LMK5B12204

JAJSJG0A - MAY 2020 - REVISED JANUARY 2021

# LMK5B122042つの周波数ドメインに対応した超低ジッタ・ネットワーク・ シンクロナイザ・クロック

## 1 特長

- デジタル・フェーズ・ロック・ループ (DPLL) ×1:

- ヒットレス・スイッチング: ±50ps の位相過渡応答

- プログラミング可能な Fastlock によるループ帯域 幅

- 低コストの TCXO/OCXO を使用する規格準拠の 同期およびホールドオーバー

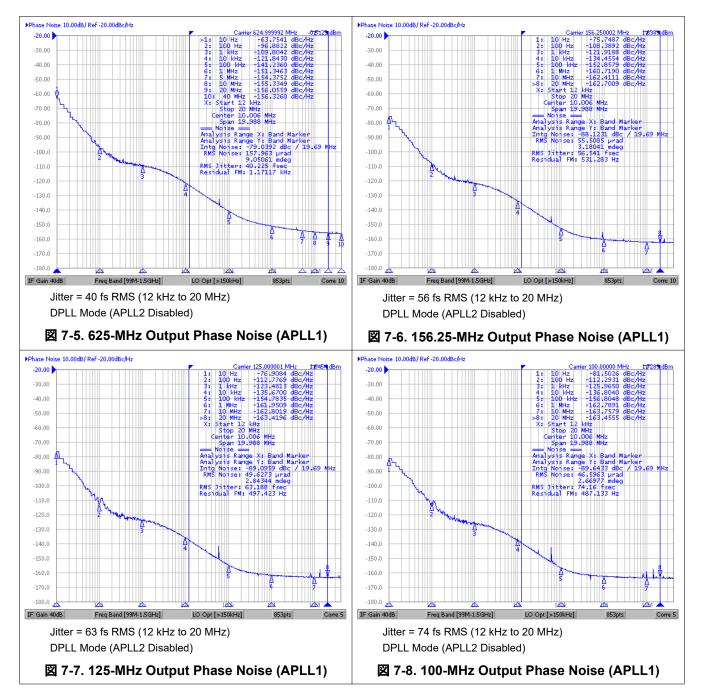

- 業界をリードするジッタ性能を備えたアナログ・フェー ズ・ロック・ループ (APLL) ×2:

- 312.5MHz で 50fs の RMS ジッタ (APLL1)

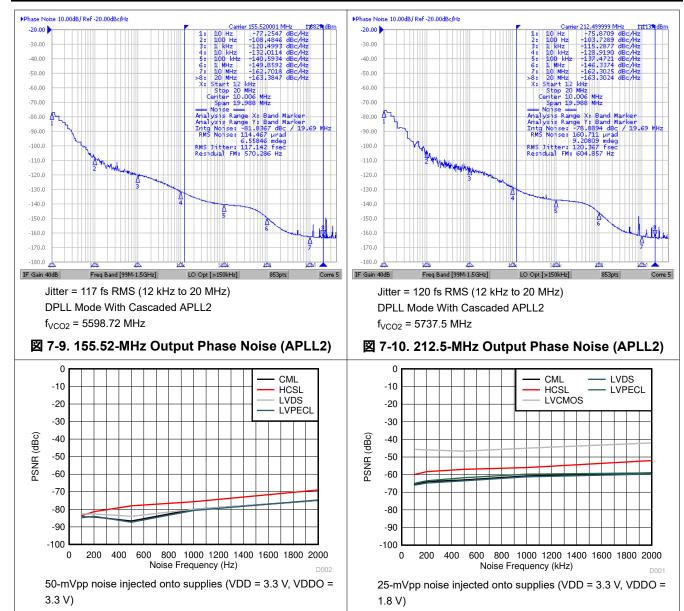

- 155.52MHz で 125fs の RMS ジッタ (APLL2)

- 基準クロック入力 ×2

- 優先度に基づく入力選択

- 基準喪失時のデジタル・ホールドオーバー

- とプログラマブル・ドライバ付きの 4 つのクロック出力

- 最大4種類の出力周波数

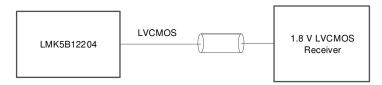

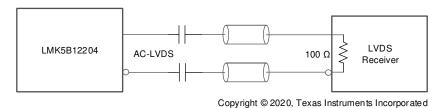

- AC-LVDS、AC-CML、AC-LVPECL、HCSL、およ び 1.8V の LVCMOS 出力フォーマット

- 起動時のカスタム・クロック用 EEPROM/ROM

- 柔軟な構成オプション

- 入力で 1Hz (1PPS)~800MHz

- XO/TCXO/OCXO 入力: 10~100MHz

- DCO モード: 0.001ppb/ステップ未満で高精度のク ロック・ステアリングを実現 (IEEE 1588 PTP スレー

- 高度なクロック監視およびステータス

- PSNR:-83dBc (3.3V 電源で 50mVpp のノイズ)

- 3.3V 電源、1.8V、2.5V、または 3.3V 出力

- 産業用温度範囲:-40℃~+85℃

## 2 アプリケーション

- SyncE (G.8262), SONET/SDH (Stratum 3/3E, G.813、GR-1244、GR-253)、IEEE 1588 PTP スレー ブ・クロック、または光伝送ネットワーク(G.709)

- イーサネット・スイッチおよびルーター用 400G ライン・ カード、ファブリック・カード

- 無線基地局 (BTS)、ワイヤレス・バックホール

- 試験および測定機器、医用画像処理

- 56G/112G PAM-4 PHY、ASIC、FPGA、SoC、プロセ ッサにおけるジッタ・クリーニング、ワンダ減衰、基準ク ロック生成

## 3 概要

LMK5B12204 は高性能のネットワーク・シンクロナイザ・ク ロックであり、ジッタ・クリーニング、クロック生成、高度なク ロック監視、優れたヒットレス・スイッチング性能により、通 信インフラおよび産業機器の厳しいタイミング要件を満た すことができます。超低ジッタ・高 PSNR (電源ノイズ除去 性能)により、高速シリアル・リンクにおけるビット誤り率 (BER) を低減します。

TI 独自のバルク弾性波 (BAW) VCO テクノロジー によ り、XO および基準入力のジッタおよび周波数に関係な く、50fs の RMS ジッタで出力クロックを生成できます。

## 製品情報

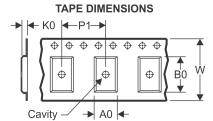

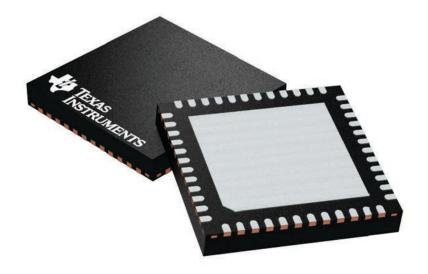

| 部品番号       | パッケージ <sup>(1)</sup> | 本体サイズ (公称)      |

|------------|----------------------|-----------------|

| LMK5B12204 | VQFN (48)            | 7.00mm × 7.00mm |

利用可能なすべてのパッケージについては、このデータシートの 末尾にある注文情報を参照してください。

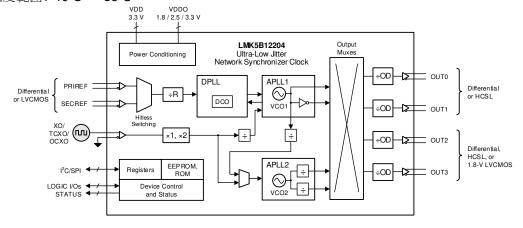

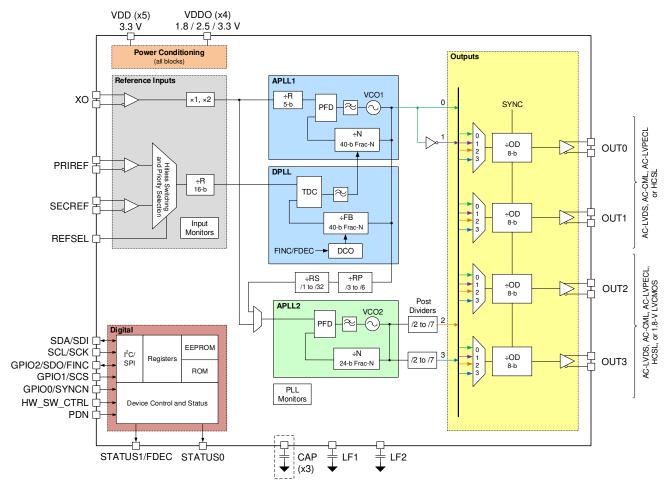

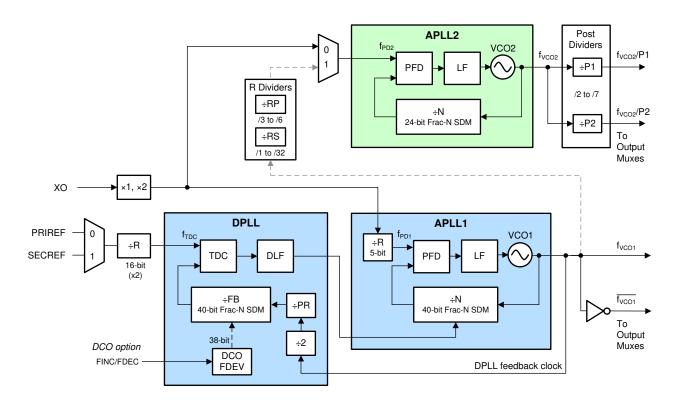

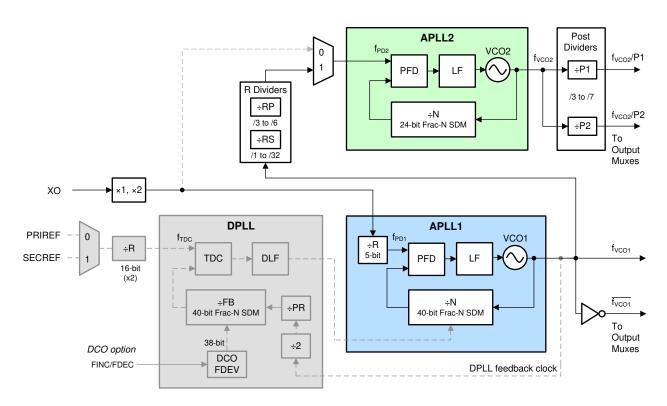

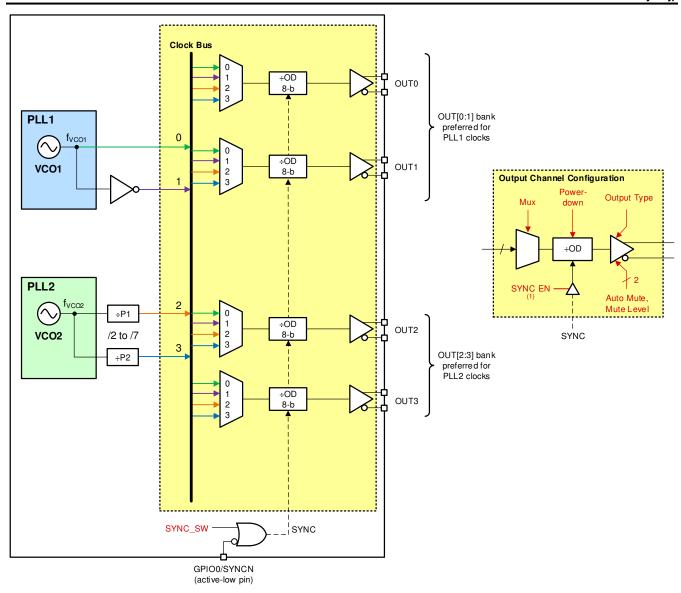

ブロック概略図

## **Table of Contents**

| 1 特長                                            | 1  | 9.4 Device Functional Modes               | <mark>52</mark>  |

|-------------------------------------------------|----|-------------------------------------------|------------------|

| 2 アプリケーション                                      |    | 9.5 Programming                           | <mark>58</mark>  |

| 3 概要                                            |    | 10 Application and Implementation         | 66               |

| 4 Revision History                              |    | 10.1 Application Information              | 66               |

| 5 概要 (続き)                                       |    | 10.2 Typical Application                  |                  |

| 6 Pin Configuration and Functions               |    | 10.3 Do's and Don'ts                      |                  |

| 6.1 Device Start-Up Modes                       |    | 11 Power Supply Recommendations           | 75               |

| 7 Specifications                                |    | 11.1 Power Supply Bypassing               | 75               |

| 7.1 Absolute Maximum Ratings                    |    | 11.2 Device Current and Power Consumption | 75               |

| 7.2 ESD Ratings                                 |    | 12 Layout                                 |                  |

| 7.3 Recommended Operating Conditions            |    | 12.1 Layout Guidelines                    | <mark>77</mark>  |

| 7.4 Thermal Information: 4-Layer JEDEC Standard |    | 12.2 Layout Example                       | <mark>77</mark>  |

| PCB                                             | 9  | 12.3 Thermal Reliability                  | <mark>77</mark>  |

| 7.5 Thermal Information: 10-Layer Custom PCB    |    | 13 Device and Documentation Support       | <mark>7</mark> 9 |

| 7.6 Electrical Characteristics                  |    | 13.1 Device Support                       | 79               |

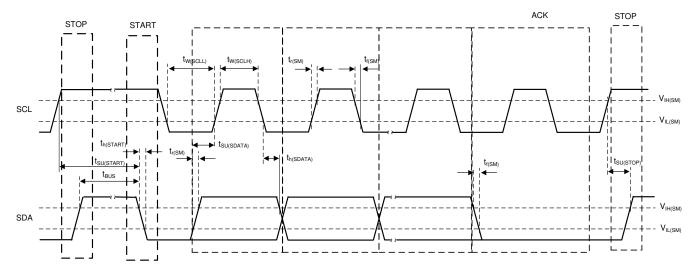

| 7.7 Timing Diagrams                             |    | 13.2ドキュメントの更新通知を受け取る方法                    | 79               |

| 7.8 Typical Characteristics                     |    | 13.3 サポート・リソース                            | 79               |

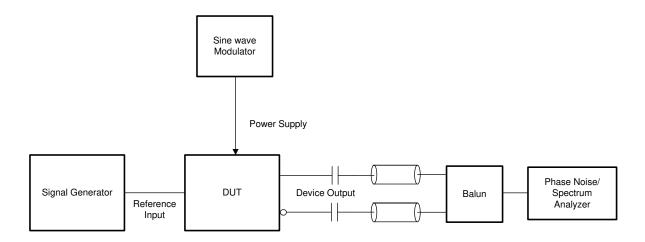

| 8 Parameter Measurement Information             |    | 13.4 Trademarks                           | <mark>79</mark>  |

| 8.1 Output Clock Test Configurations            |    | 13.5 静電気放電に関する注意事項                        | 79               |

| 9 Detailed Description                          |    | 13.6 用語集                                  | 79               |

| 9.1 Overview                                    |    | 14 Mechanical, Packaging, and Orderable   |                  |

| 9.2 Functional Block Diagram                    |    | Information                               | 79               |

| 9.3 Feature Description                         |    | 14.1 Package Option Addendum              |                  |

| 9.3 Feature Description                         | 27 | 14.1 Package Option Addendum              |                  |

**4 Revision History** 資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision * (M                    | lay 2020) to Revision A (January 2021)                    | Page |

|-----------------------------------------------|-----------------------------------------------------------|------|

| • 155.52MHz での標準 RMS                          | ジッタを 130fs から 125fs に変更                                   | 1    |

| · Changed the maximum AF                      | PLL1 PFD frequency from 50 MHz to 80 MHz                  | 9    |

| <ul> <li>Changed the maximum AC</li> </ul>    | C-LVDS output frequency from 800 MHz to 1250 MHz          | 9    |

| <ul> <li>Changed the maximum AC</li> </ul>    | C-CML output frequency from 800 MHz to 1250 MHz           | 9    |

| <ul> <li>Changed the maximum AC</li> </ul>    | C-LVPECL output frequency from 800 MHz to 1250 MHz        | 9    |

| · Changed the output forma                    | t in RMS jitter test conditions from AC-DIFF to AC-LVPECL | 9    |

| · Changed the max RMS jitt                    | er for 312.5 MHz from 100 fs to 80 fs                     | 9    |

| · Changed the max RMS jitt                    | er for 156.25 MHz from 100 fs to 90 fs                    | 9    |

| · Changed the max RMS jitt                    | er for 153.6 MHz from 250 fs to 200 fs                    | 9    |

| · Changed the max RMS jitt                    | er for 155.52 MHz from 250 fs to 200 fs                   | 9    |

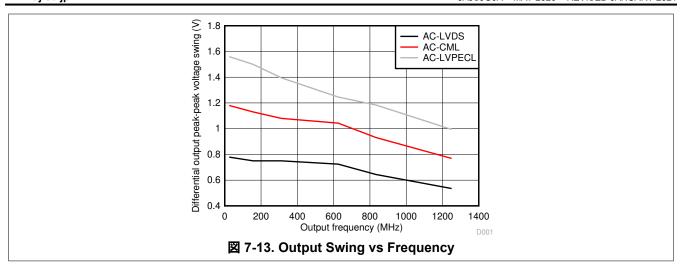

| <ul> <li>Added typical performance</li> </ul> | e plot for output voltage swing vs. output frequency      | 17   |

| · Added descriptions for refe                 | erence frequency monitoring                               | 36   |

| •                                             | -                                                         |      |

## 5 概要 (続き)

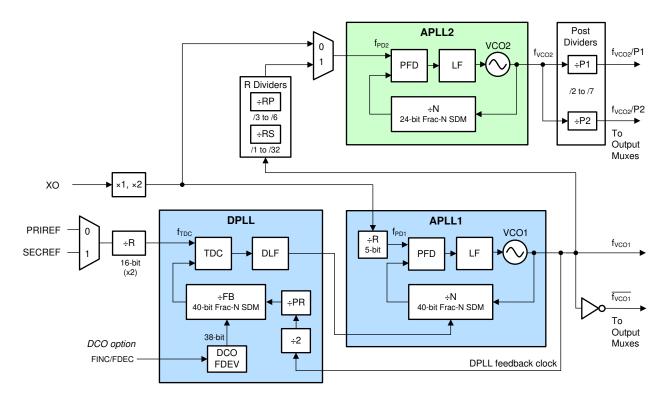

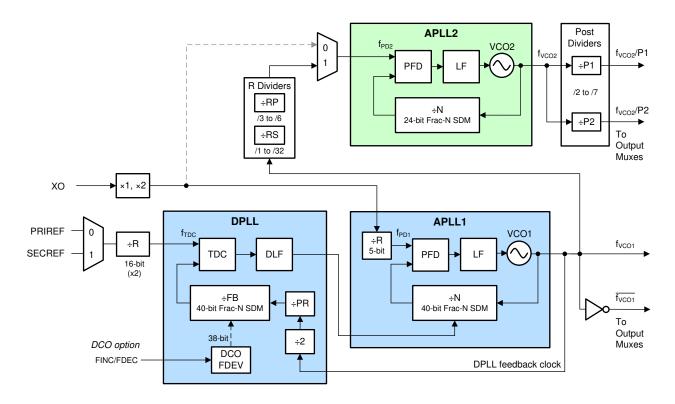

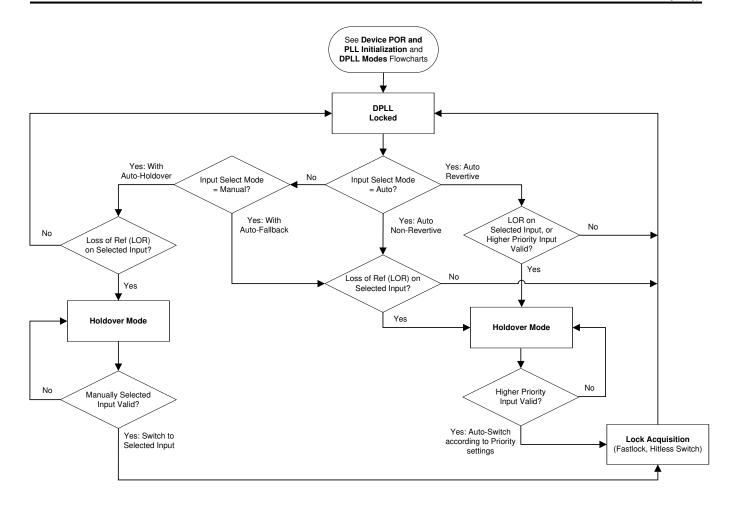

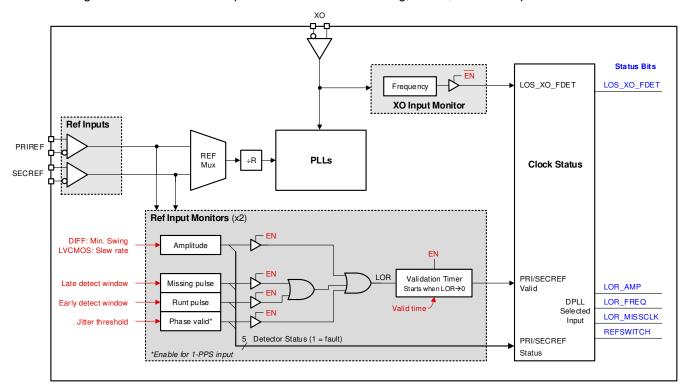

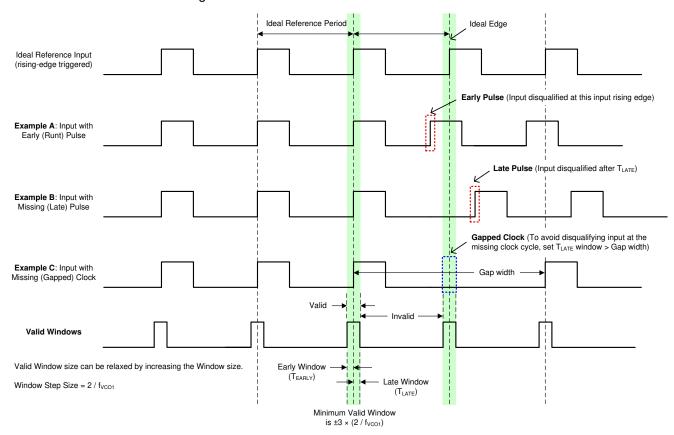

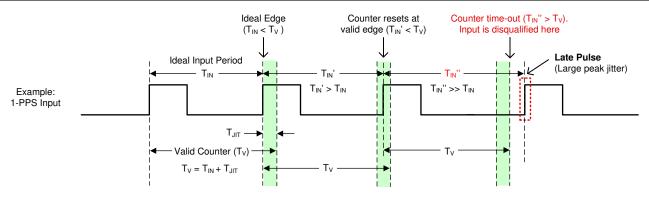

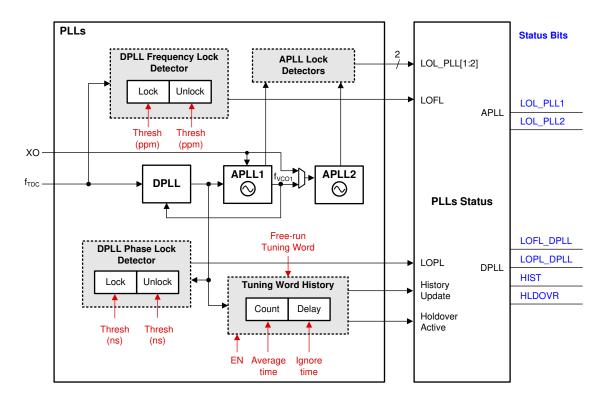

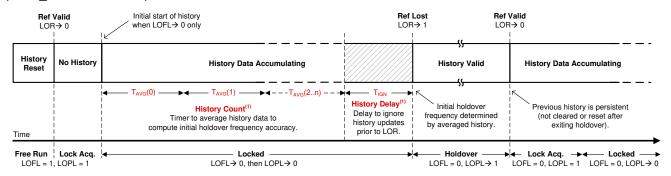

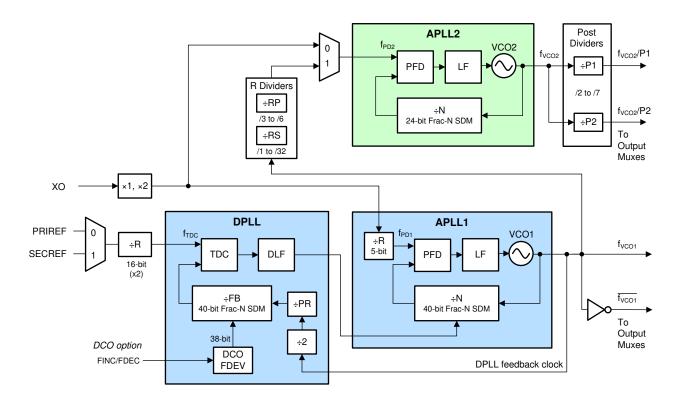

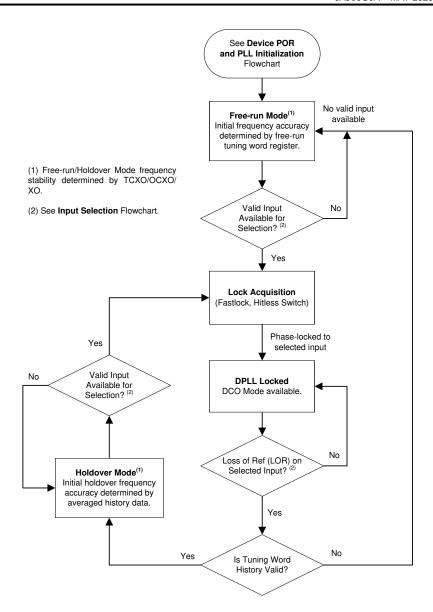

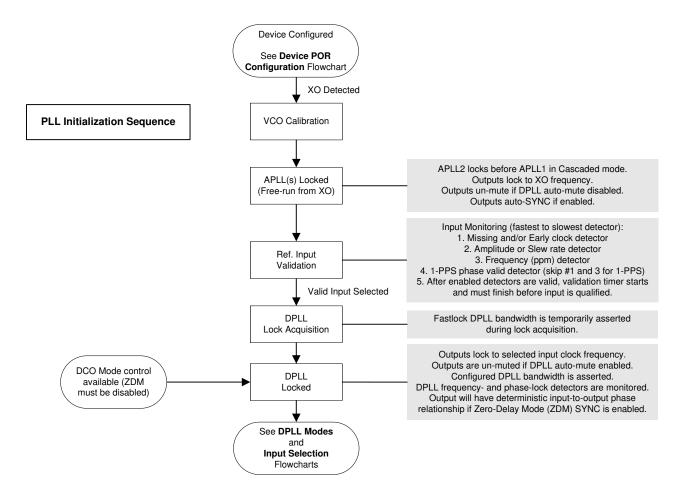

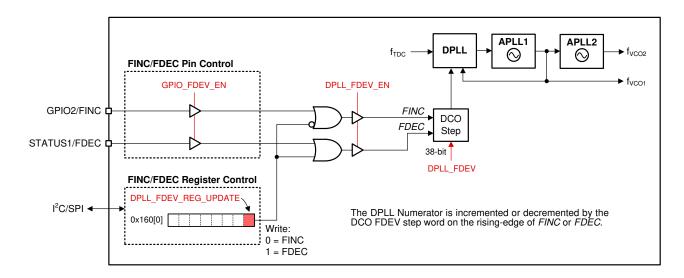

DPLL はジッタおよびワンダ減衰用のプログラミング可能なループ帯域幅をサポートし、2 つの APLL はフラクショナル周波数変換をサポートしていることから、柔軟なクロック生成が実現します。DPLL でサポートする同期オプションには、位相キャンセレーションによるヒットレス・スイッチング、デジタル・ホールドオーバー、および 0.001ppb 未満の周波数ステップ・サイズにより高精度のクロック・ステアリング (IEEE 1588 PTP スレーブ) を実現する DCO モードがあります。DPLL は1PPS (pulse-per-second) の基準入力にフェーズ・ロックします。高度な基準入力監視ブロックが、強力なクロック異常検出を実行し、基準喪失 (LOR) 時の出力クロックの乱れを最小限に抑えることができます。

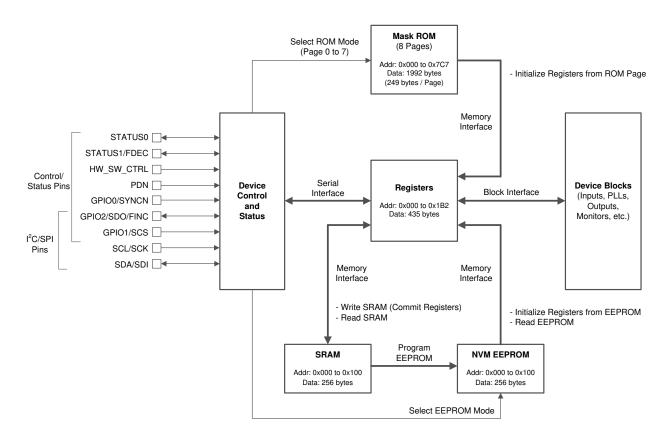

一般的な低周波数の TCXO/OCXO を使用して、同期標準に準拠したフリーランまたはホールドオーバー出力周波数安定性を確保できます。あるいは、フリーランまたはホールドオーバー時の周波数安定性やワンダが重視されない場合には、標準の XO を使用できます。I<sup>2</sup>C または SPI インターフェイスによって完全にプログラミング可能であり、内蔵 EEPROM または ROM による起動時のカスタム周波数設定にも対応しています。EEPROM は出荷時に書き込み済みであり、必要に応じてインシステム・プログラミングも可能です。

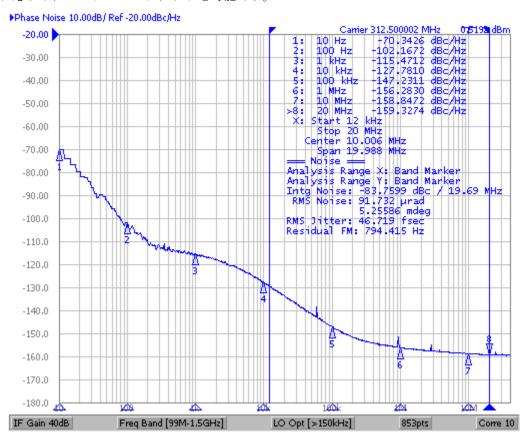

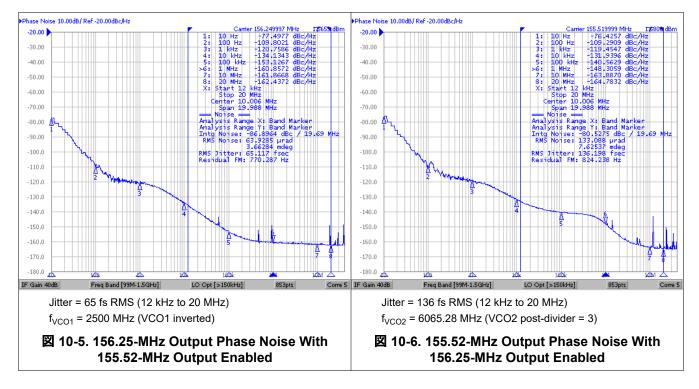

テスト条件については、セクション 7.8 を参照してください。

図 5-1. 312.5MHz での出力位相ノイズ (APLL1)、RMS ジッタ 50fs 未満

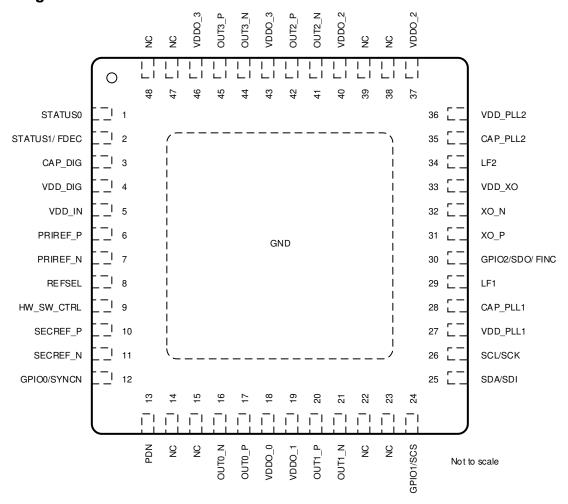

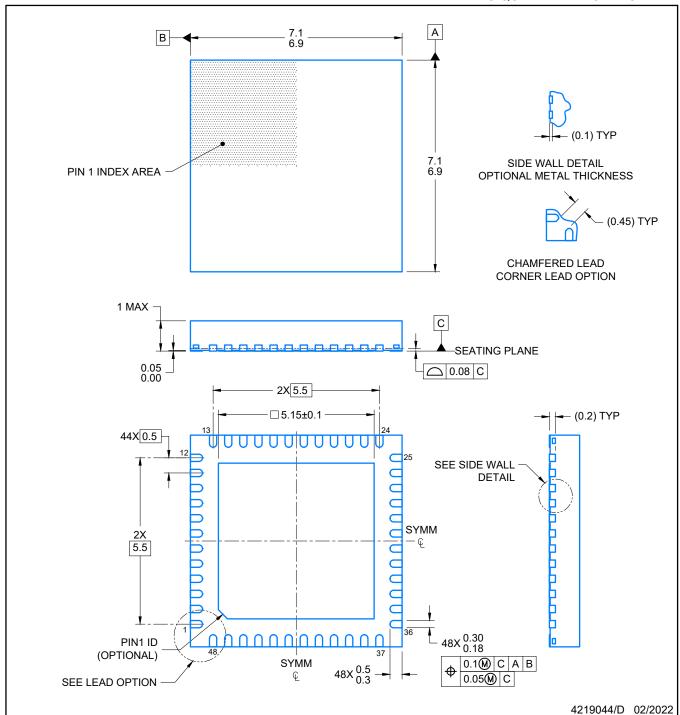

## **6 Pin Configuration and Functions**

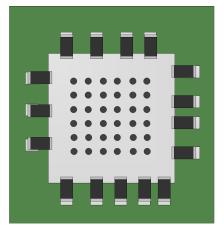

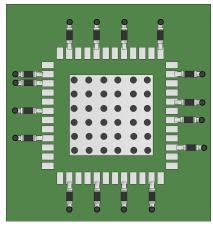

図 6-1. RGZ Package 48-Pin VQFN Top View

表 6-1. Pin Functions

| PIN         |        | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                    |

|-------------|--------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME        | NO.    | 1166                | DESCRIPTION                                                                                                                                                                                                    |

| POWER       |        |                     |                                                                                                                                                                                                                |

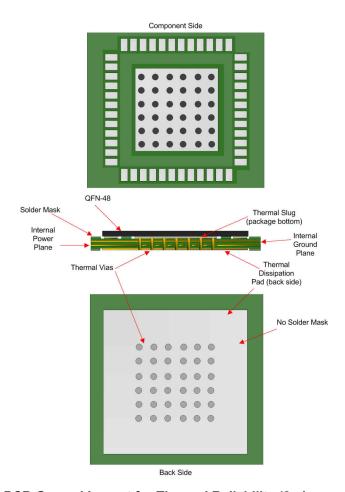

| GND         | PAD    | G                   | Ground / Thermal Pad.  The exposed pad must be connected to PCB ground for proper electrical and thermal performance.  A 5×5 via pattern is recommended to connect the IC ground pad to the PCB ground layers. |

| VDD_IN      | 5      | Р                   | Core Supply (3.3 V) for Primary and Secondary Reference Inputs. Place a nearby 0.1-µF bypass capacitor on each pin.                                                                                            |

| VDD_XO      | 33     | Р                   | Core Supply (3.3 V) for XO Input. Place a nearby 0.1-µF bypass capacitor on each pin.                                                                                                                          |

| VDD_PLL1    | 27     | Р                   |                                                                                                                                                                                                                |

| VDD_PLL2    | 36     | Р                   | Core Supply (3.3 V) for PLL1, PLL2, and Digital Blocks.  Place a nearby 0.1-μF bypass capacitor on each pin.                                                                                                   |

| VDD_DIG     | 4      | Р                   | Those a hearby c. Fig. bypace capacitor on each pin.                                                                                                                                                           |

| VDDO_0      | 18     | Р                   |                                                                                                                                                                                                                |

| VDDO_1      | 19     | Р                   | Output Supply (1.8, 2.5, or 3.3 V) for Clock Outputs 0 to 3.                                                                                                                                                   |

| VDDO_2      | 37, 40 | Р                   | Place a nearby 0.1-μF bypass capacitor on each pin.                                                                                                                                                            |

| VDDO_3      | 43, 46 | Р                   |                                                                                                                                                                                                                |

| CORE BLOCKS |        |                     |                                                                                                                                                                                                                |

表 6-1. Pin Functions (continued)

| PIN                                                         |     |                     | DECORPORA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|-------------------------------------------------------------|-----|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                                                        | NO. | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

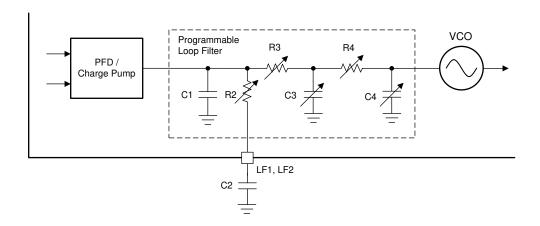

| LF1                                                         | 29  | Α                   | External Loop Filter Capacitor for APLL1 and APLL2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| LF2                                                         | 34  | А                   | ace a nearby capacitor on each pin. For LF1, a 0.47-µF capacitor is suggested for typical APLL1 op bandwidths around 1.0 kHz. For LF2, a 0.1-µF capacitor is suggested for typical APLL2 loop andwidth around 500 kHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| CAP_PLL1                                                    | 28  | Α                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| CAP_PLL2                                                    | 35  | Α                   | External Bypass Capacitors for APLL1, APLL2, and Digital Blocks.  Place a nearby 10-uF bypass capacitor on each pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| CAP_DIG                                                     | 3   | Α                   | That a hearby to an appear capacitor of cash pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| INPUT BLOCKS                                                |     | •                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

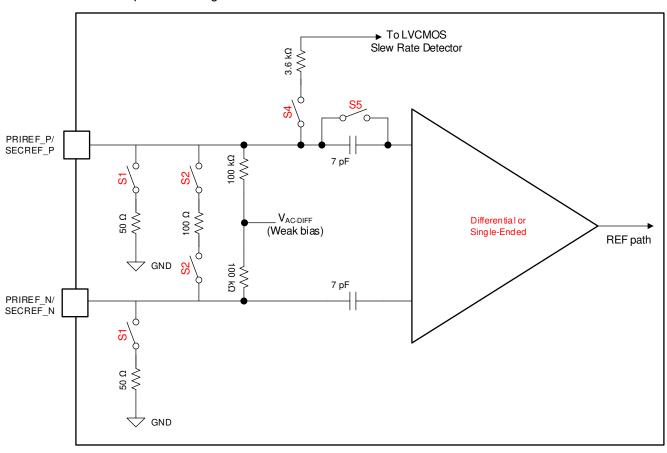

| PRIREF_P                                                    | 6   | I                   | DPLL Primary and Secondary Reference Clock Inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| PRIREF_N                                                    | 7   | ı                   | Each input pair can accept a differential or single-ended clock as a reference to the DPLL. Each pair has a programmable input type with internal termination to support AC- or DC-coupled clocks. A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| SECREF_P                                                    | 10  | I                   | single-ended LVCMOS clock can be applied to the P input with the N input pulled down to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| SECREF_N                                                    | 11  | ı                   | An unused input pair can be left floating.  For low-frequency input, an internal AC-coupling capacitor can be disabled to improve noise immunity. Differential Input and LVCMOS input can be DC-coupled to the receiver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

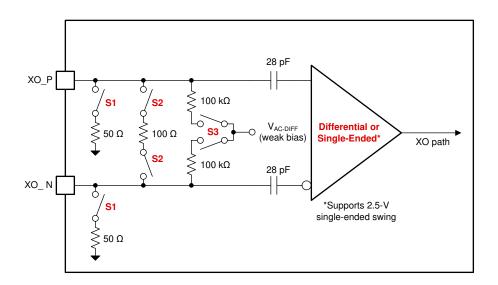

| XO_P                                                        | 31  | I                   | XO/TCXO/OCXO Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| XO_N                                                        | 32  | I                   | This input pair can accept a differential or single-ended clock signal from a low-jitter local oscillator as a reference to the APLLs. This input has a programmable input type with internal termination to support AC- or DC-coupled clocks. A single-ended LVCMOS clock (up to 2.5 V) can be applied to the P input with the N input pulled down to ground. A low-frequency TCXO or OCXO can be used to set the clock output frequency accuracy and stability during free-run and holdover modes. In DPLL mode, the XO frequency must have a non-integer relationship to the VCO1 frequency so APLL1 can operate in fractional mode (required for proper DPLL operation). In APLL-only mode, the XO frequency can have either an integer or non-integer relationship to the VCO1 frequency. |  |  |  |

| OUTPUT BLOCK                                                | S   |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| OUT0_P                                                      | 17  | 0                   | Clock Outputs 0 and 1 Bank.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| OUT0_N                                                      | 16  | 0                   | Each programmable output driver pair can support AC-LVDS, AC-CML, AC-LVPECL, and HCSL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| OUT1_P                                                      | 20  | 0                   | Unused differential outputs should be terminated if active or left floating if disabled through registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| OUT1_N                                                      | 21  | 0                   | The OUT[0:1] bank is preferred for PLL1 clocks to minimize output crosstalk.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| OUT2_P                                                      | 42  | 0                   | Clock Outputs 2 and 3 Bank.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| OUT2_N                                                      | 41  | 0                   | Each programmable output driver pair can support AC-LVDS, AC-CML, AC-LVPECL, HCSL, or 1.8-<br>V LVCMOS clocks (one or two per pair). Unused differential outputs should be terminated if active                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| OUT3_P 45 O or left floating if disabled through registers. |     | 0                   | or left floating if disabled through registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| OUT3_N                                                      | 44  | 0                   | The OUT[2:3] bank is preferred for PLL2 clocks to minimize output crosstalk. When PLL2 is not used, the OUT[2:3] bank can be used for PLL1 clocks without risk of cross-coupling from PLL2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

## 表 6-1. Pin Functions (continued)

| PIN                |         | TYPE(1)   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------|---------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME               | NO.     | ITPE      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LOGIC CONTROL      | / STATU | S (2) (3) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| HW_SW_CTRL         | 9       | I         | Device Start-Up Mode Select (3-level, 1.8-V compatible). This input selects the device start-up mode that determines the memory page used to initialize the registers, serial interface, and logic pin functions. The input level is sampled only at device power-on reset (POR). See 表 6-2 for start-up mode descriptions and logic pin functions.                                                                                                                                                                                                                                                                                                                                         |

| PDN                | 13      | I         | Device Power-Down (active low).  When PDN is pulled low, the device is in hard-reset and all blocks including the serial interface are powered down. When PDN is pulled high, the device is started according to device mode selected by HW_SW_CTRL and begins normal operation with all internal circuits reset to their initial state.                                                                                                                                                                                                                                                                                                                                                    |

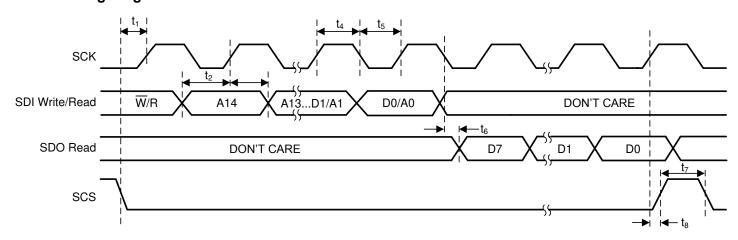

| SDA/SDI            | 25      | I/O       | I <sup>2</sup> C Serial Data I/O (SDA) or SPI Serial Data Input (SDI). See 表 6-2. When HW_SW_CTRL is 0 or 1, the serial interface is I <sup>2</sup> C. SDA and SCL pins (open-drain) require external I <sup>2</sup> C pullup resistors. The default 7-bit I <sup>2</sup> C address is 11001xxb, where the MSB bits (11001b) are initialized from on-chip EEPROM and the LSB bits (xxb) are determined by the logic input pins. When HW_SW_CTRL is 0, the LSBs are determined by the GPIO1 input state (3-level) during POR. When HW_SW_CTRL is 1, the LSBs are fixed to 00b. When HW_SW_CTRL is Float, the serial interface is SPI (4-wire, Mode 0) using the SDI, SCK, SCS, and SDO pins. |

| SCL/SCK            | 26      | I         | I <sup>2</sup> C Serial Clock Input (SCL) or SPI Serial Clock Input (SCK). See 表 6-2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GPIO0/SYNCN        | 12      | I         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| GPIO1/SCS          | 24      | I         | Multifunction Inputs or Outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| GPIO2/SDO/<br>FINC | 30      | I/O       | See 表 6-2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

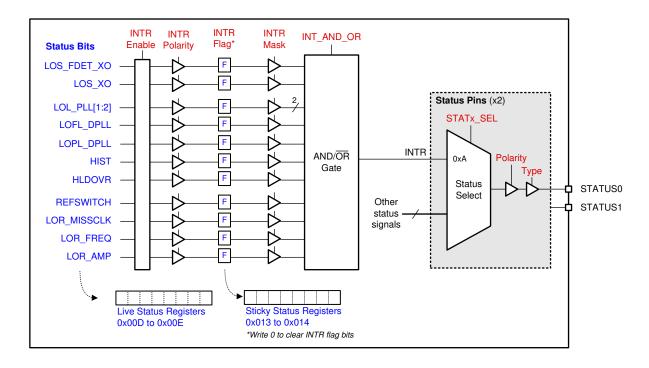

| STATUS0            | 1       | I/O       | Status Outputs 0 and 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| STATUS1/<br>FDEC   | 2       | I/O       | Each output has programmable status signal selection, driver type (3.3-V LVCMOS or open-drain), and status polarity. Open-drain requires an external pullup resistor. Leave pin floating if unused. In I <sup>2</sup> C mode, the STATUS1/FDEC pin can function as a DCO mode control input pin. See 表 6-2.                                                                                                                                                                                                                                                                                                                                                                                 |

| REFSEL             | 8       | ı         | Manual DPLL Reference Clock Input Selection. (3-level, 1.8-V compatible).  REFSEL = 0 (PRIREF), 1 (SECREF), or Float or V <sub>IM</sub> (Auto Select). This control pin must be enabled by register default or programming. Leave pin floating if unused.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

- (1)

- G = Ground, P = Power, I = Input, O = Output, I/O = Input or Output, A = Analog. Internal resistors: PDN pin has 200-k $\Omega$  pullup to VDD\_IN. HW\_SW\_CTRL, GPIO, REFSEL, and STATUS pins each have a 150-k $\Omega$ bias to  $V_{IM}$  (approximately 0.8 V) when PDN = 0 or 400-k $\Omega$  pulldown when PDN = 1.

- Unless otherwise noted: Logic inputs are 2-level, 1.8-V compatible inputs. Logic outputs are 3.3-V LVCMOS levels.

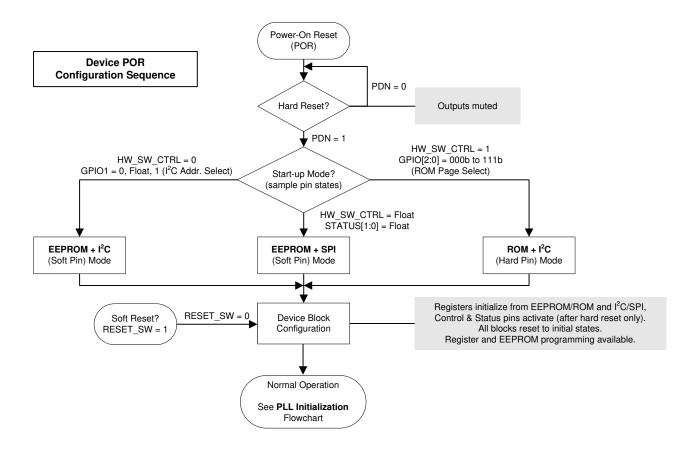

## 6.1 Device Start-Up Modes

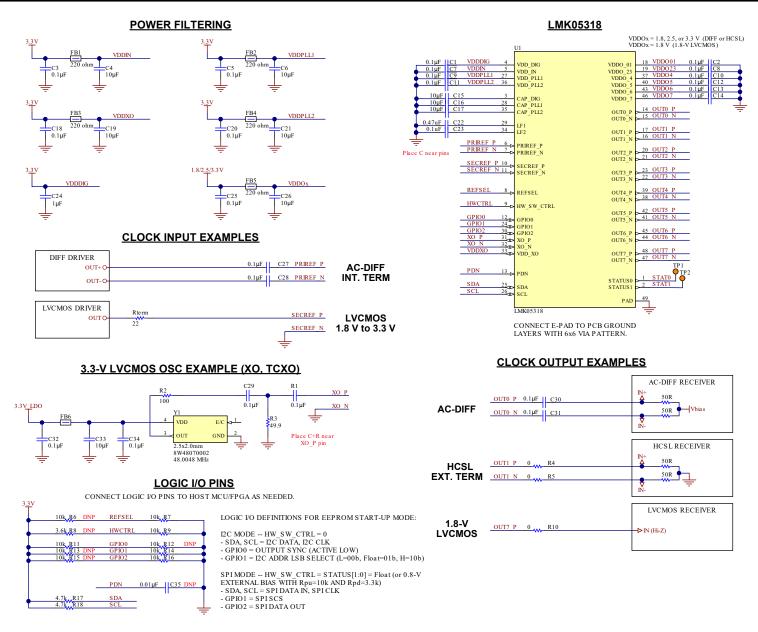

The HW\_SW\_CTRL input pin selects the device start-up mode that determines the memory page (EEPROM or ROM) used to initialize the registers, the serial interface, and the logic pin functions at power-on reset. The initial register settings determine the frequency configuration of the device on start-up. After start-up, the device registers can be accessed through the serial interface for device monitoring and programming, and the logic pins will function as defined by the selected mode.

表 6-2. Device Start-Up Modes

| HW_SW_CTRL<br>INPUT LEVEL <sup>(1)</sup> | START-UP<br>MODE                             | MODE DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                                        | EEPROM + I <sup>2</sup> C<br>(Soft pin mode) | Registers are initialized from EEPROM, and I <sup>2</sup> C interface is enabled. Logic pins:  SDA/SDI, SCL/SCK: I <sup>2</sup> C Data, I <sup>2</sup> C Clock (open-drain)  GPIO0/SYNCN: Output SYNC Input (active low). Pull up externally if not used.  GPIO1/SCS (1): I <sup>2</sup> C Address LSB Select (Low = 00b, Float = 01b, High = 10b)  GPIO2/SDO/FINC (2): DPLL DCO Frequency Increment (active high)  STATUS1/FDEC (2): DPLL DCO Frequency Decrement (active high), or Status output |

| Float<br>(V <sub>IM</sub> )              | EEPROM + SPI<br>(Soft pin mode)              | Registers are initialized from EEPROM, and SPI interface is enabled. Logic pins:  SDA/SDI, SCL/SCK: SPI Data In (SDI), SPI Clock (SCK)  GPIO0/SYNCN: Output SYNC Input (active low). Pull up externally if not used.  GPIO1/SCS: SPI Chip Select (SCS)  GPIO2/SDO/FINC: SPI Data Out (SDO)                                                                                                                                                                                                         |

| 1                                        | ROM + I <sup>2</sup> C<br>(Hard pin mode)    | Registers are initialized from the ROM page selected by GPIO pins, and I <sup>2</sup> C interface is enabled.  Logic pins:  SDA/SDI, SCL/SCK: I <sup>2</sup> C Data, I <sup>2</sup> C Clock (open-drain)  GPIO[2:0] (1): ROM Page Select Inputs (000b to 111b) during POR.  After POR, GPIO2/SDO/FINC and STATUS1/FDEC pins can function the same as for HW_SW_CTRL = 0.                                                                                                                           |

- (1) The input levels on these pins are sampled only during POR.

- (2) FINC and FDEC pins are only available when DCO mode and GPIO pin control are enabled by registers.

#### Note

To ensure proper start-up into EEPROM + SPI Mode, the HW\_SW\_CTRL, STATUS0, and STATUS1 pins must all be floating or biased to  $V_{IM}$  (0.8-V typical) before the PDN pin is pulled high. These three pins momentarily operate as 3-level inputs and get sampled at the low-to-high transition of PDN to determine the device start-up mode during POR. If any of these pins are connected to a system host (MCU or FPGA), TI recommends using external biasing resistors on each pin (10-k $\Omega$  pullup to 3.3 V with 3.3-k $\Omega$  pulldown to GND) to set the inputs to  $V_{IM}$  during POR. After power up, the STATUS pins can operate as LVCMOS outputs to overdrive the external resistor bias for normal status operation.

## 7 Specifications

## 7.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)(1)

|                        |                                                | MIN  | MAX      | UNIT |

|------------------------|------------------------------------------------|------|----------|------|

| VDD <sup>(2)</sup>     | Core supply voltages                           | -0.3 | 3.6      | V    |

| VDDO <sup>(3)</sup>    | Output supply voltages                         | -0.3 | 3.6      | V    |

| V <sub>IN</sub>        | Input voltage range for clock and logic inputs | -0.3 | VDD+0.3  | V    |

| V <sub>OUT_LOGIC</sub> | Output voltage range for logic outputs         | -0.3 | VDD+0.3  | V    |

| V <sub>OUT</sub>       | Output voltage range for clock outputs         | -0.3 | VDDO+0.3 | V    |

| T <sub>J</sub>         | Junction temperature                           |      | 150      | °C   |

| Tstg                   | Storage temperature range                      | -65  | 150      | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) VDD refers to all core supply pins or voltages. All VDD core supplies should be powered-on before the PDN is pulled high to trigger the internal power-on reset (POR).

- (3) VDDO refers to all output supply pins or voltages. VDDO\_x refers to the output supply for a specific output channel, where x denotes the channel index.

## 7.2 ESD Ratings

|                    |                         |                                                                                          | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|------|

|                    | Electrostatic           | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±750  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

|                       |                                                              | MIN   | NOM | MAX   | UNIT   |

|-----------------------|--------------------------------------------------------------|-------|-----|-------|--------|

| VDD <sup>(1)</sup>    | Core supply voltages                                         | 3.135 | 3.3 | 3.465 | V      |

|                       | Output supply voltage for AC-LVDS/CML/LVPECL or HCSL driver  | 1.71  | 1.8 | 1.89  | V      |

| VDDO_x <sup>(2)</sup> |                                                              | 2.375 | 2.5 | 2.625 | V      |

|                       |                                                              | 3.135 | 3.3 | 3.465 | V      |

| VDDO_x <sup>(2)</sup> | Output supply voltage for 1.8-V LVCMOS driver <sup>(3)</sup> | 1.71  | 1.8 | 1.89  | V      |

| V <sub>IN</sub>       | Input voltage range for clock and logic inputs               | 0     |     | 3.465 | V      |

| T <sub>J</sub>        | Junction temperature                                         |       |     | 135   | °C     |

| t <sub>VDD</sub>      | Power supply ramp time <sup>(4)</sup>                        | 0.01  |     | 100   | ms     |

| n <sub>EEcyc</sub>    | EEPROM program cycles <sup>(5)</sup>                         |       |     | 100   | cycles |

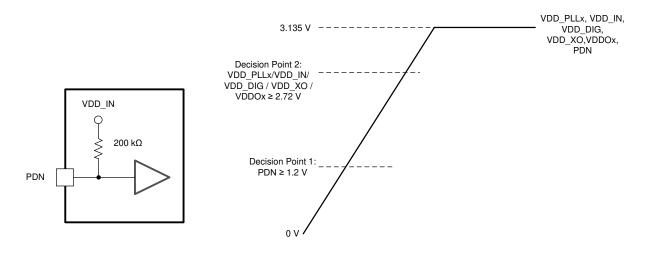

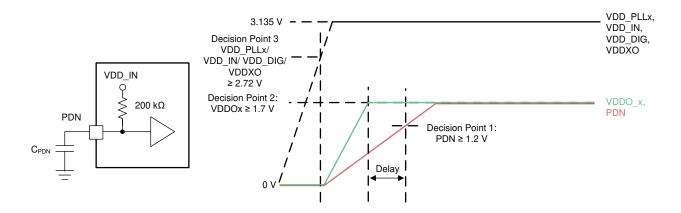

- (1) VDD refers to all core supply pins or voltages. All VDD core supplies should be powered-on before internal power-on reset (POR).

- (2) VDDO refers to all-output supply pins or voltages. VDDO\_x refers to the output supply for a specific output channel, where x denotes the channel index.

- (3) The LVCMOS driver supports full rail-to-rail swing when VDDO\_x is 1.8 V ±5%. When VDDO\_x is 2.5 V or 3.3 V, the LVCMOS driver will not fully swing to the positive rail due to the dropout voltage of the internal LDO regulator of output channel.

- (4) Time for VDD to ramp monotonically above 2.7 V for proper internal power-on reset. For slower or non-monotonic VDD ramp, hold PDN low until after VDD voltages are valid.

- (5) n<sub>EEcyc</sub> specifies the maximum EEPROM program cycles allowed for customer programming. The initial count of factory-programmed cycles is non-zero due to production tests, but factory-programmed cycles are excluded from the n<sub>EEcyc</sub> limit. The total number of EEPROM program cycles can be read from the 8-bit NVM count status register (NVMCNT), which automatically increments by 1 on each successful programming cycle. TI does not ensure EEPROM endurance if the n<sub>EEcyc</sub> limit is exceeded by the customer.

Submit Document Feedback

## 7.4 Thermal Information: 4-Layer JEDEC Standard PCB

|                       |                                              | LMK05318B  |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup> (2) (3)        | RGZ (VQFN) | UNIT |

|                       |                                              | 48 PINS    |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 23.3       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 13.2       | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 7.4        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.4        | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.2        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 7.3        | °C/W |

- For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

- (2) The thermal information is based on a 4-layer JEDEC standard board with 25 thermal vias (5 x 5 pattern, 0.3-mm holes).

- (3) Ψ<sub>JB</sub> can allow the system designer to measure the board temperature (T<sub>PCB</sub>) with a fine-gauge thermocouple and back-calculate the device junction temperature, T<sub>J</sub> = T<sub>PCB</sub> + (Ψ<sub>JB</sub> x Power). Measurement of Ψ<sub>JB</sub> is defined by JESD51-6.

## 7.5 Thermal Information: 10-Layer Custom PCB

|                 |                                              | LMK05318B  | UNIT |

|-----------------|----------------------------------------------|------------|------|

|                 | THERMAL METRIC <sup>(1)</sup> (2) (3)        | RGZ (VQFN) |      |

|                 |                                              | 48 PINS    |      |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance       | 9.1        | °C/W |

| $R_{\theta JB}$ | Junction-to-board thermal resistance         | 4.4        | °C/W |

| ΨЈТ             | Junction-to-top characterization parameter   | 0.2        | °C/W |

| ΨЈВ             | Junction-to-board characterization parameter | 4.4        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

#### 7.6 Electrical Characteristics

|           | PARAMETER                           | TEST CONDITIONS        | MIN | TYP | MAX | UNIT |

|-----------|-------------------------------------|------------------------|-----|-----|-----|------|

| POWER SUP | PLY CHARACTERISTICS                 |                        |     |     | '   |      |

| IDD_DIG   | Core Current Consumption (VDD_DIG)  |                        |     | 21  |     | mA   |

| IDD_IN    | Core Current Consumption (VDD_IN)   |                        |     | 43  |     | mA   |

| IDD_PLL1  | Core Current Consumption (VDD_PLL1) | DPLL and APLL1 enabled |     | 110 |     | mA   |

| IDD_XO    | Core Current Consumption (VDD_XO)   |                        |     | 20  |     | mA   |

| IDD_PLL2  | Core Current Consumption            | APLL2 disabled         |     | 20  |     | mA   |

|           | (VDD_PLL2)                          | APLL2 enabled          |     | 120 |     | mA   |

<sup>(2)</sup> The thermal information is based on a 10-layer 200-mm x 250-mm x 1.6-mm board with 25 thermal vias (5 x 5 pattern, 0.3-mm holes).

<sup>(3)</sup> Ψ<sub>JB</sub> can allow the system designer to measure the board temperature (T<sub>PCB</sub>) with a fine-gauge thermocouple and back-calculate the device junction temperature, T<sub>J</sub> = T<sub>PCB</sub> + (Ψ<sub>JB</sub> x Power). Measurement of Ψ<sub>JB</sub> is defined by JESD51-6.

|                      | PARAMETER                                                | TEST CONDITIONS                                                                 | MIN      | TYP  | MAX      | UNIT |

|----------------------|----------------------------------------------------------|---------------------------------------------------------------------------------|----------|------|----------|------|

|                      |                                                          | Output mux and divider enabled,<br>excludes driver(s)<br>Divider value = 2 to 6 |          | 65   |          | mA   |

| IDDO                 | Output Current Consumption, per                          | Output mux and divider enabled, excludes driver(s) Divider value > 6            |          | 70   |          | mA   |

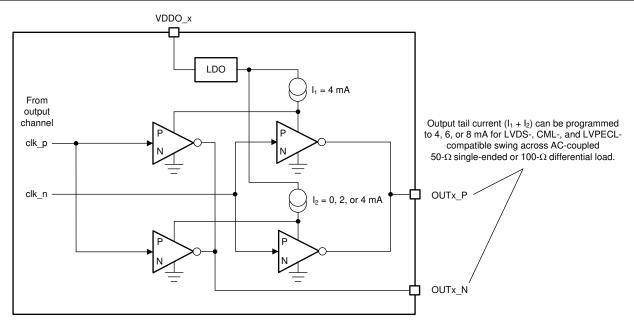

| IDDO_x               | channel <sup>(3)</sup><br>(VDDO_x)                       | AC-LVDS                                                                         |          | 11   |          | mA   |

|                      | /                                                        | AC-CML                                                                          |          | 16   |          | mA   |

|                      |                                                          | AC-LVPECL                                                                       |          | 18   |          | mA   |

|                      |                                                          | HCSL, 50-Ω load to GND                                                          |          | 25   |          | mA   |

|                      |                                                          | 1.8-V LVCMOS (x2), 100 MHz                                                      |          | 6    |          | mA   |

| IDD <sub>PDN</sub>   | Total Current Consumption (all VDD and VDDO pins, 3.3 V) | Device powered-down (PDN pin held low)                                          |          | 56   |          | mA   |

| XO INPUT C           | CHARACTERISTICS (XO)                                     |                                                                                 |          |      |          |      |

| f <sub>IN</sub>      | Input frequency range                                    |                                                                                 | 10       |      | 100      | MHz  |

| V <sub>IN-SE</sub>   | Single-ended input voltage swing                         | LVCMOS input, DC-coupled to XO_P                                                | 1        |      | 2.6      | Vpp  |

| V <sub>IN-DIFF</sub> | Differential input voltage swing <sup>(11)</sup>         | Differential input                                                              | 0.4      |      | 2        | Vpp  |

| V <sub>ID</sub>      | Differential input voltage swing <sup>(11)</sup>         | Differential input                                                              | 0.2      |      | 1        | V    |

| dV/dt                | Input slew rate <sup>(13)</sup>                          |                                                                                 | 0.2      | 0.5  |          | V/ns |

| IDC                  | Input duty cycle                                         |                                                                                 | 40       |      | 60       | %    |

| I <sub>IN</sub>      | Input leakage                                            | $50$ - $\Omega$ and $100$ - $\Omega$ internal terminations disabled             | -350     |      | 350      | μA   |

| REFERENC             | E INPUT CHARACTERISTICS (PRIRE                           | F, SECREF)                                                                      |          |      | -        |      |

| £                    | Input frequency range                                    | Differential input <sup>(4)</sup>                                               | 5        |      | 800      | MHz  |

| f <sub>IN</sub>      | Input frequency range                                    | LVCMOS input                                                                    | 1E-6     |      | 250      | MHz  |

| V <sub>IH</sub>      | Input high voltage                                       | LVCMOS input, DC-coupled to REF_P. Internally DC-coupled                        | 1.8      |      |          | V    |

| V <sub>IL</sub>      | Input low voltage                                        | LVCMOS input, DC-coupled to REF_P. Internally DC-coupled                        |          |      | 0.6      | V    |

| V <sub>IN-SE</sub>   | Single-ended input voltage swing                         | LVCMOS input, DC-coupled to REF_P. Internally AC-coupled                        | 1        |      | 2.6      | Vpp  |

| \/                   | Differential input voltage swing <sup>(11)</sup>         | Differential input, , V <sub>HYST</sub> = 50 mV                                 | 0.4      |      | 2        | Vpp  |

| $V_{\text{IN-DIFF}}$ | Differential input voltage swing <sup>(11)</sup>         | Differential input, , V <sub>HYST</sub> = 200 mV                                | 0.7      |      | 2        | Vpp  |

| \/                   | Differential input voltage swing <sup>(11)</sup>         | Differential input, V <sub>HYST</sub> = 50 mV                                   | 0.2      |      | 1        | V    |

| $V_{ID}$             | Differential input voltage swing <sup>(11)</sup>         | Differential input, V <sub>HYST</sub> = 200 mV                                  | 0.35     |      | 1        | V    |

| dV/dt                | Input slew rate <sup>(13)</sup>                          |                                                                                 | 0.2      | 0.5  |          | V/ns |

| I <sub>IN</sub>      | Input leakage                                            | 50- $\Omega$ and 100- $\Omega$ internal terminations disabled                   | -350     |      | 350      | μA   |

| VCO CHAR             | ACTERISTICS                                              |                                                                                 |          |      | -        |      |

| f <sub>VCO1</sub>    | VCO1 Frequency Range                                     |                                                                                 | 2499.750 | 2500 | 2500.250 | MHz  |

| f <sub>VCO2</sub>    | VCO2 Frequency Range                                     |                                                                                 | 5500     |      | 6250     | MHz  |

|                                | PARAMETER                                                 | TEST CONDITIONS                                                           | MIN | TYP               | MAX  | UNIT    |

|--------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------|-----|-------------------|------|---------|

| APLL CHAR                      | ACTERISTICS                                               |                                                                           |     |                   |      |         |

| £                              | APLL1 Phase Detector                                      |                                                                           | 4   |                   | 00   | N 41 1- |

| f <sub>PD1</sub>               | Frequency  APLL2 Phase Detector                           |                                                                           | 1   |                   | 80   | MHz     |

| f <sub>PD2</sub>               | Frequency                                                 |                                                                           | 10  |                   | 150  | MHz     |

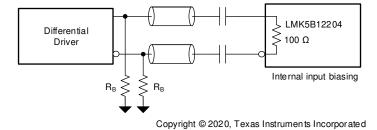

| AC-LVDS OU                     | UTPUT CHARACTERISTICS (OUTx)                              |                                                                           |     |                   |      |         |

| f <sub>OUT</sub>               | Output frequency <sup>(5)</sup>                           |                                                                           |     |                   | 1250 | MHz     |

| V <sub>OD</sub>                | Output voltage swing (V <sub>OH</sub> - V <sub>OL</sub> ) | 25 MHz ≤ f <sub>OUT</sub> ≤ 800 MHz; TYP at 156.25 MHz                    | 250 | 350               | 450  | mV      |

|                                |                                                           | f <sub>OUT</sub> = 1250 MHz                                               |     | 280               |      | mV      |

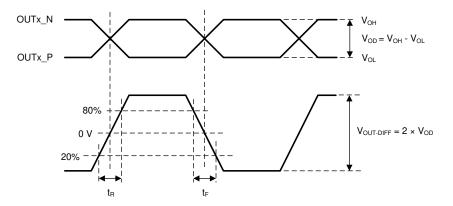

| V <sub>OUT-DIFF</sub>          | Differential output voltage swing, peak-to-peak           |                                                                           |     | 2×V <sub>OD</sub> |      | Vpp     |

| Vos                            | Output common mode                                        |                                                                           | 100 |                   | 430  | mV      |

| t <sub>SK</sub>                | Output-to-output skew                                     | Same post divider, output divide values, and output type                  |     |                   | 100  | ps      |

|                                |                                                           | 20% to 80%, < 300 MHz                                                     |     | 225               | 350  | ps      |

| t <sub>R</sub> /t <sub>F</sub> | Output rise/fall time <sup>(12)</sup>                     | ± 100 mV around center point,<br>300 MHz ≤ f <sub>OUT</sub> ≤ 800 MHz     |     | 85                | 250  | ps      |

| $PN_{FLOOR}$                   | Output phase noise floor                                  | f <sub>OUT</sub> = 156.25 MHz; f <sub>OFFSET</sub> > 10 MHz               | ,   | -160              |      | dBc/Hz  |

| ODC                            | Output duty cycle <sup>(9)</sup>                          |                                                                           | 45  |                   | 55   | %       |

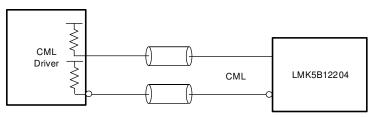

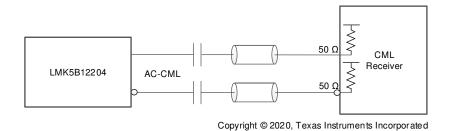

| AC-CML OU                      | TPUT CHARACTERISTICS (OUTx)                               |                                                                           |     |                   |      |         |

| f <sub>OUT</sub>               | Output frequency <sup>(5)</sup>                           |                                                                           |     |                   | 1250 | MHz     |

| V <sub>OD</sub>                | Output voltage swing (V <sub>OH</sub> - V <sub>OL</sub> ) | 25 MHz ≤ f <sub>OUT</sub> ≤ 800 MHz; TYP at f <sub>OUT</sub> = 156.25 MHz | 400 | 600               | 800  | mV      |

|                                |                                                           | f <sub>OUT</sub> = 1250 MHz                                               |     | 400               |      | mV      |

| V <sub>OUT-DIFF</sub>          | Differential output voltage swing, peak-to-peak           |                                                                           |     | 2×V <sub>OD</sub> |      | Vpp     |

| V <sub>OS</sub>                | Output common mode                                        |                                                                           | 150 |                   | 550  | mV      |

| t <sub>SK</sub>                | Output-to-output skew                                     | Same post divider, output divide values, and output type                  |     |                   | 100  | ps      |

|                                |                                                           | 20% to 80%, < 300 MHz                                                     |     | 225               | 300  | ps      |

| t <sub>R</sub> /t <sub>F</sub> | Output rise/fall time <sup>(12)</sup>                     | ± 100 mV around center point,<br>300 MHz ≤ f <sub>OUT</sub> ≤ 800 MHz     |     | 50                | 150  | ps      |

| PN <sub>FLOOR</sub>            | Output phase noise floor                                  | f <sub>OUT</sub> = 156.25 MHz; f <sub>OFFSET</sub> > 10 MHz               |     | -160              |      | dBc/Hz  |

| ODC                            | Output duty cycle <sup>(9)</sup>                          |                                                                           | 45  |                   | 55   | %       |

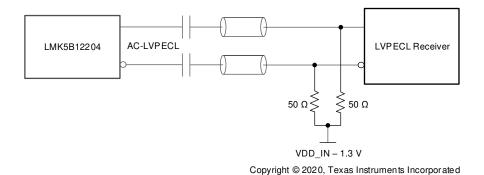

| AC-LVPECL                      | OUTPUT CHARACTERISTICS (OUT)                              | κ)                                                                        | ,   |                   |      |         |

| f <sub>OUT</sub>               | Output frequency <sup>(5)</sup>                           |                                                                           |     |                   | 1250 | MHz     |

| V <sub>OD</sub>                | Output voltage swing (V <sub>OH</sub> - V <sub>OL</sub> ) | 25 MHz ≤ f <sub>OUT</sub> ≤ 800 MHz; TYP at f <sub>OUT</sub> = 156.25 MHz | 500 | 800               | 1000 | mV      |

|                                | . 5 5 6 6 611 627                                         | f <sub>OUT</sub> = 1250 MHz                                               |     | 510               |      | mV      |

| V <sub>OUT-DIFF</sub>          | Differential output voltage swing, peak-to-peak           |                                                                           |     | 2×V <sub>OD</sub> |      | Vpp     |

| V <sub>OS</sub>                | Output common mode                                        |                                                                           | 300 |                   | 700  | mV      |

| t <sub>SK</sub>                | Output-to-output skew                                     | Same post divider, output divide values, and output type                  |     |                   | 100  | ps      |

|                                |                                                           | 20% to 80%, < 300 MHz                                                     |     | 200               | 300  | ps      |

| $t_R/t_F$                      | Output rise/fall time <sup>(12)</sup>                     | ± 100 mV around center point,<br>300 MHz ≤ f <sub>OUT</sub> ≤ 800 MHz     |     | 35                | 100  | ps      |

| PN <sub>FLOOR</sub>            | Output phase noise floor                                  | f <sub>OUT</sub> = 156.25 MHz; f <sub>OFFSET</sub> > 10 MHz               |     | -162              |      | dBc/Hz  |

| ODC                            | Output duty cycle <sup>(9)</sup>                          |                                                                           | 45  |                   | 55   | %       |

|                                | PARAMETER                                               | TEST CONDITIONS                                            | MIN   | TYP  | MAX | UNIT   |

|--------------------------------|---------------------------------------------------------|------------------------------------------------------------|-------|------|-----|--------|

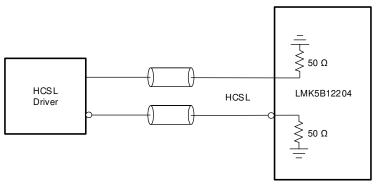

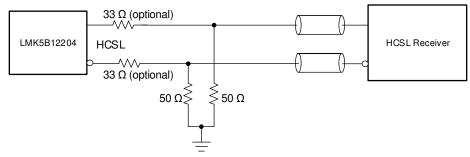

| HCSL OUTP                      | PUT CHARACTERISTICS (OUTx)                              |                                                            |       |      |     |        |

| f <sub>OUT</sub>               | Output frequency <sup>(5)</sup>                         |                                                            |       |      | 400 | MHz    |

| V <sub>OH</sub>                | Output high voltage                                     |                                                            | 600   |      | 880 | mV     |

| V <sub>OL</sub>                | Output low voltage                                      |                                                            | -150  |      | 150 | mV     |

| t <sub>SK</sub>                | Output-to-output skew                                   | Same post divider, output divide values, and output type   |       |      | 100 | ps     |

| dV/dt                          | Output slew rate <sup>(12)</sup>                        | ± 150 mV around center point                               | 1.6   |      | 4   | V/ns   |

| PN <sub>FLOOR</sub>            | Output phase noise floor (f <sub>OFFSET</sub> > 10 MHz) | 100 MHz                                                    |       | -160 |     | dBc/Hz |

| ODC                            | Output duty cycle <sup>(9)</sup>                        |                                                            | 45    |      | 55  | %      |

| 1.8-V LVCM                     | OS OUTPUT CHARACTERISTICS (OL                           | JT[4:7])                                                   |       |      | '   |        |

| f <sub>OUT</sub>               | Output frequency                                        |                                                            | 1E-6  |      | 200 | MHz    |

| V <sub>OH</sub>                | Output high voltage                                     | I <sub>OH</sub> = 1 mA                                     | 1.2   |      |     | V      |

| V <sub>OL</sub>                | Output low voltage                                      | I <sub>OL</sub> = 1 mA                                     |       |      | 0.4 | V      |

| I <sub>OH</sub>                | Output high current                                     |                                                            |       | -23  |     | mA     |

| I <sub>OL</sub>                | Output low current                                      |                                                            |       | 20   |     | mA     |

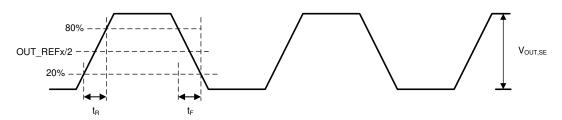

| t <sub>R</sub> /t <sub>F</sub> | Output rise/fall time                                   | 20% to 80%                                                 |       | 250  |     | ps     |

| •                              | Output-to-output skew                                   | Same post divider, output divide values, and output type   |       |      | 100 | ps     |

| t <sub>SK</sub>                | Output-to-output skew                                   | Same post divider, output divide values, LVCMOS-to-DIFF    |       |      | 1.5 | ns     |

| PN <sub>FLOOR</sub>            | Output phase noise floor                                | f <sub>OUT</sub> = 66.66 MHz; f <sub>OFFSET</sub> > 10 MHz |       | -160 |     | dBc/Hz |

| ODC                            | Output duty cycle <sup>(9)</sup>                        |                                                            | 45    |      | 55  | %      |

| R <sub>OUT</sub>               | Output impedance                                        |                                                            |       | 50   |     | Ω      |

| 3-LEVEL LO                     | GIC INPUT CHARACTERISTICS (HW                           | _SW_CTRL, GPIO1, REFSEL, STATUS[                           | 1:0]) |      |     |        |

| V <sub>IH</sub>                | Input high voltage                                      |                                                            | 1.4   |      |     | V      |

| V <sub>IM</sub>                | Input mid voltage                                       | Input floating with internal bias and PDN pulled low       | 0.7   |      | 0.9 | ٧      |

| V <sub>IL</sub>                | Input low voltage                                       |                                                            |       |      | 0.4 | V      |

| I <sub>IH</sub>                | Input high current                                      | V <sub>IH</sub> = VDD                                      | -40   |      | 40  | μΑ     |

| I <sub>IL</sub>                | Input low current                                       | V <sub>IL</sub> = GND                                      | -40   |      | 40  | μA     |

| 2-LEVEL LO                     | GIC INPUT CHARACTERISTICS (PDI                          | N, GPIO[2:0], SDI, SCK, SCS)                               |       |      |     |        |

| V <sub>IH</sub>                | Input high voltage                                      |                                                            | 1.2   |      |     | V      |

| V <sub>IL</sub>                | Input low voltage                                       |                                                            |       |      | 0.6 | V      |

| I <sub>IH</sub>                | Input high current                                      | V <sub>IH</sub> = VDD                                      | -40   |      | 40  | μA     |

| I <sub>IL</sub>                | Input low current                                       | V <sub>IL</sub> = GND                                      | -40   |      | 40  | μA     |

www.tij.co.jp

|                                | PARAMETER                            | TEST CONDITIONS                              | MIN | TYP | MAX | UNIT |

|--------------------------------|--------------------------------------|----------------------------------------------|-----|-----|-----|------|

| LOGIC OUT                      | PUT CHARACTERISTICS (STATUS[1:       | 0], SDO)                                     |     |     | '   |      |

| V <sub>OH</sub>                | Output high voltage                  | I <sub>OH</sub> = 1 mA                       | 1.2 |     |     | V    |

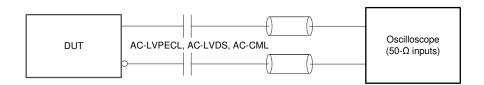

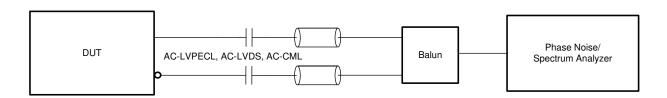

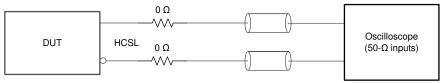

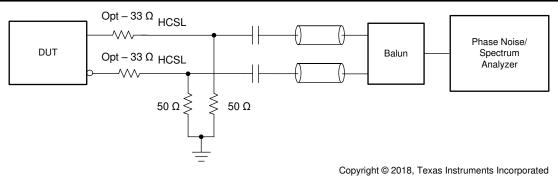

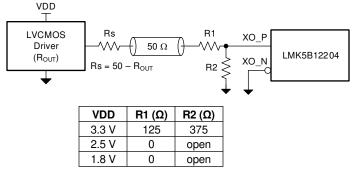

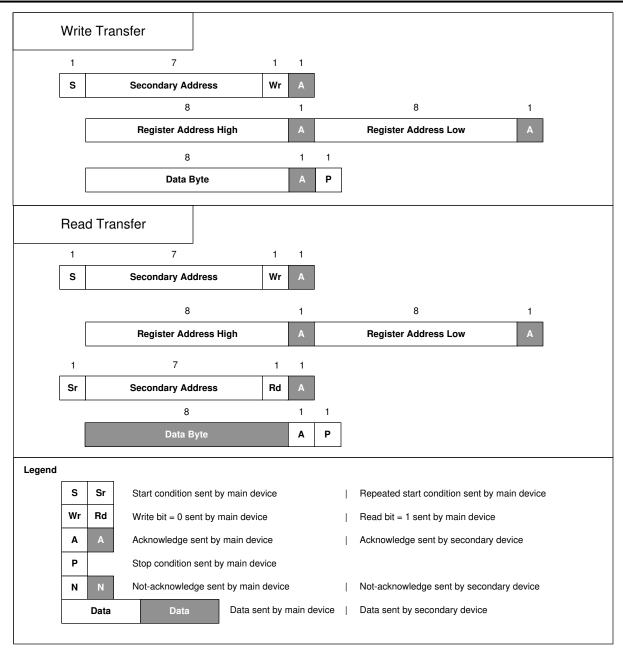

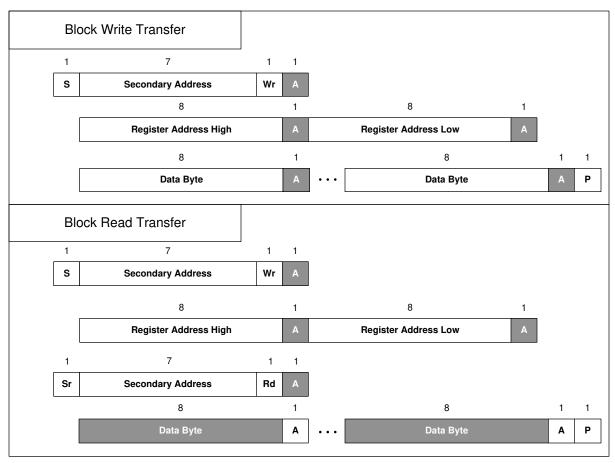

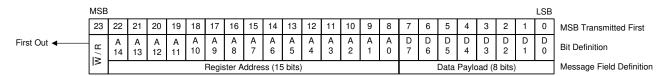

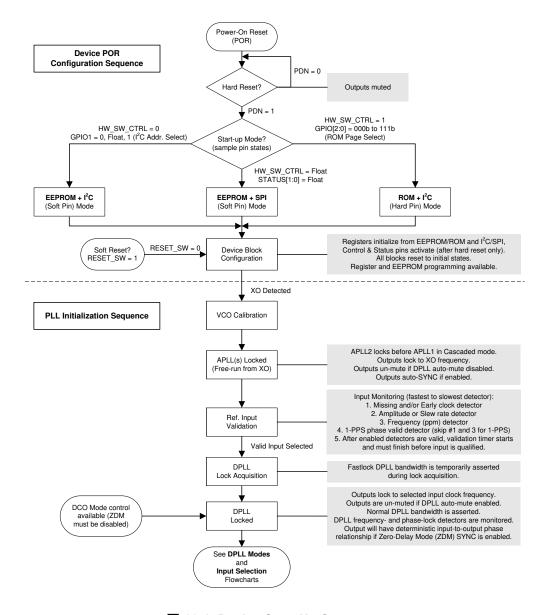

| V <sub>OL</sub>                | Output low voltage                   | I <sub>OL</sub> = 1 mA                       |     |     | 0.6 | V    |