# LMK3H2104 および LMK3H2108 4 および 8 出力 PCIe Gen 1 ~ 7 準拠、低ジッタ汎用 BAW クロック ジェネレータ

## 1 特長

- BAW 共振器を内蔵

- 外部 XTAL/XO は不要

- 柔軟な出力周波数

- 2 つの分数出力分周器 (FOD)、個別のチャネル分周器

- 最大 400MHz の出力周波数

- 柔軟な出力フォーマット

- 1.2/1.8/2.5/3.3V LVCMS

- DC または AC 結合 LVDS

- プログラム可能なスイング付きの LP-HCSL、LVPECL、CML、その他の形式は、LP-HCSL から派生できます

- 非常に小さいジッタ

- SSC ジッタ付き、最大 61fs の PCIe Gen 5 CC

- SSC ジッタ付き、最大 36.4fs の PCIe Gen 6 CC

- SSC ジッタ付き、最大 25.5fs の PCIe Gen 7 CC

- PCIe Gen 1 ~ Gen 7 準拠

- 構成可能な SSC

- プログラム可能なダウンスプレッド: 0.05% ~ -3%、センター スプレッド: ±0.025% ~ ±1.5%、またはプリセット -0.1%、-0.25%、-0.3%、-0.5% のダウンスプレッド

- 3 つの入力 LMK3H2108) または 1 つの入力 (LMK3H2104) を任意の出力にバイパス可能

- 最大スタートアップ時間 5ms

- フェイルセーフ入力ピンは、デバイスの電源がオフのときは high にプルアップできます

- 柔軟な電源

- 各 VDD ピンは、1.8V、2.5V、3.3V に個別に接続できます

- 各 VDDO ピンは、1.8V、2.5V、3.3V に設定して個別に接続できます

- 周囲温度範囲: -40°C ~ 105°C

## 2 アプリケーション

- 高性能コンピュータ サーバー マザーボード

- NIC、SmartNIC、ハードウェア アクセラレーション

- PCIe Gen 1 ~ Gen 7 のクロック生成

- 汎用クロック生成と XO/XTAL の代替

## 3 説明

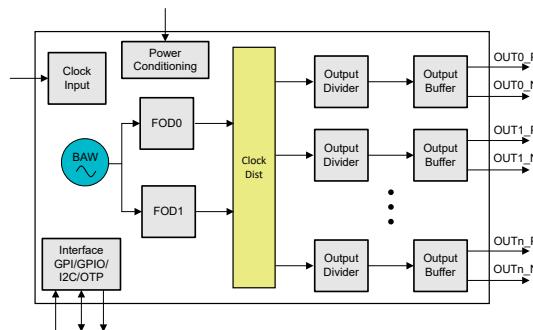

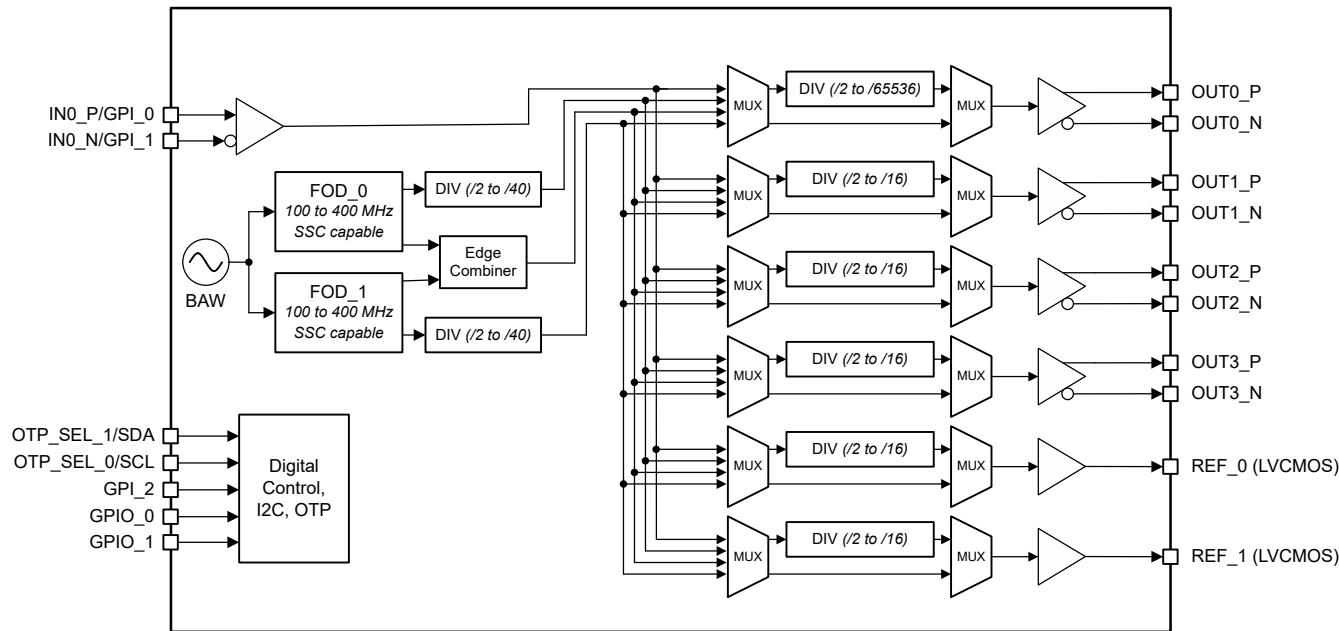

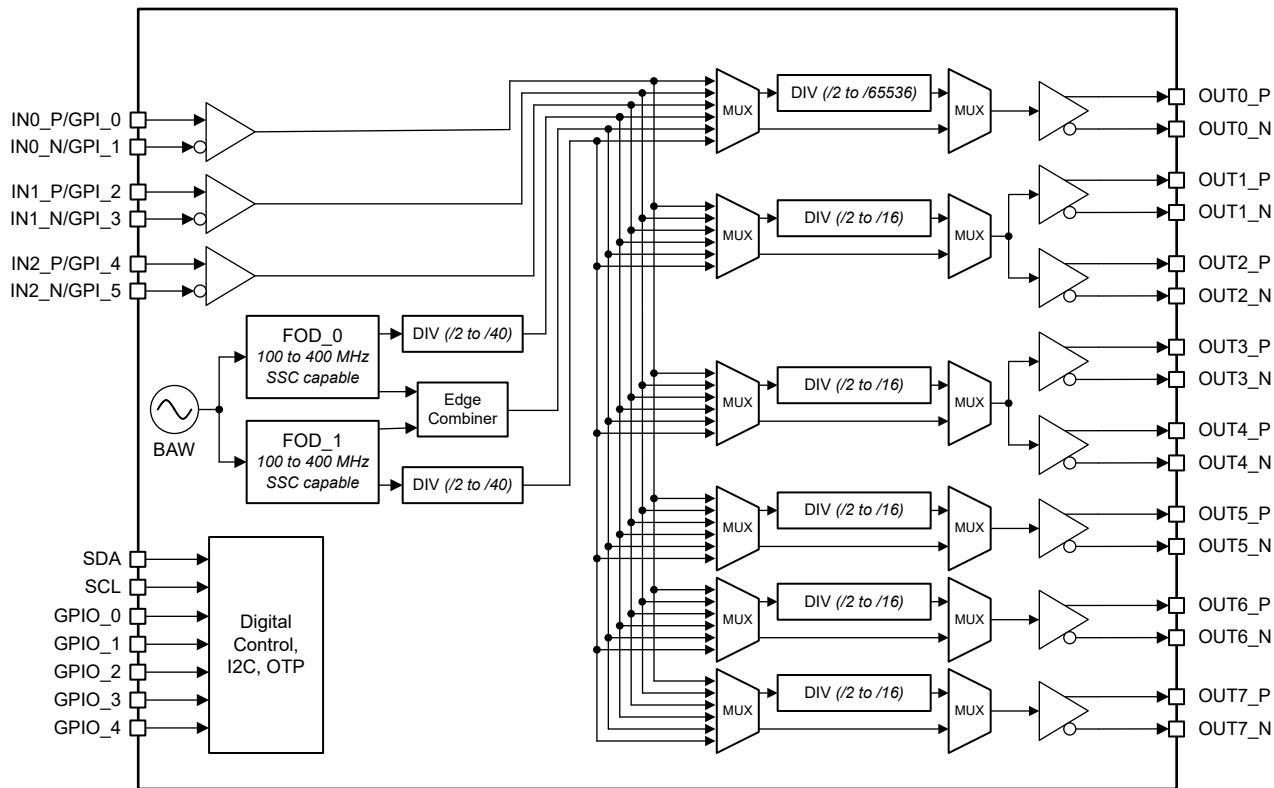

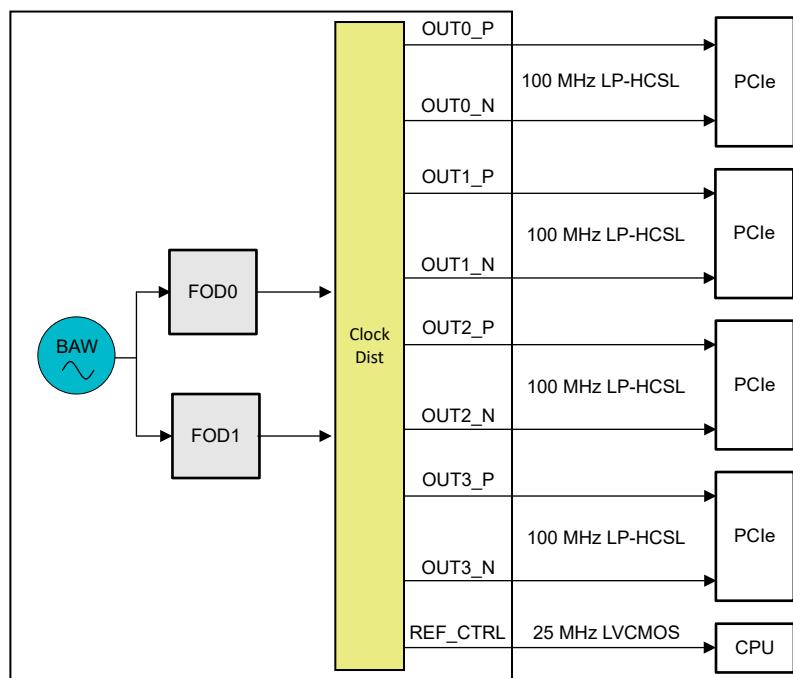

LMK3H2104 および LMK3H2108 は、BAW ベースのクロック ジェネレータで、外部の XTAL や XO を必要としません。これらのデバイスは、PCIe クロック ジェネレータま

たは汎用クロック ジェネレータとして使用できます。2 つの FOD (フラクショナル出力デバイス) は、柔軟な周波数、低消費電力、低ジッタを同時に実現します。

LMK3H2104 は、最大 4 つの差動出力と 2 つの LVCMS 出力、または最大 10 個の LVCMS 出力を供給できます。LMK3H2108 は、最大 8 つの差動出力または 16 個の LVCMS 出力を備えています。

LMK3H2104 には 1 つのクロック入力、LMK3H2108 には 3 つのクロック入力があります。クロック入力には、クロック多重化およびバッファリング機能があります。各出力バンクは独立して任意のクロックソースを選択できます。

GPI ピンと GPIO ピンにより、制御の柔軟性が向上します。これらのピンは、個別の OE、グループ化された OE、I2C アドレスの選択、OTP ページの選択、PWRGD/PWRDN#、ステータス出力、その他の機能として構成できます。

このデバイスは、ワンタイム プログラマブル (OTP) 不揮発性メモリをサポートしており、カスタマイズと出荷時に事前プログラムが可能です。

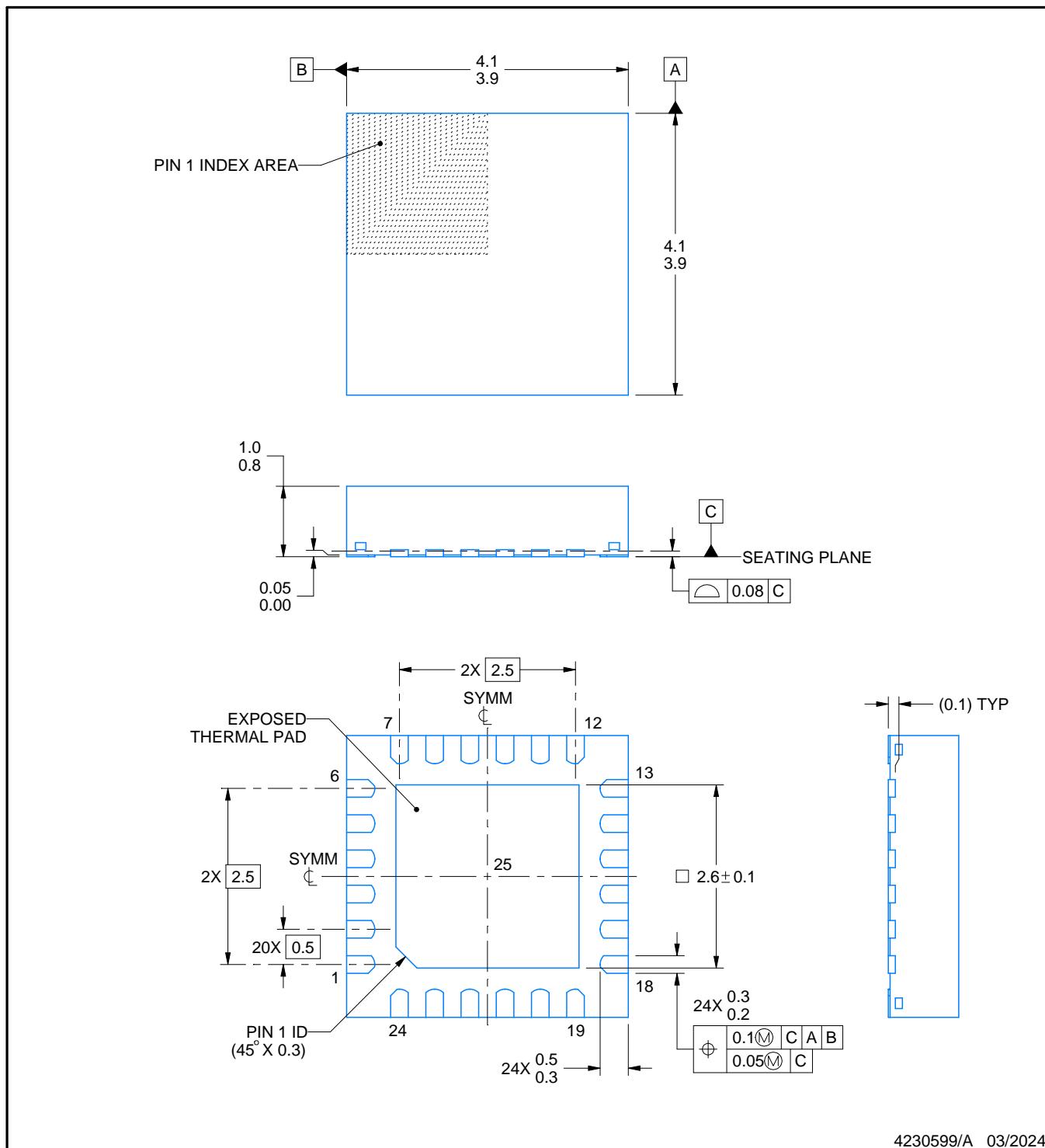

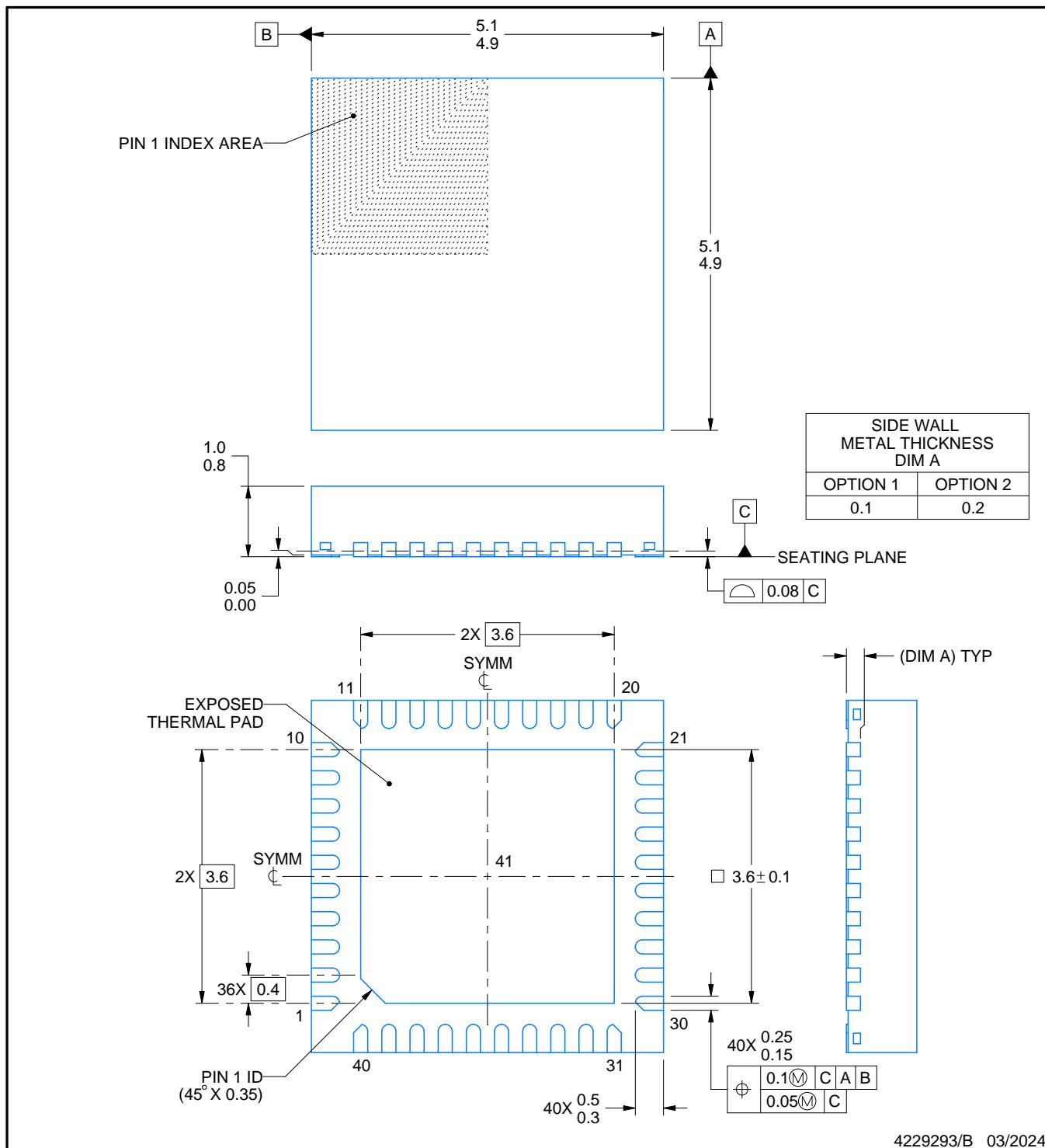

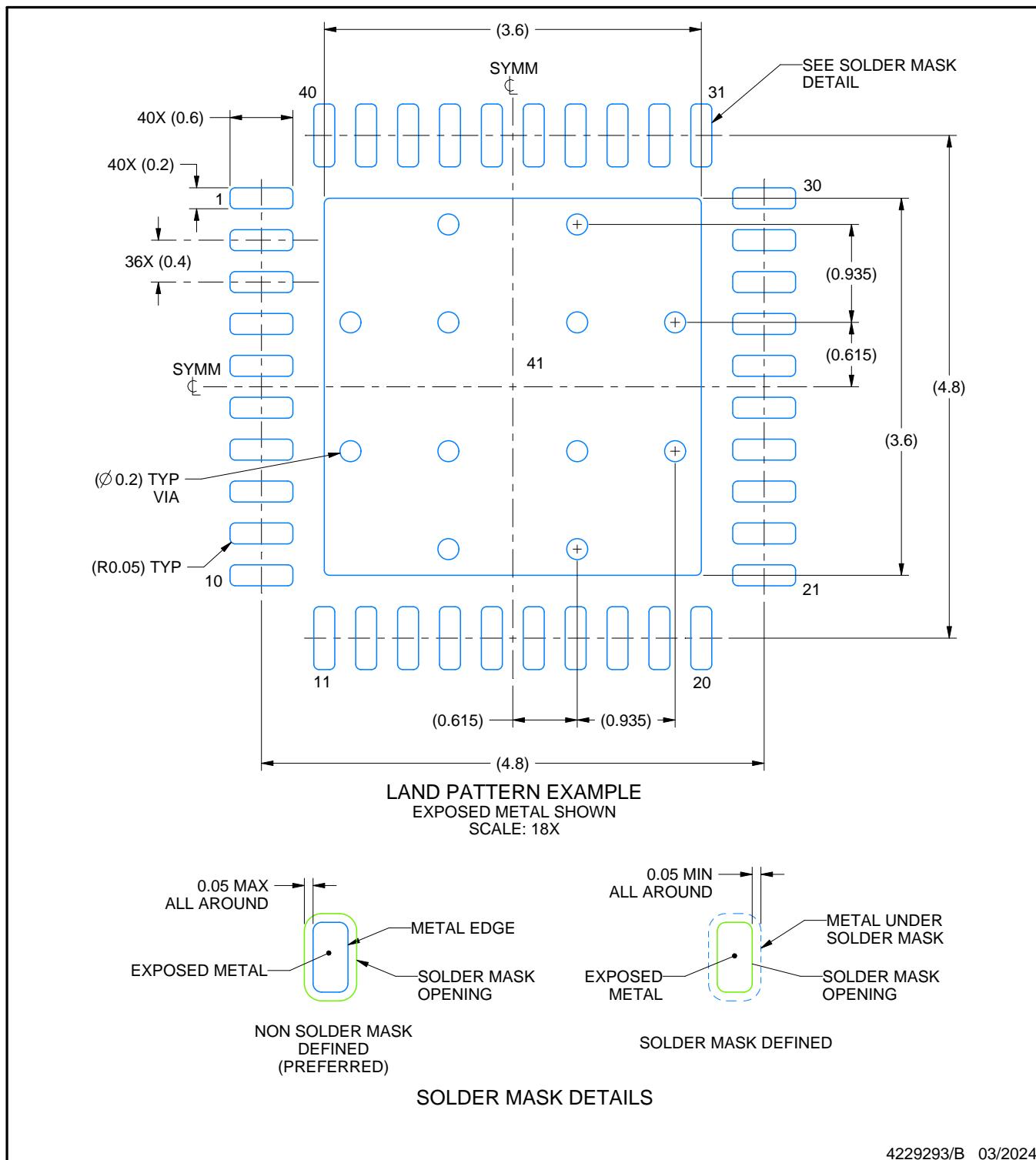

## パッケージ情報

| 部品番号      | パッケージ (1)            | パッケージ サイズ (2) |

|-----------|----------------------|---------------|

| LMK3H2104 | RGE0024AA (QFN) (24) | 4.0mm × 4.0mm |

| LMK3H2104 | RGE0024AB (QFN) (24) | 4.0mm × 4.0mm |

| LMK3H2108 | RKP0040A (QFN) (40)  | 5.0mm × 5.0mm |

(1) 詳細については、[セクション 11](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

概略ブロック図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                              |    |                        |    |

|------------------------------|----|------------------------|----|

| 1 特長                         | 1  | 7.4 SSC                | 55 |

| 2 アプリケーション                   | 1  | 7.5 デバイスの機能モード         | 56 |

| 3 説明                         | 1  | 7.6 プログラミング            | 57 |

| 4 ピン構成および機能                  | 3  | 8 アプリケーションと実装          | 60 |

| 5 仕様                         | 7  | 8.1 アプリケーション情報         | 60 |

| 5.1 絶対最大定格                   | 7  | 8.2 代表的なアプリケーション       | 60 |

| 5.2 ESD 定格                   | 7  | 8.3 電源に関する推奨事項         | 66 |

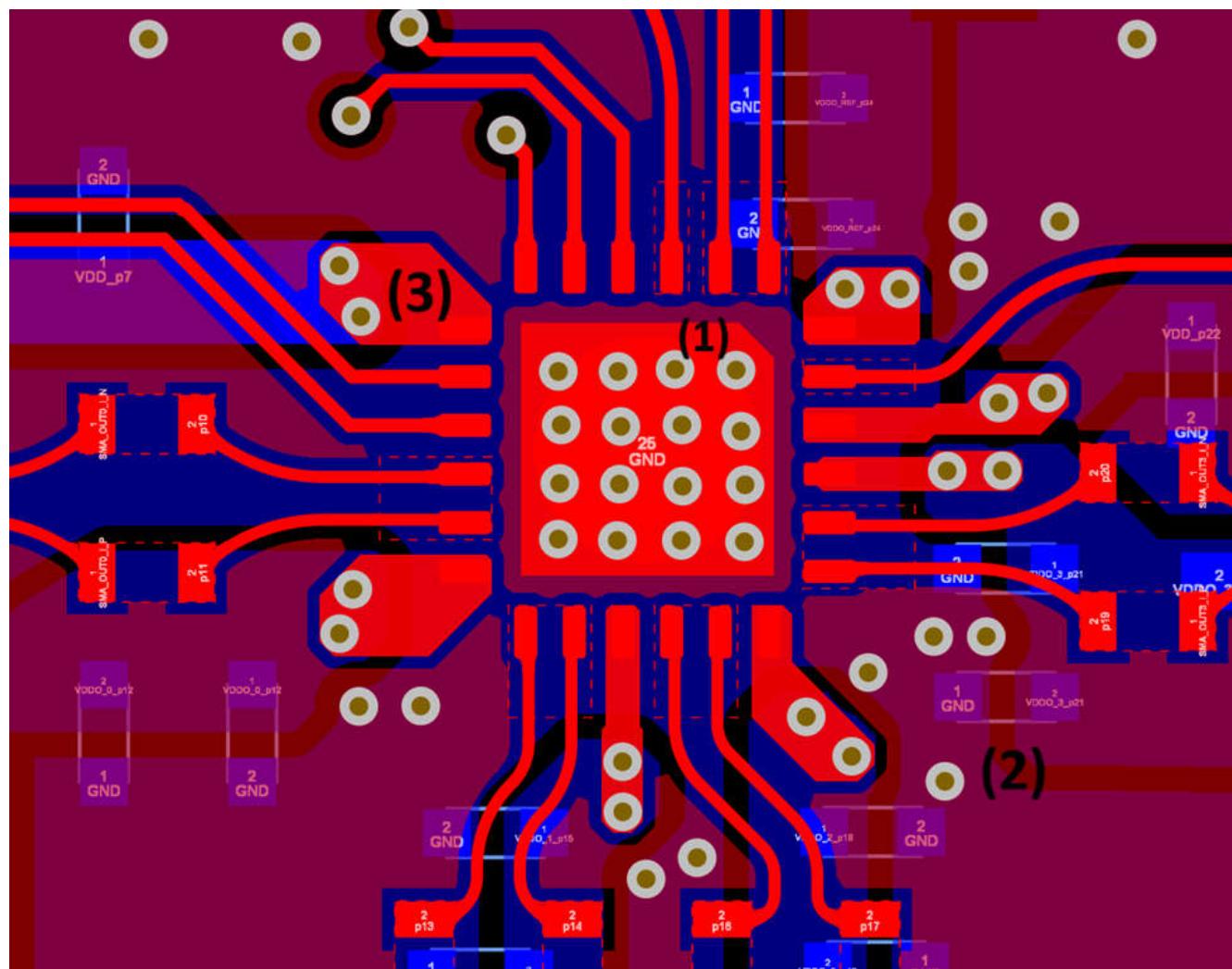

| 5.3 推奨動作条件                   | 7  | 8.4 レイアウト              | 67 |

| 5.4 熱に関する情報                  | 8  | 9 デバイスおよびドキュメントのサポート   | 68 |

| 5.5 電気的特性                    | 8  | 9.1 ドキュメントのサポート        | 68 |

| 5.6 I <sub>2</sub> C の特性     | 24 | 9.2 ドキュメントの更新通知を受け取る方法 | 68 |

| 6 パラメータ測定情報                  | 26 | 9.3 サポート・リソース          | 68 |

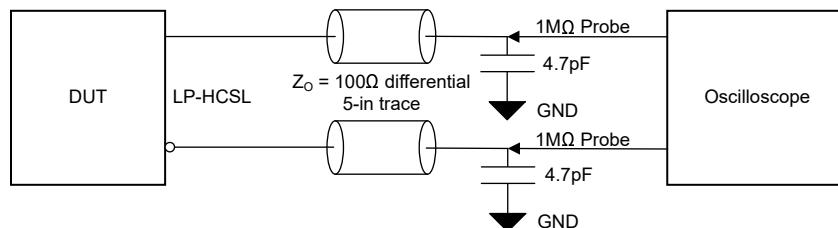

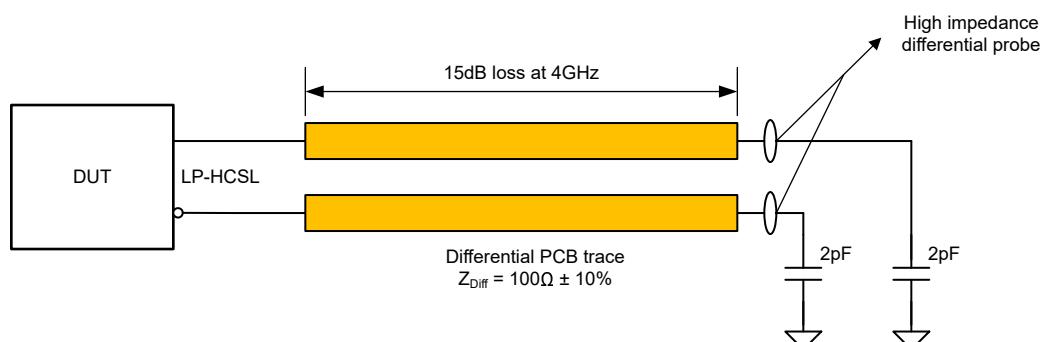

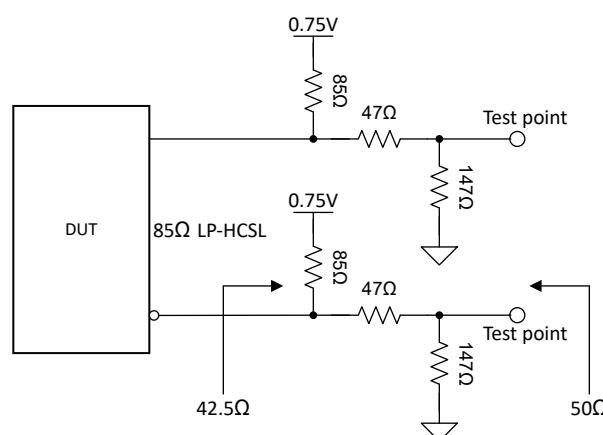

| 6.1 LP-HCSL テストまたはシミュレーション負荷 | 26 | 9.4 商標                 | 68 |

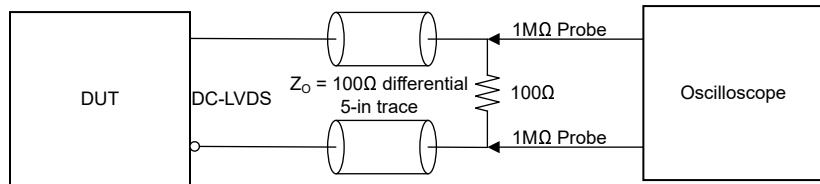

| 6.2 LVDS テスト負荷               | 27 | 9.5 静電気放電に関する注意事項      | 68 |

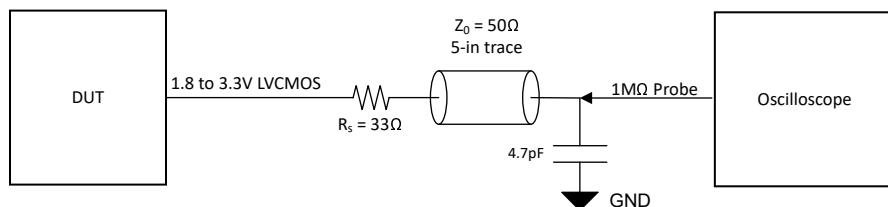

| 6.3 LVC MOS テスト負荷            | 27 | 9.6 用語集                | 68 |

| 7 詳細説明                       | 28 | 10 改訂履歴                | 68 |

| 7.1 概要                       | 28 | 11 メカニカル、パッケージ、および注文情報 | 69 |

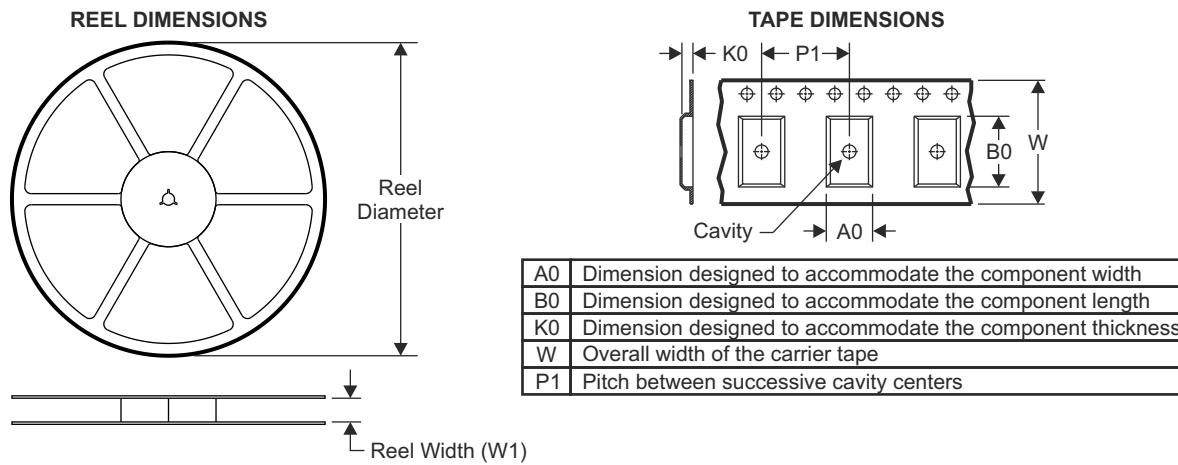

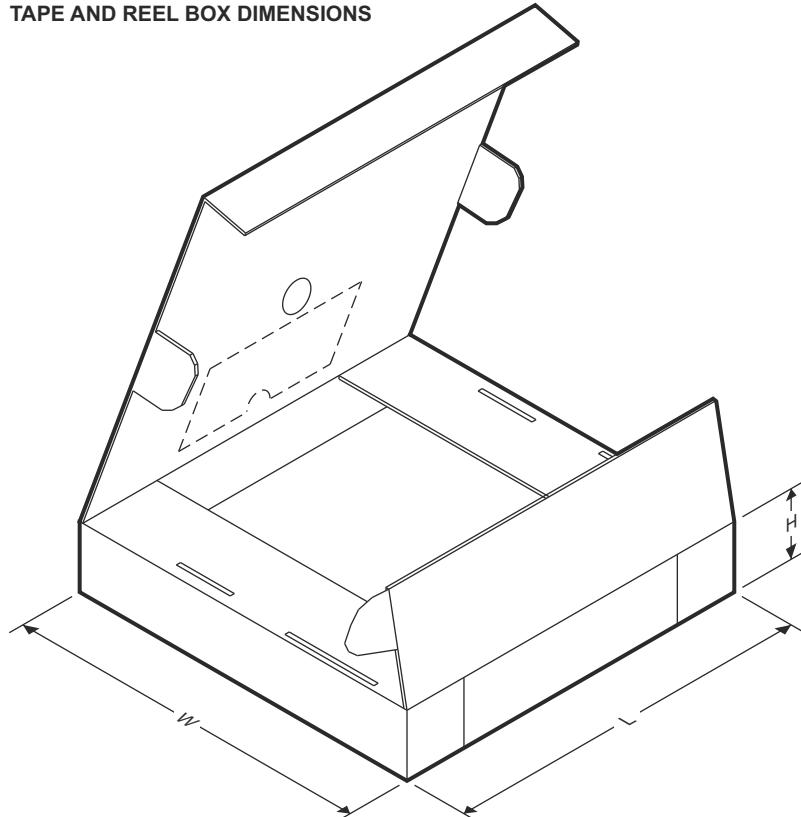

| 7.2 機能ブロック図                  | 28 | 11.1 テープおよびリール情報       | 69 |

| 7.3 機能説明                     | 29 |                        |    |

## 4 ピン構成および機能

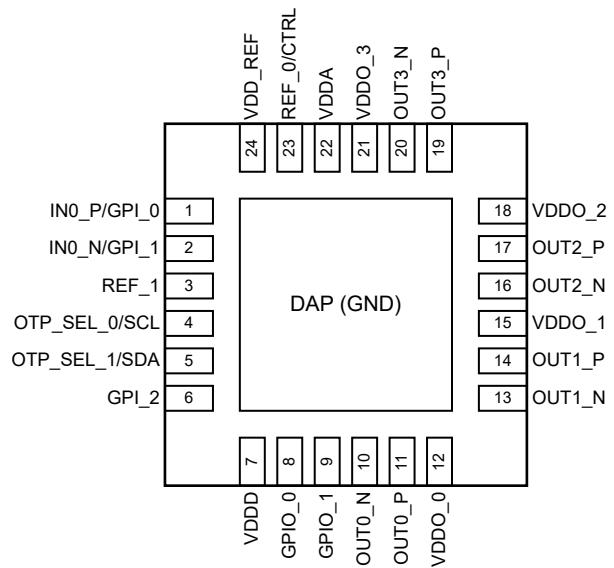

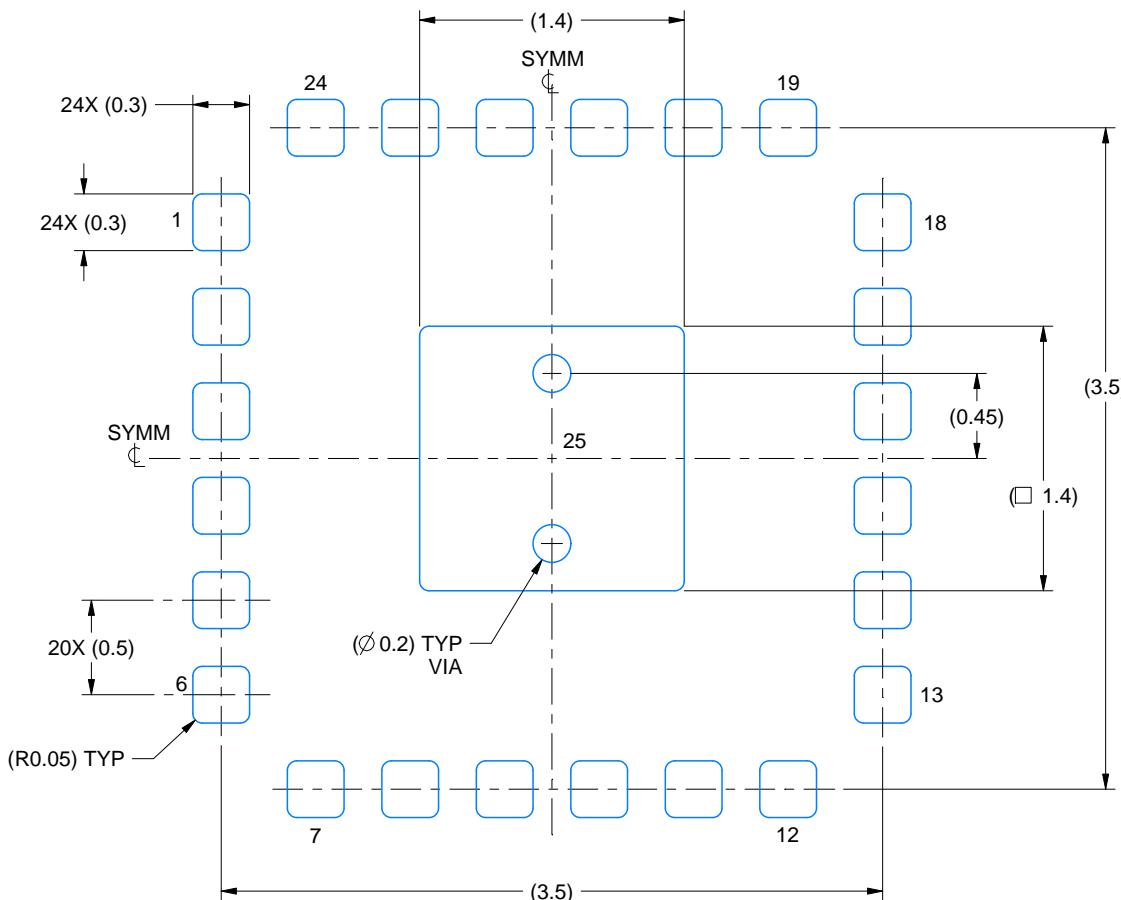

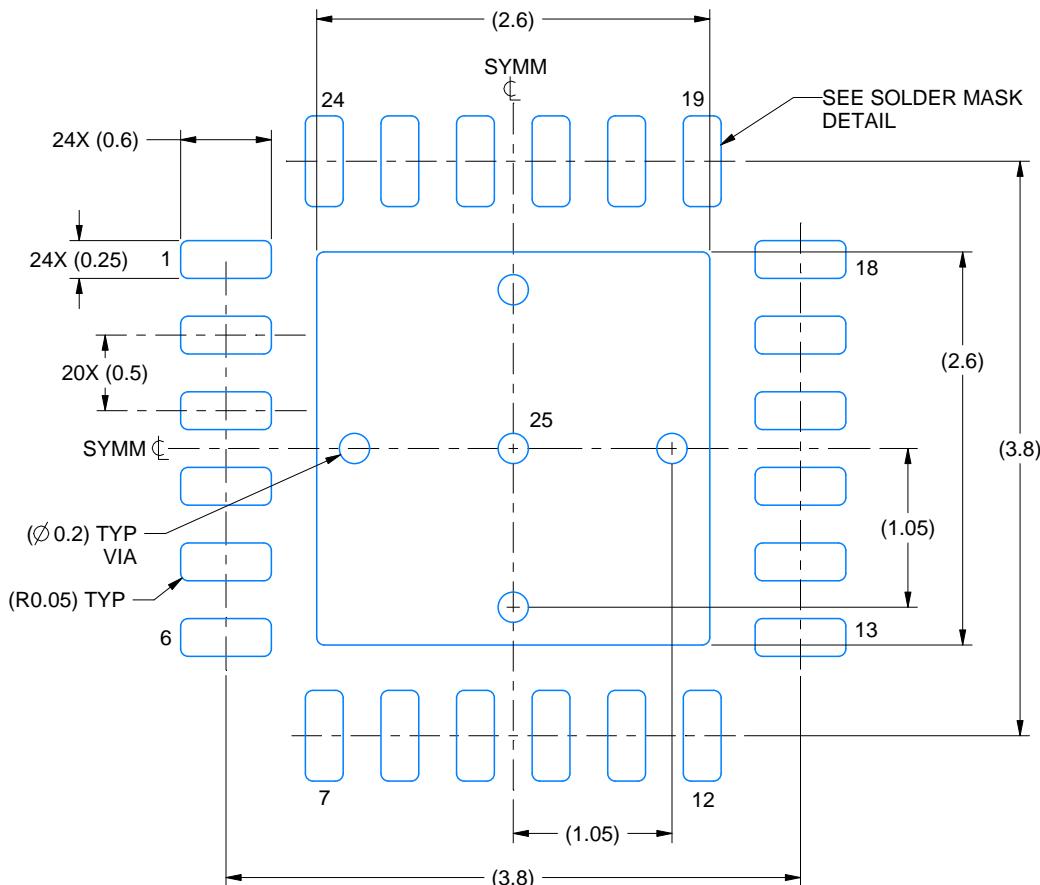

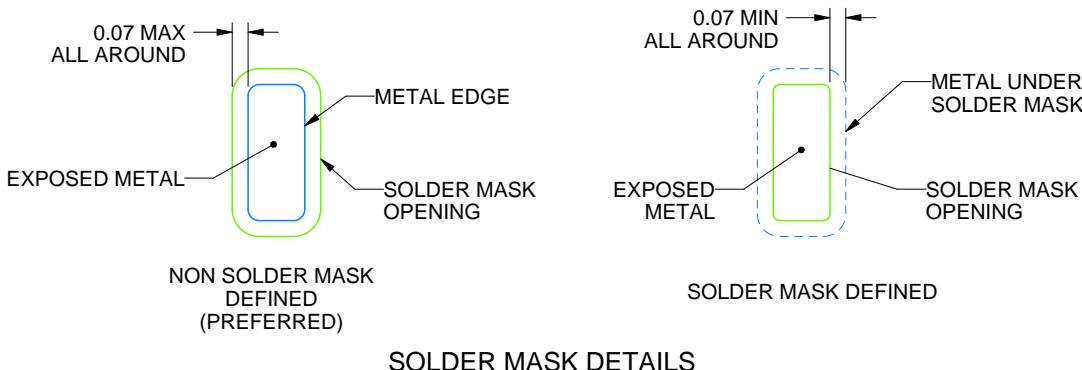

図 4-1. LMK3H2104 RGE パッケージ、24 ピン QFN (上面図)

表 4-1. ピンの機能

| ピン            |    | タイプ <sup>(1)</sup> | 説明                                                                                                                        |

|---------------|----|--------------------|---------------------------------------------------------------------------------------------------------------------------|

| 名称            | 番号 |                    |                                                                                                                           |

| IN0_P/GPI_0   | 1  | I                  | 差動クロック入力または汎用入力。これらはフェイルセーフ入力ピンです。未使用の場合は、フローティングのままにします。                                                                 |

| IN0_N/GPI_1   | 2  | I                  |                                                                                                                           |

| REF_1         | 3  | O                  | 1.8V、2.5V、3.3V の LVCMOS クロック出力。この出力はディスエーブルにして low またはトライステートにできます。未使用の場合は、フローティングのままにします。                                |

| OTP_SEL_0/SCL | 4  | I                  | 多機能ピン。機能は、パワーアップ時にピン 23 によって決定されます。デフォルトでは、両方のピンの内部プルダウン抵抗。SCL はフェイルセーフです。                                                |

| OTP_SEL_1/SDA | 5  | I/O                | <ul style="list-style-type: none"> <li>OTP モード:OTP_SEL_[1:0] 4 つの OTP ページのうち 1 を選択します</li> <li>I2C モード:SCL、SDA</li> </ul> |

| GPI_2         | 6  | I                  | 汎用入力。フェイルセーフ ピン。未使用の場合は、フローティングのままにします                                                                                    |

| VDDD          | 7  | P                  | 1.8、2.5 または 3.3V の電源。VDD マッピングについては、 <a href="#">電源ピン マッピング</a> を参照してください                                                 |

| GPIO_0        | 8  | I/O                | 汎用入出力。未使用の場合は、フローティングのままにします。                                                                                             |

| GPIO_1        | 9  | I/O                | 汎用入出力。使用しない場合は、フローティングのままにするか、VDD に接続します。GPIO_1 を VDD に接続する場合は、出力として構成しないでください。                                           |

| OUT0_N        | 10 | O                  | 差動クロック出力 0。LP-HCSL (85Ω または 100Ω)、LVDS および 1.2V、1.8V、2.5V、または 3.3V LVCMOS をサポートしています。未使用の場合は、フローティングのままにします。              |

| OUT0_P        | 11 | O                  |                                                                                                                           |

| VDDO_0        | 12 | P                  | 1.8、2.5 または 3.3V の電源。VDD マッピングについては、 <a href="#">電源ピン マッピング</a> を参照してください                                                 |

| OUT1_N        | 13 | O                  | 差動クロック出力 1。LP-HCSL (85Ω または 100Ω)、LVDS および 1.2V、1.8V、2.5V、または 3.3V LVCMOS をサポートしています。未使用の場合は、フローティングのままにします。              |

| OUT1_P        | 14 | O                  |                                                                                                                           |

| VDDO_1        | 15 | P                  | 1.8、2.5 または 3.3V の電源。VDD マッピングについては、 <a href="#">電源ピン マッピング</a> を参照してください                                                 |

| OUT2_N        | 16 | O                  | 差動クロック出力 2。LP-HCSL (85Ω または 100Ω)、LVDS および 1.2V、1.8V、2.5V、または 3.3V LVCMOS をサポートしています。未使用の場合は、フローティングのままにします。              |

| OUT2_P        | 17 | O                  |                                                                                                                           |

| VDDO_2        | 18 | P                  | 1.8、2.5 または 3.3V の電源。VDD マッピングについては、 <a href="#">電源ピン マッピング</a> を参照してください                                                 |

表 4-1. ピンの機能 (続き)

| ピン         |    | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                                              |

|------------|----|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称         | 番号 |                    |                                                                                                                                                                                                                                                                                                                                                 |

| OUT3_P     | 19 | O                  | 差動クロック出力 3。LP-HCSL (85Ω または 100Ω)、LVDS および 1.2V、1.8V、2.5V、または 3.3V LVCMOS をサポートしています。未使用の場合は、フローティングのままにします。                                                                                                                                                                                                                                    |

| OUT3_N     | 20 | O                  |                                                                                                                                                                                                                                                                                                                                                 |

| VDDO_3     | 21 | P                  | 1.8、2.5 または 3.3V の電源。VDD マッピングについては、 <a href="#">電源ピン マッピング</a> を参照してください                                                                                                                                                                                                                                                                       |

| VDDA       | 22 | P                  | 1.8、2.5 または 3.3V の電源。VDD マッピングについては、 <a href="#">電源ピン マッピング</a> を参照してください                                                                                                                                                                                                                                                                       |

| REF_0/CTRL | 23 | I/O                | 多機能ピン。パワーアップ時、ピン 4 とピン 5 の機能を決定するために、このピンの状態がラッチされます。内部プルアップまたはプルダウン抵抗は利用できません。このピンは、外部で high または low にプルアップする必要があります。 <ul style="list-style-type: none"> <li>電源オン時に低:I2C モード。ピン 4, 5 = SCL, SDA</li> <li>電源投入時に高:OTP モード。ピン 4, 5 = OTP_SEL_0, OTP_SEL_1</li> </ul> 電源投入後、このピンは 1.8V、2.5V、3.3V LVCMOS クロックを出力するか、ディスエーブルして low またはトライステートにできます。 |

| VDD_REF    | 24 | P                  | 1.8、2.5 または 3.3V の電源。VDD マッピングについては、 <a href="#">電源ピン マッピング</a> を参照してください                                                                                                                                                                                                                                                                       |

| DAP        | 25 | G                  | グランドに接続                                                                                                                                                                                                                                                                                                                                         |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源。

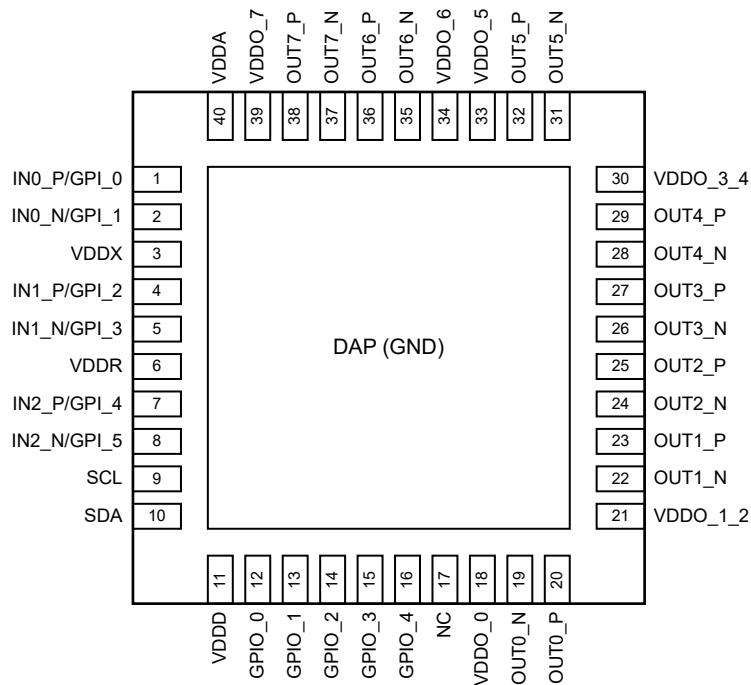

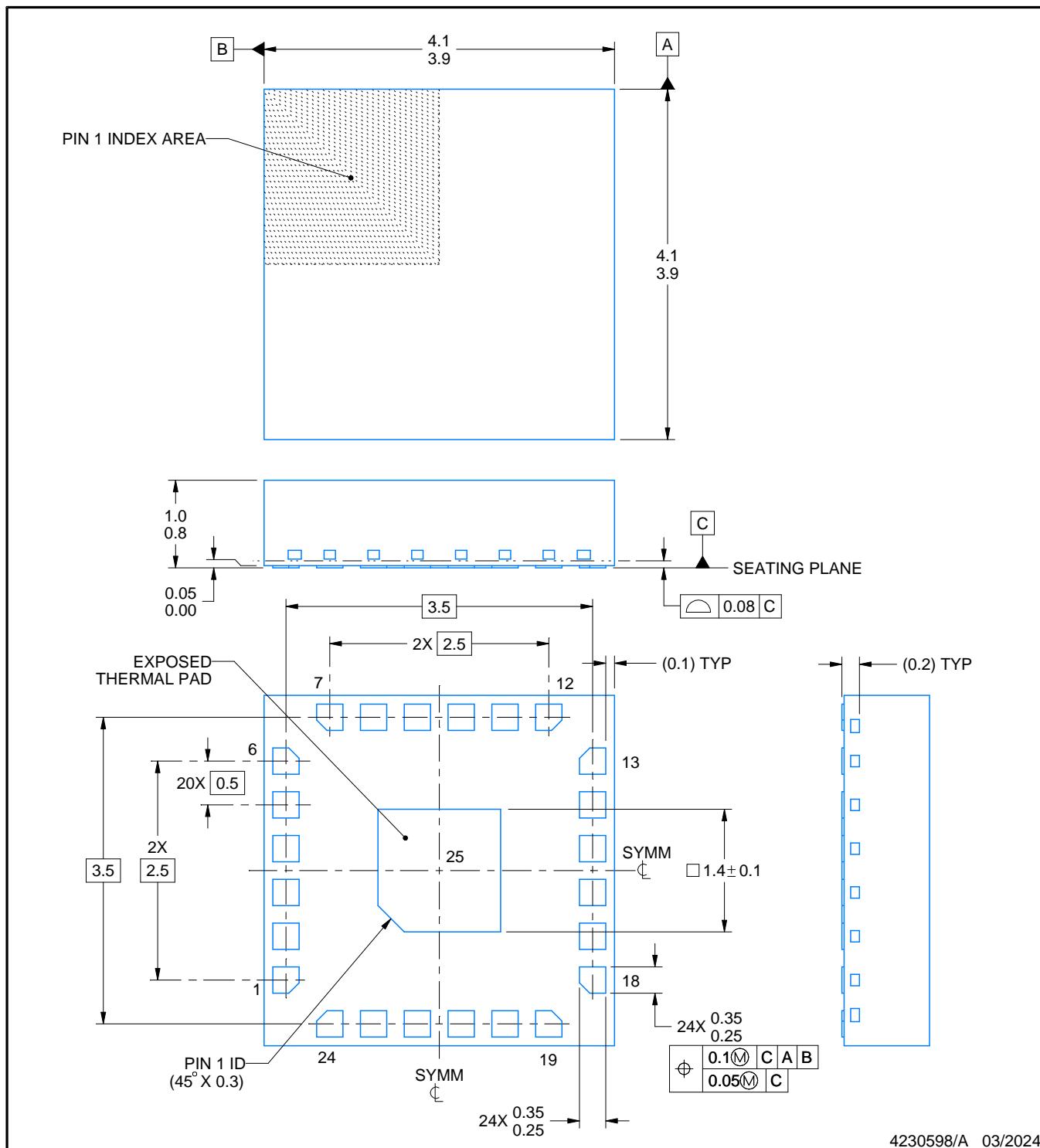

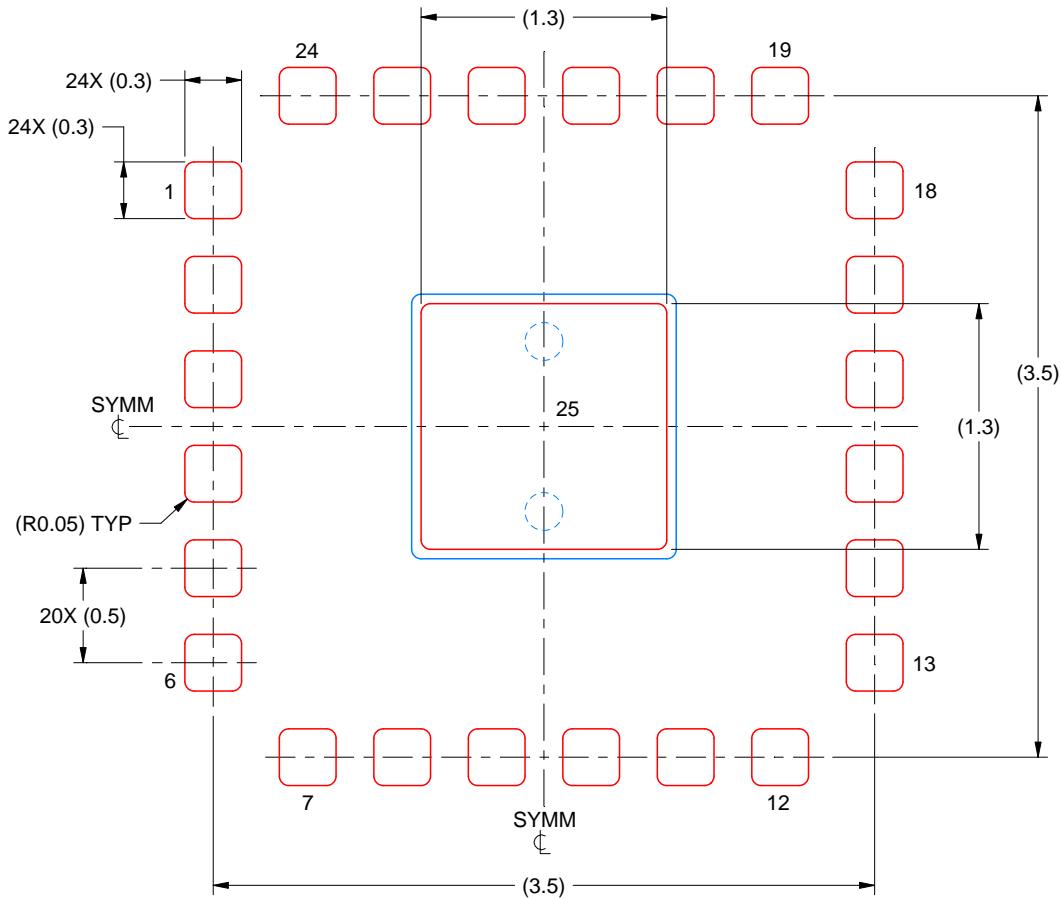

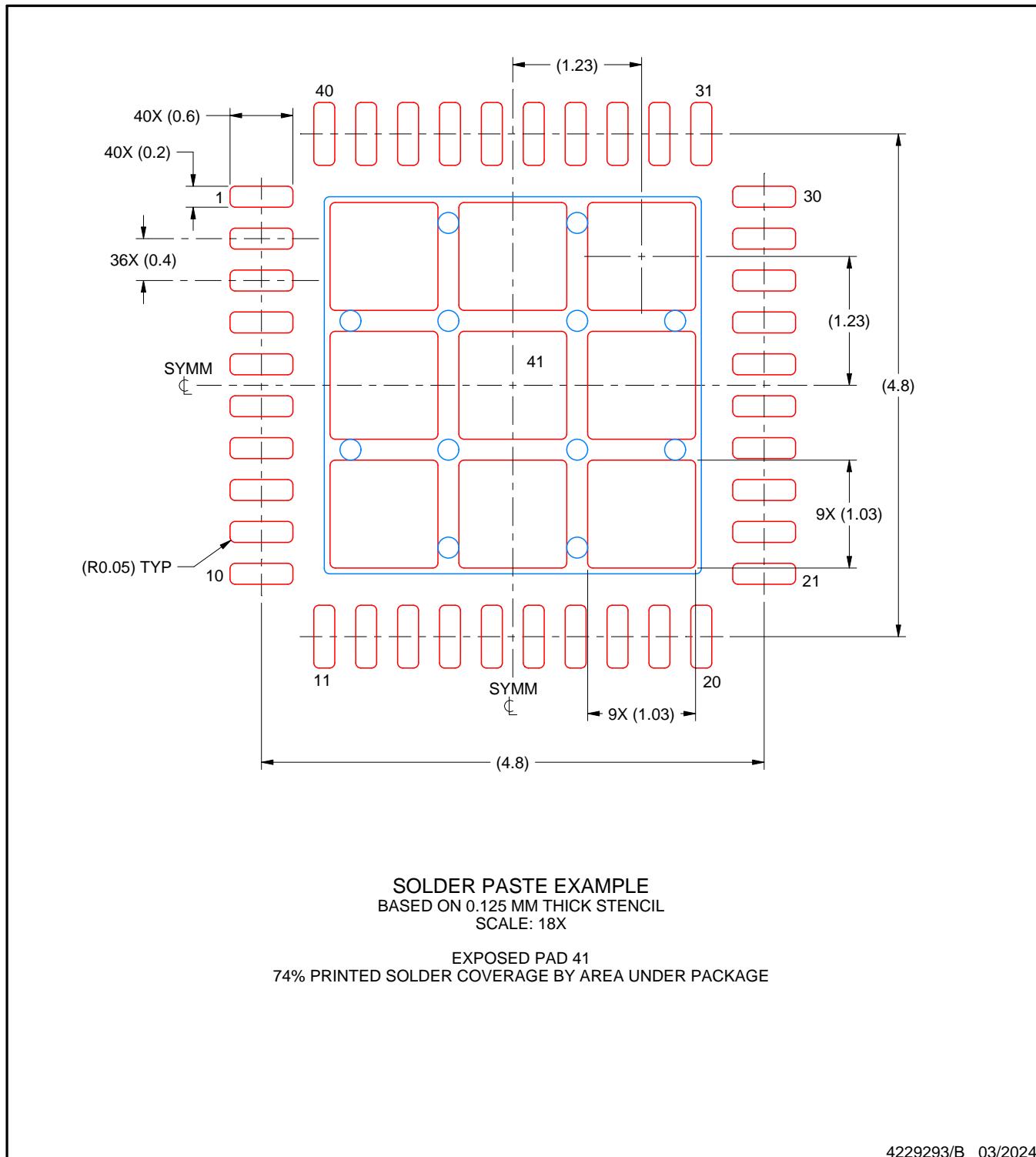

図 4-2. LMK3H2108 RKP パッケージ 40 ピン QFN 上面図

表 4-2. ピンの機能

| ピン          |    | タイプ <sup>(1)</sup> | 説明                                                                        |

|-------------|----|--------------------|---------------------------------------------------------------------------|

| 名称          | 番号 |                    |                                                                           |

| IN0_P/GPI_0 | 1  | I                  | 差動クロック入力または汎用入力。これらはフェイルセーフ入力ピンです。未使用の場合は、フローティングのままにします。                 |

| IN0_N/GPI_1 | 2  | I                  |                                                                           |

| VDDX        | 3  | P                  | 1.8、2.5 または 3.3V の電源。VDD マッピングについては、 <a href="#">電源ピン マッピング</a> を参照してください |

**表 4-2. ピンの機能 (続き)**

| ピン          |    | タイプ <sup>(1)</sup> | 説明                                                                                                           |

|-------------|----|--------------------|--------------------------------------------------------------------------------------------------------------|

| 名称          | 番号 |                    |                                                                                                              |

| IN1_P/GPI_2 | 4  | I                  | 差動クロック入力または汎用入力。これらはフェイイルセーフ入力ピンです。未使用の場合は、フローティングのままにします。                                                   |

| IN1_N/GPI_3 | 5  | I                  |                                                                                                              |

| VDDR        | 6  | P                  | 1.8、2.5 または 3.3V の電源。VDD マッピングについては、 <a href="#">電源ピン マッピング</a> を参照してください                                    |

| IN2_P/GPI_4 | 7  | I                  | 差動クロック入力または汎用入力。これらはフェイイルセーフ入力ピンです。未使用の場合は、フローティングのままにします。                                                   |

| IN2_N/GPI_5 | 8  | I                  |                                                                                                              |

| SCL         | 9  | I                  | I <sup>2</sup> C クロック                                                                                        |

| SDA         | 10 | I/O                | I <sup>2</sup> C データ                                                                                         |

| VDDD        | 11 | P                  | 1.8、2.5 または 3.3V の電源。VDD マッピングについては、 <a href="#">電源ピン マッピング</a> を参照してください                                    |

| GPIO_0      | 12 | I/O                | 汎用入出力。未使用の場合は、フローティングのままにします。                                                                                |

| GPIO_1      | 13 | I/O                | 汎用入出力。未使用の場合は、フローティングのままにします。                                                                                |

| GPIO_2      | 14 | I/O                | 汎用入出力。未使用の場合は、フローティングのままにします。                                                                                |

| GPIO_3      | 15 | I/O                | 汎用入出力。未使用の場合は、フローティングのままにします。                                                                                |

| GPIO_4      | 16 | I/O                | 汎用入出力。未使用の場合は、フローティングのままにします。                                                                                |

| NC          | 17 | 該当なし               | 接続なし。フローティングのままにするか、GND に接続します                                                                               |

| VDDO_0      | 18 | P                  | 1.8、2.5 または 3.3V の電源。VDD マッピングについては、 <a href="#">電源ピン マッピング</a> を参照してください                                    |

| OUT0_N      | 19 | O                  | 差動クロック出力 0。LP-HCSL (85Ω または 100Ω)、LVDS および 1.2V、1.8V、2.5V、または 3.3V LVCMOS をサポートしています。未使用の場合は、フローティングのままにします。 |

| OUT0_P      | 20 | O                  |                                                                                                              |

| VDDO_1_2    | 21 | P                  | 1.8、2.5 または 3.3V の電源。VDD マッピングについては、 <a href="#">電源ピン マッピング</a> を参照してください                                    |

| OUT1_N      | 22 | O                  | 差動クロック出力 1。LP-HCSL (85Ω または 100Ω)、LVDS および 1.2V、1.8V、2.5V、または 3.3V LVCMOS をサポートしています。未使用の場合は、フローティングのままにします。 |

| OUT1_P      | 23 | O                  |                                                                                                              |

| OUT2_N      | 24 | O                  | 差動クロック出力 2。LP-HCSL (85Ω または 100Ω)、LVDS および 1.2V、1.8V、2.5V、または 3.3V LVCMOS をサポートしています。未使用の場合は、フローティングのままにします。 |

| OUT2_P      | 25 | O                  |                                                                                                              |

| OUT3_N      | 26 | O                  | 差動クロック出力 3。LP-HCSL (85Ω または 100Ω)、LVDS および 1.2V、1.8V、2.5V、または 3.3V LVCMOS をサポートしています。未使用の場合は、フローティングのままにします。 |

| OUT3_P      | 27 | O                  |                                                                                                              |

| OUT4_N      | 28 | O                  | 差動クロック出力 4。LP-HCSL (85Ω または 100Ω)、LVDS および 1.2V、1.8V、2.5V、または 3.3V LVCMOS をサポートしています。未使用の場合は、フローティングのままにします。 |

| OUT4_P      | 29 | O                  |                                                                                                              |

| VDDO_3_4    | 30 | P                  | 1.8、2.5 または 3.3V の電源。VDD マッピングについては、 <a href="#">電源ピン マッピング</a> を参照してください                                    |

| OUT5_N      | 31 | O                  | 差動クロック出力 5。LP-HCSL (85Ω または 100Ω)、LVDS および 1.2V、1.8V、2.5V、または 3.3V LVCMOS をサポートしています。未使用の場合は、フローティングのままにします。 |

| OUT5_P      | 32 | O                  |                                                                                                              |

| VDDO_5      | 33 | P                  | 1.8、2.5 または 3.3V の電源。VDD マッピングについては、 <a href="#">電源ピン マッピング</a> を参照してください                                    |

| VDDO_6      | 34 | P                  | 1.8、2.5 または 3.3V の電源。VDD マッピングについては、 <a href="#">電源ピン マッピング</a> を参照してください                                    |

| OUT6_N      | 35 | O                  | 差動クロック出力 6。LP-HCSL (85Ω または 100Ω)、LVDS および 1.2V、1.8V、2.5V、または 3.3V LVCMOS をサポートしています。未使用の場合は、フローティングのままにします。 |

| OUT6_P      | 36 | O                  |                                                                                                              |

| OUT7_N      | 37 | O                  | 差動クロック出力 7。LP-HCSL (85Ω または 100Ω)、LVDS および 1.2V、1.8V、2.5V、または 3.3V LVCMOS をサポートしています。未使用の場合は、フローティングのままにします。 |

| OUT7_P      | 38 | O                  |                                                                                                              |

| VDDO_7      | 39 | P                  | 1.8、2.5 または 3.3V の電源。VDD マッピングについては、 <a href="#">電源ピン マッピング</a> を参照してください                                    |

| VDDA        | 40 | P                  | 1.8、2.5 または 3.3V の電源。VDD マッピングについては、 <a href="#">電源ピン マッピング</a> を参照してください                                    |

**表 4-2. ピンの機能 (続き)**

| ピン  |    | タイプ <sup>(1)</sup> | 説明      |

|-----|----|--------------------|---------|

| 名称  | 番号 |                    |         |

| DAP | 41 | G                  | グランドに接続 |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源。

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|           |                                                                                          | 最小値  | 最大値                | 単位 |

|-----------|------------------------------------------------------------------------------------------|------|--------------------|----|

| $V_{DD}$  | デバイス電源電圧                                                                                 | -0.3 | 3.9                | V  |

| $V_{DDO}$ | 出力電源電圧                                                                                   | -0.3 | 3.9                | V  |

| $V_{OUT}$ | OUT <sub>x</sub> _P ピンと OUT <sub>x</sub> _N ピンに印加される電圧 (出力が High または Low の場合)            | -0.3 | $V_{DDO\_x} + 0.3$ | V  |

|           | OUT <sub>x</sub> _P ピンと OUT <sub>x</sub> _N ピンに印加される電圧 (出力が LVCMOS トライステートの場合)           | -0.3 | 1.89               | V  |

|           | OUT <sub>x</sub> _P ピンと OUT <sub>x</sub> _N ピンに印加される電圧 (出力が LP-HCSL または LVDS トライステートの場合) | -0.3 | 1.5                | V  |

| $T_{stg}$ | 保存温度                                                                                     | -65  | 125                | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|             |      |                                                              | 値          | 単位 |

|-------------|------|--------------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup> | $\pm 2000$ | V  |

|             |      | デバイス帶電モデル (CDM)、JEDEC 仕様 JS-002 に準拠、すべてのピン <sup>(2)</sup>    | $\pm 500$  |    |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 5.3 推奨動作条件

$V_{DD} = V_{DDO} = 1.8, 2.5$ 、または  $3.3V \pm 5\%$ 、 $T_A = T_{A,min} \sim T_{A,max}$

|            |                                  | 最小値   | 公称値 | 最大値            | 単位 |

|------------|----------------------------------|-------|-----|----------------|----|

| $V_{DD}$   | デバイス電源電圧                         | 1.71  | 1.8 | 1.89           | V  |

|            |                                  | 2.375 | 2.5 | 2.625          | V  |

|            |                                  | 3.135 | 3.3 | 3.465          | V  |

| $V_{DDO}$  | 出力電源電圧                           | 1.71  | 1.8 | 1.89           | V  |

|            |                                  | 2.375 | 2.5 | 2.625          | V  |

|            |                                  | 3.135 | 3.3 | 3.465          | V  |

| $V_{IN}$   | IN_x、GPI、OTP_SEL、SCL、SDA ピンの入力電圧 | -0.3  |     | 3.6            | V  |

|            | GPIO または CTRL ピンの入力電圧            | -0.3  |     | $V_{DD} + 0.3$ | V  |

| $T_A$      | 周囲温度                             | -40   |     | 105            | °C |

| $T_J$      | 接合部温度                            | -40   |     | 110            | °C |

| $t_{ramp}$ | 電源ランプ時間。 $VDD = 1.8V$            | 0.05  |     | 5              | ms |

|            | 電源ランプ時間。 $VDD = 2.5$ または $3.3V$  | 0.05  |     | 5              | ms |

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> |                   | LMK3H2108       | LMK3H2104        | LMK3H2104        | 単位   |

|----------------------|-------------------|-----------------|------------------|------------------|------|

|                      |                   | RKP0040A (VQFN) | RGE0024AA (VQFN) | RGE0024AB (VQFN) |      |

|                      |                   | 40 ピン           | 24 ピン            | 24 ピン            |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗      | 31.8            | 53.0             | 39.6             | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース(上面)への熱抵抗 | 22.0            | 32.5             | 32.4             | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗      | 12.7            | 26.1             | 16.9             | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ  | 0.6             | 0.9              | 0.6              | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ  | 12.7            | 26.0             | 16.8             | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース(底面)への熱抵抗 | 0.3             | 5.1              | 3.9              | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 5.5 電気的特性

| パラメータ                                                   |                                              | テスト条件                                    | 最小値  | 標準値  | 最大値  | 単位   |

|---------------------------------------------------------|----------------------------------------------|------------------------------------------|------|------|------|------|

| 周波数安定性                                                  |                                              |                                          |      |      |      |      |

| $\Delta f_{total}$                                      | 総合周波数誤差。これには、すべての要因と、25°C での 10 年の経年劣化が含まれます | $T_A = -40 \sim 105^\circ\text{C}$       | -25  | 25   | 25   | ppm  |

| $\Delta f_{aging,25^\circ\text{C}}$ 25°C での経年劣化による周波数誤差 |                                              |                                          |      |      |      |      |

|                                                         |                                              | $T_A = 25^\circ\text{C}$ 、1 年前の経年劣化      | 1.0  | 3.6  | 3.6  | ppm  |

|                                                         |                                              | $T_A = 25^\circ\text{C}$ 、3 年前の経年劣化      | 1.2  | 5.0  | 5.0  | ppm  |

|                                                         |                                              | $T_A = 25^\circ\text{C}$ 、5 年前の経年劣化      | 1.3  | 5.7  | 5.7  | ppm  |

|                                                         |                                              | $T_A = 25^\circ\text{C}$ 、10 年前の経年劣化     | 1.4  | 6.5  | 6.5  | ppm  |

|                                                         |                                              | $T_A = 25^\circ\text{C}$ 、20 年前の経年劣化     | 1.6  | 7.4  | 7.4  | ppm  |

| クロック入力の要件                                               |                                              |                                          |      |      |      |      |

| $f_{IN}$                                                | 入力周波数                                        | LVC MOS 入力バッファ                           | 0    | 200  | 200  | MHz  |

|                                                         |                                              | 差動入力バッファ                                 | 25   | 400  | 400  | MHz  |

| $DC_{IN}$                                               | クロック入力デューティ サイクル                             |                                          | 40   | 60   | 60   | %    |

| $V_{IN}$                                                | 差動クロック入力振幅(差動ピーク・ピーク電圧の半分)                   | $f_0 \leq 300\text{MHz}$                 | 150  | 1200 | 1200 | mV   |

|                                                         |                                              | $300\text{MHz} < f_0 \leq 400\text{MHz}$ | 150  | 1200 | 1200 | mV   |

| $V_{CM}$                                                | 差動入力同相コード                                    |                                          | 0.2  | 3.3  | 3.3  | V    |

| $V_{IH}$                                                | シングルエンド入力 high 電圧                            |                                          | 1.2  | 3.6  | 3.6  | V    |

| $V_{IL}$                                                | シングルエンドクロック入力 low 電圧                         |                                          | -0.3 | 0.5  | 0.5  | V    |

| $dV_{IN}/dt$                                            | クロックの入力スルーレート                                | 20%~80%                                  | 0.15 |      |      | V/ns |

| パラメータ    |                                                                | テスト条件                                       | 最小値 | 標準値 | 最大値 | 単位 |

|----------|----------------------------------------------------------------|---------------------------------------------|-----|-----|-----|----|

| $C_{IN}$ | ピンごとのクロック入力容量。INx がクロック入力として構成されている場合の、INx_P ピンまたは INx_N ピンの容量 | 同相コード電圧 = 0.7V。<br>内部入力終端はディスエーブル           |     | 2.7 |     | pF |

|          |                                                                | 同相モード電圧 = 0.7V<br>内部 $100\Omega$ 差動終端がイネーブル |     | 1.4 |     | pF |

|          |                                                                | 同相コード電圧 = 1.2V。<br>内部入力終端はディスエーブル           |     | 2.5 |     | pF |

|          |                                                                | 同相モード電圧 = 1.2V<br>内部 $100\Omega$ 差動終端がイネーブル |     | 1.3 |     | pF |

|          |                                                                | 同相コード電圧 = 3.3V。<br>内部入力終端はディスエーブル           |     | 3.4 |     | pF |

|          |                                                                | 同相モード電圧 = 3.3V<br>内部 $100\Omega$ 差動終端がイネーブル |     | 1.4 |     | pF |

**LP-HCSL クロック出力特性**

|                 |                           |                          |     |     |     |

|-----------------|---------------------------|--------------------------|-----|-----|-----|

| $f_{out}$       | 出力周波数                     |                          | 2.5 | 400 | MHz |

| $V_{min}$       | アンダーシュートを含む出力低電圧          |                          | -85 | 85  | mV  |

| $V_{overshoot}$ | 出力電圧 high オーバーシュート電圧      | $V_{max} - V_{OH}$       |     | 120 | mV  |

| $V_{OH}$        | 出力 HIGH 電圧 <sup>(4)</sup> | OUTx_LPHCSL_VOD_SEL = 0  | 612 | 686 | mV  |

|                 |                           | OUTx_LPHCSL_VOD_SEL = 1  | 638 | 714 | mV  |

|                 |                           | OUTx_LPHCSL_VOD_SEL = 2  | 663 | 741 | mV  |

|                 |                           | OUTx_LPHCSL_VOD_SEL = 3  | 687 | 768 | mV  |

|                 |                           | OUTx_LPHCSL_VOD_SEL = 4  | 712 | 793 | mV  |

|                 |                           | OUTx_LPHCSL_VOD_SEL = 5  | 734 | 817 | mV  |

|                 |                           | OUTx_LPHCSL_VOD_SEL = 6  | 704 | 794 | mV  |

|                 |                           | OUTx_LPHCSL_VOD_SEL = 7  | 727 | 820 | mV  |

|                 |                           | OUTx_LPHCSL_VOD_SEL = 8  | 726 | 823 | mV  |

|                 |                           | OUTx_LPHCSL_VOD_SEL = 9  | 748 | 847 | mV  |

|                 |                           | OUTx_LPHCSL_VOD_SEL = 10 | 769 | 872 | mV  |

|                 |                           | OUTx_LPHCSL_VOD_SEL = 11 | 792 | 896 | mV  |

|                 |                           | OUTx_LPHCSL_VOD_SEL = 12 | 815 | 921 | mV  |

|                 |                           | OUTx_LPHCSL_VOD_SEL = 13 | 836 | 945 | mV  |

|                 |                           | OUTx_LPHCSL_VOD_SEL = 14 | 858 | 969 | mV  |

|                 |                           | OUTx_LPHCSL_VOD_SEL = 15 | 879 | 993 | mV  |

| パラメータ                          |                                                                      | テスト条件                                                     | 最小値   | 標準値   | 最大値    | 単位   |

|--------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------|-------|-------|--------|------|

| $Z_{\text{diff}}$              | LP-HCSL 静的差動インピーダンス                                                  | 85Ω LP-HCSL                                               | 68    | 85    | 102    | Ω    |

|                                |                                                                      | 100Ω LP-HCSL                                              | 80    | 100   | 120    | Ω    |

| $dV/dt$                        | 出力スルーレート (立ち上がりおよび立ち下がりエッジ)。ゼロ交差点を中心に、差動波形の -150mV ~ +150mV で測定されます。 | OUTx_SLEW_RATE = 0 <sup>(1)</sup>                         | 2.4   | 3.1   | 3.7    | V/ns |

|                                |                                                                      | OUTx_SLEW_RATE = 1 <sup>(1)</sup>                         | 2.2   | 2.9   | 3.4    | V/ns |

|                                |                                                                      | OUTx_SLEW_RATE = 2 <sup>(1)</sup>                         | 2     | 2.6   | 3.1    | V/ns |

|                                |                                                                      | OUTx_SLEW_RATE = 3 <sup>(1)</sup>                         | 1.8   | 2.3   | 2.8    | V/ns |

| $\Delta dV/dt$                 | 立ち上がりエッジレートと立ち下がりエッジレートの一一致                                          | <sup>(1)</sup>                                            |       |       | 20     | %    |

| ODC                            | 出力デューティサイクル                                                          | <sup>(1)</sup>                                            | 45    | 55    | 55     | %    |

|                                |                                                                      | $f_{\text{out}} \leq 325\text{MHz}$                       | 45    | 55    | 55     | %    |

|                                |                                                                      | $325\text{MHz} < f_{\text{out}} \leq 400\text{MHz}$       | 45    | 55    | 55     | %    |

| $t_{\text{skew}}$              | 出力間スキー                                                               | 同じクロックソース                                                 |       |       | 100    | ps   |

| $V_{\text{cross}}$             | 絶対交差点電圧                                                              | <sup>(1)</sup>                                            | 250   | 550   | 550    | mV   |

| $\Delta V_{\text{cross}}$      | クロックエッジ全体における $V_{\text{cross}}$ の変動                                 | <sup>(1)</sup>                                            |       |       | 140    | mV   |

| $ V_{\text{RB}} $              | リングバック電圧の絶対値                                                         | <sup>(1)</sup>                                            | 100   |       |        | mV   |

| $t_{\text{stable}}$            | $V_{\text{RB}}$ が許容されるまでの時間                                          | <sup>(1)</sup>                                            | 500   |       |        | ps   |

| $J_{\text{cycle-to-cycle}}$    | サイクル間ジッタ、共通クロック、SSCなし                                                | <sup>(1)</sup>                                            |       |       | 150    | ps   |

| $J_{\text{cycle-to-cycle}}$    | サイクル間ジッタ、共通クロック、-0.5% SSC                                            | <sup>(1)</sup>                                            |       |       | 150    | ps   |

| $t_{\text{period_abs}}$        | ジッタと SSC を含む絶対周期                                                     | <sup>(1)</sup>                                            | 9.949 | 10    | 10.101 | ns   |

| $t_{\text{period_avg_C}}$      | 平均クロック周期精度、共通クロック                                                    | <sup>(1)</sup>                                            | -100  |       | 2600   | ppm  |

| $t_{\text{period_avg_S}}$      | 平均クロック周期精度、SRIS                                                      | <sup>(1)</sup>                                            | -100  |       | 1600   | ppm  |

| $V_{\text{OH-DC}}$             | 出力電圧 High                                                            | DC シミュレーション負荷、<br>85Ω LP-HCSL、<br>OUTx_LPHCSL_VOD_SEL = 4 | 225   | 270   | 270    | mV   |

| $V_{\text{OL-DC}}$             | 出力電圧 Low                                                             |                                                           | 10    | 150   | 150    | mV   |

| $V_{\text{cross-DC}}$          | 絶対交差点電圧                                                              |                                                           | 130   | 200   | 200    | mV   |

| <b>LVDS クロック出力特性</b>           |                                                                      |                                                           |       |       |        |      |

| $f_{\text{out}}$               | 出力周波数                                                                |                                                           | 2.5   | 400   | 400    | MHz  |

| $ V_{\text{ODL}}$              | 差動出力電圧の定常状態の振幅 $ V_{\text{OUTP}} - V_{\text{OUTN}} $                 |                                                           | 250   | 450   | 450    | mV   |

| $\Delta V_{\text{pp-diff}}$    | 相補出力状態間の差動出力電圧スイングの変化                                                |                                                           |       |       | 50     | mV   |

| $V_{\text{OS}}$                | 定常状態の出力オフセット電圧 (同相電圧)                                                | VDDO_x = 3.3V                                             | 1.075 | 1.425 | 1.425  | V    |

|                                |                                                                      | VDDO_x = 2.5V                                             | 1.05  | 1.4   | 1.4    | V    |

|                                |                                                                      | VDDO_x = 1.8V                                             | 1     | 1.25  | 1.25   | V    |

| $\Delta V_{\text{OS}}$         | 相補出力状態間の $V_{\text{OS}}$ の変化                                         |                                                           |       |       | 50     | mV   |

| $I_{\text{SA}}, I_{\text{SB}}$ | 短絡電流。ジェネレータ出力端子がジェネレータ回路の共通端子に短絡されたときの電流の大きさ                         |                                                           | -24   | 24    | 24     | mA   |

| $I_{\text{SAB}}$               | 短絡電流。ジェネレータ出力端子が互いに短絡されたときの電流の大きさ                                    |                                                           | -12   | 12    | 12     | mA   |

| パラメータ      |                            | テスト条件              | 最小値 | 標準値 | 最大値 | 単位 |

|------------|----------------------------|--------------------|-----|-----|-----|----|

| $t_R, t_F$ | 20%~80% の差動立ち上がり / 立ち下がり時間 | OUTx_SLEW_RATE = 0 |     | 385 |     | ps |

|            |                            | OUTx_SLEW_RATE = 1 |     | 545 |     | ps |

|            |                            | OUTx_SLEW_RATE = 2 |     | 710 |     | ps |

|            |                            | OUTx_SLEW_RATE = 3 |     | 850 |     | ps |

| $t_{skew}$ | 出力間スキー                     | 同じクロック ソース         |     | 100 |     | ps |

| ODC        | 出力デューティ サイクル               |                    | 45  | 55  | 55  | %  |

**LVCMOS クロック 出力特性**

|           |                                                                        |                         |                         |     |      |

|-----------|------------------------------------------------------------------------|-------------------------|-------------------------|-----|------|

| $f_{out}$ | 出力周波数。クロック ソースは FOD またはエッジ コンバインです                                     | OUT0                    | $38.15 \times 10^{-6}$  | 200 | MHz  |

|           |                                                                        | その他のすべての出力              | $156.25 \times 10^{-3}$ | 200 | MHz  |

|           | 出力周波数。クロック ソースは IN0、IN1、または IN2                                        |                         | 0                       | 200 | MHz  |

| $dV/dt$   | 出力スルーレート。VDDO = 3.3V±5%。20% ~ 80% で測定、4.7pF 負荷                         | OUTx_CMOS_SLEW_RATE = 0 | 2                       | 5.2 | V/ns |

|           |                                                                        | OUTx_CMOS_SLEW_RATE = 1 | 1.7                     | 5   | V/ns |

|           |                                                                        | OUTx_CMOS_SLEW_RATE = 2 | 1.35                    | 4   | V/ns |

|           |                                                                        | OUTx_CMOS_SLEW_RATE = 3 | 1                       | 3.5 | V/ns |

| $dV/dt$   | 出力スルーレート。VDDO = 2.5V±5%。20% ~ 80% で測定、4.7pF 負荷                         | OUTx_CMOS_SLEW_RATE = 0 | 1.5                     | 3.9 | V/ns |

|           |                                                                        | OUTx_CMOS_SLEW_RATE = 1 | 1.3                     | 3.8 | V/ns |

|           |                                                                        | OUTx_CMOS_SLEW_RATE = 2 | 1                       | 3.1 | V/ns |

|           |                                                                        | OUTx_CMOS_SLEW_RATE = 3 | 0.75                    | 2.7 | V/ns |

| $dV/dt$   | 出力スルーレート。VDDO = 1.8V±5%。20% ~ 80% で測定、4.7pF 負荷                         | OUTx_CMOS_SLEW_RATE = 0 | 1.25                    | 2.9 | V/ns |

|           |                                                                        | OUTx_CMOS_SLEW_RATE = 1 | 1.1                     | 2.8 | V/ns |

|           |                                                                        | OUTx_CMOS_SLEW_RATE = 2 | 0.85                    | 2.4 | V/ns |

|           |                                                                        | OUTx_CMOS_SLEW_RATE = 3 | 0.65                    | 2.1 | V/ns |

| $dV/dt$   | 出力スルーレート。1.2V LVCMOS モード。VDDO = (3.3V または 2.5V)。20% ~ 80% で測定、4.7pF 負荷 | OUTx_SLEW_RATE = 0      | 1.5                     | 2.1 | V/ns |

|           |                                                                        | OUTx_SLEW_RATE = 1      | 1.3                     | 1.9 | V/ns |

|           |                                                                        | OUTx_SLEW_RATE = 2      | 1.1                     | 1.6 | V/ns |

|           |                                                                        | OUTx_SLEW_RATE = 3      | 1                       | 1.5 | V/ns |

| パラメータ                        |                                                                                       | テスト条件                                    | 最小値        | 標準値  | 最大値  | 単位   |

|------------------------------|---------------------------------------------------------------------------------------|------------------------------------------|------------|------|------|------|

| dV/dt                        | 出力スルーレート。1.2V LVC MOSモード。VDDO = 1.8V。20% ~ 80% で測定、4.7pF 負荷                           | OUTx_SLEW_RATE = 0                       | 1.2        | 2.3  | 2.3  | V/ns |

|                              |                                                                                       | OUTx_SLEW_RATE = 1                       | 1          | 2    | 2    | V/ns |

|                              |                                                                                       | OUTx_SLEW_RATE = 2                       | 0.9        | 1.8  | 1.8  | V/ns |

|                              |                                                                                       | OUTx_SLEW_RATE = 3                       | 0.8        | 1.6  | 1.6  | V/ns |

| V <sub>OH</sub>              | 出力 HIGH 電圧                                                                            | I <sub>OH</sub> = -15mA、3.3V 時           | 0.8 × VDDO | VDDO | V    | V    |

|                              |                                                                                       | I <sub>OH</sub> = -12mA、2.5V 時           | 0.8 × VDDO | VDDO | V    | V    |

|                              |                                                                                       | I <sub>OH</sub> = -8mA、1.8V 時            | 0.8 × VDDO | VDDO | V    | V    |

| V <sub>OL</sub>              | 出力 LOW 電圧                                                                             | I <sub>OL</sub> = 15mA、3.3V 時            | 0          | 0.4  | 0.4  | V    |

|                              |                                                                                       | I <sub>OL</sub> = 12mA、2.5V 時            | 0          | 0.4  | 0.4  |      |

|                              |                                                                                       | I <sub>OL</sub> = 8mA、1.8V 時             | 0          | 0.4  | 0.4  |      |

| V <sub>OH,1.2V</sub>         | 1.2V CMOS モードでの出力 high 電圧                                                             | 1.2V に設定されます。<br>I <sub>OH</sub> = -3mA  | 0.93       | 1.2  | 1.2  | V    |

|                              |                                                                                       | 1.1V に設定されます。<br>I <sub>OH</sub> = -3mA  | 0.86       | 1.1  | 1.1  | V    |

| V <sub>OL,1.2V</sub>         | 1.2V CMOS モードでの出力 low 電圧                                                              | I <sub>OL</sub> = 3mA                    | 0          | 0.24 | 0.24 | V    |

| V <sub>OD,1.2V</sub><br>Diff | V <sub>OUTP</sub> - V <sub>OUTN</sub>  。差動出力終端による 1.2V CMOS モードでの出力スイング               | 1.2V に設定されます。<br>100Ω 差動外部ライン終端。2pF の負荷。 | 539        | 600  | 660  | mV   |

|                              |                                                                                       | 1.1V に設定されます。<br>100Ω 差動外部ライン終端。2pF の負荷。 | 495        | 550  | 617  | mV   |

| V <sub>OS,1.2V</sub><br>Diff | 出力オフセット電圧。差動出力終端付き 1.2V CMOS モードにおける出力同相モード                                           | 1.2V に設定されます。<br>100Ω 差動外部ライン終端。2pF の負荷。 | 540        | 600  | 660  | mV   |

|                              |                                                                                       | 1.1V に設定されます。<br>100Ω 差動外部ライン終端。2pF の負荷。 | 495        | 550  | 605  | mV   |

| dV/dt                        | 100Ω の差動外部終端付き 1.2V CMOS モードでの差動出力スルーレート。VDDO = 3.3V または 2.5V±5%。20% ~ 80% で測定、2pF 負荷 | OUTx_SLEW_RATE = 0                       | 2.8        | 3.3  | 3.3  | V/ns |

|                              |                                                                                       | OUTx_SLEW_RATE = 1                       | 2.2        | 2.6  | 2.6  | V/ns |

|                              |                                                                                       | OUTx_SLEW_RATE = 2                       | 1.8        | 2.1  | 2.1  | V/ns |

|                              |                                                                                       | OUTx_SLEW_RATE = 3                       | 1.5        | 1.7  | 1.7  | V/ns |

|                              | 100Ω の差動外部終端付き 1.2V CMOS モードでの差動出力スルーレート。VDDO = 1.8V±5%。20% ~ 80% で測定、2pF 負荷          | OUTx_SLEW_RATE = 0                       | 2.5        | 3.3  | 3.3  | V/ns |

|                              |                                                                                       | OUTx_SLEW_RATE = 1                       | 2          | 2.6  | 2.6  | V/ns |

|                              |                                                                                       | OUTx_SLEW_RATE = 2                       | 1.6        | 2.1  | 2.1  | V/ns |

|                              |                                                                                       | OUTx_SLEW_RATE = 3                       | 1.3        | 1.8  | 1.8  | V/ns |

| I <sub>leak</sub>            | 出力リーク電流                                                                               | トライステート出力。VDD = VDDO = 3.465V            | -35        | 35   | 35   | μA   |

| パラメータ                     |                                             | テスト条件                                                  | 最小値             | 標準値       | 最大値 | 単位            |

|---------------------------|---------------------------------------------|--------------------------------------------------------|-----------------|-----------|-----|---------------|

| $R_{out}$                 | 出力インピーダンス                                   | 3.3V LVCMOS                                            |                 | 17        |     | $\Omega$      |

|                           |                                             | 2.5V LVCMOS                                            |                 | 17        |     | $\Omega$      |

|                           |                                             | 1.8V LVCMOS                                            |                 | 17        |     | $\Omega$      |

|                           |                                             | 1.2V LVCMOS                                            | 40              | 50        | 60  | $\Omega$      |

| ODC                       | 出力デューティ サイクル                                | $f_{out} \leq 156.25\text{MHz}$                        | 45              | 55        |     | %             |

|                           |                                             | $f_{out} > 156.25\text{MHz}$                           | 45              | 55        |     | %             |

| $t_{skew}$                | 出力間スキー                                      | 同じクロック ソース                                             |                 | 100       |     | ps            |

| $C_{load}$                | 最大負荷容量                                      |                                                        |                 |           | 15  | pF            |

| <b>LVC MOS REFCLK の特性</b> |                                             |                                                        |                 |           |     |               |

| $f_{out}$                 | 出力周波数                                       |                                                        | 0               | 200       |     | MHz           |

| $dV/dt$                   | 出力スルーレート、20% ~ 80% で測定                      | $V_{DDO} = 3.3V \pm 5\%$ <sup>(2)</sup>                | 2.2             | 6.1       |     | V/ns          |

|                           |                                             | $V_{DDO} = 2.5V \pm 5\%$ <sup>(2)</sup>                | 1.7             | 4.6       |     | V/ns          |

|                           |                                             | $V_{DDO} = 1.8V \pm 5\%$ <sup>(2)</sup>                | 1.45            | 3.4       |     | V/ns          |

| $V_{OH}$                  | 出力 HIGH 電圧                                  | $I_{OH} = -15\text{mA}, 3.3V \pm 5\%$ <sup>(2)</sup>   | 0.8 x $V_{DDO}$ | $V_{DDO}$ |     | V             |

|                           |                                             | $I_{OH} = -12\text{mA}, 2.5V \pm 5\%$ <sup>(2)</sup>   | 0.8 x $V_{DDO}$ | $V_{DDO}$ |     | V             |

|                           |                                             | $I_{OH} = -8\text{mA}, 1.8V \pm 5\%$ <sup>(2)</sup>    | 0.8 x $V_{DDO}$ | $V_{DDO}$ |     | V             |

| $V_{OL}$                  | 出力 LOW 電圧                                   | $I_{OL} = 15\text{mA}, 3.3V \pm 5\%$ の時 <sup>(2)</sup> | 0               | 0.4       |     | V             |

|                           |                                             | $I_{OL} = 12\text{mA}, 2.5V \pm 5\%$ の時 <sup>(2)</sup> | 0               | 0.4       |     | V             |

|                           |                                             | $I_{OL} = 8\text{mA}, 1.8V \pm 5\%$ の時 <sup>(2)</sup>  | 0               | 0.4       |     | V             |

| $I_{leak}$                | 出力リーケ電流                                     | トライステート出力。 $V_{DD} = V_{DDO} = 3.465V$ <sup>(4)</sup>  | -6              | 13        |     | $\mu\text{A}$ |

| $R_{out}$                 | 出力インピーダンス                                   | 3.3V LVCMOS                                            |                 | 17        |     | $\Omega$      |

| $R_{out}$                 | 出力インピーダンス                                   | 2.5V LVCMOS                                            |                 | 17        |     | $\Omega$      |

| $R_{out}$                 | 出力インピーダンス                                   | 1.8V LVCMOS                                            |                 | 17        |     | $\Omega$      |

| ODC                       | 出力デューティ サイクル                                | $f_{out} \leq 156.25\text{MHz}$ <sup>(2)</sup>         | 45              | 55        |     | %             |

|                           |                                             | $f_{out} > 156.25\text{MHz}$ <sup>(2)</sup>            | 45              | 55        |     | %             |

| $C_{load}$                | 最大負荷容量                                      | <sup>(2)</sup>                                         |                 |           | 15  | pF            |

| RJ                        | 12kHz ~ 20MHz 統合 RMS ジッタ                    | $f_{out} = 50\text{MHz}$ <sup>(2)</sup>                |                 |           | 1   | ps            |

| <b>SSC 特性</b>             |                                             |                                                        |                 |           |     |               |

| $f_{out}$                 | SSC をサポートする出力周波数範囲                          |                                                        | 2.5             | 200       |     | MHz           |

| $f_{SSC}$                 | SSC 変調周波数                                   |                                                        | 30              | 31.5      | 33  | kHz           |

| $f_{SSC-deviation}$       | SSC 偏差 (変調深度)                               | ダウンスプレッド (ログラムブル)                                      | -0.05           | -3        |     | %             |

|                           |                                             | センター スプレッド (ログラムブル)                                    | $\pm 0.025$     | $\pm 1.5$ |     | %             |

| $df/dt$                   | SSC 最大周波数スルーレート                             | $0 < f_{SSC-deviation} \leq -0.5\%$                    |                 | 1250      |     | ppm/us        |

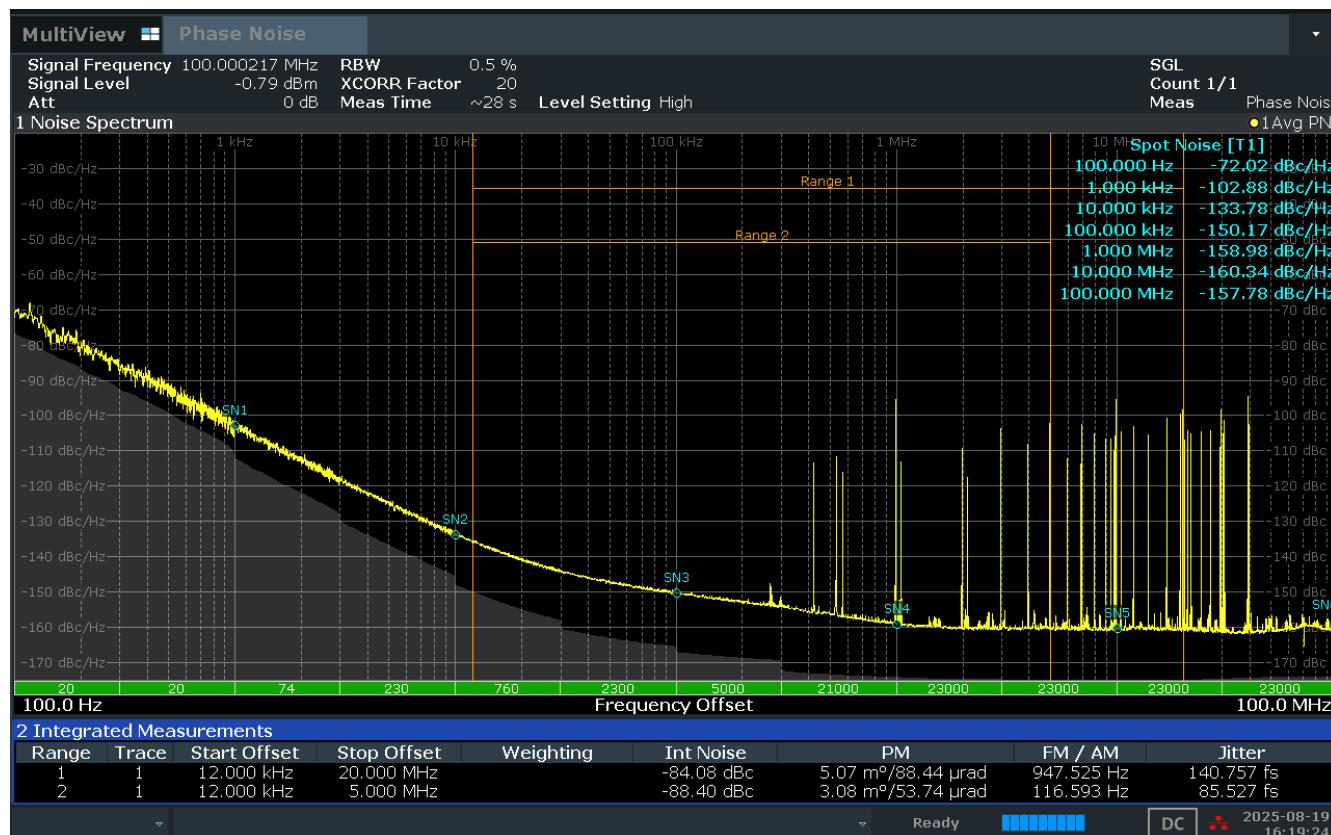

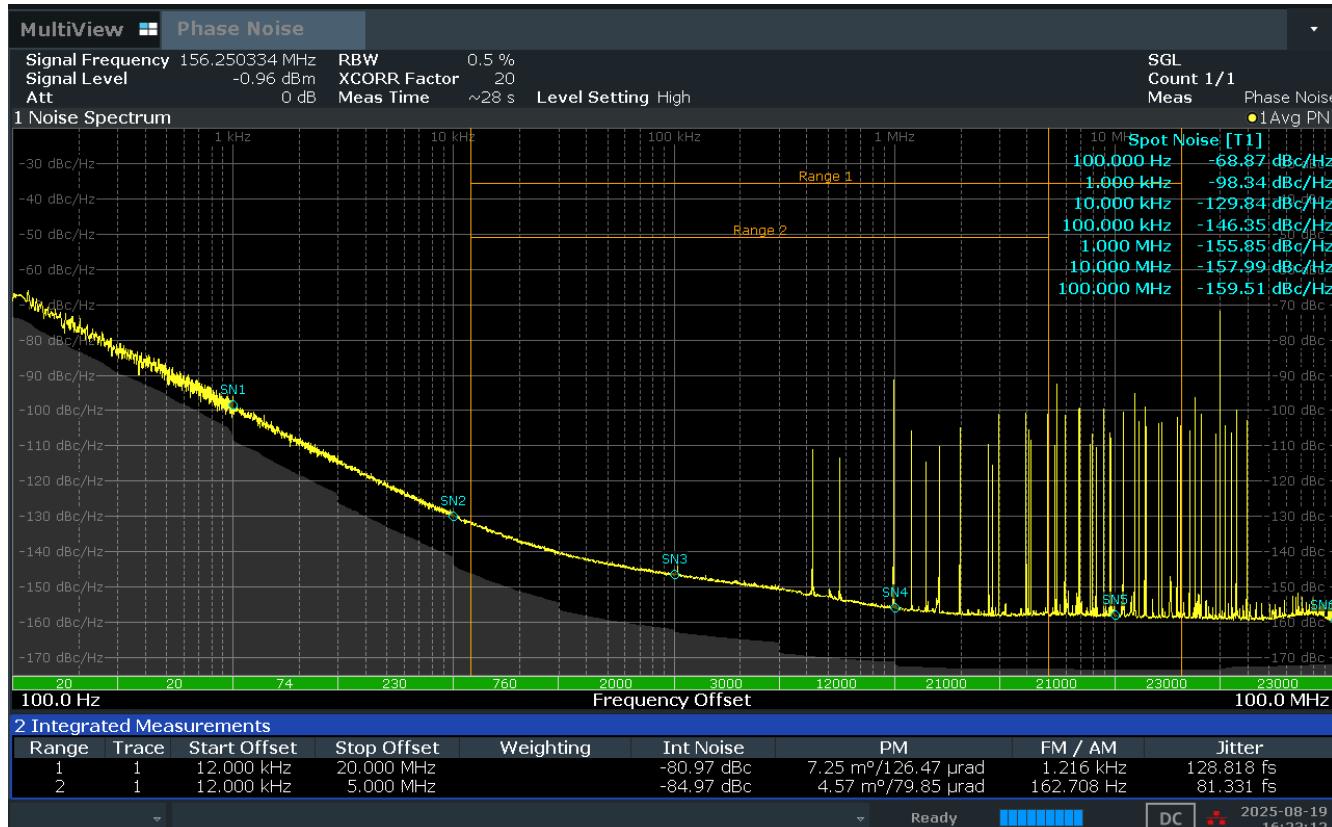

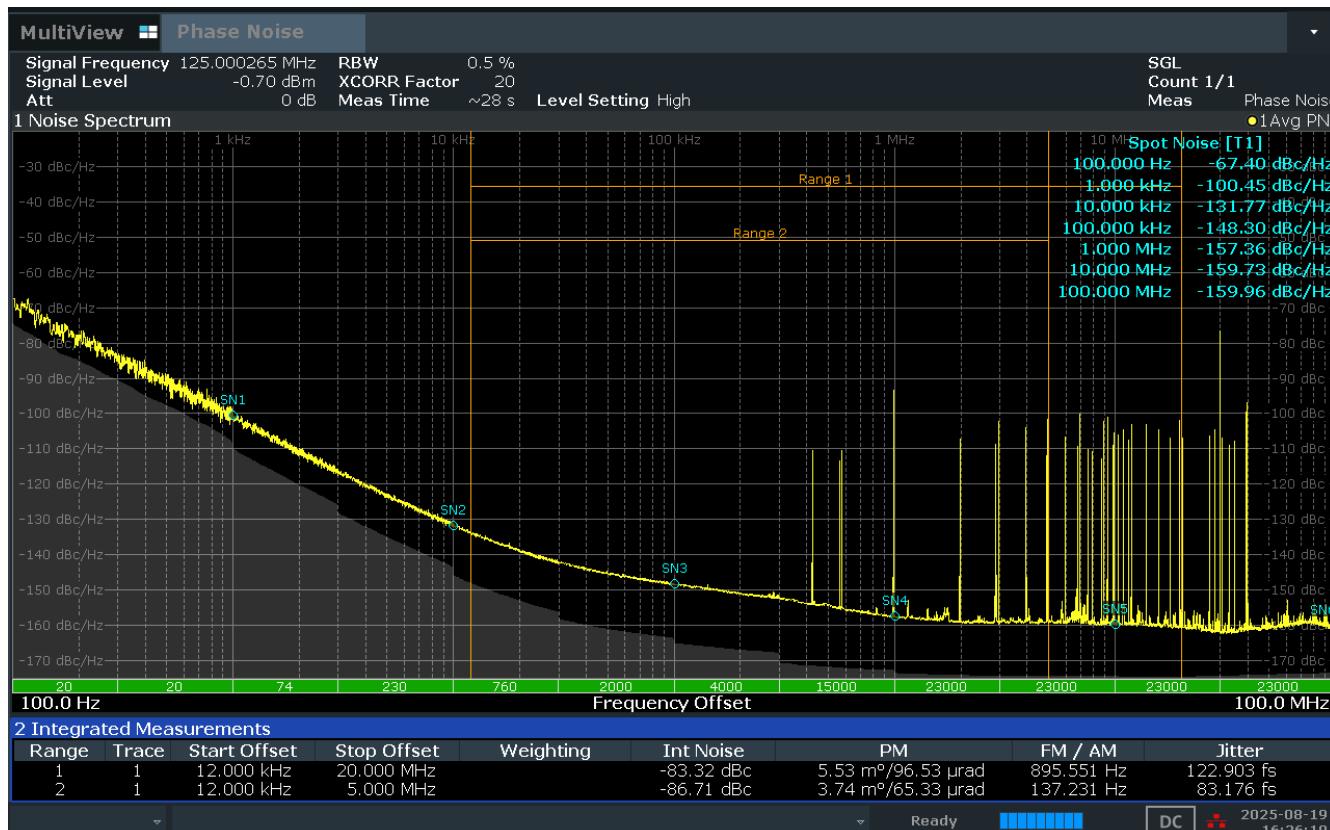

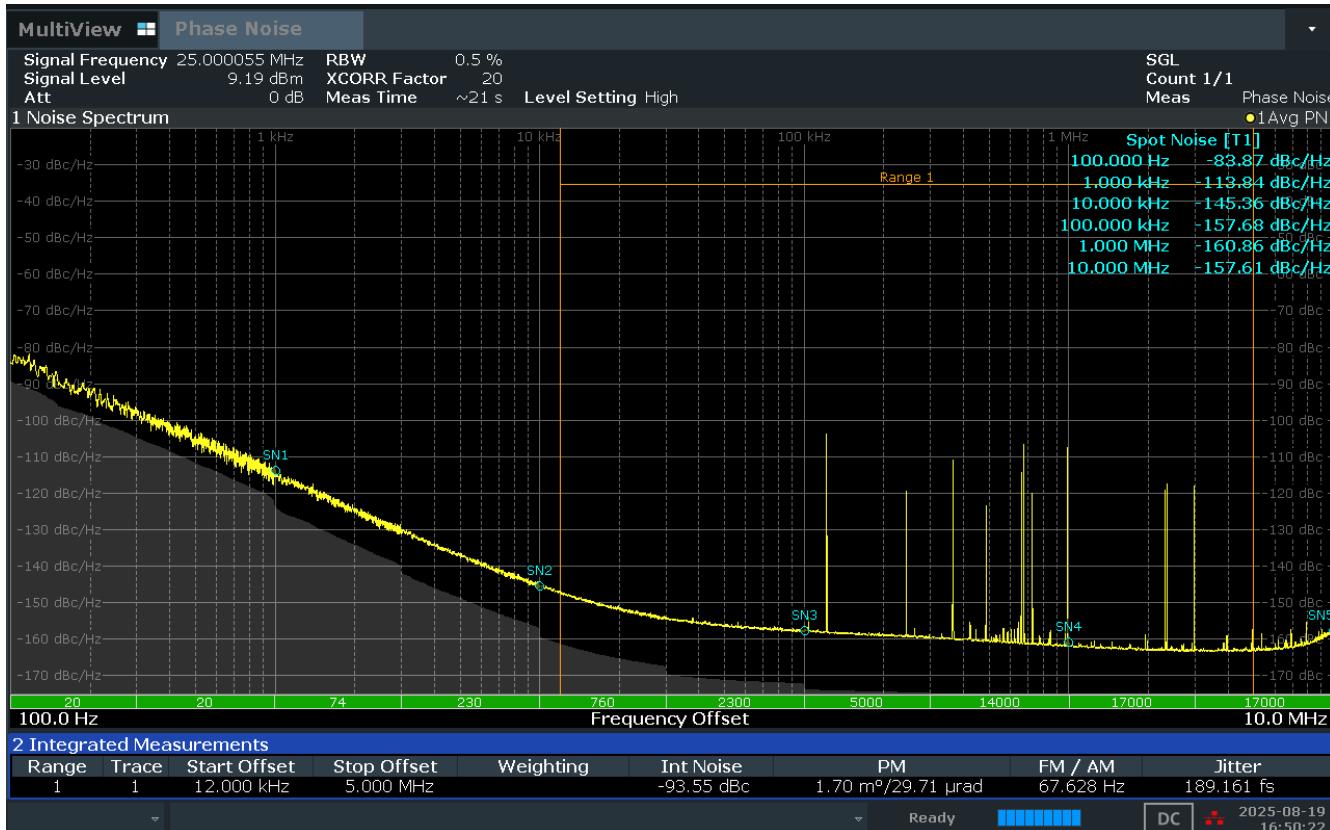

| <b>ジッタ特性</b>              |                                             |                                                        |                 |           |     |               |

| $J_{PCIe2-cc-SSC\_off}$   | PCIe Gen 2 共通クロックのジッタ、SSC はオフ (ジッタ制限 = 3ps) | FOD0 または FOD1 のみがイネーブル。SSC はディセーブル                     |                 | 0.27      |     | ps            |

| パラメータ                              |                                                                       | テスト条件                              | 最小値 | 標準値 | 最大値  | 単位 |

|------------------------------------|-----------------------------------------------------------------------|------------------------------------|-----|-----|------|----|

| J <sub>PCle2-cc-<br/>SSC_on</sub>  | PCIe Gen 2 共通クロックのジッタ、 $-0.5\% \leq \text{SSC} < 0\%$ (ジッタ制限 = 3ps)   | FOD0 または FOD1 のみがイネーブル。SSC はイネーブル  |     |     | 0.48 | ps |

| J <sub>PCle2-SRNS</sub>            | PCIe Gen 2 の SRNS ジッタ                                                 | FOD0 または FOD1 のみがイネーブル。SSC はディセーブル |     |     | 0.32 | ps |

| J <sub>PCle2-SRIS</sub>            | PCIe Gen 2 の SRIS ジッタ、 $-0.3\% \leq \text{SSC} < 0\%$                 | FOD0 または FOD1 のみがイネーブル。SSC はイネーブル  |     |     | 0.51 | ps |

| J <sub>PCle3-cc-<br/>SSC_off</sub> | PCIe Gen 3 共通クロックのジッタ、SSC はオフ (ジッタ制限 = 1ps)                           | FOD0 または FOD1 のみがイネーブル。SSC はディセーブル |     |     | 80   | fs |

| J <sub>PCle3-cc-<br/>SSC_on</sub>  | PCIe Gen 3 共通クロックのジッタ、 $-0.5\% \leq \text{SSC} < 0\%$ (ジッタ制限 = 1ps)   | FOD0 または FOD1 のみがイネーブル。SSC はイネーブル  |     |     | 145  | fs |

| J <sub>PCle3-SRNS</sub>            | PCIe Gen 3 の SRNS ジッタ                                                 | FOD0 または FOD1 のみがイネーブル。SSC はディセーブル |     |     | 95   | fs |

| J <sub>PCle3-SRIS</sub>            | PCIe Gen 3 の SRIS ジッタ、 $-0.3\% \leq \text{SSC} < 0\%$                 | FOD0 または FOD1 のみがイネーブル。SSC はイネーブル  |     |     | 440  | fs |

| J <sub>PCle4-cc-<br/>SSC_off</sub> | PCIe Gen 4 共通クロックのジッタ、SSC はオフ (ジッタ制限 = 500fs)                         | FOD0 または FOD1 のみがイネーブル。SSC はディセーブル |     |     | 76   | fs |

| J <sub>PCle4-cc-<br/>SSC_on</sub>  | PCIe Gen 4 共通クロックのジッタ、 $-0.5\% \leq \text{SSC} < 0\%$ (ジッタ制限 = 500fs) | FOD0 または FOD1 のみがイネーブル。SSC はイネーブル  |     |     | 144  | fs |

| J <sub>PCle4-SRNS</sub>            | PCIe Gen 4 の SRNS ジッタ                                                 | FOD0 または FOD1 のみがイネーブル。SSC はディセーブル |     |     | 95   | fs |

| J <sub>PCle4-SRIS</sub>            | PCIe Gen 4 の SRIS ジッタ、 $-0.3\% \leq \text{SSC} < 0\%$                 | FOD0 または FOD1 のみがイネーブル。SSC はイネーブル  |     |     | 215  | fs |

| J <sub>PCle5-cc-<br/>SSC_off</sub> | PCIe Gen 5 共通クロックのジッタ、SSC はオフ (ジッタ制限 = 150fs)                         | FOD0 または FOD1 のみがイネーブル。SSC はディセーブル |     |     | 29   | fs |

| J <sub>PCle5-cc-<br/>SSC_on</sub>  | PCIe Gen 5 共通クロックのジッタ、 $-0.5\% \leq \text{SSC} < 0\%$ (ジッタ制限 = 150fs) | FOD0 または FOD1 のみがイネーブル。SSC はイネーブル  |     |     | 61   | fs |

| J <sub>PCle5-SRNS</sub>            | PCIe Gen 5 の SRNS ジッタ                                                 | FOD0 または FOD1 のみがイネーブル。SSC はディセーブル |     |     | 36   | fs |

| J <sub>PCle5-SRIS</sub>            | PCIe Gen 5 の SRIS ジッタ、 $-0.3\% \leq \text{SSC} < 0\%$                 | FOD0 または FOD1 のみがイネーブル。SSC はイネーブル  |     |     | 66   | fs |

| J <sub>PCle6-cc-<br/>SSC_off</sub> | PCIe Gen 6 共通クロックのジッタ、SSC はオフ (ジッタ制限 = 100fs)                         | FOD0 または FOD1 のみがイネーブル。SSC はディセーブル |     |     | 19.3 | fs |

| J <sub>PCle6-cc-<br/>SSC_on</sub>  | PCIe Gen 6 共通クロックのジッタ、 $-0.5\% \leq \text{SSC} < 0\%$ (ジッタ制限 = 100fs) | FOD0 または FOD1 のみがイネーブル。SSC はイネーブル  |     |     | 36.4 | fs |

| J <sub>PCle6-SRNS</sub>            | PCIe Gen 6 の SRNS ジッタ                                                 | FOD0 または FOD1 のみがイネーブル。SSC はディセーブル |     |     | 29.3 | fs |

| パラメータ                          |                                                        | テスト条件                                                       | 最小値 | 標準値  | 最大値 | 単位 |

|--------------------------------|--------------------------------------------------------|-------------------------------------------------------------|-----|------|-----|----|

| $J_{\text{PCIe6-SRIS}}$        | PCIe Gen 6 の SRIS ジッタ、 $-0.3\% \leq \text{SSC} < 0\%$  | FOD0 または FOD1 のみがイネーブル。SSC はイネーブル                           |     | 48.3 |     | fs |

| $J_{\text{PCIe7-cc-SSC\_off}}$ | PCIe Gen 7 共通クロックのジッタ、SSC はオフ                          | FOD0 または FOD1 のみがイネーブル。SSC はディセーブル                          |     | 13.5 |     | fs |

| $J_{\text{PCIe7-cc-SSC\_on}}$  | PCIe Gen 7 共通クロックのジッタ、 $-0.5\% \leq \text{SSC} < 0\%$  | FOD0 または FOD1 のみがイネーブル。SSC はイネーブル                           |     | 25.5 |     | fs |

| $J_{\text{PCIe7-SRNS}}$        | PCIe Gen 7 の SRNS ジッタ                                  | FOD0 または FOD1 のみがイネーブル。SSC はディセーブル                          |     | 20.6 |     | fs |

| $J_{\text{PCIe7-SRIS}}$        | PCIe Gen 7 の SRIS ジッタ、 $-0.15\% \leq \text{SSC} < 0\%$ | FOD0 または FOD1 のみがイネーブル。SSC はイネーブル                           |     | 26.4 |     | fs |

| $RJ_{\text{RMS}}$              | 12kHz ~ 20MHz RMS ジッタ                                  | $f_{\text{out}} = 156.25\text{MHz}$ FOD0 または FOD1 のみがイネーブル。 | 154 | 211  |     | fs |

**パップア モードの特性**

|                           |                                    |                                                                   |     |     |    |

|---------------------------|------------------------------------|-------------------------------------------------------------------|-----|-----|----|

| $J_{\text{PCIe1-CC}}$     | PCIe Gen 1 CC                      | 差動入力スルーレート $\geq 3.5\text{ V/ns}$ 。差動入力スイシング $\geq 1600\text{mV}$ | 977 | fs  |    |

| $J_{\text{PCIe2-CC}}$     | PCIe Gen 2 CC                      |                                                                   | 229 | fs  |    |

| $J_{\text{PCIe3-CC}}$     | PCIe Gen 3 CC                      |                                                                   | 88  | fs  |    |

| $J_{\text{PCIe4-CC}}$     | PCIe Gen 4 CC                      |                                                                   | 88  | fs  |    |

| $J_{\text{PCIe5-CC}}$     | PCIe Gen 5 CC                      |                                                                   | 34  | fs  |    |

| $J_{\text{PCIe6-CC}}$     | PCIe Gen 6 CC                      |                                                                   | 22  | fs  |    |

| $J_{\text{PCIe2-IR}}$     | PCIe Gen 2 IR                      |                                                                   | 268 | fs  |    |

| $J_{\text{PCIe3-IR}}$     | PCIe Gen 3 IR                      |                                                                   | 72  | fs  |    |

| $J_{\text{PCIe4-IR}}$     | PCIe Gen 4 IR                      |                                                                   | 72  | fs  |    |

| $J_{\text{PCIe5-IR}}$     | PCIe Gen 5 IR                      |                                                                   | 28  | fs  |    |

| $J_{\text{PCIe6-IR}}$     | PCIe Gen 6 IR                      |                                                                   | 23  | fs  |    |

| $J_{\text{PCIe1-CC}}$     | PCIe Gen 1 CC                      | 差動入力スルーレート $\geq 1.5\text{ V/ns}$ 。差動入力スイシング $\geq 800\text{mV}$  | 977 | fs  |    |

| $J_{\text{PCIe2-CC}}$     | PCIe Gen 2 CC                      |                                                                   | 231 | fs  |    |

| $J_{\text{PCIe3-CC}}$     | PCIe Gen 3 CC                      |                                                                   | 90  | fs  |    |

| $J_{\text{PCIe4-CC}}$     | PCIe Gen 4 CC                      |                                                                   | 90  | fs  |    |

| $J_{\text{PCIe5-CC}}$     | PCIe Gen 5 CC                      |                                                                   | 34  | fs  |    |

| $J_{\text{PCIe6-CC}}$     | PCIe Gen 6 CC                      |                                                                   | 23  | fs  |    |

| $J_{\text{PCIe2-IR}}$     | PCIe Gen 2 IR                      |                                                                   | 273 | fs  |    |

| $J_{\text{PCIe3-IR}}$     | PCIe Gen 3 IR                      |                                                                   | 73  | fs  |    |

| $J_{\text{PCIe4-IR}}$     | PCIe Gen 4 IR                      |                                                                   | 73  | fs  |    |

| $J_{\text{PCIe5-IR}}$     | PCIe Gen 5 IR                      |                                                                   | 28  | fs  |    |

| $J_{\text{PCIe6-IR}}$     | PCIe Gen 6 IR                      |                                                                   | 23  | fs  |    |

| $J_{\text{RMS-additive}}$ | 100MHz 時の加算性 12kHz ~ 20MHz RMS ジッタ | 差動入力スルーレート $\geq 3.5\text{ V/ns}$ 。差動入力スイシング $\geq 1600\text{mV}$ | 73  | 145 | fs |

|                           |                                    | 差動入力スルーレート $\geq 1.5\text{ V/ns}$ 。差動入力スイシング $\geq 800\text{mV}$  | 77  | 153 | fs |

| パラメータ              |                                       | テスト条件                                                                                            | 最小値 | 標準値 | 最大値   | 単位 |

|--------------------|---------------------------------------|--------------------------------------------------------------------------------------------------|-----|-----|-------|----|

| $J_{RMS-additive}$ | 156.25MHz 時の加算性 12kHz ~ 20MHz RMS ジッタ | 差動入力スルーレート $\geq 3.5 \text{ V/ns}$ 。差動入力スイング $\geq 1600\text{mV}$                                | 57  | 122 | fs    |    |

|                    |                                       | 差動入力スルーレート $\geq 1.5 \text{ V/ns}$ 。差動入力スイング $\geq 800\text{mV}$                                 | 59  | 124 | fs    |    |

| $J_{RMS-additive}$ | 156.25MHz 時の加算性 12kHz ~ 70MHz RMS ジッタ | 差動入力スルーレート $\geq 3.5 \text{ V/ns}$ 。差動入力スイング $\geq 1600\text{mV}$                                | 106 | 156 | fs    |    |

|                    |                                       | 差動入力スルーレート $\geq 1.5 \text{ V/ns}$ 。差動入力スイング $\geq 800\text{mV}$                                 | 108 | 161 | fs    |    |

| $J_{RMS-additive}$ | 312.5MHz 時の加算性 12kHz ~ 20MHz RMS ジッタ  | 差動入力スルーレート $\geq 3.5 \text{ V/ns}$ 。差動入力スイング $\geq 1600\text{mV}$                                | 48  | 90  | fs    |    |

|                    |                                       | 差動入力スルーレート $\geq 1.5 \text{ V/ns}$ 。差動入力スイング $\geq 800\text{mV}$                                 | 51  | 94  | fs    |    |

| $J_{RMS-additive}$ | 312.5MHz 時の加算性 12kHz ~ 70MHz RMS ジッタ  | 差動入力スルーレート $\geq 3.5 \text{ V/ns}$ 。差動入力スイング $\geq 1600\text{mV}$                                | 81  | 123 | fs    |    |

|                    |                                       | 差動入力スルーレート $\geq 1.5 \text{ V/ns}$ 。差動入力スイング $\geq 800\text{mV}$                                 | 82  | 128 | fs    |    |

| $t_{skew}$         | 出力間スキー                                | 同じクロックソース                                                                                        |     | 100 | ps    |    |

| $t_{PD}$           | 入出力間遅延                                |                                                                                                  |     | 1.1 | ns    |    |

| $\Delta t_{PD}$    | 入出力間遅延の変動                             | 单一デバイスにおける温度および電圧条件。<br>100MHz, LP-HCSL 出力                                                       |     | 2   | ps/°C |    |

| DCD                | デューティサイクルの歪み                          | 差動入力、 $f \leq 400\text{MHz}$ 、<br>差動入力スルーレート $\geq 1.5\text{V/ns}$ 、差動入力スイング $\geq 800\text{mV}$ | -3  | 3   | %     |    |

|                    |                                       | CMOS 入力、 $f \leq 200\text{MHz}$ 、立ち上がり/立ち下がり時間は $\leq 1\text{ns}$                                | -11 | 11  | %     |    |

|                    |                                       | CMOS 入力、 $f \leq 156.25\text{MHz}$ 、立ち上がり/立ち下がり時間は $\leq 1\text{ns}$                             | -9  | 9   | %     |    |

|                    |                                       | CMOS 入力、 $f \leq 50\text{MHz}$ 、立ち上がり/立ち下がり時間は $\leq 1\text{ns}$                                 | -3  | 3   | %     |    |

| タイミング特性            |                                       |                                                                                                  |     |     |       |    |

| $t_{startup}$      | 起動時間                                  | $VDD = 2.5/3.3\text{V}$ 。すべての VDD ピンが $1.62\text{V}$ に達してから最初の出力クロックの立ち上がりエッジまでの経過時間             |     | 2.4 | 5     | ms |

|                    |                                       | $VDD = 1.8\text{V}$ 。すべての VDD ピンが $1.62\text{V}$ に達してから最初の出力クロックの立ち上がりエッジまでの経過時間                 |     | 1.6 | 5     | ms |

| パラメータ     |                                                                         | テスト条件                                                  | 最小値           | 標準値                  | 最大値 | 単位 |

|-----------|-------------------------------------------------------------------------|--------------------------------------------------------|---------------|----------------------|-----|----|

| $t_{OE}$  | 出力イネーブル時間 CLOCK_READY ステータスが「1」になった後、OE アサートから最初の出力クロックの立ち上がりエッジまでの経過時間 | フル同期モード                                                | 3 出力クロック サイクル | 7 出力クロック サイクル + 40ns |     |    |

|           |                                                                         | セルフ同期モード                                               | 3 出力クロック サイクル | 7 出力クロック サイクル + 40ns |     |    |

|           |                                                                         | SYNC モードなし                                             | 0             | 40                   | ns  |    |

| $t_{OD}$  | 出力ディスエーブル時間 OE デアサートから最後の出力クロックの立ち下がりエッジまでの経過時間。                        | フル同期モード                                                | 3 出力クロック サイクル | 7 出力クロック サイクル + 40ns |     |    |

|           |                                                                         | セルフ同期モード                                               | 3 出力クロック サイクル | 7 出力クロック サイクル + 40ns |     |    |

|           |                                                                         | SYNC モードなし                                             | 0             | 40                   | ns  |    |

| $t_{OTP}$ | 動的 OTP スイッチ時間                                                           | OTP ページが変化するとき、クロック出力の最後の立ち下がりエッジと最初の立ち上がりエッジの間で測定されます |               | 900                  |     | μs |

**電源電流特性**

|           |                                  |                                       |      |    |

|-----------|----------------------------------|---------------------------------------|------|----|

| $I_{DDR}$ | $V_{DDR}$ ピンの電源電流 (LMK3H2108 のみ) | IN1 と IN2 の電源がオフになります                 | 5.1  | mA |

|           |                                  | IN1 または IN2 イネーブルです                   | 14.1 | mA |

|           |                                  | IN1 と IN2 機能がイネーブルです                  | 25.1 | mA |

| $I_{DDX}$ | $V_{DDX}$ ピンの電源電流 (LMK3H2108 のみ) | IN0 の電源がオフになります                       | 2.5  | mA |

|           |                                  | IN0 はイネーブル                            | 13.4 | mA |

| $I_{DDA}$ | $V_{DDA}$ ピン電源電流                 | 1 つの FOD がイネーブルです。FOD 周波数 = 200 MHz   | 49.6 | mA |

|           |                                  | 1 つの FOD がイネーブルです。FOD 周波数 = 400 MHz   | 55.7 | mA |

|           |                                  | 両方の FOD がイネーブルになります。FOD 周波数 = 200 MHz | 59.2 | mA |

|           |                                  | 両方の FOD がイネーブルになります。FOD 周波数 = 400 MHz | 74.4 | mA |

| $I_{DDD}$ | $V_{DDD}$ ピン電源電流                 | 1 つの FOD がイネーブルです。FOD 周波数 = 200 MHz   | 45.8 | mA |

|           |                                  | 1 つの FOD がイネーブルです。FOD 周波数 = 400 MHz   | 52.4 | mA |

|           |                                  | 両方の FOD がイネーブルになります。FOD 周波数 = 200 MHz | 58.4 | mA |

|           |                                  | 両方の FOD がイネーブルになります。FOD 周波数 = 400 MHz | 70   | mA |

| パラメータ               |                                         | テスト条件                                                                                 | 最小値 | 標準値 | 最大値  | 単位 |

|---------------------|-----------------------------------------|---------------------------------------------------------------------------------------|-----|-----|------|----|

| $I_{DDO\_CMOS}$     | $V_{DDO}$ ピンの LVC MOS 出力ペアあたりの電源電流      | $V_{DDO} = 1.8V \pm 5\%$ 。<br>$f_{out} = 50MHz$                                       |     |     | 5    | mA |

|                     |                                         | $V_{DDO} = 2.5V \pm 5\%$ 。<br>$f_{out} = 50MHz$                                       |     |     | 6.4  | mA |

|                     |                                         | $V_{DDO} = 3.3V \pm 5\%$ 。<br>$f_{out} = 50MHz$                                       |     |     | 7.7  | mA |

|                     |                                         | $V_{DDO} = 1.8V \pm 5\%$ 。<br>$f_{out} = 200MHz$                                      |     |     | 13.4 | mA |

|                     |                                         | $V_{DDO} = 2.5V \pm 5\%$ 。<br>$f_{out} = 200MHz$                                      |     |     | 17.3 | mA |

|                     |                                         | $V_{DDO} = 3.3V \pm 5\%$ 。<br>$f_{out} = 200MHz$                                      |     |     | 21.7 | mA |

| $I_{DDO\_1.2VCMOS}$ | 1.2V LVC MOS 出力ペアあたりの $V_{DDO}$ ピンの消費電流 | $V_{DDO} = 1.8V \pm 5\%$ 。<br>1.2V LVC MOS がイネーブル。 $f_{out} = 50MHz$ 。ハイインピーダンス終端。    |     |     | 11.9 | mA |

|                     |                                         | $V_{DDO} = 1.8V \pm 5\%$ 。<br>1.2V LVC MOS がイネーブル。 $f_{out} = 200MHz$ 。ハイインピーダンス終端。   |     |     | 15.6 | mA |

|                     |                                         | $V_{DDO} = 1.8V \pm 5\%$ 。<br>1.2V LVC MOS がイネーブル。 $f_{out} = 50MHz$ 。<br>100Ω 差動終端。  |     |     | 15.8 | mA |

|                     |                                         | $V_{DDO} = 1.8V \pm 5\%$ 。<br>1.2V LVC MOS がイネーブル。 $f_{out} = 200MHz$ 。<br>100Ω 差動終端。 |     |     | 18.2 | mA |

| $I_{DDO\_LPHCS_L}$  | $V_{DDO}$ ピンの LP-HCSL 出力ペアごとの電源電流       | $V_{DDO} = 1.8, 2.5$ または<br>$3.3V \pm 5\%$ 。 $f_{out} = 100MHz$                       |     |     | 10.8 | mA |

|                     |                                         | $V_{DDO} = 1.8, 2.5$ または<br>$3.3V \pm 5\%$ 。 $f_{out} = 400MHz$                       |     |     | 16.4 | mA |

| $I_{DDO\_LVDS}$     | $V_{DDO}$ ピンの LVDS 出力ペアあたりの電源電流         | $V_{DDO} = 1.8, 2.5$ または<br>$3.3V \pm 5\%$ 。 $f_{out} = 100MHz$                       |     |     | 8    | mA |

|                     |                                         | $V_{DDO} = 1.8, 2.5$ または<br>$3.3V \pm 5\%$ 。 $f_{out} = 400MHz$                       |     |     | 11.3 | mA |

| $I_{DD\_PD}$        | 合計パワーダウン電流                              | $V_{DDO} = 1.8V \pm 5\%$                                                              |     |     | 53   | mA |

|                     |                                         | $V_{DDO} = 3.3V \pm 5\%$                                                              |     |     | 67   | mA |

| <b>PSNR 特性</b>      |                                         |                                                                                       |     |     |      |    |

| パラメータ                                |                                                                                                                              | テスト条件  | 最小値 | 標準値   | 最大値 | 単位  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--------|-----|-------|-----|-----|

| PSNR <sub>2.5/3.3</sub><br>V_CLK_GEN | 電源ノイズ除去。VDDx = 2.5 または 3.3V。クロックジェネレータ モード (クロック ソースは FOD またはエッジコンバイナ)。VDDO 以外のすべての電源ピンに印加されるリップル <sup>(3)</sup>             | 10kHz  |     | -88.9 |     | dBc |

|                                      |                                                                                                                              | 50kHz  |     | -89.9 |     | dBc |

|                                      |                                                                                                                              | 100kHz |     | -89.2 |     | dBc |

|                                      |                                                                                                                              | 500kHz |     | -82.6 |     | dBc |

|                                      |                                                                                                                              | 1MHz   |     | -93.3 |     | dBc |

|                                      |                                                                                                                              | 5MHz   |     | -86.8 |     | dBc |

|                                      |                                                                                                                              | 10MHz  |     | -89.3 |     | dBc |

|                                      | 電源ノイズ除去。VDDx = 2.5 または 3.3V。クロックジェネレータ モード (クロック ソースは FOD またはエッジコンバイナ)。すべての VDDO ピンに印加されるリップル。LVCMOS 出力フォーマット <sup>(3)</sup> | 10kHz  |     | -72   |     | dBc |

|                                      |                                                                                                                              | 50kHz  |     | -72.6 |     | dBc |

|                                      |                                                                                                                              | 100kHz |     | -72.1 |     | dBc |

|                                      |                                                                                                                              | 500kHz |     | -71.4 |     | dBc |

|                                      |                                                                                                                              | 1MHz   |     | -92.5 |     | dBc |

|                                      |                                                                                                                              | 5MHz   |     | -90.7 |     | dBc |

|                                      |                                                                                                                              | 10MHz  |     | -92.6 |     | dBc |

|                                      | 電源ノイズ除去。VDDx = 2.5 または 3.3V。クロックジェネレータ モード (クロック ソースは FOD またはエッジコンバイナ)。すべての VDDO ピンに印加されるリップル。LVDS 出力フォーマット <sup>(3)</sup>   | 10kHz  |     | -87.5 |     | dBc |

|                                      |                                                                                                                              | 50kHz  |     | -87.9 |     | dBc |

|                                      |                                                                                                                              | 100kHz |     | -83.7 |     | dBc |

|                                      |                                                                                                                              | 500kHz |     | -72.3 |     | dBc |

|                                      |                                                                                                                              | 1MHz   |     | -91.8 |     | dBc |

|                                      |                                                                                                                              | 5MHz   |     | -87.6 |     | dBc |

|                                      |                                                                                                                              | 10MHz  |     | -89.9 |     | dBc |

|                                      | 電源ノイズ除去。VDDx = 2.5 または 3.3V。クロックジェネレータ モード (クロック ソースは FOD またはエッジコンバイナ)。すべての VDDO ピンに印加されるリップル。HCSL 出力フォーマット <sup>(3)</sup>   | 10kHz  |     | -87.1 |     | dBc |

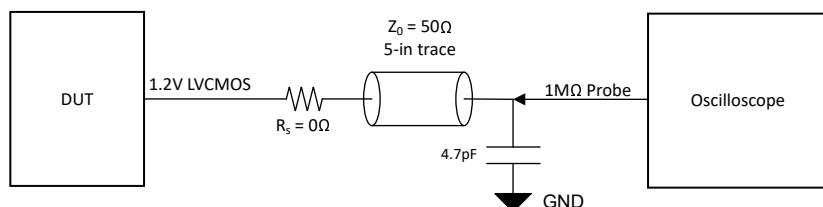

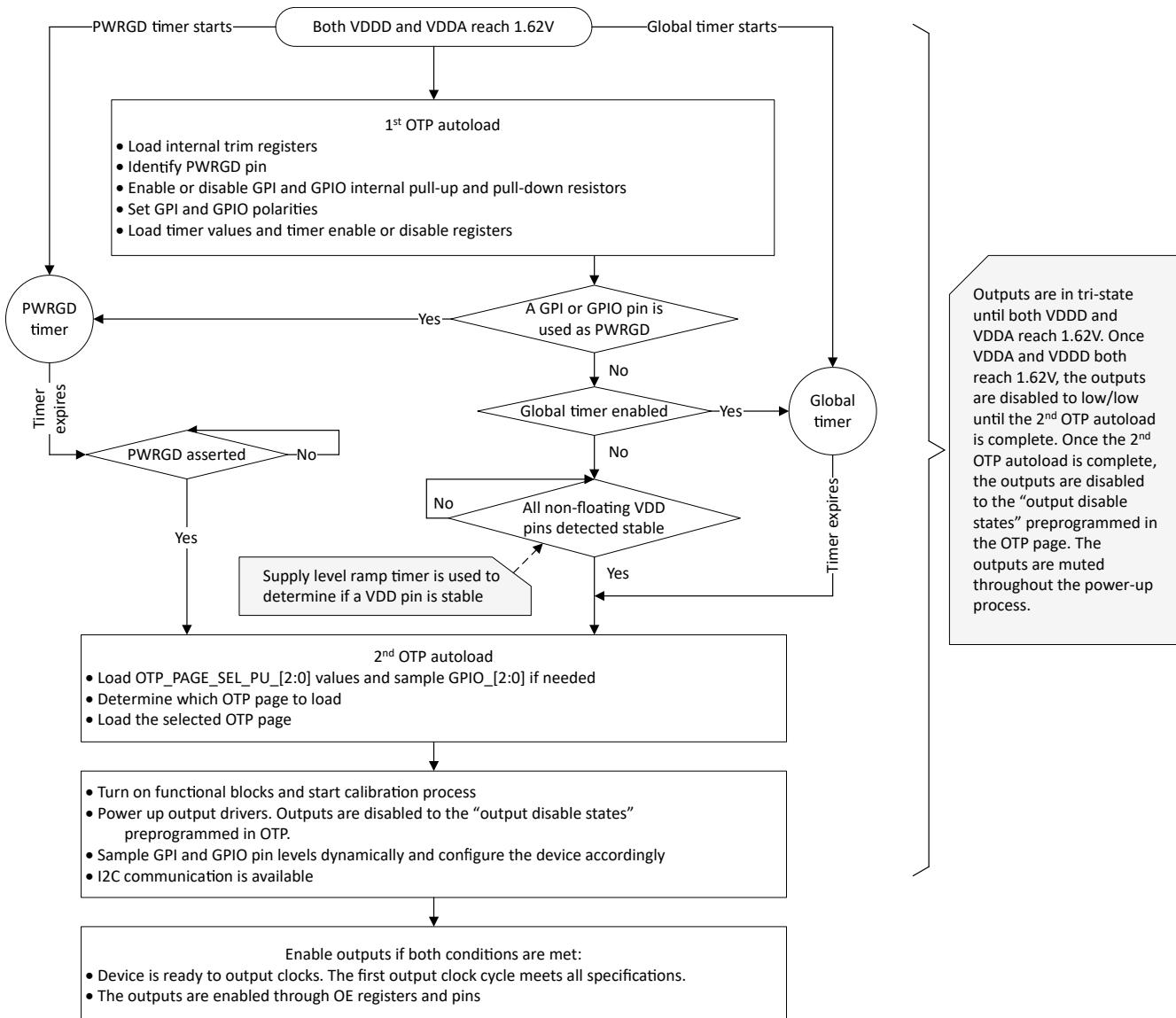

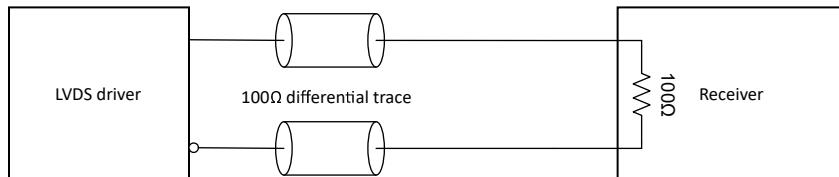

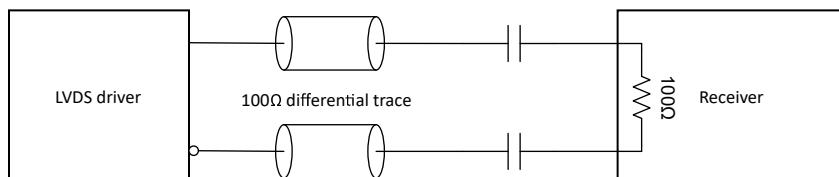

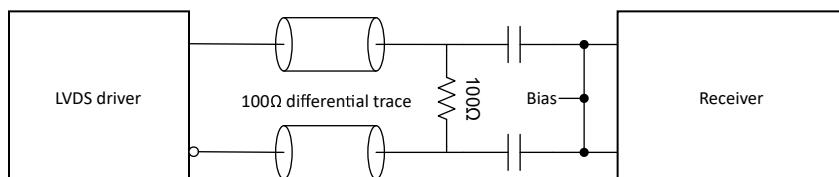

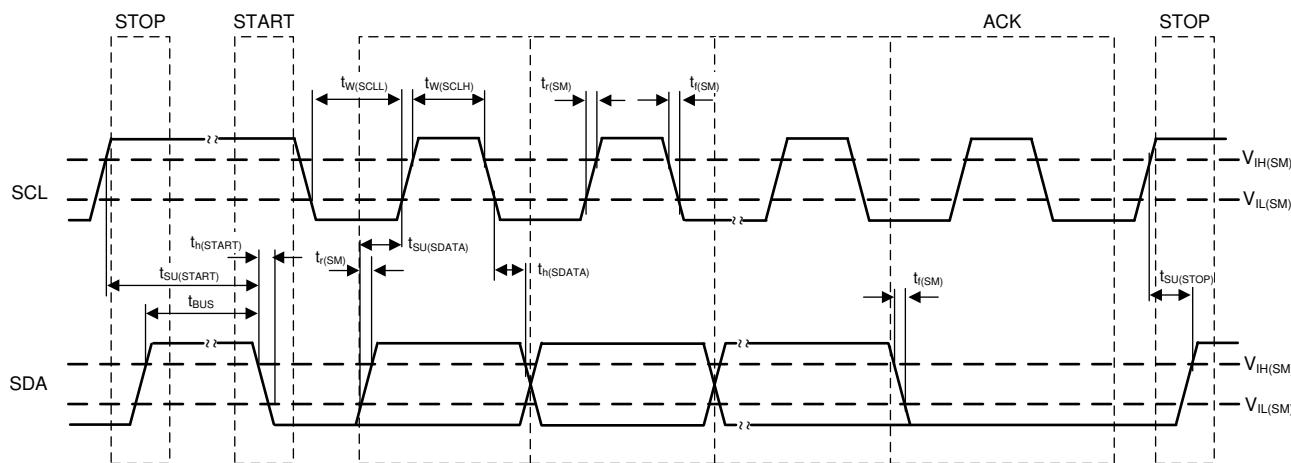

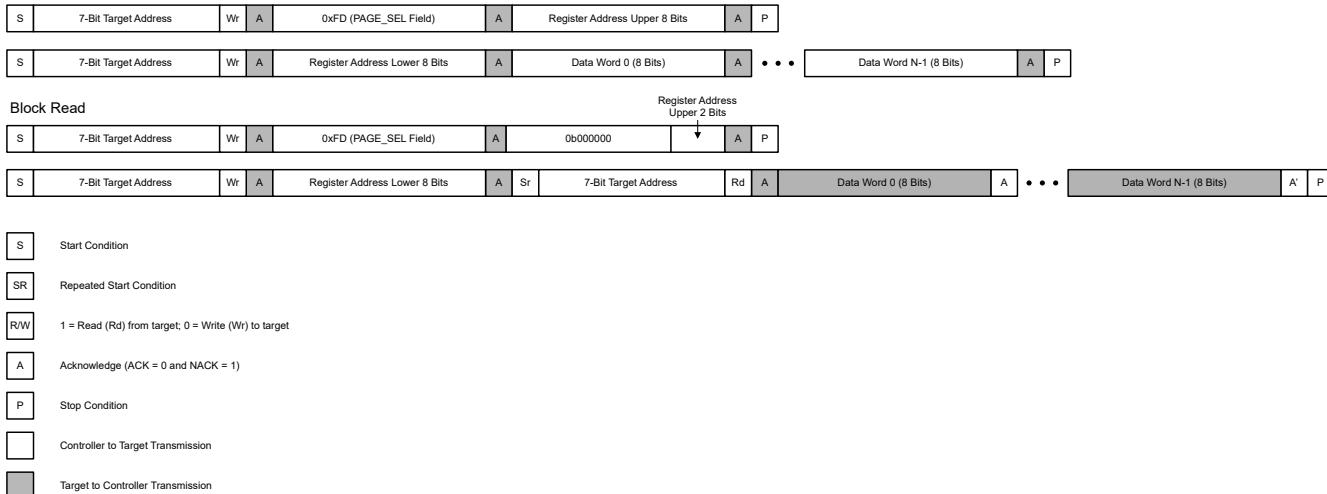

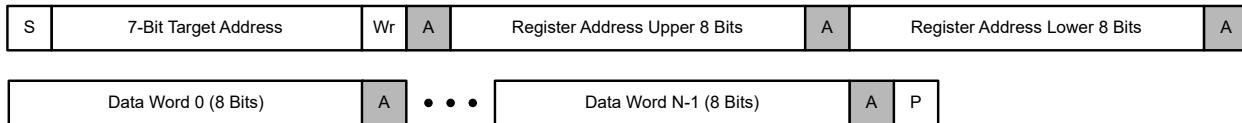

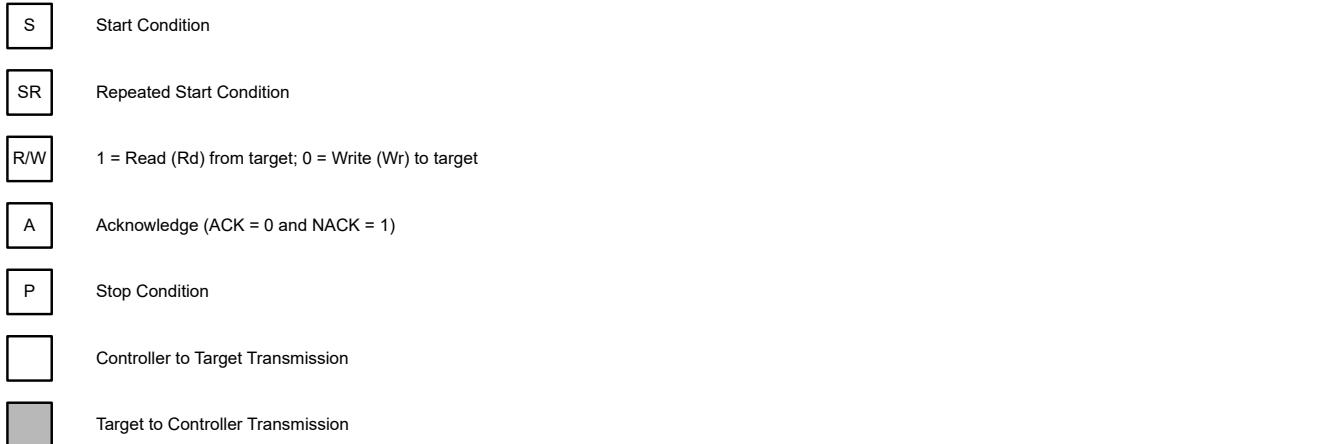

|                                      |                                                                                                                              | 50kHz  |     | -88.8 |     | dBc |