LMH2832 JAJSCA4A – JULY 2016 – REVISED JULY 2016

# LMH2832 完全差動デュアル、1.1GHz、デジタル可変ゲイン・アンプ

## 1 特長

- 2チャネルで独立に SPI™制御されるDVGA

- 5V単一電源

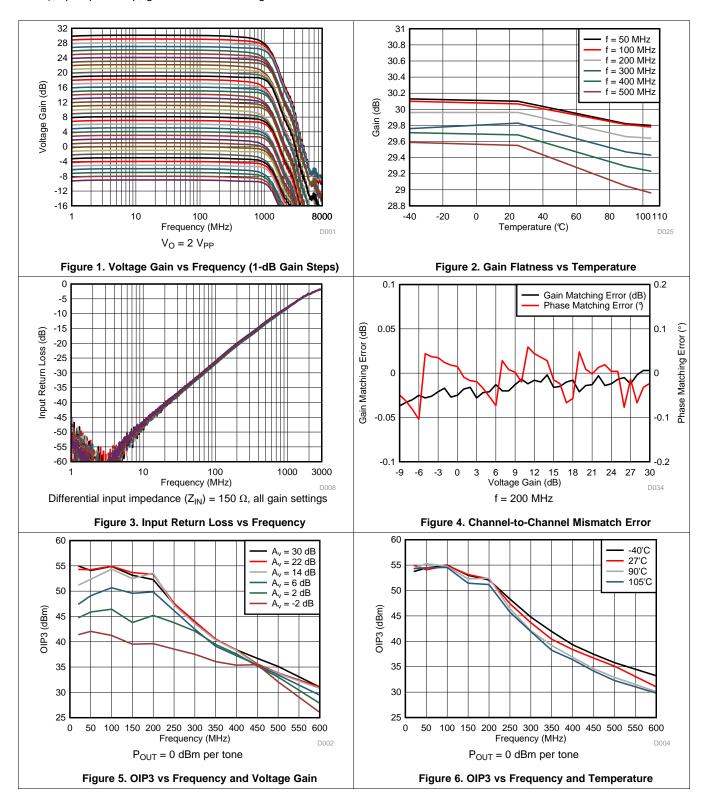

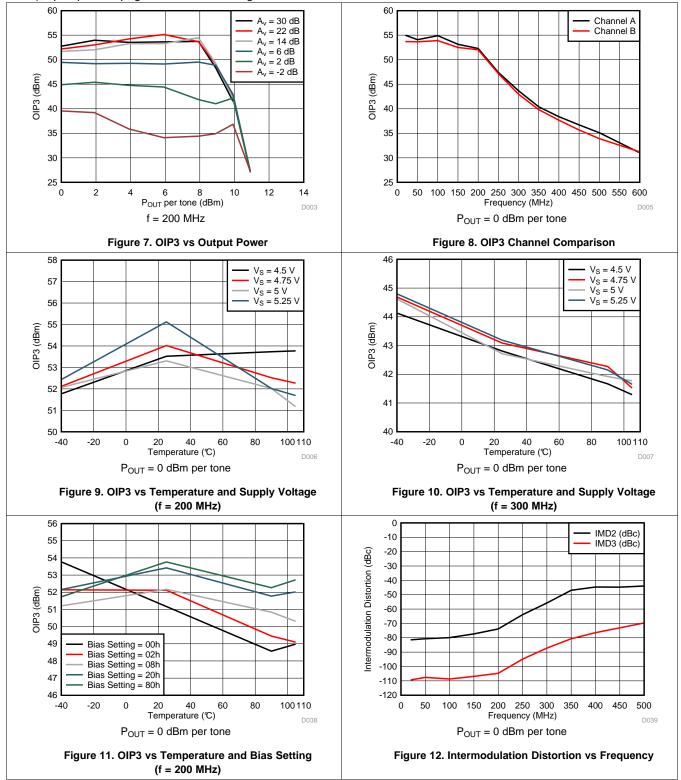

- -3dB帯域幅: 1.1GHz (最大ゲイン)

- フラット帯域幅応答: 300MHz

- チャネル間ゲイン・マッチング: ±0.05dB

- チャネル間位相マッチング: ±0.1°

- ゲイン

- 30dB~-9dB

- 1dBステップ、±0.2dB

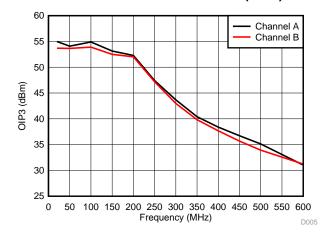

- 出力の3次インターセプト・ポイント(OIP3)

- 300MHzで43dBm

- 200MHzで51dBm

- ノイズ値(NF)

- 300MHzで6.5dB (最大ゲイン)、 $Z_{IN} = 150\Omega$

- 可変消費電力

- チャネルごとに90mA~108mA

- パワーセービングおよびパワーダウン機能

- チャネルごとにlo < 4.5 mA

- パワーダウン・ピンとSPIでプログラム可能

- 300MHzでの入力リターン・ロス

- 17dB (R<sub>S</sub> = 150Ω)

## 2 アプリケーション

- DOCSIS 3.1 CMTSアップストリーム直接サンプ リング受信機

- CATVモデム信号スケーリング

- プログラマブル・ゲインのIFアンプ

- 汎用RF、IFゲイン・ステージ

- ADCドライバ

## 3 概要

LMH2832は直線性が高い2チャネルのデジタル可変ゲイ ン・アンプ(DVGA)で、高速信号チェーンおよびデータ収 集システム用です。LMH2832は高い帯域幅、低い歪み、 低いノイズを実現するよう最適化されているため、2チャネ ル、14ビットのA/Dコンバータ(ADC)ドライバに理想的で す。このデバイスは、1つの固定ゲイン・ブロックと、1つの 可変アッテネータで構成され、合計ゲインは30dB、最大 減衰は39dBです。ゲインの範囲は30dB~-9dBで、1dB ステップで設定でき、ゲイン精度は±0.2dBです。入力イン ピーダンスは $1:3\Omega$ または $1:2\Omega$ 比率のバランを使用して、 それぞれ50Ωまたは75Ωに簡単にマッチングできます。 LMH2832は汎用ADCを駆動するよう設計されており、 ケーブル上データ・サービス・インターフェイス仕様 (DOCSIS) 3.0の32直交振幅変調(QAM)キャリア、および DOCSIS 3.1の広帯域直交周波数分割多重化(OFDM)シ ステムの両方の要件も満たしています。LMH2832は非常 に優れたNF (6.5dB)と直線性を持ち、DOCSISの仕様内 で動作するよう設計されています。パワーダウン状態での 静止電流はチャネルごとに5mA未満で、動作時の標準消 費電流はチャネルごとに105mAです。

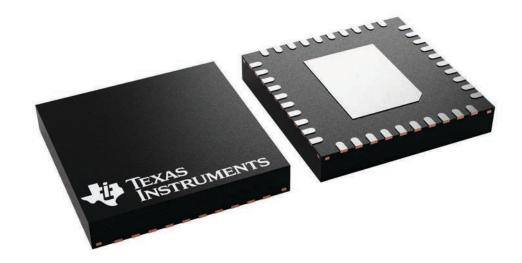

### 製品情報(1)

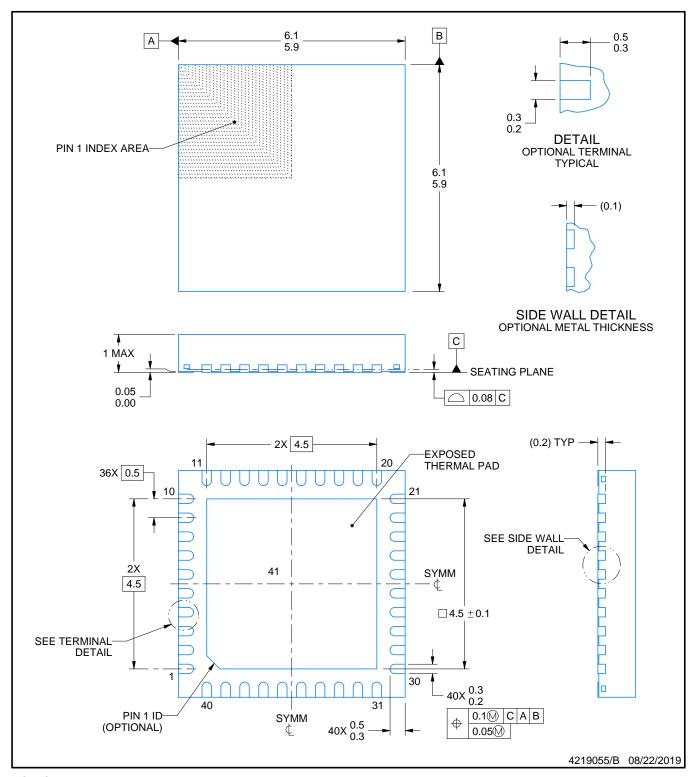

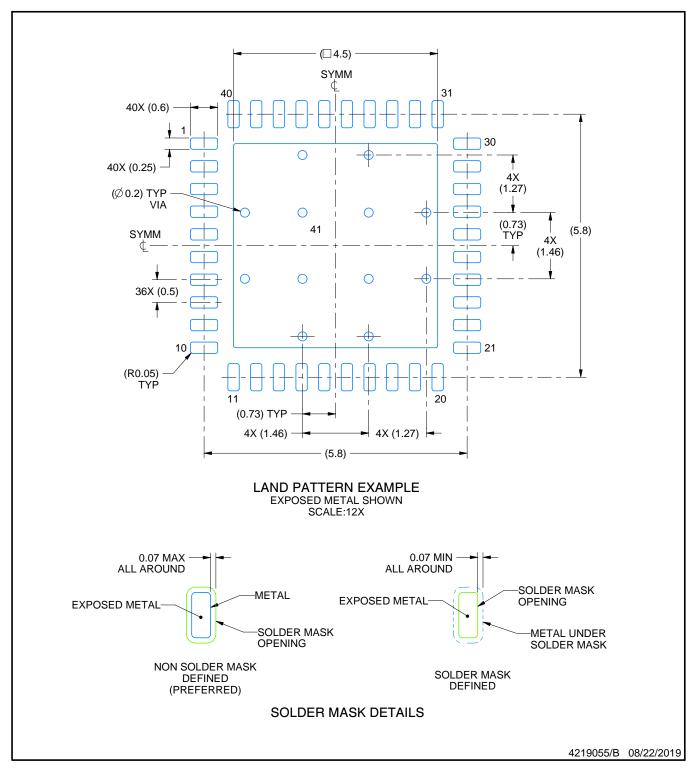

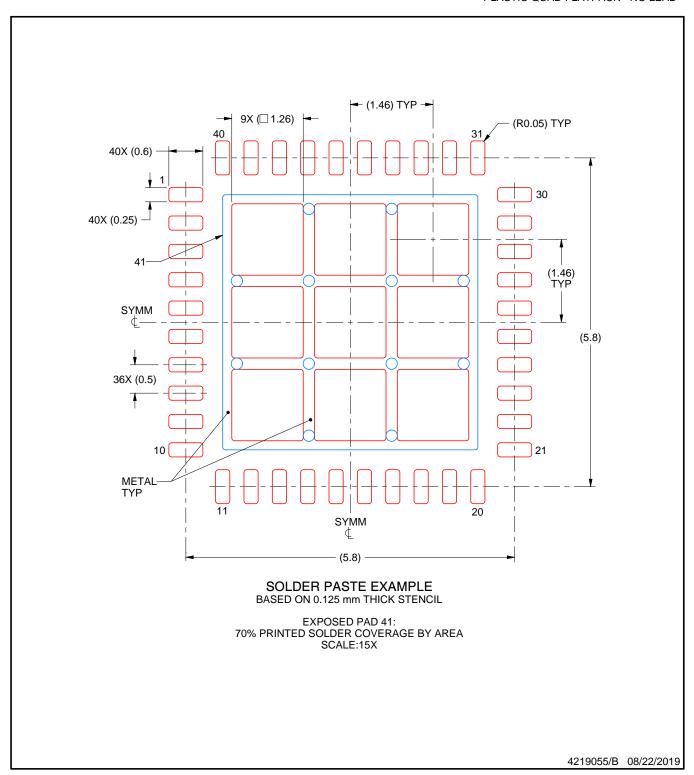

| 型番      | パッケージ     | 本体サイズ(公称)     |

|---------|-----------|---------------|

| LMH2832 | VQFN (40) | 6.00mm×6.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

### 出力の3次インターセプト・ポイント(OIP3)特性

# 目次

| 2        | .4 Thermal Information       5         .5 Electrical Characteristics       6         .6 Timing Requirements: SPI       8         .7 Typical Characteristics       9         arameter Measurement Information       16         .1 Setup Diagrams       16         .2 ATE Testing and DC Measurements       17         .3 Frequency Response       17         .4 Distortion       17         .5 Noise Figure       17         .6 Pulse Response, Slew Rate, and Overdrive Recovery       18         .7 Power-Down       18 |    | 11.1 Split Supplies         11.2 Supply Decoupling         Layout         12.1 Layout Guidelines         12.2 Layout Example         デバイスおよびドキュメントのサポート         13.1 デバイス・サポート         13.2 ドキュメントのサポート         13.3 ドキュメントの更新通知を受け取る方法         13.4 コミュニティ・リソース         13.5 商標         13.6 静電気放電に関する注意事項 | . 19<br>. 19<br>. 21<br>. 24<br>. 29<br>. 35<br>. 35<br>. 35<br>. 36<br>. 36<br>. 37<br>. 37<br>. 37<br>. 37<br>. 37<br>. 37 |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 8.<br>8. | .7 Power-Down                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 14 |                                                                                                                                                                                                                                                                                                             | . 38<br>. 38                                                                                                                 |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 20 | 016年7月発行のものから更新 | Page |  |  |

|----|-----------------|------|--|--|

| •  | 量産にリリース         | 1    |  |  |

# 5 Device Comparison Table

**Table 1. DVGA Device Comparison**

| DEVICE  | MAX GAIN, BW   | DISTORTION                                     | NOISE FIGURE |

|---------|----------------|------------------------------------------------|--------------|

| LMH6401 | 26 dB, 4.5 GHz | 43-dBm OIP3 at 200 MHz, -80-dBc HD3 at 200 MHz | 7.7 dB       |

| LHM6517 | 22 dB, 1.2 GHz | 43-dBm OIP3 at 200 MHz, -74-dBc HD3 at 200 MHz | 5.5 dB       |

| LMH6521 | 26 dB, 1.2 GHz | 49-dBm OIP3 at 200 MHz, -84-dBc HD3 at 200 MHz | 7.3 dB       |

| LMH6881 | 26 dB, 2.4 GHz | 42-dBm OIP3 at 200 MHz, -76-dBc HD3 at 200 MHz | 9.7 dB       |

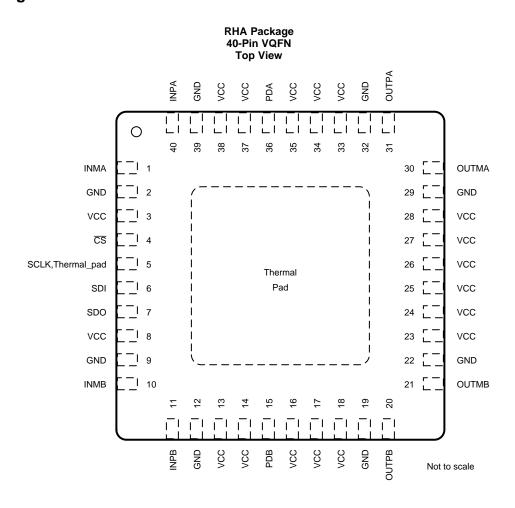

# 6 Pin Configuration and Functions

## **Pin Functions**

|             | PIN                                                                  | 1/0 | DESCRIPTION                                             |  |  |

|-------------|----------------------------------------------------------------------|-----|---------------------------------------------------------|--|--|

| NAME NO.    |                                                                      | 1/0 | DESCRIPTION                                             |  |  |

| CS          | 4                                                                    | 1   | Serial interface enable, active low                     |  |  |

| GND         | 2, 9, 12, 19, 22, 29, 32, 39                                         | 1   | Analog ground                                           |  |  |

| INMA        | 1                                                                    | 1   | Negative differential input, channel A                  |  |  |

| INMB        | 10                                                                   | 1   | Negative differential input, channel B                  |  |  |

| INPA        | 40                                                                   | I   | Positive differential input, channel A                  |  |  |

| INPB        | 11                                                                   | I   | Positive differential input, channel B                  |  |  |

| OUTMA       | 30                                                                   | 0   | Negative differential output, channel A                 |  |  |

| OUTMB       | 21                                                                   | 0   | Negative differential output, channel B                 |  |  |

| OUTPA       | 31                                                                   | 0   | Positive differential output, channel A                 |  |  |

| OUTPB       | 20                                                                   | 0   | Positive differential output, channel B                 |  |  |

| PDB         | 15                                                                   | I   | Power-down control, channel B (logic high = power-down) |  |  |

| PDA         | 36                                                                   | I   | Power-down control, channel A (logic high = power-down) |  |  |

| SCLK        | 5                                                                    | I   | Serial interface clock input                            |  |  |

| SDI         | 6                                                                    | I   | Serial interface data input                             |  |  |

| SDO         | 7                                                                    | 0   | Serial interface data output                            |  |  |

| VCC         | 3, 8, 13, 14, 16, 17, 18, 23, 24, 25, 26, 27, 28, 33, 34, 35, 37, 38 | I   | Analog voltage supply                                   |  |  |

| Thermal pad |                                                                      | _   | Connected to ground                                     |  |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                                |                        | MIN  | MAX | UNIT |

|------------------------------------------------|------------------------|------|-----|------|

| Power supply                                   |                        | -0.5 | 5.5 | V    |

| Input applied to analog inputs                 | INPA, INMA, INPB, INMB | -0.5 | 5.5 | V    |

| Voltage applied to input pins                  | •                      | -0.5 | 5.5 | V    |

| Digital input/output voltage range             |                        | -0.3 | 2   | V    |

| Operating junction temperature, T <sub>J</sub> |                        |      | 125 | °C   |

| Storage temperature, T <sub>stg</sub>          |                        | -40  | 125 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| .,                 |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|    |                                       | MIN  | NOM | MAX  | UNIT |

|----|---------------------------------------|------|-----|------|------|

| Vs | Power-supply voltage                  | 4.75 | 5   | 5.25 | V    |

|    | Specified operating temperature range | -40  |     | 85   | °C   |

### 7.4 Thermal Information

|                        |                                              | LMH2832    |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RHA (VQFN) | UNIT |

|                        |                                              | 40 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 29.5       | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 20.4       | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 6.6        | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.3        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 6.5        | °C/W |

| R <sub>θ</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 2.3        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report (SPRA953).

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 7.5 Electrical Characteristics

|                | PARAMETER                          | TEST CONDITIONS                                                                        | MIN  | TYP        | MAX  | UNIT               | TEST<br>LEVEL <sup>(1)</sup> |

|----------------|------------------------------------|----------------------------------------------------------------------------------------|------|------------|------|--------------------|------------------------------|

| AC PER         | RFORMANCE                          |                                                                                        |      |            |      |                    |                              |

| LSBW           | Large-signal,                      | $G = 30 \text{ dB}, V_O = 2 V_{PP}$                                                    |      | 1140       |      | NAL I-             | С                            |

| L2BW           | -3-dB bandwidth                    | $G = 0 dB$ , $V_O = 2 V_{PP}$                                                          |      | 2350       |      | MHz                | С                            |

| BW             | Bandwidth for 0.1-dB flatness      |                                                                                        |      | 300        |      | MHz                | С                            |

|                |                                    | f = 100 MHz, V <sub>O</sub> = 2 V <sub>PP</sub>                                        |      | -88        |      |                    | С                            |

| LIDO           | Second-order harmonic              | $f = 200 \text{ MHz}, V_O = 2 V_{PP}$                                                  |      | -76        |      | dDa                | С                            |

| HD2            | distortion                         | f = 300 MHz, V <sub>O</sub> = 2 V <sub>PP</sub>                                        |      | -63        |      | dBc                | С                            |

|                |                                    | f = 450 MHz, V <sub>O</sub> = 2 V <sub>PP</sub>                                        |      | -58        |      |                    | С                            |

|                |                                    | f = 100 MHz, V <sub>O</sub> = 2 V <sub>PP</sub>                                        |      | -94        |      |                    | С                            |

| LIDO           | Third-order harmonic               | f = 200 MHz, V <sub>O</sub> = 2 V <sub>PP</sub>                                        |      | -90        |      | JD -               | С                            |

| HD3            | distortion                         | f = 300 MHz, V <sub>O</sub> = 2 V <sub>PP</sub>                                        |      | -81        |      | dBc                | С                            |

|                |                                    | f = 450 MHz, V <sub>O</sub> = 2 V <sub>PP</sub>                                        |      | -75        |      |                    | С                            |

|                | Third-order intermodulation        | f = 100 MHz, tone spacing = 2 MHz,<br>P <sub>OUT</sub> <sup>(2)</sup> = 0 dBm per tone |      | -106       |      |                    | С                            |

| IMD3           | distortion                         | f = 200 MHz, tone spacing = 2 MHz                                                      |      | -102       |      | dBc                | С                            |

|                |                                    | f = 300 MHz, tone spacing = 2 MHz                                                      |      | -86        |      |                    | С                            |

|                |                                    | f = 100 MHz, tone spacing = 2 MHz,<br>P <sub>OUT</sub> = 0 dBm per tone                |      | 53         |      |                    | С                            |

| OIP3           | Output third-order intercept point | f = 200 MHz, tone spacing = 2 MHz,<br>P <sub>OUT</sub> = 0 dBm per tone                |      | 51         |      | dBm                | С                            |

|                |                                    | f = 300 MHz, tone spacing = 2 MHz,<br>P <sub>OUT</sub> = 0 dBm per tone                |      | 43         |      |                    | С                            |

|                |                                    | $f = 100 \text{ MHz}, R_L = 150 \Omega$                                                |      | 16         |      |                    | С                            |

| P1dB           | 1-dB compression point             | f = 200 MHz, R <sub>L</sub> = 150 Ω                                                    |      | 16         |      | dBm                | С                            |

|                |                                    | $f = 300 \text{ MHz}, R_L = 150 \Omega$                                                |      | 16.5       |      |                    | С                            |

| NF             | Noise figure                       | $R_i$ = 150 $\Omega$ , f = 300 MHz, max gain                                           |      | 6.5        |      | dB                 | С                            |

|                | Output-referred voltage noise      | f = 300 MHz, max gain                                                                  |      | 47.7       |      | nV/√ <del>Hz</del> | С                            |

| S11            | Input return loss                  | f = 300 MHz                                                                            |      | 17         |      | dB                 | С                            |

| S22            | Reverse Isolation                  | Including input transformer, f < 300 MHz                                               |      | 53         |      | dB                 | С                            |

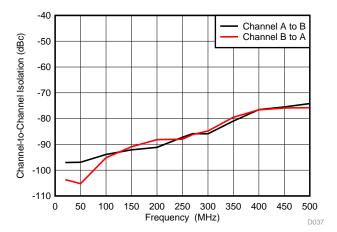

|                | Channel to abound arountally       | f = 300 MHz, channel A to B                                                            |      | <b>-77</b> |      | ٩D                 |                              |

|                | Channel-to-channel crosstalk       | f = 300 MHz, channel B to A                                                            |      | -81        |      | dB                 | С                            |

|                | Channel-to-channel phase matching  | f = 200 MHz                                                                            |      | ±0.1       |      | 0                  | С                            |

|                | Channel-to-channel gain matching   | f = 200 MHz                                                                            |      | ±0.05      |      | dB                 | С                            |

| GAIN P         | ARAMETERS                          |                                                                                        |      |            |      |                    |                              |

|                | Maximum voltage gain               | f = dc, gain code = 00h                                                                | 29.5 | 30         | 30.5 | dB                 | Α                            |

|                | Minimum voltage gain               | f = dc, gain code = 27h                                                                | -9.5 | -9         | -8.5 | dB                 | Α                            |

|                | Gain range                         |                                                                                        |      | 39         |      | dB                 | С                            |

|                | Gain step size                     | Between any two adjacent gain settings                                                 | 0.75 | 1          | 1.25 | dB                 | Α                            |

| E <sub>G</sub> | Gain error                         | For any gain value                                                                     | -0.5 | 0          | 0.5  | dB                 | Α                            |

|                | Cumulative gain error              | Referenced to max gain                                                                 | -1   |            | 1    | dB                 | Α                            |

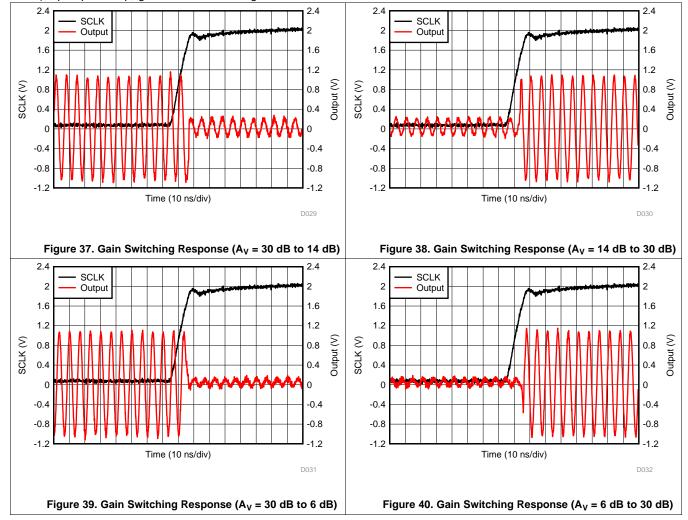

|                | Gain step transition time          |                                                                                        |      | 6          |      | ns                 | С                            |

<sup>(1)</sup> Test levels: (A) 100% tested at 25°C. Overtemperature limits by characterization and simulation. (B) Limits set by characterization and simulation. (C) Typical value only for information.

<sup>(2)</sup> P<sub>OUT</sub> is the signal tone power at the output of the device.

## **Electrical Characteristics (continued)**

|                  | PARAMETER                        | TEST CONDITIONS                                                          | MIN             | TYP                   | MAX  | UNIT | TEST<br>LEVEL <sup>(1)</sup> |

|------------------|----------------------------------|--------------------------------------------------------------------------|-----------------|-----------------------|------|------|------------------------------|

| ANALOG           | INPUT CHARACTERISTICS            |                                                                          |                 |                       | 1    |      |                              |

| z <sub>in</sub>  | Input resistance                 | f = dc, differential                                                     | 135             | 150                   | 165  | Ω    | Α                            |

| C <sub>in</sub>  | Input capacitance                | Differential                                                             |                 | 0.6                   |      | pF   | С                            |

|                  | Single-ended input resistance    | f = dc                                                                   | 67.5            | 75                    | 82.5 | Ω    | Α                            |

|                  | Single-ended input capacitance   |                                                                          |                 | 1.2                   |      | pF   | С                            |

| V <sub>ICM</sub> | Input common-mode voltage        | Internally biased to mid-supply                                          | -0.2            |                       | 0.2  | V    | Α                            |

| $V_{IL}$         | Low-level input voltage range    | Differential gain shift < 1 dB                                           | (V <sub>S</sub> | <sub>3</sub> _) + 1.5 |      | V    | С                            |

| V <sub>IH</sub>  | High-level input voltage range   | Differential gain shift < 1 dB                                           | (V <sub>S</sub> | <sub>S+</sub> ) – 1.5 |      | V    | С                            |

| ANALOG           | OUTPUT CHARACTERISTICS           |                                                                          |                 |                       |      |      |                              |

| Z <sub>O</sub>   | Output resistance                | Differential                                                             |                 | 20                    |      | Ω    | С                            |

| $V_{OL}$         | Low-level output voltage range   | V <sub>S</sub> = 5 V, GND = 0 V                                          |                 | 1.15                  | 1.25 | ٧    | А                            |

| $V_{OH}$         | High-level output voltage range  | V <sub>S</sub> = 5 V, GND = 0 V                                          | 3.75            | 3.85                  |      | V    | А                            |

| V                | Maximum output voltage           | T <sub>A</sub> = 25°C                                                    | 5               | 5.4                   |      | V    | Α                            |

| $V_{OM}$         | swing                            | $T_A = -40$ °C to +85°C                                                  |                 | 5.4                   | 6.4  | V    | В                            |

| CMRR             | Common-mode rejection ratio      |                                                                          |                 | 56                    |      | dB   | С                            |

| POWER            | SUPPLY                           |                                                                          |                 |                       |      |      |                              |

| V <sub>S</sub>   | Supply voltage                   |                                                                          | 4.75            | 5.0                   | 5.25 | V    | Α                            |

|                  |                                  | Default current, default bias setting                                    | 102             | 105                   | 108  |      | Α                            |

| $I_Q$            | Quiescent current per channel    | Min current, lowest power setting                                        |                 | 90                    |      | mA   | С                            |

|                  |                                  | Max current, highest bias setting                                        |                 | 108                   |      |      | С                            |

| ±PSRR            | Power-supply rejection ratio (3) | Gain = 30 dB                                                             |                 | -48                   |      | dB   | С                            |

| POWER-           | -DOWN <sup>(4)</sup>             |                                                                          |                 |                       |      |      |                              |

|                  | Power-down quiescent current     | T <sub>A</sub> = 25°C                                                    |                 | 2.5                   | 6    | Δ    | Α                            |

|                  | (per channel)                    | $T_A = -40$ °C to +85°C                                                  |                 |                       | 6.5  | mA   | В                            |

|                  | Power-down bias current          |                                                                          | -2              | -1                    |      | μΑ   | Α                            |

|                  | Turn-on time delay               | Time to $V_0 = 90\%$ of final value, gain = 0 dB, $V_1 = 2 \text{ V}$    |                 | 55                    |      | ns   | С                            |

|                  | Turn-off time delay              | Time to $V_0 = 10\%$ of original value, gain = 0 dB, $V_1 = 2 \text{ V}$ |                 | 110                   |      | ns   | С                            |

|                  | Forward isolation in PD mode     | f = 300 MHz                                                              |                 | -67                   |      | dB   | С                            |

| DIGITAL          | INPUTS/OUTPUTS                   |                                                                          |                 |                       |      |      |                              |

| V <sub>IH</sub>  | High-level input voltage         |                                                                          | 1.4             |                       | 2    | ٧    | Α                            |

| V <sub>IL</sub>  | Low-level input voltage          |                                                                          | -0.3            |                       | 0.8  | V    | Α                            |

|                  | TP-sh Tarrell and the P          | I <sub>OH</sub> = -100 μA                                                | 1.65            |                       |      |      | Α                            |

| $V_{OH}$         | High-level output voltage        | I <sub>OH</sub> = −2 mA                                                  | 1.55            |                       |      | V    | Α                            |

| .,               | Laurelanda et al                 | I <sub>OL</sub> = 100 μA                                                 |                 |                       | 0.1  |      | Α                            |

| $V_{OL}$         | Low-level output voltage         | I <sub>OL</sub> = 2 mA                                                   |                 |                       | 0.2  | V    | Α                            |

<sup>(3)</sup> PSRR is defined with respect to a differential output.

<sup>(4)</sup> The device power-down function can be controlled by the PDx pins or by the power-down register accessible from the SPI interface.

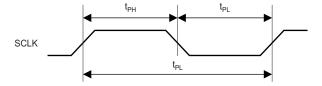

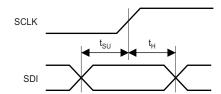

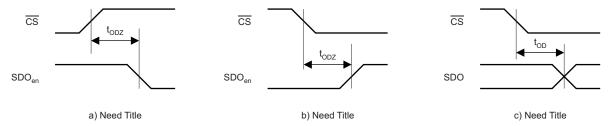

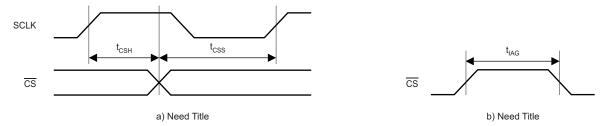

# 7.6 Timing Requirements: SPI

|                  |                                 | MIN | TYP | MAX | UNIT |

|------------------|---------------------------------|-----|-----|-----|------|

| f <sub>S_C</sub> | SCLK frequency <sup>(1)</sup>   | 0   | 25  | 50  | MHz  |

| t <sub>PH</sub>  | SCLK pulse duration, high       |     | 10  |     | ns   |

| t <sub>PL</sub>  | SCLK pulse duration, low        |     | 10  |     | ns   |

| t <sub>SU</sub>  | SDI setup                       |     | 3   |     | ns   |

| t <sub>H</sub>   | SDO hold                        |     | 3   |     | ns   |

| $t_{IZ}$         | SDO tri-state                   |     | 3   |     | ns   |

| t <sub>ODZ</sub> | SDO driven to tri-state (2)     | 0   | 10  | 20  | ns   |

| t <sub>OZD</sub> | SDO tri-state to driven         | 0   | 2   | 5   | ns   |

| t <sub>OD</sub>  | SDO output delay <sup>(2)</sup> | 0   | 10  | 12  | ns   |

| t <sub>CSS</sub> | CS setup <sup>(3)</sup>         | 3   | 5   |     | ns   |

| t <sub>CSH</sub> | CS hold                         |     | 3   |     | ns   |

| t <sub>IAG</sub> | Inter-access gap                |     | 20  |     | ns   |

Tested on the automated test equipment (ATE) only up to 25 MHz.

Referenced to the negative edge of SCLK.

Referenced to the positive edge of SCLK.

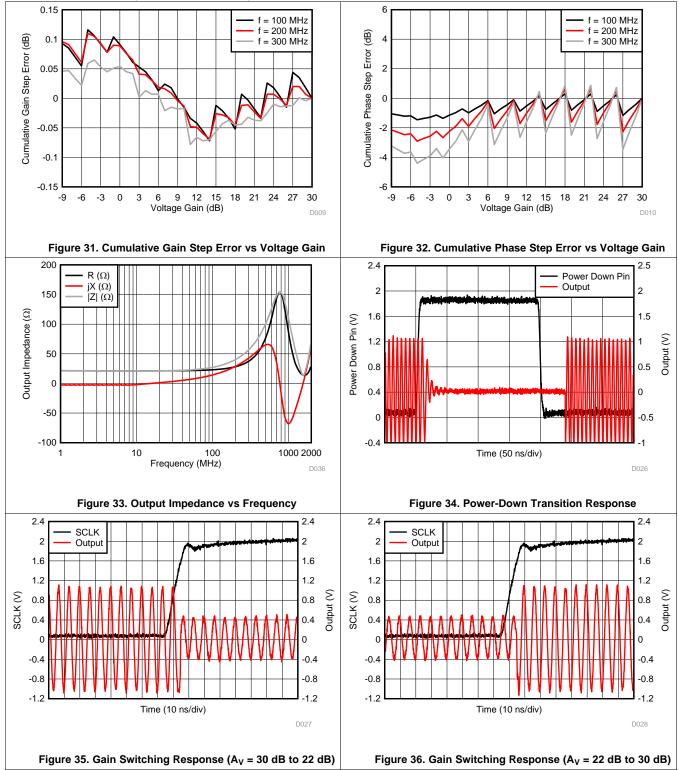

## 7.7 Typical Characteristics

### 8 Parameter Measurement Information

### 8.1 Setup Diagrams

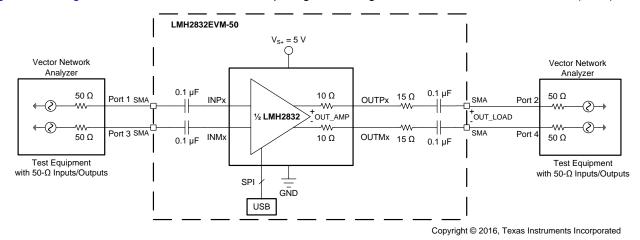

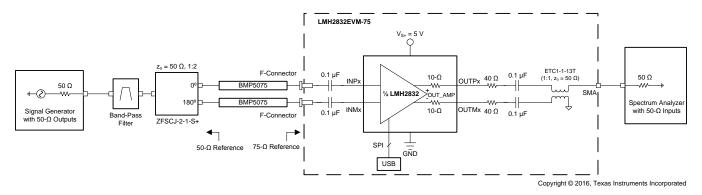

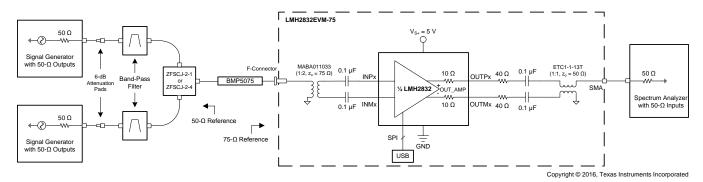

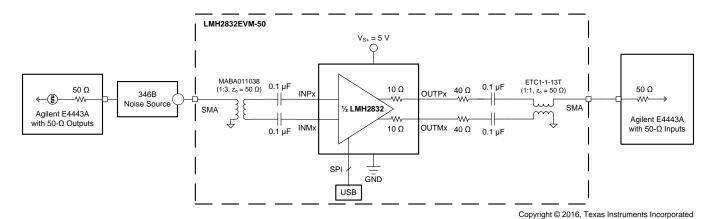

Figure 41 to Figure 44 illustrate various test setup diagrams using the LMH2832 evaluation module (EVM).

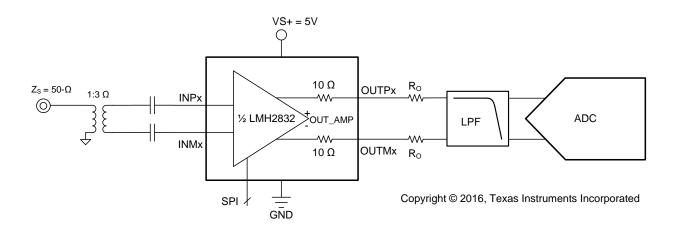

Figure 41. Frequency Response Differential Test Setup

Figure 42. Single-Tone Harmonic Distortion Test Setup

Figure 43. Two-Tone Linearity Test Setup (OIP3, OIP2)

### **Setup Diagrams (continued)**

Figure 44. Noise Figure Test Setup

### 8.2 ATE Testing and DC Measurements

All production testing and dc parameters are measured on automated test equipment (ATE) capable of dc measurements only. Some measurements (such as voltage gain) are referenced to the output of the internal amplifier and do not include losses attributed to the on-chip output resistors. The *Electrical Characteristics* values specify these conditions. When the measurement is referred to the amplifier output, the output resistors are not included in the measurement. If the measurement is referred to the device pins, then the output resistor loss is included in the measurement.

### 8.3 Frequency Response

This test is done by running an S-parameter sweep on a 4-port differential network analyzer using the standard EVM with no baluns; see Figure 41. The inputs and outputs of the EVM are connected to the network analyzer using 75- $\Omega$  coaxial cables with the input ports set to a characteristic impedance of 75  $\Omega$ , and the output ports set to a characteristic impedance of 50  $\Omega$ .

The frequency response test with capacitive load is done by soldering the capacitor across the LMH2832 output pins. In this configuration, the on-chip,  $10-\Omega$  resistors on each output leg isolate the capacitive load from the amplifier output pins.

#### 8.4 Distortion

The standard EVM is used for measuring both the single-tone harmonic distortion and two-tone intermodulation distortion; see Figure 42 and Figure 43, respectively. The distortion is measured with differential input signals to the LMH2832. In order to interface with  $50-\Omega$ , single-ended test equipment,  $50-\Omega$  to  $75-\Omega$  impedance matching pads followed by external baluns (1:2,  $z_0 = 75~\Omega$ ) are required between the EVM output ports and the test equipment. These baluns are used to combine two single tones in the two-tone test plots as well as to convert the single-ended input to differential output for harmonic distortion tests. The use of 6-dB attenuator pads on both the inputs and outputs is recommended to provide a balanced match between the external balun and the EVM.

#### 8.5 Noise Figure

This test is done by matching the input of the LMH2832 to a 50- $\Omega$  noise source using a 50- $\Omega$  to 75- $\Omega$  impedance transformation pad followed by a 1:2 balun (Figure 44), with the noise figure being referred to the input impedance (R<sub>S</sub> = 150  $\Omega$ ). As noted in Figure 44, a Keysight Technologies<sup>TM</sup> E4443A with NF features is used for the testing.

### 8.6 Pulse Response, Slew Rate, and Overdrive Recovery

For time-domain measurements, the standard EVM is driven through an impedance transformation pad and a balun again to convert a single-ended output from the test equipment to the differential inputs of the LMH2832. The differential outputs are directly connected to the oscilloscope inputs, with the differential signal response calculated using trace math from the two separate oscilloscope inputs.

#### 8.7 Power-Down

The standard EVM is used for this test by completely removing the shorting block on jumper JPD. A high-speed,  $50-\Omega$  pulse generator is used to drive the PDx pin that toggles the output signal on or off depending upon the PDx pin voltage.

#### 8.8 Crosstalk, Gain Matching, and Phase Matching

The standard EVM is used for these tests with both channels enabled. For gain and phase matching, the responses of both channels are measured on a network analyzer and the gain and phase values are compared. For crosstalk, a single channel is driven with a signal on the network analyzer when the other channel is measured.

## 8.9 Output Measurement Reference Points

The LMH2832 has two on-chip,  $10-\Omega$  output resistors on each channel. When matching the output to a  $100-\Omega$  load, the evaluation module (EVM) uses an external  $40-\Omega$  resistor on each output leg to complete the output matching. The inclusion of on-chip output resistors creates two potential reference points for measuring the output voltage. The first reference point is at the internal amplifier output (OUT\_AMP), and the second reference point is at the externally-matched  $100-\Omega$  load (OUT\_LOAD). The measurements in the *Electrical Characteristics* table and in the *Typical Characteristics* section are referred to the (OUT\_AMP) reference point unless otherwise specified. The conversion between reference points is a straightforward correction of 3 dB for power and 6 dB for voltage, as shown in Equation 1 and Equation 2. The measurements are referenced to OUT\_AMP when not specified.

$$VOUT_LOAD = (VOUT_AMP - 6 dB)$$

(1)

$$POUT_LOAD = (POUT_AMP - 3 dB)$$

(2)

## 9 Detailed Description

#### 9.1 Overview

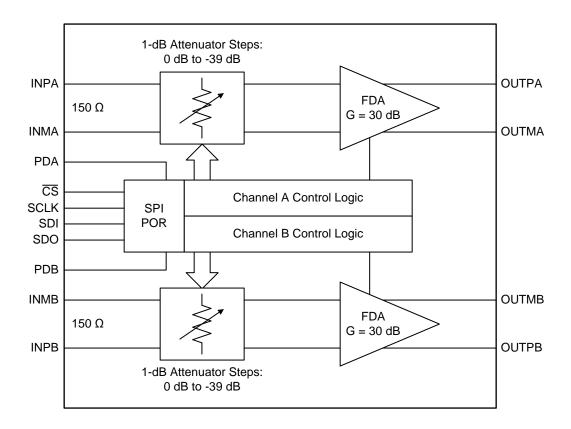

Each channel of the LMH2832 consists of an input attenuator block followed by a fully differential amplifier that has a gain of 30 dB. The attenuator has a range of 0 dB to -39 dB in 1-dB steps that is controlled by an SPI interface. The two channels can be controlled independently using the digital interface including power-down and bias settings. A separate analog power-down pin (PDA, PDB) is also included for each channel so that the device can bet set to a low-power state without waiting for a serial write to a register. The internal registers also include a power-on-reset (POR) that ensures the device starts in a known state after the power is reset.

## 9.2 Functional Block Diagram

#### 9.3 Feature Description

### 9.3.1 Analog Input Characteristics

The LMH2832 is a dual-channel device with two identical channels (A and B) that each have differential input pins (INP and INM) that denote the positive and negative inputs, respectively. The inputs are expected to be accoupled only, typically through a transformer or capacitor. The amplifier self-biases the input common-mode to mid-supply for the maximum input voltage range. The inputs of the LMH2832 can only be driven differentially. For single-ended input source applications, use a balun or fully differential amplifier (such as the LMH3401 or LMH5401) that can convert single-ended to differential signals before the LMH2832.

### **Feature Description (continued)**

At maximum gain, the digital attenuator is set to 0 dB of attenuation, causing the input signal to be much larger than the output signal and forcing the maximum output voltage swing to be limited by the outputs of the device. However at minimum gain, the maximum voltage swing is limited by the inputs of the device because the attenuator causes the output voltage to be 9 dB lower than the input voltage. In minimum gain, the input voltage limits against the electrostatic discharge (ESD) devices before the output reaches the maximum swing limits. For linear operation, the input voltage must be kept within the maximum input voltage ratings described in the *Electrical Characteristics* table.

The input impedance of the LMH2832 is set by internal termination resistors to a nominal value of 150  $\Omega$ , differential. Process variations result in a range of values, as described in the *Electrical Characteristics* table. The input impedance is also affected by device parasitic effects at higher frequencies that cause the impedance to shift away from the nominal value.

#### 9.3.2 Analog Output Characteristics

The LMH2832 has series,  $10-\Omega$ , on-chip resistors on each output to provide isolation from board parasitics that can cause instability. When designing a filter following the LMH2832, the filter source impedance calculation must include the two  $10-\Omega$ , on-chip resistors. Table 2 shows the calculated external source impedance values required for various matched filter loads.

**Table 2. Output Resistor Values for Matched Loads**

| MATCHED FILTER IMPEDANCE ( $\Omega$ ) | EXTERNAL SERIES RESISTOR PER OUTPUT $(\Omega)$ |  |  |  |  |

|---------------------------------------|------------------------------------------------|--|--|--|--|

| 100                                   | 80                                             |  |  |  |  |

| 150                                   | 130                                            |  |  |  |  |

| 200                                   | 180                                            |  |  |  |  |

| 300                                   | 280                                            |  |  |  |  |

#### 9.3.3 Driving Low Insertion-Loss Filters

When driving high-speed ADCs, a filter is commonly driven with a matched impedance to the ADC. This impedance is matched by the amplifier by setting the combination of the output resistors to the same impedance as the ADC inputs. Impedance matching is often done to minimize any transmission reflections caused by the physical signal path. The drawback to using a matched impedance is that a voltage swing is required from the amplifier outputs that is twice the desired ADC input voltage swing, which can cause output voltage limitation issues.

To avoid using a matched impedance, a low insertion loss filter can be driven where there is little to no resistance added at the amplifier outputs. The amplifier outputs then only must swing to the value of the ADC full-scale input voltage, thus eliminating most of the potential amplifier output headroom issues. The requirements of this technique are that the amplifier must be able to provide enough current to the load of the ADC and that the path between the amplifier outputs and ADC inputs must be minimized to prevent any reflections.

#### 9.3.4 Input Impedance Matching

The LMH2832 has a differential input impedance of 150  $\Omega$  that can be easily matched to single-ended, 50- $\Omega$  or 75- $\Omega$  systems using baluns. For a single-ended, 50- $\Omega$  input, a 1:3- $\Omega$  ratio balun can be used to create a 150- $\Omega$  differential source impedance to the device with a balun gain of 4.8 dB. For a single-ended, 75- $\Omega$  input, a 1:2- $\Omega$  ratio balun creates a 150- $\Omega$  differential source impedance to the device with a voltage gain of 3 dB.

#### 9.3.5 Power-On Reset (POR)

The LMH2832 has a built-in, power-on-reset (POR) that sets the device registers to their default state (see the *Register Maps* section) on power-up. Note that the LMH2832 register information is lost when power is removed. When power is reapplied, the POR ensures that the device enters a default state. Power glitches (of sufficient duration) can also initiate the POR and return the device to a default state.

#### 9.4 Device Functional Modes

### 9.4.1 Power-Down (PD)

The device supports power-down control using an external power-down (PDx) pin or by writing a logic high to bit 6 of SPI register 2h (see the *Register Maps* section). The external PDx pins are active high; when left floating, the device defaults to an on condition resulting from the internal pulldown resistors that cause a logic low on the PDx pins. The device PDx thresholds are noted in the *Electrical Characteristics* table. The device consumes approximately 7 mA in power-down mode. Note that the SPI register contents are preserved in power-down mode.

#### 9.4.2 Gain Control

The LMH2832 gain can be controlled from 30-dB gain (0-dB attenuation) to –9-dB gain in 1-dB steps by digitally programming the SPI register 2h; see the *Register Maps* section for more details.

#### 9.5 Programming

#### 9.5.1 Details of the Serial Interface

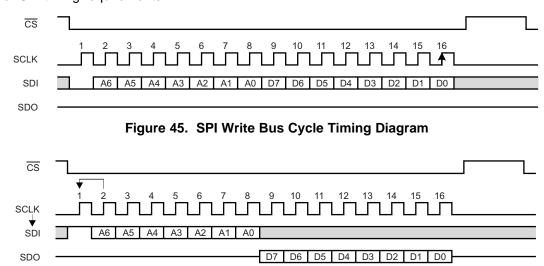

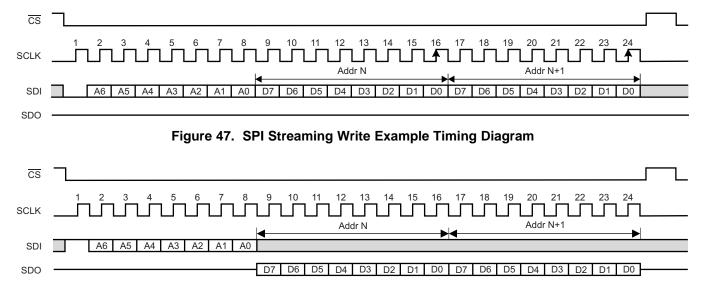

The LMH2832 has a set of internal registers that can be accessed by the serial interface formed by the  $\overline{\text{CS}}$  (serial interface enable), SCLK (serial interface clock), SDI (serial interface input data), and SDO (serial interface read-back data) pins. Serially shifting bits into the device is enabled when  $\overline{\text{CS}}$  is low. SDI serial data are latched at every SCLK rising edge when  $\overline{\text{CS}}$  is active (low). The serial data are loaded into the register at every 16th SCLK rising edge when  $\overline{\text{CS}}$  is low. When the word length exceeds a multiple of 16 bits, the excess bits are ignored. Data can be loaded in multiples of 16-bit words within a single active  $\overline{\text{CS}}$  pulse. The first eight bits form the register address and the remaining eight bits are the register data. The interface can function with SCLK frequencies from 25 MHz down to very low speeds (of a few hertz) and also with a non-50% SCLK duty cycle. A summary of the LMH2832 SPI protocol is:

- 1. SPI-1.1 interface

- 2. Independent channel A, B attenuation programming (6-bit gain control)

- 3. SPI register contents are preserved in power-down mode

- 4. SPI-controlled power modes (3-bit control for eight options to step down the power)

- 5. Powered for the main 5-V power supply

- 6. 1.8-V logic

### **Programming (continued)**

#### 9.5.2 Timing Diagrams

Figure 45 and Figure 46 show timing diagrams for the SPI write and read bus cycles, respectively. Figure 47 shows an example timing diagram for a streaming write cycle and Figure 48 shows an example timing diagram for a streaming read cycle. Figure 49, Figure 50, Figure 51, and Figure 52 illustrate timing diagrams and requirements for the clock, data input, data output, and chip select, respectively. See the *Timing Requirements: SPI* table for SPI timing requirements.

Figure 46. SPI Read Bus Cycle Timing Diagram

Figure 48. SPI Streaming Read Example Timing Diagram

Figure 49. SPI Clock Timing Diagram

# **Programming (continued)**

Figure 50. SPI Data Input Timing Diagram

Figure 51. SPI Data Output Timing Diagrams

Figure 52. SPI Chip Select Timing Diagrams

www.ti.com

# 9.6 Register Maps

Table 3 shows the SPI registers for the LMH2832.

# Table 3. SPI Register Map

| ADDRESS  |     | DEFAULT |                                   |                           |   |   | REGISTI | ER DATA |   |   |   |

|----------|-----|---------|-----------------------------------|---------------------------|---|---|---------|---------|---|---|---|

| (A[6:0]) | R/W | (Hex)   | REGISTER NAME                     | 7                         | 6 | 5 | 4       | 3       | 2 | 1 | 0 |

| 0        | R   | В3      | Revision ID                       | 1                         | 0 | 1 | 1       | 0       | 0 | 1 | 1 |

| 1        | R   | 23      | Product ID                        | 0                         | 0 | 1 | 0       | 0       | 0 | 1 | 1 |

| 2        | R/W | 00      | SW reset                          | Reserved Reset B Reserved |   |   | Reset A |         |   |   |   |

| 3        | R/W | 00      | Power-down                        | Reserved PD B Reserved    |   |   |         | PD A    |   |   |   |

| 4        | R/W | 20      | Channel A RW0, bias control       |                           |   |   | Channe  | I A RW0 |   |   | · |

| 5        | R/W | 14      | Channel A RW1, attenuator control |                           |   |   | Channe  | I A RW1 |   |   |   |

| 6        | R/W | 20      | Channel B RW0, bias control       | Channel B RW0             |   |   |         |         |   |   |   |

| 7        | R/W | 14      | Channel B RW1, attenuator control | Channel B RW1             |   |   |         |         |   |   |   |

| 8-127    | R   | 00      | Reserved                          | 0                         | 0 | 0 | 0       | 0       | 0 | 0 | 0 |

### 9.6.1 Register Descriptions

Exercising the SW reset function returns all registers to the default values of the respective channel.

## 9.6.1.1 SW Reset Register (address = 2)

Figure 53. SW Reset Register

| 7 | 6        | 5 | 4       | 3 | 2        | 1 | 0       |

|---|----------|---|---------|---|----------|---|---------|

|   | Reserved |   | Reset B |   | Reserved |   | Reset A |

|   | R-0h     |   | R/W-0h  |   | R-0h     |   | R/W-0h  |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## **Table 4. SW Reset Register Field Descriptions**

| Bit | Field    | Туре   | Reset | Description                                              |  |  |

|-----|----------|--------|-------|----------------------------------------------------------|--|--|

| 7-5 | Reserved | R      | 0h    | Reserved.                                                |  |  |

| 4   | Reset B  |        |       | s bit is a self-clearing bit.<br>No action<br>Reset      |  |  |

| 3-1 | Reserved | R      | 0h    | Reserved.                                                |  |  |

| 0   | Reset A  | R/W 0h |       | This bit is a self-clearing bit. 0 = No action 1 = Reset |  |  |

## 9.6.2 Power-Down Control Register (address = 3)

## Figure 54. Power-Down Control Register

| 7 | 6        | 5 | 4      | 3 | 2        | 1 | 0      |

|---|----------|---|--------|---|----------|---|--------|

|   | Reserved |   | PD B   |   | Reserved |   | PD A   |

|   | R-∩h     |   | R/W-0h |   | R-0h     |   | R/W-0h |

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

#### **Table 5. Power-Down Control Register Field Descriptions**

| Bit | Field    | Туре | Reset | Description          |

|-----|----------|------|-------|----------------------|

| 7-5 | Reserved | R    | 0h    | Reserved.            |

| 4   | PD B     | R/W  | 0h    | 0 = Active<br>1 = PD |

| 3-1 | Reserved | R    | 0h    | Reserved.            |

| 0   | PD A     | R/W  | 0h    | 0 = Active<br>1 = PD |

## 9.6.3 Channel A RW0 Register (address = 4)

#### Figure 55. Channel A RW0 Register

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 6. Channel A RW0 Register Field Descriptions

| Bit | Field         | Type Reset |  | Description                                                                                                                     |  |  |

|-----|---------------|------------|--|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7-0 | Channel A RW0 | R/W        |  | These bits drive the output CHA_RW0[7:0] and are reset by a device reset or Reset A. Table 10 lists controls for this register. |  |  |

## 9.6.4 Channel A RW1 Register (address = 5)

#### Figure 56. Channel A RW1 Register

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 7. Channel A RW1 Register Field Descriptions

| Bit | Field         | Туре | Reset | Description                                                                                                                     |

|-----|---------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | Channel A RW1 | R/W  | 0h    | These bits drive the output CHA_RW1[7:0] and are reset by a device reset or Reset A. Table 11 lists controls for this register. |

## 9.6.5 Channel B RW0 Register (address = 6)

## Figure 57. Channel B RW0 Register

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 8. Channel B RW0 Register Field Descriptions

| Bit | Field Type Reset |     |    | Description                                                                                                                     |  |  |

|-----|------------------|-----|----|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7-0 | Channel B RW0    | R/W | 0h | These bits drive the output CHB_RW0[7:0] and are reset by a device reset or Reset B. Table 10 lists controls for this register. |  |  |

## 9.6.6 Channel B RW1 Register (address = 7)

## Figure 58. Channel B RW1 Register

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

## Table 9. Channel B RW1 Register Field Descriptions

| Bit | Field         | Туре | Reset | Description                                                                                                                     |

|-----|---------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | Channel B RW1 | R/W  | 0h    | These bits drive the output CHB_RW1[7:0] and are reset by a device reset or Reset B. Table 11 lists controls for this register. |

# Table 10. Bias Control Register Bit Settings (Channels A, B)<sup>(1)</sup>

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | X |

| 0 | 0 | 0 | 0 | 0 | 1 | X | X |

| 0 | 0 | 0 | 0 | 1 | X | X | X |

| 0 | 0 | 0 | 1 | X | X | X | X |

| 0 | 0 | 1 | X | X | X | X | X |

| 0 | 1 | X | X | X | X | X | X |

| 1 | X | X | X | X | X | X | X |

<sup>(1)</sup> Default value: 001xxxxx. Highest power: 1xxxxxxx. Lower power: 00000000.

# Table 11. Attenuator Control Register Bit Settings (Channels A, B)<sup>(1)</sup>

|               | Iubic       | i i. Atteriuator | lator Control Register Bit Settings (Channels A, B) |   |   |   |   |  |  |  |  |

|---------------|-------------|------------------|-----------------------------------------------------|---|---|---|---|--|--|--|--|

| 7             | 6           | 5                | 4                                                   | 3 | 2 | 1 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 0                                                   | 0 | 0 | 0 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 0                                                   | 0 | 0 | 0 | 1 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 0                                                   | 0 | 0 | 1 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 0                                                   | 0 | 0 | 1 | 1 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 0                                                   | 0 | 1 | 0 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 0                                                   | 0 | 1 | 0 | 1 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 0                                                   | 0 | 1 | 1 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 0                                                   | 0 | 1 | 1 | 1 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 0                                                   | 1 | 0 | 0 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 0                                                   | 1 | 0 | 0 | 1 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 0                                                   | 1 | 0 | 1 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 0                                                   | 1 | 0 | 1 | 1 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 0                                                   | 1 | 1 | 0 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 0                                                   | 1 | 1 | 0 | 1 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 0                                                   | 1 | 1 | 1 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 0                                                   | 1 | 1 | 1 | 1 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 1                                                   | 0 | 0 | 0 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 1                                                   | 0 | 0 | 0 | 1 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 1                                                   | 0 | 0 | 1 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 1                                                   | 0 | 0 | 1 | 1 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 1                                                   | 0 | 1 | 0 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 1                                                   | 0 | 1 | 0 | 1 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 1                                                   | 0 | 1 | 1 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 1                                                   | 0 | 1 | 1 | 1 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 1                                                   | 1 | 0 | 0 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 1                                                   | 1 | 0 | 0 | 1 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 1                                                   | 1 | 0 | 1 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 1                                                   | 1 | 0 | 1 | 1 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 1                                                   | 1 | 1 | 0 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 1                                                   | 1 | 1 | 0 | 1 |  |  |  |  |

| Reserved, alw | vays read 0 | 0                | 1                                                   | 1 | 1 | 1 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 0                | 1                                                   | 1 | 1 | 1 | 1 |  |  |  |  |

| Reserved, alv | vays read 0 | 1                | 0                                                   | 0 | 0 | 0 | 0 |  |  |  |  |

| Reserved, alw | vays read 0 | 1                | 0                                                   | 0 | 0 | 0 | 1 |  |  |  |  |

| Reserved, alv | vays read 0 | 1                | 0                                                   | 0 | 0 | 1 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 1                | 0                                                   | 0 | 0 | 1 | 1 |  |  |  |  |

| Reserved, alv | vays read 0 | 1                | 0                                                   | 0 | 1 | 0 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 1                | 0                                                   | 0 | 1 | 0 | 1 |  |  |  |  |

| Reserved, alv | vays read 0 | 1                | 0                                                   | 0 | 1 | 1 | 0 |  |  |  |  |

| Reserved, alv | vays read 0 | 1                | 0                                                   | 0 | 1 | 1 | 1 |  |  |  |  |

<sup>(1)</sup> Default attenuation setting: xx001011. Maximum attenuation (lowest gain setting): xx100111. Minimum attenuation (highest gain setting): xx000000.

## 10 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 10.1 Application Information

The LMH2832 is designed as a general-purpose, analog-to-digital converter (ADC) driver that also meets the performance requirements for DOCSIS 3.X upstream CMTS solutions. This section describes various requirements and considerations for using the LMH2832 and also some design examples.

#### 10.1.1 Driving ADCs

When the amplifier is driving an ADC, the key points to consider for implementation are the signal-to-noise ratio (SNR), spurious-free dynamic range (SFDR), and ADC input considerations, as described in this section.

A typical application of the LMH2832 involves driving a wideband, 14-bit ADC (such as the ADS54J40), as shown in Figure 59. The LMH2832 can drive the full Nyquist bandwidth of ADCs with sampling rates up to 900 MSPS. If the front-end bandwidth of the ADC is more than 450 MHz, then use a simple noise filter to improve SNR. Otherwise, the ADC can be connected directly to the amplifier output pins with appropriate matching resistors to limit the full-scale input of the ADC. Note that the LMH2832 inputs must be driven differentially using a balun or fully differential amplifiers (FDAs). For dc-coupled applications, an FDA (such as the LMH3401 or LMH5401) that can convert a single-ended input to a differential output with low distortion is preferred.

Figure 59. ADC Driver with a 50- $\Omega$  Source

(3)

## **Application Information (continued)**

#### 10.1.1.1 SNR Considerations

When using the LMH2832 with a filter, the signal-to-noise ratio (SNR) of the amplifier and filter can be calculated from the amplitude of the signal and the bandwidth of the filter. The noise from the amplifier is band-limited by the filter with the equivalent brick-wall filter bandwidth. The amplifier and filter noise can be calculated using Equation 3:

$$SNR_{AMP+FILTER} = 10 \cdot log \left( \frac{V_O^2}{e_{FILTEROUT}^2} \right) = 20 \cdot log \left( \frac{V_O}{e_{FILTEROUT}} \right)$$

where:

- $e_{FILTEROUT} = e_{NAMPOUT} \sqrt{ENB}$

- $e_{NAMPOUT}$  = the output noise density of the LMH2832 (50.4 nV/ $\sqrt{Hz}$ ) at A<sub>V</sub> = 30 dB

- ENB = the brick-wall equivalent noise bandwidth of the filter

- V<sub>O</sub> = the amplifier output signal

For example, with a first-order (N = 1) band-pass or low-pass filter with a 1000-MHz cutoff, ENB is 1.57 • f<sub>-3dB</sub> = 1.57 • 1000 MHz = 1570 MHz. For second-order (N = 2) filters, ENB is 1.22 • f<sub>-3dB</sub>. When the filter order increases, ENB approaches f<sub>-3dB</sub> (N = 3  $\rightarrow$  ENB = 1.15 • f<sub>-3dB</sub>; N = 4  $\rightarrow$  ENB = 1.13 • f<sub>-3dB</sub>). Both V<sub>O</sub> and e<sub>FILTEROUT</sub> are in RMS voltages. For example, with a 2-V<sub>PP</sub> (0.707 V<sub>RMS</sub>) output signal and a 300-MHz, first-order, low-pass filter, the SNR of the amplifier and filter is 56 dB with e<sub>FILTEROUT</sub> = 50.4 nV/ $\sqrt{\text{Hz}}$  •  $\sqrt{471}$  MHz = 1.09 mV<sub>RMS</sub>.

The SNR of the amplifier, filter, and ADC sum in RMS fashion, as shown in Equation 4 (SNR values in dB):

$$SNR_{SYSTEM} = -20 \cdot log \left( \sqrt{10^{\frac{-SNR_{AMP,FILTER}}{10}} + 10^{\frac{-SNR_{ADC}}{10}}} \right)$$

(4)

This formula shows that if the SNR of the amplifier and filter equals the SNR of the ADC, then the combined SNR is 3 dB lower (worse). Thus, for minimal degradation (< 1 dB) on the ADC SNR, the SNR of the amplifier and filter must be 10 dB greater than the ADC SNR. The combined SNR calculated in this manner is usually accurate to within ±1 dB of the actual implementation.

#### 10.1.1.2 SFDR Considerations

The SFDR of the amplifier is usually set by the second- or third-order harmonic distortion for single-tone inputs, and by the second-order or third-order intermodulation distortion for two-tone inputs. Harmonics and second-order intermodulation distortion can be filtered to some degree, but third-order intermodulation spurs cannot be filtered. The ADC generates the same distortion products as the amplifier, but also generates additional spurs (not harmonically related to the input signal) as a result of sampling and clock feed through.

When the spurs from the amplifier and filter are known, each individual spur can be directly added to the same spur from the ADC, as shown in Equation 5, to estimate the combined spur (spur amplitudes in dBc):

$$HDx_{SYSTEM} = -20 \cdot log \left[ 10^{\frac{-HDx_{AMP-PILTER}}{20}} + 10^{\frac{-HDx_{ADC}}{20}} \right]$$

(5)

This calculation assumes that the spurs are in phase, but usually provides a good estimate of the final combined distortion.

For example, if the spur of the amplifier and filter equals the spur of the ADC, then the combined spur is 6 dB higher. To minimize the amplifier contribution (< 1 dB) to the overall system distortion, the spur from the amplifier and filter must be approximately 15 dB lower in amplitude than that of the converter. The combined spur calculated in this manner is usually accurate to within ±6 dB of the actual implementation; however, higher variations can be detected as a result of phase shift in the filter, especially in second-order harmonic performance.

### **Application Information (continued)**

This worst-case spur calculation assumes that the amplifier and filter spur of interest is in phase with the corresponding spur in the ADC, such that the two spur amplitudes can be added linearly. There are two phase-shift mechanisms that cause the measured distortion performance of the amplifier-ADC chain to deviate from the expected performance calculated using Equation 5; one mechanism is the common-mode phase shift and the other is the differential phase shift.

Common-mode phase shift is the phase shift detected equally in both branches of the differential signal path including the filter. Common-mode phase shift nullifies the basic assumption that the amplifier, filter, and ADC spur sources are in phase. This phase shift can lead to better performance than predicted when the spurs become phase shifted, and there is the potential for cancellation when the phase shift reaches 180°. However, there is a significant challenge in designing an amplifier-ADC interface circuit to take advantage of a common-mode phase shift for cancellation: the phase characteristics of the ADC spur sources are unknown, thus the necessary phase shift in the filter and signal path for cancellation is also unknown.

Differential phase shift is the difference in the phase response between the two branches of the differential filter signal path. Differential phase shift in the filter is a result of mismatched components caused by nominal tolerances and can severely degrade the even harmonic distortion of the amplifier-ADC chain. This effect has the same result as mismatched path lengths for the two differential traces, and causes more phase shift in one path than the other. Ideally, the phase responses over frequency through the two sides of a differential signal path are identical, such that even harmonics remain optimally out of phase and cancel when the signal is taken differentially. However, if one side has more phase shift than the other, then the even harmonic cancellation is not as effective.

Single-order, resistor-capacitor (RC) filters cause very little differential phase shift with nominal tolerances of 5% or less, but higher-order, inductor-capacitor (LC) filters are very sensitive to component mismatch. For instance, a third-order Butterworth band-pass filter with a 100-MHz center frequency and a 20-MHz bandwidth displays as much as 20° of differential phase imbalance in a SPICE Monte Carlo analysis with 2% component tolerances. Therefore, although a prototype may work, production variance is unacceptable. For ac-coupled or dc-coupled applications where a transformer or balun cannot be used, using first- or second-order filters is recommended to minimize the effect of differential phase shift.

#### 10.1.1.3 ADC Input Common-Mode Voltage Considerations (AC-Coupled Input)

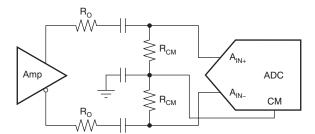

When interfacing to an ADC, the input common-mode voltage range of the ADC must be taken into account for proper operation. In an ac-coupled application between the amplifier and the ADC, the input common-mode voltage bias of the ADC can be accomplished in different ways. Some ADCs use internal bias networks such that the analog inputs are automatically biased to the required input common-mode voltage if the inputs are accoupled with capacitors (or if the filter between the amplifier and ADC is a band-pass filter). Other ADCs supply the required input common-mode voltage from a reference voltage output pin (often termed CM or  $V_{CM}$ ). With these ADCs, the ac-coupled input signal can be re-biased to the input common-mode voltage by connecting resistors from each input to the CM output of the ADC, as shown in Figure 60. AC coupling provides dc common-mode isolation between the amplifier and the ADC; thus, the output common-mode voltage of the amplifier is a don't care for the ADC.

Figure 60. Biasing AC-Coupled ADC Inputs Using the ADC CM Output

### **Application Information (continued)**

#### 10.1.1.4 ADC Input Common-Mode Voltage Considerations (DC-Coupled Input)

The LMH2832 is designed to primarily be used in ac-coupled applications only. However, the LMH2832 can be dc-coupled if certain strict conditions are met. The LMH2832 has an internal common-mode bias equal to the mid-supply voltage, so any dc coupling on the input or output must have a common-mode voltage that is also set to mid-supply. To dc couple to an ADC input, the mid-supply voltage of the LMH2832 must be centered around the ADC input common-mode. This common-mode matching can be accomplished by shifting the supplies to center the mid-supply voltage around the ADC input common-mode voltage. However, shifting the supplies also changes the ground reference for the digital inputs, which then likely requires a voltage-shifted interface as well. The LMH2832 is not recommended to be operated as dc-coupled unless absolutely necessary.

#### 10.2 Typical Applications

#### 10.2.1 DOCSIS 3.X Driver

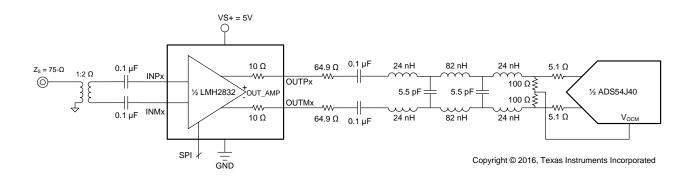

The LMH2832 is designed to perform best when driving differential input ADCs in high-speed applications. Figure 61 shows an example diagram of the LMH2832 driving an ADC with a fifth-order, low-pass filter for a 75- $\Omega$  impedance, data over cable service interface specification (DOCSIS) 3.X upstream receiver return path application. The primary interface between the amplifier and the ADC is usually an antialiasing filter to suppress high-frequency harmonics that otherwise alias back into the ADC FFT spectrum. Filters range from single-order real RC poles to higher-order, resistor-inductor-capacitor (RLC) filters, depending on the application requirements. Series output resistors (R<sub>O</sub>) help isolate the amplifier from any capacitive load presented by the filter, and can also be used to create a matched impedance to drive transmission lines.

Figure 61. DOCSIS 3.X Driver with the ADS54J40 and a 300-MHz, 4th-Order, Butterworth, Low-Pass Filter

#### 10.2.1.1 Design Requirements

Table 12 shows example design requirements for the LMH2832 in an upstream receiver application.

**Table 12. Example Design Requirements**

| SPECIFICATION                                | DESIGN REQUIREMENTS                 |  |  |

|----------------------------------------------|-------------------------------------|--|--|

| Supply voltage                               | 4.75 to 5.25 V                      |  |  |

| Usable input frequency range                 | 300 MHz                             |  |  |

| System voltage gain and range                | 33-dB voltage gain with 30-dB range |  |  |

| Source impedance                             | 75 $\Omega$ , single-ended          |  |  |

| Signal path SNR at 175 MHz (measured at ADC) | > 50 dBFS                           |  |  |

#### 10.2.1.2 Detailed Design Procedure

To begin the design process, make sure that none of the following design parameters exceed the limits listed in the *Electrical Characteristics* table, such as:

- Supply voltage

- Temperature range

- · Input voltage range across gain

- Output current requirements

- · Digital I/O voltages and currents

#### 10.2.1.2.1 Source Resistance Matching

Standard DOCSIS systems use a characteristic single-ended impedance of 75  $\Omega$  that must be properly matched to the 150- $\Omega$  differential impedance of the LMH2832. The circuit in Figure 61 uses a transformer with a 1:2- $\Omega$  ratio to convert the signal from single-ended to differential, and also to match the differential impedance. The transformer also adds a signal gain of approximately 3 dB to the system with some insertion loss depending on the chosen transformer.

#### 10.2.1.2.2 Output Impedance Matching

For the circuit in Figure 61, the output impedance is matched to a 150- $\Omega$  characteristic impedance filter to maximize the performance of the LMH2832. On the amplifier output side, the output impedance is matched to 150  $\Omega$  by including a 65- $\Omega$  series resistor on each output. Combined with the internal 10- $\Omega$  resistors on each output, the total differential impedance becomes 150  $\Omega$ . The ADS54J40 has an input impedance of approximately 600  $\Omega$  that is reduced to 150  $\Omega$  by using two 5- $\Omega$  series input resistors in parallel with two 100- $\Omega$  series resistors. The 5- $\Omega$  series resistors are included to isolate the input capacitance of the ADC so that the response of the filter is not affected. With both the amplifier and ADC impedances matched, any transmission line effects of the connection are minimized.

If the ADC is physically located close enough to the amplifier, a matched impedance may not be needed; see *Driving Low Insertion-Loss Filters* section for more information on driving non-matched filters.

#### 10.2.1.2.3 Voltage Headroom Considerations

Because of the series resistors included on both the amplifier outputs and ADC inputs, the amplifier must drive a voltage that is significantly higher than the ADC full-scale input. For the circuit in Figure 61, the ADS54J40 full-scale input voltage is 1.9  $V_{PP}$ , so the required voltage at the amplifier output pins is 3.6  $V_{PP}$ . This voltage is less than the specified output voltage of 5  $V_{PP}$  for the LMH2832, thus system performance is not limited. If the required output voltage is higher than what the amplifier can support, then the matched resistance value can be reduced. However, this reduction can have performance implications because more current output is required from the amplifier.

The input voltage swing can be larger than the output voltage swing because the LMH2832 can operate as an attenuator. To maintain the full-scale voltage of the ADS54J40 input in this application, the amplifier cannot attenuate more than 1 dB from input to output; otherwise, the maximum input voltage swing is exceeded. If the amplifier must be operated with more attenuation, then the output voltage must be reduced.

#### 10.2.1.3 Application Curve

Figure 62. Amplifier Dual Channel Isolation Presented to ADC Interface

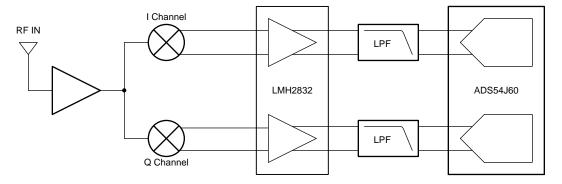

#### 10.2.2 IQ Receiver

The LMH2832 is a dual-channel device; therefore, the device has excellent gain and phase matching between channels A and B. This matching makes the LMH2832 an excellent choice for systems that require two matched channels (such as an IQ demodulation receiver), as shown in Figure 63. For an IQ system, both the gain and phase must match for the real and imaginary channel. When using two single-channel amplifiers, the matching characteristics are subject to process lot and packaging variations for two individual devices, and there is often no way to make sure that the amplifiers match without testing each amplifier. However, the dual-channel architecture of the LMH2832 allows for much tighter gain and phase matching with minimal crosstalk effects. For more matching information, see the *Electrical Characteristics* table.

Copyright © 2016, Texas Instruments Incorporated

Figure 63. IQ Receiver Block Diagram

#### 10.3 Do's and Don'ts

#### 10.3.1 Do:

- Include a thermal analysis at the beginning of the project

- · Use well-terminated transmission lines for all signals

- Maintain symmetrical input and output trace layouts

- Use solid metal layers for the power supplies

- · Keep signal lines as straight as possible

#### 10.3.2 Don't:

- Use a lower power-supply voltage than necessary

- Forget about the common-mode response of filters and transmission lines

- · Rout digital line traces close to the analog signals and supply line traces

## 11 Power Supply Recommendations

The LMH2832 is designed to be used with a single supply with a range of 4.75 V to 5.25 V. The ideal supply voltage is a 5.0-V total single-ended supply. If the supply is reduced to the minimum voltage, then the maximum input and output voltage range is reduced by 0.25 V.

### 11.1 Split Supplies

Ideally, the LMH2832 uses a single-ended, 5-V supply, but the device can be operated on a split supply if necessary. However, the digital logic is referenced to the GND pins, meaning that the logic reference shifts with the GND supply if connected to a negative voltage and must be accounted for in the logic connections. In general, the LMH2832 is not suggested to be operated with a split-supply configuration.

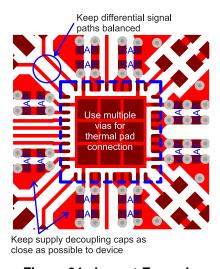

## 11.2 Supply Decoupling

Power-supply decoupling is critical to high-frequency performance. Onboard bypass capacitors are used on the LMH2832EVM; however, the most important component of the supply bypassing is provided by the printed circuit board (PCB). As illustrated in Figure 64, there are multiple vias connecting the LMH2832 power planes to the power-supply traces. These vias connect the internal power planes to the LMH2832. Both  $V_{\rm CC}$  and GND must be connected to the internal power planes with several square centimeters of continuous plane in the immediate vicinity of the amplifier. The capacitance between these power planes provides the bulk of the high-frequency bypassing for the LMH2832.

## 12 Layout

#### 12.1 Layout Guidelines

With a small bandwidth greater than 1 GHz, layout for the LMH2832 is critical and nothing can be neglected. In order to simplify board design, the LMH2832 has on-chip resistors that reduce the affect of off-chip capacitance. For this reason, make sure that the ground layer below the LMH2832 is not cut. The recommendation to not cut the ground plane under the amplifier input and output pins is different than many other high-speed amplifiers, but the reason is that parasitic inductance is more harmful to the LMH2832 performance than parasitic capacitance. By leaving the ground layer under the device intact, parasitic inductance of the output and power traces is minimized. The DUT portion of the evaluation board layout is shown in Figure 64.