# LMG365xR035 ドライバと保護機能を内蔵した 650V、35mΩ GaN FET

# 1 特長

- ゲートドライバ内蔵、650V、35mΩの GaN 電力 FET

- >200V/ns の FET ホールド オフ

- 調整可能なスルーレートによるスイッチングパフォ ーマンスの最適化と EMI の軽減

- 10V/ns から 100V/ns の有効化スルーレート

- 10V/ns からフルスピードの有効化スルーレート

- 電源ピンと入力ロジックピンの 9V から 26V の電 圧範囲で動作します

- 堅牢な保護

- サイクル単位の過電流保護と応答時間 300ns 未 満のラッチ付き短絡保護

- ハードスイッチング中のサージ耐性:720V

- 内部過熱および UVLO 監視機能による自己保護

- サーマル パッド付きの 9.8mm × 11.6mm TOLL パッ ケージ

# 2 アプリケーション

- 商用ネットワークとサーバーの電源

- 商用テレコム整流器

- ソーラー インバータと産業用モータードライブ

- 無停電電源

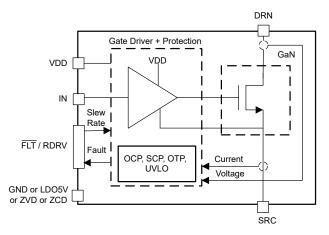

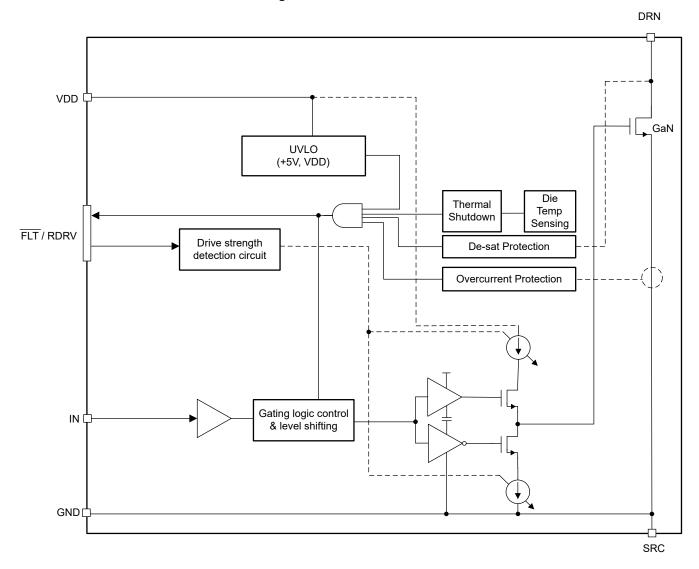

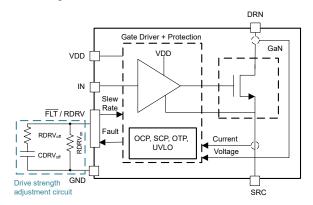

概略ブロック図

# 3 概要

ドライバと保護機能を内蔵した LMG365xR035 GaN FET は、スイッチ モード パワー コンバータを対象としていま す。このデバイスを使うと、設計者は比類ない電力密度と 効率を実現できます。

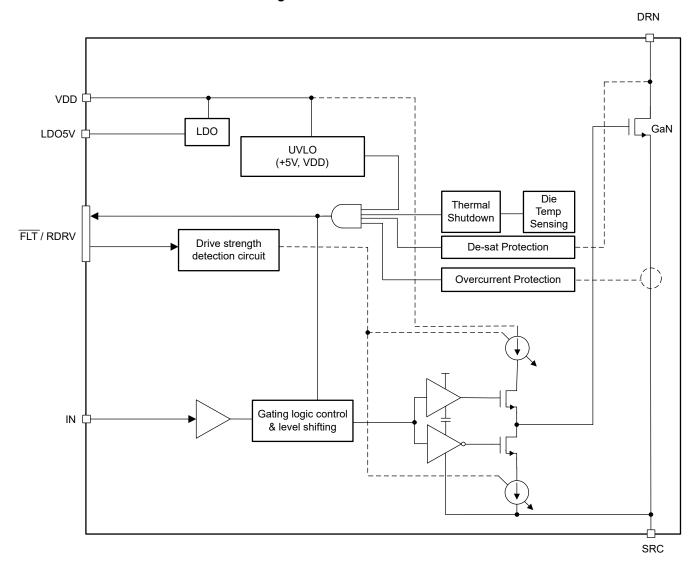

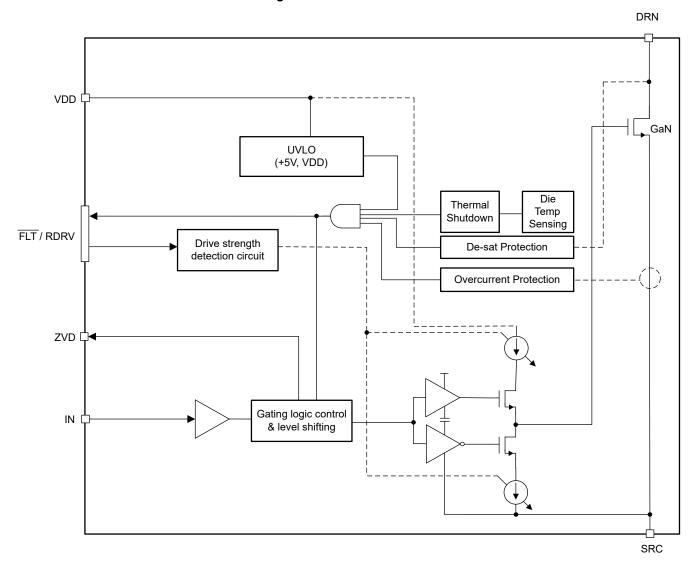

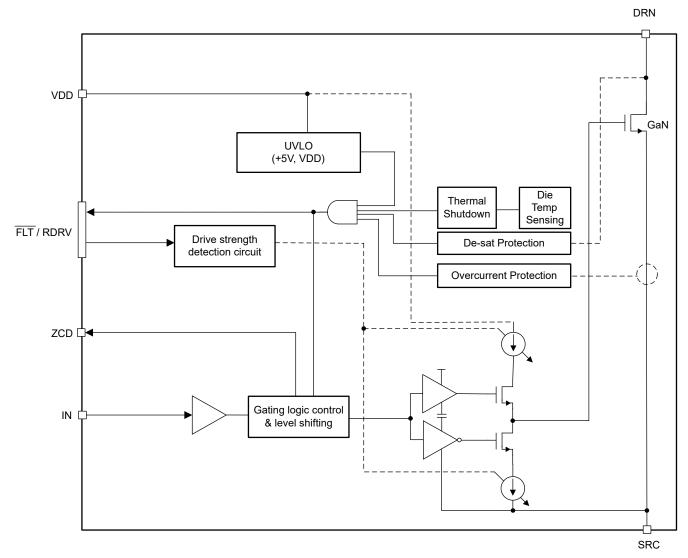

調整可能なゲートドライブ強度により、独立な有効化と最 大限無効化スルーレートの制御が可能で、EMIのアクティ ブ制御とスイッチング性能の最適化に使用できます。有効 化スルーレートは 100V/ns10 から V/ns まで変動する可 能性がありますが、負荷電流の大きさに基づいて 10V/ns の範囲で無効化スルーレートの最大値に制限することが できます。保護機能として、低電圧誤動作防止 (UVLO)、 サイクル単位の電流制限、短絡保護、および過熱保護が 搭載されています。LMG3651R035 は、外部デジタルア イソレータへの電力供給に使用できる LDO5V ピンで 5V LDO 出力を供給します。LMG3656R035 は、ゼロ電圧検 出 (ZVD) 機能を備えており、ゼロ電圧スイッチングが発生 したとき ZVD ピンからパルスを出力します。 LMG3657R035 は、ドレイン-ソース間電流が負であり、ゼ ロクロスポイント検出時に Low に遷移すると ZCD ピンを High に設定するゼロ電流検出 (ZCD) 機能を備えていま

### パッケージ情報

| 部品番号        | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-------------|----------------------|--------------------------|

| LMG365xR035 | KLA (TOLL, 9)        | 9.8 mm × 11.6mm          |

- 供給されているすべてのパッケージについては、セクション 12 を 参照してください。

- パッケージ サイズ (長さ×幅) は公称値で、該当する場合はピンも 含まれます。

### 製品情報

| 部品番号 <sup>(1)</sup> | ピン7   |

|---------------------|-------|

| LMG3650R035         | GND   |

| LMG3651R035         | LDO5V |

| LMG3656R035         | ZVD   |

| LMG3657R035         | ZCD   |

製品比較表を参照してください。

# **Table of Contents**

| 1 特長                                 | 1 8.3 Feature Description | 15                     |

|--------------------------------------|---------------------------|------------------------|

| 2 アプリケーション                           |                           |                        |

| 3 概要                                 |                           | ntion23                |

| 4 Device Comparison                  | 0 1 1 1 1: 1: 1 - f 1:    | 23                     |

| 5 Pin Configuration and Functions    | 0.0 T                     |                        |

| 6 Specifications                     |                           | ndations31             |

| 6.1 Absolute Maximum Ratings         |                           | 32                     |

| 6.2 ESD Ratings                      |                           | Support36              |

| 6.3 Recommended Operating Conditions |                           | 受け取る方法 <mark>36</mark> |

| 6.4 Thermal Information              |                           | 36                     |

| 6.5 Electrical Characteristics       |                           | 36                     |

| 6.6 Switching Characteristics        |                           | 事項36                   |

| 7 Parameter Measurement Information  | 9 10.5 用語集                | 36                     |

| 7.1 Switching Parameters             |                           |                        |

| 8 Detailed Description               |                           |                        |

| 8.1 Overview                         | , , ,                     |                        |

| 8.2 Functional Block Diagram         |                           |                        |

|                                      | •                         |                        |

# **4 Device Comparison**

# 表 4-1. Device Comparison

| DEVICE NAME | R <sub>DS(on)</sub> | Pin 7 |

|-------------|---------------------|-------|

| LMG3650R025 |                     | GND   |

| LMG3651R025 | 25mΩ                | LDO5V |

| LMG3656R025 |                     | ZVD   |

| LMG3657R025 |                     | ZCD   |

| LMG3650R035 | 35mΩ                | GND   |

| LMG3651R035 |                     | LDO5V |

| LMG3656R035 | 3311152             | ZVD   |

| LMG3657R035 |                     | ZCD   |

| LMG3650R070 |                     | GND   |

| LMG3651R070 | 70mΩ                | LDO5V |

| LMG3656R070 | 7 011152            | ZVD   |

| LMG3657R070 |                     | ZCD   |

# 5 Pin Configuration and Functions

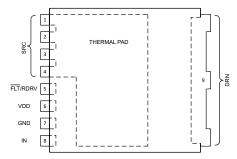

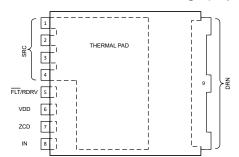

図 5-1. LMG3650R035, TOLL Package (Top View)

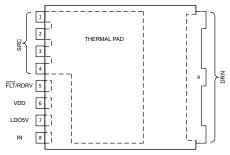

図 5-2. LMG3651R035, TOLL Package (Top View)

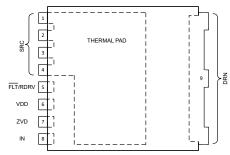

図 5-3. LMG3656R035, TOLL Package (Top View)

図 5-4. LMG3657R035, TOLL Package (Top View)

表 5-1. Pin Functions

|             |                 |                 | 2               | Ç 3-1. FIII     | · unou | 0.10                                                                                                                                                                                                                                                                                                                               |  |  |

|-------------|-----------------|-----------------|-----------------|-----------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|             |                 | PIN             |                 |                 | TYPE   | DE                                                                                                                                                                                                                                                                                                                                 |  |  |

| NAME        | LMG3650<br>R035 | LMG3651<br>R035 | LMG3656<br>R035 | LMG3657<br>R035 | (1)    | DESCRIPTION                                                                                                                                                                                                                                                                                                                        |  |  |

| SRC         | 1 - 4           | 1 - 4           | 1 - 4           | 1 - 4           | Р      | GaN FET source.                                                                                                                                                                                                                                                                                                                    |  |  |

| FLT/RDRV    | 5               | 5               | 5               | 5               | 0,1    | Fault monitoring and drive strength selection pin. Connect a resistor from this pin to GND to set the turn-on drive strength. Connect a resistor in series with capacitor from this pin to GND to set the turn-off drive strength. Slew rates are set one time at the time of power up, then the pin is used for fault monitoring. |  |  |

| VDD         | 6               | 6               | 6               | 6               | Р      | Device input supply                                                                                                                                                                                                                                                                                                                |  |  |

| GND         | 7               | _               | _               | _               | G      | Signal ground. Internally connected to SRC, and THERMAL PAD.                                                                                                                                                                                                                                                                       |  |  |

| LDO5V       | _               | 7               | _               | _               | Р      | 5V LDO output for external digital isolator.                                                                                                                                                                                                                                                                                       |  |  |

| ZVD         | _               | _               | 7               | _               | 0      | Push-pull digital output that provides zero-voltage detection signal to indicate if device achieves zero-voltage switching in current switching cycle.                                                                                                                                                                             |  |  |

| ZCD         | _               | _               | _               | 7               | 0      | Push-pull digital output that sets ZCD pin high when the drain-to-source current is negative and transitions to low upon detecting the zero-crossing point.                                                                                                                                                                        |  |  |

| IN          | 8               | 8               | 8               | 8               | ı      | CMOS compatible non inverting input used to turn the FET on and off                                                                                                                                                                                                                                                                |  |  |

| DRN         | 9               | 9               | 9               | 9               | Р      | GaN FET drain                                                                                                                                                                                                                                                                                                                      |  |  |

| THERMAL PAD | _               | _               | _               | _               | _      | Thermal pad.                                                                                                                                                                                                                                                                                                                       |  |  |

(1) I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

# 6 Specifications

# 6.1 Absolute Maximum Ratings

Unless otherwise noted: voltages are respect to GND/SRC<sup>(1)</sup>

|                            |                                                                       |          | MIN  | MAX                   | UNIT |

|----------------------------|-----------------------------------------------------------------------|----------|------|-----------------------|------|

| V <sub>DS</sub>            | Drain-source voltage, FET off                                         |          |      | 650                   | V    |

| V <sub>DS(surge)</sub>     | S(surge) Drain-source voltage, surge condition, FET off               |          |      | 720                   | V    |

| V <sub>DS(tr)(surge)</sub> | Drain-source transient ringing peak voltage, surge condition, FET off |          |      | 800                   | V    |

|                            |                                                                       | VDD      | -0.5 | 28                    | V    |

|                            | Pin voltage                                                           | IN       | -0.5 | 28                    | V    |

|                            |                                                                       | FLT/RDRV | -0.5 | 5.5                   | V    |

| I <sub>D</sub>             | Peak drain current, FET on                                            | •        |      | TBD                   | Α    |

| I <sub>D(pulse)</sub>      | Pulse drain current, FET on, t <sub>p</sub> < 10μs.                   |          | -68  | Internally<br>Limited | Α    |

| TJ                         | Operating junction temperature                                        |          | -40  | 175                   | °C   |

| T <sub>stg</sub>           | Storage temperature                                                   |          | -65  | 150                   | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 6.2 ESD Ratings

|  |                               |                                                                |                                                                       | VALUE | UNIT |

|--|-------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------|-------|------|

|  | (ESD) Electrostatic discharge | Electrostatio discharge                                        | Human body model (HBM), per ANSI/<br>ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000 | .,,  |

|  |                               | Charged-device model (CDM), per ANSI/<br>ESDA/JEDEC JS-002 (2) | ±500                                                                  | V     |      |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

Unless otherwise noted: voltages are respect to GND/SRC

|                |                                                                                     |     | MIN  | NOM MAX | UNIT |

|----------------|-------------------------------------------------------------------------------------|-----|------|---------|------|

|                | Supply voltage                                                                      | VDD | 9    | 26      | V    |

|                | Input voltage                                                                       | IN  | 0    | 26      | V    |

| I <sub>D</sub> | Drain current, FET on                                                               |     |      | 20      | Α    |

| R <sub>1</sub> | Resistance from external turn-on slew rate control resistor between FLT/RDRV to GND |     | 29.4 | open    | kΩ   |

| R2             | resistance and capacitance from external furnion siew rate control series resistor  |     | 2    | open    | kΩ   |

| C2             |                                                                                     |     | 0    | 680     | pF   |

# 6.4 Thermal Information

|                      | THERMAL METRIC(1)                            | KLA (TOLL) | UNIT |  |

|----------------------|----------------------------------------------|------------|------|--|

|                      | THERMAL WETRIO                               | 9 PINS     | ONT  |  |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 0.38       | °C/W |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

English Data Sheet: SNOSDL1

# **6.5 Electrical Characteristics**

Unless otherwise noted: voltage, resistance, capacitance, and inductance are respect to GND/SRC; –40°C ≤ T<sub>J</sub> ≤ 150°C: VDD = 12V: FTT/RDRV resistances R1 & R2 are open

|                             | PARAMETER                                                | TEST CONDITIONS                                                                         | MIN | TYP | MAX  | UNIT |

|-----------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|-----|------|------|

| GAN POWER FI                | ET                                                       |                                                                                         |     |     |      |      |

| _                           |                                                          | T <sub>J</sub> = 25°C, I <sub>L</sub> = 16A                                             |     | 35  | 55   | mΩ   |

| $R_{DS(on)}$                | Drain-source on resistance                               | T <sub>J</sub> = 150°C, I <sub>L</sub> = 16A                                            |     | 80  |      | mΩ   |

|                             |                                                          | T <sub>J</sub> = 25°C, I <sub>SD</sub> = 0.1A                                           |     | 1.8 |      | V    |

|                             | Source-drain third-quadrant voltage                      | T <sub>J</sub> = 150°C, I <sub>SD</sub> = 0.1A                                          |     | 1.8 |      | V    |

| $V_{SD}$                    |                                                          | T <sub>J</sub> = 25°C, I <sub>SD</sub> = 20A                                            |     | 2.9 |      | V    |

|                             |                                                          | T <sub>J</sub> = 150°C, I <sub>SD</sub> = 20A                                           |     | 3   |      | V    |

|                             | Desire to also we assume the                             | T <sub>J</sub> = 25°C, V <sub>DS</sub> = 650V                                           |     | TBD |      | μA   |

| I <sub>DSS</sub>            | Drain leakage current                                    | T <sub>J</sub> = 150°C, V <sub>DS</sub> = 650V                                          |     | TBD |      | μA   |

| Q <sub>OSS</sub>            | Output charge                                            | V <sub>DS</sub> = 400V                                                                  |     | 125 |      | nC   |

| C <sub>OSS</sub>            | Output capacitance                                       | V <sub>DS</sub> = 400V                                                                  |     | 173 |      | pF   |

| E <sub>oss</sub>            | Output capacitance stored energy                         | V <sub>DS</sub> = 400V                                                                  |     | 15  |      | μJ   |

| C <sub>OSS(tr)</sub>        | Time related effective output capacitance                | V <sub>DS</sub> = 400V                                                                  |     | 255 |      | pF   |

| C <sub>OSS(er)</sub>        | Energy related effective output capacitance              | V <sub>DS</sub> = 400V                                                                  |     | 200 |      | pF   |

| Q <sub>RR</sub>             | Reverse recovery charge                                  |                                                                                         |     | 0   |      | nC   |

| OVERCURRENT                 | AND SHORT-CIRCUIT PROTECTIONS                            |                                                                                         |     |     |      |      |

| I <sub>T(OC)</sub>          | Overcurrent protection threshold                         |                                                                                         | 26  | 29  | 32   | Α    |

| V <sub>T(Idsat)</sub>       | Saturation current detection - threshold voltage         |                                                                                         | 8.7 | 9   | 9.6  | V    |

| OVERTEMPERA                 | ATURE PROTECTION                                         |                                                                                         |     |     |      |      |

| T <sub>T+</sub>             | Temperature fault - positive-going threshold temperature |                                                                                         |     | 190 |      | °C   |

| T <sub>T-</sub>             | Temperature fault - negative-going threshold temperature |                                                                                         |     | 175 |      | °C   |

| $T_{T(hyst)}$               | Temperature fault - threshold temperature hysterisis     |                                                                                         |     | 20  |      | °C   |

| IN                          |                                                          |                                                                                         |     |     |      |      |

| $V_{IN,IT+}$                | Positive-going input threshold voltage                   |                                                                                         | 1.7 | 2   | 2.45 | V    |

| V <sub>IN,IT-</sub>         | Negative-going input threshold voltage                   |                                                                                         | 0.7 | 1   | 1.3  | V    |

| V <sub>IN,IT(hyst)</sub>    | Input threshold voltage hysteresis                       |                                                                                         |     | 1   |      | V    |

| R <sub>PDN</sub>            | Pull-down input resistance                               |                                                                                         | 115 | 150 | 185  | kΩ   |

| FLT/RDRV                    |                                                          |                                                                                         |     |     |      |      |

| V <sub>OL</sub>             | Low-level output voltage                                 | Output sink 8mA                                                                         |     | 0.2 | 0.4  | V    |

| V <sub>OH</sub>             | High-level output voltage                                | Output source 8mA                                                                       | 4.6 | 4.8 |      | V    |

| VDD                         |                                                          |                                                                                         |     |     |      |      |

| I <sub>VDD(ON)</sub>        | Quiescent current when FET is ON                         | IN=1                                                                                    |     | 1.9 | 11.5 | mA   |

| I <sub>VDD(OFF)</sub>       | Quiescent current when FET is OFF                        | IN=0                                                                                    |     | 0.7 | 1.1  | mA   |

| I <sub>VDD(op)</sub>        | Operating current at 140 kHz                             | f <sub>sw</sub> = 140kHz, V <sub>bus</sub> = 400V,<br>Hard-switched, 50% duty<br>cycle. |     | 3.5 | 6.5  | mA   |

| V <sub>VDD, T+ (UVLO)</sub> | UVLO- positive-going threshold voltage                   |                                                                                         | 8.1 | 8.5 | 8.9  | V    |

| V <sub>VDD, T- (UVLO)</sub> | UVLO- negative-going threshold voltage                   |                                                                                         | 7.6 | 8   | 8.4  | V    |

| V <sub>VDD, T (hyst)</sub>  | UVLO- threshold voltage hystresis                        |                                                                                         |     | 0.5 |      | V    |

# **6.6 Switching Characteristics**

Unless otherwise noted: voltage, resistance, capacitance, and inductance are respect to GND/SRC;  $-40^{\circ}\text{C} \le T_{\text{J}} \le 150^{\circ}\text{C}$ ;  $V_{\text{DD}} = 12\text{V}$ ;  $\overline{\text{FLT}}/\text{RDRV}$  resistances R1 & R2 are open

|                             | PARAMETER                                                      | TEST CONDITIONS                                                                                                                       | MIN | TYP | MAX | UNIT |

|-----------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| SWITCHING TIM               | IES                                                            |                                                                                                                                       |     |     |     |      |

| t <sub>d(on)</sub>          | Turn-on delay time                                             | From $V_{IN} > V_{IN,IT+}$ to $V_{DS} < 320V$ , $V_{BUS} = 400V$ , $L_{HB}$ current = 0A, 100V/ns                                     |     | 30  | 45  | ns   |

| t <sub>ir(on)</sub>         | Turn-on current rise time + delay time                         | From V <sub>IN</sub> > V <sub>IN,IT+</sub> to V <sub>DS</sub> < 320V, V <sub>BUS</sub> = 400V, L <sub>HB</sub> current = 10A, 100V/ns |     | 35  | 60  | ns   |

| $t_{vf(on)}$                | Turn-on voltage falling time                                   | From $V_{DS}$ < 320V to $V_{DS}$ < 80V, $V_{BUS}$ = 400V, $L_{HB}$ current = 10A, 100V/ns                                             | 1   | 2.3 | 3   | ns   |

| t <sub>vf_peak(on)</sub>    | Turn-on slew rate                                              |                                                                                                                                       | 90  | 115 | 150 | V/ns |

|                             | Pulse width distortion                                         | slew-rate setting at 100V/ns                                                                                                          |     |     | 20  | ns   |

|                             | Minimum input pulse changing the output L-H-L                  | slew-rate setting at 100V/ns<br>such that SW crosses 200V                                                                             |     |     | 50  | ns   |

| $t_{d(off)}$                | Turn-off delay time at full speed                              | From $V_{IN}$ < 2.5V to $V_{DS}$ >= 10V. $V_{BUS}$ = 400V, $I_{L}$ = 34A, fastest or full turn-off speed.                             | 12  | 17  | 35  | ns   |

| $t_{\text{vr(off)}}$        | Turn-off voltage rise time at full speed                       | From $V_{DS} >= 20V$ to $V_{DS} >= 380V$ . $V_{BUS} = 400V$ , $I_L = 34A$ , fastest or full turn-off speed.                           | 3   | 4.5 | 7   | ns   |

| STARTUP TIMES               | 5                                                              |                                                                                                                                       |     |     |     |      |

| T <sub>DRV_START</sub>      | Driver startup delay                                           | From Driver supply crossing UVLO to switch turning on if IN is high.                                                                  |     | 35  | 65  | μs   |

| FAULT TIMES                 |                                                                |                                                                                                                                       |     |     |     |      |

| $t_{ m off(OC)}$            | Overcurrent fault FET turn-off time, FET on before overcurrent | From $I_D >= I_{T(OC)}$ to $V_{ds} > 10V$ ,<br>di/dt = 100A/ $\mu$ s, in the fastest<br>turn-off speed                                |     | 370 | 480 | ns   |

| t <sub>off(OC_ON)</sub>     | Overcurrent total on time, turn-on into overcurrent.           | From $V_{ds} \le 10V$ to $V_{ds} \ge 10V$ , turning on at 110% of OC level, at 100 V/ns turn-on slew rate and fastest turn-off speed. |     | 420 | 580 | ns   |

| t <sub>off_cur(SC_ON)</sub> | SC on time measured through drain current                      | From LS I <sub>ds</sub> > 50A to I <sub>ds</sub> < 50A, at 100 V/ns turn-on slew rate in a half-bridge configuration.                 | 100 |     | 500 | ns   |

| t <sub>off_cur(SC)</sub>    | SC response time with source current measurement               | From LS Vds>9V to LS<br>Ids<50A, at 100 V/ns turn-on<br>slew rate in a half-bridge<br>configuration.                                  |     |     | 300 | ns   |

|                             | Latched-Fault reset time                                       | Time required to hold both gate driver input low to clear latched-fault                                                               | 300 | 380 | 450 | μs   |

| ZCD/ZVD                     |                                                                |                                                                                                                                       |     |     |     |      |

|                             | ZCD delay                                                      | Current crossing zero (low to high) to ZCD output pulse di/dt = 0.03A/ns                                                              | 12  | 25  | 40  | ns   |

|                             | ZVD delay                                                      | In rising to ZVD output pulse. 100V/ns turn-on speed.                                                                                 | 13  | 20  | 50  | ns   |

| t <sub>WD_ZVD</sub>         | ZVD pulse width                                                | V <sub>bus</sub> = 10V, I <sub>L</sub> = 5A, measure<br>ZVD pulse width                                                               | 90  | 120 | 170 | ns   |

# 6.6 Switching Characteristics (続き)

Unless otherwise noted: voltage, resistance, capacitance, and inductance are respect to GND/SRC;  $-40^{\circ}\text{C} \le T_{\text{J}} \le 150^{\circ}\text{C}$ ;  $V_{\text{DD}} = 12\text{V}$ ;  $\overline{\text{FLT}}/\text{RDRV}$  resistances R1 & R2 are open

| PARAMETER        | TEST CONDITIONS                              | MIN | TYP | MAX | UNIT |

|------------------|----------------------------------------------|-----|-----|-----|------|

| ZVD sensing time | Sensing time to fet turn on (100V/ns). IL=2A |     | 11  | 25  | ns   |

# 7 Parameter Measurement Information

# 7.1 Switching Parameters

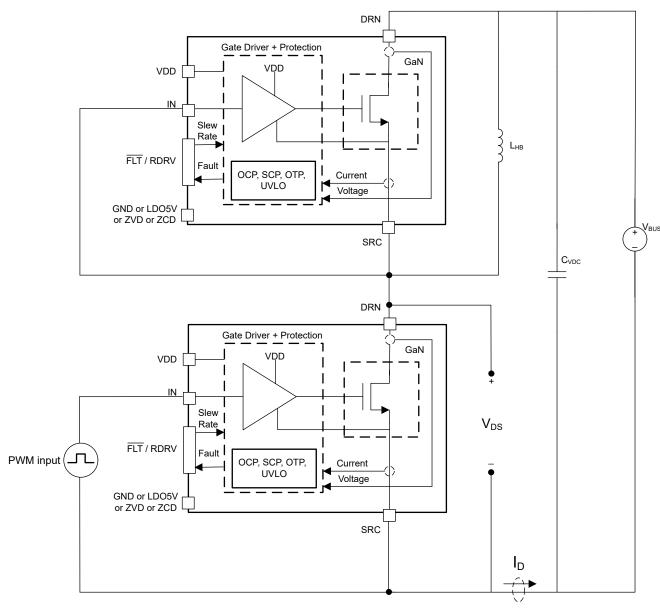

☑ 7-1 shows the circuit used to measure most switching parameters. The top device in this circuit is used to recirculate the inductor current and functions in third-quadrant mode only. The bottom device is the active device that turns on to increase the inductor current to the desired test current. The bottom device is then turned off and on to create switching waveforms at a specific inductor current. Both the drain current (at the source) and the drain-source voltage is measured. ☑ 7-2 shows the specific timing measurement. TI recommends to use the half-bridge as a double pulse tester. Excessive third-quadrant operation can overheat the top device.

図 7-1. Circuit Used to Determine Switching Parameters

図 7-2. Measurement to Determine Propagation Delays and Slew Rates

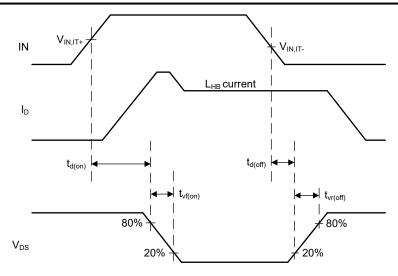

### 7.1.1 Turn-On Times

The turn-on transition has two timing components: turn-on delay time, and turn-on voltage fall time. The turn-on delay time is from when IN goes high to when the drain-source voltage falls 20% below the bus voltage. The turn-on voltage fall time is from when drain-source voltage falls 20% below the bus voltage to when the drain-source voltage falls 80% below the bus voltage. Note that the turn-on timing components are a function of the turn-on drive strength resistance RDRV\_on connected to the FLT/RDRV pin.

### 7.1.2 Turn-Off Times

The turn-off transition has two timing components: turn-off delay time, and turn-off voltage rise time. The turn-off delay time is from when IN goes low to when the drain-source voltage rises to 20% of the bus voltage. The turn-off voltage rise time is from when the drain-source voltage rises from 20% of the bus voltage to when the drain-source voltage to 80% of the bus voltage. Note that the turn-off timing components are dependent on the L<sub>HB</sub> load current, however LMG365xR035 also features the ability to limit turn-off drive strength. When the drain-to-source current is sufficiently high and the turn-off drive strength is limited, the timing components become dependent on the programming resistors RDRV\_on, RDRV\_off, and capacitance CDRV\_off connected to the FLT/RDRV pin.

### 7.1.3 Drain-Source Turn-On and Turn-off Slew Rate

The drain-source turn-on and turn-off slew rate is measured on  $V_{DS}$  around the midpoint of the bus voltage, with units in volts per nanosecond. The resistors RDRV\_on, RDRV\_off, and capacitance CDRV\_off connected to the FLT/RDRV pin is used to program the turn-on slew rate and limit the turn-off slew rate.

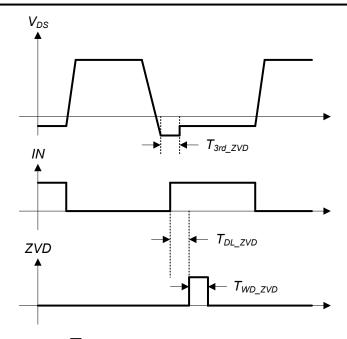

# 7.1.4 Zero-Voltage Detection Times (LMG3656R035 only)

$\boxtimes$  7-3 defines the switching timings related to the zero-voltage detection (ZVD) block, and the device's drain-to-source voltage, IN pin signal, and ZVD output signals are demonstrated. When the device achieves zero-voltage switching (ZVS), the ZVD pin outputs a pulse-signal with width  $T_{WD\_ZVD}$ , and the delay time in between IN pin's rising edge and ZVD pulse's rising edge is defined as  $T_{DL\_ZVD}$ . A certain third quadrant conduction time is required to allow the device detecting a zero-voltage switching, and  $T_{3rd\_ZVD}$  indicates this timing. See the ZD  $\cong$  8.3.8 section for more information about the ZVD timing parameters.

図 7-3. ZVD Timing Specifications

# 8 Detailed Description

# 8.1 Overview

The LMG365xR035 is a high-performance power GaN device with integrated gate driver. The GaN device offers zero reverse recovery and ultra-low output capacitance, which enables high efficiency in bridge-based topologies.

The integrated driver ensures the device stays off for high drain slew rates. The integrated driver protects the GaN device from overcurrent, short-circuit, overtemperature, VDD undervoltage, and a high-impedance RDRV pin.

Unlike Si MOSFETs, GaN devices do not have a p-n junction from source to drain and thus have no reverse recovery charge. However, GaN devices still conduct from source to drain similar to a p-n junction body diode, but with higher voltage drop and higher conduction loss. Therefore, source-to-drain conduction time must be minimized while the LMG365xR035 GaN FET is turned off.

# 8.2 Functional Block Diagram

# 8.2.1 LMG3650R035 Functional Block Diagram

# 8.2.2 LMG3651R035 Functional Block Diagram

# 8.2.3 LMG3656R035 Functional Block Diagram

# 8.2.4 LMG3657R035 Functional Block Diagram

# 8.3 Feature Description

### 8.3.1 Drive Strength Adjustment

The LMG365xR035 allows users to adjust the drive strength of the device and obtain a desired slew rate, which provides flexibility when optimizing switching losses and minimizing EMI. The typical value of turn-on slew rate and the maximum value of turn-off slew rate can be independently controlled by connecting the resistors and capacitor as shown in the ☑ 8-1. The resistance and capacitance on FLT/RDRV pin is sensed once at power-up. To do so, the device forces a step-function from 0V to 1.2V on the external R1-R2-C2 network and measures the resulting current waveform. The DC measurement determines the turn-on slew rate setting, which is programmed by the resistance R1. The AC measurement dependent on R1-R2-C2 determines the turn-off slew rate setting, which is dependent on the magnitude of the drain-to-source current charging the output capacitance but can be limited to a maximum value programmed by the resistance R2 and capacitance C2, connected in parallel to R1. 表 8-1 shows the recommended typical resistances and capacitance programming values at each slew rate setting.

The slew rate settings are determined one time at power up, then the  $\overline{FLT}/RDRV$  pin is used as a push-pull 5V digital output for fault monitoring, as described in *Fault Reporting*. If R2 and C2 are not used, the device turns-off

at full-speed and the turn-off slew rate is strictly determined by the Coss and the load current. If R1 is not used, the device defaults to the 100V/ns slew rate setting. Using slower turn-on settings results in higher Eon losses, and slower turn-off settings results in higher Eoff losses.

図 8-1. Drive Strength Adjustment Circuit

# 表 8-1. Recommended Typical Programming Resistance (kΩ) and Capacitance (pF) for Adjusting Slew Rates

| TYPICAL TURN-ON SLEW RATE (V/ns) |                      | MAXIMUM TURN-OFF SLEW RATE (V/ns) |     |      |     |      |     |                               |    |  |  |

|----------------------------------|----------------------|-----------------------------------|-----|------|-----|------|-----|-------------------------------|----|--|--|

|                                  |                      | 10                                |     | 20   |     | 40   |     | No limit (1)                  |    |  |  |

|                                  | R1                   | R2                                | C2  | R2   | C2  | R2   | C2  | R2                            | C2 |  |  |

| 10                               | 29.4                 | 2                                 | 680 | 4.87 | 270 | 9.09 | 150 | ,                             |    |  |  |

| 20                               | 35.7                 | 2                                 | 680 | 4.75 | 270 | 8.66 | 150 | high impedance <sup>(2)</sup> |    |  |  |

| 40                               | 43.2                 | 2                                 | 680 | 4.64 | 270 | 8.25 | 150 |                               |    |  |  |

| 60                               | 53.6                 | 2                                 | 680 | 4.64 | 270 | 8.06 | 150 |                               |    |  |  |

| 80                               | 69.8                 | 2                                 | 680 | 4.53 | 270 | 7.68 | 150 |                               |    |  |  |

| 100                              | > 400 <sup>(2)</sup> | 2                                 | 680 | 4.22 | 270 | 6.98 | 180 |                               |    |  |  |

- Fully dependent on the magnitude of the drain-to-source current charging the output capacitance

- (2) Open-circuit connection for programming resistances is acceptable

For example, setting R1 =  $53.6k\Omega$ , R2 =  $4.64k\Omega$  and C2 = 270pF results in turn-on slew rate of 60V/ns and turn-off slew rate is limited to a maximum of 20V/ns.

# 8.3.2 VDD Supply

VDD is the input supply for the internal circuits. Wide voltage ranges from 9V to 26V are supported on VDD pin.

### 8.3.3 Overcurrent and Short-Circuit Protection

There are two types of current faults which can be detected by the driver: overcurrent fault and short-circuit fault.

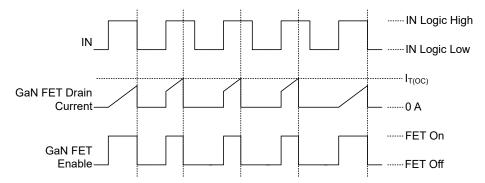

The overcurrent protection (OCP) circuit monitors drain current and compares that current signal with an internally set limit  $I_{T(OC)}$ . Upon detection of the overcurrent, the LMG365xR035 performs cycle-by-cycle protection as shown in  $\boxtimes$  8-2. In this mode, the GaN device is shut off when the drain current crosses the  $I_{T(OC)}$  plus a delay  $t_{off(OC)}$ , but the overcurrent signal clears after the IN pin signal goes low. In the next cycle, the GaN device can turn on as normal. The cycle-by-cycle function can be used in cases where steady-state operation current is below the OCP level but transient response can still reach current limit, while the circuit operation cannot be paused. The cycle-by-cycle function also prevents the GaN device from overheating by overcurrent induced conduction losses.

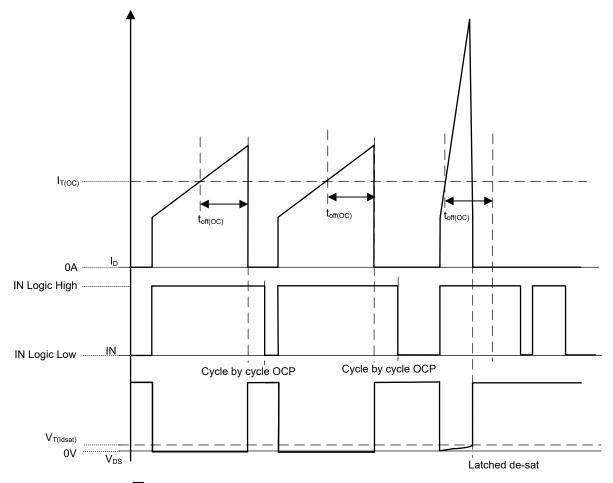

The short-circuit protection is based on desaturation (de-sat) detection, which monitors the drain-source voltage  $V_{DS}$  and compares the voltage with an internally set limit  $V_{T(Idsat)}$ . If the OC occurs before the de-sat, the  $V_{DS}$  is below the threshold, then OC is triggered, else de-sat is triggered as shown in  $\boxtimes$  8-3. Saturation can be

damaging for the GaN to continue to operate in that condition. Therefore, if a de-sat is detected, the GaN device is turned off with an intentionally slowed driver so that a lower overshoot voltage and ringing can be achieved during the turn-off event. This fast response circuit helps protect the GaN device even under a hard short-circuit condition. In this protection, the GaN device is shut off and held off until the fault is reset by either holding the IN pin low for a period of time defined in the *Specifications* or removing power from VDD.

For safety considerations, OCP allows cycle-by-cycle operation while de-sat latches the device until reset. Both faults are reported on the FLT/RDRV pin.

図 8-2. Cycle-by-Cycle Overcurrent Protection Operation

図 8-3. Overcurrent Detection vs Desaturation Detection

### 8.3.4 Overtemperature Protection

The overtemperature protection holds off the GaN power FET if the LMG365xR035 temperature is above the overtemperature protection threshold. The overtemperature protection hysteresis avoids erratic thermal cycling. An overtemperature fault is reported on the FLT/RDRV pin when the overtemperature protection is asserted. FLT/RDRV de-asserts and the device automatically returns to normal operation after the device temperature fall below the negative-going trip point.

# 8.3.5 UVLO Protection

The LMG365xR035 supports a wide range of  $V_{DD}$  voltages. However, when the  $V_{DD}$  voltage is below  $V_{DD}$  UVLO threshold, the GaN device stops switching and is held off. The  $V_{DD}$  UVLO voltage hysteresis prevents on-off chatter near the UVLO voltage trip point. The  $\overline{FLT}/RDRV$  pin is pulled low as an indication of UVLO.

# 8.3.6 Fault Reporting

All faults are reported on the FLT/RDRV pin, which serves as both an input and output pin.

The FLT/RDRV is configured as an input only at the time of powerup to adjust the drive-strength, as described in *Drive Strength Adjustment*.

The FLT/RDRV then used as an active low digital output, indicating the fault status thereafter. The pin is a push-pull 5V digital output which goes high when all faults have cleared, which means that there is additional quiescent current through R1 when the pin is forced high.

Depending on the input threshold levels for the external digital receiver connected to the fault pin, the 1.2V which is forced on this pin at power-up could be interpolated as either high or low. For this reason, it is recommended that the receiver has higher thresholds such as those common for CMOS-compatible inputs and not use TTL compatible inputs. If the input thresholds are lower, the 1.2V at power-up can be interpreted as a "high" and therefore showing that the device is not faulted when still powering up.

# 8.3.7 Auxiliary LDO (LMG3651R035 Only)

There is a 5V voltage regulator inside the part used to supply external loads, such as digital isolators for the high-side drive signal. The digital outputs of the part use this rail as their supply. No capacitor is required for stability, but transient response is poor if no external capacitor is provided. If the application uses this rail to supply external circuits, TI recommends to have a capacitor of at least 0.1µF for improved transient response. A larger capacitor can be used for further transient response improvement. The decoupling capacitor used here must be a low-ESR ceramic type. Capacitances above 0.47µF will slow down the start-up time of the LMG365xR035 due to the ramp-up time of the 5V rail.

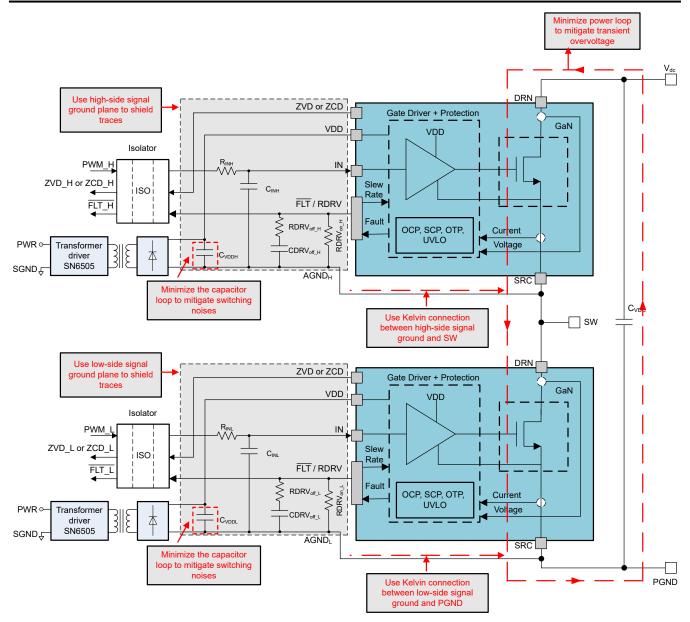

### 8.3.8 Zero-Voltage Detection (ZVD) (LMG3656R035 Only)

The zero-voltage switching (ZVS) converters are widely used to improve the power converter's efficiency. However, in those soft-switching topologies like LLC and triangular current mode (TCM) totem pole PFC, the device can lose ZVS depending on the load condition, inductor, magnetic parameters and control techniques, which affects the system efficiency. To insure ZVS, certain design margins or additional circuits are needed which sacrifices the converter performance and adds components.

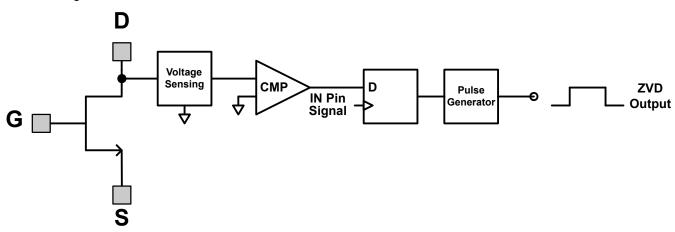

To simplify the system design for soft-switching converters,LMG3656R035 part integrates a zero-voltage detection (ZVD) circuit that provides a digital feedback signal to indicate if the device has achieved ZVS in the current switching cycle. The circuit diagram is shown in  $\boxtimes$  8-4. When the IN pin signal goes high, the logic circuit checks if the device V<sub>DS</sub> has reached below 0V to determine whether the device has achieved zero voltage switching in this switching cycle. Once a ZVS is identified, a pulse-output with a width of T<sub>WD\_ZVD</sub> will be sent out from the ZVD pin after a delay time of T<sub>DL\_ZVD</sub> as indicated in  $\boxtimes$  7-3. Note a certain third quadrant conduction time is required to allow the device detecting a zero-voltage switching, and T<sub>3rd\_ZVD</sub> is a function of the gate driver strength.

図 8-4. Circuit Diagram for Zero-Voltage Detection Circuit Block Diagram

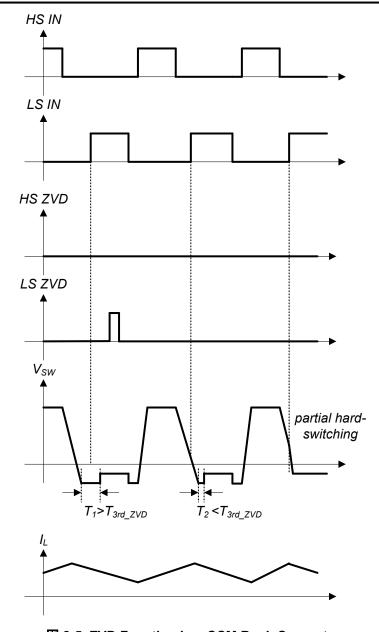

The timings of the ZVD output corresponding to a continuous conduction mode Buck converter is shown in  $\boxtimes$  8-5, and the purpose is to demonstrate how ZVD function works in both hard-switching and soft-switching conditions. The load current going out of the switch node is defined as positive. In CCM buck operation, the high-side the hard-switching device while the low-side device can achieve zero-voltage switching with a proper dead-time settings. In the first switching cycle when low-side GaN IN pin rises, the switch-node voltage  $V_{DS}$  has dropped below zero and stays in third quadrant conduction for a period of  $T_1$ . Since this third quadrant conduction time  $T_1$  is larger than the detection time  $T_{3rd\_ZVD}$  specified in electrical characteristic table, a zero-voltage switching is identified and the ZVD pin outputs a pulse signal to indicate that, and the pulse width of the ZVD pulse is also defined in the electrical characteristic table as  $T_{WD}$ . In the second switching cycle, the device is turned on earlier, and the third quadrant conduction time  $T_2$  is less than  $T_{3rd\_ZVD}$ . In this case, the ZVD signal stays low though the device has achieved ZVS. In the third switching cycle, the IN pin signal is advanced even earlier, and the device is in partial hard-switching. Accordingly, the ZVD output stays low in this case. Note the high side ZVD output stays low in this CCM buck operation as it always has hard-switching.

図 8-5. ZVD Function in a CCM Buck Converter

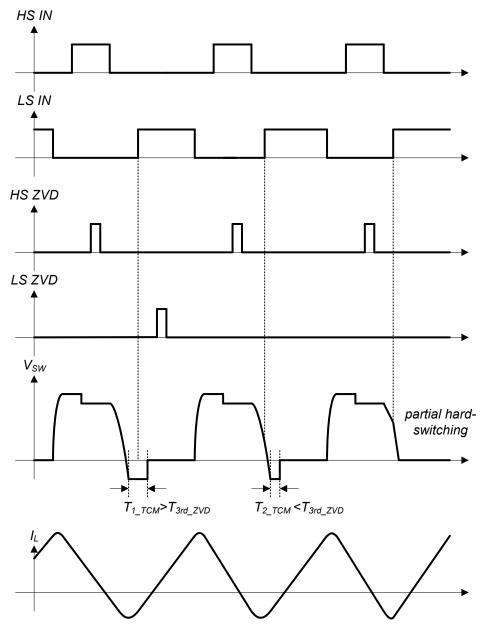

The ZVD function can facilitate the control in soft-switching topology, to illustrate it, the ZVD waveforms in a TCM totem pole PFC is shown in 🗵 8-6. In this diagram, the positive cycle is considered with V<sub>IN</sub> > 0.5 V<sub>OUT</sub>, and the load current going into the switch node is defined as positive. In the first switching cycle, the load current builds enough negative current, and the low-side device achieves ZVS with a clear third quadrant conduction time beyond T<sub>3rd DET</sub>. Therefore, the ZVD outputs a pulse signal and provide the ZVS information back. The ZVD pulses are missing in the next two switching cycles because the third quadrant conduction time becomes shorter in second cycle and the device actual loses ZVS in the third cycle.

**ADVANCE INFORMATION**

図 8-6. ZVD Function in a TCM TP PFC Converter

# 8.3.9 Zero-Current Detection (ZCD) (LMG3657R035 Only)

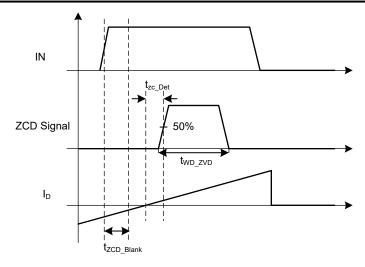

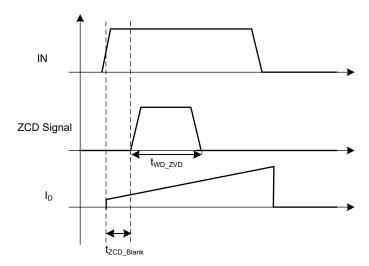

GaN FET is usually used for high frequency soft-switching and the detection of FET current zero-crossing is needed for system control. LMG3657R035 integrates a zero current detection (ZCD) circuit that provides a digital feedback signal to indicate the when the drain-to-source current is positive. When the IN pin signal goes high, the ZCD circuit includes a blanking time  $t_{ZCD\_Blank}$ , to prevent nuisance ZCD triggering during the turn-on transient. Following the blanking period, the ZCD circuit monitors the drain-to-source current. If the current is negative, a pulse-output with a width of  $t_{WD\_ZVD}$  is set on the ZCD pin after detecting the zero-crossing point, with a delay time of  $t_{zc\_Det}$ . If the current is positive, the pulse output is set on the ZCD pin immediately, as indicated in the timing diagrams below.

English Data Sheet: SNOSDL1

図 8-7. ZCD Timing Diagram When FET Turns ON Into Negative Current

図 8-8. ZCD Timing Diagram When FET Turns ON Into Positive Current

# 8.4 Device Functional Modes

The device has one mode of operation that applies when operated within the Recommended Operating Conditions.

# 9 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes, as well as validating and testing their design implementation to confirm system functionality.

# 9.1 Application Information

The LMG365xR035 is a power IC targeting hard-switching and soft-switching applications operating up to 480V bus voltages. GaN devices offer zero reverse-recovery charge enabling high-frequency, hard-switching in applications like the totem-pole PFC. Low  $Q_{oss}$  of GaN devices also benefits soft-switching converters, such as the LLC and phase-shifted full-bridge configurations. As half-bridge configurations are the foundation of the two mentioned applications and many others, this section describes how to use the LMG365xR035 in a half-bridge configuration.

(1)

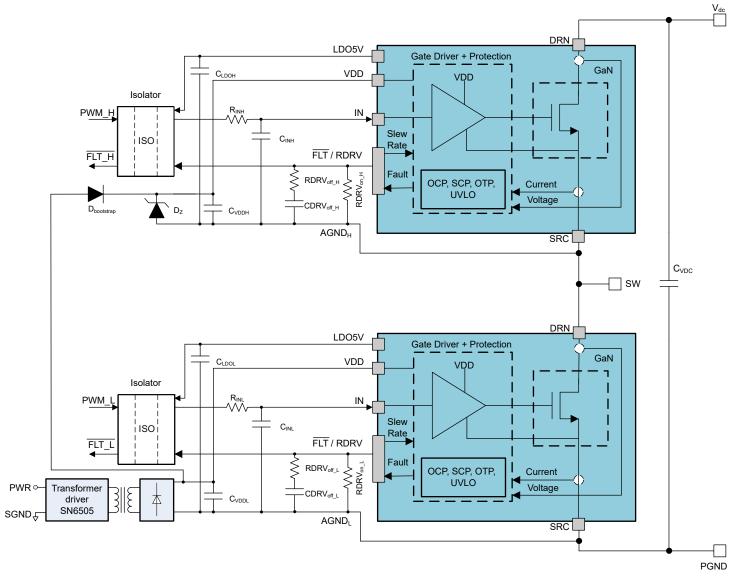

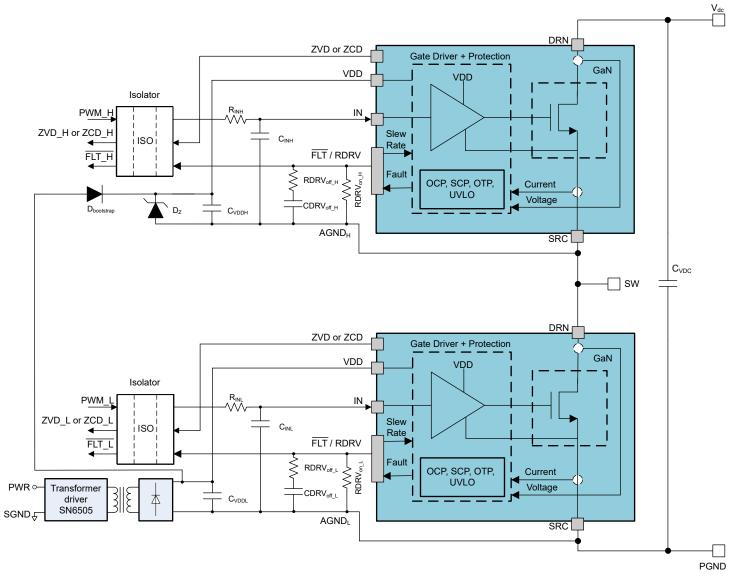

# 9.2 Typical Application

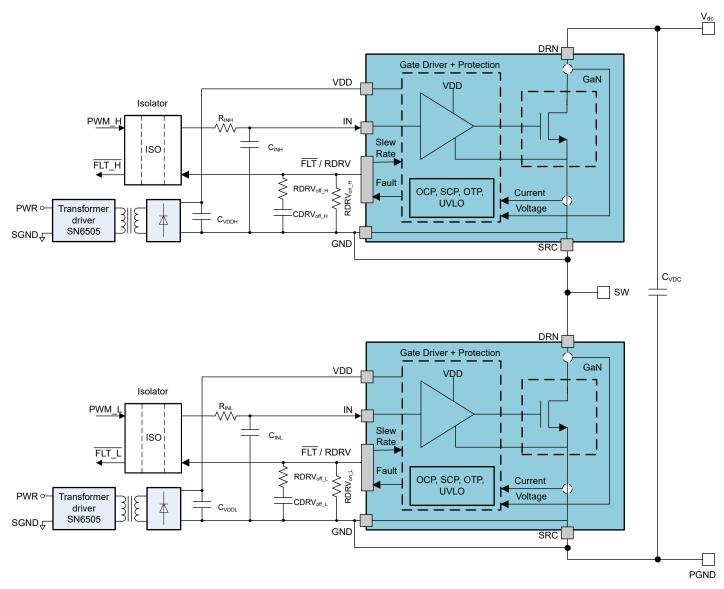

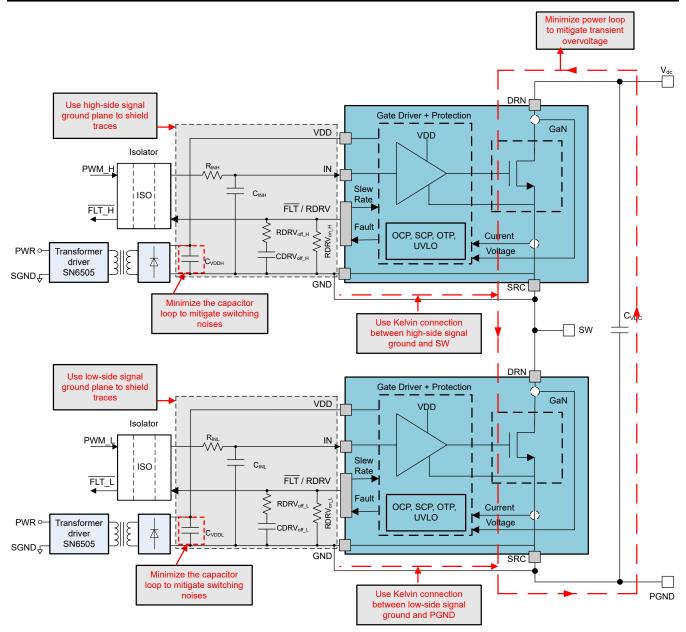

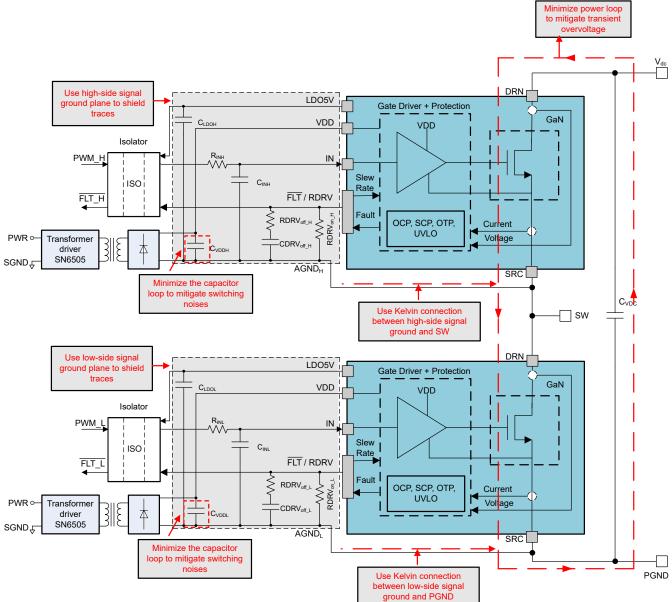

図 9-1. LMG3650R035 Typical Half-Bridge Application With Isolated Power Supply

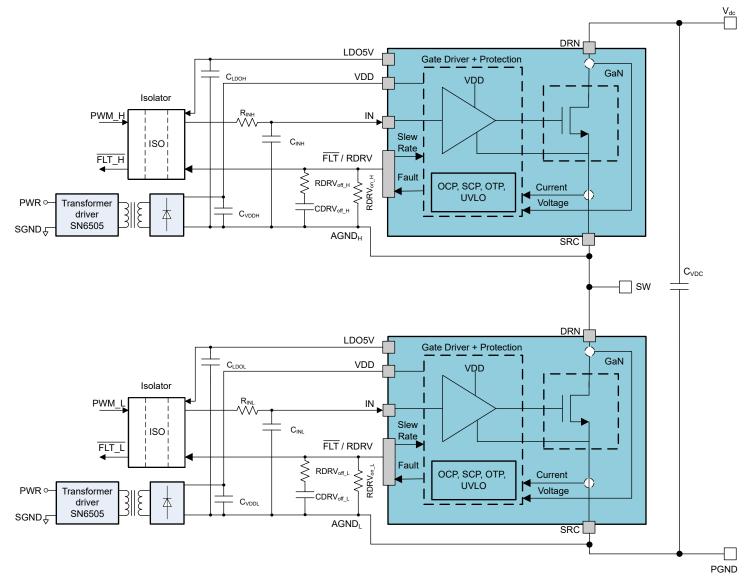

図 9-2. LMG3651R035 Typical Half-Bridge Application With Isolated Power Supply

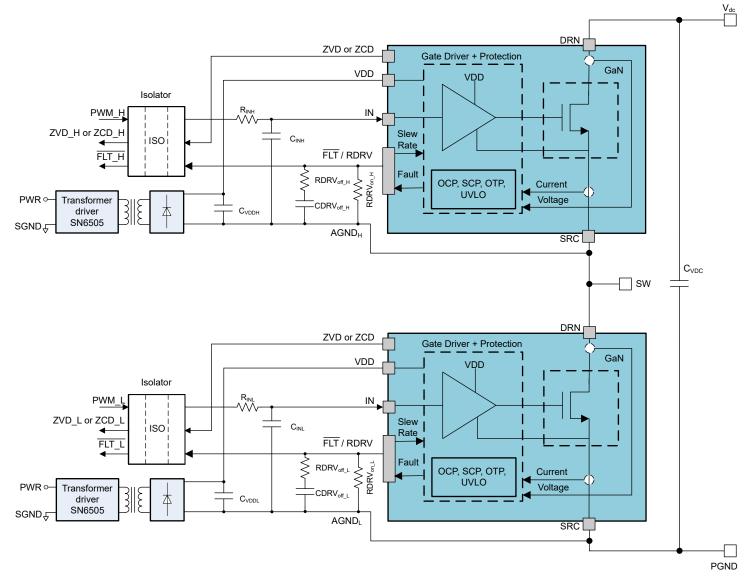

図 9-3. LMG3656R035 or LMG3657R035 Typical Half-Bridge Application With Isolated Power Supply

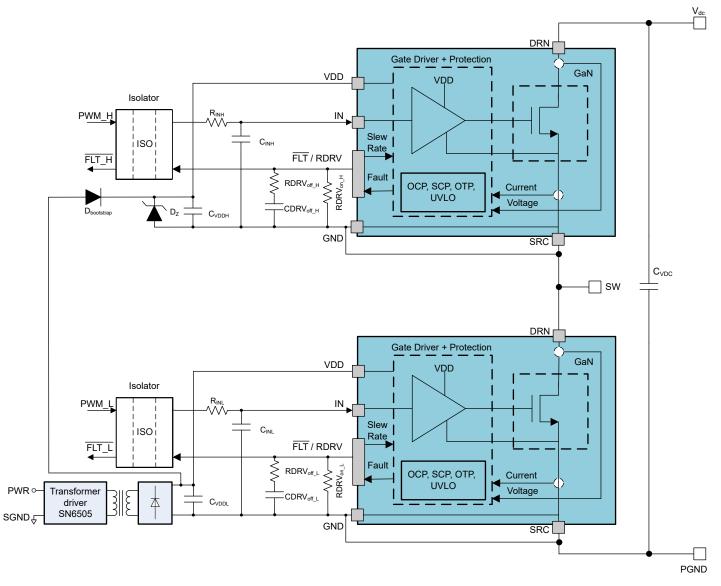

図 9-4. LMG3650R035 Typical Half-Bridge Application With Bootstrap

図 9-5. LMG3651R035 Typical Half-Bridge Application With Bootstrap

図 9-6. LMG3656R035 or LMG3657R035 Typical Half-Bridge Application With Bootstrap

# 9.2.1 Design Requirements

This design example is for a hard-switched boost converter which is representative of PFC applications. Design Parameters shows the system parameters for this design.

表 9-1. Design Parameters

| PARAMETER                | VALUE  |

|--------------------------|--------|

| Input voltage            | 200VDC |

| Output voltage           | 400VDC |

| Input (inductor) current | 20A    |

| Switching frequency      | 100kHz |

# 9.2.2 Detailed Design Procedure

In high-voltage power converters, circuit design and PCB layout are essential for high-performance power converters. As designing a power converter is out of the scope of this document, this data sheet describes how to build well-behaved half-bridge configurations with the LMG365xR035.

### 9.2.2.1 Slew Rate Selection

The slew rate of LMG365xR035 can be adjusted between approximately 10 V/ns and 100V/ns by connecting drive strength adjustment circuit. Refer to Drive Strength Adjustment for the details.

The slew rate affects GaN device performance in terms of:

- Switching loss

- Voltage overshoot

- Noise coupling

- EMI emission

Generally, high slew rates provide low switching loss, but high slew rates can also create higher voltage overshoot, noise coupling, and EMI emissions. Following the design recommendations in this data sheet helps mitigate the challenges caused by a high slew rate. The LMG365xR035 offers circuit designers the flexibility to select the proper slew rate for the best performance of their applications.

### 9.2.2.2 Signal Level-Shifting

In half-bridges, high-voltage level shifters or digital isolators must be used to provide isolation for signal paths between the high-side device and control circuit. Using an isolator is optional for the low-side device. However, using and isolator equalizes the propagation delays between the high-side and low-side signal paths, and provides the ability to use different grounds for the GaN device and the controller. If an isolator is not used on the low-side device, the control ground and the power ground must be connected at the device and nowhere else on the board. For more information, see *Layout Guidelines*. With fast-switching devices, common ground inductance can easily cause noise issues without the use of an isolator.

Choosing a digital isolator for level-shifting is important for improvement of noise immunity. As GaN device can easily create high dv/dt, > 50V/ns, in hard-switching applications, TI highly recommends to use isolators with high common-mode transient immunity (CMTI) and low barrier capacitance. Isolators with low CMTI can easily generate false signals, which could cause shoot-through. The barrier capacitance is part of the isolation capacitance between the signal ground and power ground, which is in direct proportion to the common mode current and EMI emission generated during the switching. Additionally, TI strongly encourages to select isolators which are not edge-triggered. In an edge-triggered isolator, a high dv/dt event can cause the isolator to flip states and cause circuit malfunction.

Generally, ON/OFF keyed isolators with default output low are preferred. Default low state ensures the system will not shoot-through when starting up or recovering from fault events. As a high CMTI event would only cause a very short (a few nanoseconds) false pulse, TI recommends a low pass filter, like  $300\Omega$  and 22pF R-C filter, to be placed at the driver input to filter out these false pulses.

# 9.3 Power Supply Recommendations

The LMG365xR035 only requires an unregulated VDD power supply from 9V to 26V. The low-side supply can be obtained from the local controller supply. The supply of the high-side device must come from an isolated supply or a bootstrap supply.

# 9.3.1 Using an Isolated Power Supply

Using an isolated power supply to power the high-side device has the advantage that it works regardless of continued power-stage switching or duty cycle. Using an isolated power supply can also power the high-side device before power-stage switching begins for a smooth start-up.

The isolated supply can be obtained with a push-pull converter, a flyback converter, a FlyBuck™ converter, or an isolated power module. When using an unregulated supply, the input of LMG365xR035 must not exceed the maximum supply voltage. A 24V TVS diode can be used to clamp the VDD voltage of LMG365xR035 for additional protection. Minimizing the inter-winding capacitance of the isolated power supply or transformer is necessary to reduce switching loss in hard-switched applications. Furthermore, capacitance across the isolated bias supply inject high currents into the signal-ground of the LMG365xR035 and can cause problematic ground-bounce transients. A common-mode choke can alleviate most of these issues.

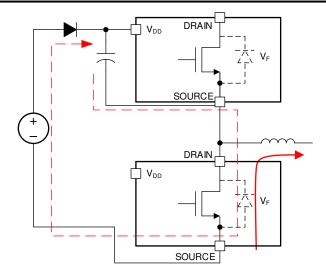

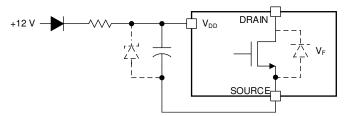

# 9.3.2 Using a Bootstrap Diode

In half-bridge configuration, a floating supply is necessary for the high-side device. To obtain the best performance of LMG365xR035, TI highly recommends *Using an Isolated Power Supply*. A bootstrap supply can be used with the recommendations of this section.

### 9.3.2.1 Diode Selection

The LMG365xR035 offers no reverse-recovery charge and very limited output charge. Hard-switching circuits using the LMG365xR035 also exhibit high voltage slew rates. A compatible bootstrap diode must not introduce high output charge and reverse-recovery charge.

A silicon carbide diode, like the GB01SLT06-214, can be used to avoid reverse-recovery effects. The SiC diode has an output charge of 3nC. Although there is additional loss from its output charge, it does not dominate the losses of the switching stage.

### 9.3.2.2 Managing the Bootstrap Voltage

In a synchronous buck or other converter where the low-side switch occasionally operates in third-quadrant, the bootstrap supply charges through a path that includes the third-quadrant voltage drop of the low-side LMG365xR035 during the dead time as shown in Charging Path for Bootstrap Diode. This third-quadrant drop can be large, which can over-charge the bootstrap supply in certain conditions. The  $V_{DD}$  supply of LMG365xR035 must be kept below 18V.

English Data Sheet: SNOSDL1

**図 9-7. Charging Path for Bootstrap Diode**

As shown in Suggested Bootstrap Regulation Circuit, the recommended bootstrap supply includes a bootstrap diode, a series resistor, and a 16V TVS or Zener diode in parallel with the  $V_{DD}$  bypass capacitor to prevent damaging the high-side LMG365xR035. The series resistor limits the charging current at start-up and when the low-side device is operating in third-quadrant mode. This resistor must be selected to allow sufficient current to power the LMG365xR035 at the desired operating frequency. At 100kHz operation, TI recommends a value of approximately  $2\Omega$ . At higher frequencies, this resistor value must be reduced or the resistor omitted entirely to ensure sufficient supply current.

☑ 9-8. Suggested Bootstrap Regulation Circuit

# 9.4 Layout

### 9.4.1 Layout Guidelines

The layout of the LMG365xR035 is critical to its performance and functionality. Because the half-bridge configuration is typically used with these GaN devices, layout recommendations are considered with this configuration. A four-layer or higher layer count board is required to reduce the parasitic inductances of the layout to achieve suitable performance. Critical layout guidelines are summarized below, and more details are further elaborated in the following sections.

図 9-9. LMG3650R035 Typical Schematic With Layout Considerations

図 9-10. LMG3651R035 Typical Schematic With Layout Considerations

図 9-11. LMG3656R035 or LMG3657R035 Typical Schematic With Layout Considerations

# 10 Device and Documentation Support

TI offers an extensive line of development tools. Tools and software to evaluate the performance of the device, generate code, and develop solutions are listed below.

# 10.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、www.tij.co.jp のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。 変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

# 10.2 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 10.3 Trademarks

FlyBuck<sup>™</sup> and テキサス・インスツルメンツ E2E<sup>™</sup> are trademarks of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

# 10.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

# 10.5 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

# 11 Revision History

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| DATE          | REVISION | NOTES           |

|---------------|----------|-----------------|

| December 2024 | *        | Initial Release |

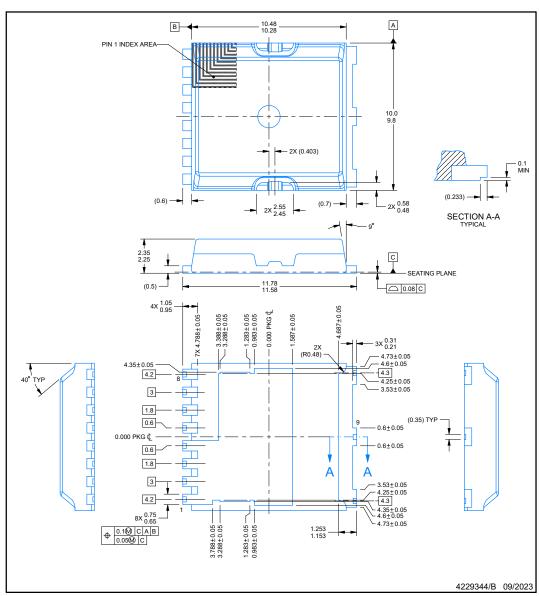

# 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

**KLA0009A**

# **PACKAGE OUTLINE**

# TOLL - 2.35 mm max height

TO LEADLESS

### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

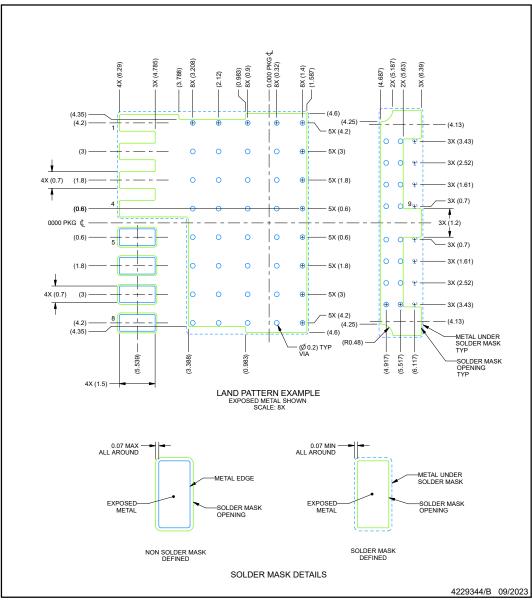

# **EXAMPLE BOARD LAYOUT**

# **KLA0009A**

# TOLL - 2.35 mm max height

TO LEADLESS

NOTES: (continued)

- This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- number SLDAZ/1 (www.u.com/uicsuaz/1).

S. Visa are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

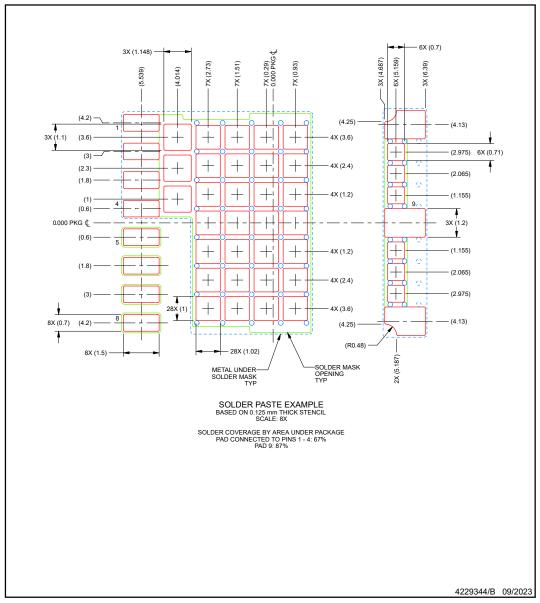

# **EXAMPLE STENCIL DESIGN**

# **KLA0009A**

TOLL - 2.35 mm max height

TO LEADLESS

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

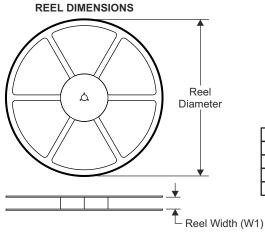

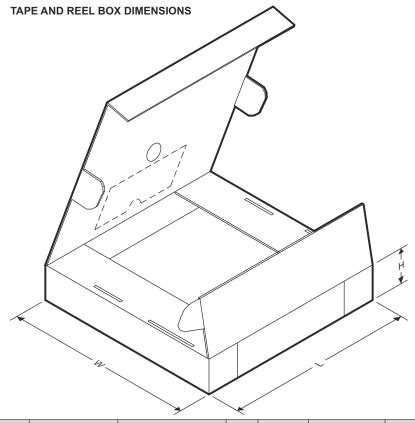

# 12.1 Tape and Reel Information

# TAPE DIMENSIONS + K0 + P1 + B0 W Cavity + A0 +

|    | D: 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                  |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

|    |                                                           |

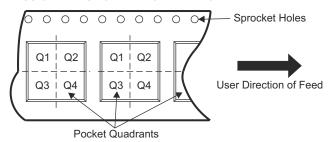

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| Device           | Package<br>Type | Package<br>Drawing | Pins | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|-----------------|--------------------|------|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| XLMG3650R035KLAT | то              | KLA                | 9    | 2000 | 330.0                    | 24.4                     | 10.20      | 11.98      | 2.6        | 12.0       | 21.0      | Q2               |

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| XLMG3650R035KLAT | ТО           | KLA             | 9    | 2000 | 356.0       | 356.0      | 45.0        |

www.ti.com 22-Oct-2025

### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|----------------|-----------------------|------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                |                       |      | (4)                           | (5)                        |              |                  |

| XLMG3650R035KLAT      | Active | Preproduction | TO (KLA)   9   | 250   LARGE T&R       | -    | Call TI                       | Call TI                    | -40 to 150   |                  |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

- (3) RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

- (4) Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

- (5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

- (6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

# 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、TIの総合的な品質ガイドライン、 ti.com または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。 TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日: 2025 年 10 月