# LMG352xR050 650V 50mΩ GaN FET、統合型ドライバと保護機能および温度レポート機能搭載

## 1 特長

- ゲート ドライバ内蔵の 650 650V GaN オン Si FET

- 高精度のゲートバイアス電圧を内蔵

- FET ホールド オフ : 200V/ns

- 3.6MHz のスイッチング周波数

- 15V/ns ~ 150V/ns のスルーレートによるスイッチング性能の最適化と EMI の軽減

- 7.5V ~ 18V 電源で動作

- 堅牢な保護

- サイクル単位の過電流保護と 100ns 未満の応答時間を持つラッチ付き短絡保護

- ハードスイッチング中のサージ耐性 : 720V

- 内部過熱および UVLO 監視機能による自己保護

- 高度なパワー マネージメント

- デジタル温度 PWM 出力

- LMG3526R050 は、ソフトスイッチング コンバータを容易にするゼロ電圧検出機能を装備

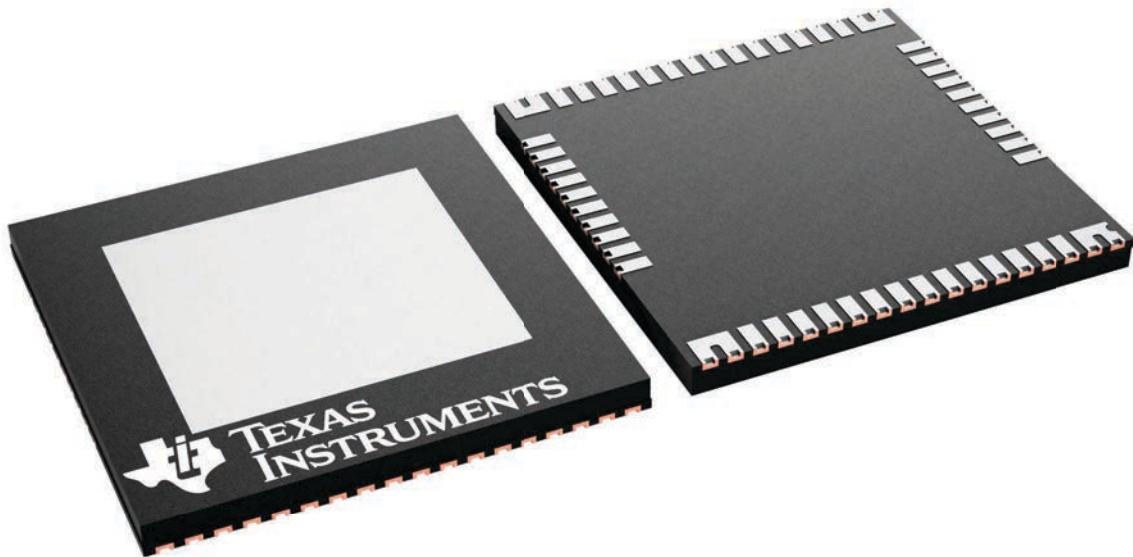

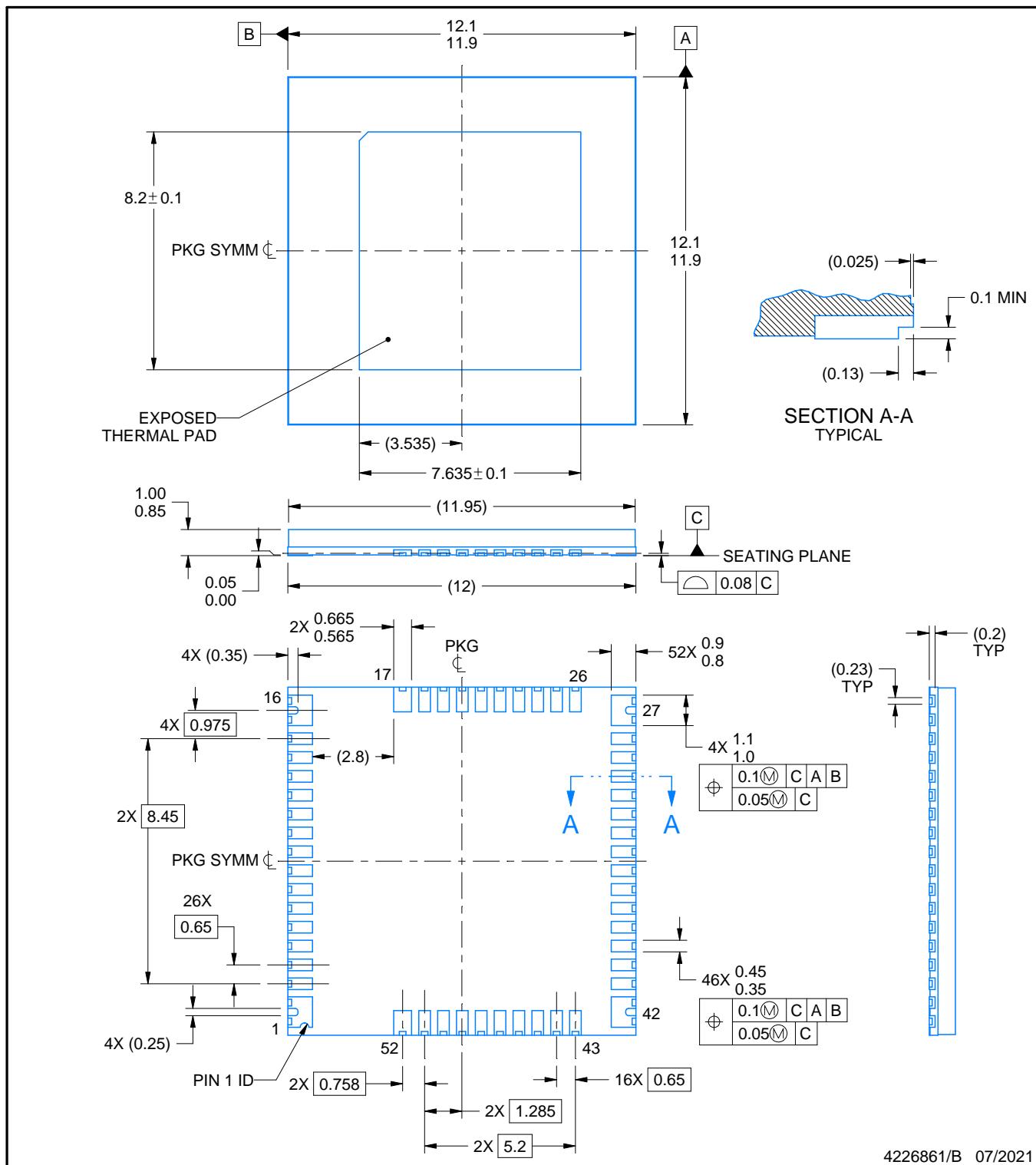

- 上面から放熱する 12mm × 12mm の VQFN パッケージにより、電気的経路と熱的経路を分離することで電力ループのインダクタンスを最小化

## 2 アプリケーション

- スイッチモード パワー コンバータ

- 商用ネットワークとサーバーの電源

- 商用テレコム整流器

- ソーラー インバータと産業用モーター ドライバ

- 無停電電源

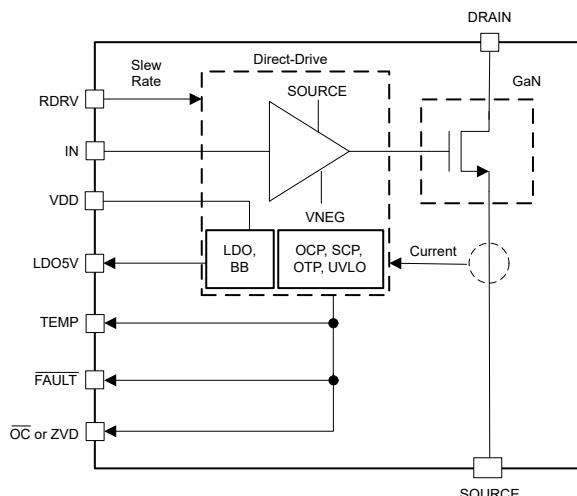

概略ブロック図

## 3 概要

統合型ドライバと保護機能を搭載した LMG352xR050 GaN FET は、スイッチモード パワー コンバータを対象としています。このデバイスを使うと、設計者は新しいレベルの電力密度と効率を実現できます。

LMG352xR050 は、最大 150V/ns のスイッチング速度を実現できるシリコン ドライバを内蔵しています。テキサス・インスツルメンツの統合型高精度ゲート バイアスは、ディスクリートシリコン ゲート ドライバと比較して、より広いスイッチング SOA をもたらします。この統合とテキサス・インスツルメンツの低インダクタンス パッケージの組み合わせにより、ハードスイッチング電源トポロジでもノイズの少ないスイッチングとリングングの最小化を実現できます。調整可能なゲート ドライブ強度により、15V/ns ~ 150V/ns のスルーレートの制御が可能で、EMI のアクティブ制御とスイッチング性能の最適化に使用できます。LMG3526R050 は、ゼロ電圧検出 (ZVD) 機能を備えており、ゼロ電圧スイッチングが発生したとき ZVD ピンからパルスを出力します。

先進的な電源管理機能として、デジタル温度レポート、フォルト検出を備えています。GaN FET の温度は可変デューティ サイクル PWM 出力により通知されるため、デバイスの負荷の管理が簡単になります。報告される障害には、過電流、短絡、過熱、VDD UVLO、高インピーダンス RDRV ピンがあります。

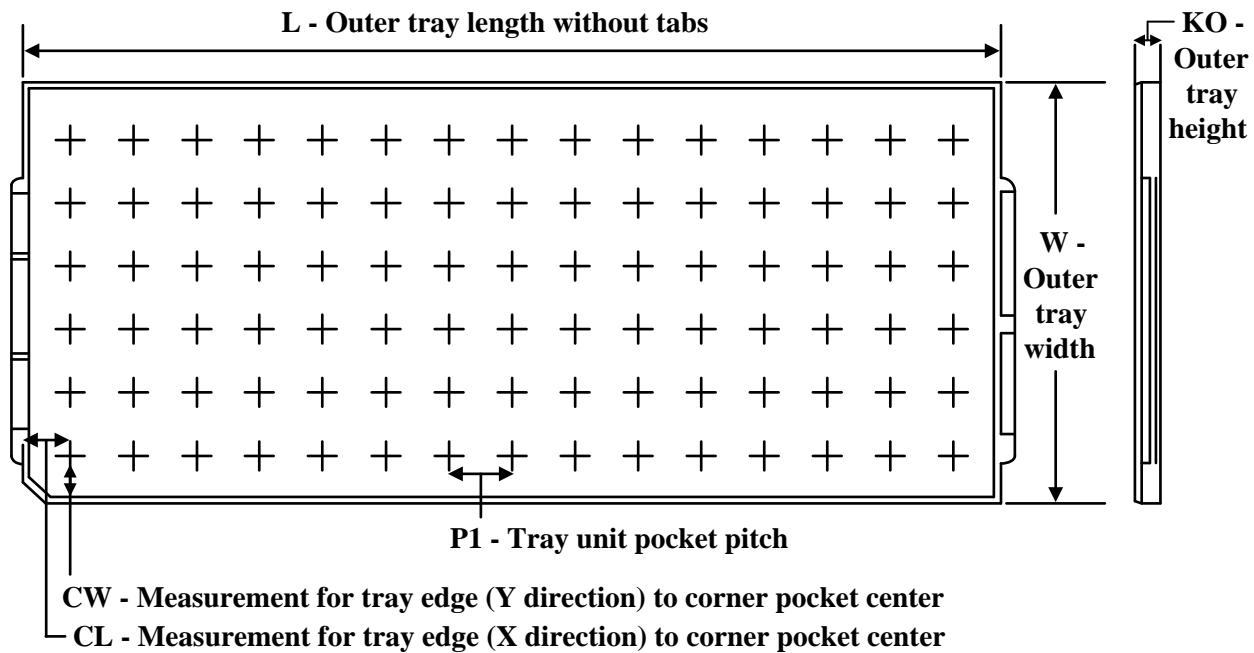

### パッケージ情報

| 部品番号        | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-------------|----------------------|--------------------------|

| LMG3522R050 |                      |                          |

| LMG3526R050 | RQS (VQFN, 52)       | 12.00mm × 12.00mm        |

(1) 詳細については、「[メカニカル、パッケージ、および注文情報](#)」を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

### 製品情報

| 部品番号        | ゼロ電圧検出機能 |

|-------------|----------|

| LMG3522R050 | —        |

| LMG3526R050 | あり       |

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                           |    |                           |    |

|---------------------------|----|---------------------------|----|

| 1 特長                      | 1  | 7.4 スタート-アップ・シーケンス        | 32 |

| 2 アプリケーション                | 1  | 7.5 デバイスの機能モード            | 33 |

| 3 概要                      | 1  | 8 アプリケーションと実装             | 34 |

| 4 ピン構成および機能               | 3  | 8.1 アプリケーション情報            | 34 |

| 5 仕様                      | 5  | 8.2 代表的なアプリケーション          | 35 |

| 5.1 絶対最大定格                | 5  | 8.3 推奨事項と禁止事項             | 40 |

| 5.2 ESD 定格                | 6  | 8.4 電源に関する推奨事項            | 40 |

| 5.3 推奨動作条件                | 6  | 8.5 レイアウト                 | 42 |

| 5.4 熱に関する情報               | 6  | 9 デバイスおよびドキュメントのサポート      | 46 |

| 5.5 電気的特性                 | 7  | 9.1 ドキュメントのサポート           | 46 |

| 5.6 スイッチング特性              | 9  | 9.2 ドキュメントの更新通知を受け取る方法    | 46 |

| 5.7 代表的特性                 | 11 | 9.3 サポート・リソース             | 46 |

| 6 パラメータ測定情報               | 13 | 9.4 商標                    | 46 |

| 6.1 スイッチング パラメータ          | 13 | 9.5 静電気放電に関する注意事項         | 46 |

| 6.2 安全 operation 領域 (SOA) | 16 | 9.6 Export Control Notice | 46 |

| 7 詳細説明                    | 17 | 9.7 用語集                   | 46 |

| 7.1 概要                    | 17 | 10 改訂履歴                   | 47 |

| 7.2 機能ブロック図               | 18 | 11 メカニカル、パッケージ、および注文情報    | 47 |

| 7.3 機能説明                  | 20 |                           |    |

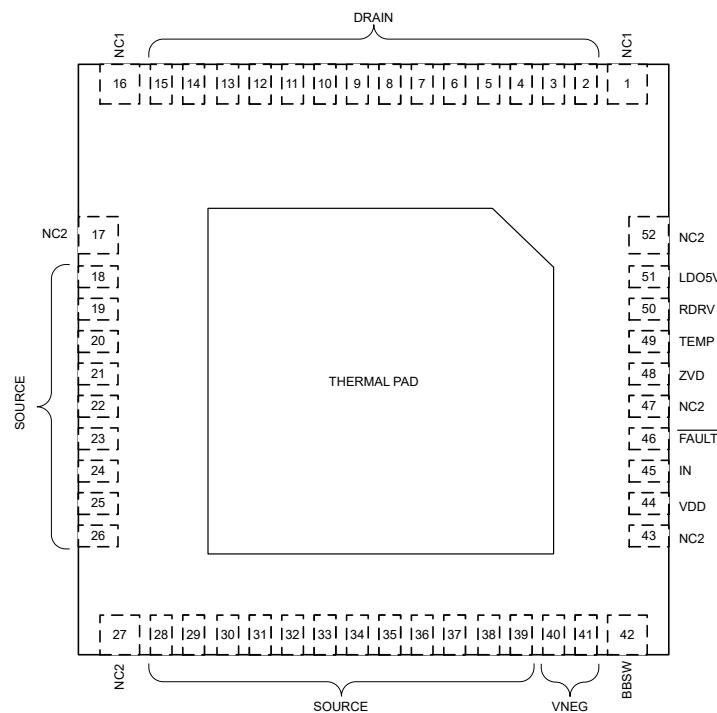

## 4 ピン構成および機能

図 4-1. LMG3522R050 RQS パッケージ、52 ピン VQFN ( 上面図 )

図 4-2. LMG3526R050 RQS パッケージ、52 ピン VQFN ( 上面図 )

表 4-1. ピンの機能

| ピン      |                |                | 種類 <sup>(1)</sup> | 説明                                                                                                                                            |

|---------|----------------|----------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 名称      | LMG3522R050    | LMG3526R050    |                   |                                                                                                                                               |

| NC1     | 1、16           | 1、16           | —                 | QFN パッケージを PCB にアンカーするために使用します。ピンは、PCB ランディング・パッドに半田付けする必要があります。PCB のランド・パッドは半田なしのマスク定義のパッドであり、PCB 上の他の金属に物理的に接続することはできません。DRAIN への内部接続。      |

| DRAIN   | 2 ~ 15         | 2 ~ 15         | P                 | GaN FET のドレイン。NC1 に内部接続されています。                                                                                                                |

| NC2     | 17、27、43、47、52 | 17、27、43、47、52 | —                 | QFN パッケージを PCB にアンカーするために使用します。ピンは、PCB ランディング・パッドに半田付けする必要があります。PCB のランド・パッドは半田なしのマスク定義のパッドであり、PCB 上の他の金属に物理的に接続することはできません。内部でソースとサーマルパッドに接続。 |

| ソース     | 18–26、28–39    | 18–26、28–39    | P                 | GaN FET ソース。NC2 およびサーマルパッドに内部接続されています。                                                                                                        |

| VNEG    | 40、41          | 40、41          | P                 | 内部昇降圧コンバータの負出力。デブレッショングループ型 GaN FET をオフにするために、負電源として使用します。2.2 $\mu$ F のコンデンサでソースにバイパスします。                                                     |

| BBSW    | 42             | 42             | P                 | 内部バック・ブースト・コンバータ・スイッチ・ピン。このポイントからソースにインダクタを接続します。                                                                                             |

| VDD     | 44             | 44             | P                 | デバイス入力電源。                                                                                                                                     |

| IN      | 45             | 45             | I                 | FET のオン/オフ用に使用される CMOS 互換非反転入力。                                                                                                               |

| FAULT   | 46             | 46             | O                 | 故障状態中に Low にアサートするプッシュプルデジタル出力。詳細については、 <a href="#">故障検出</a> を参照してください。                                                                       |

| OC      | 48             | —              | O                 | 過電流および短絡フォルト状態中に Low にアサートするプッシュプルデジタル出力。詳細については、 <a href="#">故障検出</a> を参照してください。                                                             |

| ZVD     | —              | 48             | O                 | デバイスが電流スイッチングサイクルにおいてゼロ電圧スイッチングを達成しているかどうかを示す、ゼロ電圧検出信号を出力するプッシュプルデジタル出力。詳細については、 <a href="#">ゼロ電圧検出 (ZVD)</a> を参照してください。                      |

| TEMP    | 49             | 49             | O                 | GaN FET の温度に関する情報を提供するプッシュプル・デジタル出力。9kHz の固定パルス波形を出力します。デバイスの温度は、波形のデューティサイクルとしてエンコードされます。                                                    |

| RDRV    | 50             | 50             | I                 | ドライブ強度選択ピン。このピンと SOURCE との間に抵抗を接続して、ターンオン駆動強度を設定し、スルーレートを制御します。このピンを SOURCE に接続すると 150V/ns を有効にし、このピンを LDO5V に接続すると、100V/ns を有効にできます。         |

| LDO5V   | 51             | 51             | P                 | 外部デジタルアイソレーター用の 5V LDO 出力。これを外部で使用する場合は、0.1 $\mu$ F 以上のコンデンサをソースに接続します。                                                                       |

| サーマルパッド | —              | —              | —                 | サーマルパッド。ソースと NC2 に内部接続されています。                                                                                                                 |

(1) I = 入力、O = 出力、P = 電源、

## 5 仕様

### 5.1 絶対最大定格

特に記述のない限り：電圧はソース<sup>(1)</sup>を基準にしています

|                                   |                                                        | 最小値                               | 最大値                 | 単位 |

|-----------------------------------|--------------------------------------------------------|-----------------------------------|---------------------|----|

| $V_{DS}$                          | ドレインソース間電圧、FET オフ                                      |                                   | 650                 | V  |

| $V_{DS(\text{surge})}$            | ドレインソース間電圧、FET スイッチング、サージ条件 <sup>(2)</sup>             |                                   | 720                 | V  |

| $V_{DS(\text{tr})(\text{surge})}$ | ドレインソース間過渡リンクギング・ピーク電圧、FET オフ、サージ状態 <sup>(2) (3)</sup> |                                   | 800                 | V  |

| ピン電圧                              | $V_{DD}$                                               | -0.3                              | 20                  | V  |

|                                   | LDO5V                                                  | -0.3                              | 5.5                 | V  |

|                                   | VNEG                                                   | -16                               | 0.5                 | V  |

|                                   | BBSW                                                   | $V_{VNEG-1} \text{ } V_{VDD+0.5}$ |                     | V  |

|                                   | IN                                                     | -0.3                              | 20                  | V  |

|                                   | 故障、 $\overline{OC}$ 、TEMP                              | -0.3                              | $V_{LDO5V+0}$<br>.3 | V  |

|                                   | RDRV                                                   | -0.3                              | 5.5                 | V  |

| $I_{D(\text{RMS})}$               | ドレイン RMS 電流、FET オン                                     |                                   | 44                  | A  |

| $I_{D(\text{pulse})}$             | ドレインパルス電流、FET オン、 $t_p < 10\mu\text{s}$ <sup>(4)</sup> | -96                               | 内部的に制限              | A  |

| $I_{S(\text{pulse})}$             | ソースパルス電流、FET オフ、 $t_p < 1\mu\text{s}$                  |                                   | 60                  | A  |

| $T_J$                             | 動作時接合部温度 <sup>(5)</sup>                                | -40                               | 150                 | °C |

| $T_{\text{stg}}$                  | 保存温度                                                   | -55                               | 150                 | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) スイッチング・サイクルのドレインソース間電圧定格の説明については、セクション 7.3.3 を参照してください。

- (3)  $t_1 < 200\text{ns}$  ( インチ ) 図 7-1 で。

- (4) FET が自動的にシャットオフされないように、正のパルス電流は過電流スレッショルドを下回る必要があります。 $t_p < 10\mu\text{s}$  に対して、FET のドレイン固有の正のパルス電流定格は 96A です。

- (5) 接合部温度のテスト条件については、「電気的およびスイッチング特性」表を参照してください。

## 5.2 ESD 定格

| パラメータ       |      |                                                          | 値     | 単位 |

|-------------|------|----------------------------------------------------------|-------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>     | ±2000 | V  |

|             |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 準拠 <sup>(2)</sup> | ±500  | V  |

- (1) JEDEC ドキュメント JEP157 には、500V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

- (2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

## 5.3 推奨動作条件

特に記述のない限り：電圧はソースを基準にしています

|              |                                                     | 最小値                                           | 公称値 | 最大値 | 単位 |

|--------------|-----------------------------------------------------|-----------------------------------------------|-----|-----|----|

|              | 電源電圧                                                | VDD( $V_{VDD} < 9V$ でディレーティングされる最大スイッチング周波数 ) | 7.5 | 12  | 18 |

|              | 入力電圧                                                | IN                                            | 0   | 5   | 18 |

| $I_{D(RMS)}$ | ドレイン RMS 電流                                         |                                               |     | 32  | A  |

|              | 正のソース電流                                             | LDO5V                                         |     | 25  | mA |

| $R_{RDRV}$   | 外部スルーレート制御抵抗からソースへの RDRV                            | 0                                             | 500 |     | kΩ |

| $C_{VNEG}$   | 外部バイパスコンデンサからソースへの容量                                | 1                                             | 10  |     | μF |

| $L_{BBSW}$   | 外部昇降圧インダクタから SOURCE への BBSW のインダクタンス <sup>(1)</sup> | 3                                             | 4.7 | 10  | μH |

- (1) 1A より大きい電流定格を推奨します。

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> |                     | LMG352xR050  | 単位   |

|----------------------|---------------------|--------------|------|

|                      |                     | RQS ( VQFN ) |      |

|                      |                     | 52 ピン        |      |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 0.68         | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.5 電気的特性

特に記述のない限り：電圧、抵抗、容量、およびインダクタンスは SOURCE を基準としています。 $-40^{\circ}\text{C} \leq T_J \leq 125^{\circ}\text{C}$ 、 $V_{\text{DS}} = 520\text{V}$ 、 $9\text{V} \leq V_{\text{VDD}} \leq 18\text{V}$ 、 $V_{\text{IN}} = 0\text{V}$ 、RDRV は LDO5V に接続、 $L_{\text{BBSW}} = 4.7\mu\text{H}$

| パラメータ                        | テスト条件                                          | 最小値                                                                         | 標準値  | 最大値  | 単位                   |

|------------------------------|------------------------------------------------|-----------------------------------------------------------------------------|------|------|----------------------|

| <b>GAN パワー ドランジスタ</b>        |                                                |                                                                             |      |      |                      |

| $R_{\text{DS(on)}}$          | ドレインソース間オン抵抗                                   | $V_{\text{IN}} = 5\text{V}$ 、 $T_J = 25^{\circ}\text{C}$                    | 43   | 55   | $\text{m}\Omega$     |

|                              |                                                | $V_{\text{IN}} = 5\text{V}$ 、 $T_J = 125^{\circ}\text{C}$                   | 73   |      |                      |

| $V_{\text{SD}}$              | 第3象限モードのソース-ドレイン電圧                             | $I_{\text{S}} = 0.1\text{A}$                                                | 3.8  |      | $\text{V}$           |

|                              |                                                | $I_{\text{S}} = 15\text{A}$                                                 | 3    | 5.3  |                      |

| $I_{\text{DSS}}$             | ドレイン リーク電流                                     | $V_{\text{DS}} = 650\text{V}$ 、 $T_J = 25^{\circ}\text{C}$                  | 1    |      | $\mu\text{A}$        |

|                              |                                                | $V_{\text{DS}} = 650\text{V}$ 、 $T_J = 125^{\circ}\text{C}$                 | 7    |      |                      |

| $C_{\text{OSS}}$             | 出力容量                                           | $V_{\text{DS}} = 400\text{V}$                                               | 148  |      | $\text{pF}$          |

| $C_{\text{O(er)}}$           | エネルギーに関連した実効出力キャパシタンス                          |                                                                             | 185  |      | $\text{pF}$          |

| $C_{\text{O(tr)}}$           | 時間に関連した実効出力キャパシタンス                             | $V_{\text{DS}} = 0\text{V} \sim 400\text{V}$                                | 260  |      | $\text{pF}$          |

| $Q_{\text{OSS}}$             | 出力電荷量                                          |                                                                             | 100  |      | $\text{nC}$          |

| $Q_{\text{RR}}$              | 逆方向回復電荷                                        |                                                                             | 0    |      | $\text{nC}$          |

| <b>VDD – 電源電流</b>            |                                                |                                                                             |      |      |                      |

|                              | $V_{\text{DD}}$ 静止電流                           | $V_{\text{VDD}} = 12\text{V}$ 、 $V_{\text{IN}} = 0\text{V}$ または $5\text{V}$ | 700  | 1200 | $\mu\text{A}$        |

|                              | $V_{\text{DD}}$ 動作時電流                          | $V_{\text{VDD}} = 12\text{V}$ 、 $f_{\text{IN}} = 140\text{kHz}$ 、ソフトスイッチング  | 9.7  | 11   | $\text{mA}$          |

| <b>バックブーストコンバータ</b>          |                                                |                                                                             |      |      |                      |

|                              | VNEG 出力電圧                                      | VNEG シンク電流 $40\text{mA}$                                                    | -14  |      | $\text{V}$           |

| $I_{\text{BBSW, PK(low)}}$   | 低いピーク電流モード設定時のピーク BBSW ソース電流 (ピーク外部昇降圧インダクタ電流) |                                                                             | 0.3  | 0.4  | 0.5 $\text{A}$       |

| $I_{\text{BBSW, PK(high)}}$  | 高いピーク電流モード設定時のピーク BBSW ソース電流 (ピーク外部昇降圧インダクタ電流) |                                                                             | 0.8  | 1    | 1.2 $\text{A}$       |

|                              | 高ピーク電流モード設定有効化 – 正方向のスレッショルド周波数                |                                                                             | 280  | 420  | 515 $\text{kHz}$     |

| <b>LDO5V</b>                 |                                                |                                                                             |      |      |                      |

|                              | 出力電圧                                           | LDO5V のソース $25\text{mA}$                                                    | 4.75 | 5    | 5.25 $\text{V}$      |

|                              | 短絡電流                                           |                                                                             | 25   | 50   | 100 $\text{mA}$      |

| <b>IN</b>                    |                                                |                                                                             |      |      |                      |

| $V_{\text{IN, IT+}}$         | 正方向入力スレッショルド電圧                                 |                                                                             | 1.7  | 1.9  | 2.45 $\text{V}$      |

| $V_{\text{IN, IT-}}$         | 負方向入力スレッショルド電圧                                 |                                                                             | 0.7  | 1    | 1.3 $\text{V}$       |

|                              | 入力スレッショルドのヒステリシス                               |                                                                             | 0.7  | 0.9  | 1.3 $\text{V}$       |

|                              | 入力プルダウン抵抗                                      | $V_{\text{IN}} = 2\text{V}$                                                 | 100  | 150  | 200 $\text{k}\Omega$ |

| <b>故障、OC/ZVD、TEMP – 出力駆動</b> |                                                |                                                                             |      |      |                      |

|                              | 低レベル出力電圧                                       | 出力シンク $8\text{mA}$                                                          | 0.16 | 0.4  | $\text{V}$           |

|                              | 高レベル出力電圧                                       | 出力ソース $8\text{mA}$ 、 $V_{\text{LDO5V}} - V_{\text{O}}$ で測定                  | 0.2  | 0.45 | $\text{V}$           |

| <b>VDD、VNEG – 低電圧誤動作防止</b>   |                                                |                                                                             |      |      |                      |

| $V_{\text{VDD, T+ (UVLO)}}$  | VDD UVLO – 正方向のスレッショルド電圧                       |                                                                             | 6.4  | 7    | 7.6 $\text{V}$       |

|                              | VDD UVLO – 負方向のスレッショルド電圧                       |                                                                             | 6    | 6.5  | 7.1 $\text{V}$       |

|                              | VDD UVLO – 入力スレッショルド電圧のヒステリシス                  |                                                                             | 510  |      | $\text{mV}$          |

## 5.5 電気的特性 (続き)

特に記述のない限り：電圧、抵抗、容量、およびインダクタンスは SOURCE を基準としています。 $-40^{\circ}\text{C} \leq T_J \leq 125^{\circ}\text{C}$ 、 $V_{\text{DS}} = 520\text{V}$ 、 $9\text{V} \leq V_{\text{VDD}} \leq 18\text{V}$ 、 $V_{\text{IN}} = 0\text{V}$ 、RDRV は LDO5V に接続、 $L_{\text{BBSW}} = 4.7\mu\text{H}$

| パラメータ                     | テスト条件                                                                                                                                                                                                                                               | 最小値                                                   | 標準値    | 最大値   | 単位               |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------|-------|------------------|

| VNEG UVLO – 負方向のスレッショルド電圧 |                                                                                                                                                                                                                                                     | -13.6                                                 | -13.0  | -12.3 | V                |

| VNEG UVLO – 正方向のスレッショルド電圧 |                                                                                                                                                                                                                                                     | -13.3                                                 | -12.75 | -12.1 | V                |

| <b>ゲート ドライバ</b>           |                                                                                                                                                                                                                                                     |                                                       |        |       |                  |

| ターンオンのスルーレート              | $V_{\text{DS}} < 320\text{V}$ から $V_{\text{DS}} < 80\text{V}$ まで、RDRV を LDO5V から切断、 $R_{\text{RDRV}} = 300\text{k}\Omega$ 、 $T_J = 25^{\circ}\text{C}$ 、 $V_{\text{BUS}} = 400\text{V}$ 、 $L_{\text{HB}}$ 電流 = 10A、 <a href="#">図 6-1</a> を参照してください | 15                                                    |        |       | V/ns             |

|                           | $V_{\text{DS}} < 320\text{V}$ から $V_{\text{DS}} < 80\text{V}$ まで、RDRV を LDO5V に接続、 $T_J = 25^{\circ}\text{C}$ 、 $V_{\text{BUS}} = 400\text{V}$ 、 $L_{\text{HB}}$ 電流 = 10A、 <a href="#">図 6-1</a> を参照してください                                          | 100                                                   |        |       | V/ns             |

|                           | $V_{\text{DS}} < 320\text{V}$ から $V_{\text{DS}} < 80\text{V}$ まで、RDRV を LDO5V から切断、 $R_{\text{RDRV}} = 0\Omega$ 、 $T_J = 25^{\circ}\text{C}$ 、 $V_{\text{BUS}} = 400\text{V}$ 、 $L_{\text{HB}}$ 電流 = 10A、 <a href="#">図 6-1</a> を参照してください           | 150                                                   |        |       | V/ns             |

| GaN FET の最大スイッチング周波数      | $V_{\text{NEG}}$ の立ち上がりから-13.25V 超まで、ソフトスイッチングの最大スイッチング周波数は $V_{\text{VDD}} < 9\text{V}$ のときディレーティング                                                                                                                                                | 3.6                                                   |        |       | MHz              |

| <b>故障</b>                 |                                                                                                                                                                                                                                                     |                                                       |        |       |                  |

| $I_{\text{T(OC)}}$        | ドレイン過電流故障 – スレッショルド電流                                                                                                                                                                                                                               | 45                                                    | 55     | 65    | A                |

| $I_{\text{T(SC)}}$        | ドレイン短絡故障 – スレッショルド電流                                                                                                                                                                                                                                | 65                                                    | 80     | 95    | A                |

| $di/dt_{\text{T(SC)}}$    | 過電流と短絡の間の $di/dt$ スレッショルド故障                                                                                                                                                                                                                         | 150                                                   |        |       | A/ $\mu\text{s}$ |

|                           | GaN 温度故障 – 正方向スレッショルド温度                                                                                                                                                                                                                             | 175                                                   |        |       | °C               |

|                           | GaN 温度故障 – スレッショルド温度ヒステリシス                                                                                                                                                                                                                          | 30                                                    |        |       | °C               |

|                           | ドライバ温度故障 – 正方向スレッショルド温度                                                                                                                                                                                                                             | 185                                                   |        |       | °C               |

|                           | ドライバ温度故障 – スレッショルド温度ヒステリシス                                                                                                                                                                                                                          | 20                                                    |        |       | °C               |

| <b>TEMP</b>               |                                                                                                                                                                                                                                                     |                                                       |        |       |                  |

|                           | 出力周波数                                                                                                                                                                                                                                               | 4.5                                                   | 9      | 14    | kHz              |

| 出力 PWM デューティ・サイクル         | $GaN T_J = 150^{\circ}\text{C}$                                                                                                                                                                                                                     | 82                                                    |        |       | %                |

|                           | $GaN T_J = 125^{\circ}\text{C}$                                                                                                                                                                                                                     | 58.5                                                  | 64.6   | 70    |                  |

|                           | $GaN T_J = 85^{\circ}\text{C}$                                                                                                                                                                                                                      | 36.2                                                  | 40     | 43.7  |                  |

|                           | $GaN T_J = 25^{\circ}\text{C}$                                                                                                                                                                                                                      | 0.3                                                   | 3      | 6     |                  |

| <b>理想ダイオードのモード制御</b>      |                                                                                                                                                                                                                                                     |                                                       |        |       |                  |

| $V_{\text{T(3rd)}}$       | ドレインソース間の第 3 象限検出 – スレッショルド電圧                                                                                                                                                                                                                       | -0.15                                                 | 0      | 0.15  | V                |

| $I_{\text{T(ZC)}}$        | ドレインゼロ電流検出 – スレッショルド電流                                                                                                                                                                                                                              | $0^{\circ}\text{C} \leq T_J \leq 125^{\circ}\text{C}$ | -0.2   | 0     | 0.2              |

|                           |                                                                                                                                                                                                                                                     | $-40^{\circ}\text{C} \leq T_J \leq 0^{\circ}\text{C}$ | -0.35  | 0     | 0.35             |

## 5.6 スイッチング特性

特に記述のない限り：電圧、抵抗、容量、およびインダクタンスは SOURCE を基準としています。 $-40^{\circ}\text{C} \leq T_J \leq 125^{\circ}\text{C}$ 、 $V_{\text{DS}} = 520\text{V}$ 、 $9\text{V} \leq V_{\text{VDD}} \leq 18\text{V}$ 、 $V_{\text{IN}} = 0\text{V}$ 、RDRV は LDO5V に接続、 $L_{\text{BBSW}} = 4.7\mu\text{H}$

| パラメータ                                  | テスト条件                                                                                                                                                                                          | 最小値                                                                                                                                                       | 標準値 | 最大値 | 単位  |    |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|----|

| <b>時間の切り替え</b>                         |                                                                                                                                                                                                |                                                                                                                                                           |     |     |     |    |

| $t_{\text{d(on)}} \text{ (l_{drain})}$ | $V_{\text{IN}} > V_{\text{IN, IT+}}$ から $I_{\text{D}} > 1\text{A}$ 、 $V_{\text{BUS}} = 400\text{V}$ 、 $L_{\text{HB}}$ 電流 = 10A、図 6-1 および図 6-2 を参照してください                                        | 28                                                                                                                                                        | 40  | 40  | ns  |    |

| $t_{\text{d(on)}}$                     | $V_{\text{IN}} > V_{\text{IN, IT+}}$ から $V_{\text{DS}} < 320\text{V}$ 、 $V_{\text{BUS}} = 400\text{V}$ 、 $L_{\text{HB}}$ 電流 = 10A、図 6-1 および図 6-2 を参照してください                                     | 37                                                                                                                                                        | 45  | 45  | ns  |    |

| $t_{\text{r(on)}}$                     | $V_{\text{DS}} < 320\text{V}$ から $V_{\text{DS}} < 80\text{V}$ 、 $V_{\text{BUS}} = 400\text{V}$ 、 $L_{\text{HB}}$ 電流 = 10A、図 6-1 および図 6-2 を参照してください                                             | 2.5                                                                                                                                                       | 4   | 4   | ns  |    |

| $t_{\text{d(off)}}$                    | $V_{\text{IN}} < V_{\text{IN, IT-}}$ から $V_{\text{DS}} > 80\text{V}$ 、 $V_{\text{BUS}} = 400\text{V}$ 、 $L_{\text{HB}}$ 電流 = 10A、図 6-1 および図 6-2 を参照してください                                      | 44                                                                                                                                                        | 60  | 60  | ns  |    |

| $t_{\text{r(off)}}$                    | $V_{\text{DS}} > 80\text{V}$ から $V_{\text{DS}} > 320\text{V}$ 、 $V_{\text{BUS}} = 400\text{V}$ 、 $L_{\text{HB}}$ 電流 = 10A、図 6-1 および図 6-2 を参照してください                                             | 15                                                                                                                                                        | ns  | ns  | ns  |    |

|                                        | $V_{\text{IN}}$ 立ち上がり/立ち下がり時間が 1ns 未満、 $V_{\text{DS}}$ が 200V 未満、 $V_{\text{BUS}} = 400\text{V}$ 、 $L_{\text{HB}}$ 電流 = 10A、図 6-1 を参照してください                                                    | 24                                                                                                                                                        | ns  | ns  | ns  |    |

| <b>起動時間</b>                            |                                                                                                                                                                                                |                                                                                                                                                           |     |     |     |    |

| $t_{\text{(start)}}$                   | $V_{\text{VDD}} > V_{\text{VDD, T+}} \text{ (UVLO)}$ から 故障 High、 $C_{\text{LDO5V}} = 100\text{nF}$ 、 $C_{\text{VNEG}} = 2.2\mu\text{F}$ ( 0V / バイアス ) から 15V バイアスでは、 $1.5\mu\text{F}$ まで直線的に減少 | 470                                                                                                                                                       | 470 | 470 | μs  |    |

| <b>故障時間</b>                            |                                                                                                                                                                                                |                                                                                                                                                           |     |     |     |    |

| $t_{\text{off(OC)}}$                   | 過電流フォルト FET のターンオフ時間、過電流の前の FET オン                                                                                                                                                             | $V_{\text{IN}} = 5\text{V}$ 、 $I_{\text{D}} > I_{\text{T(OC)}}$ から $I_{\text{D}} < 50\text{A}$ まで、 $I_{\text{D}} \text{ di/dt} = 100\text{A}/\mu\text{s}$ | 110 | 170 | ns  |    |

| $t_{\text{off(SC)}}$                   | 短絡電流故障 FET のターンオフ時間、短絡の前の FET オン                                                                                                                                                               | $V_{\text{IN}} = 5\text{V}$ 、 $I_{\text{D}} > I_{\text{T(SC)}}$ から $I_{\text{D}} < 50\text{A}$ まで、 $I_{\text{D}} \text{ di/dt} = 700\text{A}/\mu\text{s}$ | 55  | 100 | ns  |    |

|                                        | 過電流フォルト FET のターンオフ時間、FET が過電流にターンオン                                                                                                                                                            | $I_{\text{D}} > I_{\text{T(OC)}}$ から $I_{\text{D}} < 50\text{A}$                                                                                          | 200 | 250 | ns  |    |

|                                        | 短絡フォルト FET のターンオフ時間、FET が短絡時にオンになる                                                                                                                                                             | $I_{\text{D}} > I_{\text{T(SC)}}$ から $I_{\text{D}} < 50\text{A}$                                                                                          | 115 | 180 | ns  |    |

|                                        | 故障ラッチをクリアするためのリセット時間です                                                                                                                                                                         | $V_{\text{IN}} < V_{\text{IN, IT-}}$ から 故障 High へ                                                                                                         | 250 | 380 | 580 | μs |

| $t_{\text{(window)}} \text{ (OC)}$     | 過電流フォルトから短絡フォルトのウィンドウ時間                                                                                                                                                                        |                                                                                                                                                           | 50  | 50  | ns  |    |

| <b>理想ダイオード・モードの制御時間</b>                |                                                                                                                                                                                                |                                                                                                                                                           |     |     |     |    |

|                                        | 理想ダイオード・モード FET のターンオン時間                                                                                                                                                                       | $V_{\text{DS}} < V_{\text{T(3rd)}}$ から FET ターンオンまで、 $V_{\text{DS}}$ はハーフブリッジ構成インダクタによって 5A で放電されます                                                        | 50  | 75  | ns  |    |

|                                        | 理想ダイオード・モード FET のターンオフ時間                                                                                                                                                                       | $I_{\text{D}} > I_{\text{T(ZC)}}$ から FET ターンオフまで、ハーフブリッジ構成で作成された $I_{\text{D}} \text{ di/dt} = 100\text{A}/\mu\text{s}$                                   | 55  | 76  | ns  |    |

|                                        | 過熱シャットダウン理想ダイオードモード IN ブランкиング時間                                                                                                                                                               |                                                                                                                                                           | 150 | 230 | 360 | ns |

## 5.6 スイッチング特性(続き)

特に記述のない限り：電圧、抵抗、容量、およびインダクタンスは SOURCE を基準としています。 $-40^{\circ}\text{C} \leq T_J \leq 125^{\circ}\text{C}$ 、 $V_{\text{DS}} = 520\text{V}$ 、 $9\text{V} \leq V_{\text{VDD}} \leq 18\text{V}$ 、 $V_{\text{IN}} = 0\text{V}$ 、RDRV は LDO5V に接続、 $L_{\text{BBSW}} = 4.7\mu\text{H}$

| パラメータ                 |                                     | テスト条件                                                                                                                                | 最小値 | 標準値 | 最大値 | 単位 |

|-----------------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|----|

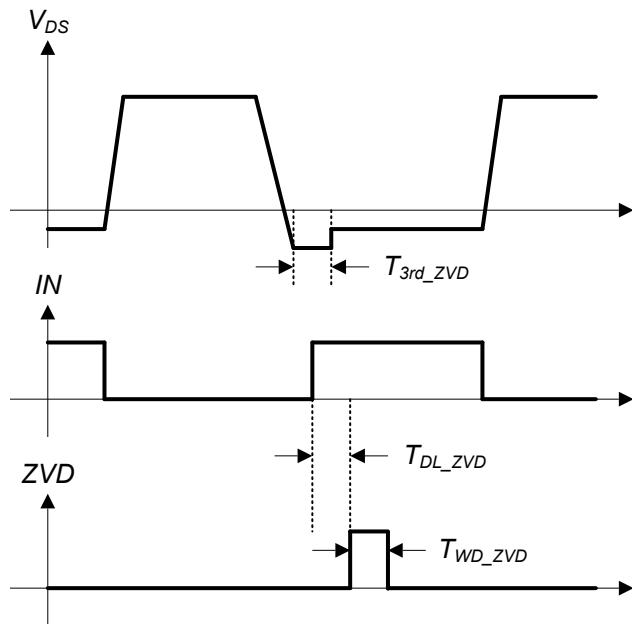

| <b>ゼロ電圧検出時間</b>       |                                     |                                                                                                                                      |     |     |     |    |

| $t_{\text{WD\_ZVD}}$  | ZVD パルス幅                            | 図 6-3 を参照してください                                                                                                                      | 75  | 100 | 140 | ns |

| $t_{\text{DL\_ZVD}}$  | IN の立ち上がりから ZVD パルスの立ち上がりエッジまでの時間遅延 | 図 6-3 を参照してください                                                                                                                      |     | 15  | 30  | ns |

| $t_{\text{3rd\_ZVD}}$ | ZVD パルスが出現し始めたときの第 3 象限導通時間         | $V_{\text{bus}} = 10\text{V}$ 、 $I_L = 5\text{A}$ 、 $R_{\text{drv}} = 5\text{V}$ で、ZVD パルスが出現し始めたとき、第 3 象限導通時間を測定します。図 6-3 を参照してください | 42  | 56  |     | ns |

(1) ターンオフ中の  $V_{\text{DS}}$  立ち上がり時間は、 $C_{\text{OSS}}$  とループインダクタンス、および負荷電流の共振の結果です。

## 5.7 代表的特性

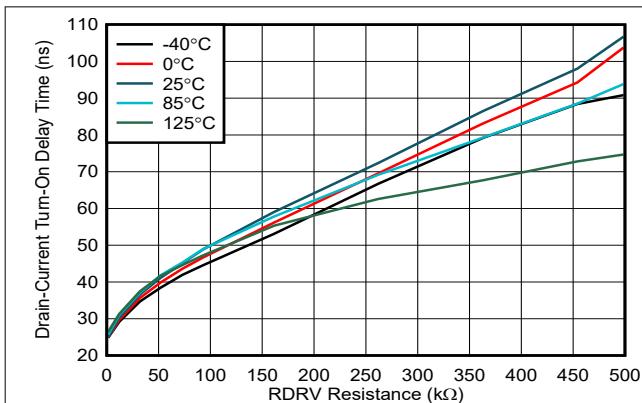

図 5-1. ドレイン電流ターンオン遅延時間と駆動強度抵抗との関係

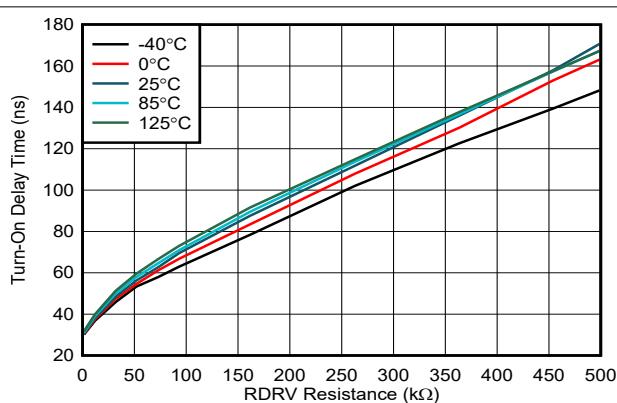

図 5-2. ターンオン遅延時間と駆動強度抵抗との関係

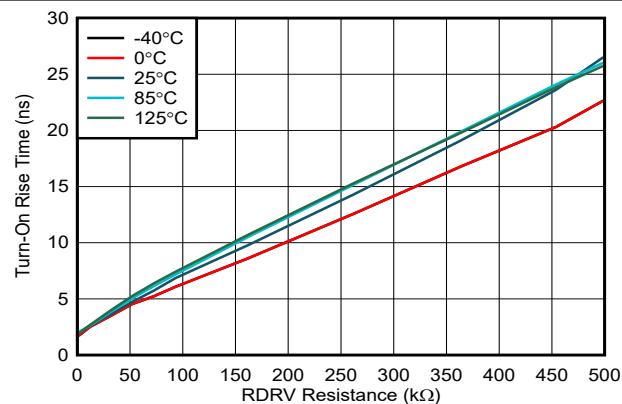

図 5-3. ターンオン立ち上がり時間と駆動強度抵抗との関係

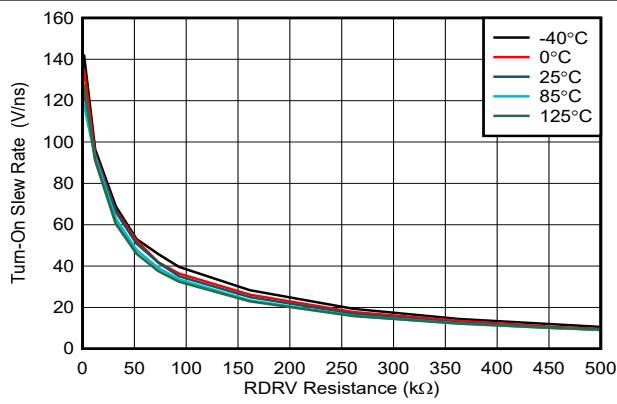

図 5-4. ターンオン・スルーレートと駆動強度抵抗との関係

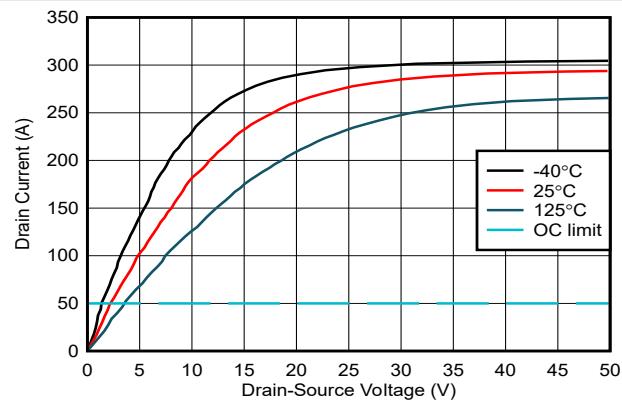

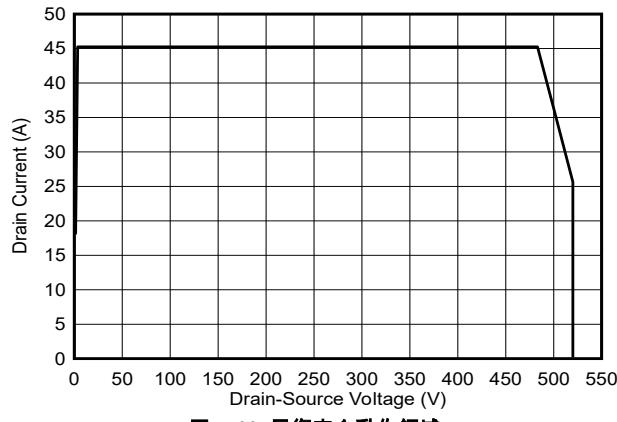

図 5-5. ドレイン電流とドレイン-ソース間電圧との関係

IN = 0V

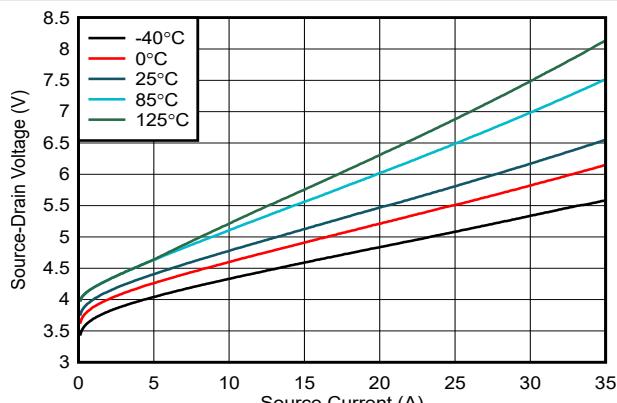

図 5-6. オフ状態のソースドレイン電圧とソース電流との関係

## 5.7 代表的特性(続き)

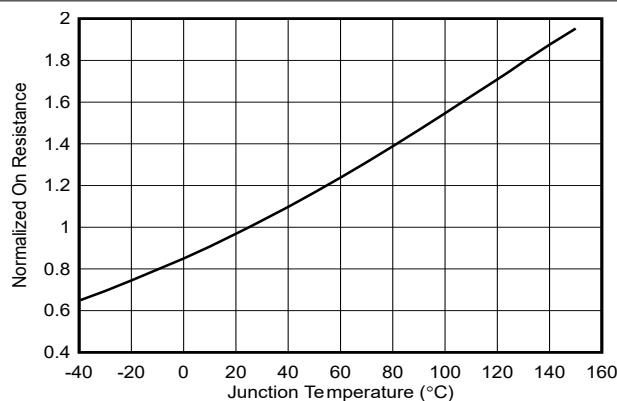

図 5-7. 接合部温度と正規化オン抵抗との関係

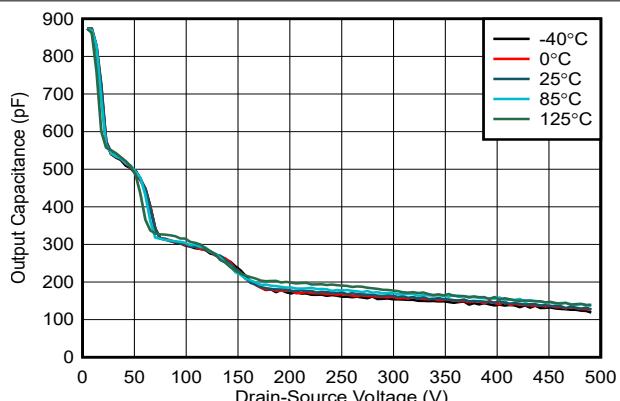

図 5-8. 出力キャパシタンスとドレン-ソース間電圧との関係

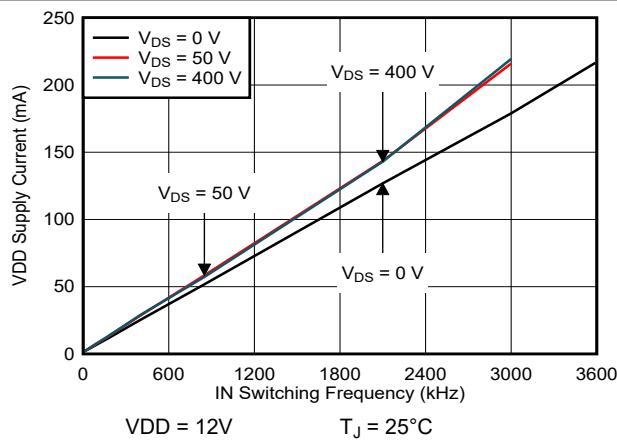

図 5-9. VDD 電源電流と入力スイッチング周波数との関係

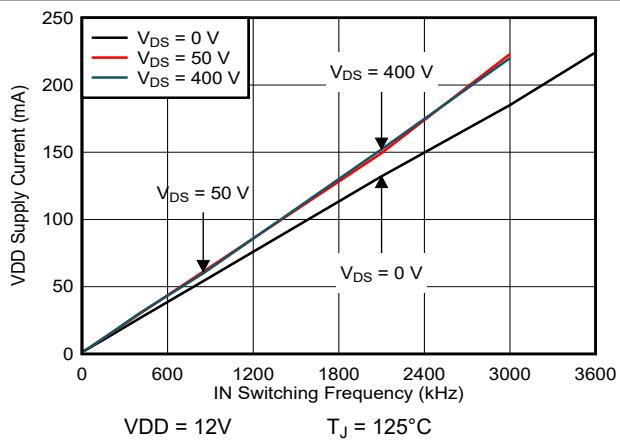

図 5-10. VDD 電源電流と入力スイッチング周波数との関係

図 5-11. 反復安全動作領域

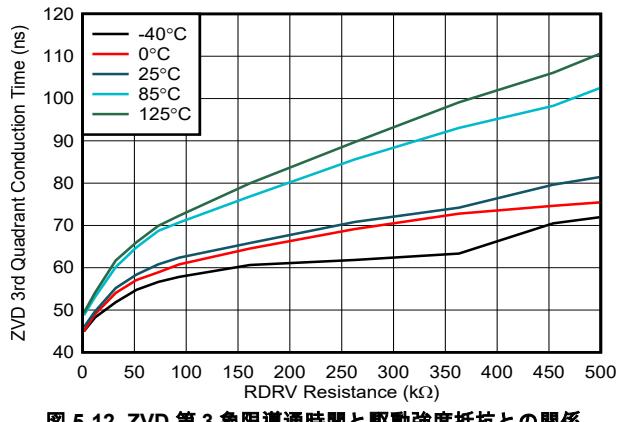

図 5-12. ZVD 第3象限導通時間と駆動強度抵抗との関係

## 6 パラメータ測定情報

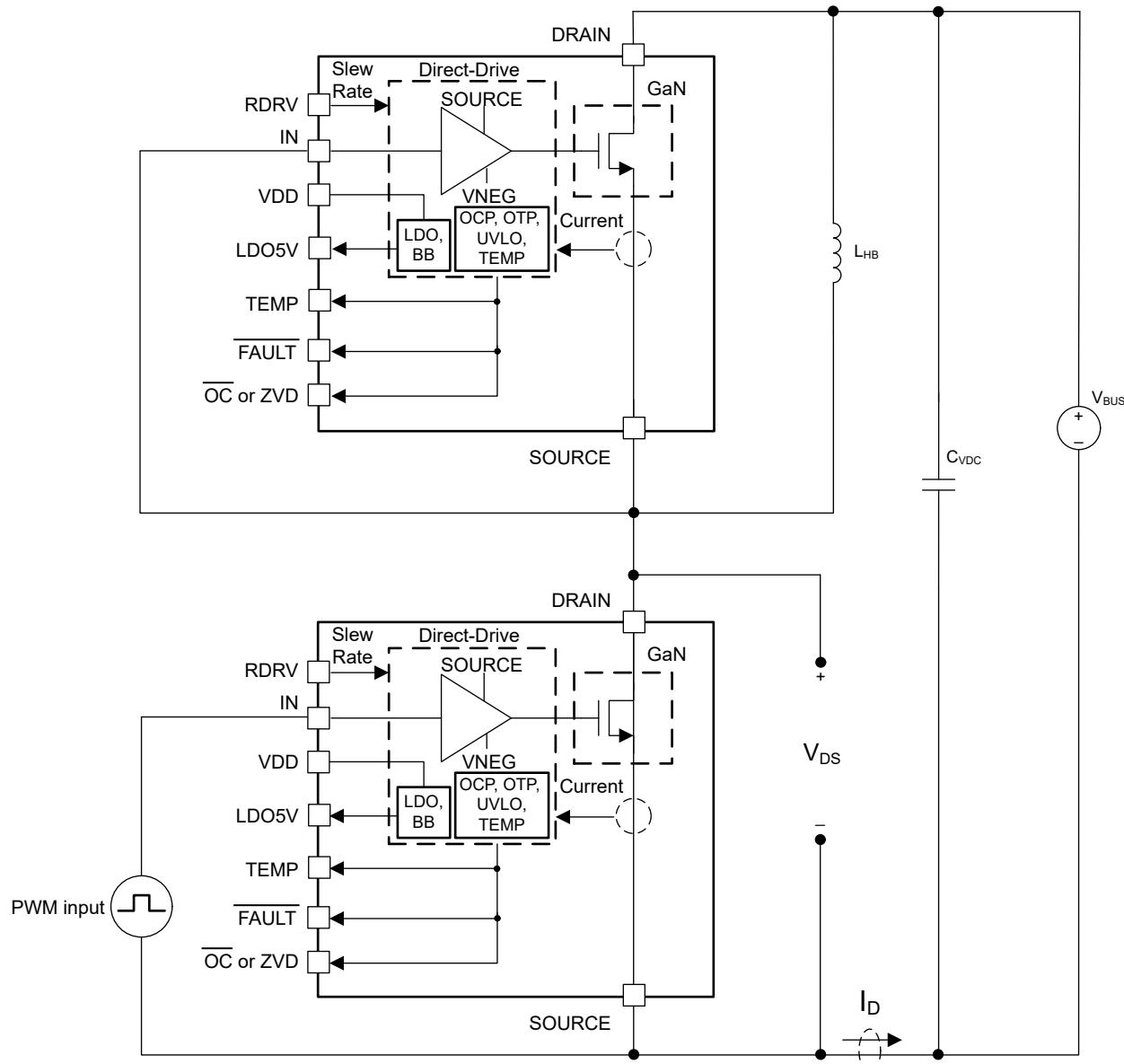

### 6.1 スイッチング パラメータ

図 6-1 に、ほとんどのスイッチング・パラメータの測定に使用する回路を示します。この回路の上部デバイスは、第 3 象限モードでのみインダクタ電流を再循環するために使用されます。下部デバイスはアクティブ・デバイスで、目的のテスト電流までインダクタ電流を増加させます。その後下部デバイスがオフおよびオンになり、特定のインダクタ電流でスイッチング波形が生成されます。ドレイン電流（ソース側）とドレインソース間電圧の両方を測定します。図 6-2 に、具体的なタイミング測定値を示します。TI は、ダブル・パルス・テストとしてハーフブリッジを使用することを推奨します。過剰な第 3 象限動作により、上部デバイスが過熱する可能性があります。

図 6-1. スイッチング・パラメータの決定に使用する回路

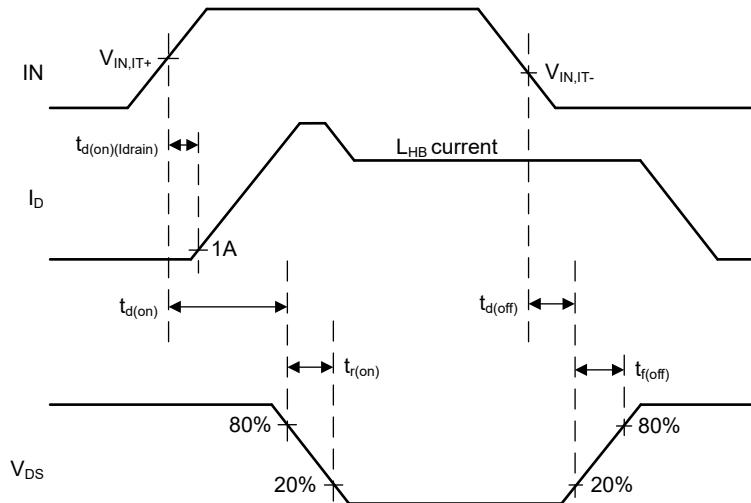

図 6-2. 伝搬遅延とスルーレートを決定するための測定値

### 6.1.1 ターンオン時間

ターンオン遷移には、ドレイン電流のターンオン遅延時間、ターンオン遅延時間、ターンオン立ち上がり時間の3つのタイミング要素があります。ドレイン電流のターンオン遅延時間は、IN が High になってから、GaN FET のドレイン電流が 1A に達するまでの時間です。ターンオン遅延時間は、IN が High になってから、ドレインソース間電圧がバス電圧より 20% 低くなるまでの時間です。最後に、ターンオンの立ち上がり時間は、ドレインソース間電圧がバス電圧より 20% 低くなっているから、ドレインソース間電圧がバス電圧より 80% 低くなった時点までになります。ターンオンの立ち上がり時間は、 $V_{DS}$  の 80% ~ 20% の立ち下がり時間と同じであることに注意します。3つのターンオン・タイミング部品はすべて、RDRV ピンの設定に依存します。

### 6.1.2 ターンオフ時間

ターンオフ遷移には、ターンオフ遅延時間と、ターンオフの立ち下がり時間の2つのタイミング要素があります。ターンオフ遅延時間は、IN が LOW になってから、ドレインソース間電圧がバス電圧の 20% まで上昇するまでの時間です。ターンオフの立ち下がり時間は、ドレインソース間電圧がバス電圧の 20% に上昇してから、ドレインソース間電圧がバス電圧の 80% に上昇するまでの期間です。ターンオフの立ち下がり時間は  $V_{DS}$  20% ~ 80% の立ち上がり時間と同じであることに注意します。ターンオフ・タイミング部品は RDRV ピン設定から独立していますが、 $L_{HB}$  負荷電流に大きく依存します。

### 6.1.3 ドレインソース間のターンオン・スルーレート

ドレインソース間のターンオン・スルーレートは、ターンオン立ち上がり時間の逆数、または  $V_{DS}$  の 80% から 20% の立ち下がり時間の逆数です。RDRV ピンを使用して、スルーレートをプログラムします。

### 6.1.4 ゼロ電圧検出時間

図 6-3 は、ゼロ電圧検出 (ZVD) ブロックに関連するスイッチングタイミングを定義し、デバイスのドレイン-ソース間電圧、IN ピン信号、ZVD 出力信号を実証しています。デバイスがゼロ電圧スイッチング (ZVS) に達すると、ZVD ピンは幅  $T_{WD\_ZVD}$  のパルス信号を出力し、IN ピンの立ち上がりエッジから ZVD パルスの立ち上がりエッジまでの遅延時間は  $T_{DL\_ZVD}$  として定義されます。本デバイスがゼロ電圧スイッチングを検出できるようにするには、一定の第3象限導通時間が必要であり、 $T_{3rd\_ZVD}$  はこのタイミングを示します。ZVD タイミングパラメータの詳細については、「[ゼロ電圧検出 \(ZVD\)](#)」セクションを参照してください。

図 6-3. ZVD タイミング仕様

## 6.2 安全 operation 領域 (SOA)

### 6.2.1 反復的 SOA

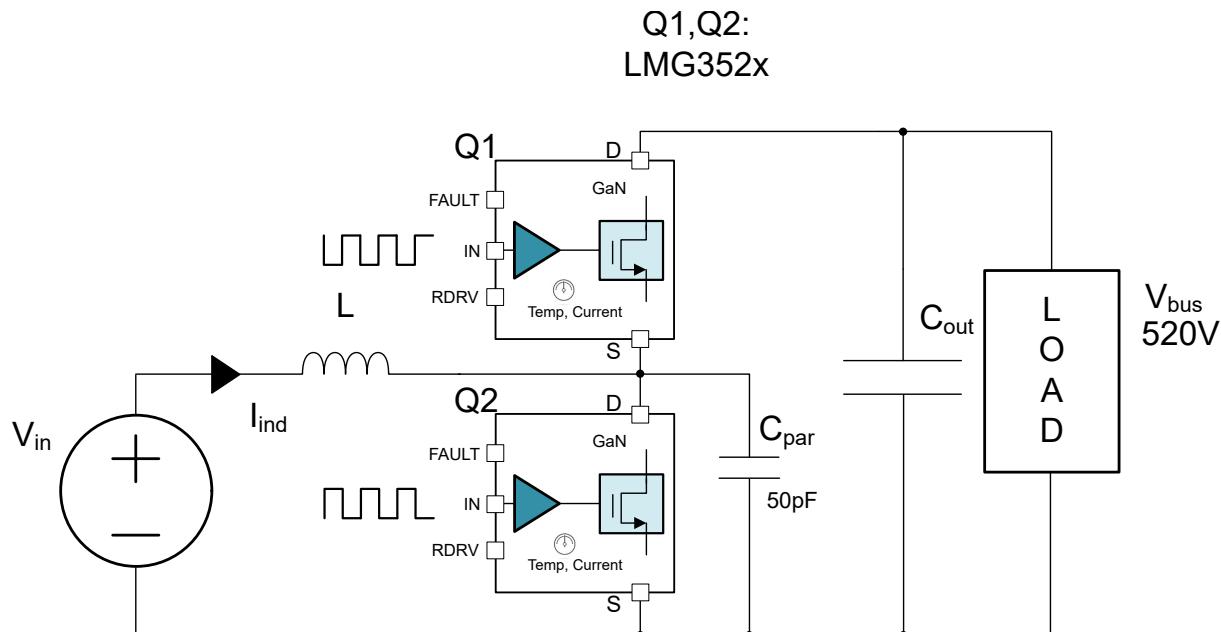

LMG352xR050 (図 5-11)の許容反復 SOA は、ターンオン時のデバイスのピークドレイン電流 ( $I_{DS}$ ) とドレインソース間電圧 ( $V_{DS}$ ) によって定義されます。スイッチング時のピークドレイン電流は、ドレイン端子に流入するいくつかの電流の合計です。インダクタ電流 ( $I_{ind}$ )、トーテムポールのもう一方の GaN デバイスの  $C_{OSS}$  を充電するために必要な電流、スイッチングノードの寄生容量 ( $C_{par}$ ) を充電するために必要な電流です。190pF はスイッチング中のデバイスの平均  $C_{OSS}$  として使われます。スイッチ・ノードの寄生容量は、PCB のオーバーラップ容量を使用して推定できます。SOA テストには昇圧トポロジを使用します。図 6-4 に示す回路は、図 5-11 の SOA 曲線を生成するために使用されます。信頼性の高い動作を確保するには、デバイスの接合部温度も 125°C に制限する必要があります。図 5-11 の  $I_{DS}$  は以下で計算できます。

$$I_{DS} = I_{ind} + (190\text{pF} + C_{par}) * \text{Drain slew rate at peak current} \quad (1)$$

ここで、ピーク電流でのドレインスルーレートはバス電圧の 70% ~ 30% の間で推定され、 $C_{par}$  はスイッチ・ノードの寄生基板容量です。

図 6-4. SOA 曲線に使用する回路

詳細については、[寿命にわたる信頼性を備えた GaN 製品を実現](#)をご覧ください。

## 7 詳細説明

### 7.1 概要

LMG352xR050 は、ゲート・ドライバが内蔵された高性能パワー GaN デバイスです。GaN デバイスは、ゼロ逆回復と超低出力キャパシタンスを実現し、ブリッジ・ベースのトポロジーで効率のイネーブル ハイを実現します。ディレクティブ駆動アーキテクチャは、内蔵ゲートドライバにより GaN デバイスを直接制御するために適用されます。このアーキテクチャにより、従来のカスコード方式に比べて優れたスイッチング性能を発揮し、GaN アプリケーションの多数の課題を解決できます。

内蔵ドライバにより、の高いドレイン・スルーレートの場合に本デバイスを確実にオフに維持できます。内蔵ドライバは、過電流、短絡、過熱、VDD 低電圧、ハイインピーダンスの RDRV ピンから GaN デバイスを保護します。また、内蔵ドライバはダイ温度を検出し、変調された PWM 信号を介して温度信号を送出することもできます。LMG3526R050 は、ゼロ電圧検出 (ZVD) 機能を備えており、ゼロ電圧スイッチングが発生したとき ZVD ピンからパルスを出力します。

Si MOSFET とは異なり、GaN デバイスにはソースからドレインへの p-n 接合がないため、逆方向回復電荷がありません。ただし、GaN デバイスは依然として、p-n 接合のボディ・ダイオードと同様にソースからドレインへ導通しますが、電圧降下が大きく、導通損失が大きくなります。したがって、LMG352xR050GaN FET がオフの間、ソースドレイン間導通時間を最小限に抑える必要があります。

## 7.2 機能ブロック図

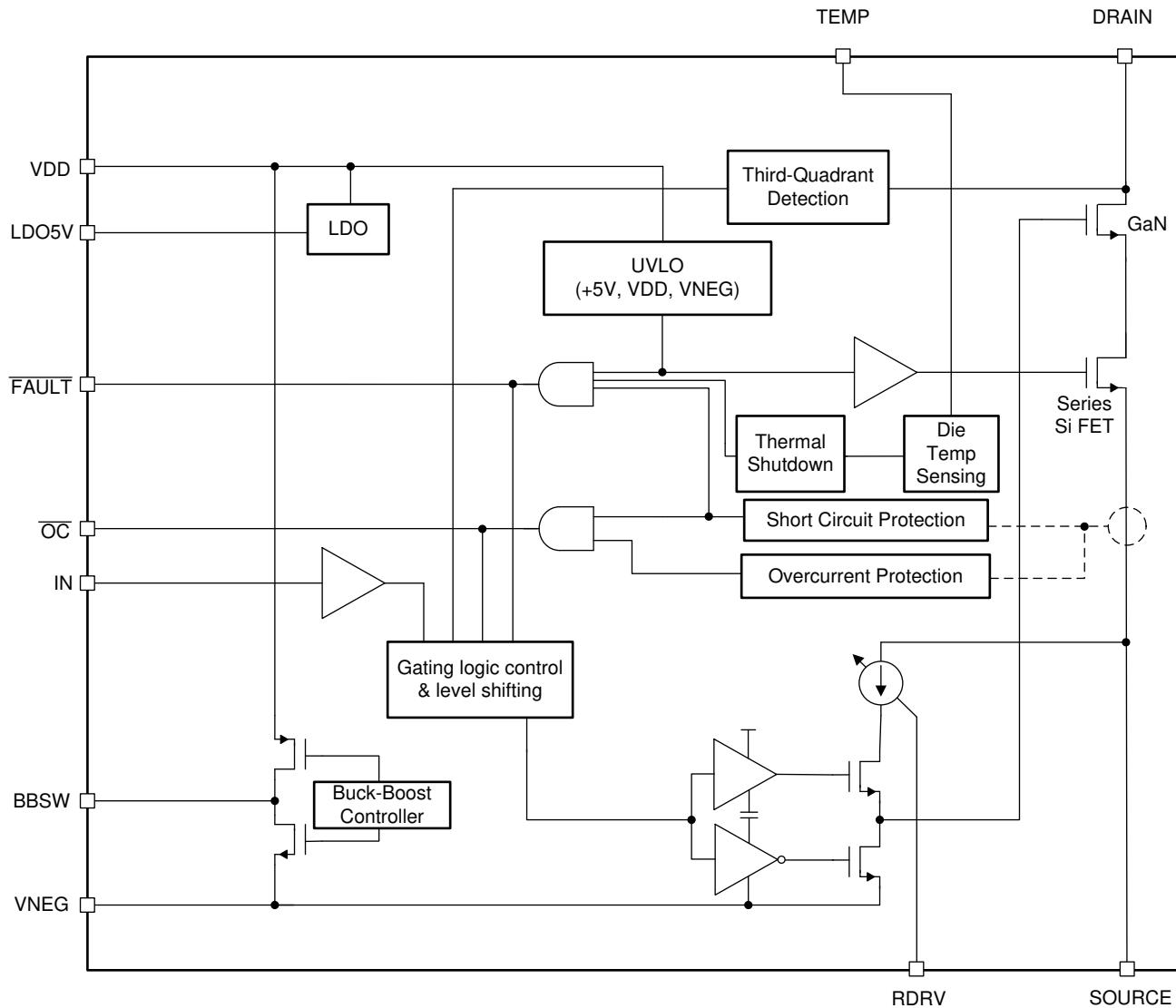

### 7.2.1 LMG3522R050 機能ブロック図

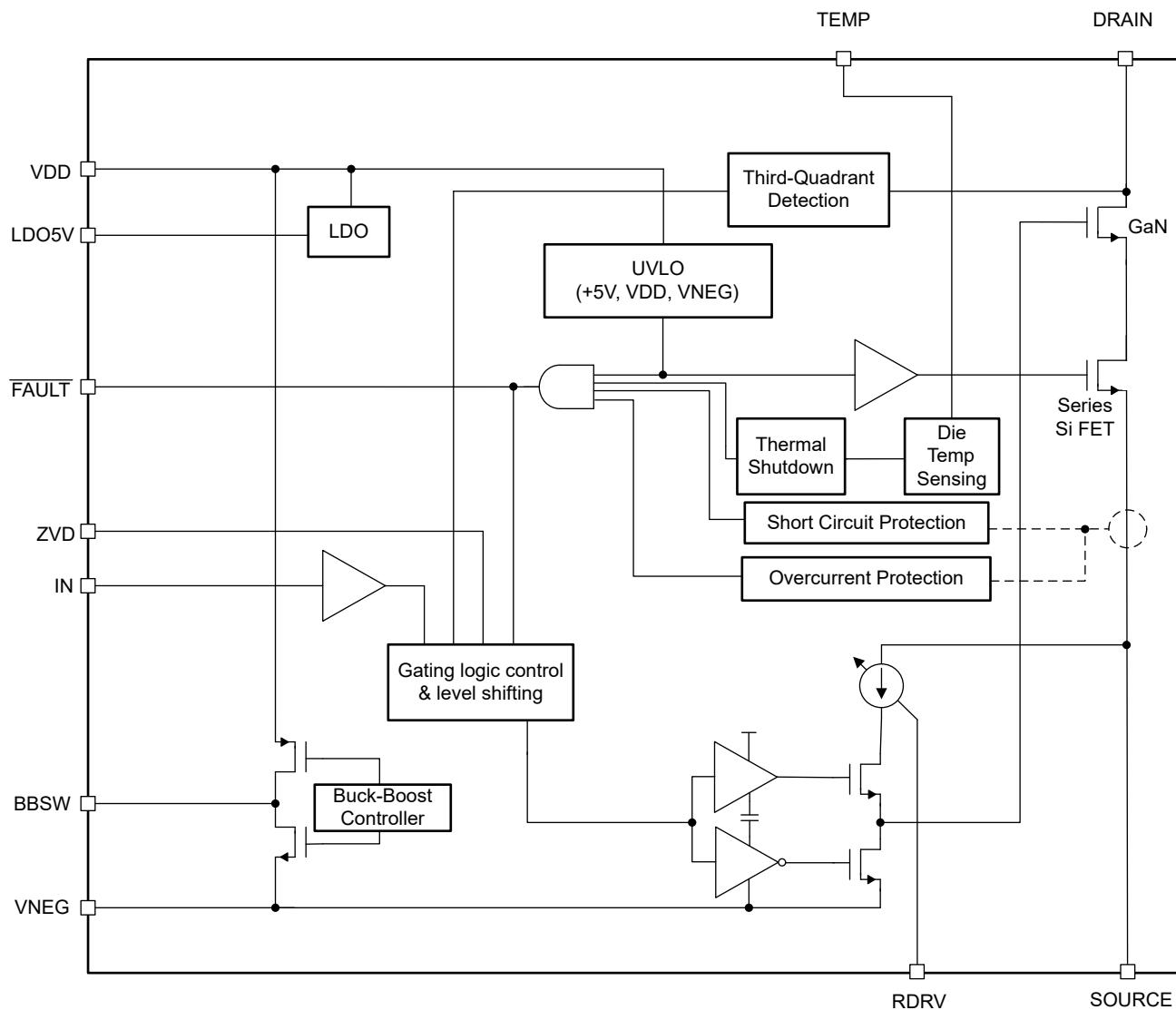

### 7.2.2 LMG3526R050 機能ブロック図

## 7.3 機能説明

LMG352xR050 は、優れたスイッチング性能とコンバータ効率を実現するための高度な機能を備えています。

### 7.3.1 GaN FET の operation 定義

このデータシートでは、以下の用語を以下のように定義します。この定義では、ソース・ピンは 0V であると想定します。

**第 1 象限電流**=ドレイン・ピンからソース・ピンに内部で流れる正電流です。

**第 3 象限電流**=ソース・ピンからドレイン・ピンに内部で流れる正電流です。

**第 1 象限電圧**=ドレイン・ピン電圧 – ソース・ピン電圧 = ドレイン・ピン電圧

**第 3 象限電圧**=ソース・ピン電圧 – ドレイン・ピン電圧 = – ドレイン・ピン電圧

**FET オン状態**=FET チャネルは定格  $R_{DS(on)}$  です。第 1 象限電流と第 3 象限電流の両方が定格  $R_{DS(on)}$  で流れることができます。

**オン状態**で LMG352xR050 は、定格の  $R_{DS(on)}$  を実現するため、GaN FET の内部ゲート電圧をソース・ピン電圧に保持します。LMG352xR050GaN FET チャネルはディブリーション・モード FET であるため、 $V_{GS} = 0V$  において定格  $R_{DS(on)}$  となります。

**FET オフ状態**=正の第 1 象限電圧では FET チャネルは完全にオフです。第 1 象限の電流は流れません。第 1 象限の電流は FET オフ状態では流れませんが、ドレイン電圧が十分に負の値 ( 正の第 3 象限電圧 ) になっていれば、第 3 象限の電流は流れます。固有の p-n 接合ボディ・ダイオードを備えたデバイスでは、ドレイン電圧が p-n 接合に順方向バイアスをかけるのに十分低下したときに電流が流れ始めます。

GaN FET には、固有の p-n 接合ボディ・ダイオードは存在しません。代わりに、GaN FET チャネルが再びオンになったので、電流が流れます。この場合、ドレイン・ピンが電気的ソースになり、ソース・ピンが電気的ドレインになります。第 3 象限のチャネルを拡張するには、ドレイン ( 電気的ソース ) 電圧を十分に低くして、GaN FET のスレッショルド電圧よりも高い  $V_{GS}$  電圧を確立する必要があります。GaN FET チャネルは飽和状態で動作しており、第 3 象限の電流を飽和電流としてサポートするのに十分なだけオンになります。

**オフ状態**で LMG352xR050 は、GaN FET の内部ゲート電圧が VNEG ピンの電圧に保持され、すべての第 1 象限電流がブロックされます。VNEG の電圧はチャネルをカットオフするため、GaN FET の負のスレッショルド電圧よりも低くなっています。

オフ状態の第 3 象限でチャネルを拡張するには、LMG352xR050 ドレイン ( 電気的ソース ) 電圧を VNEG に十分近くし、 $V_{GS}$  電圧が GaN FET のスレッショルド電圧より高く設定する必要があります。LMG352xR050GaN FET は負のスレッショルド電圧を持つディブリーションモード FET であるため、ドレイン ( 電気的ソース ) 電圧が 0V ~ VNEG の間にある状態で、GaN FET がオンになります。典型的なオフ状態の第 3 象限電圧は、第 3 象限電流が 5.3 A の場合に 15 V となります。したがって、LMG352xR050 のオフ状態の第 3 象限損失は、本質的な p-n 接合ボディダイオードを備えた同等の電力デバイスよりもはるかに高くなります。

### 7.3.2 ディレクティブ駆動 GaN アーキテクチャ

LMG352xR050 は、直列の Si FET を使用して、VDD バイアス電力が印加されていないときもパワー IC をオフに維持します。VDD バイアス電源がオフになった場合、直列 Si FET はカスコード・モードで GaN デバイスに相互接続されます。これを **機能ブロック図** に示します。GaN デバイスのゲートは、直列 Si FET のソース電圧の範囲内に保持されます。ドレインに高い電圧が印加され、シリコン FET がドレイン電圧をブロックすると、GaN デバイスがスレッショルド電圧を超えるまで GaN デバイスの  $V_{GS}$  は低下します。その後、GaN デバイスはオフになります、ドレイン電圧の残りの主要部分をブロックします。Si FET の  $V_{DS}$  が最大定格を超えないように、内部クランプがあります。この機能は、バイアス電力がない場合に直列 Si FET のアバランシェを防止します。

LMG352xR050 が VDD バイアス電源でパワーアップすると、内部昇降圧コンバータは、GaN デバイスを直接オフにするのに十分な負電圧 ( $V_{VNEG}$ ) を生成します。この場合、直列 Si FET をオンに保持し、負電圧で GaN デバイスを直接ゲートします。

GaN ゲートを接地し、Si MOSFET のゲートを駆動して GaN デバイスを制御する、従来のカスコード駆動 GaN アーキテクチャに比べると、ディレクティブ駆動構成には複数の利点があります。第 1 に、Si MOSFET はスイ

ツチングサイクルごとにスイッチングを実行する必要があるため、GaN ゲート-ソース間電荷 ( $Q_{GS}$ ) は低く、Si MOSFET の逆回復に関連する損失はありません。第 2 に、カスコード構成でオフモードでの GaN と Si MOSFET の間の電圧分布により、GaN のドレインソース間静電容量 ( $C_{DS}$ ) が大きいことから、MOSFET のアバランシェが発生する可能性があります。最後に、ディレクティブ駆動構成でのスイッチング・スルーレートを制御できますが、カスコード・ドライブでは制御できません。ディレクティブ駆動 GaN アーキテクチャの詳細については、[GaN デバイスのディレクティブ駆動構成](#)を参照してください。

### 7.3.3 ドレインソース間電圧

シリコン FET が長きにわたって支配的なパワースイッチ技術であったため、多くの設計者は、ドレインソース間電圧のヘッドライン値を、異なる技術のデバイスを比較する際の等価点として使用できないことを知りません。シリコン FET のヘッドライン・ドレインソース間電圧は、アバランシェ・ブレークダウン電圧によって設定されます。GaN FET のヘッドラインドレインソース間電圧は、データシートの仕様を基準とする長期的な信頼性によって設定されます。

シリコン FET のヘッドライン・ドレインソース間電圧を超えると、即座に永続的な損傷を引き起こすことがあります。一方、GaN FET のブレークダウン電圧はヘッドラインのドレインソース間の見出し電圧よりもはるかに高くなっています。たとえば、LMG352xR050 のブレークダウン電圧は 800V を超えています。

通常、シリコン FET は電源アプリケーションで入力電圧サージの発生時に最も弱いリンクです。シリコン FET のアバランシェ能力を超えないように、サージ保護回路を注意深く設計する必要があります。シリコン FET のブレークダウン電圧未満にサージをクランプするのは不可能なためです。また、サージ電圧を GaN FET のブレークダウン電圧以下にクランプすることは容易です。事実、GaN FET はサージ・イベントの発生中もスイッチングを継続できます。つまり、出力電力は切断にも安全です。

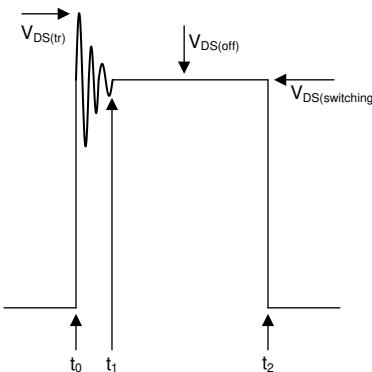

LMG352xR050 ドレインソース間能力は、[図 7-1](#) を参照して説明します。この図には、スイッチングアプリケーション内のシングルスイッチサイクルについて、GaN FET のドレインソース間電圧と時間との関係を示しています。スイッチング周波数またはデューティ・サイクルに関する請求は行われません。このデバイスは、非スイッチング・アプリケーションで連続的な電圧ストレスを印加する場合には推奨されません。

図 7-1. ドレインソース間電圧スイッチングサイクル

波形は  $t_0$  より先に開始し、FET がオン状態になります。 $t_0$  の時点で GaN FET はターンオフし、寄生素子によってドレインソース間電圧に高周波でリングが生じます。ピーク・リング電圧は  $V_{DS(tr)}$  と呼ばれます。高周波リングは、 $t_1$  だけ減衰しました。 $t_1$  と  $t_2$  の間の FET のドレインソース間電圧は、スイッチングアプリケーションの特性応答によって設定されます。特性はフラットラインとして表示されますが、他の応答も可能です。 $t_1$  と  $t_2$  の間の電圧は  $V_{DS(off)}$  と呼ばれます。 $t_2$  の時点で、ドレインソース間電圧がゼロではない状態で GaN FET がオンになります。 $t_2$  のドレインソース間電圧は  $V_{DS(switching)}$  と呼ばれます。独自の  $V_{DS(tr)}$ 、 $V_{DS(off)}$ 、 $V_{DS(switching)}$  パラメータを示しています。それぞれが GaN FET の寿命全体にわたってストレスに寄与する可能性があるからです。

LMG352xR050 のドレインソース間サージ電圧耐量は、[仕様書](#)の絶対最大定格  $V_{DS(tr)(surge)}$  および  $V_{DS(surge)}$  で確認できます。 $V_{DS(tr)(surge)}$  は [図 7-1](#) の  $V_{DS(surge)}$  に、 $V_{DS(surge)}$  は [図 7-1](#) の  $V_{DS(off)}$  および  $V_{DS(switching)}$  の両方にマッピ

ングされています。TI の GaN FET のサージ能力の詳細については、[使用条件の下で電力線サージに対するGaN FET の信頼性を検証するための新しいアプローチを参照してください。](#)

#### 7.3.4 内蔵型昇降圧 DC/DC コンバータ

内部の反転型降圧-昇圧コンバータは、GaN デバイスのターンオフ時の電源供給用に安定化された負のレールを生成します。バック・ブースト・コンバータは、ピーク電流モードのヒステリシス制御器によって制御されます。通常動作では、コンバータは不連続導通モードにとどまりますが、スタートアップ時には連続導通モードに移行できます。コンバータは内部で制御されており、必要なのは単一の表面実装インダクタと出力バイパス・コンデンサのみです。通常、コンバータは、4.7- $\mu$ H のインダクタと 2.2- $\mu$ F の出力コンデンサを使用するように設計されています。

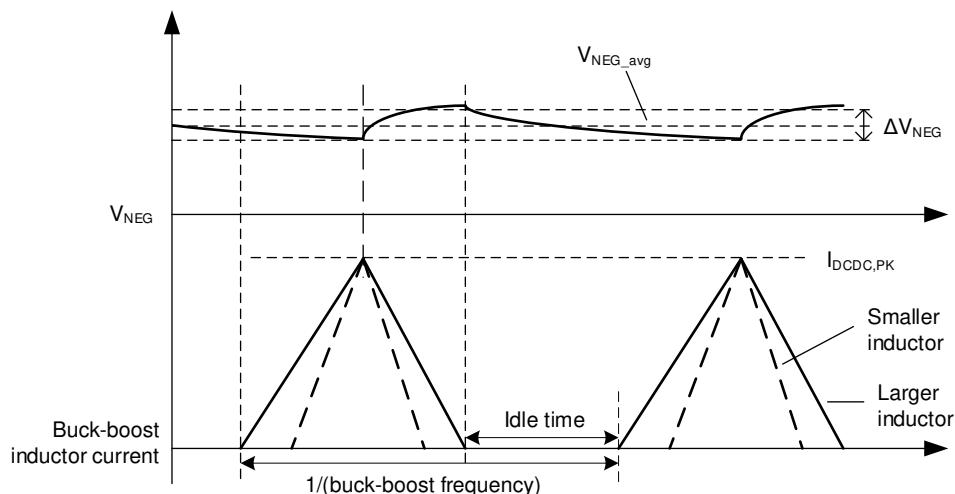

昇降圧コンバータは、ピーク電流のヒステリシス制御を使用しています。図 7-2 に示すように、スイッチングサイクルの開始時にインダクタ電流が増加し、インダクタがピーク電流制限に達するまで増加します。それからインダクタ電流はゼロに下がります各電流パルス間のアイドル時間は、昇降圧コントローラによって自動的に決定され、ゼロまで下がることができます。したがって、最大出力電流はアイドル時間がゼロのときに発生し、ピーク電流によって決定されますが、一次的にはインダクタ値には依存しません。ただし、昇降圧が-14-V レールに供給できるピーク出力電流は、VDD 入力電圧に比例します。したがって、このバックブーストがサポートする GaN の最大スイッチング周波数は VDD 電圧によって異なり、VDD 電圧が 9V 以上の場合は、3.6MHz までの動作にのみ指定されています。

図 7-2. 昇降圧コンバータのインダクタ電流

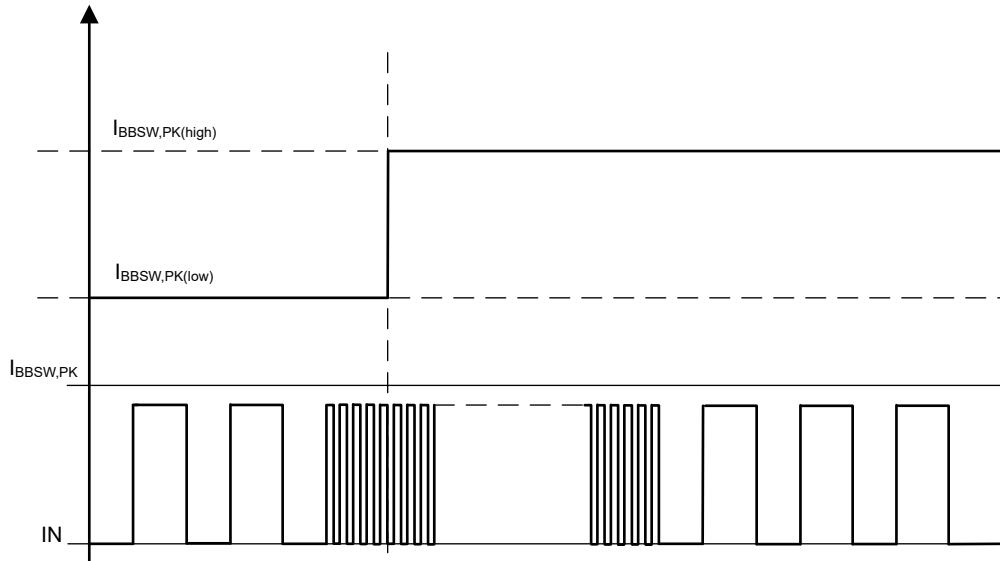

LMG352xR050 は、最大 3.6MHz の GaN 動作をサポートしています。GaN デバイスでは、広いスイッチング周波数範囲と消費電力が大きく異なるため、昇降圧コンバータを制御するために 2 つのピーク電流制限を使用します。この 2 つの範囲は、IN 正方向のスレッショルド周波数でも分離されます。図 7-3 に示すように、スイッチング周波数が低い範囲内のとき、ピーク電流は最初は低い値の  $I_{BBSW,M(low)}$  ( 標準値は 0.4A ) に設定されます。スイッチング周波数が高い範囲の場合、ピーク電流は高い値  $I_{BBSW,M(high)}$  ( 通常 1A ) まで上昇し、より大きなインダクタが必要になります。この周波数検出ロジックにはフィルタがあるため、LMG352xR050 では高い周波数で連続 5 サイクルが必要となり、その後で昇降圧ピーク電流制限値に設定されます。上限値を設定した後、電源がオフになるまで、電流制限は再度ダウンされません。スイッチング周波数が下限に戻っても、電流制限は下限にまで低下しません。

図 7-3. 昇降圧コンバータのピーク電流

昇降圧のピーク電流は、低周波および高周波動作に対して 0.4A および 1A という 2 つの異なるピーク電流制限を受けるため（[内部昇降圧 DC-DC コンバータ](#)」を参照）。インダクタの飽和電流は定格ピーク電流制限をはるかに上回る必要があります。より高い周波数でスイッチングすることでより高い制限が確立された後では、GaN デバイスがより低い周波数でスイッチングされても、電流制限がより低いレベルには戻りません。したがって、より高い 1A 制限に従ってインダクタを選択することをお勧めします。

### 7.3.5 VDD バイアス電源

内部レギュレータにより、7.5V ~ 18V の広い VDD 電圧範囲がサポートされており、内部回路が機能するために必要なバイアス電源が供給されます。VDD 入力電圧が 9V 未満の場合、最大スイッチング周波数はディレーティングされます。

### 7.3.6 補助 LDO

ハイサイド駆動信号用のデジタル・アイソレータなど、外部負荷に電力を供給するために使用する部品の内部には 5V 電圧レギュレータがあります。部品のデジタル出力は、このレールを電源として使用します。安定性のためにコンデンサは不要ですが、外付けコンデンサを使用しないと、過渡応答は悪くなります。アプリケーションでこのレールを使用して外部回路に電力を供給する場合は、TI は過渡応答の向上のために、少なくとも 0.1 $\mu$ F のコンデンサを使用することを推奨します。さらに過渡応答を改善するために、より大容量のコンデンサを使用することもできます。ここで使用するデカップリング・コンデンサには、低 ESR のセラミック・コンデンサを使用する必要があります。0.47 $\mu$ F を超える容量は、5V レールの立ち上がり時間により、LMG352xR050 の起動時間を遅くします。

### 7.3.7 フォルト保護

GaN パワー IC には、過電流保護 (OCP)、短絡保護 (SCP)、過熱保護 (OTP)、低電圧誤動作防止 (UVLO) 保護、高インピーダンス RDRV ピン保護が内蔵されています。

#### 7.3.7.1 過電流保護および短絡保護

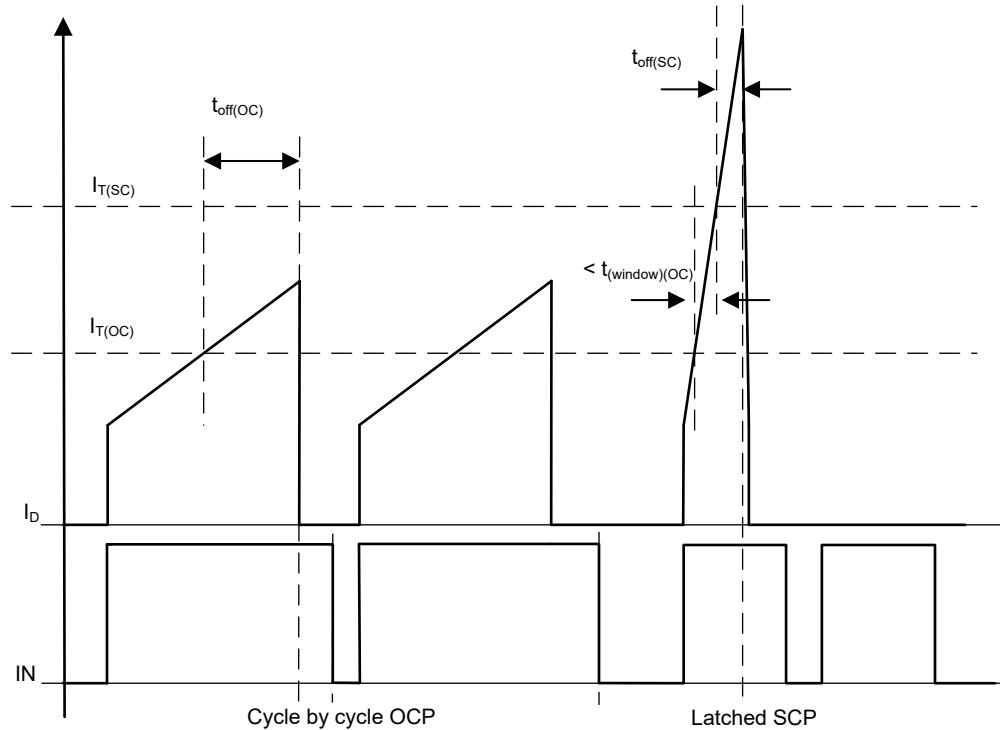

ドライバが検出できる電流故障には、過電流故障と短絡故障の 2 種類があります。

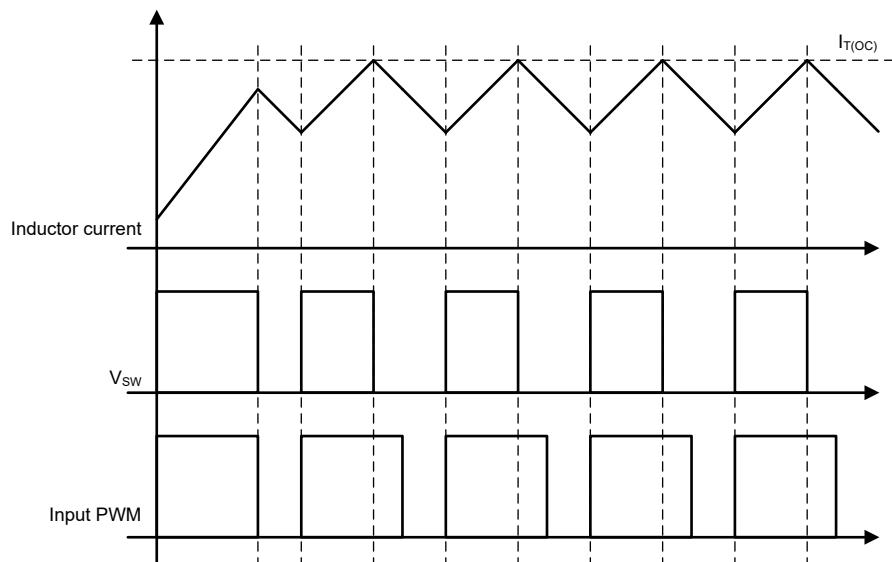

過電流保護 (OCP) 回路は、ドレイン電流を監視し、電流信号を内部で設定された制限値  $I_{T(OC)}$  と比較します。過電流を検出すると、LMG352xR050 はサイクル単位の過電流保護を行います（[図 7-4](#) を参照）。このモードでは、ドレイン電流が  $I_{T(OC)}$  に遅延  $t_{off(OC)}$  を加えた値を超えると、GaN デバイスがシャットオフされますが、IN ピン信号が LOW になると過電流信号はクリアされます。次のサイクルで、GaN デバイスは通常どおりオンすることができます。サイクル単位の機能は、定常状態の動作電流が OCP レベルを下回っているが、過渡応答が依

然として電流制限に達する可能性があり、回路の動作を一時停止できない場合に使用できます。サイクル単位の機能により、過電流によって発生する導通損失によって GaN デバイスが過熱することも防止されます。

短絡保護 (SCP) はドレイン電流を監視し、電流が OC スレッショルドと SC スレッショルドとの間を横切るときに、電流の  $di/dt$  がスレッショルド  $di/dt_{T(SC)}$  を超えた場合にトリガします。OC 検出信号を  $t_{OC,window}$  分遅延させ、より高い電流 SC 検出スレッショルドを使用することで、この  $di/dt$  検出を実行します。遅延 OC が遅延 SC の前に発生すると、 $di/dt$  がスレッショルドを下回る場合に、OC がトリガされます。最初に SC が検出されると、 $di/dt$  は十分高速で、図 7-5 に示すように SC が検出されます。この非常に大きい  $di/dt$  電流は通常、ハーフブリッジの出力が短絡することによって発生し、その状況で GaN が動作を継続するのに損傷を与える可能性があります。したがって、短絡故障が検出された場合、意図的に低速化されたドライバで GaN デバイスがオフになるため、ターンオフイベント中にオーバーシュート電圧とリングングを低減できます。この高速応答回路により、急激な短絡状況が発生した場合でも GaN デバイスを保護できます。この保護では、GaN デバイスをシャットオフして、仕様に定義されている時間にわたって IN ピンを Low に保持するか、または VDD の電源をオフにすることによって、故障がリセットされるまで保持します。

ハーフブリッジの OCP または SCP 中、電流が上限値に達し、保護によってデバイスがオフになった後でも、デバイスの PWM 入力は依然として High であり、相補型デバイスの PWM 入力を Low に維持している可能性があります。この場合、同期整流を行わずに、負荷電流が相補型デバイスの第 3 象限を通過する可能性があります。GaN デバイスのドレインからソースへの高い負の  $V_{DS}$  (-3V ~ -5V) は、第 3 象限損失が大きくなる可能性があります。これはデッド・タイム損失と同様ですが、より長い時間です。

安全性についての考慮事項として、SCP でリセットが行われるまでデバイスがラッチされている間、OCP ではサイクルバイサイクル動作が可能です。OCP および SCP 故障の通知方法については、[故障通知セクション](#)を参照してください。

図 7-4. サイクル単位の OCP operation

図 7-5. 過電流検出と短絡保護との関係

#### 7.3.7.2 過熱時のシャットダウン保護

LMG3522xR050 には、2 つの過熱シャットダウン ( OTSD ) 保護機能 ( GaN OTSD およびドライバ OTSD ) が実装されています。デバイス内のさまざまな場所を検出して各種の熱故障シナリオから保護することで、デバイスを最大限に保護するためには、2 つの OTSD 機能が必要です。

GaN OTSD は GaN FET の温度を検出します。GaN FET は、第 1 象限電流と第 3 象限電流の両方で過熱する可能性があります。GaN FET operation 定義で説明されているように、FET はオフ状態になることで第 1 象限の電流を防止することができますが、第 3 象限の電流を防止することはできません。FET の第 3 象限損失は、FET テクノロジー、電流の大きさ、および FET がオン状態またはオフ状態で動作している場合の関数です。GaN FET operation 定義で説明したように、LMG3522xR050 はオフ状態での GaN FET の第 3 象限損失がはるかに大きくなります。

GaN FET が高温の場合、最良の保護策は、第 1 象限の電流が流れようとしたときに GaN FET をオフにし、第 3 象限の電流が流れたときに GaN FET をオンにすることです。このタイプの FET 制御を、最適ダイオード・モード ( IDM ) と呼びます。GaN OTSD のトリップポイントを超えると、GaN OTSD は GaN FET を過熱シャットダウン最適ダイオードモード ( IDM ) 動作に移行させ、この最適な保護を実現します。OTSD-IDM は、最適ダイオード・モード operation で説明されています。

ドライバ OTSD は内蔵ドライバの温度を検出し、GaN OTSD よりも高い温度でトリップします。この 2 番目の OTSD 機能は、OTSD-IDM が動作するのに十分な温度差を確保しながら、ドライバの過熱故障イベントから LMG3522xR050 を保護します。これらのドライバ温度イベントには、LDO5V、BBSW、および VNEG デバイス・ピンの短絡が含まれます。ドライバ OTSD トリップ・ポイントを超過すると、ドライバ OTSD によって LDO5V レギュレータ、VNEG 昇降圧コンバータ、GaN FET がシャットオフされます。IDM はドライバ OTSD では機能しないことに注意してください。このため、ドライバ OTSD は GaN OTSD 機能よりも高くトリップする必要があります。それ以外の場合、GaN FET の第 3 象限での過熱には対処できません。

GaN OTSD とドライバ OTSD のトリップポイントの温度差に加えて、GaN OTSD とドライバ OTSD のセンスポイントの温度勾配差により、さらに温度分離が得られます。GaN OTSD センサは通常、GaN FET の消費電力によりデバイスが GaN OTSD の場合、ドライバ OTSD センサよりも少なくとも 20°C 高温になります。

故障ピンが GaN OTSD 状態とドライバ OTSD 状態のいずれかまたは両方に対してアサートされます。GaN OTSD とドライバ OTSD の両方が負方向のトリップ・ポイントを下回ると、故障がデアサートされ、デバイスは自動的に通常動作に戻ります。クールダウン中、デバイスがドライバ OTSD 状態を終了しても OTSD 状態のままになると、デバイスは自動的に IDM 動作を再開します。

#### 7.3.7.3 UVLO 保護

LMG352xR050 は幅広い VDD 電圧をサポートただし、デバイスが UVLO スレッショルドを下回ると、GaN デバイスはスイッチングを停止してオフに保持します。UVLO を通知すると、故障ピンは Low にプルされます。VIN UVLO の立ち上がりエッジに応じて LDO と昇降圧はオンになり、5V ~ 6V でシャットオフされます。

#### 7.3.7.4 ハイ・インピーダンスの RDRV ピン保護

RDRV ピンが継続的に監視される場合 ( [ドライブ強度の調整](#) を参照 ) LMG352xR050R<sub>RDRV</sub> の推奨動作条件範囲より高いインピーダンスが得られるように RDVR を継続的に監視することで、危険な低速ターンオン時間を防止します。ハイ・インピーダンス RDRV ピンを検出すると、GaN FET がオフに保持され、故障ピンがアサートされます。ハイ・インピーダンスの RDRV 端子が検出されなくなると、通常動作に復帰し、故障ピンがデアサートされます。

#### 7.3.7.5 障害通知

LMG3522R050 は、故障ピンと OC ピンの両方、または単に故障ピンの故障を通知するように構成できます。デバイスの VDD の電源投入時に OC ピンを接地に短絡すると、LMG3522R050 は故障ピンの故障のみを通知するように構成されます。

LMG3526R050 には OC ピンがなく、故障ピンの故障が通知されるのみです。

故障および OC ピンはプッシュプル出力です。High レベル出力電圧は LDO5V ピンにプルアップされます。

表 7-1 に、故障ピンと OC ピンの両方で故障が通知されたときの故障通知の真理値表を示します。

表 7-1. 故障通知の真理値表 ( 故障と OC ピンの両方が故障を報告 )

|       | 故障なし | VDD UVLO | 過熱 | ハイ・インピーダンス RDRV 端子 | 過電流 | 短絡 |

|-------|------|----------|----|--------------------|-----|----|

| FAULT | 1    | 0        | 0  | 0                  | 1   | 0  |

| OC    | 1    | 1        | 1  | 1                  | 0   | 0  |

表 7-2 に、故障ピンのみが故障を通知したときの故障通知の真理値表を示します。

表 7-2. 故障ピンのみによる故障通知の真理値表

|       | 故障なし | VDD UVLO | 過熱 | ハイ・インピーダンス RDRV 端子 | 過電流 | 短絡 |

|-------|------|----------|----|--------------------|-----|----|

| FAULT | 1    | 0        | 0  | 0                  | 0   | 0  |

#### 7.3.8 ドライブ強度調整

LMG352xR050 により、デバイスのドライブ強度を調整し、希望のスルーレートを得ることができます。これにより、スイッチング損失とノイズ結合の最適化に柔軟性をもたらします。

駆動強度を調整するため、RDRV ピンとソース・ピンの間に抵抗を配置できます。この抵抗により、ターンオン時のデバイスのスルーレートが 15V/ns ~ 150V/ns の範囲で決定されます。一方、抵抗なしで選択できる dv/dt 値は 2 つあります。RDRV ピンを接地に短絡すると、スルーレートが 150V/ns に設定され、RDRV ピンを LDO5V に短絡すると、スルーレートが 100V/ns に設定されます。デバイスは、電源オン時に LDO5V への短絡を 1 回検出します。LDO5V への短絡状態が検出されると、デバイスは RDRV ピンを監視しなくなります。そうでない場合、RDRV ピンを継続的に監視し、デバイス動作中の抵抗を変調することで dv/dt 設定を変更できます。スイッチングノイズを除去するための内部フィルタリングが十分に大きいため、変調はかなり低速であることが求められます。

注

寄生電力ループのインダクタンスは、 $V_{DS}$  スイッチング波形からの電圧スルーレートの読み出しに影響を与える可能性があります。電圧立ち下がリフェーズの前の立ち上がりフェーズで、インダクタンスにより  $V_{DS}$  の降下が生じます。この電圧降下が  $V_{DC}$  の 20%より大きい場合、電圧スルーレートの読み取り値が影響を受ける可能性があります。電力ループ設計ガイドラインと寄生電力ループインダクタンスの推定方法については、[セクション 8.5.1.2](#) を参照してください。

### 7.3.9 温度検出出力

統合ドライバーは GaN ダイの温度を感知し、TEMP ピン上の変調 PWM 信号を通じてその情報を出力します。同じリフレッシュレートの場合、典型的な PWM 周波数は 9kHz です。最小 PWM パルス幅は約 30ns であり、25°C 未満の温度で観測できます。目標温度範囲は 25°C から 150°C までで、対応する PWM デューティ・サイクルは通常 3% ~ 82% です。式 2 は、デューティ・サイクル  $D_{TEMP}$  から標準的な接合部温度 ( $T_J, typ$  標準値 (°C)) で計算するために使用できます。

$$T_{J,typ} (\text{°C}) = 162.3 * D_{TEMP} + 20.1 \quad (2)$$

に表 7-3、標準測定時の許容誤差を示します。

表 7-3. TEMP 信号および許容誤差に基づく標準的な接合部温度測定

| TEMP 信号 (°C) に基づく標準的な $T_J$ 測定 | 25 | 85 | 125 |

|--------------------------------|----|----|-----|

| 許容誤差 (°C)                      | ±5 | ±6 | ±10 |

温度が 150°C を超えると、過熱故障が発生するまで、デューティ・サイクルは直線的に増加し続けます。過熱が発生すると、TEMP ピンが HIGH にプルされ、温度が通常範囲まで低下するまでこの故障が通知されます。過熱フォルトをクリアするためのヒステリシスが備わっています。

### 7.3.10 最適ダイオード・モード動作

オフ状態の FET は、電流を一方向にブロックし (第 1 象限)、対応するダイオードのような電圧降下を伴う電流を他の方向 (第 3 象限) に流すことで、ダイオードのように動作します。ただし、FET は、非常に小さい電圧降下でオン状態で第 3 象限の電流を伝導することもできます。最適ダイオード・モード (IDM) とは、オフ状態に移行することで第 1 象限の電流をブロックするよう FET を制御し、オン状態に移行して第 3 象限の電流を伝導することで、最適な低い電圧降下を実現します。

FET オフ状態の第 3 象限電流は、通常状態とフォルト状態の両方で、パワー・コンバータで一般的に見られます。GaN FET の operation 定義で説明しているように、GaN FET には、オフ状態の第 3 象限電流を導通するための固有の p-n 接合ボディ・ダイオードはありません。代わりに、LMG352xR050 のオフ状態の第 3 象限の電圧降下は、p-n 接合部の電圧降下の数倍になります。このため、通常動作時の効率と、故障条件でのデバイスの耐久性に影響を及ぼす可能性があります。

GaN FET 過熱故障状況でのデバイスの耐久性を高めるため、LMG352xR050 デバイスには過熱シャットダウン保護に記載されているように、GaN FET 過熱シャットダウン最適ダイオードモード (OTSD-IDM) 機能が実装されています。OTSD-IDM 機能については、次のセクションで詳細に説明します。

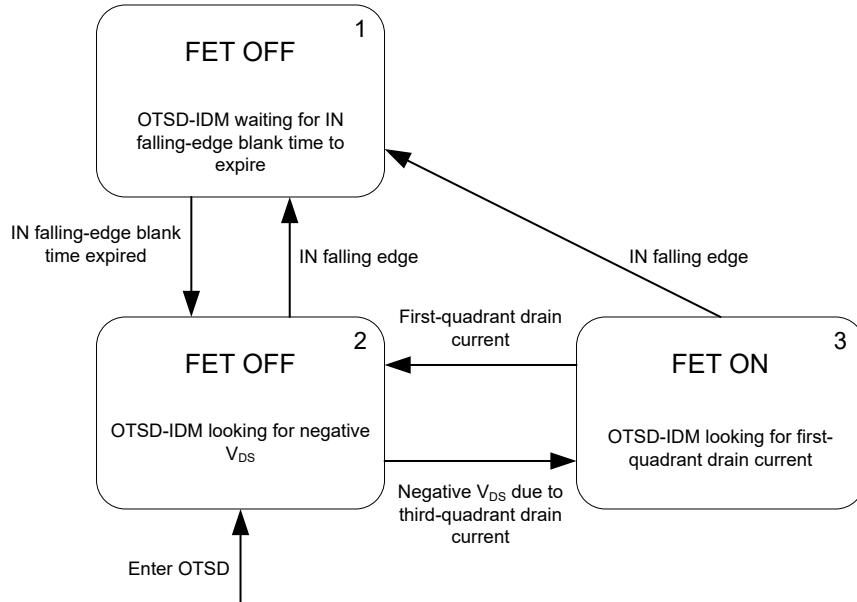

#### 7.3.10.1 過熱シャットダウンの理想ダイオードモード

過熱シャットダウンの理想ダイオード・モード (OTSD-IDM) を LMG352xR050 に実装しています。過熱シャットダウン保護で説明されているように、GaN FET が過熱したとき、理想ダイオードモードは最高の GaN FET 保護を提供します。

OTSD-IDM は、GaN FET を保護している際に、電力システムの動作のすべて、一部、またはまったく影響を与えるません。GaN OTSD イベントで LMG352xR050 が故障ピンをアサートした場合、電源システムはシャットダウンする機能を持たず、ただ動作を継続しようとするだけかもしれません。電源システムの一部は、コントローラーソフトウェアのバグ、半田接合の破損、デバイスのシャットオフなどの理由で動作を停止することがあります。電源システムがシャットダウンした瞬間、電源システムはゲート駆動信号の供給を停止しますが、誘導性素子は放電中も強制的に電流を流れ続けます。

OTSD-IDM ステート・マシンを図 7-6 に示します。各状態には、状態ボックスの右上に状態番号が割り当てられます。

図 7-6. 過熱シャットダウンの理想ダイオード・モード (OTSD-IDM) ステート・マシン

1. IN ピンで立ち下がりエッジが検出されると、LMG352xR050GaN FET は常に状態#1 になります。OTSD-IDM は、OTSD-IDM 状態#1 で GaN FET をオフにします。OTSD-IDM は、IN 立ち下がりエッジでのブランク時間が経過するまで待機しています。この時間により、反対側の FET に切り替わる時間が得られ、正のドレイン電圧が生成されます。ブランク時間が経過すると、デバイスは OTSD-IDM 状態#2 に移行します。

2. OTSD-状態#2 の場合、OTSD-IDM は IDM 状態#1 から来ている場合、IDM FET をオフの状態に維持し、OTSD-IDM 状態#3 から来ている場合、GaN FET をオフにします。OTSD-IDM は、OP-IDM 状態#2 における GaN FET ドレイン電圧を監視しています。これは、第 3 象限電流が流れていることを意味する負のドレイン電圧を探しています。これは、デバイスが OTSD に移行したときの開始状態でもあります。負の GaN FET ドレイン電圧が検出されると、デバイスは OTSD-IDM 状態#3 に移行します。

3. OTSD-IDM は、OTSD-IDM 状態#3 で GaN FET をオンにします。OTSD-IDM は、この状態のドレイン電流を監視します。第 1 象限のドレイン電流が検出されると、本デバイスは OTSD-IDM 状態#2 に移行します。

状態#1 は、です。状態#1 は、状態#2 に進む前に一定の期間待機します。固定時間は、反対側スイッチがスイッチングする時間を与え、正のドレイン電圧を生成するためです。固定時間を使用して、正のドレイン電圧が生成されない場合の固着状態を防止します。

状態 1 は、LMG352xR050 が OTSD に移行したときにコンバータがスイッチングを継続した場合に、貫通電流に対する保護に役立ちます。一方、コンバータがすでに OTSD 内の LMG352xR050 でスイッチングを開始した場合は、状態#1 でも OTSD デバイスを強制的に進行させることで、貫通電流保護が得られます。たとえば、昇圧 PFC の同期整流器は、初期入力電力アプリケーションで PFC 出力コンデンサを充電するときに OTSD に移行することができます。昇圧 PFC FET をスイッチングする前に同期整流 FET のスイッチングが開始された場合、貫通電流イベントを回避できます。

信号が存在しない場合、ステート・マシンは、従来型の理想ダイオードモード・ステート・マシンとして、状態 2 と#3 の間のみ移動します。これにより、電源システムがオフになったときにすべての誘導性素子が放電されます。GaN FET で発生する放電ストレスは最小限です。

OTSD-IDM ステート・マシンには、反復的な貫通電流イベントに対する保護がないことに注意してください。LMG352xR050 がコンバータ動作中に IN 信号を失うなど、劣化事例もあります。これにより、OTSD-IDM が繰り返しシートスルー電流イベントにさらされる可能性があります。このシナリオでは、適切なソリューションはありません。OTSD-FET IDM が貫通電流イベントを繰り返し許容しない場合、代わりに GaN FET はオフ状態の過剰な第 3 象限損失にさらされます。

### 7.3.11 ゼロ電圧検出 (ZVD)

ゼロ電圧スイッチング (ZVS) コンバータは、パワーコンバータの効率を改善するために広く使用されています。ただし、LLC や三角波電流モード (TCM) トーテムポール PFC などのソフトスイッチングトポロジでは、負荷条件、インダクタ、磁気パラメータ、制御手法によって ZVS が失われる可能性があり、システム効率に影響を及ぼします。ZVS を確実に実現するには、特定の設計マージンや追加回路が必要で、それによりコンバータの性能が低下し、部品が追加されます。

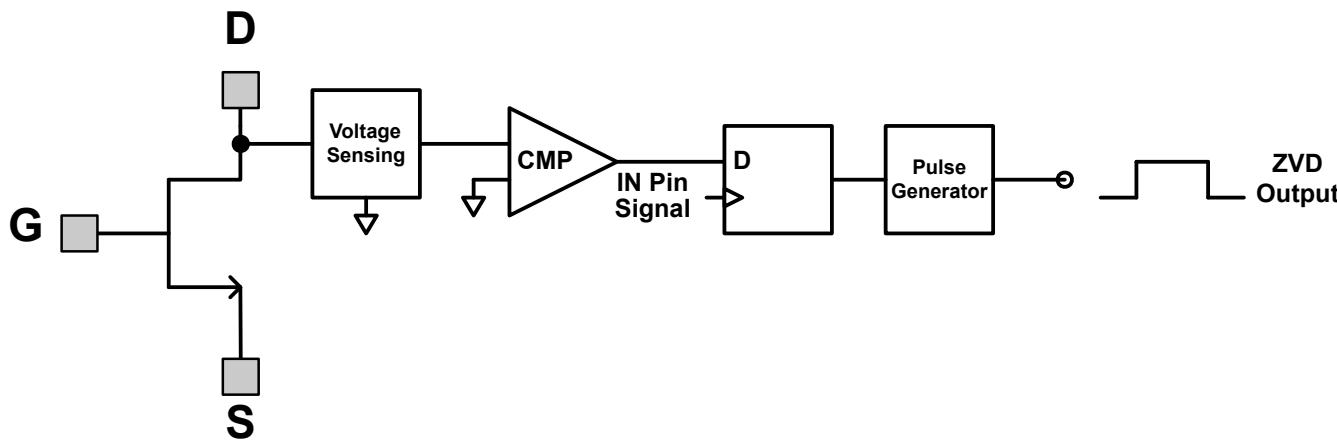

ソフトスイッチングコンバータのシステム設計を簡素化するため、LMG3526R030 部品には、ゼロ電圧検出 (ZVD) 回路が内蔵されており、電流スイッチングサイクル内で ZVS が達成されたかどうかを示すデジタル帰還信号を供給します。この回路を、図 7-7 に示します。IN ピン信号が High になると、ロジック回路はデバイスの  $V_{DS}$  が 0V を下回ったかどうかをチェックし、このスイッチングサイクルでデバイスがゼロ電圧スイッチングに成功したかどうかを判定します。ZVS が識別されると、図 6-3 に示すように、 $T_{DL\_ZVD}$  の遅延時間後に  $T_{WD\_ZVD}$  幅のパルス出力が ZVD ピンから送信されます。本デバイスがゼロ電圧スイッチングを検出できるようにするには、一定の第 3 象限導通時間が必要であり、 $T_{3rd\_ZVD}$  はゲートドライバ強度の閾値です (図 5-12 を参照)。

図 7-7. ゼロ電圧検出回路のブロック図

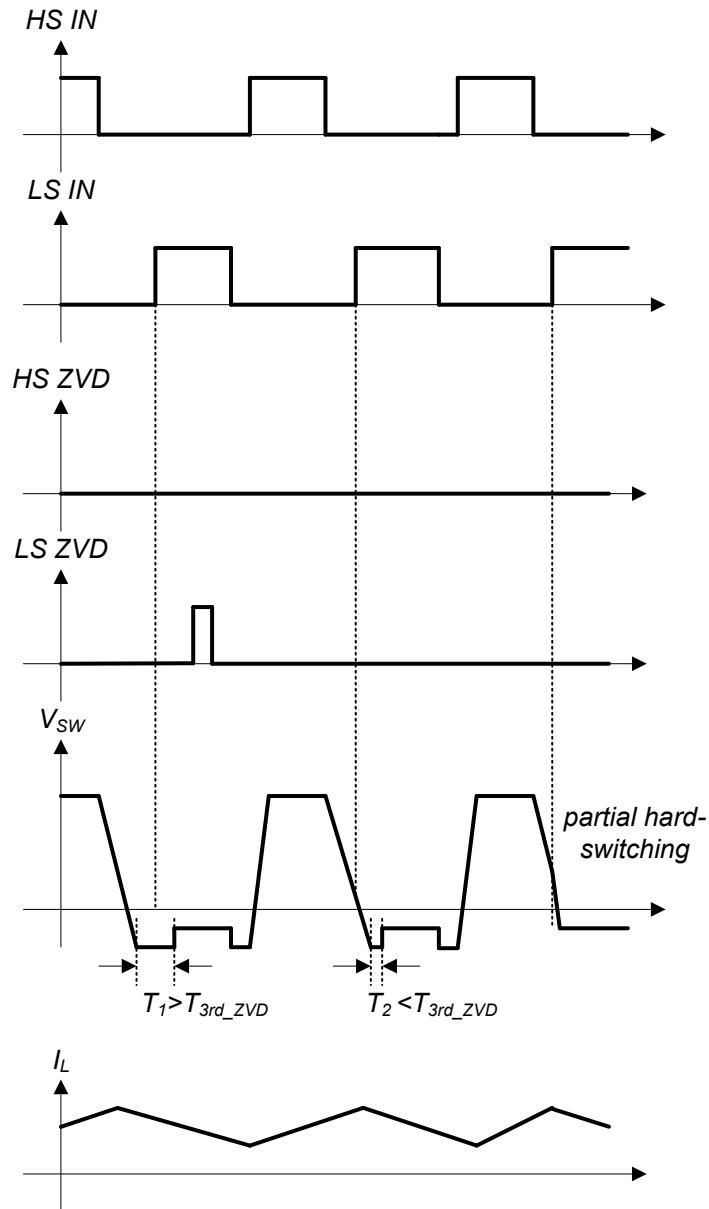

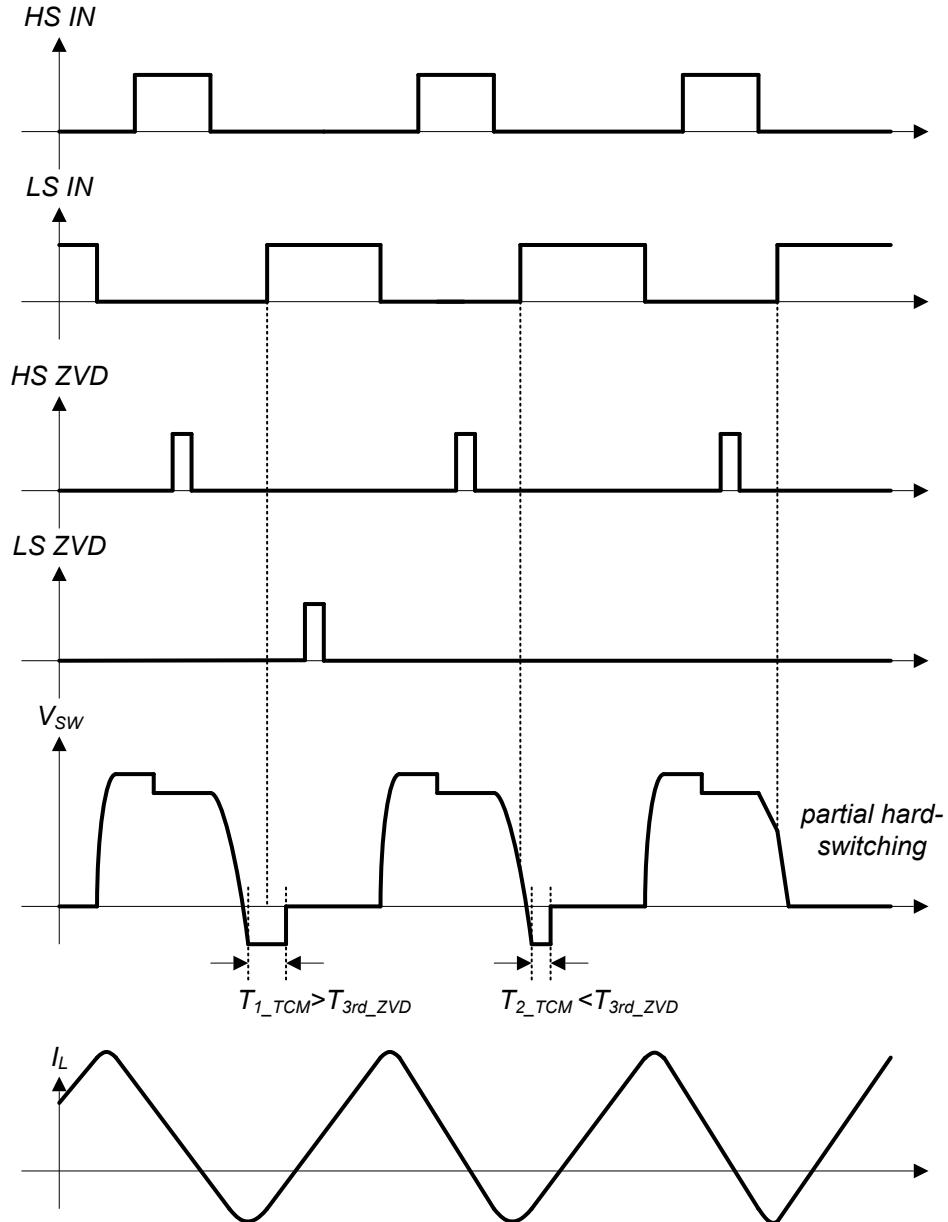

連続導通モード降圧コンバータに対応する ZVD 出力のタイミングを図 7-8 に示しますが、目的は、ハードスイッチングとソフトスイッチングの両方において ZVD 機能がどのように動作するかを示すことです。スイッチ・ノードから流れ出る負荷電流は、正と定義されます。CCM 降圧動作では、ハイサイドのハードスイッチングデバイスが動作し、ローサイドのデバイスは適切なデッドタイムの設定によりゼロ電圧スイッチングを実現できます。ローサイド GaN IN ピンが上昇する最初のスイッチング・サイクルでは、スイッチ・ノード電圧  $V_{DS}$  は 0 を下回り、 $T_1$  の期間にわたって第 3 象限導通を維持します。この第 3 象限導通時間  $T_1$  は、電気的特性表に規定されている検出時間  $T_{3rd\_ZVD}$  より大きいため、ゼロ電圧スイッチングが識別され、ZVD ピンはそれを示すパルス信号を出力し、ZVD パルスのパルス幅も電気的特性表に  $T_{WD}$  として定義されます。2 番目のスイッチングサイクルでは、本デバイスがより早くオンになり、第 3 象限導通時間  $T_2$  は  $T_{3rd\_ZVD}$  より小さくなります。この場合、デバイスが ZVS を達成しているにもかかわらず、ZVD 信号は Low のままでです。3 番目のスイッチングサイクルでは、IN ピン信号がより早く進み、デバイスは部分的にハードスイッチングを行います。したがって、この場合は ZVD 出力は Low のままでです。この CCM 降圧動作では、常にハードスイッチングが行われているため、ハイサイド ZVD 出力が Low に維持されることに注意します。

図 7-8. CCM 降圧コンバータでの ZVD 機能

ZVD 機能は、ソフトスイッチングトポロジでの制御を容易にし、それを示すために、TCM トーテムポール PFC の ZVD 波形を図 7-9 に示します。この図では、 $V_{IN} > 0.5V_{OUT}$  で正のサイクルを考慮し、スイッチ・ノードに流れ込む負荷電流を正と定義します。最初のスイッチングサイクルでは、負荷電流によって十分な負電流が形成され、ローサイドデバイスは  $T_{3rd\_DET}$  を超える明確な第 3 象限導通時間で ZVS を実現します。そのため、ZVD はパルス信号を出力し、ZVS 情報を返します。次の 2 つのスイッチングサイクルでは、ZVD パルスが欠けています。これは、第 3 象限の導通時間が 2 番目のサイクルで短くなり、デバイスが実際に 3 番目のサイクルで ZVS を失うためです。

図 7-9. TCM TP PFC コンバータでの ZVD 機能

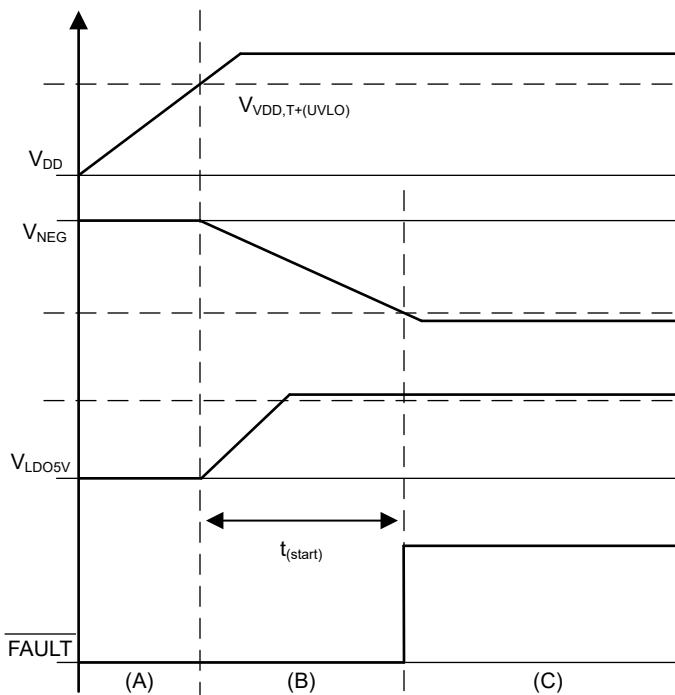

## 7.4 スタート-アップ・シーケンス

図 7-10 は、LMG352xR050 の起動シーケンスを示します。

時間間隔 A :  $V_{DD}$  が蓄積を開始します。故障信号は最初に Low にプルされます。

時間間隔 B :  $V_{DD}$  が UVLO スレッショルド  $V_{VDD,T+(UVLO)}$  を超えると、LDO5V と  $V_{NEG}$  の両方が正常に起動します。 $C_{LDO5V} = 100nF$ 、 $C_{VNEG} = 2.2 \mu F$  の場合、LDO5V は  $V_{NEG}$  より前に UVLO スレッショルドに達します。異なるコンデンサを使用すると、スタートアップ時間が異なる可能性があります。この時間間隔で  $V_{DD}$  にグリッヂが発生し、UVLO スレッショルド  $V_{VDD,T+(UVLO)}$  を下回った場合、LDO5V と  $V_{NEG}$  は蓄積を停止し、 $V_{DD}$  が再び  $V_{VDD,T+(UVLO)}$  を上回った場合にのみ再開します。この場合は、より長いスタートアップ時間が予想されます。

時間間隔 C : LDO5V と  $V_{NEG}$  の両方がスレッショルドに達すると、故障 (異常検知) 信号はクリアされ (「High」)、デバイスは IN ピン信号に追従してスイッチングを行うことができます。

図 7-10. スタート-アップのタイミング図を更新

## 7.5 デバイスの機能モード

このデバイスには 1 つの動作モードがあり、推奨動作条件内で動作した場合に適用されます。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

LMG352xR050 は、最大 520V BUS 電圧で動作するハード・スイッチングおよびソフト・スイッチングを行うアプリケーションを対象としたパワー IC です。GaN デバイスは逆回復電荷がゼロであり、トーテムポール PFC などのアプリケーションで高周波のハード・スイッチングを可能にします。GaN デバイスの低い  $Q_{oss}$  は、LLC や位相シフトフルブリッジ構成などのソフトスイッチングコンバータにも利点があります。ハーフブリッジ構成は、前述の 2 つのアプリケーションとその他多くのアプリケーションの基礎であるため、このセクションでは LMG352xR050 をハーフブリッジ構成で使用する方法について説明します。

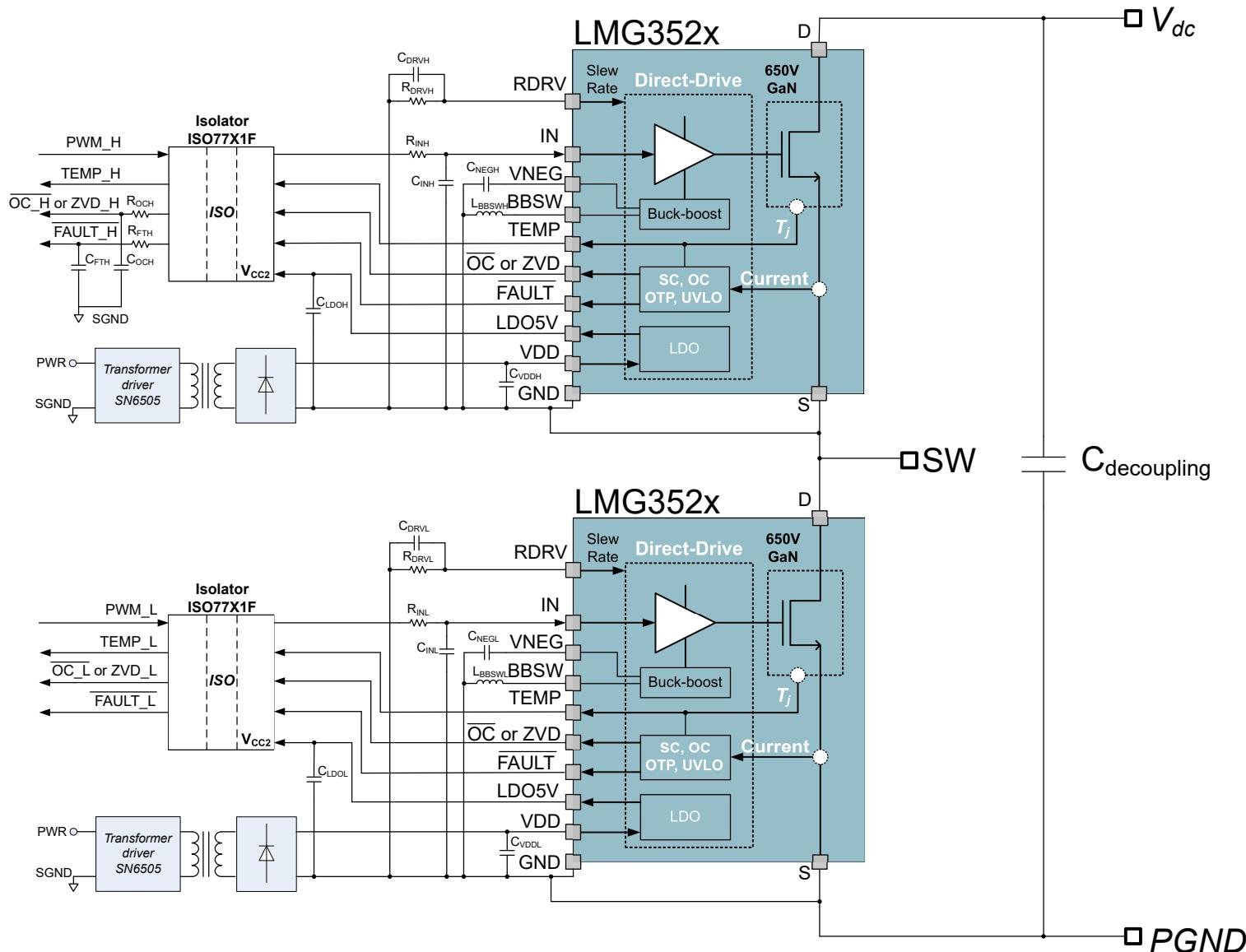

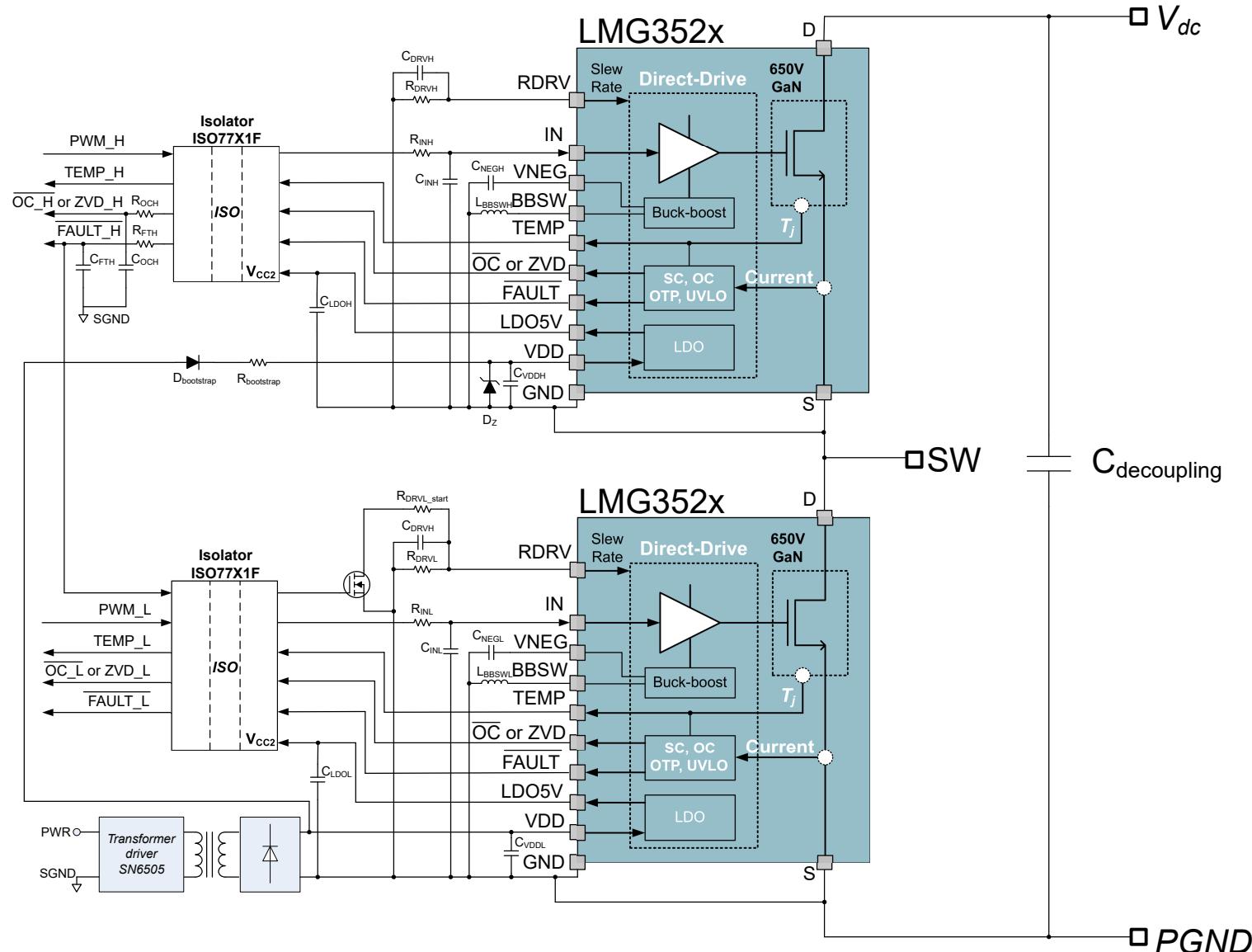

## 8.2 代表的なアプリケーション

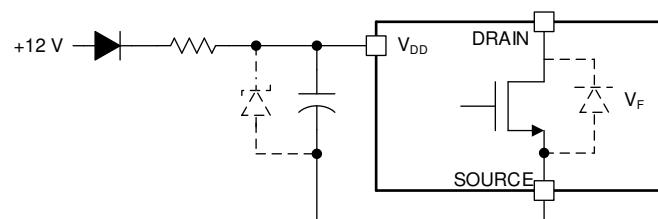

図 8-1. 絶縁型電源を使用した標準的なハーフブリッジアプリケーション

図 8-2. ブートストラップ付きの標準的なハーフブリッジ・ アプリケーション

### 8.2.1 設計要件

この設計例は、PFC アプリケーションを代表するハードスイッチ昇圧コンバータについて示しています。表 8-1 は、この設計のシステムパラメータを示します。

表 8-1. 設計パラメータ

| 設計パラメータ         | 数値の例    |

|-----------------|---------|

| 入力電圧            | 200VDC  |

| 出力電圧            | 400VDC  |

| 入力 ( インダクタ ) 電流 | 20A     |

| スイッチング周波数       | 100 kHz |

### 8.2.2 詳細な設計手順

高電圧パワーコンバータでは、高性能パワーコンバータには回路設計と PCB レイアウトが不可欠です。本書では、電力変換器の設計は対象外であるため、このデータシートでは、LMG352xR050 を使用して適切に動作するハーフブリッジ構成を構築する方法について説明します。

#### 8.2.2.1 スルーレートの選択

LMG352xR050 のスルーレートは、RDRV ピンと GND の間に抵抗  $R_{RDRV}$  を接続することで、約 15V/ns ~ 150V/ns の範囲で調整できます。大きな  $R_{RDRV}$  抵抗を使用する場合には、RDRV ピンがハイ・インピーダンス・ノードとなります。したがって、適切にシールドされていない場合、ドレインや他の高速スルーリング高電圧ノードからの結合の影響を受けやすい可能性があります。これは、不安定なスイッチング  $dv/dt$  として表面化し、極端な場合には RDRV が開放と検出されて過渡故障が発生します。ピンをレイアウトでシールドすることを優先しますが、それでも問題がある場合は、RDRV と GND の間に最大 1nF のコンデンサを追加してピン電圧を安定させることができます。

スルーレートは、GaN デバイスの性能に次の点で影響を及ぼします。

- スイッチング損失

- 電圧オーバーシュート

- ノイズ結合

- EMI ( 電磁干渉 ) 放出

一般に、スルーレートが高いとスイッチング損失は小さくなりますが、高いスルーレートは電圧オーバーシュート、ノイズ結合、および EMI 放射を増加させる可能性もあります。このデータシートに掲載されている設計上の推奨事項に従うと、スルーレートの高い要因に起因する課題を軽減できます。LMG352xR050 を使用すると、回路設計者がアプリケーションの性能を最大限に引き出すために、適切なスルーレートを柔軟に選択できます。

#### 8.2.2.1.1 ブートストラップ/ハイサイド電源でのスタートアップおよびスルーレート

ブートストラップ電源を使用すると、ハイサイド LMG352xR050 のスタートアップにさらに制約が生じます。電源投入前は、GaN デバイスは性能が低下したカスコード・モードで動作します。一部の回路では、ブートストラップ電源のハーフブリッジ構成の起動には、より低速なスルーレートが必要な場合があります。詳細については、[ブートストラップダイオードの使用](#)を参照してください。

#### 8.2.2.2 信号レベル・シフト

ハーフブリッジでは、ハイサイドデバイスと制御回路の間の信号バスを絶縁するために、高電圧レベルシフタまたはデジタルアイソレータを使用する必要があります。ローサイドデバイスでは、アイソレータを使用することもオプションです。しかし、アイソレータを使用することで、ハイサイドとローサイドの信号バスの間の伝搬遅延を均等化し、GaN デバイスとコントローラに異なるグランドを使用することができます。ローサイド・デバイスでアイソレータを使用しない場合、制御グランドと電源グランドはデバイスで接続し、基板上の他の場所には接続しない必要があります。詳細については、[レイアウトガイドライン](#)を参照してください。高速スイッチングデバイスでは、アイソレーターを使用しないと、コモン・グラウンド・インダクタンスがノイズ問題を引き起こす原因となりやすいです。

ノイズ耐性の向上には、レベル変換用のデジタルアイソレータの選択が重要です。GaN デバイスは、ハード・スイッチング・アプリケーションで 50V/ns を超える高い  $dv/dt$  を容易に実現できるため、同相過渡耐性 ( CMTI )

が高く、バリア容量が小さいアイソレータを使用することを強くお勧めします。CMTI が小さいアイソレータは容易に誤信号を発生させ、貫通電流を引き起こす可能性があります。バリア容量は信号グランドと電源グランドとの間の絶縁容量の一部で、この容量はスイッチング中に発生する同相電流と EMI 放射に正比例します。また、エッジトリガではないアイソレータを選択することを TI は強くお勧めします。エッジトリガアイソレータでは、高  $dv/dt$  イベントが発生すると、アイソレータが動作状態を反転させ、回路の誤動作を引き起こす可能性があります。

一般に、TI ISO77xxF や ISO67xxF シリーズなど、デフォルト出力が LOW のオン/オフキー付きアイソレータが推奨されます。デフォルトの Low 状態により、起動時または故障イベントからの回復時にシステムが貫通電流を防止します。CMTI イベントが大きいと、非常に短い（数ナノ秒）の誤パルスが発生するため、TI では、300Ω および 22pF の R-C フィルタなどのローパスフィルタをドライバ入力に配置して、これらの誤ったパルスをフィルタして除去することをお勧めします。

### 8.2.2.3 昇降圧コンバータの設計

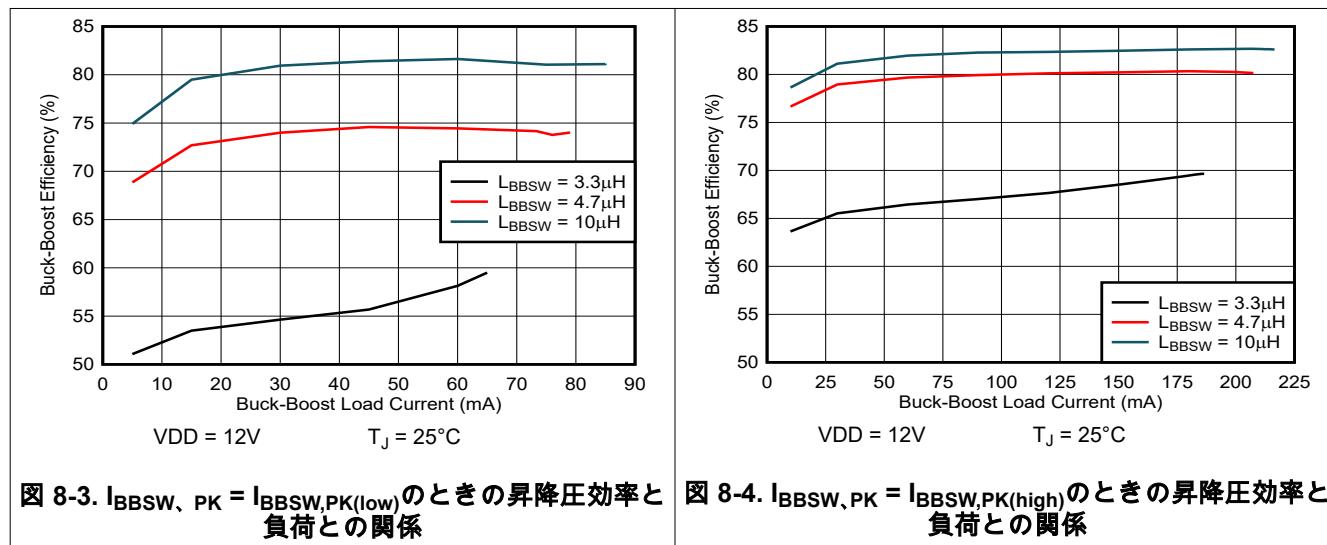

図 8-3 と図 8-4 に、さまざまなインダクタとピーク電流モードにおける昇降圧コンバータの効率と負荷電流との関係を示します。昇降圧コンバータには、インダクタの両端の  $di/dt$  が大きすぎないように、3μH の最小インダクタンス値が推奨されます。これによって、制御ループが応答するのに十分なマージンが確保されます。その結果、インダクタの最大  $di/dt$  は 6A/μs に制限されます。一方、インダクタンスが大きいと、安定した出力電圧を得るために過渡応答も制限されるため、10μH 未満のインダクタを使用することを推奨します。

図 8-3.  $I_{BBSW,PK} = I_{BBSW,PK(\text{low})}$  のときの昇降圧効率と負荷との関係

図 8-4.  $I_{BBSW,PK} = I_{BBSW,PK(\text{high})}$  のときの昇降圧効率と負荷との関係

### 8.2.3 アプリケーション曲線

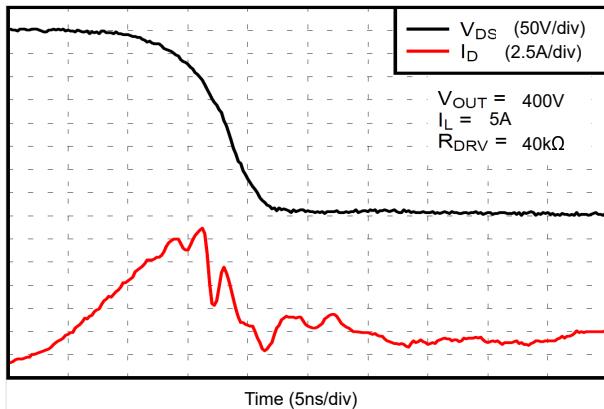

図 8-5. 「アプリケーション例」のターンオン波形

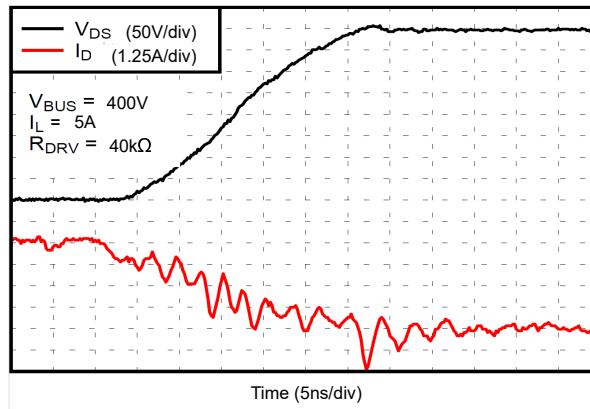

図 8-6. 「アプリケーション例」のターンオフ波形

## 8.3 推奨事項と禁止事項

一般的に GaN デバイス、特に LMG352xR050 の正常な使用は、デバイスの適切な使用に依存します。LMG352xR050 を使用するときは、次の操作を行います。

- アプリケーションノートやレイアウトの推奨事項を含め、データシートを読み、十分に理解してください。

- 電力ループ・インダクタンスを最小化するため、4 層基板を使用し、リターン・パワー・バスを内部層に配置します。

- 寄生インダクタンスを最小限に抑えるために、小型の表面実装バイパスコンデンサとバスコンデンサを使用します。

- 適切なサイズのデカップリング・コンデンサを使用し、[レイアウトのガイドライン](#)で説明されているように、これらのコンデンサは IC の近くに配置します。

- ローサイド・デバイスの入力信号を供給するには、信号アイソレータを使用します。そうでない場合、信号源が LMG352xR050IC のみの電源に接続されている信号 GND プレーンに接続されていることを確認します。

- 故障ピンを使用して電源オン状態を判定し、過電流および過熱イベントを検出し、コンバータを安全にシャットオフすることができます。

LMG352xR050 を使用するときにシステムの問題を回避するには、次のことをしないでください。

- 電源ループおよびバイパスコンデンサのインダクタンスが過剰なため、LMG352xR050 については単層または 2 層の PCB を使用して、IC が適切に動作しないようにしてください。

- バイパスコンデンサの値は、推奨値よりも小さくします。

- デバイスに損傷を与える可能性があるため、650V を超えるドレイン過渡電圧が発生することを許容します。

- デバイスの電源がオフのとき、または電源がオフのときに大きな第 3 象限導通を許可します。これにより、過熱が発生する可能性があります。この動作モードでは、自己保護機能によってデバイスを保護することはできません。

- 故障ピンの出力は無視します。

## 8.4 電源に関する推奨事項

LMG352xR050 は、7.5V ~ 18V の非レギュレート VDD 電源のみが必要です。ローサイドの電源は、ローカルのコントローラ電源から取得できます。ハイサイドデバイスの電源は、絶縁型電源またはブートストラップ電源から供給する必要があります。

### 8.4.1 絶縁型電源の使用

絶縁型電源を使用してハイサイドデバイスに電力を供給すると、電力段スイッチングやデューティ・サイクルが継続しても動作するという利点があります。また、絶縁電源を使用して、電力段のスイッチングが開始される前にハイサイドデバイスに電力を供給してこともできます。これにより、電源が供給されていない LMG352xR050 でのスイッチングに関する懸念がなくなります（詳細については、[ブートストラップ・ダイオードの使用](#)を参照）。

絶縁型電源は、プッシュプル・コンバータ、フライバック・コンバータ、FlyBuck™コンバータ、または絶縁型電源モジュールを使用して取得できます。レギュレートされていない電源を使用する場合、LMG352xR050 の入力は最大電源電圧を超えないようにする必要があります。16V TVS ダイオードを使用して、LMG352xR050 の VDD 電圧をクランプし、保護を強化できます。ハード・スイッチ・アプリケーションでスイッチング損失を低減するには、絶縁型電源またはトランジスタの巻線間容量を最小限に抑える必要があります。さらに、絶縁型バイアス電源の両端間にある容量は、LMG352xR050 の信号-グランドに大電流を注入し、グランドバウンス過渡が問題となる可能性があります。コモン・モード・チョークを使用すると、これらの問題のほとんどを軽減できます。

### 8.4.2 ブートストラップダイオードの使用

ハーフブリッジ構成では、ハイサイドデバイスにフローティング電源が必要になります。LMG352xR050 の性能を最大限に引き出すため、TI では、[絶縁電源を使用すること](#)を強くお勧めします。ブートストラップ供給は、このセクションの推奨事項と併用できます。

昇圧コンバータのようなアプリケーションでは、ハイサイド LMG352xR050 には電源が供給されていない間、ローサイド LMG352xR050 は常にスイッチングを開始します。ハイサイドバイアスが完全にセッティングする前に

非常に高いスルーレートを実現するようにローサイドを調整した場合、高スルーレートでの寄生結合が原因で、ハイサイドが意図せずターンオンする可能性があります。ローサイドのRDRVピンの抵抗を変更して、スタートアップ・スルーレートを100V/nsに減速する必要があります。この低速化は、[ブートストラップ付きの代表的なハーフブリッジ・アプリケーション](#)に示すように、ハイサイドの故障によりローサイドRDRV抵抗を制御することで実現します。

#### 8.4.2.1 ダイオードの選択

LMG352xR050は逆方向回復電荷がなく、出力電荷が非常に制限されています。また、LMG352xR050を使用したハードスイッチング回路は、電圧の高スルーレートを実現します。互換のブートストラップダイオードは、高い出力電荷と逆方向回復電荷をもたらさないようにしてください。

GB01SLT06-214などのシリコンカーバイドダイオードを使用して、逆方向回復効果を回避することができます。SiCダイオードの出力電荷は3nCです。その出力電荷には追加の損失がありますが、スイッチングステージの損失に支配されることはありません。

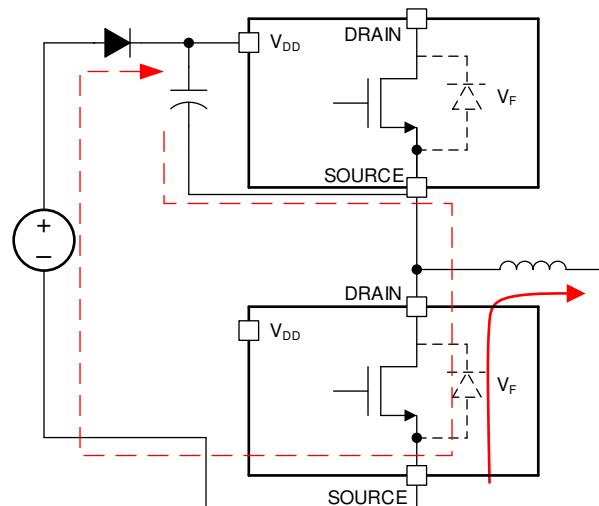

#### 8.4.2.2 ブートストラップ電圧の管理

同期降圧コンバータやその他のコンバータで、ローサイドスイッチが第3象限で動作する場合、ブートストラップ電源は、[図8-7](#)で示されているように、デッドタイム中にローサイドLMG352xR050の第3象限電圧降下を含む経路で充電されます。この第3象限の電圧降下は大きくなる可能性があり、特定の条件でブートストラップ電源を過充電する可能性があります。LMG352xR050のV<sub>DD</sub>電源電圧は、18V未満に維持する必要があります。

図8-7. ブートストラップダイオードの充電パス

図8-8に示すように、ブートストラップダイオード、直列抵抗、16V TVSまたはツエナーダイオードをV<sub>DD</sub>バイパスコンデンサと並列に接続して、ハイサイドLMG352xR050の損傷を防止することが推奨されます。直列抵抗は、スタートアップ時とローサイドデバイスが第3象限モードで動作しているときの充電電流を制限します。この抵抗は、目的の動作周波数でLMG352xR050を駆動するのに十分な電流が得られるよう選択する必要があります。100kHzで動作させる場合、TIは約2Ωの値を推奨しています。高い周波数では、この抵抗の値を減らすか、十分な供給電流を確保するため、抵抗を完全に省略する必要があります。

図8-8. 推奨されるブートストラップ・レギュレータ回路

## 8.5 レイアウト

### 8.5.1 レイアウトのガイドライン

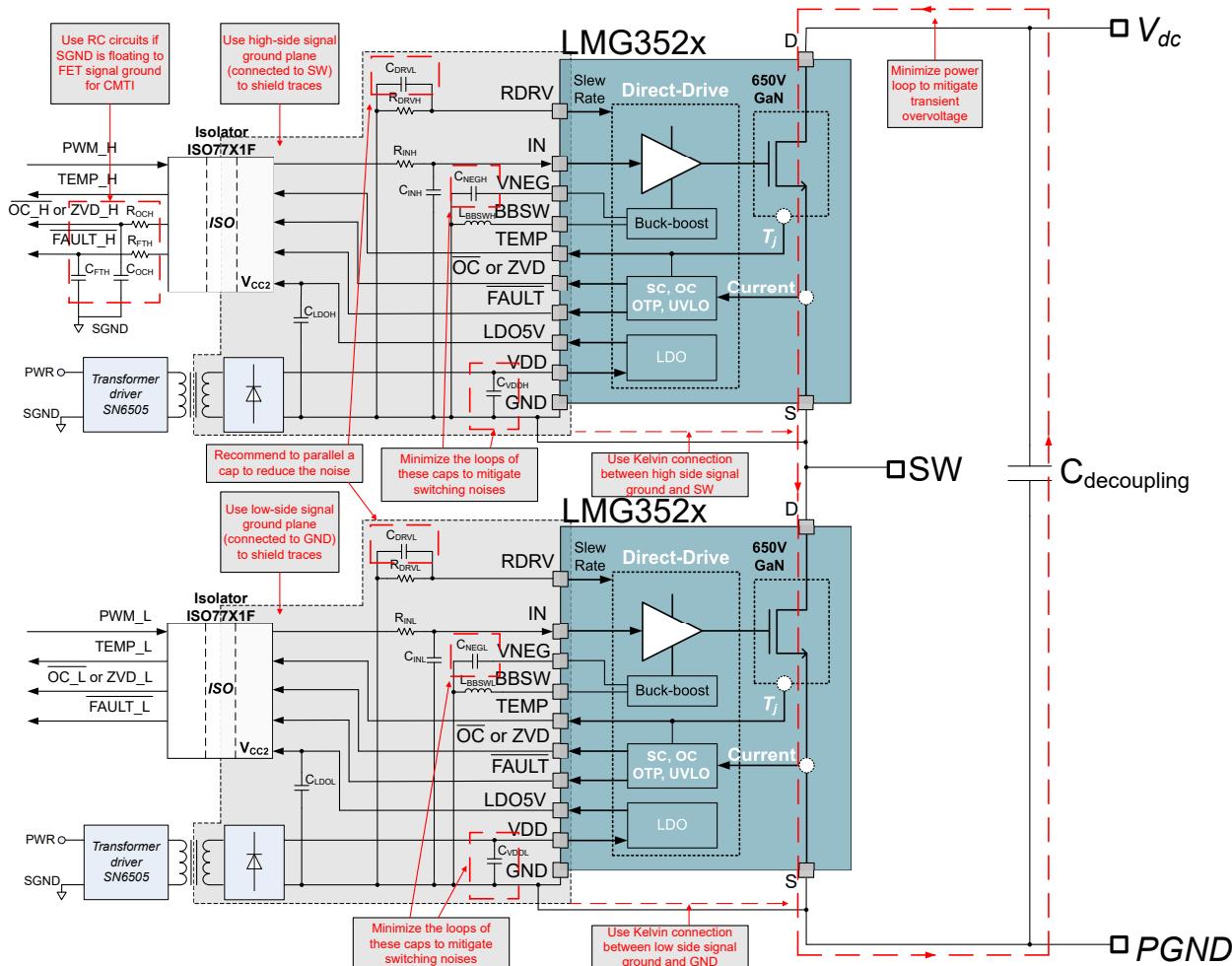

LMG352xR050 のレイアウトは、そのパフォーマンスと機能にとって重要です。通常、ハーフブリッジ構成はこれらの GaN デバイスで使用されるため、この構成ではレイアウトに関する推奨事項を考慮します。適切な性能を実現するには、レイアウトの寄生インダクタンスを低減するために、4 層以上の基板が必要です。図 8-9 重要なレイアウトのガイドラインをまとめます。詳細については、以下のセクションで詳しく説明します。

図 8-9. レイアウトに関する考慮事項付きの代表的な回路図

#### 8.5.1.1 半田接合に対する信頼性

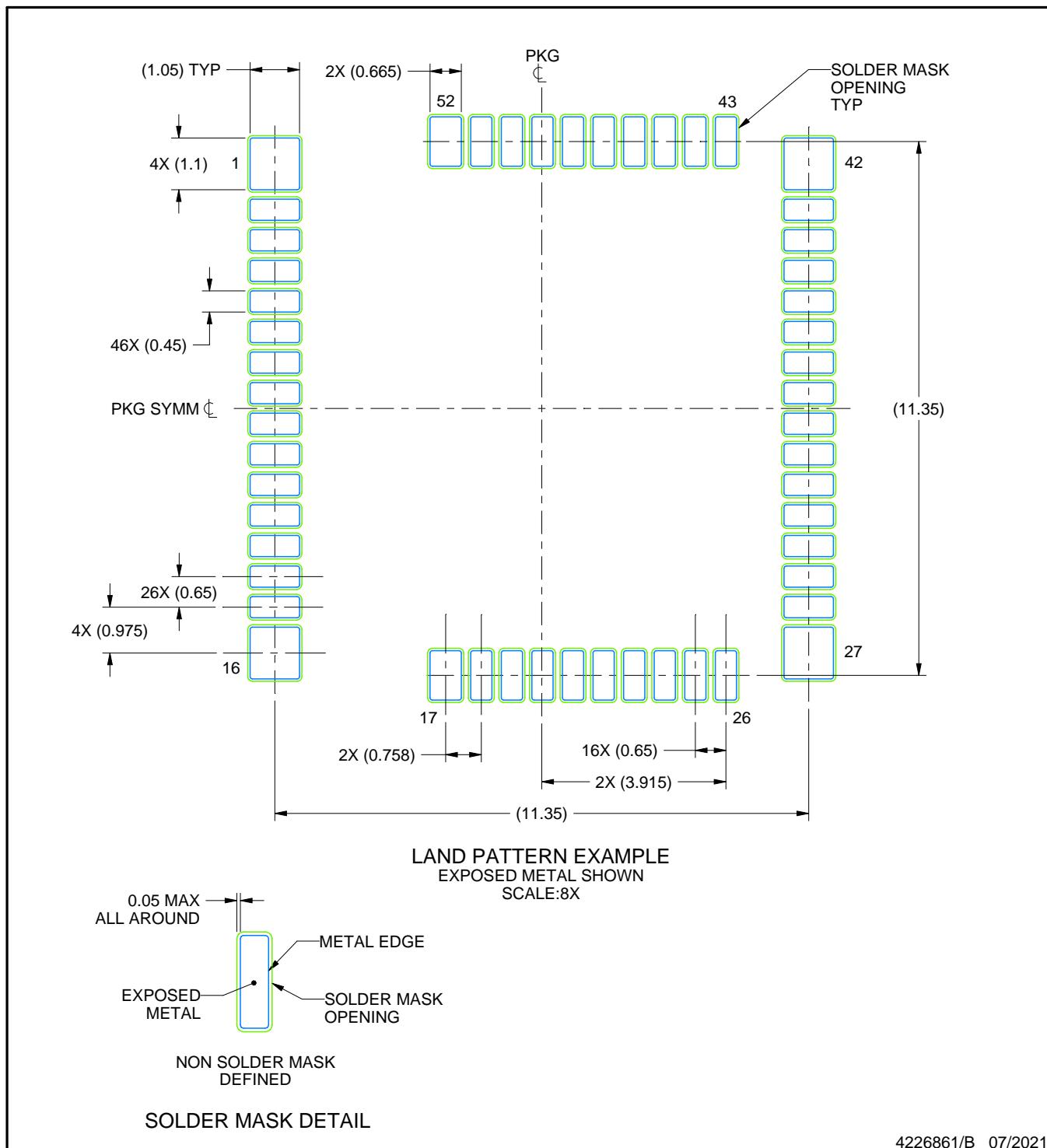

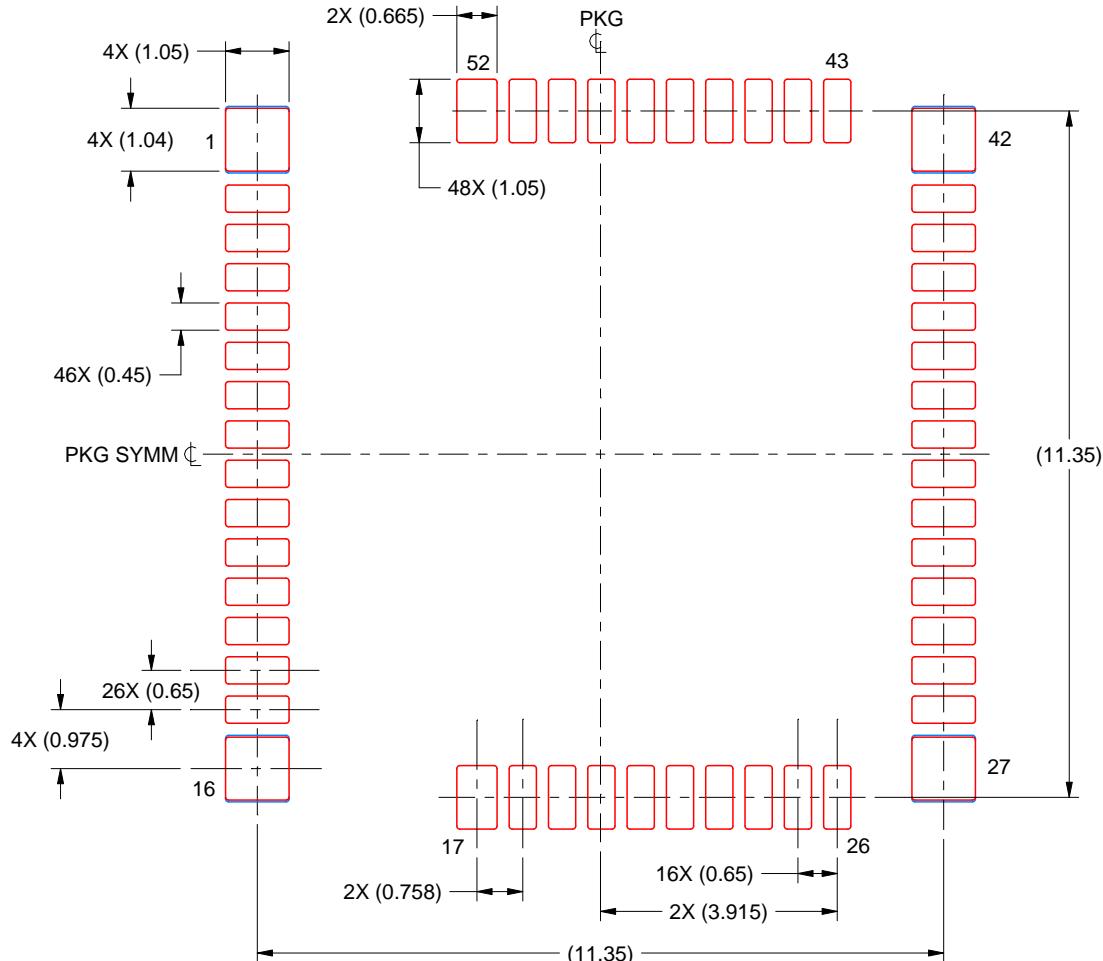

大型の QFN パッケージでは、はんだ接合部に高い応力がかかることがあります。TI は、半田接合の信頼性を確保するため、いくつかのベスト・プラクティスを推奨します。最初に、表 4-1 に記載されている NC1 および NC2 アンカーピンの指示に従う必要があります。第 2 に、すべての LMG352xR050 基板ハンダ・パッドは、メカニカル、パッケージ、および注文情報のランド・パターン例に示すように、ハンダ・マスク未定義 (NSMD) の必要があります。最後に、NSMD パッドに接続される基板トレースは、接続されるパッド側でパッド幅の 2/3 未満にする必要があります。このトレースは、ハンダ・マスクで覆われていない間は、この 2/3 幅制限を維持する必要があります。トレースがハンダ・マスク下の場合、トレースの寸法に制限はありません。レイアウト例では、これらすべての推奨事項に従っています。

### 8.5.1.2 電力ループのインダクタンス

ハーフ・ブリッジの2つのデバイスと高電圧バス容量で構成される電源ループは、スイッチング・イベント中に高い  $di/dt$  を印加します。このループのインダクタンスを最小化することで、リンクギングと電磁干渉 (EMI) を低減し、デバイスの電圧ストレスを低減することができます。

電源ループのインダクタンスを最小限に抑えるため、電源デバイスをできるだけ近くに配置します。デカップリングコンデンサは、2つのデバイスと並んで配置されています。これらは、各デバイスの近くに配置できます。レイアウト例の場合、デバイスは最下層に、デカップリング・コンデンサは最上層に配置されます。PGNDは上層に配置し、HVBUSは上層と3番目の層に、スイッチング・ノードは上層に配置します。これらのビアは、ビアを使用して最下層の電源デバイスに接続されています。ヒートシンクと導体の間の空間距離を保つため、デバイスに近接したトレースの面積は下層によって最小限に抑えられています。

電力ループ・インダクタンスは、ドレインソース間電圧スイッチング波形のリンクギング周波数  $f_{ring}$  に基づいて、次の式で推定できます。

$$L_{pl} = \frac{1}{4\pi^2 f_{ring}^2 C_{ring}} \quad (3)$$

ここで、 $C_{ring}$  は、バス電圧での  $C_{oss}$  (標準値については図 5-8 を参照) と、基板および負荷インダクタまたはトランジスタからのドレインソース間寄生容量を加算した値に等しくなります。

負荷部品の寄生容量の特性評価は困難なため、負荷部品なしで  $V_{DS}$  スイッチング波形をキャプチャし、電源ループのインダクタンスを推定することを推奨します。通常、レイアウト例の電源ループのインダクタンスは約 2.5nH です。

### 8.5.1.3 信号-グランド接続

LMG3522xR050 のソース・ピンは、内部でパワー IC 信号グランドに接続されています。ドライバに関連する受動部品の帰路 (バイパスキャパシタンスなど) は、ソース・ピンに接続する必要があります。ローカル信号のグランド・プレーンは、「Low」インピーダンスのスター接続を持つソース・ピンに接続してください。レイアウト例では、ローカル信号のグランド・プレーンは3層上に配置され、ローカル回路の帰路として機能し、3層目と最下層の間にビアを持つソース・ピンに接続されています。

### 8.5.1.4 バイパスコンデンサ

優れた性能を実現するには、ゲート駆動のループ・インピーダンスを最小化する必要があります。ゲート・ドライバはパッケージに内蔵されていますが、ドライバのバイパスキャパシタンスは外部に配置します。GaN デバイスが負電圧になると、外部 VNEG コンデンサへの経路のインピーダンスがゲート駆動ループに含まれます。この VNEG コンデンサは、VNEG と SOURCE ピンの近くに配置する必要があります。セクション 8.5.2 では、バイパス・コンデンサ C3 と C13 は最上層に配置されており、ビアとソース・ピンを経由してローカル信号グランド・プレーンから VNEG ピンに接続されています。

また、VDD 低インピーダンスで接続する場合、VDD ピンの近くにバイパス・コンデンサ (C1 および C11) を配置する必要があります。

### 8.5.1.5 スイッチ・ノードの静電容量

GaN デバイスは出力容量が非常に低く、高  $dv/dt$  で高速にスイッチングするため、スイッチング損失も非常に小さくなります。この低いスイッチング損失を維持するため、出力ノードに追加容量を最小限に抑える必要があります。スイッチ・ノードの PCB 容量は、以下のガイドラインに従って最小化できます。

- スイッチ・ノードのプレーンと他の電源プレーンおよびグランド・プレーンとの間のオーバーラップを最小限に抑えます。

- ハイサイドデバイスの下の GND リターンパスを細くしながら、低インダクタンスパスを維持します。

- ハイサイド・アイソレータ IC とブーストストラップ・ダイオードは、静電容量の小さいものを選定します。

- パワーインダクタは、GaN デバイスにできるだけ近づけて配置してください。

- パワーインダクタは、巻線間の静電容量を最小限に抑えるため、単層巻線を使用して構築する必要があります。

- 1層インダクタを使用できない場合は、追加の静電容量から GaN デバイスを効果的にシールドするために、一次インダクタと GaN デバイスの間に小型インダクタを配置することを検討してください。

- 裏面のヒートシンクを使用する場合は、放熱性能を向上させるため、下層の銅層でスイッチ・ノードの銅領域の面積が最小限のものを使用します。

#### 8.5.1.6 シグナル インテグリティ

LMG352xR050 への制御信号は、高速スイッチングによって発生する高  $dv/dt$  から保護する必要があります。制御信号とドレインの間の結合は、回路が不安定になり、破壊の可能性があります。制御信号 (IN、故障、OC / ZVD) は、隣接する層に配置されたグランド・プレーンの上に配線します。たとえば、[レイアウト例](#)では、すべての信号がローカル信号グランドプレーンに近い層に配線されています。

ハイサイド・デバイスのパターンと、PGND や HVBUS などの静的プレーンとの間の容量性結合により、同相電流とグランド・バウンスが発生する可能性があります。ハイサイド・パターンと静的プレーンの間のオーバーラップを小さくすることで、結合を低減できます。ハイサイド・レベル・シフタの場合、入力側と出力側のいずれの銅箔がアイソレータの下に伸びないことを確認してください。そうでないと、デバイスの CMTI が損なわれるおそれがあります。

#### 8.5.1.7 高電圧間隔

LMG352xR050 を使用する回路は、最大で 650V の高電圧に対応する可能性があります。LMG352xR050 を使用して回路をレイアウトする場合には、アプリケーションの沿面距離と空間距離の要件と、それらが GaN デバイスにどのように適用されるかを理解してください。各トランジスタのソースとドレイン間、および高電圧電源とグランドの間で、機能的 (または動作中) の絶縁が必要です。LMG352xR050 への入力回路と電源コントローラの間に機能絶縁、またはより強力な絶縁 (強化絶縁など) が必要になることがあります。絶縁要件を満たす信号アイソレータと PCB 間隔 (沿面距離と空間距離) を選定します。

LMG352xR050 の放熱を管理するためにヒートシンクを使用する場合は、ヒートシンクと PCB の間に必要な電気的絶縁と機械的間隔を確保してください。

#### 8.5.1.8 基板に関する推奨事項

LMG352xR050 は Si 基板上に成長した横方向デバイスです。サーマルパッドはデバイスのソースに接続されています。LMG352xR050 は、ハード・スイッチング・パワー・コンバータなど、消費電力が非常に大きいアプリケーションで使用できます。TI は、このようなコンバータでは、LMG352xR050 の上面にヒートシンクを接続することを推奨します。このヒートシンクは、電気的絶縁を備えたサーマル・パッドなどの熱インターフェイス材料 (TIM) と併用することができます。

熱レイアウトの推奨事項と性能データの詳細については、[LMG3410 スマート GaN FET の高電圧ハーフブリッジ設計ガイド](#)アプリケーションノートを参照してください。

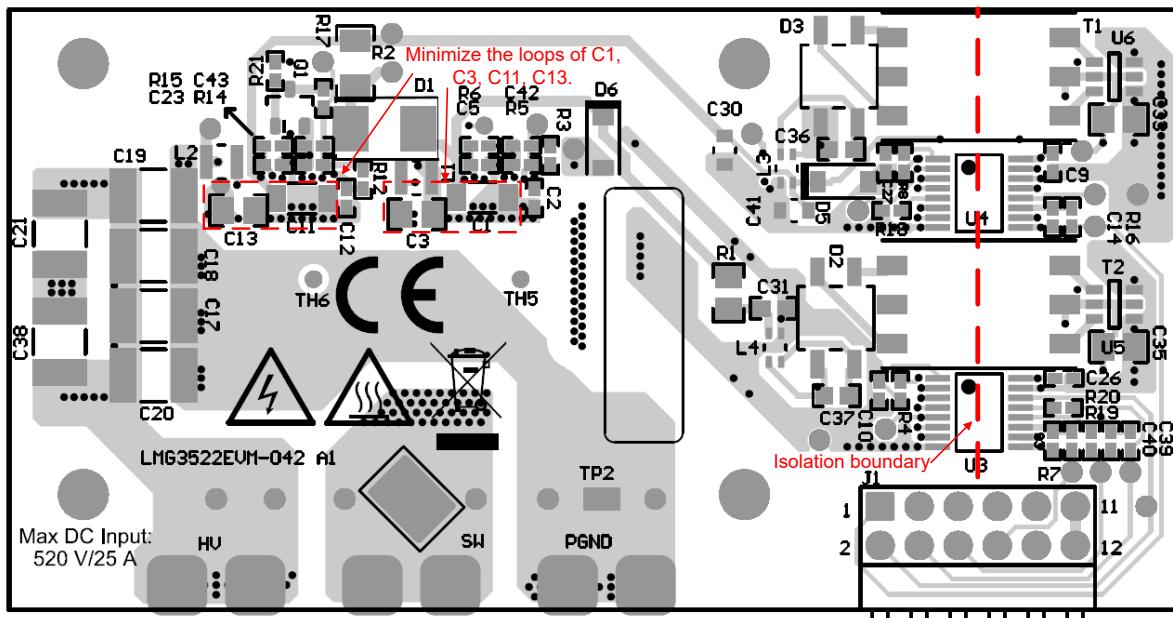

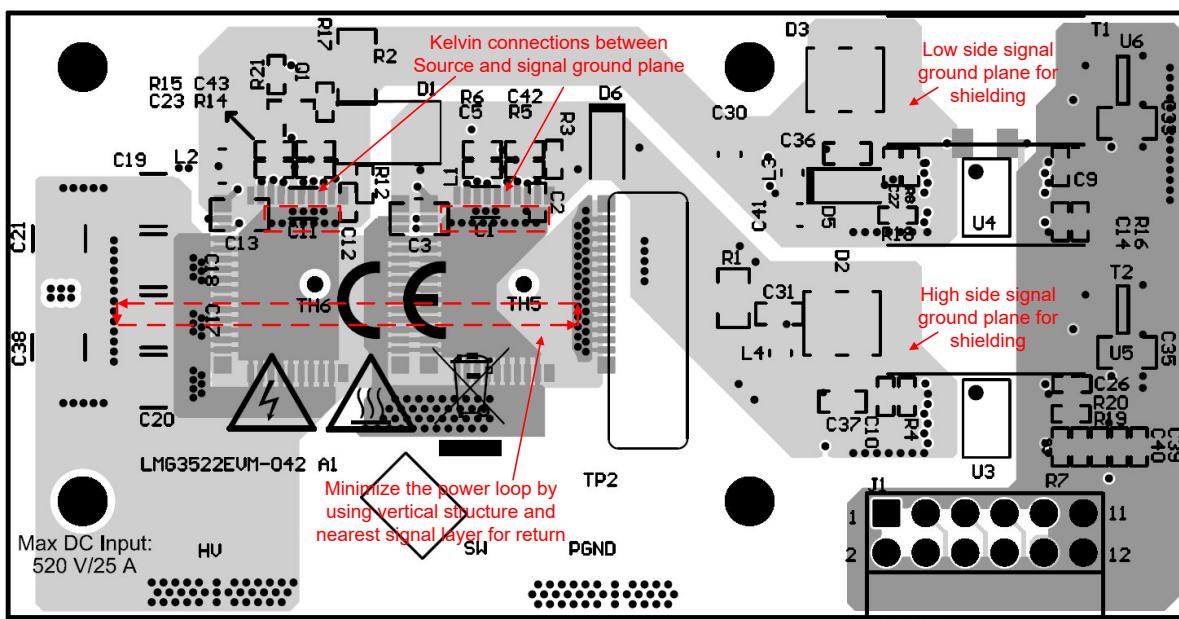

### 8.5.2 レイアウト例

LMG352xR050 およびその周辺部品の正しいレイアウトは、正しい動作に不可欠です。ここに示すレイアウトは、図 8-1 に示す GaN デバイスの回路図を反映しています。これらのレイアウトは良好な結果が得られることが示されており、ガイドラインを意図しています。しかし、別のレイアウト方法で、許容される性能を得ることもできます。また、デバイスの最新の推奨 PCB フットプリントについては、メカニカル、パッケージ、および注文情報のランド・パターンの例を参照してください。

最上層レイアウト、中間層、最下層レイアウトが示されています。中間層レイアウトには、リーダーが最上層と中間層のレイアウトを整列できるように、最上層の部品のアウトラインが含まれています。

図 8-10. ハーフブリッジの最上層レイアウト

図 8-11. ハーフブリッジの 3 層目 (ライトグレー) と最下層 (ダークグレー) レイアウト

## 9 デバイスおよびドキュメントのサポート

### 9.1 ドキュメントのサポート

#### 9.1.1 関連資料

- テキサス・インスツルメンツ、[LMG3410 スマート GaN FET の高電圧ハーフブリッジ設計ガイド](#)アプリケーションノート

- テキサス・インスツルメンツ、[使用条件下における電力線サージに対する GaN FET の信頼性を検証する新たなアプローチ](#)

- テキサス・インスツルメンツ、[寿命にわたる信頼性を備えた GaN 製品を実現](#)

- テキサス・インスツルメンツ、『[GaN デバイス用のディレクティブ駆動構成](#)』

### 9.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントを工キスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 9.4 商標

FlyBuck™ and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

### 9.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 9.6 Export Control Notice

Recipient agrees to not knowingly export or re-export, directly or indirectly, any product or technical data (as defined by the U.S., EU, and other Export Administration Regulations) including software, or any controlled product restricted by other applicable national regulations, received from disclosing party under nondisclosure obligations (if any), or any direct product of such technology, to any destination to which such export or re-export is restricted or prohibited by U.S. or other applicable laws, without obtaining prior authorization from U.S. Department of Commerce and other competent Government authorities to the extent required by those laws.

### 9.7 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision * (September 2023) to Revision A (May 2024)</b>                              | <b>Page</b> |

|-------------------------------------------------------------------------------------------------------|-------------|

| • データシートに LMG3526R050 デバイスを追加.....                                                                    | 1           |

| • 100V/ns を超える時のスイッチング性能のグラフを削除.....                                                                  | 1           |

| • 「概要」セクションにテキストを更新し、表を追加。.....                                                                       | 1           |

| • 「絶対最大定格」、「推奨動作条件」、「電気的特性」、「スイッチング特性」の各セクションで、「基準グランドに接続する」というフレーズを削除。.....                          | 5           |

| • 「電気的特性」セクションの GaN パワー・トランジスタ・サブセクションのドレインリーグ電流仕様のテスト条件で $V_{DS} = 600V$ を $V_{DS} = 650V$ に変更。..... | 5           |