# ドライバおよび電流検出エミュレーション機能内蔵、LMG2650 650V 95mΩ GaN ハーフブリッジ

## 1 特長

- GaN パワー FET ハーフ ブリッジ: 650V

- ローサイドおよびハイサイド GaN FET: 95mΩ

- 伝搬遅延時間が短いゲートドライバを内蔵: 100ns 未満

- プログラマブルなターンオン スルーレート制御機能

- 広い帯域幅で高精度の電流検出エミュレーション

- ローサイド基準 (INH) とハイサイド基準 (GDH) のハイサイド ゲートドライブ ピン

- ローサイド (INL) およびハイサイド (INH) ゲートドライブ インターロック

- ハイサイド (INH) ゲートドライブ信号レベルシフタ

- スマートスイッチ付きブートストラップ ダイオード機能

- ハイサイドの起動:<8μs

- ローサイドおよびハイサイドのサイクル単位の過電流保護

- 過熱保護

- AUX アイドル静止電流: 250μA

- AUX スタンバイ静止電流: 50μA

- BST アイドル静止電流: 70μA

- デュアル サーマル パッド付き 6mm × 8mm QFN パッケージ

## 2 アプリケーション

- モバイル向け充電器の設計

- USB 電源コンセント

- AC/DC 補助電源

- モーター ドライブ

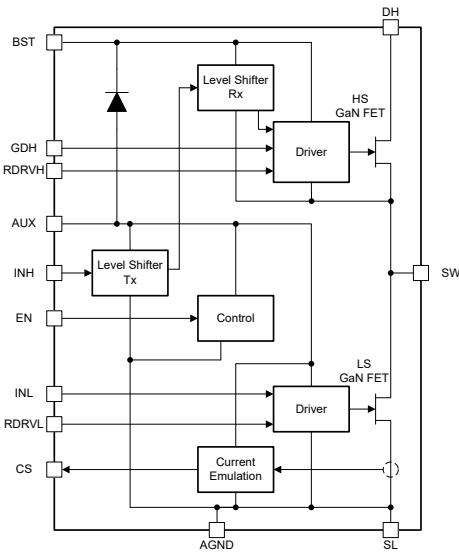

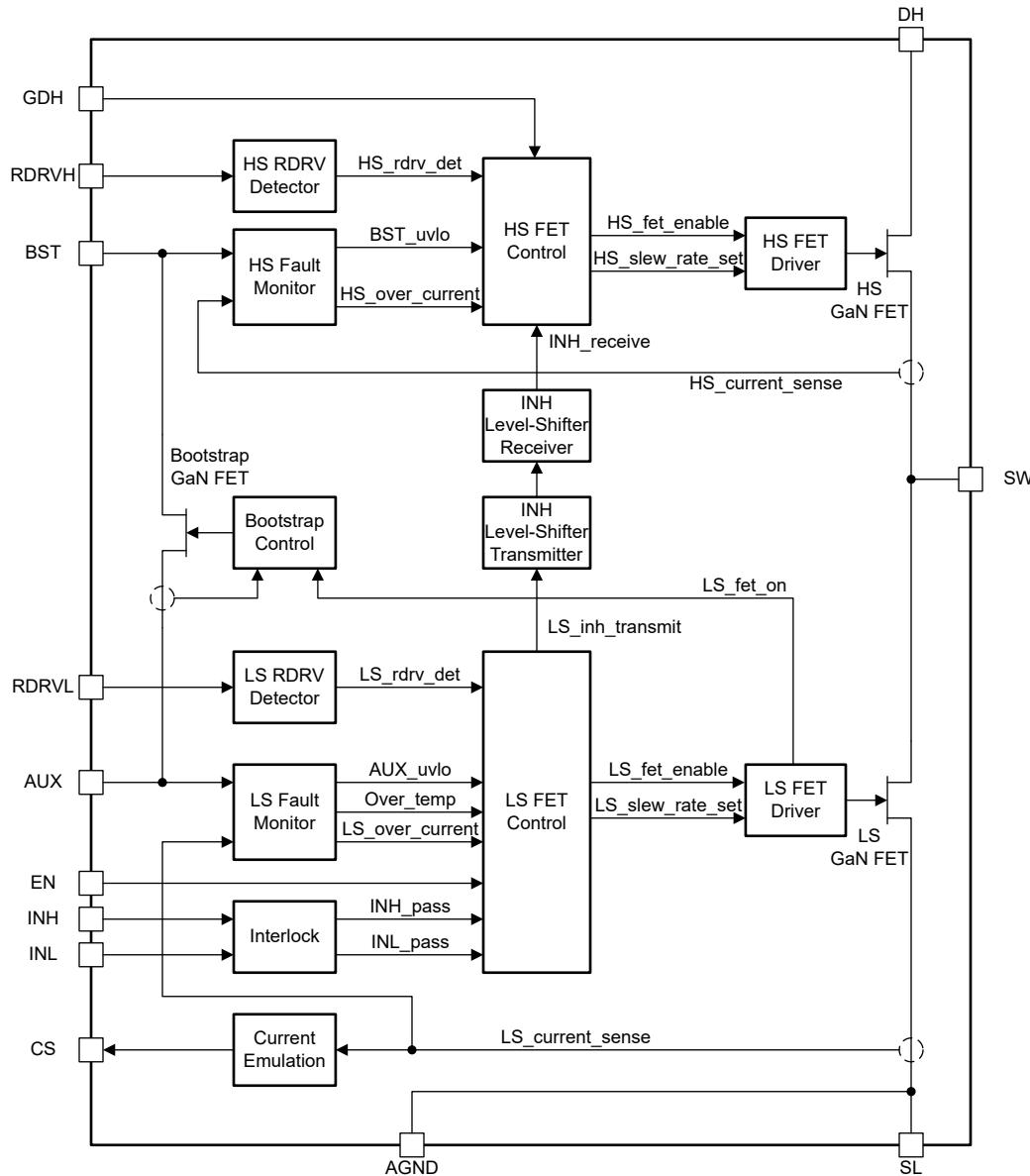

概略ブロック図

## 3 説明

LMG2650 は 650V 95mΩ GaN パワー FET ハーフブリッジです。LMG2650 は、ハーフブリッジ パワー FET、ゲートドライバ、ブートストラップ FET、ハイサイド ゲートドライブ レベル シフタを 6mm × 8mm の QFN パッケージに統合することで、設計の簡素化、部品点数の低減、基板面積の低減を実現しています。

プログラマブルなターンオン スルーレートにより、EMI とリニンググを制御できます。ローサイド電流センス エミュレーションにより、従来の電流センス抵抗方式よりも消費電力を低減でき、またローサイドのサーマル パッドを PCB 電源グランドに接続できます。

ハイサイド GaN パワー FET は、ローサイド基準ゲートドライブ ピン (INH) またはハイサイド基準ゲートドライブ ピン (GDH) で制御します。ハイサイド ゲートドライブ信号レベルシフタは、厳しいパワー スイッチング環境でも、INH ピンの信号を確実にハイサイド ゲート ドライバに伝えます。スマートスイッチ付き GaN ブートストラップ FET を使うと、ダイオードの順方向電圧降下がなく、ハイサイド電源を過充電せずに、逆方向回復電荷はありません。

LMG2650 は、小さい静止電流と高速な起動時間によって、コンバータの軽負荷効率要件とバースト モード動作に対応しています。保護機能には、FET ターンオン インターロック、低電圧誤動作防止 (UVLO)、サイクル単位の電流制限、過熱シャットダウンが含まれます。超低スルーレート設定はモータードライブ アプリケーションに対応します。

### パッケージ情報

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|---------|----------------------|--------------------------|

| LMG2650 | RFB (VQFN, 19)       | 6.00mm × 8.00mm          |

(1) 詳細については、[セクション 11](#) を参照してください。

(2) パッケージ サイズ (幅 × 長さ) は公称値であり、該当する場合はピンも含まれます。

パッケージ ビュー

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SNOSDI8](#)

## 目次

|                                    |    |                             |    |

|------------------------------------|----|-----------------------------|----|

| 1 特長.....                          | 1  | 7.2 機能ブロック図.....            | 20 |

| 2 アプリケーション.....                    | 1  | 7.3 機能説明.....               | 20 |

| 3 説明.....                          | 1  | 7.4 デバイスの機能モード.....         | 26 |

| 4 ピン構成および機能.....                   | 3  | 8 アプリケーションと実装.....          | 28 |

| 5 仕様.....                          | 5  | 8.1 アプリケーション情報.....         | 28 |

| 5.1 絶対最大定格.....                    | 5  | 8.2 代表的なアプリケーション.....       | 28 |

| 5.2 ESD 定格.....                    | 5  | 8.3 電源に関する推奨事項.....         | 31 |

| 5.3 推奨動作条件.....                    | 5  | 8.4 レイアウト.....              | 32 |

| 5.4 熱に関する情報.....                   | 6  | 9 デバイスおよびドキュメントのサポート.....   | 34 |

| 5.5 電気的特性.....                     | 7  | 9.1 ドキュメントの更新通知を受け取る方法..... | 34 |

| 5.6 スイッチング特性.....                  | 9  | 9.2 サポート・リソース.....          | 34 |

| 5.7 代表的特性.....                     | 13 | 9.3 商標.....                 | 34 |

| 6 パラメータ測定情報.....                   | 17 | 9.4 静電気放電に関する注意事項.....      | 34 |

| 6.1 GaN パワー FET のスイッチング パラメータ..... | 17 | 9.5 用語集.....                | 34 |

| 7 詳細説明.....                        | 19 | 10 改訂履歴.....                | 34 |

| 7.1 概要.....                        | 19 | 11 メカニカル、パッケージ、および注文情報..... | 34 |

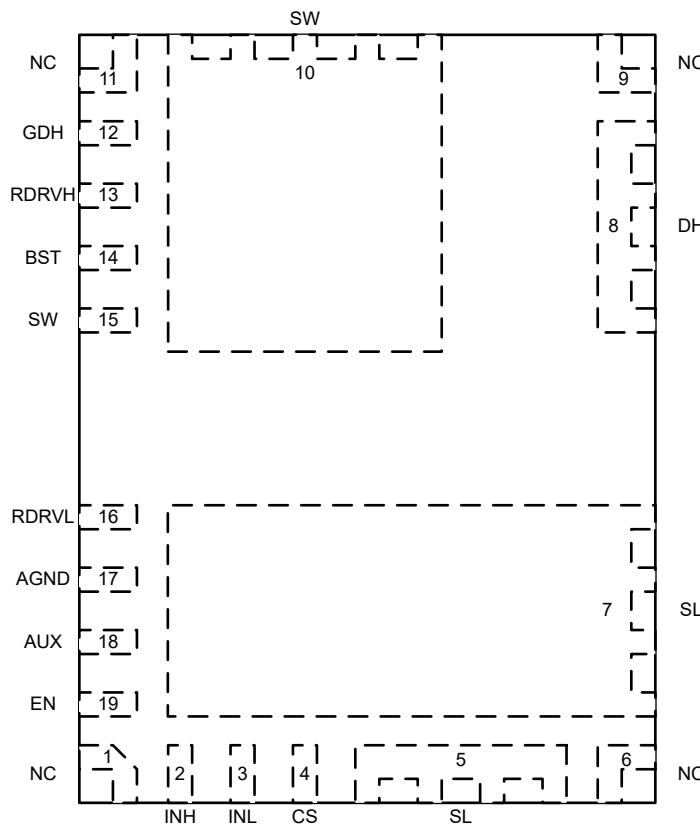

## 4 ピン構成および機能

図 4-1. RFB パッケージ、19 ピン VQFN (上面図)

表 4-1. ピンの機能

| ピン  |             | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                          |

|-----|-------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称  | 番号          |                    |                                                                                                                                                                             |

| NC  | 1, 6, 9, 11 | NC                 | QFN パッケージを PCB にアンカーするために使用します。ピンは、PCB ランディング パッドに半田付けする必要があります。PCB のランドディング パッドは半田なしのマスク定義のパッドであり、PCB 上の他の金属に物理的に接続することはできません。                                             |

| INH | 2           | I                  | ハイサイド ゲート ドライブの制御入力。AGND を基準とします。信号は内部でハイサイド GaN FET ドライバにレベル シフトされます。INH から AUX への順方向ベースの ESD ダイオードがあるため、INH が AUX よりも高く駆動される状態が防止されます。GDH ピン機能を使用する場合は、このピンを AGND に短絡します。 |

| INL | 3           | I                  | ローサイド ゲート ドライブの制御入力。AGND を基準とします。INL から AUX への順方向ベースの ESD ダイオードがあるため、INL が AUX よりも高く駆動される状態が防止されます。                                                                         |

| CS  | 4           | O                  | 電流検出エミュレーションの出力。GaN FET 電流のスケーリングされた複製を出力します。出力電流を抵抗に送り、電流センス電圧信号を生成します。抵抗は電源コントローラ IC のローカル グランドを基準にします。この機能は、ローサイド FET ソースと直列に使用される外部電流センス抵抗を置き換えます。                      |

| SL  | 5, 7        | P                  | ローサイド GaN FET ソース。ローサイドのサーマルパッド。AGND に内部接続します。                                                                                                                              |

| DH  | 8           | P                  | ハイサイド GaN FET ドレイン。                                                                                                                                                         |

| SW  | 10, 15      | P                  | ハイサイド GaN FET ソースとローサイド GaN FET ドレインの間の GaN FET ハーフブリッジ スイッチノード。ハイサイドのサーマルパッド。                                                                                              |

| GDH | 12          | I                  | ハイサイド ゲート ドライブの制御入力。SW を基準とします。信号は、ハイサイド GaN FET ドライバに直接接続します。GDH から BST への順方向ベースの ESD ダイオードがあるため、GDH が BST よりも高く駆動される状態が防止されます。INH ピン機能を使用する場合は、このピンを SW に短絡します。           |

**表 4-1. ピンの機能 (続き)**

| ピン     |    | タイプ <sup>(1)</sup> | 説明                                                                                                                                                 |

|--------|----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称     | 番号 |                    |                                                                                                                                                    |

| RDRVH  | 13 | I                  | ハイサイド駆動能力制御抵抗。RDRVH と SW の間の抵抗を設定し、ハイサイド GaN FET ターンオン スルーレートをプログラミングします。                                                                          |

| BST    | 14 | P                  | ブートストラップ電圧レール。ハイサイド電源電圧。AUX と BST の間のブートストラップ ダイオード機能は内部的に提供されます。BST と SW の間に適切なサイズのブートストラップ コンデンサを接続します。                                          |

| RDRVRL | 16 | I                  | ローサイド駆動能力制御抵抗。RDRVRL と AGND の間の抵抗を設定し、ローサイド GaN FET ターンオン スルーレートをプログラミングします。                                                                       |

| AGND   | 17 | G                  | ローサイドのアナログ グランド。SL に内部接続します。                                                                                                                       |

| AUX    | 18 | P                  | 補助電圧レール。ローサイド電源電圧。AUX と AGND の間にローカルバイパスコンデンサを接続します。                                                                                               |

| EN     | 19 | I                  | イネーブル。アクティブ モードとスタンバイモードを切り替えるために使用します。スタンバイ モードは、静止電流を減少して、コンバータの軽負荷効率目標をサポートします。EN から AUX への順方向ベースの ESD ダイオードがあるため、EN が AUX よりも高く駆動される状態が防止されます。 |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源、NC = 接続なし

## 5 仕様

### 5.1 絶対最大定格

特に記述のない限り: 電圧は AGND を基準にしています<sup>(1)</sup>

|                           |                                                                              | 最小値   | 最大値                       | 単位  |    |

|---------------------------|------------------------------------------------------------------------------|-------|---------------------------|-----|----|

| V <sub>DS</sub>           | ドレインソース間 (DH から SW) または (SW から SL) 電圧、FET オフ                                 |       | 650                       | V   |    |

| V <sub>DS(surge)</sub>    | ドレインソース間 (DH から SW) または (SW から SL) 電圧、サージ状態、FET オフ <sup>(2)</sup>            |       | 720                       | V   |    |

| V <sub>DS(tr)surge</sub>  | ドレインソース間 (DH から SW) または (SW から SL) 過渡リンギング ピーク電圧、サージ状態、FET オフ <sup>(2)</sup> |       | 800                       | V   |    |

| ピンの電圧から AGND へ            | AUX                                                                          | -0.3  | 30                        | V   |    |

|                           | EN, INL, INH                                                                 | -0.3  | V <sub>AUX</sub> + 0.3    | V   |    |

|                           | CS                                                                           | -0.3  | 5.5                       | V   |    |

|                           | RDRVRL                                                                       | -0.3  | 4                         | V   |    |

|                           | BST                                                                          | -0.3  | 30                        | V   |    |

|                           | RDRVH                                                                        | -0.3  | 4                         | V   |    |

|                           | GDH                                                                          | -0.3  | V <sub>BST_SW</sub> + 0.3 | V   |    |

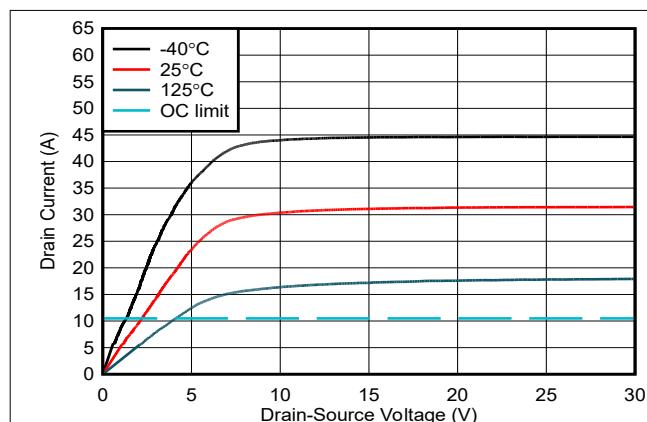

| I <sub>D(cnts)</sub>      | ドレイン (DH から SW) & (SW to SL) 連続電流、FET オン                                     | -12.1 | 内部的に制限                    | A   |    |

| I <sub>D(pulse)(oc)</sub> | 過電流応答時間中のドレイン (DH から SW) & (SW to SL) パルス電流 <sup>(3)</sup>                   |       | 28                        | A   |    |

| I <sub>S(cnts)</sub>      | ソース (SW から DH) & (SL から SW) 連続電流、FET オフ                                      |       | 12.1                      | A   |    |

|                           | 正のシンク電流                                                                      | CS    | 10                        | mA  |    |

| T <sub>J</sub>            | 動作時接合部温度                                                                     |       | -40                       | 150 | °C |

| T <sub>stg</sub>          | 保存温度                                                                         |       | -40                       | 150 | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) GaN パワー FET スイッチング機能の詳細については、『[GaN パワー FET スイッチング機能](#)』を参照してください。

- (3) 飽和状態になった場合、GaN パワー FET がこの値を自己制限値より低くする可能性があります。

### 5.2 ESD 定格

| パラメータ              |      |                                                            | 値     | 単位 |

|--------------------|------|------------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM) ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>       | ±2000 | V  |

|                    |      | デバイス帯電モデル (CDM), ANSI/ESDA/JEDEC JS-002 に準拠 <sup>(2)</sup> | ±500  | V  |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 5.3 推奨動作条件

特に記述のない限り: 電圧は AGND を基準にしています

|                 |              | 最小値                     | 公称値 | 最大値                 | 単位 |

|-----------------|--------------|-------------------------|-----|---------------------|----|

|                 | 電源電圧         | AUX                     | 10  | 26                  | V  |

|                 | SW への電源電圧    | BST                     | 7.5 | 26                  | V  |

|                 | 入力電圧         | EN, INL, INH            | 0   | V <sub>AUX</sub>    | V  |

|                 | SW への入力電圧    | GDH                     | 0   | V <sub>BST_SW</sub> | V  |

| V <sub>IH</sub> | High レベル入力電圧 | EN, INL, INH, GDH から SW | 2.5 |                     | V  |

| V <sub>IL</sub> | Low レベル入力電圧  |                         |     | 0.6                 | V  |

特に記述のない限り: 電圧は AGND を基準にしています

|                      |                               | 最小値                  | 公称値 | 最大値 | 単位            |

|----------------------|-------------------------------|----------------------|-----|-----|---------------|

| $I_{D(\text{cnts})}$ | 連続電流、FET オン                   | -9                   |     | 9   | A             |

| $C_{\text{AUX}}$     | 外付けバイパスコンデンサから AGND への AUX 容量 | 3 x $C_{\text{BST}}$ |     |     | $\mu\text{F}$ |

| $C_{\text{BST\_SW}}$ | 外付けバイパスコンデンサから SW への BST 容量   | 0.010                |     |     | $\mu\text{F}$ |

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> |                   | LMG2650    | 単位   |

|----------------------|-------------------|------------|------|

|                      |                   | RFB (VQFN) |      |

|                      |                   | 19 ピン      |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗      | 22.3       | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース(底面)への熱抵抗 | 0.85       | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.5 電気的特性

1) シンボルの定義:  $V_{DS(ls)} = SW$  から  $SL$  への電圧、 $I_{DS(ls)} = SW$  から  $SL$  への電流、 $V_{DS(hs)} = DH$  から  $SW$  への電圧、 $I_{D(hs)} = DH$  から  $SW$  への電流、 $I_{SW} = デバイスへの SW ポイント電流$ 、2) 特に記述のない限り: 電圧、抵抗、容量は AGND を基準としています、 $-40^\circ C \leq T_J \leq 125^\circ C$ 、 $V_{DS(ls)} = 520V$ 、 $V_{DS(hs)} = 520V$ 、 $10V \leq V_{AUX} \leq 26V$ 、 $7.5V \leq V_{BST\_SW} \leq 26V$ 、 $V_{EN} = 5V$ 、 $V_{INL} = 0V$ 、 $V_{INH} = 0V$ 、 $V_{GDH\_SW} = 0V$ 、 $R_{CS} = 100\Omega$

| パラメータ                                 | テスト条件                                      | 最小値                                                                                                              | 標準値   | 最大値  | 単位        |    |

|---------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------|------|-----------|----|

| <b>GAN パワー FET</b>                    |                                            |                                                                                                                  |       |      |           |    |

| $R_{DS(on)}$                          | ドレインソース間 (DH から SW) または (SW から SL) オン抵抗    | $V_{INL}$ または $V_{INH} = 5V$ , $I_D = 5.25A$ , $T_J = 25^\circ C$                                                | 95    |      | $m\Omega$ |    |

| $R_{DS(on)}$                          | ドレインソース間 (DH から SW) または (SW から SL) オン抵抗    | $V_{INL}$ または $V_{INH} = 5V$ , $I_D = 5.25A$ , $T_J = 125^\circ C$                                               | 171   |      | $m\Omega$ |    |

| $V_{SD}$                              | ソースドレン間 (SW から DH) または (SL から SW) 第 3 象限電圧 | SW から DH または SL から SW への電流 = 0.525A                                                                              | 1.9   |      | V         |    |

| $V_{SD}$                              | ソースドレン間 (SW から DH) または (SL から SW) 第 3 象限電圧 | SW から DH または SL から SW への電流 = 5.25A                                                                               | 2.6   |      | V         |    |

| $I_{DSS}$                             | ドレイン (DH から SW) または (SW から SL) リーク電流       | ( $V_{DS(ls)} = 0V$ , $V_{DS(hs)} = 650V$ ) または ( $V_{DS(hs)} = 0V$ , $V_{DS(ls)} = 650V$ ), $T_J = 25^\circ C$  | 3.6   |      | $\mu A$   |    |

| $I_{DSS}$                             | ドレイン (DH から SW) または (SW から SL) リーク電流       | ( $V_{DS(ls)} = 0V$ , $V_{DS(hs)} = 650V$ ) または ( $V_{DS(hs)} = 0V$ , $V_{DS(ls)} = 650V$ ), $T_J = 125^\circ C$ | 18.2  |      | $\mu A$   |    |

| $Q_{OSS}$                             | 出力電荷量                                      |                                                                                                                  | 34.7  |      | nC        |    |

| $C_{OSS}$                             | 出力容量                                       |                                                                                                                  | 54.2  |      | pF        |    |

| $E_{OSS}$                             | 出力キャパシタンスの蓄積エネルギー                          | ( $V_{DS(ls)} = 0V$ , $V_{DS(hs)} = 400V$ ) または ( $V_{DS(hs)} = 0V$ , $V_{DS(ls)} = 400V$ )                      | 4.69  |      | $\mu J$   |    |

| $C_{OSS,er}$                          | エネルギーに関連した実効出力キャパシタンス                      |                                                                                                                  | 58.1  |      | pF        |    |

| $C_{OSS,tr}$                          | 時間に関連した実効出力キャパシタンス                         | ( $V_{DS(ls)} = 0V$ , $V_{DS(hs)} = 0V \sim 400V$ ) または ( $V_{DS(hs)} = 0V$ , $V_{DS(ls)} = 0V \sim 400V$ )      | 86.3  |      | pF        |    |

| $Q_{RR}$                              | 逆方向回復電荷                                    |                                                                                                                  | 0     |      | nC        |    |

| <b>過電流保護</b>                          |                                            |                                                                                                                  |       |      |           |    |

| $I_{T(OC)}$                           | 過電流フォルト - スレッショルド電流                        | 9                                                                                                                | 10.5  | 12.1 | A         |    |

| <b>ポートストラップ整流器</b>                    |                                            |                                                                                                                  |       |      |           |    |

| $R_{DS(on)}$                          | AUX から BST への オン抵抗                         | $V_{INL} = 5V$ , $V_{AUX\_BST} = 1V$ , $T_J = 25^\circ C$                                                        | 8     |      | $\Omega$  |    |

|                                       |                                            | $V_{INL} = 5V$ , $V_{AUX\_BST} = 1V$ , $T_J = 125^\circ C$                                                       | 14    |      |           |    |

|                                       | AUX から BST への 電流制限                         | $V_{INL} = 5V$ , $V_{AUX\_BST} = 7V$                                                                             | 210   | 240  | 270       | mA |

|                                       | BST から AUX への 逆電流ブロック スレッショルド              | $V_{INL} = 5V$                                                                                                   | 3     | 10   | 20        | mA |

| <b>CS</b>                             |                                            |                                                                                                                  |       |      |           |    |

|                                       | 電流センス ゲイン ( $I_{CS(src)} / I_{D(LS)}$ )    | $V_{INL} = 5V$ , $0V \leq V_{CS} \leq 2V$ , $0A \leq I_{D(ls)} < I_{T(OC)(ls)}$                                  | 0.554 |      | $mA/A$    |    |

|                                       | 電流センス入力オフセット電流                             | $V_{INL} = 5V$ , $0V \leq V_{CS} \leq 2V$ , $0A \leq I_{D(ls)} < I_{T(OC)(ls)}$                                  | -91   | 91   | mA        |    |

|                                       | INL が High のままである間、過電流フォルトが発生した後に初期出力を保持   | $V_{INL} = 5V$ , $0V \leq V_{CS} \leq 2V$                                                                        |       | 7    | mA        |    |

|                                       | INL が High のままである間、過電流フォルトが発生した後に最終出力を保持   | $V_{INL} = 5V$ , $0V \leq V_{CS} \leq 2V$                                                                        | 8.5   | 12   | 15.5      | mA |

|                                       | 出力クランプ電圧                                   | $V_{INL} = 5V$ , $I_{D(ls)} = 9.0A$ , 外部ソースからの 5mA CS シング                                                        | 2.6   |      | V         |    |

| <b>EN, INL, INH から AGND。GDH から SW</b> |                                            |                                                                                                                  |       |      |           |    |

| $V_{IT+}$                             | 正方向の入力スレッショルド電圧                            | 1.7                                                                                                              | 2.45  |      | V         |    |

| $V_{IT-}$                             | 負方向の入力スレッショルド電圧                            | 0.7                                                                                                              | 1.3   |      | V         |    |

## 5.5 電気的特性 (続き)

1) シンボルの定義:  $V_{DS(ls)} = SW$  から  $SL$  への電圧、 $I_{DS(ls)} = SW$  から  $SL$  への電流、 $V_{DS(hs)} = DH$  から  $SW$  への電圧、 $I_{D(hs)} = DH$  から  $SW$  への電流、 $I_{SW} = デバイスへの SW ポイント電流、2) 特に記述のない限り: 電圧、抵抗、容量は AGND を基準としています、 $-40^\circ C \leq T_J \leq 125^\circ C$ 、 $V_{DS(ls)} = 520V$ 、 $V_{DS(hs)} = 520V$ 、 $10V \leq V_{AUX} \leq 26V$ 、 $7.5V \leq V_{BST\_SW} \leq 26V$ 、 $V_{EN} = 5V$ 、 $V_{INL} = 0V$ 、 $V_{INH} = 0V$ 、 $V_{GDH\_SW} = 0V$ 、 $R_{CS} = 100\Omega$$

| パラメータ              | テスト条件                                         | 最小値 | 標準値 | 最大値 | 単位 |

|--------------------|-----------------------------------------------|-----|-----|-----|----|

| 入力スレッショルド電圧のヒステリシス |                                               | 1   |     |     | V  |

| プルダウン入力抵抗          | $0V \leq V_{PIN} \leq 3V$                     | 200 | 400 | 600 | kΩ |

| プルダウン入力電流          | $10V \leq V_{PIN} \leq 26V$ 、 $V_{AUX} = 26V$ |     | 10  |     | μA |

### 過熱保護

|                          |  |     |     |    |

|--------------------------|--|-----|-----|----|

| 温度フォルト – 正方向のスレッショルド温度   |  | 150 | 165 | °C |

| 温度フォルト – 負方向のスレッショルド温度   |  |     | 150 | °C |

| 温度フォルト – スレッショルド温度ヒステリシス |  |     | 15  | °C |

### AUX

|                        |                        |                                                                                     |     |      |      |    |

|------------------------|------------------------|-------------------------------------------------------------------------------------|-----|------|------|----|

| $V_{AUX,T+}$<br>(UVLO) | UVLO – 正方向のスレッショルド電圧   |                                                                                     | 8.9 | 9.3  | 9.75 | V  |

|                        | UVLO – 負方向のスレッショルド電圧   |                                                                                     | 8.6 | 9.0  | 9.5  | V  |

|                        | UVLO – スレッショルド電圧ヒステリシス |                                                                                     |     | 250  |      | mV |

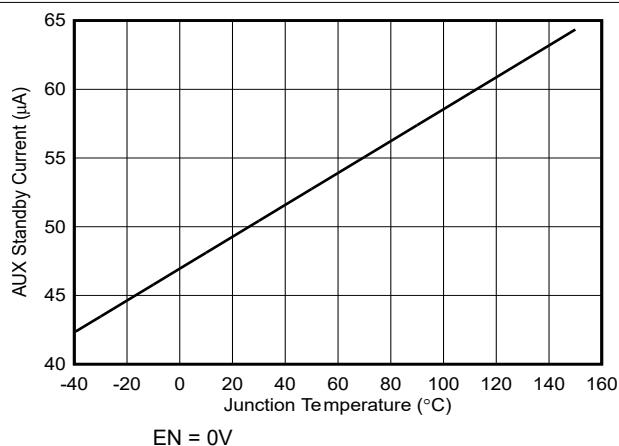

|                        | スタンバイ静止時電流             | $V_{EN} = 0V$                                                                       |     | 50   | 110  | μA |

|                        | 静止時電流                  |                                                                                     |     | 250  | 400  | μA |

|                        |                        | $V_{INL} = 5V$ 、 $I_{D(ls)} = 0A$                                                   |     | 1550 |      |    |

|                        | 動作電流                   | $V_{INL} = 0V$ または $5V$ 、 $V_{DS(ls)} = 0V$ 、 $I_{D(ls)} = 0A$ 、 $f_{INL} = 500kHz$ |     | 4.5  |      | mA |

### BST

|                             |                                                 |                                                                                             |     |     |     |    |

|-----------------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------|-----|-----|-----|----|

| $V_{BST\_SW}$<br>$T+(UVLO)$ | FET をオンにする $V_{BST\_SW}$ UVLO – 正方向のスレッショルド電圧   |                                                                                             | 6.8 | 7   | 7.4 | V  |

|                             | FET をオンに維持する $V_{BST\_SW}$ UVLO – 負方向のスレッショルド電圧 |                                                                                             | 4.8 | 5.1 | 5.4 | V  |

| 静止時電流                       |                                                 |                                                                                             |     | 70  | 120 | μA |

|                             |                                                 | $V_{INH} = 5V$ 、 $I_{D(hs)} = 0A$                                                           |     | 900 |     |    |

|                             |                                                 | $V_{GDH\_SW} = 5V$ 、 $I_{D(hs)} = 0A$                                                       |     | 900 |     |    |

| 動作電流                        |                                                 | $V_{INH} = 0V$ または $5V$ 、 $V_{DS(hs)} = 0V$ 、 $I_{DS(hs)} = 0A$ 、 $f_{INH} = 500kHz$        |     | 2.3 |     | mA |

|                             |                                                 | $V_{INH} = 0V$ または $5V$ 、 $V_{DS(hs)} = 400V$ または $0V$ 、 $I_{SW} = 1A$ 、 $f_{INH} = 500kHz$ |     | 3   |     |    |

## 5.6 スイッチング特性

1) シンボルの定義:  $V_{DS(ls)} = SW$  から  $SL$  への電圧、 $I_{DS(ls)} = SW$  から  $SL$  への電流、 $V_{DS(hs)} = DH$  から  $SW$  への電圧、 $I_{D(hs)} = DH$  から  $SW$  への電流、 $I_{SW} = デバイスへの SW ポイント電流$ 、2) 特に記述のない限り: 電圧、抵抗、容量は AGND を基準としています、 $-40^\circ\text{C} \leq T_J \leq 125^\circ\text{C}$ 、 $V_{DS(ls)} = 520\text{V}$ 、 $V_{DS(hs)} = 520\text{V}$ 、 $10\text{V} \leq V_{AUX} \leq 26\text{V}$ 、 $7.5\text{V} \leq V_{BST\_SW} \leq 26\text{V}$ 、 $V_{EN} = 5\text{V}$ 、 $V_{INL} = 0\text{V}$ 、 $V_{INH} = 0\text{V}$ 、 $R_{CS} = 100\Omega$

| パラメータ                            |                  | テスト条件                                                                                                                                                                                                           | 最小値 | 標準値 | 最大値 | 単位   |

|----------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| <b>ローサイド GaN パワー FET</b>         |                  |                                                                                                                                                                                                                 |     |     |     |      |

| $t_{d(on)}$<br>$(t_{drain})(ls)$ | ドレイン電流のターンオン遅延時間 | $V_{INL} > V_{INL,IT+}$ から $I_{D(ls)} > 50\text{mA}$ まで、<br>$V_{BUS} = 400\text{V}$ 、 $I_{SW} = 2.65\text{A}$ 、以下のローサイド スルーレート設定の場合、『 <a href="#">GaN パワー FET のスイッチング パラメータ</a> 』を参照                            |     |     |     |      |

|                                  |                  | スルーレート設定 0 (最低速)                                                                                                                                                                                                | 48  | 165 |     | ns   |

|                                  |                  | スルーレート設定 1                                                                                                                                                                                                      | 48  | 100 |     |      |

|                                  |                  | スルーレート設定 2                                                                                                                                                                                                      | 43  | 80  |     |      |

|                                  |                  | スルーレート設定 3 (最高速)                                                                                                                                                                                                | 34  | 65  |     |      |

| $t_{d(on)}(ls)$                  | ターンオン遅延時間        | $V_{INL} > V_{INL,IT+}$ から $V_{DS(ls)} < 390\text{V}$ まで、<br>$V_{BUS} = 400\text{V}$ 、 $I_{SW} = 2.65\text{A}$ 、以下のローサイド スルーレート設定の場合、『 <a href="#">GaN パワー FET のスイッチング パラメータ</a> 』を参照                           |     |     |     |      |

|                                  |                  | スルーレート設定 0 (最低速)                                                                                                                                                                                                | 89  | 255 |     | ns   |

|                                  |                  | スルーレート設定 1                                                                                                                                                                                                      | 70  | 137 |     |      |

|                                  |                  | スルーレート設定 2                                                                                                                                                                                                      | 59  | 100 |     |      |

|                                  |                  | スルーレート設定 3 (最高速)                                                                                                                                                                                                | 41  | 75  |     |      |

| $t_{r(on)}(ls)$                  | ターンオンの立ち上がり時間    | $V_{DS(ls)} < 320\text{V}$ から $V_{DS(ls)} < 80\text{V}$ まで、<br>$V_{BUS} = 400\text{V}$ 、 $I_{SW} = 2.65\text{A}$ 、以下のローサイド スルーレート設定の場合、『 <a href="#">GaN パワー FET のスイッチング パラメータ</a> 』を参照                         |     |     |     |      |

|                                  |                  | スルーレート設定 0 (最低速)                                                                                                                                                                                                | 131 | 180 |     | ns   |

|                                  |                  | スルーレート設定 1                                                                                                                                                                                                      | 51  | 65  |     |      |

|                                  |                  | スルーレート設定 2                                                                                                                                                                                                      | 11  | 19  |     |      |

|                                  |                  | スルーレート設定 3 (最高速)                                                                                                                                                                                                | 5   | 10  |     |      |

| $t_{d(off)}(ls)$                 | ターンオフ遅延時間        | $V_{INL} < V_{INL,IT-}$ から $V_{DS(ls)} > 80\text{V}$ まで、<br>$V_{BUS} = 400\text{V}$ 、 $I_{SW} = 2.65\text{A}$ (スルーレート設定に依存しない)、『 <a href="#">GaN パワー FET のスイッチング パラメータ</a> 』を参照                                 |     | 45  | 65  | ns   |

| $t_{f(off)}(ls)$                 | ターンオフ立ち下がり時間     | $V_{DS(ls)} > 80\text{V}$ から $V_{DS(ls)} > 320\text{V}$ まで、<br>$V_{BUS} = 400\text{V}$ 、 $I_{SW} = 2.65\text{A}$ (スルーレート設定に依存しない)、『 <a href="#">GaN パワー FET のスイッチング パラメータ</a> 』を参照                              |     | 20  |     | ns   |

|                                  | ターンオンのスルーレート     | $V_{DS(ls)} < 320\text{V}$ から $V_{DS(ls)} < 80\text{V}$ まで、 $T_J = 25^\circ\text{C}$ 、 $V_{BUS} = 400\text{V}$ 、 $I_{SW} = 2.65\text{A}$ 、以下のローサイド スルーレート設定の場合、『 <a href="#">GaN パワー FET のスイッチング パラメータ</a> 』を参照 |     |     |     |      |

|                                  |                  | スルーレート設定 0 (最低速)                                                                                                                                                                                                | 2   |     |     | V/ns |

|                                  |                  | スルーレート設定 1                                                                                                                                                                                                      | 5   |     |     |      |

|                                  |                  | スルーレート設定 2                                                                                                                                                                                                      | 23  |     |     |      |

|                                  |                  | スルーレート設定 3 (最高速)                                                                                                                                                                                                | 50  |     |     |      |

## 5.6 スイッチング特性(続き)

1) シンボルの定義:  $V_{DS(ls)} = SW$  から  $SL$  への電圧、 $I_{DS(ls)} = SW$  から  $SL$  への電流、 $V_{DS(hs)} = DH$  から  $SW$  への電圧、 $I_{D(hs)} = DH$  から  $SW$  への電流、 $I_{SW}$  = デバイスへの  $SW$  ポイント電流、2) 特に記述のない限り: 電圧、抵抗、容量は AGND を基準としています、 $-40^\circ C \leq T_J \leq 125^\circ C$ 、 $V_{DS(ls)} = 520V$ 、 $V_{DS(hs)} = 520V$ 、 $10V \leq V_{AUX} \leq 26V$ 、 $7.5V \leq V_{BST\_SW} \leq 26V$ 、 $V_{EN} = 5V$ 、 $V_{INL} = 0V$ 、 $V_{INH} = 0V$ 、 $R_{CS} = 100\Omega$

| パラメータ                                           |                  | テスト条件                                                                                                                                                             | 最小値 | 標準値  | 最大値 | 単位 |

|-------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|----|

| <b>ハイサイド GaN パワー FET</b>                        |                  |                                                                                                                                                                   |     |      |     |    |

| $t_{d(on)}$<br>( $I_{drain}$ )<br>( $hs, INH$ ) | ドレイン電流のターンオン遅延時間 | $V_{INH} > V_{INH,IT+}$ から $I_{D(hs)} > 50mA$ まで、<br>$V_{BUS} = 400V$ 、 $I_{SW} = -2.65A$ 、以下のハイサイド スルーレート設定の場合、『 <a href="#">GaN パワー FET のスイッチング パラメータ</a> 』を参照  |     |      |     |    |

|                                                 |                  | スルーレート設定 0 (最低速)                                                                                                                                                  | 51  | 160  |     | ns |

|                                                 |                  | スルーレート設定 1                                                                                                                                                        | 51  | 95   |     |    |

|                                                 |                  | スルーレート設定 2                                                                                                                                                        | 45  | 78   |     |    |

|                                                 |                  | スルーレート設定 3 (最高速)                                                                                                                                                  | 34  | 62   |     |    |

| $t_{d(on)}$<br>( $I_{drain}$ )<br>( $hs, GDH$ ) | ドレイン電流のターンオン遅延時間 | $V_{GDH} > V_{GDH,IT+}$ から $I_{D(hs)} > 50mA$ まで、<br>$V_{BUS} = 400V$ 、 $I_{SW} = -2.65A$ 、以下のハイサイド スルーレート設定の場合、『 <a href="#">GaN パワー FET のスイッチング パラメータ</a> 』を参照  |     |      |     |    |

|                                                 |                  | スルーレート設定 0 (最低速)                                                                                                                                                  | 46  | 150  |     | ns |

|                                                 |                  | スルーレート設定 1                                                                                                                                                        | 46  | 90   |     |    |

|                                                 |                  | スルーレート設定 2                                                                                                                                                        | 41  | 75   |     |    |

|                                                 |                  | スルーレート設定 3 (最高速)                                                                                                                                                  | 32  | 63   |     |    |

| $t_{d(on)}$<br>( $hs, INH$ )                    | ターンオン遅延時間        | $V_{INH} > V_{INH,IT+}$ から $V_{DS(hs)} < 390V$ まで、<br>$V_{BUS} = 400V$ 、 $I_{SW} = -2.65A$ 、以下のハイサイド スルーレート設定の場合、『 <a href="#">GaN パワー FET のスイッチング パラメータ</a> 』を参照 |     |      |     |    |

|                                                 |                  | スルーレート設定 0 (最低速)                                                                                                                                                  | 75  | 250  |     | ns |

|                                                 |                  | スルーレート設定 1                                                                                                                                                        | 67  | 133  |     |    |

|                                                 |                  | スルーレート設定 2                                                                                                                                                        | 56  | 97   |     |    |

|                                                 |                  | スルーレート設定 3 (最高速)                                                                                                                                                  | 39  | 73   |     |    |

| $t_{d(on)}$<br>( $hs, GDH$ )                    | ターンオン遅延時間        | $V_{GDH} > V_{GDH,IT+}$ から $V_{DS(hs)} < 390V$ まで、<br>$V_{BUS} = 400V$ 、 $I_{SW} = -2.65A$ 、以下のハイサイド スルーレート設定の場合、『 <a href="#">GaN パワー FET のスイッチング パラメータ</a> 』を参照 |     |      |     |    |

|                                                 |                  | スルーレート設定 0 (最低速)                                                                                                                                                  | 110 | 233  |     | ns |

|                                                 |                  | スルーレート設定 1                                                                                                                                                        | 83  | 126  |     |    |

|                                                 |                  | スルーレート設定 2                                                                                                                                                        | 68  | 96   |     |    |

|                                                 |                  | スルーレート設定 3 (最高速)                                                                                                                                                  | 46  | 74   |     |    |

| $t_{r(on)(hs)}$                                 | ターンオンの立ち上がり時間    | $V_{DS(hs)} < 320V$ から $V_{DS(hs)} < 80V$ まで、<br>$V_{BUS} = 400V$ 、 $I_{SW} = -2.65A$ 、以下のハイサイド スルーレート設定の場合、『 <a href="#">GaN パワー FET のスイッチング パラメータ</a> 』を参照      |     |      |     |    |

|                                                 |                  | スルーレート設定 0 (最低速)                                                                                                                                                  | 133 | 178  |     | ns |

|                                                 |                  | スルーレート設定 1                                                                                                                                                        | 50  | 65   |     |    |

|                                                 |                  | スルーレート設定 2                                                                                                                                                        | 10  | 18.5 |     |    |

|                                                 |                  | スルーレート設定 3 (最高速)                                                                                                                                                  | 4   | 10   |     |    |

## 5.6 スイッチング特性(続き)

1) シンボルの定義:  $V_{DS(ls)} = SW$  から  $SL$  への電圧、 $I_{DS(ls)} = SW$  から  $SL$  への電流、 $V_{DS(hs)} = DH$  から  $SW$  への電圧、 $I_{D(hs)} = DH$  から  $SW$  への電流、 $I_{SW}$  = デバイスへの  $SW$  ポイント電流、2) 特に記述のない限り: 電圧、抵抗、容量は AGND を基準としています、 $-40^\circ C \leq T_J \leq 125^\circ C$ 、 $V_{DS(ls)} = 520V$ 、 $V_{DS(hs)} = 520V$ 、 $10V \leq V_{AUX} \leq 26V$ 、 $7.5V \leq V_{BST\_SW} \leq 26V$ 、 $V_{EN} = 5V$ 、 $V_{INL} = 0V$ 、 $V_{INH} = 0V$ 、 $R_{CS} = 100\Omega$

| パラメータ                    |                           | テスト条件                                                                                                                                                       | 最小値 | 標準値 | 最大値 | 単位   |

|--------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| $t_{d(off)}$<br>(hs,INH) | ターンオフ遅延時間                 | $V_{INH} < V_{INH,IT-}$ から $V_{DS(hs)} > 80V$ まで、 $V_{BUS} = 400V$ 、 $I_{SW} = -2.65A$ (スルーレート設定に依存しない)、『GaN パワー FET のスイッチング パラメータ』を参照                      | 40  | 55  |     | ns   |

| $t_{d(off)}$<br>(hs,GDH) | ターンオフ遅延時間                 | $V_{GDH} < V_{GDH,IT-}$ から $V_{DS(hs)} > 80V$ まで、 $V_{BUS} = 400V$ 、 $I_{SW} = -2.65A$ (スルーレート設定に依存しない)、『GaN パワー FET のスイッチング パラメータ』を参照                      | 40  | 65  |     | ns   |

| $t_{f(off)(hs)}$         | ターンオフ立ち下がり時間              | $V_{DS(hs)} > 80V$ から $V_{DS(hs)} > 320V$ まで、 $V_{BUS} = 400V$ 、 $I_{SW} = -2.65A$ (スルーレート設定に依存しない)、『GaN パワー FET のスイッチング パラメータ』を参照                          |     | 20  |     | ns   |

| ターンオンのスルーレート             |                           | $V_{DS(hs)} < 320V$ から $V_{DS(hs)} < 80V$ まで、 $T_J = 25^\circ C$ 、 $V_{BUS} = 400V$ 、 $I_{SW} = -2.65A$ 、以下のハイサイドスルーレート設定の場合、『GaN パワー FET のスイッチング パラメータ』を参照 |     |     |     |      |

|                          |                           | スルーレート設定 0 (最低速)                                                                                                                                            | 2   |     |     | V/ns |

|                          |                           | スルーレート設定 1                                                                                                                                                  | 5   |     |     |      |

|                          |                           | スルーレート設定 2                                                                                                                                                  | 23  |     |     |      |

|                          |                           | スルーレート設定 3 (最高速)                                                                                                                                            | 50  |     |     |      |

| <b>ローサイド過電流保護</b>        |                           |                                                                                                                                                             |     |     |     |      |

| $t_{(OC)(ls)}$           | 過電流フォルト応答時間、過電流の前の FET オン | $I_{D(ls)} > I_{T(OC)(ls)}$ から $I_{D(ls)} < 0.5 \times I_{T(OC)(ls)}$ まで、 $I_{D(ls)} di/dt = 125A/\mu s$                                                    | 75  | 120 |     | ns   |

| $t_{(OC)(en)}$<br>(ls)   | 過電流フォルト応答時間、短絡に FET イネーブル | $V_{DS(ls)} = 100V$ 、 $I_{D(ls)} > I_{T(OC)(ls)}$ から $I_{D(ls)} < 0.5 \times I_{T(OC)(ls)}$ まで、以下のスルーレート設定の場合                                               |     |     |     |      |

|                          |                           | スルーレート設定 0 (最低速)                                                                                                                                            | 390 | 470 |     | ns   |

|                          |                           | スルーレート設定 1                                                                                                                                                  | 205 | 235 |     | ns   |

|                          |                           | スルーレート設定 2                                                                                                                                                  | 175 | 205 |     | ns   |

|                          |                           | スルーレート設定 3 (最高速)                                                                                                                                            | 125 | 172 |     | ns   |

| <b>ハイサイド過電流保護</b>        |                           |                                                                                                                                                             |     |     |     |      |

| $t_{(OC)(hs)}$           | 過電流フォルト応答時間、過電流の前の FET オン | $I_{D(ls)} > I_{T(OC)(ls)}$ から $I_{D(ls)} < 0.5 \times I_{T(OC)(ls)}$ まで、 $I_{D(hs)} di/dt = 125A/\mu s$                                                    | 65  | 125 |     | ns   |

| $t_{(OC)(en)}$<br>(hs)   | 過電流フォルト応答時間、短絡に FET イネーブル | $V_{DS(hs)} = 100V$ 、 $I_{D(hs)} > I_{T(OC)(hs)}$ から $I_{D(hs)} < 0.5 \times I_{T(OC)(hs)}$ まで、以下のスルーレート設定の場合                                               |     |     |     |      |

|                          |                           | スルーレート設定 0 (最低速)                                                                                                                                            | 330 | 375 |     | ns   |

|                          |                           | スルーレート設定 1                                                                                                                                                  | 175 | 190 |     | ns   |

|                          |                           | スルーレート設定 2                                                                                                                                                  | 145 | 170 |     | ns   |

|                          |                           | スルーレート設定 3 (最高速)                                                                                                                                            | 100 | 150 |     | ns   |

| <b>CS</b>                |                           |                                                                                                                                                             |     |     |     |      |

| $t_f$                    | 立ち上がり時間                   | $I_{CS(src)} > 0.2 \times I_{CS(src)(final)}$ から $I_{CS(src)} > 0.9 \times I_{CS(src)(final)}$ まで、 $0V \leq V_{CS} \leq 2V$ 、 $2.65A$ 負荷へのローサイドイネーブル        |     | 30  |     | ns   |

## 5.6 スイッチング特性(続き)

1) シンボルの定義:  $V_{DS(ls)} = SW$  から  $SL$  への電圧、 $I_{DS(ls)} = SW$  から  $SL$  への電流、 $V_{DS(hs)} = DH$  から  $SW$  への電圧、 $I_{D(hs)} = DH$  から  $SW$  への電流、 $I_{SW} = デバイスへの SW ポイント電流、2) 特に記述のない限り: 電圧、抵抗、容量は AGND を基準としています、 $-40^{\circ}\text{C} \leq T_J \leq 125^{\circ}\text{C}$ 、 $V_{DS(ls)} = 520\text{V}$ 、 $V_{DS(hs)} = 520\text{V}$ 、 $10\text{V} \leq V_{AUX} \leq 26\text{V}$ 、 $7.5\text{V} \leq V_{BST\_SW} \leq 26\text{V}$ 、 $V_{EN} = 5\text{V}$ 、 $V_{INL} = 0\text{V}$ 、 $V_{INH} = 0\text{V}$ 、 $R_{CS} = 100\Omega$$

| パラメータ      |                             | テスト条件                                                                                                                                          | 最小値 | 標準値 | 最大値 | 単位            |

|------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|---------------|

| <b>EN</b>  |                             |                                                                                                                                                |     |     |     |               |

|            | EN ウエークアップ時間                | $V_{EN} > V_{IT+}$ から $I_{D(ls)} > 10\text{mA}$ まで、 $V_{INL} = 5\text{V}$                                                                      |     | 1.5 |     | $\mu\text{s}$ |

| <b>BST</b> |                             |                                                                                                                                                |     |     |     |               |

|            | 深い BST から SW 放電までのスタートアップ時間 | $V_{BST\_SW} > V_{BST\_SW,T+(UVLO)}$ からハイサイドは、 $1\mu\text{s}$ で $V_{BST\_SW}$ が $0\text{V}$ から $10\text{V}$ まで上昇し、INH または GDH High レベルに応答します   |     | 5   |     | $\mu\text{s}$ |

|            | 浅い BST から SW 放電までのスタートアップ時間 | $V_{BST\_SW} > V_{BST\_SW,T+(UVLO)}$ からハイサイドは、 $0.5\mu\text{s}$ で $V_{BST\_SW}$ が $5\text{V}$ から $10\text{V}$ まで上昇し、INH または GDH High レベルに応答します |     | 3.2 |     | $\mu\text{s}$ |

## 5.7 代表的特性

図 5-1. ドレイン電流とドレインソース間電圧との関係

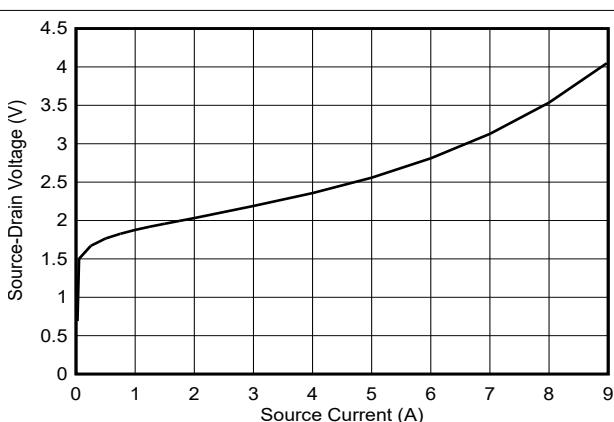

図 5-2. オフ状態のソースドレイン電圧とソース電流との関係

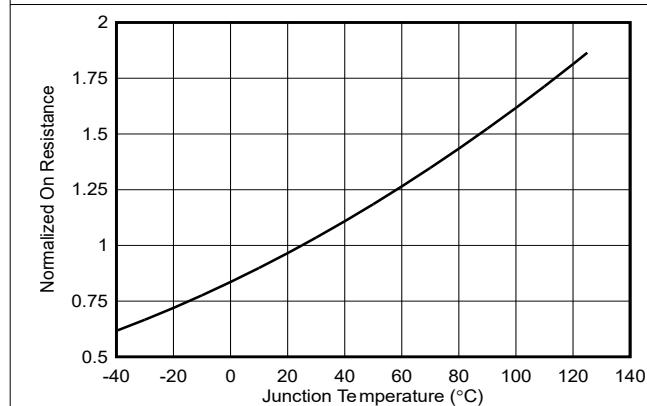

図 5-3. 正規化されたドレインソース間オン抵抗と接合部温度との関係

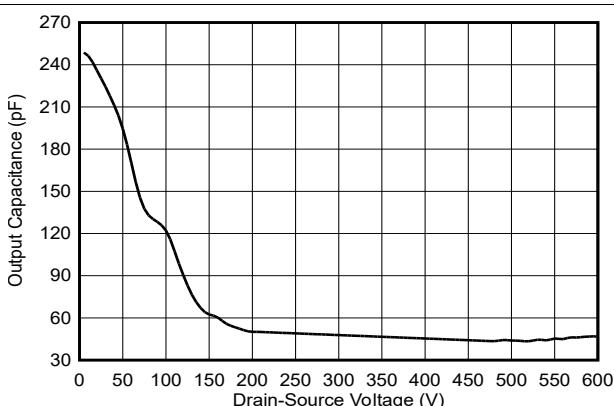

図 5-4. 出力キャパシタンスとドレインソース間電圧との関係

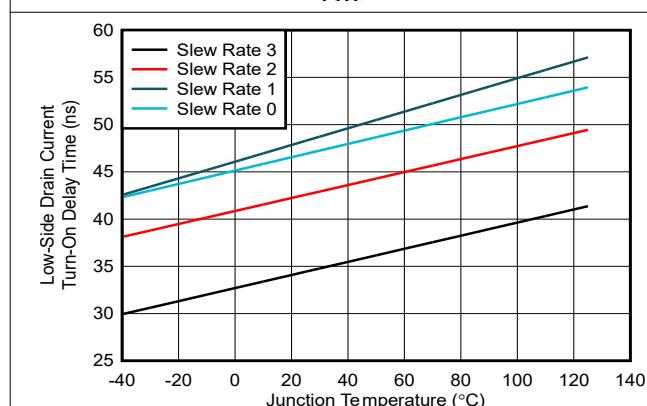

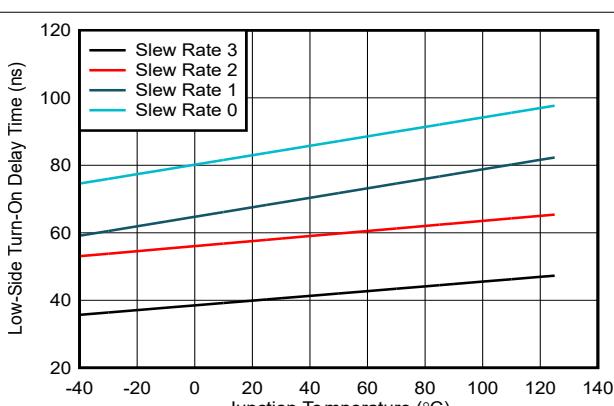

図 5-5. ローサイドドレイン電流ターンオン遅延時間と接合部温度との関係

図 5-6. ローサイドターンオン遅延時間と接合部温度との関係

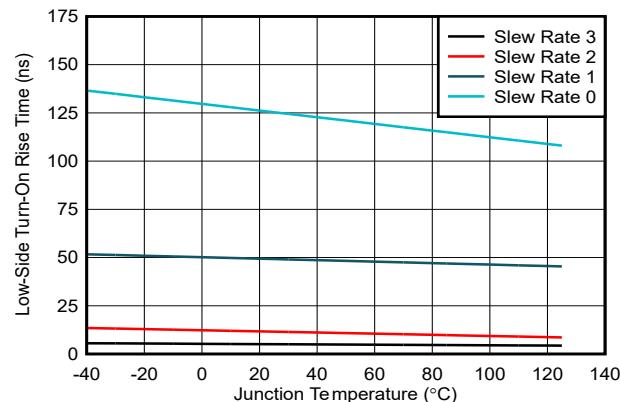

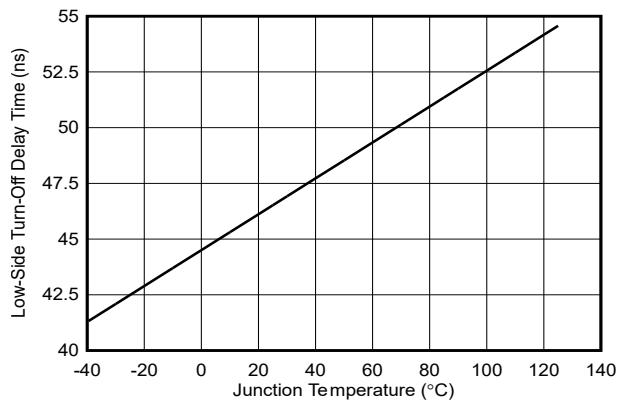

## 5.7 代表的特性 (続き)

図 5-7. ローサイド ターンオン立ち上がり時間と接合部温度との関係

図 5-8. ローサイド ターンオフ遅延時間と接合部温度との関係

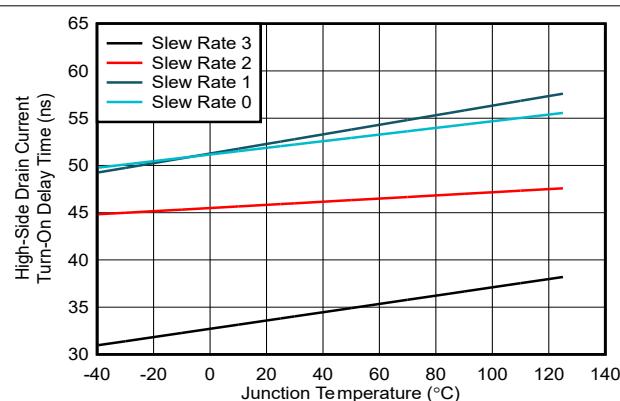

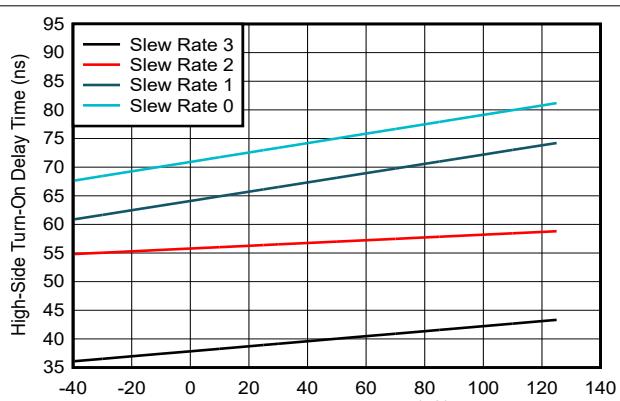

図 5-9. ハイサイド ドレイン電流のターンオン遅延時間と接合部温度との関係

図 5-10. ハイサイド ターンオン遅延時間と接合部温度との関係

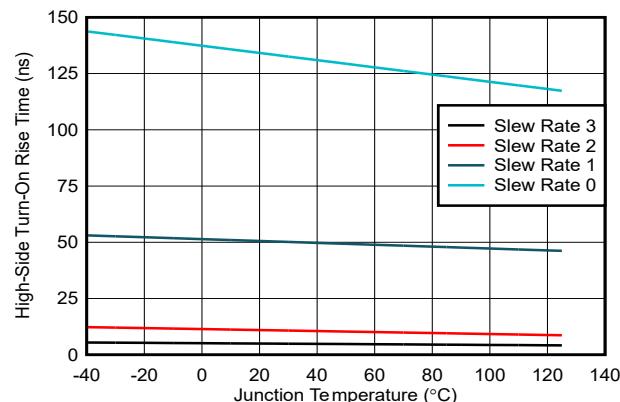

図 5-11. ハイサイド ターンオン立ち上がり時間と接合部温度との関係

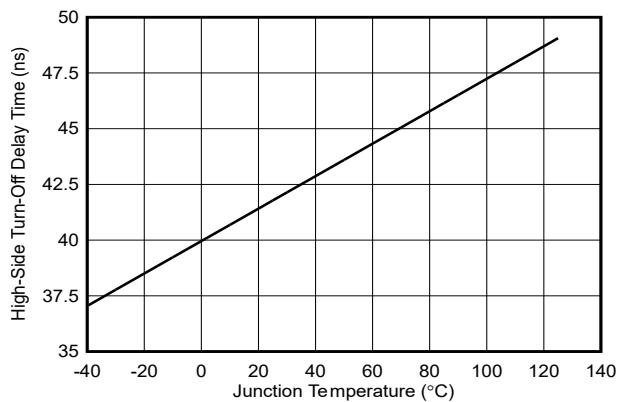

図 5-12. ハイサイド ターンオフ遅延時間と接合部温度との関係

## 5.7 代表的特性 (続き)

図 5-13. AUX スタンバイ電流と接合部温度との関係

図 5-14. AUX 静止電流と接合部温度との関係

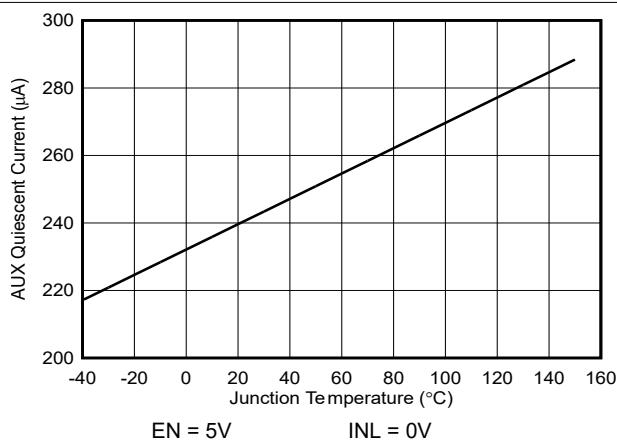

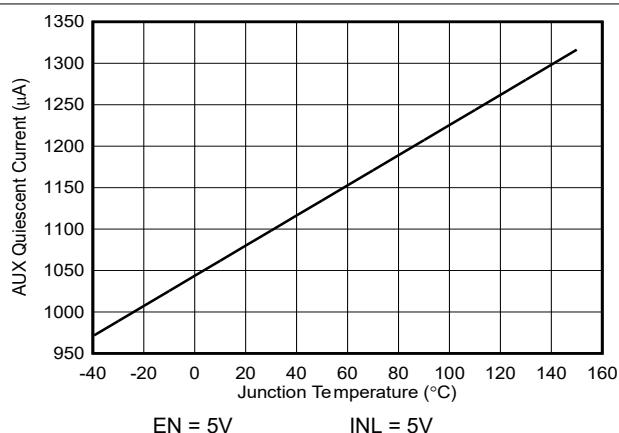

図 5-15. AUX 静止電流と接合部温度との関係

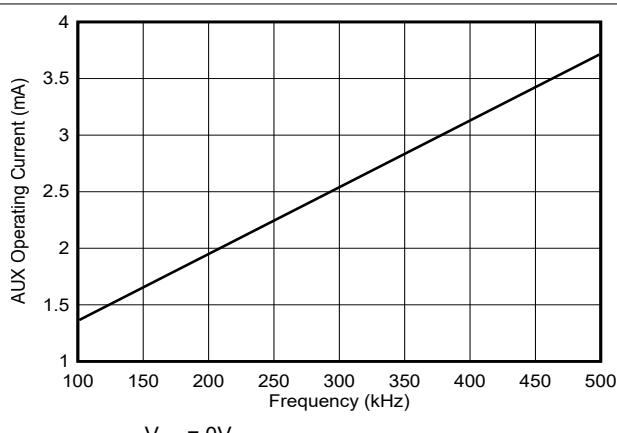

図 5-16. AUX の動作電流と周波数との関係

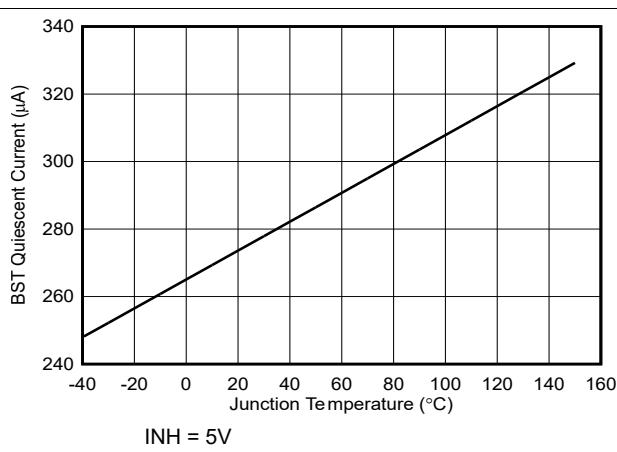

図 5-17. BST 静止電流と接合部温度との関係

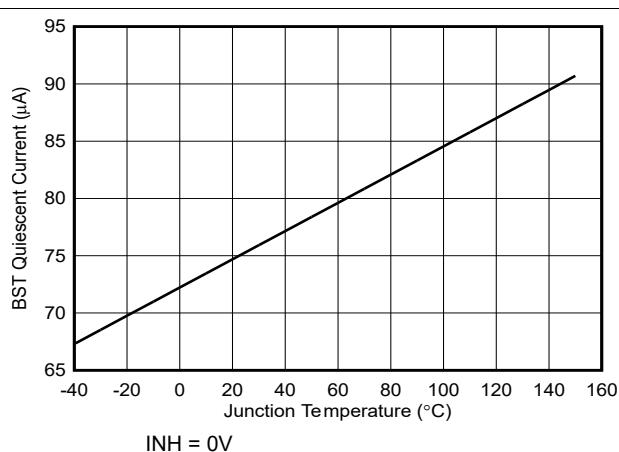

図 5-18. BST 静止電流と接合部温度との関係

## 5.7 代表的特性 (続き)

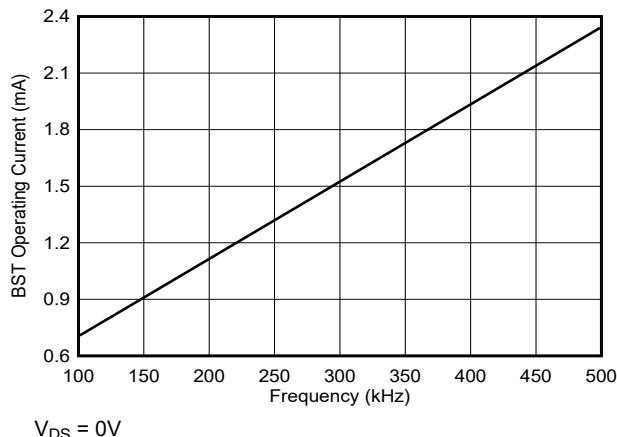

図 5-19. BST の動作電流と周波数との関係

## 6 パラメータ測定情報

### 6.1 GaN パワー FET のスイッチング パラメータ

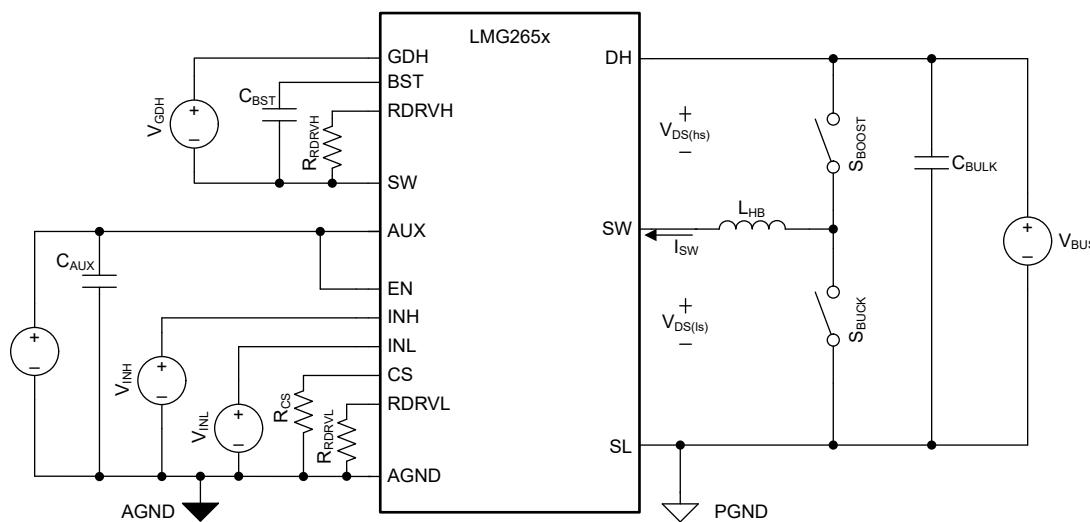

図 6-1 に、GaN パワー FET のスイッチング パラメータの測定に使用する回路を示します。回路はダブル パルス テスターとして動作します。ダブル パルス テスターの詳細については、外部リファレンスを参照してください。この回路は昇圧構成の中に配置され、ローサイド GaN のスイッチング パラメータを測定します。この回路は降圧構成の中に配置され、ハイサイド GaN のスイッチング パラメータを測定します。各構成で測定されていない GaN FET (昇圧のハイサイド、降圧のローサイド) は、ダブル パルス テスター ダイオードとして機能し、オフ状態の第 3 象限導通モードでインダクタ電流を循環させます。表 6-1 に、各構成の詳細を示します。

図 6-1. GaN パワー FET のスイッチング パラメータのテスト回路

表 6-1. GaN パワー FET のスイッチング パラメータのテスト回路構成の詳細

| 構成 | テスト対象の GaN FET | ダイオードとして動作する GaN FET | S <sub>BOOST</sub> | S <sub>BUCK</sub> | V <sub>INL</sub> | V <sub>INH</sub> | V <sub>GDH</sub> |

|----|----------------|----------------------|--------------------|-------------------|------------------|------------------|------------------|

| 昇圧 | ローサイド          | ハイサイド                | クローズド              | オープン              | ダブル パルス 波形       | 0V               | 0V               |

| 降圧 | ハイサイド          | ローサイド                | オープン               | クローズド             | 0V               | ダブル パルス 波形       | 0V               |

| 降圧 | ハイサイド          | ローサイド                | オープン               | クローズド             | 0V               | 0V               | ダブル パルス 波形       |

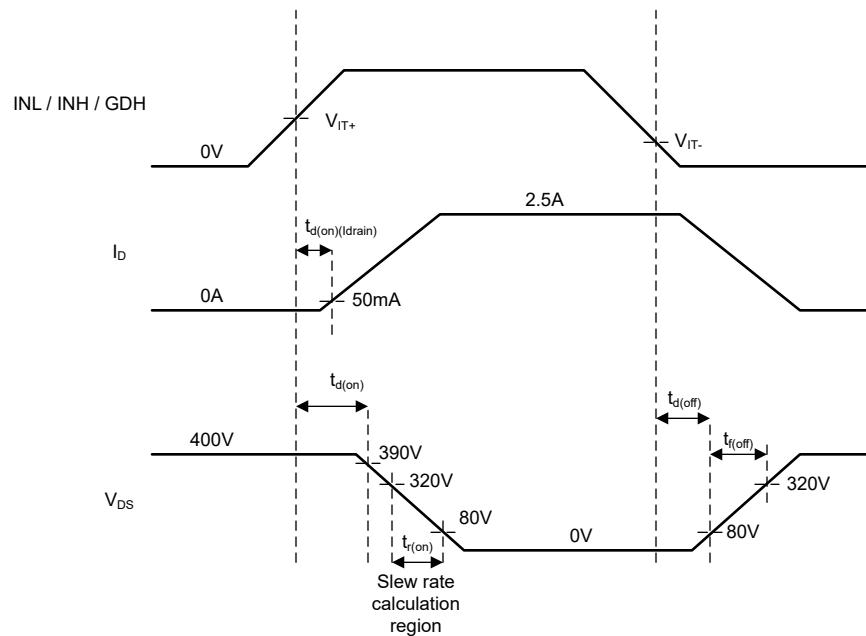

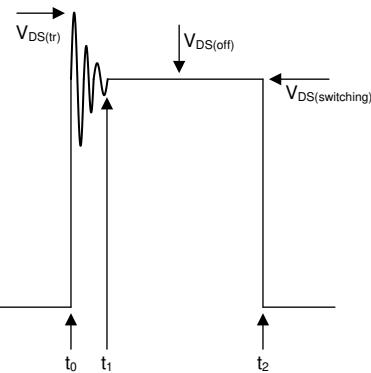

図 6-2 に、GaN パワー FET のスイッチング パラメータを示します。

GaN パワー FET ターンオン遷移には、ドレイン電流のターンオン遅延時間  $t_{d(on)}(I_{drain})$ 、ターンオン遅延時間  $t_{d(on)}$ 、ターンオン立ち上がり時間  $t_{r(on)}$  の 3 つのタイミング要素があります。ターンオンの立ち上がり時間は、 $V_{DS}$  の 80% ~ 20% の立ち下がり時間と同じであることに注意します。3 つのターンオン タイミング部品はすべて、RDRVx ピンの設定に依存します。

GaN パワー FET ターンオフ遷移には、ターンオフ遅延時間  $t_{d(off)}$ 、ターンオフの立ち下がり時間  $t_{f(off)}$  の 2 つのタイミング要素があります。ターンオフの立ち下がり時間は  $V_{DS}$  20% ~ 80% の立ち上がり時間と同じであることに注意します。ターンオフ タイミング部品は RDRVx ピン設定から独立していますが、 $L_{HB}$  電流に大きく依存します。

ターンオン スルーレートは、ターンオン立ち上がり時間の電圧デルタ (240V) にわたって測定され、EMI 設計に役立つスルーレートを取得します。RDRVx ピンを使用して、スルーレートをプログラムします。

図 6-2. GaN パワー FET のスイッチング パラメータ

## 7 詳細説明

### 7.1 概要

LMG2650 は、スイッチ モード電源アプリケーションでの使用を目的とした高集積 650V 95mΩ GaN パワー FET ハーフブリッジです。LMG2650 は、ハーフブリッジ パワー FET、ゲートドライバ、ローサイド電流センス エミュレーション機能、ハイサイド ゲートドライブ レベル シフタ、ブートストラップ ダイオード機能を 6mm x 8mm の QFN パッケージに統合しています。

650V 定格の GaN FET は、オフライン パワー スイッチング アプリケーションで発生する高電圧に対応します。GaN FET の低出力容量電荷は、パワー コンバータのスイッチングに必要な時間とエネルギーの両方を削減します。これは、小型で高効率のパワー コンバータ設計に必要とされる重要な特性です。

LMG2650 の内部ゲートドライバは GaN FET のゲート電圧を制御し、最適なオン抵抗を実現します。また、内部ドライバは、総ゲートインダクタンスと GaN FET コモンソース インダクタンスを低減し、スイッチング性能を向上させます。ローサイド / ハイサイド GaN FET のターンオン スルーレートは、4 つのディスクリート設定のいずれかに個別にプログラムできるため、電力損失、スイッチングに起因するリング、EMI に関して柔軟な設計が可能です。

電流センス エミュレーションにより、CS ピンの出力にローサイド ドレイン電流を複製します。CS ピンは、AGND への抵抗で終端され、外部電源コントローラへの電流センス入力信号を生成します。この CS ピン抵抗は、従来の電流センス抵抗をローサイド GaN FET ソースと直列に接続したものに置き換え、消費電力と占有面積を大幅に削減します。さらに、GaN ソースと直列に電流センス抵抗を接続していない場合、ローサイド GaN FET のサーマル パッド (SL ピン) を PCB 電源グランドに直接接続できるため、システムの熱性能が向上します。

ハイサイド GaN FET は、ローサイド基準の INH ピンとハイサイド基準の GDH ピンの両方で制御されるため、LMG2650 はハイサイド ゲートドライブのリファレンス電圧方式を採用したコントローラと接続できます。内部ハイサイド ゲートドライブ レベル シフタは、デバイスの静止電流への影響を最小限に抑えながら、INH 信号を確実にハイサイドに送信します。また、デバイスの起動時間への影響もありません。

AUX と BST 間のブートストラップ ダイオード機能は、スマートスイッチ付き GaN ブートストラップ FET を使用して実装されます。オン状態の GaN ブートストラップ FET には従来のブートストラップ ダイオードの順方向電圧降下がないため、BST-SW コンデンサをより完全に充電できます。スマートスイッチ付き GaN ブートストラップ FET により、ローサイド ハーフブリッジ GaN パワー FET のオフ状態の第 3 象限電流による BST-SW コンデンサの過充電という従来のブートストラップ ダイオードの問題も回避できます。ブートストラップ機能は、従来のブートストラップ ダイオードと比較して容量が小さく、逆方向回復電荷がないため、より効率的なスイッチングが実現します。

AUX 入力電源の電圧範囲は広いため、電源コントローラによって生成される広範囲の電源レールに適合します。BST 入力電源電圧範囲は、ブートストラップ再充電サイクル間の容量性ドループを考慮して、下限側ではさらに広くなります。低い AUX/BST アイドル静止電流と高速 BST 起動時間により、政府の軽負荷効率要件を満たす上で不可欠なコンバータバーストモード動作に対応できます。EN ピンを使用してデバイスをスタンバイ モードにすると、AUX 静止電流をさらに低減できます。

EN、INL、INH、GDH 制御ピンは、入力インピーダンスが高く、入力スレッショルド電圧が低く、最大入力電圧がローカル電源ピン電圧 (AUX または BST から SW) と同じです。このため、このピンは、低電圧と高電圧の両方の入力信号に対応し、低電力出力で駆動できます。

LMG2650 の保護機能には、ローサイドまたはハイサイドの電流制限低電圧ロックアウト (UVLO)、INL/INH 入力ゲートドライブ インターロック、ローサイドまたはハイサイドのサイクル単位の電流制限、ローサイドまたはハイサイドの過熱シャットダウンがあります。UVLO 機能は、コンバータの動作の良好な実現にも役立ちます。

## 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 GaN パワー FET のスイッチング機能

シリコン FET が長きにわたって支配的なパワースイッチ技術であったため、多くの設計者は、ドレインソース間電圧の銘板を、異なる技術のデバイスを比較する際の等価点として使用できないことを知りません。シリコン FET の銘板のドレインソース間電圧は、アバランシェ ブレークダウン電圧によって設定されます。GaN FET の銘板のドレインソース間電圧は、データシートの仕様への長期的な準拠によって設定されます。

シリコン FET の銘板のドレインソース間電圧を超えると、即座に永続的な損傷を引き起こすことがあります。一方、GaN FET のブレークダウン電圧は銘板のドレインソース間の見出し電圧よりもはるかに高くなっています。たとえば、LMG2650 GaN パワー FET のブレークダウン ドレイン ソース間電圧は 800V を上回るため、LMG2650 は同じ銘板の定格を持つシリコン FET を超える条件下で動作できます。

図 7-1 を使用して、LMG2650 GaN パワー FET のスイッチング機能を説明します。図に、スイッチング アプリケーション内のシングル スイッチ サイクルについて、LMG2650 GaN パワー FET のドレイン ソース間電圧と時間との関係を示します。スイッチング周波数またはデューティ・サイクルに関する請求は行われません。

図 7-1. GaN パワー FET のスイッチング機能

波形は  $t_0$  より先に開始し、FET がオン状態になります。 $t_0$  の時点では GaN FET はターンオフし、寄生素子によってドレインソース間電圧に高周波でリギングが生じます。高周波リギングは、 $t_1$  減衰します。 $t_1$  と  $t_2$  の間の FET のドレインソース間電圧は、スイッチングアプリケーションの特性応答によって設定されます。特性はフラットライン（プラトー）として表示されますが、他の応答も可能です。 $t_2$  の時点で、GaN FET がオンになります。通常動作では、過渡リギング電圧は 650V に制限され、プラート電圧は 520V に制限されます。まれなサージ現象の場合、過渡リギング電圧は 800V に制限され、プラート電圧は 720V に制限されます。

### 7.3.2 ターンオン スルーレート制御

ローサイドとハイサイド両方の GaN パワー FET のターンオン スルーレートは、4 つの個別設定のいずれかに個別にプログラムされます。ローサイド スルーレートは、RDRV1 ピンと AGND ピンの間の抵抗によってプログラムされます。ハイサイド スルーレートは、RDRVH ピンと SW ピンの間の抵抗によって設定されます。ローサイド スルーレートの設定は、AUX 電源オン中に AUX 電圧が AUX パワーオン リセット電圧を 1 回上回ると決まります。ハイサイド スルーレートの設定は、BST から SW への電源オン中に BST から SW への電圧が BST パワーオン リセット電圧を 1 回上回ると決まります。スルーレート設定の決定時間は指定されていませんが、約 0.4μs です。

表 7-1 に、4 つのスルーレート設定の推奨プログラミング抵抗値（標準値）、および各設定でのターンオン スルーレートの標準値を示します。表に記載されているように、スルーレート設定 0 のプログラムでは開回路接続が許容され、スルーレート設定 3 のプログラムでは短絡接続（ローサイドのターンオン スルーレートの場合は RDRV1 を AGND に短絡）（ハイサイドのターンオン スルーレートの場合は RDRVH を SW に短絡）が許容されます。

表 7-1. スルーレートの設定

| ターンオン スルーレートの設定 | 推奨標準プログラミング抵抗値 (kΩ) | 標準ターンオン スルーレート (V/ns) | 備考                                                                                           |

|-----------------|---------------------|-----------------------|----------------------------------------------------------------------------------------------|

| 0               | 120                 | 2                     | プログラミング抵抗の開回路接続は許容されます。                                                                      |

| 1               | 47                  | 5                     |                                                                                              |

| 2               | 22                  | 23                    |                                                                                              |

| 3               | 5.6                 | 50                    | 抵抗のプログラミングでは短絡接続（ローサイド スルーレートの場合は RDRV1 を AGND に短絡）（ハイサイド スルーレートの場合は RDRVH を SW に短絡）が許容されます。 |

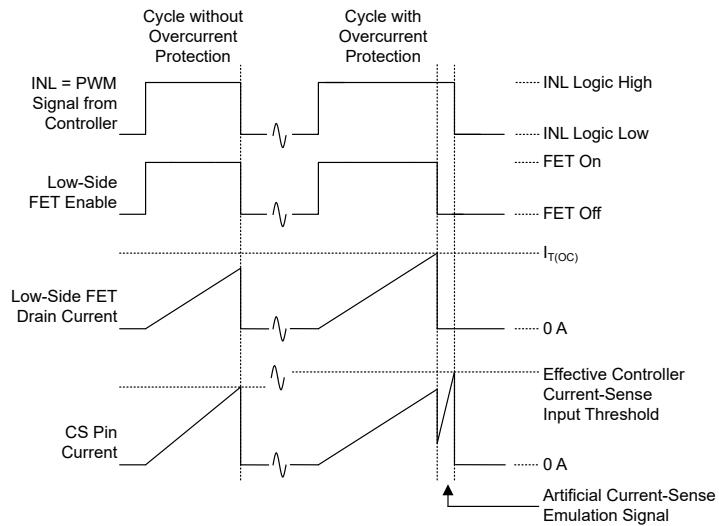

### 7.3.3 電流検出エミュレーション

電流検出エミュレーション機能により、CS ピンの出力にある GaN パワー FET の正のドレイン電流をスケーリングして複製します。電流検出エミュレーションのゲイン  $G_{CE}$  は、ローサイド GaN パワー FET  $I_D$  のドレインに 1A が流れるごとの CS ピン  $I_{CS}$  からの 0.554mA 出力です。

$$G_{CSE} = I_{CS} \div I_D = 0.554mA \div 1A = 0.000554 \quad (1)$$

CS ピンは、AGND および  $R_{CS}$  への抵抗によって終端され、外部電源コントローラへの電流センス電圧入力信号が生成されます。

$R_{CS}$  は従来の電流センス設計抵抗  $R_{CS(trad)}$  を求め、 $G_{CSE}$  の逆数を乗算して決定されます。従来の電流センス設計では、GaN パワー FET のドレイン電流  $I_D$  を  $R_{CS(trad)}$  経由で渡すことで、電流センス電圧  $V_{CS(trad)}$  が生成されます。LMG2650 は、CS ピンの出力電流  $I_{CS}$  を  $R_{CS}$  経由で渡すことで、電流センス電圧  $V_{CS}$  を生成します。電流センス電圧は、どちらの設計でも同じである必要があります。

$$V_{CS} = I_{CS} \times R_{CS} = V_{CS(trad)} = I_D \times R_{CS(trad)} \quad (2)$$

$$R_{CS} = I_D \div I_{CS} \times R_{CS(trad)} = 1 \div G_{CSE} \times R_{CS(trad)} \quad (3)$$

$$R_{CS} = 1805 \times R_{CS(trad)} \quad (4)$$

CS ピンは、内部で標準値 2.5V にクランプされます。このクランプにより、CS ピンの電流センス抵抗が切り離された場合などに、脆弱な電源コントローラの電流センス入力ピンが過電圧から保護されます。

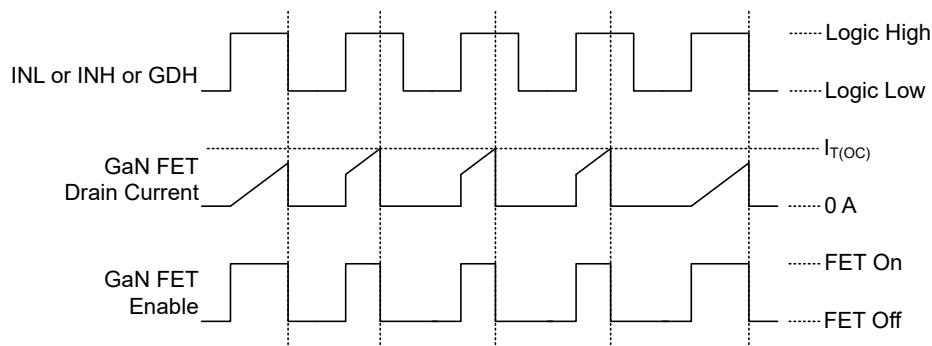

図 7-2 に、電流センス エミュレーションの動作を示します。どちらのサイクルでも、GaN FET が有効化されている間の CS ピン電流によって GaN パワー FET のドレイン電流がエミュレートされます。最初のサイクルは、電流センスの入力スレッショルドがトリップされたときに、コントローラが GaN パワー FET をオフにする通常動作を示しています。2 番目のサイクルは、コントローラの電流センス入力スレッショルドがトリップされる前に、LMG2650 の過電流保護が GaN パワー FET をオフにするフォルト状況を示しています。この 2 番目のサイクルでは、LMG2650 は、高速ランプによる人工的な電流検出エミュレーション信号を生成してコントローラの電流センス入力スレッショルドをトリップすることで、コントローラの IN パルスのハングを回避します。人工信号は、IN ピンがロジック Low になるまで保持されます。このロジック Low は、コントローラがスイッチ動作の制御に復帰することを示します。

図 7-2. 電流検出エミュレーションの動作

### 7.3.4 ブートストラップダイオード機能

内部ブートストラップ ダイオード機能は、スマートスイッチ付き GaN ブートストラップ FET によって実装されています。GaN ブートストラップ FET は、GaN ブートストラップ FET がオフのとき、AUX と BST の間の両方向の電流を遮断します。

ブートストラップ ダイオード機能は、ローサイド GaN パワー FET がオンになるとアクティブになり、ローサイド GaN パワー FET がオフになると非アクティブになります。ブートストラップ ダイオードの非アクティブ位相中は、GaN ブートストラップ FET はオフに保持されます。GaN ブートストラップ FET は、ブートストラップのアクティブ位相が開始されると 1 回オンになり、AUX から BST にダイオード電流が流れて BST-SW 間コンデンサを充電する理想ダイオードとして制御されます。GaN ブートストラップ FET がオンになった後に BST から AUX への小さな逆電流が検出されると、ブートストラップのアクティブ位相の残りの期間、GaN ブートストラップ FET はオフになります。

ブートストラップ ダイオード機能には、ブートストラップ アクティブ位相が開始された際に BST-SW 間コンデンサが著しく放電された場合に GaN ブートストラップ FET を保護するための電流制限が組み込まれています。GaN ブートストラップ FET のターンオン時間中に電流制限状態がない場合や、BST-SW 間コンデンサの充電に伴ってブートストラップ機能が電流制限値を外れた場合、GaN ブートストラップ FET のターンオン時間の残りの期間、電流制限機能が無効化されます。静止電流を節約するため、電流制限機能は無効化されています。

### 7.3.5 入力制御ピン (EN, INL, INH, GDH)

EN ピンは AGND を基準としています。このピンを使用して、[セクション 7.4](#) で説明されているアクティブ モードとスタンバイモードを切り替えることができます。

INL ピンは AGND を基準としています。このピンは、ローサイド GaN パワー FET のオン / オフを切り替えるために使用されます。

INH ピンは AGND を基準としています。このピンは、ハイサイド GaN パワー FET のオン / オフを切り替えるために使用されます。INH ピンは、ローサイド基準ゲートドライブ信号を使用してハイサイド GaN パワー FET を制御するコントローラと互換性があります。

GDH ピンは SW を基準としています。このピンは、ハイサイド GaN パワー FET のオン / オフを切り替えるために使用されます。GDH ピンは、ハイサイド基準信号を使用してハイサイド GaN パワー FET を制御するコントローラと互換性があります。

LMG2650 は、INH ピンまたは GDH ピンと組み合わせて使用し、ハイサイド GaN パワー FET を制御することを意図しています。未使用的ピンをピン (INH から AGND または GDH から SW) のリファレンス電圧に短絡します。

入力制御ピンには、ノイズ耐性のため、標準値 1V の入力電圧スレッショルドヒステリシスがあります。また、このピンには、フローティング入力に対して保護するための標準値 400kΩ プルダウン抵抗もあります。400kΩ は、標準入力電圧が 4V を超えると飽和して、最大入力プルダウン電流を標準値 10uA に制限します。EN、INL、INH ピンから AUX ピンへの個別の順方向ベースの ESD ダイオードがあります。EN、INL、INH 電圧を AUX 電圧よりも高い電圧に駆動することは避けてください。また、GDH ピンから BST ピンへの順方向ベースの ESD ダイオードもあります。GDH から SW への電圧を、BST から SW への電圧よりも高く駆動することは避けてください。

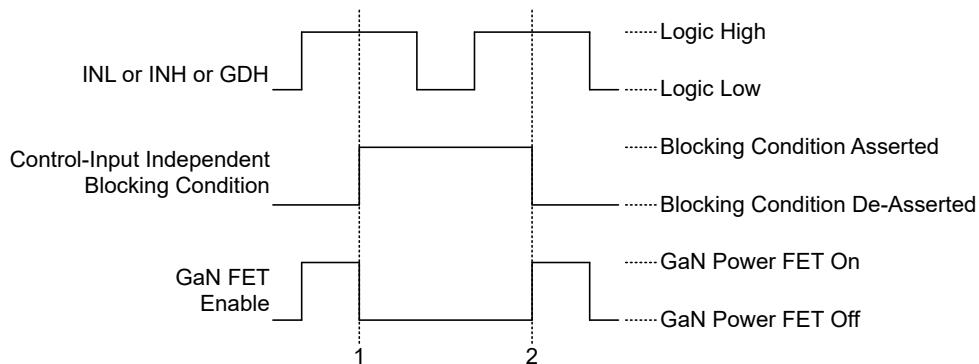

以下の条件により、INL ターンオンアクションがブロックされます。

- スタンバイ モード (上記の EN ピンで設定される通り)

- INL/INH インターロック制御における INH

- AUX 低電圧ロックアウト (UVLO)

- ローサイド過熱保護

- ローサイド GaN パワー FET の過電流保護

以下の条件により、INH ターンオンアクションがブロックされます。

- スタンバイ モード (上記の EN ピンで設定される通り)

- INL/INH インターロック制御における INH

- AUX UVLO

- ローサイド過熱保護

- BST UVLO

- ハイサイド過電流保護

以下の条件により、GDH ターンオンアクションがブロックされます。

- BST UVLO

- ハイサイド過熱保護

- ハイサイド過電流保護

ローサイド温度保護機能は INH ピンをブロックし、ハイサイド温度保護機能は GDH ピンをブロックすることに注意してください。

INL/INH インターロックと過電流保護を除くすべてのブロッキング状態は、INL、INH、GDH ロジック状態とは無関係に動作します。図 7-3 に、これらの制御入力の独立したブロッキング状態の動作を示します。

図 7-3. 制御入力に依存しないブロッキング状態の動作

セクション 7.3.6 に、INL/INH インターロック ブロックの動作を示します。また、過電流保護ブロック動作は、制御入力が制御入力のそれぞれの GaN パワー FET をオンにした後にのみアサートされます。詳細については、セクション 7.3.9 を参照してください。

### 7.3.6 INL - INH インターロック

インターロック機能により、INL ピンと INH ピンの両方がロジック High のとき、ローサイドとハイサイドの GaN パワー FET が同時にオンにならないようにします。もう一方のピンがロジック Low のとき、INL と INH のどちらかのピンがロジック High の場合、インターロックは制御されます。INL または INH ピンがインターロックの制御を取得すると、ピンがロジック High に維持されている限り、ピンの制御は維持されます。インターロックの制御の INL ピン (INH ピン) のみが、インターロックを通してロジック High 信号を渡します。

GDH ピンにはインターロック機能がないことに注意してください。これは、INL ピンと GDH ピンの両方がロジック High の場合、ローサイドとハイサイドの GaN パワー FET を同時にオンにできることを意味します。

### 7.3.7 AUX 電源ピン

AUX ピンはローサイド内部回路の入力電源であり、内部ブートストラップ ダイオード機能を経由して BST-SW 間コンデンサを充電する電源です。AUX 外部容量は、さまざまな動作条件にわたって BST から SW への外部容量の 3 倍以上にするセラミック コンデンサにすることを推奨します。

#### 7.3.7.1 AUX パワーオン リセット

AUX 電圧が AUX パワーオンリセット電圧を下回ると、AUX パワーオンリセットにより、INH ピン機能を含むすべてのローサイド機能が無効化されます。AUX パワーオンリセット電圧は指定されていませんが、約 5V です。AUX 電圧が AUX パワーオンリセット電圧を上回ると、AUX パワーオンリセットにより、RDRVRL ピンにプログラミングされるローサイドスルーレート設定の 1 回限りの判定が初期化されます。AUX 電圧が AUX パワーオンリセット電圧を上回ると、AUX パワーオンリセットにより、過熱保護機能が有効化されます。

### 7.3.7.2 AUX 低電圧誤動作防止 (UVLO)

AUX UVLO は、INL ピンがローサイド GaN パワー FET をオンにするのを阻止し、AUX 電圧が AUX UVLO 電圧を下回ると INH ピンがハイサイド GaN パワー FET をオンにするのをブロックします。図 7-3 に、AUX UVLO ブロッキング動作を示します。AUX UVLO 電圧は BST UVLO 電圧よりも高い値に設定されるため、ローサイド GaN パワー FET が動作しているときにハイサイド GaN パワー FET を動作できます。AUX UVLO 電圧と BST UVLO 電圧との間の電圧分離は、AUX 電源からの BST-SW 間コンデンサのブートストラップ充電が不完全な動作条件を考慮しています。AUX UVLO 電圧ヒステリシスは、UVLO 電圧トリップポイント付近でのオン/オフのチャタリングを防止します。

### 7.3.8 BST 電源ピン

BST ピンは、ハイサイド内部回路の入力電源です。BST ピンと対応するハイサイド回路は、SW ピンを基準としています。BST ピンは、内部ブートストラップダイオード機能を経由して、ローサイド AUX 電源ピンから電力が供給されます。ローサイド GaN FET がオフのとき、ブートストラップ機能は非アクティブになり、BST ピンは BST 電源用の BST-SW 間外部コンデンサに頼る必要があります。

BST から SW への容量の設計は、ハイサイドの充電時間とホールドアップ時間の間のトレードオフです。BST から SW への外部容量を、動作条件全体にわたって少なくとも  $10\text{nF}$  のセラミックコンデンサにすることが推奨されます。

#### 7.3.8.1 BST パワーオン リセット

BST パワーオンリセット電圧は、SW ピンを基準としています。BST から SW への電圧が BST パワーオンリセット電圧を下回ると、BST パワーオンリセットにより、すべてのハイサイド機能が無効化されます。BST パワーオンリセット電圧は指定されていませんが、約 5V です。BST から SW への電圧が BST パワーオンリセット電圧を上回ると、BST パワーオンリセットにより、RDRVH ピンにプログラムされたハイサイドスルーレート設定の 1 回限りの判定が初期化されます。

#### 7.3.8.2 BST 低電圧誤動作防止 (UVLO)

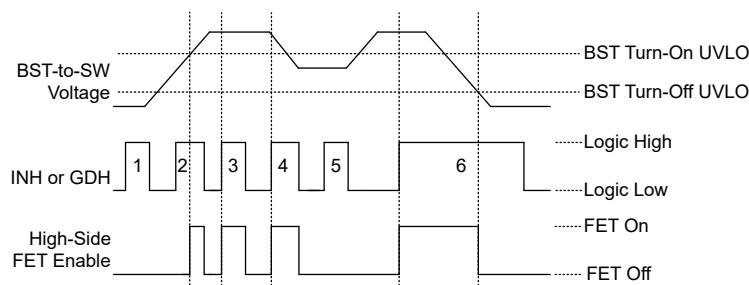

BST UVLO 電圧は、SW ピンを基準としています。以下に示されているように、BST から SW への電圧が該当する BST UVLO 電圧を下回ると、BST UVLO は、INH ピンと GDH ピンの両方がハイサイド GaN パワー FET をオンにするのをブロックします。図 7-3 に、BST UVLO ブロッキング動作を示します。BST UVLO は、2 レベルの BST UVLO を作成する 2 つの独立した UVLO 機能で構成されています。上側の BST UVLO は BST ターンオン UVLO と呼ばれ、ハイサイド GaN パワー FET をオンにできるかどうかのみを制御します。下側の BST UVLO は BST ターンオフ UVLO と呼ばれ、ハイサイド GaN パワー FET がすでにオンになった後、ハイサイド GaN パワー FET をオフにできるかどうかのみを制御します。2 レベル UVLO の動作は、ヒステリシスを持つ 1 つの UVLO とは同じではありません。

図 7-4 に、2 レベル BST UVLO の動作を示します。BST ターンオン UVLO は、BST から SW への電圧が BST ターンオン UVLO 電圧 (INH/GDH パルス #1、パルス #2 の最初の部分、パルス #5) を下回ると、ハイサイド GaN パワー FET が INH または GDH ロジック High の場合にオンになるのを防止します。ハイサイド GaN パワー FET が正常にオンになった後、BST ターンオン UVLO は無視され、INH または GDH ロジック High パルスの残り (パルス #2、#3、#4、#6 の INH/GDH の 2 番目の部分) の間、BST ターンオフ UVLO 出力が監視されます。BST ターンオフ UVLO は、BST から SW への電圧が BST ターンオフ UVLO 電圧 (INH/GDH パルス #6) を下回ると、INH/GDH ロジック High パルスの残りの間、ハイサイド GaN パワー FET をターンオフします。

図 7-4. BST UVLO の動作

2 レベル BST UVLO の実効電圧ヒステリシスは、BST UVLO 電圧の上側と下側の差です。同じヒステリシスを使用してシングル レベル BST UVLO を実装できますが、それに続くハイサイド GaN パワー FET をヒステリシス範囲の任意の場所でオンにすることができます。シングル レベル BST UVLO により、INH/GDH パルス #5 でハイサイド GaN 電源をオンにできます。2 レベル UVLO 設計により、ヒステリシス範囲でオンになることは防止されます。

2 レベル BST UVLO を使用すると、すべての INH または GDH パルスの開始時に BST-SW 間コンデンサが適切に充電されるように、広いヒステリシスを確保できます。広いヒステリシスにより、ハイサイドの起動時間を高速化するのに有用となる小さい BST-SW 間コンデンサを使用できます。INH または GDH パルスの開始時にコンデンサを適切に充電すると、ハイサイド GaN パワー FET が INH または GDH パルスの早い段階でオフになり、コンバータの動作が不安定になることがなくなります。

### 7.3.9 過電流保護

LMG2650 は、両方のハーフブリッジ GaN パワー FET のサイクル単位の過電流保護を実装しています。図 7-5 に、サイクル単位の過電流動作を示します。INL、INH、GDH のロジック High サイクルごとに、制御された GaN パワー FET がオンになります。GaN パワー FET のドレイン電流が過電流スレッショルド電流を超えると、過電流保護によって INL または INH または GDH ロジック High 期間の残りの部分で GaN パワー FET がオフになります。

図 7-5. サイクル単位の過電流保護動作

サイクル単位の過電流保護では、イベントが報告されず、保護によって GaN パワー FET が INL または INH または GDH サイクルごとにオンになるため、システムの中止が最小限に抑えられます。

セクション 7.3.3 に示されているように、ローサイド過電流保護によってローサイド GaN パワー FET がオフになった後に、コントローラがハング状態にならないように、人工的な CS ピン電流が生成されます。

### 7.3.10 過熱保護

LMG2650 は、ローサイド デバイス回路とハイサイド デバイス回路の両方に対して個別の過熱保護を実装しています。ローサイド過熱保護は、INL ピンがローサイド GaN パワー FET がオンになるのを阻止し、ローサイド温度が過熱保護温度を上回ると、INH ピンがハイサイド GaN パワー FET をオンにするのをブロックします。ハイサイド過熱保護は、ハイサイド温度が過熱保護温度を上回ると、GDH ピンがハイサイド GaN パワー FET をオフにするのをブロックします。図 7-3 に、過熱ブロッキング動作を示します。過熱保護ヒステリシスにより、誤った熱サイクルが防止されます。

AUX 電圧が AUX パワーオンリセット電圧を上回ると、ローサイド過熱保護が有効になります。AUX パワーオンリセット電圧が低いため、パワー コンバータの冷却フェーズ中に AUX レールがドリープした場合でも、過熱保護が動作し続けることができます。BST から SW への電圧が BST パワーオンリセット電圧を上回ると、ハイサイド過熱保護が有効になります。

## 7.4 デバイスの機能モード

LMG2650 には、EN ピンで制御される 2 つの動作モードがあります。デバイスは、EN がロジック High のときはアクティブ モード、EN ピンがロジック Low のときはスタンバイ モードになります。アクティブ モードでは、ハーフブリッジ GaN パワー FET は INL、INH、GDH ピンによって制御されます。スタンバイ モードでは、INL ピンと INH ピンは無視され、ロー

サイド GaN パワー FET とブートストラップ ダイオードはオフに保持され、INH ピンはハイサイド FET のオンをブロックし、AUX 静止電流は AUX スタンバイ静止電流まで低減されます。スタンバイ モードでは、BST ピンに外部電源から電力が供給されている場合、ハイサイド GaN パワー FET は GDH ピンによって制御されることに注意してください。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インストルメンツの製品仕様に含まれるものではなく、テキサス・インストルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

LMG2650 は、ハーフブリッジ FET、FET ゲートドライバ、ハイサイド ゲートドライブ レベル シフタ、ブートストラップ ダイオード機能、電流センス エミュレーションが 1 つのパッケージに統合されているため、これはプラグ アンド プレイの簡素化を実現した GaN パワー FET ハーフブリッジです。内蔵ゲートドライバ、低 IN 入力スレッショルド電圧、広い補助入力電源電圧により LMG2650 一般的な業界電源コントローラとシームレスに組み合わせられます。

### 8.2 代表的なアプリケーション

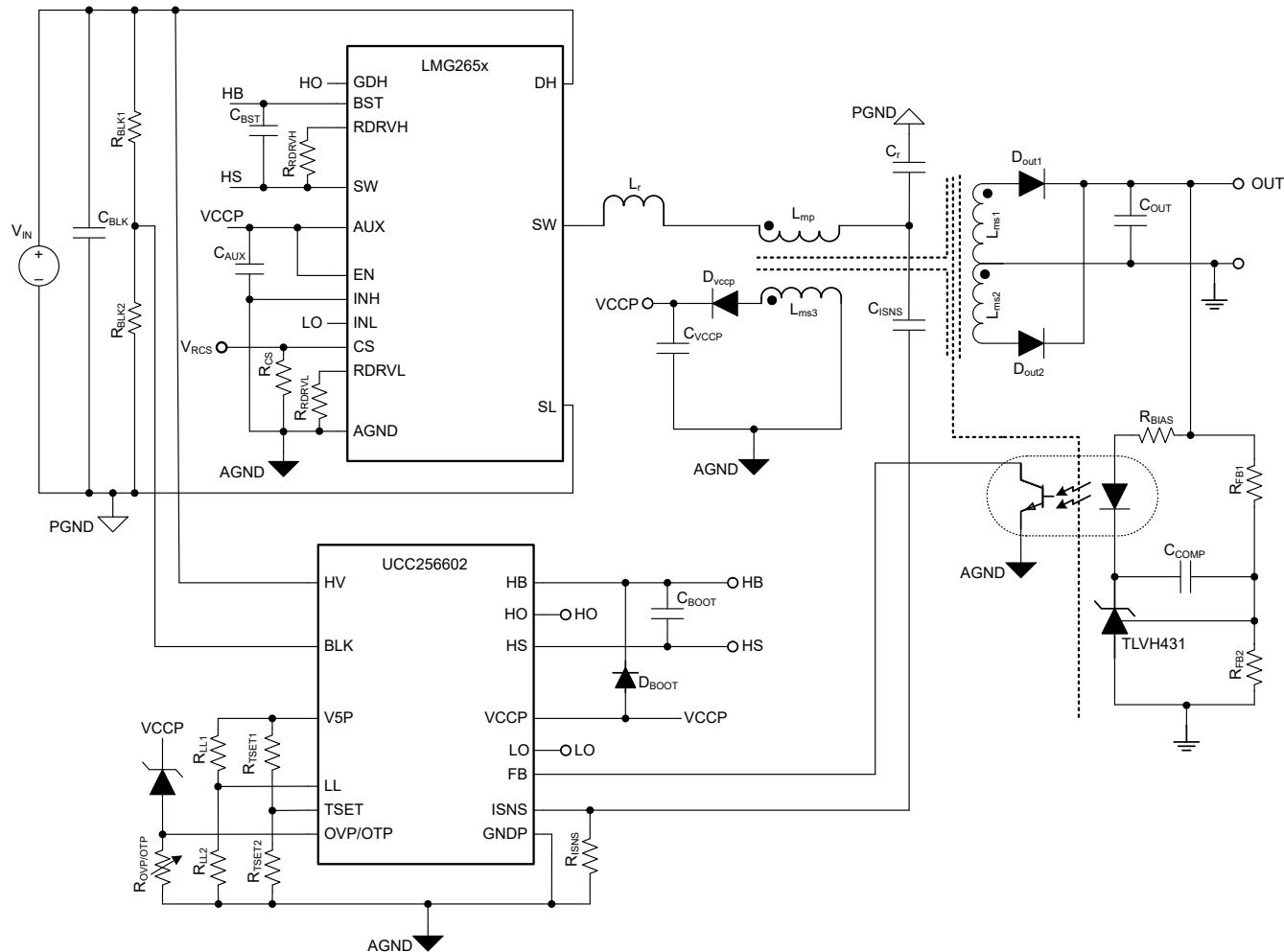

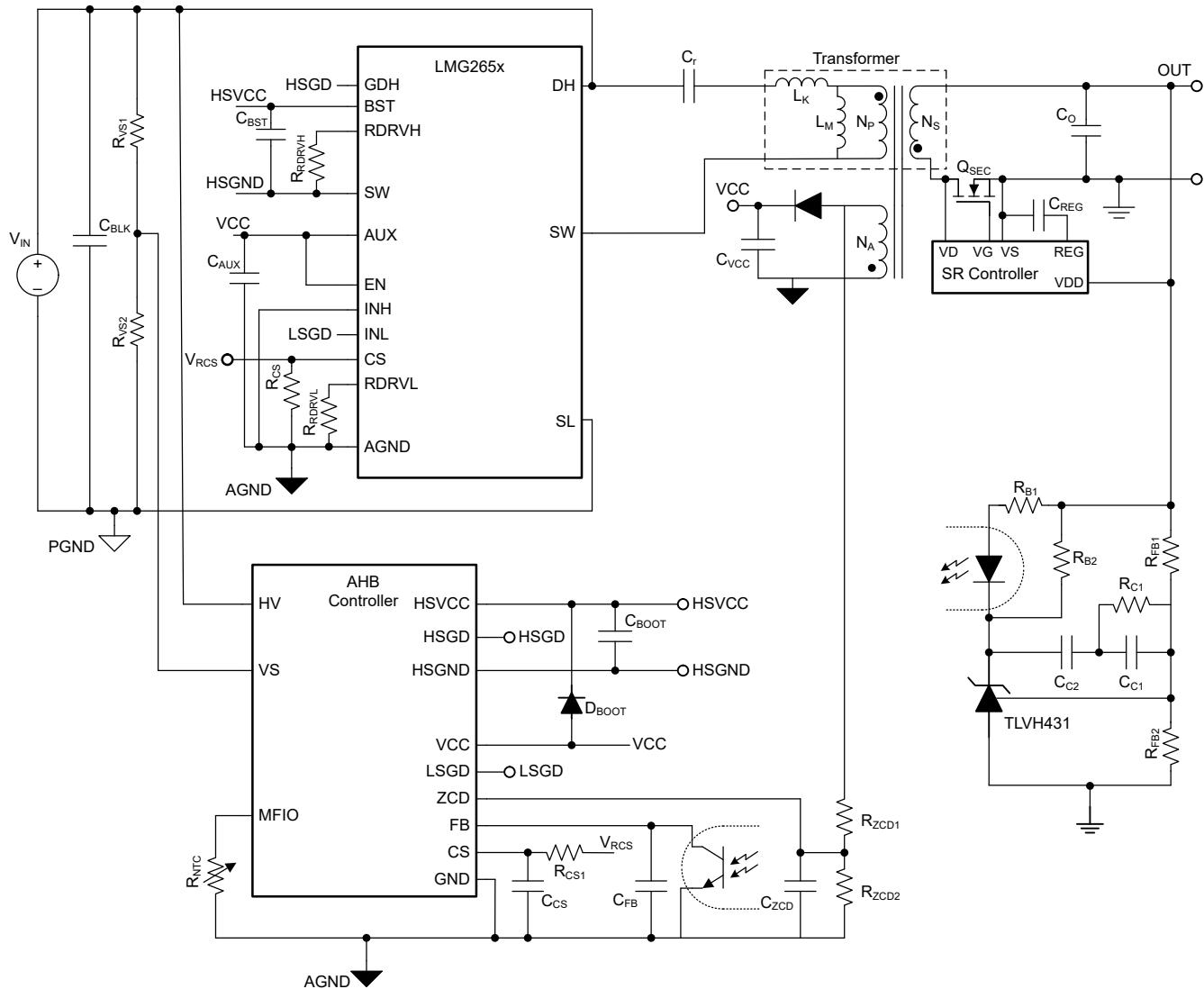

#### 8.2.1 LLC アプリケーション

図 8-1. 240W LLC コンバータ アプリケーション

### 8.2.1.1 設計要件

表 8-1. 設計仕様

| 仕様               | 値             |

|------------------|---------------|

| 入力 DC 電圧範囲       | 365VDC～410VDC |

| 出力 DC 電圧         | 48V           |

| 出力定格電流           | 5A            |

| 390VDC の出力電圧リップル | 120mVpp       |

| 390VDC 時にピーク効率   | 93%           |

### 8.2.1.2 詳細な設計手順

代表的なアプリケーションでは、LMG2650 を LLC コントローラと組み合わせて、高電力密度、高効率の 240W LLC コンバータを作成します。240W LLC コンバータ アプリケーションは、標準的なアプリケーションに適用されます。この詳細な設計手順では、アプリケーションで LMG2650 を使用する際の詳細を中心に説明します。

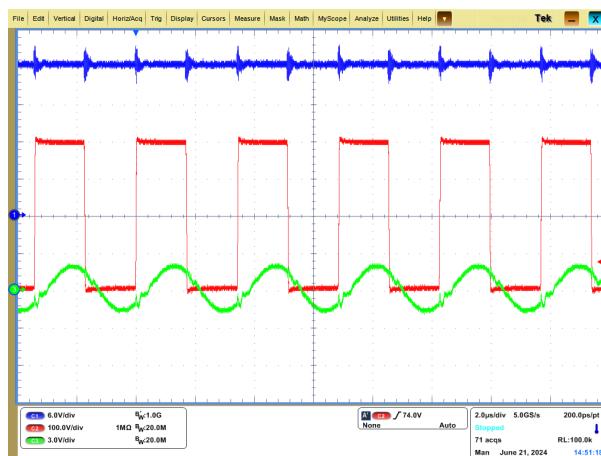

### 8.2.1.3 アプリケーション曲線

以下の波形は、代表的なスイッチング波形を示しています。赤のパターンは LMG2650 のスイッチ ノード電圧、緑のパターンは  $R_{ISNS}$  全体の電流センス電圧、青のパターンは  $V_{OUT}$  です。

図 8-2.  $V_{IN} = 400\text{VDC}$

### 8.2.2 AHB アプリケーション

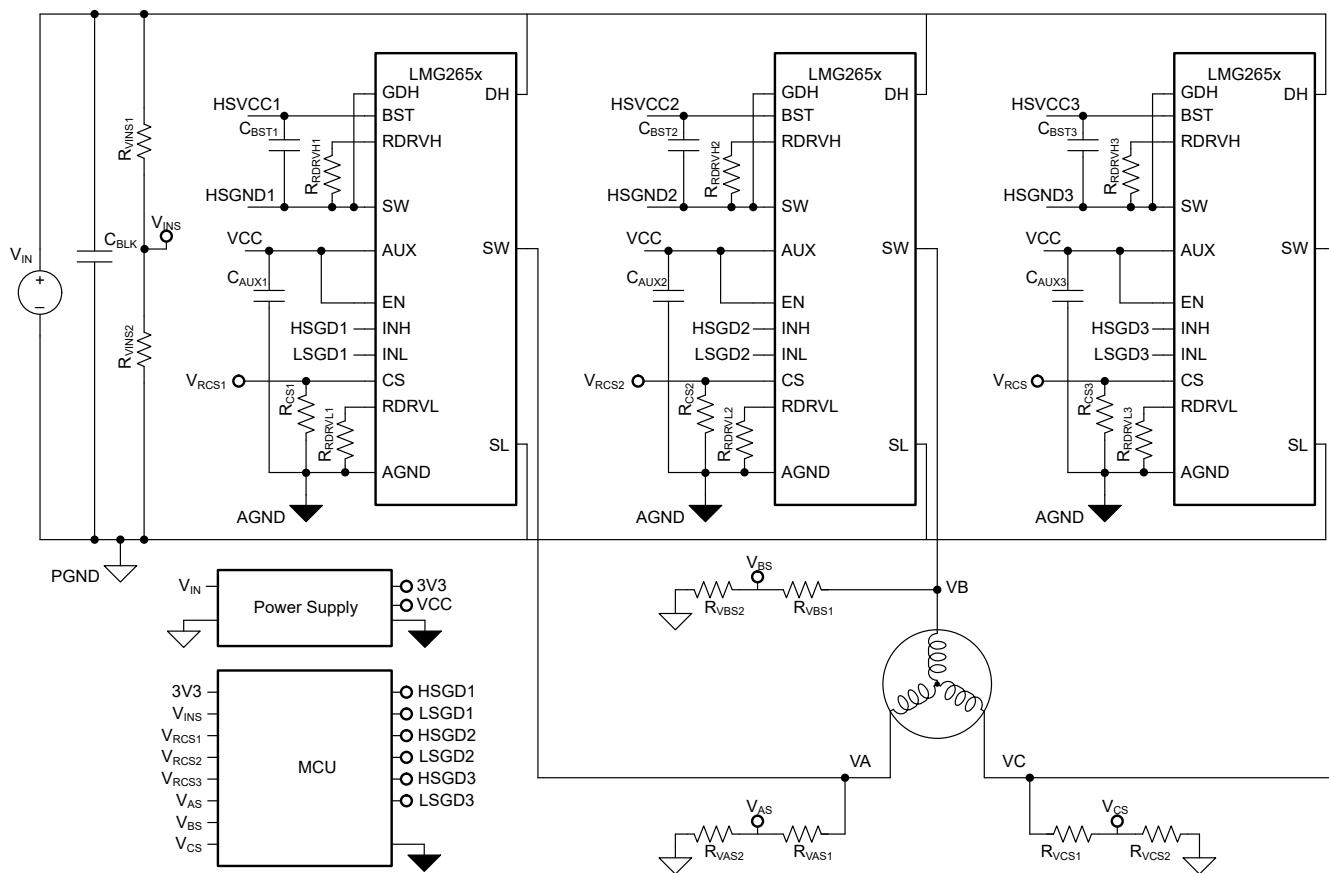

図 8-3. 180W AHB コンバータ アプリケーション

### 8.2.3 モーター ドライブ アプリケーション

図 8-4. 8A モーター ドライバ アプリケーション

### 8.3 電源に関する推奨事項

LMG2650 は、AUX ピンに接続された単一の入力電源で動作します。BST ピンは内部で AUX ピンによって電力が供給されます。LMG2650 は、電源コントローラが管理および使用するのと同じ電源で動作することを意図しています。10V ~ 26V の広い推奨 AUX 電圧範囲が、一般的なコントローラ電源ピンのターンオンおよび UVLO 電圧制限と重複しています。

AUX 外部容量は、さまざまな動作条件にわたって BST から SW への外部容量の 3 倍以上にするセラミックコンデンサにすることを推奨します。

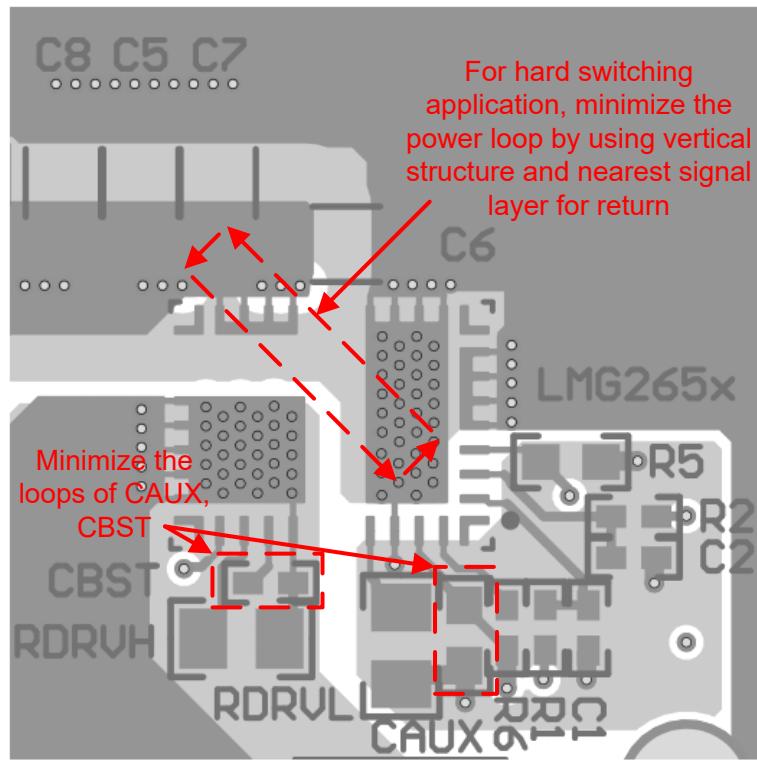

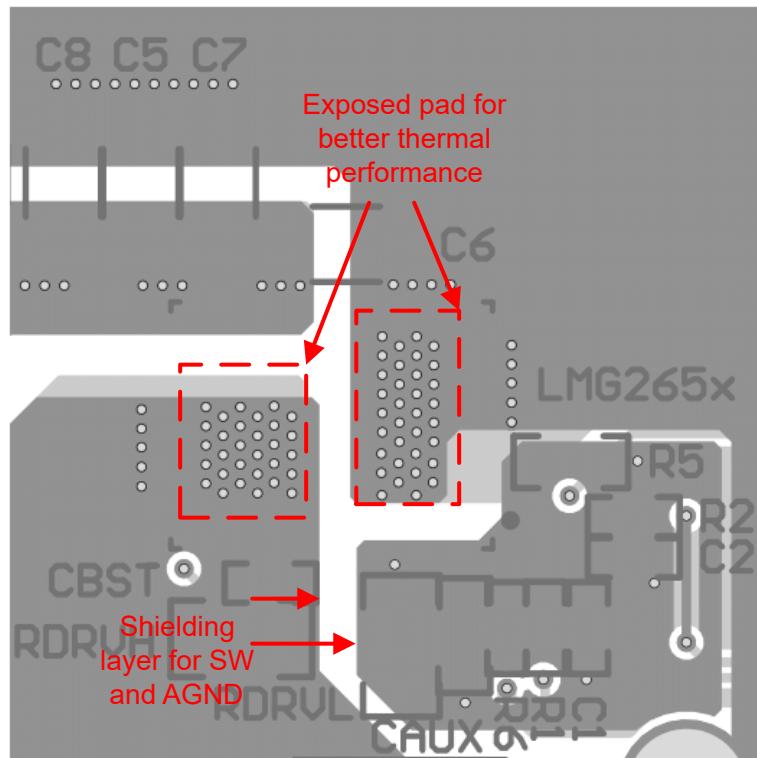

## 8.4 レイアウト

### 8.4.1 レイアウトのガイドライン

#### 8.4.1.1 半田接合部のストレス リリーフ

大型の QFN パッケージでは、はんだ接合部に高い応力がかかることがあります。半田接合部への応力を軽減するため、複数のベスト プラクティスが推奨されます。まず、「セクション 4」セクションに記載されている NC アンカー ピンの指示に従う必要があります。第 2 に、すべての基板半田パッドは、「セクション 11」セクションのランド パターン例に示されているように、非半田マスク定義 (NSMD) にする必要があります。最後に、NSMD パッドに接続される基板トレースは、接続されるパッド側でパッド幅の 2/3 未満にする必要があります。このトレースは、ハンダ・マスクで覆われていない間は、この 2/3 幅制限を維持する必要があります。トレースがハンダ・マスク下の場合、トレースの寸法に制限はありません。[セクション 8.4.2](#) は、これらすべての推奨事項に従っています。

#### 8.4.1.2 信号-グランド接続

信号グランドと電源グランドを別々にして、それらを 1 か所にのみ接続する電源を設計します。LMG2650 の AGND ピンを信号グランドに接続します。LMG2650 SL ピンとローサイド サーマル パッドを電源グランドに接続します。LMG2650 は、AGND ピン、SL ピン、およびローサイド サーマル パッドが内部で接続されるため、信号グランドと電源グランドとの間の単一の接続ポイントとして機能します。以下で推奨されている場合を除き、信号グランドと電源グランドは、ボードの他の場所には接続しないでください。

#### 8.4.1.3 CS ピン信号

式 4 に示されているように、電流センス信号のインピーダンスは、従来の電流センス信号より 3 衡高くなります。このようにインピーダンスが大きいと、電流センス信号のノイズ感受性に影響します。ノイズの多いトレースの近くに電流センス信号を配線することは、最小限に抑えてください。電流センス抵抗とすべてのフィルタリング コンデンサは、トレースの右端に、コントローラの電流センス入力ピンの隣に配置します。

#### 8.4.2 レイアウト例

図 8-5. PCB 最上層 (ダークグレー) と第 2 層 (ライトグレー) のレイアウト

図 8-6. PCB 第 3 層 (ダークグレー) と最下層 (ライトグレー) のレイアウト

## 9 デバイスおよびドキュメントのサポート

テキサス・インスツルメンツでは、幅広い開発ツールを提供しています。デバイスの性能の評価、コードの生成、ソリューションの開発を行うためのツールとソフトウェアを以下で紹介します。

### 9.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.2 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 9.3 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 9.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 9.5 用語集

#### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

#### Changes from Revision \* (May 2024) to Revision A (November 2025)

Page

- |                           |   |

|---------------------------|---|

| • 「事前情報」から「量産データ」に更新..... | 1 |

|---------------------------|---|

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| LMG2650RFBR           | Active        | Production           | VQFN (RFB)   19 | 2000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | LMG2650             |

| XLMG2650RFBR          | Active        | Preproduction        | VQFN (RFB)   19 | 2000   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

| XLMG2650RFBR.A        | Active        | Preproduction        | VQFN (RFB)   19 | 2000   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

| XLMG2650RFBR.B        | Active        | Preproduction        | VQFN (RFB)   19 | 2000   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

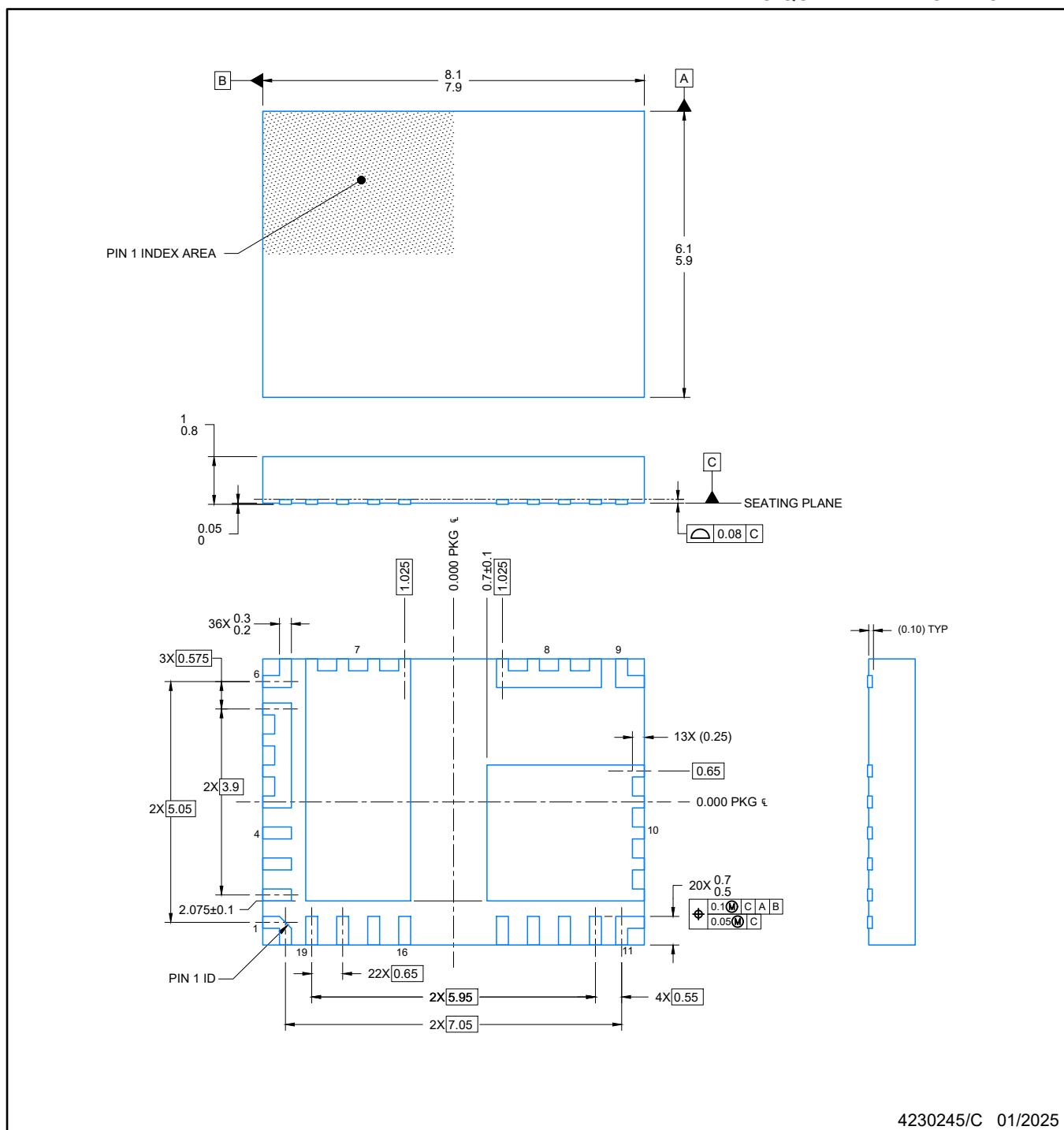

# RFB0019A

## PACKAGE OUTLINE VQFN - 1 mm max height

PLASTIC QUAD FLAT PACK- NO LEAD

4230245/C 01/2025

### NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

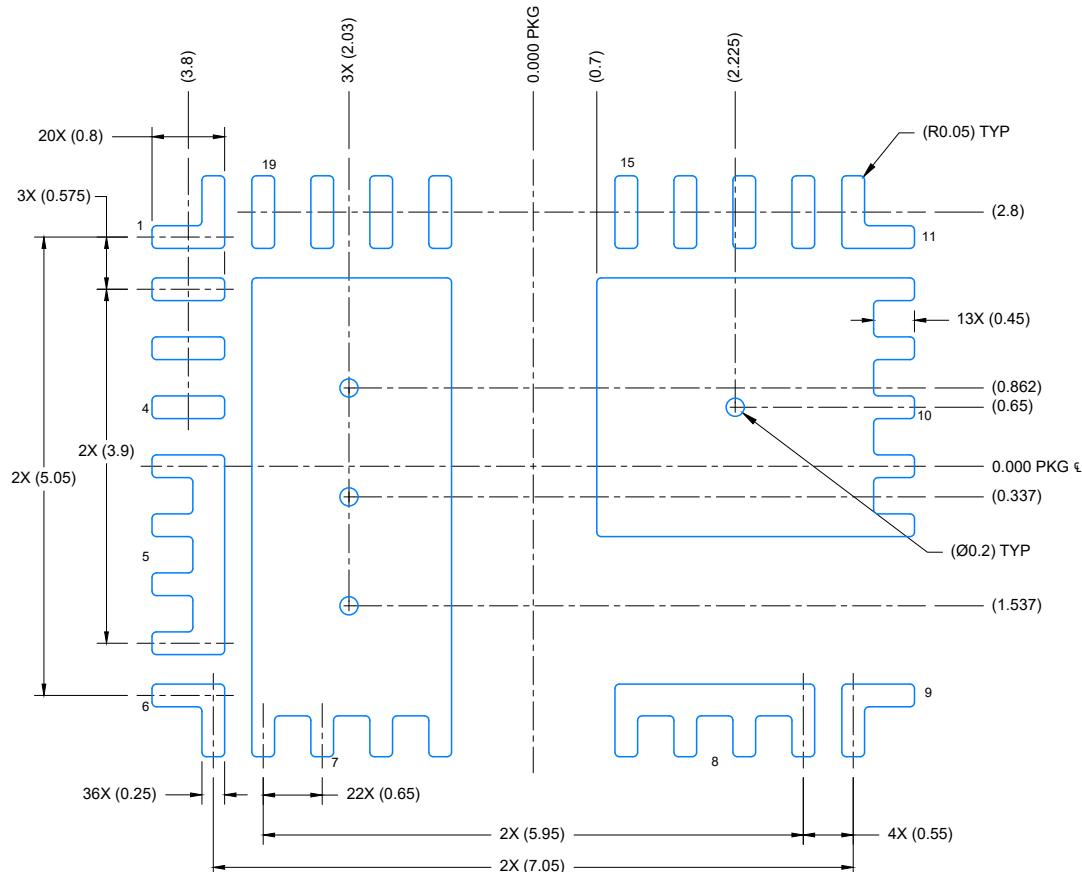

# RFB0019A

## EXAMPLE BOARD LAYOUT

VQFN - 1 mm max height

PLASTIC QUAD FLAT PACK- NO LEAD

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 12X

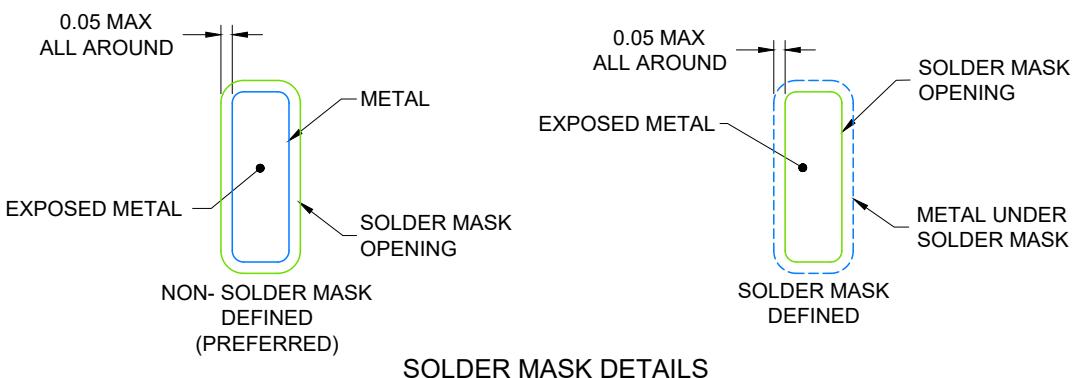

SOLDER MASK DETAILS

4230245/C 01/2025

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

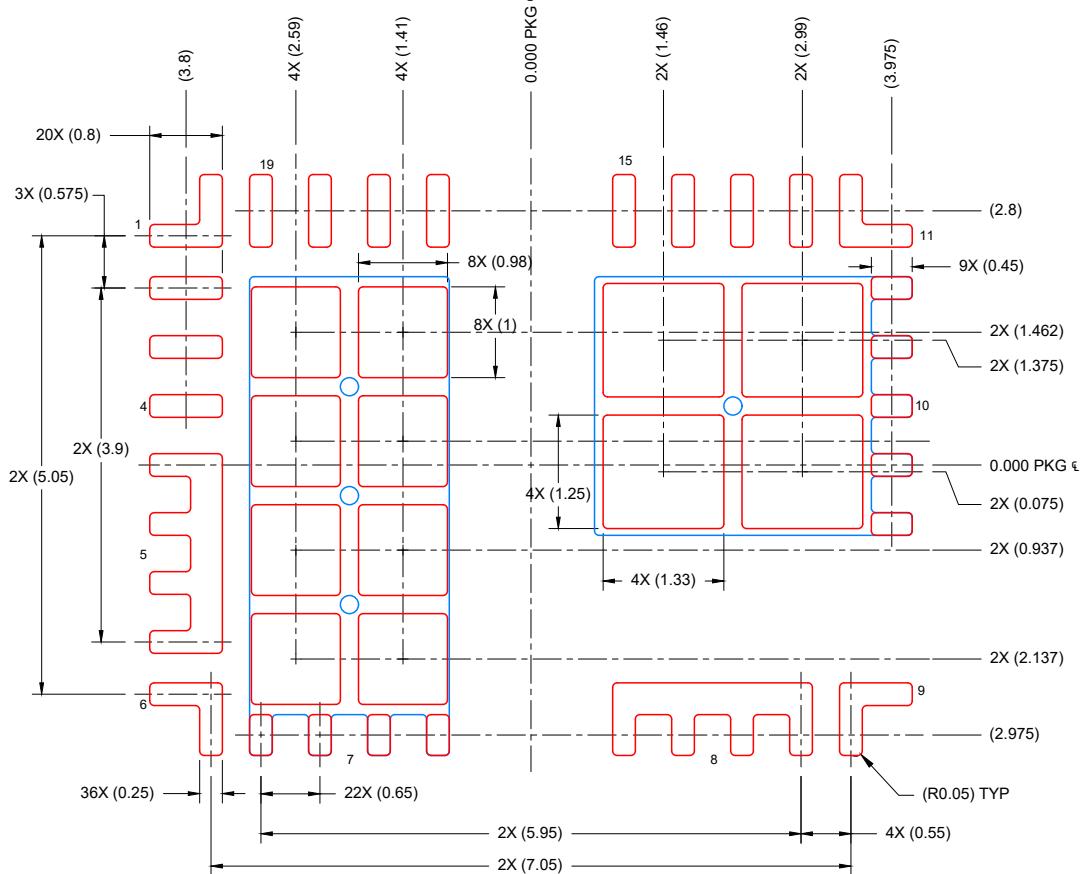

## EXAMPLE STENCIL DESIGN

## VQFN - 1 mm max height

RFB0019A

**PLASTIC QUAD FLAT PACK- NO LEAD**

**SOLDER PASTE EXAMPLE

BASED ON 0.1 mm THICK STENCIL

SCALE: 12X**

4230245/C 01/2025

**NOTES: (continued)**

- Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月