I MG1205 JAJSD27B - MARCH 2017 - REVISED APRIL 2023

# LMG1205 ブートストラップ・ダイオード内蔵の 80V、1.2A~5A、ハー リッジ GaN ドライバ

### 1 特長

- ハイサイドとローサイドで独立した TTL ロジック入力

- ピーク・ソース 1.2A、シンク電流 5A

- ハイサイドのフローティング・バイアス電圧レールは 最高 DC 100V で動作可能

- 内部ブートストラップ電源電圧クランプ

- 出力の分割により、ターンオンおよび ターンオフの強度を調整可能

- プルダウン 0.6Ω、プルアップ 2.1Ω の抵抗

- 短い伝播遅延 (標準値 35ns)

- 優れた伝搬遅延マッチング (標準値 1.5ns)

- 電源レールの低電圧誤動作防止

- 低消費電力

# 2 アプリケーション

- 電流供給プッシュプル・コンバータ

- ハーフおよびフルブリッジ・コンバータ

- 同期整流降圧コンバータ

- 2 スイッチ・フォワード・コンバータ

- アクティブ・クランプ型フォワード・コンバータ

### 3 概要

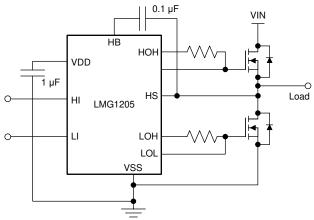

LMG1205 は、同期整流降圧、昇圧、またはハーフブリッ ジ構成で、ハイサイドとローサイドの両方のエンハンスメン ト・モード窒化ガリウム (GaN) FET を駆動できるように設 計されています。このデバイスには 100V のブートストラッ プ・ダイオード、およびハイサイドとローサイド出力用に独 立した入力が内蔵され、最大の柔軟性で制御が可能で す。ハイサイドのバイアス電圧はブートストラップ技法を使 用して生成され、内部で 5V にクランプされます。これによ って、ゲート電圧がエンハンスメント・モード GaN FET の 最大ゲート・ソース電圧定格を超過しなくなります。 LMG1205 の入力は TTL ロジック互換で、VDD 電圧に 関係なく最大 14V の入力電圧に耐えることができます。 LMG1205 には分割ゲート出力があり、ターンオンとター ンオフの強度を別々に調整可能な柔軟性があります。

さらに、LM1205 の強力なシンク能力によりゲートが LOW 状態で維持され、スイッチング時に意図しないターンオン が防止されます。LMG1205 の最大動作周波数は数 MHz です。LMG1205 は、占有面積が小さく、パッケージ のインダクタンスが最小化された、12 ピンの DSBGA パッ ケージで供給されます。

#### デバイス情報(1)

| 部品番号    | パッケージ      | 本体サイズ (公称)      |

|---------|------------|-----------------|

| LMG1205 | DSBGA (12) | 2.00mm × 2.00mm |

利用可能なすべてのパッケージについては、このデータシートの 末尾にある注文情報を参照してください。

Copyright © 2017, Texas Instruments Incorporated

アプリケーション概略図

# **Table of Contents**

| 1 特長                                 | 1 | 7.4 Device Functional Modes         | 12 |

|--------------------------------------|---|-------------------------------------|----|

| 2 アプリケーション                           |   | 8 Application and Implementation    | 13 |

| 3 概要                                 |   | 8.1 Application Information         | 13 |

| 4 Revision History                   |   | 8.2 Typical Application             | 13 |

| 5 Pin Configuration and Functions    |   | 9 Power Supply Recommendations      | 17 |

| 6 Specifications                     |   | 10 Layout                           | 18 |

| 6.1 Absolute Maximum Ratings         |   | 10.1 Layout Guidelines              | 18 |

| 6.2 ESD Ratings                      |   | 10.2 Layout Examples                | 18 |

| 6.3 Recommended Operating Conditions |   | 11 Device and Documentation Support | 19 |

| 6.4 Thermal Information              |   | 11.1 Device Support                 | 19 |

| 6.5 Electrical Characteristics       |   | 11.2 Documentation Support          | 19 |

| 6.6 Switching Characteristics        |   | 11.3ドキュメントの更新通知を受け取る方法              | 19 |

| 6.7 Typical Characteristics          |   | 11.4 サポート・リソース                      | 19 |

| 7 Detailed Description               |   | 11.5 Trademarks                     |    |

| 7.1 Overview                         |   | 11.6 静電気放電に関する注意事項                  | 19 |

| 7.2 Functional Block Diagram         |   | 11.7 用語集                            |    |

| 7.3 Feature Description              |   |                                     |    |

# **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Page |

|------|

| 1    |

| 12   |

| 14   |

| Page |

| 1    |

|      |

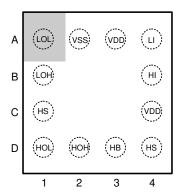

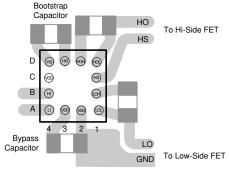

# **5 Pin Configuration and Functions**

図 5-1. YFX Package 12-Pin DSBGA Top View

表 5-1. Pin Functions

| PIN                   |      | TYPE (2) | DESCRIPTION                                                                                                                                                                                                  |  |  |

|-----------------------|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NUMBER                | NAME | 11175    | DESCRIPTION                                                                                                                                                                                                  |  |  |

| A1                    | LOL  | 0        | Low-side gate driver sink-current output: connect to the gate of the low-side GaN FET with a short, low inductance path. A gate resistor can be used to adjust the turnoff speed.                            |  |  |

| A2                    | VSS  | G        | Ground return: all signals are referenced to this ground.                                                                                                                                                    |  |  |

| A3, C4 <sup>(1)</sup> | VDD  | Р        | 5-V positive gate drive supply: locally decouple to VSS using low ESR/ESL capacitor located as close as possible to the IC.                                                                                  |  |  |

| A4                    | LI   | I        | Low-side driver control input. The LMG1205 inputs have TTL type thresholds. Unused inputs must be tied to ground and not left open.                                                                          |  |  |

| B1                    | LOH  | 0        | Low-side gate driver source-current output: connect to the gate of low-side GaN FET with short, low inductance path. A gate resistor can be used to adjust the turnon speed.                                 |  |  |

| B4                    | НІ   | I        | High-side driver control input. The LMG1205 inputs have TTL type thresholds. Unused inputs must be tied to ground and not left open.                                                                         |  |  |

| C1, D4 <sup>(1)</sup> | HS   | Р        | High-side GaN FET source connection: connect to the bootstrap capacitor negative terminal and the source of the high-side GaN FET.                                                                           |  |  |

| D1                    | HOL  | 0        | High-side gate driver turnoff output: connect to the gate of high-side GaN FET with a short, low inductance path. A gate resistor can be used to adjust the turnoff speed.                                   |  |  |

| D2                    | нон  | 0        | High-side gate driver turnon output: connect to the gate of high-side GaN FET with a short, low inductance path. A gate resistor can be used to adjust the turnon speed.                                     |  |  |

| D3                    | НВ   | Р        | High-side gate driver bootstrap rail: connect the positive terminal of the bootstrap capacitor to HB and the negative terminal to HS. The bootstrap capacitor must be placed as close as possible to the IC. |  |  |

<sup>(1)</sup> A3 and C4, C1 and D4 are internally connected

<sup>(2)</sup> I = Input, O = Output, G = Ground, P = Power

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                                       | MIN                   | MAX                  | UNIT |

|---------------------------------------|-----------------------|----------------------|------|

| VDD to VSS                            | -0.3                  | 7                    | V    |

| HB to HS                              | -0.3                  | 7                    | V    |

| LI or HI input                        | -0.3                  | 15                   | V    |

| LOH, LOL output                       | -0.3                  | VDD +0.3             | V    |

| HOH, HOL output                       | V <sub>HS</sub> - 0.3 | V <sub>HB</sub> +0.3 | V    |

| HS to VSS                             | <b>-</b> 5            | 93                   | V    |

| HS to VSS (2)                         | -5                    | 100                  | V    |

| HB to VSS                             | 0                     | 100                  | V    |

| HB to VSS <sup>(2)</sup>              | 0                     | 107                  | V    |

| Operating junction temperature        |                       | 150                  | °C   |

| Storage temperature, T <sub>stg</sub> | <b>–</b> 55           | 150                  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                 |                             |                                                                                | VALUE | UNIT                                  |

|-----------------|-----------------------------|--------------------------------------------------------------------------------|-------|---------------------------------------|

| V               |                             | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±1000 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| V <sub>(E</sub> | SD) Liectrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V                                     |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                                | MIN                 | NOM MAX               | UNIT |

|--------------------------------|---------------------|-----------------------|------|

| VDD                            | 4.5                 | 5.5                   | V    |

| LI or HI input                 | 0                   | 14                    | V    |

| HS                             | <b>-</b> 5          | 90                    | V    |

| НВ                             | V <sub>HS</sub> + 4 | V <sub>HS</sub> + 5.5 | V    |

| HS slew rate                   |                     | 50                    | V/ns |

| Operating junction temperature | -40                 | 125                   | °C   |

#### 6.4 Thermal Information

|                       |                                            | LMG1205     |      |

|-----------------------|--------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>              | YFX (DSBGA) | UNIT |

|                       |                                            | 12 PINS     |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance     | 76.8        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance  | 0.6         | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance       | 12.0        | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter | 1.6         | °C/W |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

<sup>(2)</sup> Device can withstand 1000 pulses up to the value indicated in the table of 100-ms duration and less than 1% duty cycle over its lifetime.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.4 Thermal Information (continued)

|                                                          | LMG1205     |      |

|----------------------------------------------------------|-------------|------|

| THERMAL METRIC(1)                                        | YFX (DSBGA) | UNIT |

|                                                          | 12 PINS     |      |

| $\psi_{JB}$ Junction-to-board characterization parameter | 12.0        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### **6.5 Electrical Characteristics**

Specifications are  $T_J$  = 25°C. Unless otherwise specified:  $V_{DD}$  =  $V_{HB}$  = 5 V,  $V_{SS}$  =  $V_{HS}$  = 0 V. No load on LOL and HOL or HOH and HOL<sup>(1)</sup>.

|                   | PARAMETER                       | TEST CON                                            | DITIONS                         | MIN  | TYP  | MAX  | UNIT |

|-------------------|---------------------------------|-----------------------------------------------------|---------------------------------|------|------|------|------|

| SUPPL             | Y CURRENTS                      |                                                     |                                 |      |      |      |      |

|                   | 1/00                            | LI = HI = 0 V, V <sub>DD</sub> = V <sub>HB</sub> =  | T <sub>J</sub> = 25°C           |      | 0.09 |      |      |

| I <sub>DD</sub>   | VDD quiescent current           | 4 V                                                 | T <sub>J</sub> = -40°C to 125°C |      |      | 0.12 | mA   |

|                   |                                 |                                                     | T <sub>J</sub> = 25°C           |      | 2    |      |      |

| I <sub>DDO</sub>  | VDD operating current           | f = 500 kHz                                         | T <sub>J</sub> = -40°C to 125°C |      |      | 3    | mA   |

|                   | T-A-LUD                         | LI = HI = 0 V, V <sub>DD</sub> = V <sub>HB</sub> =  | T <sub>J</sub> = 25°C           |      | 0.10 |      | 1    |

| I <sub>HB</sub>   | Total HB quiescent current      | 4 V                                                 | T <sub>J</sub> = -40°C to 125°C |      |      | 0.12 | mA   |

|                   | T-A-LUD                         | £ 500 H.L.                                          | T <sub>J</sub> = 25°C           | ,    | 1.5  |      | 4    |

| Інво              | Total HB operating current      | f = 500 kHz                                         | T <sub>J</sub> = -40°C to 125°C |      |      | 2.5  | mA   |

|                   | LID to MOO mails and assess     | 110 110 001/                                        | T <sub>J</sub> = 25°C           |      | 0.1  |      |      |

| I <sub>HBS</sub>  | HB to VSS quiescent current     | HS = HB = 80 V                                      | T <sub>J</sub> = -40°C to 125°C |      |      | 8    | μA   |

|                   | LID to MOO on another an arrant | £ 500 H.L.                                          | T <sub>J</sub> = 25°C           | ,    | 0.4  |      | 4    |

| I <sub>HBSO</sub> | HB to VSS operating current     | f = 500 kHz                                         | T <sub>J</sub> = -40°C to 125°C | ,    |      | 1    | mA   |

| INPUT             | PINS                            |                                                     |                                 |      |      |      |      |

|                   |                                 | B                                                   | T <sub>J</sub> = 25°C           |      | 2.06 |      | V    |

| $V_{IR}$          | Input voltage threshold         | Rising edge                                         | T <sub>J</sub> = -40°C to 125°C | 1.89 |      | 2.18 |      |

| . ,               |                                 |                                                     | T <sub>J</sub> = 25°C           |      | 1.66 |      |      |

| $V_{IF}$          | Input voltage threshold         | Falling edge                                        | T <sub>J</sub> = -40°C to 125°C | 1.48 |      | 1.76 | V    |

| V <sub>IHYS</sub> | Input voltage hysteresis        |                                                     |                                 |      | 400  |      | mV   |

|                   |                                 | T <sub>J</sub> = 25°C                               |                                 |      | 200  |      |      |

| R <sub>I</sub>    | Input pulldown resistance       | $T_J = -40^{\circ}\text{C to } 125^{\circ}\text{C}$ |                                 | 100  |      | 300  | kΩ   |

| UNDE              | RVOLTAGE PROTECTION             |                                                     | I                               |      |      |      |      |

|                   |                                 | T <sub>J</sub> = 25°C                               |                                 |      | 3.8  |      |      |

| $V_{DDR}$         | VDD rising threshold            | T <sub>J</sub> = -40°C to 125°C                     |                                 | 3.2  |      | 4.5  | V    |

| V <sub>DDH</sub>  | VDD threshold hysteresis        |                                                     |                                 |      | 0.2  |      | V    |

|                   |                                 | T <sub>J</sub> = 25°C                               |                                 |      | 3.2  |      |      |

| $V_{HBR}$         | HB rising threshold             | $T_J = -40^{\circ}\text{C to } 125^{\circ}\text{C}$ |                                 | 2.5  |      | 3.9  | V    |

| V <sub>HBH</sub>  | HB threshold hysteresis         |                                                     |                                 |      | 0.2  |      | V    |

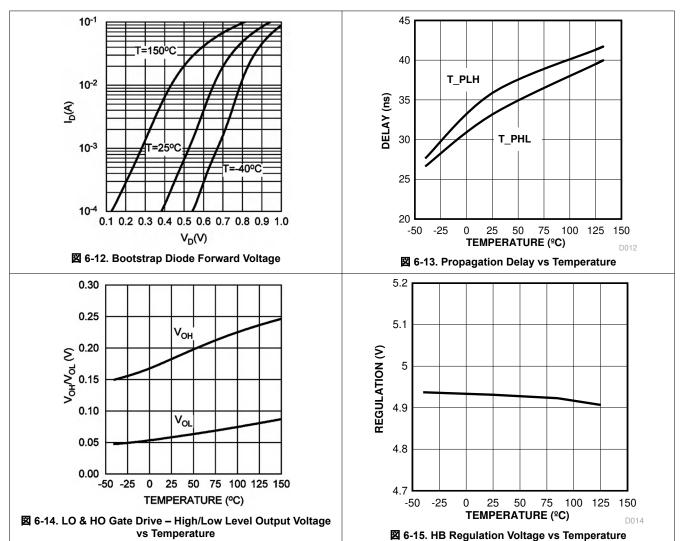

| воот              | STRAP DIODE AND CLAMP           |                                                     |                                 |      |      |      |      |

|                   |                                 |                                                     | T <sub>J</sub> = 25°C           |      | 0.45 |      |      |

| $V_{DL}$          | Low-current forward voltage     | I <sub>VDD-HB</sub> = 100 μA                        | T <sub>J</sub> = -40°C to 125°C |      |      | 0.65 | V    |

|                   |                                 |                                                     | T <sub>J</sub> = 25°C           |      | 0.9  |      |      |

| $V_{DH}$          | High-current forward voltage    | I <sub>VDD-HB</sub> = 100 mA                        | T <sub>J</sub> = -40°C to 125°C | ,    |      | 1    | V    |

|                   |                                 | 1                                                   | T <sub>J</sub> = 25°C           |      | 1.85 |      |      |

| $R_D$             | Dynamic resistance              | $I_{VDD-HB} = 100 \text{ mA}$                       | T <sub>J</sub> = -40°C to 125°C |      |      | 3.6  | Ω    |

|                   |                                 |                                                     | T <sub>J</sub> = 25°C           |      | 5    |      |      |

|                   | HB-HS clamp regulation voltage  |                                                     | T <sub>J</sub> = -40°C to 125°C | 4.5  |      | 5.25 | V    |

# **6.5 Electrical Characteristics (continued)**

Specifications are  $T_J$  = 25°C. Unless otherwise specified:  $V_{DD}$  =  $V_{HB}$  = 5 V,  $V_{SS}$  =  $V_{HS}$  = 0 V. No load on LOL and HOL or HOH and HOL<sup>(1)</sup>.

|                  | PARAMETER                                                    | TEST CO                              | NDITIONS                                            | MIN | TYP  | MAX  | UNIT |

|------------------|--------------------------------------------------------------|--------------------------------------|-----------------------------------------------------|-----|------|------|------|

| LOW-             | and HIGH-SIDE GATE DRIVER                                    |                                      |                                                     |     |      |      |      |

| V <sub>OL</sub>  | Low-level output voltage                                     | 1 -1 -100 mA                         | T <sub>J</sub> = 25°C                               |     | 0.06 |      | V    |

|                  |                                                              | $I_{HOL} = I_{LOL} = 100 \text{ mA}$ | $T_J = -40^{\circ}\text{C to } 125^{\circ}\text{C}$ |     |      | 0.1  |      |

|                  | High-level output voltage                                    |                                      | T <sub>J</sub> = 25°C                               |     | 0.21 |      |      |

| V <sub>OH</sub>  | V <sub>OH</sub> = VDD – LOH<br>or V <sub>OH</sub> = HB – HOH | $I_{HOH} = I_{LOH} = 100 \text{ mA}$ | $T_J = -40^{\circ}\text{C to } 125^{\circ}\text{C}$ |     |      | 0.31 | V    |

| I <sub>OHL</sub> | Peak source current                                          | HOH, LOH = 0 V                       |                                                     |     | 1.2  |      | Α    |

| I <sub>OLL</sub> | Peak sink current                                            | HOL, LOL = 5 V                       |                                                     |     | 5    |      | Α    |

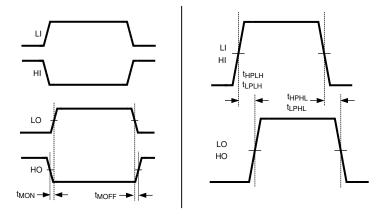

# **6.6 Switching Characteristics**

over operating free-air temperature range (unless otherwise noted)

|                   | PARAMETER                                         | TEST CON                                         | DITIONS                                             | MIN | TYP  | MAX | UNIT |  |

|-------------------|---------------------------------------------------|--------------------------------------------------|-----------------------------------------------------|-----|------|-----|------|--|

| t <sub>LPHL</sub> | LO turnoff propagation delay                      | LI falling to LOL falling                        | T <sub>J</sub> = 25°C                               |     | 33.5 |     |      |  |

|                   |                                                   |                                                  | $T_J = -40^{\circ}\text{C to } 125^{\circ}\text{C}$ |     |      | 50  | ns   |  |

| t <sub>LPLH</sub> | LO turnon propagation delay                       | LI rising to LOH rising                          | T <sub>J</sub> = 25°C                               |     | 35   |     | ns   |  |

|                   |                                                   |                                                  | $T_J = -40^{\circ}\text{C to } 125^{\circ}\text{C}$ |     |      | 50  | 115  |  |

| t <sub>HPHL</sub> | HO turnoff propagation delay                      | HI falling to HOL falling                        | T <sub>J</sub> = 25°C                               |     | 33.5 |     | ns   |  |

|                   |                                                   |                                                  | $T_J = -40^{\circ}\text{C to } 125^{\circ}\text{C}$ |     |      | 50  | 113  |  |

| t <sub>HPLH</sub> | HO turnon propagation delay                       | HI rising to HOH rising                          | T <sub>J</sub> = 25°C                               |     | 35   |     | ns   |  |

|                   |                                                   |                                                  | $T_J = -40^{\circ}\text{C to } 125^{\circ}\text{C}$ |     |      | 50  | 113  |  |

| t <sub>MON</sub>  | Delay matching                                    | T <sub>J</sub> = 25°C                            |                                                     |     | 1.5  |     | ns   |  |

|                   | LO on and HO off                                  | T <sub>J</sub> = -40°C to 125°C                  |                                                     |     | 8    | 8   | 115  |  |

| t <sub>MOFF</sub> | Delay matching                                    | T <sub>J</sub> = 25°C                            |                                                     |     | 1.5  |     | ns   |  |

|                   | LO off and HO on                                  | T <sub>J</sub> = -40°C to 125°C                  |                                                     |     |      | 8   | 115  |  |

| t <sub>HRC</sub>  | HO rise time (0.5 V – 4.5 V)                      | C <sub>L</sub> = 1000 pF                         |                                                     |     | 7    |     | ns   |  |

| t <sub>LRC</sub>  | LO rise time (0.5 V – 4.5 V)                      | C <sub>L</sub> = 1000 pF                         |                                                     |     | 7    |     | ns   |  |

| t <sub>HFC</sub>  | HO fall time (0.5 V – 4.5 V)                      | C <sub>L</sub> = 1000 pF                         |                                                     |     | 3.5  |     | ns   |  |

| t <sub>LFC</sub>  | LO fall time (0.5 V – 4.5 V)                      | C <sub>L</sub> = 1000 pF                         |                                                     |     | 3.5  |     | ns   |  |

| t <sub>PW</sub>   | Minimum input pulse width that changes the output |                                                  |                                                     |     | 10   |     | ns   |  |

| t <sub>BS</sub>   | Bootstrap diode reverse recovery time             | I <sub>F</sub> = 100 mA, I <sub>R</sub> = 100 mA |                                                     |     | 40   |     | ns   |  |

<sup>(1)</sup> Parameters that show only a typical value are ensured by design and may not be tested in production.

図 6-1. Timing Diagram

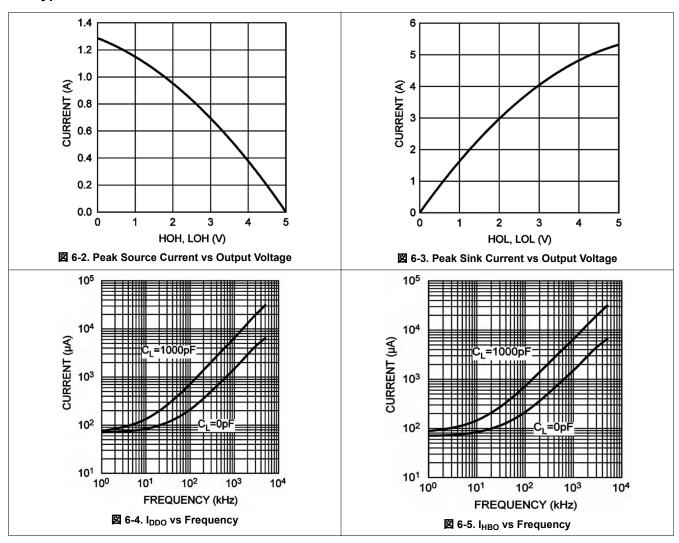

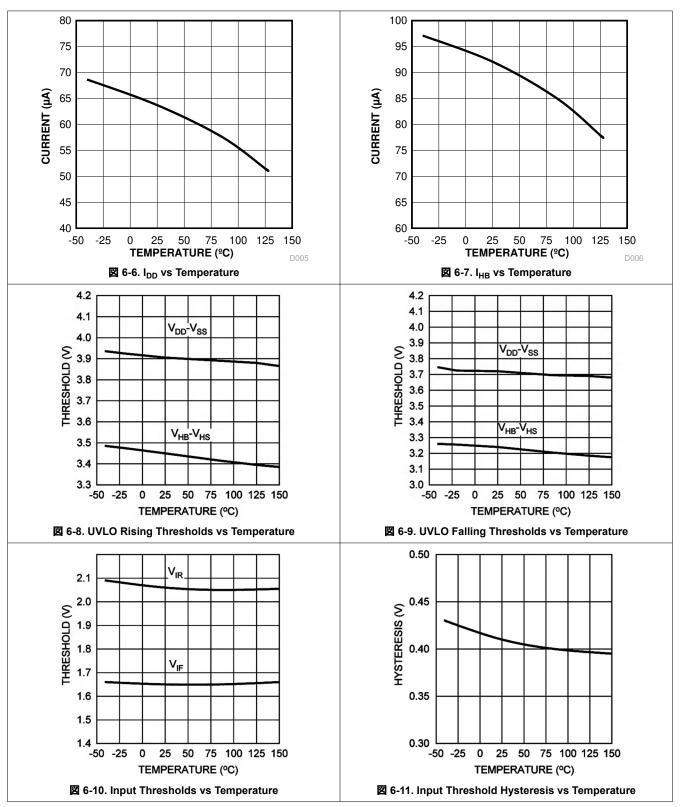

# **6.7 Typical Characteristics**

English Data Sheet: SNOSD37

# **6.7 Typical Characteristics (continued)**

# 6.7 Typical Characteristics (continued)

English Data Sheet: SNOSD37

# 7 Detailed Description

### 7.1 Overview

The LMG1205 is a high frequency high- and low- side gate driver for enhancement mode Gallium Nitride (GaN) FETs in a synchronous buck, boost, or half-bridge configuration. The high-side bias voltage is generated using a bootstrap technique and is internally clamped at 5 V, which prevents the gate voltage from exceeding the maximum gate-source voltage rating of enhancement mode GaN FETs. The LMG1205 has split-gate outputs with strong sink capability, providing flexibility to adjust the turnon and turnoff strength independently.

The LMG1205 can operate up to several MHz, and is available in a 12-pin DSBGA package that offers a compact footprint and minimized package inductance.

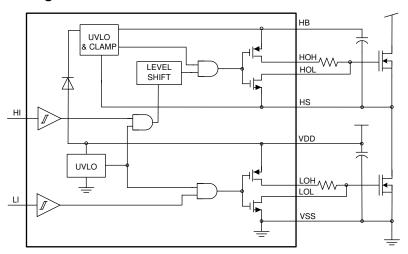

### 7.2 Functional Block Diagram

Copyright © 2017, Texas Instruments Incorporated

# 7.3 Feature Description

## 7.3.1 Input and Output

The input pins of the LMG1205 are independently controlled with TTL input thresholds and can withstand voltages up to 12 V regardless of the VDD voltage. This allows the inputs to be directly connected to the outputs of an analog PWM controller with up to 12-V power supply, eliminating the need for a buffer stage.

The output pulldown and pullup resistance of LMG1205 is optimized for enhancement mode GaN FETs to achieve high frequency and efficient operation. The 0.6- $\Omega$  pulldown resistance provides a robust low impedance turnoff path necessary to eliminate undesired turnon induced by high dv/dt or high di/dt. The 2.1- $\Omega$  pullup resistance helps reduce the ringing and over-shoot of the switch node voltage. The split outputs of the LMG1205 offers flexibility to adjust the turnon and turnoff speed by independently adding additional impedance in either the turnon path and/or the turnoff path.

If the input signal for either of the two channels, HI or LI, is not used, the control pin must be tied to either VDD or VSS. These inputs must not be left floating.

### 7.3.2 Start-up and UVLO

The LMG1205 has an undervoltage lockout (UVLO) on both the VDD and bootstrap supplies. When the VDD voltage is below the threshold voltage of 3.8 V, both the HI and LI inputs are ignored, to prevent the GaN FETs from being partially turned on. Also, if there is insufficient VDD voltage, the UVLO actively pulls the LOL and HOL low. When the VDD voltage is above its UVLO threshold, but the HB to HS bootstrap voltage is below the UVLO threshold of 3.2 V, only HOL is pulled low. Both UVLO threshold voltages have 200 mV of hysteresis to avoid chattering.

表 7-1. VDD UVLO Feature Logic Operation

| CONDITION (V <sub>HB-HS</sub> > V <sub>HBR</sub> for all cases below)                         | HI | LI | НО | LO |

|-----------------------------------------------------------------------------------------------|----|----|----|----|

| V <sub>DD</sub> - V <sub>SS</sub> < V <sub>DDR</sub> during device start-up                   | Н  | L  | L  | L  |

| V <sub>DD</sub> - V <sub>SS</sub> < V <sub>DDR</sub> during device start-up                   | L  | Н  | L  | L  |

| V <sub>DD</sub> - V <sub>SS</sub> < V <sub>DDR</sub> during device start-up                   | Н  | Н  | L  | L  |

| V <sub>DD</sub> - V <sub>SS</sub> < V <sub>DDR</sub> during device start-up                   | L  | L  | L  | L  |

| V <sub>DD</sub> - V <sub>SS</sub> < V <sub>DDR</sub> - V <sub>DDH</sub> after device start-up | Н  | L  | L  | L  |

| V <sub>DD</sub> - V <sub>SS</sub> < V <sub>DDR</sub> - V <sub>DDH</sub> after device start-up | L  | Н  | L  | L  |

| V <sub>DD</sub> - V <sub>SS</sub> < V <sub>DDR</sub> - V <sub>DDH</sub> after device start-up | Н  | Н  | L  | L  |

| V <sub>DD</sub> - V <sub>SS</sub> < V <sub>DDR</sub> - V <sub>DDH</sub> after device start-up | L  | L  | L  | L  |

表 7-2. V<sub>HB-HS</sub> UVLO Feature Logic Operation

| CONDITION (V <sub>DD</sub> > V <sub>DDR</sub> for all cases below)             | HI | LI | НО | LO |

|--------------------------------------------------------------------------------|----|----|----|----|

| V <sub>HB-HS</sub> < V <sub>HBR</sub> during device start-up                   | Н  | L  | L  | L  |

| V <sub>HB-HS</sub> < V <sub>HBR</sub> during device start-up                   | L  | Н  | L  | Н  |

| V <sub>HB-HS</sub> < V <sub>HBR</sub> during device start-up                   | Н  | Н  | L  | Н  |

| V <sub>HB-HS</sub> < V <sub>HBR</sub> during device start-up                   | L  | L  | L  | L  |

| V <sub>HB-HS</sub> < V <sub>HBR</sub> - V <sub>HBH</sub> after device start-up | Н  | L  | L  | L  |

| V <sub>HB-HS</sub> < V <sub>HBR</sub> - V <sub>HBH</sub> after device start-up | L  | Н  | L  | Н  |

| V <sub>HB-HS</sub> < V <sub>HBR</sub> - V <sub>HBH</sub> after device start-up | Н  | Н  | L  | Н  |

| V <sub>HB-HS</sub> < V <sub>HBR</sub> - V <sub>HBH</sub> after device start-up | L  | L  | L  | L  |

### 7.3.3 HS Negative Voltage and Bootstrap Supply Voltage Clamping

Due to the intrinsic nature of enhancement mode GaN FETs, the source-to-drain voltage of the bottom switch is usually higher than a diode forward voltage drop when the gate is pulled low. This causes negative voltage on HS pin. Moreover, this negative voltage transient may become even more pronounced due to the effects of board layout and device drain/source parasitic inductances. With high-side driver using the floating bootstrap configuration, negative HS voltage can lead to an excessive bootstrap voltage, which can damage the high-side GaN FET. The LMG1205 solves this problem with an internal clamping circuit that prevents the bootstrap voltage from exceeding 5 V typical. The clamping circuit works by opening an internal switch in series with the internal bootstrap diode when the bootstrap voltage exceeds the threshold, preventing further charging. The clamping circuit has a delay of about 270 ns between the threshold being exceeded and charging being stopped. In addition, the clamping circuit is bypassed if an external bootstrap diode is used.

#### 7.3.4 Level Shift

The level-shift circuit is the interface from the high-side input to the high-side driver stage which is referenced to the switch node (HS). The level shift allows control of the HO output, which is referenced to the HS pin and provides excellent delay matching with the low-side driver. Typical delay matching between LO and HO is around 1.5 ns.

#### 7.4 Device Functional Modes

表 7-3 shows the device truth table.

表 7-3. Truth Table

| HI | LI | нон  | HOL  | LOH  | LOL  |

|----|----|------|------|------|------|

| L  | L  | Open | L    | Open | L    |

| L  | Н  | Open | L    | Н    | Open |

| Н  | L  | Н    | Open | Open | L    |

| Н  | Н  | Н    | Open | Н    | Open |

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

# 8 Application and Implementation

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 Application Information

To operate GaN transistors at very high switching frequencies and to reduce associated switching losses, a powerful gate driver is employed between the PWM output of controller and the gates of the GaN transistor. Also, gate drivers are indispensable when the outputs of the PWM controller do not meet the voltage or current levels needed to directly drive the gates of the switching devices. With the advent of digital power, this situation is often encountered because the PWM signal from the digital controller is often a 3.3-V logic signal, which cannot effectively turn on a power switch. A level-shift circuit is needed to boost the 3.3 V signal to the gate-drive voltage (such as 12 V) in order to fully turn on the power device and minimize conduction losses.

Traditional buffer drive circuits based on NPN/PNP bipolar transistors in totem-pole arrangement prove inadequate with digital power because they lack level-shifting capability. Gate drivers effectively combine both the level-shifting and buffer-drive functions. Gate drivers also address other needs such as minimizing the effect of high-frequency switching noise (by placing the high-current driver IC physically close to the power switch), driving gate-drive transformers and controlling floating power-device gates, reducing power dissipation and thermal stress in controllers by moving gate charge power losses from the controller into the driver.

The LMG1205 is a MHz high- and low-side gate driver for enhancement mode GaN FETs in a synchronous buck, boost, or half-bridge configuration. The high-side bias voltage is generated using a bootstrap technique and is internally clamped at 5 V, which prevents the gate voltage from exceeding the maximum gate-source voltage rating of enhancement mode GaN FETs. The LMG1205 has split-gate outputs with strong sink capability, providing flexibility to adjust the turnon and turnoff strength independently.

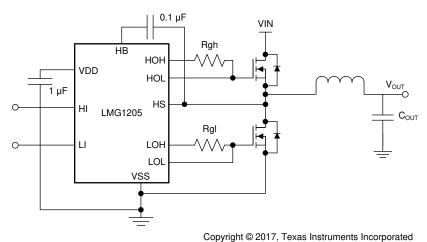

# 8.2 Typical Application

The circuit in 図 8-1 shows a synchronous buck converter to evaluate LMG1205. Detailed synchronous buck converter specifications are listed in セクション 8.2.1. Optimization of he power loop (loop impedance from VIN capacitor to PGND) is critical to the performance of the design. Having a high power loop inductance causes significant ringing in the SW node and also causes an associated power loss. For more information, please refer to セクション 11.2.1.

図 8-1. Application Circuit

Product Folder Links: LMG1205

### 8.2.1 Design Requirements

When designing a synchronous buck converter application that incorporates the LMG1205 gate driver and GaN power FETs, some design considerations must be evaluated first to make the most appropriate selection. Among these considerations are the input voltages, passive components, operating frequency, and controller selection. 表 8-1 shows some sample values for a typical application. See セクション 9, セクション 10, and セクション 8.2.2.3 for other key design considerations for the LMG1205.

表 8-1. Design Parameters

| PARAMETER                                         | SAMPLE VALUE |

|---------------------------------------------------|--------------|

| Half-bridge input supply voltage, V <sub>IN</sub> | 48 V         |

| Output voltage, V <sub>OUT</sub>                  | 12 V         |

| Output current                                    | 8 A          |

| Dead time                                         | 8 ns         |

| Inductor                                          | 4.7 μH       |

| Switching frequency                               | 1 MHz        |

### 8.2.2 Detailed Design Procedure

This procedure outlines the design considerations of LMG1205 in a synchronous buck converter with enhancement mode GaN FET. For additional design help, see セクション 11.2.1.

### 8.2.2.1 VDD Bypass Capacitor

The VDD bypass capacitor provides the gate charge for the low-side and high-side transistors and to absorb the reverse recovery charge of the bootstrap diode. The required bypass capacitance can be calculated with  $\pm$  1.

$$C_{VDD} > \frac{Q_{gH} + Q_{gL} + Q_{rr}}{\Delta V}$$

(1)

#### where

- Q<sub>qH</sub> and Q<sub>qL</sub> are gate charge of the high-side and low-side transistors, respectively

- Q<sub>rr</sub> is the reverse recovery charge of the bootstrap diode, which is typically around 4nC

- ΔV is the maximum allowable voltage drop across the bypass capacitor

TI recommends a 0.1–µF or larger value, good-quality ceramic capacitor. The bypass capacitor must be placed as close as possible to the device pins to minimize the parasitic inductance.

#### 8.2.2.2 Bootstrap Capacitor

The bootstrap capacitor provides the gate charge for the high-side switch, DC bias power for HB undervoltage lockout circuit, and the reverse recovery charge of the bootstrap diode. The required bypass capacitance can be calculated with 式 2.

$$C_{BST} > \frac{Q_{gH} + (I_{HB} + I_{GSS}) \times T_{ON} + Q_{rr}}{\Delta V}$$

(2)

#### where

- · IHB is the quiescent current of the high-side driver

- · Ton is the maximum on-time period of the high-side transistor

- I<sub>GSS</sub> is the gate leakage current of the high-side transistor

A good-quality ceramic capacitor must be used for the bootstrap capacitor. TI recommends placing the bootstrap capacitor as close as possible to the HB and HS pins.

Submit Document Feedback

Copyright © 2023 Texas Instruments Incorporated

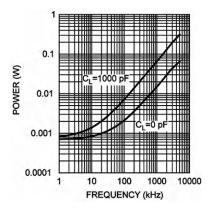

### 8.2.2.3 Power Dissipation

The power consumption of the driver is an important measure that determines the maximum achievable operating frequency of the driver. It must be kept below the maximum power dissipation limit of the package at the operating temperature. The total power dissipation of the LMG1205 is the sum of the gate driver losses and the bootstrap diode power loss.

The gate driver losses are incurred by charge and discharge of the capacitive load. It can be approximated as

$$P = (C_{LoadH} + C_{LoadL}) \times V_{DD}^{2} \times f_{SW}$$

(3)

where

C<sub>LoadH</sub> and C<sub>LoadL</sub> are the high-side and the low-side capacitive loads, respectively

It can also be calculated with the total input gate charge of the high-side and the low-side transistors as

$$P = (Q_{gH} + Q_{gL}) \times V_{DD} \times f_{SW}$$

(4)

There are some additional losses in the gate drivers due to the internal CMOS stages used to buffer the LO and HO outputs.  $\boxtimes$  8-2 shows the measured gate driver power dissipation versus frequency and load capacitance. At higher frequencies and load capacitance values, the power dissipation is dominated by the power losses driving the output loads and agrees well with the above equations.  $\boxtimes$  8-2 can be used to approximate the power losses due to the gate drivers.

Gate driver power dissipation (LO+HO), VDD = 5 V

#### 図 8-2. Neglecting Bootstrap Diode Losses

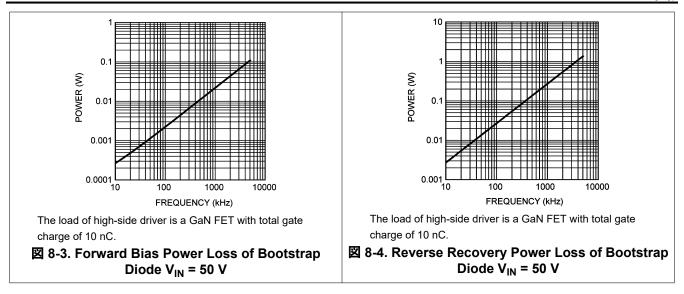

The bootstrap diode power loss is the sum of the forward bias power loss that occurs while charging the bootstrap capacitor and the reverse bias power loss that occurs during reverse recovery. Because each of these events happens once per cycle, the diode power loss is proportional to the operating frequency. Larger capacitive loads require more energy to recharge the bootstrap capacitor resulting in more losses. Higher input voltages (V<sub>IN</sub>) to the half bridge also result in higher reverse recovery losses.

図 8-3 and 図 8-4 show the forward bias power loss and the reverse bias power loss of the bootstrap diode respectively. The plots are generated based on calculations and lab measurements of the diode reverse time and current under several operating conditions. 図 8-3 and 図 8-4 can be used to predict the bootstrap diode power loss under different operating conditions.

Product Folder Links: LMG1205

The sum of the driver loss and the bootstrap diode loss is the total power loss of the IC. For a given ambient temperature, the maximum allowable power loss of the IC can be defined as  $\pm 5$ .

$$P = \frac{(T_J - T_A)}{\theta_{JA}} \tag{5}$$

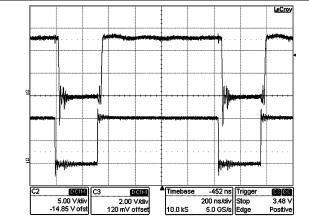

### 8.2.3 Application Curves

Conditions: Input Voltage = 48 V DC, Load Current = 5

ATraces: Top Trace: Gate of Low-Side eGaN FET, Volt/div = 2

V Bottom Trace: LI of LMG1205, Volt/div = 5 V Bandwidth Limit

= 600 MHz Horizontal Resolution = 0.2 µs/div

図 8-5. Low-Side Driver Input and Output

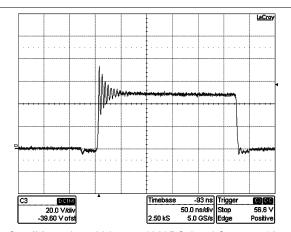

Conditions: Input Voltage = 48 V DC, Load Current = 10

ATraces: Trace: Switch-Node Voltage, Volts/div = 20 V

Bandwidth Limit = 600 MHz Horizontal Resolution = 50 ns/div

図 8-6. Switch-Node Voltage

# 9 Power Supply Recommendations

The recommended bias supply voltage range for LMG1205 is from 4.5 V to 5.5 V. The lower end of this range is governed by the internal UVLO protection feature of the VDD supply circuit. TI recommends keeping proper margin to allow for transient voltage spikes while not violating the LMG1205 absolute maximum VDD voltage rating and the GaN transistor gate breakdown voltage limit.

The UVLO protection feature also involves a hysteresis function. This means that once the device is operating in normal mode, if the VDD voltage drops, the device continues to operate in normal mode as far as the voltage drop does not exceeds the hysteresis specification, VDDH. If the voltage drop is more than hysteresis specification, the device shuts down. Therefore, while operating at or near the 4.5-V range, the voltage ripple on the VDD power supply output must be smaller than the hysteresis specification of LMG1205 UVLO to avoid triggering device shutdown.

A local bypass capacitor must be placed between the VDD and VSS pins. This capacitor must be located as close as possible to the device. TI recommends a low-ESR, ceramic, surface-mount capacitor. TI also recommends using 2 capacitors across VDD and GND: a 100-nF ceramic surface-mount capacitor for high frequency filtering placed very close to VDD and GND pin, and another surface-mount capacitor, 220 nF to 10  $\mu$ F, for IC bias requirements.

# 10 Layout

# 10.1 Layout Guidelines

Small gate capacitance and Miller capacitance enable enhancement mode GaN FETs to operate with fast switching speed. The induced high dv/dt and di/dt, coupled with a low gate threshold voltage and limited headroom of enhancement mode GaN FETs gate voltage, make the circuit layout crucial to the optimum performance. Following are some recommendations:

- The first priority in designing the layout of the driver is to confine the high peak currents that charge and discharge the GaN FETs gate into a minimal physical area. This decreases the loop inductance and minimize noise issues on the gate terminal of the GaN FETs. The GaN FETs must be placed close to the driver.

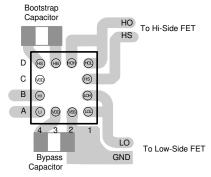

- 2. The second high current path includes the bootstrap capacitor, the local ground referenced VDD bypass capacitor and low-side GaN FET. The bootstrap capacitor is recharged on a cycle-by-cycle basis through the bootstrap diode from the ground referenced VDD capacitor. The recharging occurs in a short time interval and involves high peak current. Minimizing this loop length and area on the circuit board is important to ensure reliable operation.

- 3. The parasitic inductance in series with the source of the high-side FET and the low-side FET can impose excessive negative voltage transients on the driver. TI recommends connecting the HS pin and VSS pin to the respective source of the high-side and low-side transistors with a short and low-inductance path.

- 4. The parasitic source inductance, along with the gate capacitor and the driver pull-down path, can form an LCR resonant tank, resulting in gate voltage oscillations. An optional resistor or ferrite bead can be used to damp the ringing.

- 5. Low ESR/ESL capacitors must be connected close to the IC, between VDD and VSS pins and between the HB and HS pins to support the high peak current being drawn from VDD during turnon of the FETs. Keeping bullet #1 (minimized GaN FETs gate driver loop) as the first priority, it is also desirable to place the VDD decoupling capacitor and the HB to HS bootstrap capacitor on the same side of the PC board as the driver. The inductance of vias can impose excessive ringing on the IC pins.

- 6. To prevent excessive ringing on the input power bus, good decoupling practices are required by placing low-ESR ceramic capacitors adjacent to the GaN FETs.

図 10-1 and 図 10-2 show recommended layout patterns for the LMG1205. Two cases are considered: (1) without any gate resistors, and (2) with an optional turnon gate resistor. Note that 0402 surface mount package is assumed for the passive components in the drawings. For information on DSBGA package assembly, refer to セクション 11.2.1.

### 10.2 Layout Examples

図 10-1. Layout Example Without Gate Resistors

図 10-2. Layout Example with HOH and LOH Gate Resistors

# 11 Device and Documentation Support

## 11.1 Device Support

### 11.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

### 11.2 Documentation Support

#### 11.2.1 Related Documentation

For related documentation see the following:

- AN-1112 DSBGA Wafer Level Chip Scale Package

- Using the LMG1205HBEVM GaN Half-Bridge EVM

### 11.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.com のデバイス製品フォルダを開いてください。「更新の通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 11.4 サポート・リソース

TI E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

#### 11.5 Trademarks

TI E2E<sup>™</sup> is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 11.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 11.7 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

## Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this datasheet, refer to the left-hand navigation.

www.ti.com 23-May-2025

### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins   | Package qty   Carrier | RoHS | Lead finish/  | MSL rating/        | Op temp (°C) | Part marking |

|-----------------------|--------|---------------|------------------|-----------------------|------|---------------|--------------------|--------------|--------------|

|                       | (1)    | (2)           |                  |                       | (3)  | Ball material | Peak reflow        |              | (6)          |

|                       |        |               |                  |                       |      | (4)           | (5)                |              |              |

| LMG1205YFXR           | Active | Production    | DSBGA (YFX)   12 | 3000   LARGE T&R      | Yes  | SNAGCU        | Level-1-260C-UNLIM | -40 to 125   | 1205         |

| LMG1205YFXR.A         | Active | Production    | DSBGA (YFX)   12 | 3000   LARGE T&R      | Yes  | SNAGCU        | Level-1-260C-UNLIM | -40 to 125   | 1205         |

| LMG1205YFXT           | Active | Production    | DSBGA (YFX)   12 | 250   SMALL T&R       | Yes  | SNAGCU        | Level-1-260C-UNLIM | -40 to 125   | 1205         |

| LMG1205YFXT.A         | Active | Production    | DSBGA (YFX)   12 | 250   SMALL T&R       | Yes  | SNAGCU        | Level-1-260C-UNLIM | -40 to 125   | 1205         |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 26-Oct-2024

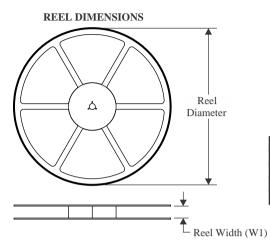

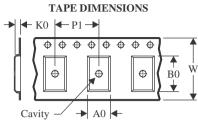

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

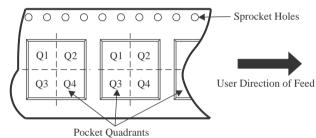

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      |       | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| LMG1205YFXR | DSBGA | YFX                | 12 | 3000 | 178.0                    | 8.4                      | 1.85       | 2.01       | 0.76       | 4.0        | 8.0       | Q1               |

| LMG1205YFXT | DSBGA | YFX                | 12 | 250  | 178.0                    | 8.4                      | 1.85       | 2.01       | 0.76       | 4.0        | 8.0       | Q1               |

www.ti.com 26-Oct-2024

## \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LMG1205YFXR | DSBGA        | YFX             | 12   | 3000 | 208.0       | 191.0      | 35.0        |

| LMG1205YFXT | DSBGA        | YFX             | 12   | 250  | 208.0       | 191.0      | 35.0        |

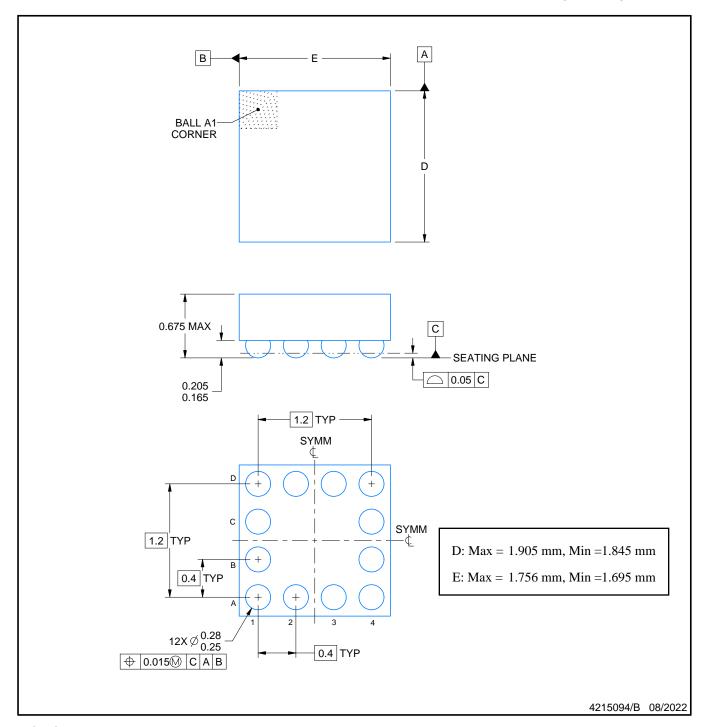

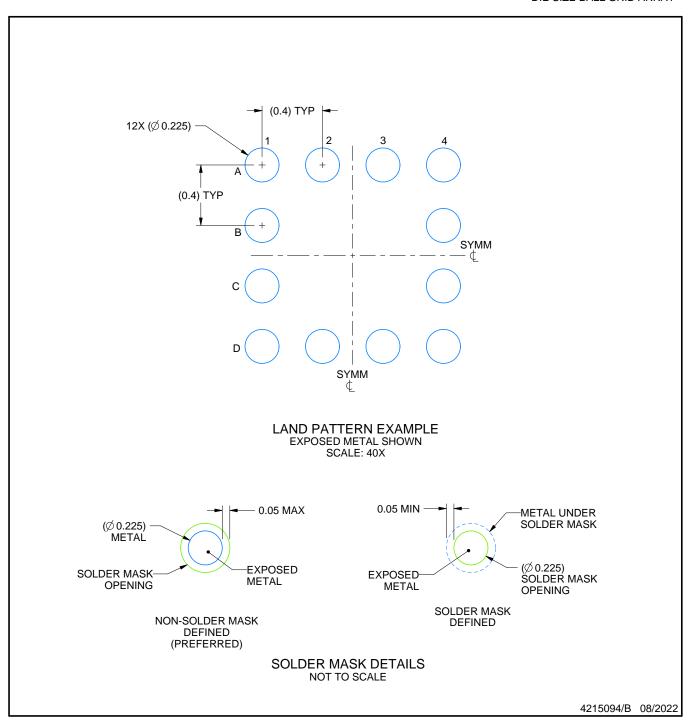

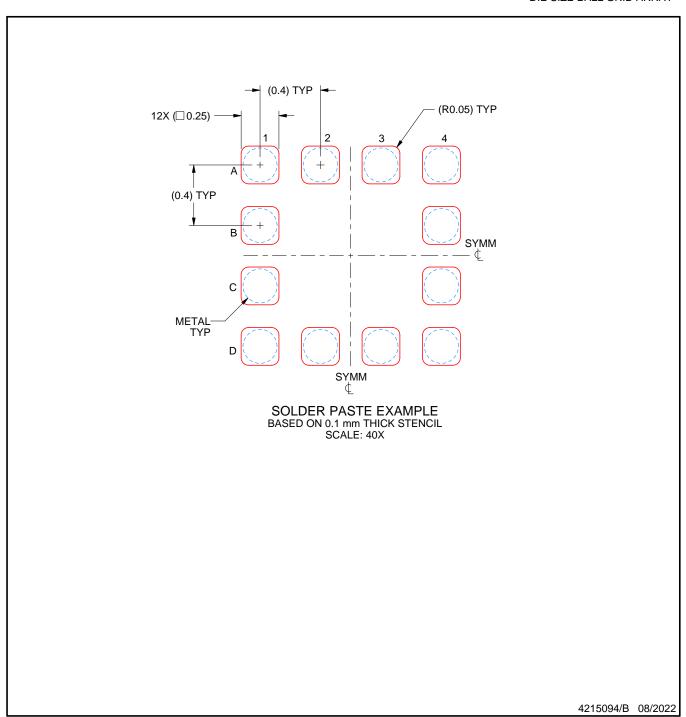

DIE SIZE BALL GRID ARRAY

# NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

DIE SIZE BALL GRID ARRAY

NOTES: (continued)

Final dimensions may vary due to manufacturing tolerance considerations and also routing constraints. See Texas Instruments Literature No. SNVA009 (www.ti.com/lit/snva009).

DIE SIZE BALL GRID ARRAY

NOTES: (continued)

4. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release.

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、 テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、 テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。 テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、 テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、 テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、 テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ 製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。 テキサス・インスツルメンツがこれらのリソ 一スを提供することは、適用される テキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、 テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2025, Texas Instruments Incorporated