# LM74912-Q1、フォルト出力および過電圧、低電圧、短絡保護付き車載用理想ダイオード・コントローラ

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認定済み

- デバイス温度グレード 1:

動作時周囲温度範囲: -40°C ~ +125°C

- 機能安全対応

- 機能安全システム設計に役立つ資料を利用可能

- 3V ~ 65V の入力範囲

- 最低 -65V までの逆入力保護

- 共通ドレイン構成で外付けの逆並列 N チャネル MOSFET を駆動

- アノードからカソードへ 10.5mV の順方向電圧降下レギュレーションを行う理想ダイオード動作

- 低いスレッショルド (-10.5mV) と高速応答 (0.5μs) の逆電流検出

- 20mA のピーク・ゲート (DGATE) ターンオン電流

- 2.6A のピーク DGATE ターンオフ電流

- 可変過電圧および低電圧保護

- MOSFET のラッチオフ状態による出力短絡保護

- 超低消費電力モード、2.5μA のシャットダウン電流 (EN = Low)

- 6μA 電流のスリープ・モード (EN = High, SLEEP = Low)

- 適切な過渡電圧サプレッサ (TVS) ダイオードにより車載用 ISO7637 過渡要件に適合

- 4mm × 4mm の 24 ピン VQFN パッケージで供給

## 2 アプリケーション

- 車載用バッテリ保護

- ADAS ドメイン・コントローラ

- インフォテインメントおよびクラスター

- 車載用外部アンプ

- 冗長化電源用のアクティブ OR

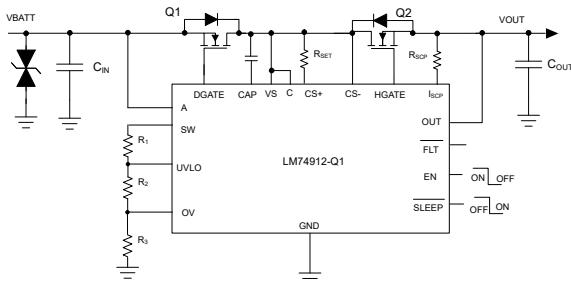

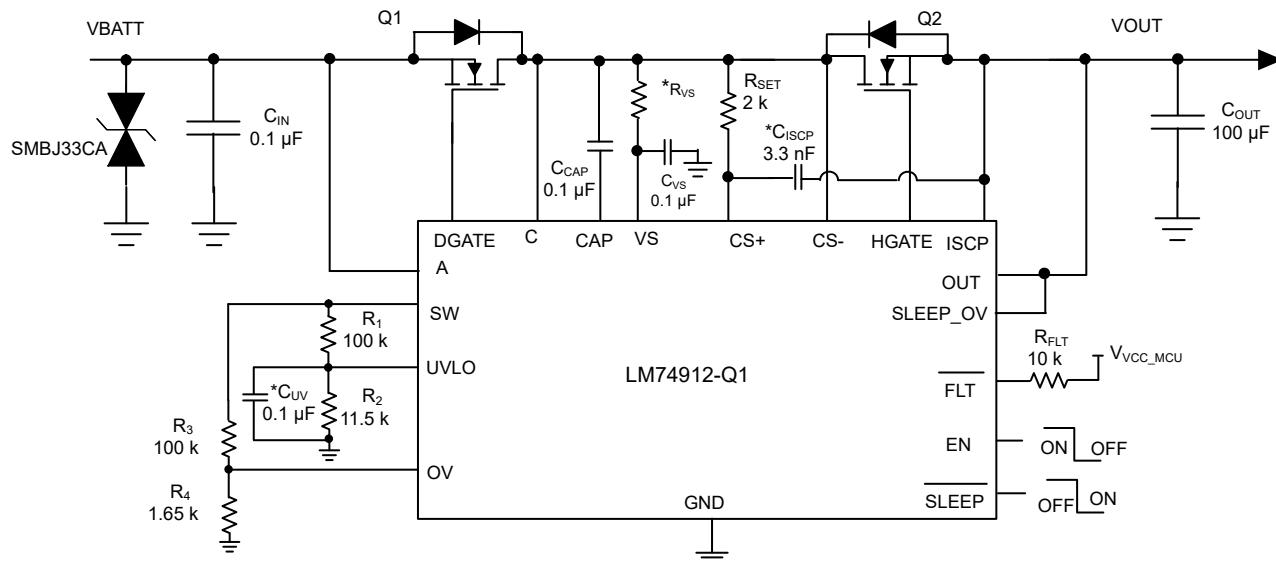

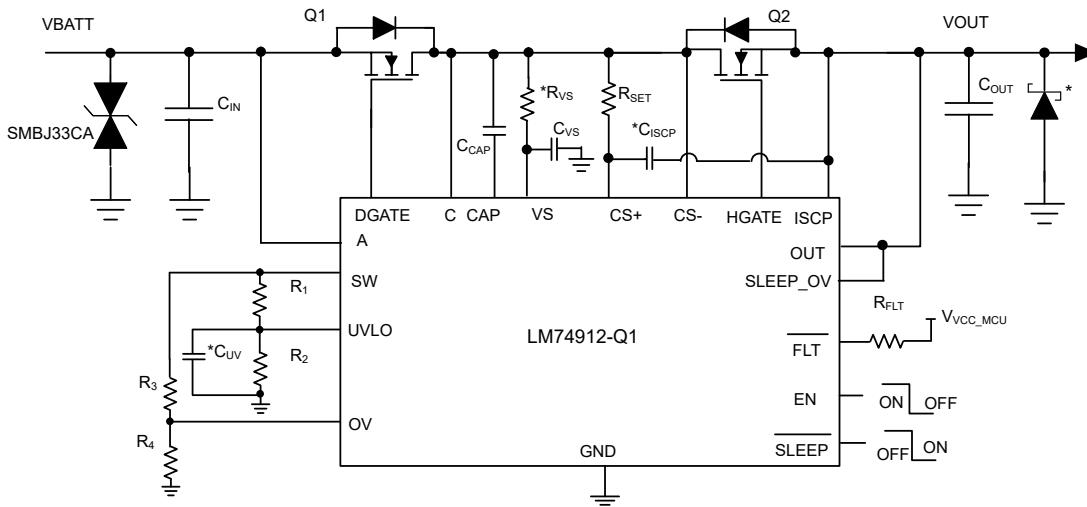

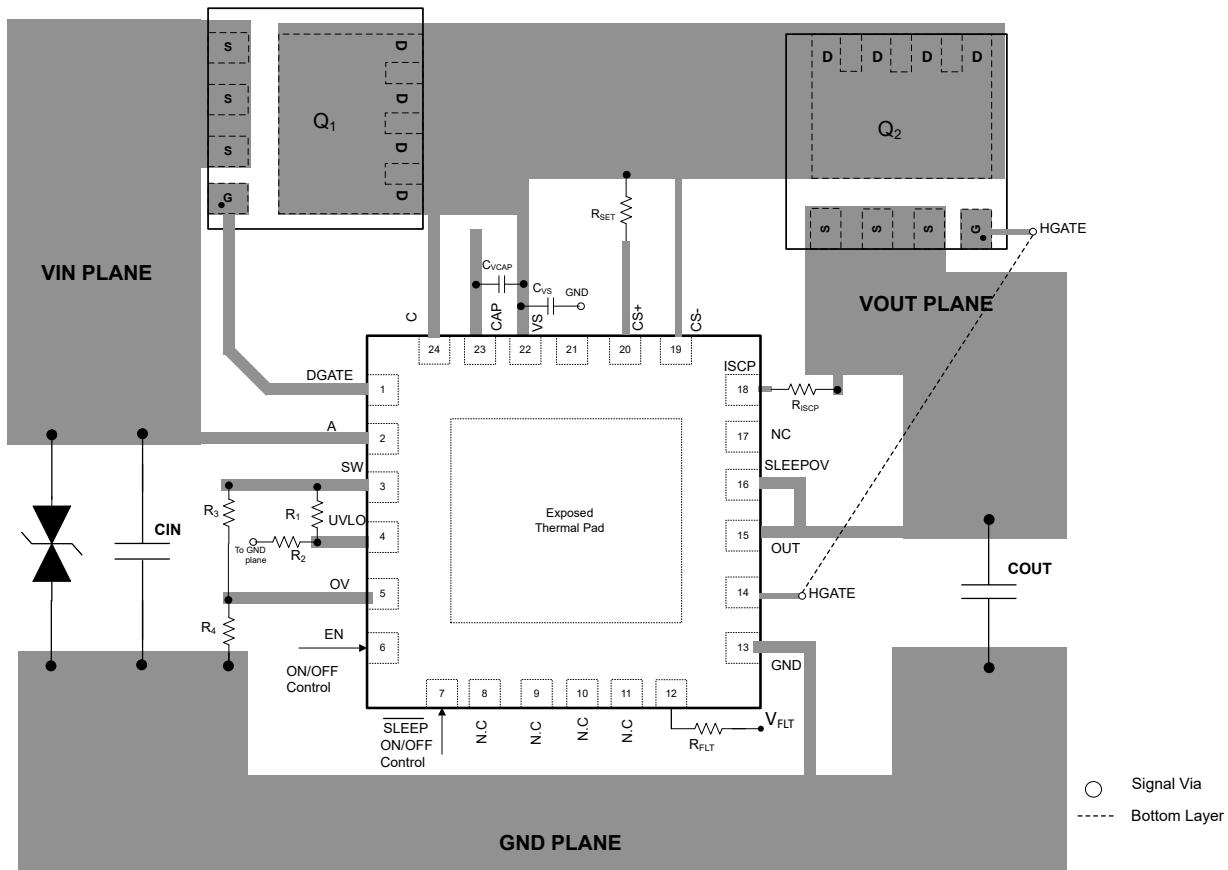

代表的なアプリケーション回路

## 3 概要

LM74912-Q1 理想ダイオード・コントローラは外付けの逆並列 N チャネル MOSFET を駆動および制御して、電力パスのオン / オフ制御と過電圧、低電圧、出力短絡保護を備えた理想ダイオード整流器をエミュレートします。入力電源電圧範囲が 3V ~ 65V と広いため、12V および 24V 車載用バッテリ駆動 ECU を保護および制御できます。このデバイスは最低 -65V の負の電源電圧に耐え、この電圧から負荷を保護できます。内蔵の理想ダイオード・コントローラ (DGATE) は第 1 の MOSFET を駆動し、逆入力保護および出力電圧保持用のショットキー・ダイオードを置き換えます。電力パスの第 2 の MOSFET により、過電流および過電圧が発生した場合に、HGATE 制御を使用して負荷の切断 (オン / オフ制御) が可能です。このデバイスには電流検出アンプが内蔵されており、可変電流制限機能により、外部 MOSFET VDS センスに基づく短絡保護を実現します。出力に短絡状態が検出されると、デバイスは負荷切断 MOSFET をラッчикオフします。このデバイスには可変過電圧カットオフ保護機能があります。このデバイスにはスリープ・モードが搭載されており、非常に低い静止電流消費 (6 μA) を実現すると同時に、車両が駐車状態のときは常時オンの負荷にリフレッシュ電流を供給します。LM74912-Q1 の最高電圧定格は 65V です。

### パッケージ情報

| 部品番号       | パッケージ (1)      | パッケージ・サイズ (2) |

|------------|----------------|---------------|

| LM74912-Q1 | RGE (VQFN, 24) | 4.0mm × 4.0mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ・サイズ (長さ×幅) は公称値であり、該当する場合はピンも含まれます。

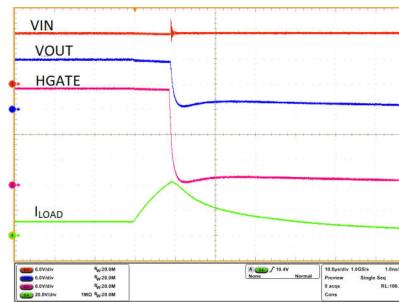

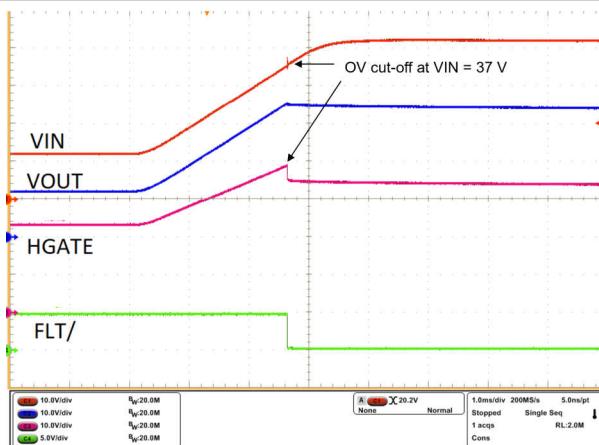

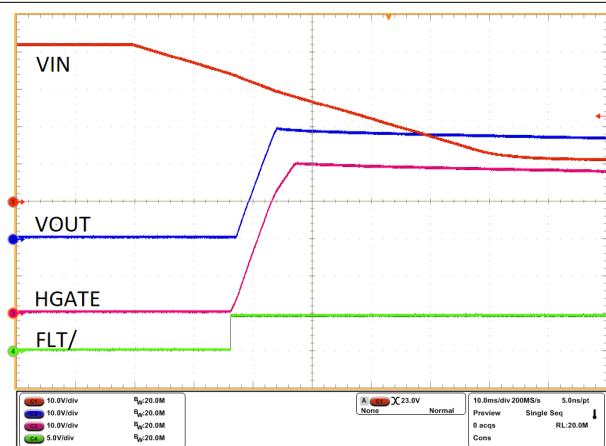

短絡応答

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、必ず最新版の英語版をご参照ください。

## 目次

|              |    |                                 |    |

|--------------|----|---------------------------------|----|

| 1 特長         | 1  | 8.2 機能ブロック図                     | 16 |

| 2 アプリケーション   | 1  | 8.3 機能説明                        | 16 |

| 3 概要         | 1  | 8.4 デバイスの機能モード                  | 21 |

| 4 改訂履歴       | 2  | 9 アプリケーションと実装                   | 22 |

| 5 ピン構成および機能  | 3  | 9.1 アプリケーション情報                  | 22 |

| 6 仕様         | 5  | 9.2 12V (代表値) バッテリ逆接続保護アプリケーション | 22 |

| 6.1 絶対最大定格   | 5  | 9.3 設計のベスト・プラクティス               | 31 |

| 6.2 ESD 定格   | 5  | 9.4 電源に関する推奨事項                  | 31 |

| 6.3 推奨動作条件   | 5  | 9.5 レイアウト                       | 33 |

| 6.4 熱に関する情報  | 6  | 10 デバイスおよびドキュメントのサポート           | 35 |

| 6.5 電気的特性    | 6  | 10.1 ドキュメントの更新通知を受け取る方法         | 35 |

| 6.6 スイッチング特性 | 8  | 10.2 サポート・リソース                  | 35 |

| 6.7 標準的特性    | 10 | 10.3 商標                         | 35 |

| 7 パラメータ測定情報  | 14 | 10.4 静電気放電に関する注意事項              | 35 |

| 8 詳細説明       | 15 | 10.5 用語集                        | 35 |

| 8.1 概要       | 15 | 11 メカニカル、パッケージ、および注文情報          | 35 |

## 4 改訂履歴

### Changes from Revision \* (July 2023) to Revision A (September 2023)

|                                   | Page |

|-----------------------------------|------|

| • ドキュメントのステータスを「事前情報」から「量産データ」に変更 | 1    |

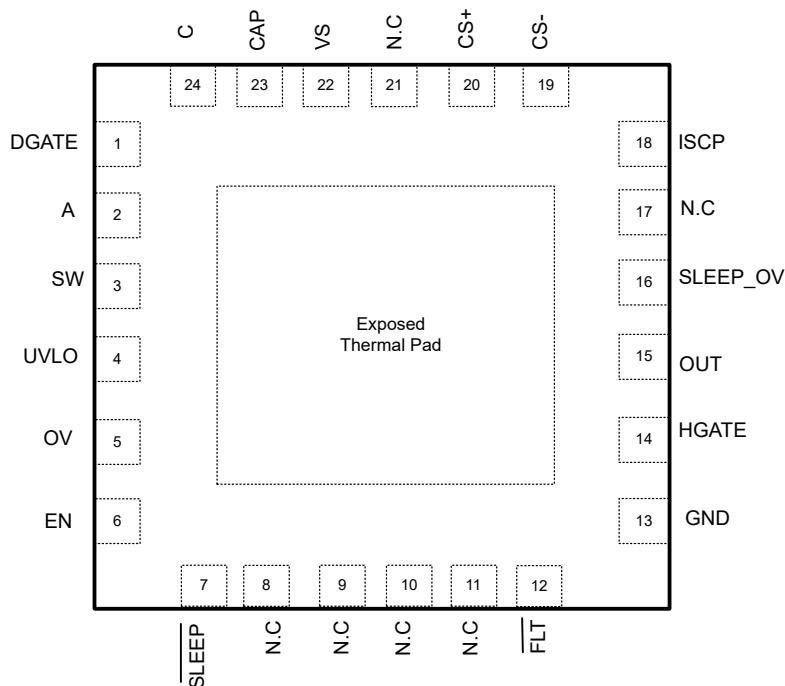

## 5 ピン構成および機能

図 5-1. RGE パッケージ、24 ピン VQFN (透過上面図)

表 5-1. ピンの機能

| ピン    |    | 種類 (1) | 概要                                                                                                                                                                                                                              |

|-------|----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称    | 番号 |        |                                                                                                                                                                                                                                 |

| DGATE | 1  | O      | ダイオード・コントローラのゲート・ドライブ出力。外部 MOSFET の GATE に接続します。                                                                                                                                                                                |

| A     | 2  | I      | 理想ダイオードのアノード。外部 MOSFET のソースに接続します。                                                                                                                                                                                              |

| SW    | 3  | I      | 電圧センシング接続解除スイッチ端子。A と SW はスイッチを介して内部接続されています。SW をバッテリ・センシングまたは OV 抵抗ラダー・ネットワークの上側接続として使用します。EN / SLEEP が Low になると、スイッチがオフになり、バッテリ・ラインからの抵抗ラダーの接続が切断され、リーク電流が遮断されます。A と SW の間の内部接続解除スイッチを使用しない場合は、SW ピンをフローティングのままにするか、A にプルします。 |

| UVLO  | 4  | I      | 可変低電圧スレッショルド入力。SW から GND への UVLO 端子間の抵抗ラダーを接続します。UVLO の電圧が低電圧カットオフ・スレッショルドを下回ると、HGATE が Low になり、HSFET をオフにします。センス電圧が UVLO 立ち下がりスレッショルドを上回ると、HGATE がオンになります。                                                                     |

| OV    | 5  | I      | 可変過電圧スレッショルド入力。SW から OV 端子間に抵抗ラダーを接続します。OV の電圧が過電圧カットオフ・スレッショルドを超えると、HGATE が Low になり、HSFET がオフになります。センス電圧が OV 立ち下がりスレッショルドを下回ると、HGATE がオンになります。                                                                                 |

| EN    | 6  | I      | EN 入力。常時オン動作の場合は VS ピンに接続します。マイコン I/O から、外部から駆動できます。このピンを $V_{(ENF)}$ 未満にプルすると、デバイスは低 IQ シャットダウン・モードに移行します。                                                                                                                     |

| SLEEP | 7  | I      | アクティブ Low の SLEEP モード入力。マイコンから駆動できます。Low にプルされると、デバイスは低消費電力状態に移行し、チャージ・ポンプとゲート・ドライブがオフになります。内部バイパス・スイッチにより出力電圧が供給され、電流容量は制限されます。使用されていない場合は、EN または VS に接続する必要があります。                                                             |

| N.C.  | 8  | —      | 接続なし。このピンはフローティングのままになります。                                                                                                                                                                                                      |

| N.C.  | 9  | —      | 接続なし。このピンはフローティングのままになります。                                                                                                                                                                                                      |

| N.C.  | 10 | —      | 接続なし。このピンはフローティングのままになります。                                                                                                                                                                                                      |

| N.C.  | 11 | —      | 接続なし。このピンはフローティングのままになります。                                                                                                                                                                                                      |

**表 5-1. ピンの機能 (continued)**

| ピン       |       | 種類 <sup>(1)</sup> | 概要                                                                                                    |

|----------|-------|-------------------|-------------------------------------------------------------------------------------------------------|

| 名称       | 番号    |                   |                                                                                                       |

| FLT      | 12    | O                 | オーブン・ドレン・フォルト出力。低電圧、過電圧、または出力短絡イベントの場合、FLT ピンは Low にプルされます。                                           |

| GND      | 13    | G                 | システム・グランド・プレーンに接続します。                                                                                 |

| HGATE    | 14    | O                 | HSFET の GATE ドライバ出力。外部 FET の GATE に接続します。                                                             |

| OUT      | 15    | I                 | 出力レール (外部 MOSFET ソース) に接続します。                                                                         |

| SLEEP_OV | 16    | I                 | SLEEP モード過電圧保護ピン。過電圧カットオフ機能の場合、このピンを Vs に接続します。過電圧クランプ機能の場合、OUT に接続します。                               |

| N.C.     | 17    | —                 | 接続なし。このピンはフローティングのままになります。                                                                            |

| ISCP     | 18    | I                 | 可変短絡保護の電流検出の負入力。ISCP が高出力に接続されると、デバイスは内部固定スレッショルドの標準値 50mV に対して CS+ ピンと ISCP ピン間の外部 HFET の電圧降下を監視します。 |

| CS-      | 19    | I                 | 電流検出アンプ電源入力。                                                                                          |

| CS+      | 20    | I                 | 可変短絡保護の電流検出の正入力。                                                                                      |

| N.C.     | 21    | —                 | 接続なし。このピンはフローティングのままになります。                                                                            |

| VS       | 22    | P                 | IC の入力電源。VS を共通ドレンの逆並列 MOSFET 構成の中間点に接続します。VS ピンと GND ピンとの間に 100nF のコンデンサを接続します。                      |

| CAP      | 23    | O                 | チャージ・ポンプの出力。CAP と VS ピンとの間に 100nF のコンデンサを接続します。                                                       |

| C        | 24    | I                 | 理想ダイオードのカソード。外部 MOSFET のドレンに接続します。                                                                    |

| RTN      | 放熱パッド | —                 | 露出したパッドはフローティングにします。GND プレーンには接続しないでください。                                                             |

(1) I: 入力、O: 出力、I/O: 入力または出力、P: 電源、G = グランド

## 6 仕様

### 6.1 絶対最大定格

自由空気での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                                 |                                                        | 最小値       | 最大値              | 単位 |

|---------------------------------|--------------------------------------------------------|-----------|------------------|----|

| 入力ピン                            | A から GND へ                                             | -65       | 70               | V  |

|                                 | VS, CS+, CS-, ISCP から GND へ                            | -1        | 70               |    |

|                                 | OUT, SLEEP_OV から GND へ                                 | -1        | 70               |    |

|                                 | C, SW, EN, SLEEP, UVLO, OV から GND へ、 $V_{(A)} > 0V$    | -0.3      | 70               |    |

|                                 | C, SW, EN, SLEEP, UVLO, OV から GND へ、 $V_{(A)} \leq 0V$ | $V_{(A)}$ | $(70 + V_{(A)})$ |    |

|                                 | RTN から GND へ                                           | -65       | 0.3              |    |

|                                 | $I_{SW}, I_{FLT}$                                      | -1        | 10               |    |

| 出力ピン                            | $I_{EN}, I_{SLEEP}, I_{OV}, I_{UVLO} V_{(A)} > 0V$     | -1        |                  | mA |

|                                 | $I_{EN}, I_{SLEEP}, I_{OV}, I_{UVLO} V_{(A)} \leq 0V$  | 内部的に制限    |                  |    |

|                                 | CAP から VS へ                                            | -0.3      | 15               |    |

| 出力から入力ピンへ                       | CAP から A へ                                             | -0.3      | 85               | V  |

|                                 | DGATE から A へ                                           | -0.3      | 15               |    |

|                                 | FLT から GND へ                                           | -1        | 70               |    |

|                                 | HGATE から OUT へ                                         | -0.3      | 15               |    |

|                                 | C から A へ                                               | -5        | 85               |    |

| 動作時の接合部温度、 $T_j$ <sup>(2)</sup> | OUT から VS へ                                            | -65       | 5                | °C |

|                                 | 動作時の接合部温度、 $T_j$                                       | -40       | 150              |    |

| 保存温度、 $T_{stg}$                 |                                                        | -40       | 150              |    |

(1) 「絶対最大定格」の範囲外の動作は、デバイスの恒久的な損傷の原因となる可能性があります。「絶対最大定格」は、このデータシートの「推奨動作条件」に示された値を超える状態で本製品が正常に動作することを暗黙的に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しなくなる可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

(2) 接合部温度が高くなると、動作寿命が短くなります。接合部温度が 125°Cを超えると、動作寿命が短くなります。

### 6.2 ESD 定格

|             |      |                                                | 値          | 単位 |

|-------------|------|------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、AEC Q100-002 準拠 <sup>(1)</sup>     | $\pm 2000$ | V  |

|             |      | 荷電デバイス・モデル (CDM)、AEC Q100-011 準拠               | $\pm 750$  |    |

|             |      | コーナー・ピン (DGATE, GND, EN, ISCP, CS-, C) および他のピン | $\pm 500$  |    |

(1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施することを示しています。

### 6.3 推奨動作条件

自由空気での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|      |                                   | 最小値 | 公称値 | 最大値 | 単位      |

|------|-----------------------------------|-----|-----|-----|---------|

| 入力ピン | A から GND へ                        | -60 | 65  |     | V       |

|      | VS, SW, CS+, CS-, ISCP から GND へ   | 0   | 65  |     | V       |

|      | EN, UVLO, OV, SLEEP から GND へ      | 0   | 65  |     | V       |

| 出力ピン | FLT から GND へ                      | 0   | 65  |     | V       |

| 外部容量 | CAP から A へ、VS から GND へ、A から GND へ | 0.1 |     |     | $\mu F$ |

## 6.3 推奨動作条件 (continued)

自由空気での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                            |                           | 最小値 | 公称値 | 最大値 | 単位 |

|----------------------------|---------------------------|-----|-----|-----|----|

| 外部 MOSFET の最大ゲート - ソース 間定格 | DGATE を A へ、HGATE を OUT へ | 15  |     |     | V  |

| T <sub>j</sub>             | 動作時接合部温度 <sup>(2)</sup>   | -40 |     | 150 | °C |

- (1) 推奨動作条件は、デバイスが機能すると想定されている条件を示します。仕様およびテスト条件については、「電気的特性」を参照してください。

(2) 接合部温度が高くなると、動作寿命が短くなります。接合部温度が 125°Cを超えると、動作寿命が短くなります。

## 6.4 熱に関する情報

| 熱評価基準                 |                     | LM74912-Q1 | 単位   |

|-----------------------|---------------------|------------|------|

|                       |                     | RGE (VQFN) |      |

|                       |                     | 24 ピン      |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 44         | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 38.3       | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 21.3       | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 0.8        | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 21.3       | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | 5.1        | °C/W |

## 6.5 電気的特性

T<sub>j</sub> = -40°C~+125°C、T<sub>j</sub> = 25°C、V<sub>(A)</sub> = V<sub>(OUT)</sub> = V<sub>(VS)</sub> = 12V、C<sub>(CAP)</sub> = 0.1μF、V<sub>(EN)</sub>、V<sub>(SLEEP)</sub> = 2V の標準値、自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                  | テスト条件                              | 最小値                                                               | 代表値   | 最大値  | 単位    |

|------------------------|------------------------------------|-------------------------------------------------------------------|-------|------|-------|

| <b>電源電圧</b>            |                                    |                                                                   |       |      |       |

| V <sub>(VS)</sub>      | 動作時入力電圧                            | 3                                                                 | 65    |      | V     |

| V <sub>(VS_PORR)</sub> | VS POR スレッショルド、立ち上がり               | 2.4                                                               | 2.65  | 2.9  | V     |

| V <sub>(VS_PORF)</sub> | VS POR スレッショルド、立ち下がり               | 2.2                                                               | 2.45  | 2.7  | V     |

| I <sub>(SHDN)</sub>    | SHDN 電流、I <sub>(GND)</sub>         | V <sub>(EN)</sub> = 0V                                            | 2.5   | 5    | μA    |

| I <sub>(SLEEP)</sub>   | SLEEP モード電流、I <sub>(GND)</sub>     | V <sub>(EN)</sub> = 2V、V <sub>(SLEEP)</sub> = 0V                  | 5.5   | 10   | μA    |

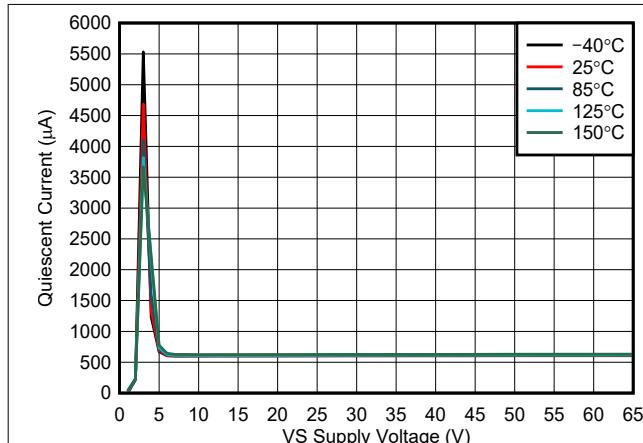

| I <sub>(Q)</sub>       | システム全体の静止電流、I <sub>(GND)</sub>     | V <sub>(EN)</sub> = 2V                                            | 610   | 730  | μA    |

|                        |                                    | V <sub>(A)</sub> = V <sub>(VS)</sub> = 24V、V <sub>(EN)</sub> = 2V | 615   | 735  | μA    |

| I <sub>(REV)</sub>     | 逆極性時の I <sub>(A)</sub> リーク電流       | 0V ≤ V <sub>(A)</sub> ≤ -65V                                      | -100  | -35  | μA    |

|                        | 逆極性時の I <sub>(OUT)</sub> リーク電流     |                                                                   | -1    | -0.3 | μA    |

| <b>イネーブル</b>           |                                    |                                                                   |       |      |       |

| V <sub>(ENR)</sub>     | 低 IQ シャットダウンのイネーブル・スレッショルド電圧、立ち上がり |                                                                   | 0.8   | 1.05 | V     |

| V <sub>(ENF)</sub>     | 低 IQ シャットダウンのイネーブル立ち下がりスレッショルド電圧   |                                                                   | 0.41  | 0.7  | V     |

| I <sub>(EN)</sub>      |                                    | V <sub>(EN)</sub> = 65V                                           | 55    | 200  | nA    |

| <b>低電圧誤動作防止コンパレータ</b>  |                                    |                                                                   |       |      |       |

| V <sub>(UVLOR)</sub>   | UVLO スレッショルド電圧、立ち上がり               |                                                                   | 0.585 | 0.6  | 0.63  |

| V <sub>(UVLOF)</sub>   | UVLO スレッショルド電圧、立ち下がり               |                                                                   | 0.533 | 0.55 | 0.573 |

| I <sub>(UVLO)</sub>    | UVLO ピンのリーク電流                      | 0V ≤ V <sub>(UVLO)</sub> ≤ 5V                                     | 52    | 200  | nA    |

| <b>SLEEP モード</b>       |                                    |                                                                   |       |      |       |

## 6.5 電気的特性 (continued)

$T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$ ,  $T_J = 25^\circ\text{C}$ ,  $V_{(\text{A})} = V_{(\text{OUT})} = V_{(\text{VS})} = 12\text{V}$ ,  $C_{(\text{CAP})} = 0.1\mu\text{F}$ ,  $V_{(\text{EN})}$ ,  $V_{(\text{SLEEP})} = 2\text{V}$  の標準値、自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                       |                                                            | テスト条件                                                                                          | 最小値  | 代表値   | 最大値   | 単位       |

|-----------------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|-------|-------|----------|

| $V_{(\text{SLEEP}_R)}$      | 低 $I_Q$ モードの $\overline{\text{SLEEP}}$ スレッショルド電圧           |                                                                                                |      | 0.8   | 1.05  | V        |

| $V_{(\text{SLEEP}_F)}$      | 低 $I_Q$ シャットダウンの $\overline{\text{SLEEP}}$ スレッショルド電圧、立ち下がり |                                                                                                |      | 0.41  | 0.7   | V        |

| $I_{(\text{SLEEP})}$        | $\overline{\text{SLEEP}}$ 入力リーク電流                          | $0\text{V} \leq V_{(\text{SLEEP})} \leq 12\text{V}$                                            |      |       | 100   | nA       |

| 過電流スレッショルド                  | SLEEP モード過電流スレッショルド                                        |                                                                                                |      | 150   | 250   | 310      |

| 過電圧スレッショルド                  | 過電圧コンパレータの立ち上がりスレッショルド                                     |                                                                                                |      | 19.3  | 21.5  | 23       |

|                             | 過電圧コンパレータの立ち下がりスレッショルド                                     |                                                                                                |      | 18.4  | 21.04 | 22.2     |

| FET 抵抗                      | SLEEP モード・バイパス FET 抵抗                                      |                                                                                                |      | 4.5   | 7.5   | $\Omega$ |

| TSD                         | SLEEP モード時のサーマル・シャットダウン立ち上がりスレッショルド                        |                                                                                                |      | 155   |       | °C       |

| <b>過電圧保護およびバッテリ・センシング入力</b> |                                                            |                                                                                                |      |       |       |          |

| $R_{(\text{SW})}$           | バッテリ・センシング接続解除スイッチの抵抗                                      | $3\text{V} \leq V_{(\text{SNS})} \leq 65\text{V}$                                              | 10   | 22    | 46    | $\Omega$ |

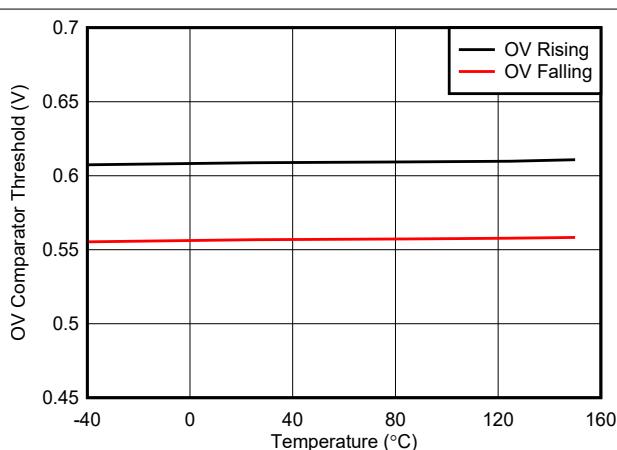

| $V_{(\text{OVR})}$          | 過電圧スレッショルド入力、立ち上がり                                         |                                                                                                |      | 0.585 | 0.6   | 0.63     |

| $V_{(\text{OVF})}$          | 過電圧スレッショルド入力、立ち下がり                                         |                                                                                                |      | 0.533 | 0.55  | 0.573    |

| $I_{(\text{OV})}$           | OV ピン入力リーク電流                                               | $0\text{V} \leq V_{(\text{OV})} \leq 5\text{V}$                                                |      |       | 52    | nA       |

| <b>電流検出アンプ</b>              |                                                            |                                                                                                |      |       |       |          |

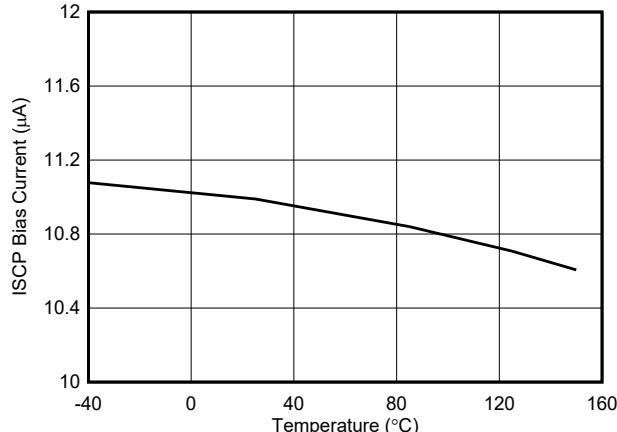

| $I_{(\text{CS+})}$          | CS+ ピン・シンク電流                                               |                                                                                                |      | 10    | 11    | 11.85    |

| $I_{(\text{SCP})}$          | ISCP ピンのバイアス電流                                             |                                                                                                |      | 10    | 11    | 11.85    |

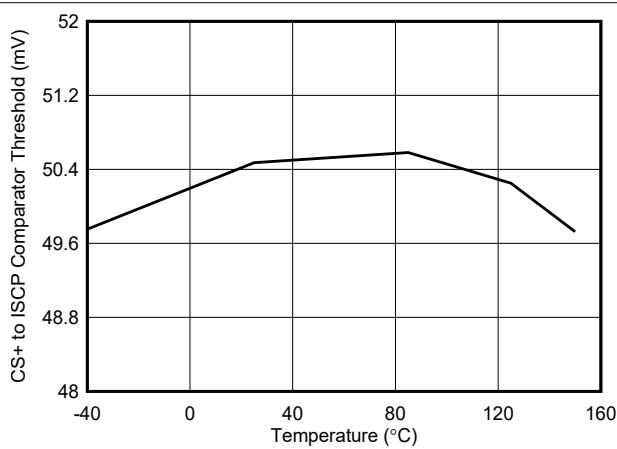

| $V_{(\text{SNS\_SCP})}$     | 短絡保護スレッショルド                                                | $R_{(\text{SCP})} = R_{(\text{SET})} = 0\Omega$                                                | 47.3 | 50    | 53.4  | mV       |

|                             |                                                            | $R_{(\text{SET})} = 1\text{k}\Omega$ , $R_{(\text{SCP})} = 0\Omega$                            |      |       | 61    | mV       |

|                             |                                                            | $R_{(\text{SCP})} = 1\text{k}\Omega$ , $R_{(\text{SET})} = 0\Omega$                            |      |       | 39    | mV       |

| <b>フォルト</b>                 |                                                            |                                                                                                |      |       |       |          |

| $R_{(\text{FLT})}$          | FLT ブルダウントラップ抵抗                                            |                                                                                                |      | 11    | 25    | 60       |

| $I_{(\text{FLT})}$          | FLT ピンのリーク電流                                               |                                                                                                |      | -100  | 400   |          |

| <b>チャージ・ポンプ</b>             |                                                            |                                                                                                |      |       |       |          |

| $I_{(\text{CAP})}$          | チャージ・ポンプのソース電流                                             | $V_{(\text{CAP})} - V_{(\text{A})} = 7\text{V}, 6\text{V} \leq V_{(\text{S})} \leq 65\text{V}$ | 2.5  | 4     | mA    |          |

| $V_{(\text{CAP\_VS})}$      | チャージ・ポンプのターンオン電圧                                           |                                                                                                |      | 11    | 12.2  | 13.2     |

|                             | チャージ・ポンプのターンオフ電圧                                           |                                                                                                |      | 11.9  | 13.2  | 14.1     |

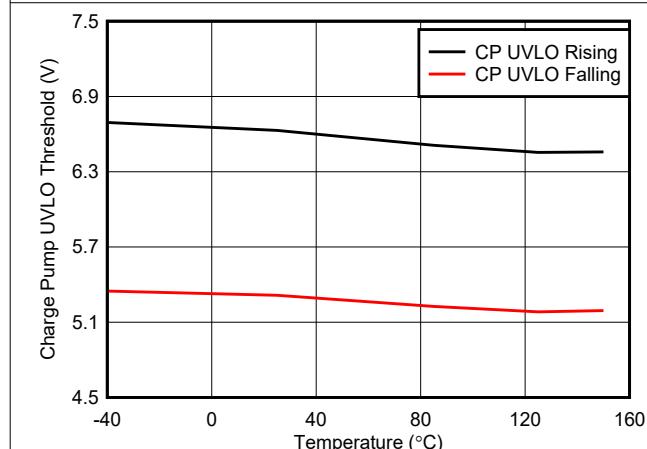

| $V_{(\text{CAP\_UVLO})}$    | チャージ・ポンプ UVLO 電圧スレッショルド、立ち上がり                              |                                                                                                |      | 5.4   | 6.6   | 7.9      |

|                             | チャージ・ポンプ UVLO 電圧スレッショルド、立ち下がり                              |                                                                                                |      | 4.4   | 5.4   | 6.6      |

| <b>理想ダイオードの MOSFET 制御</b>   |                                                            |                                                                                                |      |       |       |          |

| $V_{(\text{A\_PORR})}$      | $V_{(\text{A})}$ POR スレッショルド、立ち上がり                         |                                                                                                |      | 2.2   | 2.4   | 2.7      |

| $V_{(\text{A\_PORF})}$      | $V_{(\text{A})}$ POR スレッショルド、立ち下がり                         |                                                                                                |      | 2     | 2.2   | 2.45     |

| $V_{(\text{AC\_REG})}$      | レギュレートされた順方向 $V_{(\text{A})} - V_{(\text{C})}$ スレッショルド     |                                                                                                |      | 3.6   | 10.5  | 13.4     |

| $V_{(\text{AC\_REV})}$      | 高速逆電流ブロックの $V_{(\text{A})} - V_{(\text{C})}$ スレッショルド       |                                                                                                |      | -16   | -10.5 | -5       |

## 6.5 電気的特性 (continued)

$T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$ ,  $T_J = 25^\circ\text{C}$ ,  $V_{(\text{A})} = V_{(\text{OUT})} = V_{(\text{VS})} = 12\text{V}$ ,  $C_{(\text{CAP})} = 0.1\mu\text{F}$ ,  $V_{(\text{EN})}$ ,  $V_{(\text{SLEEP})} = 2\text{V}$  の標準値、自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                                   |                                                          | テスト条件                                                                                                 | 最小値 | 代表値  | 最大値 | 単位 |

|-----------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----|------|-----|----|

| $V_{(\text{AC\_FWD})}$                  | 逆方向から順方向への遷移時の $V_{(\text{A})} - V_{(\text{C})}$ スレッショルド |                                                                                                       | 150 | 177  | 200 | mV |

| $V_{(\text{DGATE})} - V_{(\text{A})}$   | ゲート駆動電圧                                                  | $3\text{V} < V_{(\text{S})} < 5\text{V}$                                                              | 7   |      |     | V  |

|                                         |                                                          | $5\text{V} < V_{(\text{S})} < 65\text{V}$                                                             | 9.2 | 11.5 | 14  | V  |

| $I_{(\text{DGATE})}$                    | ピーク・ゲート・ソース電流                                            | $V_{(\text{A})} - V_{(\text{C})} = 300\text{mV}$ , $V_{(\text{DGATE})} - V_{(\text{A})} = 1\text{V}$  |     | 20   |     | mA |

|                                         | ピーク・ゲート・シンク電流                                            | $V_{(\text{A})} - V_{(\text{C})} = -12\text{mV}$ , $V_{(\text{DGATE})} - V_{(\text{A})} = 11\text{V}$ |     | 2670 |     | mA |

|                                         | レギュレーション・シンク電流                                           | $V_{(\text{A})} - V_{(\text{C})} = 0\text{V}$ , $V_{(\text{DGATE})} - V_{(\text{A})} = 11\text{V}$    | 6   | 15   |     | μA |

| $I_{(\text{C})}$                        | カソード・リーク電流                                               | $V_{(\text{A})} = -14\text{V}$ , $V_{(\text{C})} = 12\text{V}$                                        | 4   | 9    | 32  | μA |

| ハイサイド MOSFET 制御                         |                                                          |                                                                                                       |     |      |     |    |

| $V_{(\text{HGATE})} - V_{(\text{OUT})}$ | ゲート駆動電圧                                                  | $3\text{V} < V_{(\text{S})} < 5\text{V}$                                                              | 7   |      |     | V  |

|                                         |                                                          | $5\text{V} < V_{(\text{S})} < 65\text{V}$                                                             | 10  | 11.1 | 14  | V  |

| $I_{(\text{HGATE})}$                    | ソース電流                                                    |                                                                                                       | 39  | 55   | 75  | μA |

|                                         | シンク電流                                                    |                                                                                                       | 128 | 180  |     | mA |

| $V_{(\text{HGATE-OUT})\_SCP}$           | 短絡保護イネーブルの HGATE-OUT スレッショルド                             |                                                                                                       |     | 6.4  |     | V  |

## 6.6 スイッチング特性

$T_J = -40^\circ\text{C} \sim +125^\circ\text{C}$ ,  $T_J = 25^\circ\text{C}$ ,  $V_{(\text{A})} = V_{(\text{OUT})} = V_{(\text{VS})} = 12\text{V}$ ,  $C_{(\text{CAP})} = 0.1\mu\text{F}$ ,  $V_{(\text{EN})}$ ,  $V_{(\text{SLEEP})} = 2\text{V}$  の標準値、自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                              |                            | テスト条件                                                                                                                                            | 最小値 | 代表値 | 最大値  | 単位 |

|------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|----|

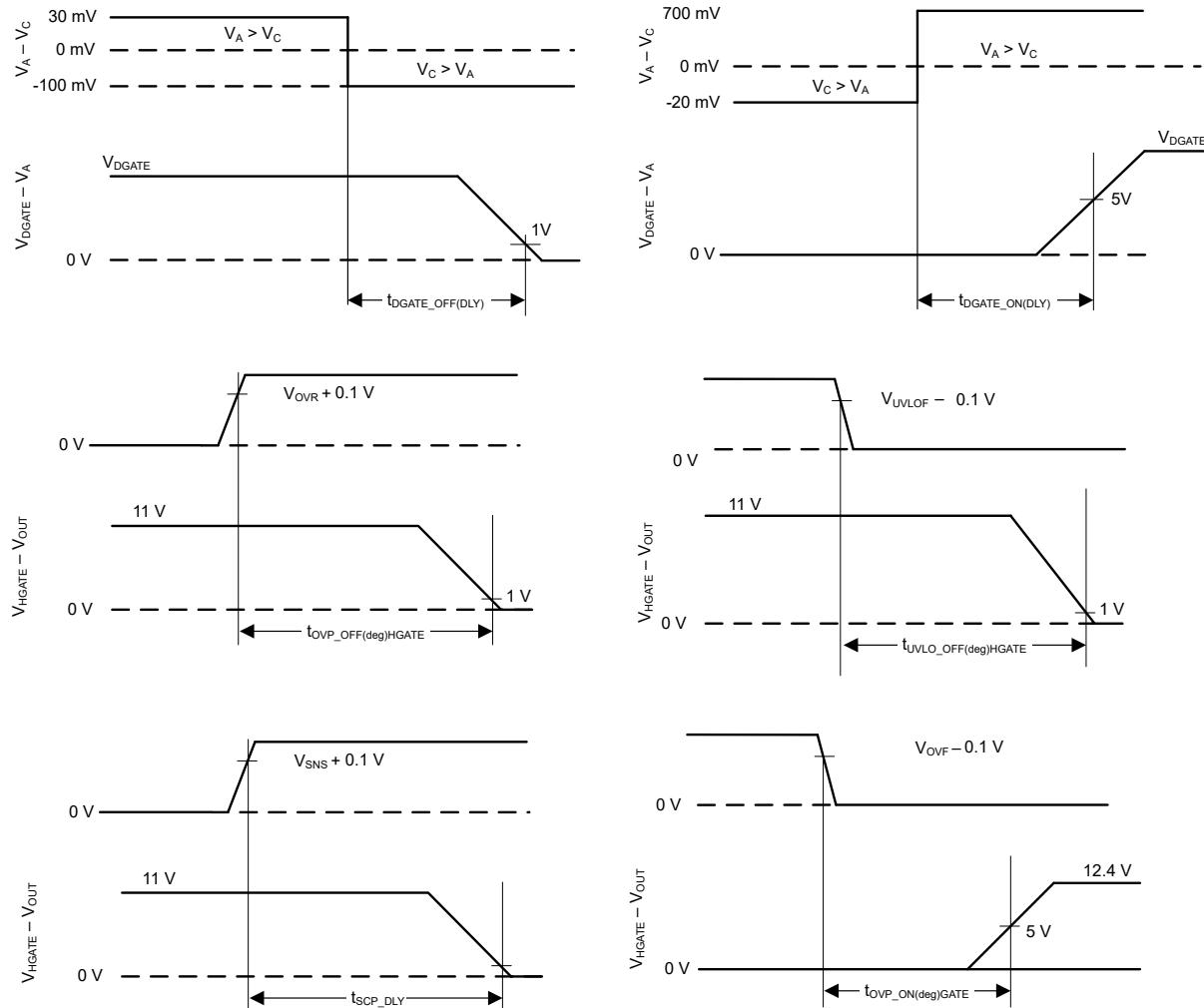

| $t_{\text{DGATE\_OFF(dly)}}$       | 逆電圧検出中の DGATE ターンオフ遅延      | $V_{(\text{A})} - V_{(\text{C})} = +30\text{mV} \sim -100\text{mV} \sim V_{(\text{DGATE-A})} < 1\text{V}$ , $C_{(\text{DGATE-A})} = 10\text{nF}$ |     | 0.5 | 0.95 | μs |

| $t_{\text{DGATE\_ON(dly)}}$        | 順方向電圧検出時の DGATE ターンオン遅延    | $V_{(\text{A})} - V_{(\text{C})} = -20\text{mV} \sim +700\text{mV} \sim V_{(\text{DGATE-A})} > 5\text{V}$ , $C_{(\text{DGATE-A})} = 10\text{nF}$ |     | 0.8 | 1.6  | μs |

| $t_{\text{EN(dly)}\_DGATE}$        | デバイス・イネーブル中の DGATE ターンオン遅延 | $\text{EN} \uparrow \sim V_{(\text{DGATE-A})} > 5\text{V}$                                                                                       |     | 185 | 270  | μs |

| $t_{\text{UVLO\_OFF(deg)}\_HGATE}$ | UVLO 中の HGATE ターンオフ・グリッヂ除去 | $\text{UVLO} \downarrow \sim \text{HGATE} \downarrow$                                                                                            |     | 5   | 7    | μs |

| $t_{\text{UVLO\_ON(deg)}\_HGATE}$  | UVLO 中の HGATE ターンオン・グリッヂ除去 | $\text{UVLO} \uparrow \sim \text{HGATE} \uparrow$                                                                                                |     | 7   |      | μs |

| $t_{\text{OVP\_OFF(deg)}\_HGATE}$  | OV 中の HGATE ターンオフ・グリッヂ除去   | $\text{OV} \uparrow \sim \text{HGATE} \downarrow$ , $C_{(\text{HGATE-OUT})} = 4.7\text{nF}$                                                      |     | 4   | 7    | μs |

| $t_{\text{OVP\_ON(deg)}\_HGATE}$   | OV 中の HGATE ターンオン・グリッヂ除去   | $\text{OV} \downarrow \sim \text{HGATE} \uparrow$                                                                                                |     | 7   |      | μs |

| $t_{\text{SCP\_DLY}}$              | 短絡保護のターンオフ遅延               | $(V_{\text{CS}} - V_{\text{ISCP}}) = 0\text{mV} \sim 100\text{mV}$ , $\text{HGATE} \downarrow$ , $C_{(\text{HGATE-OUT})} = 10\text{nF}$          |     | 2   | 4.5  | μs |

| $t_{\text{FLT\_ASSERT}}$           | 短絡状態中のフォルト・アサート遅延          | $(V_{\text{CS}} - V_{\text{ISCP}}) \uparrow \sim \text{FLT} \downarrow$                                                                          |     | 2.5 |      | μs |

| $t_{\text{FLT\_DE-ASSERT}}$        | フォルト・デアサート遅延               | $(V_{\text{CS}} - V_{\text{ISCP}}) \downarrow \sim \text{FLT} \uparrow$                                                                          |     | 3.5 |      | μs |

| $t_{\text{SLEEP\_OCP\_LATCH}}$     | SLEEP OCP ラッチ遅延            | $\text{SLEEP} = \text{Low}$ , $\text{EN} = \text{High}$                                                                                          |     | 3.5 | 7.5  | μs |

| $t_{\text{SLEEP\_OV\_OFF}}$        | スリープ・モードでの過電圧ターンオフ応答遅延     | $\text{SLEEP} = \text{Low}$ , $\text{EN} = \text{High}$                                                                                          |     | 3.5 |      | μs |

## 6.6 スイッチング特性 (continued)

$T_J = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$ 、 $T_J = 25^{\circ}\text{C}$ 、 $V_{(\text{A})} = V_{(\text{OUT})} = V_{(\text{VS})} = 12\text{V}$ 、 $C_{(\text{CAP})} = 0.1\mu\text{F}$ 、 $V_{(\text{EN})}$ 、 $V_{(\text{SLEEP})} = 2\text{V}$  の標準値、自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                           | テスト条件           | 最小値 | 代表値 | 最大値 | 単位            |

|---------------------------------|-----------------|-----|-----|-----|---------------|

| $t_{\text{SLEEP\_MODE\_ENTRY}}$ | スリープ・モード・エントリ遅延 |     | 100 |     | $\mu\text{s}$ |

## 6.7 標準的特性

図 6-1. 動作時静止電流と電源電圧との関係

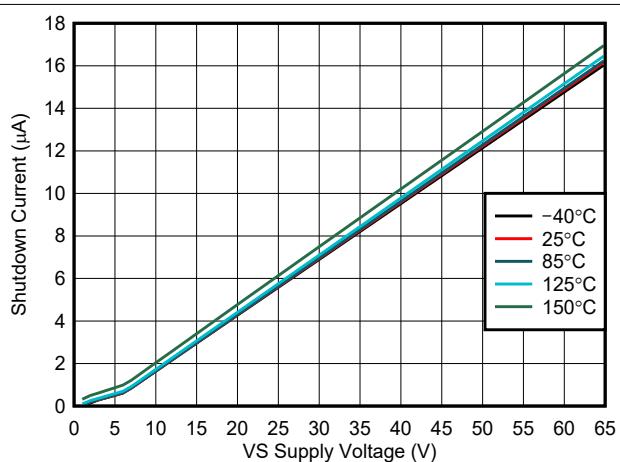

図 6-2. シャットダウン電流と電源電圧との関係

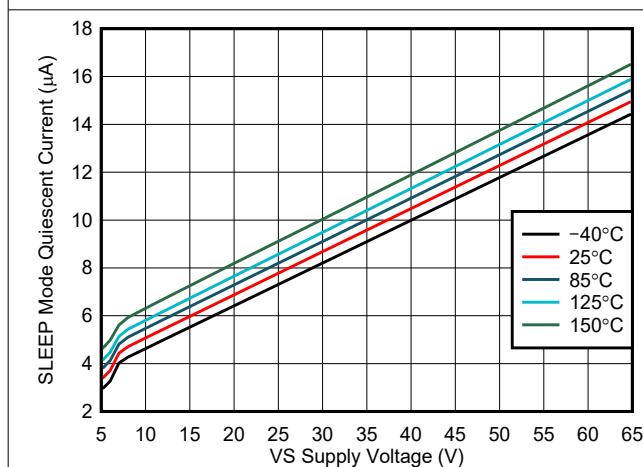

図 6-3. SLEEP モード電流と電源電圧との関係

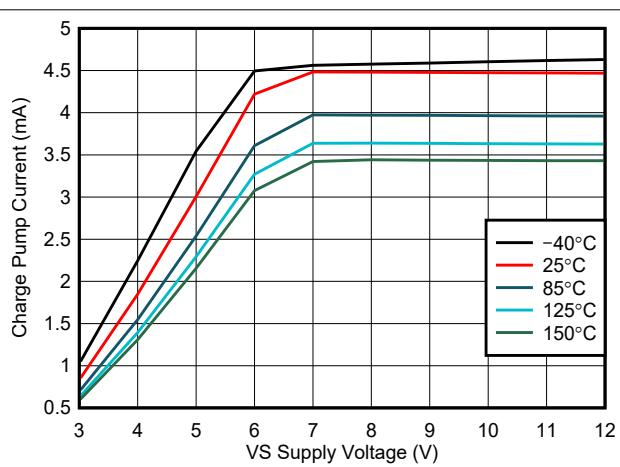

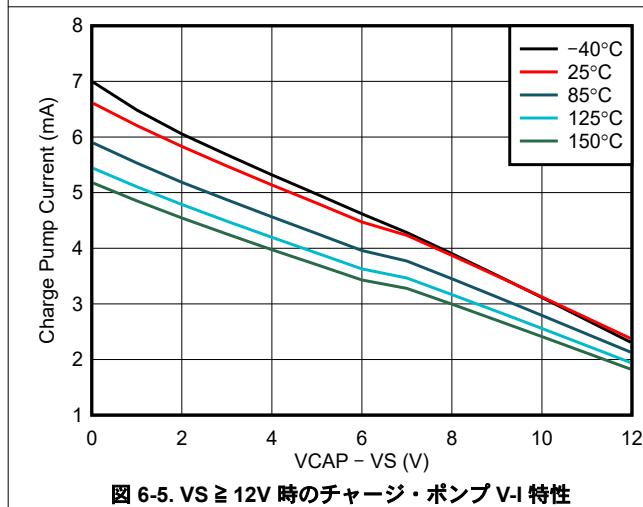

図 6-4. CAP – VS  $\geq 6$  V 時のチャージ・ポンプ電流と電源電圧との関係図 6-5. VS  $\geq 12$  V 時のチャージ・ポンプ V-I 特性

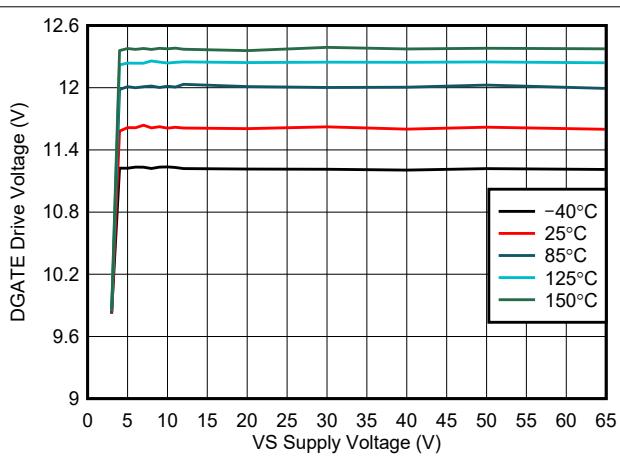

図 6-6. DGATE 駆動電圧と電源電圧との関係

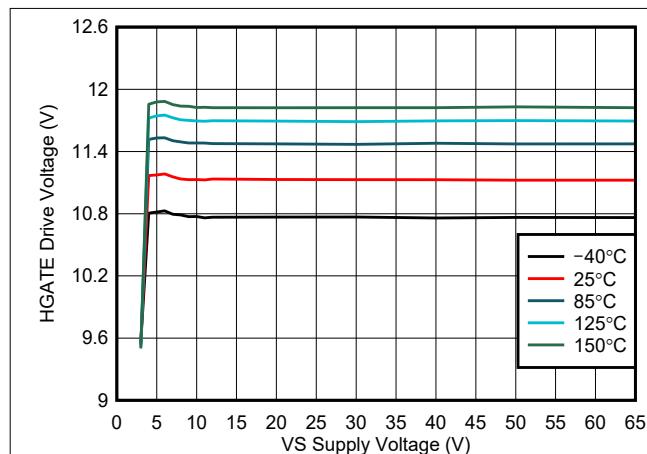

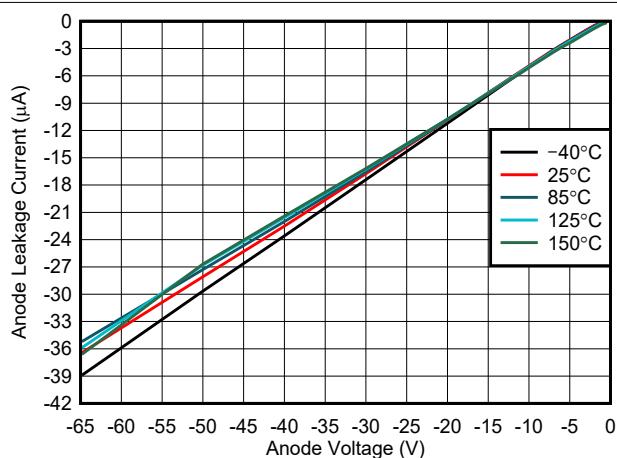

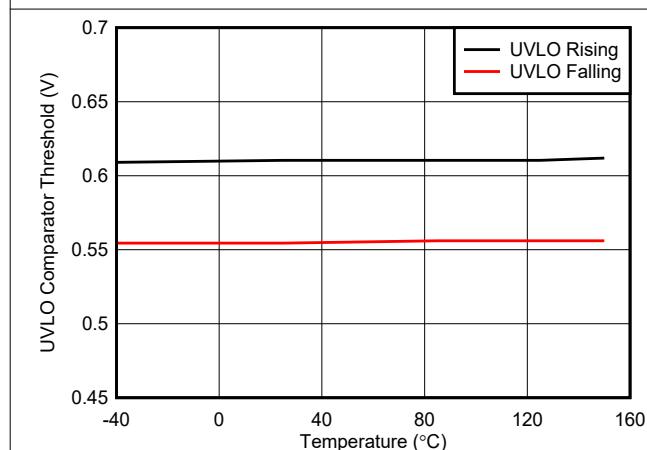

## 6.7 標準的特性 (continued)

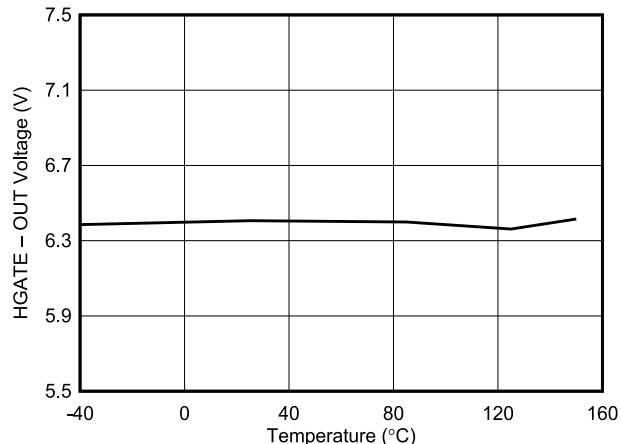

図 6-7. H-GATE 駆動電圧と電源電圧との関係

図 6-8. アノード・リーク電流と逆アノード電圧との関係

図 6-9. UVLO スレッショルドと温度との関係

図 6-10. OVP スレッショルドと温度との関係

図 6-11. チャージ・ポンプ UVLO スレッショルドと温度との関係

図 6-12. CS+ から ISCP へのコンパレータ・スレッショルドと温度との関係

## 6.7 標準的特性 (continued)

図 6-13. ISCP バイアス電流と温度との関係

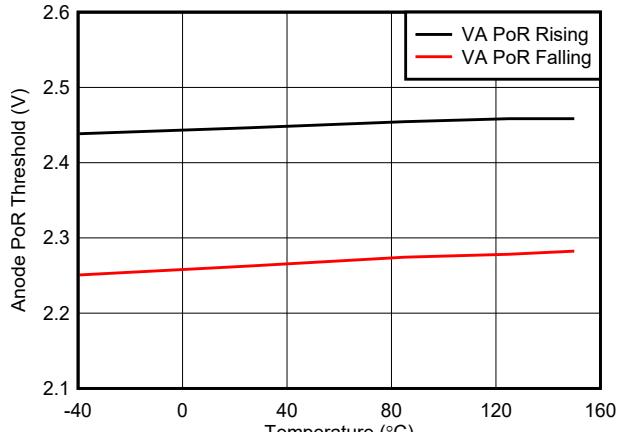

図 6-14. VA POR スレッショルドと温度との関係

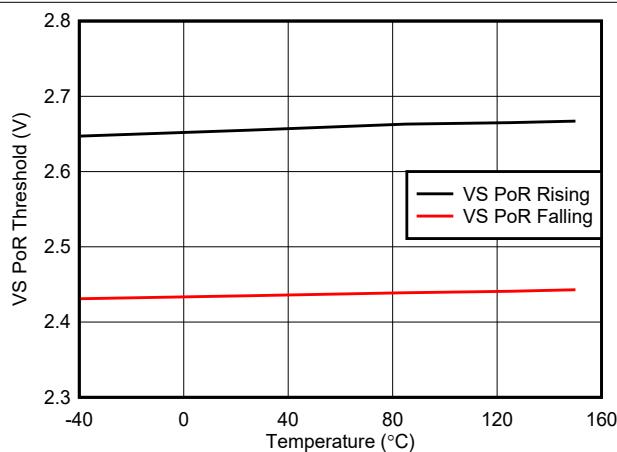

図 6-15. VS POR スレッショルドと温度との関係

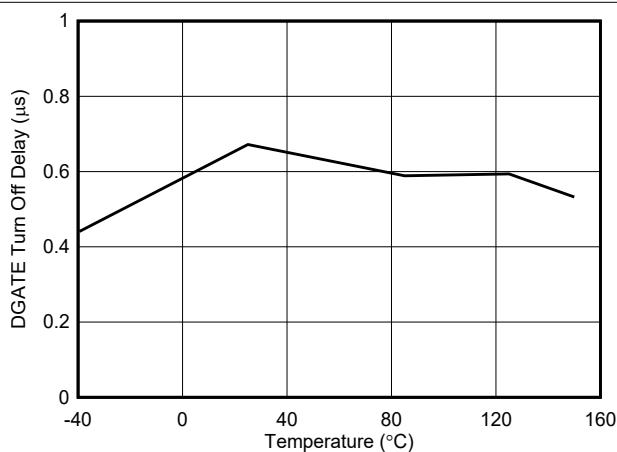

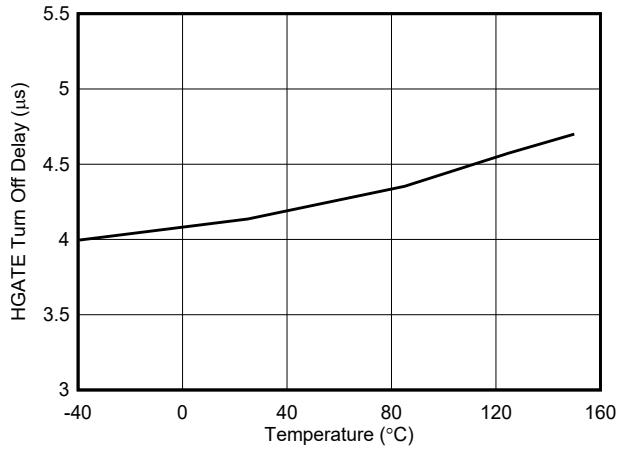

図 6-16. DGATE ターンオフ遅延

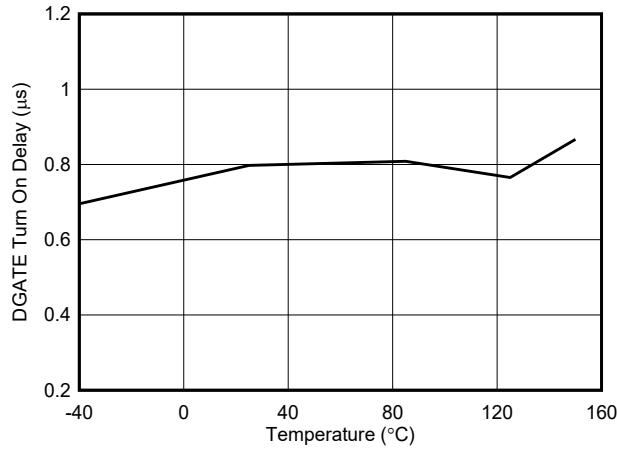

図 6-17. 順方向導通中の DGATE ターンオン遅延

図 6-18. 過電圧中の HGATE ターンオフ遅延

## 6.7 標準的特性 (continued)

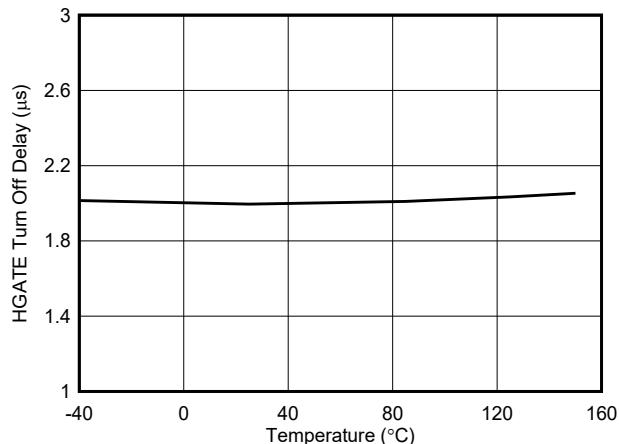

図 6-19. 短絡中の HGATE ターンオフ遅延

図 6-20. 短絡検出イネーブル・スレッショルド電圧 (HGATE-OUT)

## 7 パラメータ測定情報

図 7-1. タイミング波形

## 8 詳細説明

### 8.1 概要

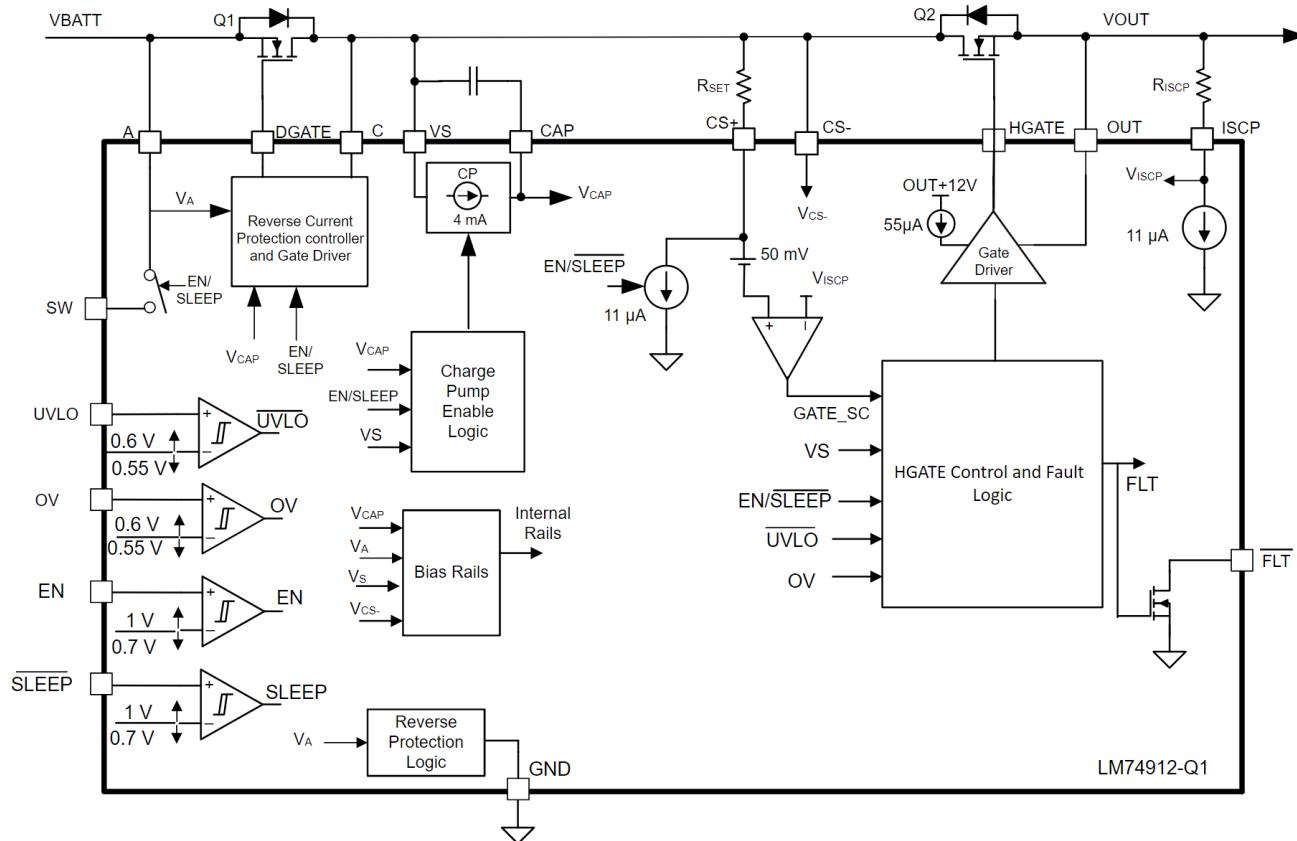

LM74912-Q1 理想ダイオード・コントローラは、逆並列外部 N チャネル MOSFET を駆動し、短絡、低電圧、過電圧保護機能により、低損失の電力パス保護を実現します。

入力電源電圧範囲が 3V～65V と広いため、12V および 24V 車載用バッテリ駆動 ECU を保護および制御できます。このデバイスは最低 -65V の負の電源電圧に耐え、この電圧から負荷を保護できます。内蔵の理想ダイオード・コントローラ (Dgate) は第 1 の MOSFET を駆動し、逆入力保護および出力電圧保持用のショットキー・ダイオードを置き換えます。電力パスの第 2 の MOSFET により、Hgate 制御を使用した負荷の切断 (オン / オフ制御) と過電圧保護が可能です。このデバイスには可変過電圧カットオフ保護機能があります。共通ドレイン構成のパワー MOSFET の場合、もう 1 つの理想ダイオードを使用した OR 接続設計のために中間点を利用できます。LM74912-Q1 の最高電圧定格は 65V です。

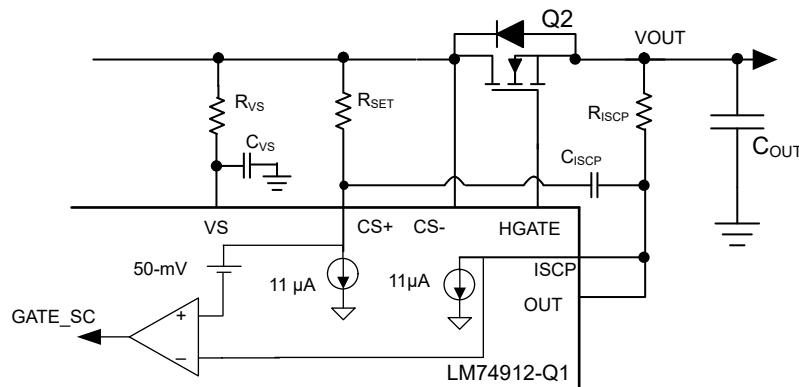

電流検出アンプを内蔵しており、外部 MOSFET (Q2) VDS 電圧を監視して短絡保護を実現します。このデバイスにはデフォルトの短絡コンパレータのスレッショルドが 50mV であり、外付け部品 ( $R_{ISCP}$  および  $R_{SET}$ ) を使用してこのスレッショルドをシフトする徹底的な柔軟性があります。いったん短絡状態が検出されると、EN, SLEEP, または VS ピンが Low から High に切り替わるまで、デバイスは MOSFET Q2 をラッチ・オフします。

このデバイスは可変過電圧および低電圧保護機能を備えており、電圧過渡事象が発生した場合に堅牢な負荷切断を行うことができます。

LM74912-Q1 には、EN および SLEEP ピンのステータスに基づいて 2 種類の低消費電力モードがあります。SLEEP モード (SLEEP=Low, EN=High) では、デバイスは外部 MOSFET ゲート・ドライブと内部チャージ・ポンプの両方をオフにすることでわずか  $5.5\mu A$  の電流しか消費しませんが、同時に内部バイパス・パスを備えているため、電流容量が制限されている状態で常時オンの負荷に電力を供給できます。イネーブル・ピンが Low のとき、デバイスは負荷を完全に切断して超低消費電力モードに移行し、消費電流は標準値  $2.5\mu A$  です。LM74912-Q1 は電圧定格が高いため、車載用 ISO7637 保護のシステム設計が簡単になります。LM74912-Q1 は OR 接続アプリケーションにも適しています。

## 8.2 機能ブロック図

このセクションでは、LM74912-Q1 の機能ブロック図を示します。

## 8.3 機能説明

### 8.3.1 チャージ・ポンプ

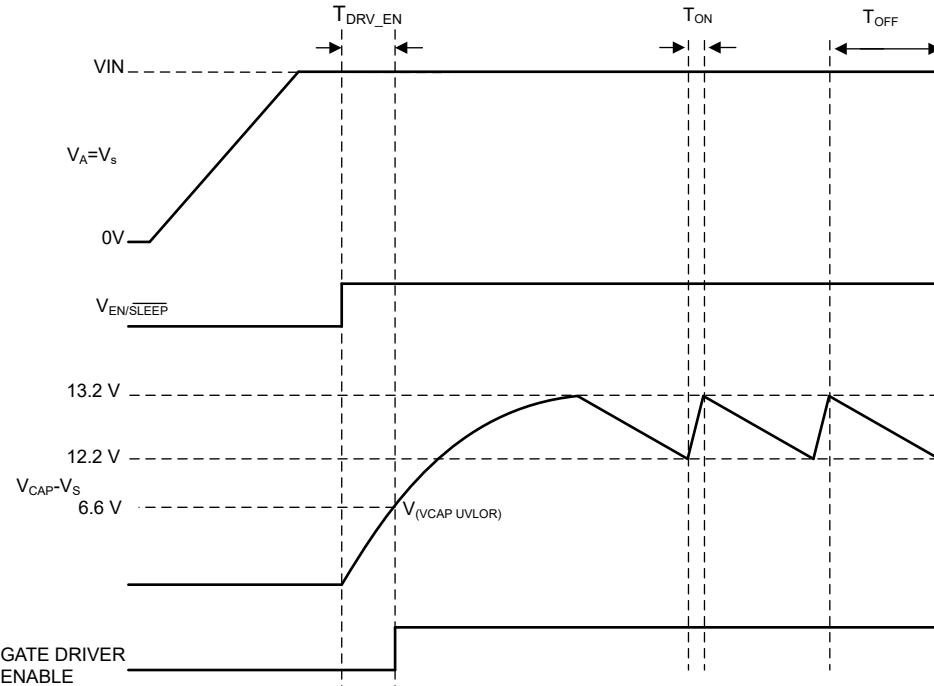

チャージ・ポンプは、外部の N チャネル MOSFET の駆動に必要な電圧を供給します。CAP ピンと VS ピンの間に外付けチャージ・ポンプ・コンデンサを配置して、外部 MOSFET をオンにするための電力を供給します。チャージ・ポンプが外部コンデンサに電流を供給するには、EN および SLEEP ピンの電圧が、指定された入力 High スレッショルドよりも高い必要があります。イネーブルにすると、チャージ・ポンプは標準値 4mA の充電電流を供給します。EN または SLEEP ピンが Low にプルされると、チャージ・ポンプはディセーブルのままです。外部 MOSFET を規定のスレッショルド電圧よりも高く駆動できるように、内部ゲート・ドライバがイネーブルになる前に、CAP から VS への電圧が低電圧誤動作防止スレッショルド (標準 6.6V) よりも高くなっている必要があります。ゲート・ドライバの初期イネーブル遅延を計算するには、式 1 を使用します。

$$T_{(DRV\_EN)} = 175 \mu s + \frac{C_{(CAP)} \times V_{(CAP\_UVLOR)}}{4 \text{ mA}} \quad (1)$$

ここで、

- $C_{(CAP)}$  は、VS ピンと CAP ピンの間に接続されているチャージ・ポンプ容量です

- $V_{(CAP\_UVLOR)} = 6.6V$  (標準値)

ゲート・ドライブのチャタリング除去には、VCAP 低電圧誤動作防止に約 1V のヒステリシスを加えます。チャージ・ポンプは、CAP から VS への電圧が標準 13.2V に達するまでイネーブルに維持され、この時点でチャージ・ポンプはディセーブルされ、VS ピンに流れる電流が減少します。CAP から VS への電圧が標準 12.2V を下回るまで、チャージ・ポンプはイネーブルのままであります。

ンプはディセーブルのまま維持され、その時点でチャージ・ポンプはイネーブルになります。図 8-1 に示すように、CAP と VS の間の電圧は 12.2V~13.2V の間で充電および放電を継続します。チャージ・ポンプをイネーブル / ディセーブルすることで、LM74912-Q1 の動作時静止電流が減少します。チャージ・ポンプがディセーブルになると、15μA の電流をシンクします。

図 8-1. チャージ・ポンプ動作

### 8.3.2 デュアル・ゲート制御 (DGATE, HGATE)

LM74912-Q1 は、2 つの独立したゲート制御およびドライバ出力、つまり DGATE および HGATE を備えており、逆並列 N チャネル MOSFET を駆動します。

#### 8.3.2.1 バッテリ逆接続保護 (A, C, DGATE)

A、C、DGATE は理想ダイオード段で構成されています。外部 MOSFET のソースを A に、ドレンを C に、ゲートを DGATE に接続します。LM74912-Q1 には、最低 -65V までの逆入力保護機能が内蔵されています。

DGATE ドライバをイネーブルにする前に、以下の条件を満たす必要があります。

- EN および SLEEP ピンの電圧は、指定された入力 High 電圧よりも高い必要があります。

- CAP から VS への電圧は、低電圧誤動作防止電圧よりも高い必要があります。

- A ピンの電圧は、VA POR 立ち上がりスレッショルドよりも高い必要があります。

- VS ピンの電圧は VS POR 立ち上がりスレッショルドよりも高い必要があります。

上記の条件が満たされない場合、DGATE ピンは A ピンに内部的に接続され、外部 MOSFET が確実にディセーブルされます。

LM74912-Q1 では、MOSFET の両端での電圧降下が A ピンと C ピンの間で継続的に監視され、DGATE から A への電圧は、順方向電圧降下を 10.5mV (標準値) でレギュレートするために必要に応じて調整されます。この閉ループ・レギュレーション方式により、逆電流発生時に MOSFET を穏やかにオフにでき、DC 逆電流を確実にゼロにします。この方式により、低速の入力電圧降下テスト中も堅牢な性能が保証されます。リニア・レギュレーション・アンプ方式に加えて、LM74912-Q1 には高速の逆電圧コンパレータも内蔵されています。A と C の両端間の電圧降下が  $V_{(AC\_REV)}$  スレッショルドに達すると、DGATE は 0.5μs (標準値) 以内で Low になります。この高速逆電圧コンパレータ方式により、入力マイクロ短絡などの高速入力電圧降下テスト時に堅牢な性能が保証されます。A と C の両端間の電圧が 0.8μs (標準値) 以内に  $V_{(AC\_FWD)}$  スレッショルドに達すると、外部 MOSFET が再びオンになります。

### 8.3.2.2 負荷切断スイッチ制御 (HGATE, OUT)

HGATE および OUT は、負荷切断スイッチ制御段で構成されています。外部 MOSFET のソースを OUT に、ゲートを HGATE に接続します。

HGATE ドライバをイネーブルにする前に、以下の条件を満たす必要があります。

- EN および SLEEP ピンの電圧は、指定された入力 High 電圧よりも高い必要があります。

- CAP から VS への電圧は、低電圧誤動作防止電圧よりも高い必要があります。

- VS ピンの電圧は Vs POR 立ち上がりスレッショルドよりも高い必要があります。

上記の条件が満たされない場合、HGATE ピンは OUT ピンに内部的に接続され、外部 MOSFET が確実にディセーブルされます。

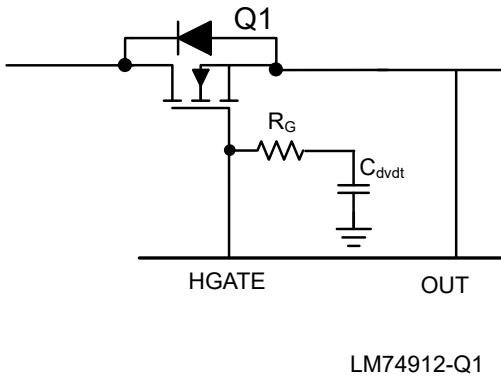

突入電流制限を行うには、図 8-2 に示すように  $C_{dvdt}$  コンデンサと  $R_1$  を接続します。

図 8-2. 突入電流制限

$C_{dvdt}$  コンデンサは、突入電流を制限するため、電源投入時の HGATE 電圧の上昇を遅くするために必要です。 $C_{dvdt}$  容量値を計算するには、式 2 を使用します。

$$C_{(dvdt)} = C_{OUT} \times \frac{I_{(HGATE\_DRV)}}{I_{INRUSH}} \quad (2)$$

$I_{HATE\_DRV}$  が  $55\mu A$  (標準値)の場合、 $I_{INRUSH}$  は突入電流、 $C_{OUT}$  は出力負荷容量です。 $C_{dvdt}$  コンデンサと直列に追加の抵抗  $R_1$  を使用すると、ターンオフ時間が短縮されます。

追加の  $C_{dvdt}$  コンデンサを接続して突入電流を制限することで、HGATE の応答が遅くなります。これにより、HGATE の回復が遅くなり、入力ラインに正のライン過渡があると、HGATE OUT の実効電圧が公称値から低下する可能性があります。

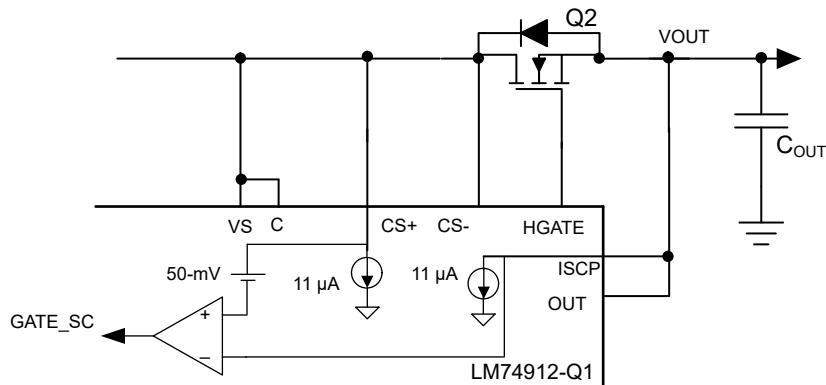

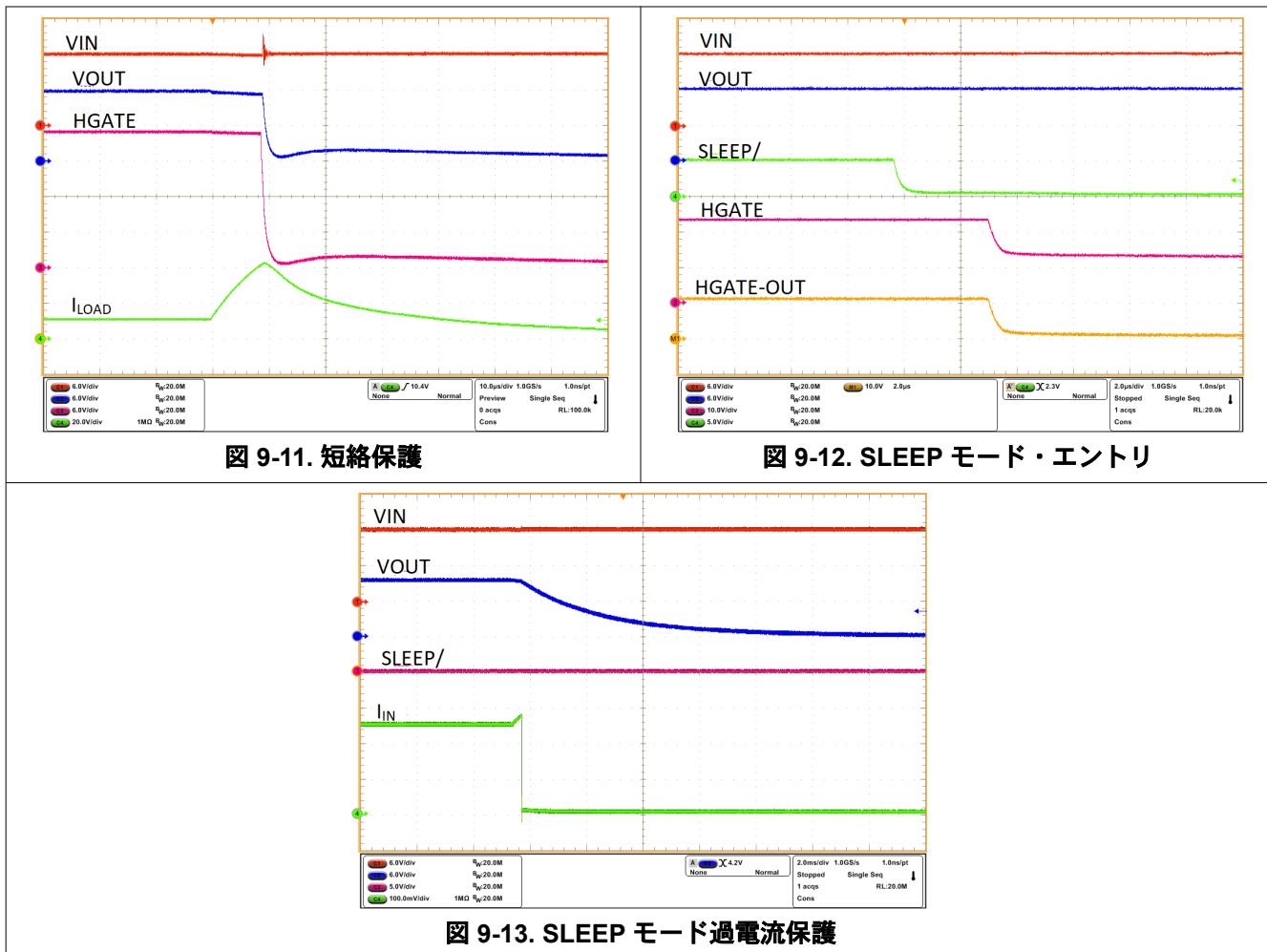

### 8.3.3 短絡保護 (CS+、CS-、ISCP)

LM74912-Q1 は、短絡保護機能により、短絡イベントを出力するのに高速に応答します。内部短絡コンパレータは、HGATE-OUT 電圧が標準  $6.4V$  を上回るとイネーブルになります。これにより、外部 FET が完全に機能強化され、デバイスの起動時に誤った短絡トリガが発生しないようにします。出力に短絡状態が発生し、CS+ と ISCP の両端の電圧がデフォルトの短絡コンパレータ・スレッショルドである標準  $50mV$  を超えると、HGATE は  $2\mu s$  以内に OUT にプルされ HFET を保護します。FLT は同時に Low にアサートします。いったん短絡状態が検出されると、EN、SLEEP、または VS ピンが Low から High に切り替わるまで、デバイスは MOSFET Q2 をラッチ・オフします。

図 8-3. 短絡保護コンパレータ

図 8-4 に示すように、短絡保護スレッショルドは、CS+ ピンからの外付け直列抵抗  $R_{SET}$  または ISCP ピンからの  $R_{ISCP}$  を使用して、デフォルトの 50mV スレッショルドから増減できます。 $R_{SET}$  抵抗はスレッショルドを正の方向にシフトし、 $R_{ISCP}$  抵抗はスレッショルドを負の方向にシフトします。短絡保護スレッショルドのシフトは、式 3 および式 4 を使用して計算できます。

$$V_{DS\_SNS} = 50 \text{ mV} + (11 \mu\text{A} \times R_{SET}) \quad (3)$$

$$V_{DS\_SNS} = 50 \text{ mV} - (11 \mu\text{A} \times R_{ISCP}) \quad (4)$$

図 8-4 に示すように、CS+ ピンと ISCP ピンの間にグリッチ除去コンデンサ  $C_{ISCP}$  を追加することで、短いスプリアス電流スパイクに対してブランкиングを行い、入力マイクロ・カット (LV124, E-10), AC 重畠 (LV124, E-06), ISO7637-2 パルス 2A などの高速な車載過渡事象が発生した場合の誤った短絡トリガを防止します。

また、短絡状態のために MOSFET Q2 がオフになると、基板の寄生容量および入力配線ハーネスのインダクタンスによる誘導性の影響により、電源ラインで電圧発振が発生する可能性があります。これらの発振がデバイスの電源ピン VS に達して誤リセットが引き起こされないよう、直列抵抗  $R_{VS}$  を追加で挿入できます。この直列抵抗  $R_{VS}$  は、VS 側のデカップリング・コンデンサ  $C_{VS}$  とともに R-C ロー・パス・フィルタを形成し、発振の減衰に役立ちます。

図 8-4. グリッチ除去フィルタによる短絡保護

LM74912-Q1 は、高精度の電流センシングは不要ですが、何らかのレベルのフォルト保護が必要なアプリケーションを対象としています。たとえば、電源バスのインダクタンスやインピーダンスが、短絡状態での電流の上昇を制限するアプリケーションなどです。

ピーク・ドレイン - ソース間電流と短絡保護応答時間が MOSFET の SOA 定格内に収まるように、外部 N チャネル MOSFET の安全動作領域 (SOA) を慎重に考慮する必要があります。また、与えられた温度範囲における外部 N チャネル MOSFET の RDS(ON) 変動が過電流検出の精度に影響を及ぼすことにも注意してください。

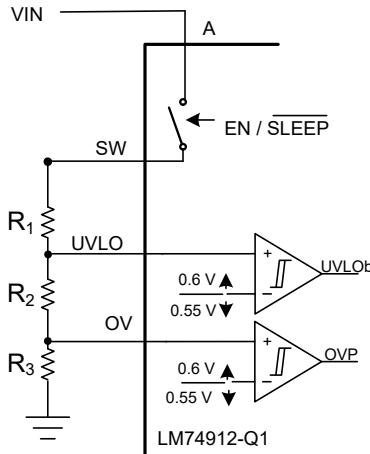

### 8.3.4 過電圧保護およびバッテリ電圧センシング (SW、OV、UVLO)

過電圧および低電圧スレッショルドのプログラミングには、図 8-5 に示すように抵抗ラダーを接続します。

図 8-5. 過電圧スレッショルドのプログラミングとバッテリ・センシング

A ピンと SW ピンの間には切断スイッチが内蔵されています。EN ピンまたは SLEEP ピンが Low になると、このスイッチはオフになります。これにより、システムのシャットダウン状態 (IGN\_OFF 状態) 時に分圧抵抗回路を流れるリーク電流を低減できます。

入力側から過電圧または低電圧状態が解消されると、HGATE は再度オンになります。

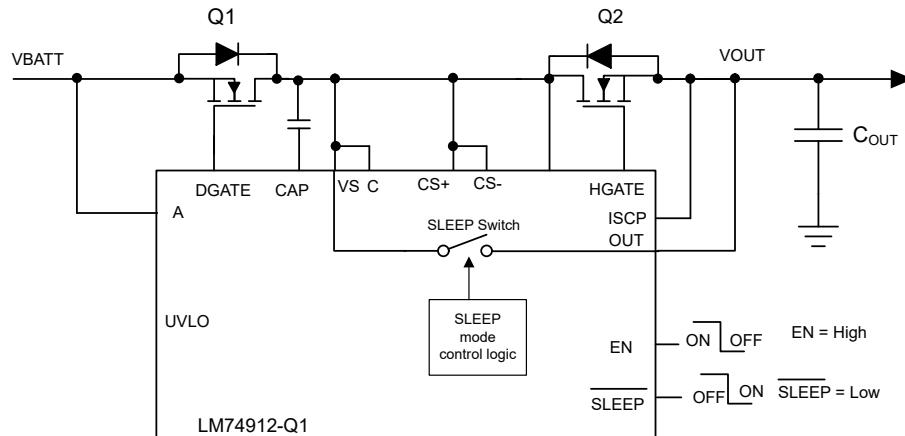

### 8.3.5 低 IQ SLEEP モード (SLEEP、SLEEP\_OV)

LM74912-Q1 は、低 IQ の SLEEP モード動作をサポートしています。このモードは、SLEEP ピンを Low (EN = High) にプルすることでイネーブルできます。SLEEP モードでは、デバイスは内部チャージ・ポンプと SW スイッチをオフにし、DGATE および HGATE 駆動をディセーブルにすることで、標準値  $5.5\mu\text{A}$  の低消費電流を実現します。ただし、同時にデバイスは、標準オン抵抗  $7\Omega$  の内部低消費電力 MOSFET を経由して OUT ピンに接続された常時オンの負荷を起動します。このモードでは、デバイスは  $100\text{mA}$  のピーク負荷電流をサポートできます。負荷が大きくなると、内部 MOSFET の両端での電圧降下が大きくなります。このデバイスは、標準  $250\text{mA}$  の過電流スレッショルドにより、スリープ・モード中の過電流保護を提供します。スリープ・モード中に過電流が発生した場合、デバイスは内部 MOSFET スイッチを切断し、デバイスをラッチオフすることで内部 FET を保護します。追加の保護層として、SLEEP モードでデバイスが過熱した場合に備えて、SLEEP モードではサーマル・シャットダウンとラッチオフ機能も備えています。本デバイスをラッチ・モードから解除するには、ユーザーは SLEEP ピンまたは EN ピンを切り替える必要があります。

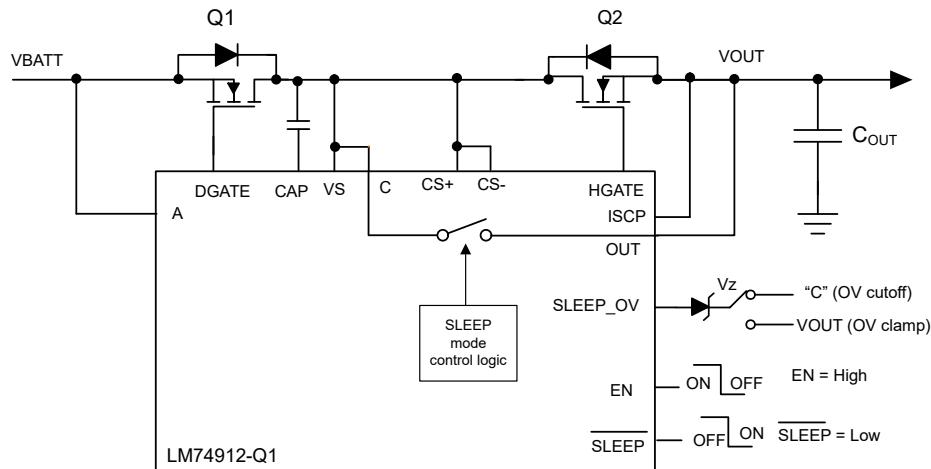

SLEEP モードでは、LM74912-Q1 は入力過電圧イベントに対する保護を行います。デバイスは、過電圧カットオフ (SLEEP\_OV を C に接続) または過電圧クラップ・モード (SLEEP\_OV を  $V_{OUT}$  に接続) に構成でき、デフォルトの過電圧スレッショルドは標準  $21\text{V}$  です。

SLEEP モード機能が不要な場合は、SLEEP ピンを EN に接続する必要があります。使用しない場合、SLEEP\_OV ピンをフローティングのままにできます。

図 8-6. LM74912-Q1 SLEEP モード

図 8-7 に示すように、SLEEP\_OV ピンと OUT/C の間に外部ツエナー・ダイオードを追加することで、SLEEP モードでより高い過電圧スレッショルドを実現できます。この機能は、24V または 48V 電源システムの過電圧スレッショルドを構成するときに役立ちます。

図 8-7. SLEEP モードでの過電圧スレッショルドの拡張

## 8.4 デバイスの機能モード

### シャットダウン・モード

イネーブル・ピンにより、外部信号を使用してゲート・ドライバをイネーブルまたはディセーブルできます。EN ピンの電圧が立ち上がりスレッショルドより高い場合、ゲート・ドライバとチャージ・ポンプは「チャージ・ポンプ」に記載されているように動作します。EN ピンの電圧が入力 Low スレッショルド  $V_{(ENF)}$  よりも低い場合、チャージ・ポンプと両方のゲート・ドライバ (DGATE および HGATE) がディセーブルされ、LM74912-Q1 はシャットダウン・モードになります。消費電流が  $2.5\mu\text{A}$  と非常に低くなります。EN ピンは  $65\text{V}$  の最大電圧に耐えることができます。常時オン動作を行うには、EN ピンを VS に接続します。

## 9 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インストルメンツの製品仕様に含まれるものではなく、テキサス・インストルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 9.1 アプリケーション情報

LM74912-Q1 は 2 つの N チャネル・パワー MOSFET を制御し、DGATE を使用してダイオード MOSFET を制御して理想ダイオードをエミュレートします。また、HGATE を使用して 2 番目の MOSFET を制御し、ディセーブル時や過電流、過電圧、低電圧イベント時に電力パスをカットオフします。HGATE 制御の MOSFET を使用して、過電圧または負荷ダンプ状態で出力をクランプできます。LM74912-Q1 は、EN または SLEEP を使用して低静止電流モードに移行でき、ここで DGATE と HGATE の両方がオフになります。このデバイスには、独立した電源入力ピン (VS) があります。チャージ・ポンプは、この電源入力から生成されます。独立した電源入力供給と独立した GATE 制御アーキテクチャにより、LM74912-Q1 デバイスはコモン・ドレイン・トポロジで逆並列接続された MOSFET を駆動するため、電源 OR 接続や電源優先マルチプレクサ・アプリケーションなど、さまざまなシステム・アーキテクチャが可能になります。これらのさまざまなトポロジを使用することで、システム設計者はさまざまなシステム設計要件を満たすフロント・エンド電源システムを設計できます。

このデバイスには、独立した電源入力ピン (VS) があります。チャージ・ポンプは、この電源入力から生成されます。独立した電源入力供給と独立した GATE 制御アーキテクチャにより、LM74912-Q1 デバイスはコモン・ドレイン・トポロジで逆並列接続された MOSFET を駆動するため、電源 OR 接続や電源優先マルチプレクサ・アプリケーションなど、さまざまなシステム・アーキテクチャが可能になります。これらのさまざまなトポロジを使用することで、システム設計者はさまざまなシステム設計要件を満たすフロント・エンド電源システムを設計できます。

### 9.2 12V (代表値) バッテリ逆接続保護アプリケーション

過電圧保護付きで逆バッテリ保護を行うコモン・ドレイン・トポロジで構成されている LM74912-Q1 の代表的なアプリケーション回路を図 9-1 に示します。

\* Optional component

図 9-1. 代表的なアプリケーション回路 - 12V のバッテリ逆接続保護と過電圧保護

### 9.2.1 12V バッテリ保護の設計要件

システム設計要件を表 9-1 に示します。

**表 9-1. 設計パラメータ - 12V のバッテリ逆接続保護および過電圧保護**

| 設計パラメータ   | 値の例                                           |

|-----------|-----------------------------------------------|

| 動作時入力電圧範囲 | 12V バッテリ、公称 12V、3.2V のコールド・クランク、35V の負荷ダンプ    |

| 出力電力      | 50W                                           |

| 出力電流範囲    | 公称 4A、最大 5A                                   |

| 短絡電流レベル   | 14A                                           |

| 入力容量      | 最小 0.1μF                                      |

| 出力容量      | 最小 0.1μF (E-10 機能クラス A パフォーマンスのオプション 100μF)   |

| 過電圧カットオフ  | 37.0V、出力カットオフ > 37.0V                         |

| AC 重畠テスト  | 2V ピーク・ツー・ピーク 30KHz、6V ピーク・ツー・ピーク 30KHz に拡張可能 |

| 車載過渡耐性準拠  | ISO 7637-2、ISO 16750-2、および LV124              |

### 9.2.2 車載バッテリ逆接続保護

LM74912-Q1 は、2 つの独立したゲート制御およびドライバ出力、DGATE および HGATE を備えており、逆並列 N チャネル MOSFET を駆動します。このため、LM74912-Q1 は ISO 7637-2 および ISO 16750-2 規格や他の車載 OEM 規格に準拠した各種車載過渡テストにおいて、堅牢なシステム保護とともに包括的な耐性を実現できます。詳細については、「[車載用 EMC 準拠、理想ダイオード・コントローラによる逆バッテリ保護](#)」の記事を参照してください。

LM74912-Q1 のゲート駆動出力 DGATE は MOSFET Q1 を制御し、逆バッテリ保護と真の逆電流ブロック機能を実現します。HGATE は、入力過電圧状態時に電力バスをオフにするように MOSFET Q2 を制御します。OV と SW に接続された抵抗ネットワーク R1、R2、R3 を構成して、過電圧保護を実現できます。また、通常の動作条件とバッテリ逆接続条件でのバッテリ監視も実現できます。双方向 TVS D1 は、12V バッテリの車載用過渡入力電圧を、正と負の両方の過渡電圧として、MOSFET Q1 および LM74912-Q1 にとって安全な電圧レベルにクランプします。

LM74912-Q1 は、高速な逆電流ブロック応答と迅速な逆回復により、ISO 16750-2 と LV124 E-06 で規定されている AC 重畠入力時に MOSFET Q1 をオン / オフし、AC 入力を DC バッテリ電圧に重畠してアクティブ整流できます。LM74912-Q1 の高速な逆電流ブロック応答により、ISO 7637-2 で規定されている -150V 2ms パルス 1 などの負の過渡入力や、LV124 E-10 テストなどの入力マイクロ短絡状態時に MOSFET Q1 をオフにできます。

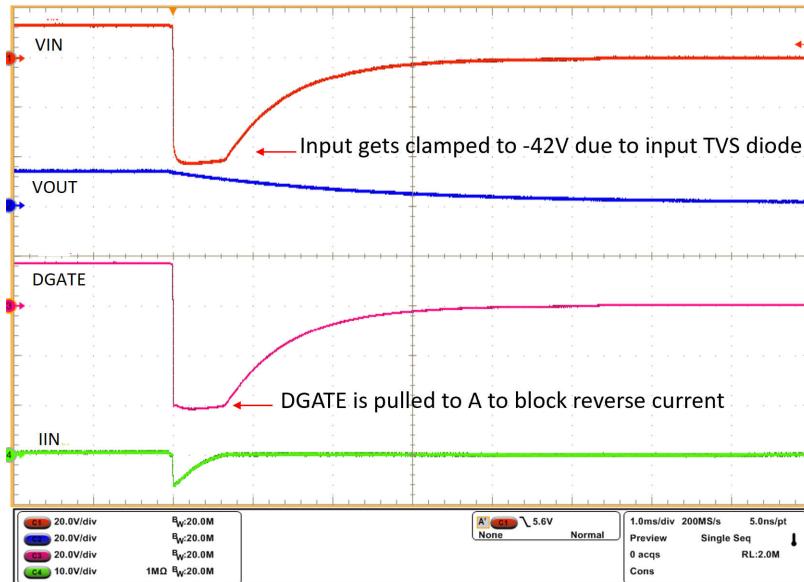

#### 9.2.2.1 入力過渡保護 : ISO 7637-2 パルス 1

ISO 7637-2 パルス 1 は、バッテリが接続されていない時に誘導性負荷と並列に接続された電子モジュールの負の過渡耐性を規定しています。ISO 7637-2 に規定されている標準的なパルス 1 はバッテリの切断から始まり、電源電圧が 0V に低下してから -150V 2ms が、スルーレート  $1\mu\text{s}$  でソース・インピーダンス  $10\Omega$  により電源入力に印加されます。LM74912-Q1 は逆電流をブロックし、出力電圧が負にスイギングしないようにします。これにより、負の過渡電圧により残りの電子回路が損傷しないようにします。LM74912-Q1 の高速逆極性コンパレータにより、MOSFET Q1 は  $0.5\mu\text{s}$  以内に迅速にオフになります。単一の双方向 TVS は、負の過渡パルスをカソード - アノード間の動作時最大電圧である 85V 内にクランプするため入力時に必要で、MOSFET Q1 のドレイン - ソース間ブレークダウン電圧定格に違反していません。

図 9-2 に、LM74912-Q1 の ISO 7637-2 パルス 1 性能を示します。

図 9-2. ISO 7637-2 パルス 1

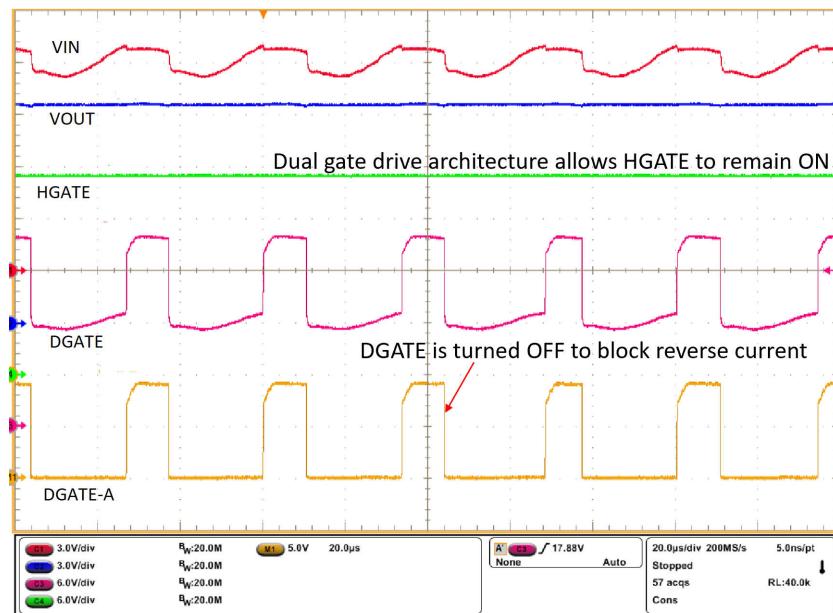

### 9.2.2.2 AC 重畠入力の整流 : ISO 16750-2 およびLV124 E-06

オルタネータは、車載電気システムに電力を供給し、車両の通常動作時間中にバッテリを充電するために使用されます。整流されたオルタネータ出力には、エンジン回転数の変動、フィールド・スイッチングオン／オフによるレギュレータのデューティ・サイクル、および電気負荷の変動といったさまざまな理由で、残留 AC リップル電圧が DC バッテリ電圧に重畠されています。12V のバッテリ電源では、オルタネータの回転子のフィールド電流を制御することにより、電圧レギュレータによってオルタネータの出力電圧が 14.5V～12.5V の範囲内にレギュレートされます。すべての電子モジュールは、DC バッテリ電圧に AC リップルを重畠した状態で適切に動作することをテスト済みです。ISO 16750-2 と LV124 E-06 に規定されている AC 重畠テストでは、15Hz～30KHz で掃引された 13.5V DC バッテリ電圧で 2V ピーク・ツー・ピークの AC リップルが必要です。LM74912-Q1 は、MOSFET Q1 を素早くオフにして逆電流をカットオフし、順方向導通中に MOSFET Q1 を素早くオンにすることで、AC 重畠電圧を整流します。MOSFET の高速なターンオフと迅速なターンオンにより、MOSFET Q1 の消費電力が低減され、アクティブ整流によって出力ホールドアップ・コンデンサの ESR の消費電力が半分に低減されます。図 9-3 に、2V ピーク・ツー・ピーク 30KHz AC 入力のアクティブ整流を示します。

図 9-3. AC 重量テスト - 2V ピーク・ツー・ピーク 30KHz

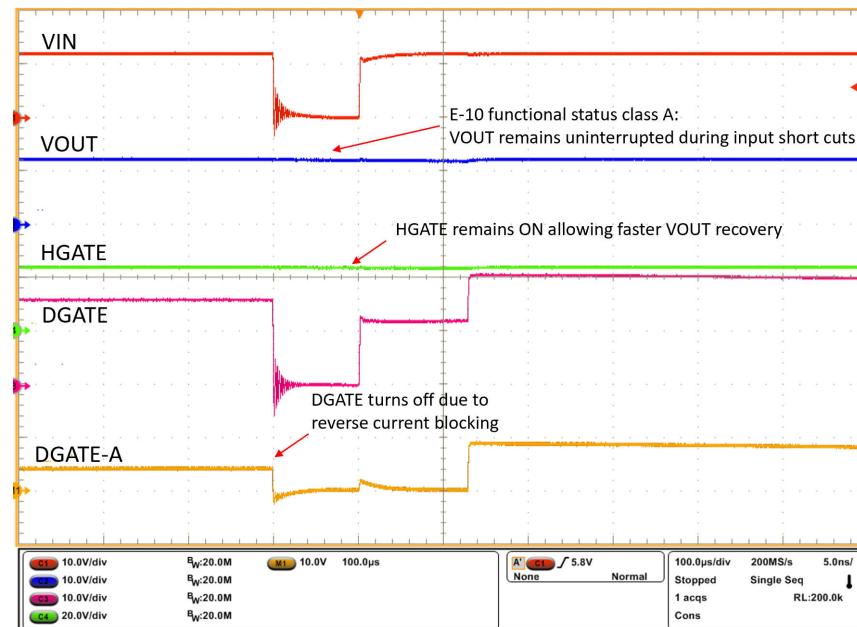

### 9.2.2.3 入力マイクロ短絡保護 : LV124 E-10

LV124 規格で規定されている E-10 テストは、接点の問題またはリレー・バウンスによる電源入力の短時間中断に対する電子モジュールの耐性をチェックします。このテスト(ケース 2)では、わずか  $10\mu\text{s}$ ～数 ms の間、入力にマイクロ短絡を印加します。機能パス・ステータス A を取得するには、電子モジュールが E-10 テスト(ケース 2)中に  $100\mu\text{s}$  の持続時間で中断なく動作することが求められます。LM74912-Q1 - D GATE および H GATE のデュアル・ゲート駆動アーキテクチャにより、シングル・ゲート駆動コントローラに比べて出力のホールドアップ容量が最適な機能パス・ステータス A を実現できます。入力のマイクロ短絡が  $100\mu\text{s}$  に印加されると、LM74912-Q1 は D GATE を  $0.5\mu\text{s}$  以内にアノード(MOSFET のソース)に短絡することで MOSFET Q1 を迅速にオフにして出力の放電を防止します。また、H GATE は MOSFET Q2 をオンに維持し、入力短絡が解消した後に迅速に回復できるようにします。

E10 入力電源切断テスト・ケース 2 中の LM74912-Q1 の性能を図 9-4 に示します。入力短絡が解消した後、入力電圧は回復し、MOSFET Q1 は  $130\mu\text{s}$  以内に再びオンになります。デュアル・ゲート・ドライブ・トポロジにより、テスト中 MOSFET Q2 をオンに維持できるため、入力電力をより高速に復元できる点に注意してください。持続時間全体にわたって出力電圧が変動しないため、機能ステータス A を実現します。

図 9-4. 入力マイクロ短絡 - LV124 E10 TC 2 100μs

### 9.2.3 詳細な設計手順

#### 9.2.3.1 設計上の考慮事項

表 9-1 に、過電圧カットオフ機能を備えた車載バッテリ逆接続保護回路を設計する際に知っておく必要のある設計パラメータをまとめています。電源投入時には、MOSFET が SOA 内で適切に動作するように、MOSFET Q2 を流れる突入電流を制限する必要があります。PCB の最大負荷電流、最大周囲温度、熱特性によって MOSFET Q2 の  $R_{DS(on)}$  が決まり、最大動作電圧によって MOSFET Q2 の電圧定格が決まります。MOSFET Q2 の選択は、主に最大動作負荷電流、最大周囲温度、AC 重畠電圧リップルの最大周波数、ISO 7637-2 のパルス 1 の要件により決まります。過電圧スレッショルドは、バッテリ逆接続保護回路の後段にあるダウントリーム DC / DC コンバータまたは他の部品の定格に基づいて決まります。MOSFET Q1、Q2、LM74912-Q1 の安全な動作レベルに入力過渡電圧をクランプするには、1 つの双方向 TVS または 2 つの逆並列單方向 TVS が必要です。

#### 9.2.3.2 チャージ・ポンプ容量 VCAP

チャージ・ポンプ VCAP に必要な最小容量は、MOSFET Q1、 $C_{ISS(MOSFET\_Q1)}$  の入力容量、および Q2  $C_{ISS(MOSFET)}$  の入力容量に基づきます。

チャージ・ポンプ VCAP: 0.1 $\mu$ F 以上が必要です。推奨値は  $VCAP (\mu F) \geq 10 \times (C_{ISS(MOSFET\_Q1)} + C_{ISS(MOSFET\_Q2)}) (\mu F)$

#### 9.2.3.3 入力、電源、および出力容量

最小入力容量  $C_{IN}$  は 0.1 $\mu$ F、出力容量  $C_{OUT}$  は 0.1 $\mu$ F をお勧めします。VS ピンは、デバイスへの電源入力として機能します。VS ピンとグランドの間には、最小 0.1 $\mu$ F のデカップリング・コンデンサをお勧めします。

#### 9.2.3.4 ホールドアップ容量

通常、出力にバルク・コンデンサを配置するのは、電源切断時の連続動作や入力側のマイクロ短絡、モジュールが停止する前にメモリ・ダンプを実行するためのホールドアップ要件、フィルタリング要件など、さまざまな理由があります。この設計は、LV124 E10 テスト・ケース 2 で 100 $\mu$ s の入力中断が発生している間に、機能ステータス「A」を満たすために、バルク・コンデンサの最小要件を考慮しています。機能パス・ステータス A を実現するため、LM74912-Q1 の出力で許容される電圧ドループは、ダウントリームの DC / DC コンバータの UVLO 設定に基づいています。この設計では、100 $\mu$ s について 12V から 6.5V へ出力電圧の降下を考慮し (5V 出力のダウントリーム・コンバータを想定)、必要な最小ホールドアップ容量は次で計算されます。

$$C_{HOLD\_UP\_MIN} = \frac{I_{LOAD} \times 100 \mu s}{\Delta V_{OUT}} \quad (5)$$

100 $\mu$ s で 5.5V の電圧降下を実現するために必要な最小ホールドアップ容量は、100 $\mu$ F です。すべての設計でホールドアップ容量が必要とされるわけではないため、代表的なアプリケーション回路ではホールドアップ・コンデンサがオプションとして示されていることに注意してください。

#### 9.2.3.5 過電圧保護とバッテリ監視

SW ピンとグランドの間に接続された抵抗 R1、R2、R3、R4 を使用して、低電圧と過電圧スレッショルドをプログラミングします。低電圧スレッショルド (UVLO から 5.5V) と過電圧スレッショルド (OV から 37.0V) を設定するために必要な抵抗値は、式 6 および式 6 を解くことで計算できます。

$$V_{UVLOF} = \frac{R_2 \times V_{UVSET}}{(R_1 + R_2)} \quad (6)$$

$$V_{OVR} = \frac{R_4 \times V_{OVSET}}{(R_3 + R_4)} \quad (7)$$

抵抗 R1、R2、R3 を経由してバッテリから引き出される入力電流を最小限に抑えるため、より大きな抵抗値の使用を推奨します。値の大きい抵抗を使用すると、計算に誤差が追加されます。これは、値の大きい抵抗を流れる電流が、OV ピンへ

のリーク電流と同等になるためです。OV ピンへの最大リーク電流は  $1\mu\text{A}$  であり、 $(R_1 + R_2 + R_3) < 120\text{k}\Omega$  を選択すると、抵抗を流れる電流が OV ピンを流れるリークの 100 倍になることが保証されます。

デバイスの電気的特性に基づき、 $V_{UVLOF}$  は  $0.55\text{V}$  です。 $R_1 = 100\text{k}\Omega$  を選択します。式 14 を解くと、 $R_2 = 11.5\text{k}\Omega$  が得られます。 $R_3$  に  $100\text{k}\Omega$ 、 $V_{OVR} = 0.6\text{V}$  を選択して式 15 を解くと、計算された抵抗値に最も近い標準 1% の抵抗値として  $R_4 = 1.65\text{k}\Omega$  が得られます。

オプションのコンデンサ  $C_{UV}$  を UVLO 抵抗ラダーの  $R_2$  と並列に配置することで、バッテリ・ラインの高速低電圧過渡をフィルタして UVLO トリガの誤検出を防止できます。

このアプリケーション例では、過電圧および低電圧スレッショルドをプログラムするため、別の抵抗ラダーを選択しています。ただし、セクション 8.3.4 に示すように、SW ピンとグランドの間に一般的な抵抗ラダーを使用することもできます。

### 9.2.3.6 短絡電流スレッショルドの選択

LM74912-Q1 には電流検出アンプが内蔵されています。このアンプは、外部 MOSFET の両端の  $V_{DS}$  降下を監視し、内部の  $50\text{mV}$  のデフォルト・スレッショルドと比較します。外部 MOSFET の両端の電圧降下が  $50\text{mV}$  のスレッショルドを超えると、ラッチ状態で MOSFET Q2 がオフになります。

外付け MOSFET Q2  $R_{DSON}$  は、以下に従って選択できます

$$R_{DSON} = \frac{50 \text{ mV}}{I_{SCP}} \quad (8)$$

MOSFET  $R_{DSON}$  は通常、 $-40^\circ\text{C} \sim 125^\circ\text{C}$  の温度範囲にわたって最大 2 倍変化する可能性があり、 $R_{DSON}$  は  $125^\circ\text{C}$  で高くなります。これは、短絡電流検出の精度に影響を与える可能性があるため、この点を考慮する必要があります。

#### 9.2.3.6.1 短絡保護用のスケーリング抵抗 $R_{SET}$ と $R_{ISCP}$ の選択

$R_{SET}$  は、共通ドレイン・ポイントと CS+ ピンの間に接続される抵抗です。この抵抗は短絡保護スレッショルド電圧を正方向にスケーリングし、ISCP ピンから VOUT に接続された抵抗  $R_{ISCP}$  は短絡スレッショルドを負方向にスケーリングします。短絡検出時の  $V_{DS}$  検出スレッショルド電圧のシフトは、以下の式で計算できます

$$V_{DS\_SNS} = 50 \text{ mV} + (11 \mu\text{A} \times R_{SET}) \quad (9)$$

$$V_{DS\_SNS} = 50 \text{ mV} - (11 \mu\text{A} \times R_{ISCP}) \quad (10)$$

図 9-1 に示すように、 $R_{SCP}$  と  $C_{SCP}$  からなる追加のグリッチ除去フィルタ（オプション）を ISCP ピンから CS- ピンに追加することで、入力マイクロ・カット (LV124、E-10)、AC 重畠 (LV124、E-06)、または ISO7637-2 パルス 2A などの高速な車載過渡事象が発生した場合の誤った短絡トリガを回避できます。

### 9.2.4 MOSFET の選択：ブロッキング MOSFET Q1

ブロッキング MOSFET Q1 の選択に重要な電気的パラメータは、最大連続ドレイン電流  $I_D$ 、最大ドレイン - ソース間電圧  $V_{DS(MAX)}$ 、最大ドレイン - ソース間電圧  $V_{GS(MAX)}$ 、ボディ・ダイオードを流れる最大ソース電流、ドレイン - ソース間オン抵抗  $R_{DSON}$  です。

最大連続ドレイン電流  $I_D$  定格は、最大連続負荷電流を超える必要があります。

最大ドレイン - ソース間電圧  $V_{DS(MAX)}$  は、このアプリケーションで見られる最大の差動電圧に耐えるのに十分な高さが必要です。これには、すべての車載用過渡事象と予測される障害条件が含まれます。 $V_{DS}$  電圧定格  $60\text{V}$  の MOSFET、単一の双向 TSV または最大定格  $40\text{V}$  の  $V_{DS}$ 、および入力に逆並列接続された 2 つの单方向 TSV を使用することをお勧めします。

LM74912-Q1 が駆動できる最大  $V_{GS}$  は  $14\text{V}$  であるため、 $V_{GS}$  の最小定格が  $15\text{V}$  の MOSFET を選択する必要があります。 $V_{GS}$  定格が  $15\text{V}$  未満の MOSFET を選択した場合、ツェナー・ダイオードを使用して  $V_{GS}$  を安全なレベルにクラシップできますが、これにより  $I_Q$  電流が増加します。

MOSFET の導通損失を低減するために、可能な限り低い  $R_{DS(ON)}$  が好ましいですが、低い  $R_{DS(ON)}$  に基づいて MOSFET を選択することは必ずしも有益ではない場合があります。 $R_{DS(ON)}$  が大きいと、逆電流が低い時に、LM74912-Q1 の逆方向コンパレータに電圧上昇に関する情報が提供されます。 $R_{DS(ON)}$  を大きくすると、逆電流検出が改善されます。最大電流時に順方向電圧降下が 50mV 未満の MOSFET を選択することが、適切な出発点です。

バッテリ電源電圧に AC 重畠リップルをアクティブ整流するには、必要な AC リップル周波数を満たすように Q1 のゲート - ソース間電荷  $Q_{GS}$  を選択する必要があります。各サイクルのアクティブ整流における最大ゲート - ソース間電荷  $Q_{GS}$  (4.5V  $V_{GS}$  時) は以下のようになります

$$Q_{GS\_MAX} = \frac{2.5 \text{ mA}}{f_{AC\_RIPPLE}} \quad (11)$$

ここで、2.5mA は 7V での最小チャージ・ポンプ電流 ( $V_{DGATE} - V_A$ ) です。 $f_{AC\_RIPPLE}$  はバッテリに重畠される AC リップルの周波数で、 $Q_{GS\_MAX}$  は 6-V  $V_{GS}$  時のメーカー・データシートに規定されている  $Q_{GS}$  値です。

接合部温度 ( $T_J$ ) を適切に制御するには、MOSFET の予想最大消費電力と比較して MOSFET の熱抵抗を考慮する必要があります。

### 9.2.5 MOSFET の選択 : ホットスワップ MOSFET Q2

MOSFET Q2 の  $V_{DS}$  定格は、最大システム電圧と入力過渡電圧を処理するのに十分な値である必要があります。この 12V 設計では、過渡過電圧イベントが抑制された負荷ダンプ 35V 400ms、および 50μs の ISO 7637-2 パルス 2A 50V 中に発生します。さらに、ISO 7637-2 パルス 3B は 100V 100ns の非常に高速な反復パルスであり、通常は入力と出力のセラミック・コンデンサに吸収されます。12V バッテリの最大電圧は 40V 未満に制限でき、推奨される最小入力容量は 0.1μF です。50V ISO 7637-2 パルス 2A は入力および出力コンデンサにも吸収され、入力および出力に十分な容量を配置することで、その振幅を 40V ピークに低減できます。ただし、この 12V 設計では、最大システム電圧は 50V で、60V  $V_{DS}$  定格の MOSFET が選択されています。

MOSFET Q2 の  $V_{GS}$  定格は、その最大 HGATE OUT 電圧 15V を上回っている必要があります。

12V バッテリへの入力ホット・プラグ時に MOSFET に流れる突入電流は、出力容量によって決まります。HGATE、 $C_{dvdt}$  の外付けコンデンサを使用して、入力ホット・プラグ時またはスタートアップ時の突入電流を制限します。式 2 で決定される突入電流の値は、MOSFET Q2 がその安全動作領域 (SOA) 内で適切に動作するように選択する必要があります。

Q2 では、60V  $V_{DS}$  と ±20V  $V_{GS}$  定格を持つ MOSFET BUK7Y4R8-60E が選択されています。突入電流時の消費電力は、MOSFET の安全動作領域 (SOA) 内に十分収まっています。

### 9.2.6 TVS の選択

入力過渡クランプと保護のため、SMBJ33CA などの 600W SMBJ シリーズ TVS をお勧めします。12V バッテリ・システム用の TVS 選択の詳細については、『12V バッテリ・システム用の TVS 選択』を参照してください。

### 9.2.7 アプリケーション曲線

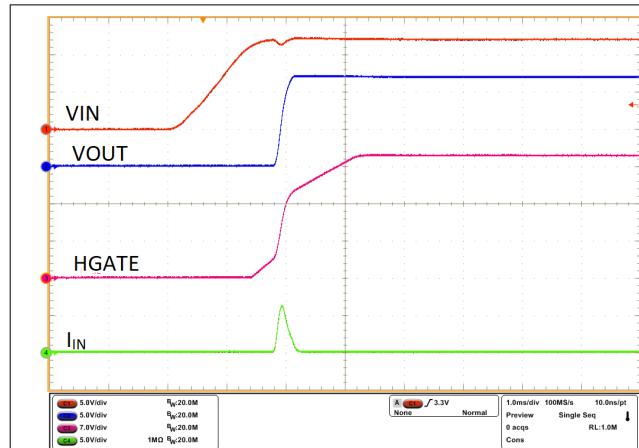

図 9-5. EN が VS にプルされているときのスタートアップ 12V

図 9-6. EN が Low から High になるときのスタートアップ

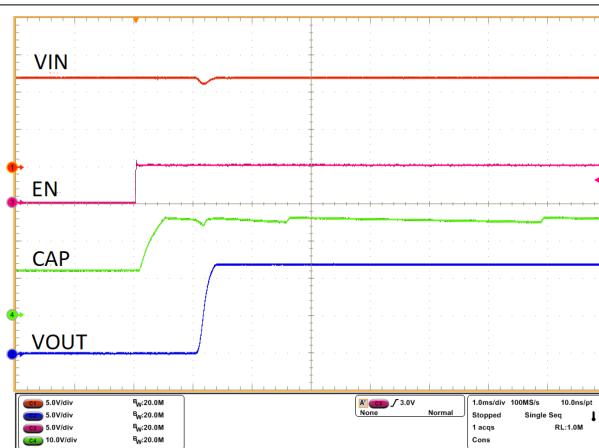

図 9-7. 逆入力電圧 -14V

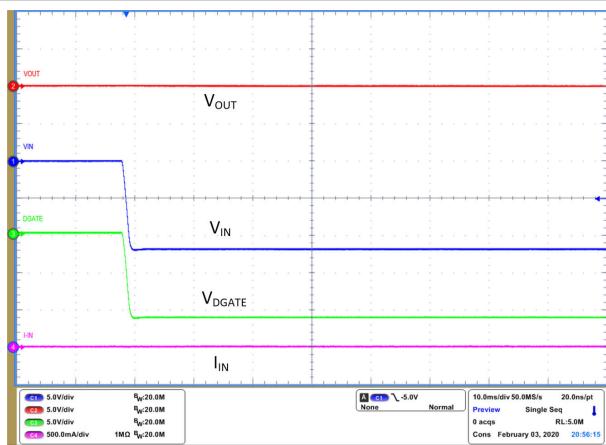

図 9-8. 過電圧保護

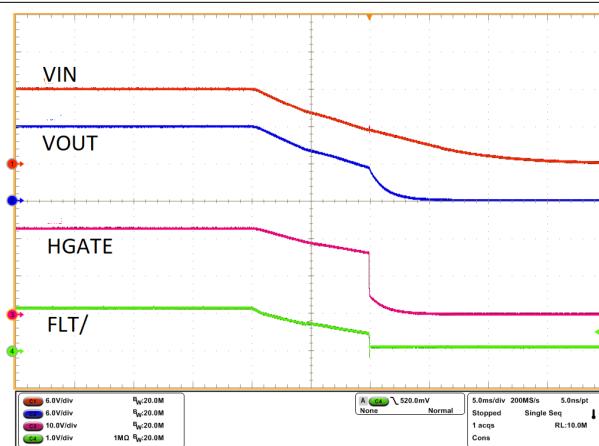

図 9-9. 過電圧復帰

図 9-10. 低電圧カットオフ応答

### 9.3 設計のベスト・プラクティス

IC の露出パッド (RTN) はフローティングのままにしてください。GND プレーンには接続しないでください。RTN を GND に接続すると、逆極性保護機能がディスエーブルになります。

### 9.4 電源に関する推奨事項

#### 9.4.1 過渡保護

電流フローの中止となる過電流、過電圧、低電圧カットオフ、逆電流ブロックなどの条件中に外部 MOSFET がオフになると、入力ライン・インダクタンスによって入力に正の電圧スパイクが発生し、出力インダクタンスによって出力に負の電圧スパイクが発生します。電圧スパイク (過渡現象) のピーク振幅は、デバイスの入力または出力に存在する直列インダクタンスの値に依存します。この問題に何等かの策を講じない場合は、上記の過渡現象によって、デバイスのセクション 6.1 を超える可能性があります。

過渡現象に対処する一般的な方法は、以下のとおりです。

- デバイスの入出力において、リード長を短くしインダクタンスを最小限に抑える。

- PCB には、大きい GND プレーンを使用する。

- 出力と GND の両端にショットキー・ダイオードを使用して、負のスパイクを吸収する。

- 低値のセラミック・コンデンサ ( $C_{(IN)}$  から約  $0.1\mu F$ ) を使用して、エネルギーを吸収し、過渡現象を減衰させる。

入力容量の近似値は、式 12 を使用して推定できます。

$$V_{\text{spike}(\text{Absolute})} = V_{(\text{IN})} + I_{(\text{Load})} \times \sqrt{\frac{L_{(\text{IN})}}{C_{(\text{IN})}}} \quad (12)$$

ここで、

- $V_{(\text{IN})}$  は公称電源電圧

- $I_{(\text{LOAD})}$  は負荷電流

- $L_{(\text{IN})}$  はソースから見た実効インダクタンスに等しい値

- $C_{(\text{IN})}$  は入力に存在する容量

一部のアプリケーションでは、過渡がデバイスのセクション 6.1 を超えないように、追加の過渡電圧サプレッサ (TVS) が必要になる場合があります。これらの過渡は、車載用 ISO7637 パルスなどの EMC テスト中に発生する可能性があります。

オプションの保護部品 (セラミック・コンデンサ、TVS、ショットキー・ダイオード) を使用した回路実装例を、図 9-14 に示します。

\* 過渡の抑制に必要なオプション部品

図 9-14. オプションの保護部品を使用した LM74912-Q1 の回路実装

#### 9.4.2 12V バッテリ・システム用の TVS の選択

TVS を選択する際に重要な仕様は、ブレークダウン電圧とクランプ電圧です。TVS+ のブレークダウン電圧は、24V のジャンプ・スタート電圧および 35V の抑制負荷ダンプ電圧より高く、LM74912-Q1 の最大定格 (65V) 未満である必要があります。TVS- のブレークダウン電圧は、逆接続されたバッテリに長時間さらされて TVS- が損傷しないように、最大逆バッテリ電圧 -16V より低くする必要があります。

クランプ電圧は、大電流パルス状況で TVS ダイオードがクランプする電圧であり、この電圧はブレークダウン電圧よりもはるかに高くなります。ISO 7637-2 パルス 1 の場合、ジェネレータ・インピーダンスが  $10\Omega$  で、入力電圧は最大  $-150V$  に上昇します。これは TVS を流れる  $15A$  に相当し、TVS の両端の電圧はクランプ電圧に近い値になります。

次の基準は、LM74912-Q1 のカソード - アノード間電圧の絶対最大定格 ( $85V$ ) と、 $V_{DS}$  MOSFET の最大定格を超えないことです。この設計例では、 $60V$  定格の MOSFET が選択されており、カソード - アノード間電圧の最大制限は  $60V$  です。

ISO 7637-2 パルス 1 の間、LM74912-Q1 のアノードは ISO パルスによってプルダウンされ、TVS- によってクランプされます。MOSFET Q1 は迅速にオフになり、逆電流によるバルク出力コンデンサの放電を防止します。MOSFET がオフになると、確認されるカソード - アノード間電圧は (TVS クランプ電圧 + 出力コンデンサ電圧) と等しくなります。出力コンデ

ンサの最大電圧が 16V (最大バッテリ電圧) の場合、TVS- のクランプ電圧は  $(60V - 16V) / 2 = 22V$  を超えないようにする必要があります。

SMBJ33CA TVS ダイオードは、12V バッテリ保護アプリケーションに使用できます。36.7V のブレークダウン電圧は、正側でジャンプ・スタートと負荷ダンプの要件、負側で 16V の逆バッテリ接続の要件を満たしています。ISO 7637-2 パルス 1 テスト中、示されているように SMBJ33CA は -44V で 12A のピーク・サージ電流をクランプし、44V 以下のクランプ電圧を満たしています。

SMBJ シリーズの TVS は、最大 600W のピーク・パルス電力レベルを定格とし、ISO 7637-2 パルスに十分です。

#### 9.4.3 24V バッテリ・システム用の TVS の選択

24V バッテリ保護アプリケーションの場合、図 9-1 の TVS と MOSFET を 24V バッテリの要件に合わせて変更する必要があります。

TVS+ のブレークダウン電圧は、48V のジャンプ・スタート電圧より高く、LM74912-Q1 のアノードおよびイネーブル・ピンの絶対最大定格 (70V) 未満で、65V の抑制負荷ダンプに耐える必要があります。TVS- のブレークダウン電圧は、逆接続されたバッテリに長時間さらされて TVS- が損傷しないように、最大逆バッテリ電圧である -32V より低くする必要があります。

ISO 7637-2 パルス 1 の間、入力電圧は  $50\Omega$  のジェネレータ・インピーダンスで -600V まで上昇します。これは、TVS- を流れる 12A に相当します。TVS- のクランプ電圧を 12V バッテリ保護回路のクランプ電圧と同じにすることはできません。ISO 7637-2 パルスの間は、確認されるアノード - カソード間電圧が ( $-TVS$  クランプ電圧 + 出力コンデンサ電圧) と等しくなるからです。24V バッテリ・アプリケーションの場合、最大バッテリ電圧は 32V なので、TVS- のクランプ電圧は  $85V - 32V = 53V$  を超えないようにする必要があります。

単一の双方向 TVS を 24V バッテリ保護に使用することはできません。これは、TVS + ブレークダウン電圧が 65V 以上、最大クランプ電圧が 53V 以下であり、クランプ電圧がブレークダウン電圧を下回ることはできないためです。入力では、逆並列接続された 2 つの単方向 TVS を使用する必要があります。正側 TVS+ については、ブレークダウン電圧が 64.4V (最小値)、67.8 (標準値) での SMBJ58A をお勧めします。負側の TVS- に対しては、ブレークダウン電圧が 32V 近く (最大逆バッテリ電圧 -32V に耐えるため)、最大クランプ電圧 42.1V の SMBJ28A をお勧めします。

24V バッテリ保護のため、75V 定格の MOSFET と、SMBJ28A および SMBJ58A を入力に逆並列接続することをお勧めします。

### 9.5 レイアウト

#### 9.5.1 レイアウトのガイドライン

- 理想ダイオード段については、LM74912-Q1 の A ピン、DGATE ピン、C ピンを MOSFET の SOURCE ピン、GATE ピン、DRAIN ピンの近くに接続します。

- 負荷切断段を行うには、LM74912-Q1 の HGATE ピンと OUT ピンを MOSFET の GATE ピンと SOURCE ピンの近くに接続します。

- このソリューションの大電流パスは MOSFET を流れるため、抵抗性損失を最小限に抑えるためには、MOSFET のソースとドレインに太く短い配線を使用することが重要です。

- LM74912-Q1 の DGATE ピンは、短い配線で MOSFET GATE に接続する必要があります。

- 過渡抑制部品は、LM74912-Q1 の近くに配置します。

- デカップリング・コンデンサ  $C_{VS}$  は、VS ピンとチップ GND の近くに配置します。

- 容量値への熱効果を低減するため、CAP ピンと VS ピンの間のチャージ・ポンプ・コンデンサは MOSFET から離して配置する必要があります。

- デバイスの露出パッド (RTN) はフローティングのままにします。RTN をグランド・プレーンに接続しないでください。

- 別のレイアウト方式で許容可能な性能を得ることもできますが、「[レイアウト例](#)」に示すレイアウトをガイドラインとしており、良好な結果が得られることを意図しています。

### 9.5.2 レイアウト例

図 9-15. PCB のレイアウト例

## 10 デバイスおよびドキュメントのサポート

### 10.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[ti.com](http://ti.com) のデバイス製品フォルダを開いてください。「更新の通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 10.2 サポート・リソース

**TI E2E™ サポート・フォーラム**は、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。**TI の使用条件**を参照してください。

### 10.3 商標

TI E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 10.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 10.5 用語集

[テキサス・インスツルメンツ用語集](#) この用語集には、用語や略語の一覧および定義が記載されています。

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更され、本ドキュメントの改訂に従って修正される場合があります。本データシートのブラウザ版を使用している場合は、画面左側のナビゲーションをご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| LM74912QRGERQ1        | Active        | Production           | VQFN (RGE)   24 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | LM<br>74912Q        |

| LM74912QRGERQ1.A      | Active        | Production           | VQFN (RGE)   24 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | LM<br>74912Q        |

| PLM74912QRGERQ1       | Active        | Preproduction        | VQFN (RGE)   24 | 3000   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

| PLM74912QRGERQ1.A     | Active        | Preproduction        | VQFN (RGE)   24 | 3000   LARGE T&R      | -           | Call TI                              | Call TI                           | -40 to 125   |                     |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## GENERIC PACKAGE VIEW

RGE 24

VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

Images above are just a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4204104/H

RGE0024T

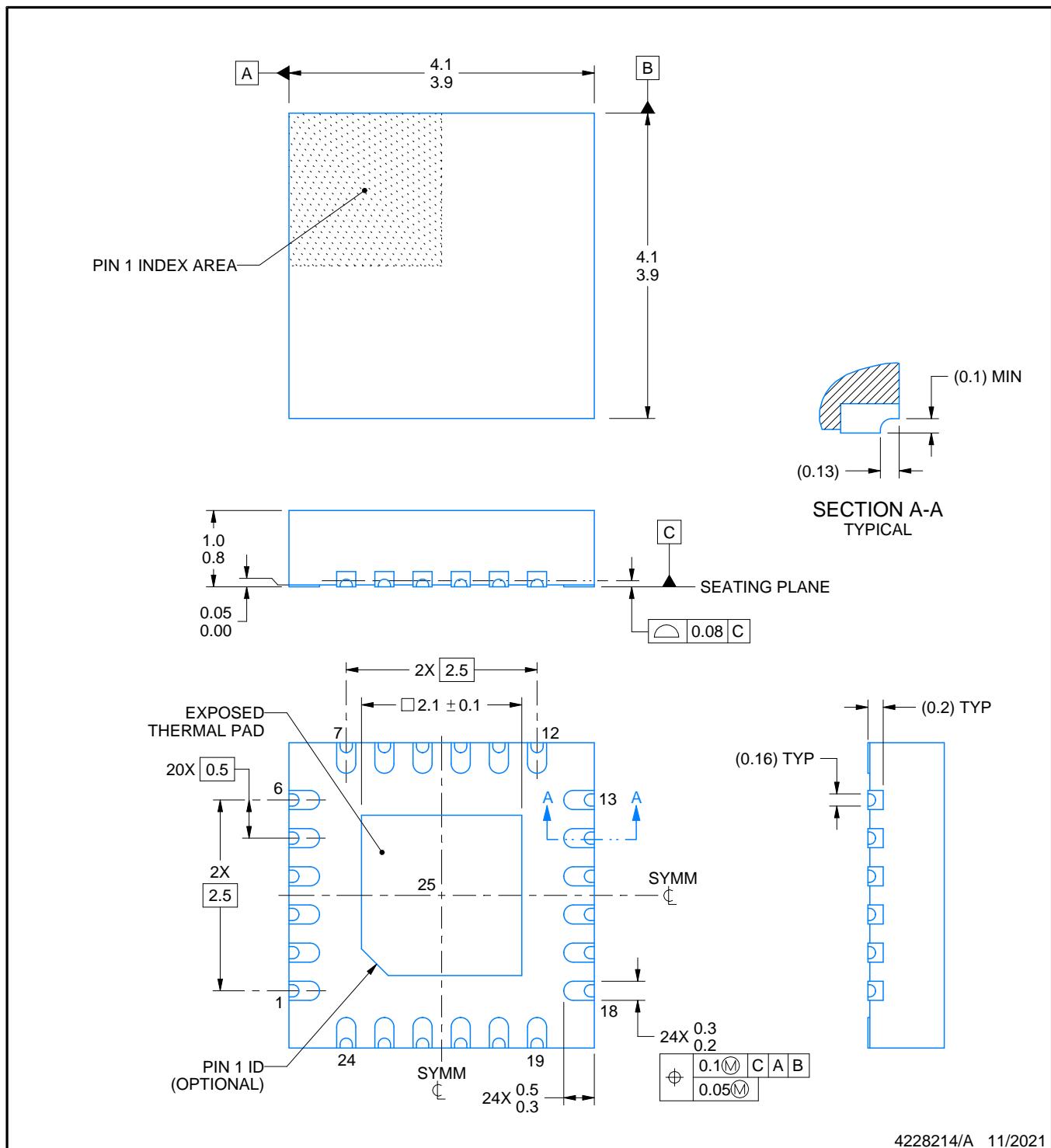

## PACKAGE OUTLINE

## VQFN - 1 mm max height

## PLASTIC QUAD FLATPACK - NO LEAD

4228214/A 11/2021

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

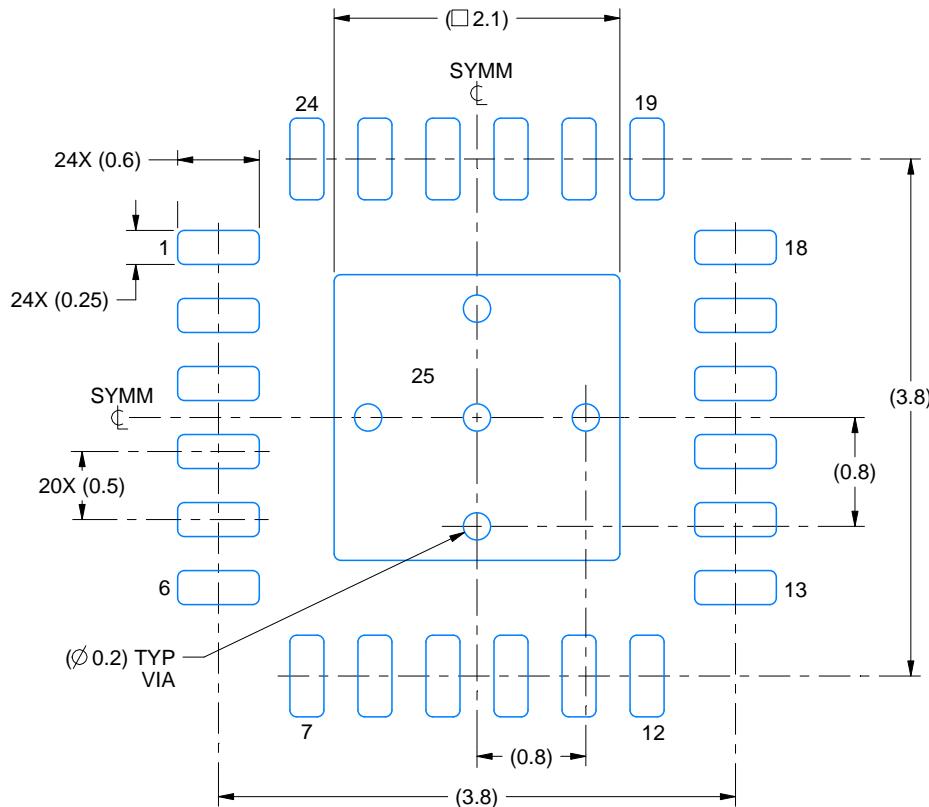

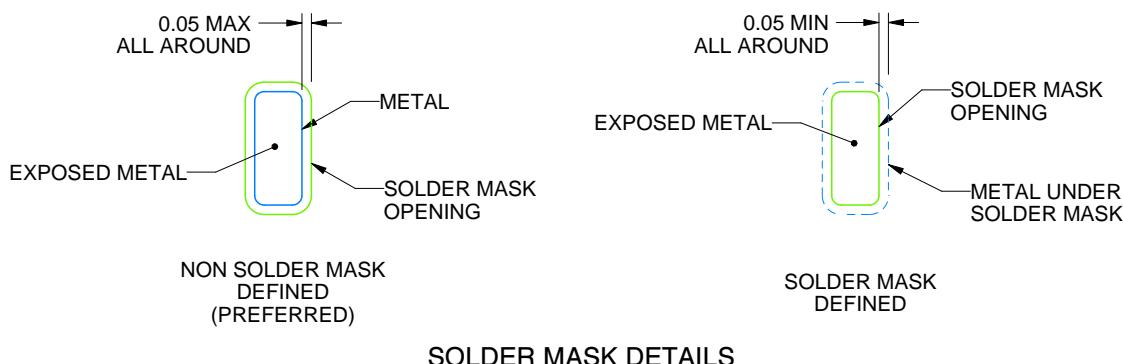

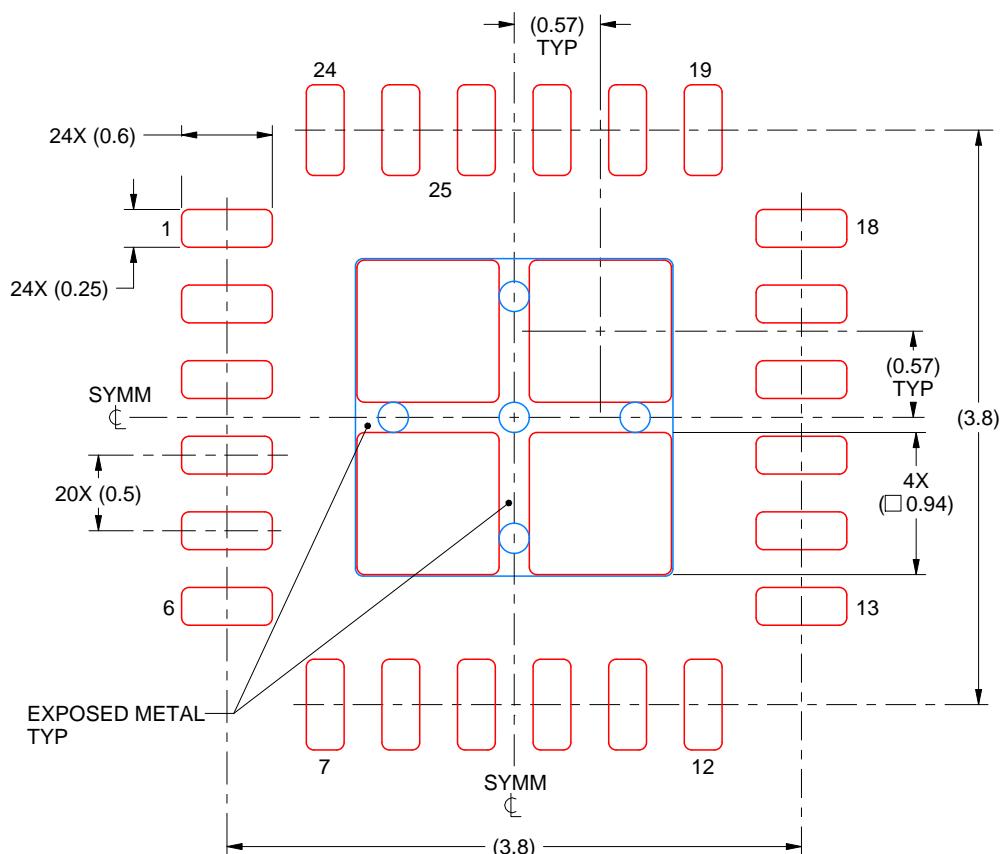

## **EXAMPLE BOARD LAYOUT**

RGE0024T

## VQFN - 1 mm max height

## PLASTIC QUAD FLATPACK - NO LEAD

**LAND PATTERN EXAMPLE**

**EXPOSED METAL SHOWN**

**SCALE:18X**

4228214/A 11/2021

---

**NOTES: (continued)**

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

# EXAMPLE STENCIL DESIGN

RGE0024T

VQFN - 1 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

## SOLDER PASTE EXAMPLE BASED ON 0.1 mm THICK STENCIL

THERMAL PAD 25:

77% PRINTED SOLDER COVERAGE BY AREA UNDER PACKAGE

SCALE:20X

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月