# LM684x5-Q1 42V 1.5A/2.5A、車載用同期整流降圧 DC/DC コンバータ、低 EMI ZEN 1 スイッチャ テクノロジー搭載、安全関連アプリケーションに最適化

## 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み:

- 温度グレード 1: -40°C ~ +125°C, T<sub>A</sub>

- 機能安全準拠**

- ISO 26262 システムの設計に役立つ資料を利用可能予定済み

- ASIL Dまでの決定論的対応能力

- ASIL Cまでのハードウェア機能

- 起動時のアナログ内蔵セルフテスト

- 冗長および高速 (0.35μs) V<sub>OUT</sub> モニタ

- フィードバック パス障害検出

- 冗長化温度センサ

- 非常に優れたピン FMEA およびピン間隔

- 幅広い入力電圧範囲: 3V ~ 42V

- ZEN 1 スイッチャ技術**

- CISPR 25 Class 5 準拠

- ±5% デュアルランダムスペクトラム拡散機能

- 拡張 HotRod™ QFN パッケージ

- スイッチング周波数: 300kHz ~ 2.2MHz

- ピンで構成可能な自動または FPWM 動作

- 補償、電流制限、TSD を内蔵

- 短い最小オン時間: 40ns (最大値)

- 2.2MHz で 36V<sub>IN</sub> から 3.3V<sub>OUT</sub> を実現

- あらゆる負荷で高効率の電力変換

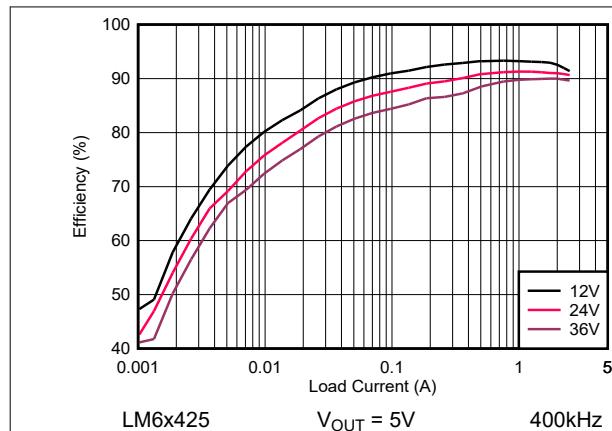

- 94% 超のピーク効率 (24V<sub>IN</sub>、5V<sub>OUT</sub>、400kHz)

- 無負荷時の 2.5μA スイッチング入力電流

- 高い電力密度

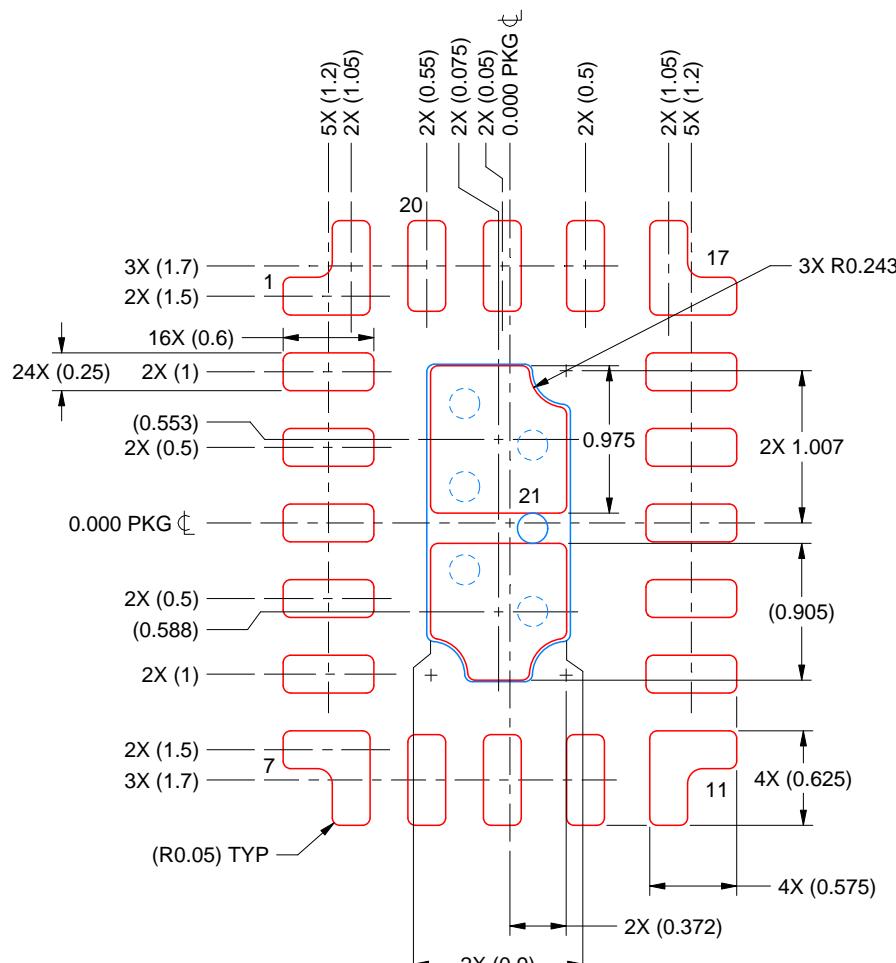

- 3.6mm × 2.6mm のコンパクトな 20 ピン eQFN パッケージで、ウェッタブル フランク構造を採用

- 36V 4/6/8A 対応の LM654x0-Q1 とピン互換

- 65V 2.5/3.5/4.5A 対応の LM656x5-Q1 とピン互換

- $\Theta_{JA} = 24.0^{\circ}\text{C}/\text{W}$  (LM65645-Q1EVM)

- WEBENCH® Power Designer** により、LM684x5-Q1 を使用するカスタム設計を作成

## 2 アプリケーション

- 先進運転支援システム (ADAS)

- 車載用インフォテインメントおよびクラスター

- ハイブリッド、電動、パワートレインシステム

## 3 説明

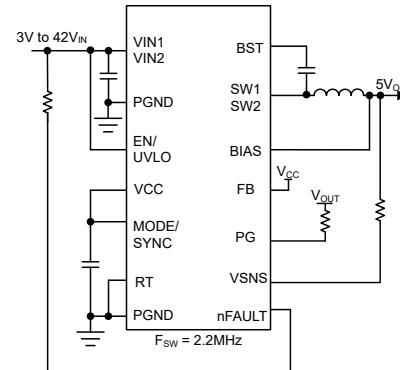

LM684x5-Q1 は、高効率、高い電力密度、超低電磁干渉 (EMI) を実現するように設計された車載用降圧コンバータ ファミリです。これらのコンバータは、3V ~ 42V の広い入力電圧範囲で動作します。

LM684x5-Q1 は、3.3V および 5V または可変構成でのピン選択可能な固定出力電圧を備えています。ループ インダクタンスを最小化し、スイッチ ノードのスルーレートを最適化することで、低 EMI での動作がイネーブルになります。電流モード制御アーキテクチャの標準最小オン時間は 30ns で、高周波数での高い変換比、高速過渡応答、優れた負荷およびライン レギュレーションを実現します。AUTO モードでは軽負荷動作時に周波数フォールドバックが有効になり、無負荷時の消費電流を最小で 1.36μA (代表値) まで低減できます。また、軽負荷時の高効率を維持するため、バッテリ駆動システムでの動作時間を延長します。

### 製品情報

| 部品番号 <sup>(3)</sup> | パッケージ <sup>(1)</sup> | パッケージサイズ <sup>(2)</sup> |

|---------------------|----------------------|-------------------------|

| LM68425-Q1          | RZT (WQFN-FCRLF、20)  | 3.60mm × 2.60mm         |

| LM68415-Q1          |                      |                         |

(1) 詳細については、[セクション 11](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

(3) 「[デバイス比較表](#)」を参照してください。

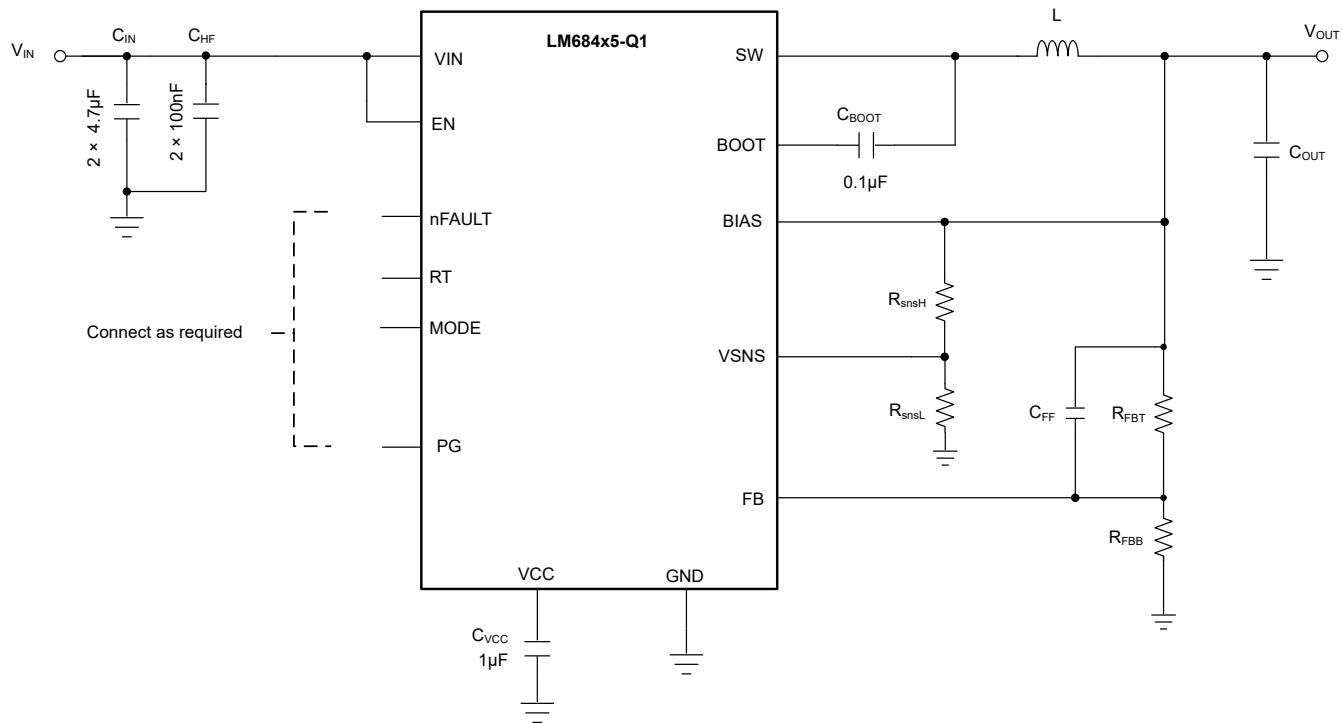

概略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

LM684x5-Q1 降圧コンバータは、特に機能安全に関連するアプリケーションを対象としています。スタートアップ時の ABIST、冗長で高速な  $V_{OUT}$  監視、フィードバック パス障害検出、冗長温度センサ、サーマル シャットダウン、電流制限などの一連の安全機能により、残存故障率 (FIT) が大幅に減少します。

LM684x5-Q1 には、CISPR 25 の放射エミッション要件への適合を容易にするための複数の機能が搭載されています。まず、対称的なピン配置により入力コンデンサを最適に配置でき、電源ループの寄生インダクタンスの実効値を極めて低く抑えます。これにより、スイッチング損失が低減され、高入力電圧および高スイッチング周波数での EMI 性能が向上します。ピンで選択可能なスイッチ ノードのスルーレート制御機能により、高周波数領域での放射ノイズをさらに低減します。スイッチング周波数は最高 2.2MHz まで抵抗により設定可能で、外部クロック ソースと同期できるため、ノイズに敏感な用途のビート周波数を除去できます。

LM684x5-Q1 の追加機能には、最大接合温度 150°C での動作、故障報告および出力電圧モニタリング用のオープンドレイン式パワーグッド (PG) インジケータ、入力 UVLO 保護のための高精度イネーブル入力、事前バイアス負荷へのモノトニックな立ち上がり、VIN または BIAS から電源供給されるデュアル入力 VCC バイアス サブレギュレータ、ヒップ モードの過負荷保護、自動復帰機能付きのサーマル シャットダウン保護が含まれます。

LM684x5-Q1 は、3.6mm×2.6mm の熱的に強化された 20 ピン eQFN パッケージで供給され、信頼性を向上させるための追加ピン クリアランスが付属しています。また、ウェッタブル フランク ピンも搭載されており、製造現場で光学検査を容易に行えます。フリップチップ配線対応リードフレーム (FCRLF) パッケージ技術を採用した LM684x5-Q1 は、実用電流能力、長期信頼性、およびコスト面での利点を活かし、高電力密度を要求するアプリケーションを対象としています。広い入力電圧範囲、低い静止電流消費、高温での動作、サイクルごとの電流制限、低い EMI シグネチャ、小型設計サイズにより、堅牢性と耐久性の強化向上が求められるアプリケーションに最適なポイント オブ ロード レギュレータ デザインを実現できます。

## 目次

|                    |           |                               |           |

|--------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>        | <b>1</b>  | <b>8 アプリケーションと実装</b>          | <b>32</b> |

| <b>2 アプリケーション</b>  | <b>1</b>  | <b>8.1 アプリケーション情報</b>         | <b>32</b> |

| <b>3 説明</b>        | <b>1</b>  | <b>8.2 代表的なアプリケーション</b>       | <b>33</b> |

| <b>4 ピン構成および機能</b> | <b>4</b>  | <b>8.3 設計のベスト プラクティス</b>      | <b>46</b> |

| <b>5 デバイス比較表</b>   | <b>6</b>  | <b>8.4 電源に関する推奨事項</b>         | <b>46</b> |

| <b>6 仕様</b>        | <b>7</b>  | <b>8.5 レイアウト</b>              | <b>46</b> |

| 6.1 絶対最大定格         | 7         | <b>9 デバイスおよびドキュメントのサポート</b>   | <b>50</b> |

| 6.2 ESD 定格         | 7         | 9.1 デバイス サポート                 | 50        |

| 6.3 推奨動作条件         | 7         | 9.2 ドキュメントのサポート               | 50        |

| 6.4 熱に関する情報        | 8         | 9.3 ドキュメントの更新通知を受け取る方法        | 50        |

| 6.5 電気的特性          | 8         | 9.4 サポート・リソース                 | 51        |

| 6.6 代表的特性          | 12        | 9.5 商標                        | 52        |

| <b>7 詳細説明</b>      | <b>14</b> | 9.6 静電気放電に関する注意事項             | 52        |

| 7.1 概要             | 14        | 9.7 用語集                       | 52        |

| 7.2 機能ブロック図        | 15        | <b>10 改訂履歴</b>                | <b>52</b> |

| 7.3 機能説明           | 16        | <b>11 メカニカル、パッケージ、および注文情報</b> | <b>53</b> |

| 7.4 デバイスの機能モード     | 26        |                               |           |

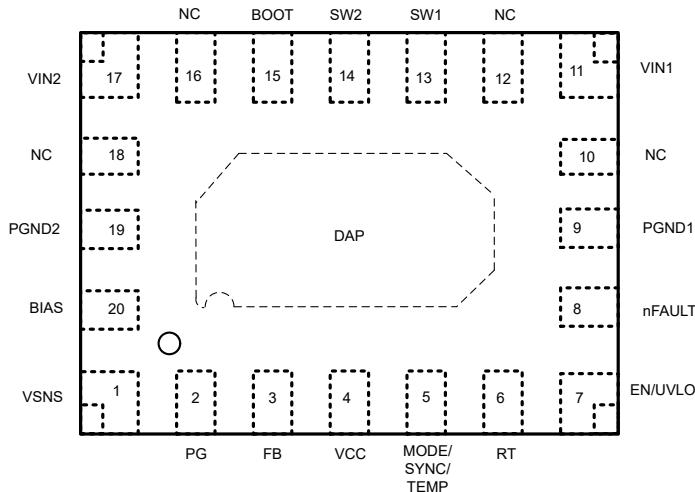

## 4 ピン構成および機能

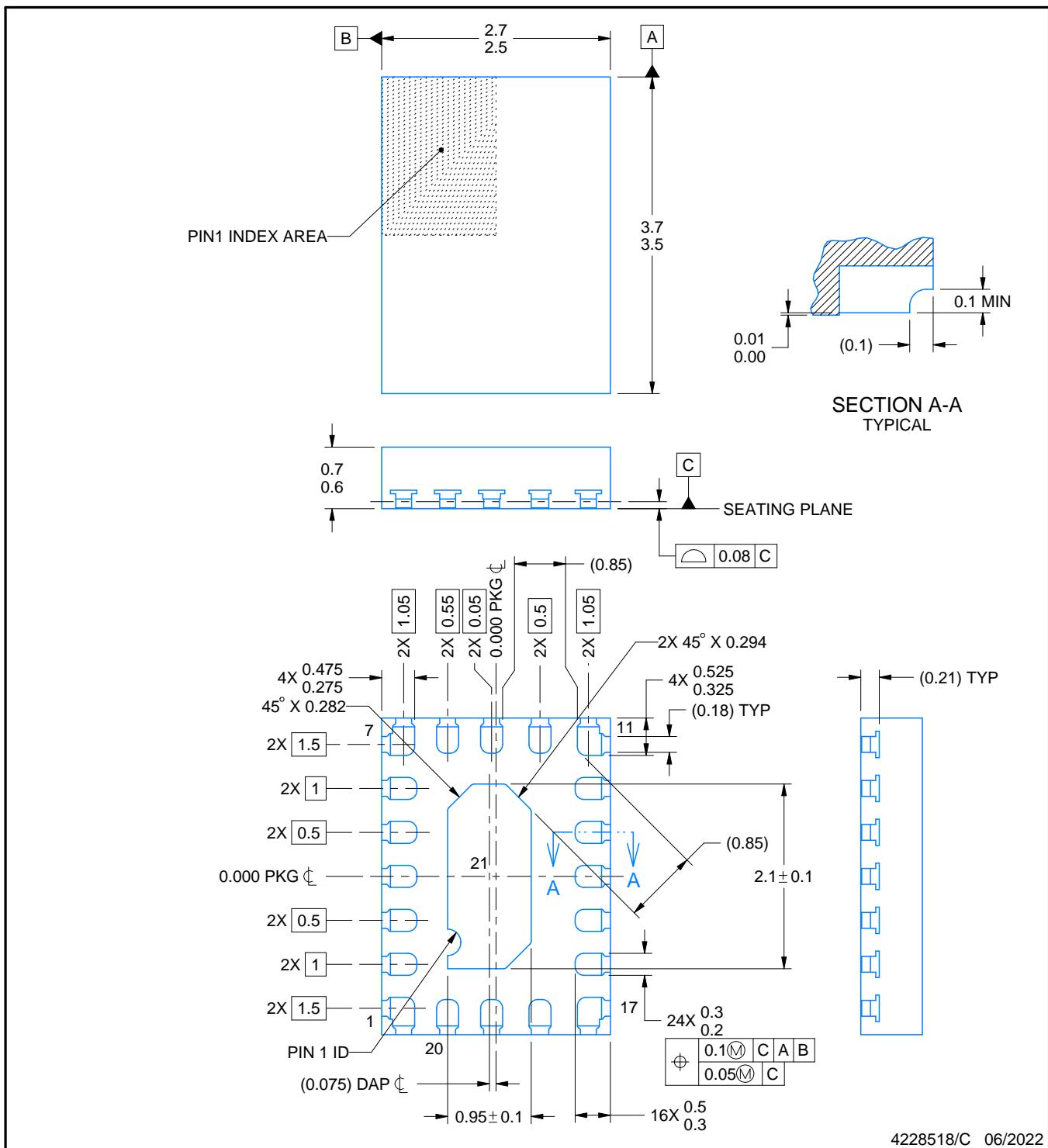

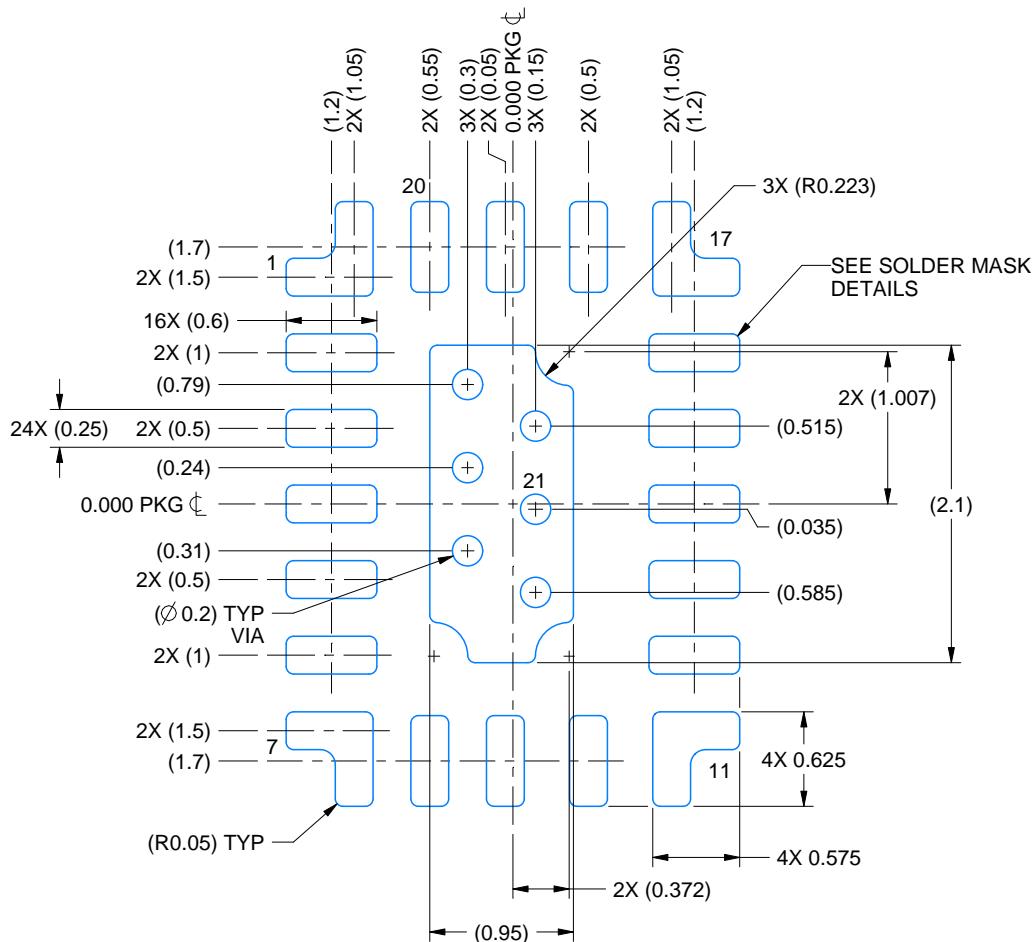

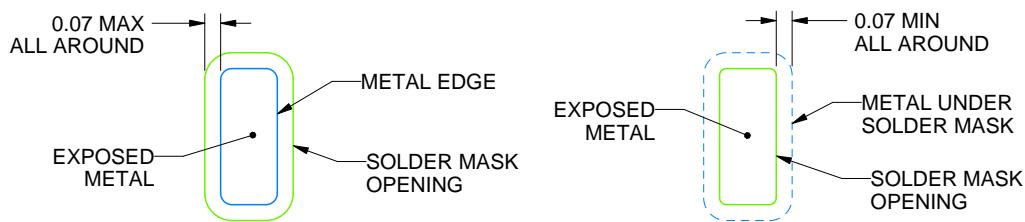

図 4-1. 20 ピン RZT、WQFN-FCRLF パッケージ (上面図)

表 4-1. ピンの機能

| ピン              |    | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                             |

|-----------------|----|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称              | 番号 |                    |                                                                                                                                                                                                                                                                                                                                |

| VSNS            | 1  | A                  | 冗長出力電圧監視ピン。固定 VOUT 構成の場合、4.99kΩ を VSNS ピンと VOUT ノードの間に接続します。可変 VOUT 構成の場合、FB ピンの抵抗ラダーと一致する外付け抵抗ラダーを接続します。                                                                                                                                                                                                                      |

| PG              | 2  | O                  | パワー グッド フラグの出力。VOUT が指定されたレギュレーション ウィンドウの範囲外である場合に Low になるオープン ドレイン出力。このピンには 100kΩ プルアップ抵抗を使用します。                                                                                                                                                                                                                              |

| FB              | 3  | A                  | 帰還構成ピン。3.3V の固定出力電圧を構成するには、GND に接続します。5V の固定出力電圧を構成するには、VCC に接続します。可変出力オプションの場合、帰還分圧器にこのピンを接続します。レギュレーション 閾値は 0.8V です。                                                                                                                                                                                                         |

| VCC             | 4  | P                  | 内部 LDO 出力。内部制御回路への電源として使用されます。このピンは、いずれの外部負荷にも接続しないでください。制御またはフラグ ピンのロジック プルアップに使用できます。このピンから GND へ、高品質な 1μF コンデンサを接続してください。                                                                                                                                                                                                   |

| MODE/SYNC /TEMP | 5  | I/O                | MODE および同期入力ピン。GND に接続するか、このピンを Low に駆動して、自動モードで動作させます。VCC に接続するか、ピンを High に駆動するか、同期クロック信号を送信して FPWM モードで動作させます。外部クロックに同期している場合、RT ピンを使用して内部周波数を同期した周波数に近い値に設定します。このピンと GND との間に 49.9kΩ 抵抗を接続して温度監視機能をアクティブにし、デバイスを FPWM モードにロックします。このピンと GND との間に 150kΩ 抵抗を接続して温度監視機能をアクティブにし、デバイスを自動モードにロックします。詳細については、「温度監視」セクションを参照してください。 |

| RT              | 6  | I/O                | スイッチング周波数のプログラミング用ピン。このピンは、400kHz 動作の場合は VCC に、2.2MHz 動作の場合は GND に接続します。このピンを抵抗を介してグランドに接続すると、スイッチング周波数を 300kHz ~ 2200kHz に設定できます。フローティングにはしないでください。                                                                                                                                                                           |

| EN/UVLO         | 7  | P                  | 高精度イネーブル ピン。High = オン、Low = オフ。このピンは VIN に直接接続できます。この入力には高精度レッショルドがあるため、調整可能な UVLO として使用できます。安全アプリケーション用に構成されている場合、このピンは、内部冗長回路に電力を供給する常時オンのレギュレータへの入力としても使用されます。フローティングにはしないでください。                                                                                                                                            |

| nFAULT          | 8  | O                  | フォルト出力ピン。故障が検出されると Low になるオープン ドレイン出力。このピンには 100kΩ プルアップ抵抗を使用します。                                                                                                                                                                                                                                                              |

| PGND1           | 9  | G                  | ローサイド MOSFET の電源グランド。システム グランドに接続。このピンと VIN1 との間に高品質のバイパス コンデンサ 1つまたは複数のコンデンサを接続します。                                                                                                                                                                                                                                           |

| NC              | 10 | —                  | 接続の無いピンフローティングのままにします。                                                                                                                                                                                                                                                                                                         |

| VIN1            | 11 | P                  | レギュレータへの入力電源。このピンと PGND1 との間に高品質のバイパス コンデンサを接続します。                                                                                                                                                                                                                                                                             |

**表 4-1. ピンの機能 (続き)**

| ピン      |       | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                          |

|---------|-------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称      | 番号    |                    |                                                                                                                                                                             |

| NC      | 12    | —                  | 接続の無いピンフローティングのままにします。                                                                                                                                                      |

| SW1、SW2 | 13、14 | P                  | デバイススイッチピン。出力インダクタに接続します。                                                                                                                                                   |

| BOOT    | 15    | P                  | ハイサイドドライバの上側電源レール。 <b>SW</b> ノードと <b>BOOT</b> との間に高品質の100nFコンデンサを接続します。 <b>SW</b> ノードが <b>Low</b> の間は、内部ダイオードによってコンデンサが充電されます。                                              |

| NC      | 16    | —                  | 接続の無いピンフローティングのままにします。                                                                                                                                                      |

| VIN2    | 17    | P                  | レギュレータへの入力電源。このピンとPGND2との間に高品質のバイパスコンデンサを接続します。                                                                                                                             |

| NC      | 18    | —                  | 接続の無いピンフローティングのままにします。                                                                                                                                                      |

| PGND2   | 19    | G                  | 内部ローサイドMOSFETの電源グランド。システムグランドに接続。このピンとVIN2との間に高品質のバイパスコンデンサを接続します。                                                                                                          |

| BIAS    | 20    | P                  | 内部電圧レギュレータへの入力。固定VOUT用に構成されている場合、このピンをVOUTノードに接続して、制御ループを閉じます。可変VOUTを構成している場合、このピンをVOUTノードに接続するか、または3.3V～30Vの外部バイアス電源に接続します。出力電圧が30Vよりも高く、外部電源を使用しない場合は、ピンをGNDに接続してください。    |

| DAP     | —     | G                  | 露出したグランドパッド。PCB上のシステムGNDに接続。このピンはダイの主要な放熱パスです。このパッドは、PCB上のGND銅箔に半田付けすることで、ヒートシンクに使用する必要があります。サンプル基板レイアウトで推奨されているようにできるだけ多くのサーマルビアを実装することで、最小限のパッケージ熱抵抗と可能な限り最高の放熱性能が保証されます。 |

(1) I = 入力、O = 出力、A = アナログ、P = 電源、G = グランド

## 5 デバイス比較表

| 発注用製品型番         | CURRENT |

|-----------------|---------|

| LM68425SFRZTRQ1 | 2.5A    |

| LM68415SFRZTRQ1 | 1.5A    |

## 6 仕様

### 6.1 絶対最大定格

接合部の動作時温度範囲  $-40^{\circ}\text{C} \sim +150^{\circ}\text{C}$  (特に記載がない場合) <sup>(1)</sup>

|      |                           | 最小値  | 最大値                    | 単位                 |

|------|---------------------------|------|------------------------|--------------------|

| 入力電圧 | VIN から PGND へ             | -0.3 | 45                     | V                  |

| 入力電圧 | EN/UVLO から PGND へ         | -0.3 | 45                     | V                  |

| 入力電圧 | RT から PGND                | -0.3 | 45                     | V                  |

| 入力電圧 | VSNS から PGND へ            | -0.3 | 40                     | V                  |

| 入力電圧 | BIAS から PGND へ            | -0.3 | 40                     | V                  |

| 入力電圧 | MODE/CLKIN/TEMP から PGND へ | -0.3 | 5.5                    | V                  |

| 入力電圧 | FB から PGND                | -0.3 | 5.5                    | V                  |

| 出力電圧 | SW～PGND                   | -0.6 | $\text{V}_{\text{IN}}$ | V                  |

| 出力電圧 | SW から PGND (過渡 10ns 未満)   | -5.0 | $\text{V}_{\text{IN}}$ | V                  |

| 出力電圧 | nFAULT から PGND へ          | -0.3 | 40                     | V                  |

| 出力電圧 | PGOOD から PGND             | -0.3 | 40                     | V                  |

| 出力電圧 | BST から SW へ               | -0.3 | 5.5                    | V                  |

| 出力電圧 | VCC から PGND へ             | -0.3 | 5.5                    | V                  |

| 温度   | 動作時の接合部温度 $T_J$           | -40  | 150                    | $^{\circ}\text{C}$ |

| 温度   | 保管温度 $T_{\text{stg}}$     | -65  | 150                    | $^{\circ}\text{C}$ |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 6.2 ESD 定格

|                           |      |            | 値                                           | 単位           |

|---------------------------|------|------------|---------------------------------------------|--------------|

| $\text{V}_{(\text{ESD})}$ | 静電放電 | 荷電デバイス モデル | デバイス帶電モデル (CDM)、AEC Q100-011 準拠             | $\pm 750$ V  |

|                           |      | 人体モデル      | 人体モデル (HBM)、AEC Q100-002 に準拠 <sup>(1)</sup> | $\pm 2000$ V |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI/ESDA/JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 6.3 推奨動作条件

接合部温度の動作範囲が  $-40^{\circ}\text{C} \sim +150^{\circ}\text{C}$  である場合 (特に記述のない限り)

|                |                                | 最小値 | 最大値 | 単位         |

|----------------|--------------------------------|-----|-----|------------|

| 入力電圧           | VIN                            | 3   | 42  | V          |

| 入力電圧           | EN                             | 0   | 42  | V          |

| 入力電圧           | nFAULT                         | 0   | 42  | V          |

| 入力電圧           | バイアス、PG                        | 0   | 30  | V          |

| 入力電圧           | FB、VSNS                        | 0   | 5.5 | V          |

| 入力電圧           | MODE/SYNC, RT                  | 0   | 5.5 | V          |

| プルアップ抵抗        | $R_{\text{PU}}(\text{PG})$     | 50  |     | k $\Omega$ |

| プルアップ抵抗        | $R_{\text{PU}}(\text{nFAULT})$ | 4   | 100 | k $\Omega$ |

| プルアップ リファレンス電圧 | $V_{\text{PU}}(\text{PG})$     | 0.8 | 30  | V          |

| 入力電流           | $I_{(\text{nFAULT})}$          |     | 0.5 | mA         |

## 6.3 推奨動作条件 (続き)

接合部温度の動作範囲が  $-40^{\circ}\text{C} \sim +150^{\circ}\text{C}$  である場合 (特に記述のない限り)

|                 |                      | 最小値 | 最大値 | 単位                 |

|-----------------|----------------------|-----|-----|--------------------|

| プルアップ リファレンス 電圧 | $V_{PU(nFAULT)}$     | 0   | 42  | V                  |

| 出力電圧            | $V_{OUT}$            | 0.8 |     | V                  |

| 出力電流            | LM6xx25 / LM6xx25-Q1 | 0   | 2.5 | A                  |

| 出力電流            | LM6xx15 / LM6xx15-Q1 | 0   | 1.5 | A                  |

| 温度              | 動作時の接合部温度 $T_J$      | -40 | 150 | $^{\circ}\text{C}$ |

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> |                                         | デバイス       | 単位                          |

|----------------------|-----------------------------------------|------------|-----------------------------|

|                      |                                         | RZT (WQFN) |                             |

|                      |                                         | 20 ピン      |                             |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗 <sup>(3)</sup>             | 24.0       | $^{\circ}\text{C}/\text{W}$ |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗 (JESD 51-7) <sup>(2)</sup> | 43.4       | $^{\circ}\text{C}/\text{W}$ |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗                     | 14.9       | $^{\circ}\text{C}/\text{W}$ |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗                            | 12.0       | $^{\circ}\text{C}/\text{W}$ |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ                        | 1.0        | $^{\circ}\text{C}/\text{W}$ |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ                        | 11.9       | $^{\circ}\text{C}/\text{W}$ |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗                     | 6.0        | $^{\circ}\text{C}/\text{W}$ |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

- (2) この表に示す  $R_{\theta JA}$  の値は他のパッケージとの比較にのみ有効であり、設計目的に使用することはできません。これらの値は JESD 51-7 に従つて計算されており、4 層 JEDEC 基板上でシミュレーションされています。この熱パラメータは、実際のアプリケーションで得られた性能を表すものではありません。たとえば、EVM  $R_{\theta JA} = 24.0^{\circ}\text{C}/\text{W}$  です。設計情報については、「最大周囲温度」セクションを参照してください。

- (3) 基板レイアウトと追加情報については、『LM65645EVM ユーザー ガイド』を参照してください。熱設計情報については、「最大周囲温度」セクションを参照してください。

## 6.5 電気的特性

特に記述のない限り、各制限値は推奨動作接合部温度 ( $T_J$ ) 範囲 ( $-40^{\circ}\text{C} \sim +150^{\circ}\text{C}$ ) にわたって適用されます。最小値および最大値は、試験、設計、および統計的相関に基づいて規定されています。標準値は  $T_J = 25^{\circ}\text{C}$  における最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。特に記述のない限り、次の条件が適用されます。 $V_{IN} = 13.5\text{V}$ 、 $V_{EN} = V_{IN}$ 、 $V_{OUT} = 3.3\text{V}$ 、 $f_{SW} = 2.2\text{MHz}$ 、 $V_{IN} \sim R_{nFAULT} = 100\text{k}\Omega$  でプルアップ

| パラメータ                | テスト条件                                   | 最小値                                                                | 標準値  | 最大値  | 単位            |

|----------------------|-----------------------------------------|--------------------------------------------------------------------|------|------|---------------|

| <b>電源 (VIN ピン)</b>   |                                         |                                                                    |      |      |               |

| $V_{IN_{UVLO\_R}}$   | $V_{IN}$ UVLO 立ち上がりスレッショルド              | $V_{IN}$ の立ち上がり (起動に必要)、 $I_{VCC} = 0\text{A}$                     | 3.25 | 3.5  | 3.65          |

| $V_{IN_{UVLO\_F}}$   | $V_{IN}$ UVLO 立ち下がりスレッショルド              | $V_{IN}$ の立ち下がり (動作後)、 $I_{VCC} = 0\text{A}$                       |      | 2.5  | 2.6           |

| $V_{IN_{UVLO\_H}}$   | $V_{IN}$ UVLO ヒステリシス                    |                                                                    |      | 0.9  | V             |

| $I_{Q\_SD}$          | $V_{IN}$ のシャットダウン時消費電流                  | $V_{EN} = 0\text{V}$ 、 $T_J = 25^{\circ}\text{C}$                  |      | 0.85 | $\mu\text{A}$ |

| $I_{VIN}$            | $VIN$ ピン入力電流、スイッチングなし                   | $V_{BIAS} = 3.3\text{V} + 2\%$                                     |      | 1.36 | $\mu\text{A}$ |

| $I_{BIAS(FIX-3.3V)}$ | BIAS ピン入力電流、3.3V 固定出力、スイッチングなし          | $V_{BIAS} = 3.3\text{V} + 2\%$ 、自動モード、                             |      | 9.22 | $\mu\text{A}$ |

| $I_{Q(FIX-3.3V)}$    | $V_{IN}$ 静止電流の合計、3.3V 固定出力、スイッチングなし     | $V_{BIAS} = 3.3\text{V} + 2\%$ 、 $T_J = 25^{\circ}\text{C}$ 、自動モード |      | 3.66 | $\mu\text{A}$ |

|                      |                                         | $T_J =$                                                            |      | 5.4  | $\mu\text{A}$ |

| $I_{Q(ADJ-3.3V)}$    | $V_{IN}$ 静止電流の合計、調整可能な 3.3V 出力、スイッチングなし | $V_{IN} = 13.5\text{V}$ 、 $V_{FB} = 0.8\text{V} + 2\%$ 、自動モード      |      | 2.4  | $\mu\text{A}$ |

| <b>イネーブル (EN ピン)</b> |                                         |                                                                    |      |      |               |

| $V_{EN\_TH\_R}$      | イネーブル電圧立ち上がりスレッショルド                     | $V_{EN}$ 立ち上がり                                                     | 1.15 | 1.25 | 1.35          |

| $V_{EN\_TH\_F}$      | イネーブル入力 Low スレッショルド                     | $V_{EN}$ 立ち下がり                                                     | 0.9  | 1    | 1.1           |

## 6.5 電気的特性 (続き)

特に記述のない限り、各制限値は推奨動作接合部温度 ( $T_J$ ) 範囲 (-40°C ~ +150°C) にわたって適用されます。最小値および最大値は、試験、設計、および統計的相関に基づいて規定されています。標準値は  $T_J = 25^\circ\text{C}$ における最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。特に記述のない限り、次の条件が適用されます。 $V_{IN} = 13.5\text{V}$ 、 $V_{EN} = V_{IN}$ 、 $V_{OUT} = 3.3\text{V}$ 、 $f_{SW} = 2.2\text{MHz}$ 、 $V_{IN} \geq R_{nFAULT} = 100\text{k}\Omega$  でプルアップ

| パラメータ                   |  | テスト条件                                     | 最小値                                                                  | 標準値   | 最大値  | 単位    |      |

|-------------------------|--|-------------------------------------------|----------------------------------------------------------------------|-------|------|-------|------|

| $V_{EN\_HYS}$           |  | イネーブル電圧のヒステリシス                            |                                                                      | 250   |      | mV    |      |

| $I_{EN\_LKG}$           |  | イネーブル入力リーキ電流                              |                                                                      | 0.2   | 1.0  | μA    |      |

| <b>内部 LDO (VCC ピン)</b>  |  |                                           |                                                                      |       |      |       |      |

| $V_{VCC}$               |  | 内部 LDO 出力電圧                               | 3.4V ≤ $V_{IN}$ ≤ 42V, $V_{BIAS} = 0\text{V}$                        | 3.35  |      | V     |      |

|                         |  |                                           | 3.4V ≤ $V_{BIAS} \leq 30\text{V}$                                    | 3.35  |      | V     |      |

| $V_{VCC-UVLO\_R}$       |  | VCC UVLO 立ち上がりスレッショルド                     | $V_{VCC-UVLO\_R}$ 低電圧立ち上がりスレッショルド、 $I_{VCC} = 0\text{A}$             | 3.20  | 3.5  | 3.65  | V    |

| $V_{VCC-UVLO\_H}$       |  | VCC UVLO ヒステリシス                           | $V_{VCC-UVLO\_R}$ 未満でのヒステリシス                                         | 0.9   |      |       | V    |

| <b>電圧リファレンス (FB ピン)</b> |  |                                           |                                                                      |       |      |       |      |

| $V_{FB}$                |  | 内部フィードバック リファレンス電圧                        | FPWM モード                                                             | 0.792 | 0.8  | 0.808 | V    |

| $I_{FB-LKG}$            |  | フィードバック ピン入力リーキ電流                         | $V_{FB} = 0.8\text{V}$ 、可変バージョン                                      | 0.025 |      | nA    |      |

| $R_{FB-SEL-5V}$         |  | FB ピンと VCC の間の 5.0V 固定設定の抵抗               |                                                                      |       | 200  | Ω     |      |

| $R_{FB-SEL-3V}$         |  | FB ピンと GND の間の 3.3V 固定設定の抵抗               |                                                                      |       | 200  | Ω     |      |

| $R_{FB-SEL-ADJ}$        |  | 可変出力電圧設定を選択するための FB ピン上の外部 FB 分圧器のテクノロジ   |                                                                      | 4     | 100  | kΩ    |      |

| <b>固定出力電圧 (BIAS ピン)</b> |  |                                           |                                                                      |       |      |       |      |

| $V_{OUT(3.3V)}$         |  | 3.3V 固定出力電圧                               | FB の GND への短絡のマスク                                                    | 3.267 | 3.3  | 3.333 | V    |

| $V_{OUT(5V)}$           |  | 5.0V 固定出力電圧                               | FB の VCC への短絡のマスク                                                    | 4.95  | 5    | 5.05  | V    |

| <b>スタートアップ (SS ピン)</b>  |  |                                           |                                                                      |       |      |       |      |

| $t_{EN\_HIGH}$          |  | イネーブル High からスイッチング開始までの遅延                | $V_{FB} = V_{RT} = V_{MODE} = GND$ , $V_{VSNS} = V_{BIAS} = V_{OUT}$ | 3.0   |      | ms    |      |

| $t_{SS}$                |  | 内部固定ソフトスタート時間                             | 最初の SW パルスから $V_{REF}$ が設定点の 90% に達するまでの時間。                          | 2.9   | 5.3  | 8.1   | ms   |

| <b>電流制限およびヒップ</b>       |  |                                           |                                                                      |       |      |       |      |

| $I_{HS-LIM}$            |  | ハイサイド ピーク電流制限、2.5A トリム オプション              | デューティ サイクルを 0% に近付ける                                                 | 3.75  | 4.1  | 4.9   | A    |

| $I_{LS-LIM}$            |  | ローサイド バレー電流制限、2.5A トリム オプション              | ローサイド FET のバレー電流制限                                                   | 2.4   | 3.0  | 3.4   | A    |

| $I_{L-PEAK-MIN}$        |  | 最小デューティ サイクルでの最小ピークインダクタ電流、2.5A トリム オプション | $V_{VCC} = 3.3\text{V}$ , $t_{pulse} \leq 100\text{ns}$ 、自動モード       | 0.8   | 1.1  | 1.35  | A    |

| $I_{L-PEAK-MAX}$        |  | 最大デューティ サイクルでの最小ピークインダクタ電流、2.5A トリム オプション | $V_{VCC} = 3.3\text{V}$ , $t_{pulse} \geq 1\mu\text{s}$ 、自動モード       | 0.43  |      |       | A    |

| $I_{HS-LIM}$            |  | ハイサイド ピーク電流制限、1.5A トリム オプション              | デューティ サイクルを 0% に近付ける                                                 | 1.7   | 2.25 | 3     | A    |

| $I_{LS-LIM}$            |  | ローサイド バレー電流制限、1.5A トリム オプション              | ローサイド FET のバレー電流制限                                                   | 1.3   | 1.8  | 2.3   | A    |

| $I_{L-PEAK-MIN}$        |  | 最小デューティ サイクルでの最小ピークインダクタ電流、1.5A トリム オプション | $V_{VCC} = 3.3\text{V}$ , $t_{pulse} \leq 100\text{ns}$ 、自動モード       | 0.5   |      |       | A    |

| $I_{L-PEAK-MAX}$        |  | 最大デューティ サイクルでの最小ピークインダクタ電流、1.5A トリム オプション | $V_{VCC} = 3.3\text{V}$ , $t_{pulse} \geq 1\mu\text{s}$ 、自動モード       | 0.15  |      |       | A    |

| $I_{LS-NEG-LIM}$        |  | ローサイド負電流制限、すべての電流制限トリム オプション              | LS FET のシンク電流制限、FPWM モード                                             | -6    | -4.3 | -2.8  | A    |

| $I_{L-ZC-LIM}$          |  | ゼロクロスの電流制限値                               | $V_{VCC} = 3.3\text{V}$ 、自動モード                                       | 45    |      |       | mA   |

| $V_{HIC}$               |  | FB ピンの過電流ヒップ スレッショルド                      | LS FET オン時間 > 165ns、ソフトスタート中ではない                                     | 0.32  |      |       | V    |

| $t_{HIC\_DLY}$          |  | ヒップ モードの起動遅延                              |                                                                      | 64    |      |       | サイクル |

| $t_{HIC}$               |  | ヒップ モードの持続時間                              |                                                                      | 45    |      |       | ms   |

| <b>パワー グッド (PG ピン)</b>  |  |                                           |                                                                      |       |      |       |      |

## 6.5 電気的特性 (続き)

特に記述のない限り、各制限値は推奨動作接合部温度 ( $T_J$ ) 範囲 (-40°C ~ +150°C) にわたって適用されます。最小値および最大値は、試験、設計、および統計的相関に基づいて規定されています。標準値は  $T_J = 25^\circ\text{C}$ における最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。特に記述のない限り、次の条件が適用されます。 $V_{IN} = 13.5\text{V}$ 、 $V_{EN} = V_{IN}$ 、 $V_{OUT} = 3.3\text{V}$ 、 $f_{SW} = 2.2\text{MHz}$ 、 $V_{IN} \geq R_{nFAULT} = 100\text{k}\Omega$  でプルアップ

| パラメータ               | テスト条件                     | 最小値                                                                             | 標準値 | 最大値  | 単位                |

|---------------------|---------------------------|---------------------------------------------------------------------------------|-----|------|-------------------|

| $V_{PG-OVP-R}$      | PG 過電圧立ち上がりスレッショルド        | FB 電圧 (可変) またはバイアス電圧 (固定) の %                                                   | 103 | 105  | 107 %             |

| $V_{PG-OVP-F}$      | PG 過電圧立ち下がりスレッショルド        | FB 電圧 (可変) またはバイアス電圧 (固定) の %                                                   | 101 | 104  | 106 %             |

| $V_{PG-UVP-R}$      | PG 低電圧立ち上がりスレッショルド        | FB 電圧 (可変) またはバイアス電圧 (固定) の %                                                   | 94  | 96   | 98 %              |

| $V_{PG-UVP-F}$      | PG 低電圧立ち下がりスレッショルド        | FB 電圧 (可変) またはバイアス電圧 (固定) の %                                                   | 93  | 95   | 97 %              |

| $t_{PG-DEGLITCH-F}$ | PG 立ち下がりエッジでのグリッチ除去フィルタ遅延 |                                                                                 | 55  | 120  | 175 $\mu\text{s}$ |

| $t_{PG-DEGLITCH-R}$ | PG 立ち上がりエッジでのグリッチ除去フィルタ遅延 |                                                                                 | 1.4 | 2    | 4.5 ms            |

| $V_{IN-PG-VALID}$   | 有効な PG 出力の最小 $V_{IN}$     | $V_{OL(PG)} < 0.4\text{V}$ , $R_{PU} = 50\text{k}\Omega$ , $V_{PU} = 5\text{V}$ |     | 1.25 | V                 |

| $V_{OL-PG}$         | 出力 LOW 電圧                 | $I_{OL} = 1\text{mA}$ , $V_{IN} = 1.2\text{V}$                                  |     | 0.4  | V                 |

| $R_{ON-PG}$         | PGOOD オン抵抗                | $I_{PG} = 1\text{mA}$                                                           |     | 40   | $\Omega$          |

### 冗長出力電圧監視 (VSNS および nFAULT ピン)

|                         |                                              |                                |     |       |                   |

|-------------------------|----------------------------------------------|--------------------------------|-----|-------|-------------------|

| $V_{nFAULT-F-OVP(R)}$   | 高速過電圧立ち上がりスレッショルド                            | VSNS 電圧の %                     | 110 | 112.5 | 115 %             |

| $t_{nFAULT-F-RESPONSE}$ | 迅速な OVP 応答時間                                 | まで                             |     | 0.35  | 0.6 $\mu\text{s}$ |

| $V_{EN(nFAULT_VALID)}$  | nFault ピンが適切に機能するための最小イネーブル電圧                | $R_{PU} = 100.0\text{k}\Omega$ |     | 1.25  | V                 |

| $V_{EN(LATCH_RESET)}$   | nFault ラッチリセットのイネーブル電圧立ち下がりスレッショルド           | $R_{PU} = 100.0\text{k}\Omega$ |     | 0.5   | V                 |

| $V_{OL(nFAULT)}$        | 出力 LOW 電圧                                    | $I_{OL} = 0.5\text{mA}$        |     | 0.4   | V                 |

| $R_{PD(BIST)}$          | スタートアップ時の nFault ピンの内部プルダウン抵抗 <sup>(1)</sup> |                                |     | 150   | $\text{k}\Omega$  |

### スイッチング周波数 (RT ピン)

|                 |                   |                                    |      |      |          |

|-----------------|-------------------|------------------------------------|------|------|----------|

| $f_{SW1(FPWM)}$ | スイッチング周波数、FPWM 動作 | $R_{RT} = \text{GND}$              | 1.98 | 2.2  | 2.42 MHz |

| $f_{SW2(FPWM)}$ | スイッチング周波数、FPWM 動作 | $R_{RT} = 15.8\text{k}\Omega$ , 1% | 900  | 1000 | 1100 kHz |

| $f_{SW3(FPWM)}$ | スイッチング周波数、FPWM 動作 | $R_{RT} = \text{VCC}$              | 360  | 400  | 440 kHz  |

### 同期 (MODE/SYNC ピン)

|                         |                                   |                                    |      |      |     |

|-------------------------|-----------------------------------|------------------------------------|------|------|-----|

| $V_{IH(MODE/CLKIN)}$    | MODE/CLKIN 入力の High レベル スレッショルド   |                                    |      | 1.3  | V   |

| $V_{IL(MODE/CLKIN)}$    | MODE/CLKIN 入力の Low レベル スレッショルド    |                                    | 0.45 |      | V   |

| $f_{CLKIN-RANGE(FPWM)}$ | 2.2MHz $f_{SW}$ を設定する同期周波数範囲      | $R_{RT} = 6.81\text{k}\Omega$ , 1% | 1.76 | 2.64 | MHz |

| $t_{CLKIN(TON)}$        | 外部 SYNC 信号の最小正パルス幅                |                                    |      | 80   | ns  |

| $t_{CLKIN(TOFF)}$       | 外部 SYNC 信号の最小負パルス幅                |                                    |      | 80   | ns  |

| $t_{CLKIN-SW-DLY}$      | CLKIN から SW への遅延時間 <sup>(1)</sup> |                                    | -15  | 15   | ns  |

### デュアルランダムスペクトラム拡散

|                     |                           |                                       |     |    |          |

|---------------------|---------------------------|---------------------------------------|-----|----|----------|

| $\Delta f_{SS1-LF}$ | 低周波数の三角波スペクトラム拡散変調範囲 - 標準 | Mode ピンはグランドへ短絡                       | 8.5 |    | %        |

| $\Delta f_{SS2-LF}$ | 低周波数の三角波スペクトラム拡散変調範囲 - 拡張 | $R_{MODE} = 149.9\text{k}\Omega$ , 1% | 17  |    | %        |

| $f_{m1-LF}$         | 三角波変調周波数 - 標準             | Mode ピンはグランドへ短絡                       | 7.2 | 12 | 16.8 kHz |

| $f_{m2-LF}$         | 三角波変調周波数 - 拡張             | $R_{MODE} = 149.9\text{k}\Omega$ , 1% | 3.6 | 6  | 8.4 kHz  |

| $\Delta f_{SS-HF}$  | 高周波の疑似ランダム拡散スペクトラム変調範囲    | $R_{MODE} = 149.9\text{k}\Omega$ , 1% | 2.0 |    | %        |

### 電力段

## 6.5 電気的特性 (続き)

特に記述のない限り、各制限値は推奨動作接合部温度 ( $T_J$ ) 範囲 (-40°C ~ +150°C) にわたって適用されます。最小値および最大値は、試験、設計、および統計的相関に基づいて規定されています。標準値は  $T_J = 25^\circ\text{C}$ における最も一般的なパラメータ基準値を表しており、参考目的にのみ提供されています。特に記述のない限り、次の条件が適用されます。 $V_{IN} = 13.5\text{V}$ 、 $V_{EN} = V_{IN}$ 、 $V_{OUT} = 3.3\text{V}$ 、 $f_{SW} = 2.2\text{MHz}$ 、 $V_{IN} \geq R_{nFAULT} = 100\text{k}\Omega$  でプルアップ

| パラメータ                |                             | テスト条件                                                            | 最小値   | 標準値   | 最大値  | 単位                         |

|----------------------|-----------------------------|------------------------------------------------------------------|-------|-------|------|----------------------------|

| $R_{DS-ON-HS}$       | ハイサイド FET オン抵抗              | $I_{SW} = 500\text{mA}$ , $V_{BOOT-SW} = 3.3\text{V}$            | 99    |       |      | $\text{m}\Omega$           |

| $R_{DS-ON-LS}$       | ローサイド FET オン抵抗              |                                                                  | 50    |       |      | $\text{m}\Omega$           |

| $t_{ON-MIN(FPWM)}$   | 最小オン時間 <sup>(1)</sup>       | FPWM: $I_{OUT} = 0\text{A}$ , $V_{IN} = 36\text{V}$ , $RT = GND$ | 30    | 40    | ns   |                            |

| $t_{ON-MIN(AUTO)}$   | 最小オン時間 <sup>(1)</sup>       | 自動: $I_{OUT} = 2\text{A}$ , $V_{IN} = 36\text{V}$ , $RT = GND$   | 28    | 40    | ns   |                            |

| $t_{OFF-MIN}$        | 最小オフ時間                      | $V_{IN} = 4\text{V}$                                             | 80    | 110   | ns   |                            |

| $t_{ON-MAX}$         | 最大オン時間                      | $f_{SW} = 400\text{kHz}$ , $R_{RT} = 40.2\text{k}\Omega$         | 13.3  |       |      | $\mu\text{s}$              |

| 冗長化温度センサ             |                             |                                                                  |       |       |      |                            |

| $V_{MODE_TEMP}$      | 温度モニタ電流精度 <sup>(1)</sup>    | $T_a = 27^\circ\text{C}$ , $R_{TEMP} = 49.9\text{k}\Omega$ , 1%  | 0.814 | 0.844 | 0.90 | V                          |

| $V_{MODE_TEMP_GAIN}$ | 温度モニタ ゲイン <sup>(1)</sup>    | $R_{TEMP} = 49.9\text{k}\Omega$ , 1%                             | 2.95  |       |      | $\text{mV}/^\circ\text{C}$ |

| サーマル シャットダウン         |                             |                                                                  |       |       |      |                            |

| $T_{SD}$             | サーマル シャットダウン <sup>(1)</sup> | シャットダウン スレッショルド                                                  | 155   | 165   | 177  | $^\circ\text{C}$           |

|                      |                             | 復帰スレッショルド                                                        | 156   |       |      | $^\circ\text{C}$           |

(1) 設計により規定されています。

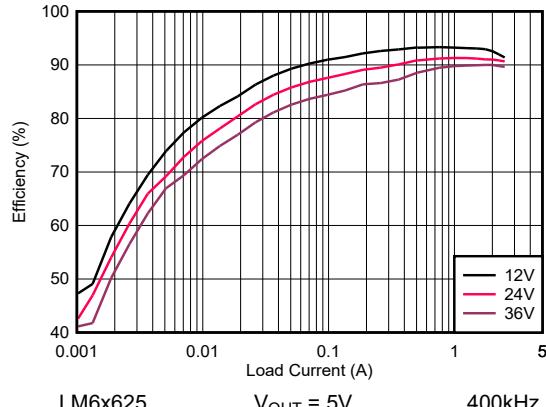

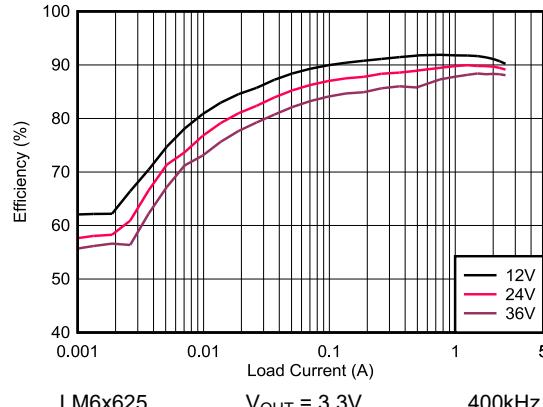

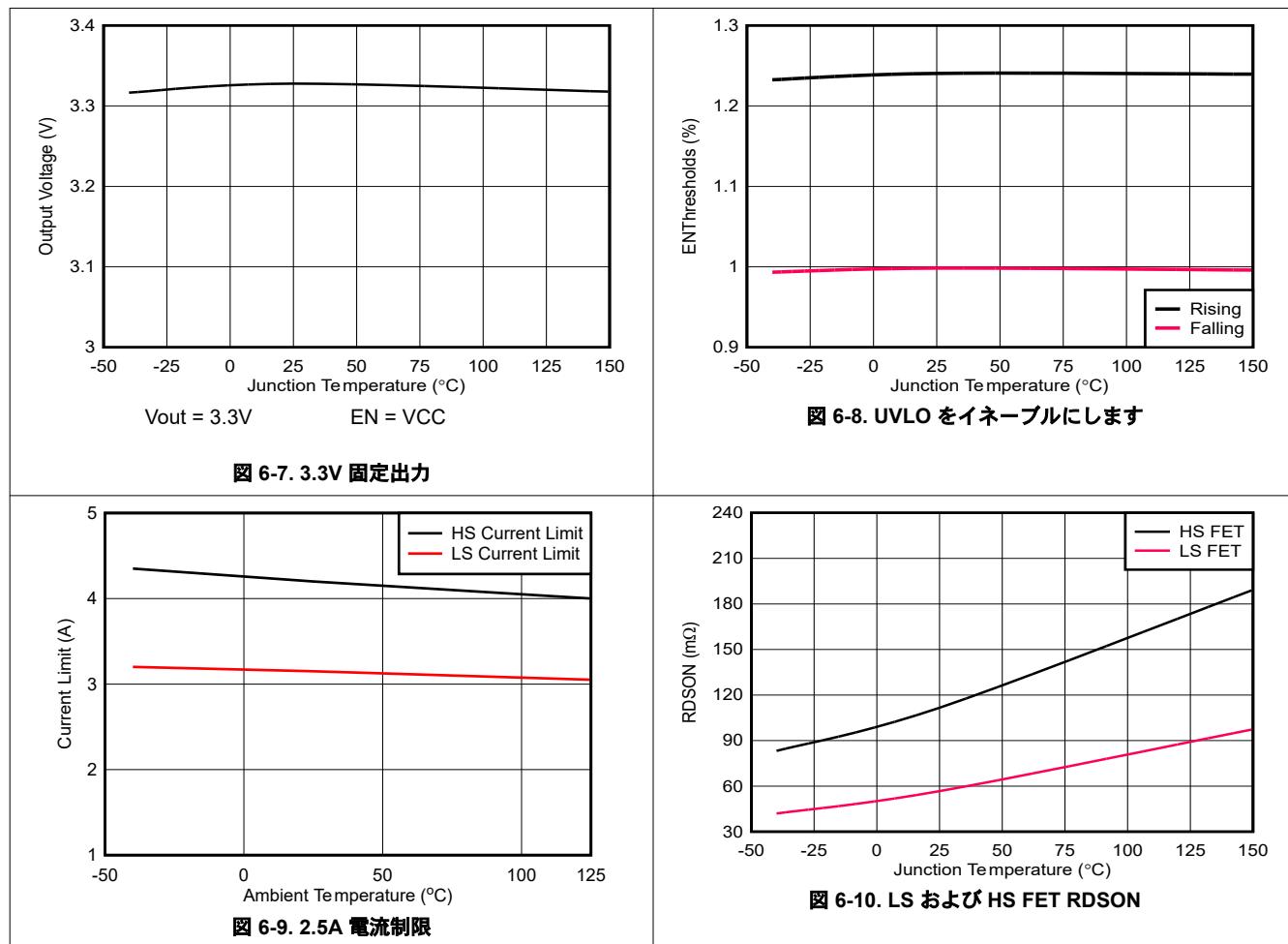

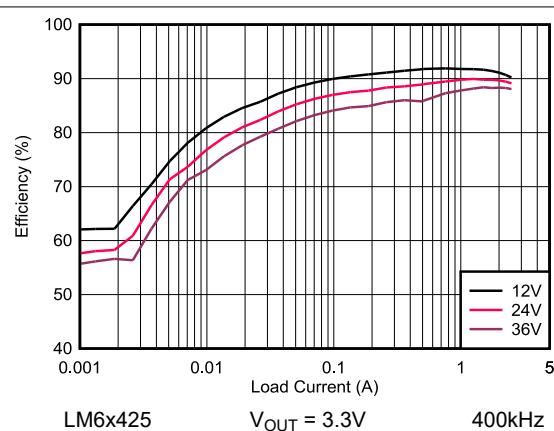

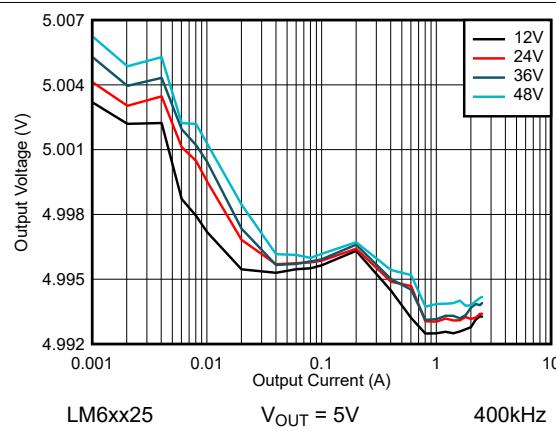

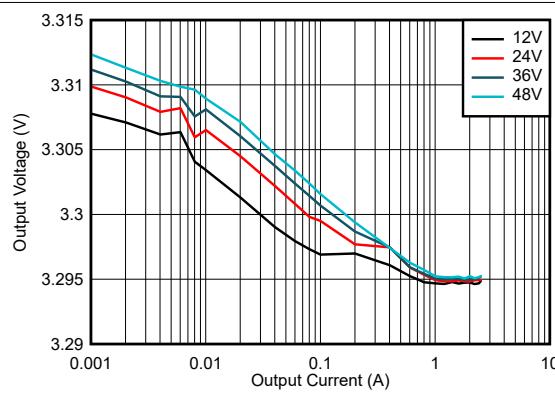

## 6.6 代表的特性

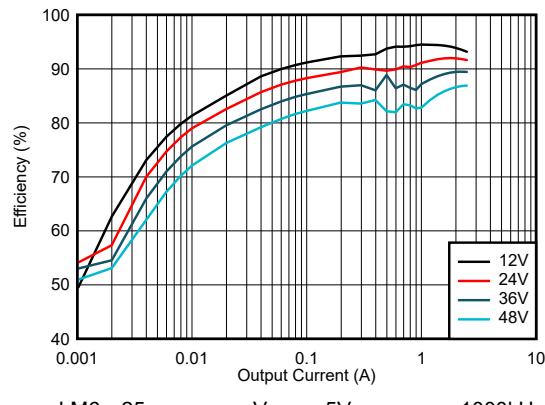

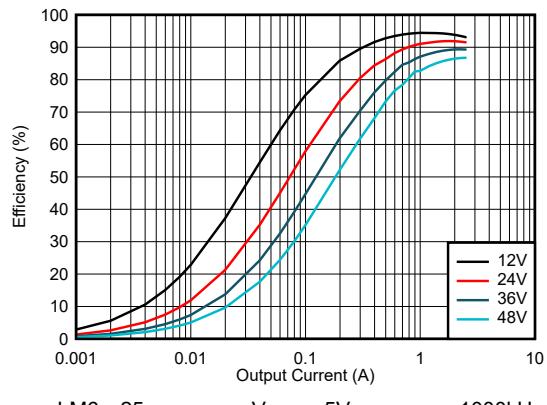

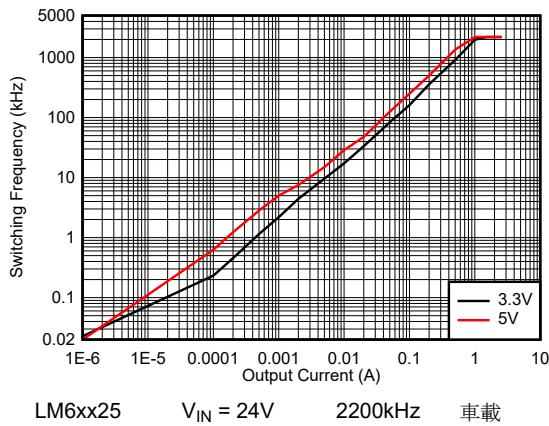

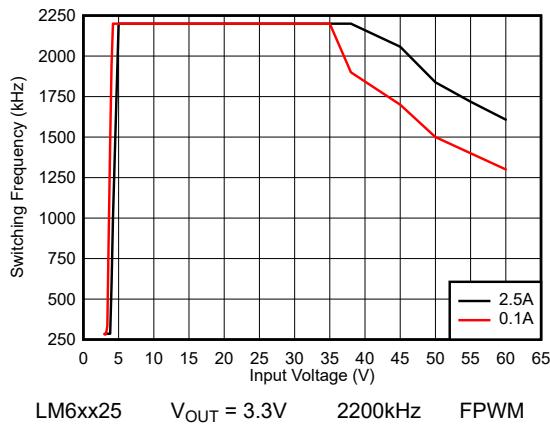

特に記述のない限り、 $V_{IN} = 13.5V$ 。

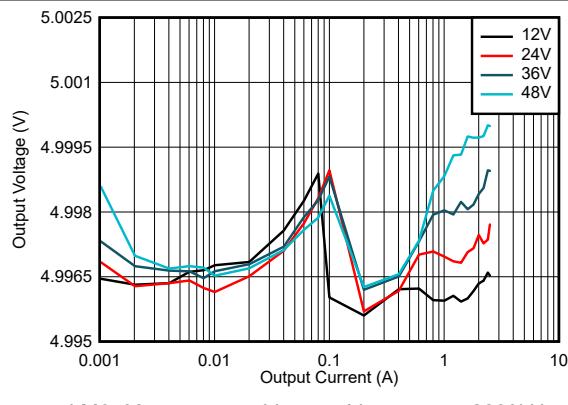

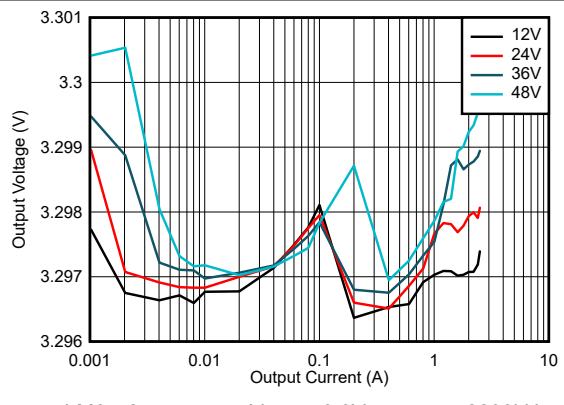

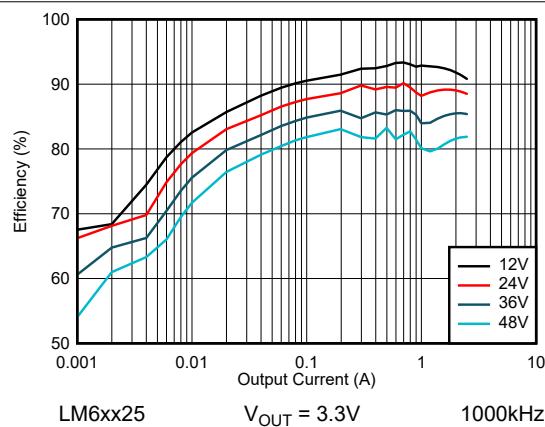

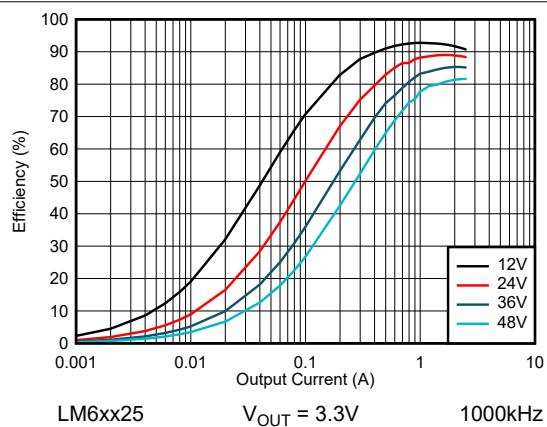

図 6-1. LM6x625 効率 - 自動モード

図 6-2. LM6x625 効率 - 自動モード

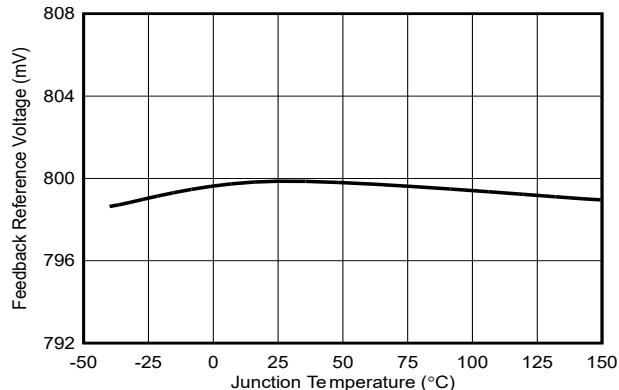

図 6-3. 帰還電圧

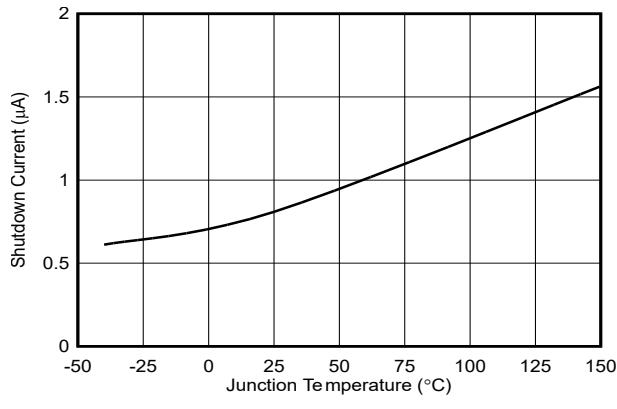

図 6-4. シャットダウン入力電流

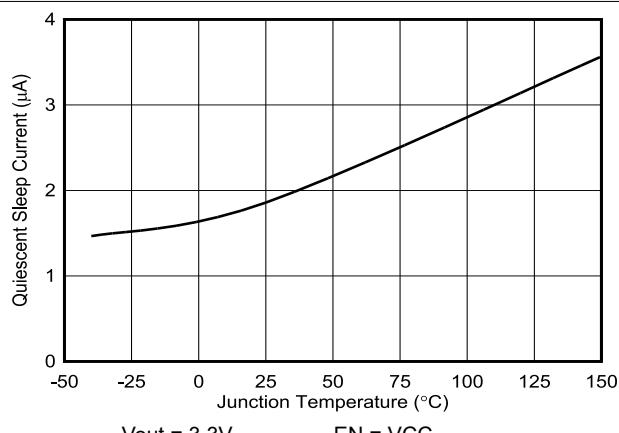

図 6-5. スリープ静止電流 3.3V 出力

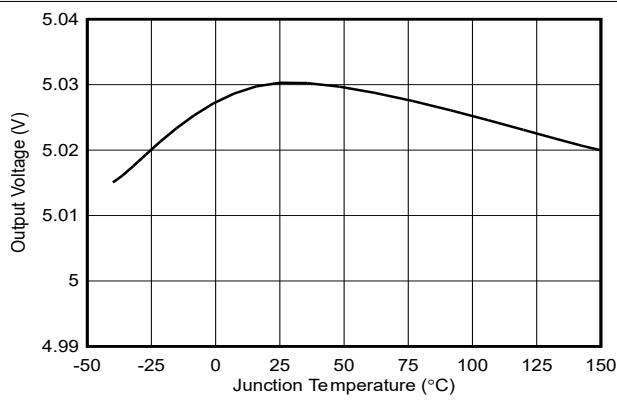

図 6-6. 5V 固定出力

## 6.6 代表的特性 (続き)

## 7 詳細説明

### 7.1 概要

LM684x5-Q1 は、機能安全関連アプリケーション向けに開発された、高効率、高電力密度、超低 EMI 降圧コンバータのファミリです。これらのコンバータは 3V ~ 42V の広い入力電圧範囲で動作し、固定出力電圧は 3.3V、5V、または可変出力構成をピンで選択できます。

代表的な最小オン時間 30ns の電流モード制御アーキテクチャにより、高周波数での高い変換比、高速過渡応答、優れた負荷およびライン レギュレーションを可能にします。最小オン時間または最小オフ時間が目的の変換比をサポートしない場合、スイッチング周波数は自動的に低下します。この機能により、ロード ダンプ イベントやコールド クランク状況中もレギュレーションを維持できます。

このデバイスは、要求の厳しい車載用および高性能産業用環境で動作しながら、最終製品のコストとサイズが最小化されるように設計されています。LM684x5-Q1 は、RT ピンを使用して固定 400kHz または固定 2.2MHz で動作させるか、300kHz ~ 2.2MHz の可変モードで動作するように設定できます。内蔵の補償回路と高精度の電流制限方式を組み合わせることで、部品表コストと部品点数を最小化できます。

LM684x5-Q1 は、低 EMI を意図して設計されています。このデバイスには、次のような事項が含まれます。

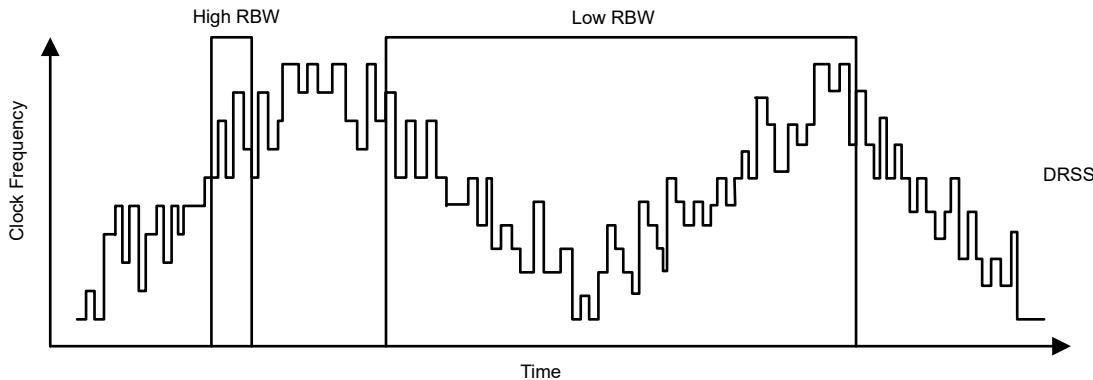

- $\pm 5\%$  デュアル ランダム スペクトラム拡散 (DRSS) により、ピーク放射を大幅に低減

- 寄生パッケージのインダクタンスを最小化する対称型のピン配置

- AM ラジオ帯域より上、および下の周波数範囲での動作

- 外部クロック同期機能とともに、自動または FPWM モードをピンで構成可能

これらの機能により、シールドとその他の高価な EMI 軽減対策を不要にできます。

LM684x5-Q1 は、安全性アプリケーション用にも設計されています。以下の安全機能が含まれています。

- 出力 UV/OV 保護機能付きパワーグッド モニタおよびオープンドレイン PG ピン出力

- 冗長出力電圧監視、高速応答の OV 保護、オープンドレイン nFAULT 出力、フォルトラッチ、自動再試行機能

- 完全に冗長化された内部電圧リファレンスおよびモニタ

- スタートアップ診断

- ヒップ モードによる過電流および出力短絡保護回路

- サーマル シャットダウン

- 接合部温度モニタ

これらの安全性機能は、ダイとパッケージの残存 FIT (故障率) を大幅に低減し、目的の ASIL/SIL レベルを実現します。

このデバイスを信頼性を重視する環境で使用するため、LM684x5-Q1 は大きくしたコーナー端子付きパッケージを採用しており、ボードレベルの信頼性の向上と、ウェッタブルフランクによる光学検査が可能です。

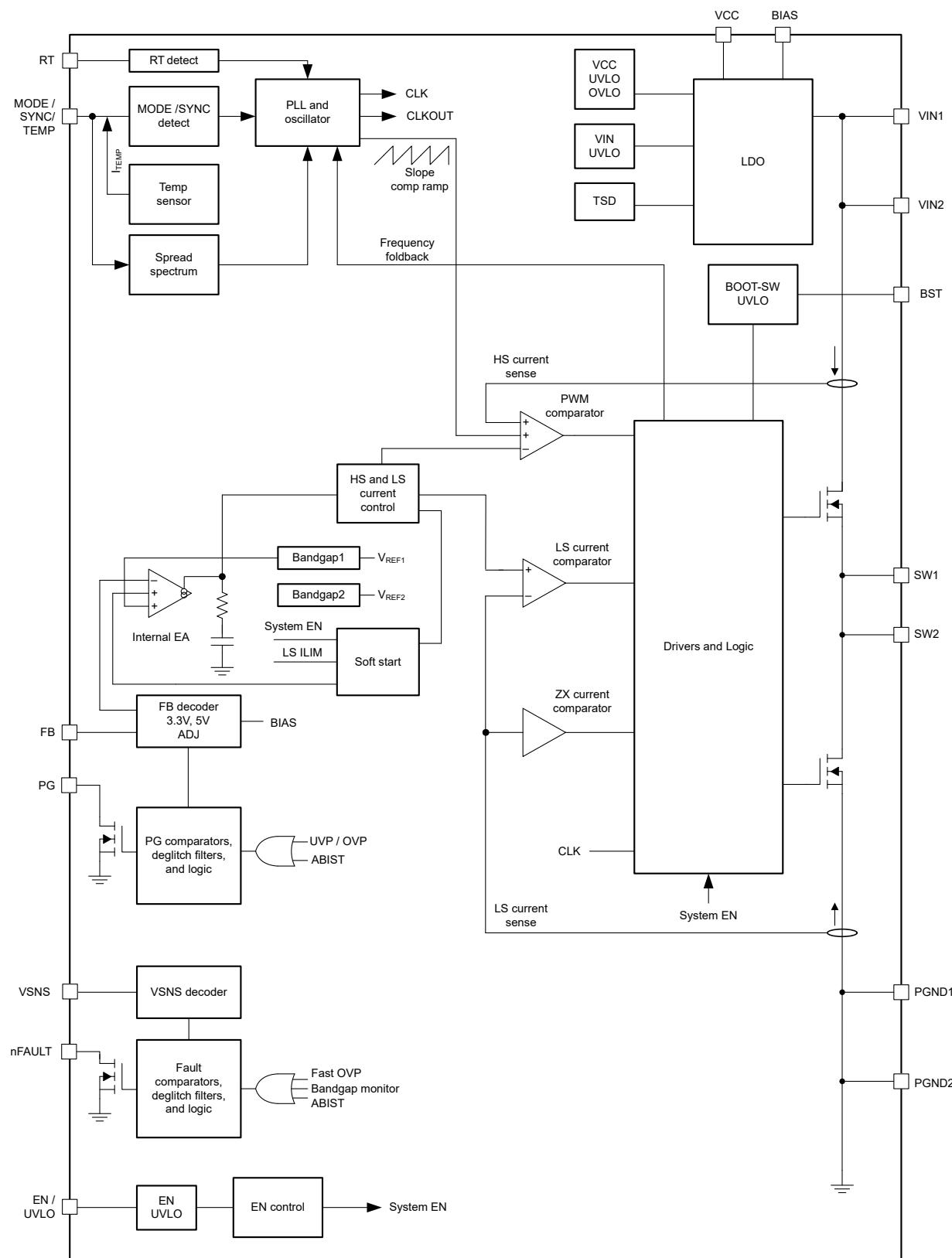

## 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 出力電圧の選択

LM684x5-Q1 は、固定出力電圧モードと可変出力電圧モードをピンで選択できることが特徴です。固定出力電圧モードでは、出力電圧は FB ピンによって選択されます。FB ピンを GND に接続して固定 3.3V 出力を選択するか、VCC に接続して固定 5V 出力を選択します。固定出力電圧モードを選択すると、BIAS ピンをレギュレータの出力に直接接続します。このモードでは、BIAS ピンがレギュレータの帰還ループを閉じ、内部バイアス レギュレータに入力電力を供給します。内部 LDO にはこのピンから電力が供給されるため、信頼性の高いボード線図を固定出力電圧モードでは取得できませんが、この測定は可変モードで行うことができます。図 8-1 に示すように、BIAS を VOUT に接続します。

表 7-1. 出力電圧の選択

| FB                    | VOUT |

|-----------------------|------|

| GND への短絡              | 3.3V |

| VCC への短絡              | 5V   |

| 帰還抵抗分圧器に接続します (図 7-1) | ADJ  |

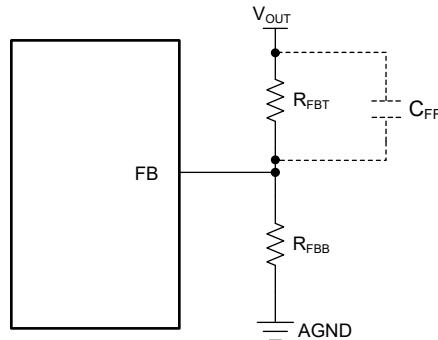

可変出力電圧モードでは、レギュレータの出力電圧と FB ピンとの間に分圧器を接続します。抵抗値は、目的の出力電圧とレギュレータの 0.8V 電圧リファレンスに基づいて計算します。接続の詳細については、図 7-1 を参照してください。

図 7-1. 可変バージョンの出力電圧の設定

$R_{FBT}$  の目的の値に基づいて  $R_{FBB}$  の値を選択するには、式 1 を使用します。 $R_{FBT}$  の値を  $100\text{k}\Omega$  以下に制限するのが最適なやり方です。抵抗値が大きいと、環境汚染によって PCB 上のリーク電流の影響を受けやすくなり、目的の出力電圧がシフトする可能性があります。PCB の過剰なリーク電流がない場合、無負荷時の電源電流を低減するために、約  $1\text{M}\Omega$  までの値を使用できます。

$$R_{FBB} = R_{FBT} \times \frac{0.8}{V_{OUT} - 0.8} \quad (1)$$

場合によっては、可変モードを使用する際に、フィードフォワード コンデンサを使用することで、ループ位相マージンまたは負荷過渡応答を改善できます。 $C_{FF}$  の正確な値は、設計の初期ベンチ評価時に経験的に選択するのが最適です。開発中のいざれかの段階で必要に応じて、このコンデンサのためのプレースホールドを PCB レイアウトに配置します。

安全機能がイネーブルの場合 (nFAULT ピンが High にプルされる)、内蔵のスタートアップ診断によって FB ピンの誤った構成が検出されると、デバイスを強制的に安全状態 (スイッチングなし) にして、nFAULT ピンを Low に駆動します。

安全機能も、スタートアップ時または通常動作時に、FB ピン抵抗の開放フォルトまたは短絡フォルトを検出して、VOUT が目標のレギュレーション値を超えないようにします。

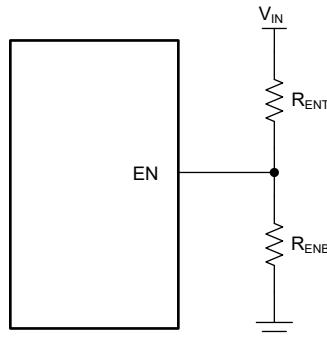

### 7.3.2 EN ピンおよび $V_{IN\_UVLO}$ としての使用

起動とシャットダウンは、EN 入力により制御されます。この入力には高精度のスレッショルドが搭載されており、必要に応じて、外付け分割電圧を使用して可変の入力低電圧ロックアウト (UVLO) を行えます。 $V_{EN\_TH\_R}$  を超える電圧を印加す

ると、本デバイスは完全にイネーブルになり、本デバイスは起動モードに移行し、ソフトスタート期間を開始できます。EN 入力が  $V_{EN\_TH\_F}$  を下回ると、レギュレータはスイッチングを停止し、VIN 入力電流は  $0.85\mu A$  (最大値) 未満でシャットダウン モードに移行します。この機能が必要ない場合は、EN 入力を VIN に直接接続できます。イネーブル ピンがフローティング状態になるとデバイスがオフになるので、イネーブルをフローティングにしないでください。各種の EN スレッショルドの値については、電気的特性表を参照してください。

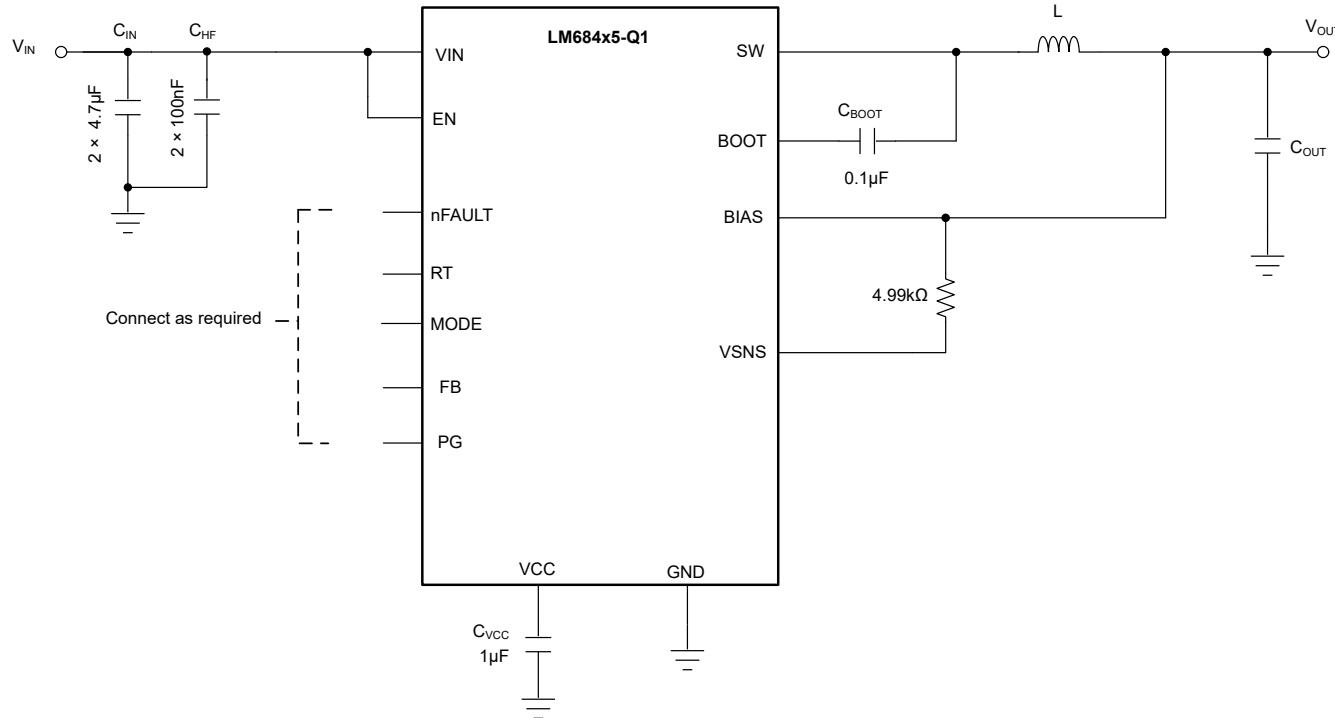

図 7-2. EN ピンを使った VIN/UVLO

場合によっては、本デバイスが内部的に備えているものとは異なる入力 UVLO レベルが必要とされることがあります。この機能は、特別なシーケンシング、または電源ケーブルが過度に長いことによる入力電圧の発振の防止に使用できます。外付けの UVLO は、図 7-2 に示す回路を使うことで実現できます。本デバイスがオンする入力電圧を  $V_{ON}$ 、オフする入力電圧を  $V_{OFF}$  と呼びます。精度を維持するため、分圧器の電流は EN 入力に流れる電流 ( $I_{EN\_LKG}$ ) より大きくする必要があります。 $R_{ENB}$  の値が  $10k\Omega$  と  $50k\Omega$  の間であれば妥当です。次に 式 2 を使って  $R_{ENT}$  を計算し、式 3 を使って  $V_{OFF}$  を計算します。

$$R_{ENT} = R_{ENB} \times \left( \frac{V_{ON}}{V_{EN\_TH\_R}} - 1 \right) \quad (2)$$

$$V_{OFF} = V_{ON} \times \left( \frac{V_{EN\_TH\_F}}{V_{EN\_TH\_R}} \right) \quad (3)$$

ここで、

- $V_{ON} = V_{IN}$  のターンオン電圧

- $V_{OFF} = V_{IN}$  のターンオフ電圧

また、EN ピンは冗長安全回路に電力を供給し、フォルト検出時に nFAULT ピンを Low にラッチします。EN ピンを再びオンにすると、nFAULT ピンがクリアされます。デバイスを eFuse の入力ホットスワップ デバイスなどの入力保護デバイスと組み合わせて安全システムに使用する場合は、EN ピンの電圧が  $V_{EN(nFAULT\_valid)}$  の最大スレッショルドの  $1.25V$  を上回っている限り安全回路に電力が供給されるように、ホットスワップ デバイスまたは eFuse デバイスの前に EN ピンを接続することを推奨します。

### 7.3.3 モード選択

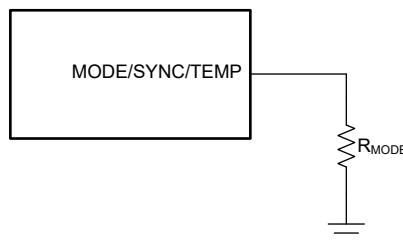

MODE/SYNC/TEMP ピンは、動作モードを設定し、外部の同期信号の入力、またはデバイス温度監視のために外部抵抗に温度依存の電流を供給するための出力として機能するマルチファンクション ピンです。このピンが接地されているか、ロジック Low に駆動されると、コンバータは自動モードで動作します。このピンが VCC に接続されているか、ロジック High に駆動されている場合、または外部クロック ソースに同期している場合、コンバータは FPWM モードで動作します。

$49.9k\Omega$  または  $149.9k\Omega$  抵抗によって GND にプルダウンされると、このピンは温度依存電流を供給し、それぞれ FPWM モードまたは自動モードで動作します。レギュレータの最初のスタートアップ シーケンス中に、このピンのステータスがテストされ、モードがロックされます。スタートアップ完了後は、入力電源が取り外された場合、または EN 入力がサイクルされない限り、モードを変更できません。

表 7-2. モード選択

| MODE/SYNC/TEMP      | モード  | 動的モード変更                  |

|---------------------|------|--------------------------|

| GND に短絡または Low に駆動  | 自動   | 有効                       |

| 49.9kΩ から GND へ     | FPWM | ディスエーブル。 $I_{TEMP}$ の供給。 |

| 149.9kΩ から GND へ    | 自動   | ディスエーブル。 $I_{TEMP}$ の供給。 |

| VCC に短絡または High に駆動 | FPWM | 有効                       |

| 信号の同期               | FPWM | 有効                       |

スタートアップ シーケンス中に抵抗が検出されない場合は、スタートアップ後に動作モードを変更できます。デバイスを自動モードから FPWM モードに移行するには、ピンを Low から High に駆動するか、同期信号を送信する必要があります。デバイスを FPWM モードから自動モードに遷移させるには、ピンを High から Low に駆動するか、同期信号の送信を停止する必要があります。グランドへの短絡または VCC へのプルアップには、200Ω 未満の抵抗が必要であることに注意してください。

### 7.3.3.1 MODE/SYNC/TEMP ピンを使用した同期

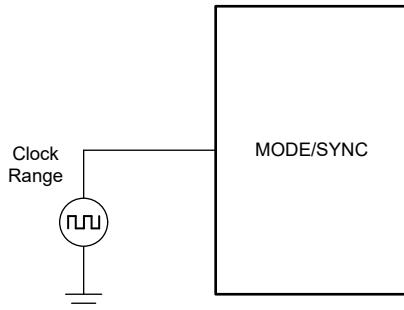

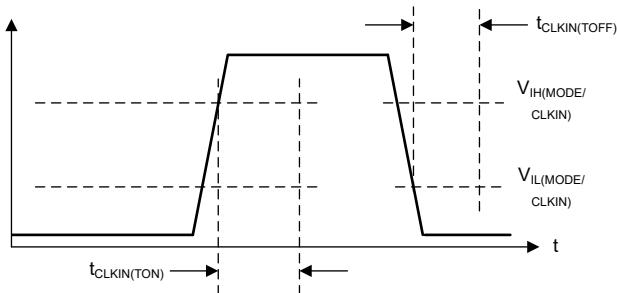

LM684x5-Q1 の MODE/SYNC/TEMP ピンを使用して、内部発振器を外部クロックに同期することができます。内部発振器は、立ち上がりエッジをピンにカップリングすることで同期できます。内部同期パルス検出器をトリップさせるには、ピンの結合エッジ電圧が SYNC 振幅スレッショルド ( $V_{IH(MODE/CLKIN)}$ ) を上回る必要があります。最小 SYNC オンパルスおよびオフパルス幅は、それぞれ  $t_{CLKIN(TON)}$  および  $t_{CLKIN(TOFF)}$  よりも長くする必要があります。LM684x5-Q1 のスイッチング動作は、300kHz～2.2MHz の外部クロックと同期することができます。

外部同期信号は、ピンの検出の前または後にのみ適用できることに注意してください。ピン検出中に印加されると、SYNC 信号は検出できません。

図 7-3. MODE/SYNC/TEMP ピンを使用した同期ができる代表的な実装

この図に、同期信号を検出するために必要な条件を示します。

図 7-4. 代表的な SYNC 波形

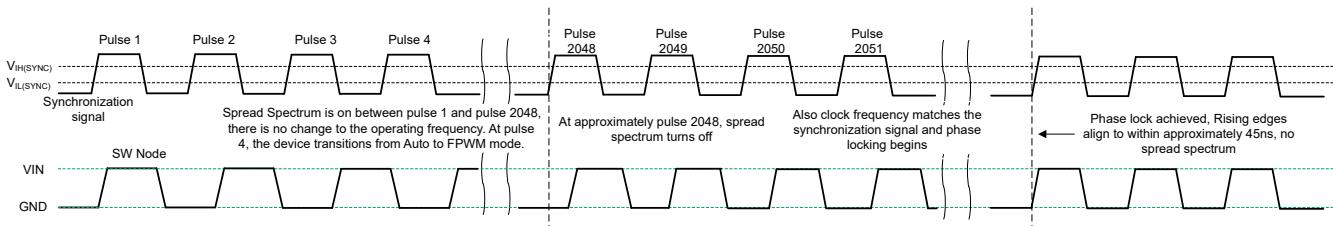

### 7.3.3.2 クロックのロック

有効な同期信号が検出された後、クロック ロック手順が開始されます。約 2048 パルスの後、クロック周波数は同期信号の周波数にロックされます。スイッチング周波数が調整されると同時に、そのクロック サイクルは、デフォルトの周波数で動作する際のクロック サイクルと同期周波数で動作する際のクロック サイクルとの中間の長さになるように位相が維持されます。長すぎる、または短すぎるパルスはありません。周波数が調整された後、立ち上がり同期エッジが立ち上がり SW ノード パルスに対応するように、数 10 サイクルかけて位相が調整されます。図 7-5 を参照してください。

4 番目のパルスで、同期信号が検出されます。約 2048 パルスの後、同期信号は同期する準備ができ、グリッチ フリーの手法を使用して周波数を調整し、位相をロックします。

図 7-5. 同期プロセス

### 7.3.4 可変スイッチング周波数

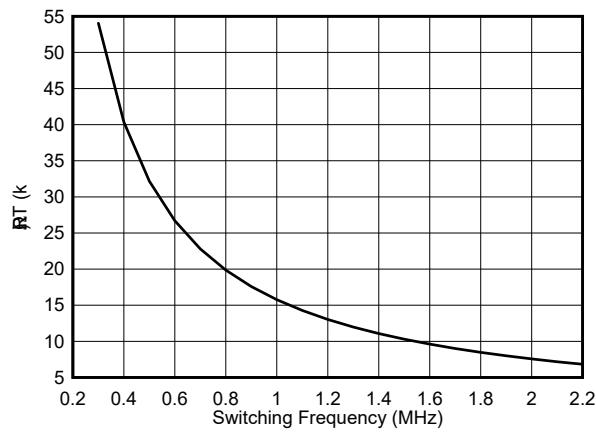

RT ピンは設定可能です。このピンを VCC に接続すると 400kHz で動作し、グランドに接続すると 2.2MHz で動作します。また、抵抗を GND に接続すると可変動作周波数に設定することができます。表 7-3 を参照してください。抵抗値が推奨範囲外になると、LM684x5-Q1 が 400kHz または 2.2MHz に戻ることに注意してください。強制的に同期させる目的で、このピンにパルス信号を印加することはしないでください。同期が必要な場合は、セクション 7.3.3.1 の SYNC/MODE ピンを参照してください。RT ピンと GND との間に抵抗を配置することで、スイッチング周波数を 300kHz ~ 2200kHz の範囲でプログラムできます。式 4 と図 7-6 を参照してください。

$$R_T(k\Omega) = \frac{16.4}{f_{SW}(\text{MHz})} - 0.633 \quad (4)$$

たとえば、 $f_{SW} = 400\text{kHz}$ 、 $R_T = 40.37\text{k}\Omega$  の場合、最も近い値として  $40.2\text{k}\Omega$  抵抗を選択できます。

図 7-6. スイッチング周波数と RT との関係

表 7-3. スイッチング周波数の設定

| RT  | スイッチング周波数 |

|-----|-----------|

| VCC | 400kHz    |

| GND | 2200kHz   |

表 7-3. スイッチング周波数の設定 (続き)

| RT            | スイッチング周波数        |

|---------------|------------------|

| RT 抵抗から GND へ | 300kHz ~ 2200kHz |

| 浮動            | フローティングしないでください  |

グランドへの短絡または VCC へのプルアップには、 $200\Omega$  未満の抵抗が必要であることに注意してください。

### 7.3.5 デュアルランダムスペクトラム拡散機能(DRSS)

LM684x5-Q1 にはデュアルランダムスペクトラム拡散(DRSS)機能があり、広い周波数範囲にわたって電源の EMI を低減します。DRSS 機能は、低周波数の三角波変調プロファイル(標準または幅広)と、高周波数のサイクル単位の疑似ランダム変調プロファイルを組み合わせたものです。低周波数の三角波変調は低い無線周波数帯域で性能を向上させ、高周波のランダム変調は高い無線周波数帯域で性能を向上させます。

低周波数の三角波変調は、12kHz の変調周波数でスイッチング周波数を  $\pm 5\%$  拡散します。

スペクトラム拡散は、狭帯域信号を広帯域信号に変換し、エネルギーを複数の周波数にわたって拡散することで機能します。業界規格では、周波数帯域ごとに異なるスペクトラムアナライザの解像度の帯域幅(RBW)の設定を要求しています。RBW はスペクトラム拡散の性能に影響を及ぼします。たとえば、CISPR-25 は、150kHz から 30MHz の周波数帯域で 9kHz の RBW を必要とします。30MHz を超える周波数の場合、必要な RBW は 120kHz です。DRSS は、低周波数の三角波変調と高周波数のサイクル単位疑似ランダム変調により、高 RBW および低 RBW での EMI 性能を同時に向上できます。DRSS 関数を使用すると、低周波数帯域(150kHz ~ 30MHz)では伝導エミッションを最大  $15\text{dB}\mu\text{V}$ 、高周波帯域(30MHz ~ 108MHz)では最大  $5\text{dB}\mu\text{V}$  低減できます。MODE/SYNC/TEMP ピンに外部クロックが印加されると、DRSS 機能はディスエーブルになります。

図 7-7. デュアルランダムスペクトラム拡散機能の実装

### 7.3.6 内部LDO、VCC UVLO、BIAS 入力

LM684x5-Q1、VCC に電力を供給する 2 つの内部レギュレータが内蔵されています。メイン VCC レギュレータは、ゲートドライブなどデバイスの機能の大部分に電力を供給します。LM684x5-Q1 は、VCC メイン レギュレータ用のデュアル入力を備えており、VIN または BIAS から供給されます。LM684x5-Q1 がアクティブになった後、BIAS が約 3.1V 未満の場合、VIN から電力が供給されます。ただし、BIAS が  $3.2V_{MAX}$  より大きい場合、BIAS から電力が供給されます。VCC は大半の条件下で通常 3.3V ですが、VIN が非常に低い場合はそれより低くなる可能性があります。不適切な動作を防止するため、VCC には、内部電圧が低すぎる場合にスイッチングを止める UVLO が備わっています。「電気的特性」の  $V_{CC-UVLO\_R}$  および  $V_{CC-UVLO\_HYST}$  を参照してください。テキサス・インスツルメンツでは、VCC コンデンサ用に X7R 以上の誘電体を使用した、定格 10V の  $1\mu\text{F}$  コンデンサを推奨します。EN pn が  $V_{EN\_TH\_F}$  未満の場合、メイン VCC レギュレータはオフになります。

LM684x5-Q1 は、VCC ピンに電力を供給する独立した常時オンのレギュレータも備えており、認証ペリフェラルおよび安全関連機能に使用されます。EN ピンが  $V_{EN\_TH\_F}$  未満であっても、常時オンのレギュレータはオンのままでです。

### 7.3.7 ブートストラップ電圧(BST ピン)

電源スイッチ (HS スイッチ) のドライバには、HS スイッチがオンのときに、VIN より高いバイアス電圧が必要となります。BST と SW の間に接続されたコンデンサは、BST 端子の電圧を (SW + VCC) に昇圧するチャージ ポンプとして機能します。物理的な設計サイズを最小化するため、LM684x5-Q1 のダイにはブートダイオードが内蔵されています。テキサス・インスツルメンツでは、BST コンデンサ用に X7R 以上の誘電体を使用した、定格 10V の 100nF コンデンサを推奨します。

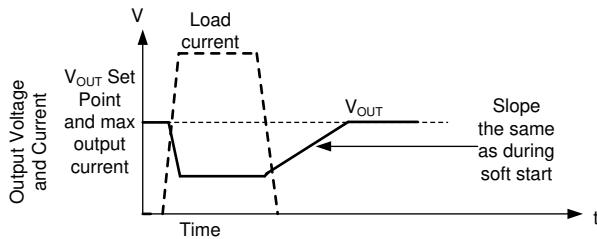

### 7.3.8 ソフトスタートとドロップアウトからの回復

LM684x5-Q1 を使用して設計する場合、ドロップアウトからの回復に起因する出力電圧のゆっくりとした上昇とソフトスタートは、2 つの個別の事象と見なす必要があります。ソフトスタートは、以下のいずれかの条件によってトリガされます。

- 本デバイスをオンにするために EN が使われました。

- ヒップ待機期間からの回復。[セクション 7.3.9.7 参照](#)。

- 過熱保護によるシャットダウンから回復した。

- IC の VIN に電力が供給されるか、VCC の UVLO が解除されます

ソフトスタートが開始された後、本 IC は以下の動作を実行します。

- 出力電圧を制御するために本 IC が使用する基準電圧が、ゆっくりと 0 から上昇します。その結果、出力電圧が (それまで 0V だった場合)、 $t_{SS}$  の時間をかけて制御値の 90% に達します。

- 動作モードが自動的に設定され、ダイオード エミュレーションを有効化する。この動作により、電圧がすでに出力されている場合、出力電圧を Low にすることなく起動できます。

- ヒップは、ソフトスタート中ディスエーブルになります ([セクション 7.3.9.7 を参照](#))。

これらの動作をすべて組み合わせることで、スタートアップを制御でき、突入電流も制限できます。また、これらの動作により、起動時に電流を制限する原因となる可能性がある出力コンデンサと負荷条件を、ヒップをトリガすることなく使用できます。また、出力電圧がすでに存在している場合、出力電圧は放電しません。

どのような理由であれ、出力電圧が数 % 以上低くなると、出力電圧はゆっくりと上昇してきます。この動作はドロップアウト条件からの回復で、ソフトスタートとは以下の 3 つの重要な点で異なります。

- 出力電圧がその設定点の 40% 未満である場合に限り、ヒップが許可される。ドロップアウト レギュレーションの間、ヒップは禁止されることに注意します。[セクション 7.3.9.7 を参照](#)してください。

- ドロップアウトからの回復中、FPWM モードが許可される。外部電源によって出力電圧が突然プルアップされた場合、LM684x5-Q1 は出力をプルダウンする場合があります。通常動作中に存在するすべての保護機能は作動しており、出力が高い電圧またはグランドに短絡した場合にデバイスを保護していることに注意します。

- 基準電圧は、現在の出力電圧を実現するために必要な値よりも約 1% 高い値に設定されます。基準電圧はゼロからはスタートしません。

名前にもかかわらず、十分に長い間、出力電圧が設定点よりも数パーセント以上低くなると、必ずドロップアウトからの回復がアクティブになるので次のいずれかになります。

- デューティ係数が、最小オン時間によって制御されるか、あるいは、

- デバイスが電流制限で動作している。

この動作は主に、以下の条件で発生します。

- ドロップアウト：目的の出力電圧を生成するのに十分な入力電圧がない場合。

- ヒップをトリガするのに十分な大きさではない過電流、または時間が短すぎてヒップをトリガできない場合。[セクション 7.3.9.7 を参照](#)してください。

出力電圧の低下が、高負荷と低入力電圧のどちらによるものであっても、出力がその設定点を下回る原因となっている条件が解消された後、起動時と同じ速度で出力は上昇します。ドロップアウトが原因でヒップがトリガされなかったとしても、回復中、64 クロック サイクル以上にわたって出力電圧が設定点の 0.4 倍を下回った場合、原則として、回復中にヒップがトリガされます。

図 7-8. ドロップアウトからの回復

### 7.3.9 安全関連の特長

LM684x5-Q1 は、以下の包括的な安全機能セットを備えています。

- 出力低電圧 (UV) および過電圧 (OV) 保護機能を備えたパワーグッドモニタ

- 高速出力過電圧 (OV) 保護機能を備えた冗長  $V_{OUT}$  監視

- フォルト出力、フォルトラッチ、自動再試行機能

- 冗長化された内部電圧リファレンスおよび監視機能

- スタートアップ診断

- ヒップ モードによる過電流および出力短絡保護回路

- サーマル シャットダウン (TSD)

- 冗長化温度センサ

#### 7.3.9.1 パワーグッドモニタ

LM684x5-Q1 は、システムの電源シーケンシングと監視を簡素化するためのパワーグッド機能を備えています。パワーグッド機能を使用すると、LM684x5-Q1 から電源を供給されるダウンストリームの回路をイネーブルにしたり、ロードスイッチなどのダウンストリームの保護回路を制御したり、あるいはシーケンス電源を起動したりできます。この機能は、可変  $V_{OUT}$  の設定では FB ピンを、固定  $V_{OUT}$  の設定では BIAS ピンを使用して、ウインドウコンパレータにより出力電圧を監視します。パワーグッド出力 (PG) は、出力電圧がレギュレーション状態のときに、高インピーダンスのオープンドレイン状態に切り替わります。出力電圧が設定電圧から  $\pm 5\%$  の範囲を超えると、PG ピンが Low ( $< V_{OL(PG)}$ ) に駆動され、出力の過電圧または低電圧状態をシステムに警告します。PG の立下りエッジの 114μs のグリッチ除去フィルタにより、遷移中のパワーグッド信号の誤トリップが防止されます。出力電圧がレギュレーションウインドウ内に戻ると、PG の立ち上がりエッジに 2ms のフィルタが接続されているため、ダウンストリーム部品のための追加の処理時間が得られます。

TI は、PG ピンと関連する 30V 以下のロジックレールとの間に 100kΩ プルアップ抵抗を入れることを推奨しています。ソフトスタート中および LM684x5-Q1 がディセーブルのとき、PG は Low にアサートされます。

安全機能がイネーブルの場合は、ABIST シーケンスによって、スタートアップ時に PG ピンのプルダウン FET の機能がチェックされます。チェックの結果、負となった場合、nFAULT ピンが Low にラッチされます。また、起動時に ABIST シーケンスによって nFAULT、RT または MODE ピンがフローティングであることが検出されると、起動後に PG ピンは Low に保持されます。

#### 7.3.9.2 冗長 $V_{OUT}$ 監視

パワーグッド監視に加えて、LM684x5-Q1 には冗長出力電圧監視機能が内蔵されているため、安全関連アプリケーションの残留 FIT (故障率) をさらに低減できます。この機能は、VSNS ピンを介して出力電圧を監視します。出力電圧がレギュレーション状態になると、冗長  $V_{OUT}$  モニタのオープンドレイン出力 (nFAULT) が高インピーダンスに切り替わります。出力電圧が設定電圧より 12.5% 高いスレッショルドを超えると、デバイスは 0.5μs の応答時間内に nFAULT ピンを Low

にアサートして応答し、スイッチングを停止します。ラッチをクリアし、スイッチング動作を再開するには、イネーブル (EN) ピンをトグルする必要があります。

図 7-9. 可変  $V_{OUT}$  の冗長監視

冗長出力電圧監視機能は EN ピンにより給電され、冗長化内部電圧リファレンスを使って出力電圧を完全に監視する冗長化を実現しています。この機能は、nFAULT ピンを GND に短絡することで無効化できます。

### 7.3.9.3 フォルト出力

LM684x5-Q1 の nFAULT ピンは、冗長  $V_{OUT}$  監視の出力として機能する以外に、スタートアップ診断回路および内部基準監視によって検出された故障も通知します。nFAULT ピンは 42V のオープンドレイン出力で、図 7-10 に示すように、アップストリームの保護回路に直接接続できます。nFAULT ピンに以下のフォルトが通知されます。

- 冗長  $V_{OUT}$  監視によって検出された出力過電圧イベント。

- 冗長  $V_{OUT}$  監視により検出された FB または VSNS パス (ピン障害オープン、ピン障害短絡、抵抗障害オープン、パラメータシフト) の障害。

- 電圧リファレンス モニタによって検出された内部電圧リファレンスまたは冗長電圧リファレンスの故障。

- スタートアップ診断回路で検出された FB、VSNS ピンでの接続の問題。

- 起動診断回路によって検出されたパワーグッド機能の問題。

上記の故障が検出されるとスイッチング動作は直ちに停止し、nFAULT ピンが Low にラッチされます ( $< V_{OL(nFAULT)}$ )。ラッチをクリアし、スイッチング動作を再開するには、EN ピンをトグルする必要があります。

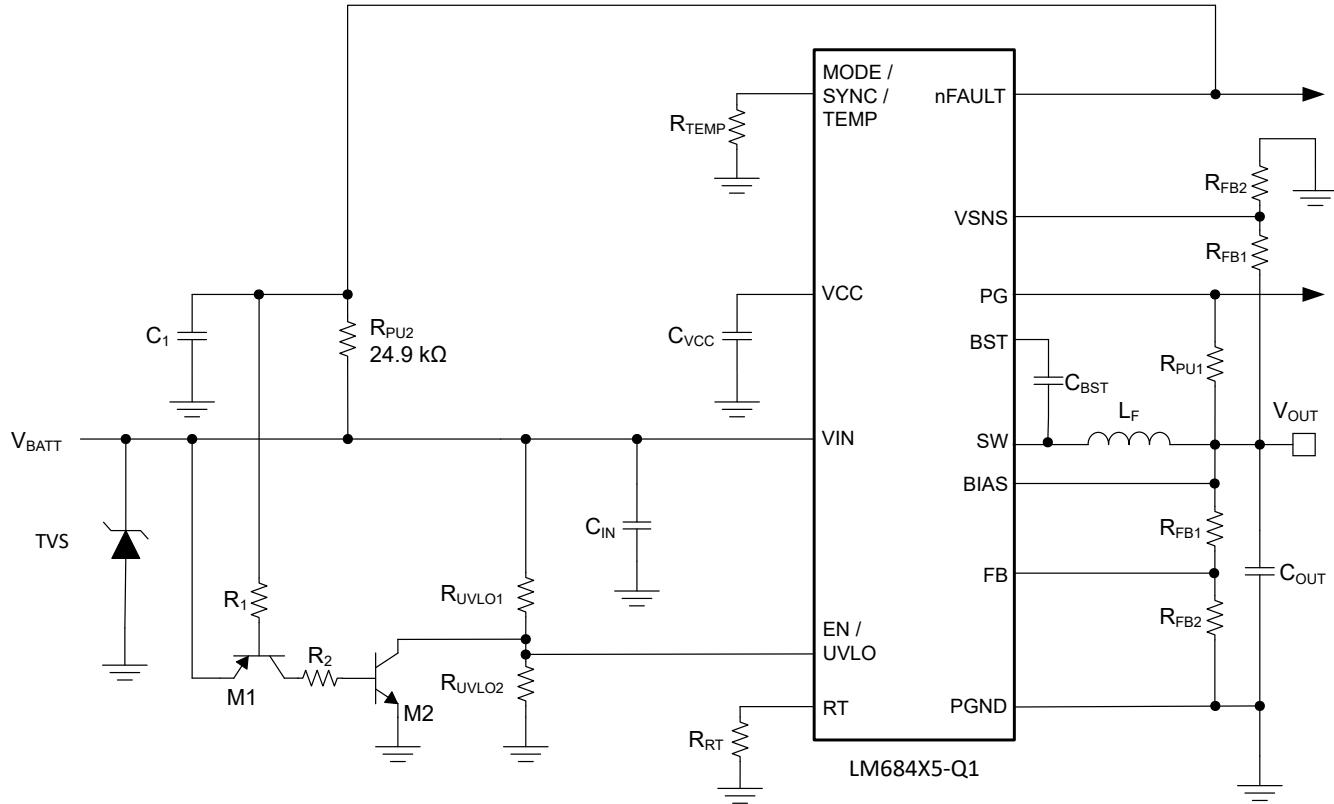

LM684x5-Q1 には、過渡的または一時的な故障の場合にユーザーの介入を不要にするため、以下の図に示すように自動再試行方式を実装するための機能も含まれています。

図 7-10. 自動再試行方式による可変 VOUT の冗長監視

この方式では、内部カウンタと、M1、M2、C1、R1、R2 で構成される外部回路を使用して、故障検出後にスタートアップシーケンスを自動的に再試行します。以下に、自動再試行方式の動作を示します。

1. 故障検出後、内部フォルトカウンタがインクリメントすると、nFAULT ピンが Low にラッチされ、M1 (PNP) ベースが Low に駆動されます。

2. M1 がオンになり、M2 (NPN) のベースが High にプルされます。

3. M2 がオンになり、EN ピンが Low にプルされてデバイスがディスエーブルされ、nFAULT ラッチがクリアされます。

4. 起動診断とソフトスタートシーケンスをすべて実行して、デバイスを再起動します。故障が検出されない場合、デバイスは定常状態で動作します。

5. 故障が解消しない場合、本デバイスはフォルトカウンタが 4 に進むまで、手順 1 ~ 4 を繰り返します。

6. nFAULT ピンは Low にラッチされるので、ラッチをクリアするには VIN ピンをトグルするかバッテリを切断する必要があります。

TI は、nFAULT ピンから 42V 以下の関連するロジック レールへの 100kΩ プルアップ抵抗を使用することを推奨します。

#### 7.3.9.4 電圧リファレンス モニタ

LM684x5-Q1 には冗長電圧リファレンスとウインドウコンパレータが内蔵されており、プライマリおよび冗長電圧リファレンスの両方を継続的に監視できます。電圧リファレンスがスタートアップ時に互いに  $\pm 5\%$  以上離れている場合、デバイスは起動しません。定常状態動作中に電圧リファレンスのドリフトが  $\pm 5\%$  を超えて離れると、スイッチング動作は即座に停止し、nFAULT ピンは Low にラッチされます。

電圧リファレンス監視機能は、nFAULT ピンが GND に短絡し、その他の安全機能が無効化されていてもアクティブです。

#### 7.3.9.5 スタートアップ診断

LM684x5-Q1 は、ソフトスタートシーケンスの前に FB、VSNS、nFAULT、MODE、RT ピンのインピーダンスチェックを実行するアナログ内蔵セルフテスト (ABIST) を備えています。

- FB および VSNS ピン: 開放が検出されると、nFAULT ピンが Low にラッピングされ、デバイスは起動しません。

- nFAULT、MODE、RT ピン: 開放が検出された場合、ソフトスタートシーケンスの完了後でも、PG ピンは Low に保持されます。

インピーダンスチェックに加えて、ABIST シーケンスは PG ピンのプルダウン FET の機能もチェックします。フォルトが検出された場合、nFAULT ピンが Low にラッピングされ、デバイスは起動しません。

スタートアップ診断または ABIST は、nFAULT ピンを GND に短絡して無効化することはできません。nFAULT がグランドに短絡された場合、デバイスは起動しません。

#### 7.3.9.6 過電流および短絡保護

LM684x5-Q1 は、ハイサイド MOSFET とローサイド MOSFET の両方でサイクル毎に電流を制限することで、過電流状態から保護されます。

下限側 MOSFET 過電流保護機能は、ピーク電流のモード制御の性質を利用して実装されています。HS スイッチ電流は、短いブランギング時間の後に HS がオンになると検出されます。固定電流設定点と、電圧レギュレーションループの出力からスロープ補償を引いた値のどちらか小さい方と HS スイッチ電流がスイッチングサイクルごとに比較されます。電圧ループには最大値があり、スロープ補償はデューティサイクルに対応して大きくなるため、デューティサイクルが 35% より大きい場合、デューティサイクルが大きくなると HS 電流制限値は下がります。

LS スイッチがオンになると、LS スイッチを流れる電流も検出、監視されます。ローサイド MOSFET は、ハイサイド MOSFET と同様に、電圧制御ループの指示に従ってオフになります。ローサイドデバイスでは、発振器が正常に新しいスイッチングサイクルを開始したとしても、電流制限を超えるとターンオフは禁止されます。また、ハイサイドデバイスと同様に、ターンオフ電流に許容される高さに限界があります。この制限値はローサイド電流制限と呼ばれます。値については、「電気的特性」を参照してください。LS 電流制限を超えた場合、LS MOSFET はオン状態を維持し、HS スイッチはターンオフしません。LS 電流が制限値を下回ると、LS スイッチがオフになります。HS デバイスが最後にオンになってから 1クロック周期以上が経過しあれば、HS スイッチは再度オンになります。

図 7-11. 電流制限波形

ハイサイドおよびローサイド電流制限の動作による正味の影響は、IC がヒステリシス制御で動作することです。電流波形は I<sub>L-HS</sub> と I<sub>L-LS</sub> の間の値をとるため、デューティサイクルが極めて高い場合を除き、出力電流はこれらの 2 つの値の平均値に近い値になります。電流制限での動作後、出力電圧がゼロに近づくにつれて、ヒステリシス制御が使われ電流は増加しなくなります。

デューティサイクルが非常に大きい場合は、不安定性を防止するためリップル電流を非常に小さくする必要があります。セクション 8.2.2.4 を参照してください。電流リップルが低いため、このデバイスは全負荷電流を供給できます。供給される電流は I<sub>L-LS</sub> に近くなります。

過負荷状態が解消されると、本デバイスはソフトスタート中であるかのように回復します（セクション 7.3.8 を参照）。出力電圧が意図した出力電圧の約 0.4 倍を下回り、64 回の連続スイッチング サイクルが経過した場合、ヒップがトリガされる可能性があることに注意してください。

### 7.3.9.7 ヒップ

LM684x5-Q1 は、64 の連続スイッチング サイクルにわたって、以下のすべての条件が満たされた場合、ヒップ過電流保護に入ります。

- ・ ソフトスタートが開始されてから、 $t_{SS}$  以上の時間が経過した（セクション 7.3.8 を参照）。

- ・ 出力電圧が、出力設定点の約 0.4 倍を下回っている。

- ・ 本デバイスがドロップアウト（最小オフ時間がデューティ係数によって制御されている状態）で動作していない。

ヒップ モードに入ると、本デバイスはシャットダウンし、 $t_{HI}$  後にソフトスタートを試みます。ヒップ モードは、極度の過電流と短絡状態の際に本デバイスの消費電力を低減するのに役立ちます。

### 7.3.9.8 サーマル シャットダウン

サーマル シャットダウンでは、本 IC の接合部温度が 165°C（標準値）を超えると、パワーグッド（PG）がアサートされたときに内部スイッチをオフにすることで、総電力損失を制限します。サーマル シャットダウンは 155°C 未満ではトリガされません。サーマル シャットダウンが作動した後、ヒステリシスにより、接合部温度が約 156°C に低下するまで本デバイスのスイッチングが止められます。接合部温度が 156°C（標準値）を下回ると、LM684x5-Q1 はソフトスタートを試みます。

接合部温度が上昇して、LM684x5-Q1 がシャットダウンされても、電力は VCC に供給され続け、機能安全メカニズムがアクティブになります。

### 7.3.9.9 冗長温度センサ

LM684x5-Q1 には冗長温度センサが内蔵されており、サーマル シャットダウン機能とは独立して、レギュレータの接合部温度を監視するために使用できます。図 7-12 に示すように、センサの出力は、MODE/SYNC/TEMP ピンから  $R_{MODE}$  に流れる温度依存電流として供給されます。このようにして、温度に依存する電圧が  $R_{MODE}$  の両端に現れます。接合部温度 27°C の場合、電圧は通常 0.844V です。この電圧は一般的に、2.95mV/°C の傾きで増加します。

起動時に MODE/SYNC/TEMP ピンに 49.9kΩ（FPWM モード）または 149.9kΩ（自動モード）抵抗が検出されると、冗長温度センサが有効になります。

外部 ADC を使用して、このピンの電圧を測定し、負荷管理またはその他の接合部温度の上昇軽減アクションのためにシステムのマイクロプロセッサに情報を伝達できます。

図 7-12. 温度センサ

## 7.4 デバイスの機能モード

### 7.4.1 シャットダウンモード

EN ピンは、本デバイスの電気的オン / オフ制御に使用できます。EN ピンの電圧が 0.9V を下回ると、レギュレータと内部 LDO の両方が電圧を出力しなくなり、本デバイスはシャットダウン モードに入ります。シャットダウン モードでは、静止電流は 0.85μA 未満に低下し、PG ピンが Low になります。

### 7.4.2 アクティブモード

LM684x5-Q1 は、次の事象が発生するとアクティブ モードになります。

- EN ピンが  $V_{EN\_TH\_R}$  を上回る。

- $V_{IN}$  が  $V_{IN\_UVLO\_R}$  を上回る。

- $V_{IN}$  が、 $V_{IN}$  の最小動作入力電圧を満たすのに十分な大きさである。

- その他の障害条件は存在しない。

保護機能については、[セクション 7.3](#) を参照してください。この動作を可能にする最も簡単な方法は、EN ピンを VIN に接続することです。これにより、印加された入力電圧が最小  $V_{IN\_OPERATE}$  を超えると自動的に起動できます。

アクティブ モードでは、負荷電流、入力電圧、出力電圧に応じて、LM684x5-Q1 は次の 6 つのサブモードのいずれかになります。

- 固定スイッチング周波数とピーク電流モード動作による連続導通モード (CCM)。

- 不連続導通モード (DCM) (自動モードのときに負荷電流がインダクタリップル電流の 1/2 未満である場合) 電流が減少し続けると、デバイスはパルス周波数変調 (PFM) に移行します。これにより、軽負荷時にスイッチング周波数が低下して、スイッチング損失を低減しながらレギュレーションを維持し、高効率を実現します。

- 要求された低デューティサイクルでの全周波数動作に必要なデバイスのオン時間の最小オン時間動作は、 $T_{ON\_MIN}$  ではサポートされていません。

- 固定スイッチング周波数の CCM に類似した強制パルス幅変調 (FPWM)、ただし、動作の固定周波数範囲を全負荷から無負荷まで拡張。

- 出力電圧が出力設定点の 0.4 倍を上回ったままの電流制限条件。

- 低下を最小限に抑えるためにスイッチング周波数が低下したときのドロップアウト モード。

- 出力電圧の設定点を除く他の動作モードと類似のドロップアウトからの回復は、プログラムされた設定点に達するまで徐々に上昇します。

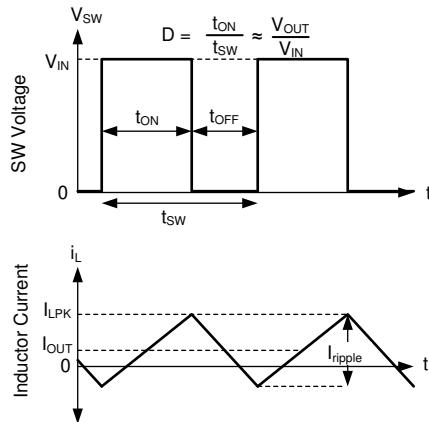

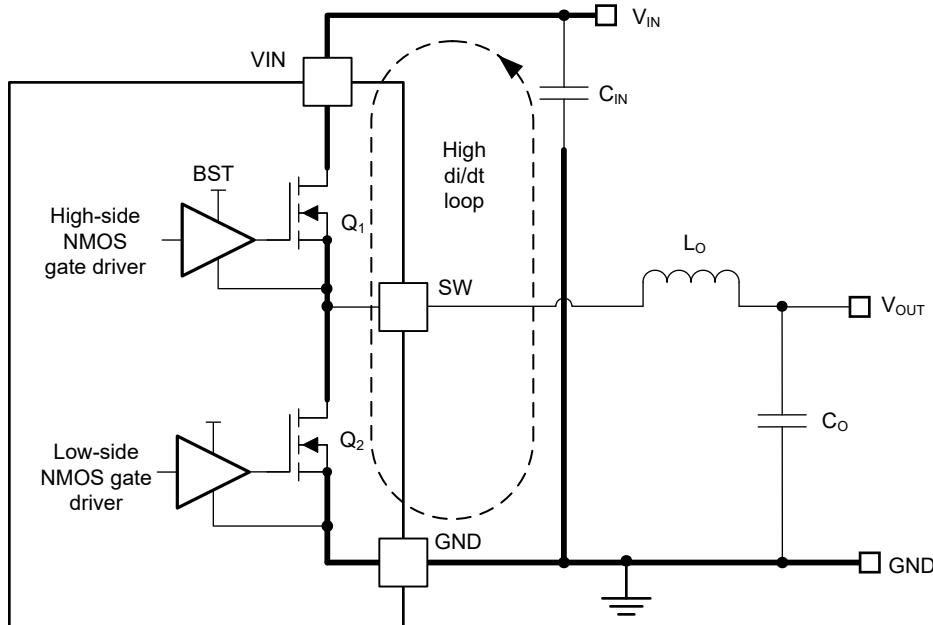

#### 7.4.2.1 ピーク電流モード動作

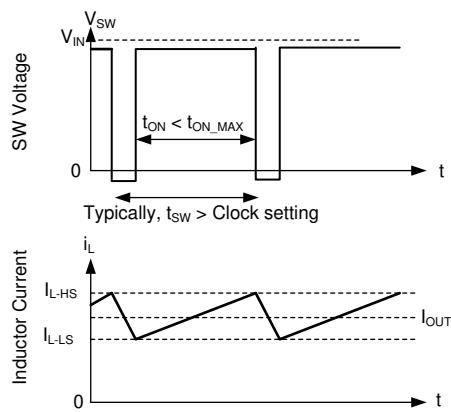

LM684x5-Q1 の以下の動作の説明は、[セクション 7.2](#) と [図 7-13](#) の波形を参照しています。両方とも、内蔵ハイサイド (HS) およびローサイド (LS) NMOS スイッチを各種デューティサイクル (D) でオンにすることで、制御された出力電圧を供給します。HS スイッチのオン時間の間、SW 端子の電圧 ( $V_{SW}$ ) は  $V_{IN}$  の付近までスイングし、インダクタ電流 ( $i_L$ ) は線形的な傾きで増加します。HS スイッチは、制御ロジックによってオフにされます。HS スイッチのオフ時間 ( $t_{OFF}$ ) の間、LS スイッチはオンにされます。インダクタ電流は LS スイッチを通して放電され、LS スイッチの両端の電圧降下によって  $V_{SW}$  をグランドより低い電圧まで強制的にスイングさせます。一定の出力電圧を維持するため、レギュレータ ループはデューティサイクルを調整します。D は、HS スイッチのオン時間をスイッチング周期で割った値として次のように定義されます。 $D = T_{ON} / (T_{ON} + T_{OFF})$ 。

損失が無視される理想的な降圧コンバータでは、次のように D は出力電圧に比例し、入力電圧に反比例します。 $D = V_{OUT} / V_{IN}$ 。

図 7-13. 連続モード (CCM) における SW 電圧とインダクタ電流の波形

高精度の DC 負荷レギュレーションを実現するため、電圧帰還ループを使用しています。ピーク電流モード制御と電流保護のために、ピークおよびバレー インダクタ電流を検出します。負荷レベルが最小ピーク インダクタ電流の 1/2 を上回っている場合、レギュレータは一定のスイッチング周波数の連続導通モードで動作します。内部的に補償された制御ネットワークは、小型外付け部品と低 ESR コンデンサを使った高速で安定した動作を実現します。

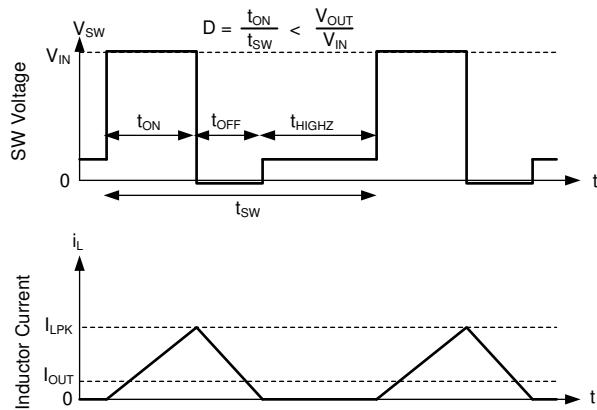

#### 7.4.2.2 自動モード動作

軽負荷時、LM684x5-Q1 は 2 種類の動作を行うことができます。自動モード動作と呼ばれる動作を使うと、負荷が重い際の通常電流モードと高効率の軽負荷動作との間をシームレスに移行できます。FPWM モードと呼ばれるもう 1 つの動作では、無負荷時でも最大周波数が維持されます。LM684x5-Q1 がどちらのモードで動作するかは、SYNC/MODE ピンによって決まります。SYNC/MODE が High のとき、本デバイスは FPWM モードになります。SYNC/MODE が Low の場合、本デバイスは PFM モードになります。

自動モードでは、定格最大出力電流の約 1/10 未満の負荷の場合、LM684x5-Q1 では軽負荷動作が使われます。軽負荷動作では、効率を向上させるため次の 2 つの手法が使われます。

- DCM 動作が可能なダイオード エミュレーション

- 周波数フォールドバック

これら 2 つの機能が同時に動作することで、非常に優れた軽負荷動作を実現しますが、互いに独立して動作することに注意します。

##### 7.4.2.2.1 ダイオード エミュレーション

ダイオード エミュレーションは、インダクタを流れる逆電流を防止します。固定ピーク インダクタ電流の場合、レギュレートするために周波数をより低くする必要があります。ダイオード エミュレーションは、周波数が下がった際のリップル電流も制限します。ピーク インダクタ電流が  $I_{PEAK-MIN}$  を下回ると、周波数が低下します。固定ピーク電流では、出力電流がゼロに向かって低下するにつれて、レギュレーションを維持するために周波数をゼロに近い値まで下げる必要があります。

自動モードでは、インダクタ電流がゼロに近づくとローサイド デバイスはオフになります。その結果、出力電流が CCM でインダクタリップルの 1/2 未満になると、本デバイスは DCM で動作します。これは、ダイオード エミュレーションが機能していることと等価です。

図 7-14. PFM 動作

自動モードでは、LM684x5-Q1 は最小ピーク インダクタ電流設定値を持っています。しかしながら、入力電圧を一定にした状態で、電流値が下がると、オン時間は一定になります。その後、周波数を調整することで、レギュレーションが達成されます。この動作モードを PFM モード レギュレーションと呼びます。

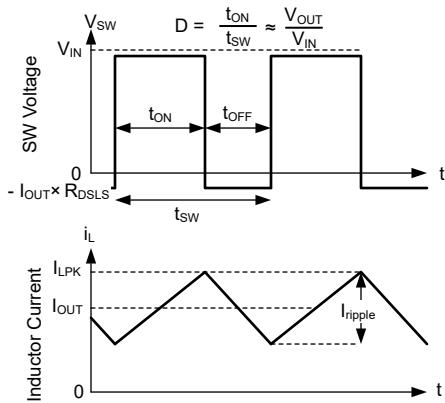

#### 7.4.2.3 FPWM モード動作

自動モード動作と同様に、軽負荷動作時の FPWM モード動作は SYNC/MODE ピンを使って選択します。

FPWM モードでは、軽負荷時に周波数が維持されます。周波数を維持するため、インダクタを流れる逆電流が制限されます。逆電流制限回路により、逆電流が制限されます。逆電流制限の値については、「電気的特性」を参照してください。

FPWM モードの連続導通 (CCM) は、 $i_{OUT}$  が  $i_{ripple}$  の半分未満でも可能です。

**図 7-15. FPWM モード動作**

FPWM モードでは、軽負荷時でも最小オン時間をコマンドできるほど入力電圧が高ければ周波数の低減が可能です。このフォールドバック機能により、入力電圧過渡事象が発生してもレギュレーションを維持できます。

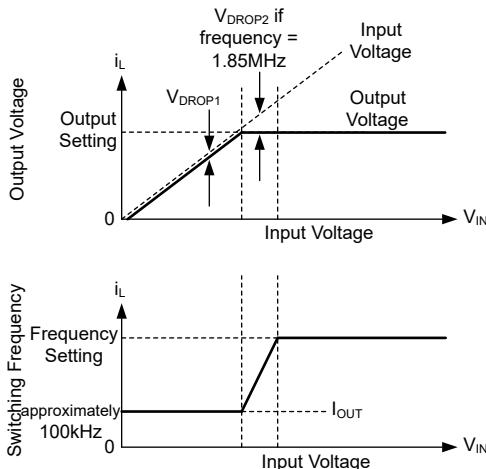

#### 7.4.2.4 ドロップアウト

ドロップアウト動作とは、必要なデューティ係数を達成するために周波数を下げ、入力電圧に対する出力電圧の比を任意の値に制御することです。与えられたクロック周波数において、デューティ係数は最小オフ時間によって制限されます。この制限値に達した後、仮にクロック周波数が維持される場合、出力電圧は低下します。LM684x5-Q1 は、出力電圧が下がるのを許容するのではなく、クロック サイクルが終わっても必要なピーク インダクタ電流が達成されるまでオン時間を延長します。ピーク インダクタ電流に達するか、または設定済みの最大オン時間 ( $t_{ON-MAX}$ 、約 9μs) が経過すると、クロックは新しいサイクルを開始できます。その結果、最小オフ時間の存在に起因して、選択されたクロック周波数において必要なデューティ係数が達成できない場合、レギュレーションを維持するために周波数が低下します。オン時間 ( $t_{ON\_MAX}$ ) を使っても出力電圧をレギュレートできないほど入力電圧が低い場合、出力電圧は入力電圧よりもわずかに ( $V_{DROP1}$ ) 低い値に下がります。[セクション 6](#) を参照してください。

出力電圧および周波数と入力電圧との関係: 入力電圧と出力電圧設定値との差がほとんどない場合、本 IC はレギュレーションを維持するために周波数を下げます。入力電圧が低すぎて、約 110kHz で目的の出力電圧を供給できない場合、出力電圧は入力電圧に追従します。

図 7-16. ドロップアウト時の周波数と出力電圧

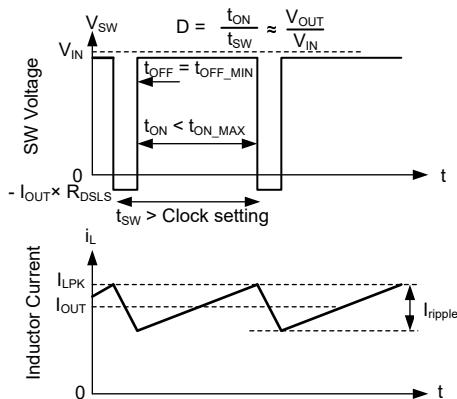

この図は、ドロップアウト中のスイッチング波形を示しています。インダクタ電流は、目的のピーク値に達するのに通常のクロックよりも長い時間を要します。その結果、周波数は低下します。この周波数の低下は  $t_{ON\_MAX}$  によって制限されます。

図 7-17. ドロップアウト波形

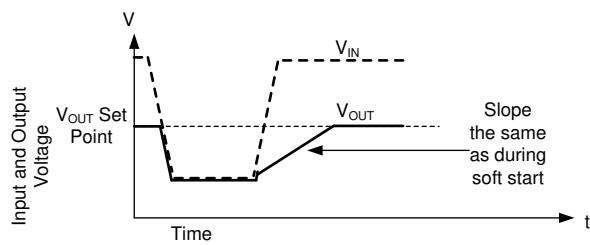

#### 7.4.2.5 ドロップアウトからの回復

一部のアプリケーションでは、目的の出力電圧よりも入力電圧が下がった後、より高い値に突然回復する場合があります。ほとんどのレギュレータは、入力電圧が急激に上昇すると、レギュレーションが達成されるまでの間、電流制限によってのみ制限されたレートで出力電圧が上昇します。入力電圧が目的の出力電圧に達すると、制御ループでのワインドアップによるオーバーシュートが発生します。出力容量が小さい（負荷が軽い）アプリケーションでは、このオーバーシュートは大きくなる可能性があります。また、レギュレータが出力電圧のレギュレーションを開始した後、大きな突入電流が入力ラインで大きな変動を引き起こす可能性があります。これは、通常、この初期突入時よりも少ない電流しか必要ありません。

LM684x5-Q1 は突入電流およびオーバーシュートを大幅に低減します。これは、入力電圧が突然上昇したときに常にソフトスタート回路を起動することで行われ、十分に下がった後で出力電圧低下を引き起します。この機能が誤って作動しないようにするには、出力電圧が 1% 以上下がるまでこの機能を使えなくする必要があります。また、この機能はドロップアウト状態または電流制限状態で動作している場合にのみ動作するため、通常の過渡応答の干渉は避けられますが、動作中に数パーセントのオーバーシュートは許容されてしまいます。出力電圧が目的のレベルに非常に近い場合、レギュレーションを開始する前にインダクタ電流が High レベルに上昇する時間がないため、オーバーシュートが低減されます。

図 7-18. 出力電圧が低下すると、出力電圧はゆっくりと回復をして、オーバーシュートや大きな突入電流を防止します

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

LM684x5-Q1 降圧 DC/DC コンバータは、2.5A の最大出力電流で、高い DC 電圧を低い DC 電圧に変換するために使われることが一般的です。LM684x5-Q1 の部品を選択する際には、次の設計手順を使用します。あるいは、WEBENCH 回路設計と選択シミュレーションサービス設計ツールを使用して、完全な設計を生成することもできます ([WEBENCH](#))。このツールは、反復的な設計手順を使用し、包括的な部品データベースにアクセスします。この機能により、このツールで最適化された設計を作成し、ユーザーはさまざまなオプションを実験できます。

### 注

以下のアプリケーション情報に記載されているすべての容量値は、特に記述のない限り実効値を指しています。実効値は、定格値や銘板値ではなく、DC バイアスおよび温度における実際の容量として定義されます。X7R 以上の誘電体を使用した、高品質で低 ESR のセラミックコンデンサを全体にわたって使用してください。値の大きいセラミックコンデンサは、すべて、通常の許容誤差と温度効果に加えて、電圧係数が大きくなります。DC バイアスを印加すると、静電容量は大幅に低下します。この点については、ケースサイズが大きく、より高い電圧定格のものが望ましいです。これらの影響を軽減するために、複数のコンデンサを並列に使用すれば、最小実効静電容量を必要な値まで大きくすることができます。この対策により、個別のコンデンサの RMS 電流要件も緩和されます。「実効」静電容量の最小値を確実に実現するために、コンデンサ バンクのバイアスおよび温度変動を慎重に検討する必要があります。

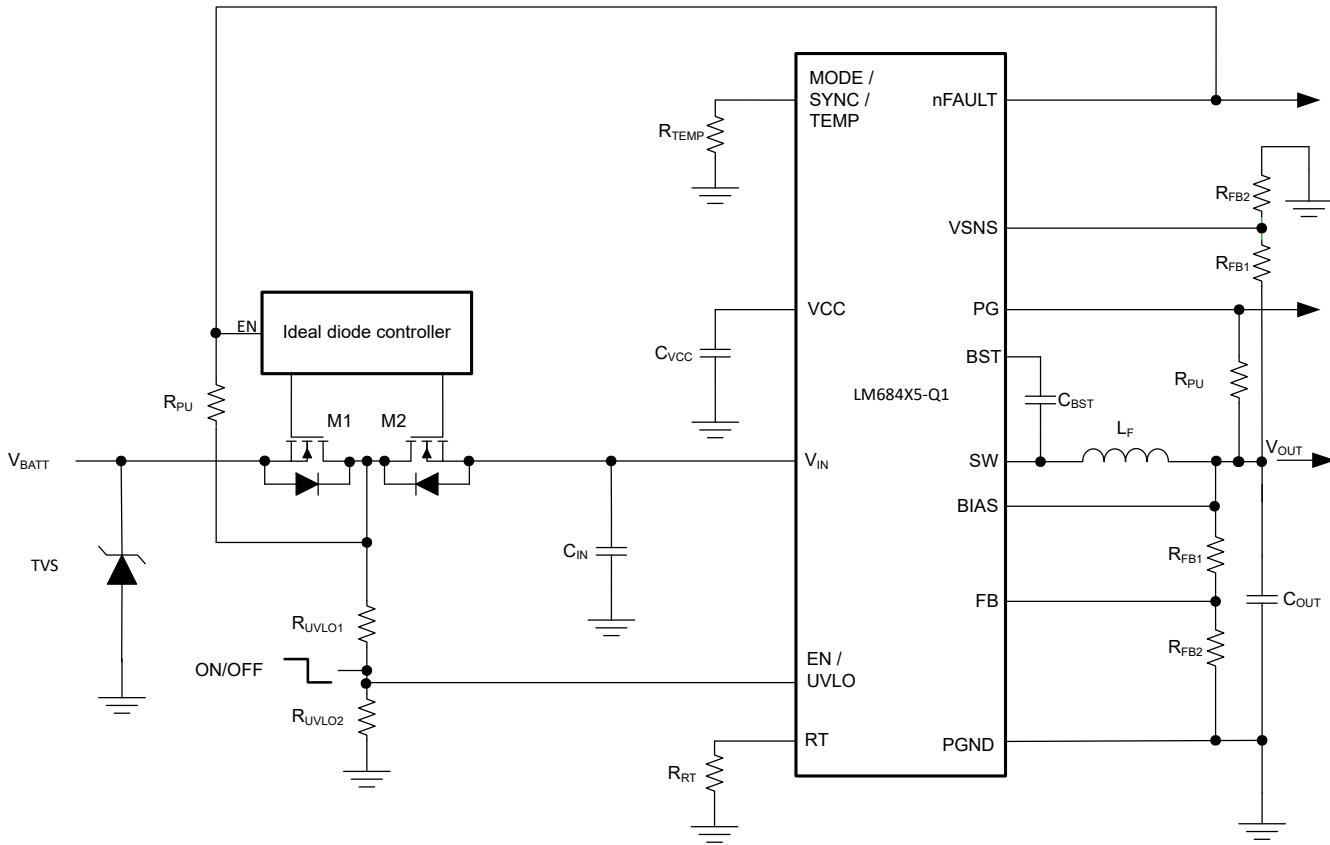

## 8.2 代表的なアプリケーション

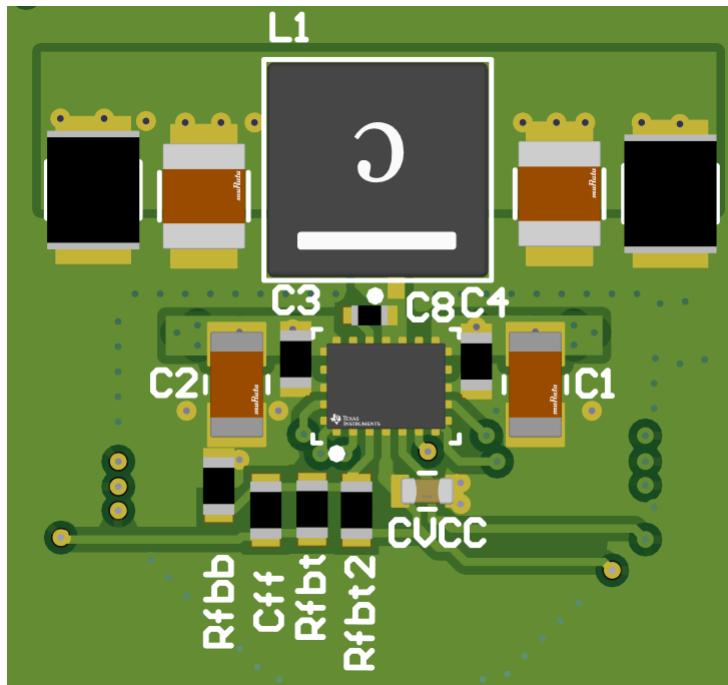

図 8-1 および図 8-2 に、可変出力モードまたは固定出力モードを使用する場合の LM684x5-Q1 の代表的なアプリケーション回路をそれぞれ示します。本デバイスは、幅広い外付け部品とシステム パラメータで機能するように設計されています。しかし、内部補償は、一定の範囲の外付けインダクタンスおよび出力容量に合わせて設計されています。クリックスタートガイドとして、表 8-1 からにさまざまな出力電圧範囲に対する代表的な部品値を示しています。これらの表の部品の値は安定した設計を表しており、必ずしも最適化されているとは限りません。これらの表に記載されている設計は、標準的な入力電圧 12V (24V 出力の場合は 36V) を基準としていますので注意してください。

図 8-1. LM684x5-Q1 を用いた可変出力電圧モードのアプリケーション回路例

図 8-2. LM684x5-Q1 を用いた固定出力電圧モードのアプリケーション回路例

表 8-1. 可変出力電圧における LM6x425 の代表的な外付け部品

| 出力電圧    | FREQUENCY | L     | COUT <sup>(1)</sup> | R <sub>FBT</sub> | R <sub>FBB</sub> | C <sub>FF</sub> |

|---------|-----------|-------|---------------------|------------------|------------------|-----------------|

| 3.3V    | 400kHz    | 8.2μH | 75μF                | 100kΩ            | 31.6kΩ           | 20pF            |

| 5V      | 400kHz    | 10μH  | 50μF                | 100kΩ            | 19.1kΩ           | 20pF            |

| 400kHz  | 47μH      | 15μF  | 205kΩ               | 7.15kΩ           | 31.6kΩ           | 5pF             |

| 3.3V    | 2200kHz   | 1.5μH | 25μF                | 100kΩ            |                  |                 |

| 5V      | 2200kHz   | 1.5μH | 15μF                | 100kΩ            | 19.1kΩ           | 5pF             |

| 2200kHz | 8.2μH     | 10μF  | 205kΩ               | 7.15kΩ           |                  |                 |

### 8.2.1 設計要件

以下の例では、表 8-2 に示した仕様に基づく詳細な設計手順を示します。

表 8-2. 詳細設計パラメータ

| 設計パラメータ   | 数値の例      |

|-----------|-----------|

| 入力電圧      | 24V (標準値) |

| 出力電圧      | 5V        |

| 最大出力電流    | 0A~2.5A   |

| スイッチング周波数 | 2200kHz   |

### 8.2.2 詳細な設計手順

以下の設計手順は、図 8-2 と 表 8-2 に適用されます。

#### 8.2.2.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer により、LM684x5-Q1 デバイスを使用するカスタム設計を作成できます。

1. 最初に、入力電圧 ( $V_{IN}$ )、出力電圧 ( $V_{OUT}$ )、出力電流 ( $I_{OUT}$ ) の要件を入力します。

2. オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

3. 生成された設計を、テキサス・インスツルメンツが提供する他の方式と比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- 熱シミュレーションを実行し、基板の熱特性を把握する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

WEBENCH ツールの詳細は、[www.ti.com/ja-jp/WEBENCH](http://www.ti.com/ja-jp/WEBENCH) でご覧になれます。

### 8.2.2.2 スイッチング周波数の選択

スイッチング周波数の選択は、変換効率と設計全体のサイズとのトレードオフとなります。スイッチング周波数を低くすると、スイッチング損失は減少し、一般的にシステム効率が高くなります。一方、スイッチング周波数を高くすると、より小型のインダクタと出力コンデンサを使用できるようになりますため、よりコンパクトな設計が可能となります。このアプリケーション例では、2200kHz の周波数を選択します。この場合、RT ピンを GND へ接続します。詳細については、[セクション 7.3.4](#) を参照してください。

### 8.2.2.3 可変または固定出力電圧モード用 FB

この例では、固定出力電圧モードを使用して、FB ピンを VCC ピンに接続することによって出力電圧を 5V に設定します。

また、VSNS ピンと出力電圧ノードとの間に  $4.99\text{k}\Omega$  抵抗を接続する必要があります。[図 8-2](#) を参照

3.3V または 5V と異なる出力電圧が必要な場合は、可変出力電圧モードを使用する必要があります。この場合、外部分圧器は出力ノードと FB ピンとの間に接続する必要があり、[式 5](#) および [式 6](#) を使用して分圧値を決定します。

$$R_{FBB} = R_{FBT} \times \frac{0.8}{V_{OUT} - 0.8} \quad (5)$$

$$100\text{k}\Omega \geq R_{FBB} \| R_{FBT} \geq 4\text{k}\Omega \quad (6)$$

[式 6](#) では、 $R_{FBB}$  と  $R_{FBT}$  の並列組み合わせは、 $4\text{k}\Omega$  より大きく、 $100\text{k}\Omega$  より小さい必要があると述べていることに注意してください。出力電圧モードを正しく設定するため、レギュレータはスタートアップ シーケンス中、FB ピンの状態を確実に検出する必要があるのでこの制限が必要です。PCB レイアウトの FB ピンからグランドへの容量を最小限に抑える必要があります。

可変出力電圧モードを使用する場合、出力電圧ノードと VSNS ピンとの間に補助分圧器が必要です。この分圧器の抵抗値と比は、メイン帰還分圧器と一致させる必要があります。[図 8-2](#) を参照してください。PCB レイアウトの VSNS ピンからの容量を最小限に抑える必要があります。

この例で可変出力電圧モードを選択していた場合、 $R_{FBT} = 100\text{k}\Omega$  かつ  $R_{FBB} = 19.1\text{k}\Omega$  の値は [式 5](#) と [式 6](#) の両方を満たします。

詳細については、[セクション 7.3.1](#) を参照してください。

### 8.2.2.4 インダクタの選択

インダクタを選択するためのパラメータはインダクタンスと飽和電流です。インダクタンスは目的のピークツー ピークリップル電流を元に選択し、通常はデバイスの最大出力電流定格の 20%~40% の範囲に収まるようにします。経験上、インダクタのリップル電流の最適な値は最大出力電流定格の 30% であることがわかっています。リップル電流の値が大きいと、

電流制限に達する前に最大出力電流が制限される場合があります。リップル電流の値が小さいと、電流モードコントローラの **SNR** が低下し、デューティサイクルのジッタが増加する可能性があります。インダクタとスイッチング周波数の許容誤差は、どちらもリップル電流の選択、したがってインダクタの値に影響を及ぼします。このデバイスで利用可能な最大負荷よりもはるかに小さな最大負荷のアプリケーションの場合でも、リップル電流の計算にはデバイスの最大電流定格を使用してください。最大出力電流に対するインダクタリップル電流の比率は **K** と表されます。[式 7](#) を使用して、インダクタンスの値を決定します

$$L = \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN} \times K \times I_{OUT - rated} \times F_{SW}} \quad (7)$$

アプリケーションの標準的な入力電圧は、通常で [式 7](#) 使用されます。ただし、アプリケーションが非常に広い入力電圧範囲を必要とする場合は、範囲の上限に近い電圧を使用できます。いずれの場合も、インダクタを選択した後で、最大入力電圧でリップル電流を確認する必要があります。上記のように、リップル電流が大きすぎると、最大出力電流が制限される可能性があります。これらの懸念を確認するために [式 8](#) を使用します。

$$I_{OUT - max} \cong I_{HS - LIM} - \frac{1}{2} \times \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN} \times L \times F_{SW}} \quad (8)$$

理想的には、インダクタの飽和電流定格は、ハイサイドスイッチの電流制限値 **I<sub>HS-LIM</sub>** 以上にする必要があります。この大きさであれば、出力の短絡時にもインダクタが飽和しないようになります。インダクタのコア材が飽和すると、インダクタンスは非常に小さい値に低下し、インダクタ電流は急増します。バレー電流制限値は、電流が暴走しづらいように設計されているとはいっても、インダクタが飽和することで電流値が急増する可能性があります。この増加は部品の損傷につながる可能性があります。フェライトコア材を採用したインダクタは飽和特性が非常に急峻ですが、コア損失は通常、圧粉コアよりも小さいです。圧粉コアは穏やかな飽和特性を示すため、インダクタの電流定格をある程度緩和できます。ただし、圧粉コアは約 **1MHz** を超える周波数でコア損失が大きくなります。いずれにしても、インダクタの飽和電流が、全負荷時のピークインダクタ電流の最大値よりも小さくならないようにする必要があります。

分数調波発振を防止するため、[式 9](#) で与えられる値よりインダクタンス値を小さくしないようにします。この制限は、あらゆる動作条件でスイッチのデューティサイクルが **50%** 以上になるアプリケーションに適用されます。

$$L_{min} \geq M \times \frac{V_{OUT}}{F_{SW}} \quad (9)$$

ここで、

- **M = 0.47 (2.5A デバイス)**

最大インダクタンスは、電流モード制御を正しく行うために必要な最小電流リップルによって制限されます。決まり事として、インダクタの最小リップル電流は、公称条件でのデバイスの最大定格電流の約 **10%** 以上とする必要があります。

この例においては、部品の選択について次の表を参照してください。ま標準的な入力電圧の **12V** に対してインダクタの値を選択するために [表 8-1](#) も使用できます。

### 8.2.2.5 出力コンデンサの選択

LM684x5-Q1 デバイスは、電流モード制御方式により、広い範囲の出力容量で動作できます。出力コンデンサ バンクは、通常、出力電圧リップルではなく負荷過渡要件および安定性によって制限されます。必要な出力キャパシタンスを推定するための最適な開始点は、[表 8-1](#)。これらの表に記載されている値は、他の出力電圧またはスイッチング周波数で補間できます。一般に、出力キャパシタンスが高く、スイッチング周波数が高いと、出力容量は小さくなります。また、可変出力電圧モードを使用する場合、C<sub>FF</sub> コンデンサを使用してループ性能を最適化できます。

出力キャパシタンスを選択した後で、低 ESR のセラミックを使用すると、ピーク ツー ピーク出力電圧リップルのおおよその値は、[式 10](#) と [式 11](#) を使って推定できます。

$$V_r \cong \frac{\Delta I}{8 \times F_{SW} \times C_{OUT}} \quad (10)$$

$$\Delta I = \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN} \times F_{SW} \times L} \quad (11)$$

実際には、過渡応答とループ位相マージンに最も影響を与えるのは出力コンデンサです。負荷過渡テストおよびボード線図は、特定の設計を検証する最善の方法であり、アプリケーションを量産に移行する前に必ず完了する必要があります。必要な出力容量に加えて、出力に小さなセラミックコンデンサを配置すると、高周波ノイズを低減するのに役立ちます。小さいケースサイズで  $1\text{nF} \sim 100\text{nF}$  の範囲のセラミックコンデンサは、インダクタや基板の寄生成分に起因する出力のスパイクを低減するのに非常に役立ちます。

最大出力キャパシタンスは、設計値の約 10 倍、または  $1000\mu\text{F}$  のいずれか小さい方に制限する必要があります。出力容量の値が大きいと、レギュレータのスタートアップ動作やループの安定性に悪影響を及ぼす可能性があります。ここに記載した値よりも大きい値を使用する必要がある場合、全負荷でのスタートアップおよびループ安定性を慎重に検討する必要があります。

この例では、表 8-1に基づき、出力キャパシタンス  $15\mu\text{F}$  を使用しています。この例が、D.C. バイアスディレーティングを印加した後の値を表すこと、および容量に適用されるその他の許容誤差を表していることに注意してください。これは、表に示されているすべての値に当てはまります。 $5\text{V}$  バイアスの  $15\mu\text{F}$  を実現する、X7R 以上の誘電体を使用したセラミックコンデンサ、またはコンデンサの組み合わせで使用できます。この表に示す値は、安定した設計を実現するために、標準値と考える必要があります。上記のように、出力キャパシタンスの最大制限値および最小制限値は、アプリケーションをテストすることで求められます。

### 8.2.2.6 入力コンデンサの選択

セラミック入力コンデンサは、レギュレータに低インピーダンスソースを供給するだけでなく、リップル電流を供給して、他の回路からスイッチングノイズを絶縁します。レギュレータの入力には、少なくとも 2 つの  $4.7\mu\text{F}$  のセラミックコンデンサが必要です。パッケージの両側に 1 個のコンデンサを配置し、デバイスの **VIN** および **GND** ピンに直接接続します。このコンデンサは、少なくともアプリケーションが必要とする最大入力電圧を定格とする必要があり、可能であれば、最大入力電圧の 2 倍が推奨されます。この値を増やすことで、入力電圧リップルを低減し、負荷過渡時の入力電圧を維持できます。また、入力に 2 つの  $100\text{nF}$  のセラミックコンデンサを高周波バイパスキャパシタンスとして使用し、レギュレータのできるだけ近くに配置する必要があります。パッケージの両側に 1 個のコンデンサを配置し、デバイスの **VIN** および **GND** ピンに直接接続します。この要件により、デバイス内部の制御回路に高周波バイパスができます。

この例では、 $2 \times 4.7\mu\text{F}$ 、 $100\text{V}$ 、X7R (またはそれ以上) のセラミックコンデンサを選択しています。また、 $100\text{nF}$  コンデンサも、X7R 誘電体を使用した  $100\text{V}$  定格とする必要があります。

多くの場合、入力にセラミックと並列に電解コンデンサを使用することが推奨されます。これは、長い配線またはパターンを使って入力電源をレギュレータに接続したり、入力 EMI フィルタを使用したりする場合に特に当てはまります。ここに中程度の ESR を持つコンデンサを使うことは、入力のインダクタンスによる入力電源のリンクギングを減衰させるのに有効です。この追加コンデンサの使用は、インピーダンスの非常に高い入力電源によって生じる電圧低下の防止にも有効です。

入力スイッチング電流のほとんどは、セラミック入力コンデンサを流れます。この電流の RMS 近似値は 式 12 から計算でき、メーカーの最大定格に照らしてチェックする必要があります。

$$I_{RMS} \approx \frac{I_{OUT}}{2} \quad (12)$$

### 8.2.2.7 C<sub>BOOT</sub>

LM684x5-Q1 では、**BOOT** ピンと **SW** ピンの間にブートストラップコンデンサを接続する必要があります。このコンデンサは、他の重要な制御回路と共に、パワー MOSFET のハイサイドゲートドライバに電力を供給するために使用するエネルギーを蓄積します。 $16\text{V}$  以上の  $100\text{nF}$  高品質セラミックコンデンサが必要です。

### 8.2.2.8 外部 UVLO

場合によっては、本デバイスが内部的に備えているものとは異なる入力 UVLO レベルが必要とされることがあります。このニーズは、図 8-3 に示す回路を使うことで実現できます。ターンオン電圧は  $V_{ON}$ 、ターンオフ電圧は  $V_{OFF}$  と指定されて

います。最初に、 $R_{ENT}$  の値を  $10\text{k}\Omega \sim 100\text{k}\Omega$  の範囲で選択し、次に、式 13 および 式 14 を使って  $R_{ENT}$  と  $V_{OFF}$  を計算します。

図 8-3. 外部 UVLO アプリケーション用のセットアップ

$$R_{ENT} = R_{ENB} \times \left( \frac{V_{ON}}{V_{EN-H}} - 1 \right) \quad (13)$$

$$V_{OFF} = V_{EN} - L \times \left( \frac{V_{ON}}{V_{EN-H}} \right) \quad (14)$$

ここで、

- $V_{ON} = V_{IN}$  のターンオン電圧

- $V_{OFF} = V_{IN}$  のターンオフ電圧

#### 8.2.2.9 最大周囲温度

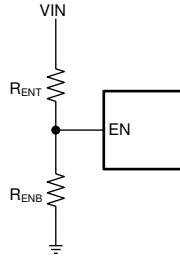

他の電力変換デバイスと同様に、レギュレータは動作中に内部で電力を消費します。この消費電力の影響により、コンバータの内部温度が周囲温度よりも高くなります。内部ダイ温度 ( $T_J$ ) は、周囲温度、電力損失、デバイスと PCB の組み合わせの実効熱抵抗  $R_{\theta JA}$  の関数です。LM684x5-Q1 の最大接合部温度は、 $150^\circ\text{C}$  に制限する必要があります。この制限により、デバイスの最大消費電力が制限され、それに伴って負荷電流も制限されます。式 15 に、重要なパラメータ間の関係を示します。周囲温度 ( $T_A$ ) が高いほど、また、 $R_{\theta JA}$  が高いほど、利用可能な最大出力電流が低減されます。コンバータの効率は、このデータシートに示す曲線を使用して推定できます。いずれかの曲線に目的の動作条件が見つからない場合は、補間によって効率を推定できます。または、目的のアプリケーション要件に合わせて EVM を調整し、効率を直接測定することもできます。 $R_{\theta JA}$  の正確な値を推定するのは、より困難です。『半導体および IC パッケージの熱評価基準』アプリケーションノートで述べているように、「熱に関する情報」表に記載されている値は、設計目的には有効ではなく、アプリケーションの熱性能の推定には使用してはなりません。この表に報告されている値は、実際のアプリケーションではめったに見られない特定の一連の条件で測定されたものです。 $R_{\theta JC(bott)}$  と  $\Psi_{JT}$  のデータは、放熱性能を判定する際に役立ちます。詳細とリソースについては、このセクションの末尾にある『半導体および IC パッケージの熱評価基準』アプリケーションノートを参照してください。

$$I_{OUT MAX} = \left( \frac{T_J - T_A}{R_{\theta JA}} \right) \times \left( \frac{\eta}{1-\eta} \right) \times \left( \frac{1}{V_{OUT}} \right) \quad (15)$$

ここで、

- $\eta$  = 効率

実効  $R_{\theta JA}$  は重要なパラメータであり、以下のような多くの要因に依存します。

- 消費電力

- 空気温度、フロー

- PCB 面積

- 銅箔ヒートシンク面積

- パッケージの下にあるサーマル リビアの数

- 隣接する部品の配置

このレギュレータで採用されている高度なパッケージには、ダイ接着パドル、または「サーマルパッド」(DAP) を使用しており、PCB の放熱用銅箔へのはんだ付け箇所を提供します。この機能により、レギュレータの接合部から放熱板への優れた熱伝導経路が確保され、PCB の放熱用銅箔に適切にはんだ付けされる必要があります。図 8-4 に、銅基板面積に対する  $R_{\theta JA}$  の代表曲線を示します。グラフに示す銅箔面積は、各層に対するものです。トップ層とボトム層は各 2oz 銅、内層は 1oz 銅です。このグラフのデータはあくまで参考用であり、実際の性能は前述のすべての要因に依存します。一例として、この EVM では、約 58cm<sup>2</sup> の銅箔面積の場合、約 24°C/W の約  $R_{\theta JA}$  を示します。

図 8-4. 热抵抗と銅面積との関係

優れた熱 PCB 設計および特定のアプリケーション環境における  $R_{\theta JA}$  を推定するためのガイドとして、以下の資料を使用してください。

- 『過去ではなく、現在の識見による熱設計』アプリケーション レポート

- 『露出パッド パッケージで最良の熱抵抗を実現するための基板レイアウト ガイド』アプリケーション レポート

- 『熱評価基準を使用して接合部温度を適切に評価する方法』アプリケーション レポート

### 8.2.3 アプリケーション曲線

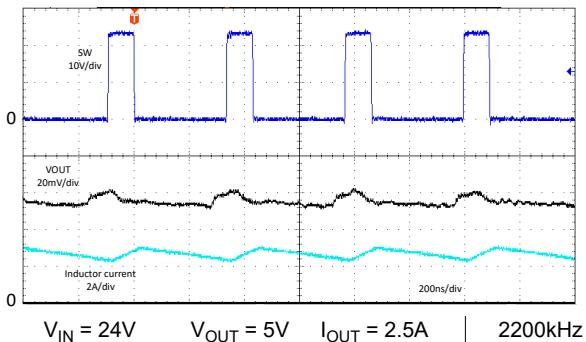

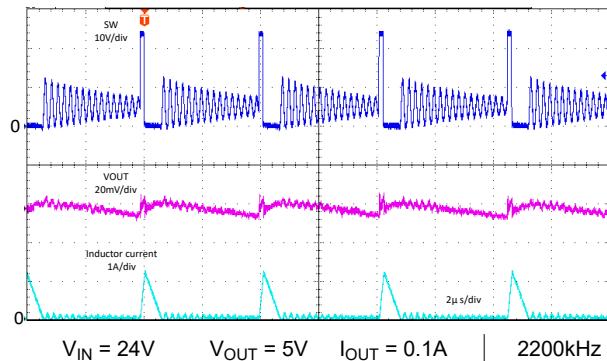

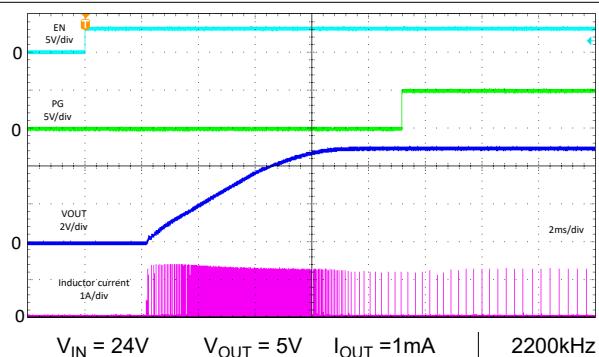

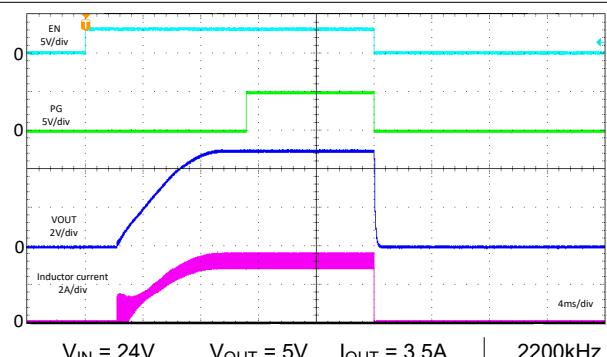

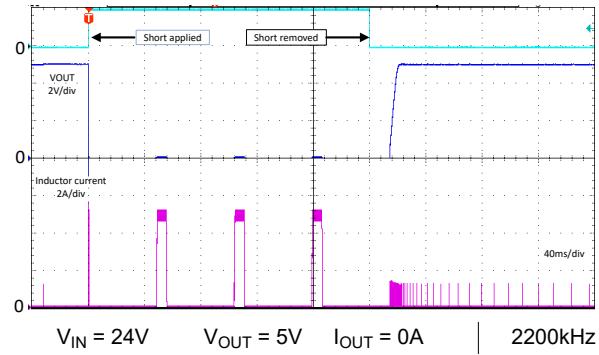

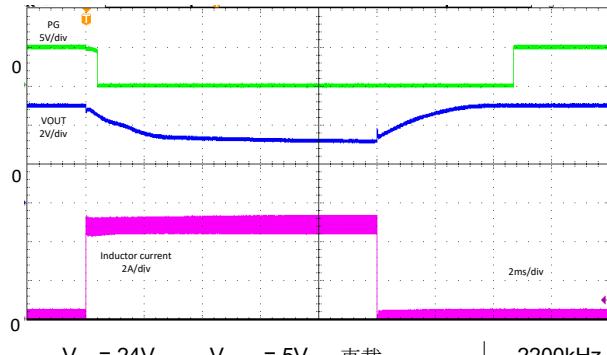

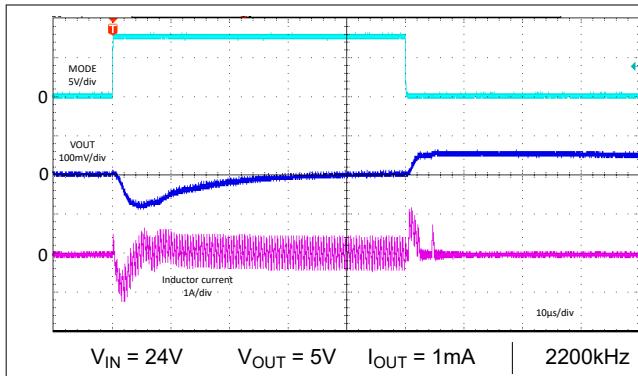

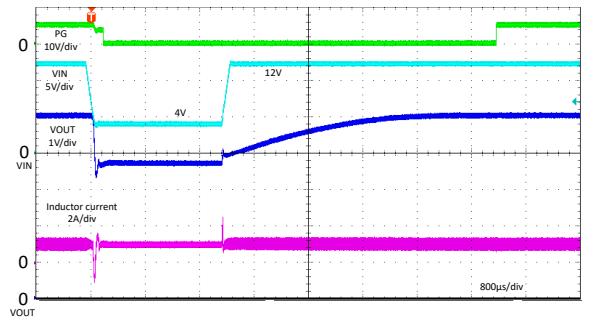

特記のない限り、次の条件が適用されます。 $V_{IN} = 24V$ 、固定出力電圧モード、 $V_{OUT}$  に BIAS 接続、 $T_A = 25^\circ C$ 。すべてのデータは標準 EVM で取得。BOM については表 8-3 を参照してください。標準的な EMI フィルタについては、図 8-30 および図 8-29 を参照してください。標準的なシステム仕様については、表 8-4 を参照してください。

図 8-5. LM6x425 効率 - 自動モード

図 8-6. LM6x425 効率 - 自動モード

図 8-7. LM6xx25 のラインレギュレーションおよび負荷レギュレーション - 自動モード

図 8-8. LM6xx25 のラインレギュレーションおよび負荷レギュレーション - 自動モード

図 8-9. LM6xx25 のライン レギュレーションおよび負荷レギュレーション - 自動モード

図 8-10. LM6xx25 のライン レギュレーションおよび負荷レギュレーション - 自動モード

図 8-11. LM6xx25 効率 - 自動モード

図 8-12. LM6xx25 効率 - FPWM モード

図 8-13. LM6xx25 効率 - 自動モード

図 8-14. LM6xx25 効率 - FPWM モード

図 8-15. LM6xx25 のスイッチング周波数と負荷電流との関係

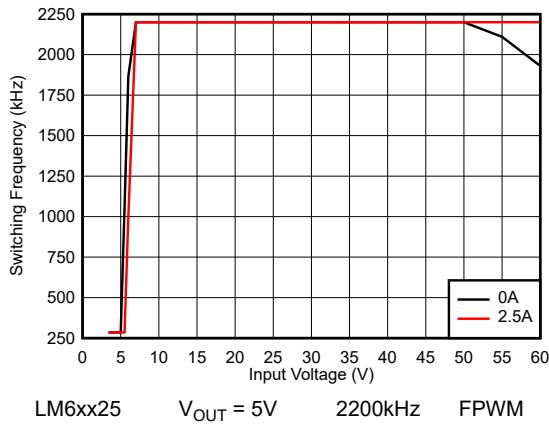

図 8-16. LM6xx25 のスイッチング周波数と入力電圧との関係

図 8-17. LM6xx25 のスイッチング周波数と入力電圧との関係

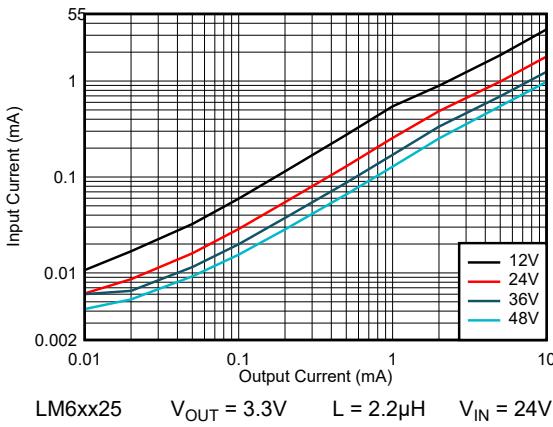

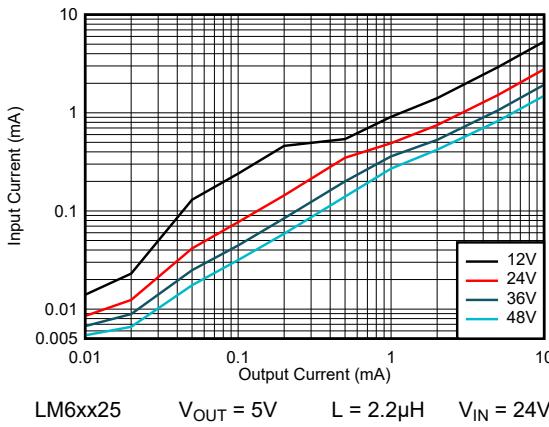

図 8-18. 入力電源電流 - 自動モード

図 8-19. 入力電源電流 - 自動モード

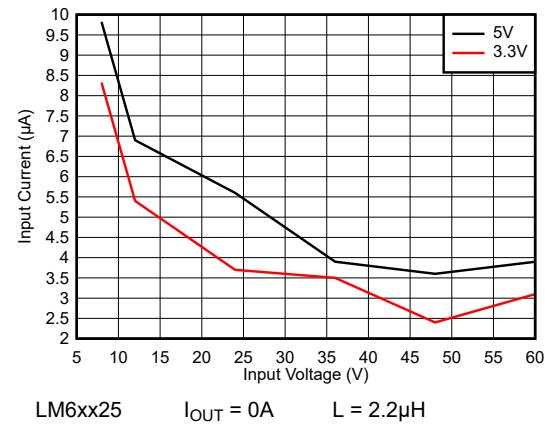

図 8-20. 無負荷時入力電源電流 - 自動モード

図 8-21. 代表的なスイッチング波形 - LM6xx25 - FPWM

図 8-22. 代表的なスイッチング波形 - LM6xx25 - 自動

図 8-23. スタートアップ - 自動

図 8-24. 起動、シャットダウン - FPWM

図 8-25. 出力短絡と回復 - 自動

図 8-26. 電流制限 (過渡)

図 8-27. MODE 変化(過渡)

図 8-28. ドロップアウト過渡と回復

**表 8-3. アプリケーション曲線データの BOM**

| デバイス    | 出力電圧 | スイッチング周波数 | インダクタ | インダクタ D.C.R. | V <sub>OUT</sub> 時の C <sub>OUT</sub> (過渡テスト用) |

|---------|------|-----------|-------|--------------|-----------------------------------------------|

| LM6x25  | 5V   | 400kHz    | 10μH  | 0.03 Ω       |                                               |

| LM6x625 | 5V   | 2200kHz   | 2.2μH | 0.02 Ω       |                                               |

| LM6x625 | 3.3V | 400kHz    | 10μH  | 0.03 Ω       |                                               |

| LM6x625 | 3.3V | 2200kHz   | 2.2μH | 0.02 Ω       |                                               |

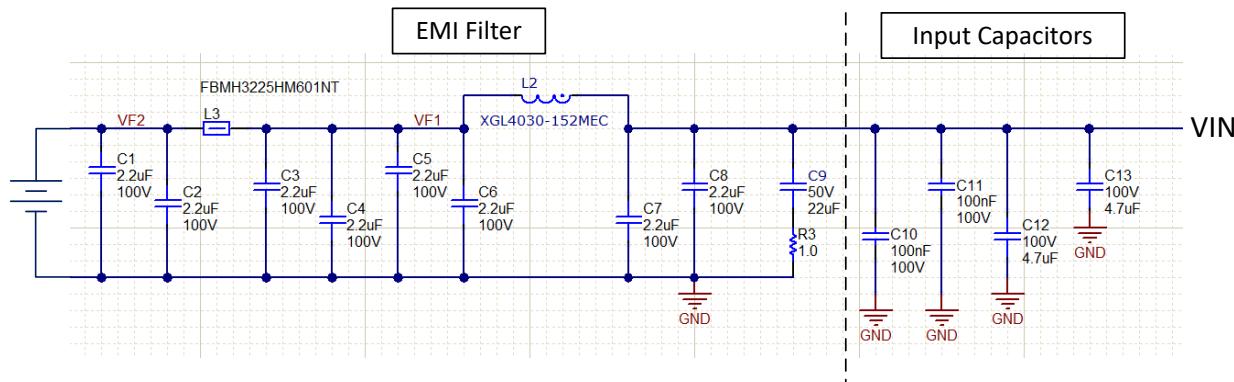

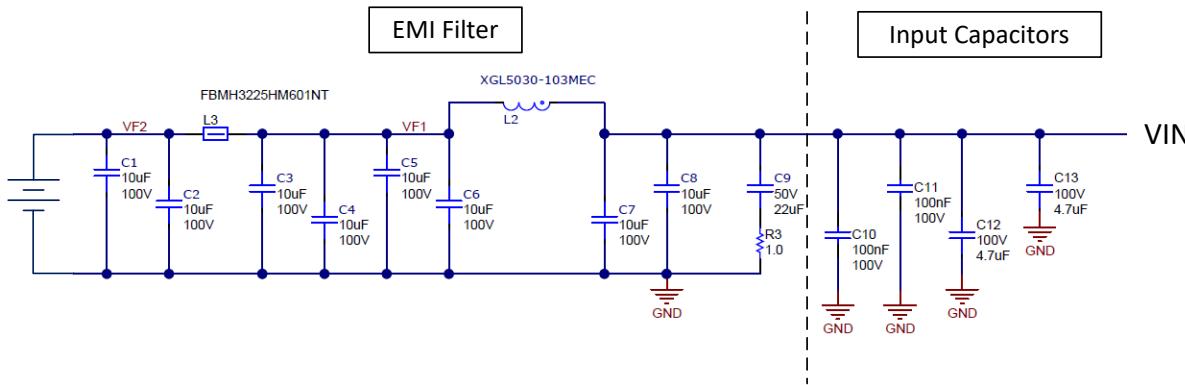

**図 8-29. 2200kHz 用 EMI 入力フィルタ**

**図 8-30. 400kHz 用 EMI 入力フィルタ**

以下の表に記載されているデータは、標準的なアプリケーション回路にのみ適用され、コンポーネントの公称値が設定されています。「代表値 (TYP)」列の仕様は、 $T_J = 25^\circ\text{C}$  にのみ適用されます。 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  の温度範囲での標準的な部品の場合、最小 (MIN) および最大 (MAX) 列の仕様が適用されます。これらの仕様は、製造試験では指定されていません。

**表 8-4. 代表的なシステム仕様**

| パラメータ  |             | テスト条件                                          | 最小値   | 標準値   | 最大値   | 単位 |

|--------|-------------|------------------------------------------------|-------|-------|-------|----|

| 入力電源   | 入力電源電流      | Vin = 24V、Vout = 3.3V、Iout = 0A、LM65635、2.2MHz |       | 2.4   |       | μA |

| Vout   | Vout = 5V   | Vin = 7V ~ 40V、Iout = 0A ~ 全負荷、FPWM            | -1.5% |       | +1.5% |    |

|        | Vout = 5V   | Vin = 7V ~ 40V、Iout = 0A ~ 全負荷、AUTO            | -1.5% |       | +2.5% |    |

| Vout   | Vout = 3.3V | Vin = 5V ~ 40V、Iout = 0A ~ 全負荷、FPWM            | -1.5% |       | +1.5% |    |

|        | Vout = 3.3V | Vin = 5V ~ 40V、Iout = 0A ~ 全負荷、AUTO            | -1.5% |       | +2.5% |    |

| $\eta$ | ピーク効率       | Vin = 12V、Vout = 5V、Iout = 1.5A、LM65645、400kHz |       | 95%   |       |    |

|        |             | Vin = 24V、Vout = 5V、Iout = 1.5A、LM65645、400kHz |       | 93.6% |       |    |

## 8.3 設計のベスト プラクティス

- 絶対最大定格を超過してはなりません。

- 推奨動作条件を超過してはなりません。

- ESD 定格を超過してはなりません。

- EN 入力をフローティングにしないでください。

- 出力電圧が入力電圧を超えないように、またグランドを下回らないようにしてください。

- 設計を量産用に確定する前に、このデータシートに記載されているすべてのガイドラインと推奨事項に従ってください。TI のアプリケーション エンジニアが、設計段階から PCB レイアウトの評価まで包括的にサポートすることで、プロジェクトの成功を確実なものにします。

## 8.4 電源に関する推奨事項

入力電源は、負荷時のレギュレータに必要な入力電流を供給できる特性を持っている必要があります。平均入力電流は、式 16 を使って見積もることができます。

$$I_{IN} = \frac{V_{IN}}{V_{OUT}} \times \frac{I_{OUT}}{\eta} \quad (16)$$

ここで、

$\eta$  は効率です。

レギュレータを長いワイヤや PCB パターンで入力電源に接続している場合は、良好な性能を実現するために特別な注意が必要です。入力ケーブルの寄生インダクタンスと抵抗は、レギュレータの動作に悪影響を及ぼすおそれがあります。寄生インダクタンスと低 ESR セラミック入力コンデンサを組み合わせることで、不足減衰共振回路を形成することが可能です。この動作により、レギュレータへの入力で過電圧過渡が発生したり、UVLO のトリップが発生したりする可能性があります。ハーネスの寄生抵抗とインダクタンスや電源の特性に応じて、負荷過渡が出力に発生したときに、電源電圧が低下する可能性があることを考慮してください。アプリケーションが最小入力電圧に近い値で動作している場合、この低下によってレギュレータが瞬時にシャットダウンし、リセットされる可能性があります。この種の問題を解決する最善策は、入力電源からレギュレータまでの距離を短くすることです。さらに、セラミック入力コンデンサと並列にアルミニウム入力コンデンサを使用してください。中程度の ESR を持つこのタイプのコンデンサを使うことは、入力共振回路の振動を減衰させ、あらゆるオーバーシュートまたはアンダーシュートを低減するのに有効です。通常、20μF~100μF の範囲の値は入力のダンピングに十分であり、大きな負荷過渡中も入力電圧を安定した状態に保持できます。

場合によっては、コンバータの入力に過渡電圧サプレッサ (TVS) が使われています。この素子の種類には、スナップバック特性を持つもの (サイリスタ型) があります。テキサス・インスツルメンツでは、このタイプの特性を持つデバイスの使用を推奨していません。このタイプの TVS が作動すると、クランプ電圧は非常に低い値に低下します。この電圧がレギュレータの出力電圧よりも低い場合、出力コンデンサは本デバイスを通して入力に向かって放電します。この制御されない電流は、デバイスに損傷を与える可能性があります。

入力電圧は、出力電圧を下回ることはできません。この状況 (入力短絡テストなど) では、出力コンデンサは、本デバイスの VIN ピンと SW ピンの間に形成された内部寄生ダイオードを通じて放電されます。この状況では電流は制御できなくなる可能性があり、デバイスが損傷するおそれがあります。このシナリオが想定される場合は、入力電源と出力の間にショットキー ダイオードを使用してください。

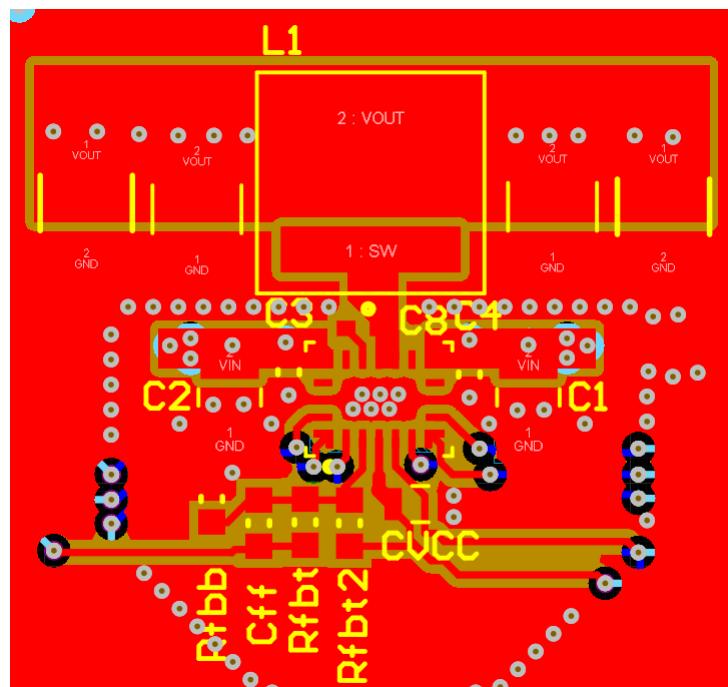

## 8.5 レイアウト

### 8.5.1 レイアウトのガイドライン

DC/DC コンバータの PCB レイアウトは、優れた設計性能を実現するために重要です。PCB レイアウトが不適切な場合、適正な回路図設計の動作の妨げとなる可能性があります。コンバータが適切にレギュレートしている場合でも、PCB レイアウトが不適切では、堅牢な設計と量産できない設計という違いが生じる可能性があります。さらに、レギュレータの EMI 性能は、PCB レイアウトに大きく依存します。降圧コンバータにおける PCB の最も重要な機能は、入力コンデンサと電源グランドによって形成されるループです (図 8-31 を参照)。このループは、トレースのインダクタンスに応答して大きな過渡電圧を発生させる可能性がある大きな過渡電流を流します。これらの望ましくない過渡電圧は、コンバータの正常な動作

を妨げます。このことから、寄生インダクタンスを低減するため、このループ内のパターンは広く短くする必要があり、ループの面積はできる限り小さくする必要があります。[セクション 8.5.2](#) は、LM684x5-Q1 の重要な部品の推奨レイアウトを示しています。

- 入力コンデンサは **VIN** ピンにできる限り近づけて配置し、短くて幅の広いパターンでグランドに接続します。

- **EVM** に示すように、対称型入力コンデンサの技法を適用します

- $C_{BOOT}$  コンデンサには広いパターンを使用します。 $C_{BOOT}$  コンデンサは、デバイスのできる限り近くに、**BOOT** および **SW** ピンに短くて幅の広いパターンで配置します。 $C_{BOOT}$  コンデンサを簡単に配置できるように、**BOOT** ピンと **SW** ピンは隣接しています。

- 帰還分圧器は、本デバイスの **FB** ピンのできるだけ近くに配置します。 $R_{FBB}$ 、 $R_{FBT}$ 、 $C_{FF}$  は、使用する場合、本デバイスに物理的に近付けて配置します。**FB** および **GND** への接続は、短くする必要があり、かつ本デバイスのそれらのピンに近付ける必要があります。**V<sub>OUT</sub>** への接続は、多少長くなってもかまいません。ただし、この後者のパターンは、レギュレータの帰還経路に静電容量結合する可能性があるすべてのノイズ源 (**SW** ノードなど) の近くには配線しないでください。

- 内層の 1 つを使って、少なくとも 1 つのグランドプレーンを配置します。このプレーンは、ノイズシールドと放熱経路として機能します。

- サーマルパッドをグランドプレーンに接続します。**WQFN** パッケージは、サーマル・パッド (PAD) 接続を備えており、PCB のグランドプレーンに半田付けできます。このパッドはヒートシンク接続として機能します。この半田接続の完全性は、アプリケーションの総合的な実効  $R_{\theta JA}$  に直接影響します。

- **VIN**、**V<sub>OUT</sub>**、**GND** に広いプレーンを使用します。コンバータの入力または出力経路でのすべての電圧降下を低減し、効率を最大化するため、これらの配線はできるだけ広くかつ真っすぐにする必要があります。

- 適切なヒートシンクのために十分な PCB 領域を確保します。最大負荷電流と周囲温度に見合った低  $R_{\theta JA}$  を実現するため、十分な銅箔面積を確保してください。PCB の上層と下層は 2 オンス銅箔とし、最低でも 1 オンス以上とします。**WQFN** パッケージでは、6 つ以上のヒートシンクビアを使用して、サーマルパッド (PAD) を PCB 下層のグランドプレーンに接続します。PCB 設計に複数の銅層を使用している場合は (推奨設計)、サーマルビアも内部層の熱拡散グランドプレーンに接続することができます。

- スイッチングする領域は、小さく保ちます。**SW** ピンをインダクタに接続する銅箔領域は、できるだけ短くかつ広くします。同時に、放射 **EMI** を低減するため、このノードの総面積を最小化する必要があります。

その他の重要なガイドラインについては、以下の PCB レイアウト資料を参照してください。

- [『スイッチング電源のレイアウトのガイドライン』アプリケーション レポート](#)

- [『Simple Switcher PCB レイアウトガイドライン』アプリケーション レポート](#)

- [『独自電源の構築 - レイアウトの考慮事項』セミナー](#)