LM5171 JAJSUV0 - JUNE 2024

# LM5171 デュアル チャネル双方向コントローラ

# 1 特長

- 機能安全 対応

- 最大定格は HV ポート 85V、LV ポート 80V

- 双方向電流レギュレーションの標準精度 1%

- チャネル電流監視の標準精度 1%

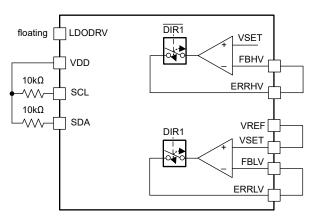

- 監視および診断用の I<sup>2</sup>C インターフェイス

- 3.5V 1% の基準電圧を内蔵

- 5V 10mA バイアス電源を内蔵

- ピーク 5A のハーフ ブリッジ ゲートドライバ

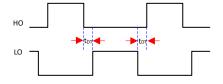

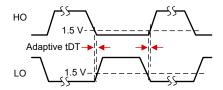

- プログラム可能またはアダプティブ デッドタイム制御

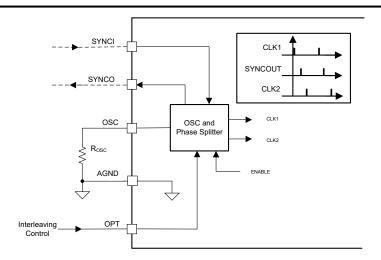

- 最大 1MHz まで、発振器の周波数をプログラム可能 で、オプションとして外部クロックへの同期も可能

- 独立したチャネルイネーブル制御入力

- 電流と電圧の両方のループ制御機能を内蔵

- ピーク電流制限をサイクル単位でプログラム可能

- 過熱シャットダウン

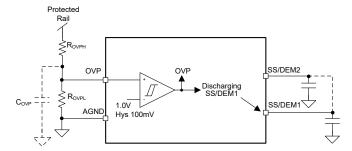

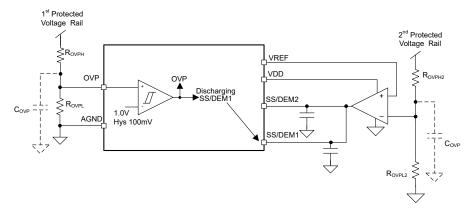

- HV および LV ポートの過電圧保護

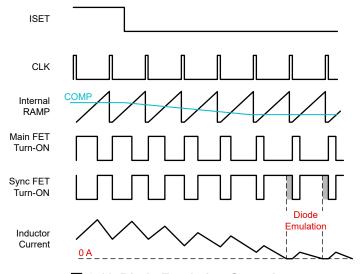

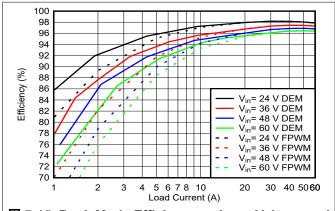

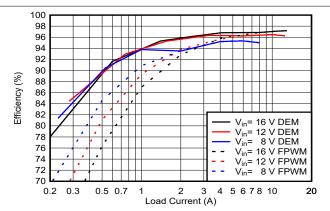

- 動的に選択可能なダイオード エミュレーション モード と強制 PWM 動作モード

- ソフトスタートタイマをプログラム可能

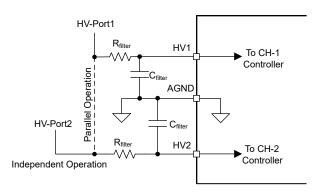

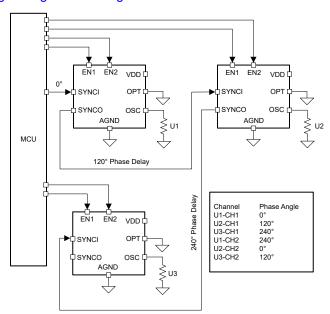

- マルチフェーズと独立チャネルの両方の動作をサポー

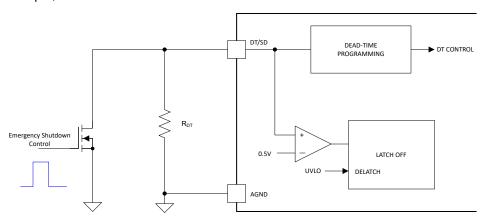

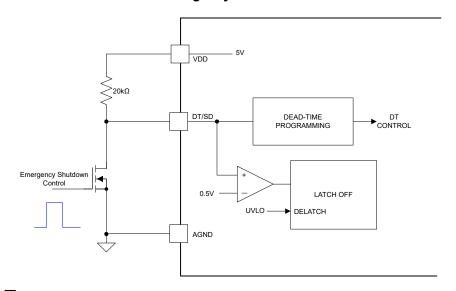

- 緊急シャットダウン ラッチをサポート

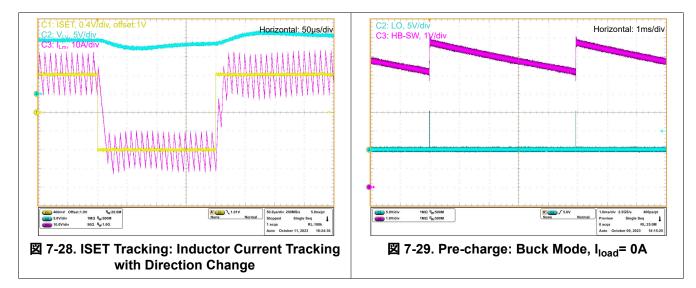

# C1: ISET, 0.4V/div, offset:1V Horizontal: 50us/div \aikkkkkkkkkkkkkk#kkkk V <sup>1</sup>W:20.0 1MΩ <sup>8</sup>W:500M 50Ω <sup>8</sup>W:1.0G

方向変更によるインダクタ電流のトラッキング

# 2 アプリケーション

- バッテリ テスト システム (BTS)

- スーパー キャパシタまたはバッテリ バックアップ電力コ ンバータ

- スタッカブルな大電力降圧または昇圧アプリケーション

# 3 概要

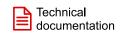

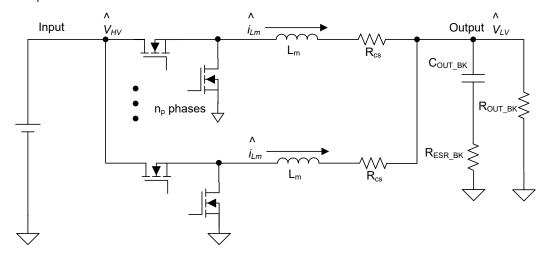

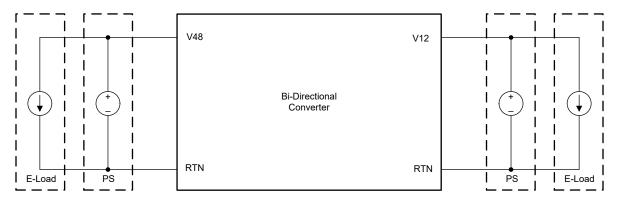

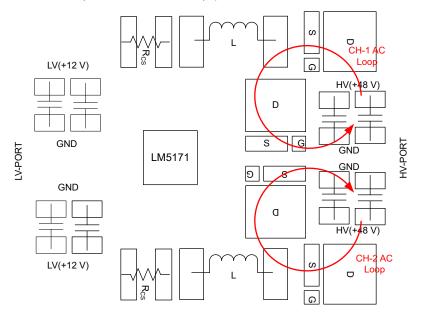

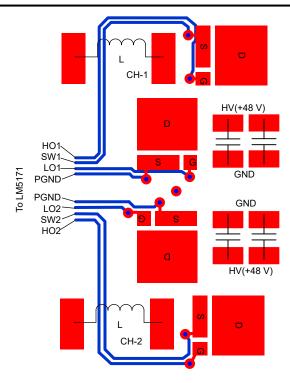

LM5171 コントローラは、高電圧かつ高精度なデュアル チャネル双方向コンバータを実現するための基本的な構 成要素を備えています。例として、デュアルバッテリシス テムがあります。LM5171 はマルチフェーズの並列動作を サポートし、各位相で平衡な電流共有を行います。また、 LM5171 は独立チャネルの双方向動作もサポートしてい るため、多相の昇降圧、または独立した昇降圧として動作 するスタンドアロンのコントローラとして多用途に使用でき

デュアル チャネルの差動電流センシング アンプと、専用 のチャネル電流モニタにより、標準値で1%の精度が得ら れます。 堅牢な 5A ハーフブリッジ ゲート ドライバは、並 列 MOSFET を駆動して、チャネルあたりの電力をより大き くできます。 コントローラは、ダイオード エミュレーション モ ード (DEM) または強制 PWM (FPWM) モードで動作す るように動的にプログラムできます。多用途な保護機能とし て、サイクル単位の電流制限、HV と LV の両方のポート における過電圧保護、および過熱保護と緊急シャットダウ ンラッチがあります。

#### 製品情報(1)

| 部品番号   | パッケージ     | 本体サイズ (公称)      |

|--------|-----------|-----------------|

| LM5171 | TQFP (48) | 7.00mm × 7.00mm |

利用可能なすべてのパッケージについては、データシートの末尾 にある注文情報を参照してください。

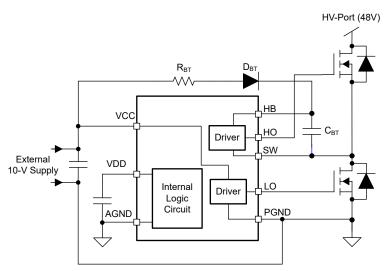

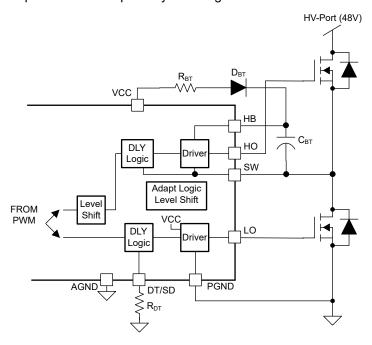

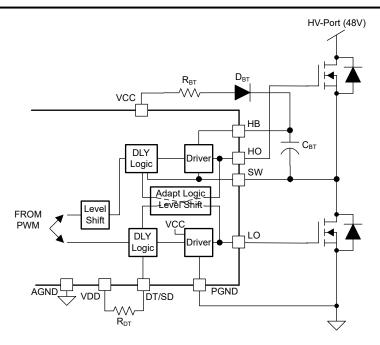

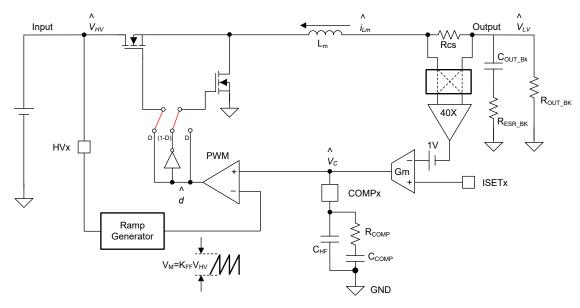

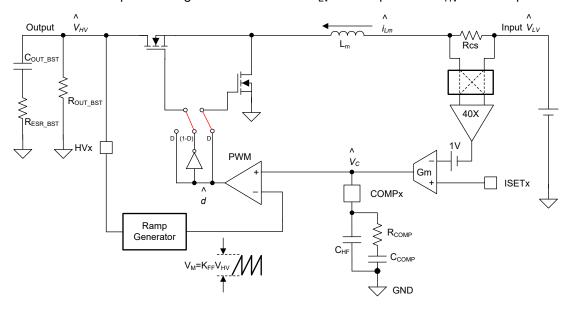

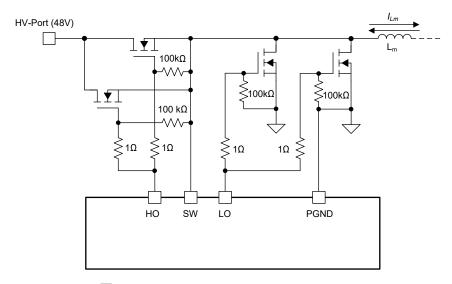

アプリケーションの簡略回路図

# **Table of Contents**

| 1 特長                                 | 1  |

|--------------------------------------|----|

| 2 アプリケーション                           | 1  |

| 3 概要                                 |    |

| 4 Pin Configuration and Functions    |    |

| 5 Specifications                     |    |

| 5.1 Absolute Maximum Ratings         |    |

| 5.2 ESD Ratings                      |    |

| 5.3 Recommended Operating Conditions |    |

| 5.4 Thermal Information              |    |

| 5.5 Electrical Characteristics       | 6  |

| 5.6 Timing Requirements              | 11 |

| 5.7 Typical Characteristics          |    |

| 6 Detailed Description               |    |

| 6.1 Overview                         |    |

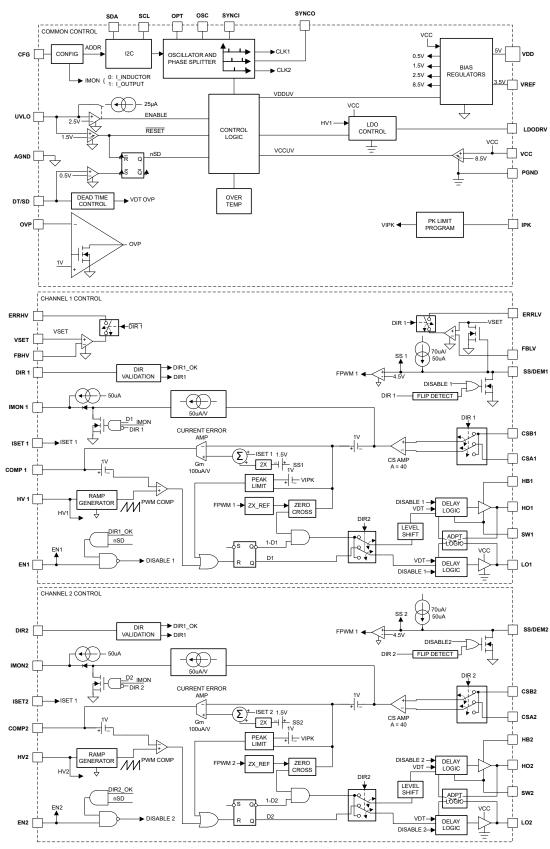

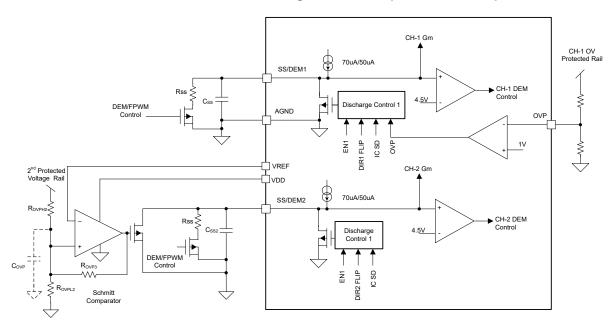

| 6.2 Functional Block Diagram         | 16 |

| 6.3 Feature Description              |    |

| 6.4 Programming                      |    |

|    | 0.5 Registers                          | 44 |

|----|----------------------------------------|----|

|    | Application and Implementation         |    |

|    | 7.1 Application Information            | 53 |

|    | 7.2 Typical Application                | 65 |

|    | 7.3 Power Supply Recommendations       | 83 |

|    | 7.4 Layout                             | 84 |

| 8  | Device and Documentation Support       | 88 |

|    | 8.1 Device Support                     | 88 |

|    | 8.2ドキュメントの更新通知を受け取る方法                  | 88 |

|    | 8.3 サポート・リソース                          | 88 |

|    | 8.4 Trademarks                         | 88 |

|    | 8.5 静電気放電に関する注意事項                      | 88 |

|    | 8.6 用語集                                | 88 |

| 9  | Revision History                       | 88 |

| 1( | 0 Mechanical, Packaging, and Orderable |    |

|    | Information                            | 89 |

|    |                                        |    |

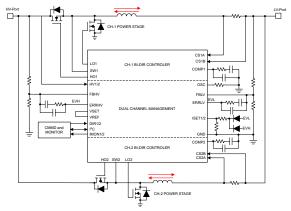

# 4 Pin Configuration and Functions

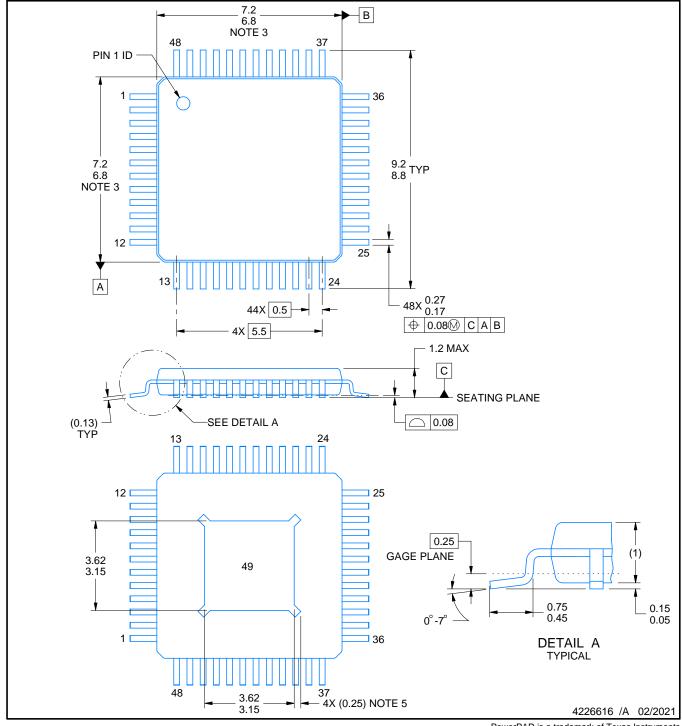

図 4-1. PHP Package 48-Pin TQFP Top View

表 4-1. Pin Functions

|     | PIN     | I/O <sup>(1)</sup>                           | DESCRIPTION                                                                                                  |

|-----|---------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| NO. | NAME    | 1/0(1)                                       | DESCRIPTION                                                                                                  |

| 1   | VREF    | Р                                            | Output of the built-in 3.5V +/- 1% reference voltage.                                                        |

| 2   | FBLV    | ı                                            | The inverting input pin for the buck error voltage amplifier.                                                |

| 3   | ERRLV   | 0                                            | Output pin of the buck error voltage amplifier.                                                              |

| 4   | IMON2   | 0                                            | CH-2 current monitor pin.                                                                                    |

| 5   | CSA2    | CIL 2 differential assessment agency in mate |                                                                                                              |

| 6   | CSB2    | ı                                            | CH-2 differential current sense inputs.                                                                      |

| 7   | ISET2   | ı                                            | CH-2 analog current programming pin.                                                                         |

| 8   | COMP2   | 0                                            | Output of the CH-2 transconductance (gm) error amplifier and the inverting input of the CH-2 PWM comparator. |

| 9   | SS/DEM2 | I                                            | The soft-start programming pin for CH-2 controller. It also sets CH-2 in either DEM or FPWM.                 |

| 10  | EN2     | ı                                            | CH-2 enable pin.                                                                                             |

| 11  | DIR2    | ı                                            | CH-2 direction command input.                                                                                |

| 12  | VDD     | Р                                            | Output of 5V internal LDO.                                                                                   |

| 13  | HV2     | I                                            | The input pin connecting to the HV-Port line voltage for CH-2 controller.                                    |

| 14  | HB2     | I                                            | CH-2 high-side gate driver bootstrap supply input.                                                           |

| 15  | HO2     | 0                                            | CH-2 high-side gate driver output.                                                                           |

| 16  | SW2     | Р                                            | CH-2 switch node.                                                                                            |

| 17  | LO2     | 0                                            | CH-2 low-side gate driver output.                                                                            |

# 表 4-1. Pin Functions (続き)

| PIN I/O(1) |                                                | (4)    |                                                                                                               |  |  |

|------------|------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------|--|--|

| NO.        | NAME                                           | 1/0(1) | DESCRIPTION                                                                                                   |  |  |

| 18         | PGND                                           | G      | Power ground connection pin.                                                                                  |  |  |

| 19         | VCC                                            | Р      | VCC bias supply pin.                                                                                          |  |  |

| 20         | LO1                                            | 0      | CH-1 low-side gate driver output.                                                                             |  |  |

| 21         | SW1                                            | Р      | CH-1 switch node.                                                                                             |  |  |

| 22         | HO1                                            | 0      | CH-1 high-side gate driver output.                                                                            |  |  |

| 23         | HB1                                            | ı      | CH-1 high-side gate driver bootstrap supply input.                                                            |  |  |

| 24         | HV1                                            | ı      | The input pin connecting to the HV-Port line voltage for CH-1 controller.                                     |  |  |

| 25         | LDODRV                                         | 0      | Control pin for the external VCC LDO MOSFET.                                                                  |  |  |

| 26         | DIR1                                           | ı      | CH-1 direction command input.                                                                                 |  |  |

| 27         | EN1                                            | ı      | CH-1 enable pin.                                                                                              |  |  |

| 28         | SS/DEM1                                        | ı      | The soft-start programming pin for CH-1 controller. It also sets CH-1 in either DEM or FPWM.                  |  |  |

| 29         | COMP1                                          | 0      | Output of the CH-1 trans-conductance (gm) error amplifier and the inverting input of the CH-1 PWM comparator. |  |  |

| 30         | ISET1                                          | ı      | CH-1 analog current programming pin.                                                                          |  |  |

| 31         | CSB1                                           | ı      | CH 1 differential current conce inputs                                                                        |  |  |

| 32         | CSA1 I CH-1 differential current sense inputs. |        |                                                                                                               |  |  |

| 33         | IMON1                                          | 0      | CH-1 current monitor pin.                                                                                     |  |  |

| 34         | ERRHV                                          | 0      | Output pin of the boost error voltage amplifier.                                                              |  |  |

| 35         | FBHV                                           | I      | The inverting input pin for the boost error voltage amplifier.                                                |  |  |

| 36         | OVP                                            | ı      | Input of the built-in over-voltage comparator.                                                                |  |  |

| 37         | SDA                                            | I/O    | Data of I <sup>2</sup> C interface.                                                                           |  |  |

| 38         | SCL                                            | ı      | Clock of I <sup>2</sup> C interface.                                                                          |  |  |

| 39         | SYNCO                                          | 0      | Clock synchronization output pin.                                                                             |  |  |

| 40         | SYNCI                                          | I      | Clock synchronization input pin.                                                                              |  |  |

| 41         | OPT                                            | ı      | Multiphase configuration pin.                                                                                 |  |  |

| 42         | osc                                            | ı      | The internal oscillator frequency programming pin.                                                            |  |  |

| 43         | AGND                                           | G      | Analog ground reference.                                                                                      |  |  |

| 44         | CFG                                            | I      | The I <sup>2</sup> C address setting and current monitor mode selection pin.                                  |  |  |

| 45         | UVLO                                           | I      | The UVLO pin, which also serves as the Controller-Peripheral enable pin.                                      |  |  |

| 46         | DT/SD                                          | ı      | Dead-time programming and emergent latched shutdown pin.                                                      |  |  |

| 47         | IPK                                            | I      | Peak current limit programming pin.                                                                           |  |  |

| 48         | VSET                                           | ı      | Voltage error amplifier reference input pin.                                                                  |  |  |

| _          | EP                                             | _      | Exposed pad of the package.                                                                                   |  |  |

(1) Note: G = Ground, I = Input, O = Output, P = Power

# 5 Specifications

# 5.1 Absolute Maximum Ratings

Over the recommended operating junction temperature range<sup>(1)</sup>

|             |                                                                                                              | MIN  | MAX     | UNIT |

|-------------|--------------------------------------------------------------------------------------------------------------|------|---------|------|

|             | HV1, HV2 to AGND                                                                                             | -0.3 | 85      |      |

|             | HV1, HV2 to AGND (50ns Transient)                                                                            |      | 90      |      |

|             | SW1, SW2 to PGND                                                                                             | -5   | 85      |      |

|             | SW1, SW2 to PGND (20ns Transient)                                                                            |      | 90      |      |

|             | SW1, SW2 to PGND (50ns Transient)                                                                            | -16  |         |      |

|             | HB1 to SW1, HB2 to SW2                                                                                       | -0.3 | 14      |      |

|             | HO1 to SW1, HO2 to SW2                                                                                       | -0.3 | HB+0.3  |      |

|             | HO1 to SW1, HO2 to SW2 (20ns Transient)                                                                      | -2   |         |      |

| Input       | LO1, LO2 to PGND                                                                                             | -0.3 | VCC+0.3 |      |

|             | LO1, LO2 to PGND (20ns Transient)                                                                            | -2   |         | V    |

|             | CSA1, CSB1,CSA2,CSB2 to PGND                                                                                 | -0.3 | 80      | v    |

|             | CSA1 to CSB1, CSA2 to CSB2                                                                                   | -0.3 | 0.3     |      |

|             | CFG, DIR1, DIR2, EN1, EN2, FBHV, FBLV, IPK, ISET1, ISET2, OPT, OVP, SCL, SDA, SYNCI, UVLO, VDD, VSET to AGND | -0.3 | 5.5     |      |

|             | COMP1, COMP2, DT/SD, ERRHV, ERRLV, IMON1, IMON2, OSC, SS/DEM1, SS/DEM2, SYNCO, VREF to AGND                  | -0.3 | VDD+0.3 |      |

|             | LDODRV TO VCC                                                                                                | -0.3 | 5       |      |

|             | VCC to PGND                                                                                                  | -0.3 | 14      |      |

|             | PGND to AGND                                                                                                 | -0.3 | 0.3     |      |

| Junction te | mperature, T <sub>J</sub> <sup>(2)</sup>                                                                     | -40  | 150     | °C   |

| Storage ter | nperature, T <sub>stg</sub>                                                                                  | -55  | 150     | C    |

<sup>1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

# 5.2 ESD Ratings

|                    |                         |                                                                              |                                      | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------|--------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) HBM ESD Classification | 1)                                   | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM) per V ANSI/ESDA/JEDEC                             | All pins                             | ±500  | V    |

|                    |                         | JS-002 <sup>(2)</sup>                                                        | Corner pins (1,12,13,24,25,36,37,48) | ±750  |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions. Pins listed as ±2000 V may actually have higher performance.

資料に関するフィードバック(ご意見やお問い合わせ) を送信

5

<sup>(2)</sup> High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions. Pins listed as ±500 V may actually have higher performance.

# **5.3 Recommended Operating Conditions**

Over the recommended operating junction temperature range of -40°C to 150°C (unless otherwise specified)(1)

|                       |                                                             | MIN                   | NOM MAX               | UNIT |

|-----------------------|-------------------------------------------------------------|-----------------------|-----------------------|------|

| HV-Port<br>(HV1, HV2) | Buck Mode                                                   | 3                     | 80                    | V    |

| HV-Port<br>(HV1, HV2) | Boost Mode                                                  | 3                     | 80                    | V    |

| LV-Port               | Buck Mode                                                   | 0                     | 75                    | V    |

| LV-Port               | Boost Mode                                                  | 1                     | 75                    | V    |

| VCC                   | Applicable External Voltage to VCC Pin                      | 9.5                   | 12                    | V    |

| TJ                    | Operating Junction Temperature <sup>(2)</sup>               | -40                   | 150                   | °C   |

| Fosc                  | Oscillator Frequency                                        | 50                    | 1000                  | kHz  |

| F <sub>EX_CLK</sub>   | Synchronization to External Clock Frequency (Minimal 50kHz) | 0.8x F <sub>OSC</sub> | 1.2x F <sub>OSC</sub> | kHz  |

| F <sub>EX_CLK</sub>   | SYNCI Pulse                                                 | 50                    | 0.8/ F <sub>OSC</sub> | ns   |

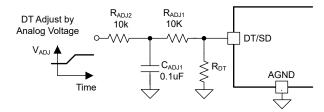

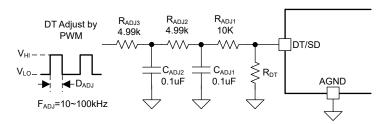

| t <sub>DT</sub>       | Programmable Dead Time Range                                | 15                    | 200                   | ns   |

<sup>(1)</sup> Operating Ratings are conditions under the device is intended to be functional. For specifications and test conditions, see Electrical Characteristics.

#### **5.4 Thermal Information**

|                       |                                              | LM5171     |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PHP (TQFP) | UNIT |

|                       |                                              | 48 PINS    |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 30.7       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 18.8       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 13.5       | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.3        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 13.4       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.5        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 5.5 Electrical Characteristics

Typical values correspond to  $T_J$  = 25°C. Minimum and maximum limits apply over  $T_J$  = -40°C to 150°C. Unless otherwise stated,  $F_{OSC}$  = 100 kHz;  $V_{VCC}$  = 10 V;  $V_{HV1}$  =  $V_{HV2}$  =  $V_{HV-Port}$  = 48V and  $V_{LV-Port}$  = 12 V.

| SYMBOL                 | PARAMETER                                 | TEST CONDITIONS                                                | MIN  | TYP | MAX  | UNIT |

|------------------------|-------------------------------------------|----------------------------------------------------------------|------|-----|------|------|

| HV Port (HV1           | , HV2)                                    |                                                                |      |     |      |      |

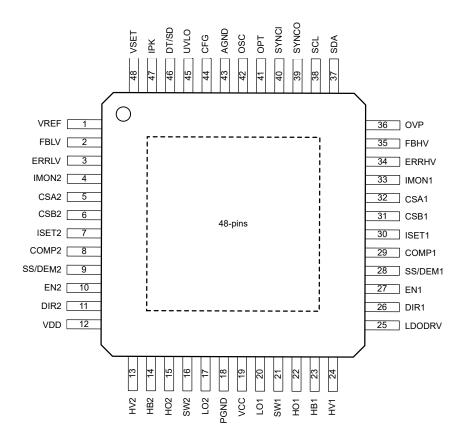

| I <sub>SHUTDOWN1</sub> | HV1 pin current in shutdown mode          | V <sub>UVLO</sub> = 0V                                         |      |     | 10   | μA   |

| I <sub>SHUTDOWN2</sub> | HV2 pin current in shutdown mode          | V <sub>UVLO</sub> = 0V                                         |      |     | 10   | μA   |

| I <sub>OPERATING</sub> | HV1 and HV2 pin current in operating      | V <sub>UVLO</sub> > 2.6V, V <sub>VCC</sub> > 9V                |      | 1   |      | mA   |

| VCC Bias Su            | pply (VCC)                                |                                                                |      |     |      |      |

| V <sub>VCC_reg</sub>   | VCC LDO regulation setting point          | V <sub>HV1</sub> > 10V                                         | 8.55 | 9   | 9.45 | V    |

| V <sub>CCUVLO</sub>    | VCC under voltage detection               | VCC falling                                                    | 7.7  | 8   | 8.2  | V    |

| V <sub>CCHYS</sub>     | VCC UVLO hysteresis                       | VCC rising                                                     | 8.2  | 8.5 | 8.7  | V    |

| I <sub>VCC_SD</sub>    | VCC sink current in shutdown mode         | V <sub>UVLO</sub> = 0V, V <sub>VCC</sub> =10V                  |      |     | 25   | μA   |

| I <sub>VCC_SB</sub>    | VCC sink current in standby: no switching | V <sub>UVLO</sub> > 2.6V, V <sub>VCC</sub> > 9V,<br>EN1=EN2=0V |      |     | 10   | mA   |

| VDD Analog             | Bias Supply (VDD)                         |                                                                | ,    |     | 11   |      |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2024 Texas Instruments Incorporated

<sup>(2)</sup> High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

| SYMBOL                                | PARAMETER                                                                                                            | TEST CONDITIONS                                                                | MIN   | TYP   | MAX   | UNIT  |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------|-------|-------|-------|

| $V_{\mathrm{VDD}}$                    | VDD voltage                                                                                                          | V <sub>UVLO</sub> > 2.6V, V <sub>VCC</sub> > 9V                                | 4.75  | 5     | 5.25  | V     |

| V <sub>DDUV</sub>                     | VDD undervoltage detection                                                                                           | VDD falling                                                                    | 4.25  | 4.5   | 4.75  | V     |

| V <sub>DDHYS</sub>                    | VDD UVLO hysteresis                                                                                                  | VDD rising above V <sub>DDUV</sub>                                             | 0.1   | 0.2   | 0.3   | V     |

| I <sub>VDD</sub>                      | VDD source current limit                                                                                             | V <sub>VDD</sub> = 4.6V                                                        | 10    |       |       | mA    |

| VOLTAGE RE                            | FERENCE (VREF)                                                                                                       |                                                                                |       |       |       |       |

| $V_{REF}$                             | Voltage reference                                                                                                    | $V_{\rm UVLO}$ > 2.6V, $V_{\rm VCC}$ > 9V, $V_{\rm VDD}$ > $V_{\rm DDUV}$      | 3.465 | 3.500 | 3.535 | V     |

| I <sub>VREF</sub>                     | VREF source current limit                                                                                            | V <sub>VREF</sub> = 3.5V                                                       | 2     |       |       | mA    |

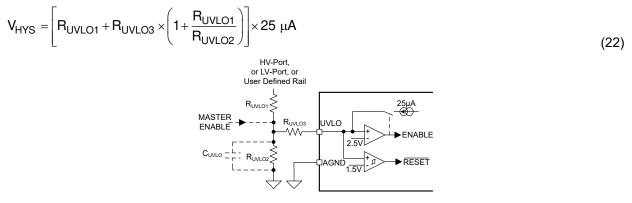

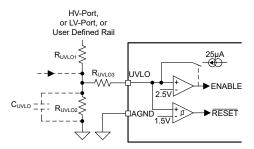

| Master ON/O                           | FF Control (UVLO)                                                                                                    |                                                                                |       |       |       |       |

| V <sub>UVLO_TH</sub>                  | UVLO release threshold                                                                                               | UVLO voltage rising                                                            | 2.4   | 2.5   | 2.6   | V     |

| I <sub>HYS</sub>                      | UVLO hysteresis current                                                                                              | UVLO source current when V <sub>UVLO</sub> > 2.6V                              | 21    | 25    | 29    | μA    |

| V <sub>RES</sub>                      | UVLO shutdown and IC reset voltage threshold                                                                         | UVLO voltage falling                                                           | 1     | 1.25  | 1.5   | ٧     |

|                                       | UVLO shutdown release                                                                                                | UVLO voltage rising above V <sub>RES</sub>                                     | 0.15  | 0.25  | 0.35  | V     |

| t <sub>UVLO</sub>                     | UVLO 2.5V threshold glitch filter                                                                                    | UVLO voltage both rising and falling                                           |       | 2.5   |       | μs    |

| t <sub>VRES</sub>                     | UVLO 1.25V V <sub>RES</sub> threshold glitch filter                                                                  |                                                                                |       | 5     | 10    | μs    |

|                                       | UVLO internal pull-down current                                                                                      |                                                                                |       | 100   |       | nA    |

| Enable Input                          | s EN1 and EN2                                                                                                        |                                                                                |       |       |       |       |

| V <sub>IL</sub>                       | Enable input low state                                                                                               | The driver outputs disabled                                                    |       |       | 1.0   | V     |

| V <sub>IH</sub>                       | Enable input high state                                                                                              | The driver outputs enabled                                                     | 2.0   |       |       | V     |

|                                       | Internal pulldown impedance                                                                                          | EN1, EN2 logic inputs internal pulldown resistor                               |       | 1     |       | MegΩ  |

|                                       | EN glitch filter time (the rising and falling edges)                                                                 |                                                                                |       | 2.5   |       | μs    |

| DIRECTION (                           | COMMANDS (DIR1, DIR2)                                                                                                |                                                                                |       |       |       |       |

| V <sub>DIR1</sub> , V <sub>DIR2</sub> | Command for current flowing from LV-Port to HV-Port (boost mode 12 V to 48 V), for CH-1 and CH-2, respectively       | Actively pulled low by external circuit                                        |       |       | 1     | V     |

| V <sub>DIR1</sub> , V <sub>DIR2</sub> | Command for current flowing from HV-<br>Port to LV-Port (buck mode 48 V to 12<br>V), for CH-1 and CH-2, respectively | Actively pulled high by external circuit                                       | 2     |       |       | V     |

| V <sub>DIR1</sub> , V <sub>DIR2</sub> | Standby (invalid DIR command)                                                                                        | DIR pin (DIR1 or DIR2) neither active<br>High nor active Low                   |       | 1.5   |       | V     |

|                                       | DIR glitch filter (the rising and falling edges)                                                                     | Both Rising and Falling Edges                                                  |       | 10    |       | μs    |

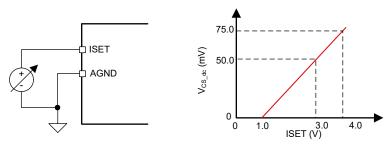

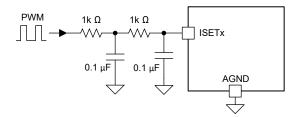

| ISET INPUTS                           | (ISET1, ISET2)                                                                                                       |                                                                                |       | ,     | 1     |       |

|                                       | ISET DC Offset Voltage                                                                                               |                                                                                |       | 1.0   |       | V     |

| G <sub>ISET</sub>                     | Gain of the regulated inductor DC current sense voltage to ISET voltage                                              | V <sub>CSA</sub> - V <sub>CSB</sub>   = 50mV                                   |       | 25    |       | mV/V  |

|                                       | ISET internal pull-down current sink                                                                                 |                                                                                |       | 75    | 200   | nA    |

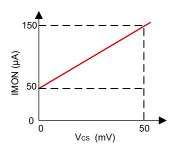

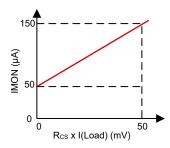

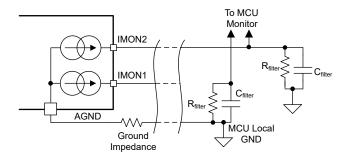

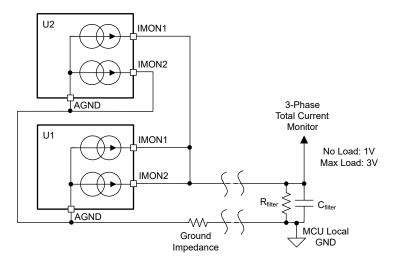

| Output Curre                          | ent Monitor (IMON1, IMON2)                                                                                           |                                                                                |       |       |       |       |

| -                                     | Gain of IMON1 and IMON2 current source versus channel current sense voltage                                          | CSA-CSB  = 50mV, CONFIG =<br>'Inductor current monitor", V <sub>DIR</sub> > 2V |       | 2     |       | μA/mV |

|                                       | Gain of IMON1 and IMON2 current source versus channel current sense voltage                                          | CSA-CSB  = 50mV, CONFIG = "Inductor current monitor", V <sub>DIR</sub> < 1V    |       | 2     |       | uA/mV |

|                                       |                                                                                                                      |                                                                                |       |       |       |       |

| SYMBOL                | PARAMETER                                                                                                 | TEST CONDITIONS                                                                                                                        | MIN   | TYP  | MAX   | UNIT  |

|-----------------------|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

|                       | Gain of IMON1 and IMON2 current source versus channel current sense voltage                               | CSA-CSB  = 50mV, CONFIG = 'Output current monitor", V <sub>DIR</sub> < 1V, Duty cycle = 0.75                                           | 0.475 | 0.5  | 0.525 | uA/mV |

|                       | Gain of IMON1 and IMON2 current source versus channel current sense voltage                               | CSA-CSB  = 10mV, CONFIG =<br>'Inductor current monitor", V <sub>DIR</sub> > 2V                                                         |       | 2    |       | uA/mV |

|                       | Gain of IMON1 and IMON2 current source versus channel current sense voltage                               | CSA-CSB  = 10mV, CONFIG =<br>'Inductor current monitor", V <sub>DIR</sub> < 1V                                                         | 1.96  | 2    | 2.04  | uA/mV |

|                       | Gain of IMON1 and IMON2 current source versus channel current sense voltage                               | CSA-CSB  = 10mV, CONFIG = 'Output current monitor", V <sub>DIR</sub> < 1V, Duty cycle = 0.75                                           | 0.475 | 0.5  | 0.525 | uA/mV |

|                       | IMON1 and IMON2 DC offset current                                                                         | CSA-CSB  = 0mV                                                                                                                         |       | 50   |       | μA    |

| CURRENT S             | SENSE AMPLIFIER (BOTH CHANNELS)                                                                           |                                                                                                                                        |       |      |       |       |

| G <sub>CS_BK1</sub>   | Gain of amplifier output to current sense voltage in buck mode                                            | V <sub>CSA</sub> - V <sub>CSB</sub>   = 50mV, V <sub>DIR</sub> > 2V                                                                    |       | 40   |       | V/V   |

| G <sub>CS_BST1</sub>  | Gain of amplifier output to current sense voltage in boost mode                                           | V <sub>CSA</sub> - V <sub>CSB</sub>   = 50mV, V <sub>DIR</sub> < 1V                                                                    |       | 40   |       | V/V   |

| G <sub>CS_BK2</sub>   | Gain of amplifier output to current sense voltage in buck mode                                            | $ V_{CSA} - V_{CSB}  = 10 \text{mV}, V_{DIR} > 2 \text{V}$                                                                             |       | 40   |       | V/V   |

| G <sub>CS_BST2</sub>  | Gain of amplifier output to current sense voltage in boost mode                                           | $ V_{CSA} - V_{CSB}  = 10$ mV, $V_{DIR} < 1$ V                                                                                         |       | 40   |       | V/V   |

| TRANSCON              | DUCTION AMPLIFIER (COMP1, COMP                                                                            | 2)                                                                                                                                     |       |      |       |       |

| Gm                    | Transconductance                                                                                          |                                                                                                                                        |       | 100  |       | μA/V  |

|                       | Output source current limit                                                                               | $V_{ISET} = 4V$ , $ V_{CSA} - V_{CSB}  = 0$ mV                                                                                         |       | 250  |       | μΑ    |

| I <sub>COMP</sub>     | Output sink current limit                                                                                 | $V_{\rm ISET}$ = 0V, $V_{\rm CSA}$ – $V_{\rm CSB}$ = 50mV in the buck mode, or $V_{\rm CSA}$ – $V_{\rm CSB}$ = -50mV in the boost mode |       | -250 |       | μА    |

| VOLTAGE L             | OOP ERROR AMPLIFIERS (VSET, LVF                                                                           | 3, LVERR, HVFB, HVERR)                                                                                                                 |       |      |       |       |

| A <sub>OL</sub>       | Open loop gain                                                                                            | V <sub>VCC</sub> > 9 V, V <sub>VDD</sub> > V <sub>DDUV</sub>                                                                           |       | 80   |       | dB    |

| F <sub>BW</sub>       | Unity gain bandwidth                                                                                      |                                                                                                                                        |       | 2.1  |       | MHz   |

| V <sub>OS</sub>       | Input offset voltage                                                                                      |                                                                                                                                        |       |      | 5     | mV    |

| V <sub>ERR_MIN</sub>  | Minimum amplifier output voltage                                                                          | Sourcing 2mA                                                                                                                           | 4     |      |       | V     |

| V <sub>ERR_MAX</sub>  | Maximum amplifier output voltage                                                                          | Sinking 2mA                                                                                                                            |       |      | 0.5   | V     |

| PWM Comp              | arator                                                                                                    |                                                                                                                                        |       |      |       |       |

|                       | COMP to output delay                                                                                      |                                                                                                                                        |       | 50   |       | ns    |

|                       | COMP to PWM comparator offset                                                                             |                                                                                                                                        |       | 1    |       | V     |

| T <sub>OFF_MIN</sub>  | Minimum off time                                                                                          |                                                                                                                                        |       | 100  | 150   | ns    |

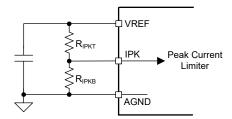

|                       | RENT LIMIT (IPK)                                                                                          |                                                                                                                                        |       |      |       |       |

| G <sub>IPK_BK1</sub>  | Gain from current sense voltage to cycle-by-cycle limit threshold voltage given at IPK pin, in buck mode  | V <sub>IPK</sub> = 3V, V <sub>DIR</sub> >2V                                                                                            | 45    | 50   | 55    | mV/V  |

| G <sub>IPK_BK2</sub>  | Gain from current sense voltage to cycle-by-cycle limit threshold voltage given at IPK pin, in buck mode  | V <sub>IPK</sub> = 1V, V <sub>DIR</sub> >2V                                                                                            | 45    | 50   | 55    | mV/V  |

| G <sub>IPK_BST1</sub> | Gain from current sense voltage to cycle-by-cycle limit threshold voltage given at IPK pin, in boost mode | V <sub>IPK</sub> = 3V, V <sub>DIR</sub> <1V                                                                                            | 45    | 50   | 55    | mV/V  |

| G <sub>IPK_BST2</sub> | Gain from current sense voltage to cycle-by-cycle limit threshold voltage given at IPK pin, in boost mode | V <sub>IPK</sub> = 1V, V <sub>DIR</sub> <1V                                                                                            | 45    | 50   | 55    | mV/V  |

| SYMBOL                 | $_{\rm c}$ = 100 kHz; $V_{\rm VCC}$ = 10 V; $V_{\rm HV1}$ = $V_{\rm HV}$ PARAMETER | TEST CONDITIONS                                                                 | MIN  | TYP  | MAX  | UNIT   |

|------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|------|------|--------|

| OVER VOLT              | AGE PROTECTION (OVP)                                                               |                                                                                 |      |      |      |        |

|                        | OVP threshold                                                                      |                                                                                 | 0.99 | 1    | 1.01 | V      |

| OVP <sub>HYS</sub>     | OVP Hysteresis                                                                     |                                                                                 |      | 100  |      | mV     |

| t <sub>OVP</sub>       | OVP Glitch Filter                                                                  |                                                                                 |      | 5    |      | us     |

| OSCILLATO              | R (OSC)                                                                            |                                                                                 |      |      |      |        |

|                        | Oscillator frequency 1                                                             | $R_{OSC}$ = 41.5k $\Omega$ , no external clock signal at SYNCI pin              | 90   | 100  | 110  | kHz    |

| F <sub>osc</sub>       | Oscillator frequency 2                                                             | $R_{OSC}$ = 4.15k $\Omega$ , no external clock signal at SYNCI pin              | 900  | 1000 | 1100 | kHz    |

| V <sub>OSC</sub>       | OSC pin DC voltage                                                                 | OSC DC Level                                                                    |      | 1    |      | V      |

| SYNCHRON               | IZATION CLOCK INPUT (SYNCI)                                                        |                                                                                 |      |      |      |        |

| V <sub>SYNIH</sub>     | SYNCI input threshold for high state                                               |                                                                                 | 2    |      |      | V      |

| V <sub>SYNIL</sub>     | SYNCI input threshold for low state                                                |                                                                                 |      |      | 1    | V      |

|                        | Delay to establish synchronization                                                 | 0.8 x F <sub>OSC</sub> < F <sub>SYNCI</sub> < 1.2 x Fosc                        |      | 200  |      | us     |

|                        | Internal pull-down impedance                                                       | V <sub>SYNCI</sub> = 2.5V                                                       |      | 1000 |      | kΩ     |

| SYNCHRON               | IZATION CLOCK OUTPUT (SYNCO)                                                       |                                                                                 | 1    |      |      |        |

| V <sub>SYNOH</sub>     | SYNCO high state                                                                   |                                                                                 | 2.5  |      |      | V      |

| V <sub>SYNOL</sub>     | SYNCO low state                                                                    |                                                                                 |      |      | 0.4  | V      |

|                        | Sourcing current when SYNCO in high state                                          | V <sub>SYNCO</sub> = 2.5V                                                       |      | 1    |      | mA     |

|                        | Sinking current when SYNCO in low state                                            | V <sub>SYNCO</sub> = 0.5V                                                       |      | 1    |      | mA     |

|                        | SYNCO pulse width                                                                  |                                                                                 | 60   | 90   | 120  | ns     |

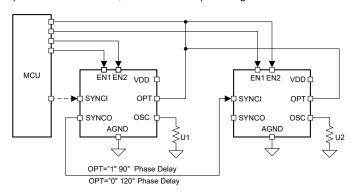

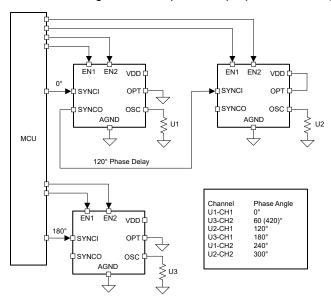

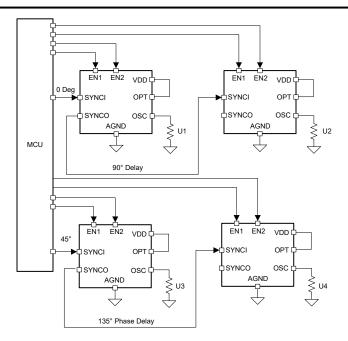

|                        | SYNCO pulse delay for multiphase                                                   | $V_{OPT} > 2V$ , $R_{SYNCO} > 61.9k\Omega$                                      |      | 90   |      | Degree |

|                        | daisy chain connection                                                             | V <sub>OPT</sub> < 1V <sub>,</sub> R <sub>SYNCO</sub> > 61.9kΩ                  |      | 120  |      | Degree |

| BOOTSTRA               | P (HB1, HB2)                                                                       |                                                                                 |      |      |      |        |

| V <sub>HB-UV</sub>     | Bootstrap undervoltage threshold                                                   | (V <sub>HB</sub> – V <sub>SW</sub> ) voltage rising                             | 6    | 6.5  | 7    | V      |

| V <sub>HB-UV-HYS</sub> | Bootstrap undervoltage hysteresis                                                  |                                                                                 |      | 0.5  |      | V      |

| I <sub>HB LK</sub>     | Bootstrap quiescent current                                                        | $V_{HB} - V_{SW} = 10V, V_{HO} - V_{SW} = 0V$                                   |      |      | 100  | μA     |

| HIGH SIDE (            | GATE DRIVERS (HO1, HO2)                                                            |                                                                                 |      |      |      |        |

| V <sub>OLH</sub>       | HO low-state output voltage                                                        | I <sub>HO</sub> = 100mA                                                         |      | 0.1  |      | V      |

| V <sub>OHH</sub>       | HO high-state output voltage                                                       | I <sub>HO</sub> = -100mA, V <sub>OHH</sub> = V <sub>HB</sub> - V <sub>HO</sub>  |      | 0.15 |      | V      |

|                        | HO rise time (10% to 90% pulse magnitude)                                          | C <sub>LD</sub> = 1000pF                                                        |      | 5    |      | ns     |

|                        | HO fall time (90% to 10% pulse magnitude                                           | C <sub>LD</sub> = 1000pF                                                        |      | 4    |      | ns     |

| Іонн                   | HOpeak sourcecurrent                                                               | V <sub>HB</sub> – V <sub>SW</sub> = 10V                                         |      | 4    |      | Α      |

| I <sub>OLH</sub>       | HOpeak sink current                                                                | V <sub>HB</sub> – V <sub>SW</sub> = 10V                                         |      | 5    |      | Α      |

| LOW SIDE G             | GATE DRIVERS (LO1, LO2)                                                            |                                                                                 |      |      |      |        |

| V <sub>OLL</sub>       | LO low-state output voltage                                                        | I <sub>LO</sub> = 100mA                                                         |      | 0.1  |      | V      |

| V <sub>OHL</sub>       | LO high-state output voltage                                                       | I <sub>LO</sub> = -100mA, V <sub>OHL</sub> = V <sub>VCC</sub> - V <sub>LO</sub> |      | 0.15 |      | V      |

|                        | LO rise time (10% to 90% pulse magnitude)                                          | C <sub>LD</sub> = 1000pF                                                        |      | 5    |      | ns     |

|                        | LO fall time (90% to 10% pulse magnitude)                                          | C <sub>LD</sub> = 1000pF                                                        |      | 4    |      | ns     |

| I <sub>OHL</sub>       | LOpeak source current                                                              | V <sub>VCC</sub> = 10V                                                          |      | 4    |      | Α      |

| I <sub>OLL</sub>       | LOpeak sink current                                                                | V <sub>VCC</sub> = 10V                                                          |      | 5    |      | Α      |

| SYMBOL              | $_{\text{C}}$ = 100 kHz; $V_{\text{VCC}}$ = 10 V; $V_{\text{HV1}}$ = $V_{\text{HV}}$                                             | TEST CONDITIONS                                                                            | MIN   | TYP | MAX   | UNIT              |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------|-----|-------|-------------------|

| INTERLEAV           | □<br>E PHASE DELAY FROM CH-2 To CH-1 (                                                                                           | (OPT)                                                                                      |       |     |       |                   |

| V <sub>OPTL</sub>   | OPT Input Low State                                                                                                              | OPT="0"                                                                                    |       |     | 1.0   | V                 |

| V <sub>OPTH</sub>   | OPT Input High State                                                                                                             | OPT="1"                                                                                    | 2.0   |     | 1.0   | V                 |

| VOPTH               | HO2 <sub>rising</sub> -HO1 <sub>rising</sub> in the buck mode, or LO2 <sub>rising</sub> -LO1 <sub>rising</sub> in the boost mode | OPT = "0" for 3 Phases in Daisy Chain<br>Interleaving Operation                            | 2.0   | 240 |       | Degree            |

|                     | HO2 <sub>rising</sub> -HO1 <sub>rising</sub> in the buck mode, or LO2 <sub>rising</sub> -LO1 <sub>rising</sub> in the boost mode | OPT= "1" for 1, 2, or 4 phases in Daisy<br>Chain Interleaving Operation                    |       | 180 |       | Degree            |

|                     | Internal Pull down impedance                                                                                                     |                                                                                            |       | 1   |       | ${\sf Meg}\Omega$ |

| DEAD TIME           | and LATCHED SHUTDOWN (DT/SD)                                                                                                     |                                                                                            |       |     |       |                   |

| •                   | LO falling edge to HO rising edge delay                                                                                          | R <sub>DT</sub> = 19.1kΩ                                                                   |       | 50  |       | ns                |

| t <sub>DT</sub>     | HO falling edge to LO rising edge delay                                                                                          | R <sub>DT</sub> = 19.1kΩ                                                                   |       | 50  |       | ns                |

| $V_{DT}$            | DC voltage level for dead time programming                                                                                       |                                                                                            |       | 1.2 |       | V                 |

|                     | DC voltage level for adaptive dead time programming                                                                              |                                                                                            | 3.1   |     |       | V                 |

| $V_{ADPT}$          | HO-SW or LO-GND voltage threshold to enable cross output for adaptive dead time scheme                                           | V <sub>VCC</sub> > 9V, (V <sub>HB</sub> – V <sub>SW</sub> ) > 8V, HO or LO voltage falling |       | 1.5 |       | V                 |

|                     | LO falling edge to HO rising edge delay                                                                                          | $V_{DT} = V_{VDD}$                                                                         |       | 40  |       | ns                |

| t <sub>ADPT</sub>   | HO falling edge to LO rising edge delay                                                                                          | $V_{DT} = V_{VDD}$                                                                         |       | 40  |       | ns                |

| t <sub>SD</sub>     | Latched shutdown glitch filter                                                                                                   |                                                                                            | 1.875 | 2.5 | 3.125 | μs                |

| R <sub>SD</sub>     | Shutdown latch pulldown resistance                                                                                               | Resistor in series with an external pull-down NFET                                         |       |     | 2     | kΩ                |

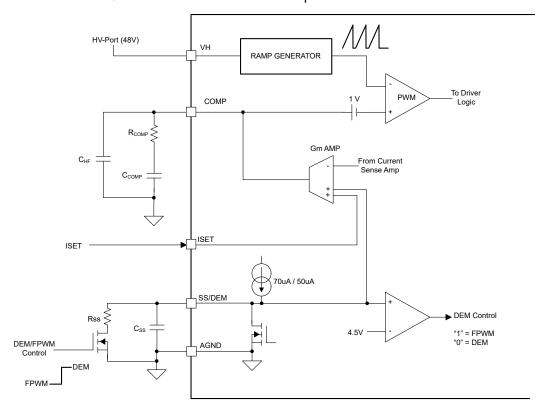

| SOFT STAR           | T and FORCED PWM and DIODE EMUL                                                                                                  | ATION PRGRAMMING (SS/DEM1, SS/D                                                            | EM2)  |     |       |                   |

| I <sub>SS</sub>     | SS charging current source during startup                                                                                        | $V_{SS} \le 3.3V, \ V_{EN} > 2V, \ V_{UVLO} > 2.5V, \ DIR < 1 \text{ or } DIR > 2$         |       | 70  |       | μΑ                |

| I <sub>SS</sub>     | SS charging current source after startup                                                                                         | $V_{SS} \ge 3.9V, \ V_{EN} > 2V, \ V_{UVLO} > 2.5V, \ DIR < 1 \text{ or } DIR > 2$         |       | 50  |       | μΑ                |

|                     | SS to gm input offset                                                                                                            |                                                                                            |       | 1   |       | V                 |

| R <sub>SS</sub>     | SS discharge device Rds(ON)                                                                                                      | V <sub>SS</sub> = 2V                                                                       |       | 20  |       | Ω                 |

| V <sub>SS_LOW</sub> | SS discharge completion threshold                                                                                                | Once it is discharged by internal logic                                                    |       | 0.3 |       | V                 |

|                     | ATIONS (CFG)                                                                                                                     |                                                                                            |       |     |       |                   |

| R <sub>CFG1</sub>   | I2C Address: b0100000. IMON = Inductor Current                                                                                   |                                                                                            |       | 0   |       | kΩ                |

| R <sub>CFG2</sub>   | I2C Address: b0100001. IMON = Inductor Current                                                                                   |                                                                                            | 0.316 |     | 0.324 | kΩ                |

| R <sub>CFG3</sub>   | I2C Address: b0100010. IMON = Inductor Current                                                                                   |                                                                                            | 0.649 |     | 0.665 | kΩ                |

| R <sub>CFG4</sub>   | I2C Address: b0100011. IMON = Inductor Current                                                                                   |                                                                                            | 1.1   |     | 1.13  | kΩ                |

| R <sub>CFG5</sub>   | I2C Address: b0100100. IMON = Inductor Current                                                                                   |                                                                                            | 1.65  |     | 1.69  | kΩ                |

| R <sub>CFG6</sub>   | I2C Address: b0100101. IMON = Inductor Current                                                                                   |                                                                                            | 2.43  |     | 2.49  | kΩ                |

| SYMBOL             | PARAMETER                                      | TEST CONDITIONS | MIN      | TYP MAX | UNIT |

|--------------------|------------------------------------------------|-----------------|----------|---------|------|

| R <sub>CFG7</sub>  | I2C Address: b0100110. IMON = Inductor Current |                 | 3.32     | 3.4     | kΩ   |

| R <sub>CFG8</sub>  | I2C Address: b0100111. IMON = Inductor Current |                 | 4.53     | 4.64    | kΩ   |

| R <sub>CFG9</sub>  | I2C Address: b0100111. IMON = Output Current   |                 | 6.65     | 6.81    | kΩ   |

| R <sub>CFG10</sub> | I2C Address: b0100110. IMON = Output Current   |                 | 10.2     | 10.5    | kΩ   |

| R <sub>CFG11</sub> | I2C Address: b0100101. IMON = Output Current   |                 | 13.7     | 14.0    | kΩ   |

| R <sub>CFG12</sub> | I2C Address: b0100100. IMON = Output Current   |                 | 18.7     | 19.1    | kΩ   |

| R <sub>CFG13</sub> | I2C Address: b0100011. IMON = Output Current   |                 | 26.1     | 26.7    | kΩ   |

| R <sub>CFG14</sub> | I2C Address: b0100010. IMON = Output Current   |                 | 37.4     | 38.3    | kΩ   |

| R <sub>CFG15</sub> | I2C Address: b0100001. IMON = Output Current   |                 | 60.4     | 61.9    | kΩ   |

| R <sub>CFG16</sub> | I2C Address: b0100000. IMON = Output Current   |                 | 95.3     | 97.6    | kΩ   |

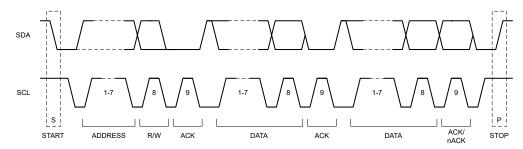

| 2C INTERF          | ACE (SLC, SDA)                                 |                 |          |         |      |

| V <sub>SDAL</sub>  | SDA input low state                            |                 |          | 1.0     | V    |

| V <sub>SDAH</sub>  | SDA input high state                           |                 | 2.0      |         | V    |

| V <sub>SCLL</sub>  | SCL input low state                            |                 |          | 1.0     | V    |

| V <sub>SCLH</sub>  | SCL input high state                           |                 | 2.0      |         | V    |

| Thermal Shu        | utdown                                         |                 | <u>'</u> |         |      |

| T <sub>J_SD</sub>  | Thermal shutdown                               |                 | 155      | 175     | °C   |

|                    | Thermal shutdown hysteresis                    |                 |          | 15      | °C   |

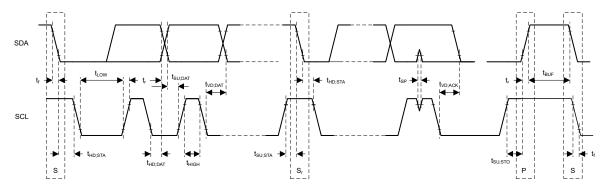

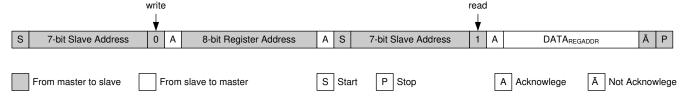

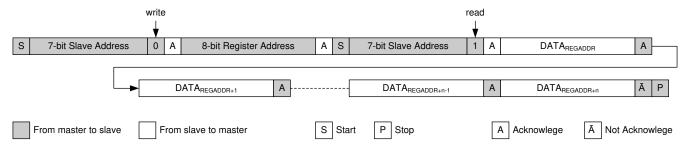

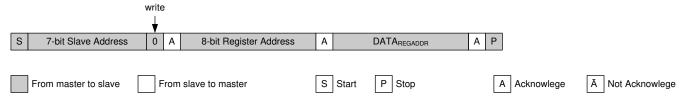

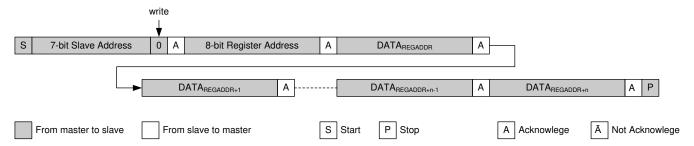

# 5.6 Timing Requirements

Over operating junction temperature range and recommended supply voltage range (unless otherwise noted)

|                       |                                                    |                               | MIN  | NOM MAX | UNI |

|-----------------------|----------------------------------------------------|-------------------------------|------|---------|-----|

| I <sup>2</sup> C INTE | RFACE                                              |                               |      |         |     |

|                       |                                                    | Standard mode                 | 0    | 100     |     |

| f <sub>SCL</sub>      | SCL clock frequency                                | Fast mode                     | 0    | 400     | kHz |

|                       |                                                    | Fast mode plus <sup>(1)</sup> | 0    | 1000    | 1   |

|                       | LOW period of the SCL clock                        | Standard mode                 | 4.7  |         |     |

| t <sub>LOW</sub>      |                                                    | Fast mode                     | 1.3  |         | μs  |

|                       |                                                    | Fast mode plus <sup>(1)</sup> | 0.5  |         |     |

|                       | HIGH period of the SCL clock                       | Standard mode                 | 4.0  |         |     |

| t <sub>HIGH</sub>     |                                                    | Fast mode                     | 0.6  |         | μs  |

|                       |                                                    | Fast mode plus <sup>(1)</sup> | 0.26 |         | 1   |

|                       | Bus free time between a STOP and a START condition | Standard mode                 | 4.7  |         |     |

| t <sub>BUF</sub>      |                                                    | Fast mode                     | 1.3  |         | μs  |

|                       |                                                    | Fast mode plus <sup>(1)</sup> | 0.5  |         | 1   |

|                       | Set-up time for a repeated START condition         | Standard mode                 | 4.7  |         |     |

| t <sub>SU:STA</sub>   |                                                    | Fast mode                     | 0.6  |         | μs  |

|                       |                                                    | Fast mode plus (1)            | 0.26 |         | 1   |

Over operating junction temperature range and recommended supply voltage range (unless otherwise noted)

|                     |                                       |                               | MIN                         | NOM MAX | UNI |

|---------------------|---------------------------------------|-------------------------------|-----------------------------|---------|-----|

|                     |                                       | Standard mode                 | 4.0                         |         |     |

| t <sub>HD:STA</sub> | Hold time (repeated) START condition  | Fast mode                     | 0.6                         |         | μs  |

|                     |                                       | Fast mode plus (1)            | 0.26                        |         | 1   |

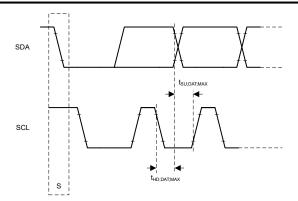

|                     |                                       | Standard mode                 | 0                           |         |     |

| t <sub>HD:DAT</sub> | Data hold time                        | Fast mode                     | 0                           |         | μs  |

|                     |                                       | Fast mode plus (1)            | 0                           |         | 1   |

|                     |                                       | Standard mode                 |                             | 1000    | 1   |

| t <sub>r</sub>      | Rise time of both SDA and SCL signals | Fast mode                     | 20                          | 300     | ns  |

|                     | Signals                               | Fast mode plus (1)            |                             | 20      | -]  |

|                     | Fall time of both SDA and SCL signals | Standard mode                 |                             | 300     | 1   |

| t <sub>f</sub>      |                                       | Fast mode                     | 20×V <sub>DD</sub> /<br>5.5 | 300     | ns  |

|                     |                                       | Fast mode plus <sup>(1)</sup> | 20×V <sub>DD</sub> /<br>5.5 | 120     | ,   |

|                     | Set-up time for STOP condition        | Standard mode                 | 4.0                         |         |     |

| t <sub>su:STO</sub> |                                       | Fast mode                     | 0.6                         |         | μs  |

|                     |                                       | Fast mode plus (1)            | 0.26                        |         | 1   |

|                     | Data valid time                       | Standard mode                 |                             | 3.45    | ,   |

| $t_{VD;DAT}$        |                                       | Fast mode                     |                             | 0.9     | μs  |

|                     |                                       | Fast mode plus (1)            |                             | 0.45    | , ] |

| t <sub>VD;ACK</sub> | Data valid acknowledge time           | Standard mode                 |                             | 3.45    | ,   |

|                     |                                       | Fast mode                     |                             | 0.9     | μs  |

|                     |                                       | Fast mode plus (1)            |                             | 0.45    | , ] |

| <u></u>             | Conscitive lead for each kind line    | Standard mode                 |                             | 400     | 1   |

| Сь                  | Capacitive load for each bus line     | Fast mode                     |                             | 400     | pF  |

<sup>(1)</sup> Fast mode plus is supported but not fully compliant with I<sup>2</sup>C standard

# **5.7 Typical Characteristics**

$V_{VIN}$  = 48V,  $V_{VCC}$  = 10V,  $V_{UVLO}$  = 3.3V,  $T_J$  = 25°C, unless otherwise stated.

# 6 Detailed Description

#### 6.1 Overview

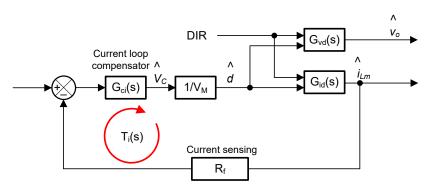

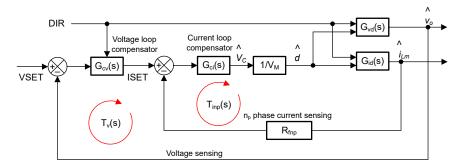

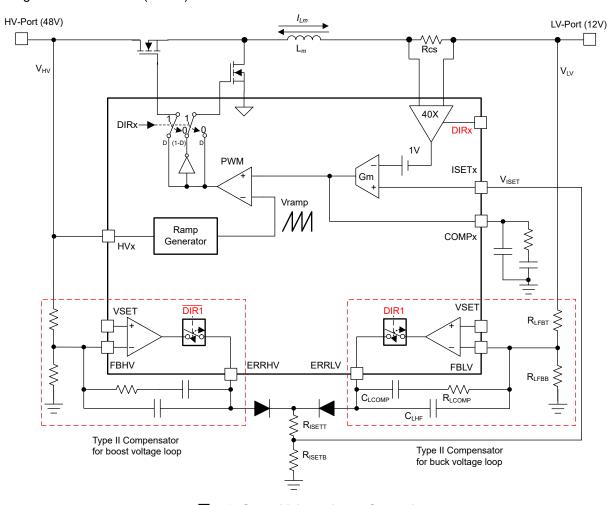

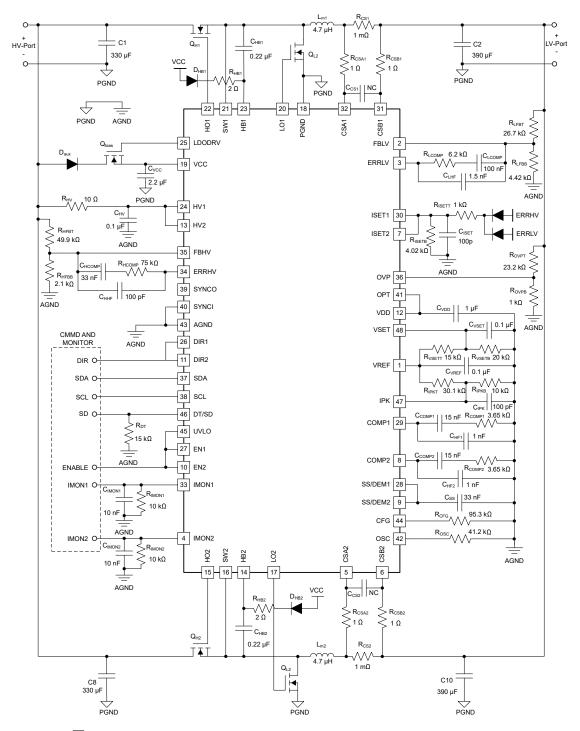

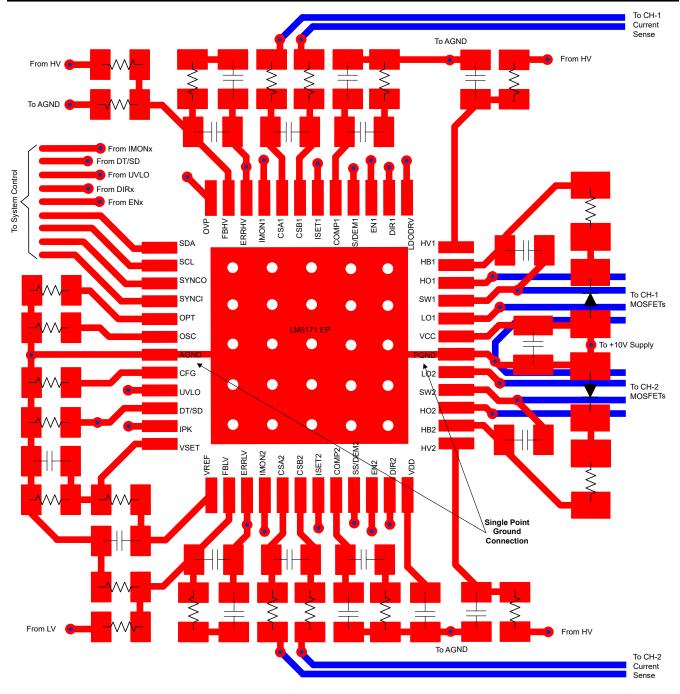

The LM5171 device is a high performance, dual-channel bidirectional PWM controller intended to manage power transfer between a Higher Voltage Port (HV-Port) and a Lower Voltage Port (LV-Port) . LM5171 integrates essential analog functions that enable the design of high-power converters with a minimal number of external components. Depending on the operating mode, device can regulate both the output port voltages, or currents, in either direction designated by the DIR input signal.

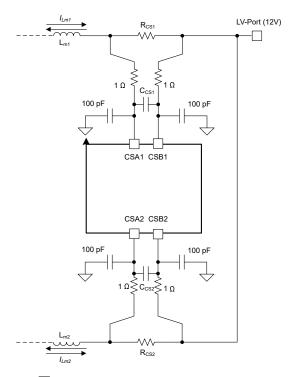

The dual-channel differential current sense amplifiers and dedicated channel current monitors achieve typical accuracy of 1%. The robust 5A half-bridge gate drivers are capable of controlling parallel MOSFET switches delivering higher power per channel. The device offers dynamically selectable Diode Emulation Mode (DEM) and Forced PWM (FPWM). With DEM, the buck or boost synchronous rectifiers enables discontinuous mode operation for improved efficiency under light load conditions, and it also prevents negative current. With FPWM, the synchronous rectifier allows negative current and hence helps achieving fast dynamic response under large circuit transients. Versatile protection features include the cycle-by-cycle peak current limit, overvoltage protection of both HV and LV Ports, detection and protection of MOSFET switch failures, and overtemperature protection.

The LM5171 uses an innovative average current mode control technology which simplifies the inner current loop compensation by maintaining a constant loop gain regardless of the power flow direction and the operating voltages and load level. The device also integrates two error amplifiers and a 1% accurate voltage reference to facilitate the bi-directional output voltage regulation. The free-running oscillator is adjustable up to 1000kHz and can be synchronized to an external clock within ±20% of the free running oscillator frequency. The stackable multiphase parallel operation is achieved by connecting two LM5171 controllers in parallel for 3 or 4 phase operation, or by synchronizing multiple LM5171 controllers to external multiphase clocks for a higher number of phases. In addition, the two channels of the LM5171 can implement two independent bi-directional converters. The UVLO pin provides commander ON/OFF control that disables the LM5171 in a low quiescent current shutdown state when the pin is held low.

The LM5171 also features the I2C port, through which the status of operation and alarms of the device can be monitored.

www.ti.com/ja-jp

#### 6.1.1 Device Configurations (CFG) and I2C Address

A single resistor placed across the CFG and AGND pins sets the IMON1 and IMON2 of the LM5171 to monitor each inductor current or load current of a channel, and it also programs the I2C address as listed in 表 6-1.

表 6-1. CFG Programming for IMONs and I2C Address

| CFG Resistor Selecti | on (kΩ) (1% Resistor) | I2C Address | IMON1 and IMON2 Function  |  |

|----------------------|-----------------------|-------------|---------------------------|--|

| Min Max              |                       | 120 Address | IMON I and IMON2 Function |  |

| 0                    | 0.1                   | 0x00        | Inductor Current          |  |

| 0.316                | 0.324                 | 0x01        | Inductor Current          |  |

| 0.649                | 0.665                 | 0x02        | Inductor Current          |  |

| 1.10                 | 1.13                  | 0x03        | Inductor Current          |  |

| 1.65                 | 1.69                  | 0x04        | Inductor Current          |  |

| 2.43                 | 2.49                  | 0x05        | Inductor Current          |  |

| 3.32                 | 3.40                  | 0x06        | Inductor Current          |  |

| 4.53                 | 4.64                  | 0x07        | Inductor Current          |  |

| 6.65                 | 6.81                  | 0x07        | Load Current              |  |

| 10.2                 | 10.5                  | 0x06        | Load Current              |  |

| 13.7                 | 14.0                  | 0x05        | Load Current              |  |

| 18.7                 | 19.1                  | 0x04        | Load Current              |  |

| 26.1                 | 26.7                  | 0x03        | Load Current              |  |

| 37.4                 | 38.3                  | 0x02        | Load Current              |  |

| 60.4                 | 61.9                  | 0x01        | Load Current              |  |

| 95.3                 | 97.6                  | 0x00        | Load Current              |  |

#### 6.1.2 Definition of IC Operation Modes

- Shutdown Mode: When the UVLO pin is < 1.25V, the LM5171 is in the shutdown mode with all gate drivers in the low state, and all internal logic reset. When UVLO < 1.25V, the device draws < 10µA through each of the HV1, HV2 and VCC pins.

- Initialization Mode: When the UVLO pin is > 1.5V but < 2.5V, and DT/SD > 0.5V, the LM5171 establishes proper internal logic states, and the LDODRV is turned on to control the external MOSFET to produce the VCC, and LM5171 prepares for circuit operation. Once VCC voltage is >8.5V, VDD and VREF are also established at approximately 5.0V and 3.5V, respectively.

- Standby Mode: When the UVLO pin is > 2.5V, and VCC > 8.5V, VDD> 4.5V, and DT/SD > 0.5V, the LM5171 is ready to operate. The oscillator is activated and the SYNCO is firing phase-shifted clock signals, but the four gate drive outputs remain off until the EN1 or EN2 initiate the power delivery mode.

- Power Delivery Mode: When the UVLO pin > 2.5V, VCC > 8.5V, VDD > 4.5V, DT/SD > 0.5V, EN1 or EN2 > 2V, DIR1 and/or DIR2 is valid (> 2V or < 1V), the SS capacitor is released. Once the SS voltage rises above 1V, the LM5171 gate drivers start to switch and start the power delivery.

- Latch-ed Shutdown mode serves as an emergency shutdown function, and it is achieved by pulling DT/SD pin below 1V for at least 2.5µs by an external circuit during operation. In latched shutdown mode, all gate drivers remain in the low state, and both SS/DEM1 and SS/DEM2 pins are held low. The latch can be reset by pulling the UVLO to below 1.25V for at least 10µs.

資料に関するフィードバック(ご意見やお問い合わせ)を送信

15

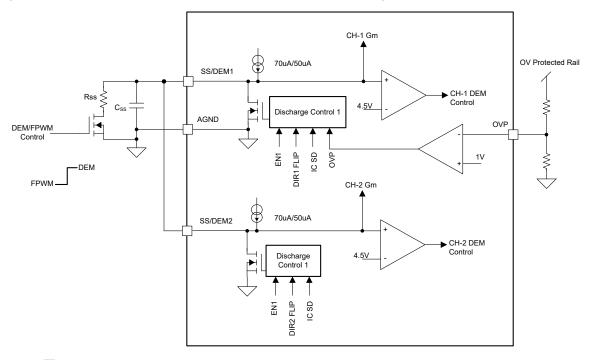

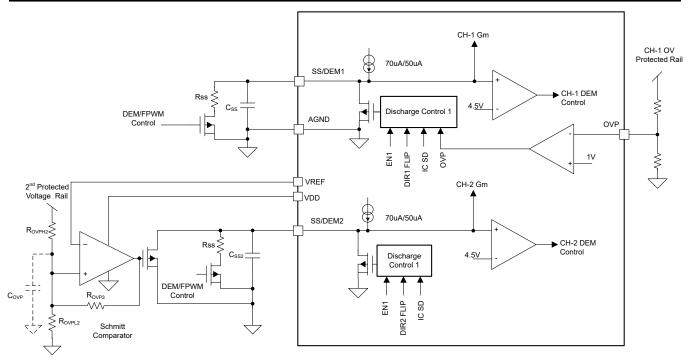

# 6.2 Functional Block Diagram

#### **6.3 Feature Description**

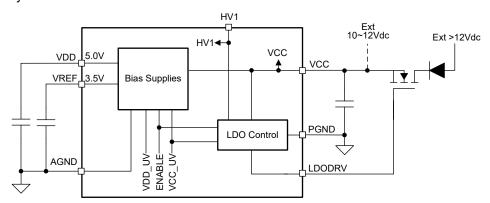

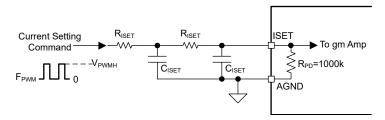

#### 6.3.1 Bias Supplies and Voltage Reference (VCC, VDD, and VREF)