## LM5168E 115V、0.3A、同期整流降圧コンバータ、

### 1 特長

- 機能安全対応

- 機能安全システムの設計に役立つ資料を利用可能

- 高信頼性の堅牢なアプリケーション用に設計

- 6V～115V の広い入力電圧範囲

- 接合部温度範囲:-55°C～+150°C

- 固定 3ms の内部ソフトスタートタイマ

- ピークおよびバレー電流制限保護

- 入力 UVLO およびサーマルシャットダウン保護機能

- スケーラブルな産業用電源およびバッテリパック用に設計

- 短い最小オン/オフ時間: 50ns

- 1MHz の可変スイッチング周波数

- ダイオード エミュレーションにより軽負荷時の効率を向上

- 自動モードでの 10µA スリープ電流

- シャットダウン時静止電流: 3µA

- LM5164、LM5163、LM5013 とピン互換

- LM5017 および LM34927 と類似のピン配置と機能。

- 統合により設計のサイズとコストを低減

- COT モード制御アーキテクチャ

- 1.9Ω の NFET 降圧スイッチを内蔵

- 0.71Ω の NFET 同期整流器を内蔵

- 1.2V の内部基準電圧

- ループ補償部品が不要

- VCC バイアスレギュレータとブートダイオードを内蔵

- オープンドレインのパワーグッドインジケータ

- パッケージ: SOIC PowerPAD™-8 IC パッケージ、間隔 1.27mm

### 2 アプリケーション

- 宇宙 — 太陽光発電、蓄電

- 航空宇宙および防衛 — スマート弾薬、アクチュエータ

- 航空 — センサ画像処理、レーダー

### 3 説明

The LM5168E は、拡張温度範囲 (-55°C ~ +150°C) の同期整流降圧コンバータです。これは、最小限の外部サージ抑制部品で、広い入力電圧範囲でレギュレーションを行えるように設計されています。制御可能な最短のオン時間は 50ns で、大きな降圧率を使用できるため、48V 公称入力から低電圧レールへの直接降圧変換が可能になります。システムの複雑性と設計のコストを下げることができます。LM5168E は最低 6V の入力電圧ディップ時にも動作し、必要に応じて 100% に近いデューティサイクルで動作するため、幅広い入力電源電圧範囲の産業用および多セルのバッテリパック機器に理想的です。

ハイサイドおよびローサイドパワー MOSFET を内蔵した LM5168E は、最大 0.3A の出力電流を供給できます。コンスタントオン時間 (COT) 制御アーキテクチャにより、スイッチング周波数はほぼ一定で、負荷およびライン過渡応答が非常に優れています。LM5168E は自動モードバージョンで使用でき、非常に低い  $I_Q$  とダイオードエミュレーションモード動作により、軽負荷時に高効率が実現します。

#### パッケージ情報

| 部品番号    | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|---------|----------------------|--------------------------|

| LM5168E | DDA (HSOIC, 8)       | 4.9mm × 6mm              |

(1) 詳細については、セクション 11 を参照してください。

(2) パッケージサイズ(長さ × 幅)は公称値であり、該当する場合はピンを含みます。

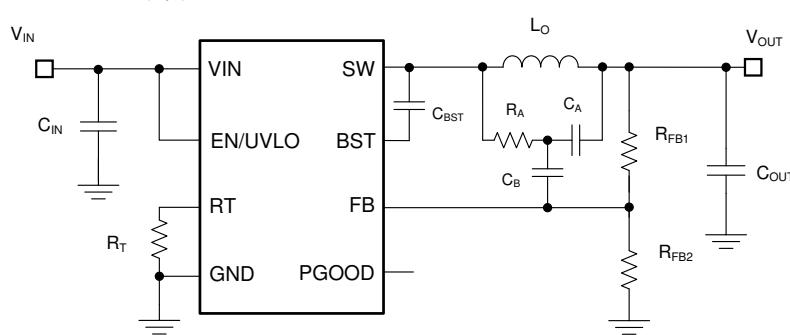

代表的な降圧コンバータの回路図

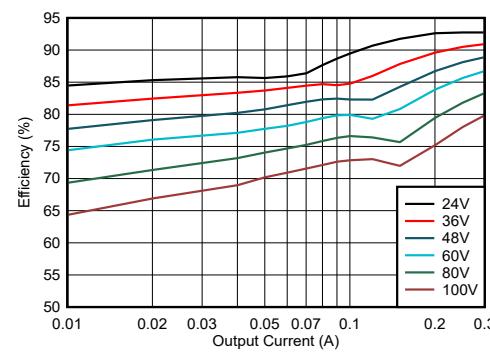

降圧コンバータの効率 :  $V_{OUT} = 12V$

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあります。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                      |    |                             |    |

|----------------------|----|-----------------------------|----|

| 1 特長.....            | 1  | 7.4 デバイスの機能モード.....         | 15 |

| 2 アプリケーション.....      | 1  | 8 アプリケーションと実装.....          | 16 |

| 3 説明.....            | 1  | 8.1 アプリケーション情報.....         | 16 |

| 4 デバイス比較表.....       | 3  | 8.2 代表的な降圧アプリケーション.....     | 17 |

| 5 ピン構成および機能.....     | 4  | 8.3 電源に関する推奨事項.....         | 26 |

| 6 仕様.....            | 5  | 8.4 レイアウト.....              | 26 |

| 6.1 絶対最大定格.....      | 5  | 9 デバイスおよびドキュメントのサポート.....   | 31 |

| 6.2 ESD Ratings..... | 5  | 9.1 デバイス サポート.....          | 31 |

| 6.3 推奨動作条件.....      | 5  | 9.2 ドキュメントのサポート.....        | 31 |

| 6.4 熱に関する情報.....     | 6  | 9.3 ドキュメントの更新通知を受け取る方法..... | 31 |

| 6.5 電気的特性.....       | 6  | 9.4 サポート・リソース.....          | 31 |

| 6.6 代表的特性.....       | 8  | 9.5 商標.....                 | 31 |

| 7 詳細説明.....          | 9  | 9.6 静電気放電に関する注意事項.....      | 32 |

| 7.1 概要.....          | 9  | 9.7 用語集.....                | 32 |

| 7.2 機能ブロック図.....     | 10 | 10 改訂履歴.....                | 32 |

| 7.3 機能説明.....        | 10 | 11 メカニカル、パッケージ、および注文情報..... | 32 |

#### 4 デバイス比較表

| 部品番号         | パッケージ             | 説明                      | 出力電流 | 軽負荷時のモード | 電流制限        |

|--------------|-------------------|-------------------------|------|----------|-------------|

| LM5168PEDDAR | DDA<br>(HSOIC, 8) | 0.3A、降圧、自動、ヒップなし、拡張温度範囲 | 0.3A | PFM      | 0.42A、ヒップなし |

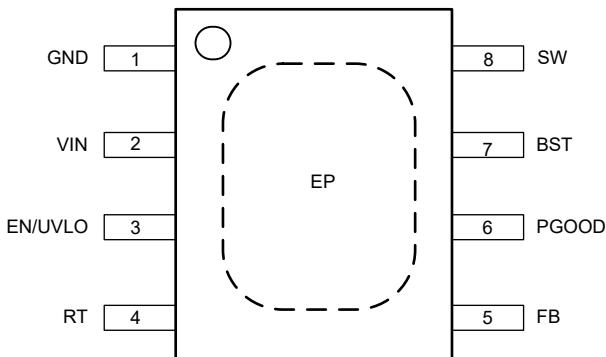

## 5 ピン構成および機能

図 5-1. 8 ピン SO PowerPAD™ 集積回路パッケージ (上面図)

表 5-1. ピンの機能

| ピン |         | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                       |

|----|---------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 番号 | 名称      |                    |                                                                                                                                                                                                                                                          |

| 1  | GND     | G                  | 内部回路のグランド接続                                                                                                                                                                                                                                              |

| 2  | VIN     | P                  | ハイサイドパワー MOSFET および内部バイアスレギュレータへのレギュレータ電源入力ピンです。短い低インピーダンスのパスを経由して、降圧コンバータの入力電源に直接接続します。                                                                                                                                                                 |

| 3  | EN/UVLO | I                  | 高精度のイネーブルおよび低電圧誤動作防止 (UVLO) のプログラミングピン。EN/UVLO 立ち上がりの電圧が 1.1V より低くなると、コンバーターはシャットダウン モードとなり、すべての機能がディセーブルされます。UVLO の電圧が 1.1V よりも高く、1.5V よりも低い場合、コンバーターはスタンバイ モードになり、内部 VCC レギュレータは動作しますが、スイッチングは行われません。EN/UVLO ピンの電圧が 1.5V よりも高い場合、スタートアップ シーケンスが開始されます。 |

| 4  | RT      | I                  | オン タイム プログラミング ピン。このピンと GND との間に抵抗によって、降圧スイッチのオン時間が設定されます。                                                                                                                                                                                               |

| 5  | FB      | I                  | 電圧レギュレーション コンパレータの帰還入力                                                                                                                                                                                                                                   |

| 6  | PGOOD   | O                  | パワーグッド インジケータ。このピンはオープンドレイン出力ピンです。10kΩ と 100kΩ の間の外付けプルアップ抵抗を介して、ソース電圧に接続します。PGOOD 機能が不要な場合は GND に接続します。                                                                                                                                                 |

| 7  | BST     | P                  | ブートストラップ ゲートドライブ電源。内部ハイサイド ゲートドライバにバイアスを印加するために、BST と SW との間に高品質の 2.2nF X7R セラミックコンデンサを接続するために必要です。                                                                                                                                                      |

| 8  | SW      | P                  | ハイサイド NMOS 降圧スイッチのソースおよびローサイド NMOS 同期整流器のドレインに内部接続されているスイッチング ノード。パワー インダクタのスイッチング ノードに接続します。                                                                                                                                                            |

| —  | EP      | —                  | パッケージの露出パッド。内部で電気的に接続されていません。EP を GND ピンに半田付けし、大きな銅プレーンに接続して熱抵抗を減らします。                                                                                                                                                                                   |

(1) P = 電源、G = グランド、I = 入力、O = 出力

## 6 仕様

### 6.1 絶対最大定格

動作時接合部温度範囲内 (特に記述のない限り)<sup>(1) (2)</sup>

|                |                  | 最小値  | 最大値   | 単位 |

|----------------|------------------|------|-------|----|

| ピン電圧           | VIN              | -0.3 | 118   | V  |

|                | SW               | -1.5 | 118   |    |

|                | SW、過渡 < 20ns     | -3   |       |    |

|                | BST              | -0.3 | 123.5 |    |

|                | BST から SW へ      | -0.3 | 5.5   |    |

|                | EN               | -0.3 | 118   |    |

|                | FB               | -0.3 | 5.5   |    |

|                | RT               | -0.3 | 5.5   |    |

|                | PGOOD            | -0.3 | 14    |    |

| ポートストラップ コンデンサ | BST-SW 間の容量      |      | 2.5   | nF |

| 動作時接合部温度       | T <sub>J</sub>   | -55  | 150   | °C |

| 保存温度           | T <sub>stg</sub> | -65  | 150   | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、デバイスは完全に機能するとは限らず、このことがデバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) PCB レイアウトに関する推奨事項 ([レイアウトガイドライン](#)) については、「アプリケーション」セクションを参照してください。

### 6.2 ESD Ratings

|                    |      | 値                                                          | 単位    |

|--------------------|------|------------------------------------------------------------|-------|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>       | ±2000 |

|                    |      | 荷電デバイス モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠 <sup>(2)</sup> | ±500  |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 6.3 推奨動作条件

動作時接合部温度範囲内 (特に記述のない限り)

|                      |             |         | 最小値 | 公称値 | 最大値  | 単位  |

|----------------------|-------------|---------|-----|-----|------|-----|

| V <sub>IN</sub>      | ピン電圧        | VIN     | 6   | 115 |      | V   |

| V <sub>EN/UVLO</sub> | ピン電圧        | EN/UVLO |     |     | 115  | V   |

| I <sub>OUT</sub>     | 出力電流範囲      | LM5168E |     | 0.3 |      | A   |

| C <sub>BST</sub>     | BST-SW 間の容量 |         |     | 2.2 |      | nF  |

| F <sub>sw</sub>      | スイッチング周波数   |         | 100 |     | 1000 | kHz |

## 6.4 热に関する情報

| 热評価基準 <sup>(1)</sup>  |                                  | LM5168E    | 単位   |

|-----------------------|----------------------------------|------------|------|

|                       |                                  | DDA (SOIC) |      |

|                       |                                  | 8 ピン       |      |

| R <sub>θJA(EVM)</sub> | 評価基板の接合部から周囲への熱抵抗 <sup>(2)</sup> | 22         | °C/W |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗                     | 38.9       | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗                | 51.7       | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ                 | 2.9        | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗                     | 14.1       | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ                 | 14.1       | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース(底面)までの熱抵抗               | 3.3        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーションノートを参照してください。

(2) この値は、LM5168PEVM で、銅の面積が約 49cm<sup>2</sup>で取得されています。詳細については、「熱に関する検討事項」セクションを参照ください。

## 6.5 電気的特性

T<sub>J</sub> = -55°C ~ +150°C。代表値は、T<sub>J</sub> = 25°C、V<sub>IN</sub> = 24V です(特に記述のない限り)。

| パラメータ                      |                                                                                      | テスト条件                                           | 最小値   | 標準値   | 最大値   | 単位 |

|----------------------------|--------------------------------------------------------------------------------------|-------------------------------------------------|-------|-------|-------|----|

| <b>電源</b>                  |                                                                                      |                                                 |       |       |       |    |

| I <sub>Q(VIN)</sub>        | V <sub>IN</sub> 静止電流                                                                 | V <sub>EN/UVLO</sub> = 2.5V、PFM 動作              | 10    | 25    | μA    |    |

| I <sub>Q(STANDBY)</sub>    | V <sub>IN</sub> スタンバイ電流                                                              | V <sub>EN/UVLO</sub> = 1.25V                    | 17    | 35    | μA    |    |

| I <sub>SD(VIN)</sub>       | V <sub>IN</sub> のシャットダウン時消費電流                                                        | V <sub>EN/UVLO</sub> = 0V、T <sub>J</sub> = 25°C | 3     | 6     | μA    |    |

| <b>イネーブル</b>               |                                                                                      |                                                 |       |       |       |    |

| V <sub>EN(R)</sub>         | EN/UVLO 電圧立ち上がりスレッショルド                                                               | EN/UVLO 立ち上がり、スイッチングが有効                         | 1.45  | 1.5   | 1.55  | V  |

| V <sub>EN(F)</sub>         | EN/UVLO 電圧立ち下がりスレッショルド                                                               | EN/UVLO 立ち下がり、スイッチングが無効                         | 1.35  | 1.4   | 1.44  | V  |

| V <sub>SD(R)</sub>         | EN/UVLO スタンバイ立ち上がりスレッショルド                                                            | EN/UVLO 立ち上がり、内部 LDO が有効、スイッチングなし。              |       | 1.1   |       | V  |

| V <sub>SD(F)</sub>         | EN/UVLO スタンバイ立ち下がりスレッショルド                                                            | EN/UVLO 立ち下がり、内部 LDO が無効。                       | 0.45  |       |       | V  |

| <b>基準電圧</b>                |                                                                                      |                                                 |       |       |       |    |

| V <sub>FB</sub>            | FB 電圧                                                                                | V <sub>FB</sub> 立ち下がり                           | 1.181 | 1.2   | 1.218 | V  |

| <b>スタートアップ</b>             |                                                                                      |                                                 |       |       |       |    |

| t <sub>SS</sub>            | 内部固定ソフトスタート時間                                                                        |                                                 | 1.75  | 3     | 4.75  | ms |

| <b>電力段</b>                 |                                                                                      |                                                 |       |       |       |    |

| R <sub>DSON(HS)</sub>      | ハイサイド MOSFET オン抵抗                                                                    | I <sub>SW</sub> = -100mA                        | 1.91  |       |       | Ω  |

| R <sub>DSON(LS)</sub>      | ローサイド MOSFET オン抵抗                                                                    | I <sub>SW</sub> = 100mA                         | 0.74  |       |       | Ω  |

| t <sub>ON(min)</sub>       | 最小 ON パルス幅                                                                           |                                                 | 50    |       |       | ns |

| t <sub>ON(1)</sub>         | On-time1                                                                             | V <sub>VIN</sub> = 6V、R <sub>RT</sub> = 75kΩ    | 5000  |       |       | ns |

| t <sub>ON(2)</sub>         | On-time2                                                                             | V <sub>VIN</sub> = 6V、R <sub>RT</sub> = 25kΩ    | 1650  |       |       | ns |

| t <sub>ON(3)</sub>         | On-time3                                                                             | V <sub>VIN</sub> = 12V、R <sub>RT</sub> = 75kΩ   | 2550  |       |       | ns |

| t <sub>ON(4)</sub>         | On-time4                                                                             | V <sub>VIN</sub> = 12V、R <sub>RT</sub> = 25kΩ   | 830   |       |       | ns |

| t <sub>OFF(min)</sub>      | 最小 OFF パルス幅                                                                          |                                                 | 50    |       |       | ns |

| <b>ブート回路</b>               |                                                                                      |                                                 |       |       |       |    |

| V <sub>BOOT-SW(UV_R)</sub> | BOOT-SW UVLO 立ち上がりスレッショルド                                                            | V <sub>BST-SW</sub> 立ち上がり                       | 2.6   | 3.4   | 3.4   | V  |

| <b>過電流保護</b>               |                                                                                      |                                                 |       |       |       |    |

| I <sub>HS_PK(OC)</sub>     | ハイサイド ピーク電流制限                                                                        |                                                 | 0.356 | 0.42  | 0.484 | A  |

| I <sub>LS_PK(OC)</sub>     | ローサイド ピーク電流制限                                                                        |                                                 | 0.356 | 0.42  | 0.484 | A  |

| I <sub>DELTA(OC)</sub>     | I <sub>HS_PK(OC)</sub> または I <sub>LS_PK(OC)</sub> の最小値から I <sub>LS_V(OC)</sub> を引いた値 |                                                 |       | 0.084 |       | A  |

| I <sub>LS_V(OC)</sub>      | ローサイドのバレー電流制限                                                                        | LS FET のローサイド バレー電流制限                           | 0.27  | 0.336 | 0.42  | A  |

## 6.5 電気的特性 (続き)

$T_J = -55^{\circ}\text{C} \sim +150^{\circ}\text{C}$ 。代表値は、 $T_J = 25^{\circ}\text{C}$ 、 $V_{IN} = 24\text{V}$  です (特に記述のない限り)。

| パラメータ               |                                     | テスト条件                   | 最小値   | 標準値  | 最大値                | 単位 |

|---------------------|-------------------------------------|-------------------------|-------|------|--------------------|----|

| $I_{ZC}$            | ゼロクロス検出電流のスレッショルド                   |                         | 0     |      | A                  |    |

| $T_W$               | 再スタート前のヒカップ時間                       |                         | 64    |      | ms                 |    |

| <b>パワー グッド</b>      |                                     |                         |       |      |                    |    |

| $V_{PGTH}$          | パワー グッド スレッショルド                     | FB 立ち下り、PG high から low  | 1.055 | 1.08 | 1.1                | V  |

|                     |                                     | FB 立ち上がり、PG low から high | 1.105 | 1.14 | 1.175              | V  |

| $R_{PG}$            | パワー グッド オン状態抵抗                      | $V_{FB} = 1\text{V}$    | 7     |      | $\Omega$           |    |

| <b>サーマル シャットダウン</b> |                                     |                         |       |      |                    |    |

| $T_{J-SHD}$         | サーマル シャットダウン スレッショルド <sup>(1)</sup> | 温度上昇                    | 175   |      | $^{\circ}\text{C}$ |    |

| $T_{J-SHD-HYS}$     | サーマル シャットダウン ヒステリシス <sup>(1)</sup>  |                         | 10    |      | $^{\circ}\text{C}$ |    |

(1) 設計による仕様で、製品テストは未実施

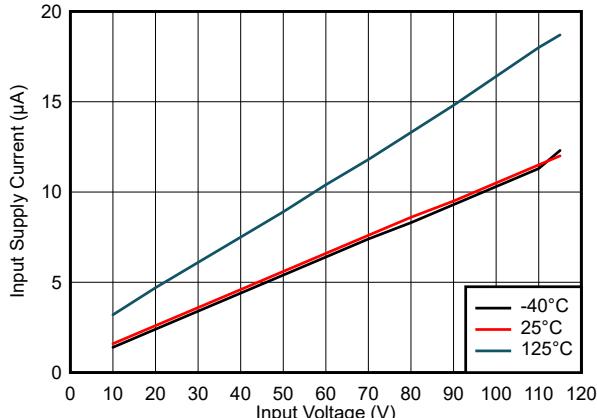

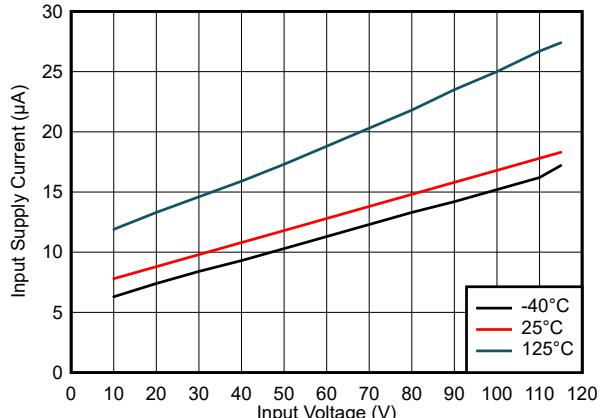

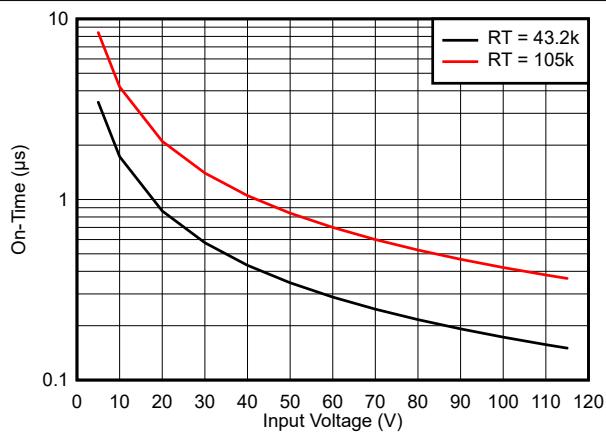

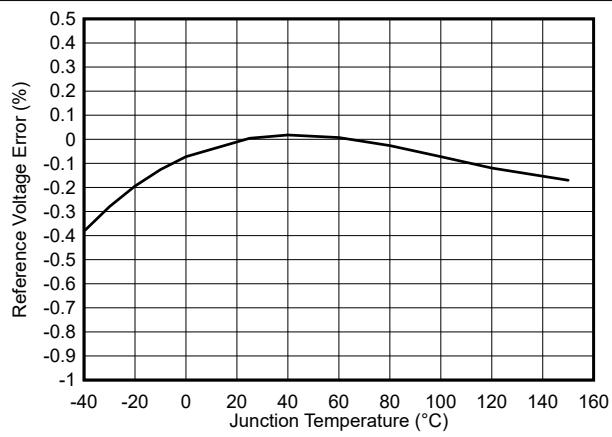

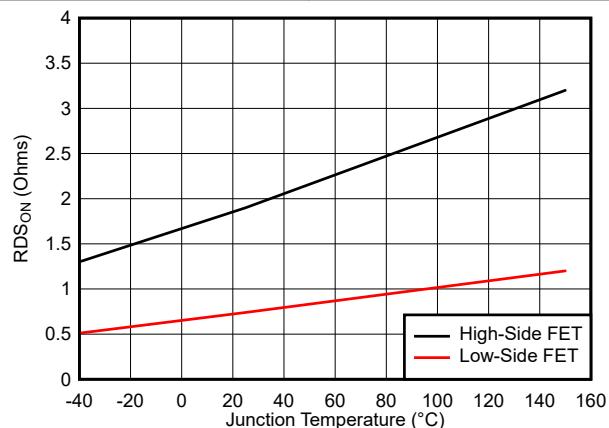

## 6.6 代表的特性

特記のない限り、次の条件が適用されます。 $T_A = 25^\circ\text{C}$  の場合、 $V_{IN} = 24\text{V}$ 。

図 6-1. シャットダウン電源電流と入力電圧との関係

図 6-2. スリープモード電源電流と入力電圧との関係

(DEM、非スイッチング)

図 6-3. COT オン時間と入力電圧との関係

図 6-4. 帰還コンパレータ スレッショルドと温度との関係

図 6-5. MOSFET のオン状態抵抗と温度との関係

## 7 詳細説明

### 7.1 概要

LM5168E は、超低  $I_Q$  の使いやすいコンスタント オンタイム (COT) 同期整流降圧レギュレータです。ハイサイドおよびローサイドパワー MOSFET を内蔵した LM5168E は低コスト、高効率の降圧コンバータであり、6V ~ 118V の広い入力電圧範囲で動作し、最大 0.3A DC 負荷電流を供給できます。LM5168E は、高電圧アプリケーションで適切な間隔を確保するために 1.27mm のピンピッチを備えた 8 ピン SO PowerPAD IC パッケージで供給されます。このコンスタント オンタイム (COT) コンバータは低ノイズ、低電流、高速負荷過渡要件に最適な選択肢で、予測型オン時間スイッチング パルスで動作します。入力電圧範囲全体にわたって、入力電圧フィードフォワードを採用して、擬似固定スイッチング周波数を実現します。制御可能なオン時間はわずか 50ns で、高い降圧率を実現でき、最小の強制オフ時間は 50ns で、非常に高いデューティサイクルを実現できます。この機能により、VIN が VOUT に近い値に低下したときの固定周波数動作が可能になります。強制オフ時間 50ns に達すると、デバイスは周波数フォールドバック動作に移行し、一定の出力電圧を維持します。LM5168E は、スマートピークおよびバレー電流制限検出回路を実装しており、出力短絡状態の発生時にも堅牢な保護が実現します。このレギュレータでは制御ループ補償は不要で、設計時間が短縮し、外部部品点数が減ります。

LM5168E は、自動モードで動作するように事前にプログラムされています。自動モードで動作するように構成されている場合、軽負荷時にはデバイスは超低  $I_Q$  モードに遷移して、高い効率を維持し、システムがスタンバイ状態のときに入力に接続されているバッテリセルの消耗を防止します。

LM5168E には、包括的なシステム要件に対応するための以下の追加機能が搭載されています。

- 電源レール シーケンシングと障害報告機能

- 内部固定ソフトスタート

- プリバイス負荷への単調なスタートアップ

- 高精度のイネーブルによるプログラム可能なライン低電圧誤動作防止 (UVLO)

- スマートなサイクル単位の電流制限によりインダクタの小型化を実現

- 自動回復機能付きサーマル シャットダウン。

LM5168E は、過渡電圧が DC レベルから逸脱する高入力電源からの安定化出力を必要とする広範な最終機器をサポートしています。このような最終製品システムの例を以下に示します。

- 多セルのバッテリパックシステム

- 24V 産業用システム

- 48V のテレコムと PoE 電圧範囲

ピン配置は、少数の外部コンポーネントのみを必要とするシンプルなレイアウトになるように設計されています。

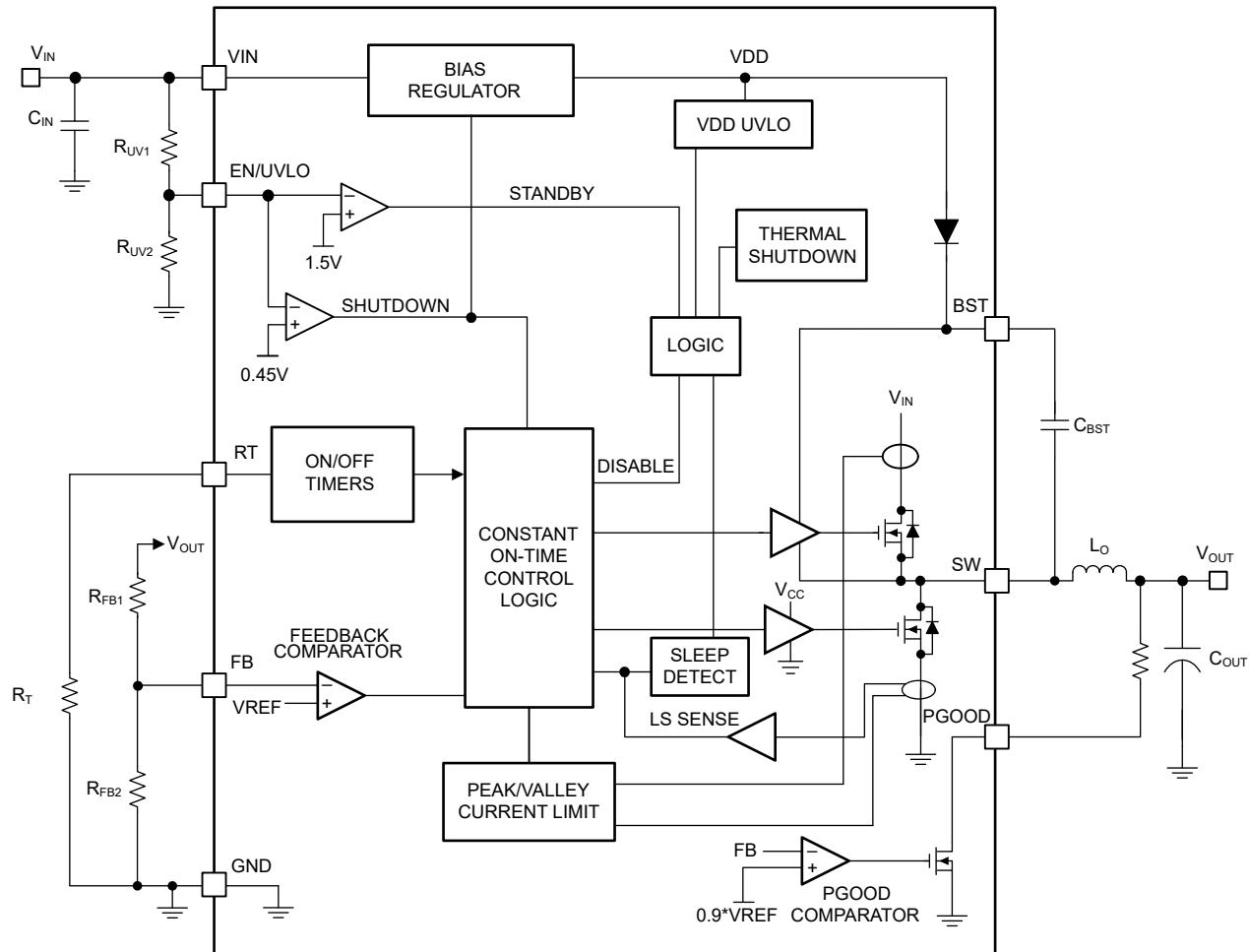

## 7.2 機能ブロック図

## 7.3 機能説明

### 7.3.1 制御アーキテクチャ

LM5168E 降圧スイッチングコンバータは、コンスタント オンタイム (COT) 制御方式を採用しています。COT 制御方式により、タイミング抵抗 ( $R_T$ ) を使用してハイサイド FET の固定のオン時間  $t_{ON}$  を設定します。 $t_{ON}$  は  $V_{IN}$  が変化するにつれて調整され、連続導通モード (CCM) の場合に固定周波数が維持されます。 $t_{ON}$  が経過した後、FB 電圧が 1.2V のリファレンス電圧と等しくなるか下回るまで、ハイサイド FET はオフのままであります。安定性を維持するため、帰還コンパレータは、オフ時間時にインダクタ電流と同相となる最小のリップル電圧を必要とします。さらに、オフ時間時の帰還電圧のこの変化は、帰還ノードに存在するすべてのノイズを支配するのに十分な大きさである必要があります。推奨される最小リップル電圧は 20mV です。堅牢な動作が必要な場合は、より多くのリップル電圧が使用されます。この動作は、SW ピンまたは BST ピンから FB ピンへ過剰な結合が発生している場合に特に当てはまります。また、入力電圧範囲全体にわたって安定性が確保される各種のリップル注入方式については、表 7-1 を参照してください。

急速スタートアップまたは正の負荷ステップ中、レギュレータはレギュレーションが達成されるまで最小オフ時間で動作します。この機能により、最小の出力電圧アンダーシュートで非常に高速な負荷過渡応答を実現します。定常状態動作で出力をレギュレートする場合、オフ時間は自動的に調整され、出力電圧レギュレーションが固定スイッチング周波数を維持するのに必要なスイッチノードのデューティサイクルが生成されます。CCM では、スイッチング周波数  $F_{SW}$  は  $R_T$  抵抗によってプログラムされます。

**表 7-1. リップル生成方法**

| TYPE 1                                                             | TYPE 2                                                          | TYPE 3                                                                 |

|--------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------|

| 最安コスト                                                              | リップルの低減                                                         | 最小リップル                                                                 |

|                                                                    |                                                                 |                                                                        |

| $RESR \geq \frac{20 \text{ mV} \times VOUT}{VFB \times \Delta IL}$ | $RESR \geq \frac{20 \text{ mV}}{\Delta IL}$                     | $C_A \geq \frac{10}{F_{SW} \times (R_{FB}    R_{FBT})}$                |

| $RESR \geq \frac{VOUT}{2 \times VIN \times FSW \times COUT}$       | $RESR \geq \frac{VOUT}{2 \times VIN \times FSW \times COUT}$    | $R_A \times C_A \leq \frac{(VIN - VOUT) \times T_{ON}}{20 \text{ mV}}$ |

|                                                                    | $CFF \geq \frac{1}{2\pi \times FSW \times (R_{FB}    R_{FBT})}$ | $C_B \geq \frac{T_{settle}}{3 \times R_{FBT}}$                         |

表 7-1 は、帰還ノードで適切な電圧リップルを生成するための 3 つの異なる方法を示しています。タイプ 1 リップル生成方式では、出力コンデンサと直列に 1 つの抵抗  $R_{ESR}$  を使用します。生成される電圧リップルには、出力コンデンサを充電および放電するインダクタリップル電流に起因する容量性リップルと、出力コンデンサに流れるインダクタリップル電流と直列抵抗  $R_{ESR}$  を介して流れる抵抗性リップルという 2 つの要素があります。容量性リップル成分はインダクタ電流と位相差があり、オフ時間中に単調に減少することはありません。抵抗性リップル成分は、インダクタ電流と同相になり、オフ時間中は単調に減少します。安定した動作を行うには、抵抗性リップルが  $V_{OUT}$  において容量性リップルを上回る必要があります。この条件が満たされていない場合、COT コンバータではスイッチングが不安定になり、複数のオン時間バーストが連続して発生し、その後長いオフ時間が続きます。タイプ 1 の式は、帰還ノードで十分な位相内リップルを確保するための直列抵抗  $R_{ESR}$  の値を定義します。

タイプ 2 のリップル生成では、直列抵抗に加えて、 $C_{FF}$  コンデンサが使用されます。出力電圧リップルは  $C_{FF}$  によって帰還ノードに直接 AC 結合されるため、 $R_{ESR}$  と最終的に出力電圧リップルは  $V_{OUT}/V_{FB}$  の係数で低減されます。

タイプ 3 リップル生成は、 $R_A$  と  $C_A$  で構成される RC ネットワークと、スイッチノード電圧を使用して、インダクタ電流と位相が一致する三角波ランプを生成します。この三角波は、コンデンサ  $C_B$  とともに帰還ノードに AC 結合されます。この回路は出力電圧リップルを使用しないため、この回路は低出力電圧リップルが重要なアプリケーションに最適な選択肢となります。また、COT 制御メソッドの詳細については、「[関連ドキュメント](#)」を参照してください。

軽負荷モード動作は、PFM と DEM 動作に設定できます。ダイオード エミュレーションモード (DEM) は負のインダクタ電流を防止し、パルス スキップは実効スイッチング周波数を下げることで軽負荷電流時に最大の効率を維持します。DEM 動作は、インダクタ バレー電流が 0 に達したときに、同期整流パワー MOSFET がオフになるときに発生します。ここで、負荷電流は CCM のピークツーピークインダクタ電流リップルの半分未満になります。ローサイド MOSFET をゼロ電流でオフにすると、スイッチング損失が低減し、負電流の伝導を防ぐことで導通損失が低減します。DEM コンバータの電力変換効率は、同等の強制 PWM CCM コンバータよりも高くなります。DEM 動作では、負荷電流が減少するにつれて、両方のパワー MOSFET がオフのままである時間が徐々に長くなります。このアイドル期間が 15μs を超えると、コンバータは超低  $I_Q$  モードに遷移し、入力からの静止電流がわずか 10μA になります。

### 7.3.2 内蔵 VCC レギュレータとブートストラップコンデンサ

LM5168E には、VIN から公称出力 5V で電力を供給される内部リニア レギュレータが内蔵されているため、VCC サブレギュレータを安定させるための外部コンデンサは必要ありません。VCC サブレギュレータは、同期 FET ドライバやロジック回路を含む内部回路ブロックに電流を供給します。入力ピン (VIN) は、最大 115V のライン電圧に直接接続できます。パワー MOSFET は総ゲート電荷量が低いため、ブートストラップコンデンサの値を小さくして、内部レギュレータへのストレスを低減します。「[絶対最大定格](#)」に指定されている高品質の 2.2nF X7R セラミック ブートストラップ コンデンサを選択します。これより大きい容量を選択すると、内部 VCC レギュレータにストレスがかかり、デバイスが損傷する可能性があります。

す。内部ブートストラップダイオードは VCC から BST に接続し、スイッチノード電圧が低いときにハイサイドゲートドライブブートストラップコンデンサの電荷を補充します。

### 7.3.3 内部ソフトスタート

LM5168E は、ソフトスタート制御ランプを内蔵しており、出力電圧を定常状態の動作点に徐々に到達させることで、起動時ストレスと電流サージを低減できます。ソフトスタート機能により、制御された単調な出力電圧スタートアップが生成されます。ソフトスタート時間は内部的に 3ms に設定されています。

### 7.3.4 オン時間ジェネレータ

LM5168E ハイサイド FET のオン時間は  $R_T$  抵抗によって決定され、入力電圧  $V_{IN}$  に反比例します。 $V_{IN}$  の反比例により、 $V_{IN}$  が変化すると、周波数はほぼ一定になります。セクション 7.3.4 を使用してオン時間を計算します。ここで、 $R_T$  は kΩ 単位です。

$$T_{ON} = \frac{R_T}{2.5 \times V_{IN}} \quad (9)$$

式 10 を使用して  $R_T$  抵抗を決定し、CCM で特定のスイッチング周波数を設定します。 $F_{SW}$  は kHz 単位です。

$$R_T = \frac{2500 \times V_{OUT}}{F_{SW}} \text{ [k}\Omega\text{]} \quad (10)$$

適切な降圧動作を実現するために、最小オン時間(最大  $V_{IN}$ )が 50ns を超える  $R_T$  を選択します。この最小オン時間に加えて、このデバイスの最大周波数は 1MHz に制限されます。

### 7.3.5 電流制限

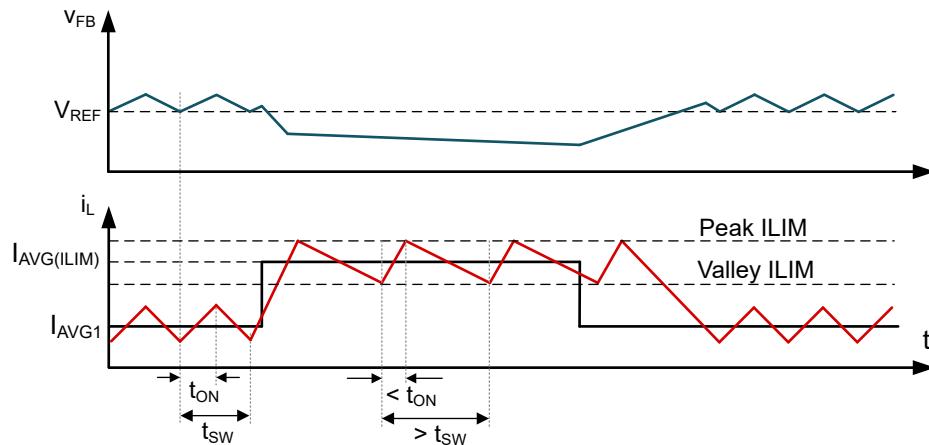

LM5168E は、ピークインダクタ電流をサイクルごとに制限することで過電流状態を管理します。ハイサイド MOSFET で検出された電流は、スイッチングサイクルごとに電流制限スレッショルド(標準値 0.42A)と比較されます。電流暴走の可能性からコンバータを保護するため、LM5168E は 0.34A に設定されたフォールドバックバレー電流制限機能を備えており、ピーク電流制限が検出された場合に有効になります。図 7-1 に示されているように、LM5168E のハイサイド MOSFET のピーク電流が 0.42A(標準値)を超えると、プログラムされたオン時間( $t_{ON}$ )に関係なく、現在のサイクルが直ちに終了し、ハイサイド MOSFET がオフになり、フォールドバックバレー電流制限が作動します。ローサイド MOSFET は、インダクタ電流がこのフォールドバックバレー電流制限値を下回るまでオンのままで、その後で次のオンパルスが開始されます。この方式は、過熱を防止するためにスイッチング周波数をフォールドバックし、LM5168E では平均出力電流を 0.3A 未満に制限して、適切な短絡および重負荷保護を提供します。

図 7-1. 電流制限のタイミング図

ハイサイド MOSFET のターンオン遷移後、リーディング エッジのプランギング時間の後に電流が検出されます。電流制限コンパレータの伝播遅延は 100ns です。オン時間が 100ns 未満の高ステップダウン状態では、ローサイド MOSFET のバックアップ ピーク電流制限コンパレータも 0.42A に設定され、フォールドバック バレー電流制限が 0.34A に設定されるようになります。この電流制限方式により、非常に低いデューティ サイクルで動作できるため、大きな降圧電圧変換が可能になり、コンバータの堅牢な保護が保証されます。

LM5168E は電流制限オフタイマとヒップ保護を実装しています。ハイサイド MOSFET の電流が  $I_{HS\_PK(OC)}$  を超えると、ハイサイド MOSFET が直ちにオフになり、リセット不可能なオフタイマが開始されます。オフ時間の長さは、FB 電圧と入力電圧によって制御されます。ヒップ保護機能により、ソフトスタート カウンタにより、電流制限サイクル連続 16 の間過電流イベントが検出された後で、の出力電圧が適切に回復できるようになります。電流制限検出なしで連続 4 サイクル後、ヒップ保護カウンタを再起動します。デバイスは、64ms の「ヒップ期間」の後に、ソフトスタートを試みます。

### 7.3.6 N チャネル降圧スイッチおよびドライバ

LM5168E は、N チャネル降圧スイッチと関連するフローティング ハイサイド ゲートドライバを内蔵しています。このゲートドライバ回路は、外付けのブートストラップ コンデンサおよび内部の高電圧ブートストラップ ダイオードと連動して動作します。BST ピンと SW ピンの間に接続された高品質セラミック コンデンサは、降圧スイッチのオン時間中にハイサイド ドライバに電圧を供給します。制限事項については、[セクション 7.3.2](#) も参照してください。オフ時間中は、SW ピンが約 0V にプルダウンされ、ブートストラップ コンデンサは内部ブートストラップ ダイオードを経由して内部 VCC から充電されます。最小オフタイマを 50ns (標準値) に設定すると、各サイクルでブートストラップ コンデンサを再充電するための最小時間が確保されます。オン時間が 300ns 未満の場合、BST コンデンサが 1 サイクルで充電されるように、最小オフタイマは強制的に 250ns になります。この動作は、BST コンデンサが最も放電された可能性が高い状態で、スリープ モードからのウェークアップ時に非常に重要です。

### 7.3.7 同期整流器

LM5168E にはローサイド同期整流 N チャネル MOSFET が内蔵されており、ハイサイド MOSFET がオフになったときにインダクタ電流が流れるための低抵抗パスとなります。

同期整流器は、ダイオード エミュレーション モードで動作します。ダイオード エミュレーションにより、軽負荷状況でレギュレータはパルスをスキップ モードで動作できます。このモードでは、軽負荷時に平均スイッチング周波数が低下します。その結果、スイッチング損失と MOSFET ゲートドライバ損失 (どちらもスイッチング周波数に比例) を低減するため、軽負荷時の効率が向上します。このパルス スキップ モードでは、軽負荷時に従来の CCM に関する循環インダクタの電流と損失も低減されます。

### 7.3.8 イネーブル/低電圧誤動作防止 (EN/UVLO)

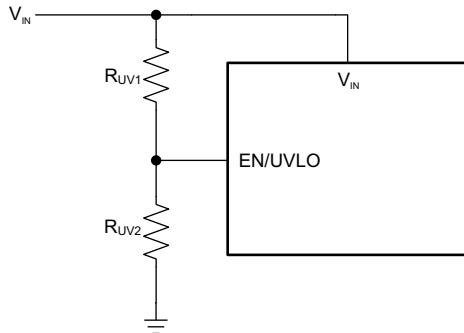

LM5168E には、デュアルレベル EN/UVLO 回路が含まれています。EN/UVLO 電圧が 0.45V (標準値) を下回ると、コンバータは低電流のシャットダウン モードになり、入力静止電流 ( $I_Q$ ) は 3µA まで低下します。電圧が 1.1V より高く、1.5V (標準値) を下回る場合、コンバータはスタンバイ モードになります。スタンバイ モードでは、制御回路がディスエーブルの間、内部バイアス レギュレータがアクティブです。電圧が立ち上がりスレッショルドの 1.5V (標準値) を超えると、通常動作が開始します。VIN と GND の間に分圧抵抗を取り付けて、レギュレータの最小動作電圧を設定します。入力電圧 UVLO の実装を希望する場合は [図 7-2](#)、[式 11](#)、および [式 12](#) の詳細を参照してください。通常、 $R_{UV1}$  の値を選択し、[式 11](#) を使用して目的の  $V_{ON}$  に基づいて  $R_{UV2}$  の値を計算します。 $R_{UV1}$  の妥当な値は 1MΩ の範囲です。次に、[式 12](#) を使用して結果として得られる  $V_{OFF}$  を計算します。 $V_{ON}$  と  $V_{OFF}$  は、それぞれデバイスがオンとオフを切り替える入力電圧です。

図 7-2. 入力 UVLO の接続

$$R_{UV2} = R_{UV1} \times \left( \frac{V_{EN(R)}}{V_{ON} - V_{EN(R)}} \right) \quad (11)$$

$$V_{OFF} = V_{EN(F)} \times \left( 1 + \frac{R_{UV1}}{R_{UV2}} \right) \quad (12)$$

入力 UVLO が不要な場合、EN/UVLO をロジック信号によって駆動されるイネーブル入力として駆動するか、VIN に直接接続できます。EN/UVLO が VIN に直接接続されている場合、レギュレータは、内部バイアスレールがアクティブになるとすぐにスイッチングを開始します。VIN で約 4.5V です。

### 7.3.9 パワー グッド (PGOOD)

LM5168E は、出力電圧がレギュレーション レベル内にあることを示す PGOOD インジケータ (PG) を備えています。PGOOD 信号は、下流コンバータの起動シーケンスや障害保護および出力監視に使用します。PGOOD は、14V 以下の DC 電源へのプルアップ抵抗を必要とするオーピンドレイン出力です。プルアップ抵抗の標準範囲は 10kΩ から 100kΩ です。必要に応じて、高い電圧プルアップ レールからの電圧を下げるために、抵抗分圧器を使用します。FB 電圧が内部リファレンス  $V_{REF}$  の 95% を超えると、内部 PGOOD スイッチがオフになり、外部プルアップにより PGOOD が high にプルアップされます。FB 電圧が  $V_{REF}$  の 90% を下回ると、内部の 7Ω PGOOD スイッチがオンになり、PGOOD が low にプルされて、出力電圧が安定化範囲を外れたことを示します。PGOOD の立ち上がりエッジには、5μs のグリッチ除去遅延が組み込まれています。

### 7.3.10 過熱保護

LM5168E には、通常の接合部温度よりも高くなった場合にデバイスを保護するため、接合部温度モニタが内蔵されています。接合部温度が 175°C (標準値) を超えると、それ以上の電力消費および温度上昇を防ぐためにサーマル シャットダウンが発生します。LM5168E は、10°C の標準的なサーマル シャットダウン ヒステリシスに基づいて、接合部温度が 165°C に低下すると再起動シーケンスを開始します。この保護は非ラッチ保護の役割を果たしているため、障害が継続している場合は、デバイスはサーマル シャットダウン状態の開始と終了を繰り返します。

## 7.4 デバイスの機能モード

### 7.4.1 シャットダウンモード

EN/UVLO は、LM5168E のオン/オフを制御します。 $V_{EN/UVLO}$  が約 0.45V を下回ると、デバイスはシャットダウン モードになります。内部 VCC サブレギュレータとスイッチング レギュレータの両方がオフになります。シャットダウン モードでの静止電流は、 $V_{IN} = 24V$  で  $3\mu A$  まで低下します。LM5168E は内部バイアス レールの低電圧保護も採用しています。入力電圧が約 4.5V 未満の場合、レギュレータはオフのままになります。

### 7.4.2 アクティブモード

LM5168E は、 $V_{EN/UVLO}$  が高精度有効化スレッショルドを超えており、内部バイアス レールが UV スレッショルドを超えている場合にアクティブ モードになります。COT アクティブ モードでは、LM5168E は負荷電流に応じて、次のいずれかのモードになります。

1. 負荷電流がピークツーピーク インダクタ電流リップルの半分を超える場合の固定スイッチング周波数による CCM

2. 自動モード (P デバイス指定子) — 軽負荷動作: CCM 動作時に負荷電流がピークツーピークのインダクタ電流リップルの半分未満の場合は、パルス スキップとダイオード エミュレーション モード (DEM) になります。

3. 出力に過電流状態が印加された際のピークおよびバレー電流制限保護付きの電流制限 CCM

### 7.4.3 スリープモード

制御アーキテクチャでは、LM5168E ダイオード エミュレーション モード (DEM) 機能について簡単に説明します。軽負荷状態において、インダクタ電流がゼロに減衰し、同期 MOSFET がオフになると、コンバータは DEM に移行して、システムに負の電流を防止します。DEM 状態では、負荷電流はピークツーピーク インダクタ リップル電流の半分未満になり、デバイスがパルス スキップ モードで動作するため、負荷がさらに減少するとスイッチング周波数は低下します。 $V_{FB}$  が 1.2V を下回ると、スイッチング パルスが設定されます。

動作周波数が減少し、 $V_{FB}$  が 1.2V ( $V_{REF}$ ) を超えて負荷電流を供給する出力コンデンサが  $15\mu s$  を超えると、コンバータは超低  $I_Q$  スリープ モードに移行して、入力電源が消費されないようにします。LM5168E で必要とされる入力静止電流 ( $I_Q$ ) は、スリープ モードでは  $10\mu A$  まで減少し、レギュレータの軽負荷効率を向上させます。このモードでは、デバイスの消費電流を非常に低くするため、すべての内部コントローラ回路がオフになります。このように  $I_Q$  が低いため、M5168E は、バッテリ直結型アプリケーションで動作寿命を延ばすための最適な選択肢となります。FB コンバータと内部バイアス レールがアクティブになり、FB 電圧が内部リファレンス  $V_{REF}$  を下回ったときに、コンバータがスリープ モードからアクティブ モードへ移行することを検出します。スリープからアクティブ状態への  $9\mu s$  ウエークアップ遅延があります。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インストルメンツの製品仕様に含まれるものではなく、テキサス・インストルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

LM5168E では、広範囲の電源電圧から固定出力電圧に降圧する降圧コンバータを作成するために、わずかな外部コンポーネントのみが必要です。このデバイスには、システム設計要件を満たすため、以下を含む複数の機能が内蔵されています。

- 高精度のイネーブル

- 入力電圧 UVLO

- 内部ソフトスタート

- プログラマブルなスイッチング周波数

- PGOOD インジケータ

LM5168E ベースのコンバータの設計プロセスを迅速化および合理化するために、設計者が特定のアプリケーションでコンポーネントを選択できるように、包括的な LM5168E クイック スタート計算ツールをダウンロードできます。このツールを補完するために、評価基板と PSPICE モデルを提供しています。

## 8.2 代表的な降圧アプリケーション

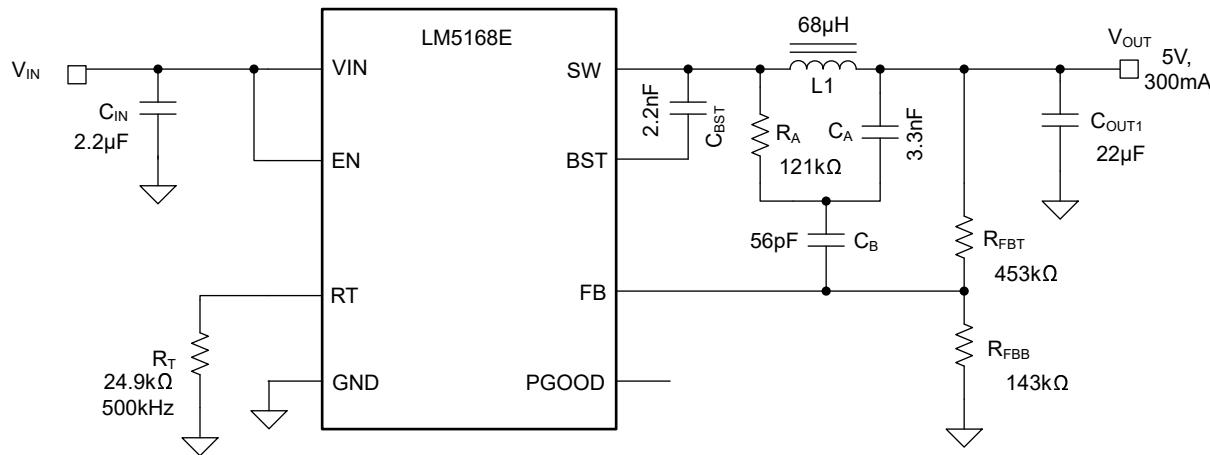

LM5168E は、軽負荷 PFM で動作する DEM モードで動作することにより、降圧アプリケーション向けに設計されています。図 8-1 に、LM5168E を使用した 300mA 負荷電流を供給可能な 5V 出力の降圧レギュレータの回路図を示します。

図 8-1. 降圧コンバータの回路図の例

### 注

このデータシートでは、静電容量の 実効値は、定格値や銘板値ではなく、D.C. バイアスおよび温度における実際の容量として定義されます。X5R 以上の誘電体を使用した、高品質で低 ESR のセラミックコンデンサを全体にわたって使用してください。値の大きいセラミックコンデンサは、すべて、通常の許容誤差と温度効果に加えて、電圧係数が大きくなります。DC バイアスを印加すると、静電容量は大幅に低下します。この点については、ケース サイズが大きく、より高い電圧定格のものが望ましいです。これらの影響を軽減するために、複数のコンデンサを並列に使用すれば、最小実効静電容量を必要な値まで大きくすることができます。この対策により、個別のコンデンサの RMS 電流要件も緩和されます。実効静電容量の最小値を確実に実現するために、コンデンサ バンクのバイアスおよび温度変動を慎重に検討する必要があります。

## 8.2.1 設計要件

表 8-1 に、LM5168E を使用した代表的な降圧アプリケーションの設計要件を示します。

表 8-1. 詳細設計パラメータ

| 設計パラメータ   | 数値の例       |

|-----------|------------|

| 公称入力電圧    | 24V        |

| 入力電圧範囲    | 12V ~ 115V |

| 出力電圧      | 5V         |

| 出力電流      | 0.3A       |

| スイッチング周波数 | 500kHz     |

## 8.2.2 詳細な設計手順

### 8.2.2.1 スイッチング周波数 ( $R_T$ )

LM5168E のスイッチング周波数は、 $R_T$  ピンに接続されたオン時間プログラミング抵抗によって設定されます。目的のスイッチング周波数と出力電圧に基づいて  $R_T$  を計算するには、式 13 を使用します。500kHz のスイッチング周波数、5V 出力の場合、24.9kΩ 抵抗を使用します。

$$R_T (k\Omega) = \frac{V_{OUT} \times 2500}{F_{SW} (\text{kHz})} \quad (13)$$

デューティ サイクルが非常に低い場合、ハイサイド MOSFET の 50ns の最小制御可能オン時間  $t_{ON(\min)}$  により、最大スイッチング周波数が制限されることに注意します。CCM では、 $t_{ON(\min)}$  により、指定されたスイッチング周波数に対する電圧変換の降圧比が制限されます。制御可能な最小デューティ サイクルを計算するには、式 14 を使用します。

$$D_{MIN} = t_{ON(\min)} \times F_{SW} \quad (14)$$

最終的に、与えられた出力電圧に対するスイッチング周波数の選択は、利用可能な入力電圧範囲、設計サイズ、および効率に影響を与えます。全スイッチング周波数を維持するため、与えられた  $t_{ON(\min)}$  に対する最大電源電圧を計算するには、式 15 を使用します。

$$V_{IN(max)} = \frac{V_{OUT}}{t_{ON(\min)} \times F_{SW}} \quad (15)$$

### 8.2.2.2 降圧インダクタの選択

ほとんどのアプリケーションでは、インダクタのリップル電流  $\Delta I_L$  が公称入力電圧での定格負荷電流の 30% ~ 50% になるようにインダクタンスを選択します。インダクタンスを計算するには、式 16 を使用します。この例では、 $V_{IN} = 24V$ 、 $F_{SW} = 500\text{kHz}$ 、リップル電流を 30%、0.3A と仮定しています。その結果、およそ 65μH のインダクタンスが得られます。この設計では、68μH として最も近い標準値を選択します。次に、式 17 を使用して、入力電圧範囲全体にわたる実際のインダクタリップル電流を計算します。最後に、式 18 を使用して最大入力電圧でのピークインダクタ電流を決定し、LM5168E の電流制限と比較します。 $V_{IN} = 115V$  に、約 0.37A のピーク電流が生じます。これは、LM5168E の電流制限を下回っています。

$$L = \frac{V_{OUT}}{F_{SW} \times \Delta I_L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \quad (16)$$

$$\Delta I_L = \frac{V_{OUT}}{F_{SW} \times L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \quad (17)$$

$$I_{L(peak)} = I_{OUT} + \frac{\Delta I_L}{2} \quad (18)$$

理想的には、インダクタの飽和電流定格は、少なくともピーク電流制限と同じ大きさです。この大きさであれば、出力の短絡時にもインダクタが飽和しないようになります。インダクタのコア材が飽和すると、インダクタンスは非常に小さい値に低下し、インダクタ電流は急増します。バレー電流制限値は、電流が暴走しづらいように設計されているとはいっても、インダクタが飽和することで電流値が急増する可能性があります。この増加は部品の損傷につながる可能性があります。したがって、インダクタを飽和させないようにしてください。フェライトコア材を採用したインダクタは飽和特性が非常に急峻ですが、コア損失は通常、圧粉コアよりも小さいです。圧粉コアは穏やかな飽和特性を示すため、インダクタの電流定格をある程度緩和できます。ただし、圧粉コアは約 1MHz を超える周波数でコア損失が大きくなります。いずれにしても、インダクタの飽和電流が、全負荷時のピークインダクタ電流の最大値よりも小さくならないようにする必要があります。

### 8.2.2.3 出力電圧の設定

LM5168E は、FB 電圧を内部基準電圧 ( $V_{REF} = 1.2V$  [標準値]) と同じ値に維持することで、出力電圧をレギュレートします。抵抗デバイダを使用して、式 19 に基づいて出力電圧をプログラムします。

$$R_{FBT} = R_{FBB} \times \left( \frac{V_{OUT}}{V_{REF}} - 1 \right) \quad (19)$$

TI は、ほとんどのアプリケーションに  $10k\Omega \sim 1M\Omega$  の範囲の  $R_{FBB}$  を選択することを推奨しています。 $R_{FBB}$  が大きいほど、消費される DC 電流が少なくなります。軽負荷時の効率が重要な場合、この抵抗値を大きくすることは必須です。フィードバック パスがノイズの影響を受けやすくなるため、TI は  $1M\Omega$  を超える  $R_{FBB}$  は推奨しません。この例では、 $R_{FBB} = 143k\Omega$  を選択しています。この動作により、 $R_{FBT} = 453k\Omega$  が得られます。帰還パターンは PCB のノイズの多い領域から離して配線し、帰還抵抗を FB ピンの近くに配置します。

### 8.2.2.4 タイプ 3 リップルネットワーク

この例では、タイプ 3 リップル注入ネットワークを使用します。このネットワークは、SW と  $V_{OUT}$  の間に  $R_A$  と  $C_A$  で構成される RC フィルタを使用して、インダクタ電流と位相が一致する三角波ランプを生成します。この三角波ランプは、コンデンサ  $C_B$  を介して帰還ノードに AC 結合されます。タイプ 3 リップル注入は、出力電圧リップルが低いことが重要なアプリケーションに最適な選択肢で、低 ESR のセラミック出力コンデンサを使用できます。

式 20 を使用して  $C_A$  を計算します。この例で使用している値を使用すると、 $C_A > 184pF$  となります。 $R_A$  を実用的な制限範囲内に維持するため、 $3300pF$  の値が選択されています。一般に、信頼性の高い動作を実現するためには、フィードバックピンで  $20mV$  のリップルが必要です。このリップルは公称入力電圧で計算されます。最小入力電圧においてリップルの最小値が  $12mV$  以上である必要があります。公称入力電圧で式 21 を使用して、 $R_A > 120k\Omega$  の値を求め、 $121k\Omega$  の値を選択しています。

$$C_A \geq \frac{10}{F_{SW} \times (R_{FBB} || R_{FBT})} \quad (20)$$

$$R_A \leq \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{0.02 \times V_{IN} \times F_{SW} \times C_A} \quad (21)$$

生成されるリップルの大きさは出力電圧リップルに影響を与えませんが、この大きさにより、生成されるリップルの振幅の約半分の DC 誤差が発生し、帰還分圧比でスケーリングされます。したがって、出力電圧で許容される DC オフセットの量により、帰還リップルに上限が生じます。

最後に、式 22 を使用して、カップリング容量  $C_B$  を計算します。式で、 $t_R$  は負荷過渡の外乱に対する制御ループのセーリング時間の概算です。これは  $50\mu s$  とみなされます。

$$C_B \geq \frac{t_R}{3 \times R_{FBT}} \quad (22)$$

ここで、

- $t_R = 50\mu s$  (標準値)

この例では、 $C_B$  に対して  $37\text{pF}$  より大きい値が計算され、 $56\text{pF}$  の値が選択されています。この値により、軽負荷動作時に、スリープ間隔中に帰還抵抗による過剰なカッピング コンデンサ放電を防止できます。 $C_B$  の最小値は  $47\text{pF}$  であることに注意してください。

### 8.2.2.5 出力コンデンサの選択

タイプ 3 リップル注入ネットワークにより小型の低 ESR セラミック出力コンデンサを使用可能となりリップル インジェクション ネットワークによりレギュレーションコンパレータに適切な信号を供給できます。

出力容量の値を選択する方法の 1 つは、式 23 を使用することです。この式では、指定された負荷電流過渡と出力電圧過渡に基づいて、出力コンデンサのサイズを決定します。

$$C_{OUT} > \frac{L \times \left( I_{OUT} + \frac{\Delta I_L}{2} \right)^2}{2 \times \Delta V \times V_{OUT}} \quad (23)$$

ここで

- $\Delta V$  = 負荷過渡時のル出力電流の変更。

- $\Delta I_L$  = 式 17 からのインダクタリップル電流

この例では、 $300\text{mA}$  の全負荷過渡に対して  $\Delta V = 50\text{mV}$  と指定します。式 18 を使用して  $I_{peak}$  を計算します。 $C_{OUT}$  が約  $17\mu\text{F}$  以上になります。セラミック コンデンサの電圧係数を考慮して、 $X7R$  誘電体を備えた  $22\mu\text{F}$ 、 $25\text{V}$  定格のコンデンサを選択します。負荷過渡を低減したり、出力電圧リップルを低減したりするため、より大きな出力容量を使用できます。最小出力容量は  $2.2\mu\text{F}$  より大きくなければならないことを念頭に置いてください。出力コンデンサの ESR が支配的ではないと仮定して、式 24 を使用してスイッチング周波数の出力リップルを推定します。

$$V_r \geq \frac{\Delta I_L}{8 \times F_{SW} \times C_{OUT}} \quad (24)$$

この場合:

- $V_r$  = スイッチング周波数におけるピークツーピークの出力電圧リップル

- $\Delta I_L$  = 式 17 からのインダクタリップル電流

### 8.2.2.6 入力コンデンサに関する検討事項

セラミック入力コンデンサは、レギュレータに低インピーダンス ソースを供給するだけでなく、リップル電流を供給して、他の回路からスイッチング ノイズを絶縁します。LM5168E レギュレータの入力には、**VIN** と **GND** 間に直接接続された最低  $2.2\mu\text{F}$  のセラミックコンデンサが必要です。これは、少なくともアプリケーションが必要とする最大入力電圧を定格とする必要があり、可能であれば、最大入力電圧の 2 倍が推奨されます。この容量を増やすことで、入力電圧リップルを低減し、負荷過渡時の入力電圧を維持できます。出力電流が大きくなると、より大きな入力容量が必要になります。 $2.2\mu\text{F}$  の値は、すべてのディレーティングが適用された後の実際の値になることに注意してください。この例では、電圧ディレーティングを考慮して、4 つの  $1\mu\text{F}$ 、 $250\text{V}$ 、 $X7R$  (またはそれ以上) のセラミックコンデンサが選択されています。より大きいケースサイズ、より高い電圧のコンデンサ、またはその両方を使用することができる場合、総数を減らすことができます。入力電圧範囲を狭い設計では、低電圧定格のコンデンサを使用できます。

多くの場合、入力にセラミックと並列に電解コンデンサを使用することが推奨されます。この方法は、長い配線またはパターン (約  $5\text{cm}$  以上) を使って入力電源をレギュレータに接続する場合に特に当てはまります。このコンデンサに中程度の ESR を持つコンデンサを使うことは、長い電源配線によって生じる入力電源のリンクギングを減衰させるのに有効です。この追加コンデンサの使用は、インピーダンスの非常に高い入力電源によって生じる電圧低下の防止にも有効です。

入力スイッチング電流のほとんどは、セラミック入力コンデンサを流れます。式 25 を使用して、おおよその RMS 電流を計算します。この値は、メーカーの最大定格に照らしてチェックする必要があります。

$$I_{RMS} \cong \frac{I_{OUT}}{2} \quad (25)$$

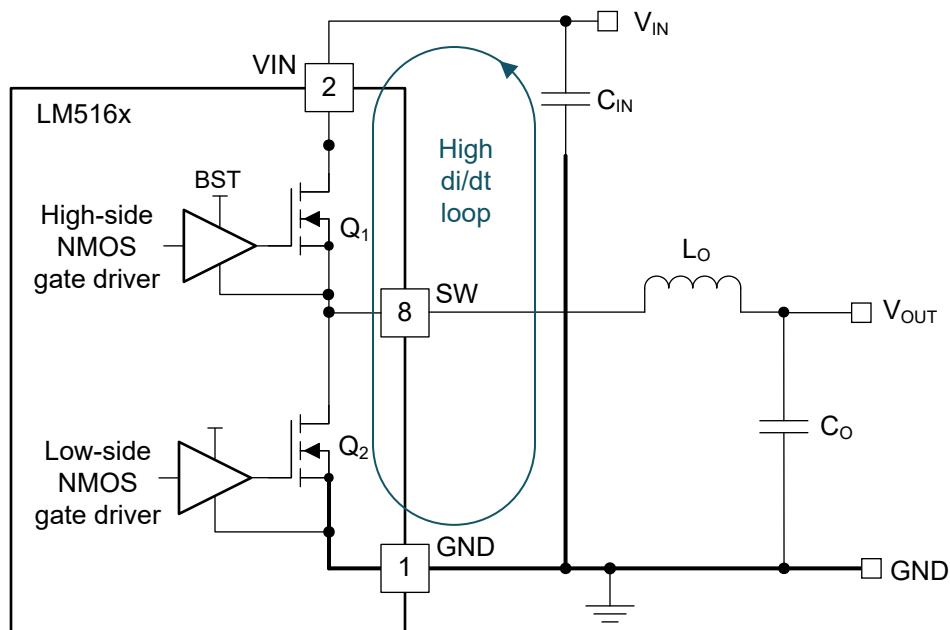

入力コンデンサは、 $di/dt$  の大きい電流ループの一部です。大きい  $di/dt$  電流と、IC と入力コンデンサの間の過剰な寄生インダクタンスの組み合わせにより、IC の SW ノードで過剰な電圧リングが発生する可能性があります。ボード上の入力コンデンサの配置は、高  $di/dt$  ループ内の寄生インダクタンスを最小化し、それに従って各スイッチング遷移における SW ノードのリングを最小化するうえで非常に重要です。

レギュレータの最大動作電圧を目標とする設計の場合は、SW ノードのリングがデバイスの絶対最大定格を超えないようにしてください。SW ノードのリングは、入力コンデンサが IC を基準として適切に配置されているかどうかに関係します。入力コンデンサの適切な配置については、図 8-28 の PCB レイアウト例を参照してください。

#### 8.2.2.7 $C_{BST}$ の選択

LM5168E では、BST と SW の間にブーストストラップ コンデンサを接続する必要があります。このコンデンサは、ハイサイド MOSFET のゲートドライバに電力を供給するために使用するエネルギーを蓄積します。高品質の 2.2nF セラミックタイプが必要です。コンデンサの DC バイアスのディレーティングを必ず考慮してください。 $C_{BST}$  の値は、2.5nF を超えないようにしてください。

#### 8.2.2.8 設計サマリ例

上記の設計手順は、LM5168E を使用して降圧レギュレータを作成するために必要な一般的な手順です。LM5168E を使用して降圧レギュレータを設計する別の例については、『LM5168PEVM ユーザー ガイド』を参照してください。COT 降圧コンバータの設計の詳細については、「[関連資料](#)」を参照してください。

### 8.2.3 アプリケーション曲線

このセクションの曲線は、LM5168E を使用して測定したものです。特に記述のない限り、次の条件が適用されます。 $T_A = 25^\circ\text{C}$ 。

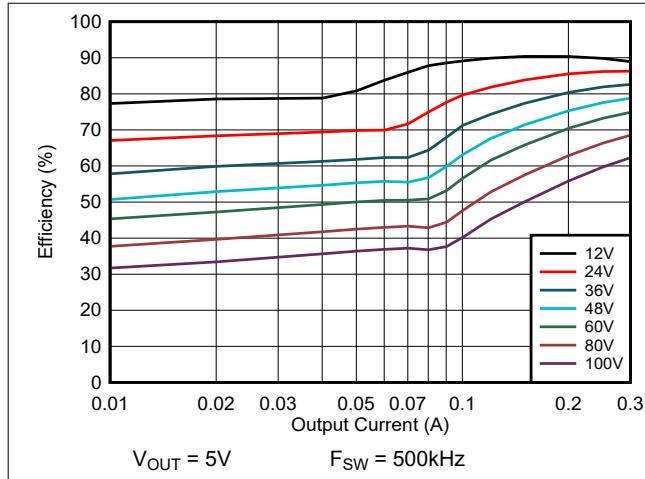

図 8-2. 効率： $V_{\text{OUT}} = 5\text{V}$

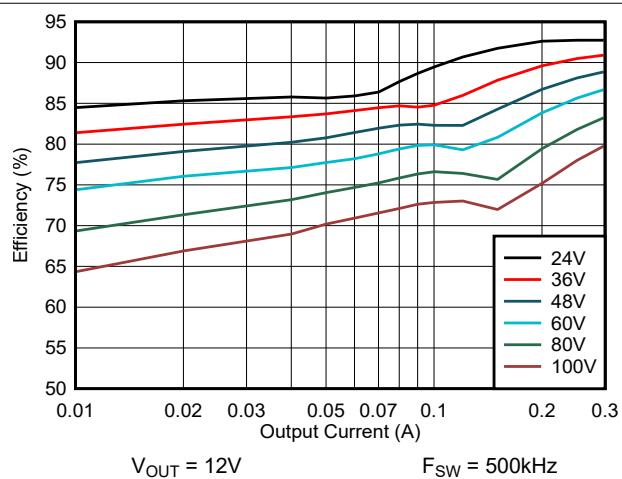

図 8-3. 効率： $V_{\text{OUT}} = 12\text{V}$

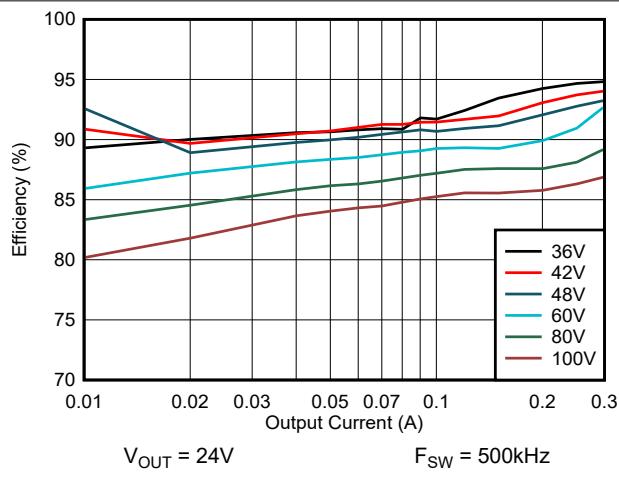

図 8-4. 効率： $V_{\text{OUT}} = 24\text{V}$

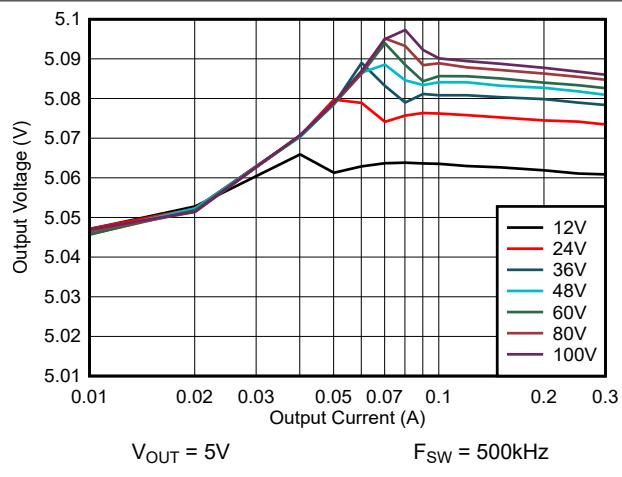

図 8-5. ラインおよびロード レギュレーション： $V_{\text{OUT}} = 5\text{V}$

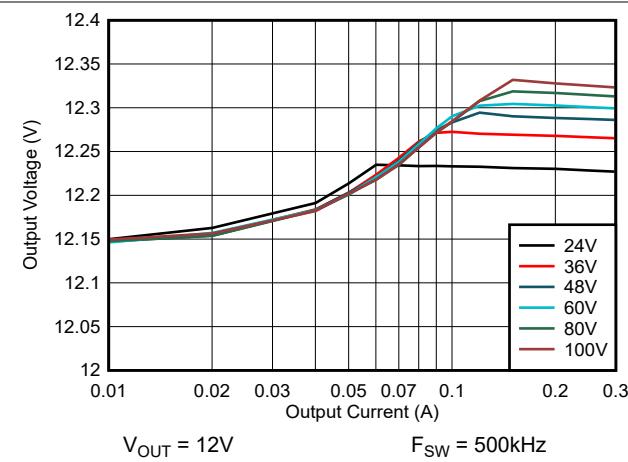

図 8-6. ラインおよびロード レギュレーション:  $V_{OUT} = 12V$

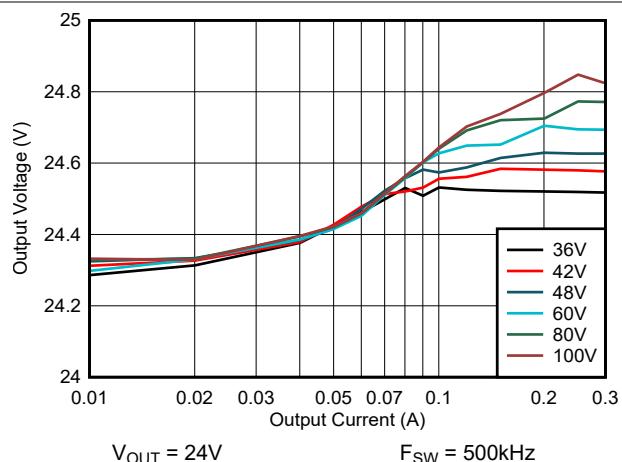

図 8-7. ラインおよびロード レギュレーション:  $V_{OUT} = 24V$

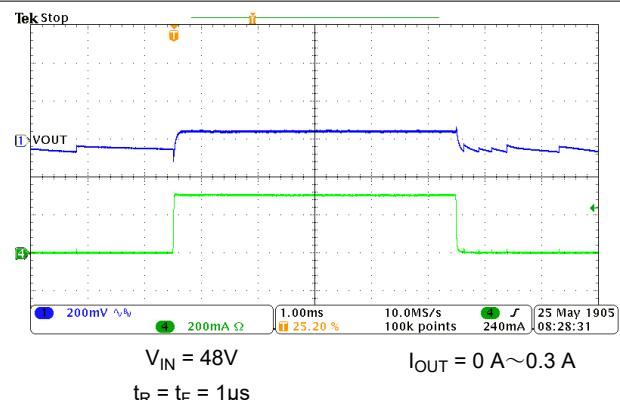

図 8-8. 負荷過渡:  $V_{OUT} = 5V$

図 8-9. 負荷過渡:  $V_{OUT} = 5V$

図 8-10. 負荷過渡:  $V_{OUT} = 12V$

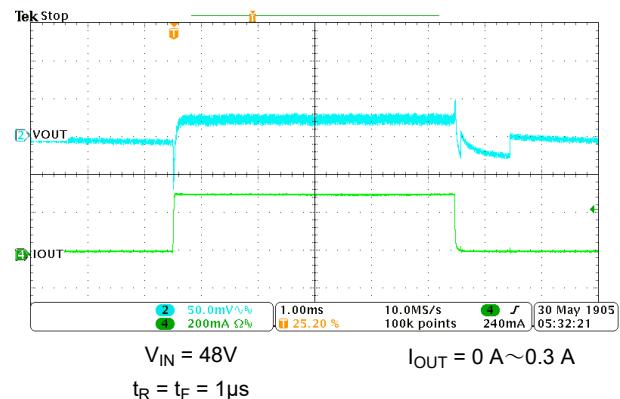

図 8-11. 負荷過渡:  $V_{OUT} = 12V$

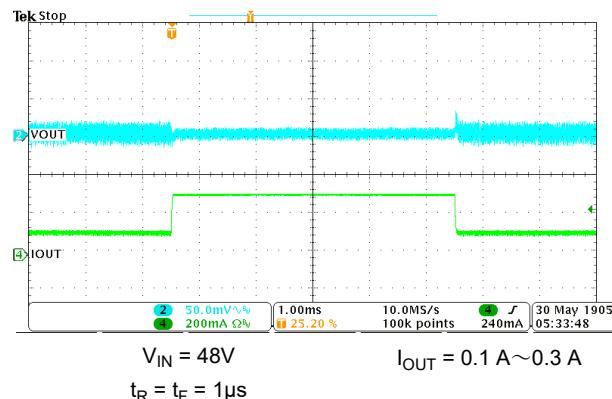

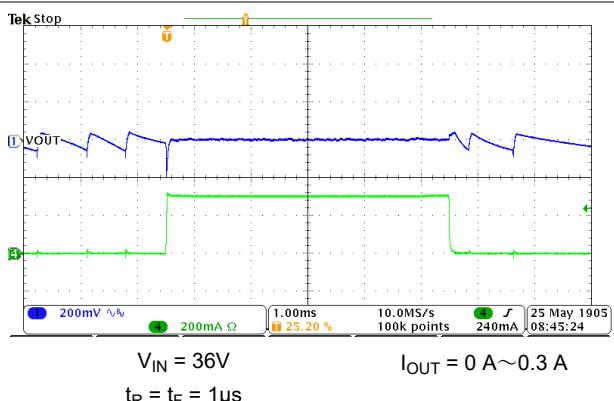

図 8-12. 負荷過渡 :  $V_{OUT} = 12V$

図 8-13. 負荷過渡 :  $V_{OUT} = 24V$

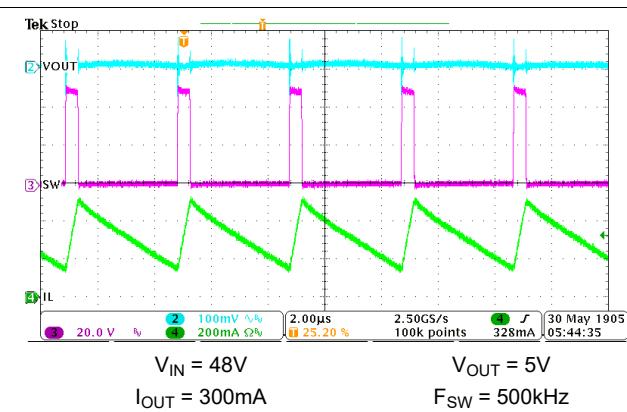

図 8-14. 代表的なスイッチング波形

図 8-15. 代表的なスイッチング波形

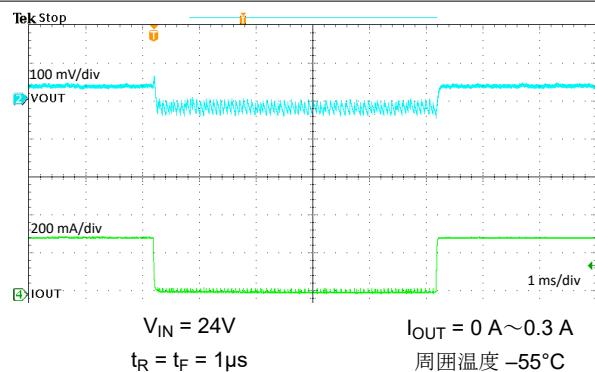

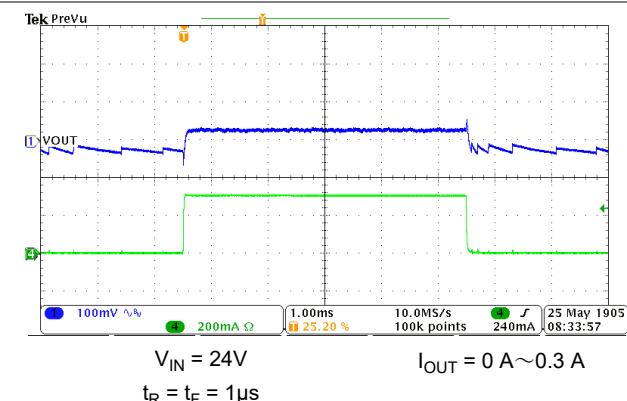

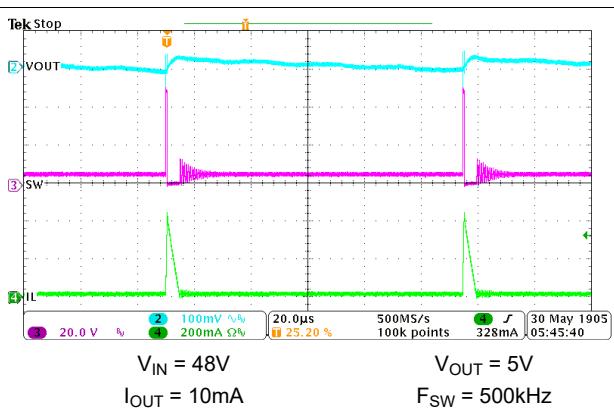

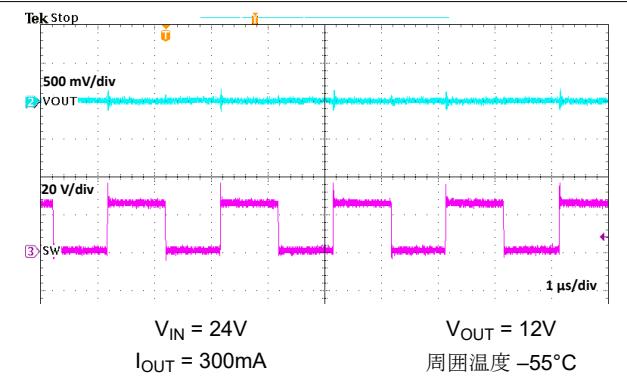

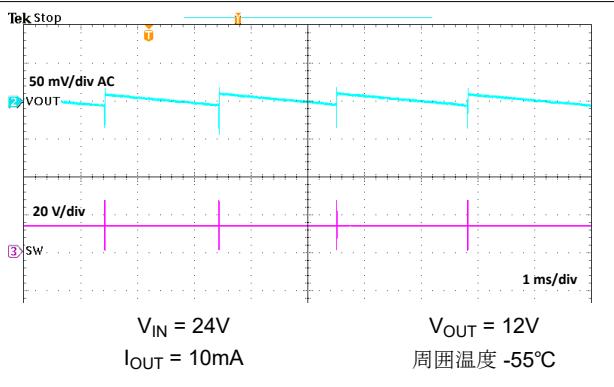

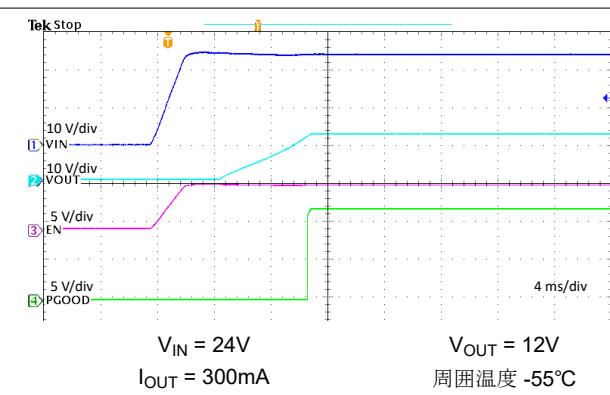

図 8-16. 代表的な拡張温度スイッチング波形

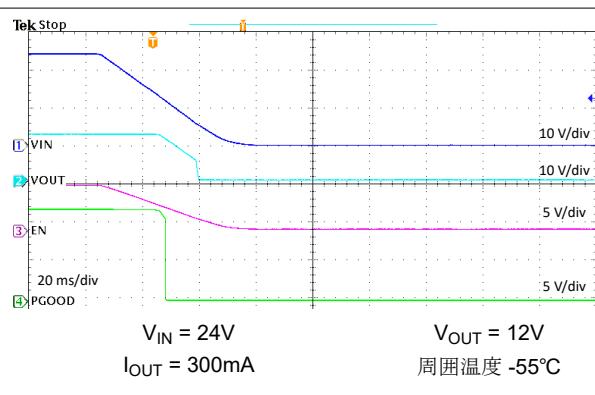

図 8-17. 代表的な拡張温度スイッチング波形

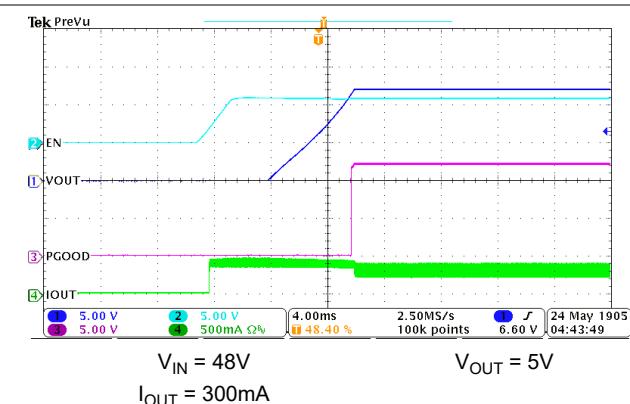

図 8-18. 代表的なスタートアップ波形

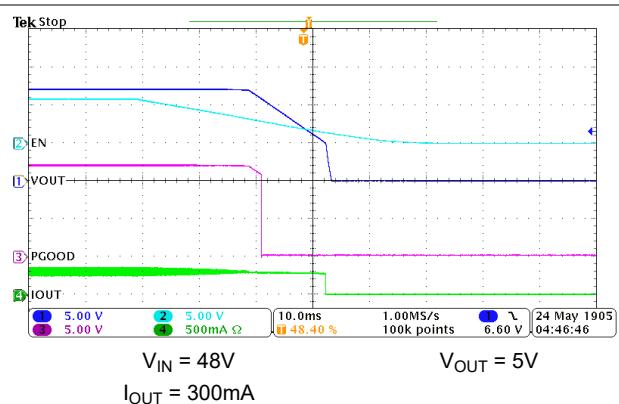

図 8-19. 代表的なシャットダウン波形

図 8-20. 代表的な拡張温度スタートアップ波形

図 8-21. 代表的な拡張温度シャットダウン波形

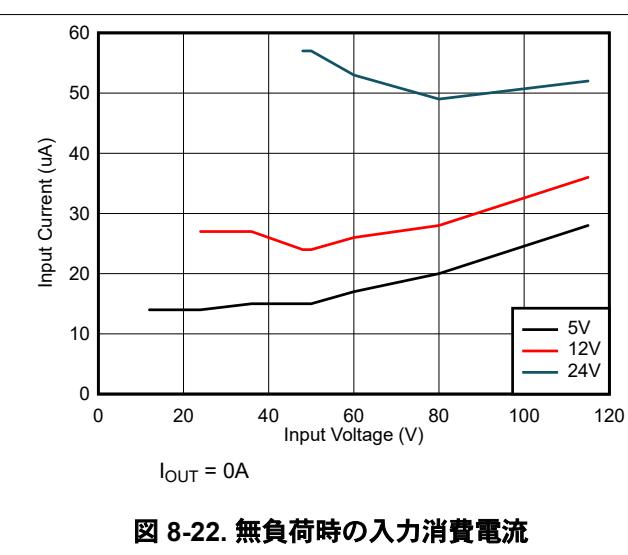

図 8-22. 無負荷時の入力消費電流

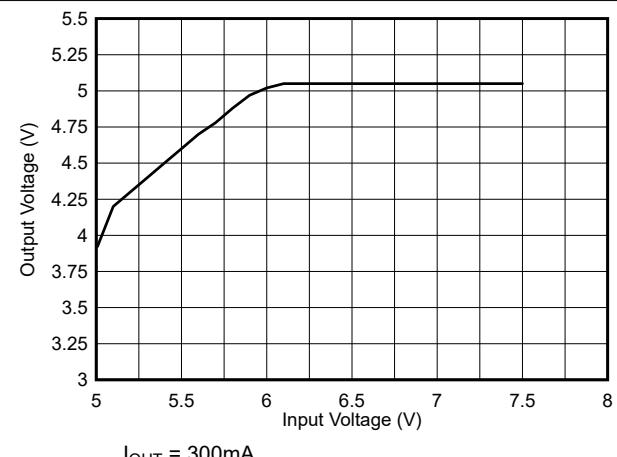

図 8-23. ドロップアウト応答

表 8-2. アプリケーションの特性曲線で使われた BOM

| $V_{OUT}$ | $R_A$         | $R_{FBB}$      | $R_{FBT}$     | $C_A$  | $C_B$ | $C_{OUT}$          | $L$                        |

|-----------|---------------|----------------|---------------|--------|-------|--------------------|----------------------------|

| 5V        | 121k $\Omega$ | 143k $\Omega$  | 453k $\Omega$ | 3300pF | 56pF  | $2 \times 22\mu F$ | 68 $\mu H$ , 0.17 $\Omega$ |

| 12V       | 182k $\Omega$ | 49.9k $\Omega$ | 453k $\Omega$ | 3300pF | 56pF  | $2 \times 22\mu F$ | 68 $\mu H$ , 0.17 $\Omega$ |

| 24V       | 243k $\Omega$ | 23.7k $\Omega$ | 453k $\Omega$ | 3300pF | 56pF  | $2 \times 22\mu F$ | 68 $\mu H$ , 0.17 $\Omega$ |

## 8.3 電源に関する推奨事項

LM5168E 降圧コンバータは、6V ~ 115V の広い入力電圧範囲で動作するように設計されています。入力電源の特性は、「[絶対最大定格](#)」表と「[推奨動作条件](#)」表に適合している必要があります。また、入力電源は、全負荷時のレギュレータに必要な入力電流を供給できる必要があります。平均入力電流を見積るには、式 26 を使用します。

$$I_{IN} = \frac{V_{OUT} \times I_{OUT}}{V_{IN} \times \eta} \quad (26)$$

ここで、

$\eta$  = 効率

コンバータが高インピーダンスを持つ長い配線や PCB パターンを経由して入力電源に接続されている場合、入力ケーブルの寄生インダクタンスと抵抗はコンバータの動作に悪影響を及ぼす可能性があります。寄生インダクタンスと低 ESR セラミック入力コンデンサを組み合わせることで、不足減衰共振回路が形成されます。この回路は、入力電源がオンとオフを周期的に切り替わるたびに、VIN で過電圧過渡が発生する可能性があります。寄生抵抗により、負荷過渡中に入力電圧が低下する場合があります。コンバーターが最小入力電圧に近い値で動作している場合、この低下によって UVLO フォルトが誤って起動され、システムがリセットされる可能性があります。こうした問題を解決する最善策は、入力電源からレギュレータまでの距離を短くして、セラミックと並列にアルミニウム電解入力コンデンサを使用することです。電解コンデンサの ESR は比較的低いため、入力共振回路は減衰し、電圧オーバーシュートを低減することができます。標準 ESR が 0.5Ω の 10μF 電解コンデンサは、ほとんどの入力回路構成で十分な減衰を実現します。

レギュレータの前に EMI 入力フィルタを使用することがあります。ただし、設計に留意しなければ、これにより不安定な状態が起きる、または前述のような影響を及ぼすおそれがあります。[『AN-2162 DC/DC コンバータ向け伝導 EMI の簡単な成功事例』](#)アプリケーションノートでは、スイッチングレギュレータの入力フィルタを設計する際に役立つ提案を紹介しています。

## 8.4 レイアウト

### 8.4.1 レイアウトのガイドライン

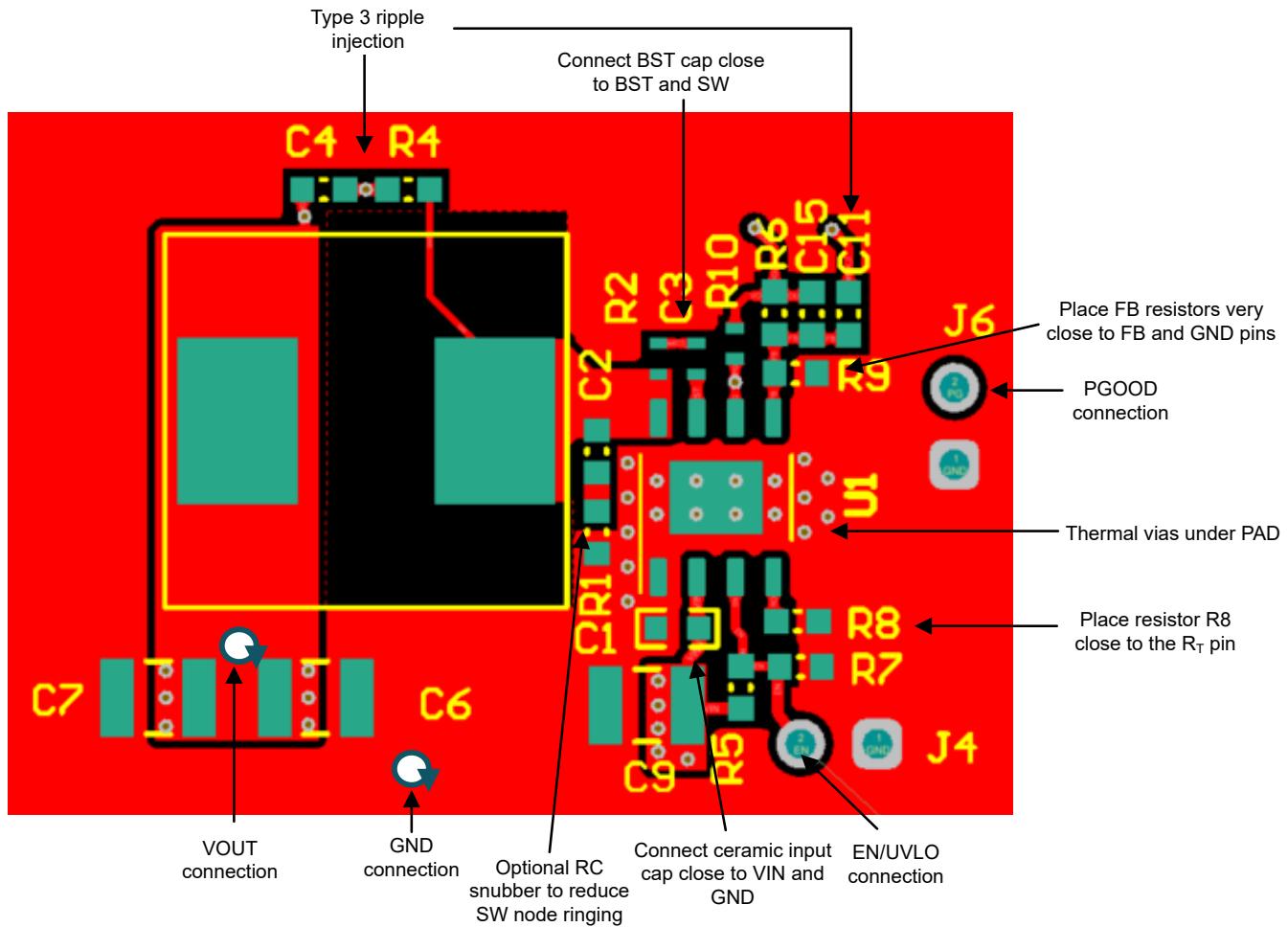

PCB レイアウトは、優れた電源設計のために重要な要素です。高スルーレートの電流や電圧を伝導するパスが複数存在し、これらが浮遊インダクタンスや寄生容量と相互作用してノイズや EMI を生成したり、電源のパフォーマンスを低下させたりする可能性があります。

- これらの問題をなくすため、高品質誘電体を使用した低 ESR のセラミックバイパスコンデンサを使用して VIN ピンを GND にバイパスします。C<sub>IN</sub> を LM5168E の VIN ピンと GND ピンにできるだけ近づけて配置します。入力コンデンサと出力コンデンサの両方の接地は、GND ピンと GND PAD に接続する局所的な上側プレーンで構成する必要があります。

- VIN および GND ピンへの入力コンデンサ接続によって形成されるループの面積を最小限に抑えます。入力コンデンサは、di/dt の大きい電流ループの一部です。大きい di/dt 電流と、IC と入力コンデンサの間の過剰な寄生インダクタンスの組み合わせにより、IC の SW ノードで過剰な電圧リンギングが発生する可能性があります。ボード上の入力コンデンサの配置は、高 di/dt ループ内の寄生インダクタンスを最小化し、それに従って各スイッチングにおける SW ノードのリンギングを最小化するうえで非常に重要です。レギュレータの最大動作電圧を目標とする設計の場合は、SW ノードのリンギングがデバイスの絶対最大定格を超えないようにしてください。SW ノード電圧のリンギングは、入力コンデンサが IC を基準として適切に配置されているかどうかに関係します。入力コンデンサの適切な配置については、図 8-28 の PCB レイアウト例を参照してください。

- インダクタを SW ピンの近くに配置します。過度の容量性結合を防止するため、SW パターンまたはプレーンの面積を最小限に抑えます。

- GND ピンはデバイスの下のパワーパッドに直接接続し、ヒートシンク PCB のグランドプレーンに接続します。

- 中間層のグランドプレーンの 1 つをノイズシールドおよび放熱経路として使用します。

- プレーンに対して単一点のグランド接続を使用します。フィードバック用のグランド接続を配線し、コンポーネントをグランドプレーンに接続します。このアクションにより、スイッチングされた電流や負荷電流がアナロググランドパターンに流れるのを防ぎます。グランドが適切に処理されないと、負荷レギュレーションが劣化したり、出力電圧リップルの動作が不安定になります。

- $V_{IN}$ ,  $V_{OUT}$ 、およびグランド バスの接続は、できる限り幅広くします。このガイドラインにより、コンバータの入力または出力パスで生じる電圧降下が低減され、効率が最大になります。

- FB ピンへのパターン長を最短にします。両方の帰還抵抗  $R_{FB1}$  と  $R_{FB2}$  を FB ピンの近くに配置します。 $C_{FF}$  (使用する場合) を  $R_{FB1}$  と直接並列に配置します。負荷での出力設定ポイントの精度が重要な場合、 $V_{OUT}$  センスを負荷に接続します。 $V_{OUT}$  センスバスをノイズの多いノードから遠ざけ、できれば接地されたシールド層の反対側の層を経由して配線します。

- $R_T$  ピンはノイズの影響を受けやすいことに注意してください。そのため、 $R_T$  抵抗はデバイスにできる限り近づけて配置し、最短のパターン長で配線します。 $R_T$  から GND への寄生容量は、20pF を超えないようにする必要があります。

- 接合部温度を 150°C 未満に維持するために、LM5168E には十分なヒートシンクを用意してください。全定格負荷で動作する場合、上面のグランド プレーンは重要な放熱面積になります。ヒートシンクビアの配列を使用して、露出パッドを PCB グランド プレーンに接続します。PCB に複数の銅層がある場合は、これらのサーマルビアも内部層の熱拡散グランド プレーンに接続する必要があります。

#### 8.4.1.1 コンパクトな PCB レイアウトによる EMI の低減

高  $di/dt$  コンポーネントによって生成される放射 EMI は、スイッチングコンバータのパルス電流に関連しています。パルス電流の経路がカバーする面積が大きいほど、より多くの電磁放射が発生します。放射 EMI を最小化するための鍵は、パルス電流経路を識別し、そのパスの面積を最小化することです。図 8-24 に、EMI という観点からの降圧コンバータ電力段の重要なスイッチング ループを示します。降圧コンバータのトポロジ アーキテクチャでは、入力コンデンサと LM5168E の統合 MOSFET で構成されるループに特に高い  $di/dt$  電流パスが存在するため、有効ループ領域を最小限に抑えてこのループの寄生インダクタンスを減らすことが必須になります。

図 8-24. 降圧コンバータの臨界電流ループ

入力コンデンサは、ハイサイド MOSFET の電流の高  $di/dt$  成分に対してプライマリ パスとなります。セラミック コンデンサを  $V_{IN}$  および GND ピンにできる限り近づけて配置することが、EMI 低減のために重要となります。SW をインダクタに接続するトレースは、できる限り短くし、過度の加熱なしに負荷電流を流すのに十分な幅にしてください。寄生抵抗を最小限に抑えるため、電流の伝導パスには、短く、太いパターン、または銅箔(形状)を使用します。出力コンデンサはインダクタの  $V_{OUT}$  側の近くに配置し、コンデンサのリターン端子を LM5168E の GND ピンと露出パッドに接続します。

#### 8.4.1.2 帰還抵抗

分圧抵抗を負荷ではなく FB ピン近くに配置することで、出力電圧帰還バスのノイズの影響を小さくします。これにより、FB 信号とノイズ結合のパターン長が短くなります。FB ピンは帰還コンパレータへの入力であるため、ノイズの影響を受け

やすいハイインピーダンスノードです。出力ノードは低インピーダンスノードであるため、 $V_{OUT}$ から分圧抵抗へのパートナーは、短いパスを使用できなければ長くても許容されます。

電圧センストレースを負荷からフィードバック抵抗分割器まで配線し、SWノード、インダクタ、および $V_{IN}$ から離して、フィードバック信号がスイッチノイズによって汚染されるのを防ぎながら、トレース長を最小限に抑えます。出力電圧を設定するために100kΩより大きな帰還抵抗を使う場合、これは最も重要です。また、電圧センスパターンは、インダクタ、SWノード、 $V_{IN}$ とは異なる層に配線します。そのため、帰還パターンをインダクタとSWノードの銅ポリゴンから分離するグランドプレーンがあります。この動作により、スイッチングノイズ源からの電圧帰還パスをさらにシールドできます。

#### 8.4.2 熱に関する注意事項

他の電力変換デバイスと同様に、LM5168Eは動作中に内部で電力を消費します。この消費電力の影響により、コンバータの内部温度が周囲温度よりも高くなります。内部のダイ温度( $T_J$ )は、以下の関数になります。

- 周囲温度

- 電力損失

- アプリケーションの有効熱抵抗  $R_{\theta JA}$

- PCB レイアウト

LM5168E の最大内部ダイ温度は、150°C に制限する必要があります。この制限により、デバイスの最大消費電力が制限され、それに伴って負荷電流も制限されます。[式 27](#) に、重要なパラメータ間の関係を示します。周囲温度( $T_A$ )が高いほど、また、 $R_{\theta JA}$  が大きいほど、利用可能な最大出力電流が低減されます。コンバータの効率は、このデータシートに示す曲線を使用して推定できます。これらの曲線にはインダクタ内の電力損失が含まれていることに注意してください。いずれかの曲線に目的の動作条件が見つからない場合は、補間にによって効率を推定できます。または、目的のアプリケーション要件に合わせて EVM を調整し、効率を直接測定することもできます。 $R_{\theta JA}$  の正確な値を推定するのは、より困難です。『[半導体およびIC パッケージの熱評価基準](#)』アプリケーションノートに記載されているように、「熱特性表」に記載されている  $R_{\theta JA}$  の値は設計目的には使用できず、アプリケーションの熱性能を推定するために使用してはなりません。この表に報告されている値は、実際のアプリケーションではめったに見られない特定の一連の条件で測定されたものです。 $R_{\theta JC(bott)}$  と  $\Psi_{JT}$  のデータは、放熱性能を判定する際に役立ちます。 $R_{\theta JA(EVM)}$  の値は LM5168PEVM に適用され、参考目的にのみ与えられています。詳細とリソースについては、このセクションの末尾に記載されている『[半導体およびIC パッケージの熱評価基準](#)』アプリケーションノートも参照してください。

$$I_{OUT} \Big|_{MAX} = \frac{(T_J - T_A)}{R_{\theta JA}} \times \frac{\eta}{(1-\eta)} \times \frac{1}{V_{OUT}} \quad (27)$$

ここで、

$\eta$  は効率です。

実効  $R_{\theta JA}$  は重要なパラメータであり、以下のような多くの要因に依存します。

- 消費電力

- 空気温度、フロー

- PCB 面積

- 銅箔ヒートシンク面積

- パッケージの下にあるサーマルビアの数

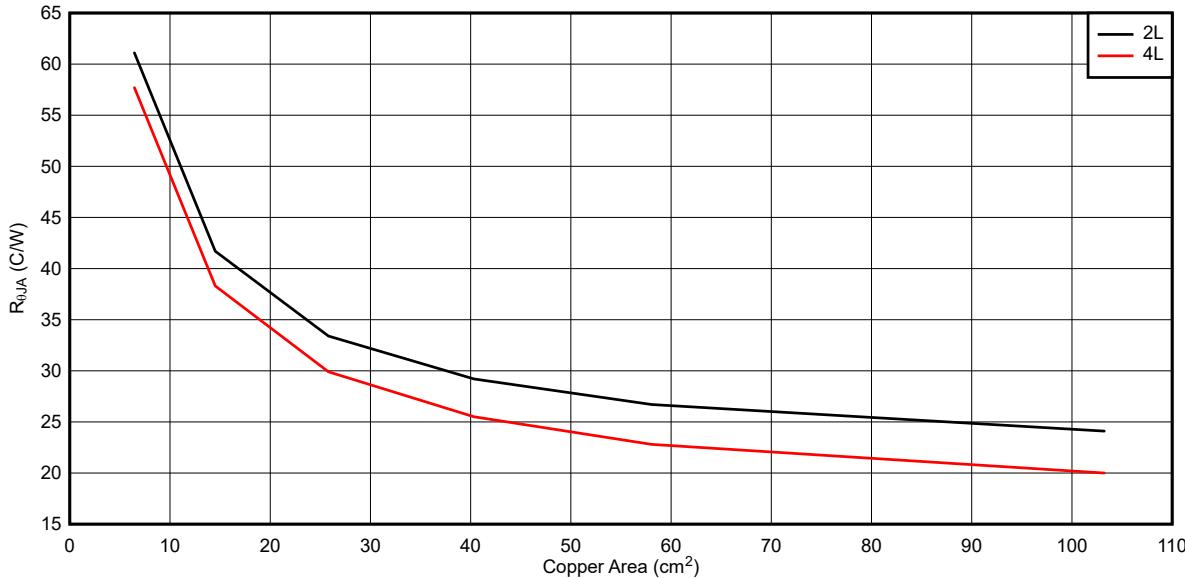

- 隣接する部品の配置

LM5168E には、ダイ接着パドル、または「露出パッド」(EP) が搭載されており、PCB の放熱用銅箔への半田付け箇所を提供します。これはレギュレータ接合部から放熱器への優れた熱伝導経路となり、PCB の放熱用銅面に適切にはんだ付けする必要があります。[図 8-25](#) に、 $R_{\theta JA}$  の代表的な例を示します。グラフに示す銅箔面積は、各層に対するものです。トップ層とボトム層は各 2oz 銅、内層は 1oz 銅です。

図 8-25. DDA パッケージの典型的な  $R_{\theta JA}$  対銅面積

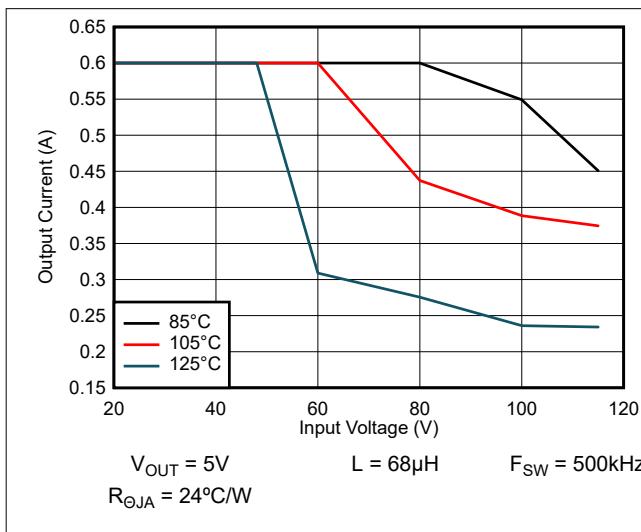

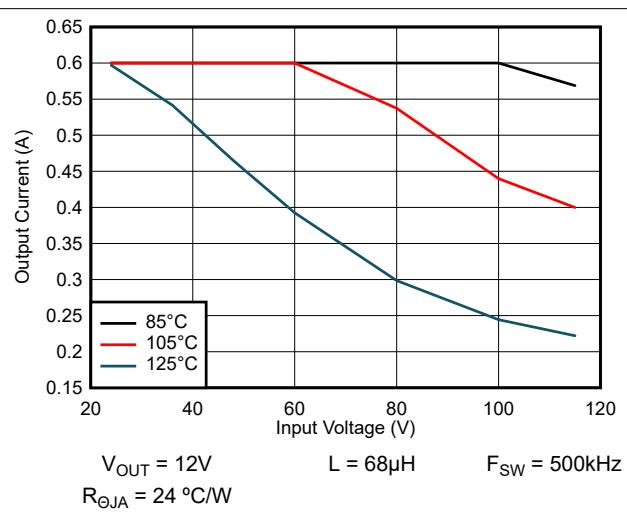

図 8-26 および 図 8-27 のデータは、特定の一連の条件における最大出力電流を決定するための指針として使用します。これらのグラフが作成された特定の条件は、各グラフの下の注記に示されています。

図 8-26. 最大出力電流 :  $V_{OUT} = 5V$

図 8-27. 最大出力電流 :  $V_{OUT} = 12V$

図 8-25 から 図 8-27 に示されているデータはあくまで参考用であり、実際の性能は前述のすべての要因に依存します。

以下の資料は、優れた熱設計のプリント基板設計および特定のアプリケーション環境における  $R_{\theta JA}$  の推定の参考として利用できます。

- 『LM501x の熱特性と PCB 設計例』アプリケーション ノート

- 『半導体および IC パッケージの熱評価基準』アプリケーション レポート

- 『AN-2020 過去ではなく、現在の識見による熱設計』アプリケーション ノート

- 『露出パッドパッケージで最良の熱抵抗を実現するための基板レイアウト ガイド』アプリケーション ノート

- 『新しい熱評価基準の解説』アプリケーション レポート

- 『車載用 DC/DC コンバータの PCB 热設計のヒント』アプリケーション ノート

### 8.4.3 レイアウト例

図 8-28 に、PCB 上層に DDA パッケージを使用し、重要な部品を上面に配置したレイアウト例を示します。

図 8-28. LM5168E の PCB レイアウト例 (DDA パッケージ)

## 9 デバイスおよびドキュメントのサポート

### 9.1 デバイス サポート

#### 9.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

### 9.2 ドキュメントのサポート

#### 9.2.1 関連資料

関連資料については、以下を参照してください。

- テキサス・インスツルメンツ、『COT タイプ III リップル回路の安定性解析』アプリケーションノート

- テキサス・インスツルメンツ、『絶縁型 Fly-Buck コンバータの設計』アプリケーションノート

- テキサス・インスツルメンツ、『オプトカプラーを使用した Fly-Buck ソリューションの設計』アプリケーションノート

- テキサス・インスツルメンツ、『LMR36520 を使用した絶縁型 s Fly-Buck コンバータの設計』アプリケーションノート

- テキサス・インスツルメンツ、『COT 降圧コンバータに最適なリップル生成ネットワークの選択』アプリケーションノート

- テキサス・インスツルメンツ、『コスト効率が高く要求の厳しいアプリケーションにおける広い  $V_{IN}$ 、低 EMI 同期降圧回路の評価』ホワイトペーパー

- テキサス・インスツルメンツ、『電源の伝導 EMI 仕様の概要』ホワイトペーパー

- テキサス・インスツルメンツ、『電源の放射 EMI 仕様の概要』ホワイトペーパー

- テキサス・インスツルメンツ、『スマートサーモスタート用の広い  $V_{IN}$  コンバータとバッテリ残量計を備えた 24V AC 電力段』デザインガイド

- テキサス・インスツルメンツ、『高精度ゲージ、50 $\mu$ A スタンバイ電流、13S、48V リチウムイオンバッテリー パック』リファレンスデザインガイド

- テキサス・インスツルメンツ、『AN-2162: DC/DC コンバータ向け伝導 EMI の簡単な成功事例』アプリケーションレポート

- テキサス・インスツルメンツ、『広い  $V_{IN}$  DC/DC コンバータによるドローンへの電力供給』アプリケーションノート

- テキサス・インスツルメンツ、『新しい熱評価基準の解説』アプリケーションノート

### 9.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.4 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの [使用条件](#) を参照してください。

### 9.5 商標

PowerPAD™ and テキサス・インスツルメンツ E2E™ are trademarks of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 9.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお奨めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 9.7 用語集

### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

| 日付          | 改訂 | 注      |

|-------------|----|--------|

| August 2025 | *  | 初版リリース |

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのプラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins           | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|--------------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| LM5168PEDDAR          | Active        | Production           | SO PowerPAD<br>(DDA)   8 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -55 to 150   | 5168PET             |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

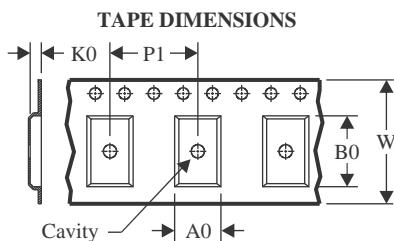

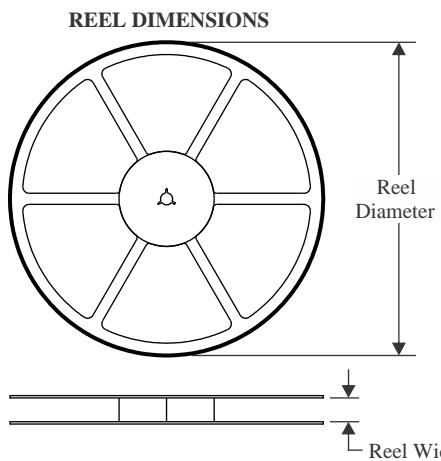

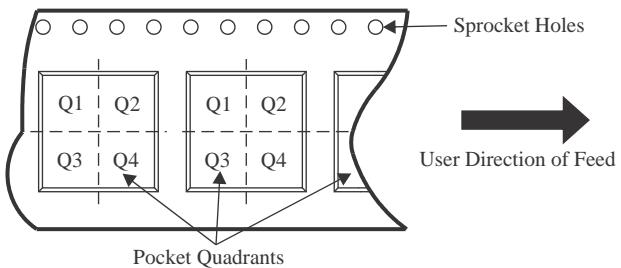

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| LM5168PEDDAR | SO PowerPAD  | DDA             | 8    | 2500 | 330.0              | 12.5               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

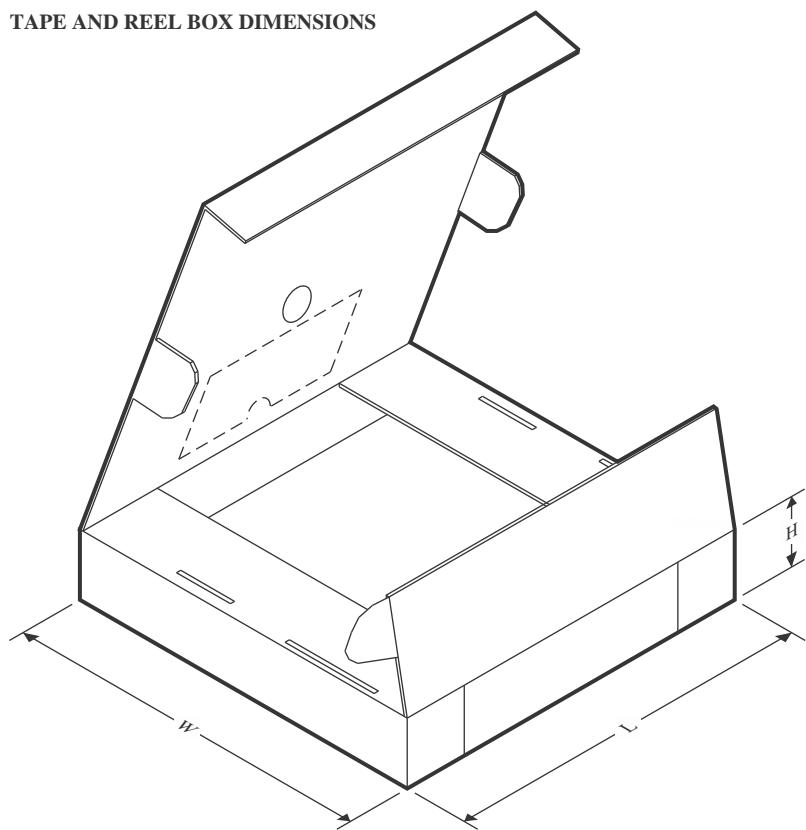

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM5168PEDDAR | SO PowerPAD  | DDA             | 8    | 2500 | 353.0       | 353.0      | 32.0        |

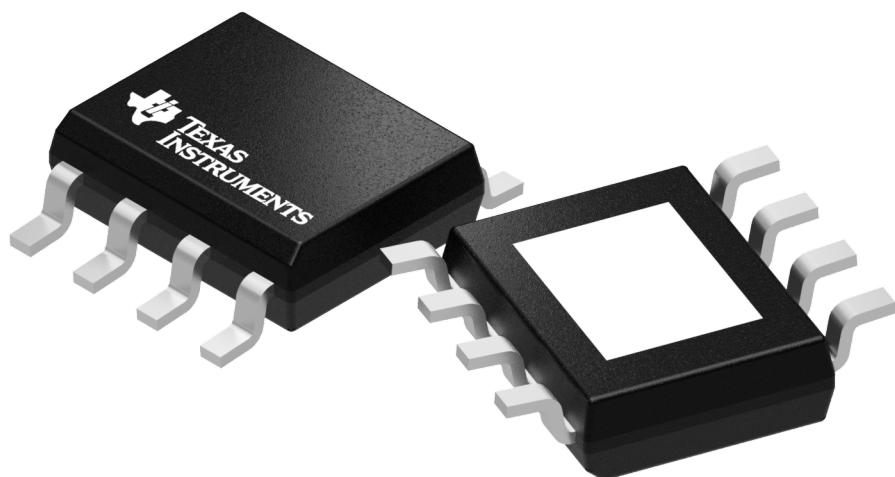

## GENERIC PACKAGE VIEW

DDA 8

PowerPAD™ SOIC - 1.7 mm max height

PLASTIC SMALL OUTLINE

Images above are just a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4202561/G

**DDA0008B**

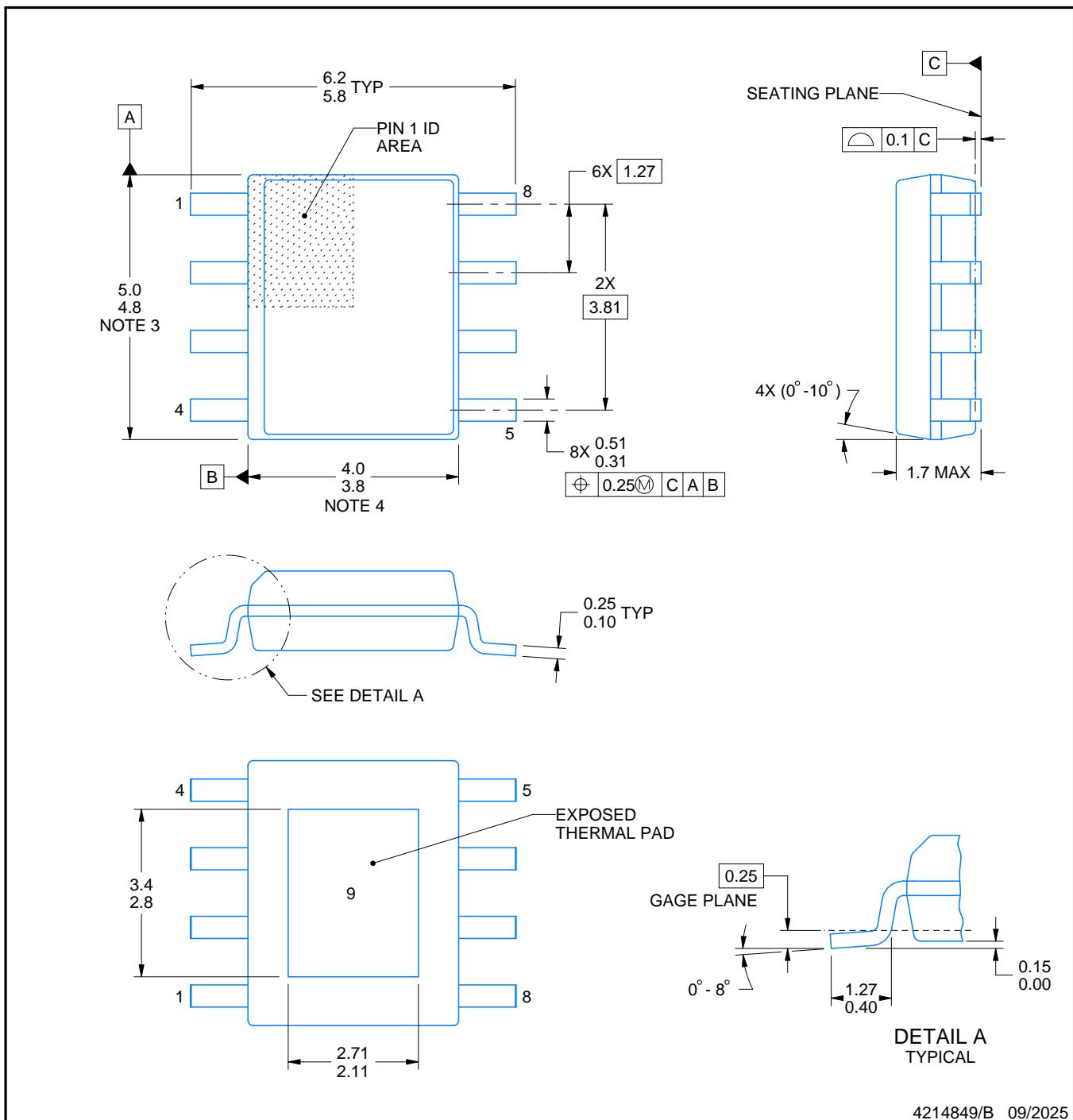

# PACKAGE OUTLINE

**PowerPAD™ SOIC - 1.7 mm max height**

PLASTIC SMALL OUTLINE

4214849/B 09/2025

PowerPAD is a trademark of Texas Instruments.

NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

5. Reference JEDEC registration MS-012.

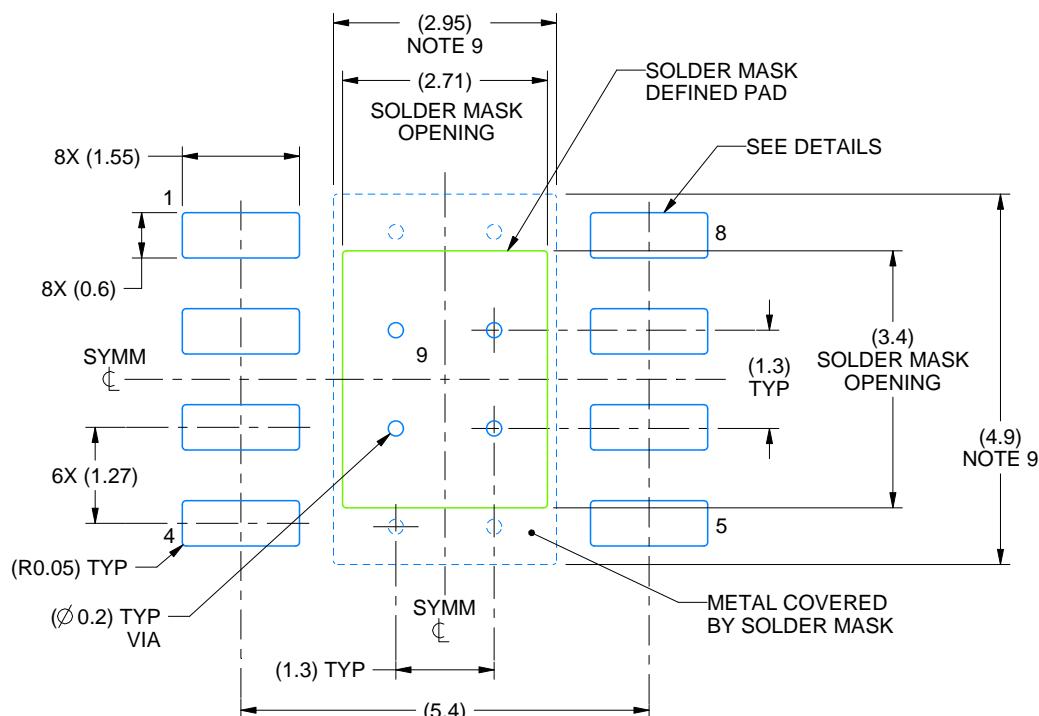

# EXAMPLE BOARD LAYOUT

DDA0008B

PowerPAD™ SOIC - 1.7 mm max height

PLASTIC SMALL OUTLINE

LAND PATTERN EXAMPLE

SCALE:10X

SOLDER MASK DETAILS

PADS 1-8

4214849/B 09/2025

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 ([www.ti.com/lit/slma002](http://www.ti.com/lit/slma002)) and SLMA004 ([www.ti.com/lit/slma004](http://www.ti.com/lit/slma004)).

9. Size of metal pad may vary due to creepage requirement.

10. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

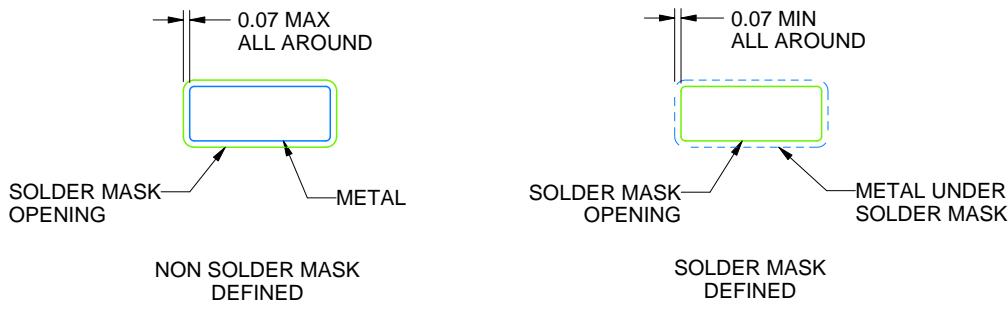

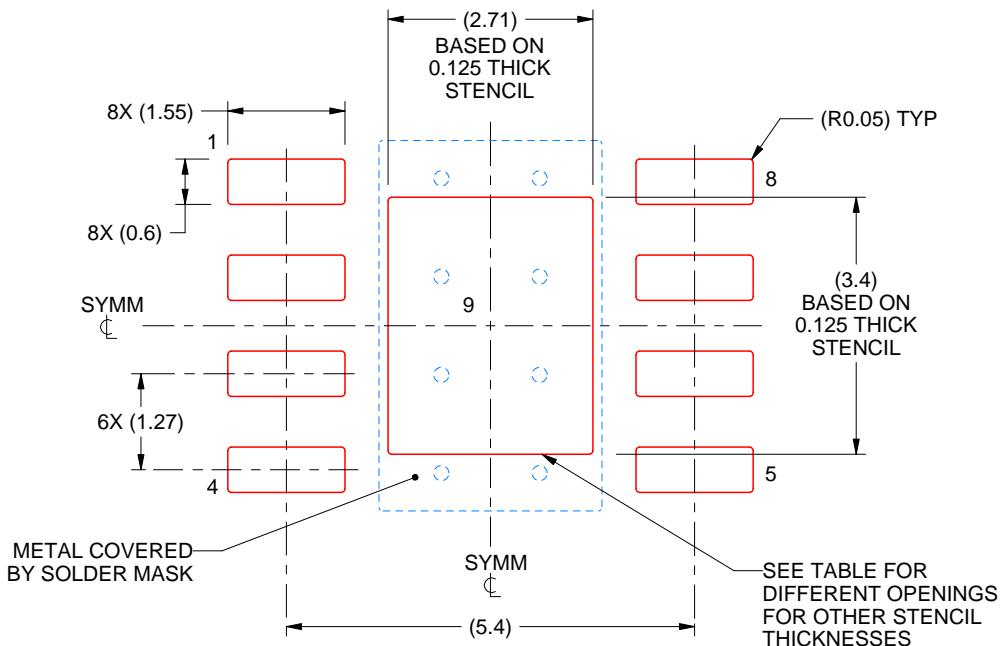

# EXAMPLE STENCIL DESIGN

DDA0008B

PowerPAD™ SOIC - 1.7 mm max height

PLASTIC SMALL OUTLINE

SOLDER PASTE EXAMPLE

EXPOSED PAD

100% PRINTED SOLDER COVERAGE BY AREA

SCALE:10X

| STENCIL THICKNESS | SOLDER STENCIL OPENING |

|-------------------|------------------------|

| 0.1               | 3.03 X 3.80            |

| 0.125             | 2.71 X 3.40 (SHOWN)    |

| 0.150             | 2.47 X 3.10            |

| 0.175             | 2.29 X 2.87            |

4214849/B 09/2025

NOTES: (continued)

11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

12. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているTI製品を使用するアプリケーションの開発の目的でのみ、TIはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TIや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TIおよびその代理人を完全に補償するものとし、TIは一切の責任を拒否します。

TIの製品は、[TIの販売条件](#)、[TIの総合的な品質ガイドライン](#)、[ti.com](#)またはTI製品などに関連して提供される他の適用条件に従い提供されます。TIがこれらのリソースを提供することは、適用されるTIの保証または他の保証の放棄の拡大や変更を意味するものではありません。TIがカスタム、またはカスタマー仕様として明示的に指定していない限り、TIの製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025年10月