# LM5155x 2.2MHz、広い入力電圧範囲、非同期整流、昇圧 / SEPIC / フライバック・コントローラ

## 1 特長

- 機能安全対応

- 機能安全システム設計に役立つ資料を利用可能

- バッテリ・アプリケーションに適した広い入力動作範囲

- 動作電圧範囲: 3.5V~45V

- BIAS = VCC のとき 2.97V~16V

- BIAS  $\geq$  3.5V のときの最小昇圧電源電圧 1.5V

- 最大 50V の入力過渡保護

- バッテリ消費の最小化

- 低いシャットダウン電流 ( $I_Q \leq 2.6\mu A$ )

- 低い動作電流 ( $I_Q \leq 480\mu A$ )

- 小さなソリューション・サイズと低コスト

- 最大スイッチング周波数: 2.2MHz

- 12 ピンの WSON パッケージ (3mm × 2mm)

- 内蔵エラー・アンプによりフォトカプラなしに 1 次側 レギュレーションが可能 (フライバック)

- クランキング中のアンダーシュートを最小化 (始動 / 停止アプリケーション)

- 高い効率と低消費電力

- 100mV  $\pm 7\%$  の低い電流制限スレッショルド

- 1.5A (ピーク) の強力な標準 MOSFET ドライバ

- 外部 VCC 電源に対応

- AM 帯域の干渉およびクロストークを回避

- 選択可能なクロック同期

- スイッチング周波数を 100kHz~2.2MHz の範囲で 動的にプログラム可能

- 保護機能内蔵

- 入力電圧範囲全体にわたって一定のピーク電流制限

- (オプション) ヒカップ・モード短絡保護 (「デバイス 比較表」を参照)

- ライン UVLO をプログラム可能

### – OVP 保護

### – サーマル・シャットダウン

### • $\pm 1\%$ 精度の高精度帰還基準電圧

### • 追加スロープ補償をプログラム可能

### • 可変ソフト・スタート

### • PGOOD インジケータ

### • WEBENCH® Power Designer により、LM5155x を 使用するカスタム設計を作成

## 2 アプリケーション

- フォトカプラを使用しない複数出力フライバック

- LED バイアス電源

- 入力範囲の広い昇圧 / SEPIC / フライバック・パワー・モジュール

- 携帯用スピーカー・アプリケーション

- バッテリ駆動の昇圧、SEPIC、フライバック

## 3 概要

LM5155x (LM5155 と LM51551) は、広い入力電圧範囲に対応した非同期昇圧コントローラであり、ピーク電流制御モードを使用しています。このデバイスは、昇圧、SEPIC、フライバックのトポロジで使用可能です。

LM5155x は、BIAS ピンが VCC ピンに接続されている場合、最小 2.97V の 1 セル・バッテリで起動できます。BIAS ピンが 3.5V を超えている場合、最小 1.5V の入力電源電圧で動作可能です。

## 製品情報

| 部品番号    | パッケージ (1) | 本体サイズ (公称)      |

|---------|-----------|-----------------|

| LM5155x | WSON (12) | 3.00mm × 2.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

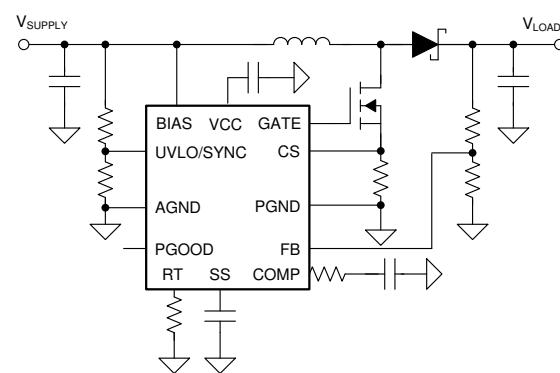

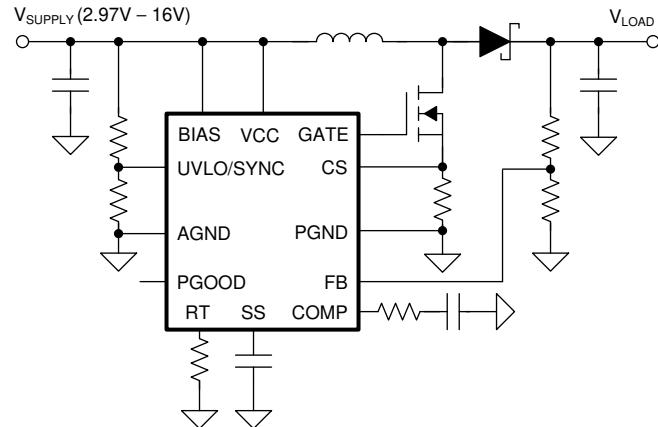

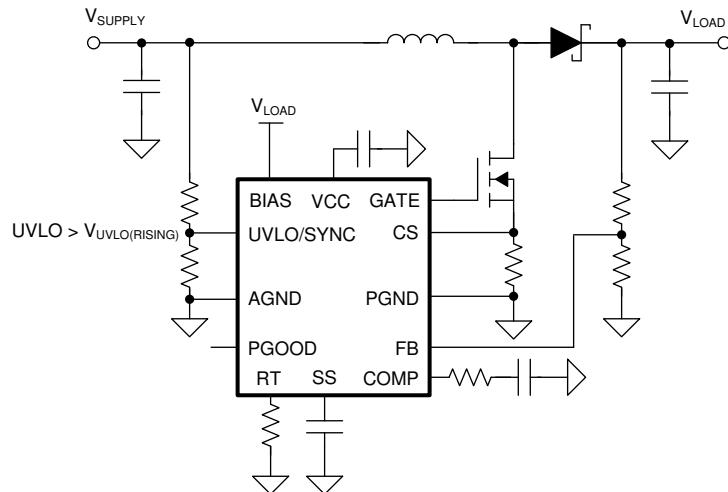

## 代表的な昇圧アプリケーション

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|             |    |                         |    |

|-------------|----|-------------------------|----|

| 1 特長        | 1  | 9.3 機能説明                | 13 |

| 2 アプリケーション  | 1  | 9.4 デバイスの機能モード          | 25 |

| 3 概要        | 1  | 10 アプリケーションと実装          | 27 |

| 4 改訂履歴      | 2  | 10.1 アプリケーション情報         | 27 |

| 5 概要 (続き)   | 3  | 10.2 代表的なアプリケーション       | 27 |

| 6 デバイス比較表   | 3  | 10.3 システム例              | 33 |

| 7 ピン構成および機能 | 4  | 10.4 電源に関する推奨事項         | 37 |

| 8 仕様        | 5  | 10.5 レイアウト              | 38 |

| 8.1 絶対最大定格  | 5  | 11 デバイスおよびドキュメントのサポート   | 41 |

| 8.2 ESD 定格  | 5  | 11.1 デバイスのサポート          | 41 |

| 8.3 推奨動作条件  | 6  | 11.2 ドキュメントのサポート        | 41 |

| 8.4 熱に関する情報 | 6  | 11.3 ドキュメントの更新通知を受け取る方法 | 41 |

| 8.5 電気的特性   | 6  | 11.4 サポート・リソース          | 41 |

| 8.6 代表的特性   | 9  | 11.5 商標                 | 42 |

| 9 詳細説明      | 12 | 11.6 静電気放電に関する注意事項      | 42 |

| 9.1 概要      | 12 | 11.7 用語集                | 42 |

| 9.2 機能ブロック図 | 12 | 12 メカニカル、パッケージ、および注文情報  | 42 |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision D (January 2021) to Revision E (August 2023)   | Page |

|----------------------------------------------------------------------|------|

| • <a href="#">図 10-11</a> を更新                                        | 33   |

| <hr/>                                                                |      |

| Changes from Revision C (June 2020) to Revision D (January 2021)     | Page |

| • 文書全体にわたって表、図、相互参照の採番方法を更新                                          | 1    |

| <hr/>                                                                |      |

| Changes from Revision B (January 2020) to Revision C (June 2020)     | Page |

| • <a href="#">図 9-16</a> のタイトルから「TBD」を削除                             | 18   |

| <hr/>                                                                |      |

| Changes from Revision A (January 2020) to Revision B (January 2020)  | Page |

| • 「特長」の一覧に機能安全対応を追加                                                  | 1    |

| <hr/>                                                                |      |

| Changes from Revision * (December 2018) to Revision A (January 2020) | Page |

| • データシートにデバイス LM51551 を追加                                            | 1    |

| <hr/>                                                                |      |

## 5 概要 (続き)

また内部 VCC レギュレータは最大 45V (絶対最大定格 50V) での BIAS ピンの動作もサポートしています。スイッチング周波数は、外付けの抵抗により 100kHz~2.2MHz の範囲で動的にプログラム可能です。2.2MHz でのスイッチングにより、AM 帯域との干渉が最小化され、ソリューション・サイズの小型化と、高速な過渡応答を実現できます。

このデバイスには、1.5A の標準 MOSFET ドライバが搭載されており、低い 100mV の電流制限スレッショルドが設定されています。また、このデバイスは外部 VCC 電源を使用して効率向上が可能です。小さい動作電流とパルス・スキッピング動作により、軽負荷時の効率を改善します。

このデバイスは、サイクル単位の電流制限、過電圧保護、ライン UVLO、サーマル・シャットダウンなどの保護機能を内蔵しています。LM51551 デバイスを選択すると、ヒップ・モード過負荷保護機能を使用できます。その他の機能には、シャットダウン時の低  $I_Q$ 、プログラム可能なソフトスタート、プログラム可能なスロープ補償、高精度基準電圧、パワー・グッド・インジケータ、外部クロック同期が含まれます。

## 6 デバイス比較表

| デバイスのオプション | ヒップ・モード保護 | 内部リファレンス |

|------------|-----------|----------|

| LM5155     | ディセーブル    | 1V       |

| LM51551    | イネーブル     | 1V       |

## 7 ピン構成および機能

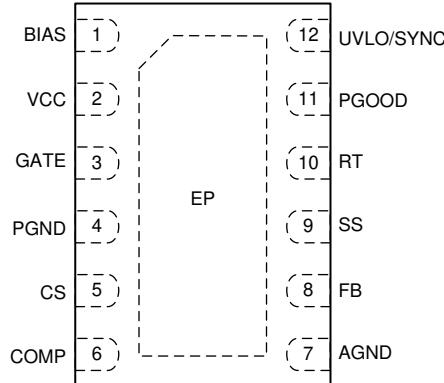

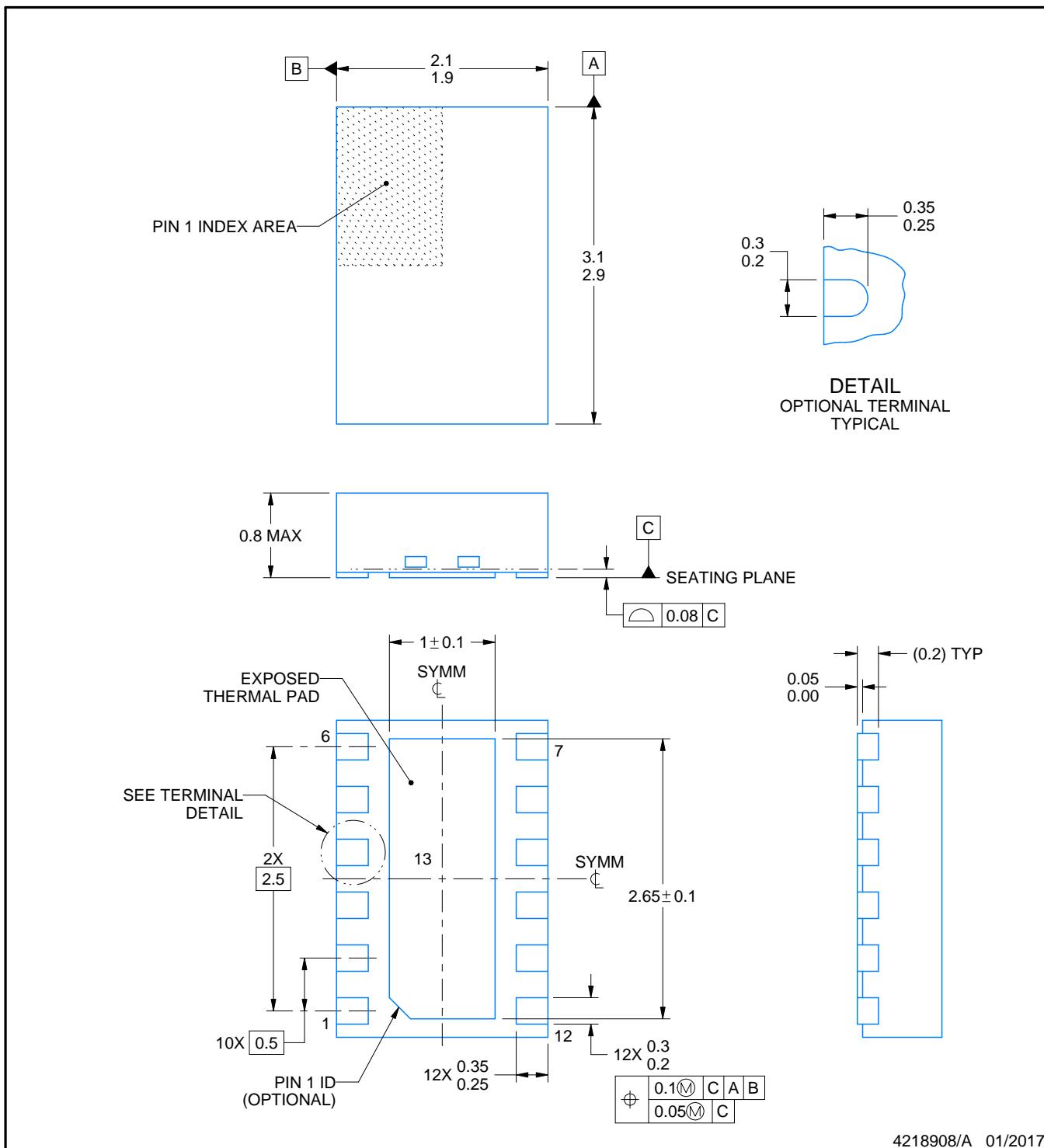

図 7-1. 12 ピン WSON DSS パッケージ (上面図)

表 7-1. ピンの機能

| ピン |               | 種類 <sup>(1)</sup> | 概要                                                                                                                                                                                                                      |

|----|---------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 番号 | 名称            |                   |                                                                                                                                                                                                                         |

| 1  | BIAS          | P                 | VCC レギュレータの電源電圧入力。このピンと PGND との間にバイパス・コンデンサを接続します。                                                                                                                                                                      |

| 2  | VCC           | P                 | 内部 VCC レギュレータの出力と MOSFET ドライバの電源電圧入力。このピンと PGND との間にセラミック・バイパス・コンデンサを接続します。                                                                                                                                             |

| 3  | GATE          | O                 | N チャネル MOSFET のゲート・ドライブ出力。短い低インダクタンスのバスを経由して、N チャネル MOSFET のゲートに直接接続します。                                                                                                                                                |

| 4  | PGND          | G                 | 電源グランド・ピン。低インダクタンスの広く短いパスを通して、センス抵抗のグランド接続に直接接続します。                                                                                                                                                                     |

| 5  | CS            | I                 | 電流センス入力ピン。短いパスを通して、電流センス抵抗の正の側に接続します。                                                                                                                                                                                   |

| 6  | COMP          | O                 | 内部の相互コンダクタンス・エラー・アンプの出力。このピンと PGND との間にループ補償部品を接続します。                                                                                                                                                                   |

| 7  | AGND          | G                 | アナログ・グランド・ピン。広く短いパスを通して、アナログ・グランド・プレーンに接続します。                                                                                                                                                                           |

| 8  | FB            | I                 | エラー・アンプの反転入力。昇圧 / SEPIC トポロジで出力電圧を設定するために、出力とこのピンとの間に分圧器を接続します。ローサイド帰還抵抗を AGND に接続します。                                                                                                                                  |

| 9  | SS            | I                 | ソフトスタート時間のプログラミング・ピン。外付けコンデンサと内部の電流ソースにより、ソフトスタート中の内部エラー・アンプのリファレンス電圧のランプ・レートが設定されます。コンデンサのグランド接続を AGND に接続します。                                                                                                         |

| 10 | RT            | I                 | スイッチング周波数の設定ピン。スイッチング周波数は、RT と AGND との間の単一の抵抗によりプログラムされます。                                                                                                                                                              |

| 11 | PGOOD         | O                 | パワーグッド・インジケータ。FB が低電圧スレッショルドを下回ると Low になるオープン・ドレイン出力。ブルアップ抵抗をシステム電圧レールに接続します。                                                                                                                                           |

| 12 | UVLO/EN/ SYNC | I                 | 低電圧誤動作防止のプログラム用ピン。このピンを抵抗デバイダを介して電源電圧に接続することで、コンバータのスタートアップおよびシャットダウン・レベルをプログラムできます。内部クロックは、UVLO/EN/SYNC ピンに負のパルス信号を印加することで、外部クロックと同期できます。このピンをフローティング状態のままにしてはいけません。未使用時は BIAS ピンに接続してください。ローサイド UVLO 抵抗を AGND に接続します。 |

| —  | EP            | —                 | パッケージの露出パッド。露出したパッドは、熱抵抗を減らすために、AGND と大きな銅のグランド・プレーンに接続する必要があります。                                                                                                                                                       |

(1) G=グランド、I=入力、O=出力、P=電源

## 8 仕様

### 8.1 絶対最大定格

接合部の動作時推奨温度範囲において<sup>(1)</sup>

|                             |                                | 最小値  | 最大値               | 単位 |

|-----------------------------|--------------------------------|------|-------------------|----|

| 入力                          | BIAS から AGND へ                 | -0.3 | 50                | V  |

|                             | UVLO から AGND へ                 | -0.3 | $V_{BIAS} + 0.3$  |    |

|                             | SS から AGND へ <sup>(2)</sup>    | -0.3 | 3.8               |    |

|                             | RT から AGND へ <sup>(2)</sup>    | -0.3 | 3.8               |    |

|                             | FB から AGND へ                   | -0.3 | 3.8               |    |

|                             | CS から AGND (DC) へ              | -0.3 | 0.3               |    |

|                             | CS から AGND へ (過渡 100ns)        | -1   |                   |    |

|                             | CS から AGND へ (過渡 20ns)         | -2   |                   |    |

|                             | PGND から AGND へ                 | -0.3 | 0.3               |    |

| 出力                          | VCC から AGND へ                  | -0.3 | 18 <sup>(3)</sup> | V  |

|                             | GATE から AGND へ (過渡 100ns)      | -1   |                   |    |

|                             | GATE から AGND へ (過渡 50ns)       | -2   |                   |    |

|                             | PGOOD から AGND へ <sup>(4)</sup> | -0.3 | 18                |    |

|                             | COMP から AGND へ <sup>(5)</sup>  | -0.3 |                   |    |

| 接合部温度、 $T_J$ <sup>(6)</sup> |                                | -40  | 150               | °C |

| 保管温度、 $T_{stg}$             |                                | -55  | 150               |    |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについての話で、絶対最大定格において、またはこのデータシートの「[推奨動作条件](#)」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

- (2) このピンは外部電圧の印加の仕様は規定されていません。

- (3) 18V または  $V_{BIAS} + 0.3V$  のいずれか低い方

- (4)  $V_{PGOOD} > V_{BIAS}$  のとき、最大電流シンクは 1mA に制限されます。

- (5) このピンには、最大 1.6mA まで処理できる最大電圧クランプが内蔵されています。

- (6) 接合部温度が高くなると、動作寿命が短くなります。接合部温度が 125°Cを超えると、動作寿命が短くなります。

### 8.2 ESD 定格

|             |       |                                                                | 値     | 単位 |

|-------------|-------|----------------------------------------------------------------|-------|----|

| $V_{(ESD)}$ | 静電気放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>   | ±2000 | V  |

|             |       | デバイス帯電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠、すべてのピン <sup>(2)</sup> | ±500  |    |

- (1) JEDEC のドキュメント JEP155 には、500V HBM であれば標準的な ESD 制御プロセスにより安全な製造が可能であると記載されています。

- (2) JEDEC のドキュメント JEP157 には、250V CDM であれば標準的な ESD 制御プロセスにより安全な製造が可能であると記載されています。

## 8.3 推奨動作条件

接合部の推奨動作温度である  $-40^{\circ}\text{C} \sim 125^{\circ}\text{C}$  の範囲内 (特に記述のない限り)<sup>(1)</sup>

|                   |                       | 最小値  | 公称値  | 最大値  | 単位  |

|-------------------|-----------------------|------|------|------|-----|

| $V_{\text{BIAS}}$ | バイアス入力 <sup>(2)</sup> | 2.97 | 45   | 45   | V   |

| $V_{\text{VCC}}$  | VCC 電圧 <sup>(3)</sup> | 2.97 | 16   | 16   | V   |

| $V_{\text{UVLO}}$ | UVLO 入力               | 0    | 45   | 45   | V   |

| $V_{\text{FB}}$   | FB 入力                 | 0    | 3.7  | 3.7  | V   |

| $f_{\text{SW}}$   | 標準スイッチング周波数           | 100  | 2200 | 2200 | kHz |

| $f_{\text{SYNC}}$ | 同期パルス周波数              | 100  | 2200 | 2200 | kHz |

| $T_{\text{J}}$    | 動作時接合部温度              | -40  | 125  | 125  | °C  |

- (1) **動作定格**は、デバイスが機能する前提の条件です。仕様およびテスト条件については、「電気的特性」を参照してください。

- (2) VCC が BIAS に直接接続されている場合、BIAS ピンの動作範囲は  $2.97\text{V} \sim 16\text{V}$  です。VCC が内部 VCC レギュレータから供給される場合、BIAS ピンの動作範囲は  $3.5\text{V} \sim 45\text{V}$  です。

- (3) このピンの電圧は  $V_{\text{BIAS}} + 0.3\text{V}$  よりも低くする必要があります。

## 8.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>        |                                  | LM5155x   | 単位   |

|-----------------------------|----------------------------------|-----------|------|

|                             |                                  | DSS(WSON) |      |

|                             |                                  | 12 ピン     |      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗 (LM5155EVM-BST)     | 40.8      | °C/W |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗                     | 63.7      | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース (上面) への熱抵抗              | 61.0      | °C/W |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗                     | 32.1      | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ (LM5155EVM-BST) | 1.5       | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ                 | 2.3       | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ (LM5155EVM-BST) | 22.5      | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ                 | 31.9      | °C/W |

| $R_{\theta JC(\text{bot})}$ | 接合部からケース (底面) への熱抵抗              | 11.2      | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション・レポートを参照してください。

## 8.5 電気的特性

代表値は  $T_{\text{J}} = 25^{\circ}\text{C}$  に対応します。最小および最大の制限値は、 $T_{\text{J}} = -40^{\circ}\text{C} \sim 125^{\circ}\text{C}$  の範囲で適用されます。特に記述のない限り、 $V_{\text{BIAS}} = 12\text{V}$ 、 $R_{\text{T}} = 9.09\text{k}\Omega$  です

| パラメータ                         | テスト条件            | 最小値                                                                                                                                    | 代表値  | 最大値   | 単位   |

|-------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|-------|------|

| <b>電源電流</b>                   |                  |                                                                                                                                        |      |       |      |

| $I_{\text{SHUTDOWN(BIAS)}}$   | BIAS シャットダウン電流   | $V_{\text{BIAS}} = 12\text{V}$ , $V_{\text{UVLO}} = 0\text{V}$                                                                         | 2.6  | 5     | μA   |

| $I_{\text{OPERATING(BIAS)}}$  | BIAS 動作電流        | $V_{\text{BIAS}} = 12\text{V}$ , $V_{\text{UVLO}} = 2\text{V}$ , $V_{\text{FB}} = V_{\text{REF}}$ , $R_{\text{T}} = 220\text{k}\Omega$ | 480  | 540   | μA   |

| <b>VCC レギュレータ</b>             |                  |                                                                                                                                        |      |       |      |

| $V_{\text{VCC-REG}}$          | VCC レギュレーション     | $V_{\text{BIAS}} = 8\text{V}$ 、無負荷                                                                                                     | 6.5  | 6.85  | 7    |

|                               | VCC レギュレーション     | $V_{\text{BIAS}} = 8\text{V}$ , $I_{\text{VCC}} = 35\text{mA}$                                                                         | 6.5  |       | V    |

| $V_{\text{VCC-UVLO(RISING)}}$ | VCC UVLO スレッショルド | VCC の立ち上がり                                                                                                                             | 2.75 | 2.85  | 2.95 |

|                               | VCC UVLO ヒステリシス  | VCC の立ち下がり                                                                                                                             |      | 0.063 | V    |

| $I_{\text{VCC-CL}}$           | VCC のソース電流制限     | $V_{\text{BIAS}} = 10\text{V}$ , $V_{\text{VCC}} = 0\text{V}$                                                                          | 35   | 105   | mA   |

| <b>イネーブル</b>                  |                  |                                                                                                                                        |      |       |      |

| $V_{\text{EN(RISING)}}$       | イネーブル・スレッショルド    | EN の立ち上がり                                                                                                                              | 0.4  | 0.52  | 0.7  |

代表値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $V_{\text{BIAS}} = 12\text{V}$ 、 $R_T = 9.09\text{k}\Omega$  です

| パラメータ                             | テスト条件                                        | 最小値                                            | 代表値   | 最大値  | 単位               |

|-----------------------------------|----------------------------------------------|------------------------------------------------|-------|------|------------------|

| $V_{\text{EN}(\text{FALLING})}$   | イネーブル・スレッショルド                                | EN の立ち下がり                                      | 0.33  | 0.49 | $\text{V}$       |

| $V_{\text{EN}(\text{HYS})}$       | イネーブル・ヒステリシス                                 | EN の立ち下がり                                      | 0.03  |      | $\text{V}$       |

| <b>UVLO/SYNC</b>                  |                                              |                                                |       |      |                  |

| $V_{\text{UVLO}(\text{RISING})}$  | UVLO / SYNC スレッショルド                          | UVLO 立ち上がり                                     | 1.425 | 1.5  | 1.575            |

| $V_{\text{UVLO}(\text{FALLING})}$ | UVLO / SYNC スレッショルド                          | UVLO 立ち下がり                                     | 1.370 | 1.45 | 1.520            |

| $V_{\text{UVLO}(\text{HYS})}$     | UVLO / SYNC スレッショルドのヒステリシス                   | UVLO 立ち下がり                                     | 0.05  |      | $\text{V}$       |

| $I_{\text{UVLO}}$                 | UVLO ヒステリシス電流                                | $V_{\text{UVLO}} = 1.6\text{V}$                | 4     | 5    | 6                |

| <b>SS</b>                         |                                              |                                                |       |      |                  |

| $I_{\text{SS}}$                   | ソフトスタート電流                                    |                                                | 9     | 10   | 11               |

|                                   | SS ブルダウン・スイッチの $R_{\text{DS}(\text{ON})}$    |                                                | 55    |      | $\Omega$         |

| <b>パルス幅変調</b>                     |                                              |                                                |       |      |                  |

| $f_{\text{sw}1}$                  | スイッチング周波数                                    | $R_T = 220\text{k}\Omega$                      | 85    | 100  | 115              |

| $f_{\text{sw}2}$                  | スイッチング周波数                                    | $R_T = 9.09\text{k}\Omega$                     | 1980  | 2200 | 2420             |

| $t_{\text{ON}(\text{MIN})}$       | 最小オン時間                                       | $R_T = 9.09\text{k}\Omega$                     | 50    |      | $\text{ns}$      |

| $D_{\text{MAX}1}$                 | 最大デューティ・サイクル制限                               | $R_T = 9.09\text{k}\Omega$                     | 80%   | 85%  | 90%              |

| $D_{\text{MAX}2}$                 | 最大デューティ・サイクル制限                               | $R_T = 220\text{k}\Omega$                      | 90%   | 93%  | 96%              |

| <b>電流検出</b>                       |                                              |                                                |       |      |                  |

| $I_{\text{SLOPE}}$                | ピーク勾配補償電流                                    | $R_T = 220\text{k}\Omega$                      | 22.5  | 30   | 37.5             |

| $V_{\text{CLTH}}$                 | 電流制限スレッショルド (CS-PGND)                        |                                                | 93    | 100  | 107              |

| <b>ヒップ・モード保護 (LM51551)</b>        |                                              |                                                |       |      |                  |

|                                   | ヒップ・イネーブル・サイクル                               |                                                | 64    |      | サイクル             |

|                                   | ヒップ・タイマ・リセット・サイクル                            |                                                | 8     |      | サイクル             |

| <b>エラー・アンプ</b>                    |                                              |                                                |       |      |                  |

| $V_{\text{REF}}$                  | FB リファレンス                                    | LM5155, LM51551                                | 0.99  | 1    | 1.01             |

| $G_m$                             | 相互コンダクタンス                                    |                                                | 2     |      | $\text{mA/V}$    |

|                                   | COMP ソース電流                                   | $V_{\text{COMP}} = 1.2\text{V}$                | 180   |      | $\mu\text{A}$    |

|                                   | COMP クランプ電圧                                  | COMP 立ち上がり ( $V_{\text{UVLO}} = 2.0\text{V}$ ) | 2.5   | 2.8  | $\text{V}$       |

|                                   | COMP クランプ電圧                                  | COMP 立ち下がり                                     | 1     | 1.1  | $\text{V}$       |

| <b>OVP</b>                        |                                              |                                                |       |      |                  |

| $V_{\text{OVTH}}$                 | 過電圧スレッショルド                                   | FB の立ち上がり ( $V_{\text{REF}}$ を基準とする)           | 107%  | 110% | 113%             |

|                                   | 過電圧スレッショルド                                   | FB の立ち下がり ( $V_{\text{REF}}$ を基準とする)           | 105%  |      |                  |

| <b>PGOOD</b>                      |                                              |                                                |       |      |                  |

|                                   | PGOOD ブルダウン・スイッチの $R_{\text{DS}(\text{ON})}$ | 1mA のシンク                                       | 90    |      | $\Omega$         |

| $V_{\text{UVTH}}$                 | 低電圧スレッショルド                                   | FB の立ち下がり ( $V_{\text{REF}}$ を基準とする)           | 87%   | 90%  | 93%              |

|                                   | 低電圧スレッショルド                                   | FB の立ち上がり ( $V_{\text{REF}}$ を基準とする)           | 95%   |      |                  |

| <b>MOSFET ドライバ</b>                |                                              |                                                |       |      |                  |

|                                   | High 状態の電圧降下                                 | 100mA のシンク                                     | 0.25  |      | $\text{V}$       |

|                                   | Low 状態の電圧降下                                  | 100mA のソース                                     | 0.15  |      | $\text{V}$       |

| <b>サーマル・シャットダウン</b>               |                                              |                                                |       |      |                  |

| $T_{\text{TSD}}$                  | サーマル・シャットダウンのスレッショルド                         | 温度上昇                                           | 175   |      | $^\circ\text{C}$ |

代表値は  $T_J = 25^\circ\text{C}$ に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ の範囲で適用されます。特に記述のない限り、 $V_{BIAS} = 12\text{V}$ ,  $R_T = 9.09\text{k}\Omega$  です

| パラメータ               | テスト条件 | 最小値 | 代表値 | 最大値 | 単位 |

|---------------------|-------|-----|-----|-----|----|

| サーマル・シャットダウンのヒステリシス |       |     | 15  |     | °C |

## 8.6 代表的特性

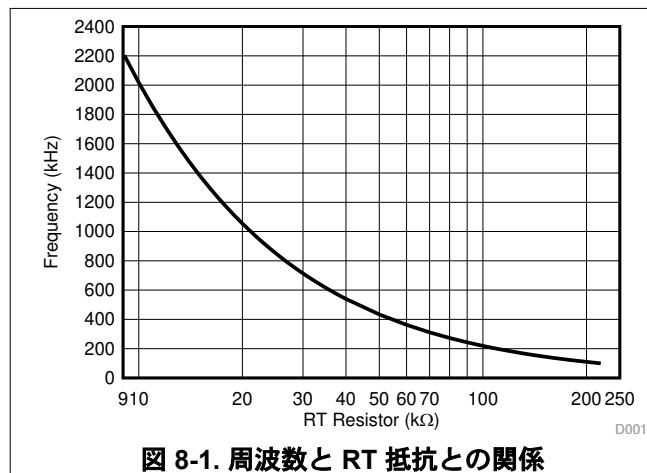

図 8-1. 周波数と RT 抵抗との関係

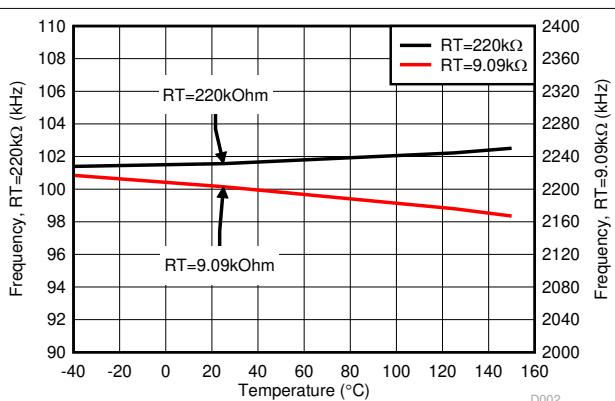

図 8-2. 周波数と温度との関係

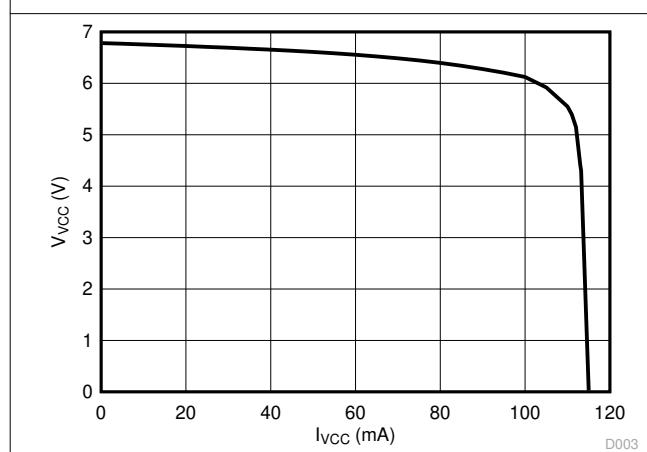

図 8-3. V<sub>VCC</sub> と I<sub>VCC</sub> との関係

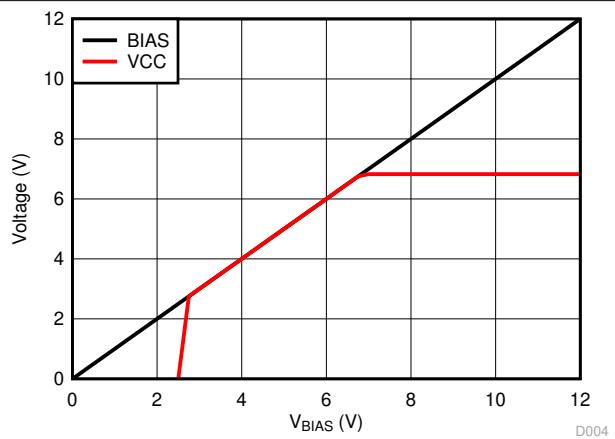

図 8-4. V<sub>VCC</sub> と V<sub>BIAS</sub> との関係 (無負荷)

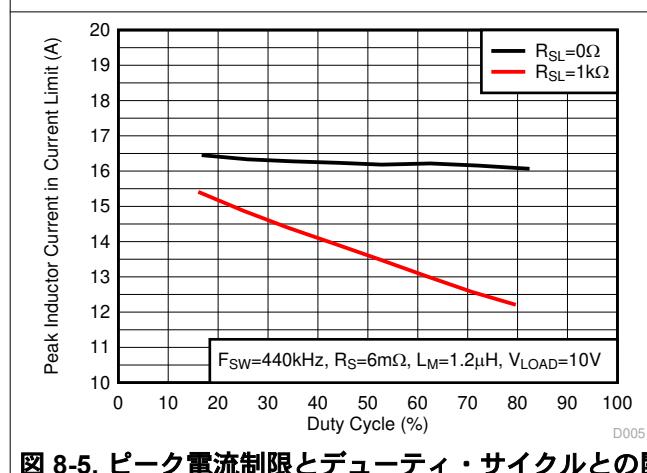

図 8-5. ピーク電流制限とデューティ・サイクルとの関係

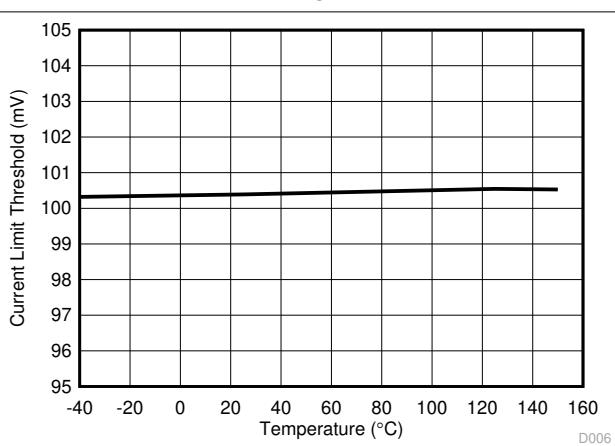

図 8-6. 電流制限スレッショルドと温度との関係

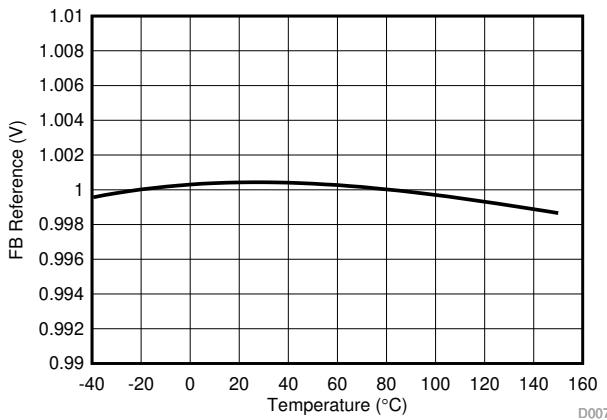

図 8-7. FB リファレンス電圧と温度との関係

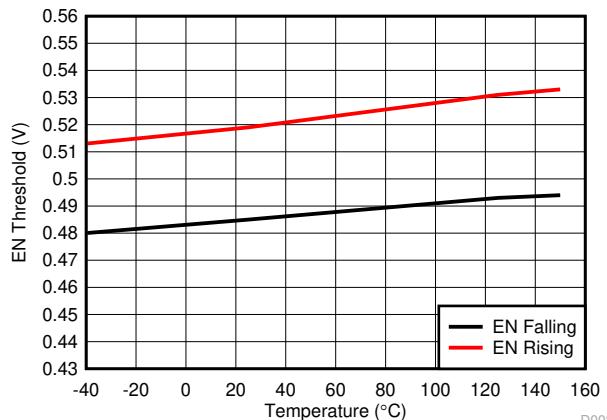

図 8-8. EN スレッショルドと温度との関係

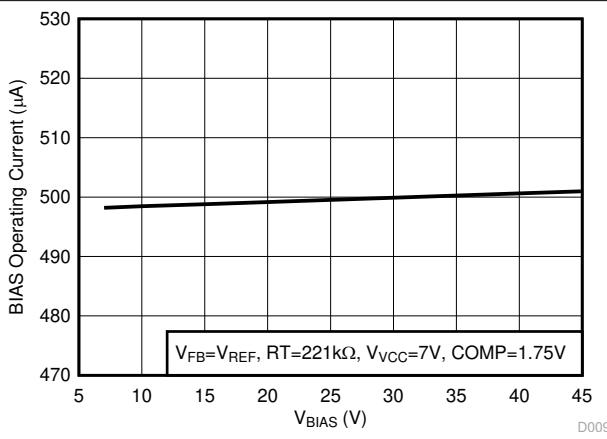

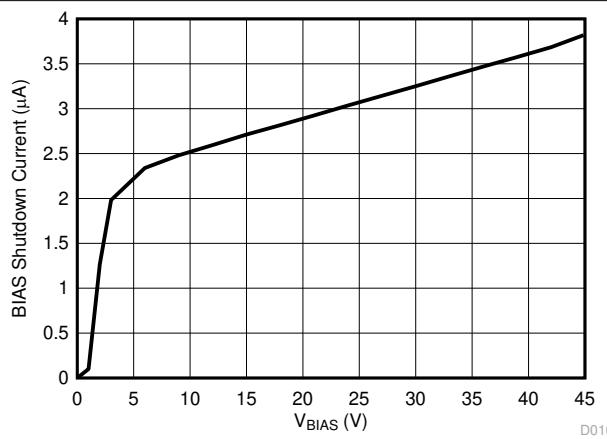

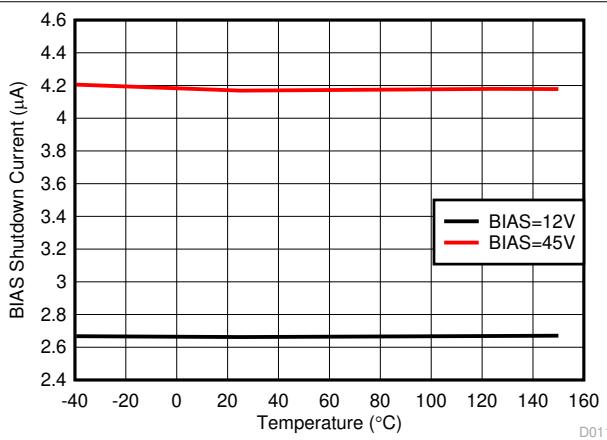

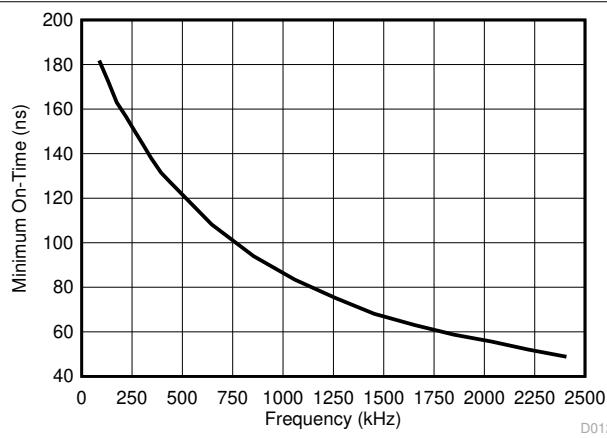

図 8-9. RT 電流を含む  $I_{OPERATING(BIAS)}$  と  $V_{BIAS}$  との関係図 8-10.  $I_{SHUTDOWN(BIAS)}$  と  $V_{BIAS}$  との関係図 8-11.  $I_{SHUTDOWN}$  と温度との関係図 8-12.  $t_{ON(MIN)}$  と周波数との関係

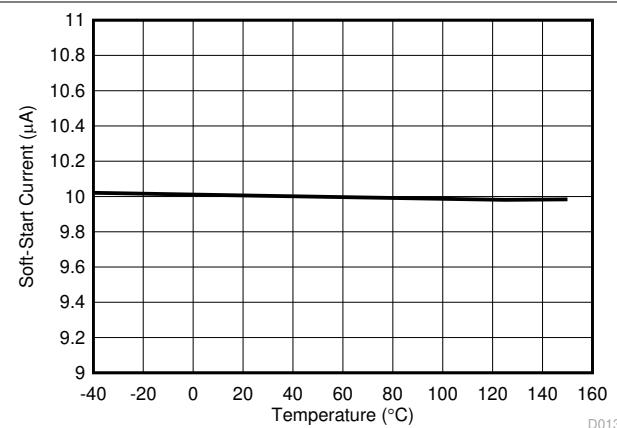

図 8-13.  $I_{ss}$  と温度との関係

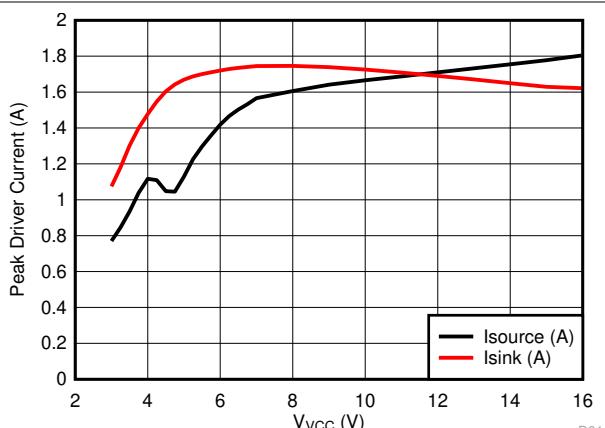

図 8-14. ピーク・ドライバ電流と  $V_{CC}$  との関係

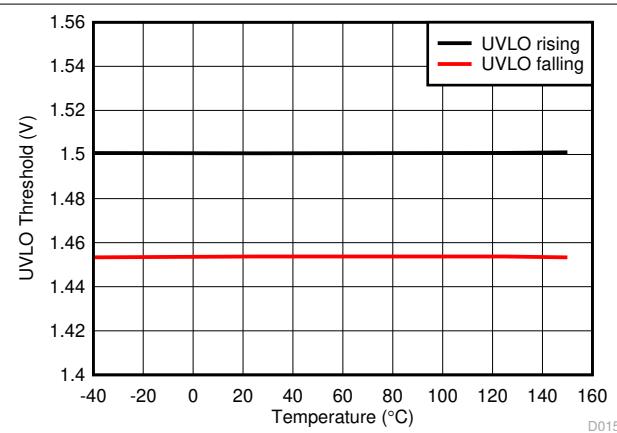

図 8-15. UVLO スレッショルドと温度との関係

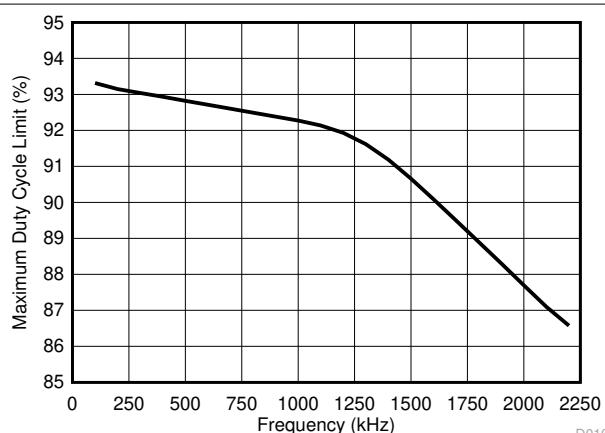

図 8-16. 最大デューティ・サイクルと周波数との関係

## 9 詳細説明

### 9.1 概要

LM5155x デバイスは、入力範囲が広い非同期昇圧コントローラで、ピーク電流モード制御を使用します。このデバイスは、昇圧、SEPIC、フライバックのトポロジで使用可能です。

LM5155x は、BIAS ピンが VCC ピンに接続されている場合、最小 2.97V の 1 セル・バッテリで起動できます。BIAS ピンが 3.5V を上回っている場合、最小 1.5V の入力電源電圧で動作できます。また内部 VCC レギュレータは、最大 45V (絶対最大定格 50V) での BIAS ピンの動作もサポートしています。スイッチング周波数は、外付けの抵抗により 100kHz ~2.2MHz の範囲で動的にプログラム可能です。2.2MHz でのスイッチングにより、AM 帯域との干渉が最小化され、ソリューション・サイズの小型化と、高速な過渡応答を実現できます。

このデバイスには、1.5A の標準 MOSFET ドライバが搭載されており、低い 100mV の電流制限スレッショルドが設定されています。また、このデバイスは外部 VCC 電源を使用して効率向上が可能です。動作電流が低く、パルス・スキッピング動作により、軽負荷時に効率が向上します。

このデバイスは、サイクル単位の電流制限、過電圧保護、ライン UVLO、サーマル・シャットダウンなどの保護機能を内蔵しています。LM51551 デバイスを選択すると、ヒップ・モード過負荷保護機能を使用できます。さらに、シャットダウン時の低  $I_Q$ 、プログラム可能なソフトスタート、プログラム可能なスロープ補償、高精度の基準電圧、パワー・グッド・インジケータ、外部クロック同期などの追加機能があります。

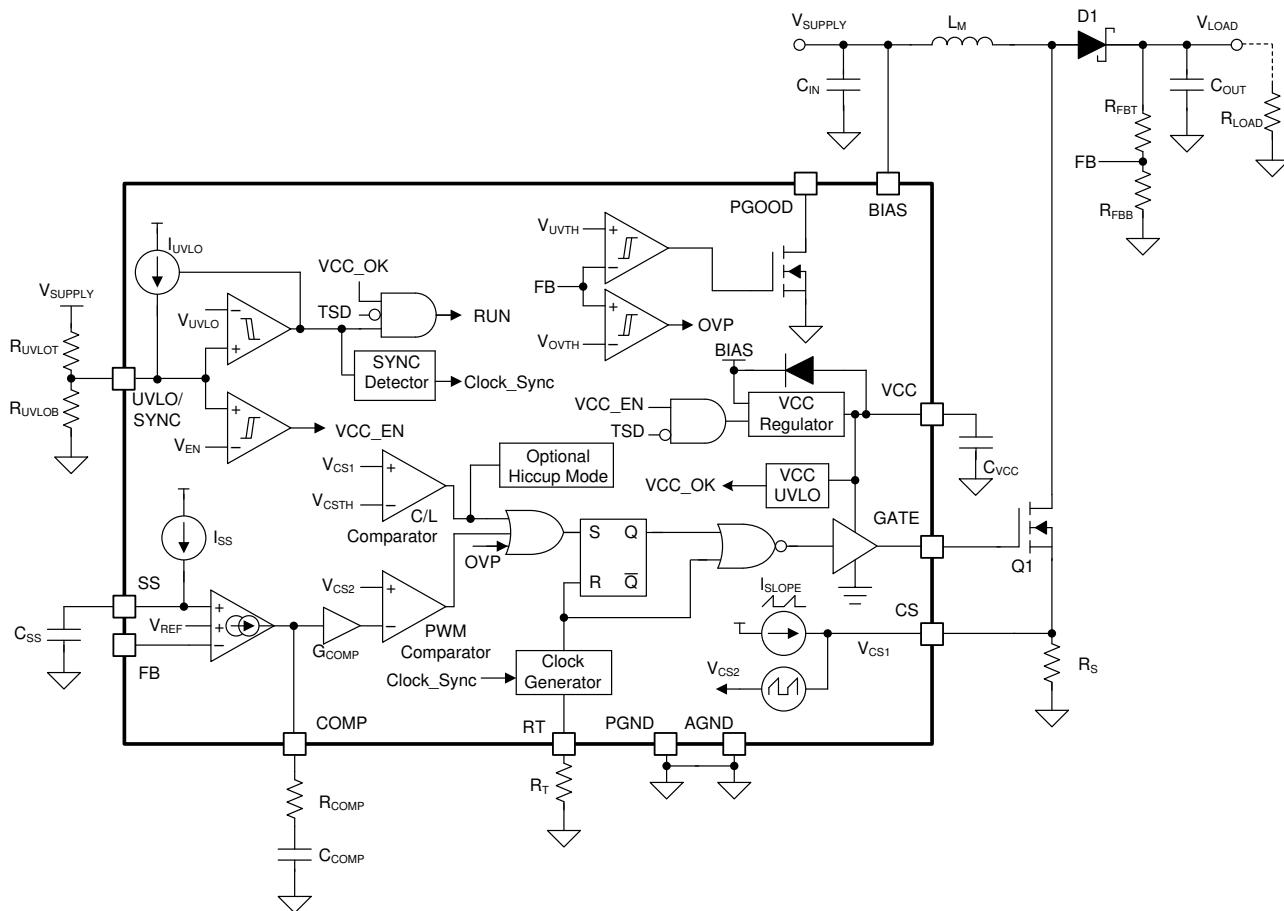

### 9.2 機能ブロック図

## 9.3 機能説明

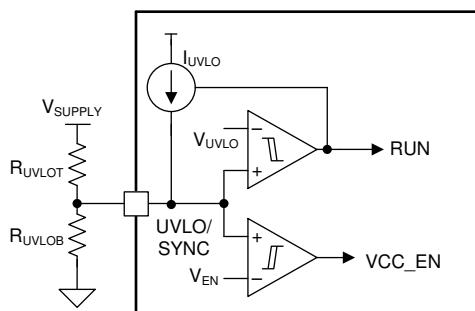

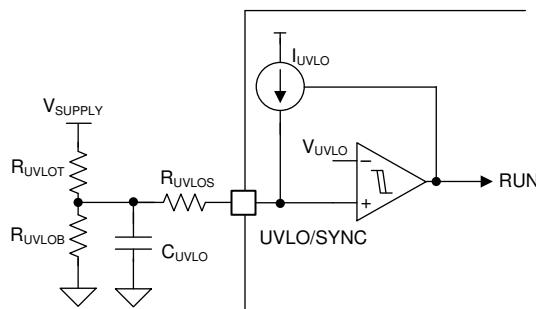

### 9.3.1 ライン低電圧ロックアウト (UVLO/SYNC ピン)

このデバイスはデュアル・レベル UVLO 回路を備えています。電源投入時に、BIAS ピンの電圧が 2.7V より高く、UVLO ピンの電圧が  $1.5\mu\text{s}$  を超えてイネーブル・スレッショルド ( $V_{\text{EN}}$ ) と UVLO スレッショルド ( $V_{\text{UVLO}}$ ) の間にある場合 (詳細は「[セクション 9.3.5](#)」を参照)、デバイスが起動し、内部構成が開始されます。このデバイスは通常、スタンバイ・モードになる前に  $65\mu\text{s}$  の内部起動遅延を必要とします。スタンバイ・モードでは、VCC レギュレータと RT レギュレータは動作し、SS ピンは接地され、GATE 出力でのスイッチングは行われません。

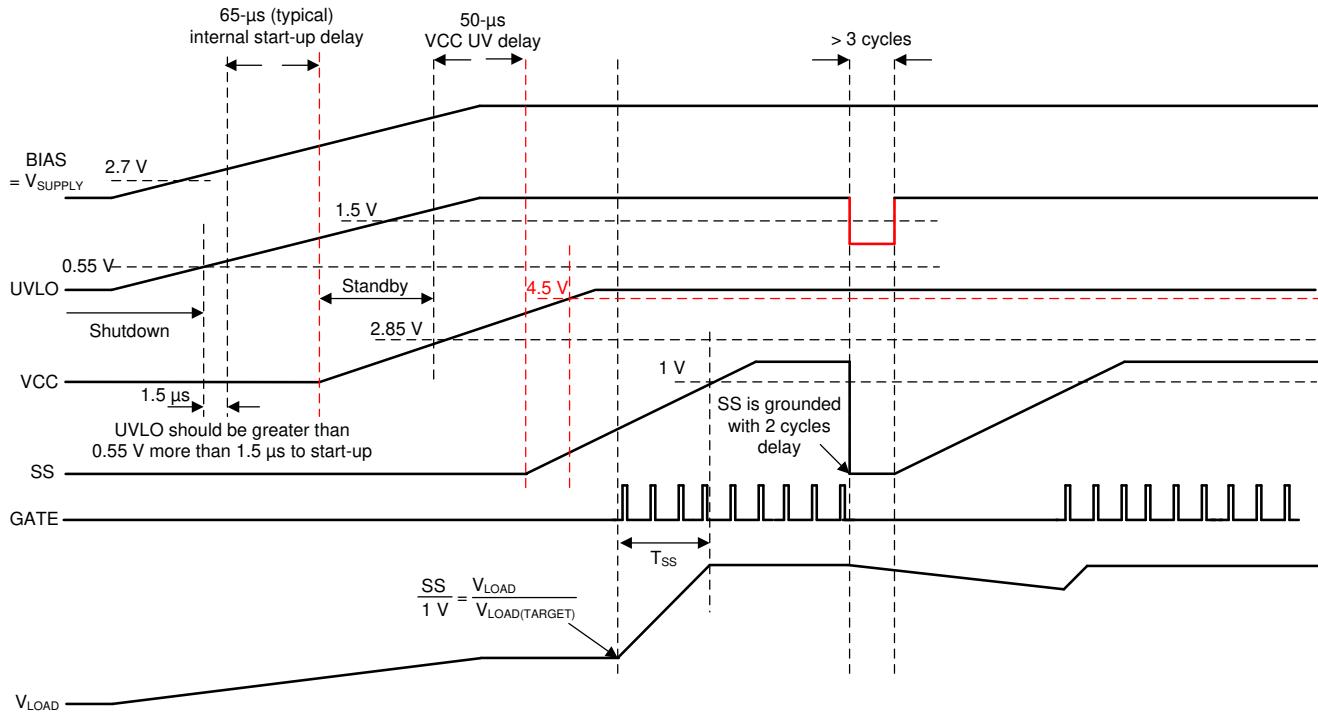

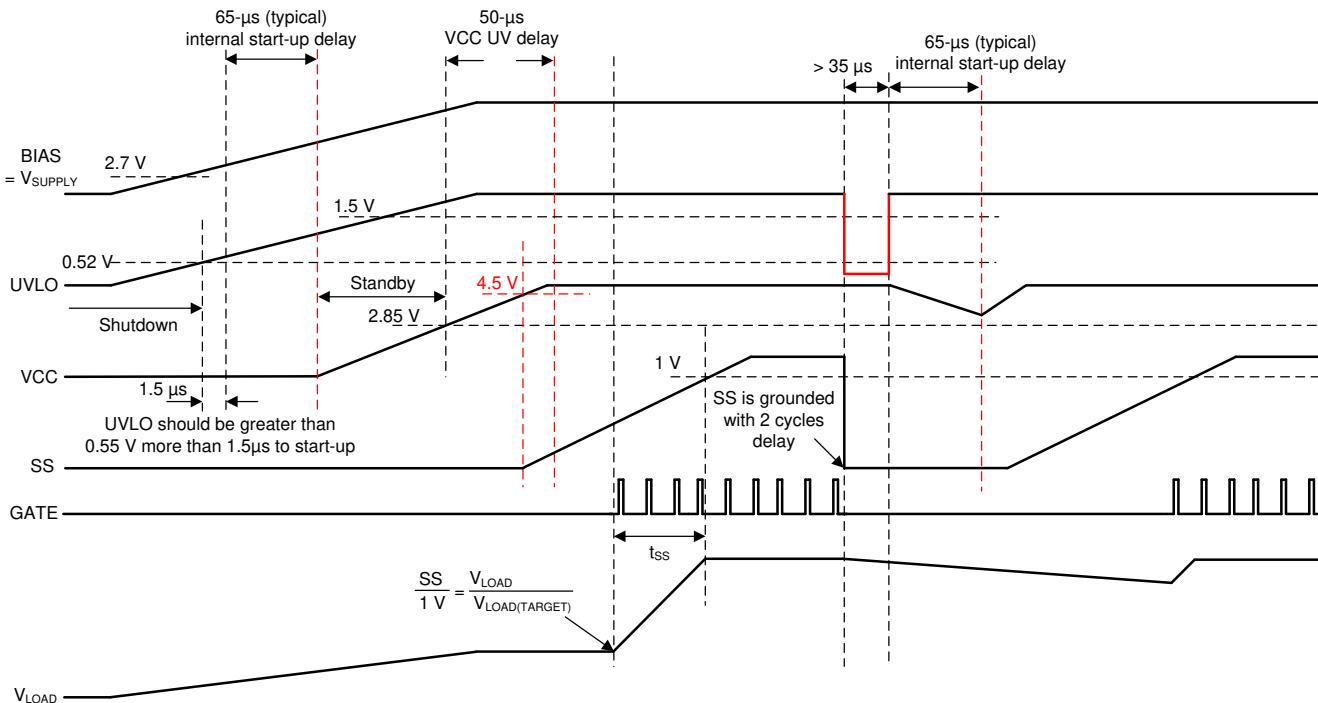

図 9-1. ライン UVLO とイネーブル

UVLO ピンの電圧が UVLO スレッショルドより高い場合、デバイスは実行モードに入ります。実行モードでは、VCC 電圧が 4.5V を超えるか、VCC 電圧が 2.85V の VCC UV スレッショルド ( $V_{\text{VCC-UVLO}}$ ) を超えてから  $50\mu\text{s}$  後かのいずれか早い方の時点で、ソフトスタート・シーケンスが開始されます。UVLO ヒステリシスは、内部の 50mV 電圧ヒステリシスと、オンまたはオフに切り替えられる追加の  $5\mu\text{A}$  電流源によって実現されます。UVLO ピンの電圧が UVLO スレッショルドより高い場合、電流ソースがイネーブルになり、UVLO ピンの電圧が急速に上昇します。UVLO ピンの電圧が UVLO スレッショルドより低くなった場合、電流ソースがディセーブルになり、UVLO ピンの電圧が急速に低下します。UVLO ピンの電圧がイネーブル・スレッショルド ( $V_{\text{EN}}$ ) より低い場合、デバイスは  $35\mu\text{s}$  (代表値) の遅延後にシャットダウン・モードに入り、すべての機能がディセーブルになります。

図 9-2. 昇圧スタートアップ波形ケース 1: 2.85V VCC UVLO によるスタートアップ、スタートアップ後の UVLO トグル

図 9-3. 昇圧スタートアップ波形ケース 2 : VCC > 4.5V のときのスタートアップ、スタートアップ後の EN トグル

外部 UVLO 抵抗デバイダは、入力電圧が望ましい動作範囲内にあるとき、UVLO ピンの電圧が 1.5V (代表値) を超えるように設計する必要があります。 $R_{UVLOT}$  と  $R_{UVLOB}$  の値は、式 1 と 式 2 に示すように計算できます。

$$R_{UVLOT} = \frac{V_{SUPPLY(ON)} \times \frac{V_{UVLO(FALLING)}}{V_{UVLO(RISING)}} - V_{SUPPLY(OFF)}}{I_{UVLO}} \quad (1)$$

ここで、

- $V_{SUPPLY(ON)}$  は、コンバータの必要なスタートアップ電圧です。

- $V_{SUPPLY(OFF)}$  は、コンバータの必要なターンオフ電圧です。

$$R_{UVLOB} = \frac{V_{UVLO(RISING)} \times R_{UVLOT}}{V_{SUPPLY(ON)} - V_{UVLO(RISING)}} \quad (2)$$

UVLO コンデンサ ( $C_{UVLO}$ ) は、スタートアップ時、または低入力電圧での厳しい負荷過渡時に入力電圧が  $V_{SUPPLY(OFF)}$  を瞬間に下回った場合に必要になります。必要な UVLO コンデンサが大きい場合、追加の直列 UVLO 抵抗 ( $R_{UVLOS}$ ) を使用することで、5 $\mu$ A のヒステリシス電流がオンになったときに UVLO ピンの電圧を急速に上昇させることができます。

図 9-4. 3 つの UVLO 抵抗を使用したライン UVLO

UVLO ピンをフローティングのままにしないでください。未使用時は BIAS ピンに接続してください。

### 9.3.2 高電圧 VCC レギュレータ (BIAS、VCC ピン)

このデバイスは、BIAS ピンから電源が供給される、広い入力範囲の内部 VCC レギュレータを備えています。広い入力範囲の VCC レギュレータにより、BIAS ピンを 3.5V~45V の電源電圧に直接接続できます。

VCC レギュレータは、デバイスがスタンバイ・モードまたは実行モードのときにオンになります。BIAS ピンの電圧が VCC レギュレーション・ターゲットを下回るとき、VCC 出力は小さなドロップアウト電圧で BIAS に追従します。BIAS ピンの電圧が VCC レギュレーション・ターゲットより高いとき、VCC レギュレータは N チャネル MOSFET ドライバに 6.85V の電源を供給します。

VCC レギュレータは、最低 35mA の能力で、VCC ピンに接続されているコンデンサに電流を供給します。推奨の VCC コンデンサの値は、1 $\mu$ F~4.7 $\mu$ F です。

このデバイスは、通常の構成で 3.5V~45V の広い入力範囲をサポートします。BIAS ピンを VCC ピンに直接接続することで、デバイスは 2.97V~16V の入力をサポートします。この構成は、デバイスが 1 セル・バッテリから起動する場合に推奨されます。

図 9-5. 2.97V スタートアップ (BIAS = VCC)

図 9-6 に示すように、昇圧コンバータ出力または外部電源から BIAS ピンに電力を供給することで、スタートアップ後の最低電源電圧をさらに下げることができます。

図 9-6. スタートアップ後の最低動作電圧の低下

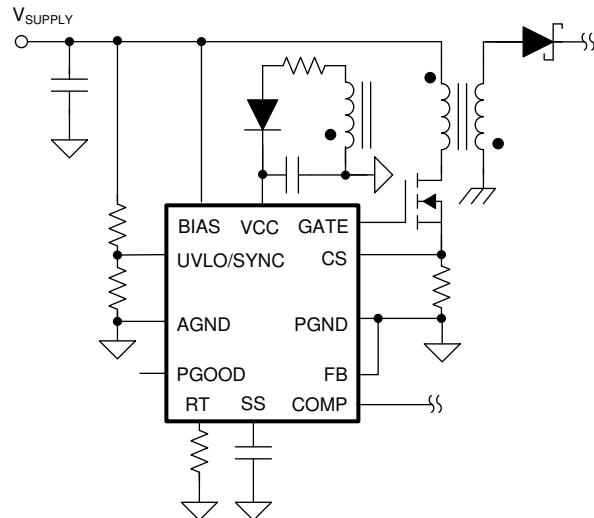

フライバック・トポロジでは、追加のトランス巻線を使用して VCC に電力を供給することで、デバイスの内部消費電力を低減できます。この構成では、外部 VCC 電源電圧は VCC レギュレーション・ターゲット ( $V_{VCC-REG}$ ) より高い必要があり、また VCC レギュレータには VCC と BIAS の間にダイオードが含まれているため、BIAS ピンの電圧は VCC 電圧より高い必要があります。

図 9-7. 外部 VCC 電源 (BIAS  $\geq$  VCC)

外部 VCC バイアス電源の電圧が BIAS ピンの電圧よりも高い場合、外部バイアス電源から VCC 経由で昇圧入力電源に電流が流れることを防止するため、入力電源と BIAS ピンの間に外付けのブロッキング・ダイオードを使用します。

### 9.3.3 ソフトスタート (SS ピン)

ソフトスタート機能は、コンバータを定常状態動作点へと徐々に到達させることで、スタートアップ時のストレスやサージを低減します。このデバイスは、SS ピンの電圧、または内部の 1.2V 基準電圧のどちらか低い方に FB ピンを調整します。

起動時、内部の  $10\mu\text{A}$  ソフトスタート電流源 ( $I_{SS}$ ) は、VCC 電圧が  $2.85\text{VCC}$  UV スレッショルドを超えてから  $50\mu\text{s}$  後、または VCC 電圧が  $4.5\text{V}$  を超えたときのいずれか早い方でオンになります。ソフトスタート電流によって、SS ピンに接続された外付けソフトスタート・コンデンサの電圧が徐々に上昇します。その結果、出力電圧が次第に上昇します。SS ピンは、VCC が VCC UVLO スレッショルド未満の場合、UVLO が UVLO スレッショルド未満の場合、ヒップ・モードのオフ時間のとき、またはサーマル・シャットダウンのときに内部スイッチによってグランドにプルダウンされます。

昇圧トポロジでは、ソフトスタート時間 ( $t_{SS}$ ) は入力電源電圧によって変化します。昇圧トポロジにおけるソフトスタート時間は、式 3 に示すように計算されます。

$$t_{SS} = \frac{C_{SS}}{I_{SS}} \times \left(1 - \frac{V_{SUPPLY}}{V_{LOAD}}\right) \times V_{REF} \quad (3)$$

SEPIC トポロジでは、ソフト・スタート時間 ( $t_{SS}$ ) は次のように計算されます。

$$t_{SS} = \frac{C_{SS}}{I_{SS}} \times V_{REF} \quad (4)$$

テキサス・インスツルメンツでは、過電流状態にならずにコンバータを起動できるよう、ソフト・スタート時間を十分に長く設定することをおすすめします。詳細については、「」を参照してください。

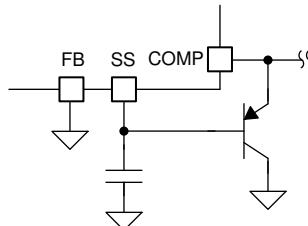

図 9-8 に、フライバック・トポロジでの 1 次側ソフトスタートの実装を示します。

図 9-8. フライバックの 1 次側ソフトスタート

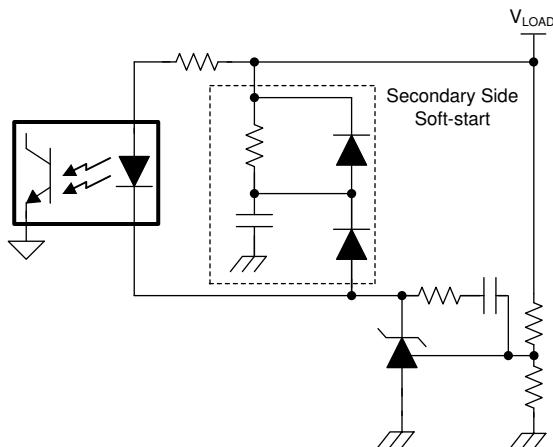

図 9-9 に、フライバック・トポロジでの 2 次側ソフトスタートの実装を示します。

図 9-9. フライバックの 2 次側ソフトスタート

#### 9.3.4 スイッチング周波数 (RT ピン)

デバイスのスイッチング周波数は、RT および AGND ピンの間に接続された単一の RT 抵抗により設定されます。RT スイッチング周波数 ( $f_{RT}$ ) を設定するための抵抗値は、式 5 を使用して計算されます。

$$R_T = \frac{2.21 \times 10^{10}}{f_{RT(TYPICAL)}} - 955 \quad (5)$$

デバイスがイネーブルの時、RT ピンは内部の RT レギュレータを使用して、0.5V に調整されます。

#### 9.3.5 クロック同期 (UVLO/SYNC ピン)

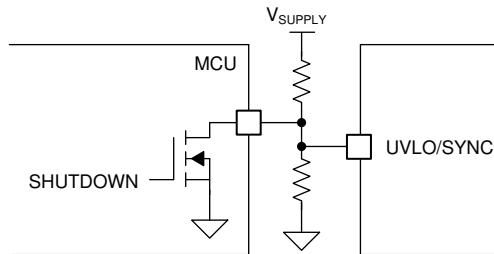

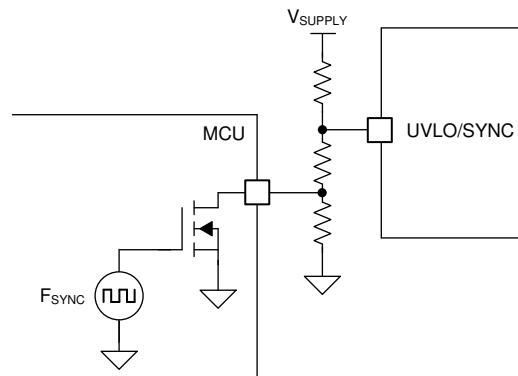

デバイスのスイッチング周波数は、UVLO/SYNC ピンをプルダウンすることにより、外部クロックに同期させることができます。デバイスの内部クロックは立ち下がりエッジで同期されますが、最大デューティ・サイクル制限によって決定される強制オフ時間中は、立ち下がりエッジの入力を無視します。外部同期クロックは、UVLO/SYNC ピンの電圧を 1.45V (代表値) 未満にプルダウンする必要があります。プルダウン・パルスのデューティ・サイクルは制限されませんが、最小プルダウン・パルス幅は 150ns より大きく、最小プルアップ・パルス幅は 250ns より大きくする必要があります。図 9-10 は、リモート・シャットダウン機能の実装を示しています。UVLO ピンは、ディスクリート MOSFET または MCU のオープン・ドレイン出力によってプルダウンできます。この構成では、デバイスは UVLO ピンがグランドに接続された直後にスイッチングを停止し、UVLO ピンがグランドに接続されてから 35μs (代表値) 後にシャットダウンします。

図 9-10. UVLO とシャットダウン

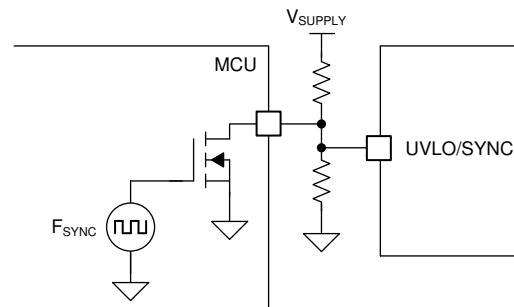

図 9-11 に、シャットダウン機能とクロック同期機能の実装をまとめて示します。この構成では、UVLO ピンがグランドに接続されると、デバイスはスイッチングを直ちに停止し、 $f_{SYNC}$  が  $35\mu\text{s}$  (代表値) を超えて High ロジック状態にとどまる場合 (UVLO が  $35\mu\text{s}$  (代表値) を超えて Low ロジック状態にある場合)、デバイスはシャットダウンします。デバイスがイネーブルされた後にクロック・パルスが供給された場合、デバイスは  $f_{SYNC}$  で動作します。

図 9-11. UVLO、シャットダウン、クロック同期

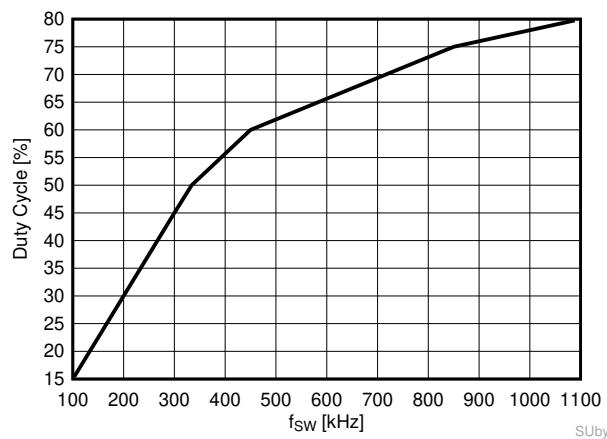

図 9-13 および 図 9-14 に、スタンバイ機能とクロック同期機能の実装をまとめて示します。この構成では、デバイスは  $f_{SYNC}$  が High ロジック状態にとどまる場合、スイッチングを直ちに停止し、 $f_{SYNC}$  が 2 スイッチング・サイクルより長い間 High ロジック状態にとどまる場合、スタンバイ・モードになります。クロック・パルスが供給されている場合、デバイスは  $f_{SYNC}$  で動作します。UVLO ピンの電圧がイネーブル・スレッショルドより  $1.5\mu\text{s}$  を超えて高いとき、デバイスがイネーブルされる可能性があるため、デバイスがイネーブルになる前に最初から外部クロック同期パルスが供給されている場合は、図 9-13 および 図 9-14 の構成を推奨します。この  $1.5\mu\text{s}$  の要件は、同期パルスのデューティ・サイクルが 50% を超える場合、緩和できます。図 9-12 に、同期パルスによる起動に必要な最小デューティ・サイクルを示します。スイッチング周波数が  $1.1\text{MHz}$  を超える場合、外部同期パルスを印加する前に、UVLO ピンの電圧が  $1.5\mu\text{s}$  より長い間、イネーブル・スレッショルドを超えている必要があります。

図 9-12. SYNC で起動するのに必要なデューティ・サイクル

図 9-13. UVLO、スタンバイ、クロック同期 (a)

図 9-14. UVLO、スタンバイ、クロック同期 (b)

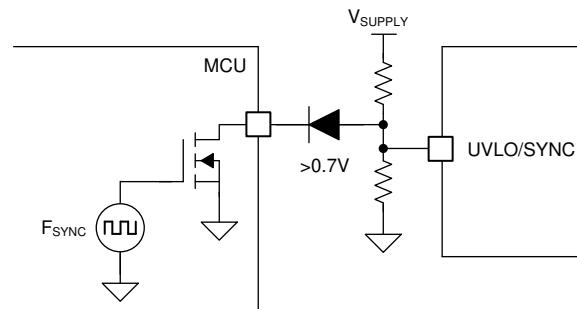

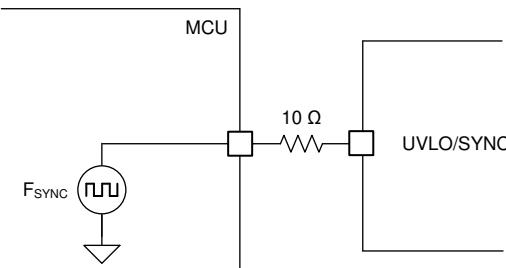

UVLO 機能が不要な場合、MCU のプッシュプル出力の 1 つを使用して、シャットダウン機能とクロック同期機能と一緒に実装できます。この構成では、 $f_{SYNC}$  が  $35\mu\text{s}$  (代表値) を超えて Low ロジック状態にとどまる場合、デバイスはシャットダウンします。 $f_{SYNC}$  が  $1.5\mu\text{s}$  を超えて High ロジック状態にとどまる場合、デバイスはイネーブルになります。デバイスがイネーブルになった後にクロック・パルスが供給された場合、デバイスは  $f_{SYNC}$  で動作します。また、この構成では、BIAS が供給された後に外部クロック・パルスを印加することを推奨します。電流制限抵抗を使用して UVLO ピンに流れる電流を  $1\text{mA}$  未満に制限することにより、BIAS が供給される前に外部クロック・パルスを供給できます (図 9-15 を参照)。

図 9-15. シャットダウンとクロック同期

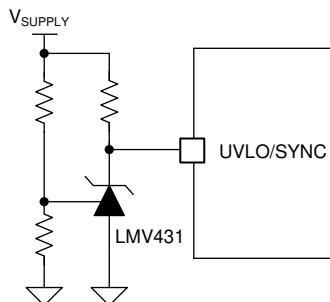

図 9-16 に、外部回路を使用した反転イネーブルの実装を示します。

図 9-16. 反転 UVLO

外部クロック周波数 ( $f_{SYNC}$ ) は、 $f_{RT(TYPICAL)}$  の +25%~−30% の範囲内である必要があります。最大デューティ・サイクル制限とスロープ抵抗 ( $R_{SL}$ ) によるピーク電流制限はクロック同期の影響を受けるため、クロック同期機能を使用する場合は特に注意してください。詳細については、「[セクション 9.3.6](#)」、「[セクション 9.3.7](#)」、および「[セクション 9.3.11](#)」を参照してください。

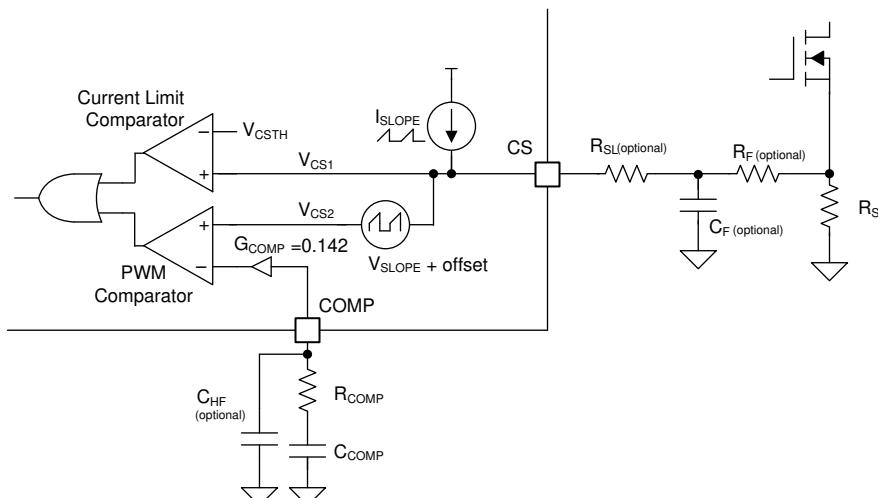

### 9.3.6 電流センスとスロープ補償 (CS ピン)

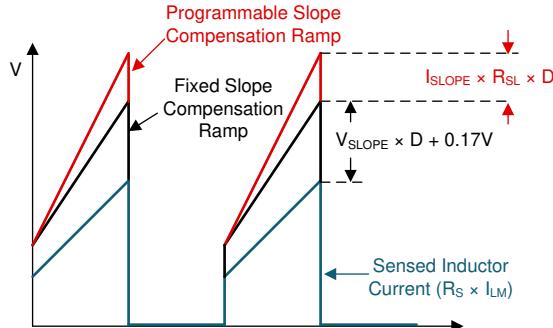

このデバイスはローサイド電流センスを持ち、固定およびオプションのプログラム可能なスロープ補償ランプを提供し、高デューティでの分数調波の発振の防止に役立ちます。PWM 動作用の検出されるインダクタ電流の入力には、固定スロープ補償ランプとプログラム可能なスロープ補償ランプの両方が追加されますが、検出されるインダクタ電流の入力には、プログラム可能なスロープ補償ランプのみが追加されます (図 9-17 を参照)。入力電源電圧に対する正確なピーク電流制限動作のために、テキサス・インスツルメンツは、固定スロープ補償のみを使用することを推奨します (図 8-5 を参照)。

このデバイスは、外部スロープ抵抗 ( $R_{SL}$ ) と  $30\mu\text{A} \times f_{RT}$  のスロープを持つこぎり波電流源を使用して、プログラム可能なスロープ補償ランプを生成することができます。この電流は CS ピンから流れ出します。

図 9-17. 電流センシングとスロープ補償

図 9-18. PWM コンバレータ入力におけるスロープ補償ランプ (a)

図 9-19. 電流制限コンバレータ入力におけるスロープ補償ランプ (b)

式 6 を使用してピーク・スロープ電流 (I<sub>SLOPE</sub>) の値を計算し、式 7 を使用してピーク・スロープ電圧 (V<sub>SLOPE</sub>) の値を計算します。

$$I_{SLOPE} = 30\mu A \times \frac{f_{RT}}{f_{SYNC}} \quad (6)$$

$$V_{SLOPE} = 40mV \times \frac{f_{RT}}{f_{SYNC}} \quad (7)$$

ここで、

- クロック同期を使用しない場合は、f<sub>SYNC</sub> = f<sub>RT</sub>。

ピーク電流モードの制御理論に従い、補償ランプのスロープは、高いデューティ・サイクルにおいて分数調波の発振を防止するため、検出されるインダクタ電流の立ち下がりスロープの半分よりも大きい必要があります。したがって、昇圧トポジにおけるスロープ補償の最小値は、次の不等式を満たす必要があります。

$$0.5 \times \frac{(V_{LOAD} + V_F) - V_{SUPPLY}}{L_M} \times R_S \times \text{Margin} < 40mV \times f_{SW} \quad (8)$$

ここで、

- V<sub>F</sub> は、外付けダイオード D1 の順方向電圧降下です。

理想的でない要因をカバーするためのマージンの推奨値は 1.2 です。必要であれば、R<sub>SL</sub> を追加して、補償ランプのスロープをさらに大きくすることができます。通常、検出されるインダクタ電流の立ち下がりスロープの 82% が、スロープ補償の最適量として知られています。検出されるインダクタ電流の立ち下がりスロープの 82% を達成するための R<sub>SL</sub> の値は、式 9 に示すように計算されます。

$$0.82 \times \frac{(V_{LOAD} + V_F) - V_{SUPPLY}}{L_M} \times R_S = (30\mu A \times R_{SL} + 40mV) \times f_{SW} \quad (9)$$

クロック同期を使用しない場合、f<sub>SW</sub> 周波数は f<sub>RT</sub> 周波数と等しくなります。クロック同期を使用する場合、f<sub>SW</sub> 周波数は f<sub>SYNC</sub> 周波数と等しくなります。R<sub>SL</sub> 抵抗の最大値は 2kΩ です。

### 9.3.7 電流制限と最小オン時間 (CS ピン)

このデバイスは、インダクタ電流とプログラム可能なスロープ補償ランプの合計が電流制限スレッショルド ( $V_{CLTH}$ ) に達したときに MOSFET をオフにする、サイクルごとのピーク電流制限保護を提供します。定常状態におけるピーク・インダクタ電流制限 ( $I_{PEAK-CL}$ ) は、式 10 に示すように計算されます。

$$I_{PEAK-CL} = \frac{V_{CLTH} - 30\mu A \times R_{SL} \times \frac{f_{RT}}{f_{SYNC}} \times D}{R_S} \quad (10)$$

実際のデューティ・サイクルは、MOSFET とセンス抵抗の電圧降下により、推定値よりも大きくなります。推定デューティ・サイクルは、式 11 に示すように計算されます。

$$D = 1 - \frac{V_{SUPPLY}}{V_{LOAD} + V_F} \quad (11)$$

昇圧コンバータには、電源からハイサイド電力ダイオード (D1) を経由する、負荷への自然なパススルー・パスがあります。このパスとデバイスの最小オン時間制限が原因となって、昇圧コンバータは出力電圧が入力電源電圧に近い、またはそれより低いときに、電流制限保護を行えません。最小オン時間は 図 8-12 に示されており、式 12 のように計算されます。

$$t_{ON(MIN)} \approx \frac{800 \times 10^{-15}}{\frac{1}{8 \times R_T} + 4 \times 10^{-6}} \quad (12)$$

必要であれば、電流センス信号の大きな先端エッジのスパイクを取り除くため、CS ピンに小さな外付け RC フィルタ ( $R_F, C_F$ ) を追加することができます。 $R_F$  の値は  $10\Omega \sim 200\Omega$  の範囲で選択し、 $C_F$  の値は  $100pF \sim 2nF$  の範囲で選択します。この RC フィルタの影響により、オン時間が  $2 \times R_F \times C_F$  より小さいときは、ピーク電流制限が有効になりません。オフ時間に  $C_F$  を完全に放電するには、RC 時定数が次の不等式を満たす必要があります。

$$3 \times R_F \times C_F < \frac{1-D}{f_{SW}} \quad (13)$$

### 9.3.8 帰還およびエラー・アンプ (FB、COMP ピン)

帰還分割抵抗は、内部の相互コンダクタンス・エラー・アンプに接続され、このアンプは高い出力抵抗 ( $R_O = 10M\Omega$ ) と広い帯域幅 ( $BW = 7MHz$ ) を備えています。内部の相互コンダクタンス・エラー・アンプは、FB ピンと SS ピンの電圧の差または内部基準電圧のいずれか低い方に比例する電流を供給します。内部の相互コンダクタンス・エラー・アンプは、通常動作中には対称的なソースおよびシンク機能を提供し、FB が OVP スレッショルドを超えるとシンク機能を低減します。

出力レギュレーション・ターゲットを設定するには、式 14 に示すように帰還抵抗の値を選択します。

$$V_{LOAD} = V_{REF} \times \left( \frac{R_{FBT}}{R_{FBB}} + 1 \right) \quad (14)$$

エラー・アンプの出力は COMP ピンに接続されるため、Type 2 のループ補償ネットワークを使用できます。 $R_{COMP}$ 、 $C_{COMP}$ 、およびオプションの  $C_{HF}$  ループ補償部品は、エラー・アンプのゲインと位相の特性を構成し、安定したループ応答を実現します。FB ピンの絶対最大定格電圧は  $3.8V$  です。必要に応じて、特に車載用の負荷ダンプ過渡時に、帰還抵抗分圧器の入力を外付けのツェナー・ダイオードでクランプできます。

COMP ピンは内部クランプを備えています。最大 COMP クランプは、シャットダウン中でも COMP ピンの最大電圧を絶対最大定格未満に制限します。最小 COMP クランプは、無負荷から重負荷への移行中にできるだけ早くスイッチングを開始できるように、COMP ピンの最小電圧を制限します。フライバック・トポロジで FB がグランドに接続されている場合、最小 COMP クランプはディセーブルになります。

### 9.3.9 パワー・グッド・インジケータ (PGOOD ピン)

このデバイスは、パワー・グッド・インジケータ (PGOOD) を備えており、シーケンシングと監視を簡素化できます。FB ピンの電圧がフィードバック低電圧スレッショルド ( $V_{UVTH}$ ) より高く、VCC が VCC UVLO スレッショルドより高く、UVLO/EN が EN スレッショルドより高い場合、PGOOD は高インピーダンスのオープン・ドレイン状態に切り替わります。25μs のグリッヂ除去フィルタは、過渡現象による PGOOD の誤ったプルダウンを防ぎます。推奨される最小プルアップ抵抗の値は 10kΩ です。

PGOOD ピンから BIAS ピンへの内部ダイオード経路により、PGOOD ピンの電圧は  $V_{BIAS} + 0.3V$  を超えることはできません。

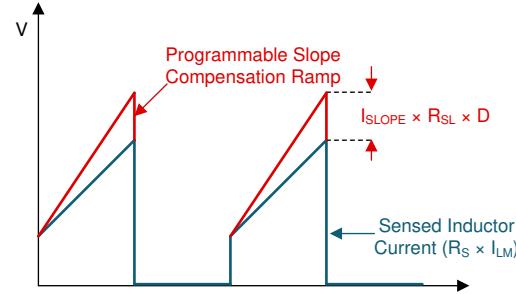

### 9.3.10 ヒカップ・モード過負荷保護 (LM51551 のみ)

長時間の電流制限状態においてコンバータをさらに保護するために、LM51551 デバイスのオプションにはヒカップ・モード過負荷保護機能があります。LM51551 の内部ヒカップ・モード・フォルト・タイマは、サイクルごとの電流制限が発生すると、PWM クロック・サイクルをカウントします。ヒカップ・モード・フォルト・タイマが 64 サイクルの電流制限を検出すると、内部のヒカップ・モード・オフ・タイマがデバイスのスイッチングを強制的に停止し、SS をプルダウンします。その後、ヒカップ・モード・オフ時間が 32768 サイクル経過した後、デバイスは再起動します。電流制限スレッショルドを超えないまま、スイッチング・サイクルが連続 8 回発生すると、64 サイクルのヒカップ・モード・フォルト・タイマはリセットされます。ヒカップ・モード・フォルト・タイマは、ソフトスタート中にイネーブルになるため、ソフトスタート時間は、ソフトスタート時間中にヒカップ・モード保護がトリガされないように十分な長さにする必要があります。

図 9-20. ヒカップ・モード過負荷保護

過酷な負荷過渡状態での予期しないヒカップ・モード動作を回避するため、ピーク電流制限をプログラムするときには、より多くのマージンを取ることを推奨します。

### 9.3.11 最大デューティ・サイクル制限と最低入力電源電圧

昇圧コンバータを設計するとき、最大デューティ・サイクルは、最低電源電圧でレビューする必要があります。目標出力電圧を達成できる最低入力電源電圧は、最大デューティ・サイクル制限によって制限され、次のように推定できます。

$$V_{SUPPLY(MIN)} \approx (V_{LOAD} + V_F) \times (1 - D_{MAX}) + I_{SUPPLY(MAX)} \times R_{DCR} + I_{SUPPLY(MAX)} \times (R_{DS(ON)} + R_S) \times D_{MAX} \quad (15)$$

ここで、

- $I_{SUPPLY(MAX)}$ =最大入力電流

- $R_{DCR}$ =インダクタの DC 抵抗

- $R_{DS(ON)}$ =MOSFET のオン抵抗

$$D_{MAX1} = 1 - 0.1 \times \frac{f_{SYNC}}{f_{RT}} \quad (16)$$

$$D_{MAX2} = 1 - 100\text{ns} \times f_{SW} \quad (17)$$

$f_{RT}$  よりも低い  $f_{SYNC}$  を供給すると、最低入力電源電圧をさらに減らすことができます。 $D_{MAX}$  は、 $D_{MAX1}$  または  $D_{MAX2}$  のいずれか低い方です。

### 9.3.12 MOSFET ドライバ (GATE ピン)

このデバイスは、1.5A のピーク電流をソースまたはシンクできる N チャネル MOSFET ドライバを備えています。ピーク・ソーシング電流は、6.75V の VCC レギュレーション・ターゲットよりも高い外部 VCC を供給すると大きくなります。スタートアップ時、特に入力電圧範囲が VCC レギュレーション・ターゲットを下回っている場合、VCC 電圧は MOSFET を完全にエンハンスするのに十分である必要があります。MOSFET の駆動電圧が、スタートアップ時に MOSFET のゲート・プライ一電圧よりも低い場合、昇圧コンバータが正しくスタートアップせず、最大デューティ・サイクルで高い消費電力の状態のままになる可能性があります。この状態は、スレッショルドの低い N チャネル MOSFET スイッチを選択し、 $V_{SUPPLY(ON)}$  を 6~7V より高く設定することで回避できます。内部 VCC レギュレータのソース能力には限界があるため、MOSFET のゲート電荷は次の不等式を満たす必要があります。

$$Q_{G@VCC} \times f_{SW} < 35\text{mA} \quad (18)$$

シャットダウン時の誤ターンオンを防ぐために、GATE と PGND の間に  $1\text{M}\Omega$  の内部抵抗が接続されています。昇圧トポジでは、MOSFET の寄生容量  $C_{DG}$  を介したカップリングに起因する誤ターンオンを回避するために、 $65\mu\text{s}$  の内部スタートアップ遅延の間、スイッチ・ノードの  $dV/dT$  を制限する必要があります。

### 9.3.13 過電圧保護 (OVP)

このデバイスは、出力電圧に OVP を備えています。OVP は FB ピンで検出されます。FB ピンの電圧が過電圧スレッショルド ( $V_{OVT\text{H}}$ ) を超えると、OVP がトリガされ、スイッチングが停止します。OVP の間、内部エラー・アンプは動作しますが、最大ソース / シンク能力は  $40\mu\text{A}$  に低下します。

### 9.3.14 サーマル・シャットダウン (TSD)

内部サーマル・シャットダウンは、接合部温度がサーマル・シャットダウン・スレッショルド ( $T_{TSD}$ ) を超えると、VCC レギュレータをオフにし、スイッチングをディセーブルにし、SS をプルダウンします。温度が  $15^\circ\text{C}$  低下すると、VCC レギュレータが再びイネーブルになり、デバイスはソフト・スタートを実行します。

## 9.4 デバイスの機能モード

### 9.4.1 シャットダウン・モード

UVLO ピンの電圧が  $35\mu\text{s}$  (代表値) より長くイネーブル・スレッショルドを下回ると、デバイスはシャットダウン・モードになります。すべての機能がディセーブルになります。シャットダウン・モードでは、デバイスは BIAS ピンの消費電流を  $2.6\mu\text{A}$  (代表値) 未満に減少させます。

### 9.4.2 スタンバイ・モード

UVLO ピンの電圧がイネーブル・スレッショルドより大きく、かつ UVLO スレッショルドを下回る状態が  $1.5\mu\text{s}$  より長く続ぐと、デバイスはスタンバイ・モードになります。VCC レギュレータは動作し、RT レギュレータは動作し、SS ピンは接地され、GATE 出力でのスイッチングは行われません。PGOOD は、VCC 電圧が VCC UV スレッショルドよりも高いとき、アクティブになります。

### 9.4.3 実行モード

UVLO ピンの電圧が UVLO スレッショルドを超え、VCC の電圧が十分である場合、デバイスは RUN モードに入ります。このモードでは、VCC 電圧が 2.85VCC UV スレッショルドを超えてから 50 $\mu$ s 後、または VCC 電圧が 4.5V を超えた場合、いずれか早い方からソフトスタートが開始されます。

## 10 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 10.1 アプリケーション情報

昇圧コンバータのループ応答と部品選択の詳細については、『LM5155-Q1 を使用した昇圧コンバータの設計方法』アプリケーション・ノートを参照してください。

### 10.2 代表的なアプリケーション

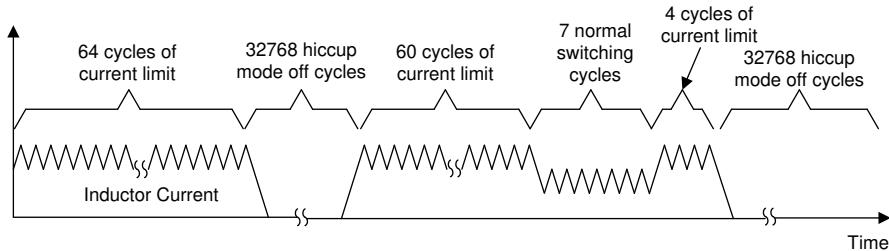

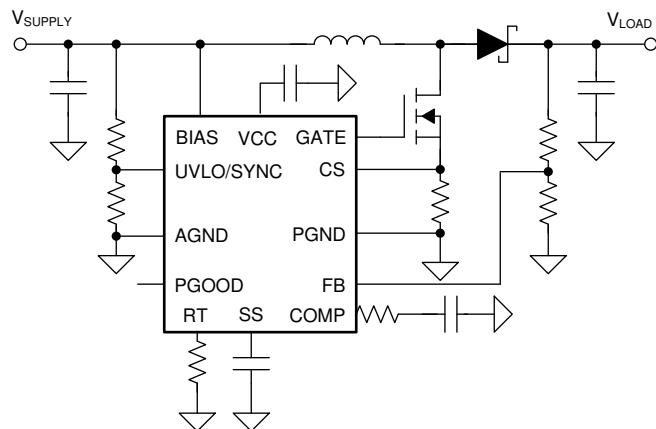

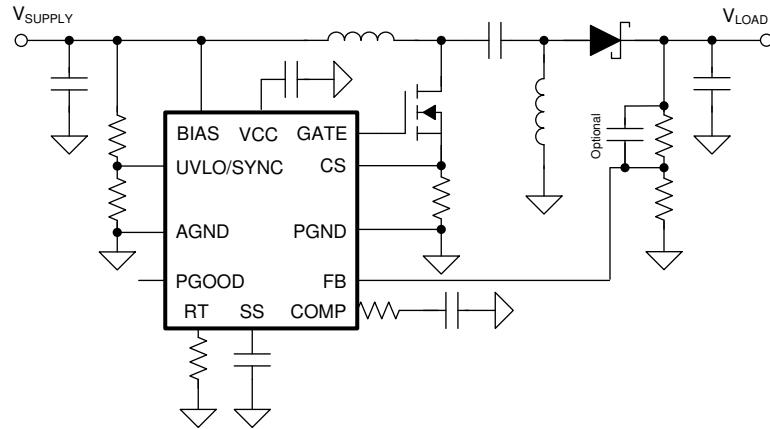

図 10-1 に、昇圧コンバータを設計するためのすべてのオプション部品を示します。

図 10-1. オプション部品を含む代表的な昇圧コンバータの回路

#### 10.2.1 設計要件

このアプリケーション例の入力、出力、性能のパラメータを、表 10-1 に示します。

表 10-1. 設計例のパラメータ

| 設計パラメータ                        | 値                    |

|--------------------------------|----------------------|

| 最低入力電源電圧 ( $V_{SUPPLY(MIN)}$ ) | 6V                   |

| 目標出力電圧 ( $V_{LOAD}$ )          | 24V                  |

| 最大負荷電流 ( $I_{LOAD}$ )          | 2A ( $\approx 48W$ ) |

| 標準スイッチング周波数 ( $f_{sw}$ )       | 440kHz               |

#### 10.2.2 詳細な設計手順

クイック・スタート・カリキュレータを使用すると、LM5155 デバイスをベースとする特定のアプリケーション用に、レギュレータを簡単に設計できます。『LM5155 昇圧コントローラ・クイックスタート・カリキュレータ』をダウンロードします。

### 10.2.2.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer により、LM5155x デバイスを使用するカスタム設計を作成できます。

- 最初に、入力電圧 ( $V_{IN}$ )、出力電圧 ( $V_{OUT}$ )、出力電流 ( $I_{OUT}$ ) の要件を入力します。

- オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

- 生成された設計を、テキサス・インスツルメンツが提供する考えられる他のソリューションと比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- 熱シミュレーションを実行し、基板の熱特性を把握する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

WEBENCH ツールの詳細は、[www.ti.com/ja-jp/WEBENCH](http://www.ti.com/ja-jp/WEBENCH) でご覧になれます。

### 10.2.2 推奨部品

表 10-2 に、この代表的なアプリケーションに推奨される部品リストを示します。

表 10-2. 部品リスト

| リファレンス指定子        | 数量 | 仕様                                                                                 | 製造元           | 部品番号 <sup>(1)</sup>  |

|------------------|----|------------------------------------------------------------------------------------|---------------|----------------------|

| $R_T$            | 1  | RES、49.9k、1%、0.1W、AEC-Q200 グレード 0、0603                                             | Vishay-Dale   | CRCW060349K9FKEA     |

| $R_{FBT}$        | 1  | RES、47.0k、1%、0.1W、AEC-Q200 グレード 0、0603                                             | Vishay-Dale   | CRCW060347K0FKEA     |

| $R_{FBB}$        | 1  | RES、2.0k、5%、0.1W、AEC-Q200 グレード 0、0603                                              | Vishay-Dale   | CRCW06032K00JNEA     |

| $L_M$            | 1  | インダクタ、シールド付き、コンポジット、6.8 $\mu$ H、18.5A、0.01 $\Omega$ 、SMD                           | Coilcraft     | XAL1010-682MEB       |

| $R_S$            | 1  | RES、0.008、1%、3W、AEC-Q200 グレード 0、2512 WIDE                                          | Susumu        | KRL6432E-M-R008-F-T1 |

| $R_{SL}$         | 1  | RES、0、5%、0.1W、0603                                                                 | Yageo America | RC0603JR-070RL       |

| $C_{OUT1}$       | 3  | CAP、CERM、4.7 $\mu$ F、50V、±10%、X7R、1210                                             | TDK           | C3225X7R1H475K250AB  |

| $C_{OUT2}$ (バルク) | 2  | CAP、アルミニウム・ポリマー、100 $\mu$ F、50V、±20%、0.025 $\Omega$ 、AEC-Q200 グレード 2、D10×L10mm SMD | Chemi-Con     | HXB500ARA101MJA10G   |

| $C_{IN1}$        | 6  | CAP、CERM、10 $\mu$ F、50V、±10%、X7R、1210                                              | MuRata        | GRM32ER71H106KA12L   |

| $C_{IN2}$ (バルク)  | 1  | CAP、ポリマー・ハイブリッド、100 $\mu$ F、50V、±20%、28 $\Omega$ 、10×10 SMD                        | Panasonic     | EEHZC1H101P          |

| $Q1$             | 1  | MOSFET、N-CH、40V、50A、AEC-Q101、SON-8                                                 | Infineon      | IPC50N04S5L5R5ATMA1  |

| $D1$             | 1  | ショットキー、60V、10A、AEC-Q101、CFP15                                                      | Nexperia      | PMEG060V100EPDZ      |

| $R_{COMP}$       | 1  | RES、11.3k、1%、0.1W、AEC-Q200 グレード 0、0603                                             | Vishay-Dale   | CRCW060311K3FKEA     |

| $C_{COMP}$       | 1  | CAP、CERM、0.022 $\mu$ F、100V、±10%、X7R、AEC-Q200 グレード 1、0603                          | TDK           | CGA3E2X7R2A223K080AA |

| $C_{HF}$         | 1  | CAP、CERM、220pF、50V、±5%、C0G/NP0、AEC-Q200 グレード 1、0603                                | TDK           | CGA3E2C0G1H221J080AA |

| $R_{UVLOT}$      | 1  | RES、21.0k、1%、0.1W、AEC-Q200 グレード 0、0603                                             | Vishay-Dale   | CRCW060321K0FKEA     |

| $R_{UVLOB}$      | 1  | RES、7.32k、1%、0.1W、AEC-Q200 グレード 0、0603                                             | Vishay-Dale   | CRCW06037K32FKEA     |

| $R_{UVLOS}$      | 0  | 該当なし                                                                               | 該当なし          | 該当なし                 |

| $C_{SS}$         | 1  | CAP、CERM、0.22 $\mu$ F、50V、±10%、X7R、AEC-Q200 グレード 1、0603                            | TDK           | CGA3E3X7R1H224K080AB |

**表 10-2. 部品リスト (続き)**

| リファレンス指定子         | 数量 | 仕様                                             | 製造元                       | 部品番号 <sup>(1)</sup> |

|-------------------|----|------------------------------------------------|---------------------------|---------------------|

| D <sub>G</sub>    | 0  | 該当なし                                           | 該当なし                      | 該当なし                |

| R <sub>G</sub>    | 1  | RES、0、5%、0.1W、0603                             | Yageo America             | RC0603JR-070RL      |

| C <sub>F</sub>    | 1  | CAP、CERM、100pF、50V、±1%、C0G/NP0、0603            | Kemet                     | C0603C101F5GACTU    |

| R <sub>F</sub>    | 1  | RES、100、1%、0.1W、0603                           | Yageo America             | RC0603FR-07100RL    |

| R <sub>SNB</sub>  | 0  | 該当なし                                           | 該当なし                      | 該当なし                |

| C <sub>SNB</sub>  | 0  | 該当なし                                           | 該当なし                      | 該当なし                |

| R <sub>BIAS</sub> | 1  | RES、0、5%、0.1W、AEC-Q200 グレード 0、0603             | Panasonic                 | ERJ-3GEY0R00V       |

| C <sub>BIAS</sub> | 1  | CAP、CERM、0.01μF、50V、±10%、X7R、0603              | Samsung Electro-Mechanics | CL10B103KB8NCNC     |

| C <sub>VCC</sub>  | 1  | CAP、CERM、1μF、16V、±20%、X7R、AEC-Q200 グレード 1、0603 | MuRata                    | GCM188R71C105MA64D  |

| R <sub>PG</sub>   | 1  | RES、24.9k、1%、0.1W、0603                         | Yageo America             | RC0603FR-0724K9L    |

(1) 「サード・パーティ製品に関する免責事項」をご覧ください。

### 10.2.2.3 インダクタの選択 ( $L_M$ )

インダクタを選択するときは、インダクタの電流リップル率 (RR)、インダクタ電流の立ち下がり勾配、R<sub>HIP</sub> ゼロ周波数 ( $f_{RHP}$ ) という 3 つの主要なパラメータを考慮します。

インダクタの電流リップル率は、コアの損失と銅線の損失でバランスが取れるように選択します。インダクタ電流の立ち下がり勾配は、高いデューティ・サイクルで分数調波の発振を防止するため、十分に低い必要があります (そうでない場合、追加の R<sub>SL</sub> 抵抗が必要です)。 $f_{RHP}$  が高い (すなわち、インダクタンスが低い) と、高いクロスオーバー周波数が可能になるため、値の小さい出力コンデンサを使用するときには常に推奨されます。

インダクタンス値は、RR、F<sub>RHP</sub>、インダクタの立ち下がり勾配との間の適切な妥協点として、インダクタの電流リップルが平均インダクタ電流の 30%~70% になるように選択できます。

### 10.2.2.4 出力コンデンサ ( $C_{OUT}$ )

出力コンデンサの正しい値 ( $C_{OUT}$ ) を選択する方法はいくつか存在します。出力コンデンサの値は、出力電圧リップルや、負荷過渡による出力オーバーシュートまたはアンダーシュートに基づいて選択できます。

出力コンデンサのリップル電流定格には、この出力リップル電流を処理するのに十分な値が必要です。複数の出力コンデンサを使用すると、リップル電流を分割できます。実践的には、セラミック・コンデンサを、大きなアルミ電解コンデンサよりも、ダイオードと MOSFET の近くに配置し、リップル電流の大部分を吸収するようにします。

### 10.2.2.5 入力コンデンサ

入力コンデンサは、入力電圧リップルを減少させます。必要な入力コンデンサの値は、ソース電源のインピーダンスの関数となります。ソース電源のインピーダンスが十分に低くない場合、より多くの入力コンデンサが必要になります。

### 10.2.2.6 MOSFET の選択

デバイスの MOSFET ゲート・ドライバは、VCC から電源を供給されます。最大ゲート電荷は、35mA の VCC のソース電流制限によって制限されます。

スイッチング周波数の高い設計では、リードなしのパッケージをお勧めします。MOSFET ゲートの容量は、オフ時間にゲート電圧が完全に放電できるよう、十分に小さい必要があります。

### 10.2.2.7 ダイオードの選択

D1 ダイオードにはショットキー・タイプが推奨されます。これは、順方向電圧降下が低く、逆方向回復荷電が小さいためです。ショットキー・ダイオードを選択するときは、逆リーク電流のパラメータが小さいことが重要です。ダイオードの定格は、

最大出力電圧に加えて、スイッチ・ノードのリンクを処理できる必要があります。また、平均出力電流を処理することも必要です。

### 10.2.2.8 効率の推定

昇圧コンバータの合計損失 ( $P_{TOTAL}$ ) は、デバイスの損失 ( $P_{IC}$ )、MOSFET の電力損失 ( $P_Q$ )、ダイオードの電力損失 ( $P_D$ )、インダクタの電力損失 ( $P_L$ )、検出抵抗での損失 ( $P_{RS}$ ) の和で表すことができます。

$$P_{TOTAL} = P_{IC} + P_Q + P_D + P_L + P_{RS} \quad (19)$$

$P_{IC}$  は、ゲート駆動損失 ( $P_G$ ) と、静止電流により発生する損失 ( $P_{IQ}$ ) に分割できます。

$$P_{IC} = P_G + P_{IQ} \quad (20)$$

それぞれの電力損失は、次のように概算されます。

$$P_G = Q_G(@VCC) \times V_{BIAS} \times f_{SW} \quad (21)$$

$$P_{IQ} = V_{BIAS} \times I_{BIAS} \quad (22)$$

各モードでの  $I_{VIN}$  および  $I_{VOUT}$  の値は、「[セクション 8.5](#)」の電源電流セクションにあります。

$P_Q$  は、スイッチング損失 ( $P_{Q(SW)}$ ) と、導通損失 ( $P_{Q(COND)}$ ) に分割できます。

$$P_Q = P_{Q(SW)} + P_{Q(COND)} \quad (23)$$

それぞれの電力損失は、次のように概算されます。

$$P_{Q(SW)} = 0.5 \times (V_{LOAD} + V_F) \times I_{SUPPLY} \times (t_R + t_F) \times f_{SW} \quad (24)$$

$t_R$  および  $t_F$  は、ローサイド N チャネル MOSFET デバイスの立ち上がりと立ち下がりの時間です。 $I_{SUPPLY}$  は、昇圧コンバータの入力電源電流です。

$$P_{Q(COND)} = D \times I_{SUPPLY}^2 \times R_{DS(ON)} \quad (25)$$

$R_{DS(ON)}$  は、MOSFET のオン抵抗で、MOSFET のデータシートに記載されています。自己発熱による  $R_{DS(ON)}$  の増大を考慮に入れてください。

$P_D$  は、ダイオードの導通損失 ( $P_{VF}$ ) と、逆方向回復損失 ( $P_{RR}$ ) に分割できます。

$$P_D = P_{VF} + P_{RR} \quad (26)$$

それぞれの電力損失は、次のように概算されます。

$$P_{VF} = (1 - D) \times V_F \times I_{SUPPLY} \quad (27)$$

$$P_{RR} = V_{LOAD} \times Q_{RR} \times f_{SW} \quad (28)$$

$Q_{RR}$  はダイオードの逆方向回復電荷で、ダイオードのデータシートに記載されています。ダイオードの逆方向回復特性は、特に出力電圧が高いとき、効率に大きな影響を及ぼします。

$P_L$  は、DCR 損失 ( $P_{DCR}$ ) と AC コア損失 ( $P_{AC}$ ) との和です。DCR はインダクタの DC 抵抗で、インダクタのデータシートで言及されています。

$$P_L = P_{DCR} + P_{AC} \quad (29)$$

それぞれの電力損失は、次のように概算されます。

$$P_{DCR} = I_{SUPPLY}^2 \times R_{DCR} \quad (30)$$

$$P_{AC} = K \times \Delta I^\beta \times f_{SW}^\alpha \quad (31)$$

$$\Delta I = \frac{V_{SUPPLY} \times D \times \frac{1}{f_{SW}}}{L_M} \quad (32)$$

$\Delta I$  は、ピーク・ツー・ピークのインダクタ電流リップルです。K,  $\alpha$ ,  $\beta$  はコアに依存する係数で、インダクタの製造業者から提供されます。

$P_{RS}$  は次のように計算されます。

$$P_{RS} = D \times I_{SUPPLY}^2 \times R_S \quad (33)$$

電力コンバータの効率は、次のように推定できます。

$$\text{Efficiency} = \frac{V_{LOAD} \times I_{LOAD}}{P_{TOTAL} + V_{LOAD} \times I_{LOAD}} \quad (34)$$

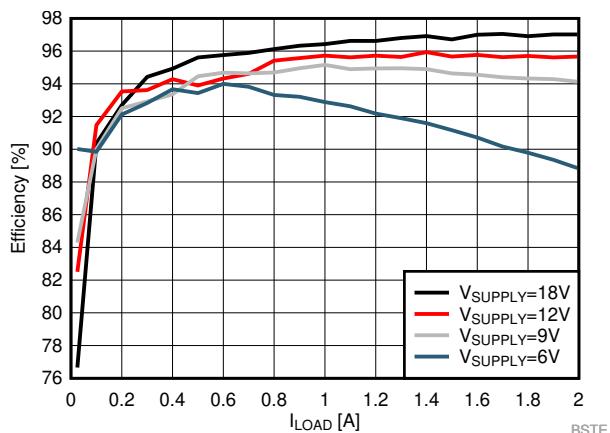

### 10.2.3 アプリケーション曲線

図 10-2. 効率

### 10.3 システム例

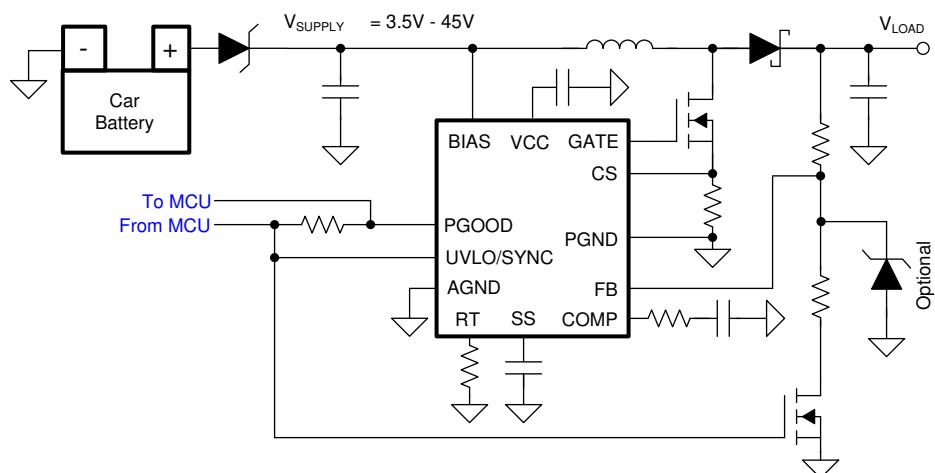

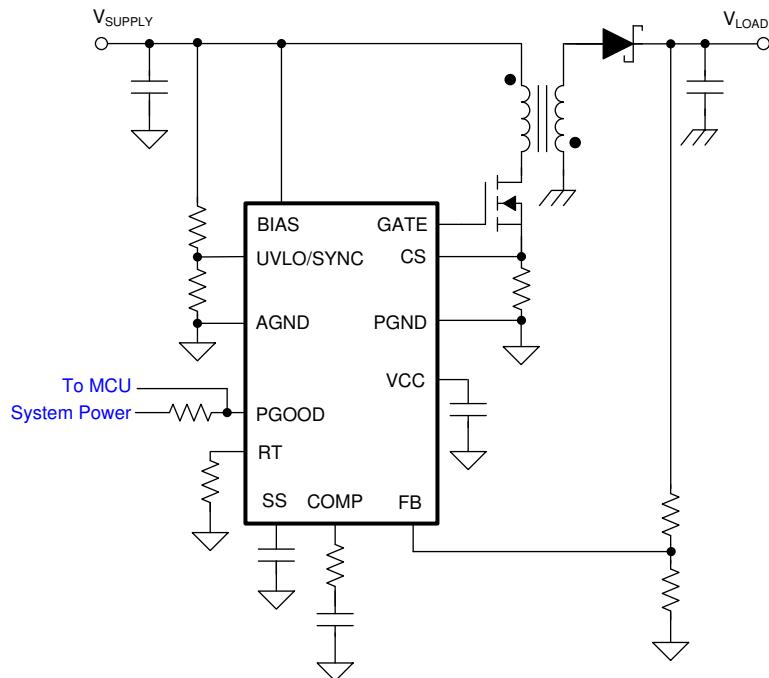

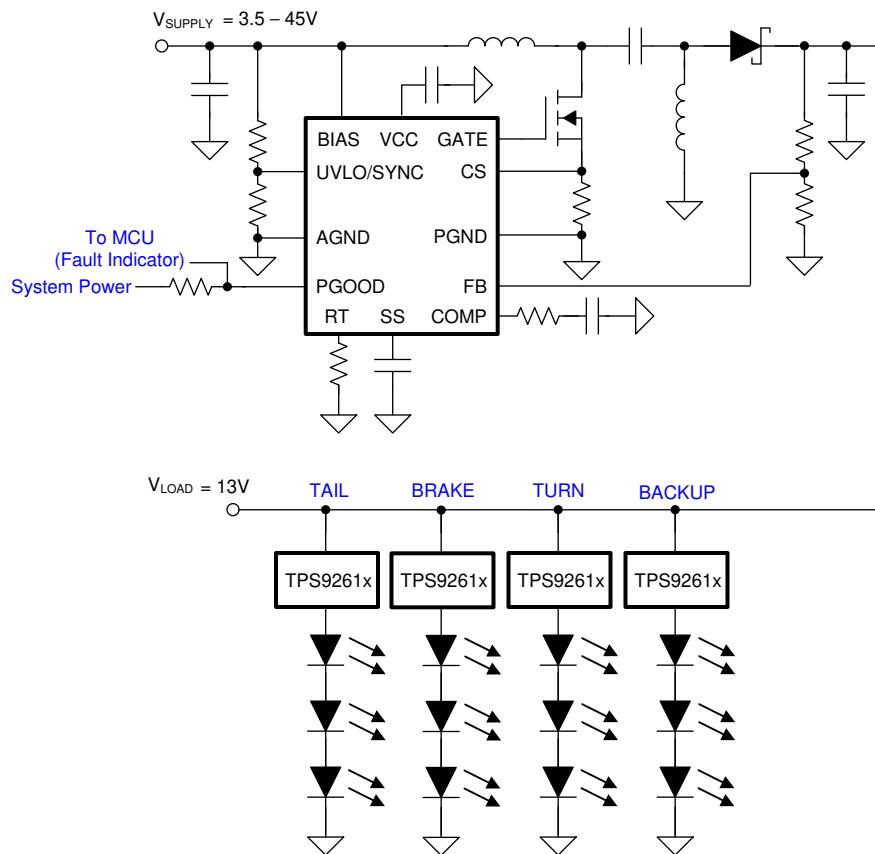

図 10-3. 代表的な昇圧アプリケーション

図 10-4. 代表的なスタート-ストップのアプリケーション

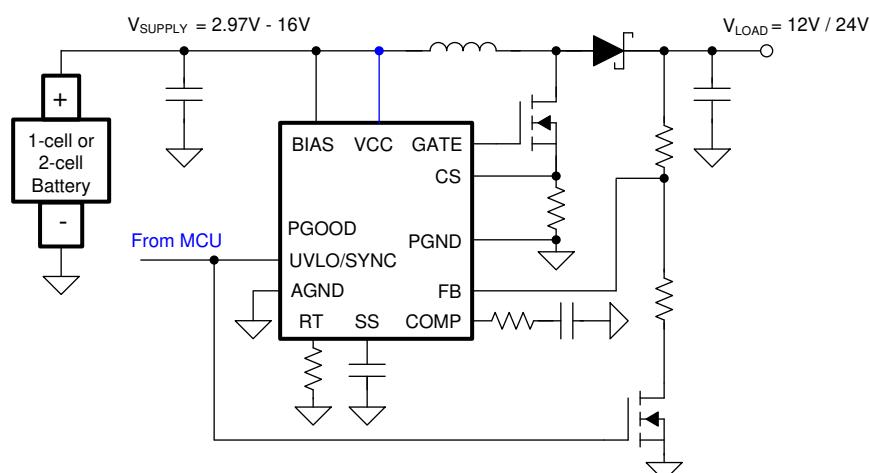

図 10-5. 緊急通報 / 昇圧オンドマンド / ポータブル・スピーカ

図 10-6. 代表的な SEPIC アプリケーション

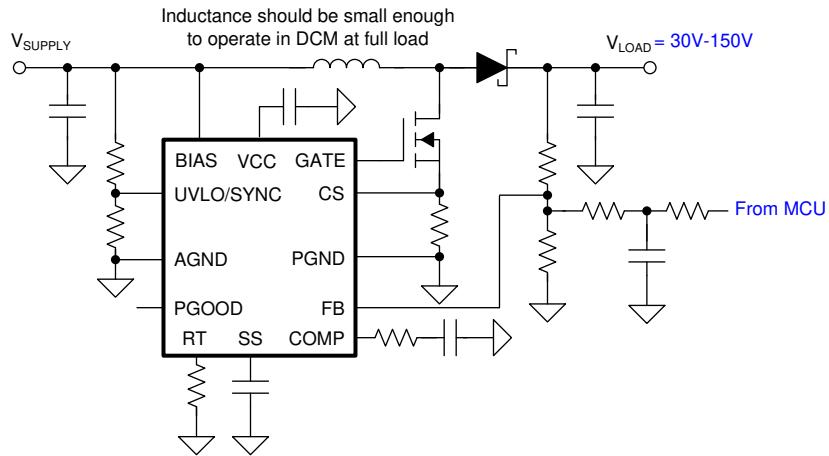

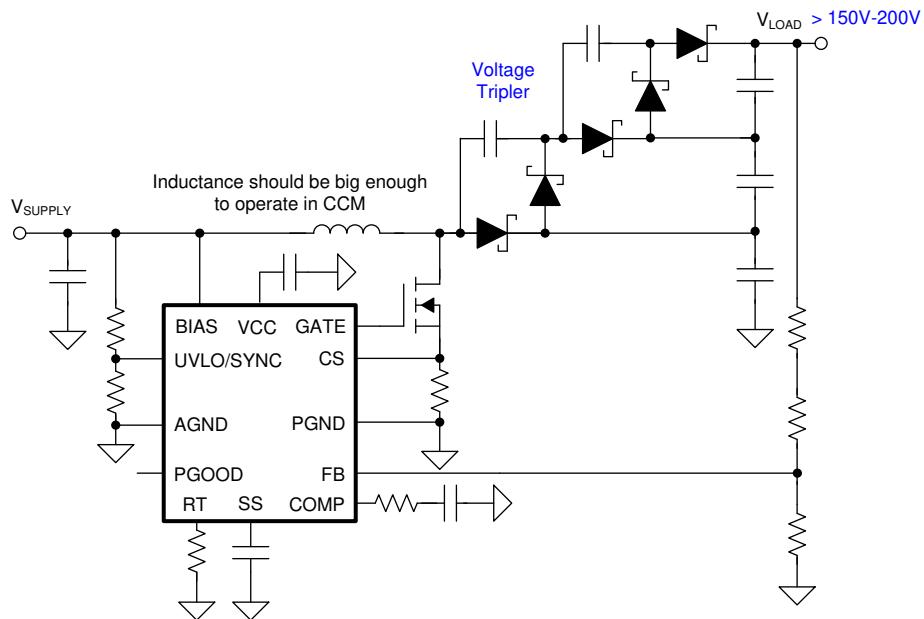

図 10-7. LIDAR バイアス電源 1

図 10-8. LIDAR バイアス電源 2

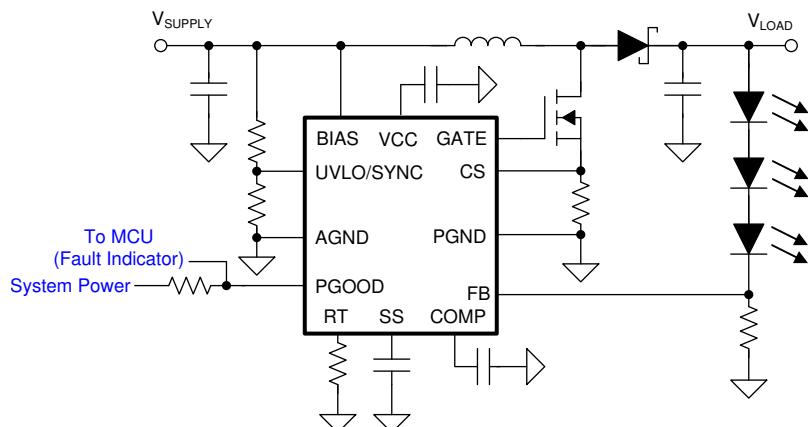

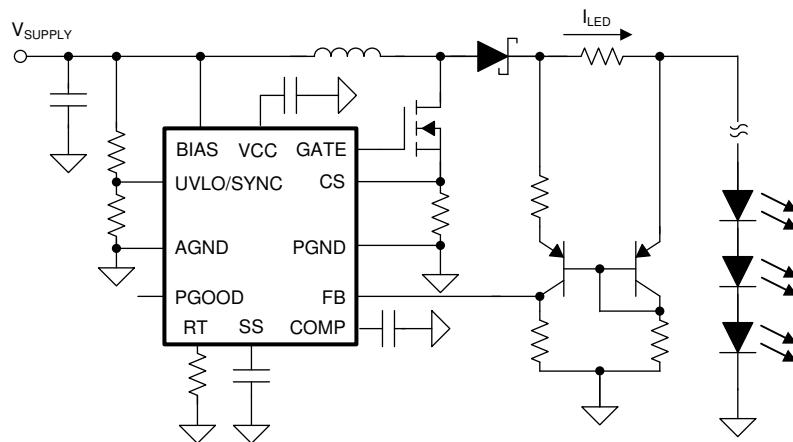

図 10-9. 低コスト LED ドライバ

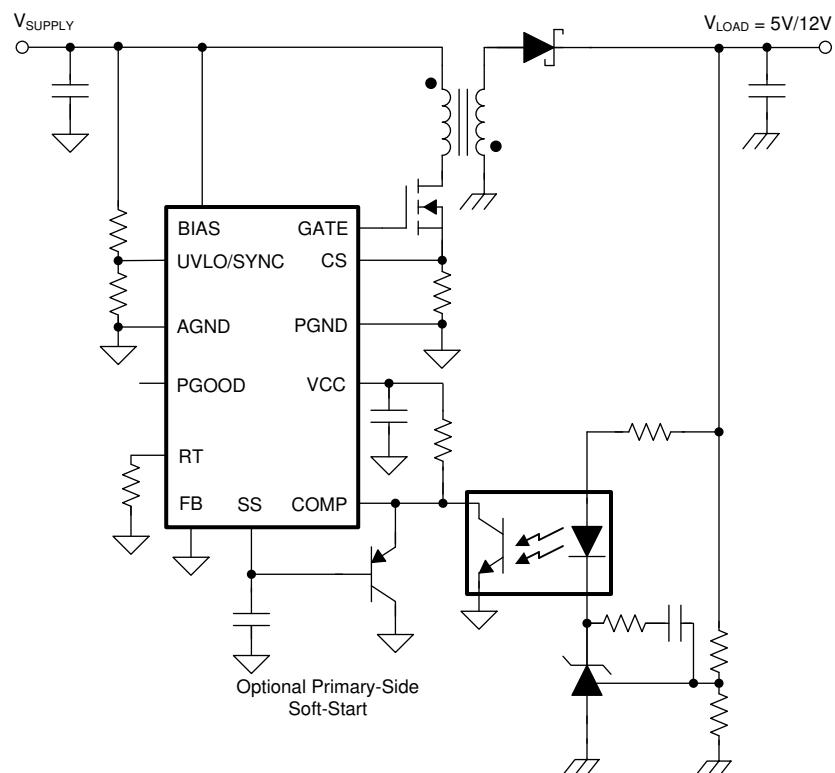

図 10-10. 2 次側レギュレーション済み絶縁型フライバック

図 10-11. 1 次側レギュレーション済み複数出力絶縁型フライバック

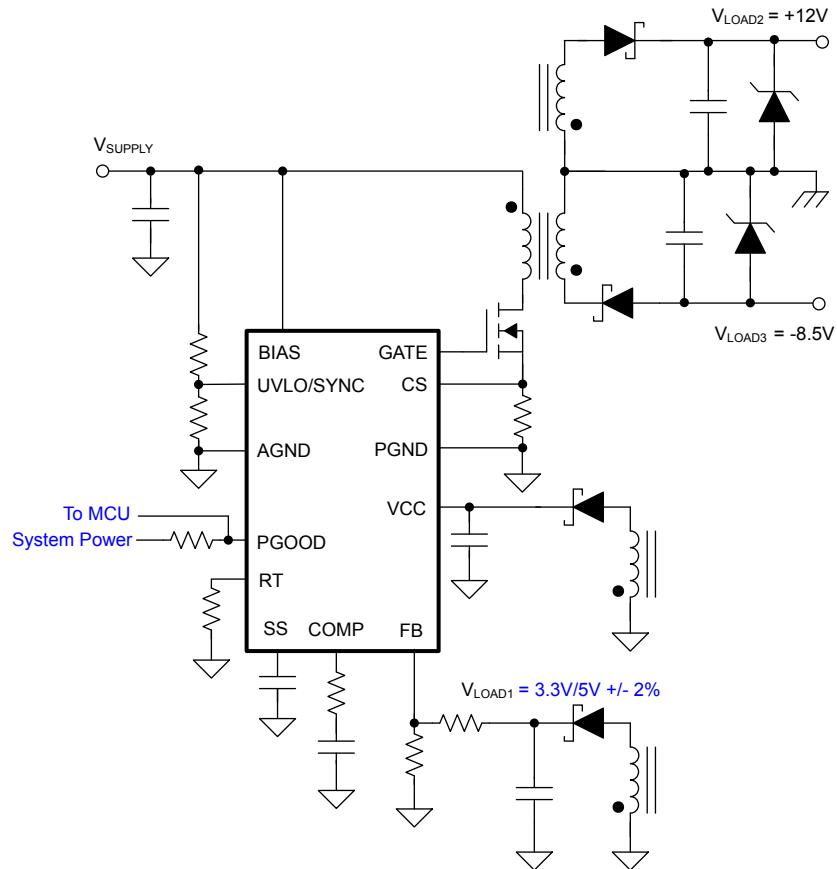

図 10-12. 代表的な非絶縁型フライバック

図 10-13. ハイサイド電流検出機能付き LED ドライバ

図 10-14. デュアル・ステージ車載用リア・ライト LED ドライバ

#### 10.4 電源に関する推奨事項

このデバイスは、1.5V～45V の電圧範囲の電源またはバッテリで動作するよう設計されています。入力電源は、最大昇圧電源電圧を供給でき、1.5V において最大入力電流を扱える必要があります。ケーブルを含めた、電源やバッテリのインピーダンスは、入力過渡電流が過剰な降下を引き起こさないよう、十分に小さい必要があります。コンバータの電源入力に、入力セラミック・コンデンサの追加が必要になることがあります。

## 10.5 レイアウト

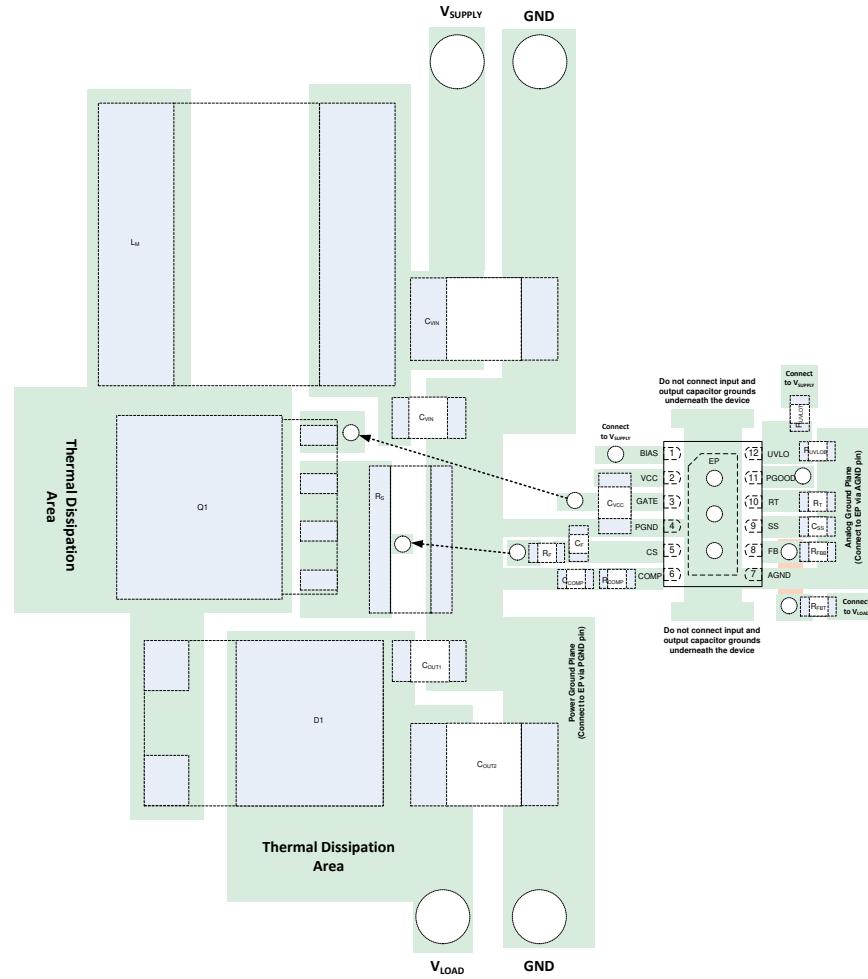

### 10.5.1 レイアウトのガイドライン

スイッチング・コンバータの性能は、PCB レイアウトの品質に大きく依存します。次のガイドラインに従うことで、最高の電力変換性能や熱性能を実現しながら、不要な EMI の生成を最小限に抑えるような PCB を設計できます。

- 最初に  $Q_1$ 、 $D_1$ 、 $R_S$  の部品を基板に取り付けます。

- $C_{OUT}$  には小型のセラミック・コンデンサを使用します。

- スイッチング・ループ ( $C_{OUT} \sim D_1 \sim Q_1 \sim R_S \sim C_{OUT}$ ) はできるだけ小さくします。

- 放熱のため、 $D_1$  ダイオードの近くに銅の領域を残します。

- デバイスを  $R_S$  抵抗の近くに配置します。

- $C_{VCC}$  コンデンサは、 $VCC$  ピンと  $PGND$  ピンの間で、デバイスのできるだけ近くに配置します。

- $PGND$  ピンは、幅が広くて短いトレースを使用して、センス抵抗の中心に直接接続します。

- $CS$  ピンはセンス抵抗の中心に接続します。必要に応じて、ビアを使用します。

- フィルタ・コンデンサを  $CS$  ピンと電源グランド・トレースの間に接続します。

- $COMP$  ピンを補償部品 ( $R_{COMP}$  および  $C_{COMP}$ ) に接続します。

- $C_{COMP}$  コンデンサを電源グランド・トレースに接続します。

- $AGND$  ピンをアナログ・グランド・プレーンに直接接続します。 $AGND$  ピンを  $R_{UVLOB}$ 、 $R_T$ 、 $C_{SS}$ 、 $R_{FBB}$  の部品に接続します。

- 露出したパッドをデバイスの下の  $AGND$  ピンと  $PGND$  ピンに接続します。

- $GATE$  ピンを  $Q_1$  FET のゲートに接続します。必要に応じて、ビアを使用します。

- スイッチング信号ループ ( $GATE \sim Q_1 \sim R_S \sim PGND \sim GATE$ ) はできるだけ小さくします。

- 露出したパッドの下にいくつかのビアを追加して、デバイスからの放熱性能を向上させます。ビアは、最下層レイヤの大きなグランド・プレーンに接続します。

## 10.5.2 レイアウト例

図 10-15. PCB のレイアウト例 1

図 10-16. PCB のレイアウト例 2

## 11 デバイスおよびドキュメントのサポート

### 11.1 デバイスのサポート

#### 11.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

#### 11.1.2 開発サポート

開発サポートについては、以下を参照してください。

- [LM5155 昇圧コントローラ・クイックスタート・カリキュレータ](#)

#### 11.1.2.1 WEBENCH® ツールによるカスタム設計

ここをクリックすると、WEBENCH® Power Designer により、LM5155x デバイスを使用するカスタム設計を作成できます。

1. 最初に、入力電圧 ( $V_{IN}$ )、出力電圧 ( $V_{OUT}$ )、出力電流 ( $I_{OUT}$ ) の要件を入力します。

2. オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化します。

3. 生成された設計を、テキサス・インスツルメンツが提供する考えられる他のソリューションと比較します。

WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格と部品の在庫情報と併せて参照できます。

通常、次の操作を実行可能です。

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- 熱シミュレーションを実行し、基板の熱特性を把握する

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットで出力する

- 設計のレポートを PDF で印刷し、設計を共有する

WEBENCH ツールの詳細は、[www.ti.com/ja-jp/WEBENCH](http://www.ti.com/ja-jp/WEBENCH) でご覧になります。

### 11.2 ドキュメントのサポート

#### 11.2.1 関連資料

関連資料については、以下を参照してください。

- テキサス・インスツルメンツ、『LM5155EVM-BST ユーザー・ガイド』

- テキサス・インスツルメンツ、『LM5155-Q1 を使用した昇圧コンバータの設計方法』

- テキサス・インスツルメンツ、『LM5155EVM-FLY ユーザー・ガイド』

- テキサス・インスツルメンツ、『LM5155-Q1 を使用した絶縁型フライバック・コンバータの設計方法』

### 11.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[ti.com](http://ti.com) のデバイス製品フォルダを開いてください。「更新の通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

### 11.4 サポート・リソース

TI E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

## 11.5 商標

TI E2E™ is a trademark of Texas Instruments.

WEBENCH® is a registered trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 11.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 11.7 用語集

### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに対して提供されている最新のデータです。このデータは、予告なしに、またドキュメントの改訂なしに変更される場合があります。本データシートのブラウザ版を使用している場合は、画面左側のナビゲーションをご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| LM51551DSSR           | Active        | Production           | WSON (DSS)   12 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 1U6H                |

| LM51551DSSR.A         | Active        | Production           | WSON (DSS)   12 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 1U6H                |

| LM51551DSSRG4         | Active        | Production           | WSON (DSS)   12 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 1U6H                |

| LM51551DSSRG4.A       | Active        | Production           | WSON (DSS)   12 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 1U6H                |

| LM51551DSST           | Active        | Production           | WSON (DSS)   12 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 1U6H                |

| LM51551DSST.A         | Active        | Production           | WSON (DSS)   12 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 1U6H                |

| LM5155DSSR            | Active        | Production           | WSON (DSS)   12 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 1U4H                |

| LM5155DSSR.A          | Active        | Production           | WSON (DSS)   12 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 1U4H                |

| LM5155DSSRG4          | Active        | Production           | WSON (DSS)   12 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 1U4H                |

| LM5155DSSRG4.A        | Active        | Production           | WSON (DSS)   12 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 1U4H                |

| LM5155DSST            | Active        | Production           | WSON (DSS)   12 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 1U4H                |

| LM5155DSST.A          | Active        | Production           | WSON (DSS)   12 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 1U4H                |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

---

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF LM5155, LM51551 :**

- Automotive : [LM5155-Q1](#), [LM51551-Q1](#)

NOTE: Qualified Version Definitions:

- Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

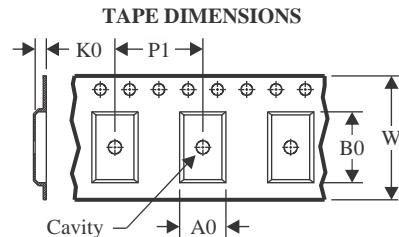

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

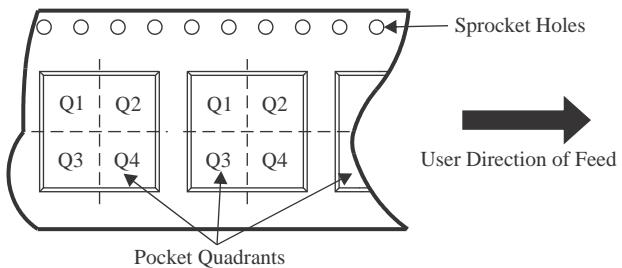

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|---------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| LM51551DSSR   | WSON         | DSS             | 12   | 3000 | 180.0              | 8.4                | 2.25    | 3.25    | 1.05    | 4.0     | 8.0    | Q1            |

| LM51551DSSRG4 | WSON         | DSS             | 12   | 3000 | 180.0              | 8.4                | 2.25    | 3.25    | 1.05    | 4.0     | 8.0    | Q1            |

| LM51551DSST   | WSON         | DSS             | 12   | 250  | 180.0              | 8.4                | 2.25    | 3.25    | 1.05    | 4.0     | 8.0    | Q1            |

| LM5155DSSR    | WSON         | DSS             | 12   | 3000 | 180.0              | 8.4                | 2.25    | 3.25    | 1.05    | 4.0     | 8.0    | Q1            |

| LM5155DSSRG4  | WSON         | DSS             | 12   | 3000 | 180.0              | 8.4                | 2.25    | 3.25    | 1.05    | 4.0     | 8.0    | Q1            |

| LM5155DSST    | WSON         | DSS             | 12   | 250  | 180.0              | 8.4                | 2.25    | 3.25    | 1.05    | 4.0     | 8.0    | Q1            |

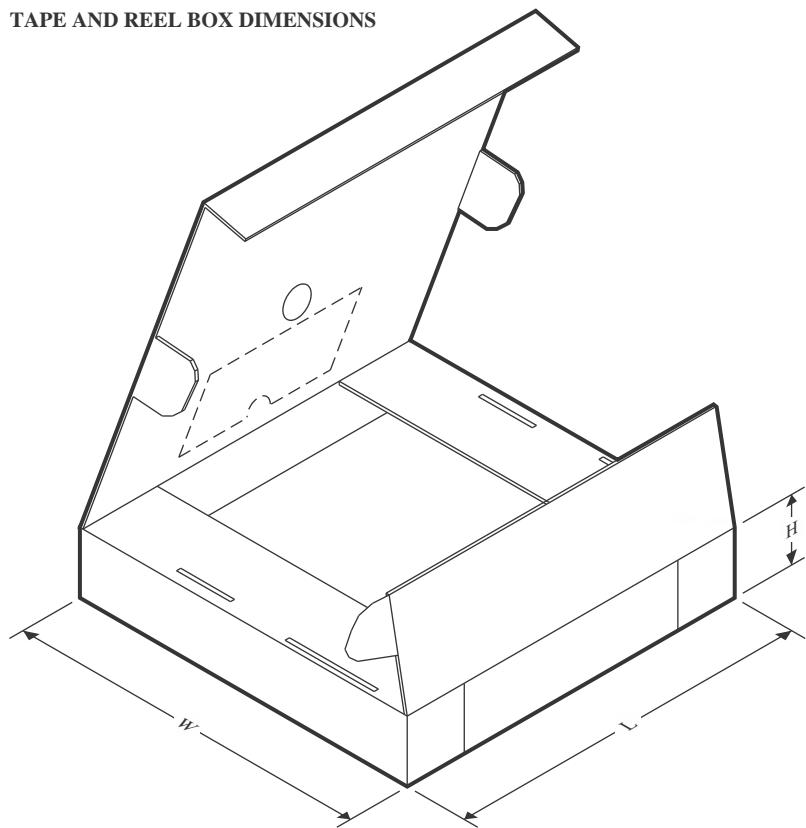

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM51551DSSR   | WSON         | DSS             | 12   | 3000 | 210.0       | 185.0      | 35.0        |

| LM51551DSSRG4 | WSON         | DSS             | 12   | 3000 | 210.0       | 185.0      | 35.0        |

| LM51551DSST   | WSON         | DSS             | 12   | 250  | 210.0       | 185.0      | 35.0        |

| LM5155DSSR    | WSON         | DSS             | 12   | 3000 | 210.0       | 185.0      | 35.0        |

| LM5155DSSRG4  | WSON         | DSS             | 12   | 3000 | 210.0       | 185.0      | 35.0        |

| LM5155DSST    | WSON         | DSS             | 12   | 250  | 210.0       | 185.0      | 35.0        |

## GENERIC PACKAGE VIEW

DSS 12

WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

Images above are just a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4209244/D

# PACKAGE OUTLINE

**DSS0012B**

**WSON - 0.8 mm max height**

PLASTIC SMALL OUTLINE - NO LEAD

4218908/A 01/2017

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

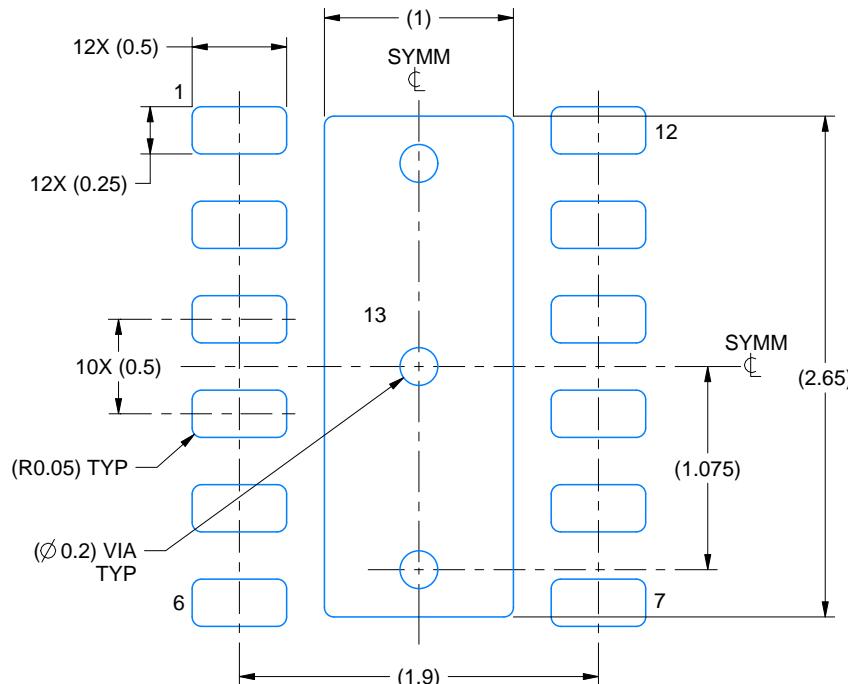

# EXAMPLE BOARD LAYOUT

DSS0012B

WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:25X

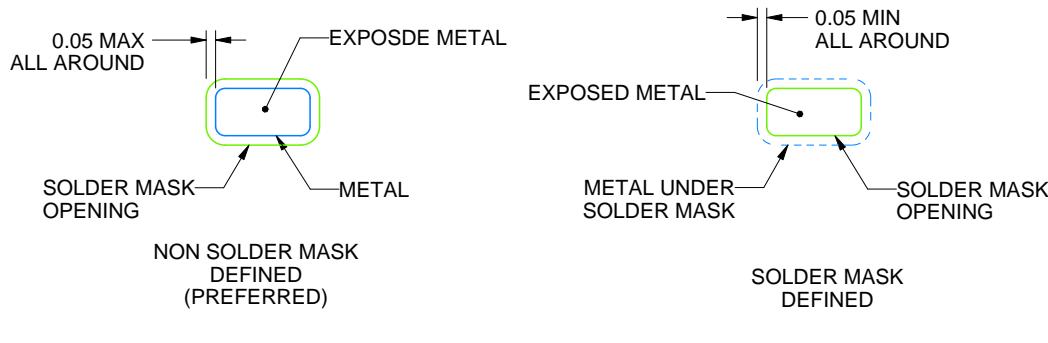

SOLDER MASK DETAILS

4218908/A 01/2017

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

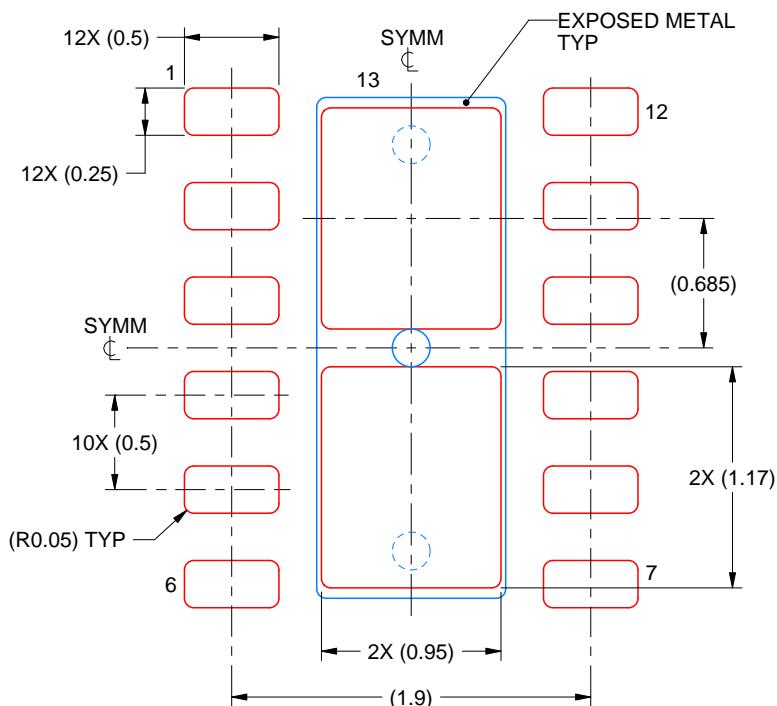

# EXAMPLE STENCIL DESIGN

DSS0012B

WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

EXPOSED PAD 13:

83% PRINTED SOLDER COVERAGE BY AREA UNDER PACKAGE

SCALE:25X

4218908/A 01/2017

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月