# LM5123-Q1 2.2MHz 広い入力電圧範囲 ( $V_{IN}$ )、低い静止電流 ( $I_Q$ )、同期整流昇圧コントローラ、 $V_{OUT}$ トラッキング付き

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認証済み

- 温度グレード 1: -40°C ~ +125°C,  $T_A$

- 機能安全対応**

- 機能安全システムの設計に役立つ資料を利用可能

- 車載用バッテリ駆動アプリケーションの広い動作範囲に適合

- 3.8V ~ 42V の入力動作範囲

- $V_{OUT}$  を 5V ~ 20V または 15V ~ 57V に動的にプログラマブル可能

- $BIAS \geq 3.8V$  のときの最小昇圧入力電圧 0.8V

- $V_{SUPPLY} > V_{LOAD}$  のときバイパス動作

- バッテリドレインの最小化

- シャットダウン電流  $\leq 3\mu A$

- 自動的なモード遷移

- ディープスリープ時のバッテリドレイン  $\leq 11\mu A$  (バイパス動作、チャージポンプオフ)

- ディープスリープ時のバッテリドレイン  $\leq 38\mu A$  (バイパス動作、チャージポンプオン)

- スリープ時の  $BIAS I_Q \leq 13\mu A$  (スキップモード)

- 強力な 5V MOSFET ドライバ

- 小さなソリューション サイズと低成本

- 最大スイッチング周波数: 2.2 MHz

- ブートダイオード内蔵

- $VIN$  に対する定ピーケ電流制限

- DCR インダクタ電流センシングをサポート

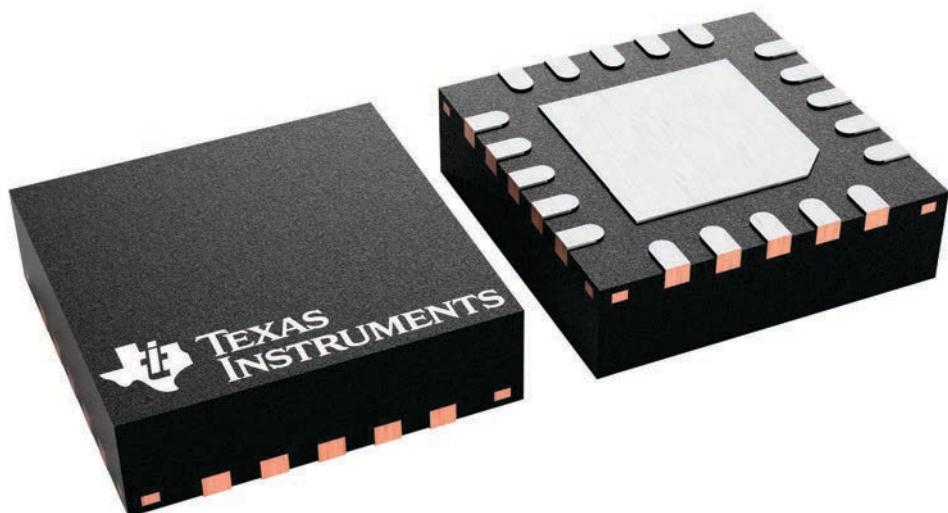

- ウェッタブル フランク付き QFN-20

- AM 帯域の干渉およびクロストークを回避

- (オプション) クロック同期

- スイッチング周波数: 100kHz ~ 2.2MHz

- スイッチングモードを選択可能 (FPWM、ダイオードエミュレーション、スキップモード)

- EMI 低減**

- プログラム可能なスペクトラム拡散 (オプション)

- 鉛レスパッケージ

- プログラマビリティとフレキシビリティ

- 動的  $V_{OUT}$  トラッキング

- 動的なスイッチング周波数のプログラミング

- プログラマブル ライン UVLO

- 可変ソフトスタート

- アダプティブ デッドタイム制御

- PGOOD インジケータ

- 保護機能内蔵

- サイクルごとのピーケ電流制限

- 過電圧保護

- HB-SW 短絡保護

- サーマル シャットダウン

## 2 アプリケーション

- トラッキング機能付き車載用オーディオ電源

- 車載用 LED バイアス電源

- 車載用 HVAC コントローラ電源

- 車載用モーター電源

## 3 説明

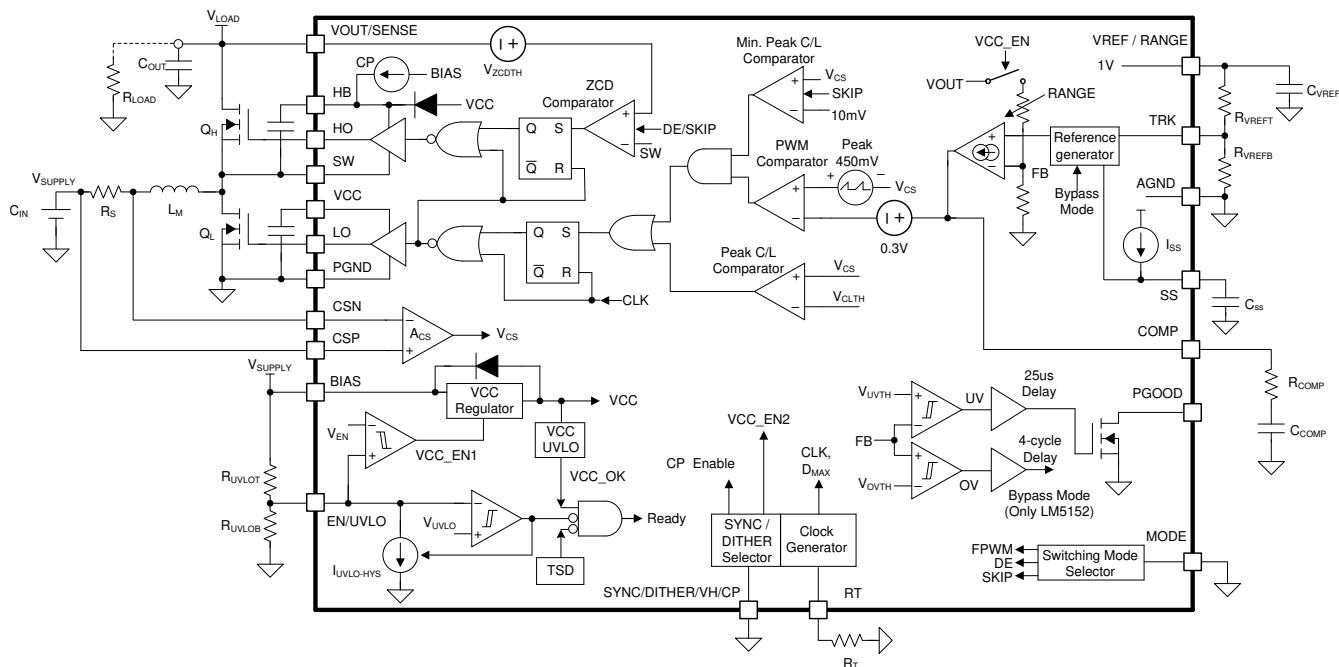

LM5123-Q1 デバイスは、広い入力電圧範囲に対応した同期整流昇圧コントローラであり、ピーケ電流モード制御を採用しています。

### パッケージ情報

| 部品番号      | パッケージ <sup>(1)</sup> | 本体サイズ(公称)     |

|-----------|----------------------|---------------|

| LM5123-Q1 | QFN (20)             | 3.5mm × 3.5mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

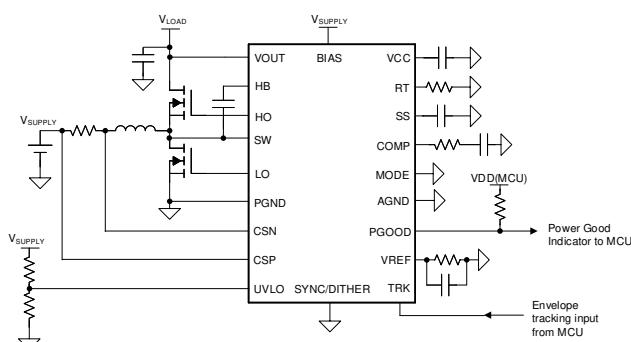

### 代表的なアプリケーション

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあり、TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                    |           |                               |           |

|--------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>        | <b>1</b>  | <b>8 アプリケーションと実装</b>          | <b>33</b> |

| <b>2 アプリケーション</b>  | <b>1</b>  | <b>8.1 アプリケーション情報</b>         | <b>33</b> |

| <b>3 説明</b>        | <b>1</b>  | <b>8.2 代表的なアプリケーション</b>       | <b>33</b> |

| <b>4 概要 (続き)</b>   | <b>3</b>  | <b>8.3 システム例</b>              | <b>36</b> |

| <b>5 ピン構成および機能</b> | <b>4</b>  | <b>9 電源に関する推奨事項</b>           | <b>37</b> |

| <b>6 仕様</b>        | <b>6</b>  | <b>10 レイアウト</b>               | <b>37</b> |

| 6.1 絶対最大定格         | 6         | 10.1 レイアウトのガイドライン             | 37        |

| 6.2 ESD 定格         | 6         | 10.2 レイアウト例                   | 38        |

| 6.3 推奨動作条件         | 7         | <b>11 デバイスおよびドキュメントのサポート</b>  | <b>39</b> |

| 6.4 熱に関する情報        | 7         | 11.1 デバイス サポート                | 39        |

| 6.5 電気的特性          | 7         | 11.2 ドキュメントの更新通知を受け取る方法       | 39        |

| 6.6 代表的特性          | 12        | 11.3 サポート・リソース                | 39        |

| <b>7 詳細説明</b>      | <b>15</b> | 11.4 商標                       | 39        |

| 7.1 概要             | 15        | 11.5 静電気放電に関する注意事項            | 39        |

| 7.2 機能ブロック図        | 15        | 11.6 用語集                      | 39        |

| 7.3 機能説明           | 16        | <b>12 改訂履歴</b>                | <b>39</b> |

| 7.4 デバイスの機能モード     | 29        | <b>13 メカニカル、パッケージ、および注文情報</b> | <b>40</b> |

## 4 概要 (続き)

このデバイスは、シャットダウン時の  $I_Q$  が低く、また、 $I_Q$  が低いスリープ モードを備えているため、無負荷および軽負荷の状況でバッテリ ドレインを最小化できます。さらに、このデバイスは、 $I_Q$  が非常に低いディープ スリープ モードでのバイパス動作にも対応しているため、電源電圧が昇圧出力レギュレーション目標よりも高い場合の外部バイパス スイッチが不要です。出力電圧は、トラッキング機能を使用して動的にプログラムできます。

デバイスの入力範囲が広いため、車載用のコールド クランクおよびロード ダンプに対応できます。BIAS が 3.8V 以上の場合、最小入力電圧は 0.8V まで下げることができます。スイッチング周波数は、外付けの抵抗により 100kHz～2.2MHz の範囲で動的にプログラム可能です。2.2MHz でのスイッチングにより、AM 帯域との干渉が最小化され、ソリューション サイズの小型化と、高速な過渡応答を実現できます。コントローラ アーキテクチャにより、コンバータ アーキテクチャと比較して、過酷な周囲温度条件での熱管理を簡素化できます。

ピーク電流制限 ( $V_{IN}$  の全範囲にわたって一定)、過電圧保護、サーマル シャットダウンなどの保護機能が内蔵されています。外部クロック同期、プログラム可能なスペクトラム拡散変調、最小限の寄生容量でのリードレス パッケージは、EMI の低減とクロストークの回避に役立ちます。その他の機能として、ライン UVLO、FPWM、ダイオード エミュレーション、DCR インダクタ電流センシング、プログラム可能なソフトスタート、パワー グッド インジケータがあります。

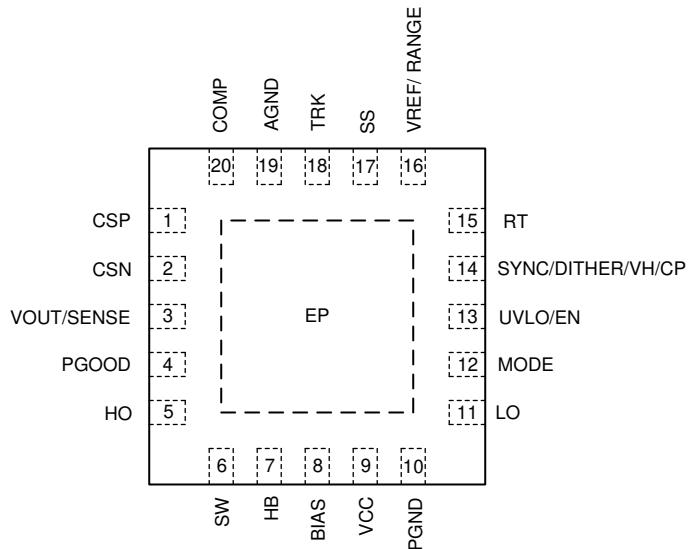

## 5 ピン構成および機能

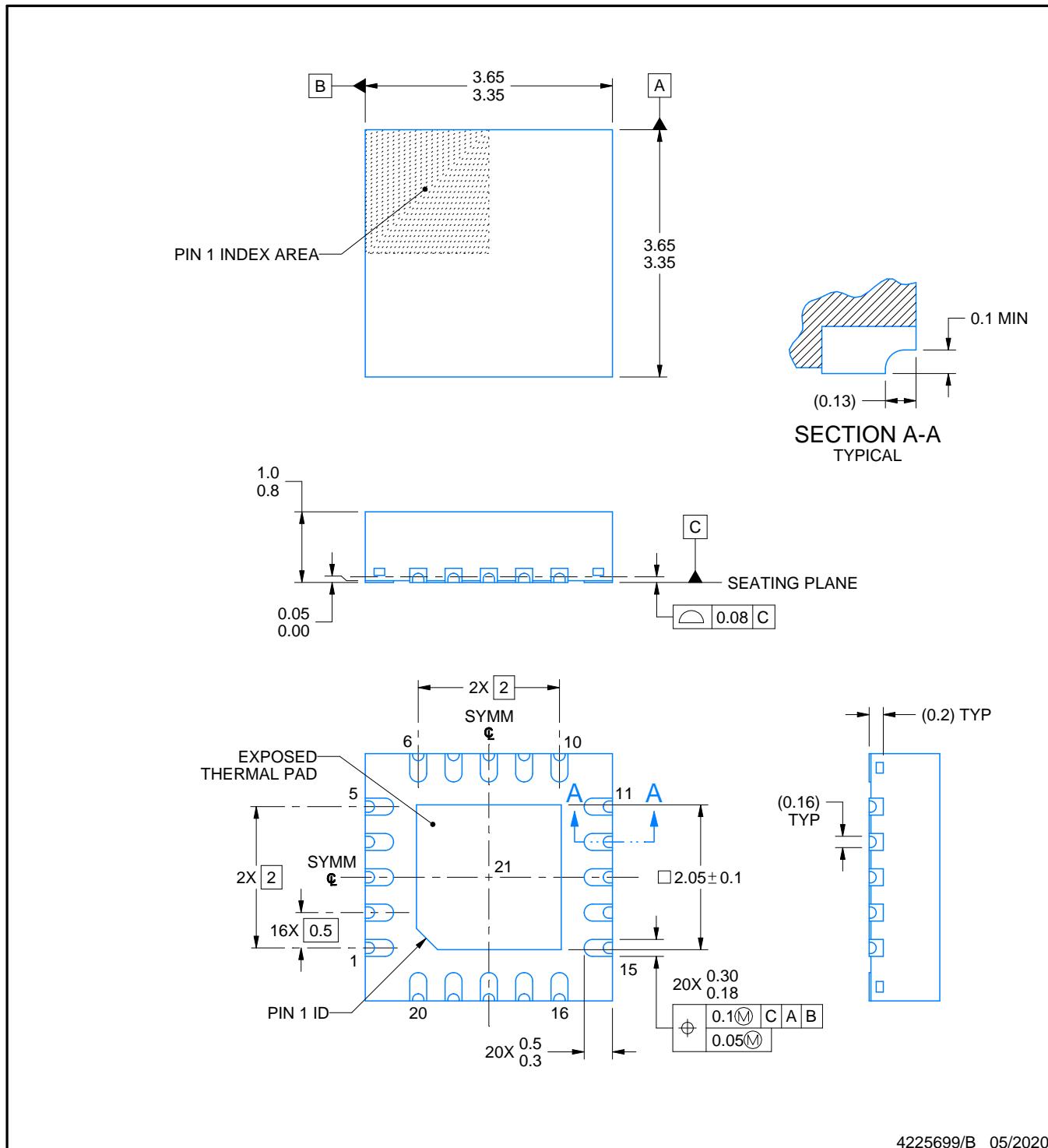

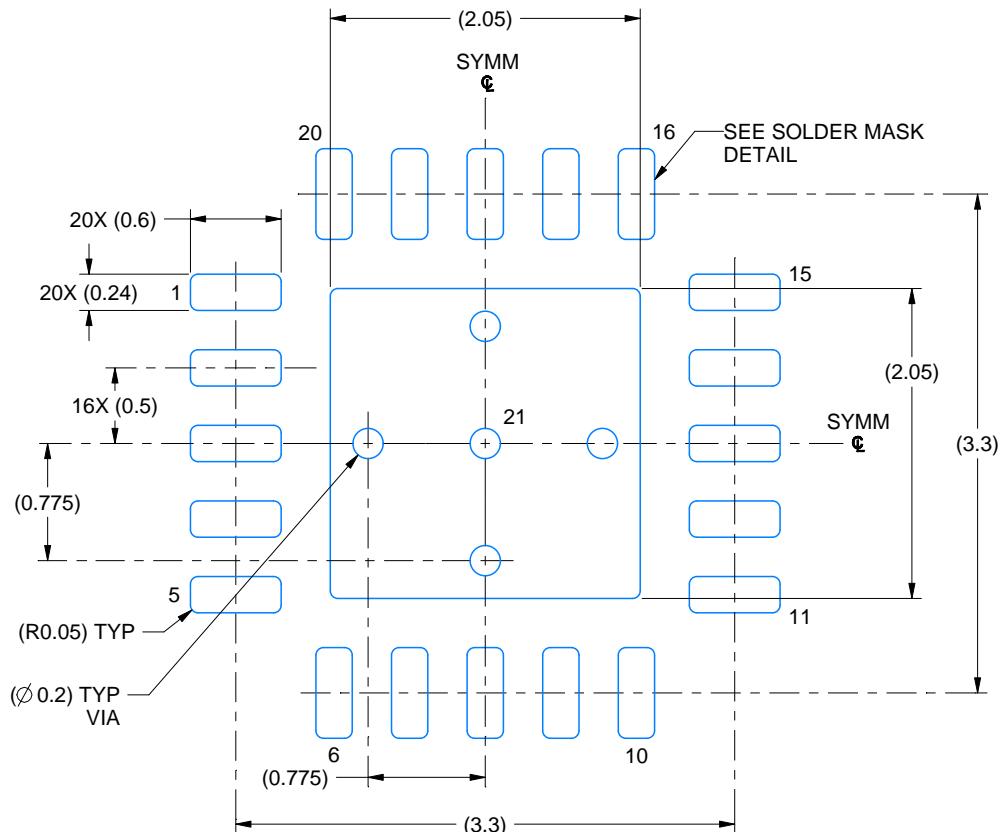

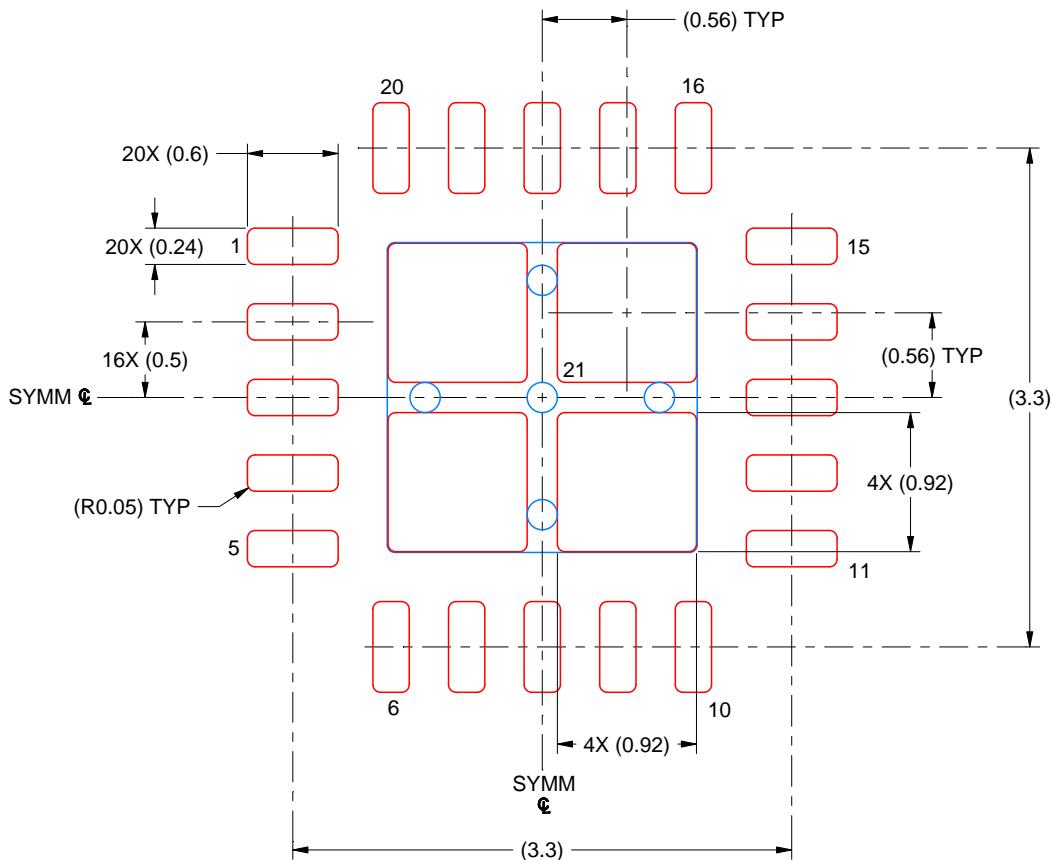

ウェッタブル フランク付き 20 ピン QFN RGR パッケージ (上面図)

表 5-1. ピンの機能

| ピン         |    | I/O <sup>(1)</sup> | 説明                                                                                                                                           |

|------------|----|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 名称         | 番号 |                    |                                                                                                                                              |

| CSP        | 1  | I                  | 電流検出アンプ入力。このピンは正の入力ピンとして動作します。                                                                                                               |

| CSN        | 2  | I                  | 電流検出アンプ入力。このピンは負の入力ピンとして動作します。                                                                                                               |

| VOUT/SENSE | 3  | I                  | 出力電圧検出ピン。内部の帰還抵抗分圧器をピンと AGND との間に接続します。0.1 $\mu$ F のローカル VOUT コンデンサを、ピンとグランドとの間に接続します。                                                       |

|            |    |                    | ハイサイド MOSFET ドレイン電圧検出ピン。短い低インダクタンスのパスを経由して、ピンをハイサイド MOSFET ドレインに接続します。                                                                       |

| PGOOD      | 4  | O                  | オープンドレイン出力段のパワー グッド インジケータ。出力電圧が低電圧スレッショルドより低い場合、このピンは接地されます。未使用時は、このピンをフローティングにできます。                                                        |

| HO         | 5  | O                  | ハイサイド ゲートドライバ出力。短い低インダクタンスのパスを経由して、ハイサイド N チャネル MOSFET のゲートに直接接続します。                                                                         |

| SW         | 6  | P                  | スイッチング ノード接続とハイサイド MOSFET ソース電圧検出ピン。短い低インダクタンスのパスを経由して、ハイサイド N チャネル MOSFET のソースとローサイド N チャネル MOSFET のドレインに直接接続します。非同期整流昇圧構成の場合は、PGND に接続します。 |

| HB         | 7  | P                  | ブートストラップ ゲート駆動のハイサイド ドライバ電源。ブートダイオードは内部で VCC からこのピンに接続されます。このピンと SW との間に 0.1 $\mu$ F コンデンサを接続します。非同期整流昇圧構成の場合は、VCC に接続します。                   |

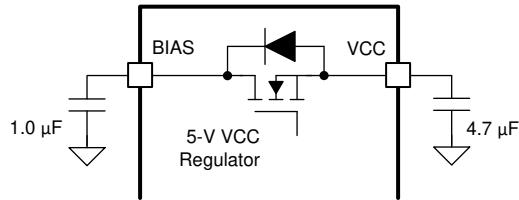

| BIAS       | 8  | P                  | VCC レギュレータの電源電圧入力。1 $\mu$ F のローカル BIAS コンデンサを、ピンとグランドとの間に接続します。                                                                              |

| VCC        | 9  | P                  | 内部 VCC レギュレータの出力と内部 MOSFET ドライバの電源電圧入力。このピンと PGND との間に 4.7 $\mu$ F コンデンサを接続します。                                                              |

| PGND       | 10 | G                  | 電源-グランド ピン。短い低インダクタンスのパスを経由して、ローサイド N チャネル MOSFET のソース端子と電源グランド プレーンを直接接続します。                                                                |

| LO         | 11 | O                  | ローサイド ゲートドライバ出力。短い低インダクタンスのパスを経由して、ローサイド N チャネル MOSFET のゲートに直接接続します。                                                                         |

表 5-1. ピンの機能 (続き)

| ピン                |    | I/O <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                | 番号 |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

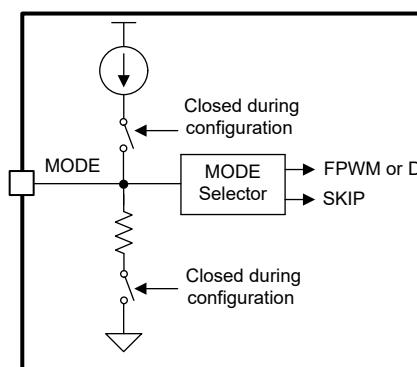

| モード               | 12 | I                  | デバイスのスイッチング モード (FPWM、ダイオード エミュレーション、またはスキップ) 選択ピン。デバイスは、ピンがオープンの場合、または最初のパワーオン時に $500\text{k}\Omega$ より大きな抵抗がピンから AGND に接続されている場合、スキップ モードに構成されます。デバイスは、ピンを VCC に接続する場合、またはパワーオン時にピンの電圧が $2.0\text{V}$ 以上の場合、FPWM モードに構成されます。デバイスは、最初のパワーオン時にピンをグランドに接続する場合、またはピンの電圧が $0.4\text{V}$ 未満場合、ダイオード エミュレーション モードに構成されます。スイッチング モードは、動作中に FPWM と DE モードとの間で動的にプログラムできます。                                                                                                                                                                                                                                                             |

| UVLO/EN           | 13 | I                  | イネーブル ピン。ピンはデバイスを有効化 / 無効化します。ピンが $0.35\text{V}$ を下回ると、デバイスはシャットダウンします。デバイスを有効化するには、このピンを $0.65\text{V}$ よりも高くする必要があります。<br>低電圧誤動作防止のプログラム用ピン。ピンを抵抗分圧器を介して電源電圧に接続することで、コンバータのスタートアップおよびシャットダウン レベルをプログラムできます。ローサイド UVLO 抵抗は AGND に接続する必要があります。未使用時は BIAS に接続してください。                                                                                                                                                                                                                                                                                                                                                             |

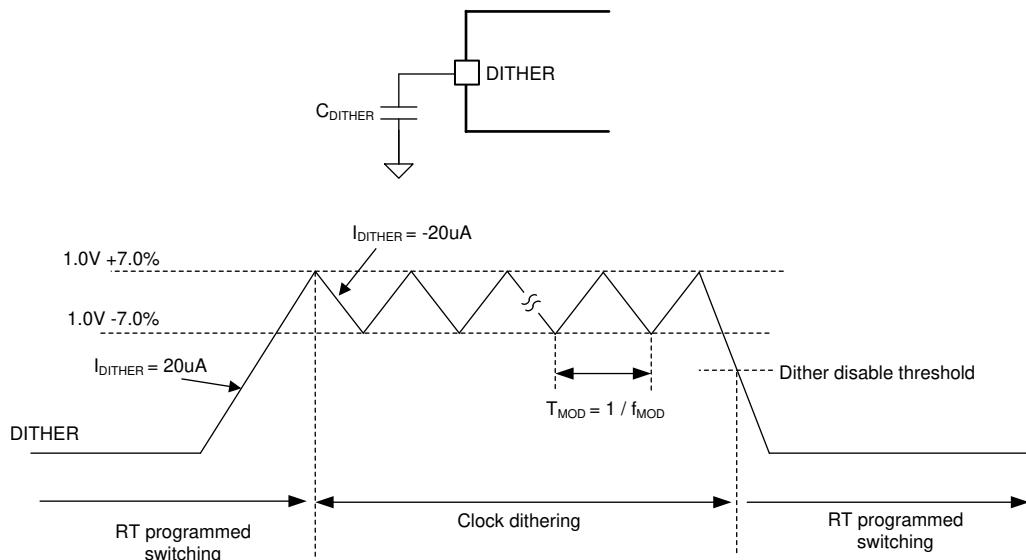

| SYNC/DITHER/VH/CP | 14 | I/O                | 同期クロック入力。内部発振器は、動作中に外部クロックと同期可能です。未使用時は AGND に接続してください。<br>クロック ディザリングおよびスペクトラム拡散変調周波数プログラミング ピン。ピンと AGND との間にコンデンサを接続すると、クロック ディザリングとスペクトラム拡散機能が有効化されます。ディザリング動作中、コンデンサは内部の $20\mu\text{A}$ の電流ソースまたは電流シンクによって充電および放電されます。このピンの電圧が上昇および下降すると、発振周波数は RT 抵抗で設定される公称周波数の $-6\% \sim +5\%$ の間で変調されます。クロック ディザリングとスペクトラム拡散は、ピンをグランドにプルダウンすることで、動作中に無効化できます。<br>VCC ホールドピン。ピンが $2.0\text{V}$ より高い場合、EN ピンが接地されているときにデバイスは VCC ピンの電圧を保持するため、再構成なしで迅速に再起動できます。<br>充電イネーブル ピン。ピンが $2.0\text{V}$ より高い場合、内部チャージ ボンプによって HB ピン電圧がバイパス動作の HB UVLO スレッショルドよりも高く維持され、バイパス動作中にハイサイド スイッチを $100\%$ オンにできます。                                     |

| RT                | 15 | I                  | スイッチング周波数の設定ピン。SYNC ピンに外部クロックが印加されていなければ、ピンと AGND との間の単一の抵抗により、スイッチング周波数がプログラムされます。スイッチング周波数は動作中に動的にプログラムできます。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| VREF/RANGE        | 16 | I/O                | $1.0\text{V}$ 内部リファレンス電圧出力。ピンと AGND の間に $470\text{pF}$ のコンデンサを接続します。 $V_{\text{OUT}}$ レギュレーション ターゲットは、ピンと TRK ピンの間に抵抗分圧器を接続することでプログラムできます。使用する場合、ピンから AGND への抵抗は常に $20\text{k}\Omega$ より大きくする必要があります。分圧器のローサイド低抵抗を AGND に接続します。<br>$V_{\text{OUT}}$ 範囲選択ピン。最初のパワーオン時に、ピンと AGND の間の抵抗が $75\text{k}\Omega$ と $100\text{k}\Omega$ の範囲内である場合、下側 $V_{\text{OUT}}$ 範囲 ( $5\text{V} \sim 20\text{V}$ ) を選択します。最初のパワーオン時に、ピンと AGND の間の抵抗が $20\text{k}\Omega$ と $35\text{k}\Omega$ の範囲内である場合、上側 $V_{\text{OUT}}$ 範囲 ( $15\text{V} \sim 57\text{V}$ ) を選択します。昇圧コンバータの出力電圧は、事前にプログラムされた範囲内で動的にプログラムできます。出力電圧レギュレーションの精度は、選択した範囲内で規定されています。 |

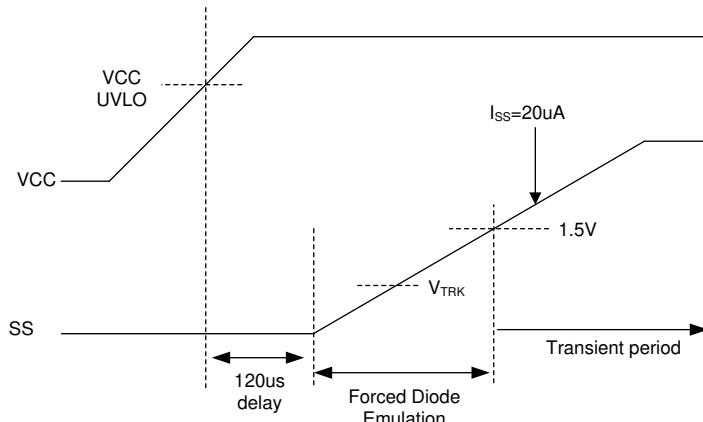

| SS                | 17 | I/O                | ソフトスタート時間のプログラミング ピン。外付けコンデンサと内部の電流ソースにより、ソフトスタート中の内部エラー アンプのリファレンス電圧のランプレートが設定されます。デバイスは、ソフトスタート時間中にダイオード エミュレーションを強制的に実行します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TRK               | 18 | I                  | 出力レギュレーション ターゲットのプログラミング ピン。 $V_{\text{OUT}}$ のレギュレーション ターゲットは、抵抗分圧器を介してピンを VREF に接続するか、D/A から直接ピン電圧を制御することでプログラムできます。このピンの推奨動作電圧範囲は $0.25\text{V} \sim 1.0\text{V}$ です。                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AGND              | 19 | G                  | アナログ グランド ピン。広く短いバスを通して、アナログ グランド プレーンに接続します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| COMP              | 20 | O                  | 内部の相互コンダクタンス エラー アンプの出力。ピンと AGND との間にループ補償部品を接続します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| EP                | —  | —                  | パッケージの露出パッド。熱抵抗を減らすため、EP を大きなグランド プレーンに半田付けする必要があります。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

(1) G=グランド、I=入力、O=出力、P=電源

## 6 仕様

### 6.1 絶対最大定格

接合部の推奨動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                                         |                                       | 最小値  | 最大値                | 単位 |

|-----------------------------------------|---------------------------------------|------|--------------------|----|

| 入力 <sup>(2)</sup>                       | BIAS から AGND へ                        | -0.3 | 50                 | V  |

|                                         | UVLO から AGND へ                        | -0.3 | BIAS + 0.3         |    |

|                                         | CSP から AGND へ                         | -0.3 | 50                 |    |

|                                         | CSP から CSN へ                          | -0.3 | 0.3                |    |

|                                         | VOUT から AGND へ                        | -0.3 | 65                 |    |

|                                         | HB ～ AGND                             | -0.3 | 65                 |    |

|                                         | HB から SW                              | -0.3 | 5.8 <sup>(3)</sup> |    |

|                                         | SW から AGND へ                          | -0.3 | 60                 |    |

|                                         | SW から AGND へ (50ns)                   | -1   |                    |    |

|                                         | SW から AGND へ (10ns)                   | -5   |                    |    |

|                                         | MODE、SYNC、TRK から AGND へ               | -0.3 | 5.5                |    |

|                                         | PGOOD から AGND へ                       | -0.3 | VOUT + 0.3         |    |

|                                         | RT から AGND へ                          | -0.3 | 2.5                |    |

|                                         | PGND から AGND へ                        | -0.3 | 0.3                |    |

| 出力 <sup>(2)</sup>                       | VCC から AGND へ                         | -0.3 | 5.8 <sup>(3)</sup> | V  |

|                                         | HO から SW へ (50ns)                     | -1   |                    |    |

|                                         | LO から PGND へ (50ns)                   | -1   |                    |    |

|                                         | VREF、SS、COMP から AGND へ <sup>(4)</sup> | -0.3 | 5.5                |    |

| 動作時の接合部温度、T <sub>J</sub> <sup>(5)</sup> |                                       | -40  | 150                | °C |

| 保管温度、T <sub>STG</sub>                   |                                       | -55  | 150                |    |

- (1) 「絶対最大定格」を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについての話で、絶対最大定格において、またはこのデータシートの「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

- (2) 外部電圧を VREF、COMP、SS、RT、LO、HO ピンに直接印加することはできません。

- (3) ピンの電圧が 5.5V を超えると、動作寿命が短くなります。

- (4) 最大 VREF ピンのソース電流は 50 $\mu$ A です。

- (5) 接合部温度が高くなると、動作寿命が短くなります。接合部温度が 125°Cを超えると、動作寿命が短くなります。

### 6.2 ESD 定格

|                    |      |                                                               | 値              | 単位 |

|--------------------|------|---------------------------------------------------------------|----------------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、AEC Q100-002 準拠 <sup>(1)</sup><br>HBM ESD 分類レベル 2 | ±2000          | V  |

|                    |      | デバイス帯電モデル (CDM)、AEC Q100-011 準拠<br>CDM ESD 分類レベル C4B          | すべてのピン<br>±500 |    |

|                    |      |                                                               | 角のピン<br>±750   |    |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

## 6.3 接合部動作条件

接合部の推奨動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                     |                                  | 最小値  | 公称値              | 最大値              | 単位  |

|---------------------|----------------------------------|------|------------------|------------------|-----|

| $V_{SUPPLY(BOOST)}$ | 昇圧コンバータ入力 (BIAS $\geq 3.8V$ のとき) | 0.8  | 42               | 42               | V   |

| $V_{LOAD(BOOST)}$   | 昇圧コンバータ出力                        | 5    | 57               | 57               |     |

| $V_{BIAS}$          | BIAS 入力                          | 3.8  | 42               | 42               |     |

| $V_{UVLO}$          | UVLO 入力                          | 0    | 42               | 42               |     |

| $V_{CSP}, V_{CSN}$  | 電流検出入力                           | 0.8  | 42               | 42               |     |

| $V_{VOUT}$          | 昇圧出力検出                           | 5    | 57               | 57               |     |

| $V_{TRK}$           | TRK 入力                           | 0.25 | 1 <sup>(3)</sup> | 1 <sup>(3)</sup> |     |

| $V_{SYNC}$          | 同期パルス入力                          | 0    | 5.25             | 5.25             |     |

| $f_{SW}$            | 標準スイッチング周波数                      | 100  | 2200             | 2200             | kHz |

| $f_{SYNC}$          | 同期パルス周波数                         | 200  | 2200             | 2200             |     |

| $T_J$               | 動作時接合部温度 <sup>(2)</sup>          | -40  | 150              | 150              | °C  |

(1) 動作定格は、デバイスが機能する前提の条件です。仕様およびテスト条件については、「電気的特性」を参照してください。

(2) 接合部温度が高くなると、動作寿命が短くなります。接合部温度が 125°C を超えると、動作寿命が短くなります。

(3) 高い VOUT 範囲を選択した場合、TRK ピンの最大電圧は 0.95V に制限されます。

## 6.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> |                     | LM5123-Q1 | 単位   |

|----------------------|---------------------|-----------|------|

|                      |                     | RGR(QFN)  |      |

|                      |                     | 20 ピン     |      |

| $R_{qJA}$            | 接合部から周囲への熱抵抗        | 43.3      | °C/W |

| $R_{qJC(top)}$       | 接合部からケース (上面) への熱抵抗 | 39.9      | °C/W |

| $R_{qJB}$            | 接合部から基板への熱抵抗        | 17.8      | °C/W |

| $\gamma_{JT}$        | 接合部から上面への特性パラメータ    | 0.8       | °C/W |

| $\gamma_{JB}$        | 接合部から基板への特性パラメータ    | 17.8      | °C/W |

| $R_{qJC(bot)}$       | 接合部からケース (底面) への熱抵抗 | 5.3       | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』を参照してください。

## 6.5 電気的特性

標準値は  $T_J = 25^\circ C$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ C \sim 125^\circ C$  の範囲で適用されます。特に記述のない限り、 $V_{BIAS} = 12V$ 、 $V_{VOUT} = 12V$ 、 $R_T = 9.09k\Omega$ 、 $R_{VREF} = 65k\Omega$  です

| パラメータ                       | テスト条件                                                                          | 最小値                                                                | 標準値 | 最大値 | 単位 |

|-----------------------------|--------------------------------------------------------------------------------|--------------------------------------------------------------------|-----|-----|----|

| <b>電源電流 (BIAS、VCC、VOUT)</b> |                                                                                |                                                                    |     |     |    |

| $I_{BIAS-SD}$               | シャットダウン時の BIAS 電流                                                              | $V_{UVLO} = 0V, V_{OUT} = 11.3V$                                   | 2.5 | 5   | μA |

| $I_{BIAS-DS1}$              | ディープ スリープ時の BIAS 電流<br>(スキップまたはダイオード エミュレーション モード、チャージ ポンプ オフ、VCC は BIAS から供給) | $V_{UVLO} = 2.5V, V_{TRK} = 0.25V, V_{SYNC} = 0V, V_{OUT} = 12V$   | 10  | 16  | μA |

| $I_{BIAS-DS2}$              | ディープ スリープ時の BIAS 電流<br>(FPWM モード、チャージ ポンプ オフ、VCC は BIAS から供給)                  | $V_{UVLO} = 2.5V, V_{TRK} = 0.25V, V_{SYNC} = 0V, V_{OUT} = 12V$   | 40  | 69  | μA |

| $I_{BIAS-DS3}$              | ディープ スリープ時の BIAS 電流<br>(スキップまたはダイオード エミュレーション モード、チャージ ポンプ オン、VCC は BIAS から供給) | $V_{UVLO} = 2.5V, V_{TRK} = 0.25V, V_{SYNC} = 2.5V, V_{OUT} = 12V$ | 32  | 60  | μA |

## 6.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $V_{BIAS} = 12\text{V}$ 、 $V_{VOUT} = 12\text{V}$ 、 $R_T = 9.09\text{k}\Omega$ 、 $R_{VREF} = 65\text{k}\Omega$  です

| パラメータ                    | テスト条件                                                   | 最小値                                                                                                     | 標準値   | 最大値   | 単位            |

|--------------------------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------|-------|---------------|

| $I_{BIAS-DS4}$           | ディープスリープ時の BIAS 電流 (FPWM モード、チャージポンプオン、VCC は BIAS から供給) | $V_{UVLO} = 2.5\text{V}$ 、 $V_{TRK} = 0.25\text{V}$ 、 $V_{SYNC} = 2.5\text{V}$ 、 $V_{OUT} = 12\text{V}$ | 114   | 154   | $\mu\text{A}$ |

| $I_{BIAS-SLEEP}$         | スリープ時の BIAS 電流 (スキップモード、VCC は BIAS から供給)                | $V_{UVLO} = 2.5\text{V}$ 、 $V_{TRK} = 0.25\text{V}$ 、MODE = OPEN、 $V_{OUT} = 5\text{V}$                 | 13    | 17.5  | $\mu\text{A}$ |

| $I_{BIAS-ACTIVE}$        | アクティブ時の BIAS 電流 (非スキッピング、VCC は BIAS から供給)               | $V_{UVLO} = 2.5\text{V}$ 、 $V_{TRK} = 0.6\text{V}$ 、MODE = VCC                                          | 1.2   | 1.5   | $\text{mA}$   |

| $I_{VOUT-SD}$            | シャットダウン時の VOUT 電流                                       | $V_{UVLO} = 0\text{V}$ 、 $V_{OUT} = 11.3\text{V}$                                                       |       | 1     | $\mu\text{A}$ |

| $I_{VOUT-DS}$            | ディープスリープ時の VOUT 電流 (ダイオードエミュレーションモード)                   | $V_{UVLO} = 2.5\text{V}$ 、 $V_{TRK} = 0.25\text{V}$ 、 $V_{OUT} = 12\text{V}$                            | 1.2   | 1.5   | $\mu\text{A}$ |

| $I_{VOUT-ACTIVE}$        | アクティブ時の VOUT 電流 (非スキッピング)                               | $V_{UVLO} = 2.5\text{V}$ 、 $V_{TRK} = 0.6\text{V}$ 、MODE = VCC                                          | 42    | 55    | $\mu\text{A}$ |

| $I_{BATTERY-SD}$         | シャットダウン時のバッテリドレイン                                       | $V_{UVLO} = 0\text{V}$ 、 $V_{OUT} = 11.3\text{V}$                                                       |       | 2.5   | $\mu\text{A}$ |

| $I_{BATTERY-DS1}$        | ディープスリープ時のバッテリドレイン (スキップまたはダイオードエミュレーションモード、チャージポンプオフ)  | $V_{UVLO} = 2.5\text{V}$ 、 $V_{TRK} = 0.25\text{V}$ 、 $V_{SYNC} = 0\text{V}$                            | 11    | 17    | $\mu\text{A}$ |

| $I_{BATTERY-DS2}$        | ディープスリープ時のバッテリドレイン (FPWM モード、チャージポンプオフ)                 | $V_{UVLO} = 2.5\text{V}$ 、 $V_{TRK} = 0.25\text{V}$ 、 $V_{SYNC} = 0\text{V}$                            | 41    | 70    | $\mu\text{A}$ |

| $I_{BATTERY-DS3}$        | ディープスリープ時のバッテリドレイン (スキップまたはダイオードエミュレーションモード、チャージポンプオン)  | $V_{UVLO} = 2.5\text{V}$ 、 $V_{TRK} = 0.25\text{V}$ 、 $V_{SYNC} = 2.5\text{V}$                          | 33    | 62    | $\mu\text{A}$ |

| $I_{BATTERY-DS4}$        | ディープスリープ時のバッテリドレイン (FPWM モード、チャージポンプオン)                 | $V_{UVLO} = 2.5\text{V}$ 、 $V_{TRK} = 0.25\text{V}$ 、 $V_{SYNC} = 2.5\text{V}$                          | 115   | 155   | $\mu\text{A}$ |

| <b>ENABLE、UVLO</b>       |                                                         |                                                                                                         |       |       |               |

| $V_{EN-RISING}$          | イネーブルスレッショルド                                            | EN 立ち上がり                                                                                                | 0.45  | 0.55  | 0.65          |

| $V_{EN-FALLING}$         | イネーブルスレッショルド                                            | EN 立ち下がり                                                                                                | 0.35  | 0.45  | 0.55          |

| $V_{EN-HYS}$             | イネーブルヒステリシス                                             | EN 立ち下がり                                                                                                | 55    | 90    | 130           |

| $I_{UVLO-HYS}$           | UVLO プルダウンヒステリシス電流                                      | $V_{UVLO} = 0.7\text{V}$                                                                                | 8     | 10    | 12            |

| $V_{UVLO-RISING}$        | UVLO スレッショルド                                            | UVLO 立ち上がり                                                                                              | 1.05  | 1.1   | 1.15          |

| $V_{UVLO-FALLING}$       | UVLO スレッショルド                                            | UVLO 立ち下がり                                                                                              | 1.025 | 1.075 | 1.125         |

| $V_{UVLO-HYS}$           | UVLO ヒステリシス                                             | UVLO 立ち下がり                                                                                              |       | 25    | $\text{mV}$   |

| <b>SYNC/DITHER/VH/CP</b> |                                                         |                                                                                                         |       |       |               |

| $V_{SYNC-RISING}$        | SYNCスレッショルド / SYNC検出スレッショルド                             | SYNC 立ち上がり                                                                                              |       | 2     | $\text{V}$    |

| $V_{SYNC-FALLING}$       | SYNCスレッショルド                                             | SYNC 立ち下がり                                                                                              | 0.4   |       | $\text{V}$    |

|                          | 最小 SYNC プルアップパルス幅                                       |                                                                                                         |       | 100   | $\text{ns}$   |

| $I_{DITHER}$             | ディザイナーソース / シンク電流                                       |                                                                                                         | 16    | 21    | 26            |

| $\Delta f_{SW1}$         | $f_{SW}$ 変調 (上限)                                        |                                                                                                         |       | 5     | %             |

| $\Delta f_{SW2}$         | $f_{SW}$ 変調 (下限)                                        |                                                                                                         |       | -6    | %             |

| $V_{DITHER-FALLING}$     | ディザイナーソースのディセーブルのスレッショルド                                |                                                                                                         | 0.65  | 0.75  | 0.85          |

| <b>VCC</b>               |                                                         |                                                                                                         |       |       | $\text{V}$    |

## 6.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $V_{\text{BIAS}} = 12\text{V}$ 、 $V_{\text{VOUT}} = 12\text{V}$ 、 $R_T = 9.09\text{k}\Omega$ 、 $R_{\text{VREF}} = 65\text{k}\Omega$  です

| パラメータ                         | テスト条件                                                               | 最小値                                                                                                     | 標準値   | 最大値  | 単位              |

|-------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------|------|-----------------|

| $V_{\text{VCC-REG1}}$         | $V_{\text{CC}}$ レギュレーション                                            | $I_{\text{VCC}} = 100\text{mA}$                                                                         | 4.75  | 5    | $5.25\text{V}$  |

| $V_{\text{VCC-REG2}}$         | $V_{\text{CC}}$ レギュレーション                                            | 無負荷                                                                                                     | 4.75  | 5    | $5.25\text{V}$  |

| $V_{\text{VCC-REG3}}$         | ドロップアウト時の $V_{\text{CC}}$ レギュレーション                                  | $V_{\text{BIAS}} = 3.8\text{V}$ 、 $I_{\text{VCC}} = 100\text{mA}$                                       | 3.45  |      | $\text{V}$      |

| $V_{\text{VCC-UVLO-RISING}}$  | $V_{\text{CC}}$ UVLO スレッショルド                                        | $V_{\text{CC}}$ 立ち上がり                                                                                   | 3.55  | 3.65 | 3.75            |

| $V_{\text{VCC-UVLO-FALLING}}$ | $V_{\text{CC}}$ UVLO スレッショルド                                        | $V_{\text{CC}}$ 立ち下がり                                                                                   | 3.2   | 3.3  | 3.4             |

| $I_{\text{VCC-CL}}$           | $V_{\text{CC}}$ のソース電流制限                                            | $V_{\text{VCC}} = 4\text{V}$                                                                            | 100   |      | $\text{mA}$     |

| <b>構成 (MODE)</b>              |                                                                     |                                                                                                         |       |      |                 |

| $V_{\text{MODE-RISING}}$      | FPWM モード スレッショルド                                                    | MODE 立ち上がり                                                                                              |       | 2.0  | $\text{V}$      |

| $V_{\text{MODE-FALLING}}$     | ダイオード エミュレーション モード のスレッショルド                                         | MODE 立ち下がり                                                                                              | 0.4   |      | $\text{V}$      |

| <b>RT</b>                     |                                                                     |                                                                                                         |       |      |                 |

| $V_{\text{RT}}$               | RT レギュレーション                                                         |                                                                                                         | 0.5   |      | $\text{V}$      |

| <b>VREF、TRK、VOUT</b>          |                                                                     |                                                                                                         |       |      |                 |

| $V_{\text{REF}}$              | $V_{\text{REF}}$ のレギュレーションターゲット                                     |                                                                                                         | 0.99  | 1    | $1.005\text{V}$ |

| $V_{\text{OUT-REG}}$          | 抵抗デバイダによる $V_{\text{OUT}}$ レギュレーションターゲット 1 (下側 $V_{\text{OUT}}$ 範囲) | $V_{\text{TRK}} = 0.25\text{V}$ 、 $R_{\text{VREF}} = 65\text{k}\Omega$ を実現するための $V_{\text{REF}}$ 抵抗デバイダ | 4.915 | 5    | $5.085\text{V}$ |

| $V_{\text{OUT-REG}}$          | 抵抗デバイダによる $V_{\text{OUT}}$ レギュレーションターゲット 2 (下側 $V_{\text{OUT}}$ 範囲) | $V_{\text{TRK}} = 0.5\text{V}$ 、 $R_{\text{VREF}} = 65\text{k}\Omega$ を実現するための $V_{\text{REF}}$ 抵抗デバイダ  | 9.9   | 10   | 10.1            |

| $V_{\text{OUT-REG}}$          | 抵抗デバイダによる $V_{\text{OUT}}$ レギュレーションターゲット 3 (下側 $V_{\text{OUT}}$ 範囲) | $V_{\text{TRK}} = 1.0\text{V}$ 、 $R_{\text{VREF}} = 65\text{k}\Omega$ を実現するための $V_{\text{REF}}$ 抵抗デバイダ  | 19.8  | 20   | 20.2            |

| $V_{\text{OUT-REG}}$          | 抵抗デバイダによる $V_{\text{OUT}}$ レギュレーションターゲット 4 (上側 $V_{\text{OUT}}$ 範囲) | $V_{\text{TRK}} = 0.25\text{V}$ 、 $R_{\text{VREF}} = 35\text{k}\Omega$ を実現するための $V_{\text{REF}}$ 抵抗デバイダ | 14.74 | 15   | 15.24           |

| $V_{\text{OUT-REG}}$          | 抵抗デバイダによる $V_{\text{OUT}}$ レギュレーションターゲット 5 (上側 $V_{\text{OUT}}$ 範囲) | $V_{\text{TRK}} = 0.5\text{V}$ 、 $R_{\text{VREF}} = 35\text{k}\Omega$ を実現するための $V_{\text{REF}}$ 抵抗デバイダ  | 29.7  | 30   | 30.3            |

| $V_{\text{OUT-REG}}$          | 抵抗デバイダによる $V_{\text{OUT}}$ レギュレーションターゲット 6 (上側 $V_{\text{OUT}}$ 範囲) | $V_{\text{TRK}} = 0.95\text{V}$ 、 $R_{\text{VREF}} = 35\text{k}\Omega$ を実現するための $V_{\text{REF}}$ 抵抗デバイダ | 56.43 | 57   | 57.57           |

| $V_{\text{OUT-REG}}$          | TRK を使用した $V_{\text{OUT}}$ レギュレーションターゲット 1 (下側 $V_{\text{OUT}}$ 範囲) | $V_{\text{TRK}} = 0.25\text{V}$ 、 $R_{\text{VREF}} = 65\text{k}\Omega$                                  | 4.91  | 5    | $5.09\text{V}$  |

| $V_{\text{OUT-REG}}$          | TRK を使用した $V_{\text{OUT}}$ レギュレーションターゲット 2 (下側 $V_{\text{OUT}}$ 範囲) | $V_{\text{TRK}} = 0.5\text{V}$ 、 $R_{\text{VREF}} = 65\text{k}\Omega$                                   | 9.88  | 10   | 10.11           |

| $V_{\text{OUT-REG}}$          | TRK を使用した $V_{\text{OUT}}$ レギュレーションターゲット 3 (下側 $V_{\text{OUT}}$ 範囲) | $V_{\text{TRK}} = 1.0\text{V}$ 、 $R_{\text{VREF}} = 65\text{k}\Omega$                                   | 19.8  | 20   | 20.2            |

| $V_{\text{OUT-REG}}$          | TRK を使用した $V_{\text{OUT}}$ レギュレーションターゲット 4 (上側 $V_{\text{OUT}}$ 範囲) | $V_{\text{TRK}} = 0.25\text{V}$ 、 $R_{\text{VREF}} = 35\text{k}\Omega$                                  | 14.71 | 15   | 15.25           |

## 6.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $V_{\text{BIAS}} = 12\text{V}$ 、 $V_{\text{VOUT}} = 12\text{V}$ 、 $R_T = 9.09\text{k}\Omega$ 、 $R_{\text{VREF}} = 65\text{k}\Omega$  です

| パラメータ                           | テスト条件                                                                | 最小値                                                                    | 標準値   | 最大値  | 単位            |

|---------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------|-------|------|---------------|

| $V_{\text{OUT-REG}}$            | TRK を使用した $V_{\text{OUT}}$ レギュレーション ターゲット 5 (上側 $V_{\text{OUT}}$ 範囲) | $V_{\text{TRK}} = 0.5\text{V}$ 、 $R_{\text{VREF}} = 35\text{k}\Omega$  | 29.6  | 30   | 30.3          |

| $V_{\text{OUT-REG}}$            | TRK を使用した $V_{\text{OUT}}$ レギュレーション ターゲット 6 (上側 $V_{\text{OUT}}$ 範囲) | $V_{\text{TRK}} = 0.95\text{V}$ 、 $R_{\text{VREF}} = 35\text{k}\Omega$ | 56.45 | 57   | 57.5          |

| $I_{\text{TRK}}$                | TRK バイアス電流                                                           |                                                                        |       | 1    | $\mu\text{A}$ |

| <b>ソフトスタート、DE から FPWM への遷移</b>  |                                                                      |                                                                        |       |      |               |

| $I_{\text{SS}}$                 | ソフトスタート電流                                                            |                                                                        | 17    | 20   | 23            |

| $V_{\text{SS-DONE}}$            | MODE 遷移開始                                                            | SS 立ち上がり                                                               | 1.3   | 1.5  | 1.7           |

| $R_{\text{SS}}$                 | SS プルダウン スイッチの $R_{\text{DSON}}$                                     |                                                                        | 30    | 70   | $\Omega$      |

| $V_{\text{SS-DIS}}$             | SS 放電検出スレッショルド                                                       |                                                                        | 30    | 50   | 75            |

| $V_{\text{SS-FB}}$              | 内部の SS から FB へのクランプ                                                  | $V_{\text{FB}}=0\text{V}$                                              | 55    | 75   | $\text{mV}$   |

| <b>電流センス (CSP、CSN、SW、SENSE)</b> |                                                                      |                                                                        |       |      |               |

| $V_{\text{SLOPE}}$              | ピーク勾配補償アンプ                                                           | CS 入力を基準とします                                                           | 45    |      | $\text{mV}$   |

| $A_{\text{CS}}$                 | 電流センス アンプのゲイン                                                        | $CSP = 3.0\text{V}$                                                    | 10    |      | $\text{V/V}$  |

|                                 | 電流センス アンプのゲイン                                                        | $CSP = 1.5\text{V}$                                                    | 10    |      | $\text{V/V}$  |

| $V_{\text{CLTH}}$               | 正のピーク電流制限スレッショルド (CSP-CSN)                                           | $CSP=3.0\text{V}$ 、 $\text{MODE} = \text{GND}$                         | 54    | 60   | 66            |

|                                 | 正のピーク電流制限スレッショルド (CSP-CSN)                                           | $CSP=1.5\text{V}$ 、 $\text{MODE} = \text{GND}$                         | 51    | 60   | 72            |

| $V_{\text{ZCD-DE}}$             | ZCD スレッショルド (SW-SENSE)                                               | $\text{MODE} = \text{GND}$                                             | 4     |      | $\text{mV}$   |

| $I_{\text{CSN}}$                | CSN バイアス電流                                                           |                                                                        |       | 1    | $\mu\text{A}$ |

| $I_{\text{CSP}}$                | CSP バイアス電流                                                           |                                                                        | 110   |      | $\mu\text{A}$ |

| <b>ポート故障保護 (HB)</b>             |                                                                      |                                                                        |       |      |               |

|                                 | 最大再補充パルス サイクル                                                        |                                                                        | 4     |      | サイクル          |

|                                 | 再補充オフ サイクル                                                           |                                                                        | 12    |      | サイクル          |

|                                 | ヒカップ モード保護に移行するためのセット数                                               |                                                                        | 4     |      | セット           |

|                                 | ヒカップ モード オフでのオフ サイクル                                                 |                                                                        | 512   |      | サイクル          |

| <b>エラー アンプ (COMP)</b>           |                                                                      |                                                                        |       |      |               |

| $G_m$                           | 相互コンダクタンス                                                            |                                                                        | 1     |      | $\text{mA/V}$ |

| $I_{\text{SOURCE-MAX}}$         | 最大 COMP ソーシング電流                                                      | $V_{\text{COMP}}=0\text{V}$                                            | 95    |      | $\mu\text{A}$ |

| $I_{\text{SINT-MAX}}$           | 最大 COMP シンキング電流                                                      | $V_{\text{COMP}}=1.8\text{V}$                                          | 90    |      | $\mu\text{A}$ |

| $V_{\text{CLAMP-MAX}}$          | COMP 最大クランプ電圧                                                        | COMP 立ち上がり                                                             | 1.8   | 2.2  | 2.55          |

| $V_{\text{CLAMP-MIN}}$          | COMP 最小クランプ電圧、スリープ およびディープ スリープ モードでアクティブ。                           | COMP 立ち下がり                                                             |       | 0.25 | $\text{V}$    |

| <b>パルス幅変調 (PWM)</b>             |                                                                      |                                                                        |       |      |               |

| $f_{\text{SW1}}$                | スイッチング周波数                                                            | $R_T = 220\text{k}\Omega$                                              | 85    | 100  | 115           |

| $f_{\text{SW2}}$                | スイッチング周波数                                                            | $R_T = 9.09\text{k}\Omega$                                             | 1980  | 2200 | 2420          |

| $t_{\text{ON-MIN}}$             | 最小の制御可能なオン時間                                                         | $R_T = 9.09\text{k}\Omega$                                             | 14    | 20   | 50            |

| $t_{\text{OFF-MIN}}$            | 最小強制オフ時間                                                             | $R_T = 9.09\text{k}\Omega$                                             | 70    | 95   | 115           |

## 6.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $V_{\text{BIAS}} = 12\text{V}$ 、 $V_{\text{VOUT}} = 12\text{V}$ 、 $R_T = 9.09\text{k}\Omega$ 、 $R_{\text{VREF}} = 65\text{k}\Omega$  です

| パラメータ                     |                                    | テスト条件                                                  | 最小値   | 標準値  | 最大値  | 単位               |

|---------------------------|------------------------------------|--------------------------------------------------------|-------|------|------|------------------|

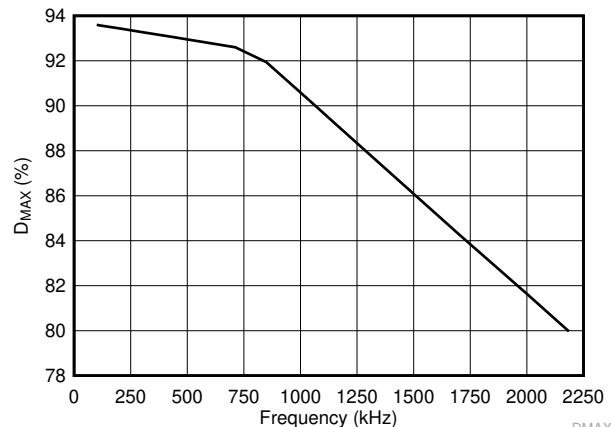

| $D_{\text{MAX1}}$         | 最大デューティサイクル制限                      | $R_T = 220\text{k}\Omega$                              | 90    | 94   | 98   | %                |

| $D_{\text{MAX2}}$         | 最大デューティサイクル制限                      | $R_T = 9.09\text{k}\Omega$                             | 75    | 80   | 83   | %                |

| <b>低静止電流のスリープ モード</b>     |                                    |                                                        |       |      |      |                  |

| $V_{\text{WAKE}}$         | 内部ウェークアップ レッショルド                   | $V_{\text{OUT-REG}}$ 立ち下がり ( $V_{\text{OUT-REG}}$ が基準) |       | 98.5 |      | %                |

|                           | スリープからウェークアップまでの遅延                 | $R_T = 9.09\text{k}\Omega$                             |       | 5    |      | $\text{us}$      |

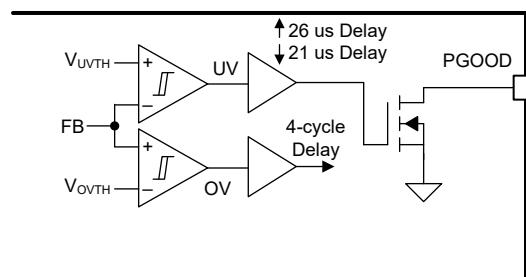

| <b>PGOOD、OVP</b>          |                                    |                                                        |       |      |      |                  |

| $V_{\text{OVTH-RISING}}$  | 過電圧レッショルド (OVP レッショルド)             | $V_{\text{OUT}}$ 立ち上がり ( $V_{\text{OUT-REG}}$ が基準)     | 104.5 | 108  | 111  | %                |

| $V_{\text{OVTH-FALLING}}$ | 過電圧レッショルド (OVP レッショルド)             | $V_{\text{OUT}}$ 立ち下がり ( $V_{\text{OUT-REG}}$ が基準)     | 100.5 | 105  | 109  | %                |

| $V_{\text{UVTH-RISING}}$  | 低電圧レッショルド (PGOOD レッショルド)           | $V_{\text{OUT}}$ 立ち上がり ( $V_{\text{OUT-REG}}$ が基準)     | 91.5  | 94   | 98   | %                |

| $V_{\text{UVTH-FALLING}}$ | 低電圧レッショルド (PGOOD レッショルド)           | $V_{\text{OUT}}$ 立ち下がり ( $V_{\text{OUT-REG}}$ が基準)     | 89.5  | 92   | 95.5 | %                |

|                           | UV コンバレータのグリッチ除去フィルタ               | 立ち上がりエッジ                                               |       | 26   |      | $\mu\text{s}$    |

|                           | UV コンバレータのグリッチ除去フィルタ               | 立ち下がりエッジ                                               |       | 21   |      | $\mu\text{s}$    |

| $R_{\text{PGOOD}}$        | PGOOD プルダウンスイッチの $R_{\text{DSON}}$ |                                                        |       | 90   | 180  | $\Omega$         |

|                           | 有効な PGOOD の最小 BIAS                 |                                                        |       |      | 2.5  | V                |

| <b>MOSFET ドライバ</b>        |                                    |                                                        |       |      |      |                  |

|                           | High 状態での電圧降下 (HO ドライバ)            | 100mA のシンク                                             |       | 0.08 | 0.15 | V                |

|                           | Low 状態での電圧降下 (HO ドライバ)             | 100mA のソース                                             |       | 0.04 | 0.1  | V                |

|                           | High 状態での電圧降下 (LO ドライバ)            | 100mA のシンク                                             |       | 0.08 | 0.17 | V                |

|                           | Low 状態での電圧降下 (LO ドライバ)             | 100mA のソース                                             |       | 0.04 | 0.1  | V                |

| $V_{\text{HB-UVLO}}$      | HB-SW UVLO レッショルド                  | HB-SW 立ち下がり                                            | 2.2   | 2.5  | 3.0  | V                |

| $I_{\text{HB-SLEEP}}$     | スリープ時の HB 静止電流                     | $HB-SW = 5\text{V}$                                    | 3.5   | 7    |      | $\mu\text{A}$    |

| $t_{\text{DHL}}$          | HO オフから LO オンまでのデッドタイム             |                                                        |       | 20   |      | ns               |

| $t_{\text{DLH}}$          | LO オフから HO オンまでのデッドタイム             |                                                        |       | 22   |      | ns               |

|                           | HB ダイオード抵抗                         |                                                        |       | 1.2  |      | $\Omega$         |

| <b>サーマル シャットダウン</b>       |                                    |                                                        |       |      |      |                  |

| $T_{\text{TSD-RISING}}$   | サーマル シャットダウンのスレッショルド               | 温度上昇                                                   |       | 175  |      | $^\circ\text{C}$ |

| $T_{\text{TSD-HYS}}$      | サーマル シャットダウン ヒステリシス                |                                                        |       | 15   |      | $^\circ\text{C}$ |

## 6.6 代表的特性

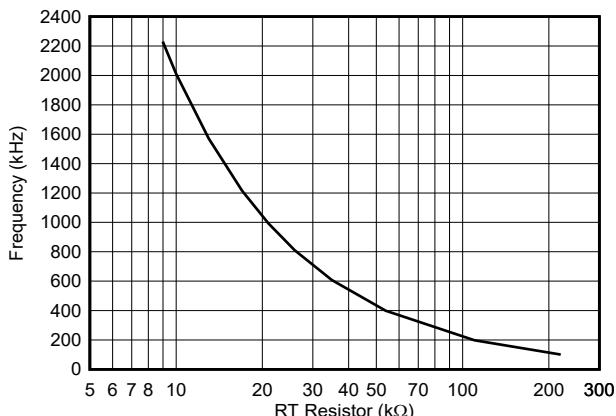

図 6-1. 周波数と RT 抵抗との関係

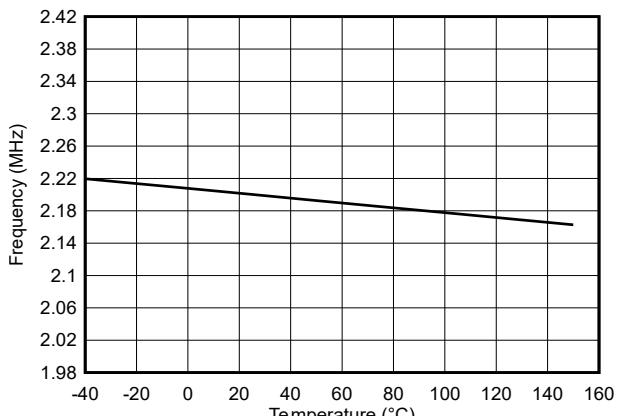

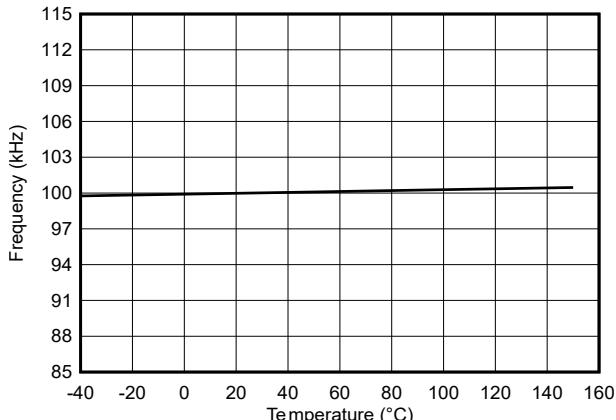

図 6-2. 周波数と温度との関係

( $RT = 9.09\text{k}\Omega$ 、2.2MHz)図 6-3. 周波数と温度との関係

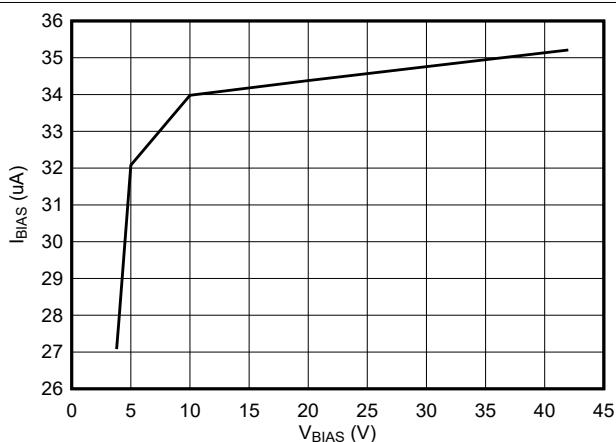

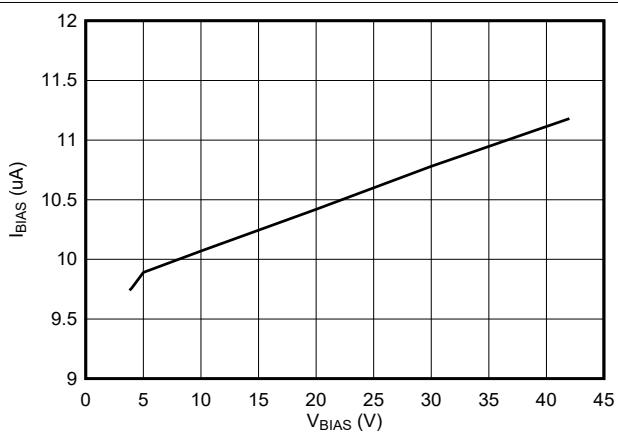

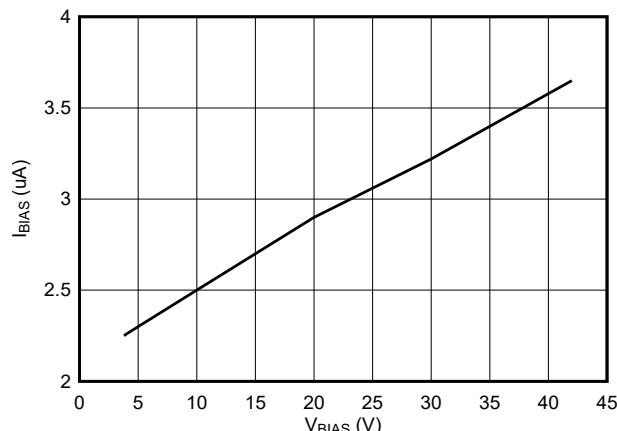

( $RT = 220\text{k}\Omega$ 、100kHz)図 6-4.  $V_{BIAS}$  と  $I_{BIAS}$  との関係 (アクティブモード)図 6-5.  $V_{BIAS}$  と  $I_{BIAS}$  との関係 (バイパスモード、チャージポンプオン)図 6-6.  $V_{BIAS}$  と  $I_{BIAS}$  との関係 (バイパスモード、チャージポンプオフ)

## 6.6 代表的特性 (続き)

図 6-7.  $V_{BIA}$  と  $I_{BIA}$  との関係 (シャットダウン モード)

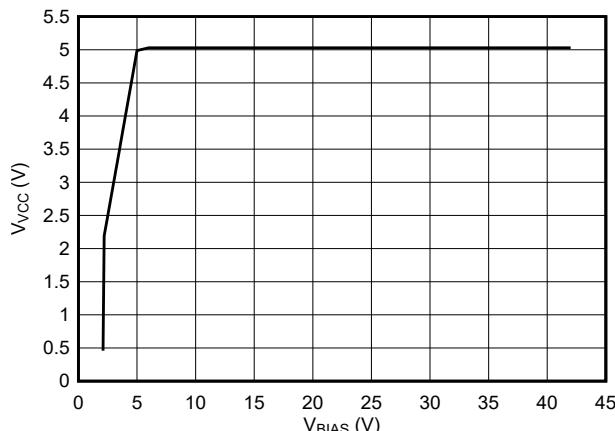

図 6-8.  $V_{BIA}$  と  $V_{VCC}$  との関係

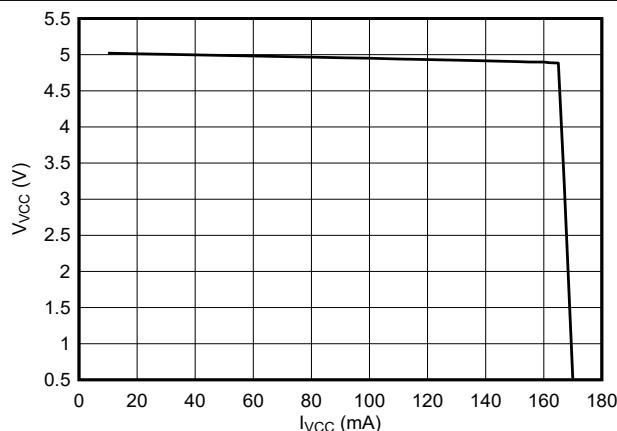

図 6-9.  $V_{VCC}$  と  $I_{VCC}$  との関係

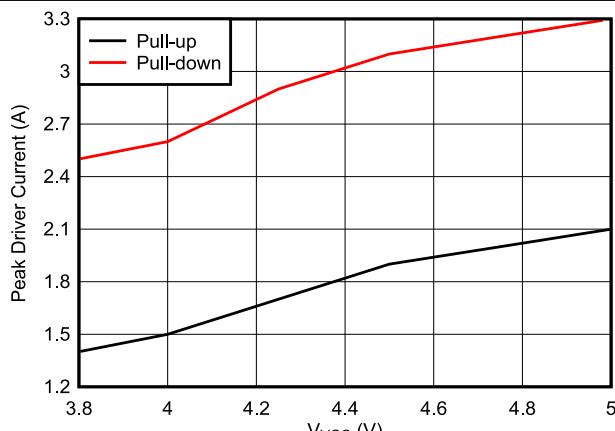

図 6-10.  $V_{VCC}$  とピーク ドライバ電流との関係

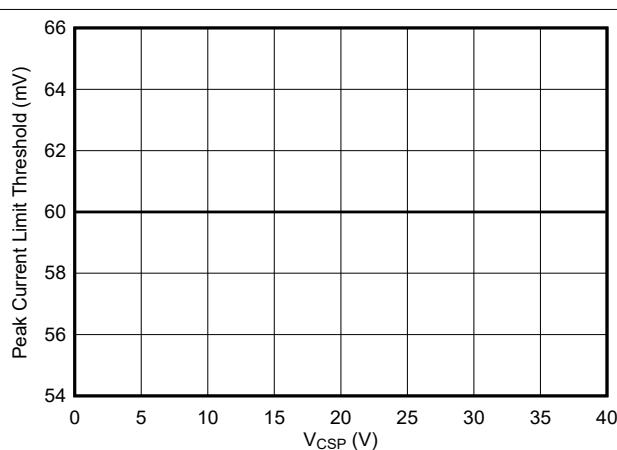

図 6-11. ピーク電流制限スレッショルドと  $V_{CSP}$  との関係

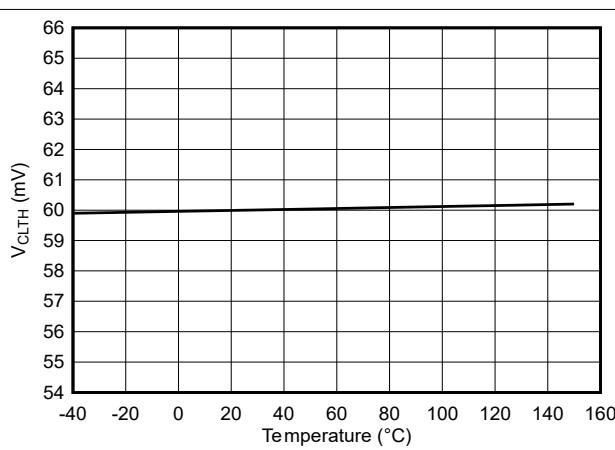

図 6-12. ピーク電流制限スレッショルド  $V_{CLTH}$  と温度との関係

( $CSP = 3V$ )

## 6.6 代表的特性 (続き)

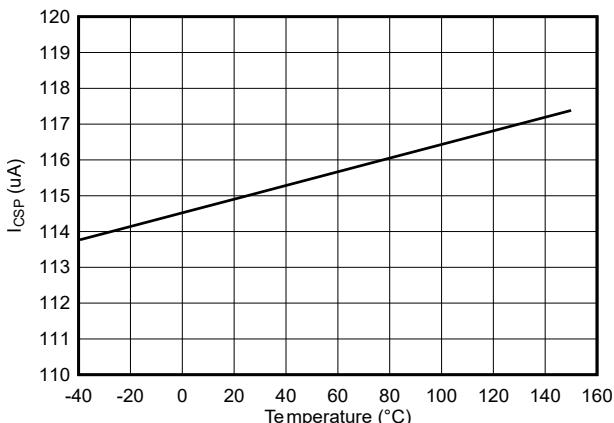

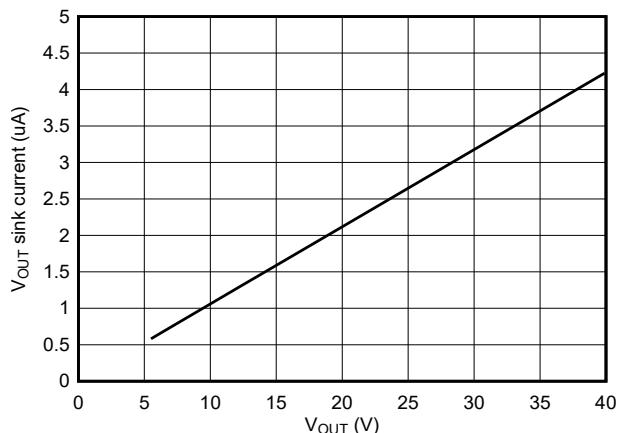

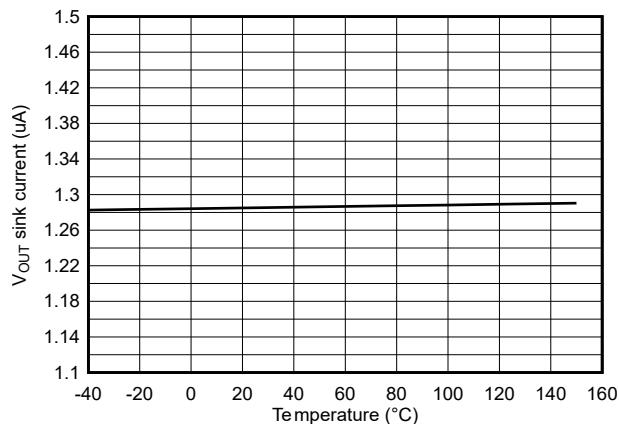

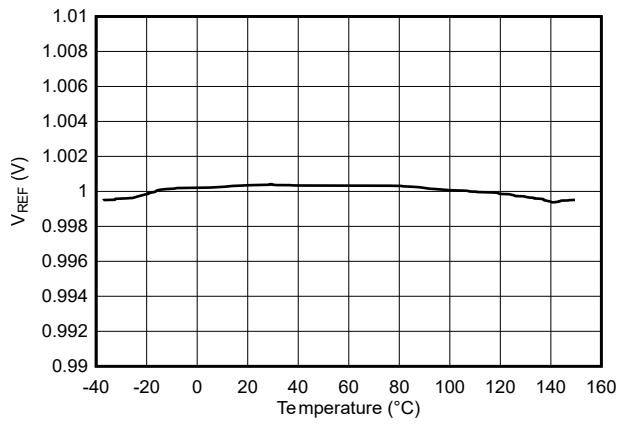

図 6-13.  $I_{CSP}$  と温度との関係 (アクティブ モード)図 6-14.  $V_{OUT}$  シンク電流と  $V_{OUT}$  との関係 (ディープ スリーブ)図 6-15.  $V_{OUT}$  シンク電流と温度との関係 (ディープ スリーブ)図 6-16.  $V_{REF}$  と温度との関係図 6-17.  $D_{MAX}$  と周波数との関係

## 7 詳細説明

### 7.1 概要

LM5123-Q1 デバイスは、ピーク電流モード制御を採用した、入力範囲が広い同期整流昇圧コントローラです。このデバイスは、シャットダウン時の  $I_Q$  が低く、また、 $I_Q$  が低いスリープモードを備えているため、無負荷および軽負荷の状況でバッテリドレインを最小化できます。さらに、このデバイスは、 $I_Q$  が非常に低いディープスリープモードでのバイパス動作にも対応しているため、電源電圧が昇圧出力レギュレーション目標よりも高い場合の外部バイパススイッチが不要です。出力電圧は、トラッキング機能を使用して動的にプログラムできます。

本デバイスの広い入力範囲は自動車のコールドクランクとロードダンプをサポートしています。BIAS が 3.8V 以上の場合、最小入力電圧は 0.8V まで下がることができます。スイッチング周波数は、外付けの抵抗により 100kHz~2.2MHz の範囲で動的にプログラマブルです。2.2MHz でのスイッチングにより、AM 帯域との干渉が最小化され、ソリューションサイズの小型化と、高速な過渡応答を実現できます。コントローラアーキテクチャにより、コンバータアーキテクチャと比較して、過酷な周囲温度条件での熱管理を簡素化できます。

ピーク電流制限 ( $V_{IN}$  の全範囲にわたって一定)、過電圧保護、サーマルシャットダウンなどの保護機能が内蔵されています。外部クロック同期、プログラマブルスペクトラム拡散変調、最小限の寄生容量でのリードレスパッケージは、EMI の低減とクロストークの回避に役立ちます。追加機能には、以下が含まれます。

- ラインUVLO

- FPWM

- ダイオードエミュレーション

- DCR インダクタ電流検出

- プログラマブルソフトスタート

- パワーグッドインジケータ

### 7.2 機能ブロック図

## 7.3 機能説明

### 注

デバイスの機能説明を読む前に、[セクション 7.4](#) を読んでください。まず、デバイスでサポートされているデバイスの機能モードおよび軽負荷スイッチング モードの種類について理解することを推奨します。

このセクションで説明するパラメータやスレッショルドの値は、特に記述のない限りリファレンス値です。最小値、最大値、標準値については、[「電気的特性」](#)を参照してください。

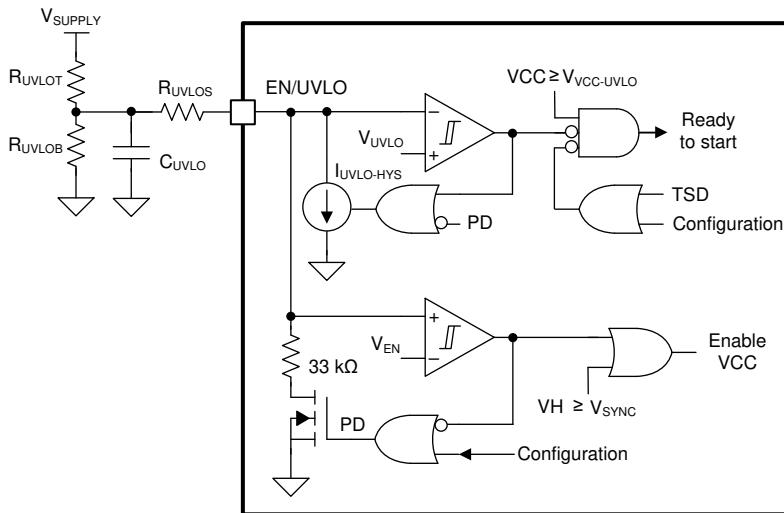

### 7.3.1 デバイスの有効化 / 無効化 (EN, VH ピン)

EN が EN スレッショルド ( $V_{EN}$ ) を下回り、VH が SYNC スレッショルド ( $V_{SYNC}$ ) を下回ると、デバイスはシャットダウンします。EN が  $V_{EN}$  を上回ると、または VH が  $V_{SYNC}$  を上回ると、デバイスは有効になります。VH ピンは、デバイスをシャットダウンする前に  $40\mu\text{s}$  の内部遅延を提供します。

シャットダウン中、EN ピンの  $33\text{k}\Omega$  内部プルダウン抵抗が GND に接続されており、ピンがフローティング時の誤ったターンオンを防止します。EN が EN スレッショルド ( $V_{EN}$ ) を上回ると、 $33\text{k}\Omega$  抵抗は切断され、 $I_{UVLO-HYS}$  電流ソースが有効になって UVLO 機能を提供します。 $I_{UVLO-HYS}$  電流は、EN スレッショルド電圧付近でのチャタリングを防止するように設計されています。

図 7-1. EN/UVLO 回路

### 7.3.2 高電圧 VCC レギュレータ (BIAS, VCC ピン)

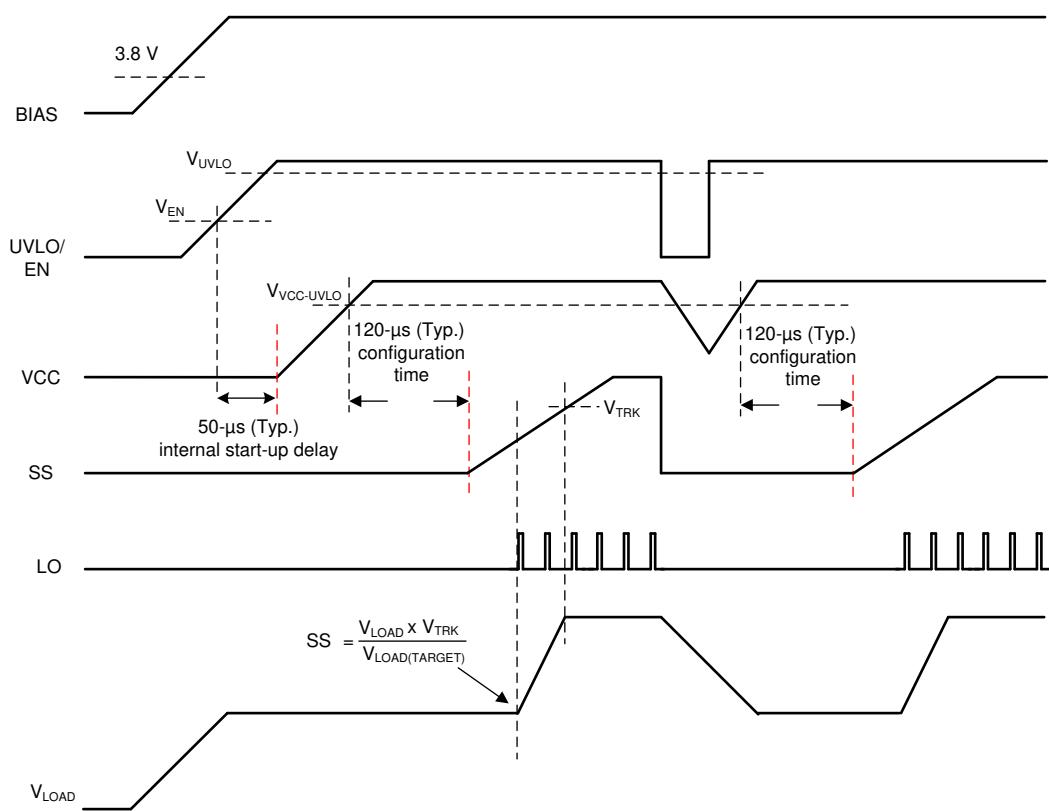

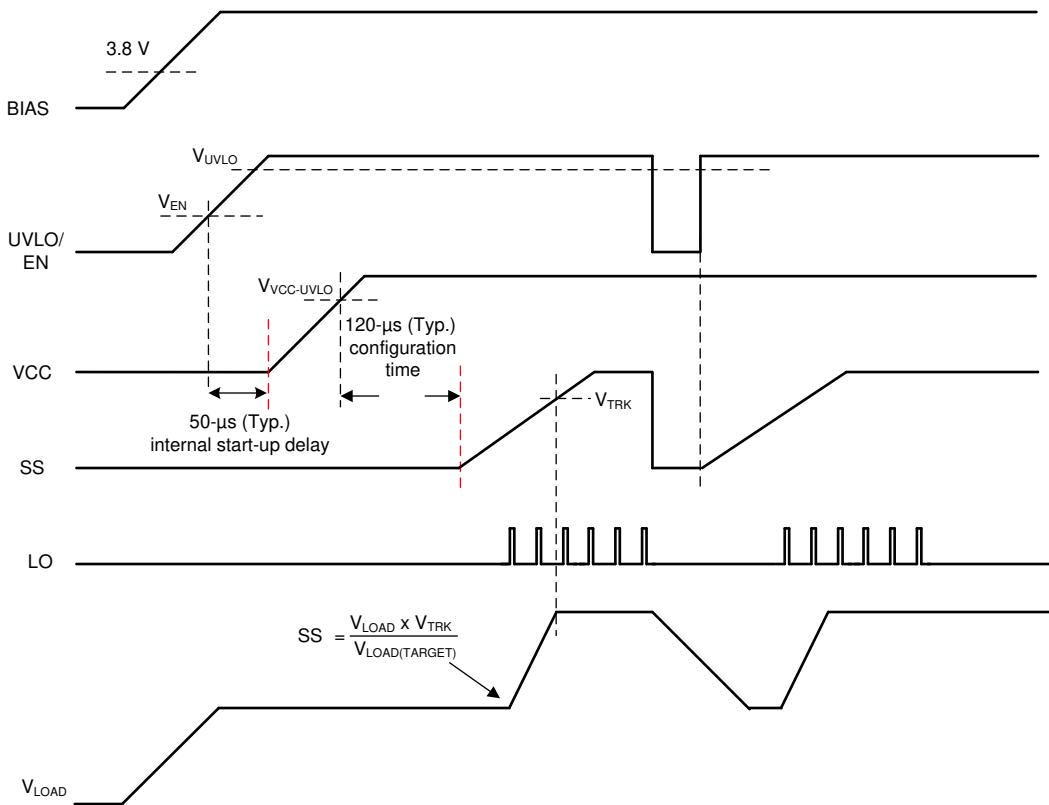

デバイスは、BIAS ピンから供給される高電圧 5V の VCC レギュレータを搭載しています。デバイスが有効になると、内部 VCC レギュレータは  $50\mu\text{s}$  をオンにし、VCC が VCC UVLO スレッショルド ( $V_{VCC-UVLO}$ ) を上回ると  $120\mu\text{s}$  デバイス構成が開始されます。デバイスがシャットダウンされるか、VCC が 2.2V を下回ると、デバイス構成がリセットされます。デバイスを再構成する場合は、デバイスをシャットダウンすることを推奨します。構成時には、軽負荷のスイッチング モードと VOUT 範囲。

高電圧 VCC レギュレータにより、BIAS ピンを  $3.8\text{V} \sim 42\text{V}$  の電源電圧に直接接続できます。BIAS が 5V VCC レギュレーション ターゲット ( $V_{VCC-REG}$ ) より低いとき、VCC 出力は、VCC レギュレータの  $1.7\Omega$  抵抗に起因する小さなドロップ アウト電圧で BIAS ピン電圧に追従します。

推奨される VCC コンデンサの値は  $4.7\mu\text{F}$  です。VCC コンデンサは、デバイスにできる限り近づけて、VCC と PGND の間に配置する必要があります。推奨される BIAS コンデンサの値は  $1.0\mu\text{F}$  です。BIAS コンデンサは、デバイスにできる限り近づけて、BIAS と PGND の間に配置する必要があります。

**図 7-2. 高電圧 VCC レギュレータ**

VCC レギュレータには VCC 電流制限機能が搭載されており、VCC ピンが誤ってグランドに短絡した場合のデバイスの損傷を防止します。VCC レギュレータの最小供給能力は、デバイスの設定時またはアクティブ モード動作時のいずれにおいても  $100\text{mA}$  ( $I_{VCC-CL}$ ) です。VCC レギュレータの最小供給能力は、スリープ モードまたはディープ スリープ モードの間、または EN が  $V_{EN}$  を下回り、VH が  $V_{SYNC}$  を上回ると  $1\text{mA}$  に低下します。VCC レギュレータは、内部ドライバおよび他の内部回路に電源を供給します。外部 MOSFET は、ドライバの消費電流が  $I_{VCC-CL}$  未満になるように注意深く選択する必要があります。ドライバの消費電流は、式 1 で計算できます。

$$I_G = 2 \times Q_{G@5V} \times f_{SW} \quad (1)$$

ここで、

- $Q_{G@5V}$  は  $5\text{V}$  のゲートソース電圧における N チャネル MOSFET ゲート電荷です。

$3.8\text{V}$  未満の VIN 動作が必要な場合は、BIAS ピンを昇圧コンバータの出力 ( $V_{LOAD}$ ) に接続する必要があります。BIAS ピンを  $V_{LOAD}$  に接続することで、BIAS が  $3.8\text{V}$  を超える場合、昇圧コンバータの入力電圧 ( $V_{SUPPLY}$ ) が  $0.8\text{V}$  まで低下することができます。最小  $V_{SUPPLY}$  の詳細については、[セクション 7.3.17](#) を参照してください。

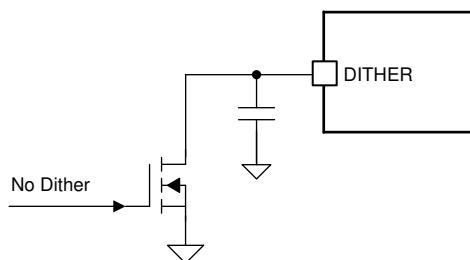

### 7.3.3 軽負荷スイッチング モードの選択(MODE ピン)

デバイス構成時に、軽負荷のスイッチング モードが選択されます。デバイスは、MODE ピンがフローティングの場合、または MODE と AGND の間に  $500\text{k}\Omega$  より大きな抵抗が接続されている場合、スキップ モードに構成されます。デバイスがスキップ モードに構成されると、ユーザーがデバイスを再構成するまで、軽負荷スイッチング モードは変更できません。

デバイスの構成時に MODE ピンの電圧が  $0.4\text{V}$  ( $V_{MODE-FALLING}$ ) 未満の場合、または接地されている場合、デバイスはダイオード エミュレーション (DE) モードに構成されます。デバイスの構成時に MODE ピンの電圧が  $2.0\text{V}$  ( $V_{MODE-RISING}$ ) 以上の場合、または VCC に接続されている場合、デバイスは強制 PWM (FPWM) モードに構成されます。デバイスが DE または FPWM モードに構成されている場合、再構成することなく、軽負荷スイッチング モードを動作中に DE と FPWM モードの間で動的に変更できます。

**図 7-3. モード選択回路**

### 7.3.4 $V_{OUT}$ 範囲の選択(RANGE ピン)

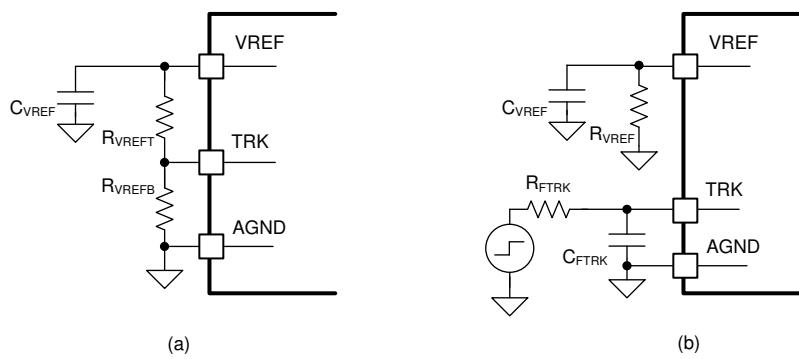

プログラム可能な  $V_{OUT}$  範囲はデバイスの構成時に選択され、ユーザーがデバイスを再構成するまで変更できません。デバイス構成時に VREF から AGND への抵抗 ( $R_{VREFT} + R_{VREFB}$ ) が  $75\text{k}\Omega \sim 100\text{k}\Omega$  の範囲内にある場合、下側  $V_{OUT}$

範囲 (5V ~ 20V) が選択されます。デバイス構成時に VREF から AGND への抵抗が 20kΩ ~ 35kΩ の範囲内にある場合、上側 V<sub>OUT</sub> 範囲 (15V ~ 57V) が選択されます。V<sub>OUT</sub> レギュレーションの精度は、選択した範囲内で規定されています。

### 7.3.5 ライン低電圧ロックアウト (UVLO ピン)

UVLO が UVLO スレッショルド (V<sub>UVLO</sub>) より高い場合、デバイスの構成が完了するとアクティブ モードに移行します。UVLO ヒステリシスは、UVLO ピンでの内部 25mV 電圧ヒステリシス (V<sub>UVLO-HYS</sub>) と、オンまたはオフに切り替えられる追加の 10μA 電流シンク (I<sub>UVLO-HYS</sub>) で達成されます。UVLO ピンの電圧が V<sub>UVLO</sub> を超えると、電流シンクが無効になり、UVLO ピンの電圧が急速に上昇します。UVLO ピンの電圧が V<sub>UVLO</sub> を下回った場合、またはデバイスの構成時間中は、電流シンクが有効になり、UVLO ピンの電圧が急速に低下します。

外部 UVLO 抵抗分圧器 (R<sub>UVLOT</sub>、R<sub>UVLOB</sub>) は、V<sub>SUPPLY</sub> が目的の動作範囲内にあるときに、UVLO ピンの電圧が V<sub>UVLO</sub> よりも高くなるように設計する必要があります。R<sub>UVLOT</sub> および R<sub>UVLOB</sub> の値は、以下のように計算できます。

$$R_{UVLOT} = \frac{\left( V_{SUPPLY\_ON} - \frac{V_{UVLO\_RISING}}{V_{UVLO\_FALLING}} \times V_{SUPPLY\_OFF} \right)}{I_{UVLO\_HYS}} \quad (2)$$

$$R_{UVLOB} = \frac{V_{UVLO\_FALLING} \times R_{UVLOT}}{V_{SUPPLY\_OFF} - V_{UVLO\_FALLING}} \quad (3)$$

UVLO コンデンサ (C<sub>UVLO</sub>) は、スタートアップ時、または低入力電圧での厳しい負荷過渡時に V<sub>SUPPLY</sub> が V<sub>SUPPLY-OFF</sub> を瞬間に下回った場合に必要となります。必要な UVLO コンデンサが大きい場合、追加の直列 UVLO 抵抗 (R<sub>UVLOS</sub>) を使用することで、I<sub>UVLO-HYS</sub> が有効のときに UVLO ピンの電圧を急速に上昇させることができます。

UVLO ピンを使用しない場合、BIAS ピンに接続できます。どのような条件でも、BIAS ピンの電圧が UVLO ピンの電圧よりも低い場合は、最小 5kΩ の抵抗を経由して UVLO ピンを駆動します。

### 7.3.6 VCC HOLD を使用した高速再起動 (VH ピン)

VH が V<sub>SYNC</sub> を上回ったとき、デバイスは高速起動または再起動する準備が整います。デバイスの構成が完了し、VCC レギュレータがアクティブになります。デバイスはスイッチングを停止しますが、EN が V<sub>EN</sub> を下回り、VH が V<sub>SYNC</sub> を上回ると、VCC レギュレータをアクティブに維持します (図 7-5 を参照)。

図 7-4. 昇圧スタートアップ波形ケース 1 : EN/UVLO によるスタートアップ、 $V_H < V_{SYNC}$  時に再起動

図 7-5. 昇圧スタートアップ波形ケース 2 : EN/UVLO によるスタートアップ、 $V_H > V_{SYNC}$  時に再起動

### 7.3.7 可変出力レギュレーションターゲット (VOUT, TRK, VREF ピン)

$V_{OUT}$  レギュレーションターゲット ( $V_{OUT-REG}$ ) は、内部エラー アンプの基準電圧である TRK ピン電圧をプログラムすることで調整できます。 $V_{OUT-REG}$  の精度は、TRK 電圧が 0.25V ~ 1.0V の間にある場合に与えられます。ハイインピーダンスの TRK ピンにより、ユーザーは D/A コンバータを使用して直接、または VREF と AGND の間の抵抗分圧器 ( $R_{VREFT}$ ,  $R_{VREFB}$ ) に接続することで、ピン電圧をプログラムできます。

このデバイスは 1V の電圧リファレンス ( $V_{REF}$ ) を供給し、抵抗分圧器により TRK ピン電圧を設定するために使用できます。デバイスはスリープ モードまたはディープ スリープ モードで  $V_{REF}$  を定期的に無効化するため、外部回路のリファレンス電圧として  $V_{REF}$  を使用することは推奨しません。安定性のため、VREF コンデンサ ( $C_{VREF}$ ) は 330pF ~ 1nF にする必要があります。470pF を推奨します。

$R_{VREFT}$  と  $R_{VREFB}$  を使用して TRK ピンの電圧をプログラムする場合、 $V_{OUT-REG}$  は以下のように計算できます。

下側  $V_{OUT}$  範囲

$$V_{OUT\_REG} = \frac{20 \times R_{VREFB}}{R_{VREFB} + R_{VREFT}} \quad (4)$$

上側  $V_{OUT}$  範囲

$$V_{OUT\_REG} = \frac{60 \times R_{VREFB}}{R_{VREFB} + R_{VREFT}} \quad (5)$$

TRK ピンの電圧はアクティブ モードで動的にプログラムできるため、エンベロープ トラッキング電源の設計が簡単です。トラッキング電源を設計する場合、 $V_{OUT}$  ピンの電圧がコマンドに追従し、過渡動作中に内部の過電圧または低電圧コンパレータがトリガされないように、TRK ピンの電圧を十分遅く調整する必要があります。特にステップ入力が印加された場合、TRK ピンでのコマンド信号のスルーレートを低速にするために、RC フィルタを TRK ピンで使用する必要があります。台形波入力または正弦波入力を印加する場合、コマンド信号のスルーレートまたは周波数を制限する必要があります。

図 7-6. 外部ステップ入力による VREF (b) を使用した TRK 制御 (a)

FPWM 動作では、 $V_{OUT-REG}$  はディープ スリープ モード中に TRK ピン電圧に直ちに追従します。スキップ モードまたはダイオード モード動作中、 $V_{OUT-REG}$  はディープ スリープ モード中に最大 20ms の遅延で TRK ピン電圧を追跡して消費電力を節約します。どのような条件でも  $V_{SUPPLY}$  が  $V_{OUT-REG}$  よりも高い場合、TRK をプログラムするときは特に注意してください。 $V_{LOAD}$  がディープ スリープ モードで  $V_{OUT-REG}$  を下回ると、デバイスは 5μs の遅延でアクティブ モードに移行しますが、ディープ スリープ モードで  $V_{OUT-REG}$  が TRK によって  $V_{LOAD}$  を超えて増加した場合、デバイスは最大 20ms の遅延でアクティブ モードに移行します。

### 7.3.8 過電圧保護 (VOUT ピン)

デバイスは、昇圧コンバータ出力の過電圧保護 (OVP) を備えています。OVP コンパレータは、内蔵の抵抗分圧器によって  $V_{OUT}$  ピンを監視します。 $V_{OUT}$  ピンの電圧が過電圧スレッショルド ( $V_{OVT\text{H}}$ ) を上回ると、OVP が起動します。OVP がトリガされると、デバイスはダイオード エミュレーションまたはスキップ モードでゼロ電流が検出されるまで、ローサイド

ライバをオフにしてハイサイド ドライバをオンにします。FPWM モードでは、OVP がトリガされてもローサイド ドライバはオフになりません。

OVP ステータスが少なくとも  $40\mu\text{s}$  になると、デバイスはディープ スリープ モードに入り、ハイサイド ドライバを 100% オンにし、推奨される  $\text{VOUT}$  コンデンサ ( $C_{\text{VOUT}}$ ) は  $0.1\mu\text{F}$  です。

### 7.3.9 パワー グッド インジケータ (PGOOD ピン)

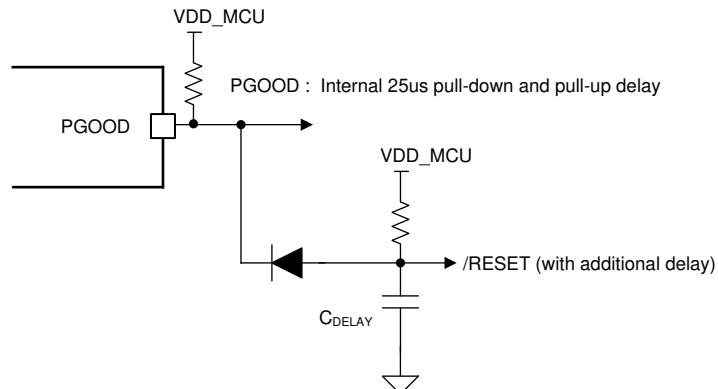

このデバイスは、パワー グッド インジケータ (PGOOD) を備えており、シーケンシングと監視を簡素化できます。PGOOD はオープンドレイン出力で、 $5\text{k}\Omega \sim 100\text{k}\Omega$  のプルアップ抵抗を外部に接続できます。 $\text{VOUT}$  ピンの電圧が低電圧スレッショルド ( $V_{\text{UVTH}}$ ) より高い場合、PGOOD スイッチはオープンになります。 $\text{VOUT}$  ピンの電圧が  $V_{\text{UVTH}}$  より低いとき、UVLO が  $V_{\text{UVLO}}$  未満であるとき、 $\text{VCC}$  が  $V_{\text{VCC-UVLO}}$  未満であるとき、またはサーマル シャットダウン中に、PGOOD ピンはグランドにプルダウンされます。 $26\mu\text{s}$  の立ち上がり時間と  $21\mu\text{s}$  の立ち下がり時間を持つグリッチ除去フィルタにより、過渡現象による PGOOD 信号の誤ったプルダウンを防ぎます。PGOOD ピンの電圧は  $V_{\text{VOUT}} + 0.3\text{V}$  を超えることはできません。

図 7-7. PGOOD インジケータ

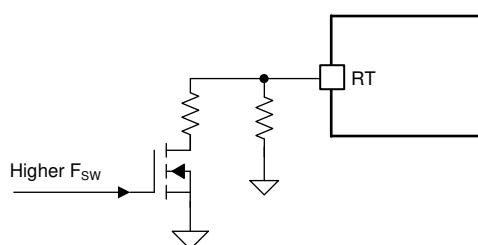

### 7.3.10 動的にプログラム可能なスイッチング周波数 (RT)

SYNC ピンに外部同期クロックが印加されていない場合、RT と AGND との間に接続された単一の RT 抵抗によってデバイスのスイッチング周波数が設定されます。RT スイッチング周波数 ( $R_T$ ) を設定するための抵抗値は、以下のように計算されます。

$$R_T = \frac{2.21 \times 10^{10}}{f_{RT(\text{typical})}} - 955 \quad (6)$$

RT ピンは、デバイスがアクティブ モードのとき、またはデバイス構成のときに、内部の RT レギュレータによって  $0.5\text{V}$  にレギュレートされます。図 7-8 に示すように、動作中にスイッチング周波数を動的にプログラムできます。

図 7-8. 周波数ホッピングの例

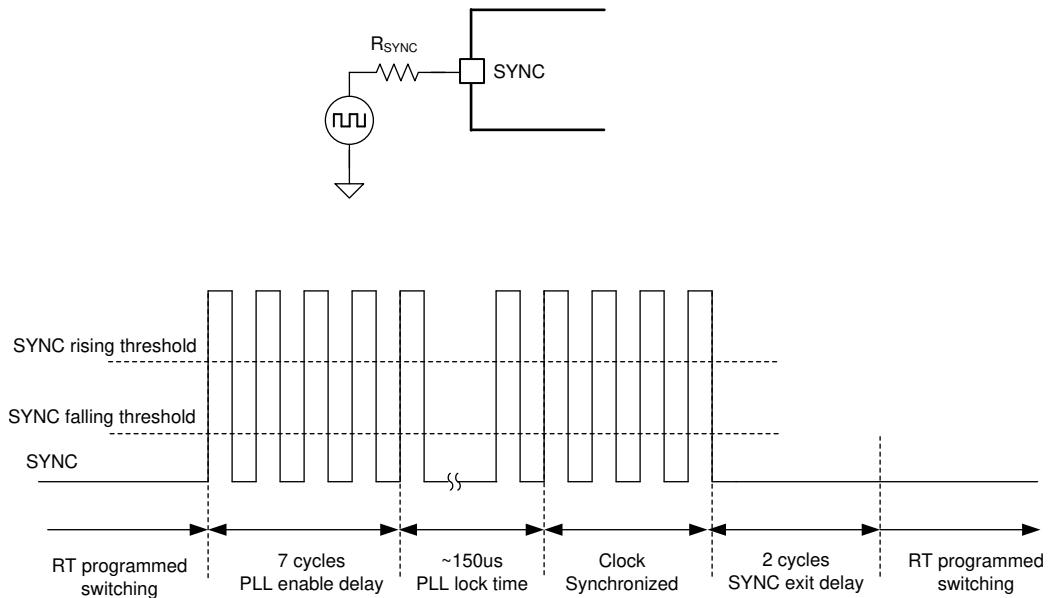

### 7.3.11 外部クロック同期 (SYNC ピン)

デバイスのスイッチング周波数は、外部パルス信号を直接 SYNC ピンに印加することで、外部クロックと同期できます。内部クロックは、内部 PLL を使用して外部同期パルスの立ち上がりエッジで同期されます。未使用時は、SYNC ピンを外部でグランドに接続します。

外部同期パルスは、High ロジック状態で  $V_{SYNC}$  より高く、Low ロジック状態で  $V_{SYNC}$  より低い必要があります。外部同期パルスのデューティサイクルに制限はありませんが、最小オンパルスおよび最小オフパルスの幅が 100ns より長い必要があります。外部同期パルスの周波数は 式 7 および 式 8 を満たす必要があります。

$$200\text{kHz} \leq f_{SYNC} \leq 2.2\text{MHz} \quad (7)$$

$$0.75 \times f_{RT(\text{typical})} \leq f_{SYNC} \leq 1.5 \times f_{RT(\text{typical})} \quad (8)$$

たとえば、350kHz (標準値) のスイッチングにおいては、RT 抵抗を変更することなく 263kHz ~ 525kHz のクロック同期をカバーするために、特定の RT 抵抗が必要です。

図 7-9. 外部クロック同期

どのような条件でも、BIAS ピンの電圧が SYNC ピンの電圧よりも低い場合は、最小 1kΩ の抵抗を経由して SYNC ピンを駆動します。

### 7.3.12 プログラマブル拡散スペクトラム (DITHER ピン)

このデバイスには、オプションのプログラマブル拡散スペクトラム (クロック ディザリング) 機能があり、DITHER と AGND との間にコンデンサを接続すると有効化されます。ディザリング コンデンサを通して、1.0V を中心とした三角波が生成されます。この三角波は、RT 抵抗によって設定される周波数から -6% ~ +5% の範囲で、発振器の周波数を変調します。ディザリング容量の値は、低周波変調のレートを設定します。

図 7-10. スイッチング周波数のディザリング

ディザリング回路でピーク EMI を効果的に低減するには、変調周波数を RT スイッチング周波数よりも大幅に低くする必要があります。特定の変調周波数 ( $f_{MOD}$ ) について必要なディザリング容量は、式 9 で計算できます。 $f_{MOD}$  を 9kHz または 10kHz に設定するのが適切な出発点です。

$$C_{DITHER} = \frac{20\mu A}{f_{MOD} \times 0.29V} \quad (9)$$

DITHER を AGND に接続すると、クロック ディザリングが無効化され、内部発振器は RT 抵抗で設定されている固定周波数で動作します。外部同期パルスが印加されているときも、クロック ディザリングはディセーブルされます。

図 7-11. ディザリングの動的なオン / オフの例

### 7.3.13 プログラマブル ソフトスタート (SS ピン)

コンバータにはソフト スタート機能があるため、定常状態の動作ポイントまで時間をかけて到達できます。スタートアップ時のストレスとサージを低減するため、デバイスは SS ピン電圧または TRK ピン電圧 ( $V_{TRK}$ ) のいざれか低い方に、エラー アンプのリファレンス電圧をレギュレートします。

内部の 20µA ソフトスタート ( $I_{SS}$ ) 電流は、VCC ピンが  $V_{VCC-UVLO}$  を超えた後、120µs だけオンになります。 $I_{SS}$  は、外部ソフトスタートコンデンサ ( $C_{SS}$ ) の電圧を徐々に上昇させます。その結果、出力電圧が次第に上昇します。

FPWM モードでは、SS ピンの電圧が 1.5V 未満の間、デバイスは強制的にダイオード エミュレーションを行います。SS ピンの電圧が 1.5V を超えると、デバイスはゼロ電流検出 (ZCD) スレッショルドを 4mV から 145mV に徐々に変化させ、ダイオード エミュレーションから FPWM モードへのスムーズな遷移を実現します。

図 7-12. ソフトスタートおよび FPWM へのスムーズな遷移

昇圧トポロジでは、昇圧出力電圧がソフトスタート シンチングの開始時の昇圧入力電圧と等しいため、ソフトスタート時間 ( $t_{SS}$ ) は入力電源電圧によって変化します。昇圧トポロジでの  $t_{SS}$  は、式 10 で計算されます。

$$t_{SS} = V_{TRK} \times \frac{C_{SS}}{20\mu A} \times \left(1 - \frac{V_{SUPPLY}}{V_{LOAD}}\right) \quad (10)$$

一般に、過電流状態にならずにコンバータを起動できるよう、ソフトスタート時間を十分に長く設定することをお勧めします。このデバイスを車載アプリケーションで事前昇圧として使用する場合は、できるだけ早く定常状態に達するように、100pF の  $C_{SS}$  を使用することを推奨します。

また、デバイスには内部の SS から FB へのクランプ ( $V_{SS-FB}$ ) も搭載されており、FB より 55mV 高い SS をクランプし、電流制限で連続 256 シンチング サイクルが発生した場合に起動します。電流制限スレッショルドを超えないまま 32 回連続してシンチング サイクルが発生した場合、SS から FB へのクランプは無効化されます。このクランプは、出力短絡または過負荷状態後のサーボを最小限に抑えるのに役立ちます。SS が 1.5V を超えると、デバイスはディープ スリープ モードに移行できます。SS をプルダウンしてシンチングを停止することは推奨しません。

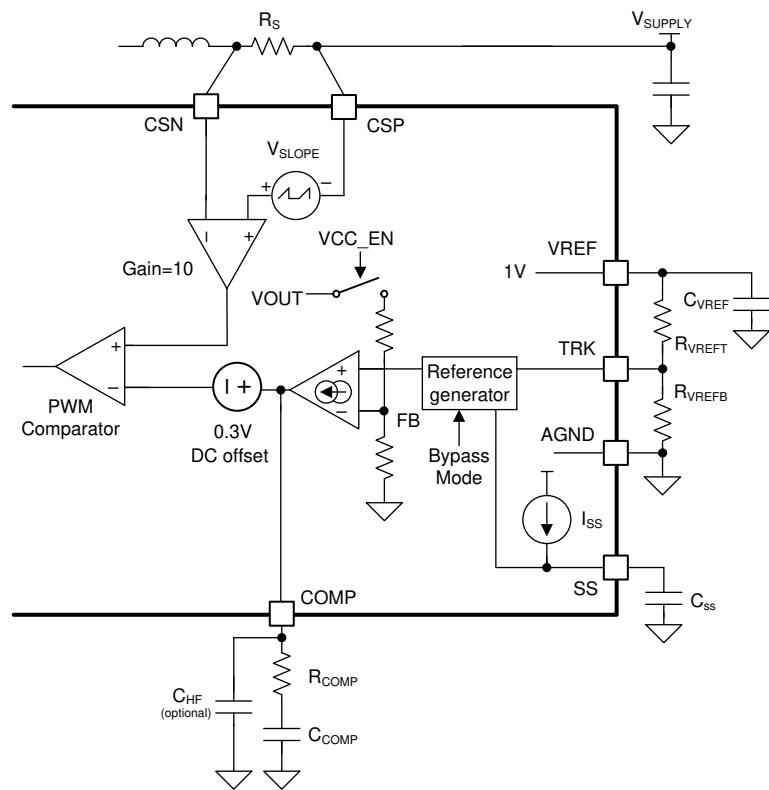

### 7.3.14 広帯域幅相互コンダクタンス エラー アンプおよび PWM (TRK, COMP ピン)

デバイスには、内部帰還抵抗分圧器が内蔵されています。内部帰還抵抗分圧器は、内部の相互コンダクタンス エラー アンプの負入力に接続され、TRK ピン電圧は、ソフトスタートが完了した後、内部相互コンダクタンス エラー アンプの正入力をプログラムします。内部相互コンダクタンス エラー アンプは、高出力抵抗 ( $R_O = 10M\Omega$ ) と広帯域幅 ( $BW = 3MHz$ ) およびシンク (またはソース) 電流を備えており、エラー アンプの負入力と正入力の差に比例します。

エラー アンプの出力は COMP ピンに接続されるため、タイプ 2 のループ補償ネットワークを使用できます。 $R_{COMP}$ 、 $C_{COMP}$ 、およびオプションの  $C_{HF}$  ループ補償部品は、エラー アンプのゲインと位相の特性を構成し、安定したループ応答を実現します。この補償ネットワークにより、非常に低い周波数の極、中間周波数の 0、高い周波数の極が生み出されます。

図 7-13 の PWM コンパレータは、増幅された検出インダクタ電流と勾配補償ランプの合計を、COMP ピン電圧と -0.3V の内部オフセットの合計と比較し、増幅された検出インダクタ電流と勾配補償ランプの合計が、COMP ピン電圧と -0.3V の内部オフセットの合計よりも大きい場合、現在のサイクルを終了します。

図 7-13. エラー アンプ、電流検出アンプ、PWM

### 7.3.15 電流検出と勾配補償 (CSP, CSN ピン)

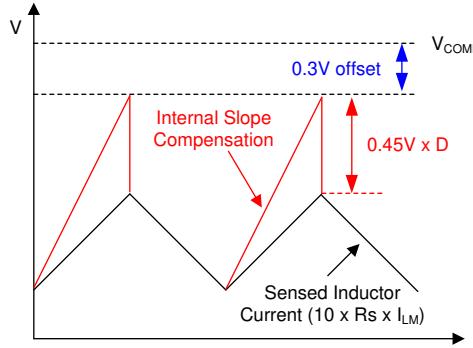

このデバイスは、実効ゲインが 10 ( $A_{CS}$ ) の電流検出アンプを搭載しており、PWM コンパレータに内部勾配補償ランプを提供して、高デューティ サイクルでの分数調波振動を防止します。デバイスは、電流センス アンプの入力に 45mV のピーク勾配補償ランプ ( $V_{SLOPE}$ ) を生成します。これは、PWM コンパレータ入力で 0.45V ピーク (100% デューティ サイクル時) の勾配補償ランプです。

ピーク電流モードの制御理論に従い、勾配補償ランプの勾配は、デューティ サイクルが高いときに分数調波振動を防止するため、検出されるインダクタ電流の立ち下がり勾配の半分よりも大きい必要があります。したがって、勾配補償の最小値は 式 11 を満たす必要があります。

$$0.5 \times (V_{LOAD} - V_{SUPPLY}) / L_M \times R_S \times \text{Margin} < V_{SLOPE} \times f_{SW} \text{ (in Boost)} \quad (11)$$

ここで、

- 理想的でない係数もカバーするため、余裕を持たせて 1.5~1.7 をおすすめします。

図 7-14. PWM コンパレータ入力

### 7.3.16 定ピーカ電流制限 (CSP, CSN ピン)

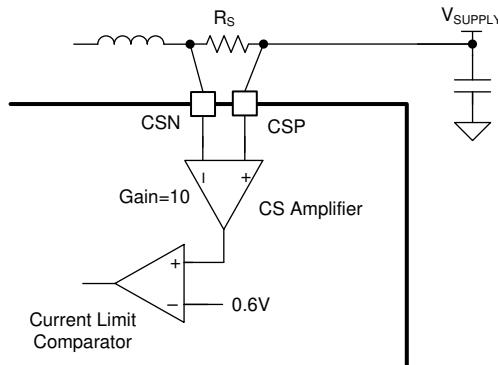

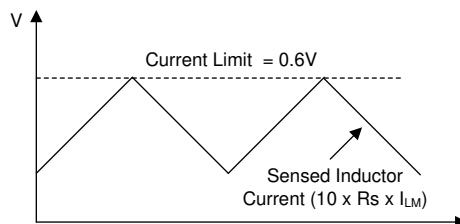

CSP-CSN 電圧がサイクル単位の電流制限スレッショルド ( $V_{CLTH}$ ) である 60mV を超えると、電流制限コンパレータが LO 出力をただちに停止します。このデバイスはピーカ電流を一定値に制限し、そのピーカインダクタ電流制限は入力および出力電圧の全体にわたって一定です。インダクタが飽和したときなど、インダクタ電流のオーバーシュートの可能性がある場合は、電流制限コンパレータは電流制限スレッショルド未満に電流が減衰するまで、パルスをスキップします。

図 7-15. 電流制限コンパレータ

サイクル単位のピーカ電流制限は、次のように計算されます。

$$I_{PEAK-CL} = \frac{0.06}{R_S} \quad (12)$$

図 7-16. 電流制限コンパレータ入力

昇圧コンバータには、電源からハイサイド MOSFET ボディダイオードを経由して負荷への、自然なパススルー パスがあります。このパスが原因で、昇圧コンバータは、出力電圧が入力電源電圧に近い場合、またはそれ以下の場合、ピーカ電流制限保護を (特に最小オン時間 ( $t_{ON-MIN}$ ) 中に動作しないピーカ電流制限保護) を提供することができません。

### 7.3.17 最大デューティ サイクルと最小の制御可能なオン時間の制限

このデバイスは、抵抗素子によって引き起こされる理想的でない要因に対応するために、最大デューティ サイクル制限 ( $D_{MAX}$ ) と最小オフ時間を提供します。 $D_{MAX}$  は、CCM 動作中にターゲット出力電圧 ( $V_{LOAD}$ ) を達成できる最低入力電源電圧 ( $V_{SUPPLY(MIN)}$ ) を決定しますが、DCM 動作中にターゲット出力電圧を達成できる  $V_{SUPPLY(MIN)}$  は  $D_{MAX}$  によって制限されません。CCM 動作中にターゲット出力電圧を達成できる  $V_{SUPPLY(MIN)}$  は以下のように推定できます。図 6-17 も参照してください。

$$V_{SUPPLY(MIN)} \approx V_{LOAD} \times (1 - D_{MAX}) + I_{SUPPLY(MAX)} \times (R_{DCR} + R_S + R_{DS(ON)}) \quad (13)$$

ここで、

- $I_{SUPPLY(MAX)}$  は、 $V_{SUPPLY(MIN)}$  での最大入力電流です。

- $R_{DCR}$  はインダクタの DC 抵抗です。

- $R_{DS(ON)}$  は MOSFET のターンオン抵抗です。

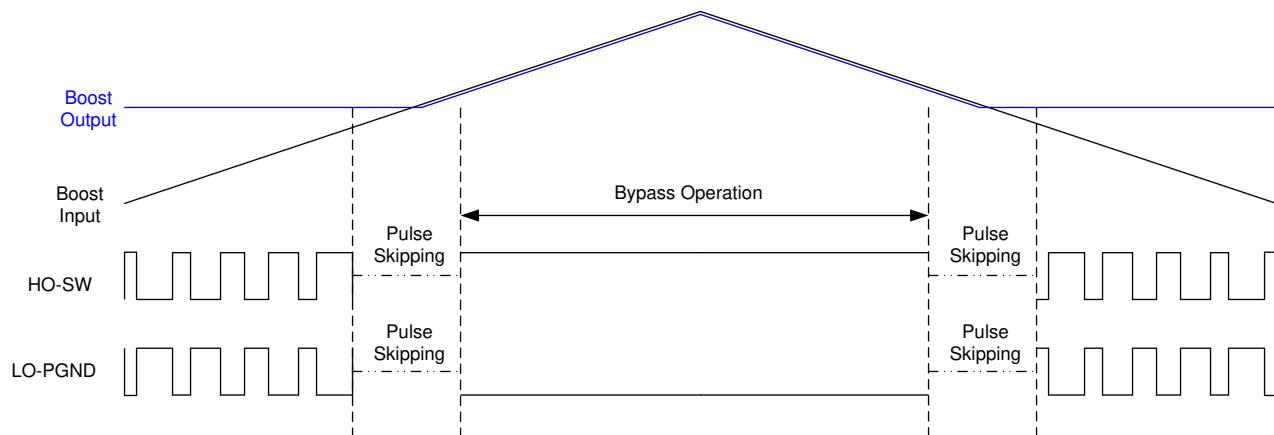

非常に軽い負荷条件、または  $V_{SUPPLY}$  が  $V_{OUT-REG}$  に近い場合、必要なオン時間が  $t_{ON-MIN}$  より短い場合、デバイスはローサイド ドライバのパルスをスキップします。このパルス スキップは、ランダムな動作のように見えます。 $V_{SUPPLY}$  が  $V_{OUT-REG}$  よりもさらに高い電圧まで上昇すると、必要なオン時間は 0 になり、最終的にデバイスはバイパス動作を開始できます。これにより、VOUT ピンの電圧が  $V_{OVTH}$  よりも高いときに、ハイサイド ドライバが 100% オンになります。

### 7.3.18 ディープスリープモードとバイパス動作(HO、CP ピン)

SS が 1.5V を超えると、デバイスは少なくとも 40 $\mu$ s が OVP ステータスになった後で、ディープ スリープ モードに移行します。V<sub>OUT</sub> が V<sub>OVP</sub> を下回ると、デバイスはアクティブ モードに戻ります。バイパス動作中、ハイサイド MOSFET のボディダイオードによって発生する損失を最小限に抑えることができます。詳細については「セクション 7.4.1.5」を参照。

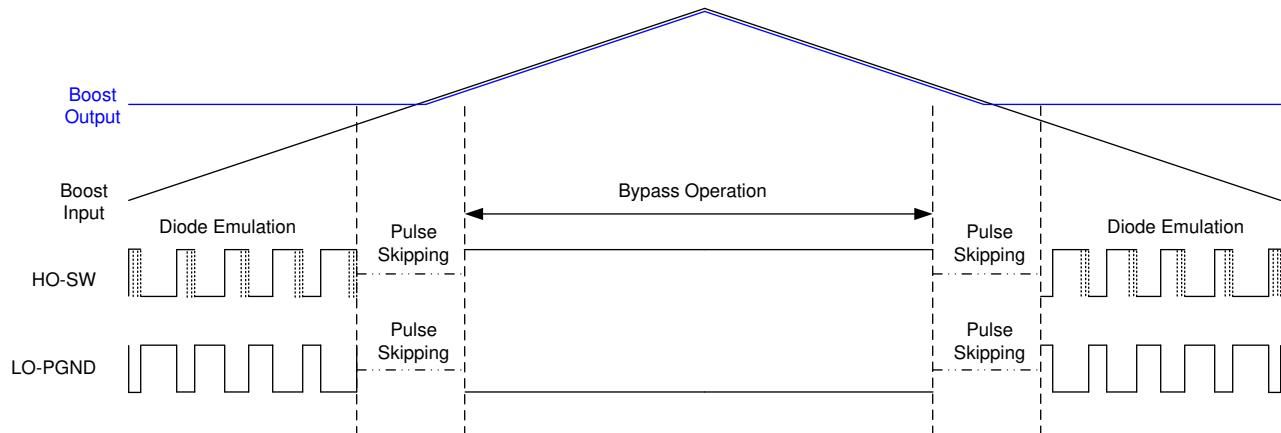

図 7-17. CCM 動作時の PWM からバイパスへの遷移

図 7-18. DCM 動作時の PWM からバイパスへの遷移

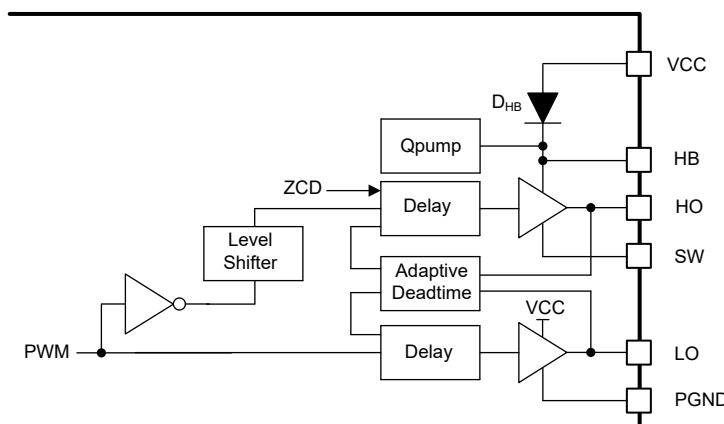

### 7.3.19 MOSFET ドライバ、内蔵ブートダイオード、ヒップモードの故障保護 (LO、HO、HB ピン)

このデバイスは、2.2A のピーク電流をソースし、3.3A のピーク電流をシンクできる N チャンネル ロジック MOSFET ドライバを備えています。LO ドライバは VCC から給電され、EN が  $V_{EN}$  を上回り、VCC が  $V_{VCC-UVLO}$  を上回ると有効になります。HO ドライバは HB から給電され、EN が  $V_{EN}$  を上回り、HB-SW 電圧が HB UVLO スレッショルド ( $V_{HB-UVLO}$ ) を上回ると有効になります。

SW ピンの電圧がローサイド MOSFET をオンにすることで約 0V になると、 $C_{HB}$  は内部ブートダイオードを経由して VCC から充電されます。 $C_{HB}$  に推奨される値は 0.1 $\mu$ F です。

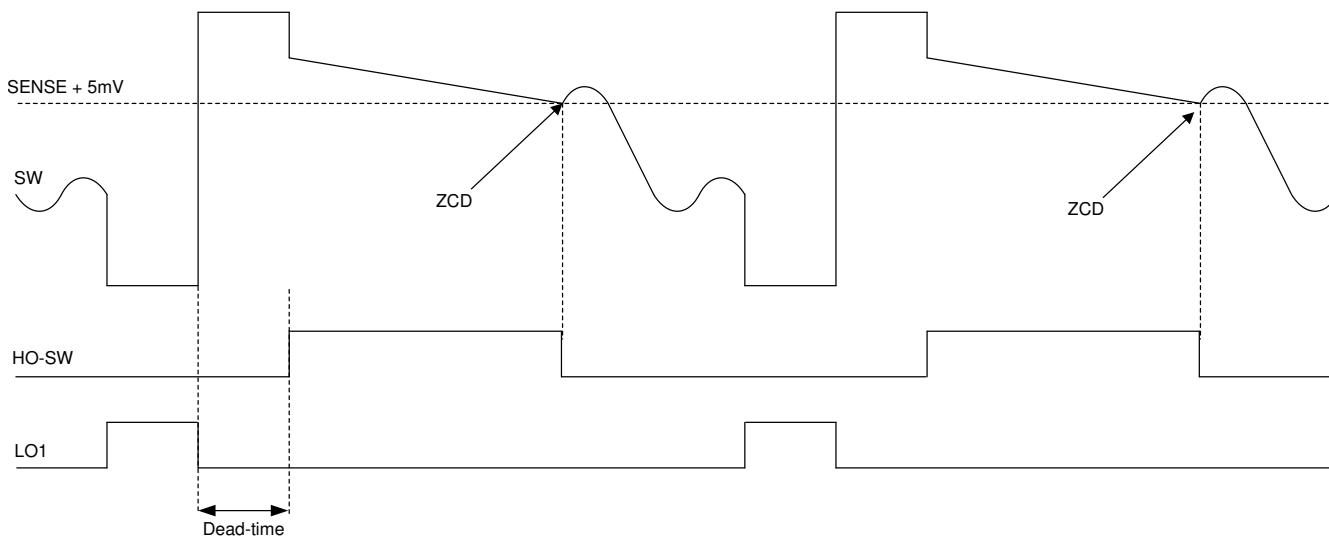

LO と HO の出力はアダプティブ デッドタイム手法により制御されるため、両方の出力が同時にターンオンされることは絶対にありません。デバイスが LO のターンオンを指示すると、アダプティブ デッドタイムのロジックにより、先に HO がオフになり、HO-SW 電圧の低下を待ちます。その後、短い遅延 ( $t_{DHL}$ ) の後で LO がオンになります。同様に、HO ドライバのターンオンは LO-PGND 電圧が放電されるまで遅延されます。その後、短い遅延 ( $t_{DLH}$ ) の後で HO がオンになります。

BIAS ピンの電圧が 5V VCC レギュレーション ターゲットを下回る場合は、MOSFET の選択に特に注意してください。特に、低 BIAS ピン電圧でのスタートアップ時に、MOSFET を完全に強化するには、MOSFET スイッチのゲート プラート電圧を BIAS ピンの電圧よりも低くする必要があります。ドライバの出力電圧が、スタートアップ時に MOSFET のゲート プラート電圧よりも低い場合、コンバータが正しくスタートアップせず、最大デューティ サイクルで高い消費電力の状態のままになる可能性があります。この条件は、より低いスレッショルドの MOSFET を選択するか、BIAS ピン電圧が十分なときにデバイスをオンにすることで回避できます。どのような条件でも、コンバータがバイパスで動作するときは注意が必要です。バイパス動作中、HO-SW の最小電圧は 3.75V です。

図 7-19. ブートダイオードを内蔵したドライバ構造

ヒップ モードの故障保護は、HB UVLO によってトリガれます。HB-SW 電圧が HB UVLO スレッショルド ( $V_{HB-UVLO}$ ) を下回ると、LO は 75ns にわたって強制的にオンになり、昇圧コンデンサを再充電します。このデバイスでは、最大 4 つの連続した再充電スイッチングが可能です。最大 4 つの連続したブート再充電スイッチングの後で、デバイスは 12 サイクルにわたってスイッチングをスキップします。4 つの連続した再充電スイッチングが 4 セット行われた後に、デバイスが昇圧コンデンサを再充電できなかった場合、デバイスはスイッチングを停止し、ヒップ モードのオフ時間は 512 サイクルに移行します。ヒップ モードのオフ時間中、PGOOD と SS は接地されます。

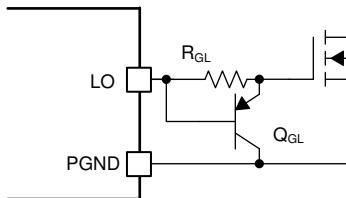

必要であれば、プルダウン PNP ロジックと並列にゲート抵抗を追加することで、スイッチング ノード電圧のスルーレートを調整できます。ゲート抵抗を追加すると実効デッドタイムが短くなる可能性があるため、十分な注意が必要です。

図 7-20. スルーレート制御

### 7.3.20 サーマルシャットダウン保護

内部サーマルシャットダウン (TSD) は、接合部温度 ( $T_J$ ) が 175°C を超えたときにデバイスを保護するために搭載されている機能です。TSD が作動すると、デバイスは低消費電力のサーマルシャットダウン状態に移行し、MOSFET ドライバと VCC レギュレータは無効になります。 $T_J$  が低下すると (ヒステリシス標準値は 15°C)、デバイスは再起動します。スリープ モードまたはディープスリープ モード中は、TSD は無効化されます。

## 7.4 デバイスの機能モード

### 7.4.1 デバイスステータス

#### 7.4.1.1 シャットダウンモード

EN が  $V_{EN}$  を下回り、VH が  $V_{SYNC}$  を下回ると、デバイスはシャットダウンし、BIAS から 3 $\mu$ A が消費されます。シャットダウン モードでは、COMP、SS、PGOOD はグランドに接続されます。EN が  $V_{EN}$  を上回ると、または VH が  $V_{SYNC}$  を上回ると、デバイスは有効になります。

#### 7.4.1.2 構成モード

デバイスが最初に有効になったとき、VCC が  $V_{VCC-UVLO}$  を上回ると、120 $\mu$ s デバイスの構成が開始されます。デバイスの構成時は、軽負荷のスイッチング モードと VOUT 範囲。デバイスがシャットダウンされるか、VCC が 2.2V を下回ると、デバイス構成がリセットされます。デバイスを再構成する場合は、デバイスをシャットダウンすることを推奨します。構成時は、33k $\Omega$  内部 EN プルダウン抵抗が接続され、VCC レギュレータの最小ソース能力は 100mA で、RT ピンは内部 RT レギュレータによって 0.5V にレギュレートされます。

#### 7.4.1.3 アクティブモード

120 $\mu$ s の初期デバイス構成が完了すると、デバイスはアクティブ モードに移行し、UVLO が  $V_{UVLO}$  を上回っていれば、すべての機能が有効になります。アクティブ モードでは、ソフトスタートシーケンスが開始され、エラー アンプが有効になります。

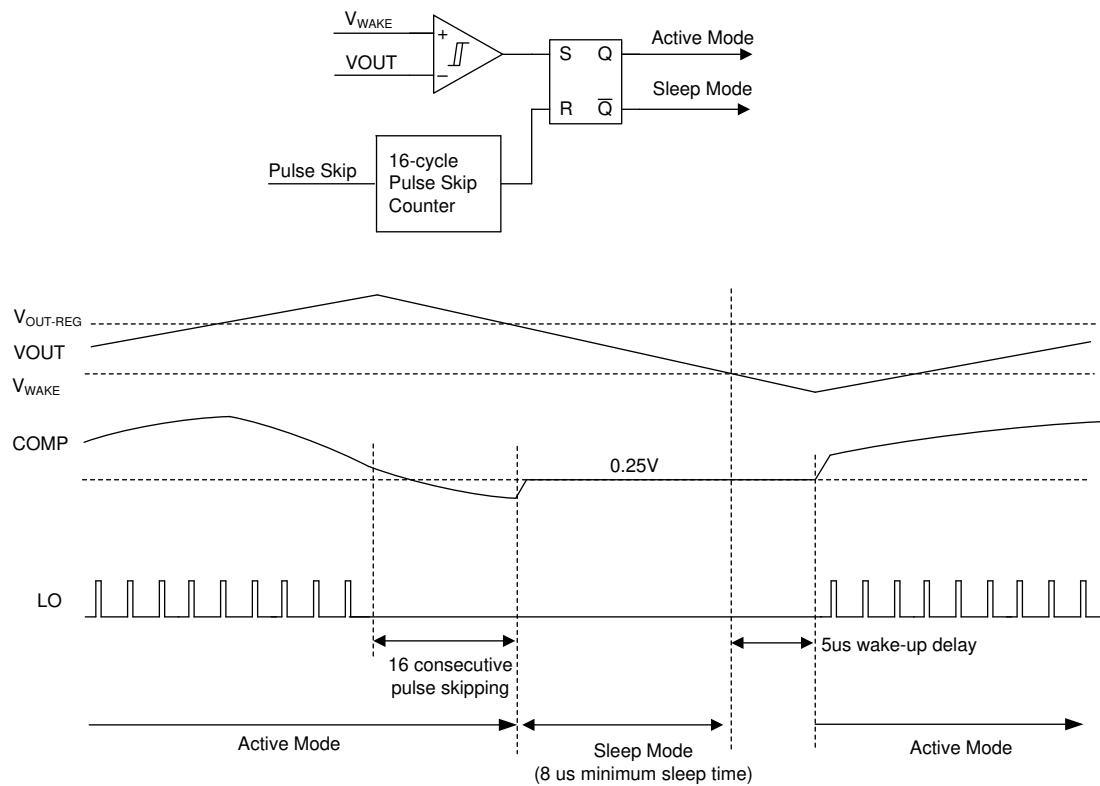

#### 7.4.1.4 スリープモード

軽負荷スイッチング モードとしてスキップ モードを選択した場合に、SS が 1.5V を超えると、ローサイド ドライバが連続 16 サイクルにわたってスイッチングをスキップすると、デバイスはスリープ モードに移行します。デバイスがスリープ モードに移行すると、8 $\mu$ s の最小スリープ時間中は、アクティブ モードに再移行できません。スリープ モード中、デバイスは内部発振器を停止して動作電流を低減し、UVLO コンパレータを無効化し、エラー アンプを無効化して COMP ピンを 0.25V にパークします。VOUT ピンの電圧が、 $V_{OUT-REG}$  よりも 1.1% 低いウェークアップ スレッショルド ( $V_{WAKE}$ ) を下回ると、デバイスはアクティブ モードに再移行します。

#### 7.4.1.5 ディープスリープモード

SS が 1.5V を超えると、デバイスは OVP ステータスが 4 サイクル経過した後でディープスリープモードに移行します。ディープスリープモード中、デバイスは内部発振器を停止して動作電流を低減し、UVLO コンパレータを無効化し、エラーアンプを無効化して COMP ピンを 0.25V にパークします。

FPWM または DE モードでは、 $V_{OUT}$  が  $V_{OVTH}$  を下回ると、デバイスはアクティブモードに戻ります。スキップモードでは、 $V_{OUT}$  が  $V_{OVTH}$  を下回ると、デバイスはアクティブモードに戻り、16 サイクル連続のパルススキップが発生した後、直ちにスリープモードに移行します。

#### 7.4.2 軽負荷スイッチングモード

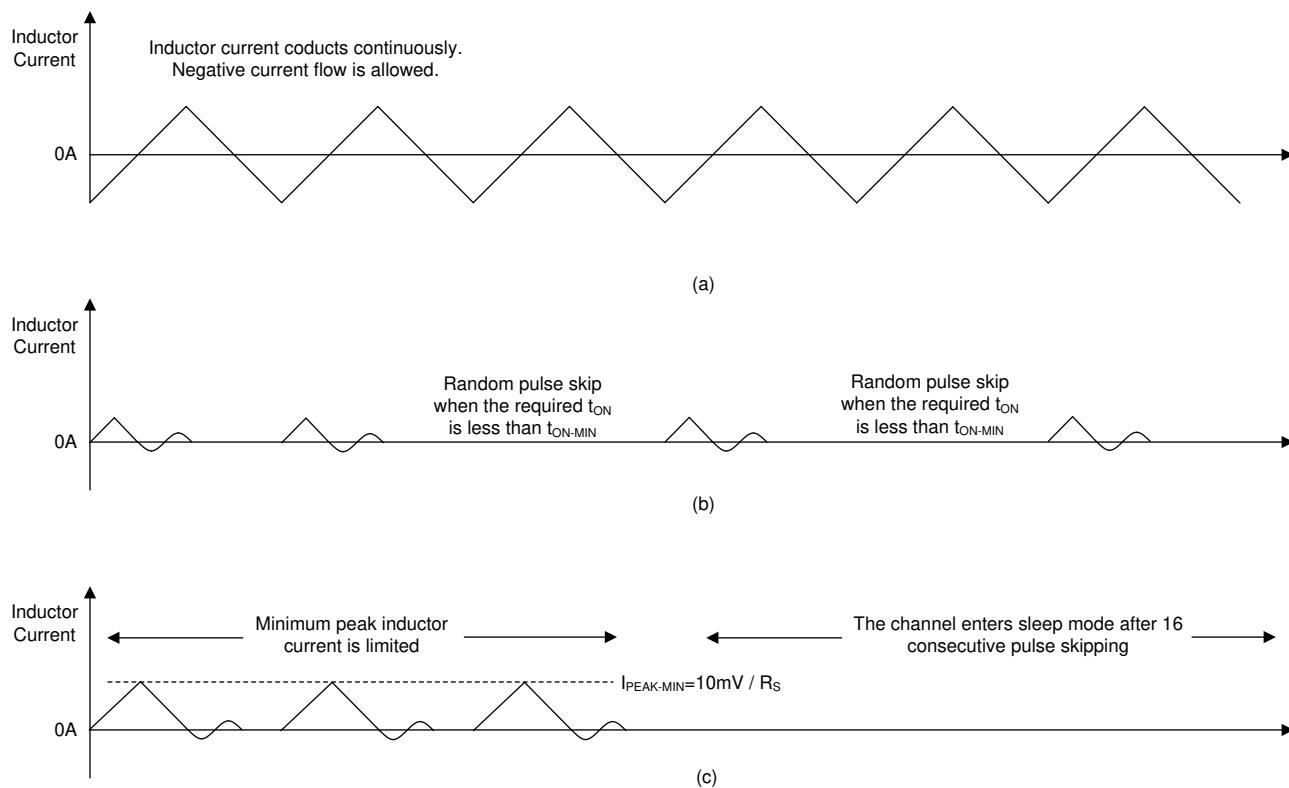

このデバイスには、3 つの軽負荷スイッチングモードがあります。各モードのインダクタ電流波形は、軽負荷または無負荷の状況で異なります。

図 7-21. 軽負荷時のインダクタの電流波形、(a) FPWM (b) ダイオード エミュレーション (c) スキップ モード

##### 7.4.2.1 強制 PWM (FPWM) モード

FPWM モードでは、軽負荷または無負荷状態でもインダクタ電流が連続的に流れ、連続導通モード (CCM) での動作が可能となります。FPWM モードの利点は、軽負荷から重負荷への過渡応答が高速で、軽負荷または無負荷状態でもスイッチング周波数が一定であることです。FPWM モードでは、最大逆電流が  $145mV/R_{DS(ON)}$  に制限されます。

##### 7.4.2.2 ダイオード エミュレーション (DE) モード

ダイオード エミュレーション (DE) モードでは、インダクタ電流の流れは、入力ソースから出力負荷への 1 方向のみ許可されます。デバイスは、ハイサイドスイッチのオン時間中に SENSE-SW 電圧を監視し、SENSE-SW 電圧が 5mV のゼロ電流検出 (ZCD) スレッショルド ( $V_{ZCD}$ ) を下回ると、PWM サイクルの残りの時間にわたってハイサイドスイッチをオフにします。ダイオード エミュレーションの利点は、軽負荷時には、FPWM モードでの効率よりも高いことです。

図 7-22. ゼロ電流検出

#### 7.4.2.3 FPWM モードでの強制ダイオード エミュレーション動作

ソフトスタート中、SS ピンの電圧が 1.5V 未満の間、デバイスは強制的にダイオード エミュレーションを行います。SS ピンが 1.5V より高い場合、ゼロ電流検出 (ZCD) スレッショルドは  $-145\text{mV}$  まで下がります。無負荷時に適切な FPWM 動作を行うには、ピークツーピーク インダクタ電流が 式 14 を満たす必要があります。

$$\frac{I_{PP} \times R_{DS(on)}}{2} < 145\text{mV} \quad (14)$$

#### 7.4.2.4 スキップ モード

軽負荷スイッチング モードとしてスキップ モードを選択する場合、デバイスはパルス スキップ カウンタがアクティブ モードで連続 16 サイクルのパルス スキップを検出するとスリープ モードに移行し、VOUT が  $V_{WAKE}$  未満に低下した場合はアクティブ モードに再移行します。

スリープ モードにより頻繁に移行し、スリープ モードを長く維持すると、軽負荷時の効率を高めることができます。スキップ モード時、かつ SS が 1.5V より大きい場合、デバイスはダイオード エミュレーション モードで動作しますが、ローサイド ライバがオンになると、最小ピーク電流は  $10\text{mV}/R_S$  に制限されます。最小ピーク電流を制限することで、昇圧コンバータはスイッチング時に必要とされる電流よりも多くの電流を供給することができ、スリープ モードに頻繁に移行して、スリープ モードを長く維持するようになります。

図 7-23. スキップ モードの動作

軽負荷スイッチング モードとしてスキップ モードを選択する場合、最小  $V_{SUPPLY}$  で  $LO$  が  $D_{MAX}$  によってオフになる前に、ピーク インダクタが  $10mV$  の最小ピーク電流制限に達するように  $L_M$  を選択する必要があります。

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

このデバイスには、システムの設計要件を満たすため、入力 UVLO、プログラマブル ソフトスタート、クロック同期、スペクトラム拡散、選択可能な軽負荷スイッチング モードなど、いくつかのオプション機能が内蔵されています。より包括的な設計のために、必要に応じて、各アプリケーションはこれらの機能を搭載しています。詳細については、『[LM5123EVM-BST ユーザー ガイド](#)』を参照してください。

### 8.2 代表的なアプリケーション

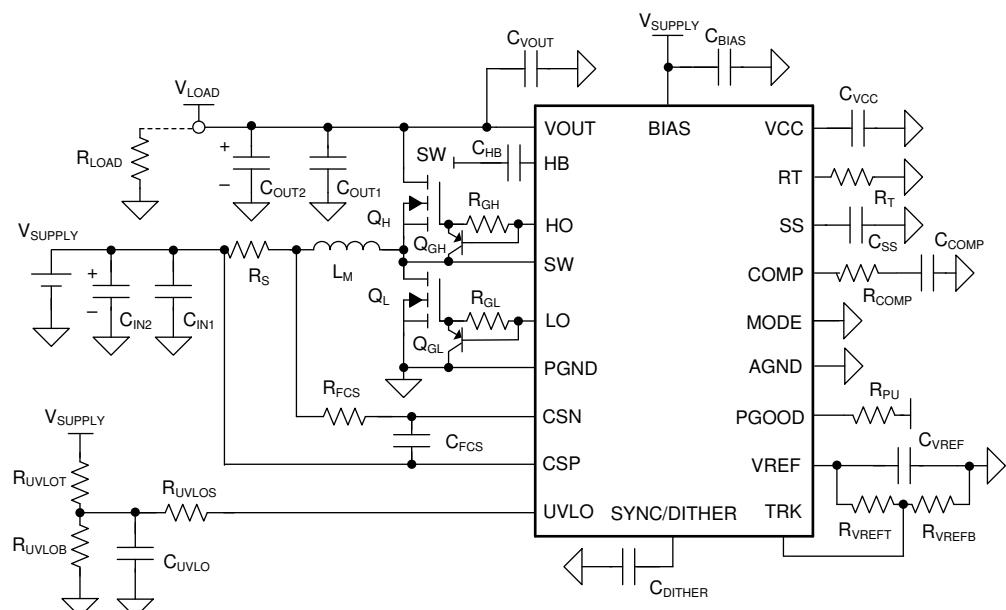

図 8-1 に、昇圧コンバータを設計するためのすべてのオプション部品を示します。

図 8-1. オプション部品を備えた代表的な同期整流昇圧コンバータ

#### 8.2.1 設計要件

このアプリケーション例の入力、出力、性能のパラメータを、表 8-1 に示します。

表 8-1. 設計例のパラメータ

| 設計パラメータ                        | 値        |

|--------------------------------|----------|

| 最低入力電源電圧 ( $V_{SUPPLY(MIN)}$ ) | 9V       |

| 目標出力電圧 ( $V_{LOAD}$ )          | 24V      |

| 最大負荷電流 ( $I_{LOAD}$ )          | 4A (96W) |

| 標準スイッチング周波数 ( $f_{SW}$ )       | 440kHz   |

## 8.2.2 詳細な設計手順

「[クイックスタート カリキュレータ](#)」を使用すると、特定のアプリケーションのレギュレータを簡単に設計できます。

推奨コンポーネントと代表的なアプリケーション曲線については、「[LM5123EVM-BST ユーザー ガイド](#)」を参照してください。

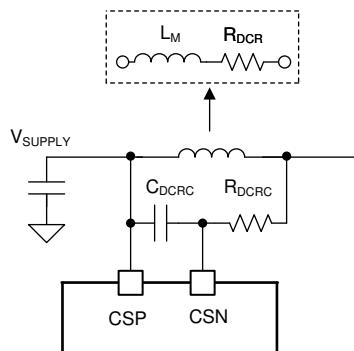

### 8.2.2.1 アプリケーションのアイデア

コストが最低限で、伝導損失も最小限であることが要求されるアプリケーションでは、検出抵抗を使用する代わりにインダクタの DC 抵抗 (DCR) を使用して、インダクタ電流の検出が行われます。時定数を一致させるには、 $R_{DCRC}$  と  $C_{DCRC}$  が式 15 を満たす必要があります。

図 8-2. DCR 電流センシング

$$\frac{L_M}{R_{DCR}} = R_{DCRC} \times C_{DCRC} \quad (15)$$

必要な場合、外部回路を使用して PGOOD の追加遅延をプログラムできます。

図 8-3. 追加の PGOOD 遅延

### 8.2.3 アプリケーション曲線

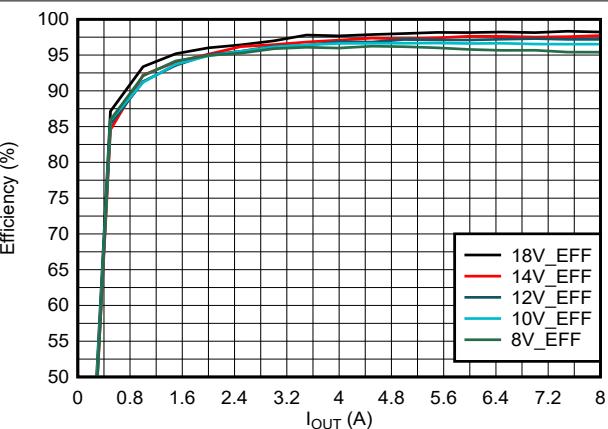

図 8-4. 効率と  $I_{OUT}$  との関係、 $V_{OUT} = 24V$  (FPWM)

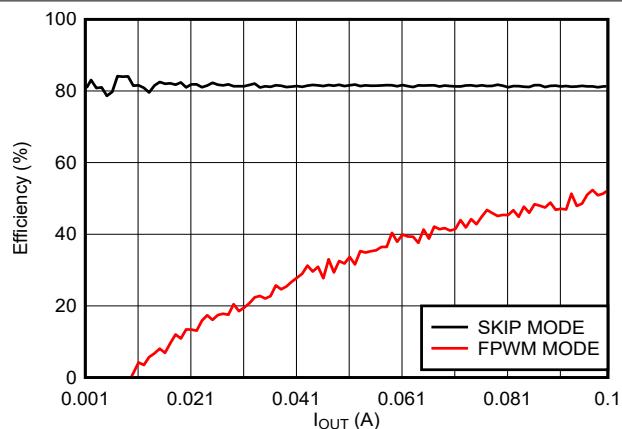

図 8-5. 効率と  $I_{OUT}$  との関係、 $V_{OUT} = 24V$  軽負荷

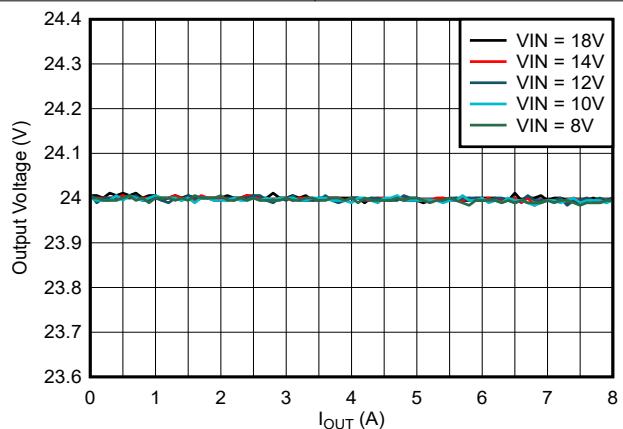

図 8-6. 24V ロード レギュレーション

### 8.3 システム例

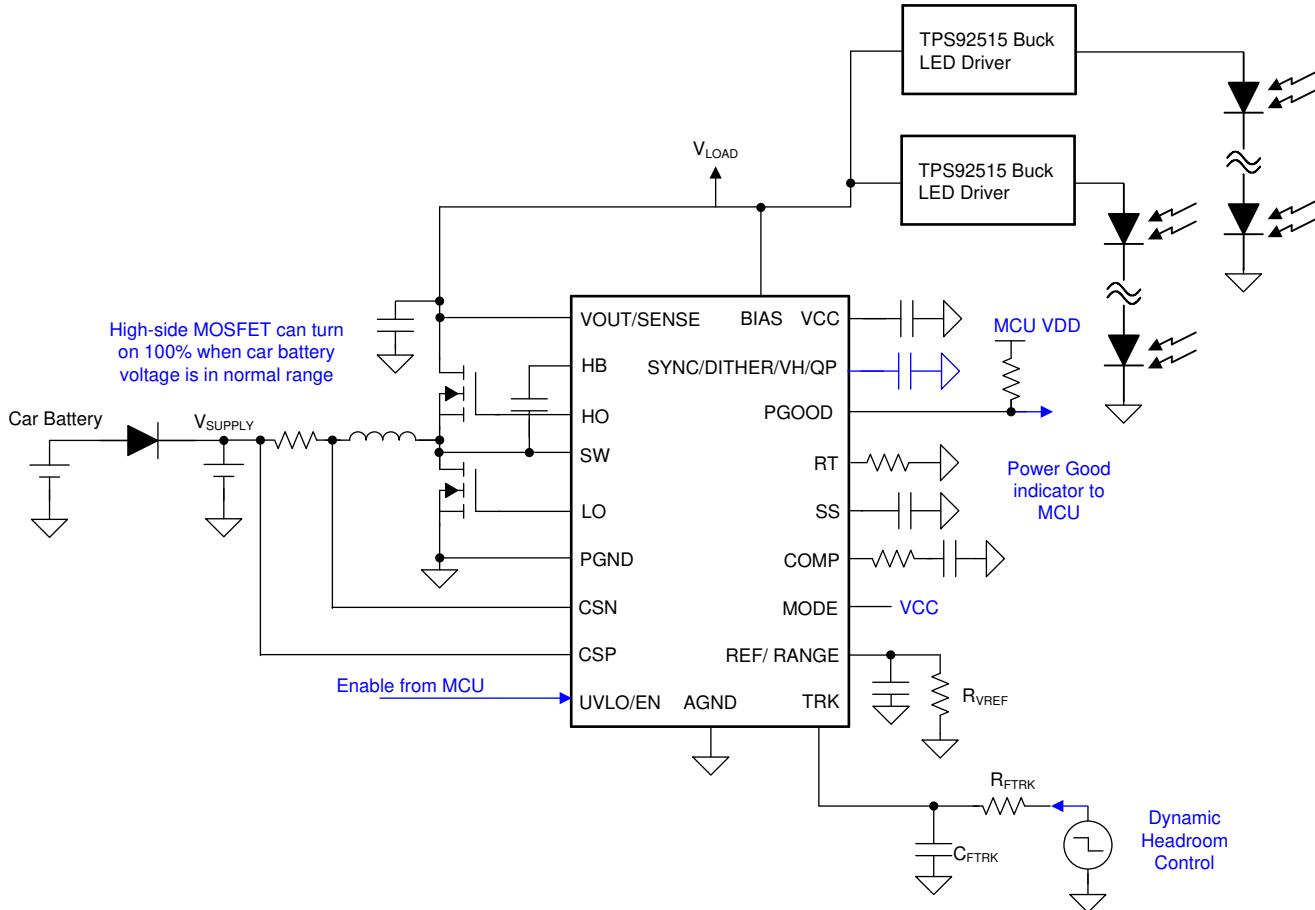

LED アプリケーションで LM5123 を使用します。TRK ピンはヘッドルームを制御するために使用できます。

図 8-7. LED アプリケーションでの LM5123

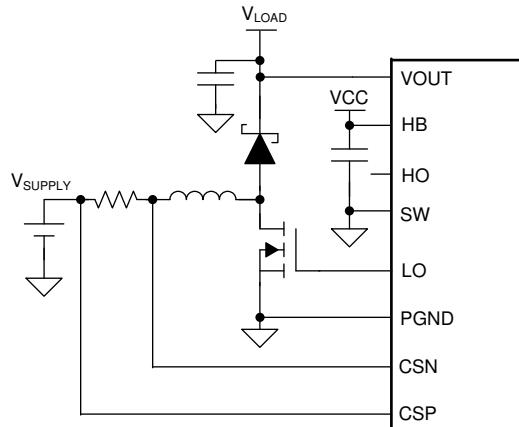

非同期整流昇圧コンバータを構成するには、SW を PGND に接続し、HB を VCC に接続します。

図 8-8. 非同期整流昇圧構成

## 9 電源に関する推奨事項

このデバイスは、電圧範囲が 0.8V ~ 42V の電源またはバッテリで動作するように設計されています。入力電源は、最大昇圧電源電圧を供給し、最大入力電流を 0.8V で処理できる必要があります。電源およびバッテリ (ケーブルを含む) のインピーダンスは、入力電流過渡によって過剰な電圧降下が発生しないように、十分に小さくする必要があります。コンバータの電源入力に、入力セラミックコンデンサの追加が必要になることがあります。

## 10 レイアウト

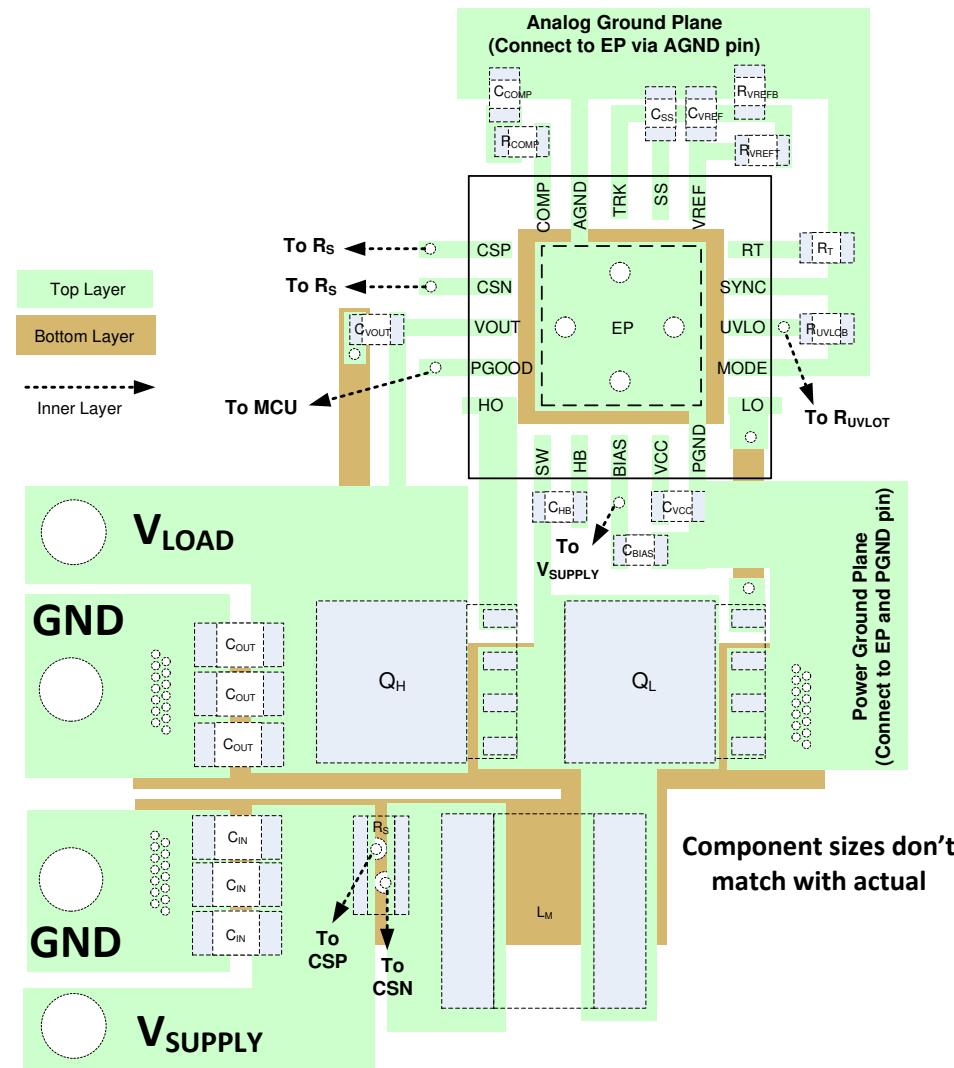

### 10.1 レイアウトのガイドライン

スイッチングコンバータの性能は、PCB レイアウトの品質に大きく依存します。次のガイドラインに従うことで、最高の電力変換性能や熱性能を実現しながら、不要な EMI の生成を最小限に抑えるような PCB を設計できます。

- $C_{VCC}$ 、 $C_{BIAS}$ 、 $C_{HB}$ 、 $C_{VOUT}$  はデバイスのできるだけ近くに配置します。ピンに直接接続します。

- $Q_H$ 、 $Q_L$ 、 $C_{OUT}$  を配置します。スイッチングループ ( $C_{OUT} \sim Q_H \sim Q_L \sim C_{OUT}$ ) はできるだけ小さくします。小型のセラミックコンデンサを採用すると、ループ長の最小化に役立ちます。熱放散のために、 $Q_H$  のドレイン接続の近くに銅の面積を残します。

- $L_M$ 、 $R_S$ 、 $C_{IN}$  を配置します。ループ ( $C_{IN} \sim R_S \sim L_M \sim C_{IN}$ ) はできるだけ小さくします。小型のセラミックコンデンサを採用すると、ループ長の最小化に役立ちます。

- $R_S$  を CSP-CSN に接続します。CSP-CSN パターンは、並列に配線し、グランドで囲む必要があります。

- $VOUT$ 、 $HO$ 、 $SW$  を接続します。これらのパターンは、短い低インダクタンスのパスを使用して並列に配線する必要があります。 $VOUT$  は、 $Q_H$  のドレイン接続に直接接続する必要があります。 $SW$  は、 $Q_H$  のソース接続に直接接続する必要があります。

- $LO$  と  $PGND$  を接続します。 $LO$ - $PGND$  パターンは、短い低インダクタンスのパスを使用して並列に配線する必要があります。 $PGND$  は、 $Q_L$  のソース接続に直接接続する必要があります。

- $R_{COMP}$ 、 $C_{COMP}$ 、 $C_{SS}$ 、 $C_{VREF}$ 、 $R_{VREFT}$ 、 $R_{VREFB}$ 、 $R_T$ 、 $R_{UVLOB}$  をデバイスの近くに配置し、共通のアナロググランドプレーンに接続します。

- 電源グランドプレーン ( $Q_L$  のソース接続) を  $PGND$  経由で  $EP$  に接続します。共通のアナロググランドプレーンを  $AGND$  経由で  $EP$  に接続します。 $PGND$  と  $AGND$  は、デバイスの下に接続する必要があります。

- $EP$  の下にいくつかのビアを追加して、デバイスからの放熱性能を向上させます。ビアは、最下層の大きなアナロググランドプレーンに接続します。

- デバイスの下、および  $EP$  に接続されている大きなアナロググランドプレーンを介して  $C_{OUT}$  と  $C_{IN}$  を接地しないでください。

## 10.2 レイアウト例

図 10-1. PCB のレイアウト例

## 11 デバイスおよびドキュメントのサポート

### 11.1 デバイス サポート

#### 11.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

### 11.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 11.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

### 11.4 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 11.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお勧めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 11.6 用語集

[テキサス・インスツルメンツ用語集](#) この用語集には、用語や略語の一覧および定義が記載されています。

## 12 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision B (January 2022) to Revision C (November 2025) | Page              |

|----------------------------------------------------------------------|-------------------|

| • SW から AGND (10ns) –5V MIN を含めて表を更新.....                            | <a href="#">6</a> |

| Changes from Revision A (December 2021) to Revision B (January 2022) | Page              |

|----------------------------------------------------------------------|-------------------|

| • ディープスリープ時のバイアス電流とバッテリドレインを更新.....                                  | <a href="#">7</a> |

| • 過電圧 (OVP) および低電圧スレッショルド (PGOOD) を更新.....                           | <a href="#">7</a> |

| • デッドタイムを更新.....                                                     | <a href="#">7</a> |

| • HB ダイオード抵抗を更新.....                                                 | <a href="#">7</a> |

| • VOUT レギュレーションターゲット電圧を更新.....                                       | <a href="#">7</a> |

| Changes from Revision * (December 2020) to Revision A (December 2021) | Page |

|-----------------------------------------------------------------------|------|

| • ドキュメントのステータスを「事前情報」から「量産データ」に変更.....                                | 1    |

## 13 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

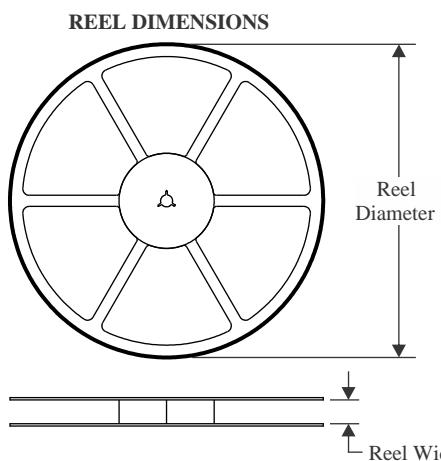

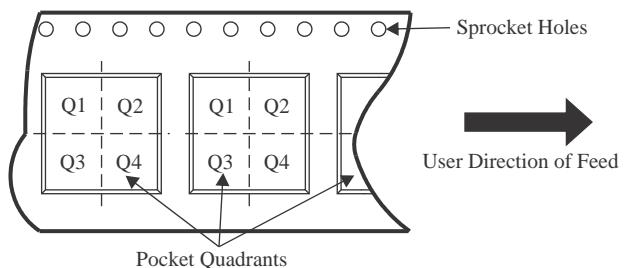

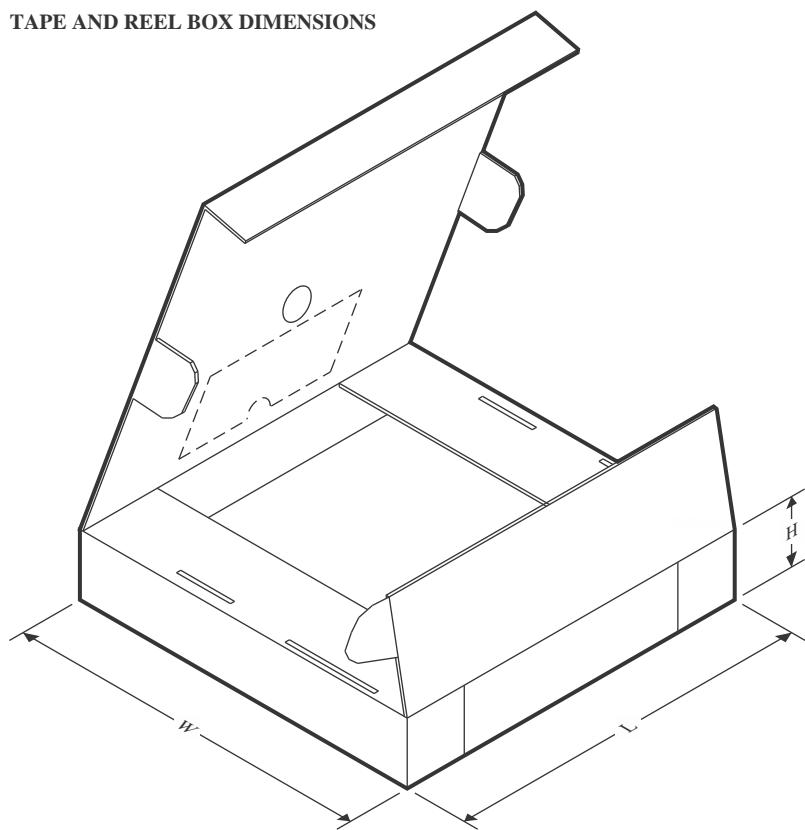

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| LM5123QRGRRQ1         | Active        | Production           | VQFN (RGR)   20 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 150   | LM5123              |

| LM5123QRGRRQ1.A       | Active        | Production           | VQFN (RGR)   20 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 150   | LM5123              |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).