LM5112, LM5112-Q1

JAJSC59C - SEPTEMBER 2004-REVISED SEPTEMBER 2016

# LM5112、LM5112-Q1 小型7A MOSFETゲート・ドライバ

## 1 特長

- LM5112-Q1は車載アプリケーション用に認定済み

- AEC-Q100グレード1認定済み

- 車載用グレードのフローで製造

- CMOSとバイポーラの複合出力によって出力電流 の変動を低減

- 7Aシンク、3Aソース電流

- 短い伝搬時間: 25ns (標準値)

- 短い立ち上がり/立ち下がり時間: 2nF負荷で 14nsまたは12ns

- 反転および非反転入力により、単一のデバイスで どちらの構成も可能

- 電源レールの低電圧誤動作防止保護

- 専用の入力グランド・ピン(IN\_REF)により 分割電源または単一電源で動作

- 電力拡張された6ピンのWSONパッケージ (3mm×3mm)または放熱特性の優れた MSOP-PowerPADパッケージ

- V<sub>CC</sub>からV<sub>EE</sub>(入力グランドに対して負電圧)までの 出力スイング

## 2 アプリケーション

- DC-DCスイッチ・モード電源

- AC-DCスイッチ・モード電源

- ソーラー・マイクロインバータ

- ソレノイドおよびモータ・ドライブ

## 3 概要

LM5112デバイスはMOSFETゲート・ドライバで、高いピーク・ゲート・ドライブ電流を供給し、小型の6ピンWSONパッケージ(SOT-23と同等の占有面積)または8ピンの露出パッド付きMSOPパッケージに搭載され、高い周波数での動作に必要な消費電力の改善が加えられています。複合出力ドライバのステージではMOSとバイポーラ・トランジスタが並列で動作し、容量性負荷から7Aを超えるピーク電流をシンクします。MOSとバイポーラ・デバイスの固有の特性を組み合わせることで、電圧および温度による駆動電流の変動が低減されます。低電圧誤動作防止保護が実装され、ゲートのターンオン電圧の不足によるMOSFETの損傷を防ぎます。LM5112デバイスには反転と非反転の両方の入力があり、単一のデバイス・タイプで反転と非反転のが一ト・ドライブの要件を満たすことができます。

#### 製品情報<sup>(1)</sup>

| <b>衣叩</b> 用我** |                   |               |  |  |  |

|----------------|-------------------|---------------|--|--|--|

| 型番             | パッケージ             | 本体サイズ(公称)     |  |  |  |

| LM5112、        | WSON (6)          | 3.00mm×3.00mm |  |  |  |

| LM5112-Q1      | MSOP PowerPAD (8) | 3.00mm×3.00mm |  |  |  |

(1) 提供されているすべてのパッケージについては、巻末の注文情報 を参照してください。

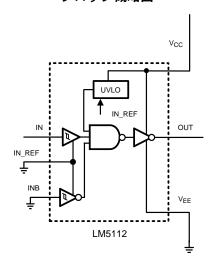

#### ブロック概略図

Copyright © 2016, Texas Instruments Incorporated

| · <b>/</b> |

|------------|

| .4         |

|            |

| 1 | 特長 1                                   |    | 7.4 Device Functional Modes    | 10 |

|---|----------------------------------------|----|--------------------------------|----|

| 2 | アプリケーション1                              | 8  | Application and Implementation | 11 |

| 3 | 概要1                                    |    | 8.1 Application Information    | 11 |

| 4 | 改訂履歴2                                  |    | 8.2 Typical Application        | 11 |

| 5 | Pin Configuration and Functions        | 9  | Power Supply Recommendations   | 13 |

| 6 | Specifications4                        | 10 | Layout                         | 13 |

| • | 6.1 Absolute Maximum Ratings           |    | 10.1 Layout Guidelines         | 13 |

|   | 6.2 ESD Ratings                        |    | 10.2 Layout Example            | 15 |

|   | 6.3 Recommended Operating Conditions 4 | 11 | デバイスおよびドキュメントのサポート             | 16 |

|   | 6.4 Thermal Information4               |    | 11.1 関連リンク                     | 16 |

|   | 6.5 Electrical Characteristics5        |    | 11.2 ドキュメントの更新通知を受け取る方法        | 16 |

|   | 6.6 Switching Characteristics 5        |    | 11.3 コミュニティ・リソース               | 16 |

|   | 6.7 Typical Characteristics            |    | 11.4 商標                        | 16 |

| 7 | Detailed Description 8                 |    | 11.5 静電気放電に関する注意事項             | 16 |

|   | 7.1 Overview 8                         |    | 11.6 Glossary                  |    |

|   | 7.2 Functional Block Diagram 8         | 12 | メカニカル、パッケージ、および注文情報            | 16 |

|   | 7.3 Feature Description9               |    |                                |    |

|   |                                        |    |                                |    |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

## Revision B (April 2006) から Revision C に変更

**Page**

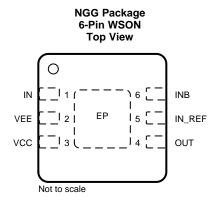

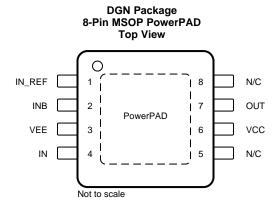

## 5 Pin Configuration and Functions

## **Pin Functions**

| F               | PIN  |      |     | DECODURE                                                                                                                                                                                                            |

|-----------------|------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | WSON | MSOP | 1/0 | DESCRIPTION                                                                                                                                                                                                         |

| Exposed Pad     | _    | _    | _   | Exposed pad, underside of package: Internally bonded to the die substrate. Connect to $V_{EE}$ ground pin for low thermal impedance.                                                                                |

| IN              | 1    | 4    | I   | Non-inverting input pin: TTL compatible thresholds. Pull up to $V_{\text{CC}}$ when not used.                                                                                                                       |

| INB             | 6    | 2    | I   | Inverting input pin: TTL compatible thresholds. Connect to IN_REF when not used.                                                                                                                                    |

| IN_REF          | 5    | 1    | _   | Ground reference for control inputs: Connect to power ground $(V_{EE})$ for standard positive only output voltage swing. Connect to system logic ground when $V_{EE}$ is connected to a negative gate drive supply. |

| N/C             | _    | 5, 8 | _   | Not internally connected                                                                                                                                                                                            |

| OUT             | 4    | 7    | 0   | Gate drive output: Capable of sourcing 3 A and sinking 7 A. Voltage swing of this output is from $V_{\text{EE}}$ to $V_{\text{CC}}$ .                                                                               |

| V <sub>CC</sub> | 3    | 6    | I   | Positive supply voltage input: Locally decouple to $V_{\text{EE}}$ . The decoupling capacitor must be placed close to the chip.                                                                                     |

| V <sub>EE</sub> | 2    | 3    | _   | Power ground for driver outputs: Connect to either power ground or a negative gate drive supply for positive or negative voltage swing.                                                                             |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                       | MIN  | MAX | UNIT |

|---------------------------------------|------|-----|------|

| V <sub>CC</sub> to V <sub>EE</sub>    | -0.3 | 15  | V    |

| V <sub>CC</sub> to IN_REF             | -0.3 | 15  | V    |

| IN/INB to IN_REF                      | -0.3 | 15  | V    |

| IN_REF to V <sub>EE</sub>             | -0.3 | 5   | V    |

| Maximum junction temperature          |      | 150 | °C   |

| Operating junction temperature        | -40  | 125 | °C   |

| Storage temperature, T <sub>stg</sub> | -55  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                        | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1) | ±2000 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                 |                                                              | MIN | MAX | UNIT |

|-----------------|--------------------------------------------------------------|-----|-----|------|

| V <sub>CC</sub> | Operating voltage, $V_{CC}$ – IN_REF and $V_{CC}$ – $V_{EE}$ | 3.5 | 14  | V    |

|                 | Operating junction temperature                               | -40 | 125 | °C   |

## 6.4 Thermal Information

|                       |                                              | LM51       | LM5112, LM5112-Q1   |      |  |  |

|-----------------------|----------------------------------------------|------------|---------------------|------|--|--|

|                       | THERMAL METRIC <sup>(1)</sup>                | NGG (WSON) | DGN (MSOP PowerPAD) | UNIT |  |  |

|                       |                                              | 6 PINS     | 8 PINS              |      |  |  |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 40         | 53.7                | °C/W |  |  |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 50.8       | 61.1                | °C/W |  |  |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 29.3       | 37.2                | °C/W |  |  |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.7        | 7.2                 | °C/W |  |  |

| ΨЈВ                   | Junction-to-board characterization parameter | 29.5       | 36.9                | °C/W |  |  |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 7.5        | 4.7                 | °C/W |  |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

### 6.5 Electrical Characteristics

$T_{.I} = -40$  °C to 125 °C,  $V_{CC} = 12$  V, INB = IN\_REF =  $V_{EE} = 0$  V, and no Load on output (unless otherwise noted).

|                     | PARAMETER                     | CONDITIONS                                                     | MIN | TYP  | MAX | UNIT |

|---------------------|-------------------------------|----------------------------------------------------------------|-----|------|-----|------|

| SUPPLY              |                               |                                                                |     |      |     |      |

| V <sub>CC</sub>     | Operating voltage             | V <sub>CC</sub> – IN_REF and V <sub>CC</sub> – V <sub>EE</sub> | 3.5 |      | 14  | V    |

| UVLO                | Undervoltage lockout (rising) | V <sub>CC</sub> – IN_REF                                       | 2.4 | 3    | 3.5 | V    |

| $V_{CCH}$           | Undervoltage hysteresis       |                                                                |     | 230  |     | mV   |

| I <sub>CC</sub>     | Supply current                |                                                                |     | 1    | 2   | mA   |

| CONTRO              | L INPUTS                      |                                                                |     |      |     |      |

| $V_{IH}$            | Logic high                    |                                                                | 2.3 |      |     | V    |

| V <sub>IL</sub>     | Logic low                     |                                                                |     |      | 0.8 | V    |

| $V_{thH}$           | High threshold                |                                                                | 1.3 | 1.75 | 2.3 | V    |

| $V_{thL}$           | Low threshold                 |                                                                | 0.8 | 1.35 | 2   | V    |

| HYS                 | Input hysteresis              |                                                                |     | 400  |     | mV   |

| I <sub>IL</sub>     | Input current low             | IN = INB = 0 V                                                 | -1  | 0.1  | 1   | μΑ   |

| I <sub>IH</sub>     | Input current high            | $IN = INB = V_{CC}$                                            | -1  | 0.1  | 1   | μA   |

| OUTPUT              | DRIVER                        |                                                                |     |      |     |      |

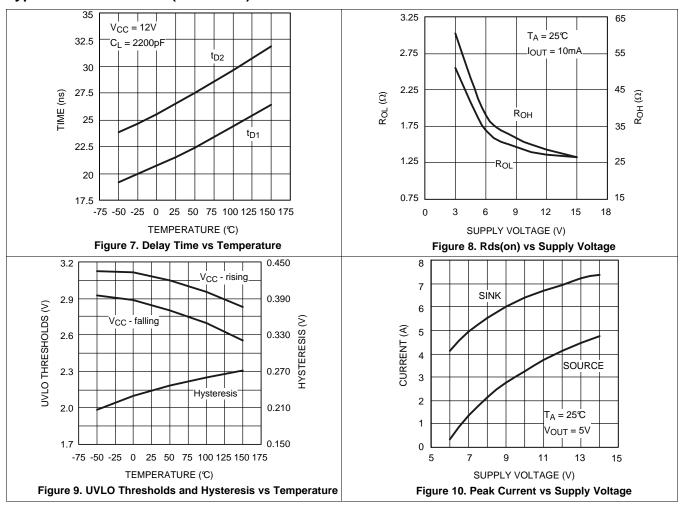

| R <sub>OH</sub>     | Output resistance high        | $I_{OUT} = -10 \text{ mA}^{(1)}$                               |     | 30   | 50  | Ω    |

| R <sub>OL</sub>     | Output resistance low         | $I_{OUT} = 10 \text{ mA}^{(1)}$                                |     | 1.4  | 2.5 | Ω    |

| I <sub>SOURCE</sub> | Peak source current           | OUT = V <sub>CC</sub> / 2,200 ns pulsed current                |     | 3    |     | Α    |

| I <sub>SINK</sub>   | Peak sink current             | OUT = V <sub>CC</sub> / 2,200 ns pulsed current                |     | 7    |     | Α    |

| LATCHUI             | PPROTECTION                   |                                                                |     |      |     |      |

|                     | AEC-Q100, METHOD 004          | T <sub>J</sub> = 150°C                                         |     | 500  |     | mA   |

<sup>(1)</sup> The output resistance specification applies to the MOS device only. The total output current capability is the sum of the MOS and bipolar devices.

## 6.6 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

|     | PARAMETER                                                         | TEST CONDITIONS                         | MIN | TYP | MAX | UNIT |

|-----|-------------------------------------------------------------------|-----------------------------------------|-----|-----|-----|------|

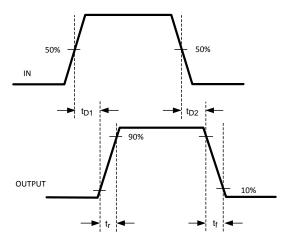

| td1 | Propagation delay time low to high, IN or INB rising (IN to OUT)  | C <sub>LOAD</sub> = 2 nF, see Figure 13 |     | 25  | 40  | ns   |

| td2 | Propagation delay time high to low, IN or INB falling (IN to OUT) | C <sub>LOAD</sub> = 2 nF, see Figure 13 |     | 25  | 40  | ns   |

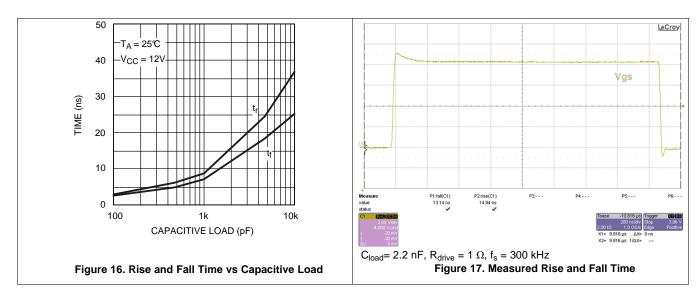

| tr  | Rise time                                                         | C <sub>LOAD</sub> = 2 nF, see Figure 13 |     | 14  |     | ns   |

| tf  | Fall time                                                         | C <sub>LOAD</sub> = 2 nF, see Figure 13 |     | 12  |     | ns   |

# TEXAS INSTRUMENTS

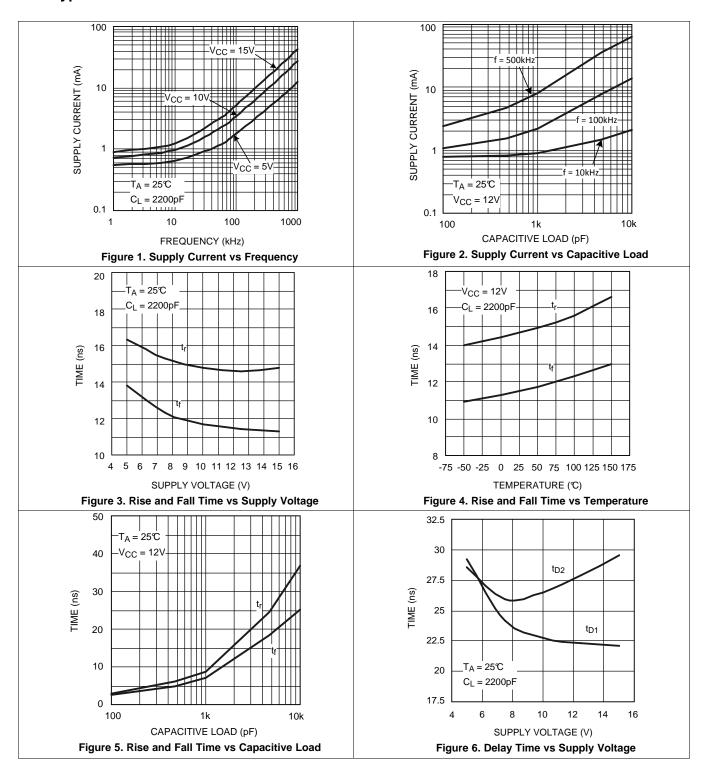

## 6.7 Typical Characteristics

## **Typical Characteristics (continued)**

## 7 Detailed Description

#### 7.1 Overview

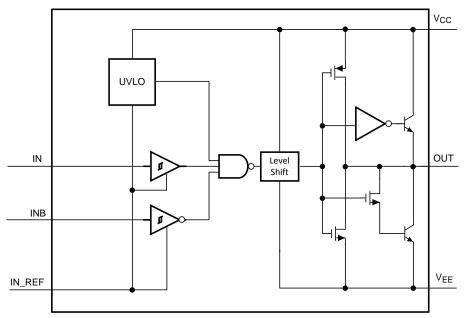

The LM5112 device is a high-speed, high-peak current (7 A) single-channel MOSFET driver. The high-peak output current of the LM5112 device switches power MOSFETs on and off with short rise and fall times, thereby reducing switching losses considerably. The LM5112 device includes both inverting and non-inverting inputs that give the user flexibility to drive the MOSFET with either active low or active high logic signals. The driver output stage consists of a compound structure with MOS and bipolar transistor operating in parallel to optimize current capability over a wide output voltage and operating temperature range. The bipolar device provides high peak current at the critical Miller plateau region of the MOSFET  $V_{\rm GS}$ , while the MOS device provides rail-to-rail output swing. The totem pole output drives the MOSFET gate between the gate drive supply voltage  $V_{\rm CC}$  and the power ground potential at the  $V_{\rm EE}$  pin.

## 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

Figure 11. LM5112 Functional Block Diagram

#### 7.3 Feature Description

The control inputs of the driver are high impedance CMOS buffers with TTL compatible threshold voltages. The negative supply of the input buffer is connected to the input ground pin IN\_REF. An internal level shifting circuit connects the logic input buffers to the totem pole output drivers. The level shift circuit and the separate input or output ground pins provide the option of single supply or split supply configurations. When driving the MOSFET gate from a single positive supply, the IN\_REF and  $V_{EE}$  pins are both connected to the power ground.

The isolated input and output stage grounds provide the capability to drive the MOSFET to a negative  $V_{GS}$  voltage for a more robust and reliable off state. In split supply configuration, the IN\_REF pin is connected to the ground of the controller which drives the LM5112 inputs. The  $V_{EE}$  pin is connected to a negative bias supply that can range from the IN\_REF potential to as low as 14 V below the  $V_{CC}$  gate drive supply. For reliable operation, the maximum voltage difference between  $V_{CC}$  and IN\_REF or between  $V_{CC}$  and  $V_{EE}$  is 14 V.

The minimum recommended operating voltage between  $V_{CC}$  and IN\_REF is 3.5 V. An undervoltage lockout (UVLO) circuit is included in the LM5112 which senses the voltage difference between  $V_{CC}$  and the input ground pin, IN\_REF. When the  $V_{CC}$  to IN\_REF voltage difference falls below 2.8 V the driver is disabled and the output pin is held in the low state. The UVLO hysteresis prevents chattering during brown-out conditions; the driver resumes normal operation when the  $V_{CC}$  to IN\_REF differential voltage exceeds 3 V.

#### 7.4 Device Functional Modes

The device output state is dependent on states of the IN and INB pins. Table 1 lists the output states for different input pin combinations.

**Table 1. Device Logic Table**

| IN PIN | INB PIN | OUT PIN |

|--------|---------|---------|

| L      | L       | L       |

| L      | Н       | L       |

| Н      | L       | Н       |

| Н      | Н       | L       |

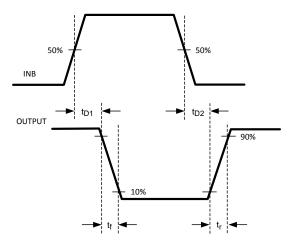

## 7.4.1 Inverting Mode

During the inverting mode of operation, INB is used as the control input and the polarity of OUT is reversed with respect to INB. Figure 12 shows a timing diagram of this mode. The IN pin is not used in this mode of operation and must be pulled up to  $V_{CC}$ .

Figure 12. Inverting

#### 7.4.2 Non-Inverting Mode

During the non-inverting mode of operation, IN is used as the control input and the polarity of OUT is the same with respect to IN. Figure 13 shows a timing diagram of this mode. The INB pin is not used in this mode of operation and must be connected to IN\_REF.

Figure 13. Non-Inverting

## 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 8.1 Application Information

A leading application for gate drivers such as the LM5112 is providing a high power buffer stage between the PWM output of a control IC and the gates of the primary power switching devices. In other cases, the driver IC is used to drive the power device gates through a drive transformer. Driver ICs are used when it is not feasible to have the primary PWM regulator IC directly drive the switching devices for one or more reasons. The PWM IC may not have the brute drive capability required for the intended switching MOSFET, limiting the switching performance in the application.

The LM5112 is used to drive a low side MOSFET with low switching losses. Either one of the control input pins, IN or INB, are used to control the gate drive to the MOSFET. The choice of the control input pin used depends on the polarity of operation.

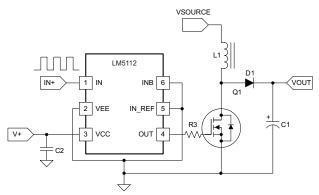

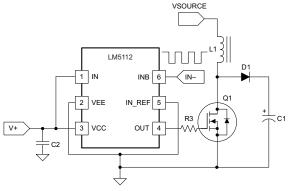

## 8.2 Typical Application

Typical application diagrams for the LM5112 device are shown below, illustrating use in non-inverting and inverting driver configurations. The high peak gate drive current of the LM5112 allows for short rise and fall times on the low-side MOSFET, thereby improving overall efficiency of the system and reducing switching losses.

Copyright © 2016, Texas Instruments Incorporated

Figure 14. Typical Application Diagram (Using Non-Inverting Control Input)

Copyright © 2016, Texas Instruments Incorporated

Figure 15. Typical Application Diagram (Using Inverting Control Input)

## **Typical Application (continued)**

#### 8.2.1 Design Requirements

When selecting the proper gate driver device for an end application, some design considerations must be evaluated first to make the most appropriate selection. Among these considerations are input-to-output configuration, the input threshold type, bias supply voltage levels, peak source and sink currents, capacitive load, and switching frequency. Table 2 shows some sample values for a typical application.

**Table 2. Design Parameters**

| PARAMETER                                                         | VALUE         |

|-------------------------------------------------------------------|---------------|

| Input-to-output logic                                             | Non-inverting |

| $V_{CC}$ bias supply voltage (measured with respect to $V_{EE}$ ) | 12 V          |

| Supply configuration                                              | Split supply  |

| Peak source current                                               | 3 A           |

| Peak sink current                                                 | 7 A           |

| Output load (MOSFET gate capacitance)                             | 2 nF          |

| Gate drive resistor                                               | 1 Ω           |

| Switching frequency                                               | 300 kHz       |

## 8.2.2 Detailed Design Procedure

See *Power Supply Recommendations*, *Layout*, and *Thermal Considerations* for key design considerations regarding the input supply, grounding, and thermal calculations specific to the LM5112.

## 8.2.3 Application Curves

The rise and fall times of the OUT signal depends on the capacitance of the MOSFET gate. Therefore, an appropriate MOSFET must be selected to meet the switching speed and efficiency requirements of the system. Figure 16 shows the rise and fall time curves as a function of capacitive load. Figure 17 shows output rise and fall time measured on an application board, showing actual device performance. The testing conditions for this figure are  $C_{load}$ = 2.2 nF,  $R_{drive}$  = 1  $\Omega$ , and  $f_s$  = 300 kHz.

## 9 Power Supply Recommendations

The recommended bias supply voltage range for LM5112 is from 3.5 V to 14 V. The lower end of this range is governed by the internal UVLO protection feature of the  $V_{CC}$  supply circuit. The upper end of this range is driven by the 14 V maximum recommended operating voltage rating of the  $V_{CC}$  supply. It is recommended to keep proper margin to allow for transient voltage spikes. The dedicated input ground pin (IN\_REF) allows split output supply operation. For such applications, ensure  $V_{EE}$  is not connected to IN\_REF.

The UVLO protection feature also involves a hysteresis function. This means that once the device is operating in normal mode, if the  $V_{CC}$  voltage drops, the device continues to operate in normal mode as long as the voltage drop does not exceed the hysteresis specification,  $V_{CCH}$ . If the voltage drop is greater than the hysteresis specification, the device shuts down. Therefore, while operating at or near the 3.5 V range, the voltage ripple on the auxiliary power supply output must be smaller than the hysteresis specification of LM5112 to avoid triggering device-shutdown.

A low-ESR or low-ESL capacitor must be connected close to the IC and between the  $V_{CC}$  and  $V_{EE}$  pins to support high peak currents being drawn from  $V_{CC}$  during turnon of the MOSFET. Also, if input pin (IN or INB) is not being used, it must be connected to  $V_{CC}$  or IN\_REF, respectively, to avoid spurious output signals.

## 10 Layout

## 10.1 Layout Guidelines

Attention must be given to board layout when using the LM5112 device. Some important considerations include:

Proper grounding is crucial. The driver required a low impedance path for current return to ground avoiding inductive loops. Two paths for returning current to ground are a) between the LM5112 device IN\_REF pin and the ground of the circuit that controls the driver inputs and b) between the LM5112 device V<sub>EE</sub> pin and the source of the power MOSFET being driven. Both paths must be as short as possible to reduce inductance and be as wide as possible to reduce resistance. These ground paths must be distinctly separate to avoid coupling between the high current output paths and the logic signals that drive the LM5112 device. With rise and fall times in the range of 10 nsec to 30 nsec, care is required to minimize the lengths of current carrying conductors to reduce their inductance and EMI from the high di/dt transients generated when driving large capacitive loads.

#### 10.1.1 Thermal Considerations

The primary goal of the thermal management is to maintain the integrated circuit (IC) junction temperature ( $T_J$ ) below a specified limit to ensure reliable long term operation. The maximum  $T_J$  of IC components must be estimated in worst case operating conditions. The junction temperature is calculated based on the power dissipated on the IC and the junction to ambient thermal resistance  $R_{\theta JA}$  for the IC package in the application board and environment. The  $R_{\theta JA}$  is not a given constant for the package and depends on the PCB design and the operating environment.

#### **Layout Guidelines (continued)**

#### 10.1.1.1 Drive Power Requirement Calculations In LM5112

The LM5112 device is a single, low-side MOSFET driver capable of sourcing and sinking 3-A or 7-A peak currents for short intervals to drive a MOSFET without exceeding package power dissipation limits. High peak currents are required to switch the MOSFET gate quickly for operation at high frequencies.

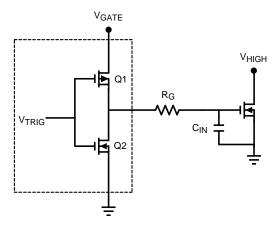

Figure 18. MOSFET Driver Diagram

Figure 18 shows a conceptual diagram of the LM5112 device output and MOSFET load. Q1 and Q2 are the switches within the gate driver.  $R_G$  is the gate resistance of the external MOSFET, and Cin is the equivalent gate capacitance of the MOSFET. The equivalent gate capacitance is a difficult parameter to measure as it is the combination of  $C_{GD}$  (gate to source capacitance) and  $C_{GD}$  (gate to drain capacitance). The  $C_{GD}$  is not a constant and varies with the drain voltage. The better way of quantifying gate capacitance is the gate charge  $Q_G$  in coloumbs.  $Q_G$  combines the charge required by  $C_{GD}$  and  $C_{GD}$  for a given gate drive voltage  $V_{GATE}$ . The gate resistance  $R_G$  is usually small and losses in it are neglected. The total power dissipated in the MOSFET driver due to gate charge is approximated by Equation 1.

$$P_{DRIVER} = V_{GATE} \times Q_G \times F_{SW}$$

where

For example, consider the MOSFET MTD6N15 whose gate charge specified as 30 nC for V<sub>GATE</sub> = 12 V.

Therefore, the power dissipation in the driver due to charging and discharging of MOSFET gate capacitances at switching frequency of 300 kHz and  $V_{GATE}$  of 12 V is equal to Equation 2.

$$P_{DRIVER} = 12 \text{ V} \times 30 \text{ nC} \times 300 \text{ kHz} = 0.108 \text{ W}$$

(2)

In addition to the above gate charge power dissipation, - transient power is dissipated in the driver during output transitions. When either output of the LM5112 device changes state, current flows from  $V_{CC}$  to  $V_{EE}$  for a brief interval of time through the output totem-pole N and P channel MOSFETs. The final component of power dissipation in the driver is the power associated with the quiescent bias current consumed by the driver input stage and Undervoltage lockout sections.

## **Layout Guidelines (continued)**

Characterization of the LM5112 device provides accurate estimates of the transient and quiescent power dissipation components. At 300 kHz switching frequency and 30 nC load used in the example, the transient power is 8 mW. The 1 mA nominal quiescent current and 12 V  $V_{GATE}$  supply produce a 12 mW typical quiescent power.

Therefore, the total power dissipation is calculated with Equation 3.

$$P_D = 0.118 + 0.008 + 0.012 = 0.138 \text{ W}$$

(3)

The junction temperature is given by Equation 4.

$$T_{J} = P_{D} \times R_{\theta JA} + T_{A} \tag{4}$$

Or the rise in temperature is given by Equation 5.

$$T_{RISE} = T_{J} - T_{A} = P_{D} \times R_{\theta JA}$$

(5)

For 6-pin WSON package, the integrated circuit die is attached to leadframe die pad which is soldered directly to the printed circuit board. This substantially decreases the junction to ambient thermal resistance ( $R_{\theta JA}$ ). By providing suitable means of heat dispersion from the IC to the ambient through exposed copper pad, which can readily dissipate heat to the surroundings,  $R_{\theta JA}$  as low as 40°C/W is achievable with the package. The resulting  $T_{RISE}$  for the driver example above is thereby reduced to just 5.5°C.

Therefore,  $T_{RISE}$  is equal to Equation 6.

$$T_{RISE} = 0.138 \times 40 = 5.5^{\circ}C$$

(6)

For MSOP-PowerPAD,  $R_{\theta JA}$  is typically 60°C/W.

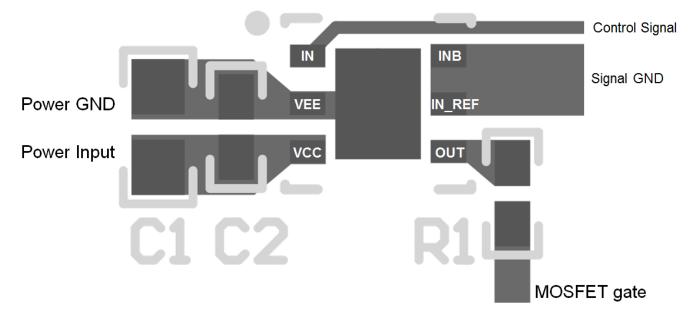

## 10.2 Layout Example

Figure 19. LM5112 Layout Example

## 11 デバイスおよびドキュメントのサポート

#### 11.1 関連リンク

次の表に、クイック・アクセス・リンクを示します。カテゴリには、技術資料、サポートおよびコミュニティ・リソース、ツールとソフトウェア、およびサンプル注文またはご購入へのクイック・アクセスが含まれます。

## 表 3. 関連リンク

| 製品        | プロダクト・フォルダ | サンプルとご購入 | 技術資料    | ツールとソフトウェア | サポートとコミュニティ |

|-----------|------------|----------|---------|------------|-------------|

| LM5112    | ここをクリック    | ここをクリック  | ここをクリック | ここをクリック    | ここをクリック     |

| LM5112-Q1 | ここをクリック    | ここをクリック  | ここをクリック | ここをクリック    | ここをクリック     |

## 11.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の隅にある「通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

## 11.3 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community T's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

## 11.4 商標

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 11.5 静電気放電に関する注意事項

これらのデバイスは、限定的なESD(静電破壊)保護機能を内蔵しています。保存時または取り扱い時は、MOSゲートに対する静電破壊を防止するために、リード線同士をショートさせておくか、デバイスを導電フォームに入れる必要があります。

### 11.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。これらの情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

# ご注意

Texas Instruments Incorporated 及びその関連会社(以下総称してTIといいます)は、最新のJESD46に従いその半導体製品及びサービスを修正し、改善、改良、その他の変更をし、又は最新のJESD48に従い製品の製造中止またはサービスの提供を中止する権利を留保します。お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての半導体製品は、ご注文の受諾の際に提示されるTIの標準販売契約約款に従って販売されます。

TIは、その製品が、半導体製品に関するTIの標準販売契約約款に記載された保証条件に従い、販売時の仕様に対応した性能を有していることを保証します。検査及びその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、適用される法令によってそれ等の実行が義務づけられている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援又はお客様の製品の設計について責任を負うことはありません。TI 製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI 製部品を使用したお客様の製品及びアプリケーションに関連する危険を最小のものとするため、適切な設計上及び操作上の安全対策は、お客様にてお取り下さい。

TIは、TIの製品又はサービスが使用されている組み合せ、機械装置、又は方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品又はサービスを使用することについてライセンスを与えるとか、保証又は是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない、又はTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブック又はデータ・シートの中にある情報の重要な部分の複製は、その情報に一切の変更を加えること無く、且つその情報と関連する全ての保証、条件、制限及び通知と共になされる限りにおいてのみ許されるものとします。TIは、変更が加えられて文書化されたものについては一切責任を負いません。第三者の情報については、追加的な制約に服する可能性があります。

TIの製品又はサービスについて TI が提示したパラメーターと異なる、又は、それを超えてなされた説明で当該 TI 製品又はサービスを再販売することは、関連する TI 製品又はサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、且つ不公正で誤認を生じさせる行為です。TI は、そのような説明については何の義務も責任も負いません。

TI からのアプリケーションに関する情報提供又は支援の一切に拘わらず、お客様は、ご自身の製品及びご自身のアプリケーションにおける TI 製品の使用に関する法的責任、規制、及び安全に関する要求事項の全てにつき、これをご自身で遵守する責任があることを認め、且つそのことに同意します。お客様は、想定される不具合がもたらす危険な結果に対する安全対策を立案し実行し、不具合及びその帰結を監視し、害を及ぼす可能性のある不具合の可能性を低減し、及び、適切な治癒措置を講じるために必要な専門的知識の一切を自ら有することを表明し、保証します。お客様は、TI 製品を安全でないことが致命的となるアプリケーションに使用したことから生じる損害の一切につき、TI 及びその代表者にその全額の補償をするものとします。

TI 製品につき、安全に関連するアプリケーションを促進するために特に宣伝される場合があります。そのような製品については、TIが目的とするところは、適用される機能上の安全標準及び要求事項を満たしたお客様の最終製品につき、お客様が設計及び製造ができるようお手伝いをすることにあります。それにも拘わらず、当該TI 製品については、前のパラグラフ記載の条件の適用を受けるものとします。

FDA クラス III(又は同様に安全でないことが致命的となるような医療機器)への TI 製品の使用は、TIとお客様双方の権限ある役員の間で、そのような使用を行う際について規定した特殊な契約書を締結した場合を除き、一切認められていません。

TIが軍需対応グレード品又は「強化プラスティック」製品として特に指定した製品のみが軍事用又は宇宙航空用アプリケーション、若しくは、軍事的環境又は航空宇宙環境にて使用されるように設計され、かつ使用されることを意図しています。お客様は、TIがそのように指定していない製品を軍事用又は航空宇宙用に使う場合は全てご自身の危険負担において行うこと、及び、そのような使用に関して必要とされるすべての法的要求事項及び規制上の要求事項につきご自身のみの責任により満足させることを認め、且つ同意します。

TIには、主に自動車用に使われることを目的として、ISO/TS 16949の要求事項を満たしていると特別に指定した製品があります。当該指定を受けていない製品については、自動車用に使われるようには設計されてもいませんし、使用されることを意図しておりません。従いまして、前記指定品以外のTI製品が当該要求事項を満たしていなかったことについては、TIはいかなる責任も負いません。

Copyright © 2016, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。 1. 静電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導電性マットにアースをとったもの等)、アースをした作業者が行うこと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、 静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

#### 2. 温·湿度環境

■温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱いを 行うこと。(但し、結露しないこと。) ● 直射日光があたる状態で保管・輸送しないこと。

#### 3. 防湿梱包

● 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

#### 4.機械的衝撃

● 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を与えないこと。

#### 5. 熱衝擊

● はんだ付け時は、最低限 260℃以上の高温状態に、10秒以上さらさないこと。(個別推奨条件がある時はそれに従うこと。)

#### 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が 一定以下に保証された無洗浄タイプのフラックスは除く。)

以上