LM5036 JAJSF96C - APRIL 2018 - REVISED OCTOBER 2021

# LM5036 補助バイアス電源搭載のハーフブリッジ PWM コントローラ

# 1 特長

- 高度に統合されたコントローラで、小さな占有面積、高 密度の DC/DC 電力コンバータを実現

- 100V、100mA の補助バイアス電源を搭載

- 完全にレギュレートされたプリバイアスへのスタートアッ

- ローサイドおよびハイサイド 1 次側 FET のパルス・マ ッチングによる拡張されたサイクル単位の電流制限

- 1次側 FET の最大デューティ・サイクルの最適化

- 電圧モード制御と入力電圧のフィードフォワード

- 100V の高電圧スタートアップ・レギュレータ

- 構成可能なラッチ、OVP 動作

- 1 次側 FET 用の 100V、2A の MOSFET ドライバを

- 1次側 FET と同期整流器 (SR) FET との間のデッドタ イムをプログラム可能

- Excel カリキュレータ・ツールまたは WEBENCH® Power Designer により、LM5036 を使用するカスタム 設計を作成

# 2 アプリケーション

- テレコムおよびデータ通信の絶縁型電源

- 産業用電源およびファクトリ・オートメーション

- 試験 / 計測機器

# 3 概要

補助バイアス電源を内蔵した LM5036 PWM コントローラ は、産業用絶縁型電源用途に適した高い電力密度を実 現します。電圧モード制御と入力電圧フィードフォワードを 使用し、ハーフブリッジ電力コンバータを実装するために 必要なすべての機能を備えています。このコントローラは、 最大 100V の DC 入力電圧で絶縁型コンバータの 1 次 側で動作するように設計されています。本コントローラは、 システム・コストを低減すると同時に電力密度と信頼性を 向上させる以下の機能を備えています。

- 補助バイアス電源としての内蔵フライバック・コンバー タ。最小限の外付け部品で1次側と2次側の両方の 回路にバイアス電力を供給します。

- 完全にレギュレートされたプリバイアスへのスタートアッ プ。プリチャージされた出力コンデンサへの起動時で も、出力電圧のオーバーシュートまたはディップを除去 します。

- パルス・マッチングによる拡張されたサイクル単位のピ ーク電流制限。本コントローラは、正と負の両方の電流 を制御します。パルス・マッチングにより、ローサイドと ハイサイド・デバイスのパルス幅が同じになるように制 御し、変圧器の飽和を防止します。出力電流制限は、 入力電圧範囲の全体にわたってほぼ一定です。

#### 製品情報

| 部品番号   | パッケージ <sup>(1)</sup> | 本体サイズ (公称)      |

|--------|----------------------|-----------------|

| LM5036 | WQFN (28)            | 5.00mm × 5.00mm |

利用可能なすべてのパッケージについては、このデータシートの 末尾にある注文情報を参照してください。

アプリケーション概略

### **Table of Contents**

| 1 特長                                                                                       | 1                     | 7.4 Device Functional Modes                                                          | 41             |

|--------------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------|----------------|

| 2 アプリケーション                                                                                 |                       | 8 Application and Implementation                                                     | 42             |

| 3 概要                                                                                       | 1                     | 8.1 Application Information                                                          |                |

| 4 Revision History                                                                         |                       | 8.2 Typical Application                                                              |                |

| 5 Pin Configuration and Functions                                                          |                       | 9 Power Supply Recommendations                                                       |                |

| 6 Specifications                                                                           |                       | 10 Layout                                                                            |                |

| 6.1 Absolute Maximum Ratings                                                               |                       | 10.1 Layout Guidelines                                                               |                |

| 6.2 ESD Ratings                                                                            |                       | 10.2 Layout Example                                                                  |                |

| 6.3 Recommended Operating Conditions                                                       | 6                     | 11 Device and Documentation Support                                                  |                |

| 6.4 Thermal Information                                                                    | 7                     | 11.1 Device Support                                                                  |                |

| 6.5 Electrical Characteristics                                                             | 7                     | 11.2 Documentation Support                                                           |                |

| 6.6 Switching Characteristics                                                              | 10                    | 11.3 サポート・リソース                                                                       |                |

| 6.7 Typical Characteristics                                                                | 11                    | 11.4 Trademarks                                                                      |                |

| 7 Detailed Description                                                                     | 13                    | 11.5 Electrostatic Discharge Caution                                                 |                |

| 7.1 Overview                                                                               | 13                    | 11.6 Glossary                                                                        | 60             |

| 7.2 Functional Block Diagram                                                               | 14                    | 12 Mechanical, Packaging, and Orderable                                              |                |

| 7.3 Feature Description                                                                    | 15                    | Information                                                                          | 61             |

| <ul><li>Changes from Revision B (April 2019) to R</li><li>・ 文書全体にわたって表、図、相互参照の採番</li></ul> |                       | (October 2021)                                                                       | Page1          |

|                                                                                            |                       |                                                                                      |                |

|                                                                                            |                       | t source for slope compensation (I <sub>SLOPE</sub> ) specif                         |                |

|                                                                                            |                       | note (1) from this parameter                                                         |                |

|                                                                                            |                       | rom 1.5 A to 1 A                                                                     |                |

|                                                                                            |                       |                                                                                      |                |

|                                                                                            |                       | (V <sub>BST_AUX(UVLO)</sub> ) specification from 2.1 V to 3.                         |                |

| Changed typical BST_AUX undervoltage if                                                    | nresnoia (V           | (BST_AUX(UVLO)) specification from 2.8 V to 5.0 V                                    | ·              |

| Changed maximum BST_AUX undervoltage                                                       | ge threshol           | d ( $V_{BST\_AUX(UVLO)}^-$ ) specification from 3.6 V to 6                           | .5 V /         |

| <ul> <li>Changed typical peak current source value</li> </ul>                              | e reference           | s from "1.5 Å" to "1 A" in セクション 7.3.6                                               | 17             |

| Changes from Revision A (June 2018) to R                                                   | evision B             | (April 2019)                                                                         | Page           |

| Added minimum recommended values for                                                       | RD <sub>1</sub> and R | D <sub>2</sub>                                                                       | <mark>6</mark> |

|                                                                                            |                       | 18V to 16V                                                                           |                |

|                                                                                            |                       | l <sub>BiasOffset</sub>                                                              |                |

|                                                                                            |                       |                                                                                      |                |

| <ul> <li>Added parameter names for some items the</li> </ul>                               | nat had nor           | ie: $I_{OVL}$ , $V_{SSSecEn}$ , $V_{SSREn}$ , $t_{CSLSG}$ , $t_{CSBLK}$ , $V_{REST}$ | Γh2,           |

|                                                                                            |                       |                                                                                      |                |

| •                                                                                          | •                     |                                                                                      |                |

| <ul> <li>Changed parameter name V<sub>PWM-OS</sub> to I<sub>PW</sub></li> </ul>            | M-OS                  | 40.01/. 401/                                                                         | /              |

| Changed parameter V <sub>AUX_UVLO</sub> maximum                                            | value from            | 16.6V to 16V                                                                         | <u>/</u>       |

| <ul> <li>Changed parameter name HC_BLK_TH to</li> </ul>                                    | V <sub>HC_BLK_T</sub> | H                                                                                    | 7              |

| <ul> <li>Added new parameters AUX SUPPLY CUI</li> </ul>                                    | KKENT LIN             | /IIT: t <sub>CSBLKA</sub> , t <sub>AUX(LIM)</sub> , t <sub>AuxSns</sub>              | 7              |

|                                                                                            |                       | r t <sub>ON</sub>                                                                    |                |

|                                                                                            |                       |                                                                                      |                |

| · Changed Positive and negative current lim                                                | it shown to           | be affected by LEB signal.                                                           | 14             |

| · Added reference to operation from voltage                                                | s above 10            | OV Values replaced with peremeter person                                             | 4.5            |

### www.tij.co.jp

| • | Added pre-biased start-up process is handled automatically by LM5036                                                  | 21   |

|---|-----------------------------------------------------------------------------------------------------------------------|------|

| • | Changed values to parameter names. V <sub>REF</sub> changed to V <sub>REFSec</sub> , TH changed to V <sub>THSec</sub> |      |

| • | Changed values to parameter names. I <sub>COMP</sub> is graphed instead of V <sub>COMP</sub>                          |      |

| • | Changed V <sub>COMP</sub> to I <sub>COMP</sub> .                                                                      |      |

| • | Changed and expanded Section: 'Enhanced Cycle-by-Cycle Current Limiting with Pulse Matching'                          |      |

| • | Changed and expanded Section: 'Reverse Current Protection'.                                                           |      |

| • | Added Section: 'CBC Threshold Accuracy'                                                                               |      |

| • | Changed values to parameter names.                                                                                    |      |

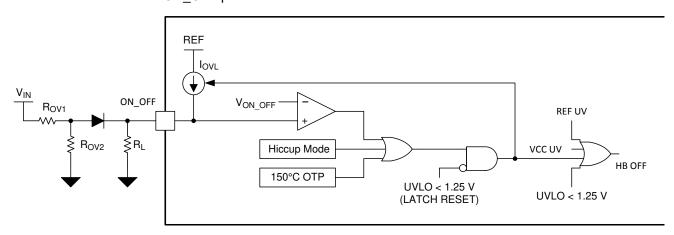

|   | Changed Section: 'ON_OFF Pin' to 'Over-Voltage / Latch (ON_OFF Pin)'. Values replaced by parameter                    |      |

|   | names.                                                                                                                | 33   |

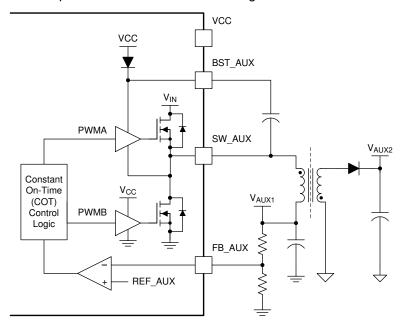

|   | Changed Section: 'Constant On-Time Control' to 'Auxiliary Constant On-Time Control'                                   |      |

|   | Changed Section: 'On-Time Generator' to 'Auxiliary On-Time Generator'                                                 |      |

|   | Added method to calculate peak Auxiliary transformer current. External schottky recommended to improve                |      |

|   | Auxiliary efficiency during ASYNCH mode.                                                                              |      |

|   | Deleted Section: 'Ripple Configuration Types'                                                                         |      |

| • | Added Section: 'Auxiliary Ripple Configuration and Control'.                                                          |      |

|   | Changed values to parameter names.                                                                                    |      |

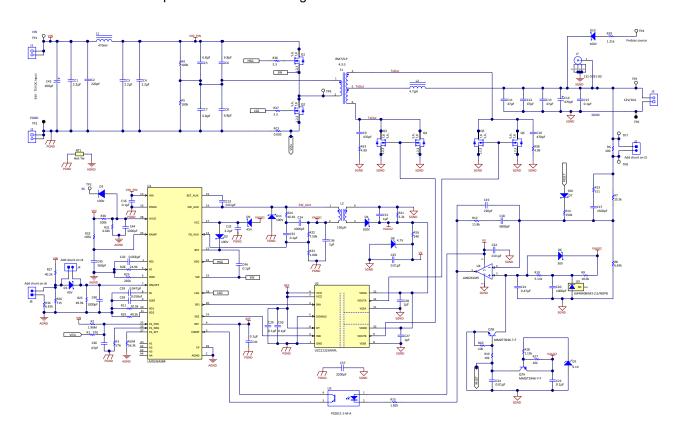

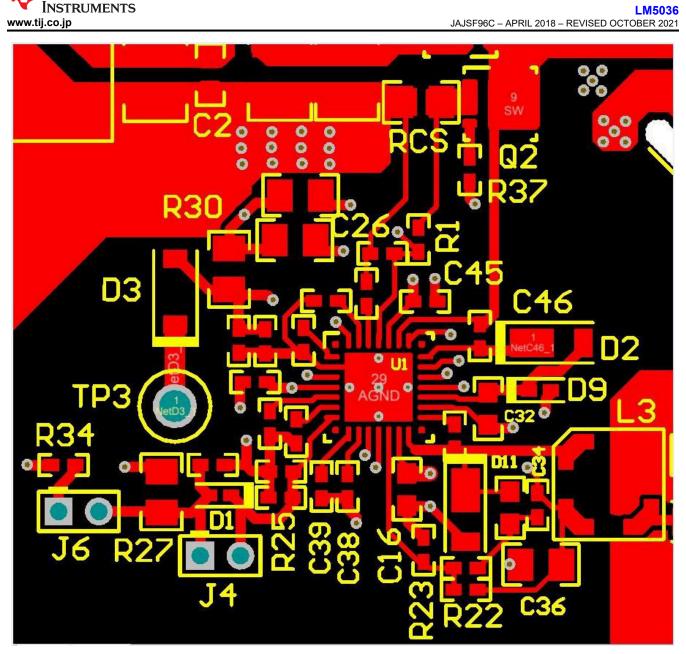

|   | Changed C26 from 330-pF to 47-pF, R29 from 165-k $\Omega$ to 220-k $\Omega$ . Added D11                               |      |

|   | Changed voltage targets for auxiliary output voltage from 12.6 V / 9 V to 11.9 V / 8.5 V.                             |      |

|   | Added reference to Excel Calculator Tool.                                                                             |      |

|   | Added restriction on use of TL431 to implement secondary side error amplifier                                         |      |

| • | Added reference to Power Stage Designer Tool.                                                                         |      |

| • |                                                                                                                       |      |

| • | Changed values to parameter names. R <sub>UV1</sub> and <sub>RUV2</sub> replace R <sub>1</sub> and R <sub>2</sub> .   |      |

| • | Changed Section: 'ON_OFF Pin Voltage Divider Selection' to 'Over Voltage / Latch (ON_OFF Pin) Voltage                 |      |

|   | Divider Selection'.                                                                                                   |      |

| • | Added new Section: 'Half-Bridge Power Stage Design'                                                                   | 47   |

| • | Changed and expanded Section:'Current Limit'                                                                          |      |

| • | Changed calculation of Auxiliary transformer inductance.                                                              |      |

| • | Changed calculated value for R <sub>ON</sub> resistor.                                                                |      |

| • | Changed calculated value of Auxiliary primary output capacitor value.                                                 | 54   |

| • | Changed calculation of secondary output capacitor. Now uses ripple peak amplitude not peak-to-peak                    |      |

|   | amplitude                                                                                                             |      |

| • | Changed calculation of Auxiliary Feedback component values.                                                           |      |

| • | Changed expression for I <sub>COMP</sub> to fix error.                                                                |      |

| • | Changed layout diagram to include external schottky diode connected between PGND and SW_AUX pins                      | 3    |

|   | 58                                                                                                                    |      |

| С | hanges from Revision * (April 2018) to Revision A (June 2018)                                                         | Page |

| • | マーケティング・ステータスを事前情報から初回リリースに変更                                                                                         | 1    |

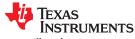

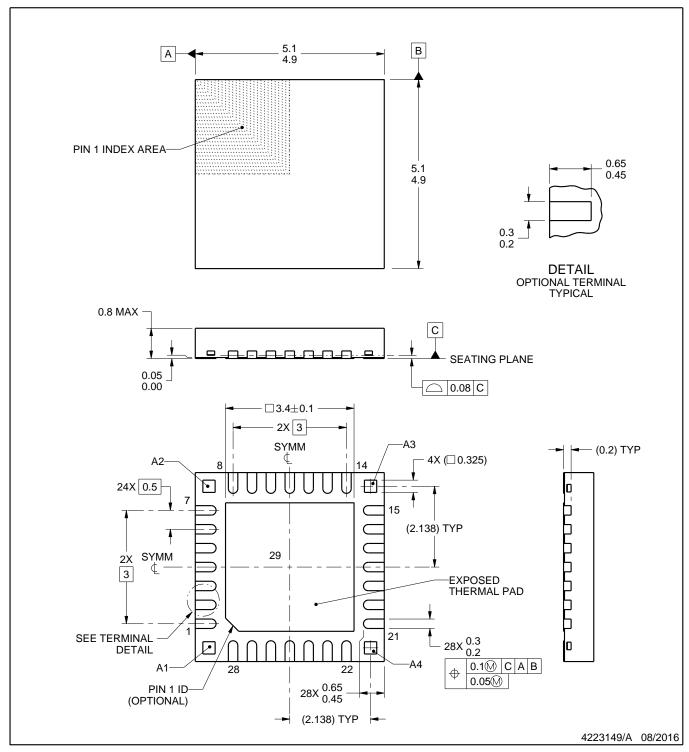

# **5 Pin Configuration and Functions**

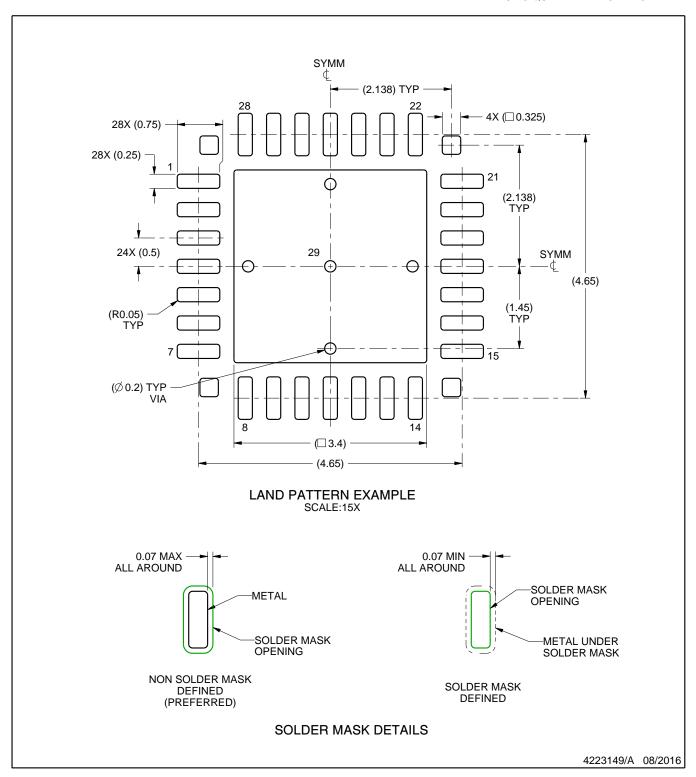

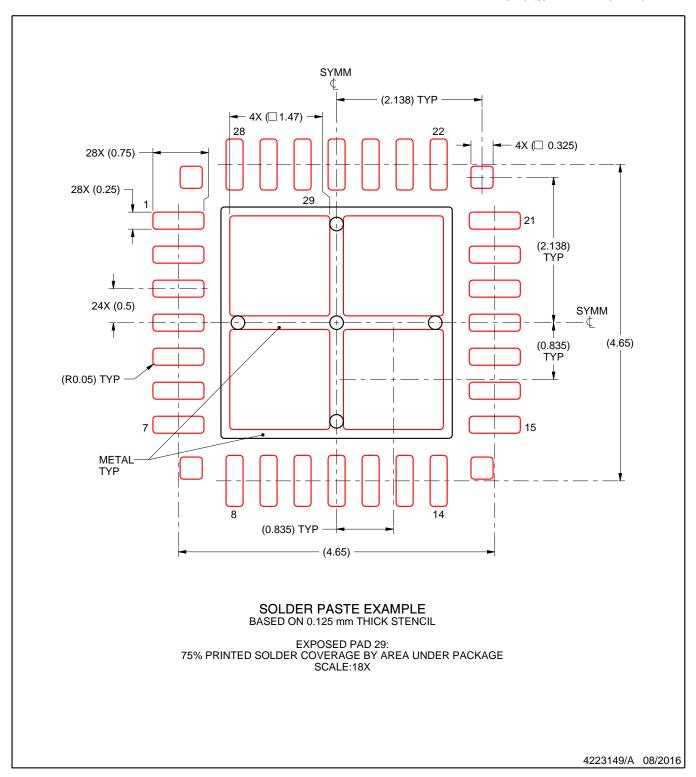

図 5-1. RJB Package, 28-Pin WQFN (Top View)

表 5-1. Pin Functions

| PIN     |     | TYPE <sup>(1)</sup> | DESCRIPTION                                                    |

|---------|-----|---------------------|----------------------------------------------------------------|

| NAME    | NO. | ITPE                | DESCRIPTION                                                    |

| AGND    | 2   | G                   | Analog ground                                                  |

| BST     | 21  | I                   | Half-bridge high-side gate drive bootstrap                     |

| BST_AUX | 15  | I                   | Auxiliary supply high-side gate drive bootstrap                |

| COMP    | 3   | I                   | Control current input to half-bridge PWM comparator            |

| CS_NEG  | 26  | I                   | Current sense amplifier negative input terminal                |

| CS_POS  | 25  | I                   | Current sense amplifier positive input terminal                |

| CS_SET  | 27  | I                   | Current limit setting                                          |

| FB_AUX  | 12  | I                   | Auxiliary supply output voltage feedback                       |

| HSG     | 22  | 0                   | Half-bridge high-side MOSFET output driver                     |

| LSG     | 18  | 0                   | Half-bridge low-side MOSFET output driver                      |

| ON_OFF  | 7   | ı                   | Configurable for over voltage protection (OVP) or latch mode   |

| PGND    | 16  | G                   | Power ground                                                   |

| RAMP    | 24  | I                   | RAMP signal input to half-bridge PWM comparator                |

| RD1     | 10  | I                   | Synchronous rectifier trailing-edge delay                      |

| RD2     | 11  | I                   | Synchronous rectifier leading-edge delay                       |

| REF     | 4   | 0                   | 5-V reference regulator output                                 |

| RES     | 1   | I                   | Hiccup mode restart timer                                      |

| RON     | 6   | I                   | Auxiliary supply on-time control                               |

| RT/SYNC | 5   | I                   | Oscillator frequency control or external clock synchronization |

| SR1     | 20  | 0                   | Synchronous rectifier PWM control output                       |

| SR2     | 19  | 0                   | Synchronous rectifier PWM control output                       |

| SS      | 8   | ı                   | Soft-start input                                               |

| SSSR    | 9   | I                   | Synchronous rectifier soft-start input                         |

# 表 5-1. Pin Functions (continued)

| PIN    | 1   | TYPE <sup>(1)</sup> | DESCRIPTION                  |

|--------|-----|---------------------|------------------------------|

| NAME   | NO. | IIFE\/              | DESCRIP HON                  |

| SW     | 23  | I                   | Half-bridge switch node      |

| SW_AUX | 14  | I                   | Auxiliary supply switch node |

| UVLO   | 28  | I                   | Input undervoltage lockout   |

| VCC    | 17  | I                   | Bias supply                  |

| VIN    | 13  | I                   | Input voltage                |

| Pad    | 29  | G                   | Exposed thermal pad          |

(1) I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

# **6 Specifications**

# **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)(1)

|                                                                         | MIN  | MAX  | UNIT |

|-------------------------------------------------------------------------|------|------|------|

| VIN to GND                                                              | -0.3 | 105  | V    |

| SW/SW_AUX to GND                                                        | -5   | 105  | V    |

| BST TO SW, BST_AUX TO SW_AUX                                            | -0.3 | 16   | V    |

| HSG to SW                                                               | -0.3 | 16   | V    |

| LSG to GND                                                              | -0.3 | 16   | V    |

| SR1/SR2 to GND                                                          | -0.3 | 5    | V    |

| VCC to GND                                                              | -0.3 | 16   | V    |

| RT, UVLO, ON/OFF, RON, RAMP, RES, FB_AUX, CS_POS, CS_NEG, CS_SET to GND | -0.3 | 5    | V    |

| COMP to GND                                                             |      | -0.3 | V    |

| COMP Input Current                                                      |      | 10   | mA   |

| Junction Temperature                                                    |      | 150  | °C   |

| Storage Temperature, Tstg                                               | -55  | 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|        |               |                                                                                         | VALUE | UNIT     |

|--------|---------------|-----------------------------------------------------------------------------------------|-------|----------|

| V      | Electrostatic | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>             | ±2000 | V        |

| V(ESD) | discharge     | Charged device model (CDM), per JEDEC specificationJESD22-C101, all pins <sup>(2)</sup> | ±750  | <b>V</b> |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                          |                                                  | MIN | NOM | MAX | UNIT |

|--------------------------|--------------------------------------------------|-----|-----|-----|------|

| V <sub>IN</sub>          | Input voltage                                    | 16  |     | 100 | V    |

| External V <sub>CC</sub> | Supply Voltage                                   | 8.5 |     | 14  | V    |

| RD <sub>x</sub>          | RD <sub>1</sub> , RD <sub>2</sub> Resistor value | 5   |     |     | kΩ   |

| T <sub>J</sub>           | Junction Temperature                             | -40 |     | 125 | °C   |

### **6.4 Thermal Information**

|                       |                                              | LM5036     |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC (1)                           | RJB (WQFN) | UNIT |

|                       |                                              | 28 PINS    |      |

| R <sub>OJA</sub>      | Junction-to-ambient thermal resistance       | 29.9       | °C/W |

| R <sub>OJC(top)</sub> | Junction-to-case (top) thermal resistance    | 18.2       | °C/W |

| R <sub>OJB</sub>      | Junction-to-board thermal resistance         | 10.4       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.2        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 10.3       | °C/W |

| R <sub>OJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Electrical Characteristics

MIN and MAX limits apply the junction temperature range of  $-40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$ . Unless otherwise specified, the following conditions apply:  $V_{IN} = 48 \text{ V}$ ,  $R_{T} = 25 \text{ k}\Omega$ ,  $RD_{1} = RD_{2} = 20 \text{ k}\Omega$ ,  $R_{ON} = 100 \text{ k}\Omega$ . No load on LSG, HSG, SR1, SR2, UVLO = 2.5 V, ON\_OFF = 0 V.

|                       | PARAMETER                                   | TEST CONDITIONS                                                                                | MIN   | TYP  | MAX   | UNIT |

|-----------------------|---------------------------------------------|------------------------------------------------------------------------------------------------|-------|------|-------|------|

| START-UP R            | EGULATOR                                    |                                                                                                |       |      |       |      |

| V <sub>CC</sub>       | V <sub>CC</sub> voltage                     | I <sub>CC</sub> = 10 mA                                                                        | 7.5   | 7.8  | 8.1   | V    |

| I <sub>CC (Lim)</sub> | Vcc current limit                           | V <sub>CC</sub> = 6 V, V <sub>IN</sub> = 20 V                                                  | 69    | 81   | 94    | mA   |

| I <sub>CC(ext)</sub>  | Vcc supply current                          | Supply current into Vcc from an externally applied source. V <sub>CC</sub> = 9 V, FB_AUX = 0 V | 6.6   | 9    | 11    | mA   |

| V <sub>CC(reg)</sub>  | Vcc load regulation                         | I <sub>CC</sub> from 0 to 50 mA                                                                | 31    | 49   | 73    | mV   |

| V <sub>CC(UV)</sub>   | Vcc undervoltage threshold                  | Positive going Vcc                                                                             | 7.4   | 7.7  | 8.0   | V    |

|                       |                                             | Negative going Vcc                                                                             | 6.1   | 6.3  | 6.7   | V    |

|                       | V <sub>IN</sub> shutdown current            | $V_{IN}$ = 20 V, $V_{UVLO}$ = 0 V, $R_{ON}$ = 100 k $\Omega$                                   | 276   | 580  | 670   | μΑ   |

|                       |                                             | $V_{IN} = 100 \text{ V}, V_{UVLO} = 0 \text{ V}, R_{ON} = 100 \text{ k}\Omega$                 | 299   | 600  | 717   | μΑ   |

|                       | V <sub>IN</sub> start-up regulator leakage  | $V_{CC}$ = 9 V, applied externally, FB_AUX > 2 V, SS = 0 V, R <sub>ON</sub> = 100 kΩ           | 180   | 234  | 304   | μA   |

| VOLTAGE RI            | EFERENCE REGULATOR (REF PIN)                |                                                                                                |       |      | '     |      |

| $V_{REF}$             | REF voltage                                 | I <sub>REF</sub> = 0 mA                                                                        | 4.85  | 5    | 5.15  | V    |

| V <sub>REF(REG)</sub> | REF load regulation                         | I <sub>REF</sub> = 0 to 25 mA                                                                  | 24    | 37   | 57    | mV   |

| I <sub>REF(LIM)</sub> | REF current limit                           | V <sub>REF</sub> = 4.5 V, V <sub>IN</sub> = 20 V                                               | 28    | 39   | 47    | mA   |

| V <sub>REF(UV)</sub>  | REF undervoltage threshold                  | Positive going V <sub>REF</sub>                                                                | 4.3   | 4.5  | 4.7   | V    |

|                       | Hysteresis                                  |                                                                                                | 0.16  | 0.26 | 0.37  | V    |

| UNDERVOLT             | TAGE LOCK OUT AND SHUTDOWN                  | (UVLO PIN)                                                                                     |       |      |       |      |

| V <sub>UVLO</sub>     | UVLO threshold                              |                                                                                                | 1.205 | 1.25 | 1.305 | V    |

| I <sub>UVLO</sub>     | UVLO Hysteresis current                     |                                                                                                | 15    | 20   | 24    | μΑ   |

| $V_{SD}$              | Internal startup regulator enable threshold | SS = 0 V, FB_AUX = 2.5 V                                                                       | 0.34  | 0.38 | 0.41  | V    |

|                       | Hysteresis                                  |                                                                                                | 90    | 135  | 175   | mV   |

| OVER-VOLT             | AGE/LATCH (ON_OFF PIN)                      |                                                                                                |       |      |       |      |

| V <sub>ON_OFF</sub>   | ON_OFF threshold                            |                                                                                                | 1.18  | 1.25 | 1.32  | V    |

| I <sub>OVL</sub>      | ON_OFF hysteresis current                   |                                                                                                | 40    | 50   | 60    | μA   |

| SOFT-START            | Γ (SS PIN, SSSR PIN)                        |                                                                                                | ,     |      |       |      |

| I <sub>SS</sub>       | SS charge current                           | SS = 0 V                                                                                       | 17    | 20   | 24    | μA   |

MIN and MAX limits apply the junction temperature range of  $-40^{\circ}\text{C} \le T_{\text{J}} \le 125^{\circ}\text{C}$ . Unless otherwise specified, the following conditions apply:  $V_{\text{IN}} = 48 \text{ V}$ ,  $R_{\text{T}} = 25 \text{ k}\Omega$ ,  $RD_{1} = RD_{2} = 20 \text{ k}\Omega$ ,  $R_{\text{ON}} = 100 \text{ k}\Omega$ . No load on LSG, HSG, SR1, SR2, UVLO = 2.5 V, ON\_OFF = 0 V.

| V <sub>SSSecEn</sub>             | SS threshold to enable SSSR charge current                                  | I <sub>COMP</sub> < 800 μA           | 1.93  | 2.00  |      |     |

|----------------------------------|-----------------------------------------------------------------------------|--------------------------------------|-------|-------|------|-----|

|                                  | onargo ourront                                                              | COMP 4 000 Pr                        | 1.93  | 2.06  | 2.2  | V   |

|                                  | SS output low voltage                                                       | Sinking 100 μA                       | 30    | 48    | 57   | mV  |

|                                  | SS threshold to disable switching                                           |                                      | 865   | 1000  | 1198 | mV  |

| I <sub>SSSR</sub>                | SSSR charge current                                                         | SS > 2 V, I <sub>COMP</sub> < 800 μA | 17    | 20    | 24   | μA  |

|                                  | SSSR output low voltage                                                     | Sinking 100 μA                       | 30    | 38.7  | 49   | mV  |

| V <sub>SSREn</sub>               | SSSR threshold to enable SR freewheeling pulse                              |                                      | 0.65  | 1.17  | 1.67 | V   |

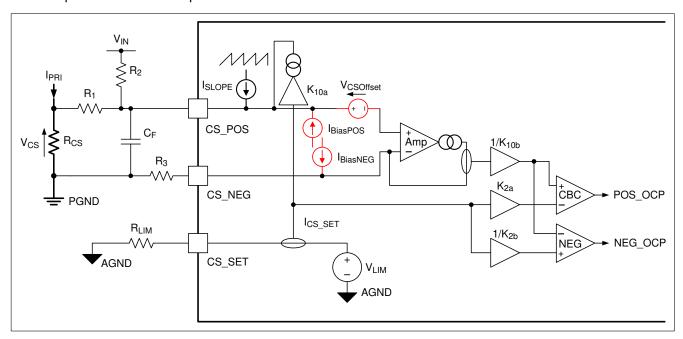

| CURRENT SE                       | NSE (CS_POS, CS_NEG, and CS_S                                               | ET PIN)                              |       |       | 1    |     |

| V <sub>LIM</sub>                 | Current limit setting voltage                                               |                                      | 0.72  | 0.75  | 0.77 | V   |

|                                  | Ratio of internal negative to positive current limit threshold              |                                      | 0.3   | 0.58  | 0.9  |     |

| t <sub>CSLSG</sub>               | CS to gate driver output delay                                              |                                      | 60    | 85    | 122  | ns  |

| t <sub>CSBLK</sub>               | CS leading-edge blanking                                                    |                                      | 33    | 53    | 76   | ns  |

| K <sub>CBC1</sub> <sup>(1)</sup> | V <sub>LIM</sub> x (K <sub>2a</sub> X K <sub>10b</sub> - K <sub>10a</sub> ) | At CBC trip threshold                | 7.28  | 7.51  | 7.81 | V   |

| V <sub>CSOffset</sub> (1)        | V <sub>CS_POS</sub> - V <sub>CS_NEG</sub>                                   | At CBC trip threshold                | -0.63 | -0.02 | 0.32 | mV  |

| I <sub>BiasOffset</sub> (1)      | I <sub>BiasPOS</sub> - I <sub>BiasNEG</sub>                                 | At CBC trip threshold                | -0.67 | 0.02  | 0.29 | μΑ  |

| I <sub>SLOPE</sub>               | Peak value of current source for slope compensation                         |                                      |       | 36    |      | μΑ  |

| REVERSE CUI                      | RRENT PROTECTION                                                            |                                      |       |       | 1    |     |

| N                                | Number of switching periods to reset negative over-current event counter    |                                      |       | 4     |      |     |

| SR_CTR_TH                        | SSSR threshold to reset SSSR cap clamp event counter                        |                                      | 4.8   | 4.94  | 5.1  | V   |

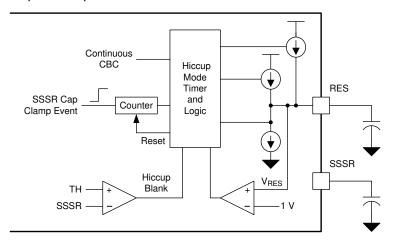

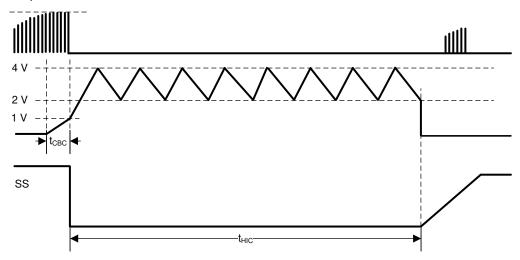

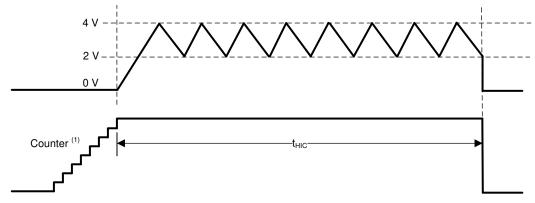

| HICCUP MODE                      | E (RES PIN)                                                                 |                                      |       |       |      |     |

| R <sub>RES</sub>                 | RES pulldown resistance                                                     | Termination of hiccup timer          | 24    | 36    | 55   | Ω   |

| V <sub>RESTh1</sub>              | RES hiccup threshold                                                        |                                      | 0.90  | 1     | 1.04 | V   |

| V <sub>RESTh3</sub>              | RES upper counter threshold                                                 |                                      | 3.91  | 4     | 4.07 | V   |

| V <sub>RESTh2</sub>              | RES lower counter threshold                                                 |                                      | 1.95  | 2     | 2.04 | V   |

| I <sub>RES-SRC1</sub>            | Charge current source1                                                      | V <sub>RES</sub> < 1 V, CBC active   | 12    | 15    | 18   | μA  |

| I <sub>RES-SRC2</sub>            | Charge current source2                                                      | 1 V < V <sub>RES</sub> < 4 V         | 25    | 30    | 36   | μA  |

| I <sub>RES-DIS1</sub>            | Discharge current source1                                                   | CBC not active                       | 3.2   | 5     | 5.5  | μA  |

| I <sub>RES-DIS2</sub>            | Discharge current source2                                                   | 2 V < V <sub>RES</sub> < 4 V         | 2.5   | 5     | 7.5  | μA  |

| HICCUP MODE                      | E BLANKING                                                                  |                                      | 1     |       |      |     |

| V <sub>HC_BLK_TH</sub>           | SSSR threshold to disable the hiccup blanking                               |                                      | 5.26  | 5.5   | 5.66 | V   |

| VOLTAGE FEE                      | ED-FORWARD (RAMP PIN)                                                       |                                      |       |       | 1    |     |

|                                  | RAMP sink impednace (clocked)                                               |                                      | 3.9   | 6.0   | 9.1  | Ω   |

| OSCILLATOR                       | (RT PIN)                                                                    |                                      |       |       | I    |     |

| f <sub>SW1</sub>                 | Frequency (half oscillator frequency)                                       | R <sub>T</sub> = 25 kΩ               | 185   | 200   | 215  | kHz |

| f <sub>SW2</sub>                 | Frequency (half oscillator frequency)                                       | R <sub>T</sub> = 10 kΩ               | 420   | 480   | 540  | kHz |

| V <sub>RTReg</sub>               | DC level                                                                    |                                      | 1.85  | 2     | 2.06 | V   |

| · KIKEG                          |                                                                             |                                      |       |       | I    |     |

MIN and MAX limits apply the junction temperature range of  $-40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$ . Unless otherwise specified, the following conditions apply:  $V_{\text{IN}} = 48 \text{ V}$ ,  $R_{\text{T}} = 25 \text{ k}\Omega$ ,  $RD_{1} = RD_{2} = 20 \text{ k}\Omega$ ,  $R_{\text{ON}} = 100 \text{ k}\Omega$ . No load on LSG, HSG, SR1, SR2, UVLO = 2.5 V, ON\_OFF = 0 V.

|                          | PARAMETER                                                    | TEST CONDITIONS                                                                                                                                       | MIN   | TYP      | MAX   | UNIT |

|--------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|-------|------|

| t <sub>1</sub>           | SR trailing edge delay SR turn-off to primary switch turn-on | RD <sub>1</sub> = 20 kΩ                                                                                                                               | 94    | 123      | 157   | ns   |

|                          |                                                              | RD <sub>1</sub> = 100 kΩ                                                                                                                              | 213   | 278      | 350   | ns   |

| t <sub>2</sub>           | SR leading edge delay primary switch turn-off to SR turn-on  | $RD_2$ = 20 kΩ                                                                                                                                        | 60    | 79       | 102   | ns   |

|                          |                                                              | RD <sub>2</sub> = 100 kΩ                                                                                                                              | 188   | 250      | 315   | ns   |

| t <sub>clk</sub>         | Pulse width of the clock                                     |                                                                                                                                                       | 47    | 65       | 87    | ns   |

| COMP PIN                 | ,                                                            |                                                                                                                                                       | ,     |          |       |      |

| I <sub>PWM-OS</sub>      | COMP current to RAMP offset                                  | RAMP = 0 V                                                                                                                                            | 596   | 800      | 1063  | μΑ   |

| V <sub>SS-OS</sub>       | SS to RAMP offset                                            | RAMP = 0 V                                                                                                                                            | 0.86  | 1        | 1.15  | V    |

|                          | COMP current to RAMP gain                                    | delta RAMP/delta I <sub>COMP</sub>                                                                                                                    | 1895  | 2400     | 2936  | Ω    |

|                          | SS to RAMP gain                                              | delta SS/delta RAMP                                                                                                                                   | 0.574 | 0.646    | 0.74  |      |

| I <sub>COSsrEn</sub>     | COMP current for SSSR charge curent enable                   | SS > 2 V                                                                                                                                              | 600   | 750      | 900   | μΑ   |

|                          | COMP to gate driver output delay                             |                                                                                                                                                       | 100   | 120      | 150   | ns   |

|                          | Minimum duty cycle                                           | I <sub>COMP</sub> = 1 mA                                                                                                                              |       |          | 0     | %    |

| BOOST (BST               | PIN)                                                         |                                                                                                                                                       | ,     |          |       |      |

| V <sub>BST(UV)</sub>     | BST under-voltage threshold                                  | V <sub>BST</sub> - V <sub>SW</sub> rising                                                                                                             | 3.2   | 4.137    | 5.6   | V    |

| ν- /                     | Hysteresis                                                   | -                                                                                                                                                     | 0.37  | 0.481    | 0.65  | V    |

| LSG, HSG G               | ATE DRIVERS                                                  |                                                                                                                                                       |       |          |       |      |

| V <sub>OL_PRI</sub>      | Low-state output voltage                                     | I <sub>HSG/LSG</sub> = 100 mA                                                                                                                         | 0.1   | 0.3      | 0.41  | V    |

| V <sub>OH_PRI</sub>      | High-state output voltage                                    | I <sub>HSG/LSG</sub> = 100 mA, V <sub>OHL_PRI</sub> = V <sub>CC</sub> - V <sub>LSG</sub> , V <sub>OHH_PRI</sub> = V <sub>BST</sub> - V <sub>HSG</sub> | 0     | 0.38     | 1     | V    |

|                          | Rise Time                                                    | C-load =1000 pF                                                                                                                                       | 2     | 8        | 12    | ns   |

|                          | Fall Time                                                    | C-load =1000 pF                                                                                                                                       | 2     | 10       | 14    | ns   |

| I <sub>SO PRI</sub>      | Peak Source Current                                          | V <sub>HSG/LSG</sub> = 0V                                                                                                                             | ,     | 1        |       | Α    |

| I <sub>SI PRI</sub>      | Peak Sink Current                                            | V <sub>HSG/LSG</sub> = VCC                                                                                                                            |       | 2        |       | A    |

|                          | ATE DRIVERS                                                  |                                                                                                                                                       |       | <u> </u> |       |      |

| V <sub>OL_SR</sub>       | Low-state output voltage                                     | I <sub>SR1/SR2</sub> = 10 mA                                                                                                                          |       |          | 0.12  | V    |

| V <sub>OH_SR</sub>       | High-state output voltage                                    | I <sub>SR1/SR2</sub> = 10 mA, V <sub>OH_SR</sub> = V <sub>REF</sub> - V <sub>SR</sub>                                                                 |       |          | 0.313 | V    |

| OH_OR                    | Rise Time                                                    | C-load = 1000 pF                                                                                                                                      | 25    | 45       | 65    | ns   |

|                          | Fall Time                                                    | C-load = 1000 pF                                                                                                                                      | 4     | 10       | 16    | ns   |

| I <sub>SO_SR</sub>       | Peak Source Current                                          | V <sub>SR</sub> = 0 V                                                                                                                                 | 0.05  | 0.09     | 0.14  | Α    |

| I <sub>SI_SR</sub>       | Peak Sink Current                                            | V <sub>SR</sub> = V <sub>REF</sub>                                                                                                                    | 0.1   | 0.2      | 0.4   | A    |

|                          | E THERMAL SHUTDOWN                                           | OIL INCI                                                                                                                                              |       |          | - "   |      |

| T <sub>SD</sub>          | Thermal Shutdown Temp                                        |                                                                                                                                                       |       | 150      |       | °C   |

| JD                       | Thermal Shutdown Hysteresis                                  |                                                                                                                                                       |       | 25       |       |      |

| AUX SUPPLY               | SWITCH CHARACTERISTICS                                       |                                                                                                                                                       |       |          |       |      |

| ·· <b>-</b> ·            | Buck Switch R <sub>DS(ON)</sub>                              | I <sub>TEST</sub> = 60 mA                                                                                                                             | 3.0   | 5.2      | 7.5   | Ω    |

|                          | Synchronous Switch R <sub>DS(ON)</sub>                       | I <sub>TEST</sub> = 60 mA                                                                                                                             | 1.2   | 2.8      | 4.5   | Ω    |

| ALIX SLIPPLY             | / UNDERVOLTAGE LOCKOUT                                       | .1E31 30 1181                                                                                                                                         | 1.2   | 2.0      | 7.0   | 32   |

| V <sub>BST_AUX(UV)</sub> | BST_AUX undervoltage threshold                               | V <sub>BST_AUX</sub> - V <sub>SW_AUX</sub> rising                                                                                                     | 3.5   | 5.0      | 6.5   | V    |

| V <sub>AUX_UVLO</sub>    | AUX supply UVLO input voltage rising threshold               |                                                                                                                                                       | 12.2  | 15       | 16.0  | V    |

|                          | AUX supply UVLO input voltage                                |                                                                                                                                                       |       |          |       |      |

MIN and MAX limits apply the junction temperature range of  $-40^{\circ}\text{C} \le T_{J} \le 125^{\circ}\text{C}$ . Unless otherwise specified, the following conditions apply:  $V_{IN}$  = 48 V,  $R_{T}$  = 25 k $\Omega$ ,  $RD_{1}$  =  $RD_{2}$  = 20 k $\Omega$ ,  $R_{ON}$  = 100 k $\Omega$ . No load on LSG, HSG, SR1, SR2, UVLO = 2.5 V, ON\_OFF = 0 V.

|                       | PARAMETER                                                                                             | TEST CONDITIONS | MIN  | TYP | MAX  | UNIT |

|-----------------------|-------------------------------------------------------------------------------------------------------|-----------------|------|-----|------|------|

| AUX SUPPL             | Y REGULATION                                                                                          |                 |      |     |      |      |

| V <sub>AUX-OFF</sub>  | OFF-State AUX Voltage<br>Regulation Level                                                             |                 | 1.26 | 1.4 | 1.53 | V    |

| V <sub>AUX-ON</sub>   | ON-State AUX Voltage<br>Regulation Level                                                              |                 | 0.95 | 1   | 1.04 | V    |

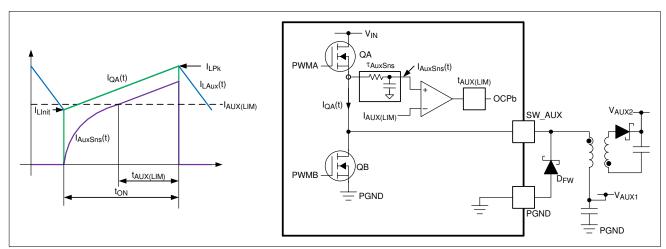

| AUX SUPPL             | Y CURRENT LIMIT                                                                                       |                 |      |     |      |      |

| I <sub>AUX(LIM)</sub> | AUX Supply Current Limit<br>Threshold                                                                 |                 | 150  | 200 | 250  | mA   |

| t <sub>CSBLKA</sub>   | Current limit comparator blanking period measured from start of t <sub>ON</sub> period <sup>(1)</sup> |                 |      | 50  |      | ns   |

| t <sub>AUX(LIM)</sub> | Delay from Comparator<br>Threshold to upper MOSFET<br>turn-OFF <sup>(1)</sup>                         |                 |      | 116 |      | ns   |

| T <sub>AuxSns</sub>   | Aux Current Limit Parasitic Filter time constant (1)                                                  |                 |      | 41  |      | ns   |

| AUX SUPPL             | Y THERMAL SHUTDOWN                                                                                    |                 |      |     |      |      |

| T <sub>SD_AUX</sub>   | AUX Supply Thermal Shutdown<br>Temp                                                                   |                 |      | 160 |      | °C   |

|                       | AUX Supply Thermal Shutdown<br>Hysteresis                                                             |                 |      | 28  |      | °C   |

<sup>(1)</sup> Specified by design. Not production tested.

# 6.6 Switching Characteristics

MIN and MAX limits apply the junction temperature range  $-40^{\circ}\text{C} \le T_{\text{J}} \le 125^{\circ}\text{C}$ . Unless otherwise specified, the following conditions apply:  $V_{\text{IN}} = 48 \text{ V}$ ,  $R_{\text{T}} = 25 \text{ k}\Omega$ ,  $RD_{1} = RD_{2} = 20 \text{ k}\Omega$ ,  $R_{\text{ON}} = 100 \text{ k}\Omega$ . No load on LSG, HSG, SR1, SR2, UVLO = 2.5 V, ON\_OFF = 0 V.

|                       | PARAMETER                       | TEST CONDITIONS                                       | MIN | TYP | MAX | UNIT |

|-----------------------|---------------------------------|-------------------------------------------------------|-----|-----|-----|------|

| t <sub>ON</sub>       | AUX SUPPLY ON-TIME              | $V_{IN} = 32 \text{ V}, R_{ON} = 100 \text{ k}\Omega$ | 240 | 330 | 440 | ns   |

| t <sub>ON</sub>       | AUX SUPPLY ON-TIME(1)           | $V_{IN}$ =54 V, $R_{ON}$ = 250 k $\Omega$             |     | 493 |     | ns   |

| t <sub>ON</sub>       | AUX SUPPLY ON-TIME(1)           | $V_{IN}$ =75V, $R_{ON}$ = 250 k $\Omega$              |     | 370 |     | ns   |

| t <sub>OFF(MIN)</sub> | AUX SUPPLY MINIMUM OFF-<br>TIME | FB_AUX = 0 V                                          | 69  | 103 | 136 | ns   |

<sup>(1)</sup> Specified by design. Not production tested.

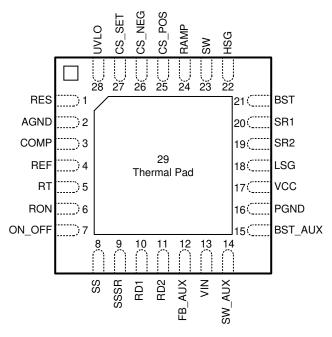

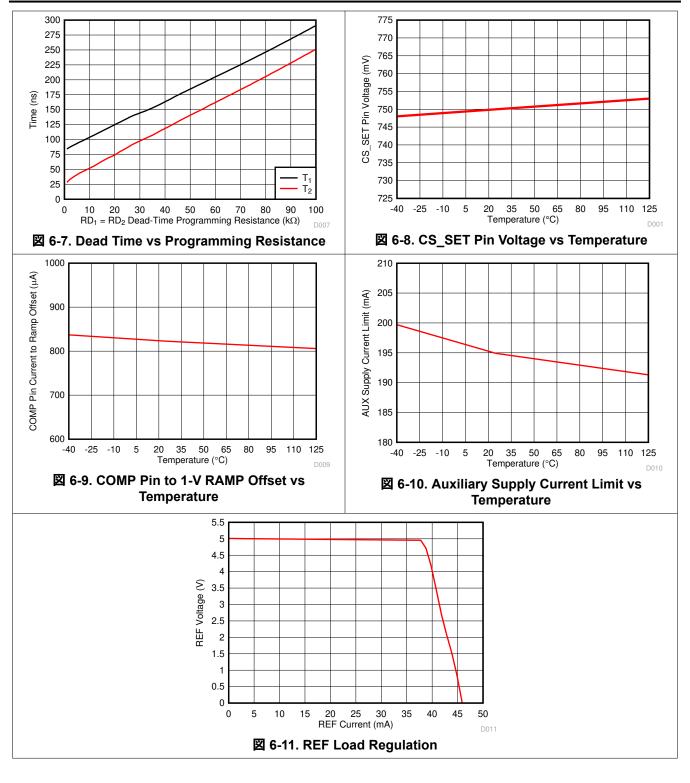

## **6.7 Typical Characteristics**

# 7 Detailed Description

### 7.1 Overview

The LM5036 device is a highly-integrated, half-bridge PWM controller with integrated auxiliary bias supply. It provides a high power-density solution for telecom, datacom and industrial power converters. The device has all of the features necessary to implement a power converter that uses half-bridge topology. The device employs voltage-mode control and includes input voltage feed-forward to improve performance. This device operates on the primary side of an isolated DC-DC power converter with input voltage up to 100-V.

The soft-start function provides a fully regulated and monotonic rise of output voltage, even when the converter energizes into a pre-biased load. The device uses an enhanced cycle-by-cycle (CBC) current limit. This function matches the pulse to maintain the voltage balance of the half-bridge capacitor divider. This method ensures flux balance of the transformer during CBC operation. The input voltage compensation function helps to minimize the variation of the current limit level across the entire input voltage range.

The LM5036 device has these other features:

- configurable latch protection

- configurable overvoltage protection (OVP)

- · optimized maximum duty cycle operation for the primary MOSFETs

- integrated half-bridge MOSFET gate drivers

- programmable dead-time between the primary MOSFETs and synchronous rectifiers

- auxiliary supply synchronous and asynchronous mode transition

- 5-V synchronous rectifier PWM outputs

- programmable line undervoltage lockout (UVLO)

- hiccup mode overcurrent protection (OCP)

- · reverse current protection

- a 2-MHz capable oscillator with synchronization capability

- two-level thermal shutdown protection

An Excel Calculator Tool is provided to ease the process of creating custom designs using this controller. This tool calculates values for all the external components required by the controller to meet a given specification. It also generates many key parameters of the power stage including, for example, the turns ratio of the half-bridge transformer. The tool generates graphs predicting, for a given set of current limit components, how the output current limit will vary with input voltage. Maximum flexibility is offered by calculating suggested values for most components, but allowing the user to input values of their own choice.

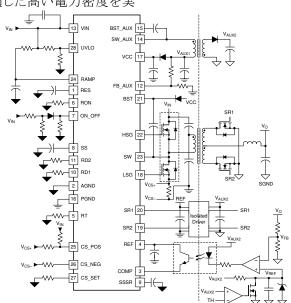

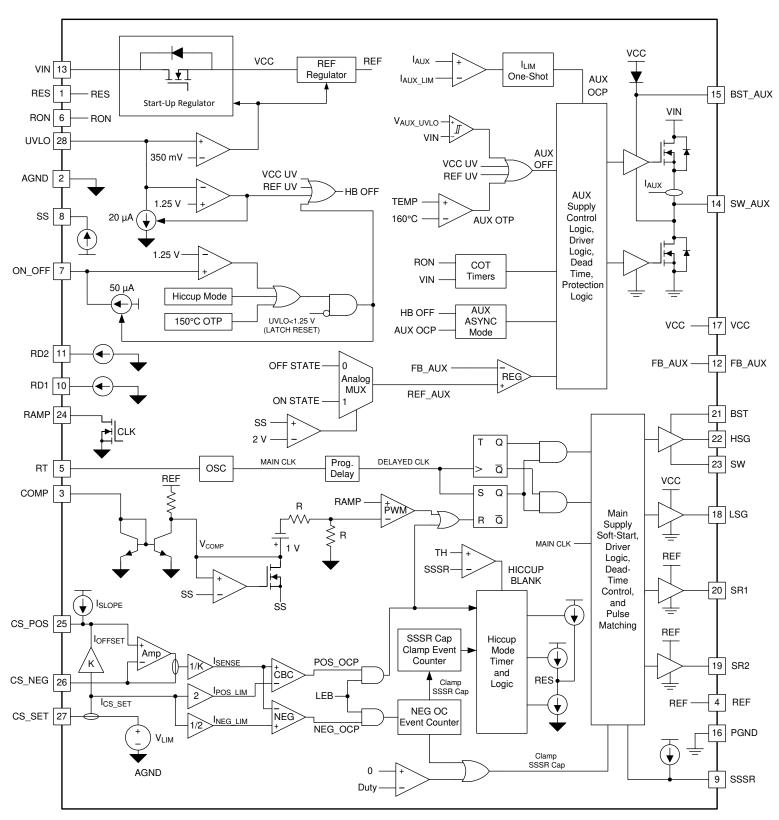

## 7.2 Functional Block Diagram

Copyright © 2018, Texas Instruments Incorporated

#### 7.3 Feature Description

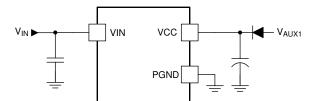

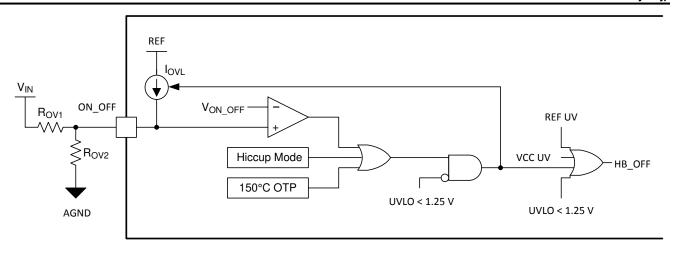

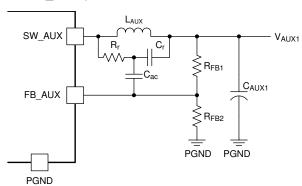

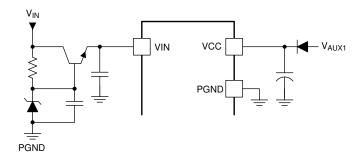

### 7.3.1 High-Voltage Start-Up Regulator

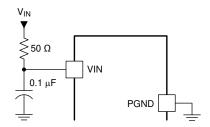

LM5036 can power itself using its internal high-voltage start-up linear regulator, but internal power dissipation can be reduced by powering VCC from an auxiliary switched mode supply. LM5036 device integrates all of the functions needed to implement a low-cost and easy-to-design isolated fly-buck auxiliary supply based on the constant-on-time (COT) control scheme. The primary output  $V_{AUX1}$  of the auxiliary supply must be connected through a diode to the VCC pin, as shown in  $\boxed{2}$  7-1. The auxiliary supply must raise the VCC voltage above the internally generated  $V_{CC}$  voltage in order to shut off the internal start-up regulator. Powering VCC from an auxiliary switched mode supply improves efficiency while reducing the power dissipation of the controller IC. The VCC under-voltage (UV) circuit will still function in this mode, requiring that VCC never falls below its UV threshold during the start-up sequence. The VCC regulator series pass transistor includes a diode between VCC and VIN that should not be forward biased in normal operation. Therefore, the auxiliary VCC voltage should never exceed the  $V_{IN}$  voltage.

図 7-1. External VCC Bias Supply Connection

#### 7.3.2 Undervoltage Lockout (UVLO)

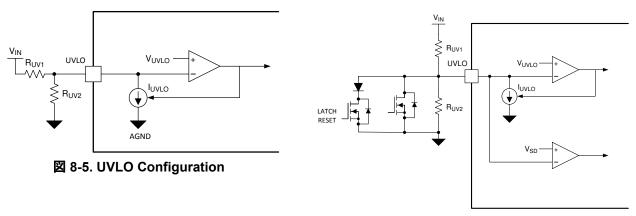

The LM5036 controller contains a three-level under-voltage lockout circuit. When the UVLO pin voltage is below  $V_{SD}$  (0.38-V typical), the controller is in a low current shutdown mode where the functional circuit blocks are not enabled including VCC startup regulator, auxiliary supply and the main half-bridge control logic and gate drive circuitry, etc.

When UVLO pin voltage is above V<sub>SD</sub>, the VCC and REF regulators become active.

When the VCC and REF outputs exceed their respective UV thresholds and the input voltage  $V_{IN}$  rises above  $V_{AUX\ UVLO}$  (15-V typical), the auxiliary supply is enabled.

When UVLO pin voltage rises above  $V_{UVLO}$  (1.25-V typical) and VCC and REF voltage are above their respective UV thresholds, the control logic of the main half-bridge converter is enabled. The soft-start capacitor is released and normal operation begins. An external set-point voltage divider from  $V_{IN}$  to GND can be used to set the minimum operating voltage of the half-bridge converter. The divider must be designed such that the voltage at the UVLO pin is greater than  $V_{UVLO}$  when  $V_{IN}$  enters the desired operating range. UVLO hysteresis is accomplished with an internal current sink  $I_{UVLO}$  (20- $\mu$ A typical) that is switched on or off into the impedance of the external set-point divider. When the UVLO pin voltage threshold of  $V_{UVLO}$  is exceeded, the current sink is deactivated to quickly raise the voltage at the UVLO pin. When the UVLO pin voltage falls below the  $V_{UVLO}$  threshold, the current sink is enabled causing the voltage at the UVLO pin to quickly fall. See  $\frac{1}{2}$  7-1 for more detail on functional modes of LM5036.

#### 7.3.3 Reference Regulator

The REF pin is the output of a 5-V linear regulator that can be used to bias an opto-coupler transistor, primary side of an isolated gate driver or digital isolator, among other housekeeping circuits. The regulator output is internally current limited to  $I_{REF(LIM)}$  (39-mA typical). The REF pin must be locally decoupled with a ceramic capacitor, the recommended range of values is from  $0.1-\mu F$  to  $10-\mu F$ .

#### 7.3.4 Oscillator, Synchronized Input

The oscillator frequency of LM5036 device is set by a resistor connected between the RT pin and AGND. The  $R_T$  resistor should be located close to the device. To set a desired oscillator frequency ( $f_{OSC}$ ), the value of  $R_T$  resistor can be calculated from  $\not\equiv$  1.

$$R_{\rm T} = \frac{1}{f_{\rm OSC} \times 1 \times 10^{-10}} \tag{1}$$

For example, if the desired oscillator frequency is 400-kHz, that is, each phase (LSG and HSG) switches at 200-kHz, the value of  $R_T$  is calculated to be 25-k $\Omega$ . If the LM5036 device is to be synchronized to an external clock, that signal must be coupled into the RT pin through a 100-pF capacitor. The RT pin voltage is nominally regulated at  $V_{RTReg}$  (2-V typical) and the external pulse amplitude should lift the pin to between 3.5-V and 5.0-V on the low-to-high transition. The synchronization pulse width should be between 15-ns and 200-ns. The  $R_T$  resistor is always required, whether the oscillator is free running or externally synchronized and SYNC frequency must be equal to or greater than the frequency set by the  $R_T$  resistor.

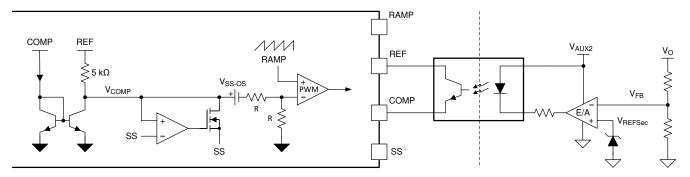

### 7.3.5 Voltage-Mode Control

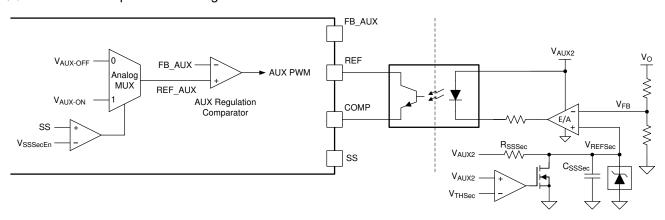

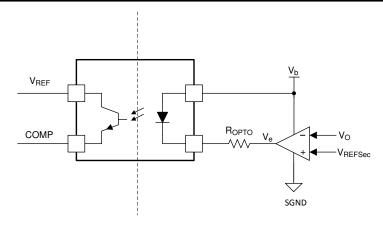

The LM5036 device employs voltage-mode control with input voltage feed-forward for the main half-bridge converter. A simplified block diagram of the voltage-mode feedback control loop is shown in  $\boxtimes$  7-2.

#### 図 7-2. Voltage-Mode Feedback Control Loop for Half-Bridge Converter

The output voltage  $(V_O)$  is sensed and compared against a reference voltage  $(V_{REFSec})$  on the secondary side which produces an error voltage which is then processed by the error amplifier. The compensated error signal is transmitted across the isolation boundary through an opto-coupler and then gets injected into the COMP pin in the form of a control current. The COMP pin current is internally mirrored by a matching pair of NPN transistors which sink current through a 5-k $\Omega$  resistor connected to the 5-V internal reference. The resulting control voltage  $V_{COMP}$  is compared with the soft-start capacitor voltage (SS) and the smaller of the two passes through an offset  $V_{SS-OS}$  (1-V typical), followed by a 2:1 resistor divider before being applied to the PWM comparator to determine the duty cycle of the half-bridge converter. The PWM comparator polarity is configured such that with no current flowing into the COMP pin, the controller produces maximum duty cycle for the primary FETs.

An opto-coupler detector can be connected between the REF pin and the COMP pin. Because the COMP pin is controlled by a current input, the voltage across the opto-coupler detector is nearly constant. The bandwidth limiting phase delay which is normally introduced by the significant capacitance of the opto-coupler is thereby greatly reduced. Higher loop bandwidths can be realized because the bandwidth limiting pole associated with the opto-coupler is now at a much higher frequency.

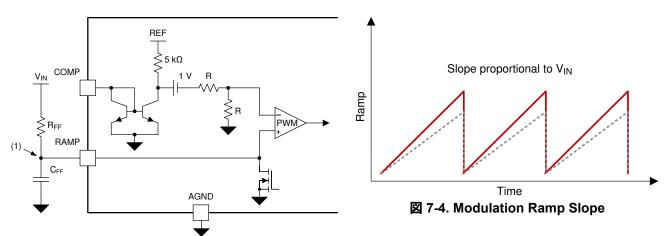

The voltage at the RAMP pin provides the modulation ramp for the PWM comparator. The PWM comparator compares the modulation ramp signal at the RAMP pin to the COMP voltage to control the duty cycle. The modulation ramp signal can be implemented as a ramp proportional to the input voltage, known as feed-forward voltage mode control, as shown in  $\boxtimes$  7-3. The RAMP pin is reset by an internal MOSFET when RAMP voltage passes COMP voltage, current limit event, or at the conclusion of each PWM cycle, whichever comes earlier.

A. Slope proportional to input voltage (see 図 7-4)

図 7-3. Feed-Forward Voltage-Mode Control Configuration

An external resistor ( $R_{FF}$ ) and capacitor ( $C_{FF}$ ) connected to VIN, AGND, and the RAMP pins are required to create a saw-tooth modulation ramp signal. The slope of the signal at RAMP will vary in proportion to the input voltage. The varying slope provides line feed-forward information necessary to improve line transient response with voltage-mode control. With a constant control signal, the on-time ( $t_{ON}$ ) varies inversely with the input voltage ( $V_{IN}$ ) to stabilize the volt-second product of the transformer. Using a line feed-forward ramp for PWM control requires very little change in the voltage regulation loop to compensate for changes in input voltage, as compared to a ramp with fixed slope. In addition, voltage-mode control is less susceptible to noise. Therefore, it is a good choice for wide input range power converter applications. However, voltage-mode control requires a Type-III compensation network due to the complex-conjugate poles of the L-C output filter.

Assistance with half-bridge voltage control loop design may be obtained using the Power Stage Designer™ tool.

The recommended capacitor value range for  $C_{FF}$  is from 100-pF to 1800-pF.  $\boxtimes$  7-3, shows that the  $C_{FF}$  value must be small enough to be discharged within the clock pulse-width ( $t_{CLK}$ ). The value of  $R_{FF}$  required can be calculated from  $\stackrel{\scriptstyle *}{\precsim}$  2

$$R_{FF} = \frac{-1}{f_{OSC} \times C_{FF} \times \ln\left(1 - \frac{V_{RAMP}}{V_{IN(min)}}\right)}$$

(2)

For example, assuming a  $V_{RAMP}$  voltage of 1.5-V (a good compromise of signal range and noise immunity),  $V_{IN(min)}$  of 36-V, oscillator frequency of 400-kHz and  $C_{FF}$  = 560-pF results in  $R_{FF}$  = 105-k $\Omega$ .

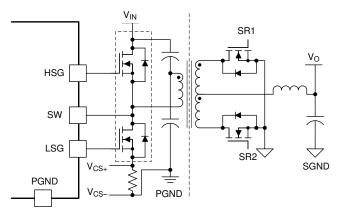

#### 7.3.6 Primary-Side Gate Driver Outputs (LSG and HSG)

The LM5036 device provides two gate driver outputs for the primary FETs of the main half-bridge converter: one floating high-side gate driver output HSG and one ground referenced low-side gate driver output LSG. Each internal gate driver is capable of sourcing 1-A peak and sinking 2-A peak (typical). Initially, the LSG output is turned on during the power transfer phase, followed by a freewheeling period during which both LSG and HSG outputs are turned off. In the subsequent power transfer phase, the HSG output is turned on followed by another freewheeling period.

Copyright © 2021 Texas Instruments Incorporated

The low-side LSG gate driver is powered directly by the VCC bias supply. The HSG gate driver is powered from a bootstrap capacitor connected between BST and SW. An external diode connected between VCC and BST provides the high-side gate driver power by charging the bootstrap capacitor from VCC when the switching node SW is low. When the high side FET is turned on, BST rises to a peak voltage equal to VCC +  $V_{IN}$ .

The BST and VCC capacitors should be placed close to the pins of the LM5036 device to minimize voltage transients due to parasitic inductance because the peak current source to the MOSFET gates can exceed 1 A (typical). The recommended value of the BST capacitor is 0.1-µF or greater. A low ESR/ESL capacitor, such as a surface mount ceramic, should be used to prevent voltage drop during the HSG transitions.

#### 7.3.7 Half-Bridge PWM Scheme

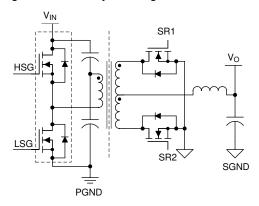

Synchronous rectification on the secondary side of the transformer provides higher efficiency, especially for low output voltage and high output current converter, compared to the diode rectification. The reduction of the diode forward voltage drop (0.5-V to 1.5-V) to 10-mV to 200-mV  $V_{DS}$  voltage for a MOSFET significantly reduces rectification losses. In a typical application, the secondary windings of the transformer can be center tapped, with the output power inductor in series with the center tap, as shown in  $\boxtimes$  7-5. The synchronous rectifiers (SRs) provide the ground path for the energized secondary winding and the inductor current.

図 7-5. Half-bridge Topology with Center-Tap Rectification

The internal SR drivers are powered by the REF regulator and each SR output is capable of sourcing 0.1-A and sinking 0.2-A peak (typical). The amplitude of the SR drivers is limited to 5-V. The 5-V SR signals enable the transfer of SR control signals across the isolation barrier either through a digital isolator or isolated gate driver. It should be noted that the actual gate sourcing and sinking currents for the SRs are provided by the secondary-side gate drivers.

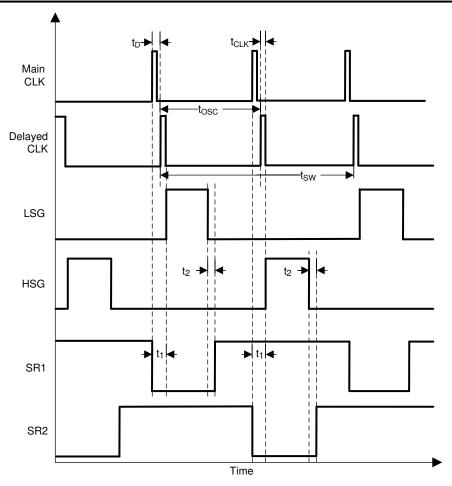

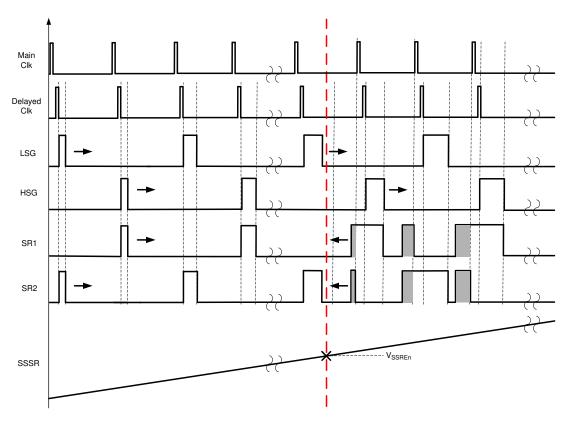

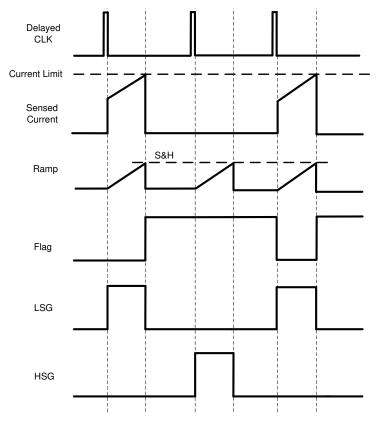

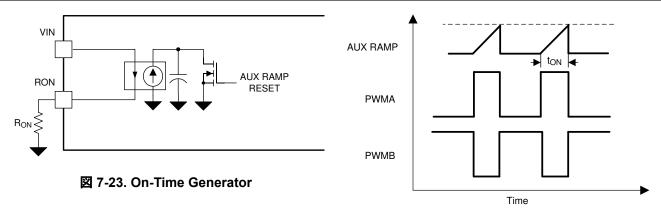

The timing diagram of the four PMW signals (LSG, HSG, SR1, and SR2) with dead-times is illustrated in  $\boxtimes$  7-6. The main clock is generated by the internal oscillator. A delayed clock is derived by adding a delay of  $t_D$  to the main clock.  $t_D$  can be calculated from  $\not\equiv$  3, where RD<sub>1</sub> is the value of the resistor connected between RD1 pin and AGND.

$$t_D = RD_1 \times 2 pF + 20 \text{ ns} \tag{3}$$

図 7-6. PWM Signal Timing Diagram

As illustrated in  $\boxtimes$  7-6, the rising edge of the main clock is used to turn off the SRs. Primary FET drive signal LSG/HSG is turned on at the falling edge of the delayed clock. Therefore, the dead-time between the falling edge of SR and the rising edge of the respective primary FET can be calculated from  $\pm$  4

$$t_1 = t_D + t_{CLK} \tag{4}$$

where

t<sub>CLK</sub> is the pulse width of the clock which is 65 ns (typical).

The minimum achievable  $t_1$  is dominated by the pulse width of the clock when  $t_D$  is set to minimum (30 ns).

After SR1 is turned off, the body diode of SR1 continues to carry about half the inductor current until the primary power raises the drain voltage of the SR1 and reverse biases its body diode. Ideally, dead-time  $t_1$  would be set to the minimum time that allows the SR to turn off before the body diode starts conducting.

Power is transferred from the primary to the secondary side when the LSG is turned on. During this power transfer period, the SR2 is still turned on while the SR1 is turned off. The drain voltage of SR1 is twice the voltage of the center tap at this time. Under the normal operation, the LSG is turned off either when the RAMP signal exceeds the COMP signal or at the rising edge of the next delayed clock signal (maximum duty cycle condition), whichever comes earlier. A dead-time  $t_2$  is inserted between the falling edge of LSG and rising edge of SR1.  $t_2$  can be calculated from  $\not\equiv$  5, where RD<sub>2</sub> is the value of the resistor connected between RD2 pin and AGND.

$$t_2 = RD_2 \times 2 \text{ pF} + 30 \text{ ns} \tag{5}$$

During the dead-time  $t_2$ , the inductor current continues to flow through the body diode of SR1. Because the body diode causes more conduction loss than the SR, efficiency can be improved by minimizing the  $t_2$  period while maintaining sufficient margin across the entire operating conditions (component tolerances, input voltages, etc.) to prevent the cross conduction between the primary FET and SR.

During the freewheeling period where both of the primary FETs are turned off while both of the SRs are turned on, the inductor current is almost equally shared between SR1 and SR2 which effectively shorts the secondary winding of the transformer. SR2 is then turned off before HSG is turned on. The power is transferred from the primary to secondary side again when HSG is turned on. After HSG is disabled and the dead-time t<sub>2</sub> expires, SR1 and SR2 both conduct again during the freewheeling period.

Resistor values of no less than 5-kΩ should be connected between the RD1/RD2 pins and AGND

#### 7.3.8 Maximum Duty Cycle Operation

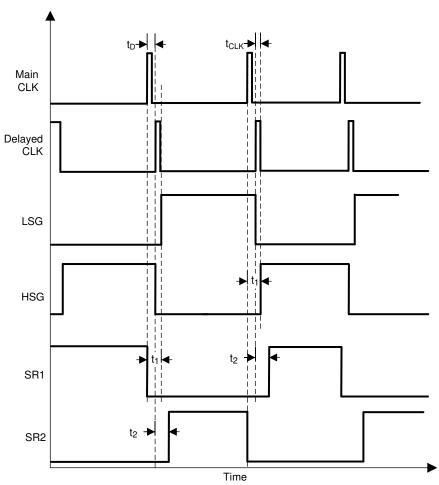

The LSG and HSG will operate at maximum duty cycle when they are turned off at the rising edge of the delayed clock, instead of by the event where RAMP voltage passes COMP voltage, as shown in  $\boxtimes$  7-7. In LM5036 device, it is intended to achieve optimized maximum duty cycle for the primary FETs in order to accommodate wider range of operation.

図 7-7. PWM Signals at Maximum Duty Cycle Condition

Use 式 6 to calculate the maximum duty cycle for the primary FETs

$$D_{MAX} = \frac{\frac{1}{f_{OSC}} - t_{CLK}}{\frac{2}{f_{OSC}}}$$

(6)

where

f<sub>OSC</sub> is the oscillator frequency which is twice the switching frequency

The pulse width of the clock is used in this case to prevent cross-conduction between the two primary FETs during the maximum duty cycle operation.

### 7.3.9 Pre-Biased Start-Up Process

The soft-start functionality limits the inrush current and voltage stress of the power converter. A common requirement for the power converters used in the telecom/datacom applications is to have a monotonic output voltage start-up into pre-biased load conditions where the output capacitor is pre-charged prior to start-up. In a pre-biased load condition, if the synchronous rectifiers are engaged prematurely they will sink current from the pre-charged output capacitors resulting in undesired output voltage dip or even power converter damage. The LM5036 device implements unique circuitry to ensure intelligent turn-on of the synchronous rectifiers such that the output voltage has monotonic start-up.

The start-up process can be divided into two phases:

- · soft-start of the primary FETs

- · soft-start of the SRs

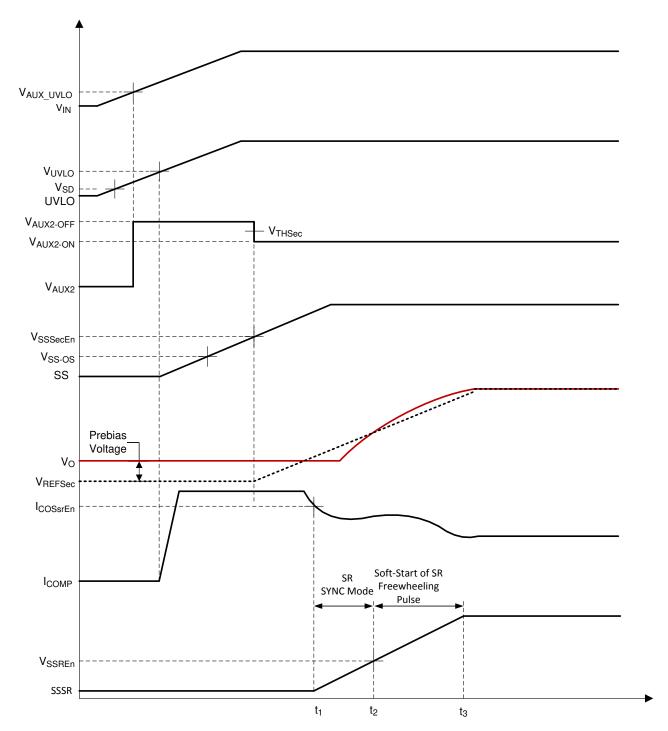

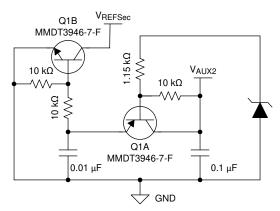

The pre-biased start-up process is handled automatically by LM5036. The user need only select values for  $C_{SS}$ ,  $C_{SSSR}$ , and the ramp rate of the secondary reference ( $V_{REFSec}$ ) soft-start  $\boxtimes$  7-8. The circuit of  $\boxtimes$  7-8 uses a comparator to, detect the voltage change of  $V_{AUX2}$  and, release the FET shorting across the secondary soft-start capacitor ( $C_{SSSec}$ ). This comparator circuit may also be replaced by the transistor based circuit of  $\boxtimes$  8-3.

#### 7.3.9.1 Primary FETs Soft-Start Process

図 7-8. Soft-Start Function

The auxiliary supply has two reference output voltage levels of  $V_{AUX-OFF}$  (1.4 -V typical, off state) and  $V_{AUX-ON}$  (1-V typical, on state) which facilitates easy voltage level shift detection on the secondary side. The auxiliary supply starts to operate as soon as  $V_{IN} > V_{AUX\_UVLO}$  (15-V typical) and VCC and REF are above the respective UV thresholds. When the soft-start capacitor is below  $V_{SSSecEn}$  (2.06-V typical), the auxiliary supply will produce the off-state voltage on the primary ( $V_{AUX1-OFF}$ ) and secondary side ( $V_{AUX2-OFF}$ ), as shown in  $\boxtimes$  7-9.

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

The off-state auxiliary output voltage level present on the secondary side  $V_{AUX2\text{-}OFF}$  is above the threshold  $V_{THSec}$ , which activates a reset circuit that discharges the output voltage reference  $V_{REFSec}$ . This ensures that the opto-coupler is producing a 0% duty-cycle command. When UVLO exceeds  $V_{UVLO}$  (1.25-V typical) and VCC and REF are above the respective UV thresholds, the soft-start capacitor starts to charge. The auxiliary supply will produce the on-state voltage level when the soft-start capacitor reaches  $V_{SSSecEn}$ .

図 7-9. Pre-biased Start-Up Waveform

The secondary side reset circuit will now be disabled because  $V_{AUX2-ON} < V_{THSec}$ , and the output voltage reference is released. The reference capacitor soft-starts the output voltage under full regulation. By modulation

of the auxiliary output voltage, the communication between the primary and secondary side is established without the need of any additional opto-coupler.

Due to the introduced programmable soft-start delay (before SS capacitor reaches  $V_{\rm SSSecEn}$ ), the duty cycle is controlled by the feedback control loop at all times without being interfered by the SS capacitor voltage (because  $V_{\rm COMP} < V_{\rm SS}$ ). When the reference voltage exceeds the pre-bias voltage at the output, the  $I_{\rm COMP}$  starts to fall as the secondary side error amplifier demands increased power. As  $I_{\rm COMP}$  falls the internal  $V_{\rm COMP}$  voltage will rise and when it exceeds  $V_{\rm SS-OS}$ , which corresponds to zero duty cycle, the duty cycle of the primary FETs starts to increase. Once the  $I_{\rm COMP}$  current falls below  $I_{\rm COSsrEn}$  the device starts to charge SSSR capacitor with current  $I_{\rm SSSR}$  (20-µA typical).

図 7-10. PWM Timing During Startup Process

### 7.3.9.2 Synchronous Rectifier (SR) Soft-Start Process

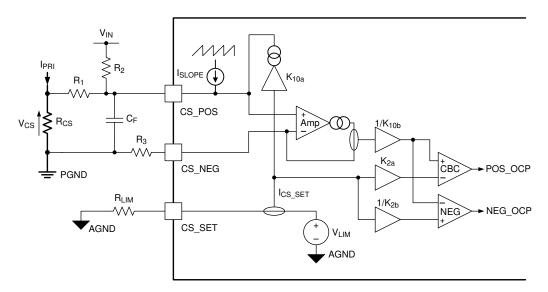

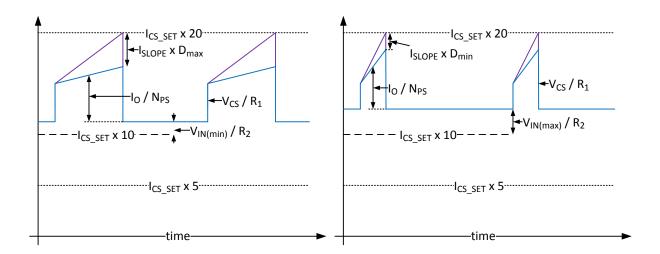

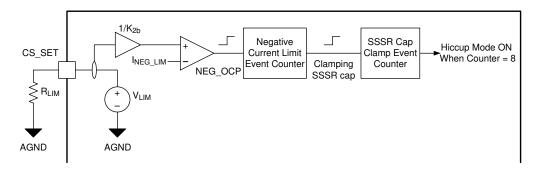

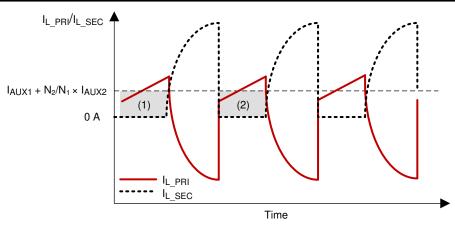

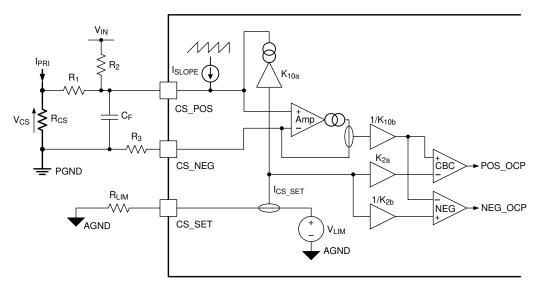

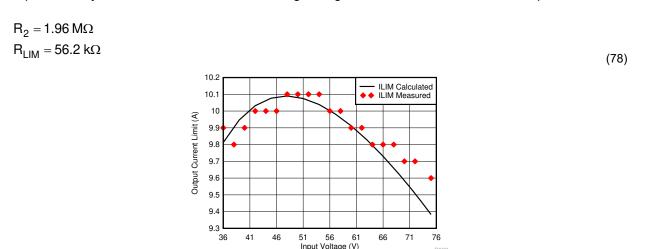

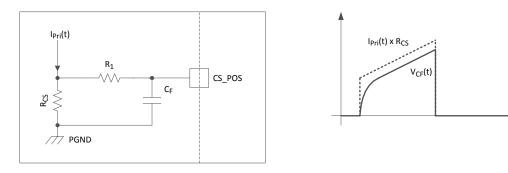

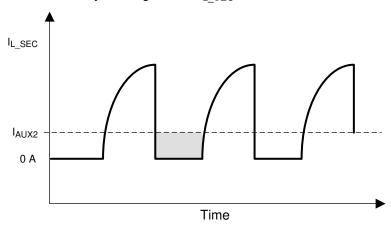

Until SSSR capacitor reaches  $V_{SSREn}$  (1-V typical), the controller operates at SR synchronization (SYNC) mode where the SR pulses are synchronized to the respective primary FET pulses, as shown in  $\boxtimes$  7-10. This helps to reduce the conduction loss of the SRs. In addition, due to the fact that the SRs only conduct during power transfer phase, there is no risk of reverse current in SYNC mode. Since the pulse width of SRs gradually increases, the output voltage disturbance due to the difference in the voltage drop between the body diode and the on resistance of the SRs is prevented.