LM3630A SNVS974B - APRIL 2013-REVISED OCTOBER 2015

# LM3630A High-Efficiency Dual-String White LED Driver

#### **Features**

- Drives up to 2 Strings of 10 Series LEDs

- Wide 2.3-V to 5.5-V Input Voltage Range

- Up to 87% Efficient

- 8-bit I<sup>2</sup>C-Compatible Programmable Exponential or Linear Brightness Control

- PWM Brightness Control for CABC Operation

- Independent Current Control per String

- True Shutdown Isolation for LEDs

- Internal Soft-Start Limits Inrush Current

- Adaptive Headroom

- Programmable 16-V/24-V/32-V/40-V Overvoltage Protection

- Selectable Boost Frequency of 500 kHz or 1 MHz with Optionally Additional Offset

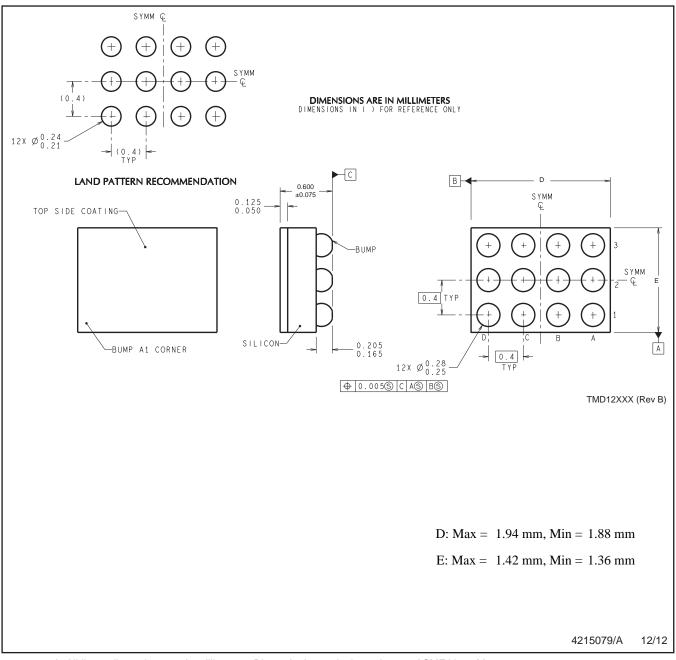

- Low Profile 12-Pin DSBGA Package

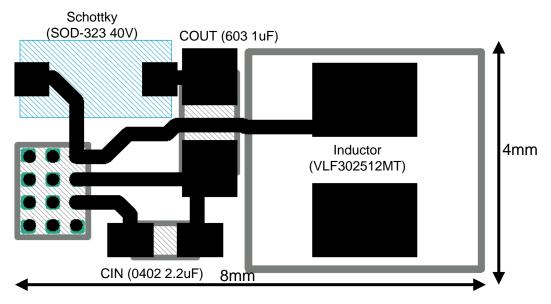

- Solution Size 32 mm<sup>2</sup>

# **Applications**

- Smart-Phone LCD Backlighting

- LCD and Keypad Lighting

# 3 Description

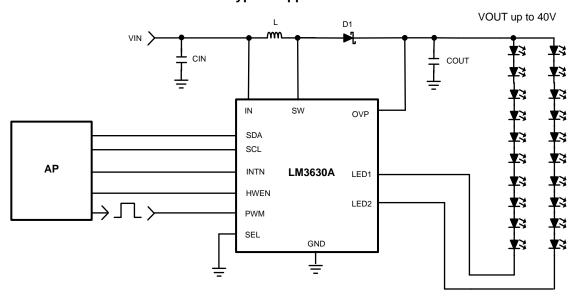

The LM3630A is a current-mode boost converter which supplies the power and controls the current in up to two strings of 10 LEDs per string. Programming is done over an I<sup>2</sup>C-compatible interface. The maximum LED current is adjustable from 5 mA to 28.5 mA. At any given maximum LED current the LED brightness is further adjusted with 256 exponential or linear dimming steps. Additionally, pulsed width modulation (PWM) brightness control can be enabled allowing for LED current adjustment by a logic level PWM signal.

The boost switching frequency is programmable at 500 kHz for low switching loss performance or 1 MHz to allow the use of tiny low-profile inductors. A setting for a 10% offset of these frequencies is available. Overvoltage protection is programmable at 16 V, 24 V, 32 V, or 40 V to accommodate a wide variety of configurations and Schottky diode/output capacitor combinations.

The device operates over a 2.3-V to 5.5-V operating voltage range and -40°C to +85°C ambient temperature range. The LM3630A is available in an ultra-small 12-bump DSBGA package.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (MAX)   |

|-------------|------------|-------------------|

| LM3630A     | DSBGA (12) | 1.94 mm x 1.42 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

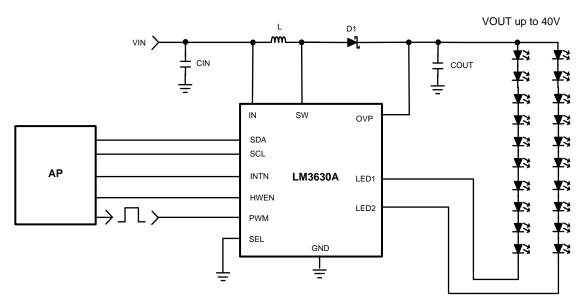

#### **Typical Application**

#### **Table of Contents**

| 1 | Features 1                                                         |    | 7.5 Programming                                  | 30         |

|---|--------------------------------------------------------------------|----|--------------------------------------------------|------------|

| 2 | Applications 1                                                     |    | 7.6 Register Maps                                | 31         |

| 3 | Description 1                                                      | 8  | Application and Implementation                   | 37         |

| 4 | Revision History2                                                  |    | 8.1 Application Information                      | 37         |

| 5 | Pin Configuration and Functions 3                                  |    | 8.2 Typical Application                          | 37         |

| 6 | Specifications4                                                    |    | 8.3 Initialization Setup                         | 40         |

| • | 6.1 Absolute Maximum Ratings                                       | 9  | Power Supply Recommendations                     | 40         |

|   | 6.2 ESD Ratings                                                    | 10 | Layout                                           | 41         |

|   | 6.3 Recommended Operating Conditions                               |    | 10.1 Layout Guidelines                           | <b>4</b> 1 |

|   | 6.4 Thermal Information                                            |    | 10.2 Layout Example                              | <b>4</b> 4 |

|   | 6.5 Electrical Characteristics                                     | 11 | Device and Documentation Support                 | 45         |

|   | 6.6 I <sup>2</sup> C-Compatible Timing Requirements (SCL, SDA) . 6 |    | 11.1 Device Support                              |            |

|   | 6.7 Typical Characteristics                                        |    | 11.2 Documentation Support                       | 45         |

| 7 | Detailed Description                                               |    | 11.3 Community Resources                         | 45         |

| • | 7.1 Overview                                                       |    | 11.4 Trademarks                                  |            |

|   | 7.2 Functional Block Diagram                                       |    | 11.5 Electrostatic Discharge Caution             | 45         |

|   | 7.3 Feature Description                                            |    | 11.6 Glossary                                    | 45         |

|   | 7.4 Device Functional Modes                                        | 12 | Mechanical, Packaging, and Orderable Information | 45         |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

# Changes from Revision A (January 2014) to Revision B

**Page**

Added Device Information and Pin Configuration and Functions sections, ESD Rating table, Feature Description,

Device Functional Modes, Application and Implementation, Power Supply Recommendations, Layout, Device and

Documentation Support, and Mechanical, Packaging, and Orderable Information sections

#### Changes from Original (April 2013) to Revision A

**Page**

Submit Documentation Feedback

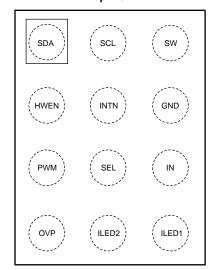

# 5 Pin Configuration and Functions

#### YFQ Package 12-Pin DSBGA Top View

#### YFQ Package 12-Pin DSBGA Bottom View

## **Pin Functions**

|     | PIN      | TVDE         | DESCRIPTION                                                                                                                                                                                                   |  |  |

|-----|----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | NO. NAME |              | DESCRIPTION                                                                                                                                                                                                   |  |  |

| A1  | SDA      | Input/Output | rial data connection for I <sup>2</sup> C-compatible interface                                                                                                                                                |  |  |

| A2  | SCL      | Input        | rial clock connection for I <sup>2</sup> C-compatible interface                                                                                                                                               |  |  |

| A3  | SW       | PWR          | Inductor connection, diode anode connection, and drain connection for internal NFET. Connect the inductor and diode as close as possible to SW to reduce inductance and capacitive coupling to nearby traces. |  |  |

| B1  | HWEN     | Input        | Logic high hardware enable                                                                                                                                                                                    |  |  |

| B2  | INTN     | Output       | Interrupt output for fault status change. Open drain active low signal.                                                                                                                                       |  |  |

| В3  | GND      | GND          | Ground                                                                                                                                                                                                        |  |  |

| C1  | PWM      | Input        | External PWM brightness control input                                                                                                                                                                         |  |  |

| C2  | SEL      | Input        | Selects I <sup>2</sup> C-compatible address. Ground selects 7-bit address 36h. V <sub>IN</sub> selects address 38h.                                                                                           |  |  |

| C3  | IN       | Input        | Input voltage connection. Connect a 2.3-V to 5.5-V supply to IN and bypass to GND with a 2.2-µF or greater ceramic capacitor.                                                                                 |  |  |

| D1  | OVP      | Input        | Output voltage sense connection for overvoltage sensing. Connect OVP to the positive terminal of the output capacitor.                                                                                        |  |  |

| D2  | ILED2    | Input        | Input terminal to internal current sink 2.                                                                                                                                                                    |  |  |

| D3  | ILED1    | Input        | Input terminal to internal current sink 1.                                                                                                                                                                    |  |  |

# 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                                           |                                                                        | MIN       | MAX       | UNIT |

|-------------------------------------------|------------------------------------------------------------------------|-----------|-----------|------|

| IN, HWEN, PWM, SCL, SDA, INTN, SEL to GND |                                                                        | -0.3      | 6         | V    |

| SW, OVP, ILED1, ILED2 to GN               | ID                                                                     | -0.3      | 45        | V    |

|                                           | Continuous power dissipation <sup>(3)</sup>                            | Internall | y limited |      |

|                                           | Maximum junction temperature                                           |           | 150       |      |

| T <sub>(J-MAX</sub> )                     | Maximum lead temperature (soldering) (4) Vapor phase (60 sec.)         |           | 215       | °C   |

|                                           | Maximum lead temperature (soldering) <sup>(4)</sup> Infrared (15 sec.) |           | 220       | °C   |

| Storage temperature, T <sub>stg</sub>     | Storage temperature, T <sub>stg</sub>                                  |           | 150       | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to the potential at the GND pin.

#### 6.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

| \/                 | Floatroatatia diaaharaa | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 | \/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|          |                               | MIN | NOM MAX | UNIT |

|----------|-------------------------------|-----|---------|------|

| $V_{IN}$ | Input voltage                 | 2.3 | 5.5     | V    |

| $T_A$    | Operating ambient temperature | -40 | 85      | °C   |

#### 6.4 Thermal Information

|                 |                                        | LM3630A     |      |

|-----------------|----------------------------------------|-------------|------|

|                 | THERMAL METRIC <sup>(1)</sup>          | YFQ (DBSGA) | UNIT |

|                 |                                        | 12 PINS     |      |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance | 78.1        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(3)</sup> Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at T<sub>J</sub> = 140°C (typical) and disengages at T<sub>J</sub> = 125°C (typical).

<sup>(4)</sup> For detailed soldering specifications and information, refer to Texas Instruments Application Note 1112: DSBGA Wafer Level Chip Scale Package (SNVA009).

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.5 Electrical Characteristics

Typical limits are for  $T_A = 25^{\circ}C$ ; minimum and maximum limits apply over the full operating ambient temperature range  $(-40^{\circ}C \le T_A \le 85^{\circ}C)$ ;  $V_{IN} = 3.6$  V, unless otherwise specified.<sup>(1)</sup>

|                      | PARAMETER                                    | TEST CONDITION                                                                                                                                                          | N                                                                   | MIN                | TYP         | MAX  | UNIT   |     |

|----------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------|-------------|------|--------|-----|

| ILED1,<br>ILED2      | Output current regulation                    | 2.5 V ≤ V <sub>IN</sub> ≤ 5.5 V, full-scale curren                                                                                                                      | it = 20 mA                                                          | 19                 | 20          | 21   | mA     |     |

|                      | ILED1 to ILED2 current                       | $2.5 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}, \text{ I}_{\text{LED}} = 10 \text{ mA}, \\ \text{T}_{\text{A}} = 25^{\circ}\text{C}$                         | ILED1 on A                                                          | -1%                | -1% 0.5% 1% |      |        |     |

| <b>І</b> матсн       | matching <sup>(2)</sup>                      | $2.5 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}, \text{ I}_{\text{LED}} = 10 \text{ mA}, \\ 0^{\circ}\text{C} \le \text{T}_{\text{A}} \le 70^{\circ}\text{C}$ | ILED2 on B                                                          | -2.5%              | 0.5%        | 2.5% |        |     |

| V <sub>REG_CS</sub>  | Regulated current sink headroom voltage      | I <sub>LED</sub> = 5 mA                                                                                                                                                 |                                                                     |                    | 250         |      | mV     |     |

| $V_{HR}$             | Current sink minimum headroom voltage        | $I_{LED} = 95\%$ of nominal, $I_{LED} = 20 \text{ m/s}$                                                                                                                 | A                                                                   |                    | 160         | 240  | IIIV   |     |

| R <sub>DSON</sub>    | NMOS switch on resistance                    | I <sub>SW</sub> = 100 mA                                                                                                                                                |                                                                     |                    | 0.25        |      | Ω      |     |

|                      |                                              |                                                                                                                                                                         |                                                                     | 480                | 600         | 720  |        |     |

| I                    | NMOS switch current limit                    | 25 / < / < 55 /                                                                                                                                                         |                                                                     | 640                | 800         | 960  | mA     |     |

| I <sub>CL</sub>      | NIVIOS SWITCH CUITERI IIIIII                 | $2.5 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$                                                                                                              |                                                                     | 800                | 1000        | 1200 | mA<br> |     |

|                      |                                              |                                                                                                                                                                         |                                                                     | 960                | 1200        | 1440 |        |     |

|                      | Output overvoltage protection                | ON threshold, 2.3 V $\leq$ V <sub>IN</sub> $\leq$ 5.5 V                                                                                                                 | 24-V option                                                         | 23                 | 24          | 25   |        |     |

| $V_{OVP}$            |                                              | ON threshold, 2.3 V ≤ V <sub>IN</sub> ≤ 5.5 V                                                                                                                           | 40-V option                                                         | 39                 | 41          | 44   | V      |     |

|                      | protection                                   | Hysteresis                                                                                                                                                              |                                                                     |                    | 1           |      |        |     |

|                      | Switching frequency                          |                                                                                                                                                                         |                                                                     | 560-kHz shift = 1  | 538         | 560  | 582    |     |

| £                    |                                              | 25777                                                                                                                                                                   | 500-kHz shift = 0                                                   | 481                | 500         | 518  | 1.11=  |     |

| $f_{\sf SW}$         |                                              | Switching frequency                                                                                                                                                     | $2.5 \text{ V} \le \text{V}_{\text{IN}} \le 5.5 \text{ V}$ 1.12-MHz | 1.12-MHz shift = 1 | 1077        | 1120 | 1163   | kHz |

|                      |                                              | 1-MHz shift                                                                                                                                                             | 1-MHz shift = 0                                                     | 962                | 1000        | 1038 |        |     |

| D <sub>MAX</sub>     | Maximum duty cycle                           |                                                                                                                                                                         | -                                                                   |                    | 94%         |      |        |     |

| IQ                   | Quiescent current into device, not switching | V <sub>IN</sub> = 3.6 V                                                                                                                                                 | ILED1 = ILED2 =<br>20 mA, feedback<br>disabled.                     |                    | 350         |      | μΑ     |     |

| I <sub>SHDN</sub>    | Shutdown current                             | 2.3 V ≤ V <sub>IN</sub> ≤ 5.5 V                                                                                                                                         | HWEN = V <sub>IN</sub> , I <sup>2</sup> C shutdown                  |                    | 1           | 4    |        |     |

|                      |                                              |                                                                                                                                                                         | HWEN = GND                                                          |                    | 1           | 4    | μΑ     |     |

| I <sub>LED_MIN</sub> | Minimum LED current in ILED1 or ILED2        | Full-scale current = 20 mA, BRT = 0x01, Exponential mapping mode                                                                                                        |                                                                     |                    | 13          |      |        |     |

| _                    | Thermal shutdown                             |                                                                                                                                                                         |                                                                     |                    | 140         |      | °C     |     |

| $T_{SD}$             | Hysteresis                                   |                                                                                                                                                                         |                                                                     |                    | 15          |      | -0     |     |

| t <sub>WAIT</sub>    | Initialization timing                        | Time period to wait from the assertic software reset, before an I <sup>2</sup> C transa During this time period an I <sup>2</sup> C transa                              | ction will be ACK'ed.                                               | 1                  |             |      | ms     |     |

Minimum and maximum limits are specified by design, test, or statistical analysis. Typical numbers are not ensured, but do represent the most likely norm. Unless otherwise specified, conditions for typical specifications are: V<sub>IN</sub> = 3.6 V and T<sub>A</sub> = 25°C.

LED current sink matching between LED1 and LED2 is given by taking the difference between ILED1 and ILED2 and dividing by the

<sup>(2)</sup> LED current sink matching between LED1 and LED2 is given by taking the difference between ILED1 and ILED2 and dividing by the sum of ILED1 and ILED2. The formula is (I<sub>LED1</sub> - I<sub>LED2</sub>)/(I<sub>LED1</sub> + I<sub>LED2</sub>) at I<sub>LED</sub> = 10 mA. I<sub>LED1</sub> is driven by Bank A and I<sub>LED2</sub> is driven by Bank B.

# **Electrical Characteristics (continued)**

Typical limits are for  $T_A = 25^{\circ}C$ ; minimum and maximum limits apply over the full operating ambient temperature range (-40°C  $\leq T_A \leq 85^{\circ}C$ );  $V_{IN} = 3.6$  V, unless otherwise specified.<sup>(1)</sup>

|                 | PARAMETER                    | TEST CONDITION                                               | MIN | TYP | MAX      | UNIT |

|-----------------|------------------------------|--------------------------------------------------------------|-----|-----|----------|------|

| LOGIC           | INPUTS (PWM, HWEN, SEL,      | SCL, SDA)                                                    |     |     |          |      |

| $V_{IL}$        | Input logic low              | $2.3 \text{ V} \leq \text{V}_{\text{IN}} \leq 5.5 \text{ V}$ | 0   |     | 0.4      | V    |

| V <sub>IH</sub> | Input logic high             | 2.3 V ≤ V <sub>IN</sub> ≤ 5.5 V                              | 1.2 |     | $V_{IN}$ | V    |

| V <sub>OL</sub> | Output logic low (SDA, INTN) | 2.3 V ≤ V <sub>IN</sub> ≤ 5.5 V                              |     |     | 400      | mV   |

| $f_{\sf PWM}$   | PWM input frequency          | 2.3 V ≤ V <sub>IN</sub> ≤ 5.5 V                              | 10  |     | 80       | kHz  |

| 0               | Innut conscitones            | SDA                                                          |     | 4.5 |          | n.E  |

| C <sub>IN</sub> | Input capacitance            | SCL                                                          |     | 5   |          | pF   |

# 6.6 I<sup>2</sup>C-Compatible Timing Requirements (SCL, SDA)

See (1).

|                |                                       | MIN | NOM | MAX | UNIT |

|----------------|---------------------------------------|-----|-----|-----|------|

| t <sub>1</sub> | SCL (clock period)                    | 2.5 |     |     | μs   |

| $t_2$          | Data in setup time to SCL high        | 100 |     |     |      |

| $t_3$          | Data in setup time to SCL low         | 0   |     |     |      |

| t <sub>4</sub> | SDA low setup time to SCL low (start) | 100 |     |     | ns   |

| t <sub>5</sub> | SDA high hold time to SCL high (stop) | 100 |     |     |      |

<sup>(1)</sup> SCL and SDA must be glitch-free in order for proper brightness to be realized.

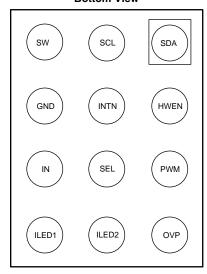

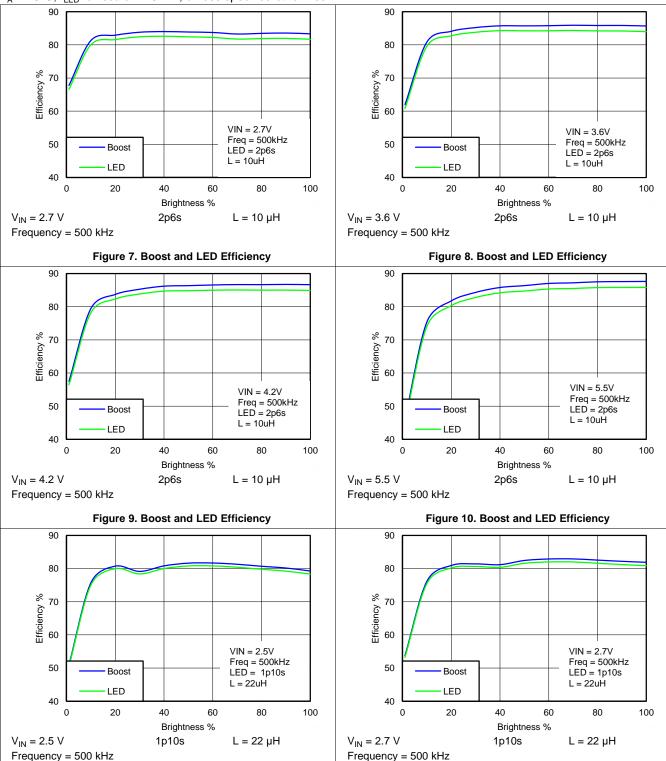

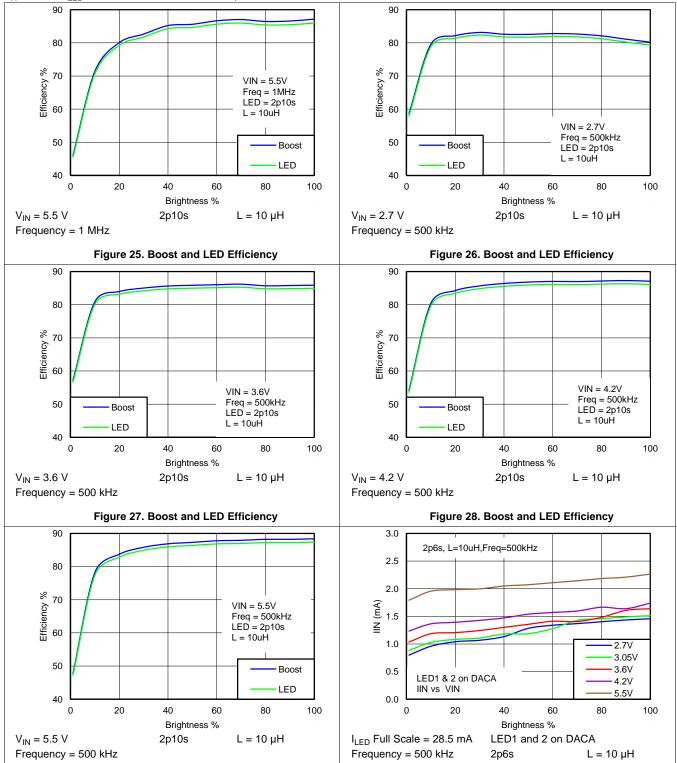

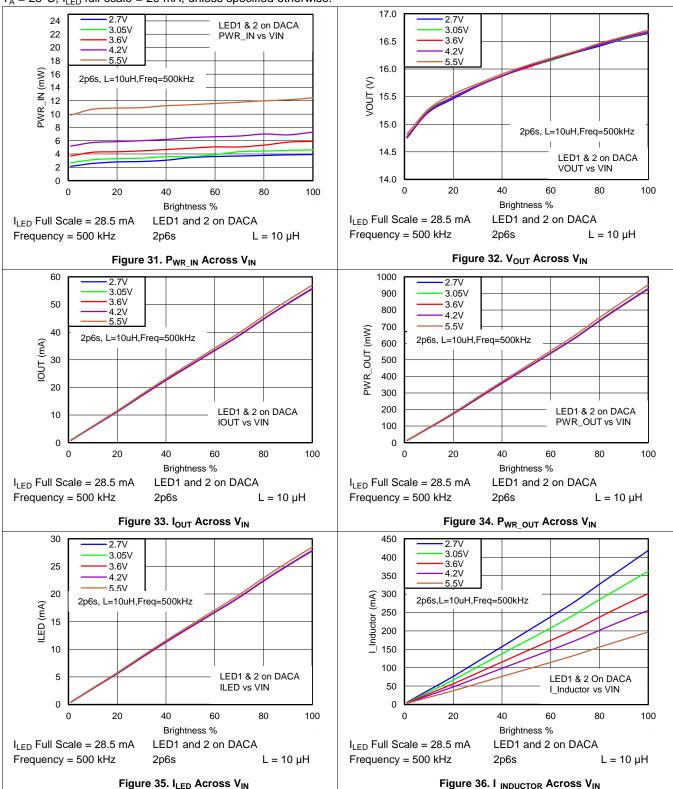

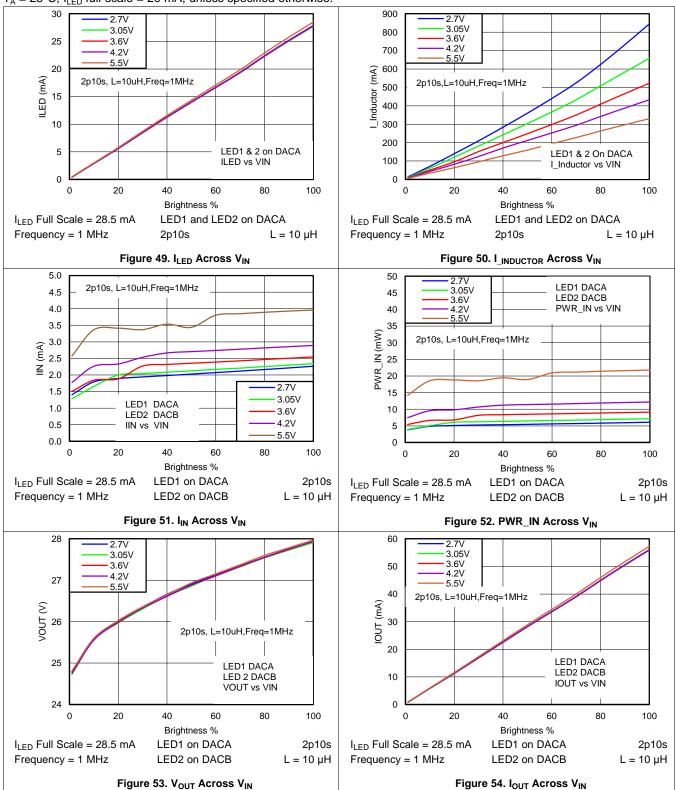

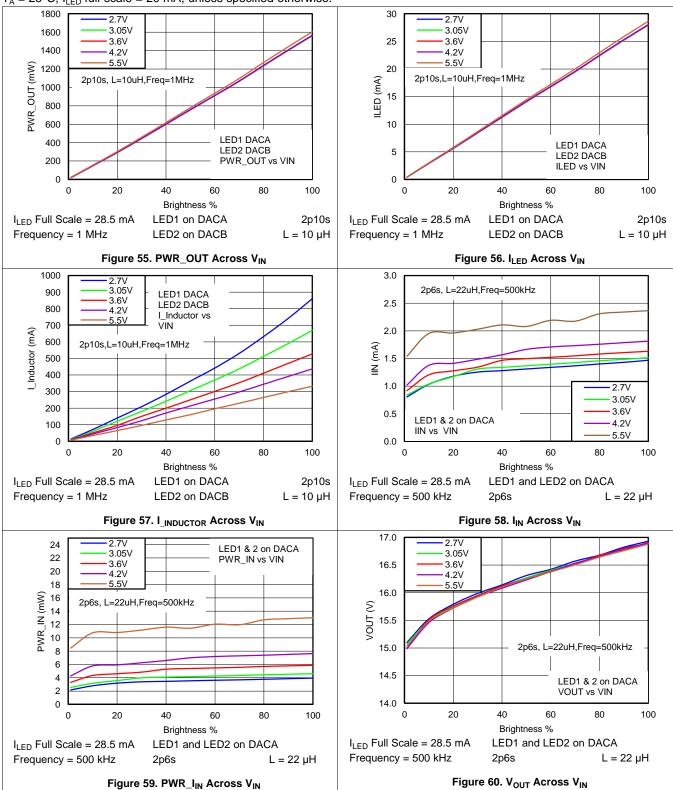

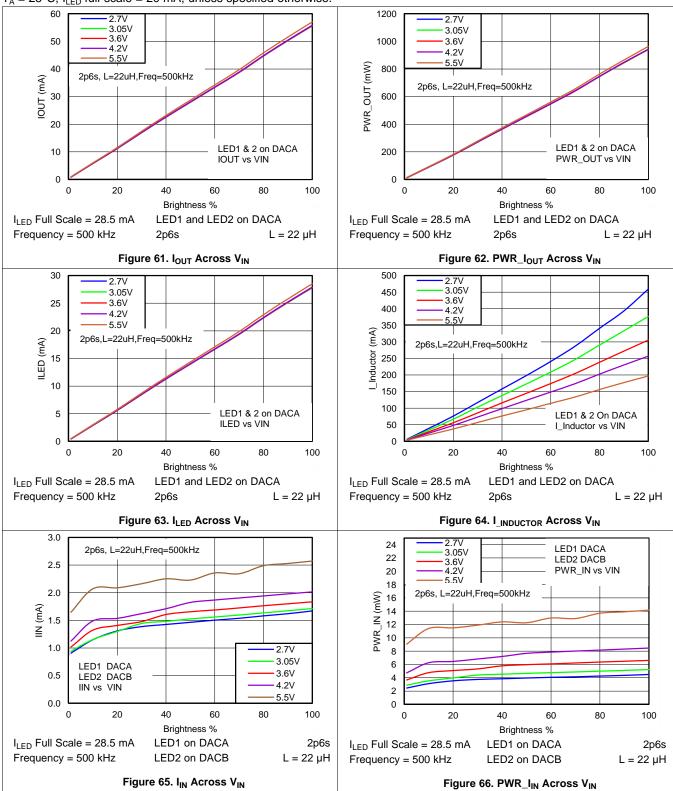

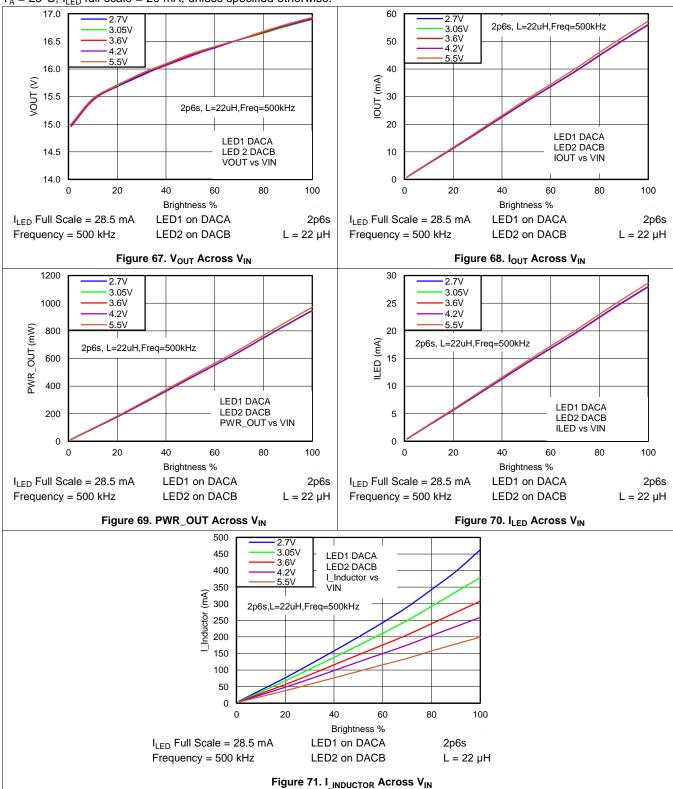

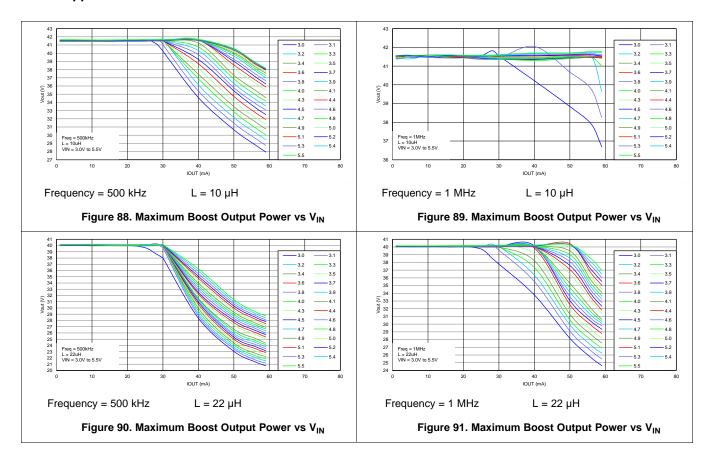

# 6.7 Typical Characteristics

$T_A = 25$ °C,  $I_{LED}$  full-scale = 20 mA, unless specified otherwise.

Copyright © 2013–2015, Texas Instruments Incorporated

Submit Documentation Feedback

# TEXAS INSTRUMENTS

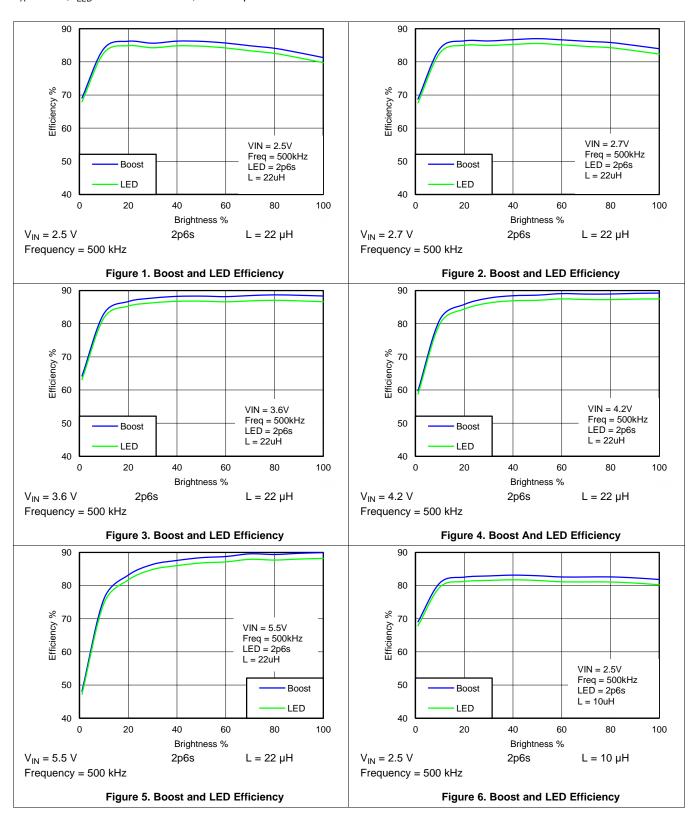

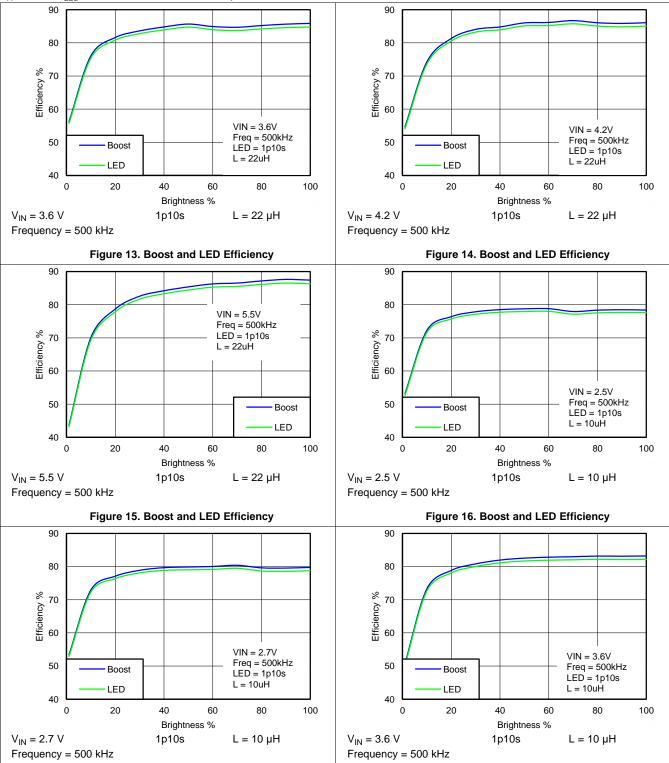

# **Typical Characteristics (continued)**

$T_A = 25$ °C,  $I_{LED}$  full-scale = 20 mA, unless specified otherwise.

Submit Documentation Feedback

Figure 11. Boost and LED Efficiency

Copyright © 2013–2015, Texas Instruments Incorporated

Figure 12. Boost and LED Efficiency

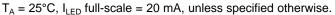

$T_A = 25$ °C,  $I_{LED}$  full-scale = 20 mA, unless specified otherwise.

Copyright © 2013–2015, Texas Instruments Incorporated

Figure 17. Boost and LED Efficiency

Submit Documentation Feedback

Figure 18. Boost and LED Efficiency

# TEXAS INSTRUMENTS

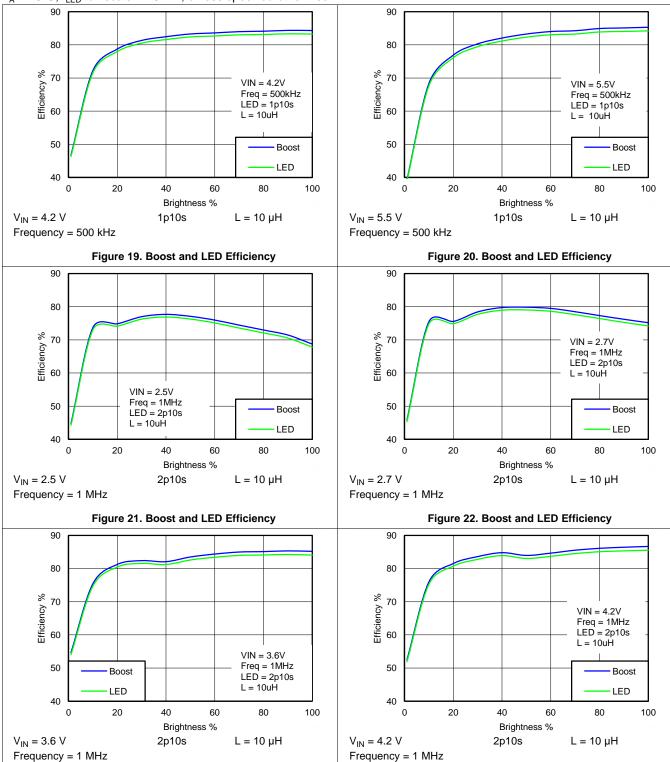

# **Typical Characteristics (continued)**

Submit Documentation Feedback

Figure 23. Boost and LED Efficiency

Copyright © 2013–2015, Texas Instruments Incorporated

Figure 24. Boost and LED Efficiency

$T_A = 25$ °C,  $I_{LED}$  full-scale = 20 mA, unless specified otherwise.

Copyright © 2013–2015, Texas Instruments Incorporated

Figure 29. Boost and LED Efficiency

Submit Documentation Feedback

Figure 30. I<sub>IN</sub> Across V<sub>IN</sub>

# TEXAS INSTRUMENTS

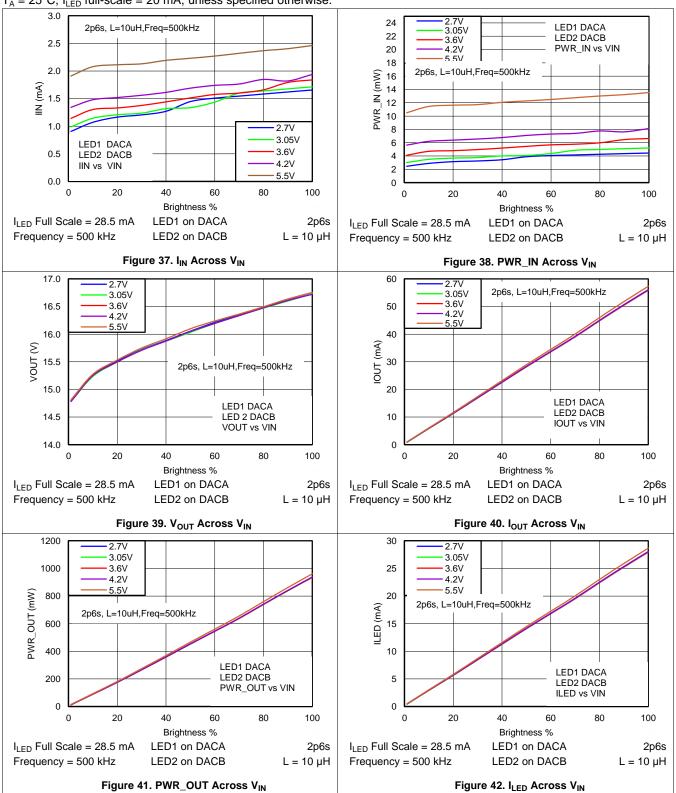

# **Typical Characteristics (continued)**

$T_A = 25$ °C,  $I_{LED}$  full-scale = 20 mA, unless specified otherwise.

Submit Documentation Feedback

Copyright © 2013–2015, Texas Instruments Incorporated

$T_A = 25$ °C,  $I_{LED}$  full-scale = 20 mA, unless specified otherwise.

# TEXAS INSTRUMENTS

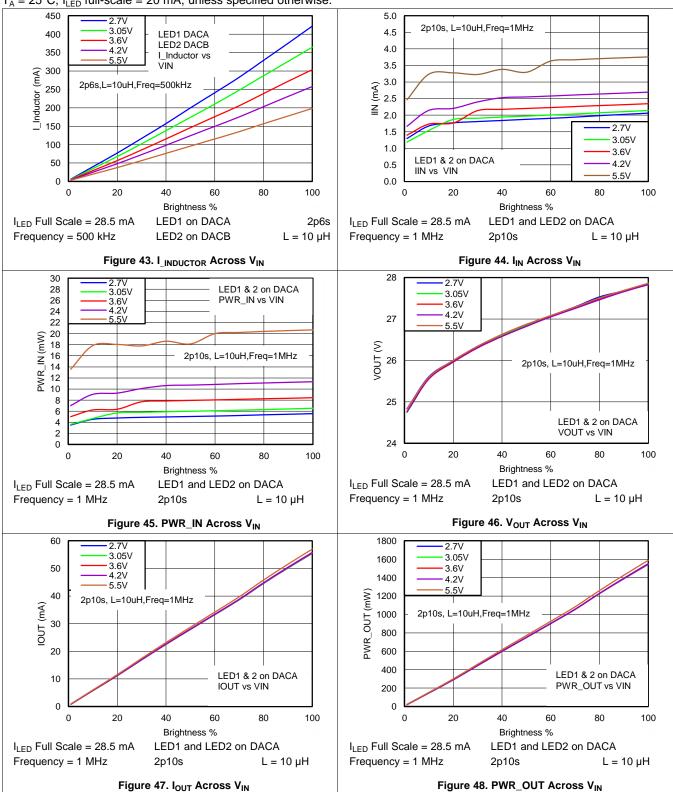

# **Typical Characteristics (continued)**

$T_A = 25$ °C,  $I_{LED}$  full-scale = 20 mA, unless specified otherwise.

Submit Documentation Feedback

Copyright © 2013–2015, Texas Instruments Incorporated

$T_A = 25$ °C,  $I_{LED}$  full-scale = 20 mA, unless specified otherwise.

Copyright © 2013–2015, Texas Instruments Incorporated

Submit Documentation Feedback

$T_A = 25$ °C,  $I_{LED}$  full-scale = 20 mA, unless specified otherwise.

Submit Documentation Feedback

Copyright © 2013–2015, Texas Instruments Incorporated

$T_A = 25$ °C,  $I_{LED}$  full-scale = 20 mA, unless specified otherwise.

Submit Documentation Feedback

# TEXAS INSTRUMENTS

# **Typical Characteristics (continued)**

$T_A = 25$ °C,  $I_{LED}$  full-scale = 20 mA, unless specified otherwise.

Submit Documentation Feedback

Copyright © 2013–2015, Texas Instruments Incorporated

# 7 Detailed Description

#### 7.1 Overview

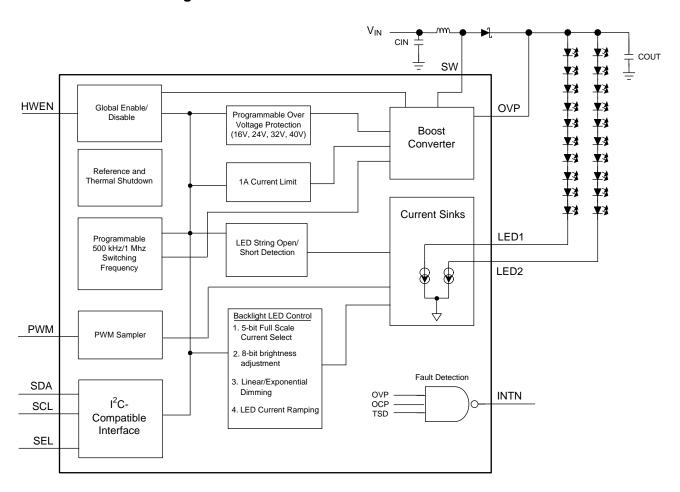

The LM3630A provides the power for two high-voltage LED strings (up to 40 V at 28.5 mA each). The two high-voltage LED strings are powered from an integrated asynchronous boost converter. The device is programmable over an I<sup>2</sup>C-compatible interface. Additional features include a PWM input for content adjustable brightness control, programmable switching frequency, and programmable overvoltage protection (OVP).

#### 7.2 Functional Block Diagram

#### 7.3 Feature Description

#### 7.3.1 Operation

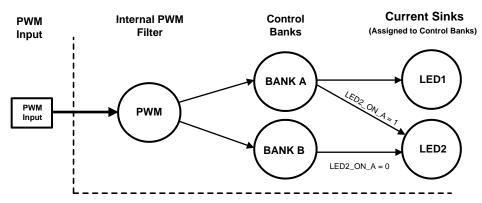

#### 7.3.1.1 Control Bank Mapping

Control of the LM3630A device current sinks is not done directly, but through the programming of Control Banks. The current sinks are then assigned to the programmed Control Bank (see Figure 72). Both current sinks can be assigned to Control Bank A or LED1 can use Control Bank A while LED2 uses Control Bank B. Assigning LED1 to Control Bank A and LED2 to Control Bank B allows for better LED current matching. Assigning each current sink to different control banks allows for each current sink to be programmed with a different current or have the PWM input control a specific current sink.

#### **Feature Description (continued)**

Figure 72. Control Diagram

Table 1. Bank Configuration Examples: Register Values

| REGISTERS TO PROGRAM | ILED1 on A, ILED2 ON B WITH PWM DIMMING <sup>(1)</sup> | ILED1 AND ILED2 ON A WITH PWM DIMMING | ILED1 ON A WITH PWM<br>ILED2 ON B NO PWM     |

|----------------------|--------------------------------------------------------|---------------------------------------|----------------------------------------------|

| Control              | 1EH linear or 06h exp                                  | 15h linear or 05h exp                 | 1EH linear or 06h exp                        |

| Configuration        | 1Bh                                                    | 09h                                   | 19h                                          |

| Brightness A         | used for A                                             | used for both                         | used for A                                   |

| Brightness B         | used for B                                             | not used                              | used for B (A and B do not have to be equal) |

<sup>(1)</sup> LED current matching is specified using this configuration.

#### 7.3.1.2 PWM Input Polaritiy

The PWM Input can be set for active high (default) or active low polarity. With active low polarity the LED current is a function of the negative duty cycle at PWM.

#### 7.3.1.3 **HWEN Input**

HWEN is the global hardware enable to the LM3630A. HWEN must be pulled high to enable the device. HWEN is a high-impedance input so it cannot be left floating. When HWEN is pulled low the LM3630A is placed in shutdown and all the registers are reset to their default state.

#### 7.3.1.4 SEL Input

SEL is the select pin for the serial bus device address. When this pin is connected to ground, the seven-bit device address is 36H. When this pin is tied to the VIN power rail, the device address is 38H.

#### 7.3.1.5 INTN Output

The INTN pin is an open-drain active-low output signal which indicates detected faults. The signal asserts low when either OCP, OVP, or TSD is detected by the LED driver. The Interrupt Enable register must be set to connect these faults to the INTN pin.

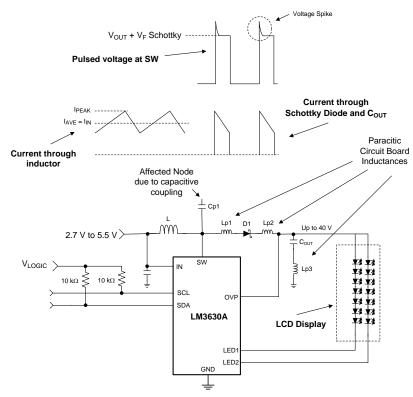

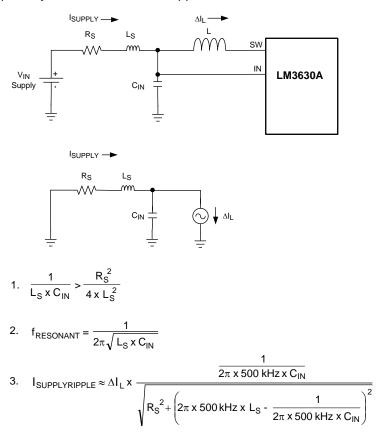

#### 7.3.1.6 Boost Converter

The high-voltage boost converter provides power for the two current sinks (ILED1 and ILED2). The boost circuit operates using a 10-µH to 22-µH inductor and a 1-µF output capacitor. The selectable 500-kHz or 1-MHz switching frequency allows for the use of small external components and provides for high boost converter efficiency. Both LED1 and LED2 feature an adaptive voltage regulation scheme where the feedback point (LED1 or LED2) is regulated to a minimum of 300 mV. When there are different voltage requirements in both high-voltage LED strings, because of different programmed voltages or string mismatch, the LM3630A regulates the feedback point of the highest voltage string to 300 mV and drop the excess voltage of the lower voltage string across the lower strings current sink.

#### 7.3.1.7 Boost Switching Frequency Select

The LM3630A's boost converter can have a 500-kHz or 1-MHz switching frequency. For a 500-kHz switching frequency the inductor value must be between 10  $\mu$ H and 22  $\mu$ H. For the 1-MHz switching frequency the inductor can be between 10  $\mu$ H and 22  $\mu$ H. Additionally, there is a Frequency Shift bit which offsets the frequency approximately 10%. For the 500 kHz setting, shift = 0. The boost frequency is shifted to 560 kHz when Shift = 1. For the 1-MHz setting, Shift = 0. The boost frequency is shifted to 1120 kHz when shift = 1.

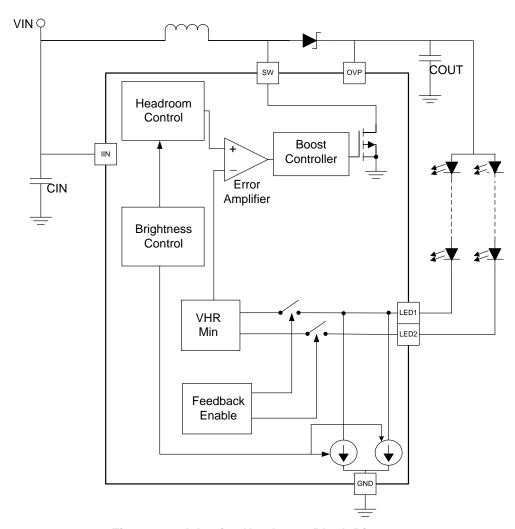

#### 7.3.1.8 Adaptive Headroom

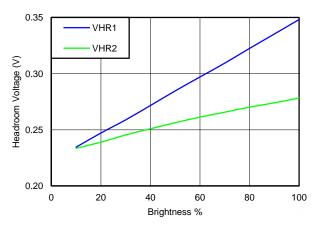

Reference Figure 73 and Figure 74 for the following description.

The adaptive headroom circuit controls the boost output voltage to provide the minimal headroom voltage necessary for the current sinks to provide the specified ILED current. The headroom voltage is fed back to the Error Amplifier to dynamically adjust the Boost output voltage. The error amplifier's reference voltage is adjusted as the brightness level is changed, because the currents sinks require less headroom at lower  $I_{LED}$  currents than at higher  $I_{LED}$  currents. Note that the VHR Min block dynamically selects the LED string that requires the higher boost voltage to maintain the  $I_{LED}$  current; this string has the lower headroom voltage. In Figure 74 this is LED string 2. The headroom voltage on LED string 1 is higher, but this is due to LED string 2 have an overall higher forward voltage than LED string 1. LED strings that have closely matched forward voltages have closely matched headroom voltages and better overall efficiency.

In a single string LED configuration the Feedback enable must be enabled for only that string (LED1 or LED2). The adaptive headroom circuit is control by that single string. In a two string LED configuration the Feedback enable must be enabled for both strings (LED1 and LED2). The VHR Min block then dynamically selects the LED string to control the adaptive headroom circuit.

Figure 73. Adaptive Headroom Block Diagram

Figure 74. Typical Headroom Voltage Curve

#### 7.3.1.9 Current Sinks

LED1 and LED2 control the current up to a 40-V LED string voltage. Each current sink has 5-bit full-scale current programmability and 8-bit brightness control. Either current sink has its current set through a dedicated brightness register and can additionally be controlled via the PWM input.

Submit Documentation Feedback

#### 7.3.1.10 Current String Biasing

Each current string can be powered from the LM3630A device's boost or from an external source. When powered from an external source the feedback input for either current sink can be disabled in the Configuration Register so it no longer controls the boost output voltage.

#### 7.3.1.11 Full-Scale LED Current

The LM3630A device's full-scale current is programmable with 32 different full-scale levels. The full-scale current is the LED current in the control bank when the brightness code is at max code (0xFF). The 5-bit full-scale current vs code is given by Equation 1:

$$I_{\text{LED FULLSCALE}} = 5 \text{ mA} + \text{Code} \times 0.75 \text{ mA}$$

(1)

With a maximum full-scale current of 28.5 mA.

## 7.3.1.12 Brightness Register

Each control bank has its own 8-bit brightness register. The brightness register code and the full-scale current setting determine the LED current depending on the programmed mapping mode.

#### 7.3.1.13 Exponential Mapping

In exponential mapping mode the brightness code to backlight current transfer function is given by Equation 2:

$$I_{LED} = I_{LED \text{ FULLSCALE}} \times 0.85 \left( 44 - \frac{\text{Code} + 1}{5.8181818} \right) \times D_{PWM}$$

where

- ILED\_FULLSCALE is the full-scale LED current setting

- · Code is the backlight code in the brightness register

- DPWM is the PWM input duty cycle

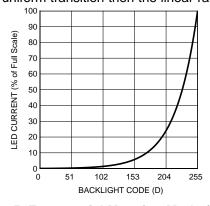

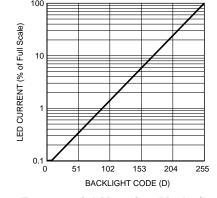

Figure 75 and Figure 76 show the approximate backlight code to LED current response using exponential mapping mode. Figure 75 shows the response with a linear Y axis, and Figure 76 shows the response with a logarithmic Y axis. In exponential mapping mode the current ramp (either up or down) appears to the human eye as a more uniform transition then the linear ramp. This is due to the logarithmic response of the eye.

Figure 75. Exponential Mapping Mode (Linear Scale)

Figure 76. Exponential Mapping Mode (Log Scale)

Submit Documentation Feedback

(2)

#### 7.3.1.14 Linear Mapping

In linear mapping mode the brightness code to backlight current has a linear relationship and follows Equation 3:

$$I_{LED} = I_{LED\_FULLSCALE} \times \frac{1}{255} \times Code \times D_{PWM}$$

where

- I<sub>LED FULLSCALE</sub> is the full scale LED current setting

- · Code is the backlight code in the brightness register

- DPWM is the PWM input duty cycle

(3)

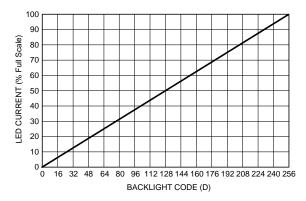

Figure 77 shows the backlight code-to-LED current response using linear-mapping mode. The Configuration Register must be set to enable linear mapping.

Figure 77. Linear Mapping Mode

#### 7.3.2 Test Features

The LM3630A contains an LED open, an LED short, and overvoltage manufacturing fault detection. This fault detection is designed to be used during the manufacturing process only and not normal operation. These faults do not set the INTN pin.

#### 7.3.2.1 Open LED String (LED1 And LED2)

An open LED string is detected when the voltage at the input to either LED1 or LED2 has fallen below 200 mV, and the boost output voltage has hit the OVP threshold. This test assumes that the LED string that is being detected for an open is being powered from the boost output (Feedback Enabled). For an LED string not connected to the boost output, and connected to another voltage source, the boost output would not trigger the OVP flag. In this case an open LED string would not be detected.

#### 7.3.2.2 Shorted LED String

The LM3630A features an LED short fault flag indicating if either of the LED strings have experienced a short. There are two methods that can trigger a short in the LED strings:

- 1. An LED current sink with feedback enabled, and the difference between OVP input and the LED current sink input voltage goes below 1 V.

- 2. An LED current sink is configured with feedback disabled (not powered from the boost output) and the difference between  $V_{IN}$  and the LED current sink input voltage goes below 1 V.

#### 7.3.2.3 Overvoltage Protection (Manufacturing Fault Detection and Shutdown)

The LM3630A provides an overvoltage Protection (OVP) mechanism specifically for manufacturing test where a display may not be connected to the device. The OVP threshold on the LM3630A has 4 different programmable options (16 V, 24 V, 32 V, and 40 V). The manufacturing protection is enabled in the Fault Status register bit 0. When enabled, this feature causes the boost converter to shutdown anytime the selected OVP threshold is exceeded. The OVP\_fault bit in the Fault Status register is set to one. The boost converter does not resume operation until the LM3630A is reset with either a write to the Software Reset bit in the Software Reset register or a cycling of the HWEN pin. The reset clears the fault.

#### 7.3.3 Fault Flags/Protection Features

The Interrupt Status register contains the status of the protection circuits of the LM3630A. The corresponding bits are set to one if an OVP, OCP, or TSD event occurs. These faults do set the INTN pin when the corresponding bit is set in the Interrupt Enable register.

#### 7.3.3.1 Overvoltage Protection (Inductive Boost Operation)

The overvoltage protection threshold (OVP) on the LM3630A has 4 different programmable options (16 V, 24 V, 32 V, and 40 V). OVP protects the device and associated circuitry from high voltages in the event the feedback enabled LED string becomes open. During normal operation, the LM3630A device's inductive boost converter boosts the output up so as to maintain at least 300 mV at the active current sink inputs. When a high-voltage LED string becomes open the feedback mechanism is broken, and the boost converterinadvertently over boosts the output. When the output voltage reaches the OVP threshold the boost converter stops switching, thus allowing the output node to discharge. When the output discharges to  $V_{\rm OVP}-1$  V the boost converter begins switching again. The OVP sense is at the OVP pin, so this pin must be connected directly to the inductive boost output capacitor's positive terminal.

For current sinks that have feedback disabled the over voltage sense mechanism is not in place to protect from potential over-voltage conditions. In this situation the application must ensure that the voltage at LED1 or LED2 doesn't exceed 40 V.

The default setting for OVP is set at 24 V. For applications that require higher than 24 V at the boost output the OVP threshold has to be programmed to a higher level at power up.

#### 7.3.3.2 Current Limit

The switch current limit for the LM3630A device's inductive boost is set at 1 A. When the current through the NFET switch hits this over current protection threshold (OCP) the device turns the NFET off and the energy of the inductor is discharged into the output capacitor. Switching is then resumed at the next cycle. The current limit protection circuitry can operate continuously each switch cycle. The result is that during high output power conditions the device can continuously run in current limit. Under these conditions the device inductive boost converter stops regulating the headroom voltage across the high voltage current sinks. This results in a drop in the LED current.

#### 7.3.3.3 Thermal Shutdown

The LM3630A contains thermal shutdown protection. In the event the die temperature reaches 140°C, the boost power supply and current sinks shut down until the die temperature drops to typically 125°C.

#### 7.3.4 Initialization Timing

#### 7.3.4.1 Initialization Timing With HWEN Tied to $V_{IN}$

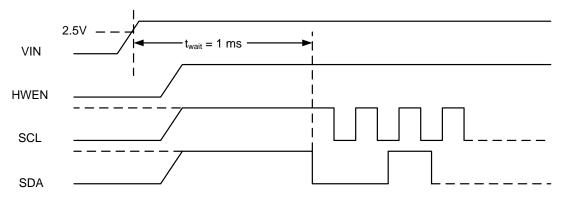

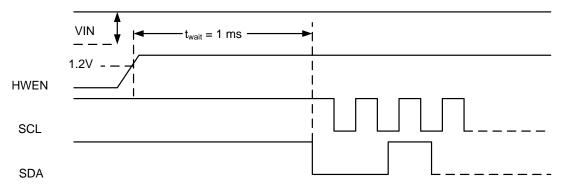

If the HWEN input is tied to  $V_{IN}$ , then the  $t_{WAIT}$  time starts when  $V_{IN}$  crosses 2.5 V as shown in Figure 78. The initial  $I^2C$  transaction can occur after the  $t_{WAIT}$  time expires. Any  $I^2C$  transaction during the  $t_{WAIT}$  period are NAK'ed.

Figure 78. Initialization Timing With HWEN Is Tied to VIN

#### 7.3.4.2 Initialization Timing With HWEN Driven by GPIO

If the HWEN input is driven by a GPIO then the  $t_{WAIT}$ time starts when HWEW crosses 1.2 V as shown in Figure 79. The initial I<sup>2</sup>C transaction can occur after the  $t_{WAIT}$  time expires. Any I<sup>2</sup>C transaction during the  $t_{WAIT}$  period are NAK'ed.

Figure 79. Initialization Timing With HWEN Driven by a GPIO

#### 7.3.4.3 Initialization After Software Reset

The time between the  $I^2C$  transaction that issues the software reset, and the subsequent  $I^2C$  transaction (that is, to configure the LM3630A) must be at greater or equal to the  $t_{WAIT}$  period of 1 ms. Any  $I^2C$  transaction during the  $t_{WAIT}$  period are NAK'ed.

#### 7.4 Device Functional Modes

#### 7.4.1 LED Current Ramping

#### 7.4.1.1 Start-Up/Shutdown Ramp

The LED current turn on time from 0 to the initial LED current set-point is programmable. Similarly, the LED current shutdown time to 0 is programmable. Both the startup and shutdown times are independently programmable with 8 different levels. The start-up times are independently programmable from the shutdown times, but not independently programmable for each Control bank. For example, programming a start-up or shutdown time, programs the same ramp time for each control bank. The start-up time is used when the device is first enabled to a non-zero brightness value. The shutdown time is used when the brightness value is programmed to zero. If HWEN is used to disable the device, the action is immediate and the Shutdown time is not used. The zero code does take a small amount of time which is approximately 0.5 ms.

**SHUTDOWN TIME** CODE START-UP TIME 000 4 ms 0 001 261 ms 261 ms 010 522 ms 522 ms 011 1.045 s 1.045 s 100 2.091 s 2.091 s 101 4.182 s 4.182 s

8.364 s

16.73 s

Table 2. Start-Up/Shutdown Times

#### 7.4.1.2 Run-Time Ramp

110

111

Current ramping from one brightness level to the next is programmable. There are 8 different ramp up times and 8 different ramp down times. The ramp up time is independently programmable from the ramp down time, but not independently programmable for each Control Bank. For example, programming a ramp up time or a ramp down time programs the same ramp time for each control bank. The run time ramps are used whenever the device is enabled with a non-zero brightness value and a new non-zero brightness value is written.

Product Folder Links: LM3630A

8.364 s

16.73 s

| CODE | RAMP-UP TIME | RAMP-DOWN TIME |  |  |

|------|--------------|----------------|--|--|

| 000  | 0            | 0              |  |  |

| 001  | 261 ms       | 261 ms         |  |  |

| 010  | 522 ms       | 522 ms         |  |  |

| 011  | 1.045s       | 1.045s         |  |  |

| 100  | 2.091s       | 2.091s         |  |  |

| 101  | 4.182s       | 4.182s         |  |  |

| 110  | 8.364s       | 8.364s         |  |  |

| 111  | 16.73s       | 16.73s         |  |  |

# 7.4.2 PWM Operation

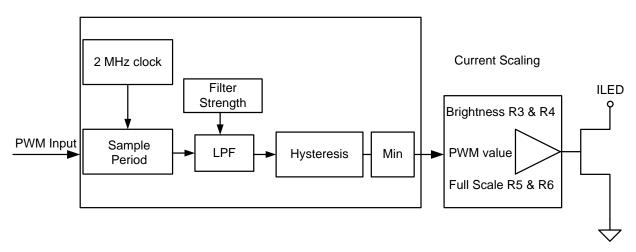

Figure 80. PWM Sampler

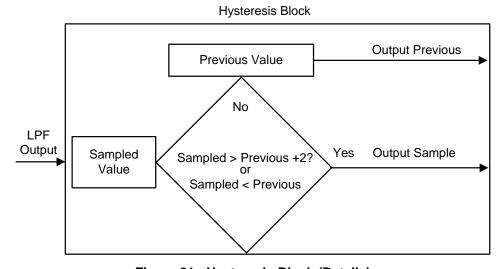

Figure 81. Hysteresis Block (Details)

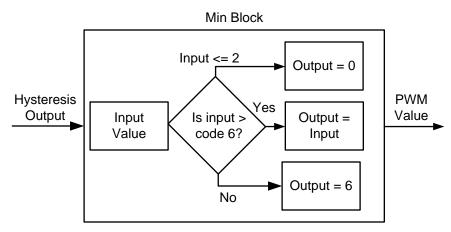

Figure 82. Min Block (Details)

#### 7.4.2.1 PWM Input

The PWM input can be assigned to any control bank. When assigned to a control bank, the programmed current in the control bank also becomes a function of the duty cycle at the PWM input. The PWM input is sampled by a digital circuit which outputs a brightness code that is equivalent to the PWM input duty cycle. The resultant brightness value is a combination of the maximum current setting, the brightness registers, and the equivalent PWM brightness code.

#### 7.4.2.2 PWM Input Frequency

The specified input frequency of the PWM signal is 10 kHz to 80 kHz. The recommended frequency is 30 kHz or greater. The PWM input sampler operates beyond those frequency limits. Performance changes based on the input frequency used. Using frequencies outside the specified range is not recommended. Lower PWM input frequency increases the likelihood that the output of the sampler may change and that a single brightness step may be visible on the screen. This may be visible at low brightness because the step change is large relative to the output level.

#### 7.4.2.3 Recommended Settings

For best performance of the PWM sampler it is recommended to have a PWM input frequency of at least 30 kHz. The Filter Strength (register 50h) must be set to 03h. The Hysteresis 1 bit must be set in register 05h to 1 when setting the maximum current for bank A. For example if max current is 20 mA, register 05h is set to 14h, change that to 94h for 1 bit hysteresis and a smooth min-to-max brightness transition.

#### 7.4.2.4 Adjustments to PWM Sampler

The digital sampler has controls for hysteresis and minimum output brightness which allow the optimization of sampler output. The default hysteresis mode of the PWM sampler requires detecting a two code change in the input to increase brightness. Reducing the hysteresis to change on 1 code allows a smoother brightness transition when the brightness control is swept across the screen in a system. The filter strength bits affect the speed of the output transitions from the PWM sampler. A lower bound to the brightness is enabled by default which limits the minimum output of the PWM sampler to an equivalent code of 6 when the LEDs are turned on. A detected code of 1 is forced to off. A minimum 2% PWM input duty cycle is recommended. Input duty cycles of 1% or less causes delayed off-to-on transitions.

#### 7.4.2.4.1 Filter Strength, Register 50h Bits [1:0]

- Filter Strength controls the amount of sampling cycles that are fed back to the PWM input sampler. A filter strength of 00b allows the output of the PWM sampler to change on every Sample Period. A filter strength of 01b allows the output of the PWM sampler to change every two Sample Periods. A filter strength of 10b allows the output of the PWM sampler to change every four Sample Periods. A filter strength of 11b allows the output of the PWM sampler to change every eight Sample Periods.

- he effect of setting this value to 11b forces the output of the PWM sampler to change less frequently then lower values. The benefit is this reduces the appearance of flicker because the output is slower to change.

The negative is that the output is slower to change.

#### 7.4.2.4.2 Hysteresis 1 Bit, Register 05h, Bit 7

- The default setting for the LM3630A has Bit 7 of register 05h is 0b. This requires the detection of a PWM input change that is at least 3 equivalent codes higher than the present code. If this bit is set to 1b, the hysteresis is turned off and the PWM sampler output is allowed to change by 2 code.

- Setting this bit to 1b turns off the 2 code requirement for the PWM sampler output to change. The benefit is that the output change is smoother. The negative is that there may be some PWM input value where the output could change by one code and it might appear as flicker.

#### 7.4.2.4.3 Lower Bound Disable, Register 05h, Bit 6

- The default setting for the LM3630A has Bit 6 of register 05h is 0b. This turns on the lower bound where the minimum output value of the PWM sampler is an equivalent code of 6. If the PWM sampler detects an equivalent code of 0 or 1, the output is 0, and the LEDs are off. If the PWM sampler detects an equivalent code of 2 through 6, a current equal to code 6 is output. Detection of any higher code outputs that code conforming to the rules of hysteresis above.

- Setting Bit 6 of register 05h to 1b can be used to allow the output to be below an equivalent code 6. The output of the PWM sampler matches the input pulse width conforming to the rules of Hysteresis and equivalent codes 1, 2, 3, 4, and 5 are also allowed. The benefit is the output is allowed to go dimmer than in the default mode. The negative is at the low codes of 1 and 2, the LEDs may not turn on or the LEDs may appear to flicker.

- Disabling the Lower Bound (05h Bit 6 = 1b) allows the minimum duty cycle to be detected at 0.35% PWM input duty cycle. At 30-kHz PWM input frequency, the minimum pulse width required to turn on the LEDs is 0.39% x 33 μS = 129 ns. There is no specified tolerance to this value.

### 7.4.2.5 Minimum T<sub>ON</sub> Pulse Width

The minimum  $T_{ON}$  pulse width required to produce a non-zero output is dependent upon the LM3630A settings. The default setting of the LM3630A requires a minimum of 0.78% duty cycle for the output to be turned on. Because the lower bound feature is enabled, a value of 0.78% (equivalent brightness code 2) up to 2.35% (equivalent brightness code 6) all produce an output equivalent to brightness code 6. At 30-kHz PWM input frequency, the minimum pulse width required to turn on the LEDs is 0.78% × 33  $\mu$ S = 260 ns.

Because of the hysteresis on the PWM input, this pulse width may not be sufficient to turn on the LEDs. It is recommended that a minimum pulse width of 2% be used.  $2\% \times 33 \,\mu\text{S} = 660 \,\text{ns}$  at 30 kHz input frequency.

Disabling the lower bound as described allows a smaller minimum pulse width.

#### 7.5 Programming

#### 7.5.1 I<sup>2</sup>C-Compatible Interface

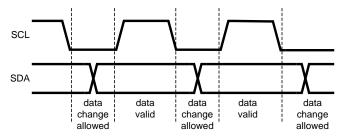

### 7.5.1.1 Data Validity

The data on SDA line must be stable during the HIGH period of the clock signal (SCL). In other words, state of the data line can only be changed when SCL is LOW.

Figure 83. Data Validity Diagram

A pullup resistor between the VIO line of the controller and SDA must be greater than  $[(V_{IO} - V_{OL}) / 3 \text{ mA}]$  to meet the  $V_{OL}$  requirement on SDA. Using a larger pullup resistor results in lower switching current with slower edges, while using a smaller pullup results in higher switching currents with faster edges.

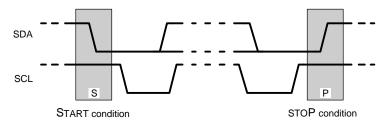

#### 7.5.1.2 Start and Stop Conditions

START and STOP conditions classify the beginning and the end of the I<sup>2</sup>C session. A START condition is defined as SDA signal transitioning from HIGH to LOW while SCL line is HIGH. A STOP condition is defined as the SDA transitioning from LOW to HIGH while SCL is HIGH. The I<sup>2</sup>C master always generates START and STOP conditions. The I<sup>2</sup>C bus is considered to be busy after a START condition and free after a STOP condition. During data transmission, the I<sup>2</sup>C master can generate repeated START conditions. First START and repeated START conditions are equivalent, function-wise.

Figure 84. Start and Stop Conditions

### 7.5.1.3 Transferring Data

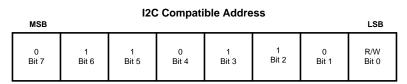

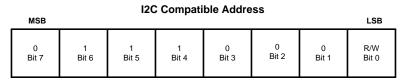

Every byte put on the SDA line must be eight bits long, with the most significant bit (MSB) transferred first. Each byte of data has to be followed by an acknowledge bit. The acknowledge related clock pulse is generated by the master. The master releases the SDA line (HIGH) during the acknowledge clock pulse. The LM3630A pulls down the SDA line during the 9th clock pulse, signifying an acknowledge. The LM3630A generates an acknowledge after each byte is received.

After the START condition, the I<sup>2</sup>C master sends a chip address. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W). The LM3630A address is 36h. For the eighth bit, a "0" indicates a WRITE and a "1" indicates a READ. The second byte selects the register to which the data is written. The third byte contains data to write to the selected register.

# **Programming (continued)**

Figure 85.  $I^2$ C-Compatible Chip Address (0x36), SEL = 0

Figure 86.  $I^2$ C-Compatible Chip Address (0x38), SEL = 1

## 7.6 Register Maps

## 7.6.1 LM3630A I<sup>2</sup>C Register Map

This table summarizes LM3630A I<sup>2</sup>C-compatible register usage and shows default register bit values after reset, as programmed by the factory. The following sub-sections provide additional details on the use of individual registers. Register bits which are blank in the following tables are considered undefined. Undefined bits should be ignored on reads and written as zero.

| SLAVE ADDRESS [0x36h for SEL = 0, 0x38h for SEL = 1] |                |      |                      |  |  |  |  |  |

|------------------------------------------------------|----------------|------|----------------------|--|--|--|--|--|

|                                                      | BASE REGISTERS |      |                      |  |  |  |  |  |

| REGISTER NAME                                        | ADDRESS        | TYPE | DEFAULT RESET VALUES |  |  |  |  |  |

| Control                                              | 0x00           | R/W  | 0xC0                 |  |  |  |  |  |

| Configuration                                        | 0x01           | R/W  | 0x18                 |  |  |  |  |  |

| Boost Control                                        | 0x02           | R/W  | 0x38                 |  |  |  |  |  |

| Brightness A                                         | 0x03           | R/W  | 0x00                 |  |  |  |  |  |

| Brightness B                                         | 0x04           | R/W  | 0x00                 |  |  |  |  |  |

| Current A                                            | 0x05           | R/W  | 0x1F                 |  |  |  |  |  |

| Current B                                            | 0x06           | R/W  | 0x1F                 |  |  |  |  |  |

| On/Off Ramp                                          | 0x07           | R/W  | 0x00                 |  |  |  |  |  |

| Run Ramp                                             | 0x08           | R/W  | 0x00                 |  |  |  |  |  |

| Interrupt Status                                     | 0x09           | R/W  | 0x00                 |  |  |  |  |  |

| Interrupt Enable                                     | 0x0A           | R/W  | 0x00                 |  |  |  |  |  |

| Fault Status                                         | 0x0B           | R/W  | 0x00                 |  |  |  |  |  |

| Software Reset                                       | 0x0F           | R/W  | 0x00                 |  |  |  |  |  |

| PWM Out Low                                          | 0x12           | Read | 0x00                 |  |  |  |  |  |

| PWM Out High                                         | 0x13           | Read | 0x00                 |  |  |  |  |  |

| Revision                                             | 0x1F           | Read | 0x02                 |  |  |  |  |  |

| Filter Strength                                      | 0x50           | R/W  | 0x00                 |  |  |  |  |  |

## 7.6.2 Register Descriptions

# Table 4. Control (Offset = 0x00, Default = 0xC0)

|              |                  |        | Register                                                                                      | Bits                                              |                 |           |           |

|--------------|------------------|--------|-----------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------|-----------|-----------|

| 7            | 6                | 5      | 4                                                                                             | 3                                                 | 2               | 1         | 0         |

| SLEEP_CMD    | SLEEP_<br>STATUS |        | LINEAR_A                                                                                      | LINEAR_B                                          | LED_A_EN        | LED_B_EN  | LED2_ON_A |

| Name         | Bit              | Access | Description                                                                                   |                                                   |                 |           |           |

| SLEEP_CMD    | 7                | R/W    | The device is put                                                                             | The device is put into sleep mode when set to '1' |                 |           |           |

| SLEEP_STATUS | 6                | Read   | Reflects the sleep mode status. A '1' indicates the part is in sleep mode.                    |                                                   |                 |           |           |

|              |                  |        | Used to determine when part has entered or exited sleep mode after writing the SLEEP_CMD bit. |                                                   |                 |           |           |

|              | 5                | Read   |                                                                                               |                                                   |                 |           |           |

| LINEAR_A     | 4                | R/W    | Enables the linea                                                                             | r output mode for                                 | Bank A when set | t to '1'. |           |

| LINEAR_B     | 3                | R/W    | Enables the linea                                                                             | r output mode for                                 | Bank B when set | t to '1'. |           |

| LED_EN_A     | 2                | R/W    | Enables the LED A output                                                                      |                                                   |                 |           |           |

| LED_EN_B     | 1                | R/W    | Enables the LED B output                                                                      |                                                   |                 |           |           |

| LED2_ON_A    | 0                | R/W    | Connect the LED                                                                               | 2 output to Bank                                  | A Control       |           |           |

# Table 5. Configuration (Offset = 0x01, Default = 0x18)

|          | Register Bits |        |                            |                            |         |          |          |  |  |

|----------|---------------|--------|----------------------------|----------------------------|---------|----------|----------|--|--|

| 7        | 6             | 5      | 4                          | 3                          | 2       | 1        | 0        |  |  |

|          |               |        | FB_EN_B                    | FB_EN_A                    | PWM_LOW | PWM_EN-B | PWM_EN_A |  |  |

| Name     | Bit           | Access | Description                |                            |         |          |          |  |  |

|          | 7             | Read   |                            |                            |         |          |          |  |  |

|          | 6             | Read   |                            |                            |         |          |          |  |  |

|          | 5             | Read   |                            |                            |         |          |          |  |  |

| FB_EN_B  | 4             | R/W    | Enable Feedback            | on Bank B                  |         |          |          |  |  |

| FB_EN_A  | 3             | R/W    | Enable Feedback            | on Bank A                  |         |          |          |  |  |

| PWM_LOW  | 2             | R/W    | Sets the PWM to a          | Sets the PWM to active low |         |          |          |  |  |

| PWM_EN_B | 1             | R/W    | Enables the PWM for Bank B |                            |         |          |          |  |  |

| PWM_EN_A | 0             | R/W    | Enables the PWM            | for Bank A                 |         |          |          |  |  |

# Table 6. Boost Control (Offset = 0x02, Default = 0x38)

|            |              |              | Registe                                                                                                | r Bits                                                            |                |       |       |

|------------|--------------|--------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|----------------|-------|-------|

| 7          | 6            | 5            | 4                                                                                                      | 3                                                                 | 2              | 1     | 0     |

|            | BOOST_OVP[1] | BOOST_OVP[0] | BOOST_OCP[1]                                                                                           | BOOST_OCP[0]                                                      | SLOW_STAR<br>T | SHIFT | FMODE |

| Name       | Bit          | Access       | Description                                                                                            |                                                                   |                |       |       |

|            | 7            | Read         |                                                                                                        |                                                                   |                |       |       |

| BOOST_OVP  | 6:5          | R/W          | Selects the voltage limit for over-voltage protection:  00 = 16 V  01 = 24 V  10 = 32 V  11 = 4 0V     |                                                                   |                |       |       |

| BOOST_OCP  | 4:3          | R/W          | Selects the current limit for over-current protection:  00 = 600 mA  01 = 800 mA  10 = 1 A  11 = 1.2 A |                                                                   |                |       |       |

| SLOW_START | 2            | R/W          | Slows the boost of                                                                                     | output transition                                                 |                |       |       |

| SHIFT      | 1            | R/W          | For FMODE = $0$ :                                                                                      | nate oscillator frequents<br>SHIFT = 0F = 500<br>SHIFT = 0F = 1 M | kHz; SHIFT 1F  |       |       |

## Table 6. Boost Control (Offset = 0x02, Default = 0x38) (continued)

|       | Register Bits |             |                                                       |  |  |  |  |  |

|-------|---------------|-------------|-------------------------------------------------------|--|--|--|--|--|

| 7     | 6             | 5 4 3 2 1 0 |                                                       |  |  |  |  |  |

| FMODE | 0             | R/W         | Selects the boost frequency:<br>0 = 500 kHz, 1 = 1MHz |  |  |  |  |  |

# Table 7. Brightness A (Offset = 0x03, Default = 0x00)<sup>(1)</sup>

|      | Register Bits |        |                                                                                                          |      |      |      |      |  |

|------|---------------|--------|----------------------------------------------------------------------------------------------------------|------|------|------|------|--|

| 7    | 6             | 5      | 4 3 2 1 0                                                                                                |      |      |      | 0    |  |

| A[7] | A[6]          | A[5]   | A[4]                                                                                                     | A[3] | A[2] | A[1] | A[0] |  |

| Name | Bit           | Access | Description                                                                                              |      |      |      |      |  |

| Α    | [7:0]         | R/W    | Sets the 8-bit brightness value for outputs connected to Bank A. Minimum brightness setting is code 04h. |      |      |      |      |  |

(1) These registers are not update if the device is in Sleep Mode (Control: SLEEP\_STATUS = 1).

# Table 8. Brightness B (Offset = 0x04, Default = 0x00)<sup>(1)</sup>

|      | Register Bits |        |                                                                                                          |      |      |      |      |  |

|------|---------------|--------|----------------------------------------------------------------------------------------------------------|------|------|------|------|--|

| 7    | 6             | 5      | 4 3 2 1 0                                                                                                |      |      |      |      |  |

| B[7] | B[6]          | B[5]   | B[4]                                                                                                     | B[3] | B[2] | B[1] | B[0] |  |

| Name | Bit           | Access | Description                                                                                              |      |      |      |      |  |

| В    | [7:0]         | R/W    | Sets the 8-bit brightness value for outputs connected to Bank B. Minimum brightness setting is code 04h. |      |      |      |      |  |

(1) These registers are not update if the device is in Sleep Mode (Control: SLEEP\_STATUS = 1).

#### Table 9. Current A (Offset = 0x05, Default 0x1F)

| Register Bits |             |        |                                                                                                                                                                                                                                                                                                                                                 |      |      |      |      |  |  |

|---------------|-------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|--|--|

| 7             | 6           | 5      | 4                                                                                                                                                                                                                                                                                                                                               | 3    | 2    | 1    | 0    |  |  |

| Hysteresis    | Lower Bound |        | A[4]                                                                                                                                                                                                                                                                                                                                            | A[3] | A[2] | A[1] | A[0] |  |  |

| Name          | Bit         | Access | Description                                                                                                                                                                                                                                                                                                                                     |      |      |      |      |  |  |

| Hysteresis    | 7           | R/W    | Determines the hysteresis of the PWM Sampler. Clearing this bit, the PWM sampler changes its output upon detecting at least 3 equivalent code changes on the PWM input. Setting this bit, the PWM sampler changes its output upon detecting 2 equivalent code changes on the PWM input.                                                         |      |      |      |      |  |  |

| Lower Bound   | 6           | R/W    | Determines the lower bound of the PWM Sampler. Clearing this bit, the PWM sampler outputs code 6 when it detects equivalent codes 2 thru 6; and code 0 when it detects equivalent codes 0 thru 1. Setting this bit, the PWM sampler can output codes below 6, based upon the Hysteresis setting and equivalent code sampled from the input PWM. |      |      |      |      |  |  |

|               | 5           | Read   |                                                                                                                                                                                                                                                                                                                                                 |      |      |      |      |  |  |

| Α             | [4:0]       | R/W    | Sets the 5-bit full-scale current for outputs connected to Bank A.                                                                                                                                                                                                                                                                              |      |      |      |      |  |  |

## Table 10. Current B (Offset = 0x06, Default = 0x1F)

| Register Bits |       |        |                                                                   |      |      |      |      |

|---------------|-------|--------|-------------------------------------------------------------------|------|------|------|------|

| 7             | 6     | 5      | 4 3 2 1 0                                                         |      |      |      |      |

|               |       |        | B[4]                                                              | B[3] | B[2] | B[1] | B[0] |

| Name          | Bit   | Access | Description                                                       |      |      |      |      |

| В             | [4:0] | R/W    | Sets the 5-bit full-scale current for outputs connected to Bank B |      |      |      |      |

# Table 11. On/Off Ramp (Offset = 0x07, Default 0x00)

|         | Register Bits |            |                               |               |           |           |           |  |

|---------|---------------|------------|-------------------------------|---------------|-----------|-----------|-----------|--|

| 7       | 6             | 5          | 4                             | 3             | 2         | 1         | 0         |  |

|         |               | T_START[2] | T_START[1]                    | T_START[0]    | T_SHUT[2] | T_SHUT[1] | T_SHUT[0] |  |

| Name    | Bit           | Access     | Description                   |               |           |           |           |  |

|         | 7             | Read       |                               |               |           |           |           |  |

|         | 6             | Read       |                               |               |           |           |           |  |

| T_START | [5:3]         | R/W        | Ramp time for startup events. |               |           |           |           |  |

| T_SHUT  | [2:0]         | R/W        | Ramp time for shu             | tdown events. |           |           |           |  |

| Code | Start-Up Time | Shutdown Time |  |  |

|------|---------------|---------------|--|--|

| 000  | 4 ms          | 0*            |  |  |

| 001  | 261 ms        | 261 ms        |  |  |

| 010  | 522 ms        | 522 ms        |  |  |

| 011  | 1.045s        | 1.045 s       |  |  |

| 100  | 2.091s        | 2.091 s       |  |  |

| 101  | 4.182s        | 4.182 s       |  |  |

| 110  | 8.364s        | 8.364 s       |  |  |

| 111  | 16.73s        | 16.73 s       |  |  |

<sup>\*</sup>Code 0 results in approximately 0.5 ms ramp time.

Table 12. Run Ramp (Offset = 0x08, Default = 0x00)

|        | Register Bits |         |                           |  |  |  |  |  |  |  |  |  |  |

|--------|---------------|---------|---------------------------|--|--|--|--|--|--|--|--|--|--|

| 7      | 6             | 5       | 4 3 2 1 0                 |  |  |  |  |  |  |  |  |  |  |

|        |               | T_UP[2] | T_UP[1]                   |  |  |  |  |  |  |  |  |  |  |

| Name   | Bit           | Access  | Description               |  |  |  |  |  |  |  |  |  |  |

|        | 7             | Read    |                           |  |  |  |  |  |  |  |  |  |  |

|        | 6             | Read    |                           |  |  |  |  |  |  |  |  |  |  |

| T_UP   | [5:3]         | R/W     | Time for ramp-up events   |  |  |  |  |  |  |  |  |  |  |

| T_DOWN | [2:0]         | R/W     | Time for ramp-down events |  |  |  |  |  |  |  |  |  |  |

| Code | Ramp-Up Time | Ramp-down Time |  |  |

|------|--------------|----------------|--|--|

| 000  | 0*           | 0*             |  |  |

| 001  | 261 ms       | 261 ms         |  |  |

| 010  | 522 ms       | 522 ms         |  |  |

| 011  | 1.045s       | 1.045 s        |  |  |

| 100  | 2.091s       | 2.091 s        |  |  |

| 101  | 4.182s       | 4.182 s        |  |  |

| 110  | 8.364s       | 8.364 s        |  |  |

| 111  | 16.73s       | 16.73 s        |  |  |

<sup>\*</sup>Code 0 results in approximately 0.5 ms ramp time.

Table 13. Interrupt Status (Offset = 0x09, Default = 0x00)

|      |     |        | Registe            | r Bits            |     |     |     |

|------|-----|--------|--------------------|-------------------|-----|-----|-----|

| 7    | 6   | 5      | 4                  | 3                 | 2   | 1   | 0   |

|      |     |        |                    |                   | OCP | OVP | TSD |

| Name | Bit | Access | Description        |                   | •   |     |     |

|      | 7   | Read   |                    |                   |     |     |     |