# LM3478Q-Q1 昇圧、SEPIC、およびフライバック DC-DC コンバータ用、高効率コントローラ

## 1 特長

- LM3478Q-Q1 は AEC-Q100 の認定を受けており、車載グレードのフローで製造

- 8 リードの VSSOP-8

- 1A のピーク電流能力を備えたプッシュプル ドライバを内蔵

- 電流制限とサーマル シャットダウン

- コンデンサと抵抗により周波数補償を最適化

- 内部ソフトスタート

- 電流モード動作

- ヒステリシス付きの低電圧誤動作防止

- 主な仕様:

- 広い電源電圧範囲: 2.97V ~ 40V

- 調整可能なクロック周波数: 100kHz ~ 1MHz

- 内部基準電圧の精度は全温度範囲で  $\pm 2.5\%$

- 10 $\mu$ A のシャットダウン電流 (全温度範囲)

- [WEBENCH Power Designer](#) により、LM3478Q-Q1 を使用したカスタム設計を作成

## 2 アプリケーション

- トラクションインバータおよびオンボード充電器の絶縁型電源 (フライバック)

- ADAS - 運転者監視

- デジタルコックピットおよびヘッドユニット

一般的な高効率昇圧 (ブースト) コンバータ

## 3 説明

LM3478Q-Q1 は、スイッチング レギュレータ用の多用途ローサイド N チャネル MOFFET コントローラです。昇圧、フライバック、SEPIC など、ローサイド MOSFET の必要な回路に適しています。さらに、LM3478Q-Q1 はきわめて高いスイッチング周波数で動作できるので、ソリューションサイズを低減することができます。LM3478Q-Q1 のスイッチング周波数は、1 個の外付け抵抗を使用することにより、100kHz ~ 1MHz の任意の値に調整できます。電流モード制御を使うと、サイクルごとの電流制限が可能になることに加え、優れた帯域幅と過渡応答が得られます。出力電流は、1 個の外付け抵抗で設定できます。

LM3478Q-Q1 にはサーマルシャットダウン、短絡保護、過電圧保護などの機能が組み込まれています。省電力シヤットダウンモードにより、5 $\mu$ A への合計消費電流が低減され、電源シーケンスが可能になります。内部ソフトスタートにより、スタートアップ時の突入電流が制限されます。

### 製品情報

| 部品番号       | パッケージ (1) | 本体サイズ (公称)       |

|------------|-----------|------------------|

| LM3478Q-Q1 | VSSOP (8) | 3.00mm × 3.00 mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあります。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                    |           |                               |           |

|--------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>        | <b>1</b>  | <b>7 アプリケーションと実装</b>          | <b>16</b> |

| <b>2 アプリケーション</b>  | <b>1</b>  | <b>7.1 アプリケーション情報</b>         | <b>16</b> |

| <b>3 説明</b>        | <b>1</b>  | <b>7.2 代表的なアプリケーション</b>       | <b>16</b> |

| <b>4 ピン構成および機能</b> | <b>3</b>  | <b>7.3 電源に関する推奨事項</b>         | <b>28</b> |

| <b>5 仕様</b>        | <b>4</b>  | <b>7.4 レイアウト</b>              | <b>28</b> |

| 5.1 絶対最大定格         | 4         | <b>8 デバイスおよびドキュメントのサポート</b>   | <b>31</b> |

| 5.2 ESD 定格         | 4         | 8.1 デバイス サポート                 | 31        |

| 5.3 推奨動作条件         | 4         | 8.2 開発サポート                    | 31        |

| 5.4 熱に関する情報        | 4         | 8.3 ドキュメントのサポート               | 31        |

| 5.5 電気的特性          | 5         | 8.4 ドキュメントの更新通知を受け取る方法        | 31        |

| 5.6 代表的特性          | 7         | 8.5 サポート・リソース                 | 31        |

| <b>6 詳細説明</b>      | <b>11</b> | 8.6 商標                        | <b>31</b> |

| 6.1 概要             | 11        | 8.7 静電気放電に関する注意事項             | <b>32</b> |

| 6.2 機能ブロック図        | 12        | 8.8 用語集                       | <b>32</b> |

| 6.3 機能説明           | 12        | <b>9 改訂履歴</b>                 | <b>32</b> |

| 6.4 デバイスの機能モード     | 15        | <b>10 メカニカル、パッケージ、および注文情報</b> | <b>32</b> |

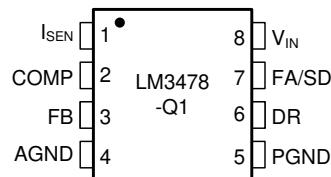

## 4 ピン構成および機能

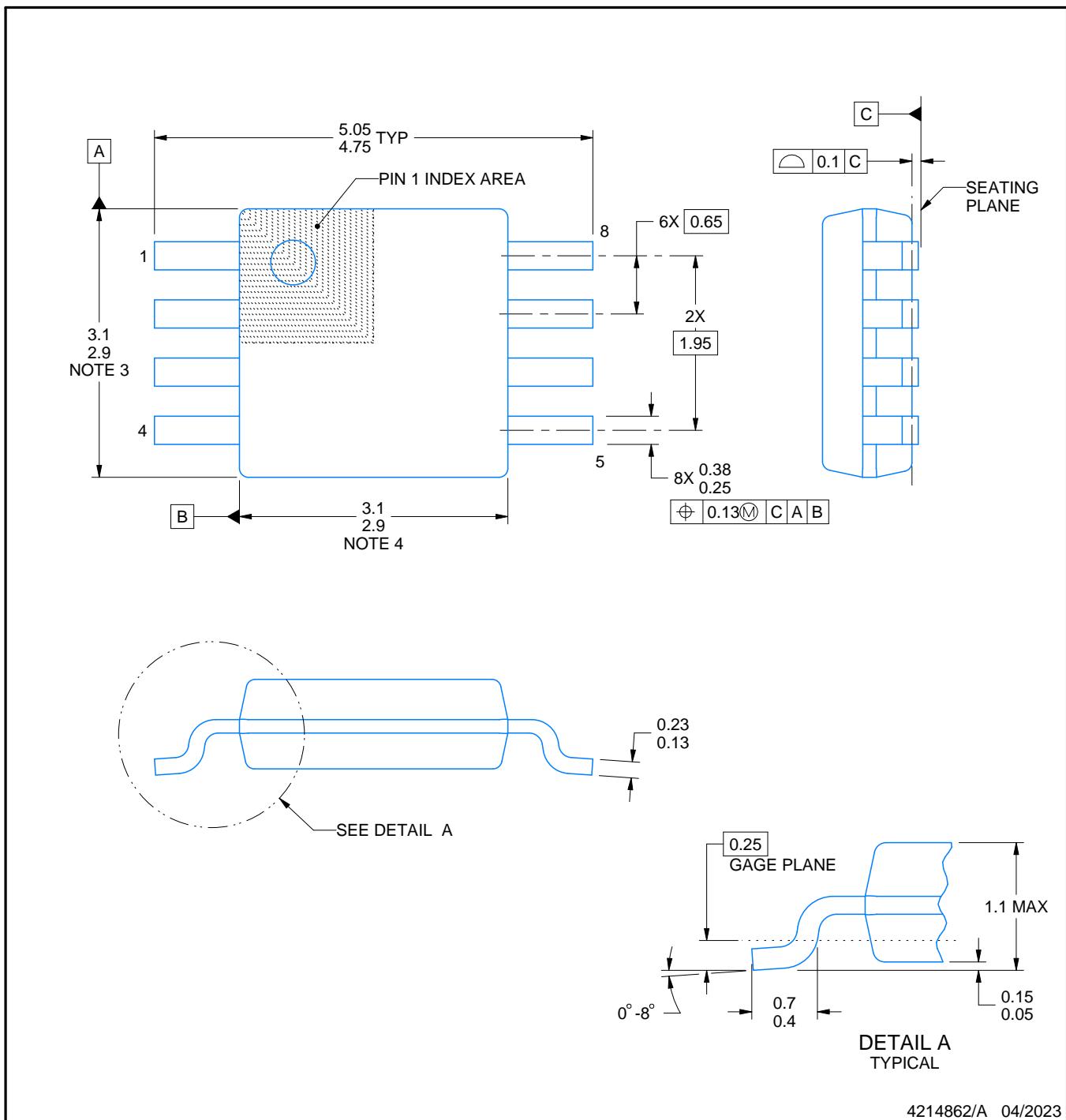

図 4-1. LM3478-Q1 DGK パッケージ、VSSOP-8 (上面図)

表 4-1. ピンの機能

| ピン               |    | I/O | 説明                                                                                                                            |

|------------------|----|-----|-------------------------------------------------------------------------------------------------------------------------------|

| 名称               | 番号 |     |                                                                                                                               |

| I <sub>SEN</sub> | 1  | I   | 電流検出入力ピン。外部センス抵抗の両端で生成される電圧がこのピンに供給されます。                                                                                      |

| COMP             | 2  | I   | 補償ピン。このピンに抵抗とコンデンサを組み合わせて接続することで、制御ループを補正できます。                                                                                |

| FB               | 3  | I   | フィードバックピン。出力電圧は、分圧抵抗を使用して、このピンに 1.26V を供給するよう調整する必要があります。                                                                     |

| AGND             | 4  | G   | アナログ グランドピン。                                                                                                                  |

| PGND             | 5  | G   | 電源グランドピン。                                                                                                                     |

| DR               | 6  | O   | 駆動ピン。外部 MOSFET のゲートをこのピンに接続する必要があります。                                                                                         |

| FA/SD            | 7  | I   | 周波数調整およびシャットダウンピン。このピンに接続する抵抗によって、発信機周波数が設定されます。このピンが 30μs よりも長い間 High になると、デバイスはオフになります。これにより、デバイスが電源から取り出す電流は 10μA 未満になります。 |

| V <sub>IN</sub>  | 8  | P   | 電源入力ピン。                                                                                                                       |

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                      |            | 最小値                | 最大値             | 単位 |

|----------------------|------------|--------------------|-----------------|----|

| 入力電圧                 |            |                    | 45              | V  |

| FB ピン電圧              |            | -0.4 < V           | $V_{FB} < 7$    | V  |

| FA/SD ピン電圧           |            | $-0.4 < V_{FA/SD}$ | $V_{FA/SD} < 7$ | V  |

| ピークドライバ出力電流 (< 10μs) |            |                    | 1               | A  |

| 電力散逸                 |            | 内部的に制限             |                 |    |

| 接合部温度                |            |                    | +150            | °C |

| リード温度                | 気相 (60 秒)  |                    | 215             | °C |

|                      | 赤外線 (15 秒) |                    | 260             | °C |

| DR ピン電圧              |            | -0.4 ≤ VDR         | $VDR \leq 8$    | V  |

| $I_{SEN}$ ピン電圧       |            |                    | 500             | mV |

| $T_{stg}$            | 保存温度       | -65                | 150             | °C |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これらはあくまでもストレス定格であり、推奨動作条件に示されている条件を超える当該の条件またはその他のいかなる条件下での、デバイスの正常な動作を保証するものではありません。絶対最大定格の状態が長時間続くと、デバイスの信頼性に影響を与える可能性があります。

### 5.2 ESD 定格

|             |      |                                            | 値     | 単位 |

|-------------|------|--------------------------------------------|-------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、AEC Q100-002 準拠 <sup>(1)</sup> | ±2000 | V  |

|             |      | デバイス帶電モデル (CDM)、AEC Q100-011 準拠            | ±750  |    |

|             |      | コーナー ピン (1, 4, 5, 8)                       | ±750  |    |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|           | 最小値                | 公称値 | 最大値                | 単位  |

|-----------|--------------------|-----|--------------------|-----|

| 電源電圧      | $2.97 \leq V_{IN}$ |     | $V_{IN} \leq 40$   | V   |

| 接合部温度範囲   | $-40 \leq T_J$     |     | $T_J \leq +125$    | °C  |

| スイッチング周波数 | $100 \leq f_{SW}$  |     | $f_{SW} \leq 1000$ | kHz |

### 5.4 热に関する情報

| 熱評価基準 <sup>(1)</sup> |                     | LM3478Q-Q1 | 単位   |

|----------------------|---------------------|------------|------|

|                      |                     | DGK        |      |

|                      |                     | 8 ピン       |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 151.2      | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 45.3       | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 85.6       | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 1.5        | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 84.2       | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 | 該当なし       | °C/W |

- (1) 従来および新しい熱評価基準の詳細については、『IC パッケージの熱評価基準』アプリケーション レポート、SPRA953 を参照してください。

## 5.5 電気的特性

特に記述のない限り、 $V_{IN} = 12V$ 、 $R_{FA} = 40k\Omega$ 、 $T_J = 25^\circ C$

| パラメータ             | テスト条件                                                                                    | 最小値    | 標準値      | 最大値       | 単位     |

|-------------------|------------------------------------------------------------------------------------------|--------|----------|-----------|--------|

| $V_{FB}$          | $V_{COMP} = 1.4V, 2.97 \leq V_{IN} \leq 40V$                                             | 1.2416 | 1.26     | 1.2843    | V      |

|                   | $V_{COMP} = 1.4V, 2.97 \leq V_{IN} \leq 40V, -40^\circ C \leq T_J \leq 125^\circ C$      | 1.228  |          | 1.292     |        |

| $\Delta V_{LINE}$ | 帰還電圧ラインレギュレーション<br>$2.97 \leq V_{IN} \leq 40V$                                           |        | 0.001    |           | %/V    |

| $\Delta V_{LOAD}$ | 出力電圧負荷レギュレーション<br>$I_{EAO}$ ソース/シンク                                                      |        |          | $\pm 0.5$ | %/A    |

| $V_{UVLO}$        | 入力低電圧誤動作防止                                                                               |        | 2.85     |           | V      |

|                   | $-40^\circ C \leq T_J \leq 125^\circ C$                                                  |        |          | 2.97      |        |

| $V_{UV(HYS)}$     | 入力低電圧誤動作防止ヒステリシス                                                                         |        | 170      |           | mV     |

|                   | $-40^\circ C \leq T_J \leq 125^\circ C$                                                  | 130    |          | 210       |        |

| $F_{nom}$         | 公称スイッチング周波数<br>$R_{FA} = 40k\Omega$                                                      |        | 400      |           | kHz    |

|                   | $R_{FA} = 40k\Omega, -40^\circ C \leq T_J \leq 125^\circ C$                              | 350    |          | 440       |        |

| $R_{DS1 (ON)}$    | ドライバスイッチオン抵抗 (上)<br>$I_{DR} = 0.2A, V_{IN} = 5V$                                         |        | 16       |           | \Omega |

| $R_{DS2 (ON)}$    | ドライバスイッチオン抵抗 (下)<br>$I_{DR} = 0.2A$                                                      |        | 4.5      |           |        |

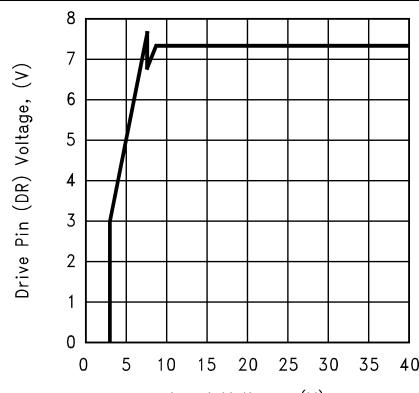

| $V_{DR (\max)}$   | 最大駆動電圧振幅 <sup>(1)</sup><br>$V_{IN} < 7.2V$                                               |        | $V_{IN}$ |           | V      |

|                   | $V_{IN} \geq 7.2V$                                                                       |        | 7.2      |           |        |

| $D_{max}$         | 最大デューティサイクル <sup>(2)</sup>                                                               |        | 100%     |           |        |

| $T_{min (on)}$    | 最小オン時間                                                                                   |        | 325      |           | ns     |

|                   | $-40^\circ C \leq T_J \leq 125^\circ C$                                                  | 210    |          | 600       |        |

| $I_{SUPPLY}$      | 電源電流 (非スイッチング)<br><sup>(3)</sup> を参照                                                     |        | 2.7      |           | mA     |

|                   | <sup>(3)</sup> を参照、 $-40^\circ C \leq T_J \leq 125^\circ C$                              |        | 3.3      |           |        |

| $I_Q$             | シャットダウン モードの静止電流<br>$V_{FA/SD} = 5V$ <sup>(4)</sup> 、 $V_{IN} = 5V$                      |        | 5        |           | \mu A  |

|                   | $V_{FA/SD} = 5V$ <sup>(4)</sup> 、 $V_{IN} = 5V, -40^\circ C \leq T_J \leq 125^\circ C$   |        | 10       |           |        |

| $V_{SENSE}$       | 電流検出スレッショルド電圧<br>$V_{IN} = 5V$                                                           | 135    | 156      | 180       | mV     |

|                   | $V_{IN} = 5V, -40^\circ C \leq T_J \leq 125^\circ C$                                     | 125    |          | 190       |        |

| $V_{SC}$          | 短絡電流制限検出電圧<br>$V_{IN} = 5V$                                                              |        | 343      |           | mV     |

|                   | $V_{IN} = 5V, -40^\circ C \leq T_J \leq 125^\circ C$                                     | 250    |          | 415       |        |

| $V_{SL}$          | 内部補償ランプ電圧<br>$V_{IN} = 5V$                                                               |        | 92       |           | mV     |

|                   | $V_{IN} = 5V, -40^\circ C \leq T_J \leq 125^\circ C$                                     | 52     |          | 132       |        |

| $V_{SL}$ 率        | $V_{SL}/V_{SENSE}$                                                                       | 0.30   | 0.49     | 0.70      |        |

| $V_{OVP}$         | $V_{COMP} = 1.4V$                                                                        | 32     | 50       |           | mV     |

|                   | $V_{COMP} = 1.4V, -40^\circ C \leq T_J \leq 125^\circ C$                                 | 25     |          |           |        |

|                   | VSSOP パッケージ                                                                              |        | 78       |           |        |

|                   | VSSOP パッケージ、 $-40^\circ C \leq T_J \leq 125^\circ C$                                     |        | 85       |           |        |

| $V_{OVP(HYS)}$    | $V_{COMP} = 1.4V$                                                                        |        | 60       |           | mV     |

|                   | $V_{COMP} = 1.4V, -40^\circ C \leq T_J \leq 125^\circ C$                                 | 20     |          | 110       |        |

| $G_m$             | エラーインプの相互コンダクタンス<br>$V_{COMP} = 1.4V, I_{EAO} = 100\mu A$ (ソース/シンク)                      | 600    | 800      | 1000      | \mu S  |

|                   | $V_{COMP} = 1.4V, I_{EAO} = 100\mu A$ (ソース/シンク)、 $-40^\circ C \leq T_J \leq 125^\circ C$ | 365    |          | 1265      |        |

| $A_{VOL}$         | エラーインプ電圧ゲイン<br>$V_{COMP} = 1.4V, I_{EAO} = 100\mu A$ (ソース/シンク)                           |        | 38       |           | V/V    |

|                   | $V_{COMP} = 1.4V, I_{EAO} = 100\mu A$ (ソース/シンク)、 $-40^\circ C \leq T_J \leq 125^\circ C$ | 26     |          | 44        |        |

| $I_{EAO}$         | エラーインプの出力電流 (ソース/シンク)<br>$V_{COMP} = 1.4V, V_{FB} = 0V$                                  | 80     | 110      | 170       | \mu A  |

|                   | $V_{COMP} = 1.4V, V_{FB} = 0V, -40^\circ C \leq T_J \leq 125^\circ C$                    | 50     |          | 220       |        |

|                   | シンク、 $V_{COMP} = 1.4V, V_{FB} = 1.4V$                                                    | -70    | -140     | -180      | \mu A  |

|                   | $V_{COMP} = 1.4V, V_{FB} = 1.4V, -40^\circ C \leq T_J \leq 125^\circ C$                  | -60    |          | -185      |        |

## 5.5 電気的特性 (続き)

特に記述のない限り、 $V_{IN} = 12V$ 、 $R_{FA} = 40k\Omega$ 、 $T_J = 25^\circ C$

| パラメータ     | テスト条件                                                                         | 最小値                                           | 標準値  | 最大値 | 単位         |

|-----------|-------------------------------------------------------------------------------|-----------------------------------------------|------|-----|------------|

| $V_{EAO}$ | 上限、 $V_{FB} = 0V$ 、COMP ピン = フローティング                                          |                                               | 2.2  |     | V          |

|           | 上限、 $V_{FB} = 0V$ 、COMP ピン = フローティング、 $-40^\circ C \leq T_J \leq 125^\circ C$ | 1.8                                           |      | 2.4 |            |

|           | 下限、 $V_{FB} = 1.4V$                                                           |                                               | 0.56 |     | V          |

|           | 下限、 $V_{FB} = 1.4V$ 、 $-40^\circ C \leq T_J \leq 125^\circ C$                 | 0.2                                           |      | 1.0 |            |

| $T_{SS}$  | 内部ソフトスタート遅延                                                                   | $V_{FB} = 1.2V$ 、 $V_{COMP} = \text{フローティング}$ | 4    |     | ms         |

| $T_r$     | 駆動ピンの立ち上がり時間                                                                  | $C_{GS} = 3000pf$ 、 $V_{DR} = 0 \sim 3V$      | 25   |     | ns         |

| $T_f$     | 駆動ピンの立ち下がり時間                                                                  | $C_{GS} = 3000pf$ 、 $V_{DR} = 0 \sim 3V$      | 25   |     | ns         |

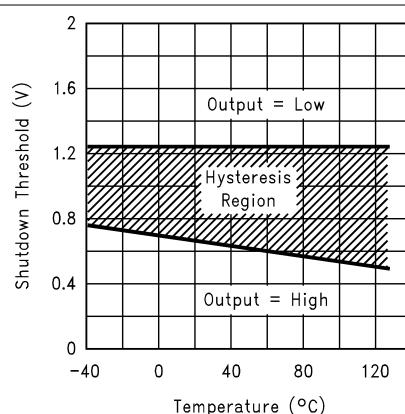

| $V_{SD}$  | 出力 = High                                                                     |                                               | 1.27 |     | V          |

|           | 出力 = High、 $-40^\circ C \leq T_J \leq 125^\circ C$                            |                                               |      | 1.4 |            |

|           | 出力 = Low                                                                      |                                               | 0.65 |     | V          |

|           | 出力 = Low、 $-40^\circ C \leq T_J \leq 125^\circ C$                             | 0.3                                           |      |     |            |

| $I_{SD}$  | シャットダウンピンの電流                                                                  | $V_{SD} = 5V$                                 | -1   |     | $\mu A$    |

| $I_{FB}$  | フィードバックピンの電流                                                                  | $V_{SD} = 0V$                                 | +1   |     | nA         |

| $T_{SD}$  | サーマルシャットダウン                                                                   |                                               |      | 165 | $^\circ C$ |

| $T_{sh}$  | サーマル シャットダウンのヒス<br>テリシス                                                       |                                               |      | 10  | $^\circ C$ |

- (1) 駆動ピンの電圧  $V_{DR}$  は、入力電圧が 7.2V より低いときは入力電圧と等しくなります。入力電圧が 7.2V 以上のとき、 $V_{DR}$  は 7.2V と等しくなります。

- (2) この部品では最大デューティサイクルが 100% 未満の動作を許可していないため、最大デューティサイクルの制限値は指定できません。

- (3) このテストでは、40-K の抵抗を使用して FA/SD ピンをグランドにプルしています。

- (4) このテストでは、40-K の抵抗を使用して FA/SD ピンを 5V にプルします。

- (5) 過電圧保護機能は、帰還電圧を基準に指定されています。これは、過電圧保護回路が帰還電圧を追跡するためです。過電圧保護スレッショルドは、過電圧保護仕様に帰還電圧  $V_{FB}$  を追加することで求められます。

- (6) レギュレータをオフにするには、FA/SD ピンを抵抗経由で  $V_{IN}$  にプルする必要があります。FA/SD ピンの電圧は、レギュレータをオフに維持するためには出力 = High の最大制限を上回る必要があり、レギュレータをオンに維持するためには出力 = Low の制限を下回る必要があります。

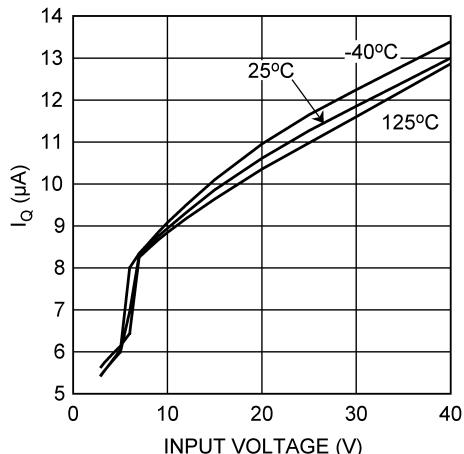

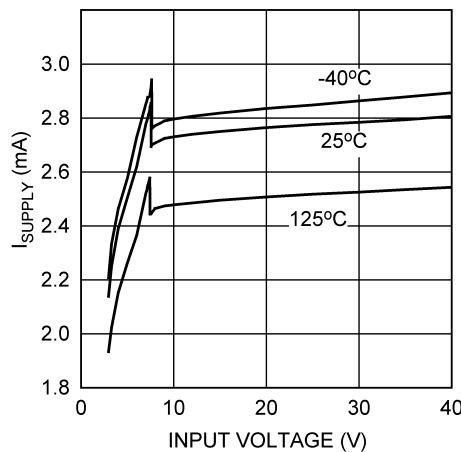

## 5.6 代表的特性

特に記述のない限り、 $V_{IN} = 12V$ 、 $T_J = 25^{\circ}\text{C}$ 。

図 5-1.  $I_Q$  と電源電圧の関係 (シャットダウン)

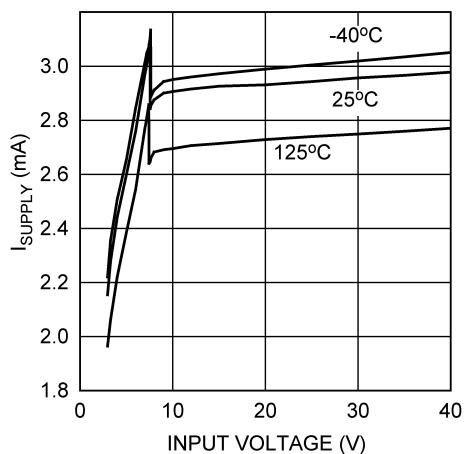

図 5-2.  $I_{\text{Supply}}$  と入力電圧との関係 (非スイッチング)

図 5-3.  $I_{\text{Supply}}$  と  $V_{IN}$  との関係 (スイッチング)

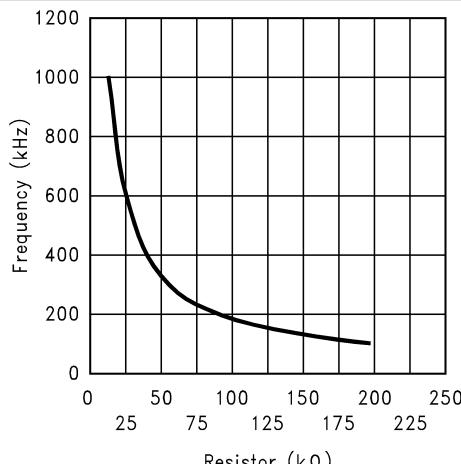

図 5-4. スイッチング周波数と  $R_{FA}$  との関係

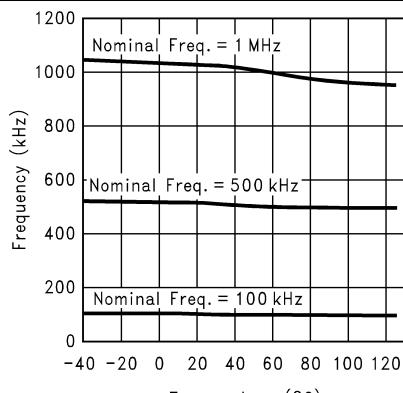

図 5-5. 周波数と温度との関係

図 5-6. 駆動電圧と入力電圧との関係

## 5.6 代表的特性 (続き)

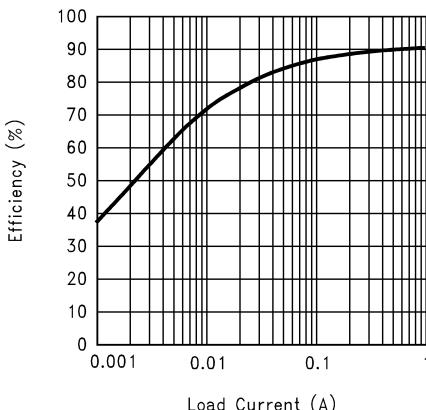

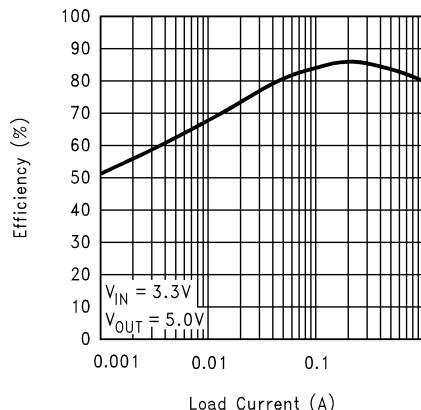

特に記述のない限り、 $V_{IN} = 12V$ 、 $T_J = 25^{\circ}\text{C}$ 。

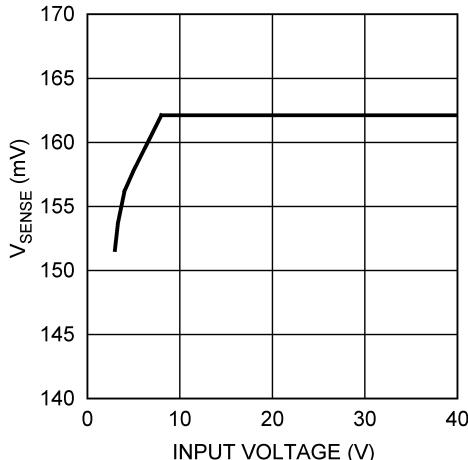

図 5-7. 電流検出スレッショルドと入力電圧との関係

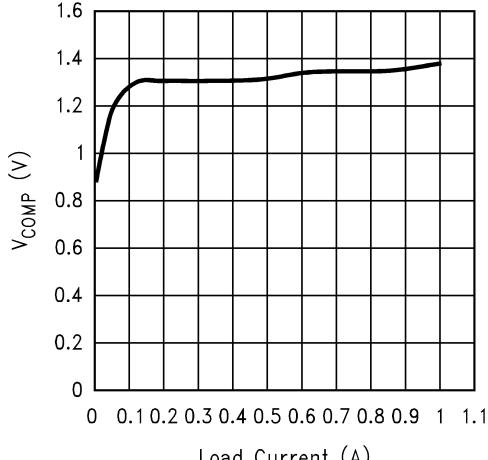

図 5-8. COMP ピンの電圧と負荷電流との関係

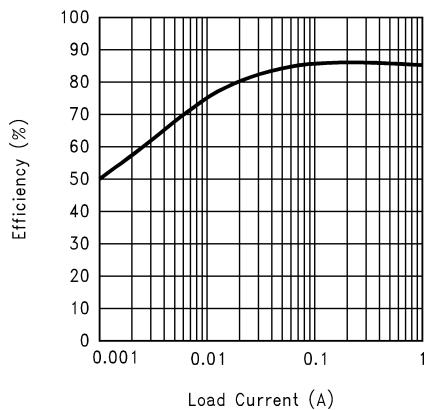

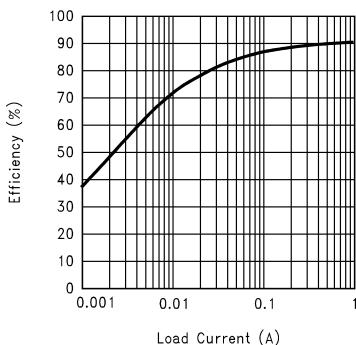

図 5-9. 効率と負荷電流との関係 (3.3-V 入力および 12-V 出力)

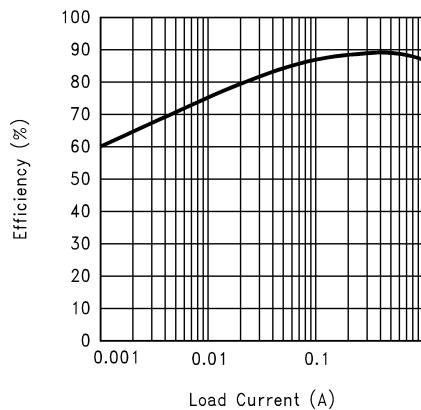

図 5-10. 効率と負荷電流との関係 (5-V 入力および 12-V 出力)

図 5-11. 効率と負荷電流との関係 (9-V 入力および 12-V 出力)

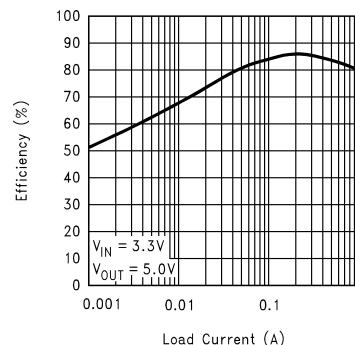

図 5-12. 効率と負荷電流との関係 (3.3-V 入力および 5-V 出力)

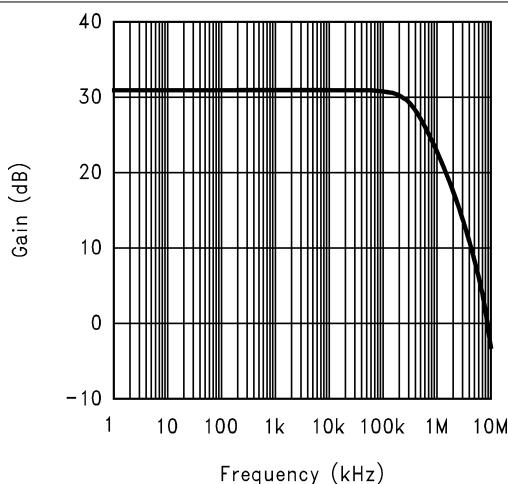

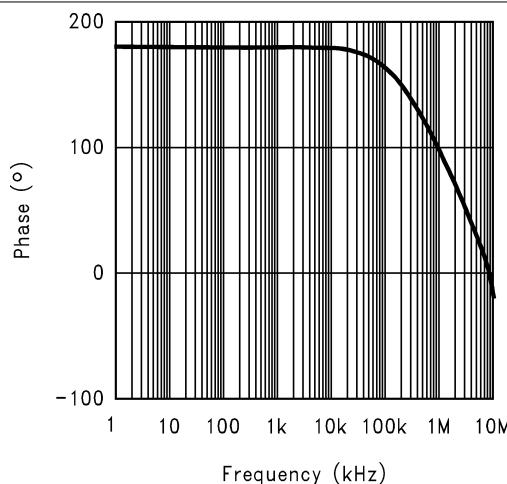

## 5.6 代表的特性 (続き)

特に記述のない限り、 $V_{IN} = 12V$ 、 $T_J = 25^{\circ}\text{C}$ 。

図 5-13. エラーアンプのゲイン

図 5-14. エラーアンプの位相

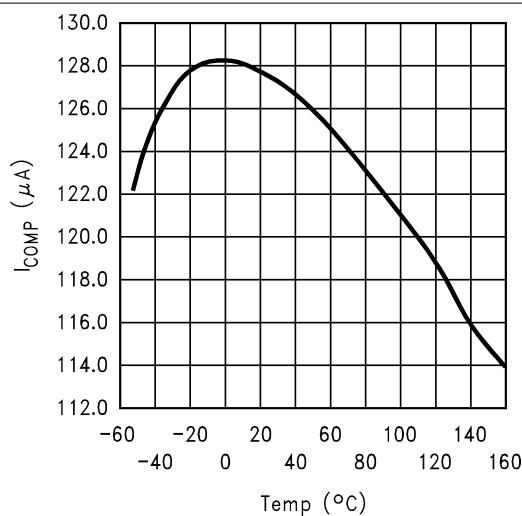

図 5-15. COMP ピンソース電流と温度との関係

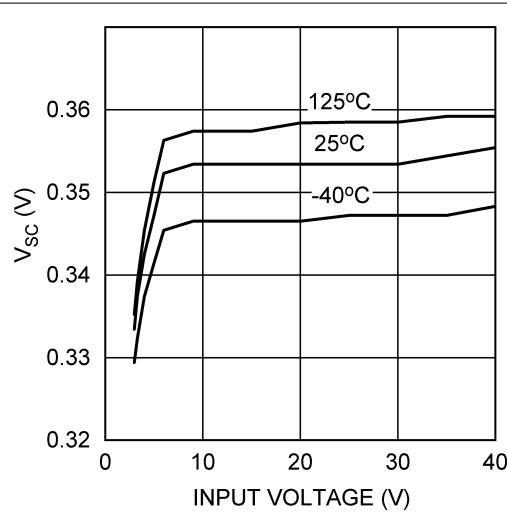

図 5-16. 短絡検出電圧と入力電圧との関係

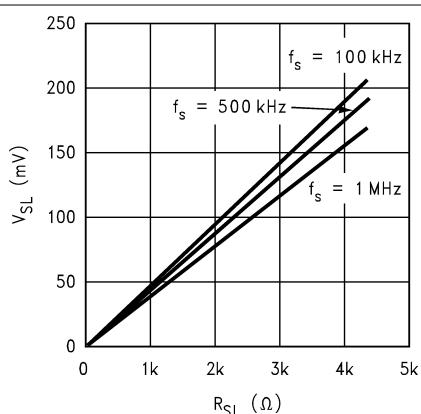

図 5-17. 準備ランプと準備抵抗との関係

図 5-18. シャットダウンスレッショルドのヒステリシスと温度との関係

## 5.6 代表的特性 (続き)

特に記述のない限り、 $V_{IN} = 12V$ 、 $T_J = 25^\circ C$ 。

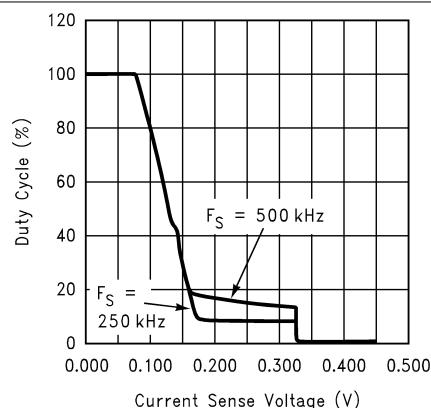

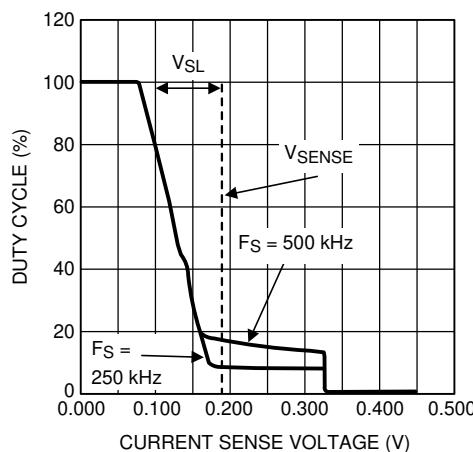

図 5-19. デューティサイクルと電流検出電圧との関係

## 6 詳細説明

### 6.1 概要

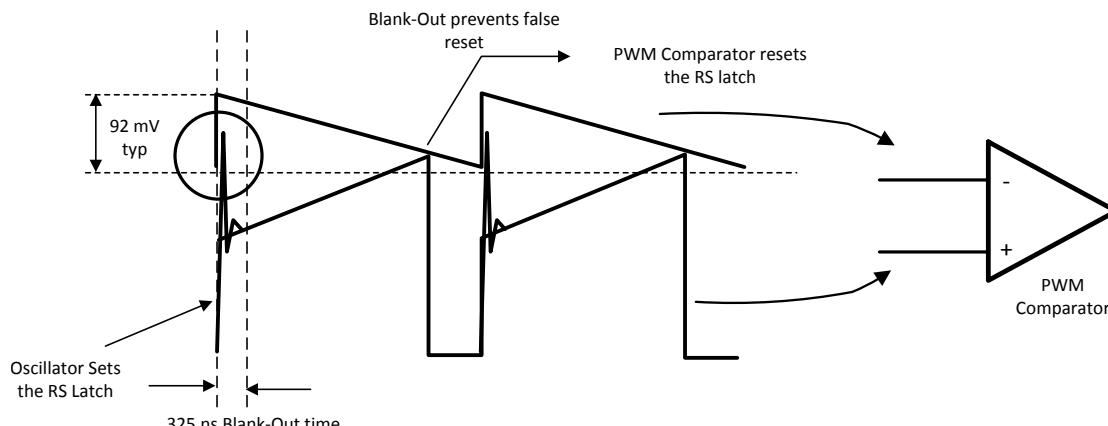

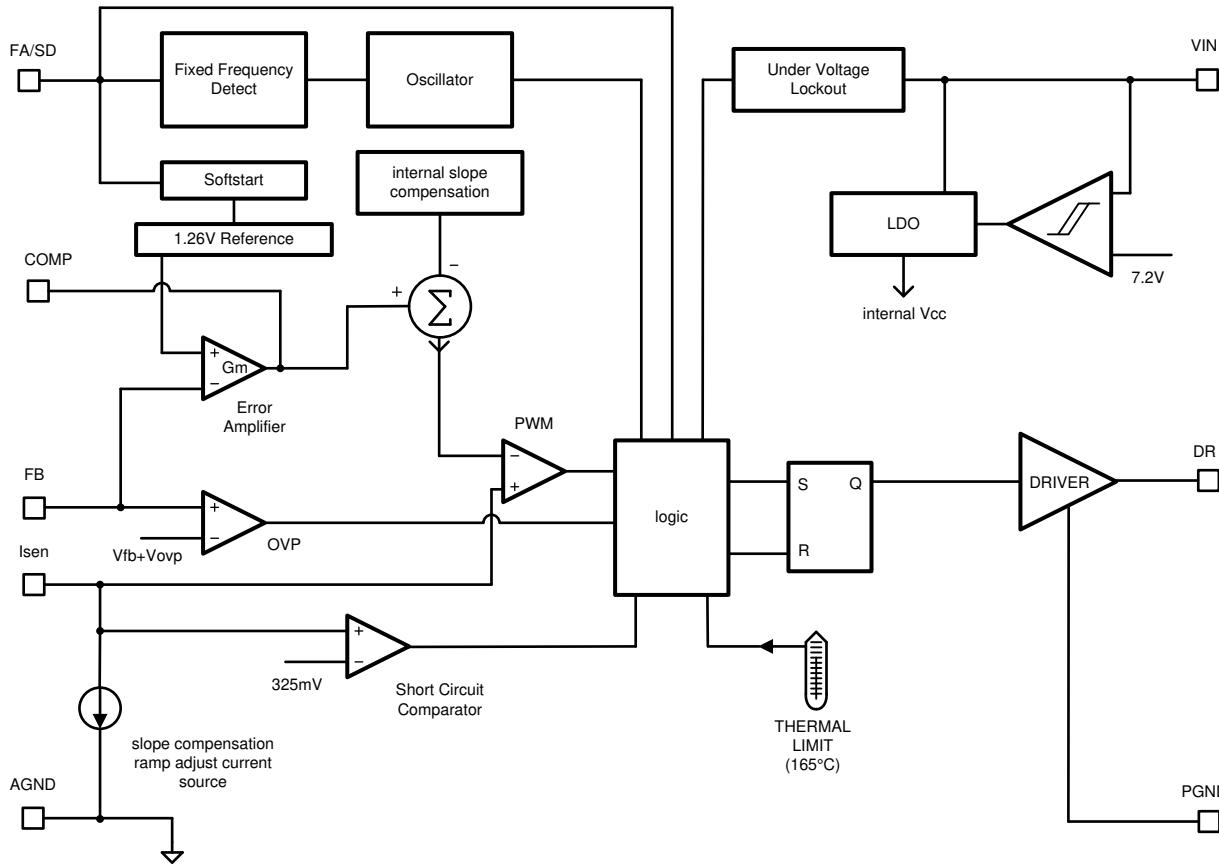

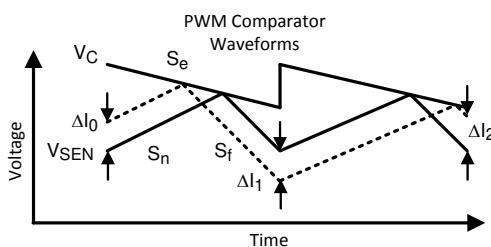

LM3478Q-Q1 デバイスは、固定周波数のパルス幅変調 (PWM) 電流モード制御アーキテクチャを使用しています。[セクション 6.2](#) に、基本機能を示します。代表的なアプリケーション回路では、外部 MOSFET を流れるピーク電流は外部センサ抵抗を介して検出されます。この抵抗の両端の電圧は、 $I_{SEN}$  ピンに供給されます。この電圧は PWM コンパレータの正の入力に供給されます。出力電圧も外部帰還抵抗分圧回路を介して検出され、エラーアンプの負入力 (フィードバックピン、FB) に供給されます。エラーアンプ (COMP ピン) の出力はスロープ補償ランプに追加され、PWM コンパレータの負入力に供給されます。スイッチングサイクルが開始されると、発振器はスイッチロジックブロックを使用して RS ラッチを設定します。これにより、DR ピン (外部 MOSFET のゲート) に High 信号が強制的に印加され、外部 MOSFET がオンになります。PWM コンパレータの正入力の電圧が負入力を超えると、RS ラッチがリセットされ、外部 MOSFET がオフになります。

図 6-1 に示すように、センサ抵抗の両端で検出される電圧には通常、スプリアスノイズスパイクが含まれています。これらのスパイクにより、PWM コンパレータが RS ラッチのリセット時期が早まる可能性があります。これらのスパイクによってラッチがリセットされないようにするために、IC 内部のブランクアウト回路は、ラッチがセットされた後の短時間 PWM コンパレータによるラッチのリセットを防止します。この時間は約 325ns で、ブランкиング間隔と呼ばれます。これは「電気的特性」セクションで最小オン時間として指定されています。非常に軽負荷または無負荷の状況では、ブランкиング期間中に外部 MOSFET がオンのときに出力コンデンサに供給されるエネルギーは、負荷に供給されるエネルギーよりも大きくなります。LM3478Q-Q1 に内蔵された過電圧コンパレータは、このような状況で出力電圧が上昇することを防止します。過電圧コンパレータは帰還 (FB ピン) 電圧を検出し、RS ラッチをリセットします。出力が減衰して公称値になるまで、ラッチはリセット状態を維持します。

図 6-1. PWM コンパレータの基本動作

## 6.2 機能ブロック図

Copyright © 2017, Texas Instruments Incorporated

## 6.3 機能説明

### 6.3.1 過電圧保護

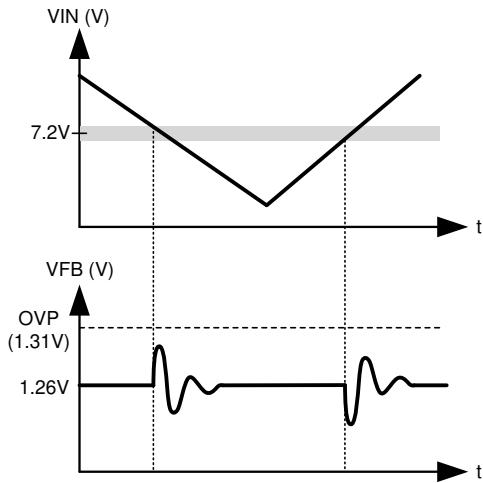

LM3478Q-Q1 は、出力電圧の過電圧保護 (OVP) 機能を備えています。OVP は帰還ピン (ピン 3) で検出されます。帰還ピンの電圧が  $V_{FB} + V_{OVP}$  まで上昇するたび、OVP がトリガれます。 $V_{FB}$  および  $V_{OVP}$  の制限については、[セクション 5.5](#) セクションを参照してください。

OVP により、駆動ピンが Low になり、パワー MOSFET が強制的にオフになります。MOSFET がオフになると、出力電圧は低下します。帰還電圧が  $V_{FB} + (V_{OVP} - V_{OVP(HYS)})$  に達すると、LM3478Q-Q1 は再びスイッチングを開始します。 $V_{OVP(HYS)}$  の制限については、[セクション 5.5](#) を参照してください。

安定していない入力電圧が 7.2V を超えると OVP がトリガれます。出力電圧は、図 6-2 に示すように反応します。LM3478Q-Q1 の内部バイアスは、ブロック図に示すように内部 LDO から供給されるか、Vin ピンの電圧が直接使用されます。Vin 電圧が 7.2V より低い場合、内部 IC バイアスは Vin 電圧になり、電圧が 7.2V を超えている場合、LM3478Q-Q1 の内部 LDO がバイアスを供給します。スイッチャーバースレッショルドの 7.2V で、LM3478Q-Q1 のすべての内部ブロックで、バイアス電圧の急激な小さな変化が見られます。バイアスが変化したため制御電圧がシフトすると、PWM コンペレータは安定化を試みます。PWM コンペレータのシナリオは負荷電流のステップ変動と同じであるため、出力電圧での応答はステップ負荷変動で観察される応答と同じになります。そのため、この場合の出力電圧オーバーシュートによって OVP もトリガされる可能性があります。LM3478Q-Q1 は、ヒステリシスモードで数サイクルにわたってレギュレーションされます。または回復せずに、負荷電流が低下するか Vin が 7.2V のスレッショルドを超えるくなるまで、単純にヒステリシスモードにとどまる可能性があります。出力はヒステリシスモードでもレギュレーションされることに注意してください。

アプリケーションの要件に応じて、この効果に何らかの影響があります。 $V_{IN}$  に直列に抵抗を追加すると、7.2V のスレッショルドを高い電圧にシフトできます。 $V_{IN}$  がスレッショルドの 7.2V に非常に近い場合は、 $V_{IN}$  のわずかなリップルにより、

スレッショルドを交差または超える可能性があります。出力電圧への影響を最小限に抑えるために、RC フィルタを使用して  $V_{IN}$  ピンをフィルタリングできます。

図 6-2. 入力電圧が 7.2V の内部バイアスレッショルドを超えると、帰還電圧に発振が生じます

### 6.3.2 スロープ補償ランプ

LM3478Q-Q1 は電流モード制御方式を使用しています。電流モード制御の主な利点は、スイッチのための固有のサイクル単位の電流制限と、単純な制御ループ特性です。電流共有が自動的であるため、電流モード制御を使用して出力段を並列接続することも容易です。ただし、図 6-3 に示すように、デューティサイクルが 50% を超えると電流モード制御は本質的に不安定です。

負荷電流がわずかに増加すると、スイッチ電流は  $\Delta I_0$  増加します。この負荷変化の影響は  $\Delta I_1$  です。

ここに示されている 2 つの立体的な波形は、内部パルス幅変調器と対比した波形で、MOSFET 駆動信号の生成に使用されます。スロープ  $S_e$  の一番上の波形は、内部で生成される制御波形  $V_C$  です。スロープ  $S_n$  と  $S_f$  の下側の波形は、検出されたインダクタ電流波形  $V_{SEN}$  です。

図 6-3.  $D > 0.5$  の分数調波振動と、分数調波の発振を防止する補償ランプ

分数調波振動は幾何学的问题として容易に理解できます。制御信号にスロープがない場合、インダクタ電流を表すスロープは制御信号に達するまで上昇し、その後再び下向きスロープになります。デューティサイクルが 50% を超えると、振動は収束せずにサイクルごとに分岐し、分数調波発振が発生します。

あるサイクルから次のサイクルへのインダクタ電流の差は、式 1 に示すように  $S_n$ 、 $S_f$ 、 $S_e$  の関数であることがわかります。

$$\Delta I_n = \frac{S_f - S_e}{S_n + S_e} \Delta I_{n-1} \quad (1)$$

したがって、量  $(S_f - S_e)/(S_n + S_e)$  が 1 より大きい場合、インダクタ電流が分岐して分数調波発振を引き起します。これはすべての電流モードのトポロジにおいて重要です。LM3478Q-Q1 には内部スロープ補償  $V_{SL}$  があり、50% のデューティサイクルを超える多くのアプリケーションで分数調波発振を回避することができます。

昇圧アプリケーションの場合、スロープ  $S_e, S_f, S_n$  は式 2、式 3、式 4 で計算できます。

$$S_e = V_{SL} \times f_s \quad (2)$$

$$S_f = R_{SEN} \times (V_{OUT} - V_{IN}) / L \quad (3)$$

$$S_n = V_{IN} \times R_{SEN} / L \quad (4)$$

$S_e$  が増加すると、分数調波発振の発生を決定する係数は小さくなります。デューティサイクルが 50% より大きく、インダクタンスが小さい場合は、係数は増加します。

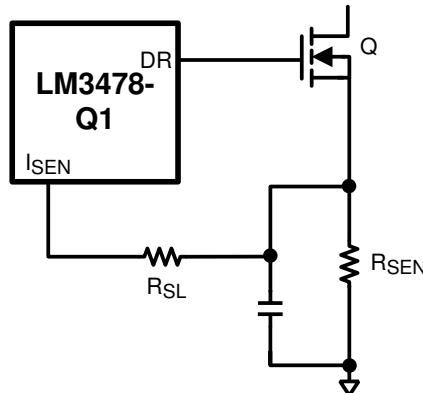

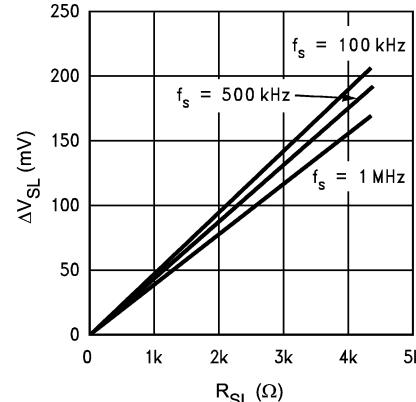

柔軟性を高めるため、 $I_{SEN}$  の経路に 1 つの外付け抵抗  $R_{SL}$  を追加することで、スロープ補償を強化できます。図 6-4 に設定を示します。外部で生成されるスロープ補償が、LM3478Q-Q1 の内部スロープ補償に追加されます。外部スロープ補償を使用する場合、 $S_e$  の式は次のようにになります：

$$S_e = (V_{SL} + (K \times R_{SL})) \times f_s \quad (5)$$

係数  $K$  の標準値は  $40\mu A$  です。

係数はスイッチング周波数に応じて変化します。図 6-5 は個々のアプリケーションの係数  $K$  を決定するために使用され、式 6 により係数  $K$  が求められます。

$$K = \Delta V_{SL} / R_{SL} \quad (6)$$

分数調波発振を防止するために、必要なだけスロープ補償を追加するのが適切な設計手法です。スロープ補償を追加することにより、制御ループで検出される電流の影響を最小限に抑えることができます。スロープ補償が非常に大きい場合の制御ループの特性は、誤差電圧をインダクタ電流ではなくのこぎり波と比較する電圧モードレギュレータと同様です。

Copyright © 2017, Texas Instruments Incorporated

図 6-4. 外部スロープ補償の追加

図 6-5. 外部スロープ補償  $\Delta V_{SL}$  と  $R_{SL}$  との関係

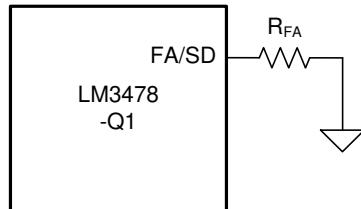

### 6.3.3 周波数調整/シャットダウン

LM3478Q-Q1 のスイッチング周波数は、1 個の外付け抵抗を使用することにより、100kHz ~ 1MHz に調整できます。図 6-6 に示すように、この抵抗は FA/SD ピンとグランドの間に接続する必要があります。目的のスイッチング周波数に必要な抵抗値を判断するには、セクション 5.6 を参照、または式 7 を使用します：

$$R_{FA} = 4.503 \times 10^{11} \times f_s^{-1.26} \quad (7)$$

図 6-6. 周波数調整

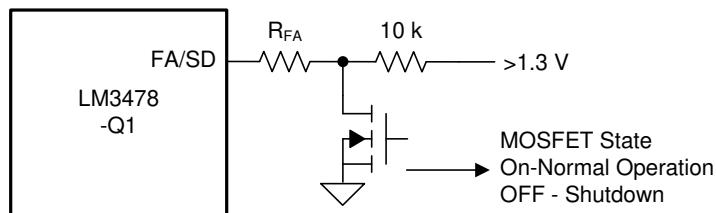

FA/SD ピンはシャットダウンピンとしても機能します。FA/SD ピンに High 信号 (1.35V 超) が発生すると、LM3478Q-Q1 はスイッチングを停止して低電流モードに移行します。これらの条件では、IC の総電源電流は  $10\mu\text{A}$  よりも小さくなります。図 6-7 に、周波数調整モードで動作しているときのシャットダウン機能の実装を示します。このモードでは、 $30\mu\text{s}$  以上 High 信号を印加すると、IC がシャットダウンします。ただし、デバイスへの損傷を防止するため、FA/SD ピンの電圧は常に絶対最大定格  $7\text{V}$  未満にする必要があります。

図 6-7. 周波数調整モードでのシャットダウン動作

#### 6.3.4 短絡保護

$I_{SEN}$  ピンで測定されたセンス抵抗の両端の電圧が  $343\text{mV}$  を超えると、短絡電流制限保護が有効になります。LM3478Q-Q1 内蔵のコンパレータによりスイッチング周波数が 5 分の 1 に低下し、短絡が解消されるまでこの状態を維持します。通常動作時は、検出された電流によってパワー MOSFET がオフになるようにトリガされます。ブランкиング期間中は、PWM コンパレータは過電流に反応しないため、短絡または重大な過負荷状態でデバイスを保護するために、この追加の  $343\text{mV}$  電流制限スレッショルドが実装されます。

#### 6.4 デバイスの機能モード

デバイスは、入力電圧が UVLO 設定点を超えるとすぐに、FA/SD ピンのプルダウン抵抗に応じて設定された周波数で動作するように設定されています。FA/SD ピンが High にプルされると、LM3478Q-Q1 はシャットダウンモードに移行します。

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

LM3478Q-Q1 は、連続導通モード (CCM) または不連続電流導通モード (DCM) のいずれかで動作可能です。以下のアプリケーションは、CCM 動作用に設計されています。この動作モードは、DCM と比較して効率が高く、通常は EMI 特性が低くなります。

### 7.2 代表的なアプリケーション

#### 7.2.1 一般的な高効率昇圧(ブースト)コンバータ

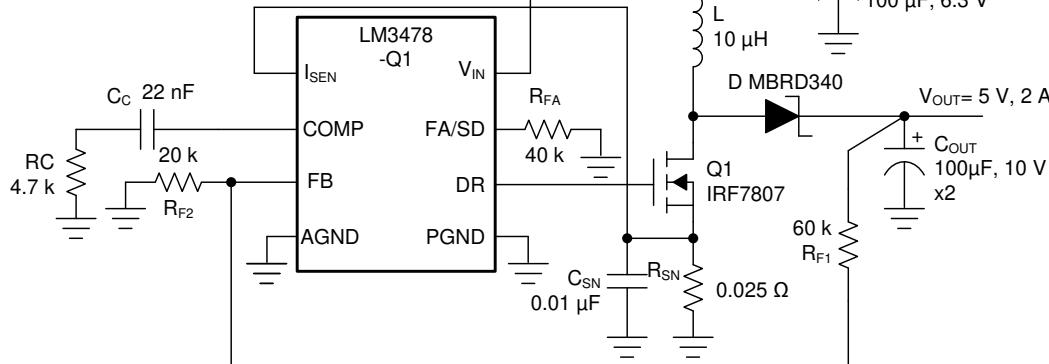

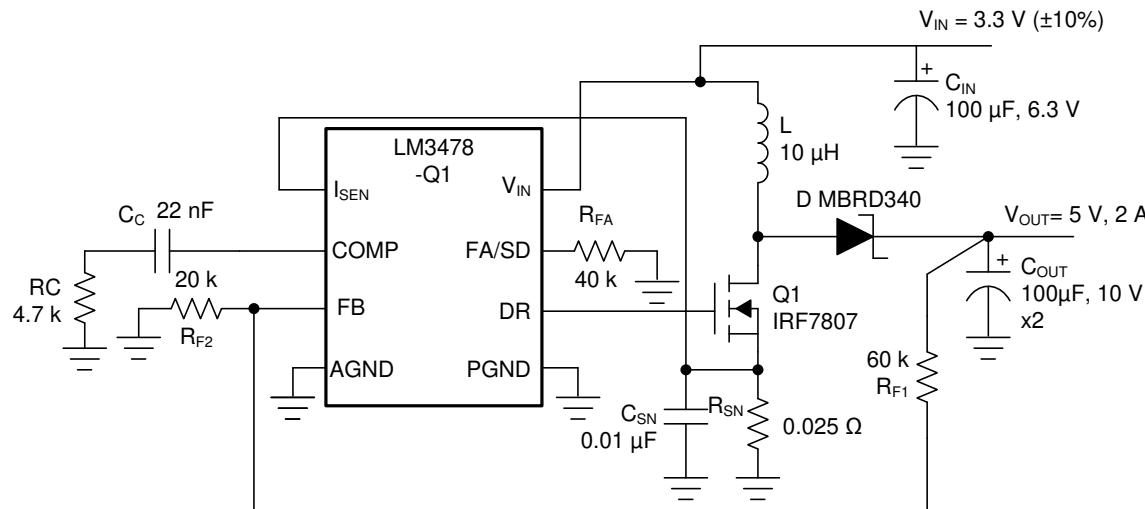

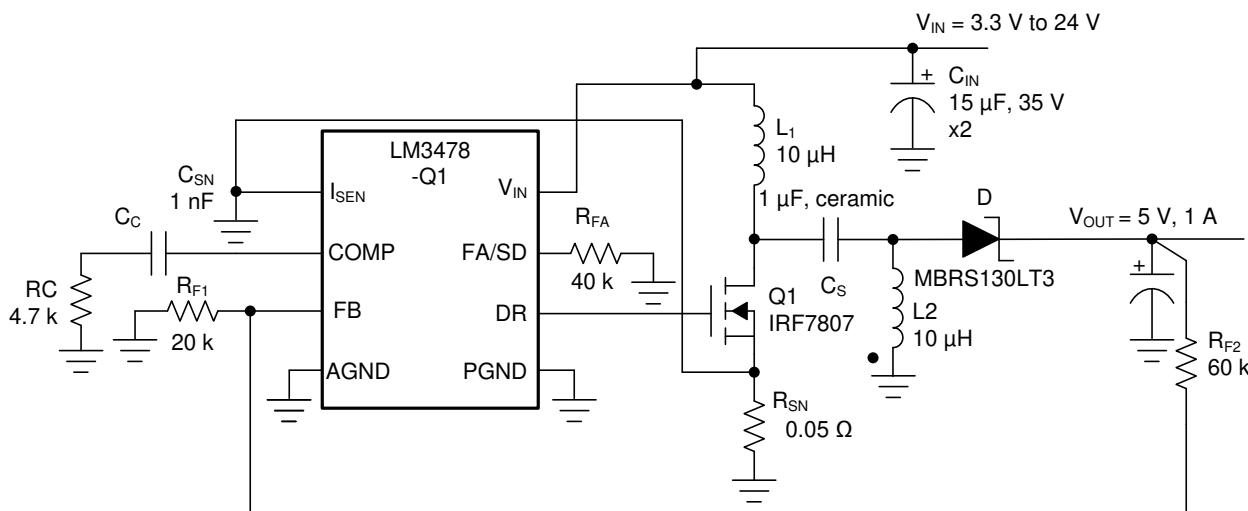

図 7-1. 一般的な高効率昇圧(ブースト)コンバータの回路図

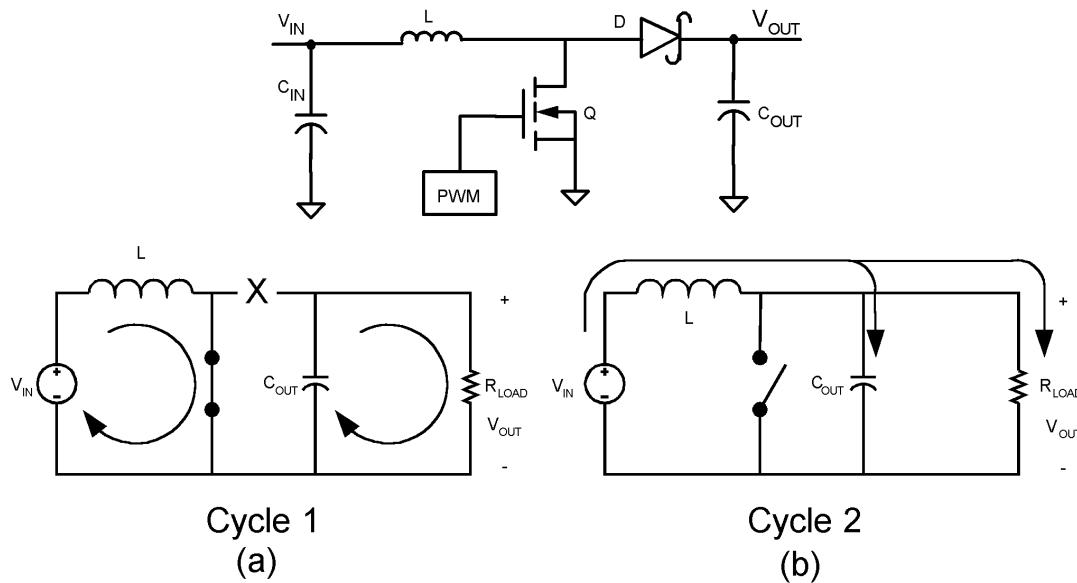

昇圧コンバータは、低入力電圧を高出力電圧に変換します。昇圧コンバータの基本構成を 図 7-2 に示します。CCM では(定常状態でインダクタ電流がゼロにならない場合)、昇圧レギュレータは 2 つの状態で動作します。最初の動作状態では、MOSFET Q がオンになり、エネルギーがインダクタに蓄積されます。この状態では、ダイオード D は逆バイアスされ、出力コンデンサ C<sub>OUT</sub> から負荷電流が供給されます。

2 番目の状態では、MOSFET Q がオフになり、ダイオードが順方向にバイアスされます。インダクタに蓄積したエネルギーは負荷と出力コンデンサに伝達されます。スイッチオン時間と合計周期の比率は、式 8 に示すように、デューティサイクル D です。

$$D = 1 - (V_{in} / V_{out}) \quad (8)$$

MOSFET とダイオードの両端間の電圧降下を含めた、デューティサイクルの定義を 式 9 に示します。

$$D = 1 - ((V_{in} - V_q) / (V_{out} + V_d)) \quad (9)$$

$V_d$  はダイオードの順方向電圧降下、 $V_q$  は MOSFET がオンのときの両端間の電圧降下です。

- A. 最初のサイクル動作

- B. 2番目のサイクル動作

図 7-2. 簡略化された昇圧コンバータ

### 7.2.1.1 設計要件

アプリケーション用の部品のサイズを適切に決定するには、入力電圧範囲、出力電圧、出力電流範囲、必要なスイッチング周波数のパラメータが必要です。これら 4 つの主要パラメータは、適切なシステム動作を実現するために利用できる部品の選択に影響します。

電源については、入力過渡電流が UVLO 値を下回らないように、電源レールの入力インピーダンスを十分に小さくする必要があります。使用するインダクタの選択を決定する要因は、平均インダクタ電流とインダクタ電流リップルです。スイッチング周波数を高く設定すると、非常に小さなインダクタ値でコンバータを動作させることができます。負荷に供給できる最大電流は、センス抵抗  $R_{SEN}$  によって設定されます。電流制限は、センス抵抗の両端に生成される電圧が電流検出スレッショルド電圧  $V_{SENSE}$  と等しいときに発生します。また、必要に応じて抵抗  $R_{SL}$  によりスロープ補償が追加されます。

以下のセクションでは、代表的な LM3478Q-Q1 昇圧アプリケーションの設計要件について説明します。

### 7.2.1.2 詳細な設計手順

#### 7.2.1.2.1 WEBENCH ツールによるカスタム設計

[ここをクリック](#)すると、WEBENCH® Power Designer により、LM3478Q-Q1 デバイスを使用するカスタム設計を作成できます。

1. 最初に、 $V_{IN}$ 、 $V_{OUT}$ 、 $I_{OUT}$  の要件を入力します。

2. オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化し、この設計と、テキサス・インスツルメンツによる他の可能なソリューションとを比較します。

3. WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格や部品の在庫情報と併せて参照できます。

4. ほとんどの場合、以下の内容も可能となります:

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- 熱シミュレーションを実行し、基板の熱性能を把握する。

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットでエクスポートする。

- 設計のレポートを PDF で印刷し、同僚と設計を共有する。

5. WEBENCH ツールの詳細は、[www.ti.com/ja-jp/webench](http://www.ti.com/ja-jp/webench) でご覧になります。

#### 7.2.1.2.2 パワーインダクタの選択

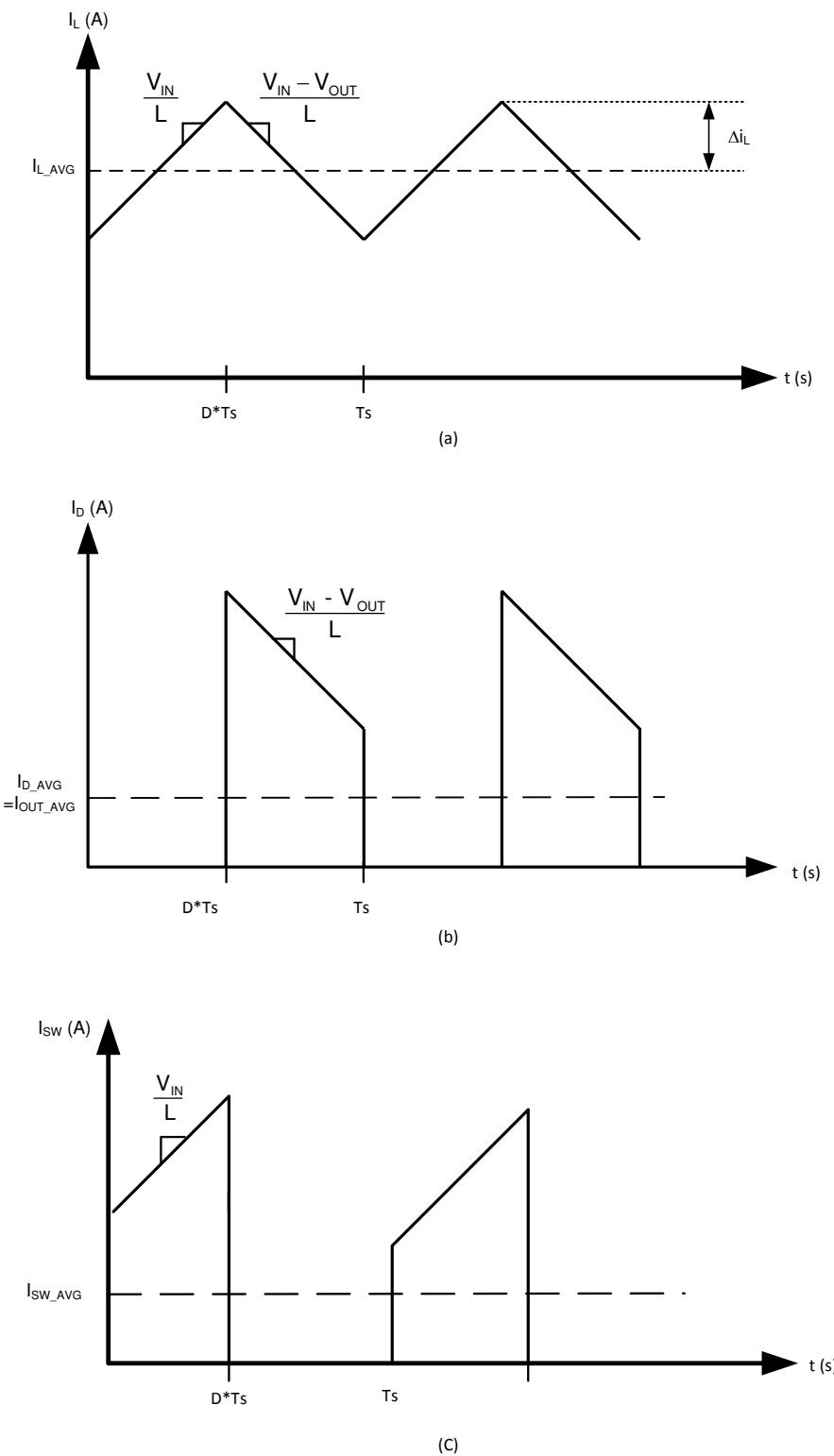

インダクタは昇圧コンバータ内にある 2 つのエネルギー蓄積素子の 1 つです。図 7-3 に、スイッチングサイクル中のインダクタ電流がどのように変化するかを示します。インダクタを流れる電流は、式 10 を使用して計測します。これは、L、I<sub>L</sub>、V<sub>L</sub> の関係を示しています。

$$V_L(t) = L \frac{di_L(t)}{dt} \quad (10)$$

適切なインダクタンス値を決定する際に重要な量は、I<sub>L</sub> (平均インダクタ電流) と ΔI<sub>L</sub> (インダクタ電流リップル) です。ΔI<sub>L</sub> が I<sub>L</sub> より大きい場合、サイクルの一部でインダクタ電流が 0 に低下し、コンバータは DCM で動作します。このデータシートに記載されているすべての分析は、CCM での動作を想定しています。CCM で動作させるには、式 11 を使用して次の条件を満たす必要があります。

$$L > \frac{D(1-D)V_{IN}}{2I_{OUT}f_S} \quad (11)$$

最小 I<sub>OUT</sub> を選択し、最小インダクタンスの値を決定します。一般的な選択は、ΔI<sub>L</sub> を I<sub>L</sub> の 30% に設定することです。インダクタの適切なコアサイズを選択するには、インダクタを流れる平均電流とピーク電流を計算する必要があります。昇圧コンバータのピークインダクタ電流に対して 式 12、式 13、式 14 を使用します。

$$I_{LPEAK} = \text{Average } I_{L(max)} + \Delta I_{L(max)} \quad (12)$$

$$\text{Average } I_{L(max)} = I_{out} / (1-D) \quad (13)$$

$$\Delta I_{L(max)} = D \times V_{in} / (2 \times f_s \times L) \quad (14)$$

これらの値よりも定格が高いインダクタを選択する必要があります。インダクタの定格が適切でない場合、飽和が発生し、回路が誤動作する可能性があります。

LM3478Q-Q1 は、非常に高い周波数でのスイッチングに設定できます。スイッチング周波数が高い場合、非常に小さなインダクタ値でコンバータを動作させることができます。LM3478Q-Q1 は、スイッチを流れるピーク電流を検出します。これは前の式で計算したピークインダクタ電流と同じです。

図 7-3. インダクタ電流とダイオード電流

### 7.2.1.2.3 出力電圧の設定

出力と FB ピンの間の抵抗分圧回路を使用して、出力電圧を設定できます。FB ピンの電圧が 1.26V になるように抵抗を選択します。以下の式を使用して、 $R_{F1}$  (出力電圧と帰還ピンの間の抵抗) と  $R_{F2}$  (帰還ピンとグランドの間の抵抗) を選択します。

$$R_{F2} = (1.26 \text{ V} \times R_{F1}) / (V_{\text{out}} - 1.26 \text{ V}) \quad (15)$$

ノイズを低減するため、帰還ピンとグランドピンの間に 100pF コンデンサを接続することもできます。

### 7.2.1.2.4 電流制限の設定

負荷に供給できる電流の最大量は、センス抵抗  $R_{\text{SEN}}$  によって設定されます。電流制限は、センス抵抗の両端に生じる電圧が電流検出スレッショルド電圧  $V_{\text{SENSE}}$  と等しいときに発生します。このスレッショルドに達すると、次のサイクルまでスイッチはオフになります。 $V_{\text{SENSE}}$  の制限は、「電気的特性」セクションで指定されています。 $V_{\text{SENSE}}$  は、図 7-4 に示すように内部制御信号  $V_{\text{CS}}$  の最大値を表します。ただし、この制御信号は一定の値ではなく、内部補償ランプ ( $V_{\text{SL}}$ ) に起因して一定期間にわたって変化します。そのため、電流制限スレッショルドも変化します。実際の電流制限スレッショルドは、検出電圧 ( $V_{\text{SENSE}}$ ) と内部補償ランプの関数です。

$$R_{\text{SEN}} \times ISW_{\text{LIMIT}} = V_{\text{CS MAX}} = V_{\text{SENSE}} - (D \times V_{\text{SL}}) \quad (16)$$

ここで、 $ISW_{\text{LIMIT}}$  はピークスイッチ電流制限で、式 17 で定義されます。

図 7-4. 電流検出電圧とデューティサイクルとの関係

図 7-4 に、 $V_{\text{CS}}$  (および電流制限スレッショルド電圧) がデューティサイクルに応じてどのように変化するかを示します。この曲線は、内部補償ランプスロープ ( $S_e$ ) に相当し、低いデューティサイクルで  $V_{\text{SENSE}}$  によって制限されます (点線で表示)。デューティサイクルが増加すると、 $V_{\text{SL}}$  の上昇に伴い制御電圧が低下します。このグラフは、325ns (標準値) のブランкиング時間の短絡電流制限スレッショルド 343mV (標準値) も示しています。高い周波数では、デューティサイクル中でこの固定ブランкиング時間が占める割合が明らかに多くなります (パーセンテージ)。電流制限スレッショルドはデューティサイクルによって異なるため、式 17 を使用して  $R_{\text{SEN}}$  を選択し、適切な電流制限スレッショルドを設定します:

$$R_{\text{SEN}} = \frac{V_{\text{SENSE}} - (D \times V_{\text{SL}})}{ISW_{\text{LIMIT}}} \quad (17)$$

式 17 の分子は  $V_{\text{CS}}$  で、式 18 は  $ISW_{\text{LIMIT}}$  を使用します。

$$ISW_{LIMIT} = \left[ \frac{I_{OUT}}{(1-D)} + \frac{(D \times V_{IN})}{(2 \times f_S \times L)} \right] \quad (18)$$

誤トリガを防止するため、電流制限値は最大動作値（標準値 120%）を多少上回るマージンを確保する必要があります。 $V_{SENSE}$  と  $V_{SL}$  の両方の値は、セクション 5.5 で指定されています。ただし、これら 2 つの仕様の制限付きで計算を行うと、非現実的に広い電流制限または  $R_{SEN}$  範囲となる場合あります。そのため、式 19 が推奨され、セクション 5.5 で指定される  $V_{SL}$  比を使用します。

$$R_{SEN} = \frac{V_{SENSE} - (D \times V_{SENSE} \times V_{SLratio})}{ISW_{LIMIT}} \quad (19)$$

$R_{SEN}$  は電流モード制御ループの一部で、制御ループの安定性に多少の影響を及ぼします。そのため、電流制限スレッショルドを設定した後、ループの安定性を検証する必要があります。「スロープ補償」セクションの説明にあるように、電流モードコンバータが安定するには、式 20 が真である必要があります。

$$S_f - S_e < S_n + S_e \quad (20)$$

この方程式が真であることを検証するには、式 21 を使用します。

$$R_{SEN} < \frac{2 \times V_{SL} \times f_S \times L}{V_o - (2 \times V_{IN})} \quad (21)$$

選択した  $R_{SEN}$  がこの値よりも大きい場合、安定性を確保するため、以下のセクションで説明するようにスロープ補償を追加する必要があります。

#### 7.2.1.2.5 外部スロープ補償を使用した電流制限

必要に応じて、 $R_{SL}$  を使用してスロープ補償を追加します。ほとんどの設計では必要なく、 $R_{SL}$  は必要以上に大きくしないでください。式 22 に従って  $R_{SL}$  を選択します。

$$R_{SL} > \frac{\frac{R_{SEN} \times (V_o - 2V_{IN})}{2 \times f_S \times L} - V_{SL}}{40 \mu A} \quad (22)$$

ここで、 $R_{SEN}$  は電流制限に基づいて選択した値です。 $R_{SL}$  を取り付けると、制御信号にはループを安定させるための追加の外部スロープが含まれるようになります。このスロープは電流制限スレッショルドにも影響を及ぼします。そのため、以下の式 23、式 24、式 25 に示すように、電流制限スレッショルドを再検証する必要があります。

$$V_{CS} = V_{SENSE} - (D \times (V_{SL} + \Delta V_{SL})) \quad (23)$$

$\Delta V_{SL}$  は、「スロープ補償ランプ」セクションで説明されているように、生成される追加のスロープ補償であり、式 24 を使用して計算されます。

$$\Delta V_{SL} = 40 \mu A \times R_{SL} \quad (24)$$

これにより、式 25 に示すように、電流制限（または  $R_{SEN}$ ）の式が変化します。

$$ISW_{LIMIT} = \frac{V_{SENSE} - (D \times (V_{SL} + \Delta V_{SL}))}{R_{SEN}} \quad (25)$$

目的の電流制限と安定動作の両方を実現するため、 $R_{SEN}$  と  $R_{SL}$  の値を繰り返し計算する必要があります。一部の設計では、 $I_{SEN}$  ピンのノイズをフィルタリングするのに  $R_{SL}$  も有効です。

リップル電流が推奨の 30% の値で、電流制限スレッショルドが最大ピークの 120% であるようにインダクタを選択する場合は、より簡単な方法を使用して  $R_{SEN}$  を決定できます。以下の 式 26 は、上記の 2 つの条件が満たされていれば、 $R_{SL}$  なしで最適な安定性を提供します。

$$R_{SEN} = \frac{V_{SENSE}}{ISW_{LIMIT} + \left( \frac{V_o - V_i}{L \times f_s} \right) \times D} \quad (26)$$

#### 7.2.1.2.6 パワーダイオードの選択

昇圧コンバータ回路を観察すると、ダイオードを流れる平均電流が平均負荷電流であり、ダイオードを流れるピーク電流がインダクタを流れるピーク電流であることがわかります。ダイオードは、そのピーク電流以上を処理可能な定格が必要です。リップルダイオード電流は、式 27 を使って計算できます。

$$I_{D(Peak)} = I_{OUT} / (1-D) + \Delta I_L \quad (27)$$

ダイオードは出力に供給される最大平均電流を熱的に処理できる必要があります。昇圧コンバータのピーク逆電圧は、レギュレーションされた出力電圧と等しくなります。ダイオードはこの電圧を処理できる必要があります。効率を向上させるには、順方向電圧降下の小さいショットキーダイオードをお勧めします。

#### 7.2.1.2.7 パワーモスFETの選択

LM3478Q-Q1 の駆動ピンは、外部 MOSFET のゲートに接続する必要があります。駆動ピン (DR) 電圧は、入力電圧により異なります (セクション 5.6 を参照)。ほとんどのアプリケーションでは、ロジックレベル MOSFET を使用できます。入力電圧が非常に低い場合は、サブロジックレベルの MOSFET を使用する必要があります。選択した MOSFET は、システムの効率に大きな影響を及ぼします。MOSFET を選択するための重要なパラメータは、次のとおりです：

1. 最小スレッショルド電圧  $V_{TH}$  (MIN)

2. オン抵抗、 $R_{DS(ON)}$

3. 総ゲート電荷量、 $Q_g$

4. 逆伝達キャパシタンス、 $C_{RSS}$

5. 最大ドレイン-ソース間電圧、 $V_{DS(MAX)}$

MOSFET のオフ状態電圧は、出力電圧とほぼ等しくなります。 $V_{DS(max)}$  は出力電圧より大きい必要があります。MOSFET の電力損失は、導通損失とスイッチング損失に分類することができます。導通損失  $P_{cond}$  を推定するには  $R_{DS(ON)}$  が必要です。

$$P_{cond} = I^2 \times R_{DS(ON)} \times D \quad (28)$$

通常、 $R_{DS(ON)}$  に対する温度の影響は非常に大きいです。高温時は 30% 増加すると想定されます。

式 28 の電流  $I$  では、平均インダクタ電流を使用できます。

特に、スイッチング周波数が高い場合、全損失の最大部分をスイッチング損失が占めている可能性があります。

動作中の MOSFET の寄生成分が変化するため、スイッチング損失の計算は非常に困難です。多くの場合、個々の MOSFET のデータシートには、有用な結果が得られるほど十分な情報は掲載されていません。式 29 と式 30 は、スイッチング損失の計算方法の概要を示しています。

$$P_{SW} = \frac{I_{Lmax} \times V_{out}}{2} \times f_{SW} \times (t_{LH} + t_{HL}) \quad (29)$$

$$t_{LH} = \left( Qgd + \frac{Qgs}{2} \right) \times \frac{Rdr_{On}}{Vdr - Vgs_{th}} \quad (30)$$

#### 7.2.1.2.8 入力コンデンサの選択

昇圧コンバータの入力にインダクタが存在するため、入力電流波形は連続して三角波になります（図 7-3 を参照）。インダクタにより、入力コンデンサに印加されるリップル電流がかなり低くなります。ただし、入力コンデンサが小さくなると、入力リップルは増加します。入力コンデンサの RMS 電流は、式 31 を使用して求められます。

$$I_{CIN(RMS)} = \Delta i_L / \sqrt{3} = \frac{1}{2\sqrt{3}} \left( \frac{V_{OUT} - V_{IN}}{V_{OUT} L f_S} \right) \times V_{in} \quad (31)$$

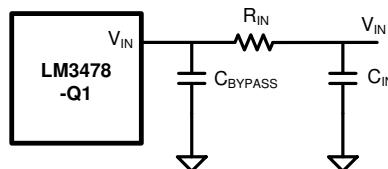

入力コンデンサは、RMS 電流を取り扱える必要があります。入力コンデンサは昇圧アプリケーションではそれほど重要ではありませんが、値が小さいとインピーダンスの相互作用が発生する可能性があります。そのため、 $10\mu F \sim 20\mu F$  の範囲で、高品質のコンデンサを選択する必要があります。 $10\mu F$  より低い値を使用すると、インピーダンスの相互作用またはスイッチングノイズの問題により LM3478Q-Q1 に影響が及ぶ可能性があります。性能を向上させるため、特に  $V_{in}$  が 8V 未満の場合には、入力に  $20\Omega$  の抵抗による RC フィルタを使用することをお勧めします。抵抗は  $V_{IN}$  ピンと直列に配置し、 $V_{IN}$  ピンにはバイパスコンデンサのみを直接接続します（図 7-5 を参照）。この構成では、 $0.1\mu F$  または  $1\mu F$  のセラミックコンデンサが必要です。バルク入力コンデンサとインダクタは、入力電源の抵抗の反対側に接続します。

Copyright © 2017, Texas Instruments Incorporated

図 7-5. IC 入力ノイズの低減

#### 7.2.1.2.9 出力コンデンサの選択

昇圧コンバータの出力コンデンサは、インダクタの充電時にすべての出力電流を供給します。その結果、大きなリップル電流が発生します。出力コンデンサは、最大 RMS 電流を取り扱える必要があります。式 32 は、出力コンデンサの RMS 電流を示しています。

$$I_{COUT(RMS)} = \sqrt{(1-D) \left[ I_{OUT}^2 \frac{D}{(1-D)^2} + \frac{\Delta i_L^2}{3} \right]} \quad (32)$$

ここで

$$\Delta i_L = \frac{DV_{IN}}{2Lf_S} \quad (33)$$

出力のリップルがコンデンサの ESR と ESL によって直接制御されます。高効率と低リップル電圧を実現するために、出力で ESR と ESL が低いコンデンサを使用します。出力には、表面実装タンタル、表面実装ポリマー電解、ポリマータンタル、または多層セラミックコンデンサを使用することを推奨します。

出力電圧リップルを非常に小さくする必要があるアプリケーションでは、多くの場合 2 段目に LC フィルタを使用するのが最善です。ほとんどの場合、電力経路に小型の 2 つ目のインダクタを使用して追加の最終的な出力コンデンサを使用する方が、LC フィルタを追加せずに出力コンデンサを増加させるだけ出力電圧リップルを低減するよりコストが低く抑えられます。

### 7.2.1.2.10 補償

昇圧トポジの補償ピンに接続する適切な補償部品の選択方法の詳細については、『LM3748 昇圧コントローラの AN-1286 補償』[SNVA067] を参照してください。

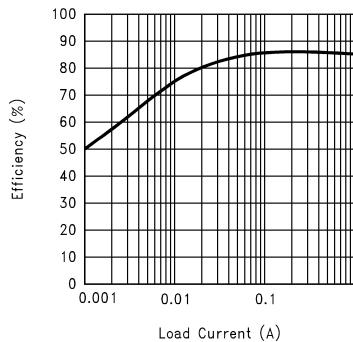

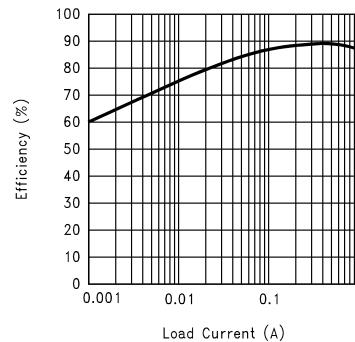

### 7.2.1.3 アプリケーション曲線

図 7-6. 効率と負荷電流との関係 (9-V In および 12V Out)

図 7-7. 効率と負荷電流との関係 (3.3-V In および 5V Out)

### 7.2.2 代表的な SEPIC コンバータ

図 7-8. 代表的な SEPIC コンバータ

LM3478Q-Q1 はローサイド N チャネル MOSFET を制御するため、SEPIC (シングルエンド 1 次インダクタンスコンバータ) アプリケーションでも使用できます。LM3478Q-Q1 を使用した SEPIC の例が 図 7-8 に示されています。出力電圧が入力電圧よりも高いまたは低い場合があることに注意してください。SEPIC は 2 つのインダクタを使用して、入力電圧の昇圧または降圧を行います。スイッチングサイクル全体でインダクタの両端に同じ電圧が印加されるため、インダクタ L1 と L2 は、2 つのディスクリートインダクタ、または結合インダクタの 2 つの巻線になります。2 つのディスクリートインダクタを使用すると、カスタムインダクタとは対照的に、カタログの磁気素子を使用できます。L1 と L2 に結合巻線を使用することで、入力リップルとサイズを小さくできます。

入力にインダクタ L1 を配置しているため、SEPIC は昇圧コンバータのすべての利点を継承します昇圧コンバータにおける SEPIC の主な利点の 1 つは、入力と出力を本質的に絶縁できることです。コンデンサの CS により入力と出力が絶縁され、負荷短絡や誤動作から保護されます。そのため、完全なシャットダウンが必要な場合の昇圧回路の置き換えに SEPIC が有用です。つまり、スイッチがオフになった時点で、出力電圧は 0V に低下します。昇圧コンバータでは、出力は入力電圧からダイオードの電圧降下を引いた値までしか降下できません。

SEPIC のデューティサイクルは 式 34 を使用して求められます。

$$D = \frac{V_{OUT} + V_{DIODE}}{V_{OUT} + V_{IN} - V_Q + V_{DIODE}} \quad (34)$$

式 34 では、 $V_Q$  は MOSFET のオン状態電圧  $Q$  で、 $V_{DIODE}$  はダイオードの順方向電圧降下です。

### 7.2.2.1 設計要件

アプリケーション用の部品のサイズを適切に決定するには、入力電圧範囲、出力電圧、出力電流範囲、必要なスイッチング周波数のパラメータが必要です。これら 4 つの主要パラメータは、適切なシステム動作を実現するために利用できる部品の選択に影響します。

電源については、入力過渡電流が UVLO 値を下回らないように、電源レールの入力インピーダンスを十分に小さくする必要があります。使用するインダクタの選択を決定する要因は、平均インダクタ電流とインダクタ電流リップルです。スイッチング周波数を高く設定すると、非常に小さなインダクタ値でコンバータを動作させることができます。負荷に供給できる最大電流は、センス抵抗  $RSEN$  によって設定されます。電流制限は、センス抵抗の両端に生成される電圧が電流検出スレッショルド電圧  $VSENSE$  と等しいときに発生します。また、必要に応じて抵抗  $RSL$  によりスロープ補償が追加されます。

以下のセクションでは、代表的な LM3478Q-Q1 昇圧アプリケーションの設計要件について説明します。

### 7.2.2.2 詳細な設計手順

#### 7.2.2.2.1 パワー MOSFET の選択

昇圧コンバータにおいて、MOSFET の選択を左右するパラメータは、最小スレッショルド電圧  $V_{TH(MIN)}$ 、オン抵抗  $R_{DS(ON)}$ 、合計ゲート電荷  $Q_g$ 、逆伝達キャパシタンス  $C_{RSS}$ 、最大ドレイン-ソース間電圧  $V_{DS(MAX)}$  です。SEPIC のピークスイッチ電圧は 式 35 を使用して求められます。

$$V_{SW(Peak)} = V_{IN} + V_{OUT} + V_{DIODE} \quad (35)$$

選択する MOSFET は、次の条件を満たす必要があります：

$$V_{DS(MAX)} > V_{SW(Peak)} \quad (36)$$

ピークスイッチ電流は、式 37 を使用して求められます。

$$I_{SW(Peak)} = I_{L1(AVG)} + I_{OUT} + \frac{\Delta I_{L1} + \Delta I_{L2}}{2} \quad (37)$$

スイッチを流れる RMS 電流は、式 38 で求められます。

$$I_{SWRMS} = \sqrt{\left[ I_{SWPEAK}^2 - I_{SWPEAK} (\Delta I_{L1} + \Delta I_{L2}) + \frac{(\Delta I_{L1} + \Delta I_{L2})^2}{3} \right] D} \quad (38)$$

#### 7.2.2.2.2 パワーダイオードの選択

ピーク電流とピーク逆電圧を処理できるパワーダイオードを選択する必要があります。SEPIC では、ダイオードのピーク電流はスイッチのピーク電流と同じになります。ダイオードのオフ状態電圧またはピーク逆電圧は  $V_{IN} + V_{OUT}$  です。昇圧コンバータと同様、平均ダイオード電流は出力電流に等しくなります。ショットキーダイオードをお勧めします。

### 7.2.2.3 インダクタ L1 および L2 の選択

連続電流導通モードを維持するようにインダクタ L1 と L2 を適切に選択するには、以下のパラメータを計算する必要があります。

インダクタの平均電流は、式 39 を使用して計算できます。

$$I_{L1AVE} = \frac{DI_{OUT}}{1-D} \quad (39)$$

$$I_{L2AVE} = I_{OUT} \quad (40)$$

コア損失を計算するためのピークツーピークリップル電流には、必要に応じて 式 41 および 式 42 を使用します。

$$\Delta I_{L1} = \frac{(V_{IN} - V_O) D}{(L1)f_s} \quad (41)$$

$$\Delta I_{L2} = \frac{(V_{IN} - V_O) D}{(L2)f_s} \quad (42)$$

連続電流導通を確保するため、条件  $I_L > \Delta I_L/2$  を維持すると、式 43 と 式 44 が得られます。

$$L1 > \frac{(V_{IN} - V_O)(1-D)}{2I_{OUT}f_s} \quad (43)$$

$$L2 > \frac{(V_{IN} - V_O)D}{2I_{OUT}f_s} \quad (44)$$

インダクタのピーク電流については、式 45 と 式 46 を使用して、インダクタが飽和しないようにしてください。

$$I_{L1PK} = \frac{DI_{OUT}}{1-D} + \frac{\Delta I_{L1}}{2} \quad (45)$$

$$I_{L2PK} = I_{OUT} + \frac{\Delta I_{L2}}{2} \quad (46)$$

$I_{L1PK}$  は、電流センス抵抗で設定された最大電流定格よりも小さくする必要があります。

入力リップルと出力リップルを低減するため、L1 の値を推奨最小値より大きくすることができます。ただし、 $D_{IL1}$  が  $I_{L1AVE}$  の 20% 未満になると、出力リップルに対する利点は最小限になります。

L2 の値を推奨最小値より大きくすると、 $\Delta_{IL2}$  を減らすことができ、結果として出力リップル電圧が低減します。

$$\Delta V_{OUT} = \left( \frac{I_{OUT}}{1-D} + \frac{\Delta I_{L2}}{2} \right) ESR \quad (47)$$

ここで、ESR は、出力コンデンサの実効直列抵抗です。

L1 と L2 が同じコア上に巻かれている場合、 $L1 = L2 = L$  となります。上記の式はすべて、インダクタンスを  $2L$  に置き換えると真になります。

#### 7.2.2.2.4 センス抵抗の選択

スイッチを流れるピーク電流  $I_{SW(Peak)}$  は、電流センス抵抗  $R_{SEN}$  を使用して調整でき、特定の出力電流を供給できます。抵抗  $R_{SEN}$  は、式 48 を使用して選択できます

$$R_{SEN} = \frac{V_{SENSE} - D(V_{SL} + \Delta V_{SL})}{I_{SWPEAK}} \quad (48)$$

#### 7.2.2.2.5 SEPIC コンデンサの選択

SEPIC コンデンサ CS の選択は、RMS 電流に依存します。SEPIC コンデンサの RMS 電流は、式 49 で求められます。

$$I_{CSRMS} = \sqrt{I_{SWRMS}^2 + (I_{L1PK}^2 - I_{L1PK}\Delta I_{L1} + \Delta I_{L1}^2)(1-D)} \quad (49)$$

SEPIC コンデンサには、出力電力に対する大きな ACrms 電流の定格が必要です。この特性があるため、SEPIC は、コンデンサを流れる RMS 電流が比較的小さい（コンデンサ テクノロジーと比較する場合）低消費電力アプリケーションに適しています。SEPIC コンデンサの電圧定格は、最大入力電圧よりも高い必要があります。CS と L1 の間にはエネルギー バランスがあり、これを用いてコンデンサ値を決定できます。式 50 に、基本エネルギー バランスを示します。

$$\frac{1}{2}C_s\Delta V_s^2 = \frac{1}{2}L_1\Delta I_{L1}^2 \quad (50)$$

ここで、

$$\Delta V_s = \left( \frac{V_{OUT}}{V_{OUT} + V_{IN} - V_Q + V_{DIODE}} \right) \frac{I_{OUT}}{f_s C_s} \quad (51)$$

は SEPIC コンデンサ両端のリップル電圧で、

$$\Delta I_{L1} = \frac{(V_{IN} - V_Q)D}{L_1 f_s} \quad (52)$$

はインダクタ L1 を流れるリップル電流です。式 53 を用いてエネルギー バランスの式を解き、 $C_s$  の最小値を求めます。

$$C_s \geq L_1 \frac{I_{OUT}^2}{(V_{IN} - V_Q)^2} \quad (53)$$

#### 7.2.2.2.6 入力コンデンサの選択

昇圧コンバータと同様に、SEPIC の入力用インダクタが 1 個あります。したがって、入力電流波形は連続的な三角波です。インダクタにより、入力コンデンサに印加されるリップル電流がかなり低くなります。ただし、入力コンデンサが小さくなると、入力リップルは増加します。入力コンデンサの RMS 電流は、式 54 を用いて求められます。

$$I_{CIN(RMS)} = \Delta I_{L1} / \sqrt{2} = \frac{D}{2\sqrt{3}} \left( \frac{V_{IN} - V_Q}{L_1 f_s} \right) \quad (54)$$

入力コンデンサは、RMS 電流を取り扱える必要があります。入力コンデンサは昇圧アプリケーションではそれほど重要ではありませんが、値が小さいとインピーダンスの相互作用が発生する可能性があります。そのため、 $10\mu F \sim 20\mu F$  の範囲で、高品質のコンデンサを選択する必要があります。 $10\mu F$  より低い値を使用すると、インピーダンスの相互作用またはス

イッティングノイズの問題により LM3478Q-Q1 に影響が及ぶ可能性があります。性能を向上させるため、特に  $V_{IN}$  が 8V 未満の場合には、入力に  $20\Omega$  の抵抗による RC フィルタを使用することを TI ではお勧めしています。抵抗は  $V_{IN}$  ピンと直列に配置し、 $V_{IN}$  ピンにはバイパスコンデンサのみを直接接続します (図 7-5 を参照)。この構成では、 $0.1\mu F$  または  $1\mu F$  のセラミックコンデンサが必要です。バルク入力コンデンサとインダクタは、入力電源の抵抗の反対側に接続します。

### 7.2.2.2.7 出力コンデンサの選択

SEPIC の出力コンデンサには非常に大きなリップル電流が発生します (昇圧コンバータの出力コンデンサと同様)。出力コンデンサを流れる RMS 電流は、式 55 を使用して求められます。

$$I_{RMS} = \sqrt{\frac{[I_{SWPK}^2 - I_{SWPK}(\Delta I_{L1} + \Delta I_{L2}) + (\Delta I_{L1} + \Delta I_{L2})^2](1-D) - I_{OUT}^2}{3}} \quad (55)$$

出力のリップルが出力コンデンサの ESR と ESL によって直接制御されます。高効率と低リップル電圧を実現するためには、出力で ESR と ESL が低い低用量コンデンサを使用します。低リップルの出力には、表面実装タンタル、表面実装ポリマー電解とポリマータンタル、Sanyo-OSCON、または多層セラミックコンデンサを推奨します。

### 7.2.2.3 アプリケーション曲線

図 7-9. 効率と負荷電流との関係 (3.3V In および 12V Out)

図 7-10. 効率と負荷電流との関係 (5V In および 12V Out)

## 7.3 電源に関する推奨事項

LM3478Q-Q1 は、車載バッテリを含む、さまざまな DC 電源で動作するように設計されています。その場合、40V を超える逆電圧と電圧ダンプから  $V_{IN}$  入力を保護する必要があります。入力過渡電流の影響で  $V_{IN}$  の UVLO レベルを下回ることがないように、入力電源レールの抵抗を十分小さい値にする必要があります。入力電源が長い配線を使用して接続されている場合、通常の入力コンデンサに加えてバルク容量の追加が必要になることがあります。

## 7.4 レイアウト

### 7.4.1 レイアウトのガイドライン

スイッチングコントローラには、適切な基板レイアウトが重要です。まず、グランドプレーン領域を放熱のために十分確保する必要があります、2 番目に、スイッチングノイズの影響を低減するために適切なガイドラインに従う必要があります。スイッチングコンバータは超高速スイッチングデバイスです。このようなデバイスでは、入力電流が急速に増加すると共にトレースの寄生インダクタンスが生じるため、望ましくない  $Ldi/dt$  ノイズスパイクが発生します。このノイズの大きさは、出力電流が大きくなるにつれて増大する傾向があります。この寄生スパイクノイズにより電磁干渉 (EMI) が発生して、デバイス性能に問題が生じる可能性もあります。そのため、このスイッチングノイズの影響を最小限に抑えるようレイアウトに注意する必要があります。電流モードデバイスの電流検知回路は、容易にスイッチングノイズの影響を受けます。このノイズによりデューティサイクルジッタが発生し、スペクトルノイズが増加します。このノイズを無視するため、LM3478Q-Q1 では各サイクルの開始時に 325ns のブランкиング時間を確保していますが、ブランкиング時間の後も多少のノイズが残っている可能性があります。

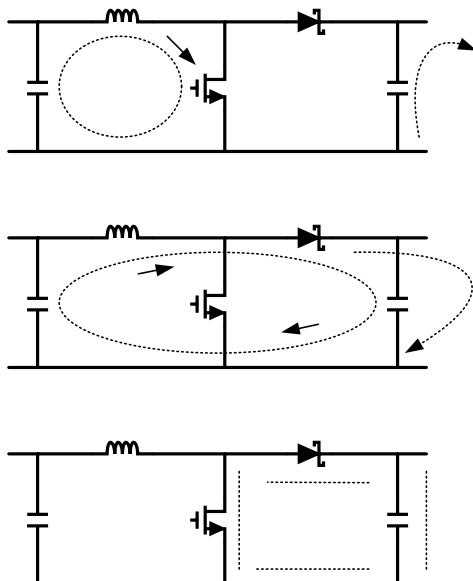

レイアウトの最も重要なルールは、AC 電流ループをできるだけ小さくすることです。図 7.11 に、昇圧コンバータの電流フローを示します。上側の回路図はオン状態での電流フローを表す点線、中央の回路図はオフ状態での電流フローを示しています。下側の回路図は AC 電流と呼ばれる電流を示しています。電流は非常に短期間で変化するので、これらは最も重要なものです。下側の回路図の点線のトレースは、できるだけ短くする必要があります。

PGND および AGND ピンは、デバイスのすぐ近くの同じグランドに接続する必要があります。グランドループ電流を避けるため、システムのすべてのグランドを 1 つの点にのみ接続してください。

セラミック入力コンデンサは、VIN ピンにできる限り近づけて接続し、GND ピンの近くにグランド接続します。

スイッチモード電源のレイアウトの詳細については、『[AN-1229 Simple Switcher PCB レイアウトガイドラインアプリケーションレポート](#)』を参照してください。

図 7.11. 昇圧アプリケーションでの電流フロー

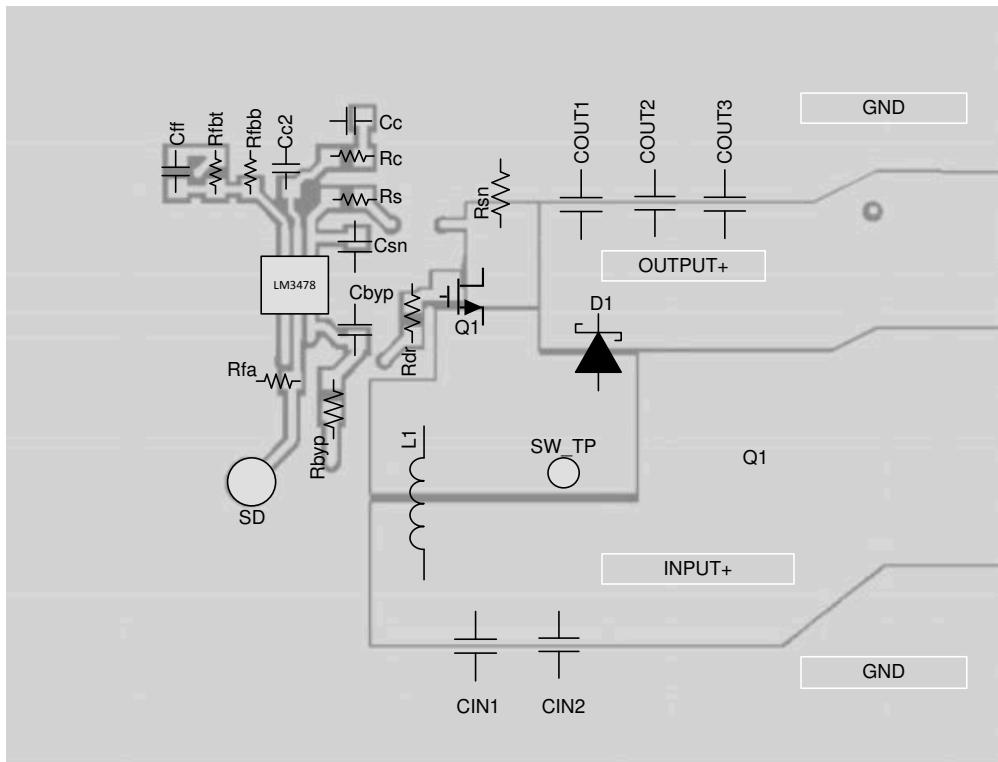

#### 7.4.2 レイアウト例

図 7-12. 昇圧コンバータの代表的なレイアウト

## 8 デバイスおよびドキュメントのサポート

### 8.1 デバイス サポート

#### 8.1.1 サード・パーティ製品に関する免責事項

サード・パーティ製品またはサービスに関するテキサス・インスツルメンツの出版物は、単独またはテキサス・インスツルメンツの製品、サービスと一緒に提供される場合に関係なく、サード・パーティ製品またはサービスの適合性に関する是認、サード・パーティ製品またはサービスの是認の表明を意味するものではありません。

### 8.2 開発サポート

この製品の開発サポートについては、以下を参照してください。

#### 8.2.1 WEBENCH ツールによるカスタム設計

[ここをクリック](#)すると、WEBENCH® Power Designer により、LM3478Q-Q1 デバイスを使用するカスタム設計を作成できます。

1. 最初に、 $V_{IN}$ 、 $V_{OUT}$ 、 $I_{OUT}$  の要件を入力します。

2. オプティマイザのダイヤルを使用して、効率、占有面積、コストなどの主要なパラメータについて設計を最適化し、この設計と、テキサス・インスツルメンツによる他の可能なソリューションとを比較します。

3. WEBENCH Power Designer では、カスタマイズされた回路図と部品リストを、リアルタイムの価格や部品の在庫情報と併せて参照できます。

4. ほとんどの場合、以下の内容も可能となります：

- 電気的なシミュレーションを実行し、重要な波形と回路の性能を確認する

- 熱シミュレーションを実行し、基板の熱性能を把握する。

- カスタマイズされた回路図やレイアウトを、一般的な CAD フォーマットでエクスポートする。

- 設計のレポートを PDF で印刷し、同僚と設計を共有する。

5. WEBENCH ツールの詳細は、[www.ti.com/ja-jp/webench](http://www.ti.com/ja-jp/webench) でご覧になれます。

### 8.3 ドキュメントのサポート

WEBENCH Power Designer により、LM3478 を使用するカスタム設計を作成します。

#### 8.3.1 関連資料

関連資料については、以下を参照してください。

- 『LM3748 昇圧コントローラ用 AN-1286 補償』[SNVA067](#)

- 『AN-1229 Simple Switcher PCB レイアウトガイドライン』[SNVA054](#)

### 8.4 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.5 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 8.6 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

WEBENCH® is a registered trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

## 8.7 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお奨めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 8.8 用語集

### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision * (April 2018) to Revision A (June 2025) | Page |

|----------------------------------------------------------------|------|

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新.....                           | 1    |

| • 熱表の値を更新.....                                                 | 4    |

| • $I_{EAO}$ の値を更新.....                                         | 5    |

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| LM3478QMM/NOPB        | Active        | Production           | VSSOP (DGK)   8 | 1000   SMALL T&R      | Yes         | NIPDAU   SN                          | Level-1-260C-UNLIM                | -40 to 125   | SSFB                |

| LM3478QMM/NOPB.A      | Active        | Production           | VSSOP (DGK)   8 | 1000   SMALL T&R      | Yes         | SN                                   | Level-1-260C-UNLIM                | -40 to 125   | SSFB                |

| LM3478QMM/NOPB.B      | Active        | Production           | VSSOP (DGK)   8 | 1000   SMALL T&R      | Yes         | SN                                   | Level-1-260C-UNLIM                | -40 to 125   | SSFB                |

| LM3478QMMX/NOPB       | Active        | Production           | VSSOP (DGK)   8 | 3500   LARGE T&R      | Yes         | NIPDAU   SN                          | Level-1-260C-UNLIM                | -40 to 125   | SSFB                |

| LM3478QMMX/NOPB.A     | Active        | Production           | VSSOP (DGK)   8 | 3500   LARGE T&R      | Yes         | SN                                   | Level-1-260C-UNLIM                | -40 to 125   | SSFB                |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

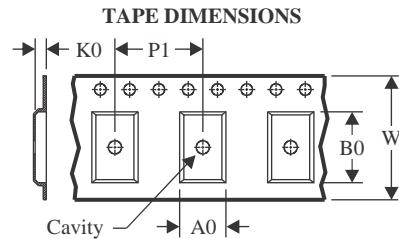

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|-----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| LM3478QMM/NOPB  | VSSOP        | DGK             | 8    | 1000 | 177.8              | 12.4               | 5.3     | 3.4     | 1.4     | 8.0     | 12.0   | Q1            |

| LM3478QMMX/NOPB | VSSOP        | DGK             | 8    | 3500 | 330.0              | 12.4               | 5.3     | 3.4     | 1.4     | 8.0     | 12.0   | Q1            |

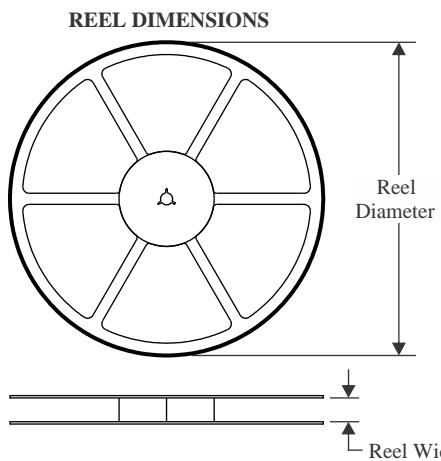

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LM3478QMM/NOPB  | VSSOP        | DGK             | 8    | 1000 | 208.0       | 191.0      | 35.0        |

| LM3478QMMX/NOPB | VSSOP        | DGK             | 8    | 3500 | 367.0       | 367.0      | 35.0        |

DGK0008A

# PACKAGE OUTLINE

VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

NOTES:

PowerPAD is a trademark of Texas Instruments.

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

5. Reference JEDEC registration MO-187.

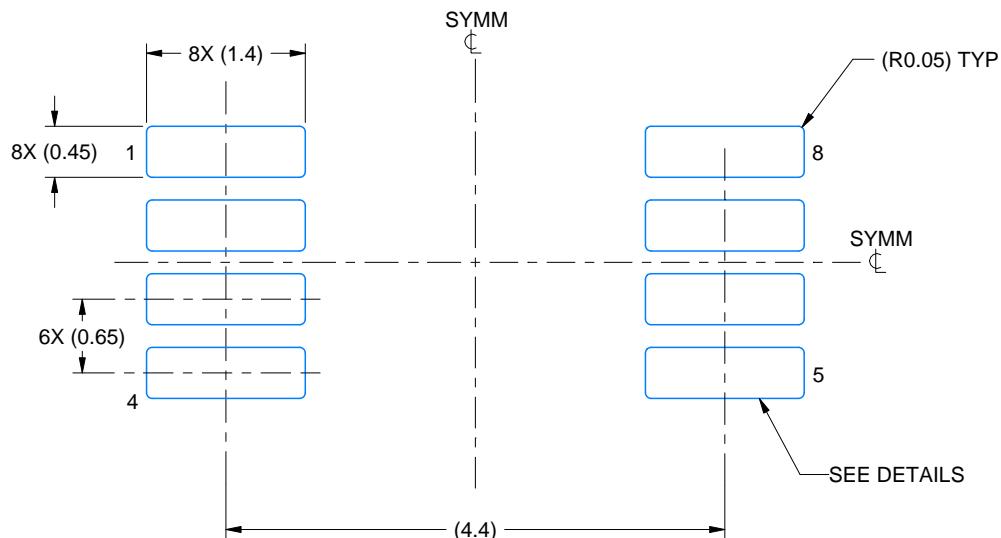

# EXAMPLE BOARD LAYOUT

DGK0008A

™ VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 15X

4214862/A 04/2023

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

9. Size of metal pad may vary due to creepage requirement.

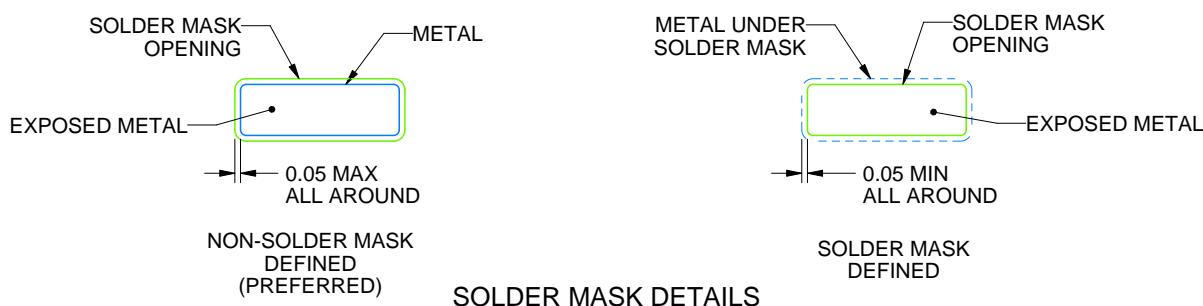

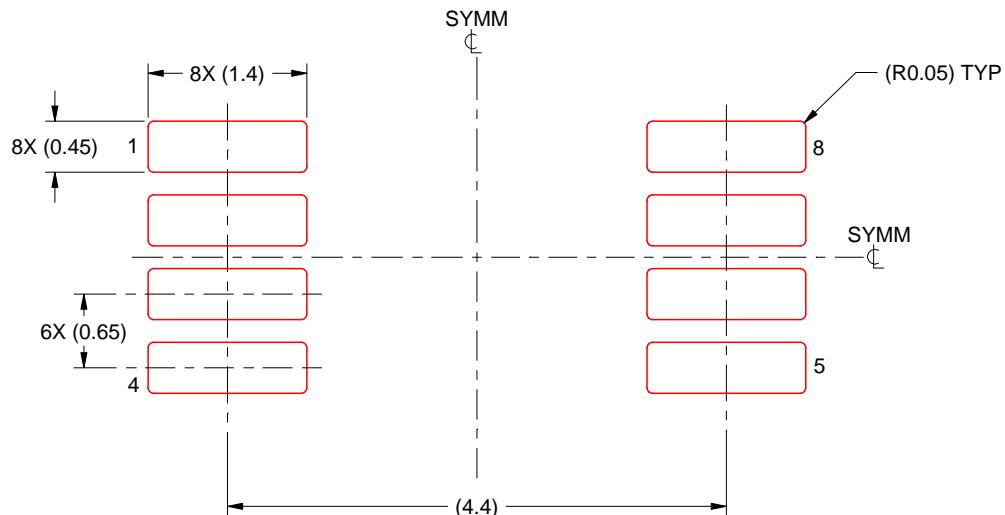

# EXAMPLE STENCIL DESIGN

DGK0008A

™ VSSOP - 1.1 mm max height

SMALL OUTLINE PACKAGE

SOLDER PASTE EXAMPLE

SCALE: 15X

4214862/A 04/2023

NOTES: (continued)

11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

12. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月