## LM251772-Q1 36V VIN4 スイッチバック昇降圧コントローラ、I<sup>2</sup>C 搭載

### 1 特長

- ・ 入力範囲: 3.5V~36V

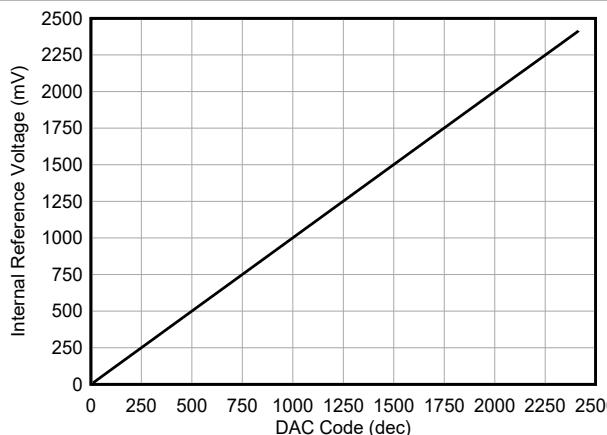

- ・ I<sup>2</sup>C を使用した動的  $V_o$  プログラミング:

- 3.3V、最大、まで 20mV 単調ステップ

- 1V から最大 23V (10mV 単調刻み)

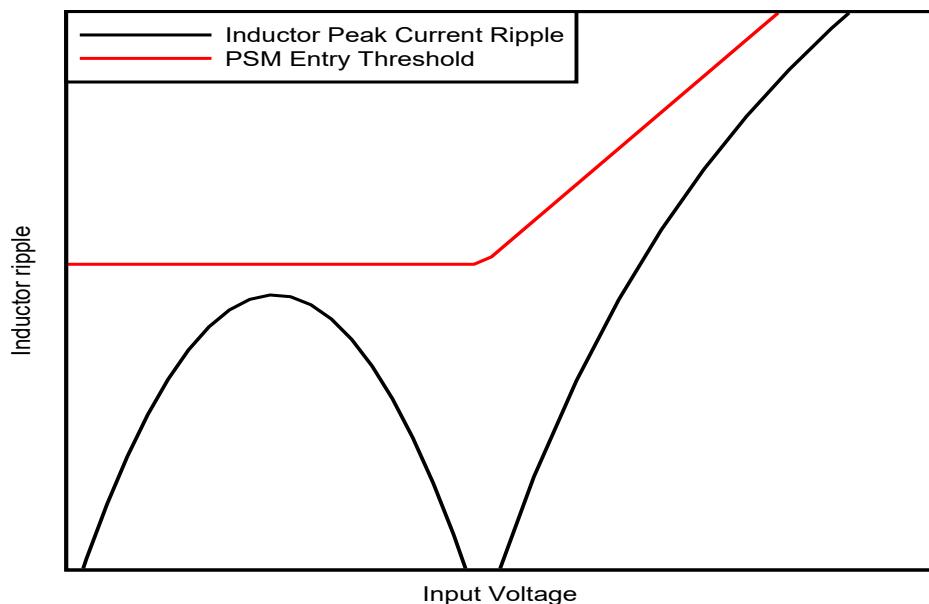

- ・ ピーク電流レギュレーション制御

- ・ すべての動作モードで小さい電圧遷移リップル

- ・ 動的な出力電圧トラッキング (デジタル PWM トラッキング入力、アナログ トラッキング入力)

- I<sup>2</sup>C インターフェイスによるプログラミング経由

- ・ シャットダウン時静止電流: 3 $\mu$ A

- ・ 動作時静止電流: 60 $\mu$ A

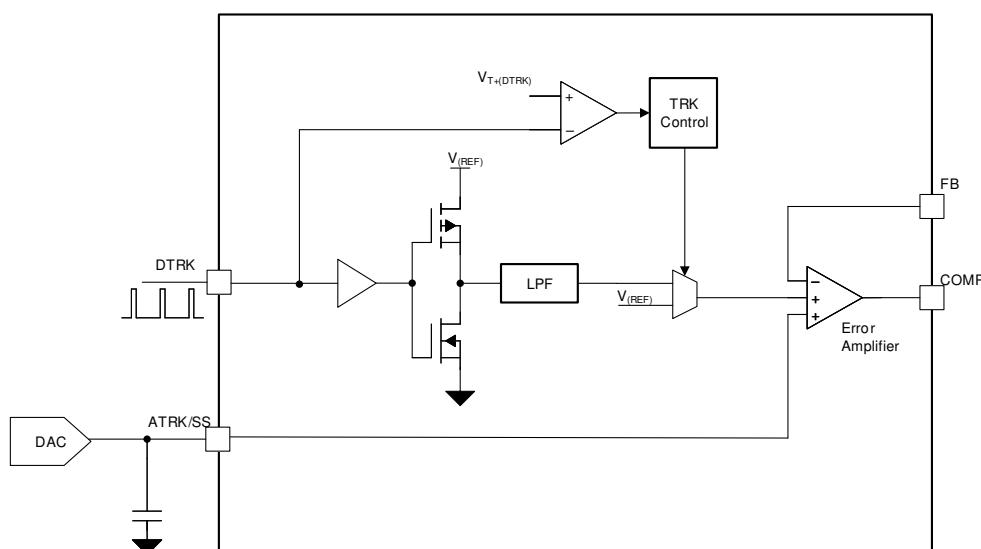

- ・ デュアル ロール ポート電力バス用の駆動 (DRV) ピン

- 高速 pMOS FET 制御用のプッシュプル出力

- nMOS FET 用チャージ ポンプ ドライバ段として構成可能

- ・ 軽負荷および高負荷条件で高効率を実現する動作モードの選択:

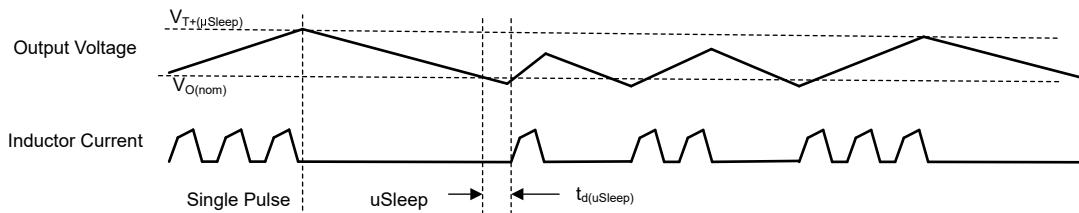

- パワー セーブ モード (单一パルス /  $\mu$ Sleep)

- 自動導通モード

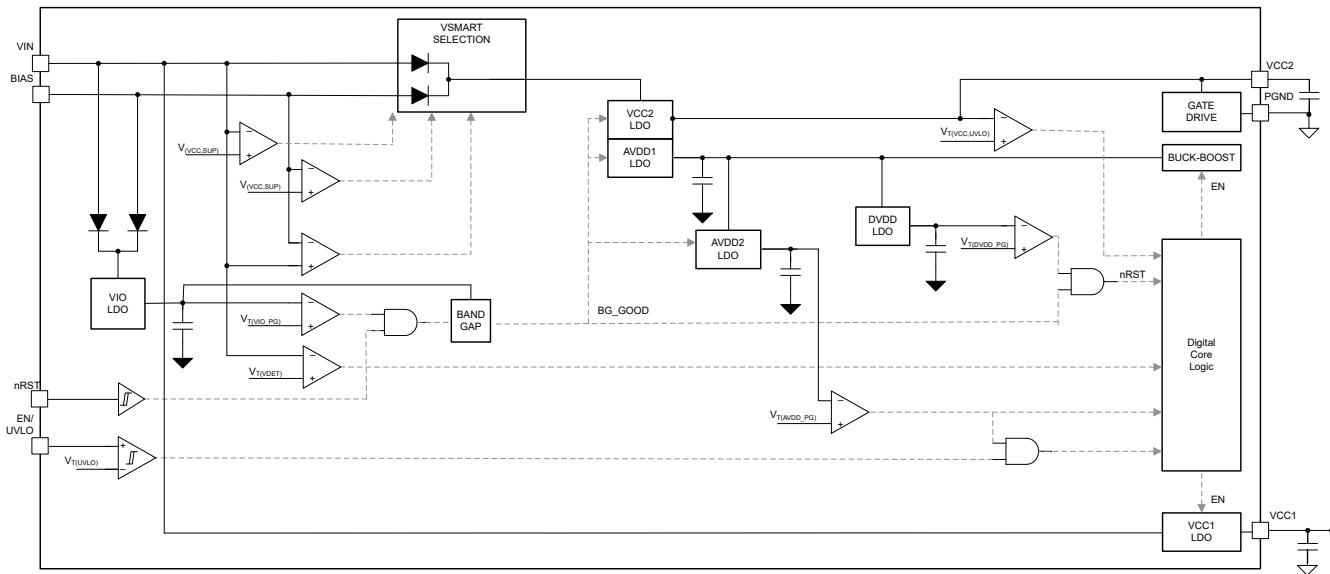

- ・ 高電圧 LDO を内蔵

- ・ マイコン電源用の補助高電圧 LDO

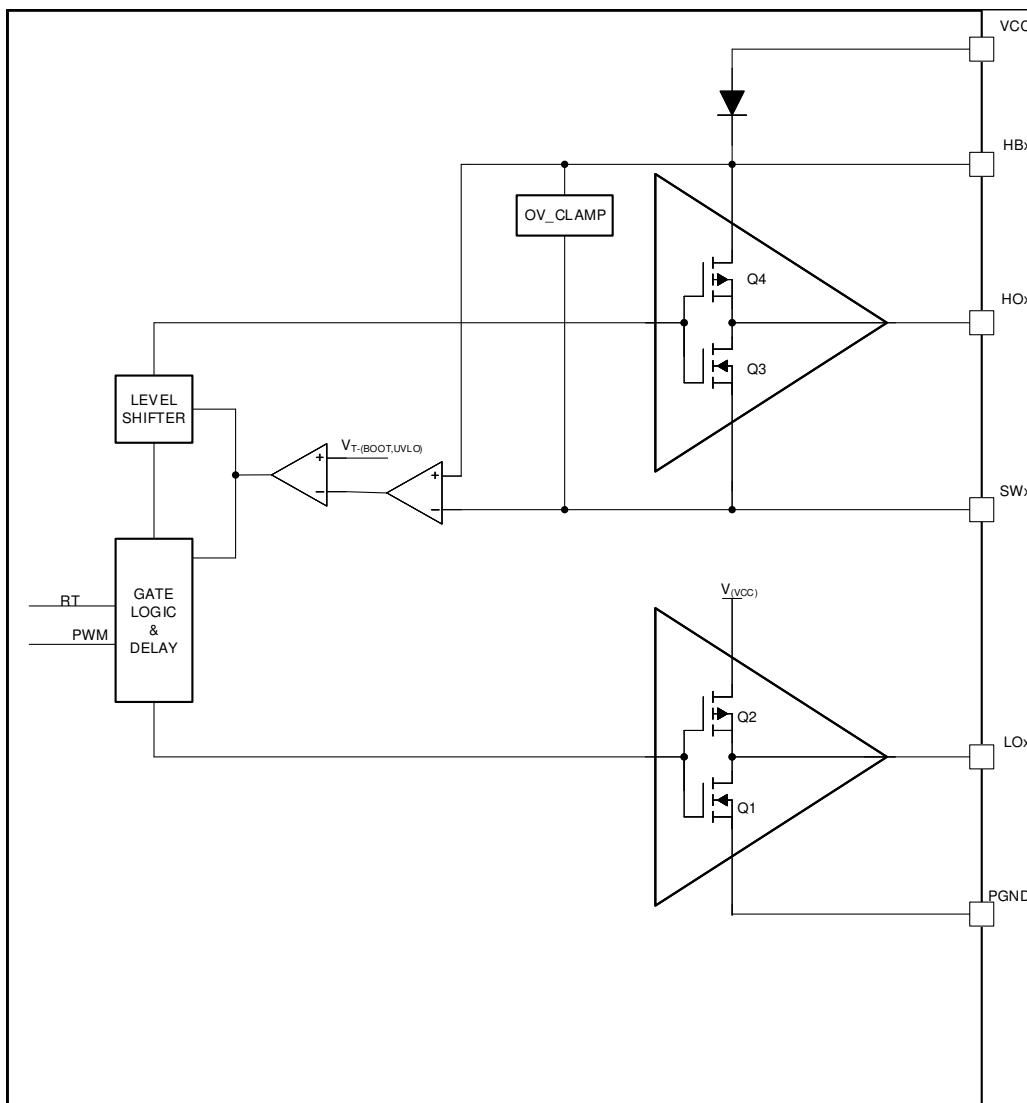

- ・ フルブリッジ ゲートドライブを内蔵

- 2A ピーク電流能力

- ブートストラップ過電圧および低電圧保護

- ブートストラップ ダイオードを内蔵

- ・ 動作モードから独立した固定周波数 (昇圧、昇降圧、降圧)

- 強制 PWM モードを選択可能

- スイッチング周波数: 100kHz~2200kHz

- 外部クロック同期およびクロック出力

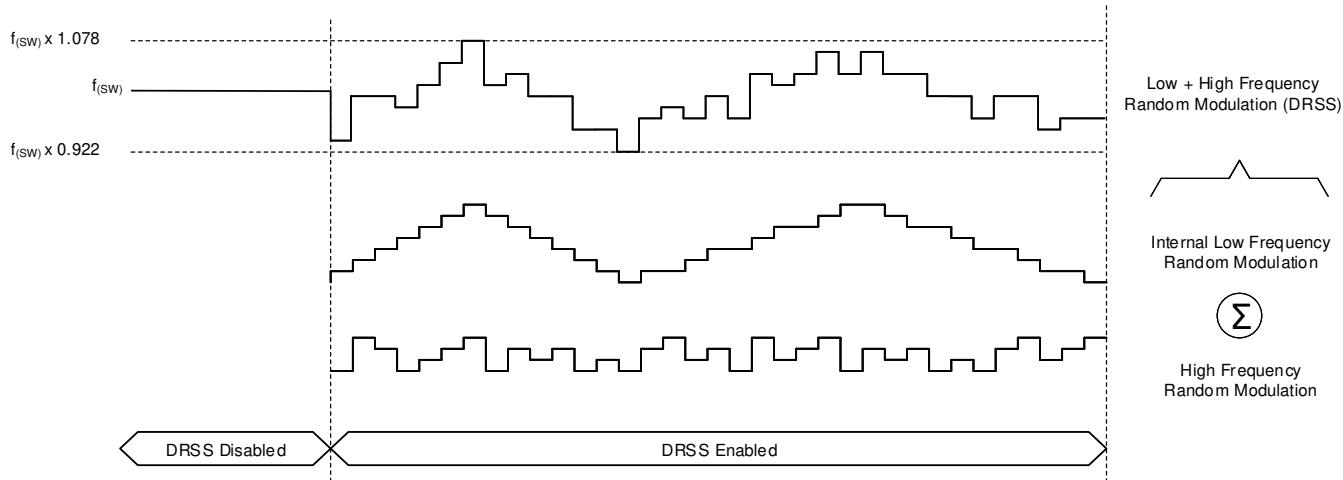

- ・ スペクトラム拡散動作を選択可能

- ・ 平均入力または出力電流センサ

- 0.5A~7A の範囲で 50mA 刻みにプログラミング可能

- ・ I<sup>2</sup>C 診断機能付きでプログラマブル

- ・ 車載用温度範囲 ( $T_j = -40^{\circ}\text{C} \sim 150^{\circ}\text{C}$ )

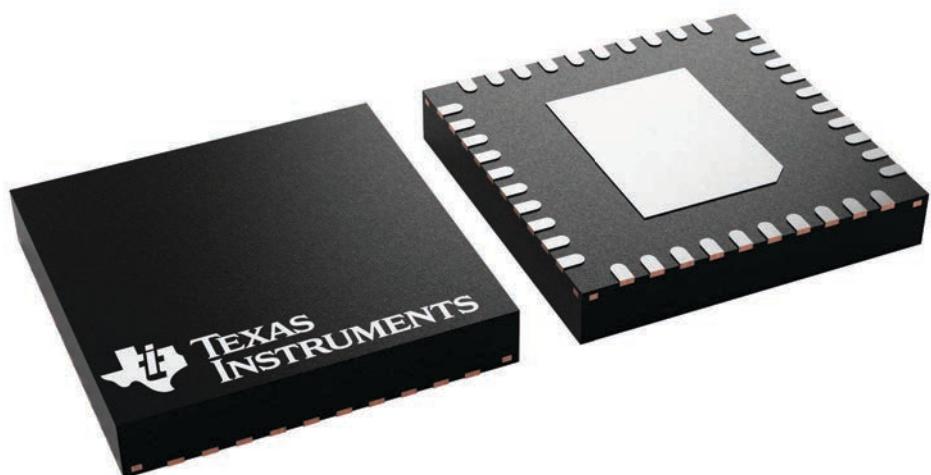

- ・ 40 ピンのウェッタブル フランク付き WSON パッケージ

- ・ 機能安全対応

- 機能安全を支援するドキュメントが利用可能

- ・ **WEBENCH® Power Designer** を使用して LM251772-Q1 を使用したカスタム設計を作成

### 2 アプリケーション

- ・ 車載用インフォテインメント、デジタル コックピット

- ・ USB-PD EPR (拡張電力範囲)

### 3 説明

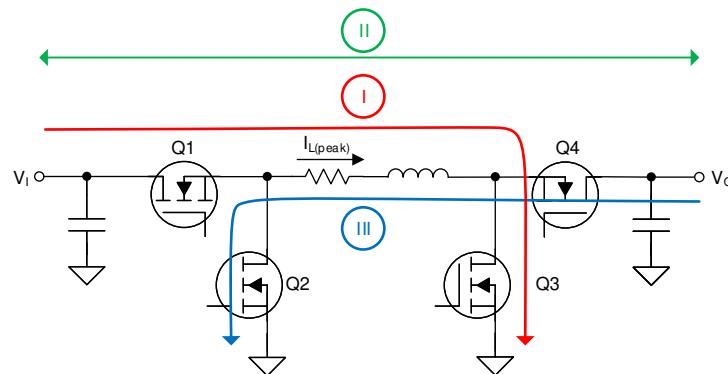

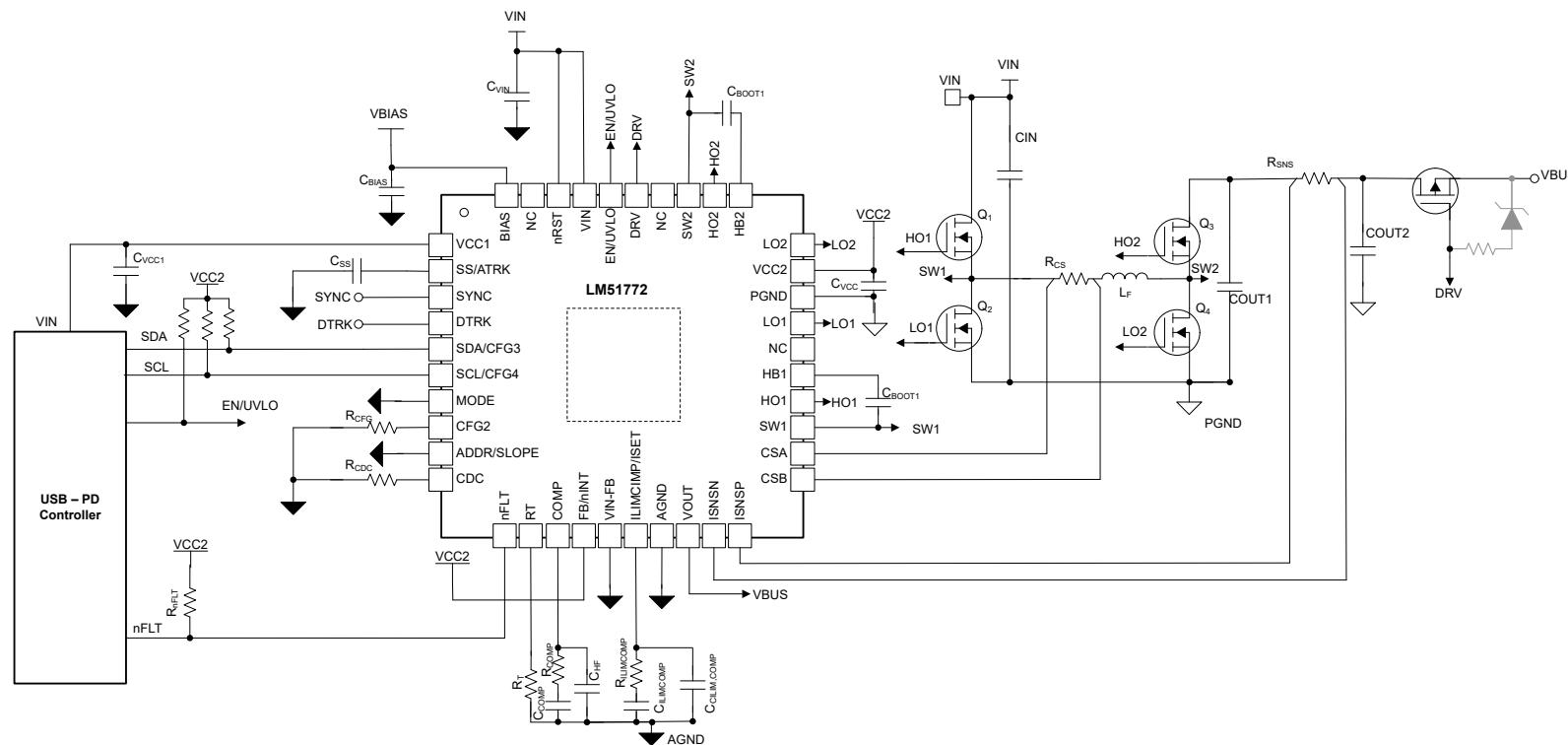

LM251772-Q1 は、4 スイッチ昇降圧コントローラです。本デバイスは入力電圧が、調整された出力電圧よりも高い、等しい、または低い場合に、レギュレートされた出力電圧を供給します。パワーセーブ モードでは、出力の動作範囲全体にわたって非常に高い効率をサポートします。出力電圧と平均電流は、内蔵の I<sup>2</sup>C インターフェースを使用して動的にプログラミング可能です。出力電圧と平均電流の設定範囲は、USB-PD 規格の要件を満たしています。システムがデュアルロールポート (DRP) 要件をサポートすることを目標としている場合、内蔵の DRV ピンはオプションの切断 FET を制御するために使用されます。

LM251772-Q1 は、RT / SYNC ピンを使用して設定される固定スイッチング周波数で動作します。降圧、昇圧、昇降圧動作中も、スイッチング周波数は同一に維持されます。このデバイスは、すべての動作モードにわたって小さなモード遷移リップルを維持します。

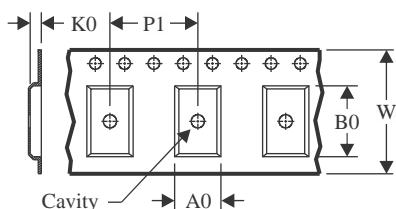

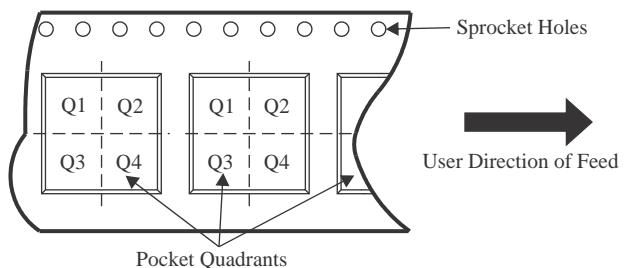

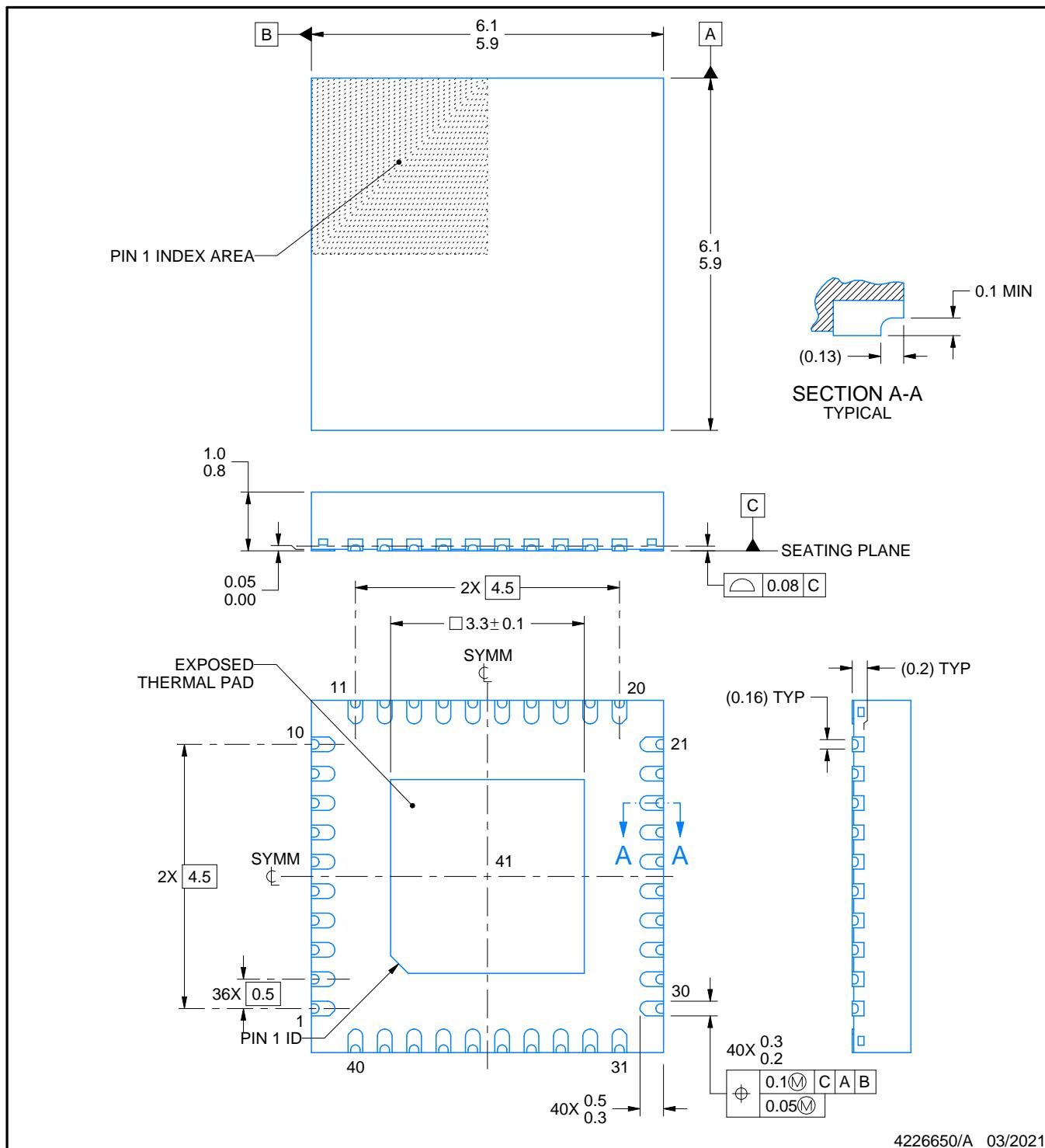

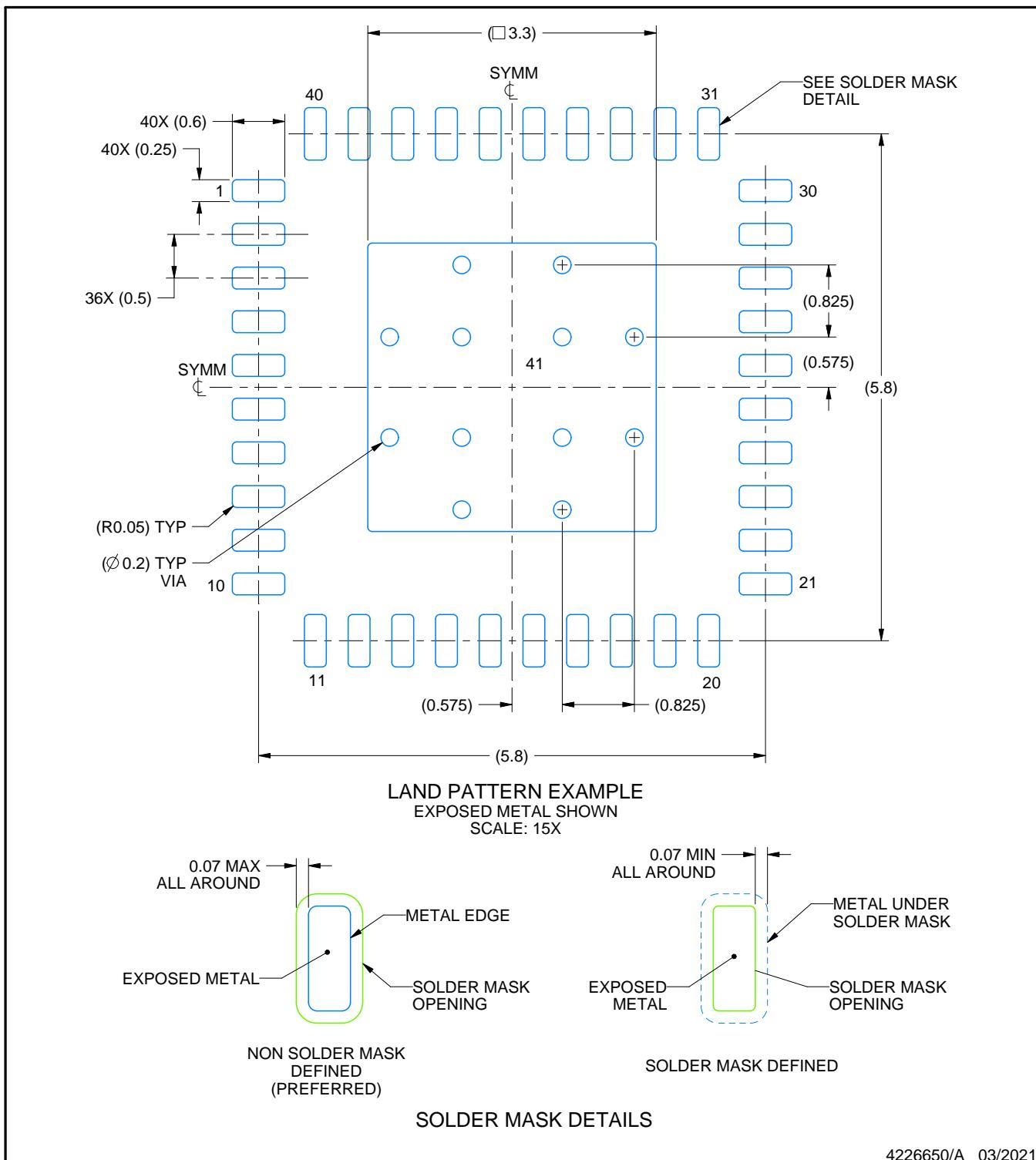

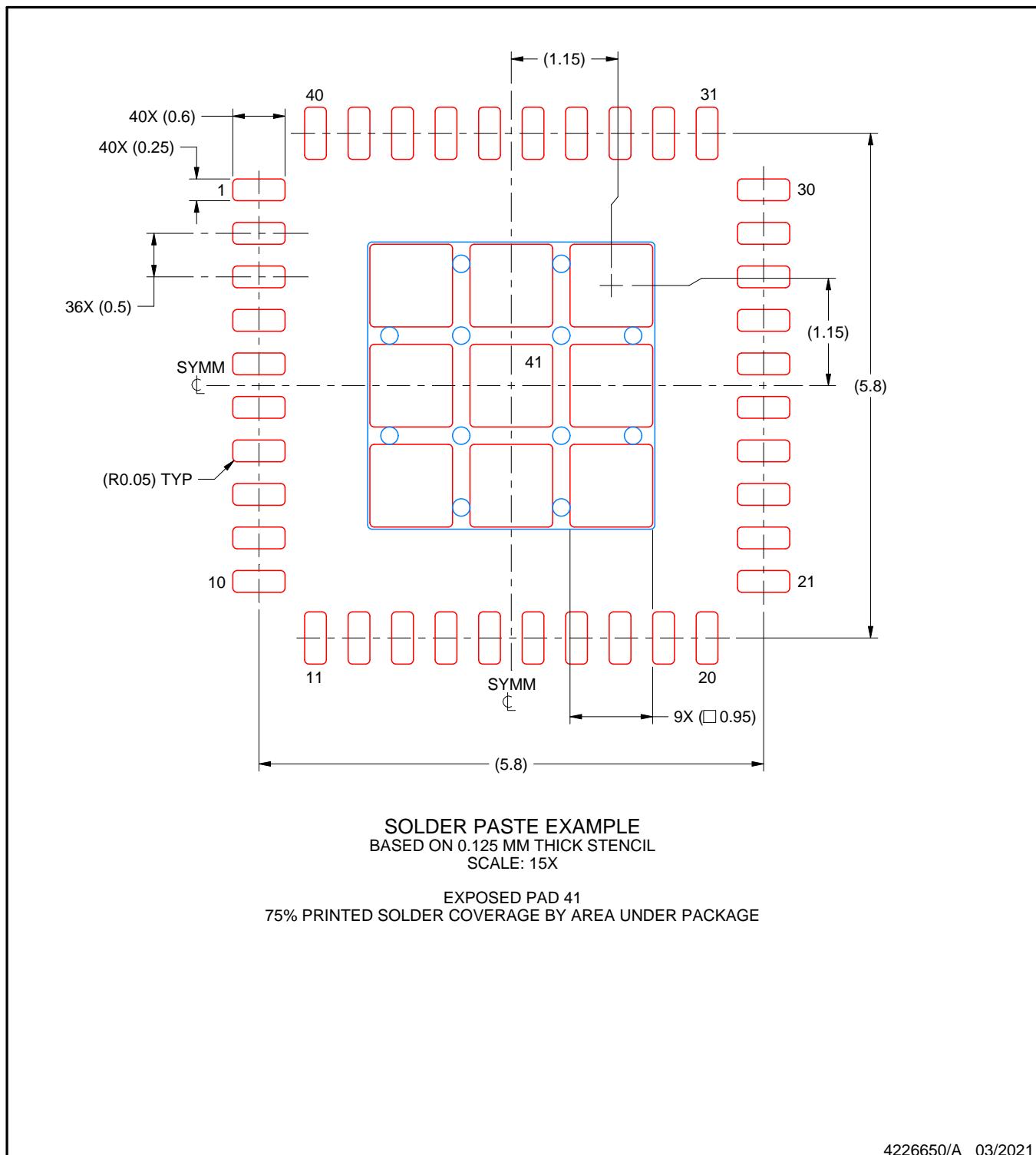

#### パッケージ情報

| 部品番号            | パッケージ (1)     | パッケージ サイズ(2) |

|-----------------|---------------|--------------|

| LM251772-Q1RHAR | RHA (VQFN、40) | 6mm × 6mm    |

(1) 詳細については、[セクション 13](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

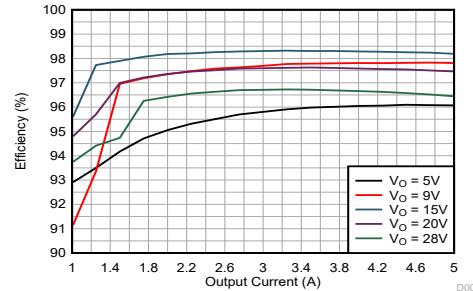

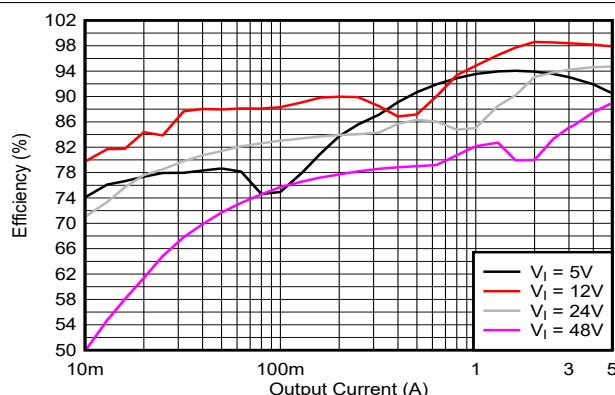

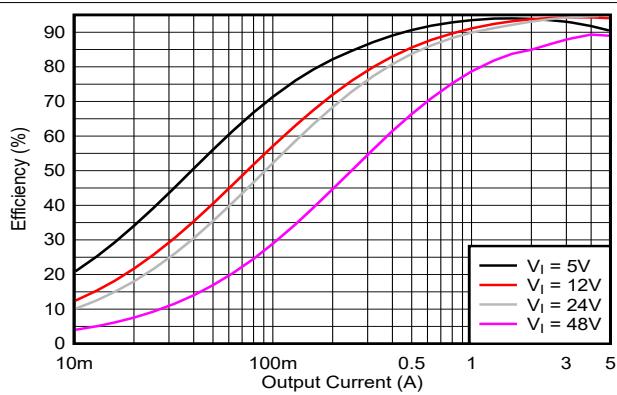

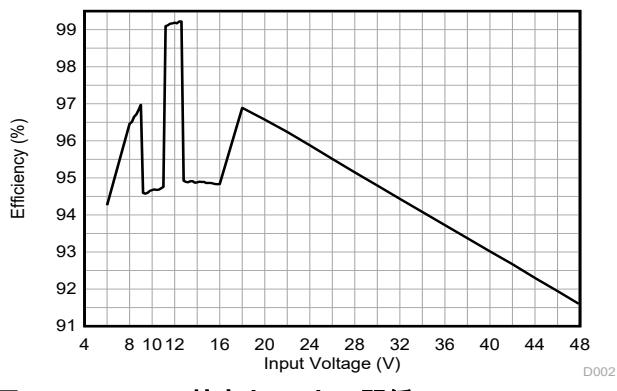

#### 効率と出力電流との関係、 $V_I = 12V$ 、PSM

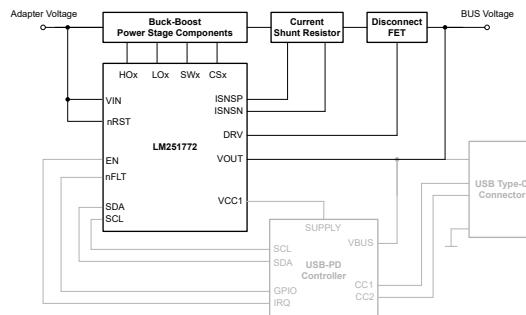

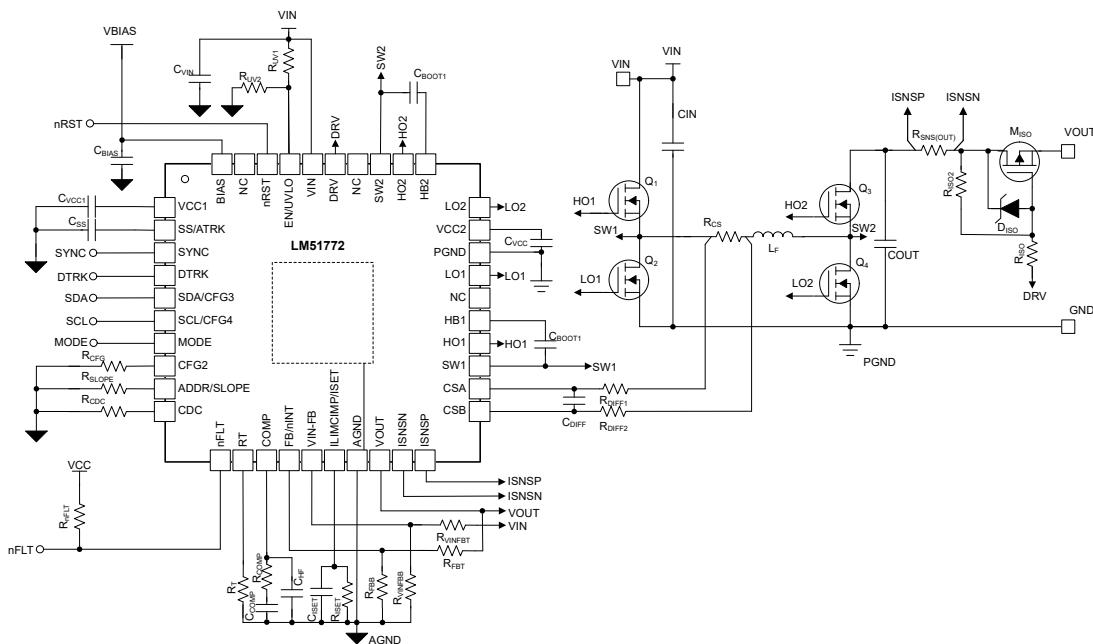

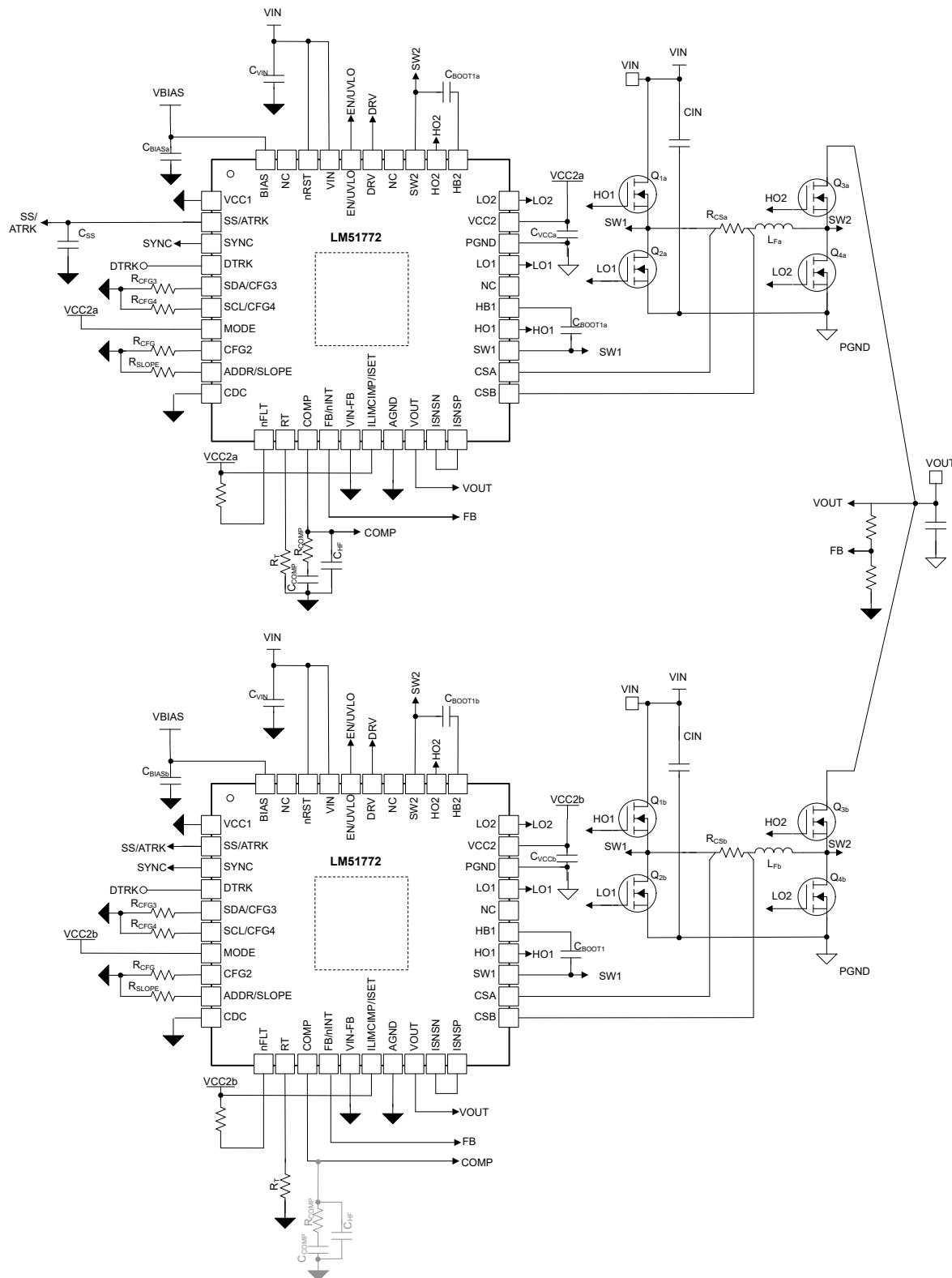

代表的なアプリケーション回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                |    |                         |     |

|----------------|----|-------------------------|-----|

| 1 特長           | 1  | 8.5 プログラミング             | 58  |

| 2 アプリケーション     | 1  | 9 LM251772 のレジスタ        | 61  |

| 3 説明           | 1  | 10 アプリケーションと実装          | 87  |

| 4 デバイスの比較      | 3  | 10.1 アプリケーション情報         | 87  |

| 5 ピン構成および機能    | 4  | 10.2 代表的なアプリケーション       | 87  |

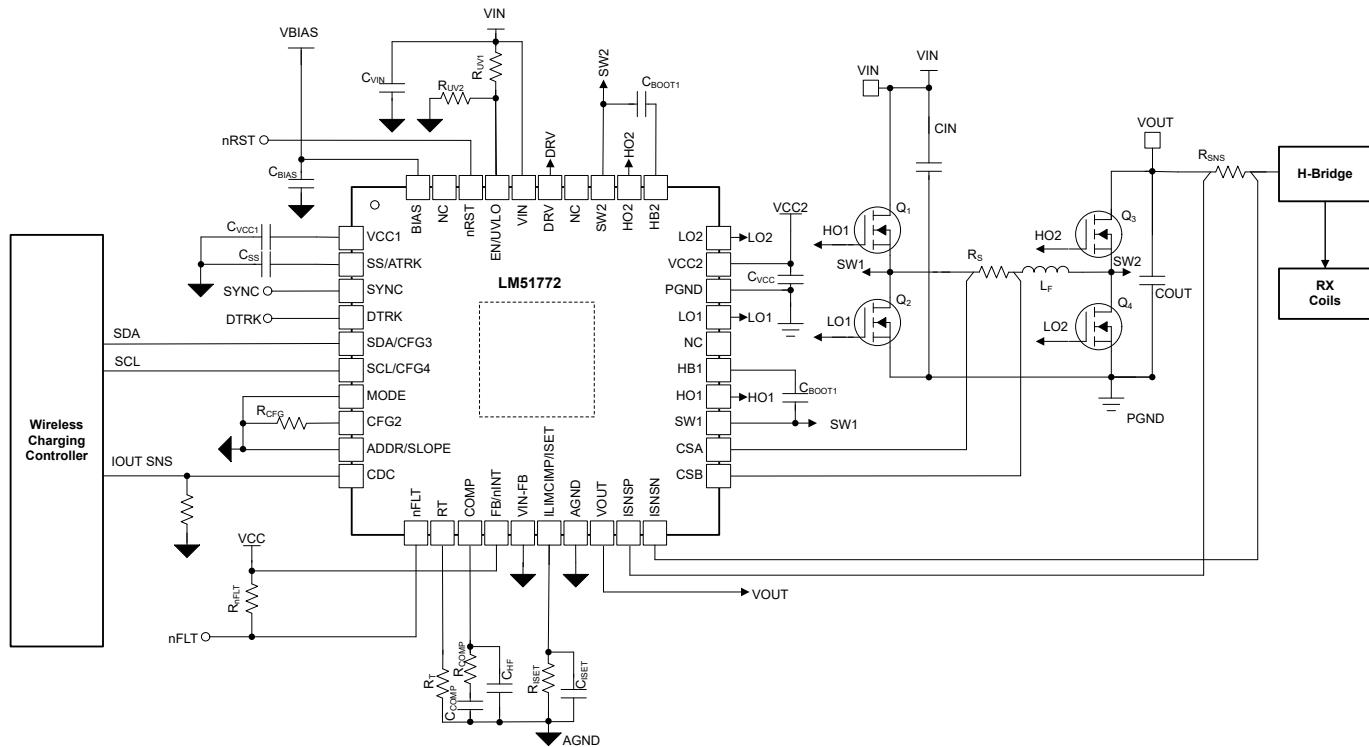

| 6 仕様           | 7  | 10.3 パワー パス付き PD ソース    | 100 |

| 6.1 絶対最大定格     | 7  | 10.4 並列 (マルチフェーズ) 動作    | 101 |

| 6.2 取り扱い定格     | 8  | 10.5 ワイヤレス充電供給          | 102 |

| 6.3 推奨動作条件     | 8  | 10.6 電源に関する推奨事項         | 103 |

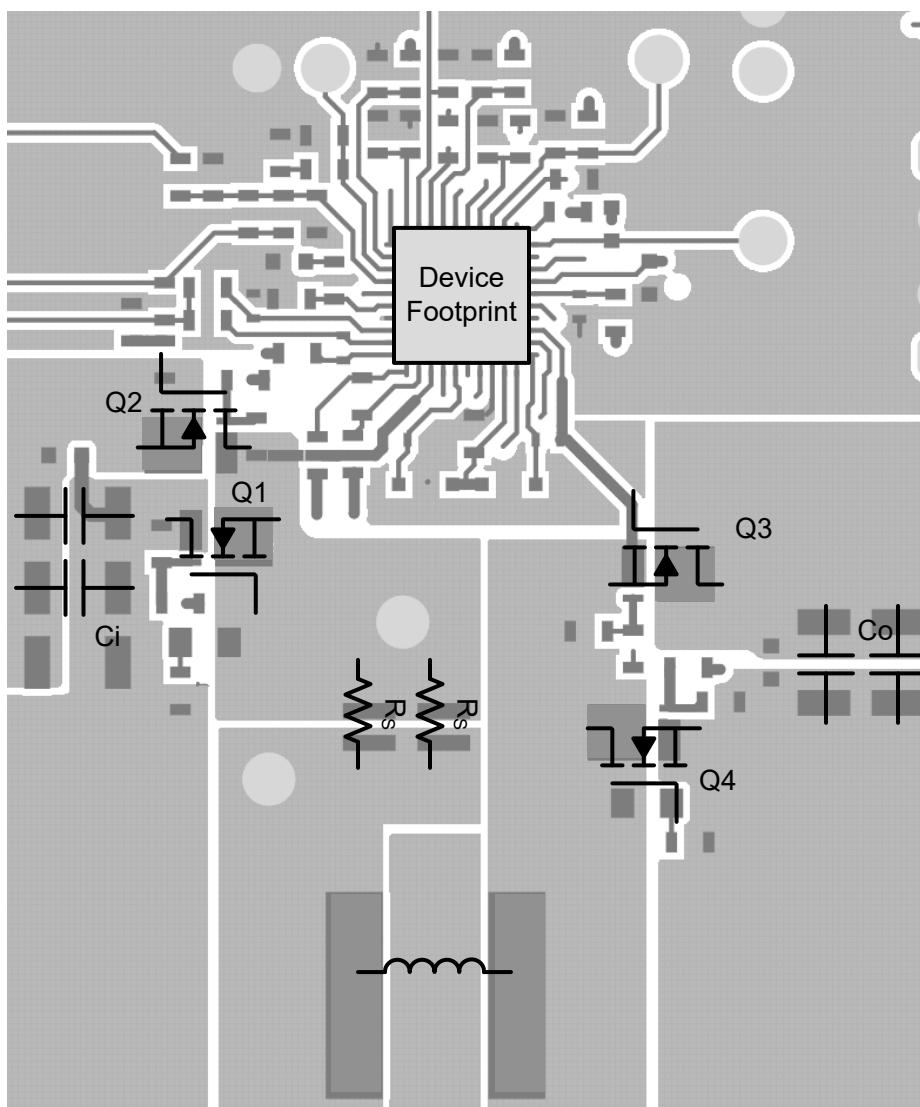

| 6.4 熱に関する情報    | 9  | 10.7 レイアウト              | 103 |

| 6.5 電気的特性      | 10 | 11 デバイスおよびドキュメントのサポート   | 106 |

| 6.6 タイミング要件    | 16 | 11.1 ドキュメントのサポート        | 106 |

| 6.7 代表的特性      | 18 | 11.2 ドキュメントの更新通知を受け取る方法 | 106 |

| 7 パラメータ測定情報    | 23 | 11.3 サポート・リソース          | 106 |

| 8 詳細説明         | 24 | 11.4 商標                 | 106 |

| 8.1 概要         | 24 | 11.5 静電気放電に関する注意事項      | 106 |

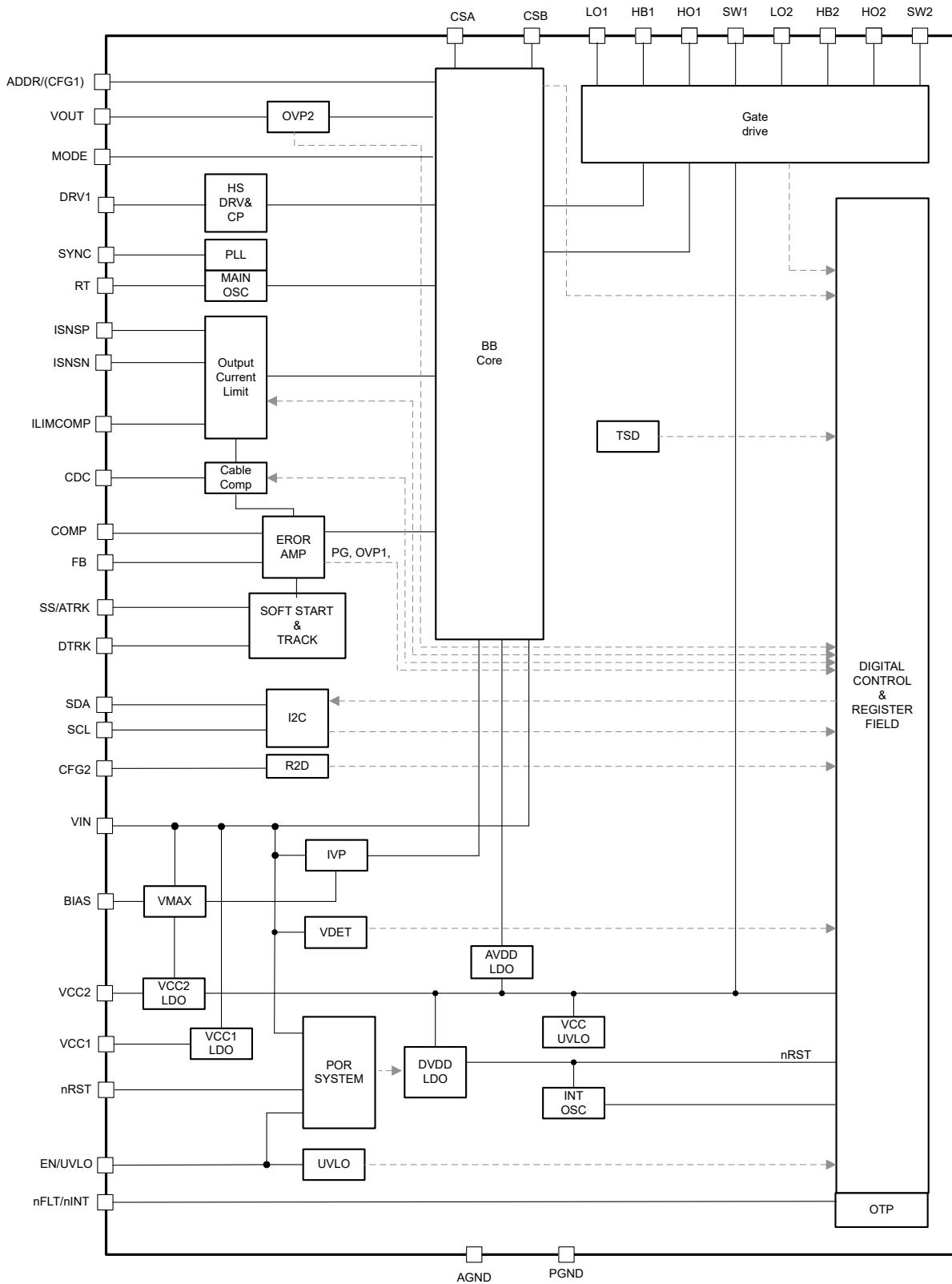

| 8.2 機能ブロック図    | 25 | 11.6 用語集                | 106 |

| 8.3 機能説明       | 26 | 12 改訂履歴                 | 106 |

| 8.4 デバイスの機能モード | 57 | 13 メカニカル、パッケージ、および注文情報  | 106 |

## 4 デバイスの比較

**表 4-1. デバイスの比較**

| 機能                        | LM251772Q1    | LM51772Q1     | LM251772 | LM51770Q1     | LM34938Q1     |

|---------------------------|---------------|---------------|----------|---------------|---------------|

| 推奨最大入力電圧                  | 36V           | 55V           | 36V      | 78V           | 36V           |

| 絶対最大入力電圧                  | 48V           | 59V           | 48V      | 85V           | 48V           |

| 推奨最大スイッチング周波数             | 2.2MHz        | 2.2MHz        | 600kHz   | 2MHz          | 2.2MHz        |

| デフォルトの出力電圧の設定値            | 5.1V          | 12V           | 5.1V     | 該当なし          | 5V            |

| デフォルトの出力電流制限値             | 900mA         | 5A            | 900mA    | 該当なし          | アナログ設定のみ      |

| プログラミングなしの出力スタートアップ状態     | 無効            | 有効            | 無効       | 有効            | 無効            |

| I <sup>2</sup> C インターフェイス | あり            | あり            | あり       | なし            | あり            |

| PSM — 自動導通モード             | あり            | あり            | あり       | あり            | あり            |

| PSM — プログラマブル導通モード        | なし            | あり            | なし       | なし            | なし            |

| 出力放電                      | あり            | あり            | あり       | なし            | あり            |

| 入力電圧レギュレーション              | あり            | あり            | あり       | 外部回路を使用する場合   | あり            |

| アナログ電流制限の設定               | なし            | あり            | なし       | なし            | あり            |

| T <sub>j</sub> 温度範囲       | −40°C ~ 150°C | −40°C ~ 150°C | 0°C~70C  | −40°C ~ 150°C | −40°C ~ 150°C |

## 5 ピン構成および機能

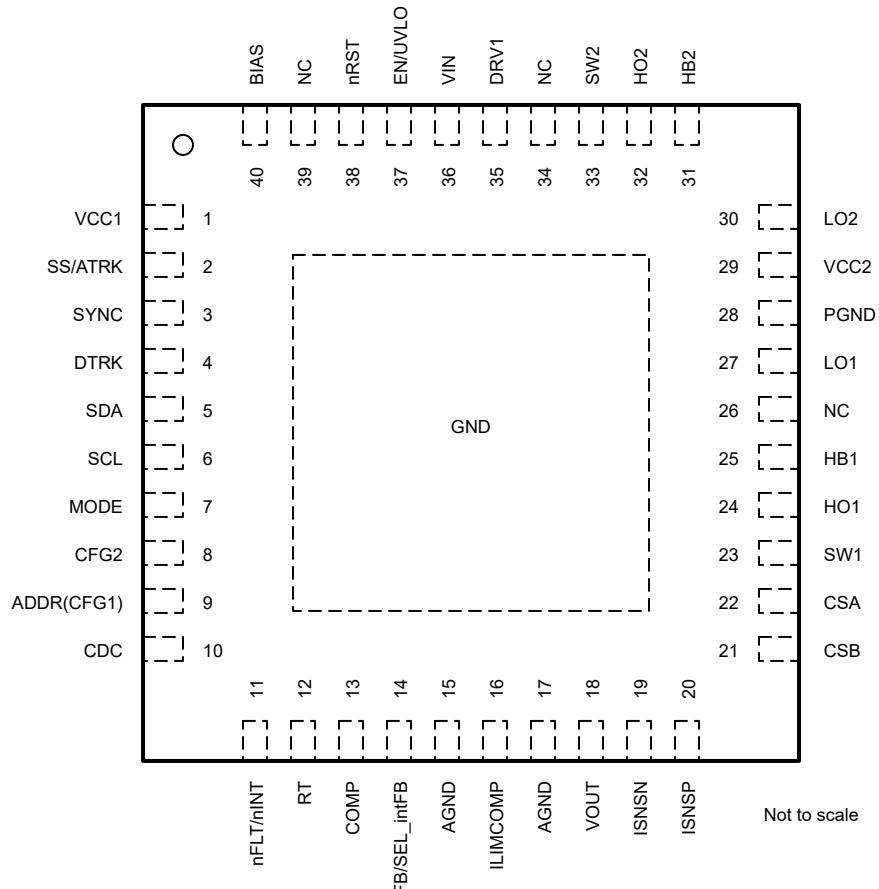

図 5-1. LM251772-Q1 RHA パッケージ、40 ピン QFN (上面図)

**表 5-1. ピン機能 LM251772Q1**

| ピン           |    | 種類 <sup>(1)</sup> | 説明                                                                                                                                                                                                                                         |

|--------------|----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称           | 番号 |                   |                                                                                                                                                                                                                                            |

| VCC1         | 1  | O                 | 補助 5V レギュレータ出力。このコンデンサは、適切なデカップリングを実現するためピンの近くに配置します。対応するロジック選択によって出力が無効になっている場合は、抵抗器を使用してピンを GND に接続するか、VCC2 にプルダウンします。ピンをフローティングのままにしないでください。                                                                                            |

| SS/ATRK      | 2  | I/O               | ソフトスタート プログラミング ピン。SS ピンと AGND ピンの間に接続するコンデンサによって、ソフトスタート時間をプログラミングします。<br>アナログ出力電圧トラッキング ピン。必要に応じて、ピンを変数電圧リファレンス (たとえば、D/A コンバータ経由) に接続することにより、VOUT 調整ターゲットをプログラムします。内部回路は、ピンの電圧と内部電圧リファレンスとの間で最低の電圧を選択します。                               |

| SYNC         | 3  | I                 | 同期クロック入力 / 出力。有効なクロック入力信号が存在する場合、内部発振器は動作中に外部クロックに同期します。このピンをフローティングのままにしないでください。この機能を使用しない場合は、ピンを VCC2 または GND に接続します。<br>SYNC ピンには、デバイスロジックを通じて設定されるクロック同期出力信号も備わっています。クロック位相は 0° と 180° を選択でき、2 つのデバイスを並列 (デュアルフェーズ) 動作で直接動作させることができます。 |

| DTRK         | 4  | I                 | 動的出力電圧トラッキング用のデジタル PWM 入力ピン。このピンをフローティングのままにしないでください。この機能を使用しない場合は、ピンを VCC または GND に接続します。                                                                                                                                                 |

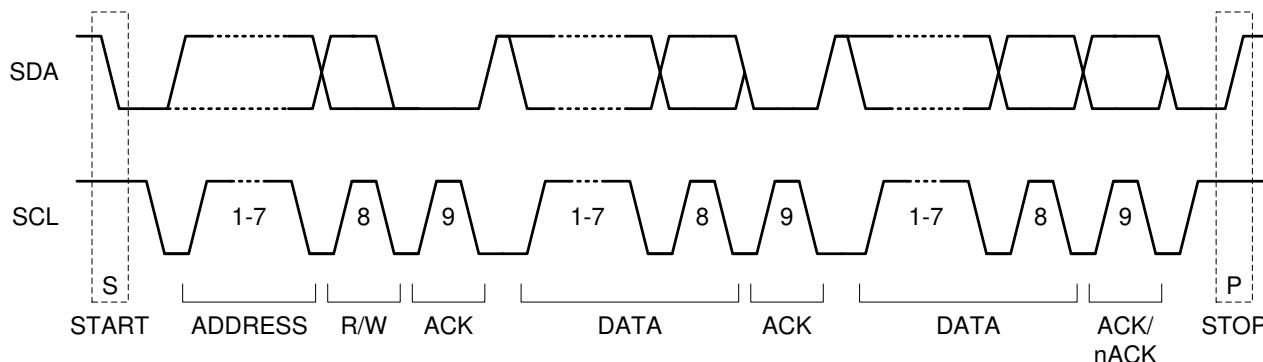

| SDA          | 5  | I <sup>2</sup> C  | I <sup>2</sup> C インターフェイスシリアルデータライン外付けプルアップ抵抗を接続します                                                                                                                                                                                        |

| SCL          | 6  | I                 | I <sup>2</sup> C インターフェイスシリアルクロックライン。外付けプルアップ抵抗を接続します                                                                                                                                                                                      |

| モード          | 7  | I                 | デバイス動作モードを選択するためのデジタル入力。このピンが low にプルされると、パワー セーブ モード (PSM) がイネーブルになります。このピンが high になると、強制 PWM または CCM 動作がイネーブルになります。動作中に動作モードを動的に変更することができます。このピンをフローティングのままにしないでください。                                                                    |

| CFG2         | 8  | I/O               | デバイス構成ピン。CFG2 ピンと GND の間に抵抗を接続し、 <a href="#">セクション 8.3.21</a> に従ってデバイスの動作を選択します                                                                                                                                                            |

| ADDR(CFG1)   | 9  | I                 | アドレス選択。I <sup>2</sup> C ターゲットアドレス LSB = 0 の場合は GND にプルダウンします。I <sup>2</sup> C ターゲットアドレス LSB = 1 の場合、VCC2 にプルします。                                                                                                                           |

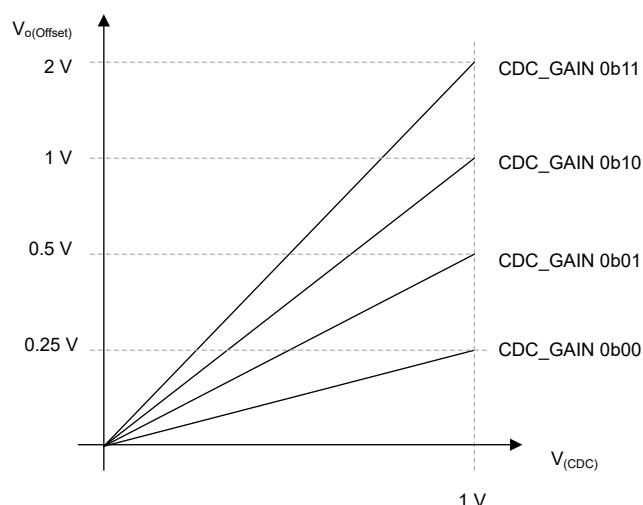

| CDC          | 10 |                   | ケーブル電圧降下補償または電流モニタ出力ピン。CDC ピンと AGND の間に抵抗を接続して、ケーブル電圧降下補償のゲインを選択します。<br>デフォルトでは、このピンは ISNSP ピンと ISNSN ピンの間で検出された電圧の電流監視信号を提供します<br>電流監視が無効になっている場合は、CDC をグランドに接続します                                                                        |

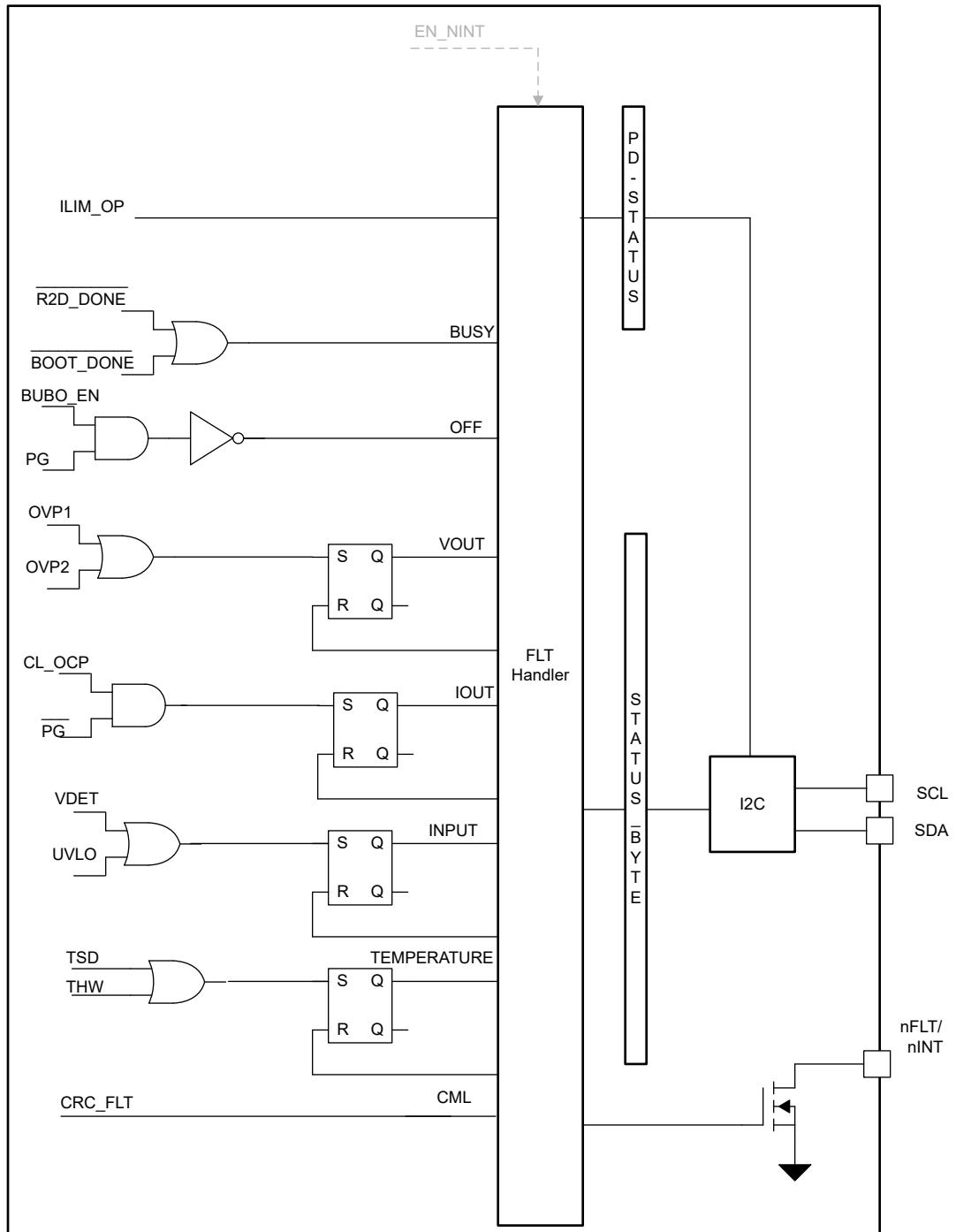

| nFLT/nINT    | 11 | O                 | 障害表示または電源正常用のオープンドレイン出力ピン。このピンは、割り込みピンとして設定されている場合、さらに別の機能を持ちます。STATUS レジスタを変更すると、256 $\mu$ s のピンが low に切り替わります。                                                                                                                           |

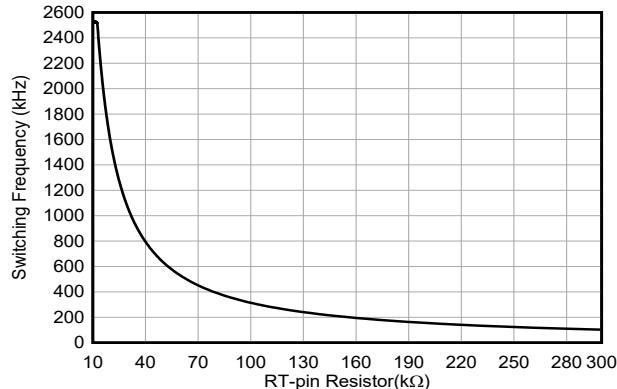

| RT           | 12 | I/O               | スイッチング周波数のプログラミング用ピン。RT ピンと AGND に外付け抵抗を接続して、スイッチング周波数を設定します                                                                                                                                                                               |

| COMP         | 13 | O                 | エラー アンプの出力。レギュレータ電圧ループの安定/補償を行うため、COMP と AGND の間に外付け RC ネットワークを接続する必要があります。                                                                                                                                                                |

| FB/SEL_INTFB | 14 | I                 | 出力電圧レギュレーション用の帰還ピン。コンバータの出力と FB ピンとの間に分圧抵抗回路を接続します。FB ピンを VCC2 に接続すると、デバイスの固定出力電圧のデフォルト設定で動作します。<br>内部帰還を選択するには、デバイスを起動する前に、このピンを VCC2 に接続します                                                                                              |

| AGND         | 15 |                   | AGND に接続                                                                                                                                                                                                                                   |

表 5-1. ピン機能 LM251772Q1 (続き)

| ピン       |    | 種類 <sup>(1)</sup> | 説明                                                                                                                                                                                                                               |

|----------|----|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称       | 番号 |                   |                                                                                                                                                                                                                                  |

| ILIMCOMP | 16 |                   | 平均電流制限ループの補償ピン。電流制限が内部 DAC によって設定されている場合、コンデンサまたはタイプ 2R-C ネットワークを接続します。<br>内部 DAC がディセーブルなら、このピンは平均電流制限の電流制限スレッショルドを設定します。<br>抵抗を AGND に接続します。アプリケーションの要件に応じて、並列コンデンサのフィルタを推奨します<br>ILIMCOMP ピンを VCC2 に接続してブロックを無効にし、静止電流を減らします。 |

| AGND     | 17 | G                 | アナログ GND                                                                                                                                                                                                                         |

| VOUT     | 18 | I                 | 出力電圧検出入力。電力段の出力レールに接続します。                                                                                                                                                                                                        |

| ISNSN    | 19 | I                 | 出力または入力平均電流センスアンプの負のセンス入力。内部平均電流センサーを使用する場合は、ISNSN と ISNSP の間にオプションの電流センス抵抗を接続する必要があります。センス抵抗は、パワーステージの入力側または出力側に配置できます。<br>オプションの電流センサがディセーブルの場合は、ISNSN と ISNSP を一緒に AGND に接続してください                                             |

| ISNSP    | 20 | I                 | 出力または入力電流センスアンプの正のセンス入力。内部平均電流センサーを使用する場合は、ISNSN と ISNSP の間にオプションの電流センス抵抗を接続する必要があります。センス抵抗は、パワーステージの入力側または出力側に配置できます。<br>オプションの電流センサが無効になっている場合は、ISNSP をグランドに接続してください                                                           |

| CSB      | 21 | I                 | インダクタピーク電流センス負入力。ケルビン接続を使用して、外部電流センス抵抗の負の側に CSB を接続します。                                                                                                                                                                          |

| CSA      | 22 | I                 | インダクタピーク電流検出正入力。ケルビン接続を使用して、外部電流センス抵抗の正の側に CSA を接続します。                                                                                                                                                                           |

| SW1      | 23 | P                 | 降圧ハーフブリッジのインダクタスイッチノード                                                                                                                                                                                                           |

| HO1      | 24 | O                 | 降圧ハーフブリッジのハイサイド ゲートドライバ出力                                                                                                                                                                                                        |

| HB1      | 25 | P                 | 降圧ハーフブリッジのブートストラップ電源ピン。ハイサイド MOSFET ゲートドライバにバイアスを提供するために、HB1 ピンと SW1 に外付けコンデンサが必要です。<br>適切なデカップリングのため、外付けコンデンサはピンとコンデンサ間の抵抗なしに、ピンに近づけて配置します                                                                                      |

| NC       | 26 | O                 | 接続なし                                                                                                                                                                                                                             |

| LO1      | 27 | O                 | 降圧ハーフブリッジのローサイド ゲートドライバ出力                                                                                                                                                                                                        |

| PGND     | 28 | G                 | 電源グランド                                                                                                                                                                                                                           |

| VCC2     | 29 | O                 | 内部リニアバイアスレギュレータ出力。VCC と PGND の間にセラミックデカップリングコンデンサを接続します。このレールは、内部ロジックおよびゲートドライバの電源となります。<br>適切なデカップリングのため、外付けコンデンサはピンとコンデンサ間の抵抗なしに、ピンに近づけて配置します。                                                                                 |

| LO2      | 30 | O                 | 昇圧ハーフブリッジのローサイド ゲートドライバ出力                                                                                                                                                                                                        |

| HB2      | 31 | P                 | 昇圧ハーフブリッジのブートストラップ電源ピン。ハイサイド MOSFET ゲートドライバにバイアスを提供するために、HB2 ピンと SW2 に外付けコンデンサが必要<br>適切なデカップリングのため、外付けコンデンサはピンとコンデンサ間の抵抗なしに、ピンに近づけて配置します                                                                                         |

| HO2      | 32 | O                 | 昇圧ハーフブリッジのハイサイド ゲートドライバ出力                                                                                                                                                                                                        |

| SW2      | 33 | P                 | 昇圧ハーフブリッジのインダクタスイッチノード                                                                                                                                                                                                           |

| NC       | 34 | O                 | 接続なし                                                                                                                                                                                                                             |

| DRV1     | 35 |                   | 外部 FET ドライブピン。このピンは、選択した構成に応じて、高電圧ブッシュプル段、オープンドレイン出力、またはチャージポンプドライバ段を備えています。<br>オプションの DRV ピンが未使用の場合は、DRV をオープンのままにしておきます。                                                                                                       |

| VIN      | 36 | I                 | 本デバイスの入力電源とセンス入力。VIN を電力段の電源電圧に接続します。                                                                                                                                                                                            |

**表 5-1. ピン機能 LM251772Q1 (続き)**

| ピン      |     | 種類 <sup>(1)</sup> | 説明                                                                                                                                    |

|---------|-----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| 名称      | 番号  |                   |                                                                                                                                       |

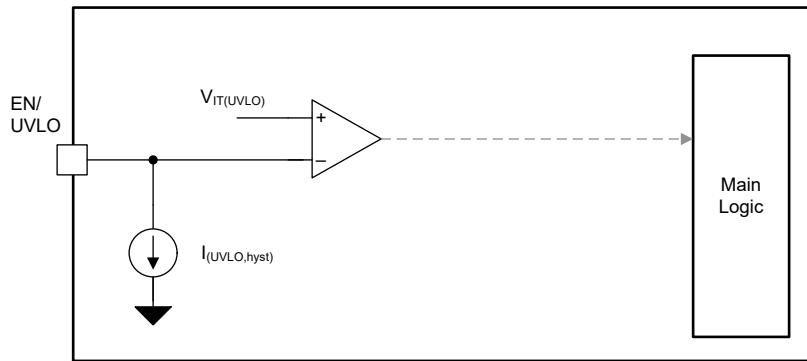

| EN/UVLO | 37  | I                 | イネーブルピン。コンバータのスイッチングをイネーブルするためのデジタル入力ピン。<br>入力には、高精度のアナログ コンバータとヒステリシスが搭載されており、入力電圧を監視します。入力電圧との間に分圧抵抗を接続して、低電圧誤動作防止 (UVLO) 機能を維持します。 |

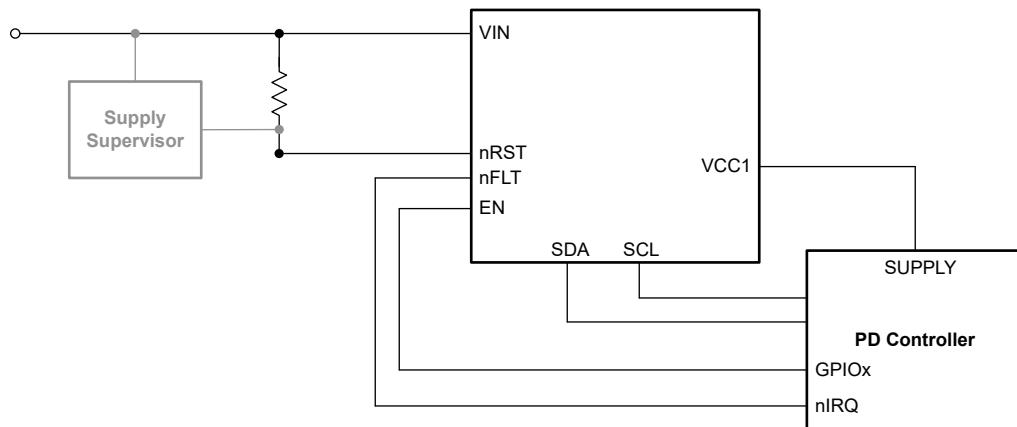

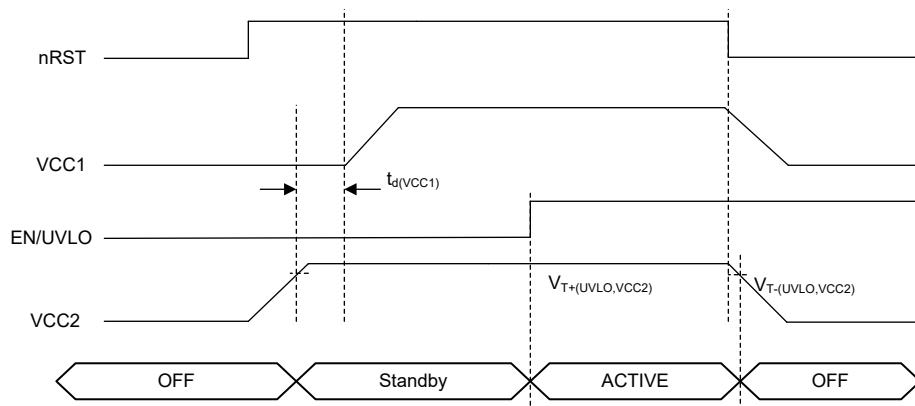

| nRST    | 38  | I                 | デジタル入力ピンを使用してデバイスの内部ロジック、インターフェイス動作、および VCC1 レギュレータをイネーブルすることができます (選択する場合)。                                                          |

| NC      | 39  | O                 | 接続なし                                                                                                                                  |

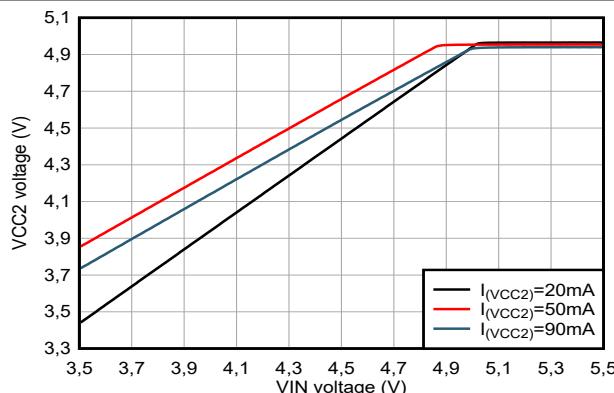

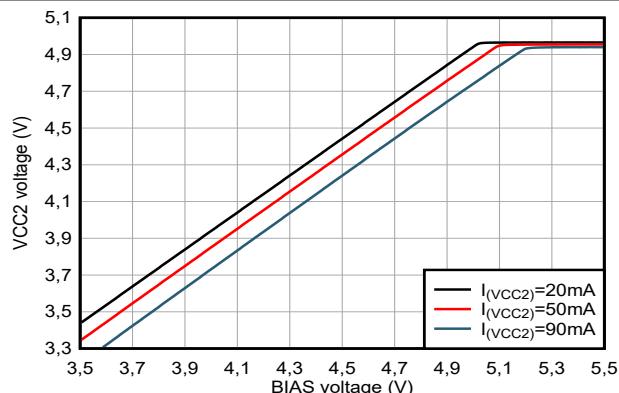

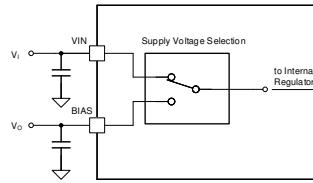

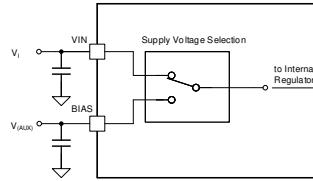

| BIAS    | 40  |                   | VCC2 バイアス レギュレータへの入力 (オプション)。VIN ではなく外部電源から VCC2 に電力を供給すると、内部 LDO の高 $V_{IN}$ 時の電力損失を削減するのに役立ちます。                                     |

| GND     | PAD | G                 | サーマル パッド                                                                                                                              |

(1) I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源。

## 6 仕様

### 6.1 絶対最大定格

自由空気での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|    |                                                                   | 最小値  | 最大値                            | 単位 |

|----|-------------------------------------------------------------------|------|--------------------------------|----|

| 入力 | BIAS から AGND へ                                                    | -0.3 | 48                             | V  |

| 入力 | VIN、ISNSP、ISNSN から AGND へ                                         | -0.3 | 48                             | V  |

| 入力 | EN/UVLO、nRST                                                      | -0.3 | 48                             | V  |

|    |                                                                   | -0.3 | $V_{(VIN)} + 5$ <sup>(4)</sup> | V  |

| 入力 | SS/ATRK、DTRK、RT、SYNC、MODE、SDA、SCL、ADDR、CFG2、AGND へ <sup>(3)</sup> | -0.3 | 5.8                            | V  |

| 入力 | FB                                                                | -0.3 | 5.8                            | V  |

| 入力 | ISNSP から ISNSN へ                                                  | -0.3 | 0.3                            | V  |

| 入力 | CSA、CSB から SW1 へ                                                  | -0.3 | 0.3                            | V  |

| 入力 | SW1 から AGND (DC) へ                                                | -0.5 | 48                             | V  |

| 入力 | SW2 から AGND(DC) まで                                                | -0.5 | 59                             | V  |

| 入力 | SW1 から AGND へ ( $\leq 100\text{ns}$ 期間)                           | -2   | 48                             | V  |

| 入力 | 、SW2 から AGND へ ( $\leq 100\text{ns}$ 期間)                          | -2   | 59                             | V  |

| 入力 | SW1 から AGND へ ( $\leq 10\text{ns}$ 期間)                            | -3   | 48                             | V  |

| 入力 | 、SW2 から AGND へ ( $\leq 10\text{ns}$ 期間)                           | -3   | 59                             | V  |

| 入力 | SW1 から AGND へ ( $\leq 5\text{ns}$ 期間)                             | -4   | 48                             | V  |

| 入力 | 、SW2 から AGND へ ( $\leq 5\text{ns}$ 期間)                            | -4   | 59                             | V  |

| 入力 | PGND から AGND へ                                                    | -0.3 | 0.3                            | V  |

| 出力 | VCC1、VCC2 から AGND へ                                               | -0.3 | 5.5                            | V  |

| 出力 | VOUT、DRV1 から AGND へ                                               | -0.3 | 59                             | V  |

| 出力 | nFLT から AGND へ                                                    | -0.3 | 5.8                            | V  |

| 出力 | COMP、ILIMCOMP、CDC から AGND へ <sup>(2)</sup>                        | -0.3 | 5.8                            | V  |

| 出力 | LO1、LO2 から PGND へ                                                 | -0.3 | $V_{(VCC2)} + 0.3$             | V  |

| 出力 | HB1 から SW1 へ、HB2 から SW2 へ                                         | -0.3 | 5.5 <sup>(5)</sup>             | V  |

| 出力 |                                                                   | -0.3 | 6                              | V  |

| 出力 | HO1～SW1                                                           | -0.3 | $V_{(HB1)} + 0.3$              | V  |

| 出力 | HO2～SW2                                                           | -0.3 | $V_{(HB2)} + 0.3$              | V  |

自由空気での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                                 |                           | 最小値  | 最大値 | 単位 |

|---------------------------------|---------------------------|------|-----|----|

| 出力                              | HO1、HO2、HB1、HB2 から AGND へ | -0.3 | 65  | V  |

| 保管温度、 $T_{STG}$                 |                           | -55  | 150 | °C |

| 動作時の接合部温度、 $T_J$ <sup>(3)</sup> |                           | -40  | 150 |    |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) このピンには、通常 1.6mA の電流を処理できる最大電圧クランプが内蔵されています。

- (3) 接合部温度が高くなると、動作寿命が短くなります。接合部温度が 125°C を超えると、動作寿命が短くなります。

- (4) 上記の両方の条件を遵守する必要があります

- (5) 電圧が規定の最大値を超えると、動作寿命が短くなります

## 6.2 取り扱い定格

|             |      |                                            |        | 値     | 単位 |

|-------------|------|--------------------------------------------|--------|-------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、AEC Q100-002 <sup>(1)</sup> 準拠 |        | ±2000 | V  |

|             |      | 荷電デバイスモデル (CDM)、AEC Q100-011 準拠            | 角のピン   | ±750  |    |

|             |      |                                            | その他のピン | ±500  |    |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

## 6.3 推奨動作条件

接合部の推奨動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|              |                                              | 最小値 | 公称値  | 最大値               | 単位  |

|--------------|----------------------------------------------|-----|------|-------------------|-----|

| $V_{(VIN)}$  | 入力電圧検出                                       | 3.5 | 20   | 36                | V   |

| $V_{(BIAS)}$ | バイアス入力電圧電源                                   | 0   |      | 36                | V   |

|              | 入力/バイアスのスタートアップ電圧                            | 3.5 |      |                   | V   |

| $V_{(VOUT)}$ | 出力電圧センス                                      | 1   | 53.5 | 55 <sup>(3)</sup> | V   |

| $V_{(DRV1)}$ | 高電圧駆動ピン出力                                    | 0   |      | 55                | V   |

|              | ISNSP, ISNSN                                 | 2.8 |      | 55                | V   |

| $R_{(SNS)}$  | 電流制限センス抵抗                                    |     | 10   |                   | mΩ  |

|              | 電流制限検出抵抗の許容誤差                                | -1  |      | 1                 | %   |

| $C_{(VCC1)}$ | VCC1 レギュレータ出力容量                              | 2   |      |                   | μF  |

| $C_{(VCC2)}$ | VCC2 レギュレータ出力容量                              | 6   |      |                   | μF  |

| $V_{FB}$     | FB 入力                                        | 0   |      | $V_{(VCC2)}$      | V   |

| $V_{IL}$     | ロジックピン low レベル (MODE, DTRK, SYNC, SDA, SCL)  |     |      | 0.4               | V   |

| $V_{IH}$     | ロジックピン high レベル (MODE, DTRK, SYNC, SDA, SCL) | 1.3 |      |                   | V   |

| $F_{SW}$     | 標準スイッチング周波数                                  | 100 |      | 2200              | kHz |

| $F_{SYNC}$   | 同期スイッチング周波数範囲                                | 100 |      | 2200              | kHz |

| $T_J$        | 動作時接合部温度 <sup>(2)</sup>                      | -40 |      | 150               | °C  |

- (1) 動作定格は、デバイスが機能する前提の条件です。仕様およびテスト条件については、「電気的特性」を参照してください。

- (2) 接合部温度が高くなると、動作寿命が短くなります。

- (3) 最小 OVP スレッショルドによって決定される公称値。

## 6.4 热に関する情報

| 热評価基準 <sup>(1)</sup> |                   | LM251772-Q1 | 単位   |

|----------------------|-------------------|-------------|------|

|                      |                   | QFN         |      |

|                      |                   | 40 ピン       |      |

| $R_{qJA}$            | 接合部から周囲への热抵抗      | 33.9        | °C/W |

| $R_{qJC(top)}$       | 接合部からケース(上面)への热抵抗 | 26.6        | °C/W |

| $R_{qJB}$            | 接合部から基板への热抵抗      | 15.4        | °C/W |

| $Y_{JT}$             | 接合部から上面への特性パラメータ  | 0.4         | °C/W |

| $Y_{JB}$             | 接合部から基板への特性パラメータ  | 15.4        | °C/W |

| $R_{qJC(bot)}$       | 接合部からケース(底面)への热抵抗 | 4.4         | °C/W |

(1) 従来および最新の热評価基準の詳細については、「[半導体およびIC パッケージの热評価基準](#)」アプリケーション ノートを参照してください。

## 6.5 電気的特性

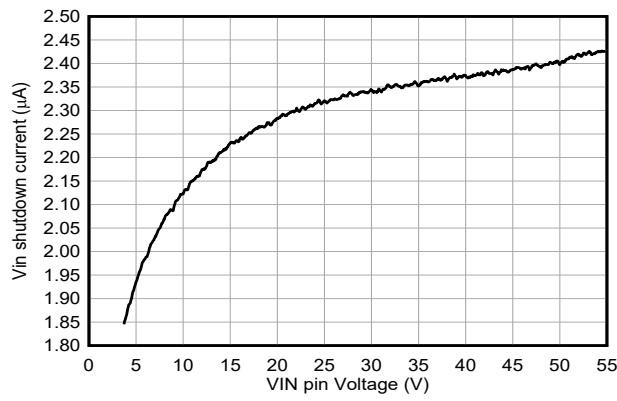

標準値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $V_{(\text{BIAS})} = 12\text{V}$

| パラメータ                  |                                                | テスト条件                                                                                                                             |                                                   | 最小値  | 標準値  | 最大値           | 単位            |

|------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------|------|---------------|---------------|

| <b>電源電流</b>            |                                                |                                                                                                                                   |                                                   |      |      |               |               |

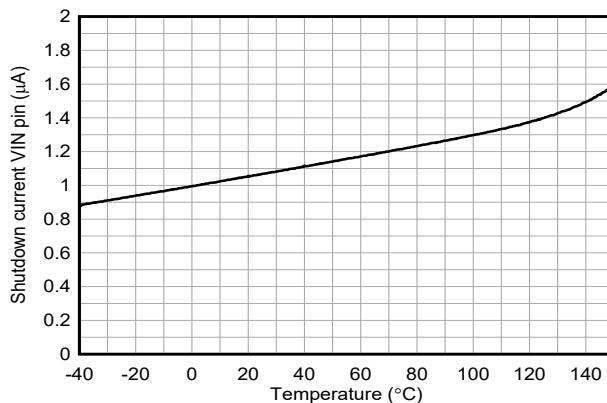

|                        | VIN へのシャットダウン電流                                | $V_{(\text{VIN})} = 48\text{V}, V_{(\text{BIAS})} = 0\text{V}$<br>$V_{(\text{EN})} = 0\text{V}$                                   | $T_J = 25^\circ\text{C}$                          | 1.1  | 1.5  | $\mu\text{A}$ |               |

|                        |                                                |                                                                                                                                   | $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$  | 1.1  | 2    | $\mu\text{A}$ |               |

|                        | BIAS へのシャットダウン電流                               | $V_{(\text{VIN})} = 0\text{V}, V_{(\text{EN})} = 0\text{V}$                                                                       | $T_J = 25^\circ\text{C}$                          | 1.3  | 1.7  | $\mu\text{A}$ |               |

|                        |                                                |                                                                                                                                   | $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$  | 1.3  | 2.2  | $\mu\text{A}$ |               |

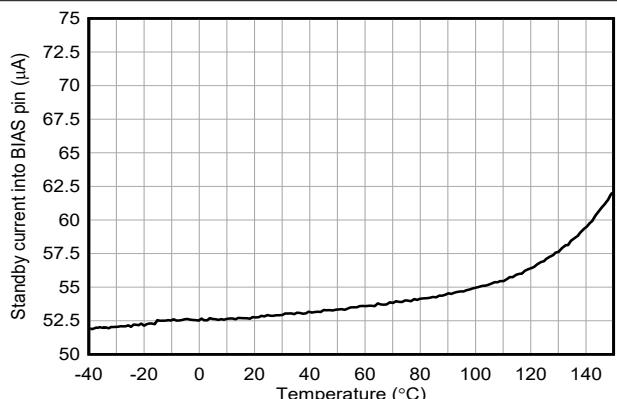

|                        | VIN へのスタンバイ電流                                  | $V_{(\text{VIN})} = 12\text{V}, V_{(\text{BIAS})} = 0\text{V}, V_{(\text{nRST})} = \text{High}$                                   | $T_J = 25^\circ\text{C}$                          | 55   | 75   | $\mu\text{A}$ |               |

|                        |                                                |                                                                                                                                   | $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$  | 55   | 100  | $\mu\text{A}$ |               |

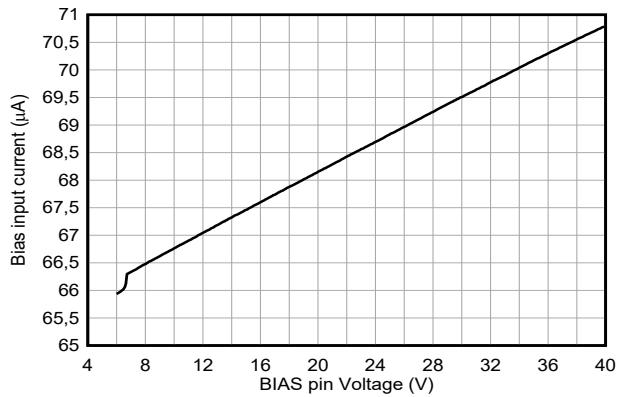

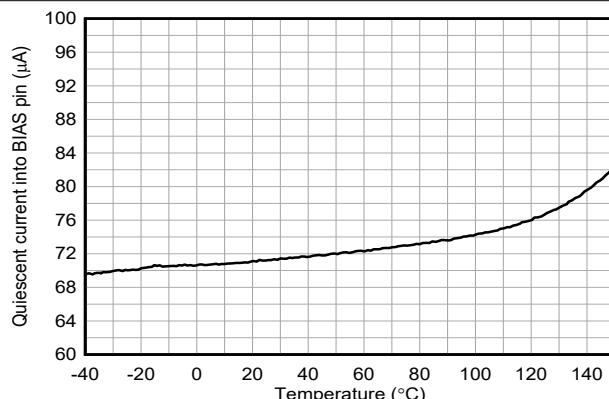

|                        | BIAS への静止電流                                    | $V_{(\text{EN})} = 3.3\text{V}, V_{(\text{FB})} > 1\text{V}$ , uSleep イネーブル、<br>ILIMCOMP = $V_{(\text{VCC2})}$ 、<br>EN_VCC1 = 0b0 | $T_J = 25^\circ\text{C}$                          | 65   | 75   | $\mu\text{A}$ |               |

|                        |                                                |                                                                                                                                   | $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$  | 65   | 100  | $\mu\text{A}$ |               |

| <b>VCC1 レギュレータ</b>     |                                                |                                                                                                                                   |                                                   |      |      |               |               |

|                        | VCC1 レギュレーション                                  | $V_I = 12.0\text{V}, I_{(\text{VCC1})} = 1\text{mA}$                                                                              |                                                   | 4.95 | 5    | 5.05          | V             |

|                        | VCC1 のドロップアウト電圧                                | $I_{(\text{VCC1})} = 34\text{mA}$                                                                                                 | $V_I = 5\text{V}$                                 | 0.6  | 1.4  | $\text{mV}$   |               |

|                        |                                                |                                                                                                                                   | $V_I = 4.5\text{V}$                               | 0.6  | 1.5  | $\text{mV}$   |               |

|                        | VCC1 ソーシング電流制限                                 | $VCC1 = \text{GND}$                                                                                                               | $V_I = 12\text{V}$                                | 34   | 70   | $\text{mA}$   |               |

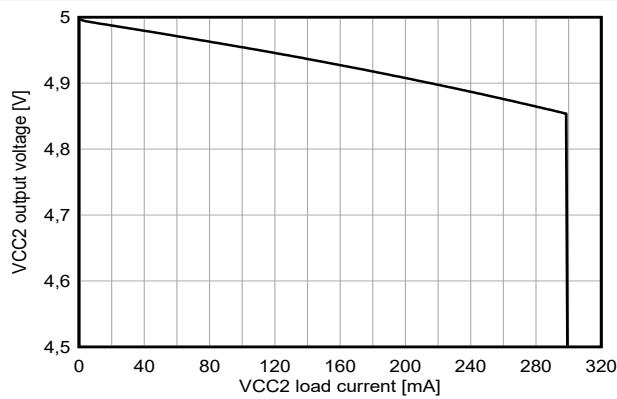

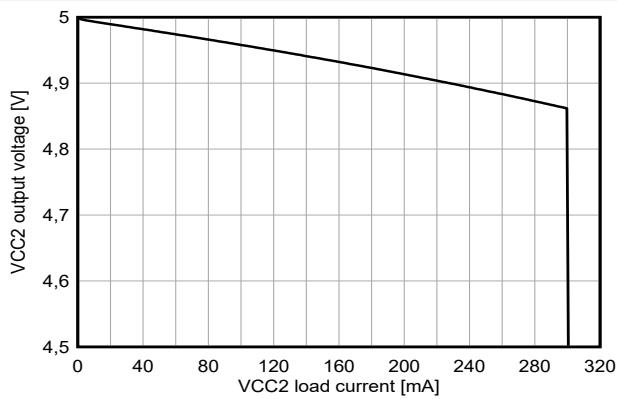

| <b>VCC2 レギュレータ</b>     |                                                |                                                                                                                                   |                                                   |      |      |               |               |

|                        | VCC2 レギュレーション                                  | $V_{(\text{BIAS})} = 12.0\text{V}, I_{(\text{VCC2})} = 20\text{mA}$                                                               |                                                   | 4.85 | 5    | 5.1           | V             |

|                        | VCC2 のドロップアウト電圧                                | $I_{(\text{VCC2})} = 45\text{mA}$                                                                                                 | $V_I = 4\text{V}$                                 | 130  | 300  | $\text{mV}$   |               |

|                        |                                                |                                                                                                                                   | $V_I = 3.5\text{V}$                               | 190  | 400  | $\text{mV}$   |               |

|                        | VCC2 ソーシング電流制限                                 | $V_{(\text{VCC2})} \geq 3\text{V}$                                                                                                | $V_I = 6\text{V}, V_{(\text{BIAS})} = 12\text{V}$ | 200  | 260  | 450           | $\text{mA}$   |

| $V_{T+(VCC2)}$         | 正方向スレッショルド                                     | $V_{(\text{VCC2})}$ 立ち上がり                                                                                                         |                                                   | 3.3  | 3.35 | 3.4           | V             |

| $V_{T-(VCC2)}$         | 負方向スレッショルド                                     | $V_{(\text{VCC2})}$ 立ち下がり                                                                                                         |                                                   | 3    | 3.05 | 3.1           | V             |

| $V_{T+(Force,BIAS)}$   | 強制 $V_{(\text{BIAS})}$ の正方向スレッショルド             | $FORCE\_BIASPIN = 0\text{b}1$                                                                                                     |                                                   | 4.5  | 4.6  | 4.7           | V             |

| $V_{hyst(Force,BIAS)}$ | 強制 $V_{(\text{BIAS})}$ 用の LDO スイッチ オーバー ヒステリシス |                                                                                                                                   |                                                   | 230  | 275  |               | $\text{mV}$   |

| $V_{T+(VCC2,SUP)}$     | LDO スイッチ オーバーの正方向スレッショルド                       | $FORCE\_BIASPIN = 0\text{b}0$                                                                                                     |                                                   | 6.7  | 6.8  | 6.9           | V             |

| $V_{hyst(VCC2,SUP)}$   | LDO スイッチ オーバー ヒステリシス                           |                                                                                                                                   |                                                   | 350  | 400  |               | $\text{mV}$   |

|                        | VCC2 UVLO 立ち上がり検出遅延時間                          | $V_{(\text{VCC2})}$ 立ち上がり                                                                                                         |                                                   | 100  |      |               | $\mu\text{s}$ |

| <b>nRST</b>            |                                                |                                                                                                                                   |                                                   |      |      |               |               |

| $V_{T+(nRST)}$         | 正方向スレッショルドを有効にする                               | $NRST$ 立ち上がり                                                                                                                      |                                                   | 1.4  |      |               | V             |

| $V_{T-(nRST)}$         | 負方向スレッショルドを有効にする                               | $NRST$ 立ち下がり                                                                                                                      |                                                   | 0.35 |      |               | V             |

| $V_{hyst(nRST)}$       | スレッショルド ヒステリシスをイネーブル                           |                                                                                                                                   |                                                   | 300  |      |               | $\text{mV}$   |

| <b>EN/UVLO</b>         |                                                |                                                                                                                                   |                                                   |      |      |               |               |

|                        | VDET 正方向のスレッショルド                               | $V_{(\text{VIN})}$ 立ち上がり、 $VDET\_RISE = 0\text{x}3$                                                                               |                                                   | 3.3  | 3.4  | 3.5           | V             |

|                        | VDET 負方向のスレッショルド                               | $V_{(\text{VIN})}$ 立ち下がり、 $VDET\_FALL = 0\text{x}0$                                                                               |                                                   | 2.6  | 2.7  | 2.799         | V             |

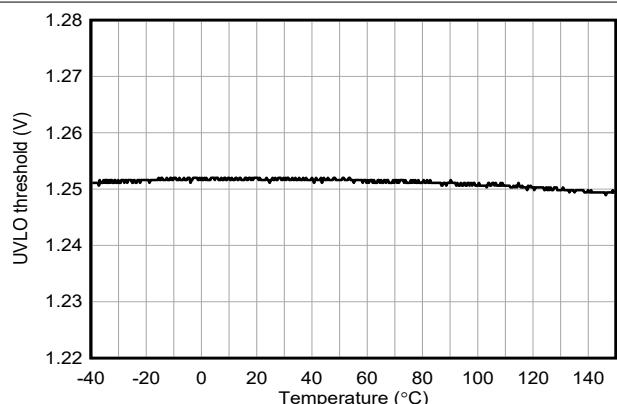

| $V_{T+(UVLO)}$         | UVLO 正方向のスレッショルド                               | $V_{(\text{EN/UVLO})}$ 立ち上がり                                                                                                      |                                                   | 1.23 | 1.25 | 1.27          | V             |

| $V_{T-(UVLO)}$         | UVLO 負方向のスレッショルド                               | $V_{(\text{EN/UVLO})}$ 立ち下がり                                                                                                      |                                                   | 1.18 | 1.2  | 1.22          | V             |

| $V_{hyst(UVLO)}$       | UVLO スレッショルド ヒステリシス                            |                                                                                                                                   |                                                   | 38   | 50   | 62            | $\text{mV}$   |

## 6.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $V_{(\text{BIAS})} = 12\text{V}$

| パラメータ                    |                                   | テスト条件                                                                             |                                                                                        | 最小値  | 標準値  | 最大値      | 単位            |

|--------------------------|-----------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|------|----------|---------------|

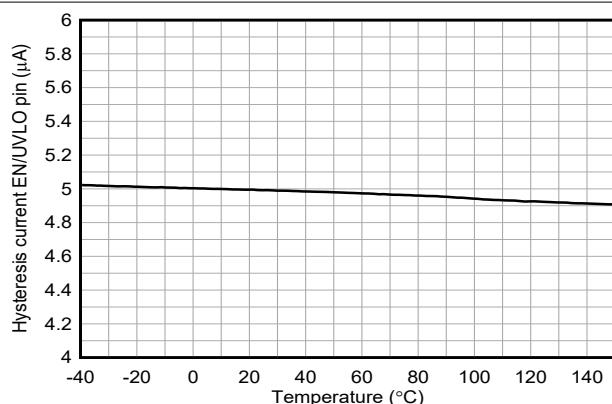

| $I_{\text{UVLO}}$        | UVLO ヒステリシスのシンク電流                 | $V_{(\text{EN/UVLO})} < 1.26\text{V}$                                             |                                                                                        | 4    | 5    | 6        | $\mu\text{A}$ |

| $t_{\text{d(UVLO)}}$     | UVLO 検出遅延時間                       | $V_{(\text{EN/UVLO})}$ 立ち下がり;                                                     |                                                                                        | 25.5 | 30   | 38.5     | $\mu\text{s}$ |

| $V_{\text{T+}(POR)}$     | POR 正方向のスレッショルド                   | POR 正方向のスレッショルド                                                                   | $V_{\text{IN}}$ の立ち上がりまたは $\text{BIAS}$ の立ち上がり                                         |      | 1.75 |          | $\text{V}$    |

| $V_{\text{T-}(POR)}$     | POR 負方向のスレッショルド                   | POR 負方向のスレッショルド                                                                   | $V_{\text{IN}}$ の立ち下がりまたは $\text{BIAS}$ の立ち下がり                                         |      | 1.7  |          | $\text{V}$    |

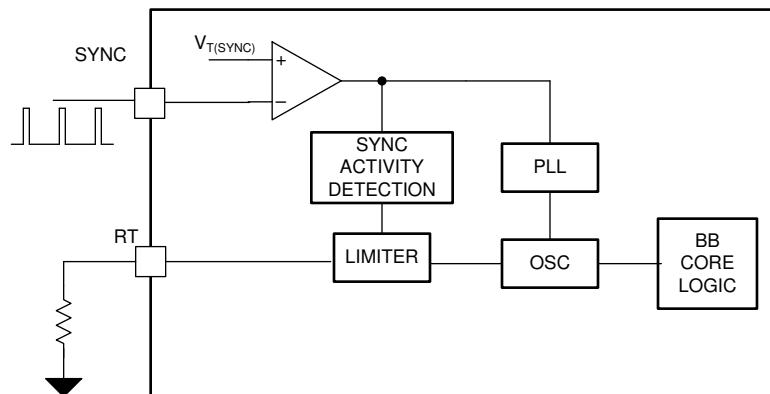

| <b>SYNC</b>              |                                   |                                                                                   |                                                                                        |      |      |          |               |

| $V_{\text{T+}(SYNC)}$    | 同期入力の正の方向スレッショルド                  |                                                                                   |                                                                                        |      | 1.19 |          | $\text{V}$    |

| $V_{\text{T-}(SYNC)}$    | 同期入力の負の方向スレッショルド                  |                                                                                   |                                                                                        | 0.41 |      |          | $\text{V}$    |

|                          | 同期アクティビティ検出周波数                    |                                                                                   |                                                                                        | 99   |      |          | $\text{kHz}$  |

| $t_{\text{d(Det,Sync)}}$ | 同期アクティビティ検出周波数スレッショルド             | $f_{(\text{SYNC})}$ を基準とします                                                       |                                                                                        |      | 3    |          | サイクル          |

|                          | 同期 PLL ロック時間                      | $f_{(\text{SYNC})}$ を基準とします                                                       | $f_{(\text{SYNC})} - 5\% < f_{(\text{sw})} < f_{(\text{SYNC})} + 5\% \text{ まで}$       | 10   |      |          | サイクル          |

|                          | 同期 high レベル出力電圧ドロップ               | $EN_{(\text{SYNC})}_{\text{OUT}} = 0\text{b}1$                                    | $V_{(\text{VCC2})}$ を基準とします                                                            |      | 0.4  |          | $\text{V}$    |

|                          | SYNC low レベル出力電圧                  | $I_{(\text{SYNC})} = 2 \text{ mA}, V_{(\text{VCC2})} \geq 3.5\text{V},$           |                                                                                        |      | 0.3  |          | $\text{V}$    |

|                          | SYNC 出力駆動能力                       | $EN_{(\text{SYNC})}_{\text{OUT}} = 0\text{b}1$<br>$V_{(\text{VCC2})} = 5\text{V}$ | シンク                                                                                    | -42  | -31  | -22      | $\text{mA}$   |

|                          |                                   |                                                                                   | ソース                                                                                    | 22   | 34   | 42       | $\text{mA}$   |

| <b>ソフトスタート</b>           |                                   |                                                                                   |                                                                                        |      |      |          |               |

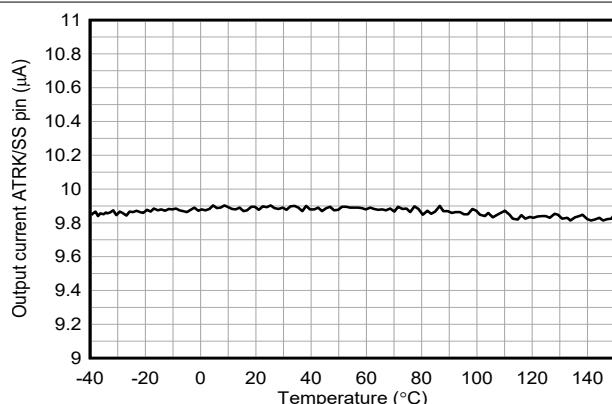

| $I_{(\text{SS})}$        | ソフトスタート電流                         |                                                                                   |                                                                                        | 9    | 10   | 11       | $\mu\text{A}$ |

|                          | SS プルダウン スイッチ $R_{\text{DS(on)}}$ | $V_{(\text{SS})} = 1 \text{ V}$                                                   |                                                                                        |      | 21   | 40       | $\Omega$      |

| $t_{\text{d(DISCH;SS)}}$ | SS ピン放電時間                         | 内部 SS 放電から、ソフトスタート電流によってピンのキャパシタが再度充電されるまでの時間                                     |                                                                                        | 500  |      |          | $\mu\text{s}$ |

| $t_{\text{d(EN_SS)}}$    | SS ピンのランプ開始遅延時間                   | ソフトスタート電流が開始するまでの内部遅延                                                             |                                                                                        | 2.5  |      | 4        | $\mu\text{s}$ |

| $V_{(\text{SS,clamp})}$  | SS ピンのクランプ電圧                      |                                                                                   |                                                                                        | 4.1  |      |          | $\text{V}$    |

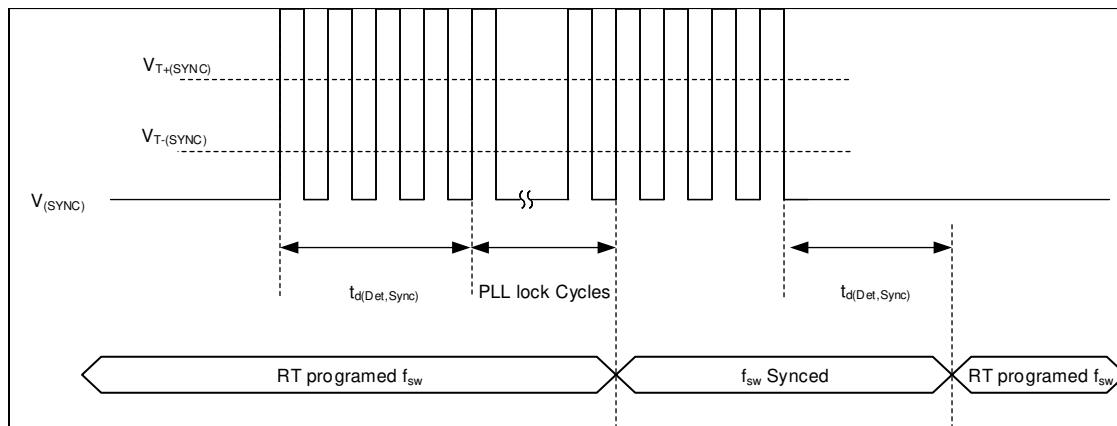

| <b>VOUT トラッキング</b>       |                                   |                                                                                   |                                                                                        |      |      |          |               |

| $V_{\text{T+}(DTRK)}$    | DTRK 正方向のスレッショルド                  | $V_{(\text{DTRK})}$ 立ち上がり                                                         |                                                                                        | 1.19 |      |          | $\text{V}$    |

| $V_{\text{T-}(DTRK)}$    | DTRK 負方向のスレッショルド                  | $V_{(\text{DTRK})}$ 立ち下がり                                                         |                                                                                        | 0.41 |      |          | $\text{V}$    |

|                          | DTRK アクティビティ検出周波数                 | DTRK アクティビティ検出周波数                                                                 |                                                                                        | 148  |      |          | $\text{kHz}$  |

| $t_{\text{d}(DTRK)}$     | DTRK 検出遅延時間                       |                                                                                   |                                                                                        |      | 3    |          | サイクル          |

| $fc(\text{LPF})$         | 内部ローパスのコーナー周波数                    |                                                                                   |                                                                                        | 40   |      |          | $\text{kHz}$  |

|                          | $V_{(\text{REF})}$ 電圧オフセット誤差      | $V_{(\text{REF})}$ 電圧オフセット誤差                                                      | $f_{(\text{DTRK})} = 500\text{kHz}, \text{デューティ} = 50\%, V_{(\text{REF})} = 1\text{V}$ |      |      | $\pm 10$ | $\text{mV}$   |

| <b>パルス幅変調</b>            |                                   |                                                                                   |                                                                                        |      |      |          |               |

|                          | スイッチング周波数                         | $R_{\text{RT}} = 14.20\text{k}\Omega$ ,                                           |                                                                                        | 2000 | 2200 | 2400     | $\text{kHz}$  |

## 6.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $V_{(\text{BIAS})} = 12\text{V}$

| パラメータ |                | テスト条件                                               |       | 最小値  | 標準値  | 最大値  | 単位  |

|-------|----------------|-----------------------------------------------------|-------|------|------|------|-----|

|       | スイッチング周波数      | $R_{\text{RT}} = 15.63\text{k}\Omega$ 、             |       | 1845 | 2000 | 2255 | kHz |

|       | スイッチング周波数      | $R_{\text{RT}} = 316\text{k}\Omega$ 、               |       | 90   | 100  | 110  | kHz |

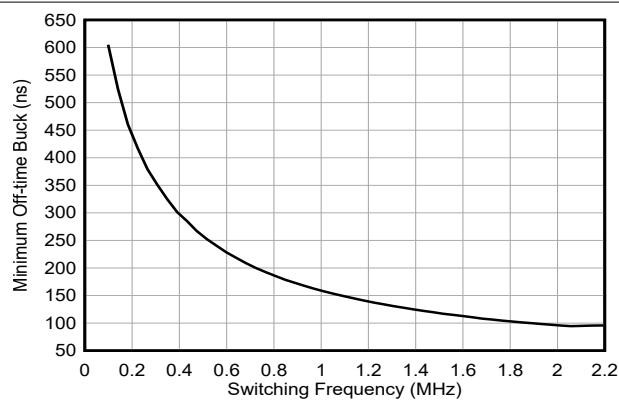

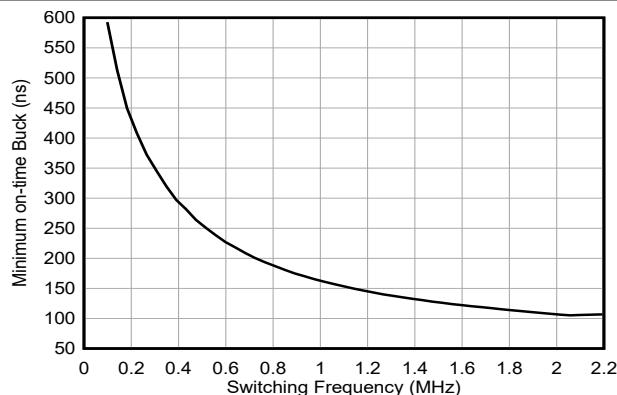

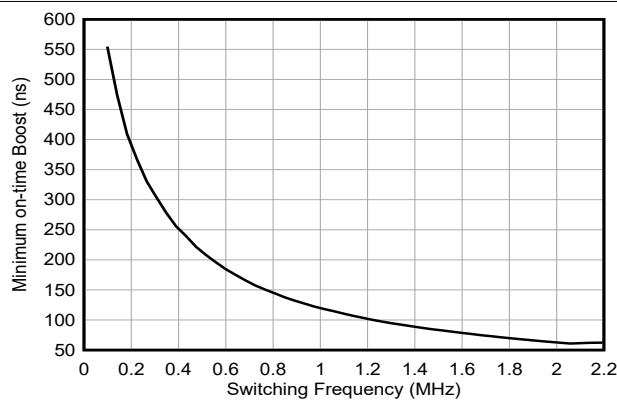

|       | 最小の制御可能なオン時間   | fPWM、 $R_{\text{RT}} = 14\text{k}\Omega$ 、正のインダクタ電流 | 昇圧モード | 64   |      |      | ns  |

|       |                |                                                     | 降圧モード | 107  |      |      | ns  |

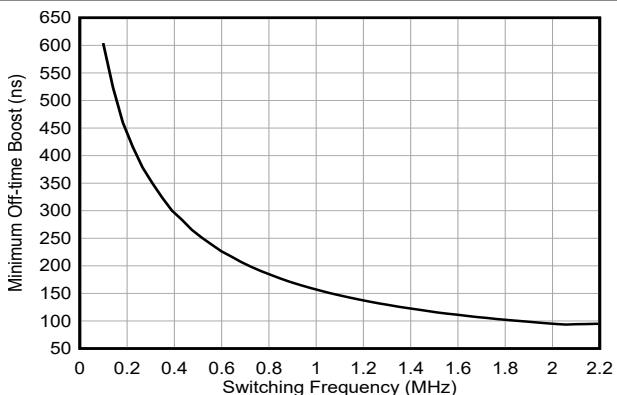

|       | 制御可能な最小オフ時間    |                                                     | 昇圧モード | 96   |      |      | ns  |

|       |                |                                                     | 降圧モード | 97   |      |      | ns  |

|       | RT のレギュレーション電圧 |                                                     |       | 0.75 |      |      | V   |

### モード選択

|                       |                   |  |  |      |   |

|-----------------------|-------------------|--|--|------|---|

| $V_{T+}(\text{MODE})$ | モード入力の正方向スレッショルド  |  |  | 1.19 | V |

| $V_{T-}(\text{MODE})$ | モード入力の負の方向スレッショルド |  |  | 0.41 | V |

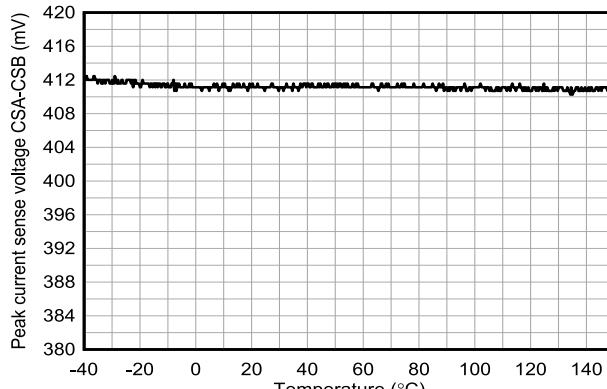

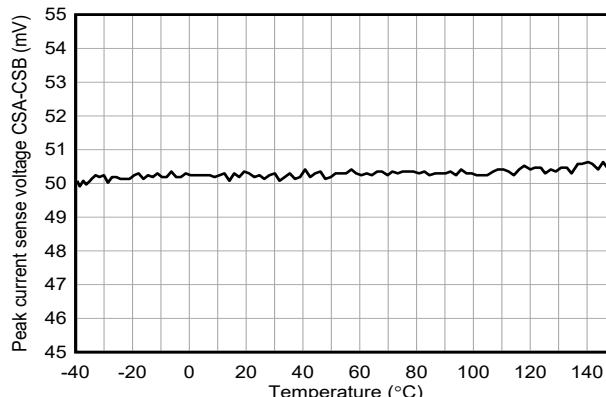

### 電流検出

|                                         |                  |  |                                                  |     |     |     |    |

|-----------------------------------------|------------------|--|--------------------------------------------------|-----|-----|-----|----|

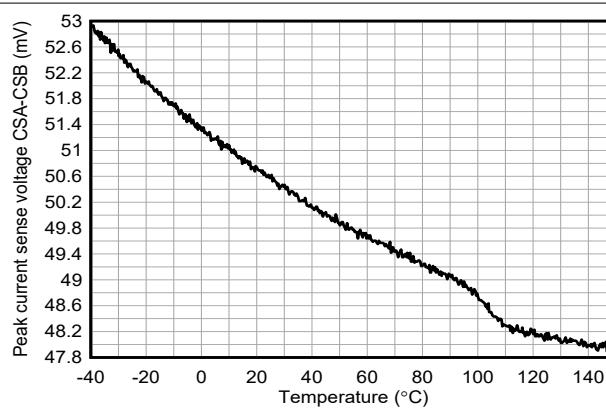

| $V_{\text{th+}}(\text{CSB-}\text{CSA})$ | 正のピーク電流制限スレッショルド |  |                                                  | 45  | 50  | 55  | mV |

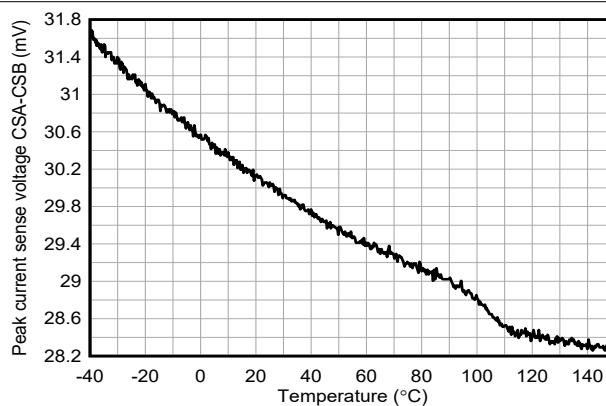

| $V_{\text{th-}}(\text{CSB-}\text{CSA})$ | 負のピーク電流制限スレッショルド |  | $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$ | -56 | -50 | -44 | mV |

### 平均電流制限

|                                 |                             |                                                                                                                                    |                                                                                                                 |                                                                                                                 |               |                 |               |    |

|---------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|---------------|-----------------|---------------|----|

| $g_{\text{m}}(\text{ISET})$     | 電流センスアンプのトランスコンダクタンス        | I2C インターフェイスはディセーブルまたは $\text{SEL\_ISET\_PIN} = 0\text{b}1$ 、 $V_{(\text{ISNSP})} > 3.3\text{V}$ 、 $\text{EN\_NEG\_CL\_LIMIT} = 0$ | $25\text{mV} \leq \Delta V_{(\text{ISNS})} \leq 50\text{mV}$                                                    | 0.9                                                                                                             | 1             | 1.1             | mS            |    |

|                                 | オフセット電圧                     | $V_{\text{ISNS}} > 4.8\text{V}$                                                                                                    | $T_J = 25^\circ\text{C}$                                                                                        | -1.5                                                                                                            | 0             | 1.5             | mV            |    |

|                                 |                             | $V_{\text{ISNS}} > 4.8\text{V}$                                                                                                    | $T_J = -40^\circ\text{C} \sim 125^\circ\text{C}$                                                                | -2.5                                                                                                            | 0             | 2.5             | mV            |    |

|                                 | 電流センシング アンプの出力電流            | I2C インターフェイスはディセーブルまたは $\text{SEL\_ISET\_PIN} = 0\text{b}1$ 、 $V_{(\text{ISNSP})} > 3.3\text{V}$ 、 $\text{EN\_NEG\_CL\_LIMIT} = 0$ | 5mV<br>25mV<br>50mV                                                                                             | 2<br>21.5<br>45                                                                                                 | 5<br>25<br>50 | 8<br>28.5<br>55 | $\mu\text{A}$ |    |

| $g_{\text{m}}(\text{ILIMCOMP})$ | 電流センスアンプのトランスコンダクタンス        | I2C インターフェイスがバイニアリで $\text{SEL\_ISET\_PIN} = 0\text{b}0$ 、 $V_{\text{ISNS}} > 4.8\text{V}$ 、 $\text{EN\_NEG\_CL\_LIMIT} = 0$       | $\Delta V_{(\text{ISNS})} = 30\text{mV}$ および $50\text{mV}$                                                      | 450                                                                                                             | 500           | 550             | $\mu\text{s}$ |    |

|                                 | 電流制限                        | $R_{(\text{ISNS})} = 10\text{m}\Omega \pm 1\%$ 、 $\text{ILIM\_THRESHOLD} = 0\text{x}64$                                            |                                                                                                                 | 4.75                                                                                                            | 5             | 5.25            | A             |    |

| $\Delta V_{(\text{ISNSx})}$     | 電流制限スレッショルド電圧               | $\text{ILIM\_THRESHOLD} = 0\text{x}14$                                                                                             |                                                                                                                 | 8.6                                                                                                             | 10            | 11.4            | mV            |    |

|                                 | 電流制限スレッショルド電圧               | $\text{ILIM\_THRESHOLD} = 0\text{x}3C$                                                                                             | $\text{EN\_NEG\_CL\_LIMIT} = 0_J = -10^\circ\text{C} \sim 70^\circ\text{C}$ ; $\text{ISNSP/N} \geq 5\text{V}$ ; | 28.8                                                                                                            | 30            | 31.2            | mV            |    |

|                                 | 電流制限スレッショルド電圧               | $\text{ILIM\_THRESHOLD} = 0\text{x}64$                                                                                             |                                                                                                                 | 48                                                                                                              | 50            | 52              | mV            |    |

| $\Delta V_{(\text{ISNSx})}$     | 電流制限スレッショルド電圧               | 電流制限スレッショルド電圧                                                                                                                      | $\text{ILIM\_THRESHOLD} = 0\text{x}FF$                                                                          | $\text{EN\_NEG\_CL\_LIMIT} = 0_J = -10^\circ\text{C} \sim 70^\circ\text{C}$ ; $\text{ISNSP/N} \geq 5\text{V}$ ; | 67.2          | 70              | 72.8          | mV |

|                                 | 電流制限スレッショルド電圧の標準的なプログラミング範囲 |                                                                                                                                    |                                                                                                                 |                                                                                                                 | 5             | 70              | mV            |    |

## 6.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $V_{(\text{BIAS})} = 12\text{V}$

| パラメータ                          |                                    | テスト条件                                                         |                                       | 最小値                                                                                                                                                                                         | 標準値  | 最大値           | 単位            |

|--------------------------------|------------------------------------|---------------------------------------------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------|---------------|

| 電流制限スレッショルドの電圧ステップ サイズ         |                                    | 5mV ~ 68.5mV に設定します                                           |                                       | 0.5                                                                                                                                                                                         |      | mV            |               |

| ILIM をディセーブルするための最小電圧          |                                    | VCC2 を基準とします                                                  |                                       | 75                                                                                                                                                                                          |      | %             |               |

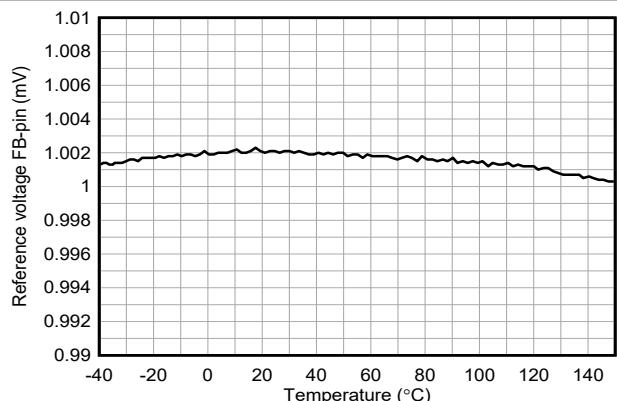

| <b>エラー・アンプ</b>                 |                                    |                                                               |                                       |                                                                                                                                                                                             |      |               |               |

| $V_{(\text{REF})}$             | FB 基準電圧                            |                                                               |                                       | 0.99                                                                                                                                                                                        | 1    | 1.01          | V             |

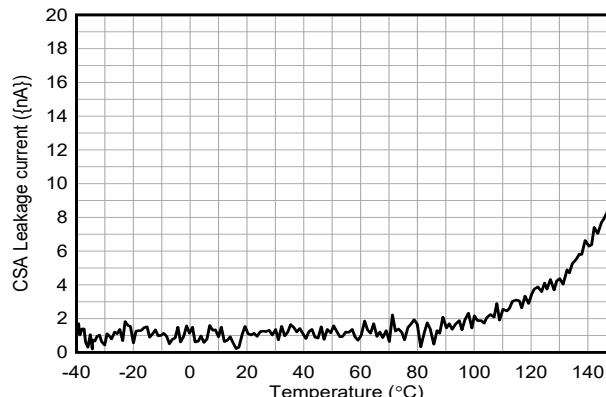

|                                | FB ピンのリーキ電流                        | $V_{(\text{FB})} = 1\text{V}$                                 |                                       |                                                                                                                                                                                             | 2    | 60            | nA            |

|                                | 出力電圧精度                             | $V_{(\text{FB})} = \text{VCC2}, \text{SEL\_DIV20}=0\text{b}1$ | $V_o, \text{nom} = 5\text{V}$         | 4.75                                                                                                                                                                                        | 5    | 5.25          | V             |

|                                |                                    |                                                               | $V_o, \text{nom} = 20\text{V}$        | 19.6                                                                                                                                                                                        | 20   | 20.4          | V             |

|                                |                                    |                                                               | $V_o, \text{nom} = 48\text{V}$        | 47.04                                                                                                                                                                                       | 48   | 48.96         | V             |

| 相互コンダクタンス                      |                                    |                                                               |                                       | 510                                                                                                                                                                                         | 600  | 690           | $\mu\text{s}$ |

| COMP ソース電流                     |                                    |                                                               |                                       |                                                                                                                                                                                             | 95   |               | $\mu\text{A}$ |

| COMP シンク電流                     |                                    |                                                               |                                       |                                                                                                                                                                                             | 120  |               | $\mu\text{A}$ |

| COMP クランプ電圧                    |                                    | $V_{(\text{FB})} = 990\text{mV}$                              |                                       | 1.2                                                                                                                                                                                         | 1.25 | 1.3           | V             |

| COMP クランプ電圧                    |                                    | $V_{(\text{FB})} = 1.01\text{V}$                              |                                       | 0.225                                                                                                                                                                                       | 0.25 | 0.275         | V             |

| $V_{T+(\text{SEL},\text{FB})}$ | 内部 FB 動作を選択するための最小電圧               |                                                               | $V_{(\text{FB})}$ 立ち上がり               | 2.6                                                                                                                                                                                         |      | V             |               |

| $t_{d(\text{uSleep})}$         | スリープ状態からウェーカアップするまでの遅延時間           |                                                               |                                       | 7                                                                                                                                                                                           |      | $\mu\text{s}$ |               |

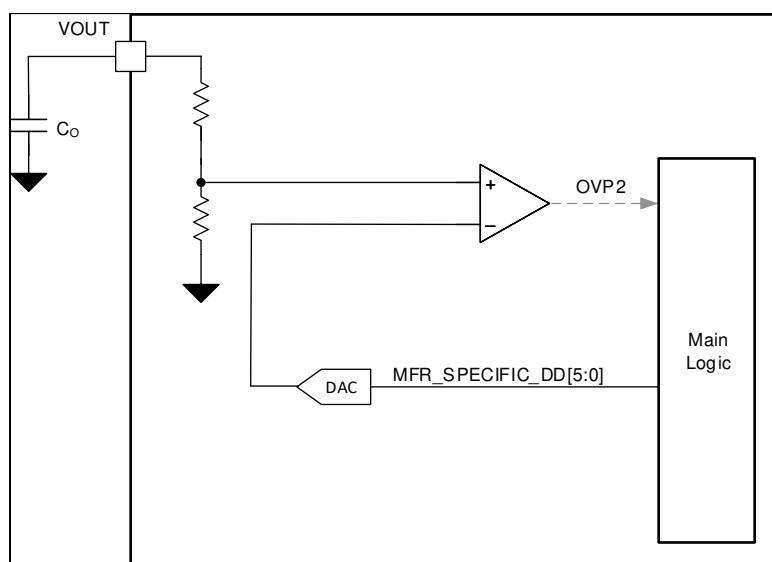

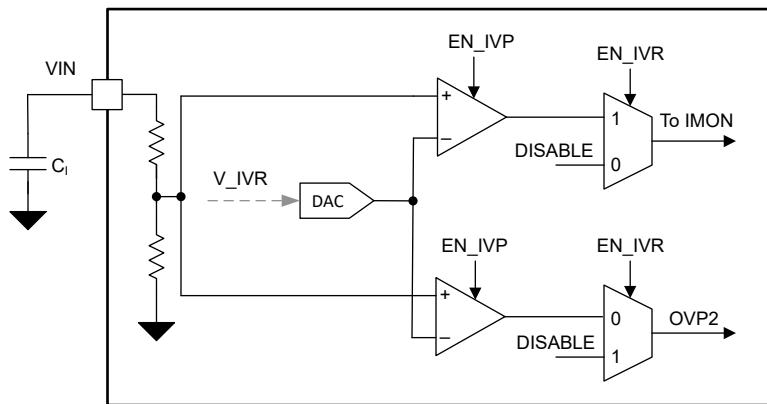

| <b>OVP</b>                     |                                    |                                                               |                                       |                                                                                                                                                                                             |      |               |               |

| VT+(OVP)                       | 過電圧立ち上がりスレッショルド                    | FB の立ち上がり ( $V_{(\text{REF})}$ を基準とする)                        |                                       | 107                                                                                                                                                                                         | 110  | 113           | %             |

| VT-(OVP)                       | 過電圧立ち下がりスレッショルド                    | FB の立ち下がり ( $V_{(\text{REF})}$ を基準とする)                        |                                       | 101                                                                                                                                                                                         | 105  | 109           | %             |

| VT+(OVP2)                      | 過電圧立ち上がりスレッショルド                    | $V_{(\text{VOUT})}$ の立ち上がり                                    | $V_{(\text{OVP2})} = 0\text{b}111111$ | 53.5                                                                                                                                                                                        | 55   | 56.5          | V             |

| VT+(IVP)                       | 入力過電圧立ち上がりスレッショルド                  | $V_{(\text{VIN})}$ 立ち上がり                                      | $IVP\_VOLTAGE = 0\text{b}00101010$    | 9.9                                                                                                                                                                                         | 10   | 10.1          | V             |

|                                | 過電圧デグリッチ時間                         |                                                               |                                       | 9                                                                                                                                                                                           | 10   | 12.5          | $\mu\text{s}$ |

| <b>nFLT</b>                    |                                    |                                                               |                                       |                                                                                                                                                                                             |      |               |               |

|                                | nFLT プルダウン スイッチの $R_{\text{DS}ON}$ | 1mA のシンク                                                      |                                       | 85                                                                                                                                                                                          |      | 140           | $\Omega$      |

| $V_{T+(\text{PG})}$            | 低電圧、正方向スレッショルド                     | FB の立ち上がり ( $V_{(\text{REF})}$ を基準とする)                        |                                       | 92                                                                                                                                                                                          | 95   | 97            | %             |

| VT-(PG)                        | 低電圧、負方向スレッショルド                     | FB の立ち下がり ( $V_{(\text{REF})}$ を基準とする)                        |                                       | 87                                                                                                                                                                                          | 90   | 93            | %             |

|                                | nFLT オフ状態リーケ                       |                                                               |                                       | 100                                                                                                                                                                                         |      | nA            |               |

| $t_{d(\text{nFLT-PIN})}$       | デグリッチ・フィルタ                         | $V_{(\text{nFLT})} = 12\text{V}$                              |                                       | 20                                                                                                                                                                                          |      | 37            | $\mu\text{s}$ |

| <b>MOSFET ドライバ</b>             |                                    |                                                               |                                       |                                                                                                                                                                                             |      |               |               |

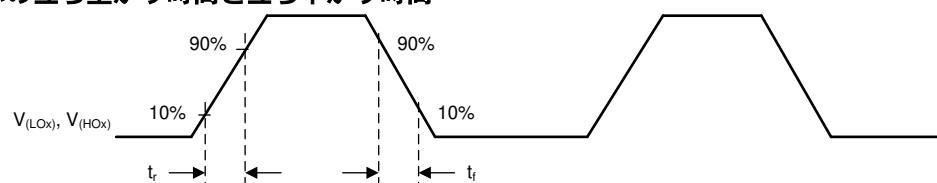

| $t_r$                          | 立ち上がり時間                            | LO1, LO2                                                      | $C_G = 3.3\text{nF}$                  | 10                                                                                                                                                                                          |      | ns            |               |

| $t_r$                          | 立ち下がり時間                            |                                                               | $C_G = 3.3\text{nF}$                  | 8                                                                                                                                                                                           |      | ns            |               |

| $t_f$                          | 立ち上がり時間                            | HO1, HO2                                                      | $C_G = 3.3\text{nF}$                  | 15                                                                                                                                                                                          |      | ns            |               |

| $t_f$                          | 立ち下がり時間                            |                                                               | $C_G = 3.3\text{nF}$                  | 15                                                                                                                                                                                          |      | ns            |               |

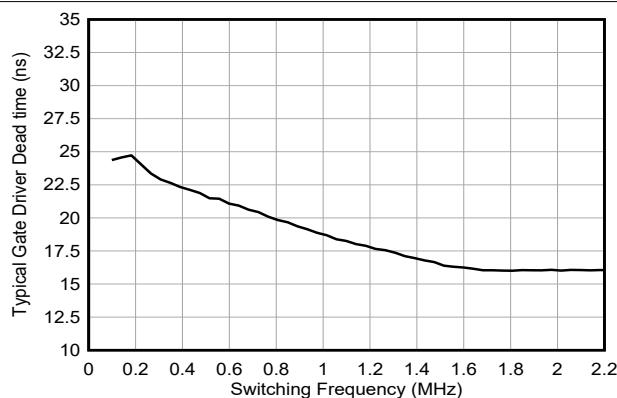

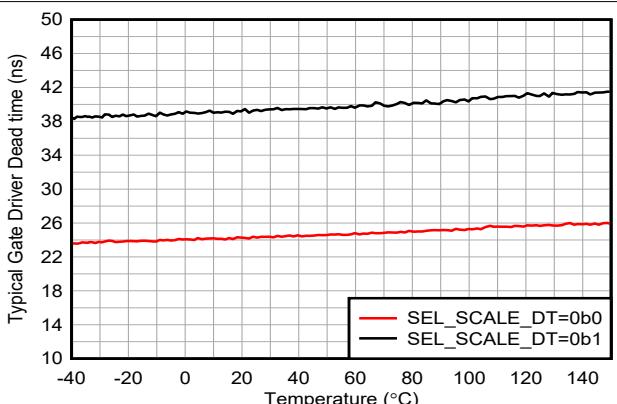

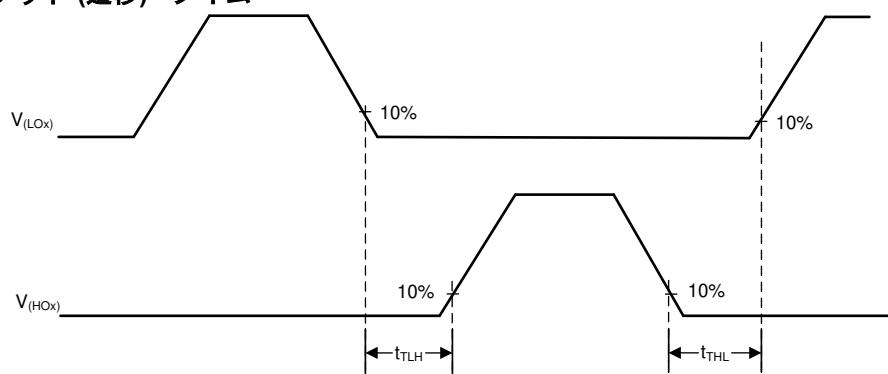

| $t_t$                          | 遷移 (デッド) 時間                        |                                                               | $C_G = 3.3\text{nF}$                  | $R_{(\text{RT})} = 316\text{k}\Omega$<br>(0.1MHz)、<br>$\text{SEL\_MIN\_DEADTIME\_GDRV} = 0\text{b}01$ 、<br>$\text{SEL\_SCALE\_DT} = 0\text{b}1$ 、<br>$\text{EN\_CONST\_TDEAD} = 0\text{b}0$ | 42   |               | ns            |

## 6.5 電気的特性 (続き)

標準値は  $T_J = 25^\circ\text{C}$  に対応します。最小および最大の制限値は、 $T_J = -40^\circ\text{C} \sim 150^\circ\text{C}$  の範囲で適用されます。特に記述のない限り、 $V_{(\text{BIAS})} = 12\text{V}$

| パラメータ                             |                               |                                                                           | テスト条件                                       |                                                                                                                                                                                              | 最小値                                | 標準値      | 最大値   | 単位               |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------|-------|------------------|

| $t_{\text{t}}$                    | 遷移 (デッド) 時間                   |                                                                           | $C_G = 3.3\text{nF}$                        | $R_{(\text{RT})} = 14.2\text{k}\Omega$<br>(2.2MHz),<br>$\text{SEL\_MIN\_DEADTIME\_GDRV} = 0\text{b}01$ ,<br>$\text{SEL\_SCALE\_DT} = 0\text{b}1$ ,<br>$\text{EN\_CONST\_TDEAD} = 0\text{b}0$ | $I_{(\text{test})} = 500\text{mA}$ | 19.5     |       | ns               |

|                                   | ゲートドライバのハイサイド<br>オン抵抗         | LO1, LO2                                                                  | 1.8                                         |                                                                                                                                                                                              |                                    | $\Omega$ |       |                  |

|                                   | ゲートドライバのハイサイド<br>オン抵抗         | HO1, HO2                                                                  | 1.5                                         |                                                                                                                                                                                              |                                    | $\Omega$ |       |                  |

|                                   | ゲートドライバのローサイド<br>オン抵抗         | LO1, LO2                                                                  | 0.9                                         |                                                                                                                                                                                              |                                    | $\Omega$ |       |                  |

|                                   | ゲートドライバのローサイド<br>オン抵抗         | HO1, HO2                                                                  | 0.8                                         |                                                                                                                                                                                              |                                    | $\Omega$ |       |                  |

| $V_{\text{TH-}}(\text{BOOT\_UV})$ | 負方向のブートストラップ UVLO スレッシ<br>ヨルド | $V(\text{HBx}) - V(\text{SWx})$ の立ち<br>下がり                                |                                             |                                                                                                                                                                                              | 2.5                                | 2.7      | 3.1   | V                |

| $V_{\text{TH-}}(\text{BOOT\_UV})$ | ブートストラップ UVLO ヒ<br>ステリシス      |                                                                           |                                             |                                                                                                                                                                                              |                                    | 300      |       | mV               |

| $V_{\text{TH+}}(\text{BST\_OV})$  | 正方向のブートストラップ過電圧スレッショ<br>ルド    | $V(\text{HBx}) - V(\text{SWx})$ 立ち上<br>がり、 $I_{\text{HBx}} = 10\text{mA}$ |                                             |                                                                                                                                                                                              | 5.1                                | 5.5      | 5.9   | V                |

| $V_{\text{TH}}(\text{GATEOUT})$   | ゲートドライバの出力スイッ<br>チング検出        | LO1, LO2                                                                  | $V_{\text{CC}}$ を基準とします                     |                                                                                                                                                                                              |                                    | 37       |       | %                |

| $V_{\text{TH}}(\text{GATEOUT})$   | ゲートドライバの出力スイッ<br>チング検出        | HO2, HO2                                                                  | $V(\text{HBx}) - V(\text{SWx})$ を基準<br>とします |                                                                                                                                                                                              |                                    | 37       |       | %                |

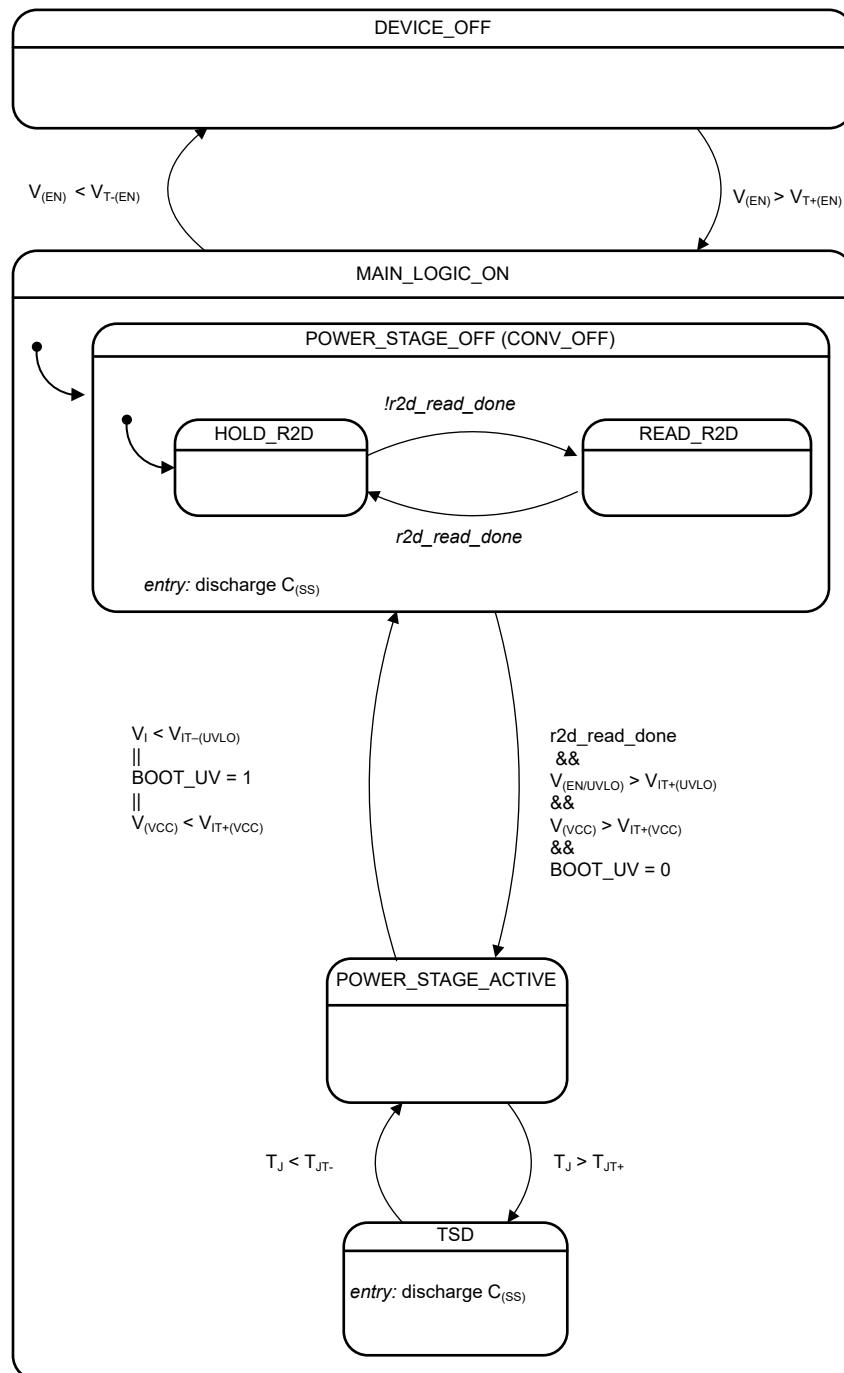

| <b>サーマル シャットダウン</b>               |                               |                                                                           |                                             |                                                                                                                                                                                              |                                    |          |       |                  |

| $T_{\text{T+J}}$                  | サーマル シャットダウンの<br>スレッショルド      | サーマル<br>シャットダウ<br>ンのスレッ<br>ショルド                                           | $T_J$ 立ち上がり                                 |                                                                                                                                                                                              |                                    | 164      |       | $^\circ\text{C}$ |

|                                   | サーマル シャットダウン ヒ<br>ステリシス       | サーマル シ<br>ヤットダウン<br>ヒステリシス                                                |                                             |                                                                                                                                                                                              |                                    | 15       |       | $^\circ\text{C}$ |

| <b>過熱警告</b>                       |                               |                                                                           |                                             |                                                                                                                                                                                              |                                    |          |       |                  |

|                                   | 過熱警告スレッショルド                   | $T_J$ 立ち上がり                                                               | $\text{THW\_THRESHOLD}=0\text{b}0$<br>0     |                                                                                                                                                                                              | 140                                |          |       | $^\circ\text{C}$ |

|                                   | 熱警告標準値プログラミング範囲               |                                                                           |                                             |                                                                                                                                                                                              | 95                                 | 140      |       | $^\circ\text{C}$ |

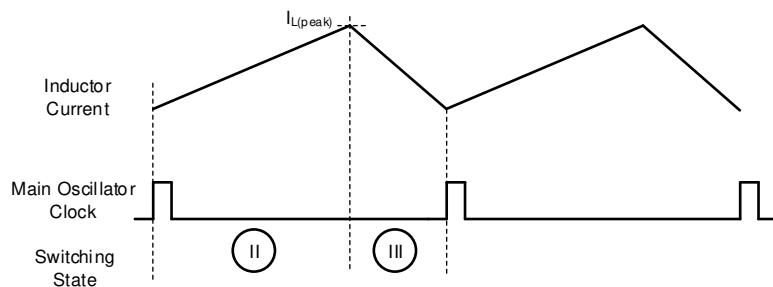

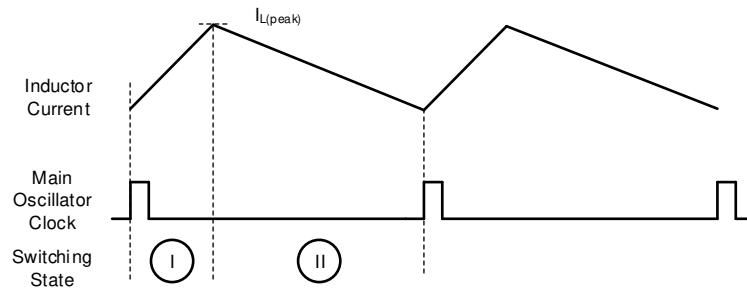

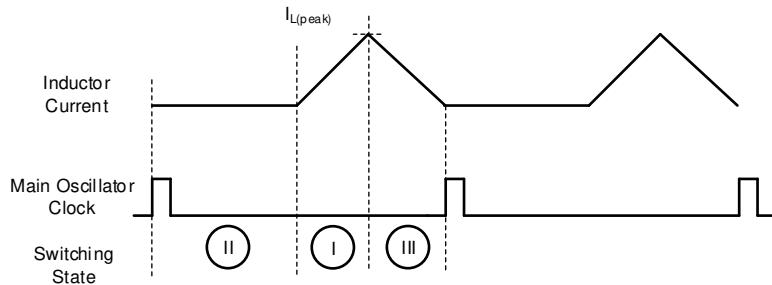

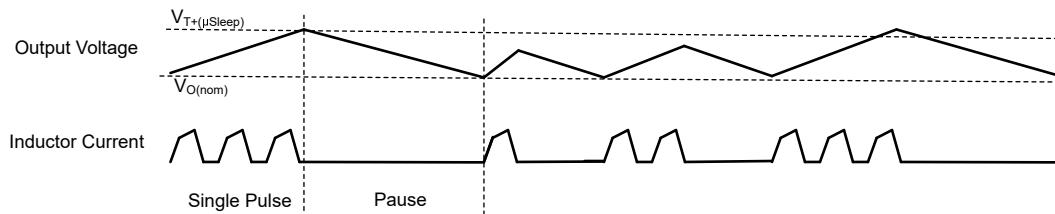

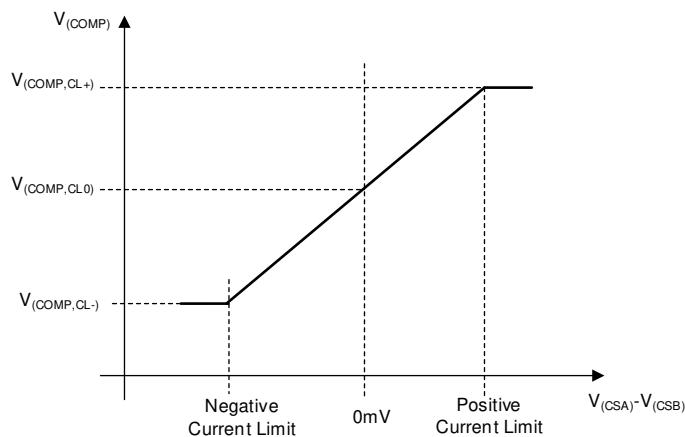

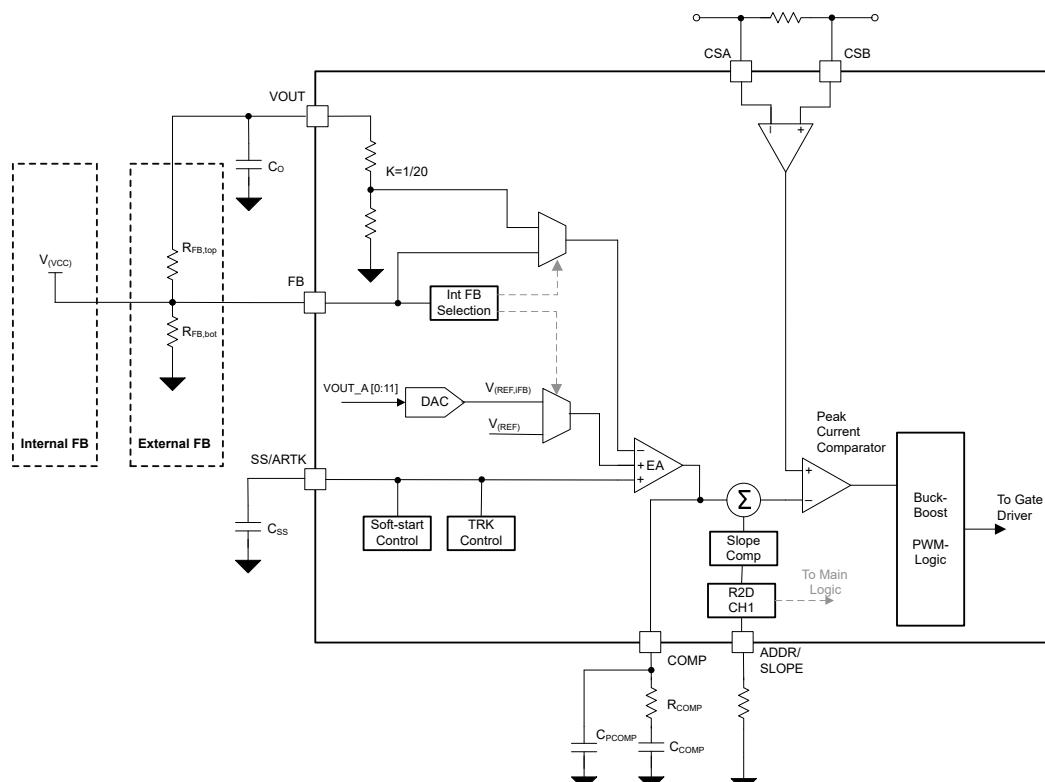

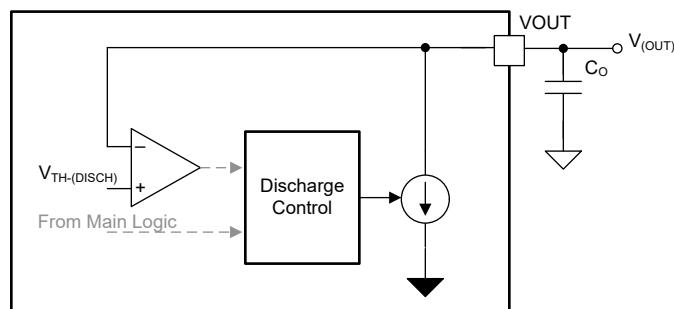

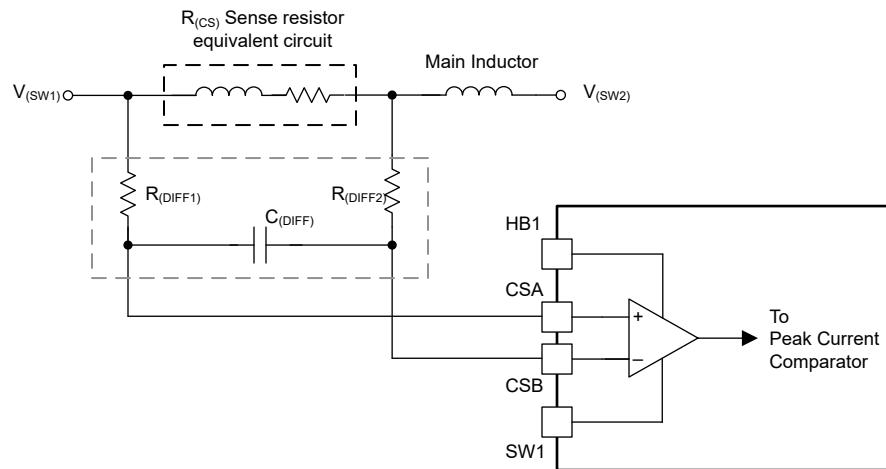

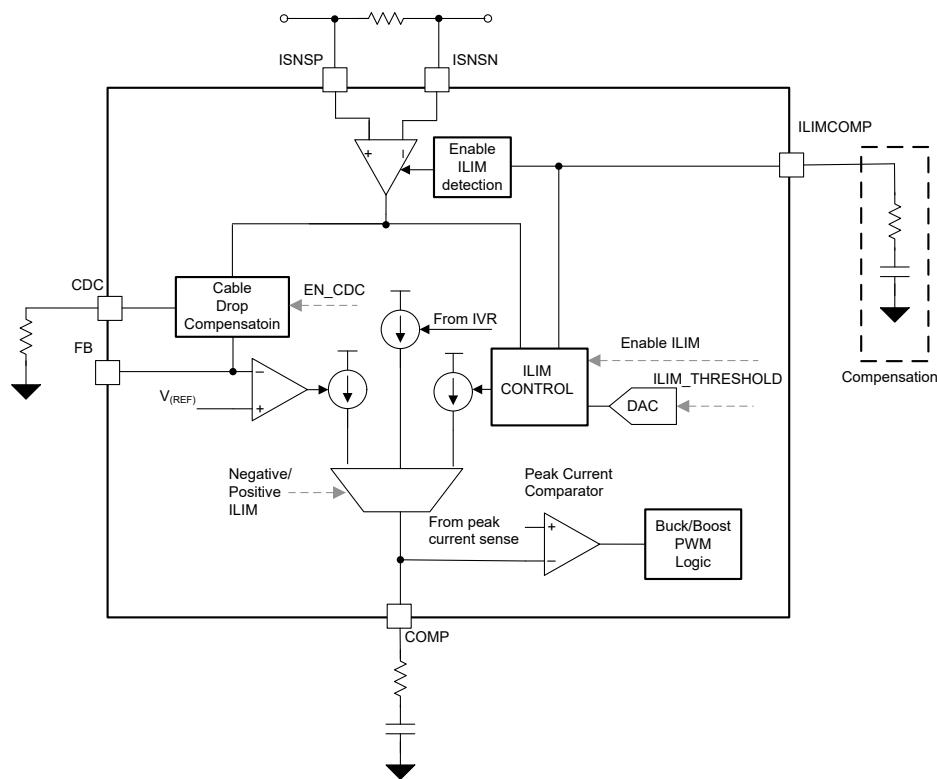

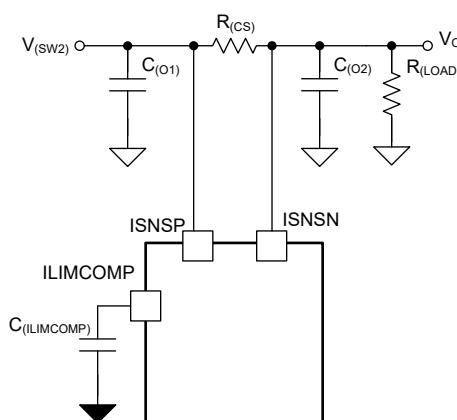

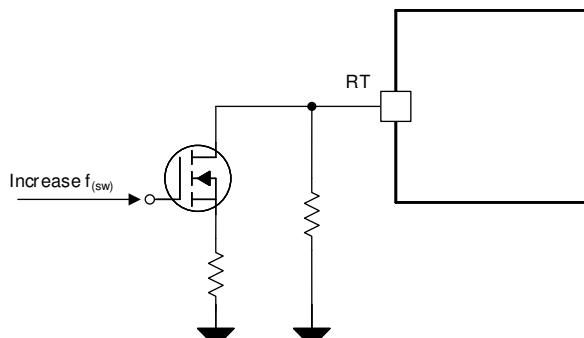

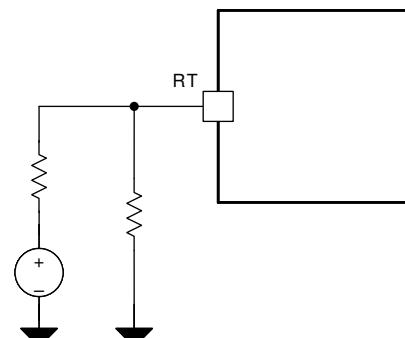

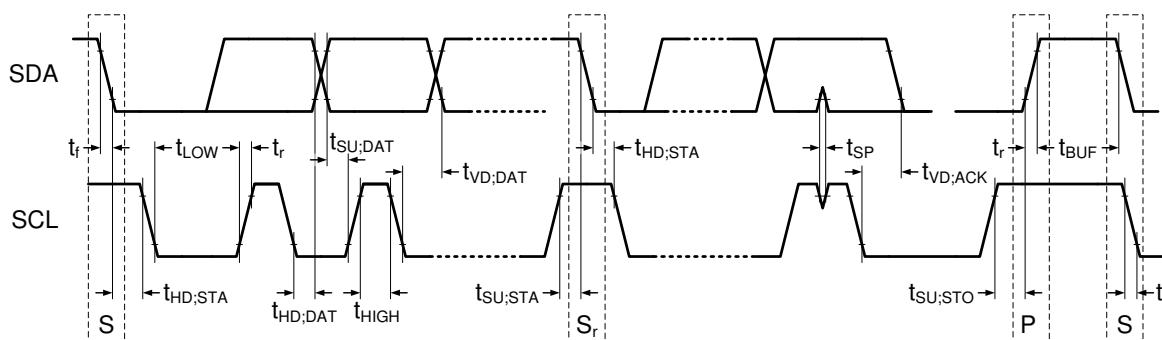

|                                   | 過熱警告精度                        |                                                                           |                                             |                                                                                                                                                                                              |                                    | $\pm 10$ |       | $^\circ\text{C}$ |