I M251772

# LM251772 USB-PD 用 I<sup>2</sup>C 搭載、36V V<sub>IN</sub> 4 スイッチ昇降圧コントローラ

## 1 特長

- 入力範囲:3.5V~36V

- 以下からの  $I^2C$  を介した動的  $V_o$  プログラミング:

- 3.3V から最大 48V (20mV 刻み)

- 1V から最大 24V (10mV 刻み)

- ピーク電流レギュレーション制御

- すべての動作モードで小さい電圧遷移リップル

- シャットダウン時静止電流:3µA

- 動作時静止電流:60µA

- デュアル ロール ポート電力パス用の駆動 (DRV) ピン

- 高速 pMOS FET 制御用のプッシュプル出力

- nMOS FET 用チャージ ポンプ ドライバ段として構

- 軽負荷および高負荷条件で高効率を実現する動作モ ードの選択:

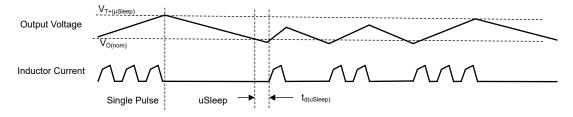

- パワー セーブ モード (単一パルス / µSleep)

- 自動導通モード

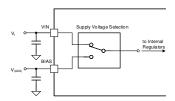

- 高電圧 LDO を内蔵

- PD コントローラ電源用の補助高電圧 LDO

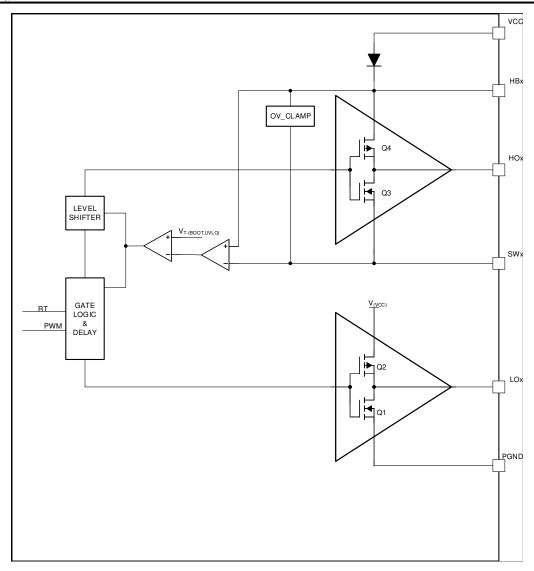

- フルブリッジ ゲートドライブを内蔵

- 2A ピーク電流能力

- ブートストラップ過電圧および低電圧保護

- ブートストラップ ダイオードを内蔵

- 動作モードから独立した固定周波数 (昇圧、昇降圧、 降圧)

- 強制 PWM モードを選択可能

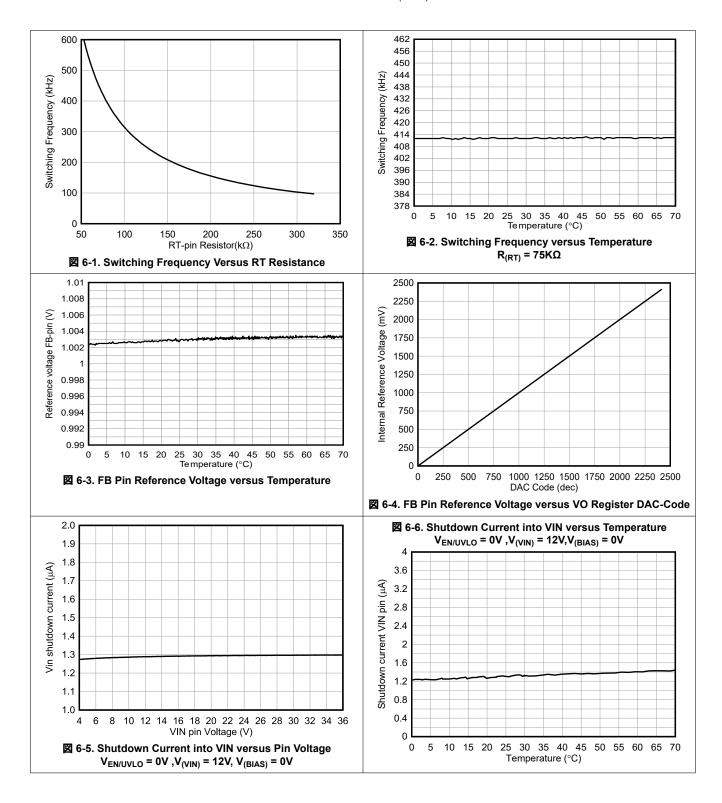

- スイッチング周波数:100kHz~600kHz

- 外部クロック同期およびクロック出力

- 平均入力または出力電流センサ

- 0.5A~7A の範囲で 50mA 刻みにプログラム可能

- 監視機能の I2C インターフェイスの読み出し値

- 民生用温度範囲 (Tj = 0℃~70℃)

- WEBENCH® Power Designer により、LM251772 を 使用するカスタム設計を作成

## 2 アプリケーション

- USB Type-C パワー デリバリ電源供給:

- ドッキング ステーション

- PC モニタ

- 産業用 PC / 高耐久性 PC

- USB AC/DC アダプタ

- ワイヤレス充電

### 3 概要

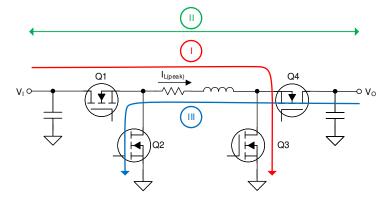

LM251772 は、4 スイッチ昇降圧コントローラです。入力 電圧が、調整された出力電圧よりも高い、等しい、または 低い場合に、レギュレートされた出力電圧を供給します。 パワーセーブ モードでは、出力の動作範囲全体にわたっ て非常に高い効率をサポートします。出力電圧と平均電 流は、内蔵の I2C インターフェイスにより動的にプログラム 可能です。出力電圧と平均電流の構成範囲は、USB-PD 標準の要件を満たしています。 内蔵の DRV ピンは切断 FET を制御でき、デュアル ロール ポート (DRP) の要件 をサポートします。

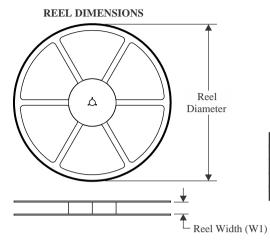

## パッケージ情報

| 部品番号         | パッケージ <sup>(1)</sup> | 本体サイズ (公称) |

|--------------|----------------------|------------|

| LM251772RHAR | RHA040               | 6 mm × 6mm |

利用可能なすべてのパッケージについては、データシートの末尾 にある注文情報を参照してください。

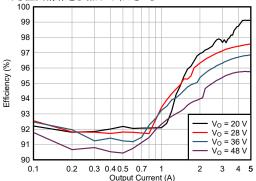

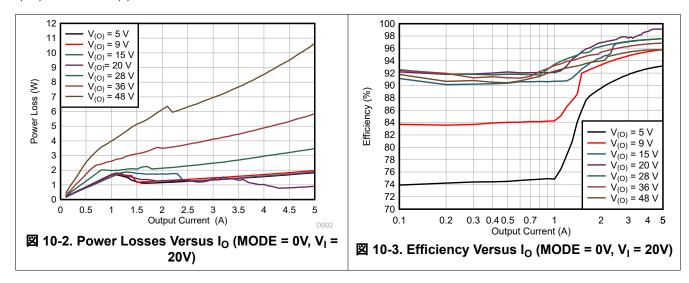

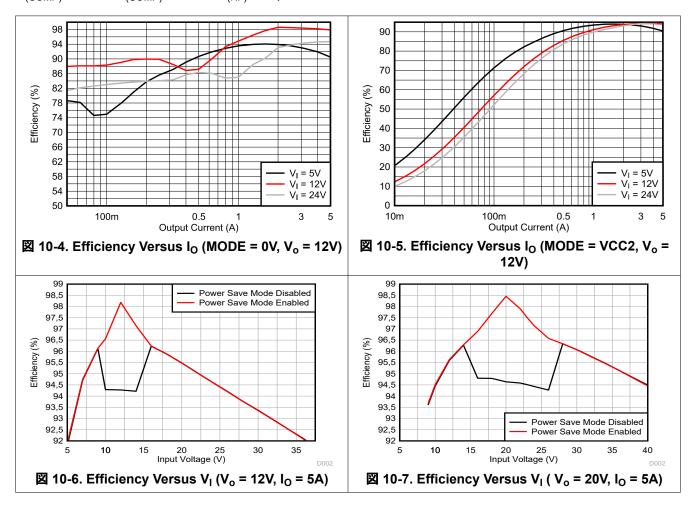

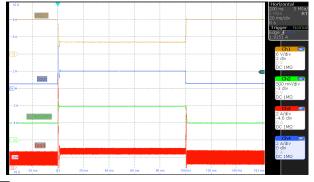

## 効率と出力電流との関係、V<sub>I</sub> = 20V、PSM

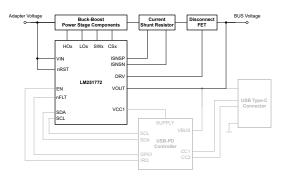

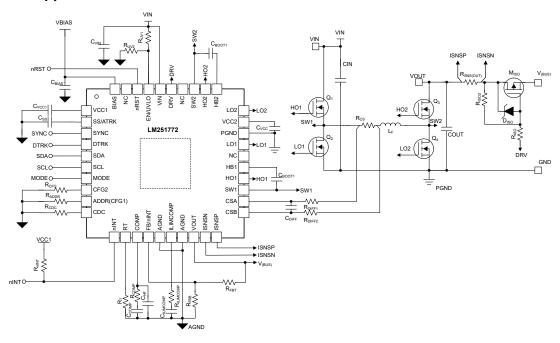

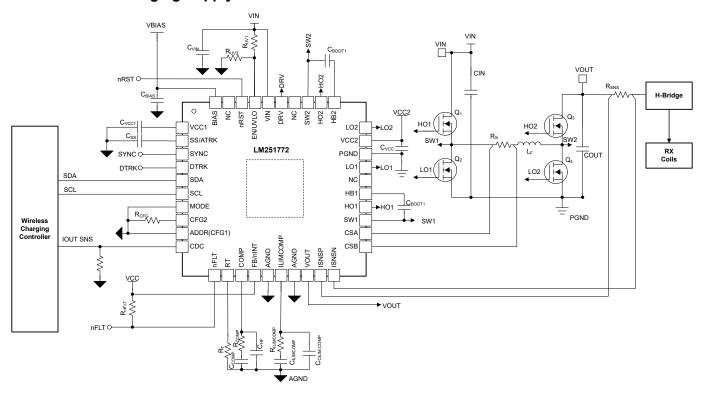

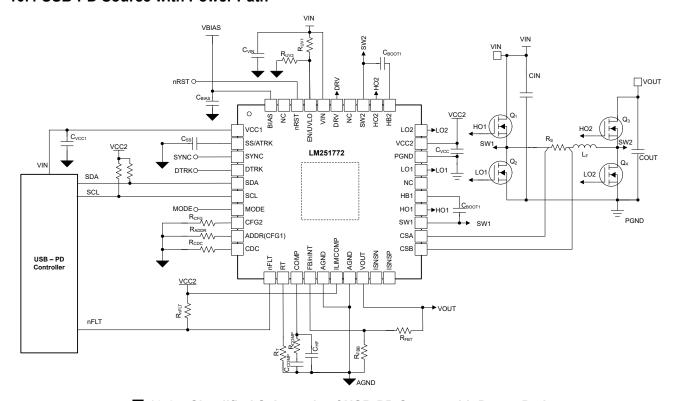

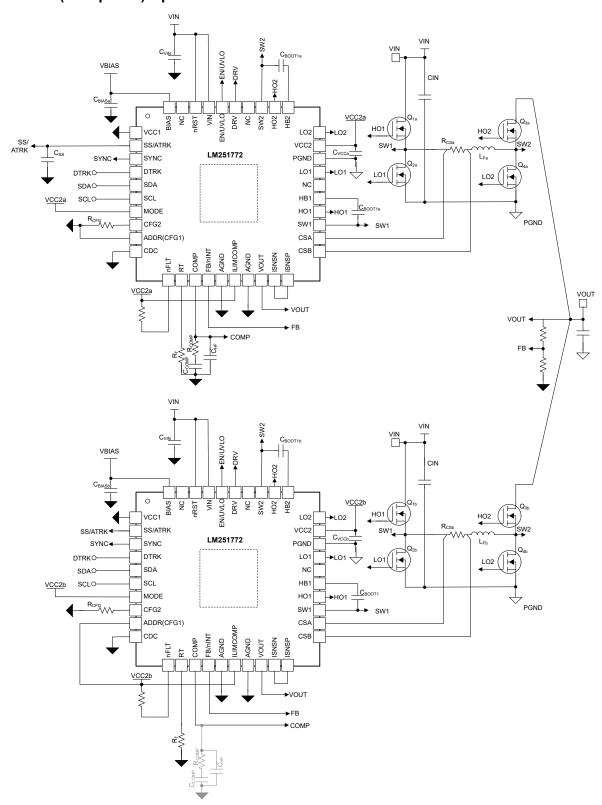

代表的なアプリケーション回路図

## **Table of Contents**

| 1 特長                                 | 1                |

|--------------------------------------|------------------|

| 2 アプリケーション                           | 1                |

| 3 概要                                 | 1                |

| 4 Device Comparison                  |                  |

| 5 Pin Configuration and Functions    |                  |

| 6 Specifications                     | 7                |

| 6.1 Absolute Maximum Ratings         | 7                |

| 6.2 Handling Ratings                 | 8                |

| 6.3 Recommended Operating Conditions | 8                |

| 6.4 Thermal Information              |                  |

| 6.5 Electrical Characteristics       |                  |

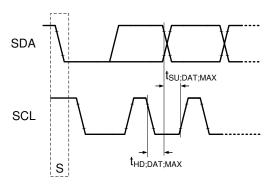

| 6.6 Timing Requirements              | 14               |

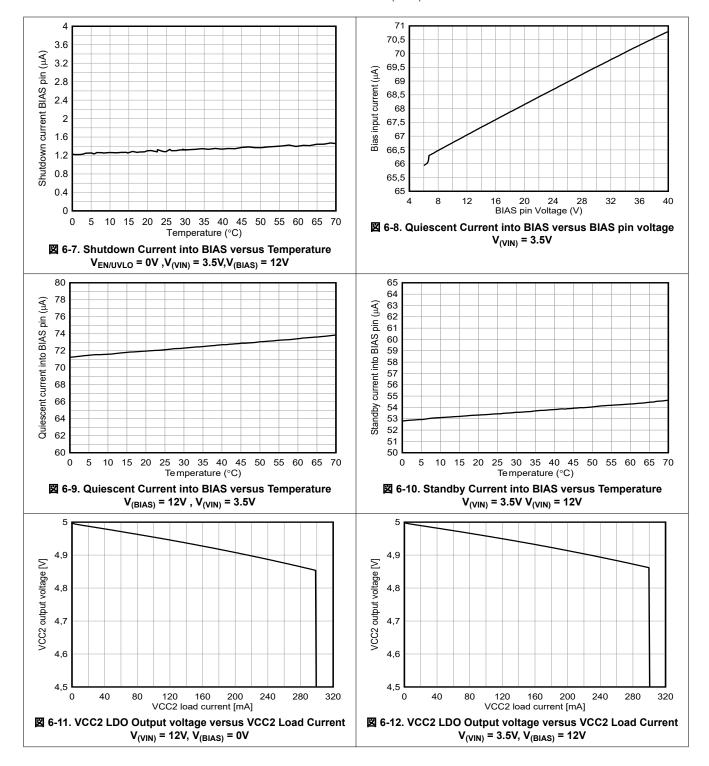

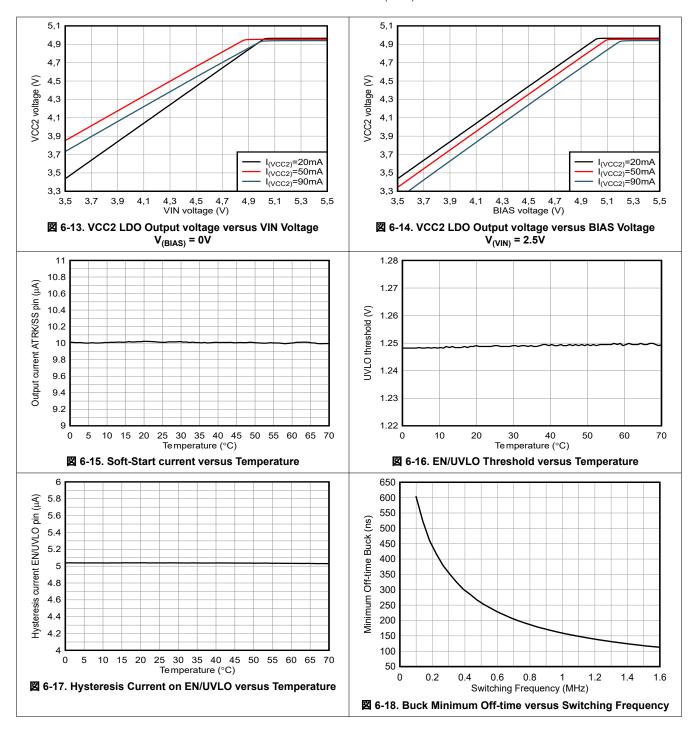

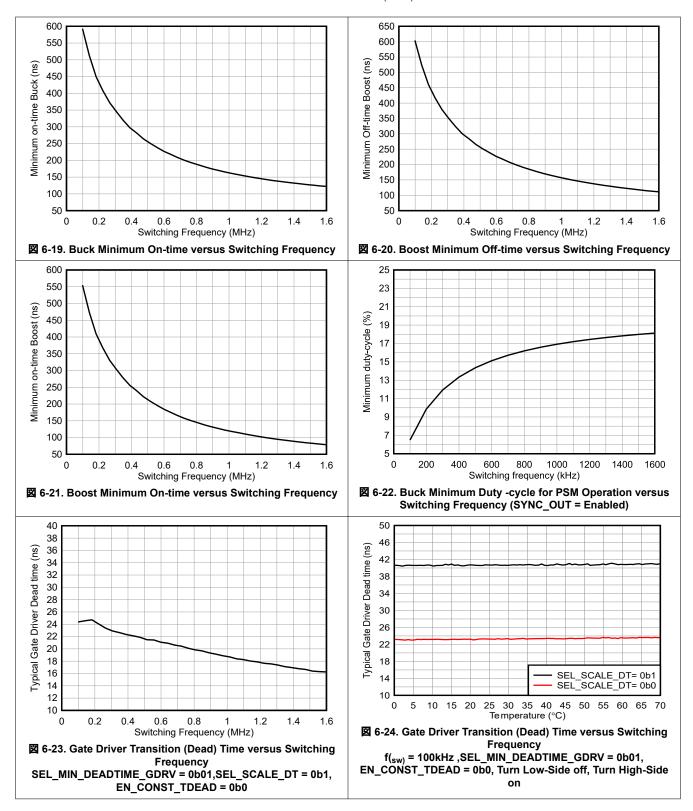

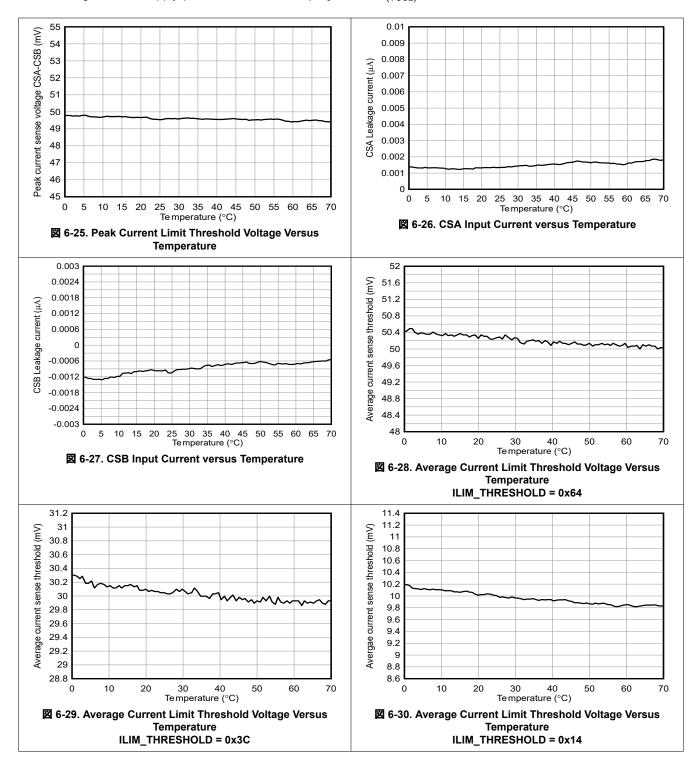

| 6.7 Typical Characteristics          | 16               |

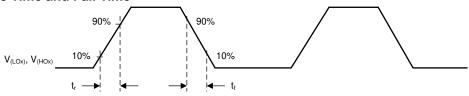

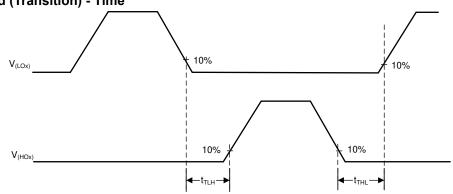

| 7 Parameter Measurement Information  | <mark>2</mark> 1 |

| 8 Detailed Description               | <mark>2</mark> 1 |

| 8.1 Overview                         | <mark>2</mark> 1 |

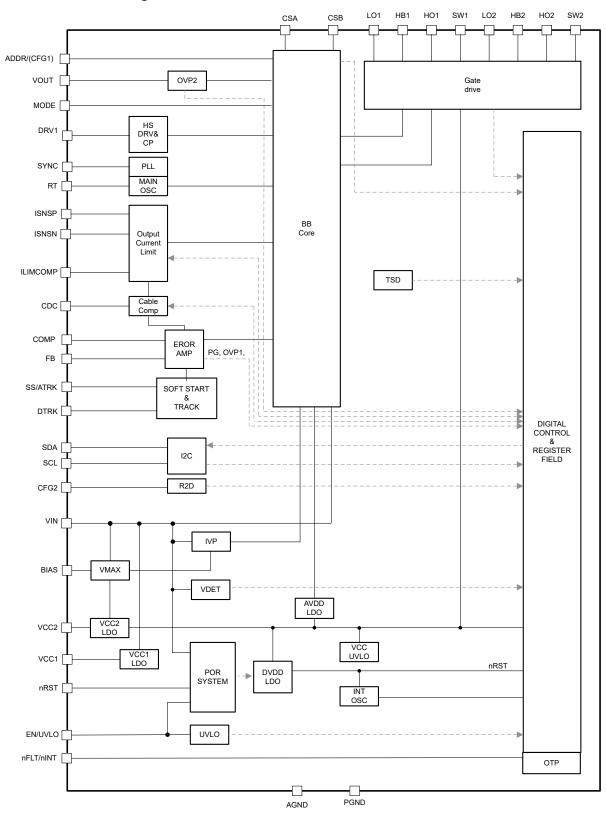

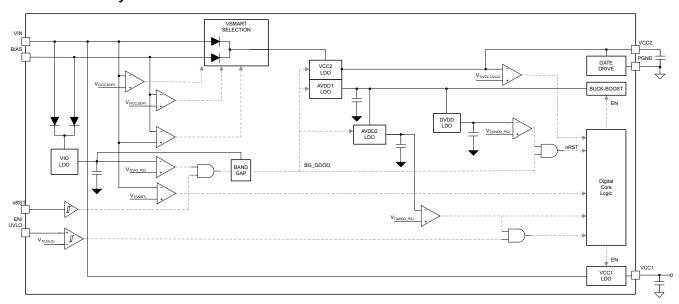

| 8.2 Functional Block Diagram         | 22               |

| 8.3 Feature Description              | <mark>2</mark> 3 |

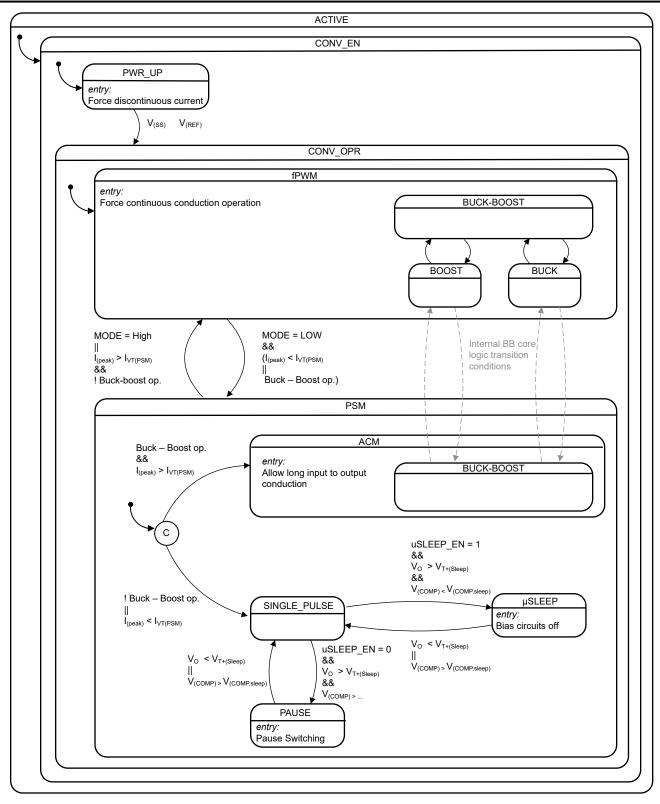

| 8.4 Device Functional Modes          | 56               |

| 8.5 Programming                         | 57              |

|-----------------------------------------|-----------------|

| 9 LM251772 Registers                    |                 |

| 10 Application and Implementation       |                 |

| 10.1 Application Information            | <mark>89</mark> |

| 10.2 Typical Application                | 89              |

| 10.3 Wireless Charging Supply           |                 |

| 10.4 USB-PD Source with Power Path      | 101             |

| 10.5 Parallel (Multiphase) Operation    | 102             |

| 11 Device and Documentation Support     | 103             |

| 11.1 Documentation Support              | 103             |

| 11.2ドキュメントの更新通知を受け取る方法                  |                 |

| 11.3 サポート・リソース                          | 103             |

| 11.4 Trademarks                         | 103             |

| 11.5 静電気放電に関する注意事項                      | 103             |

| 11.6 用語集                                | 103             |

| 12 Revision History                     | 104             |

| 13 Mechanical, Packaging, and Orderable |                 |

| Information                             | 105             |

## **4 Device Comparison**

## 表 4-1. Device Comparison

| FUNCTION                                     | LM251772    | LM51772        | LM5177                | LM51770               |

|----------------------------------------------|-------------|----------------|-----------------------|-----------------------|

| Maximum Recommended Input Voltage            | 36V         | 55V            | 60V                   | 78V                   |

| Absolute Maximum Input<br>Voltage            | 48V         | 59V            | 85V                   | 85V                   |

| Maximum Recommended Switching Frequency      | 600kHz      | 2.2MHz         | 600kHz                | 1.8MHz                |

| Default Output Voltage<br>Value              | 5.1V        | 12V            | n/a                   | n/a                   |

| Default Output Current<br>Limit Value        | 900mA       | 5A             | n/a                   | n/a                   |

| Output Start-up State<br>Without Programming | Disabled    | Enabled        | Enabled               | Enabled               |

| I <sup>2</sup> C interface                   | yes         | yes            | no                    | no                    |

| PSM - Automatic<br>Conduction Mode           | yes         | yes            | no                    | yes                   |

| PSM - Programmable<br>Conduction Mode        | no          | yes            | no                    | no                    |

| Output Discharge                             | yes         | yes            | no                    | no                    |

| Input voltage regulation                     | yes         | yes            | with external circuit | with external circuit |

| Analog Current Limit<br>Setting              | no          | yes            | no                    | no                    |

| T <sub>j</sub> Temperature Range             | 0°C to 70°C | -40°C to 125°C | -40°C to 125°C        | -40°C to 125°C        |

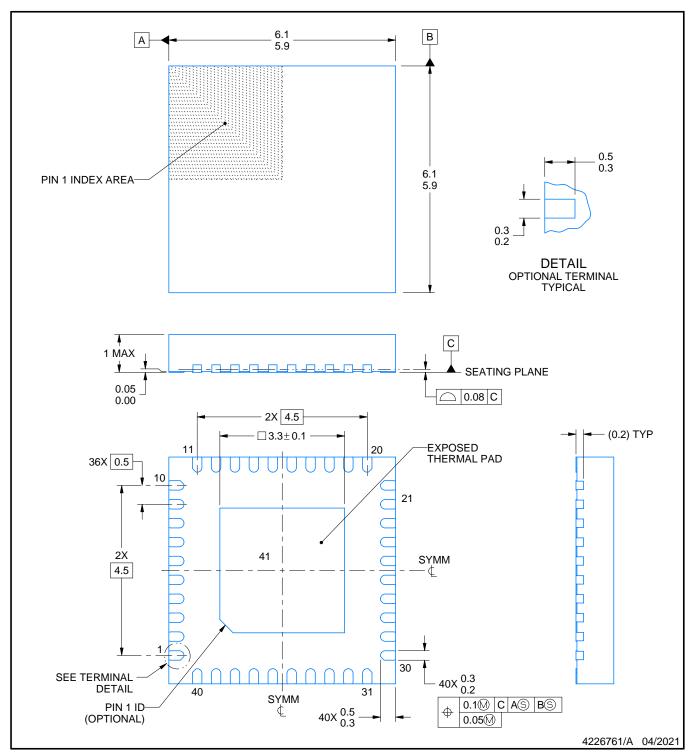

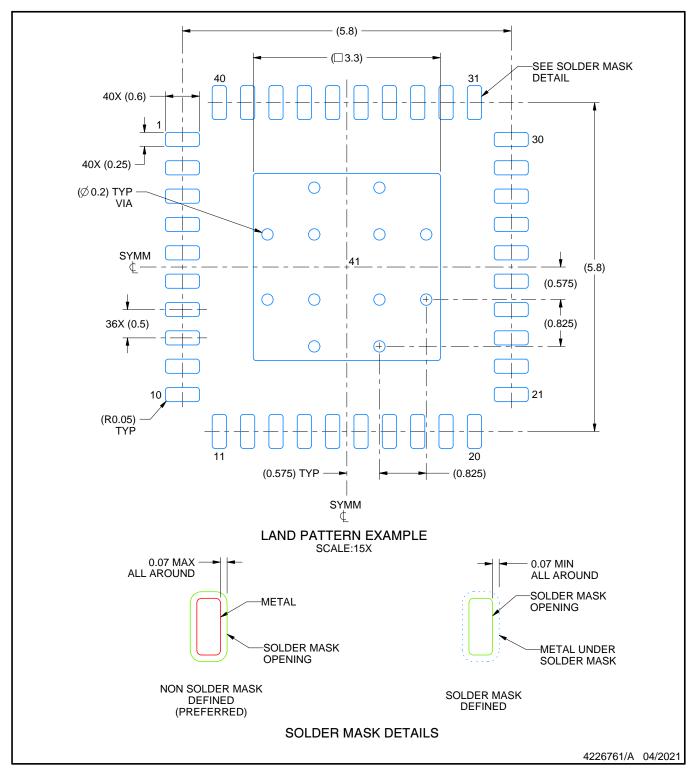

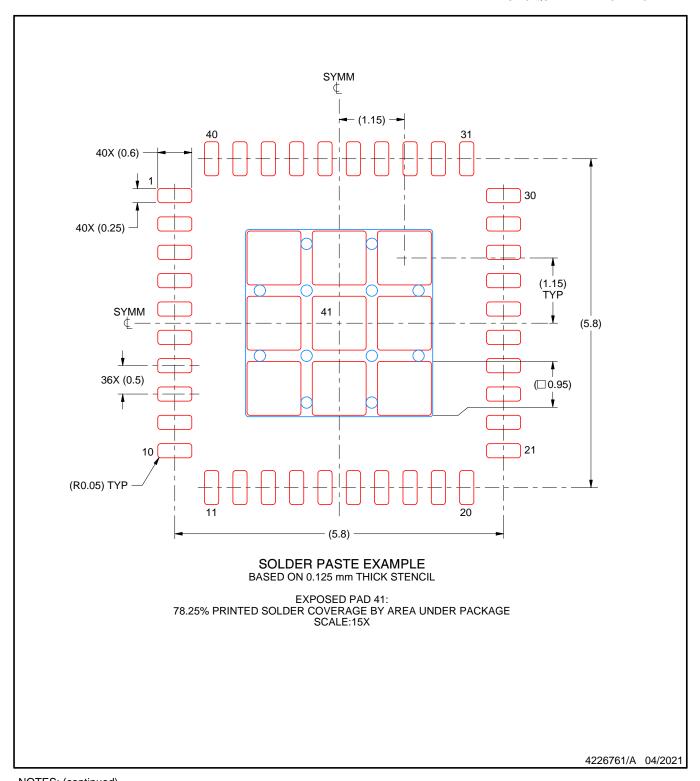

## **5 Pin Configuration and Functions**

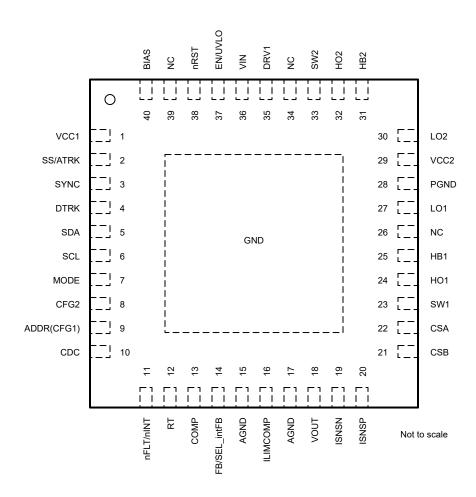

図 5-1. RHA Package 40-Pin QFN Top View

Copyright © 2025 Texas Instruments Incorporated

1

## 表 5-1. Pin Functions

| NAME   NO.   1001   DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PIN I/O <sup>(1)</sup> DESCRIPTION      |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|--|--|--|--|--|

| output is disabled by the logic it can be tied to GND with a resistor or pull leave the pin floating.  SS/ATRK  2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         |  |  |  |  |  |  |  |

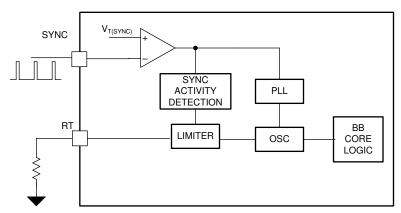

| start time.  Analog output voltage tracking pin. The VOUT regulation target can be p connecting the pin to variable voltage reference (for example, through a converter). The internal circuit selects the lowest voltage between the pin internal voltage reference.  SYNC  3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |  |  |  |  |  |  |  |

| External clock during operation. Do not leave this pin floating. If this funct connect the pin to VCC2 or GND.  The SYNC pin can be configured as clock synchronization output signal. can be selected to 0° and 180° to directly operate two devices in a paralli operation.  DTRK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | orogrammed by digital to analog         |  |  |  |  |  |  |  |

| If this function is not used, connect the pin to VCC or GND.   SDA   5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | tion is not used,<br>. The clock phase  |  |  |  |  |  |  |  |

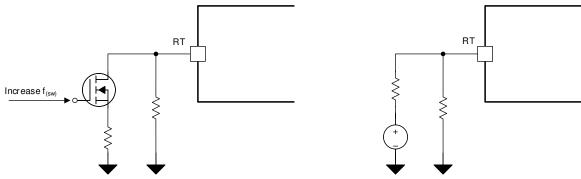

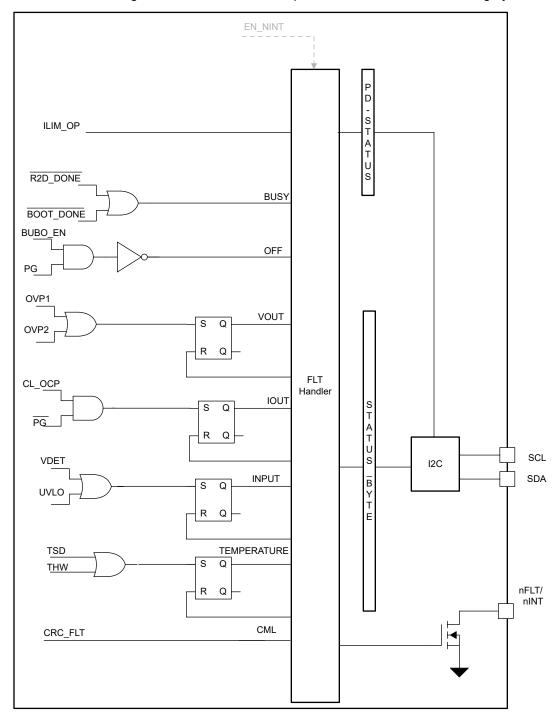

| SCL 6 I I <sup>2</sup> C interface serial clock line. Connect an external a pull-up resistor MODE 7 I Digital input to select device operation mode. If the pin is pulled low, pow (PSM) is enabled. If the pin is pulled high, the forced PWM or CCM operation can be changed dynamically during operation. Do not infloating.  CFG2 8 I/O Device configuration pin. Connect a resistor between the CFG2 pin and device operation according the セクション 8.3.21  ADDR(CFG1) 9 I Address selection. Pull to GND for I <sup>2</sup> C target address LSB = 0. Pull to VC address LSB = 1  CDC 10 Cable drop compensation or current monitor output pin. Connect a resist CDC pin and AGND to select the gain for the cable drop compensation. Per default this pin provides a current monitoring signal of the sensed vo ISNSP and ISNSN pins In case the current monitor is disabled connect CDC to ground  NFLT/nINT 11 O Open-drain output pin for fault indication or power good. This pin can be interrupt pin. In case of a STATUS register change the pin toggles low for RT 12 I/O Switching frequency programming pin. An external resistor is connected | ave this pin floating.                  |  |  |  |  |  |  |  |

| MODE   7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         |  |  |  |  |  |  |  |

| (PSM) is enabled. If the pin is pulled high, the forced PWM or CCM opera. The configuration can be changed dynamically during operation. Do not in floating.  CFG2 8 I/O Device configuration pin. Connect a resistor between the CFG2 pin and 0 device operation according the セクション 8.3.21  ADDR(CFG1) 9 I Address selection. Pull to GND for I²C target address LSB = 0. Pull to VO address LSB = 1  CDC 10 Cable drop compensation or current monitor output pin. Connect a resist CDC pin and AGND to select the gain for the cable drop compensation. Per default this pin provides a current monitoring signal of the sensed vo ISNSP and ISNSN pins In case the current monitor is disabled connect CDC to ground  nFLT/nINT 11 O Open-drain output pin for fault indication or power good. This pin can be interrupt pin. In case of a STATUS register change the pin toggles low for RT 12 I/O Switching frequency programming pin. An external resistor is connected                                                                                                                                                                               |                                         |  |  |  |  |  |  |  |

| device operation according the セクション 8.3.21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ration is enabled.                      |  |  |  |  |  |  |  |

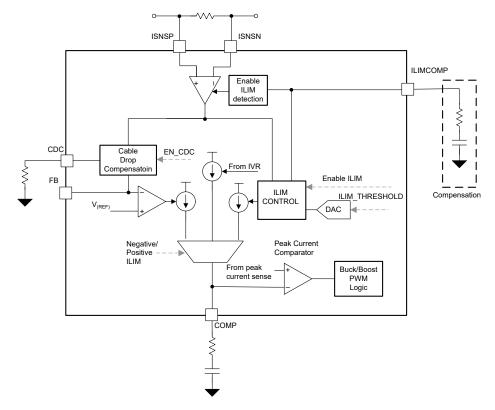

| address LSB = 1  CDC 10 Cable drop compensation or current monitor output pin. Connect a resist CDC pin and AGND to select the gain for the cable drop compensation. Per default this pin provides a current monitoring signal of the sensed vo ISNSP and ISNSN pins In case the current monitor is disabled connect CDC to ground  nFLT/nINT 11 O Open-drain output pin for fault indication or power good. This pin can be interrupt pin. In case of a STATUS register change the pin toggles low for RT 12 I/O Switching frequency programming pin. An external resistor is connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | GND to select the                       |  |  |  |  |  |  |  |

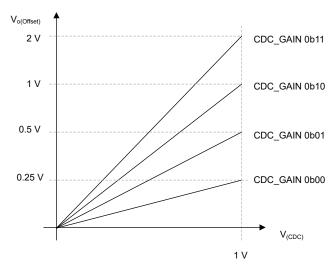

| CDC pin and AGND to select the gain for the cable drop compensation.  Per default this pin provides a current monitoring signal of the sensed vo ISNSP and ISNSN pins  In case the current monitor is disabled connect CDC to ground  nFLT/nINT  11  O Open-drain output pin for fault indication or power good. This pin can be interrupt pin. In case of a STATUS register change the pin toggles low for RT  12  I/O Switching frequency programming pin. An external resistor is connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CC2 for I <sup>2</sup> C target         |  |  |  |  |  |  |  |

| interrupt pin. In case of a STATUS register change the pin toggles low for RT 12 I/O Switching frequency programming pin. An external resistor is connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                         |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                         |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | to the RT pin and                       |  |  |  |  |  |  |  |

| COMP 13 O Output of the error amplifier. An external RC network needs to be connected COMP and AGND to stabilize/compensate the regulator voltage loop.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | cted between                            |  |  |  |  |  |  |  |

| FB/SEL_intFB  I Feedback pin for output voltage regulation. Connect a resistor divider ner output of the converter to the FB pin. Connect the FB pin to VCC2 to ope output voltage default setting of the device.  To select the internal feedback connect the pin to VCC2 before the device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | erate at a fixed                        |  |  |  |  |  |  |  |

| AGND 15 Connect to AGND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |  |  |  |  |  |  |  |

| ILIMCOMP  16  Compensation pin for average current limit loop. Connect an capacitor or network if the current limit is set by the internal DAC.  If the internal DAC is disabled the pin sets the current limit threshold for t limit. Connect a resistor to AGND. A parallel filter of capacitor is recommon the application requirements  Connect the ILIMCOMP pin to VCC2 to disable the block and reduce the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | the average current<br>nended depending |  |  |  |  |  |  |  |

| AGND 17 G Analog Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |  |  |  |  |  |  |  |

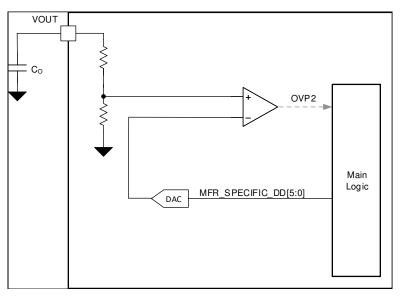

| VOUT 18 I Output voltage sense input. Connect to the power stage output rail.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                         |  |  |  |  |  |  |  |

## 表 5-1. Pin Functions (続き)

| P       | rin | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|---------|-----|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME    | NO. | 1/0(-)             | DESCRIPTION                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

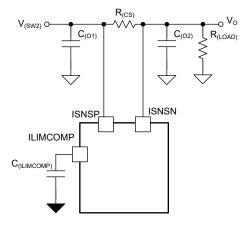

| ISNSN   | 19  | I                  | Negative sense input of the output or input average current sense amplifier. An optional current sense resistor connected between ISNSN and ISNSP can be located either on the input side or on the output side of the power stage.  In case the optional current sensor is disabled connect ISNSN and ISNSP together to AGND |  |  |  |  |

| ISNSP   | 20  | I                  | Positive sense input of the output or input current sense amplifier. An optional current sense resistor connected between ISNSN and ISNSP can be placed either on the input side or on the output side of the power stage.  In case the optional current sensor is disabled connect ISNSP to ground                           |  |  |  |  |

| CSB     | 21  | I                  | Inductor peak current sense negative input. Connect CSB to the negative side of the external current sense resistor using a Kelvin connection.                                                                                                                                                                                |  |  |  |  |

| CSA     | 22  | I                  | Inductor peak current sense positive input. Connect CSA to the positive side of the external current sense resistor using a Kelvin connection.                                                                                                                                                                                |  |  |  |  |

| SW1     | 23  | Р                  | Inductor switch node for the buck half-bridge                                                                                                                                                                                                                                                                                 |  |  |  |  |

| HO1     | 24  | 0                  | High-side gate driver output for the buck half-bridge                                                                                                                                                                                                                                                                         |  |  |  |  |

| НВ1     | 25  | Р                  | Bootstrap supply pin for buck half-bridge. An external capacitor is required between the HB1 pin and the SW1 pin, to provide bias to the high-side MOSFET gate driver. Place the external capacitor close to the pin without any resistance between the pin and capacitor for good decoupling                                 |  |  |  |  |

| NC      | 26  | 0                  | Not Connected                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| LO1     | 27  | 0                  | Low-side gate driver output for the buck half-bridge                                                                                                                                                                                                                                                                          |  |  |  |  |

| PGND    | 28  | G                  | Power Ground                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| VCC2    | 29  | 0                  | Internal linear bias regulator output. Connect a ceramic decoupling capacitor from VCC to PGND. This rail supplies the internal logic and the gate driver.  Place the external capacitor close to the pin without any resistance between the pin and capacitor for good decoupling.                                           |  |  |  |  |

| LO2     | 30  | 0                  | Low-side gate driver output for the boost half-bridge                                                                                                                                                                                                                                                                         |  |  |  |  |

| НВ2     | 31  | Р                  | Bootstrap supply pin for boost half-bridge. An external capacitor is required between the HB2 pin and the SW2 pin, to provide bias to the high-side MOSFET gate driver Place the external capacitor close to the pin without any resistance between the pin and capacitor for good decoupling                                 |  |  |  |  |

| HO2     | 32  | 0                  | High-side gate driver output for the boost half-bridge                                                                                                                                                                                                                                                                        |  |  |  |  |

| SW2     | 33  | Р                  | Inductor switch node for the boost half-bridge                                                                                                                                                                                                                                                                                |  |  |  |  |

| NC      | 34  | 0                  | Not Connected                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| DRV1    | 35  |                    | External FET drive pin. This pin features a high-voltage push pull stage, a open drain output or a charge pump driver stage according to the selected configuration.  In case the optional DRV pin is not used you can leave DRV open.                                                                                        |  |  |  |  |

| VIN     | 36  | I                  | The input supply and sense input of the device. Connect VIN to the supply voltage of the power stage.                                                                                                                                                                                                                         |  |  |  |  |

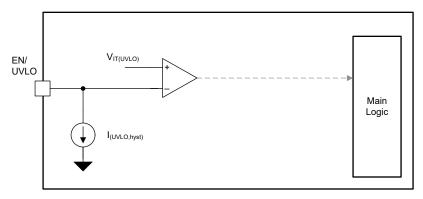

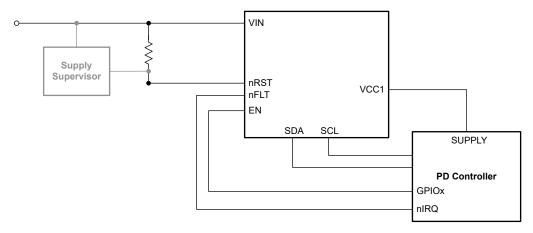

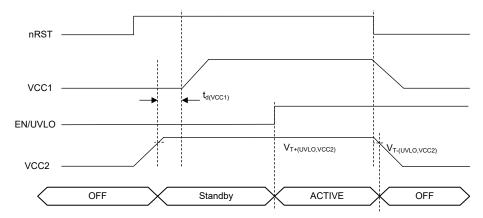

| EN/UVLO | 37  | I                  | Enable pin. Digital input pin to enable the converter switching.  The input features a precise analog comparator and a hysteresis to monitor the input voltage. Connect a resistor divider from the input voltage to maintain the under voltage lookout(UVLO) feature.                                                        |  |  |  |  |

| nRST    | 38  | I                  | Digital input pin to enable the device internal logic, interface operation and the VCC1 regulator if selected.                                                                                                                                                                                                                |  |  |  |  |

| NC      | 39  | 0                  | Not Connected                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

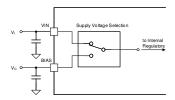

| BIAS    | 40  |                    | Optional input to the VCC2 bias regulator. Powering VCC2 from an external supply instead of VIN can reduce power loss at high $V_{\rm IN}$ .                                                                                                                                                                                  |  |  |  |  |

| GND     | PAD | G                  | Thermal pad                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

1. I = Input, O = Output, I/O = Input or Output, G = Ground, P = Power.

## **6 Specifications**

## **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise specified)(1)

|              |                                                              | MIN  | MAX                                   | UNIT |

|--------------|--------------------------------------------------------------|------|---------------------------------------|------|

| Input        | BIAS to AGND                                                 | -0.3 | 48                                    | V    |

| Input        | VIN, ISNSP, ISNSN to AGND                                    | -0.3 | 48                                    | V    |

| Input        | ENUM O PROT                                                  | -0.3 | 48 (4)                                | V    |

| Input        | EN/UVLO, nRST                                                | -0.3 | V <sub>(VIN)</sub> + 5 <sup>(4)</sup> |      |

| Input        | SS/ATRK, DTRK, RT, SYNC, MODE, SDA, SCL, ADDR, CFG2, to AGND | -0.3 | 5.8                                   | V    |

| Input        | FB                                                           | -0.3 | 5.8                                   | V    |

| Input        | CSA, CSB to SW1                                              | -0.3 | 0.3                                   | V    |

| Input        | SW1 to AGND(DC)                                              | -0.5 | 48                                    | V    |

| Input        |                                                              |      | 59                                    | V    |

| Input        |                                                              |      | 48                                    | V    |

| Input        |                                                              |      | 59                                    | V    |

| Input        | SW1 to AGND(≤ 10ns duration)                                 | -3   | 48                                    | V    |

| Input        | SW2 to AGND(≤ 10ns duration)                                 | -3   | 59                                    | V    |

| Input        | SW1 to AGND(≤ 5ns duration)                                  | -4   | 48                                    | V    |

| Input        | SW2 to AGND(≤ 5ns duration)                                  | -4   | 59                                    | V    |

| Input        | PGND to AGND                                                 | -0.3 | 0.3                                   | V    |

| Output       | VCC1, VCC2 to AGND                                           | -0.3 | 5.5                                   | V    |

| Output       | VOUT, DRV1 to AGND                                           | -0.3 | 59                                    | V    |

| Output       | nFLT to AGND                                                 | -0.3 | 5.8                                   | V    |

| Output       | COMP, ILIMCOMP, CDC to AGND <sup>(2)</sup>                   | -0.3 | 5.8                                   | V    |

| Output       | LO1, LO2, to PGND                                            | -0.3 | V <sub>(VCC2)</sub> +0.3              | V    |

| Output       | HB1 to SW1, HB2 to SW2                                       | -0.3 | 5.5 <sup>(5)</sup>                    | V    |

| Output       | HBT to SW1, HBZ to SWZ                                       | -0.3 | 6                                     | V    |

| Output       | HO1 to SW1                                                   | -0.3 | V <sub>(HB1)</sub> +0.3               | V    |

| Output       | HO2 to SW2                                                   | -0.3 | V <sub>(HB2)</sub> +0.3               | V    |

| Output       | HO1, HO2, HB1, HB2 to AGND                                   | -0.3 | 65                                    | V    |

| Storage tem  | perature, T <sub>STG</sub>                                   | -55  | 150                                   | °C   |

| Operating ju | nction temperature, T <sub>J</sub> <sup>(3)</sup>            | -40  | 150                                   | C    |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

<sup>(2)</sup> This pin has an internal max voltage clamp which can handle up to 1.6mA.

<sup>(3)</sup> High junction temperatures degrade operating lifetimes. Operating lifetime is de-rated for junction temperatures greater than 125°C.

<sup>(4)</sup> Both of the stated conditios need to be observed

<sup>(5)</sup> Operating lifetime is de-rated for voltage bigger than the specified maximum

## **6.2 Handling Ratings**

|                    |                                            |                                                         |             | VALUE | UNIT |

|--------------------|--------------------------------------------|---------------------------------------------------------|-------------|-------|------|

|                    | ( <sub>(ESD)</sub> Electrostatic discharge | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup> |             | ±2000 |      |

| V <sub>(ESD)</sub> |                                            | Charged device model (CDM), per                         | Corner pins | ±750  | V    |

|                    |                                            | AEC Q100-011                                            | Other pins  | ±500  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## **6.3 Recommended Operating Conditions**

Over the recommended operating junction temperature range (unless otherwise specified)(1)

|                     |                                                   | MIN | NOM | MAX                 | UNIT |

|---------------------|---------------------------------------------------|-----|-----|---------------------|------|

| V <sub>(VIN)</sub>  | Input Voltage Sense                               | 3.5 | 20  | 36                  | V    |

| V <sub>(BIAS)</sub> | Bias Input Voltage Supply                         | 0   |     | 36                  | V    |

|                     | Input/Bias start-up voltage                       | 3.5 |     |                     | V    |

| V <sub>(VOUT)</sub> | Output Voltage Sense                              | 1   |     | 55                  | V    |

| V <sub>(DRV1)</sub> | High voltage drive pin output                     | 0   |     | 55                  | V    |

|                     | ISNSP;ISNSN                                       | 2.8 |     | 55                  | V    |

| V <sub>(BIAS)</sub> | current limit sense resistor                      |     | 10  |                     | mΩ   |

|                     | current limit sense resistor tolerance            | -1  |     | 1                   | %    |

| C <sub>(VCC1)</sub> | VCC1 regulator output capacitance                 | 2   |     |                     | μF   |

| C <sub>(VCC2)</sub> | VCC2 regulator output capacitance                 | 6   |     |                     | μF   |

|                     | External gate resistance on LOx, HOx              |     | 2.2 |                     | Ω    |

| V <sub>FB</sub>     | FB Input                                          | 0   |     | V <sub>(VCC2)</sub> | V    |

| V <sub>IL</sub>     | Logic pin low-level (MODE, DTRK, SYNC, SDA, SCL)  |     |     | 0.4                 | V    |

| V <sub>IH</sub>     | Logic pin high-level (MODE, DTRK, SYNC, SDA, SCL) | 1.3 |     |                     | V    |

| F <sub>SW</sub>     | Typical Switching Frequency                       | 100 |     | 600                 | kHz  |

| F <sub>SYNC</sub>   | Synchronization switching Frequency range         | 100 |     | 600                 | kHz  |

| TJ                  | Operating Junction Temperature <sup>(2)</sup>     | 0   |     | 70                  | °C   |

<sup>(1)</sup> Operating Ratings are conditions under the device is intended to be functional. For specifications and test conditions, see ElectricalCharacteristics.

#### **6.4 Thermal Information**

|                       | Junction-to-case (top) thermal resistance  Junction-to-board thermal resistance  Junction-to-top characterization parameter  Junction-to-board characterization parameter | LM251772 |      |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|

|                       |                                                                                                                                                                           | QFN      | UNIT |

|                       |                                                                                                                                                                           | 40 PINS  |      |

| R <sub>qJA</sub>      | Junction-to-ambient thermal resistance                                                                                                                                    | 33.9     | °C/W |

| R <sub>qJC(top)</sub> | Junction-to-case (top) thermal resistance                                                                                                                                 | 26.6     | °C/W |

| $R_{qJB}$             | Junction-to-board thermal resistance                                                                                                                                      | 15.4     | °C/W |

| $Y_{JT}$              | Junction-to-top characterization parameter                                                                                                                                | 0.4      | °C/W |

| $Y_{JB}$              | Junction-to-board characterization parameter                                                                                                                              | 15.4     | °C/W |

| R <sub>qJC(bot)</sub> | Junction-to-case (bottom) thermal resistance                                                                                                                              | 4.4      | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Product Folder Links: LM251772

資料に関するフィードバック (ご意見やお問い合わせ) を送信

Copyright © 2025 Texas Instruments Incorporated

<sup>(2)</sup> High junction temperatures degrade operating lifetimes.

## **6.5 Electrical Characteristics**

Typical values correspond to  $T_J=25$ °C. Minimum and maximum limits apply over  $T_J=0$ °C to 70°C. Unless otherwise stated,

| V <sub>(BIAS)</sub> =12         | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                               |                                                              | MIN  | TYP  | MAX  | UNIT |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------|------|------|------|------|

| SUPPLY CU                       | IRRENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                               |                                                              |      |      |      |      |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V = 36 V V = 0                                                                | T <sub>J</sub> = 25°C                                        |      | 3.6  | 4.7  | μA   |

|                                 | Shutdown current into VIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $V_{(VIN)} = 36 \text{ V}, V_{(BIAS)} = 0$<br>V $V_{(EN)} = 0 \text{ V}$      | T <sub>J</sub> = 0°C to 70°C                                 |      | 3.6  | 7.5  | •    |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                               | T <sub>J</sub> = 25°C                                        |      | 2.8  | 4.7  |      |

|                                 | Shutdown current into BIAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $V_{(VIN)} = 0 V, V_{(EN)} = 0 V$                                             | T <sub>J</sub> = 0°C to 70°C                                 |      | 2.8  | 6    |      |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V = 12 V. V = 0                                                               | T <sub>J</sub> = 25°C                                        |      | 55   | 75   |      |

|                                 | Stand-by current into VIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $V_{(VIN)} = 12 \text{ V}, \ V_{(BIAS)} = 0$<br>V; $V_{(nRST)} = \text{High}$ | $T_{.1} = T_{.1} = 0^{\circ}\text{C to } 70^{\circ}\text{C}$ |      | 55   | 100  |      |

|                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | V <sub>(EN)</sub> = 3.3 V, V <sub>(FB)</sub> > 1 V, uSleep                    | 0 0                                                          |      | 65   | 75   |      |

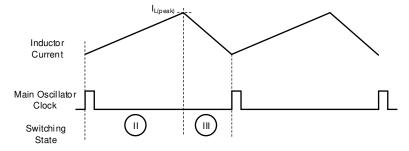

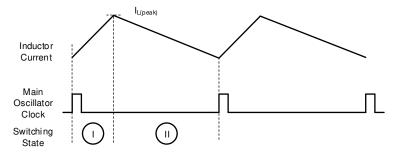

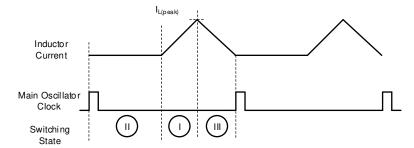

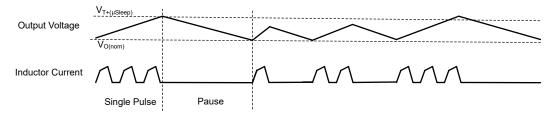

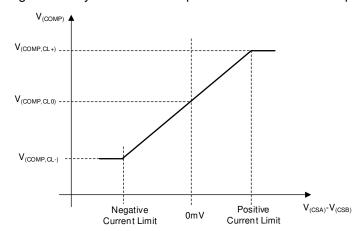

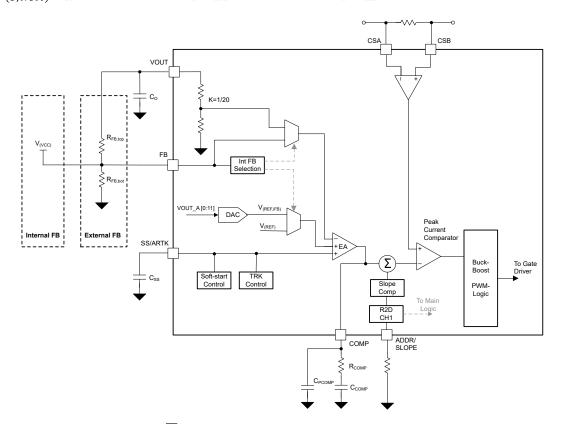

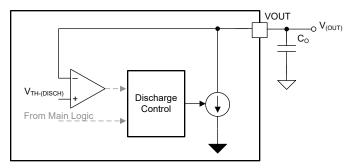

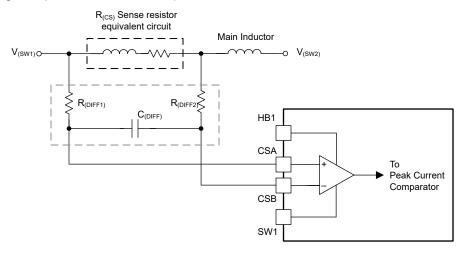

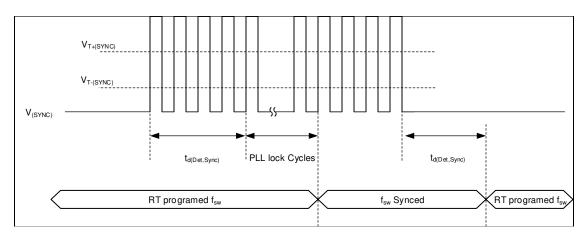

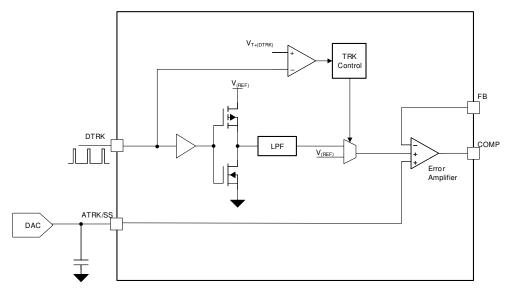

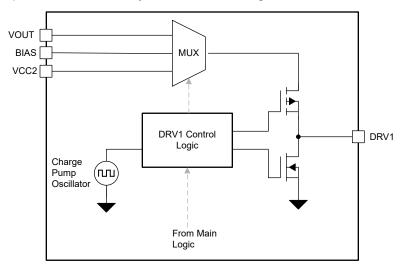

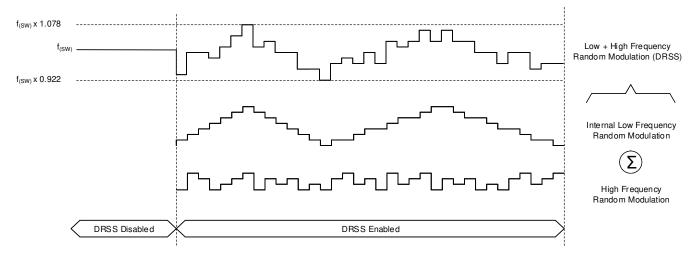

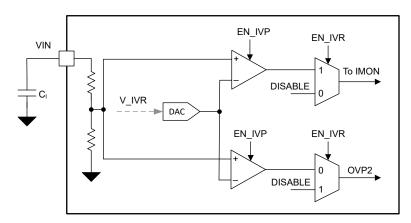

|                                 | Quiescent current into BIAS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | enabled, ILIMCOMP = V <sub>(</sub><br><sub>VCC2)</sub> , EN_VCC1 = 0b0        | T <sub>J</sub> = 0°C to 70°C                                 |      | 65   | 100  | μΑ   |