INA302, INA303

JAJSCZ9C - SEPTEMBER 2016 - REVISED MARCH 2019

# INA30x 36V、過電流保護、高精度 電流センス・アンプ、デュアル・コンパレータ内蔵

# 1 特長

- 広い同相入力電圧範囲:-0.1V~+36V

- デュアル・コンパレータ出力

- INA302:2 つの独立した制限超過アラート

- INA303:ウィンドウ・コンパレータ

- スレッショルド・レベルは個別に設定

- コンパレータ 1 のアラート応答: 1µs

- コンパレータ 2 は遅延を調整可能:2µs~10s

- 独立したラッチ制御モードによるオープン・ドレイン 出力

#### 高精度アンプ

- オフセット電圧:30µV (最大値、A3 バージョン)

- オフセット電圧ドリフト: 0.5µV/°C (最大値)

- ゲイン誤差:0.15% (最大値、A3 バージョン)

- ゲイン誤差ドリフト:10ppm/°C

- アンプ・ゲインを選択可能

- INA302A1, INA303A1:20V/V

- INA302A2、INA303A2:50V/V

- INA302A3、INA303A3:100V/V

# 2 アプリケーション

- 過電流保護

- モータ制御

- 電源保護

- コンピュータとサーバー

- 通信機器

# 3 概要

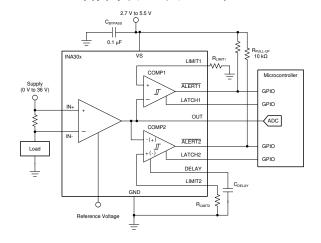

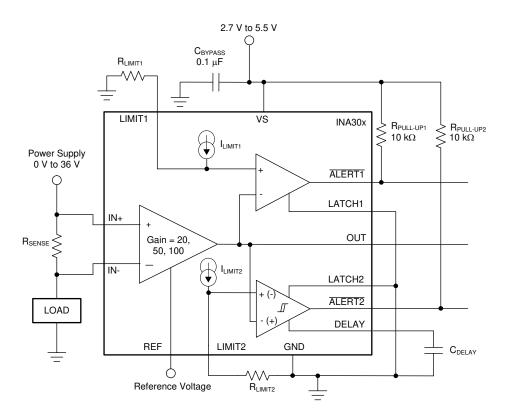

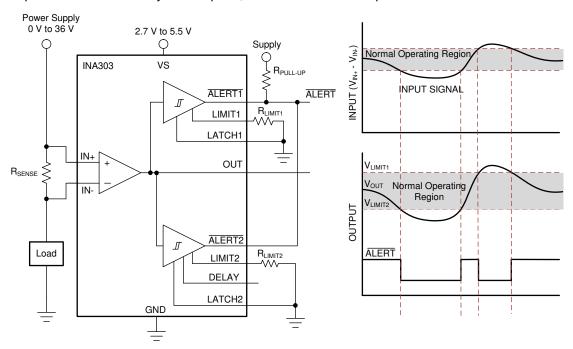

INA302 および INA303 (INA30x) デバイスは、範囲外電流条件を検出するために高コモンモード双方向電流センス・アンプと 2 つの高速コンパレータを備えています。

INA302 コンパレータは、過電流条件を検出し応答するように構成されています。INA303 コンパレータは、ウィンドウ構成で過電流と低電流の両方の条件に応答するように構成されています。これらのデバイスは、外付けの抵抗を使用して、各コンパレータ・セットについてスレッショルド範囲を設定可能です。これらの電流シャント・モニタは、電源電圧にかかわらず、-0.1V~36V の同相電圧上の差動電圧信号を測定できます。

オープン・ドレインのアラート出力は、透過モード (出力ステータスが入力状態に従う) またはラッチ・モード (ラッチがリセットされるとアラート出力がクリアされる) で動作するよう構成できます。 コンパレータ 1 のアラート応答時間は 1 μs 未満であり、コンパレータ 2 のアラート応答は外付けコンデンサにより 2 μs~10s の範囲に設定できます。

# 製品情報

| Security in |            |                 |  |  |  |  |  |  |

|-------------|------------|-----------------|--|--|--|--|--|--|

| 型番          | パッケージ      | 本体サイズ(公称)       |  |  |  |  |  |  |

| INA302      | TSSOP (14) | 4 40mm = 5 00mm |  |  |  |  |  |  |

| INA303      | 13307 (14) | 4.40mm×5.00mm   |  |  |  |  |  |  |

(1) 提供されているすべてのパッケージについては、データシートの末 尾にあるパッケージ・オプションについての付録を参照してくださ い。

# 代表的なアプリケーション

| ·— |

|----|

|    |

|    |

| 1 | 特長1                                  |    | 8.4 Device Functional Modes    | 22              |

|---|--------------------------------------|----|--------------------------------|-----------------|

| 2 | アプリケーション1                            | 9  | Application and Implementation | 24              |

| 3 | 概要1                                  |    | 9.1 Application Information    | 24              |

| 4 | 改訂履歴                                 |    | 9.2 Typical Application        | 30              |

| 5 | 概要(続き)3                              | 10 | Power Supply Recommendations   | 32              |

| 6 | Pin Configuration and Functions      | 11 | Layout                         | 32              |

| 7 | Specifications                       |    | 11.1 Layout Guidelines         | 32              |

| • | 7.1 Absolute Maximum Ratings 5       |    | 11.2 Layout Example            | 33              |

|   | 7.2 ESD Ratings                      | 12 | デバイスおよびドキュメントのサポート             | 34              |

|   | 7.3 Recommended Operating Conditions |    | 12.1 ドキュメントのサポート               | 34              |

|   | 7.4 Thermal Information 5            |    | 12.2 関連リンク                     | 34              |

|   | 7.5 Electrical Characteristics       |    | 12.3 ドキュメントの更新通知を受け取る方法        | 34              |

|   | 7.6 Typical Characteristics 8        |    | 12.4 コミュニティ・リソース               | 34              |

| 8 | Detailed Description                 |    | 12.5 商標                        | 34              |

| • | 8.1 Overview                         |    | 12.6 静電気放電に関する注意事項             | 34              |

|   | 8.2 Functional Block Diagram         |    | 12.7 Glossary                  | <mark>34</mark> |

|   | 8.3 Feature Description              | 13 | メカニカル、パッケージ、および注文情報            | 34              |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

# 5 概要(続き)

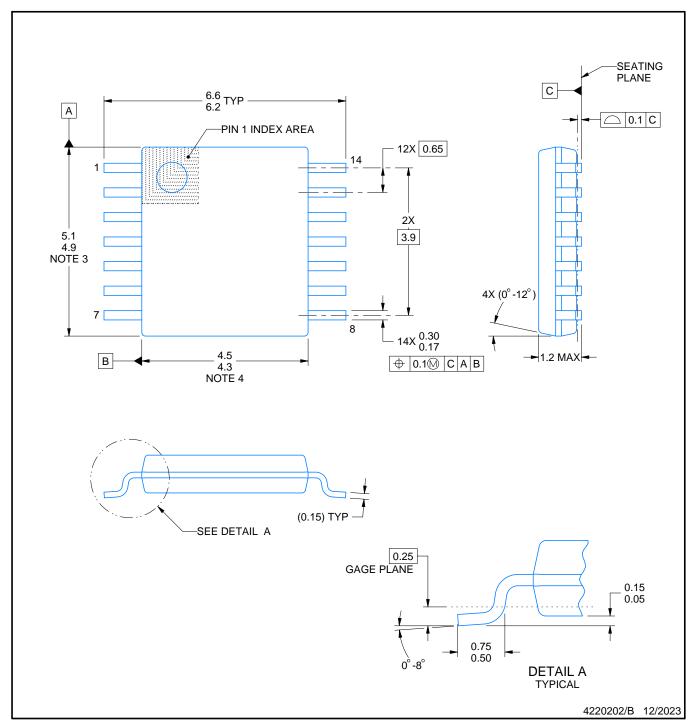

これらのデバイスは 2.7V~5.5V の単一電源で動作し、最大消費電流は 950μA です。これらのデバイスは、拡張温度範囲の -40°C~+125°C で動作が規定されており、14 ピンの TSSOP パッケージで供給されます。

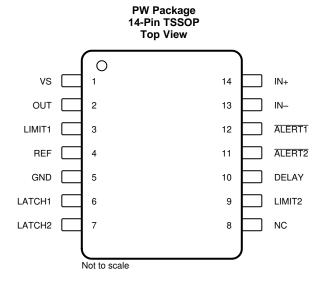

# 6 Pin Configuration and Functions

#### **Pin Functions**

| PIN |        | TVDE          | DECODIOTION                                                                                                                 |  |  |

|-----|--------|---------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | NAME   | TYPE          | DESCRIPTION                                                                                                                 |  |  |

| 1   | VS     | Analog        | Power supply, 2.7 V to 5.5 V                                                                                                |  |  |

| 2   | OUT    | Analog output | Output voltage                                                                                                              |  |  |

| 3   | LIMIT1 | Analog input  | ALERT1 threshold limit input; see the Setting Alert Thresholds section for details on setting the limit threshold           |  |  |

| 4   | REF    | Analog input  | Reference voltage, 0 V to VS                                                                                                |  |  |

| 5   | GND    | Analog        | Ground                                                                                                                      |  |  |

| 6   | LATCH1 | Digital input | Transparent or latch mode selection input                                                                                   |  |  |

| 7   | LATCH2 | Digital input | Transparent or latch mode selection input                                                                                   |  |  |

| 8   | NC     | _             | No internal connection                                                                                                      |  |  |

| 9   | LIMIT2 | Analog input  | ALERT2 threshold limit input; see the Setting Alert Thresholds section for details on setting the limit threshold           |  |  |

| 10  | DELAY  | Analog input  | Delay timing input; see the <i>Alert Outputs</i> section for details on setting the delayed alert response for comparator 2 |  |  |

| 11  | ALERT2 | Analog output | Open-drain output; active-low. This pin is an overlimit alert for the INA302 and an underlimit alert for the INA303.        |  |  |

| 12  | ALERT1 | Analog output | Open-drain output, active-low overlimit alert                                                                               |  |  |

| 13  | IN-    | Analog input  | Connect to load side of the current-sensing resistor                                                                        |  |  |

| 14  | IN+    | Analog input  | Connect to supply side of the current-sensing resistor                                                                      |  |  |

# 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                  |                          |                                                                       | MIN       | MAX           | UNIT |

|------------------|--------------------------|-----------------------------------------------------------------------|-----------|---------------|------|

| Vs               | Supply voltage           |                                                                       |           | 6             | V    |

|                  | Analog inputs (IN+, IN-) | Differential (V <sub>IN+</sub> ) – (V <sub>IN-</sub> ) <sup>(2)</sup> | -40       | 40            | V    |

|                  |                          | Common-mode <sup>(3)</sup>                                            | GND - 0.3 | 40            | V    |

| Analog input     |                          | LIMIT1, LIMIT2, DELAY, REF                                            | GND - 0.3 | $(V_S) + 0.3$ | V    |

|                  | Analog output            | OUT                                                                   | GND - 0.3 | $(V_S) + 0.3$ | V    |

|                  | Digital input            | LATCH1, LATCH2                                                        | GND - 0.3 | $(V_S) + 0.3$ | V    |

|                  | Digital output           | ALERT1, ALERT2                                                        | GND - 0.3 | 6             | V    |

| TJ               | Junction temperature     |                                                                       |           | 150           | °C   |

| T <sub>stg</sub> | Storage temperature      |                                                                       | -65       | 150           | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |  |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|--|

|                    | Human-body model (HBM   | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±3000 | 00   |  |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1500 | V    |  |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                | MIN  | NOM | MAX | UNIT |

|----------------|--------------------------------|------|-----|-----|------|

| $V_{CM}$       | Common-mode input voltage      | -0.1 | 12  | 36  | V    |

| Vs             | Operating supply voltage       | 2.7  | 5   | 5.5 | V    |

| T <sub>A</sub> | Operating free-air temperature | -40  |     | 125 | °C   |

# 7.4 Thermal Information

|                      |                                              | INA30x     |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | PW (TSSOP) | UNIT |

|                      |                                              | 14 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 110.2      | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 35.1       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 53.2       | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 2.3        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 52.4       | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | N/A        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup>  $V_{IN+}$  and  $V_{IN-}$  are the voltages at the IN+ and IN- pins, respectively.

<sup>(3)</sup> Input voltage can exceed the voltage shown without causing damage to the device if the current at that pin is limited to 5 mA.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 7.5 Electrical Characteristics

at  $T_A = 25$ °C,  $V_{SENSE} = 0$  V,  $V_{REF} = V_S$  / 2,  $V_S = 5$  V,  $V_{IN+} = 12$  V,  $V_{LIMIT1} = 3$  V, and  $V_{LIMIT2} = 3$  V (INA302) or 2 V (INA303) (unless otherwise noted)

|                      | PARAMETER                                 | TEST CONDITIONS                                                                                                                 | MIN TYP               | MAX                   | UNIT               |

|----------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|--------------------|

| INPUT                |                                           |                                                                                                                                 |                       |                       |                    |

|                      |                                           | $V_{IN} = V_{IN+} - V_{IN-}, V_{REF} = V_S / 2,$<br>A1 versions                                                                 | 0                     | ±125                  |                    |

| V <sub>IN</sub>      | Differential input voltage range          | $V_{IN} = V_{IN+} - V_{IN-}, V_{REF} = V_S / 2,$<br>A2 versions                                                                 | 0                     | ±50                   | mV                 |

|                      |                                           | $V_{IN} = V_{IN+} - V_{IN-}, V_{REF} = V_S / 2,$<br>A3 versions                                                                 | 0                     | ±25                   |                    |

|                      |                                           | $V_{IN+} = 0 \text{ V to } 36 \text{ V},$<br>$T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ A1 versions}$          | 100 114               |                       |                    |

| CMRR                 | Common-mode rejection ratio               | $V_{\text{IN+}}$ = 0 V to 36 V, $T_{\text{A}}$ = -40°C to +125°C, A2 versions                                                   | 106 118               |                       | dB                 |

|                      |                                           | $V_{IN+} = 0 \text{ V to } 36 \text{ V},$<br>$T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}, \text{ A3 versions}$          | 110 120               |                       |                    |

|                      |                                           | A1 versions                                                                                                                     | ±15                   | ±80                   |                    |

| Vos                  | Offset voltage, RTI <sup>(1)</sup>        | A2 versions                                                                                                                     | ±10                   | ±50                   | μV                 |

|                      |                                           | A3 versions                                                                                                                     | ±5                    | ±30                   |                    |

| dV <sub>OS</sub> /dT | Offset voltage drift, RTI <sup>(1)</sup>  | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                                                            | 0.02                  | 0.25                  | μV/°C              |

| PSRR                 | Power-supply rejection ratio              | $V_S = 2.7 \text{ V to } 5.5 \text{ V}, V_{\text{IN+}} = 12 \text{ V},$<br>$T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ | ±0.3                  | ±5                    | μV/V               |

| I <sub>B</sub>       | Input bias current                        | I <sub>B+</sub> , I <sub>B-</sub>                                                                                               | 115                   |                       | μA                 |

| los                  | Input offset current                      | V <sub>SENSE</sub> = 0 mV                                                                                                       | ±0.01                 |                       | μΑ                 |

| OUTPUT               | ·                                         |                                                                                                                                 |                       |                       |                    |

|                      |                                           | A1 versions                                                                                                                     | 20                    |                       | V/V                |

| G                    | Gain                                      | A2 versions                                                                                                                     | 50                    |                       |                    |

|                      |                                           | A3 versions                                                                                                                     | 100                   |                       |                    |

|                      |                                           | $V_{OUT} = 0.5 \text{ V to } V_{S} - 0.5 \text{ V, A1 versions}$                                                                | ±0.02%                | ±0.075%               |                    |

|                      | Gain error                                | $V_{OUT} = 0.5 \text{ V to } V_{S} - 0.5 \text{ V, A2 versions}$                                                                | ±0.05%                | ±0.1%                 |                    |

|                      | Gaill elloi                               | $V_{OUT} = 0.5 \text{ V to } V_{S} - 0.5 \text{ V, A3 versions}$                                                                | ±0.1%                 | ±0.15%                |                    |

|                      |                                           | $T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}$                                                                    | 3                     | 10                    | ppm/°C             |

|                      | Nonlinearity error                        | $V_{OUT} = 0.5 \text{ V to } V_{S} - 0.5 \text{ V}$                                                                             | ±0.01%                |                       |                    |

|                      | Maximum capacitive load                   | No sustained oscillation                                                                                                        | 500                   |                       | pF                 |

| VOLTAGE              | OUTPUT                                    |                                                                                                                                 |                       |                       |                    |

|                      | Swing to V <sub>S</sub> power-supply rail | $R_L = 10 \text{ k}\Omega \text{ to GND},$<br>$T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                              | $V_{\rm S}-0.05$      | V <sub>S</sub> - 0.1  | V                  |

|                      | Swing to GND                              | $R_L$ = 10 kΩ to GND,<br>$T_A$ = -40°C to +125°C                                                                                | V <sub>GND</sub> + 15 | V <sub>GND</sub> + 30 | mV                 |

| FREQUEN              | CY RESPONSE                               |                                                                                                                                 |                       |                       |                    |

|                      |                                           | A1 versions, C <sub>OUT</sub> = 500 pF                                                                                          | 550                   |                       |                    |

| BW                   | Bandwidth                                 | A2 versions, C <sub>OUT</sub> = 500 pF                                                                                          | 440                   |                       | kHz                |

|                      |                                           | A3 versions, C <sub>OUT</sub> = 500 pF                                                                                          | 400                   |                       |                    |

| SR                   | Slew rate                                 |                                                                                                                                 | 4                     |                       | V/µs               |

| NOISE, RT            | T <sup>(1)</sup>                          |                                                                                                                                 |                       |                       |                    |

|                      | Voltage noise density                     |                                                                                                                                 | 30                    |                       | nV/√ <del>Hz</del> |

<sup>(1)</sup> RTI = referred-to-input.

# **Electrical Characteristics (continued)**

at  $T_A = 25$ °C,  $V_{SENSE} = 0$  V,  $V_{REF} = V_S$  / 2,  $V_S = 5$  V,  $V_{IN+} = 12$  V,  $V_{LIMIT1} = 3$  V, and  $V_{LIMIT2} = 3$  V (INA302) or 2 V (INA303) (unless otherwise noted)

|                     | PARAMETER                                    | TEST CONDITIONS                                                                                 | MIN  | TYP  | MAX  | UNIT |

|---------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------|------|------|------|------|

| COMPAR              | ATOR                                         |                                                                                                 |      |      |      |      |

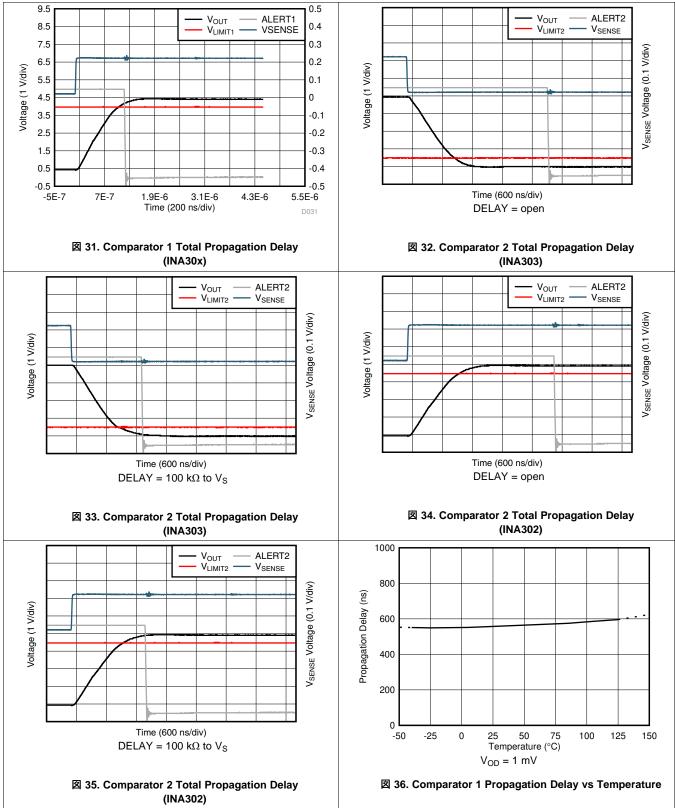

|                     |                                              | Comparator 1, input overdrive = 1 mV                                                            |      | 0.6  | 1    |      |

| t <sub>p</sub>      | Total alert propagation delay                | Comparator 2, input overdrive = 1 mV, delay = $100 \text{ k}\Omega$ to $V_S$                    |      | 1.25 | 2    | μs   |

|                     |                                              | Comparator 1, V <sub>OUT</sub> step = 0.5 V to 4.5 V, V <sub>LIMIT</sub> = 4 V                  |      | 1    | 1.5  |      |

|                     | Slew-rate-limited t <sub>p</sub>             |                                                                                                 |      | 1.5  | 2.5  | μs   |

|                     |                                              |                                                                                                 |      | 1.5  | 2.5  |      |

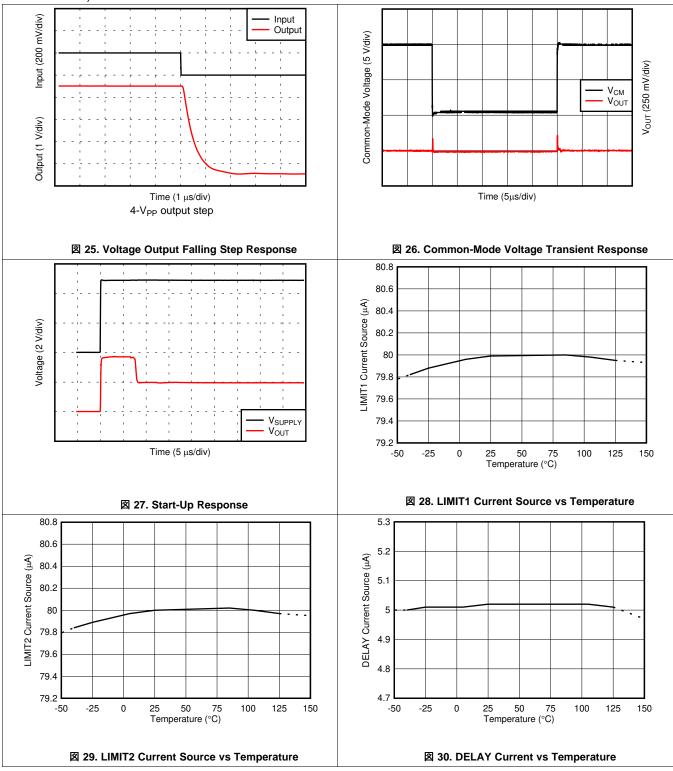

|                     | l in it the near half and a standard and a   | $T_A = 25^{\circ}C, V_{LIMIT1} < V_S - 0.6 V$                                                   | 79.2 | 80   | 80.8 |      |

| I <sub>LIMIT1</sub> | Limit threshold output current, comparator 1 | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C},$ $V_{\text{LIMIT1}} < V_S - 0.6 \text{ V}$ | 78.4 |      | 81.6 | μΑ   |

|                     | Limit threshold output current, comparator 2 | $T_A = 25^{\circ}C, V_{LIMIT2} < V_S - 0.6 V$                                                   | 79.7 | 80   | 80.4 | μА   |

| I <sub>LIMIT2</sub> |                                              | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C},$ $V_{\text{LIMIT2}} < V_S - 0.6 \text{ V}$ | 79.2 |      | 80.8 |      |

|                     | Offset voltage, both comparators             | A1 versions                                                                                     |      | 0.5  | 3.5  |      |

| $V_{OS}$            |                                              | A2 versions                                                                                     |      | 0.5  | 3.5  | mV   |

|                     |                                              | A3 versions                                                                                     |      | 0.5  | 4.0  |      |

| HYS                 | Hysteresis                                   | comparator 1, comparator 2                                                                      |      | 100  |      | mV   |

|                     | Internal programmable delay error            | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                            |      |      | 4%   |      |

| $V_{TH}$            | Delay threshold voltage                      | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                            | 1.21 | 1.22 | 1.23 | V    |

| I <sub>D</sub>      | Delay charging current                       | $T_A = -40^{\circ}\text{C}$ to +125°C, $V_{DELAY} = 0.6 \text{ V}$                              | 4.85 | 5    | 5.15 | μΑ   |

| R <sub>D</sub>      | Delay discharge resistance                   |                                                                                                 |      | 70   |      | Ω    |

| $V_{IH}$            | LATCH1, LATCH2 high-level input voltage      | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                            | 1.4  |      | 6    | V    |

| $V_{IL}$            | LATCH1, LATCH2 low-level input voltage       | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                            | 0    |      | 0.4  | V    |

| V <sub>OL</sub>     | Alert low-level output voltage               | $I_{OL} = 3 \text{ mA}, T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                     |      | 70   | 400  | mV   |

|                     | ALERT1, ALERT2 pin leakage input current     | V <sub>OH</sub> = 3.3 V                                                                         |      | 0.1  | 1    | μА   |

|                     | LATCH1, LATCH2 digital leakage input current | 0 V ≤ V <sub>LATCH1</sub> , V <sub>LATCH2</sub> ≤ V <sub>S</sub>                                |      | 1    |      | μΑ   |

| POWER S             | SUPPLY                                       |                                                                                                 |      |      |      |      |

| Io                  | Quiescent current                            | $T_A = 25^{\circ}C$                                                                             |      | 850  | 950  | μA   |

| 'Q                  | Quiescent current                            | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                                            |      |      | 1150 | μΛ   |

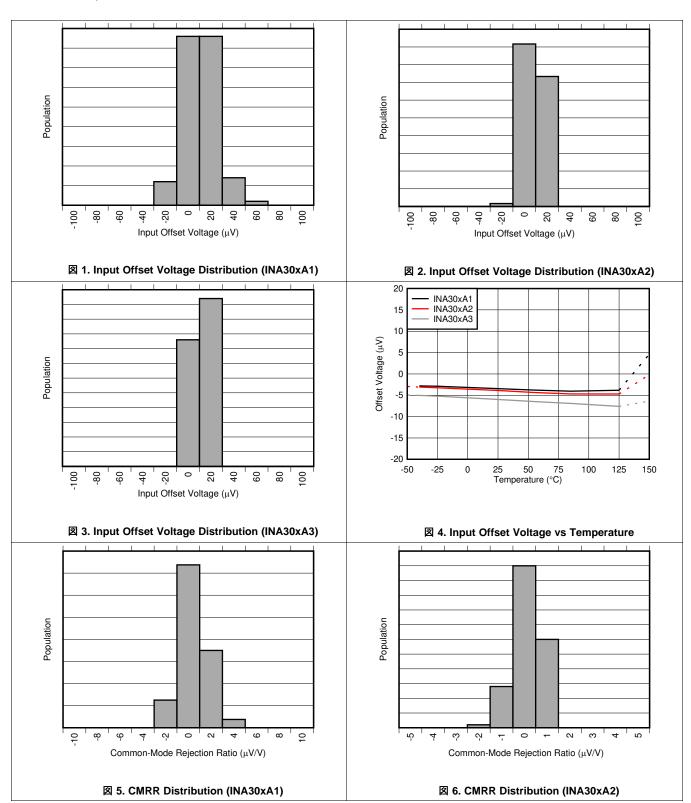

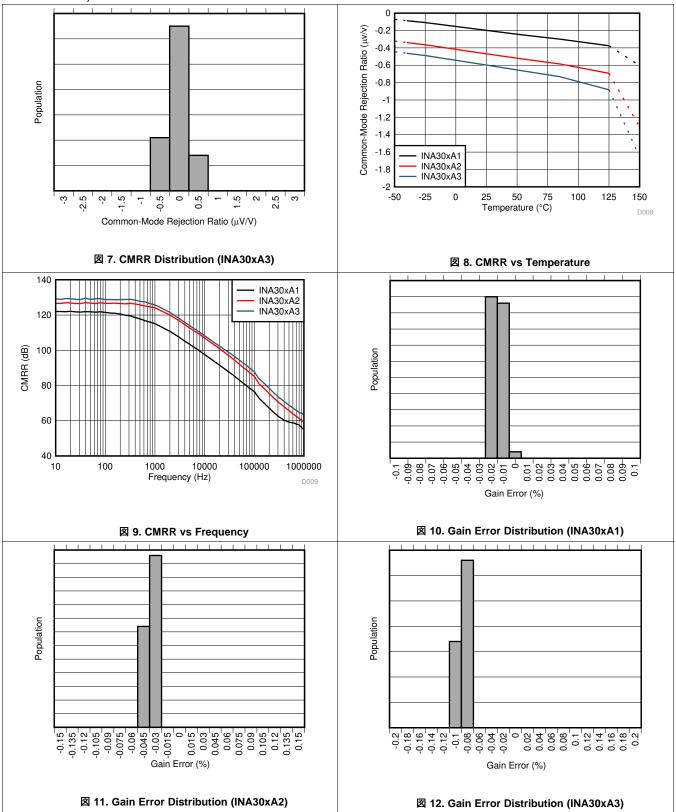

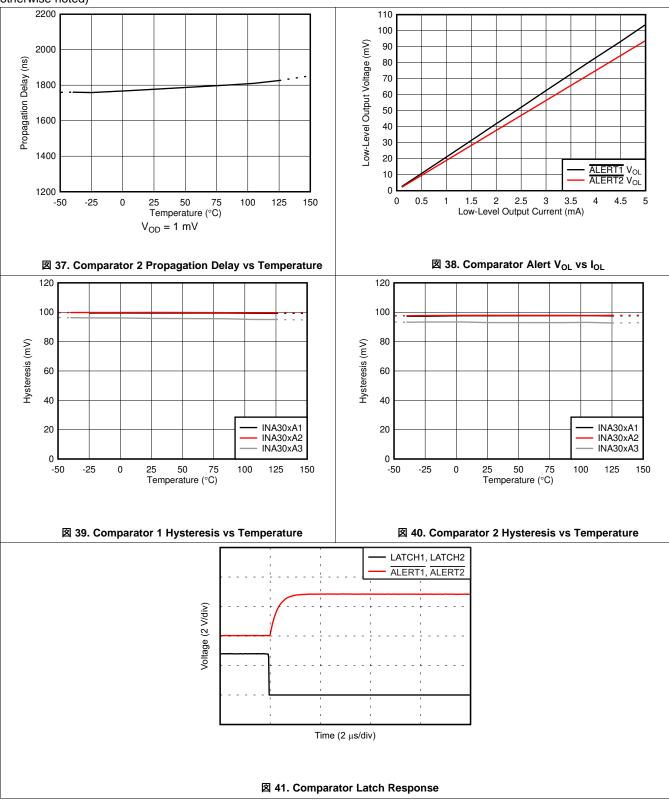

# 7.6 Typical Characteristics

# 8 Detailed Description

#### 8.1 Overview

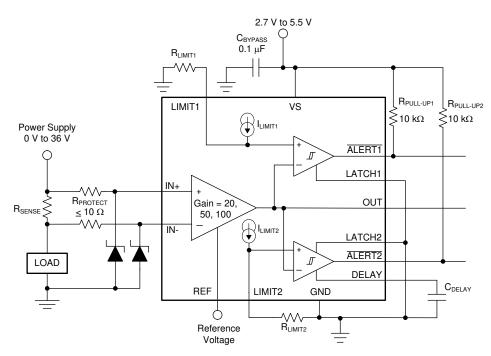

The INA30x feature a zero-drift, 36-V, common-mode, bidirectional, current-sensing amplifier, and two high-speed comparators that can detect multiple out-of-range current conditions. These specially designed, current-sensing amplifiers can be used in both low-side or high-side applications where common-mode voltages far exceed the supply voltage of the device. Currents are measured by accurately sensing voltages developed across current-sensing resistors (also known as *current-shunt resistors*). Current can be measured on input voltage rails as high as 36 V, and the device can be powered from supply voltages as low as 2.7 V.

The zero-drift topology enables high-precision measurements with maximum input offset voltages as low as  $30~\mu\text{V}$  (max) with a temperature contribution of only 0.25  $\mu\text{V}/^{\circ}\text{C}$  (max) over the full temperature range of  $-40^{\circ}\text{C}$  to +125°C. The low total offset voltage of the INA302 enables smaller current-sense resistor values to be used, improving power-efficiency without sacrificing measurement accuracy resulting from the smaller input signal.

Both devices use a single external resistor to set each out-of-range threshold. The INA302 allows for two overcurrent thresholds, and the INA303 allows for both an undercurrent and overcurrent threshold. The response time of the ALERT1 threshold is fixed and is less than 1  $\mu$ s. The response time of the ALERT2 threshold can be set with an external capacitor. The combination of a precision current-sense amplifier with onboard comparators creates a highly-accurate solution that is capable of fast detection of multiple out-of-range conditions. The ability to detect when currents are out-of-range allows the system to take corrective actions to prevent potential component or system-wide damage.

#### 8.2 Functional Block Diagram

(1)

#### 8.3 Feature Description

#### 8.3.1 Bidirectional Current Sensing

The INA30x sense current flow through a sense resistor in both directions. The bidirectional current-sensing capability is achieved by applying a voltage at the REF pin to offset the output voltage. A positive differential voltage sensed at the inputs results in an output voltage that is greater than the applied reference voltage. Likewise, a negative differential voltage at the inputs results in output voltage that is less than the applied reference voltage. The equation for the output voltage of the current-sense amplifier is shown in 式 1.

$$V_{OUT} = (I_{LOAD} \times R_{SENSE} \times GAIN) + V_{REE}$$

#### where

- I<sub>LOAD</sub> is the load current to be monitored.

- R<sub>SENSE</sub> is the current-sense resistor.

- GAIN is the gain option of the device selected.

- V<sub>REF</sub> is the voltage applied to the REF pin.

# 8.3.2 Out-of-Range Detection

The INA303 detects when negative currents are out-of-range by setting a voltage at the LIMIT2 pin that is less than the applied reference voltage. The limit voltage is set with an external resistor or externally driven by a voltage source or digital-to-analog converter (DAC); see the *Setting Alert Thresholds* section for additional information. A typical application using the INA303 to detect negative overcurrent conditions is illustrated in the *Typical Application* section.

#### 8.3.3 Alert Outputs

Both ALERTx pins are active-low, open-drain outputs that pull low when the sensed current is detected to be out of range. Both open-drain ALERTx pins require an external pullup resistor to an external supply. The external supply for the pullup voltage can exceed the supply voltage,  $V_S$ , but is restricted from operating at greater than 5.5 V. The pullup resistance is selected based on the capacitive load and required rise time; however, a  $10\text{-k}\Omega$  resistor value is typically sufficient for most applications. The response time of the ALERT1 output to an out-of-range event is less than 1  $\mu s$ , and the response time of the ALERT2 output is proportional to the value of the external  $C_{DELAY}$  capacitor. The equation to calculate the delay time for the ALERT2 output is given in  $\vec{\pm}$  2:

$$t_{DELAY} = \begin{cases} 1.5 \ \mu s & \text{If DELAY is connected to VS with } 100 \ k\Omega \\ \\ \frac{C_{DELAY} \times V_{TH}}{I_D} + 2.5 \ \mu s & \text{If } C_{DELAY} \ge 47 \ pF \end{cases}$$

#### where

- C<sub>DELAY</sub> is the external delay capacitor.

- V<sub>TH</sub> is the delay threshold voltage.

- I<sub>D</sub> is the DELAY pin current for comparator 2.

For example, if a delay time of 10  $\mu$ s is desired, the calculated value for  $C_{DELAY}$  is 492 pF. The closest standard capacitor value to the calculated value is 500 pF. If a delay time greater than 2.5  $\mu$ s on the  $\overline{ALERT2}$  output is not needed, the  $C_{DELAY}$  capacitor can be omitted. To achieve minimum delay on the  $\overline{ALERT2}$  output, connect a 100-k $\Omega$  resistor from the  $\overline{DELAY}$  pin to the VS pin. Both comparators in the INA30x have hysteresis to avoid oscillations in the  $\overline{ALERTx}$  outputs. The effect hysteresis has on the comparator behavior is described in the *Hysteresis* section.

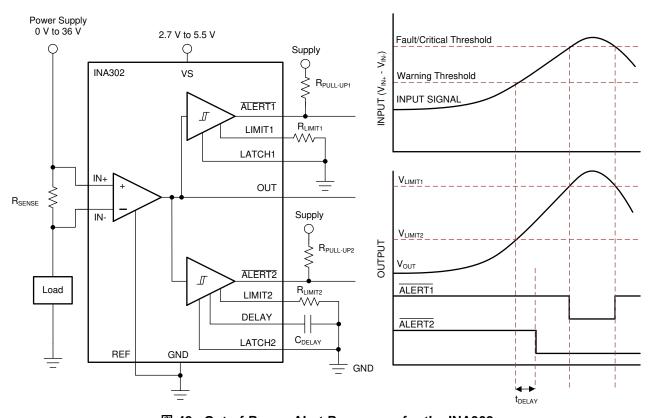

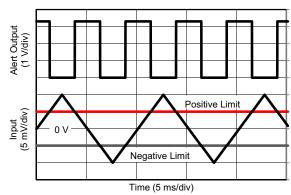

№ 42 shows the alert output response of the internal comparators for the INA302. When the output voltage of the current-sense amplifier is less than the voltage developed on either limit pin, both ALERTx outputs are in the default high state. When the current sense amplifier output is greater than the threshold voltage set by the LIMIT2 pin, the ALERT2 output pulls low after a delay time set by the external delay capacitor. The lower overcurrent threshold is commonly referred to as the overcurrent warning threshold. If the current continues to rise until the current-sense amplifier output voltage exceeds the threshold voltage set at the LIMIT1 pin, then the ALERT1 output becomes active and immediately pulls low. The low voltage on ALERT1 indicates that the measured signal at the amplifier input has exceeded the programmed threshold level, indicating an overcurrent condition has occurred. The upper threshold is commonly referred to as the fault or system critical threshold. Systems often initiate protection procedures (such as a system shutdown) when the current exceeds this threshold.

図 42. Out-of-Range Alert Responses for the INA302

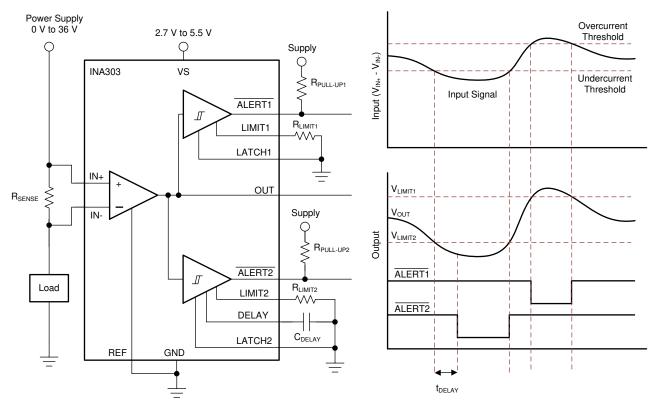

$\boxtimes$  43 shows the alert output response of the internal comparators for the INA303. Both  $\overline{\text{ALERTx}}$  outputs are in the default high state when the output voltage of the current-sense amplifier is less than the voltage developed at the LIMIT1 pin and is greater than the voltage developed at the LIMIT2 pin. The  $\overline{\text{ALERT1}}$  output becomes active and pulls low when the current-sense amplifier output voltage exceeds the threshold voltage set at the LIMIT1 pin. The low voltage on  $\overline{\text{ALERT1}}$  indicates that the measured signal at the amplifier input has exceeded the programmed threshold level, indicating an overcurrent or out-of-range condition has occurred. When the current-sense amplifier output is less than the threshold voltage set by the LIMIT2 pin, the  $\overline{\text{ALERT2}}$  output pulls low after the delay time set by the external delay capacitor expires. The delay time for the  $\overline{\text{ALERT2}}$  output is proportional to the value of the external  $C_{\text{DELAY}}$  capacitor, and is calculated by  $\vec{\pm}$  2.

図 43. Out-of-Range Alert Responses for the INA303

₹ 44 shows the alert output response of the INA303 when the two ALERTx pins are connected together. When configured in this manner, the INA303 can provide a single signal to indicate when the sensed current is operating either outside the normal operating bands or within a normal operational window. Both ALERT1 and ALERT2 outputs behave the same in regard to the alert mode. The difference with ALERT2 is that the transition of the output state is delayed by the time set by the external delay capacitor. If the overcurrent or undercurrent event is not present when the delay time expires, ALERT2 does not respond.

図 44. Current Window Comparator Implementation With the INA303

#### 8.3.3.1 Setting Alert Thresholds

The INA30x family of devices determines if an out-of-range event is present by comparing the amplifier output voltage to the voltage at the corresponding LIMITx pin. The threshold voltage for the LIMITx pins can be set using a single external resistor or by connecting an external voltage source to each pin. The INA302 allows setting limits for two overcurrent conditions. Generally, the lower overcurrent threshold is referred to as a *warning limit* and the higher overcurrent threshold is referred to as the *critical* or *fault limit*. The INA303 allows setting thresholds to detect both undercurrent and overcurrent limit conditions.

#### 8.3.3.1.1 Resistor-Controlled Current Limit

The typical approach to set the limit threshold voltage is to connect resistors from the two LIMITx pins to ground. The voltage developed across the  $R_{LIMIT1}$ ,  $R_{LIMIT2}$  resistors represents the desired fault current value at which the corresponding  $\overline{ALERTx}$  pin becomes active. The values for the  $R_{LIMIT1}$ ,  $R_{LIMIT2}$  resistors are calculated using  $\vec{x}$  3:

$$R_{LIMIT} = \frac{\left(I_{TRIP} \times R_{SENSE} \times GAIN\right) + V_{REF}}{I_{LIMIT}}$$

#### where

- I<sub>TRIP</sub> is the desired out-of-range current threshold.

- R<sub>SENSE</sub> is the current-sensing resistor.

- GAIN is the gain option of the device selected.

- V<sub>RFF</sub> is the voltage applied to the REF pin.

- I<sub>LIMIT</sub> is the limit threshold output current for the selected comparator, typically 80 μA.

(3)

#### 注

When solving for the value of  $R_{\text{LIMIT}}$ , the voltage at the corresponding LIMITx pin as determined by the product of  $R_{\text{LIMIT}}$  and  $I_{\text{LIMIT}}$  must not exceed the compliance voltage of  $V_S - 0.6 \text{ V}$ .

#### 8.3.3.1.1.1 Resistor-Controlled Current Limit: Example

For example, if the current level indicating an out-of-range condition ( $I_{TRIP}$ ) is 20 A and the current-sense resistor value ( $R_{SENSE}$ ) is 10 m $\Omega$ , then the input threshold signal is 200 mV. The INA302A1 has a gain of 20, so the resulting output voltage at the 20-A input condition is 4 V at the output of the current-sense amplifier when the REF pin is grounded. The value for  $R_{LIMIT}$  is selected to allow the device to detect this 20-A threshold, indicating that an overcurrent event has occurred. When the INA302 detects this out-of-range condition, the ALERTx pin asserts and pulls low. For this example, the value of  $R_{LIMIT}$  to detect a 4-V level is calculated to be 50 k $\Omega$ .

#### 8.3.3.1.2 Voltage-Source-Controlled Current Limit

The second method for setting the out-of-range threshold is to directly drive the LIMITx pins with a programmable DAC or other external voltage source. The benefit of this method is the ability to adjust the current-limit threshold to account for different threshold voltages used for different system operating conditions. For example, this method can be used in a system with one current-limit threshold level that must be monitored during a power-up sequence, but different threshold levels must be monitored during other system operating modes.

The voltage applied at the LIMITx pins sets the threshold voltage for out-of-range detection. The value of the voltage for a given desired current trip point is calculated using 式 4:

$$V_{SOURCE} = (I_{TRIP} \times R_{SENSE} \times GAIN) + V_{REF}$$

#### where

- ITRIP is the desired out-of-range current threshold.

- R<sub>SENSE</sub> is the current-sensing resistor.

- · GAIN is the gain option of the device selected.

- V<sub>REF</sub> is the voltage applied to the REF pin.

(4)

注

The maximum voltage that can be applied to the LIMIT2 pin is  $V_S - 0.6 \text{ V}$  and the maximum voltage that can be applied to the LIMIT1 pin must not exceed  $V_S$ .

# 8.3.3.2 Hysteresis

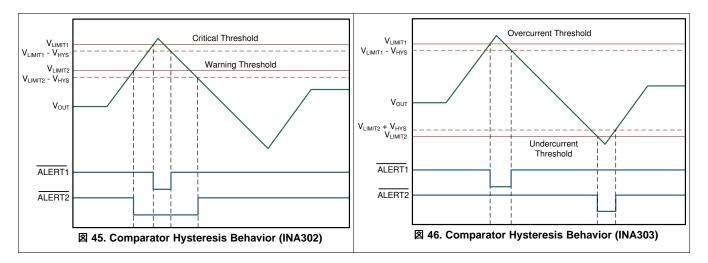

The hysteresis included in the comparators of the INA30x reduces the possibility of oscillations in the alert outputs when the measured signal level is near the overlimit threshold level. For overrange events, the corresponding ALERTx pin is asserted when the output voltage (V<sub>OUT</sub>) exceeds the threshold set at either LIMITx pin. The output voltage must drop to less than the LIMITx pin threshold voltage by the hysteresis value in order for the ALERTx pin to deassert and return to the nominal high state. Likewise for underrange events, the corresponding ALERTx pin is also pulled low when the output voltage drops to less than the threshold set by either LIMITx pin. The ALERTx pin is released when the output voltage of the current-sense amplifier rises to greater than the set threshold plus hysteresis. Hysteresis functionality for both overrange and underrange events is shown in 245 and 46 for the INA302 and INA303, respectively.

#### 8.4 Device Functional Modes

#### 8.4.1 Alert Operating Modes

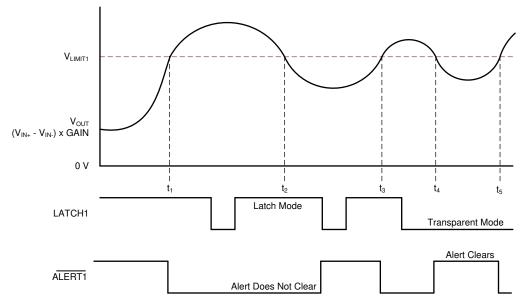

<u>Each comparator</u> has two output operating modes: transparent and latched. These modes determine how the <u>ALERTx</u> pins respond when an out-of-range condition is removed. The device is placed into either transparent or latched state based on the voltage applied to the corresponding LATCHx pin, as shown in 表 1.

### 表 1. Output Mode Settings

| OUTPUT MODE             | LATCHx PINS SETTINGS |

|-------------------------|----------------------|

| ALERTx transparent mode | LATCHx = low         |

| ALERTx latch mode       | LATCHx = high        |

# 8.4.1.1 Transparent Output Mode

The comparators are set to transparent output mode when the corresponding LATCHx pin is pulled low. When set to transparent mode, the output of the comparators changes and follows the input signal with respect to the programmed alert threshold. For example, when the amplifier output violates the set limit value, the ALERTx output pin is pulled low. As soon as the differential input signal drops to less than the alert threshold, the output returns to the default high output state. A common implementation using the device in transparent mode is to connect the ALERTx pins to a hardware interrupt input on a microcontroller. The ALERTx pin is pulled low as soon as an out-of-range condition is detected, thus notifying the microcontroller. The microcontroller immediately reacts to the alert and takes action to address the overcurrent condition. In transparent output mode, there is no need to latch the state of the alert output because the microcontroller responds as soon as the out-of-range condition occurs.

#### 8.4.1.2 Latch Output Mode

The comparators are set to latch output mode when the corresponding LATCHx pin is pulled high. Some applications do not continuously monitor the state of the ALERTx pins as described in the *Transparent Output Mode* section. For example, if the device is set to transparent output mode in an application that only polls the state of the ALERTx pins periodically, then the transition of the ALERTx pins can be missed when the out-of-range condition is not present during one of these periodic polling events. Latch output mode allows the output of the comparators to latch the output of the range condition so that the transition of the ALERTx pins is not missed when the status of the comparator ALERTx pins is polled.

The difference between latch mode and transparent mode is how the alert output responds when an overcurrent condition is removed. In transparent mode (LATCH1, LATCH2 = low), when the differential input signal drops to within normal operating range, the ALERTx pin returns to the default high setting to indicate that the overcurrent event has ended.

In latch mode (LATCHx = high), when an out-of-range condition is detected and the corresponding ALERTx pin is pulled low; the ALERTx pin does not return to the default high state when the out-of-range condition is removed. In order to clear the alert, the corresponding LATCHx pin must be pulled low for at least 100 ns. Pulling the LATCHx pins low allows the corresponding ALERTx pin to return to the default high level, provided the out-of-range condition is no longer present. If the out-of-range condition is still present when the LATCHx pins are pulled low, then the corresponding ALERTx pin remains low. The ALERTx pins can be cleared (reset to high) by toggling the corresponding LATCHx pin when the alert condition is detected by the system controller.

The latch and transparent modes are illustrated in  $\ 2$  47. As illustrated in this figure, at time  $t_1$ , the current-sense amplifier exceeds the limit threshold. During this time the LATCH1 pin is toggled with no affect to the ALERT1 output. The state of the LATCH1 pin only matters when the output of the current-sense amplifier returns to the normal operating region, as shown at  $t_2$ . At this time the LATCH1 pin is high and the overcurrent condition is latched on the ALERT1 output. As shown in the time interval between  $t_2$  and  $t_3$ , the latch condition is cleared when the LATCHx pin is pulled low. At time  $t_4$ , the LATCH1 pin is already pulled low when the amplifier output drops below the limit threshold for the second time. The device is set to transparent mode at this point and the ALERT1 pin is pulled back high as soon as the output of the current-sense amplifier drops below the alert threshold.

図 47. Transparent versus Latch Mode

# 9 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

# 9.1 Application Information

#### 9.1.1 Selecting a Current-Sensing Resistor (R<sub>SENSE</sub>)

Selecting the value of this current-sensing resistor is based primarily on two factors: the required accuracy of the current measurement and the allowable power dissipation across the current-sensing resistor. Larger voltages developed across this resistor allow for more accurate measurements to be made. Amplifiers have fixed internal errors that are largely dominated by the inherent input offset voltage. When the input signal decreases, these fixed internal amplifier errors become a larger portion of the measurement and increase the uncertainty in the measurement accuracy. When the input signal increases, the measurement uncertainty is reduced because the fixed errors are a smaller percentage of the signal being measured. Therefore, the use of larger-value, current-sensing resistors inherently improves measurement accuracy.

However, a system design trade-off must be evaluated through the use of larger input signals for improving measurement accuracy. Increasing the current-sense resistor value results in an increase in power dissipation across the current-sensing resistor. Increasing the value of the current-shunt resistor increases the differential voltage developed across the resistor when current passes through the component. This increase in voltage across the resistor increases the power that the resistor must be able to dissipate. Decreasing the value of the current-shunt resistor value reduces the power dissipation requirements of the resistor, but increases the measurement errors resulting from the decreased input signal. Selecting the optimal value for the shunt resistor requires factoring both the accuracy requirement for the specific application and the allowable power dissipation of this component.

An increasing number of very low ohmic-value resistors are becoming more widely available with values reaching down to 200  $\mu\Omega$  or lower, with power dissipations of up to 5 W that enable large currents to be accurately monitored with sensing resistors.

#### 9.1.1.1 Selecting a Current-Sensing Resistor: Example

In this example, the trade-offs involved in selecting a current-sensing resistor are discussed. This example requires 2.5% accuracy for detecting a 10-A overcurrent event where only 250 mW is allowed for the dissipation across the current-sensing resistor at the full-scale current level. Although the maximum power dissipation is defined as 250 mW, a lower dissipation is preferred to improve system efficiency. Some initial assumptions are made that are used in this example: the limit-setting resistor ( $R_{LIMIT}$ ) is a 1% component, and the maximum tolerance specification for the internal threshold setting current source (1%) is used. Given the total error budget of 2.5%, up to 0.5% of error can be attributed to the measurement error of the device under these conditions.

# **Application Information (continued)**

As shown in  $\frac{1}{8}$  2, the maximum value calculated for the current-sensing resistor with these requirements is 2.5 m $\Omega$ . Although this value satisfies the maximum power dissipation requirement of 250 mW, headroom is available from the 2.5% maximum total overcurrent detection error to reduce the value of the current-sensing resistor and to further reduce power dissipation. Selecting a 1.5-m $\Omega$ , current-sensing resistor value offers a good tradeoff for reducing the power dissipation in this scenario by approximately 40% and stays within the accuracy region.

表 2. Calculating the Current-Sensing Resistor, R<sub>SENSE</sub>

|                            | PARAMETER                            | EQUATION                                                    | VALUE | UNIT |

|----------------------------|--------------------------------------|-------------------------------------------------------------|-------|------|

| DESIGN TARGETS             | 3                                    |                                                             | 1     |      |

| I <sub>MAX</sub>           | Maximum current                      |                                                             | 10    | А    |

| P <sub>D_MAX</sub>         | Maximum allowable power dissipation  |                                                             | 250   | mW   |

|                            | Allowable current threshold accuracy |                                                             | 2.5%  |      |

| DEVICE PARAMET             | TERS                                 |                                                             |       |      |

| V <sub>OS</sub>            | Offset voltage                       |                                                             | 30    | μV   |

| E <sub>G</sub>             | Gain error                           |                                                             | 0.15% |      |

| CALCULATIONS               |                                      |                                                             |       |      |

| R <sub>SENSE_MAX</sub>     | Maximum allowable R <sub>SENSE</sub> | P <sub>D_MAX</sub> / I <sub>MAX</sub> <sup>2</sup>          | 2.5   | mΩ   |

| V <sub>OS_ERROR</sub>      | Initial offset voltage error         | $(V_{OS} / (R_{SENSE\_MAX} \times I_{MAX}) \times 100$      | 0.12% |      |

| ERROR <sub>TOTAL</sub>     | Total measurement error              | $\sqrt{(V_{OS\_ERROR}^2 + E_G^2)}$                          | 0.19% |      |

| ERROR <sub>INITIAL</sub>   | Initial threshold error              | I <sub>LIMIT</sub> tolerance + R <sub>LIMIT</sub> tolerance | 2%    |      |

| ERROR <sub>AVAILABLE</sub> | Maximum allowable measurement error  | Maximum error – ERROR <sub>INITIAL</sub>                    | 1%    |      |

| V <sub>OS_ERROR_MAX</sub>  | Maximum allowable offset error       | $\sqrt{(ERROR_{AVAILABLE}^2 - E_G^2)}$                      | 0.48% |      |

| V <sub>DIFF_MIN</sub>      | Minimum differential voltage         | V <sub>OS</sub> / V <sub>OS_ERROR_MAX</sub> (1%)            | 6.3   | mV   |

| R <sub>SENSE_MIN</sub>     | Minimum sense resistor value         | V <sub>DIFF_MIN</sub> / I <sub>MAX</sub>                    | 0.63  | mΩ   |

| P <sub>D_MIN</sub>         | Lowest-possible power dissipation    | R <sub>SENSE_MIN</sub> × I <sub>MAX</sub> <sup>2</sup>      | 63    | mW   |

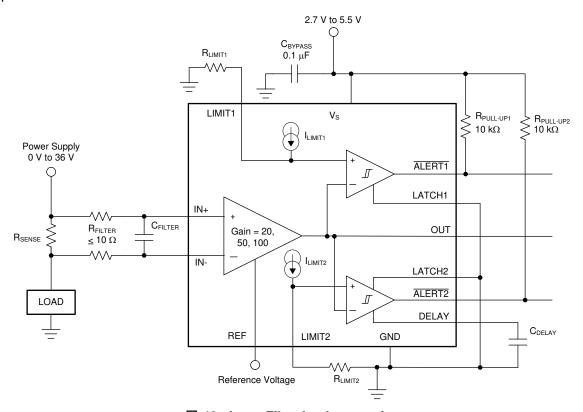

#### 9.1.2 Input Filtering

The integrated comparators in the INA30x are very accurate at detecting out-of-range events because of the low offset voltage; however, noise present at the input of the current-sense amplifier and noise internal to the device can make the offset appear larger than specified. The most obvious effect that external noise can have on the operation of a comparator is to cause a false alert condition. If a comparator detects a large noise transient coupled into the signal, the device can easily falsely interpret this transient as an overrange condition.

External filtering helps reduce the amount of noise that reaches the comparator and reduce the likelihood of a false alert from occurring because of external noise. The trade-off to adding this noise filter is that the alert response time is increased because the input signal and the noise are filtered.

48 shows the implementation of an input filter for the device.

図 48. Input Filter Implementation

Limiting the amount of input resistance used in this filter is important because this resistance can have a significant effect on the input signal that reaches the device input pins by adversely affecting the gain error of the device. A typical system implementation involves placing the current-sensing resistor very near the device so the traces are very short and the trace impedance is very small. This layout helps reduce coupling of additional noise into the measurement. Under these conditions, the characteristics of the input bias currents have minimal effect on device performance.

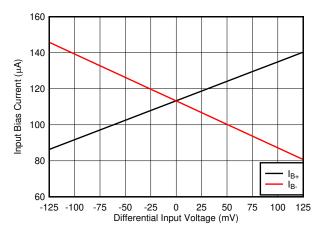

As shown in 249, the input bias currents increase in opposite directions when the differential input voltage increases. This increase results from the design of the device that allows common-mode input voltages to far exceed the device supply voltage range. When input filter resistors are placed in series with the unequal input bias currents, unequal voltage drops are developed across the input resistors. The difference between these two drops appears as an added signal that (in this case) subtracts from the voltage developed across the current-sensing resistor, thus reducing the signal that reaches the device input pins. Smaller-value input resistors reduce this effect of signal attenuation to allow for a more accurate measurement.

☑ 49. Input Bias Current vs Differential Input Voltage

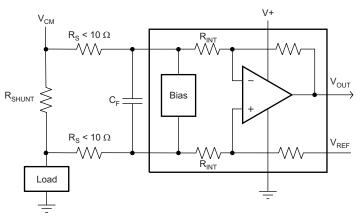

The internal bias network present at the input pins shown in  $\boxtimes$  50 is responsible for the mismatch in input bias currents that is shown in  $\boxtimes$  49. If additional external series filter resistors are added to the circuit, the mismatch in bias currents results in a mismatch of voltage drops across the filter resistors. This mismatch creates a differential error voltage that subtracts from the voltage developed at the shunt resistor. This error results in a voltage at the device input pins that is different than the voltage developed across the shunt resistor. Without the additional series resistance, the mismatch in input bias currents has little effect on device operation. The amount of error these external filter resistors add to the measurement is calculated using  $\vec{\pm}$  6, where the gain error factor is calculated using  $\vec{\pm}$  5.

NOTE: Comparators omitted for simplicity.

図 50. Filter at Input Pins

The amount of variance in the differential voltage present at the device input relative to the voltage developed at the shunt resistor is based both on the external series resistance value as well as the internal input resistors, R3 and R4 (or  $R_{INT}$  as illustrated in  $\boxtimes$  50). The reduction of the shunt voltage reaching the device input pins appears as a gain error when comparing the output voltage relative to the voltage across the shunt resistor. A factor can be calculated to determine the amount of gain error that is introduced by the addition of external series resistance. The equation used to calculate the expected deviation from the shunt voltage to what is measured at the device input pins is given in  $\vec{x}$  5:

Gain Error Factor =

$$\frac{(1250 \times R_{INT})}{(1250 \times R_{S}) + (1250 \times R_{INT}) + (R_{S} \times R_{INT})}$$

#### where

- R<sub>INT</sub> is the internal input resistor (R3 and R4).

- R<sub>S</sub> is the external series resistance.

(5)

With the adjustment factor from  $\pm$  5, including the device internal input resistance, this factor varies with each gain version, as shown in  $\pm$  3. Each individual device gain error factor is shown in  $\pm$  4.

# 表 3. Input Resistance

| PRODUCT  | GAIN | R <sub>INT</sub> (kΩ) |

|----------|------|-----------------------|

| INA30xA1 | 20   | 12.5                  |

| INA30xA2 | 50   | 5                     |

| INA30xA3 | 100  | 2.5                   |

#### 表 4. Device Gain Error Factor

| PRODUCT  | SIMPLIFIED GAIN ERROR FACTOR           |

|----------|----------------------------------------|

| INA30xA1 | $\frac{12,500}{(11\times R_S)+12,500}$ |

| INA30xA2 | $\frac{1000}{R_S + 1000}$              |

| INA30xA3 | $\frac{2500}{(3 \times R_S) + 2500}$   |

The gain error that is expected from the addition of the external series resistors is then calculated based on 式 6:

Gain Error (%) =

$$100 - (100 \times Gain Error Factor)$$

(6)

For example, using an INA302A2 and the corresponding gain error equation from  $\xi$  4, a series resistance of 10  $\Omega$  results in a gain error factor of 0.99. The corresponding gain error is then calculated using  $\sharp$  6, resulting in a gain error of approximately 1% solely because of the external 10- $\Omega$  series resistors.

#### 9.1.3 Using the INA30x With Common-Mode Transients Greater Than 36 V

With a small amount of additional circuitry, these devices can be used in circuits subject to transients higher than 36 V. Use only zener diodes or zener-type transient absorbers (sometimes referred to as *transzorbs*). Any other type of transient absorber has an unacceptable time delay. Start by adding a pair of resistors as a working impedance for the zener diode, as shown in  $\boxtimes$  51. Keep these resistors as small as possible, preferably 10  $\Omega$  or less. Larger values can be used with an additional induced error resulting from a reduced signal that actually reaches the device input pins. Many applications are satisfied with a  $10-\Omega$  resistor along with conventional zener diodes of the lowest power rating available because this circuit limits only short-term transients. This combination uses the least amount of board space. These diodes can be found in packages as small as SOT-523 or SOD-523.

図 51. Transient Protection

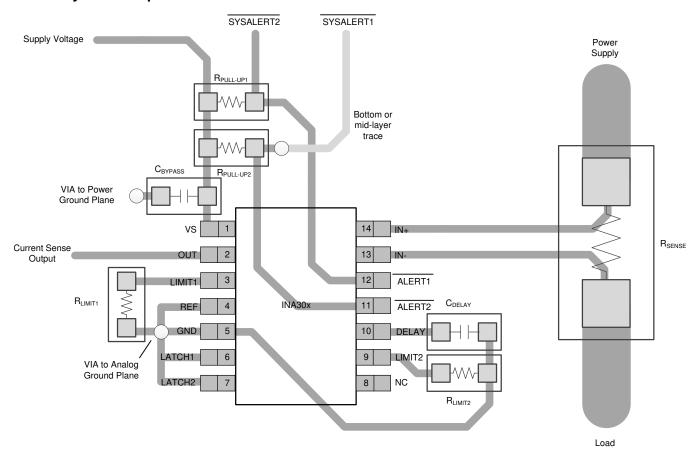

# 9.2 Typical Application

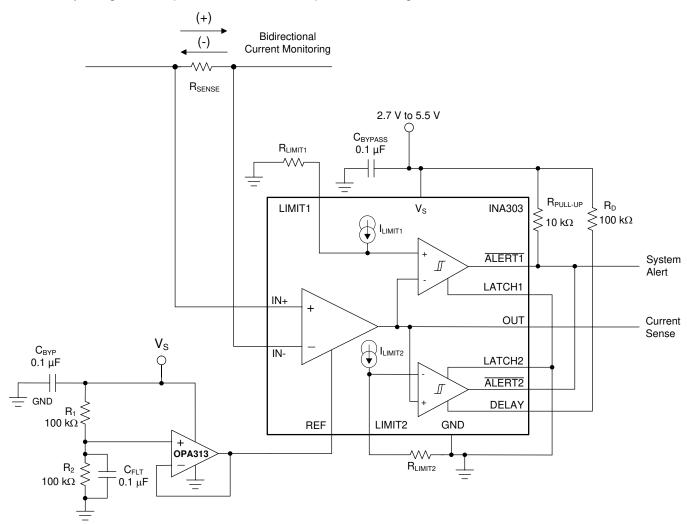

The INA30x are designed to be easily configured for detecting multiple out-of-range current conditions in an application. These devices are capable of monitoring and providing overcurrent detection of bidirectional currents. By using the REF pin of the INA303, both positive and negative overcurrent events can be detected.

# **Typical Application (continued)**

## 9.2.1 Design Requirements

To allow for bidirectional monitoring, the INA303 requires a voltage applied to the REF pin. A voltage that is half of the supply voltage is usually preferred to allow for maximum output swing in both the positive and negative current direction. To reduce the errors in the reference voltage, drive the REF pin with a low-impedance source (such as an op amp or external reference). A low-value resistor divider can be used at the expense of quiescent current and accuracy. For this design, a single alert output is preferred, so both ALERT1 and ALERT2 are connected together and use a single pullup resistor.

#### 9.2.2 Detailed Design Procedure

To achieve bidirectional monitoring, drive the reference pin halfway between the supply with a resistor divider buffered by an op amp, as shown in  $\frac{1}{8}$  5. To reduce the current draw from the supply, use 100-kΩ resistors to create the divide-by-two voltage divider. The TLV313-Q1 is selected to buffer the voltage divider because this device can operate from a single-supply rail with low  $I_Q$  and offset voltage. To minimize the response time of the ALERT2 output, a 100-kΩ pullup resistor was added from the DELAY pin to the VS pin. Select values for  $R_{SENSE}$ ,  $R_{LIMIT2}$ , and  $R_{LIMIT1}$  based on the desired current-sense levels and trip thresholds using the information in the Resistor-Controlled Current Limit and Selecting a Current-Sensing Resistor ( $R_{SENSE}$ ) sections. For this example, the values of  $R_{LIMIT1}$  and  $R_{LIMIT2}$  were selected so that the positive and negative overcurrent thresholds are the same.  $\frac{1}{8}$ 5 shows the alert output of the INA303 application circuit with the capability to detect both positive and negative overcurrent conditions.

表 5. Bidirectional Overcurrent Output Status

| OVERCURRENT PROTECTION (OCP) STATUS   | OUTPUT |

|---------------------------------------|--------|

| Positive overcurrent detection (OCP+) | 0      |

| Negative overcurrent detection (OCP-) | 0      |

| Normal operation (no OCP)             | 1      |

#### 9.2.3 Application Curve

3 shows the INA303 device being used in a bidirectional configuration to detect both negative and positive overcurrent events.

□ 53. Bidirectional Application Curve

# 10 Power Supply Recommendations

The device input circuitry accurately measures signals on common-mode voltages beyond the power-supply voltage,  $V_S$ . For example, the voltage applied to the  $V_S$  power-supply pin can be 5 V, whereas the load power-supply voltage being monitored ( $V_{CM}$ ) can be as high as 36 V. At power-up, for applications where the common-mode voltage ( $V_{CM}$ ) slew rate is greater than 6 V/ $\mu$ s with a final common-mode voltage greater than 20 V, the  $V_S$  supply is recommended to be present before  $V_{CM}$ . If the use case requires  $V_{CM}$  to be present before  $V_S$  with  $V_{CM}$  under these same slewing conditions, then a 331- $\Omega$  resistor must be added between the  $V_S$  supply and the VS pin bypass capacitor.

Power-supply bypass capacitors are required for stability, and must be placed as close as possible to the supply and ground pins of the device. A typical value for this supply bypass capacitor is 0.1 µF. Applications with noisy or high-impedance power supplies may require additional decoupling capacitors to reject power-supply noise.

During slow power-up events, current flow through the sense resistor or voltage applied to the REF pin can result in the output voltage momentarily exceeding the voltage at the LIMITx pins, resulting in an erroneous indication of an out-of-range event on the ALERTx output. When powering the device with a slow ramping power rail where an input signal is already present, all alert indications should be disregarded until the supply voltage has reached the final value.

# 11 Layout

### 11.1 Layout Guidelines

- Apply connections to the current-sense resistor, R<sub>SENSE</sub>, on the inside of the resistor pads to avoid additional

voltage losses incurred by the high current traces to the resistor. Route the traces from the current-sense

resistor symmetrically and side-by-side back to the input of the INA to minimize common-mode errors and

noise pickup.

- Place the power-supply bypass capacitor as closely as possible to the supply and ground pins. The

recommended value of this bypass capacitor is 0.1 µF. Additional decoupling capacitance can be added to

compensate for noisy or high-impedance power supplies.

- Make the connection of R<sub>LIMIT</sub> to the ground pin as direct as possible to limit additional capacitance on this

node. Routing this connection must be limited to the same plane if possible to avoid vias to internal planes. If

the routing can not be made on the same plane and must pass through vias, make sure that a path is routed

from R<sub>LIMIT</sub> back to the ground pin, and that R<sub>LIMIT</sub> is not simply connected directly to a ground plane.

- Routing to the delay capacitor <u>must be</u> short and direct. Keep the routing trace from the DELAY pin to the

delay capacitor away from the <u>ALERT2</u> trace (or any other noisy signals) to minimize any coupling effects. If

no delay capacitor is used do not have any connection to the DELAY pin. Long trace lengths on the DELAY

pin can cause noise to couple to the device, resulting in false trips.

- Pull up the open-drain output pins to the supply voltage rail; a 10-kΩ pullup resistor is recommended.

# 11.2 Layout Example

NOTE: Connect the limit resistors and delay capacitors directly to the GND pin; leave the DELAY pin unconnected or connected to VS through a pullup resistor if no delay is needed.

図 54. Recommended Layout

# 12 デバイスおよびドキュメントのサポート

#### 12.1 ドキュメントのサポート

#### 12.1.1 関連資料

関連資料については、以下を参照してください。

- テキサス・インスツルメンツ、『TLV313-Q1 低消費電力、レール・ツー・レール入出力、オフセット標準値 750μV のオペアンプ』データシート

- テキサス・インスツルメンツ、『電流に関する複数の異常状況の監視』アプリケーション・レポート

#### 12.2 関連リンク

表 6 に、クイック・アクセス・リンクの一覧を示します。カテゴリには、技術資料、サポートおよびコミュニティ・リソース、ツールとソフトウェア、およびご注文へのクイック・アクセスが含まれます。

# 表 6. 関連リンク

| 製品     | プロダクト・フォルダ | ご注文はこちら | 技術資料    | ツールとソフトウェア | サポートとコミュニティ |

|--------|------------|---------|---------|------------|-------------|

| INA302 | ここをクリック    | ここをクリック | ここをクリック | ここをクリック    | ここをクリック     |

| INA303 | ここをクリック    | ここをクリック | ここをクリック | ここをクリック    | ここをクリック     |

## 12.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の「アラートを受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

# 12.4 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E™ Online Community T's Engineer-to-Engineer (E2E) Community. Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

#### 12.5 商標

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

# 12.6 静電気放電に関する注意事項

すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## 12.7 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

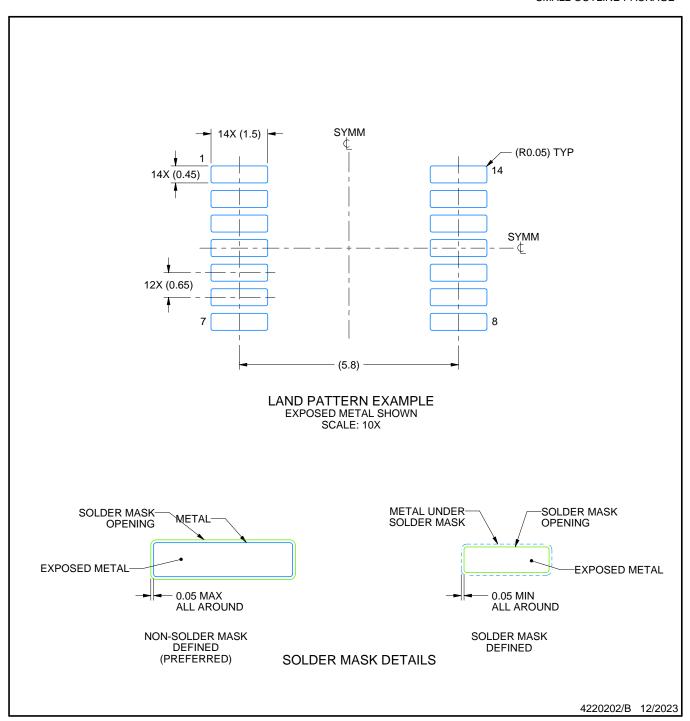

# 13 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。これらの情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあり、ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

www.ti.com

10-Nov-2025

#### **PACKAGING INFORMATION**

| Orderable part number | Status           | Material type | Package   Pins  | Package qty   Carrier | RoHS | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking |

|-----------------------|------------------|---------------|-----------------|-----------------------|------|-------------------------------|----------------------------|--------------|--------------|

|                       |                  |               |                 |                       |      | (4)                           | (5)                        |              |              |

| INA302A1IPW           | Obsolete         | Production    | TSSOP (PW)   14 | -                     | -    | Call TI                       | Call TI                    | -40 to 125   | I302A1       |

| INA302A1IPWR          | Active           | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | I302A1       |

| INA302A1IPWR.B        | Active           | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | I302A1       |

| INA302A1IPWRG4        | Active           | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | I302A1       |

| INA302A1IPWRG4.B      | Active           | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | I302A1       |

| INA302A2IPW           | Last<br>Time Buy | Production    | TSSOP (PW)   14 | 90   TUBE             | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | I302A2       |

| INA302A2IPWR          | Active           | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | I302A2       |

| INA302A2IPWR.B        | Active           | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | I302A2       |

| INA302A2IPWRG4        | Active           | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | I302A2       |

| INA302A2IPWRG4.B      | Active           | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | I302A2       |

| INA302A3IPW           | Last<br>Time Buy | Production    | TSSOP (PW)   14 | 90   TUBE             | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | I302A3       |

| INA302A3IPWR          | Active           | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | I302A3       |

| INA302A3IPWR.B        | Active           | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | I302A3       |

| INA303A1IPW           | Obsolete         | Production    | TSSOP (PW)   14 | -                     | -    | Call TI                       | Call TI                    | -40 to 125   | I303A1       |

| INA303A1IPWR          | Active           | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | I303A1       |

| INA303A1IPWR.B        | Active           | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | I303A1       |

| INA303A2IPW           | Last<br>Time Buy | Production    | TSSOP (PW)   14 | 90   TUBE             | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | I303A2       |

| INA303A2IPWR          | Active           | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | I303A2       |

| INA303A2IPWR.B        | Active           | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | I303A2       |

| INA303A3IPW           | Obsolete         | Production    | TSSOP (PW)   14 | -                     | -    | Call TI                       | Call TI                    | -40 to 125   | I303A3       |

| INA303A3IPWR          | Active           | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | I303A3       |

| INA303A3IPWR.B        | Active           | Production    | TSSOP (PW)   14 | 2000   LARGE T&R      | Yes  | NIPDAU                        | Level-2-260C-1 YEAR        | -40 to 125   | I303A3       |

$<sup>^{(1)}</sup>$  Status: For more details on status, see our product life cycle.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

# PACKAGE OPTION ADDENDUM

www.ti.com 10-Nov-2025

- (3) RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

- (4) Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

- (5) MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

- (6) Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF INA302, INA303:

Automotive: INA302-Q1, INA303-Q1

NOTE: Qualified Version Definitions:

• Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

www.ti.com 25-Jul-2025

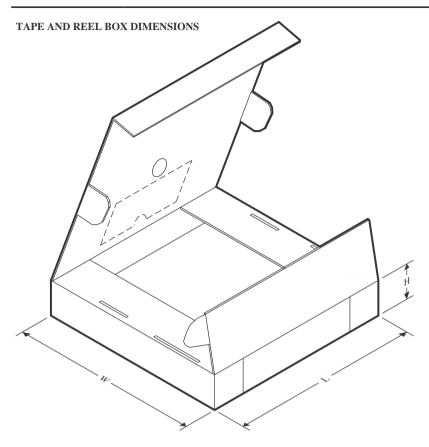

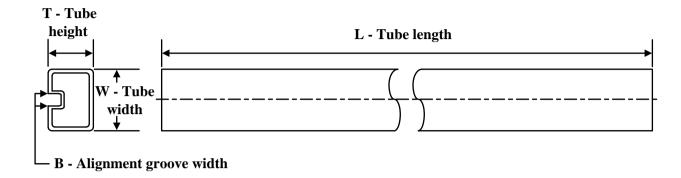

# TAPE AND REEL INFORMATION

# TAPE DIMENSIONS WHO WE PI WHO WE PI WHO WE BO WE Cavity A O WE Cavity

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device         | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| INA302A1IPWR   | TSSOP           | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| INA302A1IPWRG4 | TSSOP           | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| INA302A2IPWR   | TSSOP           | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| INA302A2IPWRG4 | TSSOP           | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| INA302A3IPWR   | TSSOP           | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| INA303A1IPWR   | TSSOP           | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| INA303A2IPWR   | TSSOP           | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| INA303A3IPWR   | TSSOP           | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

www.ti.com 25-Jul-2025

\*All dimensions are nominal

| "All dimensions are nominal |              |                 |      |      |             |            |             |

|-----------------------------|--------------|-----------------|------|------|-------------|------------|-------------|