## INAx133 高速・高精度差動アンプ

### 1 特長

- シングル、デュアルの各バージョン

- 低いオフセット電圧:  $\pm 450\mu\text{V}$  (最大値)

- 低いオフセット電圧ドリフト:  $\pm 5\mu\text{V}/^\circ\text{C}$  (最大値)

- 低ゲイン誤差: 0.05% (最大値)

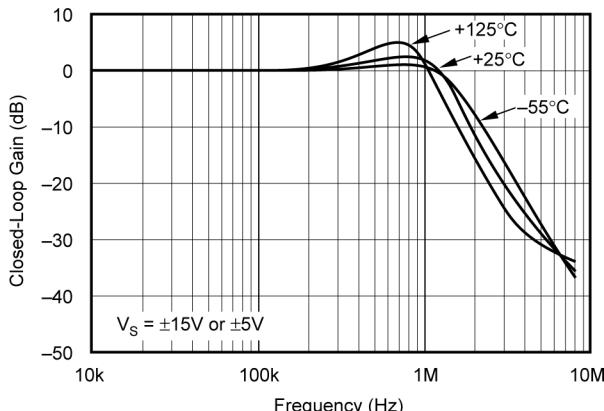

- 広い帯域幅: 1.5MHz

- 高いスルーレート: 5V/ $\mu\text{s}$

- 高速なセトリング タイム: 0.01% まで 5.5 $\mu\text{s}$

- 低い静止電流: 950 $\mu\text{A}$

- 幅広い電源電圧範囲:  $\pm 2.25\text{V}$ ~ $\pm 18\text{V}$

### 2 アプリケーション

- バッテリ セル形成とテスト機器

- センサのタグとデータロガー

- サーボ ドライブ位置フィードバック

- レベルトランスマッタ

- ストリング インバータ

### 3 概要

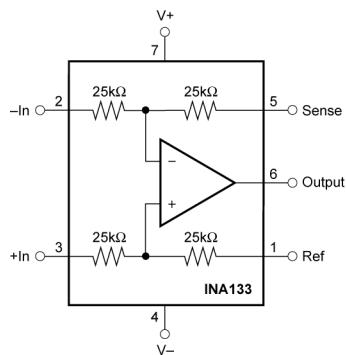

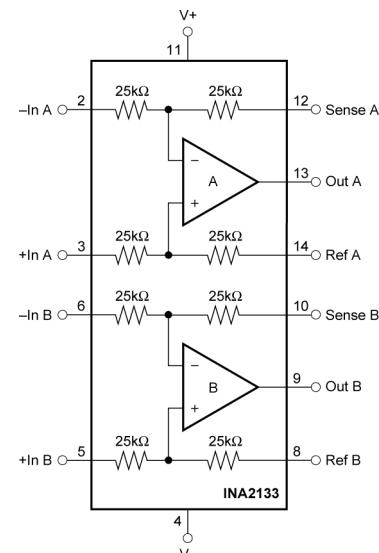

INA133 および INA2133 は、高スルーレートのユニティゲイン差動アンプであり、高精度オペアンプと高精度の抵抗ネットワークで構成されています。レーザ トリミングされたオンチップの抵抗により、高いゲイン精度と高い同相除去比を実現します。これらの抵抗温度係数 (TCR) が小さいため、温度が変化してもゲイン精度と同相モード除去が維持されます。INAx133 は、 $\pm 2.25\text{V}$ ~ $\pm 18\text{V}$  (+4.5V~+36V の単一電源) という幅広い電源範囲で動作し、その入力コモンモード電圧範囲は正および負の電源レールを超えて拡張されています。

差動アンプは、多くの一般的な回路の基礎となるものです。INAx133 は、コスト最適化設計のために、この精密回路機能を提供します。

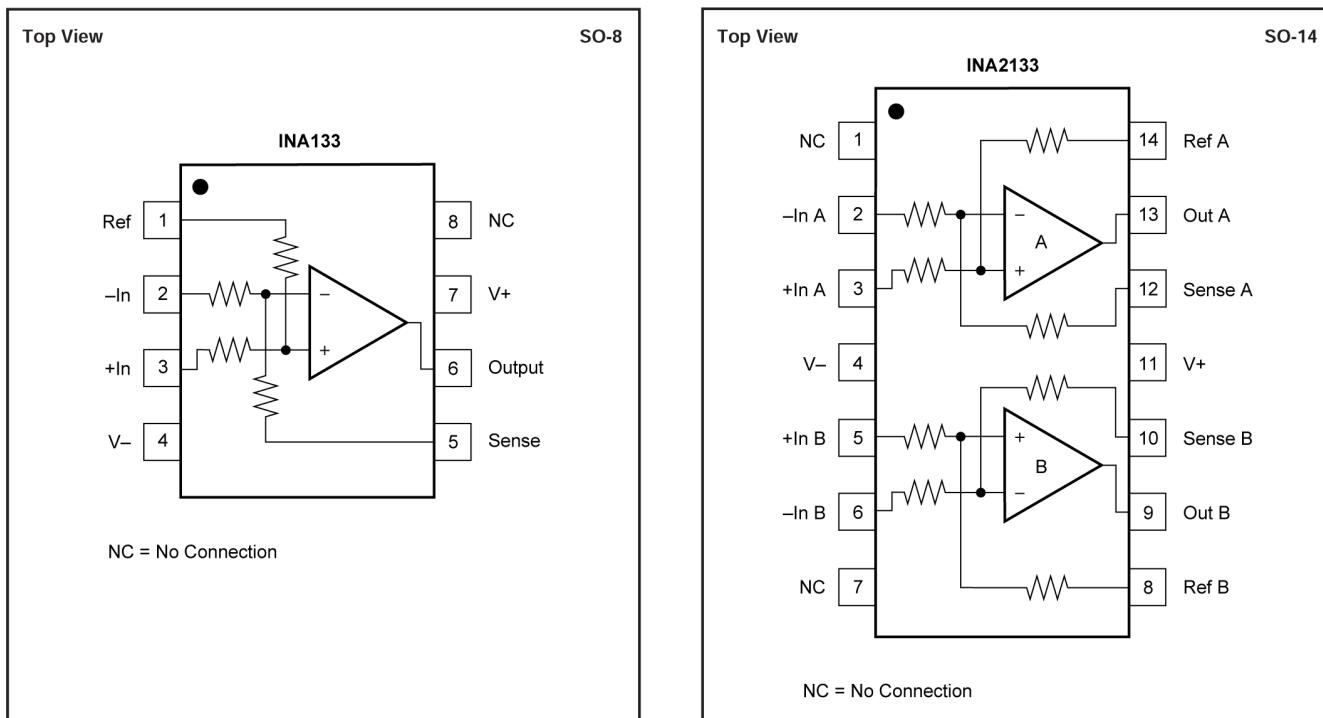

シングル INA133 バージョンは SOIC-8 表面実装パッケージで供給されます。デュアル INA2133 バージョンは SOIC-14 パッケージで供給されます。どちらも  $-40^\circ\text{C}$ ~ $+85^\circ\text{C}$  の産業用温度範囲での動作が規定されています。

#### パッケージ情報

| 部品番号    | パッケージ (1)   | パッケージ サイズ (2)   |

|---------|-------------|-----------------|

| INA133  | D (SOIC、8)  | 4.90mm × 6.00mm |

| INA2133 | D (SOIC、14) | 8.65mm × 6.00mm |

(1) 利用可能なすべてのパッケージについては、[セクション 10](#) の注文情報を参照してください。

(2) パッケージサイズ(長さ×幅)は公称値であり、ピンを含む場合もあります。

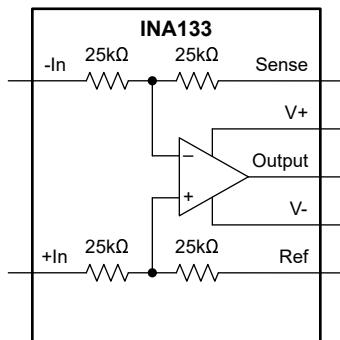

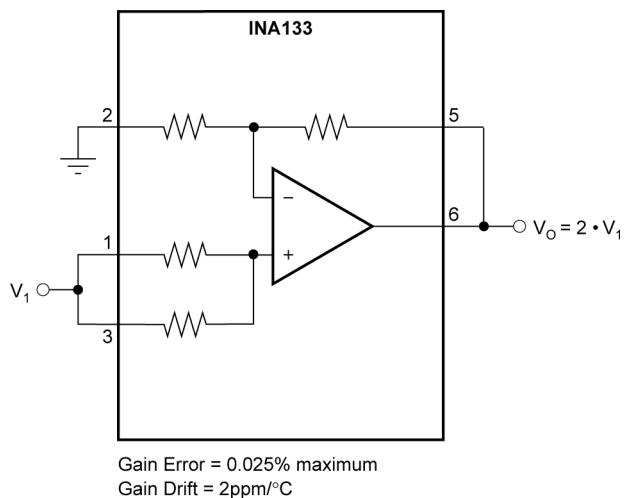

INA133 の内部概略回路図

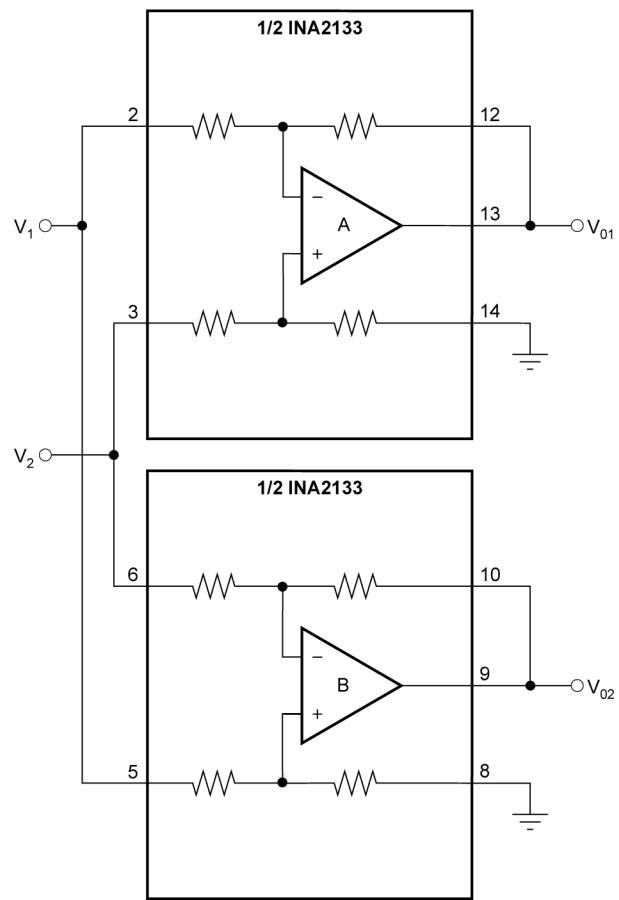

INA2133 の内部概略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、[ti.com](http://ti.com) で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                |    |                        |    |

|----------------|----|------------------------|----|

| 1 特長           | 1  | 7 アプリケーションと実装          | 14 |

| 2 アプリケーション     | 1  | 7.1 アプリケーション情報         | 14 |

| 3 概要           | 1  | 7.2 代表的なアプリケーション       | 15 |

| 4 ピン構成および機能    | 3  | 7.3 追加アプリケーション         | 16 |

| 5 仕様           | 5  | 7.4 電源に関する推奨事項         | 24 |

| 5.1 絶対最大定格     | 5  | 7.5 レイアウト              | 24 |

| 5.2 推奨動作条件     | 5  | 8 デバイスおよびドキュメントのサポート   | 26 |

| 5.3 熱に関する情報    | 5  | 8.1 デバイスサポート           | 26 |

| 5.4 電気的特性      | 6  | 8.2 ドキュメントの更新通知を受け取る方法 | 26 |

| 5.5 代表的特性      | 8  | 8.3 サポート・リソース          | 26 |

| 6 詳細説明         | 12 | 8.4 商標                 | 26 |

| 6.1 概要         | 12 | 8.5 静電気放電に関する注意事項      | 27 |

| 6.2 機能ブロック図    | 12 | 8.6 用語集                | 27 |

| 6.3 機能説明       | 12 | 9 改訂履歴                 | 27 |

| 6.4 デバイスの機能モード | 13 | 10 メカニカル、パッケージ、および注文情報 | 27 |

## 4 ピン構成および機能

表 4-1. ピンの機能 : INA133

| 名称             | 番号 | タイプ | 説明                                                 |

|----------------|----|-----|----------------------------------------------------|

| +In            | 3  | 入力  | 正(非反転)入力 — オペアンプの非反転端子に接続された $25\text{k}\Omega$ 抵抗 |

| -In            | 2  | 入力  | 負(反転)入力 — オペアンプの反転端子に接続された $25\text{k}\Omega$ 抵抗   |

| 出力             | 6  | 出力  | 出力                                                 |

| リファレンス(基準電圧)入力 | 1  | 入力  | 基準電圧入力 — オペアンプの非反転端子に接続された $25\text{k}\Omega$ 抵抗   |

| V+             | 7  | -   | 正(最高)電源                                            |

| V-             | 4  | -   | 負(最低)電源                                            |

| センス            | 5  | 入力  | センス入力 — オペアンプの反転端子に接続された $25\text{k}\Omega$ 抵抗     |

| NC             | 8  | -   | 内部接続なし(フローティングのままでも可)                              |

表 4-2. ピンの機能 : INA2133

| 名称     | 番号 | タイプ | 説明                                                         |

|--------|----|-----|------------------------------------------------------------|

| +In A  | 3  | 入力  | 正(非反転)入力(チャネル A) — オペアンプの非反転端子に接続された $25\text{k}\Omega$ 抵抗 |

| -In A  | 2  | 入力  | 負(反転)入力(チャネル A) — オペアンプの反転端子に接続された $25\text{k}\Omega$ 抵抗   |

| +In B  | 5  | 入力  | 正(非反転)入力(チャネル B) — オペアンプの非反転端子に接続された $25\text{k}\Omega$ 抵抗 |

| -In B  | 6  | 入力  | 負(反転)入力(チャネル B) — オペアンプの反転端子に接続された $25\text{k}\Omega$ 抵抗   |

| Out A  | 13 | 出力  | 出力、チャネル A                                                  |

| Out B  | 9  | 出力  | 出力、チャネル B                                                  |

| 基準電圧 A | 14 | 入力  | 基準入力(チャネル A) — オペアンプの非反転端子に接続された $25\text{k}\Omega$ 抵抗     |

| 参照 B   | 8  | 入力  | 基準入力(チャネル B) — オペアンプの非反転端子に接続された $25\text{k}\Omega$ 抵抗     |

| センス A  | 12 | 入力  | センス入力(チャネル A) — オペアンプの反転端子に接続された $25\text{k}\Omega$ 抵抗     |

| センス B  | 10 | 入力  | センス入力(チャネル B) — オペアンプの反転端子に接続された $25\text{k}\Omega$ 抵抗     |

| V+     | 11 | -   | 正(最高)電源                                                    |

表 4-2. ピンの機能 : INA2133 (続き)

| 名称 | 番号 | タイプ | 説明        |

|----|----|-----|-----------|

| V- | 4  | -   | 負 (最低) 電源 |

## 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                           |                | 最小値 | 最大値            | 単位 |

|---------------------------|----------------|-----|----------------|----|

| 電源電圧、 $V_S = (V+) - (V-)$ |                | 0   | 36             | V  |

| 信号入力ピン                    | 入力ピン           | 0   | $2 \times V_S$ | V  |

|                           | センス、および REF ピン | 0   | $V_S$          |    |

| 出力短絡 <sup>(2)</sup>       |                | 連続  |                |    |

| 温度                        | 動作温度、 $T_A$    | -55 | 125            | °C |

|                           | 接合部、 $T_J$     |     | 150            |    |

|                           | 保存、 $T_{stg}$  | -55 | 125            |    |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗示するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

- (2)  $V_S/2$  に短絡、パッケージあたり 1 チャンネル。

## 5.2 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|      |        | 最小値        | 公称値      | 最大値      | 単位 |

|------|--------|------------|----------|----------|----|

| 電源電圧 | 単一電源   | 4.5        | 30       | 36       | V  |

|      | デュアル電源 | $\pm 2.25$ | $\pm 15$ | $\pm 18$ |    |

| 規定温度 |        | -40        |          | 85       | °C |

## 5.3 热に関する情報

| 熱評価基準 <sup>(1)</sup> |                     | INA133   | INA2133  | 単位   |

|----------------------|---------------------|----------|----------|------|

|                      |                     | 8 ピン     | 14 ピン    |      |

|                      |                     | D (SOIC) | D (SOIC) |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 108.9    | 71.4     | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 45.9     | 33.1     | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 56.6     | 31.2     | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 4.8      | 3.4      | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 55.7     | 30.9     | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 | 該当なし     | 該当なし     | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、[半導体および IC パッケージの熱評価基準 アプリケーション レポート](#)を参照してください。

## 5.4 電気的特性

$T_A = 25^\circ\text{C}$ 、 $V_S = \pm 15\text{V}$ 、 $R_L = 10\text{k}\Omega$ 、グランドに接続、 $V_{\text{REF}} = 0\text{V}$ 、および  $G = 1$  すべてのパッケージと部品のバリエーションに適用されます(特に記載がない限り)。

| パラメータ              |                          | テスト条件                                                                                                                           |                                      | 最小値          | 標準値          | 最大値                          | 単位                             |

|--------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------|--------------|------------------------------|--------------------------------|

| <b>入力</b>          |                          |                                                                                                                                 |                                      |              |              |                              |                                |

| $V_{\text{OS}}$    | オフセット電圧                  | RTO <sup>(1) (2)</sup> 、 $V_{\text{CM}} = 0\text{V}$                                                                            | U型                                   | ±150         | ±450         | $\mu\text{V}$                |                                |

|                    |                          |                                                                                                                                 | UA バリエント                             | ±150         | ±900         | $\mu\text{V}$                |                                |

|                    |                          | RTO <sup>(1) (2)</sup> 、 $V_{\text{CM}} = 0\text{V}$ 、 $V_S = \pm 5\text{V}$                                                    | U型                                   | ±300         | ±750         | $\mu\text{V}$                |                                |

|                    |                          |                                                                                                                                 | UA バリエント                             | ±300         | ±1500        | $\mu\text{V}$                |                                |

|                    | オフセット電圧ドリフト              | RTO <sup>(1) (2)</sup> 、 $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                                       |                                      | ±2           | ±5           | $\mu\text{V}/^\circ\text{C}$ |                                |

|                    |                          |                                                                                                                                 | $V_S = \pm 5\text{V}$                |              | ±2           |                              | $\mu\text{V}/^\circ\text{C}$   |

| PSRR               | 電源除去比                    | RTO <sup>(1) (2)</sup> 、 $V_S = \pm 2.25\text{V} \sim \pm 18\text{V}$                                                           | U型                                   | ±10          | ±30          | $\mu\text{V}/\text{V}$       |                                |

|                    |                          |                                                                                                                                 | UA バリエント                             | 850          | 900          | 950                          | $\mu\text{V}/\text{V}$         |

| 長期安定性              |                          | RTO <sup>(1) (2)</sup>                                                                                                          |                                      |              | 0.3          |                              | $\mu\text{V}/\sqrt{\text{mo}}$ |

| $Z_{\text{IN-DM}}$ | 差動インピーダンス <sup>(3)</sup> |                                                                                                                                 |                                      |              | 50           |                              | $\text{k}\Omega$               |

| $Z_{\text{IN-CM}}$ | 同相インピーダンス <sup>(3)</sup> | $V_{\text{CM}} = 0\text{V}$                                                                                                     |                                      |              | 25           |                              | $\text{k}\Omega$               |

| $V_{\text{CM}}$    | 同相電圧範囲 <sup>(4)</sup>    | $V_O = 0\text{V}$ 、 $V_S = \pm 15\text{V}$ および $V_S = \pm 5\text{V}$                                                            | Positive                             | 2 x (V+) - 3 | 2 x (V+) - 2 |                              | V                              |

|                    |                          |                                                                                                                                 | 負                                    | 2 x (V-) + 3 | 2 x (V-) + 2 |                              | V                              |

| CMRR               | 同相除去比                    | $V_S = \pm 15\text{V}$ および $V_S = \pm 5\text{V}$ 、 $V_{\text{CM}} = 2 \times (V-) + 3 \sim 2 \times (V+) - 3$ 、 $R_S = 0\Omega$ | U型                                   | 80           | 90           |                              | dB                             |

|                    |                          |                                                                                                                                 | UA バリエント                             | 74           | 90           |                              | dB                             |

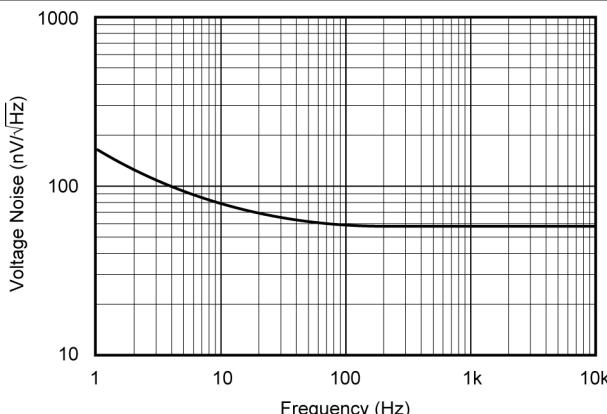

| <b>ノイズ電圧</b>       |                          |                                                                                                                                 |                                      |              |              |                              |                                |

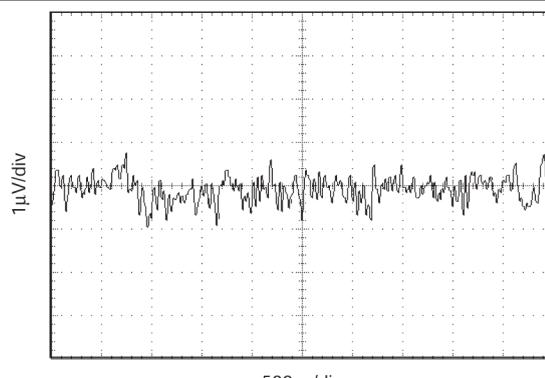

| $e_N$              | 電圧ノイズ                    | RTO <sup>(2) (5)</sup>                                                                                                          | $f = 0.01\text{Hz} \sim 10\text{Hz}$ |              | 2            |                              | $\mu\text{V}_{\text{PP}}$      |

|                    |                          |                                                                                                                                 | $f = 10\text{Hz}$                    |              | 80           |                              | $\text{nV}/\sqrt{\text{Hz}}$   |

|                    |                          |                                                                                                                                 | $f = 100\text{Hz}$                   |              | 60           |                              |                                |

|                    |                          |                                                                                                                                 | $F = 1\text{kHz}$                    |              | 57           |                              |                                |

| <b>ゲイン</b>         |                          |                                                                                                                                 |                                      |              |              |                              |                                |

| G                  | 初期ゲイン                    | $V_S = \pm 15\text{V}$ および $V_S = \pm 5\text{V}$                                                                                |                                      |              | 1            |                              | V/V                            |

| GE                 | ゲイン誤差                    | $V_S = \pm 15\text{V}$ および $V_S = \pm 5\text{V}$ 、 $(V-) + 1\text{V} \leq V_O \leq (V+) - 1.5\text{V}$                          | U型                                   | ±0.02        | ±0.05        |                              | %                              |

|                    |                          |                                                                                                                                 | UA バリエント                             | ±0.02        | ±0.1         |                              |                                |

|                    | ゲインドリフト                  | $T_A = -40^\circ\text{C} \sim +85^\circ\text{C}$                                                                                |                                      |              | ±1           | ±10                          | ppm/°C                         |

|                    |                          |                                                                                                                                 |                                      |              | ±0.0001      | ±0.001                       | FSR の %                        |

|                    |                          |                                                                                                                                 |                                      |              | ±0.0001      | ±0.002                       | FSR の %                        |

| <b>出力</b>          |                          |                                                                                                                                 |                                      |              |              |                              |                                |

| $V_O$              | 出力電圧、ゲイン誤差は 0.1%未満       | 正、 $V_S = \pm 15\text{V}$ 、および $V_S = \pm 5\text{V}$                                                                            | $(V+) - 1.5$                         | $(V+) - 1.3$ |              |                              | V                              |

|                    |                          |                                                                                                                                 | $R_L = 100\text{k}\Omega$            | $(V+) - 0.8$ |              |                              |                                |

|                    |                          | 負、 $V_S = \pm 15\text{V}$ 、および $V_S = \pm 5\text{V}$                                                                            | $(V-) + 1$                           | $(V+) - 0.8$ |              |                              |                                |

|                    |                          |                                                                                                                                 | $R_L = 100\text{k}\Omega$            | $(V-) + 0.3$ |              |                              |                                |

| 容量性負荷(安定動作)        |                          |                                                                                                                                 |                                      |              | 1000         |                              | pF                             |

| $I_{\text{SC}}$    | 短絡電流                     | $V_S/2$ まで連続                                                                                                                    |                                      |              | +32/-25      |                              | mA                             |

$T_A = 25^\circ\text{C}$ 、 $V_S = \pm 15\text{V}$ 、 $R_L = 10\text{k}\Omega$ 、グランドに接続、 $V_{\text{REF}} = 0\text{V}$ 、および  $G = 1$  すべてのパッケージと部品のバリエーションに適用されます(特に記載がない限り)。

| パラメータ          | テスト条件             | 最小値                                                           | 標準値        | 最大値       | 単位               |

|----------------|-------------------|---------------------------------------------------------------|------------|-----------|------------------|

| <b>周波数応答</b>   |                   |                                                               |            |           |                  |

| BW             | 帯域幅、-3dB          |                                                               | 1.5        |           | MHz              |

| SR             | スルーレート            |                                                               | 5          |           | V/ $\mu\text{s}$ |

| t <sub>s</sub> | セトリング時間           | 0.1%、 $V_{\text{STEP}} = 10\text{V}$ 、 $C_L = 100\text{pF}$   | 4          |           | $\mu\text{s}$    |

|                |                   | 0.01%、 $V_{\text{STEP}} = 10\text{V}$ 、 $C_L = 1000\text{pF}$ | 5.5        |           | $\mu\text{s}$    |

|                | 過負荷回復時間           | 50%オーバードライブ                                                   | 4          |           | $\mu\text{s}$    |

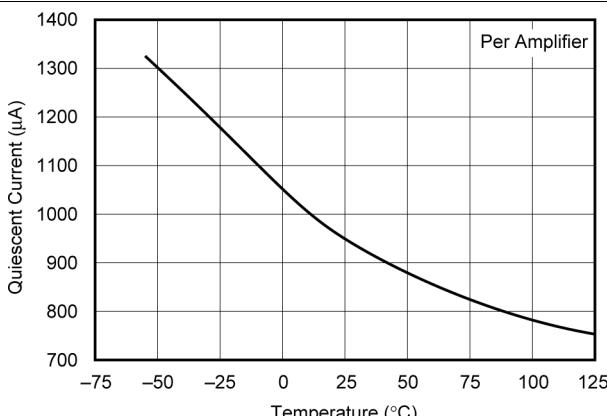

| <b>電源</b>      |                   |                                                               |            |           |                  |

| I <sub>Q</sub> | 静止電流 (アンプ 1 個あたり) | I <sub>O</sub> = 0V                                           | $\pm 0.95$ | $\pm 1.2$ | mA               |

|                |                   | I <sub>O</sub> = 0V、 $V_S = \pm 5\text{V}$                    | $\pm 0.92$ | $\pm 1.2$ | mA               |

- (1) ユニティゲイン差動構成での出力について言及。

- (2) アンプの入力バイアスとオフセット電流の影響を含みます。

- (3) 抵抗値は  $25\text{k}\Omega$  で、比率はマッチングされていますが、絶対値では  $\pm 20\%$  の誤差があります。

- (4) 保護機能なしでの最大入力電圧は、 $\pm 15\text{V}$  電源 ( $\pm 25\text{V}$ ) のいずれかより  $10\text{V}$  高い電圧です。I<sub>IN</sub> を  $1\text{mA}$  に制限。

- (5) アンプの入力電流ノイズと抵抗ネットワークの熱ノイズの影響を含みます。

## 5.5 代表的特性

$T_A = +25^\circ\text{C}$ 、 $V_S = \pm 15\text{V}$ 、 $R_L = 10\text{k}\Omega$ 、グランドに接続、 $V_{\text{REF}} = 0\text{V}$ 、特に記述のない限り

図 5-1. ゲインと周波数との関係

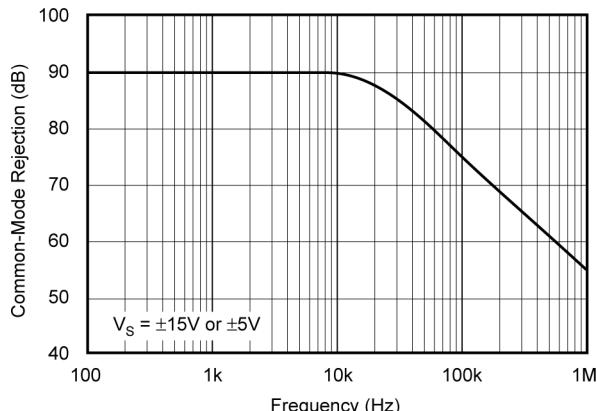

図 5-2. 同相除去比と周波数との関係

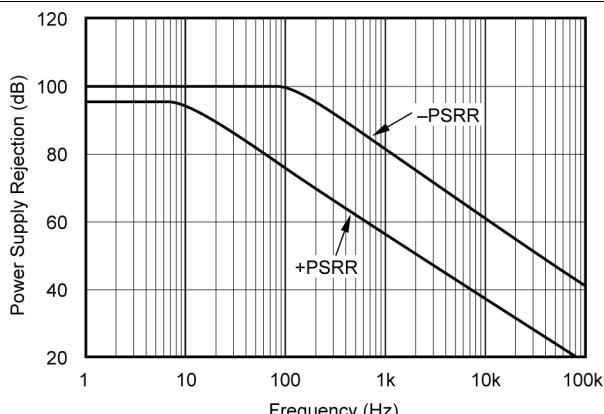

図 5-3. 電源除去特性と周波数の関係

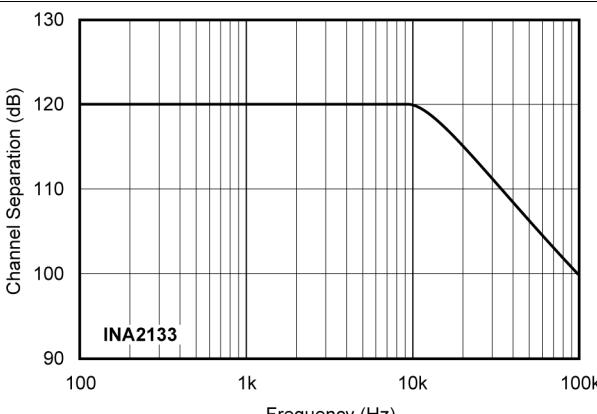

図 5-4. チャネル セパレーションと周波数との関係

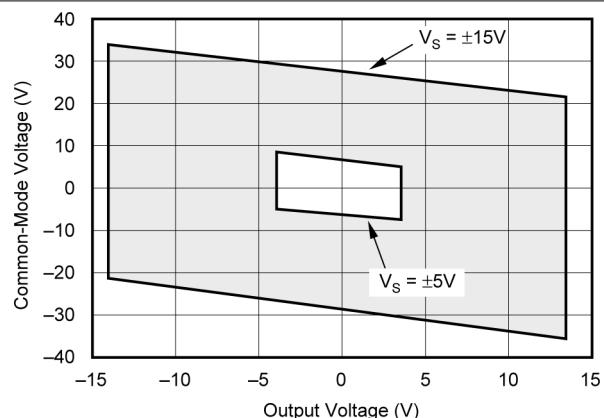

図 5-5. 入力同相電圧と出力電圧との関係

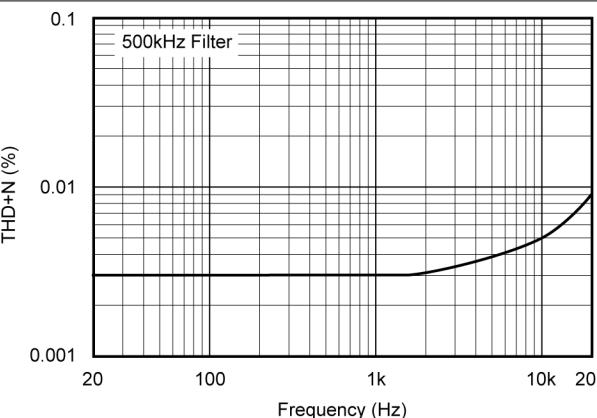

図 5-6. 全高調波歪 + ノイズと周波数との関係

## 5.5 代表的特性 (続き)

$T_A = +25^\circ\text{C}$ ,  $V_S = \pm 15\text{V}$ ,  $R_L = 10\text{k}\Omega$ , グラウンドに接続,  $V_{\text{REF}} = 0\text{V}$ , 特に記述のない限り

図 5-7. 電圧ノイズ密度と周波数との関係

図 5-8. 0.1Hz~10Hz におけるピーク・ツー・ピーク電圧ノイズ

図 5-9. 静止電流と温度との関係

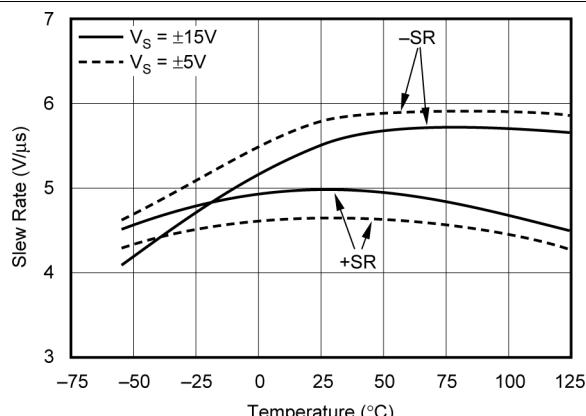

図 5-10. スルーレートと温度との関係

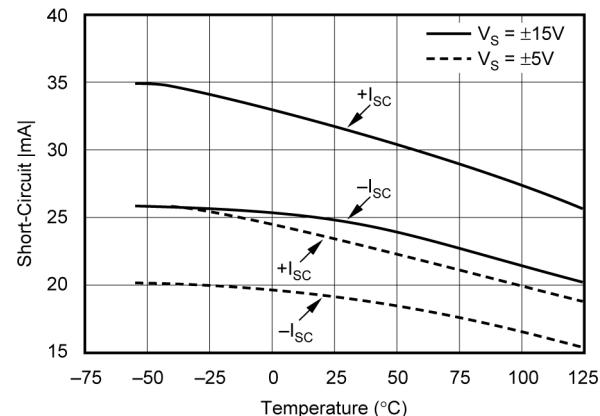

図 5-11. 短絡電流と温度との関係

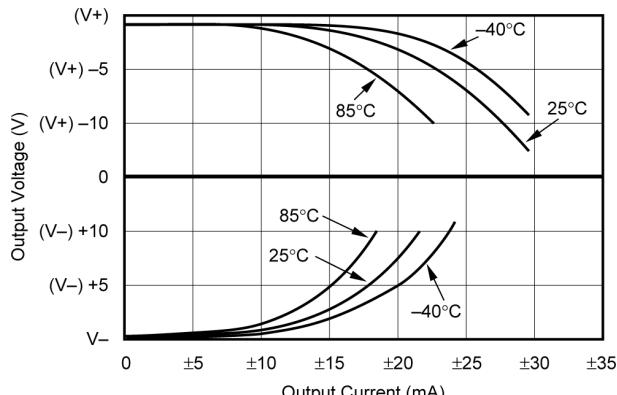

図 5-12. 出力電圧スイングと出力電流との関係

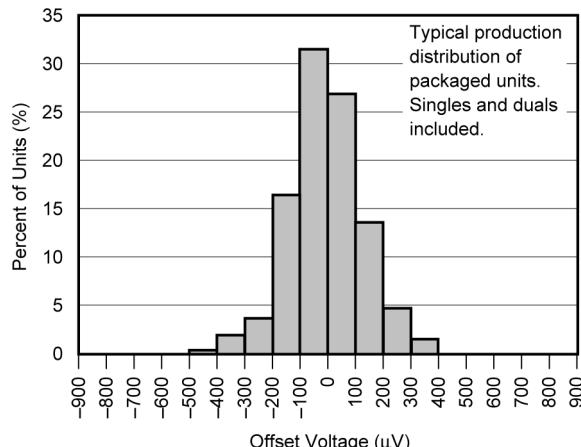

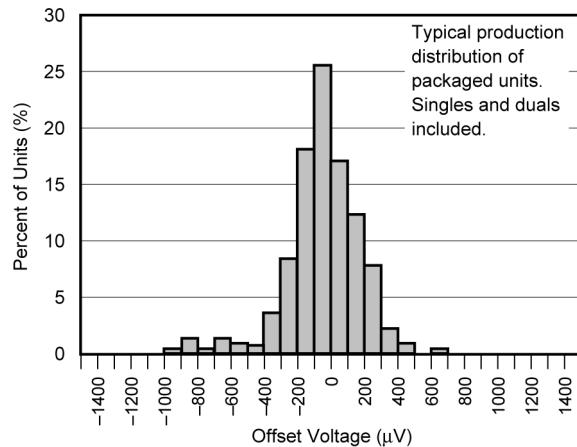

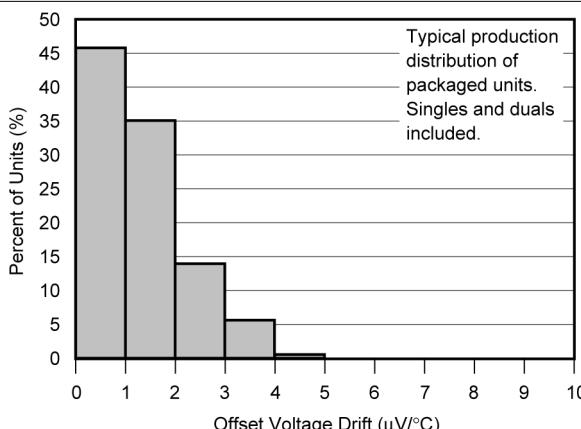

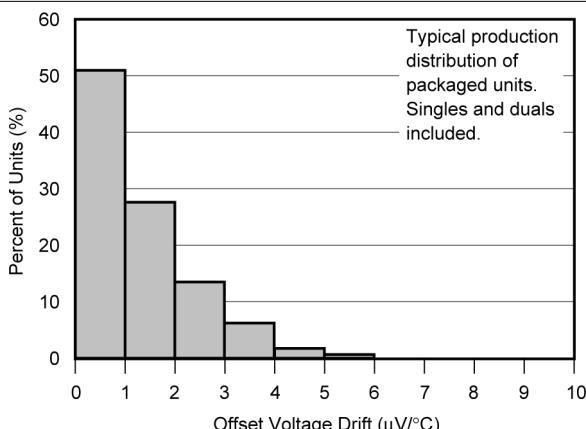

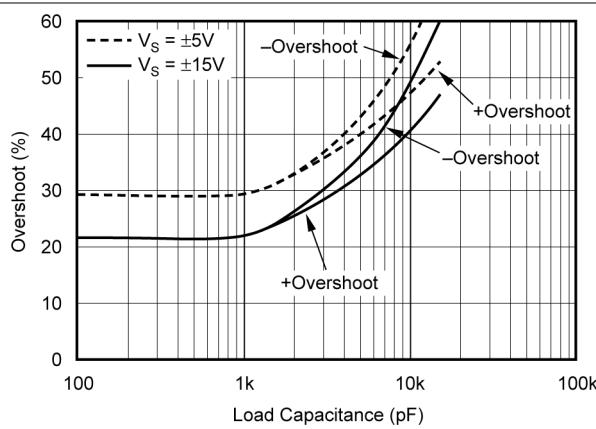

## 5.5 代表的特性 (続き)

$T_A = +25^\circ\text{C}$ ,  $V_S = \pm 15\text{V}$ ,  $R_L = 10\text{k}\Omega$ , グラウンドに接続,  $V_{\text{REF}} = 0\text{V}$ , 特に記述のない限り

図 5-13. オフセット電圧の製品分布 ( $V_S = \pm 15\text{V}$ )

図 5-14. オフセット電圧の製品分布 ( $V_S = \pm 5\text{V}$ )

図 5-15. オフセット電圧ドリフトの製品分布 ( $V_S = \pm 15\text{V}$ )

図 5-16. オフセット電圧ドリフトの製品分布 ( $V_S = \pm 5\text{V}$ )

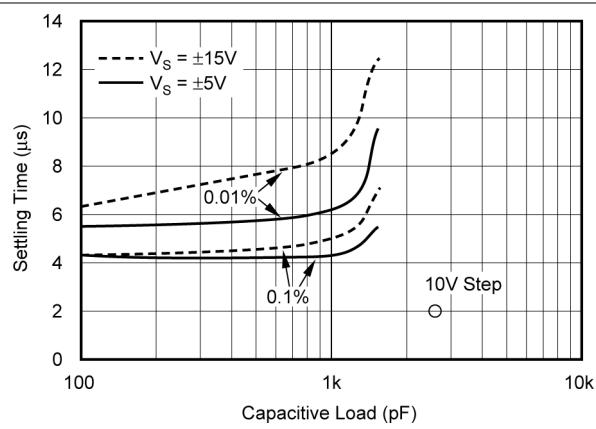

図 5-17. 小信号のオーバーシュートと負荷容量との関係

図 5-18. セトリングタイムと負荷容量との関係

## 5.5 代表的特性 (続き)

$T_A = +25^\circ\text{C}$ ,  $V_S = \pm 15\text{V}$ ,  $R_L = 10\text{k}\Omega$ , グラウンドに接続,  $V_{\text{REF}} = 0\text{V}$ , 特に記述のない限り

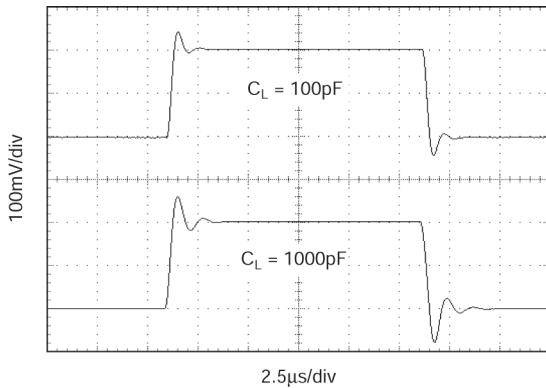

図 5-19. 小信号ステップ応答

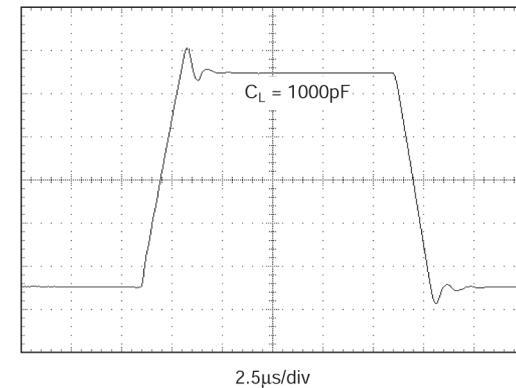

図 5-20. 大信号ステップ応答

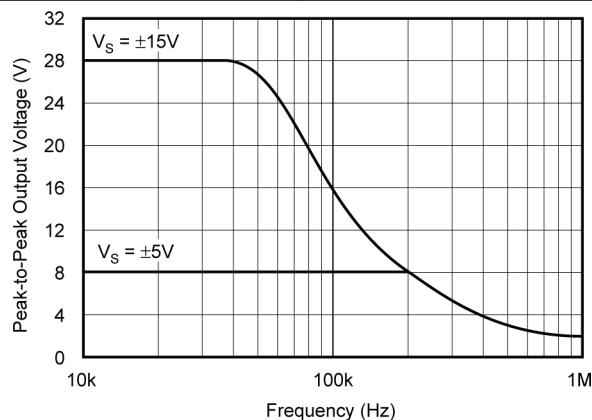

図 5-21. 最大出力電圧と周波数との関係

## 6 詳細説明

## 6.1 概要

INAx133 は高精度オペアンプと、トリムされた 4 つのオンチップ抵抗を備えています。このデバイスは、差動、非反転、反転など、さまざまなアンプ構成に設定できます。内蔵のマッチングされた抵抗は、ディスクリート実装よりも優れています。

オペアンプ回路の DC 性能の大部分は、周囲の抵抗の精度で決まります。INAx133 上の抵抗は、厳密にマッチングするようにレイアウトされています。各部の抵抗はオンチップでマッチングされ、マッチング精度も検査されています。その結果、INAx133 はゲインドリフト、同相除去比、ゲイン誤差などにおいて高い精度を実現しています。

## 6.2 機能ブロック図

### 6.3 機能說明

### 6.3.1 ゲイン誤差とドリフト係数

INAx133 のゲイン誤差は、内蔵の高精度抵抗の不一致によって制限されます。ゲインドリフトは、内蔵抵抗の温度係数のわずかな不一致によって制限されます。内蔵抵抗は、外部抵抗を使用した場合に差動増幅器が作り出すディスクリート実装と比較して、全体的なゲインドリフトを改善するために、低温度係数抵抗と精密にマッチングされています。

### 6.3.2 入力電圧範囲

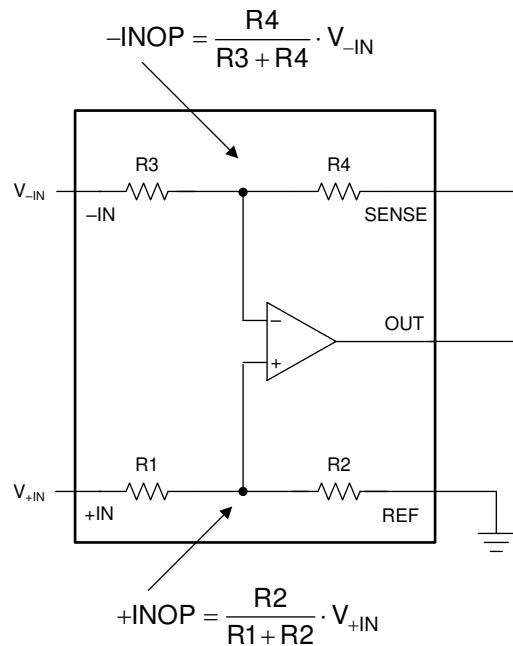

INAx133 差動アンプは、入力信号を高精度の分圧抵抗で分周することで、広い入力同相電圧範囲を実現できます。内蔵抵抗は、電圧が内部オペアンプに到達する前に分圧し、オペアンプ入力の保護を行います。図 6-1 は、差動アンプ構成において分圧がどのように機能するかの例を示しています。

図 6-1. 差動アンプ構成での分圧

### 6.4 デバイスの機能モード

INAx133 には 1 つの機能モードがあります。この装置は、 $\pm 15V$  または  $\pm 5V$  の電源で動作するように指定されており、性能が低下しますが、 $\pm 2.25V$  から  $\pm 18V$  の電源でも動作可能です。代表的特性を参照

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

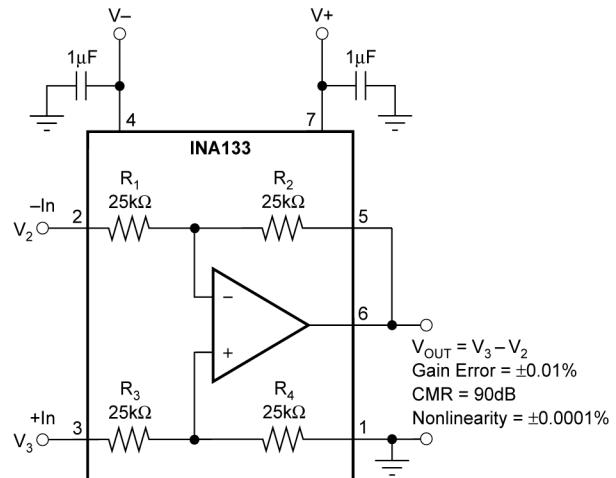

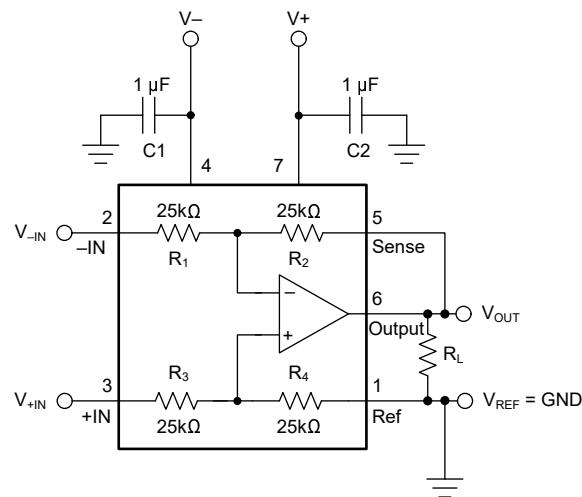

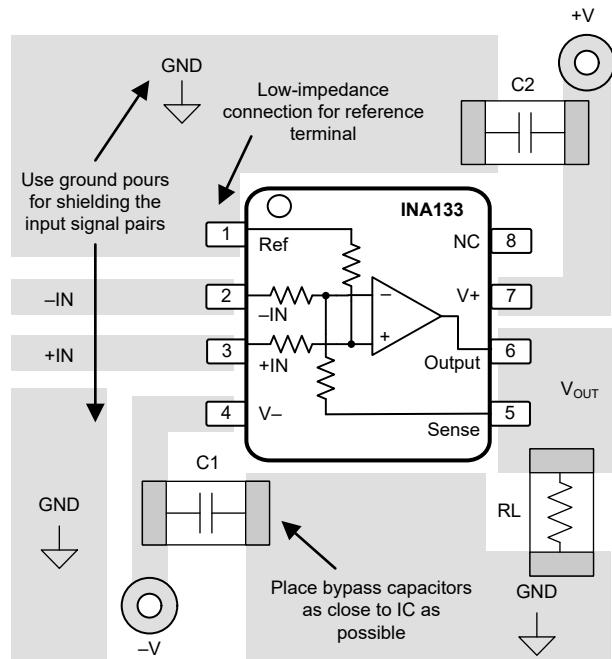

INA133 と INA2133 は、高速動作する差動アンプで、幅広い汎用アプリケーションに対応するよう設計されています。図 7-2 は、INA133 の動作に必要な基本的な接続を示しています。ノイズが多い、または高インピーダンスの電源を使用するアプリケーションでは、図 7-2 に示すように、デカップリング・コンデンサを、デバイスのピンの近くに配置します。デュアルバージョンでは、すべての回路が完全に独立しているため、一方のアンプがオーバードライブまたはショートサーキットした場合でも、クロストークを最小限に抑え、正常な動作を維持します。

差動入力信号は、図 7-2 に示すようにピン 2 と 3 に接続されています。入力に接続される各ソースインピーダンスは、良好な同相信号除去を実現するため、ほぼ等しくする必要があります。ソースインピーダンスの  $5\Omega$  の不整合は、一般的なデバイスのコモンモード除去を約  $80\text{dB}$  に低下させます ( $10\Omega$  の不整合は CMR を  $74\text{dB}$  に低下させます)。ソースに既知のインピーダンス不整合がある場合、逆の入力に直列に追加の抵抗を使用することで、良好なコモンモード除去を維持することができます。

INA133 の内蔵抵抗は、比率が正確に一致するようにトリミングされています。つまり、 $R_1$  は  $R_2$  に一致するようトリムされ、 $R_3$  は  $R_4$  に一致するようトリムされます。ただし、絶対値は等しくない場合があります ( $R_1 + R_2$  は  $R_3 + R_4$  とわずかに異なる場合があります)。したがって、入力に大きな直列抵抗 ( $250\Omega$  以上) を配置すると、たとえ整合がとれていても、コモンモード除去比が低下する可能性があります。

回路基板レイアウトの制約により、内部抵抗の接続の可能なバリエーションが示唆されることがあります。例えば、ピン 1 とピン 3 を入れ替えることができるなどです。しかし、レシオトリミング技術が使用されているため、CMRR は劣化する可能性があります。ピン 1 と 3 を入れ替える場合、適切な比率マッチングを維持するには、ピン 2 と 5 も入れ替える必要があります。

#### 7.1.1 動作電圧

INA133 および INA2133 は、優れた性能で、単一 ( $+4.5\text{V} \sim +36\text{V}$ ) またはデュアル ( $\pm 2.25\text{V} \sim \pm 18\text{V}$ ) の電源で動作します。仕様は、 $\pm 5\text{V}$  および  $\pm 15\text{V}$  の電源で量産時にテストされています。ほとんどの特性は、動作電圧範囲内で変化しません。動作電圧によって大きく変化するパラメータは、[代表特性](#)セクションに示されています。

#### 7.1.2 入力電圧

INA133 および INA2133 は、電源レールを超える上下の差動信号を正確に測定できます。リニア同相範囲は、 $2 \times (V+) - 3\text{V}$  から  $2 \times (V-) + 3\text{V}$  (電源のほぼ 2 倍) までに拡張されています。図 5-5 を参照してください。

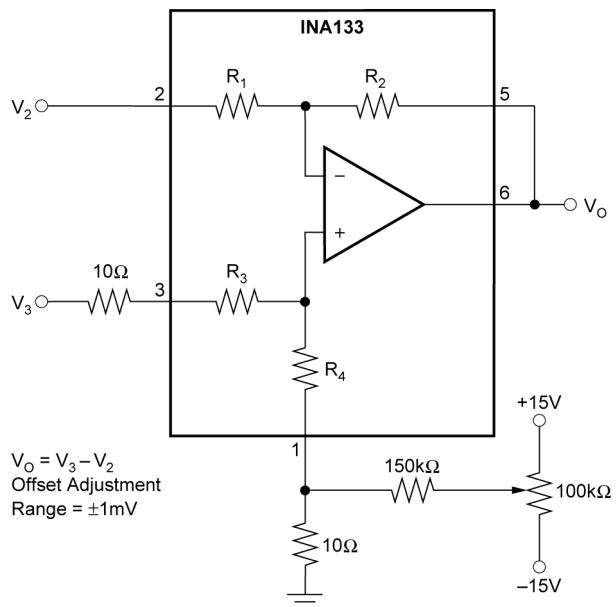

#### 7.1.3 オフセット電圧トリミング

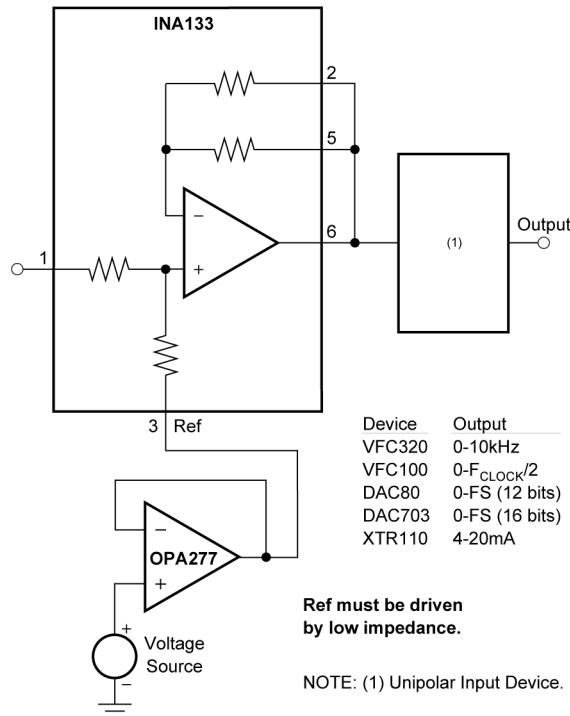

INA133 および INA2133 は、低オフセット電圧およびドリフトを実現するようにレーザートリミングされています。大半のアプリケーションでは、外部オフセット調整は必要ありません。図 7-1 は、出力オフセット電圧をトリミングするためのオプション回路を示しています。出力は、通常接地された出力基準端子 (ピン 1) を基準にします。出力信号には、Ref ピンに印加された電圧が加算されます。これは図 7-1 に示すように、オフセット電圧を打ち消すために使用できます。良好な同相除去を維持するには、Ref ピンに加える信号のソースインピーダンスを  $10\Omega$  未満に保つ必要があります。

図 7-1. オフセット調整

## 7.2 代表的なアプリケーション

INAx133 はさまざまな用途に使用できます。図 7-2 は一例を示しています。

図 7-2. 高精度差動アンプ（電源および信号の基本接続）

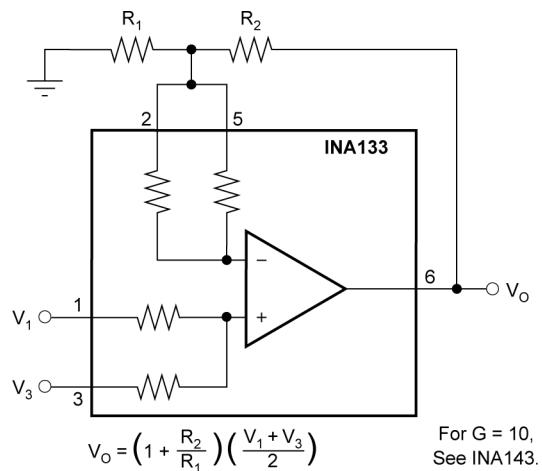

### 7.3 追加アプリケーション

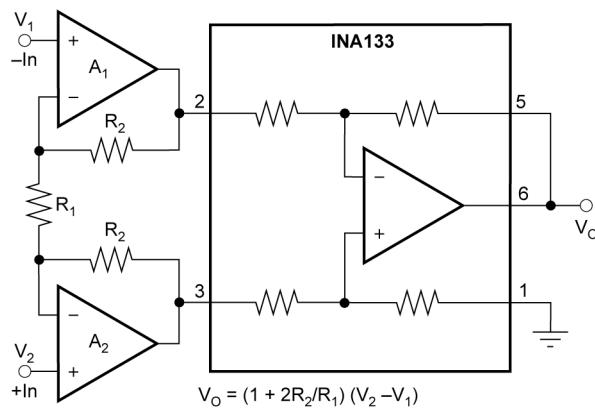

図 7-3. 高精度計測アンプ

NOTE: (1) Input series resistors should be less than 250Ω (1% max mismatch) to maintain excellent CMR. With 100Ω resistors, gain error is increased to 0.5%.

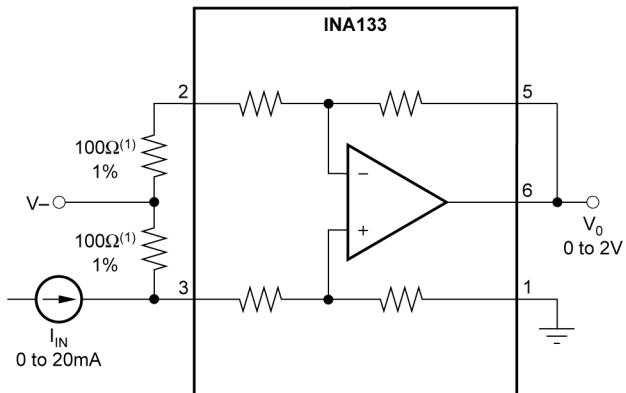

図 7-4. レール対応の電流レシーバ

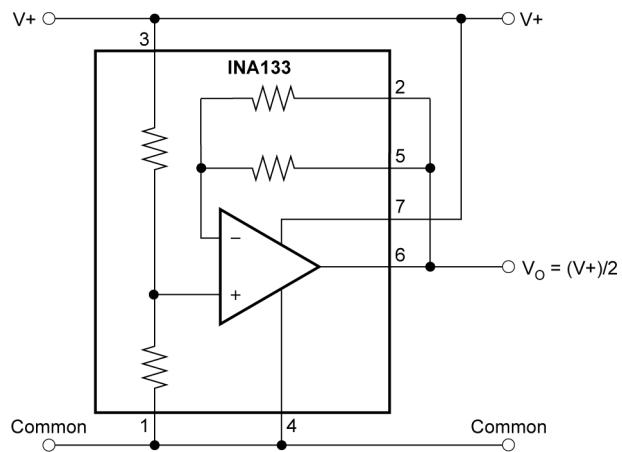

図 7-5. 疑似グラウンド ジェネレータ

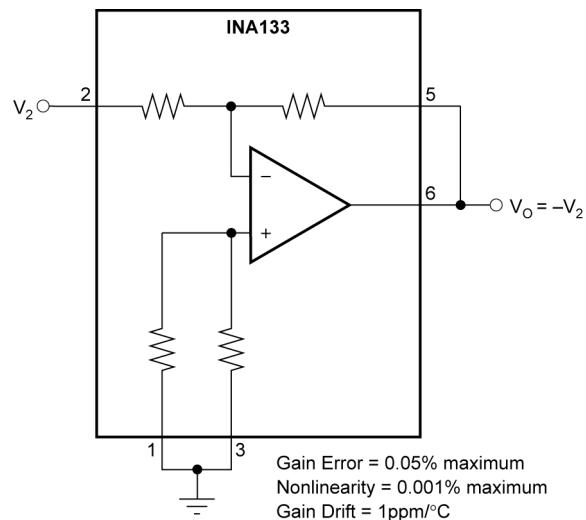

図 7-6. 高精度ユニティゲイン反転アンプ

図 7-7. 高精度 ゲイン = 2 アンプ

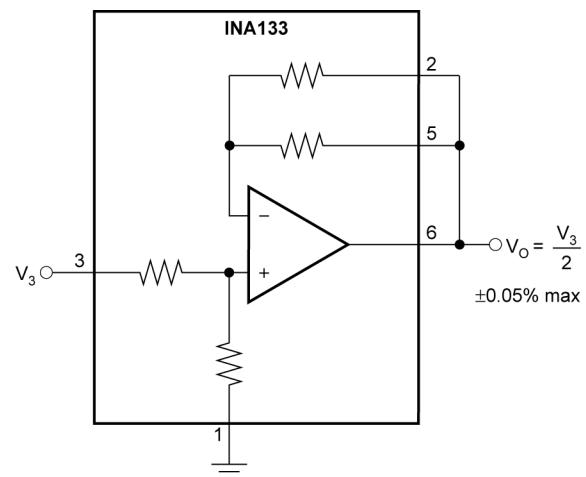

図 7-8. 高精度 ゲイン = 1/2 アンプ

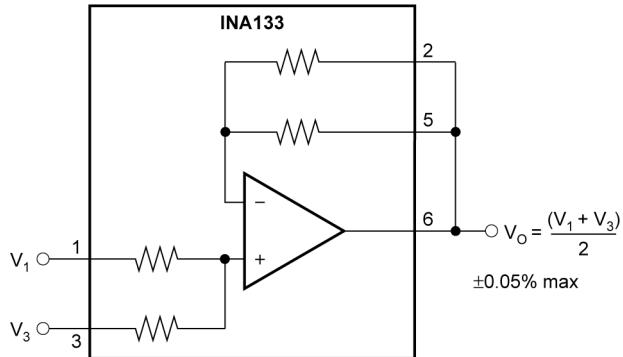

図 7-9. 高精度平均値アンプ

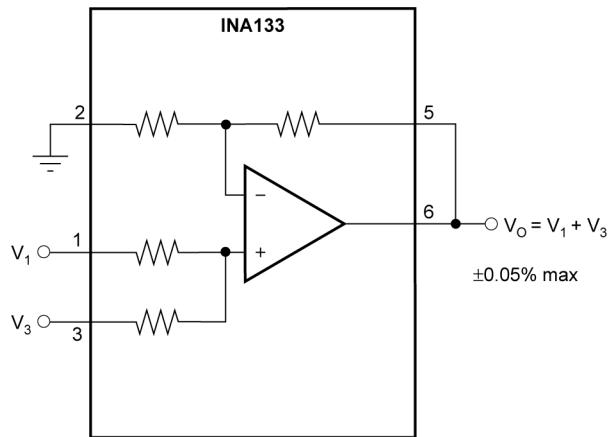

図 7-10. 高精度サミング アンプ

図 7-11. 高精度バイポーラ オフセット

図 7-12. 高精度サミング アンプ(ゲインあり)

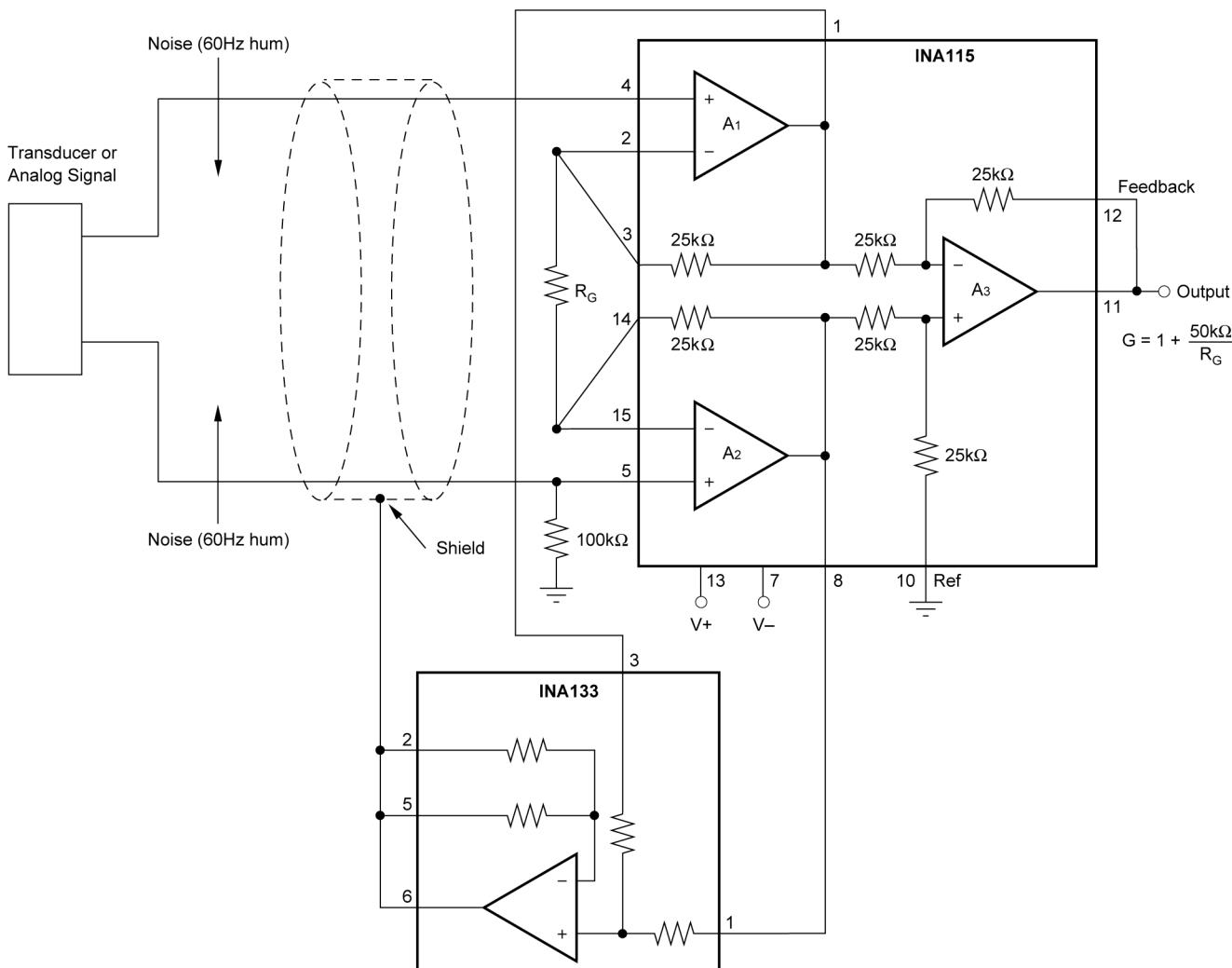

図 7-13. 計測アンプ ガード駆動ジェネレータ

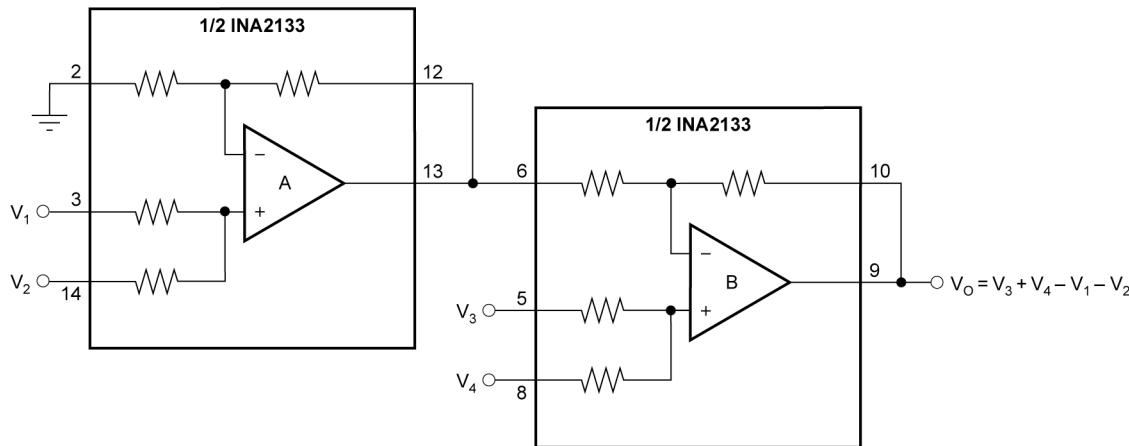

図 7-14. 高精度加算計測アンプ

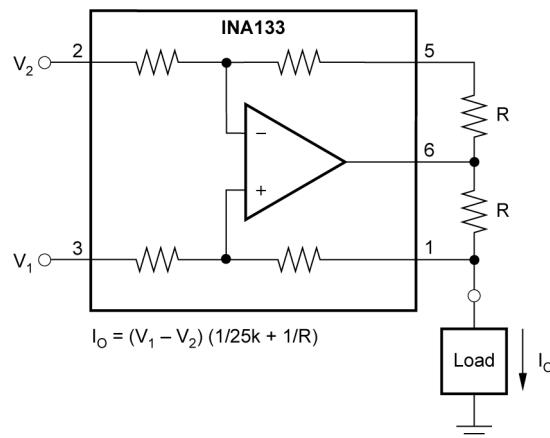

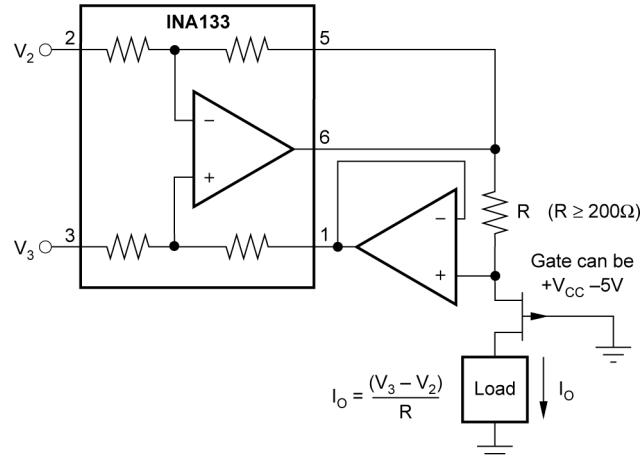

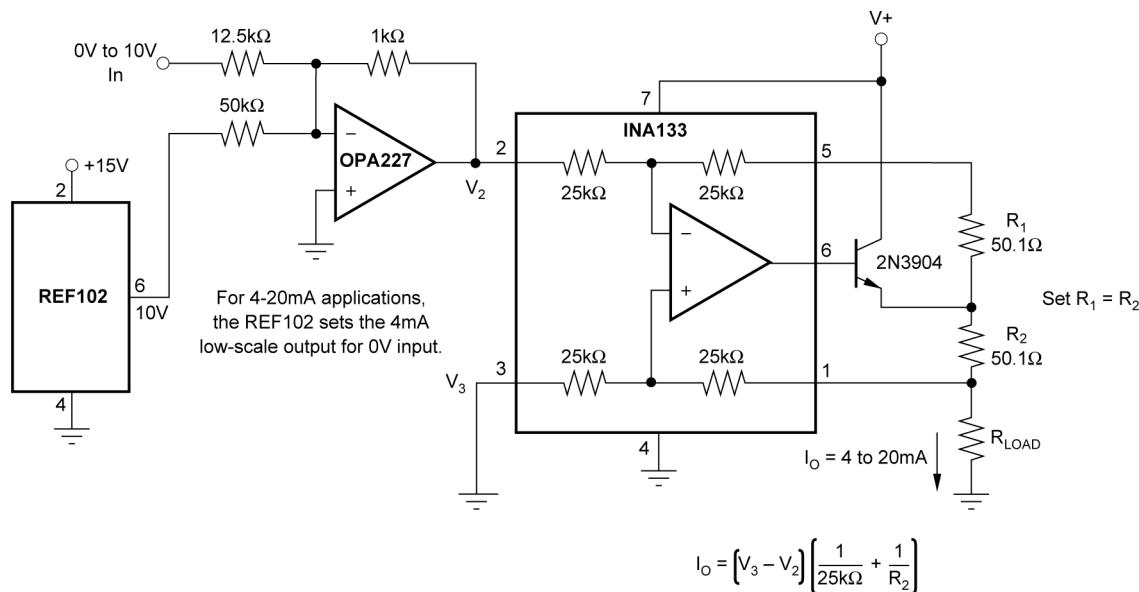

図 7-15. 高精度電圧 - 電流コンバータ (差動入力あり)

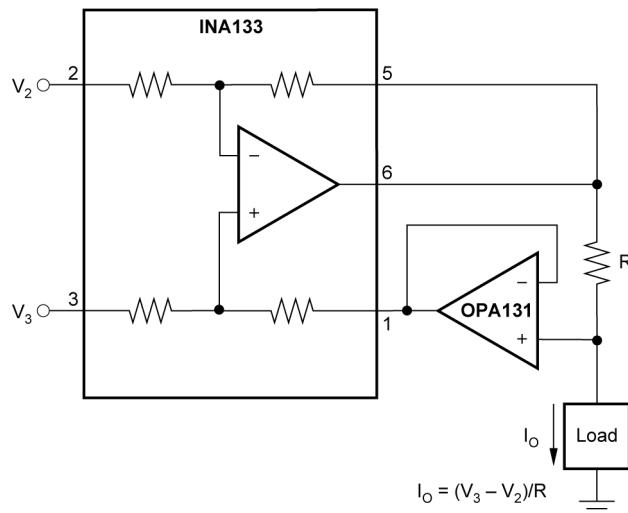

図 7-16. 小さい  $I_{o\text{UT}}$  のための差動入力電圧 - 電流コンバータ

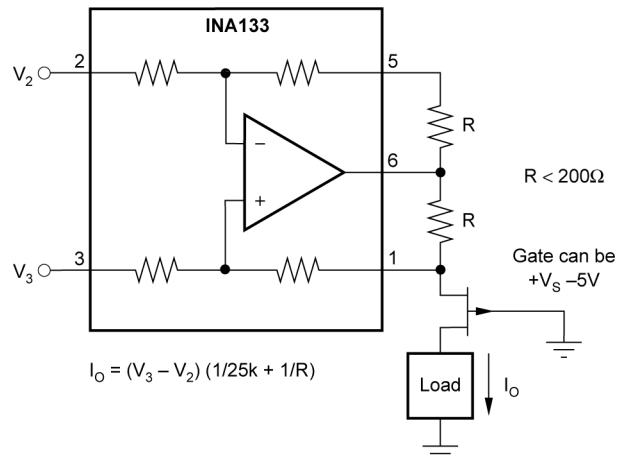

図 7-17. 電流ソースの絶縁

図 7-18. 差動出力差動アンプ

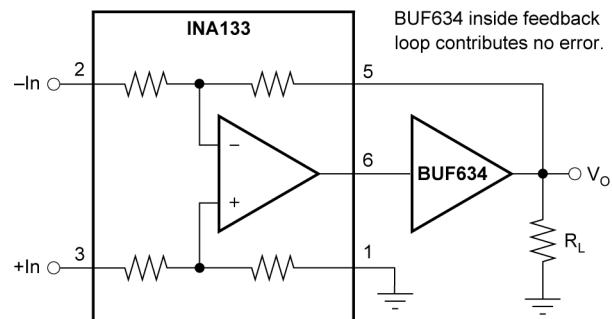

図 7-19. バッファ アンプにより電流ソースを絶縁し、高精度を実現

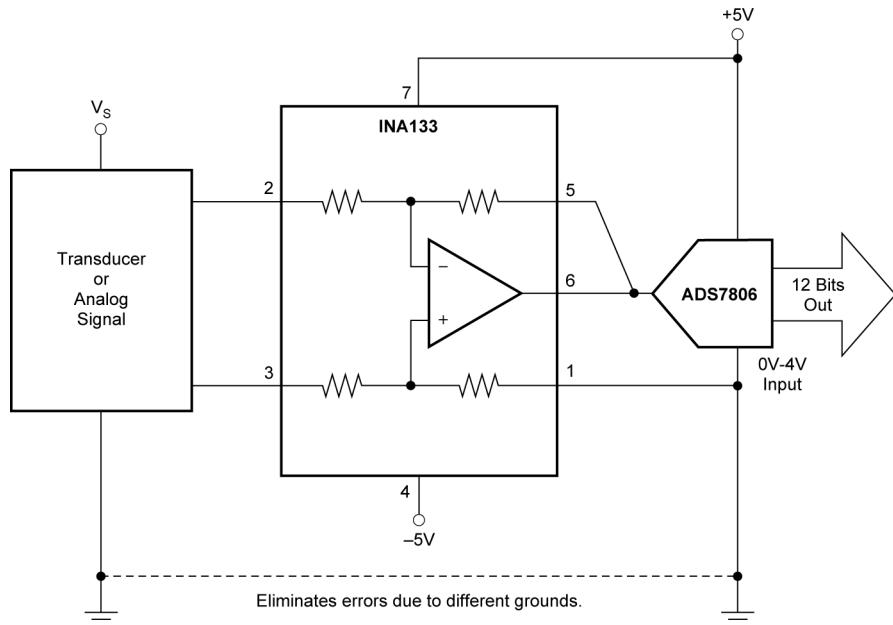

図 7-20. 差動入力データ アクイジション

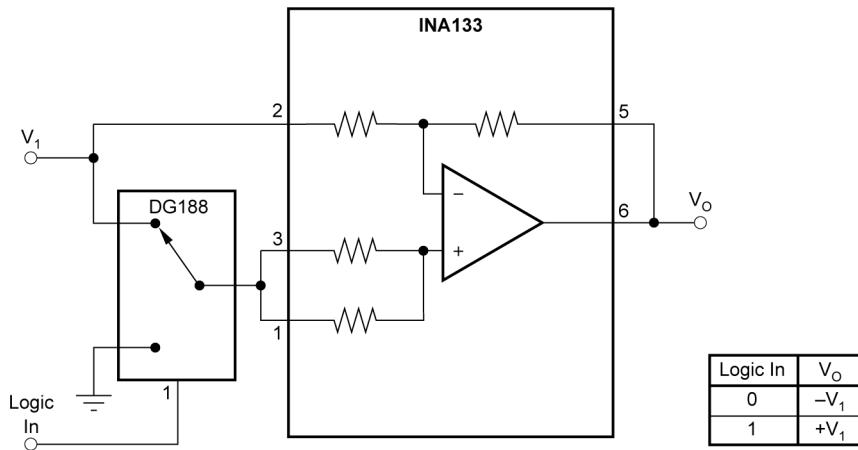

図 7-21.  $\pm 1$  のデジタル制御ゲイン アンプ

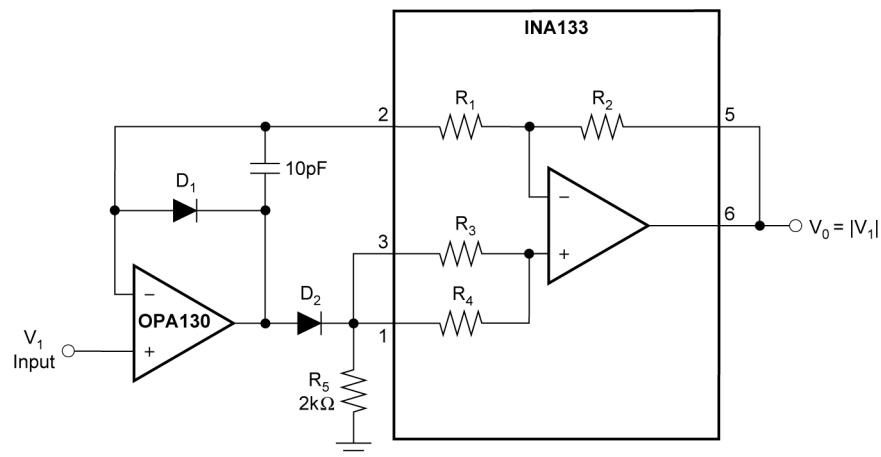

図 7-22. 高精度絶対値バッファ

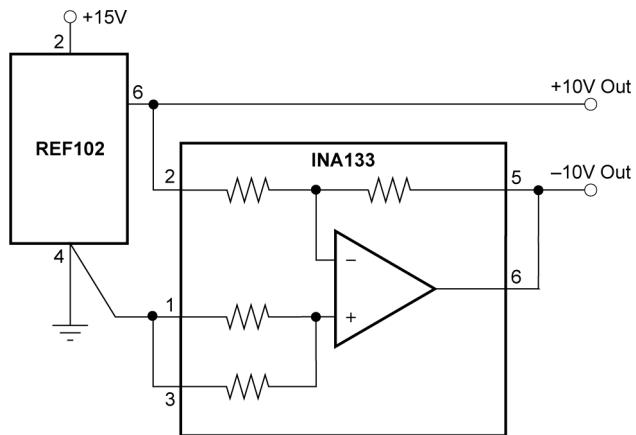

図 7-23. ±10V 高精度電圧基準

図 7-24. 高出力電流差動増幅器

図 7-25. 高精度な電圧 - 電流変換

## 7.4 電源に関する推奨事項

INA105 の公称性能は、電源電圧  $\pm 15V$  または  $\pm 5V$  で規定されています。このデバイスは  $\pm 2.25V \sim \pm 18V$  の電源で動作し、性能は電圧によって変化します。動作電圧および基準電圧範囲にわたって変化するパラメータについては、[代表的特性](#)を参照してください。

TI は、各電源ピンとグラウンドの間に低 ESR のセラミック・バイパス・コンデンサ ( $C_{BYP}$ ) を追加することを強く推奨します。単一電源での動作には、1 つの  $C_{BYP}$  のみで十分です。ノイズの多い電源や高インピーダンスの電源からの結合誤差を低減するため、 $C_{BYP}$  は可能な限りデバイスの近くに配置してください。電源トレースは、デバイスの電源端子に達する前に  $C_{BYP}$  を経由させて配線してください。詳細については、[レイアウトのガイドライン](#) を参照してください。

## 7.5 レイアウト

### 7.5.1 レイアウトのガイドライン

優れたレイアウト手法に対して、常に关心を持つことをお勧めします。デバイスで最高の動作性能を実現するには、以下のような適切な PCB レイアウト手法を使用してください。

- 同相信号が差動信号に変換されないようにするために、両方の入力パスがソースインピーダンスと容量に対して適切にマッチングされていることを確認してください。

- ノイズは、回路全体とデバイスの電源ピンを経由して、アナログ回路に伝播します。バイパスコンデンサは、アナログ回路に対して局所的に低インピーダンスの電源を供給することにより、結合ノイズを低減します。

- 各電源ピンとグラウンドの間には、低 ESR の  $0.1\mu F$  セラミックバイパスコンデンサを、可能な限りデバイスの近くに接続します。単一電源アプリケーションの場合は、V+ からグラウンドに対して 1 つのバイパスコンデンサを接続します。

- 寄生結合を低減するため、入力トレースは電源トレースや出力トレースからできるだけ遠ざけて配線します。これらの配線を分離できない場合は、ノイズの多い配線と平行に交差させるのではなく、敏感な配線は 90 度で交差させる方が望ましいです。

- 外付け部品は、可能な限りデバイスに近く配置します。

- 配線はできる限り短くします。

### 7.5.2 レイアウト例

図 7-26. 回路図の例

図 7-27. SOIC-8 パッケージ対応の PCB レイアウト

## 8 デバイスおよびドキュメントのサポート

テキサス・インスツルメンツでは、幅広い開発ツールを提供しています。デバイスの性能の評価、コードの生成、ソリューションの開発を行うためのツールとソフトウェアを以下で紹介します。

### 8.1 デバイス サポート

#### 8.1.1 開発サポート

この製品の開発サポートについては、以下を参照してください。

##### 8.1.1.1 PSpice® for TI

**PSpice® for TI** は、アナログ回路の性能評価に役立つ設計およびシミュレーション環境です。レイアウトと製造に移る前に、サブシステムの設計とプロトタイプ・ソリューションを作成することで、開発コストを削減し、市場投入までの期間を短縮できます。

##### 8.1.1.2 TINA-TI™ (無料のダウンロード ソフトウェア)

**TINA™** は、SPICE エンジンをベースにした単純かつ強力な、使いやすい回路シミュレーション プログラムです。**TINA-TI** は、TINA ソフトウェアのすべての機能を持つ無償バージョンで、パッシブ モデルとアクティブ モデルに加えて、マクロ モデルのライブラリがプリロードされています。**TINA-TI** には、SPICE の標準的な DC 解析、過渡解析、周波数ドメイン解析などの全機能に加え、追加の設計機能が搭載されています。

**TINA-TI** は **Analog eLab Design Center** から[無料でダウンロード](#)でき、ユーザーが結果をさまざまな方法でフォーマットできる、広範な後処理機能を備えています。仮想計測器により、入力波形を選択し、回路ノード、電圧、および波形をプローブして、動的なクイック スタートツールを作成できます。

#### 注

これらのファイルを使用するには、**TINA** ソフトウェア (**DesignSoft™** から入手できます) または **TINA-TI** ソフトウェアがインストールされている必要があります。[TINA-TI フォルダ](#) から、無料の **TINA-TI** ソフトウェアをダウンロードしてください。

### 8.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](#) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.3 サポート・リソース

**テキサス・インスツルメンツ E2E™ サポート・フォーラム** は、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 8.4 商標

**TINA-TI™** and **テキサス・インスツルメンツ E2E™** are trademarks of Texas Instruments.

**TINA™** and **DesignSoft™** are trademarks of DesignSoft, Inc.

**PSpice®** is a registered trademark of Cadence Design Systems, Inc.

すべての商標は、それぞれの所有者に帰属します。

## 8.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことをお奨めします。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

## 8.6 用語集

### テキサス・インスツルメンツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision * (June 1999) to Revision A (March 2025)                                                                                                                              | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 文書全体を通して、表、図、相互参照の番号付けとフォーマットを更新                                                                                                                                                            | 1    |

| 「ピン構成および機能」、「仕様」、「推奨動作条件」、「熱に関する情報」、「詳細説明」、「概要」、「機能ブロック図」、「機能説明」、「デバイスの機能モード」、「アプリケーションと実装」、「電源に関する推奨事項」、「レイアウト」、「レイアウトのガイドライン」、「レイアウト例」、「デバイスおよびドキュメントのサポート」、「メカニカル、パッケージ、および注文情報」セクションを追加 | 1    |

| 「パッケージ情報」表を変更                                                                                                                                                                               | 1    |

| INA133 および INA2133 のピン機能表を追加                                                                                                                                                                | 3    |

| 電気的特性のテーブルにテスト条件を追加                                                                                                                                                                         | 6    |

| 電気的特性で、 $V_S = \pm 15V$ および $V_S = \pm 5V$ の仕様の表を結合                                                                                                                                         | 6    |

| 電気的特性のパラメータ名をオフセット電圧初期値と温度との関係からオフセット電圧ドリフトに変更                                                                                                                                              | 6    |

| 電気的特性のパラメータ名をオフセット電圧の初期値と電源電圧との関係から電源除去比に変更                                                                                                                                                 | 6    |

| 電気的特性のパラメータ名をオフセット電圧と時間との関係から長期安定性に変更                                                                                                                                                       | 6    |

| 電気的特性のパラメータ名を電流制限、連続から同相への電流から短絡電流に変更し、テスト条件を追加                                                                                                                                             | 6    |

| 電源および温度範囲を電気的特性表から推奨動作条件および絶対最大定格表へ移動                                                                                                                                                       | 6    |

| 「アプリケーション」セクションを更新                                                                                                                                                                          | 14   |

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| INA133U               | Last Time Buy | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | Call TI                              | Level-3-260C-168 HR               | -40 to 85    | INA 133U            |

| INA133U/2K5           | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | Call TI   Nipdau                     | Level-3-260C-168 HR               | -            | INA 133U            |

| INA133U/2K5.A         | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | Call TI                              | Level-3-260C-168 HR               | -40 to 85    | INA 133U            |

| INA133UA              | Last Time Buy | Production           | SOIC (D)   8   | 75   TUBE             | Yes         | Call TI                              | Level-3-260C-168 HR               | -            | INA 133U A          |

| INA133UA/2K5          | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -            | INA (133U, 133UA) A |

| INA133UA/2K5.A        | Active        | Production           | SOIC (D)   8   | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 85    | INA (133U, 133UA) A |

| INA2133U              | Active        | Production           | SOIC (D)   14  | 50   TUBE             | Yes         | Call TI                              | Level-3-260C-168 HR               | -55 to 125   | INA2133U            |

| INA2133U.A            | Active        | Production           | SOIC (D)   14  | 50   TUBE             | Yes         | Call TI                              | Level-3-260C-168 HR               | -55 to 125   | INA2133U            |

| INA2133UA             | Active        | Production           | SOIC (D)   14  | 50   TUBE             | Yes         | Call TI                              | Level-3-260C-168 HR               | -55 to 125   | INA2133U A          |

| INA2133UA.A           | Active        | Production           | SOIC (D)   14  | 50   TUBE             | Yes         | Call TI                              | Level-3-260C-168 HR               | -55 to 125   | INA2133U A          |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

---

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

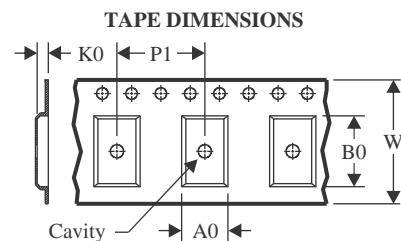

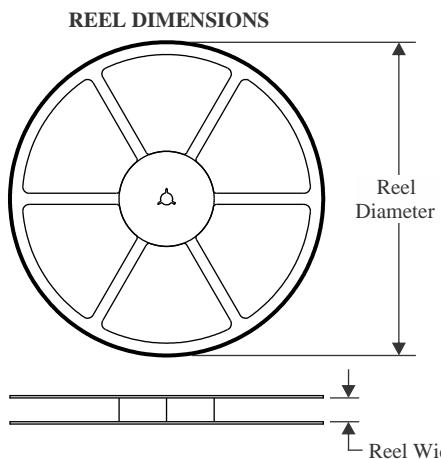

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

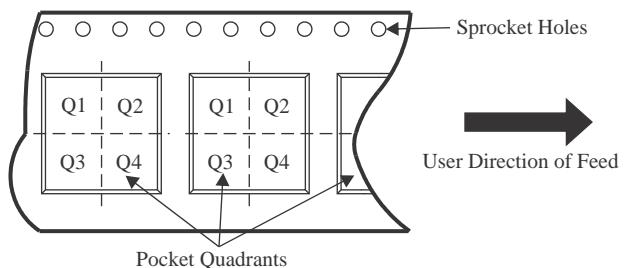

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| INA133U/2K5  | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

| INA133UA/2K5 | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.4     | 5.2     | 2.1     | 8.0     | 12.0   | Q1            |

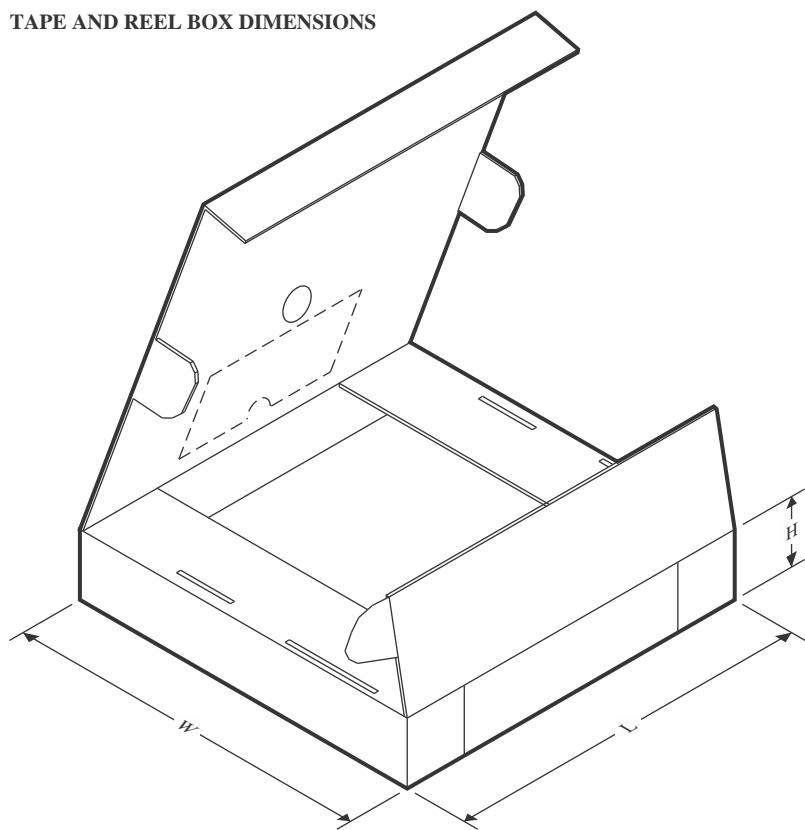

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| INA133U/2K5  | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

| INA133UA/2K5 | SOIC         | D               | 8    | 2500 | 353.0       | 353.0      | 32.0        |

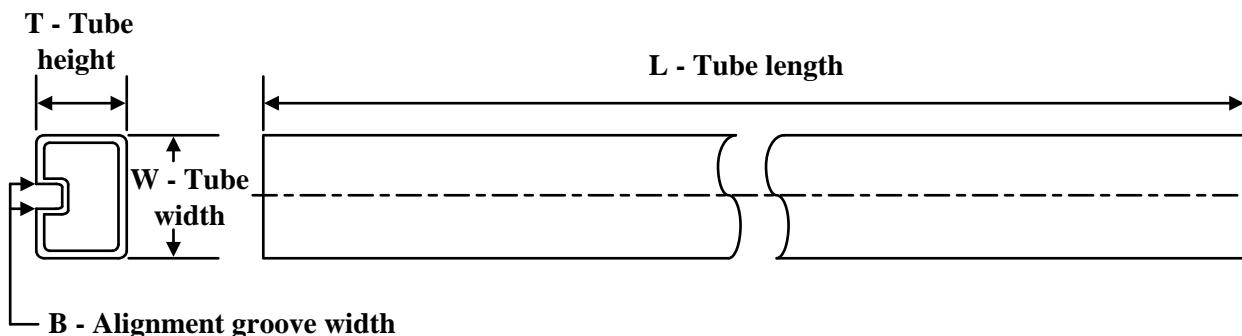

**TUBE**

\*All dimensions are nominal

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (μm) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| INA133U     | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

| INA133UA    | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

| INA2133U    | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940   | 4.32   |

| INA2133U.A  | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940   | 4.32   |

| INA2133UA   | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940   | 4.32   |

| INA2133UA.A | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940   | 4.32   |

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月