## DS160PR410-Q1 PCIe® 4.0 自動車向け 4 チャネル リニア リドライバ

### 1 特長

- PCIe® 4.0 をサポートする 4 チャネル リニア リドライバ

- PCIe 3.0、2.0、1.0 との後方互換性

- 最大 20Gbps までのほとんどの AC 結合インターフェイスをサポートする、プロトコルに依存しないリニア イコライザ

- 統合された、2 つの 2x2 クロス ポイント mux 機能

- 16dB CTLE ブーストにより PVT 上で 12dB の PCIe 4.0 リチア拡張

- 100ps の超低レイテンシ

- 16Gbps (8GHz ナイキスト) における優れた性能

- 15/-20dB Rx/Tx リターン ロス

- 1200mV AC リニアリティ

- 高い BW による優れたリニア EQ カーブ

- 3.3V 単一電源、チャネルあたり 160mW のアクティブ 電力

- 内蔵電圧レギュレータによる電源ノイズ耐性

- PCIe 用途向けの自動受信機検出

- リニア リドライバによる PCIe リンクトレーニングのシームレスなサポート

- ピン モードでの x4、x8、x16 バス幅対応、および I<sup>2</sup>C モードでの x1、x2、x4、x8、x16 対応

- ピン ストラップ、SMBus または EEPROM プログラミング

- 18 段階の EQ ブーストと 5 段階のフラット ゲイン 設定

- 40 ~ 105°C (グレード 2) の周囲温度サポート、ヒート シンク不要

- 0.5mm ピッチのウェッタブル フランクを備えた 5mm x 7mm の自動車対応パッケージ

### 2 アプリケーション

- 自動車 **先進運転支援システム (ADAS)**

- 自動車 **インフォテインメント & クラスター**

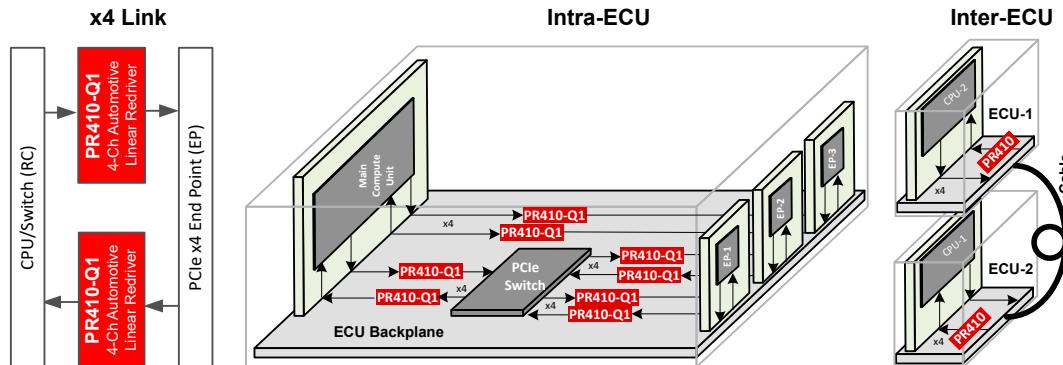

### 代表的なアプリケーション

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                                    |    |                        |    |

|------------------------------------|----|------------------------|----|

| 1 特長                               | 1  | 6.3 機能説明               | 13 |

| 2 アプリケーション                         | 1  | 6.4 デバイスの機能モード         | 15 |

| 3 説明                               | 1  | 6.5 プログラミング            | 17 |

| 4 ピン構成および機能                        | 3  | 7 アプリケーションと実装          | 22 |

| 5 仕様                               | 6  | 7.1 アプリケーション情報         | 22 |

| 5.1 絶対最大定格                         | 6  | 7.2 代表的なアプリケーション       | 22 |

| 5.2 ESD 定格                         | 6  | 7.3 電源に関する推奨事項         | 27 |

| 5.3 推奨動作条件                         | 6  | 7.4 レイアウト              | 27 |

| 5.4 熱に関する情報                        | 7  | 8 デバイスおよびドキュメントのサポート   | 29 |

| 5.5 DC の電気的特性                      | 7  | 8.1 ドキュメントのサポート        | 29 |

| 5.6 高速電気的特性                        | 8  | 8.2 ドキュメントの更新通知を受け取る方法 | 29 |

| 5.7 SMBUS/I <sup>2</sup> C タイミング特性 | 9  | 8.3 サポート・リソース          | 29 |

| 5.8 代表的特性                          | 11 | 8.4 商標                 | 29 |

| 5.9 代表的なジッタ特性                      | 11 | 8.5 静電気放電に関する注意事項      | 29 |

| 6 詳細説明                             | 12 | 8.6 用語集                | 29 |

| 6.1 概要                             | 12 | 9 改訂履歴                 | 29 |

| 6.2 機能ブロック図                        | 13 | 10 メカニカル、パッケージ、および注文情報 | 29 |

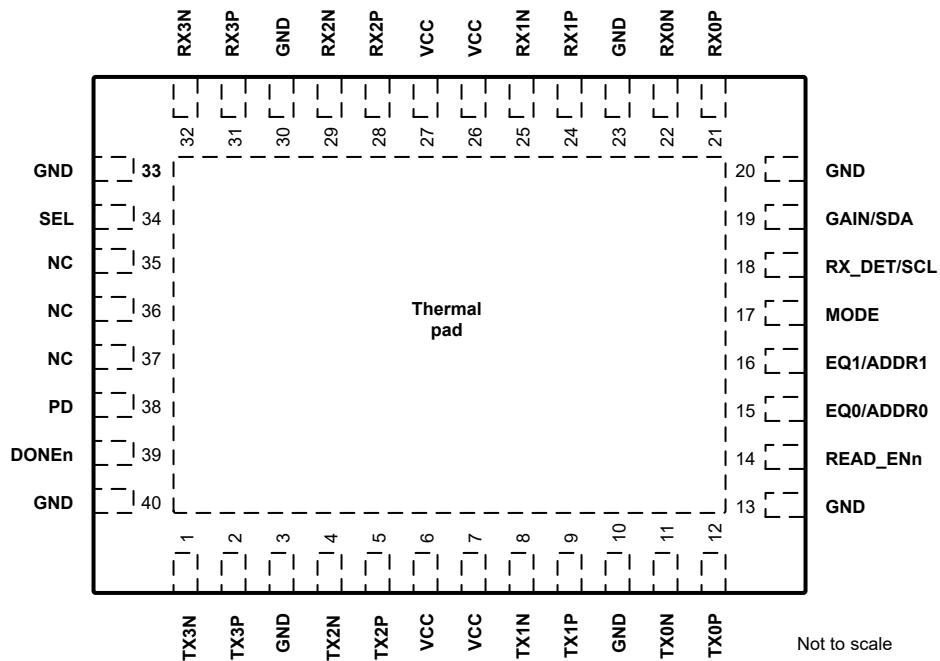

## 4 ピン構成および機能

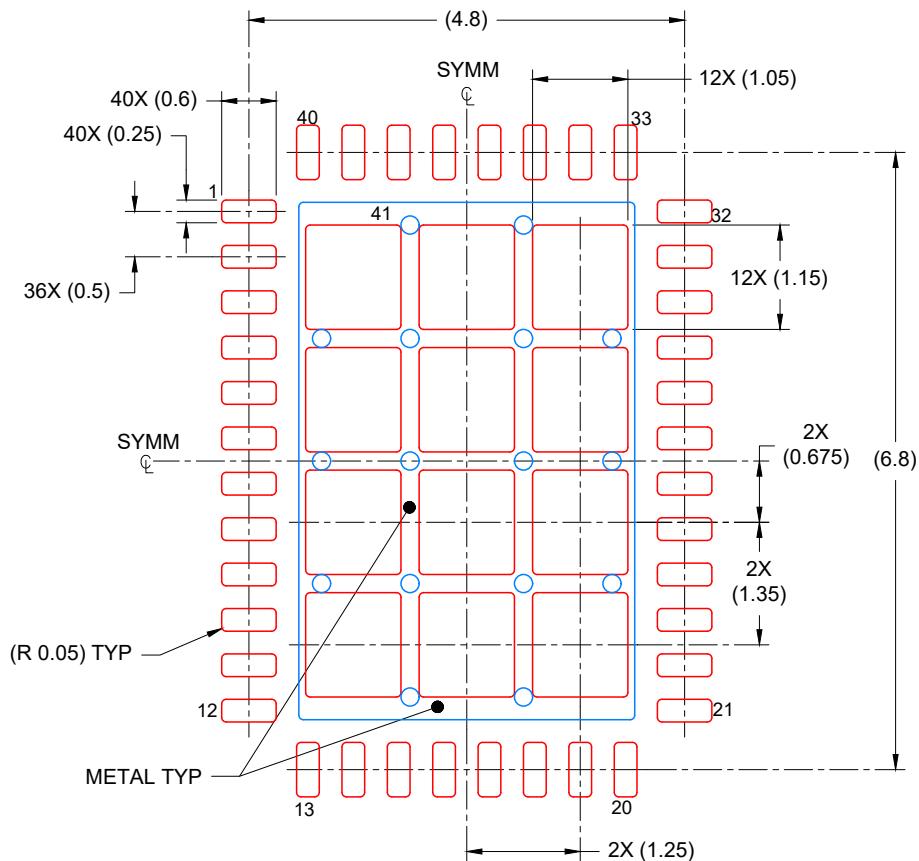

図 4-1. RGF パッケージ、40 ピン VQFN (上面図)

表 4-1. ピンの機能

| 名称          | ピン番号 | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 制御インターフェイス  |      |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| READ_ENn    | 14   | I, 3.3V<br>LVC MOS | <p><b>SMBus/I<sup>2</sup>C コントローラ モードの場合:</b><br/>デバイスのパワー アップ後、このピンが low のとき、SMBus/I<sup>2</sup>C コントローラ モードの EEPROM リード機能が開始されます。EEPROM の読み取りが完了すると (DONEn が Low にアサートされることで示されます)、このピンはデバイスの通常動作のために Low に保持できます。EEPROM ロード処理中は、デバイスの信号バスが無効になります。</p> <p><b>SMBus/I<sup>2</sup>C ターゲット モードおよびピン モードの場合:</b><br/>これらのモードでは、このピンは使用されません。ピンはフローティングのままにしてもかまいません。ピンには 1MΩ の内部弱プルダウン抵抗があります。</p>                                                                                                                                                                                                                             |

| EQ0 / ADDR0 | 15   | I, 5 レベル           | <p><b>ピン モード内:</b><br/>表 6-1 に示されるように、受信機のリニア イコライゼーション (CTLE) ブーストを設定します。これらのピンは、デバイスの電源投入時にのみサンプリングされます。</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| EQ1 / ADDR1 | 16   | I, 5 レベル           | <p><b>SMBus/I<sup>2</sup>C モード:</b><br/>表 6-5 に示されるように、SMBus/I<sup>2</sup>C ターゲット アドレスを設定します。これらのピンは、デバイスの電源投入時にのみサンプリングされます。</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| モード         | 17   | I, 5 レベル           | <p>デバイス制御構成モードを設定します。表 6-4 に示す 5 レベルの IO ピン。このピンは、デバイスの電源投入時または通常動作モード時に実行できます。</p> <p>L0: ピン モード – デバイス制御構成は、ストラップ ピンのみで行われます。</p> <p>L1: <b>SMBus/I<sup>2</sup>C コントローラ モード</b> – デバイス制御構成は外部 EEPROM から読み出されます。DS160PR410-Q1 が EEPROM の読み出しを正常に完了すると、チップは DONEn ピンを LOW に駆動します。このモードでは、EEPROM 読み出しの前、中または後のいずれでも SMBus/I<sup>2</sup>C ターゲット機能が利用可能です。注: EEPROM 読み出し中に外部 SMBus/I<sup>2</sup>C コントローラが DS160PR410-Q1 レジスタにアクセスする場合、そのコントローラはアビトリエーションをサポートする必要があります。</p> <p>L2: <b>SMBus/I<sup>2</sup>C ターゲット モード</b> – デバイス制御構成は外部 SMBus/I<sup>2</sup>C コントローラによって行われます。</p> <p>L3 と L4 (フローティング): 予約済み – TI の内部テスト モード。</p> |

表 4-1. ピンの機能 (続き)

| ピン           |    | タイプ <sup>(1)</sup>                           | 説明                                                                                                                                                                                                                                                                                                    |

|--------------|----|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称           | 番号 |                                              |                                                                                                                                                                                                                                                                                                       |

| RX_DET/SCL   | 18 | I、5 レベル/<br>I/O、3.3V<br>LVC MOS、オ<br>ープンドレイン | <b>ピン モード内:</b><br>に示されるように、レシーバ検出ステートマシンのオプションを設定します表 6-3。このピンは、デバイスの電源投入時にのみサンプリングされます。<br><b>SMBus/I<sup>2</sup>C モード:</b><br>3.3V SMBus/I <sup>2</sup> C クロック。SMBus / I <sup>2</sup> C インターフェイス規格に従い、外部 1kΩ から 5kΩ へプルアップ抵抗が必要です。                                                                 |

| ゲイン/ SDA     | 19 | I、5 レベル/<br>I/O、3.3V<br>LVC MOS、オ<br>ープンドレイン | <b>ピン モード内:</b><br>デバイスの入力から出力までのフラットゲイン (DC および AC)。このピンは、デバイスの電源投入時にのみサンプリングされます。<br><b>SMBus/I<sup>2</sup>C モード:</b><br>3.3V SMBus/I <sup>2</sup> C データ。SMBus / I <sup>2</sup> C インターフェイス規格に従い、外部 1kΩ から 5kΩ へプルアップ抵抗が必要です。                                                                        |

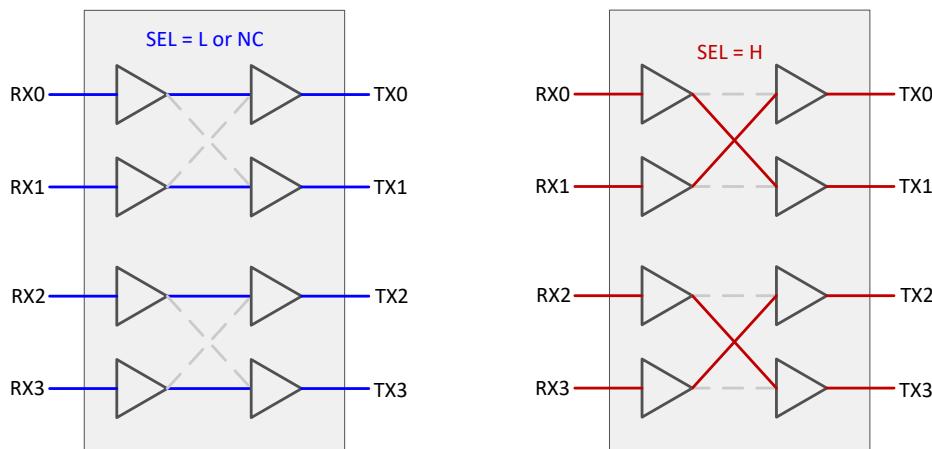

| SEL          | 34 | I、3.3V<br>LVC MOS                            | ピンはクロス ポイント Mux パスを選択します。すべてのデバイス制御モードでアクティブです。59kΩ の内部プルダウンを備えています。注: ピンをトグルすると PCIe RX 検出ステートマシンもトリガれます。Mux 機能を使用しない PCIe リドライバ用途では、ピンを未接続のままにします。Low: ストレート データ パス — RX[0/1/2/3][P/N] がリドライバを介して TX[0/1/2/3][P/N] に接続されます。High: クロス データ パス — RX[0/1/2/3][P/N] がリドライバを介して TX[1/0/3/2][P/N] に接続されます。 |

| PD           | 38 | I、3.3V<br>LVC MOS                            | リドライバの動作状態を制御する 2 レベルのロジック。すべてのデバイス制御モードでアクティブです。ピンには 1MΩ の内部弱プルダウン抵抗があります。ピンをトグルすると PCIe Rx 検出ステートマシンがトリガれます。<br>High: パワー ダウン<br>Low: パワー アップ、通常動作                                                                                                                                                  |

| DONEn        | 39 | O、3.3V オー<br>ープンドレイン                         | <b>SMBus/I<sup>2</sup>C コントローラ モードの場合:</b><br>有効な EEPROM レジスタ ロード動作が完了したことを示します。4.7kΩ などの外部プルアップ抵抗が動作に必要です。<br>High: 外部 EEPROM のロードに失敗または不完全<br>Low: 外部 EEPROM ロードが正常に完了<br><b>SMBus/I<sup>2</sup>C ターゲット/ピン モードの場合:</b><br>この出力はハイインピーダンスです。このピンはフローティングのままでかまいません。                                  |

| データ インターフェイス |    |                                              |                                                                                                                                                                                                                                                                                                       |

| TX3N         | 1  | O                                            | 100Ω 差動ドライバ出力の反転ピン。チャネル 3。                                                                                                                                                                                                                                                                            |

| TX3P         | 2  | O                                            | 100Ω 差動ドライバ出力用のノンインバーティング ピン。チャネル 3。                                                                                                                                                                                                                                                                  |

| TX2N         | 4  | O                                            | 100Ω 差動ドライバ出力の反転ピン。チャネル 2。                                                                                                                                                                                                                                                                            |

| TX2P         | 5  | O                                            | 100Ω 差動ドライバ出力用のノンインバーティング ピン。チャネル 2。                                                                                                                                                                                                                                                                  |

| TX1N         | 8  | O                                            | 100Ω 差動ドライバ出力の反転ピン。チャネル 1。                                                                                                                                                                                                                                                                            |

| TX1P         | 9  | O                                            | 100Ω 差動ドライバ出力用のノンインバーティング ピン。チャネル 1。                                                                                                                                                                                                                                                                  |

| TX0N         | 11 | O                                            | 100Ω 差動ドライバ出力の反転ピン。チャネル 0。                                                                                                                                                                                                                                                                            |

| TX0P         | 12 | O                                            | 100Ω 差動ドライバ出力 チャネル 0 用のノンインバーティング ピン。                                                                                                                                                                                                                                                                 |

| RX0P         | 21 | I                                            | イコライザへのノンインバーティング差動入力。ピンと内部 CM バイアス電圧の間に 50Ω の終端抵抗を内蔵。チャネル 0。                                                                                                                                                                                                                                         |

| RX0N         | 22 | I                                            | イコライザへの反転差動入力。ピンと内部 CM バイアス電圧の間に 50Ω の終端抵抗を内蔵。チャネル 0。                                                                                                                                                                                                                                                 |

| RX1P         | 24 | I                                            | イコライザへのノンインバーティング差動入力。ピンと内部 CM バイアス電圧の間に 50Ω の終端抵抗を内蔵。チャネル 1。                                                                                                                                                                                                                                         |

| RX1N         | 25 | I                                            | イコライザへの反転差動入力。ピンと内部 CM バイアス電圧の間に 50Ω の終端抵抗を内蔵。チャネル 1。                                                                                                                                                                                                                                                 |

| RX2P         | 28 | I                                            | イコライザへのノンインバーティング差動入力。ピンと内部 CM バイアス電圧の間に 50Ω の終端抵抗を内蔵。チャネル 2。                                                                                                                                                                                                                                         |

| RX2N         | 29 | I                                            | イコライザへの反転差動入力。ピンと内部 CM バイアス電圧の間に 50Ω の終端抵抗を内蔵。チャネル 2。                                                                                                                                                                                                                                                 |

**表 4-1. ピンの機能 (続き)**

| ピン            |                                   | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                           |

|---------------|-----------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称            | 番号                                |                    |                                                                                                                                                                              |

| RX3P          | 31                                | I                  | イコライザへのノンインバーティング差動入力。ピンと内部 CM バイアス電圧の間に $50\Omega$ の終端抵抗を内蔵。チャネル 3。                                                                                                         |

| RX3N          | 32                                | I                  | イコライザへの反転差動入力。ピンと内部 CM バイアス電圧の間に $50\Omega$ の終端抵抗を内蔵。チャネル 3。                                                                                                                 |

| <b>電源、その他</b> |                                   |                    |                                                                                                                                                                              |

| GND           | EP、3、10、<br>13、20、23、<br>30、33、40 | G                  | デバイス用のグランド リファレンス。<br>EP: QFN パッケージ底面の Exposed Pad。これはデバイスの GND リターンとして使用されます。EP は、低抵抗のパスを経由して 1 つ以上のグランド プレーンに接続する必要があります。ビア アレイにより、GND への低インピーダンス パスが実現します。EP は放熱も改善しています。 |

| VCC           | 6、7、26、27                         | P                  | 電源ピン。VCC = $3.3V \pm 10\%$ 。このデバイスの VCC ピンは、基板の VCC プレーンへの低抵抗のパスを経由して接続する必要があります。各 VCC ピンの近くで、GND との間にデカッピング コンデンサを取り付けます。                                                   |

| NC            | 35、36、37                          | -                  | 接続なし。フローティングのままにします。                                                                                                                                                         |

(1) I = 入力、O = 出力、P = 電源、G = グランド

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                             |                               | 最小値  | 最大値  | 単位 |

|-----------------------------|-------------------------------|------|------|----|

| VCC <sub>ABSMAX</sub>       | 電源電圧 (VCC)                    | -0.5 | 4.0  | V  |

| VIO <sub>CMOS,ABSMAX</sub>  | 3.3V LVC MOS ヒオーブンドレイン I/O 電圧 | -0.5 | 4.0  | V  |

| VIO <sub>5LVL,ABSMAX</sub>  | 5 レベル入力 I/O 電圧                | -0.5 | 2.75 | V  |

| VIO <sub>HS-RX,ABSMAX</sub> | 高速 I/O 電圧 (RXnP, RXnN)        | -0.5 | 3.2  | V  |

| VIO <sub>HS-TX,ABSMAX</sub> | 高速 I/O 電圧 (TXnP, TXnN)        | -0.5 | 2.75 | V  |

| T <sub>J,ABSMAX</sub>       | 接合部温度                         |      | 150  | °C |

| T <sub>stg</sub>            | 保管温度範囲                        | -65  | 150  | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。絶対最大定格は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。推奨動作条件の範囲外ではあるが、絶対最大定格の範囲内で短時間動作している場合、デバイスは損傷を受けない可能性がありますが、完全には機能しない可能性があります。この方法でデバイスを動作させると、デバイスの信頼性、機能性、性能に影響を及ぼし、デバイスの寿命を短縮する可能性があります。

### 5.2 ESD 定格

|                    |      | 値                                                         | 単位    |

|--------------------|------|-----------------------------------------------------------|-------|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM) ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>      | ±2000 |

|                    |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠 <sup>(2)</sup> | ±500  |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。±2kV と記載されたピンは、実際にはそれよりも高い性能を持つ場合があります。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

### 5.3 推奨動作条件

外気温度範囲での動作時 (特に記述がない限り)

|                                 |                                                  | 最小値                              | 公称値   | 最大値  | 単位   |

|---------------------------------|--------------------------------------------------|----------------------------------|-------|------|------|

| VCC                             | 供給電圧、VCC から GND                                  | DC と AC の電力の合計は、これらの制限を超えてはなりません | 3.0   | 3.3  | 3.6  |

| N <sub>VCC</sub> <sup>(1)</sup> | 電源ノイズ許容誤差                                        | DC から 50Hz 未満、正弦波                |       | 250  | mVpp |

|                                 |                                                  | 50Hz ~ 500kHz、正弦波                |       | 100  | mVpp |

|                                 |                                                  | 500kHz ~ 2.5MHz、正弦波              |       | 33   | mVpp |

|                                 |                                                  | 電源ノイズ、2.5MHz 超、正弦波               |       | 10   | mVpp |

| T <sub>RampVCC</sub>            | VCC 電源ランプ時間                                      | 0V~3.0V                          | 0.150 | 100  | ms   |

| T <sub>A</sub>                  | 動作時の周囲温度                                         |                                  | -40   | 105  | °C   |

| T <sub>J</sub>                  | 動作時接合部温度                                         |                                  |       | 125  | °C   |

| PW <sub>LVC MOS</sub>           | デバイスが LVC MOS 入力で有効な信号を検出するためには必要な最小ハペルス幅        | PD、SEL、および READ_ENn              | 200   |      | μs   |

| VCC <sub>SMBUS</sub>            | SMBus/I <sup>2</sup> C SDA および SCL のオーブンドレイン終端電圧 | オーブンドレイン プルアップ抵抗の電源電圧            |       | 3.6  | V    |

| F <sub>SMBus</sub>              | SMBus/I <sup>2</sup> C クロック (SCL) 周波数            | SMBus ターゲットモード                   | 10    | 400  | kHz  |

| VID <sub>LAUNCH</sub>           | ソース立ち上げ振幅                                        | 差動信号処理                           |       | 1200 | mVpp |

## 5.3 推奨動作条件 (続き)

外気温度範囲での動作時 (特に記述がない限り)

|    |         | 最小値 | 公称値 | 最大値 | 単位   |

|----|---------|-----|-----|-----|------|

| DR | データ レート | 1   |     | 20  | Gbps |

- (1) 正弦波ノイズは電源電圧に重畠されますが、デバイスの機能や、電気的表に示された重要な性能への影響はごくわずかです。AC と DC を合わせた電源ノイズが、規定された VDD 電源電圧の制限内に収まるように対策を講じる必要があります。

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>    |                     | DS160PR4<br>10-Q1 | 単位   |

|-------------------------|---------------------|-------------------|------|

|                         |                     | RGF、40 ピン         |      |

| R <sub>θJA-High K</sub> | 接合部から周囲への熱抵抗        | 29.6              | °C/W |

| R <sub>θJC(top)</sub>   | 接合部からケース (上面) への熱抵抗 | 19.0              | °C/W |

| R <sub>θJB</sub>        | 接合部から基板への熱抵抗        | 11.2              | °C/W |

| Ψ <sub>JT</sub>         | 接合部から上面への特性パラメータ    | 0.4               | °C/W |

| Ψ <sub>JB</sub>         | 接合部から基板への特性パラメータ    | 11.1              | °C/W |

| R <sub>θJC(bot)</sub>   | 接合部からケース (底面) への熱抵抗 | 3.8               | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.5 DC の電気的特性

自由気流での動作温度および電圧範囲内 (特に記述のない限り)

| パラメータ                                   |                                       | テスト条件                                                         | 最小値  | 標準値  | 最大値 | 単位 |

|-----------------------------------------|---------------------------------------|---------------------------------------------------------------|------|------|-----|----|

| <b>電源</b>                               |                                       |                                                               |      |      |     |    |

| P <sub>ACT</sub>                        | デバイスのアクティブ電力                          | 4 チャネルアクティブ、EQ = 0 ~ 2                                        | 0.57 | 0.71 |     | W  |

|                                         |                                       | 4 チャネルアクティブ、EQ = 5 ~ 19                                       | 0.69 | 0.85 |     | W  |

| P <sub>STBY</sub>                       | スタンバイ パワー モードにおけるデバイスの消費電力            | すべてのチャネルがディスエーブル (PD = H)                                     | 17   | 25   |     | mW |

| <b>制御 IO</b>                            |                                       |                                                               |      |      |     |    |

| V <sub>IH</sub>                         | High レベル入力電圧                          | SDA、SCL、PD、READ_ENn、SEL ピン                                    | 2.1  |      |     | V  |

| V <sub>IL</sub>                         | Low レベル入力電圧                           | SDA、SCL、PD、READ_ENn、SEL ピン                                    |      | 1.08 |     | V  |

| V <sub>OH</sub>                         | High レベル出力電圧                          | R <sub>pullup</sub> = 4.7kΩ (SDA、SCL、DONEn ピン)                | 2.1  |      |     | V  |

| V <sub>OL</sub>                         | Low レベル出力電圧                           | I <sub>OL</sub> = -4mA (SDA、SCL、DONEn ピン)                     |      | 0.4  |     | V  |

| I <sub>IH,SEL</sub>                     | SEL ピンの入力 High リーク電流                  | V <sub>Input</sub> = SEL ピン                                   |      | 100  |     | μA |

| I <sub>IH</sub>                         | 入力 High リーク電流                         | V <sub>Input</sub> = VCC、SCL、SDA、PD、READ_ENn ピン               |      | 10   |     | μA |

| I <sub>IL</sub>                         | 入力 Low リーク電流                          | V <sub>Input</sub> = 0V、SCL、SDA、PD、READ_ENn、SEL ピン            | -10  |      |     | μA |

| I <sub>IH,FS</sub>                      | フェイリセーフ入力ピンに対する入力 High リーク電流          | V <sub>Input</sub> = 3.6V、VCC = 0V、SCL、SDA、PD、READ_ENn、SEL ピン |      | 200  |     | μA |

| C <sub>IN-CTRL</sub>                    | 入力容量                                  | SDA、SCL、PD、READ_ENn、SEL ピン                                    | 1.6  |      |     | pF |

| <b>5 レベルの IO (MODE、GAIN、EQ0、EQ1 ピン)</b> |                                       |                                                               |      |      |     |    |

| I <sub>IH_5L</sub>                      | 入力 High リーク電流、5 レベル IO                | VIN = 2.5V                                                    |      | 10   |     | μA |

| I <sub>IL_5L</sub>                      | モードを除くすべての 5 レベル IO について入力 Low リーク電流。 | VIN = GND                                                     | -10  |      |     | μA |

## 5.5 DC の電気的特性 (続き)

自由気流での動作温度および電圧範囲内 (特に記述のない限り)

| パラメータ             |  | テスト条件                 | 最小値                                     | 標準値 | 最大値  | 単位       |

|-------------------|--|-----------------------|-----------------------------------------|-----|------|----------|

| $I_{IL\_5L,MODE}$ |  | MODE ピンの入力 Low リーク電流  | $V_{IN} = GND$                          |     | -200 | $\mu A$  |

| レシーバ              |  |                       |                                         |     |      |          |

| $V_{RX-DC-CM}$    |  | RX DC コモン モード電圧       | デバイスがアクティブまたはスタンバイ状態                    |     | 1.4  | V        |

| $Z_{RX-DC}$       |  | Rx DC シングルエンド インピーダンス |                                         |     | 50   | $\Omega$ |

| トランシミッタ           |  |                       |                                         |     |      |          |

| $Z_{TX-DIFF-DC}$  |  | DC 差動 Tx インピーダンス      | アクティブ信号中の Tx のインピーダンス, VID, diff = 1Vpp |     | 100  | $\Omega$ |

| $V_{TX-DC-CM}$    |  | レシーバの DC 同相電圧インピーダンス  |                                         |     | 1.0  | V        |

| $I_{TX-SHORT}$    |  | Tx 短絡電流               | GND に短絡したときに Tx が供給できる総電流               |     | 70   | $mA$     |

## 5.6 高速電気的特性

自由気流での動作温度および電圧範囲内 (特に記述のない限り)

| パラメータ           |                                   | テスト条件                        | 最小値 | 標準値 | 最大値 | 単位 |

|-----------------|-----------------------------------|------------------------------|-----|-----|-----|----|

| レシーバ            |                                   |                              |     |     |     |    |

| $RL_{RX-DIFF}$  | 入力差動リターン                          | 50MHz                        | -27 |     |     | dB |

|                 |                                   | 4.0GHz                       | -15 |     |     | dB |

|                 |                                   | 5.0GHz                       | -15 |     |     | dB |

|                 |                                   | 8.0GHz                       | -15 |     |     | dB |

|                 |                                   | 10.0GHz                      | -11 |     |     | dB |

| $RL_{RX-CM}$    | 入力同相モードリターン損失                     | 50MHz                        | -22 |     |     | dB |

|                 |                                   | 4.0GHz                       | -12 |     |     | dB |

|                 |                                   | 5.0GHz                       | -11 |     |     | dB |

|                 |                                   | 8.0GHz                       | -10 |     |     | dB |

|                 |                                   | 10.0GHz                      | -8  |     |     | dB |

| $XT_{RX}$       | レシーバ側ペア間絶縁                        | 10.0MHz ~ 10.0GHz の範囲全体での最小値 | -50 |     |     | dB |

| トランシミッタ         |                                   |                              |     |     |     |    |

| $RL_{TX-DIFF}$  | 出力差動リターン                          | 50.0MHz                      | -29 |     |     | dB |

|                 |                                   | 4.0GHz                       | -16 |     |     | dB |

|                 |                                   | 5.0GHz                       | -17 |     |     | dB |

|                 |                                   | 8.0GHz                       | -20 |     |     | dB |

|                 |                                   | 10.0GHz                      | -18 |     |     | dB |

| $RL_{TX-CM}$    | 出力同相モードリターン損失                     | 50.0MHz                      | -16 |     |     | dB |

|                 |                                   | 4.0GHz                       | -11 |     |     | dB |

|                 |                                   | 5.0GHz                       | -10 |     |     | dB |

|                 |                                   | 8.0GHz                       | -9  |     |     | dB |

|                 |                                   | 10.0GHz                      | -9  |     |     | dB |

| $XT_{TX}$       | 送信側のペア間絶縁                         | 10.0MHz ~ 10.0GHz の範囲全体での最小値 | -46 |     |     | dB |

| デバイス データパス      |                                   |                              |     |     |     |    |

| $T_{PLHD/PHLD}$ | データ チャネルを介した入力から出力までのレイテンシ (伝搬遅延) | ロトウハイまたはハイトウロー遷移のいずれの場合でも    | 100 |     |     | ps |

## 5.6 高速電気的特性 (続き)

自由気流での動作温度および電圧範囲内 (特に記述のない限り)

| パラメータ         |                                    | テスト条件                                                                 | 最小値  | 標準値 | 最大値 | 単位   |

|---------------|------------------------------------|-----------------------------------------------------------------------|------|-----|-----|------|

| $t_{RJ-DATA}$ | データによる付加ランダム ジッタ                   | リドライバを通過するジッタからキャリブレーションパターンを除きます。20Gbps PRBS15, 800mVpp-diff 入力スイングの | 70   |     |     | fs   |

| XT            | チャネル間クロストーク (隣接するアクティブ チャネル間、FEXT) | 50.0MHz ~ 10.0Ghz の範囲における最小値 (EQ ゲイン 0dB に正規化)                        | -38  |     |     | dB   |

| 直線性 - DC      | 出力 DC の直線性                         |                                                                       | 1650 |     |     | mVpp |

| 直線性 - AC      | 出力 AC 直線性 (GAIN = L4)              | 8Gbps                                                                 | 1250 |     |     | mVpp |

| 直線性 - AC      | 出力 AC 直線性 (GAIN = L4)              | 16Gbps                                                                | 1200 |     |     | mVpp |

| 直線性 - AC      | 出力 AC 直線性 (GAIN = L4)              | 20Gbps                                                                | 1100 |     |     | mVpp |

## 5.7 SMBUS/I<sup>2</sup>C タイミング特性

外気温度範囲での動作時 (特に記述がない限り)

| パラメータ             |                                                           | テスト条件                                  | 最小値  | 標準値 | 最大値 | 単位  |

|-------------------|-----------------------------------------------------------|----------------------------------------|------|-----|-----|-----|

| <b>ターゲット モード</b>  |                                                           |                                        |      |     |     |     |

| $t_{SP}$          | 入力フィルタにより抑制されるスパイクのパルス幅                                   |                                        |      | 50  |     | ns  |

| $t_{HD-STA}$      | ホールド時間 (繰り返し) START コンディション。<br>この期間の後に最初のクロック パルスが生成されます |                                        | 0.6  |     |     | μs  |

| $t_{LOW}$         | SCL クロック Low 期間                                           |                                        | 1.3  |     |     | μs  |

| $T_{HIGH}$        | SCL クロックの High の時間                                        |                                        | 0.6  |     |     | μs  |

| $t_{SU-STA}$      | 繰り返し START<br>条件のセットアップ時間                                 |                                        | 0.6  |     |     | μs  |

| $t_{HD-DAT}$      | データ ホールド時間                                                |                                        | 0    |     |     | μs  |

| $T_{SU-DAT}$      | データ セットアップ時間                                              |                                        | 0.1  |     |     | μs  |

| $t_r$             | SDA 信号と SCL 信号の両方の立ち上がり時間                                 | プルアップ抵抗 = 4.7kΩ, C <sub>b</sub> = 10pF | 120  |     |     | ns  |

| $t_f$             | SDA 信号と SCL 信号の両方の立ち下がり時間                                 | プルアップ抵抗 = 4.7kΩ, C <sub>b</sub> = 10pF | 2    |     |     | ns  |

| $t_{SU-STO}$      | 停止条件のセットアップ時間                                             |                                        | 0.6  |     |     | μs  |

| $t_{BUF}$         | STOP 条件と<br>START 条件の間のバス フリー時間                           |                                        | 1.3  |     |     | μs  |

| $t_{VD-DAT}$      | データ有効時間                                                   |                                        |      | 0.9 |     | μs  |

| $t_{VD-ACK}$      | データ有効アクリッジ時間                                              |                                        |      | 0.9 |     | μs  |

| $C_b$             | 各バス ラインの容量性負荷                                             |                                        |      | 400 |     | pF  |

| <b>コントローラ モード</b> |                                                           |                                        |      |     |     |     |

| $f_{SCL-M}$       | SCL クロック周波数                                               |                                        | 303  |     |     | kHz |

| $t_{LOW-M}$       | SCL の Low 期間                                              |                                        | 1.90 |     |     | μs  |

| $T_{HIGH-M}$      | SCL の High 期間                                             |                                        | 1.40 |     |     | μs  |

| $t_{SU-STA-M}$    | 繰り返し START<br>条件のセットアップ時間                                 |                                        | 2    |     |     | μs  |

## 5.7 SMBUS/I<sup>2</sup>C タイミング特性 (続き)

外気温度範囲での動作時 (特に記述がない限り)

| パラメータ          |                                                           | テスト条件                                  | 最小値 | 標準値 | 最大値 | 単位 |

|----------------|-----------------------------------------------------------|----------------------------------------|-----|-----|-----|----|

| $t_{HD-STA-M}$ | ホールド時間 (繰り返し) START コンディション。<br>この期間の後に最初のクロック パルスが生成されます |                                        | 1.5 |     |     | μs |

| $T_{SU-DAT-M}$ | データ セットアップ時間                                              |                                        | 1.4 |     |     | μs |

| $t_{HD-DAT-M}$ | データ ホールド時間                                                |                                        | 0.5 |     |     | μs |

| $t_{R-M}$      | SDA 信号と SCL 信号の両方の立ち上がり時間                                 | プルアップ抵抗 = 4.7kΩ, C <sub>b</sub> = 10pF | 120 |     |     | ns |

| $T_{F-M}$      | SDA 信号と SCL 信号の両方の立ち下がり時間                                 | プルアップ抵抗 = 4.7kΩ, C <sub>b</sub> = 10pF | 2   |     |     | ns |

| $t_{SU-STO-M}$ | STOP 条件のセットアップ時間                                          |                                        | 1.5 |     |     | μs |

### EEPROM のタイミング

|              |                     |                                                                 |     |    |

|--------------|---------------------|-----------------------------------------------------------------|-----|----|

| $T_{EEPROM}$ | EEPROM 構成のロード時間     | READ_EN <sub>n</sub> がアサートされた後に DONE <sub>n</sub> をアサートするまでの時間。 | 7.5 | ms |

| $T_{POR}$    | 最初の SMBus アクセスまでの時間 | 初期ランプ後に電源が安定します。最初のパワーオンリセット時間を含みます。                            | 50  | ms |

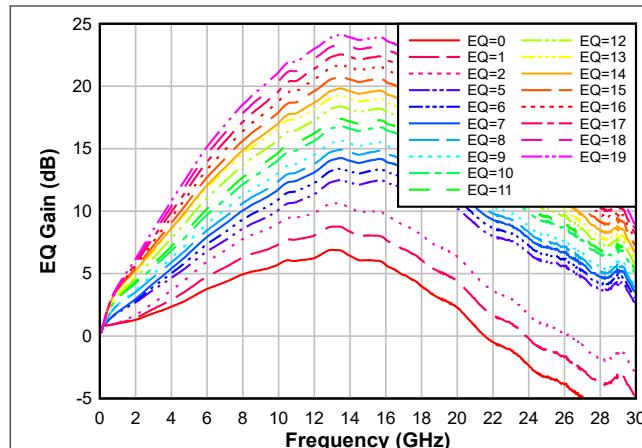

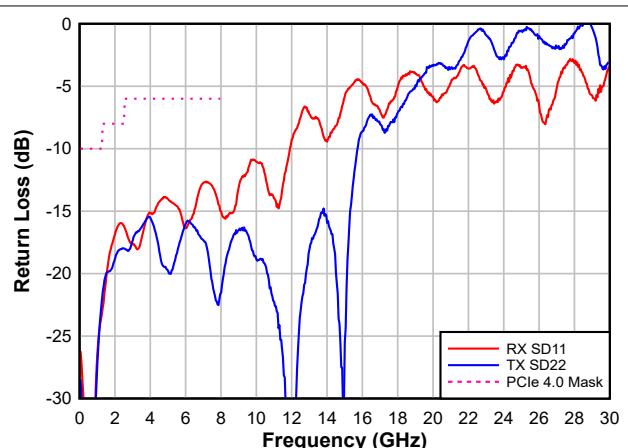

## 5.8 代表的特性

図 5-1 に、各種 EQ 設定における代表的な EQ ゲイン曲線と周波数との関係を示します。図 5-2 に、Rx および Tx ピンの代表的な差動リターン損失を示します。

図 5-1. 標準的な EQ 昇圧と周波数との関係

図 5-2. 差動リターン損失

## 5.9 代表的なジッタ特性

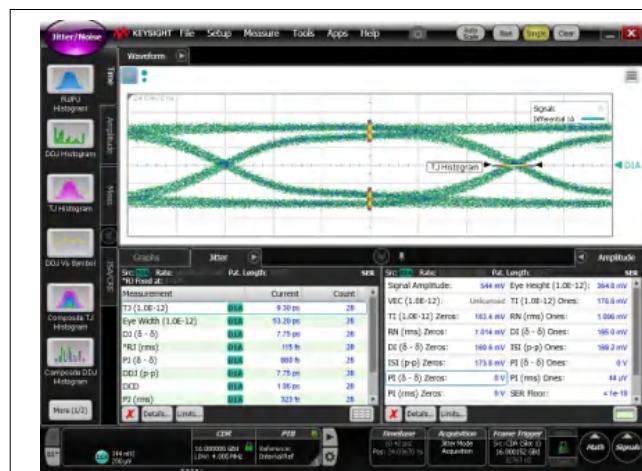

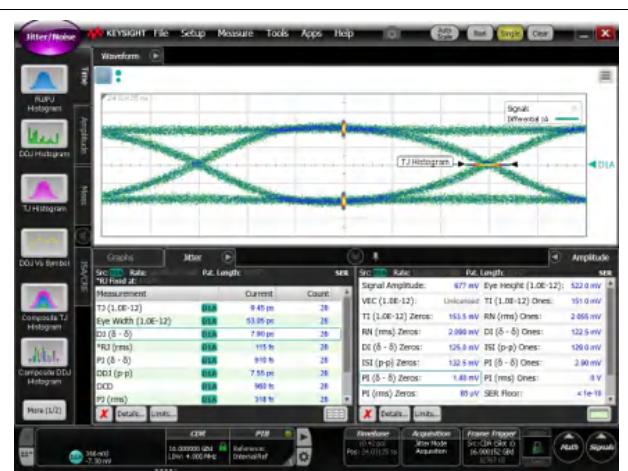

図 5-3 および 図 5-4 は、TI 評価ボードにおける最小チャネルでの 20Gbps のアイダイアグラムを示しており、キャリブレーショントレースを通したジッタ (左) と、を通したジッタ DS160PR410-Q1 (右) を比較しています。アイダイアグラムは、DS160PR410-Q1 が非常にわずかなランダムジッタ (RJ) しか追加しないことを示しており、計測器の精度以下です。キャリブレーショントレースと DUT を通した総ジッタが類似しているのは、EQ = 0 における残留イコライゼーションが入力損失に対する DJ をクリーンアップしているためと考えられます。

図 5-3. 16Gb/s 用ベースライン キャリブレーション パターン セットアップ経由

図 5-4. 16Gb/s 用 DS160PR410-Q1 経由

## 6 詳細説明

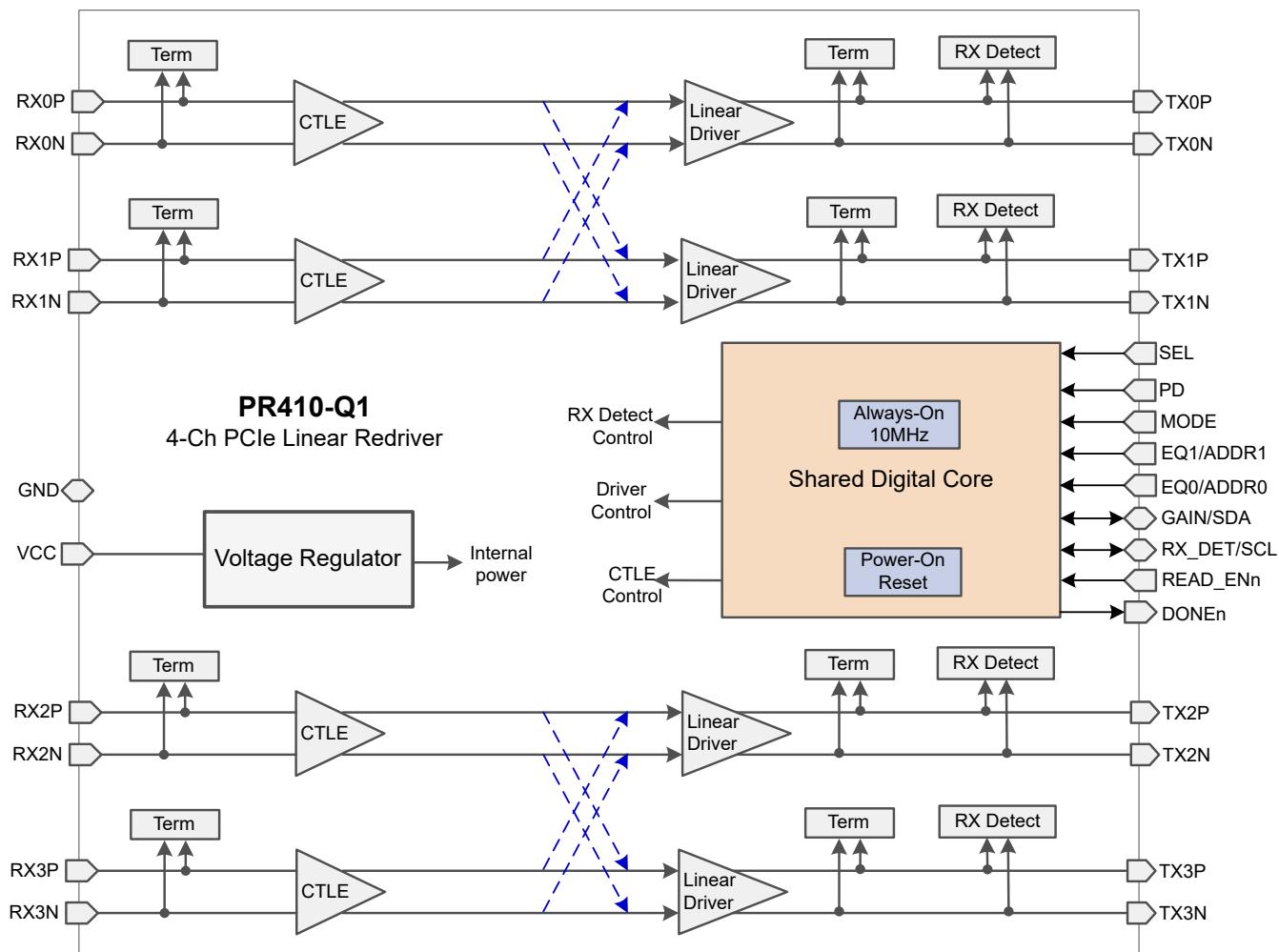

### 6.1 概要

DS160PR410-Q1 は、シグナル コンディショニングを内蔵した 4 チャネル マルチレートリニア リピータです。デバイスの信号チャネルは互いに独立して動作します。各チャネルには連続時間リニア イコライザ (CTLE) とリニア出力ドライバが含まれており、これらが連携してソース送信機と最終受信機の間の損失のある伝送チャネルを補償します。データ パスの直線性は、レシーバのイコライゼーションを効果的に維持しながら送信イコライゼーションを維持するように特に設計されています。

DS160PR410-Q1 は、次の 3 つの方法で設定できます：

**ピン モード** – デバイス制御構成は、ストラップ ピンのみで行われます。ピン モードは、多くのシステム実装ニーズに十分対応できると想定されています。

**SMBus/I<sup>2</sup>C コントローラ モード** – デバイス制御構成は外部 EEPROM から読み出されます。DS160PR410-Q1 が EEPROM の読み出しを正常に完了すると、DONEn ピンを LOW に駆動します。このモードでは、EEPROM 読み出しの前、中または後のいずれにおいても SMBus/I<sup>2</sup>C ターゲット動作が利用可能です。注：EEPROM 読み出し中に外部 SMBus/I<sup>2</sup>C コントローラが DS160PR410-Q1 レジスタにアクセスする場合、そのコントローラはアビトリエーションをサポートする必要があります。ソフトウェアの実装が不要な場合は、このモードが推奨されます。

**SMBus/I<sup>2</sup>C ターゲット モード** – 最大の柔軟性を提供します。DS160PR410-Q1 を構成するには、SMBus/I<sup>2</sup>C コントローラ デバイスがターゲット アドレスに書き込む必要があります。

## 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 リニア イコライゼーション

DS160PR410-Q1 レシーバには連続時間リニア イコライザ (CTLE) が備わっており、高周波数をブーストし低周波数を減衰させることで、パッシブ チャネルの周波数依存の挿入損失効果を等化します。このレシーバは、幅広いイコライゼーション機能のために 2 段のリニア イコライザを実装しています。イコライザ段は、幅広いチャネル媒体特性に最適な EQ ゲイン プロファイルに一致させるために、中周波数のブーストを微調整できる柔軟性も提供します。EQ プロファイル制御機能は、SMBus/I<sup>2</sup>C モードでのみ使用できます。ピン モードでは、これらの設定は FR4 パターンに最適化されています。

表 6-1 は、EQ コントロール ピンまたは SMBus/I<sup>2</sup>C レジスタを介して利用可能なイコライゼーション ブーストを提供します。ピン コントロール モードでは、EQ1 および EQ0 ピンでイコライゼーション ブーストを設定します。I<sup>2</sup>C モードでは、個々のチャネルが EQ 昇圧用に個別にプログラム可能です。

**表 6-1. イコライゼーション制御の設定**

| EQ インデックス | イコライザ設定 |     |                            |               |                |                  | EQ 昇圧標準値 (dB)<br>8GHz 時 |  |

|-----------|---------|-----|----------------------------|---------------|----------------|------------------|-------------------------|--|

|           | ピン モード  |     | SMBus/I <sup>2</sup> C モード |               |                |                  |                         |  |

|           | EQ1     | EQ0 | eq_stage1_3:0              | eq_stage2_2:0 | eq_profile_3:0 | eq_stage1_bypass |                         |  |

| 0         | L0      | L0  | 0                          | 0             | 0              | 1                | 3.0                     |  |

| 1         | L0      | L1  | 1                          | 0             | 0              | 1                | 4.0                     |  |

| 2         | L0      | L2  | 3                          | 0             | 0              | 1                | 5.5                     |  |

| 5         | L1      | L0  | 0                          | 0             | 1              | 0                | 6.5                     |  |

| 6         | L1      | L1  | 1                          | 0             | 1              | 0                | 7.0                     |  |

| 7         | L1      | L2  | 2                          | 0             | 1              | 0                | 7.5                     |  |

| 8         | L1      | L3  | 3                          | 0             | 3              | 0                | 8.5                     |  |

| 9         | L1      | L4  | 4                          | 0             | 3              | 0                | 9.0                     |  |

| 10        | L2      | L0  | 5                          | 1             | 7              | 0                | 10.0                    |  |

| 11        | L2      | L1  | 6                          | 1             | 7              | 0                | 10.5                    |  |

| 12        | L2      | L2  | 8                          | 1             | 7              | 0                | 11.0                    |  |

| 13        | L2      | L3  | 10                         | 1             | 7              | 0                | 12.0                    |  |

| 14        | L2      | L4  | 10                         | 2             | 15             | 0                | 12.5                    |  |

| 15        | L3      | L0  | 11                         | 3             | 15             | 0                | 13.0                    |  |

| 16        | L3      | L1  | 12                         | 4             | 15             | 0                | 14.0                    |  |

| 17        | L3      | L2  | 13                         | 5             | 15             | 0                | 14.5                    |  |

| 18        | L3      | L3  | 14                         | 6             | 15             | 0                | 15.5                    |  |

| 19        | L3      | L4  | 15                         | 7             | 15             | 0                | 16.0                    |  |

### 6.3.2 フラットゲイン

デバイスがピン モードのとき、ゲイン ピンを使用して、DS160PR410-Q1 のデータ パス全体のフラット ゲイン (DC および AC) を設定できます。I<sup>2</sup>C モードでは、各チャネルを独立して設定できます。表 6-2 はフラット ゲイン制御構成設定値を提供します。ほとんどのシステムに対するデフォルト推奨値は GAIN = L4 (フロート) であり、0.6dB のフラット ゲインを提供します。

DS160PR410-Q1 のフラット ゲインとイコライゼーションは、出力信号スイングが DC および高周波数において、それぞれデバイスの DC および AC の直線性の範囲を超えないように設定する必要があります。

**表 6-2. フラット ゲイン構成の設定**

| ピン モード ゲイン   | I <sup>2</sup> C モード flat_gain_2:0 | フラット ゲイン          |

|--------------|------------------------------------|-------------------|

| L0           | 0                                  | -5.6dB            |

| L1           | 1                                  | -3.8dB            |

| L2           | 3                                  | -1.3dB            |

| L3           | 7                                  | +2.5dB            |

| L4 (フローティング) | 5                                  | 0.6dB (デフォルトの推奨値) |

### 6.3.3 レシーバ検出ステート マシン

DS160PR410-Q1 は、PCI Express 仕様で定義される Rx 検出サイクルを制御する Rx 検出ステート マシンを展開します。パワー アップ時、または手動で PD または SEL をトグルした後、リドライバは遠端レシーバに有効な PCI Express 終

端が存在するかどうかを判定します。DS160PR410-Q1 の RX\_DET ピンは、表 6-3 に示されるように、システム設計者が所望のモードに適切にデバイスを設定できる追加の柔軟性を提供します。多くのアプリケーションでは、RX\_DET ピンをフロートのままにしてデフォルト設定を利用できます。SMBus/I<sup>2</sup>C モードでは、各チャネルを個別に構成できます。

表 6-3. レシーバ検出ステート マシン設定

| PD | RX_DET       | Rx コモンモード インピーダンス        | 備考                                                                                                                                                   |

|----|--------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| L  | L0           | 常に 50Ω                   | PCI Express Rx 検出ステートマシンは無効化されます。イコライゼーション付きバッファとして DS160PR410-Q1 を使用する非 PCIe インターフェイス用途に推奨されます。                                                     |

| L  | L1           | 事前検出: Hi-Z<br>事後検出: 50Ω。 | 3 回連続で有効な検出が行われるまで出力がポーリングします                                                                                                                        |

| L  | L2           | 事前検出: Hi-Z<br>事後検出: 50Ω。 | 2 回連続で有効な検出が行われるまで出力がポーリングします                                                                                                                        |

| L  | L3           | 該当なし                     | 予約済み                                                                                                                                                 |

| L  | L4 (フローティング) | 事前検出: Hi-Z<br>事後検出: 50Ω。 | 有効な終端が検出されるまで、 $\approx 150\mu\text{s}$ ごとに Tx がポーリングします。Rx CM インピーダンスは検出まで Hi-Z に保持されます。PD を $200\mu\text{s}$ の間 High にアサートしてから Low にすることでリセットされます。 |

| H  | X            | ハイインピーダンス                | Rx インピーダンスを Hi-Z に設定します                                                                                                                              |

PCIe アプリケーションでは、PD ピンを反転極性で PCIe サイドバンド信号 PERST# に、または 1 つ以上の適切な PRSNTx# 信号に接続して、所望の RX ディテクト機能を実現できます。

### 6.3.4 クロス ポイント

DS160PR410-Q1 はデュアル 2x2 クロス ポイント機能を提供します。SEL ピンを使用して、4 チャネルの信号パスをストレート接続またはクロス接続に構成できます (図 6-1 に示すように)。

図 6-1. DS160PR410-Q1 クロス ポイント Mux 動作の信号フロー ダイアグラム

## 6.4 デバイスの機能モード

### 6.4.1 アクティブ PCIe モード

デバイスは通常動作中であり、PCIe ステートマシンは RX\_DET = L1/L2/L4 によって有効化されています。このモードでは、システム内で PD ピンが Low に駆動されます (つまり、PCIe コネクタの PRSNTx# やファンダメンタル リセット PERST# 信号によって)。このモードでは、DS160PR410-Q1 は PCIe Rx または Tx 信号をリドライブし、イコライズして信号品質を改善します。

#### 6.4.2 リニア イコライザ(バッファ) モード

デバイスは通常動作中であり、PCIe ステート マシンは  $RX\_DET = L0$  によって無効化されています。このモードは非 PCIe 用途に推奨されます。このモードでは、デバイスはバッファとして動作し、リニア イコライゼーションを提供することで信号品質を改善します。

#### 6.4.3 スタンバイ モード

デバイスは、 $PD = H$  によってスタンバイ モードになります。このモードでは、デバイスは電力を節約するスタンバイ モードにあります。

## 6.5 プログラミング

### 6.5.1 ピン モード

DS160PR410-Q1 はピン ストラップ ピンを通じて完全に構成可能です。このモードでは、デバイスは 2 段階ピンと 5 段階ピンを使用して、デバイス制御と信号整合性の最適設定を行います。

#### 6.5.1.1 5 レベル制御入力

DS160PR410-Q1 は、デバイスの構成を制御するために使用される 5 レベル入力ピン (EQ0、EQ1、GAIN、MODE、RX\_DET) を備えています。これらの 5 段階入力は、抵抗分圧器を使用して 5 つの有効なレベルを設定し、より広い範囲の制御設定を可能にします。外付け抵抗は、公差 10% 以上とする必要があります。EQ0、EQ1、GAIN、RX\_DET ピンは、パワー アップ時のみサンプリングされます。MODE ピンは、デバイスの電源投入時または通常動作モード時に実行できます。

**表 6-4. 5 レベル制御ピンの設定**

| レベル | 設定              |

|-----|-----------------|

| L0  | 1kΩ から GND へ    |

| L1  | 8.25kΩ から GND へ |

| L2  | 24.9kΩ から GND へ |

| L3  | 75kΩ から GND へ   |

| L4  | F (フローティング)     |

### 6.5.2 SMBUS/I<sup>2</sup>C レジスタ制御インターフェイス

MODE = L2 (SMBus/I<sup>2</sup>C ターゲット制御モード) の場合、DS160PR410-Q1 は最大 400kHz で動作可能な標準 I<sup>2</sup>C または SMBus インターフェイスを介して構成されます。DS160PR410-Q1 のターゲット アドレスは、ADDR1 および ADDR0 ピンのピン ストラップ設定によって決定されます。DS160PR410-Q1 の各チャネル バンクに対する 16 通りのターゲット アドレスは [表 6-5](#) に示されています。SMBus/I<sup>2</sup>C モードでは、SCL および SDA ピンを 3.3V 電源にプルアップ 抵抗を介してプルアップする必要があります。この抵抗の値は、合計バス容量に依存します。4.7kΩ は、10pF のバス容量に対して適切な最初の近似値です。

**表 6-5. SMBus/I<sup>2</sup>C ターゲット アドレス設定**

| ADDR1 | ADDR0 | 7 ビットターゲット アドレス |

|-------|-------|-----------------|

| L0    | L0    | 0x18            |

| L0    | L1    | 0x1A            |

| L0    | L2    | 0x1C            |

| L0    | L3    | 0x1E            |

| L1    | L0    | 0x20            |

| L1    | L1    | 0x22            |

| L1    | L2    | 0x24            |

| L1    | L3    | 0x26            |

| L2    | L0    | 0x28            |

| L2    | L1    | 0x2A            |

| L2    | L2    | 0x2C            |

| L2    | L3    | 0x2E            |

| L3    | L0    | 0x30            |

| L3    | L1    | 0x32            |

| L3    | L2    | 0x34            |

| L3    | L3    | 0x36            |

| X     | L4    | 予約済み            |

DS160PR410-Q1 には 2 種類のレジスタがあります:

- 共有レジスタ:**これらのレジスタはいつでもアクセス可能で、デバイス レベルの設定、ステータスの読み戻し、制御、またはデバイス ID 情報のリードバックに使用されます。

- チャネル レジスタ:**これらのレジスタは、各チャネルの特定の機能を制御および設定するために使用されます。すべてのチャネルは同じレジスタ セットを持ち、それぞれを独立して構成することも、ブロードキャストライトで Bank 0 または Bank 1 に対してグループとして構成することもできます。

DS160PR410-Q1 は 4 チャネルを備えています。

| チャネル レジスタ ベース アドレス | チャネル アクセス                                        |

|--------------------|--------------------------------------------------|

| 0x00               | チャネル 0 レジスタ                                      |

| 0x20               | チャネル 1 レジスタ                                      |

| 0x40               | チャネル 2 レジスタ                                      |

| 0x60               | チャネル 3 レジスタ                                      |

| 0x80               | ブロードキャストライト チャネル Bank 0 レジスタ、<br>チャネル 0 レジスタをリード |

| 0xA0               | ブロードキャストライト チャネル 0-1 レジスタ、<br>チャネル 0 レジスタをリード    |

| 0xC0               | ブロードキャストライト チャネル 2-3 レジスタ、<br>チャネル 2 レジスタをリード    |

| 0xE0               | チャネル 0-3 がレジスタを共有                                |

### 6.5.2.1 共有レジスタ

表 6-6. 汎用レジスタ (オフセット = 0xE2)

| ビット | フィールド         | タイプ    | リセット | 説明                                                              |

|-----|---------------|--------|------|-----------------------------------------------------------------|

| 7   | 予約済み          | R      | 0x0  | 予約済み                                                            |

| 6   | rst_i2c_regs  | R/W/SC | 0x0  | デバイスリセット制御: すべての I <sup>2</sup> C レジスタをデフォルト値にリセットします (セルフクリア)。 |

| 5   | rst_i2c_mas   | R/W/SC | 0x0  | I <sup>2</sup> C コントローラをリセットします (セルフクリア)。                       |

| 4-1 | 予約済み          | R      | 0x0  | 予約済み                                                            |

| 0   | frc_eeprom_rd | R/W/SC | 0x0  | MODE および READ_ENn ステータスをオーバーライドして、手動の EEPROM 構成ロードを強制します。       |

表 6-7. EEPROM\_Status レジスタ (オフセット = 0xE3)

| ビット | フィールド         | タイプ | リセット | 説明                      |

|-----|---------------|-----|------|-------------------------|

| 7   | eecfg_cmplt   | R   | 0x0  | EEPROM のロードが完了しました。     |

| 6   | eecfg_fail    | R   | 0x0  | EEPROM のロードに失敗しました。     |

| 5   | eecfg_atmpt_1 | R   | 0x0  | EEPROM イメージのロード試行回数。    |

| 4   | eecfg_atmpt_0 | R   | 0x0  | MSB を参照してください           |

| 3   | eecfg_cmplt   | R   | 0x0  | EEPROM ロード完了 2。         |

| 2   | eecfg_fail    | R   | 0x0  | EEPROM のロードに失敗しました 2。   |

| 1   | eecfg_atmpt_1 | R   | 0x0  | EEPROM イメージ 2 のロード試行回数。 |

| 0   | eecfg_atmpt_0 | R   | 0x0  | MSB を参照してください           |

表 6-8. DEVICE\_ID0 レジスタ (オフセット = 0xF0)

| ビット | フィールド | タイプ | リセット | 説明   |

|-----|-------|-----|------|------|

| 7-4 | 予約済み  | R   | 0x0  | 予約済み |

**表 6-8. DEVICE\_ID0 レジスタ (オフセット = 0xF0) (続き)**

| ビット | フィールド        | タイプ | リセット | 説明                  |

|-----|--------------|-----|------|---------------------|

| 3   | device_id0_3 | R   | 0x0  | デバイス ID0 [3:1]: 011 |

| 2   | device_id0_2 | R   | 0x1  | MSB を参照してください       |

| 1   | device_id0_1 | R   | 0x1  | MSB を参照してください       |

| 0   | 予約済み         | R   | X    | 予約済み                |

**表 6-9. DEVICE\_ID1 レジスタ (オフセット = 0xF1)**

| ビット | フィールド        | タイプ | リセット | 説明                               |

|-----|--------------|-----|------|----------------------------------|

| 7   | device_id[7] | R   | 0x0  | デバイス ID 0010 1001: DS160PR410-Q1 |

| 6   | device_id[6] | R   | 0x0  | MSB を参照してください                    |

| 5   | device_id[5] | R   | 0x1  | MSB を参照してください                    |

| 4   | device_id[4] | R   | 0x0  | MSB を参照してください                    |

| 3   | device_id[3] | R   | 0x1  | MSB を参照してください                    |

| 2   | device_id[2] | R   | 0x0  | MSB を参照してください                    |

| 1   | device_id[1] | R   | 0x0  | MSB を参照してください                    |

| 0   | device_id[0] | R   | 0x0  | MSB を参照してください                    |

### 6.5.2.2 チャネル レジスタ

**表 6-10. RX 検出ステータス レジスタ (チャネル レジスタ ベース + オフセット= 0x00)**

| ビット | フィールド         | タイプ | リセット | 説明                                                        |

|-----|---------------|-----|------|-----------------------------------------------------------|

| 7   | rx_det_comp_p | R   | 0x0  | Rx 検出の正のデータピンのステータス:<br>0: 検出されません<br>1: 検出済み - 値がラッチされます |

| 6   | rx_det_comp_n | R   | 0x0  | Rx 検出負のデータピンのステータス:<br>0: 検出されません<br>1: 検出済み - 値がラッチされます  |

| 5-0 | 予約済み          | R   | 0x0  | 予約済み                                                      |

**表 6-11. EQ ゲイン制御レジスタ (チャネル レジスタ ベース + オフセット= 0x01)**

| ビット | フィールド            | タイプ | リセット | 説明                                                    |

|-----|------------------|-----|------|-------------------------------------------------------|

| 7   | eq_stage1_bypass | R/W | 0x0  | EQ 段 1 のバイパスを有効化:<br>0: バイパスはディスエーブル<br>1: バイパスはイネーブル |

| 6   | eq_stage1_3      | R/W | 0x0  | EQBoost ステージ 1 制御<br>詳しくは、表 6-1 を参照してください             |

| 5   | eq_stage1_2      | R/W | 0x0  |                                                       |

| 4   | eq_stage1_1      | R/W | 0x0  |                                                       |

| 3   | eq_stage1_0      | R/W | 0x0  |                                                       |

| 2   | eq_stage2_2      | R/W | 0x0  |                                                       |

| 1   | eq_stage2_1      | R/W | 0x0  | EQ ブースト ステージ 2 制御<br>詳しくは、表 6-1 を参照してください             |

| 0   | eq_stage2_0      | R/W | 0x0  |                                                       |

**表 6-12. EQ ゲイン/フラット ゲイン制御レジスタ (チャネル レジスタ ベース + オフセット= 0x03)**

| ビット | フィールド | タイプ | リセット | 説明   |

|-----|-------|-----|------|------|

| 7   | 予約済み  | R   | 0x0  | 予約済み |

**表 6-12. EQ ゲイン/フラット ゲイン制御レジスタ (チャネル レジスタ ベース + オフセット = 0x03) (続き)**

| ビット | フィールド        | タイプ | リセット | 説明                                      |

|-----|--------------|-----|------|-----------------------------------------|

| 6   | eq_profile_3 | R/W | 0x0  | EQ 中周波数昇圧プロファイル<br>詳しくは、表 6-1 を参照してください |

| 5   | eq_profile_2 | R/W | 0x0  |                                         |

| 4   | eq_profile_1 | R/W | 0x0  |                                         |

| 3   | eq_profile_0 | R/W | 0x0  |                                         |

| 2   | flat_gain_2  | R/W | 0x1  | フラット ゲインの選択:<br>詳しくは、表 6-2 を参照してください    |

| 1   | flat_gain_1  | R/W | 0x0  | 詳しくは、表 6-2 を参照してください                    |

| 0   | flat_gain_0  | R/W | 0x1  |                                         |

**表 6-13. RX 検出コントロール レジスタ (チャネル レジスタ ベース + オフセット = 0x04)**

| ビット | フィールド            | タイプ | リセット | 説明                                                                                                                                           |

|-----|------------------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 7-3 | 予約済み             | R   | 0x0  | 予約済み                                                                                                                                         |

| 2   | mr_rx_det_man    | R/W | 0x0  | rx_detect_p/n 判定の手動オーバーライド:<br>0: RX 検出ステート マシンが有効になっている<br>1: RX 検出ステート マシンがオーバーライドされ、常に有効な RX 終端が検出される                                     |

| 1   | en_rx_det_count  | R/W | 0x0  | 追加の RX 検出ポーリングを有効化<br>0: 追加の RX 検出ポーリングが無効になっている<br>1: 追加の RX 検出ポーリングが有効になっている                                                               |

| 0   | sel_rx_det_count | R/W | 0x0  | 有効な RX 検出ポーリング回数を選択 — en_rx_det_count = 1 の場合に有効<br>0: デバイストランシミッタは、2 回連続で有効な検出が行われるまでポーリングします<br>1: デバイストランシミッタは、3 回連続で有効な検出が行われるまでポーリングします |

**表 6-14. PD オーバーライド レジスタ (チャネル レジスタ ベース + オフセット = 0x05)**

| ビット | フィールド              | タイプ | リセット     | 説明                                                                                                            |

|-----|--------------------|-----|----------|---------------------------------------------------------------------------------------------------------------|

| 7   | device_en_override | R/W | 0x0      | SMBus/I <sup>2</sup> C を介してパワー ダウン オーバーライドを有効化<br>0: 手動オーバーライドがディスエーブル<br>1: 手動オーバーライドがイネーブル                  |

| 6-0 | device_en          | R/W | 0x111111 | device_en_override = 1 の場合、リドライバの各ブロックを手動でパワー ダウン可能<br>111111: すべてのブロックが有効になっている<br>000000: すべてのブロックが無効になっている |

**表 6-15. バイアス レジスタ (チャネル レジスタ ベース + オフセット = 0x06)**

| ビット       | フィールド  | タイプ | リセット    | 説明                                   |

|-----------|--------|-----|---------|--------------------------------------|

| 5-3       | バイアス電流 | R/W | 0x100   | 制御バイアス電流<br>最高のパフォーマンスを得るために 001 を設定 |

| 7, 6, 2-0 | 予約済み   | R/W | 0x00000 | 予約済み                                 |

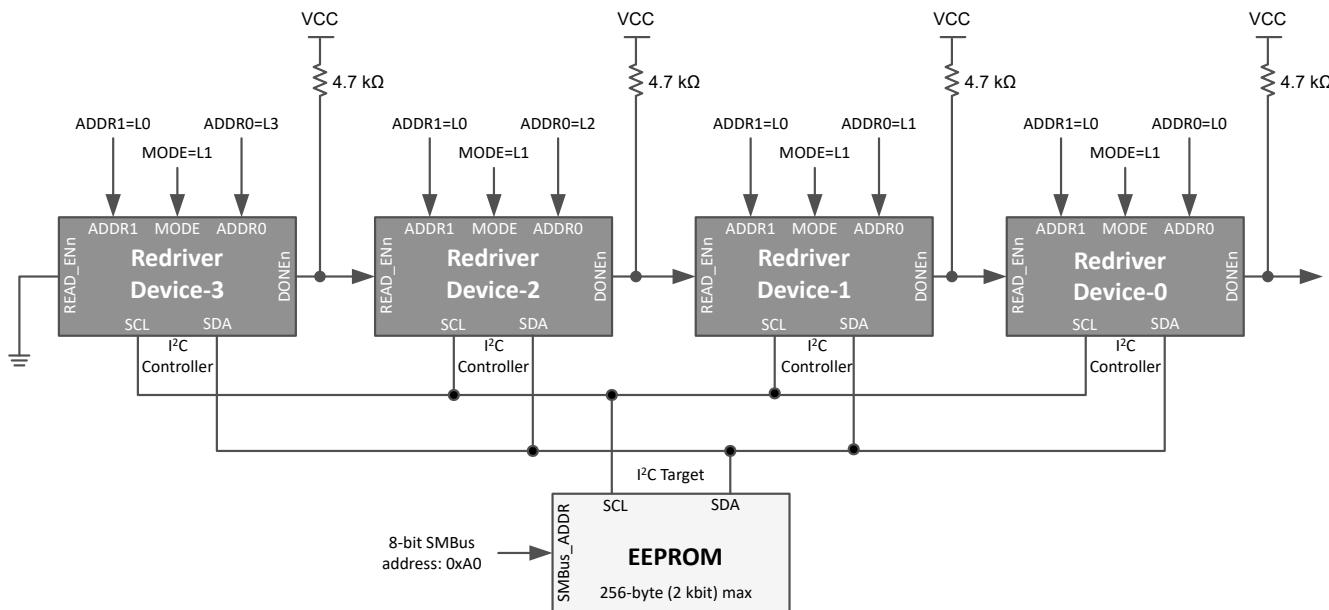

### 6.5.3 SMBus/I<sup>2</sup>C コントローラ モード構成 (EEPROM セルフロード)

DS160PR410-Q1 は、EEPROM から読み取ることで構成することもできます。このモード ピンに移行するには、L1 に設定する必要があります。EEPROM ロード動作は、デバイスの初回パワー アップ後に 1 度だけ実行されます。DS160PR410-Q1 が SMBus コントローラ モードに構成されている場合、READ\_ENn ピンが LOW にアサートされるまで SMBus IDLE 状態に留まります。READ\_ENn ピンが LOW に駆動されると、DS160PR410-Q1 は SMBus コントローラとなり、外部 EEPROM (SMBus 8 ビット アドレス 0xA0) に保存されたデバイス設定を読み出してセルフ コンフィギュレーションします。

ーションを試みます。DS160PR410-Q1 が EEPROM の読み出しを正常に完了すると、DONEn ピンを LOW に駆動します。このモードでは、EEPROM 読み出しの前、中または後のいずれにおいても SMBus/I<sup>2</sup>C ターゲット動作が利用可能です。注: EEPROM 読み出し中に外部 SMBus/I<sup>2</sup>C コントローラが DS160PR410-Q1 レジスタにアクセスする場合、そのコントローラはアビトレーションをサポートする必要があります。

外部 EEPROM を使用するシステムを設計する際には、ユーザーは以下の特定のガイドラインに従う必要があります:

- EEPROM サイズとして 2kb (256×8 ビット) を推奨します。

- MODE = L1 を設定し、SMBus コントローラ モードに構成します。

- 外部 EEPROM デバイスのアドレス バイトは 0xA0 である必要があり、3.3V 電源で 400kHz 動作が可能である必要があります

- SMBus/I<sup>2</sup>C モードでは、SCL および SDA ピンを 3.3V 電源にプルアップ抵抗を介してプルアップする必要があります。この抵抗の値は、合計バス容量に依存します。4.7kΩ は、10pF のバス容量に対して適切な最初の近似値です。

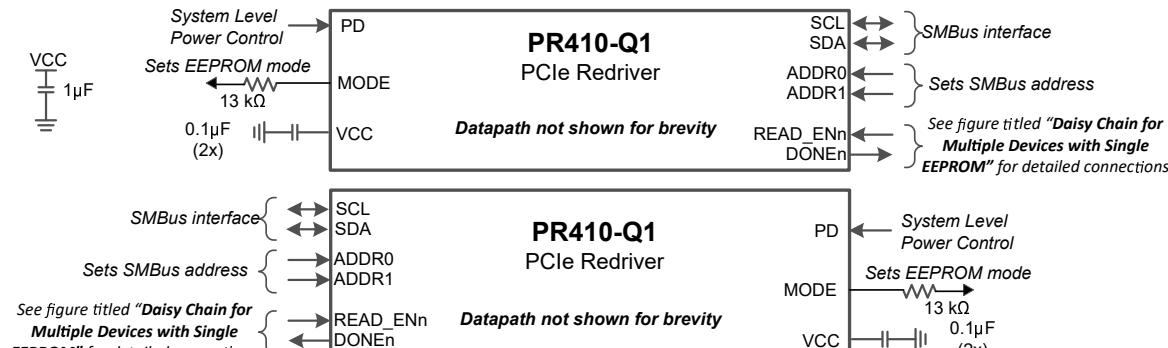

図 6-2 は、4 つの DS160PR410-Q1 を使用して PCIe x8 または 2 つの x4 構成を実装するユース ケースを示していますが、ユーザーは任意の数の DS160PR410-Q1 デバイスを同様の方法でカスケードできます。最初のデバイスの READ\_ENn ピンを Low に固定すると、パワー アップ時に自動的に EEPROM リードが開始されます。または、最初のデバイスの READ\_ENn ピンをマイクロコントローラで制御して、EEPROM リードを手動で開始することもできます。最後のデバイスの DONEn ピンはフロートのままにするか、マイクロコントローラ入力に接続して、最終 EEPROM リードの完了を監視します。

図 6-2. 単一 EEPROM から読み出すための 4 つの DS160PR410-Q1 デバイスのデイジーチェーン構成 (2 つの x4 または 1 つの x8 リンク構成)

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

DS160PR410-Q1 は、高速リニア リピータであり、PCB やケーブルなどの伝送媒体による損失で劣化した差動チャネルの到達距離を延長します。さまざまなシステムに導入可能です。以下のセクションでは、典型的なアプリケーションと、それに関連する設計上の考慮事項を概説します。

### 7.2 代表的なアプリケーション

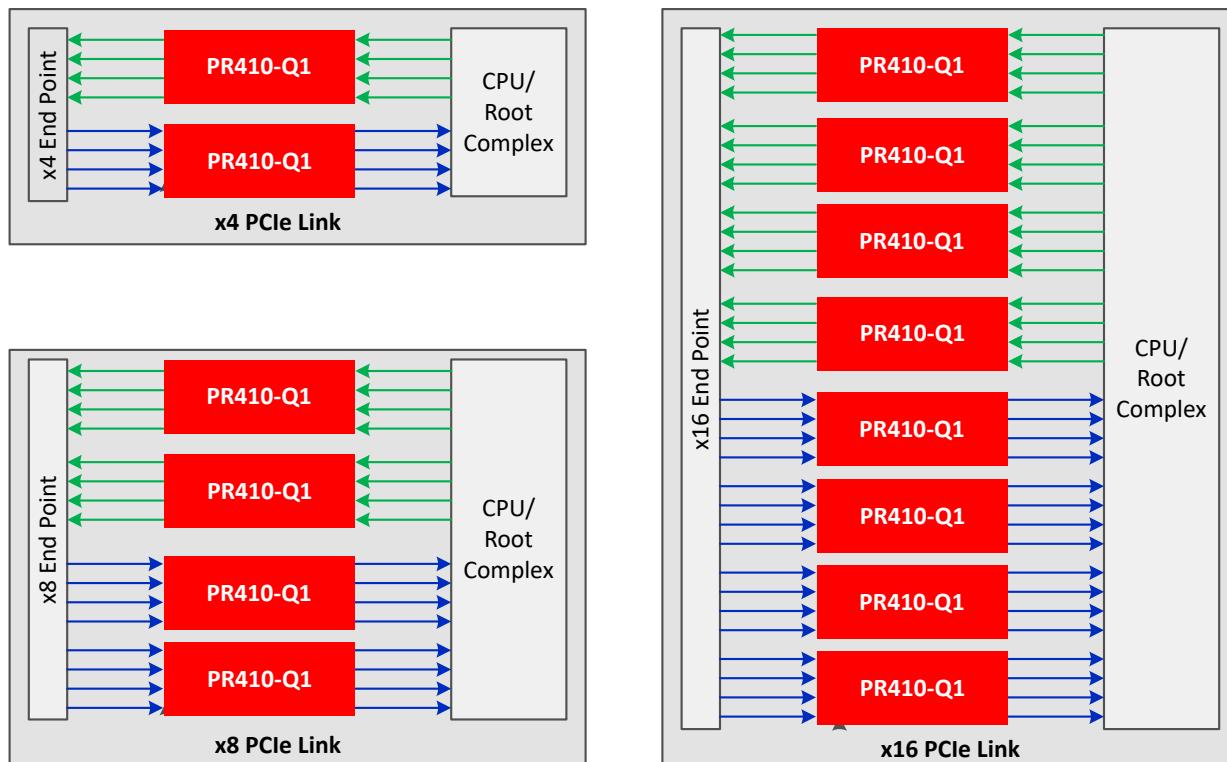

DS160PR410-Q1 は PCI Express リニア リドライバであり、Rx ディテクト機能を無効化することでインターフェイス非依存のリドライバとして構成することもできます。DS160PR410-Q1 は PCI Express レシーバ ディテクト機能を備えたプロトコル非依存の 4 チャネル リニア リドライバです。そのプロトコル非依存性により、PCI Express x4、x8、x16 アプリケーションで使用できます。図 7-1 は、複数の DS160PR410-Q1 デバイスを用いて、さまざまな幅の PCI Express バスに対して信号コンディショニングを実現する方法を示しています。

図 7-1. DS160PR410-Q1 を用いた PCI Express x4、x8、x16 のユース ケース

### 注

DS160PR410-Q1 の全 4 チャネルを同一方向に流します。したがって、x4 構成で 2 つのデバイスを使用する場合、両デバイスの PD を接続して PCIe ステートマシンを実装する必要があります。

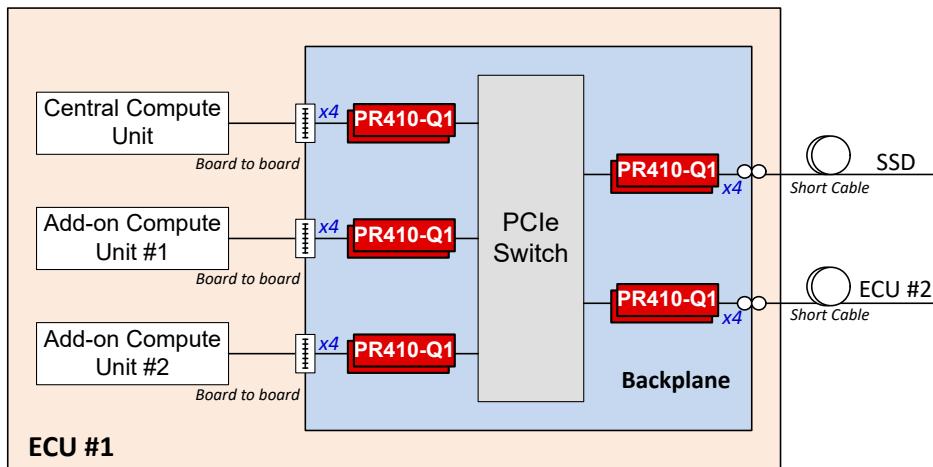

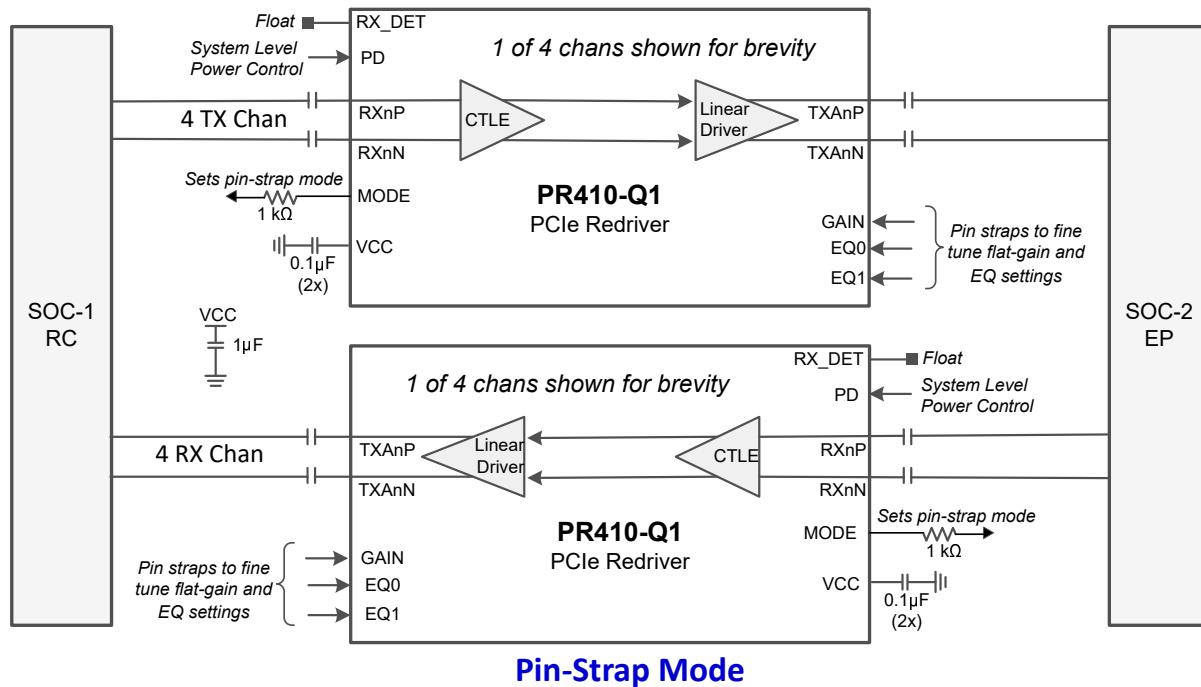

### 7.2.1 x4 レーン構成

DS160PR410-Q1 は、自動車アプリケーションで送信信号および受信信号をブーストし、ホストまたはルートコンプレックスプロセッサから PCIe Express エンドポイント (EP) へのリーチを拡張するために使用できます。図 7-2 は、自動車用 ECU (電子制御ユニット) を示しており、PCIe リンクが基板間コネクタを介して ECU 内の複数のコンピュートユニットを相互接続するために使用され、その際 DS160PR410-Q1 が信号コンディショニング機能を提供します。リドライバは、短いケーブルを用いて ECU 外部での PCIe リンクも可能にします。この例では、説明のために x4 リンクを示していますが、他のバス幅も利用可能です。

図 7-2. 自動車用 ECU における PCIe x4 リンク

以下のセクションでは、典型的な PCIe x4 レーン構成に対する詳細な手順と設計要件を示します。ただし、設計推奨事項は任意のレーン構成に使用できます。

#### 7.2.1.1 設計要件

他の高速設計と同様に、全体的な性能に影響を及ぼす要因は多数あります。以下のリストは、設計時に考慮すべき重要な領域を示しています。

- PCIe CEM コネクタと接続する場合は、 $85\Omega$  インピーダンスの配線を使用します。差動ペアのシングル エンド区間では、P トレースと N トレースの長さを一致させる必要があります。

- 差動ペアには、均一なパターン幅とパターン間隔を使用します。

- 反射を最小限に抑えるため、各チャネル セグメントのレシーバ端の近くに AC カップリング コンデンサを配置します。

- PCIe の AC カップリング コンデンサには  $220\text{nF}$  を推奨します。最大ボディ サイズを 0402 に設定し、コンデンサのランド パッド下の GND プレーンにカットアウト ポイドを追加して、GND への寄生容量を低減します。

- ドリルで背面にコネクタのビアと信号ビアを穴開けし、スタブの長さを最小化。

- リターン電流の低インダクタンス経路を確保するために、リファレンス プレーンビアを使用します。

#### 7.2.1.2 詳細な設計手順

PCIe Gen 3.0 および 4.0 アプリケーションでは、仕様によりルートコンプレックスとエンドポイントの Rx-Tx 間リンクトレーニングが要求され、それぞれ  $8\text{Gbps}$  および  $16\text{Gbps}$  で信号コンディショニング設定を確立・最適化します。リンクトレーニングでは、Rx パートナーが Tx パートナーから FIR のプリシュートおよびディエンファシス係数 (10 プリセット) を要求します。Rx パートナーには CTLE と DFE が含まれます。リンクトレーニングは信号を事前調整し、ルートコンプレックスとエンドポイント間のリンクをイコライズすることで最適化されたリンクを実現します。なお、PCIe Gen 1.0 (2.5Gbps) および PCIe Gen 2.0 (5.0Gbps) アプリケーションではリンクトレーニングは存在しません。

Gen 3.0 および 4.0 リンクでの動作において、DS160PR410-Q1 はリニア データ パスで設計されており、ルートコンプレックスとエンドポイントの Tx プリセット信号を Rx にそのまま伝達し、PCIe Gen 3.0 および 4.0 リンクがイコライゼーション設定をトレーニング・最適化できるようにします。DS160PR410-Q1 のリニア リドライバは、イコライゼーションによって減衰した信号をブーストし、PCB トレースのリーチ距離を拡張します。これにより、ユーザーはリンク パートナーの Rx によつ

て信号をより容易にリカバリできます。デバイスは、ルートコンプレックスおよびエンドポイントの Tx と Rx の間に配置し、Rx および Tx の信号スイングがデバイスのリニアリティ範囲内に収まるようにする必要があります。DS160PR410-Q1 の EQ 設定は、チャネル損失に基づいて調整し、Rx パートナーのアイ 開口を最適化してください。利用可能な EQ ゲイン設定は [表 6-1](#) に示されています。ほとんどの PCIe システムでは、デフォルトのフラット ゲイン設定である 0.6dB (GAIN = フローティング) で十分です。ただし、必要に応じてデータ パスをリニアに保つために、追加のイコライゼーションを適用するフラット ゲイン減衰を使用できます。

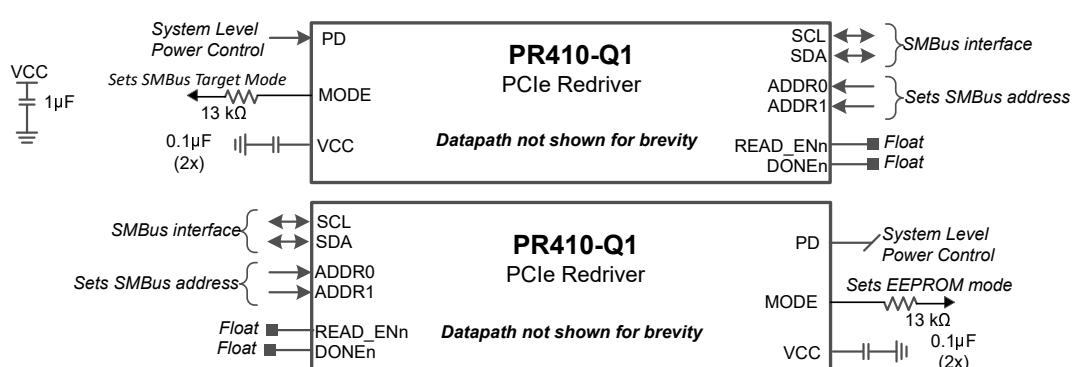

DS160PR410-Q1 は、ピン モード、SMBus/I<sup>2</sup>C コントローラ モード、および SMBus/I<sup>2</sup>C ターゲット モードという 3 つの構成モードを使用して、特定のシステムに最適化できます。SMBus/I<sup>2</sup>C モードでは、SCL および SDA ピンを 3.3V 電源にプルアップ抵抗を介してプルアップする必要があります。この抵抗の値は、合計バス容量に依存します。4.7kΩ は、10pF のバス容量に対して適切な最初の近似値です。

PCIe アプリケーションでは、PD ピンを反転極性で PCIe サイドバンド信号 PERST# に、または 1 つ以上の適切な PRSNTx# 信号に接続して、所望の RX ディテクト機能を実現できます。

DS160PR410-Q1 は、ピン モード、SMBus/I<sup>2</sup>C コントローラ モード、および SMBus/I<sup>2</sup>C ターゲット モードという 3 つの構成モードを使用して、特定のシステムに最適化できます。SMBus/I<sup>2</sup>C モードでは、SCL および SDA ピンを 3.3V 電源にプルアップ抵抗を介してプルアップする必要があります。この抵抗の値は、合計バス容量に依存します。4.7kΩ は、10pF のバス容量に対して適切な最初の近似値です。

[図 7-3](#) は、ピン ストラップ、EEPROM、SMBus ターゲット モードでの x4 レーン構成の簡略化スキーマティックを示しています。

図 7-3. ピンストラップ、EEPROM および SMBus ターゲット モードにおける PCIe x4 レーン構成の簡略化スキーマティック

### 7.2.1.3 アプリケーション曲線

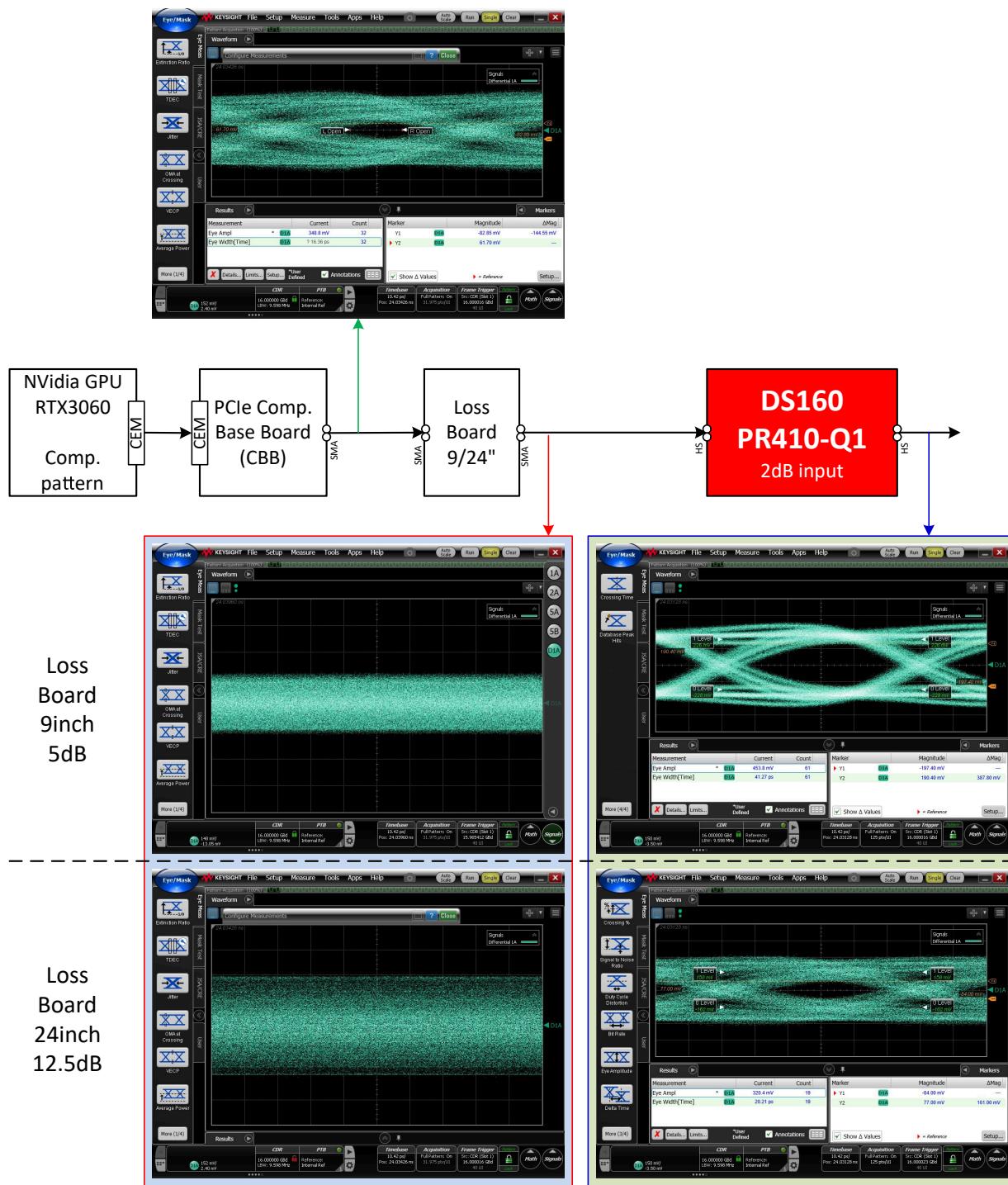

DS160PR410-Q1 はリニアリドライバであり、PCIe リンクのチャネルルーチを拡張するために使用できます。通常、PCIe 準拠の Tx および Rx には信号コンディショニング機能が備わっており、8GHz で最大 28dB のチャネル損失に対応できます。DS160PR410-Q1 を使用することで、PCIe ルートコンプレックスとエンド ポイント間の総チャネル損失は 8GHz で最大 12dB まで拡張可能です。

図 7-4. DS160PR410-Q1 によるイコライゼーションの説明

DS160PR410-Q1 のリーチ拡張機能を実証するために、GPU カードを PCIe ルート コンプレックスとして使用し、PCIe 4.0 準拠パターンを送信するセットアップを図 7-4 に示すように構築しました。GPU カードの出力は PCIe コンプライアンス ベースボード (CBB) を介してキャプチャれます。SMA ロス ボードによって損失が追加されます。DS160PR410-Q1 はボード損失によって加えられたジッタを除去し、閉じていたアイ ダイアグラムを開きます。表 7-1 はアイ 開口情報を示します。

**表 7-1. DS160PR410-Q1 を用いた PCIe 4.0 リーチ拡張**

| 構成                                      | CBB 経由の GPU 出力アイ           | ロス ボード通過後のアイ (リドライバ入力) | リドライバ出力アイ                  |

|-----------------------------------------|----------------------------|------------------------|----------------------------|

| 9 インチ ロス ボード (5dB)<br>リドライバ EQ = 17     | アイ 幅 16.4ps<br>アイ 高さ 145mV | closed                 | アイ 幅 41.3ps<br>アイ 高さ 388mV |

| 24 インチ ロス ボード (12.5dB)<br>リドライバ EQ = 19 |                            |                        | アイ 幅 20.2ps<br>アイ 高さ 161mV |

## 7.3 電源に関する推奨事項

電源を設計するときは、次の一般的なガイドラインに従ってください：

- 電源は、DC 電圧、AC ノイズ、および立ち上がりランプ時間に関して、推奨動作条件セクションで示されている動作条件を提供できるように設計する必要があります。

- 推奨動作条件が満たされている場合、DS160PR410-Q1 はフェライトビーズなど特別な電源フィルタリングを必要としません。標準的な電源デカップリングのみが必要です。典型的な電源デカップリングは、VCC ピンごとに  $0.1\mu\text{F}$  コンデンサ 1 個、デバイスごとに  $1.0\mu\text{F}$  バルクコンデンサ 1 個、そして 1 台以上の DS160PR410-Q1 デバイスに電力を供給する各電源バスごとに  $10\mu\text{F}$  バルクコンデンサ 1 個で構成されます。ローカル デカップリング ( $0.1\mu\text{F}$ ) コンデンサは、可能な限り VCC ピンの近くに接続し、DS160PR410-Q1 のグランド パッドまでの経路を最小限にする必要があります。

- DS160PR410-Q1 の電圧レギュレータの出力ピンには、それぞれのピン付近に  $0.1\mu\text{F}$  のデカップリング キャップが必要です。レギュレータは内部専用です。外部コンポーネントに電力を供給するために使用しないでください。

## 7.4 レイアウト

### 7.4.1 レイアウトのガイドライン

レイアウトを設計する際には、以下のガイドラインに従う必要があります。

- デカップリング コンデンサは、可能な限り VCC ピンの近くに配置する必要があります。基板設計が許す場合、デカップリング コンデンサはデバイスの直下に配置することを推奨します。

- 高速差動信号 TXnP/TXnN および RXnP/RXnN は、密結合、スキュー整合、およびインピーダンス制御を行う必要があります。

- 高速差動信号では、可能な限りビアの使用を避ける必要があります。ビアを使用する必要がある場合は、可能な限りビア スタブを最小化するよう注意します。その際は、多くまたはすべての層を貫通させるか、バックドリルを使用します。

- パッド容量を打ち消して信号品質を改善するために、高速差動信号パッドの下に GND リリーフを使用できます (必須ではありません)。

- GND ビアはデバイス直下に配置し、デバイスに接続された GND プレーンを他の層の GND プレーンに接続する必要があります。これには、デバイスから基板への熱伝導性を改善するという追加の利点もあります。

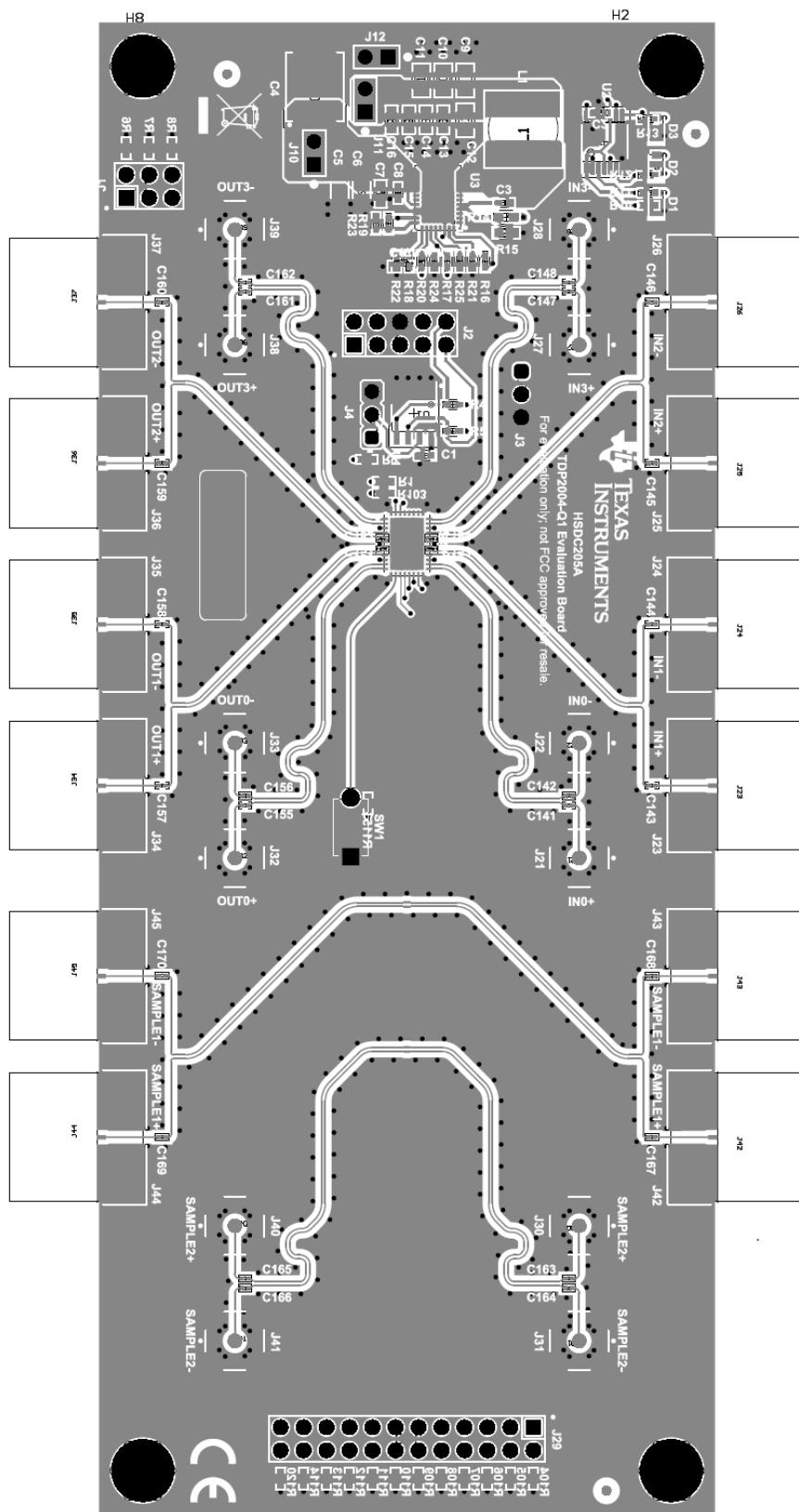

#### 7.4.2 レイアウト例

図 7-5. DS160PR410-Q1 レイアウト例—T1 評価ボード

## 8 デバイスおよびドキュメントのサポート

### 8.1 ドキュメントのサポート

#### 8.1.1 関連資料

関連資料については、以下を参照してください。

- ・ テキサス・インスツルメンツ、『[DS160PR810 プログラミング ガイド](#)』

- ・ テキサス・インスツルメンツ、『[DS160PR810 PCI-Express Gen-4 リドライバの EEPROM プログラミングについて](#)』

### 8.2 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 8.3 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの[使用条件](#)を参照してください。

### 8.4 商標

テキサス・インスツルメンツ E2E™ is a trademark of Texas Instruments.

PCIe® is a registered trademark of PCI-SIG.

すべての商標は、それぞれの所有者に帰属します。

### 8.5 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 8.6 用語集

[テキサス・インスツルメンツ用語集](#) この用語集には、用語や略語の一覧および定義が記載されています。

## 9 改訂履歴

| 日付         | 改訂 | 注      |

|------------|----|--------|

| 2025 年 6 月 | *  | 初版リリース |

## 10 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのプラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| DS160PR410RGFRQ1      | Active        | Production           | VQFN (RGF)   40 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TDP04Q1             |

| DS160PR410RGFTQ1      | Active        | Production           | VQFN (RGF)   40 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-2-260C-1 YEAR               | -40 to 125   | TDP04Q1             |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**OTHER QUALIFIED VERSIONS OF DS160PR410-Q1 :**

- Catalog : [DS160PR410](#)

---

NOTE: Qualified Version Definitions:

- Catalog - TI's standard catalog product

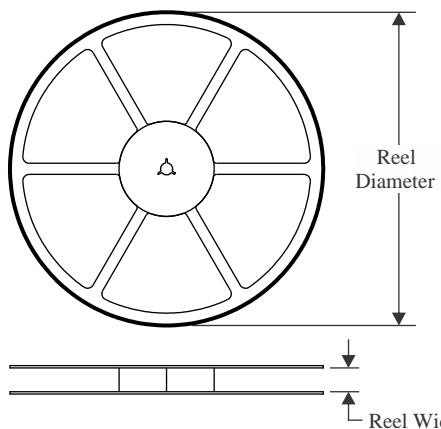

**TAPE AND REEL INFORMATION**

**REEL DIMENSIONS**

**TAPE DIMENSIONS**

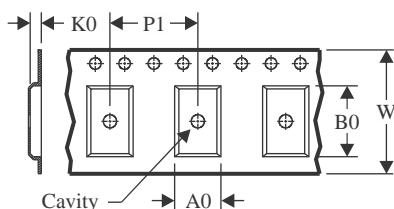

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|------------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| DS160PR410RGFRQ1 | VQFN         | RGF             | 40   | 3000 | 330.0              | 16.4               | 5.25    | 7.25    | 1.45    | 8.0     | 16.0   | Q1            |

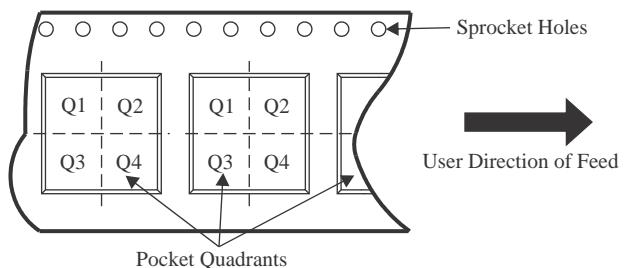

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DS160PR410RGFRQ1 | VQFN         | RGF             | 40   | 3000 | 367.0       | 367.0      | 35.0        |

## GENERIC PACKAGE VIEW

**RGF 40**

**VQFN - 1 mm max height**

**5 x 7, 0.5 mm pitch**

PLASTIC QUAD FLAT PACK- NO LEAD

This image is a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4225115/A

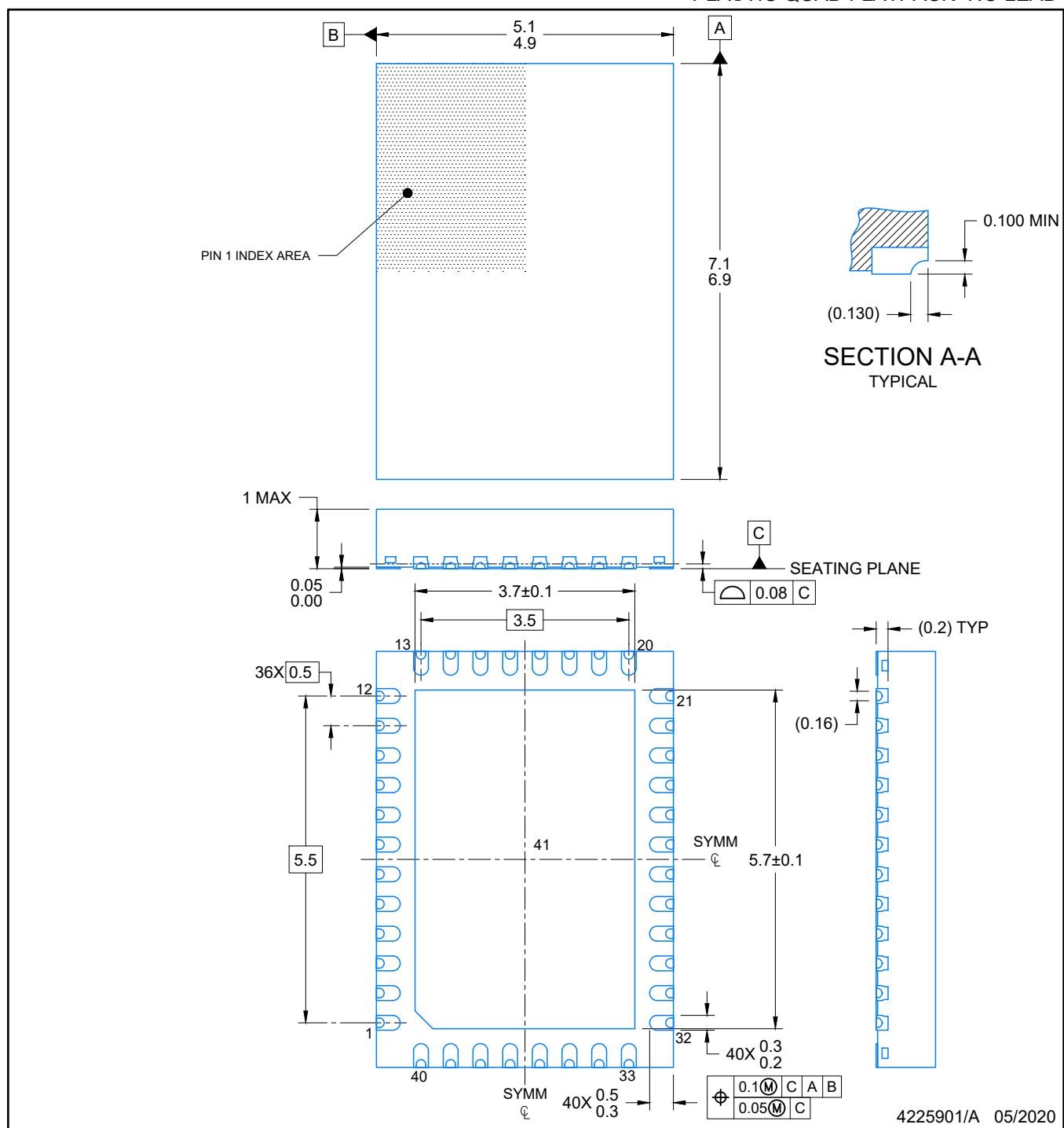

# PACKAGE OUTLINE

VQFN - 1 mm max height

RGF0040F

PLASTIC QUAD FLATPACK- NO LEAD

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

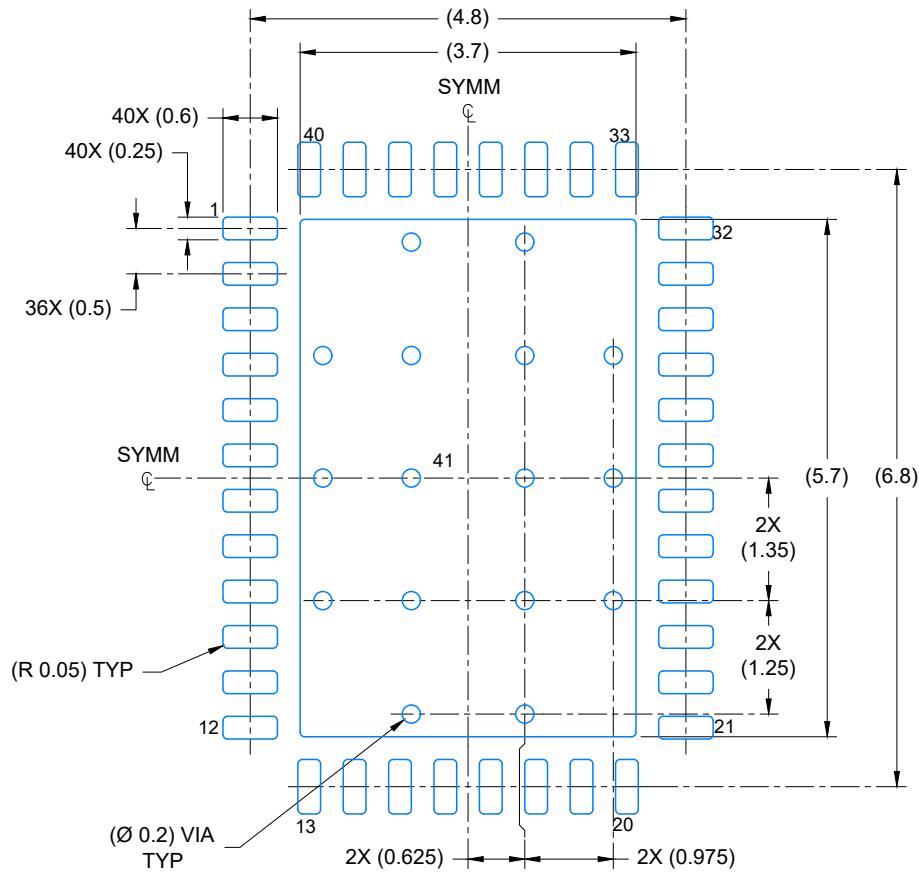

# EXAMPLE BOARD LAYOUT

RGF0040F

VQFN - 1 mm max height

PLASTIC QUAD FLATPACK- NO LEAD

## LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 12X

SOLDER MASK DETAILS

4225901/A 05/2020

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

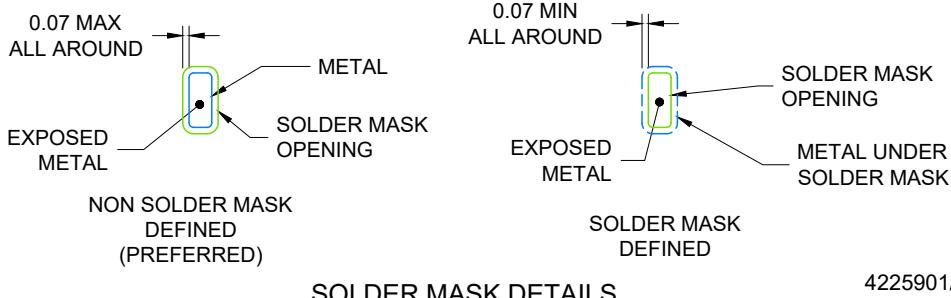

# EXAMPLE STENCIL DESIGN

VQFN - 1 mm max height

RGF0040F

PLASTIC QUAD FLATPACK- NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

EXPOSED PAD

69% PRINTED COVERAGE BY AREA

SCALE: 12X

4225901/A 05/2020

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月