DRV8873-Q1

JAJSFZ9B - OCTOBER 2017 - REVISED JANUARY 2021

# DRV8873-Q1 車載 H ブリッジ・モータ・ドライバ

## 1 特長

Texas

INSTRUMENTS

- 車載アプリケーション向けに AEC-Q100 認証を取得 - デバイス温度グレード 1:-40℃~+125℃、T<sub>A</sub>

- N チャネルの H ブリッジ・モータ・ドライバ

- 1 つの双方向ブラシ付き DC モータを駆動

- 2 つの単方向ブラシ付き DC モータ

- ソレノイドまたはその他の抵抗性および誘導性負荷

- 4.5V~38Vの動作電圧範囲

- 10A のピーク駆動電流

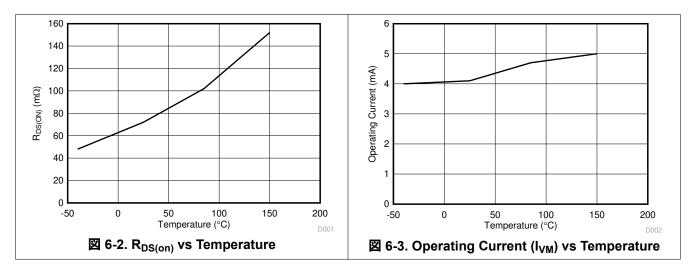

- 小さい R<sub>DS(ON)</sub> (HS + LS)

- T₁ = 25°C、13.5V 時 150mΩ

- T<sub>1</sub> = 150°C、13.5V 時 250mΩ

- 電流センス機能内蔵

- 比例電流出力 (IPROPI)

- 構成可能な制御インターフェイス

- PH/EN

- PWM (IN1/IN2)

- 独立したハーフブリッジ制御

- 1.8V、3.3V、5Vのロジック入力をサポート

- SPI またはハードウェア・インターフェイスを利用可能

- 小さなパッケージと占有面積

- 24 ピン HTSSOP PowerPAD<sup>™</sup> IC パッケージ

- 保護機能

- VM 低電圧誤動作防止 (UVLO)

- チャージ・ポンプ低電圧検出 (CPUV)

- 過電流保護 (OCP)

- 出力バッテリ短絡 / GND 短絡保護

- 開放負荷検出

- サーマル・シャットダウン (TSD)

- フォルト状態出力 (nFAULT/SPI)

- 拡散スペクトラム・クロックによる低い電磁気妨害 (EMI)

- 機能安全対応

- 機能安全システムの設計に役立つ資料を利用可 能

# 2 アプリケーション

- 電子スロットル制御

- 排気再循環

- サイドミラー・チルト

- eシフタ

- エアフロー誘導弁制御

## 3 概要

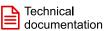

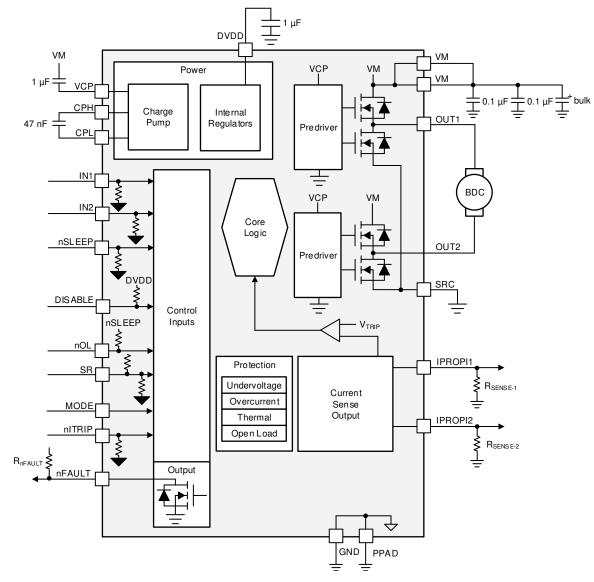

DRV8873-Q1 は車載用ブラシ付き DC モータを駆動する 統合型ドライバ IC です。2 つのロジック入力が H ブリッ ジ・ドライバを制御し、ドライバを構成する4 つの N チャネ ル MOSFET により、最大 10A のピーク電流でモータを 双方向制御できます。また単一電源で動作し、4.5V~ 38Vの広い入力電源電圧範囲に対応します。

PH/EN または PWM インターフェイスにより、制御回路に 容易に接続できる一方、独立したハーフブリッジ制御を利 用して2つのソレノイド負荷を駆動することも可能です。

内蔵の電流センス機能により、電力定格が大きいセンス抵 抗を使わなくても、両方のハイサイド FET のモータ負荷電 流に比例する出力電流を供給できます。この機能を使用 して、モータのストールまたは負荷条件の変化を検出でき ます。

低消費電力のスリープ・モードにより、内部回路の多くをシ ャットダウンして、静止電流を極めて小さく抑制できます。 内蔵する保護機能には、低電圧誤動作防止、チャージ・ ポンプ異常検出、過電流保護、短絡保護、開放負荷検 出、過熱保護があります。フォルト状態は nFAULT ピンお よび SPI レジスタにより通知されます。

#### **製品情報**(1)

|            | 34466 II ¥ I IA |                 |

|------------|-----------------|-----------------|

| 部品番号       | パッケージ           | 本体サイズ (公称)      |

| DRV8873-Q1 | HTSSOP (24)     | 7.70mm × 4.40mm |

利用可能なパッケージについては、このデータシートの末尾にあ (1) る注文情報を参照してください。

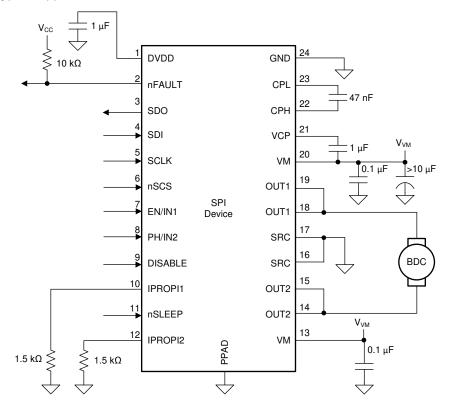

概略回路図

英語版のTI製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、 🐼 www.ti.com で閲覧でき、その内容が常に優先されます。 TI では翻訳の正確性および妥当性につきましては一切保証いたしません。 実際の設計などの前には、必ず 最新版の英語版をご参照くださいますようお願いいたします。

## **Table of Contents**

| 1 | 特長                                   | 1 |

|---|--------------------------------------|---|

|   | アプリケーション                             | 1 |

|   | 概要                                   | 1 |

|   | Revision History                     | 2 |

| 5 | Pin Configuration and Functions      |   |

|   | Pin Functions                        |   |

| 6 | Specifications                       | 5 |

|   | 6.1 Absolute Maximum Ratings         | 5 |

|   | 6.2 ESD Ratings                      | 5 |

|   | 6.3 Recommended Operating Conditions | 5 |

|   | 6.4 Thermal Information              | 5 |

|   | 6.5 Electrical Characteristics       | 3 |

|   | 6.6 SPI Timing Requirements          |   |

|   | 6.7 Typical Characteristics          | 9 |

| 7 | Detailed Description1                | 1 |

|   | 7.1 Overview                         | 1 |

|   | 7.2 Functional Block Diagram12       | 2 |

|   | 7.3 Feature Description14            | 1 |

|   | 7.4 Device Functional Modes          | 1 |

| 7.5 Programming                                       | . 31 |

|-------------------------------------------------------|------|

| 7.6 Register Maps                                     |      |

| 8 Application and Implementation                      |      |

| 8.1 Application Information                           | . 42 |

| 8.2 Typical Application                               | . 42 |

| 9 Power Supply Recommendations                        |      |

| 9.1 Bulk Capacitance Sizing                           | . 49 |

| 10 Layout                                             | .50  |

| 10.1 Layout Guidelines                                | . 50 |

| 10.2 Layout Example                                   | . 50 |

| 11 Device and Documentation Support                   | .51  |

| 11.1 Documentation Support                            | . 51 |

| 11.2 Receiving Notification of Documentation Updates. | . 51 |

| 11.3 サポート・リソース                                        | 51   |

| 11.4 Trademarks                                       | . 51 |

| 11.5 静電気放電に関する注意事項                                    | . 51 |

| 11.6 用語集                                              | . 51 |

| 12 Mechanical, Packaging, and Orderable               |      |

| Information                                           | . 51 |

|                                                       |      |

## **4 Revision History**

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision A (August 2018) to Revision B (January 2021) | Page |

|--------------------------------------------------------------------|------|

|                                                                    | 1    |

|                                                                    |      |

| Changes from Revision * (October 2017) to Revision A (August 2018) | Page |

|                                                                    | 1    |

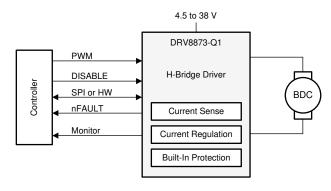

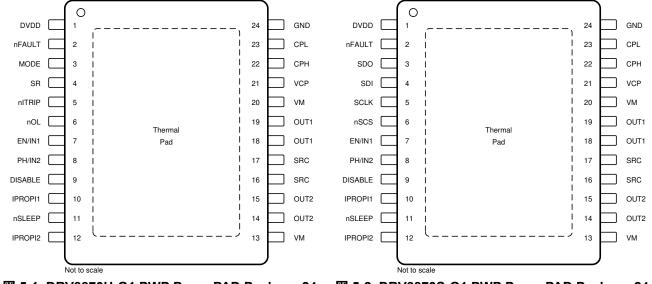

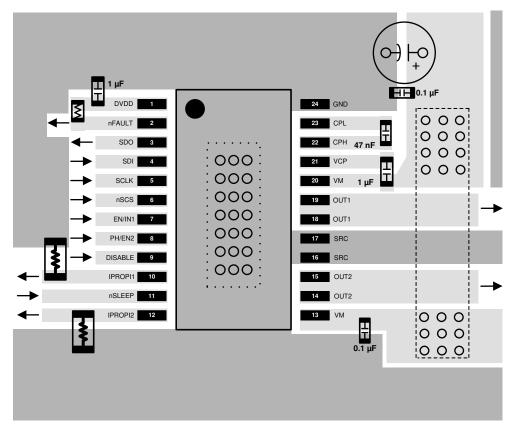

## **5** Pin Configuration and Functions

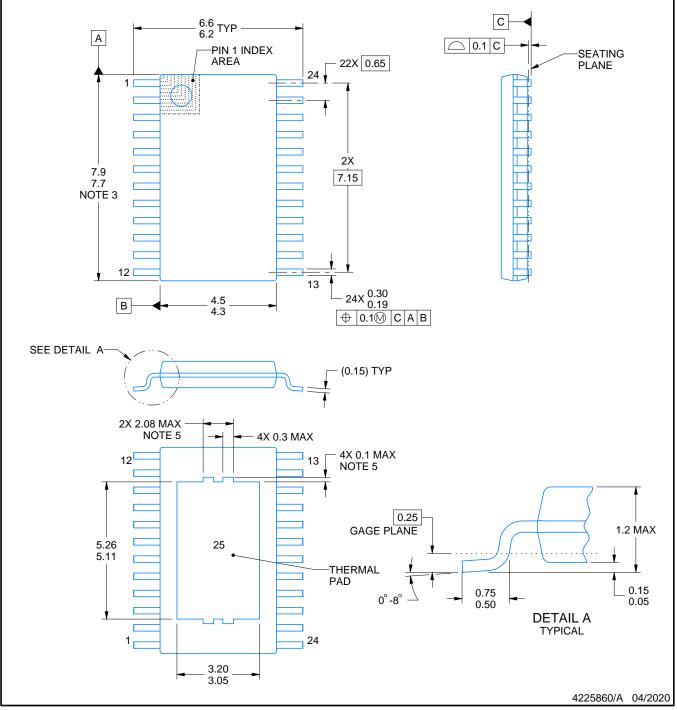

☑ 5-2. DRV8873S-Q1 PWP PowerPAD Package 24-Pin HTSSOP Top View

#### **Pin Functions**

| PIN     |             |             |                     |                                                                                                                                                                                           |  |  |

|---------|-------------|-------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME    | N           | 0.          | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                               |  |  |

| NAME    | DRV8873H-Q1 | DRV8873S-Q1 |                     |                                                                                                                                                                                           |  |  |

| СРН     | 22          | 22          | PWR                 | Charge pump switching node. Connect a X7R capacitor with a value of 47 nF between the CPH and CPL pins.                                                                                   |  |  |

| CPL     | 23          | 23          | PWR                 | Charge pump switching node. Connect a X7R capacitor with a value of 47 nF between the CPH and CPL pins.                                                                                   |  |  |

| DVDD    | 1           | 1           | PWR                 | Digital regulator. This pin is the 5-V internal digital-supply regulator. Bypass this pin to GND with a 6.3-V, $1-\mu$ F ceramic capacitor.                                               |  |  |

| EN/IN1  | 7           | 7           | I                   | Control Inputs. For details, see the セクション 7.3.1.1 section. This pin has an internal pulldown resistor to GND.                                                                            |  |  |

| DISABLE | 9           | 9           | Ι                   | Bridge disable input. A logic high on this pin disables the H-bridge Hi-Z.<br>Internal pullup to DVDD.                                                                                    |  |  |

| GND     | 24          | 24          | PWR                 | Ground pin                                                                                                                                                                                |  |  |

| IPROPI1 | 10          | 10          | 0                   | High-side FET current. The analog current proportional to the current flowing in the half bridge.                                                                                         |  |  |

| IPROPI2 | 12          | 12          | 0                   | High-side FET current. The analog current proportional to the current flowing in the half bridge.                                                                                         |  |  |

| nITRIP  | 5           | _           | I                   | Internal current-regulation control pin (ITRIP). To enable the ITRIP feature, do not connect this pin (or tie it to GND). To disable the ITRIP feature, connect this pin to the DVDD pin. |  |  |

| nOL     | 6           | _           | I                   | Open-load diagnostic control pin. To run the open-load diagnostic at power up, tie it to ground. Connect it to DVDD, open-load diagnostic will be disabled.                               |  |  |

| MODE    | 3           | _           | I                   | Input mode pin. Sets the PH/EN, PWM, or independent-PWM mode.                                                                                                                             |  |  |

| OUT1    | 18          | 18          | 0                   | Half-bridge output 1. Connect this pin to the motor or load.                                                                                                                              |  |  |

| OUT1    | 19          | 19          | 0                   | Half-bridge output 1. Connect this pin to the motor or load.                                                                                                                              |  |  |

| OUT2    | 14          | 14          | 0                   | Half-bridge output 2. Connect this pin to the motor or load.                                                                                                                              |  |  |

| OUT2    | 15          | 15          | 0                   | Half-bridge output 2. Connect this pin to the motor or load.                                                                                                                              |  |  |

Copyright © 2023 Texas Instruments Incorporated

DRV8873-Q1 JAJSFZ9B – OCTOBER 2017 – REVISED JANUARY 2021

| PIN      |             |             |                     |                                                                                                                                                    |  |  |

|----------|-------------|-------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO. |             | 0.          | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                        |  |  |

| NAME     | DRV8873H-Q1 | DRV8873S-Q1 |                     |                                                                                                                                                    |  |  |

| PH/IN2   | 8           | 8           | I                   | Control inputs. For details, see the セクション 7.3.1.1 section. This pin has an internal pulldown resistor to GND.                                     |  |  |

| SCLK     | _           | 5           | I                   | Serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin.                              |  |  |

| SDI      |             | 4           | I                   | Serial data input. Data is captured on the falling edge of the SCLK pin.                                                                           |  |  |

| SDO      | _           | 3           | PP                  | Serial data output. Data is shifted out on the rising edge of the SCLK pin. This is a push-pull output.                                            |  |  |

| SR       | 4           | —           | I                   | Slew rate adjust. This pin sets the slew rate of the H-bridge outputs.                                                                             |  |  |

| SRC      | 16          | 16          | 0                   | Power FET source. Tie this pin to GND through a low-impedance path.                                                                                |  |  |

| SRC      | 17          | 17          | 0                   | Power FET source. Tie this pin to GND through a low-impedance path.                                                                                |  |  |

| VCP      | 21          | 21          | PWR                 | Charge pump output. Connect a 16-V, $1-\mu F$ ceramic capacitor from this pin to the VM supply.                                                    |  |  |

| VM       | 13          | 13          | PWR                 | Power supply. This pin is the motor supply voltage. Bypass this pin to GND with a $0.1\mbox{-}\mu\mbox{F}$ ceramic capacitor and a bulk capacitor. |  |  |

| VM       | 20          | 20          | PWR                 | Power supply. This pin is the motor supply voltage. Bypass this pin to GND with a $0.1\mbox{-}\mu\mbox{F}$ ceramic capacitor and a bulk capacitor. |  |  |

| nFAULT   | 2           | 2           | OD                  | Fault indication pin. This pin is pulled logic low with a fault condition. This open-drain output requires an external pullup resistor.            |  |  |

| nSCS     | _           | 6           | I                   | Serial chip select. An active low on this pin enables the serial interface communications. Internal pullup to nSLEEP.                              |  |  |

| nSLEEP   | 11          | 11          | I                   | Sleep input. To enter a low-power sleep mode, set this pin logic low.                                                                              |  |  |

(1) I = input, O = output, PWR = power, NC = no connect, OD = open-drain output, PP = push-pull output

## **6** Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                   |                                  |                                                                            | MIN                  | MAX                   | UNIT |

|-------------------|----------------------------------|----------------------------------------------------------------------------|----------------------|-----------------------|------|

|                   | Power supply voltage             | VM                                                                         | -0.3                 | 40                    | V    |

|                   | Charge pump voltage              | VCP, CPH                                                                   | -0.3                 | V <sub>VM</sub> + 5.7 | V    |

|                   | Charge pump switching pin        | CPL                                                                        | -0.3                 | V <sub>VM</sub>       | V    |

|                   | Internal logic regulator voltage | DVDD                                                                       | -0.3                 | 5.7                   | V    |

|                   | Digital pin voltage              | EN/IN1, PH/IN2, nSLEEP, DISABLE, nFAULT,<br>MODE, SR, SCLK, SDI, SDO, nSCS | -0.3                 | 5.7                   | V    |

| V <sub>TRIP</sub> | Analog pin voltage               | IPROPI1, IPROPI2                                                           | 0                    | 5.5                   | V    |

| V <sub>SRC</sub>  | H-Bridge source pin voltage      |                                                                            | -0.3                 | 0.3                   | V    |

|                   | Phase node pin voltage           | OUTx                                                                       | V <sub>SRC</sub> – 1 | V <sub>VM</sub> + 1   | V    |

|                   | Open drain output current        | nFAULT                                                                     | 0                    | 10                    | mA   |

|                   | Push-pull output current         | SDO                                                                        | 0                    | 10                    | mA   |

| TJ                | Operating junction temperature   |                                                                            | -40                  | 150                   | °C   |

| T <sub>stg</sub>  | Storage temperature              |                                                                            | -65                  | 150                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                    |                            |                                                                                  |                                 | VALUE | UNIT |

|--------------------|----------------------------|----------------------------------------------------------------------------------|---------------------------------|-------|------|

|                    |                            | Human body model (HBM), per AEC Q100–002 HBM $2^{(1)}$                           | ESD Classification Level        | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic<br>discharge | Charged device model (CDM), per AEC Q100–011<br>CDM ESD Classification Level C4B | Corner pins (1, 12, 13, and 24) | ±750  | V    |

|                    |                            |                                                                                  | Other pins                      | ±500  |      |

(1) AEC Q100–002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS–001 specification.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                                     | MIN | MAX | UNIT |

|------------------|-------------------------------------|-----|-----|------|

| V <sub>VM</sub>  | Power supply voltage                | 4.5 | 38  | V    |

| VI               | Logic level input voltage           | 0   | 5.5 | V    |

| f <sub>PWM</sub> | Applied PWM signal (EN/IN1, PH/IN2) |     | 100 | kHz  |

| T <sub>A</sub>   | Operating ambient temperature       | -40 | 125 | °C   |

| TJ               | Operating junction temperature      | -40 | 150 | °C   |

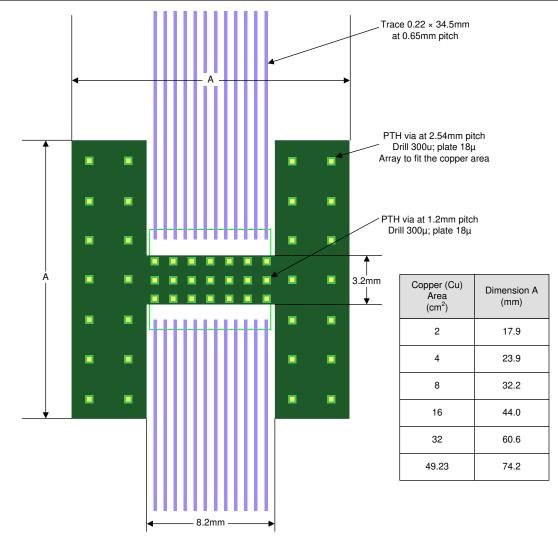

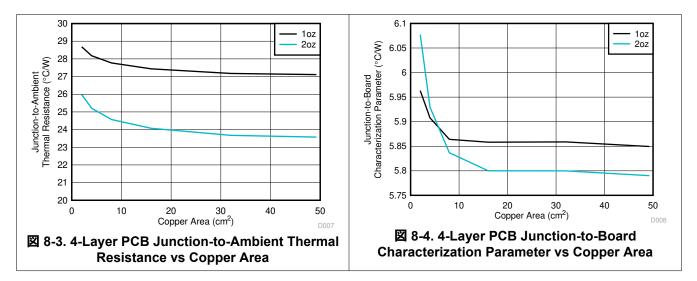

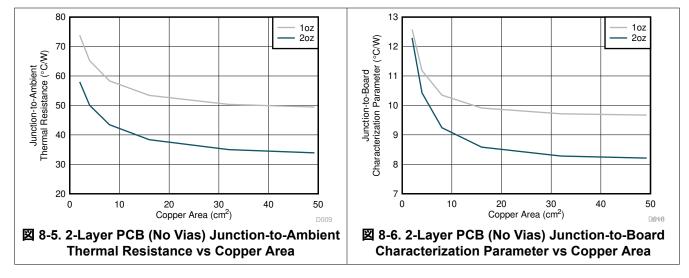

## 6.4 Thermal Information

|                       |                                            | DRV8873-Q1   |      |

|-----------------------|--------------------------------------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>              | PWP (HTSSOP) | UNIT |

|                       |                                            | 24 PINS      |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance     | 27.8         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance  | 18.8         | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance       | 5.1          | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter | 0.3          | °C/W |

Copyright © 2023 Texas Instruments Incorporated

|                       |                                              | DRV8873-Q1   |      |

|-----------------------|----------------------------------------------|--------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PWP (HTSSOP) | UNIT |

|                       |                                              | 24 PINS      |      |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 5.2          | °C/W |

| R <sub>θJC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 1.0          | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## **6.5 Electrical Characteristics**

Over recommended operating conditions unless otherwise noted. Typical limits apply for  $T_A = 25^{\circ}C$  and  $V_{VM} = 13.5 V$

|                      | PARAMETER                         | TEST CONDITIONS                                      | MIN | TYP                | MAX      | UNIT |

|----------------------|-----------------------------------|------------------------------------------------------|-----|--------------------|----------|------|

| POWER                | SUPPLIES (VM, DVDD)               |                                                      |     |                    |          |      |

| V <sub>VM</sub>      | VM operating voltage              |                                                      | 4.5 |                    | 38       | V    |

| I <sub>VM</sub>      | VM operating supply current       | V <sub>VM</sub> = 13.5 V; nSLEEP = 1; DISABLE<br>=0  |     | 5                  | 10       | mA   |

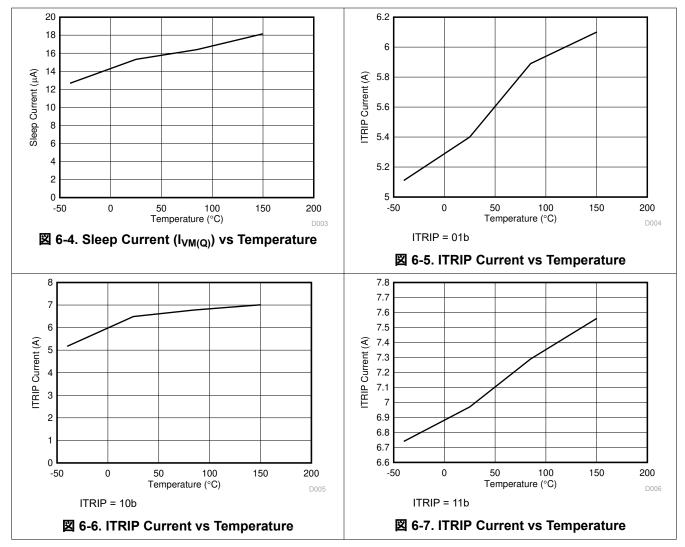

| I <sub>VM(Q)</sub>   | VM sleep mode supply current      | V <sub>VM</sub> = 13.5 V; nSLEEP = 0                 |     | 15                 | 30       | μA   |

| V <sub>DVDD</sub>    | Internal logic regulator voltage  | 2-mA load, $V_{VM}$ > 5.5 V                          | 4.7 | 5                  | 5.3      | V    |

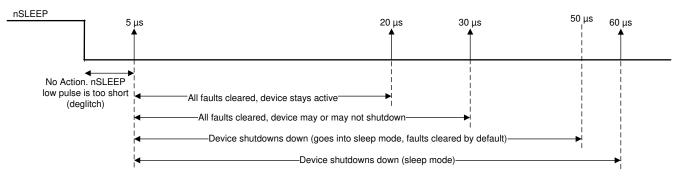

| t <sub>(SLEEP)</sub> | Sleep time                        | nSLEEP low to start device shutdown                  | 50  |                    |          | μs   |

| t <sub>(RESET)</sub> | nSLEEP reset pulse                | nSLEEP low to only clear fault registers             | 5   |                    | 20       | μs   |

| t <sub>(WAKE)</sub>  | Wake-up time                      | nSLEEP high to device ready for input signals        |     |                    | 1.5      | ms   |

| t <sub>on</sub>      | Turn-on time                      | $VM > V_{(UVLO)}$ ; nSLEEP = 1, to output transition |     |                    | 1.5      | ms   |

| t(DISABLE)           | DISABLE deglitch time             | DISABLE signal transition                            |     | 2.5                |          | μs   |

| CHARGE               | E PUMP (VCP, CPH, CPL)            |                                                      | ·   |                    | L        |      |

| V <sub>VCP</sub>     | VCP operating voltage             | with respect to VM                                   |     | V <sub>VM</sub> +5 |          | V    |

| I <sub>VCP</sub>     | VCP current                       | V <sub>VM</sub> = 13.5 V                             |     | 7                  | 10       | mA   |

| f <sub>(VCP)</sub>   | Charge pump switching frequency   | $V_{VM} > V_{(UVLO)}$ ; nSLEEP = 1                   |     | 400                |          | kHz  |

| LOGIC-L              | EVEL INPUTS (EN/IN1, PH/IN2, nSLE | EP, SCLK, SDI)                                       |     |                    | <b>i</b> |      |

| V <sub>IL</sub>      | Input logic-low voltage           |                                                      | 0   |                    | 0.8      | V    |

| VIH                  | Input logic-high voltage          |                                                      | 1.6 |                    | 5.3      | V    |

| V <sub>HYS</sub>     | Input logic hysteresis            |                                                      |     | 150                |          | mV   |

| IIL                  | Input logic-low current           | V <sub>IN</sub> = 0 V                                | -5  |                    | 5        | μA   |

| I <sub>IH</sub>      | Input logic-high current          | V <sub>IN</sub> = 5 V                                |     | 50                 |          | μA   |

| R <sub>PD</sub>      | Internal pulldown resistance      | to GND                                               |     | 100                |          | kΩ   |

|                      |                                   | SR = 000b; I <sub>O</sub> = 1 A                      |     | 1.2                |          |      |

|                      |                                   | SR = 001b; I <sub>O</sub> = 1 A                      |     | 1.6                |          |      |

|                      |                                   | SR = 010b; I <sub>O</sub> = 1 A                      |     | 2.6                |          |      |

|                      | Propagation delay (EN/IN1, PH/IN2 | SR = 011b; I <sub>O</sub> = 1 A                      |     | 3.4                |          |      |

| t <sub>pd</sub>      | to OUTx = 50%)                    | SR = 100b; I <sub>O</sub> = 1 A                      |     | 4.1                |          | μs   |

|                      |                                   | SR = 101b; I <sub>O</sub> = 1 A                      |     | 5.2                |          |      |

|                      |                                   | SR = 110b; I <sub>O</sub> = 1 A                      |     | 7.8                |          |      |

|                      |                                   | SR = 111b; I <sub>O</sub> = 1 A                      |     | 13.3               |          |      |

| LOGIC-L              | EVEL INPUT (DISABLE)              | 1                                                    | ·   |                    | I        |      |

| R <sub>PU,DIS</sub>  | Internal pull-up resistance       | DISABLE to DVDD                                      |     | 100                |          | kΩ   |

| V <sub>IL,DIS</sub>  | Input logic-low voltage           |                                                      | 0   |                    | 0.8      | V    |

|                      |                                   |                                                      | 1.6 |                    | 5.3      | V    |

TEXAS INSTRUMENTS www.ti.com/ja-jp

|                       | PARAMETER                                          | unless otherwise noted. Typical limits app TEST CONDITIONS                                        | MIN | TYP  | MAX                   | UNIT |  |

|-----------------------|----------------------------------------------------|---------------------------------------------------------------------------------------------------|-----|------|-----------------------|------|--|

| V <sub>IL,nSCS</sub>  | Input logic-low voltage                            |                                                                                                   | 0   |      | 0.8                   | V    |  |

| V <sub>IH,nSCS</sub>  | Input logic-high voltage                           |                                                                                                   | 1.6 |      | 5.3                   | V    |  |

| R <sub>PU,nSCS</sub>  | Internal pull-up resistance                        | nSCS to nSLEEP                                                                                    |     | 450  |                       | kΩ   |  |

| LOGIC-LE              | VEL INPUT (nSLEEP)                                 |                                                                                                   |     |      |                       |      |  |

| V <sub>IL,SLEEP</sub> | Input logic-low voltage                            |                                                                                                   | 0   |      | 0.8                   | V    |  |

| V <sub>IH,SLEEP</sub> | Input logic-high voltage                           |                                                                                                   | 2.7 |      | 5.3                   | V    |  |

| I <sub>IH,SLEEP</sub> | Input logic-high current                           | V <sub>IN</sub> = 5 V; nSCS is High                                                               |     | 80-  | +I <sub>SDO</sub> (1) | μA   |  |

| THREE-LI              | EVEL INPUT (MODE)                                  |                                                                                                   |     |      |                       |      |  |

| R <sub>IN-1</sub>     | Input mode 1                                       | Tied to GND                                                                                       |     |      | 105                   | Ω    |  |

| R <sub>IN-2</sub>     | Input mode 2                                       | Tied to GND                                                                                       | 190 |      |                       | kΩ   |  |

| R <sub>IN-3</sub>     | Input mode 3                                       | Tied to DVDD                                                                                      |     |      | 105                   | Ω    |  |

|                       | LL OUTPUT (SDO)                                    |                                                                                                   |     |      |                       |      |  |

| R <sub>PD,SDO</sub>   | Internal pull-down resistance                      | With respect to GND                                                                               |     | 30   | 50                    | Ω    |  |

| R <sub>PU,SDO</sub>   | Internal pull-up resistance                        | With respect to nSLEEP                                                                            |     | 120  | 240                   | Ω    |  |

|                       | AIN OUTPUT (nFAULT)                                |                                                                                                   |     |      |                       |      |  |

| V <sub>OL</sub>       | Output logic-low voltage                           | I <sub>O</sub> = 2 mA                                                                             |     |      | 0.1                   | V    |  |

|                       | Output high-impedance leakage                      | V <sub>O</sub> = 5 V                                                                              | -2  |      | 2                     | μA   |  |

| -                     | RIVER OUTPUTS (OUT1, OUT2)                         |                                                                                                   |     |      |                       |      |  |

|                       |                                                    | V <sub>VM</sub> = 13.5 V; T <sub>A</sub> = 25°C; T <sub>J</sub> = 25°C                            |     | 75   |                       |      |  |

| R <sub>DS(ON)</sub>   | High-side FET on-resistance                        | $V_{VM} = 13.5 \text{ V}; T_A = 25^{\circ}\text{C}; T_J = 150^{\circ}\text{C}$                    |     | 125  | 155                   | mΩ   |  |

|                       | Low-side FET on-resistance                         | $V_{VM} = 13.5 \text{ V}; \text{ T}_{A} = 25^{\circ}\text{C}; \text{ T}_{J} = 25^{\circ}\text{C}$ |     | 75   |                       |      |  |

| R <sub>DS(ON)</sub>   |                                                    | $V_{VM} = 13.5 \text{ V}; T_A = 25^{\circ}\text{C}; T_J = 150^{\circ}\text{C}$                    |     | 125  | 155                   | mΩ   |  |

| t <sub>(DEAD)</sub>   | Output dead time                                   | SR = 100b                                                                                         |     | 500  |                       | ns   |  |

| V <sub>F(DIODE)</sub> | Body diode forward voltage                         | I <sub>O</sub> = 1 A                                                                              |     | 0.8  |                       | V    |  |

| T (DIODE)             | , 3                                                | nSLEEP = 0                                                                                        |     | 62   |                       |      |  |

| I <sub>SINK</sub>     | Sink current when OUTx = Hi-Z                      | nSLEEP = 1, DISABLE = 1                                                                           |     | 340  |                       | μΑ   |  |

|                       |                                                    | $I_{O} = 1 \text{ A; Connect to GND}$                                                             |     | 53.2 |                       |      |  |

|                       |                                                    | $I_0 = 1 \text{ A}; \text{ R}_{(SR)} = 22 \text{ k}\Omega \pm 5\% \text{ to GND}$                 |     | 34   |                       | _    |  |

|                       | Slow rate (H/M/ Device)                            | $I_0 = 1 \text{ A}; \text{ R}_{(SR)} = 68 \text{ k}\Omega \pm 5\% \text{ to GND}$                 |     | 18.3 |                       |      |  |

| SR                    | Slew rate (H/W Device)<br>OUTx 10% to 90% changing | $I_{O} = 1 \text{ A}; \text{ No connect (Hi-Z)}$                                                  |     | 13   |                       | V/µs |  |

|                       |                                                    | $I_0 = 1 \text{ A}; \text{ R}_{(SR)} = 51 \text{ k}\Omega \pm 5\% \text{ to DVDD}$                |     | 7.9  |                       |      |  |

|                       |                                                    | $I_0 = 1 \text{ A};$ Connect to DVDD                                                              |     | 2.6  |                       |      |  |

|                       |                                                    | $I_0 = 1 \text{ A}; \text{ SR} = 000\text{b}$                                                     |     | 53.2 |                       |      |  |

|                       |                                                    | $I_{O} = 1 \text{ A}; \text{ SR} = 001\text{b}$                                                   |     | 34   |                       |      |  |

|                       |                                                    | $I_0 = 1 \text{ A}; \text{ SR} = 0.10\text{ B}$                                                   |     | 18.3 |                       |      |  |

|                       | Slow rate (SPI Device)                             | $I_0 = 1 \text{ A}; \text{ SR} = 0.11\text{ b}$                                                   |     | 13   |                       |      |  |

| SR                    | Slew rate (SPI Device)<br>OUTx 10% to 90% changing | $I_0 = 1 \text{ A}, \text{ SR} = 100\text{b}$                                                     |     | 10.8 |                       | V/µs |  |

|                       |                                                    | $I_0 = 1 \text{ A}, \text{ SR} = 1000$                                                            |     | 7.9  |                       |      |  |

|                       |                                                    | $I_0 = 1 \text{ A}, \text{ SR} = 10 \text{ B}$                                                    |     | 5.3  |                       | _    |  |

|                       |                                                    | $I_0 = 1 \text{ A}, \text{ SR} = 110 \text{ B}$                                                   |     | 2.6  |                       |      |  |

|                       | SENSE OUTPUTS (IPROPI1, IPR                        | -                                                                                                 |     | 2.0  |                       |      |  |

| k                     | Current mirror scaling                             |                                                                                                   |     | 1100 |                       | A/A  |  |

| n                     |                                                    |                                                                                                   | -50 | 1100 | 50                    | mA   |  |

| k <sub>ERR</sub>      | Current mirror scaling                             | I <sub>O</sub> < 1 A                                                                              |     |      |                       |      |  |

| EKK                   | Carone minor Soanny                                | I <sub>O</sub> ≥ 1 A                                                                              | -5  |      | 5                     | %    |  |

#### DRV8873-Q1 JAJSFZ9B – OCTOBER 2017 – REVISED JANUARY 2021

| PARAMETER             |                                     | TEST CONDITIONS                                            | MIN                    | TYP       | MAX  | UNI |  |

|-----------------------|-------------------------------------|------------------------------------------------------------|------------------------|-----------|------|-----|--|

|                       |                                     | V <sub>O</sub> = 2 V; SR = 000b                            | · · · · ·              | 2.2       |      |     |  |

| t <sub>(IPROPI)</sub> | OUTx to IPROPI                      | V <sub>O</sub> = 2 V; SR = 111b                            |                        | 10.5      |      | μs  |  |

| CURREN                | T REGULATION                        | · · · ·                                                    |                        |           |      |     |  |

|                       |                                     | ITRIP_LVL = 00b; V <sub>VM</sub> = 13.5 V                  | 3.27                   | 3.85      | 4.43 |     |  |

|                       |                                     | ITRIP_LVL = 01b; V <sub>VM</sub> = 13.5 V                  | 4.6                    | 5.4       | 6.2  | •   |  |

| TRIP                  | Current limit threshold             | ITRIP_LVL = 10b; V <sub>VM</sub> = 13.5 V                  | 5.5                    | 6.5       | 7.5  | A   |  |

|                       |                                     | ITRIP_LVL = 11b; V <sub>VM</sub> = 13.5 V                  | 5.95                   | 7         | 8.1  |     |  |

|                       |                                     | TOFF = 00b                                                 |                        | 20        |      |     |  |

|                       |                                     | TOFF = 01b                                                 |                        | 40        |      |     |  |

| OFF                   | PWM off-time                        | TOFF = 10b                                                 |                        | 60        |      | μs  |  |

|                       |                                     | TOFF = 11b                                                 |                        | 80        |      |     |  |

| t <sub>BLANK</sub>    | PWM blanking time                   |                                                            |                        | 5         |      | μs  |  |

| PROTEC                | TION CIRCUITS                       |                                                            |                        |           |      |     |  |

|                       |                                     | VM falling; UVLO report                                    |                        | 4.35 4.45 |      |     |  |

| V <sub>(UVLO)</sub>   | VM undervoltage lockout             | VM rising; UVLO recovery                                   |                        | 4.5       | 4.7  | V   |  |

| t <sub>(UVLO)</sub>   | VM UVLO falling deglitch time       | VM falling; UVLO report                                    |                        | 10        |      | μs  |  |

| V <sub>(RST)</sub>    | VM UVLO reset                       | VM falling; UVLO report; device reset                      |                        |           | 4.1  | V   |  |

| V <sub>VCP(UV)</sub>  | Charge pump undervoltage            | V <sub>VM</sub> = 12 V; T <sub>A</sub> = 25°C; CPUV report | V <sub>VM</sub> + 2.25 |           |      | V   |  |

| (OCP)                 | Overcurrent protection trip level   |                                                            | 10                     |           |      | Α   |  |

| t <sub>(OCP)</sub>    | Overcurrent deglitch time           |                                                            |                        | 3         | 5    | μs  |  |

| t <sub>(RETRY)</sub>  | Overcurrent retry time (H/W Device) |                                                            |                        | 4         |      | ms  |  |

|                       |                                     | OCP_TRETRY = 00b                                           |                        | 0.5       |      |     |  |

|                       |                                     | OCP_TRETRY = 01b                                           |                        | 1         |      |     |  |

| t <sub>(RETRY)</sub>  | Overcurrent retry time (SPI Device) | OCP_TRETRY = 10b                                           |                        | 2         |      | ms  |  |

|                       |                                     | OCP_TRETRY = 11b                                           |                        | 4         |      | 1   |  |

| V <sub>OLA</sub>      | Open load active mode               |                                                            | 150                    | 300       | 450  | m٧  |  |

|                       |                                     | OL_DLY = 0b                                                |                        | 0.3       |      |     |  |

| t <sub>d(OL)</sub>    | Open load diagnostic delay time     | OL_DLY = 1b                                                |                        | 1.2       |      | ms  |  |

| OL                    | Open load current                   |                                                            |                        | 3         |      | mA  |  |

| T <sub>OTW</sub>      | Thermal warning temperature         | Die temperature (T <sub>J</sub> )                          | 140 150                |           | 160  | °C  |  |

| T <sub>TSD</sub>      | Thermal shutdown temperature        | Die Temperature (T <sub>J</sub> )                          | 165                    | 175       | 185  | °C  |  |

| T <sub>hys</sub>      | Thermal shutdown hysteresis         | Die temperature (T <sub>J</sub> )                          | 20                     |           |      | °C  |  |

| •                     |                                     |                                                            |                        |           |      |     |  |

(1) SDO output current external to the device

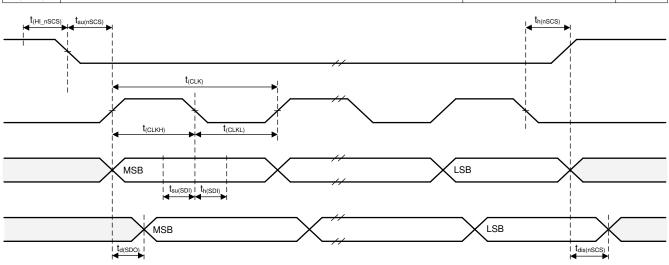

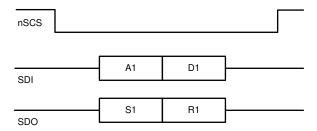

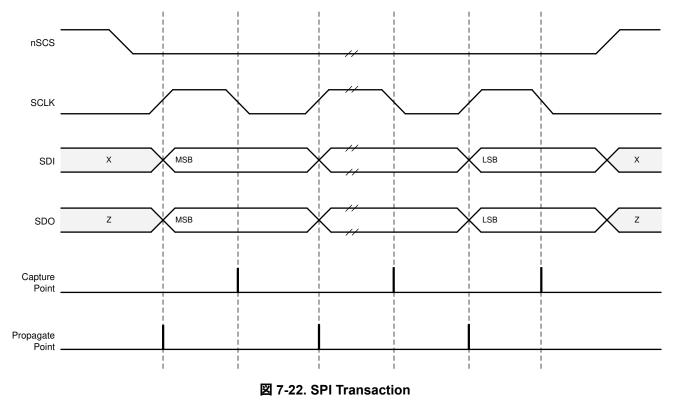

## 6.6 SPI Timing Requirements

|                       |                                                                       | MIN | NOM | MAX | UNIT |

|-----------------------|-----------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>(READY)</sub>  | SPI ready, VM > V <sub>(UVLO)</sub>                                   |     | 1   |     | ms   |

| t <sub>(CLK)</sub>    | SCLK minimum period                                                   | 100 |     |     | ns   |

| t <sub>(CLKH)</sub>   | SCLK minimum high time                                                | 50  |     |     | ns   |

| t <sub>(CLKL)</sub>   | SCLK minimum low time                                                 | 50  |     |     | ns   |

| t <sub>su(SDI)</sub>  | SDI input setup time                                                  | 20  |     |     | ns   |

| t <sub>h(SDI)</sub>   | SDI input hold time                                                   | 30  |     |     | ns   |

| t <sub>d(SDO)</sub>   | SDO output delay time, SCLK high to SDO valid, C <sub>L</sub> = 20 pF |     |     | 30  | ns   |

| t <sub>su(nSCS)</sub> | nSCS input setup time                                                 | 50  |     |     | ns   |

| t <sub>h(nSCS)</sub>  | nSCS input hold time                                                  | 50  |     |     | ns   |

|                        |                                                    | MIN | NOM | MAX | UNIT |

|------------------------|----------------------------------------------------|-----|-----|-----|------|

| t <sub>(HI_nSCS)</sub> | nSCS minimum high time before active low           | 500 |     |     | ns   |

| t <sub>dis(nSCS)</sub> | nSCS disable time, nSCS high to SDO high impedance |     | 10  |     | ns   |

G-1. SPI Slave-Mode Timing Definition

## 6.7 Typical Characteristics

## 7 Detailed Description

## 7.1 Overview

The device is an integrated, 4.5-V to 38-V motor driver for automotive brushed-motor applications. The device is capable of high output-current drive using low-R<sub>DS(ON)</sub> integrated MOSFETs.

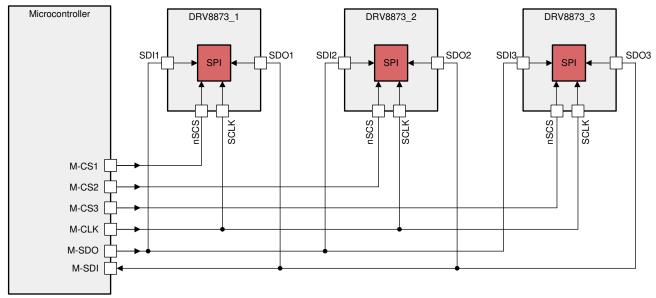

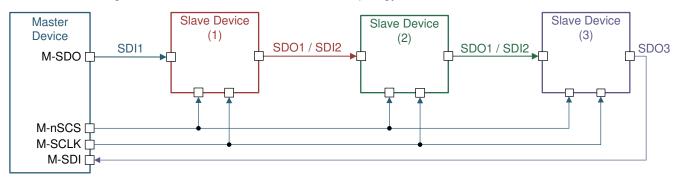

A standard 4-wire serial peripheral interface (SPI) decreases the device pin count by allowing the various device settings and fault reporting to be managed through an external controller. Alternatively a hardware interface option device is available for easy configuration with less detailed control of all device functions.

The device integrates a current mirror which provides an output current proportional to the current through the high-side FETs. This feature allows the system to monitor the motor current without the need for a large high-power resistor for current sensing. The device has a built-in current regulation feature with a fixed off-time current-chopping scheme. The current-chopping level is selected through SPI in the SPI version of the device and in the hardware version of the device is it a fixed value.

In addition to the high level of driver integration, the device provides a broad range of integrated protection features. These features include power-supply undervoltage lockout (UVLO), charge-pump undervoltage lockout, overcurrent faults, open-load detection, output short to battery and short to ground protection, and thermal shutdown. Device faults are indicated by the nFAULT pin with detailed information available in the device registers.

The device integrates a spread spectrum clocking feature for both the internal digital oscillator and internal charge pump. This feature combined with output slew rate control minimizes the radiated emissions from the device.

The device is available in a 24-pin HTSSOP package with a thermal pad.

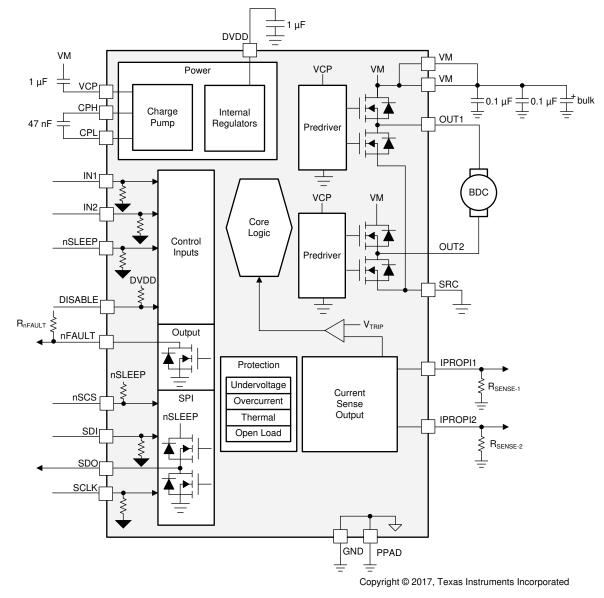

## 7.2 Functional Block Diagram

図 7-1. Hardware Device Block Diagram

🛛 7-2. SPI Device Block Diagram

## 7.3 Feature Description

| $\pm$ 7-1 lists the | recommended | external | components | for the device |

|---------------------|-------------|----------|------------|----------------|

|                     | recommended | external | components |                |

|                      | 表 /-1. External Components |             |                                                      |  |  |  |

|----------------------|----------------------------|-------------|------------------------------------------------------|--|--|--|

| COMPONENT            | PIN 1                      | PIN 2       | RECOMMENDED                                          |  |  |  |

| C <sub>VM1</sub>     | VM                         | GND         | 0.1-µF ceramic capacitor rated for VM                |  |  |  |

| C <sub>VM2</sub>     | VM                         | GND         | Bulk capacitor rated for VM                          |  |  |  |

| C <sub>VCP</sub>     | VCP                        | VM          | 16-V, 1-µF ceramic capacitor                         |  |  |  |

| C <sub>FLY</sub>     | CPH                        | CPL         | 47-nF capacitor rated for VM                         |  |  |  |

| C <sub>DVDD</sub>    | DVDD                       | GND         | 6.3-V, 1-µF ceramic capacitor                        |  |  |  |

| R <sub>nFAULT</sub>  | VCC <sup>(1)</sup>         | nFAULT      | ≥ 10-kΩ pullup resistor                              |  |  |  |

| R <sub>MODE</sub>    | MODE                       | GND or DVDD | Device hardware interface                            |  |  |  |

| R <sub>SENSE-1</sub> | IPROPI1                    | GND         | Resistors to convert mirrored current into a voltage |  |  |  |

| R <sub>SENSE-2</sub> | IPROPI2                    | GND         | Resistors to convert mirrored current into a voltage |  |  |  |

主71 External Components

SLINGE2

(1) VCC is not a pin on the device, but a VCC supply-voltage pullup is required for the open-drain output nFAULT.

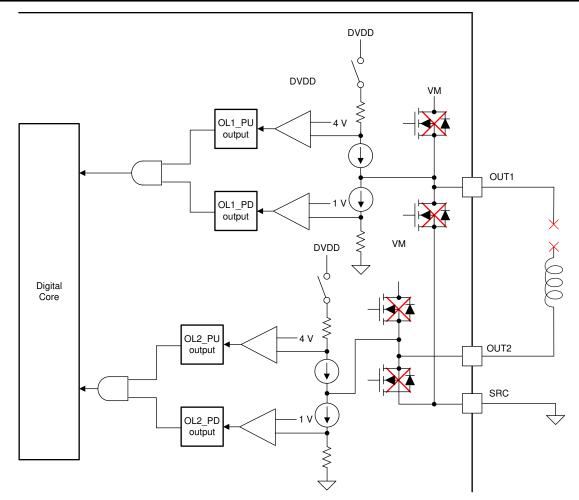

#### 7.3.1 Bridge Control

The device output has four N-channel MOSFETs configured in a H-bridge. The driver can be controlled using a PH/EN, PWM, or independent half-bridge input mode. 表 7-2 lists the control mode configurations.

| HARDWARE DEVICE<br>MODE PIN |               |                             |  |  |  |

|-----------------------------|---------------|-----------------------------|--|--|--|

| L                           | 00b           | PH/EN                       |  |  |  |

| Н                           | 01b (default) | PWM                         |  |  |  |

| 200 kΩ ± 5% to GND          | 10b           | Independent half bridge     |  |  |  |

| Not applicable              | 11b           | Input disabled, bridge Hi-Z |  |  |  |

#### 表 7-2. Control Mode Configuration

In the hardware version of the device, the MODE pin determines the control interface and latches on power-up or when exiting sleep mode. During the device power-up sequence, the DVDD pin is enabled first, and then the MODE pin latches. Tying the MODE pin directly to ground sets the mode to phase and enable. Tying the MODE pin to the DVDD pin, or an external 5 V rail, sets the mode to PWM. Connecting the MODE pin to ground with a 200 k $\Omega \pm 5\%$  resistor sets the mode to independent half-bridge where the two half-bridges can be independently controlled by their respective input (INx) pins.  $\gtrsim 7-3$  lists the different MODE pin settings.

| 表 7-3. DRV8873H-Q1 MODE Pin Settings |                         |         |  |  |  |  |

|--------------------------------------|-------------------------|---------|--|--|--|--|

| CONNECTION                           | MODE                    | CIRCUIT |  |  |  |  |

| Connect to GND                       | Phase and Enable        | MODE    |  |  |  |  |

| 200 k $\Omega$ ± 5% to GND           | Independent half-bridge |         |  |  |  |  |

| Connect to DVDD PWM                  |                         |         |  |  |  |  |

In the SPI version of the device, the mode setting can be changed by writing to the MODE register in the IC1 control register because this device version has no dedicated MODE pin. The device mode gets latched when the DISABLE signal transitions from high to low.

#### 7.3.1.1 Control Modes

The device output consists of four N-channel MOSFETs that are designed to drive high current. The MOSFETs are controlled by two logic inputs, EN/IN1 and PH/IN2, in three different input modes to support various commutation and control methods, as shown in the logic tables (表 7-4, 表 7-5, and 表 7-6). In the Independent PWM mode, the fault handling is performed independently for each half bridge. For example, if an overcurrent condition (OCP) is detected in half-bridge 1, only the half-bridge 1 output (OUT1) is disabled and half-bridge 2 continues to operate based on the IN2 input.

| AX / -4. F H/EN MODE THUIT TABLE |         |        |        |      |      |  |

|----------------------------------|---------|--------|--------|------|------|--|

| nSLEEP                           | DISABLE | EN/IN1 | PH/IN2 | OUT1 | OUT2 |  |

| 0                                | Х       | Х      | Х      | Hi-Z | Hi-Z |  |

| 1                                | 1       | Х      | Х      | Hi-Z | Hi-Z |  |

| 1                                | 0       | 0      | Х      | Н    | Н    |  |

| 1                                | 0       | 1      | 0      | L    | Н    |  |

| 1                                | 0       | 1      | 1      | Н    | L    |  |

### 素 7-4 PH/FN Mode Truth Table

| nSLEEP | DISABLE | EN/IN1 | PH/IN2 | OUT1 | OUT2 |  |

|--------|---------|--------|--------|------|------|--|

| 0      | Х       | Х      | Х      | Hi-Z | Hi-Z |  |

| 1      | 1       | Х      | Х      | Hi-Z | Hi-Z |  |

| 1      | 0       | 0      | 0      | Hi-Z | Hi-Z |  |

| 1      | 0       | 0      | 1      | L    | Н    |  |

| 1      | 0       | 1      | 0      | Н    | L    |  |

| 1      | 0       | 1      | 1      | Н    | Н    |  |

### 表 7-5. PWM Mode Truth Table

#### 表 7-6. Independent Mode Truth Table

| nSLEEP | DISABLE | EN/IN1 | PH/IN2 | OUT1 | OUT2 |

|--------|---------|--------|--------|------|------|

| 0      | X       | Х      | Х      | Hi-Z | Hi-Z |

| 1      | 1       | Х      | Х      | Hi-Z | Hi-Z |

| 1      | 0       | 0      | 0      | L    | L    |

| 1      | 0       | 0      | 1      | L    | Н    |

| 1      | 0       | 1      | 0      | Н    | L    |

| 1      | 0       | 1      | 1      | Н    | Н    |

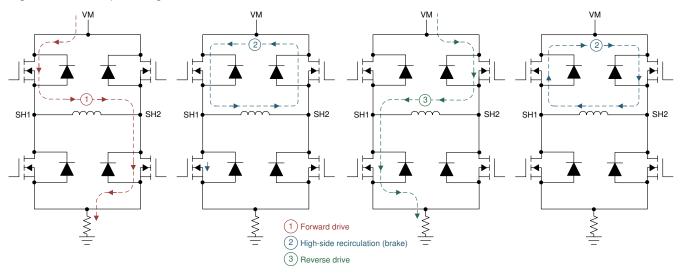

The inputs can be set to static voltages for 100% duty cycle drive, or they can be pulse-width modulated (PWM) for variable motor speed. When using PWM mode (MODE = 1), switching between driving and braking typically is best. For example, to drive a motor forward with 50% of its maximum revolutions per minute (RPM), the IN1 pin is high and the IN2 pin is low during the driving period. During the other period in this example, the IN1 pin is high and the IN2 pin is high.

☑ 7-3. Half-Bridge Current Paths

In the Independent PWM mode, to independently put the outputs of the half bridge in the high-impedance (Hi-Z) state, the OUT1\_DIS or OUT2\_DIS bit in the IC3 register must be set to 1b. Writing a logic 1 to the OUT1\_DIS bit disables the OUT1 output. Writing a logic 1 to the OUT2\_DIS bit disables the OUT2 output. The default value in these registers is 0b. The option to independently set the outputs of the half bridge in the Hi-Z state is not available for the hardware version of the device.

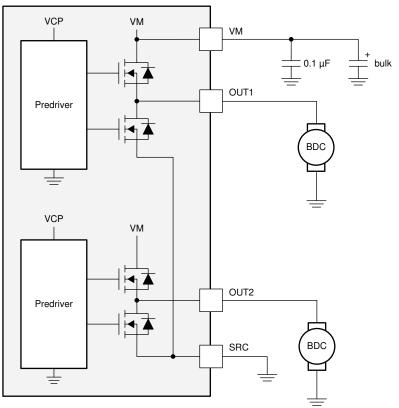

#### 7.3.1.2 Half-Bridge Operation

The device can be used to drive two solenoids or unidirectional brushed DC-motor loads instead of a brushed-DC motor in full H-bridge configuration. Independent half-bridge control is preferred for operation in this mode;

however, using the PH/EN or PWM modes is not restricted if the correct driving and braking states can be achieved.

Copyright © 2017, Texas Instruments Incorporated

図 7-4. Independent Half bridge Mode Driving Two Low-Side Loads

#### 7.3.1.3

TI does not recommend tying the OUT1 and OUT2 pins together and drive a load. The half bridges may be out of synchronization in this configuration and any mismatch in the input commands can momentarily result in shoot through condition. This mismatch can be mitigated by adding an inductor in-line with the outputs.

If loads are connected between the OUTx and VM pins, the device can draw more current than specified in the  $\frac{2}{2} \frac{2}{3} \frac{2}{6.5}$  table. To avoid this condition, TI recommends connecting loads in the configuration shown in  $\mathbb{X}$  7-4.

Depending on how the loads are connected on the outputs pin, some of the features offered by the device could have reduced functionality. For example, having a load between the OUTx and GND pins, as shown in  $\boxtimes$  7-4, results in false trips of the open-load diagnosis in active-mode (OLA). Having a load tied between the OUTx and VM pins restricts the use of internal current regulation because no means of measuring current flowing through the load with the current mirror block is available.  $\gtrsim$  7-7 lists these use cases.

|  | LOAD CONNECTIONS NODE 1 NODE 2 |     | FUNCTIONALITY |                                         |  |  |  |

|--|--------------------------------|-----|---------------|-----------------------------------------|--|--|--|

|  |                                |     | OLA           | CURRENT REGULATION (I <sub>TRIP</sub> ) |  |  |  |

|  | OUTx                           | GND | Not Available | Operational                             |  |  |  |

|  | OUTx                           | VM  | Operational   | Not Available                           |  |  |  |

#### 7.3.1.4 Internal Current Sense and Current Regulation

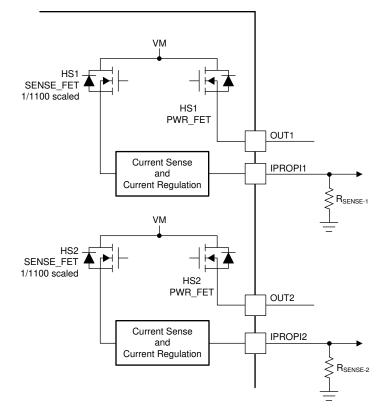

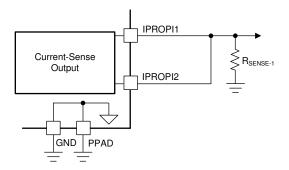

The IPROPI pin outputs an analog current that is proportional to the current flowing in the H-bridge. The output current is typically 1/1100 of the current in both high-side FETs. The IPROPI pin is derived from the current through either of the high-side FETs. Because of this, the IPROPI pin does not represent the half bridge current when operating in a fast decay mode or low-side slow decay mode. The IPROPI pin represents the H-bridge current under forward drive, reverse drive, and high-side slow decay. The IPROPI output is delayed by approximately 2  $\mu$ s for the fastest slew-rate setting (43.2 V/ $\mu$ s) after the high-side FET is switched on.

#### 図 7-5. Current-Sense Block Diagram

The selection of the external resistor should be such that the voltage on the IPROPI pin is less than 5 V. Therefore the resistor must be sized less than this value based on  $\neq$  1. The range of current that can be monitored is from 100 mA to 10 A assuming the selected external resistor meets the calculated value from  $\neq$  1. If the current exceeds 10 A, the device could reach overcurrent protection (OCP) or overtemperature shutdown (TSD). If OCP occurs, the device disables the internal MOSFETs and protects itself (for the hardware version of the device) or based on the OCP\_MODE setting (for the SPI version of the device). For guidelines on selecting a sense resistor, see the  $\frac{1}{27} \frac{1}{32} \frac{8.2.1.3}{8.2.1.3}$  section.

$$R_{(SENSE)} = k \times 5 V / I_O$$

#### where

- k is the current mirror scaling factor, which is typically 1100.

- I<sub>O</sub> is the maximum drive current to be monitored.

(1)

Texas Instruments recommends the load current not exceed 8 A during normal operation. If slew rate setting of 2.6 V/ $\mu$ s (SR = 111b) is used when the load current is about 8 A, choose TOFF to be either 40  $\mu$ s or 60  $\mu$ s.

The SPI version of the device limits the output current based on the trip level set in the SPI registers. In the hardware version of the device, the current trip limit is set to 6.5 A. The current regulation feature is enabled by default on both the outputs (OUT1 and OUT2). To disable current regulation in the hardware version of the device, the nITRIP pin must be connected to DVDD. To disable current regulation in the SPI version of the device, the DIS\_ITRIP bits in the IC4 Control register must be written to. The bit settings are:

- 01b to disable current regulation only on the OUT1 pin

- 10b to disable current regulation only on the OUT2 pin

- 11b to disable current regulation on both the OUT1 and OUT2 pins

|                   | 表 7-8. Control Regulation Threshold      |                 |     |     |     |   |  |  |  |

|-------------------|------------------------------------------|-----------------|-----|-----|-----|---|--|--|--|

|                   | PARAMETER ITRIP_LVL BIT MIN TYP MAX UNIT |                 |     |     |     |   |  |  |  |

| I <sub>TRIP</sub> | Current limit threshold                  | ITRIP_LVL = 00b | 3.4 | 4   | 4.6 | А |  |  |  |

|                   |                                          | ITRIP_LVL = 01b | 4.6 | 5.4 | 6.2 | А |  |  |  |

|                   |                                          | ITRIP_LVL = 10b | 5.5 | 6.5 | 7.5 | А |  |  |  |

|                   |                                          | ITRIP_LVL = 11b | 6   | 7   | 8   | А |  |  |  |

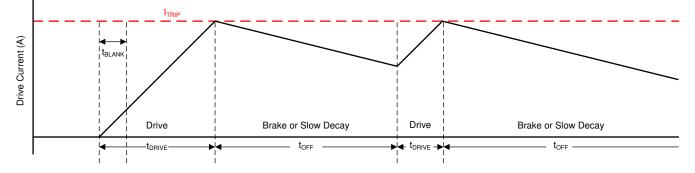

When the I<sub>TRIP</sub> current has been reached, the device enforces slow current decay by enabling both the high-side FETs for a time of  $t_{OFF}$ . In the hardware version of the device, the  $t_{OFF}$  time is 40 µs. The  $t_{OFF}$  time is selectable through SPI in the SPI version of the device, as shown in  $\frac{1}{27}$  7-9. The default setting is 01b ( $t_{OFF}$  = 40 µs).

| PARAMETER        |              | TOFF BIT   | t <sub>OFF</sub> DURATION | UNIT |  |

|------------------|--------------|------------|---------------------------|------|--|

| t <sub>OFF</sub> | PWM off time | TOFF = 00b | 20                        | μs   |  |

|                  |              | TOFF = 01b | 40                        | μs   |  |

|                  |              | TOFF = 10b | 60                        | μs   |  |

|                  |              | TOFF = 11b | 80                        | μs   |  |

#### 表 7-9. PWM Off Time Settings

#### **Z** 7-6. Current Regulation Time Periods

When the  $t_{OFF}$  time has elapsed and the current level falls below the current regulation ( $I_{TRIP}$ ) level, the output is re-enabled according to the inputs. If, after the  $t_{OFF}$  time has elapsed the current is still higher than the  $I_{TRIP}$  level, the device enforces another  $t_{OFF}$  time period of the same duration.

The drive time ( $t_{DRIVE}$ ) occurs until another ITRIP event is reached and depends heavily on the VM voltage, the back-EMF of the motor, and the inductance of the motor. During the  $t_{DRIVE}$  time, the current-sense regulator does not enforce the ITRIP limit until the  $t_{BLANK}$  time has elapsed. While in current regulation, the inputs can be

Copyright © 2023 Texas Instruments Incorporated

toggled to drive the load in the opposite direction to decay the current faster. For example, if the load was in forward drive prior to entering current regulation it can only go into reverse drive when the driver enforces current regulation.

The IPROPI1 pin represents the current flowing through the HS1 MOSFET of half-bridge 1. The IPROPI2 pin represents the current flowing through the HS2 MOSFET of half-bridge 2. To measure current with one sense resistor, the IPROPI1 and IPROPI2 pins must be connected together with the  $R_{SENSE}$  resistor as shown in  $\boxtimes$  7-7. In this configuration, the current-sense output is proportional to the sum of the currents flowing through the both high-side FETs.

図 7-7. Current Sense Output

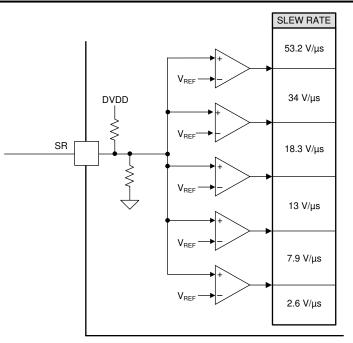

#### 7.3.1.5 Slew-Rate Control

The rise and fall times ( $t_r$  and  $t_f$ ) of the outputs can be adjusted on the hardware version of the device by changing the value of an external resistor connected from the SR pin to ground. On the SPI version of the device, the slew rate can be adjusted through the SPI. The output slew rate is adjusted internally to the device by controlling the ramp rate of the driven FET gate. The voltage or resistance on the SR pin sets the output rise and fall times in the hardware version of the device.

| CONNECTION                | SR        | CIRCUIT                     |  |  |  |

|---------------------------|-----------|-----------------------------|--|--|--|

| Connect to GND            | 53.2 V/µs |                             |  |  |  |

| 22 k $\Omega$ ± 5% to GND | 34 V/µs   | SR<br>SR<br>R <sub>SR</sub> |  |  |  |

| 表 7-10. DRV8873H-Q1 Sle | v Rate (SR) Pin Connections |

|-------------------------|-----------------------------|

|-------------------------|-----------------------------|

| 表 7-10. DRV8873H-Q1 Slew Rate (SR) Pin Connections (continued) |           |                       |  |  |  |

|----------------------------------------------------------------|-----------|-----------------------|--|--|--|

| CONNECTION                                                     | SR        | CIRCUIT               |  |  |  |

| 68 kΩ ± 5% to GND                                              | 18.3 V/µs | SR<br>R <sub>SR</sub> |  |  |  |

| > 2 MΩ to GND (Hi-Z)                                           | 13 V/µs   | × SR                  |  |  |  |

| 51 k $\Omega$ ± 5% to DVDD                                     | 7.9 V/µs  |                       |  |  |  |

| Connect to DVDD                                                | 2.6 V/µs  |                       |  |  |  |

$\boxtimes$  7-8 shows the internal circuit block for the SR pin.

### 図 7-8. SR Block Diagram

表 7-11 lists the settings in the SPI register that set the output rise and fall times in the SPI version of the device.

| SR   | RISE TIME (V/µs) | FALL TIME (V/µs) |  |  |  |  |

|------|------------------|------------------|--|--|--|--|

| 000b | 53.2             | 53.2             |  |  |  |  |

| 001b | 34               | 34               |  |  |  |  |

| 010b | 18.3             | 18.3             |  |  |  |  |

| 011b | 13               | 13               |  |  |  |  |

| 100b | 10.8             | 10.8             |  |  |  |  |

| 101b | 7.9              | 7.9              |  |  |  |  |

| 110b | 5.3              | 5.3              |  |  |  |  |

| 111b | 2.6              | 2.6              |  |  |  |  |

|      |                  |                  |  |  |  |  |

#### 表 7-11. DRV8873S-Q1 Slew Rate Settings

The typical voltage on the SR pin is 3 V and is driven internally. Changing the resistor value on the SR pin changes the slew-rate setting from approximately 2.6 V/µs to 53.2 V/µs. The recommended values for the external resistor are shown in the 2227.3.3.2 section. If the SR pin is grounded then the slew rate is 53.2 V/µs. Leaving the SR pin as a no-connect pin sets the slew rate to 13 V/µs. Tying it to the DVDD pin sets the slew rate to 2.6 V/µs.

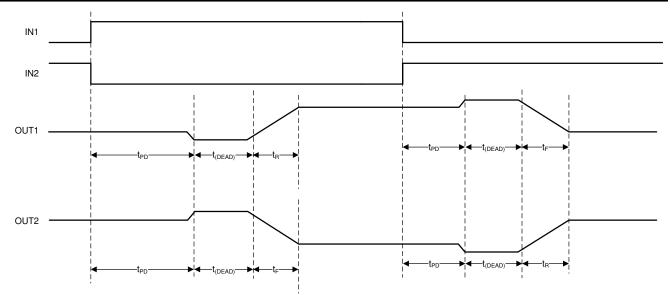

#### 7.3.1.6 Dead Time

The dead time  $(t_{(DEAD)})$  is measured as the time when the OUTx pin is in the Hi-Z state between turning off one of the half bridge MOSFETs and turning on the other. For example, the output is in the Hi-Z state between turning off the high-side MOSFET and turning on the low-side MOSFET, or turning on the high-side MOSFET and turning off the low-side MOSFET.

図 7-9. Propagation Delay Time

If the output pin is measured during the  $t_{DEAD}$  time the voltage depends on the direction of the current. If the current is leaving the pin, the voltage is a diode drop below ground. If the current is entering the pin, the voltage is a diode drop below ground. If the current is entering the pin, the voltage is a diode drop above VM. The diode drop is associated with the body diode of the high-side or the low-side FET. The dead time is dependent on the slew-rate setting because a portion of the FET gate ramp includes the observable dead time.

### 7.3.1.7 Propagation Delay

The propagation delay time  $(t_{PD})$  is measured as the time between an input edge to an output change. This time comprises two parts: an input deglitcher and output slewing delay. The input deglitcher prevents noise on the input pins from affecting the output state. The adjustable slew rate also contributes to the propagation delay time. For the fastest slew-rate setting, the  $t_{PD}$  time is typically 1.5 µs, and for the slowest slew-rate setting, the  $t_{PD}$  time is typically 4.5 µs. For the output to change state during normal operation, one FET must first be turned off.

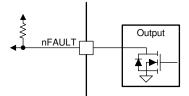

## 7.3.1.8 nFAULT Pin

The nFAULT pin has an open-drain output and should be pulled up to a 5-V or 3.3-V supply. When a fault is detected, the nFAULT line is logic low. For a 5-V pullup the nFAULT pin can be tied to the DVDD pin with a resistor (see the  $\frac{1}{2}\sqrt{3} \times 8$  section). For a 3.3-V pullup, an external 3.3-V supply must be used.

🛛 7-10. nFAULT Pin

During the device power-up sequence, or when exiting sleep mode, the nFAULT pin is held low until the digital core is alive and functional. This low level signal on the nFAULT line does not represent a fault condition. The signal can be used by the external MCU to determine when the digital core of the device is ready; however, this does not mean that the device is ready to accept input commands via the INx pins.

Copyright © 2023 Texas Instruments Incorporated

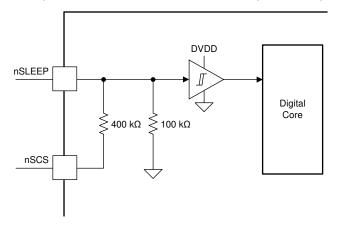

#### 7.3.1.9 nSLEEP as SDO Reference

The nSLEEP pin manages the state of the device. The device goes into sleep mode with a logic-low signal, and comes out of sleep mode when the nSLEEP pin goes high. The signal level when the nSLEEP pin goes high determines the logic level on the SDO output in the SPI version of the device. A 3.3-V signal on the nSLEEP pin provides a 3.3-V output on the SDO output. A 5-V signal on the nSLEEP pin provides a 5-V output on the SDO pin. If the sleep feature is not required, the nSLEEP pin can be connected to the MCU power supply. In that case, when the MCU is powered-up, the motor driver device is also be powered-up.

#### ☑ 7-11. nSCS and nSLEEP Circuit

In the SPI version of the device, if the nSLEEP reset pulse is used to clear faults, the SDO voltage reference is not available for the duration of the nSLEEP reset pulse. No data can be transmitted on the SDO line for the duration when the nSLEEP pin is held low. Therefore, TI recommends using the CLR\_FLT bit in the IC3 control register to clear the faults.

#### 7.3.2 Motor Driver Protection Circuits

The device is protected against VM undervoltage conditions, charge-pump undervoltage conditions, overcurrent events, and overtemperature events.

#### 7.3.2.1 VM Undervoltage Lockout (UVLO)

If at any time the voltage on the VM pin falls below the UVLO-threshold voltage,  $V_{(UVLO)}$ , for the voltage supply, all the outputs (OUTx) are disabled, and the nFAULT pin is driven low. The charge pump is disabled in this condition. The FAULT and UVLO bits are latched high in the SPI registers. Normal operation resumes (motor-driver operation and nFAULT released) when the VM undervoltage condition is removed. The UVLO bit remains set until it is cleared through the CLR\_FLT bit or an nSLEEP reset pulse.

#### 注

During the power-up sequence VM must exceed  $V_{(UVLO)}$  recovery max limit in order to power-up and function properly. After a successful power-up sequence, the device can operate down to the  $V_{(UVLO)}$  report limit before going into the undervoltage lockout condition.

#### 7.3.2.2 VCP Undervoltage Lockout (CPUV)

If at any time the voltage on the VCP pin falls below the  $V_{VCP(UV)}$  voltage for the charge pump, all the outputs (OUTx) are disabled, and the nFAULT pin is driven low. The charge pump remains active during this condition. The FAULT and CPUV bits are latched high in the SPI registers. Normal operation resumes (motor-driver operation and nFAULT released) when the VCP undervoltage condition is removed. The CPUV bit remains set until it is cleared through the CLR\_FLT bit or an nSLEEP reset pulse. This protection feature can be disabled by setting the DIS\_CPUV bit high.

#### 7.3.2.3 Overcurrent Protection (OCP)

If the current in any FET exceeds the  $I_{(ocp)}$  limits for longer than the  $t_{(OCP)}$  time, all FETs in the half bridge are disabled and the nFAULT pin is driven low. The charge pump remains active during this condition. The overcurrent protection can operate in four different modes: latched shutdown, automatic retry, report only, and disabled. In the independent PWM mode (MODE = 10b or MODE pin to ground with a 200-k $\Omega \pm 5\%$  resistor) the fault handling is performed independently for each half-bridge based on the OCP mode selected. This protection scheme protects the outputs from shorts to battery and shorts to ground.

#### 7.3.2.3.1 Latched Shutdown (OCP\_MODE = 00b)

In this mode, after an OCP event, all the outputs (OUTx) are disabled and the nFAULT pin are driven low. The FAULT, OCP, and corresponding MOSFET OCP bits are latched high in the SPI registers. Normal operation resumes (motor-driver operation and nFAULT released) when the OCP condition is removed and a clear faults command has been issued either through the CLR\_FLT bit or an nSLEEP reset pulse. This mode is the default mode for an OCP event for both the hardware version and SPI version of the device.

#### 7.3.2.3.2 Automatic Retry (OCP\_MODE = 01b)

In this mode, after an OCP event all the outputs (OUTx) are disabled and the nFAULT pin is driven low. The FAULT, OCP, and corresponding MOSFET OCP bits are latched high in the SPI registers. Normal operation resumes automatically (motor-driver operation and nFAULT released) after the t<sub>(RETRY)</sub> time has elapsed and the fault condition is removed.

#### 7.3.2.3.3 Report Only (OCP\_MODE = 10b)

In this mode, no protective action is performed when an overcurrent event occurs. The overcurrent event is reported by driving the nFAULT pin low and latching the FAULT, OCP, and corresponding MOSFET OCP bits high in the SPI registers. The motor driver continues to operate. The external controller acts appropriately to manage the overcurrent condition. The reporting is cleared (nFAULT released) when the OCP condition is removed and a clear faults command has been issued either through the CLR\_FLT bit or an nSLEEP reset pulse.

#### 7.3.2.3.4 Disabled (OCP\_MODE = 11b)

In this mode, no protective or reporting action is performed when an overcurrent event occurs. The device continues to drive the load based on the input signals.

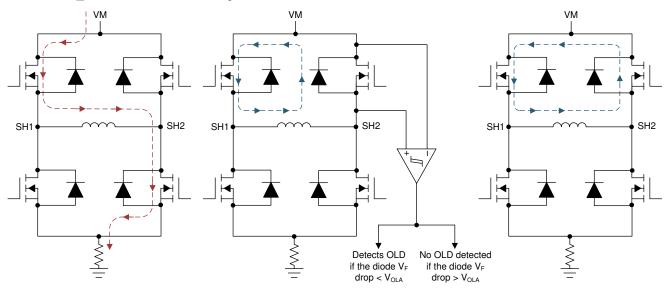

#### 7.3.2.4 Open-Load Detection (OLD)

If the motor is disconnected from the device, an open-load condition is detected and the nFAULT pin is latched low until a clear faults command is issued by the MCU either through the CLR\_FLT bit or an nSLEEP reset pulse. The fault also clears when the device is power cycled or comes out of sleep mode. The OLD test is designed for applications that have capacitance less than 15 nF when the OLP\_DLY bit set to 0b and for less than 60 nF when the OLP\_DLY bit is set to 1b on the OUTx pins. This setting is equivalent to measuring the resistance values listed in  $\frac{1}{2}$  7-12.

| NODE | 1 | NODE 2 | RESISTANCE | COMMENTS                 |  |  |  |

|------|---|--------|------------|--------------------------|--|--|--|

| OUT1 |   | OUT2   | 2 kΩ       |                          |  |  |  |

| OUTx |   | VM     | 12 kΩ      | V <sub>VM</sub> = 13.5 V |  |  |  |

| OUTx |   | GND    | 3 kΩ       |                          |  |  |  |

Open load detection works in both standby mode (OLP) and active mode (OLA). OLP detects the presence of the motor prior to commutating the motor. OLA detects the motor disconnection from the driver during commutation.

#### 7.3.2.4.1 Open-Load Detection in Passive Mode (OLP)

The open-load passive diagnostic (OLP) is different for the hardware and SPI version of the device. The OLP test is available in all three modes of operation (PN/EN, PWM, and independent half-bridge). When the open-load test is running, the internal power MOSFETs are disabled.

For the hardware version of the device, the OLP test is performed at power-up or after exiting sleep mode if the nOL pin is left as a no connect pin (or tied to GND). If the nOL pin is tied to the DVDD pin (or an external 5-V rail), the OLP test is not performed by the device.

For the SPI version of the device, the OLP test is performed when commanded. The following sequence shows how to perform the OLP test directly after the device powers up:

- 1. Power up the device (DISABLE pin high).

- 2. Select the mode through SPI.

- 3. Wait for the t<sub>(DISABLE)</sub> time to expire.

- 4. Write 1b to the EN\_OL bit in the IC1 register.

- 5. Perform the OLP test.

- If an open load (OL) is detected, the nFAULT pin is driven low, the FAULT and OLx bits are latched high. When the OL condition is removed, a clear faults command must be issued by the MCU either through the CLR\_FLT bit or an nSLEEP reset pulse which resets the OLx register bit.

- If an OL condition is not detected, the EN\_OL bits return to the default setting (0b) after the t<sub>d(OL)</sub> time expires.

- 6. Set the DISABLE pin low so that the device drives the motor or load based on the input signals.

If an open-load diagnostic is performed at any other time, the following sequence must be followed:

- 1. Set the pin DISABLE high (to disable the half bridge outputs).

- 2. Wait for the t<sub>(DISABLE)</sub> time to expire.

- 3. Write 1b to the EN\_ÓL bit in the IC1 register.

- 4. Perform the OLP test.

- If an OL condition is detected, the nFAULT pin is driven low, and the FAULT and OLx bits are latched high. When the OL condition is removed, a clear faults command must be issued by the MCU either through the CLR FLT bit or an nSLEEP reset pulse which resets the OLx register bits.

- If an OL condition is not detected, the EN\_OL bits return to the default setting (0b) after the t<sub>d(OL)</sub> time expires.

- 5. Set the DISABLE pin low so that the device drives the motor or load based on the input signals.

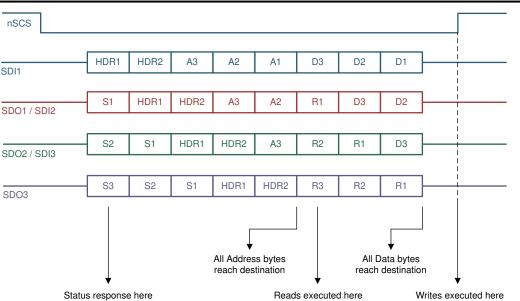

図 7-12. Open-Load Detection Circuit