# DRV8706-Q1 車載用 H ブリッジ・スマート・ゲート・ドライバ、 ワイド同相インライン電流センス・アンプ

## 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み:

- 温度グレード 1:  $-40^{\circ}\text{C} \sim +125^{\circ}\text{C}$ ,  $T_A$

- 機能安全対応**

- 機能安全システムの設計に役立つ資料を利用可能

- H ブリッジ・スマート・ゲート・ドライバ

- 動作範囲:  $4.9\text{V} \sim 37\text{V}$  (絶対最大定格  $40\text{V}$ )

- 100% PWM に対応するダブラー・チャージ・ポンプ

- ハーフブリッジおよび H ブリッジ制御モード

- ピン互換ゲート・ドライバのバリエント

- DRV8106-Q1:** ハーフブリッジ、インライン・アンプ付

- DRV8705-Q1:** H ブリッジ、ローサイド・アンプ付

- スマート・ゲート・ドライブ・アーキテクチャ

- 調整可能なスルーレート制御

- $0.5\text{mA} \sim 62\text{mA}$  のピーク・ソース電流出力

- $0.5\text{mA} \sim 62\text{mA}$  のピーク・シンク電流出力

- デッドタイム・ハンドシェイクを集積

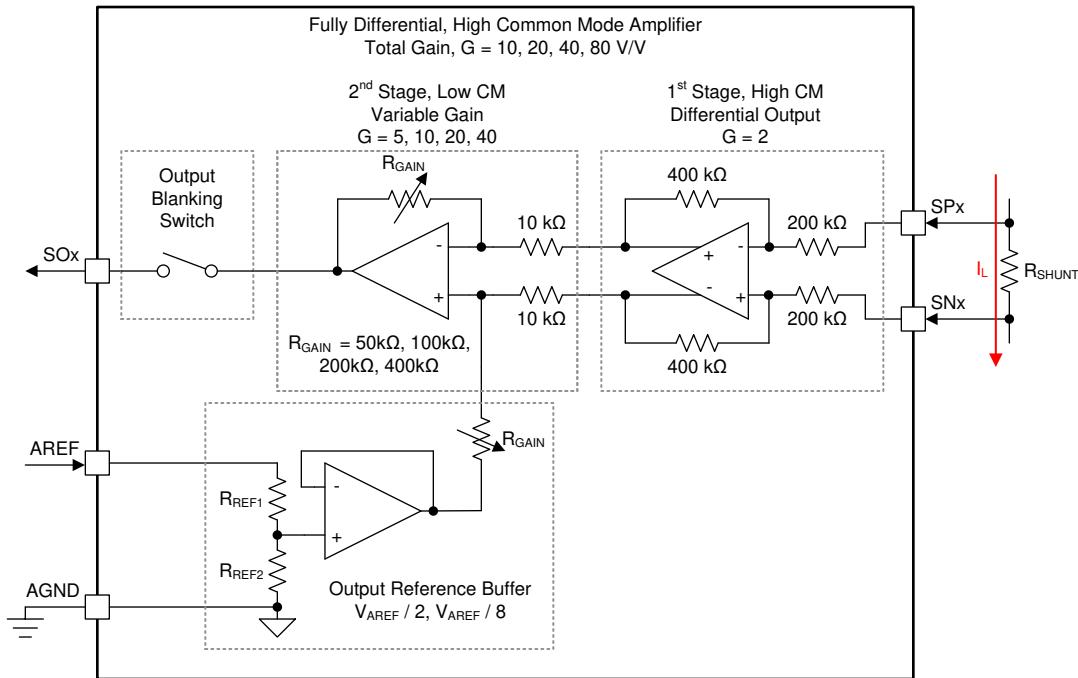

- ワイド同相電流シャント・アンプ

- インライン、ハイサイド、またはローサイドをサポート

- 可変ゲイン設定 ( $10, 20, 40, 80\text{V/V}$ )

- 高集積帰還抵抗

- 可変 PWM ブランкиング方法

- 複数のインターフェイス・オプションを利用可能

- SPI: 詳細な構成と診断

- H/W: 制御ピンの簡素化とマイコン (MCU) ピンの削減

- 拡散スペクトラム・クロック処理による EMI の低減

- コンパクトな VQFN パッケージ (ウェッタブル・フランク)

- 保護機能内蔵

- 専用ドライバ・ディセーブル・ピン (DRVOFF)

- 電源 / レギュレータ電圧監視

- MOSFET  $V_{\text{DS}}$  過電流監視

- MOSFET  $V_{\text{GS}}$  ゲート・フォルト監視

- 反転極性 MOSFET 用チャージ・ポンプ

- オフライン・オープン負荷と短絡診断

- デバイス熱警告とシャットダウン

- フォルト状況割り込みピン (nFAULT)

## 2 アプリケーション

- 車載用ブラシ付き DC モーター

- ソレノイドとリレー

- パワー・ウインドウ・リフトとスライド・ドア

- 電動サンルーフ

- パワー・シート・モジュール

- パワー・トランクとリフト・ゲート

- BDC 燃料、水、オイル・ポンプ

- ウインドシールド・ワイパー

## 3 説明

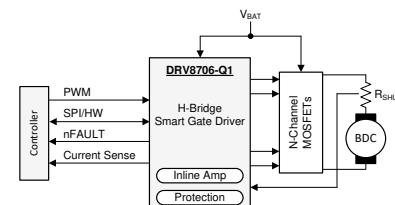

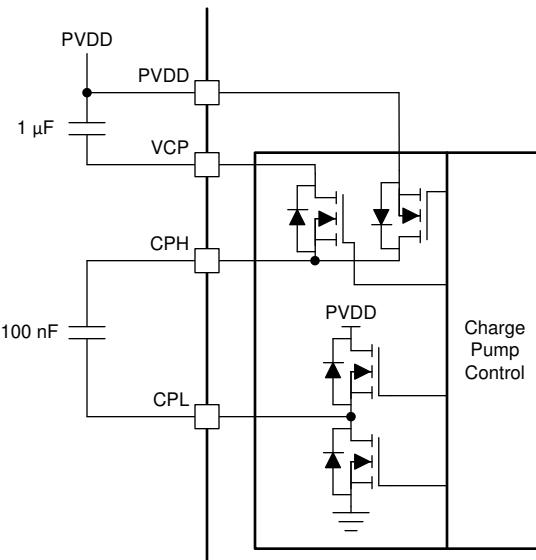

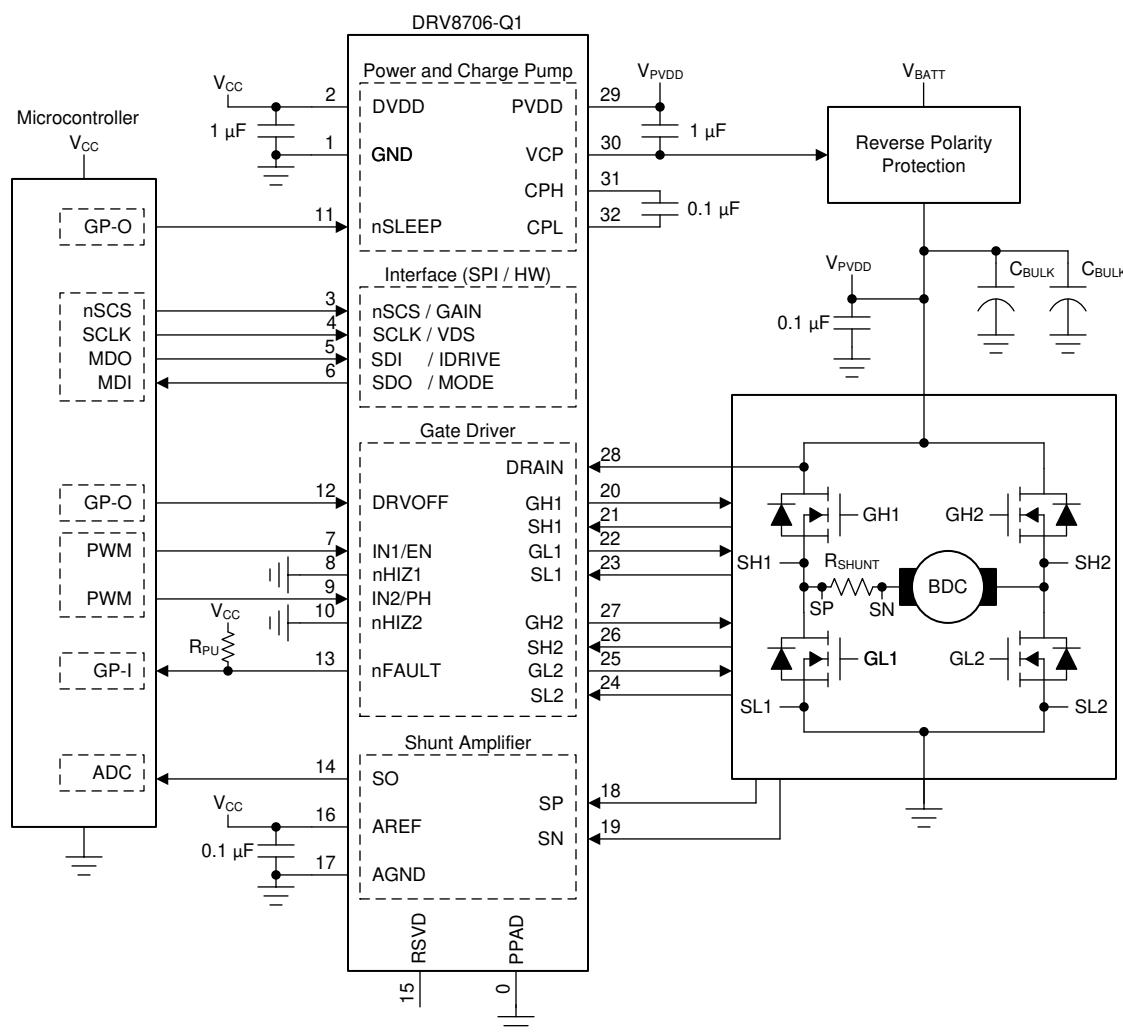

DRV8706-Q1 は高集積 H ブリッジ・ゲート・ドライバであり、ハイサイドとローサイドの各 N チャネル・パワー MOSFET を駆動することができます。ハイサイドで内蔵の電圧増倍チャージ・ポンプを使用し、ローサイドでリニア・レギュレータを使用して、適切なゲート・ドライブ電圧を生成します。

このデバイスはスマート・ゲート・ドライブ・アーキテクチャを使用し、システム・コストの削減と信頼性の向上に貢献します。ゲート・ドライバはデッドタイムを最適化して貫通電流の条件成立を回避し、調整可能なゲート・ドライブ電流を通じて電磁干渉 (EMI) を低減するための制御を実施するほか、 $V_{\text{DS}}$  モニタと  $V_{\text{GS}}$  モニタを使用して、ドレイン - ソース間、およびドレイン - ゲート間の短絡条件からの保護を実現します。

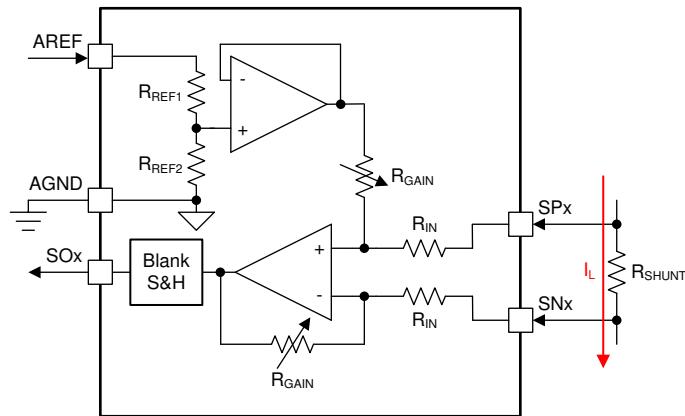

広い同相シャント・アンプにより、インライン電流検出機能が実現し、ウインドウの再循環中であっても、モーター電流を連続的に測定できます。インライン検出が必要ない場合は、ローサイドまたはハイサイドのセンス構成でアンプを使用できます。

DRV8706-Q1 は、一連の保護機能を搭載しており、信頼性の高いシステム動作の確実な実現に貢献します。保護機能には、電源とチャージ・ポンプの低電圧監視と過電圧監視、外部 MOSFET の  $V_{\text{DS}}$  過電流監視と  $V_{\text{GS}}$  ゲート障害監視、オフライン・オープン負荷および短絡の診断、内部的な温度警告と過熱保護機能があります。

### 製品情報(1)

| 部品番号       | パッケージ     | 本体サイズ (公称)      |

|------------|-----------|-----------------|

| DRV8706-Q1 | VQFN (32) | 5.00mm × 5.00mm |

(1) 利用可能なパッケージについては、このデータシートの末尾にある注文情報を参照してください。

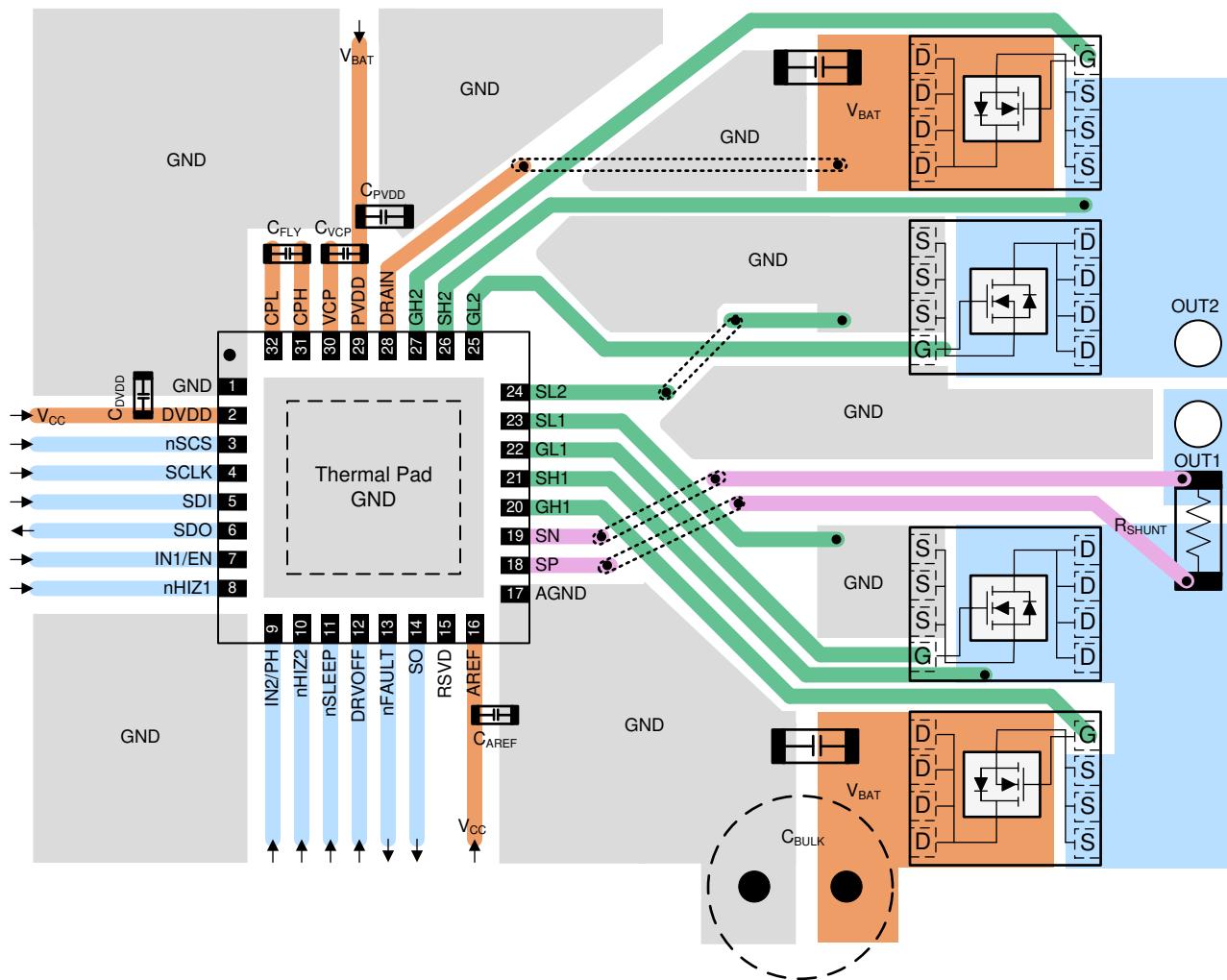

概略回路図

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、必ず最新版の英語版をご参照ください。

## 目次

|                                  |           |                                      |           |

|----------------------------------|-----------|--------------------------------------|-----------|

| <b>1 特長</b>                      | <b>1</b>  | 7.3 機能説明                             | <b>20</b> |

| <b>2 アプリケーション</b>                | <b>1</b>  | 7.4 デバイスの機能モード                       | <b>37</b> |

| <b>3 説明</b>                      | <b>1</b>  | 7.5 プログラミング                          | <b>37</b> |

| <b>4 改訂履歴</b>                    | <b>2</b>  | 7.6 レジスタ・マップ                         | <b>42</b> |

| <b>5 ピン構成</b>                    | <b>4</b>  | <b>8 アプリケーションと実装</b>                 | <b>54</b> |

| DRV8706-Q1 RHB パッケージ (VQFN) ピン機能 | 4         | 8.1 アプリケーション情報                       | 54        |

| <b>6 仕様</b>                      | <b>6</b>  | 8.2 代表的なアプリケーション                     | 54        |

| 6.1 絶対最大定格                       | 6         | <b>9 レイアウト</b>                       | <b>60</b> |

| 6.2 ESD 定格                       | 7         | 9.1 レイアウトのガイドライン                     | 60        |

| 6.3 推奨動作条件                       | 7         | 9.2 レイアウト例                           | 61        |

| 6.4 熱に関する情報                      | 7         | <b>10 デバイスおよびドキュメントのサポート</b>         | <b>62</b> |

| 6.5 電気的特性                        | 7         | 10.1 ドキュメントのサポート                     | 62        |

| 6.6 タイミング要件                      | 14        | 10.2 サポート・リソース                       | 62        |

| 6.7 タイミング図                       | 14        | 10.3 商標                              | 62        |

| 6.8 代表的特性                        | 15        | 10.4 Electrostatic Discharge Caution | 62        |

| <b>7 詳細説明</b>                    | <b>17</b> | 10.5 Glossary                        | 62        |

| 7.1 概要                           | 17        | <b>11 メカニカル、パッケージ、および注文情報</b>        | <b>63</b> |

| 7.2 機能ブロック図                      | 18        |                                      |           |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

### Changes from Revision \* (July 2020) to Revision A (April 2021)

Page

- デバイスのステータスを「量産データ」に変更..... 1

## デバイス比較表

| デバイス        | ハーフブリッジ | アンプ | インターフェイス     |

|-------------|---------|-----|--------------|

| DRV8706S-Q1 | 2       |     | シリアル (SPI)   |

| DRV8706H-Q1 | 2       | 1   | ハードウェア (H/W) |

**表 5-1. SPI と H/W 機能との比較**

| 機能                                              | SPI (S) インターフェイス   | H/W (H) インターフェイス    |

|-------------------------------------------------|--------------------|---------------------|

| PWM 入力モード                                       | 4 モード              | 4 モード               |

| ゲート・ドライブ出力電流 ( $I_{DRIVE}$ )                    | 16 設定、HS と LS に非依存 | 6 設定、HS と LS にリンク済み |

| デッドタイム                                          | ハンドシェイク + 7 固定設定   | ハンドシェイクのみ           |

| $V_{DS}$ コンパレータ・スレッショルド                         | 16 設定、HS と LS に非依存 | 6 設定、HS と LS にリンク済み |

| $V_{DS}$ および $V_{GS}$ ブランкиング時間 ( $t_{DRIVE}$ ) | 4 設定               | 固定、4 $\mu$ s        |

| $V_{DS}$ グリッヂ除去時間                               | 4 設定               | 固定、4 $\mu$ s        |

| $V_{GS}$ グリッヂ除去時間                               | 固定、2 $\mu$ s       | 固定、2 $\mu$ s        |

| $V_{DS}$ 障害応答                                   | 4 モード              | 固定、サイクルごと           |

| $V_{GS}$ 障害応答                                   | 4 モード              | 固定、サイクルごと           |

| アンプ・ゲイン                                         | 4 設定               | 4 設定                |

| アンプ・ブランкиング時間                                   | 8 設定               | N/A                 |

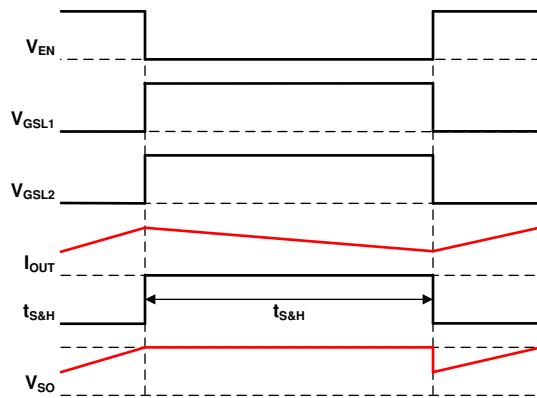

| アンプ・サンプル / ホールド                                 | 使用可能               | N/A                 |

| アンプ・リファレンス電圧                                    | 2 設定               | 固定、 $V_{AREF}/2$    |

| $V_{PVDD}$ 低電圧障害応答                              | 2 モード              | 自動リトライ              |

| $V_{PVDD}$ 過電圧障害応答                              | 4 モード              | N/A                 |

| $V_{VCP}$ 低電圧障害応答                               | 2 モード              | 自動リトライ              |

| $V_{VCP}$ 低電圧スレッショルド                            | 2 設定               | 固定、2.5V             |

| オフライン・オープン負荷診断                                  | 使用可能               | N/A                 |

| オフライン短絡診断                                       | 使用可能               | N/A                 |

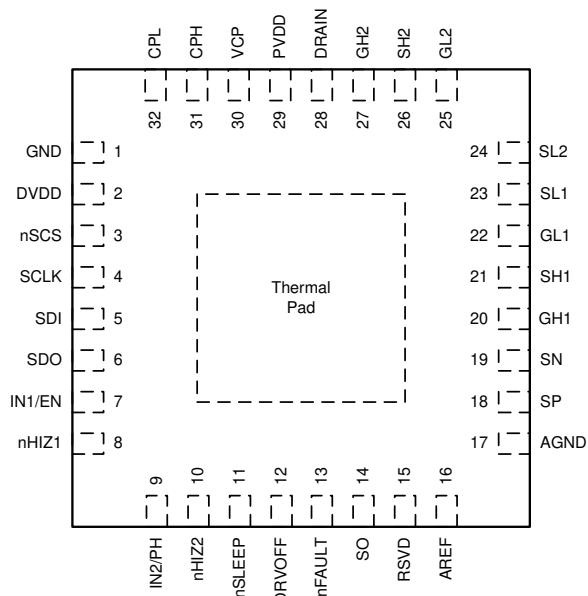

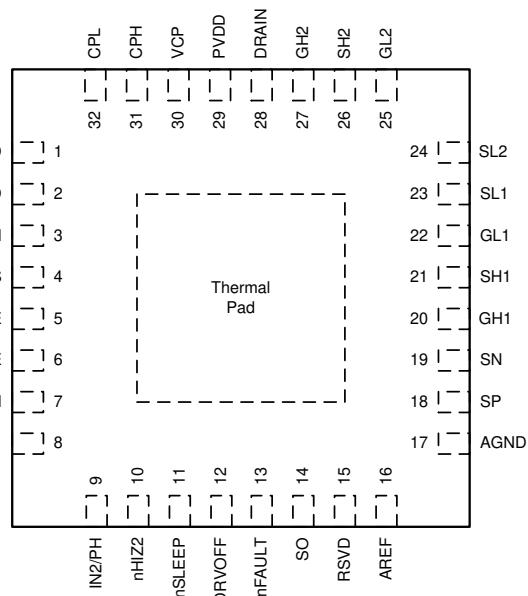

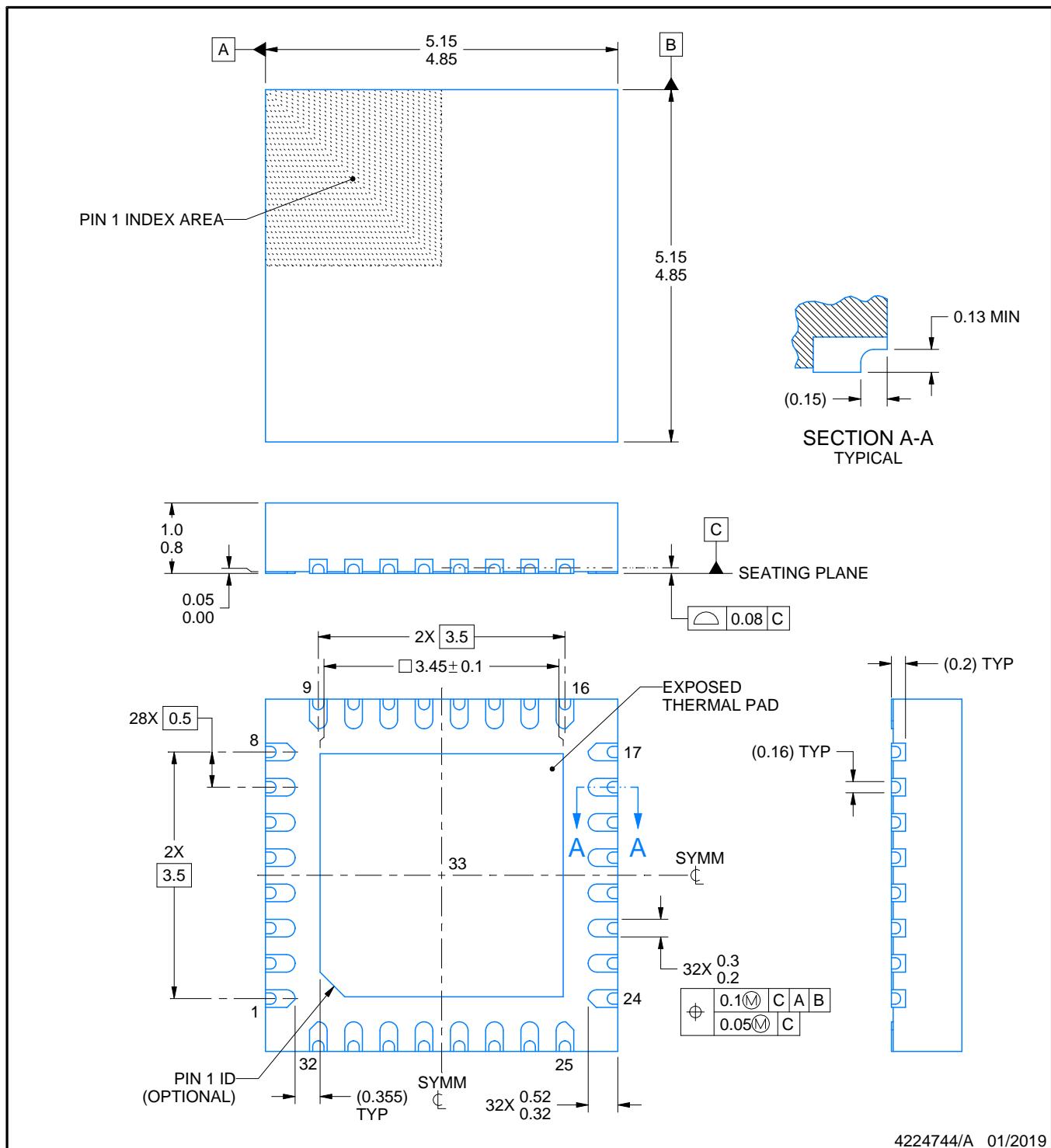

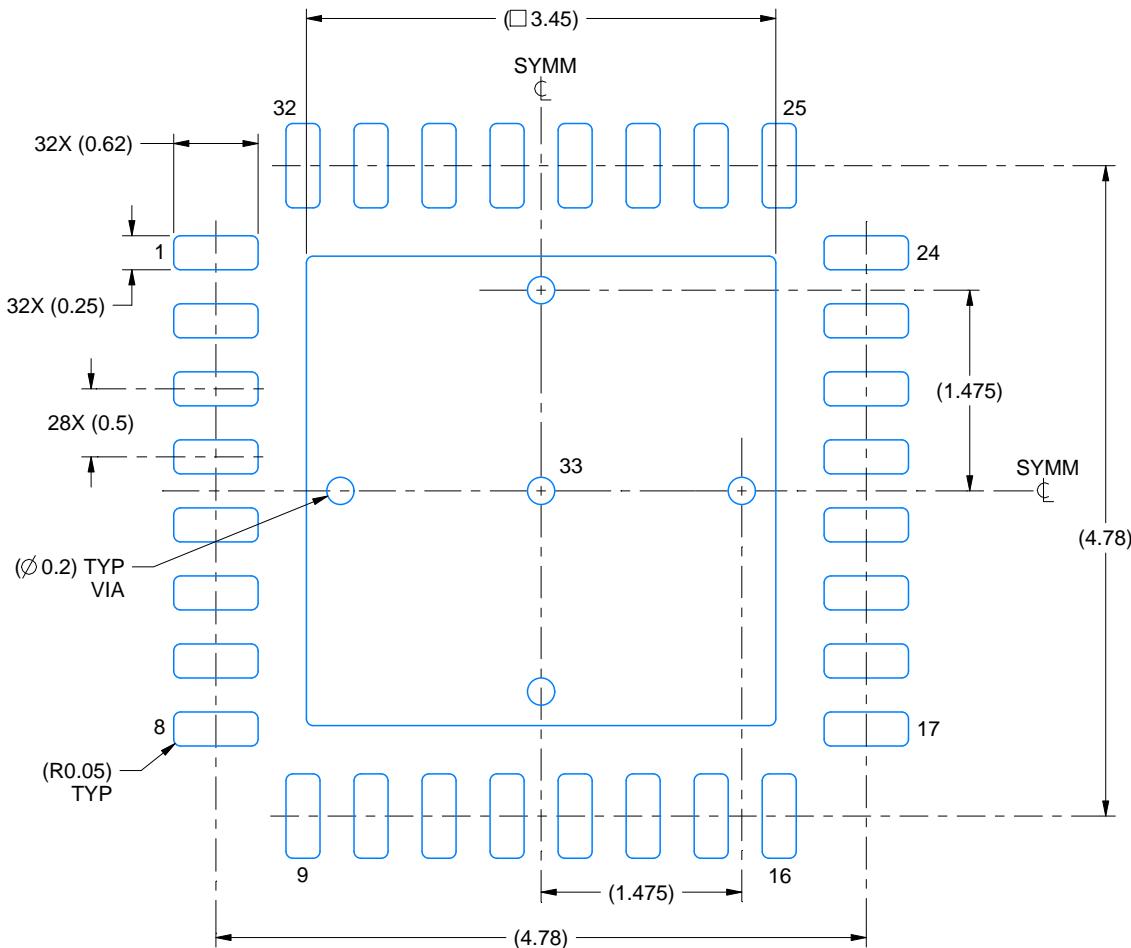

## 5 ピン構成

図 5-1. DRV8706S-Q1 RHB パッケージ 32 ピン

VQFN 上面図

図 5-2. DRV8706H-Q1 RHB パッケージ 32 ピン

VQFN 上面図

## DRV8706-Q1 RHB パッケージ (VQFN) ピン機能

| 番号 | 端子          |             | I/O | 種類   | 説明                                                                             |

|----|-------------|-------------|-----|------|--------------------------------------------------------------------------------|

|    | 名称          | 名称          |     |      |                                                                                |

|    | DRV8706S-Q1 | DRV8706H-Q1 |     |      |                                                                                |

| 1  | GND         |             | I/O | グランド | デバイスのグランド。システム・グランドに接続します。                                                     |

| 2  | DVDD        |             | I   | 電源   | デバイスのロジックおよびデジタル出力電源入力。1.0 $\mu$ F、6.3V セラミック・コンデンサを DVDD ピンと GND ピンの間に接続します。  |

| 3  | nSCS        | —           | I   | デジタル | シリアル・チップ選択。論理 Low でシリアル・インターフェイス通信をイネーブルにします。内部プルアップ抵抗。                        |

|    | —           | GAIN        | I   | アナログ | アンプのゲイン設定。4 レベル入力ピンは外付け抵抗により設定。                                                |

| 4  | SCLK        | —           | I   | デジタル | シリアル・クロック入力。シリアル・データは、このピンの対応する立ち上がりおよび立ち下がりエッジでシフト・アウトおよびキャプチャされます。内部プルダウン抵抗。 |

|    | —           | VDS         | I   | アナログ | VDS 監視しきい値設定。6 レベル入力ピンは外付け抵抗により設定。                                             |

| 5  | SDI         | —           | I   | デジタル | シリアル・データ入力。データは、SCLK ピンの立ち下がりエッジでキャプチャされます。内部プルダウン抵抗。                          |

|    | —           | IDRIVE      | I   | アナログ | ゲート・ドライバの出力電流設定。6 レベル入力ピンは外付け抵抗により設定。                                          |

| 6  | SDO         | —           | O   | デジタル | シリアル・データ出力。データは、SCLK ピンの立ち上がりエッジでシフト・アウトされます。プッシュプル出力。                         |

|    | —           | MODE        | I   | アナログ | PWM 入力モード設定。4 レベル入力ピンは外付け抵抗により設定。                                              |

| 7  | IN1/EN      |             | I   | デジタル | ハーフブリッジ制御入力。詳細については、PWM モードを参照してください。内部プルダウン。                                  |

| 8  | nHIZ1       |             | I   | デジタル | ハーフブリッジ制御入力。詳細については、PWM モードを参照してください。内部プルダウン。                                  |

| 9  | IN2/PH      |             | I   | デジタル | ハーフブリッジ制御入力。詳細については、PWM モードを参照してください。内部プルダウン。                                  |

| 端子 |             |             | I/O | 種類   | 説明                                                                                                            |

|----|-------------|-------------|-----|------|---------------------------------------------------------------------------------------------------------------|

| 番号 | 名称          | 名称          |     |      |                                                                                                               |

|    | DRV8706S-Q1 | DRV8706H-Q1 |     |      |                                                                                                               |

| 10 | nHIZ2       |             | I   | デジタル | ハーフブリッジ制御入力。詳細については、PWM モードを参照してください。内部プルダウン。                                                                 |

| 11 | nSLEEP      |             | I   | デジタル | デバイス・イネーブル・ピン。論理 Low でデバイスをシャットダウンし、スリープ・モードに移行します。内部プルダウン抵抗。                                                 |

| 12 | DRVOFF      |             | I   | デジタル | ドライバ・シャットダウン・ピン。論理 High でハイサイドとローサイド両方のゲート・ドライバ出力をプルダウンします。内部プルダウン抵抗。                                         |

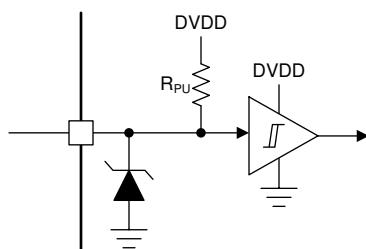

| 13 | nFAULT      |             | O   | デジタル | フォルト状態出力。論理 Low で障害状態を示します。オープン・ドレイン出力。プルアップ抵抗が必要です。                                                          |

| 14 | SO          |             | O   | アナログ | シャント・アンプ出力。                                                                                                   |

| 15 | RSVD        |             | —   | —    | 予約済みグランドに接続するか、接続を外したままにします。                                                                                  |

| 16 | AREF        |             | I   | 電源   | 電流センス・アンプ用の外部基準電圧および電源。0.1 $\mu$ F、6.3V セラミック・コンデンサを AREF ピンと AGND ピンの間に接続します。                                |

| 17 | AGND        |             | I/O | 電源   | デバイスのグランド。システム・グランドに接続します。                                                                                    |

| 18 | SP          |             | I   | アナログ | シャント・アンプの正入力。電流シャント抵抗の正端子に接続します。                                                                              |

| 19 | SN          |             | I   | アナログ | シャント・アンプの負入力。電流シャント抵抗の負端子に接続します。                                                                              |

| 20 | GH1         |             | O   | アナログ | ハイサイド・ゲート・ドライバの出力。ハイサイド・パワー MOSFET のゲートに接続します。                                                                |

| 21 | SH1         |             | I   | アナログ | ハイサイド・ソース・センス入力。ハイサイド・パワー MOSFET のソースに接続します。                                                                  |

| 22 | GL1         |             | O   | アナログ | ローサイド・ゲート・ドライバの出力。ローサイド・パワー MOSFET のゲートに接続します。                                                                |

| 23 | SL1         |             | I   | アナログ | ローサイド MOSFET のゲート・ドライブ・センス機能とパワー・リターン。ローサイド MOSFET のグランド・リターンへの低インピーダンス・パスを使用して、システム・グランドに接続します。              |

| 24 | SL2         |             | I   | アナログ | ローサイド MOSFET のゲート・ドライブ・センス機能とパワー・リターン。ローサイド MOSFET のグランド・リターンへの低インピーダンス・パスを使用して、システム・グランドに接続します。              |

| 25 | GL2         |             | O   | アナログ | ローサイド・ゲート・ドライバの出力。ローサイド・パワー MOSFET のゲートに接続します。                                                                |

| 26 | SH2         |             | I   | アナログ | ハイサイド・ソース・センス入力。ハイサイド・パワー MOSFET のソースに接続します。                                                                  |

| 27 | GH2         |             | O   | アナログ | ハイサイド・ゲート・ドライバの出力。ハイサイド・パワー MOSFET のゲートに接続します。                                                                |

| 28 | DRAIN       |             | I   | アナログ | ブリッジ MOSFET ドレイン電圧センス・ピン。ハイサイド MOSFET ドレインのコモン・ポイントに接続します。                                                    |

| 29 | PVDD        |             | I   | 電源   | デバイス・ドライバの電源入力。ブリッジ電源に接続します。0.1 $\mu$ F、PVDD 定格セラミックコンデンサと 10 $\mu$ F 以上のローカル・バルク容量を PVDD ピンと GND ピンの間に接続します。 |

| 30 | VCP         |             | I/O | 電源   | チャージ・ポンプの出力。1 $\mu$ F、16V セラミック・コンデンサを VCP ピンと PVDD ピンの間に接続します。                                               |

| 31 | CPH         |             | I/O | 電源   | チャージ・ポンプのスイッチング・ノード。100nF、PVDD 定格セラミック・コンデンサを CPH ピンと CPL ピンの間に接続します。                                         |

| 32 | CPL         |             | I/O | 電源   | チャージ・ポンプのスイッチング・ノード。100nF、PVDD 定格セラミック・コンデンサを CPH ピンと CPL ピンの間に接続します。                                         |

## 6 仕様

### 6.1 絶対最大定格

動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                               |                                                                                         | 最小値              | 最大値              | 単位 |

|-------------------------------|-----------------------------------------------------------------------------------------|------------------|------------------|----|

| ドライバ電源ピン電圧                    | PVDD                                                                                    | -0.3             | 40               | V  |

| MOSFET ドレイン・センス・ピン電圧          | DRAIN                                                                                   | -0.3             | 40               | V  |

| グランド・ピン間の電圧差                  | AGND, GND                                                                               | -0.3             | 0.3              | V  |

| チャージ・ポンプ・ピン電圧                 | VCP                                                                                     | -0.3             | 55               | V  |

| チャージ・ポンプ・ハイサイド・ピン電圧           | CPH                                                                                     | $V_{PVDD} - 0.3$ | $V_{VCP} + 0.3$  | V  |

| チャージ・ポンプ・ローサイド・ピン電圧           | CPL                                                                                     | -0.3             | $V_{PVDD} + 0.3$ | V  |

| デジタル電源ピン電圧                    | DVDD                                                                                    | -0.3             | 5.75             | V  |

| ロジック・ピン電圧                     | DRVOFF, GAIN, IDRIVE, IN1/EN, IN2/PH, MODE, nHIZx, nSLEEP, nFAULT, nSCS, SCLK, SDI, VDS | -0.3             | 5.75             | V  |

| 出力ロジック・ピン電圧                   | SDO                                                                                     | -0.3             | $V_{DVDD} + 0.3$ | V  |

| ハイサイド・ゲート・ドライブ・ピン電圧           | GHx <sup>(2)</sup>                                                                      | -2               | $V_{VCP} + 0.3$  | V  |

| 過渡 1μs ハイサイド・ゲート・ドライブ・ピン電圧    |                                                                                         | -5               | $V_{VCP} + 0.3$  |    |

| SHx を基準とするハイサイド・ゲート・ドライブ・ピン電圧 |                                                                                         | -0.3             | 13.5             |    |

| ハイサイド・センス・ピン電圧                | SHx <sup>(2)</sup>                                                                      | -2               | 40               | V  |

| 過渡 1μs ハイサイド・センス・ピン電圧         |                                                                                         | -5               | 40               |    |

| ローサイド・ゲート・ドライブ・ピン電圧           | GLx <sup>(2)</sup>                                                                      | -2               | 13.5             | V  |

| 過渡 1μs ローサイド・ゲート・ドライブ・ピン電圧    |                                                                                         | -3               | 13.5             |    |

| SLx を基準とするローサイド・ゲート・ドライブ・ピン電圧 |                                                                                         | -0.3             | 13.5             |    |

| ローサイド・センス・ピン電圧                | SLx <sup>(2)</sup>                                                                      | -2               | 2                | V  |

| 過渡 1μs のローサイド・センス・ピン電圧        |                                                                                         | -3               | 3                |    |

| ピーク・ゲート・ドライブ電流                | GHx, GLx                                                                                | 内部的に制限           | 内部的に制限           | mA |

| アンプ用電源と基準ピン電圧                 | AREF                                                                                    | -0.3             | 5.75             | V  |

| アンプ入力ピン電圧                     | SN, SP                                                                                  | -2               | $V_{VCP} + 0.3$  | V  |

| 過渡 1μs アンプ入力ピン電圧              |                                                                                         | -5               | $V_{VCP} + 0.3$  |    |

| アンプ入力差動電圧                     | SN, SP                                                                                  | -5.75            | 5.75             | V  |

| アンプ出力ピン電圧                     | SO                                                                                      | -0.3             | $V_{AREF} + 0.3$ | V  |

| 周囲温度、 $T_A$                   |                                                                                         | -40              | 125              | °C |

| 接合部温度、 $T_J$                  |                                                                                         | -40              | 150              | °C |

| 保存温度、 $T_{stg}$               |                                                                                         | -65              | 150              | °C |

- (1) 「絶対最大定格」を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を超える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

- (2) GHx, SHx, GLx、または SLx を基準とする PVDD と DRAIN は、40V を超えないようにしてください。PVDD または DRAIN が 35V を上回る場合は、GHx, SHx, GLx, SLx 上の負電圧が、この定格を超えないよう制限しなければなりません。PVDD と DRAIN が 35V 未満の場合、GHx, SHx, GLx, SLx の最大負電圧定格が利用可能です。

## 6.2 ESD 定格

|                    |       |                                                               | 値     | 単位 |

|--------------------|-------|---------------------------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電気放電 | 人体モデル (HBM)、AEC Q100-002 <sup>(1)</sup><br>HBM ESD 分類レベル 2 準拠 | ±2000 | V  |

|                    |       | デバイス帯電モデル (CDM)、AEC Q100-011<br>CDM ESD 分類レベル C4B 準拠          | ±750  |    |

|                    |       | 角のピン<br>その他のピン                                                | ±500  |    |

(1) AEC Q100-002 では、HBM ストレス試験を ANSI/ESDA/JEDEC JS-001 仕様に従って実施することを示しています。

## 6.3 推奨動作条件

動作温度範囲内 (特に記述のない限り)

|                                |                   |                                                     | 最小  | 公称  | 最大 | 単位 |

|--------------------------------|-------------------|-----------------------------------------------------|-----|-----|----|----|

| V <sub>PVDD</sub>              | ドライバ電源電圧          | PVDD                                                | 4.9 | 37  | V  |    |

| I <sub>HS</sub> <sup>(1)</sup> | ハイサイド平均ゲート・ドライブ電流 | G <sub>H</sub> x                                    | 0   | 15  | mA |    |

| I <sub>LS</sub> <sup>(1)</sup> | ローサイド平均ゲート・ドライブ電流 | G <sub>L</sub> x                                    | 0   | 15  | mA |    |

| V <sub>DVDD</sub>              | デジタル電源電圧          | DVDD                                                | 3   | 5.5 | V  |    |

| V <sub>DIN</sub>               | デジタル入力電圧          | DRVOFF、IN1/EN、IN2/PH、nHIZx、<br>nSLEEP、nSCS、SCLK、SDI | 0   | 5.5 | V  |    |

| I <sub>DOUT</sub>              | デジタル出力電流          | SDO                                                 | 0   | 5   | mA |    |

| V <sub>OD</sub>                | オープン・ドレイン・プルアップ電圧 | nFAULT                                              | 0   | 5.5 | V  |    |

| I <sub>OD</sub>                | オープン・ドレイン出力電流     | nFAULT                                              | 0   | 5   | mA |    |

| V <sub>AREF</sub>              | アンプ基準電源電圧         | AREF                                                | 3   | 5.5 | V  |    |

| I <sub>SO</sub>                | シャント・アンプ出力電流      | SO                                                  | 0   | 5   | mA |    |

| T <sub>A</sub>                 | 動作時周囲温度           |                                                     | -40 | 125 | °C |    |

| T <sub>J</sub>                 | 動作時ジャンクション温度      |                                                     | -40 | 150 | °C |    |

(1) 消費電力および温度の制限に従う必要があります。

## 6.4 热に関する情報

| 熱特性 <sup>(1)</sup>    |                          |  | DRV8706-Q1 | 単位   |

|-----------------------|--------------------------|--|------------|------|

|                       |                          |  | RHB (VQFN) |      |

|                       |                          |  | 32 ピン      |      |

| R <sub>θJA</sub>      | ジャンクションから周囲までの熱抵抗        |  | 34.9       | °C/W |

| R <sub>θJC(top)</sub> | ジャンクションからケース (上部) までの熱抵抗 |  | 25.6       | °C/W |

| R <sub>θJB</sub>      | ジャンクションから基板までの熱抵抗        |  | 15.0       | °C/W |

| Ψ <sub>JT</sub>       | ジャンクションから上部までの熱特性パラメータ   |  | 0.5        | °C/W |

| Ψ <sub>JB</sub>       | ジャンクションから基板までの熱特性パラメータ   |  | 15.0       | °C/W |

| R <sub>θJC(bot)</sub> | ジャンクションからケース (底部) までの熱抵抗 |  | 5.2        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション・レポートを参照してください。

## 6.5 電気的特性

4.9V ≤ V<sub>PVDD</sub> ≤ 37V、-40°C ≤ T<sub>J</sub> ≤ 150°C (特に記述のない限り)。標準的な制限は、V<sub>PVDD</sub> = 13.5V、T<sub>J</sub> = 25°Cに対して適用されます。

| パラメータ                           | テスト条件           | 最小値                                                                                      | 標準値  | 最大値 | 単位 |

|---------------------------------|-----------------|------------------------------------------------------------------------------------------|------|-----|----|

| <b>電源 (DRAIN、DVDD、PVDD、VCP)</b> |                 |                                                                                          |      |     |    |

| I <sub>PVDDQ</sub>              | PVDD スリープ・モード電流 | V <sub>PVDD</sub> 、V <sub>DRAIN</sub> = 13.5V、nSLEEP = 0V<br>-40 ≤ T <sub>J</sub> ≤ 85°C | 2.25 | 3   | μA |

4.9V  $\leq V_{PVDD} \leq 37V$ ,  $-40^{\circ}C \leq T_J \leq 150^{\circ}C$  (特に記述のない限り)。標準的な制限は、 $V_{PVDD} = 13.5V$ ,  $T_J = 25^{\circ}C$ に対して適用されます。

| パラメータ        |                              | テスト条件                                                                         | 最小値 | 標準値   | 最大値  | 単位      |

|--------------|------------------------------|-------------------------------------------------------------------------------|-----|-------|------|---------|

| $I_{DRAINQ}$ | DRAIN スリープ・モード電流             | $V_{PVDD}, V_{DRAIN} = 13.5V, nSLEEP = 0V$<br>$-40 \leq T_J \leq 85^{\circ}C$ |     | 2     | 2.75 | $\mu A$ |

| $I_{DVDDQ}$  | DVDD スリープ・モード電流              | $V_{PVDD}, V_{DRAIN} = 13.5V, nSLEEP = 0V$<br>$-40 \leq T_J \leq 85^{\circ}C$ |     | 2     | 3.5  | $\mu A$ |

| $I_{PVDD}$   | PVDD アクティブ・モード電流             | $V_{PVDD}, V_{DRAIN} = 13.5V, nSLEEP = 5V$                                    |     | 2     | 3    | $mA$    |

| $I_{DRAIN}$  | DRAIN アクティブ・モード電流            | $V_{PVDD}, V_{DRAIN} = 13.5V, nSLEEP = 5V, V_{DS\_LVL} \leq 500mV$            |     | 250   | 325  | $\mu A$ |

| $I_{DVDD}$   | DVDD アクティブ・モード電流             | $V_{DVDD} = 5V, SDO = 0V$                                                     |     | 3.5   | 5.5  | $mA$    |

| $f_{DVDD}$   | デジタル・オシレーター・スイッチング周波数        | 拡散スペクトラムの 1 次周波数                                                              |     | 14.25 |      | $MHz$   |

| $t_{WAKE}$   | ターンオン時間                      | $nSLEEP = 5V$ でアクティブ・モード                                                      |     | 1     |      | $ms$    |

| $t_{SLEEP}$  | ターンオフ時間                      | $nSLEEP = 0V$ でスリープ・モード                                                       |     | 1     |      | $ms$    |

| $V_{VCP}$    | PVDD を基準とするチャージ・ポンプ・レギュレータ電圧 | $V_{PVDD} \geq 13V, I_{VCP} \leq 15mA$                                        | 9.5 | 10.5  | 11   | $V$     |

|              |                              | $V_{PVDD} = 11V, I_{VCP} \leq 15mA$                                           | 8.4 | 10    | 11   |         |

|              |                              | $V_{PVDD} = 9V, I_{VCP} \leq 11mA$                                            | 7   | 8     | 9    |         |

|              |                              | $V_{PVDD} = 7V, I_{VCP} \leq 7.5mA$                                           | 5.5 | 6     | 7    |         |

|              |                              | $V_{PVDD} = 5.5V, I_{VCP} \leq 5mA$                                           | 4.5 | 5     | 5.5  |         |

| $f_{VCP}$    | チャージ・ポンプ・スイッチング周波数           | 拡散スペクトラムの 1 次周波数                                                              |     | 400   |      | $kHz$   |

#### ロジック・レベル入力 (DRV0FF, IN1/EN, IN2/PH, nHIZx, nSLEEP, nSCS, SCLK, SDI)

|           |                |                                                                  |                       |                       |         |           |

|-----------|----------------|------------------------------------------------------------------|-----------------------|-----------------------|---------|-----------|

| $V_{IL}$  | 入力ロジック Low 電圧  | DRV0FF, IN1/EN, IN2/PH, nHIZx, nSLEEP, SCLK, SDI                 | 0                     | $V_{DVDD} \times 0.3$ | $V$     |           |

| $V_{IH}$  | 入力ロジック High 電圧 | DRV0FF, IN1/EN, IN2/PH, nHIZx, nSLEEP, SCLK, SDI                 | $V_{DVDD} \times 0.7$ | 5.5                   | $V$     |           |

| $V_{HYS}$ | 入力ヒステリシス       |                                                                  |                       | $V_{DVDD} \times 0.1$ | $V$     |           |

| $I_{IL}$  | 入力ロジック Low 電流  | $V_{DIN} = 0V, DRV0FF, IN1/EN, IN2/PH, nHIZx, nSLEEP, SCLK, SDI$ | -5                    | 5                     | $\mu A$ |           |

|           |                | $V_{DIN} = 0V, nSCS$                                             | 50                    | 100                   |         |           |

| $I_{IH}$  | 入力ロジック High 電流 | $V_{DIN} = 5V, DRV0FF, IN1/EN, IN2/PH, nHIZx, nSLEEP, SCLK, SDI$ | 50                    | 100                   | $\mu A$ |           |

|           |                | $V_{DIN} = 5V, V_{DVDD} = 5V, nSCS$                              | -5                    | 5                     |         |           |

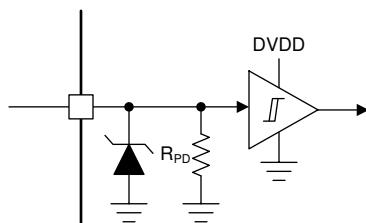

| $R_{PD}$  | 入力プルダウン抵抗      | GND, DRV0FF, IN1/EN, IN2/PH, nHIZx, nSLEEP, SCLK, SDI ～接続        | 50                    | 100                   | 150     | $k\Omega$ |

| $R_{PU}$  | 入力プルアップ抵抗      | DVDD, nSCS ～接続                                                   | 50                    | 100                   | 150     | $k\Omega$ |

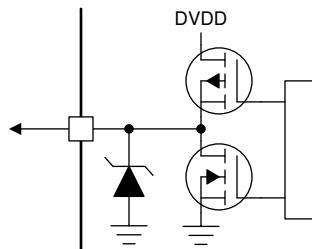

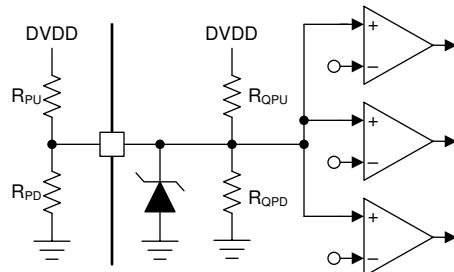

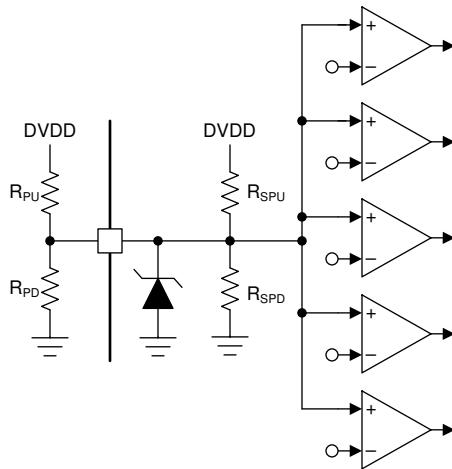

#### マルチレベル入力 (GAIN, IDRIVE, MODE, VDS)

|           |                 |                                  |                       |                       |       |           |

|-----------|-----------------|----------------------------------|-----------------------|-----------------------|-------|-----------|

| $V_{QI1}$ | クワッドレベル入力 1     | GAIN, MODE<br>電圧をレベル 1 に設定       | 0                     | $V_{DVDD} \times 0.1$ | $V$   |           |

| $R_{QI2}$ | クワッドレベル入力 2     | GAIN, MODE<br>GND への抵抗をレベル 2 に設定 | 44.65                 | 47                    | 49.35 | $k\Omega$ |

| $R_{QI3}$ | クワッドレベル入力 3     | GAIN, MODE<br>GND への抵抗をレベル 3 に設定 | 500                   | Hi-Z                  |       | $k\Omega$ |

| $V_{QI4}$ | クワッドレベル入力 4     | GAIN, MODE<br>電圧をレベル 4 に設定       | $V_{DVDD} \times 0.9$ | 5.5                   | $V$   |           |

| $R_{QPD}$ | クワッドレベル・プルダウン抵抗 | GAIN, MODE, GND ～接続              |                       | 98                    |       | $k\Omega$ |

| $R_{QPU}$ | クワッドレベル・プルアップ抵抗 | GAIN, MODE, DVDD ～接続             |                       | 98                    |       | $k\Omega$ |

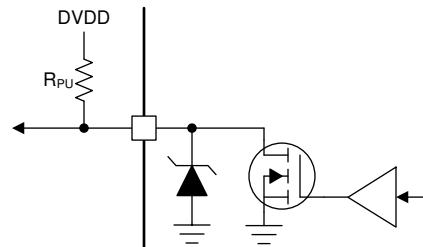

| $V_{SI1}$ | 6 レベル入力 1       | IDRIVE, VDS<br>電圧をレベル 1 に設定      | 0                     | $V_{DVDD} \times 0.1$ | $V$   |           |

4.9V  $\leq V_{PVDD} \leq 37V$ ,  $-40^\circ C \leq T_J \leq 150^\circ C$  (特に記述のない限り)。標準的な制限は、 $V_{PVDD} = 13.5V$ ,  $T_J = 25^\circ C$ に対して適用されます。

| パラメータ     |               | テスト条件                             | 最小値                   | 標準値  | 最大値  | 単位 |

|-----------|---------------|-----------------------------------|-----------------------|------|------|----|

| $R_{SI2}$ | 6 レベル入力 2     | IDRIVE、VDS<br>GND への抵抗をレベル 2 に設定  | 28.5                  | 30   | 31.5 | kΩ |

| $R_{SI3}$ | 6 レベル入力 3     | IDRIVE、VDS<br>GND への抵抗をレベル 3 に設定  | 95                    | 100  | 105  | kΩ |

| $R_{SI4}$ | 6 レベル入力 4     | IDRIVE、VDS<br>GND への抵抗をレベル 4 に設定  | 500                   | Hi-Z |      | kΩ |

| $R_{SI5}$ | 6 レベル入力 5     | IDRIVE、VDS<br>DVDD への抵抗をレベル 5 に設定 | 58.9                  | 62   | 65.1 | kΩ |

| $R_{SI6}$ | 6 レベル入力 6     | IDRIVE、VDS<br>電圧をレベル 6 に設定        | $V_{DVDD} \times 0.9$ |      | 5.5  | V  |

| $R_{SPD}$ | 6 レベル・プルダウン抵抗 | IDRIVE、VDS、GND ～接続                | 98                    |      |      | kΩ |

| $R_{SPU}$ | 6 レベル・プルアップ抵抗 | IDRIVE、VDS、DVDD ～接続               | 69                    |      |      | kΩ |

#### ロジック・レベル出力 (nFAULT, SDO)

|           |                        |                         |                       |     |    |

|-----------|------------------------|-------------------------|-----------------------|-----|----|

| $V_{OL}$  | 出力ロジック Low 電圧          | $I_{DOUT} = 5mA$        |                       | 0.5 | V  |

| $V_{OH}$  | ロジック High 出力電圧         | $I_{DOUT} = -5mA$ , SDO | $V_{DVDD} \times 0.8$ |     | V  |

| $I_{ODZ}$ | オープン・ドレイン・ロジック High 電流 | $V_{OD} = 5V$ , nFAULT  | -10                   | 10  | μA |

#### ゲート・ドライバ (GHx, GLx)

|                 |                             |                                                                                                |                   |            |            |    |

|-----------------|-----------------------------|------------------------------------------------------------------------------------------------|-------------------|------------|------------|----|

| $V_{GHx\_L}$    | GHx Low レベル出力電圧             | $I_{DRVN\_HS} = I_{STRONG}$ , $I_{GHx} = 1mA$ , $GHx \sim SHx$                                 | 0                 | 0.25       | V          |    |

| $V_{GLx\_L}$    | GLx Low レベル出力電圧             | $I_{DRVN\_LS} = I_{STRONG}$ , $I_{GLx} = 1mA$ , $GLx \sim SLx$                                 | 0                 | 0.25       | V          |    |

| $V_{GHx\_H}$    | GHx High レベル出力電圧            | $I_{DRVP\_HS} = I_{HOLD}$ , $I_{GHx} = 1mA$ , $V_{CP} \sim GHx$                                | 0                 | 0.25       | V          |    |

| $V_{GLx\_H}$    | GLx High レベル出力電圧            | $I_{DRVP\_LS} = I_{HOLD}$ , $I_{GLx} = 1mA$ , $10.5V \leq V_{PVDD} \leq 37V$ , $GLx \sim SLx$  | 10.25             | 10.5       | 12.5       | V  |

|                 |                             | $I_{DRVP\_LS} = I_{HOLD}$ , $I_{GLx} = 1mA$ , $4.9V \leq V_{PVDD} \leq 10.5V$ , $GLx \sim SLx$ | $V_{PVDD} - 0.25$ | $V_{PVDD}$ | $V_{PVDD}$ | V  |

| $I_{DRVP, SPI}$ | ピーク・ゲート電流 (ソース)<br>SPI デバイス | $IDRVP = 0000b$ , $V_{GSx} = 3V$ , $V_{PVDD} \geq 7V$                                          | 0.2               | 0.5        | 0.8        | mA |

|                 |                             | $IDRVP = 0001b$ , $V_{GSx} = 3V$ , $V_{PVDD} \geq 7V$                                          | 0.5               | 1          | 1.5        |    |

|                 |                             | $IDRVP = 0010b$ , $V_{GSx} = 3V$ , $V_{PVDD} \geq 7V$                                          | 1.3               | 2          | 2.7        |    |

|                 |                             | $IDRVP = 0011b$ , $V_{GSx} = 3V$ , $V_{PVDD} \geq 7V$                                          | 2.1               | 3          | 3.9        |    |

|                 |                             | $IDRVP = 0100b$ , $V_{GSx} = 3V$ , $V_{PVDD} \geq 7V$                                          | 2.9               | 4          | 5.1        |    |

|                 |                             | $IDRVP = 0101b$ , $V_{GSx} = 3V$ , $V_{PVDD} \geq 7V$                                          | 4.5               | 6          | 7.5        |    |

|                 |                             | $IDRVP = 0110b$ , $V_{GSx} = 3V$ , $V_{PVDD} \geq 7V$                                          | 6                 | 8          | 10         |    |

|                 |                             | $IDRVP = 0111b$ , $V_{GSx} = 3V$ , $V_{PVDD} \geq 7V$                                          | 9                 | 12         | 15         |    |

|                 |                             | $IDRVP = 1000b$ , $V_{GSx} = 3V$ , $V_{PVDD} \geq 7V$                                          | 12                | 16         | 20         |    |

|                 |                             | $IDRVP = 1001b$ , $V_{GSx} = 3V$ , $V_{PVDD} \geq 7V$                                          | 15                | 20         | 25         |    |

|                 |                             | $IDRVP = 1010b$ , $V_{GSx} = 3V$ , $V_{PVDD} \geq 7V$                                          | 18                | 24         | 30         |    |

|                 |                             | $IDRVP = 1011b$ , $V_{GSx} = 3V$ , $V_{PVDD} \geq 7V$                                          | 21                | 28         | 35         |    |

|                 |                             | $IDRVP = 1100b$ , $V_{GSx} = 3V$ , $V_{PVDD} \geq 7V$                                          | 23.25             | 31         | 38.75      |    |

|                 |                             | $IDRVP = 1101b$ , $V_{GSx} = 3V$ , $V_{PVDD} \geq 7V$                                          | 26.5              | 40         | 50         |    |

|                 |                             | $IDRVP = 1110b$ , $V_{GSx} = 3V$ , $V_{PVDD} \geq 7V$                                          | 28                | 48         | 60         |    |

|                 |                             | $IDRVP = 1111b$ , $V_{GSx} = 3V$ , $V_{PVDD} \geq 7V$                                          | 30                | 62         | 77.5       |    |

4.9V  $\leq$   $V_{PVDD}$   $\leq$  37V,  $-40^{\circ}\text{C} \leq T_J \leq 150^{\circ}\text{C}$  (特に記述のない限り)。標準的な制限は、 $V_{PVDD} = 13.5\text{V}$ 、 $T_J = 25^{\circ}\text{C}$ に対して適用されます。

| パラメータ                            |                             | テスト条件                                                                                                         | 最小値   | 標準値  | 最大値   | 単位               |

|----------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------|-------|------|-------|------------------|

| $I_{DRV_P, H/W}$                 | ピーク・ゲート電流 (ソース)<br>H/W デバイス | IDRIVE レベル 1, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                               | 0.5   | 1    | 1.5   | mA               |

|                                  |                             | IDRIVE レベル 2, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                               | 2.9   | 4    | 5.1   |                  |

|                                  |                             | IDRIVE レベル 3, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                               | 6     | 8    | 10    |                  |

|                                  |                             | IDRIVE レベル 4, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                               | 12    | 16   | 20    |                  |

|                                  |                             | IDRIVE レベル 5, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                               | 23.25 | 31   | 38.75 |                  |

|                                  |                             | IDRIVE レベル 6, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                               | 30    | 62   | 77.5  |                  |

| $I_{DRV_N, SPI}$                 | ピーク・ゲート電流 (シンク)<br>SPI デバイス | IDRVN = 0000b, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                              | 0.15  | 0.5  | 0.85  | mA               |

|                                  |                             | IDRVN = 0001b, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                              | 0.35  | 1    | 1.65  |                  |

|                                  |                             | IDRVN = 0010b, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                              | 0.85  | 2    | 3.15  |                  |

|                                  |                             | IDRVN = 0011b, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                              | 1.4   | 3    | 4.6   |                  |

|                                  |                             | IDRVN = 0100b, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                              | 2.1   | 4    | 5.9   |                  |

|                                  |                             | IDRVN = 0101b, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                              | 3.5   | 6    | 8.5   |                  |

|                                  |                             | IDRVN = 0110b, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                              | 5     | 8    | 11    |                  |

|                                  |                             | IDRVN = 0111b, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                              | 8     | 12   | 16    |                  |

|                                  |                             | IDRVN = 1000b, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                              | 11.5  | 16   | 20    |                  |

|                                  |                             | IDRVN = 1001b, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                              | 14.7  | 20   | 25    |                  |

|                                  |                             | IDRVN = 1010b, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                              | 18    | 24   | 30    |                  |

|                                  |                             | IDRVN = 1011b, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                              | 21    | 28   | 35    |                  |

|                                  |                             | IDRVN = 1100b, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                              | 23.25 | 31   | 38.75 |                  |

|                                  |                             | IDRVN = 1101b, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                              | 30    | 40   | 52    |                  |

|                                  |                             | IDRVN = 1110b, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                              | 36    | 48   | 62    |                  |

|                                  |                             | IDRVN = 1111b, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                              | 46.5  | 62   | 80    |                  |

| $I_{DRV_N, H/W}$                 | ピーク・ゲート電流 (シンク)<br>H/W デバイス | IDRIVE レベル 1, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                               | 0.35  | 1    | 1.65  | mA               |

|                                  |                             | IDRIVE レベル 2, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                               | 2.1   | 4    | 5.9   |                  |

|                                  |                             | IDRIVE レベル 3, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                               | 5     | 8    | 11    |                  |

|                                  |                             | IDRIVE レベル 4, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                               | 11.5  | 16   | 20    |                  |

|                                  |                             | IDRIVE レベル 5, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                               | 23.25 | 31   | 38.75 |                  |

|                                  |                             | IDRIVE レベル 6, $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                               | 46.5  | 62   | 80    |                  |

| $I_{HOLD}$                       | ゲート・プルアップ・ホールド電流            | $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$                                                             | 5     | 16   | 30    | mA               |

| $I_{STRONG}$                     | ゲート・プルダウン強電流                | $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$ ,<br>$0.5 \leq I_{DRV_P} \leq 12\text{mA}$                  | 30    | 62   | 100   | mA               |

|                                  |                             | $V_{GSx} = 3\text{V}$ , $V_{PVDD} \geq 7\text{V}$ ,<br>$16 \leq I_{DRV_P} \leq 62\text{mA}$                   | 45    | 128  | 205   | mA               |

| $R_{PDSA\_LS}$                   | ローサイド・セミアクティブ・プルダウン         | $GLx \sim SLx$ , $V_{GSx} = 3\text{V}$                                                                        |       | 1.8  |       | $\text{k}\Omega$ |

|                                  |                             | $GLx \sim SLx$ , $V_{GSx} = 1\text{V}$                                                                        |       | 5    |       | $\text{k}\Omega$ |

| $R_{PD\_HS}$                     | ハイサイド・パッシブ・プルダウン抵抗          | $GHx \sim SHx$                                                                                                |       | 150  |       | $\text{k}\Omega$ |

| $R_{PD\_LS}$                     | ローサイド・パッシブ・プルダウン抵抗          | $GLx \sim SLx$                                                                                                |       | 150  |       | $\text{k}\Omega$ |

| $I_{SHx}$                        | スイッチ・ノード・センス・リーケ電流          | $SHx \sim \text{流入}$ , $SHx = \text{DRAIN} \leq 37\text{V}$<br>$GHx - SHx = 0\text{V}$ , $nSLEEP = 0\text{V}$ | -5    | 0    | 25    | $\mu\text{A}$    |

|                                  |                             | $SHx \sim \text{流入}$ , $SHx = \text{DRAIN} \leq 37\text{V}$<br>$GHx - SHx = 0\text{V}$ , $nSLEEP = 5\text{V}$ | -150  | -100 | -40   | $\mu\text{A}$    |

| <b>ゲート・ドライバ・タイミング (GHx, GLx)</b> |                             |                                                                                                               |       |      |       |                  |

| $t_{PDR\_LS}$                    | ローサイド立ち上がり伝搬遅延              | GLx への入力の立ち上がり                                                                                                | 300   | 850  | ns    |                  |

4.9V  $\leq V_{PVDD} \leq 37V$ 、 $-40^{\circ}C \leq T_J \leq 150^{\circ}C$  (特に記述のない限り)。標準的な制限は、 $V_{PVDD} = 13.5V$ 、 $T_J = 25^{\circ}C$ に対して適用されます。

| パラメータ              |                              | テスト条件                                                                   | 最小値  | 標準値  | 最大値  | 単位 |

|--------------------|------------------------------|-------------------------------------------------------------------------|------|------|------|----|

| $t_{PDF\_LS}$      | ローサイド立ち下がり伝搬遅延               | $GL_x$ への入力の立ち下がり                                                       | 300  | 600  | ns   |    |

| $t_{PDR\_HS}$      | ハイサイド立ち上がり伝搬遅延               | $GH_x$ への入力の立ち上がり                                                       | 300  | 600  | ns   |    |

| $t_{PDF\_HS}$      | ハイサイド立ち下がり伝搬遅延               | $GH_x$ への入力の立ち下がり                                                       | 300  | 600  | ns   |    |

| $t_{DEAD}$         | 内部ハンドシェイク・デッドタイム             | $V_{GSx\_L}/V_{GSx\_H}$ 立ち下がり 10%～<br>$V_{GSx\_H}/V_{GSx\_L}$ 立ち上がり 10% | 350  |      | ns   |    |

| $t_{DEAD\_D, SPI}$ | 挿入可能なデジタル・デッドタイム<br>SPI デバイス | $VGS\_TDEAD = 000b$ 、ハンドシェイクのみ                                          | 0    |      |      | ns |

|                    |                              | $VGS\_TDEAD = 001b$                                                     | 150  | 250  | 350  |    |

|                    |                              | $VGS\_TDEAD = 010b$                                                     | 400  | 500  | 600  |    |

|                    |                              | $VGS\_TDEAD = 011b$                                                     | 600  | 750  | 900  |    |

|                    |                              | $VGS\_TDEAD = 100b$                                                     | 800  | 1000 | 1200 |    |

|                    |                              | $VGS\_TDEAD = 101b$                                                     | 1600 | 2000 | 2400 |    |

|                    |                              | $VGS\_TDEAD = 110b$                                                     | 3400 | 4000 | 4600 |    |

|                    |                              | $VGS\_TDEAD = 111b$                                                     | 7200 | 8000 | 8800 |    |

| $t_{DEAD\_D, H/W}$ | 挿入可能なデジタル・デッドタイム<br>H/W デバイス | ハンドシェイクのみ                                                               | 0    |      | ns   |    |

#### 電流シャント・アンプ (AREF, SN, SO, SP)

|                |                                 |                                                           |      |                |            |

|----------------|---------------------------------|-----------------------------------------------------------|------|----------------|------------|

| $V_{COM}$      | 同相入力範囲                          |                                                           | -2   | $V_{PVDD} + 2$ | V          |

| $G_{CSA, SPI}$ | センス・アンプ・ゲイン<br>SPI デバイス         | $CSA\_GAIN = 00b$                                         | 9.9  | 10.15          | 10.4       |

|                |                                 | $CSA\_GAIN = 01b$                                         | 19.5 | 20             | 20.5       |

|                |                                 | $CSA\_GAIN = 10b$                                         | 39   | 40             | 41         |

|                |                                 | $CSA\_GAIN = 11b$                                         | 78   | 80             | 82         |

| $G_{CSA, H/W}$ | センス・アンプ・ゲイン<br>H/W デバイス         | GAIN クワッドレベル 1                                            | 9.9  | 10.15          | 10.4       |

|                |                                 | GAIN クワッドレベル 2                                            | 19.5 | 20             | 20.5       |

|                |                                 | GAIN クワッドレベル 3                                            | 39   | 40             | 41         |

|                |                                 | GAIN クワッドレベル 4                                            | 78   | 80             | 82         |

| $t_{SET}$      | $\pm 1\%$ までのセンス・アンプ・セッティング・タイム | $V_{SO\_STEP} = 1.5V, G_{CSA} = 10V/V$<br>$C_{SO} = 60pF$ | 2.2  |                | $\mu s$    |

|                |                                 | $V_{SO\_STEP} = 1.5V, G_{CSA} = 20V/V$<br>$C_{SO} = 60pF$ | 2.2  |                |            |

|                |                                 | $V_{SO\_STEP} = 1.5V, G_{CSA} = 40V/V$<br>$C_{SO} = 60pF$ | 2.2  |                |            |

|                |                                 | $V_{SO\_STEP} = 1.5V, G_{CSA} = 80V/V$<br>$C_{SO} = 60pF$ | 3    |                |            |

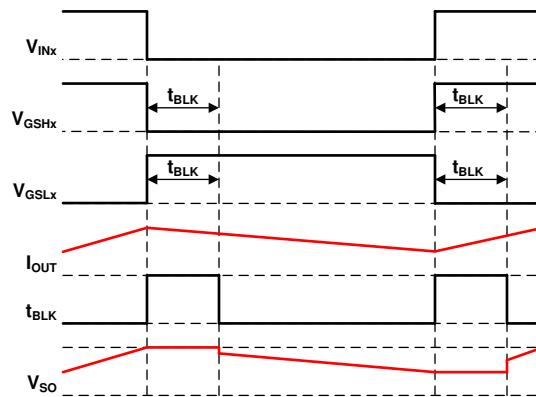

| $t_{BLK, SPI}$ | センス・アンプ出力ブランкиング時間<br>SPI デバイス  | $CSA\_BLK = 000b, t_{DRIVE}$ 期間の割合 (%)                    | 0    |                | %          |

|                |                                 | $CSA\_BLK = 001b, t_{DRIVE}$ 期間の割合 (%)                    | 25   |                |            |

|                |                                 | $CSA\_BLK = 010b, t_{DRIVE}$ 期間の割合 (%)                    | 37.5 |                |            |

|                |                                 | $CSA\_BLK = 011b, t_{DRIVE}$ 期間の割合 (%)                    | 50   |                |            |

|                |                                 | $CSA\_BLK = 100b, t_{DRIVE}$ 期間の割合 (%)                    | 62.5 |                |            |

|                |                                 | $CSA\_BLK = 101b, t_{DRIVE}$ 期間の割合 (%)                    | 75   |                |            |

|                |                                 | $CSA\_BLK = 110b, t_{DRIVE}$ 期間の割合 (%)                    | 87.5 |                |            |

|                |                                 | $CSA\_BLK = 111b, t_{DRIVE}$ 期間の割合 (%)                    | 100  |                |            |

| $t_{BLK, H/W}$ | センス・アンプ出力ブランкиング時間<br>H/W デバイス  |                                                           | 0    |                | ns         |

| $t_{SLEW}$     | 出力スルーレート                        | $C_{SO} = 60pF$                                           | 2.5  |                | V/ $\mu s$ |

4.9V  $\leq V_{PVDD} \leq$  37V,  $-40^{\circ}\text{C} \leq T_J \leq 150^{\circ}\text{C}$  (特に記述のない限り)。標準的な制限は、 $V_{PVDD} = 13.5\text{V}$ ,  $T_J = 25^{\circ}\text{C}$ に対して適用されます。

| パラメータ           |                      | テスト条件                                                        | 最小値          | 標準値               | 最大値           | 単位                             |  |  |

|-----------------|----------------------|--------------------------------------------------------------|--------------|-------------------|---------------|--------------------------------|--|--|

| $V_{BIAS, SPI}$ | 出力電圧バイアス<br>SPI デバイス | $V_{SPx} = V_{SNx} = 0\text{V}$ , CSA_DIV = 0b               | $V_{AREF}/2$ |                   | $V_{AREF}/8$  | V                              |  |  |

|                 |                      | $V_{SPx} = V_{SNx} = 0\text{V}$ , CSA_DIV = 1b               | $V_{AREF}/8$ |                   |               |                                |  |  |

| $V_{BIAS, H/W}$ | 出力電圧バイアス<br>H/W デバイス |                                                              |              | $V_{AREF}/2$      | V             |                                |  |  |

| $V_{LINEAR}$    | リニア出力電圧範囲            | $V_{AREF} = 3.3\text{V} = 5\text{V}$                         | 0.25         | $V_{AREF} - 0.25$ | V             |                                |  |  |

| $V_{OFF}$       | 入力オフセット電圧            | $V_{SPx} = V_{SNx} = 0\text{V}$ , $T_J = 25^{\circ}\text{C}$ | -1.5         | 1.5               | mV            |                                |  |  |

| $V_{OFF\_D}$    | 入力オフセット電圧ドリフト        | $V_{SPx} = V_{SNx} = 0\text{V}$                              | $\pm 10$     |                   | $\pm 25$      | $\mu\text{V}/^{\circ}\text{C}$ |  |  |

| $I_{BIAS}$      | 入力バイアス電流             | $V_{SPx} = V_{SNx} = 0\text{V}$ , ピンへ流入                      | 100          |                   | $\mu\text{A}$ |                                |  |  |

| $I_{BIAS\_OFF}$ | 入力バイアス電流オフセット        | $I_{SPx} - I_{SNx}$                                          | -1           | 1                 | $\mu\text{A}$ |                                |  |  |

| $I_{AREF}$      | AREF 入力電流            | $V_{VREF} = 3.3\text{V} = 5\text{V}$                         | 1            |                   | 1.8           | mA                             |  |  |

| CMRR            | 同相除去比                | DC, $-40 \leq T_J \leq 125^{\circ}\text{C}$                  | 72           | 90                | dB            |                                |  |  |

|                 |                      | DC, $-40 \leq T_J \leq 150^{\circ}\text{C}$                  | 69           | 90                |               |                                |  |  |

|                 |                      | 20kHz                                                        | 80           |                   |               |                                |  |  |

| PSRR            | 電源電圧除去比              | PVDD~SOx, DC                                                 | 100          |                   | dB            |                                |  |  |

|                 |                      | PVDD~SOx, 20kHz                                              | 90           |                   |               |                                |  |  |

|                 |                      | PVDD~SOx, 400kHz                                             | 70           |                   |               |                                |  |  |

#### 保護回路

|                      |                                |                                           |       |       |      |               |               |

|----------------------|--------------------------------|-------------------------------------------|-------|-------|------|---------------|---------------|

| $V_{PVDD\_UV}$       | PVDD 低電圧スレッショルド                | $V_{PVDD}$ 立ち上がり                          | 4.325 | 4.625 | 4.9  | V             |               |

|                      |                                | $V_{PVDD}$ 立ち下がり                          | 4.25  | 4.525 | 4.8  |               |               |

| $V_{PVDD\_UV\_HYS}$  | PVDD 低電圧ヒステリシス                 | 立ち上がりから立ち下がりへのスレッショルド                     |       | 100   |      | mV            |               |

| $t_{PVDD\_UV\_DG}$   | PVDD 低電圧グリッヂ除去時間               |                                           |       | 8     | 10   | 12.75         | $\mu\text{s}$ |

| $V_{PVDD\_OV}$       | PVDD 過電圧スレッショルド                | $V_{PVDD}$ 立ち上がり, PVDD_OV_LVL = 0b        | 21    | 22.5  | 24   | V             |               |

|                      |                                | $V_{PVDD}$ 立ち下がり, PVDD_OV_LVL = 0b        | 20    | 21.5  | 23   |               |               |

|                      |                                | $V_{PVDD}$ 立ち上がり, PVDD_OV_LVL = 1b        | 27    | 28.5  | 30   |               |               |

|                      |                                | $V_{PVDD}$ 立ち下がり, PVDD_OV_LVL = 1b        | 26    | 27.5  | 29   |               |               |

| $V_{PVDD\_OV\_HYS}$  | PVDD 過電圧ヒステリシス                 | 立ち上がりから立ち下がりへのスレッショルド                     |       | 1     |      | V             |               |

| $t_{PVDD\_OV\_DG}$   | PVDD 過電圧グリッヂ除去時間               | PVDD_OV_DG = 00b                          | 0.75  | 1     | 1.5  | $\mu\text{s}$ |               |

|                      |                                | PVDD_OV_DG = 01b                          | 1.5   | 2     | 2.5  |               |               |

|                      |                                | PVDD_OV_DG = 10b                          | 3.25  | 4     | 4.75 |               |               |

|                      |                                | PVDD_OV_DG = 11b                          | 7     | 8     | 9    |               |               |

| $V_{DVDD\_POR}$      | DVDD 電源 POR スレッショルド            | DVDD 立ち下がり                                | 2.5   | 2.7   | 2.9  | V             |               |

|                      |                                | DVDD 立ち上がり                                | 2.6   | 2.8   | 3    |               |               |

| $V_{DVDD\_POR\_HYS}$ | DVDD POR ヒステリシス                | 立ち上がりから立ち下がりへのスレッショルド                     |       | 100   |      | mV            |               |

| $t_{DVDD\_POR\_DG}$  | DVDD POR グリッヂ除去時間              |                                           |       | 5     | 8    | 12.75         | $\mu\text{s}$ |

| $V_{CP\_UV, SPI}$    | チャージ・ポンプ低電圧スレッショルド<br>SPI デバイス | $V_{VCP} - V_{PVDD}$ , 立ち下がり, VCP_UV = 0b | 2     | 2.5   | 3    | V             |               |

|                      |                                | $V_{VCP} - V_{PVDD}$ , 立ち下がり, VCP_UV = 1b | 4     | 5     | 6    |               |               |

| $V_{CP\_UV, H/W}$    | チャージ・ポンプ低電圧スレッショルド<br>H/W デバイス |                                           |       | 2     | 2.5  | 3             | V             |

| $t_{CP\_UV\_DG}$     | チャージ・ポンプ低電圧グリッヂ除去時間            |                                           |       | 8     | 10   | 12.75         | $\mu\text{s}$ |

| $V_{GS\_CLP}$        | ハイサイド・ドライバ $V_{GS}$ 保護クランプ     |                                           |       | 12.5  | 15   | 17            | V             |

4.9V  $\leq V_{PVDD} \leq 37V$ ,  $-40^\circ C \leq T_J \leq 150^\circ C$  (特に記述のない限り)。標準的な制限は、 $V_{PVDD} = 13.5V$ ,  $T_J = 25^\circ C$ に対して適用されます。

| パラメータ              |                                                | テスト条件                                        | 最小値  | 標準値  | 最大値  | 単位        |

|--------------------|------------------------------------------------|----------------------------------------------|------|------|------|-----------|

| $V_{GS\_LVL}$      | ゲート電圧監視スレッショルド                                 | $V_{GH/Lx} - V_{SH/Lx}$ , $V_{GS\_LVL} = 0b$ | 1.1  | 1.4  | 1.75 | V         |

|                    |                                                | $V_{GH/Lx} - V_{SH/Lx}$ , $V_{GS\_LVL} = 1b$ | 0.8  | 1    | 1.2  | V         |

| $t_{GS\_FLT\_DG}$  | $V_{GS}$ 障害監視グリッチ除去時間                          |                                              | 1.5  | 2    | 2.75 | $\mu s$   |

| $t_{GS\_HS\_DG}$   | $V_{GS}$ ハンドシェイク監視グリッチ除去時間                     |                                              |      | 210  |      | ns        |

| $t_{DRIVE, SPI}$   | $V_{GS}/V_{DS}$ 監視ブランкиング時間<br>SPI デバイス        | $VGS\_TDRV = 00b$                            | 80   | 96   | 120  | $\mu s$   |

|                    |                                                | $VGS\_TDRV = 01b$                            | 1.5  | 2    | 2.5  |           |

|                    |                                                | $VGS\_TDRV = 10b$                            | 3.25 | 4    | 4.75 |           |

|                    |                                                | $VGS\_TDRV = 11b$                            | 7.5  | 8    | 9    |           |

| $t_{DRIVE, H/W}$   | $V_{GS}$ および $V_{DS}$ 監視、ブランкиング時間<br>H/W デバイス |                                              | 3.25 | 4    | 4.75 | $\mu s$   |

| $V_{DS\_LVL, SPI}$ | $V_{DS}$ 過電流保護スレッショルド<br>SPI デバイス              | $VDS\_LVL = 0000b$                           | 0.04 | 0.06 | 0.08 | V         |

|                    |                                                | $VDS\_LVL = 0001b$                           | 0.06 | 0.08 | 0.10 |           |

|                    |                                                | $VDS\_LVL = 0010b$                           | 0.08 | 0.10 | 0.12 |           |

|                    |                                                | $VDS\_LVL = 0011b$                           | 0.10 | 0.12 | 0.14 |           |

|                    |                                                | $VDS\_LVL = 0100b$                           | 0.12 | 0.14 | 0.16 |           |

|                    |                                                | $VDS\_LVL = 0101b$                           | 0.14 | 0.16 | 0.18 |           |

|                    |                                                | $VDS\_LVL = 0110b$                           | 0.16 | 0.18 | 0.20 |           |

|                    |                                                | $VDS\_LVL = 0111b$                           | 0.18 | 0.2  | 0.22 |           |

|                    |                                                | $VDS\_LVL = 1000b$                           | 0.27 | 0.3  | 0.33 |           |

|                    |                                                | $VDS\_LVL = 1001b$                           | 0.36 | 0.4  | 0.44 |           |

|                    |                                                | $VDS\_LVL = 1010b$                           | 0.45 | 0.5  | 0.55 |           |

|                    |                                                | $VDS\_LVL = 1011b$                           | 0.54 | 0.6  | 0.66 |           |

|                    |                                                | $VDS\_LVL = 1100b$                           | 0.63 | 0.7  | 0.77 |           |

|                    |                                                | $VDS\_LVL = 1101b$                           | 0.9  | 1    | 1.1  |           |

|                    |                                                | $VDS\_LVL = 1110b$                           | 1.26 | 1.4  | 1.54 |           |

|                    |                                                | $VDS\_LVL = 1111b$                           | 1.8  | 2    | 2.2  |           |

| $V_{DS\_LVL, H/W}$ | $V_{DS}$ 過電流保護スレッショルド<br>H/W デバイス              | $VDS$ 6 レベル入力 1                              | 0.04 | 0.06 | 0.08 | V         |

|                    |                                                | $VDS$ 6 レベル入力 2                              | 0.08 | 0.10 | 0.12 |           |

|                    |                                                | $VDS$ 6 レベル入力 3                              | 0.18 | 0.2  | 0.22 |           |

|                    |                                                | $VDS$ 6 レベル入力 4                              | 0.45 | 0.5  | 0.55 |           |

|                    |                                                | $VDS$ 6 レベル入力 5                              | 0.9  | 1    | 1.1  |           |

|                    |                                                | $VDS$ 6 レベル入力 6                              |      |      | 無効   |           |

| $t_{DS\_DG, SPI}$  | $V_{DS}$ 過電流保護グリッチ除去時間<br>SPI デバイス             | $VDS\_DG = 00b$                              | 0.75 | 1    | 1.5  | $\mu s$   |

|                    |                                                | $VDS\_DG = 01b$                              | 1.5  | 2    | 2.5  |           |

|                    |                                                | $VDS\_DG = 10b$                              | 3.25 | 4    | 4.75 |           |

|                    |                                                | $VDS\_DG = 11b$                              | 7.5  | 8    | 9    |           |

| $t_{DS\_DG, H/W}$  | $V_{DS}$ 過電流保護グリッチ除去時間<br>H/W デバイス             |                                              | 3.25 | 4    | 4.75 | $\mu s$   |

| $I_{OLD}$          | オフライン診断用電流ソース                                  | プルアップ電流                                      |      | 3    |      | mA        |

|                    |                                                | プルダウン電流                                      |      | 3    |      |           |

| $R_{OLD}$          | オフライン・オープン負荷抵抗検出スレッショルド                        | $VDS\_LVL = 1.4V$ , $V_{PVDD} \leq 18V$      |      | 22   | 50   | $k\Omega$ |

|                    |                                                | $VDS\_LVL = 1.4V$ , $V_{PVDD} \leq 37V$      |      | 22   | 100  | $k\Omega$ |

|                    |                                                | $VDS\_LVL = 2V$ , $V_{PVDD} \leq 18V$        |      | 10   | 25   | $k\Omega$ |

|                    |                                                | $VDS\_LVL = 2V$ , $V_{PVDD} \leq 37V$        |      | 10   | 50   | $k\Omega$ |

4.9V  $\leq V_{PVDD} \leq 37V$ ,  $-40^{\circ}\text{C} \leq T_J \leq 150^{\circ}\text{C}$  (特に記述のない限り)。標準的な制限は、 $V_{PVDD} = 13.5V$ ,  $T_J = 25^{\circ}\text{C}$ に対して適用されます。

| パラメータ      | テスト条件            | 最小値 | 標準値 | 最大値 | 単位 |

|------------|------------------|-----|-----|-----|----|

| $T_{OTW}$  | 過熱警告温度           | 130 | 150 | 170 | °C |

| $T_{HYS}$  | 過熱警告ヒステリシス       |     | 20  |     | °C |

| $T_{OTSD}$ | 過熱シャットダウン温度      | 150 | 170 | 190 | °C |

| $T_{HYS}$  | 過熱シャットダウン・ヒステリシス |     | 20  |     | °C |

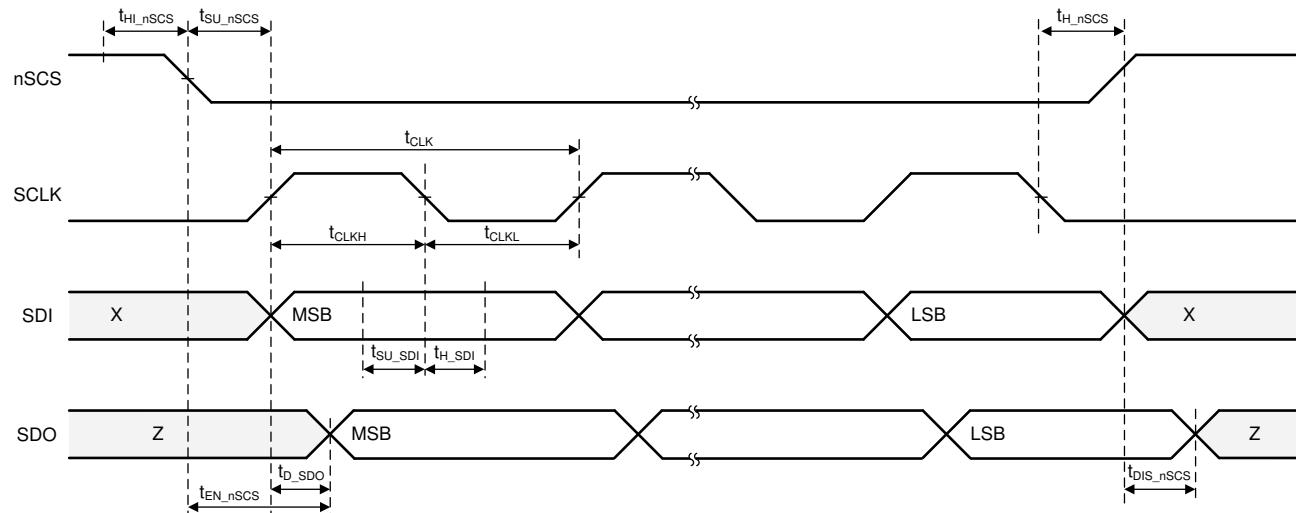

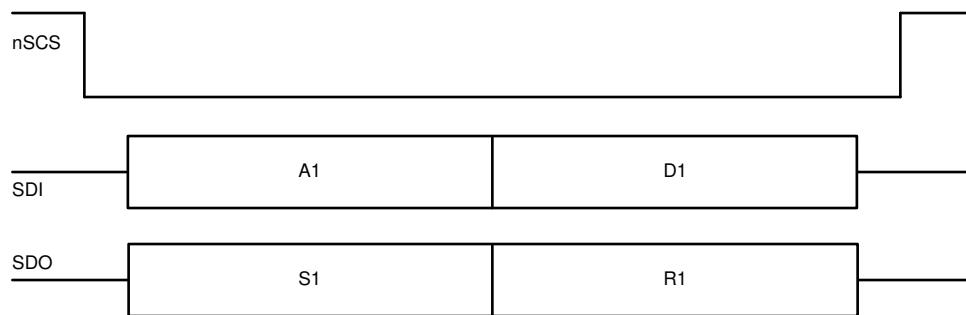

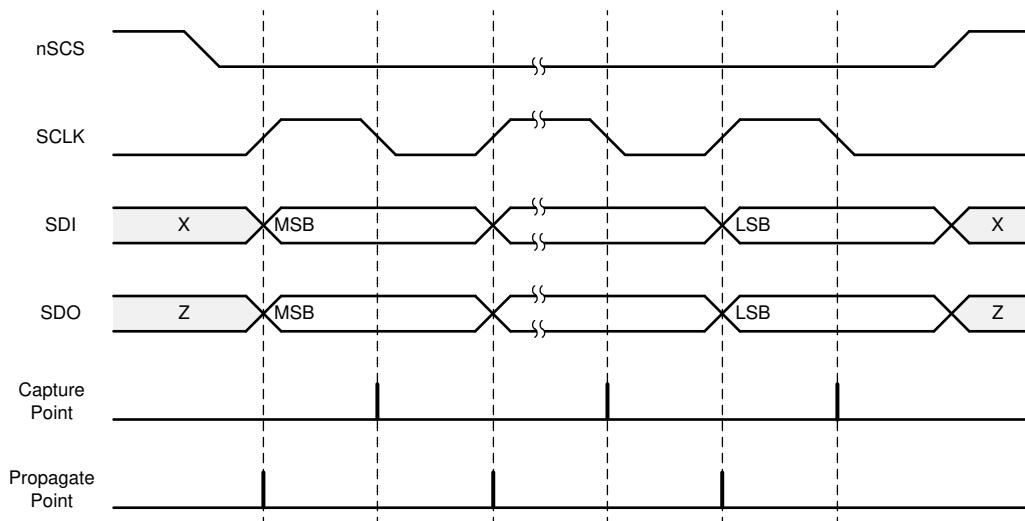

## 6.6 タイミング要件

|                 |                                     | 最小  | 公称 | 最大 | 単位 |

|-----------------|-------------------------------------|-----|----|----|----|

| $t_{SCLK}$      | SCLK の最小周期                          | 100 |    |    | ns |

| $t_{SCLKH}$     | SCLK 最小 High 時間                     | 50  |    |    | ns |

| $t_{SCLKL}$     | SCLK 最小 Low 時間                      | 50  |    |    | ns |

| $t_{SU\_SDI}$   | SDI 入力データ・セットアップ時間                  | 25  |    |    | ns |

| $t_{H\_SDI}$    | SDI 入力データ・ホールド時間                    | 25  |    |    | ns |

| $t_{D\_SDO}$    | SDO 出力データ遅延時間、 $C_L = 20\text{pF}$  |     | 30 |    | ns |

| $t_{SU\_nSCS}$  | nSCS 入力セットアップ時間                     | 25  |    |    | ns |

| $t_{H\_nSCS}$   | nSCS 入力ホールド時間                       | 25  |    |    | ns |

| $t_{HI\_nSCS}$  | nSCS 最小 High 時間                     | 450 |    |    | ns |

| $t_{EN\_nSCS}$  | イネーブル遅延時間、nSCS Low から SDO アクティブまで   |     | 50 |    | ns |

| $t_{DIS\_nSCS}$ | ディセーブル遅延時間、nSCS High から SDO Hi-Z まで |     | 50 |    | ns |

## 6.7 タイミング図

図 6-1. SPI タイミング図

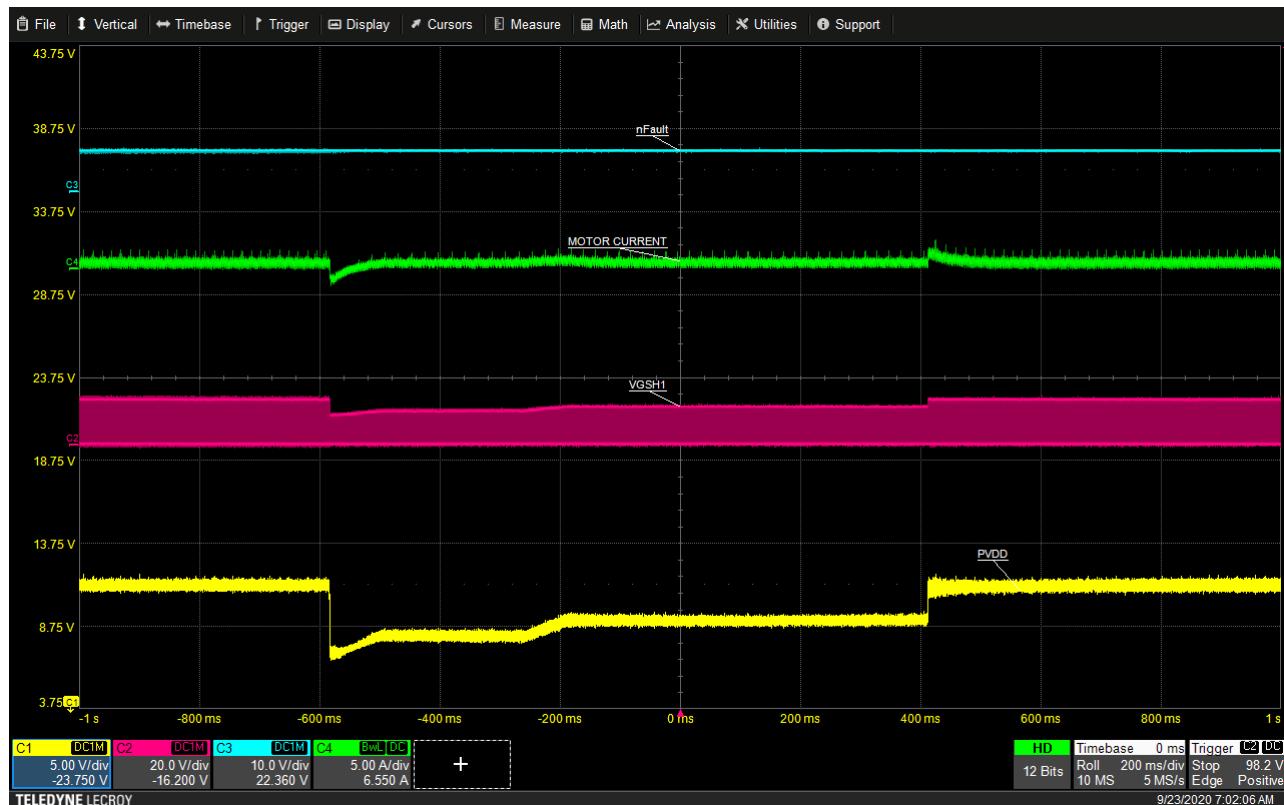

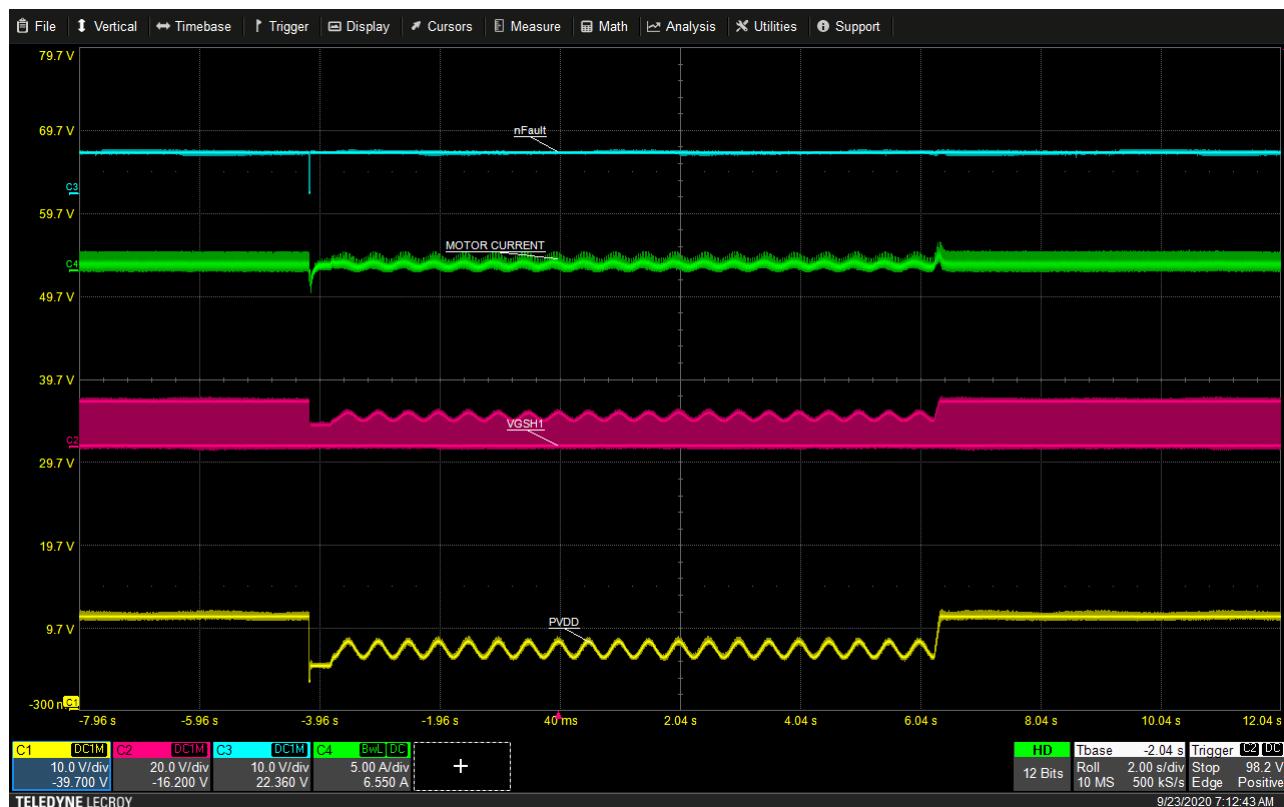

## 6.8 代表的特性

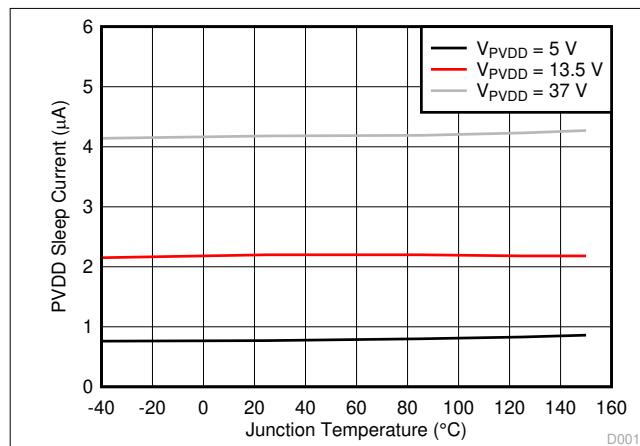

図 6-2. PVDD スリープ電流

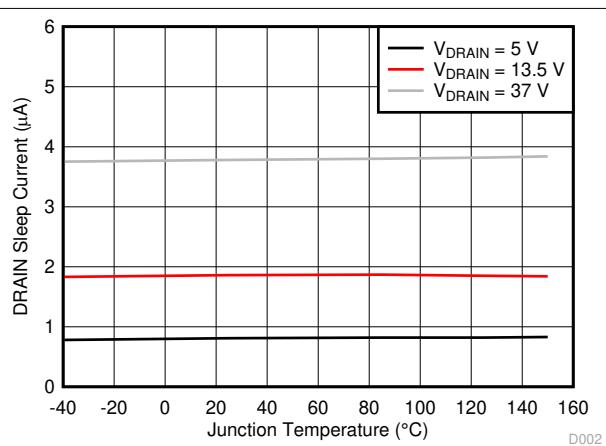

図 6-3. DRAIN スリープ電流

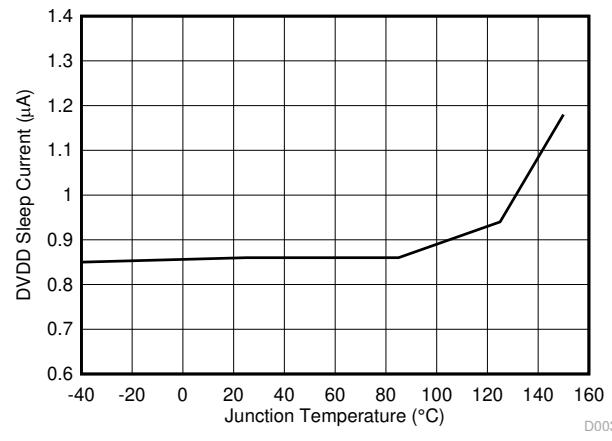

図 6-4. DVDD スリープ電流

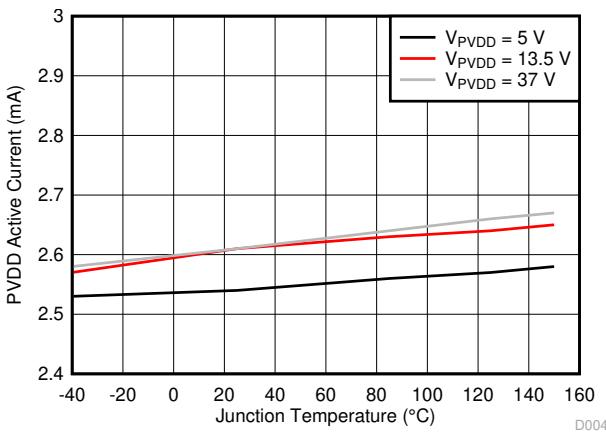

図 6-5. PVDD アクティブ電流

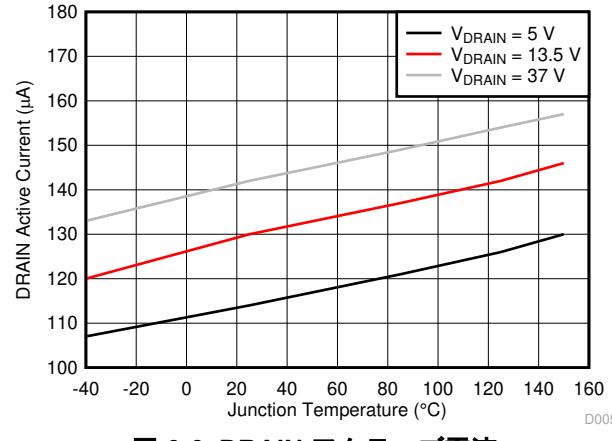

図 6-6. DRAIN アクティブ電流

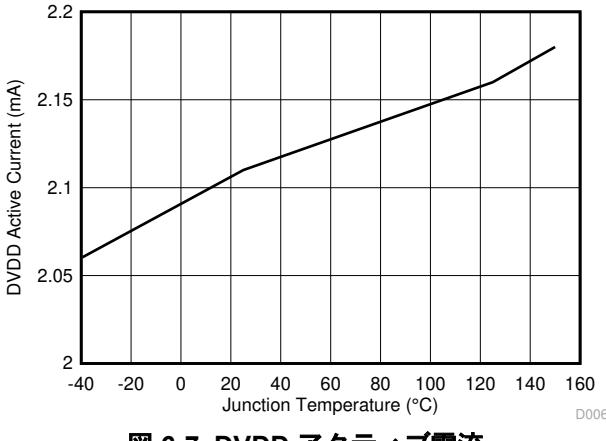

図 6-7. DVDD アクティブ電流

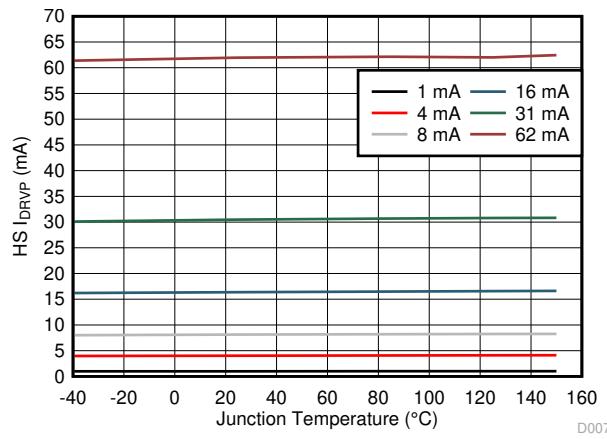

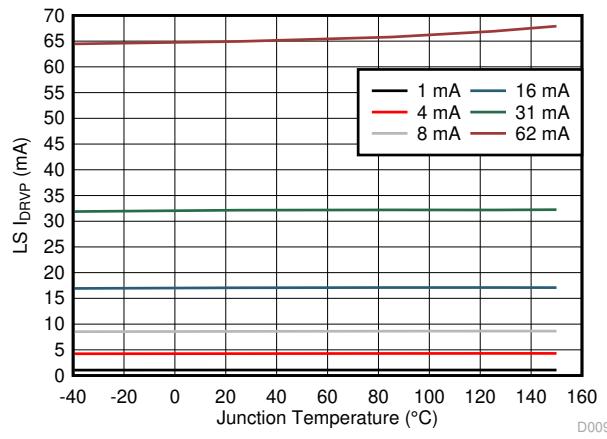

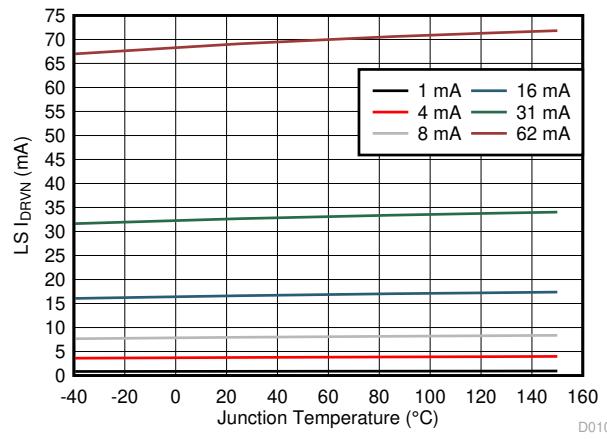

図 6-8. ハイサイド・ゲート・ドライバ・ソース電流

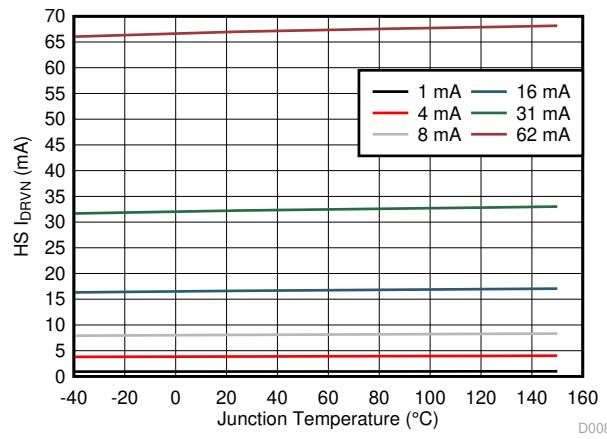

図 6-9. ハイサイド・ゲート・ドライバ・シンク電流

図 6-10. ローサイド・ゲート・ドライバ・ソース電流

図 6-11. ローサイド・ゲート・ドライバ・シンク電流

## 7 詳細説明

### 7.1 概要

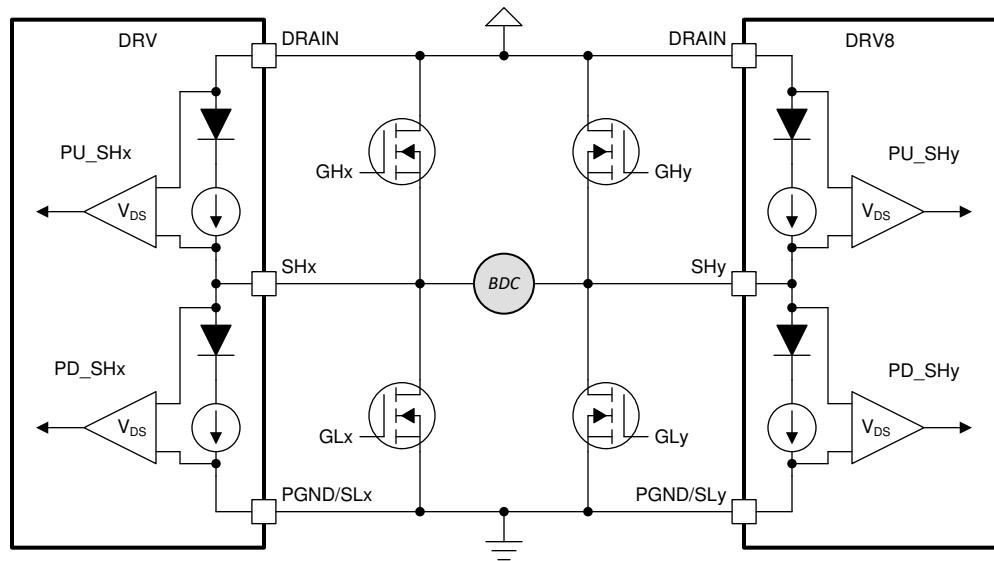

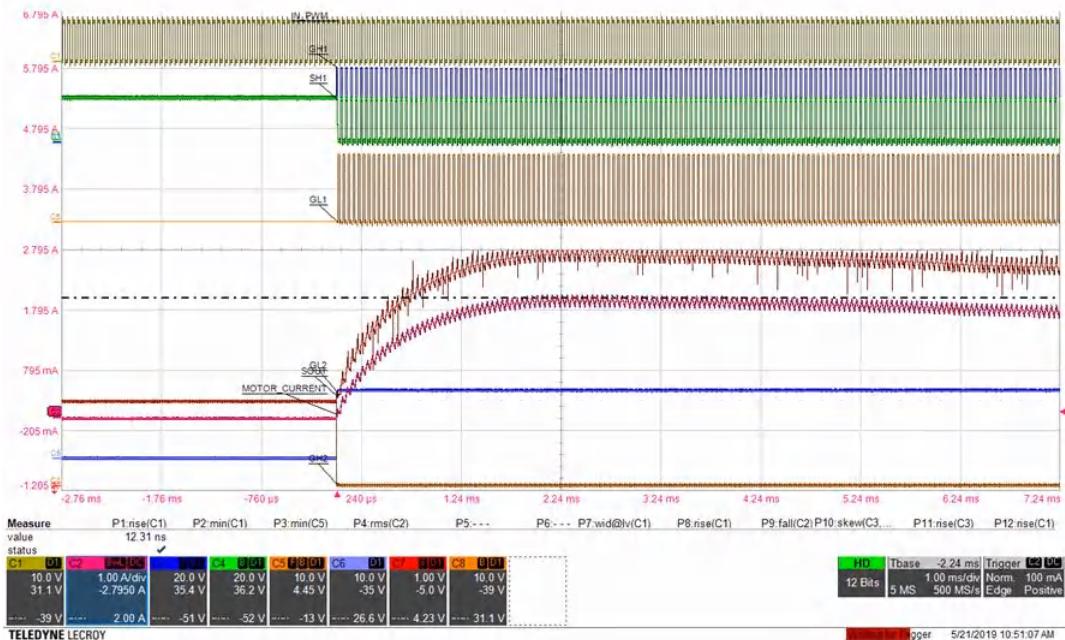

DRV8706-Q1 は、ブラシ付き DC モーター・アプリケーション用の高集積 H ブリッジ・スマート・ゲート・ドライバです。このデバイスには、2 つのハーフブリッジ・ゲート・ドライバがあり、ハイサイドとローサイドの N チャネル・パワー MOSFET を駆動できます。DRV8706-Q1 は、ハイサイドで内蔵の電圧増倍チャージ・ポンプを使用し、ローサイドでリニア・レギュレータを使用して、適切なゲート・ドライブ電圧を生成します。ゲート・ドライバは、最高 62mA のソースと 62mA のシンク・ピーク・ゲート・ドライブ電流の性能をサポートします。このデバイスは、4.9V～37V の幅広い電源電圧範囲をサポートします。

DRV8706-Q1 は、システム・コストを削減し信頼性を向上するスマート・ゲート・ドライブ・アキテクチャ (SGD) をベースにしています。SGD アキテクチャはデッドタイムを最適化して貫通電流の条件成立を回避し、調整可能なゲート・ドライブ電流を経由する MOSFET スルーレート制御により電磁干渉 (EMI) を低減するためのフレキシビリティがあるほか、 $V_{DS}$  モニタと  $V_{GS}$  モニタを使用して、ドレイン - ソース間、およびドレイン - ゲート間の短絡状況からの保護を実現します。強力なプルダウン回路は、 $dV/dt$  寄生ゲート・カップリングの防止に役立ちます。可変出力ゲート・ドライバによる外部 MOSFET のスルーレート制御がサポートされています。ゲート・ドライバのピーク・ソース電流は、0.5mA～62mA の範囲で構成できます。ゲート・ドライバのピーク・シンク電流は、0.5mA～62mA の範囲で構成できます。

DRV8706-Q1 は、3.3V または 5V の外部コントローラ (MCU) で動作可能です。専用 DVDD ピンにより、デバイスのデジタル・コアへの外部電源供給、およびコントローラの I/O 電圧を基準とするデジタル出力が可能です。これは、外部コントローラと SPI バス経由で通信し、構成設定と診断フィードバックを管理します。このデバイスには AREF ピンもあり、シャント・アンプ基準電圧を外部コントローラ ADC の基準電圧に接続できます。シャント・アンプ出力は、過剰な電圧スパイクからコントローラの入力を保護するため、AREF ピン電圧にもクランプされます。

DRV8706-Q1 は、動作前にシステムの状態を監視し、システム動作中に障害から保護するための一連の診断機能と保護機能を搭載しています。これらの機能には、電源とチャージ・ポンプ用低電圧 / 過電圧モニタ、外部 MOSFET 用  $V_{DS}$  過電流および  $V_{GS}$  ゲート障害監視、オフライン・オープン負荷 / 短絡検出、内部温度警告 / シャットダウン保護機能などがあります。電流シャント・アンプを使用して、システムの負荷電流を監視できます。このアンプは同相範囲が高いため、インライン、ハイサイド、またはローサイドのいずれかに基づく、シャント抵抗電流センシングが可能です。

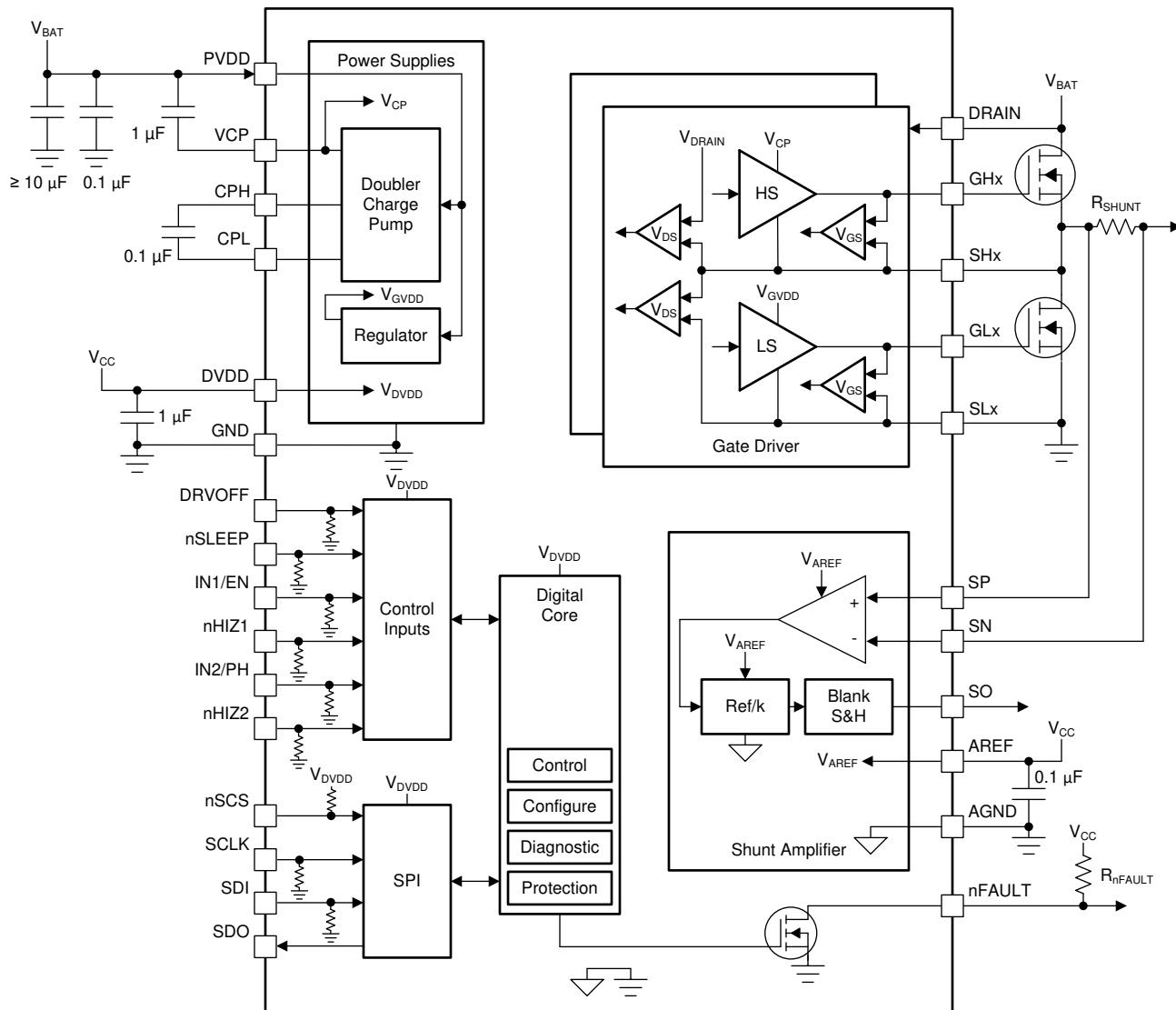

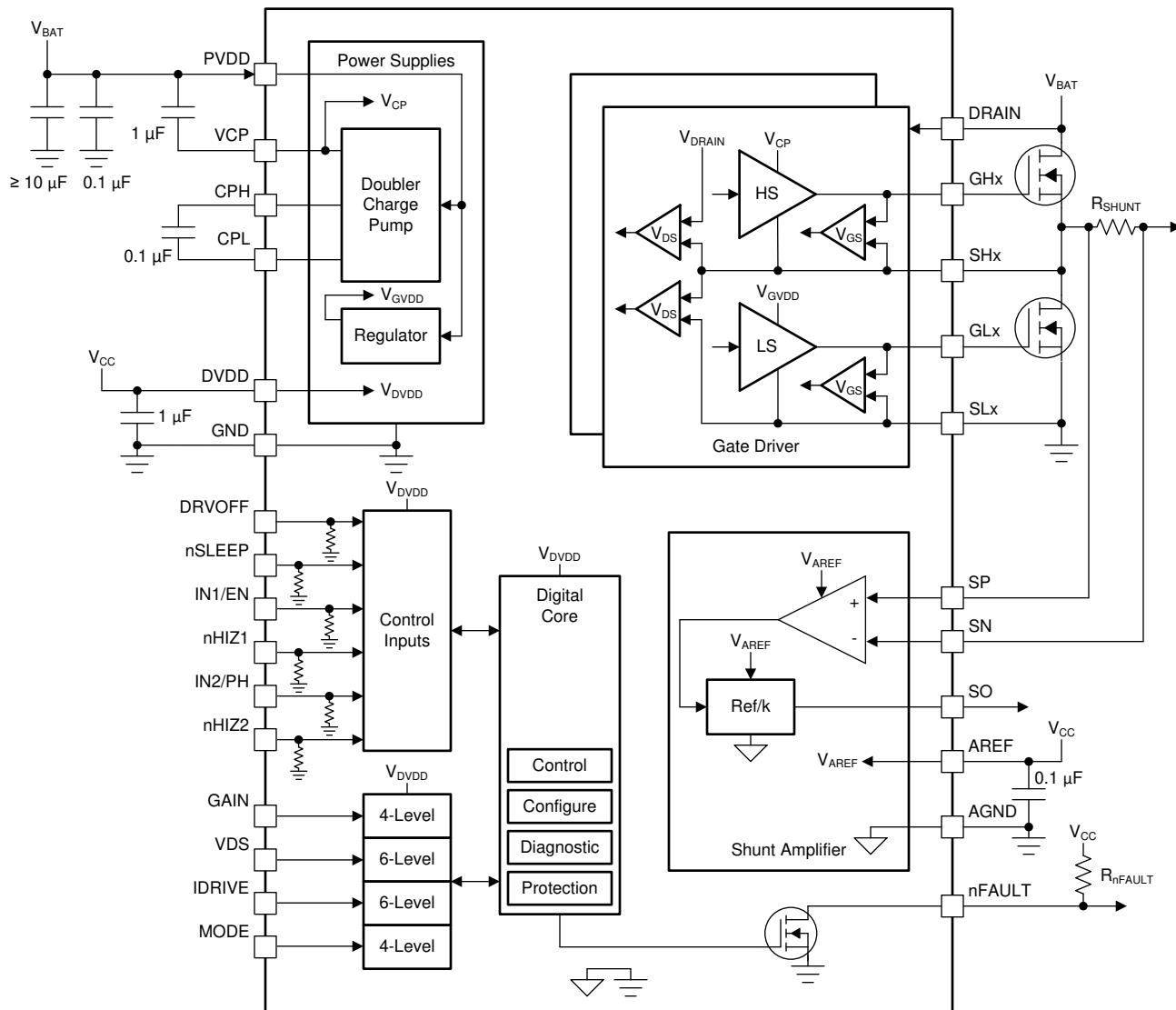

## 7.2 機能ブロック図

図 7-1. DRV8706S-Q1 の機能ブロック図

図 7-2. DRV8706H-Q1 の機能ブロック図

## 7.3 機能説明

### 7.3.1 外付け部品

表 7-1 に、推奨外付け部品を示します。

**表 7-1. 推奨外付け部品**

| 部品               | ピン 1               | ピン 2   | 推奨する事項                                 |

|------------------|--------------------|--------|----------------------------------------|

| $C_{PVDD1}$      | PVDD               | GND    | 0.1 $\mu$ F、低 ESR セラミック・コンデンサ、PVDD 定格。 |

| $C_{PVDD2}$      | PVDD               | GND    | 10 $\mu$ F 以上のローカル・パルク容量、PVDD 定格。      |

| $C_{DVDD}^{(1)}$ | DVDD               | GND    | 1.0 $\mu$ F、6.3V、低 ESR セラミック・コンデンサ     |

| $C_{AREF}^{(1)}$ | AREF               | GND    | 0.1 $\mu$ F、6.3V、低 ESR セラミック・コンデンサ     |

| $C_{VCP}$        | VCP                | PVDD   | 1 $\mu$ F、16V、低 ESR セラミック・コンデンサ        |

| $C_{FLY}$        | CPH                | CPL    | 0.1 $\mu$ F、PVDD 定格、低 ESR セラミック・コンデンサ  |

| $R_{nFAULT}$     | VCC <sup>(2)</sup> | nFAULT | ブルアップ抵抗、 $I_{OD} \leq 5$ mA            |

- (1) 外部低電圧電源のノイズを低減するため、ローカル・バイパス・コンデンサを推奨します。別のバイパス・コンデンサがデバイスと外部低電圧電源の近接した位置にあり、電源のノイズが最小限である場合は、この部品を取り外すこともできます。

- (2) VCC はデバイス上のピンではなく、低電圧外部電源です。

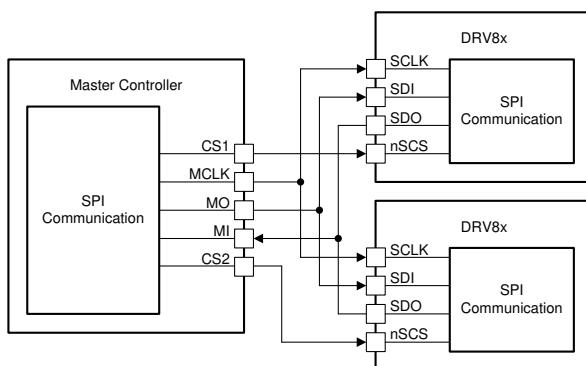

### 7.3.2 デバイス・インターフェイス・バリエント

DRV8706-Q1 ファミリのデバイスでは、最終的なアプリケーションを柔軟な設計にするか単純な設計にするか選択できるように、2 種類のインターフェイス・モード (SPI とハードウェア) をサポートしています。2 つのインターフェイス・モードで同じ 4 つのピンが共有されているので、異なるバージョン間でのピン互換が実現します。こうしたことから、アプリケーション設計者は、設計に最小限の変更を加えるだけで、評価に使用するインターフェイス・バージョンを切り替えることができます。

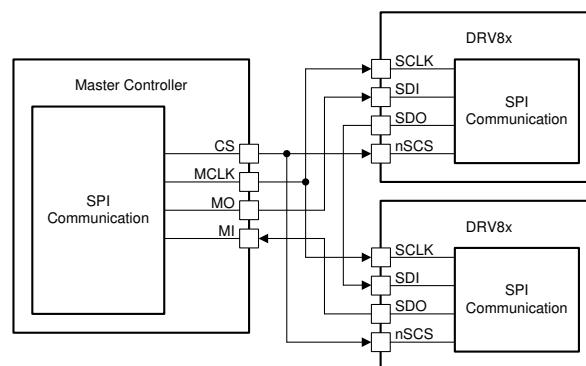

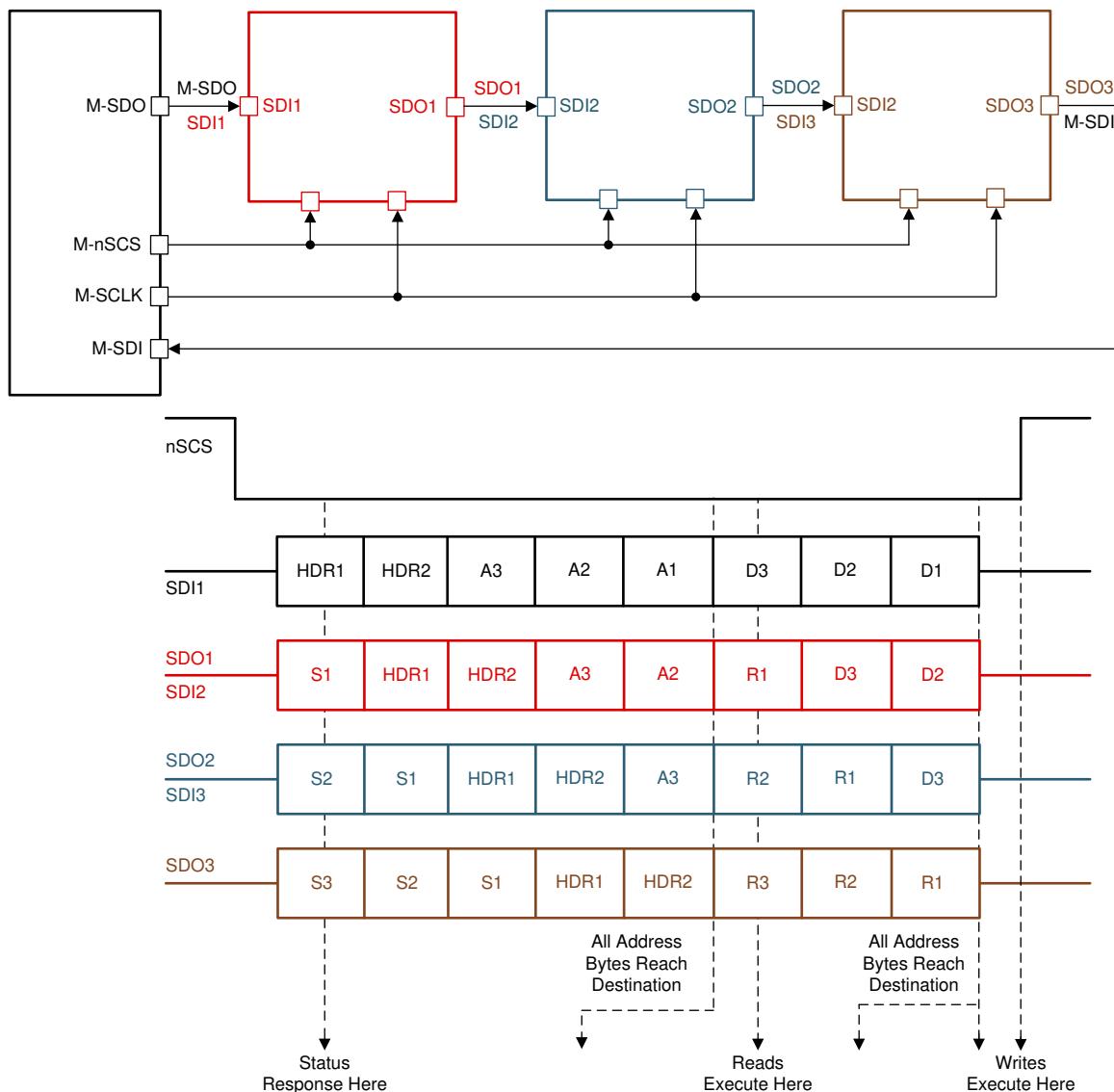

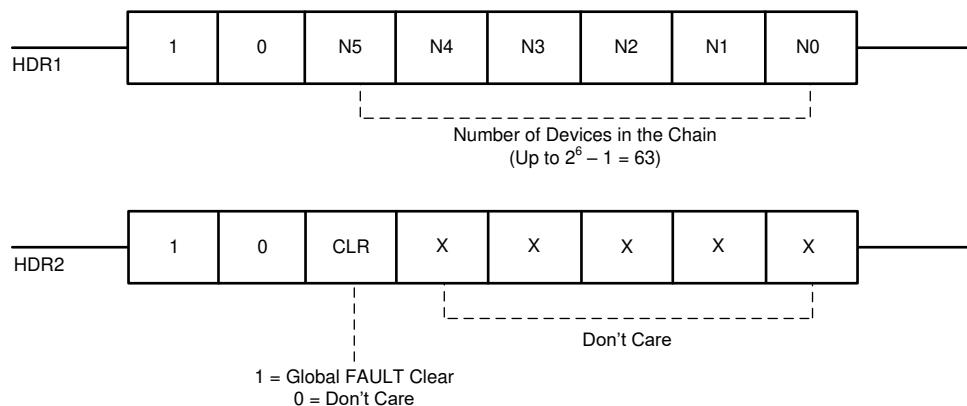

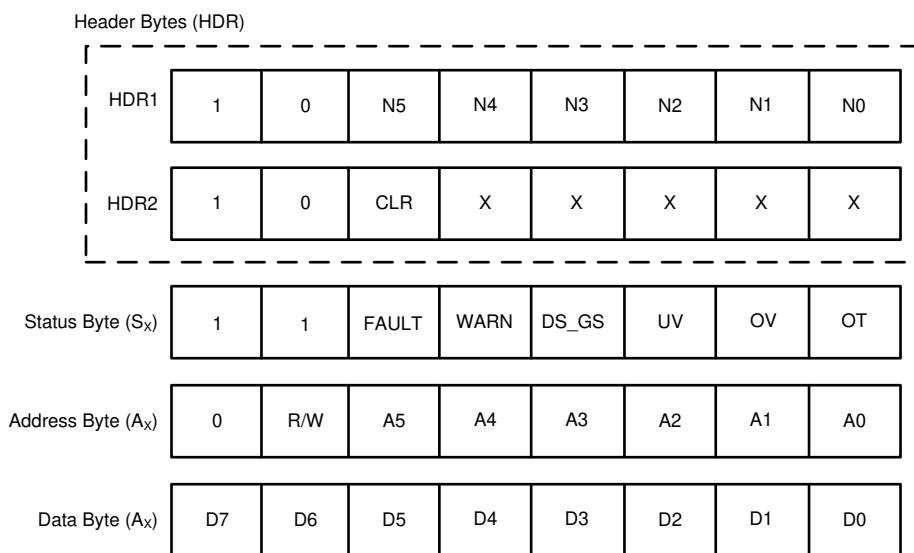

#### 7.3.2.1 シリアル・ペリフェラル・インターフェイス (SPI)

SPI デバイス・バリエントは、外部コントローラと DRV8706-Q1 の間でデータを送受信できるシリアル通信バスをサポートしています。これにより、外部コントローラがデバイスの設定を行ったり、詳細な障害情報を読み取ったりできます。このインターフェイスは SCLK、SDI、SDO、nSCS の各ピンを使用した 4 線式インターフェイスです。

- nSCS ピンはチップ選択入力です。このピンに論理 Low 信号を印加すると、SPI 通信がイネーブルになります。

- SCLK ピンは、クロック信号を受け付けて SDI と SDO 上のデータの収集と伝搬のタイミングを決める入力ピンです。

- SDI ピンはデータ入力です。

- SDO ピンはデータ出力です。SDO ピンは、DVDD 入力を基準とするプッシュプル出力構造を使用します。

SPI の詳細については、「[SPI インターフェイス](#)」セクションを参照してください。

#### 7.3.2.2 ハードウェア (HW)

ハードウェア・インターフェイス・デバイスでは、4 つの SPI ピンが抵抗によって設定可能な 4 つの入力 (GAIN、VDS、IDRIVE、MODE) に変換されます。この結果、ピンをロジック High やロジック Low に接続するか、または単純なブルアップ抵抗やブルダウン抵抗を使用することで、アプリケーション設計者がごく一般的に使用されるデバイス設定を行えるようになります。外部コントローラには SPI バスが不要になります。全般的な障害情報は、引き続き nFAULT ピンを介して取得できます。

ハードウェア・インターフェイス設定は、デバイスの電源投入時にラッチされます。nSLEEP ピンでデバイスをスリープ・モードにし、設定を変更して、nSLEEP によりデバイスを再イネーブルすることで、設定を再構成できます。

- GAIN ピンでは、電流シャント・アンプのゲインを構成します

- VDS ピンでは  $V_{DS}$  過電流監視の電圧スレッショルドを構成します。

- IDRIVE ピンではゲート・ドライブ電流の強さを構成します。

- MODE ピンでは PWM 入力制御モードを構成します。

ハードウェア・インターフェイスの詳細については、「[ピン配置](#)」セクションを参照してください。

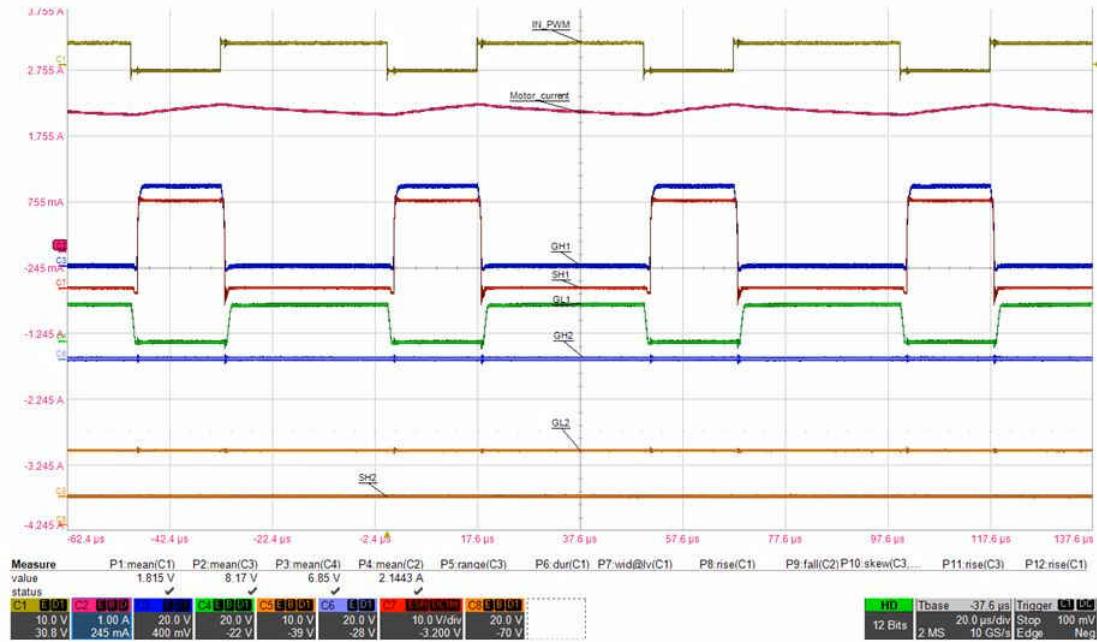

### 7.3.3 入力 PWM モード

DRV8706-Q1 には、複数の入力 PWM モードがあり、さまざまな制御スキーマと出力負荷構成をサポートします。ゲート・ドライバの出力は、IN1/EN、IN2/PH、nHIZx の入力ピンにより制御できます。SPI デバイスのバリエントでは、出力も、S\_IN1/EN、S\_IN2/PH、S\_nHIZx レジスタ設定により制御することができます。PWM モードは、SPI デバイスのバリエントでは SPI レジスタ設定 BRG\_MODE により、H/W デバイスのバリエントでは H/W MODE ピンにより設定します。各モードと、それぞれの機能の詳細は以下の通りです。

表 7-2. 入力 PWM モード

| PWM モード       | SPI インターフェイス (BRG_MODE) | H/W インターフェイス (モード・ピン) |

|---------------|-------------------------|-----------------------|

| セクション 7.3.3.1 | 00b                     | レベル 1                 |

| セクション 7.3.3.2 | 01b (PH/EN)             | レベル 2 (PH/EN)         |

|               | 10b (PWM)               | レベル 3 (PWM)           |

| セクション 7.3.3.3 | 11b                     | レベル 4                 |

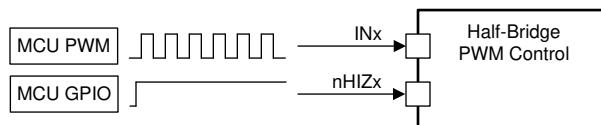

#### 7.3.3.1 ハーフブリッジ制御

ハーフブリッジ制御では、対応する IN1/EN、IN2/PH、および nHIZx 入力ピンにより、各ハーフブリッジ・ゲート・ドライバを個別に制御できます。nHIZx 信号は、IN1/EN 信号と IN2/PH 信号に対して優先されます。ハーフブリッジ制御の場合、INx 指定を参照できます。DRV8706-Q1 は、ハイサイド・スイッチングとローサイド・スイッチング間のデッドタイム生成を内部的に処理し、各ハーフブリッジを単一の PWM 入力で制御できるようにします。

DRV8706-Q1 には、nHIZx ピンにより、各ハーフブリッジ・ゲート・ドライバを独立して Hi-Z にする機能があります。この機能が必要ない場合は、nHIZx ピンを DVDD に接続する必要があります。

SPI デバイス・バリエントでは、IN1/EN、IN2/PH、HIZ1、HIZ2 信号も SPI レジスタにより制御できます。IN1/EN および IN2/PH SPI 制御は、IN1/EN\_MODE と IN2/PH\_MODE レジスタ設定でイネーブルにできます。信号は、S\_IN1/EN と S\_IN2/PH レジスタ設定によって制御されます。HIZ1 信号は、nHIZ1 ピンと S\_HIZ1 レジスタ設定の論理和です。HIZ2 信号は、nHIZ2 ピンと S\_HIZ2 レジスタ設定の論理和です。

表 7-3. ハーフブリッジ制御 (BRG\_MODE = 00b または MODE = レベル 1)

| nHIZx | INx | GHx | GLx | SHx |

|-------|-----|-----|-----|-----|

| 0     | X   | L   | L   | Z   |

| 1     | 0   | L   | H   | L   |

| 1     | 1   | H   | L   | H   |

図 7-3. ハーフブリッジ制御

#### 7.3.3.2 H ブリッジ制御

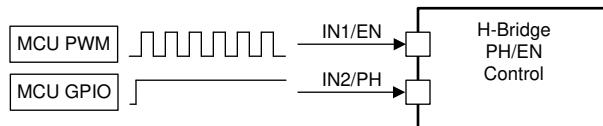

H ブリッジ制御では、IN1/EN と IN2/PH 入力ピンにより、両方のハーフブリッジ・ゲート・ドライバを H ブリッジ・ゲート・ドライバとして制御できます。

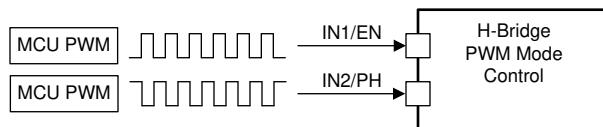

H ブリッジ・モードには 2 つの入力制御方法があり、SPI BRG\_MODE レジスタ設定または H/W モード・ピンにより構成できます。PH/EN モードでは、1 つの PWM 信号と 1 つの GPIO 信号によってコマンド制御される速度 / 方向タイプのインターフェイスにより、H ブリッジを制御できます。PWM モードでは、通常は 2 つの PWM 信号を必要とする、より高度なスキーマにより、H ブリッジを制御できます。この結果、H ブリッジ・ドライバは 4 つの異なる出力状態に入ることができます。必要に応じて制御のフレキシビリティがさらに高まります。

PH/EN モードと PWM モードの両方で、デフォルトのアクティブ・フリー・ホール・モードがローサイドでアクティブです。SPI デバイス・パリアントには、BRG\_FW レジスタ設定により、フリー・ホール状態を構成する機能があります。この設定を使用すると、ローサイドとハイサイドのアクティブ・フリー・ホール間のブリッジを変更できます。

H ブリッジ制御モードでは、nHIZx ピンと S\_HIZx レジスタ機能がディセーブルになります。nHIZx ピンは、切断または GND に接続した状態のままにできます。H ブリッジは、PWM 制御モード、DRVOFF ピン、または SPI デバイスの EN\_DRV レジスタ設定により、Hi-Z 状態に設定できます。

**表 7-4. PH/EN H ブリッジ制御 (BRG\_MODE = 01b または MODE = レベル 2)**

| IN1/EN | IN2/PH | BRG_FW | GH1 | GL1 | GH2 | GL2 | SH1 | SH2 | 説明                   |

|--------|--------|--------|-----|-----|-----|-----|-----|-----|----------------------|

| 0      | X      | 0b     | L   | H   | L   | H   | L   | L   | ローサイド・アクティブ・フリー・ホール  |

| 0      | X      | 1b     | H   | L   | H   | L   | H   | H   | ハイサイド・アクティブ・フリー・ホール  |

| 1      | 0      | X      | L   | H   | H   | L   | L   | H   | ドライブ SH2 → SH1 (逆方向) |

| 1      | 1      | X      | H   | L   | L   | H   | H   | L   | ドライブ SH1 → SH2 (順方向) |

**図 7-4. H ブリッジ PH/EN 制御**

**表 7-5. PWM H ブリッジ制御 (BRG\_MODE = 10b または MODE = レベル 3)**

| IN1/EN | IN2/PH | BRG_FW | GH1 | GL1 | GH2 | GL2 | SH1 | SH2 | 説明                   |

|--------|--------|--------|-----|-----|-----|-----|-----|-----|----------------------|

| 0      | 0      | X      | L   | L   | L   | L   | Z   | Z   | ダイオード・フリー・ホール (滑走)   |

| 0      | 1      | X      | L   | H   | H   | L   | L   | H   | ドライブ SH2 → SH1 (逆方向) |

| 1      | 0      | X      | H   | L   | L   | H   | H   | L   | ドライブ SH1 → SH2 (順方向) |

| 1      | 1      | 0b     | L   | H   | L   | H   | L   | L   | ローサイド・アクティブ・フリー・ホール  |

| 1      | 1      | 1b     | H   | L   | H   | L   | H   | H   | ハイサイド・アクティブ・フリー・ホール  |

**図 7-5. H ブリッジ PWM 制御**

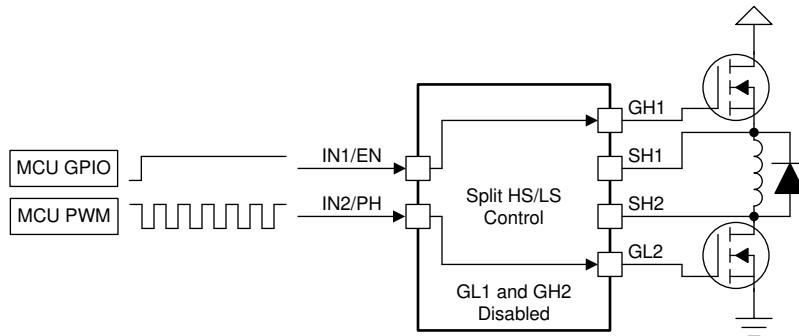

### 7.3.3.3 分割 HS/LS ソレノイド制御

分割 HS/LS ソレノイド制御モードでは、GH1 および GL2 ゲート・ドライバ出力のみがアクティブになります。GH1 出力は IN1/EN により制御され、GL2 出力は IN2/PH により制御されます。このモードでは、H ブリッジを構成して、反対のハイサイドとローサイドの外部 MOSFET 間のフローティング・ソレノイド負荷を駆動できます。

分割 HS/LS 制御モードでは、nHIZx ピンと S\_HIZx レジスタ機能がディセーブルになります。nHIZx ピンは、切断または GND に接続した状態のままにできます。H ブリッジは、DRVOFF ピンまたは SPI デバイス上の EN\_DRV レジスタ設定により、Hi-Z 状態に設定できます。

**表 7-6. 分割 HS/LS 制御 (BRG\_MODE = 11b または MODE = Level 4)**

| IN1/EN | IN2/PH | GH1 | GL1    | GH2    | GL2 | 説明             |

|--------|--------|-----|--------|--------|-----|----------------|

| 0      | X      | L   | 非アクティブ | 非アクティブ | X   | ソレノイド、ディセーブル状態 |

表 7-6. 分割 HS/LS 制御 (BRG\_MODE = 11b または MODE = Level 4) (continued)

| IN1/EN | IN2/PH | GH1 | GL1    | GH2    | GL2 | 説明            |

|--------|--------|-----|--------|--------|-----|---------------|

| 1      | X      | H   | 非アクティブ | 非アクティブ | X   | ソレノイド、イネーブル状態 |

| X      | 0      | X   | 非アクティブ | 非アクティブ | L   | ソレノイド、PWM オフ  |

| X      | 1      | X   | 非アクティブ | 非アクティブ | H   | ソレノイド、PWM オン  |

図 7-6. 分割 HS/LS PWM 制御

### 7.3.4 スマート・ゲート・ドライバ

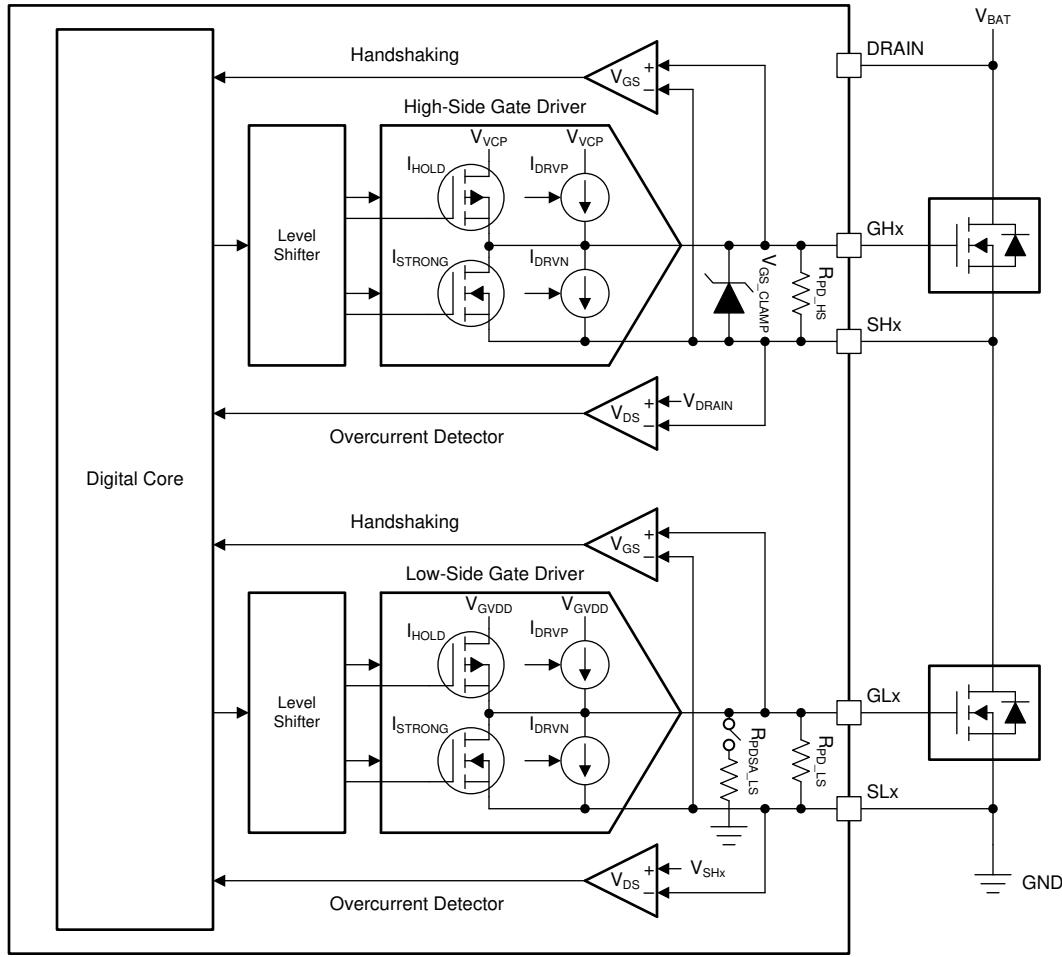

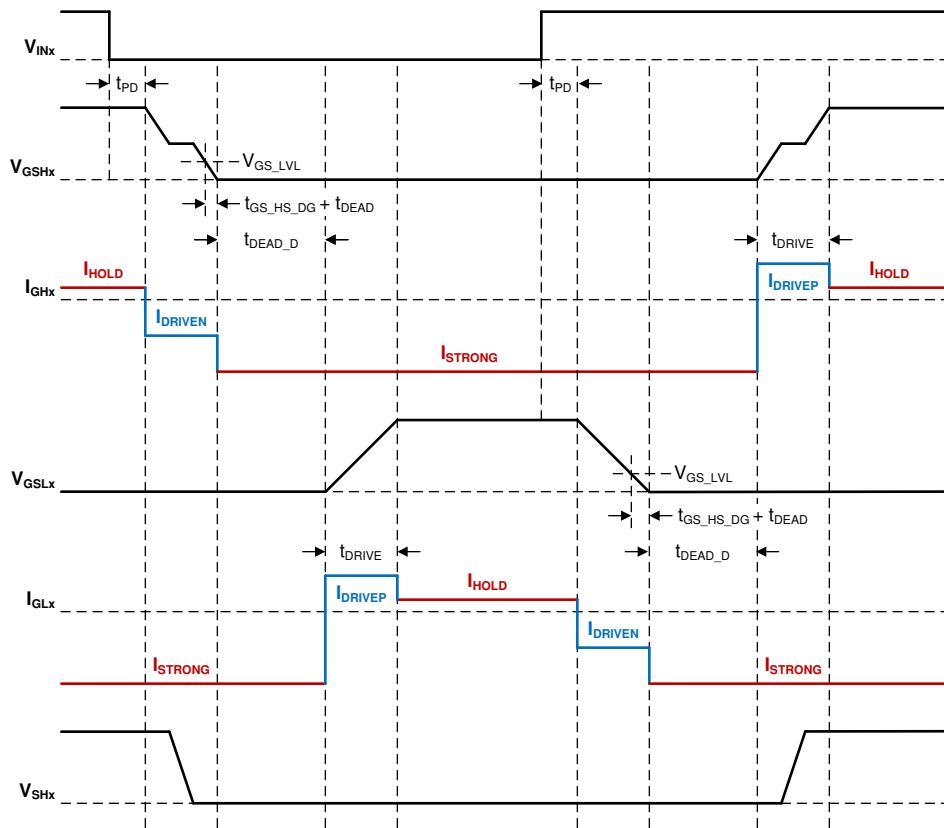

DRV8706-Q1 は、先進の可変フローティング・スマート・ゲート・ドライバ・アーキテクチャを採用し、先進の MOSFET 制御と堅牢なスイッチング性能を実現しています。DRV8706-Q1 は、スルーレート制御用ドライバ機能と、デッド・タイム・ハンドシェイク、寄生  $dV/dt$  ゲート・カップリング防止および MOSFET ゲート障害検出用のドライバ・ステートマシンを実現します。

スマート・ゲート・ドライバのコア機能：

- ゲート・ドライバの機能ブロック図

- スルーレート制御 (IDRIVE)

- ゲート駆動ステート・マシン (TDRIVE)

表 7-7. スマート・ゲート・ドライバ用語の説明

| コア機能          | 用語           | 説明                                                                                                                           |

|---------------|--------------|------------------------------------------------------------------------------------------------------------------------------|

| IDRIVE/TDRIVE | $I_{DRV_P}$  | 可変 MOSFET スルーレート制御を行うためのプログラマブル・ゲート・ドライバ駆動ソース電流。 $I_{DRV_P\_x}$ 制御レジスタまたは IDRIVE ピンを使用して構成。                                  |

|               | $I_{DRV_N}$  | 可変 MOSFET スルーレート制御を行うためのプログラマブル・ゲート駆動シンク電流。 $I_{DRV_N\_x}$ 制御レジスタまたは IDRIVE ピンを使用して構成。                                       |

|               | $I_{HOLD}$   | 非スイッチング期間中の固定ゲート・ドライバ・ホールド・プルアップ電流。                                                                                          |

|               | $I_{STRONG}$ | 非スイッチング期間中の固定ゲート・ドライバ強フルダウン電流。                                                                                               |