## DRV8376-Q1 3 相 FET 内蔵モーター ドライバ

### 1 特長

- 三相 BLDC モーター ドライバ

- 48V システムをサポート

- 最大 100kHz の PWM 周波数をサポート

- アクティブ消磁により電力損失を低減

- サイクル単位の電流制限により位相電流を制限

- 動作電圧: 4.5V~65V (絶対最大定格 70V)

- 高い出力電流能力: ピーク 4.5A

- 低い MOSFET オンステート抵抗

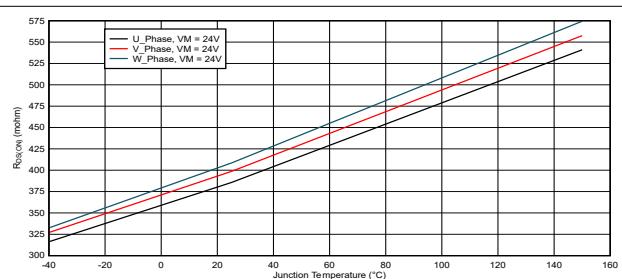

- $T_A = 25^\circ\text{C}$  で  $400\text{m}\Omega$  の  $R_{\text{DS(ON)}}$  (HS + LS)

- 1.1V/ns のスルーレートと逆方向回復損失の最小化手法により、スイッチング損失を低減します

- 調整可能なスルーレートオプション

- 200ns 未満の非常に短いデッドタイムと、100ns 未満の伝搬遅延により、小さい可聴ノイズとモーター制御が容易

- 低消費電力スリープ モード

- 1.5 $\mu\text{A}$  (標準値) ( $V_{\text{VM}} = 24\text{V}$ ,  $T_A = 25^\circ\text{C}$ )

- 複数の制御インターフェイス オプション

- 6x PWM 制御インターフェイス

- 3x PWM 制御インターフェイス

- 電流センス機能内蔵、外付け電流センス抵抗不要

- 柔軟なデバイス構成オプション

- DRV8376S: デバイスの構成とフォルトステータスのための 5MHz、16 ビット SPI

- DRV8376H: ハードウェアピンベースの構成

- 1.8V、3.3V、5V のロジック入力をサポート

- 3.3V (5%)、30mA LDO レギュレータ内蔵

- 5V (5%)、30mA LDO レギュレータ内蔵

- 保護機能内蔵

- 電源低電圧誤動作防止 (UVLO)

- チャージポンプ低電圧 (CPUV)

- 過電流保護 (OCP)

- 熱警告およびシャットダウン (OTW/OTSD)

- フォルト状況表示ピン (nFAULT)

- SPI によるフォルト診断 (オプション)

### 2 アプリケーション

- ブラシレス DC (BLDC) モーター モジュール

- HVAC モーター

- OA 機器

- ファクトリ オートメーションおよびロボティクス

- ワイヤレスアンテナ モーター

- ドローン

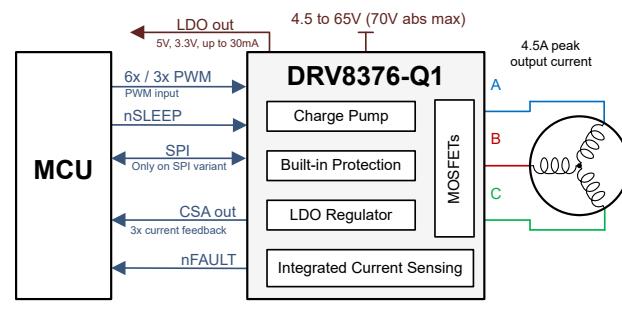

### 3 説明

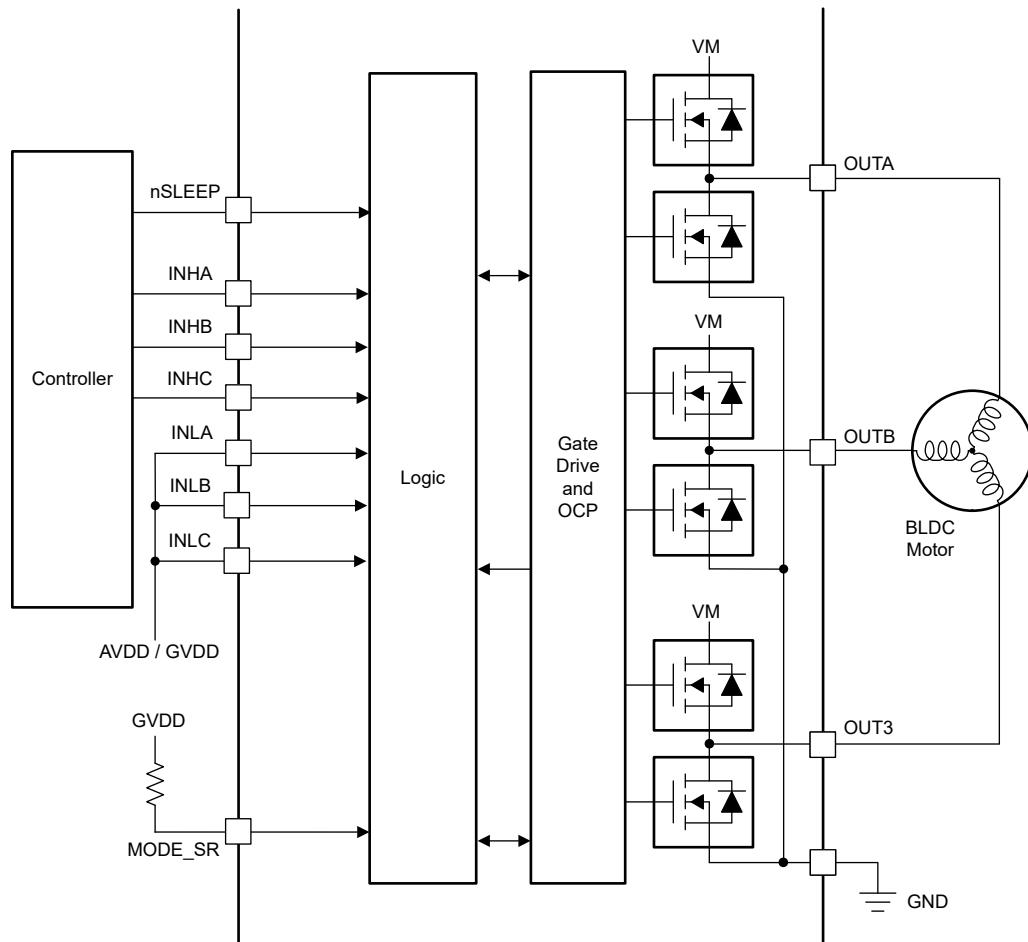

DRV8376-Q1 は、4.5V ~ 65V のブラシレス DC モーターを駆動するためのゲート ドライバと電力段を提供します。DRV8376 は、大電力駆動能力を実現するため、70V の絶対最大定格と  $400\text{m}\Omega$  (ハイサイドとローサイドの合計) という非常に小さい  $R_{\text{DS(ON)}}$  を持つ 3 つのハーフ H ブリッジを内蔵しています。内蔵の電流検出機能を使用して電流を検出するので、外付けの検出抵抗は不要です。内蔵 LDO による電源管理機能が、デバイスに必要な電圧レールを生成します。また、外部回路に電力を供給するためにも使用できます。

DRV8376-Q1 には 6x または 3x の PWM 制御方式が実装されており、センサ付きまたはセンサレスのフィールドオリエンテッド制御 (FOC)、正弦波制御、または外付けマイコンを使用した台形制御を実現できます。DRV8376 は、最大 100kHz の PWM 周波数で駆動できます。制御方式は、モーター電流制限動作からフォルト応答まで、ハードウェア ピンまたはレジスタ設定を使って詳細に設定できます。

DRV8376-Q1 は、本デバイス自身、モーター、システムをフォルト イベントから保護するための多くの保護機能を内蔵しています。

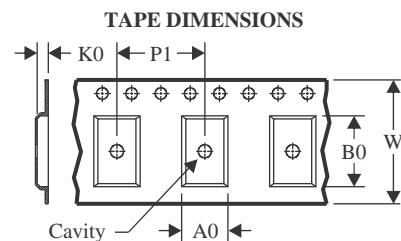

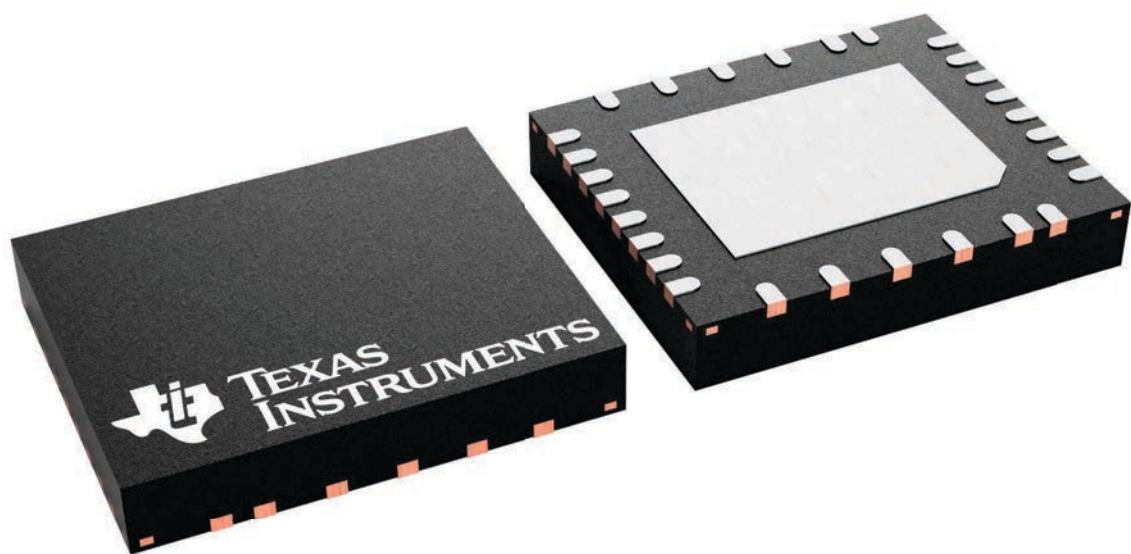

#### 製品情報

| 部品番号        | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> | 本体サイズ (公称)       |

|-------------|----------------------|--------------------------|------------------|

| DRV8376H-Q1 | VQFN (28)            | 6.00 mm × 5.00mm         | 6.00 mm × 5.00mm |

| DRV8376S-Q1 | VQFN (28)            | 6.00 mm × 5.00mm         | 6.00 mm × 5.00mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SLVSI02](#)

## 目次

|                        |           |                               |           |

|------------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>            | <b>1</b>  | 7.4 デバイスの機能モード                | <b>42</b> |

| <b>2 アプリケーション</b>      | <b>1</b>  | 7.5 SPI 通信                    | <b>43</b> |

| <b>3 説明</b>            | <b>1</b>  | <b>8 レジスタ マップ</b>             | <b>45</b> |

| <b>4 デバイス比較表</b>       | <b>3</b>  | 8.1 ステータス レジスタ                | <b>45</b> |

| <b>5 ピン構成および機能</b>     | <b>4</b>  | 8.2 制御 レジスタ                   | <b>50</b> |

| <b>6 仕様</b>            | <b>6</b>  | <b>9 アプリケーションと実装</b>          | <b>58</b> |

| 6.1 絶対最大定格             | 6         | 9.1 アプリケーション情報                | 58        |

| 6.2 ESD 定格             | 6         | 9.2 代表的なアプリケーション              | 59        |

| 6.3 推奨動作条件             | 6         | 9.3 電源に関する推奨事項                | 63        |

| 6.4 熱に関する情報            | 7         | 9.4 レイアウト                     | 64        |

| 6.5 電気的特性              | 7         | <b>10 デバイスおよびドキュメントのサポート</b>  | <b>66</b> |

| 6.6 SPI のタイミング要件       | 12        | 10.1 ドキュメントのサポート              | 66        |

| 6.7 SPI スレーブ モードのタイミング | 13        | 10.2 サポート・リソース                | 66        |

| 6.8 代表的特性              | 13        | 10.3 商標                       | 66        |

| <b>7 詳細説明</b>          | <b>14</b> | 10.4 静電気放電に関する注意事項            | 66        |

| 7.1 概要                 | 14        | 10.5 用語集                      | 66        |

| 7.2 機能ブロック図            | 15        | <b>11 改訂履歴</b>                | <b>66</b> |

| 7.3 機能説明               | 17        | <b>12 メカニカル、パッケージ、および注文情報</b> | <b>66</b> |

## 4 デバイス比較表

| デバイス     | パッケージ              | インターフェイス |

|----------|--------------------|----------|

| DRV8376S | 28 ピン VQFN (6x5mm) | SPI      |

| DRV8376H |                    | ハードウェア   |

**表 4-1. DRV8376S (SPI バリアント) と DRV8376H (ハードウェア バリアント) の構成比較**

| パラメータ                                            | DRV8376S (SPI バリアント)                                                                        | DRV8376H (ハードウェア バリアント)                                                                                                                                                                                               |

|--------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWM モード設定                                        | PWM_MODE (4 つの設定)                                                                           | MODE_SR ピン (4 つの設定)                                                                                                                                                                                                   |

| スルーレートの設定                                        | SLEW_RATE (4 つの設定)                                                                          | SLEW ピン (4 つの設定)                                                                                                                                                                                                      |

| CSA ゲイン設定                                        | CSA_GAIN (4 つの設定)                                                                           | GAIN ピン (4 つの設定)                                                                                                                                                                                                      |

| SDO ピン構成:モード、電圧                                  | SDO_ODEN (2 つの設定)、SDO_VSEL (2 つの設定)、SDO_MD (2 つの設定)                                         |                                                                                                                                                                                                                       |

| 電流制限構成:モード、nFAULT 通知、ブランギング時間、100% デューティ PWM 周波数 | ILIM_FLT_MODE (2 つの設定)、ILIM_MODE (2 つの設定)、ILIM_BLANK_SEL (4 つの設定)、PWM_100_FREQ_SEL (4 つの設定) | nFAULT 時の電流制限通知は有効化、コーストモードは固定、ブランギング時間はスルーレート 50 の場合は $5.5\mu\text{s}$ に設定、その他すべてのスルーレートの場合は $1.8\mu\text{s}$ に設定、100% デューティ入力 PWM サイクルは 20kHz に固定                                                                   |

| 過電圧保護モード                                         | OVP_MODE (2 つの設定)、OVP_SEL (2 つの設定)                                                          | 過電圧保護は無効化                                                                                                                                                                                                             |

| OCP の構成:モード、レベル、グリッヂ除去                           | OCP_MODE (4 つの設定)、OCP_LVL (2 つの設定)、OCP_DEG (4 つの設定)、OCP_RETRY (2 つの設定)                      | 自動リトライ モードで有効化、レベルは 4.5A に固定、グリッヂ除去時間は $1.25\mu\text{s}$ 、リトライ時間は 5 ms                                                                                                                                                |

| アクティブ消磁:有効、コンパレータのスレッショルド、コンパレータのマスク時間、フォルト時の動作  | EN_ASR (2 つの設定)、EN_AAR (2 つの設定)、AD_COMP_TH (2 つの設定)                                         | MODE_SR (2 つの設定)、アクティブ消磁コンパレータ スレッショルドは 100mA に設定、スルーレートが $50\text{V}/\mu\text{s}$ の場合はコンパレータのマスク時間は $5.5\mu\text{s}$ 、その他すべてのスルーレートの場合は $1.8\mu\text{s}$ に設定。ADMAG_TMARGIN は $1.6\mu\text{s}$ に設定、OCP 中はアクティブ消磁が無効化。 |

| 過熱警告                                             | OTW_MODE (2 つの設定)                                                                           | nFAULT で通知                                                                                                                                                                                                            |

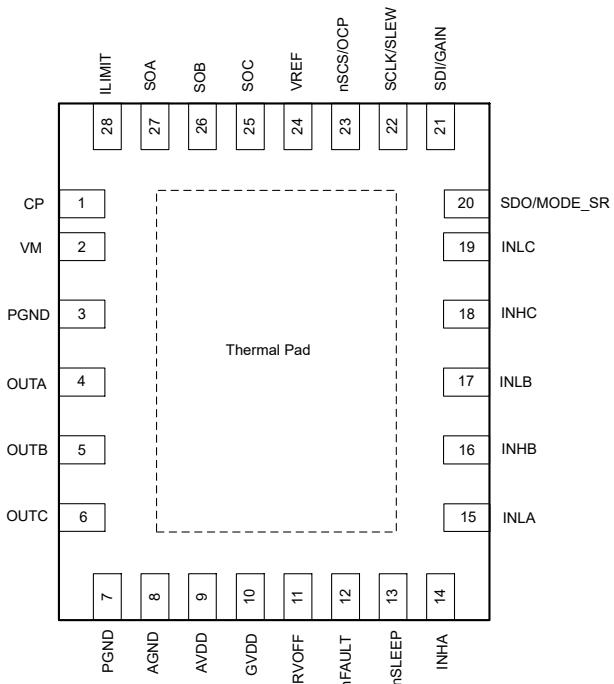

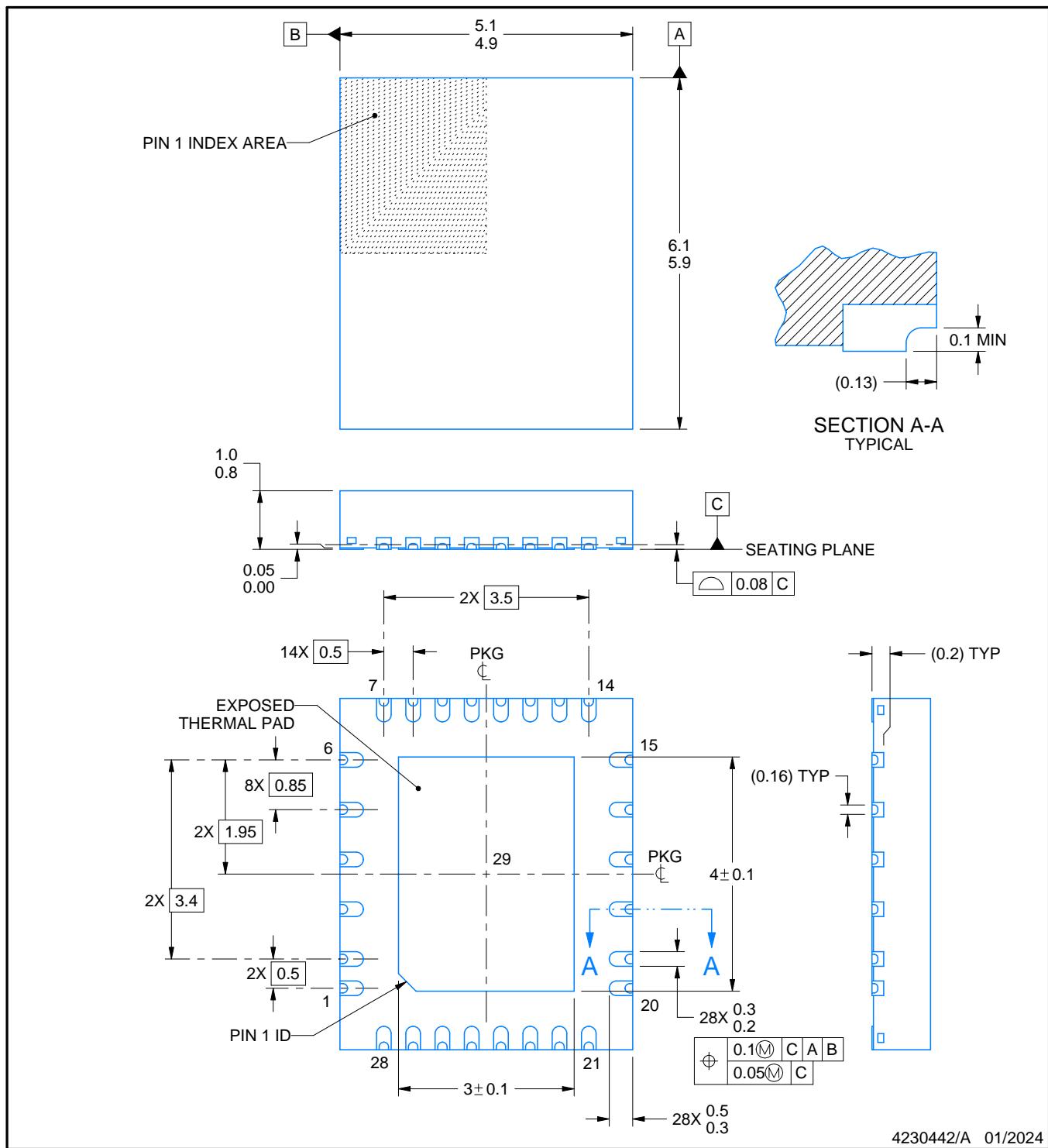

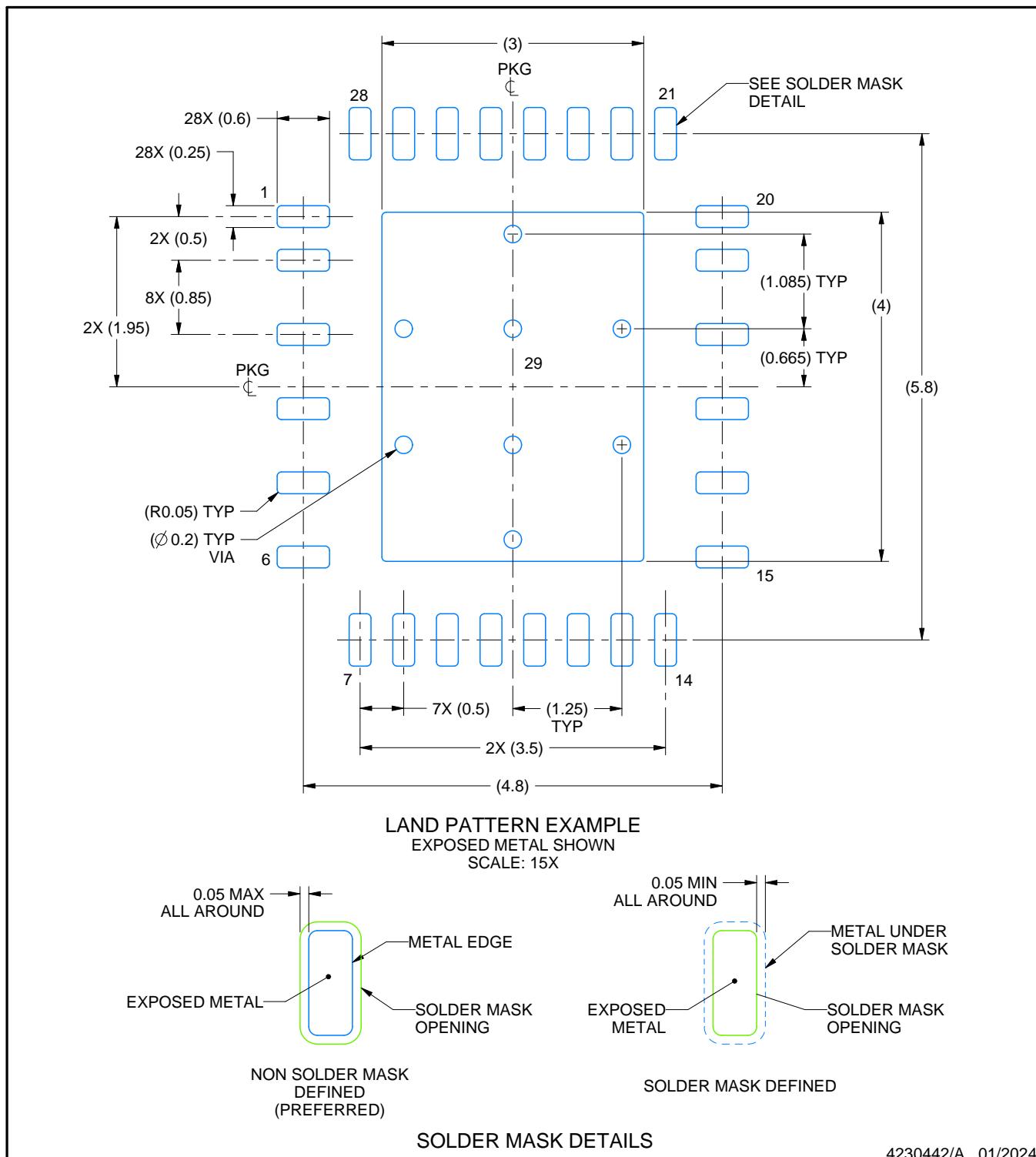

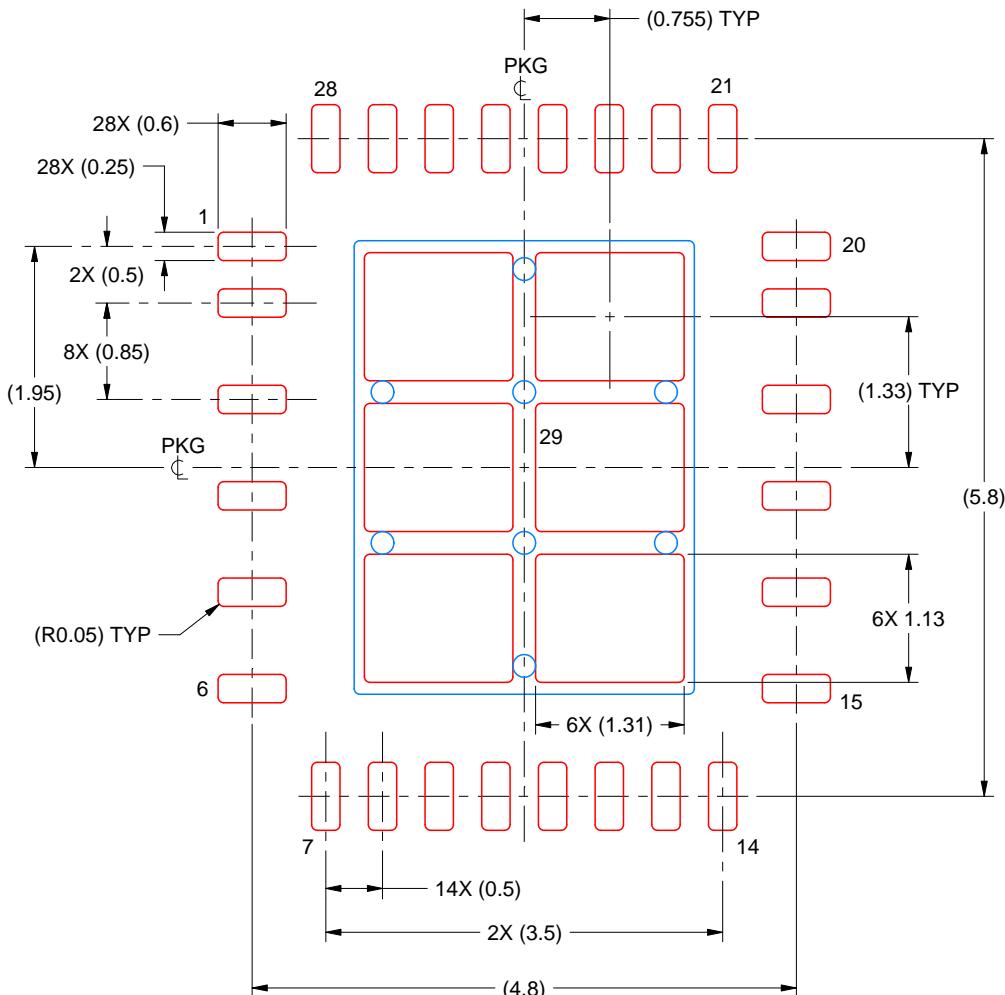

## 5 ピン構成および機能

図 5-1. DRV8376 28 ピン VQFN (露出サーマル パッド付き) 上面図

表 5-1. DRV8376 のピンの機能

| ピン     | 28 ピン VQFN パッケージ |          | タイプ <sup>(1)</sup> | 説明                                                                                                         |

|--------|------------------|----------|--------------------|------------------------------------------------------------------------------------------------------------|

| 名称     | DRV8376H         | DRV8376S |                    |                                                                                                            |

| AGND   | 8                | 8        | GND                | デバイスのアナログ グラウンド。接続に関する推奨事項については、 <a href="#">セクション 9.4.1</a> を参照してください。                                    |

| AVDD   | 9                | 9        | PWR O              | 3.3V 内部レギュレータ出力。X5R または X7R、0.1μF、6.3V セラミック コンデンサを AVDD ピンと AGND ピンの間に接続します。このレギュレータは最大 30mA を外部にソースできます。 |

| CP     | 1                | 1        | PWR O              | チャージ ポンプ出力。X5R または X7R、0.1μF、16V セラミック コンデンサを CP ピンと VM ピンの間に接続します。                                        |

| DRVOFF | 11               | 11       | I                  | このピンが High にプルされると、電力段の 6 つの MOSFET がターンオフし、すべての出力がハイインピーダンスになります。                                         |

| ゲイン    | 21               | -        | I                  | 電流センス アンプのゲイン設定。このピンは、外付け抵抗で設定される 4 レベル入力ピンです。                                                             |

| GVDD   | 10               | 10       | PWR O              | 5V 内部レギュレータ出力。X5R または X7R、1μF、10V セラミック コンデンサを AVDD ピンと AGND ピンの間に接続します。このレギュレータは最大 30mA を外部にソースできます。      |

| ILIMIT | 28               | 28       |                    | サイクル単位の電流制限で使用される相電流のスレッショルドを設定します。                                                                        |

| INHA   | 14               | 14       | I                  | OUTA のハイサイド ドライバ制御入力。このピンは、ハイサイド MOSFET の出力を制御します。                                                         |

| INHB   | 16               | 16       | I                  | OUTB のハイサイド ドライバ制御入力。このピンは、ハイサイド MOSFET の出力を制御します。                                                         |

| INHC   | 18               | 18       | I                  | OUTC のハイサイド ドライバ制御入力。このピンは、ハイサイド MOSFET の出力を制御します。                                                         |

| INLA   | 15               | 15       | I                  | OUTA のローサイド ドライバ制御入力。このピンは、ローサイド MOSFET の出力を制御します。                                                         |

**表 5-1. DRV8376 のピンの機能 (続き)**

| ピン       | 28 ピン VQFN パッケージ |          | タイプ <sup>(1)</sup> | 説明                                                                                                                                                              |

|----------|------------------|----------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称       | DRV8376H         | DRV8376S |                    |                                                                                                                                                                 |

| INLB     | 17               | 17       | I                  | OUTB のローサイド ドライバ制御入力。このピンは、ローサイド MOSFET の出力を制御します。                                                                                                              |

| INLC     | 19               | 19       | I                  | OUTC のローサイド ドライバ制御入力。このピンは、ローサイド MOSFET の出力を制御します。                                                                                                              |

| MODE_SR  | 20               | -        | I                  | PWM 入力モード設定。このピンは、外付け抵抗で設定される 4 レベル入力ピンです。                                                                                                                      |

| nFAULT   | 12               | 12       | O                  | フォルト インジケータ。フォルト条件によってロジック Low にプルされます。オーブンドライン出力には、1.8V~5.0V への外部プルアップ抵抗が必要です。nFAULT をプルアップするためには、外部電源を使用する場合は、パワーアップ時に外部電源が 2.2V を上回る値にプルアップされていることを確認してください。 |

| nSCS     | -                | 23       | I                  | シリアル チップ選択。このピンのロジック Low により、シリアル インターフェイス通信が可能になります。                                                                                                           |

| nSLEEP   | 13               | 13       | I                  | ドライバ nSLEEP。このピンをロジック Low にすると、デバイスは低消費電力のスリープ モードに移行します。20µs ~ 40µs の Low パルスを使うとフォルト状態をリセットできます。                                                              |

| OCP      | 23               | -        | I                  | OCP レベル設定。このピンは、外付け抵抗で設定される 2 レベル入力ピンです (ハードウェア デバイス)。                                                                                                          |

| OUTA     | 4                | 4        | PWR O              | ハーフブリッジ出力 A                                                                                                                                                     |

| OUTB     | 5                | 5        | PWR O              | ハーフブリッジ出力 B                                                                                                                                                     |

| OUTC     | 6                | 6        | PWR O              | ハーフブリッジ出力 C                                                                                                                                                     |

| PGND     | 3, 7             | 3, 7     | GND                | デバイスの電源グランド。接続に関する推奨事項については、 <a href="#">セクション 9.4.1</a> を参照してください。                                                                                             |

| SCLK     | -                | 22       | I                  | シリアル クロック入力。シリアル データは、このピンの対応する立ち上がりおよび立ち下がり エッジでシフト アウトおよびキャプチャされます (SPI デバイス)。                                                                                |

| SDI      | -                | 21       | I                  | シリアル データ入力。データは、SCLK ピンの立ち下がりエッジでキャプチャされます (SPI デバイス)。                                                                                                          |

| SDO      | -                | 20       | O                  | シリアル データ出力。データは、SCLK ピンの立ち上がりエッジでシフト アウトされます。このピンは外付けプルアップ抵抗を必要とします (SPI デバイス)。                                                                                 |

| SLEW     | 22               | -        | I                  | スルーレート制御設定このピンは、外付け抵抗で設定される 4 レベル入力ピンです。                                                                                                                        |

| SOA      | 27               | 27       | O                  | 電流センスアンプの出力。容量性負荷またはローパス フィルタ (直列抵抗と GND へのコンデンサ) をサポート                                                                                                         |

| SOB      | 26               | 26       | O                  | 電流センスアンプの出力。容量性負荷またはローパス フィルタ (直列抵抗と GND へのコンデンサ) をサポート                                                                                                         |

| SOC      | 25               | 25       | O                  | 電流センスアンプの出力。容量性負荷またはローパス フィルタ (直列抵抗と GND へのコンデンサ) をサポート                                                                                                         |

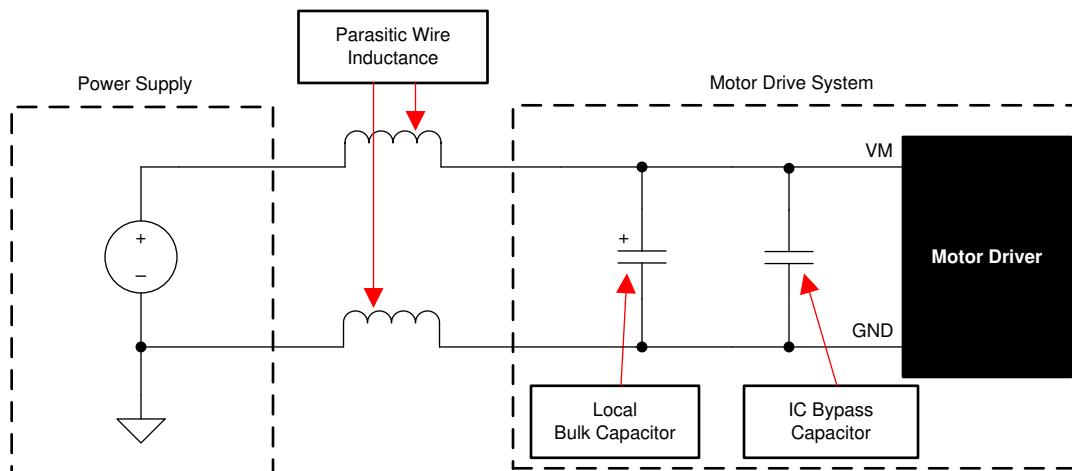

| VM       | 2                | 2        | PWR I              | 電源。モーター電源電圧に接続し、0.1µF コンデンサと VM 定格のパルク コンデンサ 1 つを使用して PGND にバイパスします。コンデンサの電圧定格は、デバイスの通常動作電圧の 2 倍以上とすることを推奨します。                                                  |

| VREF     | 24               | 24       | PWR/I              | 電流センス アンプのリファレンス X5R または X7R、0.1µF、6.3V セラミック コンデンサを VREF ピンと AGND ピンの間に接続します。                                                                                  |

| サーマル パッド |                  |          | AGND               | アナログ グランドに接続する必要があります。                                                                                                                                          |

(1) I = 入力、O = 出力、GND = グランド ピン、PWR = 電源、NC = 未接続

## 6 仕様

### 6.1 絶対最大定格

動作時周囲温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                                                          | 最小値  | 最大値         | 単位   |

|----------------------------------------------------------|------|-------------|------|

| 電源ピン電圧 (VM)                                              | -0.3 | 70          | V    |

| 電源電圧ランプ (VM)                                             |      | 4           | V/μs |

| グランドピン (PGND, AGND) 間の電圧差                                | -0.6 | 0.6         | V    |

| チャージポンプ電圧 (CP)                                           | -0.3 | $V_M + 6.2$ | V    |

| アナログレギュレータピン電圧 (GVDD)                                    | -0.3 | 5.75        | V    |

| アナログレギュレータピン電圧 (AVDD)                                    | -0.3 | 5.75        | V    |

| アナログピン入力電圧 (VREF, ILIMIT)                                | -0.3 | 5.75        | V    |

| アナログピン出力電圧 (SOx)                                         | -0.3 | 5.75        | V    |

| ロジックピン入力電圧 (DRV0FF, INHx, INLx, nSCS, nSLEEP, SCLK, SDI) | -0.3 | 5.75        | V    |

| ロジックピン出力電圧 (nFAULT, SDO, )                               | -0.3 | 5.75        | V    |

| マルチレベルピン入力電圧 (GAIN, MODE_SR, OCP, SLEW)                  | -0.3 | 5.75        | V    |

| 出力ピン電圧 (OUTA, OUTB, OUTC)                                | -1   | $V_M + 1$   | V    |

| 周囲温度、 $T_A$                                              | -40  | 125         | °C   |

| 接合部温度、 $T_J$                                             | -40  | 150         | °C   |

| 保管温度、 $T_{stg}$                                          | -65  | 150         | °C   |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 6.2 ESD 定格

|             |      | 値                                                         | 単位         |

|-------------|------|-----------------------------------------------------------|------------|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>      | $\pm 2000$ |

|             |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠 <sup>(2)</sup> | $\pm 750$  |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 6.3 推奨動作条件

動作時周囲温度範囲内 (特に記述のない限り)

|                          |                 | 最小値                                              | 公称値  | 最大値  | 単位  |

|--------------------------|-----------------|--------------------------------------------------|------|------|-----|

| $V_{VM}$                 | 電源電圧            | $V_{VM}$                                         | 4.5  | 24   | V   |

| $f_{PWM}$                | 出力 PWM 周波数      | OUTA, OUTB, OUTC                                 |      | 100  | kHz |

| $I_{OUT}$ <sup>(1)</sup> | ピーク出力巻線電流       | OUTA, OUTB, OUTC                                 |      | 4    | A   |

| $V_{IN}$                 | ロジック入力電圧        | DRV0FF, INHx, INLx, nSCS, nSLEEP, SCLK, SDI, OCP | -0.1 | 5.5  | V   |

| $V_{IN}$                 | マルチレベル入力電圧      | GAIN, MODE_SR, SLEW                              | -0.1 | GVDD |     |

| $V_{OD}$                 | オーブンドレインブルアップ電圧 | nFAULT, SDO, FG                                  | -0.1 | 5.5  | V   |

| $V_{SDO}$                | プッシュブル電圧        | SDO                                              | 2.2  | AVDD | V   |

| $I_{OD}$                 | オーブンドレイン出力電流    | nFAULT, SDO, FG                                  |      | 5    | mA  |

| $V_{VREF}$               | 電圧リファレンスピン電圧    | VREF                                             | 2.8  | 5.5  | V   |

| $ILIMIT$                 | 電流制限の電圧リファレンス   | ILIMIT                                           | -0.1 | 5.5  | V   |

動作時周辺温度範囲内 (特に記述のない限り)

|                |          | 最小値 | 公称値 | 最大値 | 単位 |

|----------------|----------|-----|-----|-----|----|

| T <sub>A</sub> | 動作時の周囲温度 | -40 |     | 125 | °C |

| T <sub>J</sub> | 動作時接合部温度 | -40 |     | 150 | °C |

(1) 消費電力および温度の制限に従う必要があります。

## 6.4 热に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | DRV8376H、DRV8376S | 単位   |

|-----------------------|---------------------|-------------------|------|

|                       |                     | VQFN (NLG)        |      |

|                       |                     | 28 ピン             |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 29.9              | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 20.8              | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 11                | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 0.3               | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 11                | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | 2.9               | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 6.5 電気的特性

T<sub>J</sub> = -40°C～+150°C、V<sub>VM</sub> = 4.5～65V (特に記述のない限り)。標準値には T<sub>A</sub> = 25°C、V<sub>VM</sub> = 24V が適用されます。

| パラメータ             | テスト条件            | 最小値                                                                                                | 標準値  | 最大値  | 単位    |    |

|-------------------|------------------|----------------------------------------------------------------------------------------------------|------|------|-------|----|

| <b>電源</b>         |                  |                                                                                                    |      |      |       |    |

| I <sub>VMQ</sub>  | VM スリープ モード電流    | V <sub>VM</sub> > 6V、nSLEEP = 0、T <sub>A</sub> = 25°C                                              | 1.5  | 3    | μA    |    |

|                   |                  | nSLEEP = 0                                                                                         | 2.5  | 8    | μA    |    |

| I <sub>VMS</sub>  | VM スタンバイ モード電流   | V <sub>VM</sub> > 6V、nSLEEP = 1、INHx = INLx = 0、SPI = 'OFF'、T <sub>A</sub> = 25°C                  | 6.6  | 8.2  | mA    |    |

|                   |                  | nSLEEP = 1、INHx = INLx = 0、SPI = 'OFF'                                                             | 6.6  | 8.2  | mA    |    |

| I <sub>VMS</sub>  | VM スタンバイ モード電流   | V <sub>VM</sub> > 6V、nSLEEP = 1、INHx = INLx = 0、SPI = 'OFF'、T <sub>A</sub> = 25°C、ASR および AAR は無効化 | 6.1  | 7.5  | mA    |    |

| I <sub>VMS</sub>  | VM スタンバイ モード電流   | nSLEEP = 1、INHx = INLx = 0、SPI = 'OFF'、ASR および AAR は無効化                                            | 6.1  | 7.5  | mA    |    |

| I <sub>VM</sub>   | VM 動作モード電流       | V <sub>VM</sub> > 6V、nSLEEP = 1、f <sub>PWM</sub> = 20kHz                                           | 7.6  | 9.8  | mA    |    |

|                   |                  | nSLEEP = 1、f <sub>PWM</sub> = 20kHz                                                                | 7.6  | 9.8  | mA    |    |

|                   |                  | nSLEEP = 1、f <sub>PWM</sub> = 100kHz                                                               | 10.1 | 13.4 | mA    |    |

| V <sub>GVDD</sub> | アナログ レギュレータの電圧   | 0mA ≤ I <sub>GVDD</sub> ≤ 30mA、(外部負荷)、VM > 6V                                                      | 4.75 | 5    | 5.25  | V  |

| V <sub>GVDD</sub> | アナログ レギュレータの電圧   | 0mA ≤ I <sub>GVDD</sub> ≤ 30mA、(外部負荷)、VM = 4.5V                                                    | 3.7  |      | 4.5   | V  |

| V <sub>AVDD</sub> | アナログ レギュレータの電圧   | 0mA ≤ I <sub>AVDD</sub> ≤ 30mA、(外部負荷)                                                              | 3.1  | 3.3  | 3.465 | V  |

| I <sub>GVDD</sub> | 外部アナログ レギュレータの負荷 | I <sub>AVDD</sub> = 0mA                                                                            |      |      | 30    | mA |

| I <sub>AVDD</sub> | 外部アナログ レギュレータの負荷 | I <sub>GVDD</sub> = 0mA                                                                            |      |      | 30    | mA |

| V <sub>VCP</sub>  | チャージポンプ レギュレータ電圧 | VM を基準とした VCP (V <sub>VM</sub> > 6V)                                                               | 4    | 5    | 6     | V  |

| t <sub>WAKE</sub> | ウェークアップ時間        | V <sub>VM</sub> > V <sub>UVLO</sub> 、nSLEEP = 1 で出力準備完了、nFAULT 解放                                  |      |      | 5.5   | ms |

$T_J = -40^\circ\text{C} \sim +150^\circ\text{C}$ ,  $V_{VM} = 4.5 \sim 65\text{V}$  (特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ ,  $V_{VM} = 24\text{V}$  が適用されます。

| パラメータ       |            | テスト条件                   | 最小値 | 標準値 | 最大値 | 単位            |

|-------------|------------|-------------------------|-----|-----|-----|---------------|

| $t_{SLEEP}$ | スリープ パルス時間 | $nSLEEP = 0$ でスリープ モード  | 120 |     |     | $\mu\text{s}$ |

| $t_{RST}$   | リセット パルス時間 | $nSLEEP = 0$ でフォルトをリセット | 20  | 40  |     | $\mu\text{s}$ |

#### ロジック レベル入力 (DRVOFF, INHx, INLx, nSLEEP, SCLK, SDI, OCP)

|           |                |                                  |     |      |               |                  |

|-----------|----------------|----------------------------------|-----|------|---------------|------------------|

| $V_{IL}$  | 入力ロジック Low 電圧  |                                  | 0   | 0.6  | V             |                  |

| $V_{IH}$  | 入力ロジック High 電圧 | $nSLEEP$                         | 1.6 | 5.5  | V             |                  |

|           |                | その他のピン                           | 1.5 | 5.5  | V             |                  |

| $V_{HYS}$ | 入力ロジック ヒステリシス  | $nSLEEP$                         | 95  | 300  | 425           | mV               |

|           |                | その他のピン                           | 180 | 300  | 425           | mV               |

| $I_{IL}$  | 入力ロジック Low 電流  | $V_{PIN}$ (ピン電圧) = 0V            | -1  | 1    | $\mu\text{A}$ |                  |

| $I_{IH}$  | 入力ロジック High 電流 | $nSLEEP$ , $V_{PIN}$ (ピン電圧) = 5V | 15  | 35   | $\mu\text{A}$ |                  |

| $I_{IH}$  | 入力ロジック High 電流 | その他のピン, $V_{PIN}$ (ピン電圧) = 5V    | 30  | 75   | $\mu\text{A}$ |                  |

| $R_{PD}$  | 入力プルダウン抵抗      | $nSLEEP$                         | 150 | 200  | 300           | $\text{k}\Omega$ |

|           |                | その他のピン                           | 70  | 100  | 130           | $\text{k}\Omega$ |

| $t_{GED}$ | グリッチ除去時間       | DRVOFF ピン                        | 0.6 | 1.15 | 1.7           | $\mu\text{s}$    |

| $C_{ID}$  | 入力容量           |                                  |     | 30   |               | pF               |

#### ロジック レベル入力 (nSCS)

|           |                |                       |     |     |               |                  |

|-----------|----------------|-----------------------|-----|-----|---------------|------------------|

| $V_{IL}$  | 入力ロジック Low 電圧  |                       | 0   | 0.6 | V             |                  |

| $V_{IH}$  | 入力ロジック High 電圧 |                       | 1.5 | 5.5 | V             |                  |

| $V_{HYS}$ | 入力ロジック ヒステリシス  |                       |     | 300 |               | mV               |

| $I_{IL}$  | 入力ロジック Low 電流  | $V_{PIN}$ (ピン電圧) = 0V |     | 75  | $\mu\text{A}$ |                  |

| $I_{IH}$  | 入力ロジック High 電流 | $V_{PIN}$ (ピン電圧) = 5V | -1  | 25  | $\mu\text{A}$ |                  |

| $R_{PU}$  | 入力プルアップ抵抗      |                       | 80  | 100 | 130           | $\text{k}\Omega$ |

| $C_{ID}$  | 入力容量           |                       |     | 30  |               | pF               |

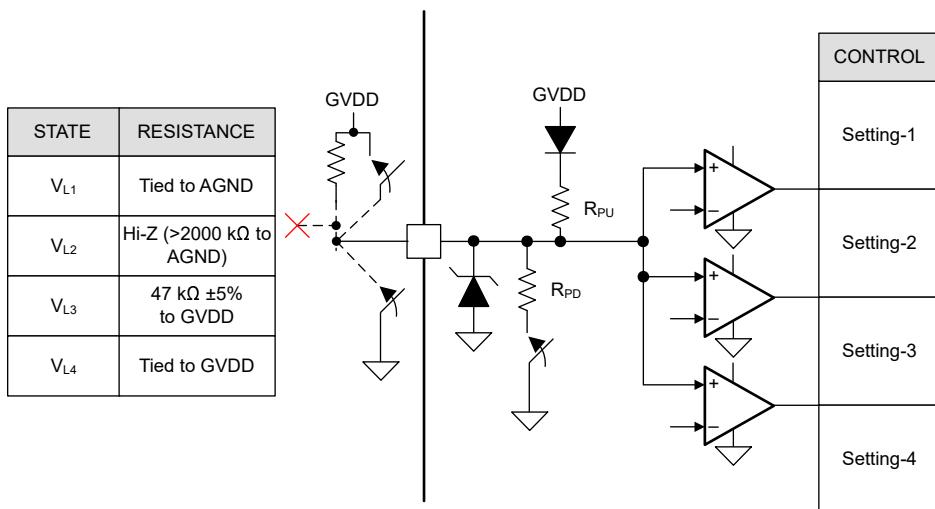

#### 4 レベル入力 (GAIN, MODE\_SR, SLEW)

|          |            |                                |           |           |           |                  |

|----------|------------|--------------------------------|-----------|-----------|-----------|------------------|

| $V_{L1}$ | 入力モード 1 電圧 | AGND に接続                       | 0         | 0.2*GVDD  | V         |                  |

| $V_{L2}$ | 入力モード 2 電圧 | ハイインピーダンス                      | 0.27*GVDD | 0.5*GVDD  | 0.55*GVDD | V                |

| $V_{L3}$ | 入力モード 3 電圧 | 47k $\Omega$ +/- 5% で GVDD に接続 | 0.6*GVDD  | 0.76*GVDD | 0.9*GVDD  | V                |

| $V_{L4}$ | 入力モード 4 電圧 | GVDD に接続                       | 0.94*GVDD |           | GVDD      | V                |

| $R_{PU}$ | 入力プルアップ抵抗  | 対 GVDD                         | 80        | 100       | 120       | $\text{k}\Omega$ |

| $R_{PD}$ | 入力プルダウン抵抗  | To AGND                        | 80        | 100       | 120       | $\text{k}\Omega$ |

#### オープンドレイン出力 (nFAULT)

|          |                |                       |    |     |               |  |

|----------|----------------|-----------------------|----|-----|---------------|--|

| $V_{OL}$ | 出力ロジック Low 電圧  | $I_{OD} = 5\text{mA}$ |    | 0.4 | V             |  |

| $I_{OH}$ | 出力ロジック High 電流 | $V_{OD} = 5\text{V}$  | -1 | 1   | $\mu\text{A}$ |  |

| $C_{OD}$ | 出力容量           |                       |    | 30  | pF            |  |

#### プッシュプル出力 (SDO)

|          |                   |                                                            |     |      |               |  |

|----------|-------------------|------------------------------------------------------------|-----|------|---------------|--|

| $V_{OL}$ | 出力ロジック Low 電圧     | $I_{OP} = 5\text{mA}$                                      | 0   | 0.4  | V             |  |

| $V_{OH}$ | ロジック High 出力電圧    | $I_{OP} = 5\text{mA}$ , SDO_VSEL = 0                       | 2.5 | AVDD | V             |  |

| $V_{OH}$ | ロジック High 出力電圧    | $I_{OP} = 5\text{mA}$ , SDO_VSEL = 1, $V_{VM} > 6\text{V}$ | 4   | GVDD | V             |  |

| $I_{OL}$ | 出力ロジック Low リーク電流  | $V_{OP} = 0\text{V}$                                       | -1  | 1    | $\mu\text{A}$ |  |

| $I_{OH}$ | 出力ロジック High リーク電流 | $V_{OP} = 5\text{V}$                                       | -1  | 1    | $\mu\text{A}$ |  |

$T_J = -40^\circ\text{C} \sim +150^\circ\text{C}$ ,  $V_{VM} = 4.5 \sim 65\text{V}$  (特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ ,  $V_{VM} = 24\text{V}$  が適用されます。

| パラメータ        |                                                         | テスト条件                                                                                                        | 最小値  | 標準値  | 最大値  | 単位   |

|--------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------|------|------|------|

| $C_{OD}$     | 出力容量                                                    |                                                                                                              |      | 30   | 30   | pF   |

| ドライバ出力       |                                                         |                                                                                                              |      |      |      |      |

| $R_{DS(ON)}$ | 全 MOSFET オン抵抗 (ハイサイド + ローサイド)                           | $V_{VM} > 6\text{V}$ , $I_{OUT} = 1\text{A}$ , $T_A = 25^\circ\text{C}$                                      | 400  | 505  | 505  | mΩ   |

|              |                                                         | $V_{VM} < 6\text{V}$ , $I_{OUT} = 1\text{A}$ , $T_A = 25^\circ\text{C}$                                      | 407  | 515  | 515  | mΩ   |

|              |                                                         | $V_{VM} > 6\text{V}$ , $I_{OUT} = 1\text{A}$ , $T_J = 150^\circ\text{C}$                                     | 690  | 790  | 790  | mΩ   |

|              |                                                         | $V_{VM} < 6\text{V}$ , $I_{OUT} = 1\text{A}$ , $T_J = 150^\circ\text{C}$                                     | 705  | 810  | 810  | mΩ   |

| SR           | Low から High へのスイッチング (20% から 80% への立ち上がり) 時の位相ピンのスルーレート | $V_{VM} = 24\text{V}$ , SLEW = 00b または SLEW ピンを AGND に接続、 $I_{OUTx} = 1\text{A}$                             | 630  | 1100 | 1760 | V/μs |

|              |                                                         | $V_{VM} = 24\text{V}$ , SLEW = 01b または SLEW ピンを ハイインピーダンスへ、 $I_{OUTx} = 1\text{A}$                           | 260  | 500  | 900  | V/μs |

|              |                                                         | $V_{VM} = 24\text{V}$ , SLEW = 10b または SLEW ピンを $47\text{k}\Omega$ +/- 5% で GVDD へ、 $I_{OUTx} = 1\text{A}$   | 135  | 250  | 455  | V/μs |

|              |                                                         | $V_{VM} = 24\text{V}$ , SLEW = 11b または SLEW ピンを GVDD に接続、 $I_{OUTx} = 1\text{A}$                             | 22   | 60   | 90   | V/μs |

| SR           | High から Low へのスイッチング (80% から 20% への立ち下がり) 時の位相ピンのスルーレート | $V_{VM} = 24\text{V}$ , SLEW = 00b または SLEW ピンを AGND に接続、 $I_{OUTx} = 1\text{A}$                             | 500  | 1100 | 1760 | V/μs |

|              |                                                         | $V_{VM} = 24\text{V}$ , SLEW = 01b または SLEW ピンを ハイインピーダンスへ、 $I_{OUTx} = 1\text{A}$                           | 240  | 500  | 845  | V/μs |

|              |                                                         | $V_{VM} = 24\text{V}$ , SLEW = 10b または SLEW ピンを $47\text{k}\Omega$ +/- 5% で GVDD へ、 $I_{OUTx} = 1\text{A}$   | 120  | 250  | 490  | V/μs |

|              |                                                         | $V_{VM} = 24\text{V}$ , SLEW = 11b または SLEW ピンを GVDD に接続、 $I_{OUTx} = 1\text{A}$                             | 30   | 50   | 85   | V/μs |

| $I_{LEAK}$   | OUTx のリーク電流                                             | $V_{OUTx} = V_{VM}$ , nSLEEP = 1                                                                             |      |      | 2    | mA   |

|              | OUTx のリーク電流                                             | $V_{OUTx} = 0\text{V}$ , nSLEEP = 1                                                                          |      |      | 1    | μA   |

| $t_{DEAD}$   | 出力デッドタイム (High から Low / Low から High)                    | $V_{VM} = 24\text{V}$ , SLEW = 00b または SLEW ピンを AGND に接続、HS ドライバ ON から LS ドライバ OFF                           | 65   | 150  | 150  | ns   |

|              |                                                         | $V_{VM} = 24\text{V}$ , SLEW = 01b または SLEW ピンを ハイインピーダンスへ、HS ドライバ ON から LS ドライバ OFF                         | 100  | 250  | 250  | ns   |

|              |                                                         | $V_{VM} = 24\text{V}$ , SLEW = 10b または SLEW ピンを $47\text{k}\Omega$ +/- 5% で GVDD へ、HS ドライバ ON から LS ドライバ OFF | 100  | 250  | 250  | ns   |

|              |                                                         | $V_{VM} = 24\text{V}$ , SLEW = 11b または SLEW ピンを GVDD に接続、HS ドライバ ON から LS ドライバ OFF                           | 250  | 550  | 550  | ns   |

| $t_{PD}$     | 伝搬遅延 (ハイサイド / ローサイド、オン/オフ)                              | $V_{VM} = 24\text{V}$ , INHx = 1 から OUTx 遷移、SLEW = 00b または SLEW ピンを AGND に接続                                 | 35   | 85   | 85   | ns   |

|              |                                                         | $V_{VM} = 24\text{V}$ , INHx = 1 から OUTx 遷移、SLEW = 01b または SLEW ピンを ハイインピーダンスへ                               | 40   | 100  | 100  | ns   |

|              |                                                         | $V_{VM} = 24\text{V}$ , INHx = 1 から OUTx 遷移、SLEW = 10b または SLEW ピンを $47\text{k}\Omega$ +/- 5% で GVDD へ       | 45   | 140  | 140  | ns   |

|              |                                                         | $V_{VM} = 24\text{V}$ , INHx = 1 から OUTx 遷移、SLEW = 11b または SLEW ピンを GVDD に接続                                 | 1200 | 1900 | 1900 | ns   |

$T_J = -40^\circ\text{C} \sim +150^\circ\text{C}$ ,  $V_{VM} = 4.5 \sim 65\text{V}$  (特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ ,  $V_{VM} = 24\text{V}$  が適用されます。

| パラメータ                |                                  | テスト条件                                                                                                 | 最小値    | 標準値 | 最大値         | 単位 |

|----------------------|----------------------------------|-------------------------------------------------------------------------------------------------------|--------|-----|-------------|----|

| $t_{MIN\_PULSE}$     | 最小出力パルス幅                         | SLEW = 00b または SLEW ピンを AGND に接続                                                                      | 110    |     | ns          |    |

| <b>電流検出アンプ</b>       |                                  |                                                                                                       |        |     |             |    |

| $G_{CSA}$            | 電流センス ゲイン (SPI デバイス)             | CSA_GAIN = 00                                                                                         | 0.4    |     | V/A         |    |

| $G_{CSA}$            | 電流センス ゲイン (SPI デバイス)             | CSA_GAIN = 01                                                                                         | 1      |     | V/A         |    |

| $G_{CSA}$            | 電流センス ゲイン (SPI デバイス)             | CSA_GAIN = 02                                                                                         | 2.5    |     | V/A         |    |

| $G_{CSA}$            | 電流センス ゲイン (SPI デバイス)             | CSA_GAIN = 03                                                                                         | 5      |     | V/A         |    |

| $G_{CSA}$            | 電流センス ゲイン (HW デバイス)              | GAIN ピンを AGND に接続                                                                                     | 0.4    |     | V/A         |    |

| $G_{CSA}$            | 電流センス ゲイン (HW デバイス)              | GAIN ピンを ハイインピーダンスへ                                                                                   | 1      |     | V/A         |    |

| $G_{CSA}$            | 電流センス ゲイン (HW デバイス)              | GAIN ピンを $47\text{k}\Omega \pm 5\%$ で GVDD へ                                                          | 2.5    |     | V/A         |    |

| $G_{CSA}$            | 電流センス ゲイン (HW デバイス)              | GAIN ピンを GVDD に接続                                                                                     | 5      |     | V/A         |    |

| $G_{CSA\_ERR}$       | 電流センス ゲイン誤差                      | $T_J = 25^\circ\text{C}$ , $0\text{A} \leq \text{LS FET 電流} \leq 2.5\text{A}$ (OUTx から PGND への電流方向)   | -4     |     | 4           |    |

|                      |                                  | $T_J = 25^\circ\text{C}$ , $2.5\text{A} \leq \text{LS FET 電流} \leq 3.5\text{A}$ (OUTx から PGND への電流方向) | -5     |     | 5           |    |

|                      |                                  | $0\text{A} \leq \text{LS FET 電流} \leq 2.5\text{A}$ (OUTx から PGND への電流方向)                              | -5     |     | 5           |    |

|                      |                                  | $2.5\text{A} \leq \text{LS FET 電流} \leq 3.5\text{A}$ , (OUTx から PGND への電流の方向)                         | -5     |     | 8.7         |    |

| $G_{CSA\_ERR}$       | 電流センス ゲイン誤差                      | $T_J = 25^\circ\text{C}$ , $0\text{A} \leq \text{LS FET 電流} \leq 2\text{A}$ (PGND から OUTx への電流の方向)    | -4     |     | 4           |    |

| $G_{CSA\_ERR}$       | 電流センス ゲイン誤差                      | $0\text{A} \leq \text{LS FET 電流} \leq 2\text{A}$ (PGND から OUTx への電流の方向)                               | -6     |     | 6           |    |

| $I_{MATCH}$          | A 相、B 相、C 相の間での電流センス ゲイン誤差のマッチング | $T_A = 25^\circ\text{C}$                                                                              | -5     |     | 5           |    |

|                      |                                  |                                                                                                       | -5     |     | 5           |    |

| $FS_{POS}$           | フルスケールの正の電流測定                    | LS FET での PGND から OUTx への電流の方向, VREF = 3.3V                                                           | 2      |     | A           |    |

| $FS_{NEG}$           | フルスケールの負の電流測定                    | LS FET での OUTx から PGND への電流の方向, VREF = 3.3V                                                           | -3.5   |     | A           |    |

| $V_{LINEAR}$         | SOx 出力電圧のリニア動作範囲                 |                                                                                                       | 0.25   |     | VREF-0.25   |    |

| $I_{OFFSET}$         | 電流センス オフセット                      | $T_J = 25^\circ\text{C}$ , 相電流 = 0A, VREF $\leq 3.6\text{V}$                                          | -20    |     | -10         |    |

| $I_{OFFSET}$         | 電流センス オフセット                      | $T_J = 25^\circ\text{C}$ , 相電流 = 0A, $3.6\text{V} \leq \text{VREF} \leq 5.5\text{V}$                  | -20    |     | -10         |    |

| $t_{SET}$            | $\pm 1\%$ までのセトリング タイム, 30 pF    | SOX のステップ = 1.2V                                                                                      | 1.2    |     | μs          |    |

| $t_{CSA\_ON\_DELAY}$ | INLx ターンオンから電流センス アンプがオンになるまでの遅延 | SR = $1000\text{V}/\mu\text{s}$ または $500\text{V}/\mu\text{s}$ または $250\text{V}/\mu\text{s}$           | 500    |     | 700         |    |

| $t_{CSA\_ON\_DELAY}$ | INLx ターンオンから電流センス アンプがオンになるまでの遅延 | SR = $50\text{V}/\mu\text{s}$                                                                         | 4300   |     | 5000        |    |

| $I_{DRIFT}$          | オフセットドリフト                        | 相電流 = 0A                                                                                              | -60    |     | 60          |    |

| $I_{VREF}$           | VREF 入力電流                        | VREF = 3.0V, nSLEEP = 0 または 1                                                                         | 15     |     | μA          |    |

| <b>パルス単位の電流制限</b>    |                                  |                                                                                                       |        |     |             |    |

| $V_{LIM}$            | サイクル単位の電流制限の ILIMIT ピンの電圧        |                                                                                                       | VREF/2 |     | VREF - 0.25 |    |

| $V_{LIM\_DIS}$       | サイクル電流制限の無効化における ILIMIT ピンの電圧    |                                                                                                       | VREF   |     | GVDD        |    |

$T_J = -40^\circ\text{C} \sim +150^\circ\text{C}$ ,  $V_{VM} = 4.5 \sim 65\text{V}$  (特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ ,  $V_{VM} = 24\text{V}$  が適用されます。

| パラメータ               |                             | テスト条件                                                                                              | 最小値  | 標準値  | 最大値  | 単位            |

|---------------------|-----------------------------|----------------------------------------------------------------------------------------------------|------|------|------|---------------|

| $I_{LIMIT}$         | VLIM ピンの電圧範囲に対応する電流制限       |                                                                                                    | 0    | 4    | 4    | A             |

| $I_{LIM\_AC}$       | 電流制限精度                      | $V_{REF} = 3.3\text{V}$ , $I_{LIMIT} > 1\text{A}$                                                  | -6   | 6    | 6    | %             |

| $I_{LIM\_AC}$       | 電流制限精度                      | $V_{REF} = 3.3\text{V}$ , $0.5\text{A} < I_{LIMIT} < 1\text{A}$                                    | -10  | 10   | 10   | %             |

| $t_{BLANK}$         | サイクル単位の電流制限ブランク時間           | $SLEW = 00\text{b}$ または $01\text{b}$ または $10\text{b}$ , $ILIM\_BLANK\_SEL = 00\text{b}$ , HW バリエント |      | 1.75 | 1.75 | $\mu\text{s}$ |

| $t_{BLANK}$         | サイクル単位の電流制限ブランク時間           | $SLEW = 00\text{b}$ または $01\text{b}$ または $10\text{b}$ , $ILIM\_BLANK\_SEL = 01\text{b}$            |      | 2.25 | 2.25 | $\mu\text{s}$ |

| $t_{BLANK}$         | サイクル単位の電流制限ブランク時間           | $SLEW = 00\text{b}$ または $01\text{b}$ または $10\text{b}$ , $ILIM\_BLANK\_SEL = 10\text{b}$            |      | 2.75 | 2.75 | $\mu\text{s}$ |

| $t_{BLANK}$         | サイクル単位の電流制限ブランク時間           | $SLEW = 00\text{b}$ または $01\text{b}$ または $10\text{b}$ , $ILIM\_BLANK\_SEL = 11\text{b}$            |      | 3.75 | 3.75 | $\mu\text{s}$ |

| $t_{BLANK}$         | サイクル単位の電流制限ブランク時間           | $SLEW = 11\text{b}$ , $ILIM\_BLANK\_SEL = 00\text{b}$ , HW バリエント                                   |      | 5.5  | 5.5  | $\mu\text{s}$ |

| $t_{BLANK}$         | サイクル単位の電流制限ブランク時間           | $SLEW = 11\text{b}$ , $ILIM\_BLANK\_SEL = 01\text{b}$                                              |      | 6    | 6    | $\mu\text{s}$ |

| $t_{BLANK}$         | サイクル単位の電流制限ブランク時間           | $SLEW = 11\text{b}$ , $ILIM\_BLANK\_SEL = 10\text{b}$                                              |      | 6.5  | 6.5  | $\mu\text{s}$ |

| $t_{BLANK}$         | サイクル単位の電流制限ブランク時間           | $SLEW = 11\text{b}$ , $ILIM\_BLANK\_SEL = 11\text{b}$                                              |      | 7.5  | 7.5  | $\mu\text{s}$ |

| 保護回路                |                             |                                                                                                    |      |      |      |               |

| $V_{UVLO}$          | 電源低電圧誤動作防止 (UVLO)           | VM 立ち上がり                                                                                           | 4.2  | 4.35 | 4.5  | V             |

|                     |                             | VM 立ち下がり                                                                                           | 4.0  | 4.15 | 4.3  | V             |

| $V_{UVLO\_HYS}$     | 電源低電圧誤動作防止ヒステリシス            | 立ち上がりから立ち下がりへのスレッショルド                                                                              | 65   | 200  | 415  | mV            |

| $t_{UVLO}$          | 電源低電圧グリッヂ除去時間               |                                                                                                    | 3    | 6    | 10   | $\mu\text{s}$ |

| $V_{OVP}$           | 電源過電圧保護 (OVP)<br>(SPI デバイス) | 電源立ち上がり、 $OVP\_EN = 1$ , $OVP\_SEL = 0$                                                            | 60   | 62.5 | 65   | V             |

|                     |                             | 電源立ち下がり、 $OVP\_EN = 1$ , $OVP\_SEL = 0$                                                            | 58   | 61   | 63.5 | V             |

|                     |                             | 電源立ち上がり、 $OVP\_EN = 1$ , $OVP\_SEL = 1$                                                            | 32.5 | 34   | 35   | V             |

|                     |                             | 電源立ち下がり、 $OVP\_EN = 1$ , $OVP\_SEL = 1$                                                            | 32   | 33   | 34   | V             |

| $V_{OVP\_HYS}$      | 電源過電圧保護 (OVP)<br>(SPI デバイス) | 立ち上がりから立ち下がりまでのスレッショルド, $OVP\_SEL = 1$                                                             | 0.74 | 0.8  | 0.85 | V             |

|                     |                             | 立ち上がりから立ち下がりまでのスレッショルド, $OVP\_SEL = 0$                                                             | 1.35 | 1.45 | 1.55 | V             |

| $t_{OVP}$           | 電源過電圧グリッヂ除去時間               |                                                                                                    | 2.5  | 6.5  | 12   | $\mu\text{s}$ |

| $V_{CPUV}$          | チャージポンプ低電圧誤動作防止 (VM より上)    | 電源立ち上がり                                                                                            | 2.1  | 2.7  | 3.2  | V             |

|                     |                             | 電源立ち下がり                                                                                            | 1.8  | 2.45 | 2.95 | V             |

| $V_{CPUV\_HYS}$     | チャージポンプ UVLO のヒステリシス        | 立ち上がりから立ち下がりへのスレッショルド                                                                              | 105  | 150  | 200  | mV            |

| $V_{AVDD\_UV}$      | アナログ レギュレータ低電圧誤動作防止         | 電源立ち上がり                                                                                            | 2.7  | 2.85 | 3    | V             |

|                     |                             | 電源立ち下がり                                                                                            | 2.5  | 2.65 | 2.8  | V             |

| $V_{AVDD\_UV\_HYS}$ | アナログ レギュレータ低電圧誤動作防止のヒステリシス  | 立ち上がりから立ち下がりへのスレッショルド                                                                              | 180  | 200  | 240  | mV            |

| $V_{GVDD\_UV}$      | GVDD レギュレータ低電圧誤動作防止         | 電源立ち上がり                                                                                            | 3.1  | 3.3  | 3.5  | V             |

| $V_{GVDD\_UV}$      | GVDD レギュレータ低電圧誤動作防止         | 電源立ち下がり                                                                                            | 2.9  | 3.1  | 3.3  | V             |

| $V_{GVDD\_UV\_HYS}$ | アナログ レギュレータ低電圧誤動作防止のヒステリシス  | 立ち上がりから立ち下がりへのスレッショルド                                                                              | 145  | 190  | 265  | mV            |

| $I_{OCP}$           | 過電流保護トリップポイント (SPI デバイス)    | $OCP\_LVL = 00\text{b}$ または $01\text{b}$                                                           | 4.5  | 9    | 9    | A             |

$T_J = -40^\circ\text{C} \sim +150^\circ\text{C}$ ,  $V_{VM} = 4.5 \sim 65\text{V}$  (特に記述のない限り)。標準値には  $T_A = 25^\circ\text{C}$ ,  $V_{VM} = 24\text{V}$  が適用されます。

| パラメータ          |                           | テスト条件                                    | 最小値 | 標準値  | 最大値 | 単位               |

|----------------|---------------------------|------------------------------------------|-----|------|-----|------------------|

| $I_{OCP}$      | 過電流保護トリップ ポイント (SPI デバイス) | $OCP\_LVL = 10\text{b}$ または $11\text{b}$ | 2.5 | 5    | A   |                  |

| $I_{OCP}$      | 過電流保護トリップ ポイント (HW デバイス)  | OCP ピンを AGND に接続または OCP ピンをハイインピーダンスに設定  | 4.5 | 9    | A   |                  |

| $I_{OCP}$      | 過電流保護トリップ ポイント (HW デバイス)  | OCP を GVDD に接続                           | 2.5 | 5    | A   |                  |

| $t_{OCP}$      | 過電流保護グリッチ除去時間 (SPI デバイス)  | $OCP\_DEG = 00\text{b}$                  | 0.2 | 0.6  | 1.2 | $\mu\text{s}$    |

|                |                           | $OCP\_DEG = 01\text{b}$                  | 0.6 | 1.25 | 1.8 | $\mu\text{s}$    |

|                |                           | $OCP\_DEG = 10\text{b}$                  | 1   | 1.6  | 2.5 | $\mu\text{s}$    |

|                |                           | $OCP\_DEG = 11\text{b}$                  | 1.4 | 2    | 3   | $\mu\text{s}$    |

| $t_{RETRY}$    | 過電流保護グリッチ除去時間 (SPI デバイス)  | $OCP\_RETRY = 0$                         | 4   | 5    | 6   | ms               |

|                |                           | $OCP\_RETRY = 1$                         | 425 | 500  | 575 | ms               |

| $t_{RETRY}$    | 過電流保護グリッチ除去時間 (HW デバイス)   |                                          | 4   | 5    | 6   | ms               |

| $T_{OTW}$      | 過熱警告温度                    | ダイ温度 ( $T_J$ )                           | 160 | 170  | 180 | $^\circ\text{C}$ |

| $T_{OTW\_HYS}$ | 過熱警告ヒステリシス                | ダイ温度 ( $T_J$ )                           | 25  | 30   | 35  | $^\circ\text{C}$ |

| $T_{TSD}$      | サーマル シャットダウン温度            | ダイ温度 ( $T_J$ )                           | 175 | 185  | 195 | $^\circ\text{C}$ |

| $T_{TSD\_HYS}$ | サーマル シャットダウン ヒステリシス       | ダイ温度 ( $T_J$ )                           | 25  | 30   | 35  | $^\circ\text{C}$ |

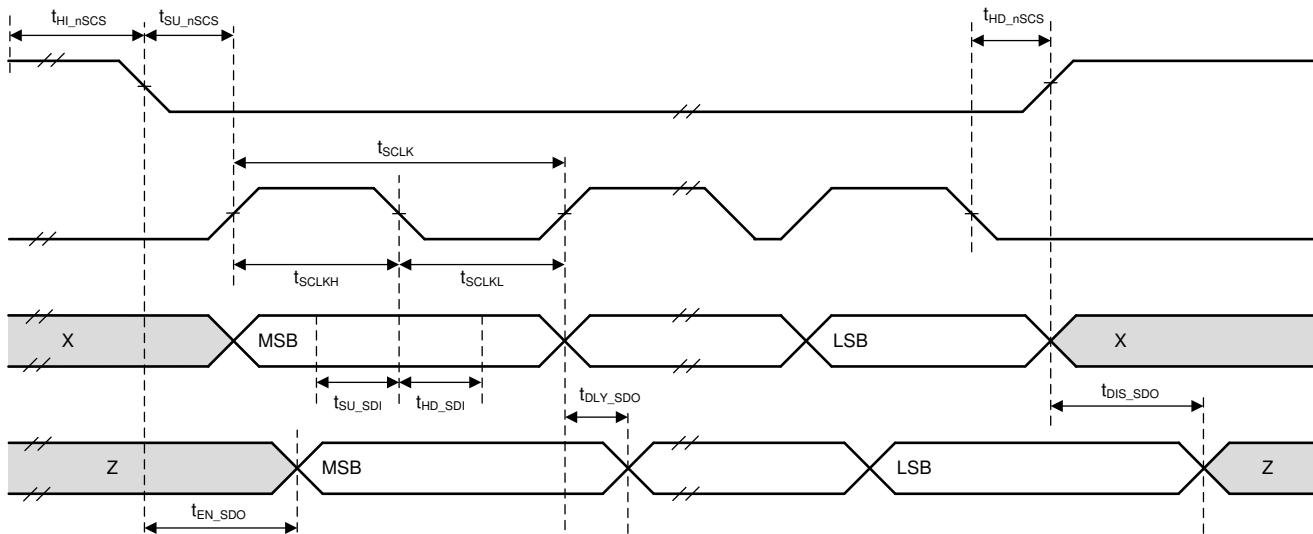

## 6.6 SPI のタイミング要件

|                |                    | 最小値 | 公称値 | 最大値 | 単位 |

|----------------|--------------------|-----|-----|-----|----|

| $t_{READY}$    | パワーアップ後、SPI レディまで  |     |     | 1   | ms |

| $t_{HI\_nSCS}$ | nSCS 最小 HIGH 時間    | 400 |     |     | ns |

| $t_{SU\_nSCS}$ | nSCS 入力セットアップ時間    | 25  |     |     | ns |

| $t_{HD\_nSCS}$ | nSCS 入力ホールド時間      | 25  |     |     | ns |

| $t_{SCLK}$     | SCLK の最小周期         | 100 |     |     | ns |

| $t_{SCLKH}$    | SCLK 最小 High 時間    | 50  |     |     | ns |

| $t_{SCLKL}$    | SCLK の最小 Low 時間    | 50  |     |     | ns |

| $t_{SU\_SDI}$  | SDI 入力データ セットアップ時間 | 25  |     |     | ns |

| $t_{HD\_SDI}$  | SDI 入力データ ホールド時間   | 25  |     |     | ns |

| $t_{DLY\_SDO}$ | SDO 出力データ遅延時間      |     |     | 25  | ns |

| $t_{EN\_SDO}$  | SDO イネーブル遅延時間      |     |     | 50  | ns |

| $t_{DIS\_SDO}$ | SDO ディスエーブル遅延時間    |     |     | 50  | ns |

## 6.7 SPI スレーブ モードのタイミング

図 6-1. SPI セカンダリ モードのタイミング

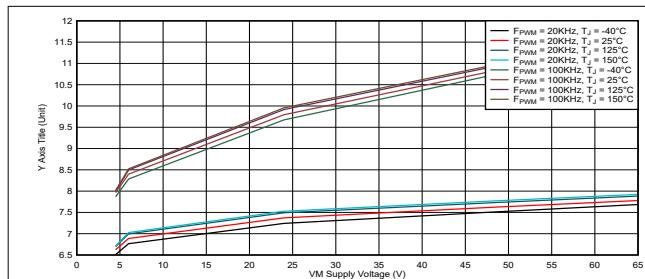

## 6.8 代表的特性

図 6-2. 電源電圧に対する電源電流

図 6-3. MOSFET の過熱の  $R_{DS(ON)}$  (ハイサイドとローサイドの合計)

## 7 詳細説明

### 7.1 概要

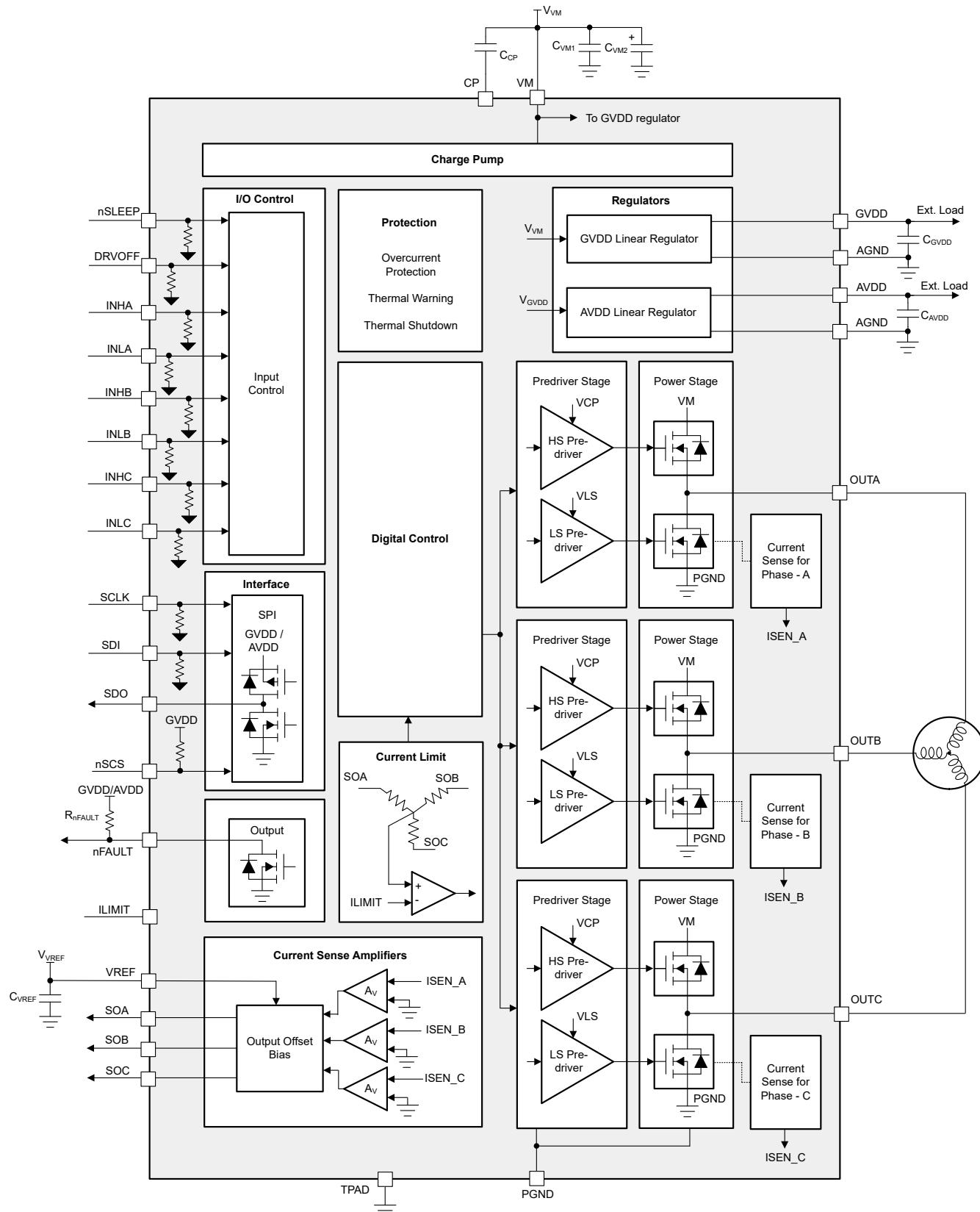

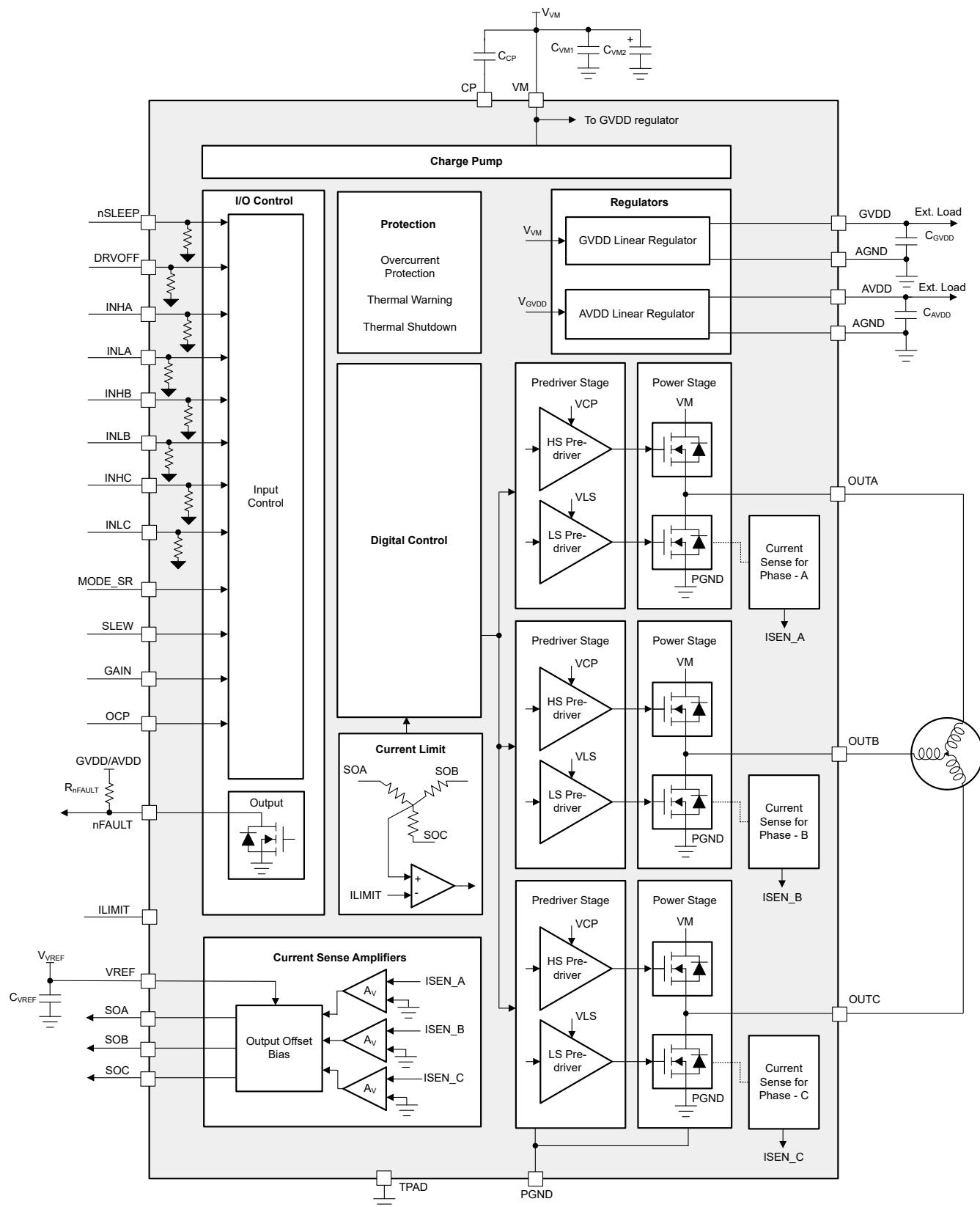

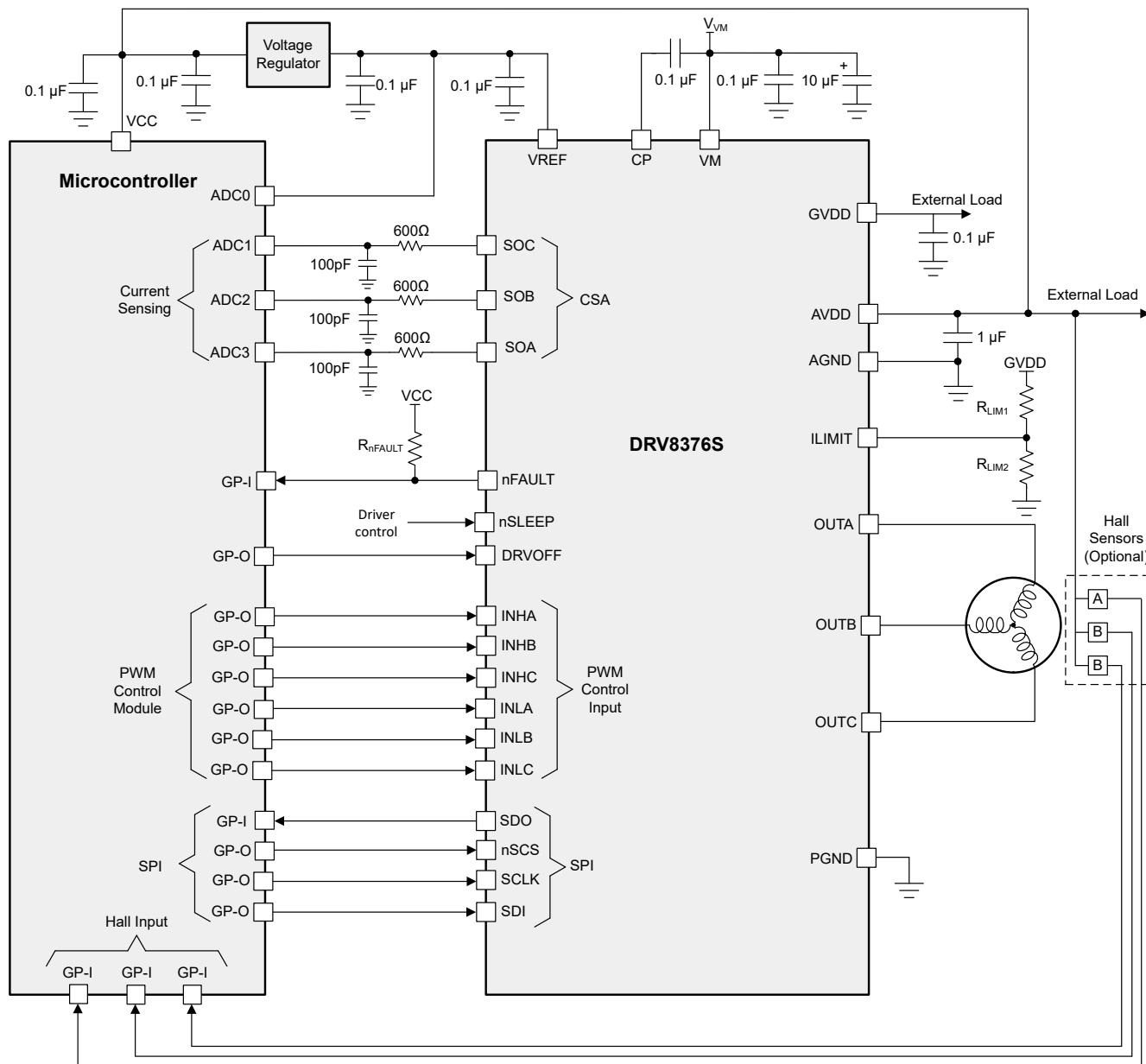

DRV8376 デバイスは、3 相モータ ドライバ アプリケーション向けの  $400\text{m}\Omega$  (ハイサイド + ローサイド MOSFET オン抵抗の合計) 統合型ドライバです。このデバイスは、3 つのハーフ ブリッジ MOSFET、ゲート ドライバ、チャージ ポンプ、電流センス アンプ、外部負荷用リニア レギュレータを統合することで、システムの部品点数、コスト、複雑さを低減しています。標準のシリアル ペリフェラル インターフェイス (SPI) を使うと、デバイスの各種設定とフォルト診断情報の読み出しを外部コントローラから簡単にできます。また、ハードウェア インターフェイス (H/W) オプションを選択した場合、固定の外部抵抗を使用して、ごく一般的な設定を行うことができます。

このアーキテクチャでは、短絡イベントや内部パワー MOSFET の  $dv/dt$  寄生ターンオンから保護するために、内部ストート マシンを使用しています。

DRV8376 デバイスには、内蔵の電流センスを使用して各ローサイド MOSFET を流れる電流を監視するための 3 つの双方向電流センス アンプが統合されています。電流センス アンプのゲイン設定は、SPI またはハードウェア インターフェイスを介して調整できます。

高いレベルでデバイスが統合されていることに加え、DRV8376 デバイスには、広範な保護機能も組み込まれています。これらの機能には、電源の低電圧誤動作防止 (UVLO)、チャージ ポンプの低電圧誤動作防止 (CPUV)、過電流保護 (OCP)、AVDD と GVDD 低電圧誤動作防止 (AVDD\_UV, GVDD\_UV)、および過熱警告シャットダウン (OTW と OTSD) などが含まれます。フォルト イベントは nFAULT ピンにより通知され、SPI 版のデバイスでは SPI レジスタで詳細情報を取得できます。

DRV8376 デバイスは、VQFN 表面実装パッケージで提供されています。この VQFN パッケージのサイズは  $6\text{mm} \times 5\text{mm}$  です。

## 7.2 機能ブロック図

図 7-1 DRV8376S のブロック図

図 7-2. DRV8376H のブロック図

## 7.3 機能説明

表 7-1 に、ドライバの外付け部品の推奨値を示します。

**表 7-1. DRV8376 の外付け部品**

| 部品            | ピン 1      | ピン 2          | 推奨                                                                  |

|---------------|-----------|---------------|---------------------------------------------------------------------|

| $C_{VM1}$     | VM        | PGND          | X5R または X7R、0.1 $\mu$ F。コンデンサの電圧定格を、本デバイスの通常動作電圧の 2 倍以上とすることを推奨します。 |

| $C_{VM2}$     | VM        | PGND          | $\geq 10\mu$ F。コンデンサの電圧定格を、本デバイスの通常動作電圧の 2 倍以上とすることを推奨します。          |

| $C_{CP}$      | CP        | VM            | X5R または X7R、16V、0.1 $\mu$ F コンデンサ                                   |

| $C_{GVDD}$    | GVDD      | AGND          | X5R または X7R、1 $\mu$ F、 $\geq 10V$                                   |

| $C_{AVDD}$    | AVDD      | AGND          | X5R または X7R、0.1 $\mu$ F、 $\geq 6.3V$                                |

| $R_{nFAULT}$  | AVDD/GVDD | nFAULT        | 5.1k $\Omega$ 、プルアップ抵抗                                              |

| $R_{MODE_SR}$ | MODE_SR   | AGND または GVDD | DRV8376H ハードウェア インターフェイス                                            |

| $R_{SLEW}$    | SLEW      | AGND または GVDD | DRV8376H ハードウェア インターフェイス                                            |

| $R_{OCP}$     | OCP       | AGND または GVDD | DRV8376H ハードウェア インターフェイス                                            |

| $R_{GAIN}$    | ゲイン       | AGND または GVDD | DRV8376H ハードウェア インターフェイス                                            |

| $C_{VREF}$    | VREF      | AGND          | X5R または X7R、0.1 $\mu$ F、VREF 定格コンデンサ (オプション)                        |

### 注

nFAULT が使われない場合でも、内部テスト モードへの望ましくない移行を避けるため、nFAULT にプルアップを接続することを TI は推奨しています。外部電源を使用して nFAULT をプルアップする場合は、パワーアップ時に nFAULT が  $>2.2V$  にプルされていることを確認します。

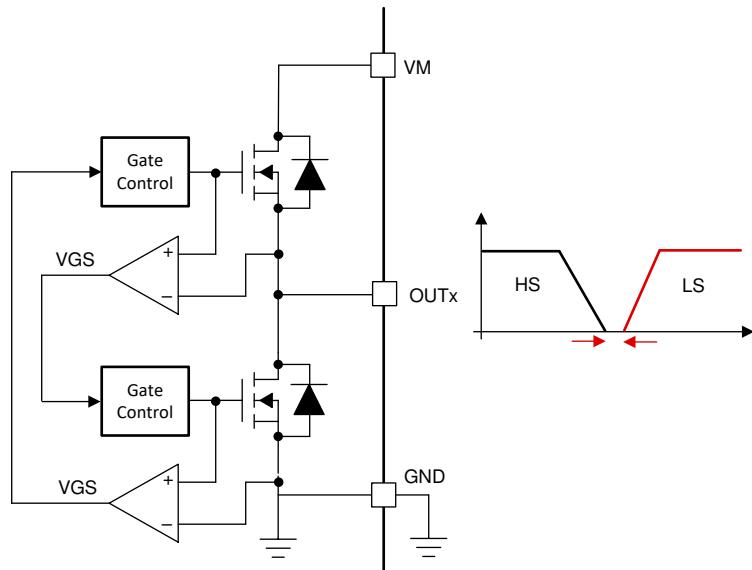

### 7.3.1 出力段

DRV8376-Q1 デバイスは、3 相ブリッジ構成で接続された統合型 400m $\Omega$  (ハイサイドとローサイドの各 FET のオン抵抗の合計) の NMOS FET で構成されています。ダブル チャージ ポンプが、100% のデューティ サイクルをサポートしつつ、広い動作電圧範囲にわたって適切なゲート バイアス電圧をハイサイド NMOS FET に供給します。ローサイド MOSFET 用のゲート バイアス電圧は、内部リニア レギュレータが供給します。

### 7.3.2 制御モード

DRV8376 ファミリのデバイスには、さまざまな整流方式や制御方式をサポートするために、4 種類の制御モードが用意されています。表 7-2 に、DRV8376 デバイスのさまざまなモードが示されています。

**表 7-2. PWM 制御モード**

| MODE のタイプ | MODE_SR ピン (ハードウェア バリアント) | PWM_MODE ビット (SPI バリアント) | SR ビット (SPI バリアント)        | PWM モード | ASR および AAR モード   |

|-----------|---------------------------|--------------------------|---------------------------|---------|-------------------|

| モード 1     | AGND に接続                  | PWM_MODE = 00b           | EN_ASR = 0、<br>EN_AAR = 0 | 6x モード  | ASR および AAR は無効化  |

| モード 2     | ハイインピーダンス                 | PWM_MODE = 01b           | EN_ASR = 1、<br>EN_AAR = 0 | 6x モード  | ASR は有効化、AAR は無効化 |

| モード 3     | $R_{MODE}$ で GVDD に接続     | PWM_MODE = 10b           | EN_ASR = 0、<br>EN_AAR = 0 | 3x モード  | ASR および AAR は無効化  |

| モード 4     | GVDD に接続                  | PWM_MODE = 11b           | EN_ASR = 1、<br>EN_AAR = 0 | 3x モード  | ASR は有効化、AAR は無効化 |

注

MODE\_SR ピンは検出され、または PWM\_MODE レジスタはパワーアップ中のみ読み出されます。そして、本デバイスは動作中の MODE\_SR/PWM\_MODE の変更をサポートしていません。

**7.3.2.1 6x PWM モード (PWM\_MODE = 00b または 01b または MODE\_SR ピンを AGND またはハイインピーダンスに接続)**

6x PWM モードでは、ハーフブリッジごとに Low、High、ハイインピーダンス(Hi-Z)の3つの出力状態がサポートされます。表 7-3 に示すように、対応する INLx および INHx 信号で出力状態を制御します。

表 7-3. 6x PWM モードの真理値表

| INLx | INHx | PHASEx    |

|------|------|-----------|

| 0    | 0    | ハイインピーダンス |

| 0    | 1    | H         |

| 1    | 0    | L         |

| 1    | 1    | ハイインピーダンス |

図 7-3 には、6x PWM モードで構成された DRV8376 のアプリケーション図が示されています。

図 7-3. 6x PWM モード

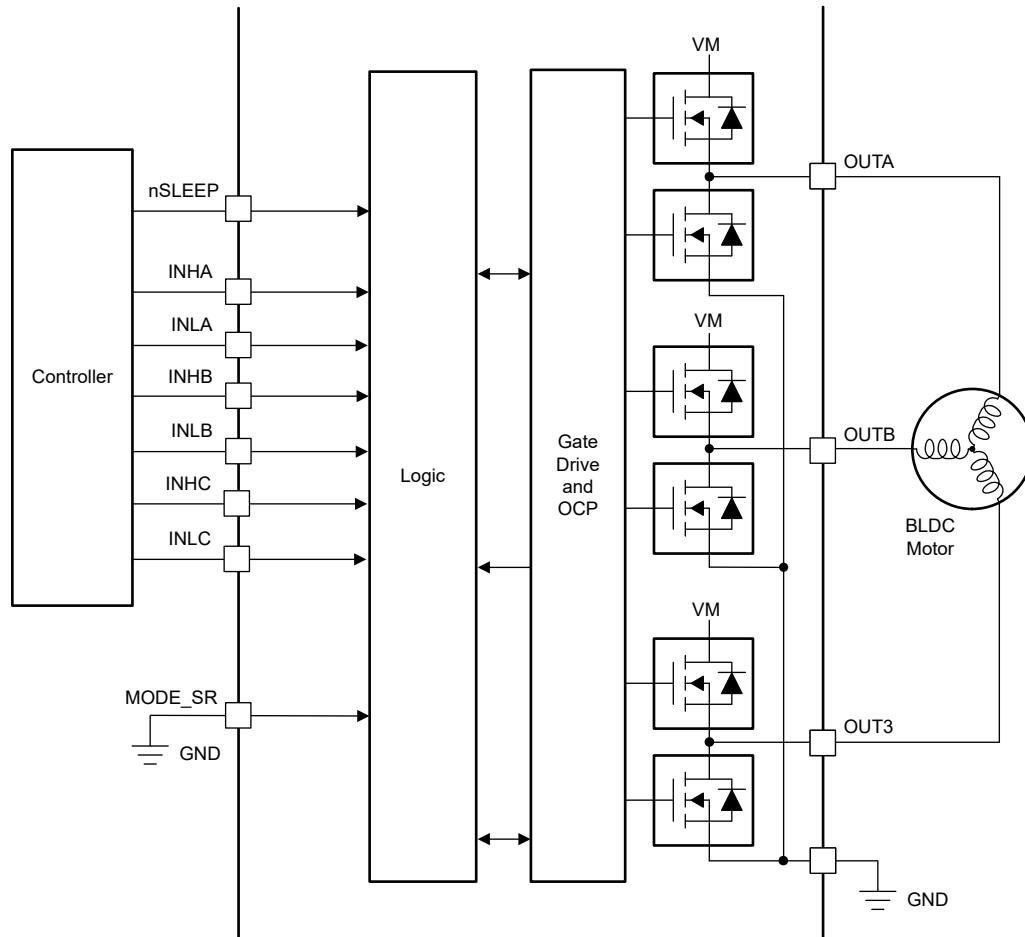

### 7.3.2.2 3x PWM モード (PWM\_MODE = 10b または 11b または MODE\_SR ピンを GVDD または R\_MODE で GVDD に接続)

この 3x PWM モードでは、INHx ピンで各ハーフブリッジを制御し、Low または High の 2 つの出力状態がサポートされます。INLx ピンは、ハーフブリッジをハイインピーダンス状態にするために使用します。ハイインピーダンス状態にする必要がない場合は、すべての INLx ピンをロジック High に固定してください。表 7-4 に示すように、対応する INHx および INLx 信号で出力状態を制御します。

表 7-4. 3x PWM モードの真理値表

| INLx | INHx | PHASEx    |

|------|------|-----------|

| 0    | X    | ハイインピーダンス |

| 1    | 0    | L         |

| 1    | 1    | H         |

図 7-4 には、3x PWM モードで構成された DRV8376 のアプリケーション図が示されています。

図 7-4. 3x PWM モード

### 7.3.3 デバイスインターフェイスモード

DRV8376-Q1 ファミリのデバイスでは、最終的なアプリケーションを柔軟な設計にするか単純な設計にするか選択できるように、2 種類のインターフェイスモード (SPI とハードウェア) をサポートしています。2 つのインターフェイスモードで同じ 4 つのピンが共有されているので、異なるバージョン間でのピン互換が実現します。こうした互換性の高さから、アプリケーション設計者は、設計に最小限の変更を加えるだけで、評価に使用するインターフェイスバージョンを切り替えることができます。

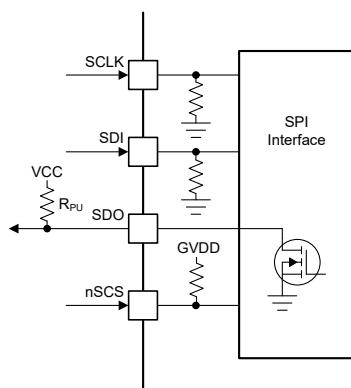

### 7.3.3.1 シリアル・ペリフェラル・インターフェイス (SPI)

SPI デバイスは、外部コントローラと DRV8376-Q1 の間でデータを送受信できるシリアル通信バスをサポートしています。これにより、外部コントローラはデバイスを設定し、詳細なフォルト情報を読み出すことができます。インターフェイスは、SCLK、SDI、SDO、nSCS ピンを使用する 4 線式インターフェイスです。以下の説明をご覧ください。

- SCLK ピンは、クロック信号を受け付けて SDI と SDO ピン上のデータの収集と伝搬のタイミングを決める入力ピンです。

- SDI ピンはデータ入力です。

- SDO ピンはデータ出力です。SDO ピンは、SDO\_MODE を通してオープンドレインまたはプッシュプルに構成できます。

- nSCS ピンはチップ選択入力です。このピンに論理 Low 信号を印加すると、SPI 通信がイネーブルになります。

SPI の詳細については、[セクション 7.5](#) を参照してください。

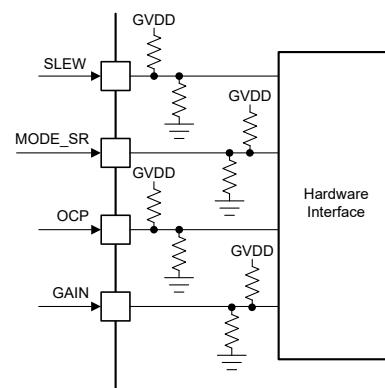

### 7.3.3.2 ハードウェア インターフェイス

ハードウェア インターフェイス デバイスでは、4 つの SPI ピンが抵抗によって設定可能な 4 つの入力、GAIN、SLEW、MODE\_SR、OCP に変換されます。

ハードウェア インターフェイスを使用すると、アプリケーション設計者は、ピンをロジック High またはロジック Low に接続するか、単純なプルアップまたはプルダウン抵抗を使用して、最も一般的なデバイスを構成できます。外部コントローラには SPI バスが不要になります。全般的なフォルト情報は、引き続き nFAULT ピンを介して取得できます。

- GAIN ピンでは電流センスアンプのゲインを設定します。

- SLEW ピンでは出力電圧のスルーレートを設定します。

- MODE\_SR では PWM 制御モードを設定します。

- OCP ピンは、OCP レベルの設定に使用されます。

ハードウェア インターフェイスの詳細については、[セクション 7.3.9](#) を参照してください。

図 7-5. DRV8376S SPI

図 7-6. DRV8376H ハードウェア インターフェイス

注

VCC は外部プルアップ電圧

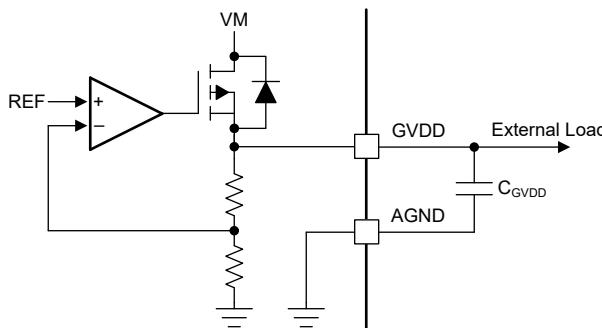

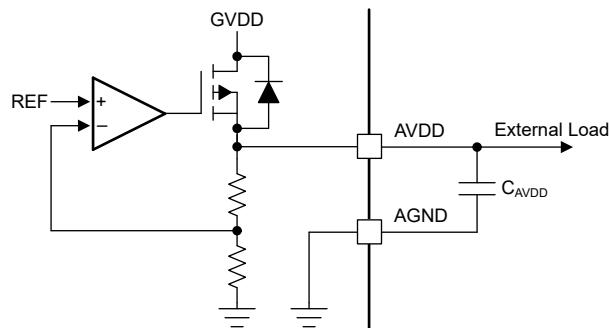

### 7.3.4 AVDD および GVDD リニア電圧レギュレータ

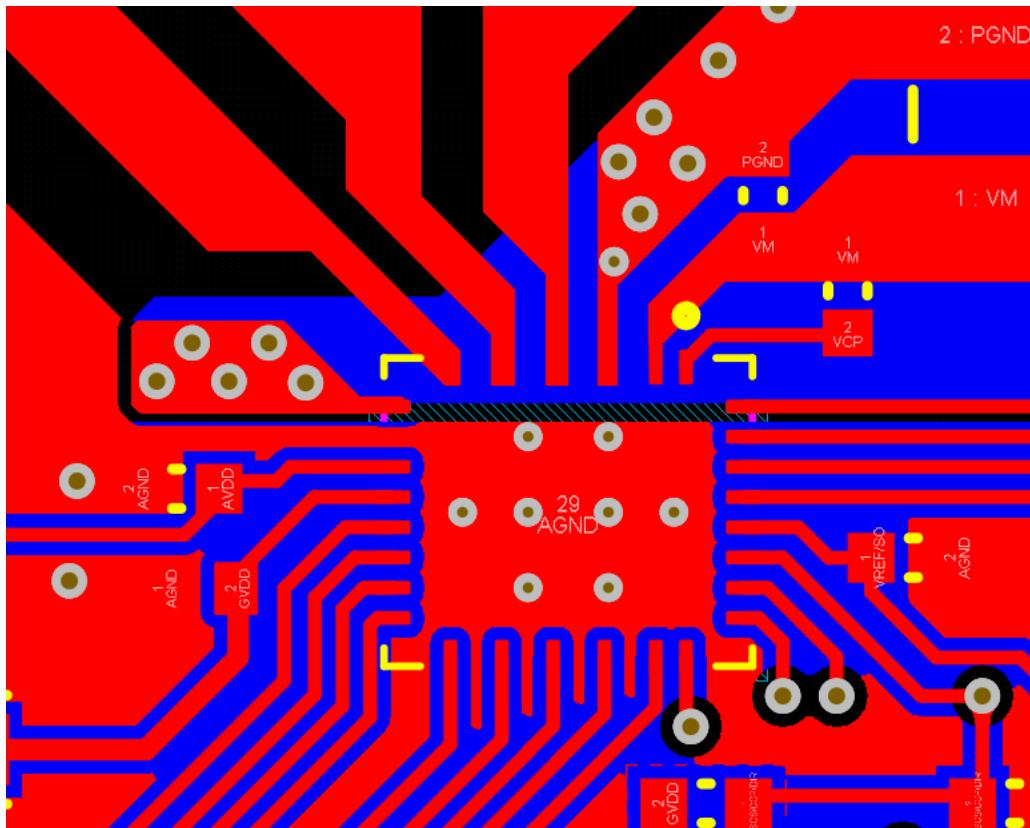

DRV8376 デバイス ファミリは、DRV83763.3V および 5V リニア レギュレータを内蔵しており、外部回路で利用できます。AVDD および GVDD レギュレータは、デバイスの内部デジタル回路に電力を供給します。また、低消費電力マイコンや他の低電流（最大 30mA）をサポートする回路に電圧を供給することもできます。X5R または X7R、0.1μF、6.3V のセラミック コンデンサを AVDD ピンの近くに配置して AVDD レギュレータの出力をバイパスし、コンデンサを隣接する AGND グランド ピンに直接配線します。X5R または X7R、1μF、10V のセラミック コンデンサを GVDD ピンの近くに配置して GVDD レギュレータの出力をバイパスし、隣接する AGND グランド ピンに直接接続します。

AVDD の公称無負荷出力電圧は 3.3V です。

図 7-7. GVDD リニア レギュレータのブロック図

図 7-8. AVDD リニア レギュレータのブロック図

式 1 および式 2 を使用して、VM を電源とする AVDD および GVDD リニア レギュレータによってデバイス内で消費される電力を計算します。

$$P = (V_{VM} - V_{AVDD}) \times I_{AVDD} \quad (1)$$

$$P = (V_{VM} - V_{GVDD}) \times I_{GVDD} \quad (2)$$

例えば、 $V_{VM} = 24V$  の場合、AVDD から 20mA の電流が流れると、消費電力は式 3 のようになります。

$$P = (24V - 3.3V) \times 20mA = 414mW \quad (3)$$

#### 注

リニア レギュレータ AVDD および GVDD の両方からの合計外部電流サポートは 30mA に制限されます。外部負荷の 30mA が AVDD に接続されている場合、外部負荷を GVDD に接続しないでください。または、その逆も行わないでください。

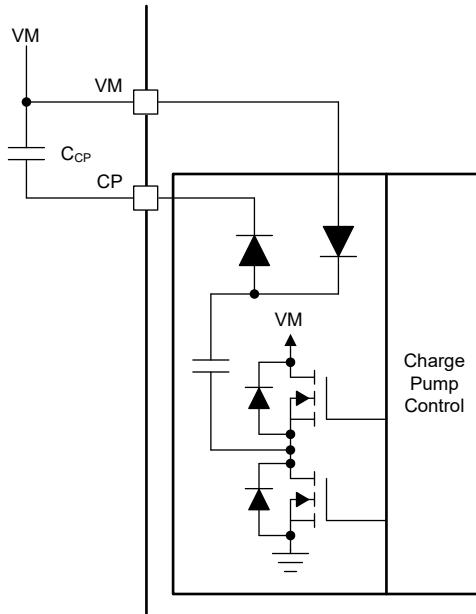

### 7.3.5 チャージポンプ

出力段では N チャネル FET を使用しているので、ハイサイド FET を完全に拡張にするには、VM 電源よりも高いゲート駆動電圧が必要です。DRV8376 は、この目的のために、VM 電源よりも高い電圧を生成するチャージ ポンプ回路を内蔵しています。

チャージ ポンプを動作させるには、1 つの外付けコンデンサが必要です。これらのコンデンサの詳細（値、接続など）については、ブロック図、ピンの説明、セクション（セクション 7.3）を参照してください。

nSLEEP が Low になるか、または過熱シャットダウンが実行されると、チャージ ポンプはシャットダウンします。

図 7-9. DRV8376 チャージポンプ

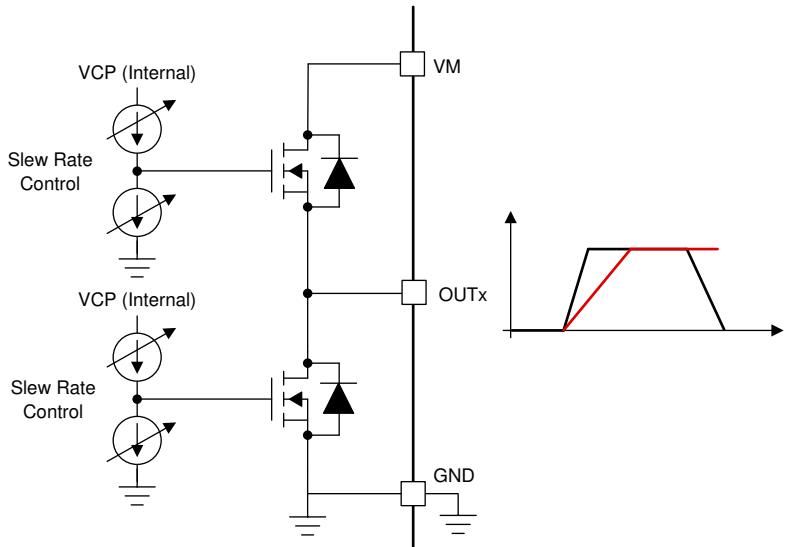

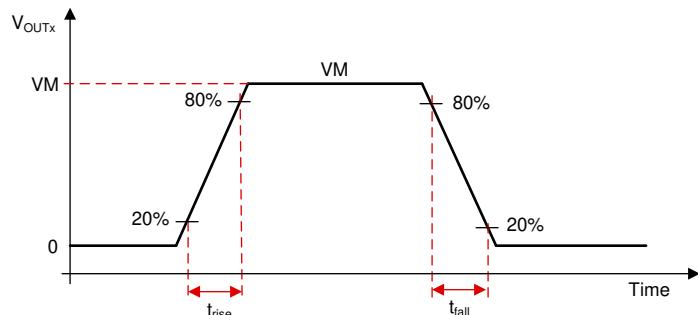

### 7.3.6 スルーレート制御

調整可能なゲートドライブ電流制御により、ハーフブリッジ内の MOSFET がアクティブに管理されてスルーレート制御が達成されます。MOSFET VDS スルーレートは、放射エミッション、エネルギーとダイオード回復スパイク期間、寄生によって発生するスイッチング電圧過渡の最適化に重大な影響を及ぼします。図 7-10 に示されているように、これらのスルーレートは、主に内部 MOSFET へのゲート電荷率によって決まります。

図 7-10. スルーレート回路の実装

各ハーフブリッジのスルーレートは、ハードウェア デバイス バリアントでは SLEW ピンによって、SPI デバイス バリアントでは SLEW ビットを使用して調整することができます。各ハーフブリッジは、スルーレート設定として 1.1V/ns、0.5V/ns、0.25V/ns、0.05V/ns のいずれかを選択できます。スルーレートは、OUTx ピンの電圧の立ち上がり時間と立ち下がり時間によって計算されます (図 7-11 を参照)。

図 7-11. スルーレート タイミング

注

パワーアップ時にのみ SLEW ピンが検出されます。DRV8376H デバイスは、動作中のスルーレート変化をサポートしていません。スルーレートは、DRV8376S デバイスのレジスタ書き込みにより、動作中に変更できます。動作中にスルーレートを変更しないことを TI は推奨しています。

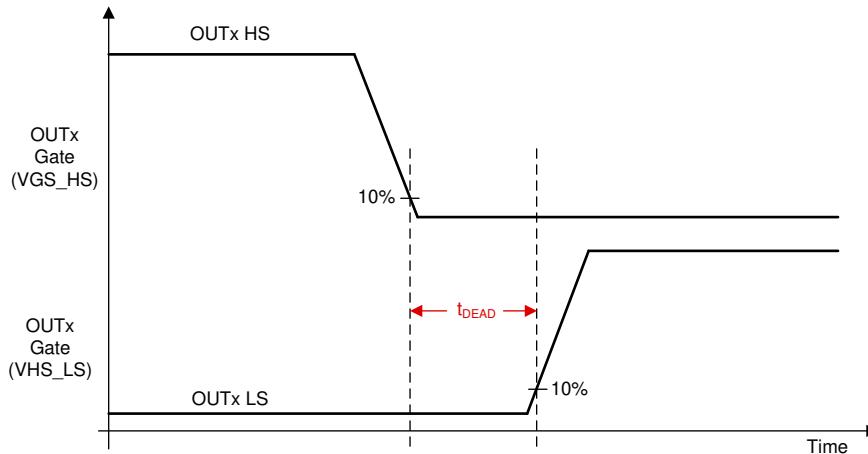

### 7.3.7 クロス導通(デッドタイム)

このデバイスは、MOSFET のクロス導通に対して包括的な保護が施されています。ハーフブリッジ構成では、デッドタイム ( $t_{DEAD}$ ) を挿入することで貫通電流を回避するため、ハイサイドおよびローサイド MOSFET の動作が維持されます。これは、ハイサイドおよびローサイド MOSFET のゲート - ソース電圧 (VGS) を検出することで実行され、同じハーフブリッジのローサイド MOSFET をオンにする前に、ハイサイド MOSFET の VGS がターンオフ レベルを確実に下回るようにしています (図 7-12 および 図 7-13 を参照)。

図 7-12. クロス導通保護

図 7-13. デッド タイム

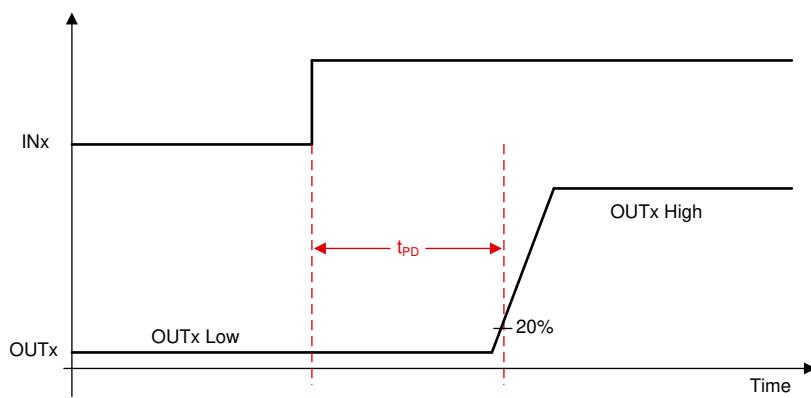

### 7.3.8 伝搬遅延

伝搬遅延時間 ( $t_{pd}$ ) は、入力ロジック エッジからゲート ドライバ電圧での変化が検出されるまでの時間として測定されます。

注

電流制限モードまたはアクティブ消磁モードでは、入力コマンドがデバイス全体に伝搬されるため、わずかなデジタル遅延が追加され、このモード中に最大 300ns 増加する可能性があります。

図 7-14. 伝搬遅延のタイミング

### 7.3.9 ピン配置図

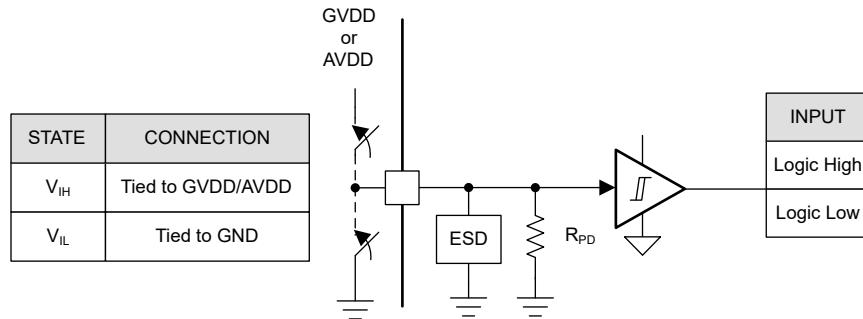

このセクションには、すべてのデジタル入出力ピンの I/O 構造が示されています。

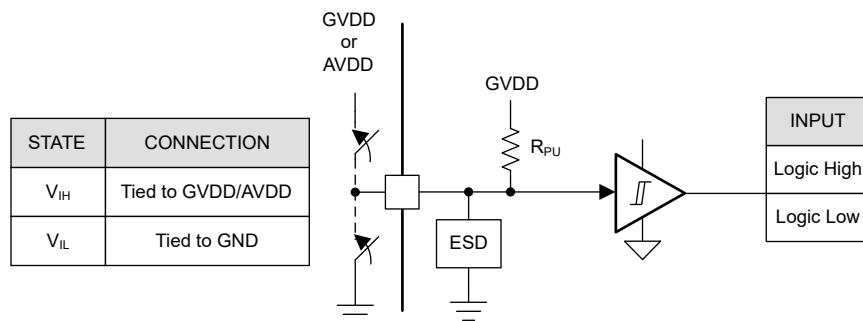

#### 7.3.9.1 ロジック レベル入力ピン (内部プルダウン)

図 7-15 に、ロジック レベルピン、DRVOFF、INHx、INLx、nSLEEP、SCLK、SDI の入力構造が示されています。入力は電圧または外部抵抗で行うことができます。内部プルダウン抵抗を介したリーコ電流を低減させるため、TI はデバイスのスリープ モードでこれらのピンを Low にすることを推奨します。

図 7-15. ロジック レベル入力ピンの構造

### 7.3.9.2 ロジック レベル入力ピン (内部プルアップ)

図 7-16 に、ロジック レベルピン nSCS の入力構造が示されています。入力は電圧または外部抵抗で駆動できます。

図 7-16. ロジック nSCS

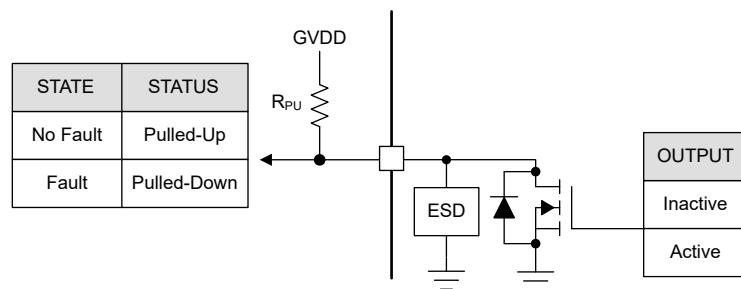

### 7.3.9.3 オープンドレインピン

図 7-17 に、オープンドレイン モードでのオープンドレイン出力ピン、nFAULT、SDO の構造が示されています。オープンドレイン出力を適切に機能させるためには、外部プルアップ抵抗が必要です。

図 7-17. オープンドレイン

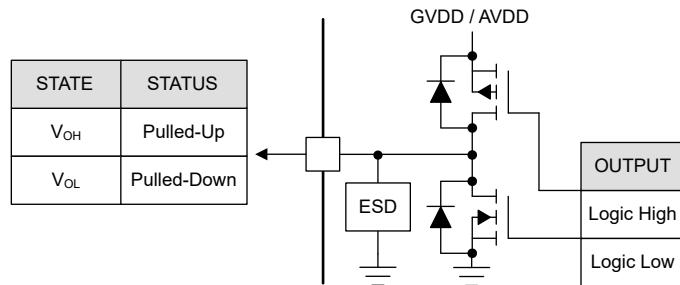

### 7.3.9.4 プッシュプルピン

図 7-18 に、プッシュプル モードでの SDO の構造が示されています。プッシュプル モードの SDO 電源は、SDO\_VSEL を設定することで、GVDD または AVDD に選択できます。

図 7-18. プッシュ プル

#### 7.3.9.5.4 レベル入力ピン

図 7-19 に、ハードウェア インターフェイス デバイス上の 4 レベル入力ピンである GAIN、MODE、\_SR、SLEW、OCP の構造が示されています。入力は外付け抵抗で設定できます。

図 7-19. 4 レベル入力ピンの構造

#### 7.3.10 電流センス アンプ

DRV8376 は、内蔵電流センシングを使った電流測定のために、3 つの高性能ローサイド電流センスアンプを内蔵しています。ローサイド電流測定は、一般に過電流保護、外部トルク制御、または外部コントローラによるブラシレス DC 整流の実装に使用されます。この 3 つのすべてのアンプは、各ハーフブリッジ レグの電流センシングに使用できます (ローサイド FET)。電流センスアンプには、プログラマブル ゲインなどの機能が含まれており、電圧リファレンスピン (VREF) で外部リファレンスが提供されます。

##### 7.3.10.1 電流センス アンプの動作

DRV8376 の SOX ピンは、ローサイド FET を流れる電流にゲイン設定 ( $G_{CSA}$ ) を乗算した値に比例するアナログ電圧を出力します。ゲイン設定は、GAIN ピン (ハードウェア デバイス バリエント) または GAIN ビット (SPI デバイス バリエント) で設定できる 4 つの異なるレベルの間で調整できます。

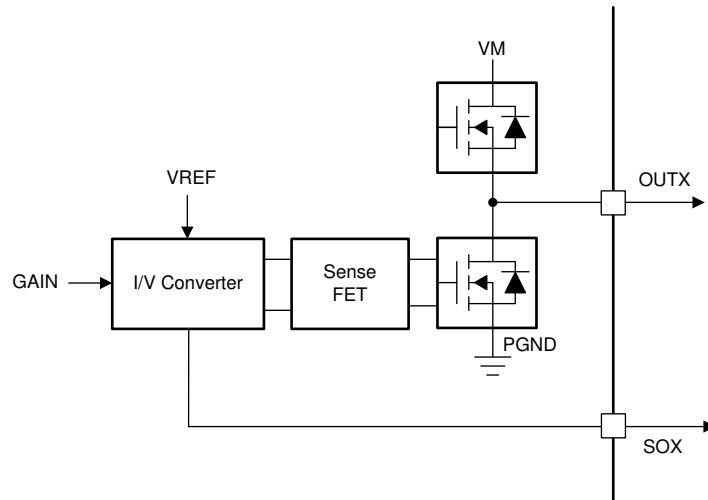

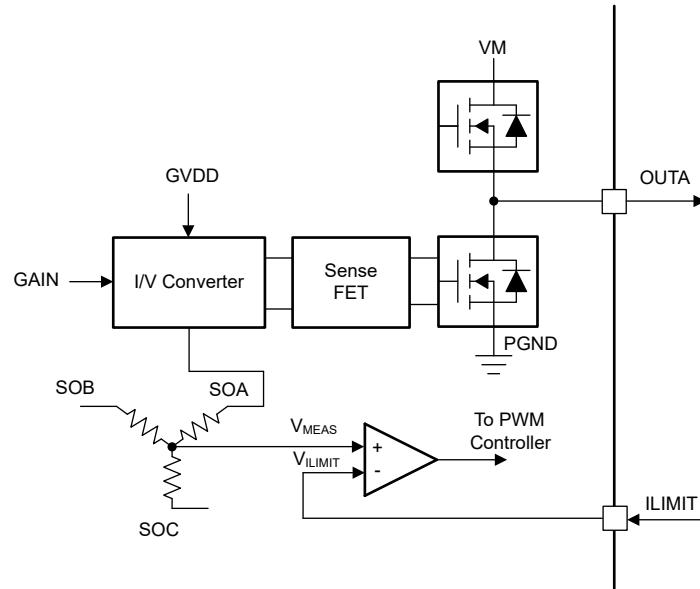

図 7-20 に、電流センスアンプの内部アーキテクチャが示されています。電流センスは、DRV8376 デバイスの各ローサイド FET のセンス FET で実装されています。この電流情報は内部 I/V コンバータに供給され、VREF ピンの電圧とゲイン設定に基づいて SO ピンに CSA 出力電圧を生成します。CSA の出力電圧は以下のように計算できます。

$$SOX = \left( \frac{V_{REF}}{2} \right) \pm GAIN \div I_{OUTX} \quad (4)$$

図 7-20. 電流センス アンプ内蔵

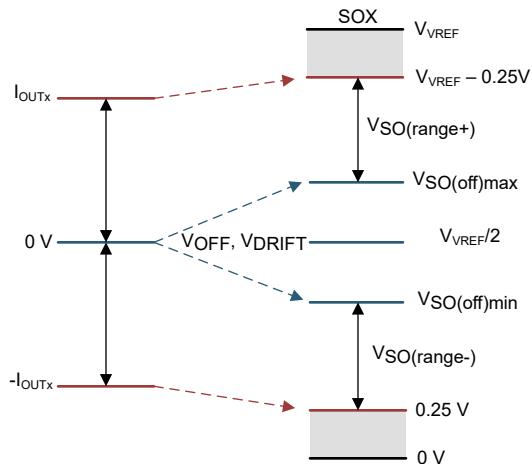

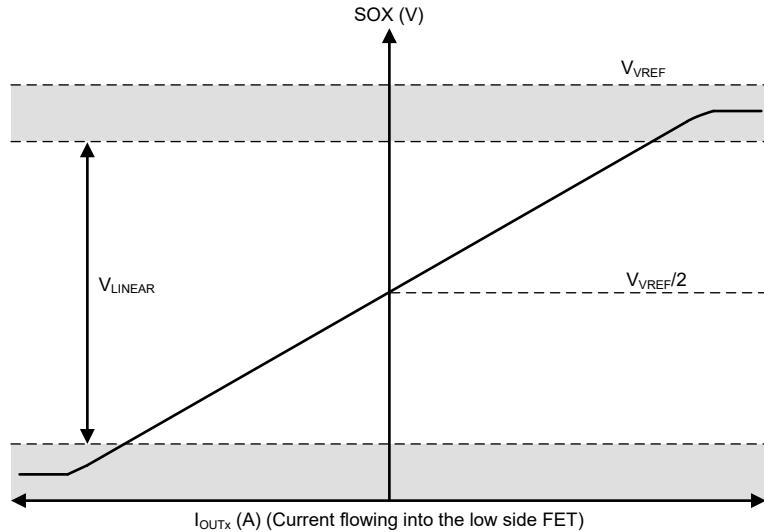

図 7-21 および 図 7-22 に、アンプの動作範囲の詳細が示されています。双方向動作では、0V 入力の場合、アンプは出力を  $V_{VREF}/2$  に設定します。差動入力の変化によって、出力に対応する変化が生じ、 $CSA\_GAIN$  係数を乗算した値が得られます。このアンプは、定義されたリニア領域内で動作を維持します。

図 7-21. 双方向電流検出の出力

図 7-22. 双方向電流検出の領域

注

電流センス アンプは、出力で連続的な電流負荷をサポートするようには設計されておらず、出力での容量性負荷のみをサポートしています。電流センス アンプの出力で、ローパス フィルタを抵抗およびコンデンサに接続することを TI は推奨しています。

注

この電流センス アンプは、動的なゲインの変更をサポートしています。HW バリエントでは、システムがピンセンシングを通じてゲインを 1ms ごとにサンプリングし、SPI バリエントでは、システムが SPI 書き込みを通じてゲインを更新します。ゲイン変更コマンドを受信した後、システムはいづれかの INLx 信号の次の立ち下がりエッジで 3 つの電流センス アンプすべてに新しいゲインを適用します。

### 7.3.11 アクティブ消磁

DRV8376 ファミリは、ダイオードの導通損失を低減することで、本デバイス内の電力損失を低減させるスマート整流機能(アクティブ消磁)を備えています。この機能が有効化されている場合、本デバイスはダイオード導通を検出すると常に、対応する MOSFET を自動的にターンオンさせます。この機能は、ハードウェアバリエントの MODE\_SR ピンにより構成できます。SPI デバイスバリエントでは、EN\_ASR および EN\_AAR ビットによってこれを構成できます。スマート整流は、自動同期整流 (ASR) モードと自動非同期整流 (AAR) モードの 2 つのカテゴリに分類されます。これらについては、以下のセクションの説明をご覧ください。

注

SPI デバイスバリエントでは、アクティブ消磁を有効にするには、EN\_ASR と EN\_AAR を両方のビットを 1 に設定する必要があります。

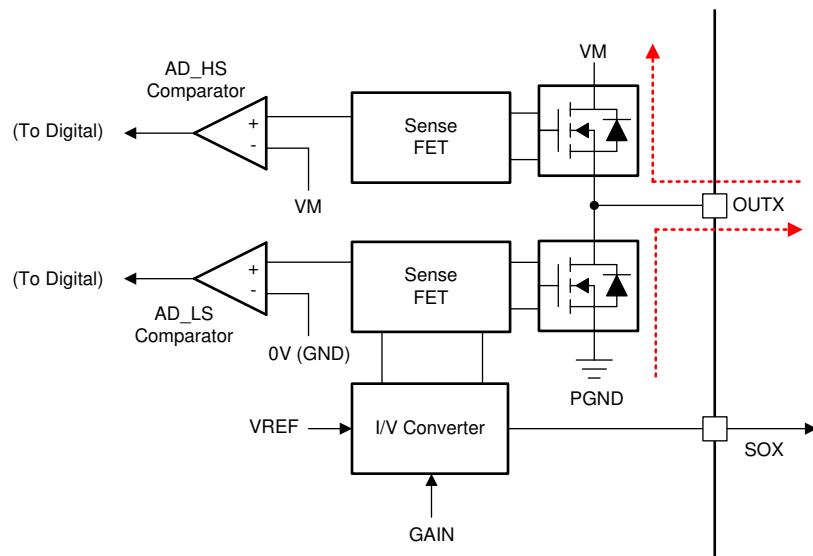

DRV8376 デバイスは、各ハーフブリッジで負の内部電流を検出するハイサイド (AD\_HS) およびローサイド (AD\_LS) コンパレータを内蔵しています。AD\_HS コンパレータはセンス FET 出力を電源電圧 (VM) スレッショルドと比較し、AD\_LS コンパレータはグランド (0V) スレッショルドと比較します。電流の流れ方 (OUTx から VM、または PGND から OUTx) に応じて、AD\_HS または AD\_LS コンパレータがトリップします。このコンパレータは、アクティブ消磁機能が動作するための基準点となります。

図 7-23. アクティブ消磁動作

表 7-2 に、DRV8376 デバイスの ASR および AAR モードの構成が示されています。

注

OCP イベント時に、アクティブ消磁が無効化されます。

#### 7.3.11.1 自動同期整流モード (ASR モード)

自動同期整流 (ASR) モードは、整流中の ASR と PWM モード時の ASR の 2 つのカテゴリに分けられます。

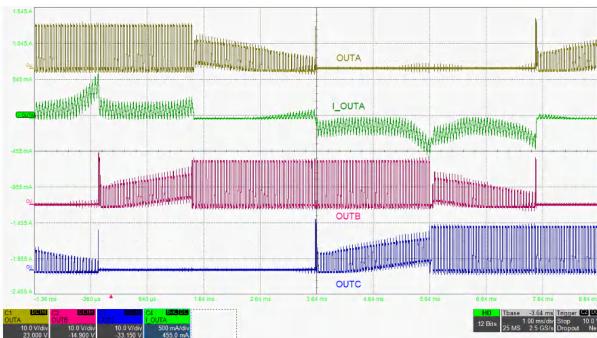

##### 7.3.11.1.1 転流時の自動同期整流

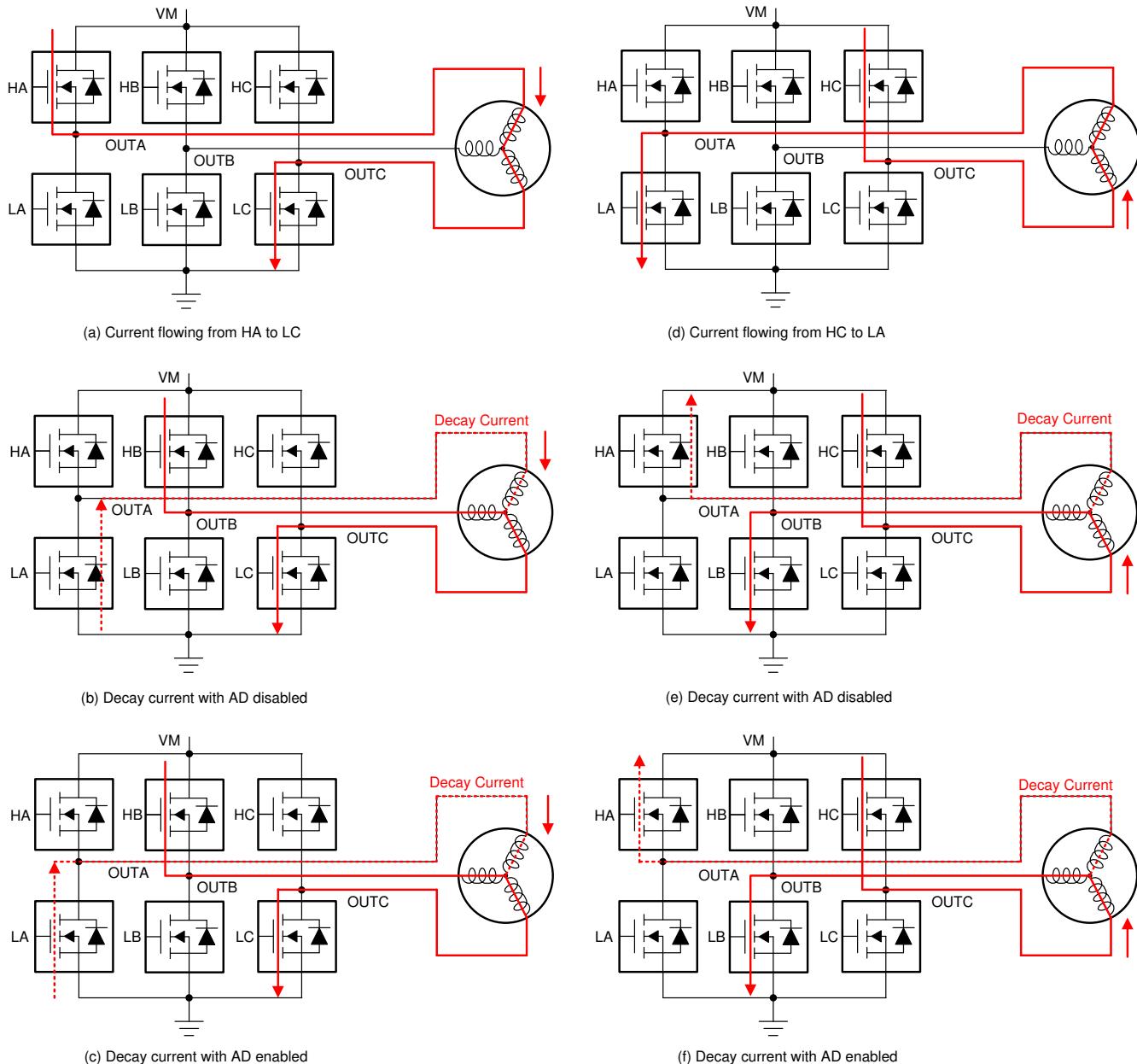

図 7-24 に、BLDC モーター整流中のアクティブ消磁の動作を示します。図 7-24 (a) に示すように、ある整流状態において、電流は HA から LC に流れています。図 7-24 (b) に示されているように、整流を切り換える間、HB スイッチはターンオンし、(モーター インダクタンスによる) OUTA の整流電流が LA のボディダイオードを流れます。これにより、整流電流によるダイオード損失が大きくなります。図 7-24 (c) に示されているように、この整流損失は、整流時間の間 LA をターンオンさせることで減少します。

図 7-24 (d)、(e)、(f) に示されているように、ハイサイド FET の動作は同様に実行されます。

図 7-24. BLDC モーター整流における ASR

図 7-25 (a) に、台形波整流で動作している BLDC モーターの自動同期整流モードに対する BLDC モーターの位相電流波形が示されています。この図は、1 つの整流サイクルにおける各種スイッチの動作を示したもので

図 7-25 (b) に、整流サイクルの拡大波形と、マージン時間 ( $t_{margin}$ ) を使用した ASR モード開始、およびアクティブな復調コンパレータのスレッショルドと遅延による ASR モードの早期停止の詳細が示されています。

図 7-25. BLDC モーター整流における ASR の電流波形

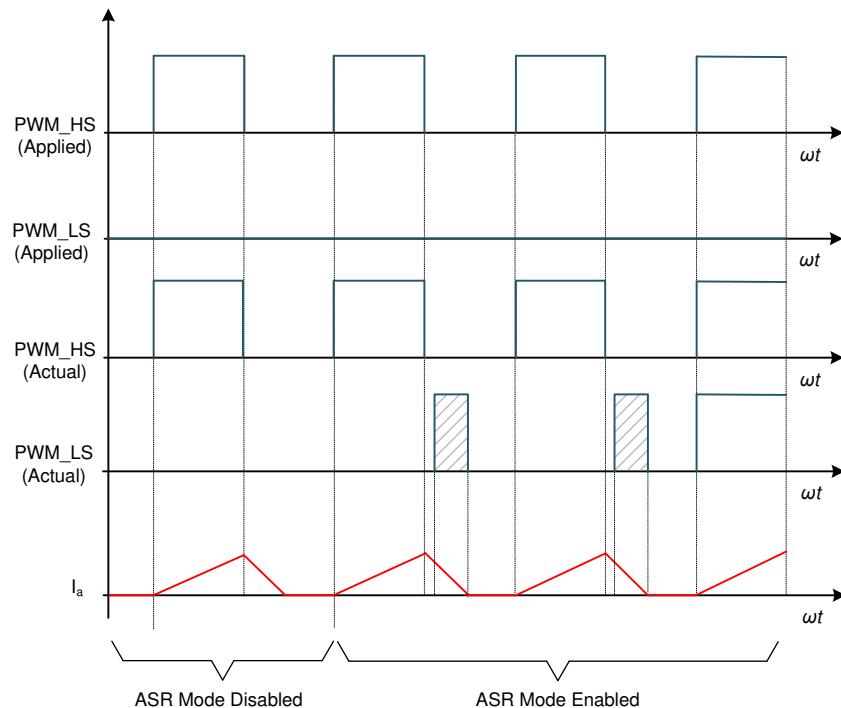

### 7.3.11.1.2 PWM モード時の自動同期整流

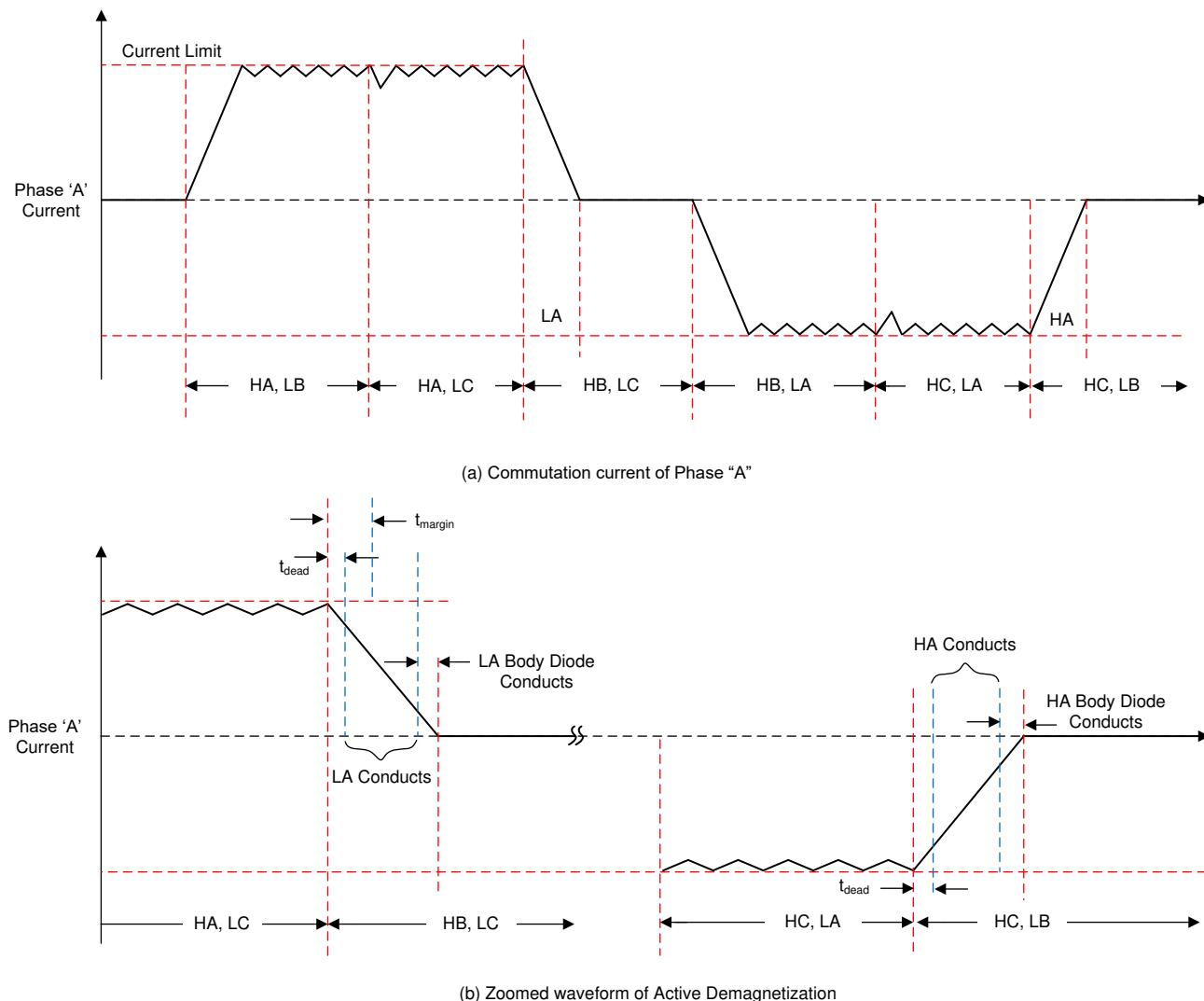

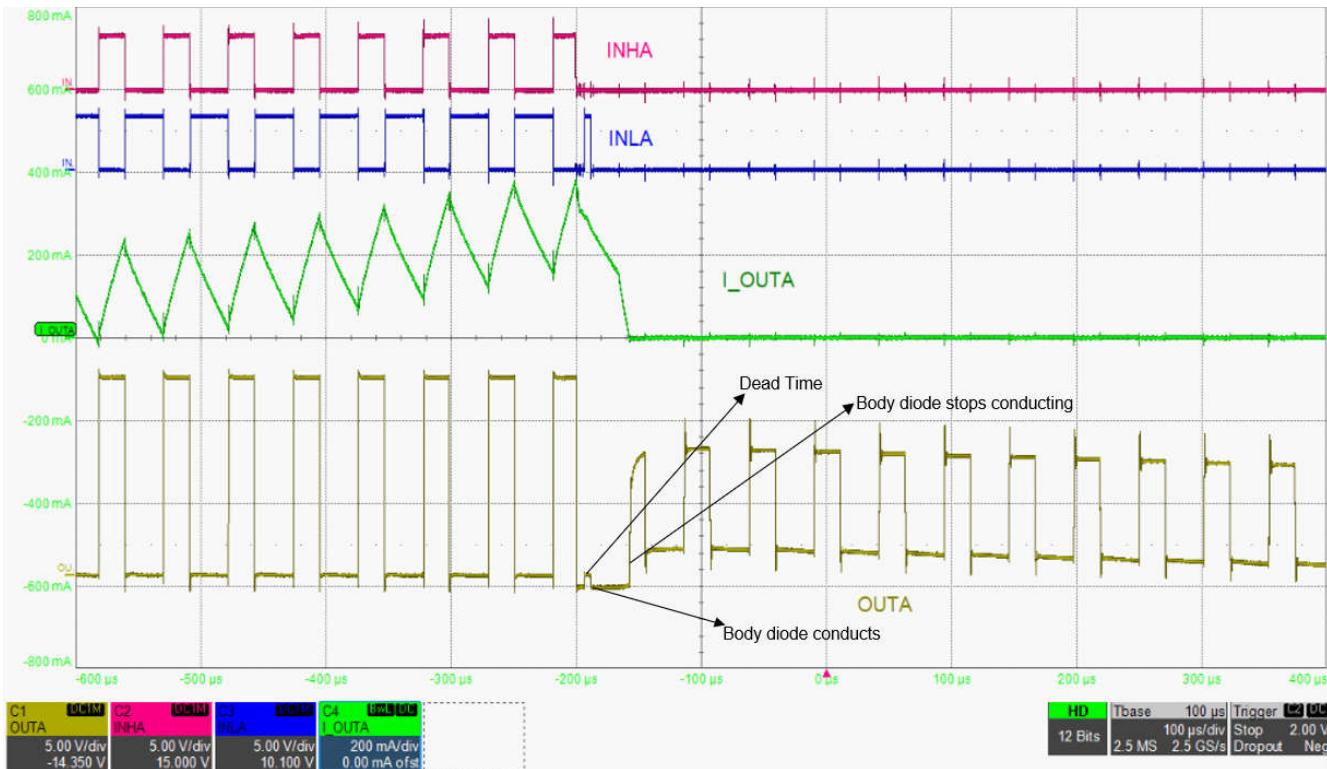

図 7-26 に、各モードでの ASR ピンの動作が示されています。この図に示されているように、PWM はハイサイド FET のみに印加されるのに対し、ローサイド FET は常にオフとなります。PWM オフ時は、電流がローサイド FET から減衰するため、電力損失が大きくなります。このため、このモードでは、ローサイドダイオードが導通している間、ローサイド FET をオンにすることができます。

図 7-26. PWM モードの ASR

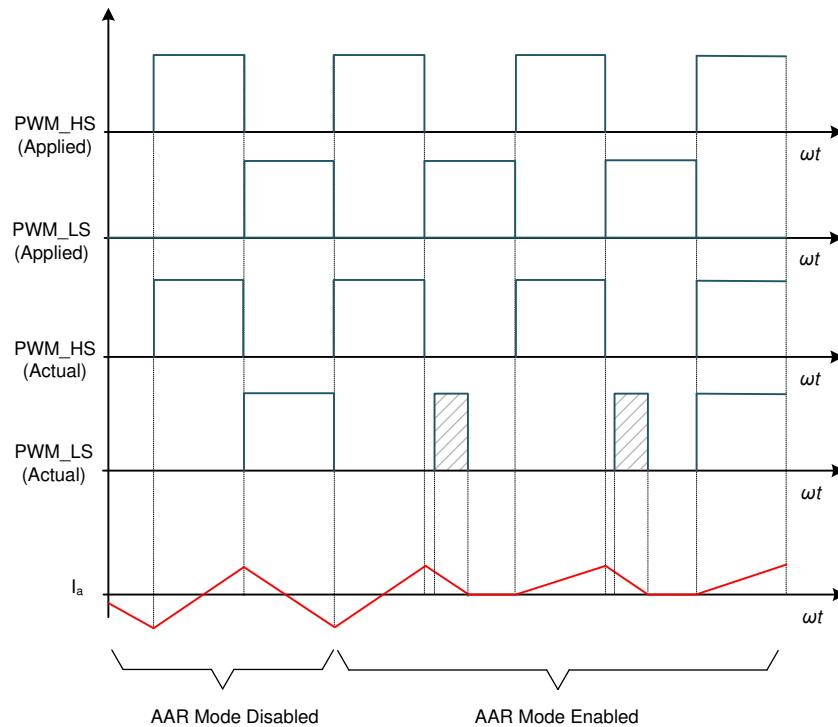

### 7.3.11.2 自動非同期整流モード (AAR モード)

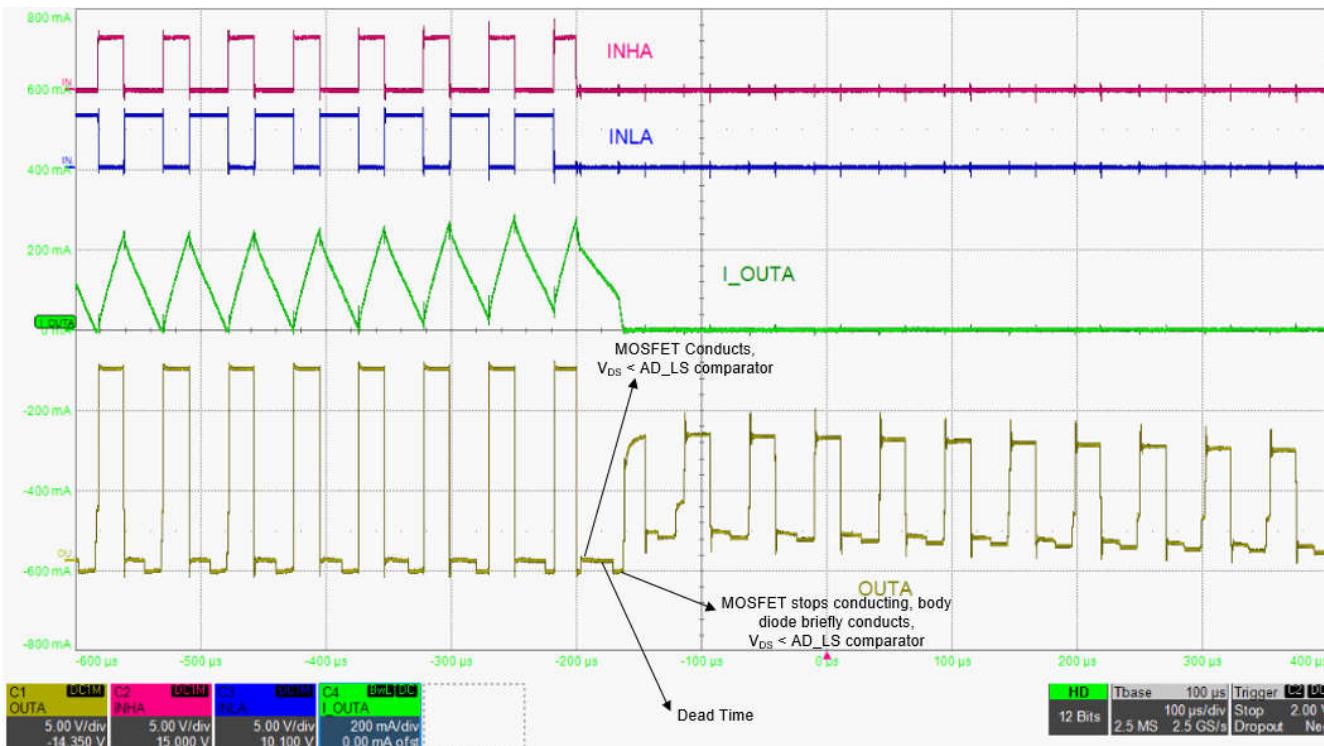

図 7-27 に、各モードでの AAR ピンの動作が示されています。この図に示されているように、ハイサイド FET とローサイド FET の同期整流で PWM を印加します。ローサイド FET が導通する間、インダクタンスの小さいモーターでは、ローサイド FET がオン状態になるため、電流は 0 に減衰して負になることがあります。この結果、BLDC モーターの動作に負のトルクが発生します。AAR モードを有効にすると、減衰中の電流が監視され、電流がゼロに近付くと直ちにローサイド FET がオフになります。これにより、BLDC モーター内を流れる負の電流を節約でき、ノイズ性能と熱管理性が向上します。

図 7-27. PWM モードの AAR

### 7.3.12 サイクル単位の電流制限

電流制限回路は、ILIMIT ピンの電圧と比較して、3 相の電流センスアンプの出力を利用します。図 7-28 電流制限回路の実装が示されています。電流センスアンプの出力は、スター型接続抵抗ネットワークと組み合わせられています。この測定電圧  $V_{MEAS}$  は、ILIMIT ピンの外部リファレンス電圧  $V_{LIM}$  と比較されることで、電流制限の実装を実現します。3 相 ( $I_{OUTx}$ ) で検出される電流と  $V_{MEAS}$  スレッショルドの関係は以下の通りです。

$$V_{MEAS} = \left( V_{REF}/2 \right) + ((I_{OUTA} + I_{OUTB} + I_{OUTC}) \times GAIN/3) \quad (5)$$

ここで、

- $V_{VREF}$ : 電流検出アンプの電源

- $I_{OUTx}$ : ローサイド MOSFET に流れる電流

- CSA\_GAIN: 電流センスアンプのゲイン

電流制限スレッショルドは、ILIMIT ピンの電圧を設定することで調整できます。ILIMIT ピンの電圧は  $V_{REF}/2$  から  $V_{MEAS}$  まで変化するため、電流制限は 0A ~ 4A の間で直線的に変化します。ILIMIT を無効化するために、 $V_{VREF}$  よりも高い電圧を印加できます。

電流制限コンパレータの出力はブランкиング時間としてブランкиングされます。ハイサイドとローサイドスイッチ制御入力の立ち上がりエッジ (INHx および INLx) ごとに、DRV8376 の出力状態はブランкиング時間中の INHx および INLx の状態によって異なります。ブランкиング時間は SPI デバイスの ILIM\_BLANK\_SEL によって構成され、ハードウェアバリアントのスルーレートが 50 の場合は 5.5μs、その他のすべてのスルーレートの場合は 1.8μs に固定されます。

図 7-28. 電流制限の実装

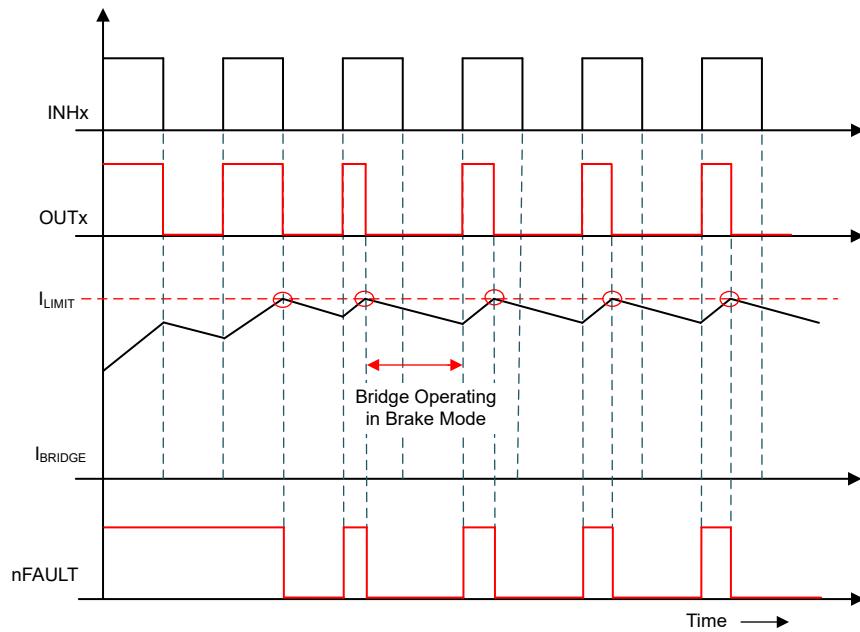

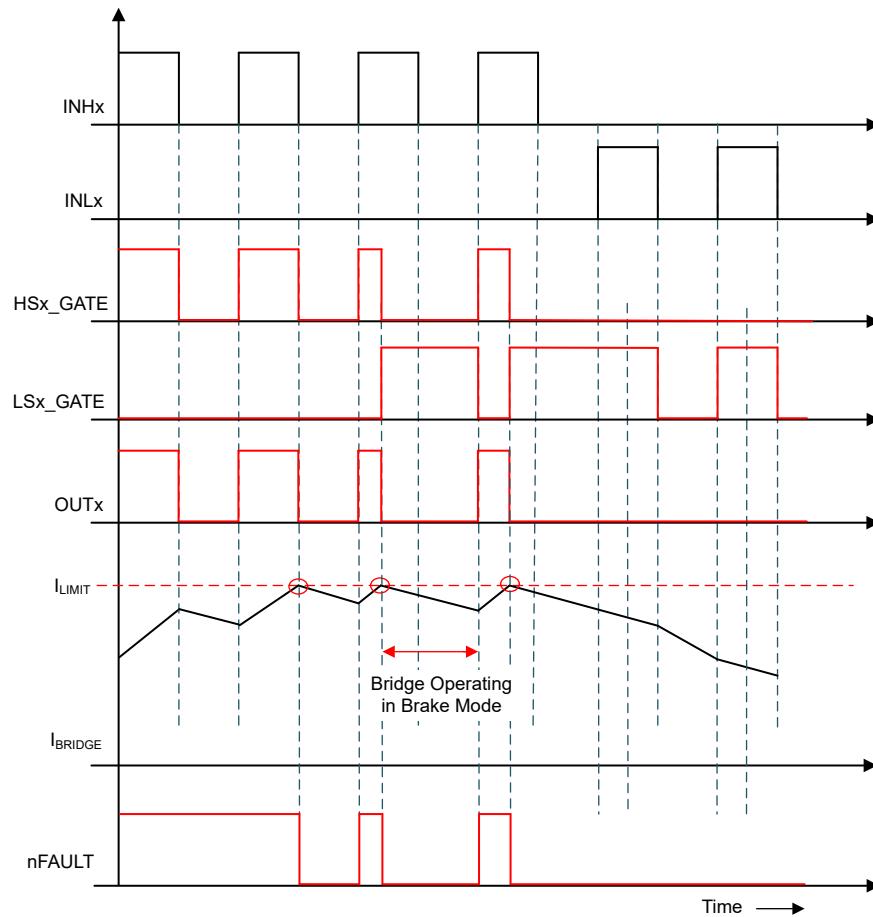

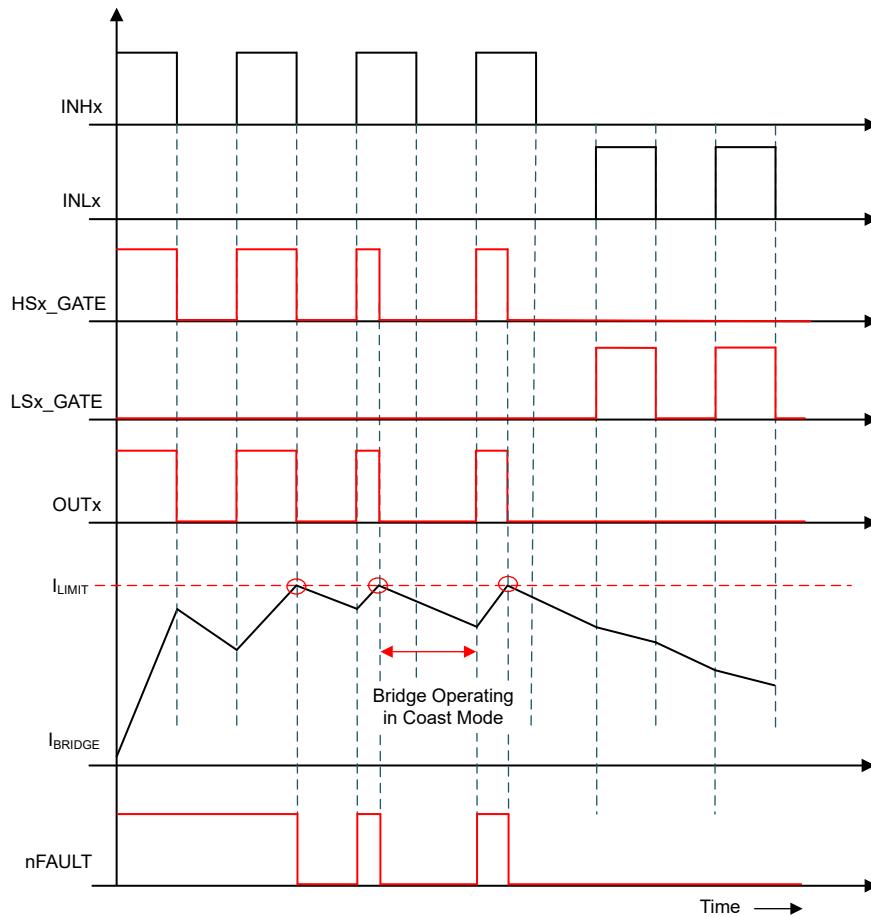

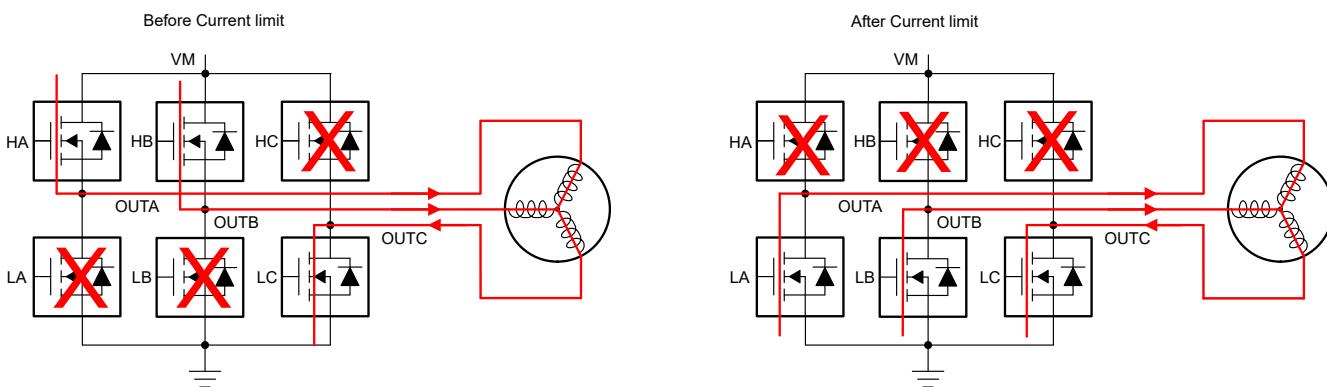

図 7-29 に示されているように、その後に電流制限が作動すると、各ハーフブリッジのハイサイド (INH<sub>x</sub>) の立ち上がりエッジまで、各ハーフブリッジのハイサイド FET が無効化されます。ローサイド FET は、SPI デバイス バリアントの ILIM\_MODE ビットを設定することで、ブレーキ モードまたはコースト (ハイインピーダンス) モードで動作できます。ハードウェア バリアントでは、ローサイド FET はコースト (ハイインピーダンス) モードで動作します。

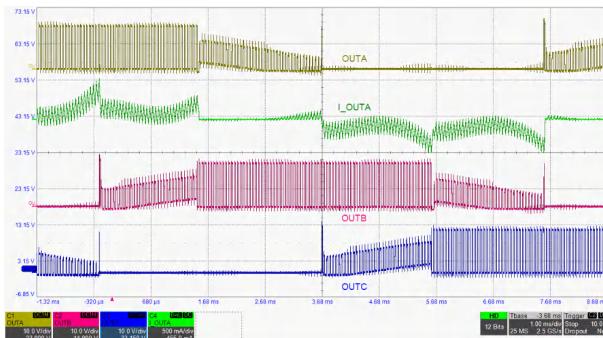

図 7-29. サイクル単位の電流制限動作

図 7-30. サイクル単位の電流制限動作 (ブレーキ モードでのローサイド スイッチングあり)

図 7-31. サイクル単位の電流制限動作 (コースト モードでのローサイド スイッチングあり)

図 7-32 に、ブレーキ モードでのドライバの動作が示されています。ここでは、ハイサイド FET が無効化されている間にローサイド FET を通って電流が循環します。に示されているように、同期整流モードで電流制限がアクティブになっている場合は、ハイサイド FET が無効化されている間にローサイド FET を通って電流が再循環します。

図 7-33 に、ハイインピーダンスマードでのドライバの動作が示されています。ここでは、ハイサイド FET が無効化されている間にローサイド FET のボディダイオードを通って電流が循環します。に示されているように、電流制限が非同期整流モードでアクティブになっている場合は、ハイサイド FET が無効化されている間にローサイド FET のボディダイオードを通って電流が再循環します。

図 7-32. ブレーキ状態

図 7-33. コースト状態

注

ブレーキ動作中、大電流がローサイド FET を流れることで、最終的に過電流保護回路がアクティブになります。この状態では、ハイサイド FET のボディダイオードが導通し、ブレーキ エネルギーを VM 電源レールに誘導します。

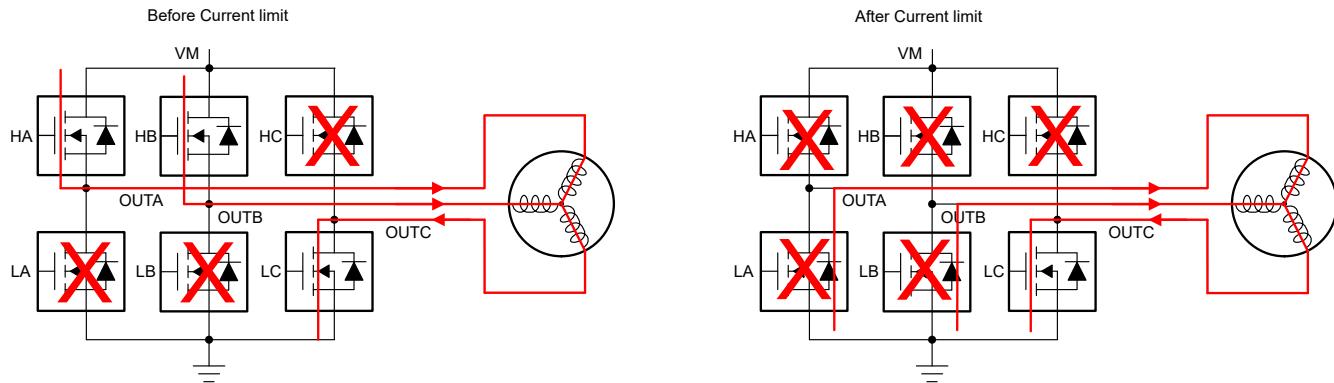

#### 7.3.12.1 100% デューティ サイクル入力でのサイクル単位の電流制限

PWM 入力に 100% デューティ サイクルが印加された場合、ハイサイド FET を再びオンにするエッジはありません。この問題を克服するため DRV8376-Q1 には内部 PWM クロックが内蔵されています。これにより、 $I_{LIMIT}$  スレッショルドを超えた後にハイサイド FET が無効化された時点でハイサイド FET がオンに戻ります。SPI バリエント DRV8376-Q1 では、この内部 PWM クロックは、PWM\_100\_DUTY\_SEL を通じて 10kHz、20kHz、または 40kHz に設定できます。H/W バリエントでは、DRV8376-Q1 PWM 内部クロックが 20kHz に設定されています。図 7-34 また、100% デューティ サイクルでの動作を示します。

図 7-34. 100% PWM デューティ サイクルでのサイクル単位の電流制限動作

#### 7.3.13 保護機能

DRV8376-Q1 ファミリのデバイスは、VM 低電圧、チャージ ポンプ低電圧、過電流イベントから保護されています。表 7-5 に、各種 フォルトの詳細が示されています。

表 7-5. フォルト時の動作と応答 (SPI デバイス)

| フォルト                | 条件                        | 構成                | 通知     | H ブリッジ     | ロジック   | 復帰                                                                         |

|---------------------|---------------------------|-------------------|--------|------------|--------|----------------------------------------------------------------------------|

| VM 低電圧 (RESET)      | $V_{VM} < V_{UVLO}$       | —                 | —      | ハイインピーダンス  | ディセーブル | 自動:<br>$V_{VM} > V_{UVLO\_R}$<br>CLR_FLT, nSLEEP リセットパルス (RESET ビット)       |

| GVDD 低電圧 (RESET)    | $V_{GVDD} < V_{GVDD\_UV}$ | —                 | —      | ハイインピーダンス  | ディセーブル | 自動:<br>$V_{GVDD} > V_{GVDD\_UV\_R}$<br>CLR_FLT, nSLEEP リセットパルス (RESET ビット) |

| AVDD 低電圧 (RESET)    | $V_{AVDD} < V_{AVDD\_UV}$ | —                 | —      | ハイインピーダンス  | ディセーブル | 自動:<br>$V_{AVDD} > V_{AVDD\_UV\_R}$<br>CLR_FLT, nSLEEP リセットパルス (RESET ビット) |

| チャージポンプ低電圧 (VCP_UV) | $V_{CP} < V_{CPUV}$       | —                 | nFAULT | ハイインピーダンス  | アクティブ  | 自動:<br>$V_{CP} > V_{CPUV}$<br>CLR_FLT, nSLEEP リセットパルス (VCP_UV ビット)         |

| 過電圧保護 (OVP)         | $V_{VM} > V_{OVP}$        | OVP_MODE = 0b     | なし     | アクティブ      | アクティブ  | 動作なし (OVP 無効)                                                              |

|                     |                           | OVP_MODE = 1b     | フォルト   | ハイインピーダンス  | アクティブ  | 自動:<br>$V_{VM} < V_{OVP}$<br>CLR_FLT, nSLEEP リセットパルス (OVP ビット)             |

| 過電流保護 (OCP)         | $I_{PHASE} > I_{OCP}$     | OCP_MODE = 00b    | nFAULT | ハイインピーダンス  | アクティブ  | ラッチ:<br>CLR_FLT, nSLEEP リセットパルス (OCP ビット)                                  |

|                     |                           | OCP_MODE = 01b    | nFAULT | ハイインピーダンス  | アクティブ  | リトライ:<br>$t_{RETRY}$<br>CLR_FLT, nSLEEP リセットパルス (OCP ビット)                  |

|                     |                           | OCP_MODE = 10b    | nFAULT | アクティブ      | アクティブ  | 通知のみ:<br>CLR_FLT, nSLEEP リセットパルス (OCP ビット)                                 |

|                     |                           | OCP_MODE = 11b    | なし     | アクティブ      | アクティブ  | 何も起こらない                                                                    |

| ILIMIT              | $V_{ILIMIT} > V_{SO}$     | ILIMFLT_MODE = 0b | なし     | ILIMIT モード | アクティブ  | 自動:<br>INHx の次の立ち上がりエッジでハイサイド<br>INLx の次の立ち上がりエッジでローサイド                    |

|                     |                           | ILIMFLT_MODE = 1b | nFAULT | ILIMIT モード | アクティブ  | 自動:<br>INHx の次の立ち上がりエッジでハイサイド<br>INLx の次の立ち上がりエッジでローサイド                    |

| SPI エラー (SPI_FLT)   | SCLK, パリティ、ADDR フォルト      | SPIFLT_MODE = 0b  | なし     | アクティブ      | アクティブ  | 何も起こらない                                                                    |

|                     |                           | SPIFLT_MODE = 1b  | nFAULT | アクティブ      | アクティブ  | 通知のみ:<br>CLR_FLT, nSLEEP リセットパルス (SPI_FLT ビット)                             |

| OTP エラー (OTP_ERR)   | OTP の読み取りが誤っています          | —                 | nFAULT | ハイインピーダンス  | アクティブ  | ラッチ:<br>パワー サイクル、CLR_FLT                                                   |

| 過熱警告 (OTW)          | $T_J > T_{OTW}$           | OTW_MODE = 0b     | なし     | アクティブ      | アクティブ  | 何も起こらない                                                                    |

|                     |                           | OTW_MODE = 1b     | nFAULT | アクティブ      | アクティブ  | 自動:<br>$T_J < T_{OTW} - T_{OTW\_HYS}$<br>CLR_FLT, nSLEEP パルス (OTW ビット)     |

| サーマル シャットダウン (OTSD) | $T_J > T_{TSD}$           | —                 | nFAULT | ハイインピーダンス  | アクティブ  | 自動:<br>$T_J < T_{TSD} - T_{TSD\_HYS}$                                      |

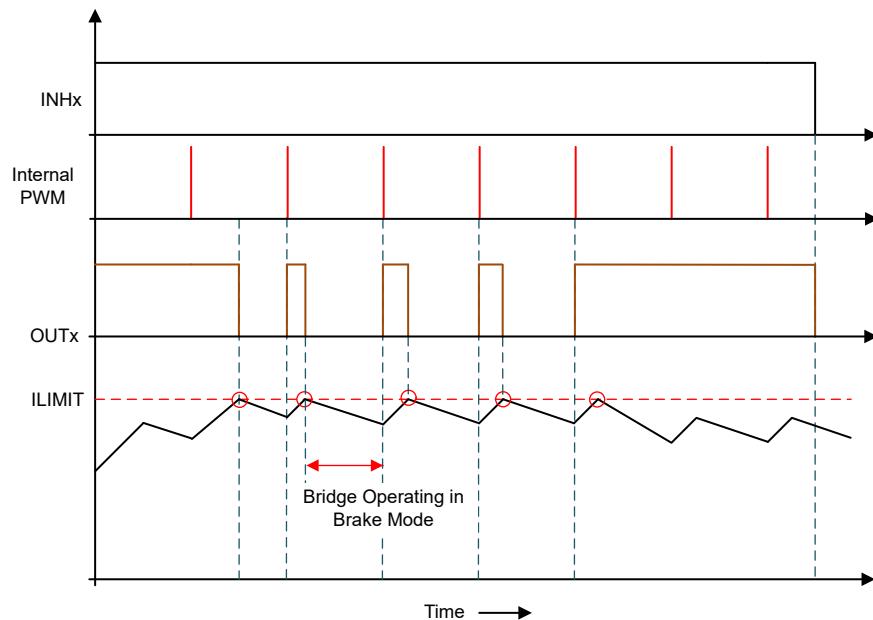

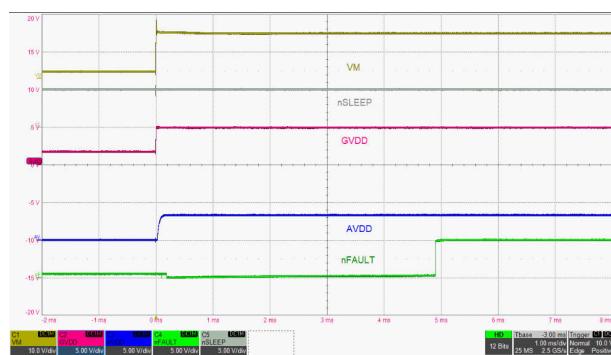

### 7.3.13.1 VM 電源低電圧誤動作防止 (RESET)

VM ピンの入力電源電圧が  $V_{UVLO}$  スレッショルド (VM UVLO 立ち下がりスレッショルド) を下回ると、常にすべての内蔵 FET、ドライバ、チャージポンプ、デジタルロジックコントローラが無効化されます (図 7-35 を参照)。VM 低電圧状態が解消されると、通常動作 (ドライバの動作) が再開されます。デバイスが VM の状態を認識すると、デバイスステータス (DEV\_STS) レジスタの RESET ビットは High にラッピングされます。RESET ビットは、CLR\_FLT ビットまたは nSLEEP ピンのリセットパルス ( $t_{RST}$ ) によってクリアされるまで High のままであります。

図 7-35. VM 電源低電圧誤動作防止

### 7.3.13.2 AVDD 低電圧保護 (AVDD\_UV)

AVDD ピンの電圧が  $V_{AVDD\_UV}$  スレッショルドを下回ると常に、内蔵 FET、ドライバ チャージポンプ、デジタル ロジック コントローラのすべてが無効化されます。AVDD 低電圧状態が解消されると、通常動作 (ドライバの動作) が再開されます。デバイスが VM の状態を認識すると、デバイスステータス (DEV\_STS) レジスタの RESET ビットは High にラッチされます。RESET ビットは、CLR\_FLT ビットまたは nSLEEP ピンのリセットパルス ( $t_{RST}$ ) によってクリアされるまで High のままでです。

### 7.3.13.3 GVDD 低電圧誤動作防止 (GVDD\_UV)

GVDD ピンの電圧が  $V_{GVDD\_UV}$  スレッショルドを下回ると常に、内蔵 FET、ドライバ チャージポンプ、デジタル ロジック コントローラのすべてが無効化されます。GVDD 低電圧状態が解消されると、通常動作 (ドライバの動作) が再開されます。デバイスが VM の状態を認識すると、デバイスステータス (DEV\_STS) レジスタの RESET ビットは High にラッチされます。RESET ビットは、CLR\_FLT ビットまたは nSLEEP ピンのリセットパルス ( $t_{RST}$ ) によってクリアされるまで High のままでです。

### 7.3.13.4 VCP チャージポンプ低電圧誤動作防止 (CPUV)

任意の時点で VCP ピン (チャージポンプ) の電圧が VCPUV スレッショルド未満に低下した場合は、統合されているすべての FET が無効化され、nFAULT ピンが Low になります。VCP の低電圧状態が解消されると、通常動作が再開されます (ドライバの動作が再開され、nFAULT ピンが解放される)。チャージポンプの低電圧は、FAULT ビットと CPUV ビットで通知されます。チャージポンプ低電圧状態が解消されると、FAULT ビットが自動的にクリアされます。CPUV ビットは、CLR\_FLT ビットまたは nSLEEP ピンのリセットパルス ( $t_{RST}$ ) によってクリアされるまでセットされたまま維持されます。CPUV 保護は、ハードウェアと SPI デバイスの両方のバリエントで常に有効化されています。

### 7.3.13.5 過電圧保護 (OVP)

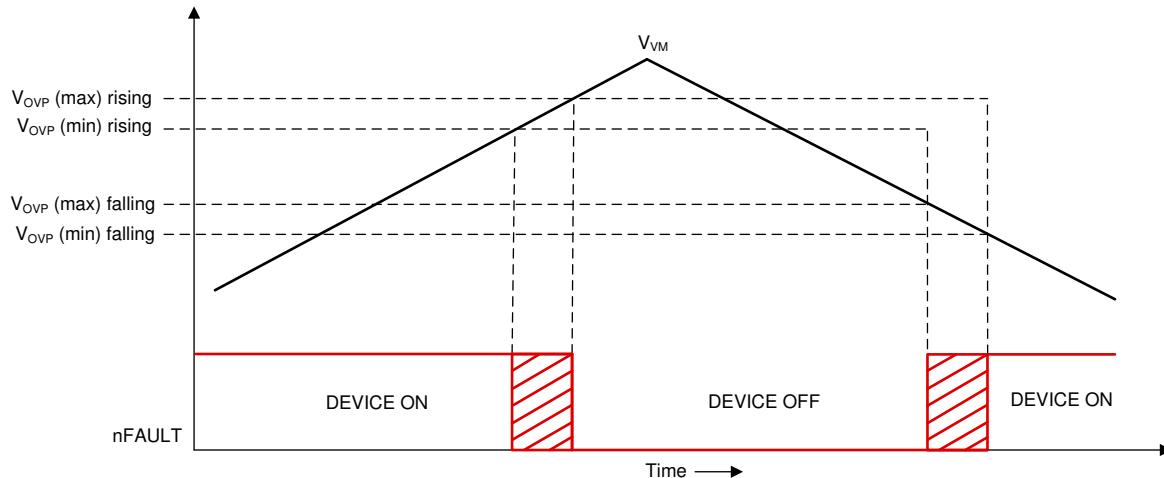

VM ピンの電源電圧が  $V_{OVP}$  スレッショルド電圧を超えると、常にすべての内蔵 FET が無効化され、nFAULT ピンが Low に駆動されます。OVP が解消されると、通常動作が再開されます (ドライバ動作が再開され、nFAULT ピンが解放される)。FAULT ビットと OVP ビットで低電圧が通知されます。過電圧状態が解消されると、FAULT ビットは自動的にクリアされます。OVP ビットは、CLR\_FLT ビットまたは nSLEEP ピンのリセットパルス ( $t_{RST}$ ) によってクリアされるまでセットされたまま維持されます。SPI デバイスの OVP\_MODE ビットを High に設定すると、この保護機能が有効になります。ハードウェア インターフェイス デバイスでは、OVP 保護が無効化されています。

OVP スレッショルドは、SPI デバイス バリエントでもプログラム可能です。OVP スレッショルドは、OVP\_SEL ビットに基づいて 35V または 65V に設定できます。

図 7-36. 過電圧保護

### 7.3.13.6 過電流保護 (OCP)

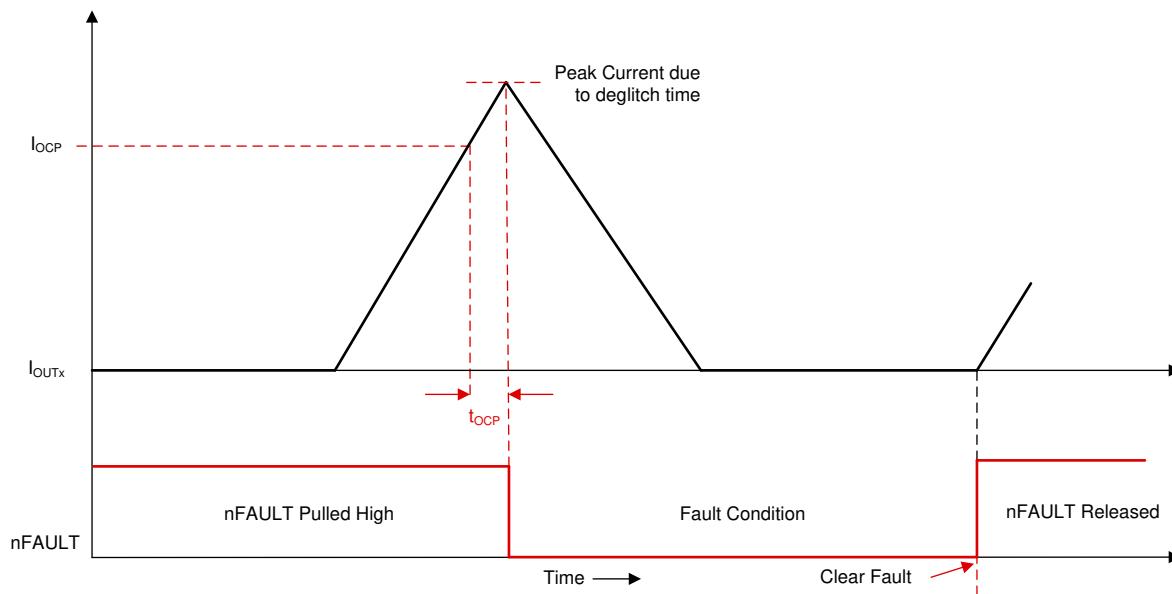

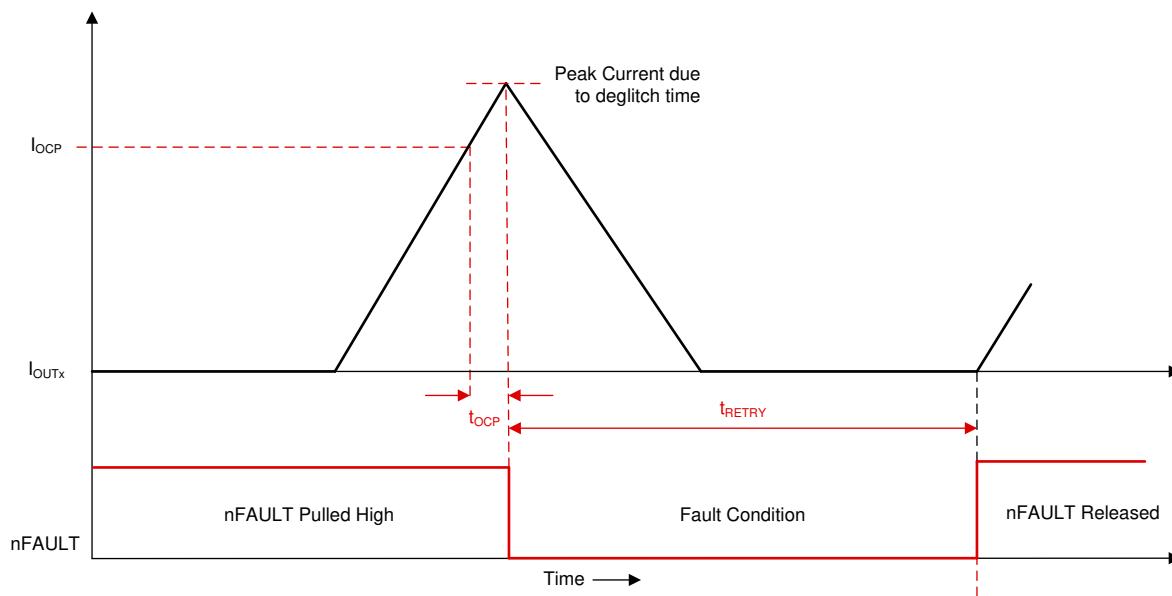

MOSFET 過電流イベントは、FET を流れる電流を監視することで検出されます。FET に流れる電流が  $t_{OCP}$  グリッチ除去時間よりも長く  $I_{OCP}$  スレッショルドを上回ると、OCP イベントが認識され、OCP\_MODE ビットに従って動作が実行されます。ハードウェア インターフェイス デバイスでは、 $I_{OCP}$  スレッショルドは OCP ピンによって設定され、 $t_{OCP\_DEG}$  は  $1.2\mu\text{s}$  に固定され、OCP\_MODE ビットはラッチ付きシャットダウンに設定されます。SPI デバイスでは、 $I_{OCP}$  スレッショルドは OCP\_LVL ビットを通じて設定され、 $t_{OCP\_DEG}$  は OCP\_DEG ビットを通じて設定されます。

表 7-6 に、DRV8376 デバイスの OCP レベルとグリッチ除去時間の構成が示されています。

表 7-6. OCP の構成

| OCP 設定 | OCP ピン (ハードウェア バリアント) | OCP_LVL ビット (SPI バリアント) | 最小 OCP レベル |

|--------|-----------------------|-------------------------|------------|

| OCP 1  | AGND に接続              | OCP_LVL = 0b            | 4.5A       |

| OCP 2  | GVDD に接続              | OCP_LVL = 1b            | 2.5A       |

OCP\_MODE ビットは以下の 4 つのモードで動作できます。OCP ラッチ付きシャットダウン、OCP 自動リトライ、OCP 通知のみ、OCP 無効。

#### 7.3.13.6.1 OCP ラッチ シャットダウン (OCP\_MODE = 00b)

このモードで OCP イベントが発生すると、すべての MOSFET が無効化され、nFAULT ピンが Low に駆動されます。SPI レジスタでは、FAULT、OCP、および対応する FET OCP ビットが High にラッチされます。OCP 状態が解消され、CLR\_FLT ビットまたは nSLEEP リセット パルス ( $t_{RST}$ ) のいずれかによってフォルト クリア コマンドが発行されると、通常動作が再開されます (ドライバの動作が再開され、nFAULT ピンが解放される)。

図 7-37. 過電流保護 - ラッチ シャットダウン モード

#### 7.3.13.6.2 OCP 自動リトライ (OCP\_MODE = 01b)

このモードで OCP イベントが発生した後、すべての MOSFET が無効化され、nFAULT ピンが Low に駆動されます。SPI レジスタでは、FAULT、OCP、および対応する FET OCP ビットが High にラッチされます。 $t_{RETRY}$  時間が経過した後は、通常動作が自動的に再開されます (ドライバ動作が再開され、nFAULT ピンが解放される)。 $t_{RETRY}$  時間が経過すると、FAULT、OCP、および対応する FET の OCP ビットは、CLR\_FLT ビットまたは nSLEEP リセット・パルス ( $t_{RST}$ ) のいずれかによってフォルトクリア コマンドが実行されるまでラッチされた状態を維持します。

図 7-38. 過電流保護 - 自動リトライ モード

#### 7.3.13.6.3 OCP 通知のみ (OCP\_MODE = 10b)

このモードでは、OCP イベントの後に保護動作は発生しません。nFAULT ピンを Low に駆動し、FAULT、OCP、および対応する FET の OCP ビットを SPI レジスタで High にラッチすることにより、過電流イベントが通知されます。DRV8376-

Q1 は通常どおり動作を継続します。外部コントローラは適切に動作することによって過電流状態を管理します。OCP 状態が解消され、CLR\_FLT ビットまたは nSLEEP リセットパルス ( $t_{RST}$ ) のいずれかによってフォルトクリアコマンドが発行されると、通知がクリアされます (nFAULT ピンが解放される)。

#### 7.3.13.6.4 OCP 無効 (OCP\_MODE = 11b)

このモードでは、OCP イベントの後に何の動作も発生しません。

#### 7.3.13.7 過熱警告 (OTW)

ダイ温度が過熱警告のトリップポイント ( $T_{OTW}$ ) を上回ると、OT ステータス (OT\_STS) レジスタの OT ビット、およびステータスレジスタ (DEV\_STS) の OTF ビットが設定されます。nFAULT ピンの OTW 通知は、構成制御レジスタの過熱警告通知 (OTW\_MODE) ビットを設定することで有効化できます。デバイスの機能は継続され、追加動作が実行されることはありません。この場合、ダイ温度が過熱警告のヒステリシスポイント ( $T_{OTW\_HYS}$ ) を下回ると、nFAULT ピンが解放されます。OTW ビットは、CLR\_FLT ビットまたは nSLEEP リセットパルス ( $t_{RST}$ ) によってクリアされ、ダイ温度が過熱警告トリップ ( $T_{OTW}$ ) を下回るまで設定されたまま維持されます。ハードウェアバリエントでは、過熱警告はデフォルトで nFAULT ピンで通知されます。

#### 7.3.13.8 サーマルシャットダウン (OTS)

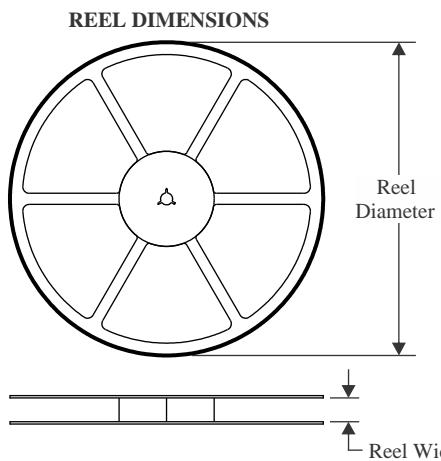

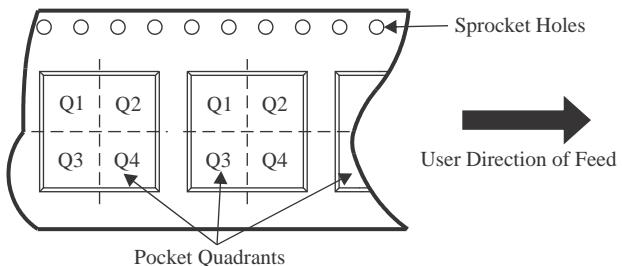

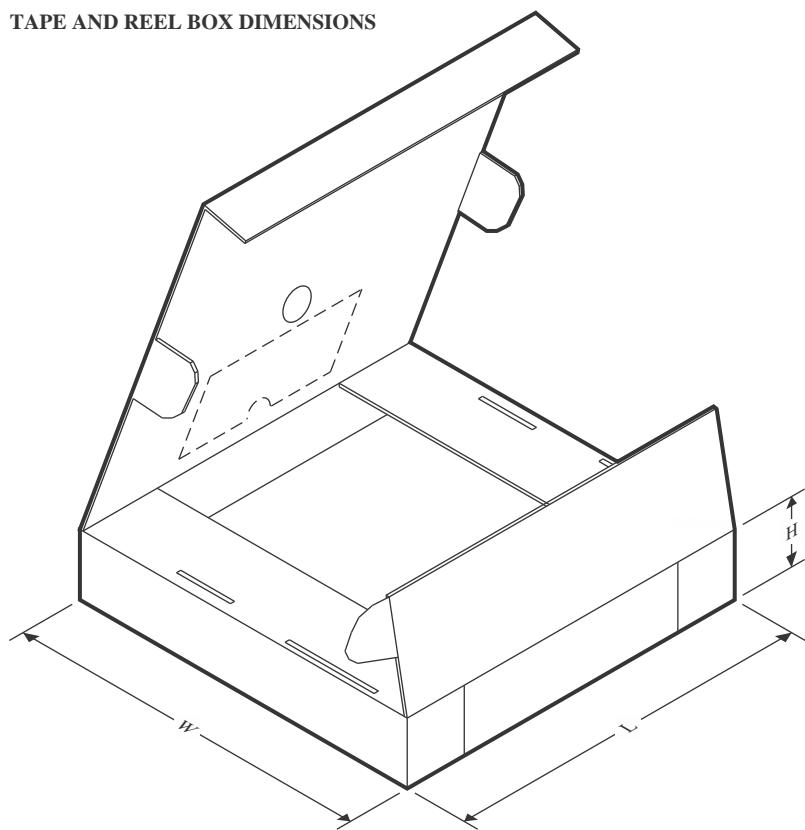

デバイスのダイ温度がサーマルシャットダウン制限のトリップポイント ( $T_{TSD}$ ) を上回ると、すべての FET が無効化され、チャージポンプがシャットダウンされ、nFAULT ピンが Low になります。さらに、OT ステータス (OT\_STS) レジスタの FAULT ビットと OTSD ビット、およびステータスレジスタ (DEV\_STS) の OTF ビットが設定されます。過熱状態が解消されると、通常動作が再開されます (ゲートドライバの動作が再開され、nFAULT ピンが解放される)。OTSD ビットが High にラッピングされたままになっている場合は、CLR\_FLT ビットまたは nSLEEP リセットパルス ( $t_{RST}$ ) のいずれかによってクリアフォルトコマンドが実行されるまで、過熱状態が発生していましたことを示しています。この保護機能をディセーブルにすることはできません。