# DRV835xF 100V 3相スマート・ゲート・ドライバ

## 1 特長

- 9~100V、トリプル・ハーフブリッジ・ゲート・ドライバ

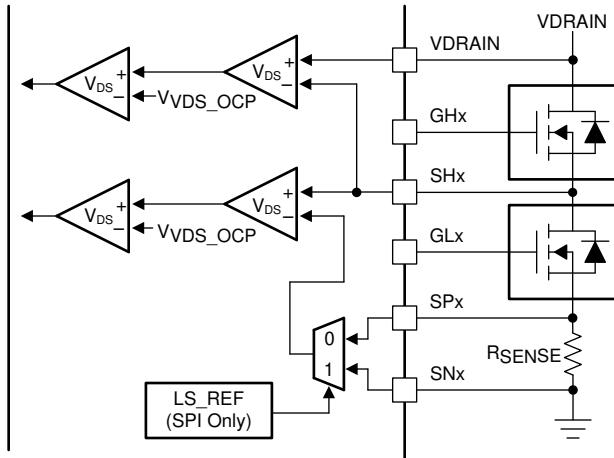

- (オプション) トリプル・ローサイド電流シャント・アンプ

- 機能安全品質管理**

- IEC 61800-5-2 機能安全準拠システム設計を支援するドキュメントを提供

- スマート・ゲート・ドライバ・アーキテクチャ

- 調整可能なスルーレート制御による EMI 性能の向上

- $V_{GS}$  ハンドシェイクおよび最小限のデッド・タイム挿入により貫通電流を回避

- 50mA~1A のピーク・ソース電流

- 100mA~2A のピーク・シンク電流

- 強力なプルダウンにより  $dV/dt$  を低減

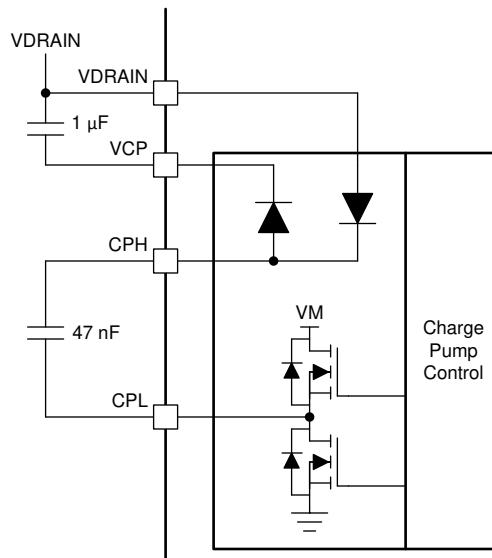

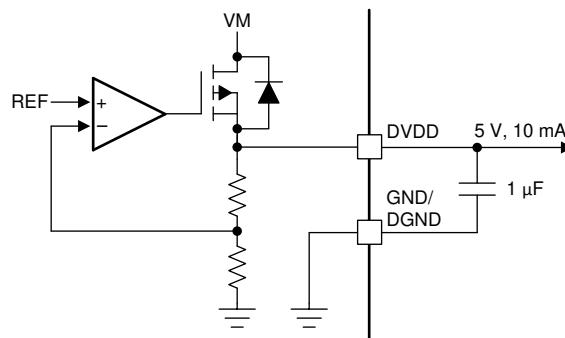

- ゲート・ドライバ電源を内蔵

- ハイサイド・ダブラー・チャージ・ポンプによる 100% PWM デューティ・サイクル制御

- ローサイドのリニア・レギュレータ

- トリプル電流シャント・アンプ内蔵

- 可変ゲイン (5, 10, 20, 40V/V)

- 双方向または単方向のサポート

- 6x, 3x, 1x、および独立 PWM モード

- 120° センサ付き動作をサポート

- SPI またはハードウェア・インターフェイスを利用可能

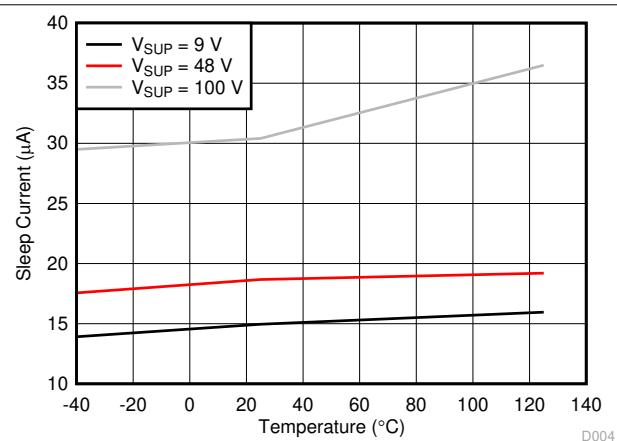

- 低消費電力のスリープ・モード ( $V_{VM} = 48V$  で  $20\mu A$ )

- 保護機能内蔵

- $VM$  低電圧誤動作防止 (UVLO)

- ゲート駆動電源低電圧 (GDUV)

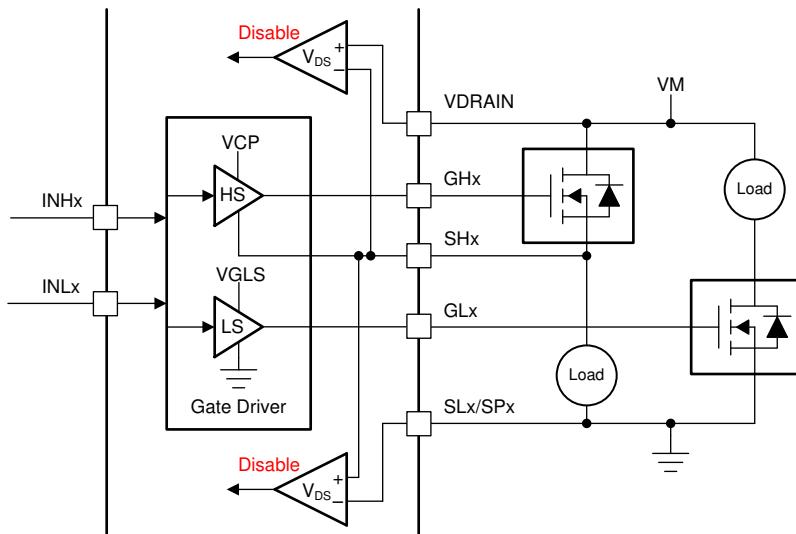

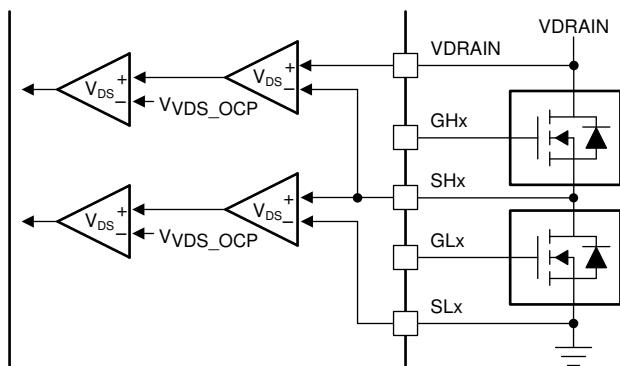

- MOSFET  $V_{DS}$  過電流保護 (OCP)

- MOSFET 貫通電流防止

- ゲート・ドライバのフォルト (GDF)

- 熱警告およびシャットダウン (OTW/OTSD)

- フォルト状態インジケータ (nFAULT)

## 2 アプリケーション

- 3相のブラシレス DC (BLDC) モータ・モジュール

- サーボ・ドライブ、ファクトリ・オートメーション

- リニア・モータ輸送用システム

- 産業用協力ロボット (コボット)

- 無人搬送車、配達用ドローン

- 電動アシスト自転車、電動スクーター、E-モビリティ

## 3 概要

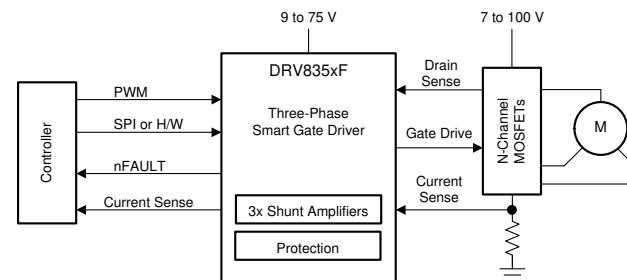

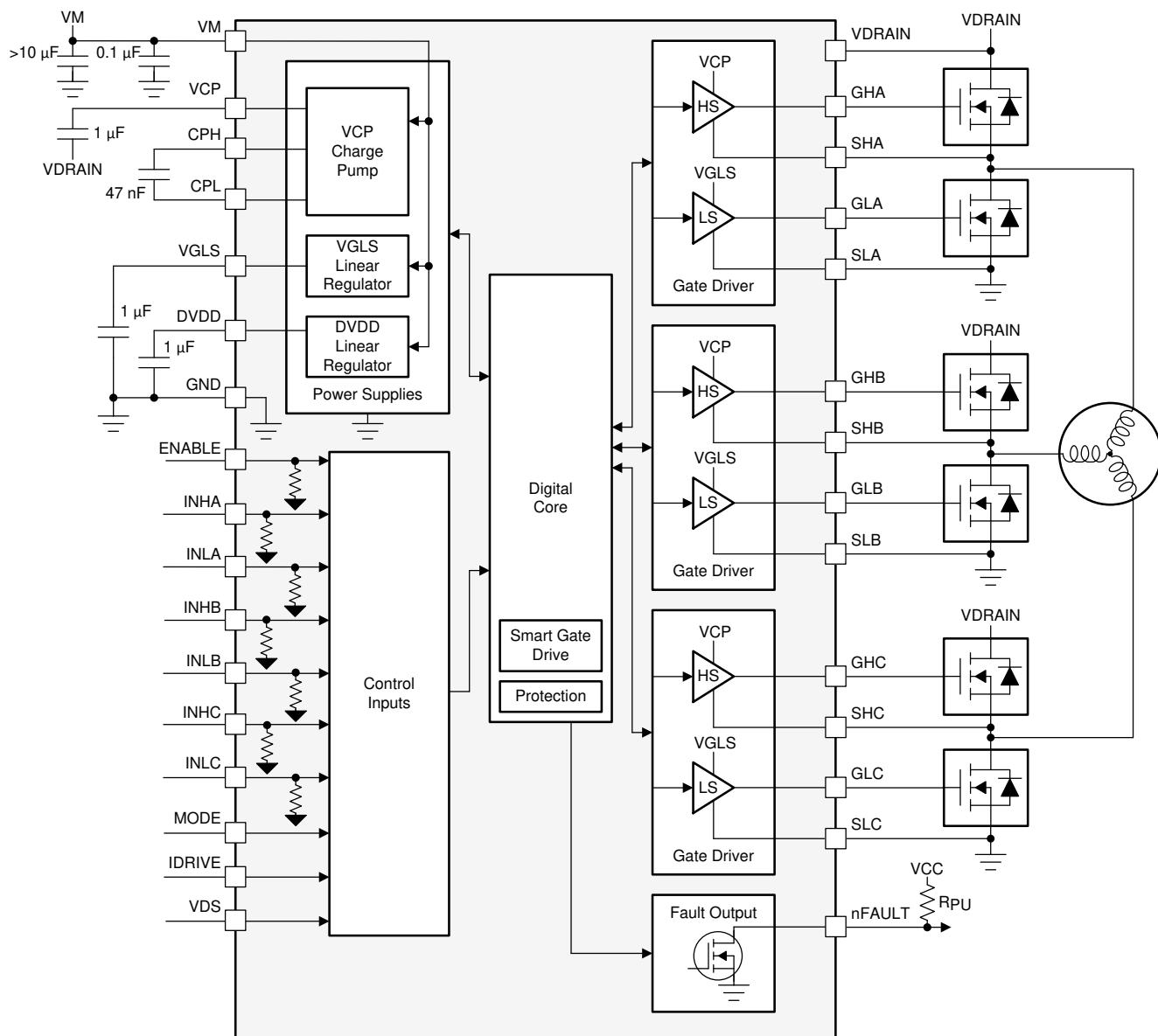

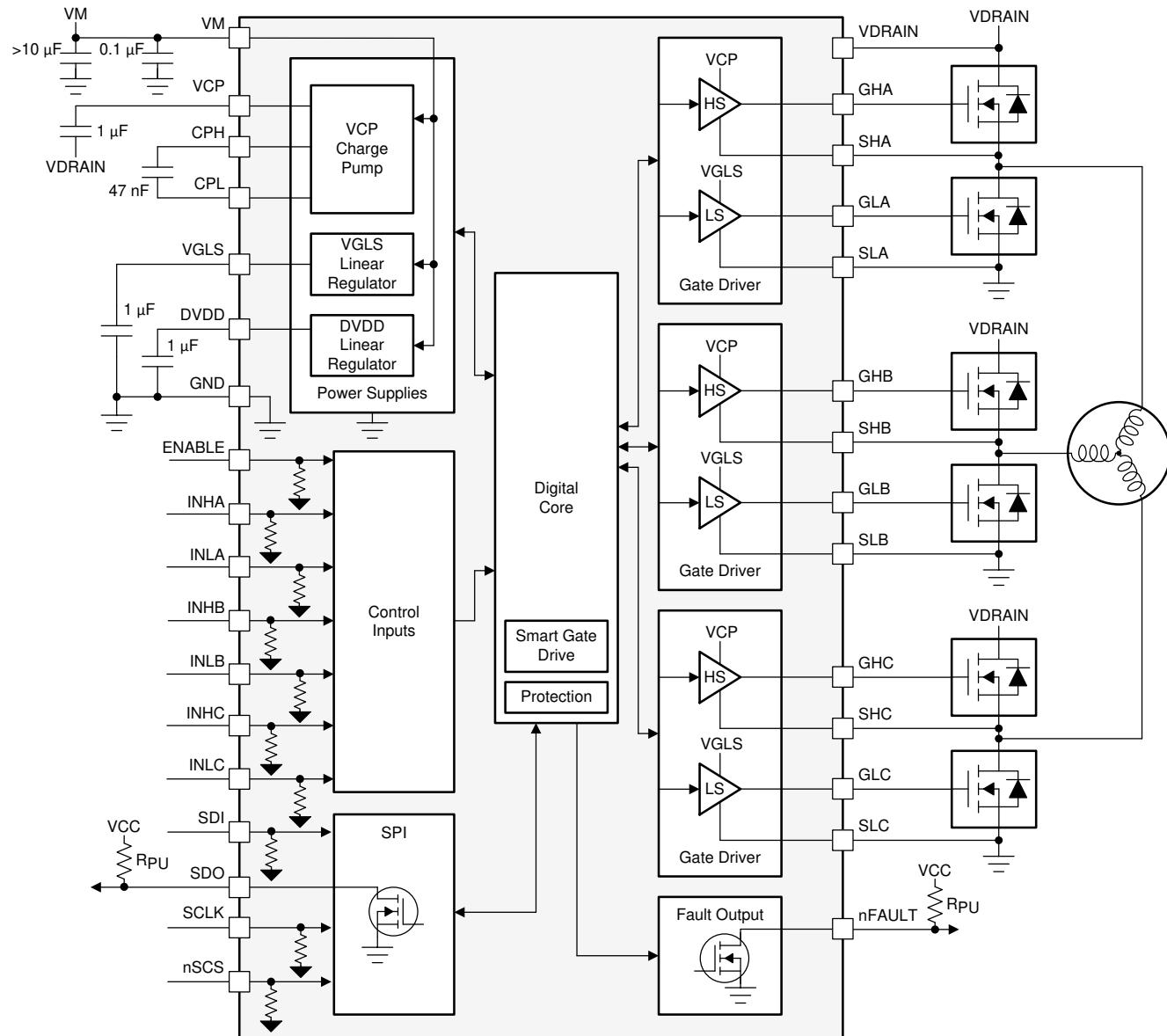

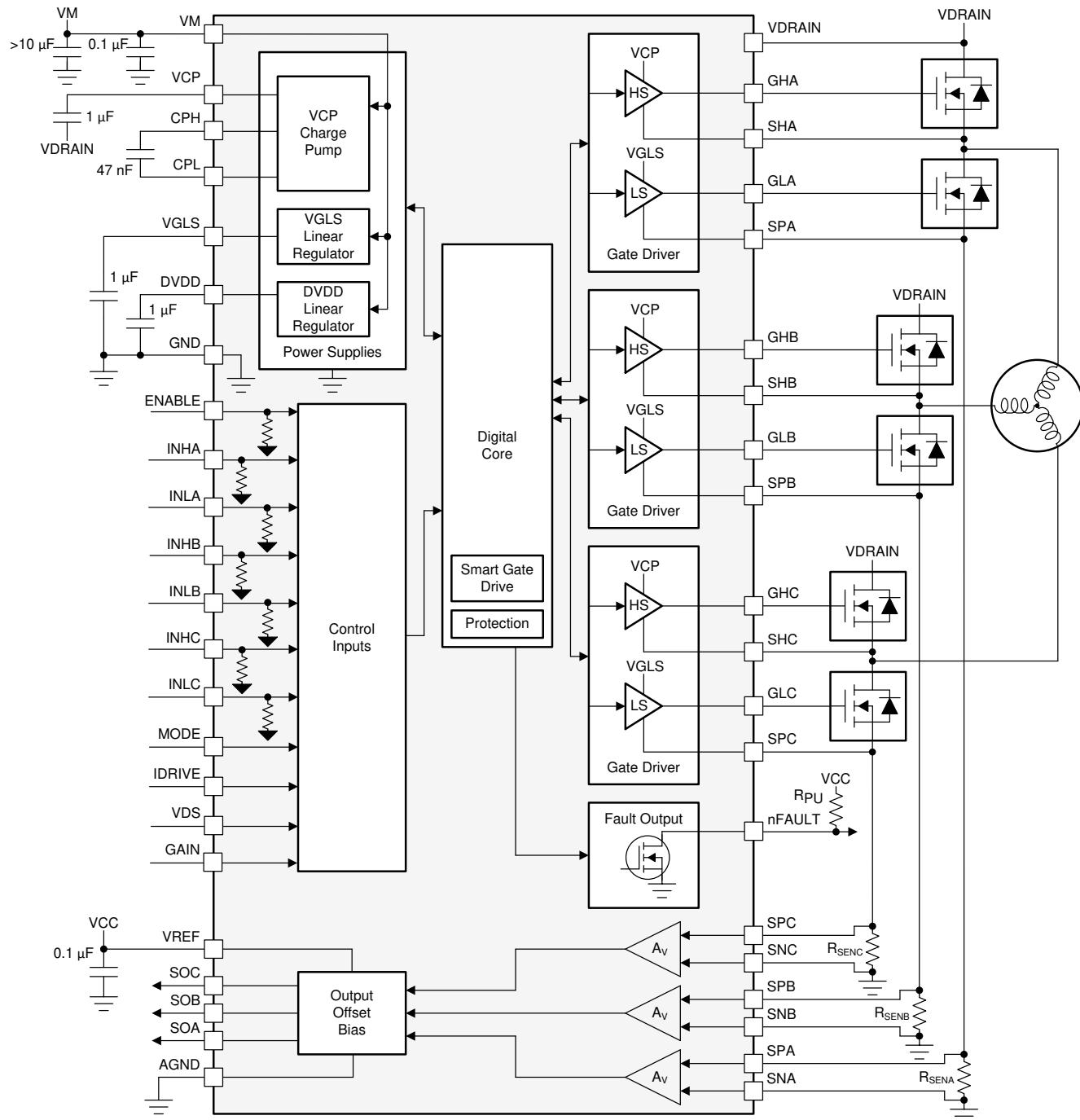

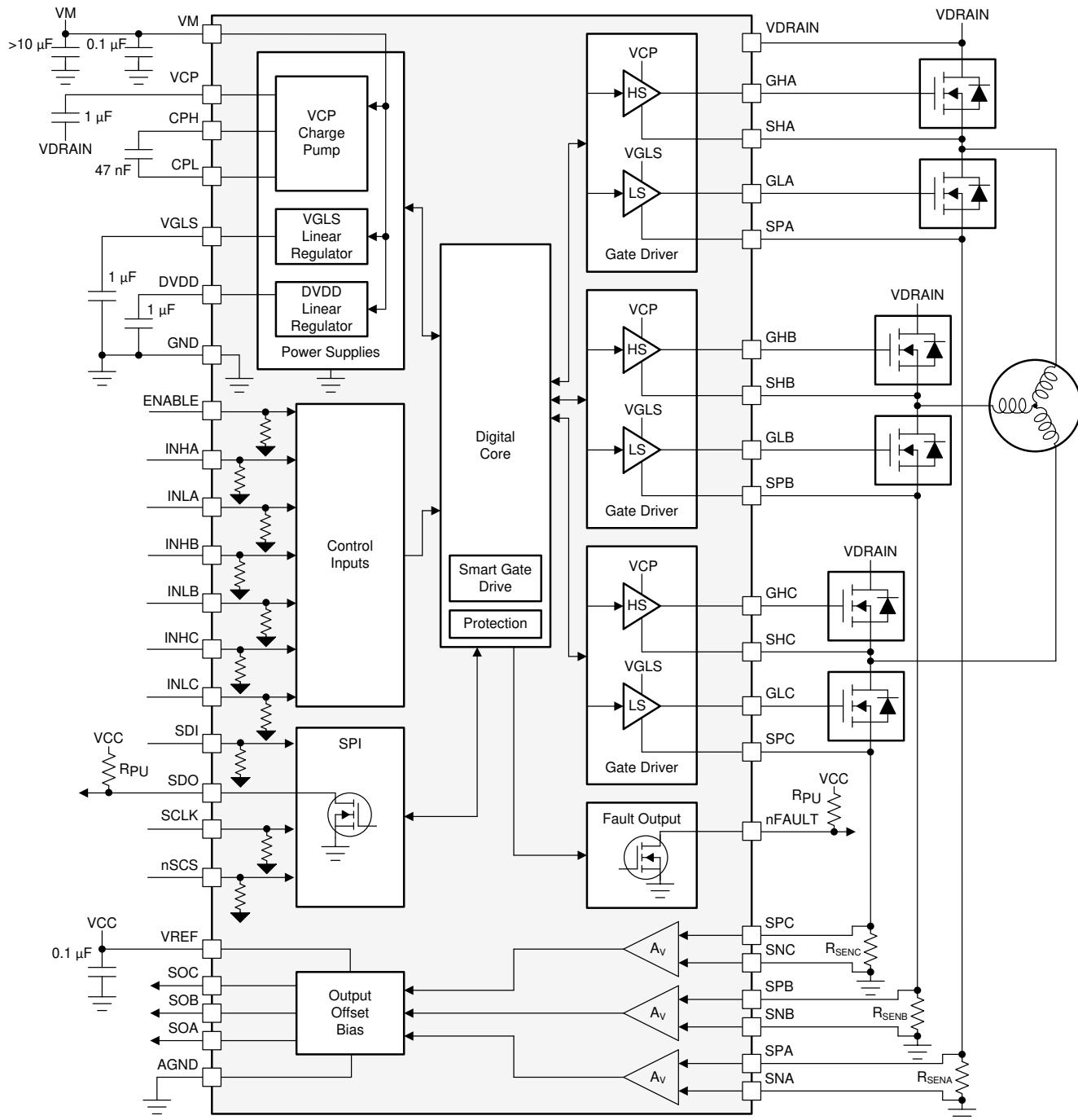

DRV835xF ファミリのデバイスは、3相ブラシレス DC (BLDC) モータ・アプリケーション向けの高度に統合されたゲート・ドライバです。一部のデバイス・バリエーションは、

各種モータ制御方式をサポートするための電流シャント・アンプを内蔵しています。

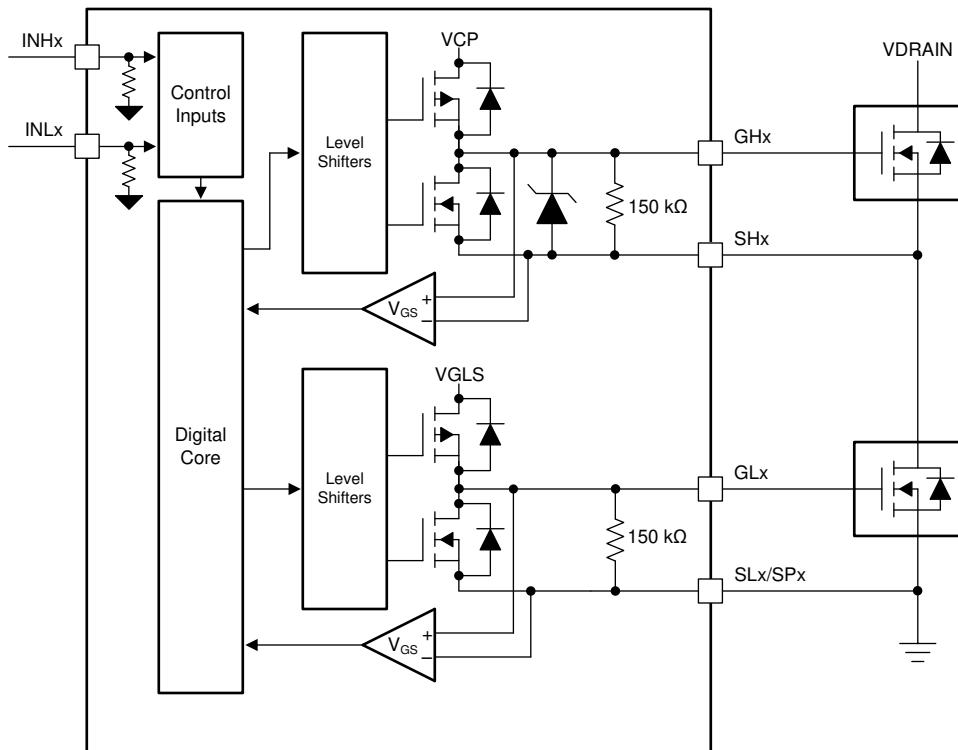

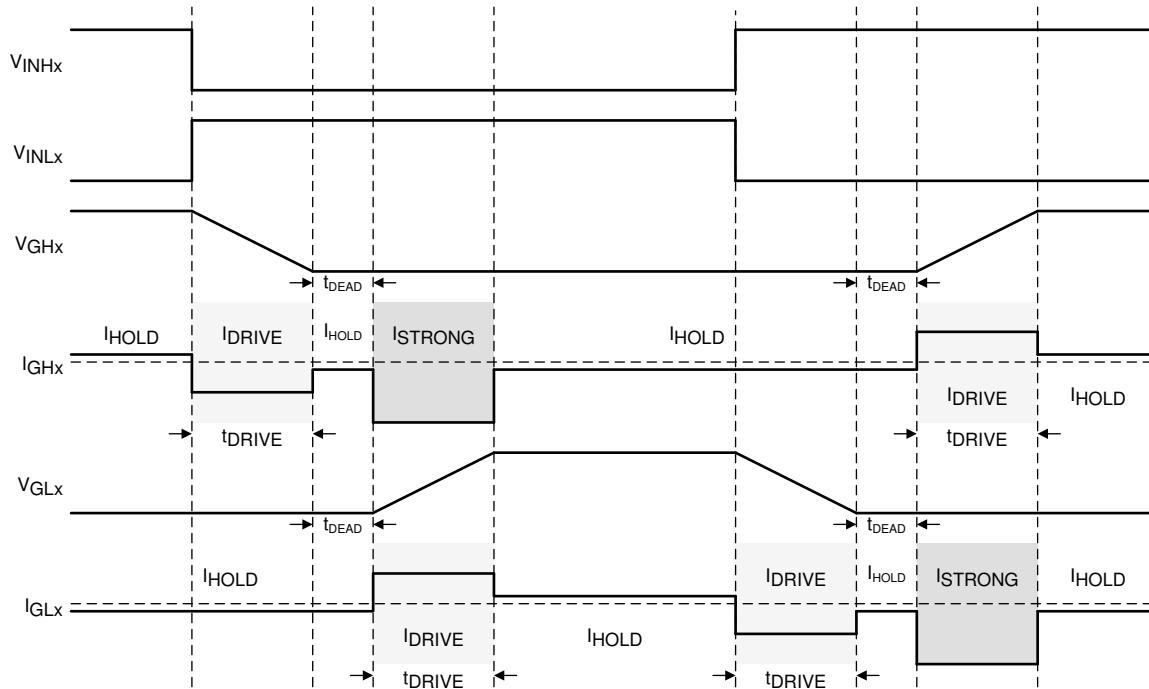

DRV835xF はスマート・ゲート・ドライバ (SGD) アーキテクチャを使用して、通常は MOSFET スルーレート制御および保護回路に必要となる外付け部品の数を減らしています。また、SGD アーキテクチャによりデッド・タイムが最適化されて貫通電流状況が防止され、MOSFET のスルーレート制御により電磁気干渉 (EMI) を柔軟に低減でき、 $V_{GS}$  監視によってゲートの短絡状況に対する保護を行えます。ゲートの強力なプルダウン回路は、望ましくない  $dV/dt$  寄生ゲート・ターンオンの防止に役立ちます。

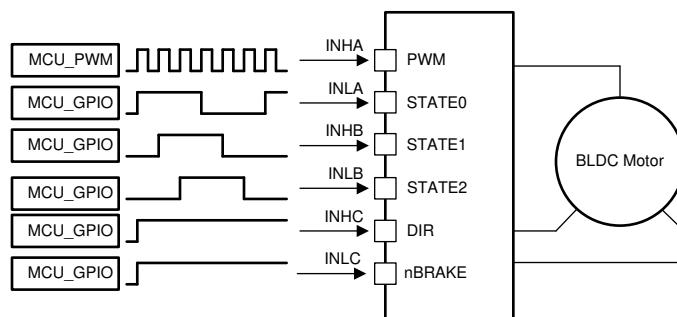

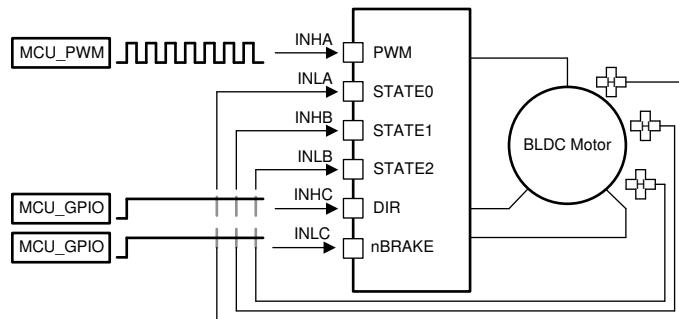

各種の PWM 制御モード (6x, 3x, 1x、および独立) がサポートされており、外部コントローラと簡単に接続できます。これらのモードにより、モータ・ドライバ PWM 制御信号のために必要なコントローラ出力の数を減らすことができます。このファミリのデバイスには 1x PWM モードも含まれており、内部ブロックの通信テーブルを使用して、BLDC モータの単純なセンサ付き台形制御に使用できます。

## 製品情報

| (1) 部品番号 | パッケージ     | 本体サイズ (公称)      |

|----------|-----------|-----------------|

| DRV8350F | WQFN (32) | 5.00mm × 5.00mm |

| DRV8353F | WQFN (40) | 6.00mm × 6.00mm |

- (1) 利用可能なパッケージについては、このデータシートの末尾にある注文情報を参照してください。

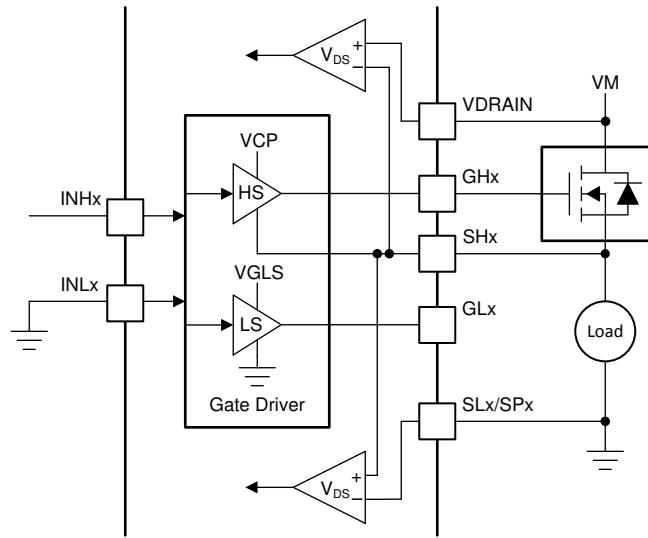

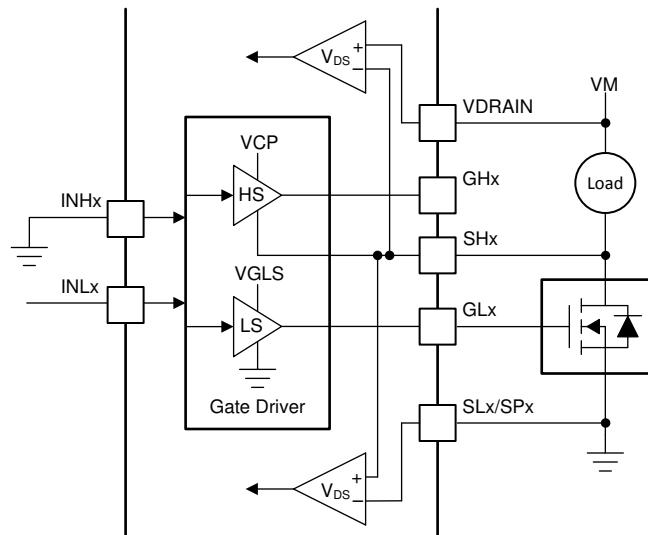

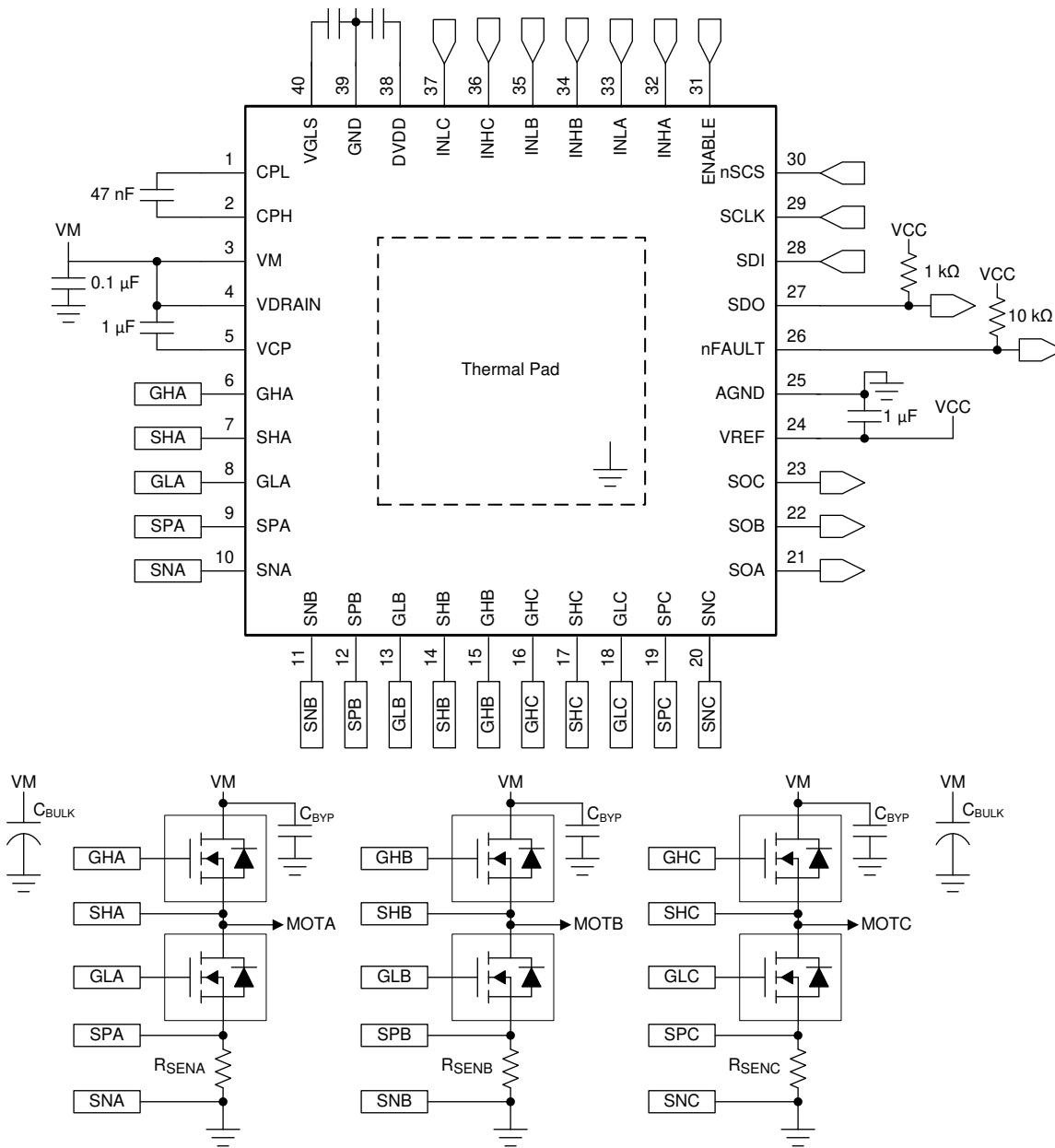

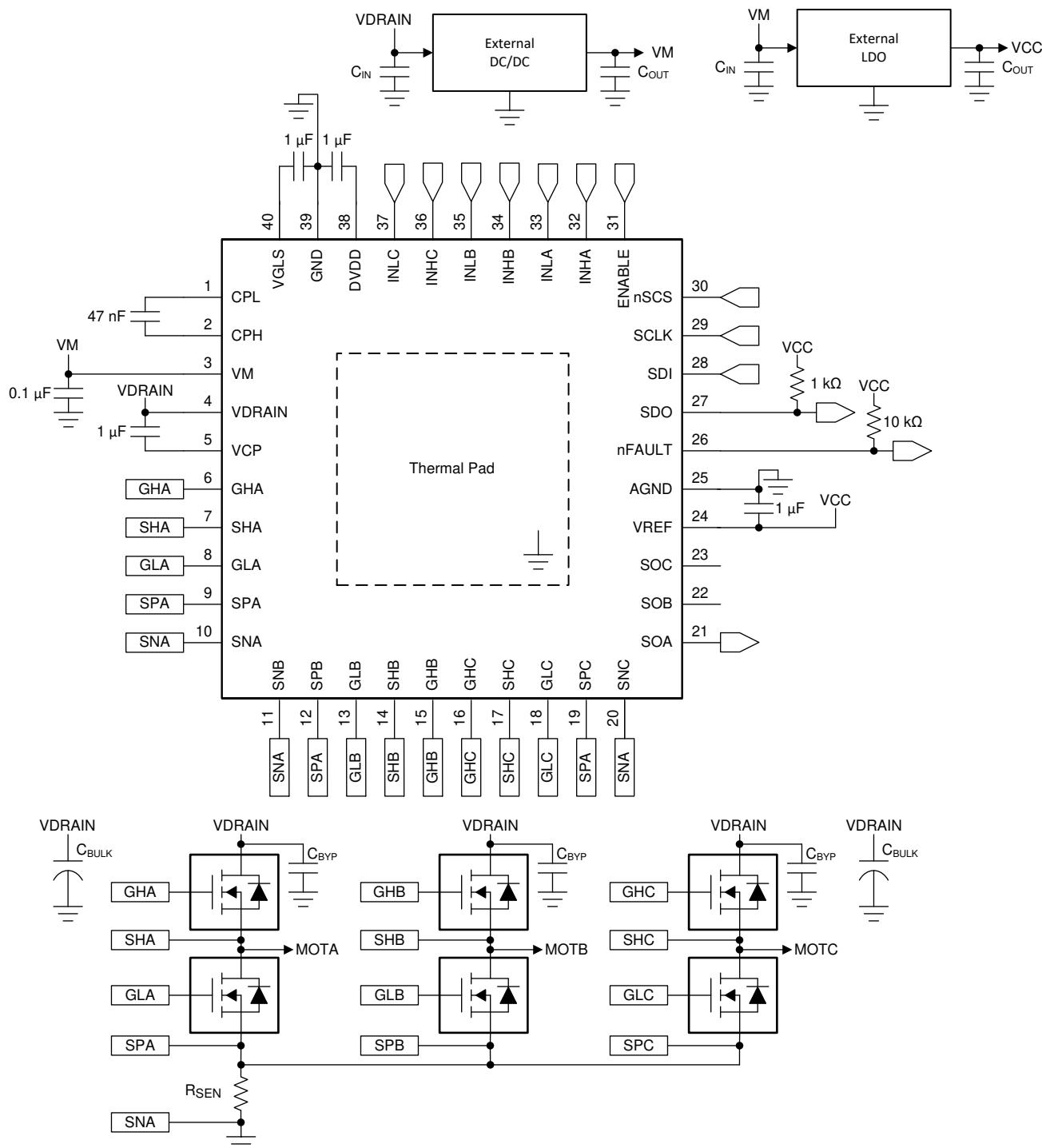

概略回路図

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、必ず最新版の英語版をご参照ください。

## 目次

|                            |           |                                                      |           |

|----------------------------|-----------|------------------------------------------------------|-----------|

| <b>1 特長</b>                | <b>1</b>  | 8.5 プログラミング                                          | <b>46</b> |

| <b>2 アプリケーション</b>          | <b>1</b>  | 8.6 レジスタ・マップ                                         | <b>48</b> |

| <b>3 概要</b>                | <b>1</b>  | <b>9 アプリケーションと実装</b>                                 | <b>59</b> |

| <b>4 改訂履歴</b>              | <b>2</b>  | 9.1 アプリケーション情報                                       | <b>59</b> |

| <b>5 デバイス比較表</b>           | <b>3</b>  | 9.2 代表的なアプリケーション                                     | <b>59</b> |

| <b>6 ピン構成と機能</b>           | <b>3</b>  | <b>10 電源に関する推奨事項</b>                                 | <b>71</b> |

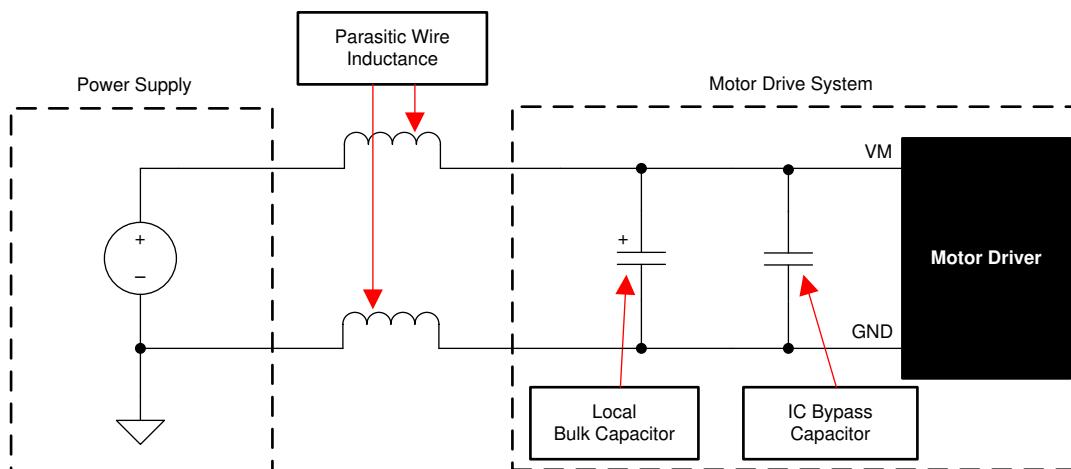

| ピン機能 — 32 ピン DRV8350F デバイス | <b>3</b>  | 10.1 バルク容量の決定                                        | <b>71</b> |

| ピン機能 — 40 ピン DRV8353F デバイス | <b>5</b>  | <b>11 レイアウト</b>                                      | <b>72</b> |

| <b>7 仕様</b>                | <b>7</b>  | 11.1 レイアウトの注意点                                       | <b>72</b> |

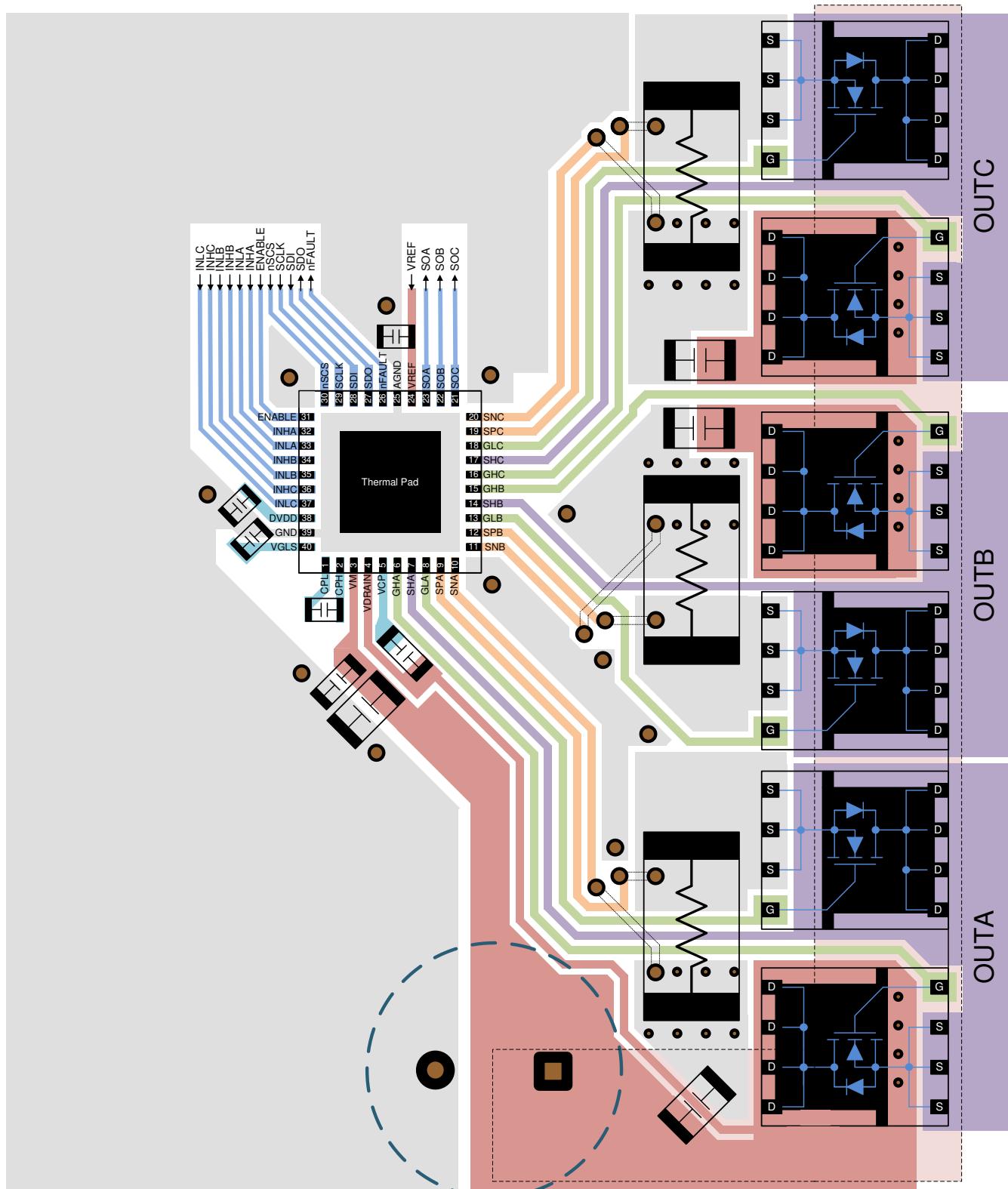

| 7.1 絶対最大定格                 | <b>7</b>  | 11.2 レイアウト例                                          | <b>73</b> |

| 7.2 ESD 定格                 | <b>7</b>  | <b>12 デバイスおよびドキュメントのサポート</b>                         | <b>74</b> |

| 7.3 推奨動作条件                 | <b>8</b>  | 12.1 デバイスのサポート                                       | <b>74</b> |

| 7.4 熱に関する情報                | <b>8</b>  | 12.2 ドキュメントのサポート                                     | <b>74</b> |

| 7.5 電気的特性                  | <b>9</b>  | 12.3 関連リンク                                           | <b>75</b> |

| 7.6 SPI のタイミング要件           | <b>15</b> | 12.4 Receiving Notification of Documentation Updates | <b>75</b> |

| 7.7 代表的特性                  | <b>16</b> | 12.5 サポート・リソース                                       | <b>75</b> |

| <b>8 詳細説明</b>              | <b>18</b> | 12.6 商標                                              | <b>75</b> |

| 8.1 概要                     | <b>18</b> | 12.7 Electrostatic Discharge Caution                 | <b>75</b> |

| 8.2 機能ブロック図                | <b>19</b> | 12.8 Glossary                                        | <b>75</b> |

| 8.3 機能説明                   | <b>22</b> | <b>13 メカニカル、パッケージ、および注文情報</b>                        | <b>75</b> |

| 8.4 デバイスの機能モード             | <b>45</b> |                                                      |           |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision A (October 2020) to Revision B (August 2021)</b> | <b>Page</b> |

|---------------------------------------------------------------------------|-------------|

| • DRV8353RF と DRV8350RF への参照を削除                                           | <b>1</b>    |

| • 主要および代替アプリケーションの図を更新                                                    | <b>59</b>   |

| • レイアウト例を更新                                                               | <b>73</b>   |

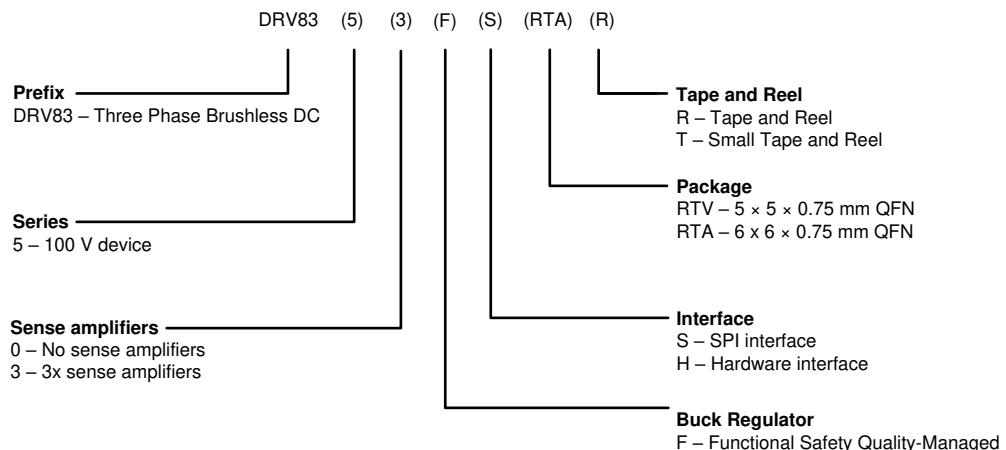

| • 「デバイス命名規則」を更新                                                           | <b>74</b>   |

| <b>Changes from Revision * (August 2018) to Revision A (October 2020)</b> | <b>Page</b> |

|---------------------------------------------------------------------------|-------------|

| • ドキュメントのステータスを「量産データ」に変更                                                 | <b>1</b>    |

| • DRV8350 および DRV8353 からプレビューのみという注記を削除                                   | <b>1</b>    |

## 5 デバイス比較表

| デバイス     | バリエーション   | シャント・アンプ | インターフェイス   |

|----------|-----------|----------|------------|

| DRV8350F | DRV8350FH | 0        | ハードウェア (H) |

|          | DRV8350FS |          | SPI (S)    |

| DRV8353F | DRV8353FH | 3        | ハードウェア (H) |

|          | DRV8353FS |          | SPI (S)    |

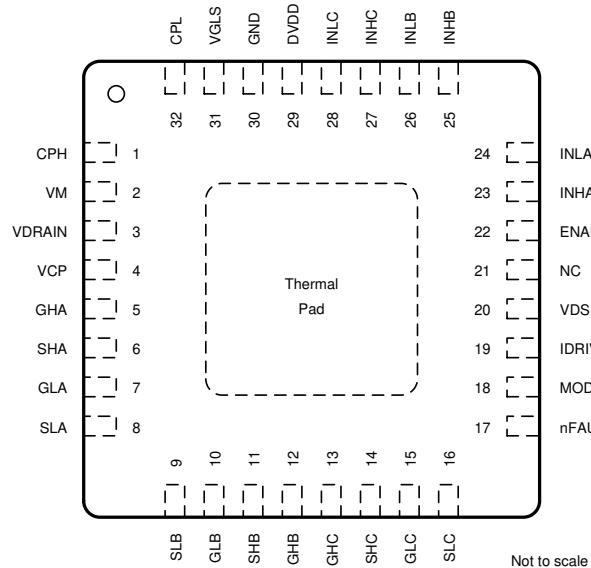

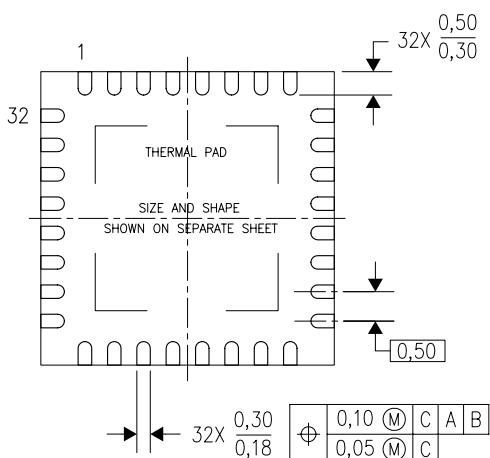

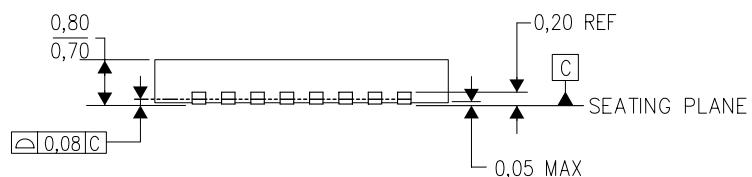

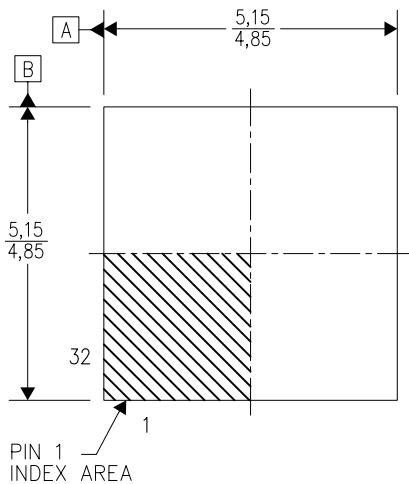

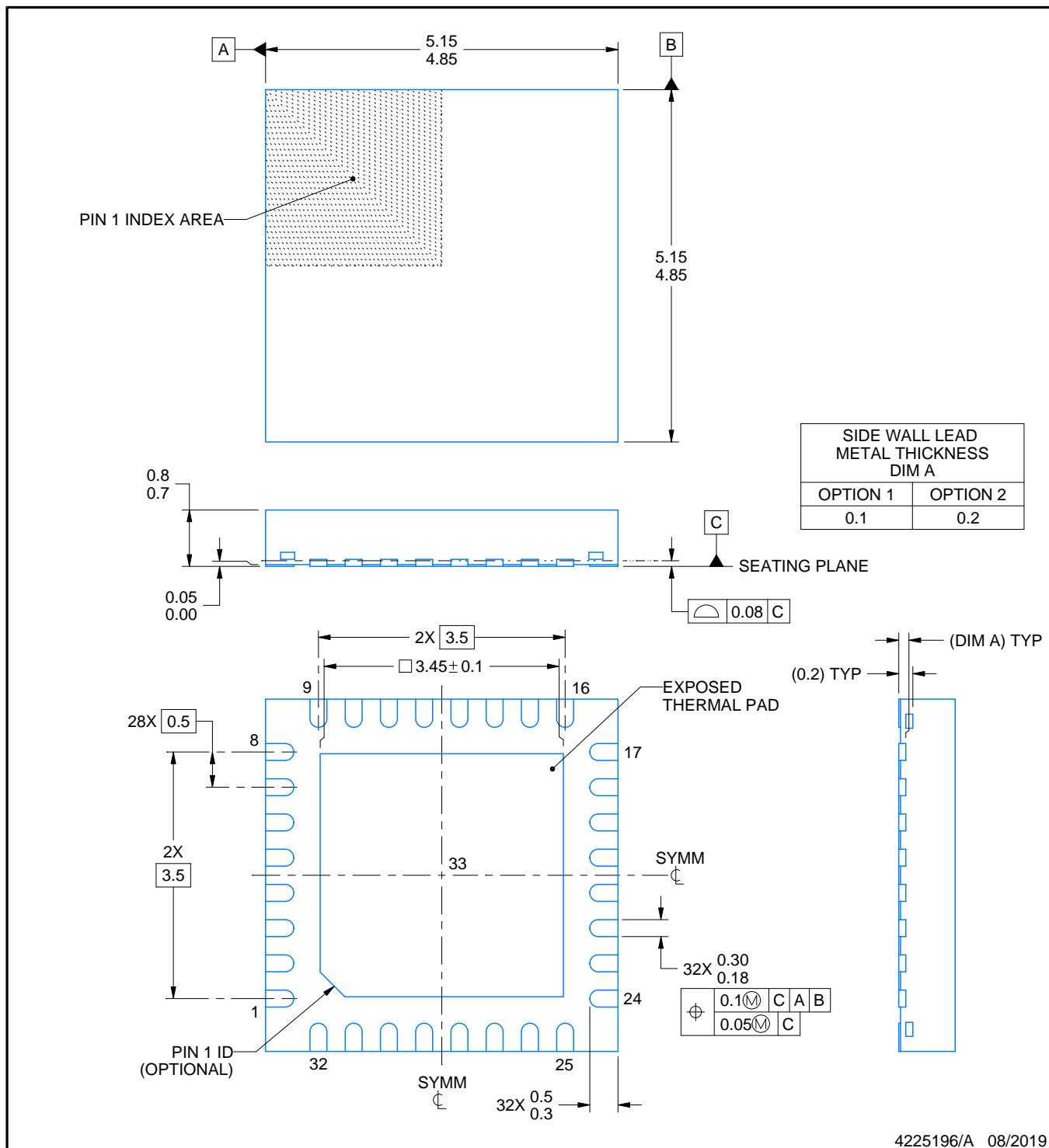

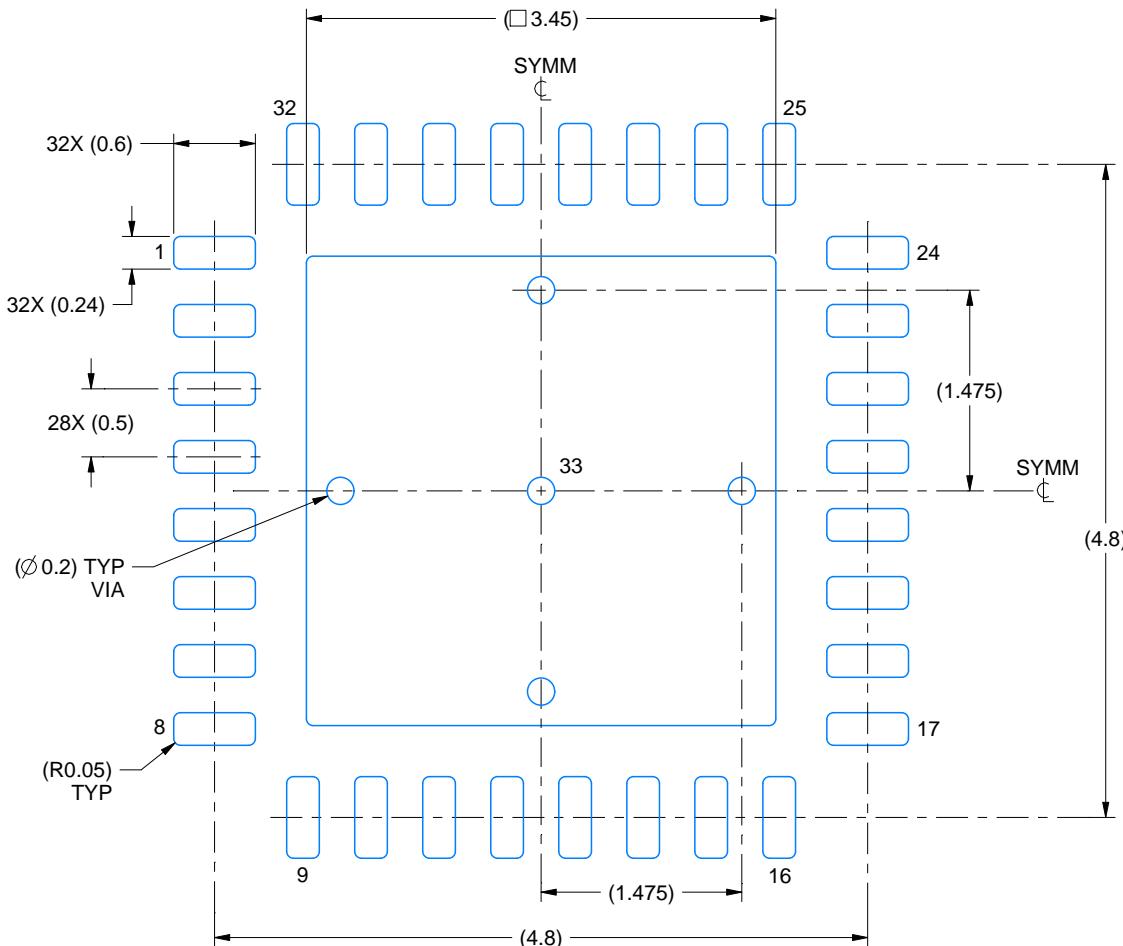

## 6 ピン構成と機能

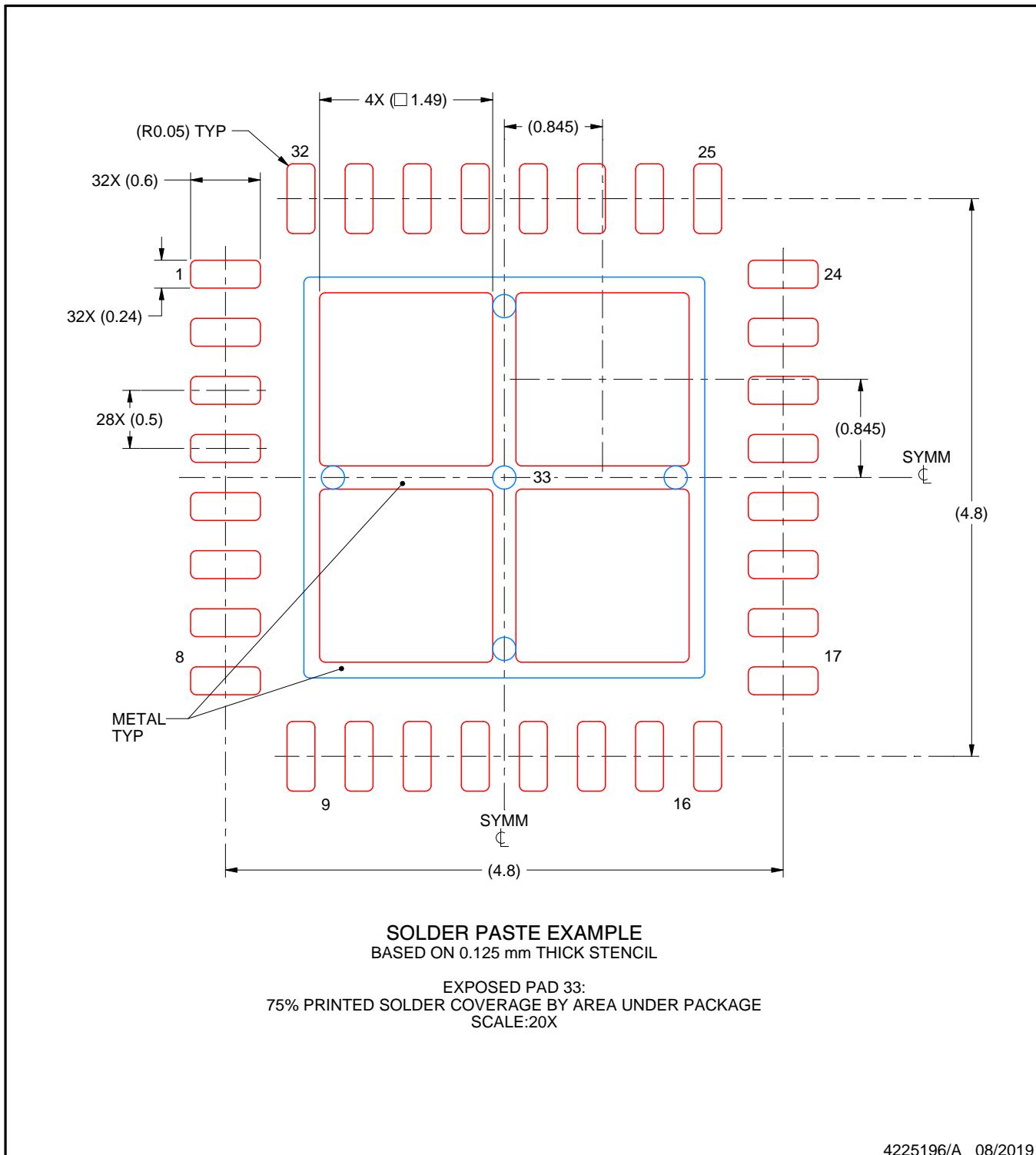

図 6-1. DRV8350FH RTV パッケージ 32 ピン WQFN

(露出サーマル・パッド付き) 上面図

図 6-2. DRV8350FS RTV パッケージ 32 ピン WQFN

(露出サーマル・パッド付き) 上面図

## ピン機能 – 32 ピン DRV8350F デバイス

| 名前     | ピン |           | タイプ (1) | 説明                                                                                                    |

|--------|----|-----------|---------|-------------------------------------------------------------------------------------------------------|

|        | 番号 | DRV8350FH |         |                                                                                                       |

| CPH    | 1  | 1         | PWR     | チャージ・ポンプのスイッチング・ノード。X5R または X7R、47nF、VDRAIN 定格セラミック・コンデンサを CPH ピンと CPL ピンの間に接続します。                    |

| CPL    | 32 | 32        | PWR     | チャージ・ポンプのスイッチング・ノード。X5R または X7R、47nF、VDRAIN 定格セラミック・コンデンサを CPH ピンと CPL ピンの間に接続します。                    |

| DVDD   | 29 | 29        | PWR     | 5V 内部レギュレータ出力。X5R または X7R、1μF、6.3V セラミック・コンデンサを DVDD ピンと GND ピンの間に接続します。このレギュレータは最大 10mA を外部にソースできます。 |

| ENABLE | 22 | 22        | I       | ゲート・ドライバのイネーブル。このピンを論理 Low にすると、本デバイスは低消費電力のスリープ・モードに移行します。8~40μs のパルスを使ってフォルト条件をリセットできます。            |

| GHA    | 5  | 5         | O       | ハイサイド・ゲート・ドライバ出力。ハイサイド・パワー MOSFET のゲートに接続します。                                                         |

| GHB    | 12 | 12        | O       | ハイサイド・ゲート・ドライバ出力。ハイサイド・パワー MOSFET のゲートに接続します。                                                         |

| GHC    | 13 | 13        | O       | ハイサイド・ゲート・ドライバ出力。ハイサイド・パワー MOSFET のゲートに接続します。                                                         |

| GLA    | 7  | 7         | O       | ローサイド・ゲート・ドライバ出力。ローサイド・パワー MOSFET のゲートに接続します。                                                         |

| GLB    | 10 | 10        | O       | ローサイド・ゲート・ドライバ出力。ローサイド・パワー MOSFET のゲートに接続します。                                                         |

| GLC    | 15 | 15        | O       | ローサイド・ゲート・ドライバ出力。ローサイド・パワー MOSFET のゲートに接続します。                                                         |

| GND    | 30 | 30        | PWR     | デバイスの基本的なグランド。システム・グランドに接続します。                                                                        |

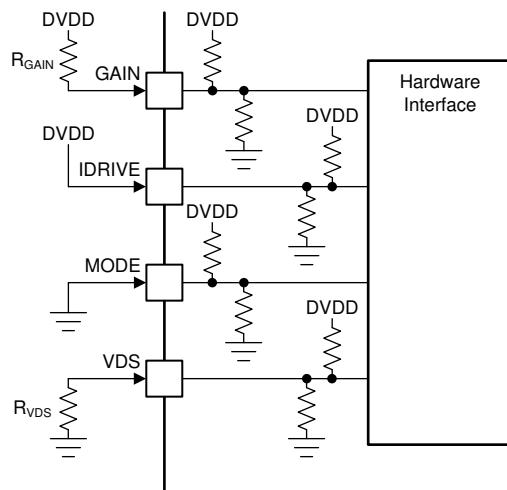

| IDRIVE | 19 | —         | I       | ゲート駆動出力電流設定。このピンは、外付け抵抗で設定される 7 レベル入力ピンです。                                                            |

| INHA   | 23 | 23        | I       | ハイサイド・ゲート・ドライバの制御入力。このピンはハイサイド・ゲート・ドライバの出力を制御します。                                                     |

| INHB   | 25 | 25        | I       | ハイサイド・ゲート・ドライバの制御入力。このピンはハイサイド・ゲート・ドライバの出力を制御します。                                                     |

| INHC   | 27 | 27        | I       | ハイサイド・ゲート・ドライバの制御入力。このピンはハイサイド・ゲート・ドライバの出力を制御します。                                                     |

| 名前     | ピン        |           | タイプ <sup>(1)</sup> | 説明                                                                                                                           |  |  |

|--------|-----------|-----------|--------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

|        | 番号        |           |                    |                                                                                                                              |  |  |

|        | DRV8350FH | DRV8350FS |                    |                                                                                                                              |  |  |

| INLA   | 24        | 24        | I                  | ローサイド・ゲート・ドライバの制御入力。このピンはローサイド・ゲート・ドライバの出力を制御します。                                                                            |  |  |

| INLB   | 26        | 26        | I                  | ローサイド・ゲート・ドライバの制御入力。このピンはローサイド・ゲート・ドライバの出力を制御します。                                                                            |  |  |

| INLC   | 28        | 28        | I                  | ローサイド・ゲート・ドライバの制御入力。このピンはローサイド・ゲート・ドライバの出力を制御します。                                                                            |  |  |

| MODE   | 18        | —         | I                  | PWM 入力モード設定。このピンは、外付け抵抗で設定される 4 レベル入力ピンです。                                                                                   |  |  |

| NC     | 21        | —         | NC                 | 内部で接続されていません。このピンはフローティングのままにしておくことも、システム・グランドに接続することもできます。                                                                  |  |  |

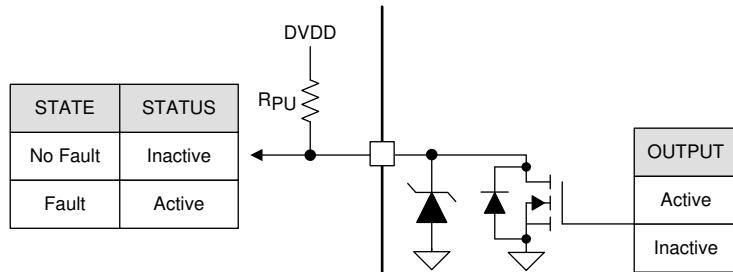

| nFAULT | 17        | 17        | OD                 | フォルト通知出力。このピンはフォルト条件中論理 Low にプルされ、外付けプルアップ抵抗を必要とします。                                                                         |  |  |

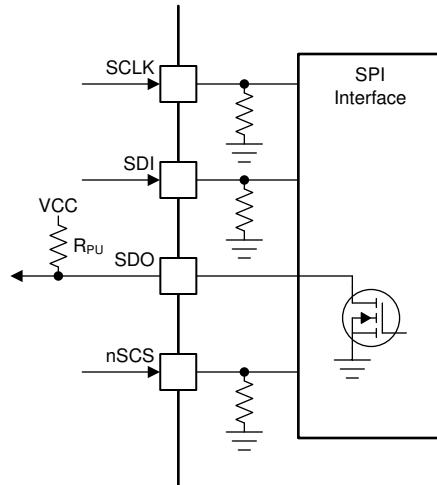

| nSCS   | —         | 21        | I                  | シリアル・チップ選択。このピンを論理 Low にすると、シリアル・インターフェイス通信が有効になります。                                                                         |  |  |

| SCLK   | —         | 20        | I                  | シリアル・クロック入力。シリアル・データは、このピンの対応する立ち上がりおよび立ち下がりエッジでシフト・アウトおよびキャプチャされます。                                                         |  |  |

| SDI    | —         | 19        | I                  | シリアル・データ入力。データは、SCLK ピンの立ち下がりエッジでキャプチャされます。                                                                                  |  |  |

| SDO    | —         | 18        | OD                 | シリアル・データ出力。データは、SCLK ピンの立ち上がりエッジでシフト・アウトされます。このピンは外付けプルアップ抵抗を必要とします。                                                         |  |  |

| SHA    | 6         | 6         | I                  | ハイサイド・ソース検出入力。ハイサイド・パワー MOSFET のソースに接続します。                                                                                   |  |  |

| SHB    | 11        | 11        | I                  | ハイサイド・ソース検出入力。ハイサイド・パワー MOSFET のソースに接続します。                                                                                   |  |  |

| SHC    | 14        | 14        | I                  | ハイサイド・ソース検出入力。ハイサイド・パワー MOSFET のソースに接続します。                                                                                   |  |  |

| SLA    | 8         | 8         | I                  | ローサイド・ソース検出入力。ローサイド・パワー MOSFET のソースに接続します。                                                                                   |  |  |

| SLB    | 9         | 9         | I                  | ローサイド・ソース検出入力。ローサイド・パワー MOSFET のソースに接続します。                                                                                   |  |  |

| SLC    | 16        | 16        | I                  | ローサイド・ソース検出入力。ローサイド・パワー MOSFET のソースに接続します。                                                                                   |  |  |

| VCP    | 4         | 4         | PWR                | チャージ・ポンプの出力。X5R または X7R、1μF、16V セラミック・コンデンサを VCP ピンと VDRAIN ピンの間に接続します。                                                      |  |  |

| VDRAIN | 3         | 3         | I                  | ハイサイド MOSFET ドレイン検出入力およびチャージ・ポンプ基準電圧。MOSFET のドレインの共通ポイントに接続します。                                                              |  |  |

| VDS    | 20        | —         | I                  | VDS モニタのトリップ・ポイント設定。このピンは、外付け抵抗で設定される 7 レベル入力ピンです。                                                                           |  |  |

| VGELS  | 31        | 31        | PWR                | 11V 内部レギュレータ出力。X5R または X7R、1μF、16V セラミック・コンデンサを VGELS ピンと GND ピンの間に接続します。                                                    |  |  |

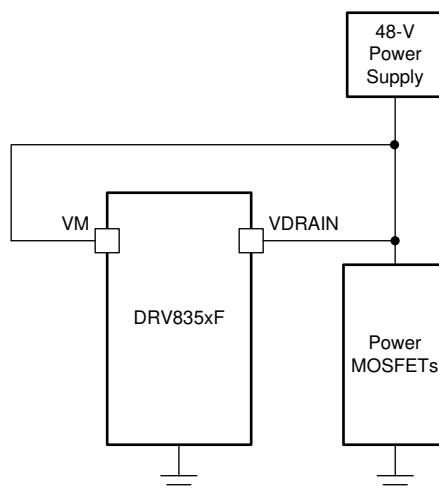

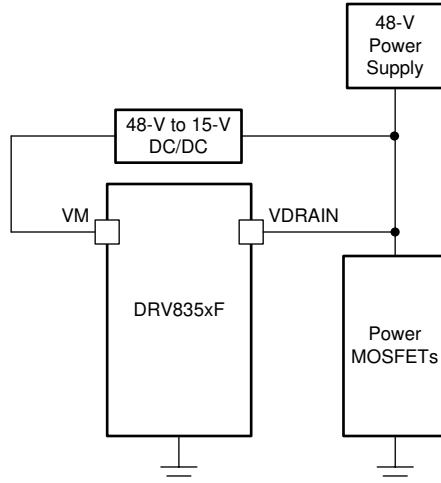

| VM     | 2         | 2         | PWR                | ゲート・ドライバの電源入力。VDRAIN または個別のゲート・ドライバ電源電圧に接続します。X5R または X7R、0.1μF、VM 定格セラミック・コンデンサと 10μF 以上のローカル・コンデンサを VM ピンと GND ピンの間に接続します。 |  |  |

(1) PWR = 電源、I = 入力、O = 出力、NC = 接続なし、OD = オープン・ドレイン

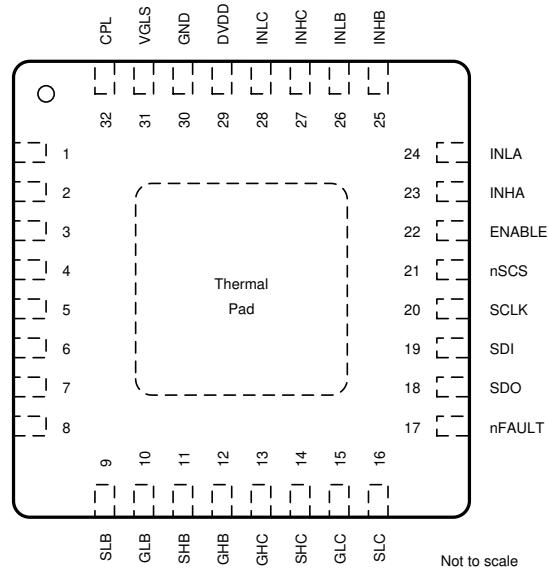

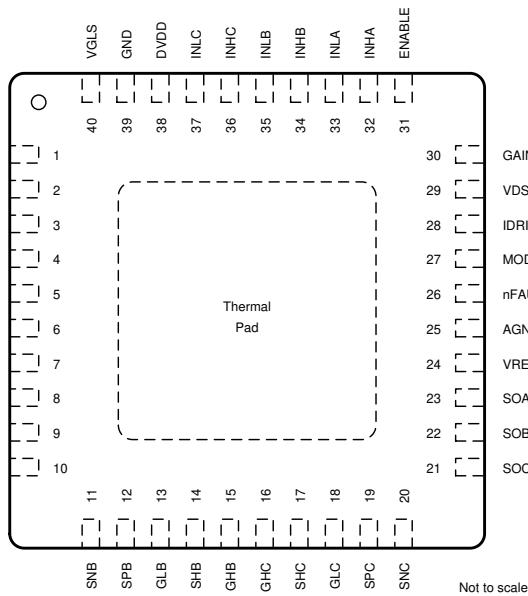

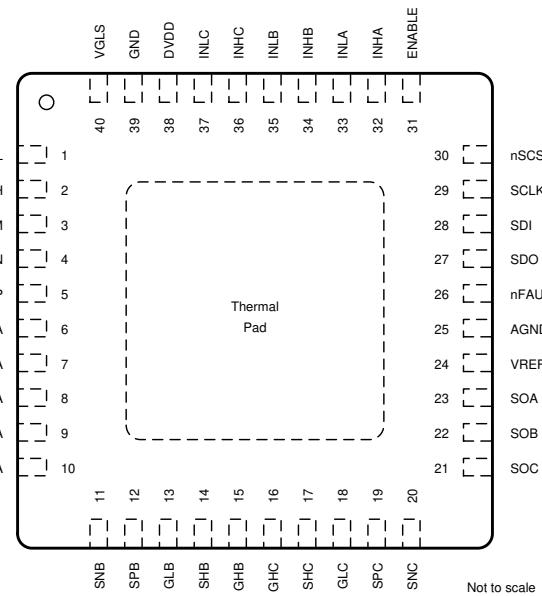

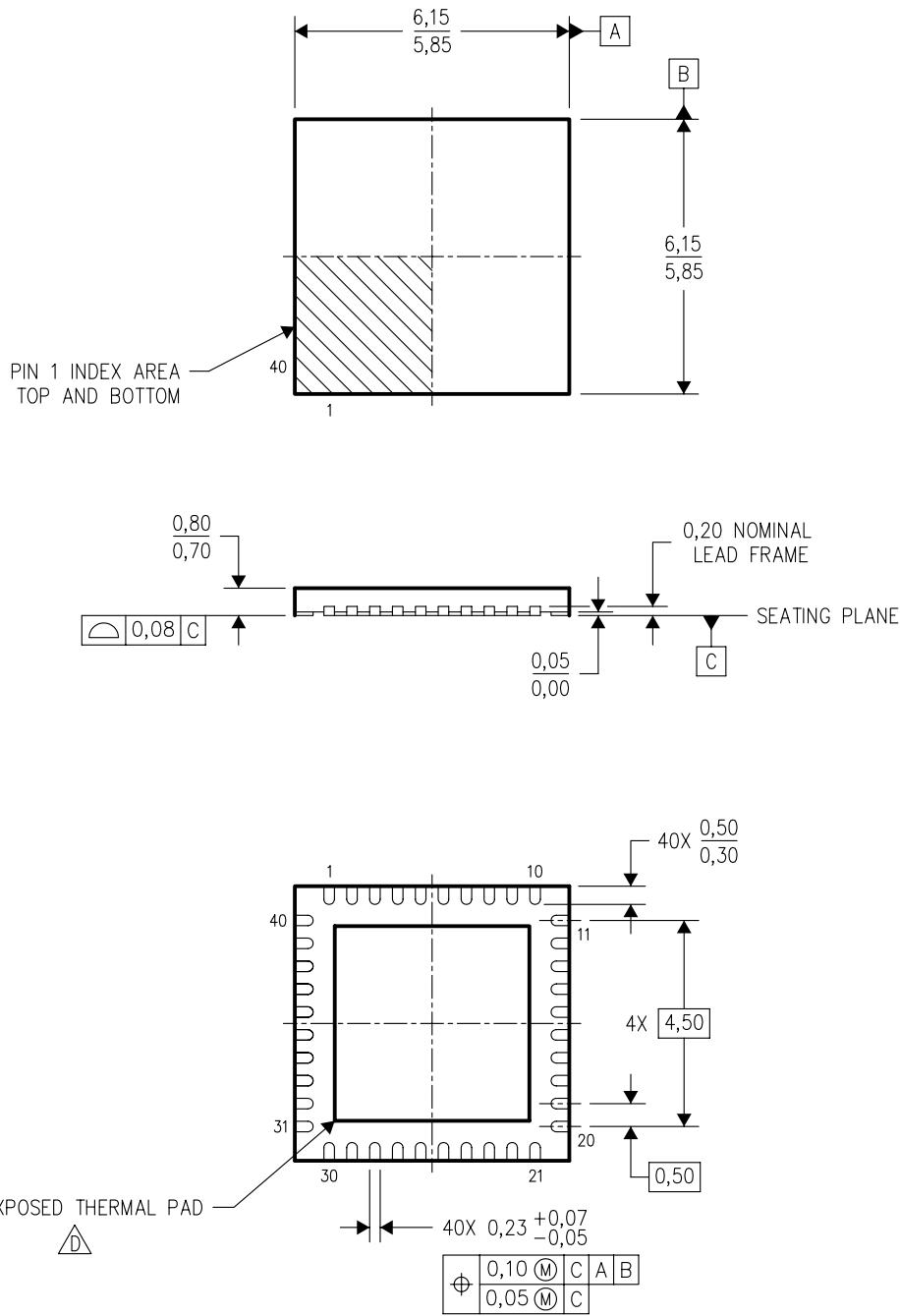

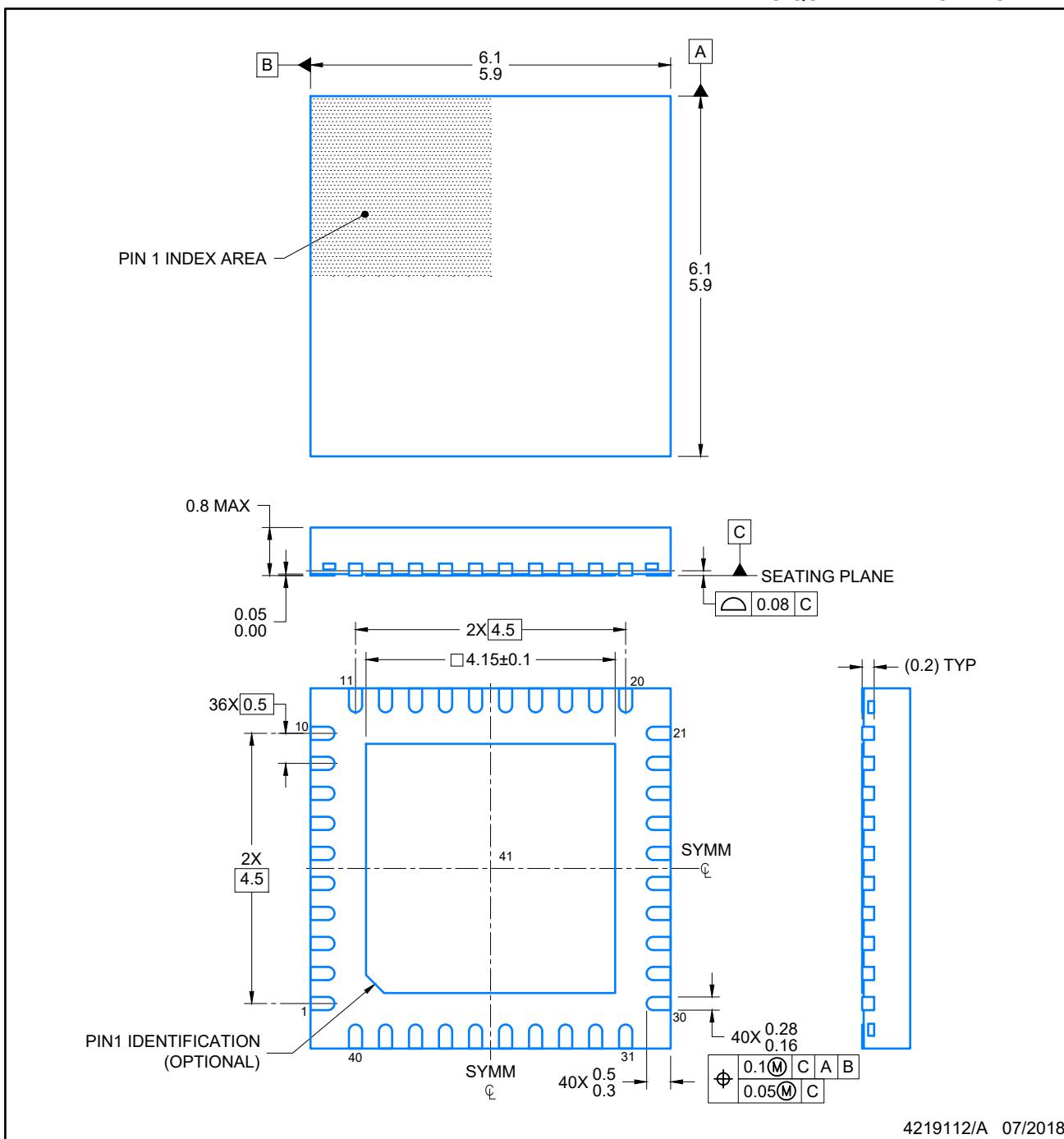

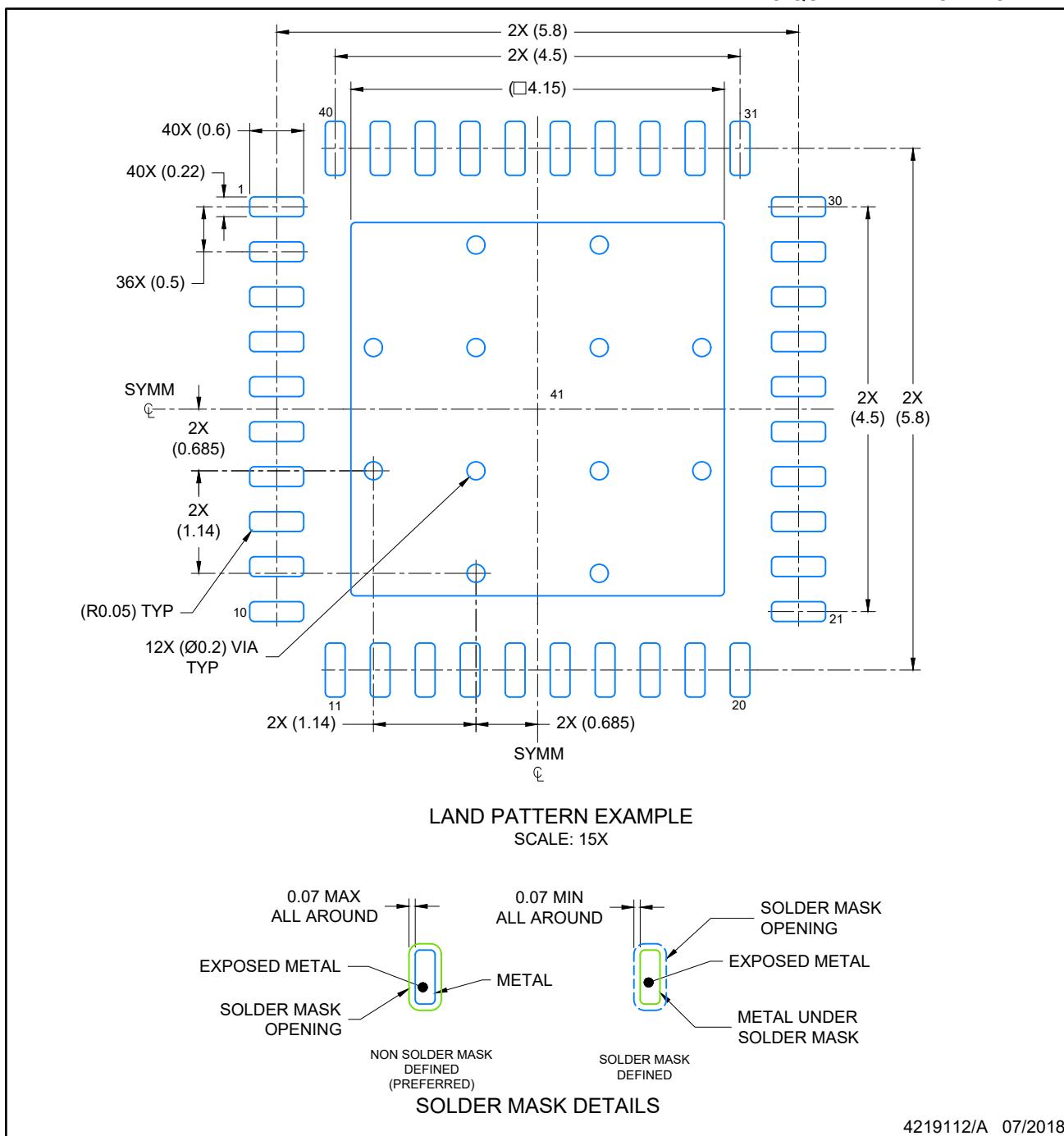

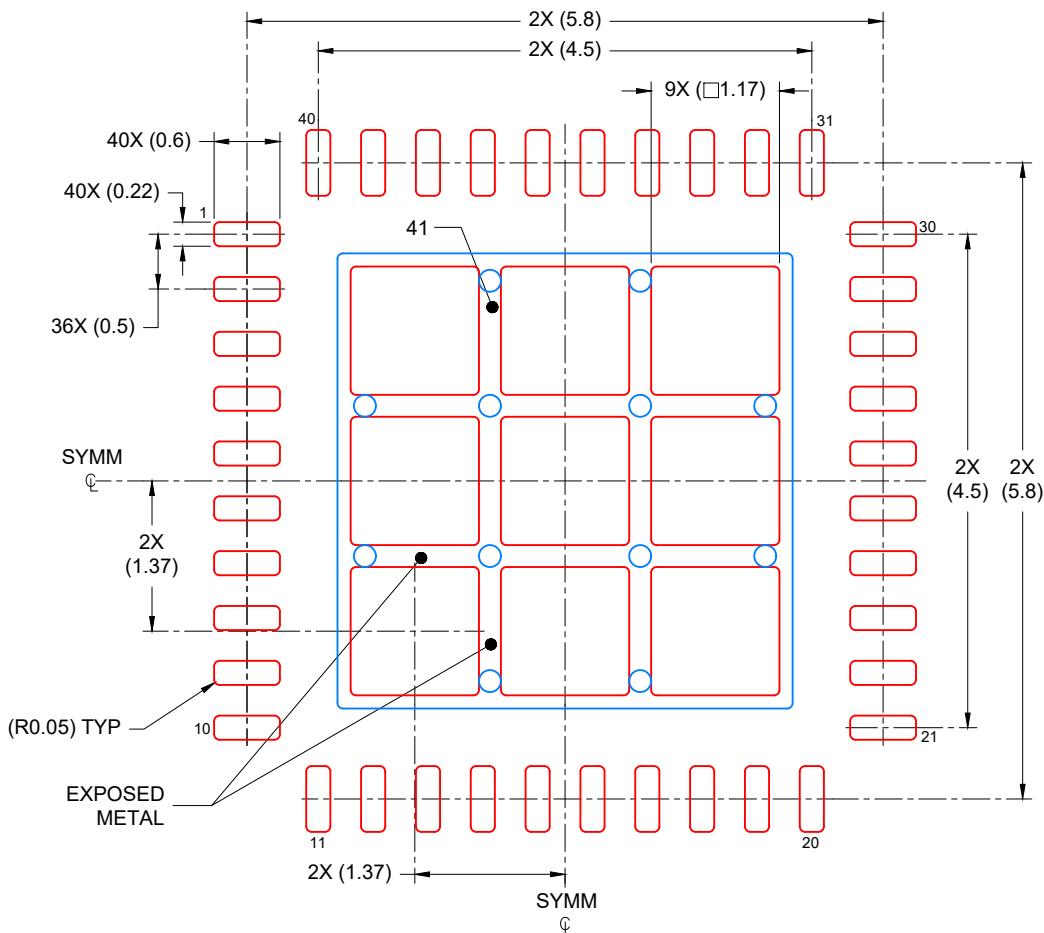

図 6-3. DRV8353FH RTA パッケージ 40 ピン WQFN

(露出サーマル・パッド付き) 上面図

図 6-4. DRV8353FS RTA パッケージ 40 ピン WQFN

(露出サーマル・パッド付き) 上面図

## ピン機能 – 40 ピン DRV8353F デバイス

| 名前     | ピン        |           | タイプ <sup>(1)</sup> | 説明                                                                                                                           |  |  |

|--------|-----------|-----------|--------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|

|        | 番号        |           |                    |                                                                                                                              |  |  |

|        | DRV8353FH | DRV8353FS |                    |                                                                                                                              |  |  |

| AGND   | 25        | 25        | PWR                | デバイスのアナログ・グランド。システム・グランドに接続します。                                                                                              |  |  |

| CPH    | 2         | 2         | PWR                | チャージ・ポンプのスイッチング・ノード。X5R または X7R、47nF、VDRAIN 定格セラミック・コンデンサを CPH ピンと CPL ピンの間に接続します。                                           |  |  |

| CPL    | 1         | 1         | PWR                | チャージ・ポンプのスイッチング・ノード。X5R または X7R、47nF、VDRAIN 定格セラミック・コンデンサを CPL ピンと CPL ピンの間に接続します。                                           |  |  |

| DVDD   | 38        | 38        | PWR                | 5V 内部レギュレータ出力。X5R または X7R、1μF、6.3V セラミック・コンデンサを DVDD ピンと GND ピンの間に接続します。このレギュレータは最大 10mA を外部にソースできます。                        |  |  |

| ENABLE | 31        | 31        | I                  | ゲート・ドライバのイネーブル。このピンを論理 Low にすると、本デバイスは低消費電力のスリープ・モードに移行します。8~40μs の Low バルスを使うとフォルト条件をリセットできます。                              |  |  |

| GAIN   | 30        | —         | I                  | アンプ・ゲイン設定。このピンは、外付け抵抗で設定される 4 レベル入力ピンです。                                                                                     |  |  |

| GND    | 39        | 39        | PWR                | デバイスの電源グランド。システム・グランドに接続します。                                                                                                 |  |  |

| GHA    | 6         | 6         | O                  | ハイサイド・ゲート・ドライバ出力。ハイサイド・パワー MOSFET のゲートに接続します。                                                                                |  |  |

| GHB    | 15        | 15        | O                  | ハイサイド・ゲート・ドライバ出力。ハイサイド・パワー MOSFET のゲートに接続します。                                                                                |  |  |

| GHC    | 16        | 16        | O                  | ハイサイド・ゲート・ドライバ出力。ハイサイド・パワー MOSFET のゲートに接続します。                                                                                |  |  |

| GLA    | 8         | 8         | O                  | ローサイド・ゲート・ドライバ出力。ローサイド・パワー MOSFET のゲートに接続します。                                                                                |  |  |

| GLB    | 13        | 13        | O                  | ローサイド・ゲート・ドライバ出力。ローサイド・パワー MOSFET のゲートに接続します。                                                                                |  |  |

| GLC    | 18        | 18        | O                  | ローサイド・ゲート・ドライバ出力。ローサイド・パワー MOSFET のゲートに接続します。                                                                                |  |  |

| IDRIVE | 28        | —         | I                  | ゲート駆動出力電流設定。このピンは、外付け抵抗で設定される 7 レベル入力ピンです。                                                                                   |  |  |

| INHA   | 32        | 32        | I                  | ハイサイド・ゲート・ドライバの制御入力。このピンはハイサイド・ゲート・ドライバの出力を制御します。                                                                            |  |  |

| INHB   | 34        | 34        | I                  | ハイサイド・ゲート・ドライバの制御入力。このピンはハイサイド・ゲート・ドライバの出力を制御します。                                                                            |  |  |

| INHC   | 36        | 36        | I                  | ハイサイド・ゲート・ドライバの制御入力。このピンはハイサイド・ゲート・ドライバの出力を制御します。                                                                            |  |  |

| INLA   | 33        | 33        | I                  | ローサイド・ゲート・ドライバの制御入力。このピンはローサイド・ゲート・ドライバの出力を制御します。                                                                            |  |  |

| INLB   | 35        | 35        | I                  | ローサイド・ゲート・ドライバの制御入力。このピンはローサイド・ゲート・ドライバの出力を制御します。                                                                            |  |  |

| INLC   | 37        | 37        | I                  | ローサイド・ゲート・ドライバの制御入力。このピンはローサイド・ゲート・ドライバの出力を制御します。                                                                            |  |  |

| MODE   | 27        | —         | I                  | PWM 入力モード設定。このピンは、外付け抵抗で設定される 4 レベル入力ピンです。                                                                                   |  |  |

| nFAULT | 26        | 26        | OD                 | フォルト通知出力。このピンはフォルト条件で論理 Low にブリッジされ、外付けプルアップ抵抗を必要とします。                                                                       |  |  |

| nSCS   | —         | 30        | I                  | シリアル・チップ選択。このピンを論理 Low にすると、シリアル・インターフェイス通信が有効になります。                                                                         |  |  |

| SCLK   | —         | 29        | I                  | シリアル・クロック入力。シリアル・データは、このピンの対応する立ち上がりおよび立ち下がりエッジでシフト・アウトおよびキャプチャされます。                                                         |  |  |

| SDI    | —         | 28        | I                  | シリアル・データ入力。データは、SCLK ピンの立ち上がりエッジでキャプチャされます。                                                                                  |  |  |

| SDO    | —         | 27        | OD                 | シリアル・データ出力。データは、SCLK ピンの立ち上がりエッジでシフト・アウトされます。このピンは外付けプルアップ抵抗を必要とします。                                                         |  |  |

| SHA    | 7         | 7         | I                  | ハイサイド・ソース検出入力。ハイサイド・パワー MOSFET のソースに接続します。                                                                                   |  |  |

| SHB    | 14        | 14        | I                  | ハイサイド・ソース検出入力。ハイサイド・パワー MOSFET のソースに接続します。                                                                                   |  |  |

| SHC    | 17        | 17        | I                  | ハイサイド・ソース検出入力。ハイサイド・パワー MOSFET のソースに接続します。                                                                                   |  |  |

| SNA    | 10        | 10        | I                  | シャント・アンプの入力。電流シャント抵抗の低電位側に接続します。                                                                                             |  |  |

| SNB    | 11        | 11        | I                  | シャント・アンプの入力。電流シャント抵抗の低電位側に接続します。                                                                                             |  |  |

| SNC    | 20        | 20        | I                  | シャント・アンプの入力。電流シャント抵抗の低電位側に接続します。                                                                                             |  |  |

| SOA    | 23        | 23        | O                  | シャント・アンプ出力。                                                                                                                  |  |  |

| SOB    | 22        | 22        | O                  | シャント・アンプ出力。                                                                                                                  |  |  |

| SOC    | 21        | 21        | O                  | シャント・アンプ出力。                                                                                                                  |  |  |

| SPA    | 9         | 9         | I                  | ローサイド・ソース検出およびシャント・アンプ入力。ローサイド・パワー MOSFET のソースと電流シャント抵抗の高電位側に接続します。                                                          |  |  |

| SPB    | 12        | 12        | I                  | ローサイド・ソース検出およびシャント・アンプ入力。ローサイド・パワー MOSFET のソースと電流シャント抵抗の高電位側に接続します。                                                          |  |  |

| SPC    | 19        | 19        | I                  | ローサイド・ソース検出およびシャント・アンプ入力。ローサイド・パワー MOSFET のソースと電流シャント抵抗の高電位側に接続します。                                                          |  |  |

| VCP    | 5         | 5         | PWR                | チャージ・ポンプの出力。X5R または X7R、1μF、16V セラミック・コンデンサを VCP ピンと VDRAIN ピンの間に接続します。                                                      |  |  |

| VDRAIN | 4         | 4         | I                  | ハイサイド MOSFET ドレイン検出入力およびチャージ・ポンプ基準電圧。MOSFET のドレインの共通ポイントに接続します。                                                              |  |  |

| VDS    | 29        | —         | I                  | VDS モニタのトリップ・ポイント設定。このピンは、外付け抵抗で設定される 7 レベル入力ピンです。                                                                           |  |  |

| VGLS   | 40        | 40        | PWR                | 11V 内部レギュレータ出力。X5R または X7R、1μF、16V セラミック・コンデンサを VGLS ピンと GND ピンの間に接続します。                                                     |  |  |

| VM     | 3         | 3         | PWR                | ゲート・ドライバの電源入力。VDRAIN または個別のゲート・ドライバ電源電圧に接続します。X5R または X7R、0.1μF、VM 定格セラミック・コンデンサと 10μF 以上のローカル・コンデンサを VM ピンと GND ピンの間に接続します。 |  |  |

**DRV8350F, DRV8353F**

JAJSJP6B – AUGUST 2018 – REVISED AUGUST 2021

| 名前   | ピン        |           | タイプ <sup>(1)</sup> | 説明                                                                                     |  |  |

|------|-----------|-----------|--------------------|----------------------------------------------------------------------------------------|--|--|

|      | 番号        |           |                    |                                                                                        |  |  |

|      | DRV8353FH | DRV8353FS |                    |                                                                                        |  |  |

| VREF | 24        | 24        | PWR                | シャント・アンプの電源入力と基準電圧 X5R または X7R、0.1 $\mu$ F、6.3V セラミック・コンデンサを VREF ピンと AGND ピンの間に接続します。 |  |  |

(1) PWR = 電源、I = 入力、O = 出力、NC = 接続なし、OD = オープン・ドレイン

## 7 仕様

### 7.1 絶対最大定格

$T_A = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  (特に記述のない限り) <sup>(1)</sup>

|                                                                                       |  | 最小                | 最大                       | 単位               |

|---------------------------------------------------------------------------------------|--|-------------------|--------------------------|------------------|

| <b>ゲート・ドライバ</b>                                                                       |  |                   |                          |                  |

| 電源ピン電圧 (VM)                                                                           |  | -0.3              | 80                       | V                |

| グランド・ピン (AGND, BGND, DGND, PGND) 間の電圧差                                                |  | -0.3              | 0.3                      | V                |

| MOSFET ドレイン検出ピン電圧 (VDRAIN)                                                            |  | -0.3              | 102                      | V                |

| MOSFET ドレイン検出ピン電圧 (VDRAIN) スルーレート                                                     |  | 0                 | 2                        | V/ $\mu\text{s}$ |

| チャージ・ポンプ・ピン電圧 (CPH, VCP)                                                              |  | -0.3              | $V_{\text{VDRAIN}} + 16$ | V                |

| チャージ・ポンプ負スイッチング・ピン電圧 (CPL)                                                            |  | -0.3              | $V_{\text{VDRAIN}}$      | V                |

| ローサイド・ゲート駆動レギュレータ・ピン電圧 (VGLS)                                                         |  | -0.3              | 18                       | V                |

| 内部ロジック・レギュレータ・ピン電圧 (DVDD)                                                             |  | -0.3              | 5.75                     | V                |

| デジタル・ピン電圧 (ENABLE, GAIN, IDRIVE, INHx, INLx, MODE, nFAULT, nSCS, SCLK, SDI, SDO, VDS) |  | -0.3              | 5.75                     | V                |

| 連続ハイサイド・ゲート駆動ピン電圧 (GHx)                                                               |  | -5 <sup>(2)</sup> | $V_{\text{VCP}} + 0.3$   | V                |

| 過渡 200ns ハイサイド・ゲート駆動ピン電圧 (GHx)                                                        |  | -10               | $V_{\text{VCP}} + 0.3$   | V                |

| SHx を基準としたハイサイド・ゲート駆動ピン電圧 (GHx)                                                       |  | -0.3              | 16                       | V                |

| 連続ハイサイド・ソース検出ピン電圧 (SHx)                                                               |  | -5 <sup>(2)</sup> | 102                      | V                |

| 連続ハイサイド・ソース検出ピン電圧 (SHx)                                                               |  | -5 <sup>(2)</sup> | $V_{\text{VDRAIN}} + 5$  | V                |

| 過渡 200ns ハイサイド・ソース検出ピン電圧 (SHx)                                                        |  | -10               | $V_{\text{VDRAIN}} + 10$ | V                |

| 連続ローサイド・ゲート駆動ピン電圧 (GLx)                                                               |  | -1.0              | $V_{\text{VGLS}} + 0.3$  | V                |

| 過渡 200ns ローサイド・ゲート駆動ピン電圧 (GLx)                                                        |  | -5.0              | $V_{\text{VGLS}} + 0.3$  | V                |

| ゲート駆動ピン・ソース電流 (GHx, GLx)                                                              |  | 内部的に制限            | 内部的に制限                   | A                |

| ゲート駆動ピン・シンク電流 (GHx, GLx)                                                              |  | 内部的に制限            | 内部的に制限                   | A                |

| 連続ローサイド・ソース検出ピン電圧 (SLx)                                                               |  | -1                | 1                        | V                |

| 過渡 200ns ローサイド・ソース検出ピン電圧 (SLx)                                                        |  | -5                | 5                        | V                |

| 連続シャント・アンプ入力ピン電圧 (SNx, SPx)                                                           |  | -1                | 1                        | V                |

| 過渡 200ns シャント・アンプ入力ピン電圧 (SNx, SPx)                                                    |  | -5                | 5                        | V                |

| 基準電圧入力ピン電圧 (VREF)                                                                     |  | -0.3              | 5.75                     | V                |

| シャント・アンプ出力ピン電圧 (SOx)                                                                  |  | -0.3              | $V_{\text{VREF}} + 0.3$  | V                |

| 周囲温度、 $T_A$                                                                           |  | -40               | 125                      | °C               |

| 接合部温度、 $T_J$                                                                          |  | -40               | 150                      | °C               |

| 保管温度、 $T_{\text{stg}}$                                                                |  | -65               | 150                      | °C               |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示しており、このデータシートの「推奨動作条件」に示された値を越える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

- (2) ハイサイド・ゲート・ピン (GHx) を基準とした VDRAIN ピンの電圧と位相ノード・ピン (SHx) の電圧は、最大 102V に制限する必要があります。これにより、VDRAIN が 92V を超える場合の GHx および SHx ピンの負電圧能力が制限されます。

### 7.2 ESD 定格

|                    |       |                                                        | 値          | 単位 |

|--------------------|-------|--------------------------------------------------------|------------|----|

| $V_{(\text{ESD})}$ | 静電気放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>   | $\pm 1000$ | V  |

|                    |       | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 準拠 <sup>(2)</sup> | $\pm 500$  |    |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 制御プロセスで安全な製造が可能であると記載されています。 $\pm 2000V$  と記載されたピンは、実際にはそれよりも高い性能を持つ場合があります。

- (2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 制御プロセスで安全な製造が可能であると記載されています。 $\pm 500V$  と記載されたピンは、実際にはそれよりも高い性能を持つ場合があります。

## 7.3 推奨動作条件

$T_A = -40^{\circ}\text{C} \sim +125^{\circ}\text{C}$  (特に記述のない限り)

|                |                                                                     | 最小値 | 最大値                | 単位                 |

|----------------|---------------------------------------------------------------------|-----|--------------------|--------------------|

| ゲート・ドライバ       |                                                                     |     |                    |                    |

| $V_{VM}$       | ゲート・ドライバの電源電圧 (VM)                                                  | 9   | 75                 | V                  |

| $V_{VDRAIN}$   | チャージ・ポンプ基準電圧およびドレイン電圧検出 (VDRAIN)                                    | 7   | 100                | V                  |

| $V_I$          | 入力電圧 (ENABLE, GAIN, IDRIVE, INHx, INLx, MODE, nSCS, SCLK, SDI, VDS) | 0   | 5.5                | V                  |

| $f_{PWM}$      | PWM 印加信号 (INHx, INLx)                                               | 0   | 200 <sup>(1)</sup> | kHz                |

| $t_{SH}$       | スイッチ・ノードのスルーレート範囲 (SHx)                                             | 0   | 2                  | V/ns               |

| $I_{GATE\_HS}$ | ハイサイド平均ゲート駆動電流 (GHx)                                                | 0   | 25 <sup>(1)</sup>  | mA                 |

| $I_{GATE\_LS}$ | ローサイド平均ゲート駆動電流 (GLx)                                                | 0   | 25 <sup>(1)</sup>  | mA                 |

| $I_{DVDD}$     | 外部負荷電流 (DVDD)                                                       | 0   | 10 <sup>(1)</sup>  | mA                 |

| $V_{VREF}$     | 基準電圧入力 (VREF)                                                       | 3   | 5.5                | V                  |

| $I_{SO}$       | シャント・アンプ出力電流 (SOx)                                                  | 0   | 5                  | mA                 |

| $V_{OD}$       | オープン・ドレイン・プルアップ電圧 (nFAULT, SDO)                                     | 0   | 5.5                | V                  |

| $I_{OD}$       | オープン・ドレイン出力電流 (nFAULT, SDO)                                         | 0   | 5                  | mA                 |

| $T_A$          | 動作時周囲温度                                                             | -40 | 125                | $^{\circ}\text{C}$ |

| $T_J$          | 動作時接合部温度                                                            | -40 | 150                | $^{\circ}\text{C}$ |

(1) 消費電力および温度の制限に従う必要があります。

## 7.4 热に関する情報

| 热評価基準 <sup>(1)</sup>        |                          | DRV8350F   | DRV8353F   | 単位                          |

|-----------------------------|--------------------------|------------|------------|-----------------------------|

|                             |                          | RTV (WQFN) | RTA (WQFN) |                             |

|                             |                          | 32 ピン      | 40 ピン      |                             |

| $R_{\theta JA}$             | ジャンクションから周囲までの熱抵抗        | 29.2       | 26.1       | $^{\circ}\text{C}/\text{W}$ |

| $R_{\theta JC(\text{top})}$ | ジャンクションからケース (上部) までの熱抵抗 | 15.2       | 13.1       | $^{\circ}\text{C}/\text{W}$ |

| $R_{\theta JB}$             | ジャンクションから基板までの熱抵抗        | 9.2        | 8.4        | $^{\circ}\text{C}/\text{W}$ |

| $\Psi_{JT}$                 | 接合部から上面への熱特性パラメータ        | 0.1        | 0.1        | $^{\circ}\text{C}/\text{W}$ |

| $\Psi_{JB}$                 | 接合部から基板への熱特性パラメータ        | 9.2        | 8.4        | $^{\circ}\text{C}/\text{W}$ |

| $R_{\theta JC(\text{bot})}$ | 接合部からケース (底面) への熱抵抗      | 1.2        | 1.1        | $^{\circ}\text{C}/\text{W}$ |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション・レポートを参照してください。

## 7.5 電気的特性

$T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ ,  $V_{VM} = 9 \sim 75\text{V}$ ,  $V_{VDRAIN} = 9 \sim 100\text{V}$ ,  $V_{VIN} = 48\text{V}$  (特に記述のない限り)

| パラメータ                           | テスト条件                   | 最小値                                                                                                 | 標準値  | 最大値  | 単位            |

|---------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------|------|------|---------------|

| <b>電源 (DVDD, VCP, VGLS, VM)</b> |                         |                                                                                                     |      |      |               |

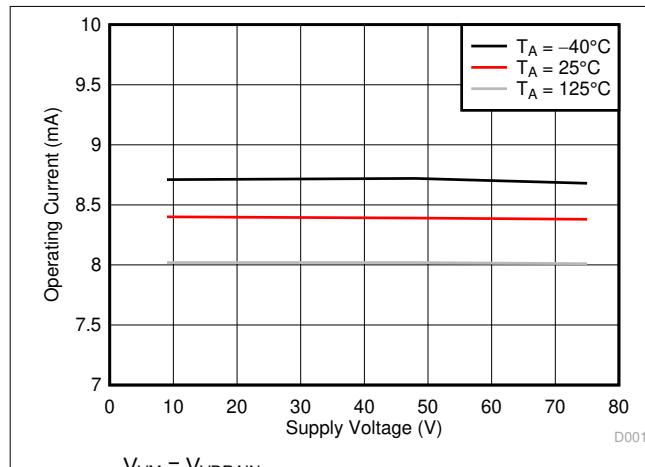

| $I_{VM}$                        | $VM$ 動作電源電流             | $V_{VM} = V_{VDRAIN} = 48\text{V}$ , $\text{ENABLE} = 3.3\text{V}$ , $\text{INHx/INLx} = 0\text{V}$ | 8.5  | 13   | mA            |

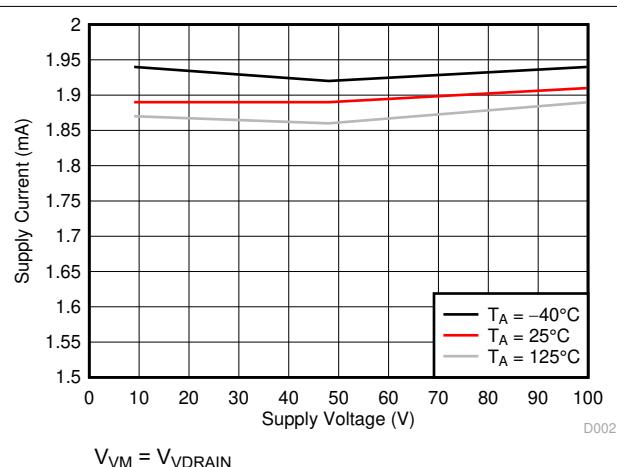

| $I_{VDRAIN}$                    | $VDRAIN$ 動作電源電流         | $V_{VM} = V_{VDRAIN} = 48\text{V}$ , $\text{ENABLE} = 3.3\text{V}$ , $\text{INHx/INLx} = 0\text{V}$ | 1.9  | 4    | mA            |

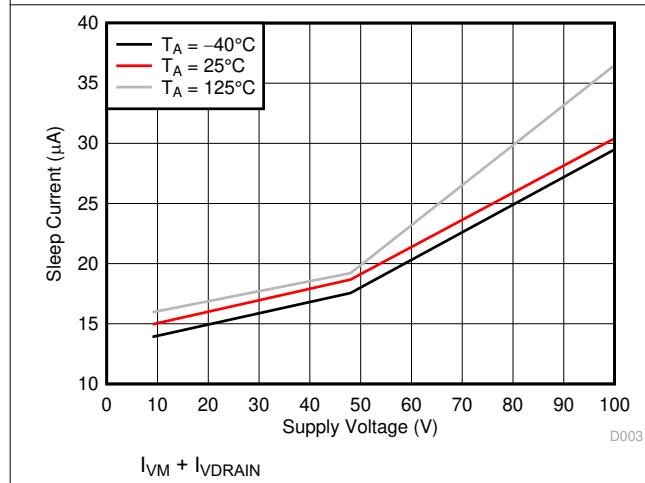

| $I_{SLEEP}$                     | スリープ・モード電源電流            | $\text{ENABLE} = 0\text{V}$ , $V_{VM} = V_{VDRAIN} = 48\text{V}$ , $T_A = 25^\circ\text{C}$         | 20   | 40   | $\mu\text{A}$ |

|                                 |                         | $\text{ENABLE} = 0\text{V}$ , $V_{VM} = V_{VDRAIN} = 48\text{V}$ , $T_A = 125^\circ\text{C}$        |      | 100  |               |

| $t_{RST}$                       | リセット・パルス時間              | フォルトをリセットするのに必要な $\text{ENABLE} = 0\text{V}$ の期間                                                    | 5    | 40   | $\mu\text{s}$ |

| $t_{WAKE}$                      | ターンオン時間                 | $V_{VM} > V_{UVLO}$ , 出力を準備完了にするのに必要な $\text{ENABLE} = 3.3\text{V}$ の期間                             |      | 1    | ms            |

| $t_{SLEEP}$                     | ターンオフ時間                 | デバイスをスリープ・モードに移行させるのに必要な $\text{ENABLE} = 0\text{V}$ の期間                                            |      | 1    | ms            |

| $V_{DVDD}$                      | DVDD レギュレータ電圧           | $I_{DVDD} = 0 \sim 10\text{mA}$                                                                     | 4.75 | 5    | 5.25          |

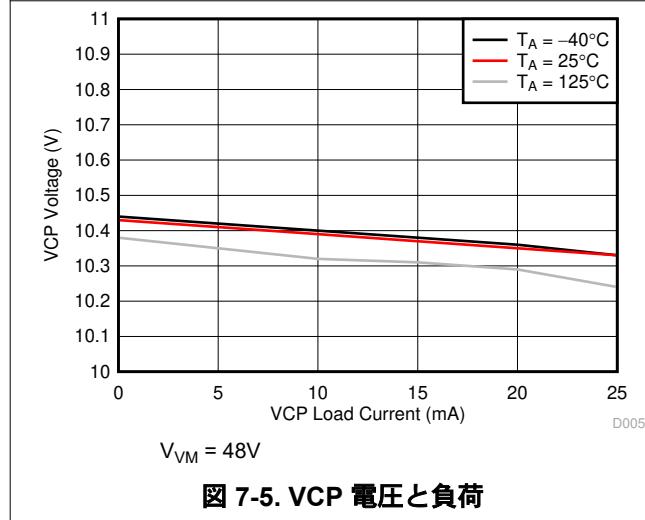

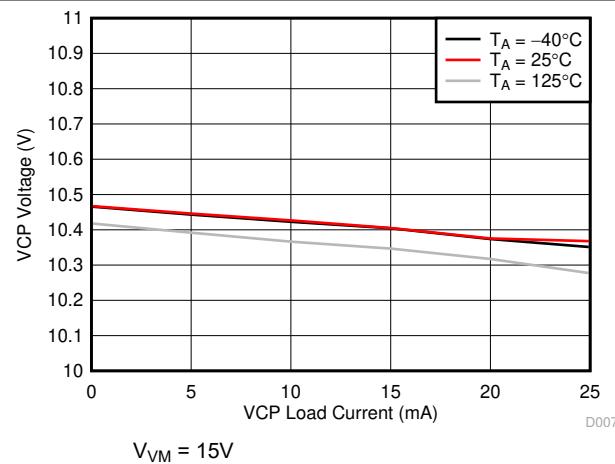

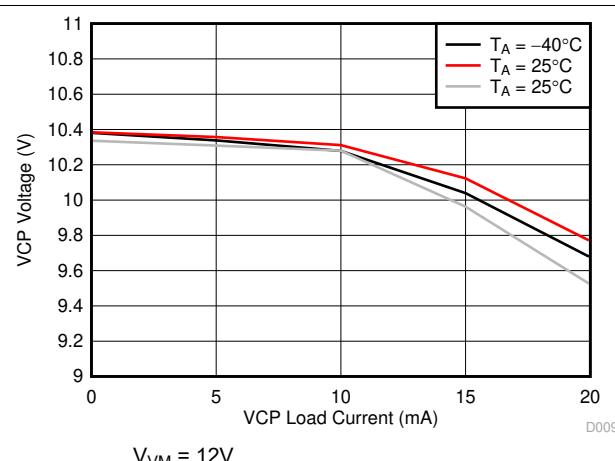

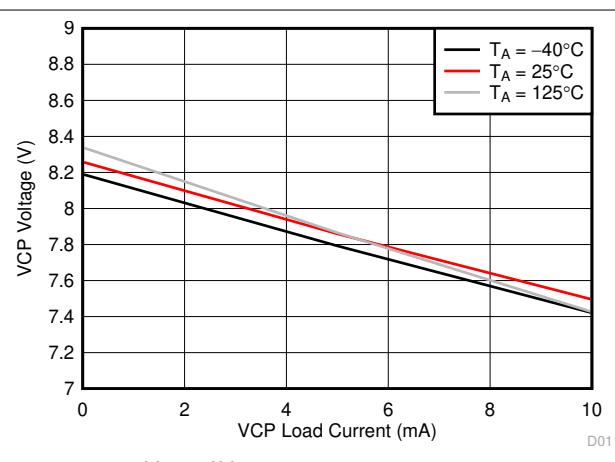

| $V_{VCP}$                       | VCP 動作電圧<br>(VDRAIN 基準) | $V_{VM} = 15\text{V}$ , $I_{VCP} = 0 \sim 25\text{mA}$                                              | 9    | 10.5 | 12            |

|                                 |                         | $V_{VM} = 12\text{V}$ , $I_{VCP} = 0 \sim 20\text{mA}$                                              | 7.5  | 10   | 11.5          |

|                                 |                         | $V_{VM} = 10\text{V}$ , $I_{VCP} = 0 \sim 15\text{mA}$                                              | 6    | 8    | 9.5           |

|                                 |                         | $V_{VM} = 9\text{V}$ , $I_{VCP} = 0 \sim 10\text{mA}$                                               | 5.5  | 7.5  | 8.5           |

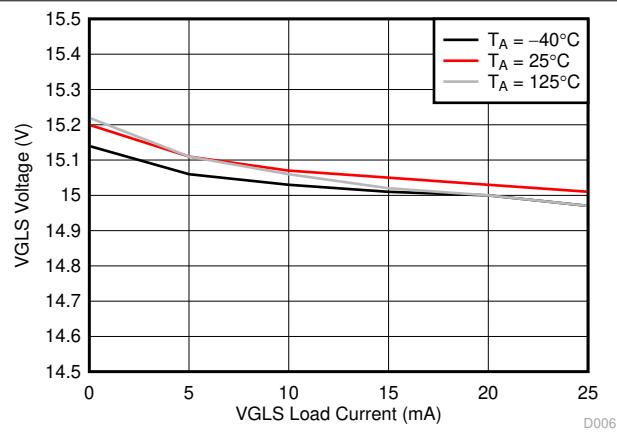

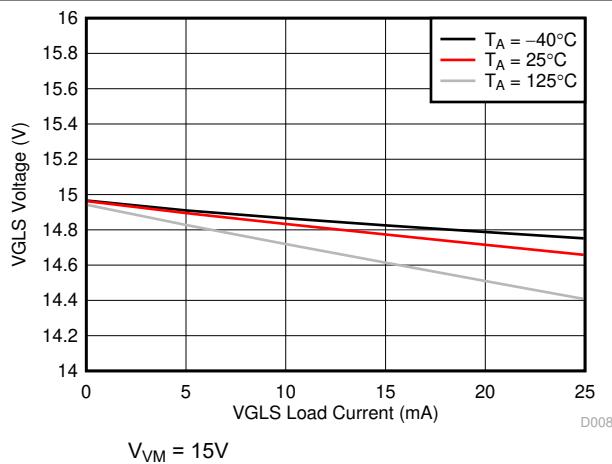

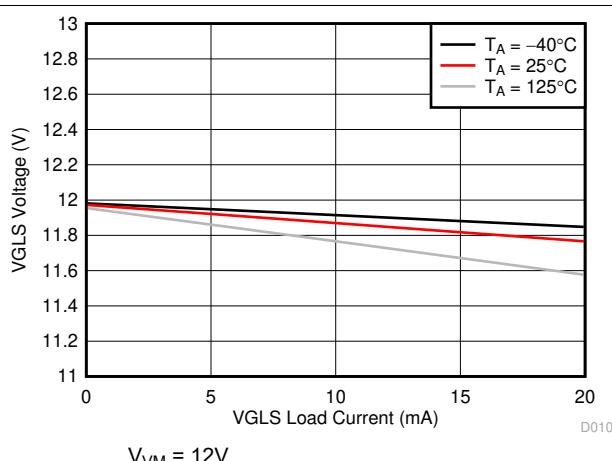

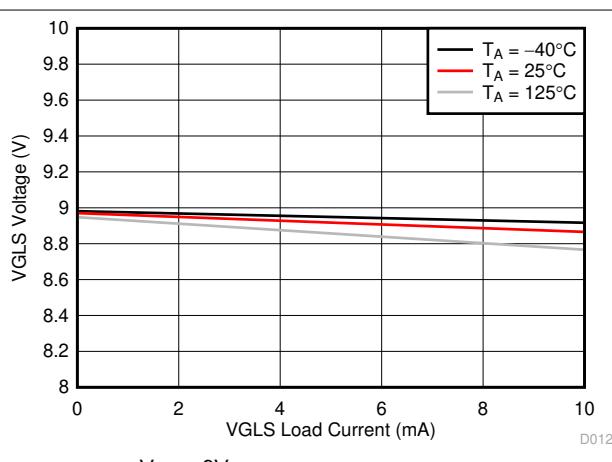

| $V_{VGLS}$                      | VGLS 動作電圧<br>(GND 基準)   | $V_{VM} = 15\text{V}$ , $I_{VGLS} = 0 \sim 25\text{mA}$                                             | 13   | 14.5 | 16            |

|                                 |                         | $V_{VM} = 12\text{V}$ , $I_{VGLS} = 0 \sim 20\text{mA}$                                             | 10   | 11.5 | 12.5          |

$T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ ,  $V_{VM} = 9 \sim 75\text{V}$ ,  $V_{VDRAIN} = 9 \sim 100\text{V}$ ,  $V_{VIN} = 48\text{V}$  (特に記述のない限り)

| パラメータ                                                | テスト条件                                                   | 最小値                                                    | 標準値   | 最大値   | 単位               |

|------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------|-------|-------|------------------|

|                                                      | $V_{VM} = 10\text{V}$ , $I_{VGLS} = 0 \sim 15\text{mA}$ | 8                                                      | 9.5   | 10.5  |                  |

|                                                      | $V_{VM} = 9\text{V}$ , $I_{VGLS} = 0 \sim 10\text{mA}$  | 7                                                      | 8.5   | 9.5   |                  |

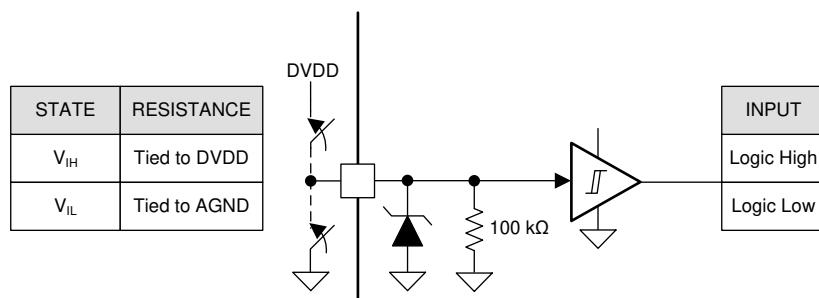

| <b>論理レベル入力 (ENABLE, INHx, INLx, nSCS, SCLK, SDI)</b> |                                                         |                                                        |       |       |                  |

| $V_{IL}$                                             | 入力論理 Low 電圧                                             | 0                                                      | 0.8   |       | V                |

| $V_{IH}$                                             | 入力論理 High 電圧                                            | 1.5                                                    | 5.5   |       | V                |

| $V_{HYS}$                                            | 入力論理ヒステリシス                                              | 100                                                    |       |       | mV               |

| $I_{IL}$                                             | 入力論理 Low 電流                                             | $V_{VIN} = 0\text{V}$                                  | -5    | 5     | $\mu\text{A}$    |

| $I_{IH}$                                             | 入力論理 High 電流                                            | $V_{VIN} = 5\text{V}$                                  | 50    | 70    | $\mu\text{A}$    |

| $R_{PD}$                                             | ブルダウン抵抗                                                 | 対 GND                                                  | 100   |       | $\text{k}\Omega$ |

| $t_{PD}$                                             | 伝搬遅延                                                    | INHx/INLx の遷移から GHx/GLx の遷移まで                          | 200   |       | ns               |

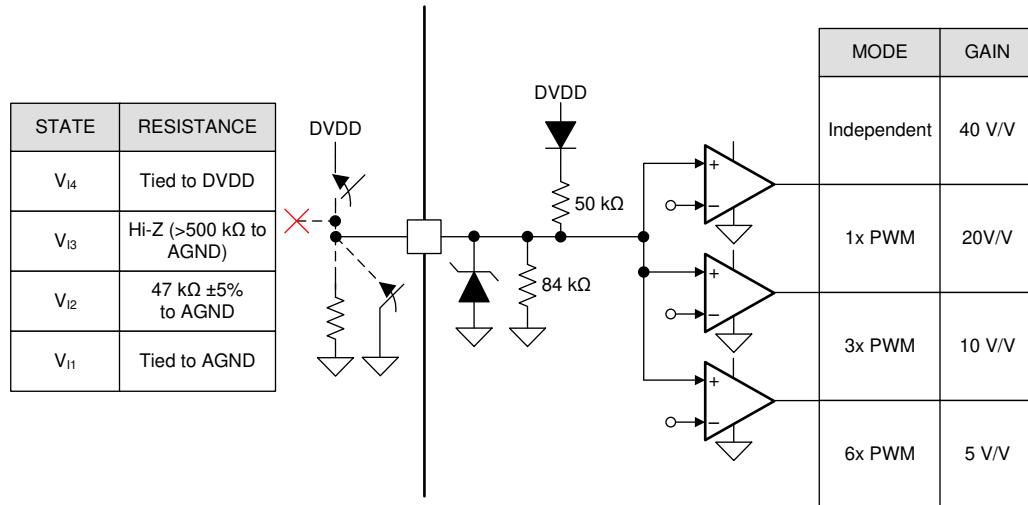

| <b>4 レベル H/W 入力 (GAIN, MODE)</b>                     |                                                         |                                                        |       |       |                  |

| $V_{I1}$                                             | 入力モード 1 電圧                                              | GND に接続                                                | 0     |       | V                |

| $V_{COMP1}$                                          | クワッドレベル電圧コンパレータ 1                                       | $V_{I1}$ と $V_{I2}$ の間の電圧コンパレータ                        | 1.156 | 1.256 | 1.356            |

| $V_{I2}$                                             | 入力モード 2 電圧                                              | $47\text{k}\Omega \pm 5\%$ で GND に接続                   | 1.9   |       | V                |

| $V_{COMP2}$                                          | クワッドレベル電圧コンパレータ 1                                       | $V_{I2}$ と $V_{I3}$ の間の電圧コンパレータ                        | 2.408 | 2.508 | 2.608            |

| $V_{I3}$                                             | 入力モード 3 電圧                                              | Hi-Z                                                   | 3.1   |       | V                |

| $V_{COMP3}$                                          | クワッドレベル電圧コンパレータ 3                                       | $V_{I3}$ と $V_{I4}$ の間の電圧コンパレータ                        | 3.614 | 3.714 | 3.814            |

| $V_{I4}$                                             | 入力モード 4 電圧                                              | DVDD に接続                                               | 5     |       | V                |

| $R_{PU}$                                             | ブルアップ抵抗                                                 | DVDD に内部ブルアップ                                          | 50    |       | $\text{k}\Omega$ |

| $R_{PD}$                                             | ブルダウン抵抗                                                 | GND に内部ブルダウン                                           | 84    |       | $\text{k}\Omega$ |

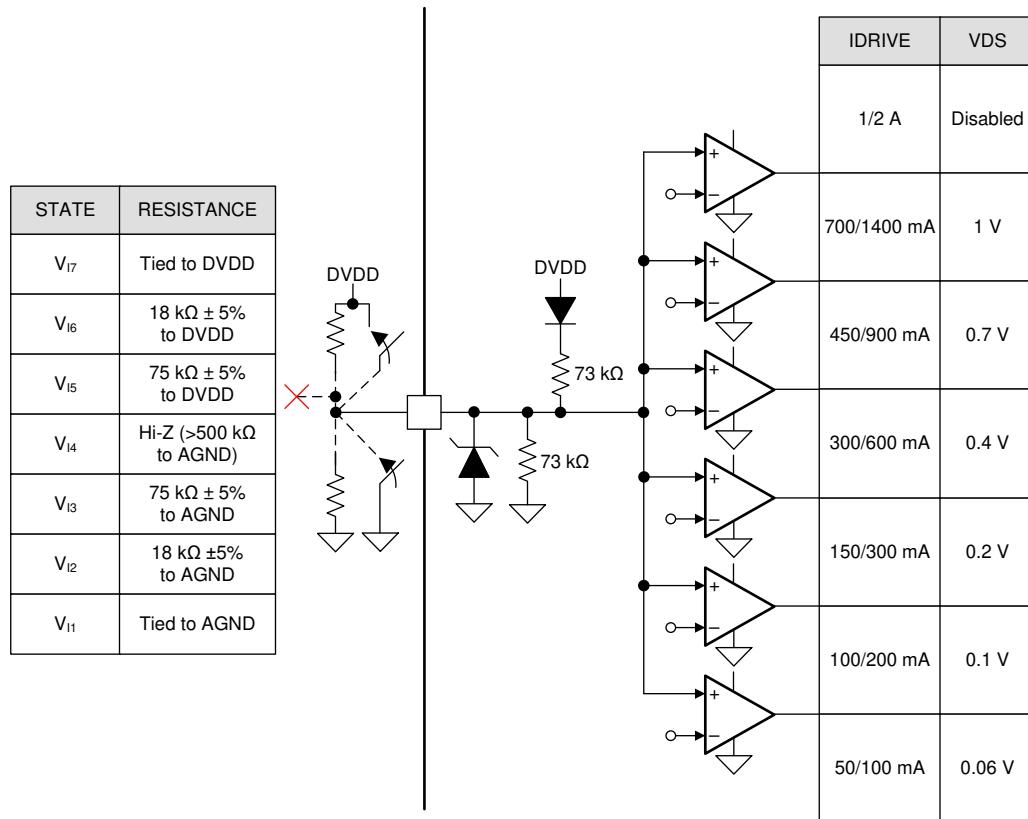

| <b>7 レベル H/W 入力 (IDRIVE, VDS)</b>                    |                                                         |                                                        |       |       |                  |

| $V_{I1}$                                             | 入力モード 1 電圧                                              | GND に接続                                                | 0     |       | V                |

| $V_{COMP1}$                                          | 7 レベル電圧コンパレータ 1                                         | $V_{I1}$ と $V_{I2}$ の間の電圧コンパレータ                        | 0.057 | 0.157 | 0.257            |

| $V_{I2}$                                             | 入力モード 2 電圧                                              | $18\text{k}\Omega \pm 5\%$ で GND に接続                   | 0.8   |       | V                |

| $V_{COMP2}$                                          | 7 レベル電圧コンパレータ 2                                         | $V_{I2}$ と $V_{I3}$ の間の電圧コンパレータ                        | 1.158 | 1.258 | 1.358            |

| $V_{I3}$                                             | 入力モード 3 電圧                                              | $75\text{k}\Omega \pm 5\%$ で GND に接続                   | 1.7   |       | V                |

| $V_{COMP3}$                                          | 7 レベル電圧コンパレータ 3                                         | $V_{I3}$ と $V_{I4}$ の間の電圧コンパレータ                        | 2.257 | 2.357 | 2.457            |

| $V_{I4}$                                             | 入力モード 4 電圧                                              | Hi-Z                                                   | 2.5   |       | V                |

| $V_{COMP4}$                                          | 7 レベル電圧コンパレータ 4                                         | $V_{I4}$ と $V_{I5}$ の間の電圧コンパレータ                        | 2.561 | 2.661 | 2.761            |

| $V_{I5}$                                             | 入力モード 5 電圧                                              | $75\text{k}\Omega \pm 5\%$ で DVDD に接続                  | 3.3   |       | V                |

| $V_{COMP5}$                                          | 7 レベル電圧コンパレータ 5                                         | $V_{I5}$ と $V_{I6}$ の間の電圧コンパレータ                        | 3.615 | 3.715 | 3.815            |

| $V_{I6}$                                             | 入力モード 6 電圧                                              | $18\text{k}\Omega \pm 5\%$ で DVDD に接続                  | 4.2   |       | V                |

| $V_{COMP6}$                                          | 7 レベル電圧コンパレータ 6                                         | $V_{I6}$ と $V_{I7}$ の間の電圧コンパレータ                        | 4.75  | 4.85  | 4.95             |

| $V_{I7}$                                             | 入力モード 7 電圧                                              | DVDD に接続                                               | 5     |       | V                |

| $R_{PU}$                                             | ブルアップ抵抗                                                 | DVDD に内部ブルアップ                                          | 73    |       | $\text{k}\Omega$ |

| $R_{PD}$                                             | ブルダウン抵抗                                                 | GND に内部ブルダウン                                           | 73    |       | $\text{k}\Omega$ |

| <b>オープン・ドレイン出力 (nFAULT, SDO)</b>                     |                                                         |                                                        |       |       |                  |

| $V_{OL}$                                             | 出力論理 Low 電圧                                             | $I_O = 5\text{mA}$                                     | 0.125 |       | V                |

| $I_{OZ}$                                             | ハイ・インピーダンス出力リード                                         | $V_O = 5\text{V}$                                      | -2    | 2     | $\mu\text{A}$    |

| <b>ゲート・ドライバ (GHx, GLx)</b>                           |                                                         |                                                        |       |       |                  |

| $V_{GSH}$                                            | ハイサイド・ゲート駆動電圧 (SHx 基準)                                  | $V_{VM} = 15\text{V}$ , $I_{VCP} = 0 \sim 25\text{mA}$ | 9     | 10.5  | 12               |

|                                                      |                                                         | $V_{VM} = 12\text{V}$ , $I_{VCP} = 0 \sim 20\text{mA}$ | 7.5   | 10    | 11.5             |

|                                                      |                                                         | $V_{VM} = 10\text{V}$ , $I_{VCP} = 0 \sim 15\text{mA}$ | 6     | 8     | 9.5              |

|                                                      |                                                         | $V_{VM} = 9\text{V}$ , $I_{VCP} = 0 \sim 10\text{mA}$  | 5.5   | 7.5   | 8.5              |

$T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ ,  $V_{VM} = 9 \sim 75\text{V}$ ,  $V_{VDRAIN} = 9 \sim 100\text{V}$ ,  $V_{VIN} = 48\text{V}$  (特に記述のない限り)

| パラメータ        |                            | テスト条件                                                   | 最小値                                            | 標準値  | 最大値  | 単位 |

|--------------|----------------------------|---------------------------------------------------------|------------------------------------------------|------|------|----|

| $V_{GSL}$    | ローサイド・ゲート駆動電圧<br>(PGND 基準) | $V_{VM} = 15\text{V}$ , $I_{VGLS} = 0 \sim 25\text{mA}$ | 9.5                                            | 11   | 12.5 | V  |

|              |                            | $V_{VM} = 12\text{V}$ , $I_{VGLS} = 0 \sim 20\text{mA}$ | 9                                              | 10.5 | 12   |    |

|              |                            | $V_{VM} = 10\text{V}$ , $I_{VGLS} = 0 \sim 15\text{mA}$ | 7.5                                            | 9    | 10.5 |    |

|              |                            | $V_{VM} = 9\text{V}$ , $I_{VGLS} = 0 \sim 10\text{mA}$  | 6.5                                            | 8    | 9.5  |    |

| $t_{DEAD}$   | ゲート駆動<br>デッド・タイム           | SPI デバイス                                                | DEAD_TIME = 00b                                | 50   |      | ns |

|              |                            |                                                         | DEAD_TIME = 01b                                | 100  |      |    |

|              |                            |                                                         | DEAD_TIME = 10b                                | 200  |      |    |

|              |                            |                                                         | DEAD_TIME = 11b                                | 400  |      |    |

|              |                            | H/W デバイス                                                |                                                | 100  |      |    |

| $t_{DRIVE}$  | ピーク電流<br>ゲート駆動時間           | SPI デバイス                                                | TDRIVE = 00b                                   | 500  |      | ns |

|              |                            |                                                         | TDRIVE = 01b                                   | 1000 |      |    |

|              |                            |                                                         | TDRIVE = 10b                                   | 2000 |      |    |

|              |                            |                                                         | TDRIVE = 11b                                   | 4000 |      |    |

|              |                            | H/W デバイス                                                |                                                | 4000 |      |    |

| $I_{DRIVEP}$ | ピーク・ソース<br>ゲート電流           | SPI デバイス                                                | IDRIVEP_HS または IDRIVEP_LS = 0000b              | 50   |      | mA |

|              |                            |                                                         | IDRIVEP_HS または IDRIVEP_LS = 0001b              | 50   |      |    |

|              |                            |                                                         | IDRIVEP_HS または IDRIVEP_LS = 0010b              | 100  |      |    |

|              |                            |                                                         | IDRIVEP_HS または IDRIVEP_LS = 0011b              | 150  |      |    |

|              |                            |                                                         | IDRIVEP_HS または IDRIVEP_LS = 0100b              | 300  |      |    |

|              |                            |                                                         | IDRIVEP_HS または IDRIVEP_LS = 0101b              | 350  |      |    |

|              |                            |                                                         | IDRIVEP_HS または IDRIVEP_LS = 0110b              | 400  |      |    |

|              |                            |                                                         | IDRIVEP_HS または IDRIVEP_LS = 0111b              | 450  |      |    |

|              |                            |                                                         | IDRIVEP_HS または IDRIVEP_LS = 1000b              | 550  |      |    |

|              |                            |                                                         | IDRIVEP_HS または IDRIVEP_LS = 1001b              | 600  |      |    |

|              |                            |                                                         | IDRIVEP_HS または IDRIVEP_LS = 1010b              | 650  |      |    |

|              |                            |                                                         | IDRIVEP_HS または IDRIVEP_LS = 1011b              | 700  |      |    |

|              |                            |                                                         | IDRIVEP_HS または IDRIVEP_LS = 1100b              | 850  |      |    |

|              |                            |                                                         | IDRIVEP_HS または IDRIVEP_LS = 1101b              | 900  |      |    |

|              |                            |                                                         | IDRIVEP_HS または IDRIVEP_LS = 1110b              | 950  |      |    |

|              |                            |                                                         | IDRIVEP_HS または IDRIVEP_LS = 1111b              | 1000 |      |    |

|              |                            | H/W デバイス                                                | IDRIVE = GND に接続                               | 50   |      |    |

|              |                            |                                                         | IDRIVE = $18\text{k}\Omega \pm 5\%$ で GND に接続  | 100  |      |    |

|              |                            |                                                         | IDRIVE = $75\text{k}\Omega \pm 5\%$ で GND に接続  | 150  |      |    |

|              |                            |                                                         | IDRIVE = Hi-Z                                  | 300  |      |    |

|              |                            |                                                         | IDRIVE = $75\text{k}\Omega \pm 5\%$ で DVDD に接続 | 450  |      |    |

|              |                            |                                                         | IDRIVE = $18\text{k}\Omega \pm 5\%$ で DVDD に接続 | 700  |      |    |

|              |                            |                                                         | IDRIVE = DVDD に接続                              | 1000 |      |    |

$T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ ,  $V_{VM} = 9 \sim 75\text{V}$ ,  $V_{VDRAIN} = 9 \sim 100\text{V}$ ,  $V_{VIN} = 48\text{V}$  (特に記述のない限り)

| パラメータ                            |                        |          | テスト条件                                                  | 最小値   | 標準値               | 最大値  | 単位                           |  |

|----------------------------------|------------------------|----------|--------------------------------------------------------|-------|-------------------|------|------------------------------|--|

| $I_{DRIVEN}$                     | ピーク・シンク<br>ゲート電流       | SPI デバイス | $IDRIVEN_{HS}$ または $IDRIVEN_{LS} = 0000b$              | 100   |                   |      | mA                           |  |

|                                  |                        |          | $IDRIVEN_{HS}$ または $IDRIVEN_{LS} = 0001b$              | 100   |                   |      |                              |  |

|                                  |                        |          | $IDRIVEN_{HS}$ または $IDRIVEN_{LS} = 0010b$              | 200   |                   |      |                              |  |

|                                  |                        |          | $IDRIVEN_{HS}$ または $IDRIVEN_{LS} = 0011b$              | 300   |                   |      |                              |  |

|                                  |                        |          | $IDRIVEN_{HS}$ または $IDRIVEN_{LS} = 0100b$              | 600   |                   |      |                              |  |

|                                  |                        |          | $IDRIVEN_{HS}$ または $IDRIVEN_{LS} = 0101b$              | 700   |                   |      |                              |  |

|                                  |                        |          | $IDRIVEN_{HS}$ または $IDRIVEN_{LS} = 0110b$              | 800   |                   |      |                              |  |

|                                  |                        |          | $IDRIVEN_{HS}$ または $IDRIVEN_{LS} = 0111b$              | 900   |                   |      |                              |  |

|                                  |                        |          | $IDRIVEN_{HS}$ または $IDRIVEN_{LS} = 1000b$              | 1100  |                   |      |                              |  |

|                                  |                        |          | $IDRIVEN_{HS}$ または $IDRIVEN_{LS} = 1001b$              | 1200  |                   |      |                              |  |

|                                  |                        |          | $IDRIVEN_{HS}$ または $IDRIVEN_{LS} = 1010b$              | 1300  |                   |      |                              |  |

|                                  |                        |          | $IDRIVEN_{HS}$ または $IDRIVEN_{LS} = 1011b$              | 1400  |                   |      |                              |  |

|                                  |                        |          | $IDRIVEN_{HS}$ または $IDRIVEN_{LS} = 1100b$              | 1700  |                   |      |                              |  |

|                                  |                        |          | $IDRIVEN_{HS}$ または $IDRIVEN_{LS} = 1101b$              | 1800  |                   |      |                              |  |

|                                  |                        |          | $IDRIVEN_{HS}$ または $IDRIVEN_{LS} = 1110b$              | 1900  |                   |      |                              |  |

|                                  |                        |          | $IDRIVEN_{HS}$ または $IDRIVEN_{LS} = 1111b$              | 2000  |                   |      |                              |  |

|                                  |                        | H/W デバイス | $IDRIVE = GND$ に接続                                     | 100   |                   |      | mA                           |  |

|                                  |                        |          | $IDRIVE = 18k\Omega \pm 5\%$ で $GND$ に接続               | 200   |                   |      |                              |  |

|                                  |                        |          | $IDRIVE = 75k\Omega \pm 5\%$ で $GND$ に接続               | 300   |                   |      |                              |  |

|                                  |                        |          | $IDRIVE = \text{Hi-Z}$                                 | 600   |                   |      |                              |  |

|                                  |                        |          | $IDRIVE = 75k\Omega \pm 5\%$ で $DVDD$ に接続              | 900   |                   |      |                              |  |

|                                  |                        |          | $IDRIVE = 18k\Omega \pm 5\%$ で $DVDD$ に接続              | 1400  |                   |      |                              |  |

|                                  |                        |          | $IDRIVE = DVDD$ に接続                                    | 2000  |                   |      |                              |  |

| $I_{HOLD}$                       | ゲート保持電流                |          | $t_{DRIVE}$ 後のソース電流                                    | 50    |                   |      | mA                           |  |

|                                  |                        |          | $t_{DRIVE}$ 後のシンク電流                                    | 100   |                   |      |                              |  |

| $I_{STRONG}$                     | ゲート強フルダウン電流            |          | $GHx$ から $SHx$ , $GLx$ から $SPx/SLx$                    | 2     |                   |      | A                            |  |

| $R_{OFF}$                        | ゲート・オフ保持抵抗             |          | $GHx$ から $SHx$ , $GLx$ から $SPx/SLx$                    | 150   |                   |      | k $\Omega$                   |  |

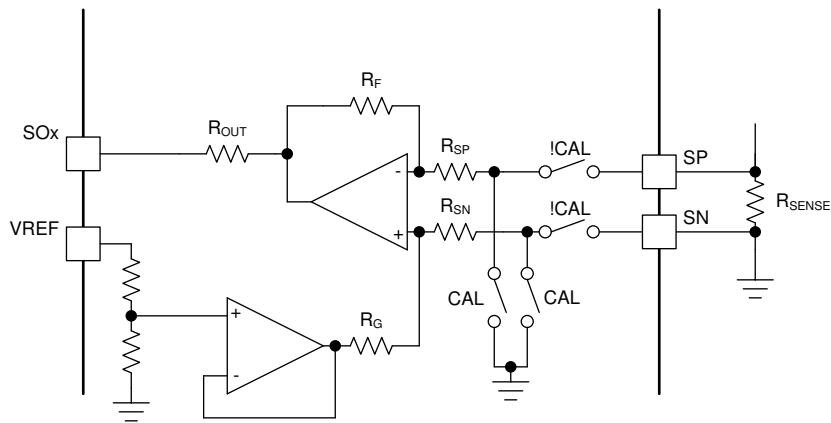

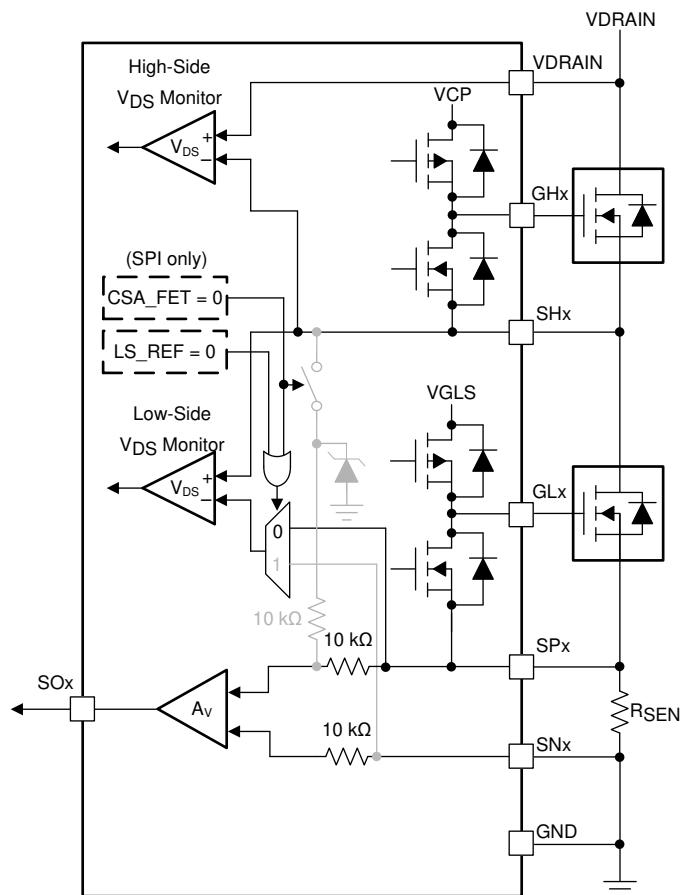

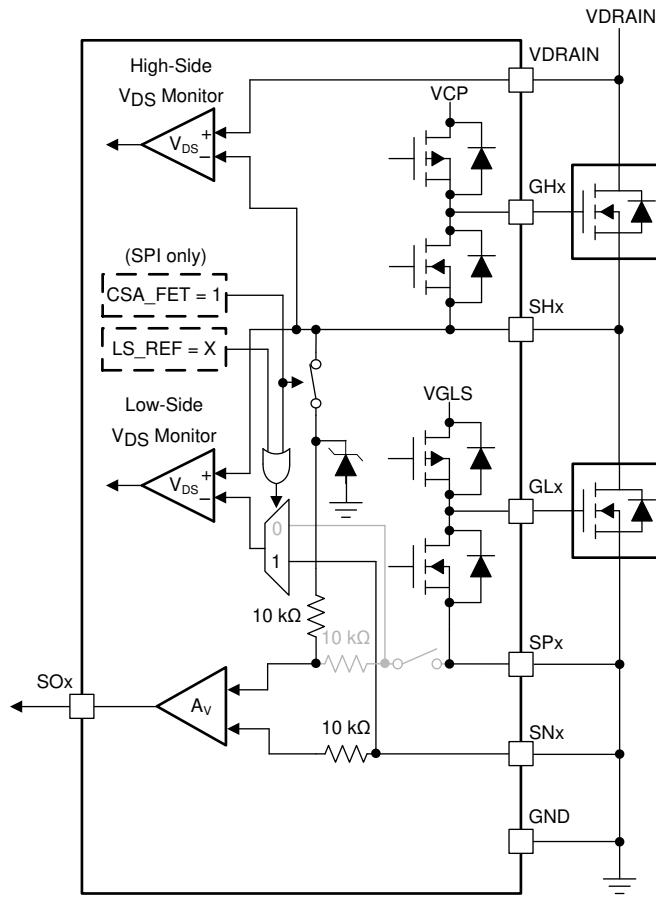

| 電流シャント・アンプ (SNx, SOx, SPx, VREF) |                        |          |                                                        |       |                   |      |                              |  |

| $G_{CSA}$                        | アンプのゲイン                | SPI デバイス | $CSA_{GAIN} = 00b$                                     | 4.85  | 5                 | 5.15 | V/V                          |  |

|                                  |                        |          | $CSA_{GAIN} = 01b$                                     | 9.7   | 10                | 10.3 |                              |  |

|                                  |                        |          | $CSA_{GAIN} = 10b$                                     | 19.4  | 20                | 20.6 |                              |  |

|                                  |                        |          | $CSA_{GAIN} = 11b$                                     | 38.8  | 40                | 41.2 |                              |  |

|                                  |                        | H/W デバイス | $GAIN = GND$ に接続                                       | 4.85  | 5                 | 5.15 |                              |  |

|                                  |                        |          | $GAIN = 47k\Omega \pm 5\%$ で $GND$ に接続                 | 9.7   | 10                | 10.3 |                              |  |

|                                  |                        |          | $GAIN = \text{Hi-Z}$                                   | 19.4  | 20                | 20.6 |                              |  |

|                                  |                        |          | $GAIN = DVDD$ に接続                                      | 38.8  | 40                | 41.2 |                              |  |

|                                  |                        |          | $V_{O\_STEP} = 0.5\text{V}$ , $G_{CSA} = 5\text{V/V}$  | 250   |                   |      | ns                           |  |

|                                  |                        |          | $V_{O\_STEP} = 0.5\text{V}$ , $G_{CSA} = 10\text{V/V}$ | 500   |                   |      |                              |  |

| $t_{SET}$                        | $\pm 1\%$ までのセトリング・タイム |          | $V_{O\_STEP} = 0.5\text{V}$ , $G_{CSA} = 20\text{V/V}$ | 1000  |                   |      |                              |  |

|                                  |                        |          | $V_{O\_STEP} = 0.5\text{V}$ , $G_{CSA} = 40\text{V/V}$ | 2000  |                   |      |                              |  |

|                                  |                        |          |                                                        |       |                   |      |                              |  |

|                                  |                        |          |                                                        |       |                   |      |                              |  |

| $V_{COM}$                        | コモン・モード入力範囲            |          |                                                        | -0.15 | 0.15              |      | V                            |  |

| $V_{DIFF}$                       | 差動モード入力範囲              |          |                                                        | -0.3  | 0.3               |      | V                            |  |

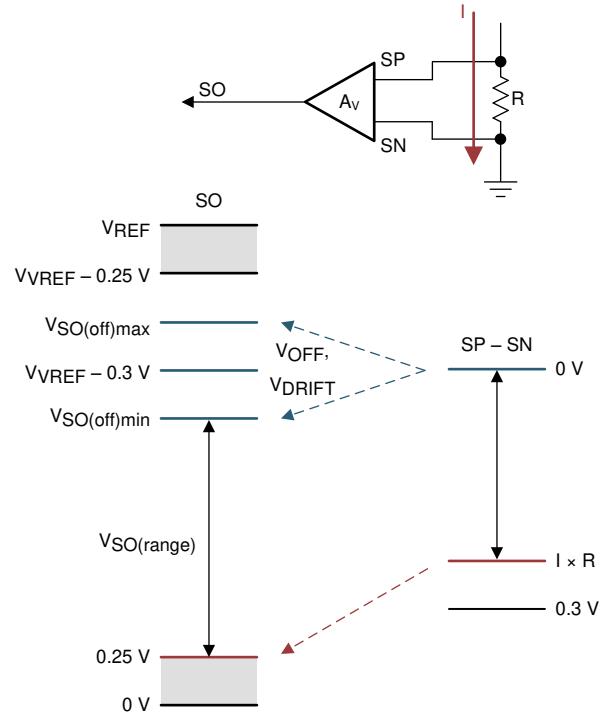

| $V_{OFF}$                        | 入力オフセット誤差              |          | $V_{SP} = V_{SN} = 0\text{V}$                          | -3    | 3                 |      | mV                           |  |

| $V_{DRIFT}$                      | オフセット・ドリフト             |          | $V_{SP} = V_{SN} = 0\text{V}$                          | 10    |                   |      | $\mu\text{V}/^\circ\text{C}$ |  |

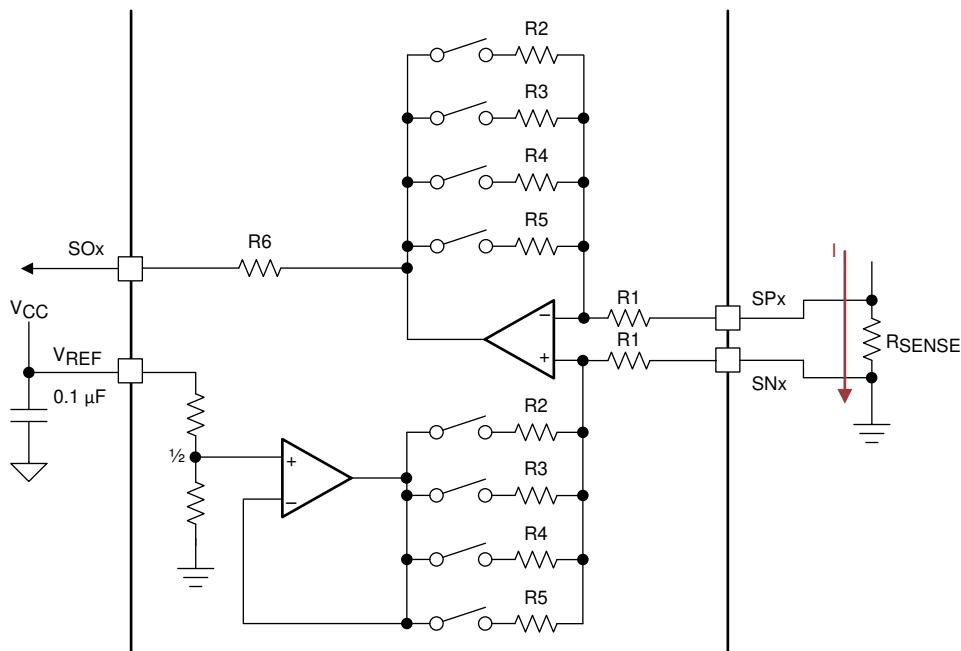

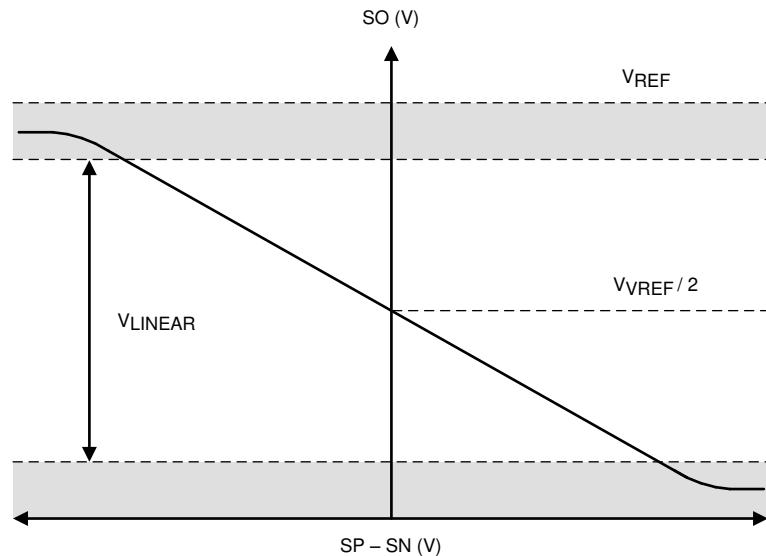

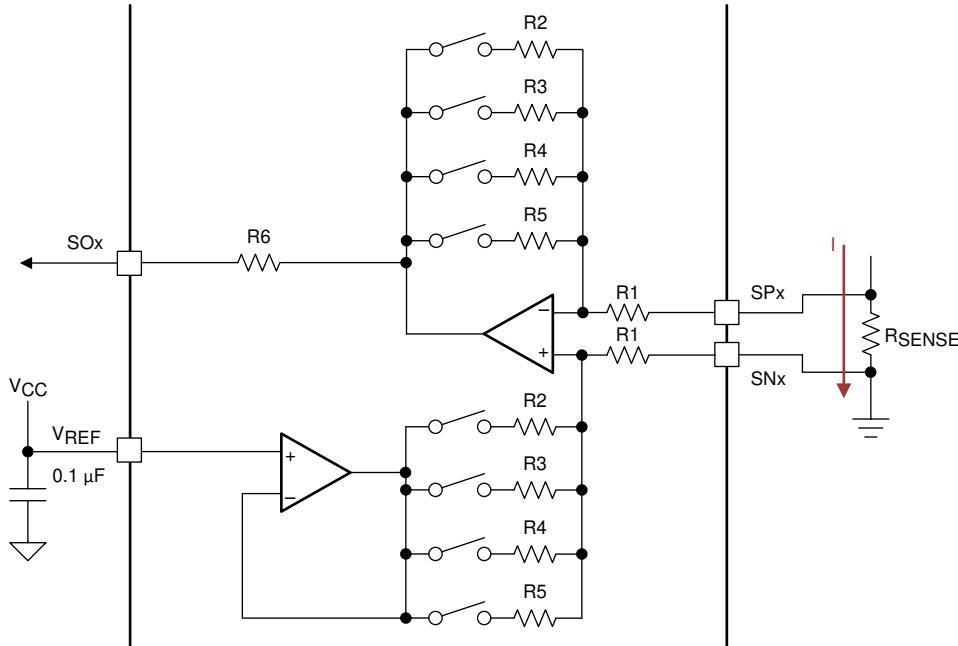

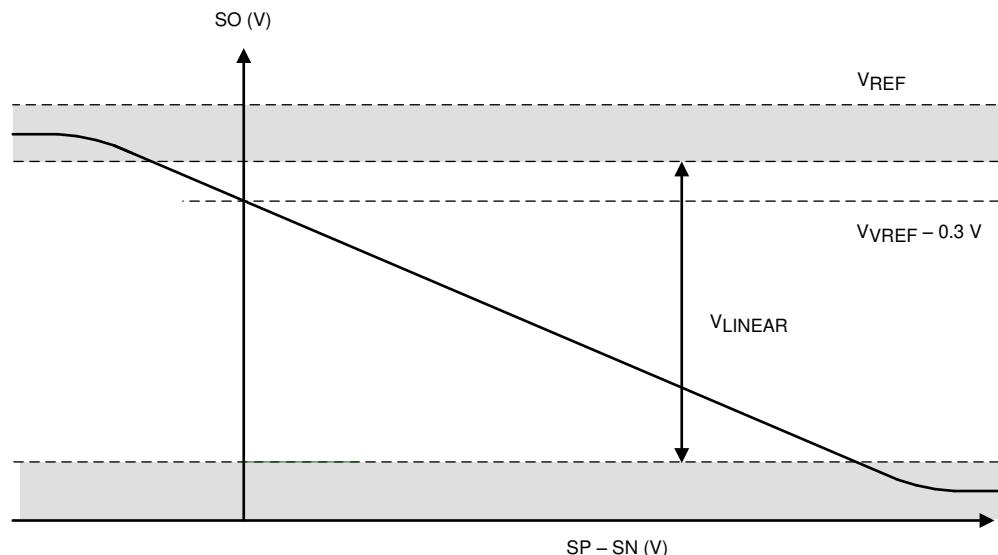

| $V_{LINEAR}$                     | SOx 出力電圧の直線範囲          |          |                                                        | 0.25  | $V_{VREF} - 0.25$ |      | V                            |  |

$T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ ,  $V_{VM} = 9 \sim 75\text{V}$ ,  $V_{VDRAIN} = 9 \sim 100\text{V}$ ,  $V_{VIN} = 48\text{V}$  (特に記述のない限り)

| パラメータ           |                           |          | テスト条件                                                      | 最小値                           | 標準値  | 最大値                    | 単位  |  |

|-----------------|---------------------------|----------|------------------------------------------------------------|-------------------------------|------|------------------------|-----|--|

| $V_{BIAS}$      | SOx 出力電圧バイアス              | SPI デバイス | $V_{SP} = V_{SN} = 0\text{V}$ , $V_{REF\_DIV} = 0\text{b}$ | $V_{VREF} - 0.3$              |      | $V_{VREF} / 2$         | V   |  |

|                 |                           |          | $V_{SP} = V_{SN} = 0\text{V}$ , $V_{REF\_DIV} = 1\text{b}$ | $V_{VREF} / 2$                |      |                        |     |  |

|                 |                           |          | H/W デバイス                                                   | $V_{SP} = V_{SN} = 0\text{V}$ |      | $V_{VREF} / 2$         |     |  |

| $I_{BIAS}$      | SPx/SNx 入力バイアス電流          |          |                                                            | 250                           |      | $\mu\text{A}$          |     |  |

| $V_{SLEW}$      | SOx 出力スルーレート              |          | 60pF 負荷                                                    | 10                            |      | $\text{V}/\mu\text{s}$ |     |  |

| $I_{VREF}$      | VREF 入力電流                 |          | $V_{VREF} = 5\text{V}$                                     | 1.5                           |      | 2.5                    | mA  |  |

| UGB             | ユニティ・ゲイン帯域幅               |          | DRV835xF:60pF 負荷                                           | 10                            |      |                        | MHz |  |

|                 |                           |          | DRV835xFR:60pF 負荷                                          | 1                             |      |                        | MHz |  |

| 保護回路            |                           |          |                                                            |                               |      |                        |     |  |

| $V_{VM\_UV}$    | VM 低電圧誤動作防止               |          | DRV835xF:VM 立ち下がり、UVLO 通知                                  | 8.0                           | 8.3  | 8.8                    | V   |  |

|                 |                           |          | DRV835xF:VM 立ち上がり、UVLO 復帰                                  | 8.2                           | 8.5  | 9.0                    |     |  |

|                 |                           |          | DRV835xFR:VM 立ち下がり、UVLO 通知                                 | 8.0                           | 8.3  | 8.6                    |     |  |

|                 |                           |          | DRV835xFR:VM 立ち上がり、UVLO 復帰                                 | 8.2                           | 8.5  | 8.8                    |     |  |

| $V_{VM\_UVH}$   | VM 低電圧ヒステリシス              |          | 立ち上がりから立ち下がりへのスレッショルド                                      | 200                           |      | $\text{mV}$            |     |  |

| $t_{VM\_UVD}$   | VM 低電圧グリッチ除去時間            |          | VM 立ち下がり、UVLO 通知                                           | 10                            |      | $\mu\text{s}$          |     |  |

| $V_{VDR\_UV}$   | VDRAIN 低電圧誤動作防止           |          | DRV835xF:VDRAIN 立ち下がり、UVLO 通知                              | 6.1                           | 6.4  | 6.8                    | V   |  |

|                 |                           |          | DRV835xF:VDRAIN 立ち上がり、UVLO 復帰                              | 6.3                           | 6.6  | 7.0                    |     |  |

|                 |                           |          | DRV835xFR:VDRAIN 立ち下がり、UVLO 通知                             | 6.1                           | 6.4  | 6.7                    |     |  |

|                 |                           |          | DRV835xFR:VDRAIN 立ち上がり、UVLO 復帰                             | 6.3                           | 6.6  | 6.9                    |     |  |

| $V_{VDR\_UVH}$  | VDRAIN 低電圧ヒステリシス          |          | 立ち上がりから立ち下がりへのスレッショルド                                      | 200                           |      | $\text{mV}$            |     |  |

| $t_{VDR\_UVD}$  | VDRAIN 低電圧グリッチ除去時間        |          | VDRAIN 立ち下がり、UVLO 通知                                       | 10                            |      | $\mu\text{s}$          |     |  |

| $V_{VCP\_UV}$   | VCP チャージ・ポンプ低電圧誤動作防止      |          | VCP 立ち下がり、GDUV 通知                                          | $V_{DRAIN} + 5$               |      | V                      |     |  |

| $V_{VGLS\_UV}$  | VGLS ローサイド・レギュレータ低電圧誤動作防止 |          | VGLS 立ち下がり、GDUV 通知                                         | 4.25                          |      | V                      |     |  |

| $V_{GS\_CLAMP}$ | ハイサイド・ゲート・クランプ            |          | 正のクランプ電圧                                                   | 12.5                          | 13.5 | 16                     | V   |  |

|                 |                           |          | 負のクランプ電圧                                                   | -0.7                          |      |                        |     |  |

$T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ ,  $V_{VM} = 9 \sim 75\text{V}$ ,  $V_{VDRAIN} = 9 \sim 100\text{V}$ ,  $V_{VIN} = 48\text{V}$  (特に記述のない限り)

| パラメータ          |                                      | テスト条件       | 最小値                                                  | 標準値     | 最大値  | 単位    |    |

|----------------|--------------------------------------|-------------|------------------------------------------------------|---------|------|-------|----|

| $V_{VDS\_OCP}$ | $V_{DS}$ 過電流トリップ電圧                   | SPI デバイス    | DRV835xF:VDS_LVL = 0000b                             | 0.041   | 0.06 | 0.072 |    |

|                |                                      |             | DRV835xF:VDS_LVL = 0001b                             | 0.051   | 0.07 | 0.084 |    |

|                |                                      |             | DRV835xF:VDS_LVL = 0010b                             | 0.061   | 0.08 | 0.096 |    |

|                |                                      |             | DRV835xF:VDS_LVL = 0011b                             | 0.071   | 0.09 | 0.108 |    |

|                |                                      |             | DRV835xF:VDS_LVL = 0100b                             | 0.081   | 0.1  | 0.115 |    |

|                |                                      |             | DRV835xFR:VDS_LVL = 0000b                            | 0.048   | 0.06 | 0.072 |    |

|                |                                      |             | DRV835xFR:VDS_LVL = 0001b                            | 0.056   | 0.07 | 0.084 |    |

|                |                                      |             | DRV835xFR:VDS_LVL = 0010b                            | 0.064   | 0.08 | 0.096 |    |

|                |                                      |             | DRV835xFR:VDS_LVL = 0011b                            | 0.072   | 0.09 | 0.108 |    |

|                |                                      |             | DRV835xFR:VDS_LVL = 0100b                            | 0.085   | 0.1  | 0.115 |    |

|                |                                      |             | VDS_LVL = 0101b                                      | 0.18    | 0.2  | 0.22  |    |

|                |                                      |             | VDS_LVL = 0110b                                      | 0.27    | 0.3  | 0.33  |    |

|                |                                      |             | VDS_LVL = 0111b                                      | 0.36    | 0.4  | 0.44  |    |

|                |                                      |             | VDS_LVL = 1000b                                      | 0.45    | 0.5  | 0.55  |    |

|                |                                      |             | VDS_LVL = 1001b                                      | 0.54    | 0.6  | 0.66  |    |

|                |                                      | H/W デバイス    | VDS_LVL = 1010b                                      | 0.63    | 0.7  | 0.77  |    |

|                |                                      |             | VDS_LVL = 1011b                                      | 0.72    | 0.8  | 0.88  |    |

|                |                                      |             | VDS_LVL = 1100b                                      | 0.81    | 0.9  | 0.99  |    |

|                |                                      |             | VDS_LVL = 1101b                                      | 0.9     | 1.0  | 1.1   |    |

|                |                                      |             | VDS_LVL = 1110b                                      | 1.35    | 1.5  | 1.65  |    |

|                |                                      |             | VDS_LVL = 1111b                                      | 1.8     | 2    | 2.2   |    |

|                |                                      |             | DRV835xF:VDS = GND に接続                               | 0.041   | 0.06 | 0.072 |    |

|                |                                      |             | DRV835xF:VDS = $18\text{k}\Omega \pm 5\%$ で GND に接続  | 0.081   | 0.1  | 0.115 |    |

| $t_{OCP\_DEG}$ | $V_{DS}$ および $V_{SENSE}$ 過電流グリッヂ除去時間 | SPI デバイス    | DRV835xFR:VDS = GND に接続                              | 0.048   | 0.06 | 0.072 |    |

|                |                                      |             | DRV835xFR:VDS = $18\text{k}\Omega \pm 5\%$ で GND に接続 | 0.085   | 0.1  | 0.115 |    |

|                |                                      |             | VDS = $75\text{k}\Omega \pm 5\%$ で GND に接続           | 0.18    | 0.2  | 0.22  |    |

|                |                                      |             | VDS = ハイ・インピーダンス                                     | 0.36    | 0.4  | 0.44  |    |

|                |                                      | H/W デバイス    | VDS = $75\text{k}\Omega \pm 5\%$ で DVDD に接続          | 0.63    | 0.7  | 0.77  |    |

|                |                                      |             | VDS = $18\text{k}\Omega \pm 5\%$ で DVDD に接続          | 0.9     | 1    | 1.1   |    |

|                |                                      |             | VDS = DVDD に接続                                       | デイスエーブル |      |       |    |

|                |                                      |             | OCP_DEG = 00b                                        | 1       |      |       |    |

|                |                                      |             | OCP_DEG = 01b                                        | 2       |      |       |    |

| $t_{SEN\_OCP}$ | $V_{SENSE}$ 過電流トリップ電圧                | SPI デバイス    | OCP_DEG = 10b                                        | 4       |      |       |    |

|                |                                      |             | OCP_DEG = 11b                                        | 8       |      |       |    |

|                |                                      |             | H/W デバイス                                             | 4       |      |       |    |

|                |                                      | H/W デバイス    | SEN_LVL = 00b                                        | 0.25    |      |       |    |

|                |                                      |             | SEN_LVL = 01b                                        | 0.5     |      |       |    |

|                |                                      |             | SEN_LVL = 10b                                        | 0.75    |      |       |    |

|                |                                      |             | SEN_LVL = 11b                                        | 1       |      |       |    |

| $t_{RETRY}$    | 過電流リトライ時間                            | SPI デバイス    | TRETRY = 0b                                          | 8       |      |       |    |

|                |                                      |             | TRETRY = 1b                                          | 50      |      |       |    |

|                |                                      | H/W デバイス    |                                                      | 8       |      |       |    |

|                |                                      |             |                                                      | ms      |      |       |    |

| $T_{OTW}$      | 過熱警告温度                               | ダイ温度、 $T_J$ |                                                      | 130     | 150  | 170   | °C |

| $T_{OTSD}$     | 過熱シャットダウン温度                          | ダイ温度、 $T_J$ |                                                      | 150     | 170  | 190   | °C |

| $T_{HYS}$      | 熱ヒステリシス                              | ダイ温度、 $T_J$ |                                                      | 20      |      |       | °C |

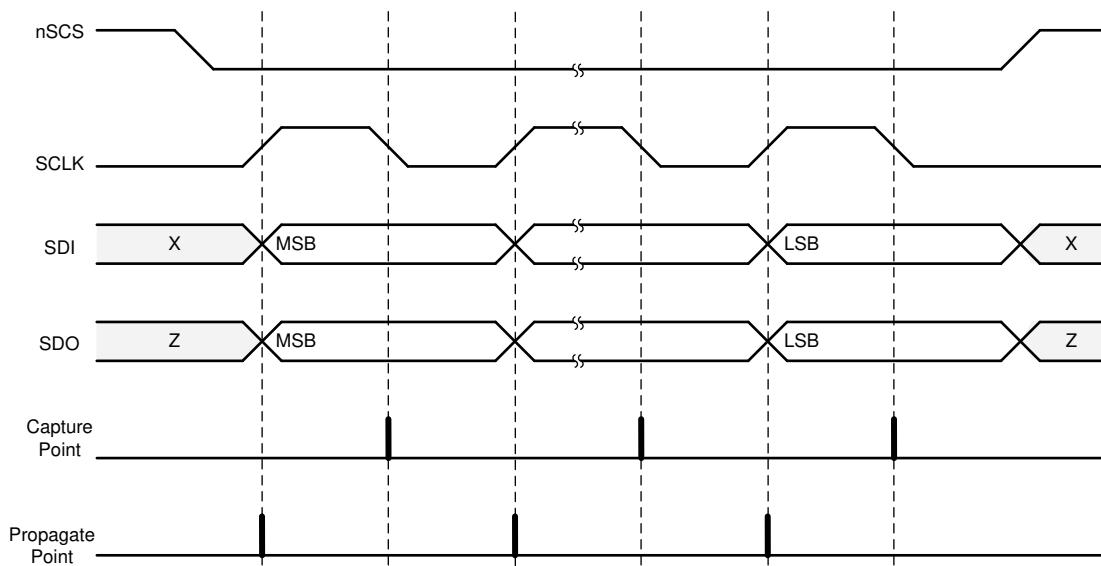

## 7.6 SPI のタイミング要件

$T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ ,  $V_{VM} = 9 \sim 75\text{V}$  (特に記述のない限り)

|                |                               |                                      | 最小値 | 公称値 | 最大値 | 単位 |

|----------------|-------------------------------|--------------------------------------|-----|-----|-----|----|

| $t_{READY}$    | イネーブル後、SPI 準備完了まで             | $VM > UVLO$ , $ENABLE = 3.3\text{V}$ |     | 1   |     | ms |

| $t_{CLK}$      | SCLK の最小周期                    |                                      | 100 |     |     | ns |

| $t_{CLKH}$     | SCLK 最小 High 時間               |                                      | 50  |     |     | ns |

| $t_{CLKL}$     | SCLK 最小 Low 時間                |                                      | 50  |     |     | ns |

| $t_{SU_SDI}$   | SDI 入力データ・セットアップ時間            |                                      | 20  |     |     | ns |

| $t_{H_SDI}$    | SDI 入力データ・ホールド時間              |                                      | 30  |     |     | ns |

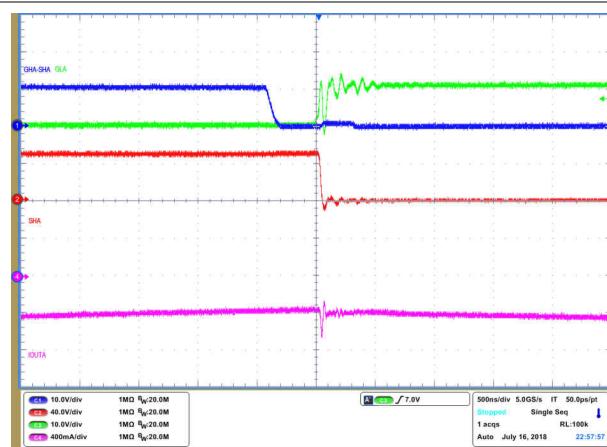

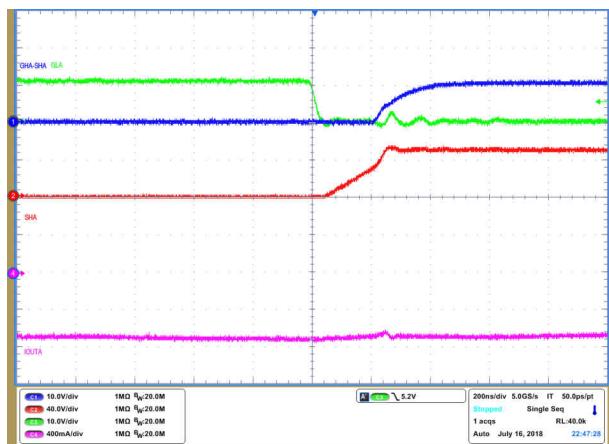

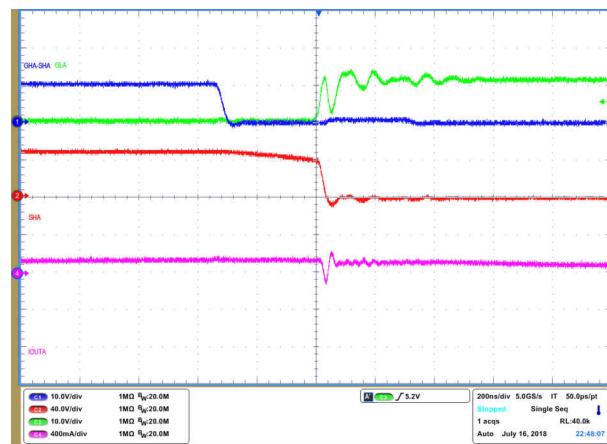

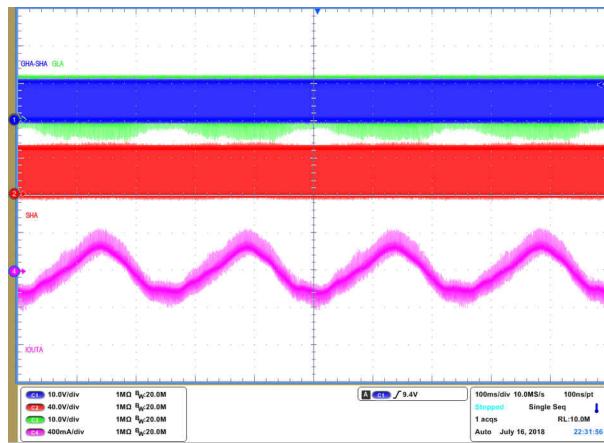

| $t_{D_SDO}$    | SDO 出力データ遅延時間                 | SCLK High から SDO 有効まで                |     | 30  |     | ns |