DRV8343-Q1

JAJSGQ9A - MARCH 2018 - REVISED APRIL 2019

# DRV8343-Q1 独立のハーフブリッジ制御と 3 つの内蔵電流センス・アンプを搭載した 12V/24V 車載用ゲート・ドライバ・ユニット (GDU)

# 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み

- 温度グレード 1: -40°C ≤ T<sub>A</sub> ≤ +125°C

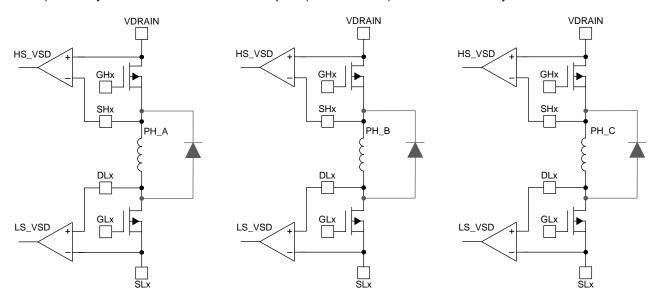

- 3つの独立したハーフブリッジ・ゲート・ドライバ

- 専用のソース (SHx) およびドレイン (DLx) ピンに より、独立の MOSFET 制御をサポート

- 3 つのハイサイドと 3 つのローサイドの N チャネル MOSFET (NMOS) を駆動

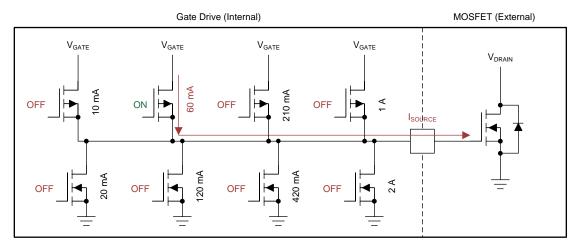

- スマート・ゲート・ドライブ・アーキテクチャ

- 調整可能なスルーレート制御

- 1.5mA~1A のピーク・ソース電流

- 3mA~2A のピーク・シンク電流

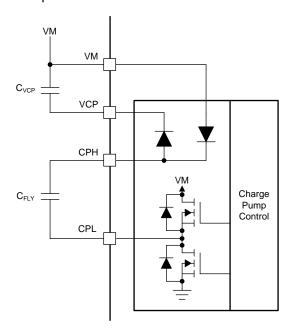

- ゲート・ドライバのチャージ・ポンプによる 100% デューティ・サイクル

- 3 つの電流センス・アンプ (CSA) を内蔵

- 可変ゲイン (5、10、20、40V/V)

- 双方向または単方向のサポート

- SPI (S) およびハードウェア (H) インターフェイスを使用可能

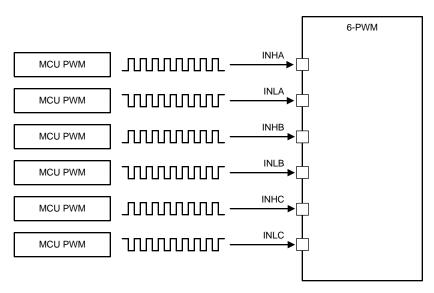

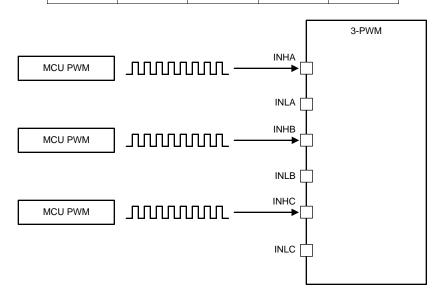

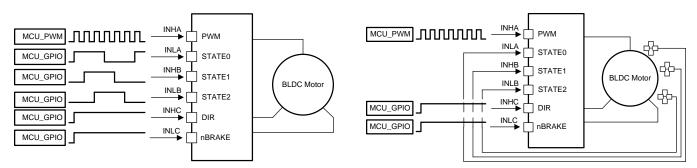

- 6x、3x、1x、および独立 PWM モード

- 3.3V と 5 Vのロジック入力電圧をサポート

- チャージ・ポンプ出力を使用して、逆電圧保護 MOSFET を駆動可能

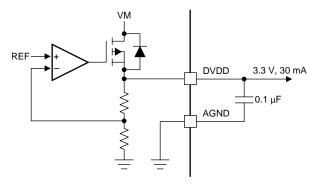

- リニア電圧レギュレータ、3.3V、30mA

- 保護機能内蔵

- VM 低電圧誤動作防止 (UVLO)

- チャージ・ポンプ低電圧 (CPUV)

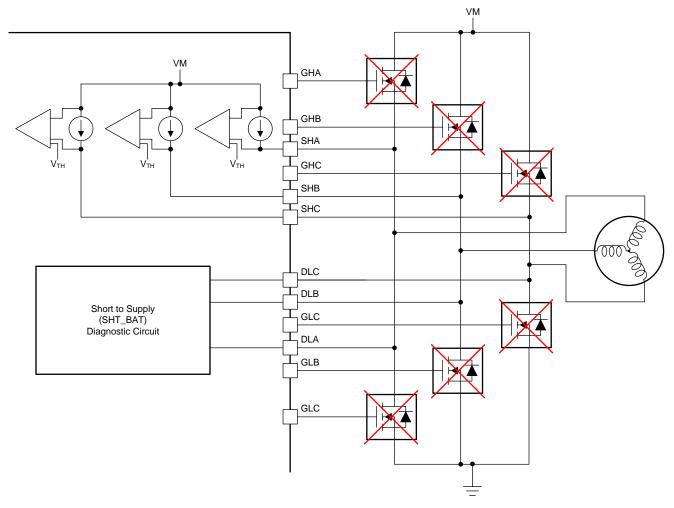

- バッテリへの短絡 (SHT BAT)

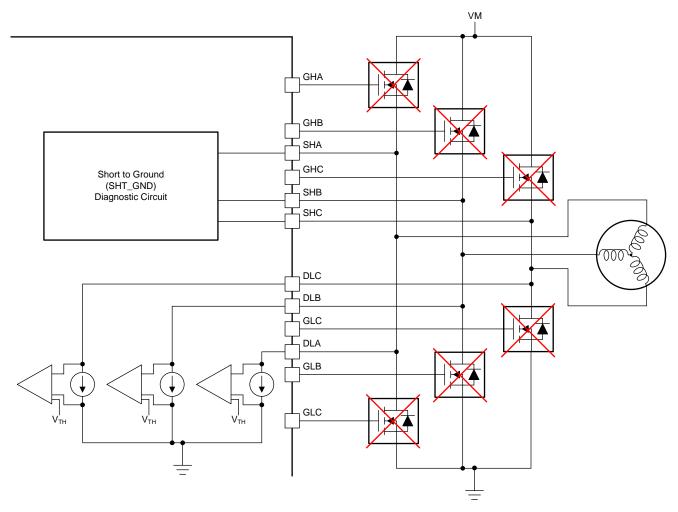

- グランドへの短絡 (SHT GND)

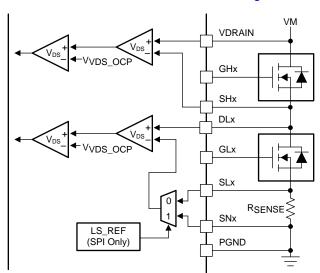

- MOSFET 過電流保護 (OCP)

- ゲート・ドライバのフォルト (GDF)

- 熱警告およびシャットダウン (OTW/OTSD)

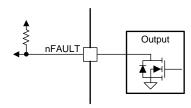

- 障害状況インジケータ (nFAULT)

# 2 アプリケーション

- 12Vおよび24Vの車載用モータ制御アプリケーション

- BLDC および BDC モータ・モジュール

- ファンと送風機

- 燃料および水ポンプ

- ソレノイド駆動

# 3 概要

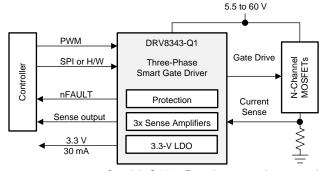

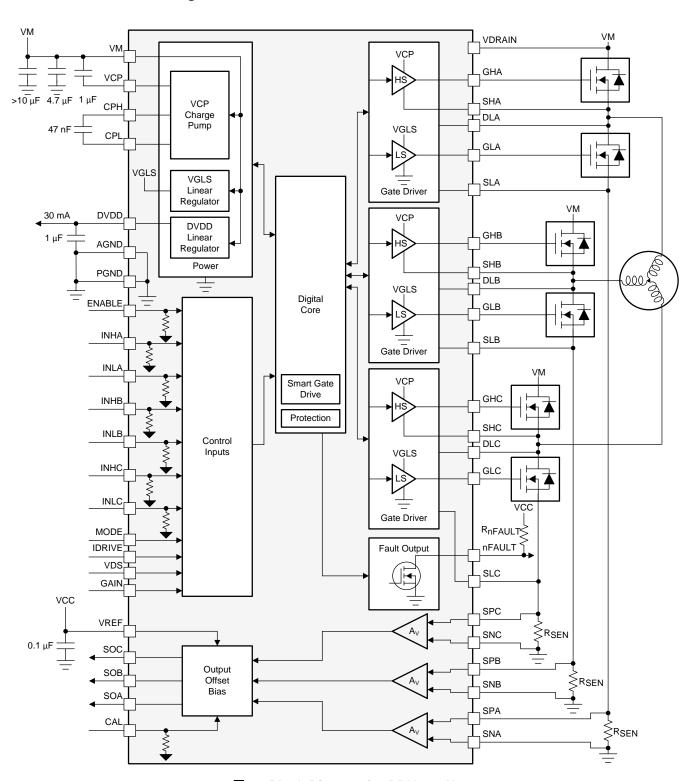

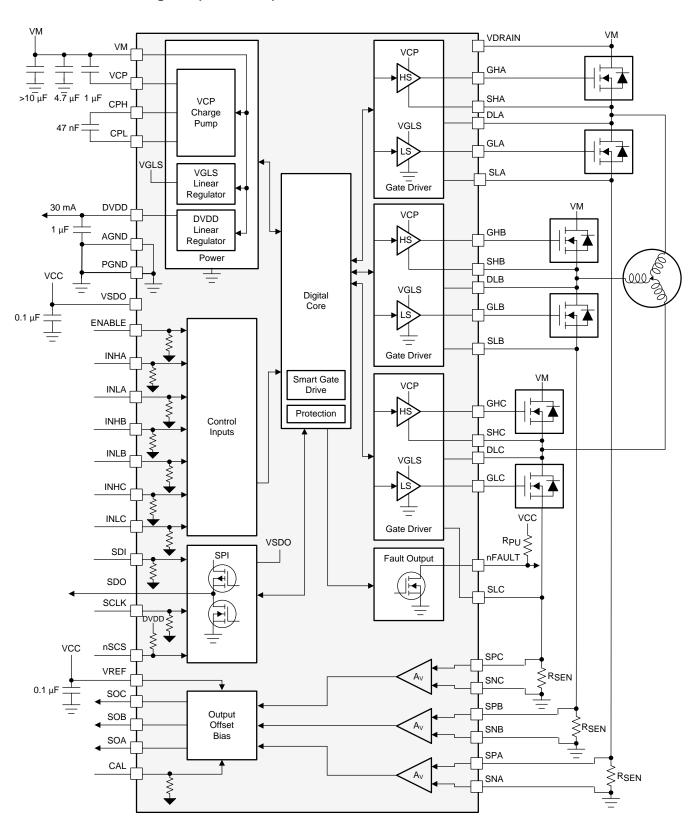

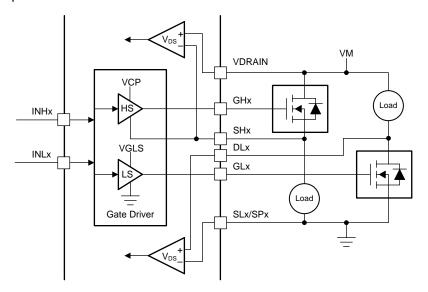

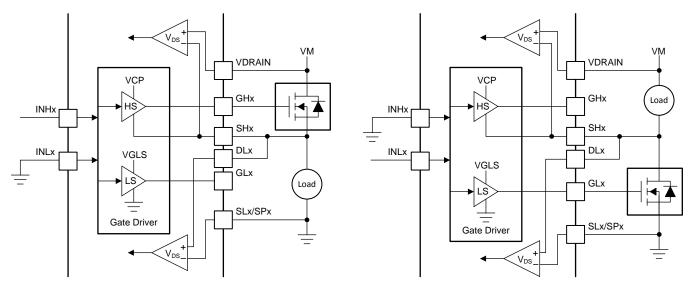

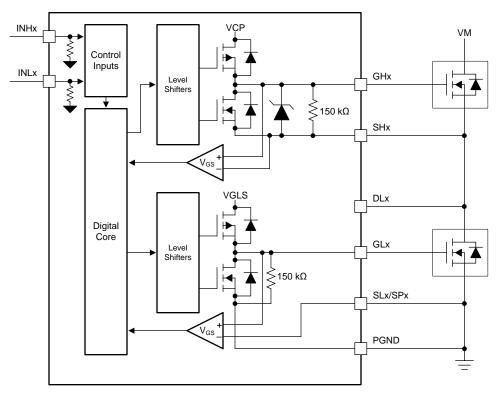

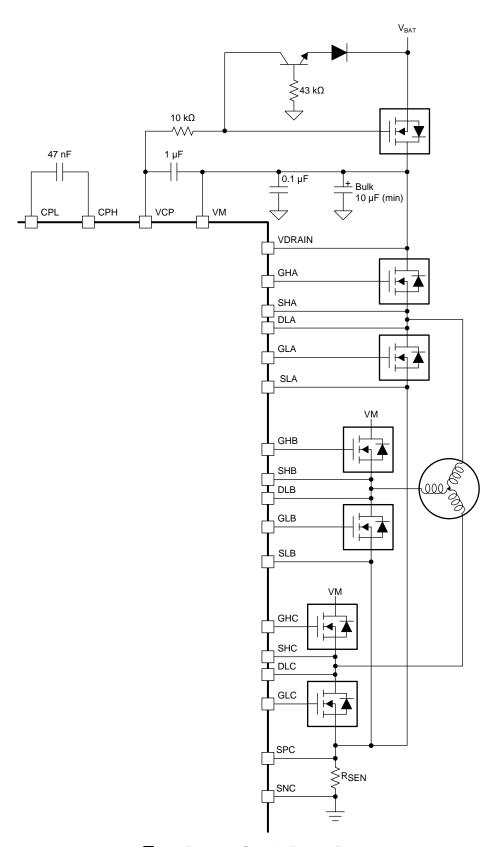

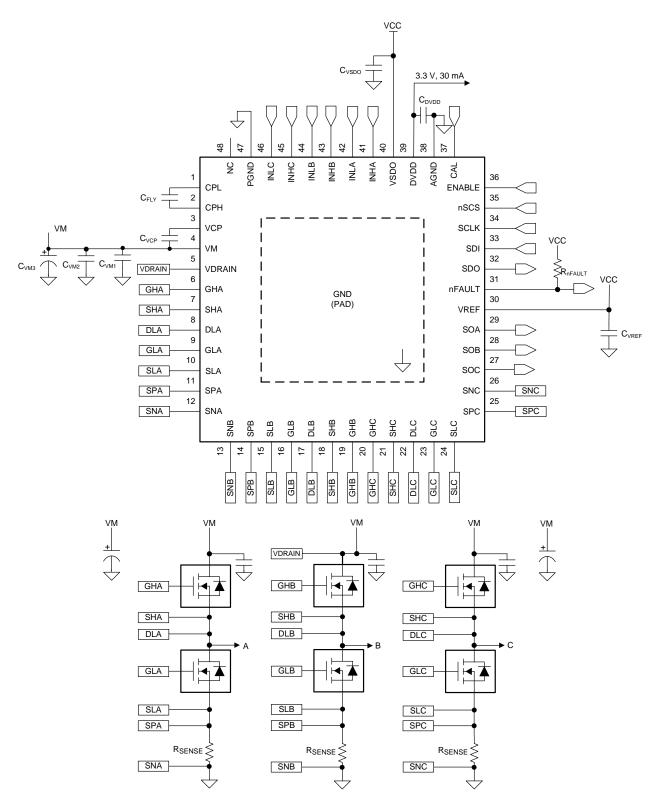

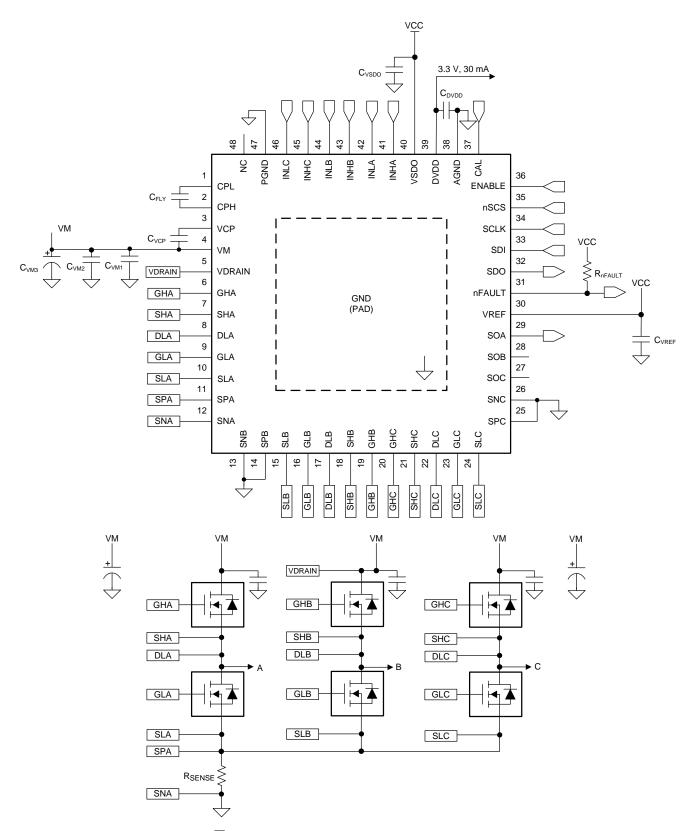

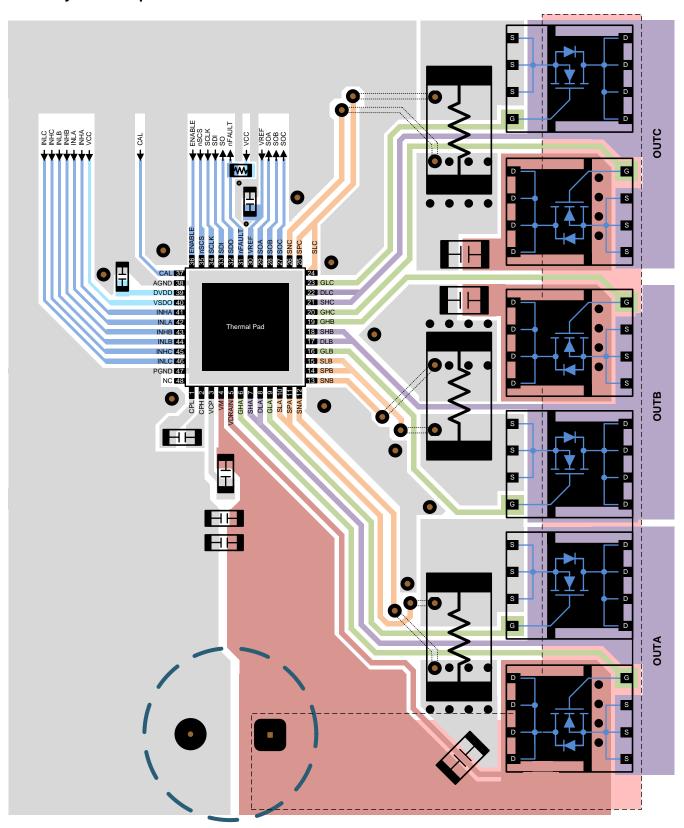

DRV8343-Q1デバイスは、3相アプリケーション用の統合 ゲート・ドライバです。このデバイスには、3つのハーフ・ブ リッジ・ゲート・ドライバがあり、それぞれがハイサイドとロー サイドのNチャネル・パワーMOSFETを駆動できます。専 用のソースおよびドレイン・ピンにより、ソレノイド・アプリ ケーションで独立のMOSFET制御が可能です。

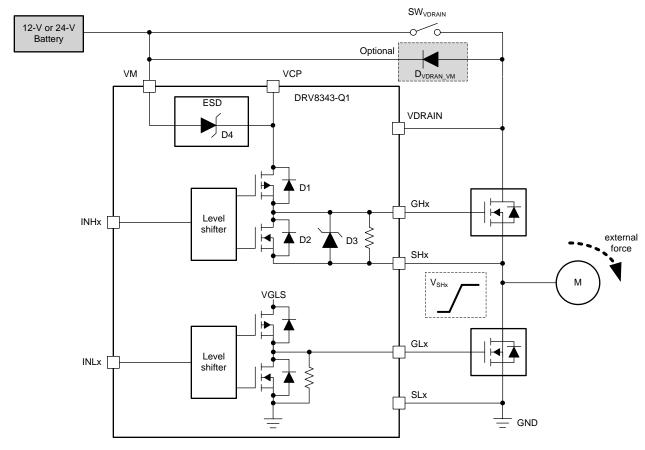

DRV8343-Q1 は、内蔵のチャージ・ポンプを使用してハイサイド MOSFET 用の、リニア・レギュレータを使用してローサイド MOSFET 用の、適切なゲート駆動電圧を生成します。スマート・ゲート・ドライブのアーキテクチャは、最大でソース1A、シンク2Aのピーク・ゲート駆動電流をサポートします。DRV8343-Q1は単一電源で動作でき、ゲート・ドライバ用に5.5~60Vの広い入力電源電圧範囲をサポートします。

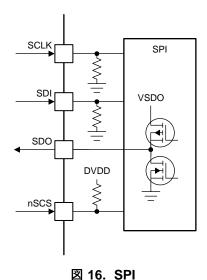

6x、3x、1x、および独立入力のPWMモードにより、コントローラの回路と簡単に接続できます。ゲート・ドライバとデバイスの構成設定は、SPIまたはハードウェア(H/W)インターフェイスにより細かく変更可能です。DRV8343-Q1デバイスには3つのローサイド電流センス・アンプが内蔵されており、駆動段の3相すべてについて、双方向の電流センシングが可能です。

#### 製品情報(1)

| 型番         | パッケージ     | 本体サイズ(公称)     |

|------------|-----------|---------------|

| DRV8343-Q1 | HTQFP(48) | 7.00mm×7.00mm |

(1) 提供されているすべてのパッケージについては、巻末の注文情報を参照してください。

## 概略回路図

Copyright © 2017, Texas Instruments Incorporated

| ·— |

|----|

|    |

|    |

| 1 | <b>株</b> E                            |    | 9.5 Programming                                   | 53                  |

|---|---------------------------------------|----|---------------------------------------------------|---------------------|

| - | 特長                                    |    | 9.6 Register Maps                                 |                     |

| 2 | アプリケーション1                             | 40 |                                                   |                     |

| 3 | 概要1                                   | 10 | Application and Implementation                    |                     |

| 4 | 改訂履歴2                                 |    | 10.1 Application Information                      | 70                  |

| 5 | 概要(続き)3                               |    | 10.2 Typical Application                          | 70                  |

| 6 | Device Comparison Table 4             | 11 | Power Supply Recommendations                      | 77                  |

| 7 | Pin Configuration and Functions 4     |    | 11.1 Power Supply Consideration in Generator Mode | e . <mark>77</mark> |

| _ | <u> </u>                              |    | 11.2 Bulk Capacitance Sizing                      | 77                  |

| 8 | Specifications8                       | 12 | Layout                                            | 79                  |

|   | 8.1 Absolute Maximum Ratings          |    | 12.1 Layout Guidelines                            |                     |

|   | 8.2 ESD Ratings 8                     |    | 12.2 Layout Example                               |                     |

|   | 8.3 Recommended Operating Conditions9 | 13 | デバイスおよびドキュメントのサポート                                |                     |

|   | 8.4 Thermal Information9              |    | 13.1 デバイス・サポート                                    |                     |

|   | 8.5 Electrical Characteristics 10     |    |                                                   |                     |

|   | 8.6 SPI Timing Requirements           |    | 13.2 ドキュメントのサポート                                  |                     |

|   | 8.7 Typical Characteristics17         |    | 13.3 ドキュメントの更新通知を受け取る方法                           |                     |

| 9 | Detailed Description 18               |    | 13.4 コミュニティ・リソース                                  |                     |

|   | 9.1 Overview 18                       |    | 13.5 商標                                           |                     |

|   | 9.2 Functional Block Diagram          |    | 13.6 静電気放電に関する注意事項                                | 82                  |

|   | 9.3 Feature Description               |    | 13.7 Glossary                                     | 82                  |

|   | •                                     | 14 | メカニカル、パッケージ、および注文情報                               | 82                  |

|   | 9.4 Device Functional Modes           |    |                                                   |                     |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| 20 | <b>118</b> 年3月発行のものから更新 | Pag | е |

|----|-------------------------|-----|---|

| •  | デバイスのステータスを量産データに 変更    |     | 1 |

# 5 概要(続き)

低消費電力のスリープ・モードがあり、静止電流を低減できます。低電圧誤動作防止、チャージ・ポンプのフォルト、MOSFET過電流、MOSFET短絡、位相ノードの電源およびグランドへの短絡、ゲート・ドライバのフォルト、過熱への保護機能が内蔵されています。フォルト状況はnFAULTピンにより通知され、SPIデバイスのバリエーションではデバイスのレジスタにより詳細が通知されます。

PΡ

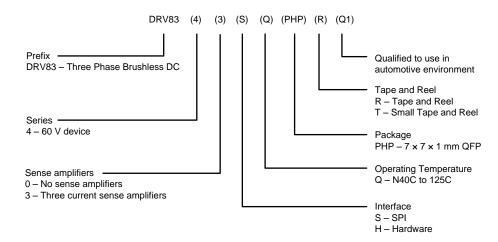

# 6 Device Comparison Table

| DEVICE     | VARIANT <sup>(1)</sup> | INTERFACE <sup>(1)</sup> |

|------------|------------------------|--------------------------|

| DRV8343-Q1 | DRV8343H               | Hardware                 |

|            | DRV8343S               | SPI                      |

(1) For more information on the device name and device options, see the デバイスの項目表記 section.

# 7 Pin Configuration and Functions

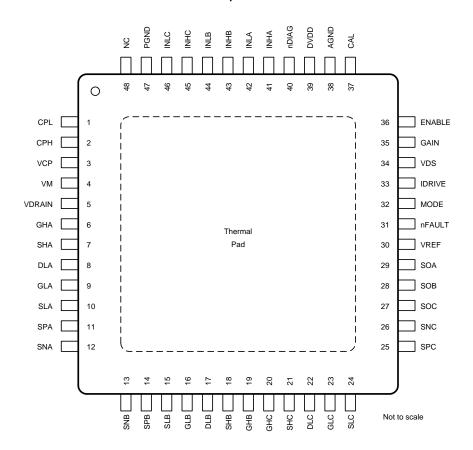

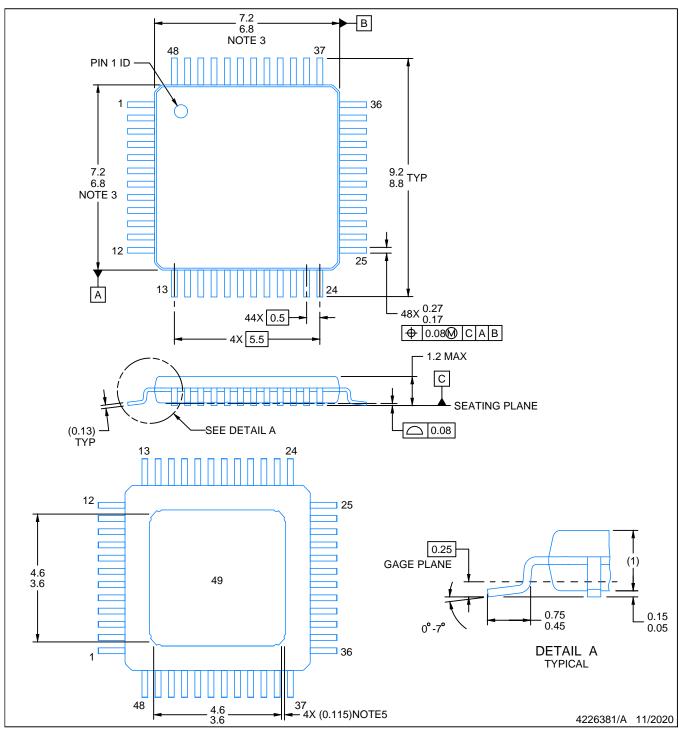

#### DRV8343H PHP PowerPAD™ Package 48-Pin HTQFP With Exposed Thermal Pad Top View

## Pin Functions—DRV8343H

|     | PIN    | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                       |  |

|-----|--------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME   | ITPE\/              | DESCRIPTION                                                                                                                       |  |

| 1   | CPL    | PWR                 | Charge pump switching node. Connect a flying capacitor between the CPH and CPL pins                                               |  |

| 2   | CPH    | PWR                 | Charge pump switching node. Connect a flying capacitor between the CPH and CPL pins                                               |  |

| 3   | VCP    | PWR                 | Charge pump output. Connect a bypass capacitor between the VCP and VM pins                                                        |  |

| 4   | VM     | PWR                 | e driver power supply input. Connect to the bridge power supply. Connect bypass capacitors VM and PGND pins                       |  |

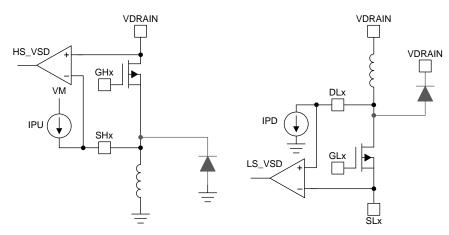

| 5   | VDRAIN | I                   | h-side MOSFET drain sense input. Connect to the common point of the MOSFET drains                                                 |  |

| 6   | GHA    | 0                   | gh-side gate driver output. Connect to the gate of the high-side power MOSFET                                                     |  |

| 7   | SHA    | I                   | High-side source sense input. Connect to the high-side power MOSFET source. If high-side power MOSFET is not used, connect to GND |  |

| 8   | DLA    | I                   | Low-side MOSFET drain sense input. Connect to the low-side MOSFET drain                                                           |  |

(1) PWR = power, I = input, O = output, NC = no connection, OD = open-drain output

# Pin Functions—DRV8343H (continued)

|     | PIN            | (4)                 |                                                                                                                                                                                                                                                              |  |

|-----|----------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME           | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                  |  |

| 9   | GLA            | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET                                                                                                                                                                                |  |

| 10  | SLA            | I                   | Low-side source sense input. Connect to the low-side power MOSFET source                                                                                                                                                                                     |  |

| 11  | SPA            | I                   | Low-side current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor                                                                                                                              |  |

| 12  | SNA            | I                   | Current sense amplifier input. Connect to the low-side of the current shunt resistor                                                                                                                                                                         |  |

| 13  | SNB            | I                   | Low-side source sense input. Connect to the low-side power MOSFET source                                                                                                                                                                                     |  |

| 14  | SPB            | I                   | Low-side current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor                                                                                                                              |  |

| 15  | SLB            | I                   | Low-side source sense input. Connect to the low-side power MOSFET source                                                                                                                                                                                     |  |

| 16  | GLB            | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET                                                                                                                                                                                |  |

| 17  | DLB            | I                   | Low-side MOSFET drain sense input. Connect to the low-side MOSFET drain                                                                                                                                                                                      |  |

| 18  | SHB            | I                   | High-side source sense input. Connect to the high-side power MOSFET source. If high-side power MOSFET is not used, connect to GND                                                                                                                            |  |

| 19  | GHB            | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET                                                                                                                                                                              |  |

| 20  | GHC            | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET                                                                                                                                                                              |  |

| 21  | SHC            | I                   | High-side source sense input. Connect to the high-side power MOSFET source. If high-side power MOSFET is not used, connect to GND                                                                                                                            |  |

| 22  | DLC            | I                   | Low-side MOSFET drain sense input. Connect to the low-side MOSFET drain                                                                                                                                                                                      |  |

| 23  | GLC            | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET                                                                                                                                                                                |  |

| 24  | SLC            | I                   | Low-side source sense input. Connect to the low-side power MOSFET source                                                                                                                                                                                     |  |

| 25  | SPC            | I                   | Low-side current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor                                                                                                                              |  |

| 26  | SNC            | I                   | Current sense amplifier input. Connect to the low-side of the current shunt resistor                                                                                                                                                                         |  |

| 27  | SOC            | 0                   | Current sense amplifier output                                                                                                                                                                                                                               |  |

| 28  | SOB            | 0                   | Current sense amplifier output                                                                                                                                                                                                                               |  |

| 29  | SOA            | 0                   | Current sense amplifier output                                                                                                                                                                                                                               |  |

| 30  | VREF           | PWR                 | Current sense amplifier power supply input and reference. Connect a bypass capacitor between VREF and AGND                                                                                                                                                   |  |

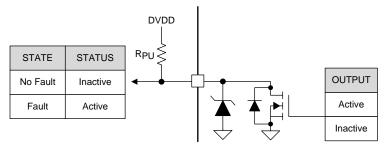

| 31  | nFAULT         | OD                  | Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pullup resistor                                                                                                                                       |  |

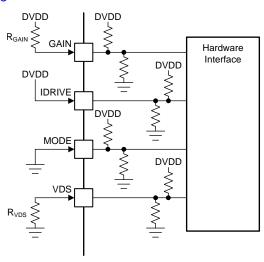

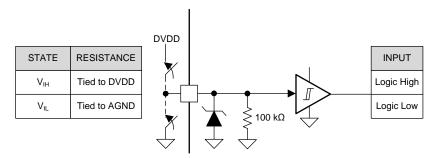

| 32  | MODE           | I                   | WM input mode setting. This pin is a 7-level input pin set by an external resistor                                                                                                                                                                           |  |

| 33  | IDRIVE         | I                   | Gate drive output current setting. This pin is a 7-level input pin set by an external resistor                                                                                                                                                               |  |

| 34  | VDS            | I                   | VDS monitor trip point setting. This pin is a 7-level input pin set by an external resistor                                                                                                                                                                  |  |

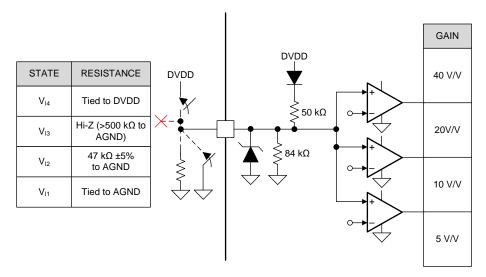

| 35  | GAIN           | I                   | Amplifier gain setting. The pin is a 4-level input pin set by an external resistor                                                                                                                                                                           |  |

| 36  | ENABLE         | I                   | Gate driver enable. When this pin is logic low the device goes to a low-power sleep mode. An 20-µs (typ) low pulse can be used to reset fault conditions                                                                                                     |  |

| 37  | CAL            | I                   | Amplifier calibration input. Set logic high to internally short amplifier inputs                                                                                                                                                                             |  |

| 38  | AGND           | PWR                 | Device analog ground. Connect to system ground                                                                                                                                                                                                               |  |

| 39  | DVDD           | PWR                 | 3.3-V internal regulator output. Connect a bypass capacitor between the DVDD and AGND pins. This regulator can externally source up to 30 mA.                                                                                                                |  |

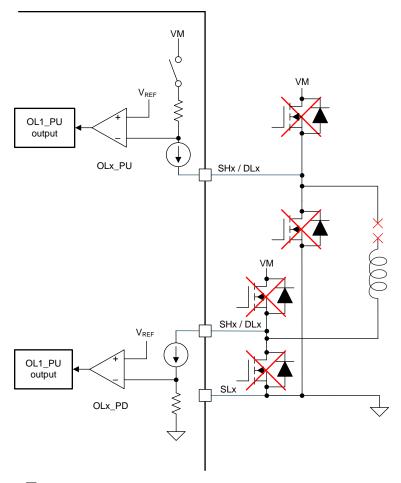

| 40  | nDIAG          | 1                   | Control pin for open load diagnostic and offline short-to-battery and short-to-ground diagnostic. To enable the diagnostics at device power-up, do not connect this pin (or tie it to ground). To disable the diagnostics, connect this pin to the DVDD pin. |  |

| 41  | INHA           | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver                                                                                                                                                               |  |

| 42  | INLA           | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver                                                                                                                                                                 |  |

| 43  | INHB           | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver                                                                                                                                                               |  |

| 44  | INLB           | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver                                                                                                                                                                 |  |

| 45  | INHC           | I                   | gh-side gate driver control input. This pin controls the output of the high-side gate driver                                                                                                                                                                 |  |

| 46  | INLC           | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver                                                                                                                                                                 |  |

| 47  | PGND           | PWR                 | Device power ground. Connect to system ground                                                                                                                                                                                                                |  |

| 48  | NC             | NC                  | No connect. Do not connect anything to this pin                                                                                                                                                                                                              |  |

| _   | Thermal<br>Pad | PWR                 | Must be connected to ground                                                                                                                                                                                                                                  |  |

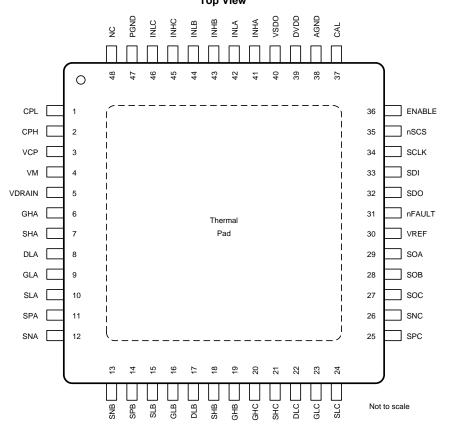

#### DRV8343S PHP PowerPAD™ Package 48-Pin HTQFP With Exposed Thermal Pad Top View

# Pin Functions—DRV8343S

|     | PIN    | TYPE <sup>(1)</sup> | DECODIDEION                                                                                                                     |  |  |

|-----|--------|---------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | NAME   | TYPE                | DESCRIPTION                                                                                                                     |  |  |

| 1   | CPL    | PWR                 | Charge pump switching node. Connect a flying capacitor between the CPH and CPL pins                                             |  |  |

| 2   | CPH    | PWR                 | Charge pump switching node. Connect a flying capacitor between the CPH and CPL pins                                             |  |  |

| 3   | VCP    | PWR                 | Charge pump output. Connect a bypass capacitor between the VCP and VM pins                                                      |  |  |

| 4   | VM     | PWR                 | Gate driver power supply input. Connect to the bridge power supply. Connect bypass capacitors between the VM and PGND pins      |  |  |

| 5   | VDRAIN | I                   | High-side MOSFET drain sense input. Connect to the common point of the MOSFET drains                                            |  |  |

| 6   | GHA    | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET                                                 |  |  |

| 7   | SHA    | I                   | side source sense input. Connect to the high-side power MOSFET source. If high-side power MOSFET is not used, ct to GND         |  |  |

| 8   | DLA    | I                   | Low-side MOSFET drain sense input. Connect to the low-side MOSFET drain                                                         |  |  |

| 9   | GLA    | 0                   | side gate driver output. Connect to the gate of the low-side power MOSFET                                                       |  |  |

| 10  | SLA    | I                   | Low-side source sense input. Connect to the low-side power MOSFET source                                                        |  |  |

| 11  | SPA    | 1                   | r-side current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt stor       |  |  |

| 12  | SNA    | I                   | Current sense amplifier input. Connect to the low-side of the current shunt resistor                                            |  |  |

| 13  | SNB    | I                   | Low-side source sense input. Connect to the low-side power MOSFET source                                                        |  |  |

| 14  | SPB    | 1                   | Low-side current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor |  |  |

| 15  | SLB    | I                   | Low-side source sense input. Connect to the low-side power MOSFET source                                                        |  |  |

| 16  | GLB    | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET                                                   |  |  |

| 17  | DLB    | I                   | Low-side MOSFET drain sense input. Connect to the low-side MOSFET drain                                                         |  |  |

(1) PWR = power, I = input, O = output, NC = no connection, OD = open-drain output, PP = push-pull

# Pin Functions—DRV8343S (continued)

|     | PIN            | (4)                 |                                                                                                                                                          |  |

|-----|----------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME           | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                              |  |

| 18  | SHB            | I                   | High-side source sense input. Connect to the high-side power MOSFET source. If high-side power MOSFET is not used, connect to GND                        |  |

| 19  | GHB            | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET                                                                          |  |

| 20  | GHC            | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET                                                                          |  |

| 21  | SHC            | 1                   | High-side source sense input. Connect to the high-side power MOSFET source. If high-side power MOSFET is not used, connect to GND                        |  |

| 22  | DLC            | I                   | Low-side MOSFET drain sense input. Connect to the low-side MOSFET drain                                                                                  |  |

| 23  | GLC            | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET                                                                            |  |

| 24  | SLC            | I                   | Low-side source sense input. Connect to the low-side power MOSFET source                                                                                 |  |

| 25  | SPC            | I                   | Low-side current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor                          |  |

| 26  | SNC            | I                   | Current sense amplifier input. Connect to the low-side of the current shunt resistor                                                                     |  |

| 27  | SOC            | 0                   | Current sense amplifier output                                                                                                                           |  |

| 28  | SOB            | 0                   | Current sense amplifier output                                                                                                                           |  |

| 29  | SOA            | 0                   | Current sense amplifier output                                                                                                                           |  |

| 30  | VREF           | PWR                 | Current sense amplifier power supply input and reference. Connect a bypass capacitors between VREF and AGND                                              |  |

| 31  | nFAULT         | OD                  | Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pullup resistor                                   |  |

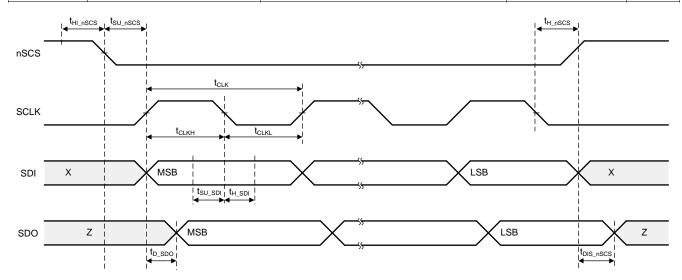

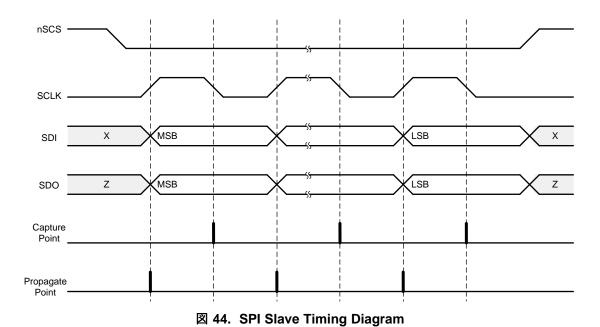

| 32  | SDO            | PP                  | Serial data output. Data is shifted out on the rising edge of the SCLK pin. VSDO determines logic level on the output                                    |  |

| 33  | SDI            | I                   | Serial data input. Data is captured on the falling edge of the SCLK pin                                                                                  |  |

| 34  | SCLK           | I                   | Serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin                                     |  |

| 35  | nSCS           | I                   | Serial chip select. A logic low on this pin enables serial interface communication                                                                       |  |

| 36  | ENABLE         | I                   | Gate driver enable. When this pin is logic low the device goes to a low-power sleep mode. An 20-µs (typ) low pulse can be used to reset fault conditions |  |

| 37  | CAL            | I                   | Amplifier calibration input. Set logic high to internally short amplifier inputs                                                                         |  |

| 38  | AGND           | PWR                 | Device analog ground. Connect to system ground                                                                                                           |  |

| 39  | DVDD           | PWR                 | 3.3-V internal regulator output. Connect a bypass capacitor between the DVDD and AGND pins. This regulator can externally source up to 30 mA.            |  |

| 40  | VSDO           | PWR                 | Supply pin for SDO output. Connect to 5-V or 3.3-V depending on the desired logic level. Connect a bypass capacitors between VSDO and AGND               |  |

| 41  | INHA           | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver                                                           |  |

| 42  | INLA           | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver                                                             |  |

| 43  | INHB           | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver                                                           |  |

| 44  | INLB           | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver                                                             |  |

| 45  | INHC           | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver                                                           |  |

| 46  | INLC           | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver                                                             |  |

| 47  | PGND           | PWR                 | Device power ground. Connect to system ground                                                                                                            |  |

| 48  | NC             | NC                  | No connect. Do not connect anything to this pin                                                                                                          |  |

| _   | Thermal<br>Pad | PWR                 | Must be connected to ground                                                                                                                              |  |

# 8 Specifications

# 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                                                                                             | MIN               | MAX                     | UNIT |

|-------------------------------------------------------------------------------------------------------------|-------------------|-------------------------|------|

| GATE DRIVER                                                                                                 |                   | <u>'</u>                |      |

| Power supply pin voltage (VM)                                                                               | -0.3              | 65                      | V    |

| Voltage differential between ground pins (AGND, BGND, DGND, PGND)                                           | -0.3              | 0.3                     | V    |

| MOSFET drain sense pin voltage (VDRAIN)                                                                     | -0.3              | 65                      | V    |

| Charge pump pin voltage (CPH, VCP)                                                                          | -0.3              | V <sub>VM</sub> + 13.5  | V    |

| Charge-pump negative-switching pin voltage (CPL)                                                            | -0.3              | V <sub>VM</sub>         | V    |

| nternal logic regulator pin voltage (DVDD)                                                                  | -0.3              | 3.8                     | V    |

| Voltage difference between VM and VDRAIN                                                                    | -10               | 10                      | V    |

| Digital pin voltage (CAL, ENABLE, GAIN, IDRIVE, INHx, INLx, MODE, nFAULT, nSCS, SCLK, SDI, SDO, VDS, nDIAG) | -0.3              | 5.75                    | V    |

| Continuous high-side gate drive pin voltage (GHx)                                                           | -5 <sup>(2)</sup> | V <sub>VCP</sub> + 0.5  | V    |

| Transient 200-ns high-side gate drive pin voltage (GHx)                                                     | -7                | V <sub>VCP</sub> + 0.5  | V    |

| High-side gate drive pin voltage with respect to SHx (GHx)                                                  | -0.3              | 13.5                    | V    |

| Continuous high-side source sense pin voltage (SHx, DLx)                                                    | -5 <sup>(2)</sup> | V <sub>VM</sub> + 5     | V    |

| Transient 200-ns high-side source sense pin voltage (SHx, DLx)                                              | -7                | V <sub>VM</sub> + 7     | V    |

| Continuous high-side source sense pin voltage (SHx, DLx)                                                    | -5 <sup>(2)</sup> | V <sub>DRAIN</sub> + 5  | V    |

| Transient 200-ns high-side source sense pin voltage (SHx, DLx)                                              | -7                | V <sub>DRAIN</sub> + 7  | V    |

| Continuous low-side gate drive pin voltage (GLx)                                                            | -0.5              | 15                      | V    |

| Gate drive pin source current (GHx, GLx)                                                                    | Internally li     | mited                   | Α    |

| Gate drive pin sink current (GHx, GLx)                                                                      | Internally li     | Α                       |      |

| Continuous low-side source sense pin voltage (SLx)                                                          | -1                | 1                       | V    |

| Transient 200-ns low-side source sense pin voltage (SLx)                                                    | -3                | 3                       | V    |

| Continuous shunt amplifier input pin voltage (SNx, SPx)                                                     | -1                | 1                       | V    |

| Transient 200-ns shunt amplifier input pin voltage (SNx, SPx)                                               | -3                | 3                       | V    |

| Reference input pin voltage (VREF)                                                                          | -0.3              | 5.75                    | V    |

| Shunt amplifier output pin voltage (SOx)                                                                    | -0.3              | V <sub>VREF</sub> + 0.3 | V    |

| Shunt amplifier output current (SOx)                                                                        | 0                 | 8                       | mA   |

| Push-pull output buffer reference voltage (VSDO)                                                            | -0.3              | 5.75                    | V    |

| Push-pull output current (SDO)                                                                              | 0                 | 10                      | mA   |

| Open drain pullup voltage (nFAULT)                                                                          | -0.3              | 5.75                    | V    |

| Open drain output current (nFAULT)                                                                          | 0                 | 10                      | mA   |

| Operating junction temperature, T <sub>J</sub>                                                              | -40               | 150                     | °C   |

| Storage temperature, T <sub>stq</sub>                                                                       | -65               | 150                     | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 8.2 ESD Ratings

|                    |                                                         |                                           |                                                 | VALUE | UNIT |

|--------------------|---------------------------------------------------------|-------------------------------------------|-------------------------------------------------|-------|------|

|                    | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> |                                           | ±2000                                           |       |      |

| V <sub>(ESD)</sub> | Electrostatic discharge                                 | Charged-device model (CDM), per AEC Q100- | All pins                                        | ±500  | V    |

|                    | distriargs                                              | 011                                       | Corner pins (1, 10, 11, 20, 21, 30, 31, and 40) | ±750  | V    |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

<sup>(2)</sup> Continuous high-side gate pin (GHx) and phase node pin voltage (SHx) should be limited to -2 V minimum for an absolute maximum of 65 V on VM. At 60 V and below, the full specification of -5 V continuous on GHx and SHx is allowable.

# 8.3 Recommended Operating Conditions

|                      |                                                                                                | MIN | MAX               | UNIT |

|----------------------|------------------------------------------------------------------------------------------------|-----|-------------------|------|

| GATE DRIVE           | ER .                                                                                           |     | '                 |      |

| M                    | Power supply voltage (VM) Continuous (1)                                                       | 5.5 | 50                | V    |

| $V_{VM}$             | Power supply voltage (VM) Transient over voltage (2)                                           | 5.5 | 60                | V    |

| VI                   | Input voltage (CAL, ENABLE, GAIN, IDRIVE, INHx, INLx, MODE, nSCS, SCLK, SDI, VDS, VSDO, nDIAG) | 0   | 5.5               | V    |

| f <sub>PWM</sub>     | Applied PWM signal (INHx, INLx)                                                                | 0   | 200(3)            | kHz  |

| I <sub>GATE_HS</sub> | High-side average gate-drive current (GHx)                                                     | 0   | 25 <sup>(3)</sup> | mA   |

| I <sub>GATE_LS</sub> | Low-side average gate-drive current (GLx)                                                      | 0   | 25 <sup>(3)</sup> | mA   |

| I <sub>DVDD</sub>    | External load current (DVDD)                                                                   | 0   | 30(3)             | mA   |

| $V_{VREF}$           | Reference voltage input (VREF)                                                                 | 3   | 5.5               | V    |

| V <sub>SDO</sub>     | Push-pull voltage (SDO)                                                                        | 3   | 5.5               | V    |

| V <sub>OD</sub>      | Open drain pullup voltage (nFAULT)                                                             | 0   | 5.5               | V    |

| T <sub>A</sub>       | Operating ambient temperature                                                                  | -40 | 125               | °C   |

- (1) Operation at VM = 5.5V only when coming from higher VM. The minimum VM voltage for startup is greater than V<sub>UVLO</sub> (rising) voltage.

(2) VM recommended operating condition for electrical characteristic table. Product life time depends on VM voltage. The device is intended for 12–V and 24–V battery automotive system with life-time nominal voltage of 5.5 V 50 V. The device can be operated during additional overvoltage events as specified in ISO16750-2:2012

- (3) Power dissipation and thermal limits must be observed

#### 8.4 Thermal Information

|                        |                                              | DRV8343-Q1  |      |

|------------------------|----------------------------------------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | PHP (HTQFP) | UNIT |

|                        |                                              | 48 PINS     |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 26.5        | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 16.3        | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 6.7         | °C/W |

| ΤιΨ                    | Junction-to-top characterization parameter   | 0.2         | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 6.8         | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 1.0         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 8.5 Electrical Characteristics

|                                  | PARAMETER                          | TEST CONDITIONS                                                                   | MIN          | TYP  | MAX  | UNIT |

|----------------------------------|------------------------------------|-----------------------------------------------------------------------------------|--------------|------|------|------|

| POWER SUPI                       | PLIES (DVDD, VCP, VM)              |                                                                                   |              |      |      |      |

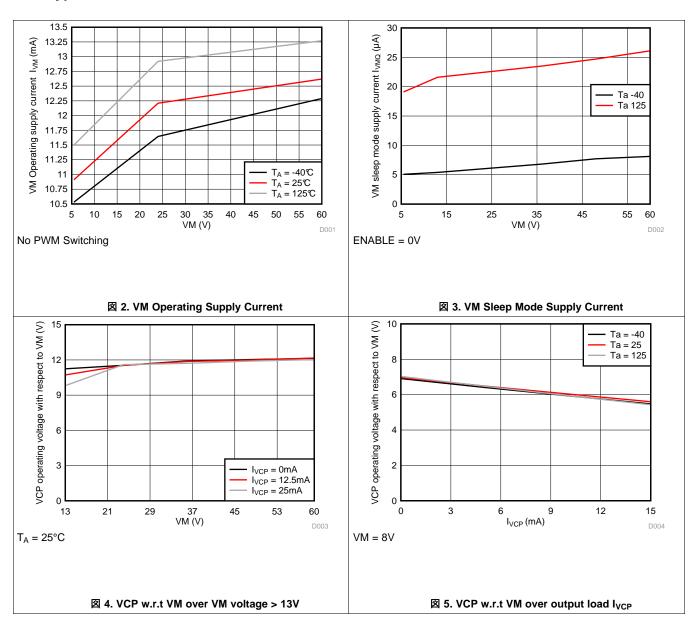

| I <sub>VM</sub>                  | VM operating supply current        | V <sub>VM</sub> = 24 V, ENABLE = 3.3 V, INHx/INLx = 0 V, SHx = 0 V                |              | 12   | 16   | mA   |

| 1                                | VM closp mode supply surrent       | ENABLE = 0 V, V <sub>VM</sub> = 24 V, T <sub>A</sub> = 25°C                       |              | 12   | 20   |      |

| I <sub>VMQ</sub>                 | VM sleep mode supply current       | ENABLE = 0 V, V <sub>VM</sub> = 24 V, T <sub>A</sub> = 125°C                      |              |      | 50   | μA   |

| t <sub>RST</sub>                 | Reset pulse time                   | ENABLE = 0 V period to reset faults                                               | 4.4          |      | 43   | μs   |

| t <sub>WAKE</sub> <sup>(1)</sup> | Turnon time                        | ENABLE = 3.3 V to outputs ready, $V_{VM} > V_{UVLO}$                              |              |      | 1    | ms   |

| t <sub>SLEEP</sub>               | Turnoff time                       | ENABLE = 0 V to device sleep mode                                                 |              |      | 1    | ms   |

| $V_{DVDD}$                       | DVDD regulator voltage             | $V_{VM} > 6 \text{ V}, I_{DVDD} = 0 \text{ to } 30 \text{ mA}$                    | 3            | 3.3  | 3.6  | V    |

| ▼DVDD                            | DVDD regulator voltage             | $V_{VM} = 5.5$ to 6 V, $I_{DVDD} = 0$ to 20 mA                                    | 3            | 3.3  | 3.6  | V    |

|                                  |                                    | $V_{VM} = 13 \text{ V}, I_{VCP} = 0 \text{ to } 25 \text{ mA}$                    | 8.4          | 11   | 12.5 |      |

| $V_{VCP}$                        | VCP operating voltage              | $V_{VM} = 10 \text{ V}, I_{VCP} = 0 \text{ to } 20 \text{ mA}$                    | 6.3          | 9    | 10   | V    |

| VCP                              | with respect to VM                 | $V_{VM} = 8 \text{ V}, I_{VCP} = 0 \text{ to } 15 \text{ mA}$                     | 5.4          | 7    | 8    | V    |

|                                  |                                    | $V_{VM} = 5.5 \text{ V}, I_{VCP} = 0 \text{ to } 5 \text{ mA}$                    | 4            | 5    | 6    |      |

| LOGIC-LEVEL                      | INPUTS (CAL, ENABLE, INHx, INLx, S | CLK, SDI)                                                                         |              |      |      |      |

| V <sub>IL</sub>                  | Input logic low voltage            |                                                                                   | 0            |      | 0.7  | V    |

| $V_{IH}$                         | Input logic high voltage           |                                                                                   | 1.6          |      | 5.5  | V    |

| V <sub>HYS</sub>                 | Input logic hysteresis             |                                                                                   |              | 182  |      | mV   |

| I <sub>IL</sub>                  | Input logic low current            | V <sub>VIN</sub> = 0 V; INHx, INLx, SDI(IDRIVE), SCLK(VDS), ENABLE                | <b>-</b> 5   |      | 5    | μΑ   |

| I <sub>IH</sub>                  | Input logic high current           | V <sub>VIN</sub> = 5 V; INHx, INLx, SDI(IDRIVE), SCLK(VDS)                        |              | 50   | 90   | μΑ   |

| I <sub>IH</sub>                  | Input logic high current           | V <sub>VIN</sub> = 5 V; ENABLE                                                    |              | 80   | 110  | μΑ   |

| R <sub>PD</sub>                  | Pulldown resistance                | To AGND; INHx, INLx, SDI(IDRIVE), SCLK(VDS)                                       | 50           | 100  | 200  | kΩ   |

| R <sub>PD</sub>                  | Pulldown resistance                | To AGND; ENABLE                                                                   | 30           | 60   | 110  | kΩ   |

| t <sub>PD</sub>                  | Propagation delay                  | INHx/INLx input buffer and digital core propagation delay. Dead time is excluded. |              | 105  |      | ns   |

| LOGIC LEVEL                      | INPUT (nSCS)                       |                                                                                   |              |      |      |      |

| V <sub>IL,nSCS</sub>             | Input logic low voltage            |                                                                                   | 0            |      | 0.7  | V    |

| V <sub>IH,nSCS</sub>             | Input logic high voltage           |                                                                                   | 1.6          |      | 5.5  | V    |

| R <sub>PU,nSCS</sub>             | Pullup resistance                  | To DVDD                                                                           | 25           | 50   | 90   | kΩ   |

| FOUR-LEVEL                       | H/W INPUT (GAIN)                   |                                                                                   |              |      |      |      |

| V <sub>I1</sub>                  | Input mode 1 voltage               | Tied to AGND                                                                      |              | 0    |      | V    |

| V <sub>I2</sub>                  | Input mode 2 voltage               | 47 kΩ ± 5% to tied AGND                                                           |              | 1.2  |      | V    |

| V <sub>I3</sub>                  | Input mode 3 voltage               | Hi-Z ( > 500 kΩ to AGND)                                                          |              | 2    |      | V    |

| V <sub>I4</sub>                  | Input mode 4 voltage               | Tied to DVDD                                                                      |              | 3.3  |      | V    |

| R <sub>PU</sub>                  | Pullup resistance                  | Internal pullup to DVDD                                                           | 25           | 50   | 80   | kΩ   |

| R <sub>PD</sub>                  | Pulldown resistance                | Internal pulldown to AGND                                                         | 40           | 84   | 130  | kΩ   |

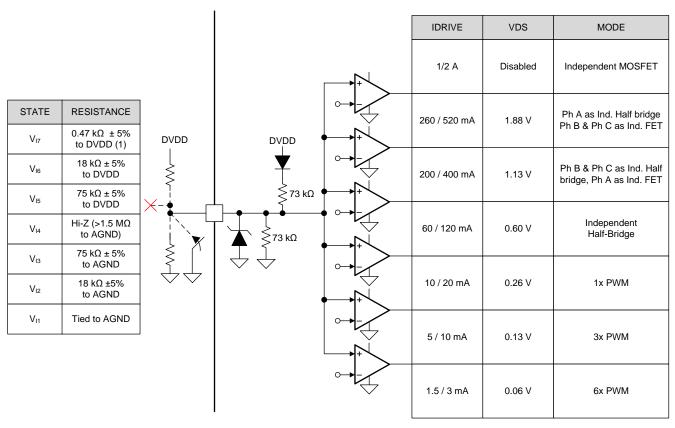

| SEVEN-LEVE                       | L H/W INPUTS (MODE, IDRIVE, VDS)   |                                                                                   |              |      |      |      |

| V <sub>I1</sub>                  | Input mode 1 voltage               | Tied to AGND                                                                      |              | 0    |      | V    |

| V <sub>I2</sub>                  | Input mode 2 voltage               | 18 k $\Omega$ ± 5% tied to AGND                                                   |              | 0.5  |      | V    |

| V <sub>I3</sub>                  | Input mode 3 voltage               | 75 k $\Omega$ ± 5% tied to AGND                                                   |              | 1.1  |      | V    |

| V <sub>I4</sub>                  | Input mode 4 voltage               | Hi-Z ( > 1.5 MΩ )                                                                 |              | 1.65 |      | V    |

| V <sub>I5</sub>                  | Input mode 5 voltage               | 75 k $\Omega$ ± 5% tied to DVDD                                                   |              | 2.2  |      | V    |

| V <sub>I6</sub>                  | Input mode 6 voltage               | 18 k $\Omega$ ± 5% tied to DVDD                                                   |              | 2.8  |      | V    |

| V <sub>I7</sub>                  | Input mode 7 voltage               | MODE : 0.47 k $\Omega$ ± 5% tied to DVDD VDS, IDRIVE : Tied to DVDD               |              | 3.3  |      | V    |

| R <sub>PU</sub>                  | Pullup resistance                  | Internal pullup to DVDD                                                           | 35           | 73   | 125  | kΩ   |

| R <sub>PD</sub>                  | Pulldown resistance                | Internal pulldown to AGND                                                         | 35           | 73   | 125  | kΩ   |

|                                  | OUTPUT (SDO)                       |                                                                                   | <del>-</del> |      |      |      |

|                        | PARAMETER                    |             | TEST CONDITIONS                                             | MIN          | TYP  | MAX  | UNIT |  |  |

|------------------------|------------------------------|-------------|-------------------------------------------------------------|--------------|------|------|------|--|--|

| D                      | Internal nullun              |             | To VSDO = 5 V                                               |              | 40   | 90   | Ω    |  |  |

| $R_{PU,SDO}$           | Internal pullup              |             | To VSDO = 3.3 V                                             |              | 60   | 120  | Ω    |  |  |

| R <sub>PD,SDO</sub>    | Internal pulldown            |             | To GND                                                      |              | 30   | 50   | Ω    |  |  |

| OPEN DRAIN             | OUTPUT (nFAULT)              |             |                                                             |              |      |      |      |  |  |

| V <sub>OL</sub>        | Output logic low volta       | ge          | $I_O = 5 \text{ mA}$                                        |              |      | 0.15 | V    |  |  |

| l <sub>oz</sub>        | Output high impedan          | ce leakage  | V <sub>O</sub> = 5 V                                        | -1           |      | 9    | μA   |  |  |

| GATE DRIVE             | RS (GHx, GLx)                |             |                                                             | Ÿ            |      |      |      |  |  |

|                        |                              |             | $V_{VM}$ = 13 V, $I_{VCP}$ = 0 to 25 mA, GHx no output load | 8.4          | 11   | 12.5 |      |  |  |

| $V_{GSH}$              | High-side gate drive         | /oltage     | $V_{VM}$ = 10 , $I_{VCP}$ = 0 to 20 mA, GHx no output load  | 6.3          | 9    | 10   | V    |  |  |

|                        | with respect to SHx          |             | $V_{VM}$ = 8 V, $I_{VCP}$ = 0 to 15 mA, GHx no output load  | 5.4          | 7    | 8    | V    |  |  |

|                        |                              |             | $V_{VM}$ = 5.5 V, $I_{VCP}$ = 0 to 5 mA, GHx no output load | 4            | 5    | 6    |      |  |  |

| .,                     |                              |             | $V_{VM}$ = 12 V, $I_{VCP}$ = 0 to 25 mA, GLx no output load | 9            | 11   | 12   |      |  |  |

|                        | Low-side gate drive v        | oltage      | $V_{VM}$ = 10 V, $I_{VCP}$ = 0 to 20 mA, GLx no output load | 9.9          | 10.0 | 10.1 | V    |  |  |

| $V_{GSL}$              | with respect to PGNE         | )           | $V_{VM}$ = 8 V, $I_{VCP}$ = 0 to 15 mA, GLx no output load  | 7.9          | 8.0  | 8.1  | V    |  |  |

|                        |                              |             | $V_{VM}$ = 5.5 V, $I_{VCP}$ = 0 to 5 mA, GLx no output load | 5.4          | 5.5  | 5.6  | .6   |  |  |

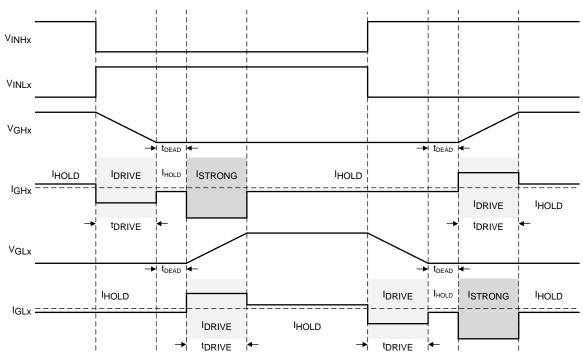

|                        |                              |             | DEAD_TIME = 00b                                             |              | 500  |      |      |  |  |

|                        |                              | SPI Device  | DEAD_TIME = 01b                                             |              | 1000 |      |      |  |  |

| t <sub>DEAD</sub>      | Gate drive dead time         | SFI Device  | DEAD_TIME = 10b                                             |              | 2000 |      | ns   |  |  |

|                        | acaa iiiiic                  |             | DEAD_TIME = 11b                                             |              | 4000 |      |      |  |  |

|                        |                              | H/W Device  |                                                             |              | 1000 |      |      |  |  |

|                        |                              |             | TDRIVE = 00b                                                |              | 500  |      |      |  |  |

|                        |                              | CDI Davisa  | TDRIVE = 01b                                                | 1000<br>2000 |      |      |      |  |  |

| t <sub>DRIVE</sub>     | Peak current gate drive time | SPI Device  | TDRIVE = 10b                                                |              |      |      | ns   |  |  |

|                        | gate anve time               |             | TDRIVE = 11b                                                | 3000         |      |      |      |  |  |

|                        |                              | H/W Device  |                                                             |              | 3000 |      |      |  |  |

| t <sub>DRIVE MAX</sub> | Peak current gate dri        | ve max time | IDRIVEP_Hx = 0000b, 0001b, 0010b, 0011b                     |              | 20   |      | μs   |  |  |

|                     | PARAMETER    |            | TEST CONDITIONS                                                                   | MIN                                           | TYP                                              | MAX  | UNIT |  |  |  |  |

|---------------------|--------------|------------|-----------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------|------|------|--|--|--|--|

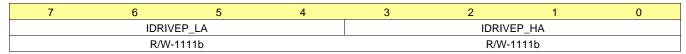

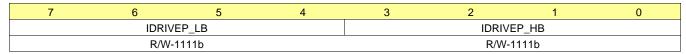

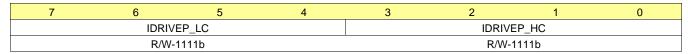

|                     |              |            | IDRIVEP_Hx = 0000b (GHx), V <sub>VM</sub> = 24 V                                  | 0.45                                          | 1.5                                              | 3.0  |      |  |  |  |  |

|                     |              |            | IDRIVEP_Lx = 0000b (GLx), V <sub>VM</sub> = 24 V                                  | 0.81                                          | 2.7                                              | 5.4  |      |  |  |  |  |

|                     |              |            | IDRIVEP_Hx = 0001b (GHx), V <sub>VM</sub> = 24 V                                  | 1.05                                          | 3.5                                              | 7    |      |  |  |  |  |

|                     |              |            | IDRIVEP_Lx = 0001b (GLx), V <sub>VM</sub> = 24 V                                  | 1.17                                          | 3.9                                              | 7.8  |      |  |  |  |  |

|                     |              |            | IDRIVEP_Hx = 0010b (GHx), $V_{VM}$ = 24 V                                         | 1.5                                           | 5                                                | 10   |      |  |  |  |  |

|                     |              |            | IDRIVEP_Lx = 0010b (GLx), V <sub>VM</sub> = 24 V                                  | 1.95                                          | 6.5                                              | 13   |      |  |  |  |  |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 0011b (GHx/GLx), V <sub>VM</sub> = 3 10                |                                               |                                                  |      |      |  |  |  |  |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 0100b (GHx/GLx), V <sub>VM</sub> = 24 V                | 4.5                                           | 15                                               | 30   |      |  |  |  |  |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 0101b (GHx/GLx), V <sub>VM</sub> = 24 V                | 15                                            | 50                                               | 100  |      |  |  |  |  |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 0110b (GHx/GLx), V <sub>VM</sub> = 24 V                | 18                                            | 60                                               | 120  |      |  |  |  |  |

|                     |              | SPI Device | IDRIVEP_Hx or IDRIVEP_Lx = 0111b (GHx/GLx), V <sub>VM</sub> = 24 V                | 19.5                                          | 65                                               | 130  |      |  |  |  |  |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 1000b (GHx/GLx), V <sub>VM</sub> = 24 V                | $V_{VM} = 76$ $V_{VM} = 79.8$ $V_{VM} = 98.8$ | 200 400                                          |      |      |  |  |  |  |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 1001b (GHx/GLx), V <sub>VM</sub> = 24 V                | 79.8                                          | 210                                              | 420  |      |  |  |  |  |

|                     | Peak source  |            | IDRIVEP_Hx or IDRIVEP_Lx = 1010b (GHx/GLx), V <sub>VM</sub> = 24 V                | 98.8                                          | 260                                              | 520  |      |  |  |  |  |

| I <sub>DRIVEP</sub> | gate current |            | IDRIVEP_Hx or IDRIVEP_Lx = 1011b (GHx/GLx), V <sub>VM</sub> = 24 V                | 100.7                                         | 265                                              | 530  | mA   |  |  |  |  |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 1100b (GHx/GLx), V <sub>VM</sub> = 24 V                | 279.3                                         | 735                                              | 1470 |      |  |  |  |  |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 1101b (GHx/GLx), V <sub>VM</sub> = 24 V                | 304                                           | 800                                              | 1600 |      |  |  |  |  |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 1110b (GHx/GLx), V <sub>VM</sub> = 24 V                | 355.3                                         | 935                                              | 1870 |      |  |  |  |  |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 1111b (GHx/GLx), V <sub>VM</sub> = 24 V                | 380                                           | 3.5 3.9 5 6.5 10 15 50 60 65 200 210 260 265 735 | 2000 |      |  |  |  |  |

|                     |              |            | IDRIVE = Tied to AGND (GHx), V <sub>VM</sub> = 24 V                               | 0.45                                          | 1.5                                              | 3.0  |      |  |  |  |  |

|                     |              |            | IDRIVE = Tied to AGND (GLx), V <sub>VM</sub> = 24 V                               | 0.81                                          | 2.7                                              | 5.4  |      |  |  |  |  |

|                     |              |            | IDRIVE = 18 k $\Omega$ ± 5% tied to AGND (GHx), V <sub>VM</sub> = 24 V            | 1.5                                           | 5                                                | 10   |      |  |  |  |  |

|                     |              |            | IDRIVE = 18 k $\Omega$ ± 5% tied to AGND (GLx), V <sub>VM</sub> = 24 V            | 1.95                                          | 6.5                                              | 13   |      |  |  |  |  |

|                     |              | H/W Device | IDRIVE = 75 k $\Omega$ ± 5% tied to AGND (GHx/GLx), V <sub>VM</sub> = 24 V        | 3                                             | 10                                               | 20   |      |  |  |  |  |

|                     |              | 501100     | IDRIVE = Hi-Z (GHx/GLx), V <sub>VM</sub> = 24 V                                   | 18                                            | 60                                               | 120  |      |  |  |  |  |

|                     |              |            | IDRIVE = 75 k $\Omega$ ± 5% tied to DVDD (GHx/GLx), V <sub>VM</sub> = 24 V 76 200 |                                               |                                                  |      |      |  |  |  |  |

|                     |              |            | IDRIVE = 18 k $\Omega$ ± 5% tied to DVDD (GHx/GLx), V <sub>VM</sub> = 24 V        | V <sub>VM</sub> = 24 98.8 260 520             |                                                  |      |      |  |  |  |  |

|                     |              |            | IDRIVE = Tied to DVDD (GHx/GLx), V <sub>VM</sub> = 24 V                           | 380                                           | 1000                                             | 2000 |      |  |  |  |  |

|                     | PARAMETER                                             |              | TEST CONDITIONS                                                  | MIN                      | TYP  | MAX  | UNIT |  |  |

|---------------------|-------------------------------------------------------|--------------|------------------------------------------------------------------|--------------------------|------|------|------|--|--|

|                     | I ANAMETER                                            |              | IDRIVEN_Hx or IDRIVEN_Lx = 0000b, V <sub>VM</sub> = 24 V         | 0.9                      | 3    | 5.4  | ONIT |  |  |

|                     |                                                       |              | IDRIVEN_Hx or IDRIVEN_Lx = 0000b, V <sub>VM</sub> = 24 V         | 2.09                     | 7    | 12.6 |      |  |  |

|                     |                                                       |              | IDRIVEN_Hx or IDRIVEN_Lx = 0001b, V <sub>VM</sub> = 24 V         | 3                        | 10   | 18   |      |  |  |

|                     |                                                       |              |                                                                  | 6                        | 20   | 36   |      |  |  |

|                     |                                                       |              | IDRIVEN Hx or IDRIVEN Lx = 0011b, V <sub>VM</sub> = 24 V         | 9                        | 30   | 54   |      |  |  |

|                     |                                                       |              | IDRIVEN Liver IDRIVEN Live 0100b, V <sub>VM</sub> = 24 V         |                          |      |      |      |  |  |

|                     |                                                       |              | IDRIVEN_Hx or IDRIVEN_Lx = 0101b, V <sub>VM</sub> = 24 V         | 30                       | 100  | 180  |      |  |  |

|                     |                                                       |              | IDRIVEN_Hx or IDRIVEN_Lx = 0110b, V <sub>VM</sub> = 24 V         | 36                       | 120  | 216  |      |  |  |

|                     |                                                       | SPI Device   | IDRIVEN_Hx or IDRIVEN_Lx = 0111b, V <sub>VM</sub> = 24 V         | 39                       | 130  | 234  |      |  |  |

|                     |                                                       |              | IDRIVEN_Hx or IDRIVEN_Lx = 1000b, V <sub>VM</sub> = 24 V         | 120                      | 400  | 720  |      |  |  |

|                     |                                                       |              | IDRIVEN LIVE TORIVEN LIVE 1001b, V <sub>VM</sub> = 24 V          | 126                      | 420  | 756  |      |  |  |

|                     | Peak sink                                             |              | IDRIVEN_Hx or IDRIVEN_Lx = 1010b, V <sub>VM</sub> = 24 V         | 156                      | 520  | 936  |      |  |  |

| IDRIVEN             | gate current                                          |              | IDRIVEN_Hx or IDRIVEN_Lx = 1011b, V <sub>VM</sub> = 24 V         | 159                      | 530  | 954  | mA   |  |  |

|                     |                                                       |              | IDRIVEN_Hx or IDRIVEN_Lx = 1100b, V <sub>VM</sub> = 24 V         | 441                      | 1470 | 2646 |      |  |  |

|                     |                                                       |              | IDRIVEN_Hx or IDRIVEN_Lx = 1101b, V <sub>VM</sub> = 24 V         | 480                      | 1600 | 2880 |      |  |  |

|                     |                                                       |              | IDRIVEN_Hx or IDRIVEN_Lx = 1110b, V <sub>VM</sub> = 24 V         | 24 V 600<br>0.9<br>4 V 3 | 1870 | 3366 |      |  |  |

|                     |                                                       |              | IDRIVEN_Hx or IDRIVEN_Lx = 1111b, V <sub>VM</sub> = 24 V         |                          | 2000 | 3600 |      |  |  |

|                     |                                                       |              | IDRIVE = Tied to AGND, V <sub>VM</sub> = 24 V                    |                          | 3    | 5.4  |      |  |  |

|                     |                                                       |              | IDRIVE = 18 k $\Omega$ ± 5% tied to AGND, V <sub>VM</sub> = 24 V |                          | 10   | 18   |      |  |  |

|                     |                                                       |              | IDRIVE = 75 k $\Omega$ ± 5% tied to AGND, V <sub>VM</sub> = 24 V |                          | 20   | 36   |      |  |  |

|                     |                                                       | H/W Device   | IDRIVE = Hi-Z, V <sub>VM</sub> = 24 V                            | 36                       | 120  | 216  |      |  |  |

|                     |                                                       |              | IDRIVE = 75 k $\Omega$ ± 5% tied to DVDD, V <sub>VM</sub> = 24 V | 120                      | 400  | 720  |      |  |  |

|                     |                                                       |              | IDRIVE = 18 k $\Omega$ ± 5% tied to DVDD, V <sub>VM</sub> = 24 V | 156                      | 520  | 936  |      |  |  |

|                     |                                                       |              | IDRIVE = Tied to DVDD, V <sub>VM</sub> = 24 V                    | 600                      | 2000 | 3600 |      |  |  |

|                     |                                                       | SPI Device   | IDRIVEP_Hx = 0000b, V <sub>VM</sub> = 24 V                       | 0.45                     | 1.5  | 3.8  |      |  |  |

|                     |                                                       |              | IDRIVEP_Hx = 0001b, V <sub>VM</sub> = 24 V                       | 3.5                      | 7    |      |      |  |  |

|                     |                                                       |              | IDRIVEP_Hx = 0010b, V <sub>VM</sub> = 24 V                       | 1.5                      | 5    | 10   |      |  |  |

|                     | Osta haldina sassasa                                  |              | IDRIVEP_Hx = 0011b, V <sub>VM</sub> = 24 V                       | 3                        | 10   | 20   |      |  |  |

| I <sub>HOLDP</sub>  | Gate holding source current after t <sub>DRIVE</sub>  |              | All other IDRIVE settings, V <sub>VM</sub> = 24 V                | 4.5                      | 15   | 30   | mA   |  |  |

|                     | 51.112                                                |              | IDRIVE tied to AGND, V <sub>VM</sub> = 24 V                      | 0.45                     | 1.5  | 3.8  |      |  |  |

|                     |                                                       |              | IDRIVE = 18 k $\Omega$ ± 5% tied to AGND, V <sub>VM</sub> = 24 V | 1.5                      | 5    | 10   |      |  |  |

|                     |                                                       |              | IDRIVE = 75 k $\Omega$ ± 5% tied to AGND, $V_{VM}$ = 24 V        | 3                        | 10   | 20   |      |  |  |

|                     |                                                       |              | All other IDRIVE settings, $V_{VM} = 24 \text{ V}$               | 4.5                      | 15   | 30   |      |  |  |

|                     |                                                       |              | IDRIVEP_Hx = 0000b, V <sub>VM</sub> = 24 V                       | 0.9                      | 3    | 5.4  |      |  |  |

|                     |                                                       |              | IDRIVEP_Hx = 0001b, V <sub>VM</sub> = 24 V                       | 2                        | 7    | 12.6 |      |  |  |

|                     |                                                       | SPI Device   | IDRIVEP_Hx = 0010b, V <sub>VM</sub> = 24 V                       | 3                        | 10   | 18   |      |  |  |

|                     |                                                       |              | IDRIVEP_Hx = 0011b, V <sub>VM</sub> = 24 V                       | 6                        | 20   | 36   |      |  |  |

| I <sub>HOLDN</sub>  | Gate holding sink<br>current after t <sub>DRIVE</sub> |              | All other IDRIVE settings, V <sub>VM</sub> = 24 V                | 9                        | 30   | 54   | mA   |  |  |

|                     | ourient after tDRIVE                                  |              | IDRIVE tied to AGND, V <sub>VM</sub> = 24 V                      | 0.9                      | 3    | 5.4  |      |  |  |

|                     |                                                       | LIAM D       | IDRIVE = 18 k $\Omega$ ± 5% tied to AGND, V <sub>VM</sub> = 24 V | 3                        | 10   | 18   |      |  |  |

|                     |                                                       | H/W Device   | IDRIVE = 75 k $\Omega$ ± 5% tied to AGND, V <sub>VM</sub> = 24 V | 6                        | 20   | 36   |      |  |  |

|                     |                                                       |              | All other IDRIVE settings, V <sub>VM</sub> = 24 V                | 9                        | 30   | 54   |      |  |  |

|                     | Gate strong pulldown                                  | current      | IDRIVEP_Hx = 0000b, 0001b, 0010b, 0011b, V <sub>VM</sub> = 24 V  | 9                        | 30   | 54   | mA   |  |  |

| I <sub>STRONG</sub> | (GHx to SHx and GLx                                   |              | All other IDRIVE settings, V <sub>VM</sub> = 24 V                | 0.6                      | 2    | 3.6  | A    |  |  |

| R <sub>OFF</sub>    | Gate hold off resistor                                |              | GHx to SHx                                                       |                          | 150  | 280  | kΩ   |  |  |

| R <sub>OFF</sub>    | Gate hold off resistor                                |              | GLx to PGND                                                      |                          | 150  | 280  | kΩ   |  |  |

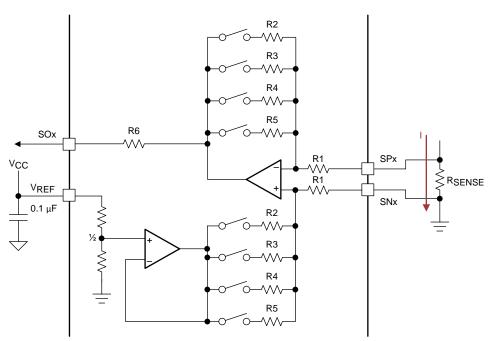

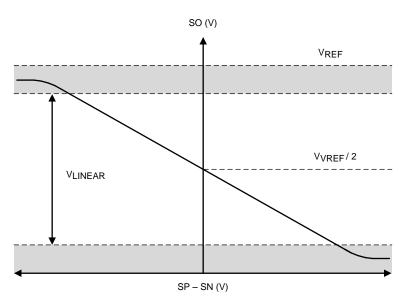

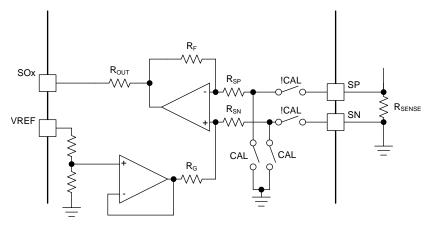

|                     | IUNT AMPLIFIER (SNx, SO)                              | . SPx. VRFF\ |                                                                  |                          |      |      |      |  |  |

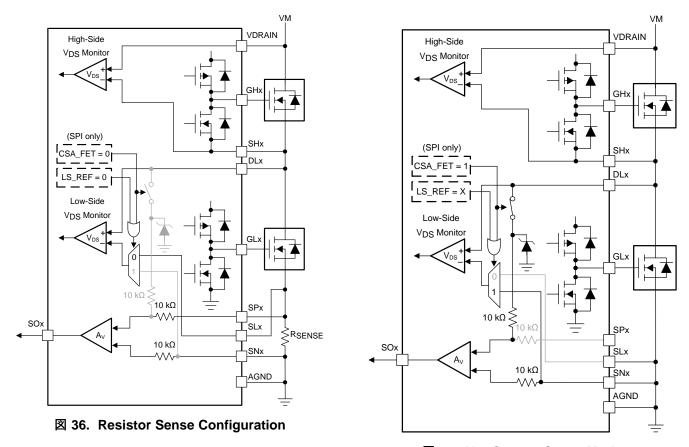

|                               | PARAMETER                       |               | TEST CONDITIONS                                                                                                    | MIN                   | TYP                     | MAX                      | UNIT  |

|-------------------------------|---------------------------------|---------------|--------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------|--------------------------|-------|

|                               |                                 |               | CSA_GAIN = 00b, CSA_FET = 0b                                                                                       | 4.9                   | 5                       | 5.1                      |       |

|                               |                                 |               | CSA_GAIN = 01b, CSA_FET = 0b                                                                                       | 9.8                   | 10                      | 10.2                     |       |

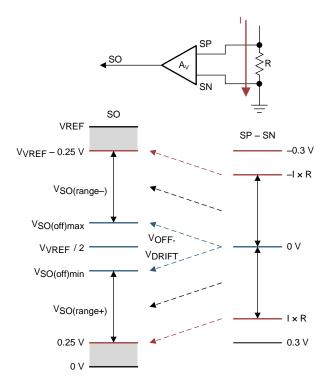

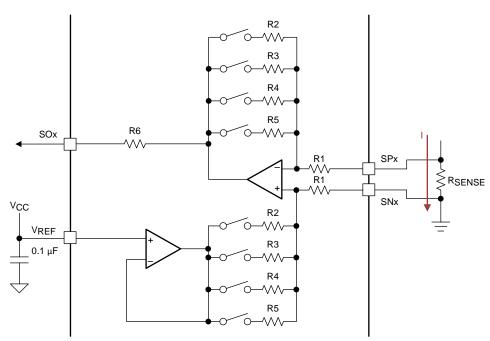

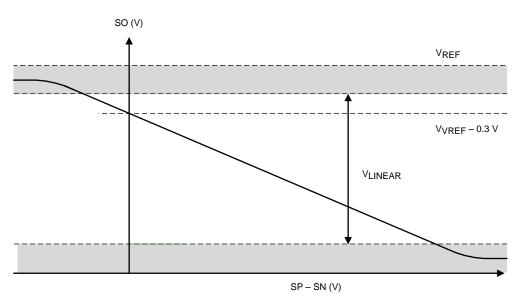

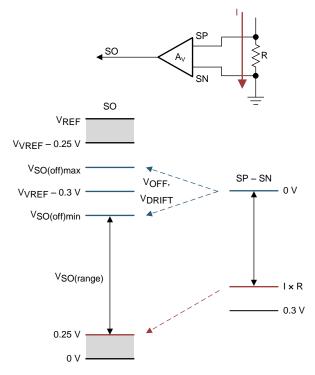

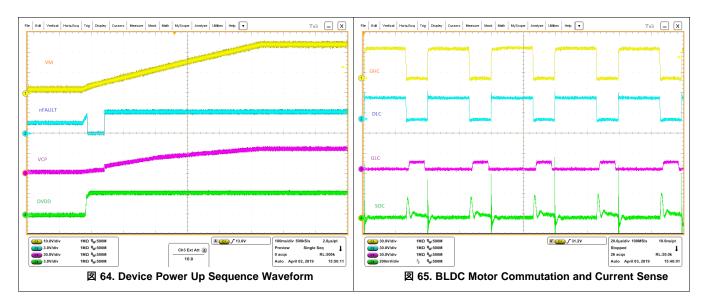

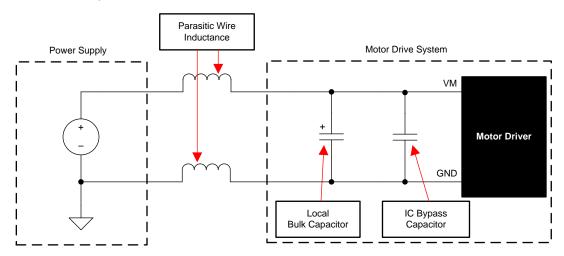

|                               |                                 | SPI Device    | CSA_GAIN = 10b, CSA_FET = 0b                                                                                       | 19.6                  | 20                      | 20.4                     |       |