# DRV8334-Q1 を搭載 車載用 24/12V バッテリ 3 相ゲート ドライバ ユニット、高精度電流センシング機能および拡張診断機能

## 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み: 温度オプション:

- DRV8334EPHP: -40°C ~ +150°C,  $T_A$

- DRV8334QPHP: -40°C ~ +125°C,  $T_A$

- 3 相ハーフブリッジ ゲートドライバ

- 6 個の N チャネル MOSFET (NMOS) を駆動

- 4.5 ~ 60V の広い動作電圧範囲

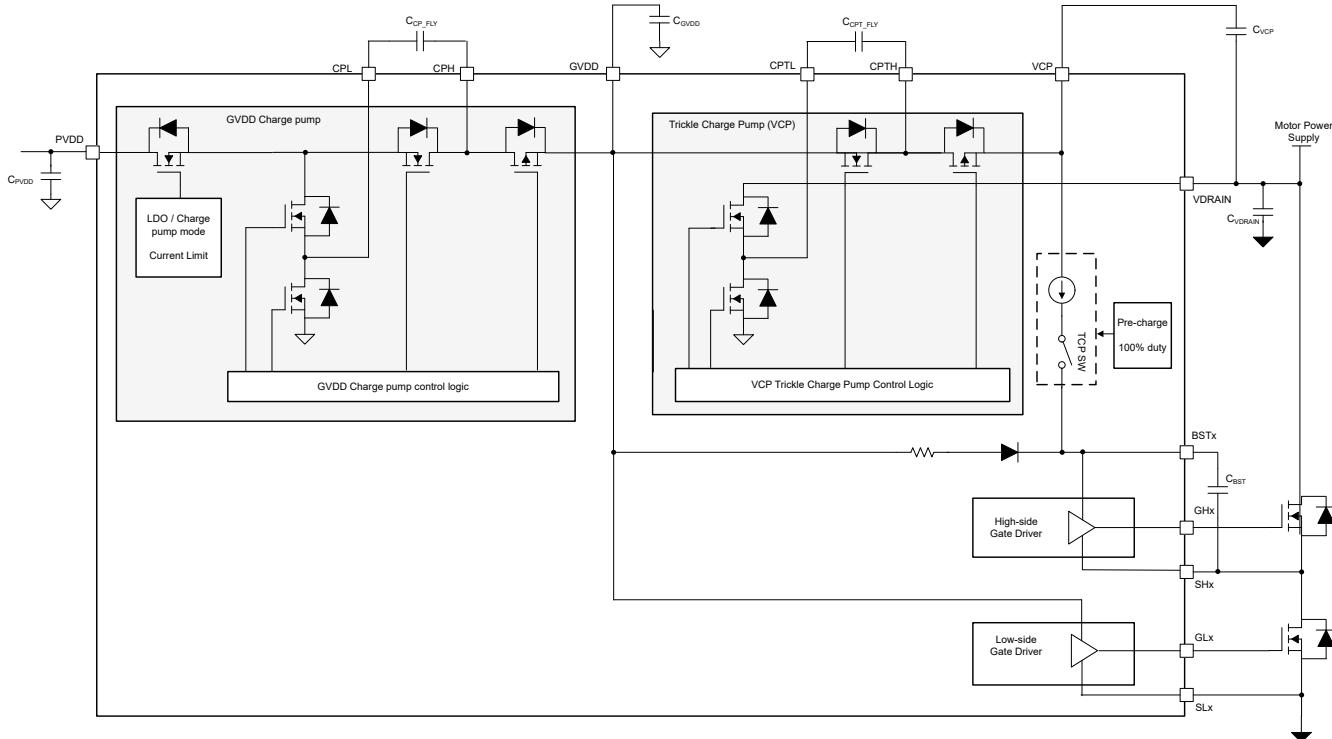

- ハイサイド ゲートドライバのブートストラップ アーキテクチャ

- 最大で平均 50mA のゲートスイッチング電流をサポートする強力な GVDD チャージポンプにより、400nC の MOSFET を 20kHz で駆動可能

- トリクル チャージ ポンプにより 100% の PWM デューティサイクルをサポートし、外付けの保護回路を駆動するためのオーバードライブ電源を生成

- スマート ゲートドライブ アーキテクチャ

- 45 レベルで構成可能な最大 1000 / 2000mA (ソース / シンク) のピーク ゲートドライブ電流

- 3 ステップの動的駆動電流制御

- 構成可能なソフトシャットダウンにより、過電流シャットダウン時の誘導性電圧スパイクを最小化

- ローサイド電流検出アンプ

- 全温度範囲にわたって 1mV 未満の低入力オフセット

- 9 レベルの可変ゲイン

- SPI ベースの詳細な構成と診断

- ドライバを個別にディセーブルする DRVOFF ピン

- 高電圧ウェークアップ ピン (nSLEEP)

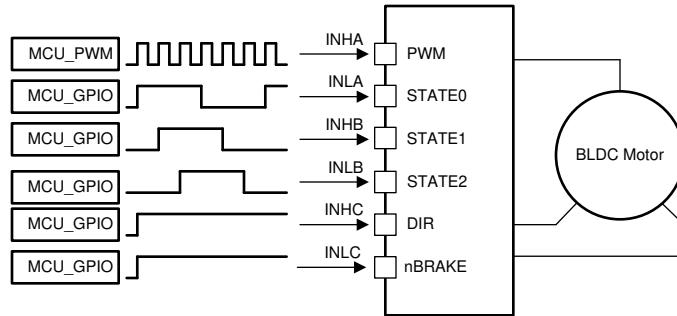

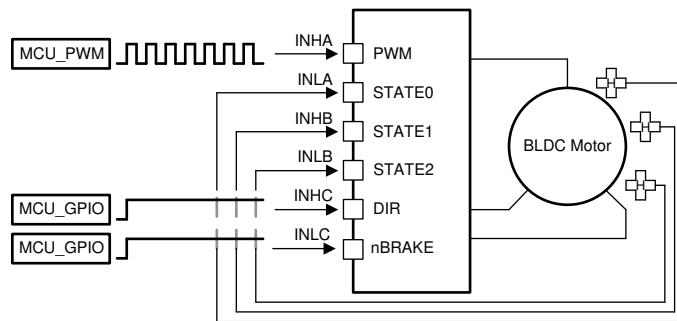

- 6x, 3x, 1x、および独立 PWM モード

- 3.3V および 5V のロジック入力をサポート

- リセット設定用のオプションのプログラム可能な OTP

- 内蔵保護機能

- バッテリおよび電源電圧モニタ

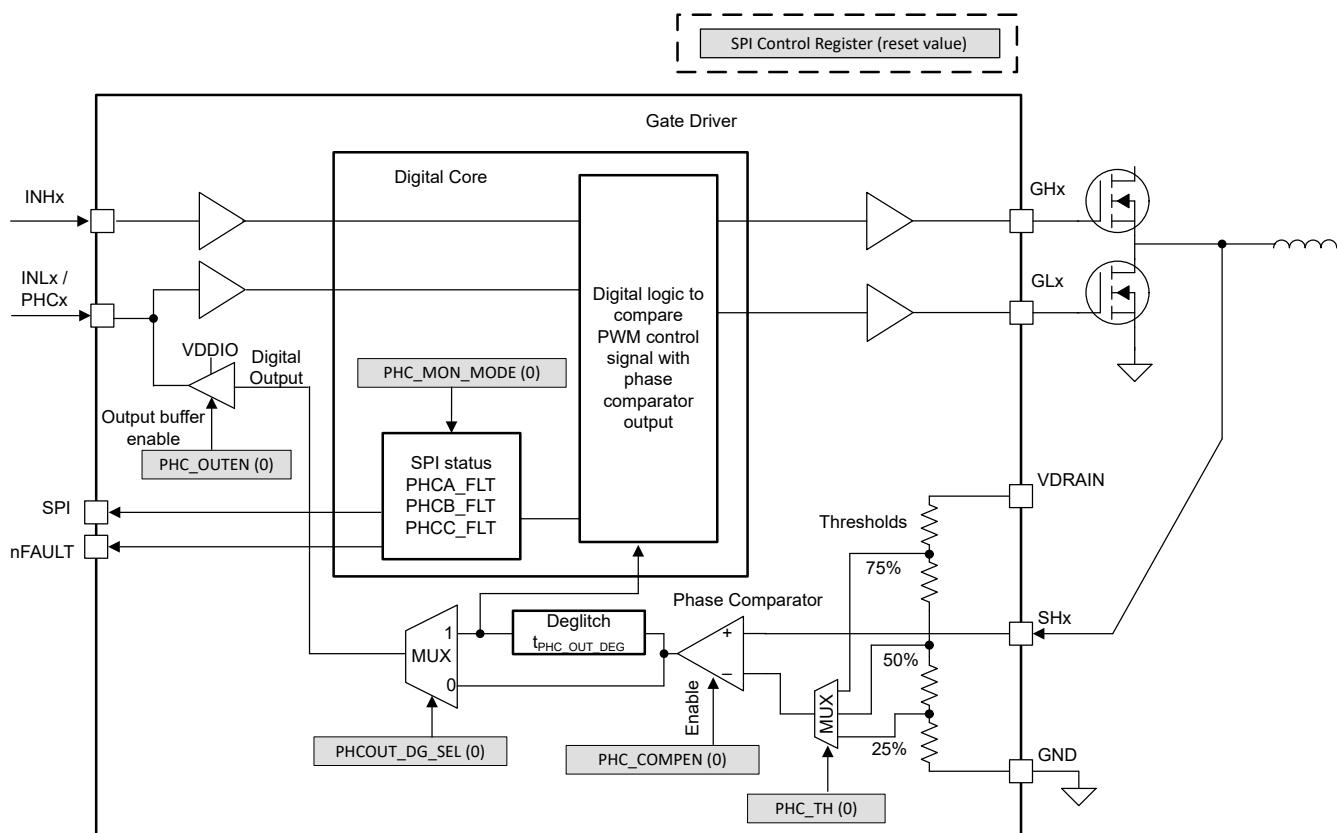

- 位相フィードバック コンパレータ

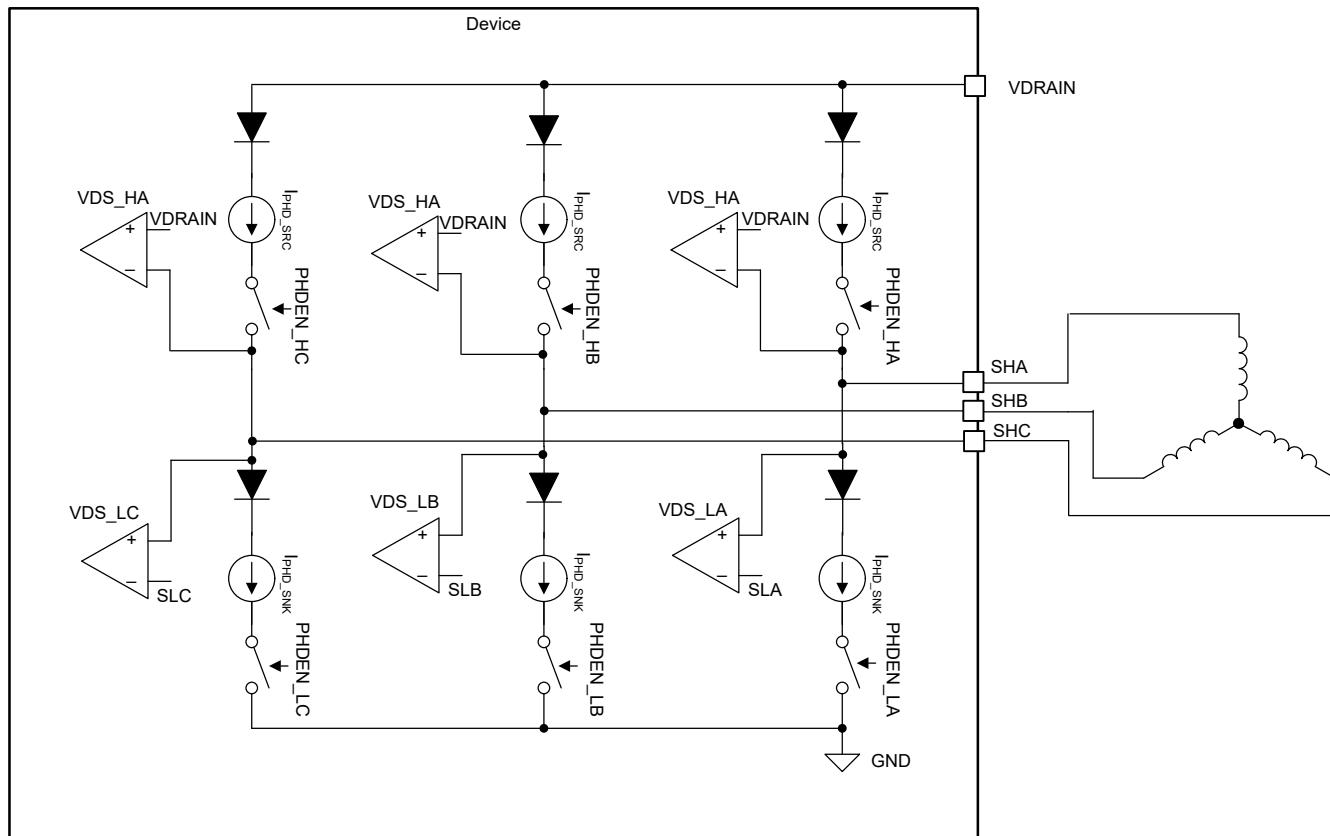

- MOSFET  $V_{DS}$  および  $R_{sense}$  過電流監視

- MOSFET  $V_{GS}$  ゲート フォルト監視

- デバイス熱警告とシャットダウン

- フォルト状態インジケータ ピン

## 2 アプリケーション

- 燃料、水、油のポンプ

- 車載用のファンとブロワー

- 車載各種ボディ用モーター

- トランスマッショングルーバー

- 車載用 BLDC および PMSM モーター

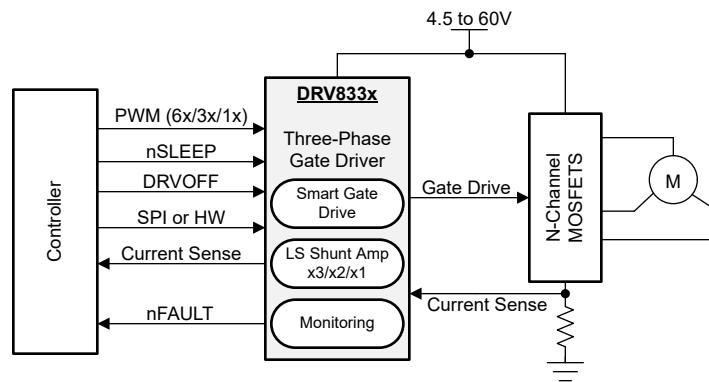

## 3 説明

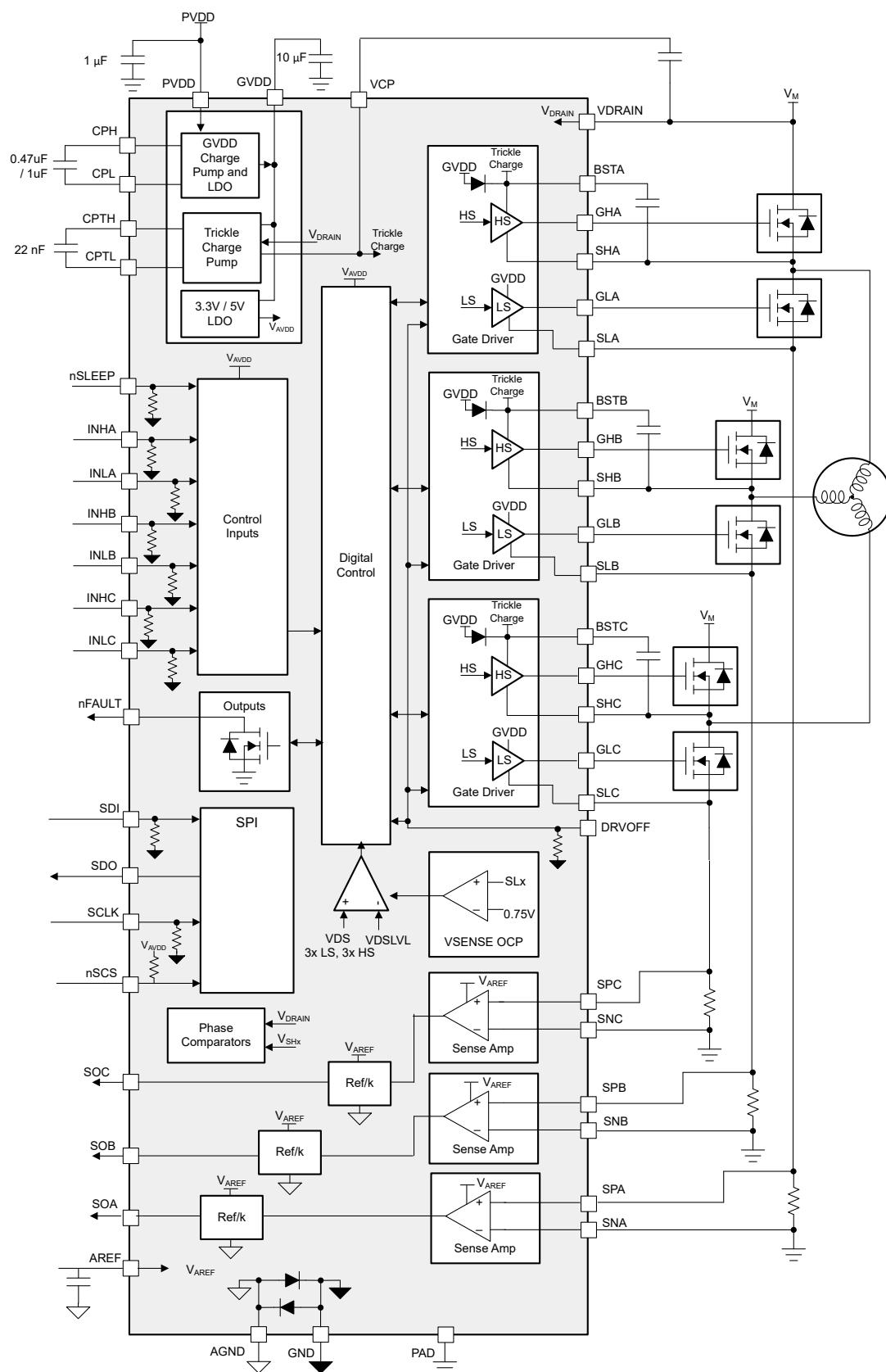

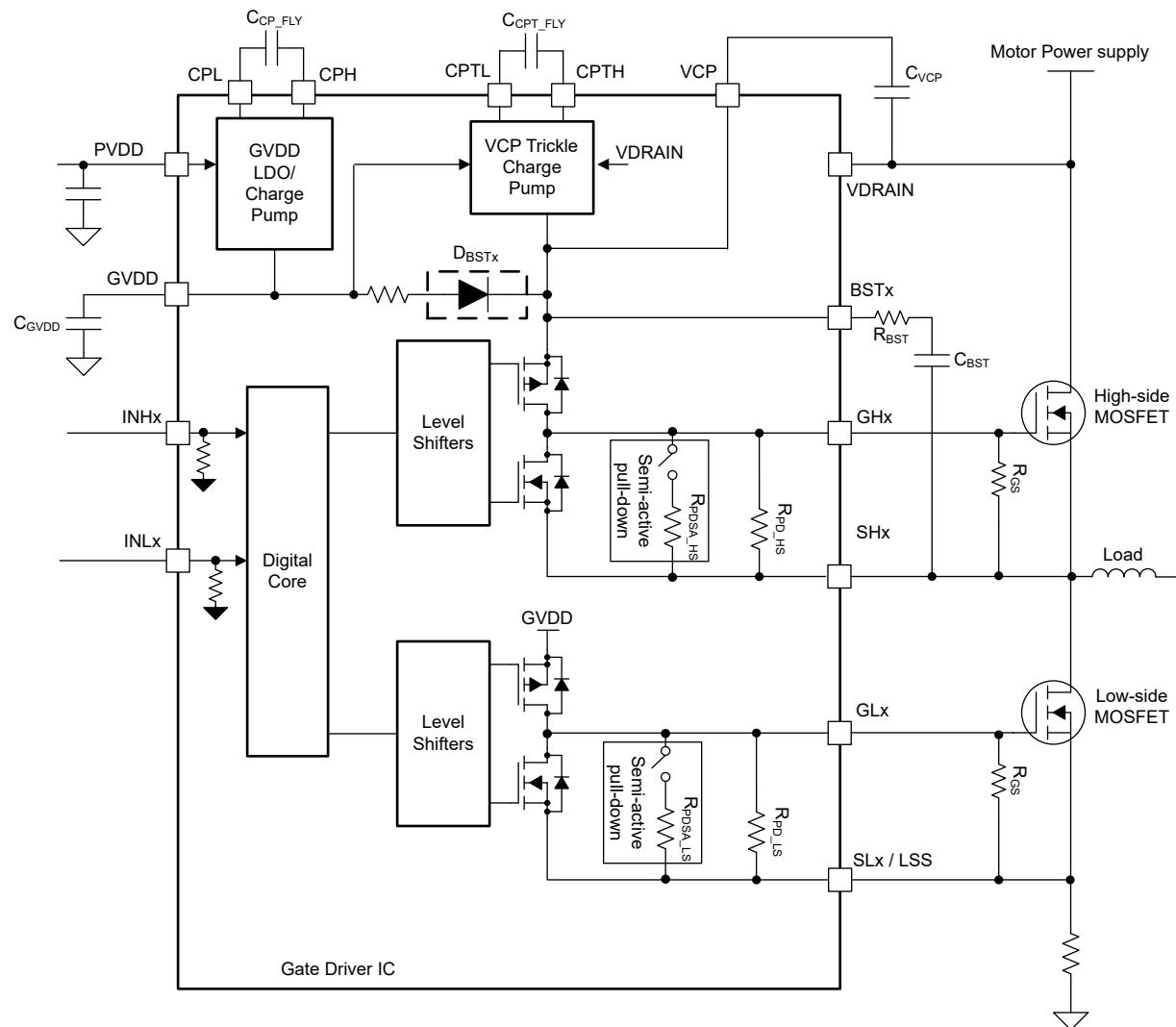

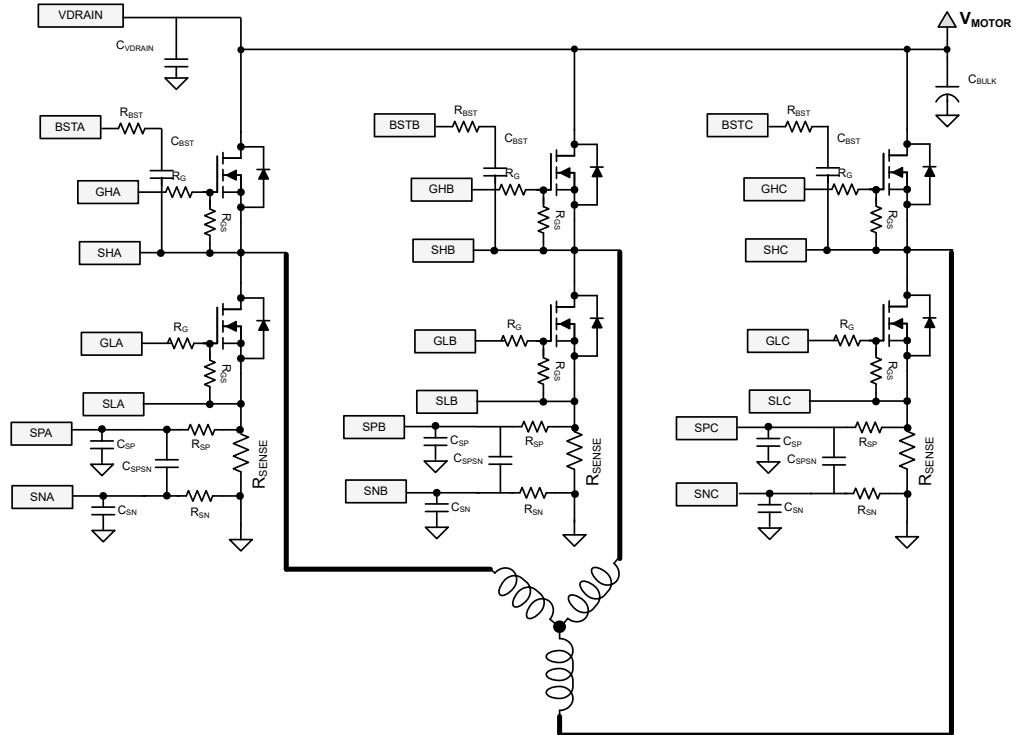

DRV8334-Q1 は、12V および 24V の車載用 3 相 BLDC アプリケーション向けの統合スマート ゲートドライバです。このデバイスには、3 つのハーフ ブリッジ ゲートドライバがあり、それぞれがハイサイドとローサイドの N チャネル パワー MOSFET を駆動できます。DRV8334-Q1 は、内蔵ブートストラップ ダイオードと GVDD チャージ ポンプを使用して、適切なゲート駆動電圧を生成します。スマート ゲートドライブのアーキテクチャは、0.8mA から最大でソース 1A、シンク 2A までの構成可能なピーク ゲート駆動電流をサポートします。DRV8334-Q1 単一電源で 4.5V ~ 60V の広い入力電圧範囲で動作できます。トリクル チャージ ポンプを使用することで、100% PWM デューティサイクル制御をサポートし、外部スイッチのオーバードライブ電源電圧を供給できます。

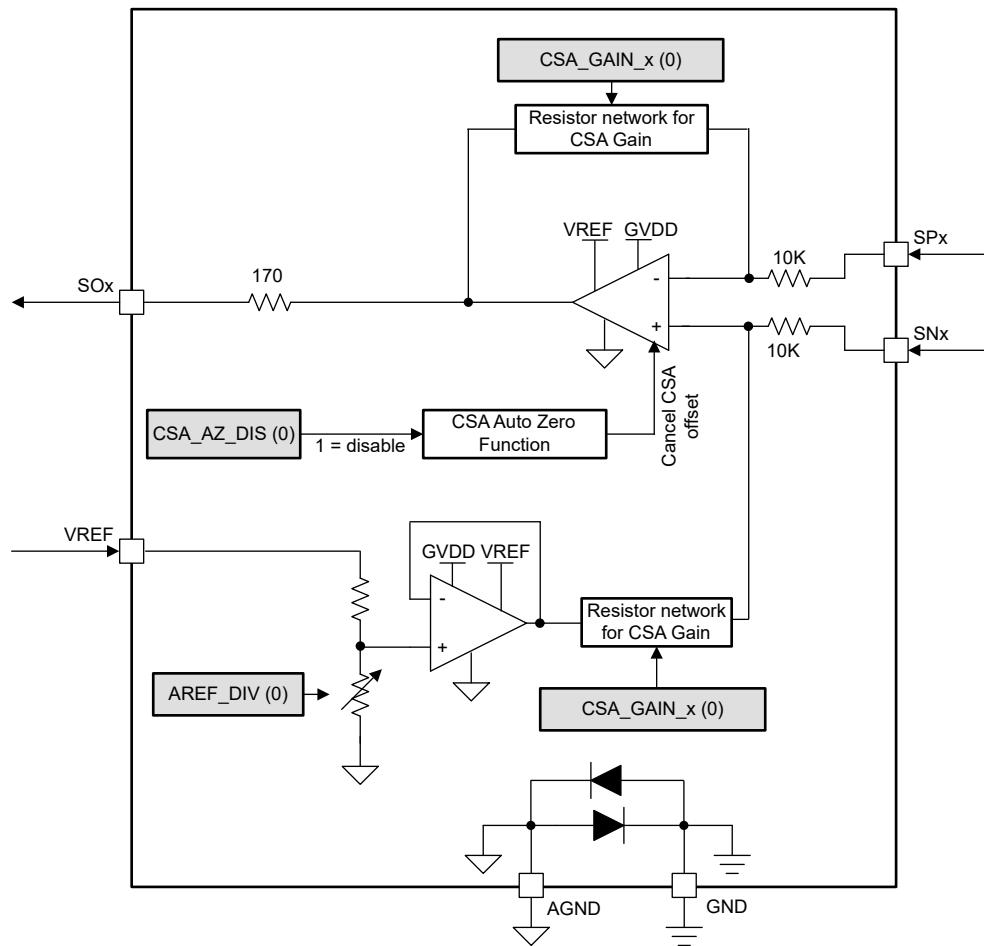

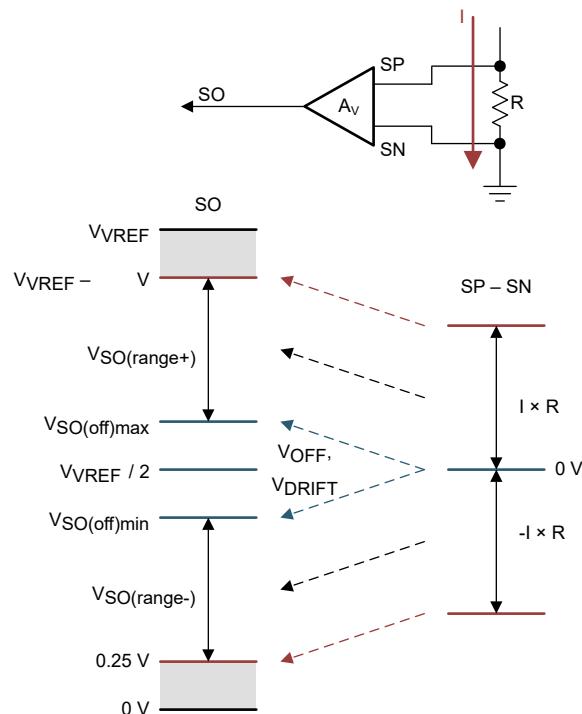

DRV8334-Q1 は、抵抗によるローサイド電流検出をサポートする、ローサイド電流検出アンプを備えています。アンプのオフセットが低いため、システムは正確なモーター電流測定を行うことができます。

DRV8334-Q1 に内蔵されている広範な診断機能と保護機能により、堅牢なモーター駆動システムの設計が可能になり、外部コンポーネントの必要性がなくなります。高度に構成可能なデバイス応答により、このデバイスは、さまざまなシステム設計にシームレスに組み込むことができます。

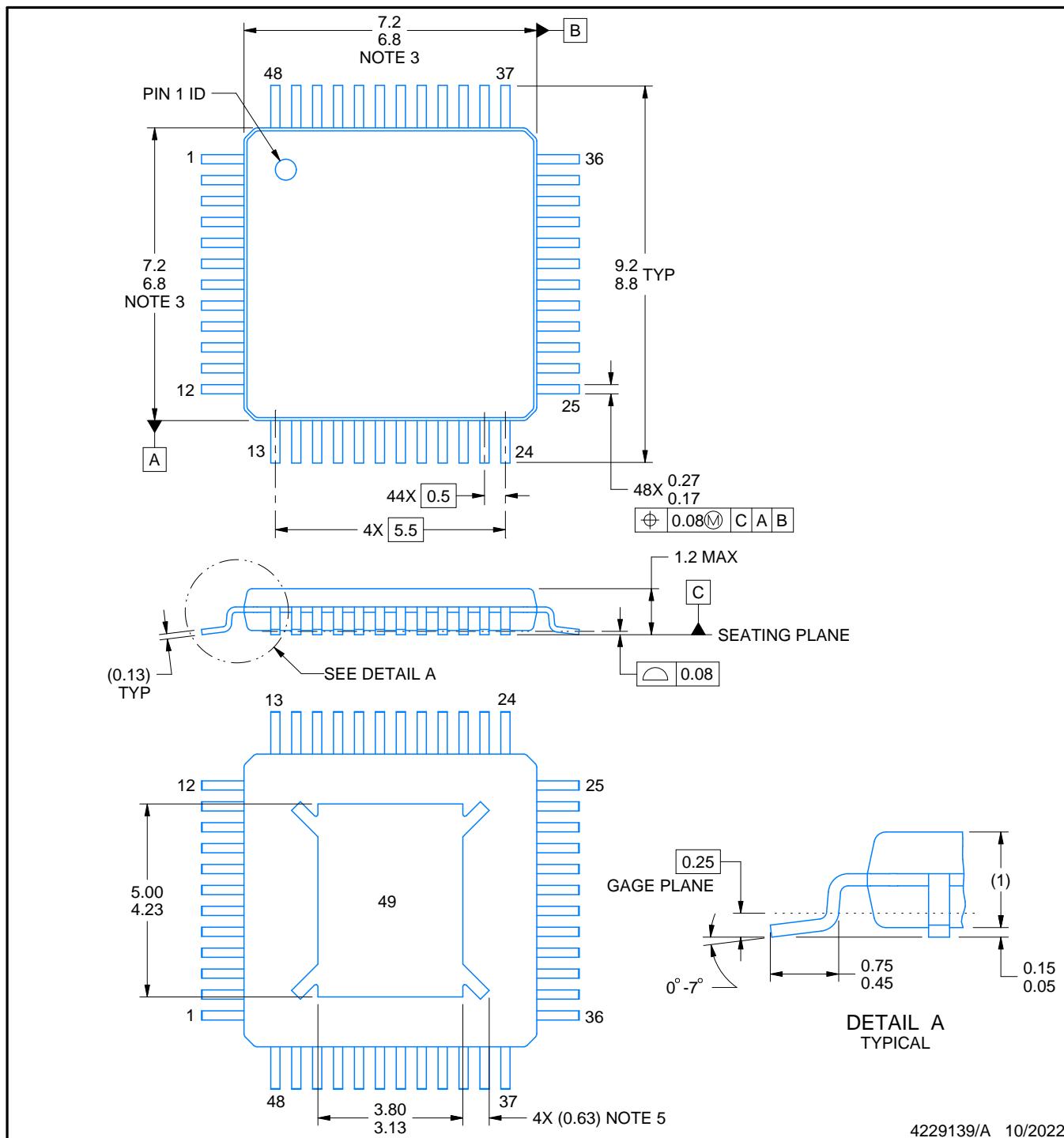

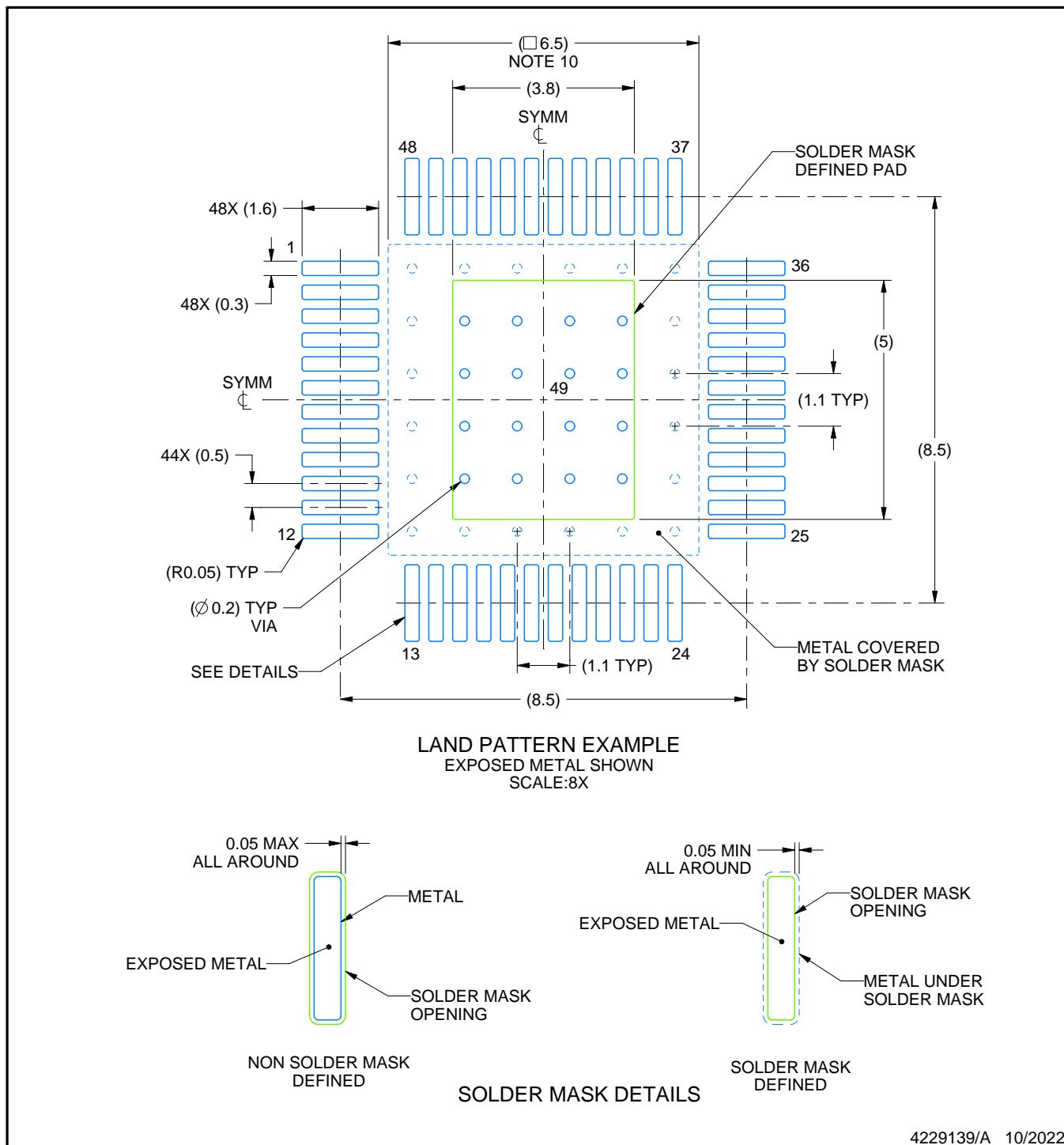

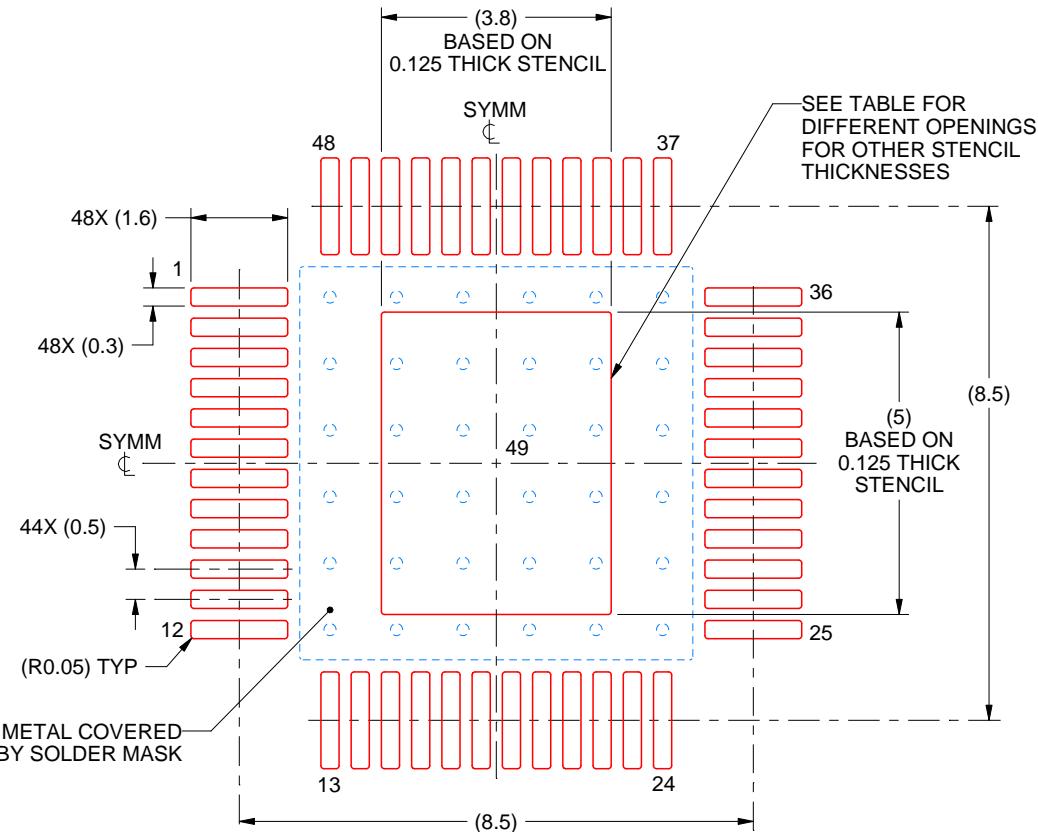

### パッケージ情報

| 部品番号       | パッケージ <sup>(1)</sup>    | パッケージ サイズ <sup>(2)</sup> | 本体サイズ (公称) |

|------------|-------------------------|--------------------------|------------|

| DRV8334-Q1 | HTQFP (48)              | 9mm × 9 mm               | 7mm × 7mm  |

|            | QFN (48) <sup>(3)</sup> | 7mm × 7mm                | 7mm × 7mm  |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ サイズには、該当する場合はピンも含まれます。

(3) 製品レビューのみ。詳細は テキサス・インスツルメンツまでお問い合わせください。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

概略回路図

## 目次

|                           |    |                        |    |

|---------------------------|----|------------------------|----|

| 1 特長                      | 1  | 6.4 デバイスの機能モード         | 44 |

| 2 アプリケーション                | 1  | 6.5 プログラミング            | 46 |

| 3 説明                      | 1  | 7 レジスタ マップ             | 48 |

| 4 ピン構成および機能               | 4  | 7.1 STATUS レジスタ        | 49 |

| 4.1 ピン機能 48 ピン DRV8334-Q1 | 4  | 7.2 制御レジスタ             | 53 |

| 5 仕様                      | 8  | 8 アプリケーションと実装          | 68 |

| 5.1 絶対最大定格                | 8  | 8.1 アプリケーション情報         | 68 |

| 5.2 ESD 定格 (車載機器)         | 9  | 8.2 代表的なアプリケーション       | 68 |

| 5.3 推奨動作条件                | 9  | 8.3 レイアウト              | 71 |

| 5.4 熱に関する情報               | 10 | 9 デバイスおよびドキュメントのサポート   | 73 |

| 5.5 電気的特性                 | 10 | 9.1 ドキュメントのサポート        | 73 |

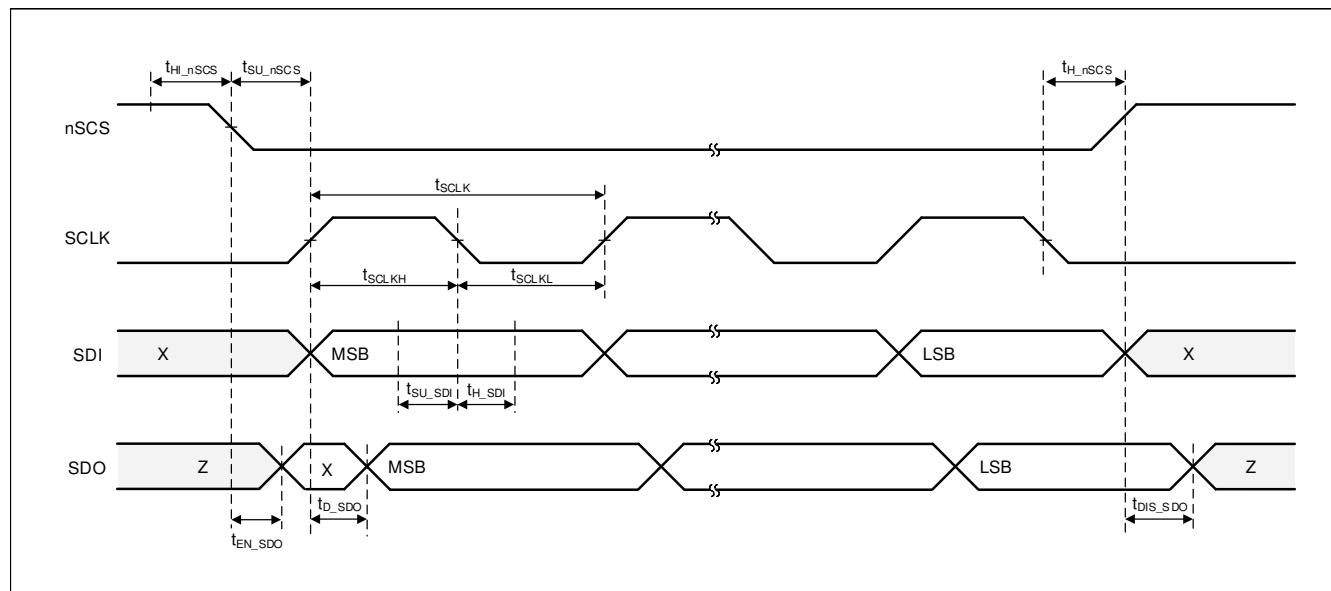

| 5.6 タイミング要件               | 23 | 9.2 ドキュメントの更新通知を受け取る方法 | 73 |

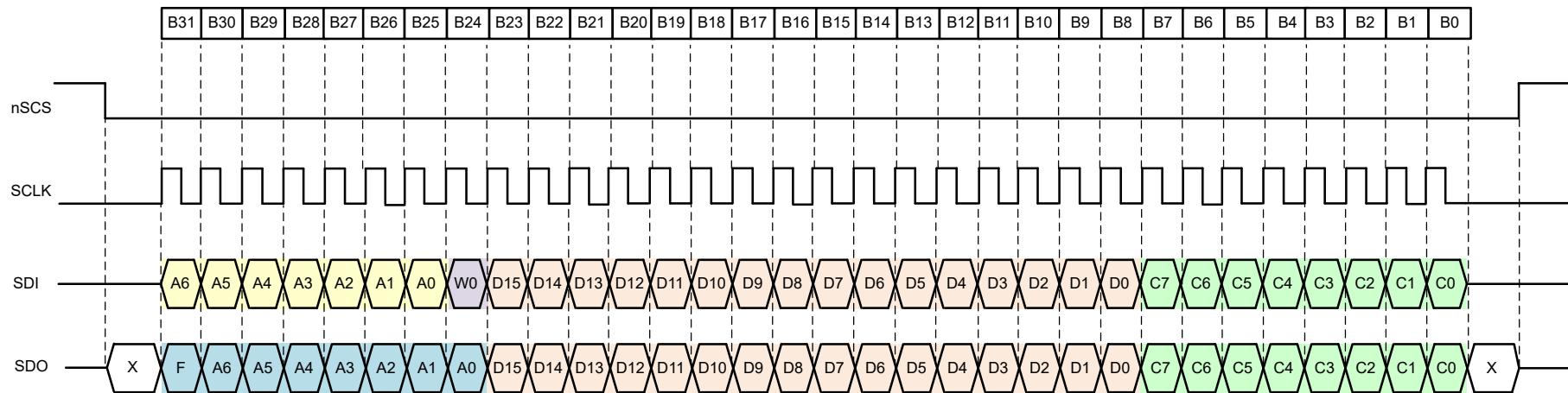

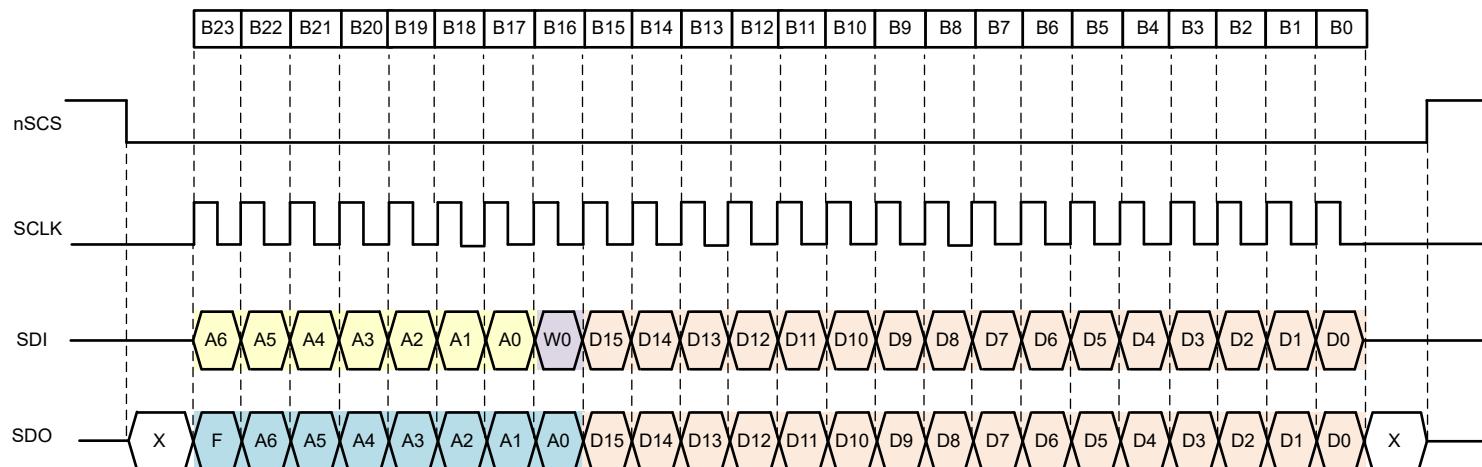

| 5.7 SPI のタイミング図           | 23 | 9.3 コミュニティリソース         | 73 |

| 6 詳細説明                    | 24 | 9.4 商標                 | 73 |

| 6.1 概要                    | 24 | 10 改訂履歴                | 73 |

| 6.2 機能ブロック図               | 25 | 11 メカニカル、パッケージ、および注文情報 | 74 |

| 6.3 機能説明                  | 26 |                        |    |

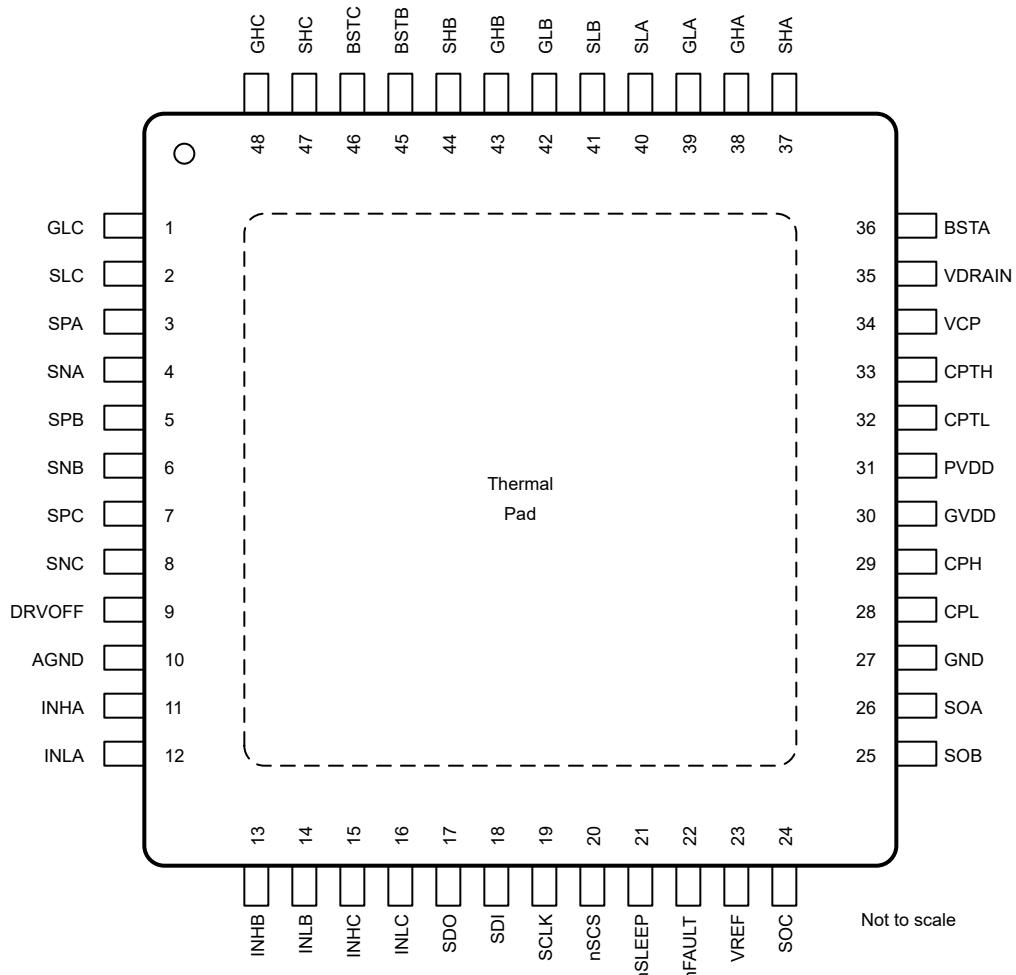

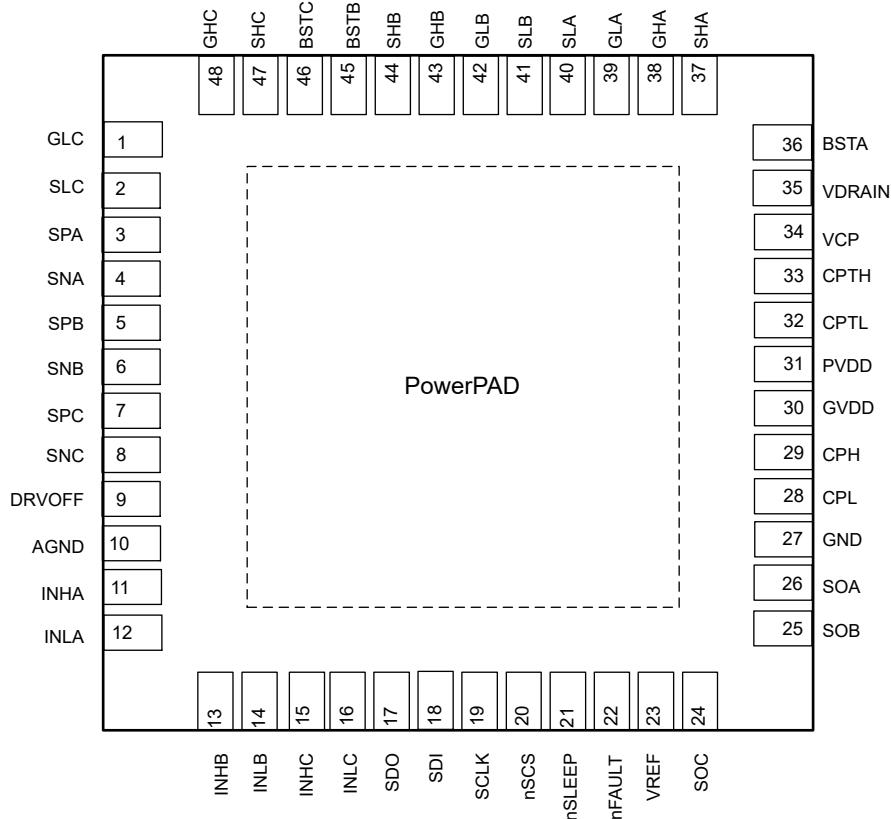

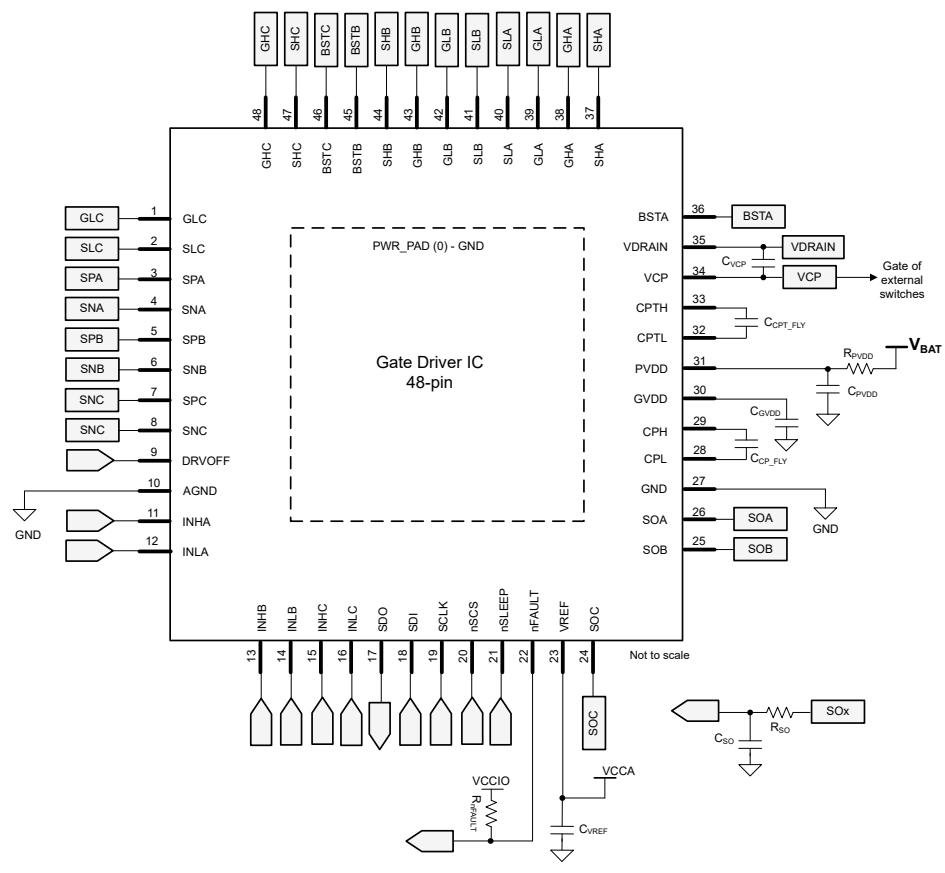

## 4 ピン構成および機能

### 4.1 ピン機能 48 ピン DRV8334-Q1

図 4-1. DRV8334-Q1 パッケージ、48 ピン、HTQFP (露出サーマル パッド付き) 上面図

図 4-2. DRV8334-Q1xRGZ パッケージ、48 ピン、QFN (開発中製品) (露出サーマル パッド付き) 上面図

表 4-1. ピンの機能 48-QFP および 48-QFN (開発中製品)

| ピン     |    | I/O <sup>(1)</sup> | 説明                                                                                                           |

|--------|----|--------------------|--------------------------------------------------------------------------------------------------------------|

| 名称     | 番号 |                    |                                                                                                              |

| GLC    | 1  | O                  | ローサイド ゲートドライバ出力。ローサイド パワー MOSFET のゲートに接続します。                                                                 |

| SLC    | 2  | I                  | ローサイド ソース検出入力。ローサイド パワー MOSFET のソースに接続します。                                                                   |

| SPA    | 3  | I                  | ローサイド電流シャントアンプ入力。ローサイド パワー MOSFET のソースと電流シャント抵抗の高電位側に接続します。                                                  |

| SNA    | 4  | I                  | 電流検出アンプ入力。電流シャント抵抗の低電位側に接続します。                                                                               |

| SPB    | 5  | I                  | ローサイド電流シャントアンプ入力。ローサイド パワー MOSFET のソースと電流シャント抵抗の高電位側に接続します。                                                  |

| SNB    | 6  | I                  | 電流検出アンプ入力。電流シャント抵抗の低電位側に接続します。                                                                               |

| SPC    | 7  | I                  | ローサイド電流シャントアンプ入力。ローサイド パワー MOSFET のソースと電流シャント抵抗の高電位側に接続します。                                                  |

| SNC    | 8  | I                  | 電流検出アンプ入力。電流シャント抵抗の低電位側に接続します。                                                                               |

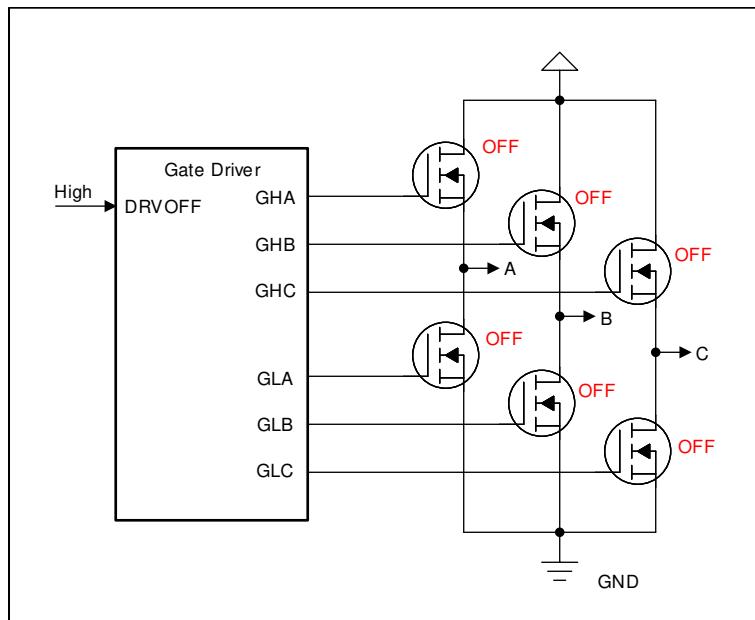

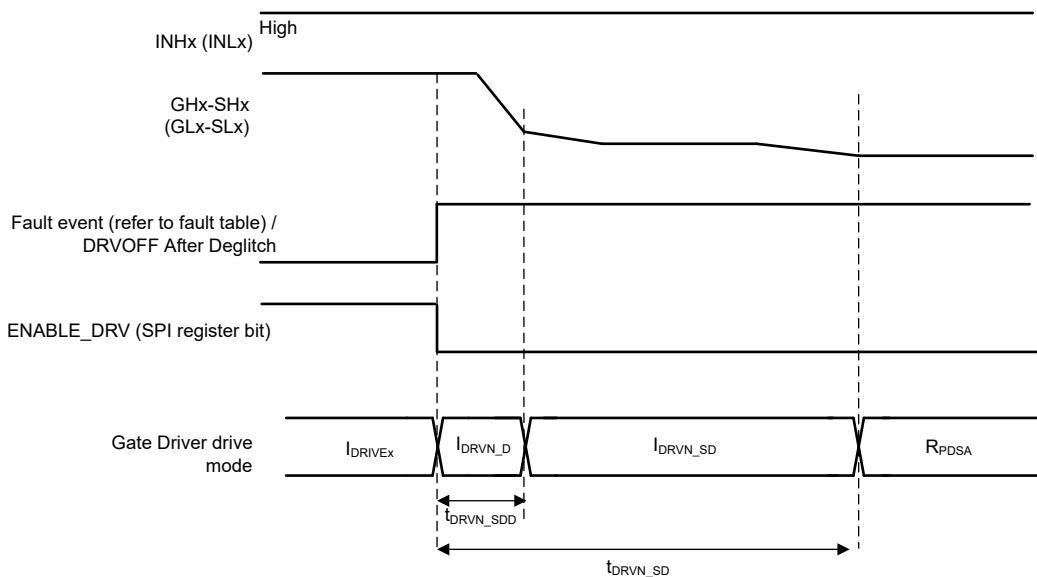

| DRVOFF | 9  | I                  | ゲートドライバ出力 GHx および GLx へのアクティブ High シャットダウン入力。                                                                |

| AGND   | 10 | PWR                | デバイスのグランド。                                                                                                   |

| INHA   | 11 | I                  | ハイサイド ゲートドライバの制御入力。このピンはハイサイド ゲートドライバの出力を制御します。                                                              |

| INLA   | 12 | I/O                | ローサイド ゲートドライバの制御入力。このピンはローサイド ゲートドライバの出力を制御します。このピンは、SPI レジスタ ビット PHC_OUTEN により、位相コンパレータのバッファを出力するように構成できます。 |

| INHB   | 13 | I                  | ハイサイド ゲートドライバの制御入力。このピンはハイサイド ゲートドライバの出力を制御します。                                                              |

| INLB   | 14 | I/O                | ローサイド ゲートドライバの制御入力。このピンはローサイド ゲートドライバの出力を制御します。このピンは、SPI レジスタ ビット PHC_OUTEN により、位相コンパレータのバッファを出力するように構成できます。 |

表 4-1. ピンの機能 48-QFP および 48-QFN (開発中製品) (続き)

| ピン     |    | I/O <sup>(1)</sup> | 説明                                                                                                           |

|--------|----|--------------------|--------------------------------------------------------------------------------------------------------------|

| 名称     | 番号 |                    |                                                                                                              |

| INHC   | 15 | I                  | ハイサイド ゲートドライバの制御入力。このピンはハイサイド ゲートドライバの出力を制御します。                                                              |

| INLC   | 16 | I/O                | ローサイド ゲートドライバの制御入力。このピンはローサイド ゲートドライバの出力を制御します。このピンは、SPI レジスタ ビット PHC_OUTEN により、位相コンパレータのバッファを出力するように構成できます。 |

| SDO    | 17 | O                  | シリアル データ出力。                                                                                                  |

| SDI    | 18 | I                  | シリアル データ入力。                                                                                                  |

| SCLK   | 19 | I                  | シリアル クロック入力。                                                                                                 |

| nSCS   | 20 | I                  | シリアル チップ選択。                                                                                                  |

| nSLEEP | 21 | I                  | ゲートドライバ nSLEEP。このピンを論理 Low にすると、本デバイスは低消費電力のスリープ モードに移行します。                                                  |

| nFAULT | 22 | OD                 | フォルト通知出力。このピンはフォルト条件中論理 Low にプルされ、外付けプルアップ抵抗を必要とします。                                                         |

| VREF   | 23 | PWR                | 電流センス アンプ用外部電圧レファレンス。                                                                                        |

| SOC    | 24 | O                  | 電流センスアンプの出力。                                                                                                 |

| SOB    | 25 | O                  | 電流センスアンプの出力。                                                                                                 |

| SOA    | 26 | O                  | 電流センスアンプの出力。                                                                                                 |

| GND    | 27 | PWR                | デバイスのグランド                                                                                                    |

| CPL    | 28 | PWR                | チャージポンプのスイッチング ノード。フライング コンデンサを CPH ピンと CPL ピンの間に接続します。                                                      |

| CPH    | 29 | PWR                | チャージポンプのスイッチング ノード。フライング コンデンサを CPH ピンと CPL ピンの間に接続します。                                                      |

| GVDD   | 30 | PWR                | ゲートドライバの電源出力。GVDD 定格セラミック コンデンサを GVDD ピンと GND ピンの間に接続します。                                                    |

| PVDD   | 31 | PWR                | ゲートドライバの電源入力。プリッジ電源に接続します。PVDD 定格セラミック コンデンサを PVDD ピンと GND ピンの間に接続します。                                       |

| CPTL   | 32 | PWR                | トリクル チャージ ポンプ スイッチング ノード。チャージ ポンプ フライング コンデンサを CPTL ピンと CPTH ピンの間に接続します。                                     |

| CPTH   | 33 | PWR                | トリクル チャージ ポンプ スイッチング ノード。チャージ ポンプ フライング コンデンサを CPTL ピンと CPTH ピンの間に接続します。                                     |

| VCP    | 34 | PWR                | トリクル チャージ ポンプ ストレージ容量。VCP ピンと VDRAIN ピンの間にセラミック コンデンサを接続します。                                                 |

| VDRAIN | 35 | PWR                | ハイサイド ドレイン検出およびチャージ ポンプ 電源入力。                                                                                |

| BSTA   | 36 | O                  | ブートストラップ出力ピン。BSTA と SHA の間にブートストラップ コンデンサを接続します。                                                             |

| SHA    | 37 | I                  | ハイサイド ソース センス入力。ハイサイド パワー MOSFET ソースに接続します。                                                                  |

| GHA    | 38 | O                  | ハイサイド ゲートドライバ出力。ハイサイド パワー MOSFET のゲートに接続します。                                                                 |

| GLA    | 39 | O                  | ローサイド ゲートドライバ出力。ローサイド パワー MOSFET のゲートに接続します。                                                                 |

| SLA    | 40 | I                  | ローサイド ソース検出入力。ローサイド パワー MOSFET のソースに接続します。                                                                   |

| SLB    | 41 | I                  | ローサイド ソース検出入力。ローサイド パワー MOSFET のソースに接続します。                                                                   |

| GLB    | 42 | O                  | ローサイド ゲートドライバ出力。ローサイド パワー MOSFET のゲートに接続します。                                                                 |

| GHB    | 43 | O                  | ハイサイド ゲートドライバ出力。ハイサイド パワー MOSFET のゲートに接続します。                                                                 |

| SHB    | 44 | I                  | ハイサイド ソース センス入力。ハイサイド パワー MOSFET ソースに接続します。                                                                  |

| BSTB   | 45 | O                  | ブートストラップ出力ピン。BSTB と SHB の間にブートストラップ コンデンサを接続します。                                                             |

| BSTC   | 46 | O                  | ブートストラップ出力ピン。BSTC と SHC の間にブートストラップ コンデンサを接続します。                                                             |

| SHC    | 47 | I                  | ハイサイド ソース センス入力。ハイサイド パワー MOSFET ソースに接続します。                                                                  |

| GHC    | 48 | O                  | ハイサイド ゲートドライバ出力。ハイサイド パワー MOSFET のゲートに接続します。                                                                 |

**表 4-1. ピンの機能 48-QFP および 48-QFN (開発中製品) (続き)**

| ピン  |      | I/O <sup>(1)</sup> | 説明                                                                     |

|-----|------|--------------------|------------------------------------------------------------------------|

| 名称  | 番号   |                    |                                                                        |

| PAD | 該当なし | 該当なし               | 露出パッド。最高の放熱能力を持つ GND プレーンに接続します。このパッドは、回路動作のための GND への電気接続としては使用されません。 |

(1) 信号タイプ:I = 入力、O = 出力、I/O = 入力または出力、PWR = 電源

## 5 仕様

### 5.1 絶対最大定格

動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                              |                                                                          | 最小値    | 最大値                | 単位   |

|------------------------------|--------------------------------------------------------------------------|--------|--------------------|------|

| 電源ピン電圧                       | PVDD                                                                     | -0.3   | 65                 | V    |

| ハイサイド MOSFET ドレインピン電圧        | VDRAIN                                                                   | -0.3   | 65                 | V    |

| グランドピン間の電圧差                  | AGND, GND                                                                | -0.3   | 0.3                | V    |

| チャージポンプピン電圧                  | CPH                                                                      | -0.3   | $V_{GVDD} + 0.3$   | V    |

| チャージポンプピン電圧                  | CPL                                                                      | -0.3   | $V_{GVDD} + 0.9$   | V    |

|                              | CPL, $V_{PVDD} < V_{GVDD}$                                               |        | $V_{PVDD} + 0.6$   |      |

| トリクルチャージポンプハイサイドピン電圧         | CPTH                                                                     | -0.3   | 80                 | V    |

| トリクルチャージポンプローサイドピン電圧         | CPTL                                                                     | -0.3   | $V_{VDRAIN} + 0.3$ | V    |

| トリクルチャージポンプの出力ピン電圧           | VCP                                                                      | -0.3   | 80                 | V    |

| ゲートドライバレギュレータピン電圧 $V_{GVDD}$ | GVDD                                                                     | -0.3   | 18                 | V    |

| ロジックピン電圧                     | nSLEEP                                                                   | -0.3   | 65                 | V    |

| ロジックピン電圧                     | DRVOFF                                                                   | -0.3   | 65                 | V    |

| ロジックピン電圧                     | INHx, INLx, nFAULT, SCLK, SDO, SDI, nSCS                                 | -0.3   | 6.5                | V    |

| ロジックピン電圧                     | INHx, INLx, nFAULT, SCLK, SDO, SDI, nSCS:過渡応答                            | -0.3   | 7.0                | V    |

| ポートストラップピン電圧                 | BSTx、連続                                                                  | -0.3   | 80                 | V    |

|                              | SHx を基準とした BSTx                                                          | -0.3   | 20                 | V    |

|                              | GHx を基準とした BSTx                                                          | -0.3   | 20                 | V    |

| ポートストラップピンの過渡電流              | BSTx、過渡 (500ns)、外付け部品 $R_{BST} = 2\Omega$ と条件 $V(R_{BST}) = -7V$ 、を想定    |        | 3.5                | A    |

| ハイサイドゲートドライブピン電圧             | GHx、連続                                                                   | -8     | 80                 | V    |

| ハイサイドゲートドライブピン電圧             | GHx、過渡応答 1μs                                                             | -15    | 80                 | V    |

| SHx を基準とするハイサイドゲートドライブピン電圧   | GHx - SHx                                                                | -0.3   | $BSTx + 0.3$       | V    |

| ハイサイドソースピン電圧                 | SHx、連続                                                                   | -8     | 70                 | V    |

| ハイサイドソースピン電圧                 | SHx、過渡応答 1μs                                                             | -15    | 72                 | V    |

| ローサイドゲートドライブピン電圧             | SLx (LSS) を基準とした GLx                                                     | -0.3   | 20                 | V    |

| ローサイドゲートドライブピン電圧             | GVDD を基準とした GLx, $V_{GLx} - V_{GVDD} < V_{GLx} > V_{GVDD}$ の場合           |        | 0.3                | V    |

| ローサイドゲートドライブピン電圧             | GLx、連続                                                                   | -8     | 20                 | V    |

| ローサイドゲートドライブピン電圧             | GLx、過渡 1μs                                                               | -15    | 20                 | V    |

| ローサイドソース検出ピン電圧               | SLx、連続                                                                   | -8     | $V_{GVDD}$         | V    |

| ローサイドソース検出ピン電圧               | SLx、過渡 1μs                                                               | -15    | $V_{GVDD}$         | V    |

| ゲート駆動電流                      | GHx, GLx                                                                 | 内部的に制限 | 内部的に制限             | A    |

| 基準電圧入力ピン電圧                   | VREF                                                                     | -0.3   | 6                  | V    |

| シャントアンプ入力ピン電圧                | SNx, SPx、連続                                                              | -5     | 5                  | V    |

| シャントアンプ入力ピン電圧                | SNx, SPx、過渡 1μs                                                          | -15    | 15                 | V    |

| シャントアンプ出力ピン電圧                | SOx                                                                      | -0.3   | $V_{REF} + 0.3$    | V    |

| 電源過渡電圧ランプ                    | PVDD, VDRAIN, VREF                                                       |        | 3                  | V/μs |

| ハイサイドソースのスルーレート              | SHx, $V_{BSTx} - V_{SHx} \geq 5.5V$<br>nSLEEP = High および ENABLE_DRV = 1b |        | 4                  | V/ns |

動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                 |              | 最小値 | 最大値 | 単位 |

|-----------------|--------------|-----|-----|----|

| 周囲温度、 $T_A$     | 周囲温度、 $T_A$  | -40 | 125 | °C |

| 接合部温度、 $T_J$    | 接合部温度、 $T_J$ | -40 | 150 | °C |

| 保管温度、 $T_{stg}$ |              | -65 | 150 | °C |

(1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

## 5.2 ESD 定格 (車載機器)

|             |      |                                                               | 値                              | 単位 |

|-------------|------|---------------------------------------------------------------|--------------------------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、AEC Q100-002 <sup>(1)</sup><br>HBM ESD 分類レベル 2 準拠 | ±2000                          | V  |

|             |      | 荷電デバイス モデル (CDM)、AEC Q100-011<br>CDM ESD 分類レベル C4B 準拠         | 角のピン<br>±750<br>その他のピン<br>±500 |    |

(1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

## 5.3 推奨動作条件

## 動作温度範囲内 (特に記述のない限り)

|               |                               | 最小値                                                                             | 公称値 | 最大値 | 単位 |

|---------------|-------------------------------|---------------------------------------------------------------------------------|-----|-----|----|

| $V_{VM}$      | 電源電圧                          | PVDD<br>デバイス完全機能。PVDD = 4.5V で動作するには、それより高い PVDD から得られる場合のみ。起動時の最小 PVDD = 4.85V | 4.5 | 60  | V  |

| $V_{VM}$      | ロジック動作の電源電圧                   | PVDD、ロジック、SPI は、起動用の最小 PVDD からバッテリ立ち下がり後機能 (すべての機器が完全に機能した状態から、バッテリを始動させたとき)    | 4.0 | 60  | V  |

| $V_{VDRAIN}$  | ハイサイド MOSFET ドレイン電圧           | VDRAIN、完全機能                                                                     | 4.5 | 60  | V  |

| $V_{VDRAIN}$  | ハイサイド MOSFET ドレイン電圧           | VDRAIN、限定期的な機能 (VDS モニタ)。GVDD、TCP/VCP、BST、ゲートドライバが機能。                           | 0   | 60  | V  |

| $V_{BST}$     | SHx を基準とするブートストラップ ピンの電圧      | nSLEEP = High、PWM スイッチング、ゲートドライバが機能 <sup>(1)</sup>                              | 3.9 | 20  | V  |

| $I_{VCP}$     | VCP 外部負荷                      | VCP、PVDD < 8V                                                                   |     | 3   | mA |

| $I_{VCP}$     | VCP 外部負荷                      | VCP、PVDD > 8V                                                                   |     | 5   | mA |

| $V_{IN}$      | ロジック入力電圧                      | DRVOFF、INHx、INLx                                                                | 0   | 5.5 | V  |

| $V_{IN}$      | ロジック入力電圧                      | nSLEEP,                                                                         | 0   | 60  | V  |

| $V_{IN}$      | ロジック入力電圧                      | SCLK、SDI、nSCS                                                                   | 0   | 5.5 | V  |

| $V_{OD}$      | オープン ドレイン ブルアップ電圧             | nFAULT                                                                          |     | 5.5 | V  |

| $I_{OD}$      | オープン ドレイン 出力 ブルアップ 抵抗         | nFAULT                                                                          | 5   |     | KΩ |

| $I_{OD}$      | オープン ドレイン 出力電流                | SDO、PHC、DC 条件                                                                   |     | -1  | mA |

| $I_{GS}$      | 総平均ゲート駆動電流 (ローサイドとハイサイドを合わせて) | $I_{GHx}$ $I_{GLx}$                                                             |     | 50  | mA |

| $V_{VREF}$    | 電流センスアンプ リファレンス 電圧            | VREF                                                                            | 3   | 5.5 | V  |

| $V_{SL}$      | SLx の DC 電圧                   | SLx ピン、DC 条件                                                                    | -2  | 2   | V  |

| $V_{CM\_CSA}$ | 電流センス入力同相電圧                   | SP、SN                                                                           | -2  | 2   | V  |

動作温度範囲内 (特に記述のない限り)

|       |                   |                                 | 最小値 | 公称値 | 最大値 | 単位 |

|-------|-------------------|---------------------------------|-----|-----|-----|----|

| $T_A$ | 動作時の周囲温度          | 動作時の周囲温度 DRV8334Q デバイス<br>バリエント | -40 | 125 | 125 | °C |

| $T_A$ | 動作時の周囲温度 (グレード 0) | 動作時の周囲温度 DRV8334E デバイス<br>バリエント | -40 | 150 | 150 | °C |

| $T_J$ | 動作時接合部温度          | 動作時接合部温度 DRV8334Q デバイス<br>バリエント | -40 | 150 | 150 | °C |

| $T_J$ | 動作時接合部温度 (グレード 0) | 動作時接合部温度 DRV8334E デバイス<br>バリエント | -40 | 175 | 175 | °C |

(1)  $V_{BST}$  は、過電圧/低電圧検出スレッショルド  $V_{BST\_OV}/V_{BST\_UV}$  と、外部 MOSFET の要件を持つユーザーがレビューする必要があります。

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup> |                     | DRV8334-Q1 | DRV8334-Q1     | 単位   |

|----------------------|---------------------|------------|----------------|------|

|                      |                     | PHP(QFP)   | RGZ(QFN) プレビュー |      |

|                      |                     | 48 ピン      | 48 ピン          |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 27.0       | 23.7           | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 15.6       | 11.6           | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 11.0       | 6.5            | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 0.2        | 0.2            | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 10.9       | 6.5            | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 | 1.1        | 1.2            | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.5 電気的特性

$4.5V \leq V_{PVDD} \leq 60V$ 、 $-40^{\circ}C \leq T_J \leq$  (特に記述のない限り)

| パラメータ            | テスト条件              | 最小値                                                                                                                                                       | 標準値 | 最大値 | 単位 |

|------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----|

| <b>電源 (PVDD)</b> |                    |                                                                                                                                                           |     |     |    |

| $I_{PVDDQ}$      | $PVDD$ スリープ モード電流  | $V_{PVDD} = 12V$ 、 $nSLEEP = 0$ 、 $T_A = 25^{\circ}C$ 、<br>$I_{PVDDQ} = PVDD + VDRAIN$                                                                    | 7   | 10  | μA |

| $I_{PVDDQ}$      | $PVDD$ スリープ モード電流  | $V_{PVDD} = 24V$ 、 $nSLEEP = 0$ 、 $T_A = 25^{\circ}C$ 、<br>$I_{PVDDQ} = PVDD + VDRAIN$                                                                    | 8   | 12  | μA |

| $I_{PVDDQ}$      | $PVDD$ スリープ モード電流  | $V_{PVDD} = < 36V$ 、 $nSLEEP = 0$ 、 $I_{PVDDQ} = PVDD + VDRAIN$                                                                                           | 9   | 30  | μA |

| $I_{PVDD}$       | $PVDD$ アクティブ モード電流 | $V_{PVDD} = 24V$ 、 $nSLEEP = HIGH$ 、 $INHx = INLX = Low$ 、FET 接続なし、 $I_{PVDD} = PVDD + VDRAIN$ 、 $V_{DRAIN} = 24V$                                        | 25  | 38  | mA |

| $I_{PVDD}$       | $PVDD$ アクティブ モード電流 | $V_{PVDD} = 60V$ 、 $nSLEEP = HIGH$ 、 $INHx = INLX = Low$ 、FET 接続なし、 $I_{PVDD} = PVDD + VDRAIN$ 、 $V_{DRAIN} = 60V$ 、<br>$VCP\_MODE = 00b, 01b, 11b$       | 26  | 40  | mA |

| $I_{PVDD}$       | $PVDD$ アクティブ モード電流 | $V_{PVDD} = 24V$ 、 $nSLEEP = HIGH$ 、 $INHx = INLX = 20kHz$ でスイッチング、FET 接続なし、 $I_{PVDD} = PVDD + VDRAIN$                                                   | 25  | 38  | mA |

| $I_{PVDD}$       | $PVDD$ アクティブ モード電流 | $V_{PVDD} = 60V$ 、 $nSLEEP = HIGH$ 、 $INHx = INLX = 20kHz$ でスイッチング。FET 接続なし、 $I_{PVDD} = PVDD + VDRAIN$ 、 $V_{DRAIN} = 60V$ 、 $VCP\_MODE = 00b, 01b, 11b$ | 26  | 40  | mA |

$4.5V \leq V_{PVDD} \leq 60V, -40^{\circ}C \leq T_J \leq$  (特に記述のない限り)

| パラメータ                                     |                                       | テスト条件                                                                                                                                     | 最小値  | 標準値  | 最大値  | 単位 |

|-------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----|

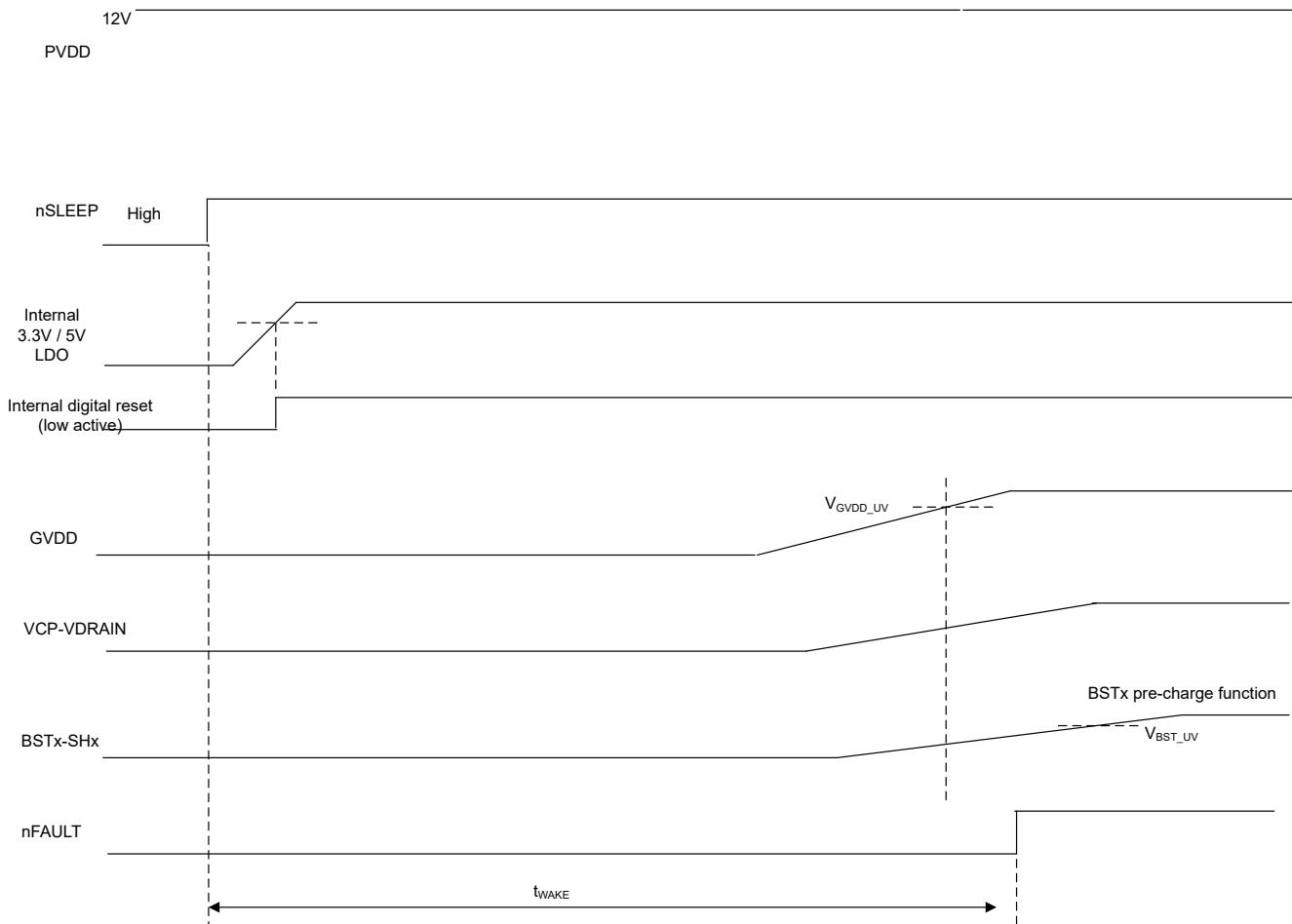

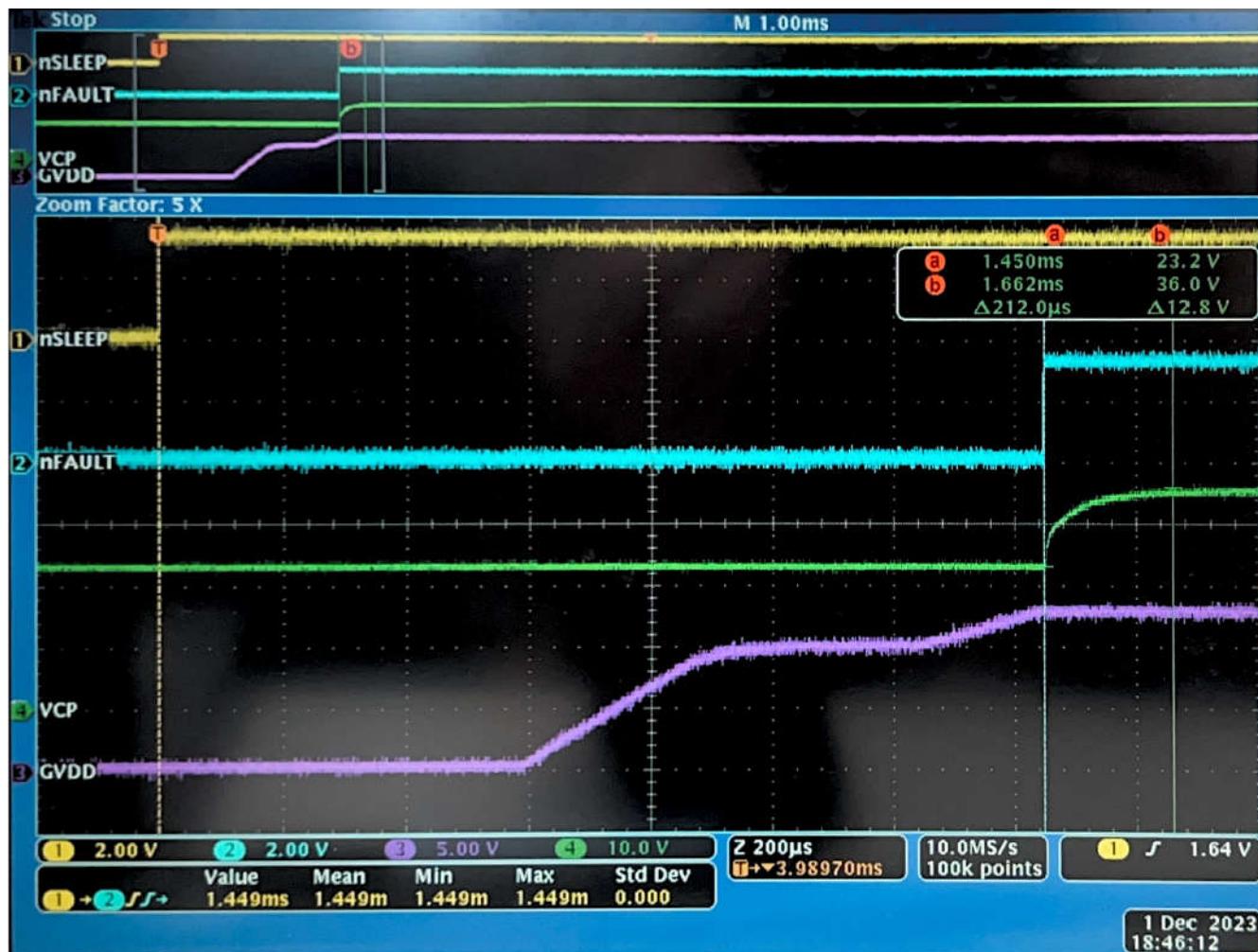

| $t_{WAKE}$                                | ターンオン時間                               | $nSLEEP = \text{Low}$ から $\text{High}$ 、 $nFAULT$ が $\text{High}$ に移行。                                                                    |      | 1    | 5    | ms |

| <b>ロジック レベル入力 (INHx, INLx, nSLEEP など)</b> |                                       |                                                                                                                                           |      |      |      |    |

| $V_{IL}$                                  | 入力ロジック Low 電圧                         |                                                                                                                                           |      | 0.8  |      | V  |

| $V_{IH}$                                  | 入力ロジック High 電圧                        |                                                                                                                                           | 2.1  |      |      | V  |

| $V_{HYS}$                                 | 入力ヒステリシス                              |                                                                                                                                           | 200  | 330  | 450  | mV |

| $V_{IL}$                                  | DRVOFF 入力ロジック Low 電圧                  | DRVOFF                                                                                                                                    |      | 0.8  |      | V  |

| $V_{IH}$                                  | DRVOFF 入力ロジック High 電圧                 | DRVOFF                                                                                                                                    | 2.1  |      |      | V  |

| $V_{HYS}$                                 | DRVOFF 入力ヒステリシス                       | DRVOFF                                                                                                                                    | 190  | 350  | 600  | mV |

| $R_{PD}$                                  | 入力プルダウン抵抗                             | 対 GND、INHx、INLx、SCLK、SDI                                                                                                                  | 50   | 100  | 150  | kΩ |

| $R_{PD}$                                  | 入力プルダウン抵抗                             | $nSLEEP$ 、DRVOFF                                                                                                                          | 460  | 800  | 1700 | kΩ |

| $I_{IL}$                                  | 入力ロジック Low 電流                         | $V_I = 0V$ 、 $nSCS$ (内部プルアップ)、 $VIO = 3.3V$                                                                                               | 11   | 33   | 66   | μA |

| $I_{IL}$                                  | 入力ロジック Low 電流                         | $V_I = 0V$ 、 $nSCS$ (内部プルアップ)、 $VIO = 5V$                                                                                                 | 25   | 50   | 100  | μA |

| $I_{IH}$                                  | 入力ロジック High 電流                        | $V_I = 5V$ 、INHx/INLx/SDI/SCLK                                                                                                            | 30   | 50   | 70   | μA |

| $V_{IH}$                                  | $nSleep$ 入力ロジック High 電圧               |                                                                                                                                           |      | 2.1  |      | V  |

| $V_{IL}$                                  | $nSleep$ 入力ロジック Low 電圧                |                                                                                                                                           | 0.8  |      |      | V  |

| $V_{HYST}$                                | $nSleep$ 入力ロジック ヒステリシス                |                                                                                                                                           | 0.1  |      |      | V  |

| <b>ロジック レベル出力 (nFAULT、SDO、PHCx)</b>       |                                       |                                                                                                                                           |      |      |      |    |

| $V_{OL}$                                  | 出力ロジック Low 電圧                         | $I_{DOUT} = 1mA$ 、PHCOMP                                                                                                                  |      | 0.5  |      | V  |

| $V_{OL}$                                  | 出力ロジック Low 電圧                         | $I_{DOUT} = 1mA$ 、SDO                                                                                                                     |      | 0.5  |      | V  |

| $V_{OH}$                                  | ロジック High 出力電圧                        | $I_{DOUT} = 1mA$ 、SDO、3.3V モード                                                                                                            | 2.7  | 3.3  | 3.6  | V  |

| $V_{OH}$                                  | ロジック High 出力電圧                        | $I_{DOUT} = 1mA$ 、PHCOMP、5V モード、 $V_{PVDD} \geq 4.5V$                                                                                     | 4.0  | 5    | 5.5  | V  |

| $V_{OH}$                                  | ロジック High 出力電圧                        | $I_{DOUT} = 1mA$ 、SDO、5V モード、 $V_{PVDD} \geq 4.5V$                                                                                        | 4.0  | 5    | 5.5  | V  |

| $V_{OH}$                                  | ロジック High 出力電圧                        | $I_{DOUT} = 1mA$ 、SDO、5V モード、 $4V \leq V_{PVDD} < 4.5V$                                                                                   | 3.6  | 3.8  | 4.5  | V  |

| $I_{OZ}$                                  | 出力ロジック High 電流                        | $nFAULT: nFAULT = 5V$ を強制、フォルトイ ベントなし、 $nSLEEP = \text{High}$<br>SDO: $V_{SDO} = 5V$ を強制、 $nSCS = \text{High}$ ま たは $nSLEEP = \text{Low}$ | -12  |      | 25   | μA |

| $I_{OZ}$                                  | 出力ロジック High 電流                        | SDO: $V_{SDO} = 0V$ を強制、 $nSCS = \text{High}$ ま たは $nSLEEP = \text{Low}$                                                                  | -12  |      | 10   | μA |

| <b>チャージ ポンプ (GVDD、VCP)</b>                |                                       |                                                                                                                                           |      |      |      |    |

| $V_{GVDD}$                                | GVDD ゲートドライバ レギュレータ電圧 (LDO モード)       | $22V \leq V_{PVDD} \leq 50mA$                                                                                                             | 11.5 | 13.5 |      | V  |

|                                           |                                       | $18V \leq V_{PVDD} \leq 22V, I_{GS} \leq 50mA$                                                                                            | 11.5 | 13.5 |      | V  |

|                                           | GVDD ゲートドライバ レギュレータ電圧 (チ ャージ ポンプ モード) | $7.2V \leq V_{PVDD} \leq 18V, I_{GS} = 50mA, I_{VCP} = 5mV$                                                                               | 11.5 | 13.5 |      | V  |

|                                           |                                       | $6.5V \leq V_{PVDD} \leq 7.2V, I_{GS} \leq 20mA, I_{VCP} = 3mA$                                                                           | 11.5 | 13.5 |      | V  |

|                                           |                                       | $5V \leq V_{PVDD} \leq 6.5V, I_{GS} \leq 20mA, I_{VCP} = 3mA$                                                                             | 9    | 13   |      | V  |

|                                           |                                       | $4.5V \leq V_{PVDD} \leq 5V, I_{GS} \leq 20mA, I_{VCP} = 3mA, ,$                                                                          | 8    | 10   |      | V  |

4.5V  $\leq$  V<sub>PVDD</sub>  $\leq$  60V,  $-40^{\circ}\text{C} \leq T_J \leq$  (特に記述のない限り)

| パラメータ                   |                                             | テスト条件                                                                                                                                                                                                                                                | 最小値  | 標準値  | 最大値  | 単位 |

|-------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----|

| V <sub>VCP</sub>        | VCP チャージポンプ電圧 (V <sub>DRAIN</sub> を基準とした場合) | V <sub>VCP</sub> = V <sub>(VCP - V<sub>DRAIN</sub>)</sub> 、13.5 $\geq$ GVDD $\geq$ 11V, V <sub>DRAIN</sub> > 4.5V, I <sub>VCP</sub> = 5mA,                                                                                                           | 9.5  |      | 13.5 | V  |

|                         |                                             | V <sub>VCP</sub> = V <sub>(VCP - V<sub>DRAIN</sub>)</sub> 、9V $\leq$ GVDD < 11V, V <sub>DRAIN</sub> > 4.5V, I <sub>VCP</sub> = 3mA,                                                                                                                  | 8.3  |      | 11   |    |

|                         |                                             | V <sub>VCP</sub> = V <sub>(VCP - V<sub>DRAIN</sub>)</sub> 、8V $\leq$ GVDD < 9V, V <sub>DRAIN</sub> > 4.5V, I <sub>VCP</sub> = 3mA,                                                                                                                   | 7.36 |      | 9    |    |

| t <sub>BST_PRECHG</sub> | VCP チャージポンプのブートストラップコンデンサのプリチャージ時間          | V <sub>BST-SHX</sub> = 5V, INL <sub>x</sub> = INH <sub>x</sub> = Low, T <sub>j</sub> = 150C, I <sub>VCP</sub> = 3mA, C <sub>VCP</sub> = 1.5 $\mu$ F, C <sub>BST</sub> = 1.5 $\mu$ F (各相), C <sub>VCP_FLY</sub> = 1 $\mu$ F, V <sub>PVDD</sub> = 4.5V |      | 1.7  | 3    | ms |

| V <sub>BST_TCPOFF</sub> | VCP の BST 監視電圧により、BST コンデンサの充電を停止 (立ち上がり電圧) | INL <sub>x</sub> = 0, SH <sub>x</sub> = 0, V <sub>DRAIN</sub> , V <sub>DRAIN</sub> = PVDD = 12V, 60V                                                                                                                                                 | 12.0 | 13.2 | 14.6 | V  |

#### ブートストラップダイオード

|                    |                                                        |                                                            |      |      |          |

|--------------------|--------------------------------------------------------|------------------------------------------------------------|------|------|----------|

| V <sub>BOOTD</sub> | ブートストラップダイオードの順方向電圧                                    | I <sub>BOOT</sub> = 100 $\mu$ A                            | 0.55 | 0.85 | V        |

|                    |                                                        | I <sub>BOOT</sub> = 10mA                                   | 0.85 | 1.1  |          |

| V <sub>BOOTD</sub> | ブートストラップダイオードの順方向電圧                                    | I <sub>BOOT</sub> = 100mA, T <sub>j</sub> < 150C           |      | 1.6  | V        |

| R <sub>BOOTD</sub> | ブートストラップの動的抵抗 ( $\Delta V_{BOOTD} / \Delta I_{BOOT}$ ) | I <sub>BOOT</sub> = 100mA および 50 mA, T <sub>j</sub> < 150C | 6.6  | 9.1  | $\Omega$ |

#### ゲートドライバ (GH<sub>x</sub>, GL<sub>x</sub>, SH<sub>x</sub>, SL<sub>x</sub>)

|                      |                      |                                                                                                                                             |   |     |     |            |

|----------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-----|------------|

| V <sub>GL_L</sub>    | ローサイド低レベル出力電圧        | IGL <sub>x</sub> = 10mA, GL <sub>x</sub> - SL <sub>x</sub> , IDR <sub>VL</sub> = 100100b, IHOLD_SEL = 0b, V <sub>GVDD</sub> = 12V,          | 0 | 0.2 | V   |            |

| V <sub>GL_H</sub>    | ローサイドハイレベル出力電圧       | IGL <sub>x</sub> = 10mA, GVDD - GL <sub>x</sub> , IDR <sub>VL</sub> = 100100b, IHOLD_SEL = 0b, V <sub>GVDD</sub> = 12V,                     | 0 | 0.2 | V   |            |

| V <sub>GH_L</sub>    | ハイサイド低レベル出力電圧        | IGH <sub>x</sub> = 10mA, GH <sub>x</sub> - SH <sub>x</sub> , IDR <sub>VL</sub> = 100100b, IHOLD_SEL = 0b, V <sub>GVDD</sub> = 12V,          | 0 | 0.2 | V   |            |

| V <sub>GH_H</sub>    | ハイサイドハウレベル出力電圧       | IGH <sub>x</sub> = 10mA, BST <sub>x</sub> - GH <sub>x</sub> , IDR <sub>VL</sub> = 100100b, IHOLD_SEL = 0b, V <sub>GVDD</sub> = 12V,         | 0 | 0.2 | V   |            |

| R <sub>PDSA_LS</sub> | ロー サイドセミアクティブプルダウン抵抗 | GL <sub>x</sub> から SL <sub>x</sub> , nSLEEP = Low, V <sub>GLx</sub> - V <sub>SLx</sub> = 2V, GVDD (BST <sub>x</sub> -SH <sub>x</sub> ) > 2V | 2 | 3   | 4.3 | k $\Omega$ |

| R <sub>PDSA_HS</sub> | ハイサイドセミアクティブプルダウン抵抗  | GH <sub>x</sub> から SH <sub>x</sub> , nSLEEP = Low, V <sub>GHx</sub> - V <sub>SHx</sub> = 2V, GVDD (BST <sub>x</sub> -SH <sub>x</sub> ) > 2V | 7 | 9   | 12  | k $\Omega$ |

4.5V  $\leq$  V<sub>PVDD</sub>  $\leq$  60V,  $-40^{\circ}\text{C} \leq T_J \leq$  (特に記述のない限り)

| パラメータ             | テスト条件                                          | 最小値 | 標準値  | 最大値 | 単位 |

|-------------------|------------------------------------------------|-----|------|-----|----|

| I <sub>DRVN</sub> | IDRVN=000000b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 0.85 |     | mA |

|                   | IDRVN=000001b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 1.2  |     |    |

|                   | IDRVN=000010b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 1.6  |     |    |

|                   | IDRVN=000011b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 2.0  |     |    |

|                   | IDRVN=000100b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 2.4  |     |    |

|                   | IDRVN=000101b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 3.0  |     |    |

|                   | IDRVN=000110b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 3.6  |     |    |

|                   | IDRVN=000111b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 4.2  |     |    |

|                   | IDRVN=001000b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 4.7  |     |    |

|                   | IDRVN=001001b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 5.7  |     |    |

|                   | IDRVN=001010b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 6.7  |     |    |

|                   | IDRVN=001011b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 7.8  |     |    |

|                   | IDRVN=001100b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 8.8  |     |    |

|                   | IDRVN=001101b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 10   |     |    |

|                   | IDRVN=001110b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 11.5 |     |    |

|                   | IDRVN=001111b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 13   |     |    |

|                   | IDRVN=010000b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 14   |     |    |

|                   | IDRVN=010001b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 17   |     |    |

|                   | IDRVN=010010b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 19   |     |    |

|                   | IDRVN=010011b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 26   |     |    |

|                   | IDRVN=010100b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 29   |     |    |

|                   | IDRVN=010101b, VGSx = 5V, BST-SHx = GVDD = 12V |     | 32   |     |    |

4.5V  $\leq$  V<sub>PVDD</sub>  $\leq$  60V,  $-40^{\circ}\text{C} \leq T_J \leq$  (特に記述のない限り)

| パラメータ           |                 | テスト条件                                                                                       | 最小値 | 標準値              | 最大値 | 単位 |

|-----------------|-----------------|---------------------------------------------------------------------------------------------|-----|------------------|-----|----|

| $I_{DRVN}$      | ピーク シンクゲート電流    | IDRVN=010110b, VGSx = 5V, BST-SHx = GVDD = 12V                                              | 37  |                  |     | mA |

|                 |                 | IDRVN=010111b, VGSx = 5V, BST-SHx = GVDD = 12V                                              | 43  |                  |     |    |

|                 |                 | IDRVN=011000b, VGSx = 5V, BST-SHx = GVDD = 12V                                              | 49  |                  |     |    |

|                 |                 | IDRVN=011001b, VGSx = 5V, BST-SHx = GVDD = 12V                                              | 58  |                  |     |    |

|                 |                 | IDRVN=011010b, VGSx = 5V, BST-SHx = GVDD = 12V                                              | 77  |                  |     |    |

|                 |                 | IDRVN=011011b, VGSx = 5V, BST-SHx = GVDD = 12V                                              | 92  |                  |     |    |

|                 |                 | IDRVN=011100b, VGSx = 5V, BST-SHx = GVDD = 12V                                              | 100 |                  |     |    |

|                 |                 | IDRVN=011101b, VGSx = 5V, BST-SHx = GVDD = 12V                                              | 120 |                  |     |    |

|                 |                 | IDRVN=011110b, VGSx = 5V, BST-SHx = GVDD = 12V                                              | 140 |                  |     |    |

|                 |                 | IDRVN=011111b, VGSx = 5V, BST-SHx = GVDD = 12V                                              | 155 |                  |     |    |

|                 |                 | IDRVN=100000b, VGSx = 5V, BST-SHx = GVDD = 12V                                              | 175 |                  |     |    |

|                 |                 | IDRVN=100001b, VGSx = 5V, BST-SHx = GVDD = 12V                                              | 210 |                  |     |    |

|                 |                 | IDRVN=100010b, VGSx = 5V, BST-SHx = GVDD = 12V                                              | 240 |                  |     |    |

|                 |                 | IDRVN=100011b, VGSx = 5V, BST-SHx = GVDD = 12V                                              | 270 |                  |     |    |

| $I_{DRVNP}$     | ピーク ソースゲート電流    | IDRV_CFG = 0b, IDRV_RATIO = 00b, IDRVN = 00000b から 100011b, VGSx = 5V, BST-SHx = GVDD = 12V |     | $1^*I_{DRVN}$    |     | mA |

|                 |                 | IDRV_CFG = 0b, IDRV_RATIO = 01b, IDRVN = 00000b から 100011b, VGSx = 5V, BST-SHx = GVDD = 12V |     | $0.75^*I_{DRVN}$ |     | mA |

|                 |                 | IDRV_CFG = 0b, IDRV_RATIO = 10b, IDRVN = 00000b から 100011b, VGSx = 5V, BST-SHx = GVDD = 12V |     | $0.5^*I_{DRVN}$  |     | mA |

|                 |                 | IDRV_CFG = 0b, IDRV_RATIO = 11b, IDRVN = 00000b から 100011b, VGSx = 5V, BST-SHx = GVDD = 12V |     | $0.25^*I_{DRVN}$ |     | mA |

| $I_{DRVN\_VAR}$ | ピーク シンク ゲート電流変動 | IDRVN=000000b - 010011b, TYP を基準とした場合                                                       | -55 | +55              |     | %  |

|                 |                 | IDRVN=010011b - 100011b, TYP を基準とした場合                                                       | -45 | +45              |     | %  |

4.5V  $\leq$  V<sub>PVDD</sub>  $\leq$  60V,  $-40^{\circ}\text{C} \leq T_J \leq$  (特に記述のない限り)

| パラメータ                |                          | テスト条件                                                                               | 最小値  | 標準値  | 最大値  | 単位 |

|----------------------|--------------------------|-------------------------------------------------------------------------------------|------|------|------|----|

| IDRVN                | ピーク シンク ゲート電流-スイッチ モード   | IDRVN=100100b, VGSx (GHx-SHx, GLx-SLx) = 12V, BST-SHx = GVDD = 12V. SGD_TMP_EN = 1b | 370  | 600  | 980  | mA |

|                      |                          | IDRVN=100101b, VGSx (GHx-SHx, GLx-SLx) = 12V, BST-SHx = GVDD = 12V. SGD_TMP_EN = 1b | 440  | 700  | 1050 | mA |

|                      |                          | IDRVN=100110b, VGSx (GHx-SHx, GLx-SLx) = 12V, BST-SHx = GVDD = 12V. SGD_TMP_EN = 1b | 500  | 795  | 1250 | mA |

|                      |                          | IDRVN=100111b, VGSx (GHx-SHx, GLx-SLx) = 12V, BST-SHx = GVDD = 12V. SGD_TMP_EN = 1b | 580  | 910  | 1365 | mA |

|                      |                          | IDRVN=101000b, VGSx (GHx-SHx, GLx-SLx) = 12V, BST-SHx = GVDD = 12V. SGD_TMP_EN = 1b | 720  | 1090 | 1600 | mA |

|                      |                          | IDRVN=101001b, VGSx (GHx-SHx, GLx-SLx) = 12V, BST-SHx = GVDD = 12V. SGD_TMP_EN = 1b | 820  | 1255 | 1820 | mA |

|                      |                          | IDRVN=101010b, VGSx (GHx-SHx, GLx-SLx) = 12V, BST-SHx = GVDD = 12V. SGD_TMP_EN = 1b | 910  | 1455 | 2200 | mA |

|                      |                          | IDRVN=101011b, VGSx (GHx-SHx, GLx-SLx) = 12V, BST-SHx = GVDD = 12V. SGD_TMP_EN = 1b | 1000 | 1685 | 2500 | mA |

|                      |                          | IDRVN=101100b, VGSx (GHx-SHx, GLx-SLx) = 12V, BST-SHx = GVDD = 12V. SGD_TMP_EN = 1b | 1080 | 2000 | 2600 | mA |

| IDRVP                | ピーク ソース ゲート電流 - スイッチ モード | IDRVP=100100b, VGSx (GHx-SHx, GLx-SLx) = 0V, GVDD = 12V                             | 160  | 300  | 450  | mA |

|                      |                          | IDRVP=100101b, VGSx (GHx-SHx, GLx-SLx) = 0V, GVDD = 12V                             | 160  | 320  | 480  | mA |

|                      |                          | IDRVP=100110b, VGSx (GHx-SHx, GLx-SLx) = 0V, GVDD = 12V                             | 200  | 380  | 570  | mA |

|                      |                          | IDRVP=100111b, VGSx (GHx-SHx, GLx-SLx) = 0V, GVDD = 12V                             | 215  | 430  | 645  | mA |

|                      |                          | IDRVP=101000b, VGSx (GHx-SHx, GLx-SLx) = 0V, GVDD = 12V                             | 250  | 500  | 750  | mA |

|                      |                          | IDRVP=101001b, VGSx (GHx-SHx, GLx-SLx) = 0V, GVDD = 12V                             | 300  | 600  | 850  | mA |

|                      |                          | IDRVP=101010b, VGSx (GHx-SHx, GLx-SLx) = 0V, GVDD = 12V                             | 360  | 700  | 970  | mA |

|                      |                          | IDRVP=101011b, VGSx (GHx-SHx, GLx-SLx) = 0V, GVDD = 12V                             | 400  | 800  | 1150 | mA |

|                      |                          | IDRVP=101100b, VGSx (GHx-SHx, GLx-SLx) = 0V, GVDD = 12V                             | 500  | 1000 | 1300 | mA |

| I <sub>HOLD_PU</sub> | ゲート プル アップ 保持電流          | I <sub>HOLD_SEL</sub> = 1b, BST-SHx = GVDD = 12V.                                   | 150  | 250  | 400  | mA |

| I <sub>HOLD_PU</sub> | ゲート プル アップ 保持電流          | I <sub>HOLD_SEL</sub> = 0b, BST-SHx = GVDD = 12V.                                   | 330  | 560  | 900  | mA |

| I <sub>HOLD_PD</sub> | ゲート プル ダウン 保持電流          | I <sub>HOLD_SEL</sub> = 1b, BST-SHx = GVDD = 12V.                                   | 140  | 267  | 480  | mA |

4.5V  $\leq V_{PVDD} \leq 60V$ ,  $-40^{\circ}C \leq T_J \leq$  (特に記述のない限り)

| パラメータ                           |                             | テスト条件                                                                                                                                                                     | 最小値  | 標準値  | 最大値  | 単位 |

|---------------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----|

| $I_{HOLD\_PD}$                  | ゲート プル ダウン保持電流              | $I_{HOLD\_SEL} = 0b$ , $BST-SHx = GVDD = 12V$ .                                                                                                                           | 580  | 1100 | 1500 | mA |

| $I_{STRONG}$                    | ゲート プル ダウン強電流               | $GHx-SHx = 12V$ (ハイ サイド) または $GLx = 12V$ (ロー サイド), $BST-SHx = GVDD = 12V$ .                                                                                               | 1000 | 2000 | 2800 | mA |

| <b>ゲートドライバ タイミング (GHx, GLx)</b> |                             |                                                                                                                                                                           |      |      |      |    |

| $t_{PD}$                        | 入力から出力までの伝搬遅延 GHx/GLx 立ち下がり | $INHx, INLx$ から $GHx, GLx.IDRVN = IDRVP = 101000b$ , $INHx/INLx$ の立ち下がりエッジ後 $VGS = VGHS/VGLS - 1V$ , $V_{GVDD} = V_{BSTMx-SHx} \geq 8V$                                   | 90   | 150  | ns   |    |

| $t_{PD}$                        | 入力から出力までの伝搬遅延 GHx/GLx 立ち下がり | $INHx, INLx$ から $GHx, GLx.IDRVN = IDRVP = 011101b$ , $INHx/INLx$ の立ち下がりエッジ後 $VGS = VGHS/VGLS - 1V$ , $V_{GVDD} = V_{BSTMx-SHx} \geq 8V$                                   | 110  | 150  | ns   |    |

| $t_{PD}$                        | 入力から出力までの伝搬遅延 GHx/GLx 立ち上がり | $INHx, INLx$ から $GHx, GLx.IDRVN = IDRVP = 101000b$ , $INHx/INLx$ の立ち上がりエッジ後 $VGS = 1V$ , $V_{GVDD} = V_{BSTMx-SHx} \geq 8V$                                               | 90   | 152  | ns   |    |

| $t_{PD}$                        | 入力から出力までの伝搬遅延 GHx/GLx 立ち上がり | $INHx, INLx$ から $GHx, GLx.IDRVN = IDRVP = 011101b$ , $INHx/INLx$ の立ち上がりエッジ後から $VGS = 1V$ , $V_{GVDD} = V_{BSTMx-SHx} \geq 8V$                                             | 100  | 150  | ns   |    |

| $t_{PD}$                        | 入力から出力までの伝搬遅延 GHx/GLx 立ち上がり | Rev2p0 新項目<br>$DRV\_BIAS\_MODE = 01b$<br>$INHx, INLx$ から $GHx, GLx.IDRVN = IDRVP = 101000b$ , $INHx/INLx$ の立ち上がりエッジ後 $VGS = 1V$ , $V_{GVDD} = V_{BSTMx-SHx} \geq 8V$      | 60   | 170  | ns   |    |

| $t_{PD}$                        | 入力から出力までの伝搬遅延 GHx/GLx 立ち上がり | Rev2p0 新項目<br>$DRV\_BIAS\_MODE = 10b, 11b$<br>$INHx, INLx$ から $GHx, GLx.IDRVN = IDRVP = 101000b$ , $INHx/INLx$ の立ち上がりエッジ後 $VGS = 1V$ , $V_{GVDD} = V_{BSTMx-SHx} \geq 8V$ | 100  | 220  | ns   |    |

| $t_{PD\_match}$                 | 位相ごとの伝搬遅延のマッチング             | $GHx$ ターン オフから $GLx$ ターン オン、<br>$GLx$ ターン オフから $GHx$ ターン オン、<br>$V_{GVDD} = V_{BSTMx-SHx} \geq 8V$                                                                        | -150 | 10   | 150  | ns |

| $t_{PD\_match}$                 | 位相間の伝搬遅延時間のマッチング            | $GHx/GLx$ ターン オフから $GHy/GLy$ ターン オン、<br>$GHx/GLx$ ターン オフから $GHy/GLy$ ターン オン、<br>$V_{GVDD} = V_{BSTMx-SHx} \geq 8V$                                                        | -50  | 10   | 50   | ns |

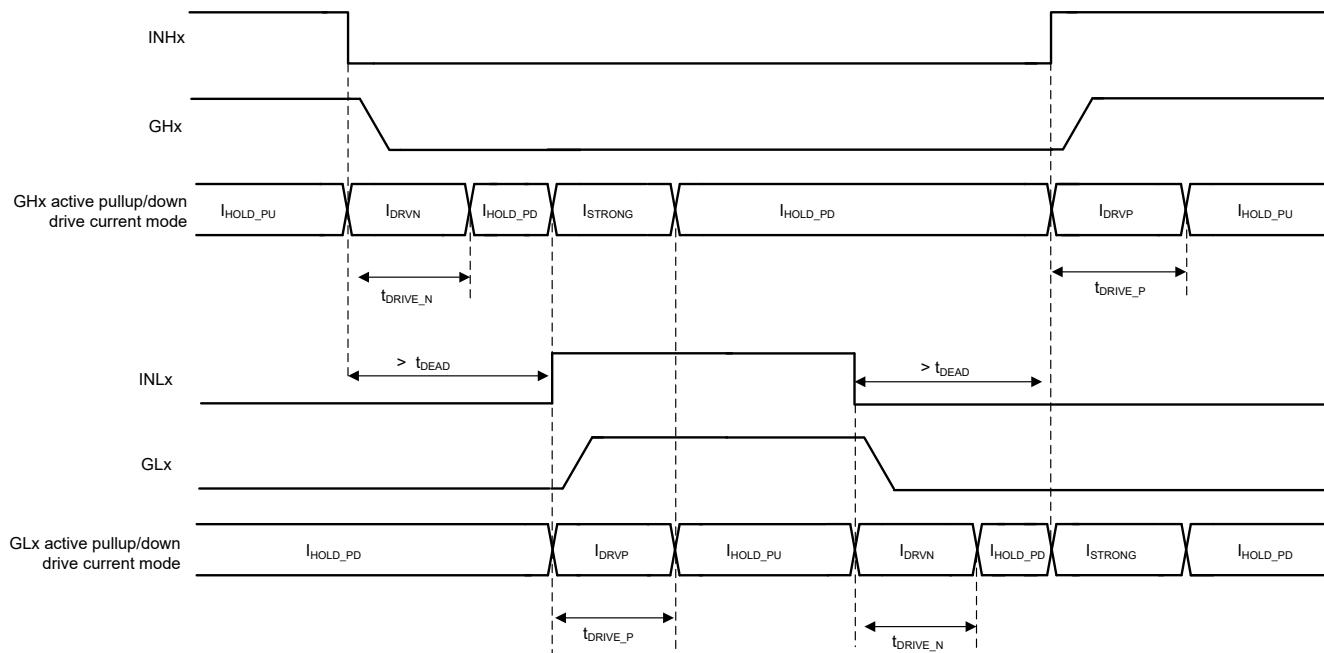

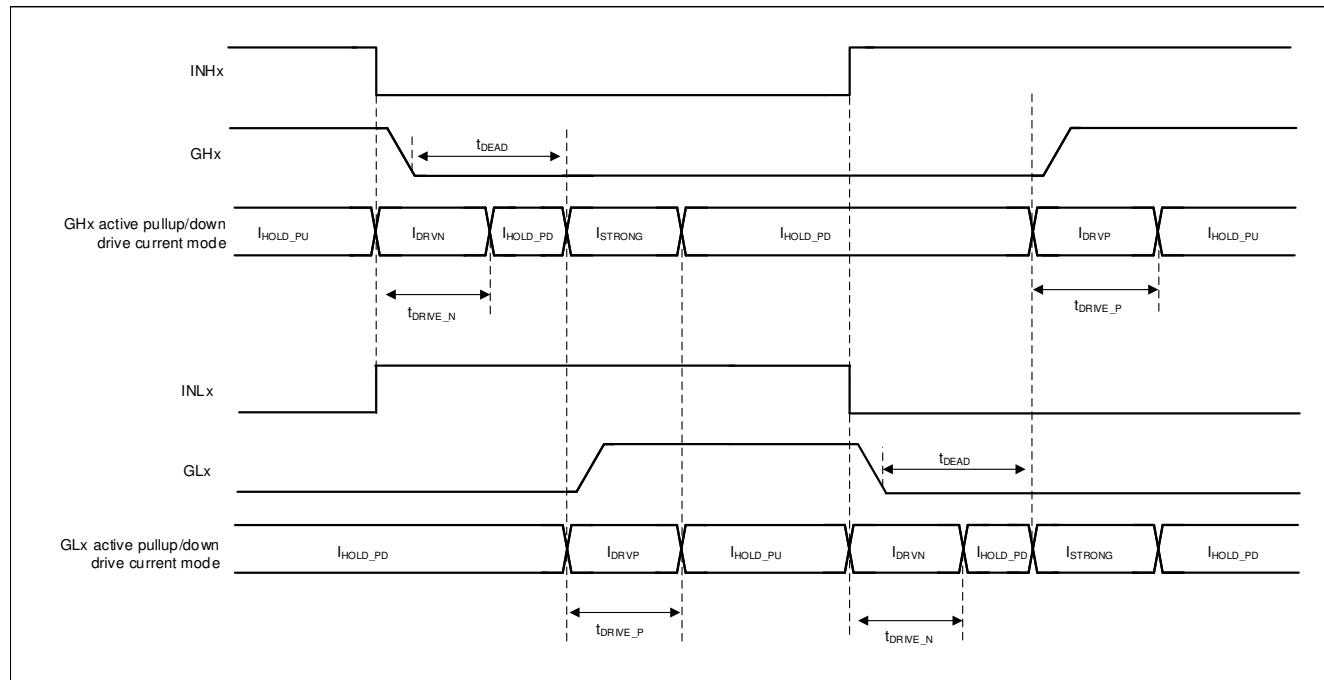

| $t_{DRIVE}$                     | ピーク電流ゲート駆動時間                | 標準値。 $TDRVP$ ( $TDRVN$ ) = $0000b - 1111b$ . 抵抗マップ $TDRNP$ および $TDRVN$ を参照。                                                                                               | 140  |      | 3821 | ns |

| $t_{DRIVE\_V}$                  | ピーク電流ゲート駆動時間の変動             | 標準値を基準にした場合。 $TDRVP$ ( $TDRVN$ ) = $0000b - 1111b$                                                                                                                        | -20  |      | 20   | %  |

| $t_{DEAD}$                      | デジタル ゲート駆動デッド タイム           | DEADTIME = $000b$ ;                                                                                                                                                       | 30   | 70   | 130  | ns |

|                                 |                             | DEADTIME = $001b$ ;                                                                                                                                                       | 170  | 214  | 300  | ns |

|                                 |                             | DEADTIME = $010b$                                                                                                                                                         | 230  | 286  | 380  | ns |

|                                 |                             | DEADTIME = $011b$                                                                                                                                                         | 420  | 500  | 640  | ns |

|                                 |                             | DEADTIME = $100b$                                                                                                                                                         | 640  | 750  | 930  | ns |

|                                 |                             | DEADTIME = $101b$                                                                                                                                                         | 880  | 1000 | 1280 | ns |

|                                 |                             | DEADTIME = $110b$                                                                                                                                                         | 1270 | 1500 | 1820 | ns |

|                                 |                             | DEADTIME = $111b$                                                                                                                                                         | 1700 | 2000 | 2400 | ns |

$4.5V \leq V_{PVDD} \leq 60V, -40^{\circ}C \leq T_J \leq$  (特に記述のない限り)

| パラメータ                                  |                        | テスト条件                                                                                     | 最小値   | 標準値               | 最大値 | 単位      |

|----------------------------------------|------------------------|-------------------------------------------------------------------------------------------|-------|-------------------|-----|---------|

| <b>電流シャントアンプ (SNx, SOx, SPx, VREF)</b> |                        |                                                                                           |       |                   |     |         |

| $A_{CSA}$                              | 検出アンプのゲイン              | $CSAGAIN = 0000b$                                                                         | 5     |                   |     | V/V     |

|                                        |                        | $CSAGAIN = 0001b$                                                                         | 10    |                   |     | V/V     |

|                                        |                        | $CSAGAIN = 0010b$                                                                         | 12    |                   |     | V/V     |

|                                        |                        | $CSAGAIN = 0011b$                                                                         | 16    |                   |     | V/V     |

|                                        |                        | $CSAGAIN = 0100b$                                                                         | 20    |                   |     | V/V     |

|                                        |                        | $CSAGAIN = 0101b$                                                                         | 23    |                   |     | V/V     |

|                                        |                        | $CSAGAIN = 0110b$                                                                         | 25    |                   |     | V/V     |

|                                        |                        | $CSAGAIN = 0111b$                                                                         | 30    |                   |     | V/V     |

|                                        |                        | $CSAGAIN = 1000b$                                                                         | 40    |                   |     | V/V     |

| $\Delta A_{CSA}$                       | 検出アンプのゲイン誤差            | すべての CSAGAIN 設定<br>$V_{GVDD} > 7.2V$ (この GVDD 条件はすべての CSA 項目に適用)                          | -0.55 | 0.55              |     | %       |

| $t_{SET}$                              | $\pm 1\%$ までのセトリング タイム | $V_{STEP} = 1.6V, A_{CSA} = 5V/V, R_{SO} = 160\Omega, C_{SO} = 470pF, VREF = 5V/3V$       | 0.6   | 1.6               |     | $\mu s$ |

| $t_{SET}$                              | $\pm 1\%$ までのセトリング タイム | $V_{STEP} = 1.6V, A_{CSA} = 10V/V, C_{LOAD} = 470pF$                                      | 0.65  | 1.5               |     | $\mu s$ |

| $t_{SET}$                              | $\pm 1\%$ までのセトリング タイム | $V_{STEP} = 1.6V, A_{CSA} = 20V/V, R_{SO} = 160\Omega, C_{SO} = 470pF VREF = 5V/3V$       | 0.7   | 1.55              |     | $\mu s$ |

| $t_{SET}$                              | $\pm 1\%$ までのセトリング タイム | $V_{STEP} = 1.6V, A_{CSA} = 30V/V, R_{SO} = 160\Omega, C_{SO} = 470pF VREF = 5V$          | 0.7   | 1.5               |     | $\mu s$ |

| $t_{SET}$                              | $\pm 1\%$ までのセトリング タイム | $V_{STEP} = 1.6V, A_{CSA} = 30V/V, R_{SO} = 160\Omega, C_{SO} = 470pF VREF = 3V$          | 0.7   | 1.6               |     | $\mu s$ |

| $t_{SET}$                              | $\pm 1\%$ までのセトリング タイム | $V_{STEP} = 1.6V, A_{CSA} = 40V/V, R_{SO} = 160\Omega, C_{SO} = 470pF VREF = 5V$          | 0.7   | 1.7               |     | $\mu s$ |

| $t_{SET}$                              | $\pm 1\%$ までのセトリング タイム | $V_{STEP} = 1.6V, A_{CSA} = 40V/V, R_{SO} = 160\Omega, C_{SO} = 470pF VREF = 3V$          | 0.7   | 1.75              |     | $\mu s$ |

| UGB                                    | ユニティゲイン帯域幅             | $C_{LOAD} = 470pF$ 、閉ループ、BW @ ユニティゲイン                                                     | 10    |                   |     | MHz     |

| BW                                     | 帯域幅                    | 閉ループ、-3db、出力負荷なし                                                                          | 1     |                   |     | MHz     |

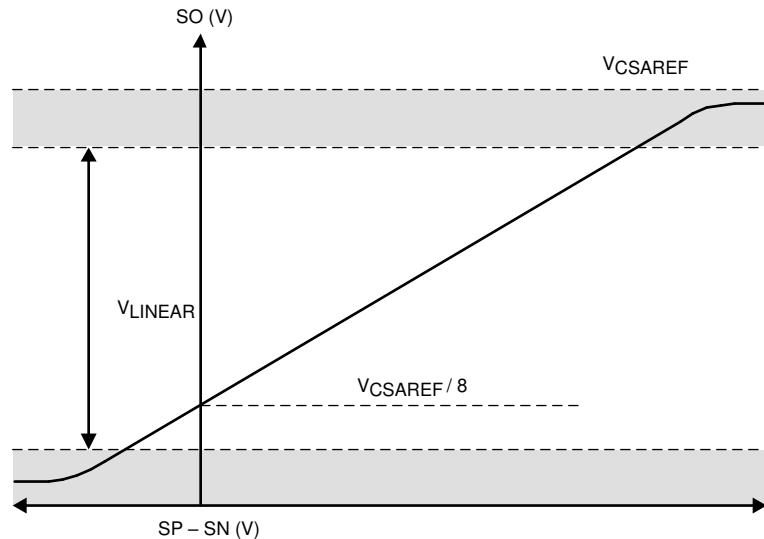

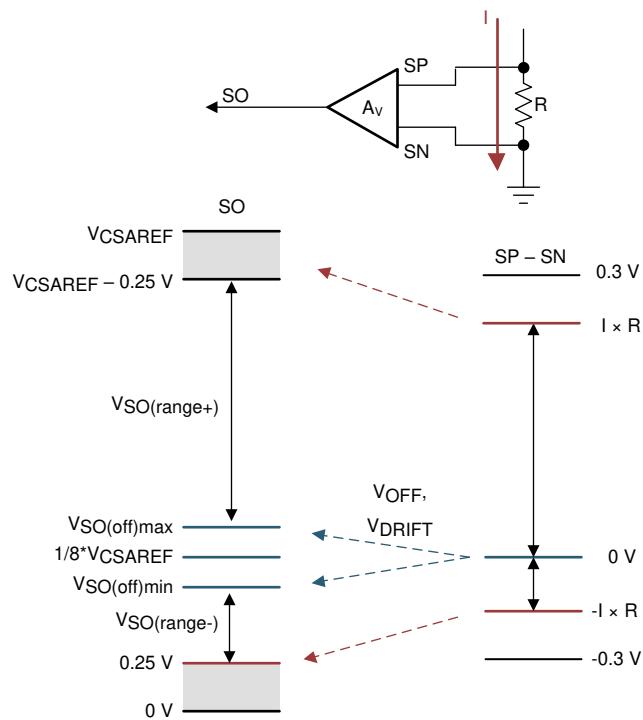

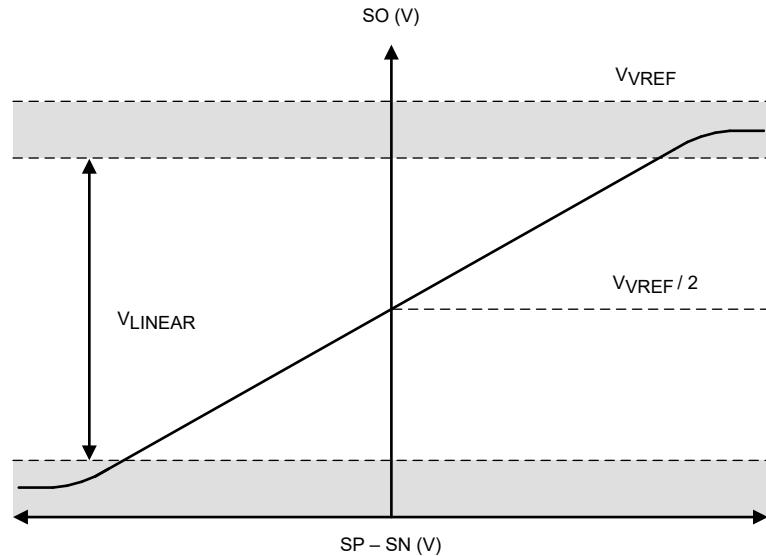

| $V_{SWING}$                            | 出力電圧範囲                 | $V_{VREF} = 3$ から $5.5V$                                                                  | 0.25  | $V_{VREF} - 0.25$ |     | V       |

| $V_{COM}$                              | 同相入力範囲                 | $V_{COM} = (V_{SP} + V_{SN})/2$                                                           | -2    | 2                 |     | V       |

| $t_{com\_rec}$                         | 同相過渡回復タイミング            | $V_{COM} = -15V$ から $0V$                                                                  |       | 2.9               |     | $\mu s$ |

| $V_{DIFF}$                             | 差動モード入力範囲              |                                                                                           | -0.3  | 0.3               |     | V       |

| $V_{OFF}$                              | 入力オフセット電圧の合計           | $V_{SP} = V_{SN} = GND, CSAGAIN = 0000b$<br>(ゲイン 5)<br>初期オフセット + オフセットドリフト、ゲイン = 5        | -0.6  | 0.5               |     | mV      |

| $V_{OFF}$                              | 入力オフセット電圧の合計           | $V_{SP} = V_{SN} = GND, CSAGAIN = 0001b - 1000b$ (ゲイン 10 - ゲイン 40)<br>初期オフセット + オフセットドリフト | -0.5  | 0.5               |     | mV      |

| $V_{OFF\_DRIFT}$                       | 入力オフセット電圧ドリフト          | $V_{SP} = V_{SN} = GND$ 、温度ドリフト + エイジング                                                   |       | $\pm 0.1$         |     | mV      |

| $I_{BIAS}$                             | 入力バイアス電流               | $V_{SP} = V_{SN} = GND$ 、CSA と SENSE_OCP の合計                                              | 20    | 100               |     | $\mu A$ |

4.5V  $\leq$   $V_{PVDD}$   $\leq$  60V,  $-40^{\circ}\text{C} \leq T_J \leq$  (特に記述のない限り)

| パラメータ             |                   | テスト条件                                  | 最小値  | 標準値 | 最大値  | 単位            |

|-------------------|-------------------|----------------------------------------|------|-----|------|---------------|

| $I_{BIAS\_OFF}$   | 入力バイアス電流オフセット     | $I_{SP} - I_{SN\_CSA}$ と SENSE_OCP の合計 | -1.5 | 1.5 |      | $\mu\text{A}$ |

| $I_{VREF}$        | 基準入力電流            | $V_{CSAREF} = 3.3\text{V}$             | 3    | 6   | 9.25 | $\text{mA}$   |

|                   |                   | $V_{CSAREF} = 5\text{V}$               | 4    | 7   | 9.5  | $\text{mA}$   |

| CMRR              | DC 同相除去比          | SN/SP = -2V から 2V                      | 60   | 90  |      | $\text{dB}$   |

| CMRR              | 過渡同相除去比           | 20KHz                                  | 60   | 90  |      | $\text{dB}$   |

| PSRR              | 電源除去比             |                                        |      | 100 |      | $\text{dB}$   |

| $t_{CSAAZ\_INIT}$ | 初期 CSA 自動ゼロ       | CSA_EN = 1b から最初の CSA 自動ゼロ機能の終了まで      | 26   | 32  | 38   | $\mu\text{s}$ |

| $t_{CSAAZ\_MIN}$  | CSA 自動ゼロ タイムアウト期間 | CSA_EN = 1b. INHx と INLx の切り替え。        | 170  |     |      | $\mu\text{s}$ |

| $t_{CSAAZ\_MAX}$  | CSA 自動ゼロ タイムアウト期間 | CSA_EN = 1b. INHx=INLx= low            |      |     | 260  | $\mu\text{s}$ |

#### 温度レポート

#### 電源電圧の監視

|                      |                      |                                                   |                       |      |      |               |               |

|----------------------|----------------------|---------------------------------------------------|-----------------------|------|------|---------------|---------------|

| $V_{PVDD\_UV}$       | PVDD 低電圧誤動作防止スレッショルド | $V_{PVDD}$ 立ち上がり                                  | 4.5                   | 4.65 | 4.8  | V             |               |

|                      |                      | $V_{PVDD}$ 立ち下がり                                  | 4.05                  | 4.2  | 4.35 |               |               |

| $V_{PVDD\_UV\_HYS}$  | PVDD 低電圧誤動作防止ヒステリシス  |                                                   | 立ち上がりから立ち下がりへのスレッショルド | 400  | 450  | 500           | mV            |

| $t_{PVDD\_UV\_DG}$   | PVDD 低電圧グリッヂ除去時間     |                                                   | 立ち上がりエッジと立ち下がりエッジ     | 8    | 12   | 16            | $\mu\text{s}$ |

| $V_{PVDD\_UVW}$      | PVDD 低電圧警告スレッショルド    | $V_{PVDD}$ 立ち上がり、 $PVDD\_UVW\_LVL = 0b$           | 6.0                   | 7    |      | V             |               |

|                      |                      | $V_{PVDD}$ 立ち下がり、 $PVDD\_ULW\_LVL = 0b$           | 5.8                   | 6.8  |      | V             |               |

|                      |                      | $V_{PVDD}$ 立ち上がり、 $PVDD\_UVW\_LVL = 1b$           | 7.3                   | 8.3  |      | V             |               |

|                      |                      | $V_{PVDD}$ 立ち下がり、 $PVDD\_UVW\_LVL = 1b$           | 7.1                   | 8.1  |      | V             |               |

| $V_{PVDD\_UVW\_HYS}$ | PVDD 低電圧警告ヒステリシス     | 立ち上がりから立ち下がりへのスレッショルド                             | 140                   | 200  | 260  | mV            |               |

| $t_{PVDD\_UVW\_DG}$  | PVDD 低電圧警告グリッヂ除去時間   | 立ち上がりエッジと立ち下がりエッジ                                 | 8                     | 12   | 16   | $\mu\text{s}$ |               |

| $V_{PVDD\_OV}$       | PVDD 過電圧スレッショルド      | $V_{PVDD}$ 立ち上がり、 $PVDD\_OV\_LVL = 00b$           | 28                    | 31   |      | V             |               |

|                      |                      | $V_{PVDD}$ 立ち下がり、 $PVDD\_OV\_LVL = 00b$           | 27                    | 30   |      |               |               |

|                      |                      | $V_{PVDD}$ 立ち上がり、 $PVDD\_OV\_LVL = 01b$           | 33                    | 36   |      |               |               |

|                      |                      | $V_{PVDD}$ 立ち下がり、 $PVDD\_OV\_LVL = 01b$           | 32                    | 35   |      |               |               |

|                      |                      | $V_{PVDD}$ 立ち上がり、 $PVDD\_OV\_LVL = 10b$           | 50                    | 55   |      |               |               |

|                      |                      | $V_{PVDD}$ 立ち下がり、 $PVDD\_OV\_LVL = 10b$           | 47                    | 52   |      |               |               |

| $V_{PVDD\_OV\_HYS}$  | PVDD 過電圧ヒステリシス       | 立ち上がりから立ち下がりまでのスレッショルド $PVDD\_OV\_LVL = 00b, 01b$ | 0.6                   | 0.9  | 1.2  | V             |               |

| $V_{PVDD\_OV\_HYS}$  | PVDD 過電圧ヒステリシス       | 立ち上がりから立ち下がりまでのスレッショルド $PVDD\_OV\_LVL = 10b$      | 2.0                   | 2.2  | 2.4  | V             |               |

| $t_{PVDD\_OV\_DG}$   | PVDD 過電圧グリッヂ除去時間     | 立ち上がりエッジと立ち下がりエッジ                                 | 8                     | 12   | 16   | $\mu\text{s}$ |               |

| $V_{GVDD\_UV}$       | GVDD 低電圧スレッショルド      | $V_{GVDD}$ 立ち上がり - 電源投入後                          | 7.0                   | 7.8  |      | V             |               |

|                      |                      | $V_{GVDD}$ 立ち上がり - 電源投入時のみ                        | 7.5                   | 8.1  |      | V             |               |

|                      |                      | $V_{GVDD}$ 立ち下がり                                  | 6.8                   | 7.6  |      | V             |               |

| $V_{GVDD\_UV\_HYS}$  | GVDD 低電圧ヒステリシス       | 立ち上がりから立ち下がりへのスレッショルド                             | 185                   | 215  | 245  | mV            |               |

| $t_{GVDD\_UV\_DG}$   | GVDD 低電圧グリッヂ除去時間     | 立ち上がりエッジと立ち下がりエッジ                                 | 8                     | 12   | 16   | $\mu\text{s}$ |               |

4.5V  $\leq V_{PVDD} \leq 60V$ ,  $-40^{\circ}C \leq T_J \leq$  (特に記述のない限り)

| パラメータ                |                     | テスト条件                                                             | 最小値  | 標準値  | 最大値  | 単位      |

|----------------------|---------------------|-------------------------------------------------------------------|------|------|------|---------|

| $V_{GVDD\_OV}$       | GVDD 過電圧スレッショルド     | $V_{GVDD}$ 立ち上がり                                                  | 15   | 17   |      | V       |

|                      |                     | $V_{GVDD}$ 立ち下がり                                                  | 14.5 | 16.5 |      |         |

| $V_{GVDD\_OV\_HYS}$  | GVDD 過電圧ヒステリシス      | 立ち上がりから立ち下がりへのスレッショルド                                             | 490  | 560  | 630  | mV      |

| $t_{GVDD\_OV\_DG}$   | GVDD 過電圧グリッチ除去時間    | 立ち上がりエッジと立ち下がりエッジ                                                 | 8    | 12   | 16   | $\mu s$ |

| $V_{BST\_UV}$        | ブートストラップ低電圧スレッショルド  | $V_{BSTx}$ - $V_{SHx}$ , $V_{BSTx}$ 立ち上がり、<br>$BST\_UV\_LVL = 1b$ | 6.3  | 7.4  | 8.5  | V       |

|                      |                     | $V_{BSTx}$ - $V_{SHx}$ , $V_{BSTx}$ 立ち下がり、<br>$BST\_UV\_LVL = 1b$ | 6.1  | 7.2  | 8.3  |         |

| $V_{BST\_UV}$        | ブートストラップ低電圧スレッショルド  | $V_{BSTx}$ - $V_{SHx}$ , $V_{BSTx}$ 立ち上がり、<br>$BST\_UV\_LVL = 0b$ | 3.8  | 4.4  | 5    | V       |

|                      |                     | $V_{BSTx}$ - $V_{SHx}$ , $V_{BSTx}$ 立ち下がり、<br>$BST\_UV\_LVL = 0b$ | 3.60 | 4.2  | 4.8  | V       |

| $V_{BST\_UV\_HYS}$   | ブートストラップ低電圧ヒステリシス   | 立ち上がりから立ち下がりまでのスレッショルド<br>$BST\_UV\_LVL = 0b$ および $1b$            | 120  | 200  | 280  | mV      |

| $t_{BST\_UV\_DG}$    | ブートストラップ低電圧グリッチ除去時間 | 立ち上がりエッジと立ち下がりエッジ                                                 | 4    | 6    | 8    | $\mu s$ |

| $V_{BST\_OV}$        | ブートストラップ過電圧スレッショルド  | $V_{BSTx} - V_{SHx}$ , $V_{BSTx}$ の立ち上がり                          | 15.2 | 18   |      | V       |

|                      |                     | $V_{BSTx} - V_{SHx}$ , $V_{BSTx}$ の立ち下がり                          | 15   | 17.8 |      |         |

| $V_{BST\_OV\_HYs}$   | ブートストラップ過電圧ヒステリシス   |                                                                   | 110  | 200  | 260  | mV      |

| $t_{BST\_OV\_DG}$    | ブートストラップ過電圧グリッチ除去時間 | 立ち上がりエッジと立ち下がりエッジ                                                 | 8    | 12   | 16   | $\mu s$ |

| $V_{CP\_UV}$         | VCP 低電圧スレッショルド      | VCP - VDRAIN、立ち上がり                                                | 6    | 6.7  | 7.36 | V       |

|                      |                     | VCP - VDRAIN、立ち下がり                                                | 5.9  | 6.6  | 7.25 |         |

| $t_{CP\_UV\_DG}$     | VCP 低電圧グリッチ除去時間     | 立ち上がりエッジと立ち下がりエッジ                                                 | 8    | 12   | 16   | $\mu s$ |

| $V_{CP\_OV}$         | VCP 過電圧スレッショルド      | VCP - VDRAIN、立ち上がり                                                | 14.1 | 17.1 |      | V       |

|                      |                     | VCP - VDRAIN、立ち下がり                                                | 13.8 | 16.7 |      |         |

| $t_{CP\_OV\_DG}$     | VCP 過電圧グリッチ除去時間     | 立ち上がりエッジと立ち下がりエッジ                                                 | 8    | 12   | 16   | $\mu s$ |

| $V_{DRAIN\_UV}$      | VDRAIN 低電圧スレッショルド   | $V_{DRAIN}$ 立ち上がり                                                 | 4.25 | 4.35 | 4.45 | V       |

| $V_{DRAIN\_UV}$      | VDRAIN 低電圧スレッショルド   | $V_{DRAIN}$ 立ち下がり                                                 | 4.05 | 4.15 | 4.25 | V       |

| $V_{DRAIN\_UV\_HYS}$ | VDRAIN 低電圧ヒステリシス    |                                                                   | 160  | 190  | 210  | mV      |

| $t_{DRAIN\_UV\_DG}$  | VDRAIN 低電圧グリッチ除去時間  | 立ち上がりエッジと立ち下がりエッジ                                                 | 8    | 12   | 16   | $\mu s$ |

| $V_{DRAIN\_OV}$      | VDRAIN 過電圧スレッショルド   | $V_{DRAIN}$ 立ち上がり, $V_{DRAIN\_OV\_LVL} = 00b$                     | 28   | 31   |      | V       |

|                      |                     | $V_{DRAIN}$ 立ち下がり, $V_{DRAIN\_OV\_LVL} = 00b$                     | 27   | 30   |      | V       |

|                      |                     | $V_{DRAIN}$ 立ち上がり, $V_{DRAIN\_OV\_LVL} = 01b$                     | 33   | 36   |      | V       |

|                      |                     | $V_{DRAIN}$ 立ち下がり, $V_{DRAIN\_OV\_LVL} = 01b$                     | 32   | 35   |      | V       |

|                      |                     | $V_{DRAIN}$ 立ち上がり, $V_{DRAIN\_OV\_LVL} = 10b, 11b$                | 50   | 55   |      | V       |

|                      |                     | $V_{DRAIN}$ 立ち下がり, $V_{DRAIN\_OV\_LVL} = 10b, 11b$                | 48   | 353  |      | V       |

| $V_{DRAIN\_OV\_HYS}$ | VDRAIN 過電圧ヒステリシス    | 立ち上がりから立ち下がりまでのスレッショルド, $V_{DRAIN\_OV\_LVL} = 00b, 01b$           | 0.7  | 1.0  | 1.3  | V       |

4.5V  $\leq$  V<sub>PVDD</sub>  $\leq$  60V,  $-40^{\circ}\text{C} \leq T_J \leq$  (特に記述のない限り)

| パラメータ                         |                              | テスト条件                                                                                                                | 最小値   | 標準値  | 最大値   | 単位 |

|-------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------|-------|------|-------|----|

| V <sub>DRAIN_OV_H</sub><br>YS | VDRAIN 過電圧ヒステリシス             | 立ち上がりから立ち下がりまでのスレッショルド、V <sub>DRAIN_OV_LVL</sub> = 10b、11b                                                           | 1.9   | 2.3  | 2.6   | V  |

| t <sub>VDRAIN_OV_DG</sub>     | VDRAIN 過電圧グリッチ除去時間           | 立ち上がりエッジと立ち下がりエッジ                                                                                                    | 8     | 12   | 16    | μs |

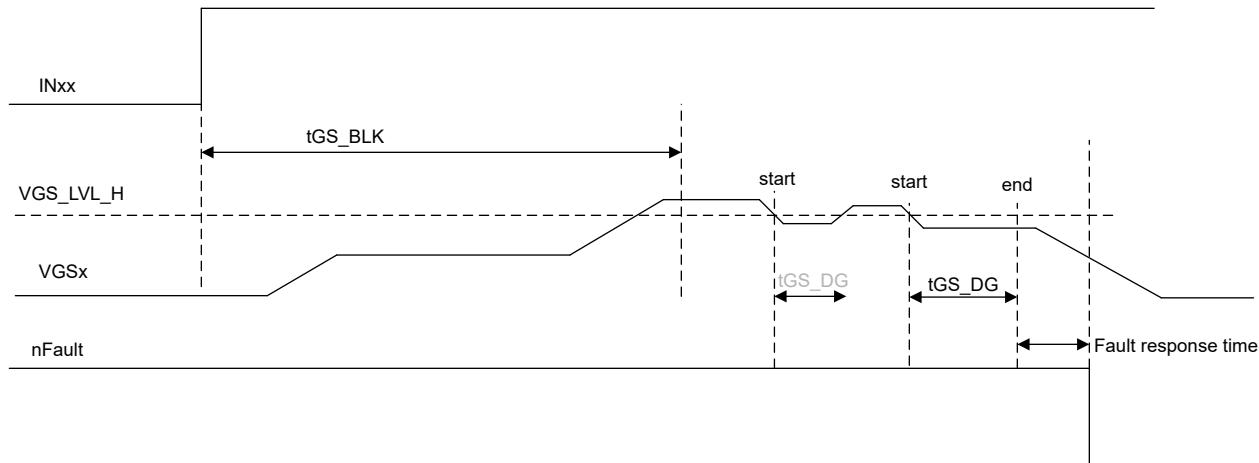

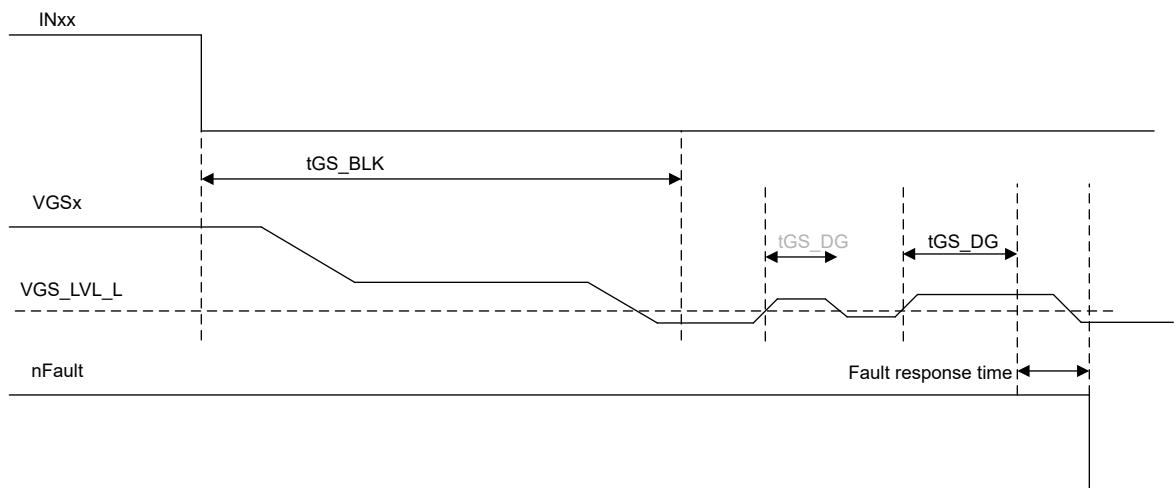

| 保護回路                          |                              |                                                                                                                      |       |      |       |    |

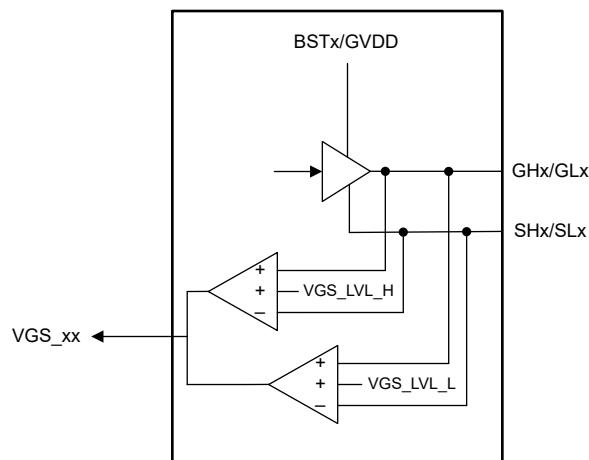

| V <sub>GS_LVL_H</sub>         | ゲート電圧監視スレッショルド               | V <sub>GHx</sub> – V <sub>SHx</sub> 、V <sub>GLx</sub> – V <sub>SLx</sub> 、INLx/<br>INHx=H、V <sub>GS_LVL</sub> = 1'b1 | 6.9   |      | 8.5   | V  |

| V <sub>GS_LVL_H</sub>         | ゲート電圧監視スレッショルド               | V <sub>GHx</sub> – V <sub>SHx</sub> 、V <sub>GLx</sub> – V <sub>SLx</sub> 、INLx/<br>INHx=H、V <sub>GS_LVL</sub> = 1'b0 | 5     |      | 6.3   | V  |

| V <sub>GS_LVL_L</sub>         | ゲート電圧監視スレッショルド               | V <sub>GHx</sub> – V <sub>SHx</sub> 、V <sub>GLx</sub> – V <sub>SLx</sub> 、INLx/INHx=L                                |       | 1.3  | 2     | V  |

| t <sub>GS_DG</sub>            | VGS ゲート電圧監視グリッチ除去時間          | V <sub>GS_DG</sub> = 000b                                                                                            | 0.3   | 0.6  | 0.8   | μs |

|                               |                              | V <sub>GS_DG</sub> = 001b                                                                                            | 0.6   | 1.0  | 1.3   | μs |

|                               |                              | V <sub>GS_DG</sub> = 010b                                                                                            | 1.1   | 1.5  | 1.9   | μs |

|                               |                              | V <sub>GS_DG</sub> = 011b, V <sub>GS_DG</sub> = 1xxb                                                                 | 1.6   | 2.0  | 2.5   | μs |

| t <sub>GS_BLK</sub>           | VGS ゲート電圧監視ブランкиング時間         | V <sub>GS_BLK</sub> = 000b                                                                                           | 1.7   | 2.25 | 2.9   | μs |

|                               |                              | V <sub>GS_BLK</sub> = 001b                                                                                           | 2.4   | 3    | 3.6   | μs |

|                               |                              | V <sub>GS_BLK</sub> = 010b                                                                                           | 4.0   | 5    | 5.8   | μs |

|                               |                              | V <sub>GS_BLK</sub> = 011b                                                                                           | 5.9   | 7    | 8.2   | μs |

|                               |                              | V <sub>GS_BLK</sub> = 100b, 101b, 110b, 111b                                                                         | 8.6   | 10   | 11.9  | μs |

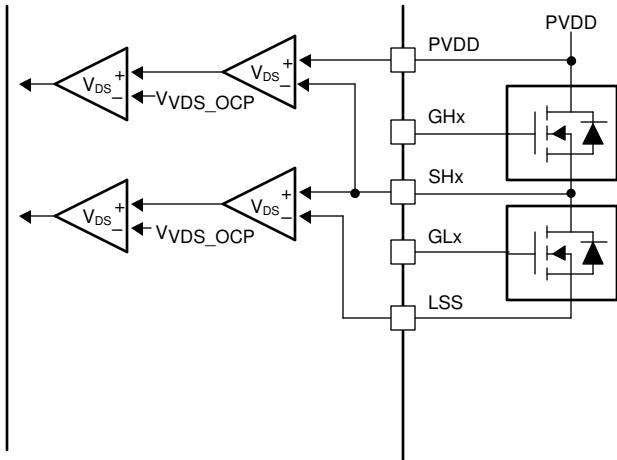

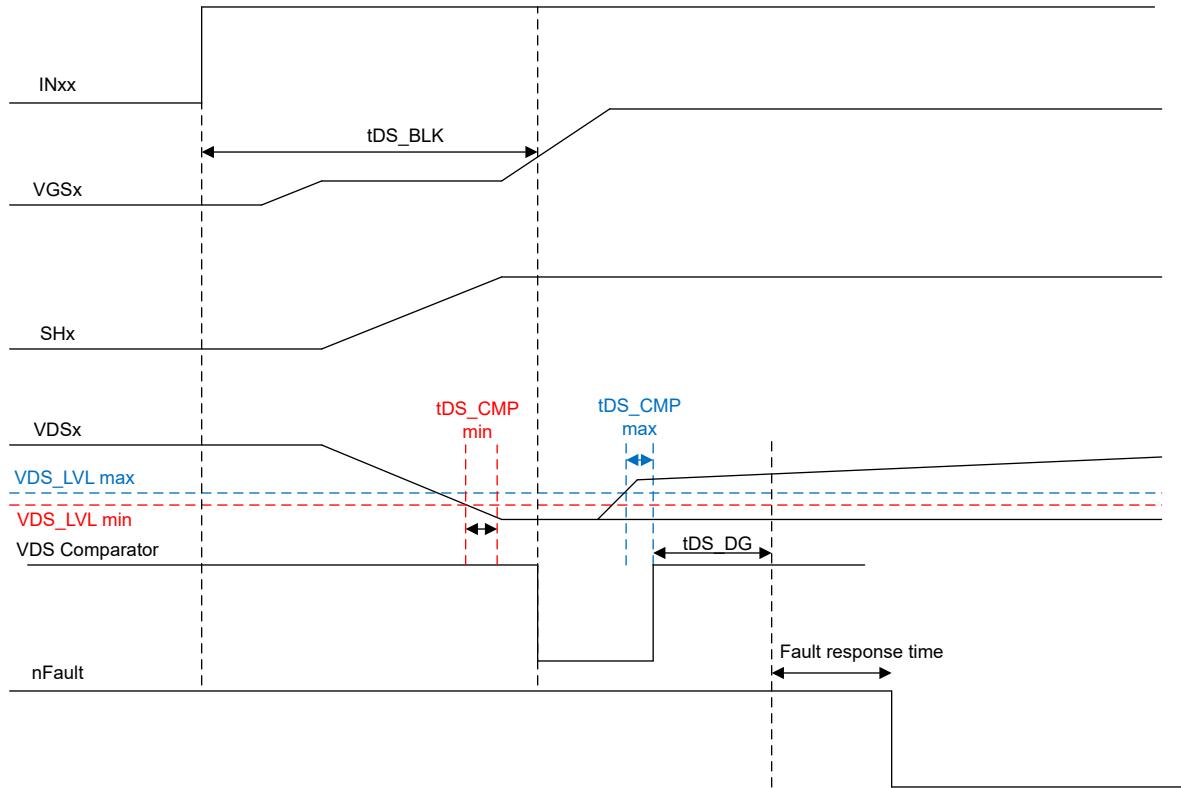

| V <sub>DS_LVL</sub>           | V <sub>DS</sub> 過電流保護スレッショルド | V <sub>DS_LVL</sub> = 0000b, SLx = -0.2V ~<br>+2.0V. V <sub>DS_CM</sub> = 0b                                         | 0.036 | 0.06 | 0.085 | V  |