**DRV8329**

# DRV8329 4.5~60V 三相 BLDC ゲート・ドライバ

## 1 特長

- **65V** 三相ハーフブリッジ・ゲート・ドライバ

- 3 つのハイサイドおよび 3 つのローサイドの N チャ ネル MOSFET (NMOS) を駆動

- 4.5~60V の動作電圧範囲

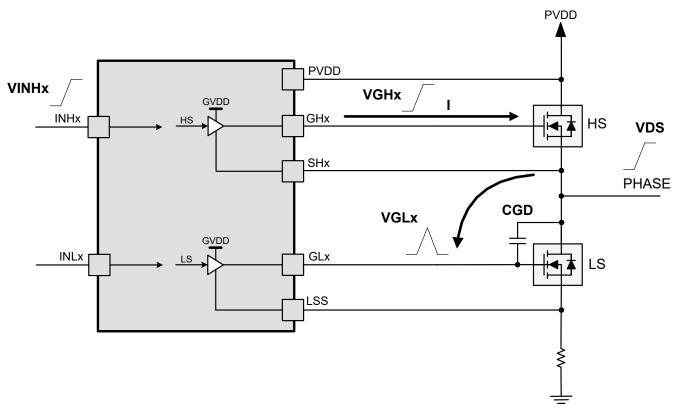

- トリクル・チャージ・ポンプにより 100% の PWM デ ューティ・サイクルをサポート

- ブートストラップ・ベースのゲート・ドライバ・アーキテク チャ

- 最大ピーク・ソース電流:1000mA

- 最大ピーク・シンク電流:2000mA

- 低入力オフセット (1 シャント用に最適化) の電流セン ス・アンプを内蔵

- 可変ゲイン (5、10、20、40V/V)

- ハードウェア・インターフェイスにより構成が容易

- 超低消費電力スリープ・モード:25℃で 1µA 未満

- 複数の相間で 4ns (標準値) の伝搬遅延マッチング

- 独立したドライバ・シャットダウン・パス (DRVOFF)

- 65V 許容のウェイク・ピン (nSLEEP)

- SHx で -10V までの負の過渡電圧をサポート

- 6x および 3x PWM モード

- 3.3V と 5V のロジック入力電圧をサポート

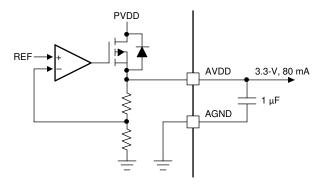

- 高精度 LDO (AVDD)、3.3V ±3%、80mA

- 小型で占有面積の小さい QFN パッケージ

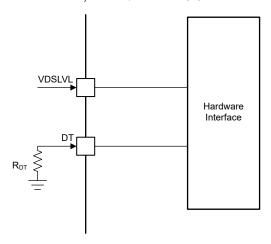

- VDSLVL ピンにより VDS 過電流スレッショルドを調整 可能

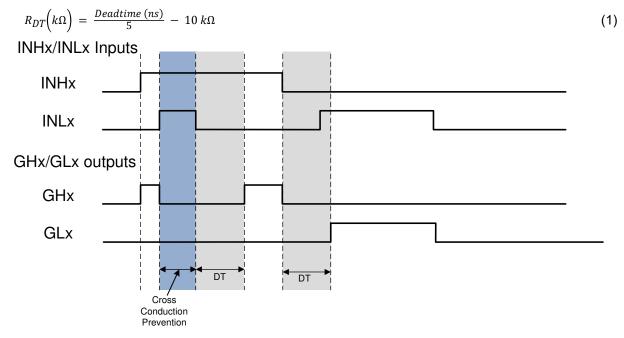

- DT ピンによりデッドタイムを調整可能

- パワー・ブロックによる効率的なシステム設計

- 内蔵保護機能

- PVDD 低電圧誤動作防止 (PVDDUV)

- GVDD 低電圧 (GVDDUV)

- ブートストラップ低電圧 (BST UV)

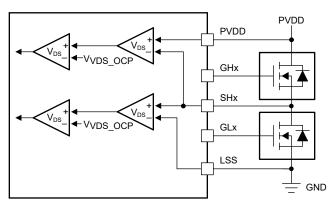

- 過電流保護 (VDS OCP、SEN OCP)

- サーマル・シャットダウン (OTSD)

- フォルト状態インジケータ (nFAULT)

# 2 アプリケーション

- ブラシレス DC (BLDC) モーター・モジュールおよび **PMSM**

- コードレスの庭園機器および電動工具、芝刈り機

- 家電製品のファンおよびポンプ

- サーボ・ドライブ

- 電動アシスト自転車、電動スクーター、E-モビリティ

- コードレス掃除機

- ・ドローン

- 産業用および物流用ロボット、ラジコン玩具

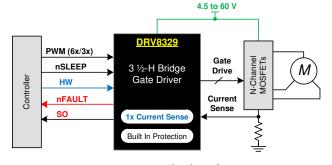

## 3 概要

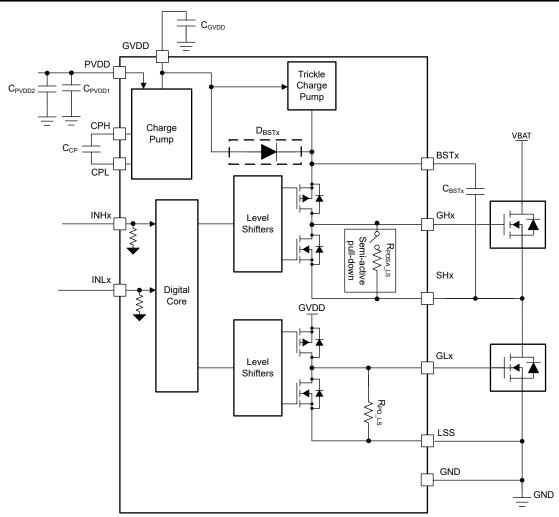

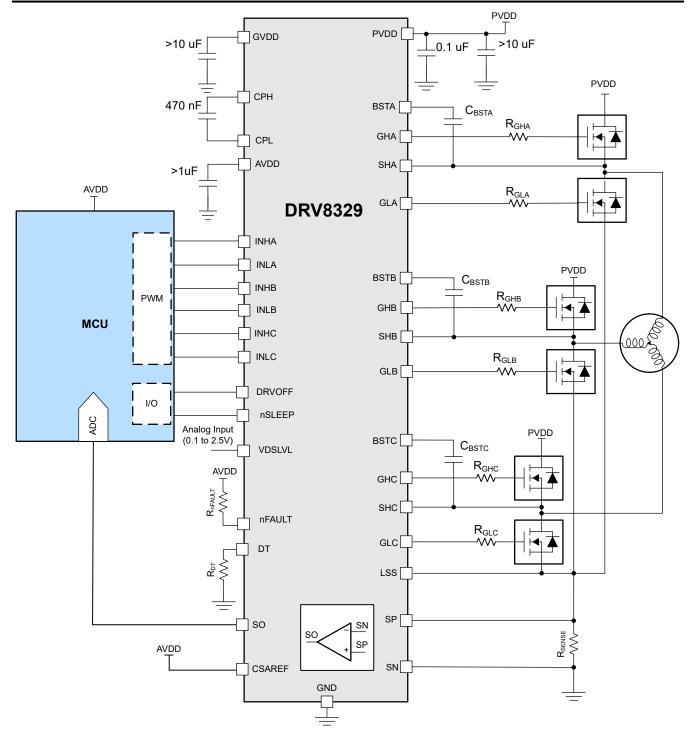

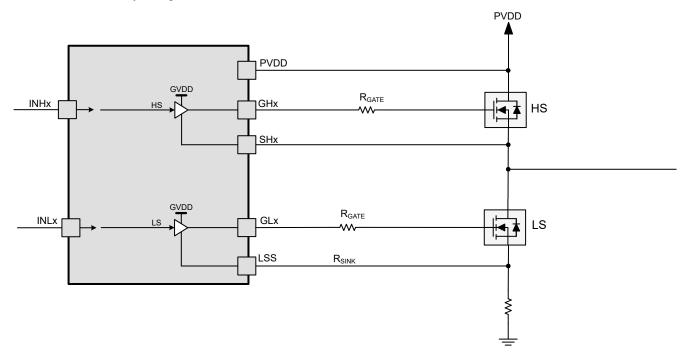

**DRV8329** ファミリのデバイスは、三相アプリケーション用 の統合ゲートドライバです。このデバイスには、3 つのハ ーフ ブリッジ ゲート ドライバがあり、それぞれがハイサイド とローサイドの N チャネル パワー MOSFET を駆動できま す。このデバイスは、内部のチャージポンプを使用して適 切なゲート駆動電圧を生成し、ブートストラップ回路を使用 してハイサイド MOSFET をオンさせます。 100% デューテ ィ サイクルをサポートするためにトリクル チャージ ポンプ を備えています。このゲートドライブのアーキテクチャは、 最大でソース 1A、シンク 2A のピーク ゲート駆動電流を サポートします。DRV8329 は、単一電源で動作可能であ り、4.5V~60Vの広い入力電源電圧範囲に対応します。

6x および 3x PWM モードにより、コントローラ回路と簡単 に接続できます。このデバイスには正確な 3.3V LDO が 内蔵されています。この LDO は外部コントローラへの電 力供給に使用でき、CSA のリファレンス電圧として使用で きます。デバイスの構成設定は、ハードウェア (H/W) ピン により変更可能です。

DRV8329 デバイスにはローサイド電流センス アンプが内 蔵されており、駆動段の3相すべてからの電流の合計を 電流センシングできます。

低消費電力のスリープ モードがあり、内部回路のほとんど をシャットダウンして静止電流を低減できます。低電圧誤 動作防止、GVDD フォルト、MOSFET 過電流、MOSFET 短絡、過熱に対する保護機能が内蔵されています。フォ ルト状態は、nFAULTピンにより通知されます。

#### 製品情報(1)

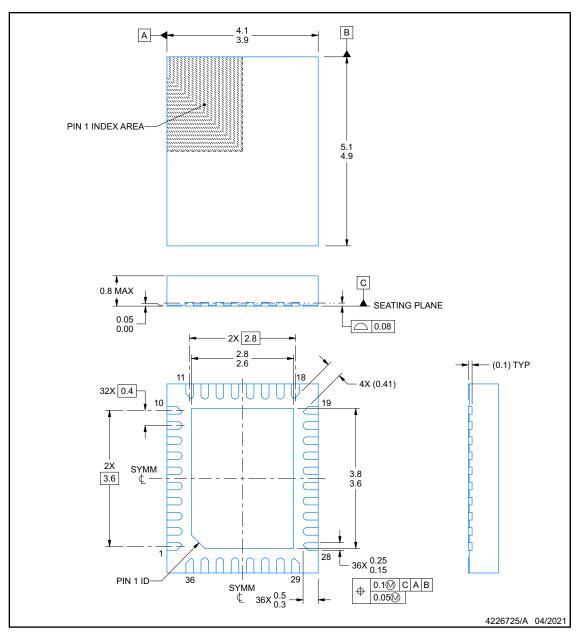

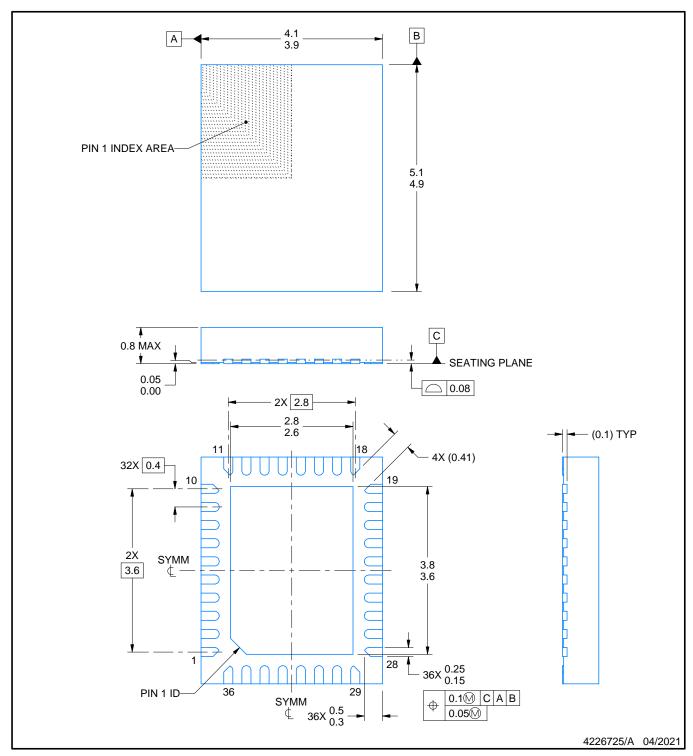

| 部品番号        | パッケージ     | 本体サイズ (公称)      |

|-------------|-----------|-----------------|

| DRV8329AREE | VQFN (36) | 5.00mm × 4.00mm |

| DRV8329BREE | VQFN (36) | 5.00mm × 4.00mm |

利用可能なすべてのパッケージについては、データシートの末尾 にある注文情報を参照してください。

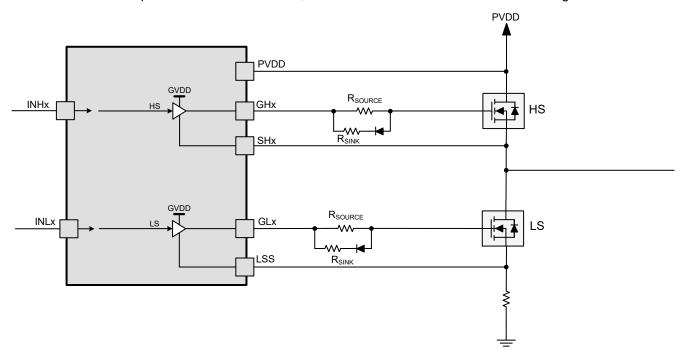

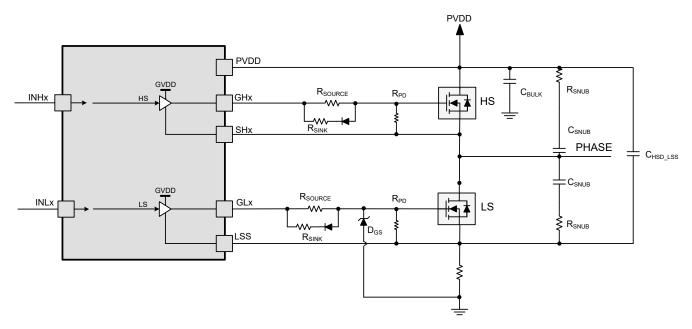

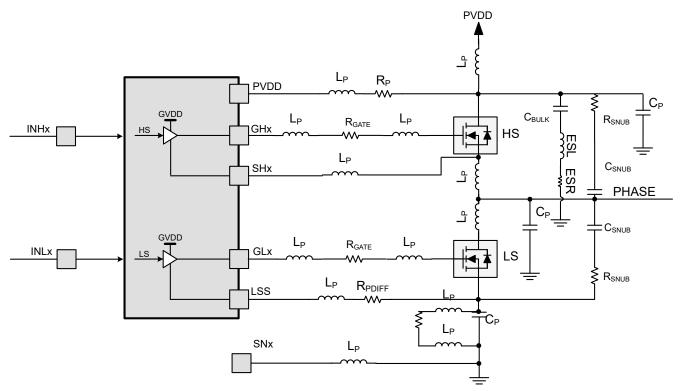

DRV8329 の概略回路図

# **Table of Contents**

| . #4 ==                              |                                       |

|--------------------------------------|---------------------------------------|

| 1 特長                                 |                                       |

| 2 アプリケーション                           | · · · · · · · · · · · · · · · · · · · |

| 3 概要                                 |                                       |

| 4 Device Comparison Table            |                                       |

| 5 Pin Configuration and Functions    |                                       |

| 6 Specification                      | (                                     |

| 6.1 Absolute Maximum Ratings         |                                       |

| 6.2 ESD Ratings Auto                 | 6                                     |

| 6.3 Recommended Operating Conditions |                                       |

| 6.4 Thermal Information 2pkg         |                                       |

| 6.5 Electrical Characteristics       |                                       |

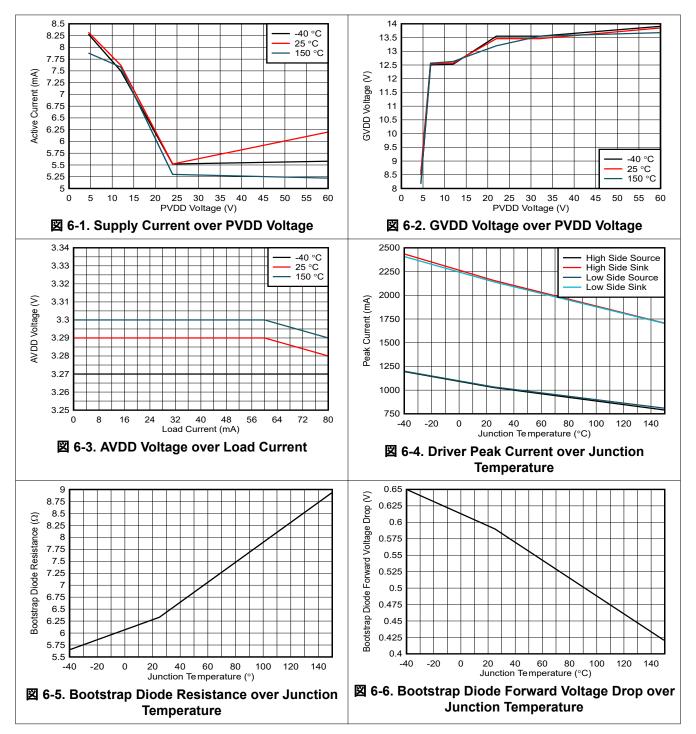

| 6.6 Typical Characteristics          | 1                                     |

| 7 Detailed Description               | 16                                    |

| 7.1 Overview                         | 10                                    |

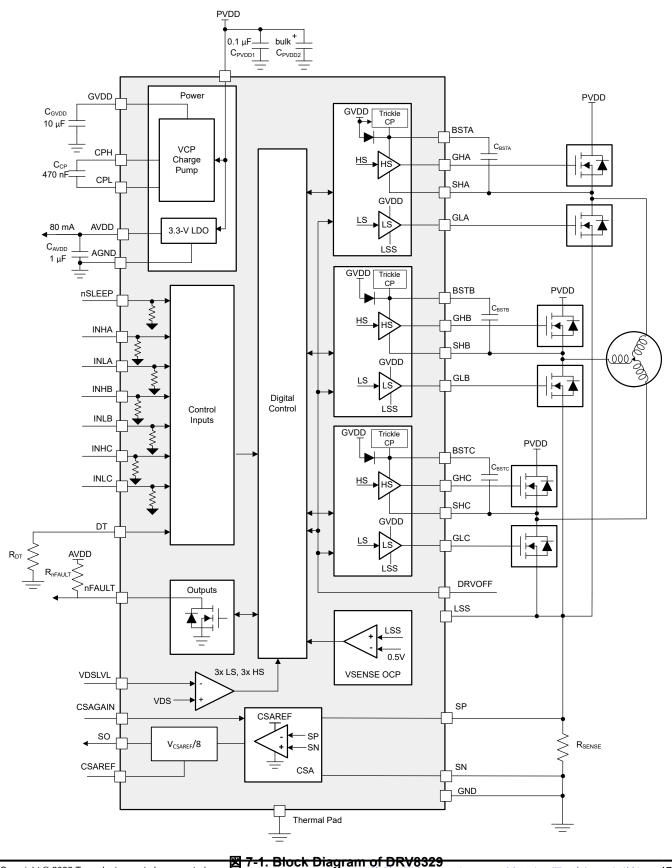

| 7.2 Functional Block Diagram         |                                       |

| 7.3 Feature Description              | 18                                    |

| 7.4 Device Functional Modes          |                                       |

| o Application and implementation                    | 29   |

|-----------------------------------------------------|------|

| 8.1 Application Information                         | . 29 |

| 8.2 Typical Application                             |      |

| 8.3 Power Supply Recommendations                    |      |

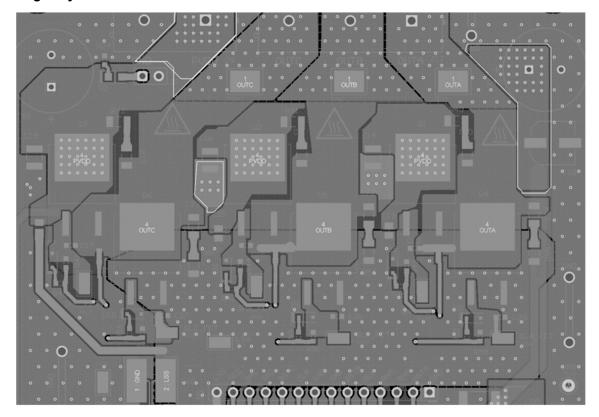

| 8.4 Layout                                          | . 44 |

| 9 Device and Documentation Support                  |      |

| 9.1 Device Support                                  | . 48 |

| 9.2 Documentation Support                           | . 48 |

| 9.3 Related Links                                   | . 48 |

| 9.4 Receiving Notification of Documentation Updates | 48   |

| 9.5 Community Resources                             | 48   |

| 9.6 Trademarks                                      | 48   |

| 10 Revision History                                 | . 48 |

| 11 Mechanical, Packaging, and Orderable             |      |

| Information                                         | . 48 |

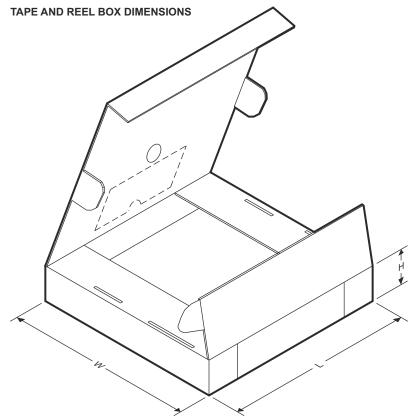

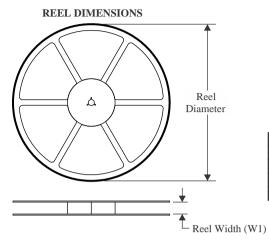

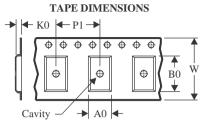

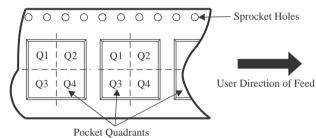

| 11.1 Tape and Reel Information                      |      |

| · · · · · · · · · · · · · · · · · · ·               |      |

# **4 Device Comparison Table**

## 表 4-1. Different Device Variants

| DEVICE  | DEVICE VARIANT | Package             | LDO output | DT pin and VDSLVL | PWM_MODE |

|---------|----------------|---------------------|------------|-------------------|----------|

| DRV8329 | DRV8329A       | 36-pin QFN          | 33\/       | Available         | 6x       |

|         | DRV8329B       | (5.00 mm x 4.00 mm) | 3.3 V      | Available         | 3x       |

3

English Data Sheet: SLVSGX4

# **5 Pin Configuration and Functions**

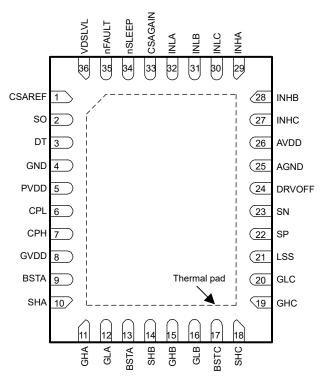

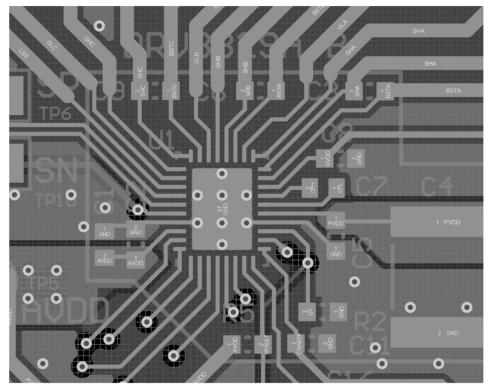

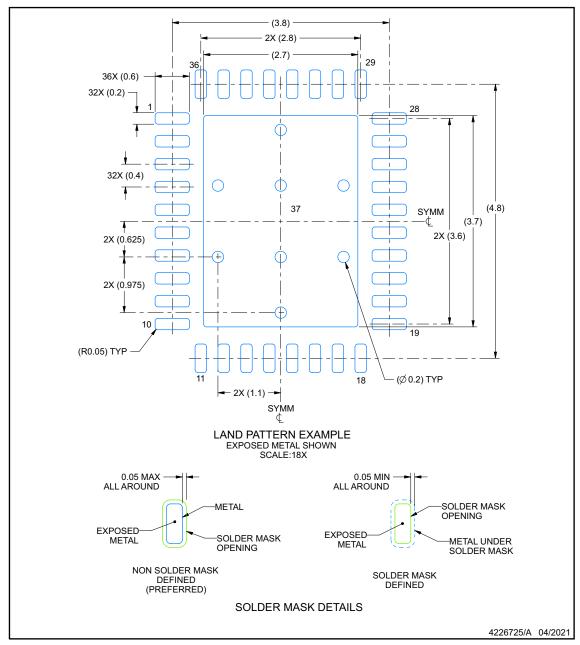

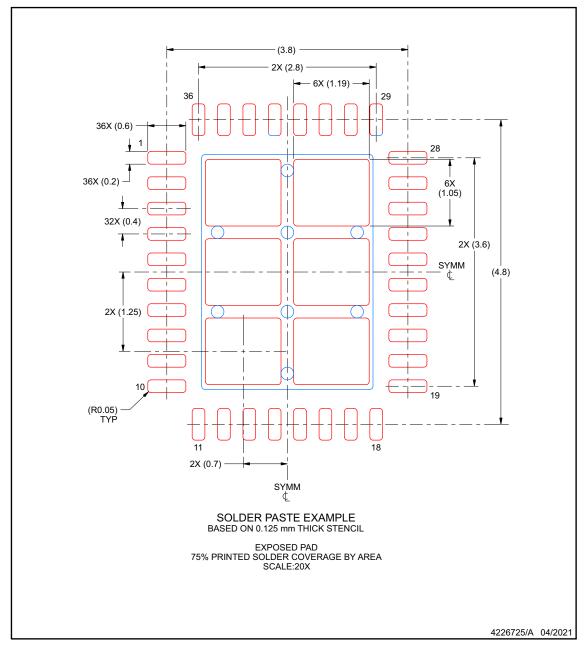

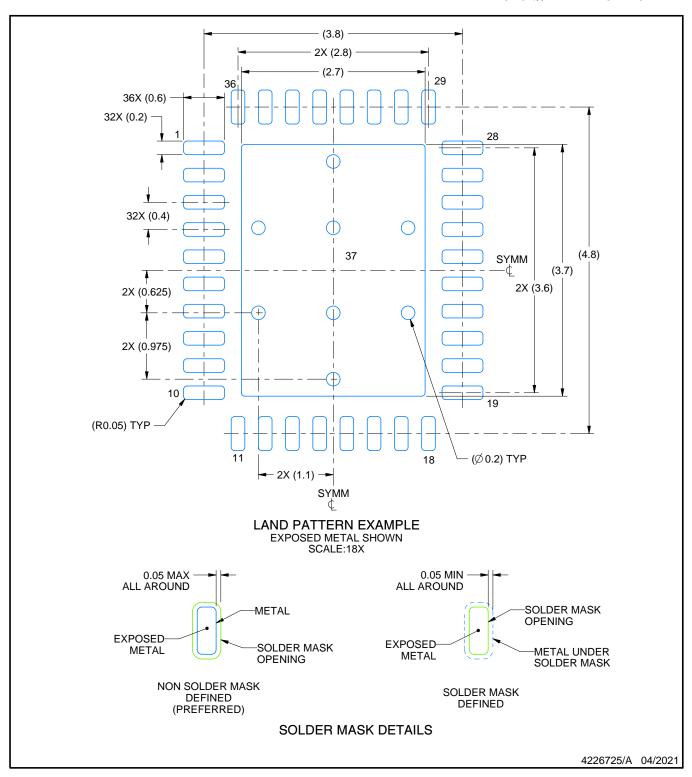

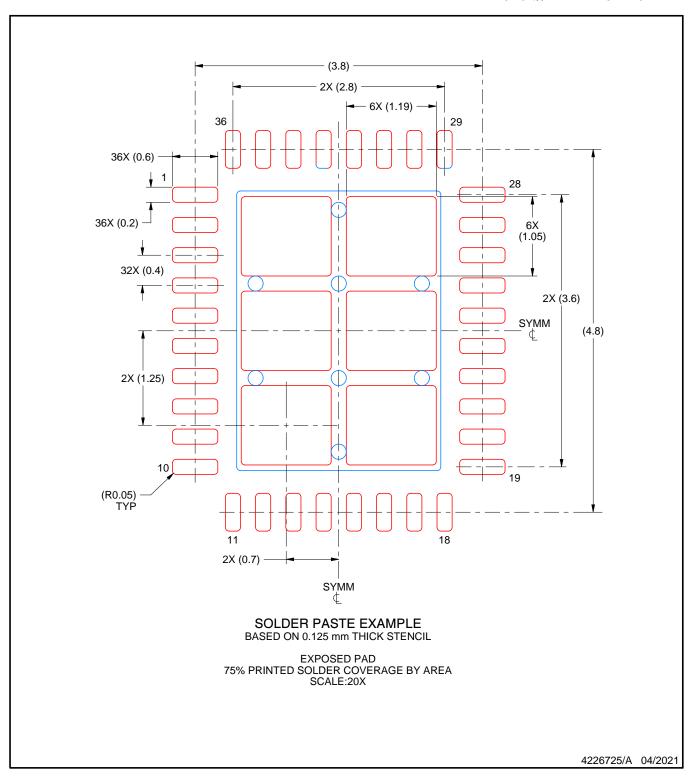

図 5-1. DRV8329 REE Package 36-pin VQFN With Exposed Thermal Pad Top View

表 5-1. Pin Functions—36-Pin DRV8329 Devices

| NAME    | PIN NO. | TVDE  | DECORIDATION                                                                                                                                                                                                                                                         |

|---------|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | DRV8329 | TYPE  | DESCRIPTION                                                                                                                                                                                                                                                          |

| AGND    | 25      | PWR   | Device analog ground. Refer for the recommendation on connection.                                                                                                                                                                                                    |

| AVDD    | 26      | PWR-O | 3.3-V regulator output. Connect a X5R or X7R, 1- $\mu$ F, >6.3-V ceramic capacitor between the AVDD and GND pins. This regulator can source up to 80 mA externally. TI recommends a capacitor voltage rating at least twice the normal operating voltage of the pin. |

| BSTA    | 9       | 0     | Bootstrap output pin. Connect a X5R or X7R, 1-μF, 25-V ceramic capacitor between BSTA and SHA                                                                                                                                                                        |

| BSTB    | 13      | 0     | Bootstrap output pin. Connect a X5R or X7R, 1-µF, 25-V ceramic capacitor between BSTB and SHB                                                                                                                                                                        |

| BSTC    | 17      | 0     | Bootstrap output pin. Connect a X5R or X7R, 1-µF, 25-V ceramic capacitor between BSTC and SHC                                                                                                                                                                        |

| CSAGAIN | 33      | I     | Gain settings for Current sense amplifier. The pin is a 4 level input pin set by an external resistor. See for more information.                                                                                                                                     |

| CSAREF  | 1       | I     | Current sense amplifier reference. Connect a X5R or X7R, 0.1-µF, 6.3-V ceramic capacitor between the CSAREF and AGND pins.                                                                                                                                           |

| CPH     | 7       | PWR   | Charge pump switching node. Connect a X5R or X7R, PVDD-rated ceramic capacitor between the                                                                                                                                                                           |

| CPL     | 6       | PWR   | CPH and CPL pins. TI recommends a capacitor voltage rating at least twice the normal operating voltage of the pin.                                                                                                                                                   |

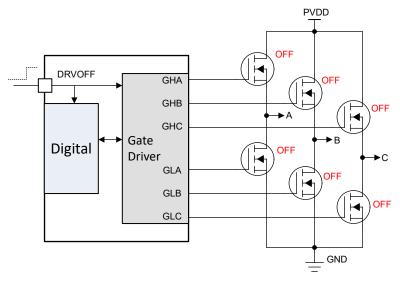

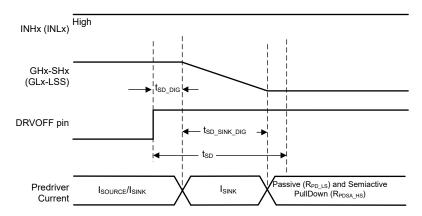

| DRVOFF  | 24      | I     | Independent driver shutdown path. Pulling DRVOFF high turns off all external MOSFETs by putting the gate drivers into the pull-down state. This signal bypasses and overrides the digital core of DRV8329.                                                           |

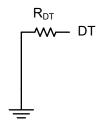

| DT      | 3       | I     | Gate drive deadtime setting. Connect a resistor of value between 10 k $\Omega$ to 390 k $\Omega$ between DT and GND to adjust deadtime between 100 ns to 2000 ns. If pin is left floating or connected to GND fixed value of 55 ns deadtime is inserted.             |

| GHA     | 11      | 0     | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                                                                                                                     |

| GHB     | 15      | 0     | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                                                                                                                     |

| GHC     | 19      | 0     | High-side gate driver output. Connect to the gate of the high-side power MOSFET.                                                                                                                                                                                     |

| GLA     | 12      | 0     | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                                                                                                                       |

Copyright © 2025 Texas Instruments Incorporated

1

Product Folder Links: DRV8329

# 表 5-1. Pin Functions—36-Pin DRV8329 Devices (続き)

| NAME       | PIN NO.                                                                                                                                                                               | TVDE  | DECORPTION                                                                                                                                                                                                                                                                            |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME       | DRV8329                                                                                                                                                                               | TYPE  | DESCRIPTION                                                                                                                                                                                                                                                                           |

| GLB        | 16                                                                                                                                                                                    | 0     | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                                                                                                                                        |

| GLC        | 20                                                                                                                                                                                    | 0     | Low-side gate driver output. Connect to the gate of the low-side power MOSFET.                                                                                                                                                                                                        |

| GVDD       | 8                                                                                                                                                                                     | PWR-O | Gate driver power supply output. Connect a X5R or X7R, 30-V rated ceramic ≥ 10-uF local capacitance between the GVDD and GND pins. TI recommends a capacitor value of >10x C <sub>BSTx</sub> and voltage rating at least twice the normal operating voltage of the pin.               |

| GND        | 4                                                                                                                                                                                     | PWR   | Device ground. Refer for the recommendation on connection.                                                                                                                                                                                                                            |

| INHA       | 29                                                                                                                                                                                    | I     | High-side gate driver control input for Phase A. This pin controls the output of the high-side FET.                                                                                                                                                                                   |

| INHB       | 28                                                                                                                                                                                    | Į.    | High-side gate driver control input for Phase B. This pin controls the output of the high-side FET.                                                                                                                                                                                   |

| INHC       | 27                                                                                                                                                                                    | I     | High-side gate driver control input for Phase C. This pin controls the output of the high-side FET.                                                                                                                                                                                   |

| INLA       | 32                                                                                                                                                                                    | I     | Low-side gate driver control input for Phase A. This pin controls the output of the low-side FET.                                                                                                                                                                                     |

| INLB       | 31                                                                                                                                                                                    | I     | Low-side gate driver control input for Phase B. This pin controls the output of the low-side FET.                                                                                                                                                                                     |

| INLC       | 30                                                                                                                                                                                    | I.    | Low-side gate driver control input for Phase C. This pin controls the output of the low-side FET.                                                                                                                                                                                     |

| LSS        | 21                                                                                                                                                                                    | PWR   | Low side source pin, connect all sources of the external low-side MOSFETs here. This pin is the sink path for the low-side gate driver, and serves as an input to monitor the low-side MOSFET VDS voltage and VSEN_OCP voltage.                                                       |

| nFAULT     | 35                                                                                                                                                                                    | OD    | Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pull-up resistor to 3.3V to 5.0V.                                                                                                                                              |

| nSLEEP     | 34                                                                                                                                                                                    | 1     | Sleep mode entry pin. When this pin is pulled logic low the device goes to a low-power sleep mode. An 1 to 1.2-µs low pulse can be used to reset fault conditions without entering sleep mode.                                                                                        |

| PVDD       | 5                                                                                                                                                                                     | PWR   | Gate driver power supply input. Connect to the bridge power supply. Connect a X5R or X7R, 0.1-µF, >2x PVDD-rated ceramic and >10-uF local capacitance between the PVDD and GND pins. TI recommends a capacitor voltage rating at least twice the normal operating voltage of the pin. |

| SHA        | 10                                                                                                                                                                                    | I/O   | High-side source pin. Connect to the high-side power MOSFET source. This pin is an input for the VDS monitor and the output for the high-side gate driver sink.                                                                                                                       |

| SHB        | 14                                                                                                                                                                                    | I/O   | High-side source pin. Connect to the high-side power MOSFET source. This pin is an input for the VDS monitor and the output for the high-side gate driver sink.                                                                                                                       |

| SHC        | 18                                                                                                                                                                                    | I/O   | High-side source pin. Connect to the high-side power MOSFET source. This pin is an input for the VDS monitor and the output for the high-side gate driver sink.                                                                                                                       |

| so         | 2                                                                                                                                                                                     | 0     | Current sense amplifier output. Supports capacitive load or low pass filter (resistor in series and capacitor to GND)                                                                                                                                                                 |

| SP         | 22                                                                                                                                                                                    | 1     | Current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor.                                                                                                                                                               |

| SN         | 23                                                                                                                                                                                    | I     | Current sense amplifier input. Connect to the low-side of the current shunt resistor.                                                                                                                                                                                                 |

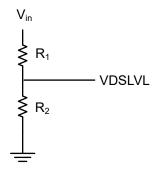

| VDSLVL     | L 36 VDS monitor trip point setting. Connect an analog level input from 0.1 V to 2.5 V to set a VDS r trip point setting for MOSFET overcurrent protection. See for more information. |       | VDS monitor trip point setting. Connect an analog level input from 0.1 V to 2.5 V to set a VDS monitor trip point setting for MOSFET overcurrent protection. See for more information.                                                                                                |

| Thermal Pa | ad                                                                                                                                                                                    | PWR   | Must be connected to GND                                                                                                                                                                                                                                                              |

English Data Sheet: SLVSGX4

# 6 Specification

# **6.1 Absolute Maximum Ratings**

over operating temperature range (unless otherwise noted)(1)

|                                                                 | ,                                      | MIN                   | MAX                       | UNIT |

|-----------------------------------------------------------------|----------------------------------------|-----------------------|---------------------------|------|

| Power supply pin voltage                                        | PVDD                                   | -0.3                  | 65                        | V    |

| Bootstrap pin voltage                                           | BSTx                                   | -0.3                  | 80                        | V    |

| Bootstrap pin voltage                                           | BSTx with respect to SHx               | -0.3                  | 20                        | V    |

| Bootstrap pin voltage                                           | BSTx with respect to GHx               | -0.3                  | 20                        | V    |

| Charge pump pin voltage                                         | CPL, CPH                               | -0.3                  | $V_{GVDD}$                | V    |

| Gate driver regulator pin voltage                               | GVDD                                   | -0.3                  | 20                        | V    |

| Analog regulator pin voltage                                    | AVDD                                   | -0.3                  | 4                         | V    |

| Logic pin voltage (nSLEEP)                                      | nSLEEP                                 | -0.3                  | 65                        | V    |

| Logic pin voltage                                               | DRVOFF, DT, INHx, INLx, nFAULT, VDSLVL | -0.3                  | 6                         | V    |

| High-side gate drive pin voltage                                | GHx                                    | -8                    | 80                        | V    |

| Transient 500-ns high-side gate drive pin voltage               | GHx                                    | -10                   | 80                        | V    |

| High-side gate drive pin voltage                                | GHx with respect to SHx                | -0.3                  | 20                        | V    |

| High-side source pin voltage                                    | SHx                                    | -8                    | 70                        | V    |

| Transient 500-ns high-side source pin voltage                   | SHx                                    | -10                   | 72                        | V    |

| Low-side gate drive pin voltage                                 | GLx with respect to LSS                | -0.3                  | 20                        | V    |

| Transient 500-ns low-side gate drive pin voltage <sup>(2)</sup> | GLx with respect to LSS                | -1                    | 20                        | V    |

| Low-side gate drive pin voltage                                 | GLx with respect to GVDD               |                       | 0.3                       | V    |

| Transient 500-ns low-side gate drive pin voltage                | GLx with respect to GVDD               |                       | 1                         | V    |

| Low-side source sense pin voltage                               | LSS                                    | -1                    | 1                         | V    |

| Transient 500-ns low-side source sense pin voltage              | LSS                                    | -10                   | 8                         | V    |

| Gate drive current                                              | GHx, GLx                               | Internally<br>Limited | Internally<br>Limited     | Α    |

| Current sense amplifer reference input pin voltage              | CSAREF                                 | -0.3                  | 5.5                       | V    |

| Shunt amplifier input pin voltage                               | SN, SP                                 | -1                    | 1                         | V    |

| Transient 500-ns shunt amplifier input pin voltage              | SN, SP                                 | -10                   | 8                         | V    |

| Shunt amplifier output pin voltage                              | so                                     | -0.3                  | V <sub>CSAREF</sub> + 0.3 | V    |

| Junction temperature, T <sub>J</sub>                            |                                        | -40                   | 150                       | °C   |

| Storage temperature, T <sub>stq</sub>                           |                                        | -65                   | 150                       | °C   |

<sup>(1)</sup> Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime

## 6.2 ESD Ratings Auto

|                    |               |                                                                                           |             | VALUE | UNIT |

|--------------------|---------------|-------------------------------------------------------------------------------------------|-------------|-------|------|

|                    | Electrostatic | Human body model (HBM), per AEC Q100-002 <sup>(1)</sup><br>HBM ESD Classification Level 2 |             | ±2000 | .,,  |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per AEC Q100-011                                              | Corner pins | ±750  | V    |

|                    |               | CDM ESD Classification Level C4B                                                          | Other pins  | ±500  |      |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

<u>資料に関するフィードバック (ご意見やお問い合わせ) を送信</u> Copyright © 2025 Texas Instruments Incorporated

<sup>(2)</sup> Supports upto 5A for 500 nS when GLx-LSS is negative

# **6.3 Recommended Operating Conditions**

over operating temperature range (unless otherwise noted)

|                                |                                                                    |                                     | MIN | NOM | MAX                | UNIT |

|--------------------------------|--------------------------------------------------------------------|-------------------------------------|-----|-----|--------------------|------|

| V <sub>PVDD</sub>              | Power supply voltage                                               | PVDD                                | 4.5 |     | 60                 | V    |

| V <sub>PVDD_RAMP</sub>         | Power supply voltage ramp rate at power up                         | PVDD                                |     |     | 30                 | V/us |

| V <sub>PVDD_RAMP</sub>         | Power supply voltage ramp rate during operation                    | PVDD                                |     |     | 4                  | V/us |

| V <sub>BST</sub>               | Bootstrap pin voltage with respect to SHx                          | nSLEEP = High, INHx is switching    | 4   |     | 20                 | V    |

| I <sub>AVDD</sub> (1)          | Regulator external load current                                    | AVDD                                |     |     | 80                 | mA   |

| I <sub>TRICKLE</sub>           | Trickle charge pump external load current                          | BSTx                                |     |     | 2                  | μΑ   |

| V <sub>IN</sub>                | Logic input voltage                                                | DRVOFF, INHx, INLx, nSLEEP          | 0   |     | 5.5                | V    |

| V <sub>IN</sub>                | Logic input voltage                                                | DT, VDSLVL                          | 0   |     | 3.4                | V    |

| f <sub>PWM</sub>               | PWM frequency                                                      | INHx, INLx                          | 0   |     | 200                | kHz  |

| V <sub>OD</sub>                | Open drain pullup voltage                                          | nFAULT                              |     |     | 5.5                | V    |

| I <sub>OD</sub>                | Open drain output current                                          | nFAULT                              |     |     | -10                | mA   |

| I <sub>GS</sub> <sup>(1)</sup> | Total average gate-drive current (Low Side and High Side Combined) | I <sub>GHx</sub> , I <sub>GLx</sub> |     |     | 30                 | mA   |

| V <sub>CSAREF</sub>            | Current sense amplifier reference voltage                          | CSAREF                              | 2.8 |     | 5.5                | V    |

| V <sub>SHSL</sub>              | Slew Rate on SHx pins                                              |                                     |     |     | 4                  | V/ns |

| C <sub>BSTx</sub>              | Capacitor between BSTx and SHx                                     |                                     |     |     | 4.7 <sup>(2)</sup> | μF   |

| C <sub>GVDD</sub>              | Capacitor between GVDD and GND                                     |                                     |     |     | 130                | μF   |

| T <sub>A</sub>                 | Operating ambient temperature                                      |                                     | -40 |     | 125                | °C   |

| T <sub>J</sub>                 | Operating junction temperature                                     |                                     | -40 |     | 150                | °C   |

<sup>(1)</sup> Power dissipation and thermal limits must be observed

# 6.4 Thermal Information 2pkg

|                       |                                              | DEVICE     |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RGF (VQFN) | UNIT |

|                       |                                              | 40         |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 30.6       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 20.1       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 12.0       | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.4        | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 12.0       | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 4.6        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Current flowing through boot diode (DBOOT) needs to be limited for  $C_{BSTx} > 4.7 \mu F$ .

## **6.5 Electrical Characteristics**

$4.5~\text{V} \le \text{V}_{\text{PVDD}} \le 60~\text{V}, -40^{\circ}\text{C} \le \text{T}_{\text{J}} \le 150^{\circ}\text{C}$  (unless otherwise noted). Typical limits apply for  $\text{T}_{\text{A}} = 25^{\circ}\text{C}, \text{V}_{\text{PVDD}} = 24~\text{V}$

|                         | PARAMETER                                               | TEST CONDITIONS                                                                                                                                                                                                                                                                                     | MIN | TYP | MAX | UNIT |

|-------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| POWER SUI               | PPLIES (AVDD, PVDD, GVDD)                               |                                                                                                                                                                                                                                                                                                     |     |     |     |      |

|                         | DVDD days and days and                                  | V <sub>PVDD</sub> =24V, nSLEEP = 0, T <sub>A</sub> = 25°C                                                                                                                                                                                                                                           |     |     | 1   | μA   |

| I <sub>PVDDQ</sub>      | PVDD sleep mode current                                 | nSLEEP = LOW                                                                                                                                                                                                                                                                                        |     |     | 2   | μA   |

|                         | DVDD standbases to                                      | V <sub>PVDD</sub> = 24 V; nSLEEP = HIGH, INHx = INLX = LOW, DRVOFF = HIGH                                                                                                                                                                                                                           |     | 2   | 4   | mA   |

| I <sub>PVDDS</sub>      | PVDD standby mode current                               | nSLEEP = HIGH, INHx = INLX = LOW,<br>DRVOFF = HIGH                                                                                                                                                                                                                                                  |     | 3   | 5.5 | mA   |

|                         |                                                         | V <sub>PVDD</sub> = 24 V, nSLEEP = HIGH, INHx = INLX = Switching@20kHz, No FETs connected                                                                                                                                                                                                           |     | 4   | 7   | mA   |

| I <sub>PVDD</sub>       | PVDD active mode current                                | nSLEEP = HIGH, INHx = INLX =<br>Switching@20kHz, No FETs connected                                                                                                                                                                                                                                  |     | 5   | 10  | mA   |

|                         |                                                         | V <sub>PVDD</sub> = 8 V, nSLEEP = HIGH, INHx = INLX = LOW, No FETs connected                                                                                                                                                                                                                        |     | 5   | 10  | mA   |

|                         |                                                         | V <sub>PVDD</sub> = 24 V, nSLEEP = HIGH, INHx = INLX = LOW, No FETs connected                                                                                                                                                                                                                       |     | 5   | 7   | mA   |

| IL <sub>BSx</sub>       | Bootstrap pin leakage current                           | $V_{BSTx} = V_{SHx} = 60V, V_{GVDD} = 0V,$<br>nSLEEP = LOW                                                                                                                                                                                                                                          | 5   | 10  | 16  | μΑ   |

| IL <sub>BS_TRAN</sub>   | Bootstrap pin active mode transient leakage current     | INLx = INHx = Switching@20kHz, No<br>FETs connected                                                                                                                                                                                                                                                 | 60  | 115 | 300 | μΑ   |

|                         | Bootstrap pin active mode leakage static source current | $\begin{split} & \text{INHx} = \text{HIGH, INLx} = \text{LOW, INLy} = \text{INLz} \\ & = \text{HIGH, nSLEEP} = \text{HIGH,} \\ & \text{V}_{\text{PVDD}} = \text{V}_{\text{SHx}} = \text{V}_{\text{GVDD}} = \text{12V, V}_{\text{BSTx}} \text{-} \\ & \text{V}_{\text{SHx}} = \text{5V} \end{split}$ | 135 | 200 | 280 | μA   |

| IL <sub>BS_DC_SRC</sub> |                                                         | $\begin{split} & \text{INHx} = \text{HIGH, INLx} = \text{LOW, INLy} = \text{INLz} \\ & = \text{HIGH, nSLEEP} = \text{HIGH,} \\ & \text{V}_{\text{PVDD}} = \text{V}_{\text{SHX}} = \text{V}_{\text{GVDD}} = 12\text{V, V}_{\text{BSTx}} - \\ & \text{V}_{\text{SHx}} = 7\text{V} \end{split}$        | 70  | 105 | 145 | μA   |

|                         |                                                         | INHx = LOW, INLx = LOW, INLy = INLz = HIGH, nSLEEP = HIGH, V <sub>PVDD</sub> = V <sub>SHX</sub> = V <sub>GVDD</sub> = 12V, V <sub>BSTx</sub> - V <sub>SHx</sub> = 5V                                                                                                                                | 25  | 50  | 90  | μA   |

|                         |                                                         | $\begin{aligned} &\text{INHx} = \text{LOW, INLx} = \text{LOW, INLy} = \text{INLz} = \\ &\text{HIGH, nSLEEP} = \text{HIGH, V}_{\text{PVDD}} = \text{V}_{\text{SHX}} = \\ &\text{V}_{\text{GVDD}} = \text{12V, V}_{\text{BSTx}} - \text{V}_{\text{SHx}} = \text{7V} \end{aligned}$                    | 16  | 28  | 50  | μA   |

| 11                      | Bootstrap pin active mode leakage static sink current   | $\begin{aligned} & \text{INHx} = \text{LOW, INLx} = \text{LOW, INLy} = \text{INLz} = \\ & \text{HIGH, nSLEEP} = \text{HIGH, V}_{\text{PVDD}} = \text{V}_{\text{SHX}} = \\ & \text{V}_{\text{GVDD}} = 12\text{V, V}_{\text{BSTx}} - \text{V}_{\text{SHx}} = 12\text{V} \end{aligned}$                | 10  | 40  | 90  | μA   |

| ILBS_DC_SINK            |                                                         | $\begin{aligned} & \text{INHx} = \text{High, INLx} = \text{LOW, INLy} = \text{INLz} = \\ & \text{HIGH, nSLEEP} = \text{HIGH, V}_{\text{PVDD}} = \text{V}_{\text{SHX}} = \\ & \text{V}_{\text{GVDD}} = 12\text{V, V}_{\text{BSTx}} - \text{V}_{\text{SHx}} = 12\text{V} \end{aligned}$               | 14  | 45  | 91  | μА   |

|                         |                                                         | $\begin{aligned} & \text{INHx} = \text{INLx} = \text{LOW},  \text{V}_{\text{BSTx}} - \text{V}_{\text{SHx}} = 15, \\ & \text{V}_{\text{SHx}} = 0 \text{ to 60V},  \text{nSLEEP} = \\ & \text{HIGH, DRVOFF} = \text{LOW} \end{aligned}$                                                               | 80  | 145 | 210 | μА   |

|                         | Source pin leakage current                              | $\begin{aligned} & \text{INHx} = \text{INLx} = \text{LOW},  \text{V}_{\text{BSTx}} \text{-V}_{\text{SHx}} = 11, \\ & \text{V}_{\text{SHx}} = 0 \text{ to 60V},  \text{nSLEEP} = \\ & \text{HIGH, DRVOFF} = \text{LOW} \end{aligned}$                                                                | 15  | 20  | 30  | μA   |

| IL <sub>SHx</sub>       | Codice piiriearaye current                              | $\begin{aligned} & \text{INHx} = \text{High, INLx} = \text{LOW, V}_{\text{BSTx}} \text{- V}_{\text{SHx}} \\ & = 15, \text{ V}_{\text{SHx}} = 0 \text{ to 60V, nSLEEP} = \\ & \text{HIGH, DRVOFF} = \text{LOW} \end{aligned}$                                                                        | 80  | 145 | 210 | μА   |

|                         |                                                         | INHx = HIGH, INLx = LOW, V <sub>BSTx</sub> - V <sub>SHx</sub> = 11, V <sub>SHx</sub> = 0 to 60V, nSLEEP = HIGH, DRVOFF = LOW                                                                                                                                                                        | 13  | 25  | 35  | μA   |

4.5 V ≤ V<sub>PVDD</sub> ≤ 60 V, -40°C ≤ T<sub>J</sub> ≤ 150°C (unless otherwise noted). Typical limits apply for T<sub>A</sub> = 25°C, V<sub>PVDD</sub> = 24 V

|                        | PARAMETER                                             | TEST CONDITIONS                                                                                                                | MIN                          | TYP  | MAX      | UNIT     |

|------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|----------|----------|

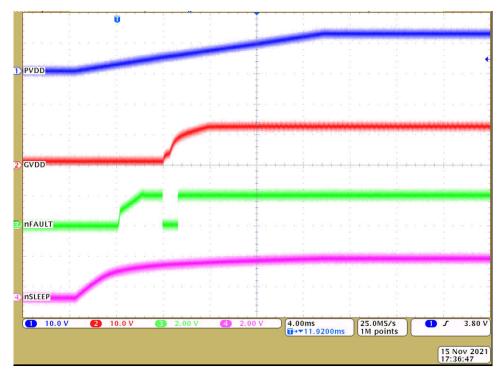

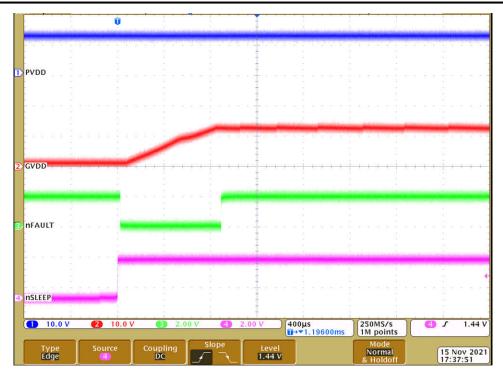

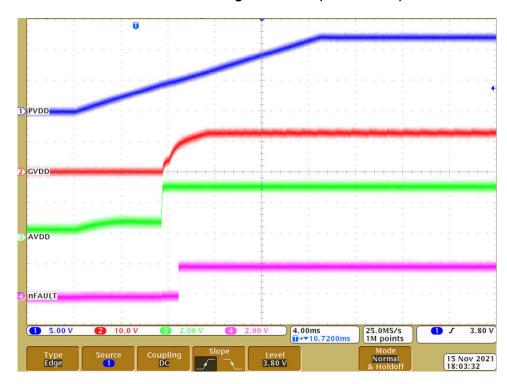

|                        |                                                       | nSLEEP = HIGH to Active mode<br>(Outputs Ready), DRVOFF =<br>LOW, C <sub>GVDD</sub> = 10 uF, C <sub>BSTx</sub> = 1 uF          |                              | 1    | 2        | ms       |

| <sup>t</sup> wake      | Turnon time (nSLEEP)                                  | nSLEEP = High to Active mode (Outputs Ready). C <sub>GVDD</sub> = 100 uF, C <sub>AVDD</sub> = 10 uF, C <sub>BSTx</sub> = 10 uF |                              | 10   | 15       | ms       |

|                        |                                                       | V <sub>PVDD</sub> = 12V, nSLEEP = HIGH to Active mode (Outputs Ready), DRVOFF = LOW, C <sub>GVDD</sub> = 10 uF                 |                              | 1    | 2        | ms       |

|                        | Turnon time (DRVOFF)                                  | DRVOFF = LOW to Active mode (Outputs Ready), nSLEEP = High                                                                     |                              | 0.05 | 0.1      | ms       |

| t <sub>SLEEP</sub>     | Turnoff time                                          | nSLEEP = LOW to Sleep mode                                                                                                     |                              |      | 20       | us       |

| t <sub>RST</sub>       | Minimum Reset Pulse Time                              | nSLEEP = LOW period to reset faults                                                                                            | 1                            |      | 1.2      | us       |

|                        |                                                       | V <sub>PVDD</sub> ≥ 40 V, I <sub>GS</sub> = 10 mA, T <sub>J</sub> = 25°C                                                       | 11.8                         | 13   | 15       | V        |

| V <sub>GVDD_RT</sub>   |                                                       | 22 V ≤V <sub>PVDD</sub> ≤ 40 V, I <sub>GS</sub> = 30 mA, T <sub>J</sub> = 25°C                                                 | 11.8                         | 13   | 15       | V        |

|                        | GVDD Gate driver regulator voltage (Room Temperature) | $8 \text{ V} \leq \text{V}_{\text{PVDD}} \leq 22 \text{ V}, I_{\text{GS}} = 30 \text{ mA}, T_{\text{J}} = 25^{\circ}\text{C}$  | 11.8                         | 13   | 15       | V        |

|                        | (                                                     | $6.75 \text{ V} \le V_{PVDD} \le 8 \text{ V}, I_{GS} = 10 \text{ mA}, T_{J} = 25^{\circ}\text{C}$                              | 11.8                         | 13   | 14.5     | V        |

|                        |                                                       | $4.5 \text{ V} \le \text{V}_{PVDD} \le 6.75 \text{ V}, I_{GS} = 10 \text{ mA}, T_{J} = 25^{\circ}\text{C}$                     | 2*V <sub>PVDD</sub><br>- 1   |      | 13.5     | V        |

|                        | GVDD Gate driver regulator voltage                    | $V_{PVDD} \ge 40 \text{ V}, I_{GS} = 10 \text{ mA}$                                                                            | 11.5                         |      | 15.5     | V        |

|                        |                                                       | 22 V ≤V <sub>PVDD</sub> ≤ 40 V, I <sub>GS</sub> = 30 mA                                                                        | 11.5                         |      | 15.5     | V        |

| $V_{GVDD}$             |                                                       | 8 V ≤V <sub>PVDD</sub> ≤ 22 V; I <sub>GS</sub> = 30 mA                                                                         | 11.5                         |      | 15.5     | V        |

|                        |                                                       | 6.75 V ≤V <sub>PVDD</sub> ≤ 8 V, I <sub>GS</sub> = 10 mA                                                                       | 11.5                         |      | 14.5     | V        |

|                        |                                                       | 4.5 V ≤V <sub>PVDD</sub> ≤ 6.75 V, I <sub>GS</sub> = 10 mA                                                                     | 2*V <sub>PVDD</sub><br>- 1.4 |      | 13.5     | V        |

|                        | AVDD Analog regulator voltage (Room Temperature)      | $V_{PVDD} \ge 6 \text{ V}, 0 \text{ mA} \le I_{AVDD} \le 30 \text{ mA}, T_J = 25^{\circ}\text{C}$                              | 3.26                         | 3.3  | 3.33     | V        |

| $V_{AVDD\_RT}$         |                                                       | $V_{PVDD} \ge 6 \text{ V}$ , 30 mA $\le I_{AVDD} \le 80 \text{ mA}$ , $T_J = 25^{\circ}\text{C}$                               | 3.2                          | 3.3  | 3.4      | V        |

|                        |                                                       | $V_{PVDD} \le 6 \text{ V}, 0 \text{ mA} \le I_{AVDD} \le 50 \text{ mA}, T_J = 25^{\circ}\text{C}$                              | 3.13                         | 3.3  | 3.46     | V        |

| $V_{AVDD}$             | AVDD Analog regulator voltage                         | $V_{PVDD} \ge 6 \text{ V}, 0 \text{ mA} \le I_{AVDD} \le 80 \text{ mA}$                                                        | 3.2                          | 3.3  | 3.4      | V        |

| * AVDD                 | /// DD / malog regulater voltage                      | $V_{PVDD} \le 6 \text{ V}, 0 \text{ mA} \le I_{AVDD} \le 50 \text{ mA}$                                                        | 3.125                        | 3.3  | 3.5      | V        |

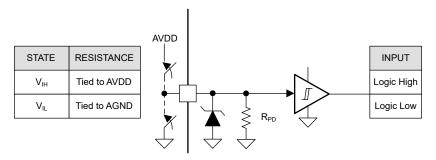

| LOGIC-LEVI             | EL INPUTS (DRVOFF, INHx, INLx, nSLE                   | ,                                                                                                                              |                              |      |          |          |

| V <sub>IL</sub>        | Input logic low voltage                               | DRVOFF                                                                                                                         |                              |      | 0.8      | V        |

|                        |                                                       | INLx, INHx pins                                                                                                                |                              |      | 8.0      | V        |

| V <sub>IH</sub>        | Input logic high voltage                              | DRVOFF                                                                                                                         | 2.2                          |      |          | V        |

|                        |                                                       | INLx, INHx pins                                                                                                                | 2.2                          | 400  | 050      | V        |

| V <sub>HYS</sub>       | Input hysteresis                                      | DRVOFF                                                                                                                         | 200                          | 400  | 650      | mV       |

| <br>I                  | Input logic low current                               | INLx, INHx pins V <sub>PIN</sub> (Pin Voltage) = 0 V;                                                                          | 45<br>-1                     | 240  | 350<br>1 | mV<br>μA |

| l <sub>IL</sub>        | input logic low current                               | nSLEEP, V <sub>PIN</sub> (Pin Voltage) = 65 V;                                                                                 | 3                            | 6.5  | 10       | μA       |

| l <sub>iH</sub>        | Input logic high current                              | nSLEEP, V <sub>PIN</sub> (Pin Voltage) = 5 V;                                                                                  | 3                            | 6    | 10       | μA       |

| ın                     | input logic nigh current                              | Other pins, V <sub>PIN</sub> (Pin Voltage) = 5 V;                                                                              | 7                            | 20   | 35       | μA       |

| R <sub>PD DRVOFF</sub> | Input pulldown resistance                             | DRVOFF To GND                                                                                                                  | 100                          | 200  | 300      | kΩ       |

| R <sub>PD_nSLEEP</sub> | Input pulldown resistance                             | nSLEEP To GND                                                                                                                  | 500                          | 800  | 1500     | kΩ       |

| R <sub>PD</sub>        | Input pulldown resistance                             | All other pins To GND                                                                                                          | 150                          | 250  | 350      | kΩ       |

| ·-Γυ                   |                                                       | p                                                                                                                              | 100                          | _00  | 300      |          |

$4.5~V \le V_{PVDD} \le 60~V, -40^{\circ}C \le T_{J} \le 150^{\circ}C$  (unless otherwise noted). Typical limits apply for  $T_{A} = 25^{\circ}C, V_{PVDD} = 24~V$

|                               | PARAMETER                                                                       | s otherwise noted). Typical limits apply  TEST CONDITIONS                                        | MIN           | TYP            | MAX           | UNIT |

|-------------------------------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------|----------------|---------------|------|

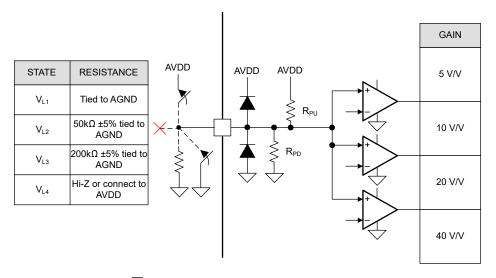

| FOUR-LEVE                     | L INPUTS (GAIN)                                                                 |                                                                                                  |               |                |               |      |

| V <sub>L1</sub>               | Input level 1 voltage                                                           | Tied to GND                                                                                      | 0             |                | 0.18*AV<br>DD | V    |

| V <sub>L2</sub>               | Input level 2 voltage                                                           | 50 kΩ +/- 5% tied to GND                                                                         | 0.48*AV<br>DD | 0.5*AVD<br>D   | 0.52*AV<br>DD | V    |

| V <sub>L3</sub>               | Input level 3 voltage                                                           | 200 kΩ +/- 5% tied to GND                                                                        | 0.82*AV<br>DD | 0.833*AV<br>DD | 0.85*AV<br>DD | V    |

| $V_{L4}$                      | Input level 4 voltage                                                           | HiZ or Connect to AVDD                                                                           |               | AVDD           |               | V    |

| R <sub>PU</sub>               | Input pullup resistance                                                         | GAIN To AVDD                                                                                     | 80            | 100            | 120           | kΩ   |

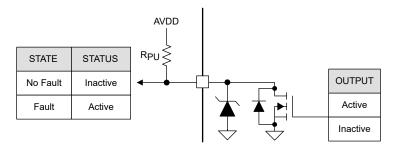

| OPEN-DRAI                     | N OUTPUTS (nFAULT etc)                                                          |                                                                                                  |               |                |               |      |

| V <sub>OL</sub>               | Output logic low voltage                                                        | I <sub>OD</sub> = 5 mA                                                                           |               |                | 0.4           | V    |

| l <sub>OZ</sub>               | Output logic high current                                                       | V <sub>OD</sub> = 5 V                                                                            | -1            |                | 1             | μA   |

| C <sub>OD</sub>               | Output capacitance                                                              | V <sub>OD</sub> = 5 V                                                                            |               |                | 30            | pF   |

| GATE DRIVE                    | ERS (GHx, GLx, SHx, SLx)                                                        |                                                                                                  | ı             |                | 1             |      |

| V <sub>GSHx_LO</sub>          | High-side gate drive low level voltage                                          | I <sub>GLx</sub> = -100 mA; V <sub>GVDD</sub> = 12V; No FETs connected                           | 0.05          | 0.11           | 0.24          | V    |

| V <sub>GSHx_HI</sub>          | High-side gate drive high level voltage (V <sub>BSTx</sub> - V <sub>GHx</sub> ) | I <sub>GHx</sub> = 100 mA; V <sub>GVDD</sub> = 12V; No FETs connected                            | 0.28          | 0.44           | 0.82          | V    |

| V <sub>GSLx_LO</sub>          | Low-side gate drive low level voltage                                           | I <sub>GLx</sub> = -100 mA; V <sub>GVDD</sub> = 12V; No FETs connected                           | 0.05          | 0.11           | 0.27          | V    |

| V <sub>GSLx_HI</sub>          | Low-side gate drive high level voltage (V <sub>GVDD</sub> - V <sub>GHx</sub> )  | I <sub>GHx</sub> = 100 mA; V <sub>GVDD</sub> = 12V; No FETs connected                            | 0.28          | 0.44           | 0.82          | V    |

|                               |                                                                                 | INHx = HIGH, INLx = LOW, INLy = INLz<br>= HIGH, V <sub>PVDD</sub> >15V, V <sub>GVDD</sub> ≥11.5V | 8.4           | 9.6            | 11.1          | V    |

| V <sub>GSH_100_PH</sub>       | High-side gate drive voltage in steady state with 100 % duty cycle (GHx- SHx)   | INHx = HIGH, INLx = LOW, INLy = INLz<br>= HIGH, V <sub>GVDD</sub> ≥11.5V                         | 7.5           | 8.3            | 9             | V    |

|                               |                                                                                 | INHx = HIGH, INLx = LOW, INLy = INLz<br>= HIGH, 7V ≥V <sub>GVDD</sub> ≥ 8V                       | 5.7           | 6.5            | 7.6           | V    |

| R <sub>DS(ON)_PU_</sub><br>HS | High-side pullup switch resistance                                              | I <sub>GHx</sub> = 100 mA; V <sub>GVDD</sub> = 12V                                               | 2.7           | 4.5            | 8.4           | Ω    |

| R <sub>DS(ON)_PD_</sub><br>HS | High-side pulldown switch resistance                                            | I <sub>GHx</sub> = 100 mA; V <sub>GVDD</sub> = 12V                                               | 0.2           | 1.1            | 2.4           | Ω    |

| R <sub>DS(ON)_PU_</sub><br>LS | Low-side pullup switch resistance                                               | I <sub>GLx</sub> = 100 mA; V <sub>GVDD</sub> = 12V                                               | 2.7           | 4.5            | 8.3           | Ω    |

| R <sub>DS(ON)_PD_</sub>       | Low-side pulldown switch resistance                                             | I <sub>GLx</sub> = 100 mA; V <sub>GVDD</sub> = 12V                                               | 0.2           | 1.1            | 2.8           | Ω    |

| I <sub>DRIVEP_HS</sub>        | High-side peak source gate current                                              | V <sub>GSHx</sub> = 12V                                                                          | 550           | 1000           | 1575          | mA   |

| I <sub>DRIVEN_HS</sub>        | High-side peak sink gate current                                                | V <sub>GSHx</sub> = 0V                                                                           | 1150          | 2000           | 2675          | mA   |

| I <sub>DRIVEP_LS</sub>        | Low-side peak source gate current                                               | V <sub>GSLx</sub> = 12V                                                                          | 550           | 1000           | 1575          | mA   |

| I <sub>DRIVEN_LS</sub>        | Low-side peak sink gate current                                                 | V <sub>GSLx</sub> = 0V                                                                           | 1150          | 2000           | 2675          | mA   |

| R <sub>PD_LS</sub>            | Low-side passive pull down                                                      | GLx to LSS                                                                                       | 80            | 100            | 120           | kΩ   |

| R <sub>PDSA_HS</sub>          | High-side semiactive pull down                                                  | GHx to SHx, V <sub>GSHx</sub> = 2V                                                               | 8             | 10             | 12.5          | kΩ   |

| GATE DRIVE                    | ERS TIMINGS                                                                     |                                                                                                  | -             |                |               |      |

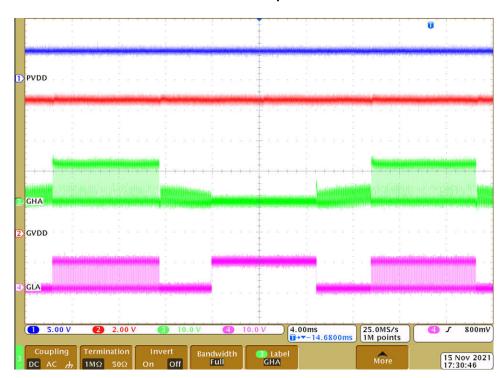

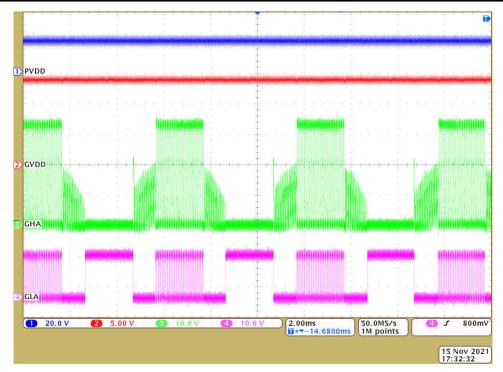

| t <sub>PDR_LS</sub>           | Low-side rising propagation delay                                               | INLx to GLx rising, V <sub>GVDD</sub> > 8V                                                       | 70            | 100            | 145           | ns   |

| t <sub>PDF_LS</sub>           | Low-side falling propagation delay                                              | INLx to GLx falling, V <sub>GVDD</sub> > 8V                                                      | 70            | 100            | 135           | ns   |

| t <sub>PDR_HS</sub>           | High-side rising propagation delay                                              | INHx to GHx rising, $V_{GVDD} = V_{BSTx} - V_{SHx} > 8V$                                         | 65            | 100            | 145           | ns   |

| t <sub>PDF_HS</sub>           | High-side falling propagation delay                                             | INHx to GHx falling, $V_{GVDD} = V_{BSTx} - V_{SHx} > 8V$                                        | 70            | 100            | 140           | ns   |

4.5 V ≤ V<sub>PVDD</sub> ≤ 60 V, −40°C ≤ T<sub>J</sub> ≤ 150°C (unless otherwise noted). Typical limits apply for T<sub>A</sub> = 25°C, V<sub>PVDD</sub> = 24 V

|                                | PARAMETER                                                                         | TEST CONDITIONS                                                                                                                                | MIN   | TYP  | MAX  | UNIT   |

|--------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|--------|

| tpd_match_p                    |                                                                                   | GLx turning ON to GLx turning OFF, $V_{GVDD} = V_{BSTx} - V_{SHx} > 8V$ ; SHx = 0V to 60V, No load on GHx and GLx                              | -25   | ±4   | 25   | ns     |

|                                | Matching propagation delay per phase                                              | GLx turning OFF to GHx turning ON, $V_{GVDD} = V_{BSTx} - V_{SHx} > 8V$ ; SHx = 0V to 60V, No load on GHx and GLx                              | -28   | ±4   | 28   | ns     |

| н                              | matering propagation delay per phase                                              | GHx turning ON to GHx turning OFF, $V_{GVDD} = V_{BSTx} - V_{SHx} > 8V$ ; SHx = 0V to 60V, No load on GHx and GLx                              | -25   | ±4   | 25   | ns     |

|                                |                                                                                   | GHx turning OFF to GLx turning ON, $V_{GVDD} = V_{BSTx} - V_{SHx} > 8V$ ; SHx = 0V to 60V, No load on GHx and GLx                              | -25   | ±4   | 25   | ns     |

|                                |                                                                                   | GHx turning ON to GHy turning ON, $V_{GVDD} = V_{BSTx} - V_{SHx} > 8V$ ; SHx = 0V to 60V, No load on GHx and GLx                               | -10   | ±4   | 10   | ns     |

| t <sub>PD MATCH</sub> P        | Matching propagation delay phase to                                               | GLx turning ON to GLy turning ON,<br>V <sub>GVDD</sub> = V <sub>BSTx</sub> - V <sub>SHx</sub> > 8V; SHx = 0V to<br>60V, No load on GHx and GLx | -10   | ±4   | 10   | ns     |

| H_PH                           | phase                                                                             | GHx turning OFF to GHy turning OFF, $V_{GVDD} = V_{BSTx} - V_{SHx} > 8V$ ; SHx = 0V to 60V, No load on GHx and GLx                             | -15   | ±4   | 15   | ns     |

|                                |                                                                                   | GLx turning OFF to GLy turning OFF, $V_{GVDD} = V_{BSTx} - V_{SHx} > 8V$ ; SHx = 0V to 60V, No load on GHx and GLx                             | -10   | ±4   | 10   | ns     |

| t <sub>PW_MIN</sub>            | Minimum input pulse width on INHx,<br>INLx that changes the output on GHx,<br>GLx |                                                                                                                                                | 18    | 32   | 45   | ns     |

| t <sub>DEAD</sub>              | Gate drive dead time configurable range                                           |                                                                                                                                                | 50    |      | 2000 | ns     |

|                                | Gate drive dead time                                                              | DT pin floating                                                                                                                                | 35    | 55   | 90   | ns     |

| •                              |                                                                                   | DT pin connected to GND                                                                                                                        | 25    | 55   | 80   | ns     |

| t <sub>DEAD</sub>              |                                                                                   | 10 kΩ between DT pin and GND                                                                                                                   | 75    | 100  | 140  | ns     |

|                                |                                                                                   | 390 kΩ between DT pin and GND                                                                                                                  | 1350  | 2000 | 2650 | ns     |

| BOOTSTRA                       | P DIODES                                                                          |                                                                                                                                                |       |      |      |        |

| \/                             | Bootstrap diode forward voltage                                                   | I <sub>BOOT</sub> = 100 μA                                                                                                                     |       |      | 0.8  | V      |

| $V_{BOOTD}$                    | Bootstrap diode forward voltage                                                   | I <sub>BOOT</sub> = 100 mA                                                                                                                     |       |      | 1.6  | V      |

| R <sub>BOOTD</sub>             | Bootstrap dynamic resistance ( $\Delta V_{BOOTD}/\Delta I_{BOOT}$ )               | I <sub>BOOT</sub> = 100 mA and 50 mA                                                                                                           | 4.5   | 5.5  | 9    | Ω      |

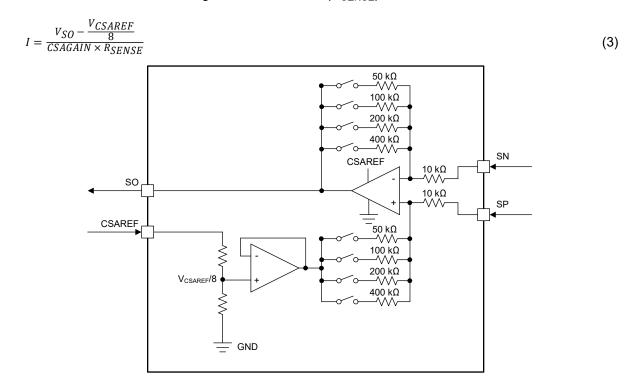

| CURRENT S                      | HUNT AMPLIFIERS (SNx, SOx, SPx, CS                                                | AREF)                                                                                                                                          |       |      |      |        |

|                                |                                                                                   | CSAGAIN = Tied to GND                                                                                                                          | 4.92  | 5    | 5.05 | V/V    |

| A <sub>CSA</sub>               | Sense amplifier gain                                                              | CSAGAIN = 50kΩ ±5% tied to GND                                                                                                                 | 9.9   | 10   | 10.1 | V/V    |

| OOA                            |                                                                                   | CSAGAIN = 200kΩ ±5% tied to GND                                                                                                                | 19.75 | 20   | 20.2 | V/V    |

|                                |                                                                                   | CSAGAIN =Hi-Z;                                                                                                                                 | 39.6  | 40   | 40.6 | V/V    |

| A <sub>CSA_ERR</sub>           | Sense amplifier gain error                                                        | T <sub>J</sub> = 25°C                                                                                                                          | -1.5  |      | 1.5  | %      |

| A <sub>CSA_ERR_D</sub><br>RIFT | Sense amplifier gain error temperature drift                                      |                                                                                                                                                | -20   |      | 20   | ppm/°C |

| NL                             | Non linearity Error                                                               |                                                                                                                                                |       | 0.01 | 0.05 | %      |

English Data Sheet: SLVSGX4

$4.5~\text{V} \leq \text{V}_{\text{PVDD}} \leq 60~\text{V}, -40^{\circ}\text{C} \leq \text{T}_{\text{J}} \leq 150^{\circ}\text{C}$  (unless otherwise noted). Typical limits apply for T<sub>A</sub> = 25°C, V<sub>PVDD</sub> = 24 V

|                        | PARAMETER                          | TEST CONDITIONS                                                                                            | MIN   | TYP   | MAX                           | UNIT  |

|------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------|-------|-------|-------------------------------|-------|

|                        |                                    | V <sub>STEP</sub> = 1.6 V, A <sub>CSA</sub> = 5 V/V, C <sub>LOAD</sub> = 500pF                             |       | 0.6   | 1                             | μs    |

| t                      | Settling time to ±1%               | V <sub>STEP</sub> = 1.6 V, A <sub>CSA</sub> = 10 V/V, C <sub>LOAD</sub> = 500pF                            |       | 0.6   | 1.1                           | μs    |

| t <sub>SET</sub>       | Setting time to 1176               | V <sub>STEP</sub> = 1.6 V, A <sub>CSA</sub> = 20 V/V, C <sub>LOAD</sub> = 500pF                            |       | 0.7   | 1.2                           | μs    |

|                        |                                    | V <sub>STEP</sub> = 1.6 V, A <sub>CSA</sub> = 40 V/V, C <sub>LOAD</sub> = 500pF                            |       | 0.8   | 1.7                           | μs    |

|                        |                                    | V <sub>STEP</sub> = 1.6 V, A <sub>CSA</sub> = 5 V/V, C <sub>LOAD</sub> = 60pF                              |       | 0.3   | 0.5                           | μs    |

| t                      | Settling time to ±1%               | V <sub>STEP</sub> = 1.6 V, A <sub>CSA</sub> = 10 V/V, C <sub>LOAD</sub> = 60pF                             |       | 0.3   | 0.5                           | μs    |

| t <sub>SET</sub>       | Setting time to £176               | V <sub>STEP</sub> = 1.6 V, A <sub>CSA</sub> = 20 V/V, C <sub>LOAD</sub> = 60pF                             |       | 0.3   | 0.65                          | μs    |

|                        |                                    | V <sub>STEP</sub> = 1.6 V, A <sub>CSA</sub> = 40 V/V, C <sub>LOAD</sub> = 60pF                             |       | 0.3   | 0.8                           | μs    |

|                        |                                    | A <sub>CSA</sub> = 5 V/V, C <sub>LOAD</sub> = 60-pF, small signal -3 dB                                    | 3     | 5     | 7                             | MHz   |

| BW                     | Bandwidth                          | A <sub>CSA</sub> = 10 V/V, C <sub>LOAD</sub> = 60-pF, small signal -3 dB                                   | 2.5   | 4.8   | 6.6                           | MHz   |

| Bandwidth              | Dariuwidii                         | A <sub>CSA</sub> = 20 V/V, C <sub>LOAD</sub> = 60-pF, small signal -3 dB                                   | 2     | 4     | 5.4                           | MHz   |

|                        |                                    | A <sub>CSA</sub> = 40 V/V, C <sub>LOAD</sub> = 60-pF, small signal -3 dB                                   | 1.75  | 3     | 4.2                           | MHz   |

|                        | Output slew rate                   | V <sub>STEP</sub> = 1.6 V, A <sub>CSA</sub> = 5 V/V, C <sub>LOAD</sub> = 60-<br>pF, low to high transition |       | 12    |                               | V/µs  |

|                        |                                    | V <sub>STEP</sub> = 1.6 V, A <sub>CSA</sub> = 10 V/V, C <sub>LOAD</sub> = 60-pF, low to high transition    |       | 13    |                               | V/µs  |

| t <sub>SR</sub>        |                                    | V <sub>STEP</sub> = 1.6 V, A <sub>CSA</sub> = 20 V/V, C <sub>LOAD</sub> = 60-pF, low to high transition    |       | 11    |                               | V/µs  |

|                        |                                    | V <sub>STEP</sub> = 1.6 V, A <sub>CSA</sub> = 40 V/V, C <sub>LOAD</sub> = 60-pF, low to high transition    |       | 11    |                               | V/µs  |

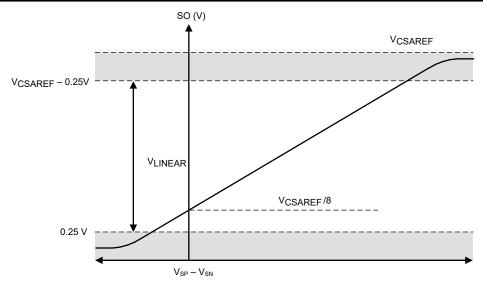

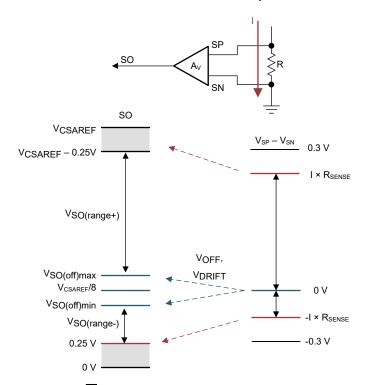

| V <sub>SWING</sub>     | Output voltage range               | V <sub>CSAREF</sub> = 3                                                                                    | 0.25  |       | 2.75                          | V     |

| V <sub>SWING</sub>     | Output voltage range               | V <sub>CSAREF</sub> = 5.5                                                                                  | 0.25  |       | 5.25                          | V     |

| V <sub>SWING</sub>     | Output voltage range               | V <sub>CSAREF</sub> = 3 to 5.5 V                                                                           | 0.25  |       | V <sub>CSAREF</sub><br>- 0.25 | V     |

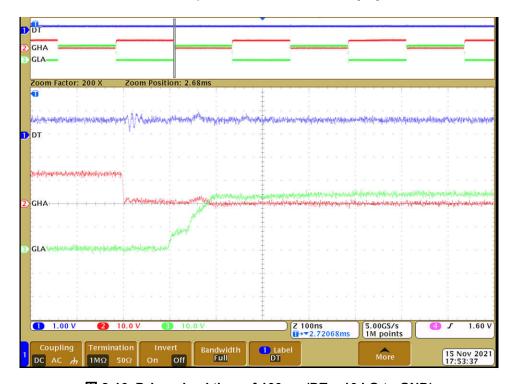

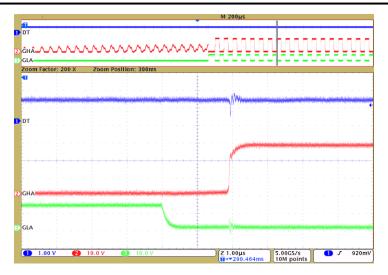

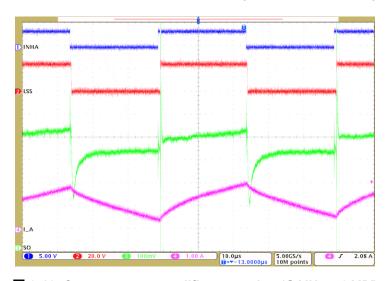

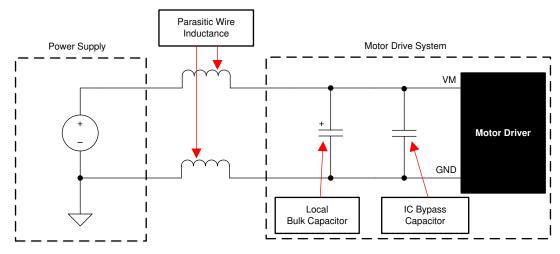

| V <sub>COM</sub>       | Common-mode input range            |                                                                                                            | -0.15 |       | 0.15                          | V     |