# DRV8220 18V H ブリッジ・モーター・ドライバ、PWM、PH/EN、ハーフブリッジ制御インターフェイス、および低消費電力スリープ・モード付き

## 1 特長

- N チャネルの H ブリッジ・モーター・ドライバ

- MOSFET オン抵抗:HS + LS 1Ω

- 1 つの双方向ブラシ付き DC モーターを駆動

- 2 つの単方向ブラシ付き DC モーター

- 単一コイルまたはデュアルコイルのラッチリレー 1 個

- プッシュプルおよび双安定ソレノイド

- その他の抵抗性、誘導性、または LED 負荷

- 4.5V~18V の動作電源電圧範囲

- 高い出力電流能力:

- フルブリッジ:ピーク 1.76A

- ハーフブリッジ:出力ごとのピーク 1.76A

- 並列ハーフブリッジ:ピーク 3.52A

- 複数のインターフェイスにより柔軟性と GPIO の削減を達成

- 標準 PWM インターフェイス (IN1/IN2)

- 1.8V、3.3V、5V のロジック入力電圧に対応

- スリープ・モードでの非常に低い消費電力

- $V_{VM} = 12V$ 、 $T_J = 25^{\circ}C$  で 960μA

- 時間指定の自動スリープ・モードにより GPIO を削減

- 保護機能

- 低電圧誤動作防止 (UVLO)

- 過電流保護 (OCP)

- サーマル・シャットダウン (TSD)

- デバイス・ファミリの詳細については、[デバイスの比較](#)をご覧ください。

- **DRV8210**: 1.65~11V、1Ω、複数のインターフェイス

- **DRV8210P**: スリープ・ピン、PWM インターフェイス

- **DRV8212**: 1.65~11V、280mΩ、複数のインターフェイス

- **DRV8212P**: スリープ・ピン、PWM インターフェイス

- **DRV8220**: 4.5~18V、1Ω、複数のインターフェイス

## 2 アプリケーション

- ブラシ付き DC モーター、ソレノイド、リレー駆動

- 水道、ガス、電気メータ

- IP ネットワークカメラの IR カットフィルタ

- ビデオ・ドアベル

- マシン・ビジョン・カメラ

- サーキット・ブレーカ

- 電子スマート・ロック

- 電子 / ロボット玩具

- 血圧計

- 点滴用ポンプ

- 電動歯ブラシ

- 美容と化粧

## 3 概要

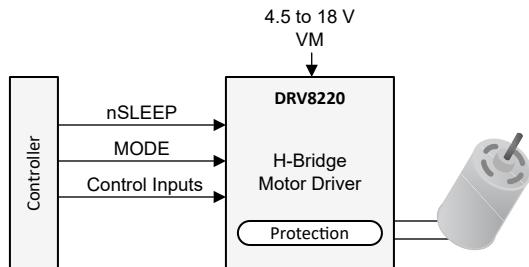

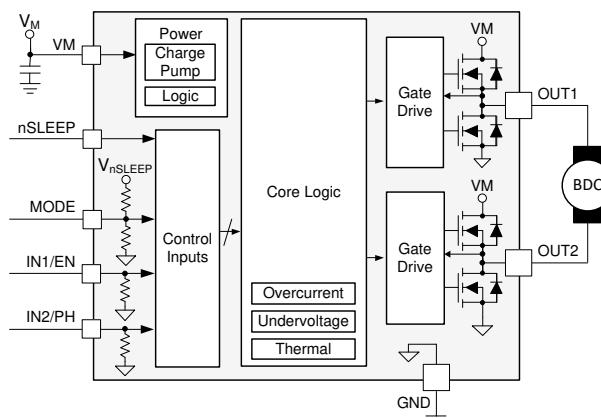

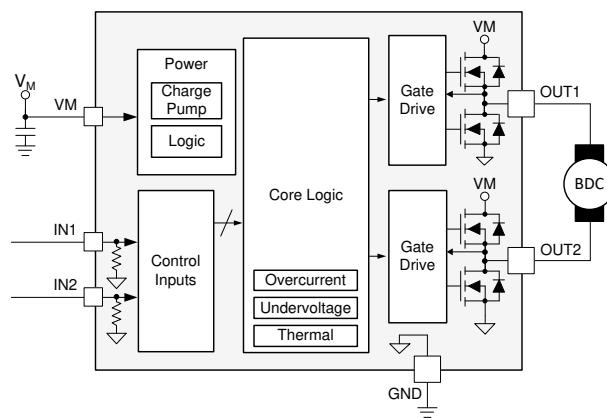

DRV8220 は、4 つの N チャネル・パワー FET、チャージ・ポンプ・レギュレータ、保護回路を内蔵した統合モーター・ドライバです。チャージ・ポンプにはすべてのコンデンサが内蔵されているため、PCB 上のモーター・ドライバのソリューション・サイズ全体が小さくなり、100% のデューティ・サイクルで動作できます。

DRV8220 は、PWM (IN1/IN2)、位相 / イネーブル (PH/EN)、独立ハーフブリッジ、並列ハーフブリッジを含む複数の制御インターフェイス・モードをサポートしています。各インターフェイスは低消費電力のスリープ・モードをサポートしており、内部回路のほとんどをシャットダウンすることで静止電流が非常に小さくなります。DSG パッケージは nSLEEP ピンをサポートしているため、ロジック信号入力を使用してスリープ・モードを制御できます。

本デバイスは、最大 1.76A の出力電流を供給できます。4.5V~18V の電源電圧で動作します。

このドライバは、電源低電圧誤動作防止 (UVLO)、出力過電流 (OCP)、デバイス過熱 (TSD) などの堅牢な内部保護機能を備えています。

DRV8220 は、各種の負荷と電源レールに最小限の設計変更で対応できるよう、スケーラブルな  $R_{DS(on)}$  と電源電圧の選択肢を取り揃えたピン互換のデバイス・ファミリの一部です。このファミリのデバイスの詳細については、[デバイスの比較](#)をご覧ください。弊社のポートフォリオ全体については、[tij.co.jp](http://tij.co.jp) の [ブラシ付きモーター・ドライバ](#)をご覧ください。

## 製品情報

| 部品番号 <sup>(1)</sup> | パッケージ      | 本体サイズ (公称)      |

|---------------------|------------|-----------------|

| DRV8220DSG          | WSON (8)   | 2.00mm × 2.00mm |

| DRV8220DRL          | SOT563 (6) | 1.20mm × 1.60mm |

(1) 利用可能なパッケージについては、このデータシートの末尾にある注文情報を参照してください。

英語版の TI 製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、必ず最新版の英語版をご参照ください。

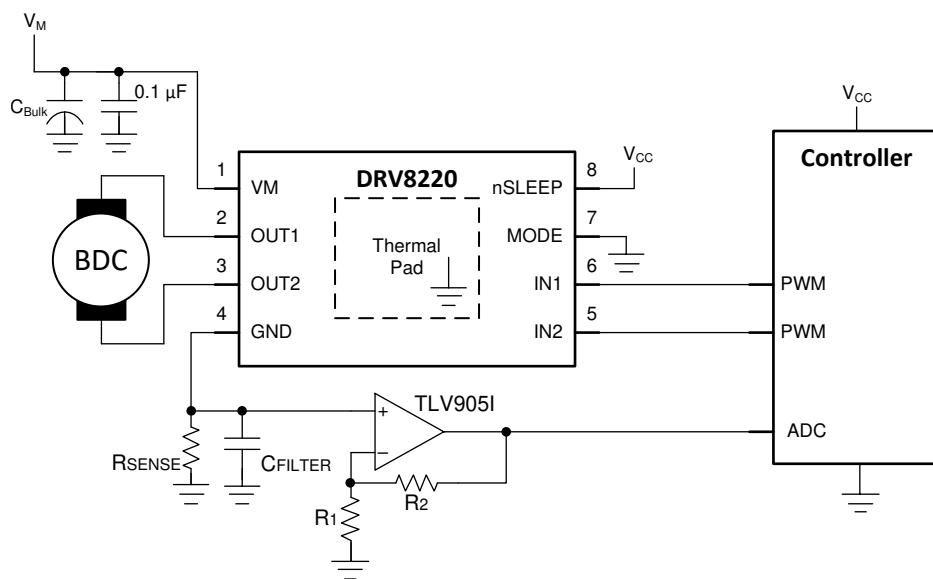

概略回路図

## 目次

|                |    |                                                      |    |

|----------------|----|------------------------------------------------------|----|

| 1 特長           | 1  | 9 アプリケーションと実装                                        | 17 |

| 2 アプリケーション     | 1  | 9.1 アプリケーション情報                                       | 17 |

| 3 概要           | 1  | 9.2 代表的なアプリケーション                                     | 17 |

| 4 改訂履歴         | 3  | 9.3 電流能力と熱性能                                         | 26 |

| 5 デバイスの比較      | 4  | 10 電源に関する推奨事項                                        | 33 |

| 6 ピン構成および機能    | 5  | 10.1 バルク容量                                           | 33 |

| 7 仕様           | 6  | 11 レイアウト                                             | 34 |

| 7.1 絶対最大定格     | 6  | 11.1 レイアウトのガイドライン                                    | 34 |

| 7.2 ESD 定格     | 6  | 11.2 レイアウト例                                          | 34 |

| 7.3 推奨動作条件     | 6  | 12 デバイスおよびドキュメントのサポート                                | 36 |

| 7.4 熱に関する情報    | 6  | 12.1 ドキュメントのサポート                                     | 36 |

| 7.5 電気的特性      | 7  | 12.2 Receiving Notification of Documentation Updates | 36 |

| 7.6 の標準特性      | 8  | 12.3 サポート・リソース                                       | 36 |

| 8 詳細説明         | 10 | 12.4 商標                                              | 36 |

| 8.1 概要         | 10 | 12.5 Electrostatic Discharge Caution                 | 36 |

| 8.2 機能ブロック図    | 10 | 12.6 Glossary                                        | 36 |

| 8.3 機能説明       | 11 | 13 メカニカル、パッケージ、および注文情報                               | 37 |

| 8.4 デバイスの機能モード | 15 |                                                      |    |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision * (February 2021) to Revision A (April 2021)                  | Page |

|-------------------------------------------------------------------------------------|------|

| • 最初のページとデバイスの比較表にある製品ファミリへの参照を更新                                                   | 1    |

| • 「ピン構成および機能」、「仕様」表、「詳細説明」、「アプリケーションと実装」、「レイアウト」の各セクションに DRL パッケージ・オプションに関する技術情報を追加 | 1    |

| Changes from Revision A (April 2021) to Revision B (August 2021) | Page |

|------------------------------------------------------------------|------|

| • デバイスのステータスを「量産データ」に更新                                          | 1    |

## 5 デバイスの比較

表 5-1. デバイス比較表

| 型番       | 電源電圧 (V) | $R_{DS(on)}$ (mΩ)        | $I_{OCP}$ (A) | 選択できるインターフェイス     | スリープ・モードの開始条件        | ピン互換デバイス                                       | パッケージ                         |

|----------|----------|--------------------------|---------------|-------------------|----------------------|------------------------------------------------|-------------------------------|

| DRV8210  | 1.65~11  | 950 (DRL)、<br>1050 (DSG) | 1.76          | PWM、PH/EN、ハーフブリッジ | 自動スリープ、<br>VCC       | DRV8210、<br>DRV8212、<br>DRV8220                | SOT563<br>(DRL)、WSON<br>(DSG) |

| DRV8212  | 1.65~11  | 280                      | 4             |                   | 自動スリープ、<br>nSLEEP ピン |                                                |                               |

| DRV8220  | 4.5~18   | 1000                     | 1.76          | PWM               | nSLEEP ピン            | DRV8837、<br>DRV8837C、<br>DRV8210P、<br>DRV8212P | WSON (DSG)                    |

| DRV8210P | 1.65~11  | 1050                     | 1.76          |                   |                      |                                                |                               |

| DRV8212P | 1.65~11  | 280                      | 4             |                   |                      |                                                | WSON (DSG)                    |

## 6 ピン構成および機能

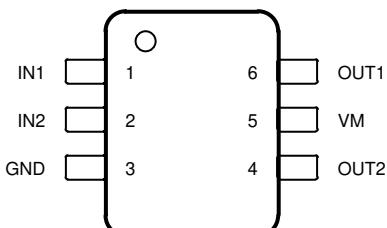

図 6-1. DRV8220 DRL パッケージ 6 ピン SOT 上面図

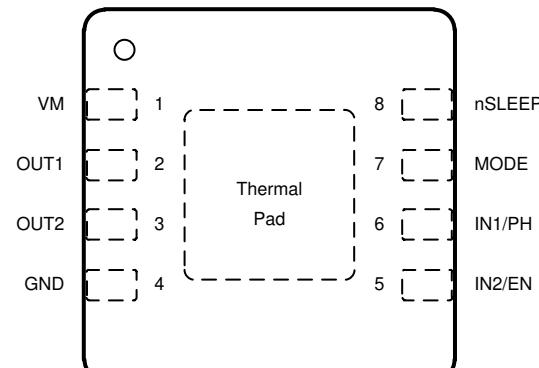

図 6-2. DRV8220 DSG パッケージ 8 ピン WSON 上面図

表 6-1. ピン機能

| ピン     |     |     | 種類  | 説明                                                                                        |

|--------|-----|-----|-----|-------------------------------------------------------------------------------------------|

| 名称     | DRL | DSG |     |                                                                                           |

| GND    | 3   | 4   | PWR | デバイスのグランド。システム・グランドに接続します。                                                                |

| IN1    | 1   | —   | I   | H ブリッジ制御入力。「セクション 8.3.2」を参照してください。内部プルダウン抵抗。                                              |

| IN1/PH | —   | 6   | I   | H ブリッジ制御入力。「セクション 8.3.2」を参照してください。内部プルダウン抵抗。                                              |

| IN2    | 2   | —   | I   | H ブリッジ制御入力。「セクション 8.3.2」を参照してください。内部プルダウン抵抗。                                              |

| IN2/EN | —   | 5   | I   | H ブリッジ制御入力。「セクション 8.3.2」を参照してください。内部プルダウン抵抗。                                              |

| MODE   | —   | 7   | I   | H ブリッジ制御入力モード。「セクション 8.3.2」を参照してください。nSLEEP ピン電圧を基準とするトライレベル入力。                           |

| nSLEEP | —   | 8   | I   | スリープ・モード入力。このピンをロジック High に設定すると、デバイスがイネーブルされます。このピンをロジック Low に設定すると、低消費電力スリープ・モードに移行します。 |

| OUT1   | 6   | 2   | O   | H ブリッジ出力。モーターまたはその他の負荷に接続します。                                                             |

| OUT2   | 4   | 3   | O   | H ブリッジ出力。モーターまたはその他の負荷に接続します。                                                             |

| VM     | 5   | 1   | PWR | モーター電源。このピンは、0.1 $\mu$ F のセラミック・コンデンサおよび VM 定格の十分なパルク容量を使用して GND ピンにバイパスします。              |

| PAD    | —   | —   | —   | サーマル・パッド。システム・グランドに接続します。                                                                 |

## 7 仕様

### 7.1 絶対最大定格

動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                       |                             | 最小値              | 最大値                               | 単位   |

|-----------------------|-----------------------------|------------------|-----------------------------------|------|

| 電源ピン電圧                | VM                          | -0.5             | 20                                | V    |

| 電源過渡電圧ランプ             | VM、                         | 0                | 2                                 | V/μs |

| ロジック・ピン電圧             | INx, nSLEEP, IN1/PH, IN2/EN | -0.5             | 5.75                              | V    |

| トライレベル・ピン電圧           | MODE                        | -0.5             | 5.75                              |      |

| 出力ピン電圧                | OUTx                        | -V <sub>SD</sub> | V <sub>VM</sub> + V <sub>SD</sub> | V    |

| 出力電流 <sup>(1)</sup>   | OUTx                        | 内部的に制限           | 内部的に制限                            | A    |

| 周囲温度、T <sub>A</sub>   |                             | -40              | 125                               | °C   |

| 接合部温度、T <sub>J</sub>  |                             | -40              | 150                               | °C   |

| 保存温度、T <sub>stg</sub> |                             | -65              | 150                               | °C   |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示しており、このデータシートの「推奨動作条件」に示された値を越える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

### 7.2 ESD 定格

|                    |       | 値                                                       | 単位    |

|--------------------|-------|---------------------------------------------------------|-------|

| V <sub>(ESD)</sub> | 静電気放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>    | ±2000 |

|                    |       | 荷電デバイス・モデル (CDM)、JEDEC 仕様 JESD22-C101 準拠 <sup>(2)</sup> | ±500  |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。±2000V と記載されたピンは、実際にはそれよりも高い性能を持つ場合があります。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。±500V と記載されたピンは、実際にはそれよりも高い性能を持つ場合があります。

### 7.3 推奨動作条件

動作温度範囲内 (特に記述のない限り)

|                                 |              | 最小                                | 公称値 | 最大   | 単位  |

|---------------------------------|--------------|-----------------------------------|-----|------|-----|

| V <sub>VM</sub>                 | モーター電源電圧     | VM                                | 4.5 | 18   | V   |

| V <sub>IN</sub>                 | ロジック・ピン電圧    | INx, nSLEEP, IN1/PH, IN2/EN, MODE | 0   | 5.5  | V   |

| f <sub>PWM</sub>                | PWM 周波数      | INx, IN1/PH, IN2/EN               | 0   | 100  | kHz |

| I <sub>OUT</sub> <sup>(1)</sup> | ピーク出力電流      | OUTx                              | 0   | 1.76 | A   |

| T <sub>A</sub>                  | 動作時周囲温度      |                                   | -40 | 125  | °C  |

| T <sub>J</sub>                  | 動作時ジャンクション温度 |                                   | -40 | 150  | °C  |

- (1) 消費電力および温度の制限に従う必要があります。

### 7.4 热に関する情報

| 熱評価基準 <sup>(1)</sup>  |                          | DRV8220      | DRV8220    | 単位   |

|-----------------------|--------------------------|--------------|------------|------|

|                       |                          | DRL (SOT563) | DSG (WSON) |      |

|                       |                          | 6 ピン         | 8 ピン       |      |

| R <sub>θJA</sub>      | ジャンクションから周囲までの熱抵抗        | 152.4        | 94.7       | °C/W |

| R <sub>θJC(top)</sub> | ジャンクションからケース (上部) までの熱抵抗 | 63.6         | 115.1      | °C/W |

| R <sub>θJB</sub>      | ジャンクションから基板までの熱抵抗        | 39.1         | 62.3       | °C/W |

| Ψ <sub>JT</sub>       | ジャンクションから上部までの熱特性パラメータ   | 2.0          | 11.6       | °C/W |

| Ψ <sub>JB</sub>       | ジャンクションから基板までの熱特性パラメータ   | 38.7         | 62.0       | °C/W |

| 熱評価基準 <sup>(1)</sup> |                        | DRV8220      | DRV8220    | 単位   |

|----------------------|------------------------|--------------|------------|------|

|                      |                        | DRL (SOT563) | DSG (WSON) |      |

|                      |                        | 6 ピン         | 8 ピン       |      |

| $R_{\theta JC(bot)}$ | ジャンクションからケース(底部)までの熱抵抗 |              | 38.6       | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーション・レポートを参照してください。

## 7.5 電気的特性

$4.5V \leq V_{VM} \leq 18V$ 、 $-40^{\circ}C \leq T_J \leq 150^{\circ}C$  (特に記述のない限り)

標準値は  $T_J = 27^{\circ}C$ 、 $V_{VM} = 12V$  の場合

| パラメータ                                          | テスト条件                            | 最小値                                                        | 標準値                      | 最大値                       | 単位 |

|------------------------------------------------|----------------------------------|------------------------------------------------------------|--------------------------|---------------------------|----|

| <b>電源電圧 (VM)</b>                               |                                  |                                                            |                          |                           |    |

| $I_{VM}$                                       | VM アクティブ・モード電流                   | IN1 = 0V、IN2 = 3.3V                                        | 1.5                      | 2                         | mA |

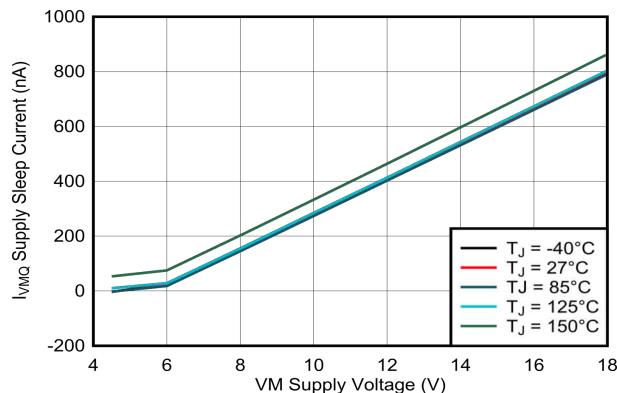

| $I_{VMQ}$                                      | VM スリープ・モード電流                    | スリープ・モード、 $V_{VM} = 12V$ 、 $T_J = 27^{\circ}C$             |                          | 960                       | nA |

| $t_{WAKE}$                                     | ターンオン時間                          | スリープ・モードからアクティブ・モードまでの遅延                                   |                          | 65                        | μs |

| $t_{AUTOSLEEP}$                                | 自動スリープのターンオフ時間                   | アクティブ・モードから自動スリープ・モードまでの遅延、<br>$nSLEEP = 3.3V$             | 0.9                      | 2.6                       | ms |

| $t_{SLEEP}$                                    | ターンオフ時間                          | アクティブ・モードからスリープ・モードまでの遅延、<br>$nSLEEP = 0V$                 | 1                        |                           | μs |

| <b>ロジックレベル入力 (INx, nSLEEP, IN1/PH, IN2/EN)</b> |                                  |                                                            |                          |                           |    |

| $V_{IL}$                                       | 入力ロジック Low 電圧                    |                                                            | 0                        | 0.35                      | V  |

| $V_{IH}$                                       | 入力ロジック High 電圧                   |                                                            | 1.45                     | 5.5                       | V  |

| $V_{HYS}$                                      | 入力ロジック・ヒステリシス                    |                                                            | 49                       |                           | mV |

| $I_{IL}$                                       | 入力ロジック Low 電流                    | $V_I = 0V$                                                 | -1                       | 1                         | μA |

| $I_{IH}$                                       | 入力ロジック High 電流、IN1/EN、<br>IN2/PH | $V_I = 3.3V$                                               | 20                       | 50                        | μA |

| $I_{IH\_nSLEEP}$                               | 入力ロジック High 電流、nSLEEP            | $V_I = 3.3V$ 、アクティブ・モード                                    | 60                       | 100                       | μA |

|                                                |                                  | $V_I = 3.3V$ 、自動スリープ・モード                                   |                          | 42                        | nA |

| $R_{PD}$                                       | 入力プルダウン抵抗、IN1/EN、IN2/PH          | 対 GND                                                      | 100                      |                           | kΩ |

| <b>トライレベル入力 (MODE)</b>                         |                                  |                                                            |                          |                           |    |

| $V_{TIL}$                                      | トライレベル入力ロジック Low 電圧              |                                                            | 0                        | $0.22 \times V_{nSLEEP}$  | V  |

| $V_{TIZ}$                                      | トライレベル入力 Hi-Z 電圧                 | $R_I = Hi-Z$                                               | $0.6 \times V_{nSLEEP}$  | $0.675 \times V_{nSLEEP}$ | V  |

| $V_{TIH}$                                      | トライレベル入力ロジック High 電圧             |                                                            | $0.75 \times V_{nSLEEP}$ | 5.5                       | V  |

| $R_{TPD}$                                      | トライレベル・プルダウン抵抗                   | 対 GND、スリープ・モード                                             | 1                        |                           | MΩ |

|                                                |                                  | 対 GND、アクティブ・モード                                            |                          | 130                       | kΩ |

| $R_{TPU}$                                      | トライレベル・プルアップ抵抗                   | 対の nSLEEP バッファ付き基準電圧                                       | 75                       |                           | kΩ |

| <b>ドライバ出力 (OUTx)</b>                           |                                  |                                                            |                          |                           |    |

| $R_{DS(on)\_HS}$                               | ハイサイド MOSFET オン抵抗                | $I_O = 0.2A$                                               | 500                      |                           | mΩ |

| $R_{DS(on)\_LS}$                               | ローサイド MOSFET オン抵抗                | $I_O = -0.2A$                                              | 500                      |                           | mΩ |

| $V_{SD}$                                       | ボディダイオード順方向電圧                    | $I_O = -0.5A$                                              | 1                        |                           | V  |

| $t_{RISE}$                                     | 出力立ち上がり時間                        | $V_{OUTx}$ の $V_{VM}$ の 10% から 90% までの立ち上がり                | 150                      |                           | ns |

| $t_{FALL}$                                     | 出力立ち下がり時間                        | $V_{OUTx}$ の $V_{VM}$ の 90% から 10% までの立ち下がり                | 150                      |                           | ns |

| $t_{PD}$                                       | 入力から出力までの伝搬遅延                    | 入力が 0.8V から $V_{OUTx} = 0.1 \times V_{VM}$ と交差、 $I_O = 1A$ | 135                      |                           | ns |

| $t_{DEAD}$                                     | 出力デッドタイム                         | 内部デッドタイム                                                   | 500                      |                           | ns |

$4.5V \leq V_{VM} \leq 18V$ 、 $-40^{\circ}C \leq T_J \leq 150^{\circ}C$  (特に記述のない限り)

標準値は  $T_J = 27^{\circ}C$ 、 $V_{VM} = 12V$  の場合

| パラメータ           |                      | テスト条件                               | 最小値 | 標準値  | 最大値 | 単位          |

|-----------------|----------------------|-------------------------------------|-----|------|-----|-------------|

| $I_{OUT}$       | OUTx へのリーク電流         | OUTx は Hi-Z、VM への $R_L = 20\Omega$  |     | 186  |     | $\mu A$     |

|                 |                      | OUTx は Hi-Z、GND への $R_L = 20\Omega$ |     | -3   |     | nA          |

| 保護回路            |                      |                                     |     |      |     |             |

| $V_{UVLO}$      | VM 電源低電圧誤動作防止 (UVLO) | 電源立ち上がり                             |     | 4.5  |     | V           |

|                 |                      | 電源立ち下がり                             |     | 3.7  |     | V           |

| $V_{UVLO\_HYS}$ | 電源 UVLO ヒステリシス       | 立ち上がりから立ち下がりへのスレッショルド               |     | 325  |     | mV          |

| $t_{UVLO}$      | 電源低電圧グリッチ除去時間        | $V_{VM}$ 立ち下がりから OUTx ディセーブルまで      |     | 11   |     | $\mu s$     |

| $I_{OCP}$       | 過電流保護トリップ・ポイント       |                                     |     | 1.76 |     | A           |

| $t_{OCP}$       | 過電流保護グリッチ除去時間        |                                     |     | 4.2  |     | $\mu s$     |

| $t_{RETRY}$     | 過電流保護リトライ時間          |                                     |     | 1.7  |     | ms          |

| $T_{TSD}$       | サーマル・シャットダウン温度       |                                     |     | 153  | 193 | $^{\circ}C$ |

| $T_{HYS}$       | 過熱シャットダウン・ヒステリシス     |                                     |     | 22   |     | $^{\circ}C$ |

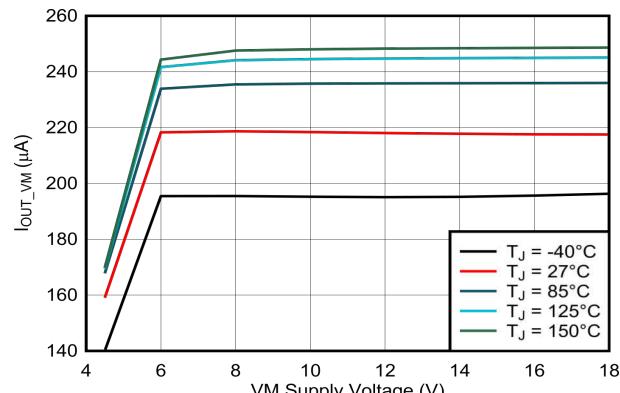

## 7.6 の標準特性

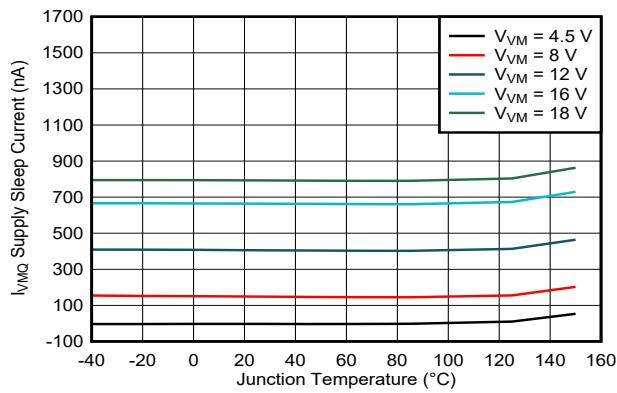

A. nSLEEP = 0V

図 7-1. スリープ電流 ( $I_{VMQ}$ ) と電源電圧 ( $V_{VM}$ ) との関係

A. nSLEEP = 0V

図 7-2. スリープ電流 ( $I_{VMQ}$ ) と接合部温度 ( $T_J$ ) との関係

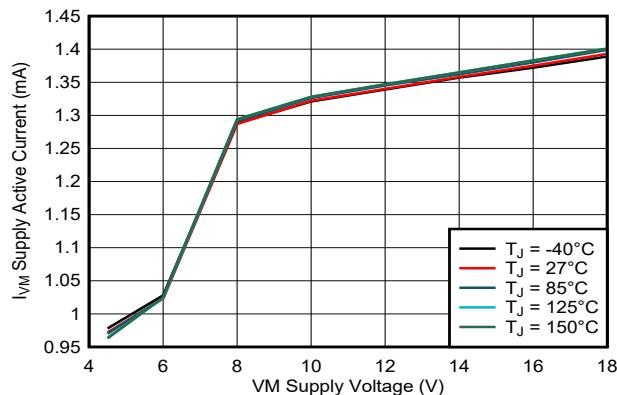

A. nSLEEP = 3.3V

図 7-3. アクティブ電流 ( $I_{VM}$ ) と電源電圧 ( $V_{VM}$ ) との関係

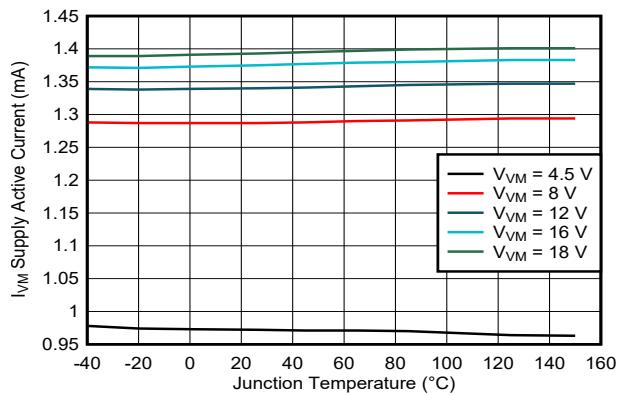

A. nSLEEP = 3.3V

図 7-4. アクティブ電流 ( $I_{VM}$ ) と接合部温度 ( $T_J$ ) との関係

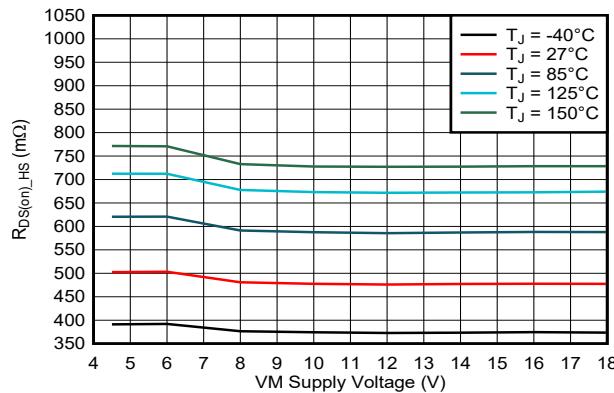

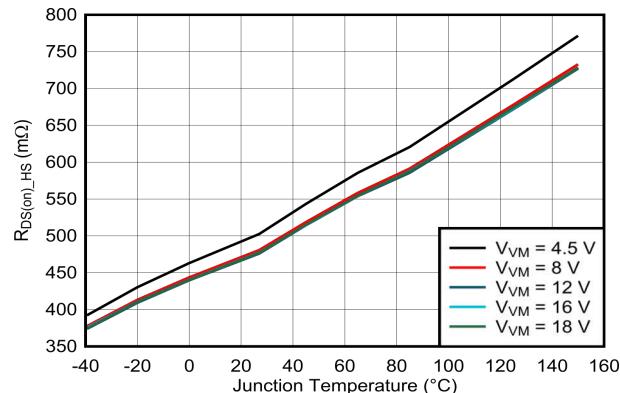

A. nSLEEP = 3.3V

図 7-5. ハイサイド  $R_{DS(on)}$  と電源電圧との関係

A. nSLEEP = 3.3V

図 7-6. ハイサイド  $R_{DS(on)}$  と接合部温度 ( $T_J$ ) との関係

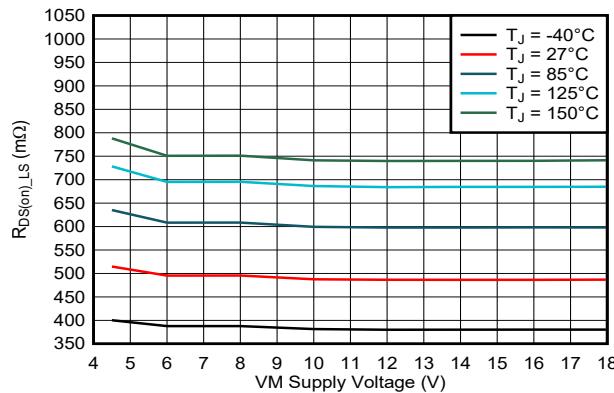

A. nSLEEP = 3.3V

図 7-7. ローサイド  $R_{DS(on)}$  と電源電圧との関係

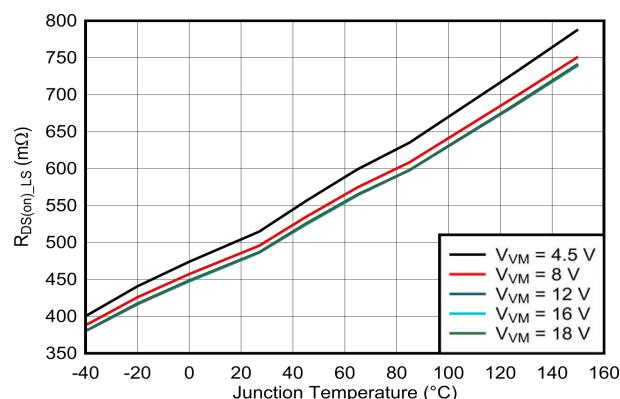

A. nSLEEP = 3.3V

図 7-8. ローサイド  $R_{DS(on)}$  と接合部温度 ( $T_J$ ) との関係

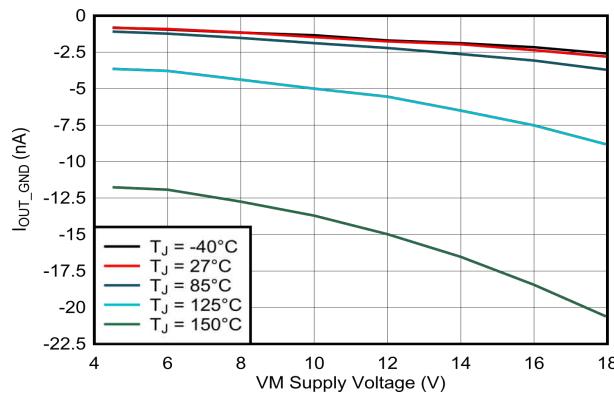

図 7-9. OUTx が GND に接続されているときの、OUTx への Hi-Z リーク電流 ( $I_{OUT}$ ) と電源電圧 ( $V_{VM}$ ) との関係

図 7-10. OUTx が VM に接続されているときの、OUTx への Hi-Z リーク電流 ( $I_{OUT}$ ) と電源電圧 ( $V_{VM}$ ) との関係

## 8 詳細説明

### 8.1 概要

DRV8220 は統合型 H ブリッジ・ドライバで、PWM (IN1/IN2) インターフェイス (DRL および DSG パッケージ)、PH/EN (DSG のみ)、またはハーフブリッジ・インターフェイス (DSG のみ) という複数の制御インターフェイスを選択できます。プリント基板の面積と外付け部品を削減するため、このデバイスにはチャージ・ポンプ・レギュレータとそのコンデンサが内蔵されています。DSG および DRL パッケージは、時間設定付き自動スリープ・モードをサポートしており、入力が 1~2ms の間非アクティブに維持されるとデバイスが自動的に低消費電力スリープ・モードに移行するため、ディセーブル / スリープ・ピンが不要になり、マイコンの GPIO 接続が少なくてすみます。PWM または PH/EN モードに自動スリープを使用する場合、nSLEEP ピンを High に接続することができます。自動スリープが使用できないときは、nSLEEP ピンによりデバイスをハーフブリッジ・モードでスリープに移行できます。

PWM インターフェイスは、標準の 2 ピン (IN1/IN2) モーター駆動インターフェイスです。PH/EN インターフェイスでは、コントローラから供給されている 1 つの PWM リソースだけを使用して双方向 PWM 制御を行えます。PWM と PH/EN のインターフェイスは、ブラシ付き DC モーターや双安定リレーのような負荷を双方向に駆動できます。独立したハーフブリッジ・モードにより、各ハーフブリッジを完全に制御できます。ハーフブリッジはチャネルごとに 2 つの負荷を独立して制御でき、フルブリッジ駆動の半分の  $R_{DS(on)}$  で、ハイサイドまたはローサイド・ドライバとして動作します。別の方針として、ハーフブリッジ・モードでは複数の入力と出力をそれぞれ相互に接続でき (これを「並列化」と呼びます)、フルブリッジ駆動の 1/4 の  $R_{DS(on)}$  で、ハイサイドまたはローサイド・ドライバとして単一の負荷を駆動できます。

システム・フォルトが発生した場合、内蔵の保護機能がデバイスを保護します。主な保護機能は、低電圧誤動作防止 (UVLO)、過電流保護 (OCP)、過熱シャットダウン (TSD) です。

### 8.2 機能ブロック図

図 8-1. DSG パッケージでの複数のインターフェイスのバリエント

図 8-2. DRL パッケージでの PWM インターフェイスのバリエント

## 8.3 機能説明

### 8.3.1 外付け部品

推奨の外付け部品を、表 8-1 に示します。

表 8-1. 推奨の外付け部品

| 部品        | ピン 1 | ピン 2 | 推奨する事項                               |

|-----------|------|------|--------------------------------------|

| $C_{VM1}$ | VM   | GND  | 0.1 $\mu$ F、低 ESR セラミック・コンデンサ、VM 定格。 |

| $C_{VM2}$ | VM   | GND  | セクション 10.1、VM 定格。                    |

### 8.3.2 制御モード

DRV8220 は、PH/IN1 ピンと EN/IN2 ピンで各種の制御方式をサポートするため、3 つのモードを備えています。MODE ピンは、表 8-2 に示すようにロジック LOW、ロジック HIGH、Hi-Z のいずれかに設定することで、制御インターフェイス・モードを選択します。MODE ピンは状態をラッピングしないため、動作中に変更できます。

DRL パッケージのバリエントは、PWM インターフェイスのみをサポートします (表 8-4 を参照)。

表 8-2. DSG バリエントの MODE ピンの機能

| MODE の状態         | 制御モード   |

|------------------|---------|

| PMODE = ロジック LOW | PWM     |

| MODE = ロジック HIGH | PH/EN   |

| MODE = Hi-Z      | ハーフブリッジ |

入力は DC、またはデューティ・サイクルが 0% から 100% の範囲のパルス幅変調 (PWM) 電圧信号に対応できます。デフォルトでは、入力がなくても INx、PH/IN1、および EN/IN2 ピンには内部プルダウン抵抗が接続されているため、出力が Hi-Z になることが保証されます (唯一の例外はハーフブリッジ・モードで、INx がフローティングなら OUTx = L です)。

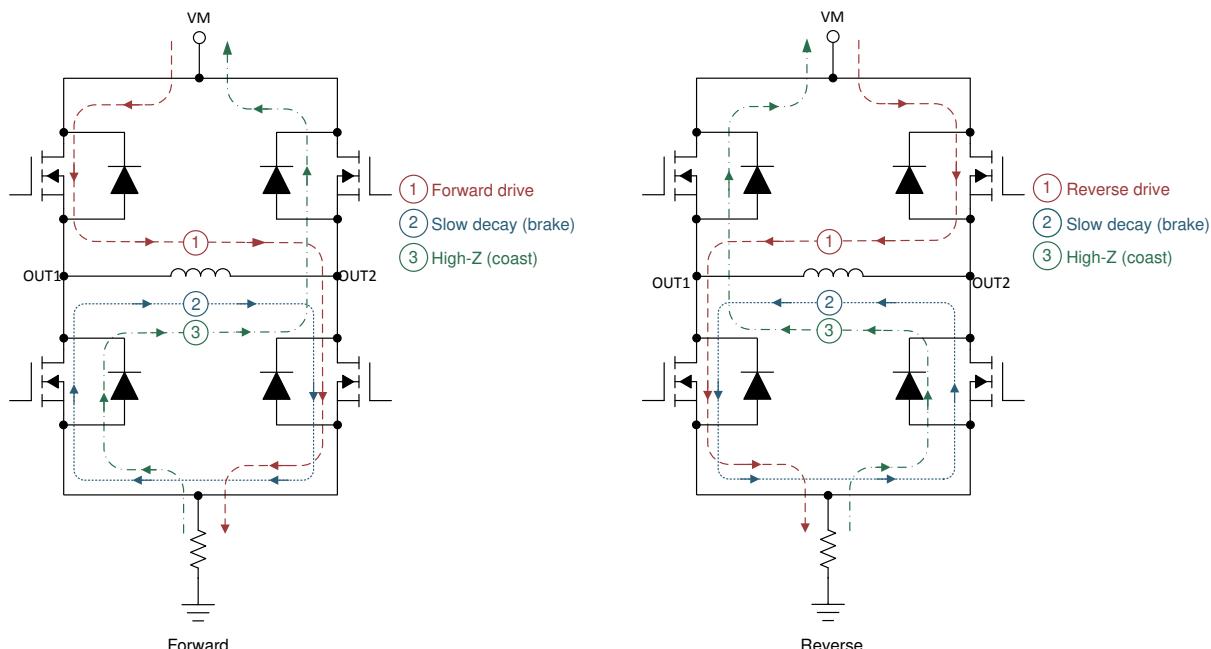

以下のセクションでは、各制御モードの真理値表を示します。また、DRV8220 では、ハーフブリッジのハイサイド MOSFET とローサイド MOSFET の切り替え時に自動的にデッドタイムが生成されます。以下のセクションで説明する H ブリッジの各種状態の呼称と構成を 図 8-3 に示します。

図 8-3. H ブリッジの状態

### 8.3.2.1 PWM 制御モード (DSG : MODE = 0 かつ DRL)

PWM インターフェイス (IN1/IN2) は、表 8-3 および表 8-4 の真理値表に基づいて OUTx ピンを制御します。DSG パッケージの場合、MODE ピンをロジック Low に設定すると PWM モードが選択されます。コースト / Hi-Z 状態は、自動スリープ・モードとしても機能します。デバイスは、 $t_{SLEEP}$  だけコースト / Hi-Z 状態に維持された後で、自動的に低消費電力スリープ・モードに移行します (自動スリープ)。PWM モードは、DRL パッケージで使用できる唯一のインターフェイス・モードです。

表 8-3. DSG パッケージでの、自動スリープとスリープ・ピンによる PWM 制御モード

| nSLEEP | IN1 | IN2 | OUT1 | OUT2 | 説明                                       |

|--------|-----|-----|------|------|------------------------------------------|

| 0      | X   | X   | Hi-Z | Hi-Z | 低消費電力スリープ・モード                            |

| 1      | 0   | 0   | Hi-Z | Hi-Z | コースト (H ブリッジ Hi-Z) /<br>低消費電力の自動スリープ・モード |

| 1      | 0   | 1   | L    | H    | 逆方向 (OUT2 → OUT1)                        |

| 1      | 1   | 0   | H    | L    | 順方向 (OUT1 → OUT2)                        |

| 1      | 1   | 1   | L    | L    | ブレーキ (ローサイド低速減衰)                         |

表 8-4. DRL パッケージでの自動スリープによる PWM 制御モード

| IN1 | IN2 | OUT1 | OUT2 | 説明                                       |

|-----|-----|------|------|------------------------------------------|

| 0   | 0   | Hi-Z | Hi-Z | コースト (H ブリッジ Hi-Z) /<br>低消費電力の自動スリープ・モード |

| 0   | 1   | L    | H    | 逆方向 (OUT2 → OUT1)                        |

| 1   | 0   | H    | L    | 順方向 (OUT1 → OUT2)                        |

| 1   | 1   | L    | L    | ブレーキ (ローサイド低速減衰)                         |

### 8.3.2.2 PH/EN 制御モード (DSG: MODE = 1)

電源投入時に PMODE ピンがロジック High の場合、このデバイスでは「位相・イネーブル」(PH/EN) モードが選択されます。PH/EN モードでは、H ブリッジのインターフェイスの速度と方向タイプを制御できます。PH/EN モードの真理値表を表 8-5 に示します。EN ピンが Low になると、デバイスはブレーキ・モードに移行します。これにより、コントローラは EN ピンに单一の PWM ジェネレータ・ペリフェラルを使用し、標準の GPIO ピンが PH ピンを使用して方向を制御します。ただし、EN ピンが  $t_{SLEEP}$  よりも長く Low に維持されると、デバイスは低消費電力スリープ・モードに移行し、出力はディセーブルされます。

表 8-5. PH/EN 制御モード

| nSLEEP | EN | PH | OUT1     | OUT2     | 説明                                                          |

|--------|----|----|----------|----------|-------------------------------------------------------------|

| 0      | X  | X  | Hi-Z     | Hi-Z     | 低消費電力スリープ・モード (H ブリッジ Hi-Z)                                 |

| 1      | 0  | X  | L → Hi-Z | L → Hi-Z | $t_{SLEEP}$ の間、ブレーキ (ローサイド低速減衰)、その後自動スリープ・モード (H ブリッジ Hi-Z) |

| 1      | 1  | 0  | L        | H        | 逆方向 (OUT2 → OUT1)                                           |

| 1      | 1  | 1  | H        | L        | 順方向 (OUT1 → OUT2)                                           |

### 8.3.2.3 ハーフブリッジ制御モード (DSG: MODE = Hi-Z)

MODE ピンがフローティング (Hi-Z) の場合、はハーフブリッジ制御モードを選択します。このモードでは、各ハーフブリッジを直接制御して、ハイサイド低速減衰 (ブレーキ) のサポート、2 つの独立した負荷の駆動、または複数の出力の並列化により単一負荷に対する大電流能力を実現できます。独立ハーフブリッジ・モードの真理値表を、表 8-6 に示します。このモードには自動スリープ状態がないため、nSLEEP ピンを使用してデバイスのスリープ・モードとアクティブ・モードを切り替える必要があります。詳細については、セクション 8.4.2 を参照してください。

**表 8-6. ハーフブリッジ制御モード Old\_Colspec : 左**

| nSLEEP | IN1 | IN2 | OUT1 | OUT2 | 説明            |

|--------|-----|-----|------|------|---------------|

| 0      | X   | X   | Hi-Z | Hi-Z | 低消費電力スリープ・モード |

| 1      | 0   | X   | L    | X    | OUT1 ローサイド・オン |

| 1      | 1   | X   | H    | X    | OUT1 ハイサイド・オン |

| 1      | X   | 0   | X    | L    | OUT2 ローサイド・オン |

| 1      | X   | 1   | X    | H    | OUT2 ハイサイド・オン |

### 8.3.3 保護回路

DRV8220 は、電源低電圧、出力過電流、デバイス過熱イベントから完全に保護されています。

#### 8.3.3.1 電源の低電圧誤動作防止 (UVLO)

電源電圧が低電圧誤動作防止スレッショルド電圧 ( $V_{UVLO}$ ) を下回ると、H ブリッジのすべての MOSFET がディセーブルになります。この状況では、チャージ・ポンプおよびデバイス・ロジックもディセーブルになります。電源電圧が  $V_{UVLO}$  スレッショルドを上回ると、通常動作が再開されます。デバイスが UVLO に移行する条件の要約を [表 8-7](#) に示します。

**表 8-7. DRV8220 の UVLO 応答条件**

| $V_{VM}$ | デバイスの応答 |

|----------|---------|

| < 4.5V   | UVLO    |

| > 4.5V   | 通常動作    |

#### 8.3.3.2 OUTx 過電流保護 (OCP)

各 MOSFET のアナログ電流制限回路により、出力端子短絡時にもデバイスのピーク出力電流を制限できます。出力電流が、過電流グリッチ除去時間  $t_{OCP}$  より長い時間にわたって、過電流スレッショルド  $I_{OCP}$  を上回ると、H ブリッジのすべての MOSFET がディセーブルになります。 $t_{RETRY}$  の経過後、PH/IN1 ピンと EN/IN2 ピンの状態に応じて MOSFET が再イネーブルされます。過電流状態がまだ解消していない場合、このサイクルを繰り返します。解消している場合、通常のデバイス動作を再開します。

ハーフブリッジ制御モードでは、OCP の動作が多少変化します。過電流イベントが検出されると、対応するハーフブリッジのみがディセーブルになります。もう一方のハーフブリッジは通常動作を継続します。これにより、本デバイスは負荷を個別に駆動する際に、フォルト・イベントを個別に管理できます。両方のハーフブリッジで過電流イベントが検出されると、両方のハーフブリッジがディセーブルになります。両方のハーフブリッジは、同じ過電流リトライ・タイマを共有します。OUT1 に過電流イベントが最初に発生すると、 $t_{RETRY}$  の間、その出力はディセーブルになります。OUT1 に過電流イベントが発生した後、 $t_{RETRY}$  が経過する前に、OUT2 に過電流イベントが発生した場合、両方の OUTx ピンが、 $t_{RETRY}$  時間の全体にわたってディセーブル状態に維持されます。

#### 8.3.3.3 過熱検出保護 (TSD)

ダイの温度が過熱限界値の  $T_{TSD}$  を超えると、H ブリッジのすべての MOSFET がディセーブルになります。過熱状態が解消し、ダイの温度が  $T_{TSD}$  スレッショルドを下回ると、通常動作を再開します。

### 8.3.4 ピン構造図

#### 8.3.4.1 ロジックレベル入力

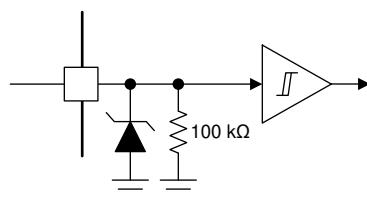

ロジックレベル入力ピン IN1、IN2、PH/IN1、EN/IN2 の入力構造を [図 8-4](#) に示します。

**図 8-4. ロジックレベル入力**

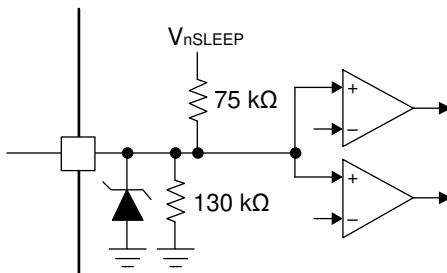

#### 8.3.4.2 トライレベル入力

トライレベル入力ピンである MODE の入力構造を [図 8-5](#) に示します。MODE ピンは、nSLEEP ピンの電圧を基準として自分の入力状態を参照し、ロジック High、ロジック Low、または高インピーダンス (Hi-Z) 入力状態を判定します。ただし、デバイスが自動スリープ・モードの場合、スリープ・ピンからこれらの内部抵抗に向かって電流は流れ込みません。これにより、スリープ・モード時のデバイス全体の消費電流を低減できます。

図 8-5. の MODE のトライレベル入力

## 8.4 デバイスの機能モード

DRV8220 は、システムの入力および条件に応じて複数のモードで動作します。

### 8.4.1 アクティブ・モード

このモードでは、H ブリッジ、チャージ・ポンプ、内部論理回路がアクティブになり、本デバイスはいつでも入力を受信できます。低消費電力のスリープ・モードやフォルト・モードに移行すると、デバイスはアクティブ・モードを終了します。スリープ・モードを終了するとき、デバイスをイネーブルするためには、nSLEEP を  $t_{WAKE}$  より長い時間 HIGH に保持する必要があります。自動スリープからウェイクアップするとき、デバイスをイネーブルするためには、INx ピン (DRL パッケージまたは DSG パッケージで MODE = 0 のとき) または EN ピン (DSG パッケージで MODE = 1 のとき) を  $t_{WAKE}$  の時間だけ HIGH に保持する必要があります。 $t_{WAKE}$  時間が経過するとデバイスはウェイクアップし、INx ピンまたは EN ピンで PWM 信号を受け取ることができます。

### 8.4.2 低消費電力スリープ・モード

DRV8220 は低消費電力のスリープ・モードをサポートし、ドライバがアクティブでないときに VM からの消費電流を低減します。低消費電力スリープ・モードでは、デバイスは  $I_{VMQ}$  で表される最小電流を消費します。DSG パッケージで低消費電力スリープ・モードに移行するには自動スリープと、nSLEEP ピンを使用する方法の 2 つがあります。低消費電力スリープ・モードに移行する方法を [表 8-8](#) に示します。DRL パッケージのバリエントは、自動スリープ・モードのみをサポートしています。

表 8-8. DRV8220 のスリープ・モードの概要

| バリエント | 入力ピンの状態                 | OUT1     | OUT2     | 概要                                                                                                                                                    |

|-------|-------------------------|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRL   | IN1 = IN2 = 0           | Hi-Z     | Hi-Z     | PWM インターフェイスの自動スリープ: この状態に移行すると、出力はディセーブルされます。デバイスはアクティブ・モードで $t_{SLEEP}$ だけ維持されてから、低消費電力モードに移行します。                                                   |

| DSG   | MODE = 0, IN1 = IN2 = 0 | Hi-Z     | Hi-Z     | PH/EN インターフェイスの自動スリープ: この状態に移行すると、ローサイド FET がオンになり、両方の出力がブレーキ・モードに移行します。デバイスは $t_{SLEEP}$ だけこの状態に維持されてから、低消費電力モードに移行します。低消費電力モードに移行すると、出力はディセーブルされます。 |

|       | MODE = 1, EN = 0        | L → Hi-Z | L → Hi-Z | スリープ・ピン:nSLEEP ピンが Low になると、出力はディセーブルされ、デバイスは直ちに低消費電力スリープ・モードに移行します。                                                                                  |

|       | nSLEEP = 0              | Hi-Z     | Hi-Z     |                                                                                                                                                       |

デバイスは、入力ピンが [表 8-8](#) に示されている以外の状態に移行すると、[アクティブ・モード](#) に復帰します。デバイスを自動スリープ・モードからウェイクアップするには、PWM 入力信号を受け取る前に、INx ピンまたは EN ピンを (MODE の状態とパッケージのバリエントに応じて)  $t_{WAKE}$  より長い時間 High にアサートする必要があります。nSLEEP ピンを使用するとき、nSLEEP は  $t_{WAKE}$  より長い時間 High にアサートされる必要があります。また、INx や EN ピンが自動スリープ状態であってはいけません。

DSG パッケージの場合、PWM または PH/EN インターフェイス・モードで自動スリープを使用するならば、nSLEEP ピンをロジック電源レールに接続することを推奨します。マイコンが nSLEEP を制御するアプリケーションでは、VM >  $V_{UVLO}$  の間、nSLEEP がフローティングでないことを設計で保証する必要があります。この状態になると、MODE、IN1/PH、IN2/EN ピンの状態によっては、予期しない出力が発生することがあります。システムでこの状態が発生する可能性がある場合は、nSLEEP に 100kΩ のプルダウン抵抗を使用することを推奨します。

### 8.4.3 フォルト・モード

DRV8220 は、フォルトが発生するとフォルト・モードに移行します。これにより、デバイスと出力負荷が保護されます。フォルト・モードでのデバイスの動作は、[セクション 8.3.3](#) に示すようにフォルト条件によって異なります。復帰条件を満たすと、本デバイスはフォルト・モードからアクティブ・モードに戻ります。フォルト条件、応答、および復帰の概要を [表 8-9](#) に示します。

**表 8-9. DRV8220 のフォルト条件の概要**

| フォルト               | 条件                     | H ブリッジ | 復帰                        |

|--------------------|------------------------|--------|---------------------------|

| 低電圧誤動作防止 (UVLO)    | $VM < V_{UVLO}$ の立ち下がり | ディセーブル | $VM > V_{UVLO}$ の立ち上がり    |

| 過電流 (OCP)          | $I_{OUT} > I_{OCP}$    | ディセーブル | $t_{RETRY}$               |

| サーマル・シャットダウン (TSD) | $T_J > T_{TSD}$        | ディセーブル | $T_J < T_{TSD} - T_{HYS}$ |

## 9 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 9.1 アプリケーション情報

DRV8220 は、ハーフブリッジまたは H ブリッジの電力段構成を必要とする各種用途に使用できます。一般的なアプリケーション例としては、ブラシ付き DC モーター、ソレノイド、双安定ラッチリレー、アクチュエータなどがあります。本デバイスは、LED、抵抗性素子、リレーなど多くの一般的な受動負荷を駆動することもできます。このセクションでは、DRV8220 のアプリケーション例をいくつか紹介します。

### 9.2 代表的なアプリケーション

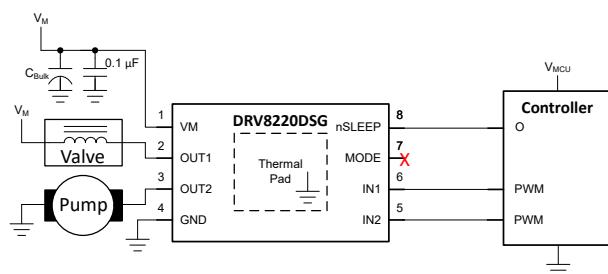

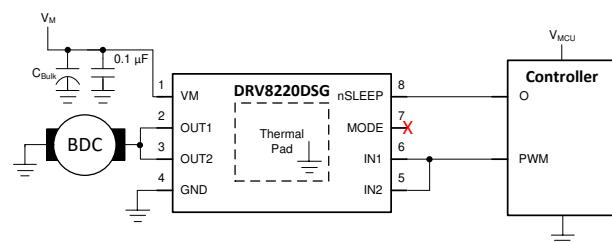

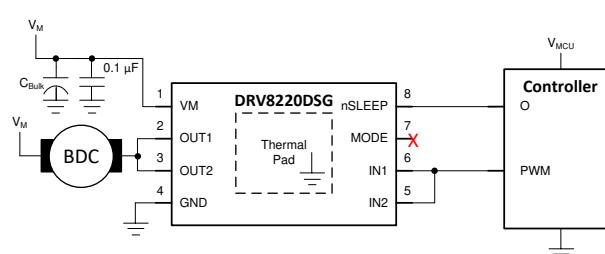

#### 9.2.1 フルブリッジ駆動

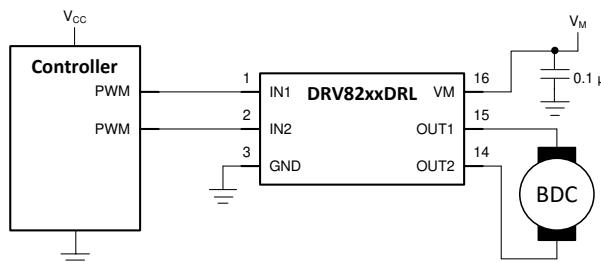

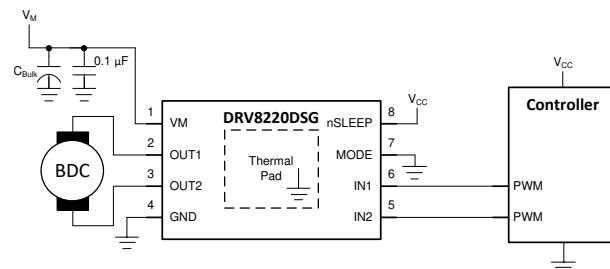

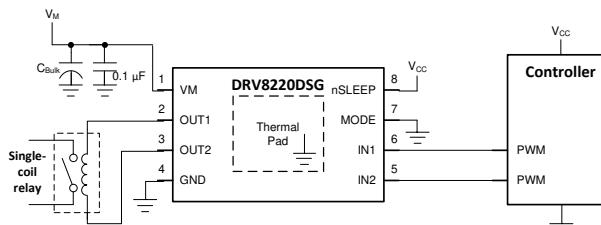

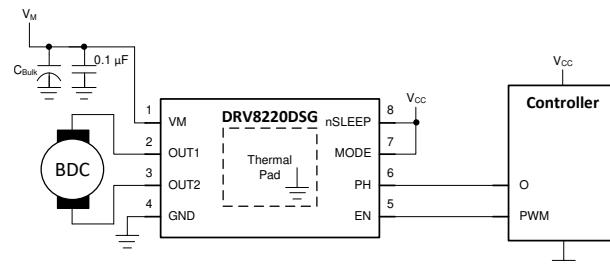

DRV8220 の標準的なアプリケーションは、出力をフルブリッジまたは H ブリッジ構成として使用し、ブラシ付き DC モーターまたはシングルコイルのラッチリレーを双方向（順方向および逆方向）で駆動します。それぞれのパッケージのバリエントについて、PWM インターフェイスでモーターを駆動する例を図 9-1 と図 9-2 に示します。PWM インターフェイスで単一コイルのラッチリレーを駆動する例を図 9-3 に示します。PH/EN インターフェイスでモーターを駆動する例を図 9-4 に示します。

図 9-1. DRL パッケージでの PWM インターフェイスのモーター駆動アプリケーション

図 9-2. DSG パッケージでの PWM インターフェイスのモーター駆動アプリケーション

図 9-3. PWM インターフェイスのシングルコイル・ラッチリレーのアプリケーション

図 9-4. PH/EN インターフェイスのモーター駆動アプリケーション

#### 9.2.1.1 設計要件

一般的な使用事例で必要なパラメータを表 9-1 に示します。

表 9-1. システム設計要件

| 設計パラメータ        | 略号              | 値の例  |

|----------------|-----------------|------|

| モーター電源電圧       | V <sub>M</sub>  | 11V  |

| マイクロコントローラ電源電圧 | V <sub>CC</sub> | 3.3V |

表 9-1. システム設計要件 (continued)

| 設計パラメータ           | 略号          | 値の例   |

|-------------------|-------------|-------|

| ターゲット・モーター RMS 電流 | $I_{motor}$ | 300mA |

| ターゲット・リレー電流       | $I_{relay}$ | 50mA  |

### 9.2.1.2 詳細な設計手順

#### 9.2.1.2.1 電源電圧

適切な供給電圧は、負荷（モーター、ソレノイド、リレーなど）の定格によって異なります。ブラシ付き DC モーターの場合、電源電圧は RPM の目標値に影響を与えます。電圧がより高ければ、パワー FET に印加されている PWM デューティ・サイクルは同じままで、ブラシ付き DC モーターをより高速に回転させることができます。また、電圧が高いと、モーター、ソレノイド、リレーの巻線を流れる電流の変化率も大きくなります。

#### 9.2.1.2.2 制御インターフェイス

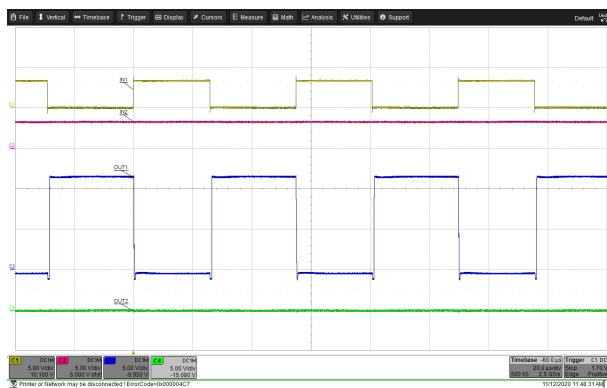

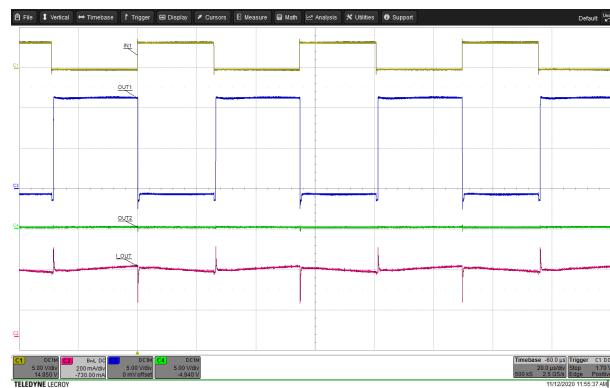

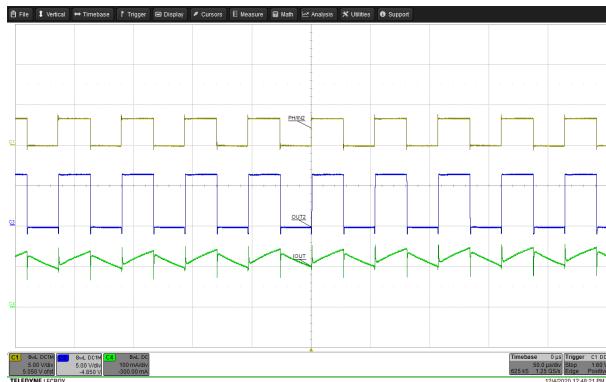

選択したパッケージに対応する PWM 制御インターフェイスを [セクション 8.3.2.1](#) に示します。図 9-2 に示すように、MODE ピンを GND ネットに直接接続することをお勧めします。ただし、アプリケーションで他のインターフェイス状態が必要な場合は、MODE ピンを GPIO ピンに接続して、動作中に他のインターフェイス・オプションを選択できます。自動スリープ機能により、わずか 2 つのピンでモーターと低消費電力モードを双方向制御できます。これにより、スリープ・ピンを制御するための別の GPIO が不要になります。PWM インターフェイスを使用したモーター駆動の波形の例を [図 9-5](#) と [図 9-6](#) に示します。

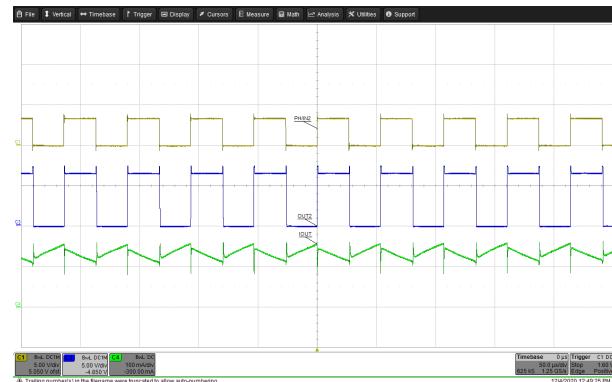

PWM インターフェイスを使用して單一コイルのリレーを駆動する波形の例を [図 9-7](#) と [図 9-8](#) に示します。これらの図に示すように、リレーは FORWARD/REVERSE 状態と、BRAKE/COAST 状態の間で駆動できます。

PH/EN 制御インターフェイスを、[セクション 8.3.2.2](#) に示します。MODE ピンをマイクロコントローラの電源に接続すると、PH/EN インターフェイスが選択されます。PH/EN モードでは、EN ピンのみをトグルすることにより、モーター駆動に必要なマイクロコントローラ PWM ジェネレータの数を減らすことができます。PH ピンは、このインターフェイスを使用してモータ駆動の方向を制御します。EN が  $t_{SLEEP}$  よりも長く LOW に保持されると、デバイスはスリープ・モードに移行します。

#### 9.2.1.2.3 低消費電力動作

低消費電力スリープ・モードの開始方法については、[セクション 8.4.2](#) で説明しています。スリープ・モードに移行するときは、すべての入力をロジック Low に設定して、システムの電力を最小化することを推奨します。

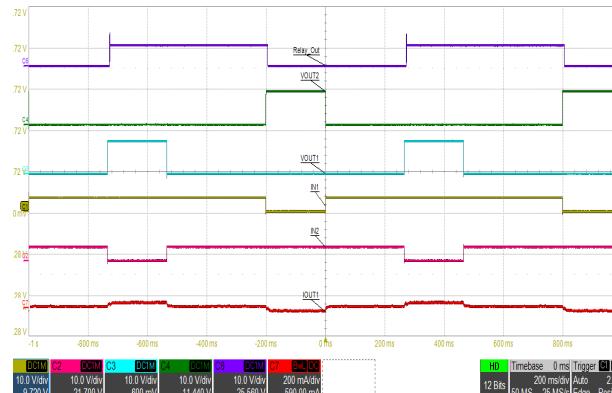

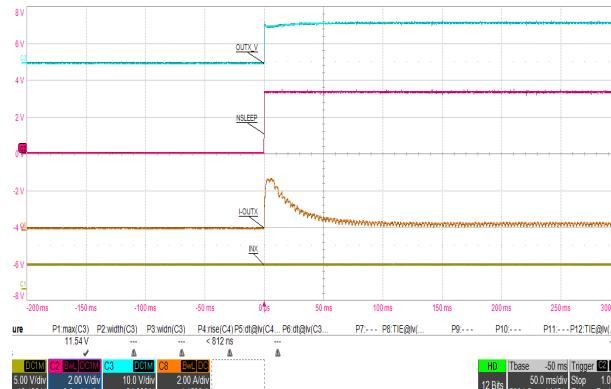

### 9.2.1.3 アプリケーション曲線

A. チャネル 1 = IN1 チャネル 2 = IN2 チャネル 3 = OUT1

チャネル 4 = OUT2

図 9-5. デューティ・サイクル 50% でのモーターの

PWM 駆動、INx と OUTx の電圧

A. チャネル 1 = IN1 チャネル 2 = モータ チャネル 3 = OUT1

チャネル 4 = OUT2

図 9-6. デューティ・サイクル 50% でのモーターの

PWM 駆動、信号とモーター電流

A. チャネル 1 = IN1 チャネル 2 = IN2 チャネル 3 = V<sub>OUT1</sub>

チャネル 4 = V<sub>OUT2</sub> チャネル 6 = リレー・ チャネル 7 = リレー・

スイッチ コイル電流

図 9-7. 単一コイルのラッチリレーによる PWM 駆動、

駆動プロファイル FORWARD → COAST →

REVERSE → COAST

A. チャネル 1 = IN1 チャネル 2 = IN2 チャネル 3 = V<sub>OUT1</sub>

チャネル 4 = V<sub>OUT2</sub> チャネル 6 = リレー・ チャネル 7 = リレー・

スイッチ コイル電流

図 9-8. 単一コイルのラッチリレーによる PWM 駆動、

駆動プロファイル FORWARD → BRAKE →

REVERSE → BRAKE

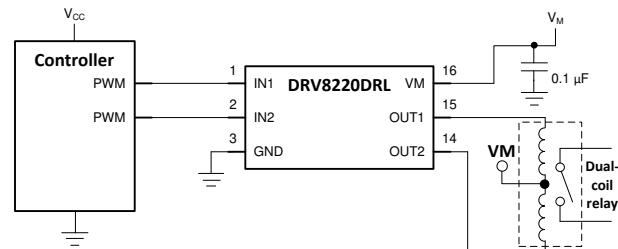

### 9.2.2 ハーフブリッジ駆動

DRV8220 は、MODE ピンをフローティング状態にすると、ハーフブリッジ・モードに設定できます。このモードでは、デバイスの出力をローサイドまたはハイサイド・ドライバとして使用できます。これにより、1 つまたは 2 つのモーターの単方向（一方向のみ）、ソレノイド、バルブ、リレーなど各種の負荷を駆動できます。デバイスの OUT1 をローサイド・ドライバ、OUT2 をハイサイド・ドライバとして使用する例を 図 9-9 に示します。両方の負荷は、ハイサイドとローサイドのどちらからでも駆動できます。図 9-10 と図 9-11 に示すように、INx ピンと OUTx ピンをそれぞれ互いに接続すると、デバイスは、半分の  $R_{DS(on)}$  で単一の負荷を駆動できます。これにより、より大きな電流要件に対応できます。この構成を「並列ハーフブリッジ・モード」と呼びます。

ハーフブリッジ・モードでは、PWM デューティ・サイクルのオフ時間に、ハーフブリッジ内にある他の FET とボディ・ダイオードがフリーホイール電流を再循環させるため、追加の外部ダイオードは不要です。

図 9-9. ハーフブリッジ・モードを、2 つの負荷用のハイサイドおよびローサイド・ドライバとして使用

図 9-10. ハーフブリッジ・モードを、出力が並列化されたハイサイド・ドライバとして使用

図 9-11. ハーフブリッジ・モードを、出力が並列化されたローサイド・ドライバとして使用

### 9.2.2.1 設計要件

図 9-9 に示されている使用事例に必要なパラメータを [表 9-2](#) に示します。

**表 9-2. システム設計要件**

| 設計パラメータ        | 略号         | 値の例                    |

|----------------|------------|------------------------|

| 負荷電源電圧         | $V_M$      | 12V                    |

| マイクロコントローラ電源電圧 | $V_{MCU}$  | 3.3V                   |

| 最大バルブ電流        | $I_{OUT1}$ | 100ms にわたって 100mA のパルス |

| 最大ポンプ電流        | $I_{OUT2}$ | 600mA (RMS)            |

### 9.2.2.2 詳細な設計手順

#### 9.2.2.2.1 電源電圧

適切な電源電圧は、負荷の定格によって異なります。

#### 9.2.2.2.2 制御インターフェイス

DSG パッケージのハーフブリッジ制御インターフェイスについては、[セクション 8.3.2.3](#) に説明されています。

#### 9.2.2.2.3 低消費電力動作

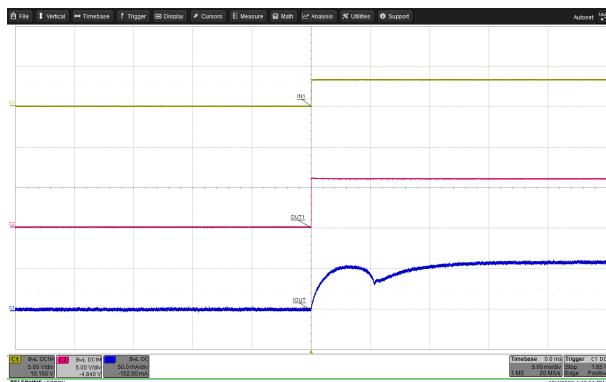

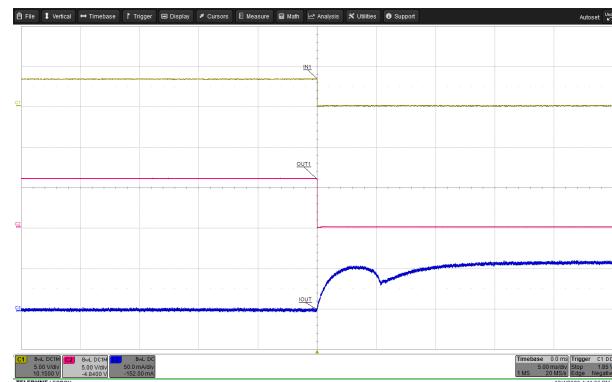

$nSLEEP$  を 0V にすると、DRV8220 はハーフブリッジ・モードでスリープ状態に移行します。低消費電力スリープ・モードの詳細な開始方法については、[セクション 8.4.2](#) で説明しています。スリープ・モードに移行するときは、システムの電力を最小化するため、すべての入力をロジック Low に設定することを推奨します。DRV8220 をハーフブリッジ・モードでウェークアップするには、 $nSLEEP$  を High にした後で、IN1 または IN2 を  $t_{WAKE}$  より長い時間だけ High に設定してから Low に戻すか、PWM 信号を送信します。このウェークアップ手順を、[図 9-16](#) と [図 9-17](#) に示します。

OUTx ピンからのリーク電流を最小限に抑えるために (特にバッテリ駆動のアプリケーションで)、OUTx から GND に負荷を接続してください。前述のように、OUTx から  $V_M$  に負荷を接続することも可能ですが、負荷がディセーブルされたときに OUTx へ多少のリーク電流が発生することがあります。負荷が H ブリッジ構成で接続されている場合、予想されるリーク電流はありません。

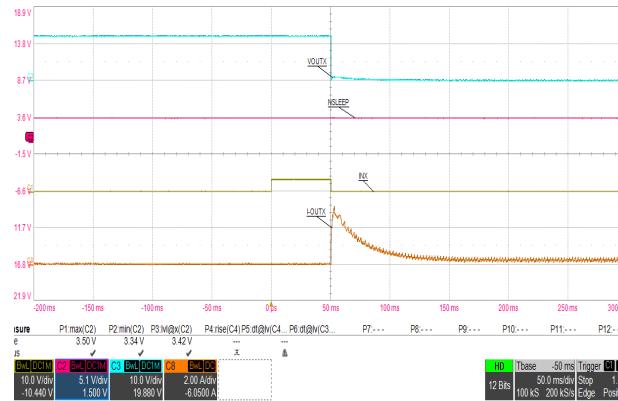

#### 9.2.2.3 アプリケーション曲線

以下の図は、ハーフブリッジ・モードでのハイサイドおよびローサイド駆動の波形の例を示しています。[図 9-12](#) と [図 9-13](#) に、ハイサイドとローサイドの駆動を使用してモーターを単方向で駆動する波形の例を示します。[図 9-14](#) と [図 9-15](#) に、ハイサイドとローサイドの駆動を使用してソレノイドを駆動する波形の例を示します。[図 9-16](#) と [図 9-17](#) に、OUTx ピンを並列に接続してシングル・ハーフブリッジを形成し、ハイサイドとローサイドの駆動を使用してモーターを駆動する例を示します。

A. チャネル 1 = IN2 チャネル 2 =  $V_{OUT2}$  チャネル 4 = モータ

一電流

図 9-12. ハイサイド FET を使用してデューティ・サイ

クル 50% のハーフブリッジ・モードでモーターを駆動

する

A. チャネル 1 = IN2 チャネル 2 =  $V_{OUT2}$  チャネル 4 = モータ

一電流

図 9-13. ローサイド FET を使用してデューティ・サイ

クル 50% のハーフブリッジ・モードでモーターを駆動

する

A. チャネル 1 = IN1 チャネル 2 =  $V_{OUT1}$  チャネル 4 = ソレノイ

ド電流

図 9-14. ハイサイド FET を使用して、ハーフブリッ

ジ・モードでソレノイドを駆動する

A. チャネル 1 = IN1 チャネル 2 =  $V_{OUT1}$  チャネル 4 = ソレノイ

ド電流

図 9-15. ローサイド FET を使用して、ハーフブリッ

ジ・モードでソレノイドを駆動する

A. チャネル 1 = IN1、

IN2 (並列)

チャネル 8 = モータ

一電流

チャネル 2 = チャネル 3 =  $V_{OUT}$

$V_{nSLEEP}$  (OUT1/2 の並列)

A. チャネル 1 = IN1、

IN2 (並列)

チャネル 8 = モータ

一電流

チャネル 2 = チャネル 3 =  $V_{OUT}$

$V_{nSLEEP}$  (OUT1/2 の並列)

図 9-16. ハイサイド FET を使用して並列ハーフブリッジ・モードでモーターを駆動する 図 9-17. ローサイド FET を使用して並列ハーフブリッジ・モードでモーターを駆動する

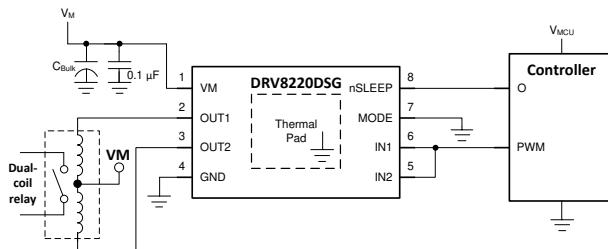

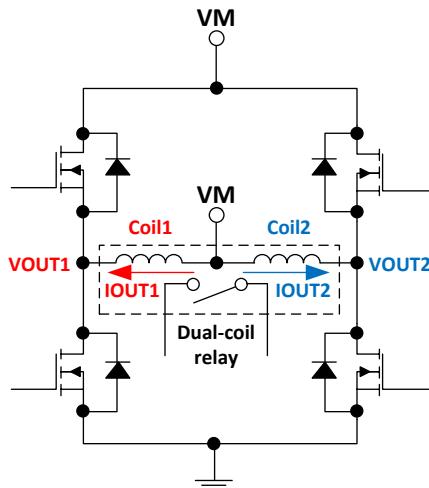

### 9.2.3 デュアルコイル・リレーの駆動

PWM インターフェイスは、デュアルコイルのラッチ・リレーを駆動するためにも使用できます。回路図の例を、このセクションの図に、回路図の例を示します。

図 9-18. デュアルコイル・リレーの駆動、DSG パッケージ 図 9-19. デュアルコイル・リレーの駆動、DRL パッケージ

#### 9.2.3.1 設計要件

デュアルコイル・リレー・アプリケーションの要件の例を [表 9-3](#) に示します。

表 9-3. システム設計要件

| 設計パラメータ        | 略号                   | 値の例                    |

|----------------|----------------------|------------------------|

| モーター電源電圧       | $V_M$                | 12V                    |

| マイクロコントローラ電源電圧 | $V_{CC}$             | 3.3V                   |

| リレー電流          | $I_{OUT1}, I_{OUT2}$ | 100ms にわたって 500mA のパルス |

#### 9.2.3.2 詳細な設計手順

##### 9.2.3.2.1 電源電圧

適切な電源電圧は、負荷の定格によって異なります。

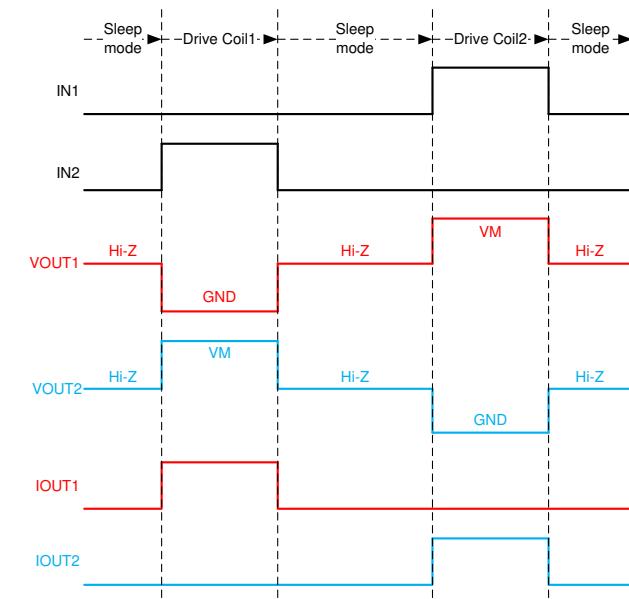

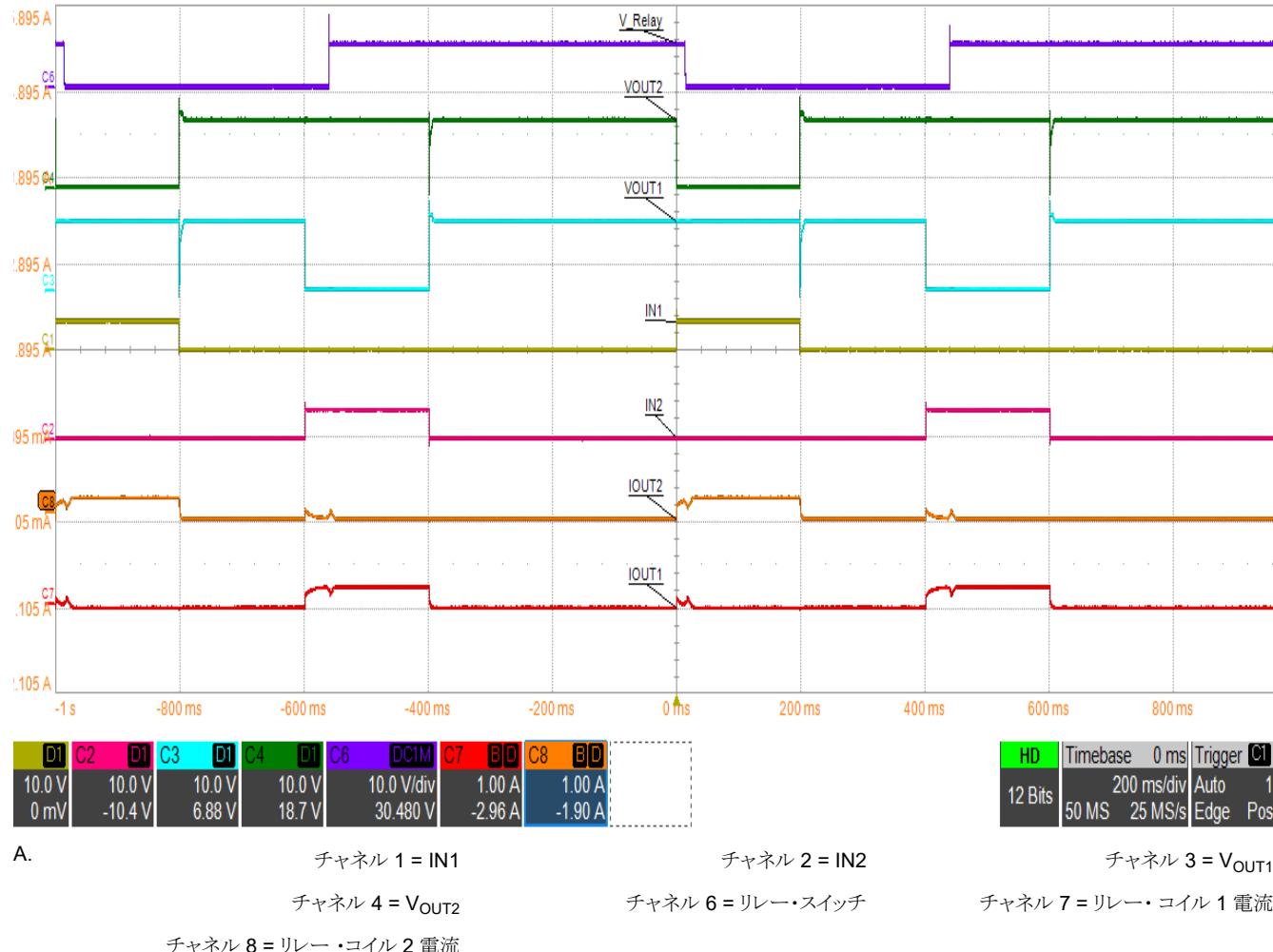

### 9.2.3.2.2 制御インターフェイス

PWMインターフェイスは、デュアルコイル・リレーの駆動に使用できます。セクション 8.3.2.1 に、PWM制御インターフェイスを示します。PWMインターフェイスを使用したデュアルコイル・リレー駆動の回路図とタイミング図を、図 9-20 と図 9-21 に示します。

図 9-20. OUTx H ブリッジで駆動するデュアルコイル・リレーの回路図

図 9-21. PWMインターフェイスを使用したデュアルコイル・リレーの駆動タイミング図

PWMインターフェイスの真理値表を表 9-4 に示します。この表の説明は、入力と出力の状態によってデュアルコイル・リレーを駆動する方法を反映しています。coil1 が駆動されるとき (OUT1 電圧が GND のとき)、OUT2 の電圧は VM になります。リレーのセンター・タップも VM なので、電流は coil2 を流れません。coil2 が駆動される場合も同様で、coil1 は VM に短絡します。ハイサイド FET のボディ・ダイオードはフリーホイール・ダイオードとして機能するため、追加の外部ダイオードは不要です。このアプリケーションのオシロスコープのパターンを、図 9-22 に示します。

表 9-4. デュアルコイル・リレー駆動用の PWM制御表

| IN1 | IN2 | OUT1 | OUT2 | 説明                                         |

|-----|-----|------|------|--------------------------------------------|

| 0   | 0   | Hi-Z | Hi-Z | 出力ディセーブル (H ブリッジ Hi-Z)                     |

| 0   | 1   | L    | H    | coil1 の駆動                                  |

| 1   | 0   | H    | L    | coil2 の駆動                                  |

| 1   | 1   | L    | L    | coil1 と coil2 の駆動 (デュアルコイル・ラッチ・リレーでは無効な状態) |

### 9.2.3.2.3 低消費電力動作

低消費電力スリープ・モードの開始方法については、セクション 8.4.2 で説明しています。スリープ・モードに移行するときは、すべての入力をロジック Low に設定して、システムの電力を最小化することを推奨します。

OUTx ピンからのリーク電流を最小限に抑えるために (特にバッテリ駆動のアプリケーションで)、OUTx から GND に負荷を接続してください。前のセクションで示したように、OUTx から VM に負荷を接続することも可能ですが、負荷がディセーブルされたときに OUTx へ多少のリーク電流が発生することがあります。

### 9.2.3.3 アプリケーション曲線

図 9-22. デュアルコイル・リレーの PWM 駆動

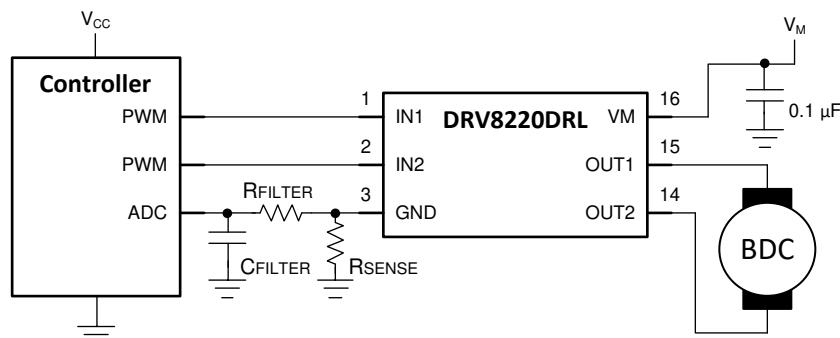

### 9.2.4 電流センス

GND ピンに小さなシャント抵抗を接続すると、電流センスの情報をマイクロコントローラの ADC に返すことができます。マイクロコントローラはこの情報を使用して、ストールなどのモーター負荷条件を検出できます。DRL パッケージを使用した回路図の例を 図 9-23 に示します。さらに優れた電流センスのダイナミック・レンジが必要な場合は、図 9-24 に示すようにアンプを追加できます。

DSG サーマル・パッドは、基板のグランド・ネット、または GND ピン / センス信号ネットに接続できます。

図 9-23. DRL パッケージの DRV8220 で GND ピンに接続するシャント抵抗

図 9-24. 電流センス・アンプの例

#### 9.2.4.1 設計要件

電流センス・アプリケーションの要件の例を [表 9-5](#) に示します。

表 9-5. システム設計要件

| 設計パラメータ               | 略号                               | 値の例   |

|-----------------------|----------------------------------|-------|

| モーター電源電圧              | $V_M$                            | 12V   |

| マイクロコントローラ電源電圧        | $V_{CC}$                         | 3.3V  |

| $R_{SENSE}$ の両端間の最大電圧 | $V_{SENSE}$                      | 150mV |

| モーター RMS 電流           | $I_{OUT1}, I_{OUT2}$             | 500mA |

| モーターのストール電流           | $I_{OUT1,stall}, I_{OUT2,stall}$ | 1A    |

#### 9.2.4.2 詳細な設計手順

##### 9.2.4.2.1 シャント抵抗の決定

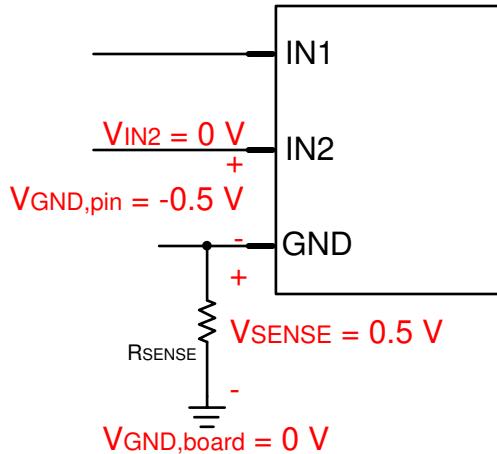

$IN_x$  ピンの絶対最大定格は、シャント抵抗の両端の最大電圧を設定するものです。 $IN_x$  ピンの信号が Low で基板グランドを基準とした場合、 $IN_x$  ピンは GND ピンの電圧を基準とした負の電圧になります。これにより、最大センス電圧 / GND ピン電圧が 0.5V に設定されます。相対ピン電圧を [図 9-25](#) に示します。

図 9-25. 電流センス抵抗を使用する基板グランドを基準としたピン電圧

この例では、最大  $V_{SENSE}$  として 150mV を使用します。これは 0.5V 未満で、安全や誤差の余裕があります。モーターに流れる最大電流はストール電流、この例では 1A です。この情報から、検出抵抗  $R_{SENSE}$  は次の式で計算できます。

$$R_{SENSE} = V_{SENSE} / I_{STALL} = 0.15 / 1 = 0.15\Omega \quad (1)$$

デバイスの GND ピンの電圧は、検出抵抗を流れる電流によって変化するため、設計者はロジック・ピンが  $V_{IL}$  と  $V_{IH}$  のパラメータを満たし、MODE ピンが  $V_{TIL}$ 、 $V_{TIZ}$ 、および  $V_{TIH}$  パラメータを満たし、電源電圧が常に  $V_{UVLO}$  より高く維持されることを確認する必要があります。

#### 9.2.4.2.2 RC フィルタ

図 9-23 に示す RC フィルタを使用して、センス信号からのノイズと過渡信号をフィルタします。 $R_{FILTER} = 1k\Omega$ 、 $C_{FILTER} = 100nF$  を推奨します。システムの特定の条件に応じて、異なる値を選択できます。

### 9.3 電流能力と熱性能

ドライバの出力電流および消費電力能力は、PCB の設計と外部システムの条件に大きく依存します。ここでは、これらの値を計算するための指針を提示します。

#### 9.3.1 消費電力および出力電流特性

本デバイスの総消費電力は、静止消費電流 ( $P_{VM}$ )、パワー MOSFET のスイッチング損失 ( $P_{SW}$ )、およびパワー MOSFET の  $R_{DS(on)}$  (伝導) 損失 ( $P_{RDS}$ ) の 3 つの主要な成分に分けられます。それ以外の要素が消費電力の増加に影響することもありますが、この 3 つの主要な要素に比べると通常わずかです。

$$P_{TOT} = P_{VM} + P_{SW} + P_{RDS} \quad (2)$$

$P_{VM}$  は、公称モーター電源電圧 ( $V_{VM}$ ) と、 $I_{VM}$  アクティブ・モード電流の仕様から計算できます。

$$P_{VM} = V_{VM} \times I_{VM} \quad (3)$$

$$P_{VM} = 16.8mW = 12V \times 1.4mA \quad (4)$$

$P_{SW}$  は、公称モーター電源電圧 ( $V_{VM}$ )、平均出力電流 ( $I_{RMS}$ )、スイッチング周波数 ( $f_{PWM}$ )、デバイス出力立ち上がり ( $t_{RISE}$ ) および立ち下がり ( $t_{FALL}$ ) 時間の仕様から計算できます。

$$P_{SW} = P_{SW\_RISE} + P_{SW\_FALL} \quad (5)$$

$$P_{SW\_RISE} = 0.5 \times V_M \times I_{RMS} \times t_{RISE} \times f_{PWM} \quad (6)$$

$$P_{SW\_FALL} = 0.5 \times V_M \times I_{RMS} \times t_{FALL} \times f_{PWM} \quad (7)$$

$$P_{SW\_RISE} = 9mW = 0.5 \times 12V \times 0.5A \times 150ns \times 20kHz \quad (8)$$

$$P_{SW\_FALL} = 9mW = 0.5 \times 12V \times 0.5A \times 150ns \times 20kHz \quad (9)$$

$$P_{SW} = 18mW = 9mW + 9mW \quad (10)$$

$P_{RDS}$  は、デバイスの  $R_{DS(on)}$  と平均出力電流 ( $I_{RMS}$ ) から計算できます。

$$P_{RDS} = I_{RMS}^2 \times (R_{DS(ON)\_HS} + R_{DS(ON)\_LS}) \quad (11)$$

$R_{DS(ON)}$  はデバイス温度と強い相関があります。デバイスの接合部温度を  $85^{\circ}C$  と仮定すると、正規化した温度データに基づき、 $R_{DS(on)}$  は約 1.5 倍に増大する可能性があります。下の計算は、このディレーティング係数を示しています。または、[セクション 7.6](#) セクションには  $R_{DS(on)}$  が温度に応じてどのように変化するかを示す曲線が記されています。

$$P_{RDS} = 375mW = (0.5A)^2 \times (500m\Omega \times 1.5 + 500m\Omega \times 1.5) \quad (12)$$

上記の計算例に基づき、以下の式でデバイスの予想される消費電力の合計を計算します。

$$P_{TOT} = P_{VM} + P_{SW} + P_{RDS} \quad (13)$$

$$P_{TOT} = 410mW = 16.8mW + 18mW + 375mW \quad (14)$$

デバイス接合部温度は、 $P_{TOT}$ 、デバイス周囲温度 ( $T_A$ )、パッケージ熱抵抗 ( $R_{\theta JA}$ ) を使って推定できます。 $R_{\theta JA}$  の値は、PCB 設計と、デバイス周りの銅のヒートシンクに大きく依存します。[セクション 9.3.2](#) に、この依存関係を詳細に説明します。

$$T_J = (P_{TOT} \times R_{\theta JA}) + T_A \quad (15)$$

$$T_J = 124^{\circ}C = (0.410W \times 94.7^{\circ}C/W) + 85^{\circ}C \quad (16)$$

デバイスの接合部温度は、システムのすべての動作条件について、絶対最大定格より低く維持する必要があります。このセクションの計算では、接合部温度の妥当な推定値を示します。ただし、システム動作中の温度測定に基づくその他の方法は、より現実的で信頼性の高いものになります。モーター・ドライバの定格電流と消費電力の詳細については、「[セクション 9.3.2](#)」および「[セクション 12.1.1](#)」を参照してください。

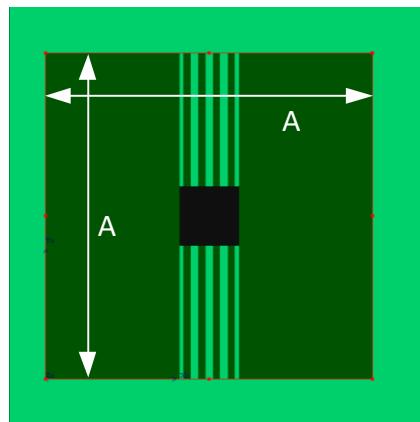

### 9.3.2 熱性能

データシートに規定する接合部から周囲への熱抵抗  $R_{\theta JA}$  は、おもに各種ドライバの比較または熱性能の概算に役立ちます。しかし、実際のシステム性能は、PCB 層構成 (スタックアップ)、配線、ビア数、サーマル・パッド周りの銅面積に応じて、この値よりも良くなったり、悪くなったりします。ドライバが特定の電流を駆動する時間の長さもまた、消費電力や熱性能に影響を与えます。ここでは、定常状態および過渡熱条件での設計方法について考察します。

このセクションのデータは、次の基準を使用してシミュレーションしたものです。

#### WSON (DSG パッケージ)

- 2 層 PCB、標準 FR4、1oz (35 $\mu$ m 銅箔厚) または 2oz 銅箔厚。サーマル・ビアはサーマル・パッドの下にのみ配置 (2 個のビア、1.2mm 間隔、0.3mm 直径、0.025mm 銅メッキ)。

- 上層: DRV8220 WSON パッケージ・フットプリントおよび銅プレーン・ヒートシンク。シミュレーションでは、上層の銅領域が変化しています。

- 下層: DRV8220 用にサーマル・パッドの下でビアを介して熱的に接続されたグランド・プレーン。下層の銅領域は、上部の銅領域によって異なります。

- 4 層 PCB、標準 FR4。外側のプレーンは 1oz (35 $\mu$ m 銅箔厚) または 2oz 銅箔厚。内側のプレーンは 1oz で一定。サーマル・ビアはサーマル・パッドの下にのみ配置 (2 個のビア、1.2mm 間隔、0.3mm 直径、0.025mm 銅メッキ)。

- 上層: DRV8220 WSON パッケージ・フットプリントおよび銅プレーン・ヒートシンク。シミュレーションでは、上層の銅領域が変化しています。

- 中間層 1: DRV8220 サーマル・パッドにビアを介して熱的に接続された GND プレーン。グランド・プレーンの領域は 74.2mm x 74.2mm です。

- 中間層 2: 電源プレーン、熱的接続なし。電源プレーンの領域は 74.2mm x 74.2mm です。

- 下層: DRV8220 の下に小さな銅パッドを設け、上層および内部 GND プレーンから打ったビアで熱的に接続した信号層。下層のサーマル・パッドはパッケージと同じサイズ (2 mm x 2 mm)。上層の銅プレーンが変化しても、下層のパッドのサイズは一定。

HTSSOP パッケージについてシミュレーションした基板の例を [図 9-26](#) に示します。表 9-6 に、各シミュレーションで変化させた基板の寸法を示します。

図 9-26. WSON PCB モデルの上層

表 9-6. 16 ピン PWP パッケージの寸法 A

| 銅 (Cu) 面積 (mm <sup>2</sup> ) | 寸法 A (mm) |

|------------------------------|-----------|

| 2                            | 15.11     |

| 4                            | 20.98     |

| 8                            | 29.27     |

| 16                           | 40.99     |

### SOT (DRL パッケージ)

- 2 層 PCB、標準 FR4、1oz (35μm 銅箔厚) または 2oz 銅箔厚。サーマル・ビアはパッケージのフットプリントの下にのみ配置 (2 個のビア、1.2mm 間隔、0.3mm 直径、0.025mm 銅メッキ)。

- 上層: DRV8220 SOT パッケージのフットプリントと、銅プレーンのヒートシンク。シミュレーションでは、上層の銅領域が変化しています。

- 下層: DRV8220DRL パッケージのフットプリントの下で、ビアを介して熱的に接続される GND プレーン。下層の銅領域は、上部の銅領域によって異なります。

- 4 層 PCB、標準 FR4。外側のプレーンは 1oz (35μm 銅箔厚) または 2oz 銅箔厚。内側のプレーンは 1oz で一定。サーマル・ビアは、DRV8220DRL パッケージのフットプリントの下にのみ配置 (2 個のビア、1.2mm 間隔、0.3mm 直径、0.025mm 銅メッキ)。

- 上層: DRV8220 SOT パッケージのフットプリントと、銅プレーンのヒートシンク。シミュレーションでは、上層の銅領域が変化しています。

- 中間層 1: DRV8220DRL パッケージのフットプリントの下で、ビアを介して熱的に接続される GND プレーン。グランド・プレーンの領域は 74.2mm x 74.2mm です。

- 中間層 2: 電源プレーン、熱的接続なし。電源プレーンの領域は 74.2mm x 74.2mm です。

- 下層: DRV8220DRL の下に小さな銅パッドを設け、上層および内部 GND プレーンから打ったビアで熱的に接続した信号層。下層のサーマル・パッドはパッケージと同じサイズ (1.2 mm x 1.6 mm)。上層の銅プレーンが変化しても、下層のパッドのサイズは一定。

HTSSOP パッケージについてシミュレーションした基板の例を [図 9-27](#) に示します。表 9-7 に、各シミュレーションで変化させた基板の寸法を示します。

図 9-27. SOT PCB モデルの上層

表 9-7. 16 ピン PWP パッケージの寸法 A

| 銅 (Cu) 面積 (mm <sup>2</sup> ) | 寸法 A (mm) |

|------------------------------|-----------|

| 2                            | 15.11     |

| 4                            | 20.98     |

| 8                            | 29.27     |

| 16                           | 40.99     |

### 9.3.2.1 定常状態熱性能

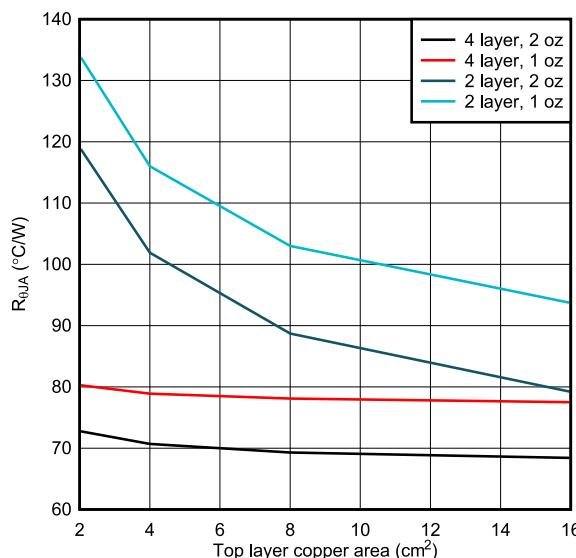

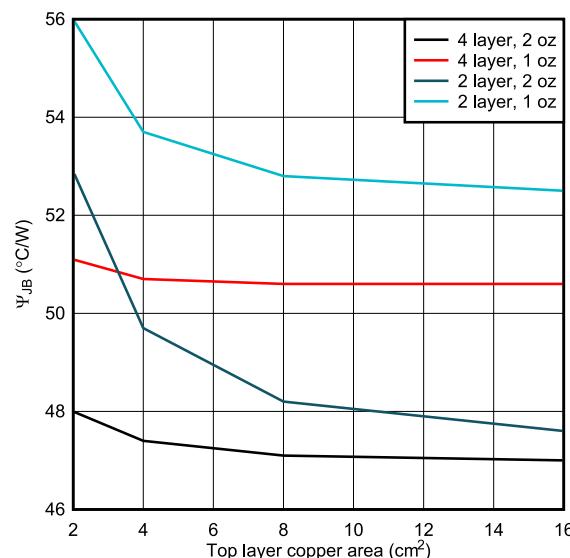

「定常状態条件」とは、モーター・ドライバが長時間にわたって一定の RMS 電流で動作することを指します。このセクションの図は、銅面積、銅厚、PCB 層数に応じた  $R_{\theta JA}$  と  $\Psi_{JB}$  (接合部から基板への熱特性) の変化を示しています。銅面積が大きく、層数が多く、銅プレーンが厚いほど、 $R_{\theta JA}$  と  $\Psi_{JB}$  は小さくなり、PCB レイアウトの熱性能が高くなることを示しています。

図 9-28. WSON、PCB の接合部から周囲への熱抵抗と

銅面積との関係

図 9-29. WSON、接合部から基板への特性パラメータ

と銅面積との関係

図 9-30. SOT、PCB の接合部から周囲への熱抵抗と銅面積との関係

図 9-31. SOT、接合部から基板への特性パラメータと銅面積との関係

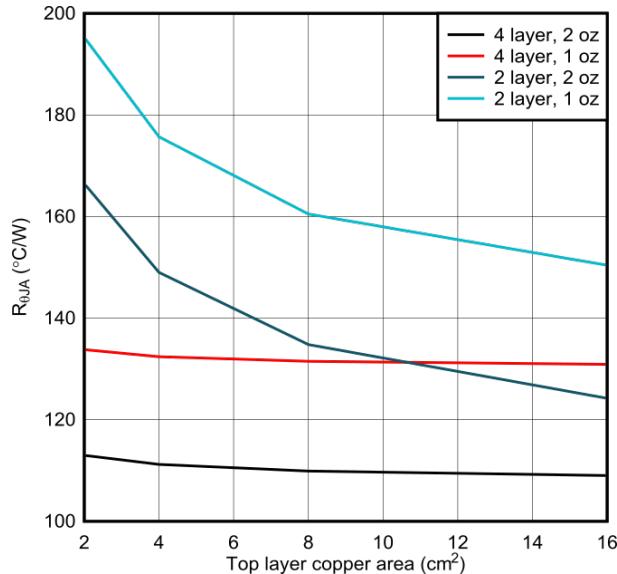

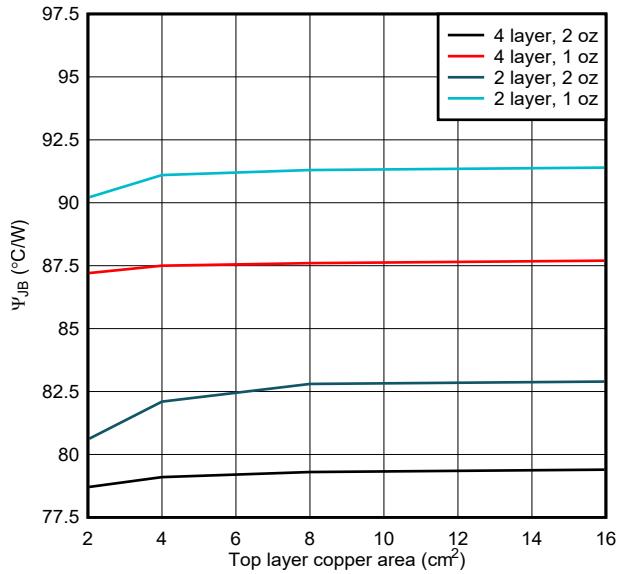

### 9.3.2.2 過渡熱性能

モーター・ドライバには、さまざまな過渡状況が発生し、短時間に大きな電流が流れる可能性があります。たとえば、次のとおりです。

- ローターが最初に静止しているときのモーター起動。

- 電源またはグランドがモーターの出力のいずれかに短絡し、過電流保護がトリガされるフォルト条件。

- モーターまたはソレノイドが短時間駆動された後、解放される。

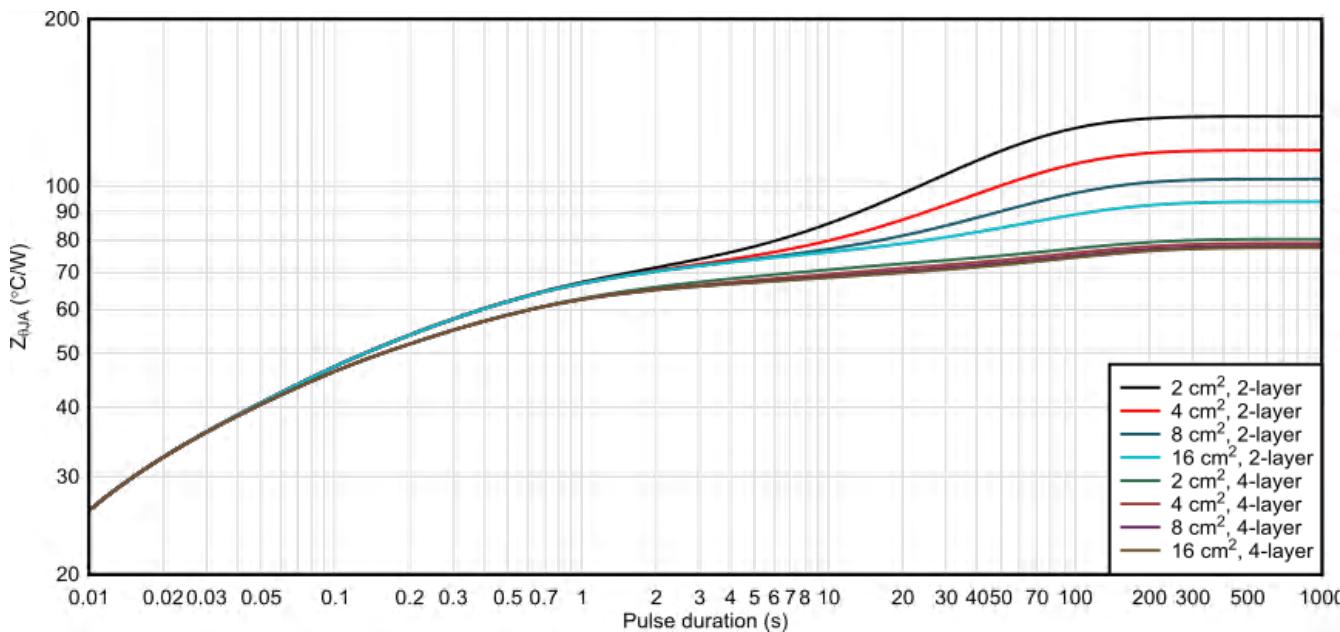

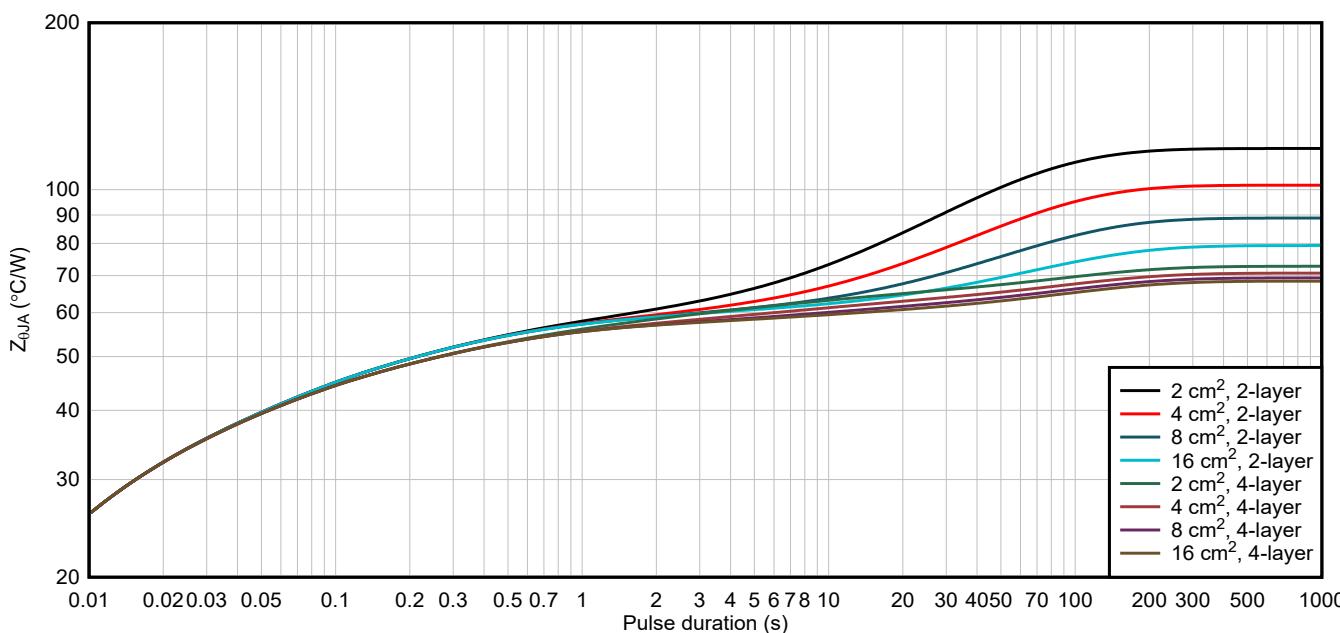

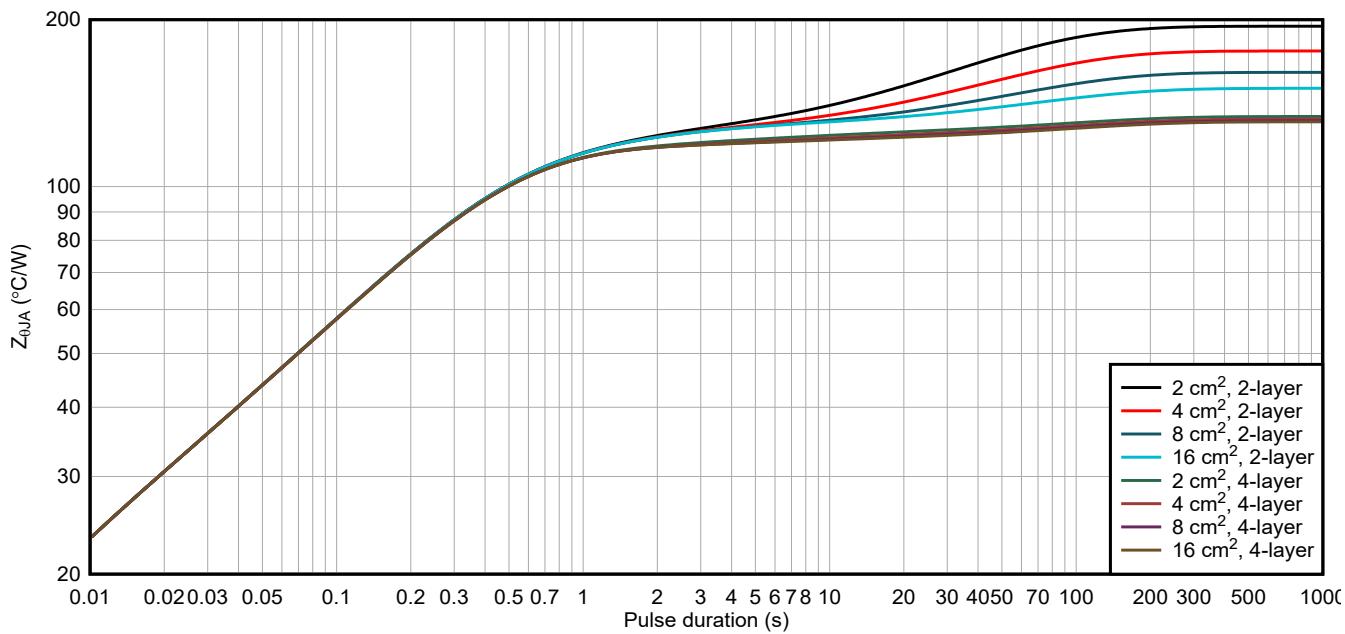

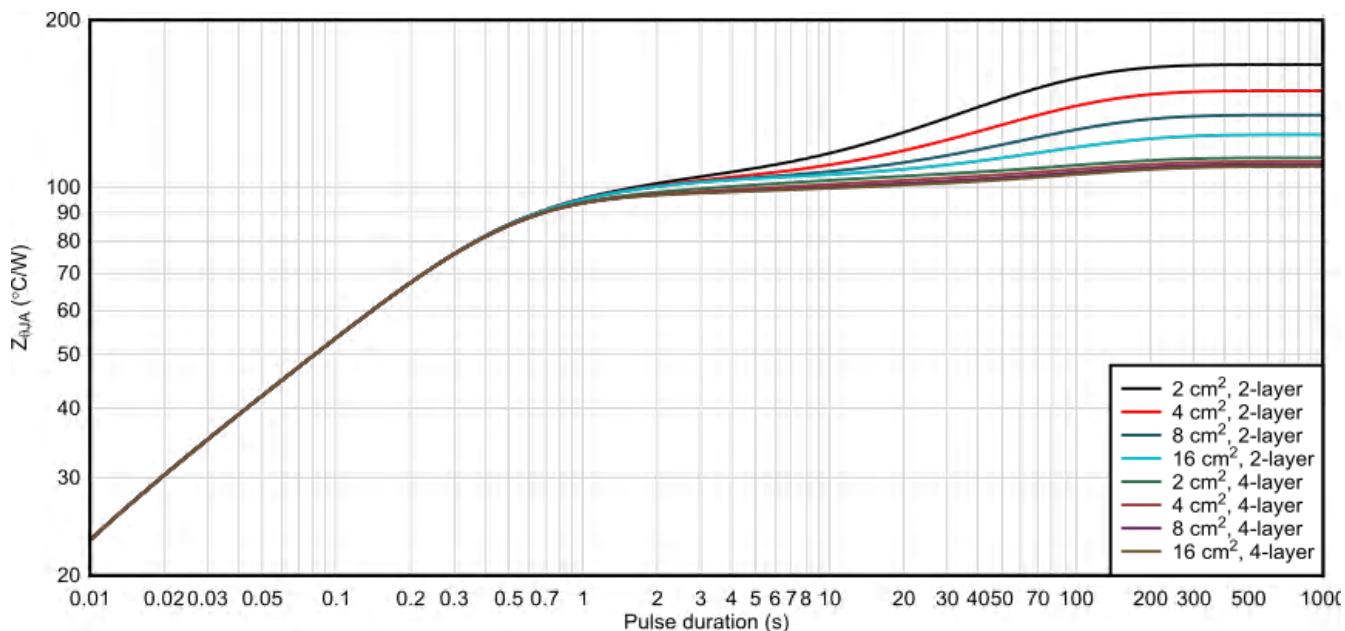

このような過渡条件では、銅の面積や厚さに加えて、駆動時間も熱性能に影響を与えます。過渡条件の場合、熱インピーダンス ( $Z_{\theta JA}$ ) パラメータは、接合部から周囲への熱性能を示します。このセクションの図は、WSON と SOT パッケージ用の 1oz および 2oz の銅のレイアウトをシミュレートしたものです。これらのグラフは、短い電流パルスで熱性能が高くなることを示しています。駆動時間が短い場合、本デバイスのダイのサイズとパッケージが熱性能を決定します。より長い駆動パルスの場合、基板レイアウトが熱性能により大きな影響を与えます。どちらのグラフの熱インピーダンス曲線も、駆動パルス期間が長くなるに従って層数と銅面積に応じた差が観測されることを示しています。パルスが長い場合、定常状態の性能とみなすことができます。

図 9-32. WSON パッケージと 1oz 銅レイアウトでの、接合部から周囲への熱インピーダンス

図 9-33. WSON パッケージと 2oz 銅レイアウトでの、接合部から周囲への熱インピーダンス

図 9-34. SOT パッケージと 1oz 銅レイアウトでの、接合部から周囲への熱インピーダンス

図 9-35. SOT パッケージと 2oz 銅レイアウトでの、接合部から周囲への熱インピーダンス

## 10 電源に関する推奨事項

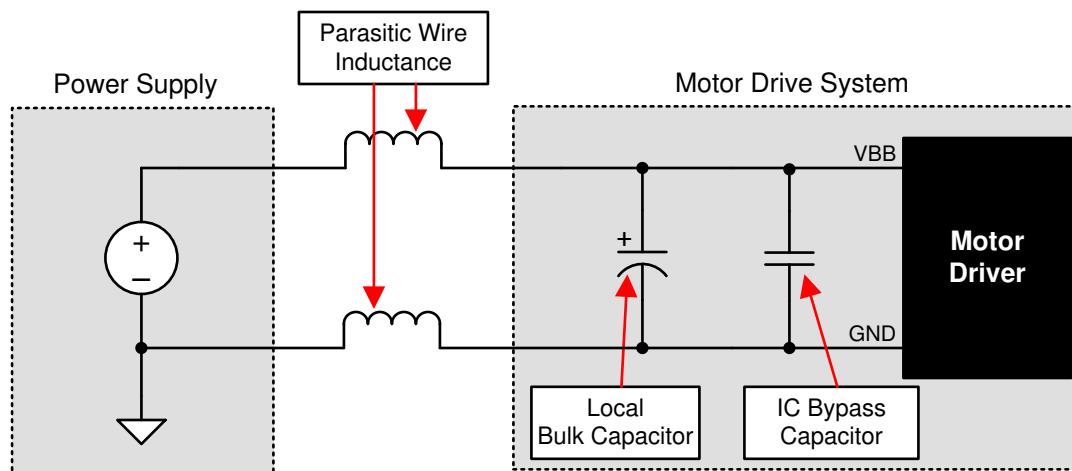

### 10.1 バルク容量

適切なローカル・バルク容量の確保は、モーター・ドライブ・システムの設計において重要な要素です。バルク容量を増やすと、一般にメリットがありますが、コストの増大と大型化というデメリットも伴います。

必要なローカル・バルク容量値は、次のようなさまざまな要素で決まります。

- モーターまたは負荷が必要とする最大電流

- 電源容量と電流供給能力

- 電源とモーター・システムの間の寄生インダクタンスの大きさ

- 許容されるシステムの電圧リップル

- モーターのブレーキ方式 (該当する場合)

電源とモーター・ドライブ・システムの間のインダクタンスにより、電源からの電流の変化する速度が制限されます。ローカル・バルク容量が小さすぎると、モーターに大電流を供給しようとする場合、または負荷ダンプが発生した場合、システムの電圧が変動します。十分なバルク容量を備えることで、モーターの電圧は安定し、大電流を素早く供給できます。

データシートには一般に、推奨最小値が記載されていますが、バルク・コンデンサの容量が適切かどうかを判断するには、システム・レベルのテストが必要です。

図 10-1. システム電源の寄生成分の例

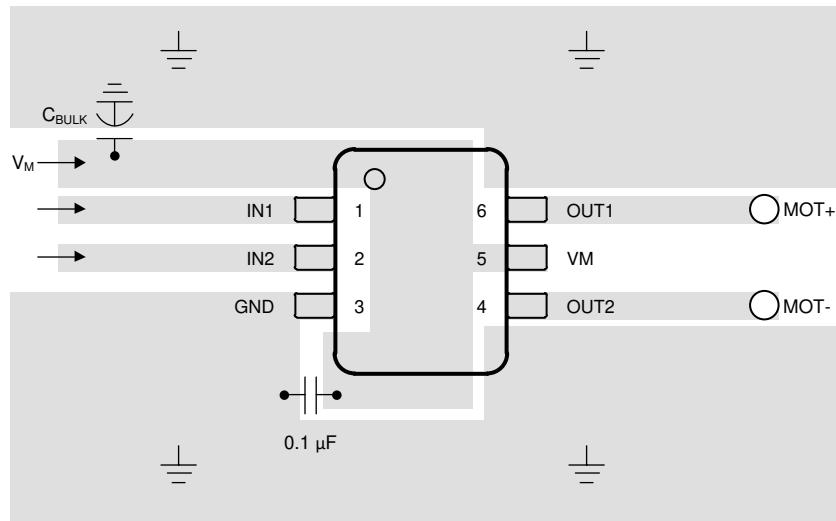

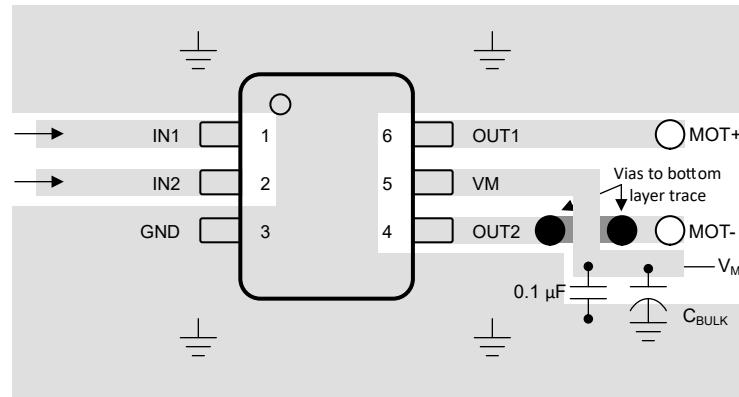

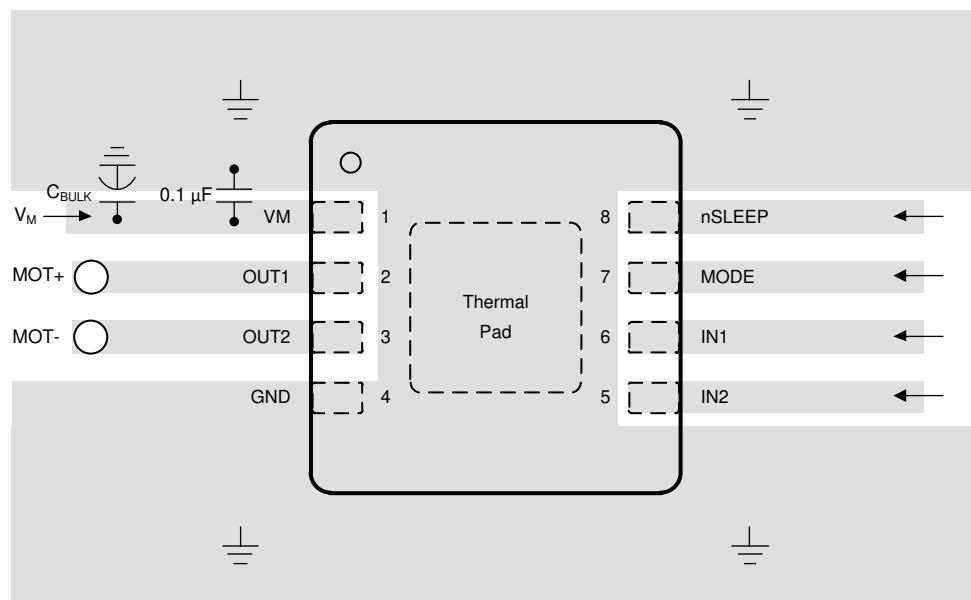

## 11 レイアウト

### 11.1 レイアウトのガイドライン

DRV8220 デバイスにはパワー MOSFET が内蔵されており、大電流を駆動できるため、レイアウト設計と外部部品の配置には細心の注意を払う必要があります。設計とレイアウトに関する指針は以下のとおりです。レイアウトに関する推奨事項の詳細については、『モータードライバの基板レイアウトのベスト・プラクティス』(英語)をご覧ください。

- VM と GND 間バイパス・コンデンサには、低 ESR のセラミック・コンデンサを使用する必要があります。X5R および X7R タイプを推奨します。

- ループ・インダクタンスを最小限に抑えるため、VM 電源コンデンサは、デバイスにできるだけ近く配置する必要があります。

- VM 電源バルク・コンデンサはセラミックまたは電解タイプとすることができますが、やはりループ・インダクタンスを最小限に抑えるため、デバイスにできるだけ近付けて配置する必要があります。

- VM、OUT1、OUT2、GND は電源から出力へ大電流を供給し、グランドに戻します。これらのトレースには、実現可能であれば、太い金属配線を使用する必要があります。

- GND は、PCB のグランド・プレーンに直接接続する必要があります。

- PCB のヒートシンクを最大限に確保するため、本デバイスのサーマル・パッドは、PCB 上層のグランド・プレーン(と、利用可能な場合、サーマル・ビアを介して内部グランド・プレーン)に取り付ける必要があります。

- 最適なヒートシンクを実現するために、サーマル・パッドを取り付ける銅プレーンの面積はできるだけ大きくする必要があります。

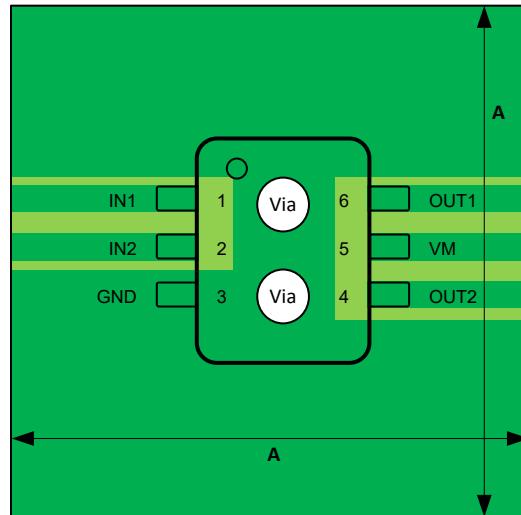

### 11.2 レイアウト例

図 11-1. ピアなしでの DRL パッケージの簡略化されたレイアウト例

図 11-2. 銅面積が大きく放熱特性に優れた、 DRL パッケージの簡略化されたレイアウト例

図 11-3. DSG パッケージの簡略化されたレイアウト例

## 12 デバイスおよびドキュメントのサポート

### 12.1 ドキュメントのサポート

#### 12.1.1 関連資料

関連資料については、以下を参照してください。

- テキサス・インスツルメンツ、『モーター・ドライバ消費電力の計算』アプリケーション・レポート (英語)

- テキサス・インスツルメンツ、『PowerPAD™の簡単な使用法』アプリケーション・レポート

- テキサス・インスツルメンツ、『熱特性強化型パッケージ PowerPAD™』アプリケーション・レポート

- テキサス・インスツルメンツ、『モーター・ドライバ電流定格の説明』アプリケーション・レポート (英語)

- テキサス・インスツルメンツ、『モータ・ドライバの基板レイアウトのベスト・プラクティス』アプリケーション・レポート

### 12.2 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on [ti.com](http://ti.com). Click on *Subscribe to updates* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

### 12.3 サポート・リソース

**TI E2E™ サポート・フォーラム**は、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、該当する貢献者により、現状のまま提供されるものです。これらは TI の仕様を構成するものではなく、必ずしも TI の見解を反映したものではありません。TI の使用条件を参照してください。

### 12.4 商標

TI E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 12.5 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### 12.6 Glossary

#### TI Glossary

This glossary lists and explains terms, acronyms, and definitions.

## 13 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに対して提供されている最新のデータです。このデータは予告なく変更されることがあります。ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins    | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| DRV8220DRLR           | Active        | Production           | SOT-5X3 (DRL)   6 | 4000   LARGE T&R      | Yes         | Call TI   Sn                         | Level-1-260C-UNLIM                | -40 to 125   | 8220                |

| DRV8220DRLR.A         | Active        | Production           | SOT-5X3 (DRL)   6 | 4000   LARGE T&R      | Yes         | SN                                   | Level-1-260C-UNLIM                | -40 to 125   | 8220                |

| DRV8220DSGR           | Active        | Production           | WSON (DSG)   8    | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 220                 |

| DRV8220DSGR.A         | Active        | Production           | WSON (DSG)   8    | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-1-260C-UNLIM                | -40 to 125   | 220                 |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

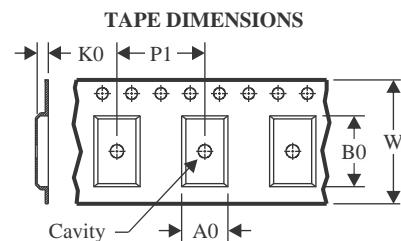

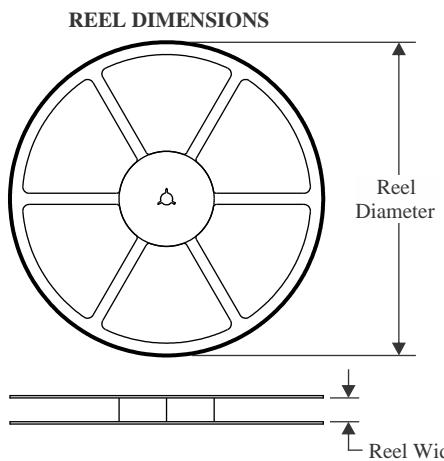

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

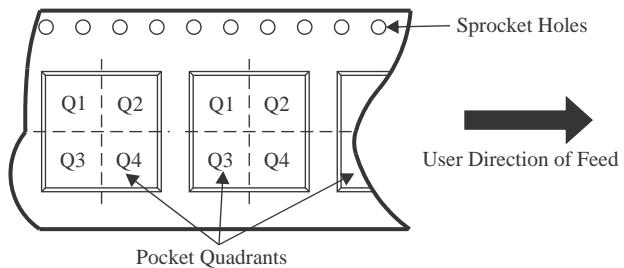

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|-------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| DRV8220DRLR | SOT-5X3      | DRL             | 6    | 4000 | 180.0              | 8.4                | 2.0     | 1.8     | 0.75    | 4.0     | 8.0    | Q3            |

| DRV8220DRLR | SOT-5X3      | DRL             | 6    | 4000 | 180.0              | 8.4                | 1.8     | 1.8     | 0.75    | 4.0     | 8.0    | Q3            |

| DRV8220DSGR | WSON         | DSG             | 8    | 3000 | 180.0              | 8.4                | 2.3     | 2.3     | 1.15    | 4.0     | 8.0    | Q2            |

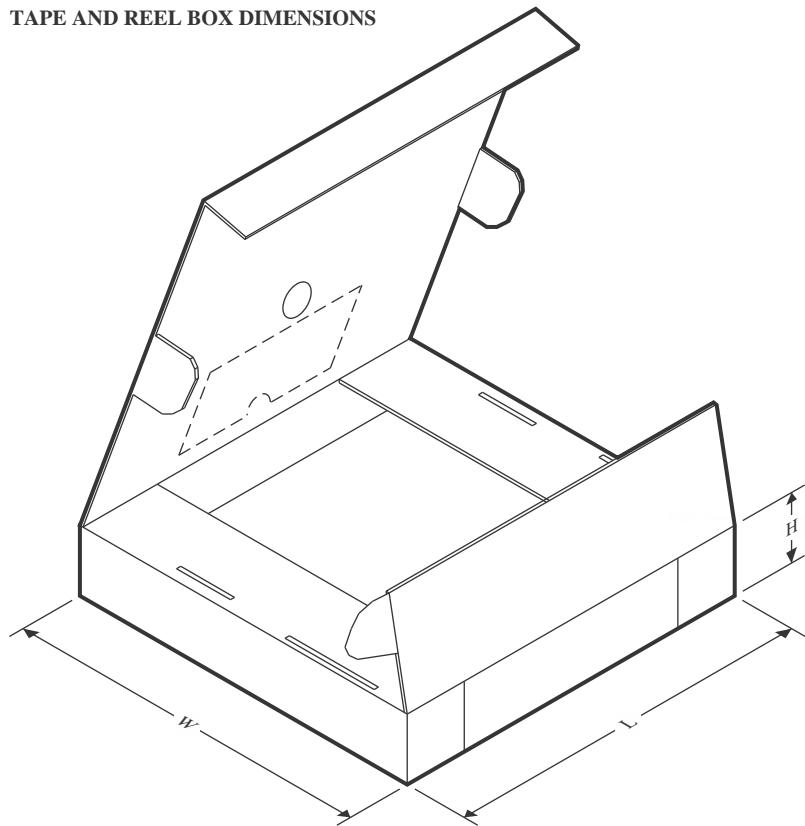

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DRV8220DRLR | SOT-5X3      | DRL             | 6    | 4000 | 210.0       | 185.0      | 35.0        |

| DRV8220DRLR | SOT-5X3      | DRL             | 6    | 4000 | 210.0       | 185.0      | 35.0        |

| DRV8220DSGR | WSON         | DSG             | 8    | 3000 | 210.0       | 185.0      | 35.0        |

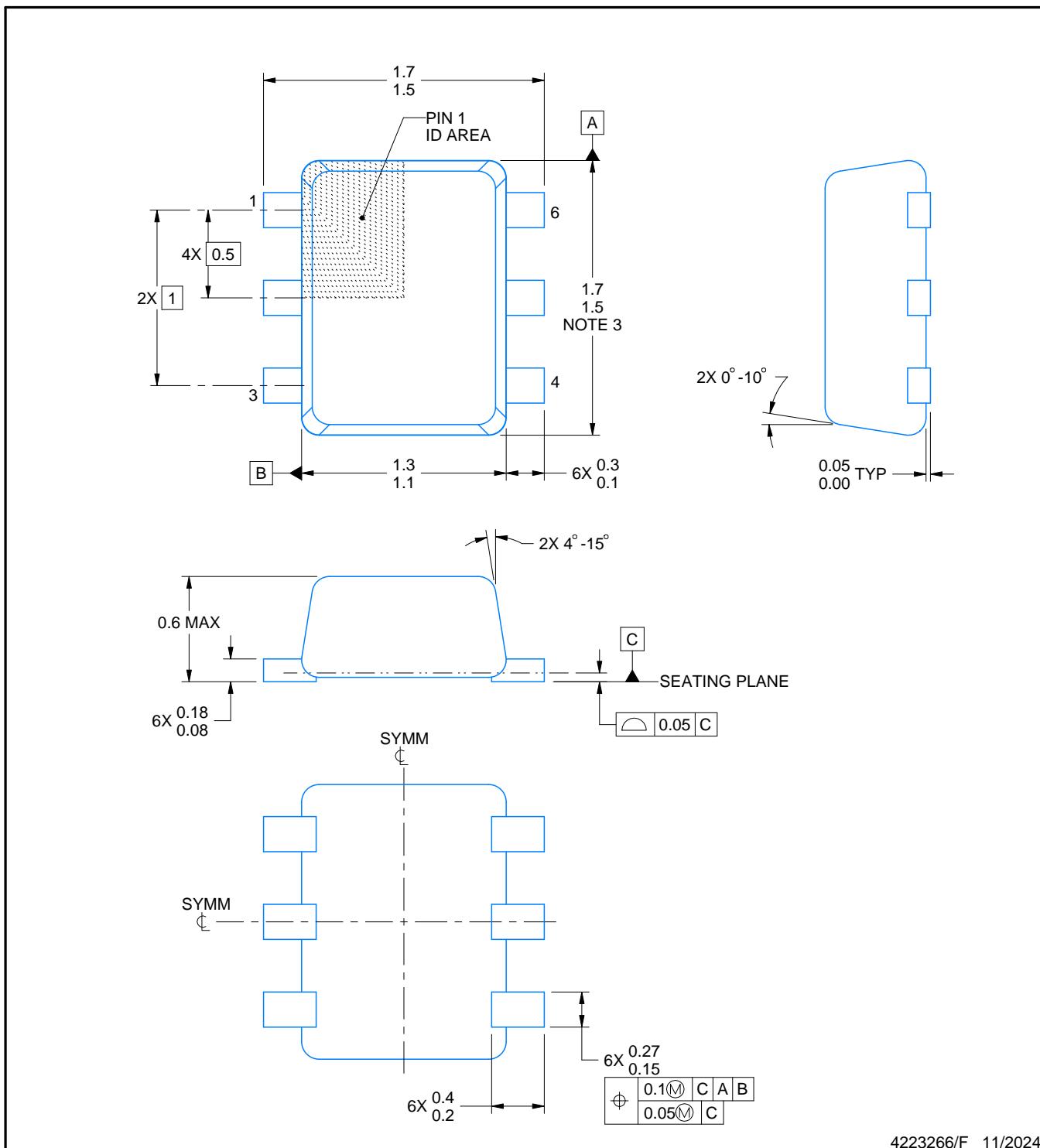

# PACKAGE OUTLINE

## SOT - 0.6 mm max height

PLASTIC SMALL OUTLINE

DRL0006A

4223266/F 11/2024

### NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. Reference JEDEC registration MO-293 Variation UAAD

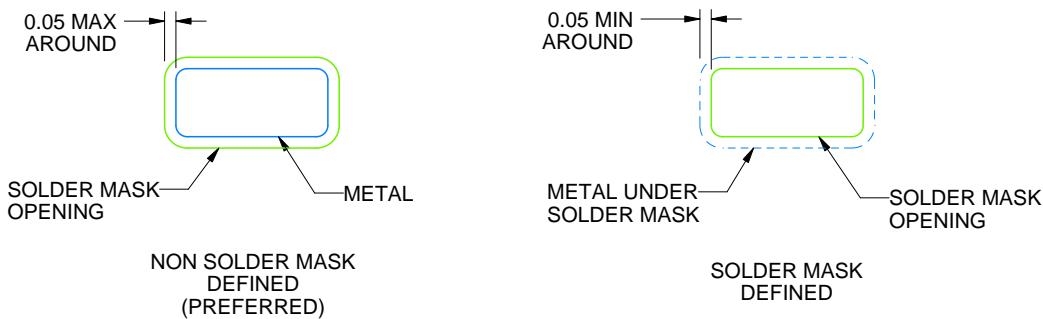

# EXAMPLE BOARD LAYOUT

DRL0006A

SOT - 0.6 mm max height

PLASTIC SMALL OUTLINE

4223266/F 11/2024

NOTES: (continued)

5. Publication IPC-7351 may have alternate designs.

6. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

7. Land pattern design aligns to IPC-610, Bottom Termination Component (BTC) solder joint inspection criteria.

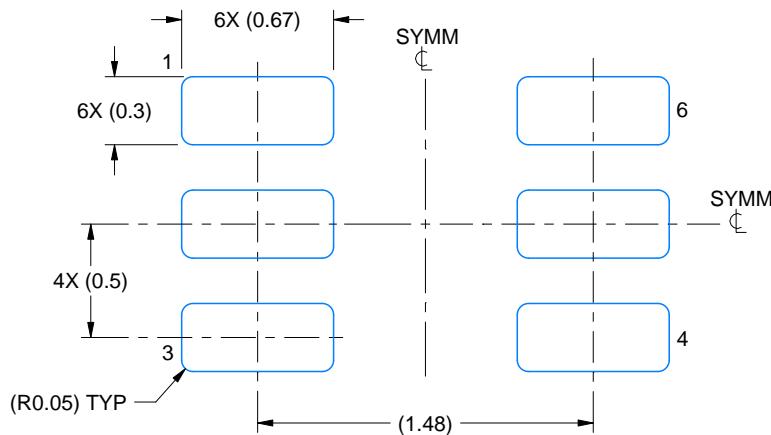

# EXAMPLE STENCIL DESIGN

DRL0006A

SOT - 0.6 mm max height

PLASTIC SMALL OUTLINE

SOLDER PASTE EXAMPLE

BASED ON 0.1 mm THICK STENCIL

SCALE:30X

4223266/F 11/2024

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

# GENERIC PACKAGE VIEW

## DSG 8

## WSON - 0.8 mm max height

2 x 2, 0.5 mm pitch

PLASTIC SMALL OUTLINE - NO LEAD

This image is a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4224783/A

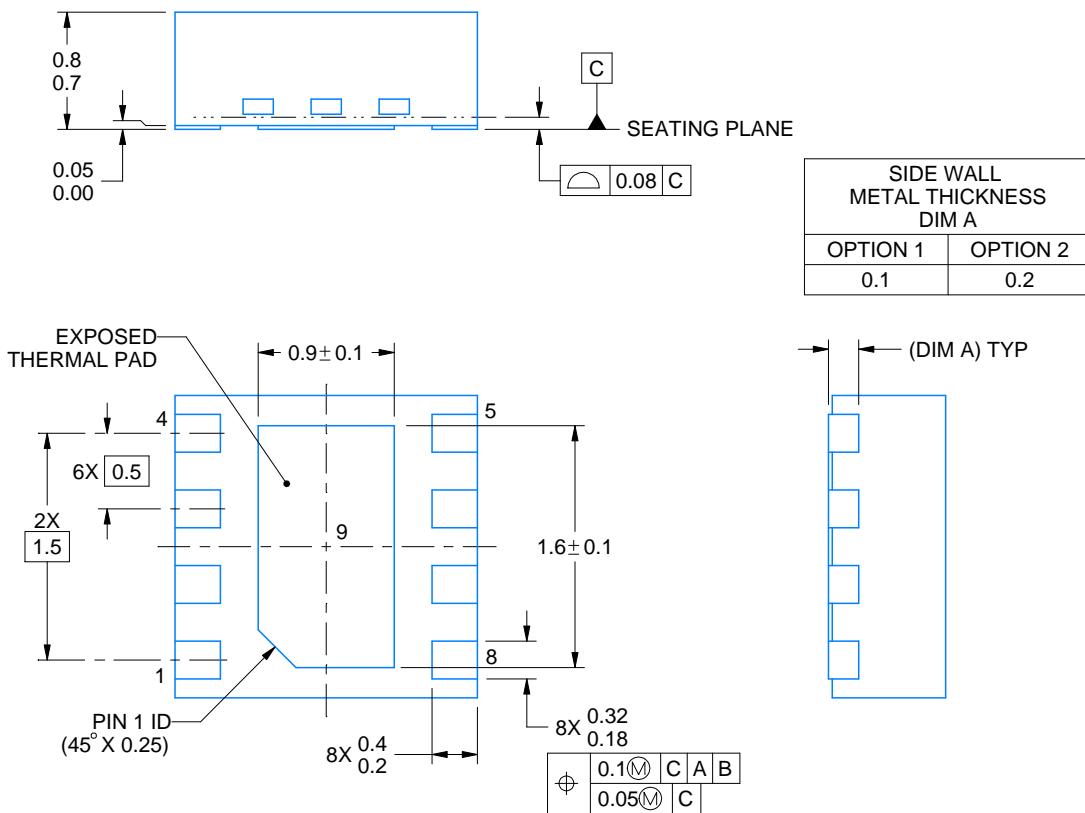

# PACKAGE OUTLINE

DSG0008A

WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

4218900/E 08/2022

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

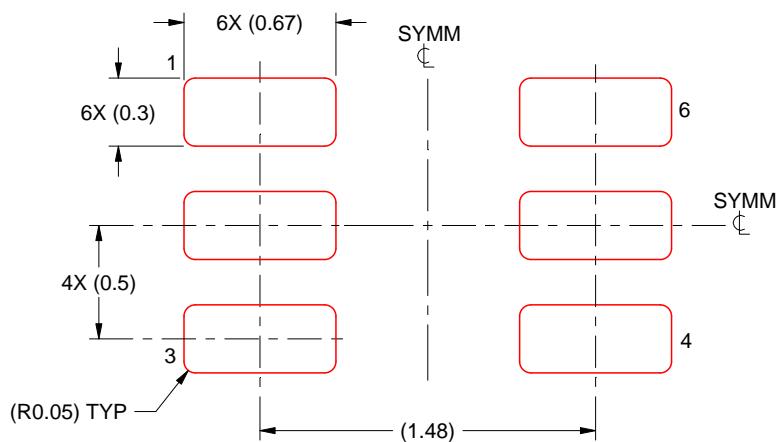

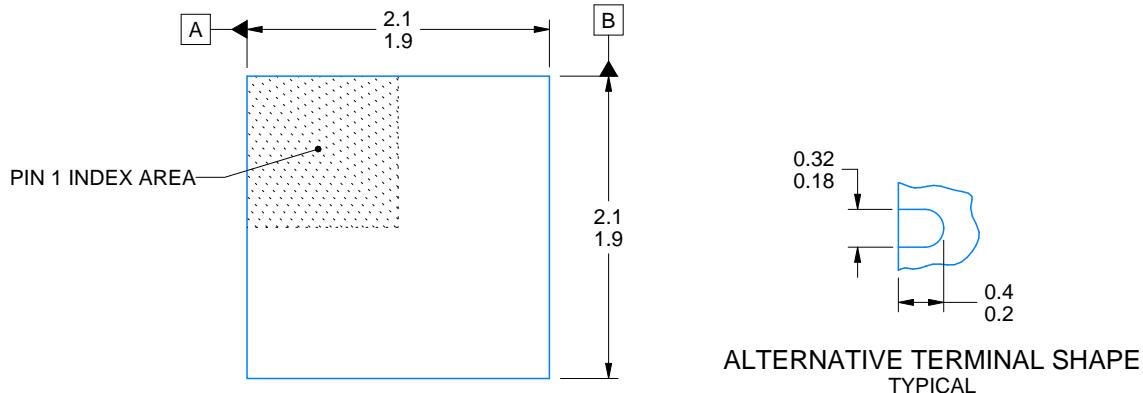

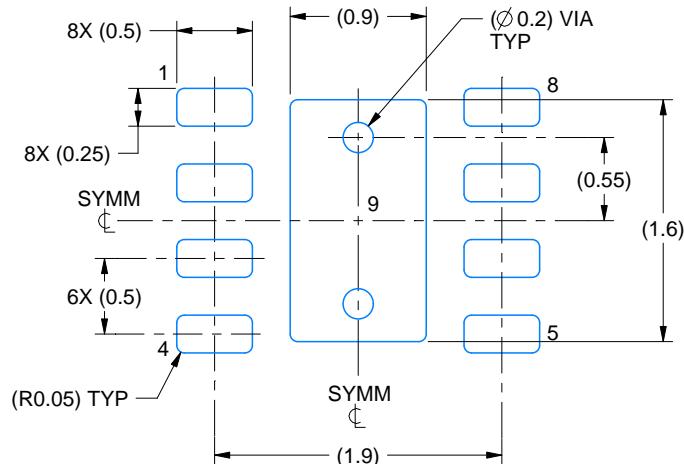

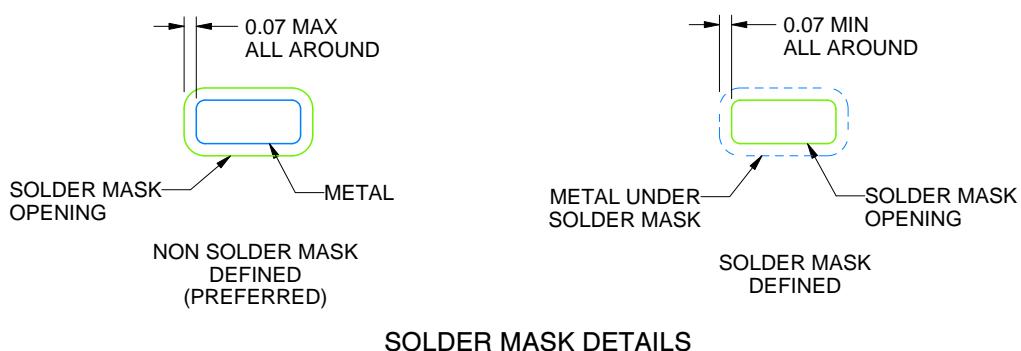

## EXAMPLE BOARD LAYOUT

**DSG0008A**

## WSON - 0.8 mm max height

## PLASTIC SMALL OUTLINE - NO LEAD

## LAND PATTERN EXAMPLE

4218900/E 08/2022

#### NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

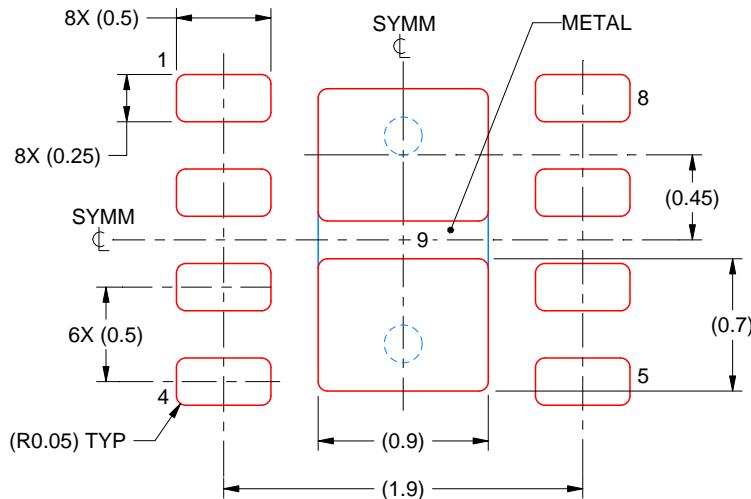

# EXAMPLE STENCIL DESIGN

DSG0008A

WSON - 0.8 mm max height

PLASTIC SMALL OUTLINE - NO LEAD

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

EXPOSED PAD 9:

87% PRINTED SOLDER COVERAGE BY AREA UNDER PACKAGE

SCALE:25X

4218900/E 08/2022

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月