**DRV8163-Q1**

JAJSW61 - FEBRUARY 2025

# DRV8163-Q1 65V 車載用、電流センス機能および診断機能搭載、 ハーフ ブリ ッジ ドライバ

# 1 特長

- 車載アプリケーション用に AEC-Q100 認定済み: - 温度グレード 1:-40℃~+125℃、T<sub>Δ</sub>

- 機能安全対応

- 機能安全システム設計に役立つ資料を利用可能

- 4.5V~65V (絶対最大定格 70V) 動作範囲

- MOSFET オン抵抗 (HS + LS):43mΩ

- 最大出力電流:40A

- 2 種類のインターフェイス オプション HW または SPI

- 最大 100kHz の PWM 周波数動作、自動デッド タイ ム生成付き

- 設定可能なスルーレートとスペクトラム拡散クロックによ る低電磁干渉 (EMI)

- 統合型の電流センス (シャント抵抗が不要)

- IPROPI への比例負荷電流出力

- IPROPI でのダイ温度監視 (SPI のみ)

- 設定可能な電流レギュレーション

- フォルト応答 (ラッチまたは再試行) を設定可能な保護 および診断機能

- オフ状態とオン状態の両方で負荷診断を行い、開 放負荷および短絡を検出

- 電源 (VM) の電圧監視

- 過電流保護

- 過熱警告 (SPI のみ)

- 過熱保護

- パワー オフブレーキ

- nFAULT ピンによるフォルト通知

- 1.8V、3.3V、5V のロジック入力をサポート

- 低いスリープ電流、25℃で7µA (標準値)

- デバイス ファミリの比較表

# 2 アプリケーション

- 24V および 48V 車載ボディシステム

- 車載用ブラシ付き DC モーター、ソレノイド

- ドア モジュール、ミラー モジュール、ワイパー モジュ ール、シートモジュール

- トランク リフト、ウィンドウ リフト

- ステアリング コラム、サンルーフ シェード

- 電気自動車、トラック、バス、その他の商用車

# 3 概要

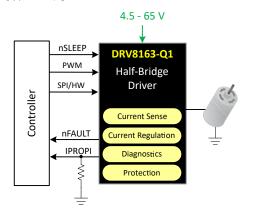

DRV8163-Q1 は、24V および 48V 車載アプリケーション 用、広電圧範囲、高出力、完全統合型 ハーフブリッジド ライバです。 パワー パッケージに収容されたこのデバイス は、BiCMOS 大電力プロセス テクノロジー ノードを採用し た設計であり、優れた電力処理能力と放熱特性を達成す ると同時に、コンパクトなパッケージ サイズ、使いやすいレ イアウト、EMI 制御能力、高精度の電流センス、堅牢性、 診断機能も実現しています。

このデバイスには、N チャネル ハーフブリッジ、チャージ ポンプ、ハイサイド電流検出およびレギュレーション、電流 比例出力、保護回路が内蔵されています。内蔵の検出機 能では電流ミラーを使用するため、シャント抵抗が不要に なり、基板面積の節約とシステム コストの削減が可能で す。低消費電力のスリープ モードにより、低い静止電流を 実現できます。

このデバイスは、電圧監視機能、負荷診断機能、さらに過 電流および過熱に対する保護機能を搭載しています。フ ォルト条件は nFAULT ピンにより示されます。これには、 次の 2 つのバリアントが用意されています。 HW インター フェイスおよび SPI インターフェイスです。 SPI バリアント は、デバイス構成とフォルト監視において、より高い柔軟性 があります。

# 製品情報

| 部品番号            | インターフェイス | パッケージ サイズ <sup>2</sup>        |

|-----------------|----------|-------------------------------|

| DRV8163HQVAKRQ1 | HW       | VQFN-HR (15) (3.5mm x<br>6mm) |

| DRV8163SQVAKRQ1 | SPI      | VQFN-HR (15) (3.5mm x<br>6mm) |

- 巻末の注文情報を参照してください。

- パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピ ンも含まれます。

概略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳)を使用していることがあり、TI では翻訳の正確性および妥当 体につきましては一切保証いたしません。 実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

# **Table of Contents**

| 1 | 特長                                   | . • |

|---|--------------------------------------|-----|

|   | アプリケーション                             |     |

|   | 概要                                   |     |

|   | Device Comparison                    |     |

|   | Pin Configuration and Functions      |     |

|   | 5.1 HW Variant                       |     |

|   | 5.2 SPI Variant                      |     |

| 6 | Specifications                       | . 7 |

|   | 6.1 Absolute Maximum Ratings         |     |

|   | 6.2 ESD Ratings                      |     |

|   | 6.3 Recommended Operating Conditions | . 7 |

|   | 6.4 Thermal Information              |     |

|   | 6.5 Electrical Characteristics       | . 8 |

|   | 6.6 Switching Waveforms              | 14  |

| 7 | Detailed Description                 |     |

|   | 7.1 Overview                         |     |

|   | 7.2 Functional Block Diagram         |     |

| 7.3 Feature Description                 |                  |

|-----------------------------------------|------------------|

| 8 Register Map - SPİ Variant Only       | 45               |

| 8.1 User Registers                      | 45               |

| 9 Application and Implementation        | 50               |

| 9.1 Application Information             | <mark>50</mark>  |

| 9.2 Typical Application                 | <mark>5</mark> 1 |

| 10 Device and Documentation Support     | 53               |

| 10.1 Device Support                     | <mark>53</mark>  |

| 10.2 Documentation Support              | <mark>53</mark>  |

| 10.3ドキュメントの更新通知を受け取る方法                  | <mark>53</mark>  |

| 10.4 サポート・リソース                          | <u>5</u> 3       |

| 10.5 Trademarks                         | 53               |

| 10.6 静電気放電に関する注意事項                      | 53               |

| 10.7 用語集                                | 53               |

| 11 Mechanical, Packaging, and Orderable |                  |

| Information                             | 53               |

|                                         |                  |

# 4 Device Comparison

表 4-1 summarizes the R<sub>ON</sub> and package differences between devices in the DRV8X6X-Q1 family.

# 表 4-1. Device Comparison

| PART NUMBER <sup>(1)</sup> | Configuration   | (LS + HS) R <sub>ON</sub> | I <sub>OUT</sub> MAX | PACKAGE      | BODY SIZE      | Interface |

|----------------------------|-----------------|---------------------------|----------------------|--------------|----------------|-----------|

| DRV8262-Q1                 | 1 or 2 H-bridge | 50mΩ or 100mΩ             | 16A or 8A            | HTSSOP (44)  | 14 mm X 6.1 mm | HW        |

| DRV8962-Q1                 | 4 Half-bridge   | 100mΩ                     | 8A                   | HTSSOP (44)  | 14 mm X 6.1 mm | HW        |

| DRV8263-Q1                 | 1 H-bridge      | 85mΩ                      | 29A                  | VQFN-HR (15) | 3.5 mm X 6 mm  | HW, SPI   |

| DRV8163-Q1                 | 1 Half-bridge   | 43mΩ                      | 40A                  | VQFN-HR (15) | 3.5 mm X 6 mm  | HW, SPI   |

<sup>(1)</sup> This is the product datasheet for the DRV8163-Q1. Please reference other device variant data sheets for additional information.

表 4-2 summarizes the feature differences between the SPI and HW interface variants in the DRV8163-Q1. In general, the SPI variant offers more configurability, bridge control options, diagnostic feedback, and additional features.

表 4-2. SPI Variant vs HW Variant Comparison

| 324                                                                       | C + 2. Of I variant von                        | variant companion                                                                            |

|---------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------|

| FUNCTION                                                                  | HW Variant                                     | SPI Variant                                                                                  |

| Bridge control                                                            | Pin only                                       | Individual pin "and/or" register bit with pin status indication (Refer Register Pin control) |

| Clear fault command                                                       | Reset pulse on nSLEEP pin                      | SPI CLR_FAULT command                                                                        |

| Over current protection (OCP)                                             | Fixed at the highest setting                   | 4 choices for thresholds, 4 choices for filter time                                          |

| ITRIP regulation                                                          | 5 levels with disable & fixed TOFF time        | 7 levels with disable & indication, with programmable TOFF time                              |

| Individual fault reaction configuration between retry or latched behavior | Not supported, either all latched or all retry | Supported                                                                                    |

| Detailed fault logging and device status feedback                         | Not supported, nFAULT pin monitoring necessary | Supported, nFAULT pin monitoring optional                                                    |

| VM over voltage                                                           | Not supported                                  | Supported                                                                                    |

| On-state (Active) diagnostics                                             | Not supported                                  | Supported for high-side loads                                                                |

| Spread spectrum clocking (SSC)                                            | Not supported                                  | Supported                                                                                    |

| Overtemperature warning                                                   | Not supported                                  | Supported                                                                                    |

| Die Temperature monitor                                                   | Not supported                                  | Supported                                                                                    |

|                                                                           |                                                |                                                                                              |

### 表 4-3. Differentiating between devices in the family

| Device      | Package Symbolization | DEVICE_ID Register |

|-------------|-----------------------|--------------------|

| DRV8262-Q1  | 8262                  | Not applicable     |

| DRV8962-Q1  | 8962                  | Not applicable     |

| DRV8263H-Q1 | 8263H                 | Not applicable     |

| DRV8163H-Q1 | 8163H                 | Not applicable     |

| DRV8263S-Q1 | 8263S                 | 0 x 34             |

| DRV8163S-Q1 | 8163S                 | 0 x 3C             |

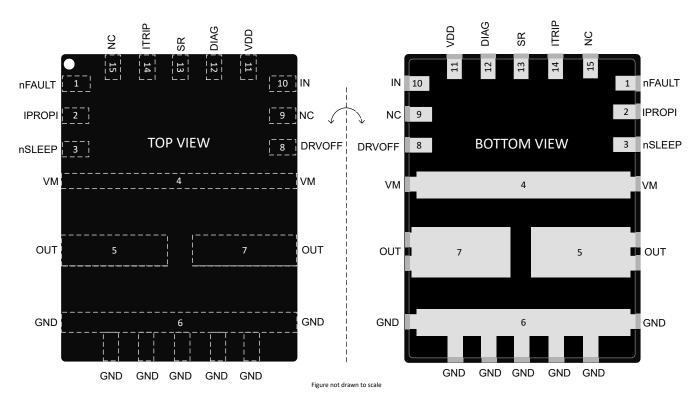

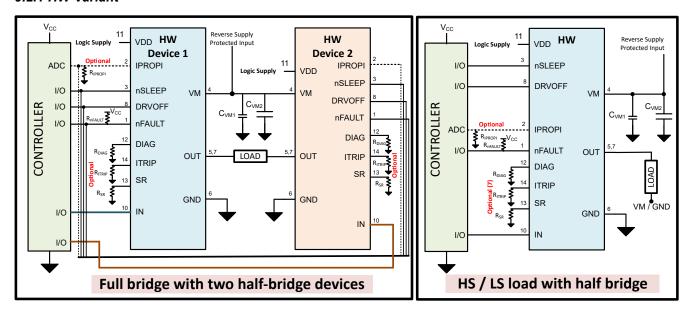

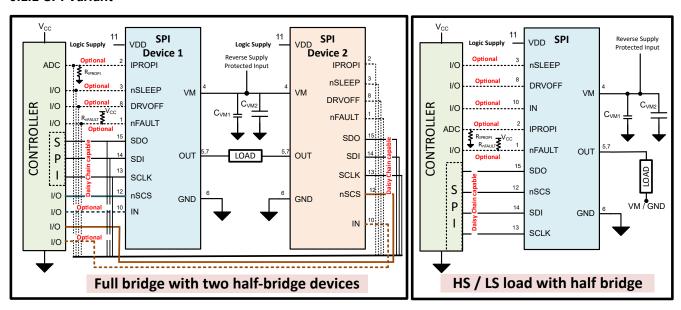

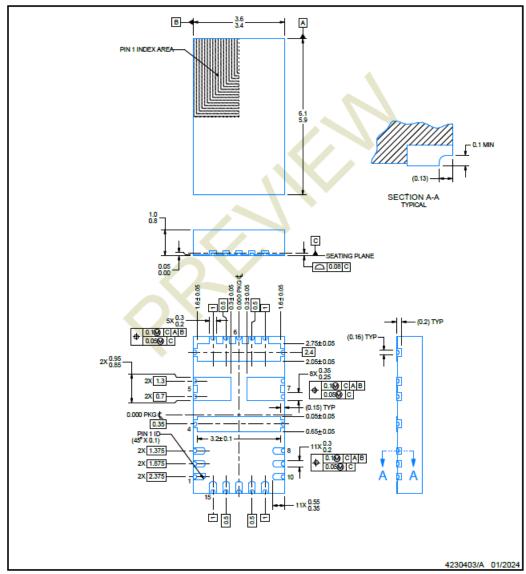

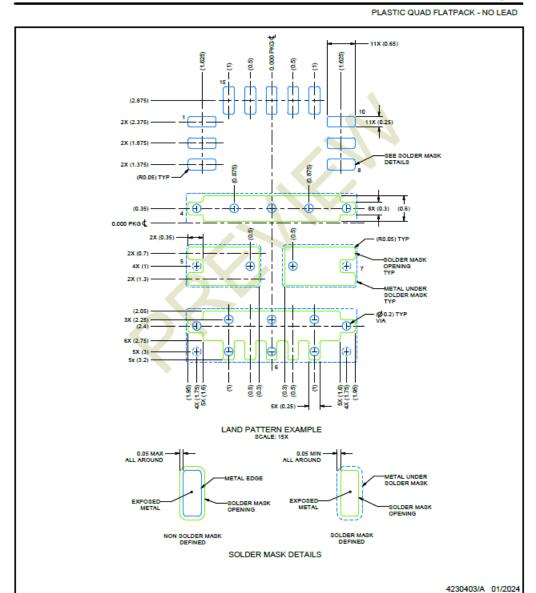

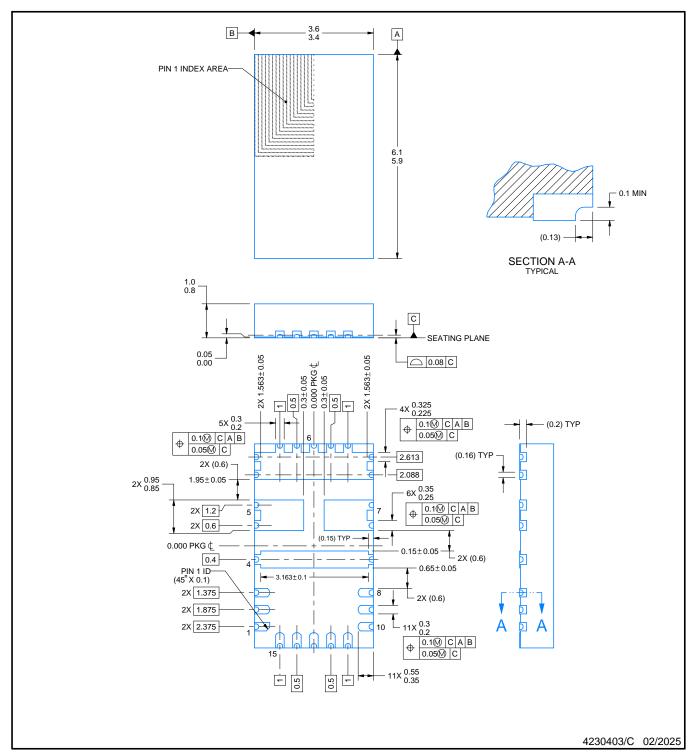

# 5 Pin Configuration and Functions5.1 HW Variant

# 図 5-1.

図 5-2. DRV8163H-Q1 in VQFN-HR(15) Package

# 表 5-1. Pin Functions

| X V-1.1 III1 Unduons |        |                                                                                                                |                                                                                                                                                     |  |  |  |  |

|----------------------|--------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| P                    | IN     | TYPE (1)                                                                                                       | DESCRIPTION                                                                                                                                         |  |  |  |  |

| NO.                  | NAME   |                                                                                                                | DEGGAII NON                                                                                                                                         |  |  |  |  |

| 1                    | nFAULT | OD                                                                                                             | Fault indication to the controller.                                                                                                                 |  |  |  |  |

| 2                    | IPROPI | I/O                                                                                                            | Driver load current analog feedback. For details, refer to IPROPI in the Device Configuration section.                                              |  |  |  |  |

| 3                    | nSLEEP | ļ                                                                                                              | Controller input pin for SLEEP . For details, see the Bridge Control section.                                                                       |  |  |  |  |

| 4                    | VM     | Р                                                                                                              | Power supply. This pin is the motor supply voltage. Bypass this pin to GND with a 0.1µF ceramic capacitor and a bulk capacitor.                     |  |  |  |  |

| 5, 7                 | OUT    | Р                                                                                                              | Half-bridge output. Connect these pins together to the motor or load.                                                                               |  |  |  |  |

| 6                    | GND    | G                                                                                                              | Ground pin                                                                                                                                          |  |  |  |  |

| 8                    | DRVOFF | I                                                                                                              | Controller input pin for bridge Hi-Z. For details, see the Bridge Control section.                                                                  |  |  |  |  |

| 9                    | NC     | -                                                                                                              | No connect.                                                                                                                                         |  |  |  |  |

| 10                   | IN     | ļ                                                                                                              | Controller input pin for bridge operation. For details, see the Bridge Control section.                                                             |  |  |  |  |

| 11                   | VDD    | Р                                                                                                              | Logic power supply to the device.                                                                                                                   |  |  |  |  |

| 12                   | DIAG   | I                                                                                                              | Device configuration pin for load type indication and fault reaction configuration. For details, refer to DIAG in the Device Configuration section. |  |  |  |  |

| 13                   | SR     | Device configuration pin for Slew Rate control . For details, refer to Slew Rate in the Configuration section. |                                                                                                                                                     |  |  |  |  |

Copyright © 2025 Texas Instruments Incorporated

Product Folder Links: DRV8163-Q1

# 表 5-1. Pin Functions (続き)

| PIN     |      | TYPE (1) | DESCRIPTION                                                                                                                               |  |

|---------|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO.     | NAME | 1115     | DECOMP HOW                                                                                                                                |  |

| 14      |      |          | Device configuration pin for ITRIP level for high-side current limiting. For details, refer to ITRIP in the Device Configuration section. |  |

| 15 NC - |      | •        | No connect.                                                                                                                               |  |

(1) I = input, O = output, I/O = input/output, G = ground, P = power, OD = open-drain output, PP = push-pull output

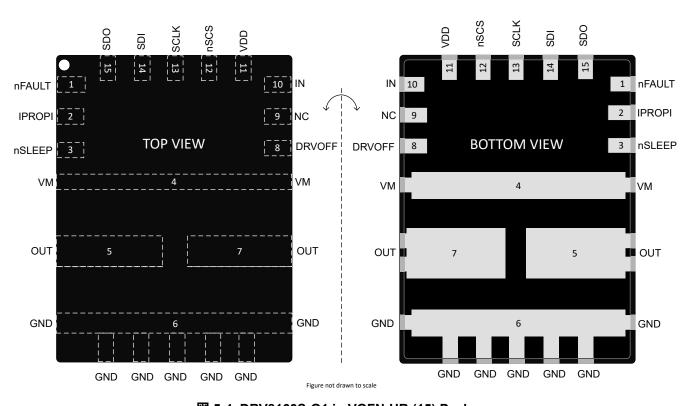

# 5.2 SPI Variant

図 5-3.

図 5-4. DRV8163S-Q1 in VQFN-HR (15) Package

# 表 5-2. Pin Functions

| PIN        |        | TYPE (1) | DESCRIPTION                                                                                                                                                                          |  |

|------------|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO.        | NAME   | IIFE ( / | DESCRIP HON                                                                                                                                                                          |  |

| 1          | nFAULT | OD       | Fault indication to the controller.                                                                                                                                                  |  |

| 2          | IPROPI | I/O      | Multi-purpose pin. Provides driver load current analog feedback or analog voltage proportional to die temperature. For details, refer to IPROPI in the Device Configuration section. |  |

| 3          | nSLEEP | I        | Controller input pin for SLEEP . For details, see the Bridge Control section.                                                                                                        |  |

| 4          | VM     | Р        | Power supply. This pin is the motor supply voltage. Bypass this pin to GND with a 0.1µF ceramic capacitor and a bulk capacitor.                                                      |  |

| 5, 7 OUT P |        | Р        | Half-bridge output. Connect these pins together to the motor or load.                                                                                                                |  |

| 6          | GND    | G        | Ground pin                                                                                                                                                                           |  |

| 8 DRVOFF I |        | I        | Controller input pin for bridge Hi-Z. For details, see the Bridge Control section.                                                                                                   |  |

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

5

# 表 5-2. Pin Functions (続き)

| PIN              |                | TYPE (1) | DESCRIPTION                                                                              |  |  |

|------------------|----------------|----------|------------------------------------------------------------------------------------------|--|--|

| NO.              | NO. NAME       |          | DESCRIPTION                                                                              |  |  |

| 9 NC - No connec |                | -        | No connect.                                                                              |  |  |

| 10 IN I          |                | I        | Controller input pin for bridge operation. For details, see the Bridge Control section.  |  |  |

| 11               | 11 VDD P Logic |          | Logic power supply to the device.                                                        |  |  |

| 12 nSCS I        |                | Į        | SPI - Chip Select. An active low on this pin enables the serial interface communication. |  |  |

| 13               | 13 SCLK I      |          | SPI - Serial Clock input.                                                                |  |  |

| 14 SDI I         |                | I        | SPI - Serial Data Input. Data is captured at the falling edge of SCLK.                   |  |  |

| 15 SDO PP        |                | PP       | SPI - Serial Data Output. Data is updated at the rising edge of SCLK.                    |  |  |

(1) I = input, O = output, I/O = input/output, G = ground, P = power, OD = open-drain output, PP = push-pull output

# 6 Specifications

# 6.1 Absolute Maximum Ratings

Over operating temperature range (unless otherwise noted)(1)

|                                         |                      | MIN                               | MAX                 | UNIT |

|-----------------------------------------|----------------------|-----------------------------------|---------------------|------|

| Power supply pin voltage                | VM                   | -0.3 <sup>(3)</sup>               | 70                  | V    |

| Power supply transient voltage ramp     | VM                   |                                   | 2                   | V/µs |

| Logic supply voltage                    | VDD                  | -0.3                              | 5.75                | V    |

| Logic supply transient voltage ramp     | VDD                  |                                   | 5                   | V/µs |

| Continuous Output pin voltage           | OUT                  | -1                                | V <sub>VM</sub> + 1 | V    |

| Transient 100 ns Output pin voltage     | OUT                  | -3                                | V <sub>VM</sub> + 3 | V    |

| Output pin current                      | OUT                  | Internally limited <sup>(2)</sup> |                     | А    |

| DRFOFF, nSLEEP pin voltage              | DRVOFF, nSLEEP       | -0.3                              | 70                  | V    |

| Logic I/O voltage                       | IN, nFAULT           | -0.3                              | 5.75                | V    |

| HW variant - Configuration pins voltage | ITRIP, SR, DIAG      | -0.3                              | 5.75                | V    |

| Analog feedback pin voltage             | IPROPI               | -0.3                              | 5.75                | V    |

| SPI I/O voltage - SPI variant           | SDI, SDO, nSCS, SCLK | -0.3                              | 5.75                | V    |

| Ambient temperature, T <sub>A</sub>     |                      | -40                               | 125                 | °C   |

| Junction temperature, T <sub>J</sub>    |                      | -40                               | 150                 | °C   |

| Storage temperature, T <sub>stg</sub>   |                      | -65                               | 150                 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) Limited by the over current and over temperature protection functions of the device

- (3) With external component support, short duration violation of this limit can be tolerated during ISO 7637 transient pulse testing

# 6.2 ESD Ratings

|                    |               |                                              |                | VALUE | UNIT |

|--------------------|---------------|----------------------------------------------|----------------|-------|------|

|                    | Electrostatic | LIDM FOR Obsesting Level O                   | VM, OUT, GND   | ±4000 |      |

| V                  |               |                                              | All other pins | ±2000 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged device model (CDM), per AEC Q100-011 | Corner pins    | ±750  | v    |

|                    |               | CDM ESD Classification Level C4B             | Other pins     | ±500  |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 6.3 Recommended Operating Conditions

over operating temperature range (unless otherwise noted)

|                    |                       |                            | MIN | MAX | UNIT |

|--------------------|-----------------------|----------------------------|-----|-----|------|

| $V_{VM}$           | Power supply voltage  | VM                         | 4.5 | 65  | V    |

| V <sub>VDD</sub>   | Logic supply voltage  | VDD                        | 3   | 5.5 | V    |

| V <sub>LOGIC</sub> | Logic I/O pin voltage | IN, nSLEEP, DRVOFF, nFAULT | 0   | 5.5 | V    |

| f <sub>PWM</sub>   | PWM frequency         | IN                         | 0   | 100 | kHz  |

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ) を送信

7

over operating temperature range (unless otherwise noted)

|                      |                                        |                      | MIN | MAX                    | UNIT |

|----------------------|----------------------------------------|----------------------|-----|------------------------|------|

| V <sub>CONFIG</sub>  | HW variant - Configuration pin voltage | ITRIP, SR, DIAG      | 0   | 5.5                    | V    |

| V <sub>IPROPI</sub>  | Analog feedback voltage                | IPROPI               | 0   | 5.5                    | V    |

| V <sub>SPI_IOS</sub> | SPI pin voltage                        | SDI, SDO, nSCS, SCLK | 0   | V <sub>VDD</sub> + 0.5 | V    |

| T <sub>A</sub>       | Operating ambient temperature          |                      | -40 | 125                    | °C   |

| TJ                   | Operating junction temperature         |                      | -40 | 150                    | °C   |

#### 6.4 Thermal Information

Refer Transient thermal impedance table for application related use case.

|                       | THERMAL METRIC <sup>(1)</sup>                | VQFN-HR package | UNIT |

|-----------------------|----------------------------------------------|-----------------|------|

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 31.5            | °C/W |

| R <sub>eJC(top)</sub> | Junction-to-case(top) thermal resistance     | TBD             | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | TBD             | °C/W |

| $\Psi_{ m JT}$        | Junction-to-top characterization parameter   | TBD             | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | TBD             | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case(bottom) thermal resistance  | TBD             | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.4.1 Transient Thermal Impedance & Current Capability

Information based on thermal simulations

# 表 6-1. Transient Thermal Impedance (R<sub>0JA</sub>) and Current Capability

|             |        | α <sub>θJA</sub> [°C/W] <sup>(1)</sup> | ı    |        |           | Current [A] <sup>(2)</sup> |        |                   |

|-------------|--------|----------------------------------------|------|--------|-----------|----------------------------|--------|-------------------|

| PART NUMBER |        | OJA [ C/44]                            |      | wi     | thout PWM | 3)                         | with P | WM <sup>(4)</sup> |

|             | 0.1sec | 1sec                                   | DC   | 0.1sec | 1sec      | DC                         | 1sec   | DC                |

| DRV8163-Q1  | 3.96   | 8.38                                   | 31.5 | TBD    | TBD       | TBD                        | TBD    | TBD               |

- (1) Based on thermal simulations using 40mm x 40mm x 1.6mm 4-layer PCB 2oz Cu on top and bottom layers, 1oz Cu on internal planes with 0.3 mm thermal via drill diameter, 0.025mm Cu plating, 1 minimum mm via pitch.

- (2) Estimated transient current capability at 85 °C ambient temperature for junction temperature rise to 150°C

- (3) Only conduction losses (I<sup>2</sup>R) are considered

- (4) Switching loss roughly estimated by the following equation:

$$P_{SW} = V_{VM} \times I_{Load} \times f_{PWM} \times V_{VM}/SR, \text{ where } V_{VM} = 48V, f_{PWM} = 20KHz, SR = 220V/\mu s$$

(1)

### 6.5 Electrical Characteristics

Typical values are at  $T_A$  = 25°C and  $V_{VM}$  = 48 V. All limits are over recommended operating conditions, unless otherwise noted.

|                  | PARAMETER                   | TEST CONDITIONS                                                        | MIN | TYP | MAX | UNIT |

|------------------|-----------------------------|------------------------------------------------------------------------|-----|-----|-----|------|

| POWER SU         | PPLIES (VM, VDD)            |                                                                        |     |     |     |      |

| I <sub>VDD</sub> | VDD current in ACTIVE state | Die temperature readout disabled                                       |     | 2   | 3.5 |      |

| I <sub>VMS</sub> | VM current in STANDBY state | V <sub>VM</sub> = 48 V, Drivers Hi-Z, Die temperature readout disabled |     | 1   | 1.8 | mA   |

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

8

|                             | PARAMETER                                                                                     | TEST CONDITIONS                                                                                                                    | MIN | TYP | MAX | UNIT |

|-----------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| I <sub>VMQ</sub>            | VM current in SLEEP state                                                                     | V <sub>VM</sub> = 48 V, POB disabled, V <sub>nSLEEP</sub> = 0<br>V or V <sub>VDD</sub> < V <sub>POR_FALL</sub>                     |     | 7   | 30  | μΑ   |

| I <sub>VMQ_POB</sub>        | VM current in SLEEP state with POB                                                            | V <sub>VM</sub> = 48 V, POB enabled, V <sub>nSLEEP</sub> = 0<br>V                                                                  |     | 8   | 35  | μA   |

| I <sub>VDDQ_POB</sub>       | VDD current in SLEEP state with POB                                                           | V <sub>VM</sub> = 48 V, POB enabled, V <sub>nSLEEP</sub> = 0<br>V                                                                  |     | 7.5 | 14  | μΑ   |

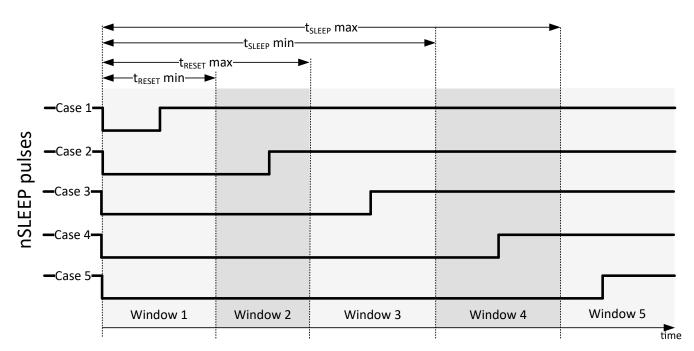

| t <sub>RESET</sub>          | RESET pulse filter time                                                                       | Reset signal on nSLEEP, HW variant                                                                                                 | 5   |     | 35  | μs   |

| t <sub>SLEEP</sub>          | Sleep command filter time                                                                     | Sleep signal on nSLEEP, HW variant                                                                                                 | 40  |     | 120 | μs   |

| t <sub>SLEEP_SPI</sub>      | Sleep command filter time                                                                     | Sleep signal on nSLEEP, SPI variant                                                                                                | 5   |     | 20  | μs   |

| t <sub>WAKEUP</sub>         | Wake-up command filter time                                                                   | Wake-up signal on nSLEEP                                                                                                           |     | 6   |     | μs   |

| t <sub>COM</sub>            | Time for communication to be available after wake-up or power-up through VM or VDD pin        | Wake-up signal on nSLEEP pin or power cycle (V <sub>VM</sub> > V <sub>POR_RISE</sub> or V <sub>VDD</sub> > V <sub>POR_RISE</sub> ) |     |     | 200 | μs   |

| t <sub>READY</sub>          | Time for driver ready to be driven after wake-up through nSLEEP or power-up through VM or VDD | Wake-up signal on nSLEEP pin or power cycle (V <sub>VM</sub> > V <sub>POR_RISE</sub> or V <sub>VDD</sub> > V <sub>POR_RISE</sub> ) |     |     | 1.2 | ms   |

| LOGIC-LEV                   | EL INPUTS (nSLEEP, DRVOFF, IN                                                                 | I, nSCS, SDI, SCLK)                                                                                                                | ,   |     | ,   |      |

| V <sub>IL</sub>             | Input logic-low voltage                                                                       | All pins                                                                                                                           | 0   |     | 0.6 | V    |

| V <sub>IH</sub>             | Input logic-high voltage                                                                      | All pins                                                                                                                           | 1.5 |     | 5.5 | V    |

| V <sub>HYS</sub>            | Input logic hysteresis                                                                        | All pins (except nSLEEP)                                                                                                           |     | 100 |     | mV   |

| V <sub>HYS</sub><br>_nSLEEP | nSLEEP logic hysteresis                                                                       |                                                                                                                                    |     | 180 |     | mV   |

| R <sub>PU</sub>             | Internal pull-up resistance on DRVOFF and nSCS                                                | Measured at min V <sub>IH</sub> level                                                                                              | 150 |     | 450 | kΩ   |

| R <sub>PD</sub>             | Internal pull-down resistance on IN, SDI, SCLK                                                | Measured at max V <sub>IL</sub> level                                                                                              | 150 |     | 450 | kΩ   |

| R <sub>PD_nSLEEP</sub>      | Internal pull-down resistance on nSLEEP                                                       | Measured at max V <sub>IL</sub> level                                                                                              | 160 |     | 400 | kΩ   |

| TRI-LEVEL                   | INPUT (MODE)                                                                                  |                                                                                                                                    |     | -   |     |      |

| R <sub>LVL1</sub>           | Level 1                                                                                       | Connect to GND                                                                                                                     |     |     | 10  | Ω    |

| R <sub>LVL2</sub>           | Level 2                                                                                       | +/- 10% resistor to GND                                                                                                            | 8   | 16  | 24  | kΩ   |

| R <sub>LVL3</sub>           | Level 3                                                                                       | Hi-Z (no connect)                                                                                                                  | 249 |     |     | kΩ   |

| QUAD-LEVE                   | EL INPUT (SR)                                                                                 |                                                                                                                                    | l   |     | l   |      |

| R <sub>LVL1</sub>           | Level 1                                                                                       | Connect to GND                                                                                                                     |     |     | 10  | Ω    |

| R <sub>LVL2</sub>           | Level 2                                                                                       | +/- 10% resistor to GND                                                                                                            | 8   | 16  | 24  | kΩ   |

| R <sub>LVL3</sub>           | Level 3                                                                                       | +/- 10% resistor to GND                                                                                                            | 45  | 75  | 110 | kΩ   |

| R <sub>LVL4</sub>           | Level 4                                                                                       | Hi-Z (no connect)                                                                                                                  | 249 |     |     | kΩ   |

| SIX-LEVEL                   | INPUTS (ITRIP, DIAG)                                                                          |                                                                                                                                    |     |     | I   |      |

| R <sub>LVL1</sub>           | Level 1                                                                                       | Connect to GND                                                                                                                     |     |     | 10  | Ω    |

|                        | PARAMETER                                                                        | TEST CONDITIONS                                | MIN | TYP  | MAX | UNIT |

|------------------------|----------------------------------------------------------------------------------|------------------------------------------------|-----|------|-----|------|

| R <sub>LVL2</sub>      | Level 2                                                                          | +/- 10% resistor to GND                        | 8   | 9    | 10  | kΩ   |

| R <sub>LVL3</sub>      | Level 3                                                                          | +/- 10% resistor to GND                        | 22  | 24   | 26  | kΩ   |

| R <sub>LVL4</sub>      | Level 4                                                                          | +/- 10% resistor to GND                        | 45  | 48   | 51  | kΩ   |

| R <sub>LVL5</sub>      | Level 5                                                                          | +/- 10% resistor to GND                        | 90  | 100  | 110 | kΩ   |

| R <sub>LVL6</sub>      | Level 6                                                                          | Hi-Z (no connect)                              | 249 |      |     | kΩ   |

| PUSH-PULI              | OUTPUT (SDO)                                                                     |                                                |     |      | '   |      |

| V <sub>OL_SDO</sub>    | Output logic-low voltage                                                         | 0.5 mA sink                                    |     | 0.1  | 0.2 | V    |

| V <sub>OH_SDO</sub>    | Output logic-high voltage                                                        | 0.5 mA source, V <sub>VDD</sub> = 5 V          | 4.7 | 4.9  |     | V    |

| I <sub>SDO</sub>       | SDO Leakage Current                                                              | V <sub>VM</sub> > 6 V                          | -2  |      | 2   | μA   |

| CONTROL                | OUTPUTS (nFAULT)                                                                 | 1                                              | '   | '    | '   |      |

| V <sub>OL</sub>        | Output logic-low voltage                                                         | I <sub>O</sub> = 5 mA                          |     |      | 0.3 | V    |

| I <sub>OH</sub>        | Output logic-high leakage                                                        |                                                | -1  |      | 1   | μΑ   |

| DRIVER OL              | TPUTS (OUT)                                                                      | ı                                              |     |      | '   |      |

|                        | Himb side FFT on maristance                                                      | T <sub>J</sub> = 25 °C, I <sub>O</sub> = -6 A  |     | 21   | 25  | mΩ   |

| R <sub>HS_ON</sub>     | High-side FET on resistance                                                      | T <sub>J</sub> = 150 °C, I <sub>O</sub> = -6 A |     | 35   | 42  | mΩ   |

| D.                     | Law side FFT on masisteness                                                      | T <sub>J</sub> = 25 °C, I <sub>O</sub> = 6 A   |     | 22   | 26  | mΩ   |

| R <sub>LS_ON</sub>     | Low-side FET on resistance                                                       | T <sub>J</sub> = 150 °C, I <sub>O</sub> = 6 A  |     | 36   | 43  | mΩ   |

| V <sub>SD</sub>        | Body diode forward voltage                                                       | I <sub>O</sub> = ±6 A (both directions)        | 0.4 | 0.8  | 1.2 | V    |

| I <sub>Hi-Z</sub>      | OUT lekage current to GND in SLEEP state                                         | V <sub>OUTx</sub> = V <sub>VM</sub> = 48 V     |     |      | 140 | μA   |

| Switching F            | Parameters with High-Side Recirc                                                 | culation                                       |     |      | l   |      |

|                        |                                                                                  | SR = 00b or LVL1                               | 180 | 220  | 260 | V/µs |

|                        | Output voltage rise/fall slew rate,                                              | SR = 01b or LVL2                               | 90  | 110  | 130 | V/µs |

| SR <sub>LS</sub>       | 10% - 90% (rise), 90% - 10% (fall), V <sub>VM</sub> = 48 V, I <sub>O</sub> = 6 A | SR = 10b or LVL3                               | 40  | 50   | 60  | V/µs |

|                        | (14), 1 (16)                                                                     | SR = 11b or LVL4                               | 16  | 20   | 24  | V/µs |

|                        | Propagation delay during output                                                  | SR = 00b or 01b or LVL1 or LVL2                |     | 0.24 |     | μs   |

| t <sub>PD_LSOFF</sub>  | voltage rise, I <sub>O</sub> = 6 A                                               | SR = 10b or 11b or LVL3 or LVL4                |     | 0.28 |     | μs   |

|                        | Propagation delay during output                                                  | SR = 00b or 01b or LVL1 or LVL2                |     | 0.32 |     | μs   |

| t <sub>PD_LSON</sub>   | voltage fall, I <sub>O</sub> = 6 A                                               | SR = 10b or 11b or LVL3 or LVL4                |     | 0.46 |     | μs   |

|                        |                                                                                  | SR = 00b or 01b or LVL1 or LVL2                |     | 0.28 |     | μs   |

| tDEAD_LSOFF            | Dead time during output voltage                                                  | SR = 10b or LVL3                               |     | 0.36 |     | μs   |

|                        | rise, I <sub>O</sub> = 6 A                                                       | SR = 11b or LVL4                               |     | 0.65 |     | μs   |

|                        |                                                                                  | SR = 00b or 01b or LVL1 or LVL2                |     | 0.68 |     | μs   |

| t <sub>DEAD_LSON</sub> | Dead time during output voltage                                                  | SR = 10b or LVL3                               |     | 0.75 |     | μs   |

| _                      | fall, I <sub>O</sub> = 6 A                                                       | SR = 11b or LVL4                               |     | 0.82 |     | μs   |

|                         | PARAMETER                                                                           | TEST CONDITIONS                  | MIN  | TYP  | MAX                                                                                  | UNIT |

|-------------------------|-------------------------------------------------------------------------------------|----------------------------------|------|------|--------------------------------------------------------------------------------------|------|

|                         |                                                                                     | SR = 00b or LVL1                 | 180  | 220  | 260                                                                                  | V/µs |

| 0.0                     | Output voltage rise/fall slew rate,                                                 | SR = 01b or LVL2                 | 90   | 110  | 130                                                                                  | V/µs |

| SR <sub>HS</sub>        | 10% - 90% (rise), 90% - 10%<br>(fall), V <sub>VM</sub> = 48 V, I <sub>O</sub> = 6 A | SR = 10b or LVL3                 | 40   | 50   | 60                                                                                   | V/µs |

|                         | ( ), VIVI - , O -                                                                   | SR = 11b or LVL4                 | 16   | 20   | 24                                                                                   | V/µs |

|                         | Propagation delay during output                                                     | SR = 00b or 01b or LVL1 or LVL2  |      | 0.24 |                                                                                      | μs   |

| t <sub>PD_HSON</sub>    | voltage rise, I <sub>O</sub> = 6 A                                                  | SR = 10b or 11b or LVL3 or LVL4  |      | 0.28 |                                                                                      | μs   |

|                         |                                                                                     | SR = 00b or 01b or LVL1 or LVL2  |      | 0.32 |                                                                                      | μs   |

| t <sub>PD_HSOFF</sub>   | Propagation delay during output voltage fall, I <sub>O</sub> = 6 A                  | SR = 10b or LVL3                 |      | 0.45 |                                                                                      | μs   |

|                         | Voltage fall, 10 = 0 A                                                              | SR = 11b or LVL4                 |      | 0.53 |                                                                                      | μs   |

|                         |                                                                                     | SR = 00b or LVL1                 |      | 0.68 |                                                                                      | μs   |

|                         | Dead time during output voltage                                                     | SR = 01b or LVL2                 |      | 0.8  |                                                                                      | μs   |

| <sup>t</sup> DEAD_HSON  | rise, I <sub>O</sub> = 6 A                                                          | SR = 10b or LVL3                 |      | 1.07 |                                                                                      | μs   |

|                         |                                                                                     | SR = 11b or LVL4                 |      | 1.8  |                                                                                      | μs   |

| t <sub>DEAD_HSOFF</sub> | Dead time during output voltage fall, I <sub>O</sub> = 6 A                          | All slew rates                   |      | 0.11 |                                                                                      | μs   |

|                         | Current regulation blanking time                                                    | TBLK = 0b. Only choice for HW.   |      | 0.8  |                                                                                      | μs   |

| t <sub>BLANK</sub>      | (Valid for only for LS recirculation)                                               | TBLK = 1b                        |      | 1.8  |                                                                                      | μs   |

| IPROPI & IT             | RIP Regulation                                                                      |                                  |      |      |                                                                                      |      |

| A <sub>IPROPI</sub>     | Current mirror gain                                                                 | I <sub>OUT</sub> > 2 A           | 190  | 202  | 215                                                                                  | μΑ/Α |

|                         |                                                                                     | I <sub>OUT</sub> > 2 A           | -5   |      | 7                                                                                    |      |

| A <sub>ERR</sub>        | Current mirror scaling error                                                        | 0.5 A < I <sub>OUT</sub> ≤ 2 A   | -8   |      | 8                                                                                    | %    |

|                         |                                                                                     | 0.2 A < I <sub>OUT</sub> ≤ 0.5 A | -15  |      | 215<br>7                                                                             |      |

| A <sub>ERR_M</sub>      | Current matching between the two half-bridges                                       | I <sub>OUT</sub> > 2 A           | -3   |      | +3                                                                                   | %    |

| V <sub>IPROPI_LIM</sub> | Internal clamping voltage on IPROPI                                                 |                                  | 3.4  |      | 5.5                                                                                  | V    |

|                         |                                                                                     | S_ITRIP = 001b or LVL2           | 1.08 | 1.2  | 1.3                                                                                  | V    |

|                         |                                                                                     | S_ITRIP = 010b (SPI only)        | 1.31 | 1.44 | 1.55                                                                                 | V    |

|                         |                                                                                     | S_ITRIP = 011b (SPI only)        | 1.53 | 1.67 | 1.81                                                                                 | V    |

| V <sub>ITRIP_LVL</sub>  | Voltage limit on V <sub>IPROPI</sub> to trigger TOFF cycle for ITRIP regulation     | S_ITRIP = 100b or LVL3           | 1.83 | 2    | 2.16                                                                                 | V    |

|                         | TOTT Gyold for TTY Togulation                                                       | S_ITRIP = 101b or LVL4           | 2.14 | 2.34 | 2.52                                                                                 | V    |

|                         |                                                                                     | S_ITRIP = 110b or LVL5           | 2.44 | 2.67 | 2.88                                                                                 | V    |

|                         |                                                                                     | S_ITRIP = 111b or LVL6           | 2.74 | 3    | 3.24                                                                                 | V    |

|                         |                                                                                     | TOFF = 00b                       | 9    | 20   | 35                                                                                   |      |

|                         | ITDID as analytical off the s                                                       | TOFF = 01b. Only choice for HW.  | 15   | 30   | 45                                                                                   |      |

| t <sub>OFF</sub>        | ITRIP regulation off-time                                                           | TOFF = 10b                       | 20   | 40   | 60                                                                                   | μs   |

|                         |                                                                                     | TOFF = 11b                       | 25   | 50   | 215<br>7<br>8<br>15<br>+3<br>5.5<br>1.81<br>2.16<br>2.52<br>2.88<br>3.24<br>35<br>45 |      |

|                        | PARAMETER                                                                  | TEST CONDITIONS                               | MIN  | TYP  | MAX  | UNIT |

|------------------------|----------------------------------------------------------------------------|-----------------------------------------------|------|------|------|------|

| PROTECTIO              | ON CIRCUITS                                                                |                                               |      |      |      |      |

| V <sub>VMOV_POB</sub>  | VM over voltage threshold while rising during POB                          |                                               | 60   |      | 69   | V    |

| $V_{VMOV}$             | VM over voltage threshold while rising                                     | OVSEL = 0b (SPI only)                         | 59.5 |      | 64.5 | V    |

| V <sub>VMOV_HYS</sub>  | VM over voltage hysteresis                                                 |                                               |      | 0.7  |      | V    |

| t <sub>VMOV</sub>      | VM over voltage deglitch time                                              |                                               | 4    | 12   | 19   | μs   |

| .,                     | VM UVLO lockout                                                            | VM falling                                    | 4.1  | 4.25 | 4.4  | V    |

| $V_{VMUV}$             | VIVI UVLU IOCKOUL                                                          | VM rising                                     | 4.15 | 4.3  | 4.45 | V    |

| V <sub>VMUV_HYST</sub> | VM UVLO hysteresis                                                         | Rising to falling threshold                   |      | 100  |      | mV   |

| t <sub>VMUV</sub>      | VM UVLO deglitch time                                                      |                                               | 3    | 12   | 20   | μs   |

| V <sub>POR_FALL</sub>  | VM or VDD voltage at which device goes into POR                            |                                               |      |      | 3.2  | V    |

| V <sub>POR_RISE</sub>  | VM or VDD voltage at which device comes out of POR                         |                                               |      |      | 3.5  | V    |

|                        |                                                                            | OCP_SEL = 11b                                 | 40   |      | 56   | Α    |

|                        |                                                                            | OCP_SEL = 10b                                 | 29   |      | 42   | Α    |

| OCP                    | Overcurrent protection threshold                                           | OCP_SEL = 01b                                 | 20   |      | 27   | Α    |

|                        |                                                                            | OCP_SEL = 00b (default), only choice for HW   | 10   |      | 14   | Α    |

| І <sub>ОСР_РОВ</sub>   | Overcurrent protection threshold with POB enabled                          |                                               | 29   |      | 40   | Α    |

|                        | Overcurrent protection deglitch                                            | TOCP = 0b                                     | 0.5  | 1    | 1.5  | μs   |

| t <sub>OCP</sub>       | time                                                                       | TOCP = 1b, only choice for HW                 | 0.6  | 2    | 3.5  | μs   |

| RETRY                  | Overcurrent protection retry time                                          | Fault reaction set to RETRY                   | 2.6  | 5    | 6.7  | ms   |

| t <sub>CLEAR</sub>     | Fault free operation time to auto-<br>clear from over current event        | Fault reaction set to RETRY                   | 70   |      | 140  | μs   |

| T <sub>TSD</sub>       | Thermal shutdown                                                           | Die temperature T <sub>J</sub>                | 155  | 170  | 185  | °C   |

| T <sub>HYS_TSD</sub>   | Thermal shutdown hysteresis                                                | Die temperature T <sub>J</sub>                |      | 20   |      | °C   |

| TSD                    | Thermal shutdown deglitch time                                             |                                               | 7    | 12   | 18   | μs   |

| CLEAR_TSD              | Fault free operation time to auto-<br>clear from over temperature<br>event | Fault reaction set to RETRY                   | 3.6  | 5    | 6.4  | ms   |

| т                      | Over Temperature Warning                                                   | Die temperature T <sub>J</sub> , OTW_SEL = 0b | 125  | 140  | 155  | °C   |

| T <sub>OTW</sub>       | Threshold                                                                  | Die temperature T <sub>J</sub> , OTW_SEL = 1b | 105  | 120  | 135  | °C   |

| T <sub>HYS_OTW</sub>   | Over Temperature Warning hysteresis                                        | Die temperature T <sub>J</sub>                |      | 20   |      | °C   |

| t <sub>OTW</sub>       | Over Temperature Warning deglitch time                                     |                                               | 7    | 12   | 18   | μs   |

|                         | PARAMETER                                                    | TEST CONDITIONS                                   | MIN | TYP  | MAX | UNIT |

|-------------------------|--------------------------------------------------------------|---------------------------------------------------|-----|------|-----|------|

| T <sub>DIE</sub>        | Die Temperature Measurement Range                            | Die temperature T <sub>J</sub>                    | -40 |      | 185 | °C   |

| I <sub>IPROPI_DIE</sub> | IPROPI Current Range for Die<br>Temperature Measurement      |                                                   | 0.5 |      | 1.5 | mA   |

| T <sub>DIE_ACC</sub>    | Die Temperature Measurement<br>Accuracy                      | Die temperature T <sub>J</sub>                    | -10 |      | 10  | %    |

| V <sub>POB_TH</sub>     | Powered off braking threshold                                |                                                   |     | 580  |     | mV   |

| t <sub>OCP_POB</sub>    | Overcurrent protection deglitch time in POB                  |                                                   | 1.2 | 2    | 2.8 | μs   |

| t <sub>POB_ON</sub>     | Powered off braking turn-on time                             |                                                   |     | 20   |     | μs   |

| t <sub>POB_RETRY</sub>  | Powered off braking retry time                               |                                                   |     | 180  |     | μs   |

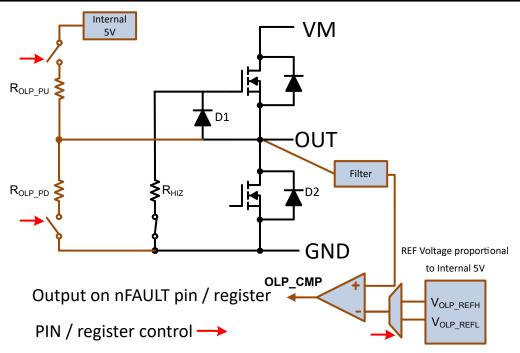

| R <sub>S_GND</sub>      | Resistance on OUT to GND that will be detected as short      |                                                   |     |      | 1.5 | kΩ   |

| R <sub>S_VM</sub>       | Resistance on OUT to VM that will be detected as short       |                                                   |     |      | 3   | kΩ   |

| R <sub>OPEN_FB</sub>    | Resistance between OUTx that will be detected as open        |                                                   | 0.5 |      |     | kΩ   |

| R <sub>OPEN_LS</sub>    | Resistance on OUT to GND that will be detected as open       | Valid for low-side load                           | 1.5 |      |     | kΩ   |

| R <sub>OPEN_HS</sub>    | Resistance on OUT to VM that will be detected as open        | Valid for high-side load, V <sub>VM</sub> = 48 V  | 30  |      |     | kΩ   |

| V <sub>OLP_REFL</sub>   | OLP Comparator Reference Low                                 | V <sub>VM</sub> > 5 V                             |     | 2.2  |     | V    |

| R <sub>OLP_PU</sub>     | Internal pull-up resistance on OUT to internal 5V during OLP | V <sub>OUTx</sub> = V <sub>OLP_REFH</sub> + 0.1 V |     | 1    |     | kΩ   |

| R <sub>OLP_PD</sub>     | Internal pull-down resistance on OUT to GND during OLP       | V <sub>OUTx</sub> = V <sub>OLP_REFL</sub> - 0.1 V |     | 1    |     | kΩ   |

|                         |                                                              | SR = 00b or LVL1                                  | 10  |      | 24  |      |

|                         | Internal sink current on OUTx to                             | SR = 01b or LVL2                                  | 5   |      | 12  | mΛ   |

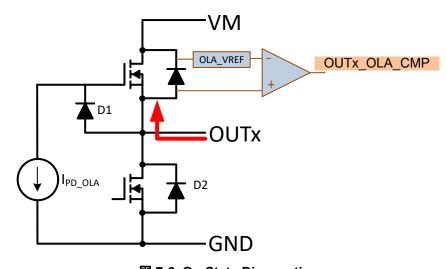

| I <sub>PD_OLA</sub>     | GND during dead-time in high-<br>side recirculation          | SR = 10b or LVL3                                  | 2.3 |      | 6   | mA   |

|                         |                                                              | SR = 11b or LVL4                                  | 0.8 |      | 2.6 |      |

| V <sub>OLA_REF</sub>    | Comparator Reference with respect to VM used for OLA         |                                                   |     | 0.28 |     | V    |

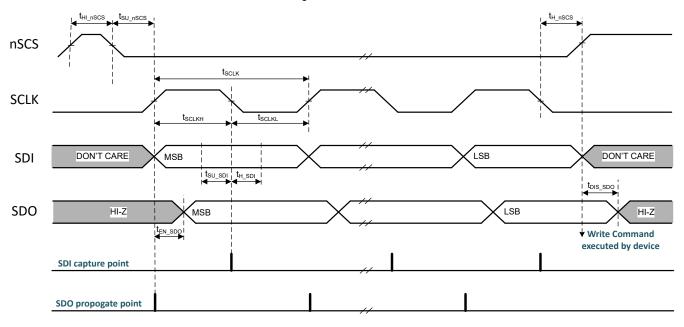

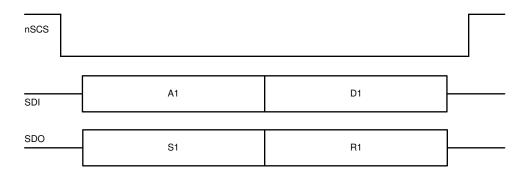

# 6.5.1 SPI Timing Requirements

|                      |                                    | MIN | TYP | MAX | UNIT |

|----------------------|------------------------------------|-----|-----|-----|------|

| t <sub>SCLK</sub>    | SCLK minimum period <sup>(1)</sup> | 110 |     |     | ns   |

| t <sub>SCLKH</sub>   | SCLK minimum high time             | 50  |     |     | ns   |

| t <sub>SCLKL</sub>   | SCLK minimum low time              | 50  |     |     | ns   |

| t <sub>HI_nSCS</sub> | nSCS minimum high time             | 600 |     |     | ns   |

|                      |                                       | MIN | TYP | MAX | UNIT |

|----------------------|---------------------------------------|-----|-----|-----|------|

| t <sub>SU_nSCS</sub> | nSCS input setup time                 | 25  |     |     | ns   |

| t <sub>H_nscs</sub>  | nSCS input hold time                  | 25  |     |     | ns   |

| t <sub>SU_SDI</sub>  | SDI input data setup time             | 25  |     |     | ns   |

| t <sub>H_SDI</sub>   | SDI input data hold time              | 25  |     |     | ns   |

| t <sub>EN_SDO</sub>  | SDO enable delay time <sup>(1)</sup>  |     |     | 45  | ns   |

| t <sub>DIS_SDO</sub> | SDO disable delay time <sup>(1)</sup> |     |     | 100 | ns   |

(1) SDO delay times are valid only with SDO external load of 5 pF. With a 20 pF load on SDO, there is an additional delay on SDO, which results in a 25% increase in SCLK minimum time, limiting the SCLK to a maximum of 8 MHz.

図 6-1. SPI Peripheral-Mode Timing Definition

# 6.6 Switching Waveforms

# 6.6.1 Output switching transients

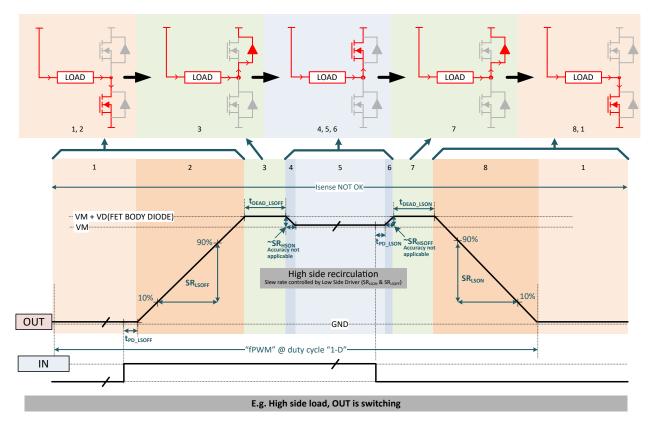

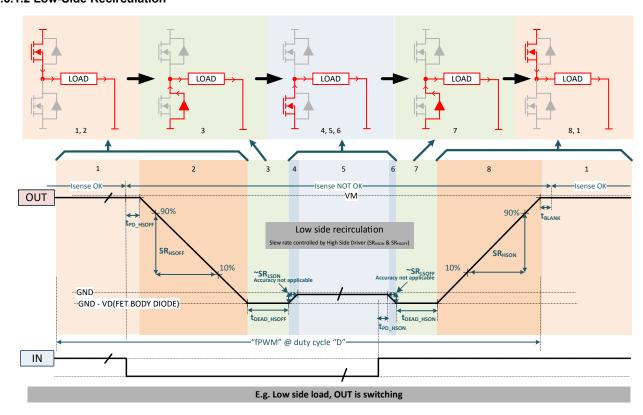

This section illustrates the switching transients for an inductive load due to external PWM or internal ITRIP regulation.

# 6.6.1.1 High-Side Recirculation

図 6-2. Output Switching Transients with High-Side Recirculation

#### 6.6.1.2 Low-Side Recirculation

図 6-3. Output Switching Transients with Low-Side Recirculation

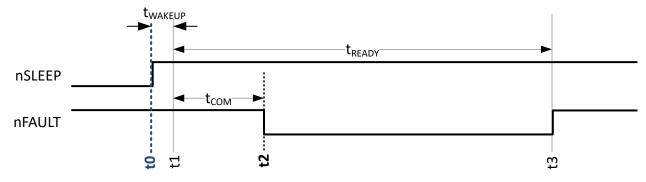

# 6.6.2 Wake-up Transients

#### 6.6.2.1 HW Variant

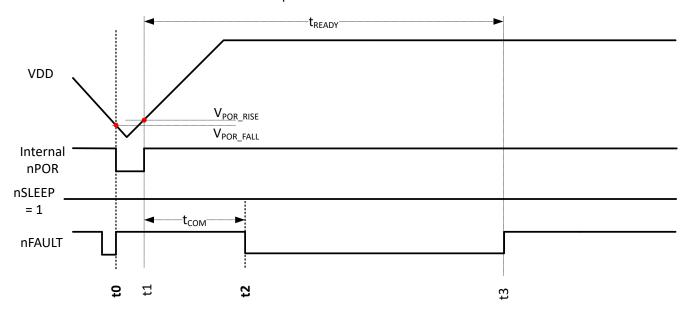

図 6-4. Wake-up from SLEEP State to STANDBY State

Hand shake between controller and device during wake-up as follows:

- t0: Controller nSLEEP asserted high to initiate device wake-up

- t1: Device internal state Wake-up command registered by device (end of Sleep state)

- t2: Device nFAULT asserted low to acknowledge wake-up and indicate device ready for communication

- t3: Device internal state Initialization complete. nFAULT de-asserted. Device in STANDBY state

資料に関するフィードバック(ご意見やお問い合わせ)を送信

Copyright © 2025 Texas Instruments Incorporated

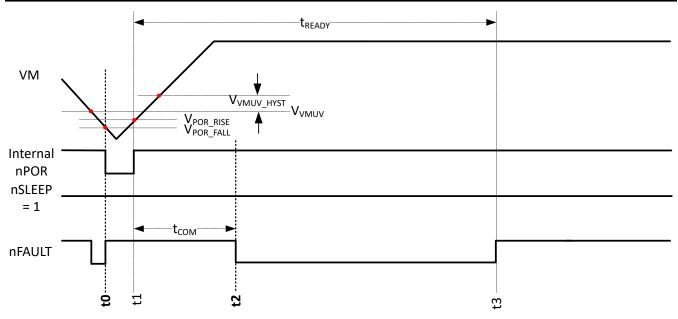

図 6-5. Power-up via VM to STANDBY State

Hand shake between controller and device during power-up as follows:

- t0: Device internal state POR asserted based on under voltage of internal LDO (VM dependent)

- t1: Device internal state POR de-asserted based on recovery of internal LDO voltage

- t2: Device nFAULT asserted low to acknowledge wake-up and indicate device ready for communication

- t3: Device internal state Initialization complete. nFAULT de-asserted. Device in STANDBY state

図 6-6. Power-up via VDD to STANDBY State

Hand shake between controller and device during power-up as follows:

- t0: Device internal state POR asserted based on under voltage on VDD (external supply)

- t1: Device internal state POR de-asserted based on recovery of voltage on VDD (external supply)

- t2: Device nFAULT asserted low to acknowledge wake-up and indicate device ready for communication

- t3: Device internal state Initialization complete. nFAULT de-asserted. Device in STANDBY state

#### 6.6.2.2 SPI Variant

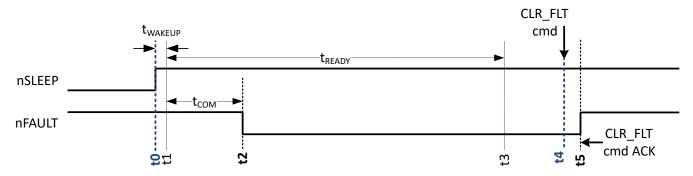

図 6-7. Wake-up from SLEEP State to STANDBY State

Hand shake between controller and device during a wake-up transient as follows:

- t0: Controller nSLEEP asserted high to initiate device wake-up

- t1: Device internal state Wake-up command registered by device (end of Sleep state)

- t2: Device nFAULT asserted low to acknowledge wake-up and indicate device ready for communication

- t3: Device internal state Initialization complete

- t4 (Any time after t2): Controller Issue CLR\_FLT command through SPI to acknowledge device wake-up

- t5: Device nFAULT de-asserted as an acknowledgment of CLR FLT command. Device in STANDBY state

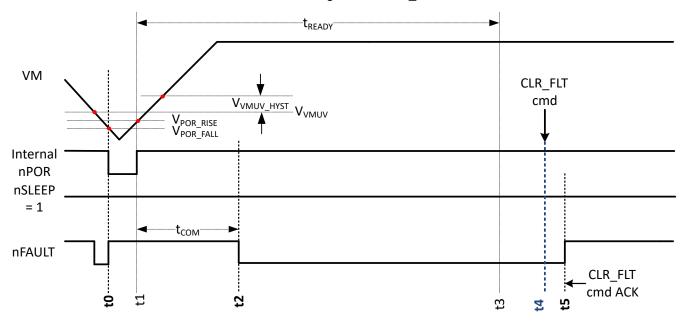

図 6-8. Power-up via VM to STANDBY State Transition

Hand shake between controller and device during power-up as follows:

- t0: Device internal state POR asserted based on under voltage of internal LDO (VM dependent)

- t1: Device internal state POR de-asserted based on recovery of internal LDO voltage

- t2: Device nFAULT asserted low to acknowledge wake-up and indicate device ready for communication

- t3: Device internal state Initialization complete

- t4 (Any time after t2): Controller Issue CLR FLT command through SPI to acknowledge device power-up

- t5: Device nFAULT de-asserted as an acknowledgment of CLR\_FLT command. Device in STANDBY state

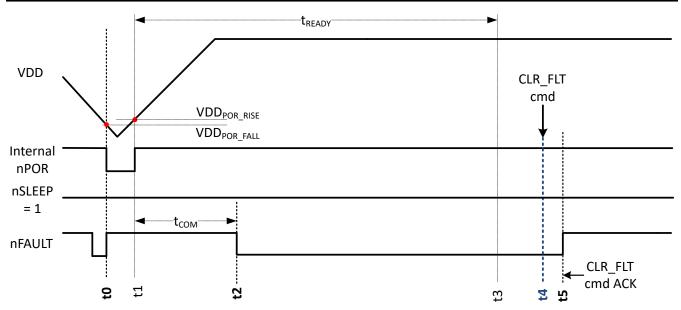

図 6-9. Power-up via VDD to STANDBY State Transition

Hand shake between controller and device during power-up as follows:

- t0: Device internal state POR asserted based on under voltage on VDD (external supply)

- t1: Device internal state POR de-asserted based on recovery of voltage on VDD (external supply)

- t2: Device nFAULT asserted low to acknowledge wake-up and indicate device ready for communication

- t3: Device internal state Initialization complete

- t4 (Any time after t2): Controller Issue CLR\_FLT command through SPI to acknowledge device power-up

- t5: Device nFAULT de-asserted as an acknowledgment of CLR FLT command. Device in STANDBY state

### 6.6.3 Fault Reaction Transients

#### 6.6.3.1 Retry setting

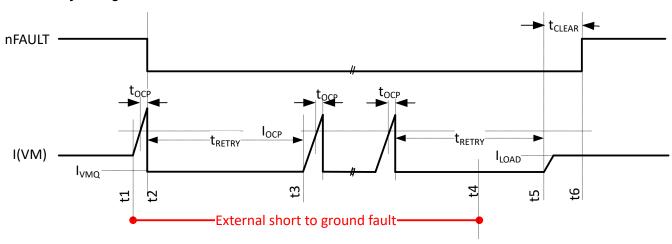

図 6-10. Fault reaction with RETRY setting (shown for OCP occurrence on high-side when OUT is shorted to ground)

Short occurrence and recovery scenario with RETRY setting:

t1: An external short occurs.

- t2: OCP (Over Current Protection) fault confirmed after t<sub>OCP</sub>, output disabled, nFAULT asserted low to indicate fault.

- t3: Device automatically attempts retry (auto retry) after t<sub>RETRY</sub>. Each time output is briefly turned on to confirm short occurrence and then immediately disabled after t<sub>OCP</sub>. nFAULT remains asserted low through out. Cycle repeats till driver is disabled by the user or external short is removed, as illustrated further. Note that, in case of a TSD (Thermal Shut Down) event, automatic retry time depends on the cool off based on thermal hysteresis.

- t4: The external short is removed.

- t5: Device attempts auto retry. But this time, no fault occurs and device continues to keep the output enabled.

- t6: After a fault free operation for a period of t<sub>CLEAR</sub> is confirmed, nFAULT is de-asserted.

- SPI variant only Fault status remains latched till a CLR FLT command is issued.

Note that, in the event of an output short to ground causing the high-side OCP fault detection, IPROPI pin will continue to be pulled up to  $V_{IPROPI\_LIM}$  voltage to indicate this type of short, while the output is disabled. This is especially useful for the HW variant to differentiate the indication of a short to ground fault from the other faults.

### 6.6.3.2 Latch setting

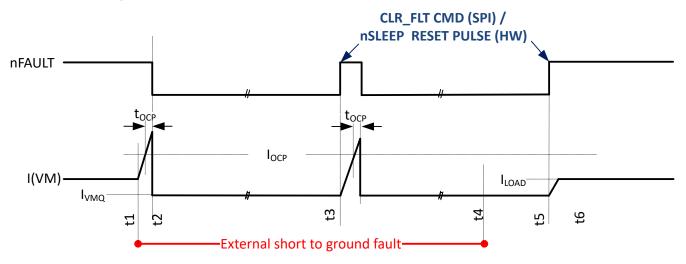

図 6-11. Fault reaction with Latch setting (shown for OCP occurrence on high-side when OUT is shorted to ground)

Short occurrence and recovery scenario with LATCH setting:

- t1: An external short occurs.

- t2: OCP (Over Current Protection) fault confirmed after t<sub>OCP</sub>, output disabled, nFAULT asserted low to indicate fault.

- t3: A CLR\_FLT command (SPI variant) or nSLEEP RESET Pulse (HW variant) issued by controller. nFAULT is de-asserted and output is enabled. OCP fault is detected again and output is disabled with nFAULT asserted low.

- · t4: The external short is removed.

- t5: A CLR\_FLT command (SPI variant) or nSLEEP RESET Pulse (HW variant) issued by controller. nFAULT is de-asserted and output is enabled. Normal operation resumes.

- SPI variant only Fault status remains latched till a CLR FLT command is issued.

Note that, in the event of an output short to ground causing the high-side OCP fault detection, IPROPI pin will continue to be pulled up to  $V_{IPROPI\_LIM}$  voltage to indicate this type of short, while the output is disabled. This is especially useful for the HW variant to differentiate the indication of a short to ground fault from the other faults.

資料に関するフィードバック (ご意見やお問い合わせ) を送信 Copyright © 2025 Texas Instruments Incorporated

# 7 Detailed Description

# 7.1 Overview

The DRV8163-Q1 is a brushed DC motor driver that operates from 4.5 to 65V supporting a wide range of output load currents for various types of motors and loads. The device integrates a charge pump regulator to support efficient high-side N-channel MOSFETs with 100% duty cycle operation. The device operates from a single power supply input (VM) which can be directly connected to a battery or DC voltage supply. The device also provides a low-power mode to minimize current draw during system inactivity. The digital block of the device is powered by an external supply input through the VDD pin.

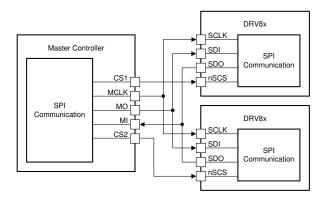

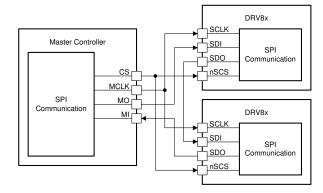

The device is available in two interface variants -

- HW variant The hardwired interface variant is available for easy device configuration. Due to the limited number of available pins in the device, this variant offers fewer configuration and fault reporting capabilities compared to the SPI variant.

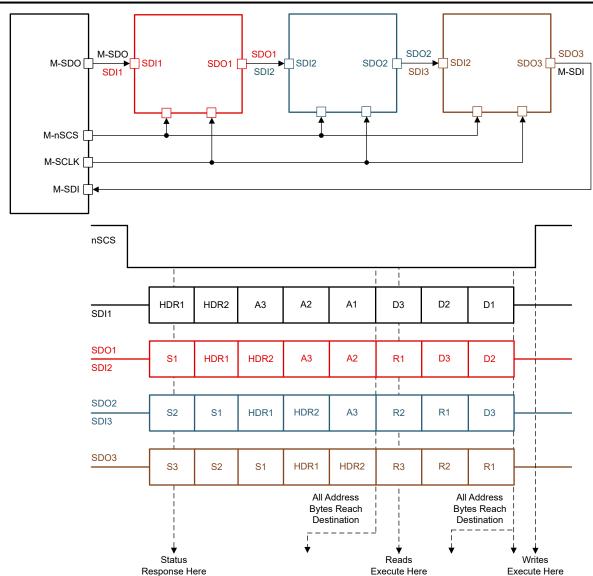

- 2. SPI variant A standard 4-wire serial peripheral interface (SPI) with daisy chain capability allows flexible device configuration and detailed fault reporting to an external controller. The feature differences of the SPI and HW variants can be found in the device comparison section.

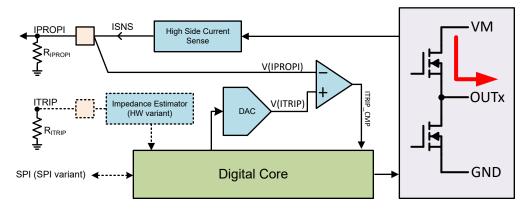

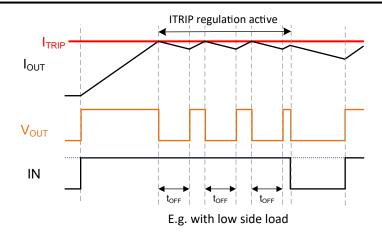

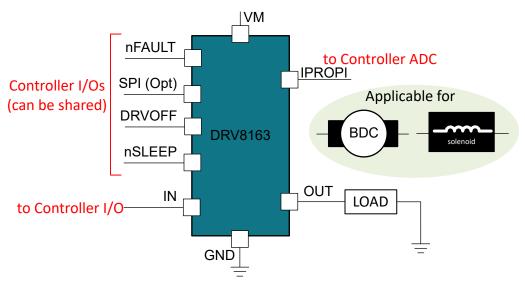

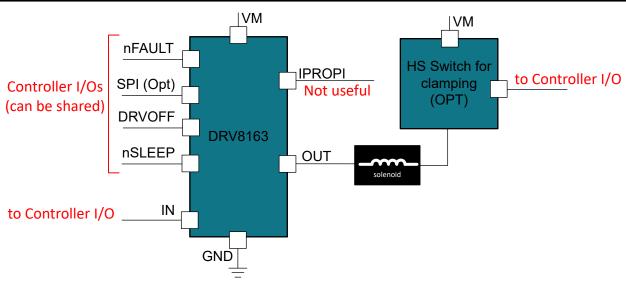

The DRV8163-Q1 device provides a load current sense output using current mirrors on the high-side power MOSFETs. The IPROPI pin sources a small current that is proportional to the current in the high-side MOSFETs (current sourced out of the OUTx pin). This current can be converted to a proportional voltage using an external resistor (R<sub>IPROPI</sub>). Additionally, for the SPI variant, the IPROPI pin can be programmed to output a voltage proportional to the die temperature. The device also supports a fixed off-time PWM chopping scheme for limiting current to the load. The current regulation level can be configured through the ITRIP function.

A variety of protection features and diagnostic functions are integrated into the device. These include supply voltage monitor (VMUV and VMOV), off-state (Passive) diagnostics (OLP), on-state (Active) diagnostics (OLA), overcurrent protection (OCP) for each power FET, powered-off braking (POB), over-temperature warning (OTW) and die temperature monitor, and over-temperature shutdown (TSD). Fault conditions are indicated on the nFAULT pin. The SPI variant has additional communication protection features such as frame errors and lock features for configuration register bits and driver control bits.

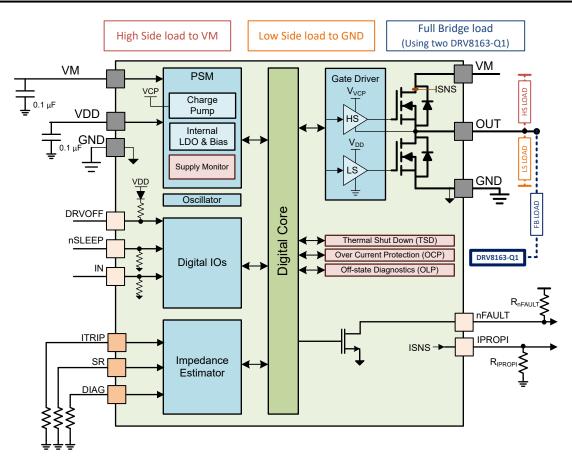

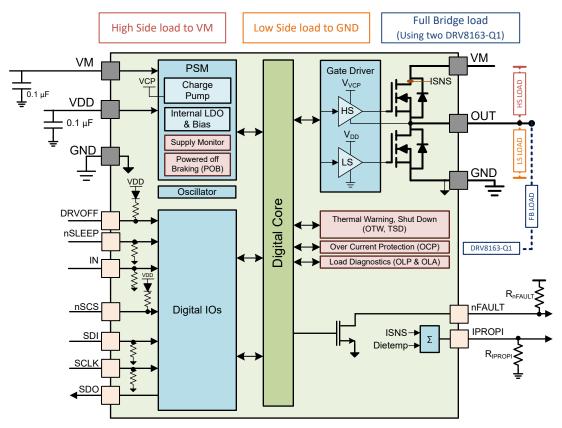

### 7.2 Functional Block Diagram

Copyright © 2025 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ)を送信

21

図 7-1. Functional Block Diagram - HW Variant

図 7-2. Functional Block Diagram - SPI Variant

# 7.3 Feature Description

# 7.3.1 External Components

表 7-1 and 表 7-2 contain the recommended external components for the device.

# 7.3.1.1 HW Variant

表 7-1. External Components Table for HW Variant

| Component           | PIN                                                | Recommendation                                                                                                                                                                   |  |  |

|---------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| C <sub>VM1</sub>    | VM                                                 | 0.1μF, low ESR ceramic capacitor to GND rated for VM                                                                                                                             |  |  |

| C <sub>VM2</sub>    | VM                                                 | Local bulk capacitor to GND, 10µF or higher, rated for VM to handle load transients. Refer to the section on bulk capacitor sizing.                                              |  |  |

| C <sub>VDD</sub>    | VDD 0.1μF, 6.3V, low ESR ceramic capacitor to GND. |                                                                                                                                                                                  |  |  |

| R <sub>IPROPI</sub> | IPROPI                                             | Typically $500 - 5000\Omega$ $0.063$ W resistor to GND, depending on the controller ADC dynamic range. The pin can be shorted to GND if ITRIP and IPROPI function is not needed. |  |  |

| C <sub>IPROPI</sub> | IPROPI                                             | Optional 10 - 100nF, 6.3V capacitor to GND to slow down the ITRIP regulation loop. Refer Over Current Protection (OCP) section.                                                  |  |  |

| R <sub>nFAULT</sub> | nFAULT                                             | Typically 1K $\Omega$ - 10K $\Omega$ , 0.063W pull-up resistor to controller supply.                                                                                             |  |  |

| R <sub>SR</sub>     | SR                                                 | Open or short to GND or 0.063W 10% resistor to GND depending on the setting. Refer SR section.                                                                                   |  |  |

| R <sub>ITRIP</sub>  | ITRIP                                              | Open or short to GND or 0.063W 10% resistor to GND depending on the setting. Refer ITRIP table.                                                                                  |  |  |

| R <sub>DIAG</sub>   | DIAG                                               | Open or short to GND or 0.063W 10% resistor to GND depending on the setting. Refer DIAG section.                                                                                 |  |  |

#### 7.3.1.2 SPI Variant

### 表 7-2. External Components Table for SPI Variant

| Component           | PIN    | Recommendation                                                                                                                                                                 |

|---------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|