# DRV81620-Q1 : 8 チャネル、40V 対応、700mΩ、完全保護機能付き、車載リレー、LED、照明、モータ制御向けのローサイド/ハイサイド切替可能ドライバ

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認証済み

- 温度グレード 1: -40°C ~ +125°C,  $T_A$

- 機能安全対応**

- 機能安全の設計に役立つ資料

- アナログ電源電圧: **3V ~ 40V**

- クランク機能: 最小 3V

- LV124 車載規格をサポート

- デジタル電源電圧: **3V ~ 5.5V**

- 3.3V および 5V マイクロコントローラと互換

- ドレインソース間のクランプ電圧: 最小 **42V**

- ソースグランド間の最大クランプ電圧: **-18V**

- $R_{DS(ON)}$ : 12V, 25°C 時の代表値 **700mΩ**

- 電流: すべてのチャネルがオンの場合、85°C 時に出力ごとに **330mA**

- マッピング機能を備えた **2 個の並列入力**

- リップル ホーム モードでのフェイルセーフ起動

- nSLEEP および IN ピンの使用

- 2 個の独立した内部 **PWM** ジェネレータ

- ランプを駆動するための電球突入モード (BIM)

- 2W/5W ランプや他の容量性負荷向け

- 低電流のスリープモード:  $T_J \leq 85^\circ\text{C}$  で  $3\mu\text{A}$  未満

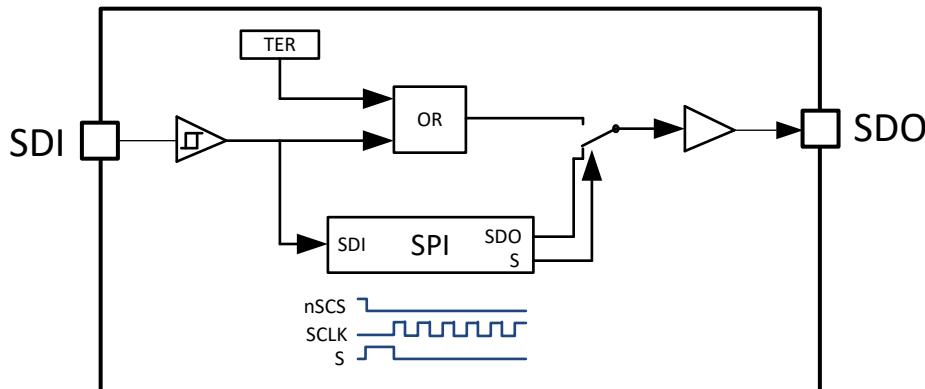

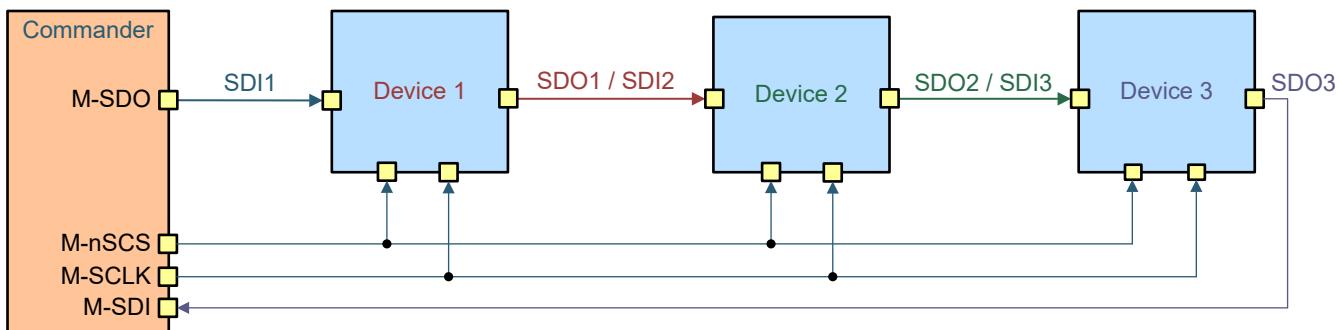

- 制御および診断用の 16 ビット SPI

- デイジーチェーン機能

- 8 ビット SPI デバイスと互換

- 各種**保護機能**をサポート

- 逆極性バッテリ保護

- グランドおよびバッテリ短絡保護

- 低電圧条件での安定した動作

- 過電流ラッチオフ

- 過熱警告

- サーマルシャットダウンラッチオフ

- 過電圧保護

- バッテリ喪失およびグランド喪失時の保護

- 静電気放電 (ESD) 保護

- 各種**診断機能**をサポート

- SPI レジスタを介した診断情報

- オン状態での過負荷検出

- オンおよびオフ状態でのオープン負荷検出

- 入力および出力ステータスモニタ

## 2 アプリケーション

- ゾーン制御モジュール (ZCM)

- 車載用ボディコントロール モジュール (BCM)

- オートモーティブ ライティング

- ガソリン / ディーゼル エンジン

- 車両制御ユニット (VCU)

- プログラマブル ロジック コントローラ (PLC)

## 3 説明

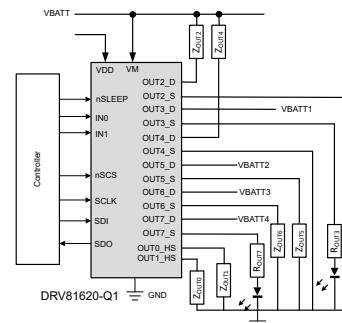

DRV81620-Q1 は保護機能と診断機能を備えた 8 チャネルのローサイド ドライバおよびハイサイド ドライバです。このデバイスは、リレー、LED、ランプ、モータを制御するために設計されています。

負荷およびデバイスの制御と診断には、デイジーチェーン対応のシリアル ペリフェラル インターフェイス(SPI)が使用されます。マッピング機能を持つ 2 つの入力ピンを利用して、出力を直接制御できます。このデバイスは、フェイルセーフ起動のためのリップル ホーム モードをサポートしています。内蔵の PWM ジェネレータは LED を駆動でき、電球の突入モードは大きな静電容量で負荷を駆動できます。各出力にあるクランプ回路が、誘導性負荷のスイッチオフ時に発生するエネルギーを放散します。

このデバイスは、低電圧、過電圧、短絡、開放負荷検出などの各種保護機能をサポートしています。保護および診断機能を内蔵し、高度に統合された DRV81620-Q1 は、車載用ボディおよびパワートレイン アプリケーションに最高です。

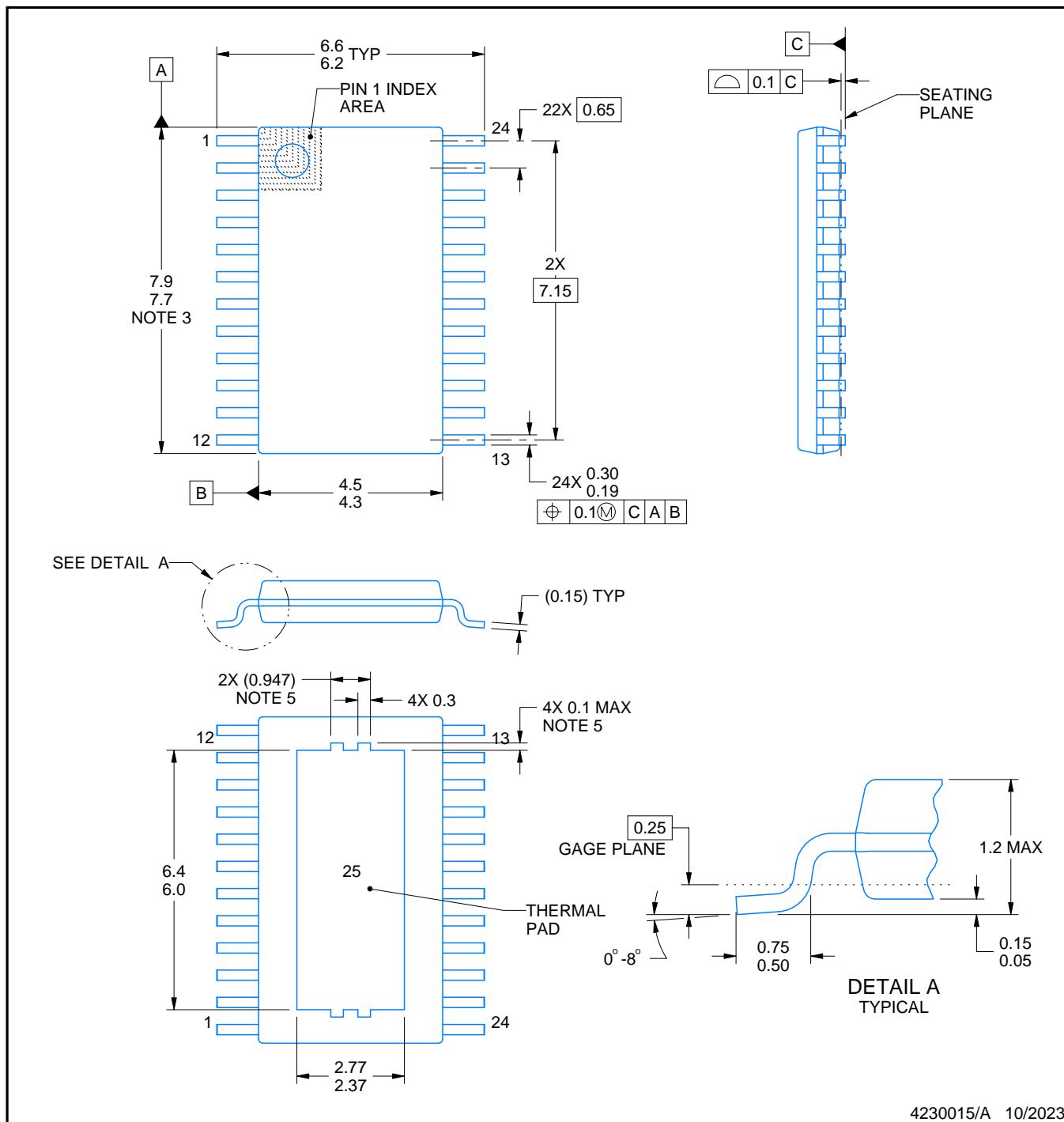

## 製品情報

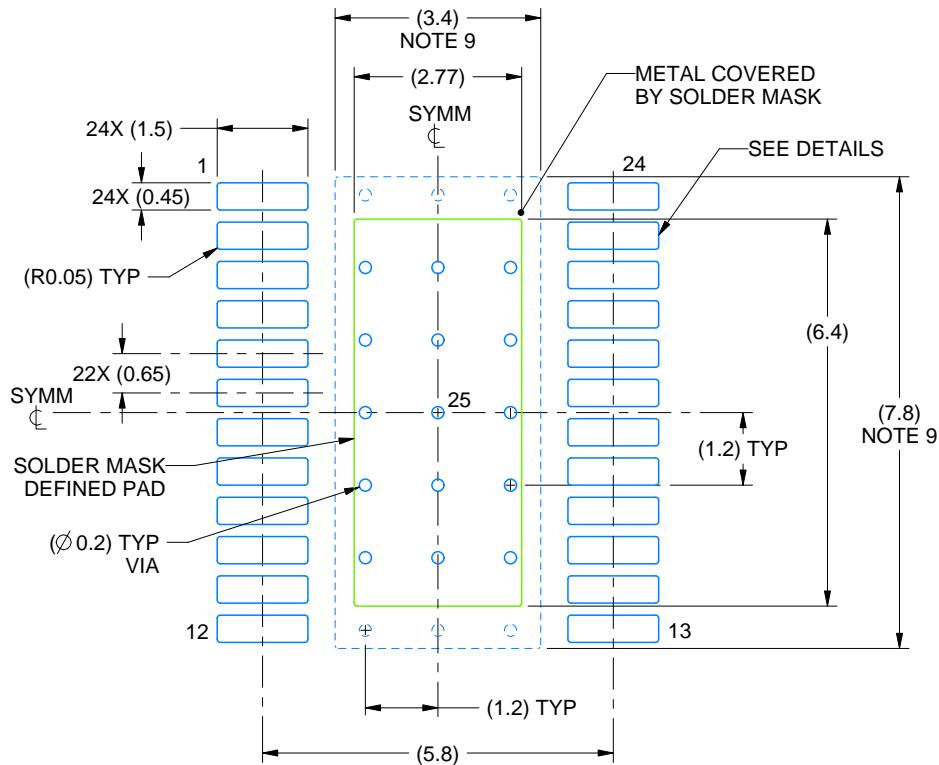

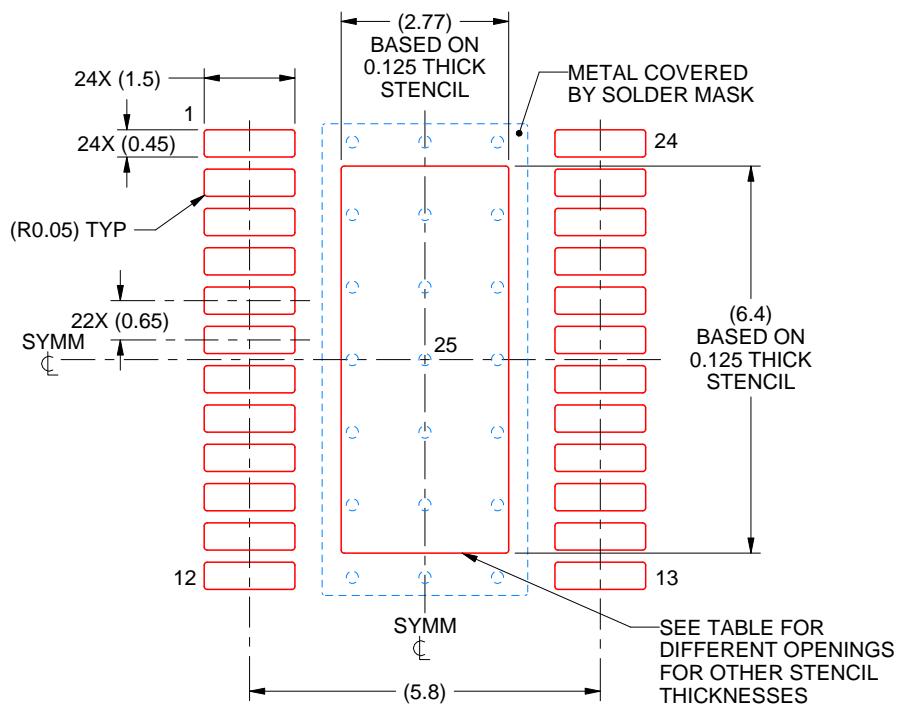

| 部品番号                | パッケージ<br>(1)   | パッケージ<br>サイズ(2) | 本体サイズ (公称)     |

|---------------------|----------------|-----------------|----------------|

| DRV81620QPWPR<br>Q1 | HTSSOP<br>(24) | 7.8mm × 6.4mm   | 7.7 mm × 4.4mm |

(1) 詳細については、[セクション 11](#) を参照してください。

(2) パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はビンも含まれます。

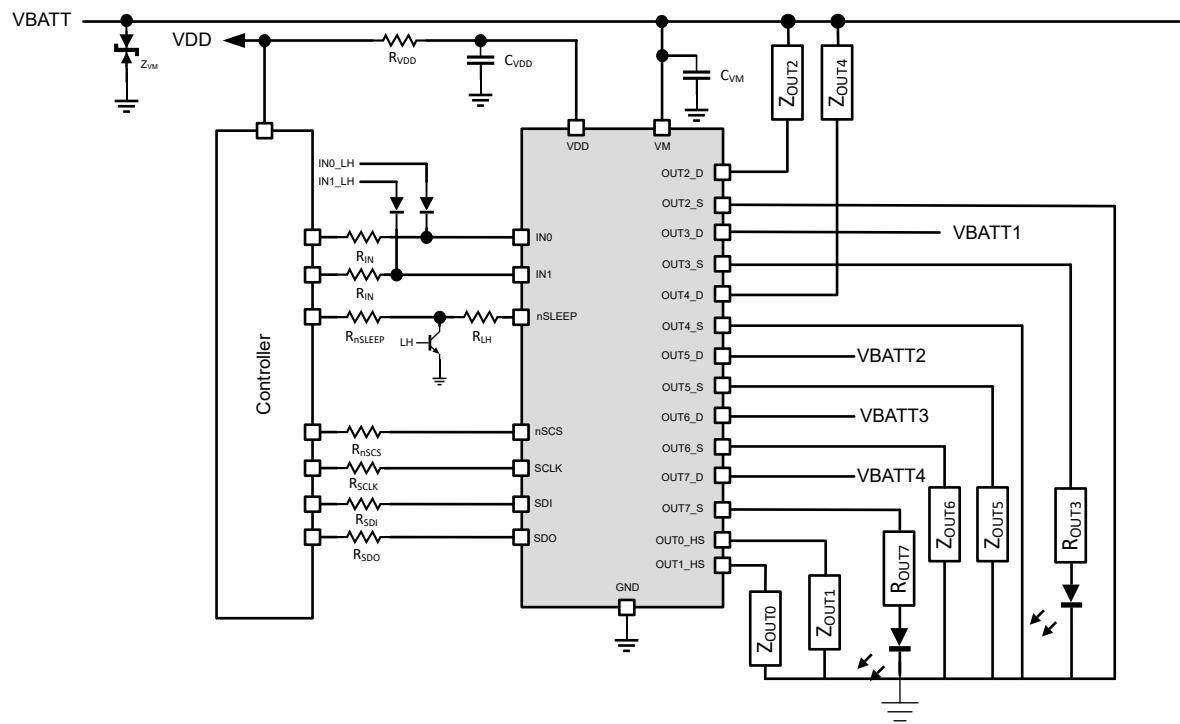

概略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                  |    |                        |    |

|------------------|----|------------------------|----|

| 1 特長             | 1  | 7.2 機能ブロック図            | 17 |

| 2 アプリケーション       | 1  | 7.3 機能説明               | 18 |

| 3 説明             | 1  | 8 アプリケーションと実装          | 51 |

| 4 デバイスの比較        | 3  | 8.1 アプリケーション情報         | 51 |

| 5 ピン構成および機能      | 4  | 8.2 代表的なアプリケーション       | 52 |

| 6 仕様             | 6  | 8.3 レイアウト              | 54 |

| 6.1 絶対最大定格       | 6  | 9 デバイスおよびドキュメントのサポート   | 56 |

| 6.2 ESD 定格       | 7  | 9.1 ドキュメントの更新通知を受け取る方法 | 56 |

| 6.3 推奨動作条件       | 7  | 9.2 サポート・リソース          | 56 |

| 6.4 熱に関する情報      | 7  | 9.3 商標                 | 56 |

| 6.5 電気的特性        | 8  | 9.4 静電気放電に関する注意事項      | 56 |

| 6.6 SPI のタイミング要件 | 13 | 9.5 用語集                | 56 |

| 6.7 代表的特性        | 14 | 10 改訂履歴                | 56 |

| 7 詳細説明           | 16 | 11 メカニカル、パッケージ、および注文情報 | 56 |

| 7.1 概要           | 16 |                        |    |

## 4 デバイスの比較

DRV81xxx-Q1 ファミリの各デバイスのローサイド、ハイサイド、および構成可能なチャネルの数を表 4-1 に示します。

表 4-1. デバイスの比較

| 型番          | ハイサイド チャネルの数 | ローサイド チャネルの数 | 構成可能 (ハイサイドまたはロー<br>サイド) チャネルの数 |

|-------------|--------------|--------------|---------------------------------|

| DRV81242-Q1 | 4            | 2            | 2                               |

| DRV81080-Q1 | 8            | 0            | 0                               |

| DRV81602-Q1 | 0            | 2            | 6                               |

| DRV81620-Q1 | 2            | 0            | 6                               |

| DRV81008-Q1 | 0            | 8            | 0                               |

| DRV81004-Q1 | 0            | 4            | 0                               |

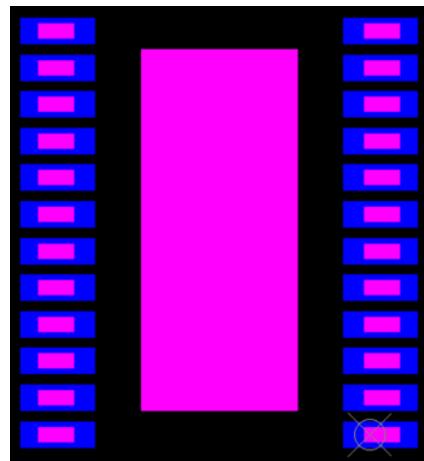

## 5 ピン構成および機能

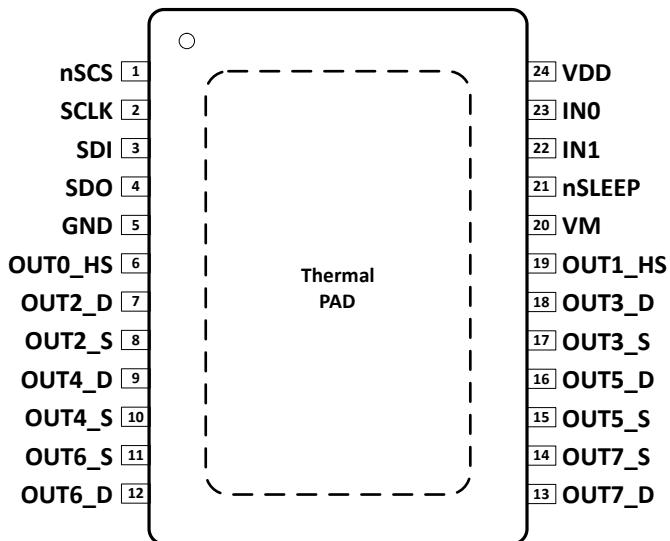

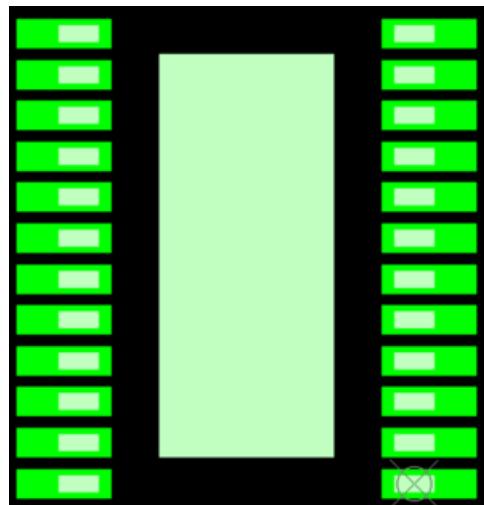

図 5-1. 24 ピン HTSSOP (PWP) 上面図

表 5-1. ピンの機能

| ピン      |    | タイプ | 説明                                                                               |

|---------|----|-----|----------------------------------------------------------------------------------|

| 名称      | 番号 |     |                                                                                  |

| VM      | 20 | P   | 出力段と保護回路のアナログ電源電圧                                                                |

| VDD     | 24 | P   | SPI デジタル電源電圧                                                                     |

| GND     | 5  | G   | グランドピン                                                                           |

| nSCS    | 1  | I   | シリアル チップ選択。このピンを <b>Low</b> にするとシリアル インターフェイス通信が有効になります。VDD に統合プルアップ。            |

| SCLK    | 2  | I   | シリアル クロック入力。シリアル データは、このピンの対応する立ち上がりおよび立ち下がりエッジでシフトアウトおよびキャプチャされます。GND に統合プルダウン。 |

| SDI     | 3  | I   | シリアル データ入力。データは、SCLK の立ち下がりエッジでキャプチャされます。GND に統合プルダウン。                           |

| SDO     | 4  | O   | シリアル データ出力。データは、SCLK の立ち上がりエッジでシフト アウトされます。                                      |

| nSLEEP  | 21 | I   | ロジック <b>High</b> にすると、アイドルモードがアクティブになります。GND に統合プルダウン。                           |

| IN0     | 23 | I   | デフォルトでチャネル 2 に接続し、リープホームモードで使用しています。GND に統合プルダウン。                                |

| IN1     | 22 | I   | デフォルトでチャネル 3 に接続し、リープホームモードで使用しています。GND に統合プルダウン                                 |

| OUT0_HS | 6  | O   | ハイサイド FET のソース (チャネル 0)                                                          |

| OUT2_D  | 7  | O   | 自動構成可能 FET のドレイン (チャネル 2)                                                        |

| OUT2_S  | 8  | O   | 自動構成可能 FET のソース (チャネル 2)                                                         |

| OUT4_D  | 9  | O   | 自動構成可能な FET のドレイン (チャネル 4)                                                       |

| OUT4_S  | 10 | O   | 自動構成可能な FET のソース (チャネル 4)                                                        |

| OUT6_S  | 11 | O   | 自動構成可能な FET のソース (チャネル 6)                                                        |

| OUT6_D  | 12 | O   | 自動構成可能な FET のドレイン (チャネル 6)                                                       |

**表 5-1. ピンの機能 (続き)**

| ピン      |    | タイプ | 説明                                           |

|---------|----|-----|----------------------------------------------|

| 名称      | 番号 |     |                                              |

| OUT7_D  | 13 | O   | 自動構成可能な FET のドレイン (チャネル 7)                   |

| OUT7_S  | 14 | O   | 自動構成可能 FET のソース (チャネル 7)                     |

| OUT5_S  | 15 | O   | 自動構成可能 FET のソース (チャネル 5)                     |

| OUT5_D  | 16 | O   | 自動構成可能な FET のドレイン (チャネル 5)                   |

| OUT3_S  | 17 | O   | 自動構成可能 FET (チャネル 3)                          |

| OUT3_D  | 18 | O   | 自動構成可能な FET のドレイン (チャネル 3)                   |

| OUT1_HS | 19 | O   | ハイサイド FET のソース (チャネル 1)                      |

| PAD     | -  | -   | 露出パッド。冷却および EMC のため、露出したパッドを PCB グランドに接続します。 |

I = 入力、O = 出力、I/O = 入力または出力、G = グランド、P = 電源。

## 6 仕様

### 6.1 絶対最大定格

$T_J = -40^{\circ}\text{C} \sim 150^{\circ}\text{C}$ 、すべてのグラウンドを基準とした電圧、ピンに流れ込む正電流 (特に記述のない限り)

|               |                                                                                                          | 最小値                | 最大値                | 単位 |

|---------------|----------------------------------------------------------------------------------------------------------|--------------------|--------------------|----|

| $V_M$         | アナログ電源電圧                                                                                                 | -0.3               | 42                 | V  |

| $V_{DD}$      | デジタル電源電圧                                                                                                 | -0.3               | 5.75               | V  |

| $V_{M\_LD}$   | ロードダンプ保護の電源電圧                                                                                            |                    | 42                 | V  |

| $V_{M\_SC}$   | 短絡保護の電源電圧                                                                                                | 0                  | 28                 | V  |

| $-V_{M\_REV}$ | 逆極性電圧、 $T_J(0) = 25^{\circ}\text{C}$ 、 $t \leq 2$ 最小値、 $R_L = 70\Omega$ をすべてのチャネルで実現                     | -                  | 18                 | V  |

| $I_{VM}$      | $VM$ ピンを流れる電流、 $t \leq 2$ 最小値                                                                            | -10                | 10                 | mA |

| $ I_L $       | 負荷電流、シングルチャネル                                                                                            | -                  | $I_{L\_OCP0}$      | A  |

| $V_{DS}$      | パワー FET の電圧                                                                                              | -0.3               | 42                 | V  |

| $V_{OUT\_S}$  | FET ソース電圧                                                                                                | -18                | $V_{OUT\_D} + 0.3$ | V  |

| $V_{OUT\_D}$  | FET ドレイン電圧 ( $V_{OUT\_S} \geq 0V$ )                                                                      | $V_{OUT\_S} - 0.3$ | 42                 | V  |

| $V_{OUT\_D}$  | FET ドレイン電圧 ( $V_{OUT\_S} < 0V$ )                                                                         | -0.3               | 42                 | V  |

| $E_{AS}$      | 最大エネルギー消費の単一パルス、 $T_J(0) = 25^{\circ}\text{C}$ 、 $I_L(0) = 2 * I_{L\_EAR}$                               | -                  | 50                 | mJ |

| $E_{AS}$      | 最大エネルギー消費の単一パルス、 $T_J(0) = 150^{\circ}\text{C}$ 、 $I_L(0) = 400\text{mA}$                                | -                  | 25                 | mJ |

| $E_{AR}$      | 反復パルスの最大エネルギー散逸 $-I_{L\_EAR}$ , $2 * 10^6$ cycles, $T_J(0) = 85^{\circ}\text{C}$ 、 $I_L(0) = I_{L\_EAR}$ | -                  | 10                 | mJ |

| $V_I$         | IN0、IN1、nSCS、SCLK、SDI の各ピンの電圧                                                                            | -0.3               | 5.75               | V  |

| $V_{nSLEEP}$  | nSLEEP ピンの電圧                                                                                             | -0.3               | 42                 | V  |

| $V_{SDO}$     | SDO ピンの電圧                                                                                                | -0.3               | $V_{DD} + 0.3$     | V  |

| $T_A$         | 周囲温度                                                                                                     | -40                | 125                | °C |

| $T_J$         | 接合部温度                                                                                                    | -40                | 150                | °C |

| $T_{stg}$     | 保存温度                                                                                                     | -55                | 150                | °C |

- 短絡保護機能は、28V を超える電圧下でインダクタンスが  $1\mu\text{H}$  未満の短絡には対応していません。

- ロードダンプは、 $t_{ON} = 400\text{ms}$ 、 $t_{ON}/t_{OFF} = 10\%$ 、100 パルスに制限されています。

- 逆極性の場合、すべてのチャネルで  $T_J(0) = 25^{\circ}\text{C}$ 、 $t \leq 2$  最小値、 $R_L = 70\Omega$  です。デバイスは JEDEC JESD51-2、-5、-7 に従って自然対流の FR4 2s2p 基板に実装されています。製品 (Chip + パッケージ) は、2 つの内銅層 ( $2 * 70\mu\text{m Cu}$ 、 $2 * 35\mu\text{m Cu}$ ) を持つ  $76.2 * 114.3 * 1.5\text{mm}$  基板上でシミュレーションされました。該当する場合、露出パッドの下のサーマルビアアレイが最初の内側の銅層に接触しています。

- 最大エネルギー消費を得るために、パルス形状は誘導性スイッチオフを表します。 $I_L(t) = I_L(0) \times (1 - t / t_{pulse})$ ;  $0 < t < t_{pulse}$ 。

- 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- 故障状態は、「通常の動作範囲外」と見なされます。

## 6.2 ESD 定格

|           |      |                                            |                         | 値          | 単位 |

|-----------|------|--------------------------------------------|-------------------------|------------|----|

| $V_{ESD}$ | 静電放電 | 人体モデル (HBM)、AEC Q100-002 <sup>(1)</sup> 準拠 | OUT ピンと VM または GND の関係  | $\pm 4000$ | V  |

|           |      |                                            | その他のピン                  | $\pm 2000$ |    |

|           |      | 荷電デバイス モデル (CDM)、<br>AECQ100-011 準拠        | コーナー ピン (1, 12, 13, 24) | $\pm 750$  |    |

|           |      |                                            | その他のピン                  | $\pm 500$  |    |

(1) AEC Q100-002 は、ANSI/ESDA/JEDEC JS-001 仕様に従って HBM ストレス試験を実施することを示しています。

## 6.3 推奨動作条件

自由空気での動作温度範囲内 (特に記述のない限り)

|              |                                             | 最小値 | 公称値 | 最大値 | 単位 |

|--------------|---------------------------------------------|-----|-----|-----|----|

| $V_{M\_NOR}$ | 通常動作の電源電圧範囲                                 | 4   | -   | 40  | V  |

| $V_{M\_LOW}$ | より低い電源電圧範囲で動作するため、パラメータ偏差も可能                | 3   | -   | 4   | V  |

| $V_{DD}$     | ロジック電源電圧、 $f_{SCLK} = 5\text{MHz}$          | 3   | -   | 5.5 | V  |

| $V_I$        | 制御および SPI 入力 (nSLEEP、IN0、IN1、nSCS、SCLK、SDI) | 0   | -   | 5.5 | V  |

| $T_A$        | 周囲温度                                        | -40 | -   | 125 | °C |

| $T_J$        | 接合部温度                                       | -40 | -   | 150 | °C |

## 6.4 热に関する情報

| 熱評価基準                |                     | PWP (HTSSOP) | 単位   |

|----------------------|---------------------|--------------|------|

|                      |                     | 24 ピン        |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 32.2         | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 27.5         | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 12.5         | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 1.3          | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 12.5         | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 | 5.7          | °C/W |

## 6.5 電気的特性

$V_{DD} = 3V \sim 5.5V$ 、 $V_M = 4V \sim 40V$ 、 $T_J = -40^{\circ}C \sim +150^{\circ}C$  (特に記述のない限り)

標準値:  $V_{DD} = 5V$ 、 $V_M = 13.5V$ 、 $T_J = 25^{\circ}C$

| パラメータ                     |                               | テスト条件                                                                                                                | 最小値                             | 標準値 | 最大値 | 単位  |

|---------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------|-----|-----|-----|

| 電源電圧 ( $V_M$ , $V_{DD}$ ) |                               |                                                                                                                      |                                 |     |     |     |

| $V_{M\_OP}$               | $V_M$ 最小動作電圧                  | $ENx = 1b$ 、 $UVRVM = 1b \sim V_{DS} \leq 1V$ 、 $R_L = 50\Omega$                                                     |                                 |     | 4   | V   |

| $V_{DD\_OP}$              | $VDD$ 動作電圧                    | $f_{SCLK} = 5MHz$                                                                                                    | 3                               |     | 5.5 | V   |

| $V_{MDIFF}$               | $V_M$ と $V_{DD}$ の電圧差         |                                                                                                                      |                                 | 200 |     | mV  |

| $I_{VM\_SLEEP}$           | スリープモードのアナログ電源電流              | $nSLEEP$ 、 $IN0$ 、 $IN1$ はフローティング、 $V_M = 5V \sim 28V$ 、 $nSCS = VDD$                                                | $T_J \leq 85^{\circ}C$          |     | 0.6 | 3   |

|                           |                               | $nSLEEP$ 、 $IN0$ 、 $IN1$ はフローティング、 $nSCS = VDD$                                                                      | $T_J = 150^{\circ}C$            |     | 0.9 | 20  |

| $I_{VDD\_SLEEP}$          | スリープモードでのロジック電源電流             | $nSLEEP$ 、 $IN0$ 、 $IN1$ はフローティング、 $nSCS = VDD$                                                                      | $T_J \leq 85^{\circ}C$          |     | 0.1 | 1   |

|                           |                               |                                                                                                                      | $T_J = 150^{\circ}C$            |     | 0.7 | 4   |

| $I_{SLEEP}$               | スリープモードでの全体消費電流               | $nSLEEP$ 、 $IN0$ 、 $IN1$ はフローティング、 $V_M = 5V \sim 28V$ 、 $nSCS = VDD$                                                | $T_J \leq 85^{\circ}C$          |     |     | 4   |

|                           |                               | $nSLEEP$ 、 $IN0$ 、 $IN1$ はフローティング、 $nSCS = VDD$                                                                      | $T_J = 150^{\circ}C$            |     |     | 24  |

| $I_{VM\_IDLE}$            | アイドルモードでのアナログ電源電流             | $nSLEEP =$ 論理 High、 $IN0$ 、 $IN1$ フローティング、 $f_{SCLK} = 0 MHz$ 、 $ACT = 0b$ 、 $ENx = 0b$ 、 $IOLx = 0b$ 、 $nSCS = VDD$ |                                 |     |     | 2.1 |

|                           |                               |                                                                                                                      | COR モード、 $V_M \leq V_{DD} - 1V$ |     |     | 0.3 |

| $I_{VDD\_IDLE}$           | アイドルモードのロジック電源電流              | $nSLEEP =$ 論理 High、 $IN0$ 、 $IN1$ フローティング、 $f_{SCLK} = 0 MHz$ 、 $ACT = 0b$ 、 $ENx = 0b$ 、 $nSCS = VDD$               |                                 |     | 0.1 |     |

|                           |                               |                                                                                                                      | COR モード、 $V_M \leq V_{DD} - 1V$ |     |     | 1.9 |

| $I_{IDLE}$                | アイドルモードでの総消費電流                | $nSLEEP =$ 論理 High、 $IN0$ 、 $IN1$ フローティング、 $f_{SCLK} = 0 MHz$ 、 $ACT = 0b$ 、 $ENx = 0b$ 、 $IOLx = 0b$ 、 $nSCS = VDD$ |                                 |     |     | 2.2 |

| $I_{VM\_ACT\_OF}$         | アクティブモード時のアナログ電源電流 - チャネル OFF | $nSLEEP =$ 論理 High、 $IN0$ 、 $IN1$ フローティング、 $f_{SCLK} = 0 MHz$ 、 $ACT = 0b$ 、 $ENx = 0b$ 、 $IOLx = 0b$ 、 $nSCS = VDD$ |                                 |     | 4.6 | mA  |

|                           |                               |                                                                                                                      | COR モード、 $V_M \leq V_{DD} - 1V$ |     | 1   | 2.3 |

## 6.5 電気的特性 (続き)

$V_{DD} = 3V \sim 5.5V$ 、 $V_M = 4V \sim 40V$ 、 $T_J = -40^{\circ}C \sim +150^{\circ}C$  (特に記述のない限り)

標準値:  $V_{DD} = 5V$ 、 $V_M = 13.5V$ 、 $T_J = 25^{\circ}C$

| パラメータ               |                                | テスト条件                                                                                                                                                                                                           | 最小値                                                                         | 標準値             | 最大値             | 単位     |

|---------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------|-----------------|--------|

| $I_{VM\_ACT\_ON}$   | アクティブ モード時のアナログ電源電流 - チャネル ON  | $nSLEEP = \text{論理 High}$ 、<br>$IN0, IN1 \text{ フローティング}$ 、<br>$f_{SCLK} = 0 \text{ MHz}$ 、 $ACT = 1b$ 、 $ENx = 1b$ 、 $IOLx = 0b$ 、<br>$nSCS = VDD$                                                             | $EN\_OLON = 0100b$                                                          |                 |                 | 4.6 mA |

|                     |                                |                                                                                                                                                                                                                 | COR モード、<br>$V_M \leq V_{DD} - 1V$                                          | 1               | 2.3             | mA     |

| $I_{VDD\_ACT\_OFF}$ | アクティブ モードでのロジック電源電流 - チャネル OFF | $nSLEEP = \text{論理 High}$ 、<br>$IN0, IN1 \text{ フローティング}$ 、<br>$f_{SCLK} = 0 \text{ MHz}$ 、 $ACT = 1b$ 、 $ENx = 0b$ 、<br>$nSCS = VDD$                                                                           |                                                                             |                 | 0.1             | mA     |

|                     |                                |                                                                                                                                                                                                                 | COR モード、<br>$V_M \leq V_{DD} - 1V$                                          |                 | 2.4             | mA     |

| $I_{VDD\_ACT\_ON}$  | アクティブ モードでのロジック電源電流 - チャネル ON  | $nSLEEP = \text{論理 High}$ 、<br>$IN0, IN1 \text{ フローティング}$ 、<br>$f_{SCLK} = 0 \text{ MHz}$ 、 $ACT = 1b$ 、 $ENx = 1b$ 、<br>$nSCS = VDD$                                                                           |                                                                             |                 | 0.1             | mA     |

|                     |                                |                                                                                                                                                                                                                 | COR モード、<br>$IOLx = 0b$ 、<br>$EN\_OLON = 0100b$ 、<br>$V_M \leq V_{DD} - 1V$ |                 | 2.4             | mA     |

| $I_{ACT\_OFF}$      | アクティブ モードでの総消費電流 - チャネル OFF    | $nSLEEP = \text{ロジック High}$ 、 $IN0, IN1 \text{ フローティング}$ 、<br>$f_{SCLK} = 0 \text{ MHz}$ 、 $ACT = 1b$ 、 $ENx = 0b$ 、<br>$IOLx = 0b$ 、 $nSCS = VDD$                                                              |                                                                             |                 | 4.7             | mA     |

| $I_{ACT\_ON}$       | アクティブ モードでの総消費電流 - チャネル ON     | $nSLEEP = \text{ロジック High}$ 、 $IN0, IN1 \text{ フローティング}$ 、<br>$f_{SCLK} = 0 \text{ MHz}$ 、 $ACT = 1b$ 、 $ENx = 1b$ 、<br>$IOLx = 0b$ 、 $EN\_OLON = 0100b$ 、<br>$nSCS = VDD$                                      |                                                                             |                 | 4.7             | mA     |

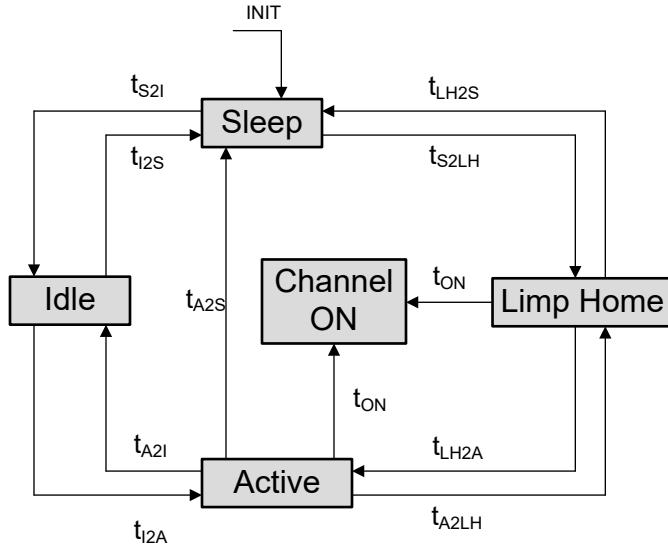

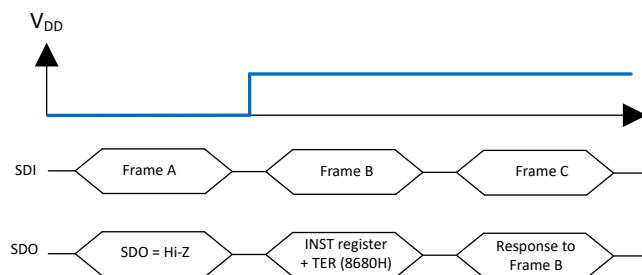

| $t_{S2I}$           | スリープからアイドルまでの遅延                | $nSLEEP$ ピンから $TER+INST$ レジスタまで = 8680H                                                                                                                                                                         |                                                                             | 200             | 300             | μs     |

| $t_{I2S}$           | アイドルからスリープまでの遅延                | $nSLEEP$ ピンから 標準診断 = 0000H、<br>SDO から GND への外部プルダウン                                                                                                                                                             |                                                                             | 100             | 150             | μs     |

| $t_{I2A}$           | アイドルからアクティブまでの遅延               | $INx$ または $nSCS$ ピンから MODE = 10b                                                                                                                                                                                |                                                                             | 100             | 150             | μs     |

| $t_{A2I}$           | アクティブからアイドルまでの遅延               | $INx$ または $nSCS$ ピンから MODE = 11b                                                                                                                                                                                |                                                                             | 100             | 150             | μs     |

| $t_{S2LH}$          | スリープからリンプホームまでの遅延              | $INx$ ピンから $V_{DS} = 10\% V_M$                                                                                                                                                                                  |                                                                             | 300 + $t_{ON}$  | $450 + t_{ON}$  | μs     |

| $t_{LH2S}$          | リンプホームからスリープまでの遅延              | $INx$ ピンから 標準診断 = 0000H、<br>SDO から GND の外部プルダウン                                                                                                                                                                 |                                                                             | 200 + $t_{OFF}$ | $300 + t_{OFF}$ | μs     |

| $t_{LH2A}$          | リンプホームからアクティブまでの遅延             | $nSLEEP$ ピンから MODE = 10b                                                                                                                                                                                        |                                                                             | 50              | 100             | μs     |

| $t_{A2LH}$          | アクティブからリンプホームまでの遅延             | $nSLEEP$ ピンから $TER + INST$ レジスタ = 8683H ( $IN0 = IN1 = \text{ロジック High}$ ) または<br>8682H ( $IN1 = \text{ロジック High}$ , $IN0 = \text{ロジック Low}$ ) または 8681H ( $IN1 = \text{ロジック Low}$ , $IN0 = \text{ロジック High}$ ) |                                                                             | 55              | 100             | μs     |

## 6.5 電気的特性 (続き)

$V_{DD} = 3V \sim 5.5V$ 、 $V_M = 4V \sim 40V$ 、 $T_J = -40^{\circ}C \sim +150^{\circ}C$  (特に記述のない限り)

標準値:  $V_{DD} = 5V$ 、 $V_M = 13.5V$ 、 $T_J = 25^{\circ}C$

| パラメータ                                                               |                                                 | テスト条件                                                                                          | 最小値  | 標準値            | 最大値          | 単位       |

|---------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------|------|----------------|--------------|----------|

| $t_{A2S}$                                                           | アクティブからスリープまでの遅延                                | $nSLEEP$ ピンから標準診断 = 0000H、 $SDO$ から GND への外部プルダウン                                              |      | 50             | 100          | $\mu s$  |

| 制御および SPI 入力 ( $nSLEEP$ 、 $IN0$ 、 $IN1$ 、 $nSCS$ 、 $SCLK$ 、 $SDI$ ) |                                                 |                                                                                                |      |                |              |          |

| $V_{IL}$                                                            | 入力ロジック Low 電圧                                   |                                                                                                | 0    |                | 0.8          | V        |

| $V_{IH}$                                                            | 入力論理 High 電圧 ( $nSLEEP$ 、 $IN0$ 、 $IN1$ )       |                                                                                                | 2    |                | 5.5          | V        |

| $V_{IH\_SPI}$                                                       | 入力ロジック High 電圧 ( $nSCS$ 、 $SCLK$ 、 $SDI$ )      |                                                                                                | 2    |                | $V_{DD}$     | V        |

| $I_{IL}$                                                            | 入力ロジック Low 電流 ( $nSCS$ を除くすべてのピン)               | $V_I = 0.8 V$                                                                                  | 8    | 12             | 16           | $\mu A$  |

| $I_{IH}$                                                            | 入力ロジック High 電流 ( $nSCS$ を除くすべてのピン)              | $V_I = 2 V$                                                                                    | 20   | 30             | 40           | $\mu A$  |

| $I_{IL\_nSCS}$                                                      | $nSCS$ 入力ロジック Low 電流                            | $V_{nSCS} = 0.8 V$ 、 $V_{DD} = 5V$                                                             | 30   | 60             | 90           | $\mu A$  |

| $I_{IH\_nSCS}$                                                      | $nSCS$ 入力ロジック High 電流                           | $V_{nSCS} = 2 V$ 、 $V_{DD} = 5V$                                                               | 10   | 40             | 65           | $\mu A$  |

| プッシュプル出力 (SDO)                                                      |                                                 |                                                                                                |      |                |              |          |

| $V_{SDO\_L}$                                                        | 出力ロジック Low 電圧                                   | $I_{SDO} = -1.5mA$                                                                             | 0    |                | 0.4          | V        |

| $V_{SDO\_H}$                                                        | ロジック High 出力電圧                                  | $I_{SDO} = 1.5mA$                                                                              |      | $V_{DD} - 0.4$ |              | $V_{DD}$ |

| $I_{SDO\_OFF}$                                                      | SDO トライステートリーク電流                                | $V_{nSCS} = V_{DD}$ 、 $V_{SDO} = 0V$ または $V_{DD}$                                              | -0.5 |                | 0.5          | $\mu A$  |

| 電力段                                                                 |                                                 |                                                                                                |      |                |              |          |

| $R_{DS(ON)}$                                                        | ON 抵抗                                           | $T_J = 25^{\circ}C$                                                                            | 0.4  | 0.7            | 0.95         | $\Omega$ |

|                                                                     |                                                 | $T_J = 150^{\circ}C$ 、 $I_L = I_{L\_EAR} = 220 mA$                                             | 0.6  | 1              | 1.4          |          |

| $I_{L\_NOM}$                                                        | 公称負荷電流 (すべてのチャネルがアクティブ)                         | $T_A = 85^{\circ}C$ 、 $T_J \leq 150^{\circ}C$                                                  |      | 330            | 500          | $mA$     |

|                                                                     |                                                 | $T_A = 105^{\circ}C$ 、 $T_J \leq 150^{\circ}C$                                                 |      | 260            | 500          | $mA$     |

| $I_{L\_NOM}$                                                        | 公称負荷電流 (アクティブなチャネルの半分)                          | $T_A = 85^{\circ}C$ 、 $T_J \leq 150^{\circ}C$                                                  |      | 470            | 500          | $mA$     |

| $I_{L\_EAR}$                                                        | 最大エネルギー消費の負荷電流 - 反復 (すべてのチャネルがアクティブ)            | $T_A = 85^{\circ}C$ 、 $T_J \leq 150^{\circ}C$                                                  |      | 220            |              | $mA$     |

| $-I_{L\_REV}$                                                       | チャネルあたりの逆電流機能 (ハイサイド動作時)                        |                                                                                                |      |                | $I_{L\_EAR}$ | $mA$     |

| $E_{AR}$                                                            | 最大エネルギー消費反復パルス - 2 * $I_{L\_EAR}$ (2 チャネルを並列接続) | $T_{J(0)} = 85^{\circ}C$ 、 $I_{L(0)} = 2 * I_{L\_EAR}$ 、 $2 * 10^6$ サイクル、影響を受けるチャネルでは PAR = 1b |      |                | 15           | $mJ$     |

| $V_{DS\_OP}$                                                        | バッテリ電圧低下時の電力段の電圧降下                              | $R_L = 50\Omega$ 、 $V_M = V_{M1} = V_{M2} = V_{M\_OP,max}$                                     |      | 0.05           | 0.2          | V        |

| $V_{DS\_OP}$                                                        | 自動構成可能なチャネルにおける、バッテリ低下時のパワーステージの電圧降下            | $R_L = 50\Omega$ 、 $V_M$ またはグランドに接続済み、 $V_M = V_{M\_OP,max}$ 、 $V_{Dx} = V_{M\_OP,max}$        |      | 0.05           | 0.3          | V        |

## 6.5 電気的特性 (続き)

$V_{DD} = 3V \sim 5.5V$ 、 $V_M = 4V \sim 40V$ 、 $T_J = -40^{\circ}C \sim +150^{\circ}C$  (特に記述のない限り)

標準値:  $V_{DD} = 5V$ 、 $V_M = 13.5V$ 、 $T_J = 25^{\circ}C$

| パラメータ              |                                                                                                            | テスト条件                                                                                                | 最小値 | 標準値  | 最大値 | 単位        |

|--------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----|------|-----|-----------|

| $V_{DS\_OP}$       | バッテリ残量が少ない時にハイサイドチャネルで発生するパワーステージの電圧降下                                                                     | $R_L = 50\Omega$ 、 $V_M = V_{M\_OP,max}$ 、 $V_{M\_HS} = V_{M\_OP,max}$                               |     | 0.05 | 0.3 | V         |

| $V_{DS\_CL}$       | ローサイドチャネルにおけるドレインからソースへの出力クランプ電圧                                                                           | $I_L = 20mA$ 、 $V_M = V_{OUT\_Dx} = 36V$                                                             | 42  | 44   | 50  | V         |

| $V_{OUT\_CL}$      | ハイサイドチャネルにおけるソースからグランドへの出力クランプ電圧                                                                           | $I_L = 20mA$ 、 $V_M = V_{OUT\_Dx} = 7V$                                                              | -24 |      | -18 | V         |

| $I_{L\_OFF}$       | 出力リーコンデンサー (各ローサイドチャネル)                                                                                    | $V_{IN} = 0V$ またはフローティング、 $V_{DS} = 28V$ 、 $ENx = 0b$ 、 $T_J \leq 85^{\circ}C$                       |     | 0.5  | 2   | $\mu A$   |

| $I_{L\_OFF}$       | 出力リーコンデンサー (各ローサイドチャネル)                                                                                    | $V_{IN} = 0V$ またはフローティング、 $V_{DS} = 28V$ 、 $ENx = 0b$ 、 $T_J = 150^{\circ}C$                         |     | 1.5  | 5   | $\mu A$   |

| $I_{L\_OFF}$       | 出力リーコンデンサー (各自動構成可能またはハイサイドチャネル)                                                                           | $V_{IN} = 0V$ またはフローティング、 $V_{DS} = 28V$ 、 $V_{OUT\_S} = 1.5V$ 、 $ENx = 0b$ 、 $T_J \leq 85^{\circ}C$ |     | 0.3  | 4   | $\mu A$   |

| $I_{L\_OFF}$       | 出力リーコンデンサー (各自動構成可能またはハイサイドチャネル)                                                                           | $V_{IN} = 0V$ またはフローティング、 $V_{DS} = 28V$ 、 $V_{OUT\_S} = 1.5V$ 、 $ENx = 0b$ 、 $T_J = 150^{\circ}C$   |     | 0.3  | 3   | $\mu A$   |

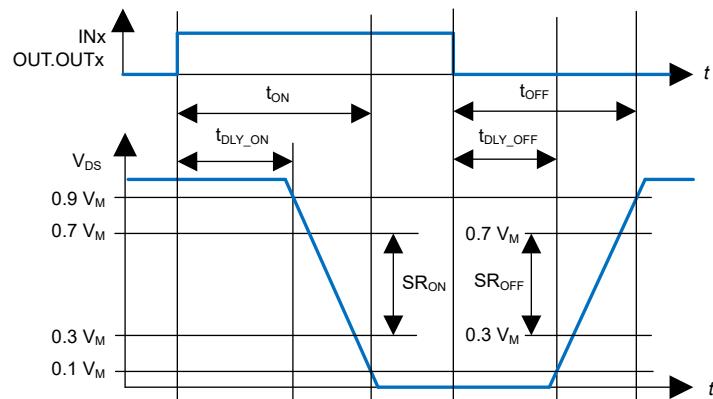

| $t_{DLY\_ON}$      | ターンオン遅延 ( $INx$ ピンまたは制御ビットの入力から、ローサイド構成では $V_{OUT} = 90\% V_M$ 、ハイサイド構成では $V_{OUT} = 10\% V_M$ )           | $R_L = 50\Omega$ 、 $V_M = 13.5V$ 、アクティブモードまたはリープホームモード                                               | 2   | 5    | 8   | $\mu s$   |

| $t_{DLY\_OFF}$     | ターンオフ遅延 ( $INx$ ピンまたは制御ビットの入力から、ローサイド構成では $V_{OUT} = 10\% V_M$ 、ハイサイド構成では $V_{OUT} = 90\% V_M$ )           | $R_L = 50\Omega$ 、 $V_M = 13.5V$ 、アクティブモードまたはリープホームモード                                               | 3   | 6    | 11  | $\mu s$   |

| $t_{ON}$           | ターンオン時間 ( $INx$ ピンまたは制御ビットの入力から、ローサイド構成では $V_{OUT} = 10\% V_M$ 、ハイサイド構成では $V_{OUT} = 90\% V_M$ )           | $R_L = 50\Omega$ 、 $V_M = 13.5V$ 、アクティブモードまたはリープホームモード                                               | 9   | 16   | 23  | $\mu s$   |

| $t_{OFF}$          | ターンオフ時間 ( $INx$ ピンまたは制御ビットの入力から、ローサイド構成では $V_{OUT} = 90\% V_M$ 、ハイサイド構成では $V_{OUT} = 10\% V_M$ )           | $R_L = 50\Omega$ 、 $V_M = 13.5V$ 、アクティブモードまたはリープホームモード                                               | 11  | 17   | 25  | $\mu s$   |

| $t_{ON} - t_{OFF}$ | ターンオン/オフマッチング                                                                                              | $R_L = 50\Omega$ 、 $V_M = 13.5V$ 、アクティブモードまたはリープホームモード                                               | -10 | 0    | 10  | $\mu s$   |

| $SR_{ON}$          | ターンオン時のスルーレート、ローサイド構成では $V_{DS} = 70\% \sim 30\% V_M$ またはハイサイド構成では $V_{DS} = 30\% \sim 70\% V_M$ へ変化する際の速度 | $R_L = 50\Omega$ 、 $V_M = 13.5V$ 、アクティブモードまたはリープホームモード、 $SR = 0b$                                    | 0.6 | 1.3  | 1.8 | $V/\mu s$ |

|                    |                                                                                                            | $R_L = 50\Omega$ 、 $V_M = 13.5V$ 、アクティブモードまたはリープホームモード、 $SR = 1b$                                    | 1.3 | 2.5  | 3.6 | $V/\mu s$ |

## 6.5 電気的特性 (続き)

$V_{DD} = 3V \sim 5.5V$ 、 $V_M = 4V \sim 40V$ 、 $T_J = -40^{\circ}C \sim +150^{\circ}C$  (特に記述のない限り)

標準値:  $V_{DD} = 5V$ 、 $V_M = 13.5V$ 、 $T_J = 25^{\circ}C$

| パラメータ            |                                                                                                            | テスト条件                                                                   | 最小値  | 標準値  | 最大値  | 単位          |

|------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------|------|------|-------------|

| $SR_{OFF}$       | ターンオン時のスルーレート、ローサイド構成では $V_{DS} = 30\% \sim 70\% V_M$ またはハイサイド構成では $V_{DS} = 70\% \sim 30\% V_M$ へ変化する際の速度 | $R_L = 50\Omega$ 、 $V_M = 13.5V$ 、アクティブ モードまたはリープ ホーム モード、 $SR = 0b$    | 0.6  | 1.3  | 1.8  | $V/\mu s$   |

|                  |                                                                                                            | $R_L = 50\Omega$ 、 $V_M = 13.5V$ 、アクティブ モードまたはリープ ホーム モード、 $SR = 1b$    | 1.3  | 2.5  | 3.6  | $V/\mu s$   |

| $t_{INRUSH}$     | バルブ突入電流モードの再起動時間                                                                                           | アクティブ モード                                                               |      |      | 40   | $\mu s$     |

| $t_{BIM}$        | 電球突入モードのリセット時間                                                                                             | アクティブ モード                                                               |      | 40   |      | ms          |

| $f_{INT}$        | 内部基準周波数                                                                                                    | FPWM = 1000b                                                            | 80   | 102  | 125  | kHz         |

| $f_{INT\_VAR}$   | 内部基準周波数変動                                                                                                  |                                                                         | -15  |      | 15   | %           |

| $t_{SYNC}$       | 内部基準周波数同期時間                                                                                                | FPWM = 1000b                                                            |      | 7    | 10   | $\mu s$     |

| PROTECTION       |                                                                                                            |                                                                         |      |      |      |             |

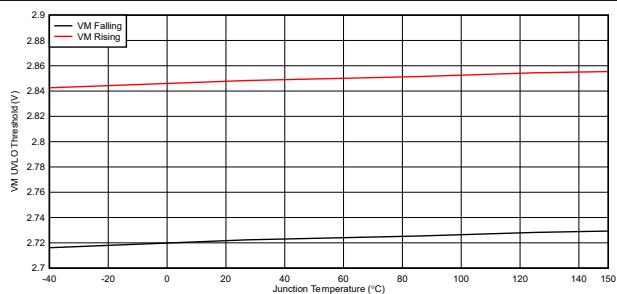

| $V_{M\_UVLO\_F}$ | VM 低電圧シャットダウン (立ち下がり)                                                                                      | $ENx = \text{オン}$ 、 $V_{DS} \leq 1V \sim UVRVM = 1b$ 、 $R_L = 50\Omega$ | 2.64 | 2.73 | 2.82 | V           |

| $V_{M\_UVLO\_R}$ | VM 低電圧シャットダウン (立ち上がり)                                                                                      |                                                                         | 2.77 | 2.86 | 2.95 | V           |

| $V_{DD\_UVLO}$   | VDD 低電圧シャットダウン                                                                                             | $V_{SDI} = V_{SCLK} = V_{nSCS} = 0V$ 、SDO を Low から Hi-Z に               | 2.5  | 2.65 | 2.8  | V           |

| $V_{DD\_HYS}$    | VDD 低電圧シャットダウン ヒステリシス                                                                                      |                                                                         |      | 120  |      | mV          |

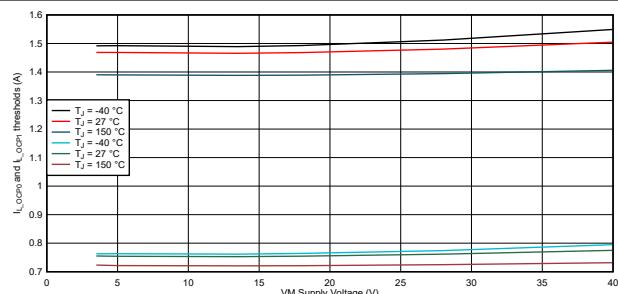

| $I_{L\_OCP0}$    | 過電流保護スレッショルド、OCP = 0b                                                                                      | $T_J = -40^{\circ}C$                                                    | 1.3  | 1.5  | 1.8  | A           |

|                  |                                                                                                            | $T_J = 25^{\circ}C$                                                     | 1.3  | 1.45 | 1.7  | A           |

|                  |                                                                                                            | $T_J = 150^{\circ}C$                                                    | 1.2  | 1.4  | 1.6  | A           |

| $I_{L\_OCP1}$    | 過電流保護スレッショルド、OCP = 0b                                                                                      | $T_J = -40^{\circ}C$                                                    | 0.7  | 0.8  | 1    | A           |

|                  |                                                                                                            | $T_J = 25^{\circ}C$                                                     | 0.65 | 0.75 | 0.9  | A           |

|                  |                                                                                                            | $T_J = 150^{\circ}C$                                                    | 0.65 | 0.72 | 0.85 | A           |

| $I_{L\_OCP0}$    | 過電流保護スレッショルド、OCP = 1b                                                                                      | $T_J = -40^{\circ}C$                                                    | 2.2  | 2.5  | 3    | A           |

|                  |                                                                                                            | $T_J = 25^{\circ}C$                                                     | 2.1  | 2.4  | 2.8  | A           |

|                  |                                                                                                            | $T_J = 150^{\circ}C$                                                    | 1.9  | 2.1  | 2.4  | A           |

| $I_{L\_OCP1}$    | 過電流保護スレッショルド、OCP = 1b                                                                                      | $T_J = -40^{\circ}C$                                                    | 1    | 1.3  | 1.6  | A           |

|                  |                                                                                                            | $T_J = 25^{\circ}C$                                                     | 1    | 1.3  | 1.55 | A           |

|                  |                                                                                                            | $T_J = 150^{\circ}C$                                                    | 1    | 1.25 | 1.5  | A           |

| $t_{OCPIN}$      | 過電流スレッショルドの切り替え遅延時間                                                                                        |                                                                         | 70   | 170  | 260  | $\mu s$     |

| $t_{OFF\_OCP}$   | 過電流シャットダウン遅延時間                                                                                             | $BIMx = PARx = 0b$                                                      | 4    | 7    | 11   | $\mu s$     |

| $T_{OTW}$        | 過熱警告                                                                                                       |                                                                         | 120  | 140  | 160  | $^{\circ}C$ |

| $T_{HYS\_OTW}$   | 過熱警告 ヒステリシス                                                                                                |                                                                         |      | 12   |      | $^{\circ}C$ |

| $T_{TSD}$        | サーマル シャットダウン温度                                                                                             |                                                                         | 150  | 175  | 200  | $^{\circ}C$ |

## 6.5 電気的特性 (続き)

$V_{DD} = 3V \sim 5.5V$ ,  $V_M = 4V \sim 40V$ ,  $T_J = -40^{\circ}C \sim +150^{\circ}C$  (特に記述のない限り)

標準値:  $V_{DD} = 5V$ ,  $V_M = 13.5V$ ,  $T_J = 25^{\circ}C$

| パラメータ            |                                            | テスト条件                                                                              | 最小値                                         | 標準値        | 最大値 | 単位        |

|------------------|--------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------|------------|-----|-----------|

| $V_{M\_AZ}$      | 過電圧保護                                      | $I_{VM} = 10mA$ 、スリープモード                                                           | 42                                          | 47         | 52  | V         |

| $V_{DS\_REV}$    | 逆極性時のドレインソースダイオード (ローサイドスイッチ構成)            | $I_L = -10mA$ 、スリープモード、 $T_J = 25^{\circ}C$                                        |                                             | 730        |     | mV        |

| $V_{DS\_REV}$    | 逆極性時のドレインソースダイオード (ローサイドスイッチ構成)            | $I_L = -10mA$ 、スリープモード、 $T_J = 150^{\circ}C$                                       |                                             | 540        |     | mV        |

| $R_{DS\_REV}$    | 逆極性時のオン抵抗(ハイサイドスイッチ構成)                     | $V_M = -V_{M\_REV}$ , $I_L = I_{L\_EAR}$                                           | $T_J = 25^{\circ}C$<br>$T_J = 150^{\circ}C$ | 0.7<br>1.1 |     | $\Omega$  |

| $t_{RETRY0\_LH}$ | リープホームモードでの再起動時間                           |                                                                                    | 7                                           | 10         | 13  | ms        |

| $t_{RETRY1\_LH}$ | リープホームモードでの再起動時間                           |                                                                                    | 14                                          | 20         | 26  | ms        |

| $t_{RETRY2\_LH}$ | リープホームモードでの再起動時間                           |                                                                                    | 28                                          | 40         | 52  | ms        |

| $t_{RETRY3\_LH}$ | リープホームモードでの再起動時間                           |                                                                                    | 56                                          | 80         | 104 | ms        |

| $t_{OSM}$        | 出力ステータスモニタコンバレータのセトリング時間                   |                                                                                    |                                             |            | 20  | $\mu s$   |

| $V_{OSM}$        | 出力ステータス監視スレッショルド電圧                         |                                                                                    | 3                                           | 3.3        | 3.6 | V         |

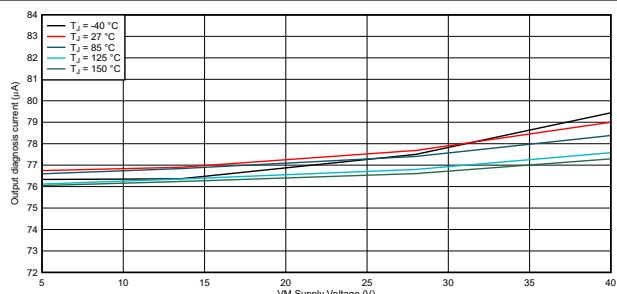

| $I_{OL}$         | 出力診断電流                                     | $V_{DS} = 3.3V$ (ローサイド構成の場合)、 $V_{OUT\_S} = 3.3V$ (ハイサイド構成の場合), $VM = 13.5V$       | 60                                          | 75         | 95  | $\mu A$   |

| $I_{OL}$         | 出力診断電流                                     | $V_{DS} = 3.3V$ (ローサイド構成の場合)、 $V_{OUT\_S} = 3.3V$ (ハイサイド構成の場合), $VM = 5V \sim 28V$ | 50                                          | 75         | 100 | $\mu A$   |

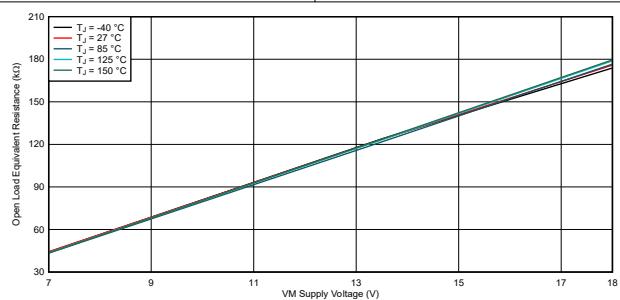

| $R_{OL}$         | 開放負荷等価抵抗                                   | $VM = 13.5V$                                                                       | 110                                         |            | 160 | $k\Omega$ |

| $R_{OL}$         | 開放負荷等価抵抗                                   | $VM = 7V \sim 18V$                                                                 | 30                                          |            | 230 | $k\Omega$ |

| $t_{ONMAX}$      | スイッチがオンの状態での開放負荷診断において、マルチプレクサが起動するまでの待機時間 | $OLMAX = 0b$                                                                       | 40                                          | 60         | 85  | $\mu s$   |

| $t_{OLONSET}$    | オン時開放負荷診断のセトリングタイム                         |                                                                                    |                                             | 25         | 40  | $\mu s$   |

| $t_{OLONSW}$     | オン診断チャネルの切り替え時間での開放負荷                      |                                                                                    |                                             | 15         | 20  | $\mu s$   |

| $I_{L\_OL}$      | 開放負荷検出スレッショルド電流                            |                                                                                    | 3                                           | 6          | 9   | mA        |

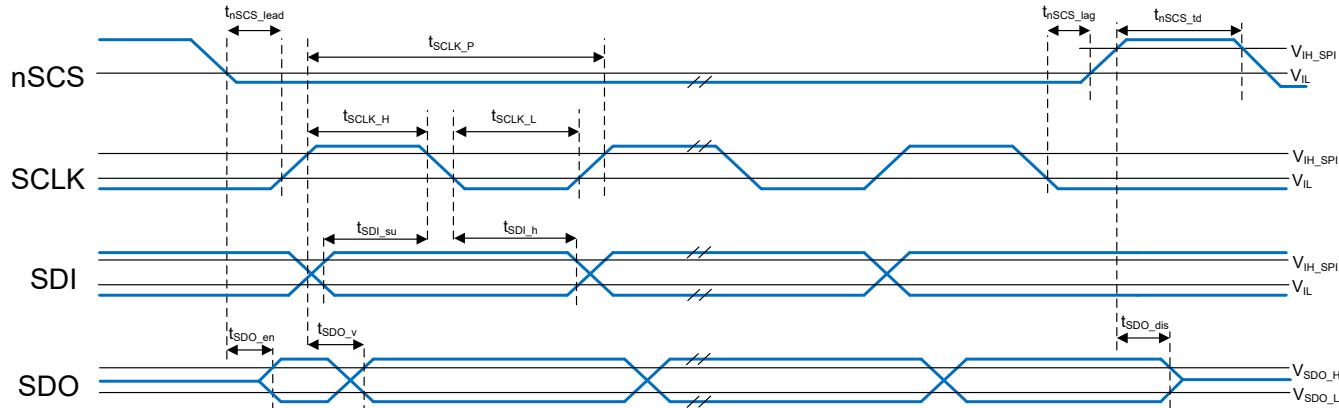

## 6.6 SPI のタイミング要件

- 製造時テストは適用されず、設計により検証されます。

| パラメータ            |                                     | テスト条件 | 最小値 | 公称値 | 最大値 | 単位 |

|------------------|-------------------------------------|-------|-----|-----|-----|----|

| $t_{nSCS\_lead}$ | イネーブルリード時間 (nSCS立ち下がりからSCLK立ち上がりまで) |       | 200 |     |     | ns |

| $t_{nSCS\_lag}$  | イネーブル遅延時間 (SCLK立ち下がりからnSCS立ち上がりまで)  |       | 200 |     |     | ns |

## 6.6 SPI のタイミング要件 (続き)

- 製造時テストは適用されず、設計により検証されます。

| パラメータ          |                                            | テスト条件                        | 最小値 | 公称値 | 最大値 | 単位  |

|----------------|--------------------------------------------|------------------------------|-----|-----|-----|-----|

| $t_{nSCS\_td}$ | 転送遅延時間 (nSCS 立ち上がりから立ち下がり nSCS まで)         |                              | 250 |     |     | ns  |

| $t_{SDO\_en}$  | 出力イネーブル時間 (nSCS 立ち下がりから SDO 有効まで)          | SDO ピンでの $C_L = 20\text{pF}$ |     |     | 200 | ns  |

| $t_{SDO\_dis}$ | 出力ディスエーブル時間 (nSCS 立ち上がりから SDO ハイインピーダンスまで) | SDO ピンでの $C_L = 20\text{pF}$ |     |     | 200 | ns  |

| $f_{SCLK}$     | シリアル クロック周波数                               |                              |     |     | 5   | MHz |

| $t_{SCLK\_P}$  | シリアルクロック周期                                 |                              | 200 |     |     | ns  |

| $t_{SCLK\_H}$  | シリアルクロックロジック High 時間                       |                              | 75  |     |     | ns  |

| $t_{SCLK\_L}$  | シリアルクロックロジック Low 時間                        |                              | 75  |     |     | ns  |

| $t_{SDI\_su}$  | データセットアップ時間 (SCLK 立ち下がりまでの必要な SDI 時間)      |                              | 20  |     |     | ns  |

| $t_{SDI\_h}$   | データホールド時間 (SCLK から SDI に立ち下がり)             |                              | 20  |     |     | ns  |

| $t_{SDO\_v}$   | 容量性負荷での出力データの有効時間                          | SDO ピンでの $C_L = 20\text{pF}$ |     |     | 100 | ns  |

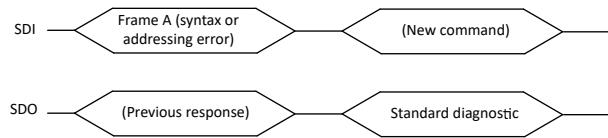

図 6-1. SPI タイミング図

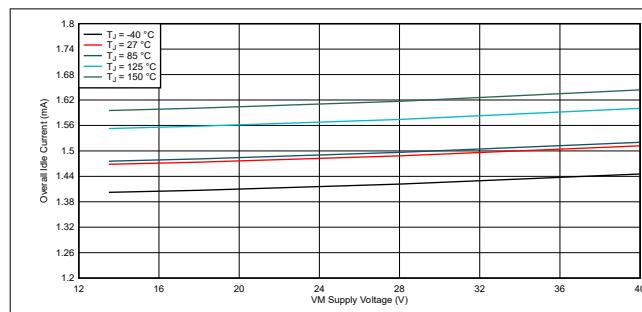

## 6.7 代表的特性

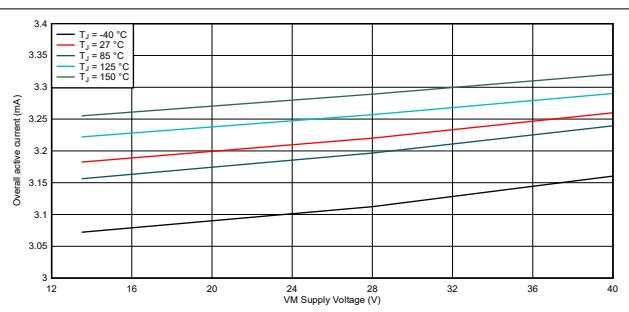

図 6-2. アイドルモード消費電流、VDD = 5.5V

図 6-3. アクティブモードの電源電流、VDD = 5.5V

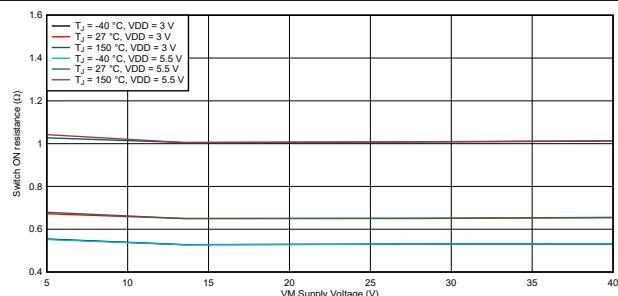

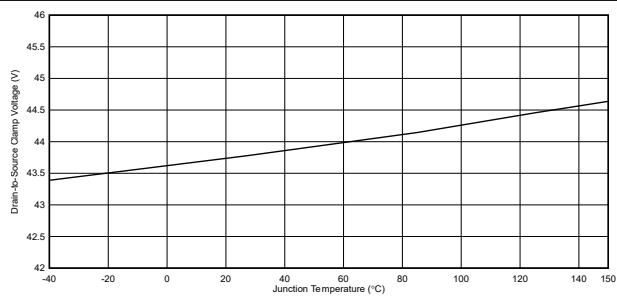

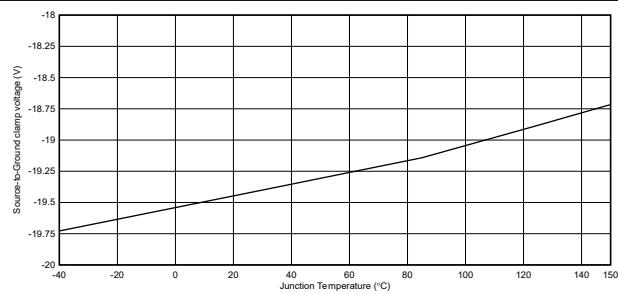

## 6.7 代表的特性 (続き)

図 6-4. スイッチ オン抵抗

図 6-5. ドレイン-ソース間クランプ電圧

図 6-6. ソース-グラウンド間クランプ電圧

図 6-7. VM UVLO スレッショルド

図 6-8. 過電流保護スレッショルド、 $VDD = 5.5\text{ V}$ 、OCP = 0b

図 6-9. 出力診断電流、 $VDD = 5.5\text{ V}$

図 6-10. 開放負荷等価抵抗

## 7 詳細説明

### 7.1 概要

DRV81620-Q1 は 8 チャネルのローサイドおよびハイサイド スイッチで、保護機能および診断機能が内蔵されています。出力ステージは、または 2 つのハイサイド スイッチと 6 つの自動構成スイッチ、(代表的な  $R_{DS(ON)} T_J$  時) = 25 °C は 700mΩ を含みます。N チャネル MOSFET には、自動構成可能チャネルとハイサイド チャネル用の 1 つのチャージポンプが備わっています。このデバイスは、低電源電圧で動作するように設計されています。デバイスはバッテリ電圧が低い状態に維持できます ( $V_M \geq 3V$ )。

自動構成可能スイッチは、負荷の接続方法に応じてハイサイド構成またはローサイド構成で使用できます。保護機能と診断機能は、ハードウェア構成に自動的に適応します。ハイサイド駆動では、通電時の開放負荷診断を実行することが可能です。

16 ビットの SPI イは、デバイスと負荷の制御および診断に使用されます。SPI はデイジーチェーンをサポートしており、同じマイコンピングを使用して複数のデバイス (8 ビット SPI も搭載したデバイス) を 1 つの SPI チェーンで接続できます。SPI 機能は、デジタル電源が存在するときのみ利用できます。

このデバイスには 2 つの入力ピンがあり、これらは 2 つの構成可能な出力を制御できます。nSLEEP ピンが ロジック Low のときは、デジタル電源電圧の有無に関係なく、入力ピンを使用してチャネル 2 および 3 を個別にアクティブ化することができます。入力マッピング機能を使用すると、入力ピンを別の出力に接続したり、同じ入力ピンにさらに多くの出力を割り当てることができます。この場合、1 つの入力信号でより多くのチャネルを制御できます。

このデバイスは、開放負荷 (オン状態とオフ状態) と短絡検出により負荷を診断できます。オフ状態での開放負荷を検出するには、SPI を使って内部電流源  $I_{OL}$  を有効にすることが可能です。各出力段は短絡から保護されています。過電流が発生した場合、該当するチャネルは過電流検出しきい値に達するとオフになり、SPI を介して再度オンにすることができます。

リープ ホーム モード動作では、ロジック High に設定された入力ピンに接続されているチャネルは、出力再起動時間が経過した後、自動的に再起動します。温度センサは、デバイスを過熱から保護するため、各チャネルで利用できます。

表 7-1. 製品概要

| パラメータ                           | 記号            | 値                           |

|---------------------------------|---------------|-----------------------------|

| アナログ電源電圧                        | $V_M$         | 3.0V ~ 40V                  |

| デジタル電源電圧                        | $V_{DD}$      | 3.0V ~ 5.5V                 |

| 最小の過電圧保護                        | $V_{M\_AZ}$   | 42V                         |

| $T_J = 150$ °C 時の最大オン抵抗         | $R_{DS(ON)}$  | 1.4Ω                        |

| 公称負荷電流( $T_A = 85$ °C、すべてのチャネル) | $I_{L\_NOM}$  | 330mA                       |

| 最大エネルギー消費-繰り返し                  | $E_{AR}$      | 10mJ @ $I_{L\_EAR} = 220mA$ |

| ドレイン ソース間のクランプ電圧                | $V_{DS\_CL}$  | 42V                         |

| ソースからグランドへの最大出力クランプ電圧           | $V_{OUT\_CL}$ | -18V                        |

| 過負荷スイッチオフの最大スレッショルド             | $I_{L\_OVLO}$ |                             |

| $T_J \leq 85$ °C での最大総静止電流      | $I_{SLEEP}$   | 4μA                         |

| 最大 SPI クロック周波数                  | $f_{SCLK}$    | 5MHz                        |

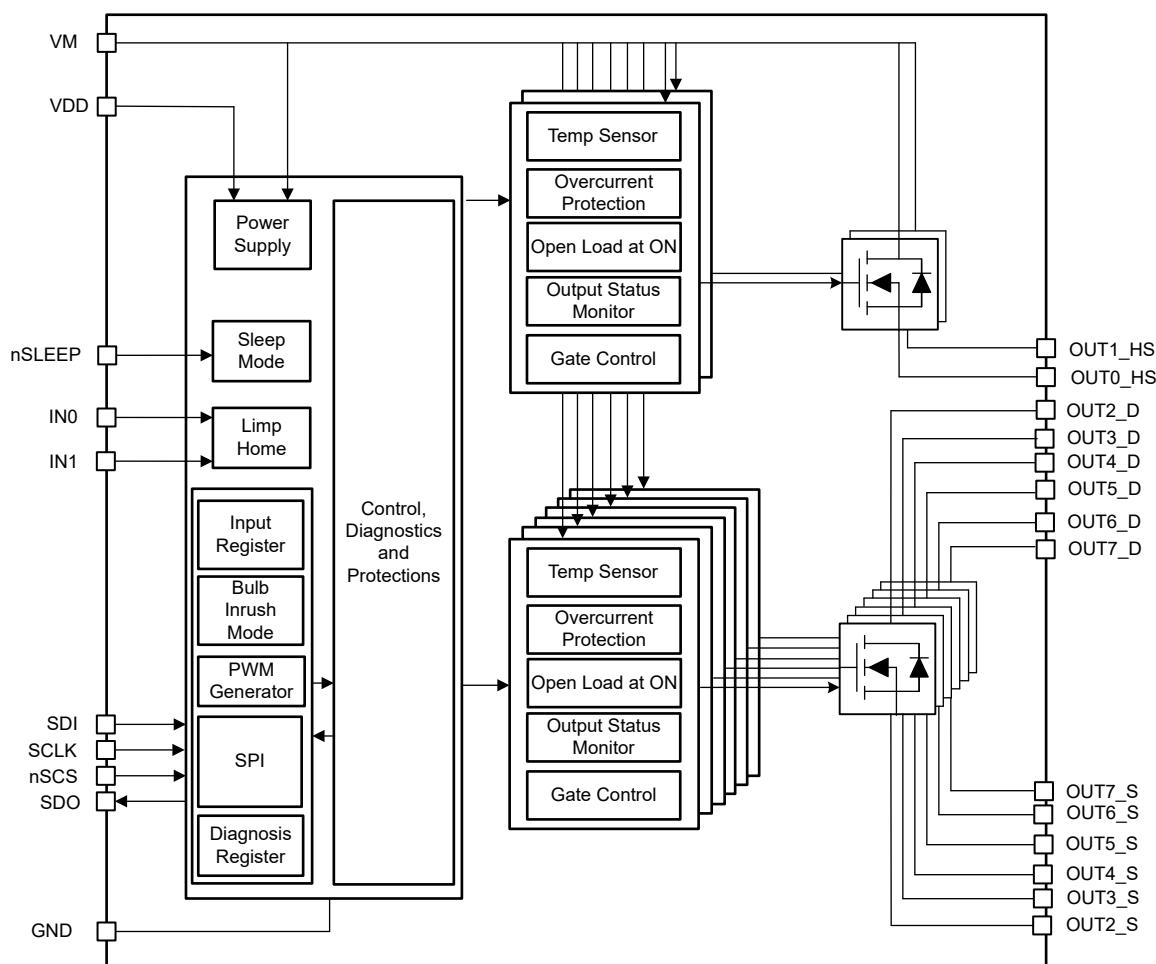

## 7.2 機能ブロック図

図 7-1. DRV81620-Q1 の機能ブロック図

## 7.3 機能説明

### 7.3.1 コントロールピン

このデバイスには 3 本のピン (IN0、IN1、nSLEEP) があり、SPI を使用せずにデバイスを直接制御できます。

#### 7.3.1.1 入力ピン :

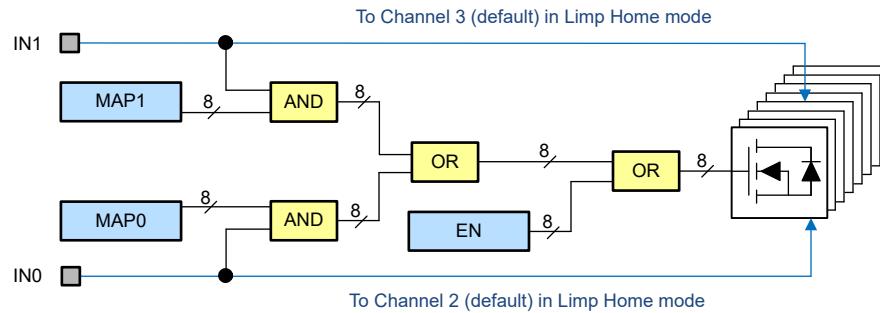

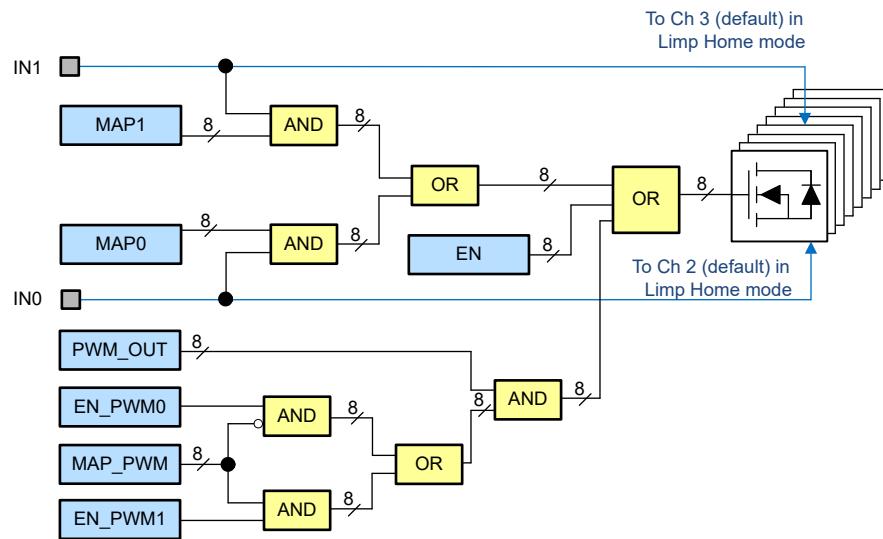

デバイスには 2 つの入力ピンがあります。各入力ピンはデフォルトで 1 つのチャネル (IN0 からチャネル 2、IN1 からチャネル 3) に接続されています。入力マッピングレジスタ MAP0 および MAP1 は、各入力ピンに追加または異なるチャネルを接続するようにプログラムできます (図 7-2 を参照)。チャネルを駆動する信号は、EN レジスタの状態、PWM ジェネレータ (PWM ジェネレータの出力マッピング状態に従う)、および IN0 と IN1 (入力マッピング レジスタの状態に従う) との論理和 (OR) の組み合わせによって決定されます。

図 7-2. 入力マッピング

入力ピンのロジックレベルは、入力ステータスマニタレジスタ (INST) を使用して監視できます。入力ステータスマニタは、デバイスがリップ ホーム モードのときも動作します。どちらかの入力ピンがロジック High に設定され、nSLEEP ピンがロジック Low に設定されると、デバイスはリップホームモードに切り替わり、デフォルトで入力ピンに割り当てられたチャネルをアクティブにします。

#### 7.3.1.2 nSLEEP ピン

nSLEEP ピンを使用して、デバイスを論理 Low に設定し、すべての入力ピンも論理 Low に設定すると、スリープモードに移行します。nSLEEP ピンがロジック Low に設定されている場合、本デバイスはリップホーム・モードに移行します。

適切なモード遷移を保証するには、nSLEEP ピンを少なくとも  $t_{I2S}$  (ロジック High からロジック Low に遷移) または  $t_{S2I}$  (ロジック Low からロジック High に遷移) の間設定する必要があります。

nSLEEP ピンを論理 Low に設定すると、次のようにになります。

- SPI 内のすべてのレジスタはデフォルト値にリセットされます。

- $V_{DD}$  および  $V_M$  低電圧検出回路は無効化され、消費電流を低減します (両方の入力がロジック Low に設定されている場合)。

- 両方の入力ピンがロジック Low に設定されている場合、SPI 通信は許可されません (nSCS ピンがロジック Low に設定されているときも、SDO ピンが高インピーダンスのままで)。

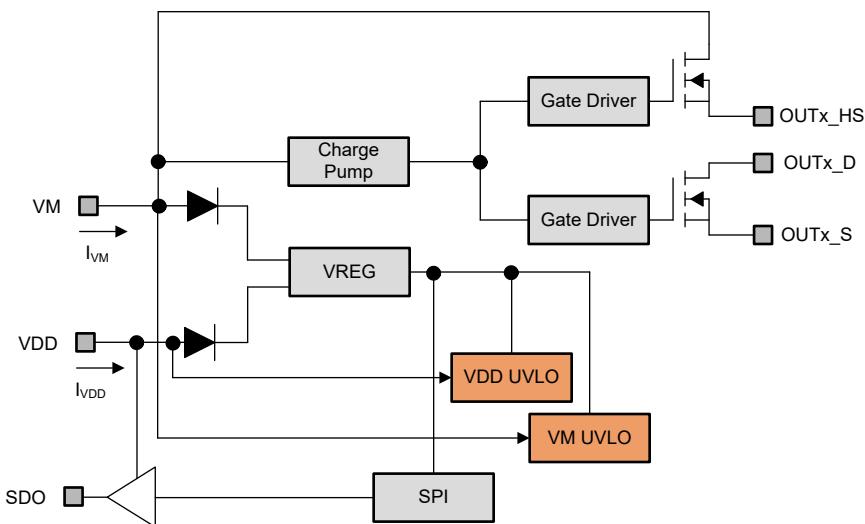

### 7.3.2 電源

DRV81620-Q1 は、それぞれ 2 系統の電源電圧によって供給されます。

- $V_M$  (ロジックにも使用されるアナログ電源電圧、およびチャネル 0 および 1 のドレインとしても使用される電源電圧)

- $V_{DD}$  (デジタル電源電圧)

$V_M$  電源をバッテリフィードに接続し、 $V_{DD}$  電源と組み合わせて電力段の駆動回路に使用します。 $V_M$  電圧が  $V_{DD}$  電圧を下回る状況 (たとえば、最小 3V までのクランキングイベント時) では、 $V_{DD}$  ピンの消費電流が増加する場合があります。 $V_M$  および  $V_{DD}$  電源電圧には、低電圧検出回路があります。

- $V_M$  と  $V_{DD}$  の両方の電源電圧が低電圧なため、電源段と SPI 通信のアクティブ化を防止できます (SPI レジスタはリセットされます)

- $V_{DD}$  電源が低電圧になると、SPI 通信は禁止されます。SPI 読み出し/書き込みレジスタはデフォルト値にリセットされます。

- $V_M$  電源が発生すると、デバイスはロジック回路に必要なすべての電流を  $V_{DD}$  電源から供給するようになります。すべてのチャネルがディセーブルされ、 $V_M \geq V_{M\_OP}$  になるとすぐにイネーブルになります。

以下の画像は、電源ピン  $V_M$  と  $V_{DD}$ 、出力段ドライバ、そして SDO 電源ライン間の相互作用を示す基本的な概念図です。

図 7-3. 内部電源アーキテクチャ

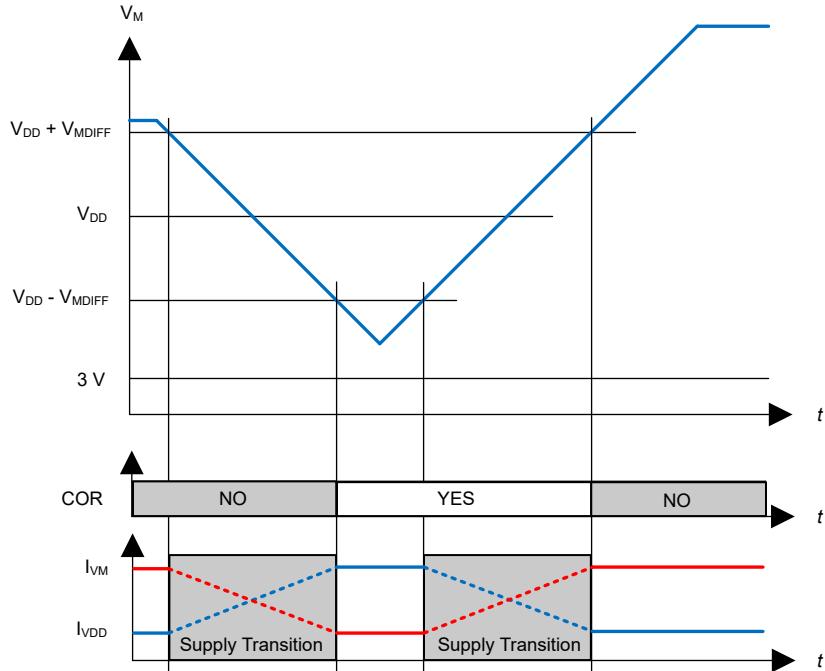

$3V \leq V_M \leq V_{DD} - V_{MDIFF}$  の場合、デバイスはクランキング動作範囲 (COR) で動作します。この状態では、 $V_{DD}$  ピンからの電流消費が増加し、 $VM$  ピンからの電流消費は減少します。合計消費電流は指定された制限内に維持されます。

図 7-4 に、デバイスが COR を出入りする  $VM$  ピンの電圧レベルを示します。COR との間の遷移中、 $I_{VM}$  と  $I_{VDD}$  は、通常動作と COR 動作用に定義された値の間で変化します。両方の電流の合計は、セクション 6.5 に規定されている制限範囲内にとどまります。

図 7-4. クランキング動作範囲

When  $V_{M\_UVLO} \leq V_M \leq V_{M\_OP}$  の場合、以前にオフになっていたチャネルをオンに切り替えることができない場合があります。すでにオンになっているすべてのチャネルは、SPI または IN ピンを使ってオフにされない限り、その状態を維持します。 $V_M$  および  $V_{DD}$  電源電圧の異なるチャネル動作の概要を表 7-2、表 7-3 および表 7-4 に示します (これらの表は、電源投入が成功した後に有効です)。

表 7-2.  $V_M$  と  $V_{DD}$  の機能としてのチャネル制御

|                           | $V_{DD} \leq V_{DD\_UVLO}$ | $V_{DD} > V_{DD\_UVLO}$                      |

|---------------------------|----------------------------|----------------------------------------------|

| $V_M \leq 3V$             | チャネルを制御できません               | チャネルのオン/オフ切り替え (SPI 制御) ( $R_{DS(on)}$ 偏差可能) |

| $3V < V_M \leq V_{M\_OP}$ | チャネルは SPI で制御できません         | チャネルのオン/オフ切り替え (SPI 制御) ( $R_{DS(on)}$ 偏差可能) |

| $V_M > V_{M\_OP}$         | チャネルは SPI で制御できません         | チャネルのオンとオフを切り替えることができます                      |

表 7-3. リンプ ホームモードを  $V_M$  および  $V_{DD}$  の関数として使用

|                           | $V_{DD} \leq V_{DD\_UVLO}$ | $V_{DD} > V_{DD\_UVLO}$    |

|---------------------------|----------------------------|----------------------------|

| $V_M \leq 3V$             | 該当なし                       | 利用可能 ( $R_{DS(ON)}$ 偏差も可能) |

| $3V < V_M \leq V_{M\_OP}$ | 利用可能 ( $R_{DS(ON)}$ 偏差も可能) | 利用可能 ( $R_{DS(ON)}$ 偏差も可能) |

| $V_M > V_{M\_OP}$         | 使用可能                       | 使用可能                       |

表 7-4. SPI レジスタと SPI 通信を  $V_M$  と  $V_{DD}$  の機能として使用

|          | $V_{DD} \leq V_{DD\_UVLO}$ | $V_{DD} > V_{DD\_UVLO}$  |

|----------|----------------------------|--------------------------|

| SPI レジスタ | リセット                       | 使用可能                     |

| SPI 通信   | 使用不可 ( $f_{SCLK} = 0MHz$ ) | 可能 ( $f_{SCLK} = 5MHz$ ) |

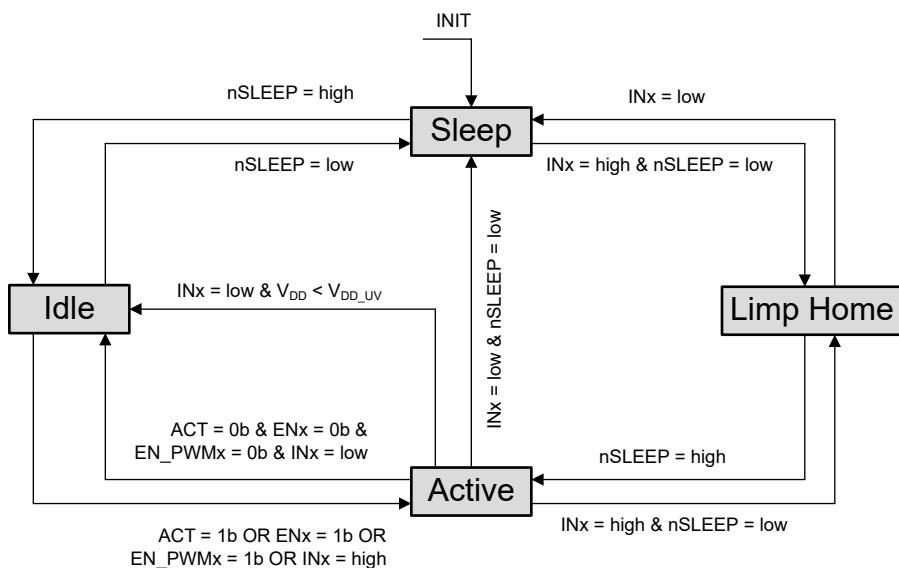

### 7.3.2.1 動作モード

このデバイスには次の動作モードがあります。

- スリープ モード

- アイドル モード

- アクティブ モード

- リンプホームモード

動作モード間の遷移は、以下のレベルと状態に応じて決定されます。

- nSLEEP ピンのロジック レベル

- INx ピンのロジック レベル

- ENx ビットの状態

- ACT ビットの状態

- EN\_PWM0 および EN\_PWM1 のビット状態

状態遷移の可能性を含む状態遷移図を図 7-5 に示します。デバイスの動作や一部のパラメータは、デバイスの動作モードによって変化することがあります。また、低電圧検出回路により、同じ動作モードでいくつかの変化が見られます。

図 7-5. 動作モードの状態図

デバイスの動作モードは、次の式で観測できます。

- 出力チャネルのステータス

- SPI レジスタのステータス

- $V_{DD}$  ピンでの消費電流 ( $I_{VDD}$ )

- VM ピンでの消費電流 ( $I_{VM}$ )

負荷をオンにするためのデフォルトの動作モードはアクティブモードです。デバイスがアクティブモードではなく、1つ以上の出力の切り替え要求が (SPI または入力ピン経由) 来る場合、nSLEEP ピンのステータスに従って、アクティブ モードまたはリンプ ホーム モードに切り替わります。

チャネルのターンオン時間は、デバイスがアクティブ モードまたはリンプ ホーム モードの場合、パラメータ  $t_{ON}$  により定義されます。それ以外の場合は、前述のいずれかの電源モードに移行するために必要な遷移時間を加味する必要があります (図 7-6 を参照)。

図 7-6. モード遷移タイミング

表 7-5 に、デバイスの動作モード、 $V_M$  と  $V_{DD}$  電源電圧、および最も重要な機能 (チャネル制御、SPI 通信、SPI レジスタ) の状態の関係を示します。

表 7-5. 動作モード、 $V_M$  および  $V_{DD}$  電圧との関係でのデバイスの機能

| 動作モード       | 機能       | $V_M$ UVLO, $V_{DD} \leq V_{DD\_UVLO}$ | $V_M$ UVLO, $V_{DD} > V_{DD\_UVLO}$ | $V_M$ は UVLO ではない、 $V_{DD} \leq V_{DD\_UVLO}$ | $V_M$ は UVLO ではない、 $V_{DD} > V_{DD\_UVLO}$ |

|-------------|----------|----------------------------------------|-------------------------------------|-----------------------------------------------|--------------------------------------------|

| スリープ        | チャネル数    | 該当なし                                   | 該当なし                                | 該当なし                                          | 該当なし                                       |

|             | SPI 通信   | 該当なし                                   | 該当なし                                | 該当なし                                          | 該当なし                                       |

|             | SPI レジスタ | リセット                                   | リセット                                | リセット                                          | リセット                                       |

| アイドル        | チャネル数    | 該当なし                                   | 該当なし                                | 該当なし                                          | 該当なし                                       |

|             | SPI 通信   | 該当なし                                   | あり                                  | 該当なし                                          | あり                                         |

|             | SPI レジスタ | リセット                                   | あり                                  | リセット                                          | あり                                         |

| アクティブ       | チャネル数    | 該当なし                                   | あり                                  | あり、ピン内のみ                                      | あり                                         |

|             | SPI 通信   | 該当なし                                   | あり                                  | 該当なし                                          | あり                                         |

|             | SPI レジスタ | リセット                                   | あり                                  | リセット                                          | あり                                         |

| リンプ ホーム モード | チャネル数    | 該当なし                                   | あり、ピン内のみ                            | あり、ピン内のみ                                      | あり、ピン内のみ                                   |

|             | SPI 通信   | 該当なし                                   | はい、読み取り専用                           | 該当なし                                          | はい、読み取り専用                                  |

|             | SPI レジスタ | リセット                                   | はい、読み取り専用                           | リセット                                          | はい、読み取り専用                                  |

### 7.3.2.1.1 パワーアップ

いずれかの電源電圧 ( $V_M$  または  $V_{DD}$ ) がデバイスに印加され、 $INx$  または  $nSLEEP$  ピンが論理 High に設定されているとき、パワーアップ条件が満たされます。 $V_M$  がスレッショルド  $V_{M\_OP}$  を上回るか、または  $V_{DD}$  が UVLO スレッショルドを上回ると、内部パワーオン信号が設定されます。

### 7.3.2.1.2 スリープモード

デバイスがスリープモードにあるときは、電源電圧とは無関係にすべての出力がオフになり、SPI レジスタがリセットされます。消費電流は最小限です。

### 7.3.2.1.3 アイドルモード

アイドルモードでは、デバイスの消費電流はパラメータ  $I_{VDD\_IDLE}$  と  $I_{VM\_IDLE}$  で与えられた制限、またはデバイス全体のパラメータ  $I_{IDLE}$  に達することができます。

- このモードでは、内部電圧レギュレータは動作しています。

- 診断機能は使用できません。

- 電源電圧とは無関係に出力チャネルがオフになります。

- $V_{DD}$  が利用可能な場合、SPI レジスタは動作しており、SPI 通信が可能です。

- アイドルモードでは、機能安全上の理由から、ERRx ビットはクリアされません。

### 7.3.2.1.4 アクティブモード

アクティブモードは、リンプホーム条件が設定されておらず、一部またはすべての負荷を駆動する必要があるときの、デバイスの通常の動作モードです。表 7-5 に示すように、 $V_{DD}$  および  $V_M$  の電圧レベルは動作に影響を及ぼします。デバイスの消費電流は、 $I_{VDD\_ACT}$  と  $I_{VM\_ACT}$  (デバイス全体の  $I_{ACT}$ ) で規定されています。

nSLEEP ピンがロジック High に設定され、入力ピンのいずれかがロジック High に設定されるか、または 1 つの ENx ビットが 1b に設定されると、デバイスはアクティブモードに移行します。

- ACT ビットが 0b に設定されている場合、すべての入力ピンがロジック Low に設定され、ENx ビットが 0b に設定されると、デバイスはすぐにアイドルモードに戻ります。

- ACT が 1b に設定されている場合、デバイスは入力ピンや ENx ビットのステータスとは無関係にアクティブモードに維持されます。

- すべての入力ピンがロジック Low に設定されていると、 $V_{DD}$  電源の低電圧状態により、デバイスはアイドルモードに移行します。

レジスタ MAP0 と MAP1 の両方が 00h に設定されていても、入力ピン INx の 1 つがロジック High に設定されている場合、デバイスはアクティブモードに移行します。

### 7.3.2.1.5 リンプホームモード

nSLEEP ピンがロジック Low で、入力ピンの 1 つがロジック High に設定されているとき、デバイスはリンプホームモードに移行し、デバイスに接続されているチャネルをオンにします。SPI 通信は可能ですが、読み出し専用モード (SPI レジスタは読み取り可能ですが、書き込みはできません) でのみ可能です。

- UVRVM を 1b に設定します

- MODE ビットを 01b (リンプホームモード) に設定します

- リンプホームモードに移行した後、最初の SPI コマンドでは、TER ビットが 1b に設定されます。その後、ビットは正常に動作します。

- OLON ビットと Oloff ビットが 0b に設定されます

- ERRx ビットは正常に動作します

- OSMx ビットは、読み取りと通常動作が可能です

- 他のすべてのレジスタはデフォルト値に設定され、デバイスがリンプホームモードである限りはプログラムできません

リンプホーム時にチャネル 2 および 3 をオンにするために必要な電源電圧条件の詳細については、表 7-3 を参照してください。他のすべてのチャネルはオフです。

アクティブからリンプホームモード、またはリンプホームからアクティブモードへの遷移中に SPI コマンドが送信されると、SPI 応答が未定義になる場合があります。

### 7.3.2.2 リセット条件

次の 3 つの条件のいずれかが、SPI レジスタをデフォルト値にリセットします。

- $V_{DD}$  は、低電圧スレッショルド  $V_{DD\_UVLO}$  を下回ってはなりません

- nSLEEP ピンをロジック Low に設定

- リセットコマンド (RST を 1b に設定) が実行されます

- ERRx ビットは、RESET コマンドによってクリアされません (機能安全の場合)。

特に、すべてのチャネルがオフになり (ロジック High に設定された入力ピンがない場合)、入力マッピングの構成がリセットされます。

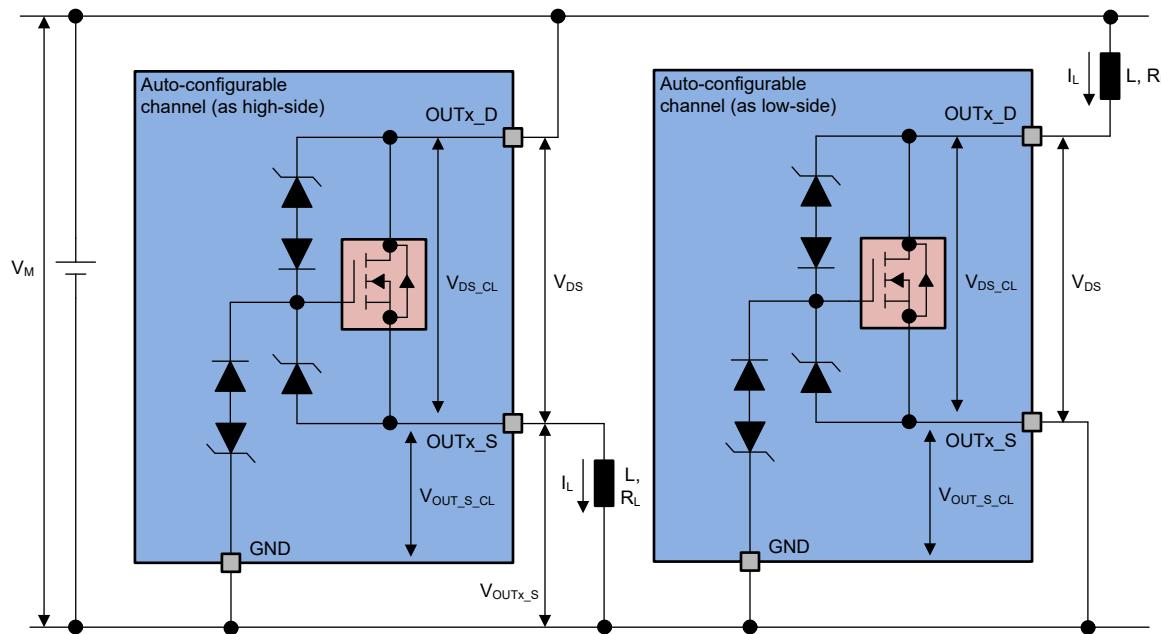

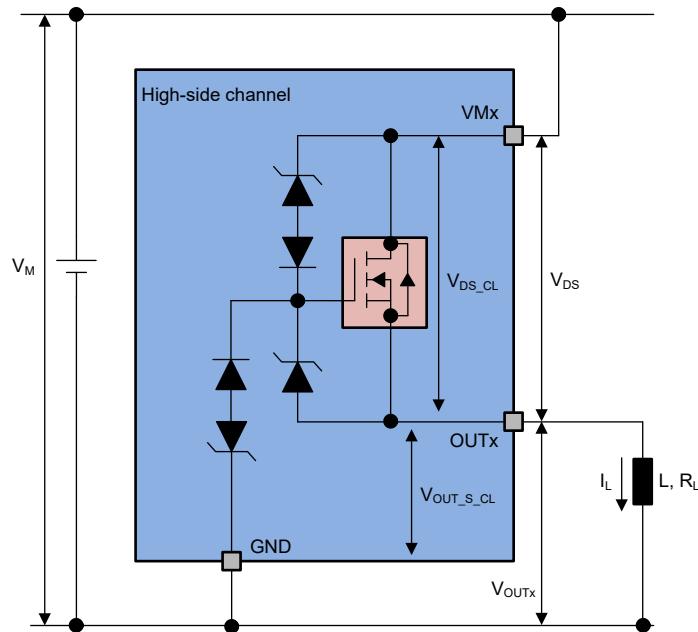

### 7.3.3 電力段

The DRV81620-Q1 は 8 チャネルの構成可能な、ハイサイド スイッチです。N チャネル MOSFET を採用して電力段を形成しています。オン抵抗  $R_{DS(ON)}$  は、電源電圧と接合部温度  $T_J$  に依存します。

自動構成可能なチャネルが 6 個あり、それぞれをローサイド スイッチまたはハイサイド スイッチとして使用することができます。各チャネルは、ドレインおよびソースの電位に応じて、診断機能および保護機能を自動的に調整します。これらのチャネルを実現するために、チャージ ポンプを出力 MOSFET ゲートに接続します。

ハイサイド構成では、負荷は FET のグランドとソースの間に接続されます (ピン OUTx\_S,  $n = 2 \dots 7$ )。FET のドレイン (OUTx\_D, 'x' は構成可能なチャネル番号を表す) は、グランドと VM の間の任意の電位に接続することができます。ドレインが VM に接続されている場合、チャネルはハイサイド スイッチのように動作します。

ローサイド構成では、パワー トランジスタのソース端子は GND ピンの電位に接続する必要があります (直接接続するか、逆電流防止用ダイオードを介して接続します)。

これらの各チャネルは個別に構成を選択できるため、一部のチャネルをローサイド構成で接続し、残りの自動構成可能チャネルをハイサイド スイッチとして使用することも可能です。

#### 7.3.3.1 スイッチング抵抗性負荷

抵抗性の負荷をスイッチングする場合、以下のスイッチング時間とスルーレートを考慮する必要があります。

デフォルトのスルーレート:  $1.3V/\mu s$ 。構成レジスタ 2 の SR ビットを使用して、スルーレートを  $2.5V/\mu s$  に増やすことができます。

図 7-7. 抵抗性負荷の切り換え

#### 7.3.3.2 誘導性出力クランプ

誘導性負荷をオフにすると、インダクタンスが継続的に電流を駆動しようとしているため、パワースイッチの両端の電圧は  $V_{DS\_CL}$  ポテンシャルまで上昇します。出力ピンの電圧を未満にすることは許可されていません。デバイスの損傷を防止するために電圧クランプが必要です。

次の図は、クランプの実装を示しています。最大許容負荷インダクタンスは制限されます。クランプ構造により、すべてのモード (スリープ、アイドル、アクティブ、リンプ ホーム) でデバイスが保護されます。

図 7-8. 自動構成可能チャネルの出力クランプ

図 7-9. ハイサイドチャネルの出力クランプ

### 7.3.3.3 最大負荷インダクタンス

誘導性負荷の消磁中、磁気エネルギーは DRV81620-Q1 で消費されます。式 2 と式 3 は、ハイサイドスイッチに使用できます (自動構成可能なスイッチでは、負荷の位置に応じて、すべての式を使用できます)。

(1)

$$E = (V_M - V_{OUTS\_CL}) \times \left[ \frac{V_{OUTS\_CL}}{R_L} \times \ln \left( 1 - \frac{R_L \times I_L}{V_{OUTS\_CL}} \right) + I_L \right] \times \frac{L}{R_L} \quad (2)$$

$$E = (V_M - V_{OUT\_CL}) \times \left[ \frac{V_{OUT\_CL}}{R_L} \times \ln\left(1 - \frac{R_L \times I_L}{V_{OUT\_CL}}\right) + I_L \right] \times \frac{L}{R_L} \quad (3)$$

熱に変換される最大エネルギーは、部品の熱設計によって制限されます。セクション 6.5 に示す  $E_{AR}$  値は、出力に接続されているインダクタンスが同時に消磁されたとき、すべてのチャネルが同じエネルギーを消費できると仮定しています。

#### 7.3.3.4 逆電流動作

ハイサイド構成において逆電流 ( $V_{OUT_X\_S} > V_{OUT_X\_D}$ ) または ( $V_{OUT_X} > V_{Mx}$ ) が発生している間、該当するチャネルはオン状態またはオフ状態のままになります。さらに、逆電流が印加されている間にチャネルがオン状態であり、過熱しきい値に達すると、ERRx ビットがセットされることがあります。

影響を受けていないチャネルの基本機能 (オン/オフの切り替え、保護機能、診断機能) は、他のチャネルに印加された逆電流の影響を受けません。特に以下のパラメータについては、ばらつきが発生する可能性があります (ただし、過温保護機能には影響しません)。

- スイッチング機能:  $t_{ON}$ ,  $t_{OFF}$ ,  $SR_{ON}$ ,  $SR_{OFF}$

- 保護機能:  $I_{L\_OCP0}$ ,  $I_{L\_OCP1}$

- 診断機能:  $V_{DS\_OL}$ ,  $V_{OUT\_OL}$ ,  $V_{OUT\_S\_OL}$ ,  $I_{L\_OL}$

影響を受けていないチャネルにおけるランプ ホーム状態での信頼性は変わりません。

#### 注

逆電流が流れている間は、温度保護や過負荷保護などの保護機能は有効になりません。逆電流は FET 内部での電力損失を引き起こし、結果としてデバイス全体の温度を上昇させます。これにより、過熱によって影響を受けていないチャネルがスイッチオフになることがあります。

#### 7.3.3.5 並列でのチャネル スイッチング

チャネルが並列に接続された場合には、2 つのチャネルが非同期にオフになることがあります。そのため、最後にオフになるチャネルに追加の熱ストレスが発生します。この状態を回避するため、SPI レジスタで、2 つの隣接チャネルの並列動作を (PAR ビットを使用して) 構成することができます。このモードで動作している場合、過負荷または過熱状態に反応した最も速いチャネルは、他のチャネルも非アクティブになります。2 つの並列チャネルが処理できる誘導性エネルギーは、1 つのチャネルエネルギーの 2 倍未満です。以下の 2 つのチャネルは互いに同期できます。

- チャネル 0 およびチャネル 2 → PAR0 を 1b に設定

- チャネル 1 およびチャネル 3 → PAR1 を 1b に設定

- チャネル 4 およびチャネル 6 → PAR2 を 1b に設定

- チャネル 5 およびチャネル 7 → PAR3 を 1b に設定

この同期ビットは、チャネルが過電流状態または過熱状態にどのように反応するかにのみ影響します。同期したチャネルは、マイコンによって個別にオン/オフする必要があります。

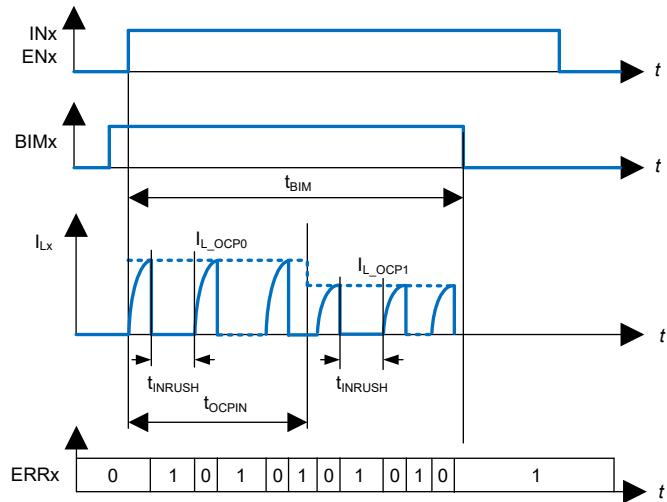

#### 7.3.3.6 電球突入モード (BIM)

場合によっては、本デバイスの出力の一部または複数が、ランプや電子機器などの容量性負荷を駆動する必要があります。このような状況では、スイッチをオンにした直後に突入電流が過負荷電流のしきい値に達し、チャネルがラッчикオフされことがあります。通常の動作では、チャネルが再びオンになるために、マイコンから SPI コマンド (CLRx ビット) でラッチをクリアする指示が送られるまで、デバイスは待機します。通常、容量性負荷を起動するには、この遅延時間が長すぎます。

対応する BIMx ビットが 1b に設定されている場合、チャネルが過電流または過熱のしきい値に達してラッчикオフされても、 $t_{INRUSH}$  の時間が経過した後にチャネルが自動的に再起動し、負荷が突入電流フェーズから抜けられるようになります。図 7-10 に、詳細なタイミング図を示します。図に示すように、チャネルがオンになるとカウンタが起動します。チャネルがオフになるたびに (そのチャネルを制御している要因に関係なく)、BIMx は 0b にリセットされます。

BIMx ビットが 1b に設定されている間は、ERRx ビットも 1b に設定される可能性がありますが、それによってチャネルがラッчикオフされることはありません。

特に出力の短絡が発生した場合に、チャネルへの過剰な熱ストレスを防止するため、内部タイマは 40ms (パラメータ  $t_{BIM}$ ) 後に  $BIMx$  ビットを 0b に設定します。このデバイスでは、信頼性に影響を与えることなく、各チャネルごとにバルブ突入電流モード (BIM) を柔軟に設定できます。

図 7-10. 電球突入モード (BIM) 動作

### 7.3.3.7 PWM ジェネレータを内蔵

このデバイスには、独立した 2 つの内蔵 PWM ジェネレータがあります。各 PWM ジェネレータは 1 つ以上のチャネルに割り当てることができ、異なるデューティサイクルおよび周波数を設定できます。

どちらの PWM ジェネレータも、内部発振器によって生成されたベース周波数  $f_{INT}$  を基準とします。このベース周波数は、以下に示すように FPWM ビットを使用して調整できます。

表 7-6. FPWM の設定

| FPWM ビット | デルタから $f_{INT}$ への変化 |

|----------|----------------------|

| 0000b    | 予約済み                 |

| 0001b    | -37.2%               |

| 0010b    | -31.9%               |

| 0011b    | -26.9%               |

| 0100b    | -21%                 |

| 0101b    | -15.5%               |

| 0110b    | -10.9%               |

| 0111b    | -5.8%                |

| 1000b    | -                    |

| 1001b    | +4.3%                |

| 1010b    | +8.9%                |

| 1011b    | +14%                 |

| 1100b    | +19.5%               |

| 1101b    | +25.6%               |

| 1110b    | +32.4%               |

| 1111b    | +40%                 |

PWM ジェネレータごとに、次の 4 つのパラメータを設定できます。

- デューティサイクル (PWM ジェネレータ 0 のビット DC0)

- 8 ビットで、0.39% のデューティサイクル分解能を実現可能

- マイコンが新しいデューティサイクルを設定すると、PWM ジェネレータは前のサイクルが完了するまで待機し、その後で新しいデューティサイクルを適用します (デューティサイクルが 0% または 100% の場合でも同様で、新しいデューティサイクルは次の PWM サイクルから反映されます)。

- 設定可能な最大デューティサイクルは 99.61% です (DC0 に 11111111b を設定した場合)。FREQ0 を 11b に設定すると、100% を実現できます。

- 周波数 (FREQ0, FREQ1, FCTR0, FCTR1 の各ビットは、 $f_{INT}$  の分周比を選択し、希望するデューティサイクルを実現するために使用されます)

**表 7-7. PWM ジェネレータ 0 の PWM 周波数選択**

| FCTR0 | FREQ0 | PWM 周波数                     |

|-------|-------|-----------------------------|

| 0b    | 00b   | $f_{INT}/1024$ (100Hz に対応)  |

| 0b    | 01b   | $f_{INT}/512$ (200Hz に対応)   |

| 0b    | 10b   | $f_{INT}/256$ (400Hz に対応)   |

| 1b    | 00b   | $f_{INT}/128$ (800Hz に対応)   |

| 1b    | 01b   | $f_{INT}/64$ (1600Hz に対応)   |

| 1b    | 10b   | $f_{INT}/51.2$ (2000Hz に対応) |

**表 7-8. PWM ジェネレータ 1 の PWM 周波数選択**

| FCTR1 | FREQ1 | PWM 周波数                     |

|-------|-------|-----------------------------|

| 0b    | 00b   | $f_{INT}/1024$ (100Hz に対応)  |

| 0b    | 01b   | $f_{INT}/512$ (200Hz に対応)   |

| 0b    | 10b   | $f_{INT}/256$ (400Hz に対応)   |

| 1b    | 00b   | $f_{INT}/128$ (800Hz に対応)   |

| 1b    | 01b   | $f_{INT}/64$ (1600Hz に対応)   |

| 1b    | 10b   | $f_{INT}/51.2$ (2000Hz に対応) |

- チャネル出力制御およびマッピング レジスタ PWM\_OUT および MAP\_PWM

- 任意のチャネルを各 PWM ジェネレータに割り当てることができます

- 2 つの並列入力と組み合わせることで、マイコンのリソースや SPI データ通信の負荷を抑えながら、4 つの独立した PWM チャネル グループを構成することができます。

図 7-11 に、PWM ジェネレータの追加に示す概念を拡張します。

図 7-11. PWM ジェネレータのマッピング

### 7.3.4 保護および診断機能

このデバイスは、複数の保護機能をサポートしており、以降のセクションで詳細に説明します。SPI は、デバイスと負荷状態に関する診断情報を提供します。各チャネル診断情報は、他のチャネルから独立しています。1 つのチャネルのエラー状態は、デバイスの他のチャネルの診断に影響を与えません（並列に動作するように構成されていない限り、詳細については、[セクション 7.3.3.5](#) を参照してください）。

1 つのチャネルで過電流または過熱が発生すると、診断ビット **ERRx** がそれに応じて設定されます。[セクション 7.3.4.2](#) と [セクション 7.3.4.3](#) で説明されているように、チャネルはオフになるため、**CLRx** ビットを 1b に設定して再度アクティブにする必要があります。

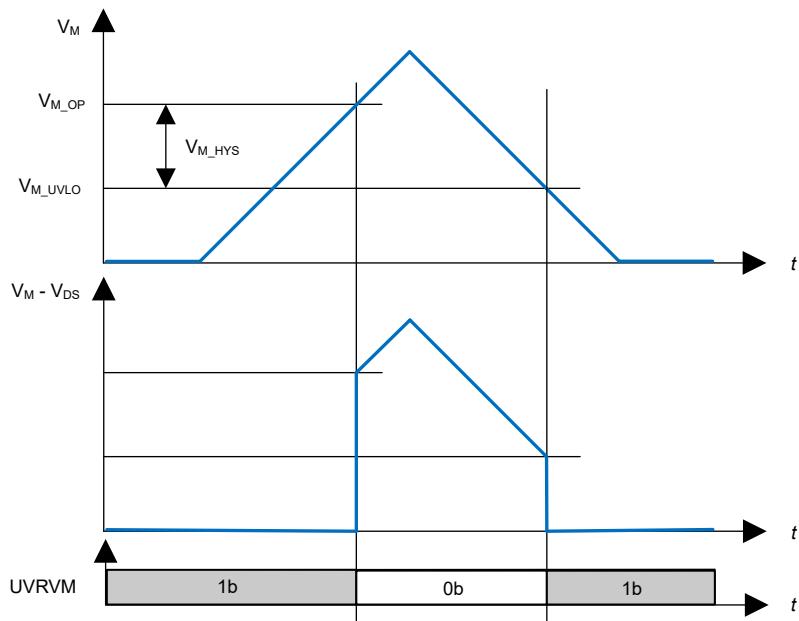

#### 7.3.4.1 $V_M$ の低電圧

$V_{M\_UVLO}$  と  $V_{M\_OP}$  の間には、低電圧機構がトリガされます。デバイスが動作しており、電源電圧が低電圧スレッショルド  $V_{M\_UVLO}$  を下回ると、ロジックはビット **UVRVM** を 1b に設定します。電源電圧  $V_M$  が最小電圧動作スレッショルド  $V_{M\_OP}$  を上回るとすぐに、最初の標準診断読み出しの後で、ビット **UVRVM** は 0b に設定されます。 $V_M$  の低電圧状態は、[セクション 7.3.2](#) で説明されているように、チャネルのステータスに影響します。低電圧動作を、[図 7-12](#) に示します。

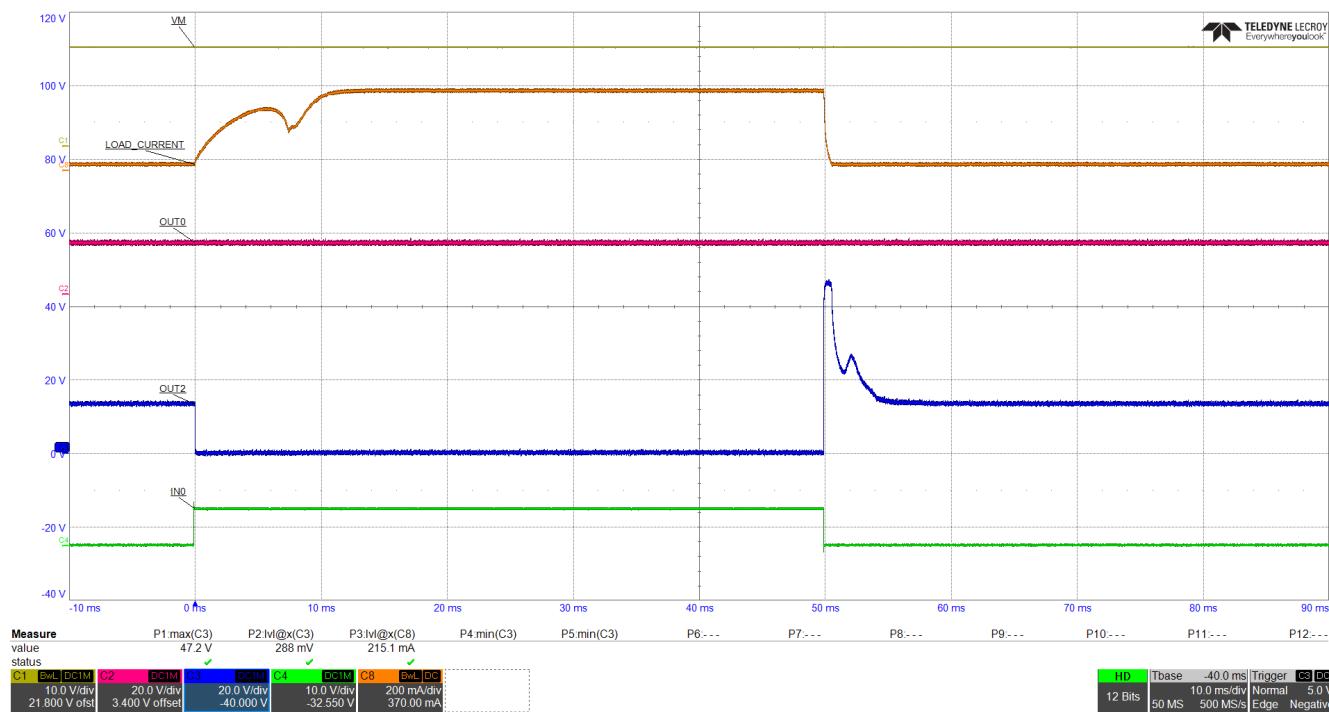

図 7-12.  $V_M$  低電圧の動作

#### 7.3.4.2 過電流保護

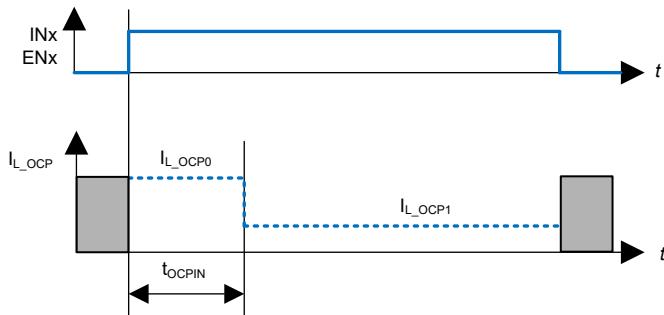

デバイスは、過電流または負荷短絡時に保護されます。2 つの過電流スレッショルドがあります（[図 7-13](#) を参照）。

- チャネルスイッチオンと  $t_{OCPIN}$  の間の  $I_{L\_OCP0}$

- $t_{OCPIN}$  の後に  $I_{L\_OCP1}$

$I_{L\_OCP0}$  および  $I_{L\_OCP1}$  の値は、OCP ビットに応じます。チャネルが  $2 * t_{SYNC}$  を超える時間オフになるたびに、過負荷電流スレッショルドは  $I_{L\_OCP0}$  に戻ります。

図 7-13. 過電流スレッショルド

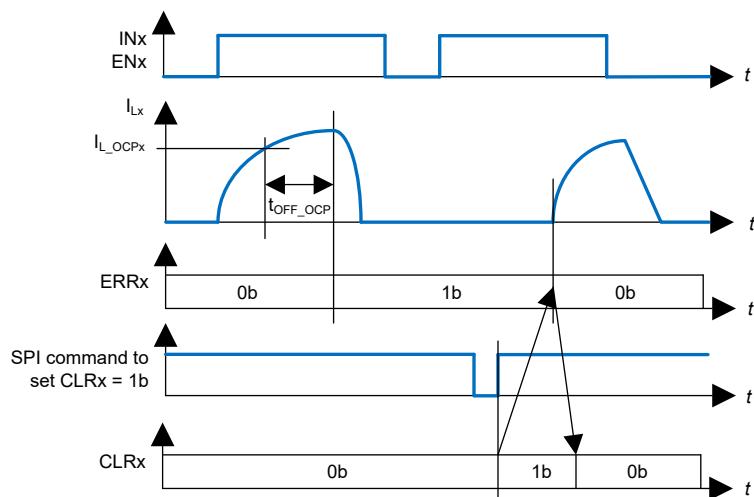

負荷電流が  $I_{L\_OCP0}$  または  $I_{L\_OCP1}$  を上回っている場合、 $t_{OFF\_OCP}$  の時間の後、過負荷チャネルがオフになり、診断ビット  $ERR_x$  が設定されます。対応する  $CLR_x$  ビットを  $1b$  に設定することで、保護ラッチをクリアした後でチャネルをオンにできます。このビットは、チャネルをデラッチした後で内部で  $0b$  にセットされます。詳細については、図 7-14 を参照してください。

図 7-14. 過電流時にラッチオフする

#### 7.3.4.3 過熱保護機能

各チャネルに温度センサが内蔵されているため、過熱したチャネルがオフになり、デバイスの損傷を防止します。対応する診断ビット  $ERR_x$  が設定されます (過負荷保護と組み合わせて)。対応する  $CLR_x$  ビットを  $1b$  に設定することで、保護ラッチをクリアした後でチャネルをオンにできます。このビットは、チャネルをデラッチした後で内部で  $0b$  にセットされます。

#### 7.3.4.4 過熱警告

ダイ温度が過熱警告トリップポイント ( $T_{OTW}$ ) を超えると、構成レジスタ 2 に  $OTW$  ビットが設定されます。デバイスの機能は継続され、追加動作が実行されることはありません。

ダイ温度が過熱警告のヒステリシス ポイント ( $T_{HYS\_OTW}$ ) を下回ると、 $OTW$  ビットは自動的にクリアされます。

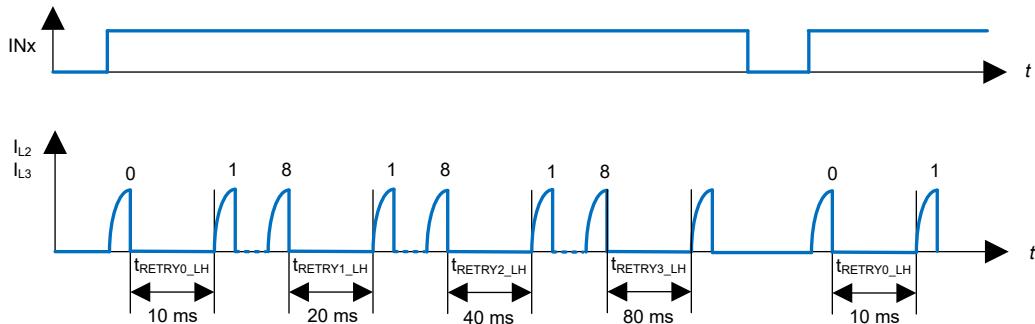

#### 7.3.4.5 リンプ ホーム モードでの過熱および過電流保護

デバイスがリンプホームモードのときは、入力ピンを使用してチャネル 2 と 3 をオンにできます。過電流、短絡、または過熱の場合は、チャネルがオフになります。入力ピンがロジック High のままの場合、チャネルは次のタイミングで再起動します。

- 10ms (最初の 8 回の再試行)

- 20ms (8 回の再試行後)

- 40ms (8 回の再試行後)

- 80ms (入力ピンがロジック High のままで、エラーが存在している限り)

入力ピンが  $2 * t_{SYNC}$  を超えてロジック Low に設定されると、再起動タイマはリセットされます。リップホームモードで、次のチャネルがアクティブになると、タイマーは再び 10ms から開始されます。詳しくは、図 7-15 を参照してください。過電流スレッショルドは、セクション 7.3.4.2 を参照してください。

図 7-15. リップホームでタイマーを再起動します

#### 7.3.4.6 逆極性保護

逆極性 (リバース バッテリ) 状態では、の電力損失が、各 FET のボディダイオード (ローサイドスイッチとして使われる自動構成チャネルの場合) で発生します。一方で、ハイサイドチャネルとして使用される自動構成チャネル、は電力損失を低減するためにオンにされます。ロジックおよび電源ピンの各 ESD ダイオードは、合計消費電力に寄与します。チャネルを流れる逆電流は、接続された負荷によって制限する必要があります。デジタル電源の (VDD) および入力ピンを流れる電流も制限する必要があります (セクション 6.1 を参照)。

#### 注

逆極性時には、温度保護や電流制限などの保護メカニズムはアクティブになりません。

#### 7.3.4.7 過電圧保護

$V_{M\_SC}$  と  $V_{M\_LD}$  の間の電源電圧の場合、出力 MOSFET は引き続き動作し、入力ピンまたは EN ビットに追従します。

セクション 7.3.3.2 に示すように、誘導性負荷の出力クランプに加えて、ロジックおよびすべてのチャネルの過電圧保護のためにクランプ機構があり、VM ピンと GND ピンの間の電圧 ( $V_{M\_AZ}$ ) を監視できます。

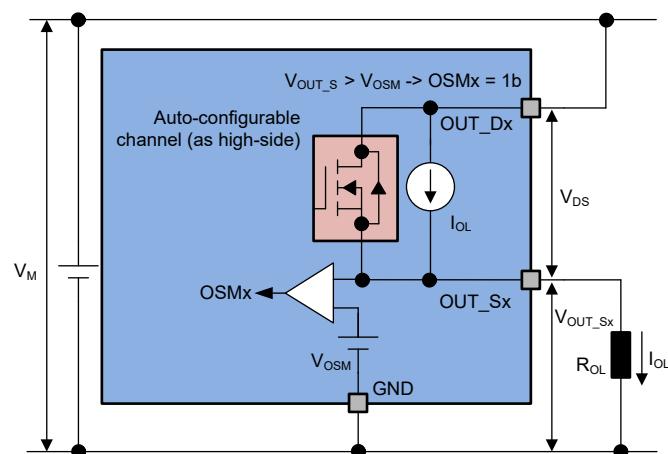

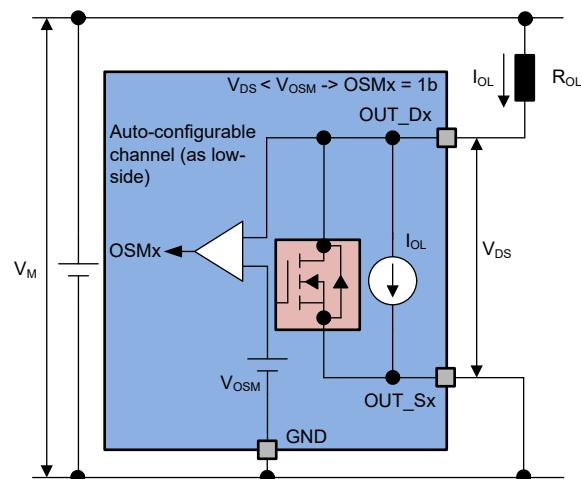

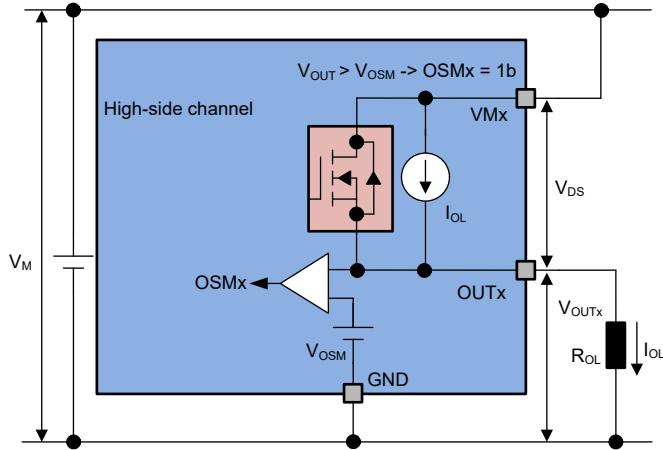

#### 7.3.4.8 出力ステータス モニタ

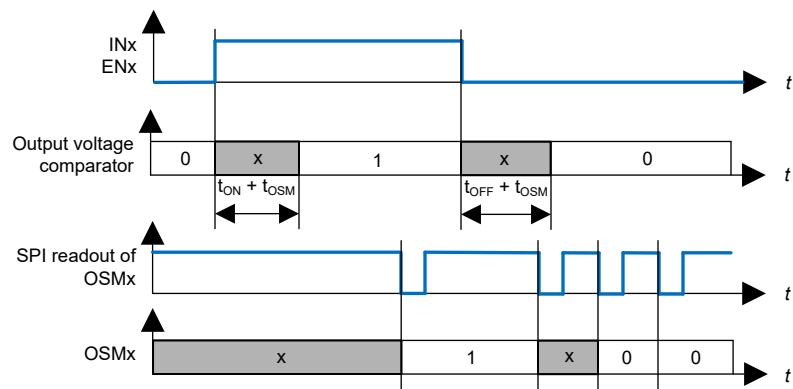

デバイスは、各チャネルの構成に応じて、 $V_{DS}$  with  $V_{OSM}$  (ローサイドスイッチ構成で使用されている自動構成可能チャネルの場合)、 $V_{OUT\_S}$  と  $V_{OSM}$  (ハイサイドスイッチ構成で使用されている自動構成可能チャネルの場合)、 $V_{OUT}$  と  $V_{OSM}$  (ハイサイドチャネルの場合) を比較し、その結果に基づいて対応する  $OSMx$  ビットを設定します。これらのビットは、 $OSM$  レジスタが読み取られるたびに更新されます。

- $V_{DS} < V_{OSM} \rightarrow OSMx = 1b$  (ローサイドスイッチ構成)

- $V_{OUT\_S} > V_{OSM} \rightarrow OSMx = 1b$  (ハイサイドとして使用される自動構成可能チャネル)

パワー・イッチと並列に接続された診断電流  $I_{OL}$  は、 $IOLx$  ビットをプログラムすることで有効にできます。この  $IOLx$  ビットは、オフ検出時のオープン負荷に使用できます。各チャネルには専用の診断電流源があります。診断現在の  $I_{OL}$  が有効になっている場合、またはチャネルの状態が変化した場合 (オン → オフまたはオフ → オン)、信頼性の高い診断を行うために  $t_{OSM}$  を待つ必要があります。 $I_{OL}$  電流源をイネーブルにすると、デバイスの消費電流が増加します。開放負荷が検出された場合でも、そのチャネルはオフにラッチされません。

タイミングの概要については、図 7-16 を参照してください ( $IOLx$  の値は、負荷に正しく接続された通常動作のチャネルを指しています)。

図 7-16. 出力ステータス モニタ タイミング

出力ステータス監視診断は、 $V_M = V_{M\ NOR}$  および  $V_{DD} \geq V_{DD\ UVLO}$  のときに利用できます。

出力ステータス モニタは出力電圧をリアルタイムで監視するため、OFF 状態での開放負荷診断を正確に行うには、チャネルの OFF 状態と OSM レジスタの読み取りを同期させる必要があります。

次のは、出力ステータス モニタが概念レベルでどのように実装されるかを示しています。

図 7-17. 出力ステータスマニタ - ハイサイド構成時自動構成可能チャネル

図 7-18. 出力状態モニタ - ローサイド構成時自動構成可能チャネル

図 7-19. 出力ステータス モニタ - ハイサイド チャネル

標準診断では、ビット **OLOFF** は、オフ状態のすべてのチャネルにおいて、対応する電流源  $I_{OL}$  アクティブになっているすべてのチャネルにおいて、すべての **OSMx** ビットの OR 組み合わせを表します。

**DISOL** ビットが 1b の場合、すべての  $I_{OL}$  電流ソースをディスエーブルすることで、開放負荷検出がディセーブルになります。

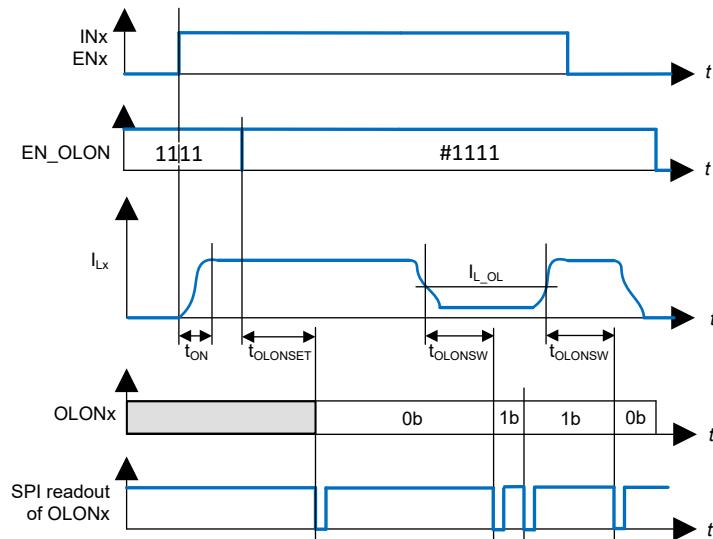

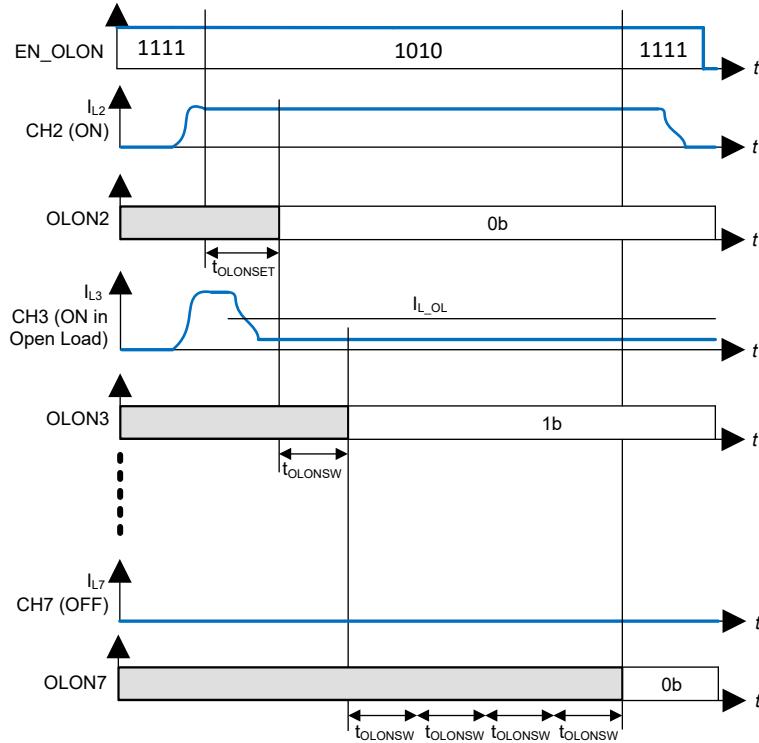

#### 7.3.4.9 オン状態での開放負荷検出

各ハイサイド スイッチおよびハイサイド スイッチとして使用される自動構成可能なチャネルは、オン状態での開放負荷を検出できます。この機能は **EN\_OLON** ビットを設定することで制御可能です。リセット後、オン状態での開放負荷検出機能はデフォルトでは無効になっています。このデバイスは  $I_{L_{Sx}}$  を  $I_{L_{OL}}$  と比較し、それに応じて **OLONx** ビットを設定します。

$I_{L_{Sx}} < I_{L_{OL}} \rightarrow OLONx = 1b \quad V_{OUTx\_S} > V_{OUT\_S\_OL}$  の場合

##### 7.3.4.9.1 オン時の開放負荷 - 直接チャネル診断

**EN\_OLON** ビットを特定チャネルに設定すると、そのチャネルについて内部マルチプレクサが通電時の開放負荷を確認します。TI は診断をアクティブにする前に、チャネルを少なくとも  $t_{ON}$  の間オンにすることを推奨します。一定時間  $t_{OLONSET}$  の経過後、選択されたチャネルに対応する **OLONx** ビットが利用可能になります。**OLONx** レジスタ内のその他のビットはすべてデフォルト値 (0b) に設定されます。これらのビットは、レジスタが読み取られるたびに更新されます。

チャネルが選択されると、それに対応する **OLONx** ビットの内容が標準診断 (**OLON** ビット) にも表示されます。複数のレジスタ読み出しが連続して行われる場合でも、マイコンからの各読み出し要求ごとにレジスタの内容は更新されます。

図 7-20. オン時の開放負荷 (直接チャネル診断)

#### 7.3.4.9.2 オン時の開放負荷 - 診断ループ

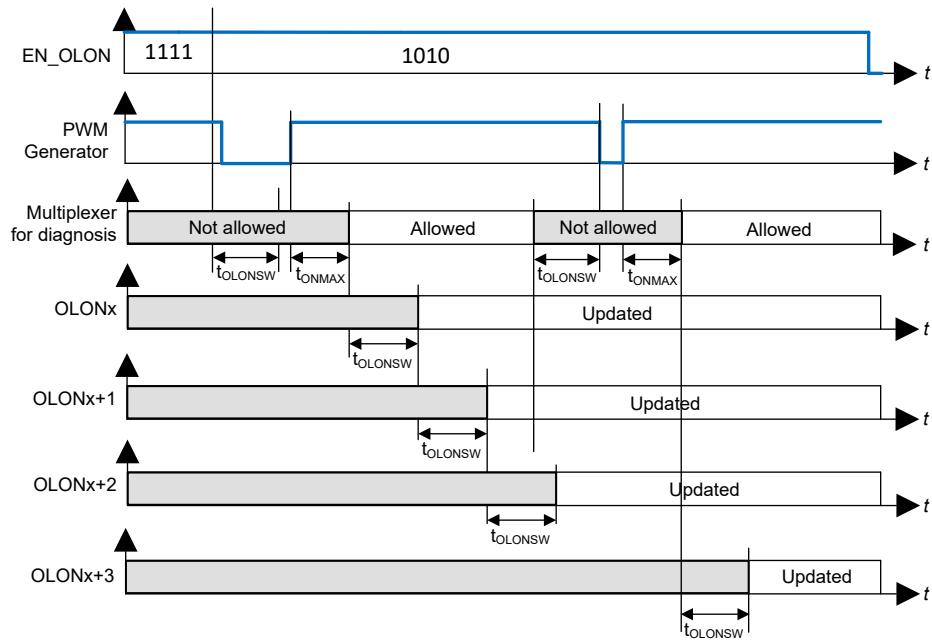

EN\_OON ビットに 1010b を設定すると、デバイスは診断ループを開始し、自動構成可能なチャネル (ハイサイドスイッチとして使われている場合) すべてについて、オン状態での開放負荷の有無をチェックします。まず、内部ロジックは、マイコンによって直接制御されており、かつ内部 PWM ジェネレータによって駆動されるように設定されていないすべてのチャネルをチェックします。その後、内部ロジックは、内部 PWM ジェネレータ制御に設定されているチャネルをすべて確認します。

- マイコンから直接駆動されるチャネルの診断シーケンス

- 最初にチェックされるチャネル: チャネル 2 診断ループをイネーブルにする前に、チャネルを少なくとも  $t_{on}$  でオンにすることを推奨します。

- $t_{OLONSET} + t_{SYNC}$  の時間が経過すると、最初のチャネルの診断が完了します (OLONx ビットが更新されます)。

- 内部マルチプレクサは、次のチャネルに設定されます。 $t_{OLONSW} + t_{SYNC}$  が経過すると、選択したチャネルの診断が完了します (OLONx ビットが更新されます)。この手順は、残りのすべての直接駆動チャネルに対して繰り返されます。

- 診断が行われた時にあるチャネルがオフになっている場合、対応する OLONx ビットは 0b に設定されます

- 内部 PWM ジェネレータによって駆動されるチャネルの診断シーケンス

- これらのチャネルは、マイコンから直接制御されているすべてのチャネルの診断が完了した後にのみチェックされます

- PWM ジェネレータ 0 にマッピングされたチャネルが最初にチェックされます

- $t_{OLONSET}$  時間が経過すると、チャネルのアクティビ化 (スイッチオン) が、最初のチャネルに対するオン時開放負荷診断を実行するためのトリガーイベントとなります。

- $t_{ONMAX} + t_{OLONSW}$  時間が経過すると、最初のチャネルの診断が完了します (OLONx ビットが更新されます)。

- 内部マルチプレクサは、次のチャネルに設定されます。 $t_{OLONSW}$  時間が経過すると、現在選択されているチャネルの診断が完了します (OLONx ビットが更新されます)。この手順は、残りの PWM ジェネレータ駆動チャネルすべてに対して繰り返されます。

- PWM 周期中にチャネルがオフ状態にある場合、診断を実行するために内部ロジックはオン状態になるのを待ちます。 $t_{ONMAX} + t_{OLONSW}$  が経過すると、そのチャネルの診断が完了します。

- 信頼性の高い診断を行うためには、最小オン時間が  $t_{ONMAX} + t_{OLONSW}$  を超えている必要があります。オン時間が  $t_{ONMAX} + t_{OLONSW}$  より小さい場合、対応する OLONx は 0b に設定されます。

診断ループが完了すると、EN\_OON ビットはデフォルト値の 1111b にリセットされ、OLONx ビットには直前の診断結果が保持されます。レジスタの内容を更新するには、新たに診断ループを開始する必要があります。

図 7-21. オン時開放負荷診断のタイミング (診断ループ - マイコン制御チャネル)

図 7-22. オン時開放負荷診断のタイミング (診断ループ - 内部 PWM ジェネレータ制御チャネル)

### 7.3.4.9.3 OLON ビット

OLON ビットは、次の値を想定できます。

- 0b = オン状態での開放負荷は検出されなかったか、診断時にチャネルがオフ状態だったことを示します

- 1b = チャネルがオン状態のときに開放負荷を検出

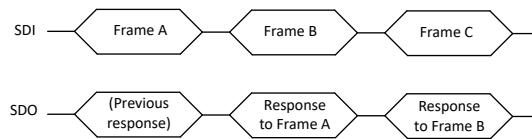

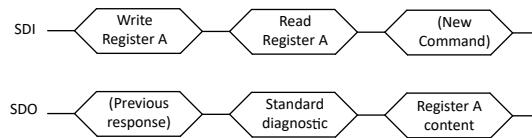

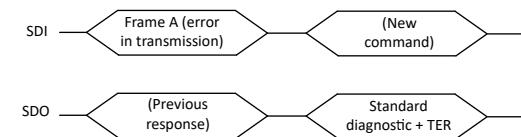

EN\_OOLON の設定に応じて、標準診断ではさまざまな情報が報告されます。