# DRV816x 保護機能および電流センスアンプ搭載、100V ハーフブリッジスマートゲートドライバ

## 1 特長

- ハーフブリッジ構成の 2 つの N チャネル MOSFET を駆動

- ハイサイド MOSFET ソース / ドレイン最大 102V (絶対最大定格)

- 8V (5V DRV8162L)~20V のゲートドライブ電源

- ブートストラップダイオードを内蔵

- 機能安全品質管理**

- 機能安全システム設計に役立つ資料を利用可能

- 内蔵トリクルチャージポンプにより 100% の PWM デューティサイクルをサポート

- 16 レベルのゲートドライブピーク電流

- 16mA~1000mA ソース電流

- 32mA~2000mA シンク電流

- ソース - シンク電流比 1:1, 1:2, 1:3

- 可変 PWM デッドタイム挿入 20ns~900ns

- モーター位相 (SH) スイッチング向けの堅牢な設計

- スルーレート 50V/μs

- 負の過渡電圧 -20V

- 2A の強力なゲートプルダウン

- 冗長シャットダウン用にゲート駆動電源入力を分割 (DRV8162, DRV8162L)

- 低オフセットの電流センスアンプ (DRV8161)

- 可変ゲイン (5, 10, 20, 40V/V)

- 柔軟な PWM 制御インターフェイス、2 ピン PWM, 1 ピン PWM、独立 PWM モード

- 13 レベル VDS 過電流スレッショルド

- 独立したシャットダウンピン (nDRV0FF)

- ゲートドライバソフトシャットダウンシーケンス

- 保護機能内蔵

- GVDD 低電圧 (GVDDUV)

- ブートストラップ低電圧 (BST\_UV)

- MOSFET 過電流保護 (VDS)

- 貫通電流保護

- サーマルシャットダウン (OTSD)

- フォルト状態インジケータ (nFAULT)

- 3.3V および 5V のロジック入力をサポート

## 2 アプリケーション

- 産業用ロボット / 協力ロボット (コボット)

- 移動ロボット (AGV/AMR)

- リニアモーター輸送用システム

- サーボドライブ**

- ドローン

- 電動アシスト自転車、電動スクーター、E-モビリティ

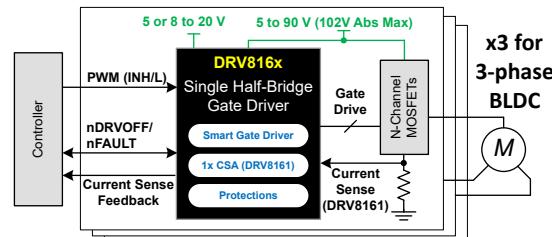

## 3 説明

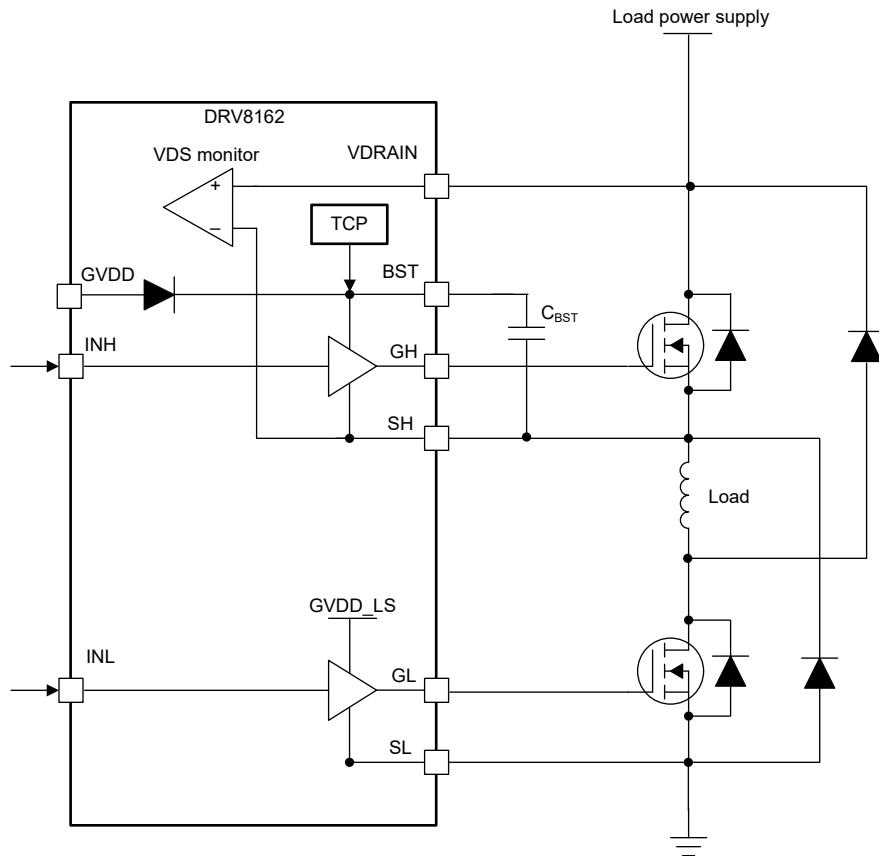

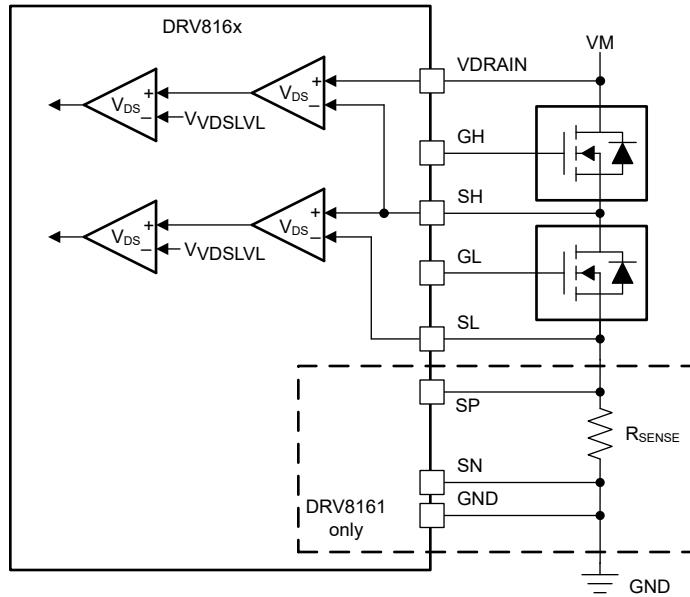

DRV816x は、ハイサイドおよびローサイドの N チャネルパワー MOSFET を駆動できる、ハーフブリッジゲートドライバです。ゲート駆動電圧は GVDD 電源ピンから生成され、内蔵ブートストラップ回路はハイサイド FET を最大 102V ドレインまで駆動するために使用されます。スマートゲートドライブアーキテクチャは、最大でソース 1A、シンク 2A の 16 レベル (48 通りの組み合わせ) のゲート駆動ピーク電流をサポートし、ゲート駆動電流の内蔵タイミング制御機能も搭載しています。これらのデバイスを使用して、ブラシレス / ブラシ付き DC モータ、PMSM、ステッピングモータ、SRM、ソレノイドなど、各種の負荷を駆動できます。

電源低電圧、FET 過電流、ダイ過熱に対する保護機能が内蔵されています。nFAULT ピンは、保護機能によって検出されたフォルトイベントを通知します。nDRV0FF ピンは、PWM 制御から独立して電力段のシャットダウンを開始します。DRV8162 および DRV8162L デバイスは、セーフトルクオフ (STO) 機能を補助するために、分割電源アーキテクチャを採用しています。

ゲート駆動電流、デッドタイム、PWM 制御インターフェイス、過電流検出など、デバイスの多くのパラメータは、いくつかの受動部品をデバイスのピンに接続して構成できます。内蔵のローサイド電流センスアンプ (DRV8161) は、電流測定情報をコントローラに返します。

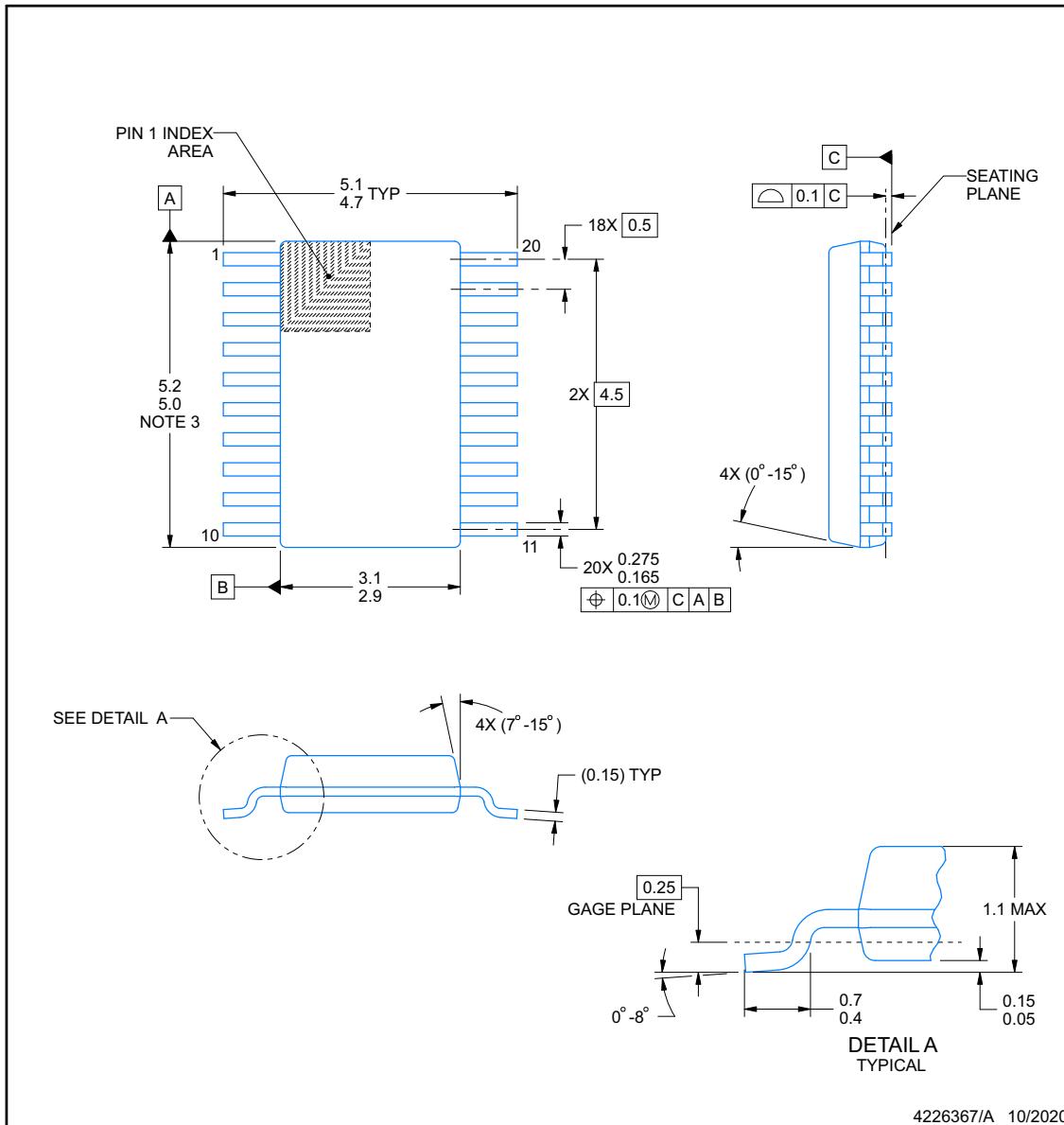

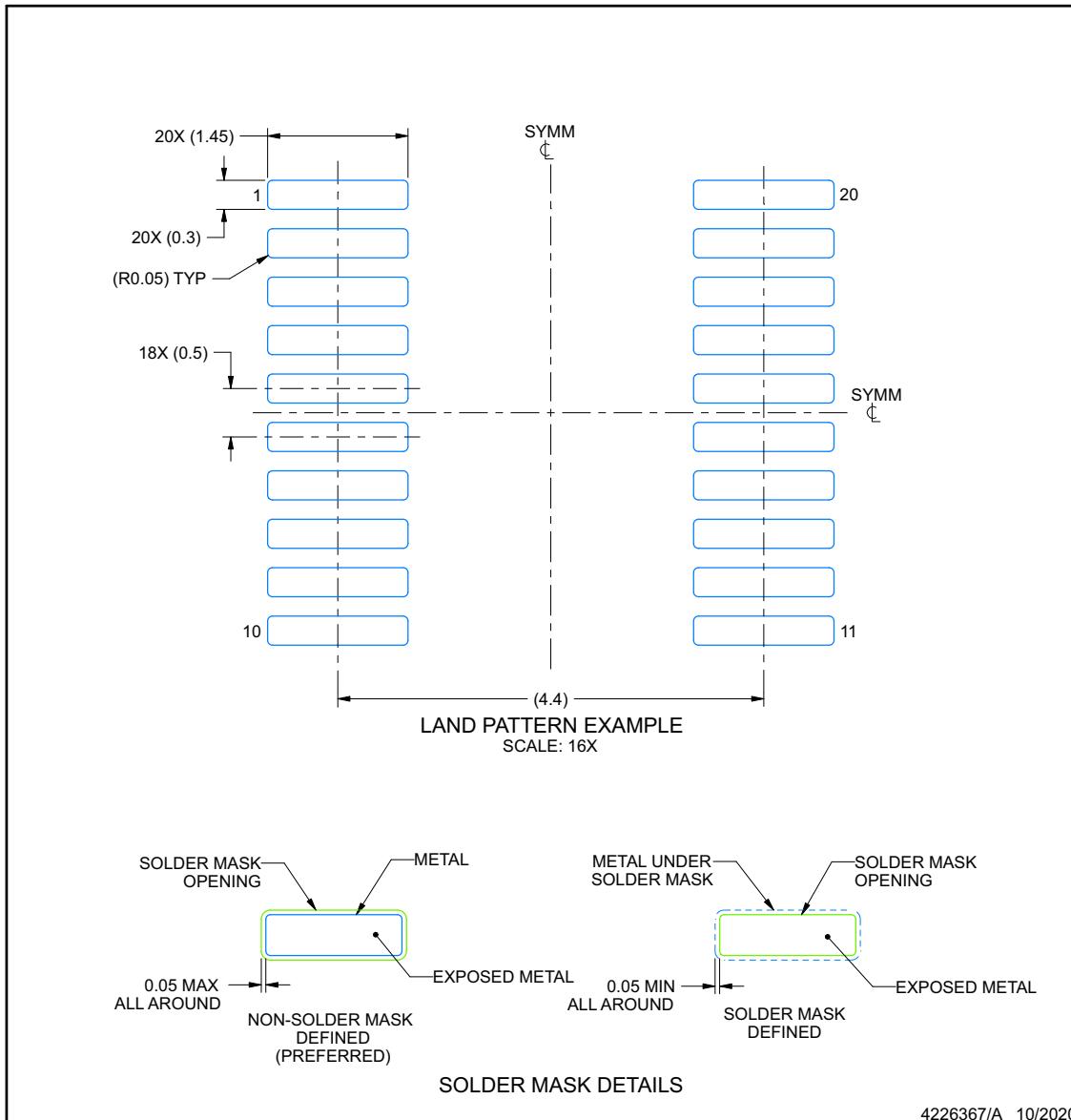

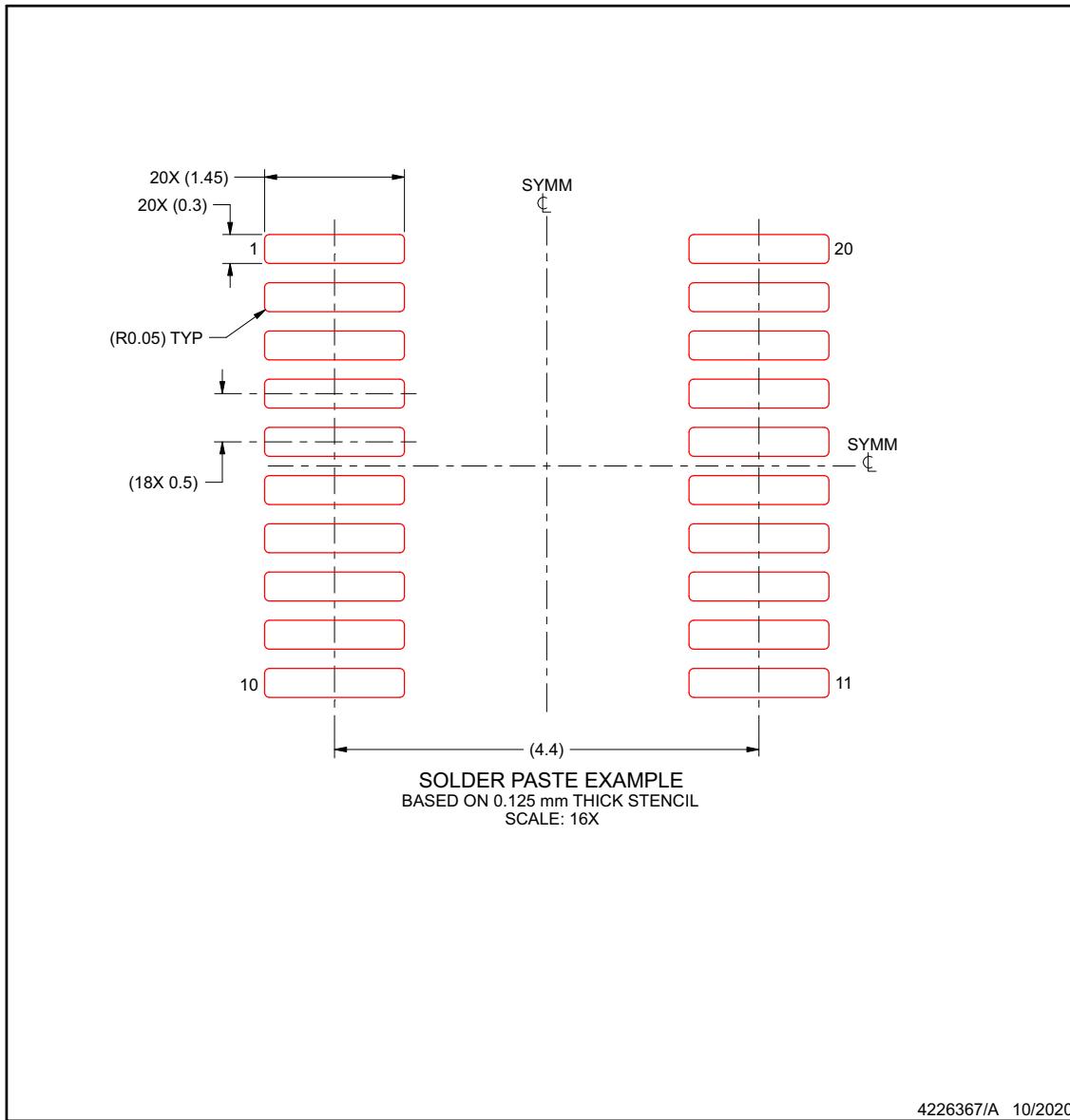

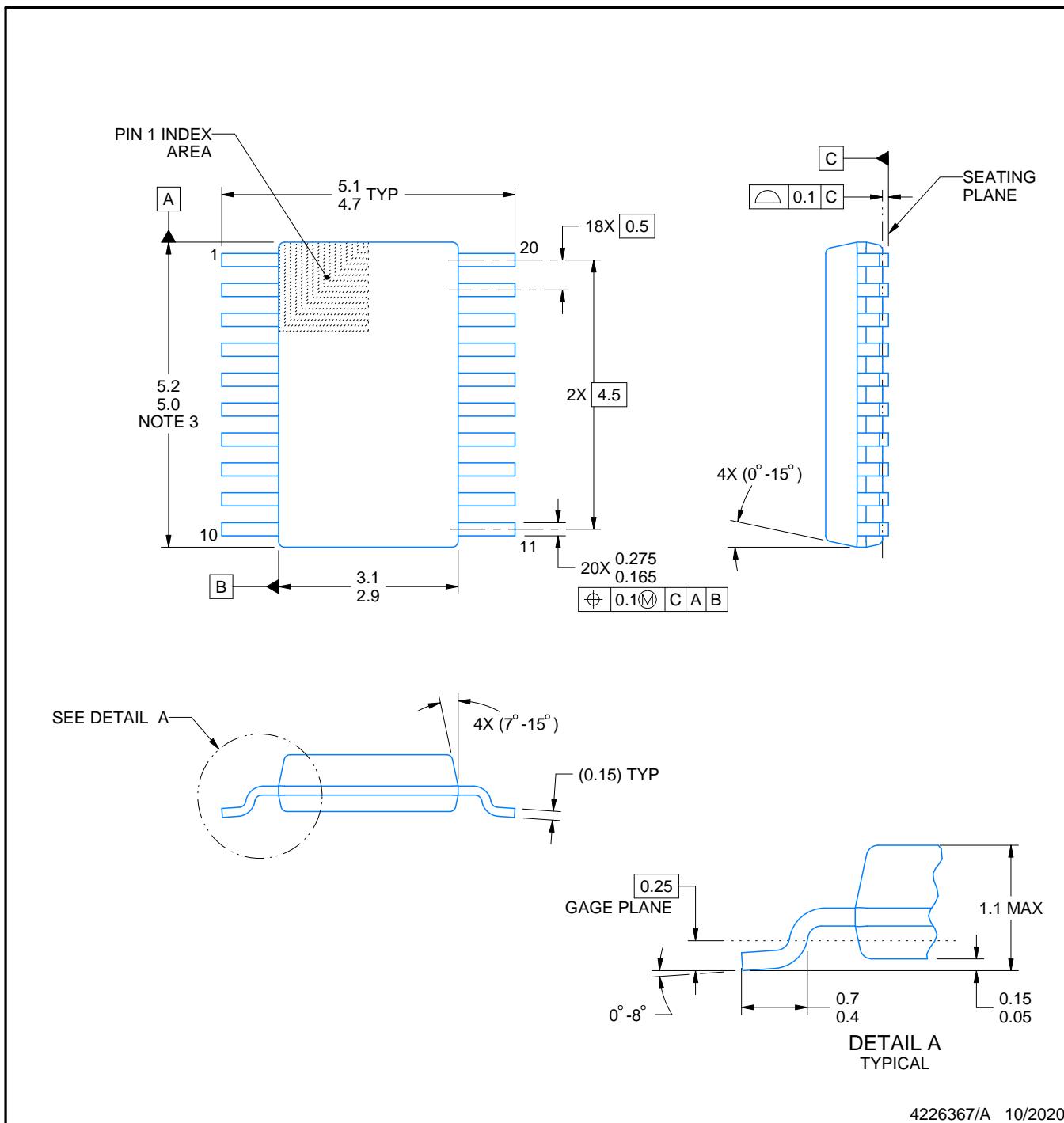

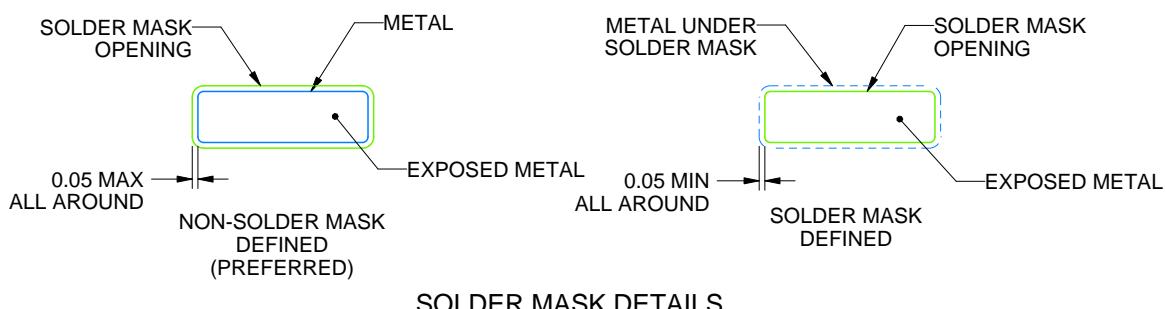

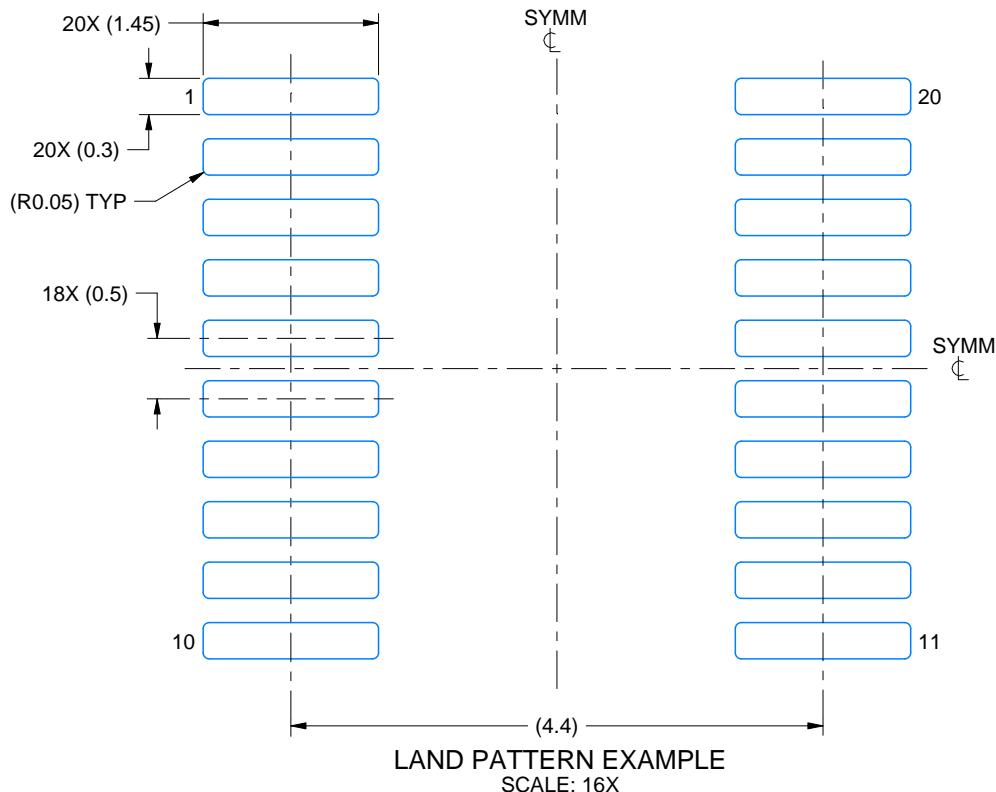

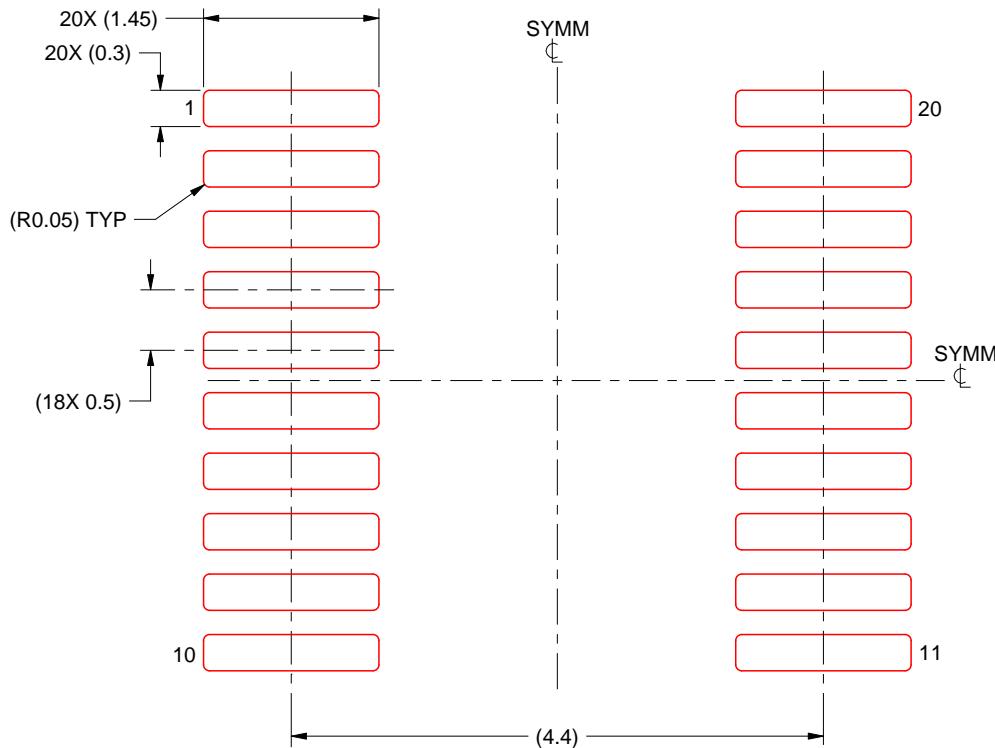

### 製品情報

| 部品番号                   | パッケージ <sup>(1)</sup> | パッケージサイズ <sup>(2)</sup> | 本体サイズ(公称)     |

|------------------------|----------------------|-------------------------|---------------|

| DRV8161                | VSSOP (20)           | 5.1mm × 4.9mm           | 5.1mm × 3.0mm |

| DRV8162 <sup>(3)</sup> | VSSOP (20)           | 5.1mm × 4.9mm           | 5.1mm × 3.0mm |

(1) 詳細については、[セクション 11](#) を参照してください。

(2) パッケージサイズ(長さ × 幅)は公称値であり、該当する場合はピンも含まれます。

(3) DRV8162 および DRV8162L デバイスのバリエントが含まれます。「[デバイス比較表](#)」を参照してください。

DRV816x の概略回路図

## 目次

|                    |           |                               |           |

|--------------------|-----------|-------------------------------|-----------|

| <b>1 特長</b>        | <b>1</b>  | <b>8 アプリケーションと実装</b>          | <b>35</b> |

| <b>2 アプリケーション</b>  | <b>1</b>  | <b>8.1 アプリケーション情報</b>         | <b>35</b> |

| <b>3 説明</b>        | <b>1</b>  | <b>8.2 代表的なアプリケーション</b>       | <b>35</b> |

| <b>4 デバイス比較表</b>   | <b>3</b>  | <b>8.3 レイアウト</b>              | <b>37</b> |

| <b>5 ピン構成および機能</b> | <b>4</b>  | <b>8.4 電源に関する推奨事項</b>         | <b>38</b> |

| <b>6 仕様</b>        | <b>6</b>  | <b>9 デバイスおよびドキュメントのサポート</b>   | <b>40</b> |

| 6.1 絶対最大定格         | 6         | 9.1 デバイス サポート                 | 40        |

| 6.2 ESD 定格         | 6         | 9.2 ドキュメントのサポート               | 40        |

| 6.3 推奨動作条件         | 7         | 9.3 ドキュメントの更新通知を受け取る方法        | 40        |

| 6.4 熱に関する情報 (1pkg) | 7         | 9.4 サポート・リソース                 | 40        |

| 6.5 電気的特性          | 8         | 9.5 商標                        | 40        |

| 6.6 タイミング図         | 13        | 9.6 静電気放電に関する注意事項             | 40        |

| <b>7 詳細説明</b>      | <b>15</b> | 9.7 用語集                       | 40        |

| 7.1 概要             | 15        | 9.8 コミュニティリソース                | 40        |

| 7.2 機能ブロック図        | 16        |                               |           |

| 7.3 機能説明           | 18        | <b>10 改訂履歴</b>                | <b>40</b> |

|                    |           | <b>11 メカニカル、パッケージ、および注文情報</b> | <b>41</b> |

## 4 デバイス比較表

| デバイス    | デバイスの種類  | パッケージのピン数 | 電流検出アンプ | ゲートドライブ電源      | 最小 GVDD 動作 | 制御モード                |

|---------|----------|-----------|---------|----------------|------------|----------------------|

| DRV8161 | DRV8161  | 20        | あり      | GVDD           | 8V         | 2 ピン、1 ピン PWM、独立 FET |

| DRV8162 | DRV8162  |           | なし      | GVDD と GVDD_LS | 8V         |                      |

|         | DRV8162L |           |         |                | 5V         |                      |

## 5 ピン構成および機能

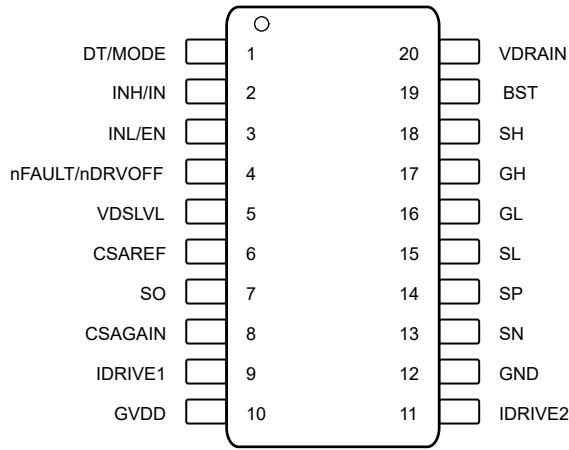

図 5-1. DRV8161 DGS パッケージ 20 ピン VSSOP 上面図

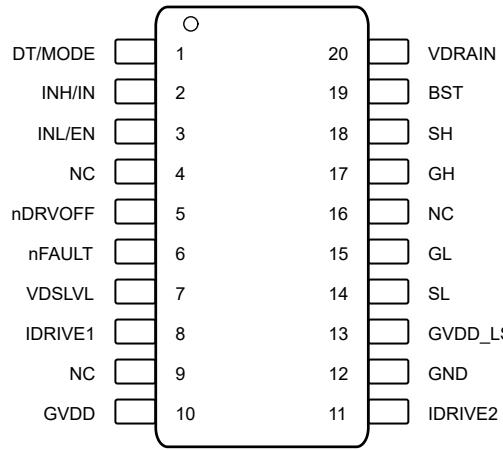

図 5-2. DRV8162 と DRV8162L DGS パッケージ 20 ピン VSSOP 上面図

表 5-1. ピン機能—DRV816x デバイス

| 名称                   | ピン               |                               | タイプ  | 説明                                                                                                                                                          |

|----------------------|------------------|-------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | DRV8161<br>20 ピン | DRV8162、<br>DRV8162L<br>20 ピン |      |                                                                                                                                                             |

| DT / MODE            | 1                | 1                             | I    | 入力ピンのインターフェイスロジックとゲート駆動デッドタイム設定を選択します。DT と GND の間に抵抗を接続してデッドタイムを 20ns~900ns の範囲で調整し、PWM モードを選択します。                                                          |

| INH/IN               | 2                | 2                             | I    | ゲートドライバの制御入力。ゲートドライバの制御は、DT/MODE ピンの設定に依存します。                                                                                                               |

| INL/EN               | 3                | 3                             | I    | ゲートドライバの制御入力。ゲートドライバの制御は、DT/MODE ピンの設定に依存します。                                                                                                               |

| NC                   | —                | 4                             | 該当なし | 未接続。オープンのままにします。                                                                                                                                            |

| nDRVVOFF             | —                | 5                             | I    | ゲートドライバシャットダウン制御。nDRVVOFF をローにプルダウンすると、ゲートドライバがプルダウン状態になることで、ハイサイドおよびローサイドの外部 MOSFET がオフになります。                                                              |

| nFAULT /<br>nDRVVOFF | 4                | —                             | I/O  | 共有の故障インジケータピンとゲートドライバシャットダウンピン。このピンをコントローラ電源またはコントローラ出力ピンへの外部プルアップ抵抗に接続します。このピンは、故障状態の間、ロジック low にプルされます。アクティブゲートドライバシャットダウンを有効にするには、外部ロジックによりピンを low にします。 |

| nFAULT               | —                | 6                             | OD   | フォルト通知出力。このピンは故障状態の間はロジック Low にプルされ、コントローラの I/O 電源への外部プルアップ抵抗 (3.3V~5.0V) が必要です。                                                                            |

| VDSLVL               | 5                | 7                             | I    | VDS 監視スレッショルド設定。このピンは、外部抵抗により設定される多段階入力ピンです。                                                                                                                |

| CSAREF               | 6                | —                             | PWR  | 電流センスアンプのリファレンスコンデンサを CSAREF ピンと GND ピンの間に接続します。                                                                                                            |

| SO                   | 7                | —                             | O    | 電流センスアンプの出力。                                                                                                                                                |

| CSAGAIN              | 8                | —                             | I    | 電流センスアンプのゲイン設定。このピンは、外部抵抗により設定される多段階入力ピンです。                                                                                                                 |

| IDRIVE1              | 9                | 8                             | I    | ゲート駆動のソースおよびシンク電流設定。このピンは、外部抵抗により設定される多段階入力ピンです。                                                                                                            |

| NC                   |                  | 9, 16                         |      | 未接続。オープンのままにします。                                                                                                                                            |

**表 5-1. ピン機能—DRV816x デバイス (続き)**

| 名称      | ピン               |                               | タイプ | 説明                                                                                |  |  |

|---------|------------------|-------------------------------|-----|-----------------------------------------------------------------------------------|--|--|

|         | 番号               |                               |     |                                                                                   |  |  |

|         | DRV8161<br>20 ピン | DRV8162、<br>DRV8162L<br>20 ピン |     |                                                                                   |  |  |

| GVDD    | 10               | 10                            | PWR | ゲートドライバの電源入力。コンデンサを GVDD ピンと GND ピンの間に接続します。                                      |  |  |

| IDRIVE2 | 11               | 11                            | I   | ゲート駆動のソースおよびシンク電流設定。このピンは、外部抵抗により設定される多段階入力ピンです。                                  |  |  |

| GND     | 12               | 12                            | PWR | デバイスのグラウンド。                                                                       |  |  |

| GVDD_LS | —                | 13                            | PWR | ローサイドゲートドライバの電源入力(DRV8162 および DRV8162L のみ)。コンデンサを GVDD_LS ピンと GND ピンの間に接続します。     |  |  |

| SN      | 13               | —                             | I   | 電流検出アンプ入力。電流シャント抵抗の低電位側に接続します。                                                    |  |  |

| SP      | 14               | —                             | I   | 電流シャントアンプの入力。ローサイドパワー MOSFET のソースと電流シャント抵抗の高電位側に接続します。                            |  |  |

| SL      | 15               | 14                            | I   | ローサイドソースピン。ローサイドパワー MOSFET のソースに接続します。このピンは VDS 監視用入力でありローサイドゲートドライバのシンクのための出力です。 |  |  |

| GL      | 16               | 15                            | O   | ローサイドゲートドライバ出力。ローサイドパワー MOSFET のゲートに接続します。                                        |  |  |

| GH      | 17               | 17                            | O   | ハイサイドゲートドライバ出力。ハイサイドパワー MOSFET のゲートに接続します。                                        |  |  |

| SH      | 18               | 18                            | I   | ハイサイドソースピン。ハイサイドパワー MOSFET ソースに接続します。このピンは VDS 監視用入力であり、ハイサイドゲートドライバのシンクのための出力です。 |  |  |

| BST     | 19               | 19                            | O   | ブートストラップ出力ピン。BST と SH の間にコンデンサを接続します。                                             |  |  |

| VDRAIN  | 20               | 20                            | PWR | VDS モニタおよびチャージポンプ基準用のハイサイド MOSFET ドレインセンス入力。ハイサイド MOSFET ドレインに接続します。              |  |  |

PWR = 電源、I = 入力、O = 出力、NC = 接続なし、OD = オープンドレイン出力

## 6 仕様

### 6.1 絶対最大定格

推奨動作条件範囲内 (特に記述のない限り)<sup>(1)</sup>

|                        |                                          | 最小値  | 最大値                       | 単位   |

|------------------------|------------------------------------------|------|---------------------------|------|

| ゲートドライバレギュレータピン電圧      | GVDD, GVDD_LS                            | -0.3 | 20                        | V    |

| ハイサイド ドレインピン電圧         | VDRAIN, T <sub>J</sub> = 25°C            | -0.3 | 102                       | V    |

| ブートストラップピン電圧           | BST, T <sub>J</sub> = 25°C               | -0.3 | 115                       | V    |

| ブートストラップピン電圧           | SH を基準とした BST                            | -0.3 | 20                        | V    |

| ロジックピン電圧               | nFAULT                                   | -0.3 | 20                        | V    |

|                        | INH(IN)、INL(EN)、nDRVOFF、VDSLVL           | -0.3 | 20                        |      |

|                        | DT/MODE、IDRIVE1、IDRIVE2、CSAGAIN          | -0.3 | 6                         |      |

| ハイサイド ゲートドライブピン電圧      | Gh, T <sub>J</sub> = 25°C<br>GVDD >= 11V | -5   | 115                       | V    |

| ハイサイド ゲートドライブピン電圧      | SH を基準とした GH                             | -0.3 | 20                        | V    |

| ハイサイド ソースピン電圧          | SH, DC                                   | -5   | 105                       | V    |

| 過度ハイサイド ソースピンマイナス電圧    | SH, 1 μs                                 | -20  |                           | V    |

| ハイサイドソースピンのスルーレート      | SH, V <sub>BST-SH</sub> > 3.5V           |      | 50                        | V/ns |

| ローサイド ゲートドライブピン電圧      | SL を基準とした GL                             | -0.3 | 20                        | V    |

| ローサイド ソース検出ピン電圧        | SL                                       | -5   | V <sub>GVDD</sub> +0.3    | V    |

| 過度ローサイド ソースセンスピニマイナス電圧 | SL, 1 μs                                 | -16  |                           | V    |

| 電流検出アンプリファレンス入力ピン電圧    | CSAREF                                   | -0.3 | 5.5                       | V    |

| シャントアンプ入力ピン電圧          | SN, SP                                   | -1   | 1                         | V    |

| 過渡 500ns シャントアンプ入力ピン電圧 | SN, SP, 500ns                            | -16  | 20                        | V    |

| シャントアンプ出力ピン電圧          | SO                                       | -0.3 | V <sub>CSAREF</sub> + 0.3 | V    |

| 接合部温度、T <sub>J</sub>   |                                          | -40  | 150                       | °C   |

| 保管温度、T <sub>stg</sub>  |                                          | -65  | 150                       | °C   |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

### 6.2 ESD 定格

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup>      | ±2000 | V |

|--------------------|------|-----------------------------------------------------------|-------|---|

|                    |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠 <sup>(2)</sup> |       |   |

- (1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

## 6.3 推奨動作条件

動作温度範囲内 (特に記述のない限り)

|               |                                       |                                                                                                                                           | 最小値 | 公称値 | 最大値 | 単位 |

|---------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|----|

| $V_{GVDD}$    | 電源電圧                                  | $GVDD, GVDD\_LS$                                                                                                                          | 8   |     | 20  | V  |

|               | 電源電圧(DRV8162Lのみ)                      | $GVDD, GVDD\_LS, DRV8162L$ デバイス<br>バリエント                                                                                                  | 5   |     |     | V  |

| $V_{GVDD-SL}$ | SLに対する電源電圧                            | $GVDD$ (DRV8161)、 $GVDD\_LS$<br>(DRV8162x)はローサイドプリドライバ<br>PWM 動作用                                                                         | 3.5 |     |     | V  |

| $V_{VDRAIN}$  | ハイサイドドレインピン電圧                         | $VDRAIN$ 、ローサイドゲート駆動、ハイサイド<br>ゲート駆動スイッチング(ブートストラップ付<br>き)                                                                                 | 0   | 90  |     | V  |

| $V_{BST-SH}$  | SHを基準とするブートストラップピンの電<br>圧             | $BST(V_{BST} - V_{SH})$ 、ハイサイドゲート駆動ス<br>イッチング、 $BST\_UV$ 検出なし、 $V_{BST-SH}$<br>$min > V_{BST\_UV} max$ (立ち上がり)、                           | 6.1 |     | 20  | V  |

|               | SHを基準とするブートストラップピンの電<br>圧(DRV8162Lのみ) | $BST(V_{BST} - V_{SH})$ 、DRV8162L デバイスバ<br>リエントのみ、ハイサイドゲート駆動スイッチ<br>ング、 $BST\_UV$ 検出なし、 $V_{BST-SH}$ $min >$<br>$V_{BST\_UV} max$ (立ち上がり) | 4.6 |     |     | V  |

| $V_{BST}$     | ブートストラップピン電圧                          | $BST$                                                                                                                                     | 0   | 105 |     | V  |

| $V_{SH}$      | ハイサイドソースピン電圧                          | $SH$                                                                                                                                      | -2  | 95  |     | V  |

| $V_I$         | デジタル/ピン検出入力電圧                         | INH、INL、IDRIVE1、IDRIVE2、<br>CSAGAIN、VDSLVL、nDRVVOFF、DT/<br>MODE                                                                           | 0   | 5.5 |     | V  |

| $V_{OD}$      | オープンドレインブルアップ電圧                       | nFAULT                                                                                                                                    |     | 5.5 |     | V  |

| $I_{OD}$      | オープンドレイン出力電流                          | nFAULT                                                                                                                                    |     | -5  |     | mA |

| $V_{CSAREF}$  | 電流センスアンプリファレンス電圧                      | CSAREF                                                                                                                                    | 3.0 | 5.5 |     | V  |

| $T_A$         | 動作時の周囲温度                              |                                                                                                                                           | -40 | 125 |     | °C |

| $T_J$         | 動作時接合部温度                              |                                                                                                                                           | -40 | 150 |     | °C |

## 6.4 热に関する情報 (1pkg)

|                      | 熱評価基準 <sup>(1)</sup> | DRV8161/DRV8162 | 単位   |

|----------------------|----------------------|-----------------|------|

|                      |                      | DGS (VSSOP)     |      |

|                      |                      | 20 ピン           |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗         | 87.0            | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース(上面)への熱抵抗    | 31.2            | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗         | 42.3            | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ     | 0.9             | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ     | 41.9            | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース(底面)への熱抵抗    | 該当なし            | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーションレポートを参照してください。

## 6.5 電気的特性

、 $V_{GVDD} = 12V$   $V_{VDRAIN} = 48V$ 、 $T_J = 25^\circ C$  (特に記述のない限り)

| パラメータ                               |                                                      | テスト条件                                                                                            | 最小値  | 標準値   | 最大値 | 単位 |

|-------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------|------|-------|-----|----|

| <b>電源(GVDD, BST)</b>                |                                                      |                                                                                                  |      |       |     |    |

| $I_{VDRAIN\_UNP\_WR}$               | $GVDD$ 電源が供給されていないときの $VDRAIN$ リーク電流                 | $GVDD = 0V$ 、 $VDRAIN = 48V$ 、 $V_{BST-SH} = 0V$<br>$VDRAIN+SH$ のリーク電流                           | 3.5  | 5     | μA  |    |

| $I_{GVDD}$                          | $GVDD$ アクティブ モード電流                                   | $INH = INL = 20kHz$ でスイッチング、<br>$V_{BST} = V_{GVDD}$ 、FET は接続なし、DT/MODE ピンはオープン。 $VDS\_LVL = 2V$ | 2    |       | mA  |    |

| $t_{WAKE}$                          | ターンオン時間                                              | $GVDD = 0V \sim 12V$<br>$GVDD\_UV$ からアクティブモード(出力準備完了) ( $nFAULT = High$ )                        | 0.4  |       | ms  |    |

| $I_{L\_BS\_TCPON}$                  | ハイサイドブースト中のポートストラップピンのリーク電流                          | $INH = High$ 、 $TCP\_ON$                                                                         | 30   |       | μA  |    |

| <b>ロジックレベル入力(INH, INL, nDRVOFF)</b> |                                                      |                                                                                                  |      |       |     |    |

| $V_{IL}$                            | 入力ロジック Low 電圧                                        | INL, INH, nDRVOFF                                                                                | 0.8  | 0.8   | V   |    |

| $V_{IH}$                            | 入力ロジック High 電圧                                       | INL, INH, nDRVOFF                                                                                | 2.2  |       | V   |    |

| $R_{PU}$                            | 入力プルアップ抵抗                                            | nDRVOFF から内部レギュレータへ、外部接続なし                                                                       | 250  |       | kΩ  |    |

| $R_{PD}$                            | 入力プルダウン抵抗                                            | INH, INL から GND へ                                                                                | 250  |       | kΩ  |    |

| $t_{nDRVOFF\_DEG}$                  | nDRVOFF 入力のグリッチ除去時間                                  | nDRVOFF の立ち下がりと立ち上がり                                                                             | 1    | 2.1   | 4.2 | μs |

| $t_{nDRVOFF\_DIAG}$                 | nDRVOFF 診断パルスの有効入力時間                                 | DRV8162 および DRV8162L のみ                                                                          | 0.5  |       | μs  |    |

| <b>オープンドレイン出力(nFAULT)</b>           |                                                      |                                                                                                  |      |       |     |    |

| $V_{OL}$                            | 出力ロジック Low 電圧                                        | $I_{OD} = 5mA$ 、 $GVDD > 4V$                                                                     | 0.4  | 0.4   | V   |    |

| <b>ポートストラップダイオード(BST)</b>           |                                                      |                                                                                                  |      |       |     |    |

| $V_{BOOTD}$                         | ポートストラップ ダイオードの順方向電圧                                 | $I_{BOOT} = 100 \mu A$                                                                           | 0.82 | 0.82  | V   |    |

| $V_{BOOTD}$                         | ポートストラップ ダイオードの順方向電圧                                 | $I_{BOOT} = 100 mA$                                                                              | 1.6  | 1.6   | V   |    |

| $R_{BOOTD}$                         | ポートストラップの動的抵抗 ( $\Delta V_{BOOTD}/\Delta I_{BOOT}$ ) | $I_{BOOT} = 100mA$ および $50mA$                                                                    | 3.9  | 4.8   | 9   | Ω  |

| <b>チャージポンプ(BST)</b>                 |                                                      |                                                                                                  |      |       |     |    |

| $V_{TCP}$                           | トリクルチャージポンプの出力電圧                                     | $V_{BST-SH} = High$ 、 $SH = VDRIVE = 20V$ 、 $BST > GVDD$ 、外部負荷 $I_{TRICKLE} = 2uA$               | 9.5  | 10.6  | 12  | V  |

| $t_{TCP\_DLY}$                      | トリクルチャージポンプのアクティブ遅延時間                                | INL = Low                                                                                        | 150  | 250   | 350 | μs |

| <b>ゲートドライバ(GH, GL, SH, SL)</b>      |                                                      |                                                                                                  |      |       |     |    |

| $V_{GSHx\_LO}$                      | ハイサイド ゲート駆動の low レベル電圧 ( $V_{GH} - V_{SH}$ )         | $I_{GHx} = -10mA$ 、 $V_{GVDD} = 12V$ 、IDRIVE = 1000mA、FET は接続されていない                              | 0    | 0.022 | 0.2 | V  |

| $V_{GSHx\_HI}$                      | ハイサイドゲート駆動の High レベル電圧 ( $V_{BST} - V_{GH}$ )        | $I_{GHx} = 10mA$ 、 $V_{GVDD} = 12V$ 、IDRIVE = 500mA、FET は接続されていない                                | 0    | 0.09  | 0.2 | V  |

| $V_{GSLx\_LO}$                      | ローサイド ゲート駆動の low レベル電圧 ( $V_{GL} - V_{SL}$ )         | $I_{GLx} = -10mA$ 、 $V_{GVDD} = 12V$ 、IDRIVE = 1000mA、FET は接続されていない                              | 0    | 0.022 | 0.2 | V  |

| $V_{GSLx\_HI}$                      | ローサイド ゲート駆動の High レベル電圧 ( $V_{GVDD} - V_{GL}$ )      | $I_{GLx} = 10mA$ 、 $V_{GVDD} = 12V$ 、IDRIVE = 500mA、FET は接続されていない                                | 0    | 0.09  | 0.2 | V  |

、 $V_{GVDD} = 12V$   $V_{VDRAIN} = 48V$ 、 $T_J = 25^\circ C$ (特に記述のない限り)

| パラメータ          | テスト条件                                                                                     | 最小値 | 標準値  | 最大値  | 単位 |

|----------------|-------------------------------------------------------------------------------------------|-----|------|------|----|

| $I_{DRIVEP0}$  | $V_{BST} - V_{SH} = V_{GVDD} = 12V$ 、 $T_J = -40^\circ C \sim 150^\circ C$<br>ピークソースゲート電流 | 9   | 16   | 26   | mA |

| $I_{DRIVEP1}$  |                                                                                           | 19  | 32   | 52   | mA |

| $I_{DRIVEP2}$  |                                                                                           | 38  | 64   | 103  | mA |

| $I_{DRIVEP3}$  |                                                                                           | 57  | 96   | 154  | mA |

| $I_{DRIVEP4}$  |                                                                                           | 76  | 128  | 205  | mA |

| $I_{DRIVEP5}$  |                                                                                           | 96  | 160  | 256  | mA |

| $I_{DRIVEP6}$  |                                                                                           | 115 | 192  | 308  | mA |

| $I_{DRIVEP7}$  |                                                                                           | 134 | 224  | 359  | mA |

| $I_{DRIVEP8}$  |                                                                                           | 153 | 256  | 410  | mA |

| $I_{DRIVEP9}$  |                                                                                           | 172 | 288  | 461  | mA |

| $I_{DRIVEP10}$ |                                                                                           | 192 | 320  | 512  | mA |

| $I_{DRIVEP11}$ |                                                                                           | 230 | 384  | 615  | mA |

| $I_{DRIVEP12}$ |                                                                                           | 268 | 448  | 717  | mA |

| $I_{DRIVEP13}$ |                                                                                           | 307 | 512  | 820  | mA |

| $I_{DRIVEP14}$ |                                                                                           | 460 | 768  | 1229 | mA |

| $I_{DRIVEP15}$ |                                                                                           | 614 | 1024 | 1639 | mA |

、 $V_{GVDD} = 12V$   $V_{VDRAIN} = 48V$ 、 $T_J = 25^\circ C$ (特に記述のない限り)

| パラメータ                 |                           | テスト条件                                                                                | 最小値  | 標準値  | 最大値  | 単位 |

|-----------------------|---------------------------|--------------------------------------------------------------------------------------|------|------|------|----|

| $I_{DRIVEN0}$         | ピークシンクゲート電流               | $V_{BST} - V_{SH} = V_{GVDD} = 12V$ 、 $T_J = -40^\circ C \sim 150^\circ C$           | 19   | 32   | 52   | mA |

| $I_{DRIVEN1}$         |                           | $V_{BST} - V_{SH} = V_{GVDD} = 12V$ 、 $T_J = -40^\circ C \sim 150^\circ C$           | 38   | 64   | 103  | mA |

| $I_{DRIVEN2}$         |                           | $V_{BST} - V_{SH} = V_{GVDD} = 12V$ 、 $T_J = -40^\circ C \sim 150^\circ C$           | 76   | 128  | 205  | mA |

| $I_{DRIVEN3}$         |                           | $V_{BST} - V_{SH} = V_{GVDD} = 12V$ 、 $T_J = -40^\circ C \sim 150^\circ C$           | 115  | 192  | 308  | mA |

| $I_{DRIVEN4}$         |                           | $V_{BST} - V_{SH} = V_{GVDD} = 12V$ 、 $T_J = -40^\circ C \sim 150^\circ C$           | 153  | 256  | 410  | mA |

| $I_{DRIVEN5}$         |                           | $V_{BST} - V_{SH} = V_{GVDD} = 12V$ 、 $T_J = -40^\circ C \sim 150^\circ C$           | 192  | 320  | 512  | mA |

| $I_{DRIVEN6}$         |                           | $V_{BST} - V_{SH} = V_{GVDD} = 12V$ 、 $T_J = -40^\circ C \sim 150^\circ C$           | 230  | 384  | 615  | mA |

| $I_{DRIVEN7}$         |                           | $V_{BST} - V_{SH} = V_{GVDD} = 12V$ 、 $T_J = -40^\circ C \sim 150^\circ C$           | 268  | 448  | 717  | mA |

| $I_{DRIVEN8}$         |                           | $V_{BST} - V_{SH} = V_{GVDD} = 12V$ 、 $T_J = -40^\circ C \sim 150^\circ C$           | 307  | 512  | 820  | mA |

| $I_{DRIVEN9}$         |                           | $V_{BST} - V_{SH} = V_{GVDD} = 12V$ 、 $T_J = -40^\circ C \sim 150^\circ C$           | 345  | 576  | 922  | mA |

| $I_{DRIVEN10}$        |                           | $V_{BST} - V_{SH} = V_{GVDD} = 12V$ 、 $T_J = -40^\circ C \sim 150^\circ C$           | 384  | 640  | 1024 | mA |

| $I_{DRIVEN11}$        |                           | $V_{BST} - V_{SH} = V_{GVDD} = 12V$ 、 $T_J = -40^\circ C \sim 150^\circ C$           | 460  | 768  | 1229 | mA |

| $I_{DRIVEN12}$        |                           | $V_{BST} - V_{SH} = V_{GVDD} = 12V$ 、 $T_J = -40^\circ C \sim 150^\circ C$           | 537  | 896  | 1434 | mA |

| $I_{DRIVEN13}$        |                           | $V_{BST} - V_{SH} = V_{GVDD} = 12V$ 、 $T_J = -40^\circ C \sim 150^\circ C$           | 614  | 1024 | 1639 | mA |

| $I_{DRIVEN14}$        |                           | $V_{BST} - V_{SH} = V_{GVDD} = 12V$ 、 $T_J = -40^\circ C \sim 150^\circ C$           | 921  | 1536 | 2458 | mA |

| $I_{DRIVEN15}$        |                           | $V_{BST} - V_{SH} = V_{GVDD} = 12V$ 、 $T_J = -40^\circ C \sim 150^\circ C$           | 1228 | 2048 | 3277 | mA |

| $R_{PD\_LS}$          | ローサイド パッシブ プルダウン          | $GL$ から $SL$ 、 $V_{GL} - V_{SL} = 2V$                                                | 60   | 85   | 120  | kΩ |

| $R_{PDSA\_HS}$        | ハイサイド セミアクティブ プルダウン       | $V_{GVDD} < V_{GVDD\_UV}$<br>$GH \sim SH$ 、 $V_{GH} - V_{SH} = 2V$                   | 2    | 4    | 8    | kΩ |

| $I_{PUHOLD\_HS}$      | ハイサイド ブルアップホールド電流         | $T_J = -40 \sim 150^\circ C$                                                         | 307  | 512  | 820  | mA |

| $I_{PDHOLD\_HS}$      | ハイサイド ブルダウンホールド電流         | $T_J = -40 \sim 150^\circ C$                                                         | 1228 | 2048 | 3277 | mA |

| $I_{PDSTRONG\_L\_S}$  | ローサイド・プルダウン強電流            | $T_J = -40 \sim 150^\circ C$                                                         | 1228 | 2048 | 3277 | mA |

| $I_{PDSTRONG\_H\_S}$  | ハイサイド ブルダウン強電流            | $T_J = -40 \sim 150^\circ C$                                                         | 1228 | 2048 | 3277 | mA |

| $I_{DRVIVENSD\_L\_S}$ | ローサイド ピークシンク ゲートシャットダウン電流 | $I_{DRIVENx}$ は $I_{DRIVEN13}$ (1024mA 標準値) またはそれ以下の設定に設定されます                        |      | 32   |      | mA |

| $I_{DRVIVENSD\_L\_S}$ | ローサイド ピークシンク ゲートシャットダウン電流 | $I_{DRIVENx}$ は $I_{DRIVEN14}$ (1536mA 標準値) または $I_{DRIVEN15}$ (2048mA 標準値) に設定されます。 |      | 64   |      | mA |

| $I_{DRVIVENSD\_H\_S}$ | ハイサイド ピークシンク ゲートシャットダウン電流 | $I_{DRIVENx}$ は $I_{DRIVEN13}$ (1024mA 標準値) またはそれ以下の設定に設定されます                        |      | 32   |      | mA |

| $I_{DRVIVENSD\_H\_S}$ | ハイサイド ピークシンク ゲートシャットダウン電流 | $I_{DRIVENx}$ は $I_{DRIVEN14}$ (1536mA 標準値) または $I_{DRIVEN15}$ (2048mA 標準値) に設定されます。 |      | 64   |      | mA |

、 $V_{GVDD} = 12V$   $V_{VDRAIN} = 48V$ 、 $T_J = 25^\circ C$ (特に記述のない限り)

| パラメータ                  | テスト条件                                                 | 最小値                                                                                                                                                                        | 標準値 | 最大値     | 単位      |

|------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|---------|

| <b>ゲートドライバのタイミング</b>   |                                                       |                                                                                                                                                                            |     |         |         |

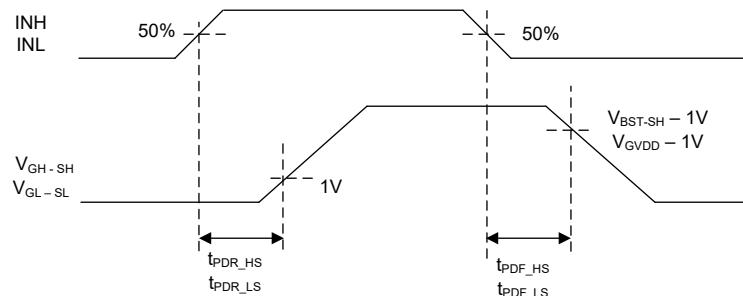

| $t_{PDR\_LS}$          | ローサイド立ち上がり伝搬遅延                                        | INL から GL 立ち上がりまで、 $V_{GVDD} > 8V$                                                                                                                                         | 25  | 40      | 80 ns   |

| $t_{PDF\_LS}$          | ローサイド立ち下がり伝搬遅延                                        | INL から GL 立ち下がりまで、 $V_{GVDD} > 8V$                                                                                                                                         | 25  | 41      | 80 ns   |

| $t_{PDR\_HS}$          | ハイサイド立ち上がり伝搬遅延                                        | INH から GH 立ち上がりまで、 $V_{GVDD} = V_{BST} - V_{SH} > 8V$                                                                                                                      | 25  | 41      | 80 ns   |

| $t_{PDF\_HS}$          | ハイサイド立ち下がり伝搬遅延                                        | INH から GH 立ち下がりまで、 $V_{GVDD} = V_{BST} - V_{SH} > 8V$                                                                                                                      | 25  | 42      | 80 ns   |

| $t_{PD\_MATCH}$        | ローサイドゲートドライバの伝搬遅延の一致                                  | GL ターンオンから GL ターンオフまで、 $V_{GL\_SL} = 1V$ から $V_{GL\_SL} = V_{GVDD} - 1V$ 、<br>$V_{GVDD} = V_{BST} - V_{SH} > 8V$ 、 $V_{SH} = 0V \sim 90V$ 、GH と GL は無負荷                    | -10 | $\pm 4$ | 10 ns   |

|                        | ハイサイドゲートドライバの伝搬遅延の一致                                  | GH ターンオンから GH ターンオフまで、 $V_{GH\_SH} = 1V$ から $V_{GH\_SH} = V_{BST\_SH} - 1V$ 、 $V_{GVDD} = V_{BST} - V_{SH} > 8V$ 、 $V_{SH} = 0V \sim 90V$ 、GH と GL は無負荷                    | -10 | $\pm 4$ | 10 ns   |

| $t_{PD\_MATCH\_PH}$    | 位相ごとの伝搬遅延のマッチング                                       | デッドタイムの無効化。GL ターンオフから GH ターンオンまで、 $V_{GL\_SL} = V_{GVDD} - 1V$ から $V_{GH\_SH} = 1V$ 、 $V_{GVDD} = V_{BST} - V_{SH} > 8V$ 、 $V_{SH} = 0V \sim 90V$ 、GH と GL は無負荷、デッドタイムは無効化 | -12 | $\pm 4$ | 12 ns   |

|                        |                                                       | デッドタイムの無効化。GH ターンオフから GL ターンオンまで、 $V_{GH\_SH} = V_{BST\_SH} - 1V$ から $V_{GL\_SL} = 1V$ 、 $V_{GVDD} = V_{BST} - V_{SH} > 8V$ 、 $V_{SH} = 0V \sim 90V$ 、GH と GL は無負荷         | -10 | $\pm 4$ | 10 ns   |

| $t_{DEAD}$             | ゲート駆動デッドタイム                                           | $R_{DT} = 470 \Omega$ 2 ピン PWM モード。                                                                                                                                        | 20  |         | ns      |

| $t_{DEAD}$             | ゲート駆動デッドタイム                                           | $R_{DT} = 1.3K\Omega$ 2 ピン PWM モード、                                                                                                                                        | 97  | 100     | 120 ns  |

| $t_{DEAD}$             | ゲート駆動デッドタイム                                           | $R_{DT} = 3.3K\Omega$ 2 ピン PWM モード、                                                                                                                                        | 316 | 370     | 422 ns  |

| $t_{DEAD\_CFG}$        | ゲート駆動デッドタイム設定範囲                                       | $T_{dead}$ リニア設定 $R_{DT} = 10K\Omega \sim 1M\Omega$ 、1 ピン PWM モード                                                                                                          | 20  |         | 900 ns  |

| $t_{DEAD}$             | ゲート駆動デッドタイム                                           | $R_{DT} = 990K\Omega$ 1 ピン PWM モード、 $T_J = -40 \sim 150^\circ C$                                                                                                           | 700 | 900     | 1250 ns |

| $t_{MINDEAD\_VGS\_HS}$ | VGS 監視モードの最小ゲート駆動デッドタイム(最短利用可能)、HS 立ち下がりから LS 立ち上がりまで | VGS モニタデッドタイム挿入モード。<br>$t_{DEAD\_CFG} < 130ns$ 、 $V_{GVDD} > 8V$ 、 $V_{BST\_SH} > 8V$ 、 $0V < V_{SH} \leq 90V$                                                             |     | 215     | ns      |

| $t_{MINDEAD\_VGS\_LS}$ | VGS 監視モードの最小ゲート駆動デッドタイム(最短利用可能)、LS 立ち下がりから HS 立ち上がりまで | VGS モニタデッドタイム挿入、 $t_{DEAD\_CFG} < 130ns$ 、 $V_{GVDD} > 8V$ 、 $V_{BST\_SH} > 8V$ 、 $0V < V_{SH} \leq 90V$                                                                   |     | 225     | ns      |

| $t_{DRVN\_SD}$         | シャットダウン中のゲートドライバのプルダウンタイミング                           |                                                                                                                                                                            | 20  |         | $\mu s$ |

#### 電流シャントアンプ (SN、SO、SP、CSAREF)

|                       |                    |                                                 |     |                    |

|-----------------------|--------------------|-------------------------------------------------|-----|--------------------|

| $A_{CSA}$             | 検出アンプのゲイン          | CSAGAIN = GND に接続 (LEVEL0)                      | 5   | V/V                |

|                       |                    | CSAGAIN = の $10k\Omega$ (標準値)を GND に接続 (LEVEL1) | 10  | V/V                |

|                       |                    | CSAGAIN = の $30k\Omega$ (標準値)を GND に接続 (LEVEL2) | 20  | V/V                |

|                       |                    | CSAGAIN = オープン、(LEVEL3)                         | 40  | V/V                |

| $A_{CSA\_ERR\_DRAFT}$ | 検出アンプのゲイン誤差の温度ドリフト | $T_J = -40^\circ C \sim 150^\circ C$            | -70 | 70 ppm/ $^\circ C$ |

$V_{GVDD} = 12V$   $V_{VDRAIN} = 48V$ ,  $T_J = 25^\circ C$  (特に記述のない限り)

| パラメータ            |                        | テスト条件                                                                        | 最小値    | 標準値                 | 最大値              | 単位  |

|------------------|------------------------|------------------------------------------------------------------------------|--------|---------------------|------------------|-----|

| $t_{SET}$        | $\pm 1\%$ までのセトリング タイム | $V_{STEP} = 1.6V$ , $A_{CSA} = 5V/V$ , $C_{SO} = 500pF$                      | 0.6    |                     | $\mu s$          |     |

|                  |                        | $V_{STEP} = 1.6V$ , $A_{CSA} = 40V/V$ , $C_{SO} = 500pF$                     | 0.8    |                     | $\mu s$          |     |

| BW               | 帯域幅                    | $A_{CSA} = 5V/V$ , $C_{LOAD} = 60pF$ 、小信号 -3dB                               | 3      | 5                   | 7                | MHz |

| $V_{SWING}$      | 出力電圧範囲                 | $V_{CSAREF} = 3\sim 5.5V$                                                    | 0.25   | $V_{CSAREF} - 0.25$ | V                |     |

| $V_{COM}$        | 同相入力範囲                 |                                                                              | -0.225 | 0.225               | V                |     |

| $V_{OFF}$        | 入力オフセット電圧              | $V_{SP} = V_{SN} = GND$ , $T_J = 25^\circ C$ , ゲイン $A_{CSA} = 10, 20, 40V/V$ | -1.94  | 1.94                | mV               |     |

| $V_{OFF}$        | 入力オフセット電圧              | $V_{SP} = V_{SN} = GND$ , $T_J = 25^\circ C$ , ゲイン $A_{CSA} = 5V/V$          | -3.34  | 3.34                | mV               |     |

| $V_{OFF\_DRIFT}$ | 入力オフセット電圧ドリフト          | $V_{SP} = V_{SN} = GND$                                                      | 8      |                     | $\mu V/^\circ C$ |     |

| $V_{BIAS}$       | 出力電圧バイアス比              | $V_{SP} = V_{SN} = GND$                                                      | 0.5    |                     |                  |     |

| $I_{BIAS}$       | 入力バイアス電流               | $V_{SP} = V_{SN} = GND$ , $V_{CSAREF} = 3V\sim 5.5V$                         | 100    |                     | $\mu A$          |     |

| $I_{BIAS\_OFF}$  | 入力バイアス電流オフセット          | $I_{SP} - I_{SN}$                                                            | -1     | 1                   | $\mu A$          |     |

| CMRR             | 同相除去比                  | DC                                                                           | 80     |                     | dB               |     |

|                  |                        | 20 kHz                                                                       | 60     |                     | dB               |     |

| $I_{CSA\_SUP}$   | CSA の消費電流              | $CSAREF$ , $V_{CSAREF} = 3V\sim 5.5V$                                        | 1.5    |                     | mA               |     |

| $T_{CMREC}$      | 同相復帰時間                 |                                                                              | 2      |                     | us               |     |

**保護回路**

|                    |                     |                                                              |         |         |

|--------------------|---------------------|--------------------------------------------------------------|---------|---------|

| $V_{GVDD\_UV}$     | GVDD 低電圧スレッショルド     | $V_{GVDD}$ 立ち上がり                                             | 7.4     | V       |

|                    |                     | $V_{GVDD}$ 立ち下がり                                             | 6.7     | V       |

| $V_{GVDD\_UV}$     | GVDD 立ち上がり、DRV8162L | $V_{GVDD}$ 立ち上がり、DRV8162L                                    | 4.8     | V       |

|                    |                     | $V_{GVDD}$ 立ち下がり、DRV8162L                                    | 4.7     | V       |

| $t_{GVDD\_UV\_DG}$ | GVDD 低電圧グリッチ除去時間    |                                                              | 5 10 15 | $\mu s$ |

| $V_{BST\_UV}$      | ブートストラップ低電圧スレッショルド  | $V_{BST} - V_{SH}$ , $V_{BST}$ 立ち上がり, $GVDD = 12V$           | 7.43    | V       |

|                    | ブートストラップ低電圧スレッショルド  | $V_{BST} - V_{SH}$ , $V_{BST}$ 立ち下がり, $GVDD = 12V$           | 7.25    | V       |

|                    | ブートストラップ低電圧スレッショルド  | $V_{BST} - V_{SH}$ , $V_{BST}$ 立ち上がり, $GVDD = 5V$ , DRV8162L | 4.08    | V       |

|                    | ブートストラップ低電圧スレッショルド  | $V_{BST} - V_{SH}$ , $V_{BST}$ 立ち下がり, $GVDD = 5V$ , DRV8162L | 3.94    | V       |

、 $V_{GVDD} = 12V$   $V_{VDRAIN} = 48V$ 、 $T_J = 25^\circ C$  (特に記述のない限り)

| パラメータ            | テスト条件                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 最小値            | 標準値  | 最大値   | 単位      |            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|-------|---------|------------|

| $V_{DS\_LVL0-0}$ | $R_{VDSLVL} = : 最大 0.1K\Omega (LEVEL0)$<br>$R_{VDSLVL} = 2K\Omega (LEVEL1)、VDSLVL ピンで 1 つのパルスが検出されました$<br>$R_{VDSLVL} = 2K\Omega (標準値、LEVEL1)、DC$<br>$R_{VDSLVL} = 5.6K\Omega (標準値) (LEVEL2)、VDSLVL ピンで 1 つのパルスが検出されました$<br>$R_{VDSLVL} = 5.6K\Omega (標準値) (LEVEL2)$<br>$R_{VDSLVL} = 12K\Omega (標準値) (LEVEL3)、VDSLVL ピンで 1 つのパルスが検出されました$<br>$R_{VDSLVL} = 12K\Omega (標準値) (LEVEL3)$<br>$R_{VDSLVL} = 26K\Omega (標準値) (LEVEL4)、VDSLVL ピンで 1 つのパルスが検出されました$<br>$R_{VDSLVL} = 26K\Omega (標準値) (LEVEL4)$<br>$R_{VDSLVL} = 62K\Omega (標準値) (LEVEL5)、VDSLVL ピンで 1 つのパルスが検出されました$<br>$R_{VDSLVL} = 62K\Omega (標準値) (LEVEL5)$<br>$R_{VDSLVL} = 130K\Omega (標準値) (LEVEL6)、VDSLVL ピンで 1 つのパルスが検出されました$<br>$R_{VDSLVL} = 130K\Omega (標準値) (LEVEL6)$ | 0.087          | 0.1  | 0.116 | V       |            |

| $V_{DS\_LVL1-1}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.136          | 0.15 | 0.166 |         |            |

| $V_{DS\_LVL1-0}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.187          | 0.2  | 0.217 |         |            |

| $V_{DS\_LVL2-1}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.28           | 0.3  | 0.319 |         |            |

| $V_{DS\_LVL2-0}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.38           | 0.4  | 0.42  |         |            |

| $V_{DS\_LVL3-1}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.482          | 0.5  | 0.53  |         |            |

| $V_{DS\_LVL3-0}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.575          | 0.6  | 0.623 |         |            |

| $V_{DS\_LVL4-1}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.67           | 0.7  | 0.73  |         |            |

| $V_{DS\_LVL4-0}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.765          | 0.8  | 0.83  |         |            |

| $V_{DS\_LVL5-1}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.87           | 0.9  | 0.934 |         |            |

| $V_{DS\_LVL5-0}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0.96           | 1.0  | 1.04  |         |            |

| $V_{DS\_LVL6-1}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.46           | 1.5  | 1.548 |         |            |

| $V_{DS\_LVL6-0}$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.945          | 2.0  | 2.05  |         |            |

| $t_{DS\_DG}$     | $V_{DS}$ 保護グリッチ除去時間                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                | 3    |       | $\mu s$ |            |

| $t_{DS\_BLK}$    | $V_{DS}$ 過電流保護ブランкиング時間                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                | 1    |       | $\mu s$ |            |

| $t_{CLRFLT}$     | $V_{DS}$ 過電流保護故障クリア時間                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | INH= INL = Low | 250  |       | $\mu s$ |            |

| $t_{VDSLVLFIL}$  | VDSLVL 1 パルスフィルタ時間                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                | 4    |       | $\mu s$ |            |

| $V_{IHVDSLVL}$   | VDSLVL 1 パルス ハイレベル検出電圧                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                | 1    |       | V       |            |

| $T_{OTSD}$       | サーマル シャットダウン温度                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $T_J$ 立ち上がり、   | 158  | 170   | 187     | $^\circ C$ |

| $T_{HYS}$        | サーマル シャットダウンヒステリシス                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                | 7    | 8.5   | 10      | $^\circ C$ |

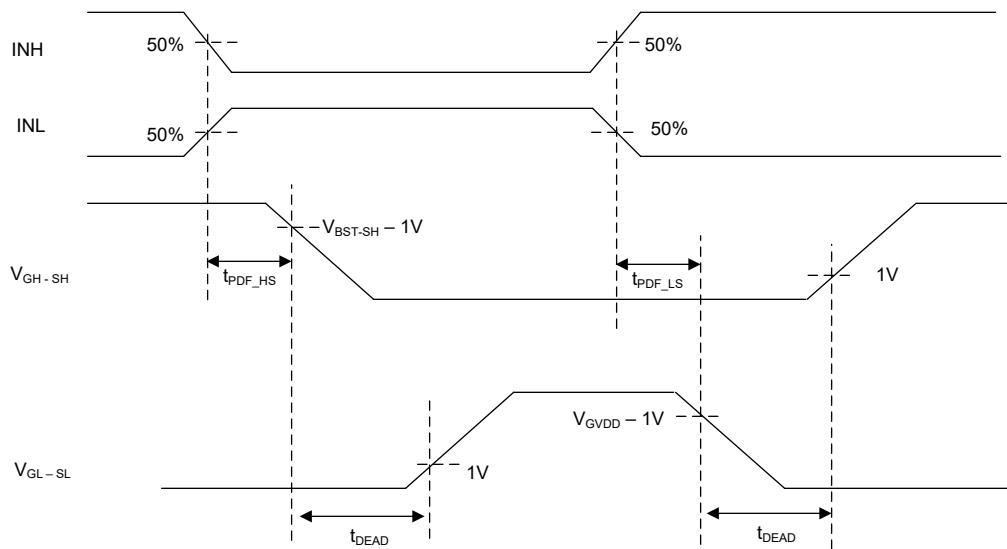

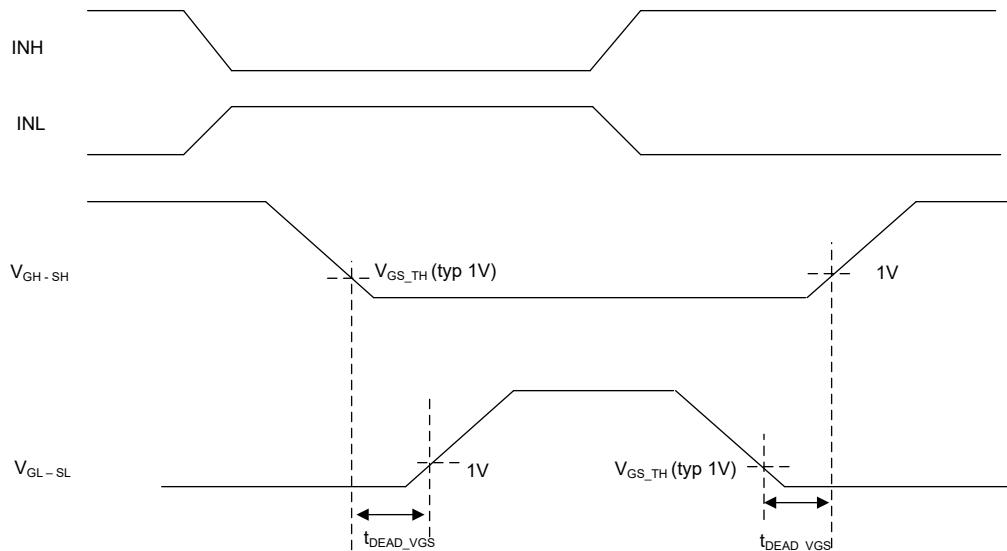

## 6.6 タイミング図

図 6-1. ゲートドライバの伝搬遅延タイミング図

図 6-2. ゲートドライバのデッドタイミングの挿入 (INH および INL モニタモード)

図 6-3. ゲートドライバのデッドタイミング挿入 (VGS モニタモード)

## 7 詳細説明

### 7.1 概要

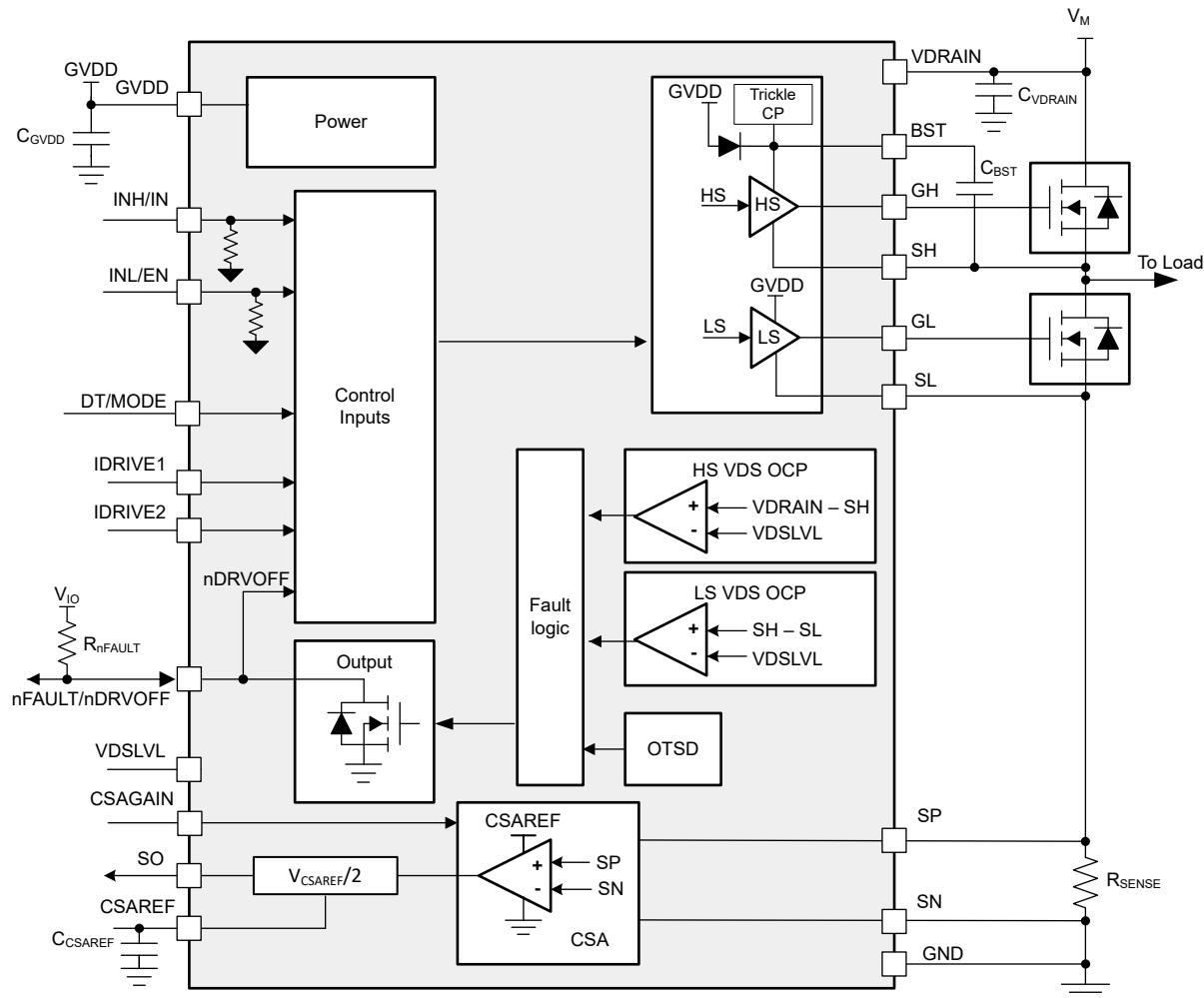

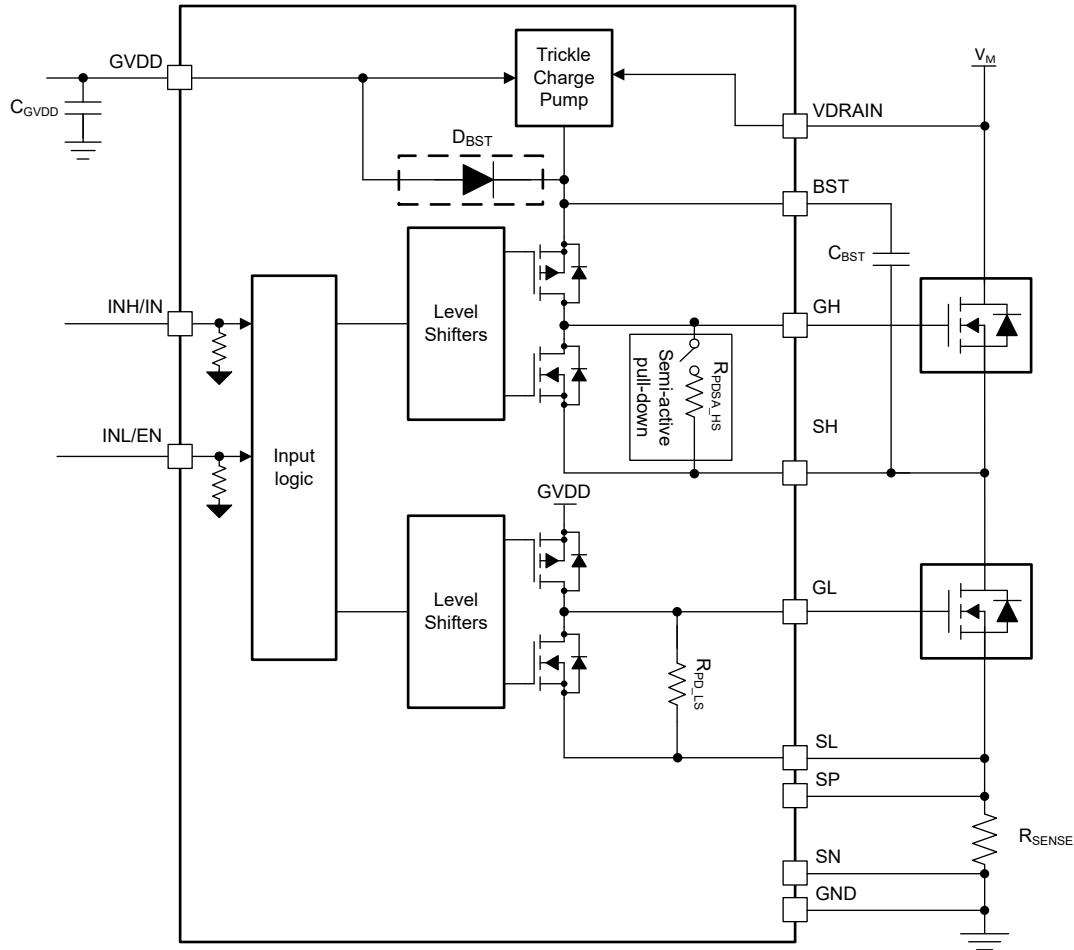

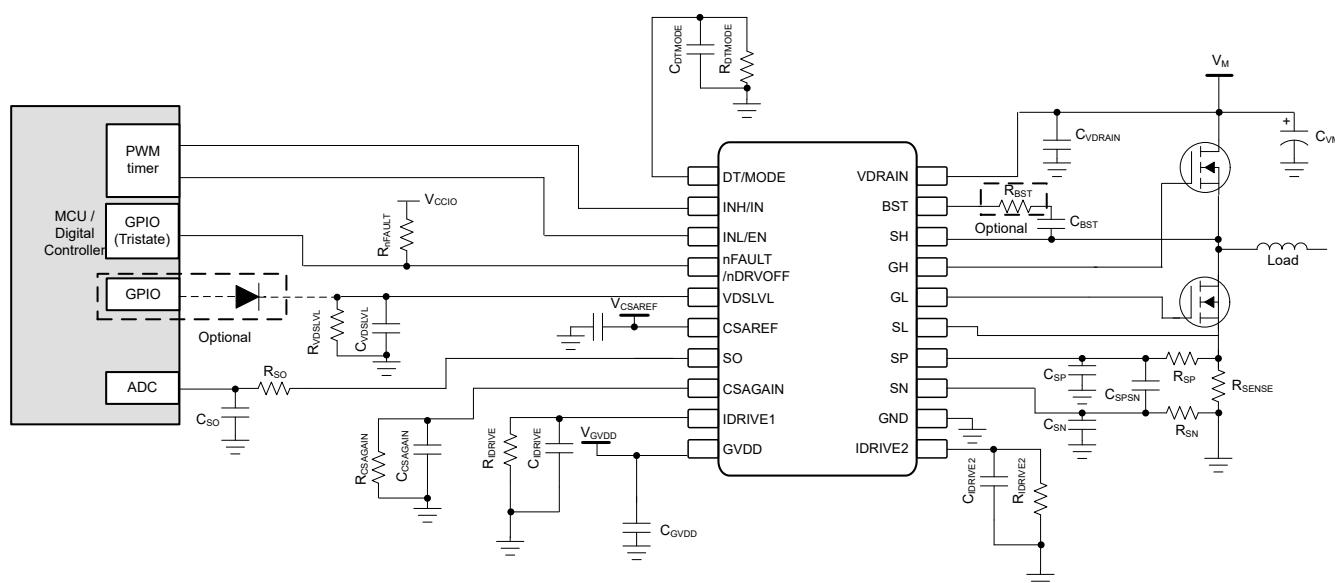

DRV816x デバイスは、ブラシレス DC (BLDC) モーター、ブラシ付き DC モーター、ステッパモーター、スイッチリラクタンスモーター、ソレノイドなど、さまざまな電気機械的負荷に対する統合型 100V ゲートドライバです。これらのデバイスでは、ハーフブリッジゲートドライバとトリクルチャージポンプ、ブートストラップダイオード、FET VDS 監視機能を統合することで、システムコンポーネントの数、コスト、複雑性を削減します。FET VDS モニタは、電源、接地、またはモータ端子間の短絡から外部 FET を保護します。DRV8161 は、コントローラの ADC への電流フィードバック用に、低側双方向電流センサアンプを内蔵しています。ハーフブリッジアーキテクチャにより、ゲートドライバを電源段 FET の近くに配置することができ、信号経路を簡素化し、放射 EMI を低減し、PCB の面積を全体的に削減することができます。

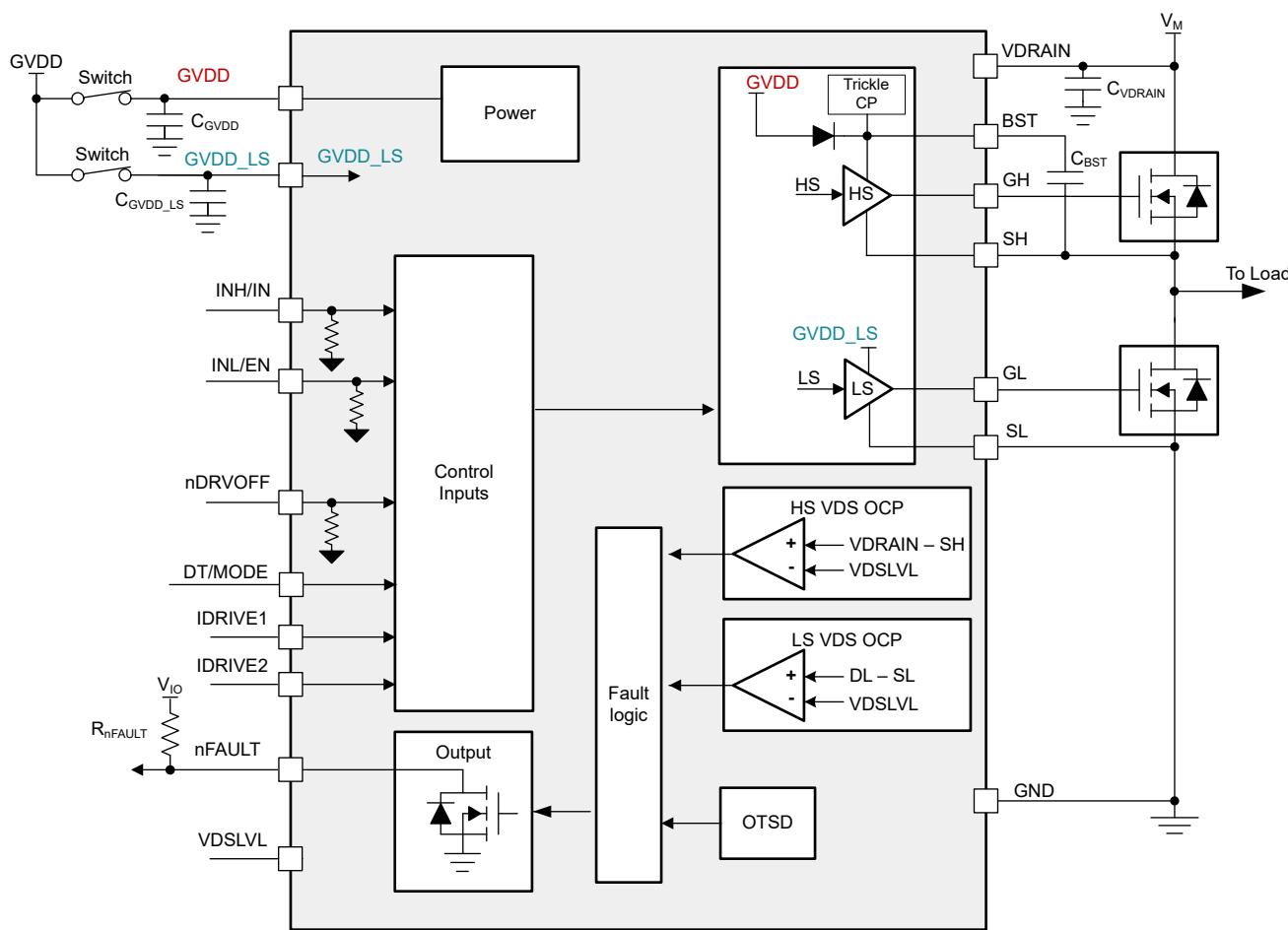

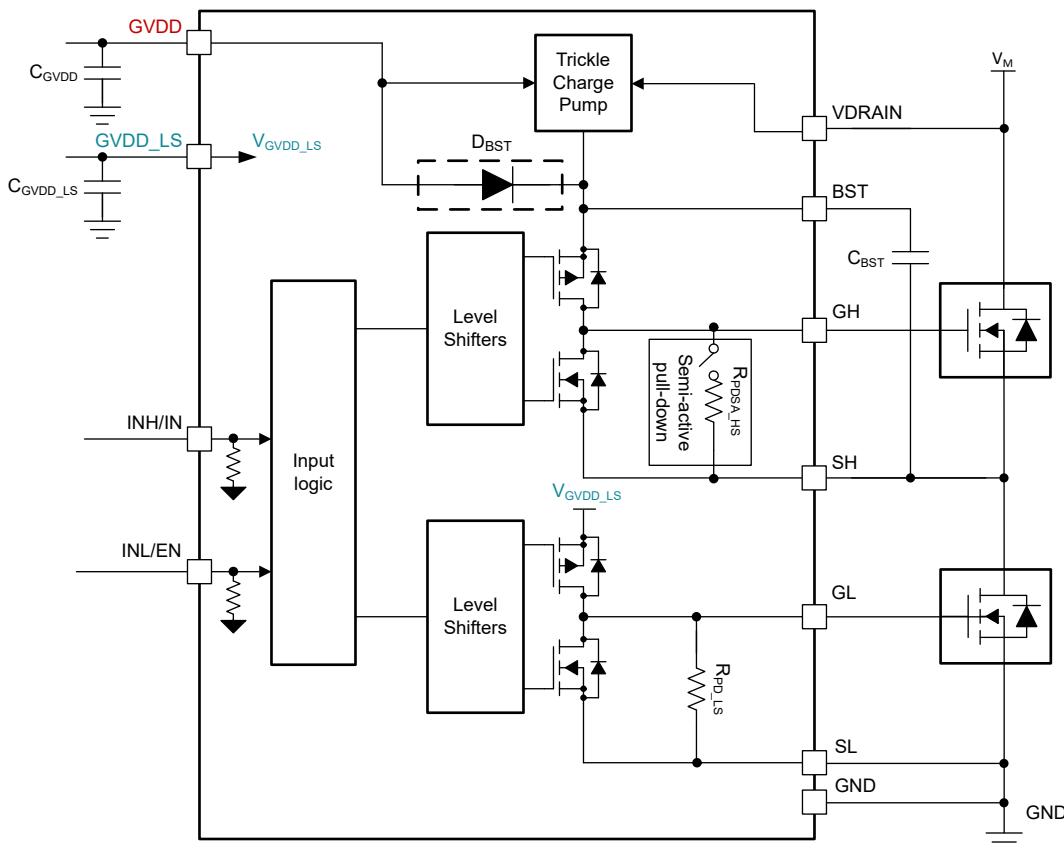

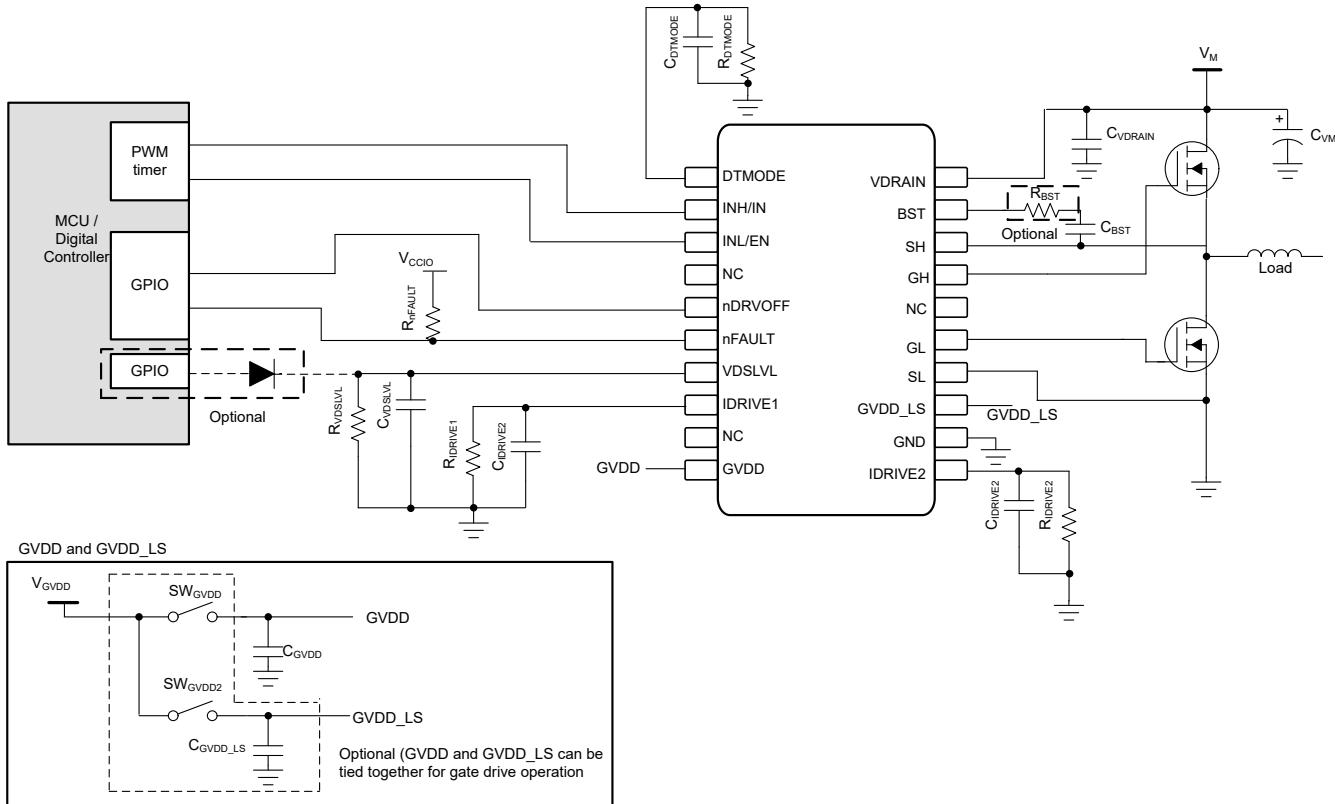

本ゲートドライバは外付け N チャネル ハイサイド / ローサイド パワー MOSFET をサポートしており、最大 1A (ソース) / 2A (シンク) のピーク電流を駆動することができます。内蔵ブートストラップダイオード、外付けブートストラップコンデンサ、内蔵トリクルチャージポンプにより、GVDD ピンからハイサイドゲートドライブ電源電圧が生成されます。GVDD ピンはローサイドゲートドライブ電源電圧を直接供給します。DRV8162 および DRV8162L のデバイスバリエーションは、個別の GVDD および GVDD\_LS ピンを装備してセーフトルクオフ (STO) のシステム設計をサポートします。

スマートゲートドライブアーキテクチャは出力ゲート駆動電流強度を動的に調整する機能を備えているため、ゲートドライバはパワー MOSFET の VDS スイッチング速度を制御できます。このため、外付けゲート駆動抵抗およびダイオードが必要になり、BOM の部品点数、コスト、PCB 面積の低減が可能です。このアーキテクチャでは、ゲート駆動の短絡に対する保護、ハーフブリッジのデッドタイムの制御、外部パワー MOSFET の dV/dt 寄生ターンオンに対する保護のために、内部ステートマシンも使っています。

高いレベルでデバイスが統合されていることに加え、DRV816x のデバイスには、広範な保護機能も組み込まれています。これらの機能には、電源電圧低下ロックアウト (UVLO)、VDS 過電流モニタリング (OCP)、過熱シャットダウン (OTSD) が含まれます。nFAULT ピンは、保護機能によって検出されたフォルトイベントを通知します。

## 7.2 機能ブロック図

図 7-1. DRV8161 のブロック図

図 7-2. DRV8162 および DRV8162L のブロック図

## 7.3 機能説明

### 7.3.1 ゲート ドライバ

DRV816x ファミリのデバイスには、ハーフブリッジ構成の N チャネルパワー MOSFET を駆動できるハイサイドとローサイドの FET ゲートドライバが統合されています。ブートストラップゲート駆動アーキテクチャは、PWM スイッチング中にハイサイドゲートドライバ電圧を生成します。GVDD ピンはハイサイドとローサイドの両方のゲートドライバに電源を供給し、FET の  $V_{GS}$  電圧を設定します。

DRV816x、ハーフブリッジ電力ステージアーキテクチャをサポートしています。このデバイスは、通常の 2 ピン PWM、1 ピン PWM 制御インターフェイスに加え、シートスルー保護を無効にし、ハイサイドとローサイドの FET を個別に制御することで、独立した PWM モードを提供します。独立した FET 制御は、ソレノイドおよびスイッチトリラクタンスマーターの駆動に便利です。DRV8162 と DRV8162L には、ハイサイドとローサイドの FET ゲート駆動用に独立した電源ピン(GVDD と GVDD\_LS)があります。これによって、システムはゲート駆動電源ピンに外部パワースイッチを追加することで、セーフルクオフ(STO)機能に対応できます。

#### 7.3.1.1 PWM 制御モード

DRV816x ファミリのデバイスには、さまざまな整流方式や制御方式をサポートするために、3 種類の PWM 制御モードが用意されています。PWM 制御モードは、1 ピン PWM、2 ピン PWM、独立 PWM モードです。これらのモードは DT/MODE ピンによって構成されます。

電源投入時に DT/MODE ピンはラッチされるため、PWM 制御モードを変更するには、電源によってデバイスをリセットする必要があります。DT/MODE ピンを使用した PWM 制御モードの構成については、表 7-6 を参照してください。

#### 7.3.1.1.2 2 ピン PWM モード

2 ピン PWM モードでは、ハーフブリッジドライバは、lowhigh、または ハイインピーダンス(Hi-Z)の 3 つの出力状態をサポートします。表 7-1 に示すように、対応する INH および INL 信号で出力状態を制御します。

表 7-1. 2 ピン PWM モードの真理値表

| INL | INH | GL | GH | SH        |

|-----|-----|----|----|-----------|

| 0   | 0   | L  | L  | ハイインピーダンス |

| 0   | 1   | L  | H  | H         |

| 1   | 0   | H  | L  | L         |

| 1   | 1   | L  | L  | ハイインピーダンス |

### 7.3.1.1.2 1 ピン PWM モード

1 ピン PWM モードでは、IN ピンでハーフブリッジを制御し、Low または High の 2 つの出力状態がサポートされます。EN ピンは、ハーフブリッジを Hi-Z 状態にするために使用します。Hi-Z 状態にする必要がない場合は、INL/EN ピンをロジックハイに固定してください。[表 7-2](#) に示すように、対応する INH/IN および INL/EN 信号で出力状態を制御します。

**表 7-2. 1 ピン PWM モードの真理値表**

| INL/EN | INH/IN | GL | GH | SH        |

|--------|--------|----|----|-----------|

| 0      | X      | L  | L  | ハイインピーダンス |

| 1      | 0      | H  | L  | L         |

| 1      | 1      | L  | H  | H         |

### 7.3.1.1.3 独立 PWM モード

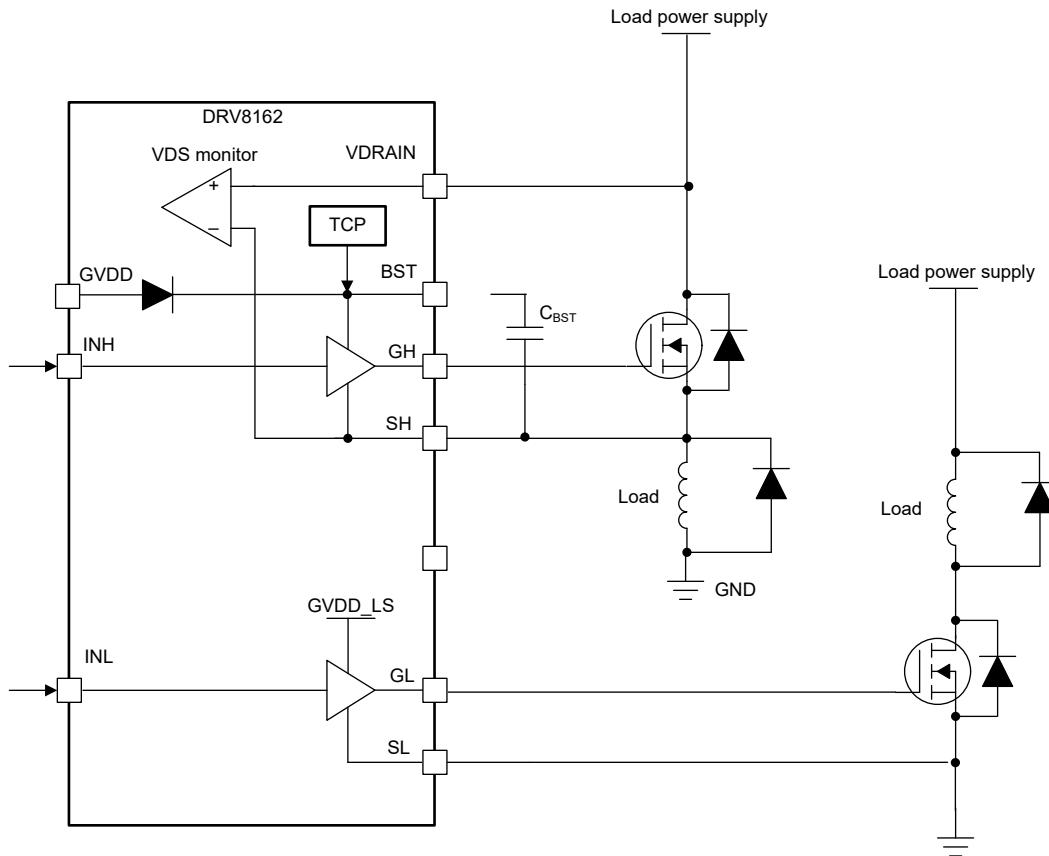

DRV816x は独立 PWM モードをサポートしており、INH および INL ピンはそれぞれ出力 GH および GL を制御します。この制御モードでは、デバイスは独立したハイサイド負荷とローサイド負荷を駆動できます。独立 PWM 駆動モードは、ソレノイド、スイッチドリラクタンスモータ(SRM)、単方向ブラシ付き DC モータ、ローサイドおよびハイサイドスイッチなど、さまざまなタイプの負荷に使用できます。このモードでは、特定のハーフブリッジゲートドライバでハイサイドとローサイド両方の MOSFET を同時にオンにすることで、このデバイスをハイサイドまたはローサイドドライバとして使用できます。モードでは、貫通電流保護とデッドタイムはバイパスされます。

**表 7-3. 独立 PWM モードの真理値表**

| INL | INH | GL | GH |

|-----|-----|----|----|

| 0   | 0   | L  | L  |

| 0   | 1   | L  | H  |

| 1   | 0   | H  | L  |

| 1   | 1   | H  | H  |

[図 7-3](#) は、このデバイスを使用して誘導負荷を接続する方法を示しており、ハイサイドとローサイドの MOSFET を同時にオンにして負荷を駆動し、貫通電流を発生させないことを可能にします。電流再循環用の外付けダイオードを推奨します。この構成は、ソレノイドまたはアプリケーションの設計に役立ちます。トクリルチャージポンプは、ローサイド PWM 動作に関係なく常時有効化されます。

**注**

独立 PWM モードが構成されている場合、DRV816x のローサイド VDS 監視は利用できません。DRV8161 の場合、MCU によって CSA 出力を監視して過電流状態を検出できます。

図 7-3. ハイサイドとローサイド間の単一負荷向けの独立 PWM モード

図 7-4 は、1 つのハーフブリッジでハイサイド負荷とローサイド負荷を同時に接続し、負荷を個別に駆動する方法を示しています。

図 7-4. ハイサイドとローサイドの独立負荷に対応する独立 PWM モード

### 7.3.1.2 ゲート ドライバーアーキテクチャ

本ドライバ デバイスは、ハイサイドとローサイド両方のドライバに対して、相補型のプッシュプルトポロジが使用されています。このトポロジにより、外部 MOSFET ゲートのプルアップとプルダウンが両方とも強化できます。ローサイド ゲートドライバには、GVDD レギュレータ電源から直接電力が供給されます。ハイサイド ゲートドライバ用には、ブートストラップ ダイオードとブートストラップ コンデンサを使ってフローティング ハイサイド ゲート電源電圧を生成します。ブートストラップ ダイオードは内蔵されており、BST ピンに外付けのブートストラップ コンデンサを使います。

電源が切り離された際に外部 MOSFET がターンオンするのを防止するため、ハイサイド ゲートドライバはセミアクティブ プルダウンを備えており、ローサイド ゲートはパッシブ プルダウンを備えています。

図 7-5. DRV8161 ゲート ドライバ ブロック図

図 7-6. DRV8162 および DRV8162L ゲートドライバのブロック図

#### 7.3.1.2.1 ティックルチャージポンプ (TCP)

ドライバと外部コンポーネントのリーク電流による電圧降下を防止するため、トリクル チャージ ポンプ (TCP) が BST ノードに接続されています。チャージポンプは、VDRAIN ピンを基準にして V<sub>TCP</sub> 電圧を生成します。独立 PWM モードでは、チャージポンプは常時アクティブです。2 ピン PWM および 1 ピン PWM モードで、INL が 250us (標準値) にわたって Low のままである場合、チャージポンプがアクティブになります。

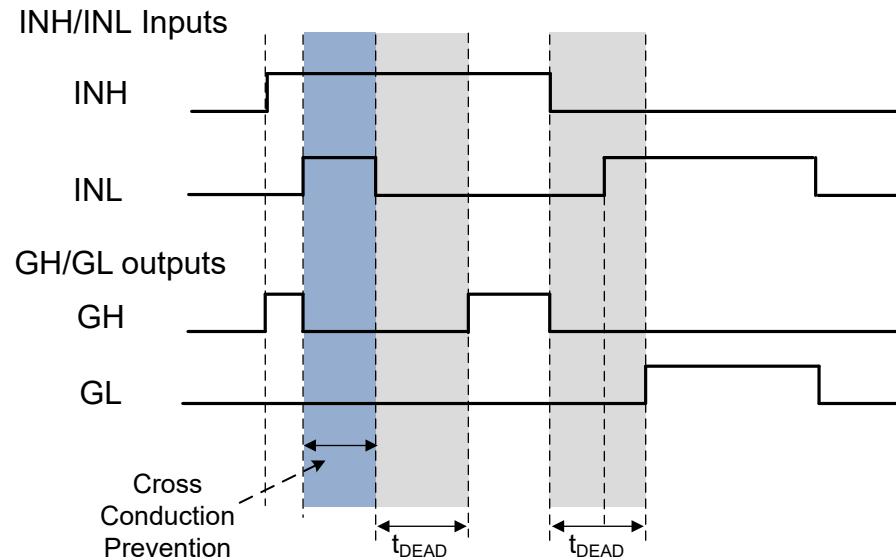

#### 7.3.1.2.2 デッドタイムとクロス導通防止 (貫通電流保護)

DRV816x はデッドタイム挿入機能を備えており、各ハーフブリッジの外部 MOSFET の両方が同時にオンに切り替わるのを防止します。デッドタイムは、DT/MODE とグランドの間に抵抗を接続することで、20ns~900ns の範囲で有効化および調整できます。セクション 7.3.2.6 を参照してください。

DRV816x では、デバイスが 2 ピン PWM モードに構成されている場合、ハイサイド入力とローサイド入力は独立して動作しますが、同じハーフブリッジのハイサイドとローサイドが同時にオンになっている場合、クロス導通を防止するための例外があります。このデバイスは、ハイサイドとローサイドの入力が同時にロジックハイになった場合に貫通電流を防止するために、ハイサイドとローサイドの出力が OFF になります。

図 7-7. クロス導通防止とデッドタイム挿入（2 ピン PWM、デッドタイム挿入有効）

### 7.3.2 ピン配置図

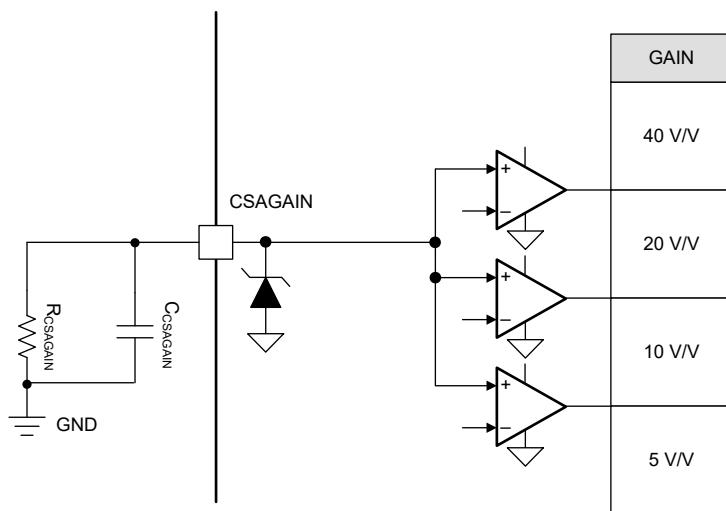

#### 7.3.2.1 4 レベル入力ピン (CSAGAIN)

図 7-8 は、ハードウェアインターフェース構成用の 4 レベル入力ピン CSAGAIN の構造を示しています。入力は外付け抵抗で設定できます。 $C_{CSAGAIN}$  は、GND ノイズの影響を低減するためのオプションです。CSA ゲイン情報は、デバイスの電源投入時にラッチされず、デバイス動作中に更新できます。

図 7-8. 4 レベル入力ピンの構造

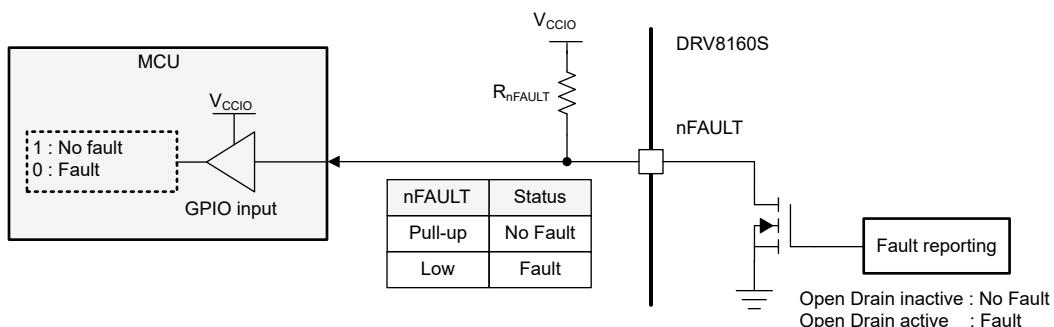

#### 7.3.2.2 デジタル出力 nFAULT (DRV8162、DRV8162L)

図 7-9 は、オープンドレイン出力ピンである nFAULT の構造を示しています。オープンドレイン出力を正しく機能させるためには、外部プルアップ抵抗が必要です。nFAULT を含むデバイスのアクションについては、を参照して表 7-7 ください。

図 7-9. nFAULT オープンドレイン出力バッファ

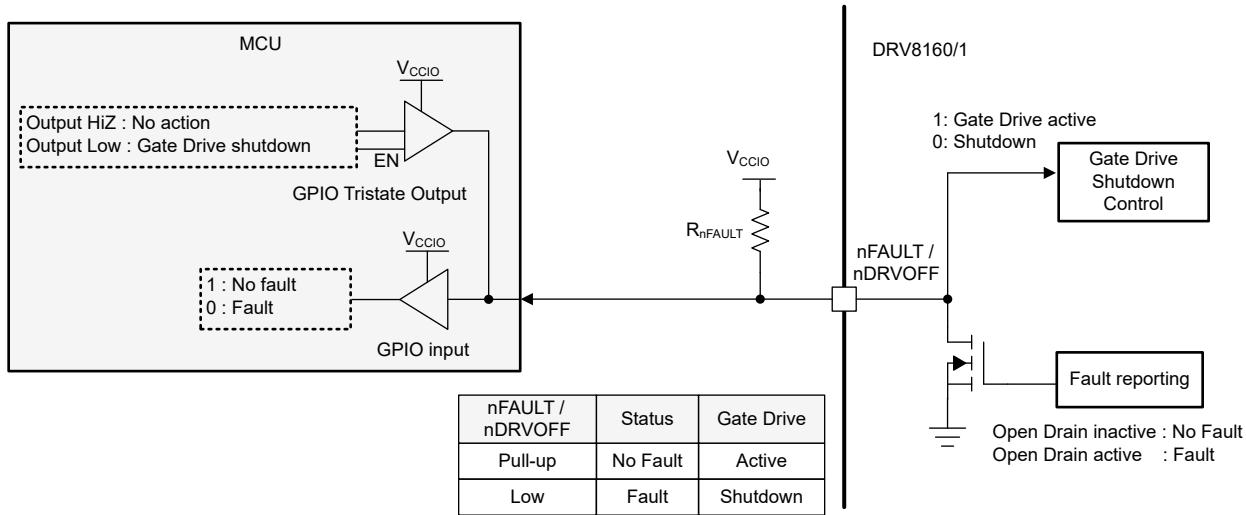

#### 7.3.2.3 デジタル入力/出力 nFAULT/nDRVOFF (DRV8161)

図 7-10 は、オープンドレイン出力ピンの構造を示しています。DRV8161 デバイス バリアントでは、1 つのデバイスピン nFAULT/nDRVOFF を共有することで、2 つの機能 nFAULT と nDRVOFF が実現されます。オープンドレイン出力を正しく機能させるためには、外部プルアップ抵抗が必要です。故障状態が検出されると、デバイスはオープンドレインバッファを起動し、nFAULT/nDRVOFF ピンが low に駆動されます。nFAULT/nDRVOFF ピンは、ゲートドライブシャットダウンロジックに内部接続されており、nFAULT/nDRVOFF ピンがローレベルの場合、ゲートドライブ出力はシャットダウン(プルダウン)されます。nFAULT を含むデバイスのアクションについては、を参照して表 7-7 ください。

図 7-10. nFAULT/nDRVOFF オープンドレイン出力および入力バッファ

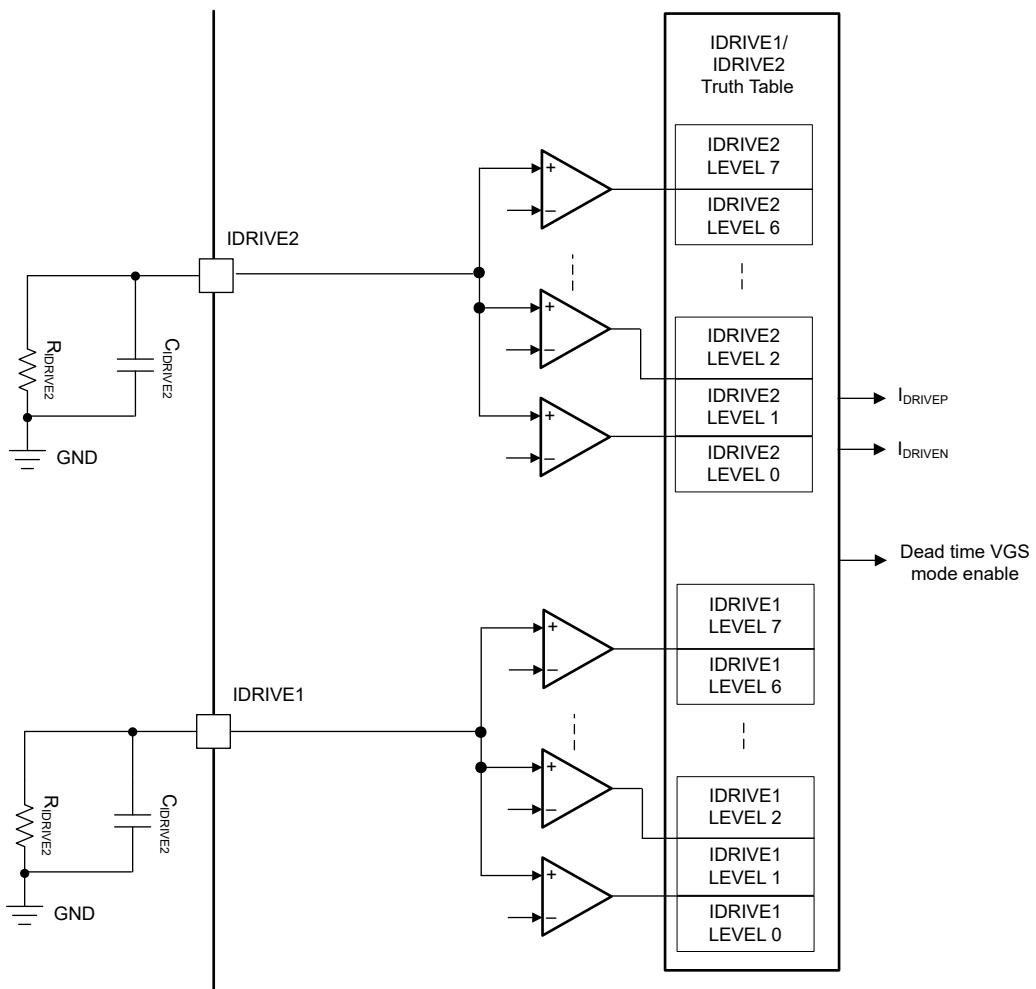

### 7.3.2.4 マルチレベル入力 (IDRIVE1 および IDRIVE2)

DRV816x にはゲート駆動電流を設定するための IDRIVE1 および IDRIVE2 デバイスピンがあります。各ピンは、デバイスのピンと GND の間に外付け抵抗を接続し LEVEL0～LEVEL7 の 8 つのレベルに設定できます。ゲート駆動電流  $I_{DRIVEN}$  と  $I_{DRIVEP}$  は表 7-4 で定義できます。表の(g)は、VGS モニタのデッドタイム挿入が無効であることを示しています。IDRIVE1 および IDRIVE2 の情報は、デバイスの電源オン時にラッチされます。

図 7-11. IDRIVE1 および IDRIVE2 のマルチレベルデジタル入力

表 7-4. ゲート駆動電流構成の IDRIVE1/IDRIVE2 真理値表

|                                |                               | IDRIVE2 入力ピン ( $R_{IDRIVE2}$ ) |                    |                     |                    |                           |                    |                          |                    |                          |                    |                          |                    |                           |                    |                    |                    |

|--------------------------------|-------------------------------|--------------------------------|--------------------|---------------------|--------------------|---------------------------|--------------------|--------------------------|--------------------|--------------------------|--------------------|--------------------------|--------------------|---------------------------|--------------------|--------------------|--------------------|

|                                |                               | LEVEL0<br>(GND への短<br>絡)       |                    | LEVEL1<br>(2KΩ、代表値) |                    | LEVEL2<br>(5.6KΩ、代表<br>値) |                    | LEVEL3<br>(12KΩ、代表<br>値) |                    | LEVEL4<br>(27KΩ、代表<br>値) |                    | LEVEL5<br>(62KΩ、代表<br>値) |                    | LEVEL6<br>(130KΩ、代表<br>値) |                    | LEVEL7 (オ<br>ープン)  |                    |

|                                |                               | ソース:シンク=<br>1:2                |                    | ソース:シンク=<br>1:2     |                    | ソース:シンク=<br>1:1.5         |                    | ソース:シンク=<br>1:1.5        |                    | ソース:シンク=<br>1:1          |                    | ソース:シンク=<br>1:3          |                    | VGS デッドタイ<br>ム挿入が有効       |                    | IDRIVE2 オー<br>プン   |                    |

|                                |                               | $I_{DRIVE_P}$ [mA]             | $I_{DRIVE_N}$ [mA] | $I_{DRIVE_P}$ [mA]  | $I_{DRIVE_N}$ [mA] | $I_{DRIVE_P}$ [mA]        | $I_{DRIVE_N}$ [mA] | $I_{DRIVE_P}$ [mA]       | $I_{DRIVE_N}$ [mA] | $I_{DRIVE_P}$ [mA]       | $I_{DRIVE_N}$ [mA] | $I_{DRIVE_P}$ [mA]       | $I_{DRIVE_N}$ [mA] | $I_{DRIVE_P}$ [mA]        | $I_{DRIVE_N}$ [mA] | $I_{DRIVE_P}$ [mA] | $I_{DRIVE_N}$ [mA] |

| IDRIVE1 入力ピン ( $R_{IDRIVE1}$ ) | LEVEL7 (オ<br>ープ<br>ン)         | 256                            | 512                | 16                  | 32                 | 256                       | 384                | 16                       | 32                 | 128                      | 128                | 64                       | 192                | 32(G)                     | 64(G)              | 16(G)              | 32(G)              |

|                                | LEVEL6<br>(130K<br>Ω、代<br>表値) | 288                            | 576                | 32                  | 64                 | 288                       | 448                | 32                       | 32                 | 192                      | 192                | 128                      | 384                | 96(G)                     | 192(G)             | 64(G)              | 128(G)             |

|                                | LEVEL5<br>(62K<br>Ω、代<br>表値)  | 320                            | 640                | 64                  | 128                | 320                       | 448                | 64                       | 64                 | 256                      | 256                | 192                      | 576                | 128(G)                    | 256(G)             | 128                | 256                |

|                                | LEVEL4<br>(27K<br>Ω、代<br>表値)  | 384                            | 768                | 96                  | 192                | 384                       | 576                | 96                       | 128                | 320                      | 320                | 256                      | 768                | 160(G)                    | 320(G)             | 192                | 384                |

|                                | LEVEL3<br>(12K<br>Ω、代<br>表値)  | 448                            | 896                | 128                 | 256                | 448                       | 640                | 128                      | 192                | 384                      | 384                | 288                      | 896                | 192(G)                    | 384(G)             | 256                | 512                |

|                                | LEVEL2<br>(5.6K<br>Ω、代<br>表値) | 512                            | 1024               | 160                 | 320                | 512                       | 768                | 160                      | 256                | 448                      | 448                | 384                      | 1024               | 224(G)                    | 448(G)             | 320                | 640                |

|                                | LEVEL1<br>(2KΩ、<br>代表<br>値)   | 768                            | 1536               | 192                 | 384                | 768                       | 1024               | 192                      | 256                | 512                      | 512                | 512                      | 1536               | 512(G)                    | 1024(G)            | 512                | 1024               |

|                                | LEVEL0<br>(GND<br>への短<br>絡)   | 1024                           | 2048               | 224                 | 448                | 1024                      | 1536               | 224                      | 384                | 1024                     | 1024               | 768                      | 2048               | 1024(G)                   | 2048(G)            | 1024               | 2048               |

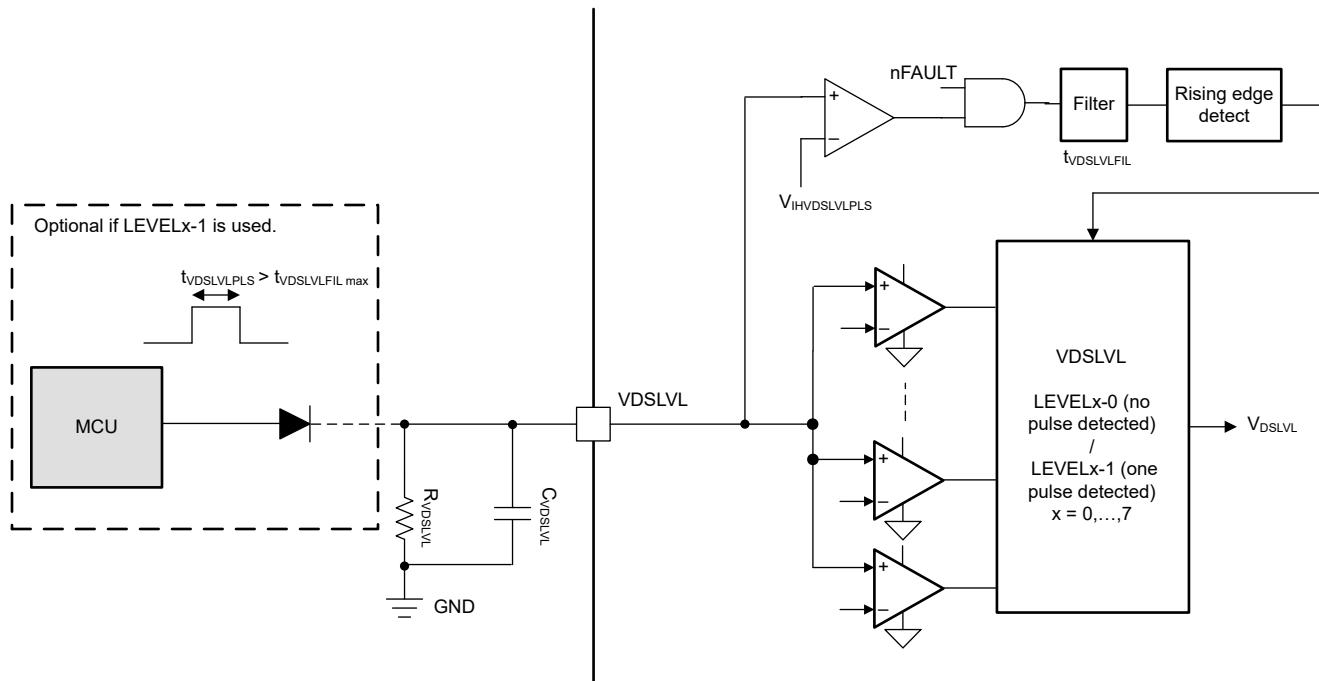

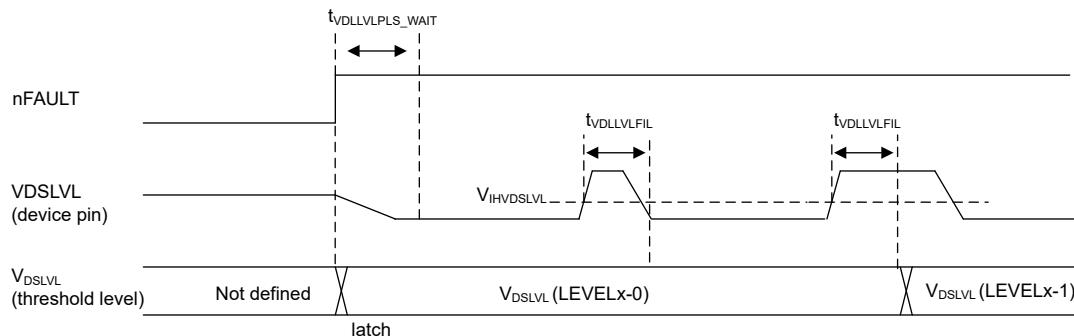

### 7.3.2.5 マルチレベルデジタル入力 (VDSLVL)

DRV816x の VDS 監視スレッショルドレベルは、VDSLVL ピンを使用して構成できます。ピンは、VDSLVL と GND の間に外部抵抗を接続することで LEVEL0 から LEVEL7 までの 8 レベルを設定できます。7 つのスレッショルドレベルは、表 7-5 によって決定されます。図 7-13 に示すように、VDSLVL ピンにデジタルパルスを 1 つ印加すると、追加の 6 スレッショルドレベルが利用可能になります。VDSLVL ピンがオープンの場合、VDS 監視機能は無効化されます。VDS 監視スレッショルドの情報は、デバイスの電源オン時にラッチされます。

図 7-12. VDSLVL 入力パルスのタイミング図

図 7-13. VDSLVL のマルチレベルデジタル入力

表 7-5. VDS スレッショルドレベル選択表

| VDSLVL 入力ピン( $R_{VDSLVL}$ ) | VDS 監視スレッショルド      |                       |

|-----------------------------|--------------------|-----------------------|

|                             | LEVELx-0 (パルス検出なし) | LEVELx-1 (1 つのパルスを検出) |

| LEVEL7 (OPEN)               | ディセーブル             | ディセーブル                |

| LEVEL6 (130KΩ、代表値)          | 2V                 | 1.5V                  |

| LEVEL5 (62KΩ、代表値)           | 1V                 | 0.9V                  |

| LEVEL4 (27KΩ、代表値)           | 0.8V               | 0.7V                  |

| LEVEL3 (12KΩ、代表値)           | 0.6V               | 0.5V                  |

| LEVEL2 (5.6KΩ、代表値)          | 0.4V               | 0.3V                  |

| LEVEL1 (2KΩ、代表値)            | 0.2V               | 0.15V                 |

| LEVEL0 (GND への短絡)           | 0.1V               | 該当なし                  |

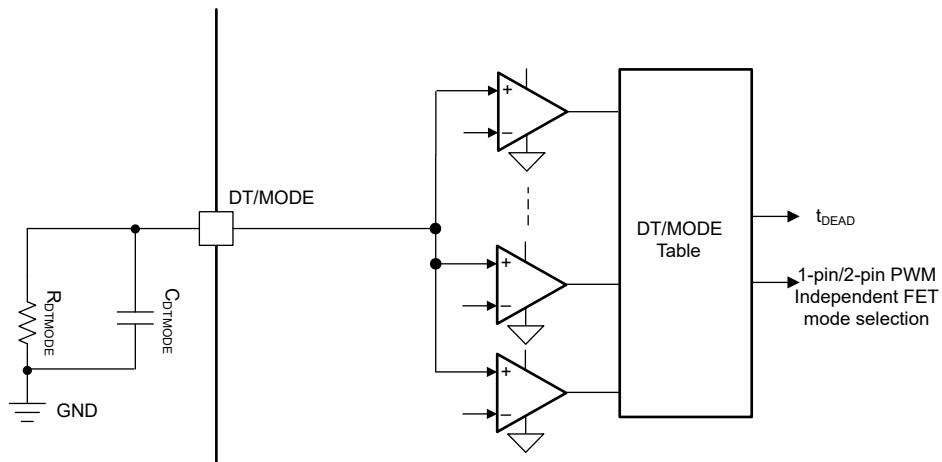

### 7.3.2.6 マルチレベルデジタル入力 DT/MODE

図 7-14 は、ハードウェアインターフェイス構成におけるマルチレベル入力ピン DT/MODE の構造を示しています。入力は、GND に接続された外付け抵抗  $R_{DTMODE}$  で設定できます。 $C_{DTMODE}$  は、GND ノイズの影響を低減するためのオプションです。表 7-6 に示すように、貫流電流機能、デッドタイム挿入、および PWM 制御モードが設定されています。LEVEL0、1、2、3、LEVEL5 の情報は、デバイスの電源オン時にラッチされます。

図 7-14. DT/MODE ピンの構造

表 7-6. DT/MODE 表

| DT/ MODE ( $R_{DTMODE}$ )   | 貫通電流保護 | デッドタイムの挿入 ( $t_{DEAD}$ )                                            | PWM 制御モード |

|-----------------------------|--------|---------------------------------------------------------------------|-----------|

| LEVEL5 (ピンがフローティング、> 3.3MΩ) | 有効     | 無効。IDRIVE により VGS デッドタイム挿入が有効にされている場合、<br>$t_{MINDEAD\_VG}$ が挿入されます | 2 ピン PWM  |

| LEVEL4 -リニア (10KΩ~1MΩ)      | 有効     | 有効 (20ns~900ns)                                                     | 1 ピン PWM  |

| LEVEL3 (3.3KΩ)              | 有効     | 有効 (370ns)                                                          | 2 ピン PWM  |

| LEVEL2 (1.3KΩ)              | 有効     | 有効 (100ns)                                                          | 2 ピン PWM  |

| LEVEL1 (470Ω)               | 有効     | 有効 (20ns)                                                           | 2 ピン PWM  |

| LEVEL0 (GND への短絡)           | ディセーブル | ディセーブル                                                              | 独立した PWM  |

式 1 を使用して、LEVEL4 のデッドタイムを計算します。

$$t_{dead}(ns) = 0.89 \times R_{DTMODE}(k\Omega) + 11.1 \quad (1)$$

### 7.3.3 ローサイド電流検出アンプ

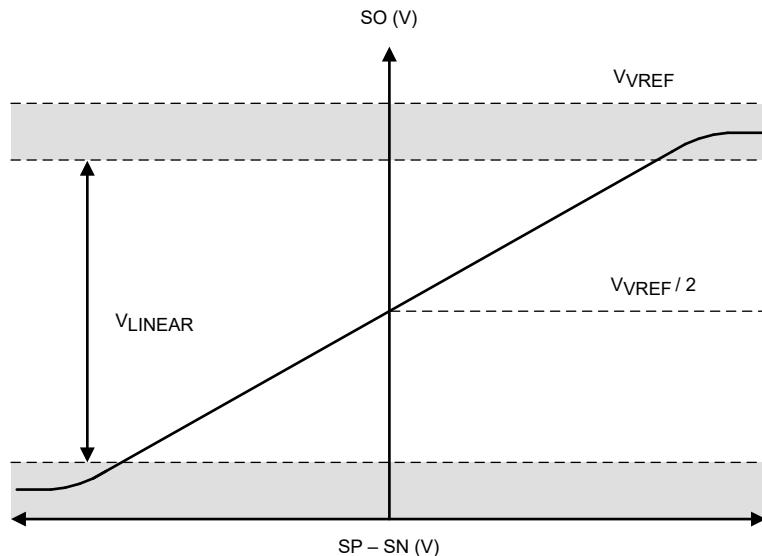

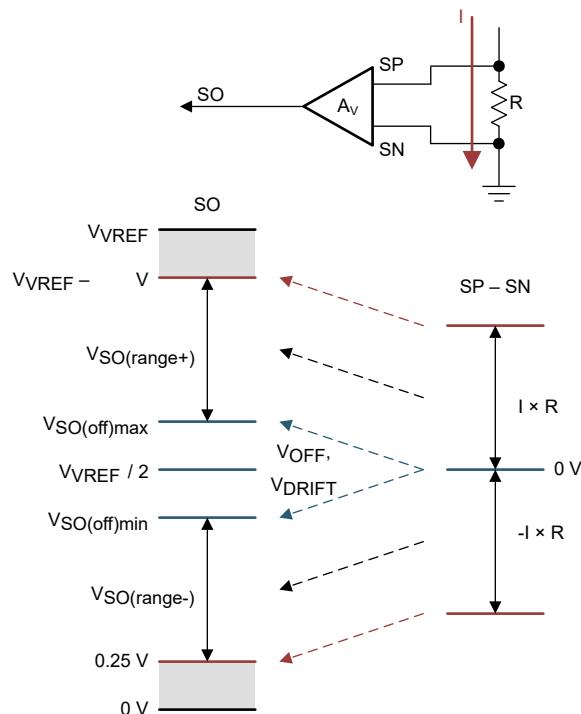

DRV8161 は、ローサイド シャント抵抗を使った電流測定のための高性能ローサイド電流検出アンプを内蔵しています。ローサイド電流測定は、一般に過電流保護、外部トルク制御、または外部コントローラによるプラシレス DC の整流を実装するために使用されます。電流センスアンプを使用して、ハーフブリッジ電流の合計を検出できます。電流センスアンプには、構成可能なゲイン、電圧リファレンスピン (CSAREF) などの機能が含まれています。DRV8161 は、 $V_{CSAREF}/2$  の共通電圧を内部で生成します。

ゲイン設定は 4 つの異なるレベル (5V/V、10V/V、20V/V、40V/V) に調整できます。ゲイン設定は、CSAGAIN ピンを使用して構成できます。

### 7.3.3.1 双方向電流検出の動作

DRV8161 は、電流測定を双方向で行うために、コモンモード電圧を内部で生成します。電流センスアンプは双方向モードとして動作し、SO ピンは、SP および SN ピン間の電圧にゲイン設定 ( $G_{CSA}$ ) と出力バイアス電圧  $V_{VREF}/2$  を乗算した値に等しいアナログ電圧を出力します。

シャント抵抗 (CSAREF / 2 case) を流れる電流値を計算するには、式 2 を使用します。

$$I = \frac{V_{SOx} - \frac{V_{VREF}}{2}}{G_{CSA} \times R_{SENSE}} \quad (2)$$

図 7-15. 双方向電流検出の出力

図 7-16. 双方向電流検出の領域

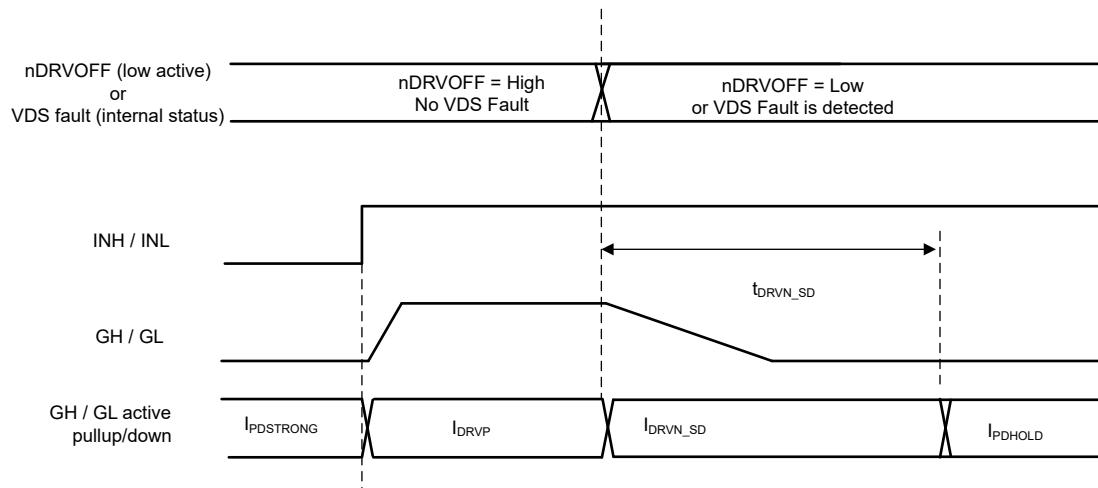

### 7.3.4 ゲート ドライバシャットダウン シーケンス (nDRVOFF)

nDRVOFF が Low に駆動されると、ゲートドライバはシャットダウンに移行し、入力ピン INH/IN および INL/EN の信号がオーバーライドされます。nDRVOFF はデバイス内部のデジタル制御ロジックをバイパスし、ゲートドライバ出力に直接接続されます。このピンを使うと、内部制御ロジックを直接バイパスできるため、ゲートドライバが無効化された際の故障を外部から監視できます。DRV816x が nDRVOFF ピンを LOW に駆動していることを検出すると、デバイスはゲートドライバを無効にし、ゲートドライバをプルダウンモードに移行します。ゲートドライバのシャットダウンシーケンスは、図 7-17 に示すように進行します。ゲートドライバがシャットダウンシーケンスを開始すると、ドライバプルダウンが  $I_{DRVN\_SD}$  の電流で  $t_{DRVN\_SD}$  時間の間アクティブプルダウンが適用されます。

図 7-17. ゲート ドライバシャットダウン シーケンス

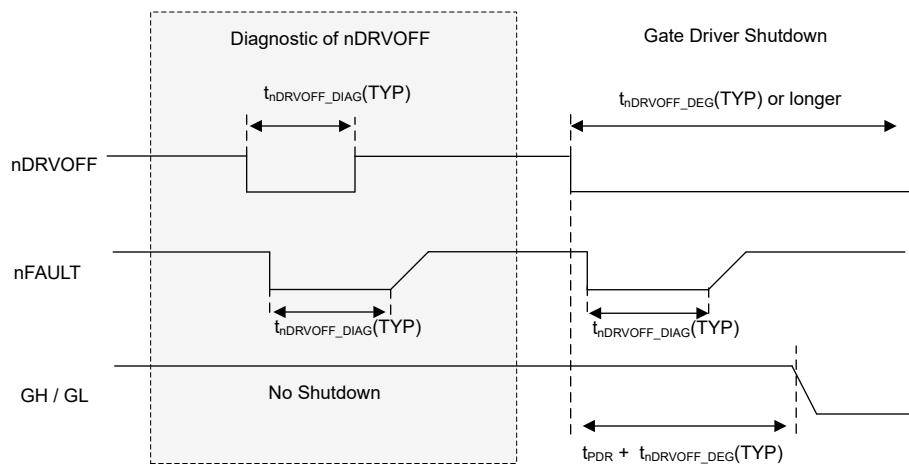

#### 7.3.4.1 nDRVOFF 診断

図 7-18 は DRV8162 および DRV8162L の nDRVOFF の診断を推奨します。nDRVOFF ピンに Low アクティブパルス  $t_{nDRVOFF\_DIAG}$  (標準値 0.5us) が印加された場合、デバイスはゲートドライバ出力をシャットダウンせず、nFAULT を Low に駆動することにより応答します。このデバイス機能は、PWM 動作を継続しながら nDRVOFF の機能を診断することを目的としています。nDRVOFF が  $t_{nDRVOFF\_DEG}$  よりも長い間 Low に駆動されると、デバイスはシャットダウンを開始します。

図 7-18. nDRVOFF 診断

### 7.3.5 ゲート ドライバ保護回路

DRV816x は、GVDD 低電圧および過電圧、ブートストラップ低電圧、MOSFET V<sub>DS</sub> および過熱(OTSD)イベントから保護されています。

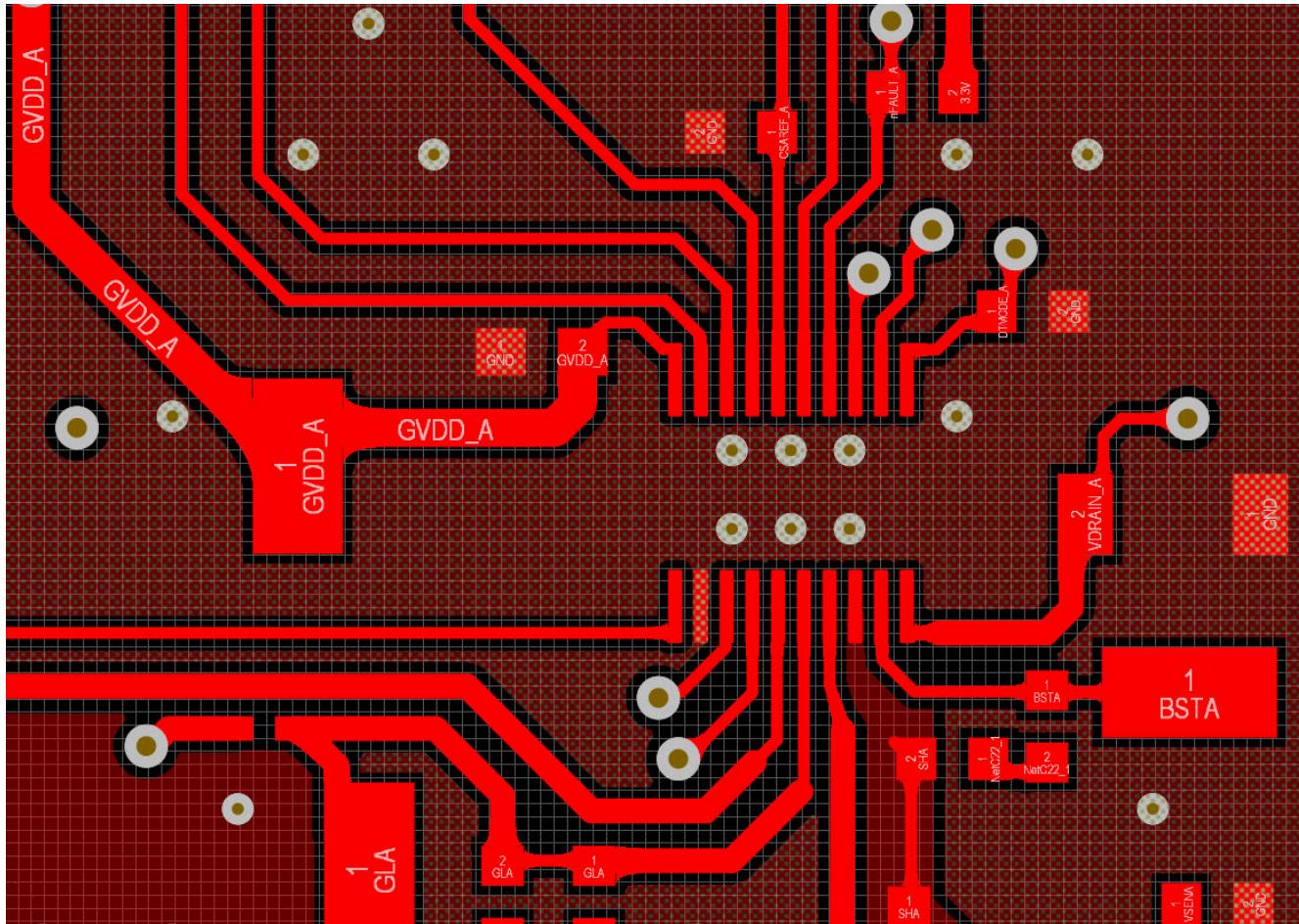

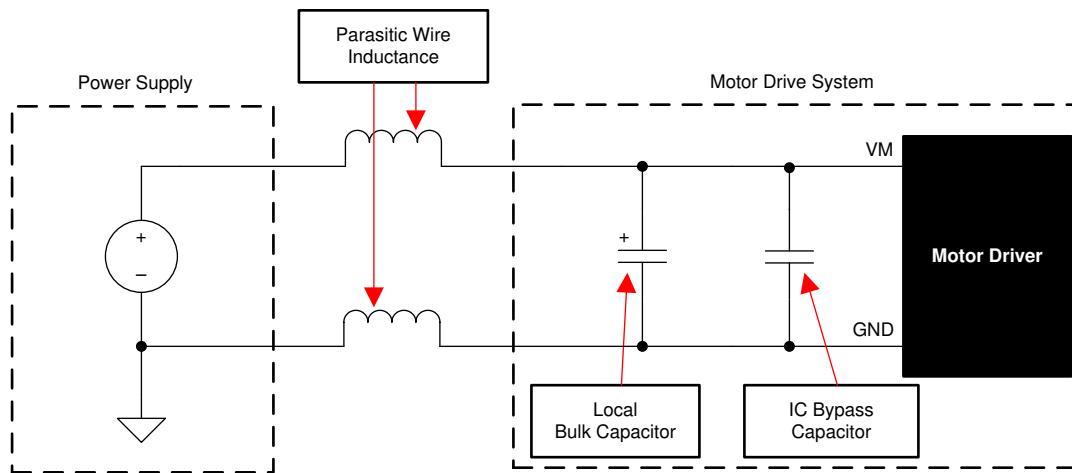

**表 7-7. フォルト動作および応答**