# DRV3946-Q1 電流レギュレーション、クランプ、診断機能搭載、デュアルチャネル車載用ソレノイドドライバ

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認証済み

- 温度グレード 1: -40°C ~ +125°C, T<sub>A</sub>

- **機能安全準拠**

- 機能安全アプリケーション向けに開発

- ISO26262 システムの設計に役立つ資料が利用可能

- ASIL Dまでのインテグリティレベル

- ASIL Cまでのハードウェア安全度

- 車載 EV 接触器リレーとソレノイド制御の各アプリケーションをターゲットとする高集積ソレノイドドライバ

- 電源、電流レギュレーション、診断、安全機能の統合

- 構成可能なピーク / ホールド電流設定による高効率ソレノイド駆動

- 電源、インターフェイス、ドライバ、モニタの内蔵セルフ テストおよび診断機能

- 冗長電源、ローサイドおよびハイサイドドライバ、2 次側監視ロジックにより信頼性の高い動作を実現するアーキテクチャ

- 動作範囲: 最大 28V (絶対最大定格 40V)

- 改良型ハーフブリッジ内蔵

- 充電、還流、クランプ用途

- 代表値 R<sub>DS(ON)</sub>: 37mΩ (ローサイド)、57mΩ (ハイサイド)

- クランプ回路内蔵による迅速なターンオフ機能

- ハイサイド クランプと冗長ローサイド クランプ

- 1 線式接続によるローサイド負荷制御

- 外部ハイサイドスイッチにより冗長シャットオフが可能

- ± 5% 精度のローサイドおよびハイサイド電流センス

- アナログ負荷電流帰還ピン (IPROPI)

- 内部制御モード:

- 閉ループ PWM 電流レギュレーション

- 構成可能なピーク時間、ピーク電流、ホールド電流

- 外部制御モード:

- 固定 PWM 周波数でデューティサイクルを変動

- 固定デューティサイクルで PWM 周波数を変動

- CRC 搭載 4 線式アドレス指定可能 24 ビット SPI

- 同じ SPI 上で複数のデバイスを動作可能

- 共有 SPI バス上のすべてのデバイスがプロードキャストコマンドを受信可能

- 包括的な保護機能と診断機能:

- デバイス内蔵セルフ テスト

- 負荷監視による開路 / 短絡の検出

- ドライバのオン / オフ中の制御喪失の検出

- 低電流または低電圧時に強制リレーがオープン

- 冗長ピン シャットオフ

- nFAULT ピンによるフォルト通知

## 2 アプリケーション

- EV 接触器リレー

- ピークおよびホールド ソレノイド

- オン / オフリレー

- 比例ソレノイド

- バッテリ切り離しユニット (BDU)

- バッテリ ジャンクション ボックス (BJB)

- パワー ディストリビューション ボックス (PDB)

- アクティブ サスペンション システム

- 車両制御ユニット (VCU)

### パッケージ情報

| 部品番号 <sup>(1)</sup> | パッケージ       | パッケージ サイズ (公称) <sup>(2)</sup> |

|---------------------|-------------|-------------------------------|

| DRV3946-Q1          | HTSSOP (28) | 9.7mm × 4.4mm                 |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はピンも含まれます。

### 製品情報

| 主要な機能                         |

|-------------------------------|

| 2 個のソレノイドを高効率で駆動可能            |

| オン抵抗の低い電力段                    |

| 迅速なターンオフを可能にするクランプ回路          |

| 閉ループ PWM 電流レギュレーション           |

| ピーク電流とホールド電流とタイミング パラメータを構成可能 |

| 最大 20kHz の PWM 周波数オプション       |

| 包括的なオン / オフ状態診断               |

| アドレス指定可能な 24 ビット SPI          |

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

English Data Sheet: [SLVSHN6](#)

### 3 概要

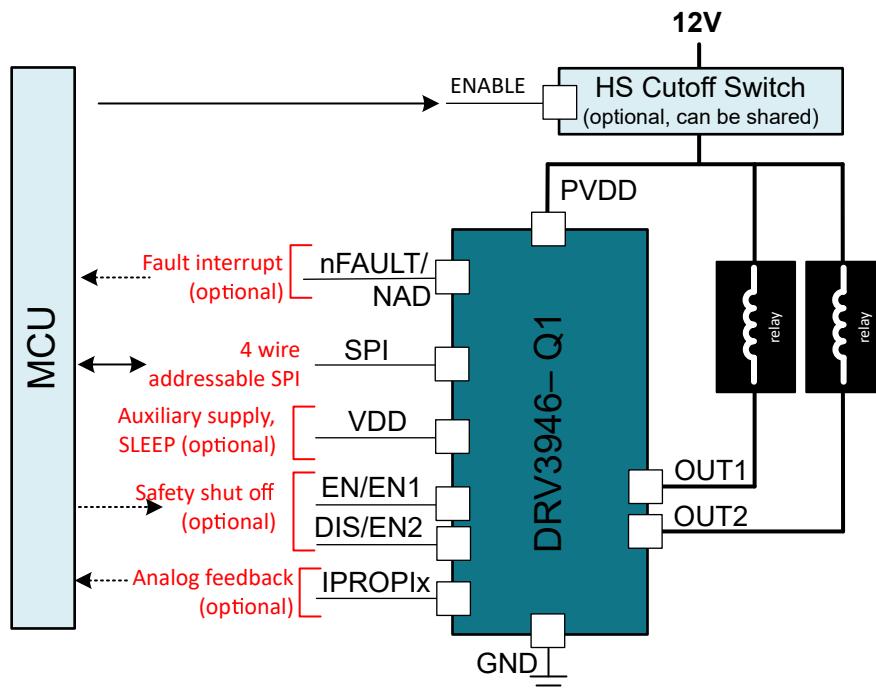

DRV3946-Q1 は、EV バッテリ管理システムの接触器リレーなど、車載アプリケーション用の 2 つのソレノイドを駆動する高集積ソリューションです。電源、電流センシングと電流レギュレーション、構成可能なピーク / ホールド電流と関連タイミング、診断機能と保護機能を搭載しています。また、従来のディスクリート ソレノイド ドライバに比べて性能を向上させる複数の独自機能も搭載しています。これらの機能には、負荷電流を迅速に放電するための内蔵冗長クランプ回路、アドレス指定可能な SPI、オン抵抗の低いスイッチを備えた変更型ハーフブリッジ ドライバ段が含まれます。

このデバイスは、1 線式のローサイド接続でソレノイド負荷を制御し、(共有可能な) 外部ハイサイド スイッチと組み合わせることで、冗長シャットオフ機能を実現できます。内蔵スイッチは、充電、還流、クランプを実行します。このデバイスは、内部および外部の電流制御モードをサポートしています。PWM 周波数は構成可能で、自動疑似ランダム周波数生成および波形整形を使用した低周波数ディザリングが追加されています。内部 PWM 電流制御ループは、MCU 電流制御ループが不要なため、ソフトウェア開発の労力削減につながります。DRV3946-Q1 は柔軟な電流制御パラメータをサポートしており、広範な種類のソレノイドをサポートしています。ピーク電流とホールド電流、および対応するタイミング パラメータが構成可能なため、システムレベルで省電力を実現できます。

DRV3946-Q1 は機能安全準拠を目標としており、リレー制御と意図しない動作の防止を目的として、ASIL-C 定格の機能安全を目標にしています。このデバイスは、開放および短絡検出のための負荷の継続的な監視、オンおよびオフ状態診断、電圧監視、短絡保護、高電圧定格 IO などの包括的な保護および診断機能をサポートしています。

アドレス指定可能な SPI により、1 つの共有 SPI バスで複数のデバイスを制御できます。必要なマイコン リソースの削減に加えて、アドレス指定可能な SPI にはブロードキャスト コマンド構造が組み込まれており、共有アドレス指定バス上のすべてのデバイスが、ある特定のアクションを同時にを行うことができます。SPI には、CRC、アドレス読み戻し機能、各種バスフォルト検出メカニズムなど、複数の堅牢性機能が組み込まれています。

概略回路図

## 目次

|                 |   |                            |   |

|-----------------|---|----------------------------|---|

| 1 特長.....       | 1 | 5 メカニカル、パッケージ、および注文情報..... | 3 |

| 2 アプリケーション..... | 1 | 5.1 付録:パッケージオプション.....     | 4 |

| 3 概要.....       | 2 | 5.2 テープおよびリール情報.....       | 5 |

| 4 改訂履歴.....     | 3 |                            |   |

## 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision * (December 2023) to Revision A (June 2024) | Page |

|-------------------------------------------------------------------|------|

| • 機能安全のテキストを更新。.....                                              | 1    |

| • ブロードキャストコマンドのテキストを更新。.....                                      | 1    |

## 5 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定したデバイスについて利用可能な最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 5.1 付録：パッケージオプション

### パッケージ情報

| 発注可能なデバイス          | 供給状況 <sup>(1)</sup> | パッケージタイプ | パッケージ図 | ピン数 | パッケージの数量 | エコ プラン <sup>(2)</sup> | リード / ボール仕上げ <sup>(6)</sup> | MSL ピーク温度 <sup>(3)</sup> | 動作温度 (°C) | デバイスマーキング <sup>(4) (5)</sup> |

|--------------------|---------------------|----------|--------|-----|----------|-----------------------|-----------------------------|--------------------------|-----------|------------------------------|

| DRV3946QPW<br>PRQ1 | アクティブ               | HTSSOP   | PWP    | 28  | 2500     | RoHS & グリーン           | NiPdAu                      | Level-3-260C-1<br>68 HR  | -40~125   | 3946                         |

- (1) マーケティング ステータスの値は次のように定義されています。

**供給中:**新しい設計への使用が推奨される量産デバイス。

**最終受注中:**テキサス・インスツルメンツはデバイスの生産終了を発表しており、現在最終受注期間中です。

**非推奨品:**新規設計には推奨しません。デバイスは既存の顧客をサポートするために生産されていますが、テキサス・インスツルメンツでは新規設計にこの部品を使用することを推奨していません。

**量産開始前:**量産されていない、市販されていない、またはウェブで発表されていない未発表デバイスで、サンプルは提供されていません。

**プレビュー:**デバイスは発表済みですが、まだ生産は開始されていません。サンプルが提供される場合と提供されない場合があります。

**生産中止品:**テキサス・インスツルメンツは、このデバイスの生産を終了しました。

- (2) エコ プラン - 環境に配慮した計画的な分類:鉛フリー (RoHS)、鉛フリー (RoHS 適用除外)、またはグリーン (RoHS 準拠、Sb/Br 非含有) があります。最新情報、および製品内容の詳細については、<http://www.ti.com/productcontent> でご確認ください。

**未定:**鉛フリー / グリーン転換プランが策定されていません。

**鉛フリー (RoHS):**テキサス・インスツルメンツにおける「Lead-Free」または「Pb-Free」(鉛フリー) は、6 つの物質すべてに対して現在の RoHS 要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が 0.1% を超えないという要件も含まれます。高温はんだに対応した テキサス・インスツルメンツ鉛フリー製品は、鉛フリー仕様プロセスでの使用に適しています。

**鉛フリー (RoHS 適用除外):**この部品は、1) ダイとパッケージとの間に鉛ベース フリップ チップのはんだシングル使用、または 2) ダイとリードフレームとの間に鉛ベースの接着剤を使用、のいずれかについて、RoHS が免除されています。この部品はそれ以外の点では、上記の定義の鉛フリー (RoHS 準拠) の条件を満たしています。

**グリーン (RoHS および Sb/Br 非含有):**テキサス・インスツルメンツにおける「グリーン」は、鉛フリー (RoHS 準拠) に加えて、臭素 (Br) およびアンチモン (Sb) をベースとした難燃材を含まない(均質な材質中の Br または Sb 重量が 0.1% を超えない)ことを意味しています。

- (3) MSL、ピーク温度-- JEDEC 業界標準分類に従った耐湿性レベル、およびピークはんだ温度です。

- (4) ロゴ、ロットトレース コード情報、または環境カテゴリに関する追加マークがデバイスに表示されることがあります。

- (5) 複数のデバイスマーキングが、括弧書きされています。カッコ内に複数のデバイスマーキングがあり、「～」で区切られている場合、その中の 1 つだけがデバイスに表示されます。行がインデントされている場合は、前行の続きということです。2 行合わせたものが、そのデバイスのデバイスマーキング全体となります。

- (6) リード / ボール仕上げ - 発注可能なデバイスには、複数の材料仕上げオプションが用意されていることがあります。複数の仕上げオプションは、縦罫線で区切られています。リード / ボール仕上げの値が最大列幅に収まらない場合は、2 行にまたがります。

**重要なお知らせと免責事項:**このページに掲載されている情報は、発行日現在のテキサス・インスツルメンツの知識および見解を示すものです。テキサス・インスツルメンツの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。テキサス・インスツルメンツでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。テキサス・インスツルメンツおよび テキサス・インスツルメンツのサプライヤは、特定の情報を機密情報として扱っているため、CAS 番号やその他の制限された情報が公開されない場合があります。

いかなる場合においても、そのような情報から生じたテキサス・インスツルメンツの責任は、このドキュメント発行時点でのテキサス・インスツルメンツ製品の価格に基づくテキサス・インスツルメンツからお客様への合計購入価格 (年次ベース) を超えることはありません。

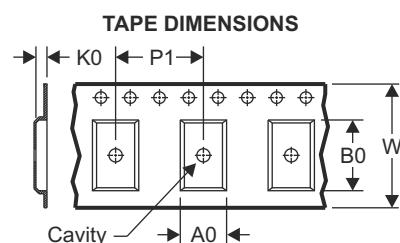

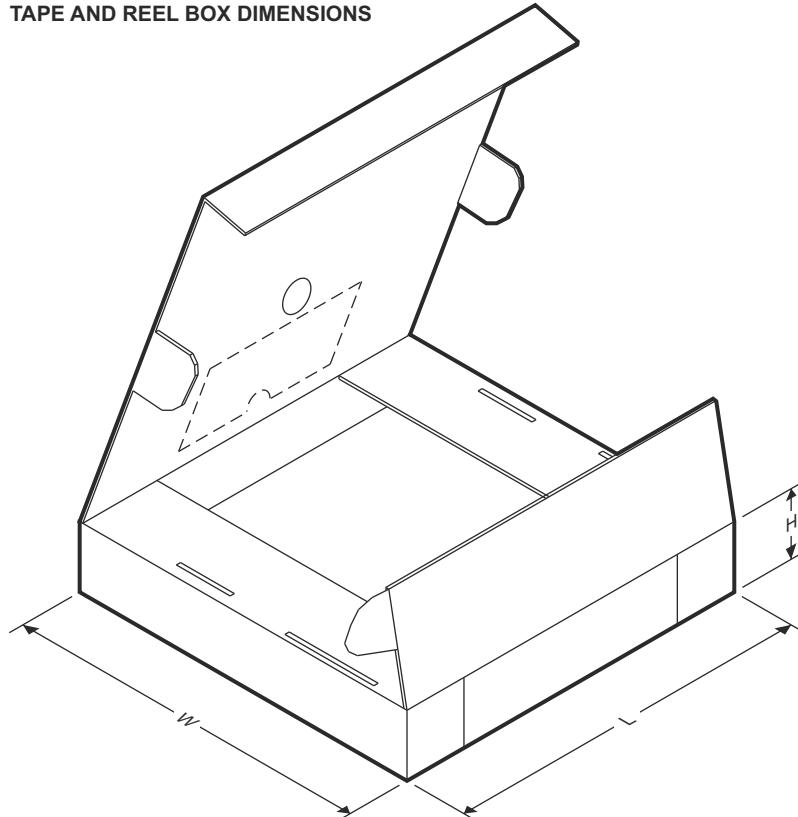

## 5.2 テープおよびリール情報

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

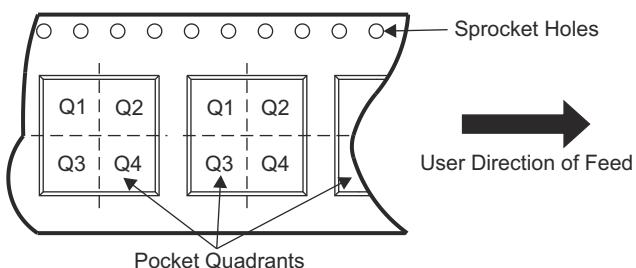

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

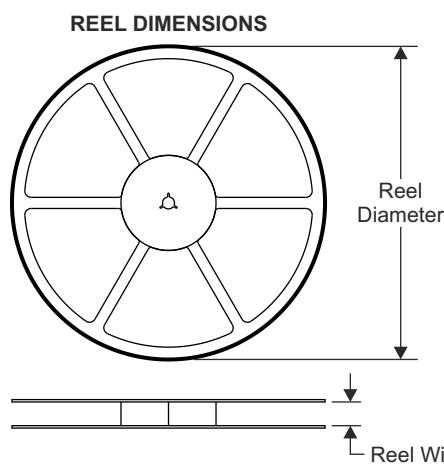

| デバイス           | パッケージタイプ | パッケージ図 | ピン数 | SPQ  | リール直径 (mm) | リール幅 W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | ピン1の象限 |

|----------------|----------|--------|-----|------|------------|--------------|---------|---------|---------|---------|--------|--------|

| DRV3946QPWPRQ1 | HTSSOP   | PWP    | 28  | 2500 | 330.0      | 16.4         | 6.75    | 10.1    | 1.8     | 12.0    | 16.0   | Q1     |

## TAPE AND REEL BOX DIMENSIONS

| デバイス           | パッケージタイプ | パッケージ図 | ピン数 | SPQ  | 長さ (mm) | 幅 (mm) | 高さ (mm) |

|----------------|----------|--------|-----|------|---------|--------|---------|

| DRV3946QPWPRQ1 | HTSSOP   | PWP    | 28  | 2500 | 356.0   | 356.0  | 35.0    |

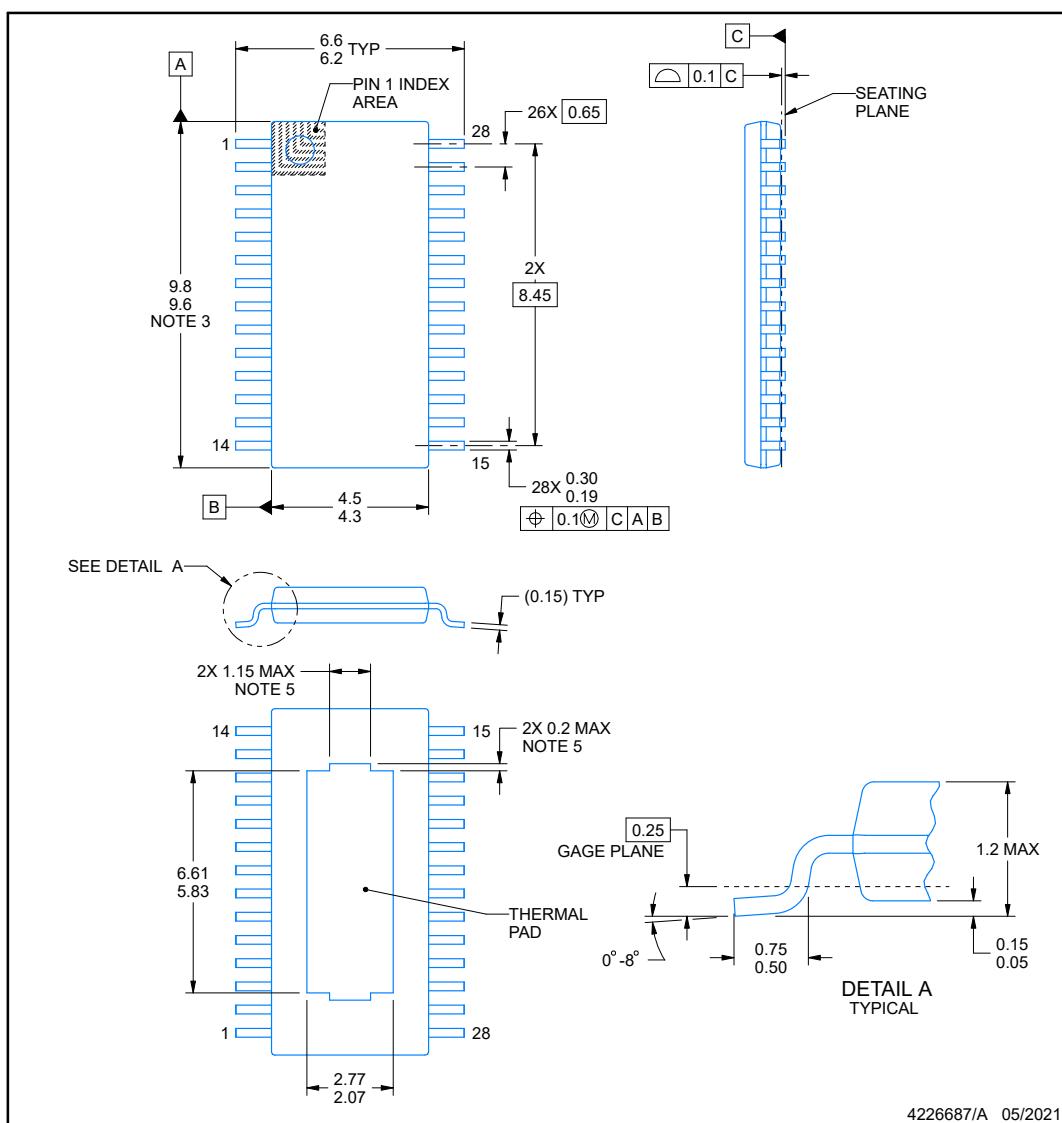

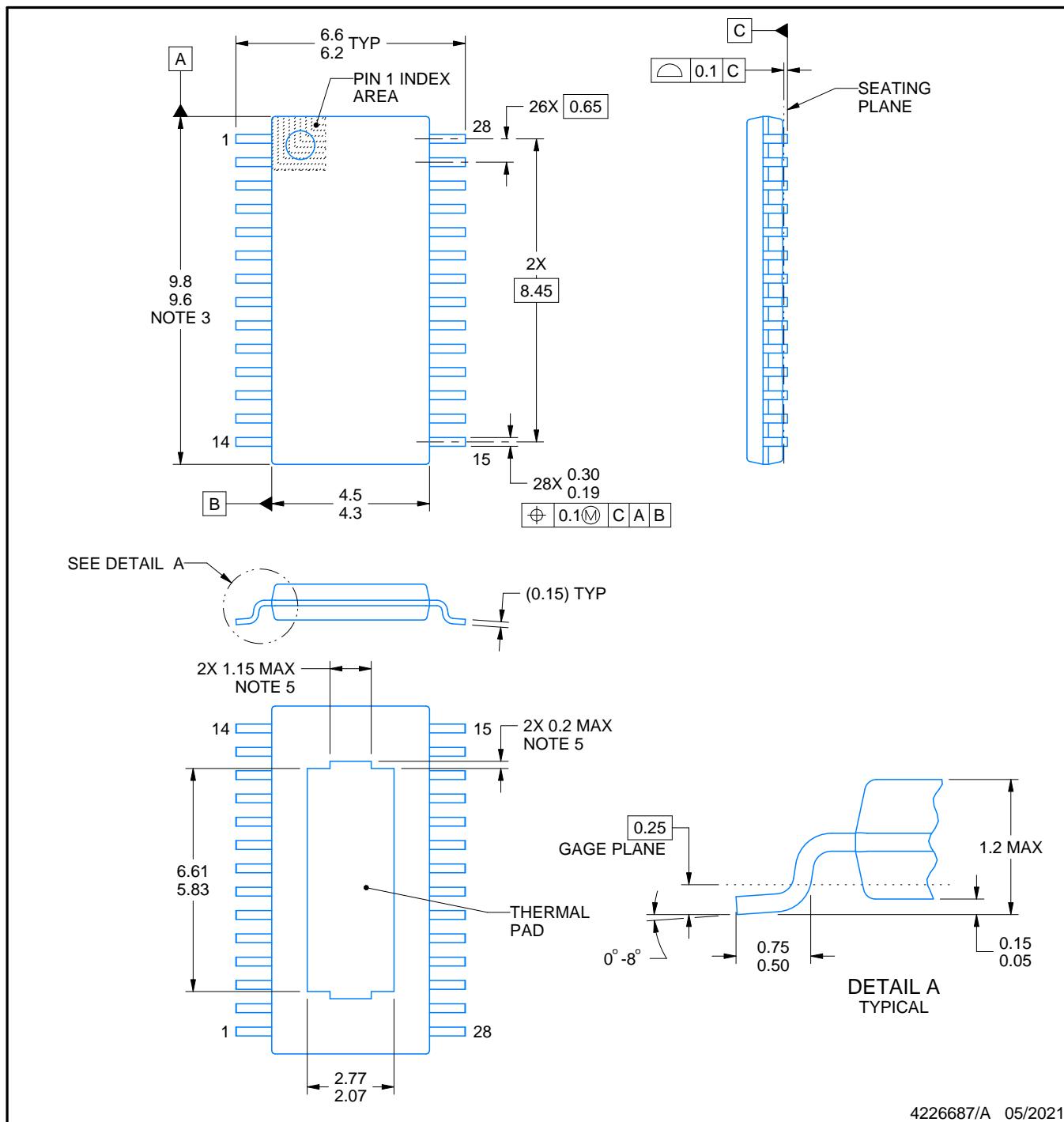

# PACKAGE OUTLINE

PWP0028T

## **PowerPAD™ TSSOP - 1.2 mm max height**

SMALL OUTLINE PACKAGE

4226687/A 05/2021

## NOTES:

PowerPAD is a trademark of Texas Instruments.

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. Reference JEDEC registration MO-153.

5. Features may differ or may not be present.

## PWP0028T

## PowerPAD™ TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 ([www.ti.com/lit/slma002](http://www.ti.com/lit/slma002)) and SLMA004 ([www.ti.com/lit/slma004](http://www.ti.com/lit/slma004)).

9. Size of metal pad may vary due to creepage requirement.

10. Vias are optional depending on application, refer to device data sheet. It is recommended that vias under paste be filled, plugged or tented.

## EXAMPLE STENCIL DESIGN

**PWP0028T**

**PowerPAD™ TSSOP - 1.2 mm max height**

SMALL OUTLINE PACKAGE

NOTES: (continued)

11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

12. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](#) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2024, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins    | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-------------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| DRV3946QPWPRQ1        | Active        | Production           | HTSSOP (PWP)   28 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | 3946                |

| DRV3946QPWPRQ1.A      | Active        | Production           | HTSSOP (PWP)   28 | 2500   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 125   | 3946                |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## GENERIC PACKAGE VIEW

**PWP 28**

**PowerPAD™ TSSOP - 1.2 mm max height**

**4.4 x 9.7, 0.65 mm pitch**

**SMALL OUTLINE PACKAGE**

This image is a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4224765/B

## **PACKAGE OUTLINE**

**PWP0028T**

**PowerPAD™ TSSOP - 1.2 mm max height**

## SMALL OUTLINE PACKAGE

## NOTES:

PowerPAD is a trademark of Texas Instruments.

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 mm per side.

4. Reference JEDEC registration MO-153.

5. Features may differ or may not be present.

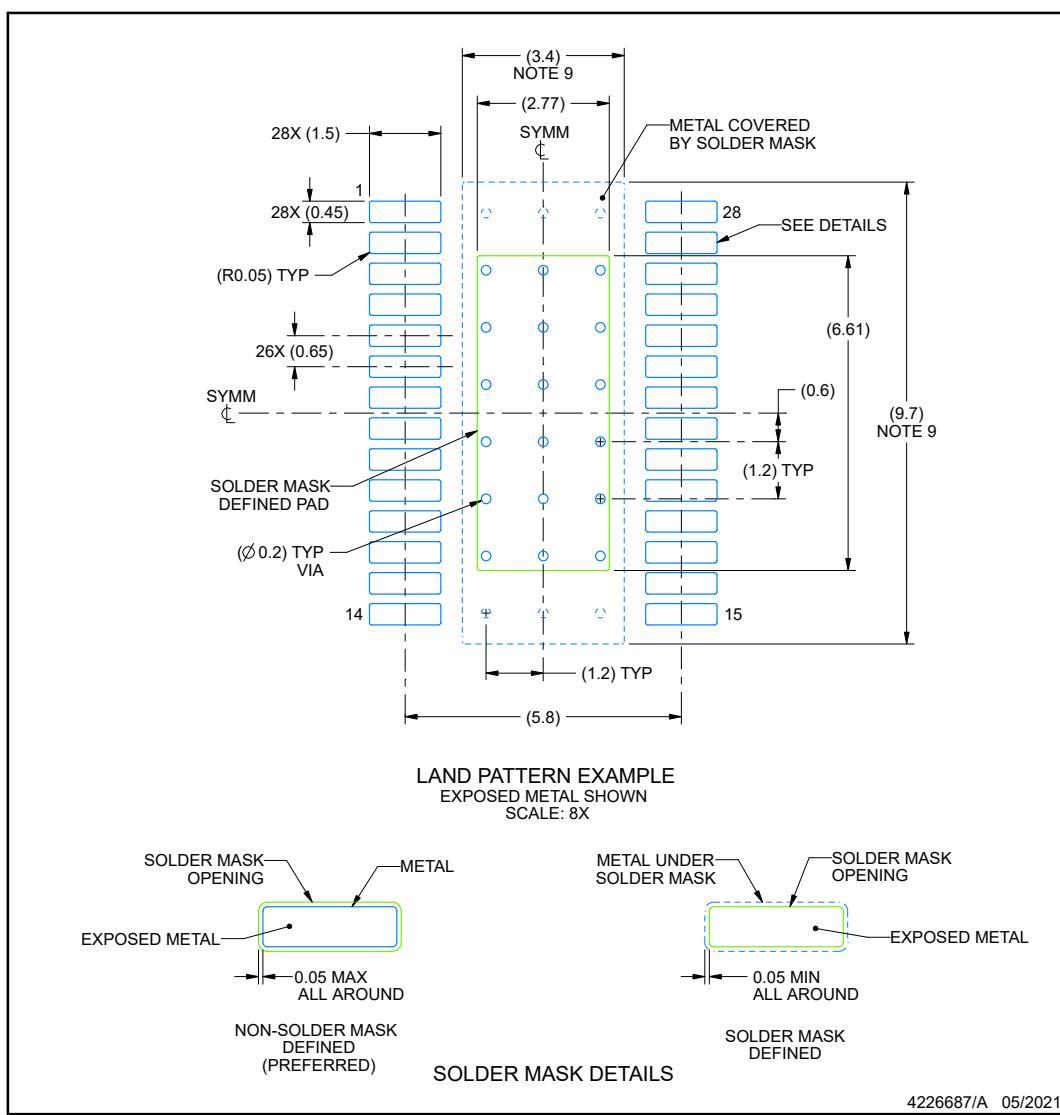

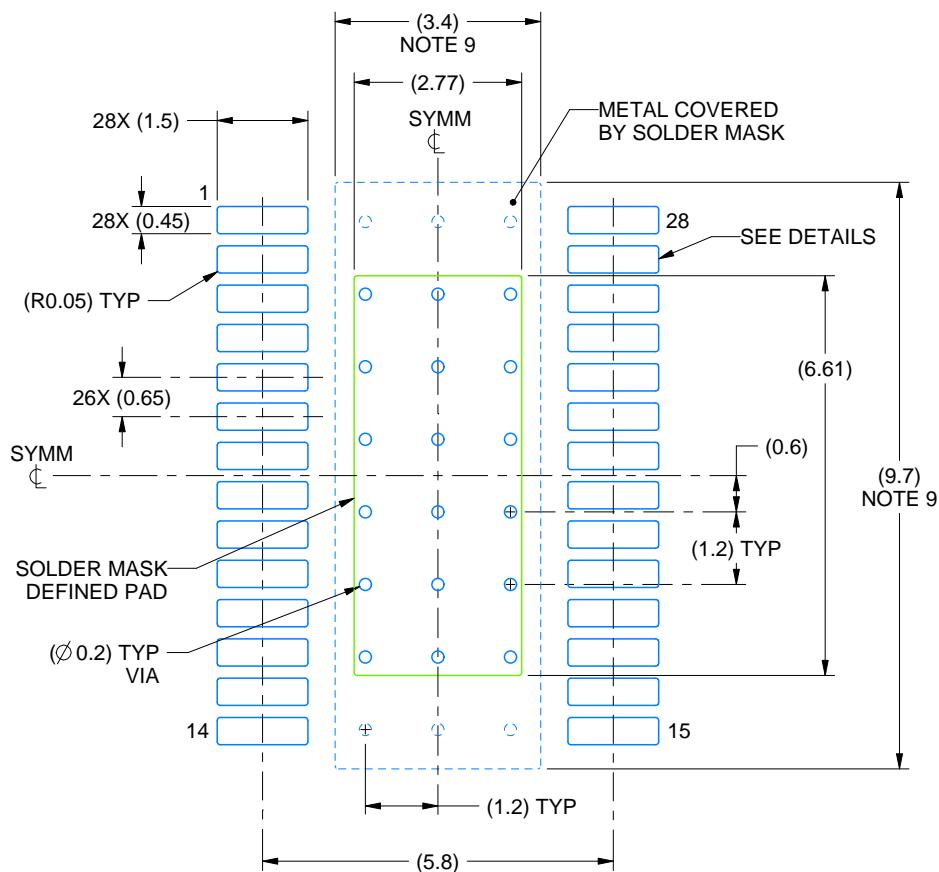

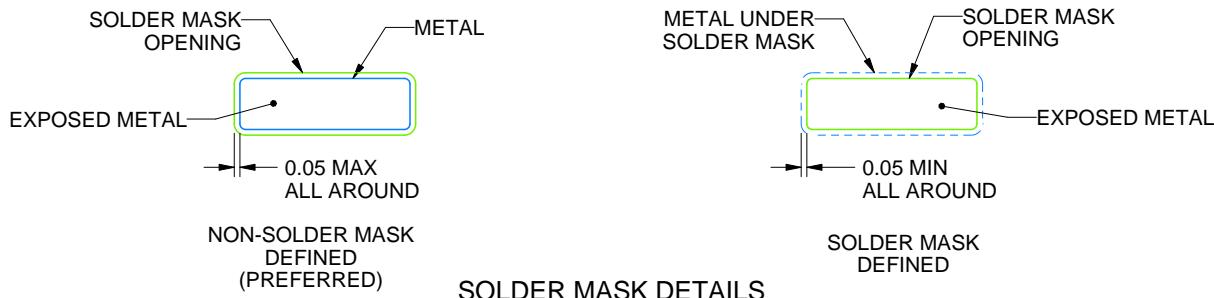

# EXAMPLE BOARD LAYOUT

PWP0028T

PowerPAD™ TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 8X

4226687/A 05/2021

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

8. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature numbers SLMA002 ([www.ti.com/lit/slma002](http://www.ti.com/lit/slma002)) and SLMA004 ([www.ti.com/lit/slma004](http://www.ti.com/lit/slma004)).

9. Size of metal pad may vary due to creepage requirement.

10. Vias are optional depending on application, refer to device data sheet. It is recommended that vias under paste be filled, plugged or tented.

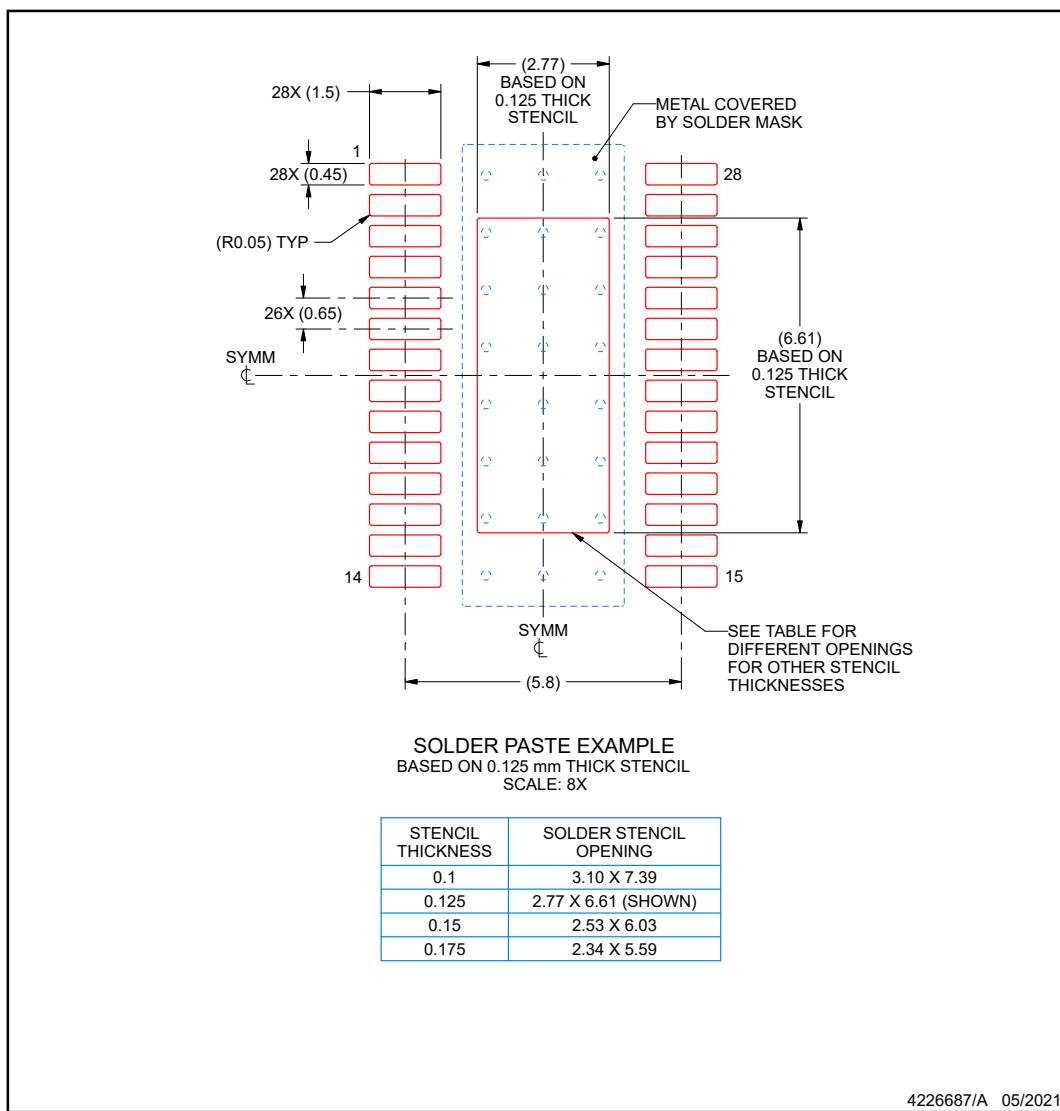

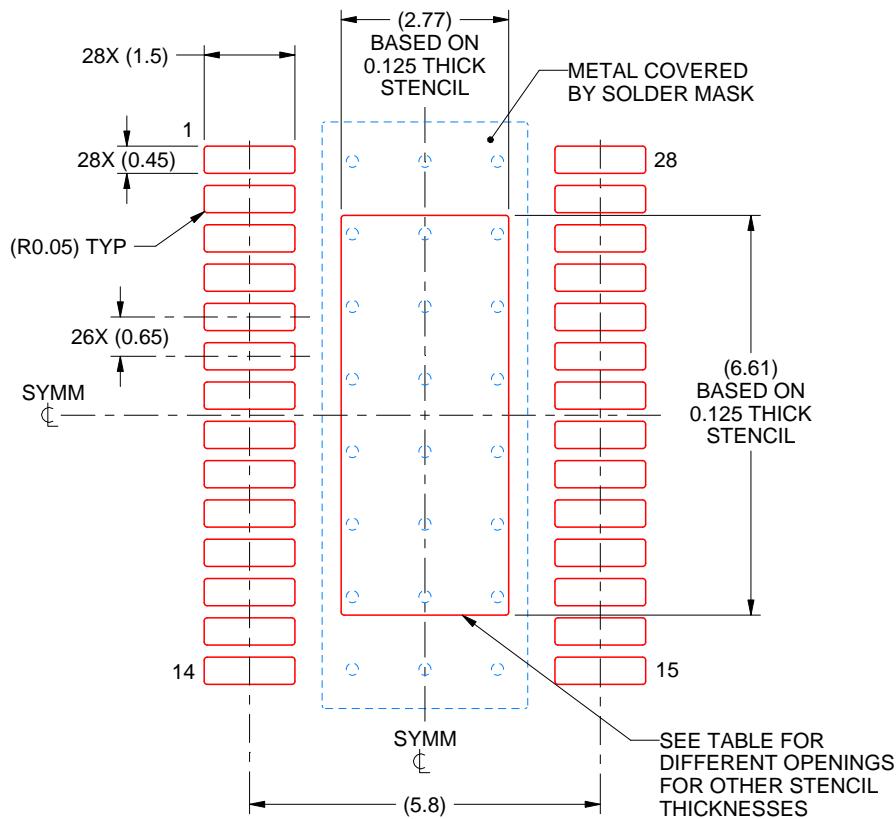

# EXAMPLE STENCIL DESIGN

PWP0028T

PowerPAD™ TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE: 8X

| STENCIL THICKNESS | SOLDER STENCIL OPENING |

|-------------------|------------------------|

| 0.1               | 3.10 X 7.39            |

| 0.125             | 2.77 X 6.61 (SHOWN)    |

| 0.15              | 2.53 X 6.03            |

| 0.175             | 2.34 X 5.59            |

4226687/A 05/2021

NOTES: (continued)

11. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

12. Board assembly site may have different recommendations for stencil design.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適した TI 製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TI の製品は、[TI の販売条件](#)、[TI の総合的な品質ガイドライン](#)、[ti.com](#) または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TI はそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日：2025 年 10 月