**DRV2667** JAJSGK4E - MARCH 2013 - REVISED JANUARY 2023

# DRV2667 ピエゾ・ハプティクス・ドライバ 昇圧、デジタル・フロント・エンド、内部波形メモリ付き

## 1 特長

Texas

INSTRUMENTS

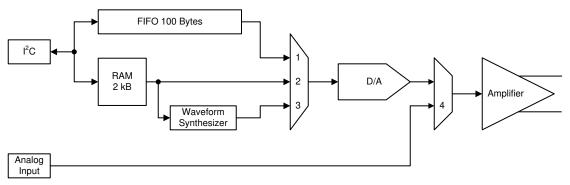

- 統合型デジタル・フロント・エンド

- 最高 400kHz の I<sup>2</sup>C バス制御

- 先進の波形シンセサイザ

- 2kBの内部波形メモリ \_

- 100 バイトの内部 FIFO インターフェイス

- Immersion TS5000 準拠

- オプションのアナログ入力

- 高電圧ピエゾ・ハプティクス・ドライバ

- 200V<sub>PP</sub>、300Hz で最大 100nF を駆動

- 150V<sub>PP</sub>、300Hz で最大 150nF を駆動

- 100V<sub>PP</sub>、300Hz で最大 330nF を駆動

- 50VPP、300Hz で最大 680nF を駆動

- 差動出力

- 105V の内蔵昇圧コンバータ

- 可変昇圧電圧

- 可変昇圧電流制限

- プログラム可能な昇圧電流制限機能

- パワー FET およびダイオードを内蔵

- 変圧器不要

- 2ms の短いスタートアップ時間

- 3.3~5.5V の広い電源電圧範囲

- 1.8V 互換、VDD 許容のデジタル・ピン

## 2 アプリケーション

- 携帯電話およびタブレット

- 携帯型コンピュータ

- キーボードとマウス

- 電子ゲーム機

- タッチ対応デバイス

## 3 概要

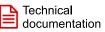

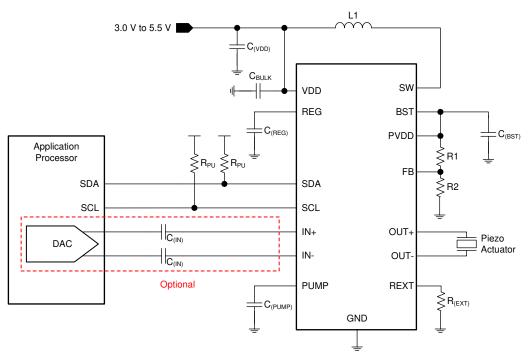

DRV2667 デバイスは、105V 昇圧スイッチ、パワー・ダイ オード、完全差動アンプ、デジタル・フロント・エンドを内蔵 したピエゾ・ハプティクス・ドライバであり、高電圧と低電圧 の両方のピエゾ・ハプティクス・アクチュエータを駆動可能 です。この多用途デバイスは、1<sup>2</sup>C ポートまたはアナログ入 力により、HD ハプティクスをサポートします。

DRV2667 デバイスのデジタル・インターフェイスは、I<sup>2</sup>C 互換バスを介して利用できます。デジタル・インターフェイ スを採用すると、PWM 生成によるコストのかかるプロセッ サの負担や、ホスト・システムでの追加のアナログ・チャネ ル要件を緩和できます。内部 FIFO への書き込みが行わ れるたびに、本デバイスは自動的に復帰し、2ms の内部 スタートアップ手順の後で波形の再生を開始します。デー タ・フローが停止するか、FIFO がアンダーランすると、本 デバイスは自動的にポップなしのシャットダウン手順に移 行します。

DRV2667 デバイスは、波形を保存して最低限のレイテン シで呼び出せる波形メモリ、最小限のメモリを使って複雑 なハプティクス波形を構築できる先進の波形シンセサイザ も備えています。これにより、ハードウェア・アクセラレーシ ョンが可能となり、ホスト・プロセッサはハプティクス生成の 役目から解放され、ハプティクス・インターフェイス上のバ ス・トラフィックも最小限になります。

昇圧電圧は2つの外付け抵抗によって設定され、昇圧電 流制限は Rext 抵抗によりプログラム可能です。標準のス タートアップ時間が 2ms である DRV2667 は、高速のハ プティクス応答に理想的なピエゾ・ドライバです。熱過負荷 保護機能により、過駆動時の損傷からデバイスを保護して います。

#### 制品情報(1)

| 部品番号 |         | パッケージ    | 本体サイズ (最大)      |  |  |  |  |

|------|---------|----------|-----------------|--|--|--|--|

|      | DRV2667 | QFN (20) | 4.00mm × 4.00mm |  |  |  |  |

利用可能なすべてのパッケージについては、このデータシートの (1)末尾にある注文情報を参照してください。

簡略回路図

英語版の工製品についての情報を翻訳したこの資料は、製品の概要を確認する目的で便宜的に提供しているものです。該当する正式な英語版の最新情報は、 、www.ti.com で閲覧でき、その内容が常に優先されます。TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、必ず 最新版の英語版をご参照くださいますようお願いいたします。

## **Table of Contents**

| 1 特長1                                 |

|---------------------------------------|

| 2 アプリケーション1                           |

| 3 概要1                                 |

| 4 Revision History                    |

| 5 Pin Configuration and Functions     |

| 6 Specifications                      |

| 6.1 Absolute Maximum Ratings4         |

| 6.2 ESD Ratings4                      |

| 6.3 Recommended Operating Conditions4 |

| 6.4 Thermal Information4              |

| 6.5 Electrical Characteristics5       |

| 6.6 Timing Requirements6              |

| 6.7 Switching Characteristics6        |

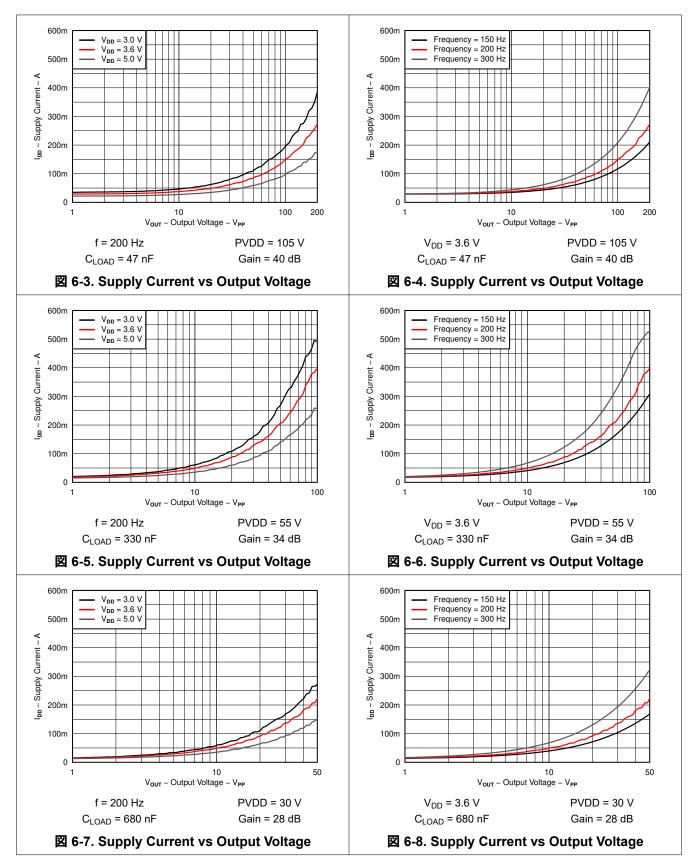

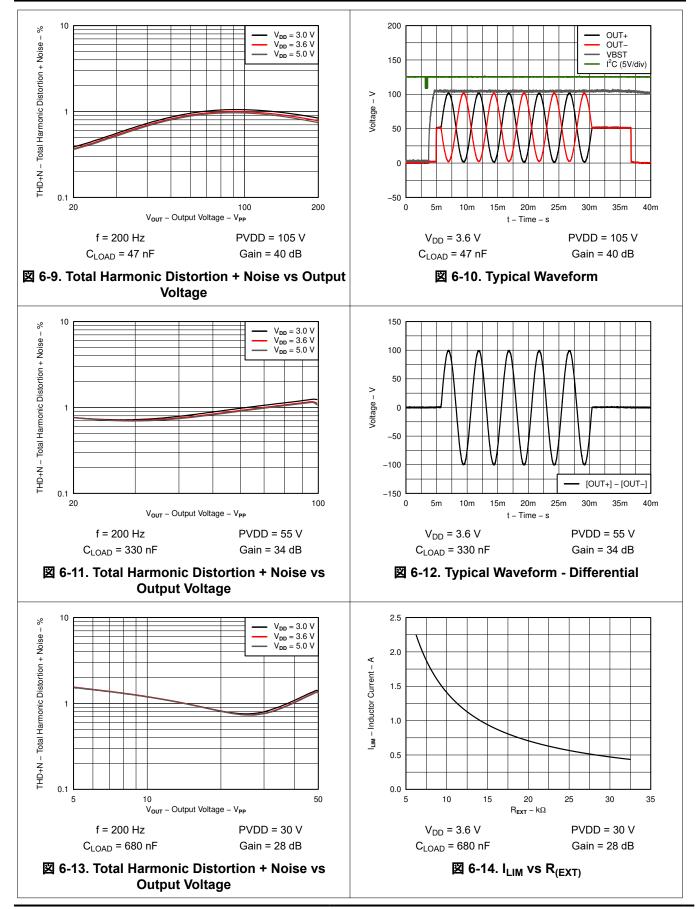

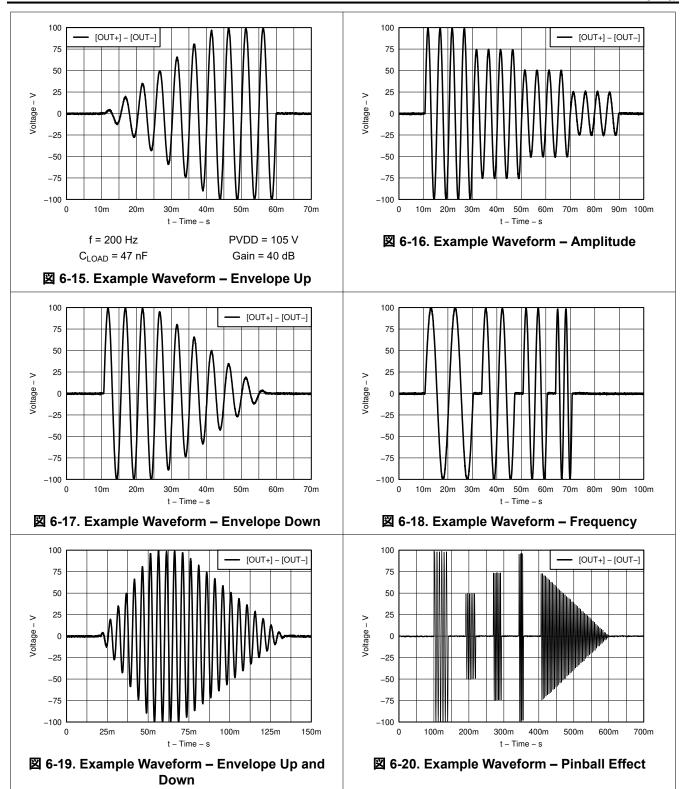

| 6.8 Typical Characteristics8          |

| 7 Detailed Description11              |

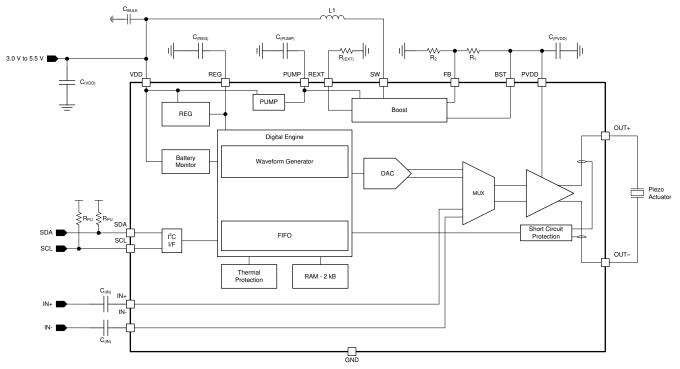

| 7.1 Overview 11                       |

| 7.2 Functional Block Diagram11        |

| 7.3 Feature Description11             |

| 7.4 Device Functional Modes                           | .14 |

|-------------------------------------------------------|-----|

| 7.5 Programming                                       | 15  |

| 7.6 Register Map                                      |     |

| 8 Application and Implementation                      |     |

| 8.1 Application Information                           |     |

| 8.2 Typical Application                               |     |

| 8.3 Initialization Setup                              |     |

| 9 Power Supply Recommendations                        | .40 |

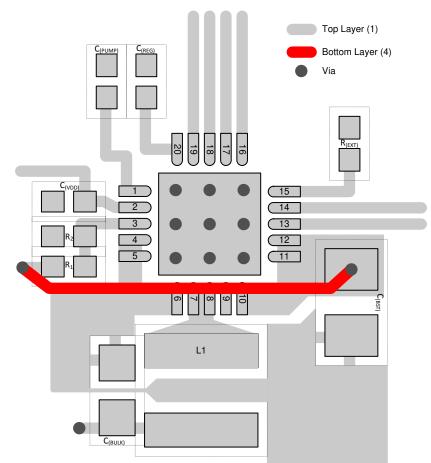

| 10 Layout                                             | .41 |

| 10.1 Layout Guidelines                                |     |

| 10.2 Layout Example                                   |     |

| 11 Device and Documentation Support                   | .42 |

| 11.1 Receiving Notification of Documentation Updates. | .42 |

| 11.2 Community Resources                              | .42 |

| 11.3 Trademarks                                       |     |

| 12 Mechanical, Packaging, and Orderable               |     |

| Information                                           | 42  |

|                                                       |     |

4 Revision History 資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Changes from Revision D (November 2018) to Revision E (January 2023)                                        |                   |  |  |  |

|-------------------------------------------------------------------------------------------------------------|-------------------|--|--|--|

| Changed V <sub>DD</sub> MIN spec from 3.0 to 3.3                                                            | 4                 |  |  |  |

| Changes from Revision C (December 2017) to Revision D (November 2018)                                       | Page              |  |  |  |

| Changed the first sentence of the second paragraph in the <i>FIFO Mode</i> section.                         |                   |  |  |  |

| Changes from Revision B (September 2015) to Revision C (December 2017)                                      | Page              |  |  |  |

| Changed Bit 6-3 in Address: 0x01                                                                            | 27                |  |  |  |

| - Changed 3.3 $\mu F$ to 22 $\mu F$ To: 3.3 $\mu H$ to 22 $\mu H$ in the <i>Inductor Selection</i> section. |                   |  |  |  |

| Changes from Revision A (January 2014) to Revision B (September 2015)                                       | Page              |  |  |  |

| • 「ESD 定格」表、「機能説明」セクション、「デバイスの機能モード」セクション、「アプリ                                                              | アーションと実装」セクション、「電 |  |  |  |

| 源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメント                                                                 | のサポート」セクション、「メカニカ |  |  |  |

| ル、パッケージ、および注文情報」セクションを追加。                                                                                   |                   |  |  |  |

| <ul> <li>Added Exception description to セクション 7.3.11.3 section</li> </ul>                                   |                   |  |  |  |

| Changes from Revision * (March 2013) to Revision A (January 2014)                                           | Page              |  |  |  |

| • 製品フォルダの1ページのデータシートを完全なデータシートに変更                                                                           | 1                 |  |  |  |

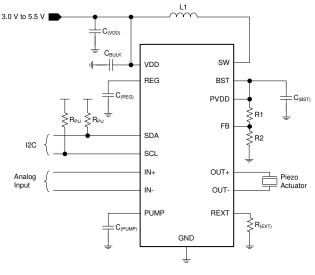

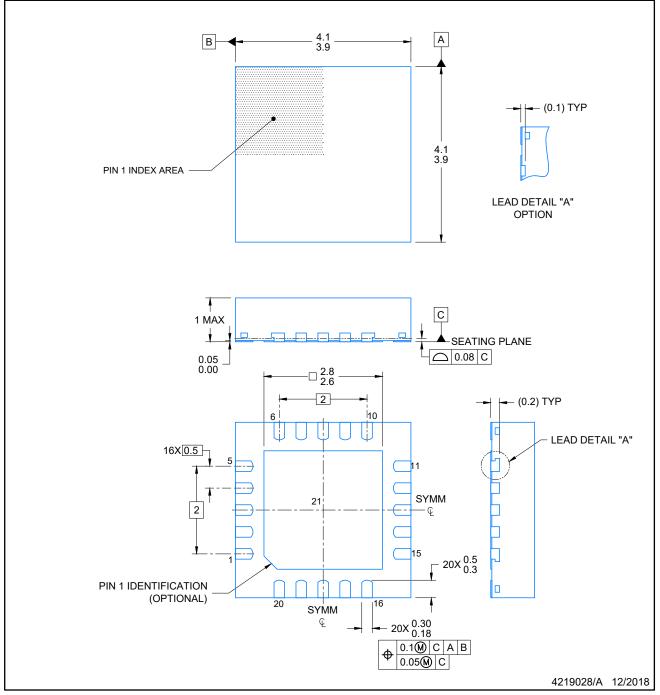

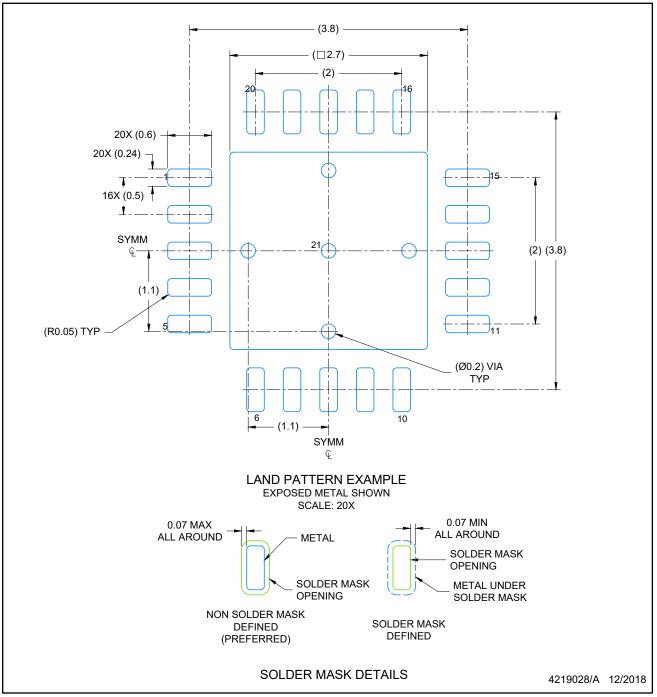

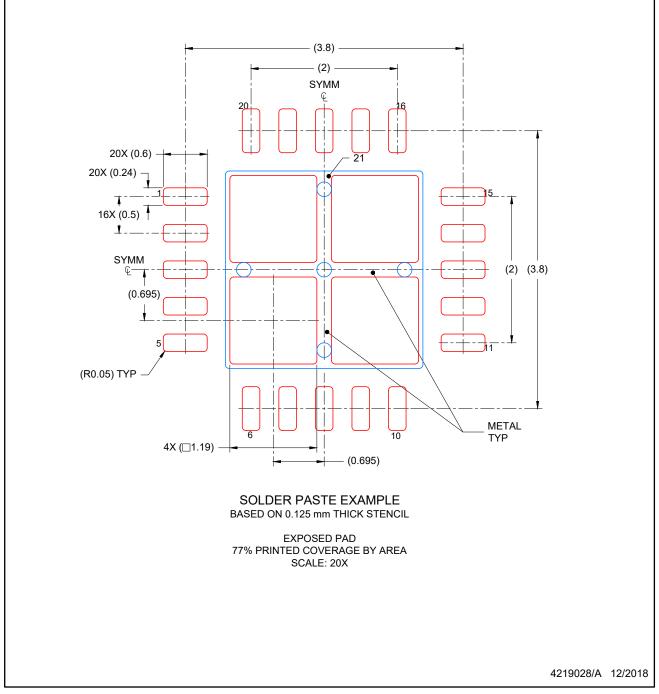

## **5** Pin Configuration and Functions

## 図 5-1. RGP Package 20-Pin QFN With Exposed Thermal Pad Top View

| 表 5 | -1. Pin | Function | S |

|-----|---------|----------|---|

|-----|---------|----------|---|

| PIN  |         | TYPE <sup>1</sup> | DESCRIPTION                                             |

|------|---------|-------------------|---------------------------------------------------------|

| NAME | NO.     |                   | DESCRIPTION                                             |

| PUMP | 1       | Р                 | Internal charge pump voltage                            |

| VDD  | 2       | Р                 | 3- to 5.5-V supply input. A 1 μF-capacitor is required. |

| FB   | 3       | I                 | Boost feedback                                          |

| GND  | 4, 5, 6 | Р                 | Supply ground                                           |

| SW   | 7, 8    | Р                 | Internal boost switch pin                               |

| NC   | 9       | _                 | No connect                                              |

| BST  | 10, 11  | Р                 | Boost output voltage. A 0.1-µF capacitor is required.   |

| PVDD | 12      | Р                 | High-voltage amplifier input voltage                    |

| OUT+ | 13      | 0                 | Positive haptic driver differential output              |

| OUT- | 14      | 0                 | Negative haptic driver differential output              |

| REXT | 15      | I                 | Sets boost current limit. Resistor to ground.           |

| IN-  | 16      | I                 | Negative analog input                                   |

| IN+  | 17      | I                 | Positive analog input                                   |

| SCL  | 18      | I                 | I <sup>2</sup> C clock                                  |

| SDA  | 19      | I/O               | I <sup>2</sup> C data                                   |

| REG  | 20      | 0                 | 1.8-V regulator output. A 0.1-µF capacitor is required. |

1. I = Input, O = Output, P = Power

## 6 Specifications

#### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                |                                       |      | MIN  | MAX                   | UNIT |

|------------------------------------------------|---------------------------------------|------|------|-----------------------|------|

| Supply Voltage, V <sub>DD</sub>                |                                       | -0.3 | 6    | V                     |      |

| Input voltage, V <sub>I</sub>                  | SDA, SCL, IN+, IN–, FB                |      | -0.3 | V <sub>DD</sub> + 0.3 | V    |

| Boost voltage                                  | BST, SW, OUT+, OUT–, PVDD             |      | -0.3 | 120                   | V    |

| Operating free-air temperate                   | ure, T <sub>A</sub>                   |      | -40  | 70                    | °C   |

| Operating junction temperature, T <sub>J</sub> |                                       |      | -40  | 150                   | °C   |

| Storage temperature, T <sub>stg</sub>          | Storage temperature, T <sub>stg</sub> |      | -65  | 85                    | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                    |                         |                                                                          | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>        | ±2500 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 $^{(2)}$ | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                  |                             |                                                                 | MIN | NOM | MAX  | UNIT |

|------------------|-----------------------------|-----------------------------------------------------------------|-----|-----|------|------|

| $V_{DD}$         | Supply voltage              |                                                                 | 3.3 |     | 5.5  | V    |

| V <sub>BST</sub> | Boost voltage               |                                                                 | 15  |     | 105  | V    |

| V <sub>IN</sub>  | Differential input voltage  |                                                                 |     | 1.8 |      | V    |

|                  |                             | $V_{BST}$ = 105 V, Frequency = 500 Hz, $V_{OUT}$ = 200 $V_{PP}$ |     |     | 50   |      |

|                  |                             | $V_{BST}$ = 105 V, Frequency = 300 Hz, $V_{OUT}$ = 200 $V_{PP}$ |     |     | 100  |      |

|                  |                             | $V_{BST}$ = 80 V, Frequency = 300 Hz, $V_{OUT}$ = 150 $V_{PP}$  |     |     | 150  |      |

| CL               | Load capacitance            | $V_{BST}$ = 55 V, Frequency = 300 Hz, $V_{OUT}$ = 100 $V_{PP}$  |     |     | 330  | nF   |

|                  |                             | $V_{BST}$ = 30 V, Frequency = 300 Hz, $V_{OUT}$ = 50 $V_{PP}$   |     |     | 680  |      |

|                  |                             | $V_{BST}$ = 25 V, Frequency = 300 Hz, $V_{OUT}$ = 40 $V_{PP}$   |     |     | 1000 |      |

|                  |                             | $V_{BST}$ = 15 V, Frequency = 300 Hz, $V_{OUT}$ = 20 $V_{PP}$   |     |     | 3000 |      |

| R <sub>EXT</sub> | Current limit control resis | stor                                                            | 6   |     | 35   | kΩ   |

| L                | Inductance for boost con    | verter                                                          | 3.3 |     |      | μH   |

#### 6.4 Thermal Information

|                       |                                              | DRV2667   |      |

|-----------------------|----------------------------------------------|-----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RGP (QFN) | UNIT |

|                       |                                              | 20 PINS   |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 32.6      | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 30.4      | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 8.2       | °C/W |

| Ψ <sub>JT</sub>       | Junction-to-top characterization parameter   | 0.4       | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 8.1       | °C/W |

|                       |                                              | DRV2667   |      |

|-----------------------|----------------------------------------------|-----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RGP (QFN) | UNIT |

|                       |                                              | 20 PINS   |      |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.2       | °C/W |

(1) For more information about traditional and new thermal metrics, see the *Semiconductor and IC Package Thermal Metrics* application report.

## **6.5 Electrical Characteristics**

| $T_{A} = 25 °C$ | ). Vnn = 3.6 | V (unless | otherwise noted) |

|-----------------|--------------|-----------|------------------|

|                 |              |           |                  |

|                      | PARAMETER                                |              | TEST CONDITIONS                                                         | MIN   | TYP  | MAX  | UNIT            |  |

|----------------------|------------------------------------------|--------------|-------------------------------------------------------------------------|-------|------|------|-----------------|--|

| V <sub>REG</sub>     | Voltage at the REG pin                   |              |                                                                         | 1.6   | 1.75 | 1.9  | V               |  |

| I <sub>IL</sub>      | Digital low-level input c                | urrent       | SDA, SCL<br>V <sub>DD</sub> = 3.6 V, V <sub>I</sub> = 0 V               |       |      | 1    | μA              |  |

| I <sub>IH</sub>      | Digital high-level input current         |              | SDA, SCL<br>V <sub>DD</sub> = 3.6 V, V <sub>I</sub> = V <sub>DD</sub>   |       |      | 1    | uA              |  |

| V <sub>IL</sub>      | Digital low-level input v                | oltage       | SDA, SCL<br>V <sub>DD</sub> = 3.6 V                                     |       |      | 0.5  | V               |  |

| V <sub>IH</sub>      | Digital high-level input                 | voltage      | SDA, SCL<br>V <sub>DD</sub> = 3.6 V                                     | 1.4   |      |      | V               |  |

| V <sub>OL</sub>      | Digital low-level output voltage         |              | SDA<br>3-mA sink current                                                |       |      | 0.4  | V               |  |

| I <sub>SD</sub>      | Shutdown current                         |              | V <sub>DD</sub> = 3.6 V, STANDBY = 1                                    |       | 10   |      | μA              |  |

|                      |                                          | Digital mode | V <sub>DD</sub> = 3.6 V, STANDBY = 0                                    |       | 130  | 175  | μA              |  |

|                      | Quiescent current                        |              | V <sub>DD</sub> = 3.6 V, analog input mode,<br>V <sub>BST</sub> = 105 V |       | 24   |      |                 |  |

| IQ                   |                                          | Analog mode  | $V_{DD}$ = 3.6 V, analog input mode,<br>V <sub>BST</sub> = 80 V         |       | 13   |      | <b>س</b> ۸      |  |

|                      |                                          | Analog mode  | $V_{DD}$ = 3.6 V, analog input mode,<br>V <sub>BST</sub> = 50 V         |       | 9    |      | mA              |  |

|                      |                                          |              | V <sub>DD</sub> = 3.6 V, analog input mode,<br>V <sub>BST</sub> = 30 V  |       | 5    |      |                 |  |

| R <sub>IN</sub>      | Input impedance                          |              | IN+, IN–; All gains                                                     |       | 100  |      | kΩ              |  |

|                      |                                          |              | GAIN[1:0] = 00                                                          | 49    | 50   | 51   |                 |  |

| V                    | Full-scale output voltage (digital mode) |              | GAIN[1:0] = 01                                                          | 98    | 100  | 102  | V               |  |

| V <sub>OUT(FS)</sub> | i un-scale output voltag                 |              | GAIN[1:0] = 10                                                          | 147   | 150  | 153  | V <sub>PP</sub> |  |

|                      |                                          |              | GAIN[1:0] = 01                                                          | 196   | 200  | 204  |                 |  |

| V <sub>OUT(OS)</sub> | Output offset                            |              | All gains                                                               | -0.25 |      | 0.25 | V               |  |

|                      |                                          |              | GAIN[1:0] = 00, V <sub>OUT</sub> = 50 V <sub>PP</sub> ,<br>no load      |       | 20   |      |                 |  |

| BW                   | Amplifics bondwidth                      |              | GAIN[1:0] = 01, V <sub>OUT</sub> = 100 V <sub>PP</sub> ,<br>no load     |       | 10   |      |                 |  |

|                      | Amplifier bandwidth                      |              | GAIN[1:0] = 10, V <sub>OUT</sub> = 150 V <sub>PP</sub> ,<br>no load     |       | 7.5  |      | kHz             |  |

|                      |                                          |              | GAIN[1:0] = 11, V <sub>OUT</sub> = 200 V <sub>PP</sub> ,<br>no load     |       | 5    |      |                 |  |

$T_A$  = 25 °C,  $V_{DD}$  = 3.6 V (unless otherwise noted)

|                       | PARAMETER                                                                                                                                                  | TEST CONDITIONS                                                                                                        | MIN | TYP | MAX  | UNIT |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|--|

|                       |                                                                                                                                                            | C <sub>L</sub> = 220 nF, f = 200 Hz, V <sub>BST</sub> = 30 V,<br>GAIN[1:0] = 00, V <sub>OUT</sub> = 50 V <sub>PP</sub> |     | 69  |      |      |  |

|                       |                                                                                                                                                            | C <sub>L</sub> = 680 nF, f = 150 Hz, V <sub>BST</sub> = 30 V,<br>GAIN[1:0] = 00, V <sub>OUT</sub> = 50 V <sub>PP</sub> |     | 75  |      |      |  |

|                       |                                                                                                                                                            | C <sub>L</sub> = 680 nF, f = 300 Hz, V <sub>BST</sub> = 30 V,<br>GAIN[1:0] = 00, V <sub>OUT</sub> = 50 V <sub>PP</sub> | 115 |     |      |      |  |

| I <sub>BAT,</sub> AVG | Average battery current during operation<br>$C_L = 22 \text{ nF, } f = 200 \text{ Hz, } V_{BST} = 80 \text{ V,}$<br>$GAIN[1:0] = 10, V_{OUT} = 150 V_{PP}$ | 67                                                                                                                     |     | mA  |      |      |  |

|                       |                                                                                                                                                            | $C_L$ = 47 nF, f = 150 Hz, $V_{BST}$ = 105 V,<br>GAIN[1:0] = 11, $V_{OUT}$ = 200 $V_{PP}$                              |     | 210 |      | -    |  |

|                       |                                                                                                                                                            | $C_L$ = 47 nF, f = 300 Hz, $V_{BST}$ = 105 V,<br>GAIN[1:0] = 11, $V_{OUT}$ = 200 $V_{PP}$                              |     | 400 |      |      |  |

| THD+N                 | Total harmonic distortion plus noise                                                                                                                       | f = 300 Hz, V <sub>OUT</sub> = 200 V <sub>PP</sub>                                                                     |     | 1%  |      |      |  |

| f <sub>S</sub>        | Output sample rate                                                                                                                                         | Digital playback engine sample rate                                                                                    | 7.8 | 8   | 8.05 | kHz  |  |

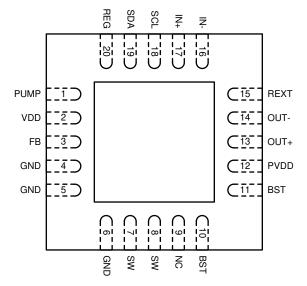

## 6.6 Timing Requirements

|                    |                                                | MIN | NOM | MAX | UNIT |

|--------------------|------------------------------------------------|-----|-----|-----|------|

| f <sub>SCL</sub>   | Frequency at the SCL pin with no wait states   |     |     | 400 | kHz  |

| t <sub>w(H)</sub>  | Pulse duration, SCL high                       | 0.6 |     |     | μs   |

| t <sub>w(L)</sub>  | Pulse duration, SCL low                        | 1.3 |     |     | μs   |

| t <sub>su(1)</sub> | Setup time, SDA to SCL                         | 100 |     |     | ns   |

| t <sub>h(1)</sub>  | Hold time, SCL to SDA                          | 10  |     |     | ns   |

| t <sub>BUF</sub>   | Bus free time between stop and start condition | 1.3 |     |     | μs   |

| t <sub>su(2)</sub> | Setup time, SCL to start condition             | 0.6 |     |     | μs   |

| t <sub>h(2)</sub>  | Hold time, start condition to SCL              | 0.6 |     |     | μs   |

| t <sub>su(3)</sub> | Setup time, SCL to stop condition              | 0.6 |     |     | μs   |

## 6.7 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

|                    | PARAMETER     |                                                                              | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------|---------------|------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

| T <sub>start</sub> | Start-up time | Time from I <sup>2</sup> C write until boost and amplifier are fully enabled |                 | 2   |     | ms  |      |

|                    | SCL           | tw(H)                                                                        | tsu(1)          |     |     |     |      |

|                    | SDA           |                                                                              |                 |     |     |     |      |

☑ 6-1. SCL and SDA Timing

図 6-2. Timing for Start and Stop Conditions

## 6.8 Typical Characteristics

DRV2667 JAJSGK4E – MARCH 2013 – REVISED JANUARY 2023

## 7 Detailed Description

#### 7.1 Overview

The DRV2667 device is a piezo haptic driver with integrated boost switch, integrated power diode, integrated fully-differential amplifier, and integrated digital front end. This versatile device is capable of driving both high-voltage and low-voltage piezo haptic actuators. The input signal can be driven over the I<sup>2</sup>C port or the analog inputs.

The digital interface of the DRV2667 device is available through an I<sup>2</sup>C compatible bus. A digital interface relieves the costly processor burden of PWM generation or additional analog channel requirements in the host system. Any writes to the internal FIFO automatically wakes up the device and begin playing the waveform after the 2 ms internal startup procedure. When the data flow stops or the FIFO under runs, the device automatically enters a pop-less shutdown procedure.

The DRV2667 device also includes waveform memory to store and recall waveforms with minimal latency as well as an advanced waveform synthesizer to construct complex haptic waveforms with minimal memory usage. This provide a means of hardware acceleration, relieving the host processor of haptic generation duties as well as minimizing bus traffic over the haptic interface.

The boost voltage is set using two external resistors, and the boost current limit is programmable through the  $R_{EXT}$  resistor. A typical start-up time of 2 ms makes the DRV2667 an ideal piezo driver for fast haptic responses. Thermal overload protection prevents the device from being damaged when overdriven.

## 7.2 Functional Block Diagram

## 7.3 Feature Description

#### 7.3.1 Support for Haptic Piezo Actuators

The DRV2667 device supports haptic piezo actuators of up to 200  $V_{PP}$ .

#### 7.3.2 Flexible Front End Interface

The DRV2667 device supports multiple approaches to launch and control haptic effects, that are detailed in  $\frac{1}{2}$   $\frac{1}{2}$   $\frac{1}{2}$  7.4.

図 7-1. Front-End Interface

#### 7.3.3 Ramp Down Behavior

If the user leaves the state of the DAC at any level other than mid-scale (0x00), the DAC automatically ramps down at a safe rate after the timeout period has expired. If the DRV2667 device is properly programmed, the ramp down sequence will never be used. This is a failsafe for any unavoidable interruptions to the playback process. Any writes to the FIFO during the ramp down period are discarded.

#### 7.3.4 Low Latency Startup

The DRV2667 device features a fast startup time, that is essential for achieving low latency in haptic applications. When the STANDBY bit is transitioned from high to low, the device is ready for operation. The device logic automatically controls the internal boost converter and amplifier enable signals. The boost converter and amplifier are enabled only when needed and otherwise remain in a lower power idle state. When the device received a data byte through the FIFO interface, or the GO bit is asserted (in Direct Playback from RAM or Waveform Synthesis Playback modes), the boost converter and amplifier wake up and the internal logic sends the first sample through the internal DAC after the wake-up is completed. In the system application, the entire system latency must be kept to less than 30 ms total to be imperceptible to the end user. At a 2-ms wake-up time, the device is a small percentage of the total system latency.

If the EN\_OVERRIDE bit is set, the device immediately enters the startup procedure and the boost converter and amplifier remain enabled, bypassing the internal controls. Subsequent transactions occur immediately with no wake-up overhead, but the boost converter and amplifier draw a quiescent current until the EN\_OVERRIDE bit is cleared by the user.

#### 7.3.5 Low Power Standby Mode

The DRV2667 device has a low-power standby mode through the I<sup>2</sup>C interface that puts the device in its lowest power state. This mode is entered when the standby bit (STANDBY) is set from low to high. When the STANDBY bit is set high, no other mode of operation is enabled. When the STANDBY bit transitions from high to low, the device is readied for operation and may receive data.

#### 7.3.6 Device Reset

The DRV2667 device has software-based reset functionality. When the DEV\_RST bit is set, the device immediately stops any transaction in process, resets all of its internal registers to the default values, and enters standby mode.

#### 7.3.7 Amplifier Gain

The amplifier gain determines the gain from IN+/IN– to OUT+/OUT– when using the analog playback mode. For digital playback, the gain is optimized for achieving approximately 50  $V_{PP}$ , 100  $V_{PP}$ , 150  $V_{PP}$ , 200  $V_{PP}$  without clipping. Note that clipping of the amplifier occurs if the expected peak voltage is greater than the boost converter output voltage (VBST)

The DRV2667 device gain is programmable according to  $\frac{1}{5}$  7-1.

| GAIN[1] | GAIN[0] | FULL SCALE PEAK VOLTAGE<br>(V) | GAIN (dB) ANALOG MODE |

|---------|---------|--------------------------------|-----------------------|

| 0       | 0       | 25                             | 28.8                  |

| 0       | 1       | 50                             | 34.8                  |

| 1       | 0       | 75                             | 38.4                  |

| 1       | 1       | 100                            | 40.7                  |

#### 表 7-1. Amplifier Gain Table

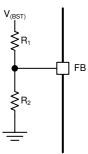

#### 7.3.8 Adjustable Boost Voltage

The output voltage of the integrated boost converter may be adjusted by a resistive feedback divider between the boost output voltage (VBST) and the feedback pin (FB). The boost voltage must be programmed to a value greater than the maximum peak signal voltage that the user expects to create with the device amplifier. Lower boost voltages achieve better system efficiency when lower amplitude signals are applied, thus the user must take care not to use a higher boost voltage than necessary. The maximum allowed boost voltage is 105 V.

#### 7.3.9 Adjustable Current Limit

The current limit of the boost switch can be adjusted through a resistor to ground placed on the REXT pin. To avoid damage to both the inductor and the DRV2667 device, the programmed current limit must be less than the rated saturation limit of the inductor selected by the user. If the combination of the programmed limit and inductor saturation is not high enough, then the output current of the boost converter will not be high enough to regulate the boost output voltage under heavy load conditions. This then causes the boosted rail to sag, possibly causing distortion of the output waveform.

#### 7.3.10 Internal Charge Pump

The DRV2667 device has an integrated charge pump to provide adequate gate drive for internal nodes. The output of this charge pump is placed on the PUMP pin. An X5R or X7R storage capacitor of 0.1  $\mu$ F with a voltage rating of 10 V or greater must be placed at this pin.

#### 7.3.11 Device Protection

#### 7.3.11.1 Thermal Protection

The DRV2667 device contains an internal temperature sensor that shuts down both the boost converter and the high-voltage amplifier when the temperature threshold is exceeded. When the device temperature falls below the threshold, the device will restart operation automatically. Continuous operation of the device is not recommended. Most haptic use models only operate the device in short bursts. The thermal shutdown function protects the device from damage when overdriven, but usage models which drive the device into thermal shutdown must always be avoided.

#### 7.3.11.2 Overcurrent Protection

If the load demands more current than what the DRV2667 device can supply, the device automatically clamps the output voltage to avoid damage.

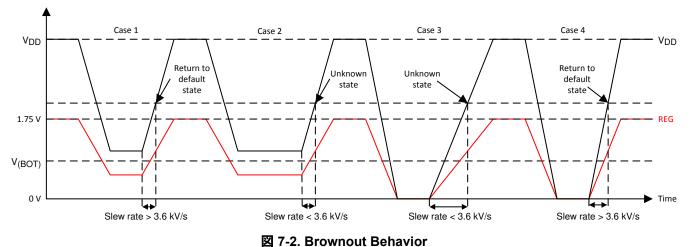

#### 7.3.11.3 Brownout Protection

The DRV2667 device has on-chip brownout protection. When activated, a reset signal is issued that returns the DRV2667 device to the initial default state. If the voltage regulator  $V_{REG}$  goes below the brownout protection threshold ( $V_{BOT}$ ) the DRV2667 device automatically shuts down. When  $V_{REG}$  returns to the typical output voltage (1.75 V), the DRV2667 device returns to the initial device state. The brownout protection threshold,  $V_{BOT}$ , is typically at 0.84 V.

There is one exception to this behavior. The brownout circuit is designed to tolerate fast brownout conditions as shown by Case 1 in  $\boxtimes$  7-2. If the V<sub>DD</sub> ramp-up rate is slower than 3.6 kV/s, then the device can fall into an unknown state. In such a situation, to return to the initial default state the device must be power-cycled with a V<sub>DD</sub> ramp-up rate that is faster than 3.6 kV/s.

## 7.4 Device Functional Modes

#### 7.4.1 FIFO Mode

The DRV2667 device includes a 100-byte FIFO for real-time haptic waveform playback. The FIFO mode accepts 8-bit digital haptic waveform data over an I<sup>2</sup>C compatible bus and writes it into an on-chip FIFO. The data is read out of the FIFO automatically at an 8-kHz sampling rate and fed into a digital-to-analog converter (DAC). The DAC then drives the high-voltage amplifier. This mode is utilized when the user writes directly to the I<sup>2</sup>C FIFO entry address (0x0B). When the first data byte is written to the FIFO, the device goes through the proper start-up sequence and begins outputting the waveform automatically. An internal timing sequence waits approximately 2 ms before the first data is sent through the DAC and output by the device. It is important that the data values start and end at or near the mid-scale code (0x00) to avoid large steps at the beginning and end of the waveform. When the FIFO is empty, the device waits for the timeout period (see  $\frac{1}{2}$   $\frac{1}{2}$

Because the speed of the serial interface could be faster than the read-out rate of the FIFO, the device issues a "not acknowledge" or "NAK" if the FIFO is full during a FIFO write transaction. If at any time the FIFO becomes completely full, the FIFO\_FULL bit is set. When in this condition, the FIFO cannot accept more data without overwriting previous data that has not yet been played. If this occurs, the user must wait until data has had a chance to empty from the FIFO before sending more data. The data must be re-sent starting at the byte that received a NAK.

Any multi-byte I<sup>2</sup>C write to the FIFO register is treated as a continuous write to the FIFO. Multi-byte writes are preferred for optimum performance. The FIFO interprets the incoming data as twos complement. This means the maximum full-scale code is 0x7F, the maximum negative voltage is 0x80, and the mid-scale is 0x00.

#### 7.4.1.1 Waveform Timeout

The DRV2667 device has a timeout period after the FIFO has emptied. This timeout period allows the user time to send a subsequent waveform before the device logic puts the device into idle mode, that then allows the host processor time to cue up an adjoining waveform from memory. After the timeout expires, the DRV2667 device must re-enter the 2 ms startup sequence before the next waveform plays. The timeout period is register-selectable to be 5, 10, 15 or 20 ms.

#### 7.4.2 Direct Playback from RAM Mode

The Direct Playback from RAM mode makes use of the on-chip 2 kB of RAM for internal waveform storage. This mode allows for immediate, low-latency recall of arbitrary haptic waveforms with very little intervention from the host processor. Haptic waveforms, be they simple or complex, may be stored in this memory at opportune times when immediate processor response is not critical. Examples of this are when the end-user product is being powered up and initialized or when an application is being launched.

The waveforms are stored as 8-bit twos-complement, Nyquist-rate data points, and are played from RAM at an 8-kHz data rate. Up to 250 ms of total waveform playback time may be stored in the Direct Playback From RAM mode format in the 2-kB memory. The waveform sizes are completely customizable, so many small waveforms may be stored or fewer long ones. The sum of the waveform lengths must not be greater than the 2-kB RAM size.

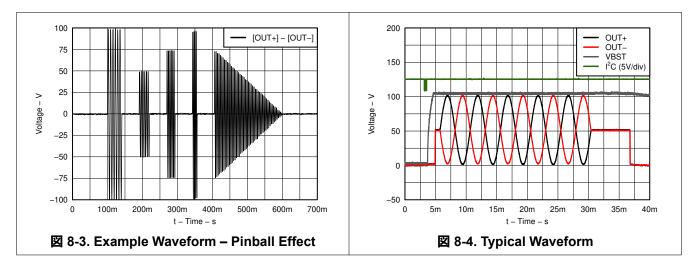

#### 7.4.3 Waveform Synthesis Playback Mode

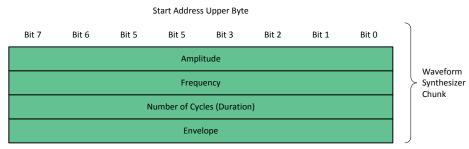

The Waveform Synthesis Playback mode is a very powerful and an efficient way of utilizing the on-chip RAM while retaining all of the low-latency and low-processor overhead benefits of the Direct Playback From RAM mode. In this mode, the actual playback data is not explicitly stored, it is synthesized based on simple sinusoidal waveform "chunks". Each sinusoidal chunk consists of the following bytes:

- Amplitude

- Frequency

- Number of Cycles (Duration)

- Envelope

Using this method, multiple chunks may be cascaded together to form a wide variety of haptic effects. In addition to programming frequency, amplitude and duration bytes, the envelope byte allows individual amplitude ramps of various rates to be applied to the beginning and end of each chunk. The Waveform Synthesis Playback mode equips the user with powerful tools to store a virtually infinite tapestry of effects in device memory.

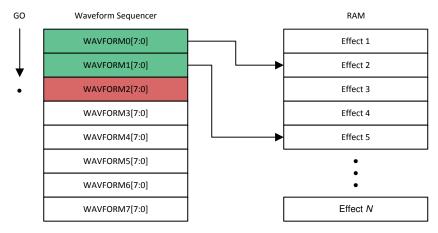

#### 7.4.4 Waveform Sequencer

For the Direct Playback from RAM and the Waveform Synthesis Playback modes, waveform identifiers are stored sequentially into a waveform header at the beginning of the waveform memory. Each waveform may be called out from memory during playback by its individual waveform identifier using the waveform sequencer. The waveform sequencer allows the user to cascade up to eight waveforms together, that can be played either as a direct waveform or a synthesized waveform using the Direct Playback from RAM and Waveform Synthesis Playback methods. When the waveform memory and the waveform sequencer are populated, this powerful feature allows the host processor to fire a chain of up to eight cascaded effects with a single I<sup>2</sup>C register write.

#### 7.4.5 Analog Playback Mode

In analog playback mode the signal in the IN+/IN- inputs is amplified and played through the high-voltage amplifier. When the INPUT\_MUX bit is set, the DRV2667 device switches the analog inputs (IN+/IN-) to the high-voltage amplifier. While in the analog mode, the gain is still register-selectable. Also, the high-voltage amplifier enable is controlled directly through the EN\_OVERRIDE bit, so the EN\_OVERRIDE bit must be set for the boost and amplifier to be active.

#### 7.4.6 Low Voltage Operation Mode

The lowest gain setting is optimized for 50 V<sub>PP</sub> with a boost voltage of 30 V. Some applications may not need 50 V<sub>PP</sub>, so the user may elect to program the boost converter as low as 15 V to improve efficiency. When using boost voltages lower than 30 V, consider the following: First, to reduce boost ripple to an acceptable level, a 50-V rater, 0.22- $\mu$ F boost capacitor is recommended. Second, the maximum code range of the digital interface is limited. For example, the user may elect to program the boost voltage to 25 V, and plan for a maximum drive signal of 40 V<sub>PP</sub> at the actuator. Any digital code given to the FIFO that is greater than 20 V<sub>P</sub> / 25 V<sub>P</sub> x 127 = ±102 may induce clipping, so the user must only send digital codes between -102 and 102. Use of codes outside this range, for this example, may clip or drive the actuator beyond its rating.

#### 7.5 Programming

#### 7.5.1 Programming the Boost Voltage

The boost output voltage is programmed through two external resistors as shown in  $\boxtimes$  7-3. The boost output voltage is given by  $\ddagger$  1.

#### 図 7-3. FB Network

$$V_{(BST)} = V_{(FB)} \cdot \left(1 + \frac{R_1}{R_2}\right)$$

(1)

(2)

#### where

$V_{(BST)}$  must be programmed to a value of 5.0 V greater than the largest peak voltage expected in the system to allow adequate amplifier headroom. Because the programming range for the boost voltage extends to 105 V, the leakage current through the resistor divider can become significant. It is recommended that the sum of the resistances  $R_1 + R_2$  be greater than 400 kΩ. When resistor values greater than 1 MΩ are used, PCB contamination may cause boost voltage inaccuracy. Exercise caution when soldering large resistances, and clean the area when finished for best results.  $\frac{1}{2}$  7-2 shows examples on how to configure the device for different output voltages.

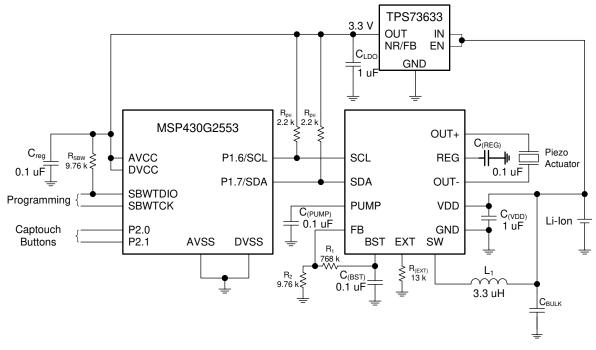

| R <sub>1</sub> | R <sub>2</sub> | GAIN[1:0] | V <sub>(BST)</sub> | FULL SCALE PEAK VOLTAGE<br>(V) |

|----------------|----------------|-----------|--------------------|--------------------------------|

| 402 kΩ         | 18.2 kΩ        | 00        | 30                 | 25                             |

| 392 kΩ         | 9.76 kΩ        | 01        | 55                 | 50                             |

| 768 kΩ         | 13 kΩ          | 10        | 80                 | 75                             |

| 768 kΩ         | 9.76 kΩ        | 11        | 105                | 100                            |

#### 表 7-2. Boost Voltage Table

#### 7.5.2 Programming the Boost Current Limit

The peak current drawn from the supply through the inductor is set solely by the  $R_{(EXT)}$  resistor. This peak current limit is independent of the inductance value chosen, but the inductor must be capable of handling this programmed limit. The relationship of  $R_{(EXT)}$  and  $I_{LIM}$  is approximated by  $rac{1}{\sim} 2$ .

$$\mathbf{R}_{(\text{EXT})} = \left(\mathbf{K} \cdot \frac{\mathbf{V}_{\text{REF}}}{\mathbf{I}_{\text{LIM}}}\right) - \mathbf{R}_{\text{INT}}$$

where

- K = 10500, , and

- V<sub>REF</sub> = 1.35 V

- R<sub>INT</sub> = 60 Ω

- ILIM is the desired peak current limit through the inductor.

#### 7.5.3 Programming the RAM

#### 7.5.3.1 Accessing the RAM

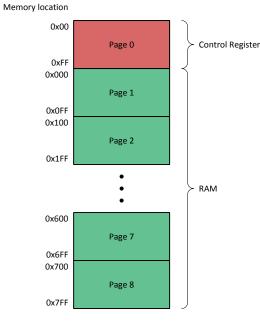

To maintain compatibility with the majority of standard  $I^2C$  controllers, the DRV2667 device uses 8-bit addressing. To access 2 kB of RAM, a paging system is employed. The page register is located at address 0xFF.

There are 8 memory pages that make up the 2048 bytes with 256 bytes on each page. Note that page 0 is reserved for register control space, as shown in  $\boxtimes$  7-4.

🛛 7-4. Page Structure

Because the device addresses are only 8-bits, a special exception exists to distinguish whether the user is trying to write the page register at address 0xFF or the memory location at 0xPFF, where P represents the page number. In order to access the page register, the programmer must use a Single-Byte I<sup>2</sup>C protocol to perform a single-byte write to memory location 0xFF (see t / 2 = 2 7.5.4.3). To access the memory location in RAM at register 0xFF, the user must use the Incremental Multiple-Byte protocol (see t / 2 = 2 7.5.4.4), and the beginning address must be less than 0xFF.

The page register automatically increments for multiple-byte writes that cross the page boundaries, as a convenience for filling memory across multiple pages. Multiple-byte reads across page boundaries are not supported. All memory is retained in the device until the device power is cycled.

#### 7.5.3.2 RAM Format

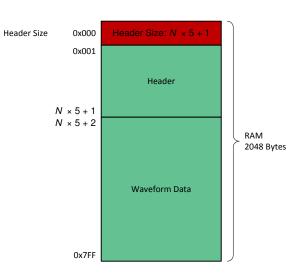

The RAM is structured into 3 main blocks as shown in  $\boxtimes$  7-5:

- Header size block; 1 byte

- Header block; *N* x 5 bytes, where *N* is the number of effects stored

- Waveform data block

Memory location

2 7-5. RAM Structure

The first byte of the RAM (at memory location 0x00 on Page 1) must contain the header size. The header size refers to the last byte in the header, so the value stored must be  $N \ge 5 + 1$ , as shown in  $\boxtimes 7-5$ .

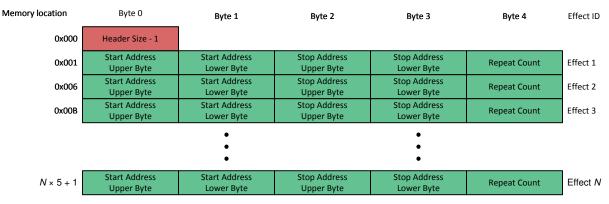

The header block describes the location of the waveform data content. The structure of the header consists of 5-byte blocks containing the following information (see  $\boxtimes$  7-6):

- · Start address, upper byte

- · Start address, lower byte

- Stop address, upper byte

- Stop address, lower byte

- Repeat count

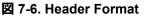

Because more than 8-bits are required to address the 2 kB of memory, each start and stop address consists of two bytes. The start address contains the location of the first byte in the waveform and the stop byte contains the locations of the last byte in the waveform. Within the address byte, the upper byte contains the page address, and the lower byte refers to the specified address within the page (see  $\boxtimes$  7-7). The upper byte interprets a 0 as Page 1, and a 7 as Page 8 because the waveform processing engine cannot access the control space in Page 0.

図 7-7. Header Address Byte Format

The repeat count byte contains the number of times this waveform identifier (which starts at the start address and ends at the stop address) is to be repeated when it is called during playback. A 0 in this byte is interpreted as an infinite loop and the waveform is played indefinitely until the GO bit is cleared by the user. Otherwise, the repeat count is simply the number of times that the waveform is repeated.

The waveform data can be interpreted in two ways:

- Direct Playback from RAM mode

- Waveform Synthesis Playback mode

Note that both modes can be stored in the RAM, and the device interprets the waveform data according to the mode specified. To signal the device which mode is desired, the MSB of the start address, upper byte is used (see  $\boxtimes$  7-7). A 0 indicates Direct Playback from RAM Mode, and a 1 indicates a Waveform Synthesis Playback Mode.

The Direct Playback from RAM mode requires no special handling: the waveform starts at the start-address location and plays each sub-sequent byte at the Nyquist-rate. The data is stored in twos complement, where 0xFF is interpreted as full-scale, 0x00 is no signal, and 0x80 is negative full-scale. The waveform is played at an 8-kHz data rate.

The Waveform Synthesis Playback Mode stores data in sinusoidal chunks, where each chunk consists of four bytes as shown in  $\boxed{2}$  7-8:

- Amplitude

- Frequency

- Number of Cycles (Duration)

- Envelope

## 図 7-8. Waveform Synthesizer Format

The interpretation of each of these four bytes is outlined in  $\frac{1}{2}$  7-3.

| BYTE | NAME                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | Amplitude                      | The amplitude byte refers to the magnitude of the synthesized sinusoid. 0xFF produces a full-<br>scale sinusoid, 0x80 produces a half-scale sinusoid, and 0x00 does not produce any signal. An<br>amplitude of 0x00 can be useful for producing timed waits or delays within the effect.<br>To calculate the absolute peak voltage, use the following equation, where <i>amplitude</i> is a single-<br>byte integer:<br>Peak voltage = amplitude / 255 x full-scale peak voltage                                             |

| 2    | Frequency                      | The frequency byte adjusts the frequency of the synthesized sinusoid. The minimum frequency is 7.8125 Hz. A value of zero is not allowed. The sinusoidal frequency is determined with the following equation, where <i>frequency</i> is a single-byte integer:<br>Sinusoid frequency (Hz) = 7.8125 x frequency                                                                                                                                                                                                               |

| 3    | Number of Cycles<br>(Duration) | The number of sinusoidal cycles to be played by the synthesizer. A convenient way to specify the duration of a coherent sinusoid is by inputting the number of cycles. This method ensures that the waveform chunk will always begin and end at zero amplitude, thus avoiding discontinuities. The actual duration in time given by this value may be calculated through the following equation, where # of cycles and frequency are both single-byte integers.<br>Duration (ms) = 1000 x # of cycles / (7.8125 x frequency) |

#### 表 7-3. Waveform Chunk Bytes for Synthesizer

| BYTE | NAME     |                                                                                                                                                                                                                               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |          | at the beginning of the synthesized sinusor<br>rate at the end of the synthesized sinusor<br>in the duration parameter of the waveform<br>parameter of the waveform. As such, if a<br>than the duration time as programmed in | bles. The upper nibble, bits [7:4], sets the ramp-up rate<br>oid, and the lower nibble, bits [3:0], sets the ramp-down<br>d. The user must note that the ramp-up time is included<br>n, and the ramp-down time is appended to the duration<br>ramp-up time is used, the ramp-up time must be less<br>byte 3. Also note that the <i>Total Ramp Time</i> is for a ramp<br>). Ramps to a fraction of full-scale have the same |

|      |          | Nibble Value                                                                                                                                                                                                                  | Total Ramp Time                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |          | 0                                                                                                                                                                                                                             | No Envelope                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |          | 1                                                                                                                                                                                                                             | 32 ms                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |          | 2                                                                                                                                                                                                                             | 64 ms                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |          | 3                                                                                                                                                                                                                             | 96 ms                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4    | Envelope | 4                                                                                                                                                                                                                             | 128 ms                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |          | 5                                                                                                                                                                                                                             | 160 ms                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |          | 6                                                                                                                                                                                                                             | 192 ms                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |          | 7                                                                                                                                                                                                                             | 224 ms                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |          | 8                                                                                                                                                                                                                             | 256 ms                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |          | 9                                                                                                                                                                                                                             | 512 ms                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |          | 10                                                                                                                                                                                                                            | 768 ms                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |          | 11                                                                                                                                                                                                                            | 1024 ms                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |          | 12                                                                                                                                                                                                                            | 1280 ms                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |          | 13                                                                                                                                                                                                                            | 1536 ms                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |          | 14                                                                                                                                                                                                                            | 1792 ms                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |          | 15                                                                                                                                                                                                                            | 2048 ms                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### 表 7-3. Waveform Chunk Bytes for Synthesizer (continued)

#### 7.5.3.2.1 Programming the Waveform Sequencer

To play the effects stored in memory, the effects must be loaded into the waveform sequencer. The effects can then be launched by the use of the GO bit.

The waveform sequencer queues up to eight waveform identifiers for playback. A waveform identifier is an integer value referring to the index position of a waveform in the Header Block (see  $\boxtimes$  7-6). Upon assertion of the GO bit, playback begins at register 0x03. When playback of that waveform ends, the waveform sequencer plays the next waveform identifier in register 0x04 if the identifier stored in register 0x04 is non-zero. Th waveform sequencer continues in this way until the sequencer reaches an identifier value of zero or until all eight identifiers are played as shown in  $\boxtimes$  7-9.

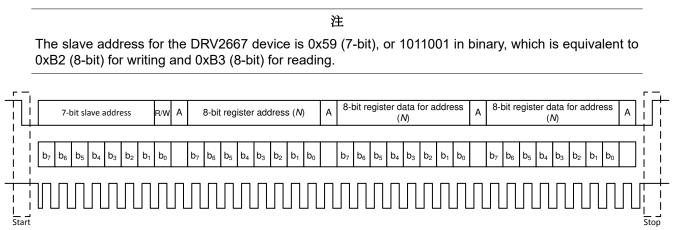

#### 7.5.4 I<sup>2</sup>C Interface

#### 7.5.4.1 General I<sup>2</sup>C Operation

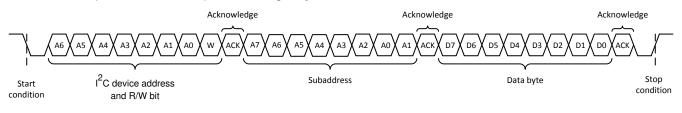

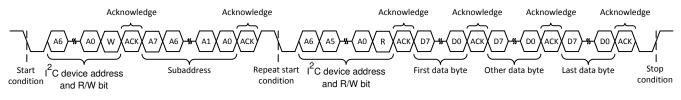

The  $l^2C$  bus employs two signals, SDA (data) and SCL (clock), to communicate between integrated circuits in a system. The bus transfers data serially, one bit at a time. The 8-bit address and data bytes are transferred with the most-significant bit (MSB) first. In addition, each byte transferred on the bus is acknowledged by the receiving device with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving a stop condition on the bus. The bus uses transitions on the data pin (SDA) while the clock is at logic high to indicate start and stop conditions. A high-to-low transition on the SDA signal indicates a start, and a low-to-high transition indicates a stop. Normal data-bit transitions must occur within the low time of the clock period.  $\boxtimes$  7-10 shows a typical sequence. The master device generates the 7-bit slave address and the read-write (R/W) bit to start communication with a slave device. The master device then waits for an acknowledge condition. The slave device holds the SDA signal low during the acknowledge clock period to indicate acknowledgment. When this acknowledgment occurs, the master transmits the next byte of the sequence. Each device is addressed by a unique 7-bit slave address plus a R/W bit (1 byte). All compatible devices share the same signals through a bidirectional bus using a wired-AND connection.

The number of bytes that can be transmitted between start and stop conditions is not limited. When the last word transfers, the master generates a stop condition to release the bus.  $\boxtimes$  7-10 shows a generic data-transfer sequence.

Use external pullup resistors for the SDA and SCL signals to set the logic-high level for the bus. Pullup resistors with values between 660  $\Omega$  and 4.7 k $\Omega$  are recommended. Do not allow the SDA and SCL voltages to exceed the DRV2667 supply voltage, V<sub>DD</sub>.

The DRV2667 device operates as an  $I^2$ C-slave with 1.8-V logic thresholds, but can operate up to the V<sub>DD</sub> voltage.

#### 図 7-10. Typical I<sup>2</sup>C Sequence

#### 7.5.4.2 Single-Byte and Multiple-Byte Transfers

The serial control interface supports both single-byte and multiple-byte read-write operations for all registers.

During multi-byte transactions, the register address provided serves as the starting address. Subsequent data transfers automatically increment the register address accessed until a stop condition is reached.

#### 7.5.4.3 Single-Byte Write

As shown in  $\boxtimes$  7-11, a single-byte data-write transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C device address and the read-write bit. The read-write bit determines the direction of the data transfer. For a write-data transfer, the read-write bit must be set to 0. After receiving the correct I<sup>2</sup>C device address and the read-write bit, the DRV2667 device responds with an acknowledge bit. Next, the master

transmits the register byte corresponding to the DRV2667 internal-memory address that is accessed. After receiving the register byte, the device responds again with an acknowledge bit. Finally, the master device transmits a stop condition to complete the single-byte data-write transfer.

2 7-11. Single-Byte Write Transfer

#### 7.5.4.4 Multiple-Byte Write and Incremental Multiple-Byte Write

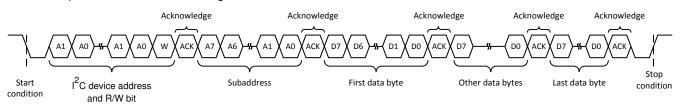

A multiple-byte data write transfer is identical to a single-byte data write transfer except that multiple data bytes are transmitted by the master device to the DRV2667 device. After receiving each data byte, the DRV2667 device responds with an acknowledge bit as shown in  $\boxtimes$  7-12.

#### 7.5.4.5 Single-Byte Read

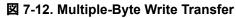

$\boxtimes$  7-13 shows that a single-byte data-read transfer begins with the master device transmitting a start condition followed by the l<sup>2</sup>C device address and the read-write bit. For the data-read transfer, both a write followed by a read actually occur. Initially, a write occurs to transfer the address byte of the internal memory address to be read. As a result, the read-write bit is set to 0.

After receiving the DRV2667 address and the read-write bit, the DRV2667 device responds with an acknowledge bit. The master then sends the internal memory address byte, after which the device issues an acknowledge bit. The master device transmits another start condition followed by the DRV2667 address and the read-write bit again. This time, the read-write bit is set to 1, indicating a read transfer. Next, the DRV2667 device transmits the data byte from the memory address that is read. After receiving the data byte, the master device transmits a not-acknowledge followed by a stop condition to complete the single-byte data read transfer. See the note in the  $\frac{1}{2}$   $\frac{1}{2} \times 7.5.4.1$  section for the device address.

図 7-13. Single-Byte Read Transfer

#### 7.5.4.6 Multiple-Byte Read

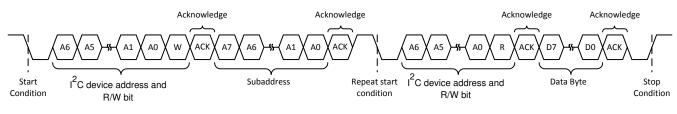

A multiple-byte data-read transfer is identical to a single-byte data-read transfer except that multiple data bytes are transmitted by the DRV2667 device to the master device as shown in  $\boxtimes$  7-14. With the exception of the last data byte, the master device responds with an acknowledge bit after receiving each data byte.

図 7-14. Multiple-Byte Read Transfer

## 7.6 Register Map

## 表 7-4. Register Map Overview

| REG NO. | DEFAULT | BIT 7    | BIT 6         | BIT 5    | BIT 4   | BIT 3    | BIT 2        | BIT 1       | BIT 0     |

|---------|---------|----------|---------------|----------|---------|----------|--------------|-------------|-----------|

| 0x00    | 0x02    |          | ·             | Reserved | •       |          | ILLEGAL_ADDR | FIFO_EMPTY  | FIFO_FULL |

| 0x01    | 0x38    | Reserved |               | CHIP     | ID[3:0] |          | INPUT_MUX    | GAIN        | I[1:0]    |

| 0x02    | 0x40    | DEV_RST  | STANDBY       | Res      | erved   | TIMEO    | UT[1:0]      | EN_OVERRIDE | GO        |

| 0x03    | 0x00    |          |               |          | WAVFO   | RM0[7:0] |              |             |           |

| 0x04    | 0x00    |          | WAVFORM1[7:0] |          |         |          |              |             |           |

| 0x05    | 0x00    |          | WAVFORM2[7:0] |          |         |          |              |             |           |

| 0x06    | 0x00    |          |               |          | WAVFO   | RM3[7:0] |              |             |           |

| 0x07    | 0x00    |          |               |          | WAVFO   | RM4[7:0] |              |             |           |

| 0x08    | 0x00    |          |               |          | WAVFO   | RM5[7:0] |              |             |           |

| 0x09    | 0x00    |          |               |          | WAVFO   | RM6[7:0] |              |             |           |

| 0x0A    | 0x00    |          | WAVFORM7[7:0] |          |         |          |              |             |           |

| 0x0B    | 0x00    |          | FIFO[7:0]     |          |         |          |              |             |           |

| 0xFF    | 0x00    |          |               |          | PAG     | E[7:0]   |              |             |           |

## 表 7-5. EEPROM Map Overview

| REG NO. | DEFAULT | BIT 7    | BIT 6 | BIT 5 | BIT 4  | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---------|---------|----------|-------|-------|--------|-------|-------|-------|-------|

| 0x01    | 0x38    | Reserved |       | CHIPI | D[3:0] |       |       |       |       |

## 7.6.1 Address: 0x00

| 図 7-15. 0x00 |   |          |   |   |                     |               |              |  |  |  |  |  |

|--------------|---|----------|---|---|---------------------|---------------|--------------|--|--|--|--|--|

| 7            | 6 | 5        | 4 | 3 | 2                   | 1             | 0            |  |  |  |  |  |

|              |   | Reserved |   |   | ILLEGAL_ADDR[0<br>] | FIFO_EMPTY[0] | FIFO_FULL[0] |  |  |  |  |  |

|              |   |          |   |   | RO-0                | RO-1          | RO-0         |  |  |  |  |  |

#### 表 7-6. Address: 0x00

| BIT | FIELD        | TYPE | DEFAULT | DESCRIPTION      | N                                                                                                                                      |  |

|-----|--------------|------|---------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| 7-3 | Reserved     |      |         |                  |                                                                                                                                        |  |

| 2   | ILLEGAL_ADDR | RO   | 0       | perform an ille  | the waveform generator attempted to<br>gal operation. This usually means<br>ntered improper header information<br>m memory.            |  |

|     |              |      |         | 0                | Normal operation                                                                                                                       |  |

|     |              |      |         | 1                | Illegal address attempted                                                                                                              |  |

| 1   | FIFO_EMPTY   | RO   | 1       | Indicates that t | the internal 100-byte FIFO is empty.                                                                                                   |  |

|     |              |      |         | 0                | FIFO is not empty                                                                                                                      |  |

|     |              |      |         | 1                | FIFO is empty                                                                                                                          |  |

| 0   | FIFO_FULL    | RO   | 0       | cannot accept    | Indicates that the internal 100-byte FIFO is full and<br>cannot accept data until another byte has played<br>through the internal DAC. |  |

|     |              |      |         | 0                | FIFO not full                                                                                                                          |  |

|     |              |      |         | 1                | FIFO is full                                                                                                                           |  |

#### 7.6.2 Address: 0x01

#### 🖾 7-16. 0x01

| 7        | 6           | 5    | 4    | 3    | 2            | 1     | 0              |

|----------|-------------|------|------|------|--------------|-------|----------------|

| Reserved | CHIPID[3:0] |      |      |      | INPUT_MUX[0] | GAIN  | <b>J</b> [1:0] |

|          | RW-0        | RW-1 | RW-1 | RW-1 | R/W-0        | R/W-0 | R/W-0          |

#### 表 7-7. Address: 0x01

| BIT | FIELD       | TYPE | DEFAULT | DESCRIPTION       |                                       |

|-----|-------------|------|---------|-------------------|---------------------------------------|

| 7   | Reserved    |      |         |                   |                                       |

| 6-3 | CHIPID[3:0] | RW   | 7       | Identifies the de | evice.                                |

|     |             |      |         | 5                 | DRV2665                               |

|     |             |      |         | 7                 | DRV2667                               |

| 2   | INPUT_MUX   | R/W  | 0       | Selects the sour  | rce to be played.                     |

|     |             |      |         | 0                 | Digital input source                  |

|     |             |      |         | 1                 | Analog input source                   |

| 1-0 | GAIN[1:0]   | R/W  | 0       | Selects the gain  | n for the amplifier.                  |

|     |             |      |         | 0                 | 25 V (Digital) - 28.8 dB<br>(Analog)  |

|     |             |      |         | 1                 | 50 V (Digital) - 34.8 dB<br>(Analog)  |

|     |             |      |         | 2                 | 75 V (Digital) - 38.4 dB<br>(Analog)  |

|     |             |      |         | 3                 | 100 V (Digital) - 40.7 dB<br>(Analog) |

#### 7.6.3 Address: 0x02

#### 図 7-17. 0x02

| 7          | 6          | 5    | 4     | 3      | 2       | 1              | 0     |

|------------|------------|------|-------|--------|---------|----------------|-------|

| DEV_RST[0] | STANDBY[0] | Rese | erved | TIMEOU | UT[1:0] | EN_OVERRIDE[0] | GO[0] |

DRV2667 JAJSGK4E – MARCH 2013 – REVISED JANUARY 2023

| 図 7-17. 0x02 (continued) |              |           |             |                                                             |                                                                                                                                         |                                                      |  |  |  |  |

|--------------------------|--------------|-----------|-------------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|--|--|