# DRV2624 内蔵メモリ搭載超低消費電力閉ループ LRA/ERM ハプティック ドライバー

## 1 特長

- 超低電力シャットダウン モード

- 低消費電力のスタンバイ状態

- 抵抗ベースのアクチュエータ診断

- SimpleDrive 1 線式振動方式**

- 自動共振トラッキングおよび報告

- 自動オーバードライブおよびブレーキ

- 自動レベル キャリブレーション

- バッテリ放電に対応する駆動補償機能

- 電力保持機能付きの構成可能なバッテリ モニタ

- 自動ブレーキを使用したオフ共振駆動

- LRA 波形形状の選択

- ループ可能な波形シーケンサを備えた、RAM

- リアルタイム再生 (RTP) モード

- I<sup>2</sup>C 制御のデジタル プレイバック エンジン

- ハードウェアとソフトウェアのトリガ オプション

- 自動ブレーキによるスタンバイへの自動的な遷移

- オプションの割り込みピン

- 1.8V 互換、VDD 許容のデジタル インターフェイス<sup>1</sup>

## 2 アプリケーション

- 携帯電話およびタブレット

- フィットネス バンドやウェアラブル デバイスなど

- リモート制御、マウス、ペリフェラル デバイス

- タッチ対応デバイス

- ヒューマン マシン インターフェイス

## 3 説明

DRV2624 デバイスは、独自の閉ループ アーキテクチャに依存したハプティクス ドライバで、消費電力を最適化しながら、シャープで強力で一貫性のあるハプティクス効果を実現します。

内部メモリとループ可能な波形シーケンサと、自動オーバードライブおよびブレーキ機能により、鮮明で最適なハプティクス効果を簡単に生成できるため、処理ユニットの負荷が軽減されます。

DRV2624 デバイスには、自動的にスタンバイ状態に移行する機能とバッテリ保存機能があり、ユーザーの介入なしに消費電力を低減できます。NRST ピンを使用すると、完全なシャットダウン状態を設定して、消費電力をさらに削減できます。

波形形状の選択を使用すると、正弦波および方形波ドライブでハプティクスの操作感と可聴性能をカスタマイズできます。自動ブレーキによるオフ共振駆動により、非共振ハプティクス設計を簡素化できます。

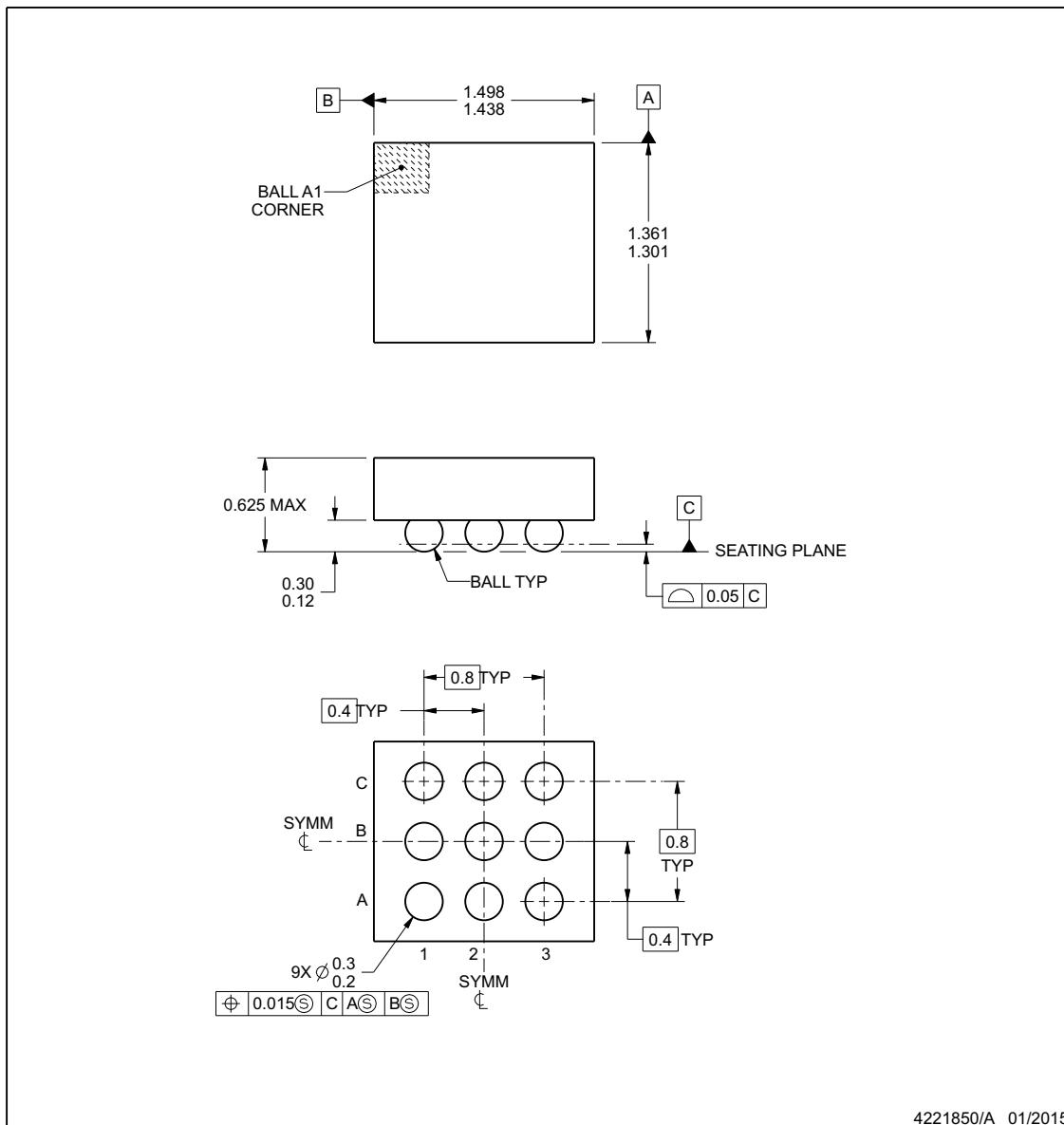

### パッケージ情報

| 型番      | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|---------|----------------------|--------------------------|

| DRV2624 | DSBGA (9)            | 1.498mm × 1.361mm        |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンを含みます。

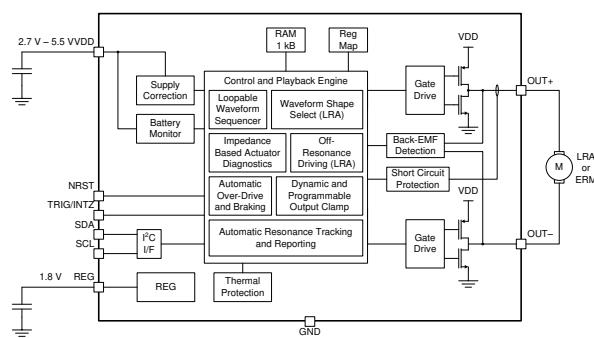

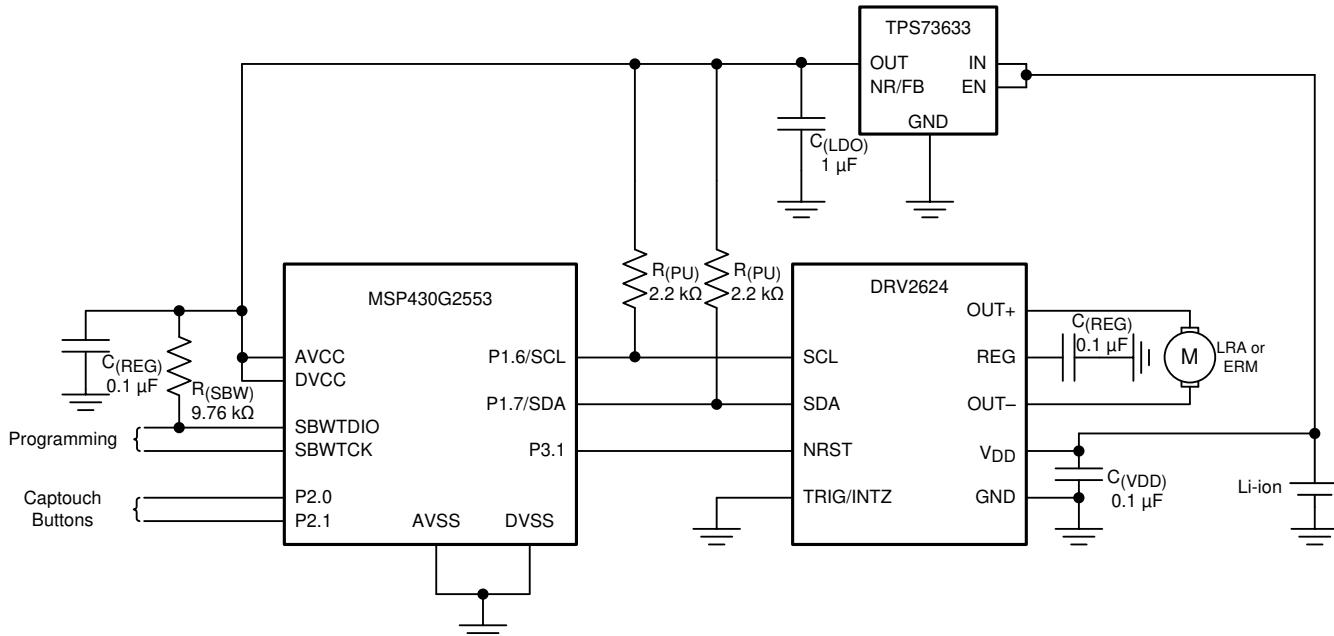

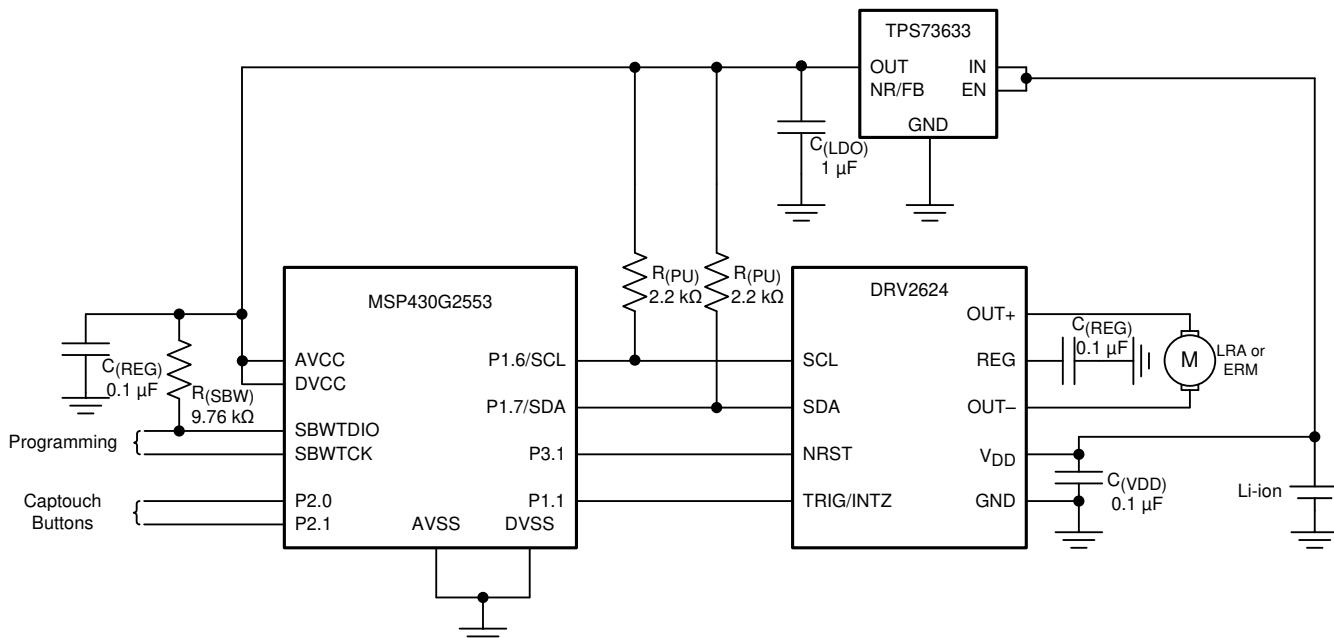

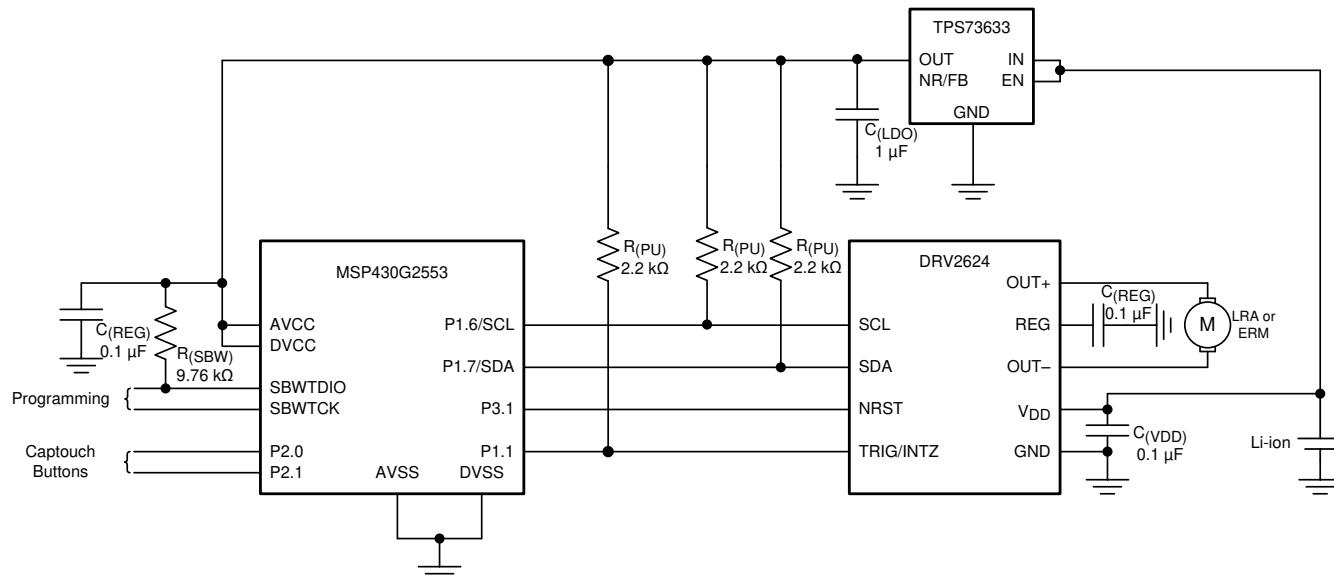

概略回路図

<sup>1</sup> による特許申請中の制御アルゴリズム

## 目次

|                     |           |                                     |           |

|---------------------|-----------|-------------------------------------|-----------|

| <b>1 特長</b>         | <b>1</b>  | 8.17 アドレス:0x10.....                 | 50        |

| <b>2 アプリケーション</b>   | <b>1</b>  | 8.18 アドレス:0x11.....                 | 50        |

| <b>3 説明</b>         | <b>1</b>  | 8.19 アドレス:0x12.....                 | 51        |

| <b>4 ピン構成および機能</b>  | <b>3</b>  | 8.20 アドレス:0x13.....                 | 51        |

| <b>5 仕様</b>         | <b>4</b>  | 8.21 アドレス:0x14.....                 | 52        |

| 5.1 絶対最大定格          | 4         | 8.22 アドレス:0x15.....                 | 52        |

| 5.2 ESD 定格          | 4         | 8.23 アドレス:0x16.....                 | 53        |

| 5.3 推奨動作条件          | 4         | 8.24 アドレス:0x17.....                 | 53        |

| 5.4 熱に関する情報         | 4         | 8.25 アドレス:0x18.....                 | 54        |

| 5.5 電気的特性           | 6         | 8.26 アドレス:0x19.....                 | 55        |

| 5.6 タイミング要件         | 6         | 8.27 アドレス:0x1A.....                 | 55        |

| 5.7 スイッチング特性        | 6         | 8.28 アドレス:0x1B.....                 | 55        |

| 5.8 代表的特性           | 8         | 8.29 アドレス:0x1C.....                 | 56        |

| <b>6 パラメータ測定情報</b>  | <b>11</b> | 8.30 アドレス:0x1D.....                 | 56        |

| 6.1 グラフのテスト構成       | 11        | 8.31 アドレス:0x1F.....                 | 56        |

| <b>7 詳細説明</b>       | <b>12</b> | 8.32 アドレス:0x20.....                 | 58        |

| 7.1 概要              | 12        | 8.33 アドレス:0x21.....                 | 58        |

| 7.2 機能ブロック図         | 12        | 8.34 アドレス:0x22.....                 | 58        |

| 7.3 機能説明            | 12        | 8.35 アドレス:0x23.....                 | 59        |

| 7.4 デバイスの機能モード      | 22        | 8.36 アドレス:0x24.....                 | 59        |

| 7.5 例外的な条件下の動作です    | 25        | 8.37 アドレス:0x25.....                 | 61        |

| 7.6 プログラミング         | 26        | 8.38 アドレス:0x26.....                 | 61        |

| <b>8 レジスタ マップ</b>   | <b>39</b> | 8.39 アドレス:0x27.....                 | 61        |

| 8.1 アドレス:0x00.....  | 41        | 8.40 アドレス:0x28.....                 | 62        |

| 8.2 アドレス:0x01.....  | 41        | 8.41 アドレス:0x29.....                 | 64        |

| 8.3 アドレス:0x02.....  | 43        | 8.42 アドレス:0x2A.....                 | 64        |

| 8.4 アドレス:0x03.....  | 43        | 8.43 アドレス:0x2C.....                 | 66        |

| 8.5 アドレス:0x04.....  | 43        | 8.44 アドレス:0x2E.....                 | 66        |

| 8.6 アドレス:0x05.....  | 44        | 8.45 アドレス:0x2F.....                 | 66        |

| 8.7 アドレス:0x06.....  | 44        | 8.46 アドレス:0x30.....                 | 68        |

| 8.8 アドレス:0x07.....  | 45        | 8.47 アドレス:0xFD.....                 | 68        |

| 8.9 アドレス:0x08.....  | 46        | 8.48 アドレス:0xFE.....                 | 68        |

| 8.10 アドレス:0x09..... | 47        | 8.49 アドレス:0xFF.....                 | 68        |

| 8.11 アドレス:0x0A..... | 47        | <b>9 デバイスおよびドキュメントのサポート</b> .....   | <b>76</b> |

| 8.12 アドレス:0x0B..... | 47        | 9.1 デバイス サポート.....                  | 76        |

| 8.13 アドレス:0x0C..... | 48        | 9.2 商標.....                         | 76        |

| 8.14 アドレス:0x0D..... | 48        | <b>10 改訂履歴</b> .....                | <b>76</b> |

| 8.15 アドレス:0x0E..... | 49        | <b>11 メカニカル、パッケージ、および注文情報</b> ..... | <b>77</b> |

| 8.16 アドレス:0x0F..... | 49        |                                     |           |

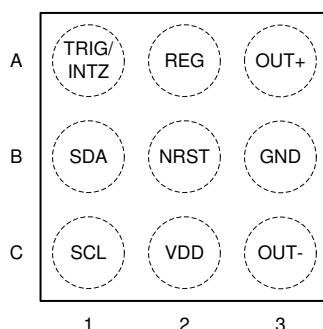

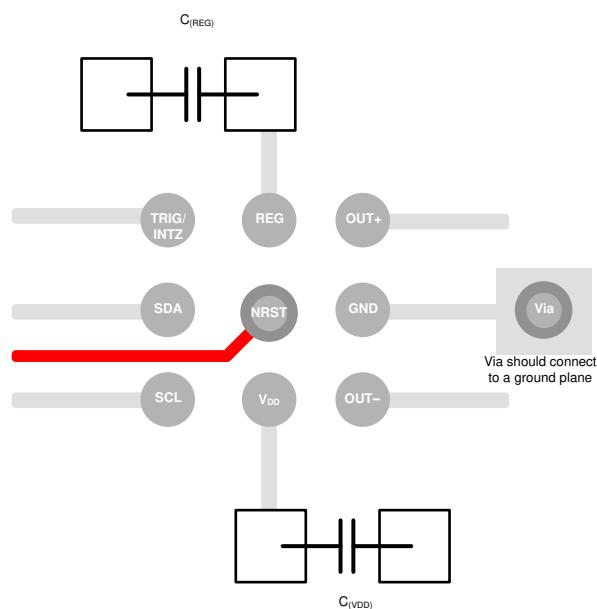

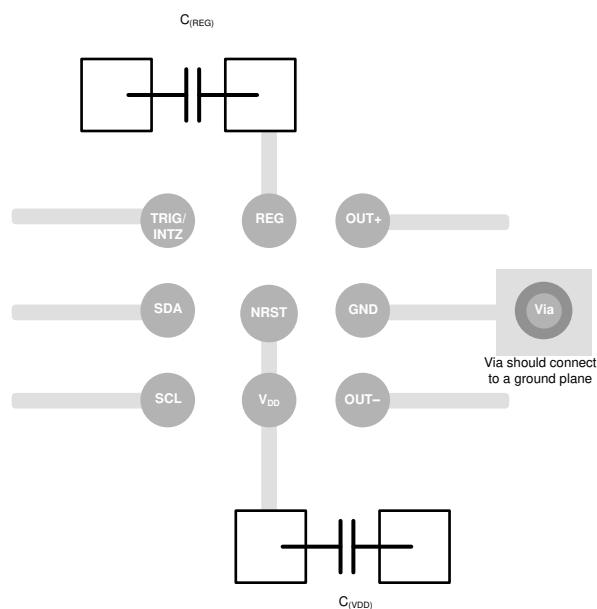

## 4 ピン構成および機能

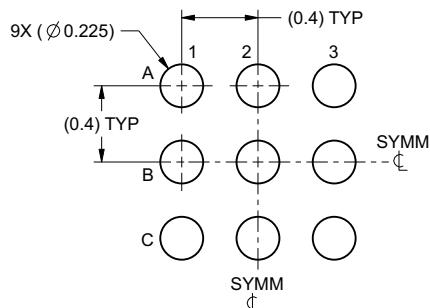

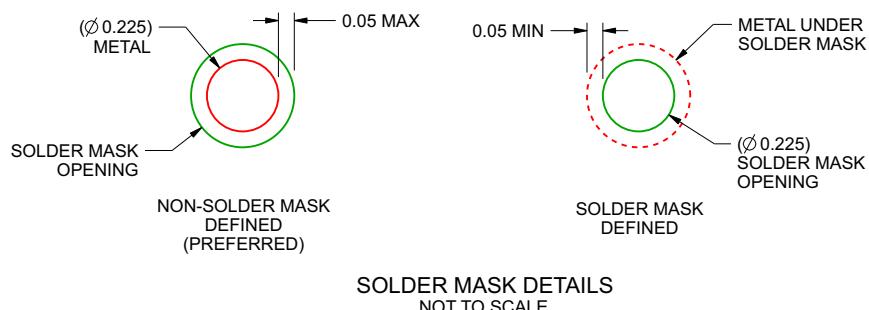

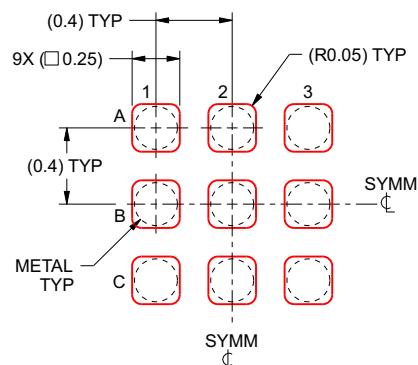

図 4-1. YFF パッケージ 9 ピン DSBGA 上面図

表 4-1. ピンの機能

| ピン        |    | I/O | 説明                                                                                                         |

|-----------|----|-----|------------------------------------------------------------------------------------------------------------|

| 名称        | 番号 |     |                                                                                                            |

| VDD       | C2 | P   | 電源電圧 (2.7V ~ 5.5V)。0.1μF セラミック コンデンサが必要です。                                                                 |

| GND       | B3 | P   | 電源グランド                                                                                                     |

| REG       | A2 | O   | 1.8V レギュレータ出力。0.1μF セラミック コンデンサが必要です                                                                       |

| OUT-      | C3 | O   | 負のハプティクス ドライバの差動出力                                                                                         |

| OUT+      | A3 | O   | 正のハプティクス ドライバの差動出力                                                                                         |

| SDA       | B1 | I/O | I <sup>2</sup> C データ                                                                                       |

| SCL       | C1 | I   | I <sup>2</sup> C クロック                                                                                      |

| TRIG/INTZ | A1 | I/O | マルチモード ピン。入力トリガ (パルス)、入力イネーブル、または出力割り込みとして選択できます。このピンには、内部にプルダウン 抵抗があります。<br>ピンを使用しない場合は、このピンはグランドに接続されます。 |

| NRST      | B2 | I   | デバイスリセット ピン (シャットダウン モード)このピンを使用しない場合、そのピンは VDD に接続されます (内部プルアップまたはプルダウンなし)。                               |

## 5 仕様

### 5.1 絶対最大定格

自由空気での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

|                    |                     | 最小値  | 最大値 | 単位 |

|--------------------|---------------------|------|-----|----|

| 電源電圧               | $V_{DD}$            | -0.3 | 6   | V  |

| 入力電圧               | NRST                | -0.3 | 6   | V  |

|                    | SDA                 | -0.3 | 6   | V  |

|                    | SCL                 | -0.3 | 6   | V  |

|                    | TRIG/INTZ           | -0.3 | 6   | V  |

|                    | 自由気流での動作温度範囲、 $T_A$ | -40  | 85  | °C |

| 動作時の接合部温度範囲、 $T_J$ |                     | -40  | 150 | °C |

| 保管温度、 $T_{stg}$    |                     | -65  | 150 | °C |

- (1) 絶対最大定格を超えた動作は、デバイスに恒久的な損傷を与える可能性があります。絶対最大定格は、これらの条件において、または推奨動作条件に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|                  |                                                                | 最小値   | 最大値  | 単位 |

|------------------|----------------------------------------------------------------|-------|------|----|

| $V_{(ESD)}$ 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>   | -1500 | 1500 | V  |

|                  | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠、すべてのピン <sup>(2)</sup> | -500  | 500  |    |

(1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|             |           | 最小値 | 公称値 | 最大値 | 単位 |

|-------------|-----------|-----|-----|-----|----|

| $V_{DD}$    | 電源電圧      | 2.7 | 5.5 | 5.5 | V  |

| $R_L$       | 負荷インピーダンス | 8   |     |     | Ω  |

| $C_L$       | 負荷容量      |     |     | 100 | pF |

| $f_{(LRA)}$ | LRA 周波数   | 45  | 300 | 300 | Hz |

### 5.4 热に関する情報

| 熱評価基準 <sup>(1)</sup> |                     | DRV2625 | 単位   |

|----------------------|---------------------|---------|------|

|                      |                     | DSBGA   |      |

|                      |                     | 9 ピン    |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 107     | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 0.9     | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 18.1    | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 3.8     | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 18.1    | °C/W |

|                      | 熱評価基準 <sup>(1)</sup> | DRV2625 | 単位   |

|----------------------|----------------------|---------|------|

|                      |                      | DSBGA   |      |

|                      |                      | 9 ピン    |      |

| $R_{\theta JC(bot)}$ | 接合部からケース(底面)への熱抵抗    | —       | °C/W |

- (1) 従来および最新の熱測定基準の詳細については、アプリケーションレポート『半導体およびICパッケージの熱評価基準』、[SPRA953](#) を参照してください。

## 5.5 電気的特性

$T_A = 25^\circ\text{C}$ ,  $V_{DD} = 3.6\text{V}$ 、特に記述のない限り

| パラメータ                                 | テスト条件                                                                   | 最小値  | 標準値  | 最大値 | 単位               |

|---------------------------------------|-------------------------------------------------------------------------|------|------|-----|------------------|

| $V_{(REG)}$ REG ピンでの電圧                |                                                                         |      | 1.84 |     | V                |

| $I_{IL}$ デジタル low レベル入力電流             | NRST, TRIG/INTZ, SDA, SCL<br>$V_{DD} = 5.5\text{V}$ , $V_I = 0\text{V}$ |      | 100  |     | nA               |

| $I_{IH}$ デジタル high レベル入力電流            | SDA, SCL<br>$V_{DD} = 5.5\text{V}$ , $V_I = V_{DD}$                     |      | 0.1  |     | $\mu\text{A}$    |

|                                       | NRST<br>$V_{DD} = 5.5\text{V}$ , $V_I = V_{DD}$                         |      | 1    |     |                  |

|                                       | TRIG/INTZ<br>$V_{DD} = 5.5\text{V}$ , $V_I = V_{DD}$                    | 2.7  | 3.5  |     |                  |

| $V_{IL}$ デジタル low レベル入力電圧             | NRST, TRIG/INTZ, SDA, SCL                                               |      | 0.4  |     | V                |

| $V_{IH}$ デジタル high レベル入力電圧            | NRST, TRIG/INTZ, SDA, SCL                                               | 1.41 |      |     | V                |

| $V_{OL}$ デジタル low レベル出力電圧             | TRIG/INTZ, SDA<br>3mA シング電流                                             |      | 0.4  |     | V                |

| $R_{DS(on)}$ ドレイン-ソース間オン抵抗 (LS + HS)  |                                                                         | 0.75 |      |     | $\Omega$         |

| $I_{(SD)}$ シャットダウン電流                  | $V_{(NRST)} = 0\text{V}$                                                | 105  | 180  |     | nA               |

| $I_{(STBY)}$ スタンバイ電流                  | $V_{(NRST)} = V_{DD}$<br>スタンバイ モードで                                     | 1.55 | 2    |     | $\mu\text{A}$    |

| $I_{(Q)}$ 静止時電流                       | $V_{(NRST)} = V_{DD}$<br>アイドル モードで - 信号無し                               | 2.5  |      |     | $\text{mA}$      |

| $Z_{O(SD)}$ シャットダウン時の出力インピーダンス        | OUT+ から GND, OUT- から GND<br>～                                           | 15   |      |     | $\text{k}\Omega$ |

| $Z_{O(STBY)}$ スタンドバイ時の出力インピーダンス       | OUT+ から GND, OUT- から GND<br>～                                           | 15   |      |     | $\text{k}\Omega$ |

| $Z_{LOAD(th)}$ 過電流検出の負荷インピーダンス スレッシング | OUT+ から GND, OUT- から GND<br>～                                           | 4    |      |     | $\Omega$         |

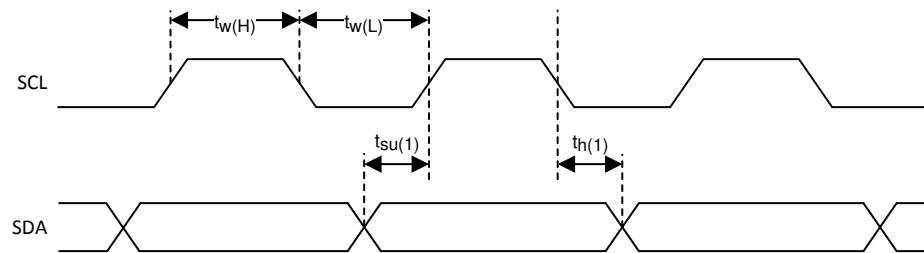

## 5.6 タイミング要件

$T_A = 25^\circ\text{C}$ ,  $V_{DD} = 3.6\text{V}$ 、特に記述のない限り

|             |                      | 最小値 | 公称値 | 最大値 | 単位            |

|-------------|----------------------|-----|-----|-----|---------------|

| $f_{(SCL)}$ | ウェイト状態なしで SCL ピンの周波数 |     | 400 |     | kHz           |

| $t_{w(H)}$  | パルス幅、SCL high        | 0.6 |     |     | $\mu\text{s}$ |

| $t_{w(L)}$  | パルス幅、SCL low         | 1.3 |     |     | $\mu\text{s}$ |

| $t_{su(1)}$ | セットアップ時間、SDA から SCL  | 100 |     |     | ns            |

| $t_{h(1)}$  | ホールド時間、SCL から SDA まで | 10  |     |     | ns            |

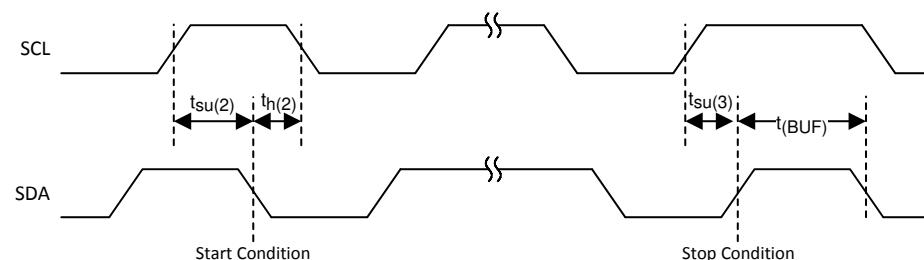

| $t_{(BUF)}$ | 停止条件と始動条件の間のバス解放時間   | 1.3 |     |     | $\mu\text{s}$ |

| $t_{su(2)}$ | セットアップ時間、SCL から開始条件  | 0.6 |     |     | $\mu\text{s}$ |

| $t_{h(2)}$  | ホールド時間、開始条件から SCL    | 0.6 |     |     | $\mu\text{s}$ |

| $t_{su(3)}$ | セットアップ時間、SCL から停止条件  | 0.6 |     |     | $\mu\text{s}$ |

## 5.7 スイッチング特性

$T_A = 25^\circ\text{C}$ ,  $V_{DD} = 3.6\text{V}$ 、特に記述のない限り

| パラメータ                | テスト条件              | 最小値 | 標準値 | 最大値 | 単位 |

|----------------------|--------------------|-----|-----|-----|----|

| $t_{(on)}$ デバイスの起動時間 | スタンバイからの電力消費を防止します | 1   |     |     | ms |

$T_A = 25^\circ\text{C}$ ,  $V_{DD} = 3.6\text{V}$ 、特に記述のない限り

| パラメータ                                         | テスト条件                | 最小値 | 標準値  | 最大値 | 単位  |

|-----------------------------------------------|----------------------|-----|------|-----|-----|

| $t_{(\text{start})}$ 波形起動時間                   | トリガから出力信号までの経路を保護します |     | 1    |     | ms  |

| $f_{O(\text{PWM})}$ PWM 出力周波数 (OUT+ および OUT-) |                      |     | 20.5 |     | kHz |

図 5-1. SCL と SDA のタイミング

図 5-2. スタート条件とストップ条件のタイミング

## 5.8 代表的特性

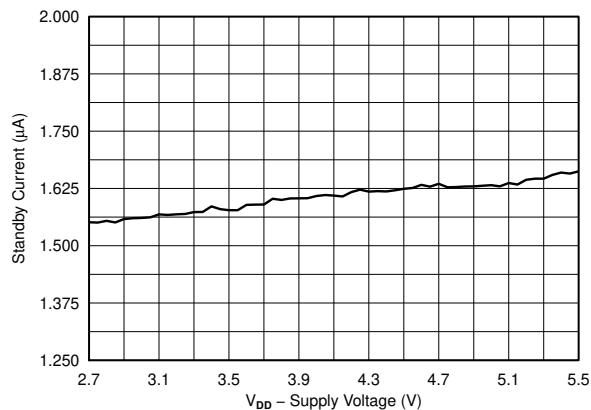

図 5-3. スタンドバイ電流と電源電圧との関係

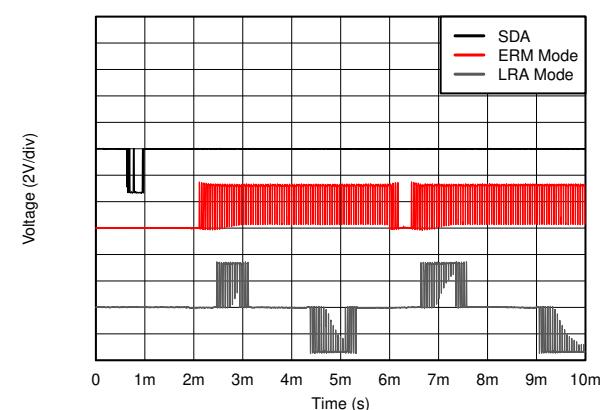

図 5-4. ERM と LRA の起動レイテンシ

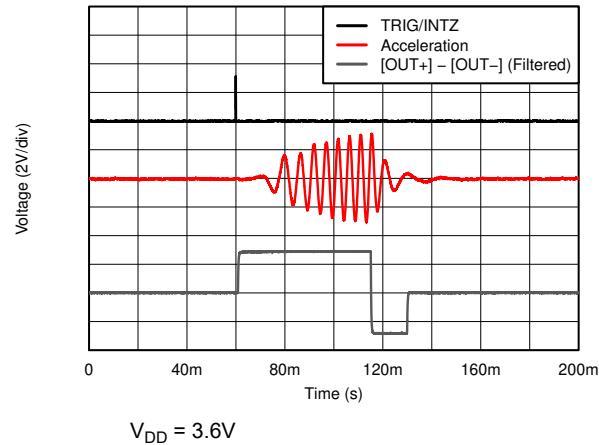

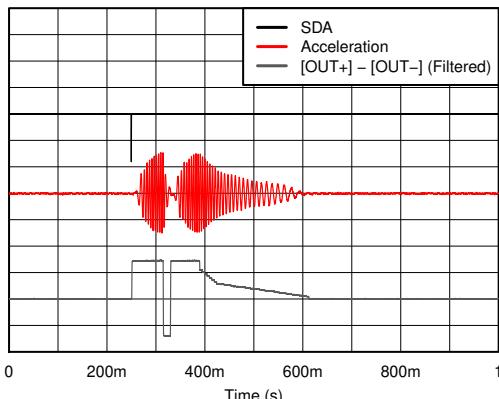

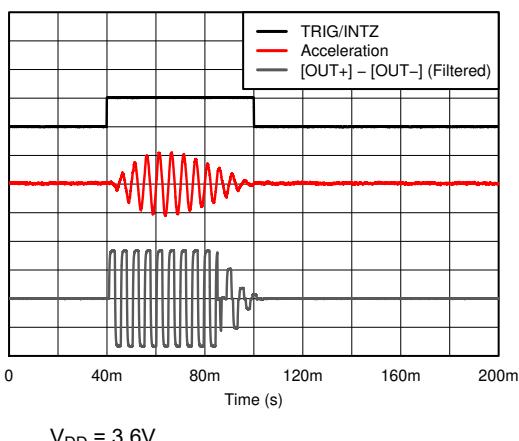

図 5-5. 外部パルス トリガによる ERM クリック (開ループ)

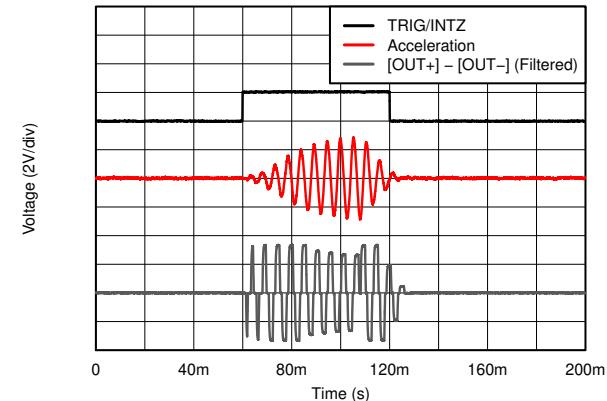

図 5-6. 外部レベル トリガによる LRA 強いクリック (閉ループ)

Voltage (2V/div)

$V_{DD} = 3.6V$

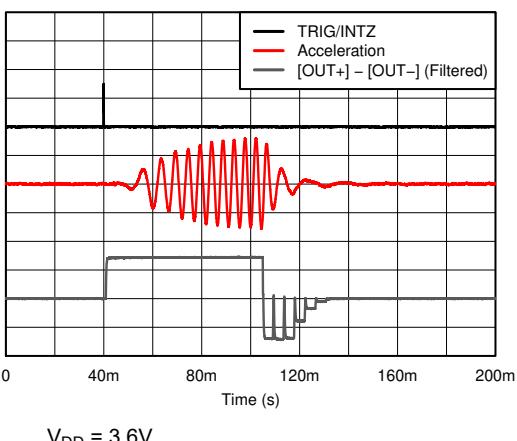

図 5-7. 内部トリガ付き ERM クリックバウンス (開ループ)

Voltage (2V/div)

$V_{DD} = 3.6V$

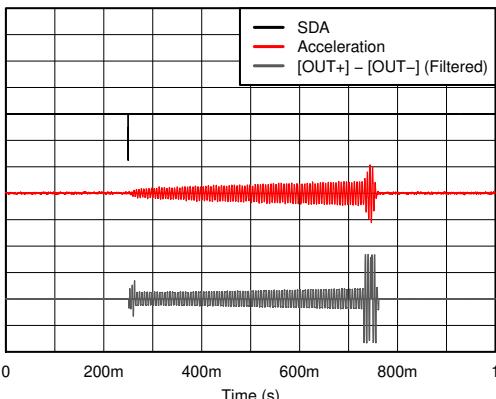

図 5-8. 内部トリガによる LRA 遷移クリック (閉ループ)

Voltage (2V/div)

$V_{DD} = 3.6V$

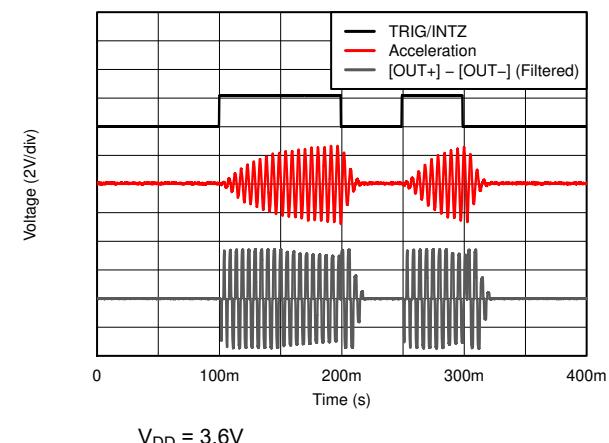

図 5-9. ERM RTP バズ (クローズドループ)、パルストリガ付き

Voltage (2V/div)

$V_{DD} = 3.6V$

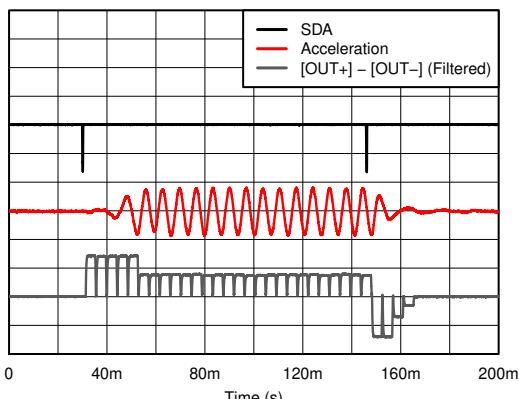

図 5-10. LRA 正弦波クリック (開ループ) と自動ブレーキ

Voltage (2V/div)

$V_{DD} = 3.6V$

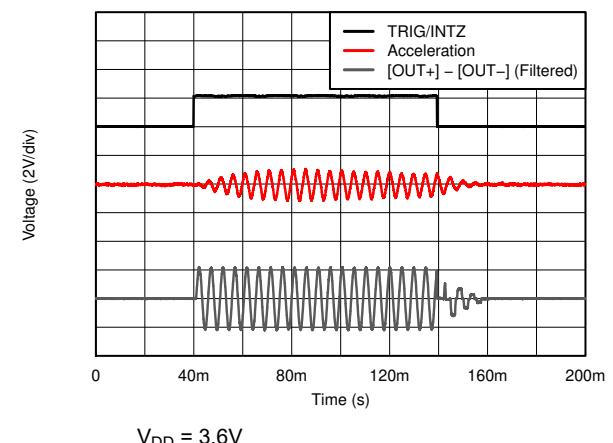

図 5-11. LRA 方形波自動ブレーキ付きクリック (開ループ)

Voltage (2V/div)

$V_{DD} = 3.6V$

図 5-12. 自動ブレーキ機能を備えた ERM クリック (開ループ)

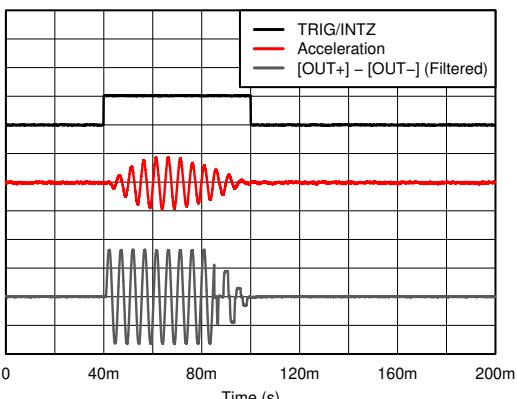

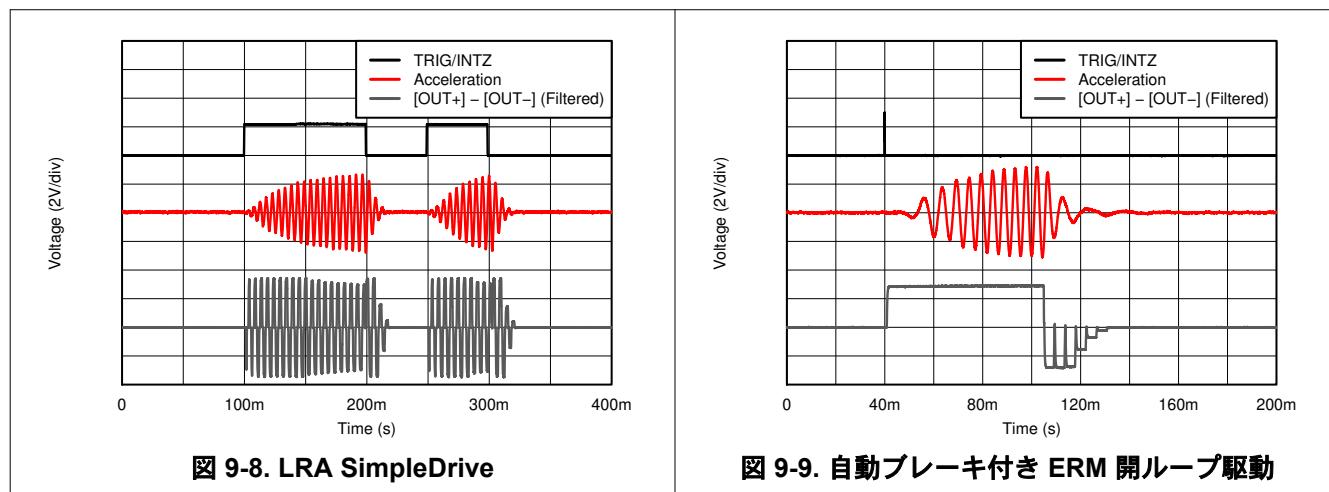

図 5-13. クローズドループを備えた LRA SimpleDrive

図 5-14. 正弦波を備えた LRA SimpleDrive

## 6 パラメータ測定情報

### 6.1 グラフのテスト構成

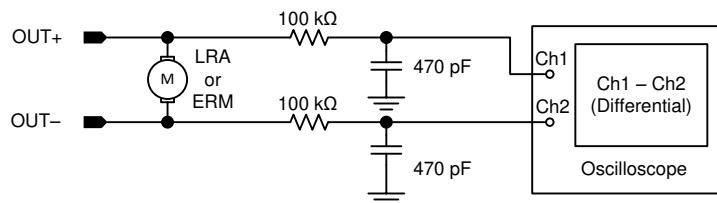

**代表的特性**セクションに表示されるグラフをキャプチャするには、出力フィルターなしでキャプチャされる図 6-1 の波形を除いて、次の 1 次 RC フィルター設定が使用されます。出力 PWM 変調はすべてのモードに搭載しているため、このフィルタはオシロスコープで出力信号を表示するときに使用します。閉ループおよび自動共振トラッキング機能に影響を与える可能性があるため、フィルタの実効インピーダンスが低すぎないようにします。そのため、出力測定にはこの正確なフィルタを使用することをお勧めします。ほとんどのオシロスコープの入力インピーダンスは各チャネルで  $1M\Omega$  であるため、フィルタによる分圧器の効果により、測定された振幅が約 1% 低下します。

図 6-1. テスト設定

#### 6.1.1 デフォルトのテスト条件

- $V_{DD} = 3.6V$ 、特に記述のない限り。

- 特に記述のない限り、ERM および LRA モードの負荷として (モデル化されたアクチュエータとは対照的に) 実際のアクチュエータを使用した。

## 7 詳細説明

### 7.1 概要

DRV2624 デバイスは、独自の閉ループ アーキテクチャに依存したハプティクスドライバで、消費電力を最適化しながら、シャープで強力で一貫性のあるハプティクス効果を実現します。内部メモリとループ可能な波形シーケンサ、自動オーバードライブおよびブレーキ機能により、鮮明で最適なハプティック効果を簡単に生成できるため、処理ユニットの負荷が軽減されます。DRV2624 デバイスには、自動的にスタンバイ状態に移行する機能とバッテリ保存機能があり、ユーザーの介入なしに消費電力を低減できます。NRST ピンを使用すると、完全なシャットダウン状態を設定して、消費電力をさらに削減できます。波形形状の選択を使用すると、正弦波および方形波ドライブでハプティクスの操作感と可聴性能をカスタマイズできます。自動ブレーキによるオフ共振駆動により、非共振ハプティクス設計を簡素化できます。

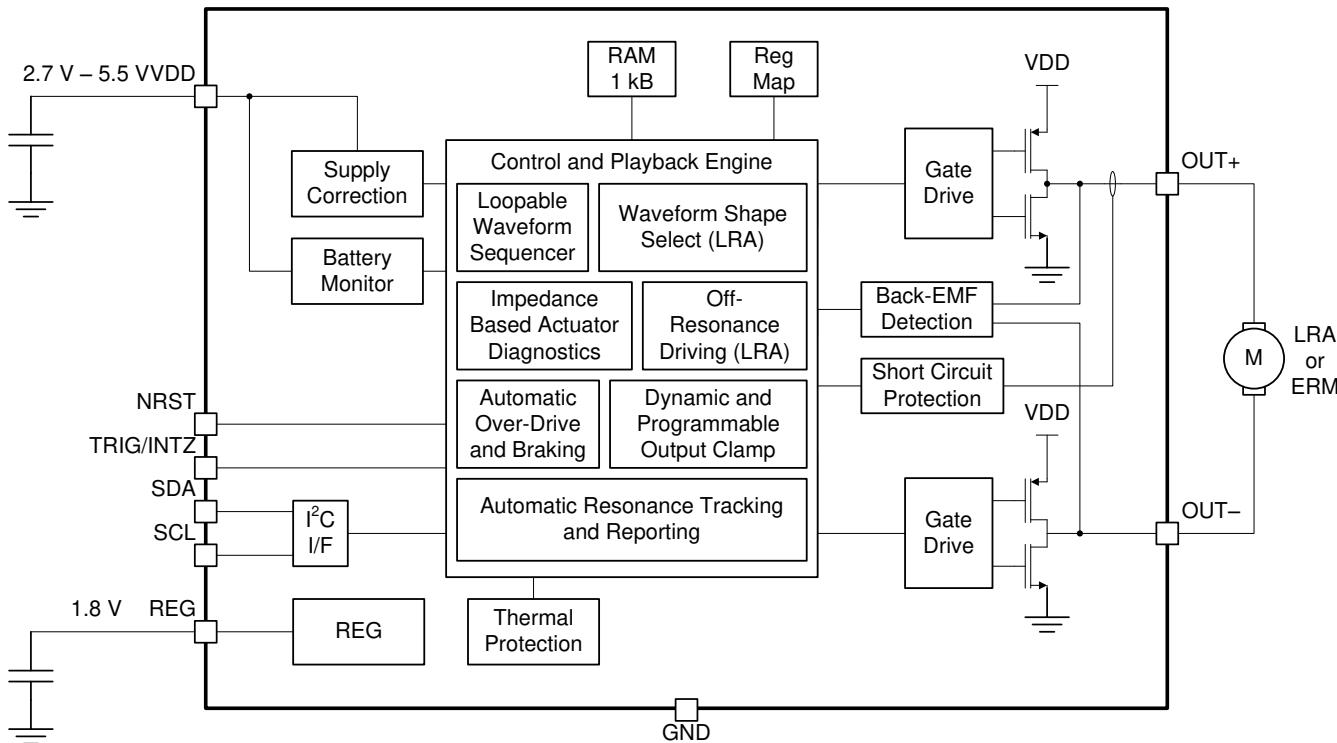

### 7.2 機能ブロック図

### 7.3 機能説明

#### 7.3.1 ERM および LRA アクチュエータ向け

DRV2624 デバイスは、ERM と LRA の両方のアクチュエータをサポートしています。LRA\_ERM ビットは、デバイスが使用するアクチュエータのタイプを選択するように設定する必要があります。

#### 7.3.2 スマートループアーキテクチャ

スマート ループ アーキテクチャは、アクチュエータの性能を最適化し、障害検出を可能にする高度な閉ループ システムです。このアーキテクチャは、自動共振トラッキングおよび報告 (LRA 用)、自動レベル キャリブレーション、起動および停止の高速化、抵抗ベースの診断ルーチン、その他の独自アルゴリズムで構成されています。

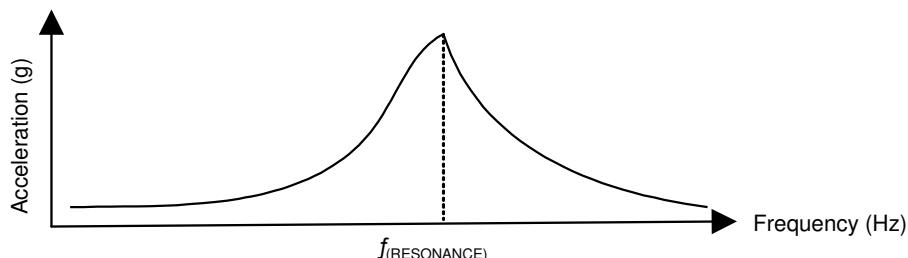

##### 7.3.2.1 LRA 用自動共振エンジン

DRV2624 自動共振エンジンは、LRA の共振周波数をリアルタイムで追跡し、半サイクル後に共振周波数に効果的にロックします。何らかの理由で波形の中央に共振周波数が変化した場合、エンジンはサイクルごとに周波数を追跡します。自動共振エンジンはアクチュエータの逆起電力を常に監視することでトラッキングを実行します。自動共振エンジンは、レ

ベル キャリブレーションにのみ使用される自動キャリブレーション プロセスの影響を受けないことに注意してください。自動共振エンジンにはキャリブレーションは不要です。

### 7.3.2.2 LRA 向けリアルタイム共振周波数レポート

スマートループ アーキテクチャにより、LRA の共振周波数は I<sup>2</sup>C 経由で利用可能になります。周波数報告はリアルタイムで行われるため、DRV2624 デバイスが LRA と同期している間に周波数記録をポーリングする必要があります。アクチュエータがアイドル状態またはブレーキ状態のとき、ポーリングされたデータはポーリングされません。

### 7.3.2.3 LRA でオープン ループに自動切り替え

LRA が有効でない逆 EMF 信号を生成した場合、DRV2624 デバイスは自動的に開ループ動作に切り替わり、デフォルトかつ設定可能な周波数でオーバードライブ モードでアクチュエータにエネルギーを供給し続けます。LRA が有効な逆 EMF 信号を生成し始めた場合、自動共振エンジンが自動的に制御を引き継ぎ、共振周波数をリアルタイムで追跡し続けます。このモードに同期すると、スマートループ アーキテクチャの利点のすべてが使用されます。

$$f_{(LRA\_NO-BEMF)} \approx \frac{1}{2 \times (t_{(DRIVE\_TIME[4:0])} - t_{(ZC\_DET\_TIME[1:0])})} \quad (1)$$

この DRV2624 デバイスは、再同期オプションなしに、開ループ モードに自動的に移行できます。この機能は LRA\_AUTO\_OPEN\_LOOP ビットの設定でイネーブルになります。オープン ループ モードへの移行は、ドライバが LRA との同期に失敗したときのみ発生します。AUTO\_OI\_CNT[1:0] パラメータを調整することで、開ループ モードへの遷移前に許容される非同期サイクルの量を設定できます。開ループ モードは、自動オーバードライブやブレーキなどのスマートループ アーキテクチャは恩恵を受けないことに注意してください。

$$f_{(LRA\_OL)} = \frac{1}{OL\_LRA\_PERIOD[6:0] \times 97.56 \times 10^{-6}} \quad (2)$$

### 7.3.2.4 自動オーバードライブおよびブレーキ

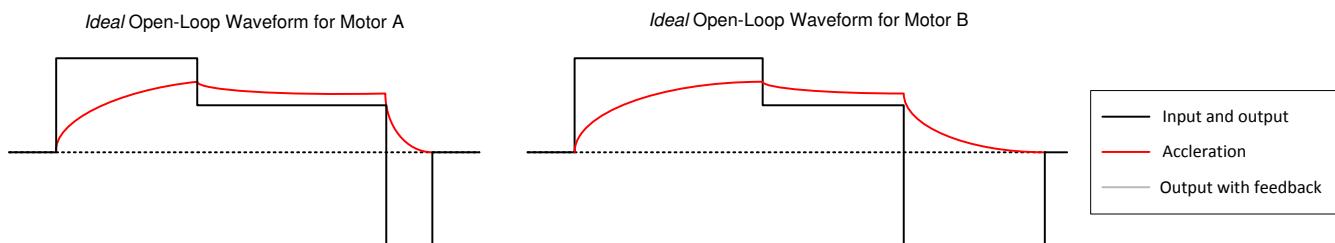

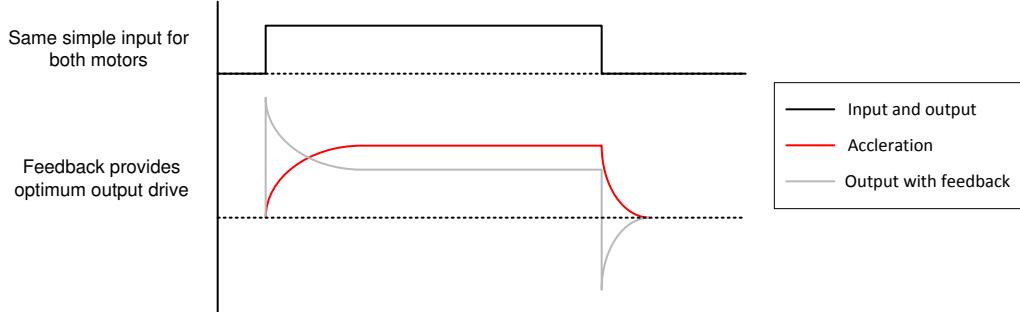

DRV2624 の重要な特長の 1 つが、ERM と LRA の両方のアクチュエータ フィードバック制御を採用したスマートループ アーキテクチャです。フィードバック制御は、自動的なオーバードライブと自動ブレーキを実現することで、モーターの応答動作から入力波形を感じません。

開ループのハプティクス システムは一般に、アクチュエータの定常状態定格電圧より高いオーバードライブ電圧を起動時に駆動して、アクチュエータの起動レイテンシを短縮します。同様に、効果的なブレーキのためにブレーキ アルゴリズムを採用する必要があります。開ループ ドライバを使用する場合、これらの動作は入力波形データに含める必要があります。モーター A とモーター B の ERM アクチュエータの例を考えてみましょう。開ループ内の入力波形は異なります (図 7-1 を参照)。一方、自動オーバードライブとブレーキを備えたスマートループ技術を使用することで、両方のアクチュエータで同じ入力波形が機能します (図 7-2 を参照)。スマートループ アーキテクチャは、フィードバック制御と自動共振エンジンの組み合わせにより、LRA に対しても同様に適切に機能します。

図 7-1. 標準的な開ループ波形

図 7-2. スマート ループによる波形単純化

#### 7.3.2.4.1 起動ブースト

アクチュエータの開始時間性能を低減するため、DRV2624 デバイスにオーバードライブ ブースト機能があり、アクチュエータの過渡応答により高いループゲインを適用します。

#### 7.3.2.4.2 ブレーキ ファクター

アクチュエータのブレーキ時間性能を最適化するため、この DRV2624 デバイスはブレーキと駆動ゲインの間のゲイン比を高める手段を提供します。フィードバックゲイン比が高いとブレーキ時間が短くなりますが、これらの比率によって閉ループシステムの安定性も低下します。FB\_BRAKE\_FACTOR パラメータは、ブレーキ係数を設定するために調整できます。

#### 7.3.2.5 自動レベル キャリブレーション

スマート ループ アーキテクチャは、アクチュエータの逆起電力動作を監視することでアクチュエータ フィードバックを使用します。逆起電力のレベルは、アクチュエータの構造によってアクチュエータメーカーによって異なる可能性があります。自動キャリブレーションはこの変動を補償し、指定された定格電圧とオーバードライブ クランプ レジスタ設定に従って目的のアクチュエータのスケーリングも実行します。自動キャリブレーションが実行されると、いずれかの DRV2624 入力インターフェイスで 100% の信号レベルがアクチュエータに定常状態で定格電圧を供給します。帰還により、出力レベルが定格電圧レベルよりも高くなると、自動オーバードライブおよびブレーキが可能になりますが、出力レベルがプログラム可能なオーバードライブ クランプ電圧を超えるません。

#### 7.3.2.5.1 抵抗性損失に対応する自動補償

この DRV2624 デバイスは、ドライバの抵抗損失を自動的に補償します。自動レベル キャリブレーション ルーチン中に、アクチュエータの抵抗をチェックし、補正係数を決定して A\_CAL\_COMP パラメータに保存します。

#### 7.3.2.5.2 自動的な逆起電力正規化

DRV2624 デバイスは、アクチュエータ間の逆起電力の大きさの違いを自動的に補償します。補償係数は、自動レベル キャリブレーション ルーチン中に決定され、その係数は A\_CAL\_BEMF パラメータに保存されます。

#### 7.3.2.5.3 キャリブレーション時間調整

自動レベル キャリブレーション ルーチンの持続時間は、精度に影響を与えます。影響はアクチュエータの開始時間特性に大きく依存します。自動較正ルーチンは、較正係数が計算される前にアクチュエータが一定の加速に達することを想定しています。開始時間の特性はアクチュエータごとに異なる可能性があるため、AUTO\_CAL\_TIME パラメータはキャリブレーション性能を最適化するために、自動レベル キャリブレーション ルーチンの持続時間を変更できます。または、較正ルーチンの期間をトリガで調整し、AUTO\_CAL\_TIME パラメータのオプションを選択することもできます。

#### 7.3.2.5.4 ループゲイン制御

DRV2624 デバイスを使用すると、ドライバが逆起電力(つまりモーター速度)と入力信号レベルを一致させる速さを制御できます。ループゲインが高い(またはセトリングが高速)オプションを選択すると、ループゲインが低い(またはセトリングが遅い)場合よりも安定しない動作が得られます。LOOP\_GAIN パラメータは、ループゲインを制御します。

### 7.3.2.5 逆起電力ゲイン制御

BEMF\_GAIN パラメータは、逆起電力アンプのアナログ ゲインを設定します。自動較正ルーチンは、アクチュエータに最適な値を BEMF\_GAIN ビットに自動的に設定します。

SAMPLE\_TIME パラメータを変更すると、逆起電力ゲインも調整されます。サンプリング時間が長いほど、ゲインは大きくなります。

### 7.3.2.6 アクチュエータ診断

DRV2624 デバイスは、アクチュエータが存在しない（開放）か短絡しているかを判断できます。診断プロセス中にフォルトが検出されると、DIAG\_RESULT ビットがアサートされます。

DRV2624 このデバイスはアクチュエータ抵抗測定機能も備えており、DIAG\_Z\_RESULT パラメータで利用できます。

$$R_{(act)} = 478.43 \cdot \frac{DIAG\_Z\_RESULT[7:0]}{719 + 4 \cdot CURRENT\_K[7:0]} \quad (3)$$

### 7.3.2.7 自動再同期

LRA アクチュエータの場合、DRV2624 デバイスには自動再同期機能があり、アクチュエータの移動中に波形の再生が開始されると、アクチュエータを正しい方向に自動的にプッシュします。波形が開始されたときにアクチュエータが静止している場合、DRV2624 デバイスはデフォルト方向に駆動されます。

### 7.3.3 閉ループ動作

閉ループ動作が必要な場合、DRV2624 デバイスはすべての閉ループ パラメータをオーバーライドする閉ループ駆動モードを備えており、デジタル インターフェイス経由で利用可能です。

このモードを有効化すると、デジタル閉ループモードを保存済み波形と RTP モードで使用できます。

閉ループ動作のダイナミック レンジは OD\_CLAMP[7:0] によって設定され、最大ピーク値が設定されます。振幅コード (RTP または内部メモリを使用) は、出力を適宜スケーリングします。

LRA アクチュエータの場合、OL\_LRA\_PERIOD パラメータは、PWM 出力周波数  $f_{O(PWM)}$  から得られる動作周波数をプログラムします。

#### 7.3.3.1 LRA 用の波形形状の選択

DRV2624 では、閉ループ モードでの正弦波または方形波の波形を選択できます。WAVE\_SHAPE\_LRA パラメータは、使用するシェイプを選択します。ERM モードおよび閉ループ モードでは、WAVE\_SHAPE\_LRA パラメータは無視されます。

#### 7.3.3.2 閉ループでの自動ブレーキ

DRV2624 は、ERM と LRA の両方について、閉ループで自動ブレーキ機能を備えています。自動ブレーキを実現するため、DRV2624 はブレーキ期間中に閉ループにスイッチするため、閉ループ波形の形状に頼っています。AUTO\_BRK\_OL パラメータを使用して、自動ブレーキ機能をイネーブルまたはディセーブルにできます。自動ブレーキ機能を使用するには、閉ループ動作に合わせてデバイスを適切に構成する必要があります。

### 7.3.4 柔軟なフロントエンド インターフェイス

DRV2624 デバイスは、ハプティクス効果の起動と制御に複数の方法を提供しています。MODE パラメータは、波形シーケンサを使用するか（このため、内部または外部のトリガで波形をトリガするか）、RTP モードを使用するかを選択します。汎用 TRIG/INTZ ピンは TRIG\_PIN\_FUNC パラメータで構成できるため、柔軟性が向上します。

#### 7.3.4.1 内部メモリ インターフェイス

DRV2624 デバイスは、再生エンジンで使用される波形保存のために 1kB の RAM を内蔵して設計されています。データは効率的な方法（電圧と時間のペア）で保存され、搬送可能な波形の数を最大化します。再生エンジンには、スタート波形および終了波形ポイントに依存し、リニア補間技法を使用して、滑らかなランプ（上下）を生成する機能もあります。

ホスト プロセッサではなく DRV2624 に波形を保存するには、次のようないくつかの利点があります。

- デジタル ストリーミング (RTP) のような処理要件のオフロード。

- DRV2624 に波形を保存し、トリガ信号のみを必要とすることで、レイテンシを改善できます。

- 波形データを転送する必要がなくなるため、I<sup>2</sup>C トライフィックが減少

#### 7.3.4.1.1 ライブリパラメーター化

内部メモリに保存されている波形は、時間オフセット パラメータによって増強されます。この拡張は、内部メモリに保存された波形に対してのみ行われ、RTP モードでは行われません。この機能の目的は、波形にタイム ストレッチ(または時間短縮)を追加することです。この機能は、特定のアクチュエータの立ち上がり時間と立ち下がり時間に合わせて、波形のライブラリ全体をカスタマイズするのに役立ちます。

ストレッチまたは縮小できる時間パラメータには、次のものがあります。

|            |              |

|------------|--------------|

| <b>ODT</b> | オーバードライブ時間   |

| <b>SPT</b> | 前向きな時間を維持します |

| <b>SNT</b> | 負の時間を維持する    |

| <b>BRT</b> | ブレーキ時間       |

時間値は加算オフセットで、8 ビット符号付き値です。これらの値のデフォルト オフセットは 0 です。正の値は加算され、負の値は現在再生されているエフェクトの時間値から減算されます。波形の最も正の値は自動的にオーバードライブ時間と解釈され、波形の最も負の値はブレーキ時間として自動的に解釈されます。これらの時間オフセット パラメータは、電圧時間のペアとリニアランプの両方に適用されます。線形勾配の場合、線形補間は、その期間の 2 つの動作ポイントにわたってストレッチ(または縮小)されます。

$$t_{(\text{final})} = t_{(\text{orig})} + t_{(\text{ofs})} \quad (4)$$

#### 7.3.4.1.2 再生間隔

内部メモリティックは、デフォルトでは 5ms 間隔と解釈されます。さらに細分化が必要な場合は、PLAYBACK\_INTERVAL ビットを使用して 1ms 間隔を選択できます。

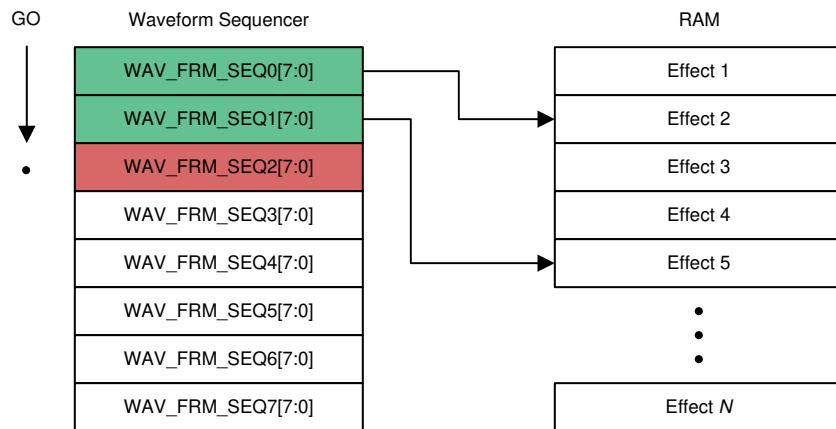

#### 7.3.4.1.3 波形シーケンサ

波形シーケンサは、再生用の波形識別子をキューに入れます。8 つのシーケンス レジスタは、シーケンシャル再生のために最大 8 つの波形をキューに入れます。波形識別子は、内部ライブラリ内の波形のインデックス位置を示す整数値です。ユーザーが MODE[1:0] パラメータで実行するプロセスとして波形再生を選択すると、ユーザーがプロセスをトリガーすると(GO ビットを使用するか、設定されている場合は外部から)、WAV\_FRM\_SEQ1 から再生が開始されます。その波形の再生が終了すると、次の波形がゼロでない場合、波形シーケンサは WAV\_FRM\_SEQ2 に保持されている波形識別子を再生します。波形シーケンサーは、シーケンサーが 0 の識別子値に達するまで、または 8 つの識別子がすべて再生されるまで、いずれかのシナリオに到達するまで、このように動作を続けます。

波形識別子の範囲は 1 ~ 127 です。各シーケンス レジスタの MSB は、シーケンス波形間の遅延を実装できます。MSB が high の場合、ビット [6:0] は待機時間の長さを示します。そのステップの待ち時間は WAV\_FRM\_SEQ[6:0] × 10ms になります。

DRV2624 では、次の波形識別子に移動する前に、各波形を何回もループすることができます。波形ループ機能は、WAV\_SEQ\_LOOP パラメータで設定できます。

また、DRV2624 では、WAV\_SEQ\_MAIN パラメータを構成することで、波形シーケンサ全体をループできます。この場合、波形シーケンサは、WAV\_SEQ\_MAIN で指定された番号に従って、すべての有効な WAV\_FRM\_SEQn 識別子をループします。たとえば、1 番目と 2 番目の識別子が有効である場合(たとえば、1 と 2)、3 番目の識別子が 0(停止する信号)、WAV\_SEQ\_MAIN が 1 回ループするように設定されている場合(波形シーケンスを 2 回再生)、DRV2624 デバイスは波形 1、波形 2、波形 1、波形 2 の順に再生し、スタンバイに移行します。

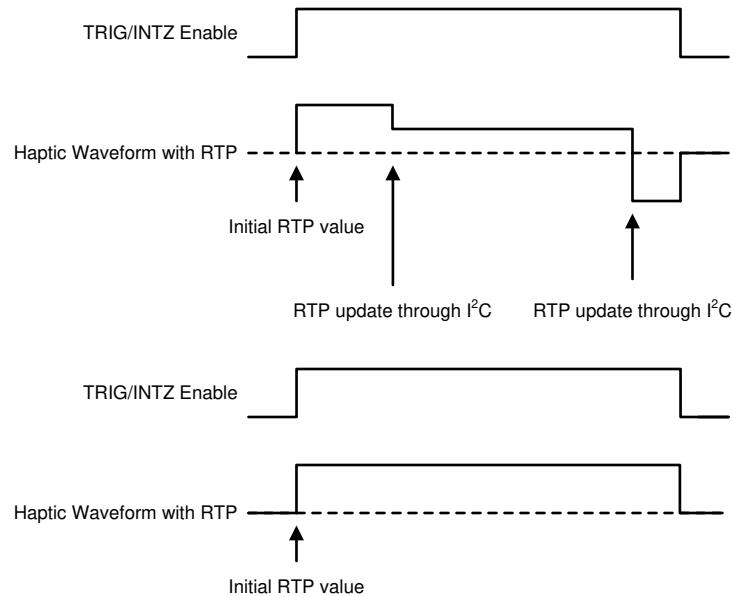

### 7.3.4.2 リアルタイム再生 (RTP) インターフェイス

リアルタイム再生モードは、振幅値を保持する単純な单一の 8 ビットレジスタインターフェイスです。リアルタイム再生を有効にすると、振幅値を表す **RTP\_INPUT** パラメータが再生エンジンに直接送信されます。トリガーされると、ユーザーが停止トリガーを送信するか、デバイスを RTP モードから削除するまで、この値が再生されます。RTP モードは、ユーザーが I<sup>2</sup>C 経由でレジスタ値を入力するデジタルストリーミングモードです。RTP モードとレガシーページ PWM モードは類似しているため、ホストプロセッサの PWM ジェネレータで使用するよう設計された API (アプリケーションプログラミングインターフェイス) は、ホストタイマにデータ値を書き込む代わりに、I<sup>2</sup>C 経由でデータ値を書き込むことができます。この機能により、元のソフトウェアとの互換性を維持しながら、ホスト内のタイマーが解放されます。

LRA の場合、**CONTROL\_LOOP** ビットが開ループ動作に設定されていない限り、DRV2624 デバイスは共振周波数を自動的に追跡します。**CONTROL\_LOOP** ビットが開ループに設定されている場合、**OL\_LRA\_PERIOD** パラメータで設定された開ループ周波数に従って LRA が駆動されます。

### 7.3.4.3 プロセストリガ

DRV2624 デバイス内のすべてのプロセス (RTP、波形シーケンサ、キャリブレーション、診断) がトリガれます。つまり、プロセスを開始する前にプロセスをトリガする必要があります。トリガは、GO ビットを使用してソフトウェアで、または TRIG/INTZ ピンを使用するハードウェアで実現できます。このプロセスは、完了すると停止するか、停止トリガーが送信された場合に停止します。外部トリガ機能の詳細については、[セクション 7.3.16](#) を参照してください。

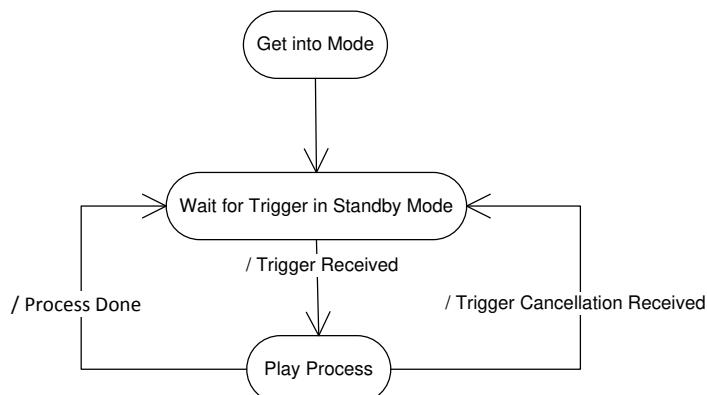

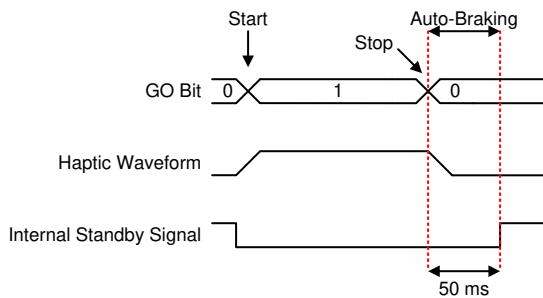

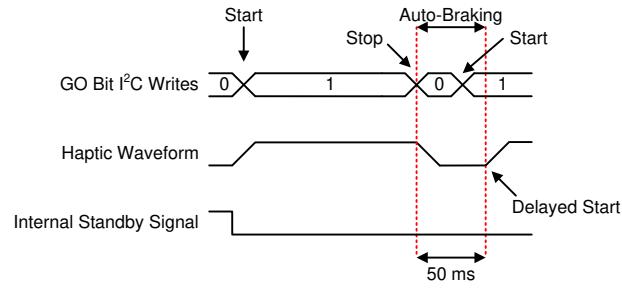

図 7-3 の図の後に、一般的なプロセス (RTP、波形シーケンサ、キャリブレーション、または診断) が開始および終了します。

図 7-3. 典型的なプロセスの実行

### 7.3.5 ノイズゲート制御

DRV2624 デバイスにはノイズゲートが搭載されており、特定のスレッショルドより低い任意の電圧をフィルタで除去して、意図しない振動を防止します。NG\_THRESH ビットは、スレッショルドを制御します。

### 7.3.6 エッジレート制御

DRV2624 出力ドライバにはエッジレート制御 (ERC) が実装されています。この制御により、出力ドライバの立ち上がりおよび立ち下がり特性が、モバイルおよびポータブルプラットフォームで一般的な他の回路に干渉する可能性のあるレベルの放射線を放射しないことが維持されます。ほとんどの ERC システムでは、外部出力フィルタ、コンデンサ、フェライトビーズは不要です。

### 7.3.7 一定の振動強度

DRV2624 デバイスには電源帰還が搭載されています。電源電圧が時間の経過とともに変動した場合 (バッテリ放電など)、必要な出力電圧を維持するのに十分な電源電圧が利用できる限り、振動強度は変わりません。

### 7.3.8 バッテリ電圧報告

再生中、デバイスは DRV2624V<sub>DD</sub> ピンのサイクル毎の電圧測定を行います。この情報は、VBAT[7:0] パラメータにより提供されます。式 5 を使用して、VBAT[7:0] に基づいて電圧を計算します。

$$\text{Voltage Level (V)} = \frac{\text{VBAT}[7:0]}{255} \times 5.6 \quad (5)$$

### 7.3.9 超低電力シャットダウン

NRST ピンを使用してデバイスをシャットダウン状態に設定すると、消費電力が 1 マイクロレベル未満に低減されるため、ハプティクスが必要ないときにシステムの電力を維持できます。この状態では、レジスタの内容は保持されません。

### 7.3.10 自動移行スタンバイ(低電力)

DRV2624 は、使用していないときは自動的に低消費電力のスタンバイ状態に移行します。この状態では、レジスタの内容は保持され、I<sup>2</sup>C 通信が利用可能です。DRV2624 は、波形の再生を要求されたときのスタンバイからの高速ターンオン時間を特長としています。以下の注意事項は、DRV2624 がスタンバイ状態に完全には戻らず、疑似スタンバイ状態で立ち往生してしまうコーナー ケースについて説明しています。追加の I<sup>2</sup>C トランザクションを使用して、疑似スタンバイ状態をクリアし、完全にスタンバイ モードに戻ります。

#### 注

このケースは、次の設定を使用する場合に適用されます。AUTO\_BRK\_INTO\_STBY = 1 (イネーブル)、TRIG\_PIN\_FUNC = 2 (I<sup>2</sup>C を使用した内部トリガモード)、MODE = 0 または 1 (RTP または波形シーケンサ モード)。GO ビットを 0 に書き込んで RTP モードを停止すると、デバイスは自動ブレーキ期間を完了し、擬似スタンバイ状態に戻ります。プログラムされた波形持続時間が終了する前に GO ビットを 0 に書き込んで波形が停止すると、デバイスは自動ブレーキ期間を完了し、疑似スタンバイ状態に戻ります。この疑似スタンバイ状態は、スタンバイ状態よりも多くの電流を消費します。RTP または波形シーケンサ モードのどちらの場合も、自動ブレーキ時間の後に任意のレジスタへの追加の I<sup>2</sup>C 書き込みまたは読み出しが行われ、疑似スタンバイ状態がクリアされます。自動ブレーキの時間は (PLAYBACK\_INTERVAL\*10) で、1ms を加算します。1ms のバッファを使用して、自動ブレーキの期間が確実に完了するようにします。

### 7.3.11 I<sup>2</sup>C ウオッチドッグタイマ

I<sup>2</sup>C が予期せず停止すると、I<sup>2</sup>C プロトコルがハンク状態のままになる可能性があります。デバイスの電源を切って再投入しなくとも通信を回復できるように、DRV2624 デバイスには自動ウォッチドッグ タイマが搭載されており、4.33ms 後にユーザーの介入なしに I<sup>2</sup>C プロトコルをリセットします。

### 7.3.12 デバイスの保護

DRV2624 デバイスには、過熱および過電流保護と、UVLO 用の保護回路が内蔵されています。このような状態が発生すると、DRV2624 デバイスは直ちに再生を停止し、スタンバイ状態になります。レジスタ 0x01 にはそれぞれのステータスビットが設定され、レジスタを読み出すとクリアされます。割り込みは、DRV2624 デバイスが起動するように構成されている場合に発生できます。

危険状態が解消された場合(過電流状態が解消される)、DRV2624 デバイスは通常動作を続行しますが、ステータスビットは粘着性があるため、ステータス レジスタが読み出されるまでビットはアサートされ続けます。

#### 7.3.12.1 サーマル センサ

DRV2624 には、過熱状態の発生時にデバイスを即座にスタンバイ状態にし、OVER\_TEMP ビットを設定する温度回路があります。

TRIG\_PIN\_FUNC パラメータで割り込み機能が選択され、割り込みがマスクされていない場合、割り込みが発生して、ホスト プロセッサに重大な状況を通知します。

### 7.3.12.2 過電流保護

波形再生中に、DRV2624 デバイスの出力ピンのインピーダンスが低すぎると、DRV2624 デバイスは直ちにスタンバイ状態に移行し、過電流フラグ (OC\_DETECT ビット) をラッチします。

TRIG\_PIN\_FUNC パラメータで割り込み機能が選択され、割り込みがマスクされていない場合、割り込みが発生して、ホストプロセッサに重大な状況を通知します。

### 7.3.12.3 VDD UVLO 保護

DRV2624 デバイスには、VDD レベルを監視して、そのレベルが設定可能なスレッショルドを上回ることを維持するバッテリモニタがあります (UVLO\_THRES[2:0] パラメータを使用)。

VDD ドループが発生した場合、DRV2624 デバイスは直ちにスタンバイ状態に移行して消費電流を低減し、UVLO フラグ (UVLO ビット) をラッチします。

TRIG\_PIN\_FUNC パラメータで割り込み機能が選択され、割り込みがマスクされていない場合、割り込みが発生して、ホストプロセッサに重大な状況を通知します。

### 7.3.12.4 ブラウンアウト保護

この DRV2624 デバイスには、ブラウンアウト保護がオンチップ搭載されています。アクティブになると、DRV2624 デバイスを初期デフォルト状態に戻すリセット信号が発行されます。レギュレータ電圧  $V_{(REG)}$  がブラウンアウト保護スレッショルド ( $V_{(BOT)}$ ) 以下になると、DRV2624 を下回ると、デバイスは自動的にシャットダウンされます。 $V_{(REG)}$  が標準出力電圧 (1.8V) に戻ると、DRV2624 デバイスは初期デバイス状態に戻ります。ブラウンアウト保護スレッショルド ( $V_{(BOT)}$ ) は通常 1.6V です。

### 7.3.13 POR

POR 回路は、VDD 電圧と REG 電圧の両方が正常なレベル REG 電圧レベルがリセットスレッショルドを下回ると、デバイスは自動的にプロセスを中止し、適切な電力レベルが利用可能になります。VDD と REG の両方に有効な電圧が印加されると、デバイスはパワーアップ シーケンスを続行し、デフォルトの状態に戻ります。VREG が正常なレベルに保たれているときに VDD が UVLO を下回ると、デバイスは直ちにスタンバイ状態に移行します。

### 7.3.14 シリコンのリビジョン制御

DRV2624 は、CHIPID[3:0] および REV[3:0] パラメータ (レジスタ 0x00 に配置) にリビジョン制御を実装しています。この機能により、外部コントローラから外部コントローラに接続されているデバイスを判定し、デバイスを制御するための適切なファームウェアを選択できるため、あるプラットフォームから別のプラットフォームへのファームウェアの移植が容易になります。

### 7.3.15 LRA および ERM アクチュエータ向け

DRV2624 デバイスは、LRA と ERM の両方のアクチュエータをサポートしています。デフォルト状態は LRA モードですが、LRA\_ERM ビットを使用して変更できます。

### 7.3.16 多用途ピン機能

DRV2624 の柔軟性を高めるため、TRIG/INTZ ピンは構成可能な多目的ピンで、動作モードに応じてさまざまな機能を実行します。このピンは、入力トリガ パルスピン、入力トリガ レベル (イネーブル) ピン、出力割り込みピンとして使用できます。TRIG/INTZ ピンは、一度に 1 つの機能 (トリガ エッジ、トリガ レベル (イネーブル)、または割り込み機能のいずれか) しか実行できないため、特定の機能 (たとえば、TRIG/INTZ を入力トリガ エッジとして構成) が選択されている場合、他の機能は利用できません (割り込みなど)。

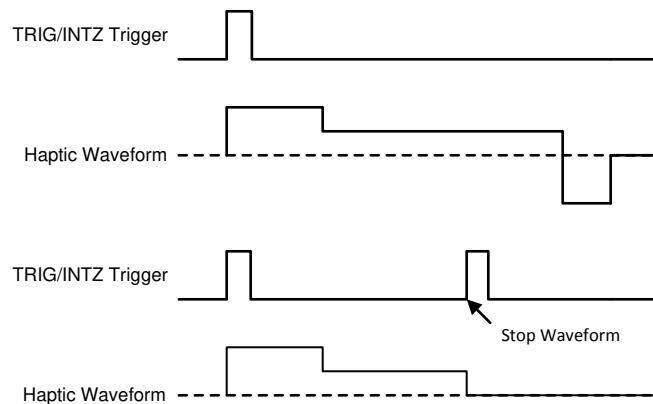

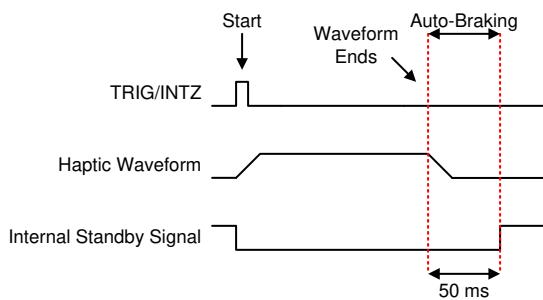

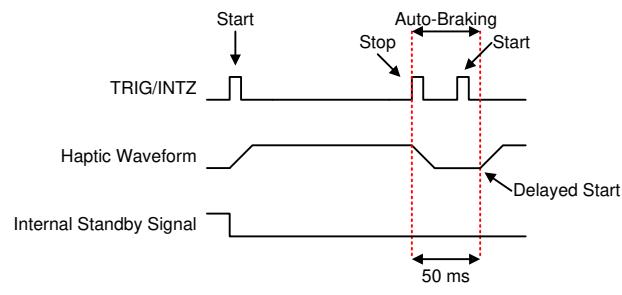

#### 7.3.16.1 トリガ パルス機能

トリガ パルス機能により、外部プロセッサは TRIG/INTZ ピンにパルスを印加してプロセス (波形シーケンサ、RTP、診断、キャリブレーション) を開始できます。このプロセスは開始されて再生が完了するまで行われ、その後、デバイスはスタンバイモードに戻り電力を維持します。ルーチンが完了する前に停止トリガ (別のトリガ パルス) が受信されると、そのルーチンは停止し、デバイスはスタンバイ状態に戻ります。診断モードの場合、停止トリガにより診断ルーチンは中止され、結果は報告されません。自動レベル キャリブレーション ルーチンの場合は、AUTO\_CAL\_TIME[2:0] がトリガ コントロールに

設定されていない限り、ストップトリガによりキャリプレーションが中止されます。この場合、キャリプレーションが完了するにはストップトリガが必要で、キャリプレーションがスムーズに終了し、期待される出力が提供されます。また、停止トリガは GO ビットに 0 を書き込むことでもできることにも注意してください。

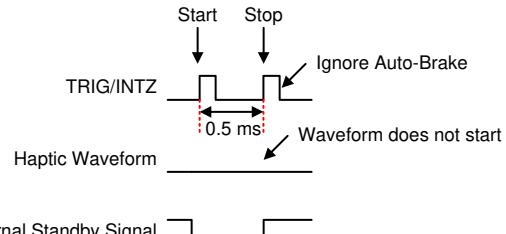

最小パルス幅の期間は 1 $\mu$ s で、標準的なパルスは短く維持されます。パルスが長すぎると、次のメモのコーナー ケースが発生する可能性があります。

#### 注

このケースは、次の設定を使用する場合に適用されます。AUTO\_BRK\_INTO\_STBY = 1 (イネーブル)、TRIG\_PIN\_FUNC = 0 (外部パルストリガ)、MODE = 1 (波形シーケンサ モード)。TRIG ピンが自動ブレーキ期間内に low に返されないと、それに続く TRIG の high 信号を見逃す可能性があります。これは、TRIG high 信号が波形シーケンスを再生できないことを意味します。自動ブレーキの時間は (PLAYBACK\_INTERVAL\*10) です。

図 7-4. トリガ パルス モードの TRIG/INTZ 機能

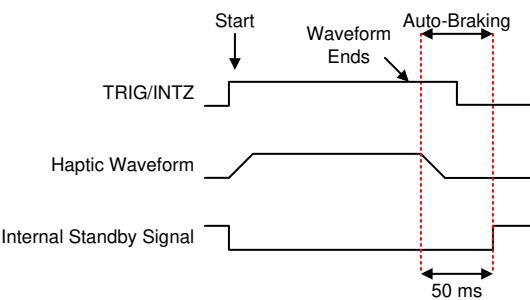

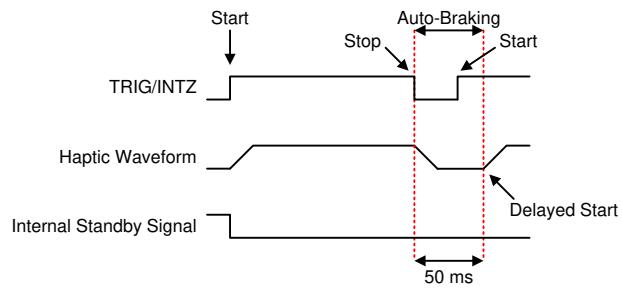

#### 7.3.16.2 トリガレベル (イネーブル) 機能

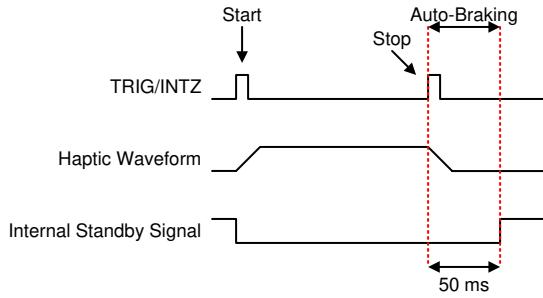

トリガ レベル (イネーブル) 機能により、外部マイクロコントローラは TRIG/INTZ ピンをアサートしてをウェイクアップ DRV2624 でき、即座にプロセスの再生を開始できます (波形シーケンサ、RTP 値、診断、自動キャリプレーション)。TRIG/INTZ ピンがアサート解除 (low) されると、デバイスはスタンバイ状態に戻り電力を維持します。スタンバイ状態に移行する前にブレーキが必要な場合、自動ブレーキを行うために AUTO\_BRK\_INTO\_STBY ビットを設定できます。自動ブレーキをスタンバイ機能に使用する際は、以下の注意事項を参照してください。キャリプレーション中は自動ブレーキは無視されることに注意してください。

#### 注

このケースは、次の設定を使用する場合に適用されます。AUTO\_BRK\_INTO\_STBY = 1 (イネーブル)、TRIG\_PIN\_FUNC = 1 (外部レベルトリガ)、MODE = 1 (波形シーケンサ モード)。TRIG ピンが自動ブレーキ期間内に low に返されないと、それに続く TRIG の high 信号を見逃す可能性があります。TRIG high 信号が波形シーケンスを再生しないことを意味します。自動ブレーキの時間は (PLAYBACK\_INTERVAL\*10) です。

図 7-5. トリガ レベル (イネーブル) モードでの TRIG/INTZ 機能

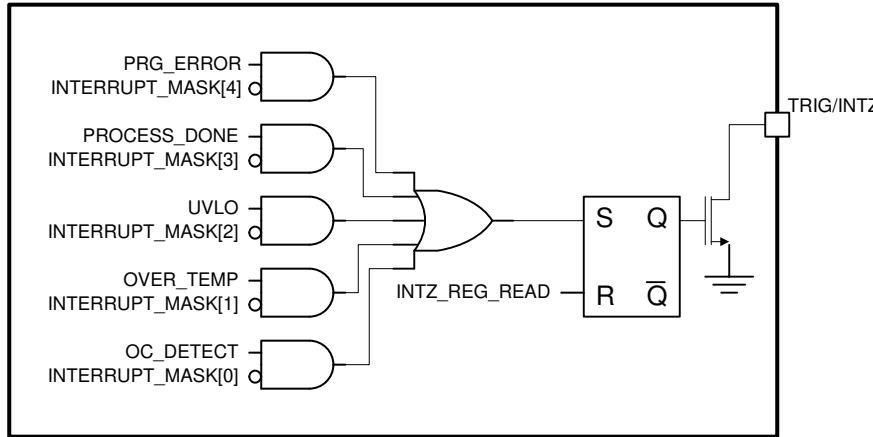

### 7.3.16.3 割り込み機能

割り込み機能により、DRV2624 は、特定の状態が発生したことを外部プロセッサと通信できます。割り込みとして構成されているとき、TRIG/INTZ ピンはオープンドレイン構成の出力になります。このモードには外部プルアップが必要です。アサートされると、TRIG/INTZ ピンによって割り込みがクリアされるまでノードがプルダウンされます（ステータス レジスタを読み取ることで実行されます）。すべての割り込みはマスク可能です。低消費電力アプリケーションについては、以下の注をご覧ください。サポートされている割り込みの説明を以下に示します。

---

注

テキサス インストルメンツでは、割り込みを検出しようとするときに、低消費電力アプリケーションで TRIG/INTZ を **high** にすることは推奨しません。プルアップによって、VDD から約 500μA の電流が追加で消費される可能性があります。割り込みを監視するには、I<sup>2</sup>C ステータス レジスタを使用します。

プロセス実行中に出力段で過電流イベントが発生した場合（波形再生や自動キャリブレーションなど）、OC\_DETECT にフラグが設定されます。

OVER\_TEMP は、プロセス実行中に接合部温度が熱スレッショルドを上回ると、フラグが設定されます（波形再生、診断、自動キャリブレーションなど）。

プロセス実行中に VDD が VDD\_THRESH 電圧を下回ると、UVLO のフラグが設定されます（波形再生、診断、自動キャリブレーションなど）。

PROCESS\_DONE には、プロセス（波形シーケンサ、診断、またはキャリブレーション）が終了するとフラグが設定されます。PROCESS\_DONE ビットは、プロセスが中断された場合（ストップトリガやクリティカル条件による場合など）はアサートされません。RTP は自動的に終了しないため、RTP によって PROCESS\_DONE がアサートされることはありません。PROCESS\_DONE を返す特定の波形については、注を参照してください。

---

注

AUTO\_BRK\_INTO\_STBY = 1 の場合、PROCESS\_DONE トリガは、マルチ クリックまたはマルチパターン化された波形を再生するときに、複数回繰り返すことができます。テキサス インストルメンツでは、スタンダバイ ビットに自動ブレーキをイネーブルにした状態で PROCESS\_DONE 機能を使用することは推奨しません。

PRG\_ERROR は、RAM 内で読み取ったデータが破損している場合にフラグが設定されます。

図 7-6. 割り込みモードの TRIG/INTZ 機能

デバイスがスタンバイ状態の間、UVLO、過熱、過電流などの重大な状態は監視されません。しかし、デバイスがスタンバイ状態の場合でも、 $\text{I}^2\text{C}$  通信が継続している間、UVLO および過熱状態は監視されます。

### 7.3.17 スタンバイ状態への自動的な遷移

DRV2624 では、自動的にスタンバイ状態に移行して電力を維持できます。デバイスがスタンバイに移行し、新しい波形がトリガされると、DRV2624 は、ウェークアップし、要求された波形を直ちに再生します。

### 7.3.18 自動ブレーキをスタンバイ状態にします

DRV2624 を使用すると、スタンバイに移行する前に自動ブレーキをかけることができます。AUTO\_BRK\_INTO\_STBY がアサートされると、デバイスは（必要に応じて）アクチュエータをブレーキしてからスタンバイに移行します。過熱、過電流、UVLO、NRST のアサートなど、重大な条件が発生した場合、この機能はバイパスされます。

### 7.3.19 バッテリ監視と電力維持

DRV2624 デバイスは VDD 電圧を継続的に監視します。UVLO\_THRES[2:0] 電圧を下回る VDD 電圧グリッチが発生した場合、DRV2624 は直ちに再生を停止して、スタンバイ状態に移行します。UVLO ステータスビットがアサートされ、構成されている場合は、TRIG/INTZ ピンがアサートされます。VDD グリッチのためにスタンバイに移行すると、AUTO\_BRK\_INTO\_STBY が有効化されても、ブレーキがバイパスされることに注意します。UVLO 条件が発生しても、 $\text{I}^2\text{C}$  通信は中断されません。ただし、UVLO 条件により通信が破壊される可能性があるため、 $\text{I}^2\text{C}$  トランザクションの後で UVLO フラグをチェックし、処理中の内容が破損していないことを確認することをお勧めします。

また、DRV2624 はバッテリを監視するバッテリ保護モードも搭載しており、VDD 電圧が指定のスレッショルドを下回ると (BAT\_LIFE\_EXT\_LVL1[7:0] および BAT\_LIFE\_EXT\_LVL2[7:0] パラメータを参照)、ユーザーの指定に従って、自動的に最大出力電圧をクランプします (OD\_CLAMP\_LVL1[7:0] および OD\_CLAMP\_LVL2[7:0] パラメータを参照)。

## 7.4 デバイスの機能モード

### 7.4.1 電源の状態

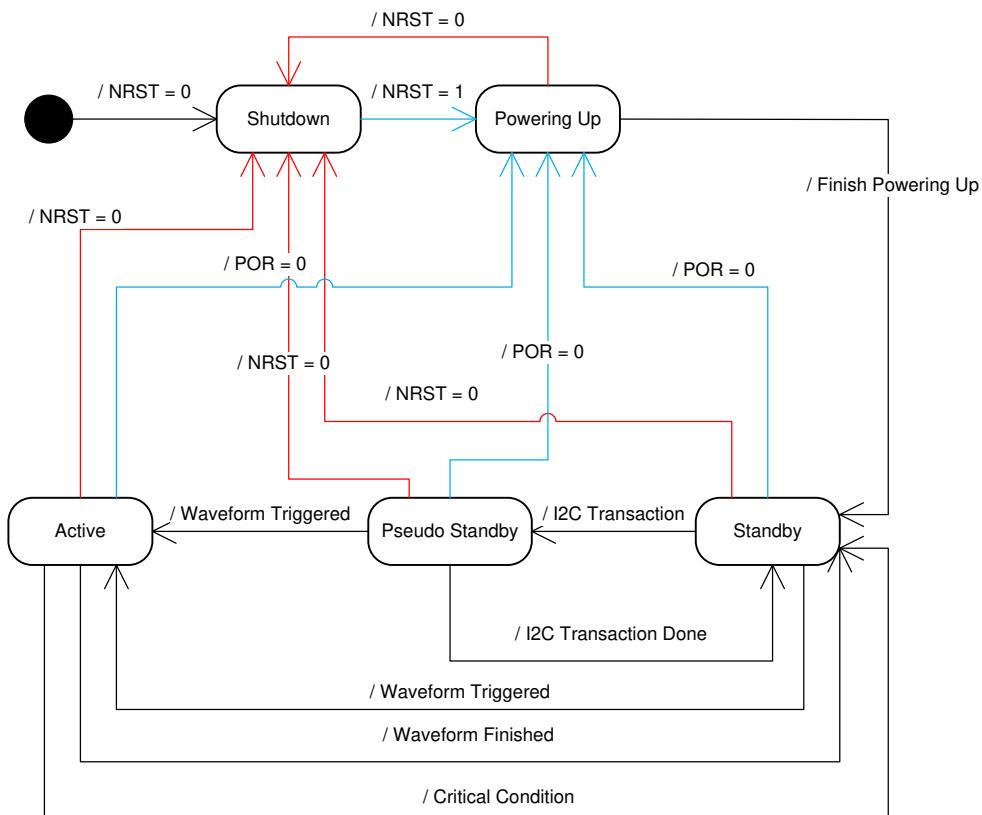

DRV2624 デバイスには、消費電力を最適化するため、複数の電力状態があります。重大な条件が発生した場合、DRV2624 デバイスは直ちにスタンバイ状態になります。図 7-7 に、各状態との間の遷移を示します。

特定のコーナー状況では、DRV2624 は疑似スタンバイ状態にとどまり、低消費電力スタンバイ状態に完全には戻らない可能性があります。自動移行スタンバイ（低電力）の注を参考してください。この疑似スタンバイ状態を終了するには、単純な  $\text{I}^2\text{C}$  トランザクションを使用できます。疑似スタンバイ状態をクリアするロジックは、図 7-7 の  $\text{I}^2\text{C}$  トランザクション完了パスに従います。

図 7-7. 電源状態図

#### 7.4.2 $V_{DD} < 2.5$ (最小 $V_{DD}$ ) での動作

デバイスの  $V_{DD}$  値が 2.5V 未満の場合、動作させることは推奨しません。

#### 7.4.3 $V_{DD} > 6V$ ( $V_{DD}$ の絶対最大定格) での動作

**DRV2624** デバイスは、最大 5.5V で動作するように設計されており、絶対最大定格電圧は 6V です。6V を超える電圧にさらされると、デバイスに永続的な損傷が発生する可能性があります。

#### 7.4.4 シャットダウン状態での動作

本デバイスの NRST ピンは、DRV2624 デバイスのパワーアップをゲートします。NRST がアサートされる (ロジック low) と、デバイスのすべての内部ブロック (I<sup>2</sup>C コントローラを含む) がオフになり、超低消費電力を実現します。

**NRST** ピンがディアサートされると (ロジック high)、DRV2624 デバイスは電源オンになり、すべてのデフォルト状態がロードされて、スタンバイ状態に移行して電力を維持します。

**NRST** ピンをアサートすると、直ちに有効になります。実行中のすべてのプロセスは直ちに中止され、デバイスはシャットダウン状態に移行します。

DRV2624 デバイスでは、NRST を VDD に永続的に接続できます。この場合、シャットダウン状態はバイパスされます。

#### 7.4.5 スタンバイ状態での動作

DRV2624 は省電力用に最適化されているため、デバイスを使用していないときは自動的にスタンバイになります。

スタンバイ状態では、I<sup>2</sup>C通信が利用可能で、レジスタの内容が保持されます。

スタンバイ状態は電力を維持するために、必須ではないブロックすべてをオフにしますが、高速なターンオン時間により、このモードからの低レイテンシのハイディクス再生が可能です。

ホストコントローラが **DRV2624** デバイスを強制的にスタンバイにする場合、ホストコントローラはストップトリガを送信することで実行できます。このトリガは、GO ビットに 0 を書き込むことで実行するか、または外部トリガを使用する場合は、[セクション 7.3.4.3](#) で説明されている適切なメカニズムに従うことで実行できます。

**DRV2624** には、スタンバイ状態になる前に駆動ブレーキをアクチュエータにかける自動ブレーキオプションが装備されています。自動ブレーキ機能は、デバイスがスタンバイ状態になるたびに実行されますが、重要な条件（過電流、サーマルシャットダウン、UVLO など）を除きます。自動ブレーキ機能は、**AUTO\_BRK\_INTO\_STBY** ビットを使って有効化または無効化できます。

#### 7.4.6 ACTIVE 状態での動作

**DRV2624** がデバイスがプロセス（波形の再生、キャリブレーション、または診断）を実行する必要がある場合のみ、アクティブモードに移行します。

デバイスがアクティブモードになったとき、最初に行う作業は重要な条件（過電流、サーマルシャットダウン、UVLO など）をチェックすることです。重大な状態が発生すると、**DRV2624** デバイスは適切なフラグを設定し（そのように設定されている場合は割り込みを発生）、直ちにスタンバイに移行します。クリティカルな状態が存在しない場合、**DRV2624** デバイスはルーチンを実行し、完了するとスタンバイ状態に戻ります。

ルーチンの実行中に重要な状態が発生した場合、このルーチンは直ちに中止され、デバイスは適切なフラグを設定し（そのように設定されている場合は割り込みを発生させ）、直ちにスタンバイに移行します。

ルーチンの実行中に停止トリガを受信すると、そのルーチンは停止され、デバイスはスタンバイ状態に移行します。自動ブレーキ機能が有効化されている場合（**AUTO\_BRK\_INTO\_STBY** ビット）、**DRV2624** デバイスはスタンバイ状態に移行する前にアクチュエータをブレーキします。

#### 7.4.7 動作モードを変更

**DRV2624** デバイスには、動作モードのさまざまな要素を制御する 8 つのパラメータがあります。**LRA\_ERM**、**MODE[1:0]**、**CONTROL\_LOOP**、**TRIG\_PIN\_FUNC**、**AUTO\_BRK\_INTO\_STBY**、**AUTO\_BRK\_DL**、**LRA\_WAVE\_SHAPE**。プロセスの実行中にこれらのパラメータのいずれかが変更された場合（波形の再生、診断、またはキャリブレーション）、**DRV2624** はその変更を中止として解釈し、スタンバイに移行します。

**LRA\_ERM** パラメータ アクチュエータタイプを選択します。

**MODE[1:0]** は、実行可能な 4 つのプロセス、すなわち波形の再生、診断、較正に RTP および波形シーケンサのいずれかを選択します。**DRV2624** デバイスは、トリガが受信されるまでスタンバイ状態になります。その時点で、デバイスは **MODE[1:0]** パラメータで選択したプロセスを実行します。終了すると、**DRV2624** デバイスはスタンバイ状態に戻ります。

**CONTROL\_LOOP** はオープンループとクローズドループを選択します。

**TRIG\_PIN\_FUNC** パラメータは、パルストリガ、レベルトリガ、割り込みという 3 つの可能性の中から、TRIG/INTZ ピンの機能を選択します。

**AUTO\_BRK\_INTO\_STBY** パラメータは、スタンバイに移行する際の自動ブレーキを有効化します。**DRV2624** デバイスは、スタンバイに移行する前にアクチュエータの逆起電力を監視し、逆起電力が移動している場合は、アクチュエータがブレーキをかけてスタンバイに移行します。この機能を開ループで実行するには、**AUTO\_BRK\_DL** ピンをイネーブルにする必要があることに注意します。

**AUTO\_BRK\_DL** パラメータは、開ループモードの自動ブレーキを有効化します。有効にすると、波形が負の振幅でコンフィグレーションされるたびに、**DRV2624** デバイスはアクチュエータをブレーキします。この機能は、アクチュエータが較正されており、閉ループ条件下で動作することを前提としています。

**LRA\_WAVE\_SHAPE** パラメータ（LRA でのみ使用可能）を使用すると、開ループで LRA を駆動するときに使用する波形形状を選択できます。クローズドループでは、このパラメータは無視されます。

## 7.5 例外的な条件下の動作です

このセクションでは、さまざまな非常に優れた条件と、そのような条件での DRV2624 デバイスの動作方法について説明します。このセクションでは、デバイスがこれらの状態に移行する方法についても説明します。

### 7.5.1 アクチュエータ非接続時の動作

開ループ モードでは、DRV2624 デバイスは、ユーザーの意図したとおりに波形が駆動されます。

LRA 閉ループ モードでは、OUT+ ピンおよび OUT- ピンにアクチュエータが接続されていなくとも波形が再生されると、出力ピンが切り替わります。ただし、トグル周波数は予測できません。

ERM 閉ループ モードでは、出力ピンが駆動を試みますが、振幅は予測できません。

### 7.5.2 非可動アクチュエータを取り付けた状態での作業

ERM の場合、移動が検出されるまで、DRV2624 デバイスはアクチュエータのオーバードライブを試みます。

非可動アクチュエータのモデルは抵抗として単純化することができます。OUT+ ピンと OUT- ピン間に抵抗 (LRA と同様の負荷、例えば  $25\Omega$ ) が接続され、DRV2624 デバイスが LRA クローズドループ モードの場合、出力ピンはデフォルトの  $f$  でトグルします。LRA オープンループ モードでは、出力ピンは指定されたオープンループ周波数でトグルします。

### 7.5.3 REG ピンで短絡による動作

REG ピンが GND に短絡されると、デバイスはオフになります。短絡が解消されると、デバイスはデフォルト状態で起動します。

### 7.5.4 OUT+、OUT-、またはその両方を短絡したときの動作

再生中に、いずれかの出力ピン (OUT+ または OUT-) が V<sub>DD</sub>、GND、または相互に短絡された場合、電流保護回路が自動的にイネーブルになり、出力段をシャットダウンし、OC\_DETECT ビットがアサートされ (および割り込みがイネーブルの場合は割り込みが発生)、DRV2624 デバイスはスタンバイ状態に移行します。

DRV2624 デバイスは、プロセス (RTP、波形シーケンサ、診断、キャリブレーション) の実行時のみ短絡をチェックします。デバイスがアイドルのときに短絡が発生した場合、デバイスがプロセスを実行しようとするまで、短絡は検出されません。

## 7.6 プログラミング

### 7.6.1 LRA 用自動共振エンジン プログラミング

#### 7.6.1.1 ドライブ時間プログラミング

各 LRA アクチュエータの共振周波数は、多くの要因に基づいて変動し、一般的には機械的特性が主に占めています。自動共振エンジントラッキング システムは、アクチュエータの共振周波数に関する情報を提供することによって最適化されています。DRIVE\_TIME[4:0] ビットは、LRA の半期間の初期推測として使用されます。ドライブ時間は自動的かつ迅速に調整され、最適なドライブが得られます。たとえば、LRA の共振周波数が 200Hz の場合、駆動時間は 2.5ms に設定されています。

ERM アクチュエータの場合、DRIVE\_TIME[4:0] ビットが逆起電力サンプリングのレートを制御します。駆動時間が短いと逆起電力サンプリング周波数が高くなり、出力信号のピーク/平均値比が高くなり、電源ヘッドルームがより大きくなります。駆動時間が長いほど、逆起電力サンプリング周波数が低くなり、フィードバックは低速で反応します。

#### 7.6.1.2 電流散逸時間のプログラミング

アクチュエータの逆起電力を検出するために、DRV2624 デバイスは高インピーダンス モードに移行します。ただし、デバイスがこのモードに移行する前に、デバイスはアクチュエータの電流を消費する必要があります。DRV2624 デバイスは、IDISS\_TIME[3:0] パラメータにより、消費電流に割り当てられた時間を制御します。

#### 7.6.1.3 ブランкиング時間のプログラミング

アクチュエータの電流が消費された後、DRV2624 デバイスは信号のブランкиング時間が安定するまで待機してから、逆起電力のアナログ/デジタル (AD) 変換が変換されます。BLANKING\_TIME[3:0] パラメータは、この時間を制御します。

#### 7.6.1.4 ゼロクロス検出時間プログラミング

ブランкиング時間が経過すると、逆起電力 AD はゼロ クロスを監視します。ZC\_DET\_TIME[1:0] パラメータは、ゼロ クロス検出に許容される最小時間を制御します。

### 7.6.2 自動レベルキャリブレーション プログラミング

#### 7.6.2.1 定格電圧プログラミング

定格電圧は、定常状態でのドライバ出力の駆動電圧です。ただし、閉ループ ドライブ モードでは、一時的に定格電圧を超える出力電圧が発生する可能性があります。

RATED\_VOLTAGE[7:0] パラメータは、閉ループ駆動モードの定格電圧を設定します。

$$V_{(ERM-CL_AV)} = 21.88 \times 10^{-3} \text{ RATED_VOLTAGE}[7:0] \quad (6)$$

$$V_{(LRA-CL_RMS)} = \frac{20.58 \times 10^{-3} \times \text{RATED_VOLTAGE}[7:0]}{\sqrt{1 - (4 \times t_{(SAMPLE\_TIME)} + 300 \times 10^{-6}) \times f_{(LRA)}}} \quad (7)$$

開ループ モードでは、RATED\_VOLTAGE[7:0] パラメータは無視されます。代わりに、OD\_CLAMP[7:0] パラメータを使用して開ループ駆動モードのフルスケール電圧を設定します。

$$V_{(ERM-OL_AV)} = 21.59 \times 10^{-3} \text{ OD_CLAMP}[7:0] \quad (8)$$

$$V_{(LRA-OL_RMS)} = 21.32 \times 10^{-3} \times \text{OD_CLAMP}[7:0] \times \sqrt{1 - f_{(LRA)} \times 800 \times 10^{-6}} \quad (9)$$

自動較正ルーチンは、RATED\_VOLTAGE[7:0] ビットと OD\_CLAMP[7:0] ビットを入力として使用するため、較正を実行する前にこれらのレジスタを書き込む必要があります。このレジスタ値を変更する場合、A\_CAL\_BEMF[7:0] を適切に設定するためにキャリブレーションが行われます。

### 7.6.2.2 オーバードライブ電圧-クランプのプログラミング

閉ループ動作中、アクチュエータ帰還により、自動オーバードライブおよび自動ブレーキ期間中に出力電圧が定格電圧を超えることができます。OD\_CLAMP[7:0] パラメータは、自動オーバードライブが境界設定されるようにクランプを設定します。OD\_CLAMP[7:0] パラメータは、閉ループ動作のフルスケール基準電圧としても機能します。OD\_CLAMP[7:0] パラメータは、モードに関係なく、常に許容される最大ピーコンデンサ電圧を表します。

#### 注

電源電圧 ( $V_{DD}$ ) がオーバードライブクランプ電圧よりも低い場合、出力電圧が電源電圧を超えることができないため、出力ドライバはクランプ電圧値に到達できません。定格電圧がオーバードライブクランプ電圧を超えると、オーバードライブクランプ電圧が定格電圧よりも優先されます。

$$V_{(ERM\_clamp)} = \frac{21.64 \times 10^{-3} \times OD\_CLAMP[7:0] \times (t_{(DRIVE\_TIME)} - 300 \times 10^{-6})}{t_{(DRIVE\_TIME)} + t_{(IDISS\_TIME)} + t_{(BLANKING\_TIME)}} \quad (10)$$

$$V_{(LRA\_clamp)} = 21.22 \times 10^{-3} \times OD\_CLAMP[7:0] \quad (11)$$

### 7.6.3 I<sup>2</sup>C インターフェイス

#### 7.6.3.1 TI のハプティクス ブロードキャスト モード

DRV2624 デバイスには TI ハプティクス ブロードキャスト モードが搭載されており、I<sup>2</sup>C\_BCAST\_EN ビットを使用してインペリフェラルにすると、デバイスはペリフェラル アドレス 0x58 (7 ビット) または 1011000 (バイナリ) に応答します。システムにインストールされている TI のハプティクス ブロードキャスト モードを複数のハプティクス ドライバが実装している場合に、このモードは便利です。このような状況では、0x58 ペリフェラル アドレスに GO ビットを書き込むことで、すべてのハプティクス ドライバが同時にプロセスをトリガできます。

#### 7.6.3.2 I<sup>2</sup>C 通信の可用性

スタンバイ、およびアクティブ状態時の読み取り/書き込み動作に I<sup>2</sup>C プロトコルを使用できます。

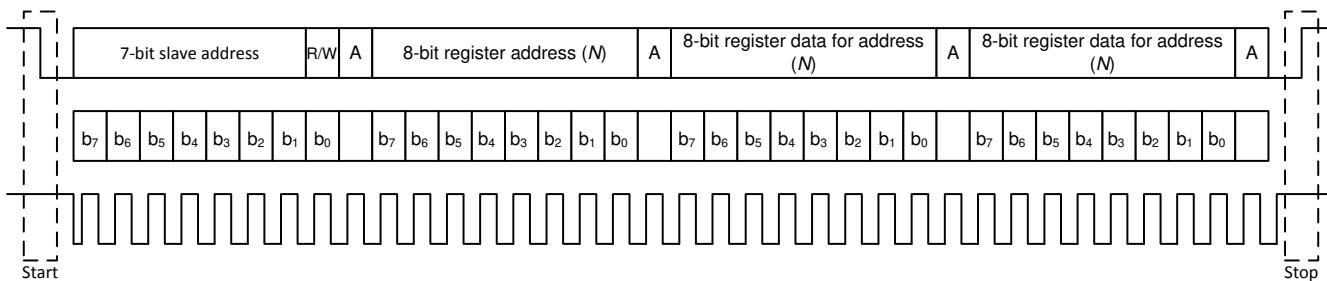

#### 7.6.3.3 一般的な I<sup>2</sup>C の動作

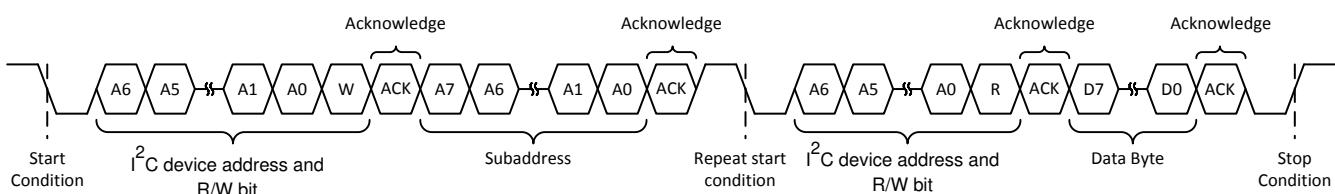

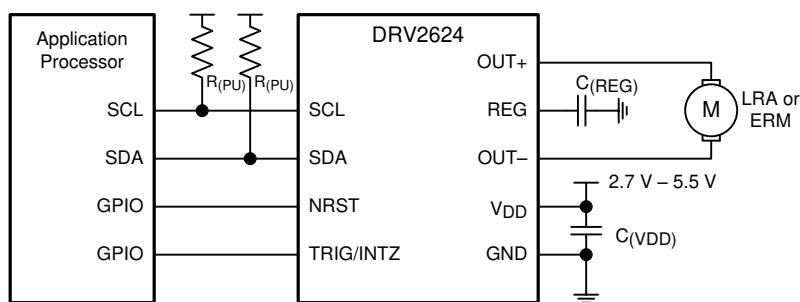

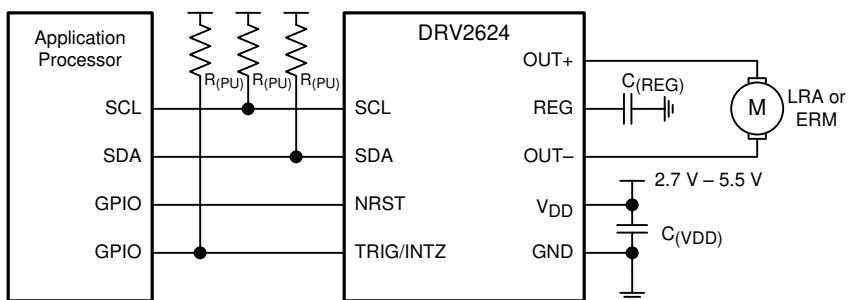

I<sup>2</sup>C バスは、SDA (データ) と SCL (クロック) の 2 つの信号を使用して、シリアル データ伝送によりシステム内の集積回路間で通信を行います。バスはデータを 1 ビットずつシリアルに転送します。8 ビットのアドレスとデータ バイトは、最上位ビット (MSB) から順に転送されます。さらに、バス上で転送される各バイトは、受信デバイスによってアクノリッジ ビットで確認されます。各転送操作は、コントローラ デバイスがバス上にスタートコンディションを発生させることで開始し、ストップコンディションを発生させることで終了します。バスは、クロックがロジック ハイの状態でデータ ピン (SDA) の遷移を使用して、スタートの条件およびストップの条件を示します。SDA 信号ラインでのハイからローへの遷移はスタート条件を示し、ローからハイへの遷移はストップ条件を示します。通常のデータビット遷移は、クロック周期の低レベル期間内に発生しなければなりません。図 7-8 に代表的なアプリケーションを示します。コントローラ デバイスは、ペリフェラルデバイスとの通信を開始するために、7 ビットのペリフェラルアドレスと読み取り/書き込み (R/W) ビットを生成します。その後、コントローラ デバイスはアクノリッジ条件を待ちます。ペリフェラルデバイスは、アクノリッジ クロック期間中に SDA 信号を低レベルに保持することで、アクノリッジを示します。確認応答が発生すると、コントローラ デバイスはシーケンスの次のバイトを送信します。各デバイスは、固有の 7 ビットのペリフェラルアドレスと R/W ビット (1 バイト) によってアドレス指定されます。すべての互換デバイスは、ワイヤード-AND 接続を使用した双方向バスを介して、同じ信号を共有します。

開始条件と停止条件の間で送信できるバイト数に制限はありません。最後のデータワードが転送されると、コントローラはバスを解放するためにストップコンディションを生成します。一般的なデータ転送シーケンスを、図 7-8 に示します。

SDA および SCL 信号に外付けプルアップ抵抗を使用して、バスの論理ハイレベルを設定します。660Ω ~ 4.7kΩ のプルアップ抵抗を推奨します。SDA と SCL 電圧が DRV2624 電源電圧  $V_{DD}$  を超えないようにしてください。

**注**

DRV2624 ペリフェラル アドレスは、0x5A (7 ビット)、または 1011010 のバイナリ アドレスです。

**図 7-8. 代表的な I<sup>2</sup>C シーケンス**

DRV2624 デバイスは、I<sup>2</sup>C ペリフェラルの 1.8V ロジック レベルとして動作しますが、最大 V<sub>DD</sub> 電圧で動作できます。デバイス アドレスは 0x5A (7 ビット)、またはバイナリで 1011010 であり、これは書き込みの場合は 0xB4 (8 ビット)、読み取りの場合は 0xB5 (8 ビット) と等価です。

#### 7.6.3.4 シングル バイトおよびマルチ バイト転送

シリアル制御インターフェイスは、シングル バイトとマルチ バイトの R/W の両方の動作を、すべてのレジスタについてサポートしています。

マルチ バイトの読み取り動作中、DRV2624 デバイスは符号付きレジスタからデータを 1 バイトずつ返します。マスター デバイスがアクノリッジで応答を継続する限り、このデバイスは応答します。

DRV2624 は、シーケンシャルな I<sup>2</sup>C アドレッシングに対応しています。書き込みトランザクションは、レジスタの後にそのレジスタに対するデータが発行される場合、I<sup>2</sup>C 順次書き込みトランザクションが実行され、その後に続く残りのレジスタも送信されます。I<sup>2</sup>C のシーケンシャルな書き込みトランザクションの場合、発行されたレジスタは開始点となり、その後に停止または開始が送信される前に、データの量が送信され、いくつのレジスタを書き込むかが決定されます。

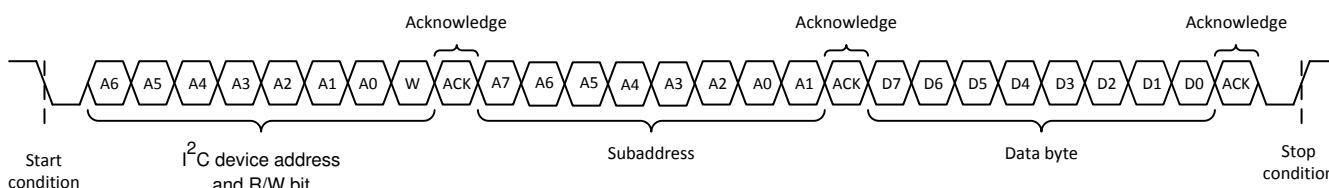

#### 7.6.3.5 シングル バイトの書き込み

図 7-9 にあるように、シングル バイトのデータ書き込み転送では、最初にマスター デバイスが開始条件を送信し、次に I<sup>2</sup>C デバイス アドレスと読み取り / 書き込みビットが続きます。データ転送方向は、読み取り / 書き込みビットによって決定されます。書き込みデータ転送を実行するには、読み取り / 書き込みビットを 0 にセットします。正しい I<sup>2</sup>C デバイス アドレスと読み取り / 書き込みビットを受信すると、DRV2624 はアクノリッジ ビットを返します。次に、コントローラはアクセスされた DRV2624 内部メモリ アドレスに対応するレジスタ バイトを送信します。デバイスは、レジスタ バイトを受信すると、再度アクノリッジ ビットを返信します。最後に、コントローラ デバイスが停止条件を送信すると、シングル バイト データの書き込み転送が完了します。

**図 7-9. シングル バイトの書き込み転送**

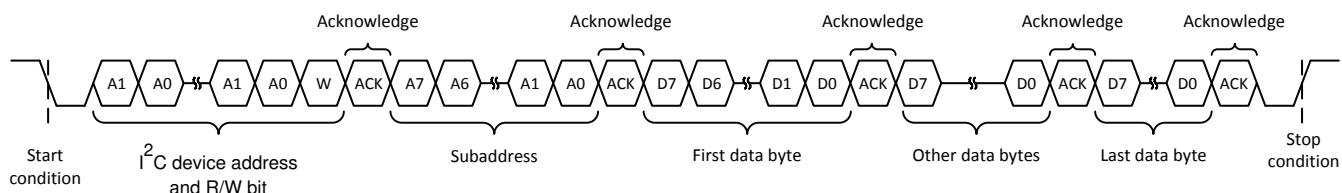

### 7.6.3.6 マルチ バイトの書き込みと増分マルチ バイトの書き込み

マルチ バイトデータの書き込み転送は、シングル バイトデータの書き込み転送と同じですが、図 7-10 に示すように、複数のデータ バイトがコントローラー デバイスによって DRV2624 デバイスに送信される点が異なります各データ バイトを受信すると、DRV2624 デバイスはアクノリッジ ビットで応答します。

図 7-10. マルチ バイトの書き込み転送

### 7.6.3.7 シングル バイトの読み取り

図 7-11 に示すように、シングル バイトのデータ読み取り転送では、コントローラ デバイスが開始条件を送信し、次に  $\text{I}^2\text{C}$  デバイス アドレスと R/W ビットを送信することで開始されます。データ読み取り転送の場合、実際には書き込みとその次の読み取りの両方が行われます。最初に、内部メモリ アドレスの読み取りに必要なアドレス バイトを転送するために、書き込みが実行されます。その結果、読み取り / 書き込みビットは 0 に設定されます。

この DRV2624 デバイスは、DRV2624 アドレスと読み取り / 書き込み ビットを受信すると、アクノリッジ ビットで応答します。次に、コントローラーが内部メモリ アドレス バイトを送信すると、デバイスはアクノリッジ ビットを送信します。コントローラ デバイスは、DRV2624 アドレスと読み取り / 書き込み ビットに続いて、もう 1 つのスタート条件を送信します。この場合、読み取り / 書き込み ビットは 1 に設定され、読み取り転送が実行されることを示します。次に、DRV2624 デバイスは読み取り中のメモリ アドレスからデータ バイトを送信します。データ バイトを受信すると、コントローラ デバイスは非応答 (not-acknowledge) を送信し、その後、停止条件を出して、シングルバイト データ読み取り転送が完了します セクション 7.6.3.3 セクションの注記を参照してください。

図 7-11. シングル バイトの読み取り転送

### 7.6.3.8 マルチ バイトの読み取り

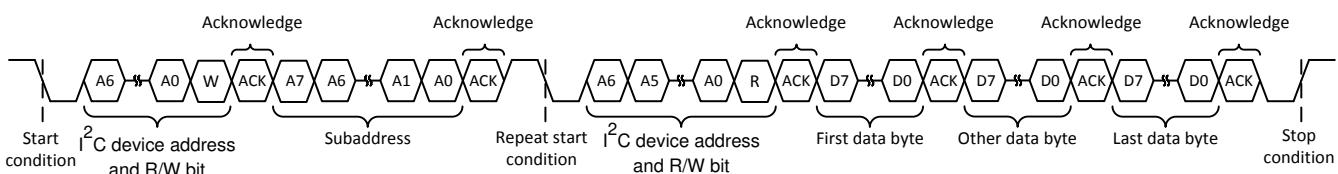

マルチ バイトデータの読み取り転送はシングル バイトのデータ読み取り転送と同じですが、図 7-12 に示すように、複数のデータ バイトが DRV2624 デバイス によってコントローラ デバイスに送信されます。コントローラ デバイスは、データ バイトを受信するごとにアクノリッジ ビットを返信します。ただし、最後のデータ バイトについては返信しません。

図 7-12. マルチ バイトの読み取り転送

## 7.6.4 開ループ動作のプログラミング

DRV2624 デバイスは、開ループモードと閉ループモードで使用できます。開ループ動作が必要な場合、最初の手順は、使用するアクチュエータのタイプ (ERM と LRA) を決定することです。

### 7.6.4.1 ERM 開ループ動作のプログラミング

DRV2624 デバイスを ERM 開ループ動作で構成するには、LRA\_ERM ビットを 0 に、CONTROL\_LOOP ビットを 1 に書き込んで ERM を選択する必要があります。

### 7.6.4.2 LRA 開ループ動作のプログラミング

DRV2624 デバイスを LRA 開ループ動作で構成するには、LRA\_ERM ビットを 1 に、CONTROL\_LOOP ビットを 1 に書き込んで LRA を選択する必要があります。さらに、OL\_LRA\_PERIOD パラメータは、適切な LRA 周波数を使用して設定する必要があります。

## 7.6.5 閉ループ動作のプログラミング

クローズドループ動作の場合、アクチュエータの選択に従ってデバイスを較正する必要があります。それに応じてキャリブレーションを行う場合、ユーザーは目的の波形を提供するだけです。DRV2624 デバイスはレベルを自動的に調整し、LRA の場合は駆動周波数を自動的に調整します。

## 7.6.6 診断ルーチン

DRV2624 には診断ルーチンがあり、MODE[1:0] パラメータで選択できます。このルーチンの目的は、アクチュエータを安全かつ正しく駆動できるかどうかを判断することです。診断ルーチンによって問題が検出されると、DIAG\_RESULT ビットがアサートされます (high)。診断ルーチンの実行後、DIAG\_RESULT をチェックして、診断ルーチンの結果を評価します。UVLO、過熱、過電流状態などの致命的な条件が原因で、診断ルーチンが完了しない場合、診断ルーチンは中止され、DIAG\_RESULT は 1 に設定されます。

診断ルーチンは、抵抗測定ルーチンと機能ルーチンの 2 つのサブルーチンで構成されている。

抵抗測定サブルーチンは、差動出力ピン (OUT+ および OUT-) からの観測結果としてアクチュエータの抵抗を報告し、DIAG\_Z\_RESULT パラメータに配置されます。抵抗測定サブルーチンは常に診断ルーチンの間に実行され、出力は DIAG\_Z\_RESULT に通知されます。唯一の例外は、過熱または UVLO 状態中であり、この場合診断ルーチンは直ちに中止され、デバイスはスタンバイ状態に移行します。

### 注

このサブルーチンでは、短絡が存在していても、過電流状態は発生しません。抵抗の測定値は、過電流検出回路によっては検出されない小さな電流を注入するためです。抵抗測定サブルーチンが最初に実行されます。また、このサブルーチンは DIAG\_RESULT ビットをアサートしません。

抵抗測定の後、診断ルーチンは (キャリブレーション波形と同じ波形) を再生して、アクチュエータを正常に駆動できるかどうかを判断します。短絡または開放状態が発生し、有効な BEMF が検出されないと、DIAG\_RESULT ビットがアサートされます。診断ルーチン中に過電流状態などの重大な問題が発生した場合、このルーチンを中止して、DIAG\_RESULT がアサートされることに注意してください。

## 7.6.7 キャリブレーションルーチン

DRV2624 には、特定のアクチュエータ (接続され、較正されているもの) を閉ループで正常に駆動するために必要なすべての重要なパラメータが自動的に入力されるキャリブレーションルーチンがあります。アクチュエータが同じモデルであっても、異なるアクチュエータ間で変動が発生します。目的の結果を維持するため、アクチュエータごとに較正ルーチンを少なくとも 1 回実行することを推奨します。

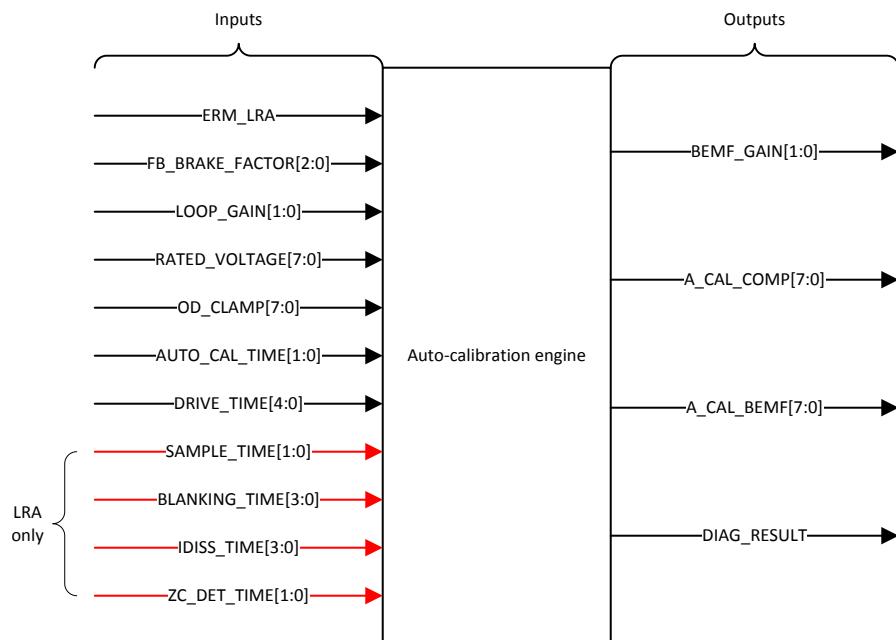

キャリブレーションエンジンは、キャリブレーションを実行する前に入力として多くのパラメータを必要とします。入力が構成されているときは、較正ルーチンを実行できます。較正が実行されると、指定されたレジスタ位置に出力パラメータが書き込まれます。[図 7-13](#) に、必要な入力と生成された出力をすべて示します。適切な自動共振動作を維持するために、

LRA アクチュエータ タイプは ERM よりも多くの入力パラメータを必要とします。デバイスが ERM モードのとき、LRA パラメータは無視されます。

図 7-13. キャリブレーション エンジンの機能図

適切な較正結果を得るには、安定した加速が得られるように十分な時間にわたって較正波形を実行する必要があります。このため、DRV2624 デバイスにはキャリブレーション波形の時間の設定が可能で、**AUTO\_CAL\_TIME[1:0]** パラメータで選択できます。さらに、**AUTO\_CAL\_TIME** パラメータで許可されている時間よりも長い時間を必要とする場合に対応するために、トリガを使用して較正時間を制御するオプションが用意されています。トリガー制御オプションでは、最初のトリガーの後にキャリブレーションの実行が開始され、停止トリガーを受信すると実行が停止します。この時点で、較正の出力値が書き込まれます。キャリブレーションを正常に動作させるには、最小期間が必要であることに注意してください。

表 7-1. 各種の **AUTO\_CAL\_TIME** 選択によるキャリブレーション ルーチンの動作

| <b>AUTO_CAL_TIME[1:0]</b> | アクション              | 備考                                                                                                                                  |

|---------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 0                         | 250ms のキャリブレーション波形 |                                                                                                                                     |

| 1                         | 500ms のキャリブレーション波形 |                                                                                                                                     |

| 2                         | 1s キャリブレーション波形     |                                                                                                                                     |

| 3                         | トリガ制御              | GO ビットまたは外部からトリガできます。外部トリガを使用するには、 <b>TRIG_PIN_FUNC</b> パラメータを適切に設定する必要があります。<br>この場合、最小期間は 1 秒です。そうしないと、キャリブレーションの結果が破損する可能性があります。 |

以下の手順は、自動較正用のレジスタ設定のステップバイステップを示しています。

1. DRV2624 デバイスに有効な電源電圧を印加してから、NRST ピンを high にプルします。供給電圧により、選択したアクチュエータの適切な駆動電圧が得られます。

2. 自動較正ルーチンを設定するため、MODE パラメータに値 0x03 を書き込みます。

3. 自動キャリブレーション エンジンに必要な入力パラメータを入力します。

- a. LRA\_ERM - 選択は、目的のアクチュエータによって異なります。

- b. FB\_BRAKE\_FACTOR[2:0] — ほとんどのアクチュエータで有効な値は 3 です。

- c. LOOP\_GAIN[1:0] — ほとんどのアクチュエータで有効な値は 2 です。

- d. RATED\_VOLTAGE[7:0] - 正しいレジスタ値を計算する方法については、[セクション 7.6.2.1](#) セクションを参照してください。

- e. OD\_CLAMP[7:0] - 正しいレジスタ値を計算するには、[セクション 7.6.2.2](#) セクションを参照してください。

- f. AUTO\_CAL\_TIME[1:0] — ほとんどのアクチュエータで 3 の値が有効です。

- g. DRIVE\_TIME[3:0] — 正しいレジスタ値を計算するには、[セクション 7.6.1.1](#) を参照してください。

- h. SAMPLE\_TIME[1:0] — ほとんどのアクチュエータで有効な値は 3 です。

- i. BLANKING\_TIME[3:0] — 値 1 はほとんどのアクチュエータで有効です。

- j. IDISS\_TIME[3:0] — 値 1 はほとんどのアクチュエータで有効です。

- k. ZC\_DET\_TIME[1:0] - 0 の値は、ほとんどのアクチュエータで有効です。

4. GO ビットに 1 を書き込み、自動較正プロセスを開始します。自動較正が完了すると、GO ビットは自動的にクリアされます。自動較正結果は、[図 7-13](#) に示すように、それぞれのレジスタに書き込まれます。

5. DIAG\_RESULT ビットのステータスを確認して、フォルトなしで自動較正ルーチンが完了したことを維持します。

6. 自動キャリブレーションされた設定を使用してシステム性能を評価します。自動較正プロセスはアクチュエータの性能と動作に影響を与える可能性があるため、評価はデバイスの最終組み立て時に行われることに注意してください。調整が必要な場合は、入力を修正して、このシーケンスを繰り返すことができます。パフォーマンスが十分である場合、ユーザーは次のいずれかを実行できます。

- a. その後の電源投入時には、キャリブレーション プロセスを繰り返します。

- b. 自動キャリブレーションの結果をホスト プロセッサのメモリに保存し、その後の電源投入時に DRV2624 デバイスに書き換えます。これらの設定は、STANDBY モードのときも、EN ピンが low のときも、デバイスによって維持されます。

## 7.6.8 波形再生プログラミング

### 7.6.8.1 波形再生用のデータ形式

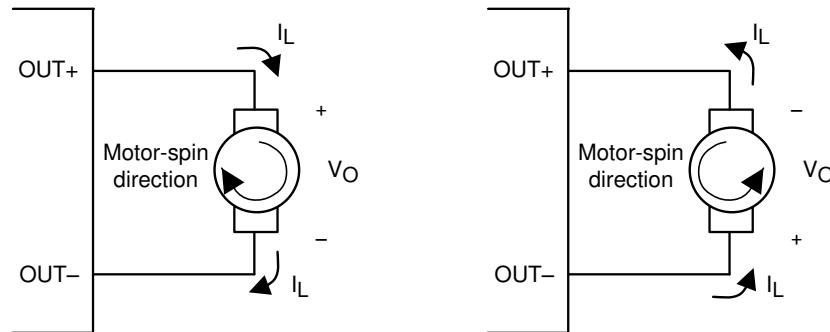

DRV2624 は符号付きデータ形式 (2 の補数) を使用して、ドライブの大きさと方向を指定します。アクチュエータは、閉ループまたは開ループのいずれかで駆動できます。閉ループでは、正の数値は必要なドライブの大きさを示します。負の数値はブレーキ信号として解釈され、閉ループでは自動的に行われます。開ループでは、ドライブとブレーキの両方の振幅の大きさを指定するために正と負の数値が必要です。自動ブレーキが閉ループに選択されている場合、負の数値はブレーキ信号として解釈されます。

### 7.6.8.2 閉ループ モード

閉ループ モードでは、フルスケール駆動の基準レベルは **OD\_CLAMP[7:0]** パラメータによって設定されます。ミッドスケール入力値は駆動信号を与えず、ミッドスケール未満の場合は負の駆動値が得られます。ERM の場合、負のドライブ値はカウンタ回転、またはブレーキになります。LRA の場合、負の駆動値によって整流が 180 度の位相シフトが得られます。

### 7.6.8.3 閉ループ モード

閉ループ モードでは、DRV2624 デバイスは ERM と LRA の両方のデバイスに対して自動的なオーバードライブとブレーキを実行します。正の値は、加速度が必要であることを示します。負の値と 0 は、ブレーキが必要であることを示します。

定常状態フルスケール駆動の基準レベルは、**RATED\_VOLTAGE[7:0]** ビット (自動キャリブレーションを実行する場合) によって設定されます。出力電圧は、自動オーバードライブとブレーキの定格電圧を一時的に上回る場合がありますが、**OD\_CLAMP[7:0]** 電圧を超えない場合があります。逆起電力フィードバックによってブレーキが必要であると判断された場合、入力信号に基づいて自動的にブレーキがかけられます。

特定のアクチュエータに対してオーバードライブ時間が大きすぎる可能性がある場合、**OD\_CLAMP\_TIME[1:0]** を使用してオーバードライブモード (定格電圧を上回る電圧) で費やす時間を制限できます。オーバードライブ時間を超えて、DRV2624 デバイスがまだアクチュエータをオーバードライブしようとしている場合は、新しいクランプが強制されます。このクランプは **RATED\_VOLTAGE\_CLAMP[7:0]** パラメータで指定され、ブレーキ信号を受信するまで強制されます。ブレーキ時に、**OD\_CLAMP\_TIME[1:0]** で指定された時間にわたってデバイスがオーバードライブされる可能性があり、これを超えると **RATED\_VOLTAGE\_CLAMP[7:0]** が強制的に適用されます。この機能は、アクチュエータが必要以上に連続的にオーバードライブされないように維持します。

## 7.6.9 波形の設定と再生

触覚効果の再生は、RTP モードまたは波形シーケンサを使用して行われます。また、このプロセス (RTP または波形シーケンサのいずれか) は、GO ビットに 1 を書き込むか、トリガ パルスまたはトリガ レベルの構成で外部トリガを使用してトリガできます。GO ビットに 0 を書き込むか、外部の TRIG/INTZ ピン経由で停止トリガを送信することで、波形を早期に終了できます。

### 7.6.9.1 RTP モードを使用した波形再生

ユーザーは、MODE[1:0] パラメータに書き込むことで、RTP モードに移行できます。RTP モードでは、デバイスがトリガを受信すると、DRV2624 デバイスは RTP\_INPUT[7:0] パラメータで指定された振幅でアクチュエータを連続的に駆動します。振幅は RTP\_INPUT[7:0] パラメータで指定された値に追従するため、I<sup>2</sup>C バスは波形をストリーミングできます。駆動を停止するには、モードを変更するか、停止トリガを送信します (GO ビットに 0 を書き込むか、外部トリガを使用)。

### 7.6.9.2 RAM へのデータのロード

DRV2624 デバイスには、顧客の波形を格納するための 1kB の RAM が内蔵されています。波形は振幅時間のペアで表現されます。波形シーケンサを使用すると、I<sup>2</sup>C または外部 GPIO トリガによって波形を呼び出し、シーケンス化、再生できます。

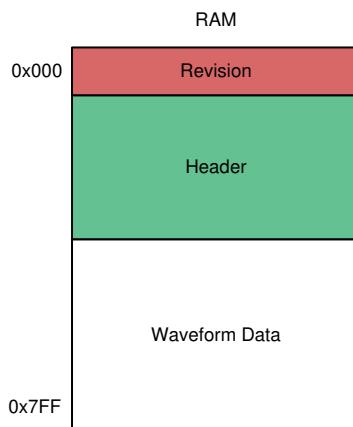

ライブラリは、リビジョン バイト (0 に設定する必要があります)、ヘッダー セクション、および波形データ コンテンツで構成されます。ライブラリ ヘッダーは、データフィールド内の各エフェクト ID のデータ境界を定義し、波形データにはエフェクトを定義する一連の振幅時間ペアが含まれています。

図 7-14. RAM メモリ構造

#### 7.6.9.2.1 ヘッダー形式

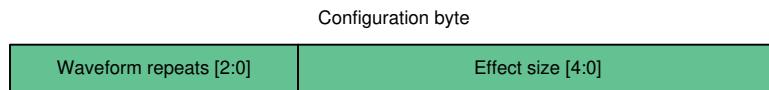

ヘッダ ブロックは、それぞれ 3 バイトの  $N$  境界定義ブロックで構成されています。 $N$  は RAM に格納される効果の数です ( $N$  は 127 を上回ることはできません)。各境界定義ブロックには、開始アドレス (2 バイト) と構成バイトが含まれています。

開始アドレスには、この効果に関連する波形データが開始されるメモリ内の位置が含まれます。ヘッダー内のエフェクト ポインタの位置がエフェクト ID になります。最初のエフェクト境界の定義はエフェクト 1 の ID を指し、2 番目の定義はエフェクト 2 の ID を指し、以下同様に続きます。結果のエフェクト ID は、波形シーケンサで使用されるエフェクト ID です。

| Memory location        | Header                   |                          |                    | Effect ID |

|------------------------|--------------------------|--------------------------|--------------------|-----------|

| 0x000                  | Revision                 |                          |                    |           |

| 0x001                  | Start address upper byte | Start address lower byte | Configuration byte | Effect 1  |

| 0x004                  | Start address upper byte | Start address lower byte | Configuration byte | Effect 2  |

| 0x007                  | Start address upper byte | Start address lower byte | Configuration byte | Effect 3  |

|                        | •                        | •                        | •                  |           |

| $(N - 1) \times 3 + 1$ | Start address upper byte | Start address lower byte | Configuration byte | Effect N  |

図 7-15. ヘッダー構造

構成バイトには、次の 2 つのパラメータが含まれています。

- エフェクト サイズには、波形データを定義するバイト数が含まれます。エフェクト サイズ 0 はエラー状態です。波形データは時間値(2 バイト)として定義されるため、奇数のエフェクトサイズはエラー状態です。したがって、効果サイズは 2 から 30 の偶数でなければなりません。

- WAVEFORM\_REPEATS[2:0] ビットを使用して、波形シーケンサから呼び出されたときに波形全体を再生する回数を選択します。0 の値は繰り返しではなく、波形は 1 回再生されます。値が 1 の場合は 1 回の繰り返しを意味し、波形が 2 回再生されます。7 の値は、GO ビットがクリアされるまでの無限の繰り返しを意味します。

波形を設計する際には、RAM に保存されている波形がスムーズに繰り返されるように、波形の末尾の適切な駆動時間を波形振幅ゼロにするように維持してください。

図 7-16. ヘッダー構成のバイト構造

#### 7.6.9.2.2 RAM 波形データ形式

ライブラリ データの内容は、電圧時間ペアとリニアランプの 2 つの形式を取ることができます。電圧と時間のペア方式は、設定と待機のプロトコルを実装しています。これは、ほとんどの種類の波形に対してアクチュエータを効率的に制御する方法です。ランプ波形が必要な場合、設定と待機方式は非効率になります。そのため、2 つの振幅値間の電圧のセットを線形補間する線形ランプ方式もサポートされています。どちらの方法も、セット ポイントごとに 2 バイトのデータしか必要としません。リニアランプ方式では、最小 4 バイトを使用するため、線形補間を次の設定点で実行できます。電圧値の最上位ビットは、リニアランプモードを示すために予約されています。

| Waveform data |               |  |

|---------------|---------------|--|

| Ramp          | Voltage [6:0] |  |

|               | Time [7:0]    |  |

| Ramp          | Voltage [6:0] |  |

|               | Time [7:0]    |  |

| •             |               |  |

| •             |               |  |

| •             |               |  |

| Ramp          | Voltage [6:0] |  |

|               | Time [7:0]    |  |

図 7-17. 波形データ構造

データは、インターリーブ形式の電圧時間ペアとして保存されます。電圧時間ペアの電圧は、符号付きデータ形式では -63 ~ 63 の範囲の 7 ビット符号付き数値、符号なしデータ形式では 0 ~ 127 の範囲の 7 ビット符号なし数値です。電圧バイトの MSB は、リニアランプ モード用に予約されています。

時間値は、電圧が持続するティックの数です。ティックのサイズは **PLAYBACK\_INTERVAL** ビットによって異なります。**PLAYBACK\_INTERVAL = 0** の場合、絶対時間はティック数×5ms です。**PLAYBACK\_INTERVAL = 1** の場合、絶対時間は数ティック×1ms です。

電圧バイトの最上位ビットが高い場合、エンジンはその電圧と次の電圧ポイント間の線形補間を解釈します。次の電圧ポイントは、通常の電圧時間ペア、またはそれに続くランプの一部になります。以下に、バイトのシーケンスを示します。

1. Byte1 — Voltage1 (MSB High)

2. Byte2 — Time1

3. Byte3 — Voltage2

4. Byte4 — Time2

エンジンは、時間 **Time1** の間に **Voltage1** と **Voltage2** の間に線形補間を作成します。ここで、**Time1** は 5ms のティック数です。ランプの開始値は、**Voltage1** に含まれる 7 ビットの値です。終了振幅は、**Voltage2** に含まれる 7 ビット値です。**Voltage2** の MSB は、次の電圧時間ペア、または後続のランプの開始点を示すことができます。

#### 7.6.9.3 波形シーケンサ

内部メモリからの触覚効果を再生するには、まずエフェクトを波形シーケンサにロードしてから、いずれかのトリガ オプションを使用してエフェクトを起動する必要があります。

波形シーケンサは、再生用に波形ライブラリ識別子をキューに入れます。8 つのシーケンス レジスタは、シーケンシャル再生のために最大 8 つのライブラリ波形をキューに入れます。波形識別子は、内部メモリ内の波形のインデックス位置を示す整数值です。ユーザーが波形シーケンサをトリガすると、再生は **WAV\_FRM\_SEQ1** から開始します。波形の再生が終了すると、**WAV\_FRM\_SEQ2** に保持されている次の波形識別子が波形シーケンサによって再生されます(ゼロ以外の場合)。波形シーケンサーは、シーケンサーが 0 の識別子値に達するか、または 8 つの識別子がいずれか早い方に再生されるまで、このように続けます。

波形識別子は 7 ビットの数値です。各シーケンス レジスタの MSB を使用して、シーケンス波形間の遅延を実装できます。MSB が **high** の場合、ビット 6-0 は待機時間の長さを示します。そのステップの待ち時間は **WAV\_FRM\_SEQ[6:0] ×10ms** になります。

DRV2624 デバイスでは、**WAVn\_SEQ\_LOOP** パラメータを使用して個別の波形をループできます。使用する場合、スタートマシンは、関連する **WAVn\_SEQ\_LOOP** パラメータで指定された回数だけ特定の波形をループしてから、次の波形に移動します。さらに、波形のシーケンサ全体を、**WAV\_SEQ\_MAIN\_LOOP** パラメータで指定した回数だけループさせることができます。波形ループ機能は、ハプティクス着信音など、長いカスタム ハプティクスの再生に役立ちます。

図 7-18. 波形シーケンサのプログラミング

#### 7.6.9.4 波形再生トリガ

DRV2624 デバイスには、次の 2 つの波形再生モードがあります。波形シーケンサおよび RTP。どちらのモードも、TRIG/INTZ ピンを使用して外部から、または GO ビットを使用して内部的にトリガすることができます。外部トリガを使用する場合は、TRIG\_PIN\_FUNC を最も適切に選択する必要があります。

##### 7.6.9.4.1 自動ブレーキを使用せずにスタンバイに再生トリガーされます

スタンバイへの自動ブレーキが無効化されている場合 (AUTO\_BRK\_INTO\_STBY ビットを 0 に設定)、GO ビットに 1 を書き込むと内部トリガにより RTP および波形シーケンサ モードの両方で再生をトリガでき、GO ビットに 0 を書き込むことで停止できます。再生は、トリガ パルスまたはトリガ レベルの指定に従って外部トリガによってトリガすることもできます (詳細については、図 7-5 および図 7-4 を参照してください)。外部トリガ ピンがトリガ レベルに設定されている場合 (TRIG\_PIN\_FUNC = 1)、内部トリガは利用できないことに注意します。

RTP 再生 (MODE[1:0]=0) は、トリガされると、波形が停止するまで無期限に実行されます。波形シーケンサ (MODE[1:0]= 1) は、シーケンサがエンドポイントに達するまで実行され、無限ループが要求されない限り、キャンセルトリガを受信せずに自動的にスタンバイに移行します。

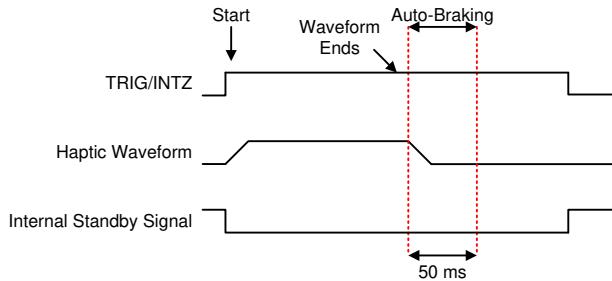

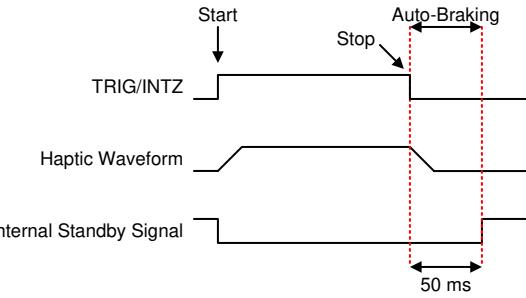

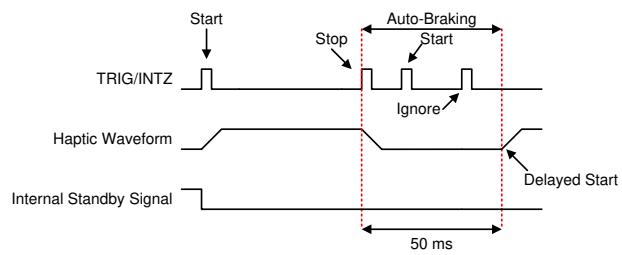

###### 7.6.9.4.1.1 自動ブレーキによるスタンバイ状態への再生トリガ (SimpleDrive)

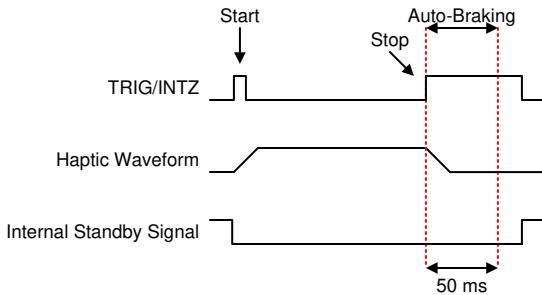

スタンバイへの自動ブレーキが有効化されている場合 (AUTO\_BRK\_INTO\_STBY ビットが 1 に設定されている)、デバイス部品はスタンバイに移行する前にブレーキ モードに移行します。この機能により、以下の図に示す新しいタイミング要件が導入されます。

図 7-19. トリガ パルス付き波形シーケンサ

図 7-20. トリガ レベルの波形シーケンサ

図 7-21. TRIG/INTZ ピンが high のままになったときのトリガ レベル動作を備えた波形シーケンサ

図 7-22. トリガ パルス (RTP または波形シーケンサ)による高速スタート/ストップ

図 7-23. 再生開始および停止トリガ (パルス) (RTP または波形シーケンサ)

図 7-24. 再生開始および停止トリガ (レベル) (RTP または波形シーケンサ)

図 7-25. 再生の開始および停止トリガ (内部 GO ビット) (RTP または波形シーケンサ)

図 7-26. 遅延スタート付きトリガ レベル (RTP または波形シーケンサ)

図 7-27. トリガ パルスと遅延スタート (RTP または波形シーケンサ)

図 7-28. トリガ パルスと遅延スタート、無視されたパルス (RTP または波形シーケンサ)

図 7-29. 遅延スタート付き GO ビット トリガ (RTP または波形シーケンサ)

図 7-30. TRIG/INTZ ピンが high のままのとき (RTP または波形シーケンサ)、トリガ パルス動作

## 7.6.10

## 8 レジスタ マップ

表 8-1. レジスタ マップの概要

| レジスタ<br>番号 | デフォルト | ビット 7                    | ビット 6              | ビット 5              | ビット 4             | ビット 3                  | ビット 2              | ビット 1     | ビット 0                  |  |  |  |

|------------|-------|--------------------------|--------------------|--------------------|-------------------|------------------------|--------------------|-----------|------------------------|--|--|--|

| 0x00       | 0x03  | CHIPID[3:0]              |                    |                    |                   | REV[3:0]               |                    |           |                        |  |  |  |

| 0x01       | 0x00  | DIAG_RESULT              | 予約済み               |                    | PRG_ERROR         | PROCESS_DONE           | UVLO               | OVER_TEMP | OC_DETECT              |  |  |  |

| 0x02       | 0x18  | 予約済み                     |                    |                    |                   | INTZ_MASK[3:0]         |                    |           |                        |  |  |  |

| 0x03       | 0x00  | DIAG_Z_RESULT[7:0]       |                    |                    |                   | VBAT[7:0]              |                    |           |                        |  |  |  |

| 0x04       | 0x00  | 予約済み                     |                    |                    |                   | LRA_PERIOD[9:8]        |                    |           |                        |  |  |  |

| 0x05       | 0x00  | LRA_PERIOD[7:0]          |                    |                    |                   | I2C_BCAST_EN           |                    |           |                        |  |  |  |

| 0x06       | 0x00  | LINEREG_COMP_SEL[1:0]    |                    |                    |                   | TRIG_PIN_FUNC[1:0]     | MODE[1:0]          |           |                        |  |  |  |

| 0x07       | 0x44  | CONTROL_LOOP             | AUTO_BRK_OL        | AUTO_BRK_INTO_STBY | INPUT_SLOPE_CHECK | 予約済み                   |                    |           |                        |  |  |  |

| 0x08       | 0x88  | BAT_LIFE_EXT_LVL_EN[1:0] | 予約済み               |                    | UVLO_THRES[2:0]   |                        |                    |           | BAT_LIFE_EXT_LVL1[7:0] |  |  |  |

| 0x09       | 0x00  | BAT_LIFE_EXT_LVL2[7:0]   |                    |                    |                   | BAT_LIFE_EXT_LVL1[7:0] |                    |           |                        |  |  |  |

| 0x0A       | 0x92  | BAT_LIFE_EXT_LVL2[7:0]   |                    |                    |                   | BAT_LIFE_EXT_LVL2[7:0] |                    |           |                        |  |  |  |

| 0x0B       | 0x8D  | 予約済み                     |                    |                    |                   | 予約済み                   |                    |           |                        |  |  |  |

| 0x0C       | 0x00  | PLAYBACK_INTERVAL        |                    |                    |                   | DIG_MEM_GAIN[1:0]      |                    |           |                        |  |  |  |

| 0x0D       | 0x00  | RTP_INPUT[7:0]           |                    |                    |                   | GO                     |                    |           |                        |  |  |  |

| 0x0E       | 0x7F  | WAIT1                    | WAV_FRM_SEQ1[6:0]  |                    |                   |                        | WAV_FRM_SEQ2[6:0]  |           |                        |  |  |  |

| 0x0F       | 0x01  | WAIT2                    | WAV_FRM_SEQ3[6:0]  |                    |                   |                        | WAV_FRM_SEQ4[6:0]  |           |                        |  |  |  |

| 0x10       | 0x00  | WAIT3                    | WAV_FRM_SEQ5[6:0]  |                    |                   |                        | WAV_FRM_SEQ6[6:0]  |           |                        |  |  |  |

| 0x11       | 0x00  | WAIT4                    | WAV_FRM_SEQ7[6:0]  |                    |                   |                        | WAV_FRM_SEQ8[6:0]  |           |                        |  |  |  |

| 0x12       | 0x00  | WAIT5                    | WAV1_SEQ_LOOP[1:0] |                    |                   |                        | WAV2_SEQ_LOOP[1:0] |           |                        |  |  |  |

| 0x13       | 0x00  | WAIT6                    | WAV3_SEQ_LOOP[1:0] |                    |                   |                        | WAV4_SEQ_LOOP[1:0] |           |                        |  |  |  |

| 0x14       | 0x00  | WAIT7                    | WAV5_SEQ_LOOP[1:0] |                    |                   |                        | WAV6_SEQ_LOOP[1:0] |           |                        |  |  |  |

| 0x15       | 0x00  | WAIT8                    | WAV7_SEQ_LOOP[1:0] |                    |                   |                        | WAV8_SEQ_LOOP[1:0] |           |                        |  |  |  |

| 0x16       | 0x00  | 予約済み                     |                    |                    |                   | WAV_SEQ_MAIN_LOOP[2:0] |                    |           |                        |  |  |  |

| 0x17       | 0x00  | ODT[7:0]                 |                    |                    |                   | SPT[7:0]               |                    |           |                        |  |  |  |

| 0x18       | 0x00  | SNT[7:0]                 |                    |                    |                   | BRT[7:0]               |                    |           |                        |  |  |  |

| 0x19       | 0x00  | 定格電圧[7:0]                |                    |                    |                   | OD_CLAMP[7:0]          |                    |           |                        |  |  |  |

| 0x1A       | 0x00  | A_CAL_COMP[7:0]          |                    |                    |                   | A_CAL_BEMF[7:0]        |                    |           |                        |  |  |  |

| 0x1B       | 0x0D  | NG_THRESH                |                    |                    |                   | FB_BRAKE_FACTOR[2:0]   |                    |           |                        |  |  |  |

| 0x1C       | 0x6D  | LOOP_GAIN[1:0]           |                    |                    |                   | BEMF_GAIN[1:0]         |                    |           |                        |  |  |  |

| 0x1D       | 0x36  | RATED_VOLTAGE_CLAMP[7:0] |                    |                    |                   |                        |                    |           |                        |  |  |  |

表 8-1. レジスタ マップの概要 (続き)

| レジスタ<br>番号 | デフォルト | ビット 7              | ビット 6              | ビット 5              | ビット 4              | ビット 3            | ビット 2 | ビット 1              | ビット 0          |

|------------|-------|--------------------|--------------------|--------------------|--------------------|------------------|-------|--------------------|----------------|

| 0x25       | 0x80  |                    |                    |                    | OD_CLAMP_LVL1[7:0] |                  |       |                    |                |

| 0x26       | 0x00  |                    |                    |                    | OD_CLAMP_LVL2[7:0] |                  |       |                    |                |

| 0x27       | 0x10  | LRA_MIN_FREQ_SEL   | LRA_RESYNC_FORMAT  | 予約済み               |                    | DRIVE_TIME[4:0]  |       |                    |                |

| 0x28       | 0x11  |                    | BLANKING_TIME[3:0] |                    |                    | IDISS_TIME[3:0]  |       |                    |                |

| 0x29       | 0x0C  | 予約済み               |                    | OD_CLAMP_TIME[1:0] |                    | SAMPLE_TIME[1:0] |       | ZC_DET_TIME[1:0]   |                |

| 0x2A       | 0x02  |                    |                    | 予約済み               |                    |                  |       | AUTO_CAL_TIME[1:0] |                |

| 0x2C       | 0x00  | LRA_AUTO_OPEN_LOOP |                    | AUTO_DL_CNT[1:0]   |                    | 予約済み             |       |                    | LRA_WAVE_SHAPE |

| 0x2E       | 0x00  |                    |                    | 予約済み               |                    |                  |       | OL_LRA_PERIOD[9:0] |                |

| 0x2F       | 0xC6  |                    |                    |                    | OL_LRA_PERIOD[9:0] |                  |       |                    |                |

| 0x30       | 0x00  |                    |                    |                    | CURRENT_K[7:0]     |                  |       |                    |                |

| FD         | 0x00  |                    |                    |                    | RAM_ADDR[15:8]     |                  |       |                    |                |

| FE         | 0x00  |                    |                    |                    | RAM_ADDR[7:0]      |                  |       |                    |                |

| FF         | 0x00  |                    |                    |                    | RAM_DATA[7:0]      |                  |       |                    |                |

## 8.1 アドレス : 0x00

**図 8-1. 0x00**

|             |     |     |     |     |          |     |     |

|-------------|-----|-----|-----|-----|----------|-----|-----|

| 7           | 6   | 5   | 4   | 3   | 2        | 1   | 0   |

| CHIPID[3:0] |     |     |     |     | REV[3:0] |     |     |

| R-0         | R-0 | R-0 | R-0 | R-0 | R-0      | R-1 | R-1 |

凡例: R/W = 読み出し / 書き込み、R = 読み出し専用、-n = リセット後の値

**表 8-2. アドレス : 0x00**

| ビット | フィールド       | タイプ | デフォルト | 説明                                   |

|-----|-------------|-----|-------|--------------------------------------|

| 7-4 | CHIPID[3:0] | R   | 0     | デバイス識別情報を提供します                       |

|     |             |     |       | 0 DRV2624                            |

|     |             |     |       | 1 DRV2625                            |

| 3-0 | REV[3:0]    | R   | 3     | デバイスリビジョンに関する情報を提供します <sup>(1)</sup> |

(1) Rev 2 および 3 は、両方とも商用リリースされています。

## 8.2 アドレス : 0x01

**表 8-3. 0x01**

|                |       |           |                 |         |              |              |     |

|----------------|-------|-----------|-----------------|---------|--------------|--------------|-----|

| 7              | 6     | 5         | 4               | 3       | 2            | 1            | 0   |

| DIAG_RESULT[0] | 予約済み  | PRG_ERROR | PROCESS_DONE[0] | UVLO[0] | OVER_TEMP[0] | OC_DETECT[0] |     |

| R-0            | R/W-0 |           | R-0             | R-0     | R-0          | R-0          | R-0 |

凡例: R/W = 読み出し / 書き込み、R = 読み出し専用、-n = リセット後の値

**表 8-4. アドレス : 0x01**

| ビット | フィールド        | タイプ | デフォルト | 説明                                                                                                                                                                                                                           |

|-----|--------------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | DIAG_RESULT  | R   | 0     | このビットの意味は、動作モードによって異なります。診断モードでは、このビットはアクチュエータが開放またはグランドに短絡しているか、VDD に短絡しているか、有効な BEMF 信号がないかのいずれかでアサートされます。インピーダンス測定モードについてでは、DIAG_Z_RESULT[7:0] を参照してください。較正モードでは、較正が失敗した場合、このビットがアサートされます。このビットは、スティッキーであり、読み取り時にクリアされます。 |

|     |              |     |       | 0 問題は見つかりませんでした。                                                                                                                                                                                                             |

|     |              |     |       | 1 診断またはキャリブレーションに失敗しました。                                                                                                                                                                                                     |

| 6-5 | 予約済み         | R/W | 0     | 予約済み                                                                                                                                                                                                                         |

| 4   | PRG_ERROR    | R   | 0     | RAM に必要な形式に準拠していないデータがある場合、このビット資産です。このビットは、スティッキーであり、読み取り時にクリアされます。                                                                                                                                                         |

|     |              |     |       | 0 RAM の読み取り中にエラーは見つかりませんでした。                                                                                                                                                                                                 |

|     |              |     |       | 1 RAM の読み取り中にエラーが見つかりました。                                                                                                                                                                                                    |

| 3   | PROCESS_DONE | R   | 0     | 実行されたプロセスが実行されたかどうかを示します。このビットは、スティッキーであり、読み取り時にクリアされます。                                                                                                                                                                     |

|     |              |     |       | 0 処理が行われていません。                                                                                                                                                                                                               |

|     |              |     |       | 1 処理が実行されます (波形シーケンサ、診断、自動キャリブレーション)。このビットは、読み出すとクリアされます。                                                                                                                                                                    |

| 2   | UVLO         | R   | 0     | VDD が UVLO_THRESH[2:0] を下回ると、このビットがアサートされます。このビットは、スティッキーであり、読み取り時にクリアされます。                                                                                                                                                  |

|     |              |     |       | 0 VDD ドループは観察されていません。                                                                                                                                                                                                        |

|     |              |     |       | 1 VDD ドループが観察されます。読み出すとクリア。                                                                                                                                                                                                  |

**表 8-4. アドレス : 0x01 (続き)**

| ビット | フィールド     | タイプ | デフォルト | 説明                                                    |

|-----|-----------|-----|-------|-------------------------------------------------------|

| 1   | OVER_TEMP | R   | 0     | 過熱保護の現在のステータスを示します。このビットは、ステイッキーであり、読み取り時にクリアされます。    |

|     |           |     |       | 0 温度が過熱スレッショルドを下回っています                                |

|     |           |     |       | 1 温度が過熱スレッショルドを上回っている。読み出すとクリア。                       |

| 0   | OC_DETECT | R   | 0     | 出力過電流保護の現在のステータスを示します。このビットは、ステイッキーであり、読み取り時にクリアされます。 |

|     |           |     |       | 0 OUT+ または OUT- で過電流を検出しません                           |

|     |           |     |       | 1 OUT+ または OUT- で過電流を検出しました。読み出すとクリア。                 |

### 8.3 アドレス : 0x02

**図 8-2. 0x02**

| 7     | 6 | 5 | 4     | 3     | 2              | 1     | 0     |

|-------|---|---|-------|-------|----------------|-------|-------|

| 予約済み  |   |   |       |       | INTZ_MASK[3:0] |       |       |

| R/W-0 |   |   | R/W-1 | R/W-1 | R/W-0          | R/W-0 | R/W-0 |

凡例: R/W = 読み出し / 書き込み、R = 読み出し専用、-n = リセット後の値

**表 8-5. アドレス : 0x02**

| ピット | フィールド          | タイプ | デフォルト | 説明                                                                    |

|-----|----------------|-----|-------|-----------------------------------------------------------------------|

| 7-5 | 予約済み           | R/W | 0     | 予約済み                                                                  |

| 4-0 | INTZ_MASK[4:0] | R/W | 24    | 割り込みモードに設定されている場合、TRIG/INTZ ピンの動作を構成するために、ステータスビットをマスクします。それ以外の場合は無視。 |

|     |                |     |       | 0 INTZ_MASK[0] = 1 のとき、OC_DETECT ステータスは割り込みを生成しません                    |

|     |                |     |       | 1 INTZ_MASK[1] = 1 の場合、OVER_TEMP ステータスは割り込みを生成しません                    |

|     |                |     |       | 2 INTZ_MASK[2] = 1 の場合、UVLO ステータスは割り込みを発生させません                        |

|     |                |     |       | 3 INTZ_MASK[3] = 1 のとき、PROCESS_DONE ステータスは割り込みを発生させません                |

### 8.4 アドレス : 0x03

**図 8-3. 0x03**

| 7                  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------------|---|---|---|---|---|---|---|

| DIAG_Z_RESULT[7:0] |   |   |   |   |   |   |   |

| R-0                |   |   |   |   |   |   |   |

凡例: R/W = 読み出し / 書き込み、R = 読み出し専用、-n = リセット後の値

**表 8-6. アドレス : 0x03**

| ピット | フィールド              | タイプ | デフォルト | 説明                                          |

|-----|--------------------|-----|-------|---------------------------------------------|

| 7-0 | DIAG_Z_RESULT[7:0] | R   | 0     | このパラメータは、診断ルーチン実行後のアクチュエータのインピーダンス測定値を示します。 |

### 8.5 アドレス : 0x04

**図 8-4. 0x04**

| 7         | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------|---|---|---|---|---|---|---|

| VBAT[7:0] |   |   |   |   |   |   |   |

| R-0       |   |   |   |   |   |   |   |

凡例: R/W = 読み出し / 書き込み、R = 読み出し専用、-n = リセット後の値

**表 8-7. アドレス : 0x04**

| ピット | フィールド     | タイプ | デフォルト | 説明                                                                        |

|-----|-----------|-----|-------|---------------------------------------------------------------------------|

| 7-0 | VBAT[7:0] | R   | 0     | このパラメータは、VDD ピンの電源電圧をリアルタイムで読み取ります。読み取りを行うには、デバイスがアケティブに波形を再生している必要があります。 |

## 8.6 アドレス : 0x05

図 8-5. 0x05

| 7     | 6 | 5 | 4 | 3 | 2 | 1               | 0 |

|-------|---|---|---|---|---|-----------------|---|

| 予約済み  |   |   |   |   |   | LRA_PERIOD[9:8] |   |

| R/W-0 |   |   |   |   |   | RO-0            |   |

凡例: R/W = 読み出し / 書き込み、R = 読み出し専用、-n = リセット後の値

表 8-8. アドレス : 0x05

| ピット | フィールド           | タイプ | デフォルト | 説明                                                                                                                                                                                                                                                                                                                  |

|-----|-----------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-2 | 予約済み            | R/W | 0     | 予約済み                                                                                                                                                                                                                                                                                                                |

| 1-0 | LRA_PERIOD[9:0] | RO  | 0     | このパラメータは、LRA の共振周波数をリアルタイムで報告します。このレジスタは継続的に更新されるため、MSB セクションが最初に読み取られ、LSB が読み取られるまで LSB (および MSB) レジスタが保持されて、一貫性を維持します。波形が終了し、LSB が読み取られていない場合、デバイスは両方のレジスタ (MSB と LSB) のロックを自動的に解除し、レジスタは次の再生時に更新を開始します。このため、正確な測定値を得るために、同じ再生中に両方のレジスタを読み取ることを推奨します。LRA 周期 = LRA_PERIOD[9:0]×24.39μs。報告された周波数の精度は、ブレーキ中に検証されません。 |

## 8.7 アドレス : 0x06

図 8-6. 0x06

| 7               | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------|---|---|---|---|---|---|---|

| LRA_PERIOD[7:0] |   |   |   |   |   |   |   |

| R-0             |   |   |   |   |   |   |   |

凡例: R/W = 読み出し / 書き込み、R = 読み出し専用、-n = リセット後の値

表 8-9. アドレス : 0x06

| ピット | フィールド           | タイプ | デフォルト | 説明                                                                                                                                                                                                                                                                                                            |

|-----|-----------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | LRA_PERIOD[9:0] | R   | 0     | このパラメータは、LRA の共振周波数をリアルタイムで報告します。このレジスタは継続的に更新されるため、MSB セクションが最初に読み取られ、LSB が読み取られるまで LSB (および MSB) レジスタが保持されて、一貫性を維持します。波形が終了し、LSB が読み取られていない場合、デバイスは両方のレジスタ (MSB と LSB) のロックを自動的に解除し、次の再生時に更新を開始します。このため、同じ再生中に両方のレジスタを読み取ることで、正確な測定値を得ることが重要です。LRA 周期 = LRA_PERIOD[9:0]×24.39μs。報告された周波数の精度は、ブレーキ中に検証されません。 |

## 8.8 アドレス : 0x07

図 8-7. 0x07