# DP83TG720S-Q1 SGMII および RGMII 対応 1000BASE-T1 車載用イーサネット PHY

## 1 特長

- IEEE802.3bp 1000BASE-T1 準拠

- Open Alliance TC12 の相互運用性と EMC に適合

- OA/IEEE 準拠 PHY との相互運用性テスト済み

- EMC 耐性、クラス IV 準拠 (UTP:シールドなしツイストペア)

- MDI ピンに LPF を内蔵

- MAC インターフェイス:RGMII、SGMII

- 対応する I/O 電圧:3.3V、2.5V、1.8V

- テキサス・インスツルメンツの 100BASE-T1 PHY とビン互換

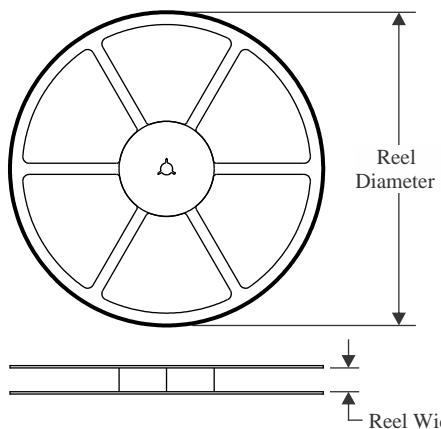

- 必要な BOM を変更することで、100BASE-T1 と 1000BASE-T1 に対応するシングル ボード設計

- パワー セービング機能:

- スタンバイ、スリープ

- ローカルおよびリモート ウェークアップ

- 診断ツール キット

- 高精度の温度モニタ

- 電圧モニタ

- ESD イベント モニタ

- データ スループット カリキュレータ:内蔵 MAC パケット ジェネレータ、カウンタ、エラー チェック

- リンク品質監視

- ケーブル開放および短絡 フォルト検出

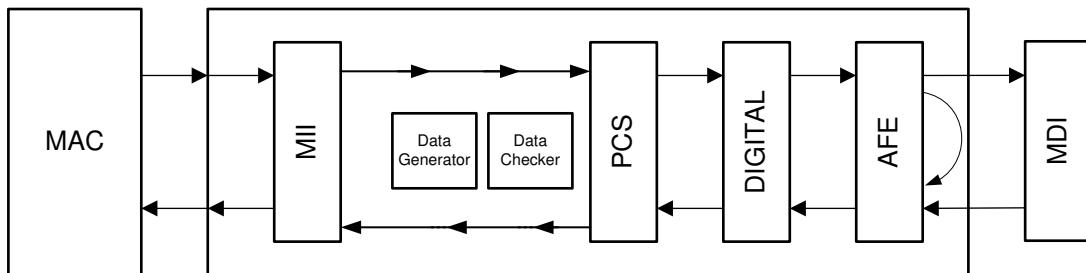

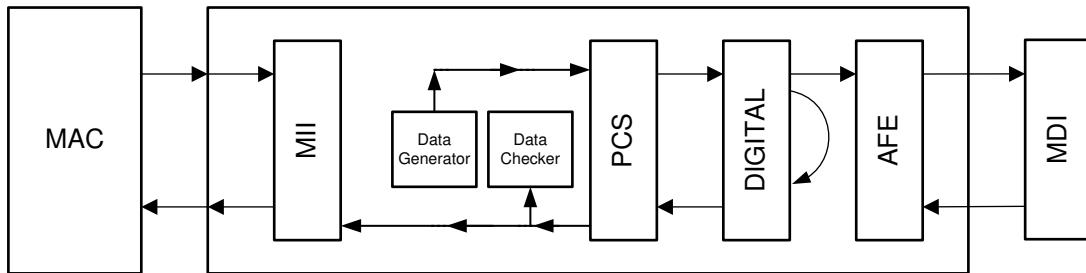

- ループバック モード

- 25MHz クロック出力源

- VQFN、ウェッタブル フランク パッケージ

- AEC-Q100 認定済み

- 内蔵 ESD 保護:IEC61000-4-2 ESD:±8kV 接触放電

- デバイス温度グレード 1:−40°C ~ +125°C の動作時周囲温度

## 2 アプリケーション

- テレマティクス制御ユニット (TCU、TBOX)

- ゲートウェイとボディ コントロール モジュール (BCM)

- ADAS:LIDAR、レーダー、フロント カメラ

## 3 概要

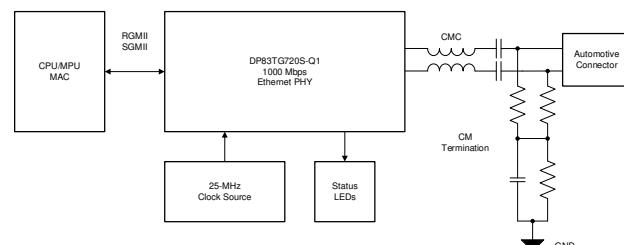

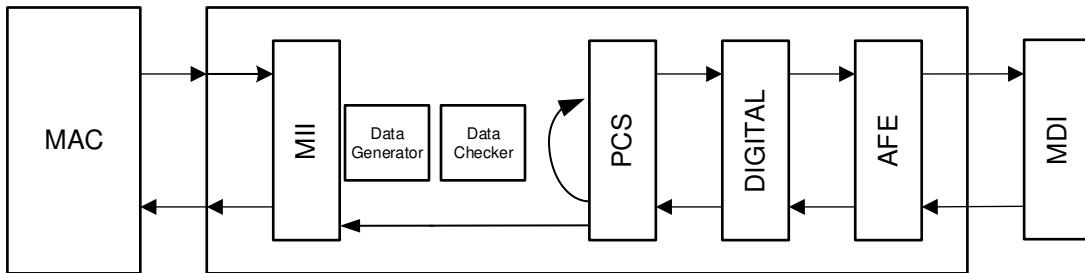

DP83TG720S-Q1 デバイスは、IEEE 802.3bp と Open Alliance に準拠した車載用イーサネット物理層トランシーバです。このデバイスには、シールドなしとシールド付きのシングル ツイストペア ケーブル上でデータを送受信するために必要な、すべての物理層機能が搭載されています。このデバイスは xMII の柔軟性があり、RGMII および SGMII MAC インターフェイスをサポートします。

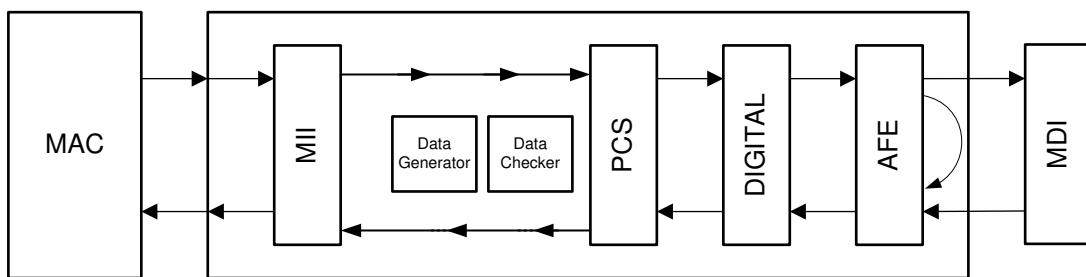

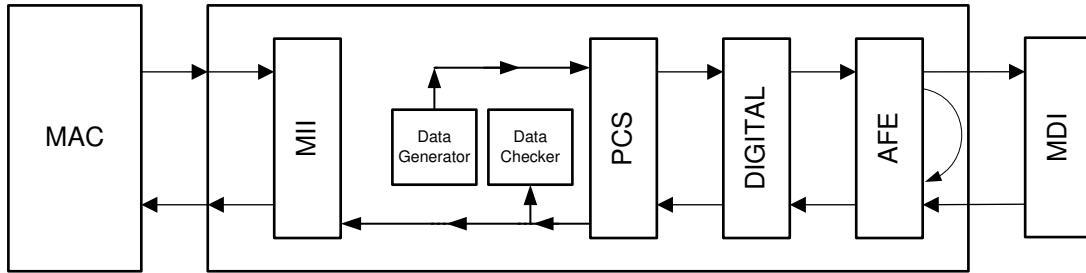

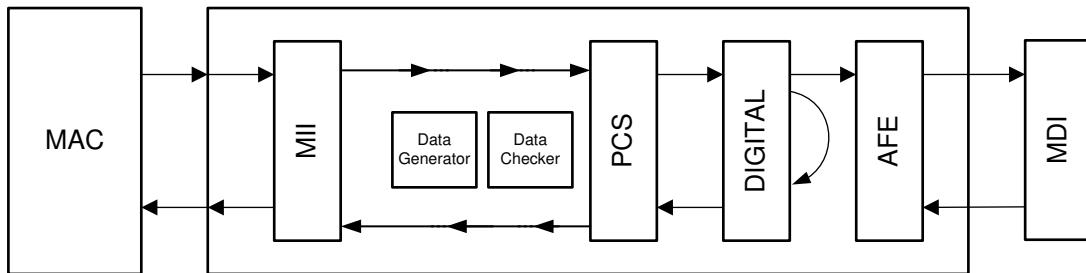

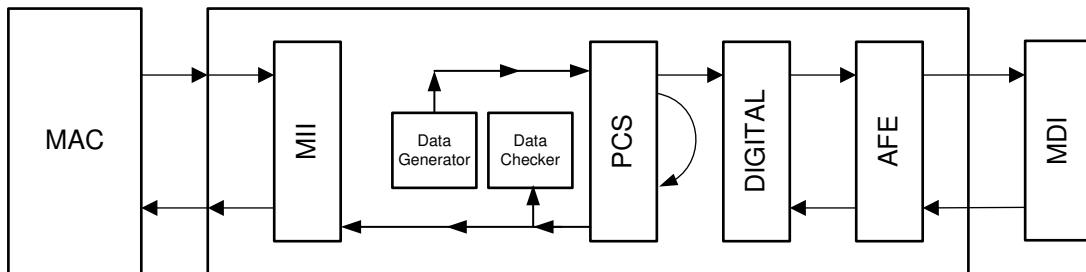

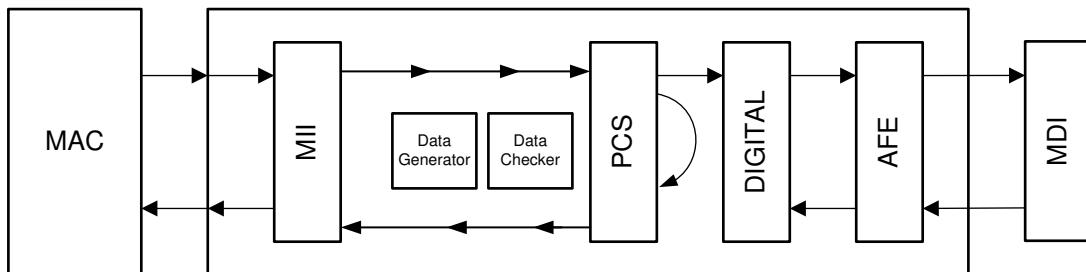

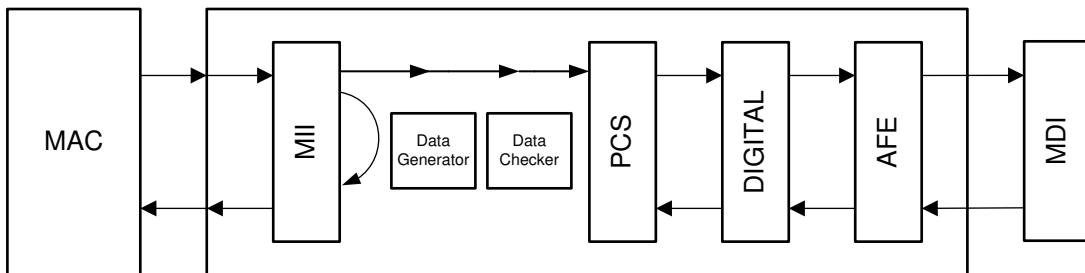

DP83TG720 は Open Alliance EMC および相互運用性仕様 (シールドなしツイストケーブル) に準拠しています。DP83TG720 は テキサス・インスツルメンツの 100BASE-T1 PHY と フットプリント互換であるため、1 枚のボードで両方の速度に対応する、拡張性に優れた設計を実現できます。このデバイスでは、リアルタイム監視ツール、デバッグツール、テスト モードを豊富に備えた診断ツール キットを提供しています。ツール キットには、初めて内蔵された静電放電 (ESD) 監視ツールが含まれています。このデバイスは xMII と MDI の両方で ESD イベントをカウントでき、プログラム可能な割り込みを使用してリアルタイム監視も行えます。また、DP83TG720S-Q1 は、カスタマイズ可能な MAC パケットの生成と受信パケットのエラー チェックを行うため、データ ジェネレータおよびチェック ツールを内蔵しています。これにより、MAC に頼らずに、データバスをシステム レベルでテスト / 最適化できます。

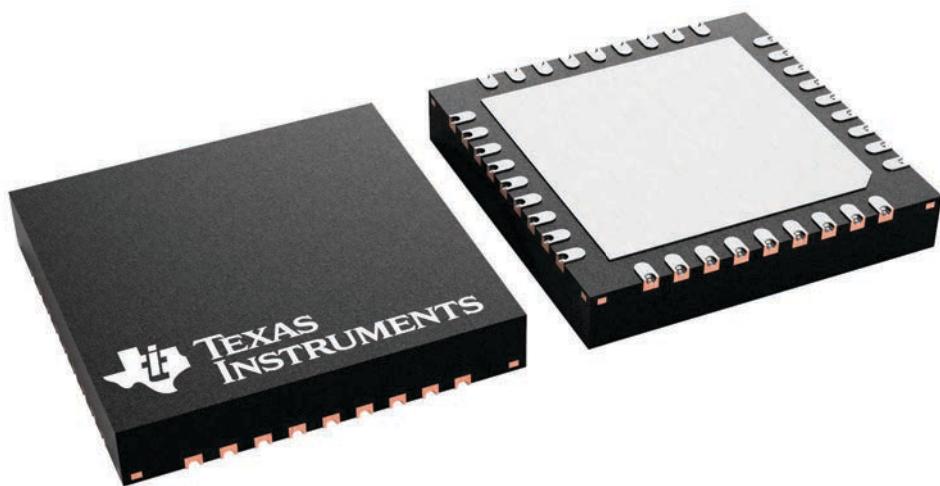

### 製品情報

| 部品番号          | パッケージ (1) | 本体サイズ (公称) (2)  |

|---------------|-----------|-----------------|

| DP83TG720S-Q1 | VQFN (36) | 6.00mm × 6.00mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ サイズ (長さ×幅) は公称値であり、該当する場合はビンも含まれます。

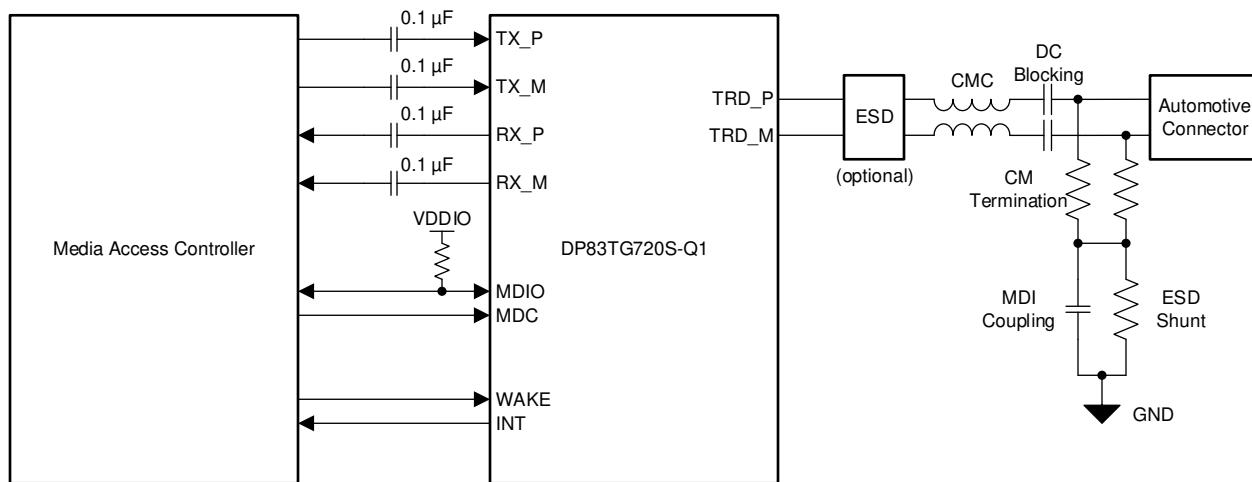

概略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                    |           |                                     |            |

|--------------------|-----------|-------------------------------------|------------|

| <b>1 特長</b>        | <b>1</b>  | 6.4 デバイスの機能モード                      | <b>40</b>  |

| <b>2 アプリケーション</b>  | <b>1</b>  | 6.5 プログラミング                         | <b>56</b>  |

| <b>3 概要</b>        | <b>1</b>  | 6.6 レジスタマップ                         | <b>60</b>  |

| <b>4 ピン構成および機能</b> | <b>3</b>  | <b>7 アプリケーションと実装</b>                | <b>172</b> |

| ピンの機能              | <b>4</b>  | 7.1 アプリケーション情報                      | <b>172</b> |

| 4.1 ピンの状態          | <b>6</b>  | 7.2 代表的なアプリケーション                    | <b>172</b> |

| 4.2 ピンの電源ドメイン      | <b>9</b>  | 7.3 電源に関する推奨事項                      | <b>172</b> |

| <b>5 仕様</b>        | <b>10</b> | 7.4 テキサス・インスツルメンツの 100BT1 PHY との互換性 | <b>175</b> |

| 5.1 絶対最大定格         | <b>10</b> | 7.5 レイアウト                           | <b>176</b> |

| 5.2 ESD 定格         | <b>10</b> | <b>8 デバイスおよびドキュメントのサポート</b>         | <b>179</b> |

| 5.3 推奨動作条件         | <b>10</b> | 8.1 ドキュメントの更新通知を受け取る方法              | <b>179</b> |

| 5.4 熱に関する情報        | <b>11</b> | 8.2 サポート・リソース                       | <b>179</b> |

| 5.5 電気的特性          | <b>11</b> | 8.3 商標                              | <b>179</b> |

| 5.6 タイミング要件        | <b>15</b> | 8.4 静電気放電に関する注意事項                   | <b>179</b> |

| 5.7 タイミング図         | <b>19</b> | 8.5 用語集                             | <b>179</b> |

| 5.8 LED の駆動特性      | <b>23</b> | <b>9 改訂履歴</b>                       | <b>179</b> |

| <b>6 詳細説明</b>      | <b>24</b> | <b>10 メカニカル、パッケージ、および注文情報</b>       | <b>181</b> |

| 6.1 概要             | <b>24</b> | 10.1 付録:パッケージ・オプション                 | <b>181</b> |

| 6.2 機能ブロック図        | <b>25</b> |                                     |            |

| 6.3 機能説明           | <b>26</b> |                                     |            |

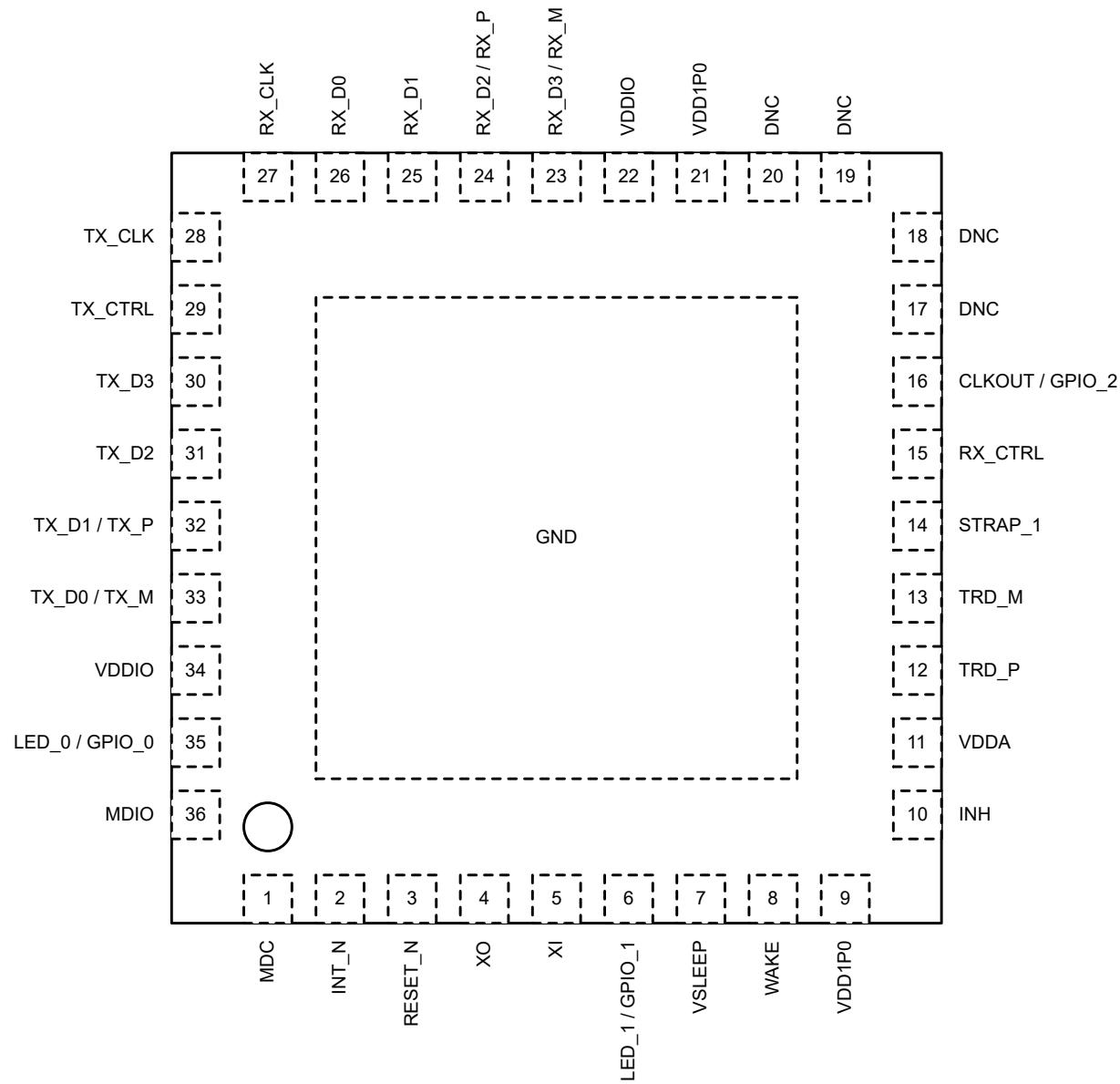

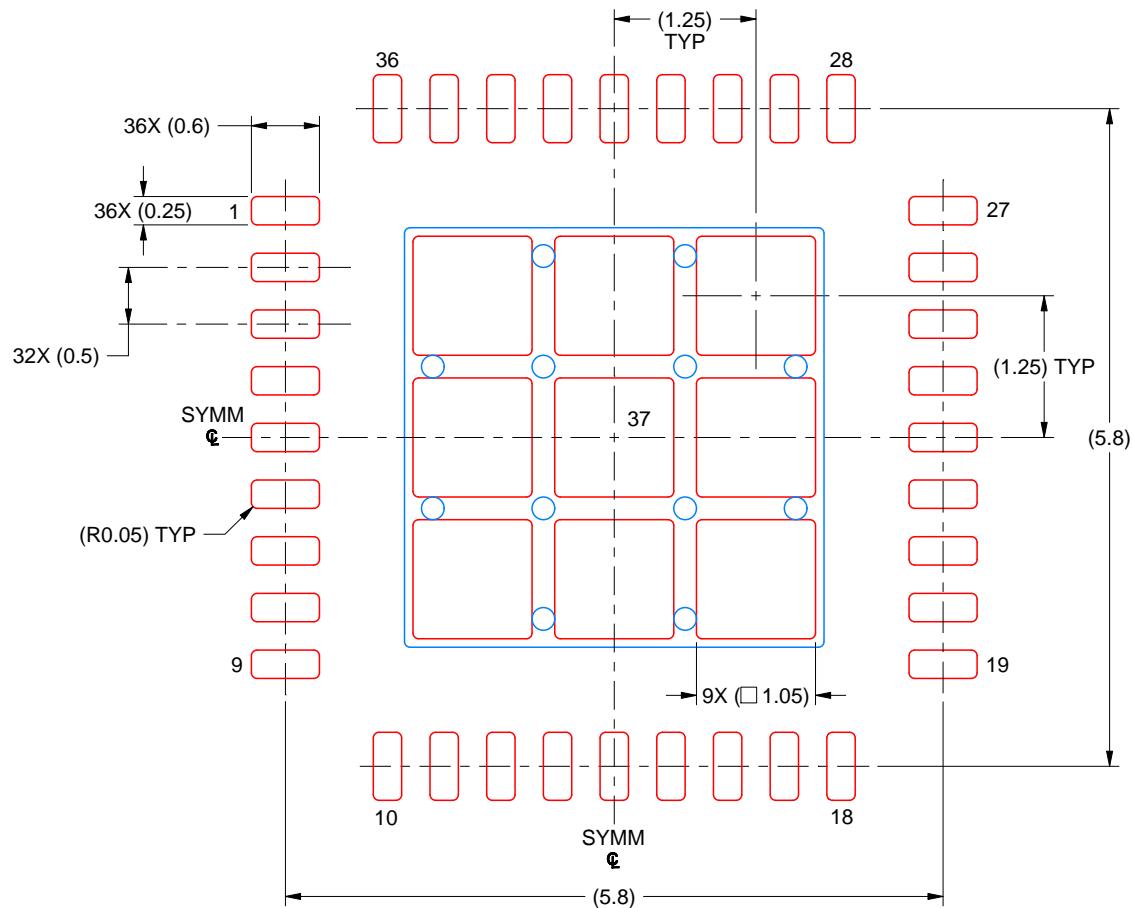

## 4 ピン構成および機能

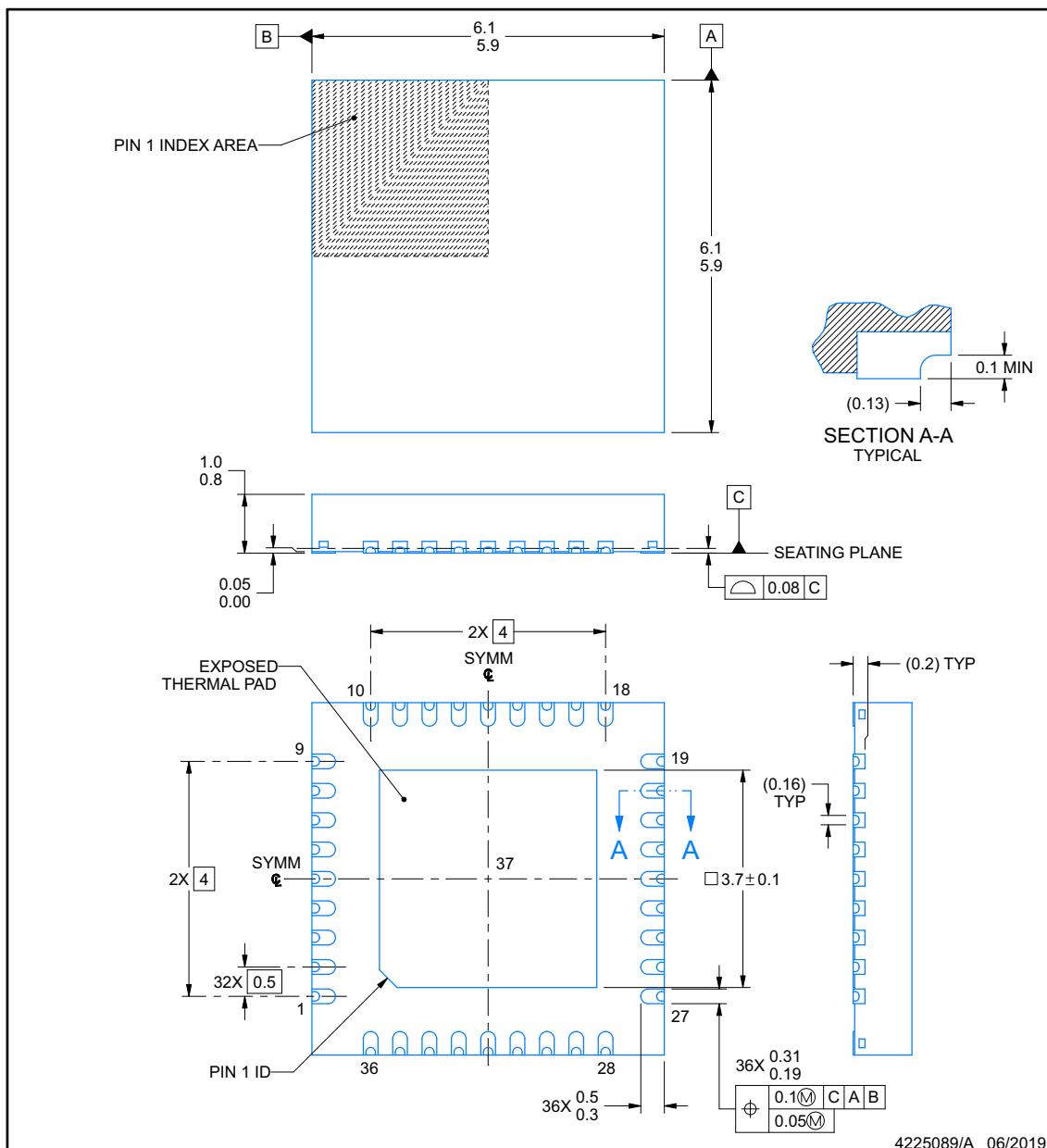

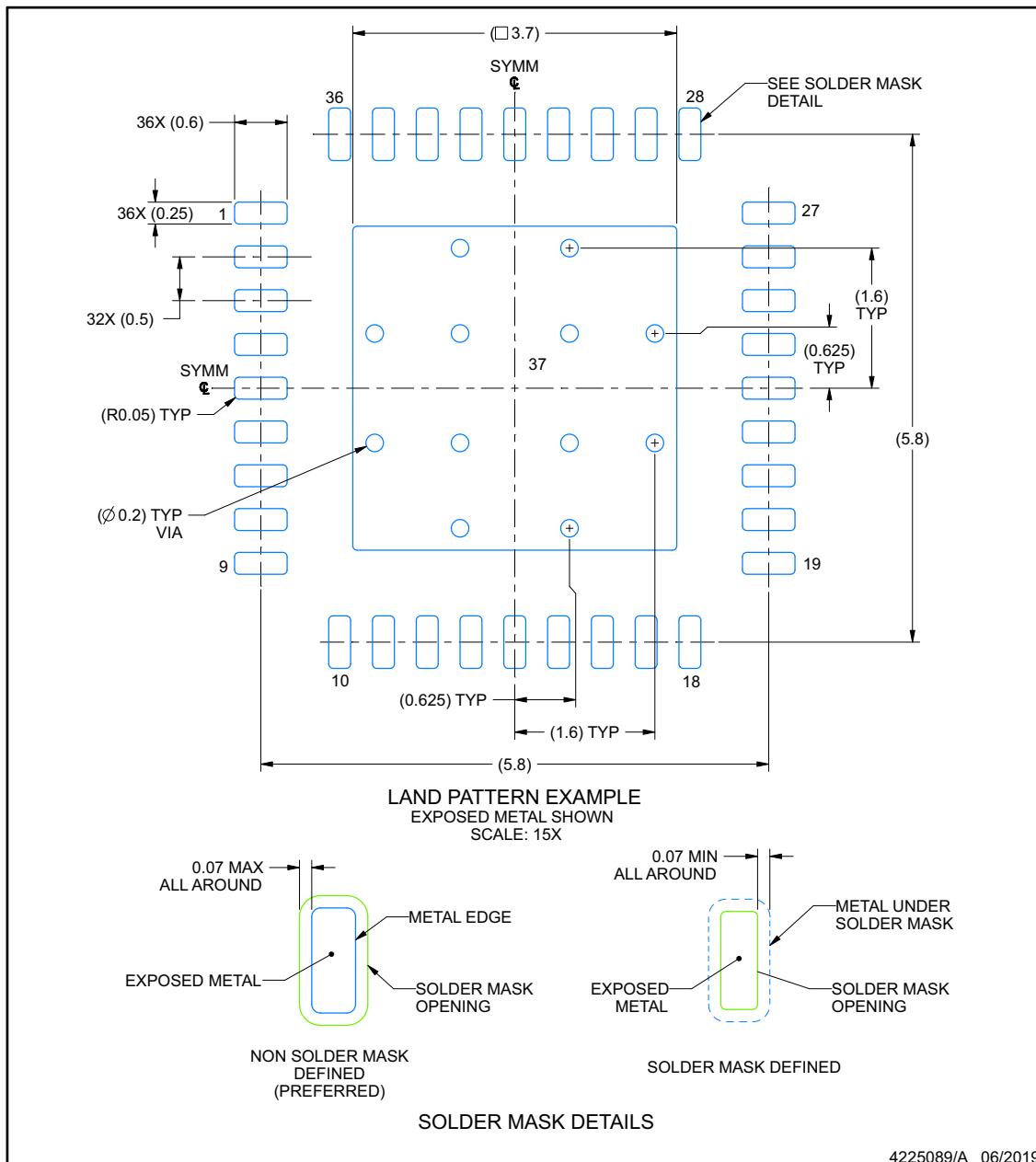

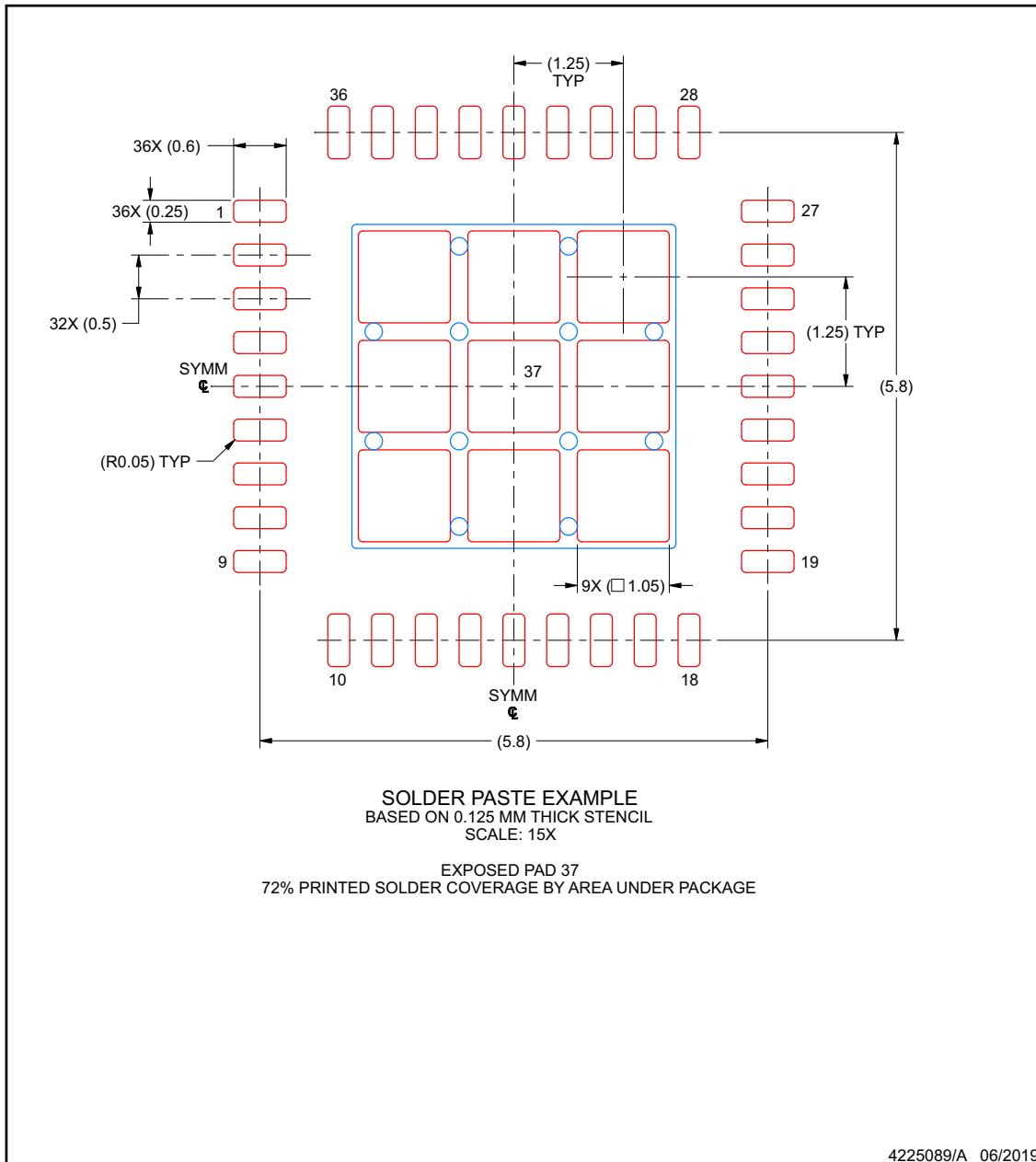

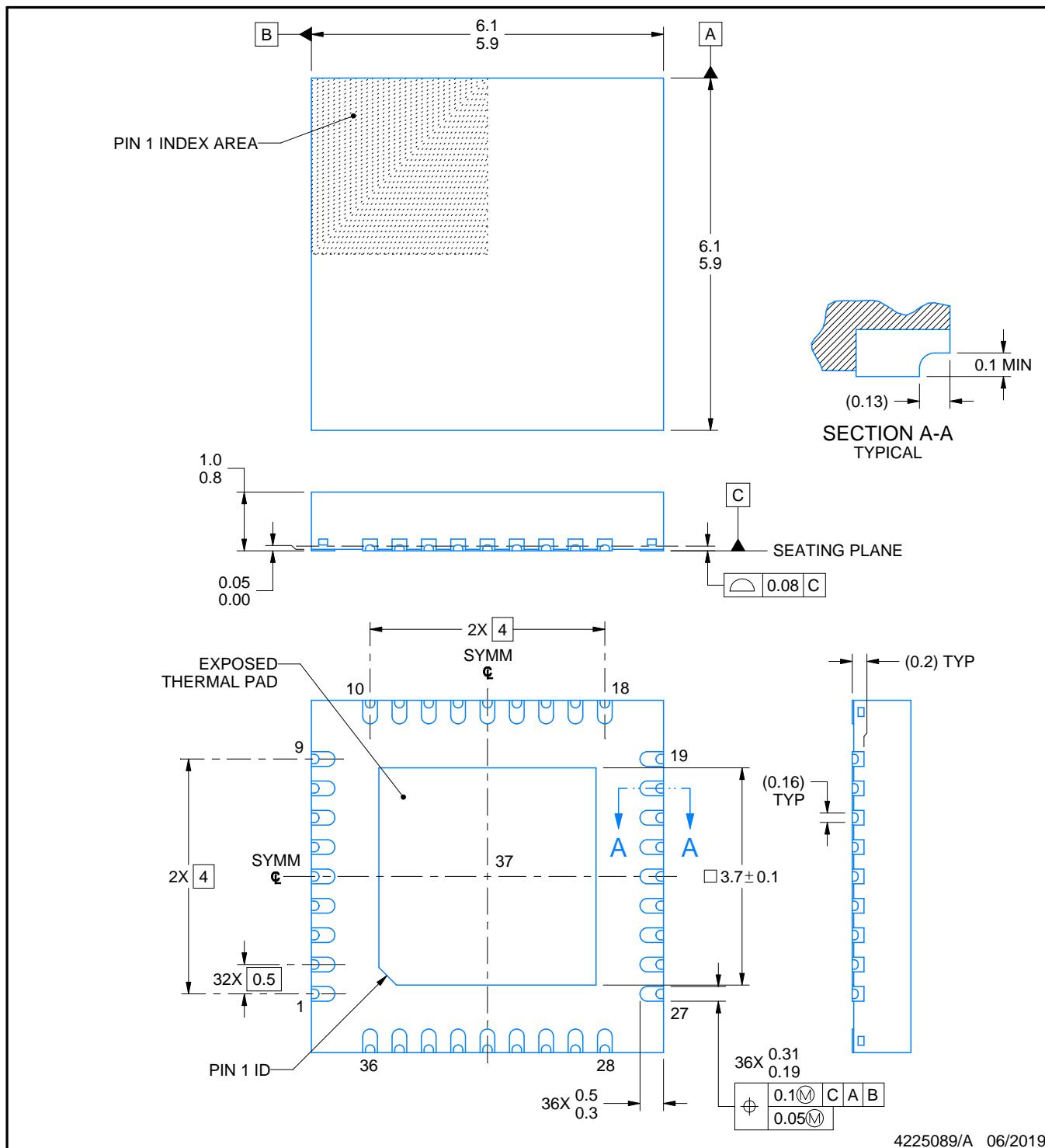

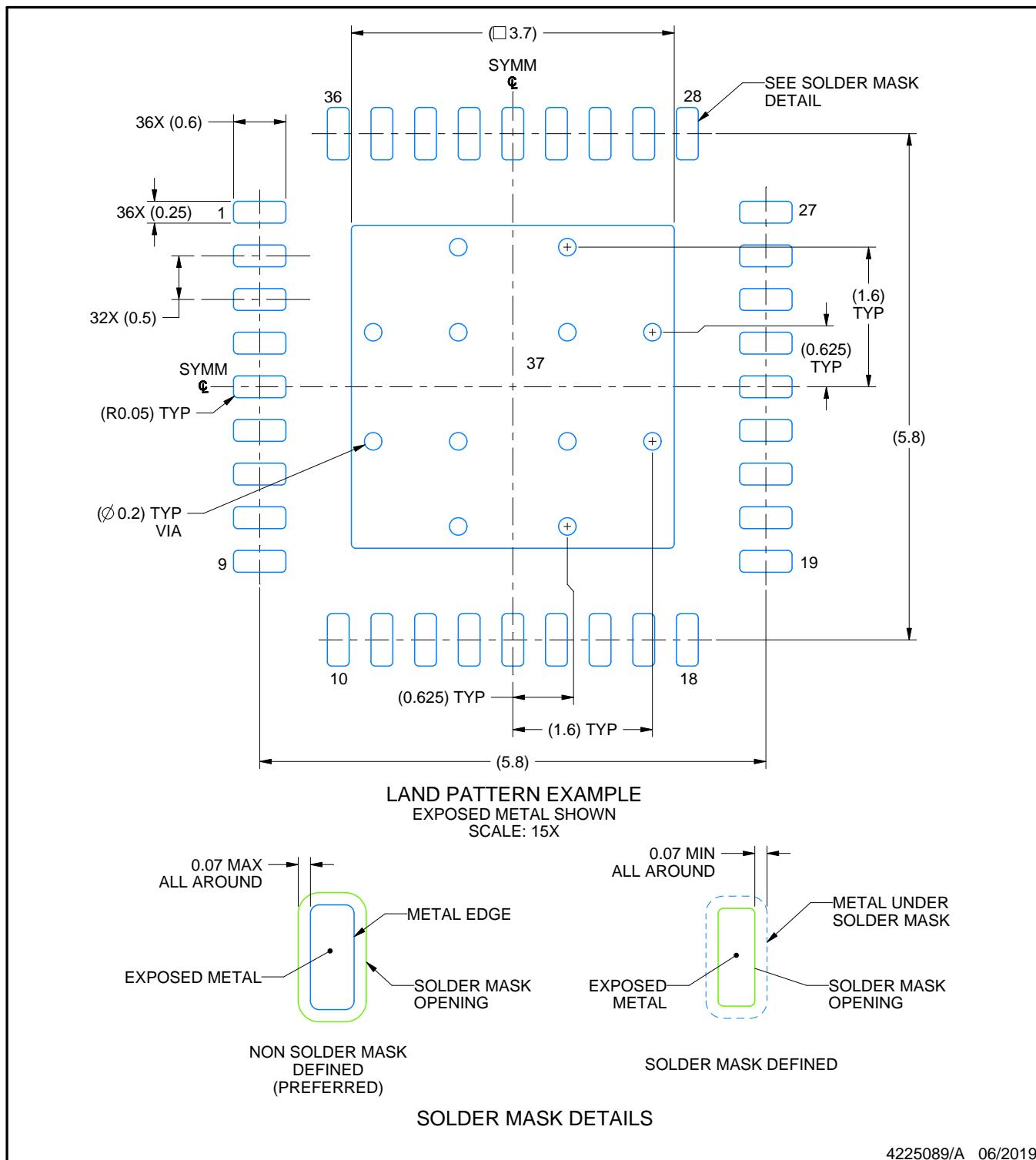

図 4-1. RHA パッケージ

36 ピン VQFN 上面図

## ピンの機能

表 4-1. ピンの機能

| ピン                           |    | 状態 <sup>(1)</sup> | 説明 <sup>(2)</sup>                                                                                                                                                                                                                                                                                                        |

|------------------------------|----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                           | 番号 |                   |                                                                                                                                                                                                                                                                                                                          |

| <b>MAC インターフェイス</b>          |    |                   |                                                                                                                                                                                                                                                                                                                          |

| RX_D3                        | 23 | S, PD, O          | <b>受信データ:</b> ケーブルで受信されたシンボルはデコードされ、RX_CLK の立ち上がりエッジに同期してこれらのピンから送信されます。RX_DV (RX_CTL からデコード) がアサートされている場合、これらには有効なデータが含まれます。RGMII モードではニブル (RX_D[3:0]) が送信されます。                                                                                                                                                         |

| RX_D2                        | 24 |                   | <b>RX_M/RX_P:</b> 差動 SGMII データ出力。これらのピンは PHY から MAC にデータを送信します。                                                                                                                                                                                                                                                          |

| RX_D1                        | 25 |                   |                                                                                                                                                                                                                                                                                                                          |

| RX_D0                        | 26 |                   |                                                                                                                                                                                                                                                                                                                          |

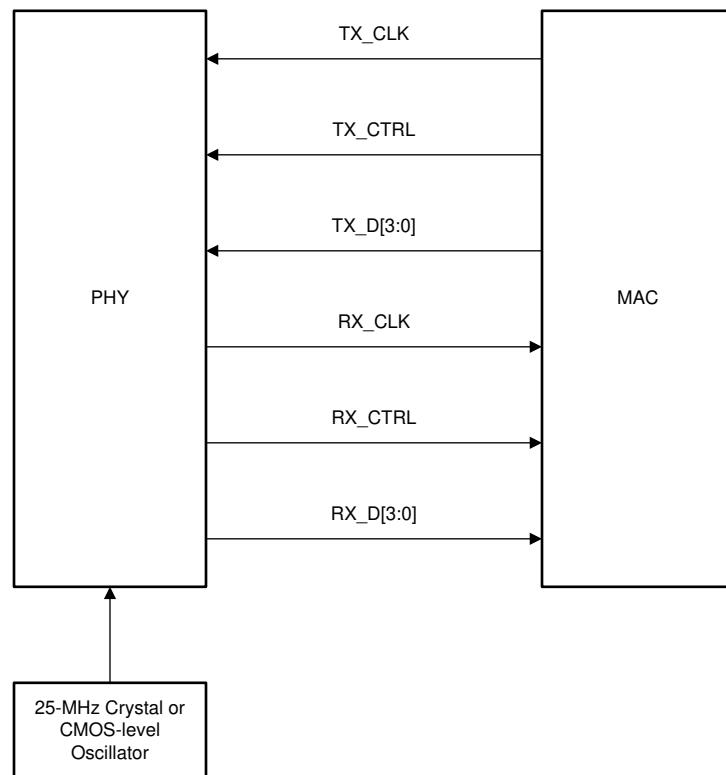

| RX_CLK                       | 27 | O                 | <b>受信クロック:</b> RGMII モードでは、PHY はこの 125MHz クロックを MAC に供給します。<br><b>SGMII モードでは未使用</b>                                                                                                                                                                                                                                     |

| RX_CTRL                      | 15 | S, PD, O          | <b>RGMII 受信制御:</b> 受信制御は、受信データ有効表示と受信エラー表示を 1 つの信号に統合したものです。RX_DV は RX_CLK の立ち上がりエッジに示され、RX_ER は RX_CLK の立ち下がりエッジに示されます。<br><b>SGMII モードではストラップとしてのみ使用</b>                                                                                                                                                               |

| TX_CLK                       | 28 | I                 | <b>送信クロック:</b> RGMII モードでは、MAC はこの 125MHz クロックを PHY に供給します。<br><b>SGMII モードでは未使用</b>                                                                                                                                                                                                                                     |

| TX_CTRL                      | 29 | I                 | <b>RGMII 送信制御:</b> 送信制御は、送信イネーブルと送信エラー表示を 1 つの信号に統合したものです。TX_EN は TX_CLK の立ち上がりエッジの前に示され、TX_ER は TX_CLK の立ち下がりエッジに示されます。<br><b>SGMII モードでは未使用</b>                                                                                                                                                                        |

| TX_D3                        | 30 | I                 |                                                                                                                                                                                                                                                                                                                          |

| TX_D2                        | 31 |                   |                                                                                                                                                                                                                                                                                                                          |

| TX_D1                        | 32 |                   | <b>送信データ:</b> RGMII モードでは、送信データニブル (TX_D[3:0]) が MAC から受信されます。<br><b>TX_M/TX_P:</b> 差動 SGMII データ入力。これらのピンは、MAC から PHY に送信されたデータを受信します。                                                                                                                                                                                   |

| TX_D0                        | 33 |                   |                                                                                                                                                                                                                                                                                                                          |

| <b>シリアル マネージメント インターフェイス</b> |    |                   |                                                                                                                                                                                                                                                                                                                          |

| MDC                          | 1  | I                 | <b>管理データクロック:</b> MDIO シリアル マネージメント入力および出力データに同期したクロック。                                                                                                                                                                                                                                                                  |

| MDIO                         | 36 | OD, IO            | <b>管理データ入出力 (Management Data Input/Output):</b> 管理ステーションまたは PHY のいづれかから出力される双方向管理データ信号。このピンには外付けプルアップ抵抗 (推奨値 = 2.2kΩ) が必要です。                                                                                                                                                                                             |

| <b>制御インターフェイス</b>            |    |                   |                                                                                                                                                                                                                                                                                                                          |

| INT                          | 2  | PU, OD, O         | <b>割り込み:</b> アクティブ Low 出力。割り込み条件が発生すると、Low にアサートされます。このピンは弱いプルアップを内蔵しています。各種割り込みトリガを有効化するには、レジスタ アクセスが必要です。割り込みイベントフラグが一度セットされると、このピンの割り込みイベントをクリアするには、レジスタ アクセスが必要です。<br>レジスタ [0x0011] を使うことで、このピンをアクティブ High 出力として構成できます。<br>割り込みソースを確実にキャプチャするため、int_n ピンで割り込みがアサートされた後に、割り込みレジスタ x12, x13, x18 からステータスを読み出すことを推奨します。 |

| RESET                        | 3  | PU, I             | <b>RESET:</b> DP83TG720S-Q1 を初期化または再初期化するアクティブ Low 入力。このピンを 10μs 以上 Low にアサートすると、リセットプロセスが強制的に開始されます。すべての内部レジスタは、「レジスタ マップ」セクションで各ビットに対して指定されたデフォルト状態に再初期化されます。リセットのデアサート時に、すべてのブートストラップピンが再サンプリングされます。                                                                                                                  |

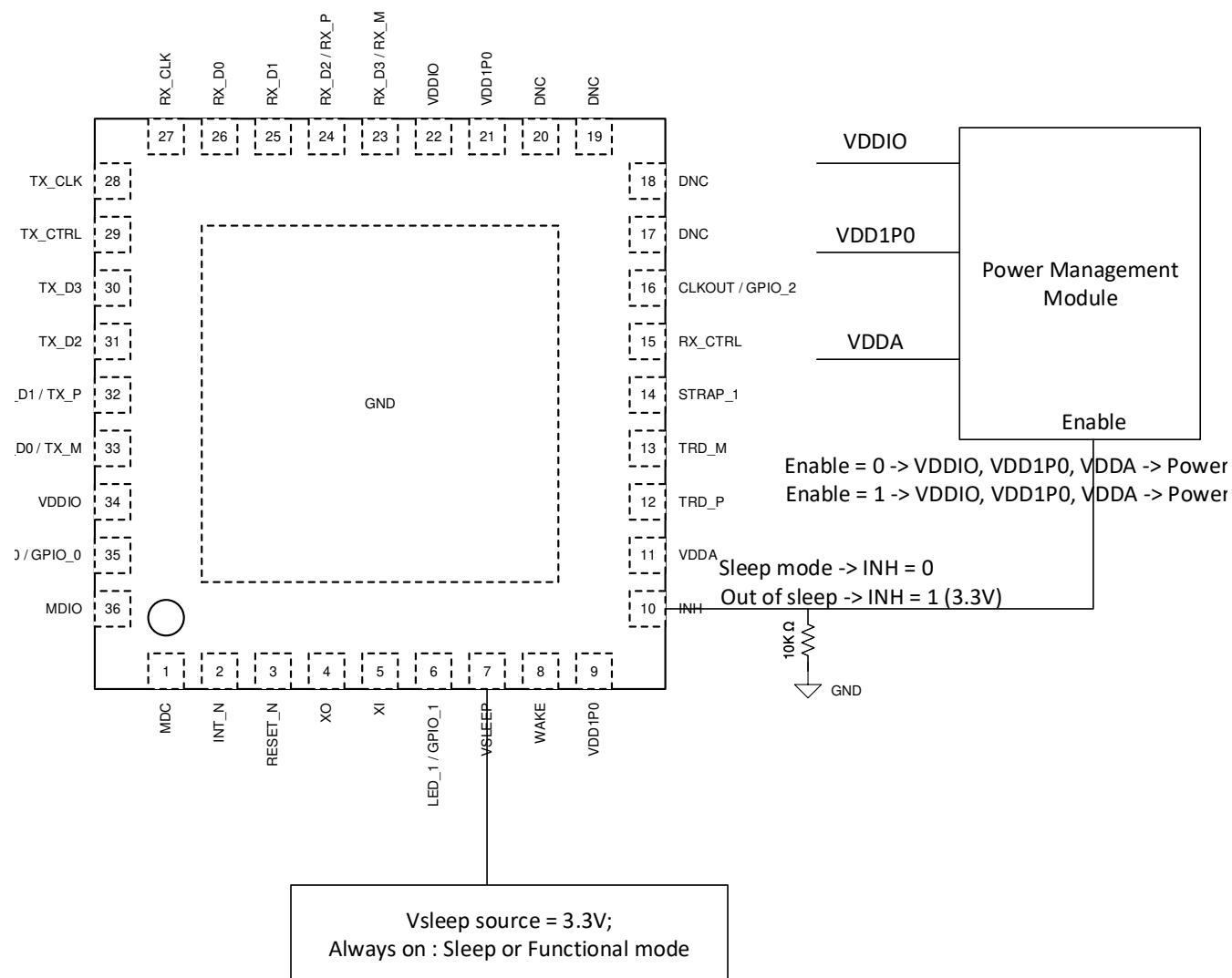

| INH                          | 10 | PMOS OD           | <b>INH:</b> アクティブ High の PMOS オープンドレイン出力。PHY がスリープ状態に移行すると、外付けプルダウン抵抗 (推奨値 = 10kΩ) がラインをグランドにプルダウンできるように、PHY は INH ピンを解放します。その他の状態では、INH ピンは VSLEEP レールに High 状態を駆動します。                                                                                                                                                  |

**表 4-1. ピンの機能 (続き)**

| ピン                       |                   | 状態 <sup>(1)</sup> | 説明 <sup>(2)</sup>                                                                                                                                                        |

|--------------------------|-------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                       | 番号                |                   |                                                                                                                                                                          |

| WAKE                     | 8                 | PD, I             | <b>WAKE:</b> ウェークアップ ピンのアクティブ High (このピンは VSLEEP ドメインで動作します) パルスにより、PHY はスリープ状態から復帰します。パルス幅については、タイミングのセクションを参照してください。スリープ状態を使わない場合、このピンを VSLEEP レールに直接接続できます。または浮動できます。 |

| STRP_1                   | 14                | I                 | <b>ストラップ 1:</b> このピンは、PHY_AD ビットをストラップするためのものです。                                                                                                                         |

| <b>クロック インターフェイス</b>     |                   |                   |                                                                                                                                                                          |

| XI                       | 5                 | I                 | <b>基準クロック入力:</b> 基準クロックの 25MHz $\pm$ 100ppm 許容誤差の水晶振動子または発振器入力。本デバイスは、外付け水晶振動子 (ピン XI とピン XO の間に接続) と外付け CMOS レベル発振器 (ピン XI のみに接続、XO は浮動) のどちらにも対応しています。                 |

| XO                       | 4                 | O                 | <b>基準クロック出力:</b> XO ピンは水晶振動子の場合にのみ使用されます。CMOS レベル発振器を XI に接続する場合、このピンは浮動したままになります。                                                                                       |

| <b>LED/GPIO インターフェイス</b> |                   |                   |                                                                                                                                                                          |

| LED_0 /<br>GPIO_0        | 35                | S, PD, IO         | <b>LED_0:</b> リンク ステータス                                                                                                                                                  |

| LED_1 /<br>GPIO_1        | 6                 | S, PD, IO         | <b>LED_1:</b> TX/RX 動作のリンク ステータスと点滅                                                                                                                                      |

| CLKOUT/<br>GPIO_2        | 16                | IO                | <b>クロック出力:</b> デフォルトでは 25MHz の基準クロック (XI のバッファリング済みレプリカ)。使用しない場合、レジスタ 0x0453 = 0x0006 を書き込むことで、クロック出力を無効化できます。                                                           |

| <b>メディア依存インターフェイス</b>    |                   |                   |                                                                                                                                                                          |

| TRD_M                    | 13                | IO                | <b>差動送信および受信:</b> 1000BASE-T1 動作用に構成された双方向差動信号。IEEE 802.3bp 準拠。                                                                                                          |

| TRD_P                    | 12                |                   |                                                                                                                                                                          |

| <b>電源およびグランド接続</b>       |                   |                   |                                                                                                                                                                          |

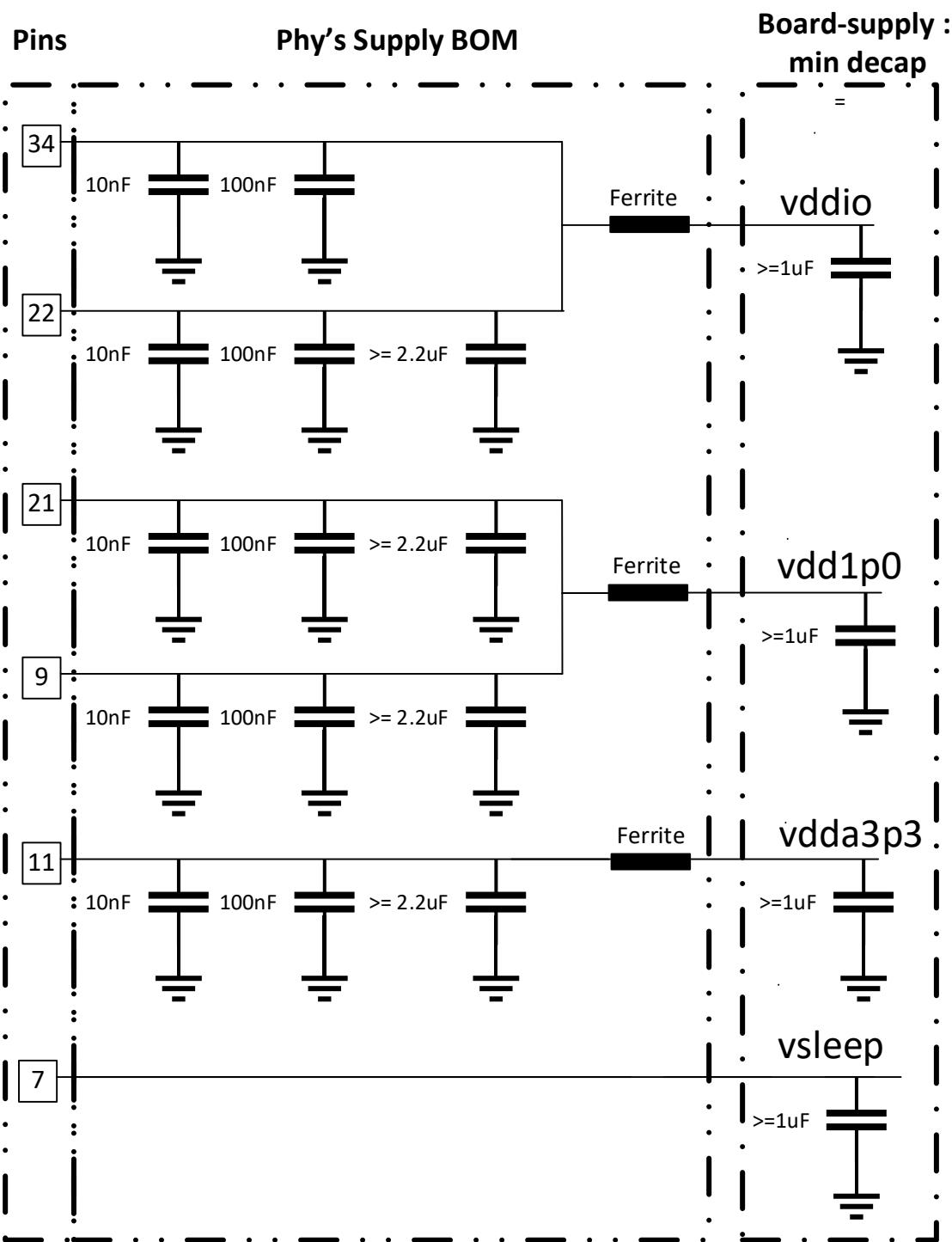

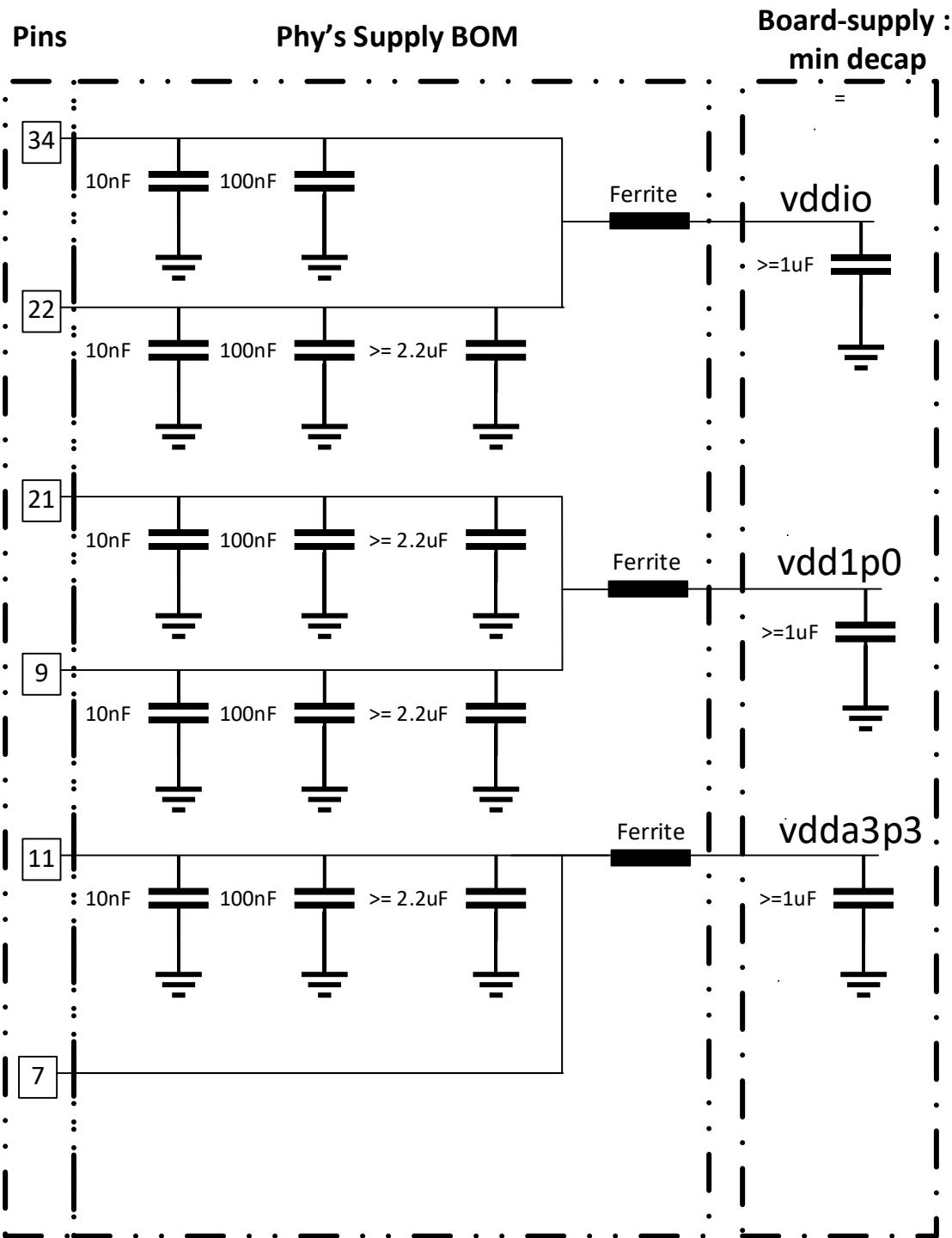

| VDDA3P3                  | 11                | 電源                | <b>コア電源:</b> 3.3V デカッピング ネットワークについては、「電源に関する推奨事項」を参照してください。                                                                                                              |

| VDDIO                    | 22, 34            | 電源                | <b>IO 電源:</b> 1.8V, 2.5V、または 3.3V。デカッピング ネットワークについては、「電源に関する推奨事項」を参照してください。                                                                                              |

| VDD1P0                   | 9, 21             | 電源                | <b>コア電源:</b> 1.0V デカッピング ネットワークについては、「電源に関する推奨事項」を参照してください。                                                                                                              |

| VSLEEP                   | 7                 | 電源                | <b>スリープ電源:</b> 3.3V デカッピング ネットワークについては、「電源に関する推奨事項」を参照してください。<br>スリープ機能を使用しない場合、このピンを VDDA3P3 に接続する必要があります。                                                              |

| グランド                     | DAP               | グランド              | <b>グランド</b>                                                                                                                                                              |

| <b>接続禁止</b>              |                   |                   |                                                                                                                                                                          |

| DNC                      | 17, 18,<br>19, 20 | DNC               | <b>DNC:</b> 接続しないでください (テスト構造がこれらのピンに接続されており、PHY の損傷または誤モードへの移行を防止するために浮動状態に保つ必要があります)。                                                                                  |

(1) 種類: I = 入力

O = 出力

IO = 入出力

OD = オープンドレイン

PD = 内部プルダウン

PU = 内部プルアップ

S = ストラップ: 構成ピン (すべての構成ピンは、弱い内部プルアップまたはプルダウンを備えています)。

(2) ピンを使用しない場合は、上記の表に示す推奨接続要件に従ってください。終端処理が必要ないピンは浮動させておくことができます。

## 4.1 ピンの状態

表 4-2. ピンの状態 - RGMII

| ピン名           | 起動 / リセット            |        |          | 通常動作 - RGMII         |        |          |

|---------------|----------------------|--------|----------|----------------------|--------|----------|

|               | ピンの状態 <sup>(1)</sup> | プル・タイプ | プル値 (kΩ) | ピンの状態 <sup>(1)</sup> | プル・タイプ | プル値 (kΩ) |

| MDC           | I                    | なし     | -        | I                    | なし     | -        |

| INT_N         | I                    | PU     | 9        | OD                   | PU     | 9        |

| RESET_N       | I                    | PU     | 9        | I                    | PU     | 9        |

| XO            | O                    | なし     | -        | O                    | なし     | -        |

| XI            | I                    | なし     | -        | I                    | なし     | -        |

| LED_1         | I                    | PD     | 9        | O                    | なし     | -        |

| WAKE          | I                    | PD     | 50       | I                    | PD     | 50       |

| STRP_1        | I                    | PD     | 6.3      | I                    | なし     | -        |

| INH           | PMOS, OD, O          | なし     | -        | PMOS, OD, O          | なし     | -        |

| RX_CTRL       | I                    | PD     | 6.3      | O                    | なし     | -        |

| CLKOUT/GPIO_2 | O                    | なし     | -        | O                    | なし     | -        |

| RX_D3         | I                    | PD     | 9        | O                    | なし     | -        |

| RX_D2         | I                    | PD     | 9        | O                    | なし     | -        |

| RX_D1         | I                    | PD     | 9        | O                    | なし     | -        |

| RX_D0         | I                    | PD     | 9        | O                    | なし     | -        |

| RX_CLK        | I                    | PD     | 9        | O                    | なし     | -        |

| TX_CLK        | I                    | なし     | -        | I                    | なし     | -        |

| TX_CTRL       | I                    | なし     | -        | I                    | なし     | -        |

| TX_D3         | I                    | なし     | -        | I                    | なし     | -        |

| TX_D2         | I                    | なし     | -        | I                    | なし     | -        |

| TX_D1         | I                    | なし     | -        | I                    | なし     | -        |

| TX_D0         | I                    | なし     | -        | I                    | なし     | -        |

| LED_0         | I                    | PD     | 9        | O                    | なし     | -        |

| MDIO          | I                    | なし     | -        | IO                   | なし     | -        |

- (1) 種類:

I = 入力

O = 出力

IO = 入出力

OD = オープン・ドレイン

PD = 内部プルダウン

PU = 内部プルアップ

**表 4-3. ピンの状態 - SGMII**

| ピン名           | 起動 / リセット            |        |          | 通常動作 - SGMII         |        |          |

|---------------|----------------------|--------|----------|----------------------|--------|----------|

|               | ピンの状態 <sup>(1)</sup> | プル・タイプ | プル値 (kΩ) | ピンの状態 <sup>(1)</sup> | プル・タイプ | プル値 (kΩ) |

| MDC           | I                    | なし     | -        | I                    | なし     | -        |

| INT_N         | I                    | PU     | 9        | OD                   | PU     | 9        |

| RESET_N       | I                    | PU     | 9        | I                    | PU     | 9        |

| XO            | O                    | なし     | -        | O                    | なし     | -        |

| XI            | I                    | なし     | -        | I                    | なし     | -        |

| LED_1         | I                    | PD     | 9        | O                    | なし     | -        |

| WAKE          | I                    | PD     | 50       | I                    | PD     | 50       |

| STRP_1        | I                    | PD     | 6.3      | I                    | なし     | -        |

| INH           | PMOS, OD, O          | なし     | -        | PMOS, OD, O          | なし     | -        |

| RX_CTRL       | I                    | PD     | 6.3      | I                    | PD     | 6.3      |

| CLKOUT/GPIO_2 | O                    | なし     | -        | O                    | なし     | -        |

| RX_D3         | I                    | PD     | 9        | O                    | なし     | -        |

| RX_D2         | I                    | PD     | 9        | O                    | なし     | -        |

| RX_D1         | I                    | PD     | 9        | Hi-Z                 | PD     | 9        |

| RX_D0         | I                    | PD     | 9        | Hi-Z                 | PD     | 9        |

| RX_CLK        | I                    | PD     | 9        | Hi-Z                 | PD     | 9        |

| TX_CLK        | I                    | なし     | -        | Hi-Z                 | なし     | -        |

| TX_CTRL       | I                    | なし     | -        | Hi-Z                 | なし     | -        |

| TX_D3         | I                    | なし     | -        | Hi-Z                 | なし     | -        |

| TX_D2         | I                    | なし     | -        | Hi-Z                 | なし     | -        |

| TX_D1         | I                    | なし     | -        | I                    | なし     | -        |

| TX_D0         | I                    | なし     | -        | I                    | なし     | -        |

| LED_0         | I                    | PD     | 9        | O                    | なし     | -        |

| MDIO          | I                    | なし     | -        | IO                   | なし     | -        |

- (1) 種類:I = 入力

O = 出力

IO = 入出力

OD = オープン・ドレイン

PD = 内部プルダウン

PU = 内部プルアップ

Hi-Z = 高インピーダンス

表 4-4. ピンの状態 - スリープおよび分離

| ピン名           | MAC 分離               |                        |          | スリープ                 |        |          |

|---------------|----------------------|------------------------|----------|----------------------|--------|----------|

|               | ピンの状態 <sup>(1)</sup> | プル・タイプ                 | プル値 (kΩ) | ピンの状態 <sup>(1)</sup> | プル・タイプ | プル値 (kΩ) |

| MDC           | I                    | なし                     | -        | 浮動                   | なし     | -        |

| INT_N         | O                    | PU                     | 9        | 浮動                   | なし     | -        |

| RESET_N       | I                    | PU                     | 9        | 浮動                   | なし     | -        |

| XO            | O                    | なし                     | -        | 浮動                   | なし     | -        |

| XI            | I                    | なし                     | -        | 浮動                   | なし     | -        |

| LED_1         | O                    | なし                     | -        | 浮動                   | なし     | -        |

| WAKE          | I                    | PD                     | 50       | I                    | なし     | 50       |

| STRP_1        | I                    | なし                     | -        | 浮動                   | なし     | -        |

| INH           | PMOS, OD, O          | なし                     | -        | PMOS, OD, O          | なし     | -        |

| RX_CTRL       | I                    | PD                     | 6.3      | 浮動                   | なし     | -        |

| CLKOUT/GPIO_2 | O                    | なし                     | -        | 浮動                   | なし     | -        |

| RX_D3         | I                    | PD / なし <sup>(2)</sup> | 9        | 浮動                   | なし     | -        |

| RX_D2         | I                    | PD / なし <sup>(2)</sup> | 9        | 浮動                   | なし     | -        |

| RX_D1         | I                    | PD                     | 9        | 浮動                   | なし     | -        |

| RX_D0         | I                    | PD                     | 9        | 浮動                   | なし     | -        |

| RX_CLK        | I                    | PD                     | 9        | 浮動                   | なし     | -        |

| TX_CLK        | I                    | なし                     | -        | 浮動                   | なし     | -        |

| TX_CTRL       | I                    | なし                     | -        | 浮動                   | なし     | -        |

| TX_D3         | I                    | なし                     | -        | 浮動                   | なし     | -        |

| TX_D2         | I                    | なし                     | -        | 浮動                   | なし     | -        |

| TX_D1         | I                    | なし                     | -        | 浮動                   | なし     | -        |

| TX_D0         | I                    | なし                     | -        | 浮動                   | なし     | -        |

| LED_0         | O                    | なし                     | -        | 浮動                   | なし     | -        |

| MDIO          | IO                   | なし                     | -        | 浮動                   | なし     | -        |

(1) 種類:I = 入力

O = 出力

IO = 入出力

OD = オープン・ドレイン

PD = 内部プルダウン

PU = 内部プルアップ

Hi-Z = 高インピーダンス

浮動 = IO に電力が供給されていないため、ピンは PHY によってバイアス印加されていません。

(2) PD は、RGMII の分離モード専用です。

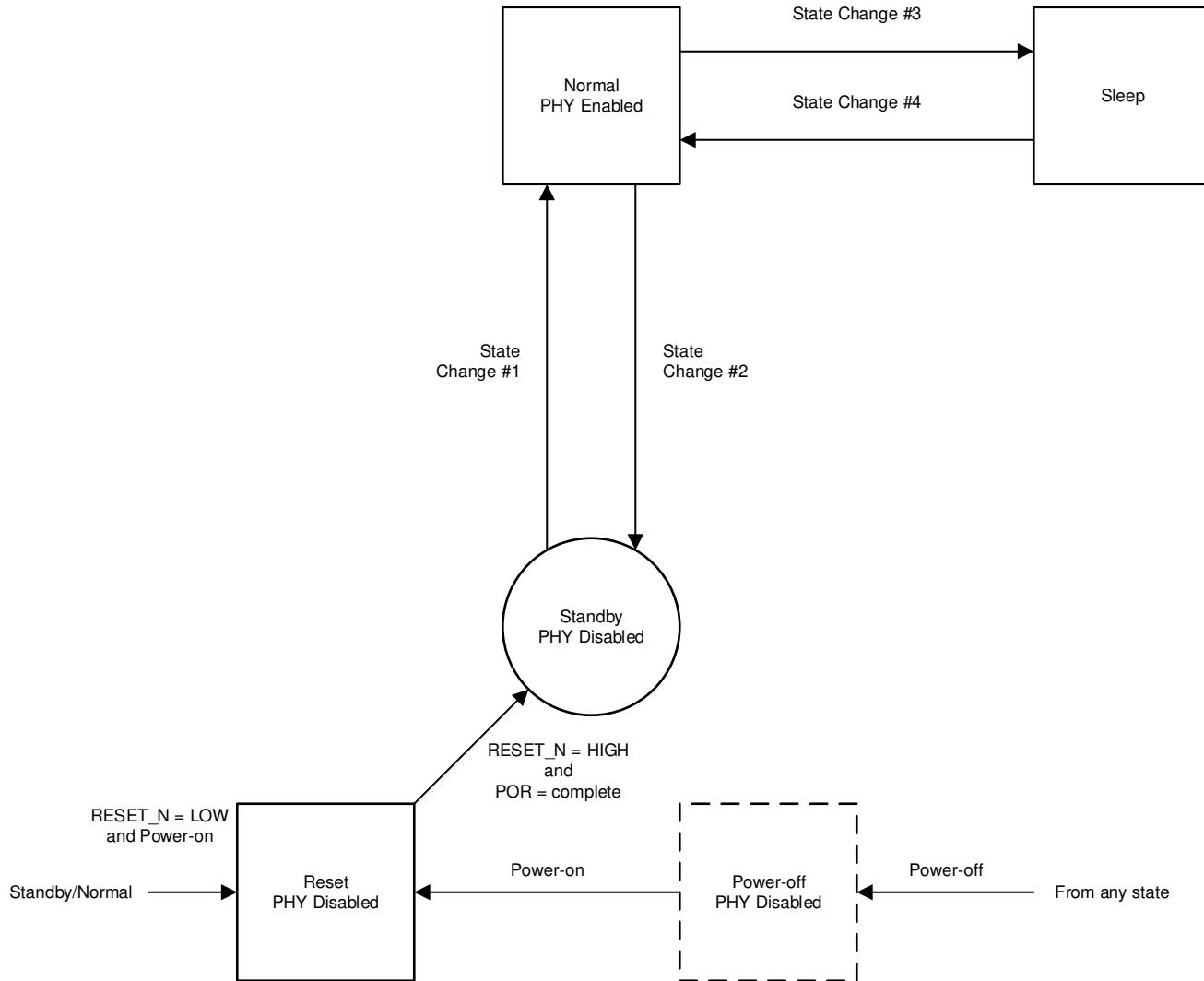

**注**

スリープ・モードに入る場合、VDDA、VDDIO、VDD1P0 はパワーダウンするものとします。詳細については、「スリープ・モードに必要な実装」の図を参照してください。

## 4.2 ピンの電源ドメイン

表 4-5. ピン電源ドメイン表

| ピン            | RGMII モード | SGMII モード |

|---------------|-----------|-----------|

| MDC           | VDDIO     | VDDIO     |

| INT_N         | VDDIO     | VDDIO     |

| RESET_N       | VDDIO     | VDDIO     |

| XI            | VDDIO     | VDDIO     |

| XO            | VDDIO     | VDDIO     |

| LED_1         | VDDIO     | VDDIO     |

| WAKE          | VSLEEP    | VSLEEP    |

| STRP_1        | VDDIO     | VDDIO     |

| INH           | VSLEEP    | VSLEEP    |

| RX_CTRL       | VDDIO     | VDDIO     |

| CLKOUT/GPIO_2 | VDDIO     | VDDIO     |

| RX_D3         | VDDIO     | VDDA      |

| RX_D2         | VDDIO     | VDDA      |

| RX_D1         | VDDIO     | VDDIO     |

| RX_D0         | VDDIO     | VDDIO     |

| RX_CLK        | VDDIO     | VDDIO     |

| TX_CLK        | VDDIO     | VDDIO     |

| TX_CTRL       | VDDIO     | VDDIO     |

| TX_D3         | VDDIO     | VDDIO     |

| TX_D2         | VDDIO     | VDDIO     |

| TX_D1         | VDDIO     | VDDA      |

| TX_D0         | VDDIO     | VDDA      |

| LED_0         | VDDIO     | VDDIO     |

| MDIO          | VDDIO     | VDDIO     |

| TRD_P         | VDDA      | VDDA      |

| TRD_M         | VDDA      | VDDA      |

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                           |                                                                                                       | 最小値  | 標準値                         | 最大値 | 単位 |

|---------------------------|-------------------------------------------------------------------------------------------------------|------|-----------------------------|-----|----|

| 電源電圧                      | VDDA3P3                                                                                               | -0.5 |                             | 4   | V  |

| 電源電圧                      | VDD1P0                                                                                                | -0.5 |                             | 1.4 | V  |

| 電源電圧                      | VDDIO (3.3V)                                                                                          | -0.5 |                             | 4   | V  |

| 電源電圧                      | VDDIO (2.5V)                                                                                          | -0.5 |                             | 2.9 | V  |

| 電源電圧                      | VDDIO (1.8V)                                                                                          | -0.5 |                             | 2.2 | V  |

| 電源電圧                      | V <sub>SLEEP</sub>                                                                                    | -0.5 |                             | 4   | V  |

| MDI ピン                    | TRD_M, TRD_P                                                                                          | -0.5 |                             | 4   | V  |

| LVCMOS/<br>LVTTL 入力電<br>圧 | MDC, RESET, XI, LED_1, STRP_1, RX_CTRL, CLKOUT,<br>RX_D[3:0], TX_CLK, TX_CTRL, TX_D[3:0], LED_0, MDIO | -0.5 | VDDIO + 0.3                 |     | V  |

| LVCMOS/<br>LVTTL 入力電<br>圧 | WAKE                                                                                                  | -0.5 | V <sub>SLEEP</sub> + 0.3    |     | V  |

| LVCMOS/<br>LVTTL 出力電<br>圧 | INT, LED_1, RX_CTRL, CLKOUT, RX_D[3:0], RX_CLK,<br>LED_0, MDIO                                        | -0.5 | VDDIO + 0.3                 |     | V  |

| LVCMOS/<br>LVTTL 出力電<br>圧 | INH                                                                                                   | -0.5 | V <sub>SLEEP</sub> +<br>0.3 |     | V  |

| T <sub>J</sub>            | 接合部温度                                                                                                 |      |                             | 150 | °C |

| T <sub>stg</sub>          | 保存温度                                                                                                  | -65  |                             | 150 | °C |

(1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについての話で、絶対最大定格において、またはこのデータシートの「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。絶対最大定格の状態に長時間置くと、デバイスの信頼性に影響を及ぼす場合があります。

### 5.2 ESD 定格

|                    |      |                                                |              | 値     | 単位 |

|--------------------|------|------------------------------------------------|--------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、AEC Q100-002<br>に準拠 <sup>(1)</sup> | すべてのピン       | ±2000 | V  |

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、AEC Q100-002<br>に準拠 <sup>(1)</sup> | TRD_M, TRD_P | ±8000 | V  |

| V <sub>(ESD)</sub> | 静電放電 | 荷電デバイス モデル (CDM)、AEC<br>Q100-011 準拠            | すべてのピン       | ±500  | V  |

| V <sub>(ESD)</sub> | 静電放電 | IEC 61000-4-2 接触放電                             | TRD_M, TRD_P | ±8000 | V  |

(1) AEC Q100-002 は、HBM ストレス試験を ANSI / ESDA / JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|         |                 | 最小値  | 公称値 | 最大値  | 単位 |

|---------|-----------------|------|-----|------|----|

| VDDIO   | IO 電源電圧、1.8V 動作 | 1.62 | 1.8 | 1.98 | V  |

|         | IO 電源電圧、2.5V 動作 | 2.25 | 2.5 | 2.75 |    |

|         | IO 電源電圧、3.3V 動作 | 2.97 | 3.3 | 3.63 |    |

| VDDA3P3 | コア電源電圧、3.3V     | 2.97 | 3.3 | 3.63 | V  |

## 5.3 推奨動作条件 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

|                    |               | 最小値  | 公称値 | 最大値  | 単位 |

|--------------------|---------------|------|-----|------|----|

| VDD1P0             | コア電源電圧、1.0V   | 0.95 | 1   | 1.1  | V  |

| V <sub>SLEEP</sub> | スリープ電源電圧、3.3V | 2.97 | 3.3 | 3.63 | V  |

| T <sub>A</sub>     | 周囲温度          | -40  |     | 125  | °C |

## 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | DP83TG720  | 単位   |

|-----------------------|---------------------|------------|------|

|                       |                     | RHA (VQFN) |      |

|                       |                     | 36 ピン      |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 32.5       | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 22.2       | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 13.3       | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ    | 0.3        | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ    | 13.3       | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース (底面) への熱抵抗 | 3.2        | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.5 電気的特性

自由気流での動作温度範囲内 (特に記述のない限り)<sup>(1)</sup>

| パラメータ                     | テスト条件        | 最小値                                                    | 標準値     | 最大値     | 単位      |

|---------------------------|--------------|--------------------------------------------------------|---------|---------|---------|

| DC 特性                     |              |                                                        |         |         |         |

| XI                        |              |                                                        |         |         |         |

| V <sub>IH</sub>           | High レベル入力電圧 |                                                        | 1.3     |         | V       |

| V <sub>IL</sub>           | Low レベル入力電圧  |                                                        | 0.5     |         | V       |

| WAKE ピン                   | WAKE ピン      | WAKE ピン                                                | WAKE ピン | WAKE ピン | WAKE ピン |

| V <sub>IH</sub>           | High レベル入力電圧 | V <sub>SLEEP</sub> = 3.3V ± 10%                        | 2       |         | V       |

| V <sub>IL</sub>           | Low レベル入力電圧  | V <sub>SLEEP</sub> = 3.3V ± 10%                        |         | 0.8     | V       |

| INH ピン                    | INH ピン       | INH ピン                                                 | INH ピン  | INH ピン  | INH ピン  |

| V <sub>OH</sub>           | High レベル出力電圧 | I <sub>OH</sub> = -2mA、V <sub>SLEEP</sub> = 3.3V ± 10% | 2.4     |         | V       |

| 3.3V VDDIO <sup>(2)</sup> |              |                                                        |         |         |         |

| V <sub>OH</sub>           | High レベル出力電圧 | I <sub>OH</sub> = -2mA、VDDIO = 3.3V ± 10%              | 2.4     |         | V       |

| V <sub>OL</sub>           | Low レベル出力電圧  | I <sub>OL</sub> = 2mA、VDDIO = 3.3V ± 10%               |         | 0.4     | V       |

| V <sub>IH</sub>           | High レベル入力電圧 | VDDIO = 3.3V ± 10%                                     | 2       |         | V       |

| V <sub>IL</sub>           | Low レベル入力電圧  | VDDIO = 3.3V ± 10%                                     |         | 0.8     | V       |

| 2.5V VDDIO <sup>(2)</sup> |              |                                                        |         |         |         |

| V <sub>OH</sub>           | High レベル出力電圧 | I <sub>OH</sub> = -2mA、VDDIO = 2.5V ± 10%              | 2       |         | V       |

| V <sub>OL</sub>           | Low レベル出力電圧  | I <sub>OL</sub> = 2mA、VDDIO = 2.5V ± 10%               |         | 0.4     | V       |

| V <sub>IH</sub>           | High レベル入力電圧 | VDDIO = 2.5V ± 10%                                     | 1.7     |         | V       |

| V <sub>IL</sub>           | Low レベル入力電圧  | VDDIO = 2.5V ± 10%                                     |         | 0.7     | V       |

| 1.8V VDDIO <sup>(2)</sup> |              |                                                        |         |         |         |

## 5.5 電気的特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

| パラメータ           |                                            | テスト条件                                                                          | 最小値            | 標準値           | 最大値   | 単位            |

|-----------------|--------------------------------------------|--------------------------------------------------------------------------------|----------------|---------------|-------|---------------|

| $V_{OH}$        | High レベル出力電圧                               | $I_{OH} = -2\text{mA}$ , $VDDIO = 1.8\text{V} \pm 10\%$                        | $VDDIO - 0.45$ |               |       | V             |

| $V_{OL}$        | Low レベル出力電圧                                | $I_{OL} = 2\text{mA}$ , $VDDIO = 1.8\text{V} \pm 10\%$                         |                |               | 0.45  | V             |

| $V_{IH}$        | High レベル入力電圧                               | $VDDIO = 1.8\text{V} \pm 10\%$                                                 | 0.7 * $VDDIO$  |               |       | V             |

| $V_{IL}$        | Low レベル入力電圧                                | $VDDIO = 1.8\text{V} \pm 10\%$                                                 |                | 0.3 * $VDDIO$ |       | V             |

| $I_{IH}$        | 入力 High 電流 (MDIO)                          | $VIN = VCC$ , $-40^\circ\text{C} \sim 125^\circ\text{C}$                       | -5             |               | 5     | $\mu\text{A}$ |

| $I_{IH}$        | 入力 High 電流 (RGMII 入力ピン、MDC)                | $VIN = VCC$ , $-40^\circ\text{C} \sim 125^\circ\text{C}$                       | -20            |               | 20    | $\mu\text{A}$ |

| $I_{OZ}$        | 入力 High 電流 (MDIO)                          | $VIN$ の掃引範囲は $0\text{V} \sim VCC$ , $-40^\circ\text{C} \sim 125^\circ\text{C}$ | -40            |               | 40    | $\mu\text{A}$ |

| $I_{IL}$        | 入力 Low 電流 (RGMII 入力ピン、MDC、MDIO)            | $VIN = GND$ , $-40^\circ\text{C} \sim 125^\circ\text{C}$                       | -40            |               | 5     | $\mu\text{A}$ |

| $I_{OZL}$       |                                            | INH                                                                            |                |               | 6     | $\mu\text{A}$ |

| $I_{OZL}$       | トライステート出力電流 <sup>(5)</sup>                 | $VIN$ の掃引範囲は $0\text{V} \sim VCC$ , $-40^\circ\text{C} \sim 125^\circ\text{C}$ | -40            |               | 10    | $\mu\text{A}$ |

| $I_{OZL}$       | トライステート出力電流 <sup>(6)</sup>                 | $VIN$ の掃引範囲は $0\text{V} \sim VCC$ , $-40^\circ\text{C} \sim 125^\circ\text{C}$ | -60            |               | 60    | $\mu\text{A}$ |

| $C_{IN}$        | 入力容量                                       | LVCMOS/LVTTL ピン <sup>(3)</sup>                                                 |                |               | 2     | pF            |

| $C_{IN}$        | 入力容量                                       | LVCMOS/LVTTL ピン <sup>(4)</sup>                                                 |                |               | 4     | pF            |

| $C_{IN}$        |                                            | XI                                                                             |                |               | 1     | pF            |

| $C_{OUT}$       | 出力容量                                       | LVCMOS/LVTTL ピン <sup>(3)</sup>                                                 |                |               | 2     | pF            |

| $C_{OUT}$       | 出力容量                                       | LVCMOS/LVTTL ピン <sup>(4)</sup>                                                 |                |               | 4     | pF            |

| $C_{OUT}$       |                                            | XO                                                                             |                |               | 1     | pF            |

| $R_{pull-up}$   | 内蔵プルアップ抵抗値                                 | INT, RESET                                                                     | 6.5            | 9             | 12.5  | k $\Omega$    |

| $R_{pull-down}$ | 内蔵プルダウン抵抗値                                 | STRP_1, RX_CTRL                                                                | 4.725          | 6.3           | 7.875 | k $\Omega$    |

| $R_{pull-down}$ | 内蔵プルダウン抵抗値                                 | LED_1, RX_D[3:0], RX_CLK, LED_0                                                | 7.3            | 9             | 13    | k $\Omega$    |

|                 |                                            | WAKE                                                                           | 35             | 50            | 62.5  | k $\Omega$    |

| $R_{pull-down}$ | 内蔵プルアップ抵抗値 (アクティブ時)                        | INH                                                                            |                |               | 106   | $\Omega$      |

| $R_{series}$    | 内蔵 MAC 直列終端抵抗値 (デフォルト)                     | RX_D[3:0], RX_CTRL, RX_CLK                                                     | 24             | 42            | 52    | $\Omega$      |

| $R_{series}$    | 内蔵 MAC 直列終端抵抗値 (レジスタ $<0x0456> = 0x0148$ ) | RX_D[3:0], RX_CTRL, RX_CLK                                                     | 30             | 52            | 65    | $\Omega$      |

| $R_{series}$    | 内蔵 MAC 直列終端抵抗値 (レジスタ $<0x0456> = 0x0168$ ) | RX_D[3:0], RX_CTRL, RX_CLK                                                     | 40             | 70            | 84    | $\Omega$      |

| 消費電流、スリープ モード   |                                            |                                                                                |                |               |       |               |

| $I_{SLEEP}$     | スリープ時の消費電流                                 | $V_{SLEEP}$                                                                    |                | 485           | 840   | $\mu\text{A}$ |

| 消費電流、リセットのアサート時 |                                            |                                                                                |                |               |       |               |

| $I_{DDIO}$      | IO 電源電流、 $VDDIO = 1.8\text{V}$             | $VDDIO$                                                                        |                | 4             | 9     | mA            |

| $I_{DDIO}$      | IO 電源電流、 $VDDIO = 2.5\text{V}$             | $VDDIO$                                                                        |                | 5             | 12    | mA            |

| $I_{DDIO}$      | IO 電源電流、 $VDDIO = 3.3\text{V}$             | $VDDIO$                                                                        |                | 6.5           | 15    | mA            |

| $I_{DDA3P3}$    | コア消費電流、 $3.3\text{V}$                      | VDDA3P3                                                                        |                | 5             | 8     | mA            |

| $I_{DD1P0}$     | コア消費電流、 $1.0\text{V}$                      | VDD1P0                                                                         |                | 30            | 110   | mA            |

| 消費電流、スタンバイ      |                                            |                                                                                |                |               |       |               |

| $I_{DDIO}$      | IO 電源電流、 $VDDIO = 1.8\text{V}$             | $VDDIO$                                                                        |                | 4             | 11    | mA            |

| $I_{DDIO}$      | IO 電源電流、 $VDDIO = 2.5\text{V}$             | $VDDIO$                                                                        |                | 6             | 13    | mA            |

## 5.5 電気的特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

| パラメータ                                                                |                         | テスト条件                                 | 最小値   | 標準値              | 最大値     | 単位       |

|----------------------------------------------------------------------|-------------------------|---------------------------------------|-------|------------------|---------|----------|

| $I_{DDIO}$                                                           | IO 電源電流、 $VDDIO = 3.3V$ | VDDIO                                 |       | 8                | 15      | mA       |

| $I_{DDA3P3}$                                                         | コア消費電流、 $3.3V$          | VDDA3P3                               |       | 16               | 18      | mA       |

| $I_{DD1P0}$                                                          | コア消費電流、 $1.0V$          | VDD1P0                                |       | 33               | 112     | mA       |

| 消費電流、アクティブ モード、電圧: $\pm 10\%$ 、トライフィック:100%、パケット サイズ:1518、コンテンツ:ランダム |                         |                                       |       |                  |         |          |

| $I_{DDIO}$                                                           | IO 電源電流、 $VDDIO = 1.8V$ | RGMII                                 | 20    | 25               | mA      |          |

| $I_{DDIO}$                                                           | IO 電源電流、 $VDDIO = 2.5V$ | RGMII                                 | 26    | 30               | mA      |          |

| $I_{DDIO}$                                                           | IO 電源電流、 $VDDIO = 3.3V$ | RGMII                                 | 33    | 40               | mA      |          |

| $I_{DDIO}$                                                           | IO 電源電流、 $VDDIO = 1.8V$ | SGMII                                 | 3.5   | 5                | mA      |          |

| $I_{DDIO}$                                                           | IO 電源電流、 $VDDIO = 2.5V$ | SGMII                                 | 5     | 7                | mA      |          |

| $I_{DDIO}$                                                           | IO 電源電流、 $VDDIO = 3.3V$ | SGMII                                 | 6.5   | 8                | mA      |          |

| $I_{DDA3P3}$                                                         | コア消費電流、 $3.3V$          | RGMII                                 | 85    | 89               | mA      |          |

| $I_{DD1P0}$                                                          | コア消費電流、 $1.0V$          | RGMII                                 | 177   | 250              | mA      |          |

| $I_{DDA3P3}$                                                         | コア消費電流、 $3.3V$          | SGMII                                 | 95    | 100              | mA      |          |

| $I_{DD1P0}$                                                          | コア消費電流、 $1.0V$          | SGMII                                 | 200   | 260              | mA      |          |

| $I_{SLEEP}$                                                          | スリープ時の消費電流              | $V_{SLEEP} = 3.3V \pm 10\%$           | 1000  | 1500             | $\mu A$ |          |

| MDI の特性                                                              |                         |                                       |       |                  |         |          |

| $V_{OD-MDI}$                                                         | 出力差動電圧                  | $R_{L(diff)} = 100\Omega$             |       | 1.3              |         | V        |

| $R_{MDI-DIFF}$                                                       | 内蔵差動 MDI 終端 (アクティブ状態)   | TRD_P、TRD_M                           | 100   |                  |         | $\Omega$ |

| $R_{MDI-DIFF}$                                                       | 内蔵差動 MDI 終端 (スリープ状態)    | TRD_P、TRD_M                           | 100   |                  |         | $\Omega$ |

| SGMII ドライバの DC 仕様                                                    |                         |                                       |       |                  |         |          |

| $V_{OD-SGMII}$                                                       | 出力差動電圧                  | $R_{L(diff)} = 100\Omega$             | 150   | 400              | $mV$    |          |

| $R_{OUT-DIFF}$                                                       | 内蔵差動出力終端                | RX_P、RX_M                             | 78    | 100              | 130     | $\Omega$ |

| SGMII レシーバの DC 仕様                                                    |                         |                                       |       |                  |         |          |

| $V_{IDTH}$                                                           | 入力差動スレッショルド             |                                       | 100   |                  |         | $mV$     |

| $R_{IN-DIFF}$                                                        | 内蔵差動入力終端                | TX_P、TX_M                             | 82    | 100              | 121     | $\Omega$ |

| ポートストラップの DC 特性                                                      |                         |                                       |       |                  |         |          |

| 2 レベル<br>のストラップ                                                      |                         |                                       |       |                  |         |          |

| $V_{bsl\_1v8}$                                                       | ポートストラップのスレッショルド        | モード 1、 $VDDIO = 1.8V \pm 10\%$ 、2 レベル | 0     | $0.35^* V_{DIO}$ |         | V        |

| $V_{bsl\_1v8}$                                                       | ポートストラップのスレッショルド        | モード 2、 $VDDIO = 1.8V \pm 10\%$ 、2 レベル | 1.175 | $VDDIO$          |         | V        |

| $V_{bsl\_2v5}$                                                       | ポートストラップのスレッショルド        | モード 1、 $VDDIO = 2.5V \pm 10\%$ 、2 レベル | 0     | 0.7              |         | V        |

| $V_{bsl\_2v5}$                                                       | ポートストラップのスレッショルド        | モード 2、 $VDDIO = 2.5V \pm 10\%$ 、2 レベル | 1.175 | $VDDIO$          |         | V        |

| $V_{bsl\_3v3}$                                                       | ポートストラップのスレッショルド        | モード 1、 $VDDIO = 3.3V \pm 10\%$ 、2 レベル | 0     | 0.7              |         | V        |

| $V_{bsl\_3v3}$                                                       | ポートストラップのスレッショルド        | モード 2、 $VDDIO = 3.3V \pm 10\%$ 、2 レベル | 1.175 | $VDDIO$          |         | V        |

| 3 レベル<br>のストラップ                                                      |                         |                                       |       |                  |         |          |

| $V_{bsl\_1v8}$                                                       | ポートストラップのスレッショルド        | モード 1、 $VDDIO = 1.8V \pm 10\%$ 、3 レベル | 0     | $0.35^* V_{DIO}$ |         | V        |

## 5.5 電気的特性 (続き)

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

| パラメータ                | テスト条件                             | 最小値                            | 標準値             | 最大値             | 単位     |

|----------------------|-----------------------------------|--------------------------------|-----------------|-----------------|--------|

| V <sub>bs2_1V8</sub> | ブートストラップのスレッショルド                  | モード 2、VDDIO = 1.8V ± 10%、3 レベル | 0.40 *<br>VDDIO | 0.75 *<br>VDDIO | V      |

| V <sub>bs3_1V8</sub> | ブートストラップのスレッショルド                  | モード 3、VDDIO = 1.8V ± 10%、3 レベル | 0.84 *<br>VDDIO | VDDIO           | V      |

| V <sub>bs1_2V5</sub> | ブートストラップのスレッショルド                  | モード 1、VDDIO = 2.5V ± 10%、3 レベル | 0               | 0.19 *<br>VDDIO | V      |

| V <sub>bs2_2V5</sub> | ブートストラップのスレッショルド                  | モード 2、VDDIO = 2.5V ± 10%、3 レベル | 0.27 *<br>VDDIO | 0.41 *<br>VDDIO | V      |

| V <sub>bs3_2V5</sub> | ブートストラップのスレッショルド                  | モード 3、VDDIO = 2.5V ± 10%、3 レベル | 0.58 *<br>VDDIO | VDDIO           | V      |

| V <sub>bs1_3V3</sub> | ブートストラップのスレッショルド                  | モード 1、VDDIO = 3.3V ± 10%、3 レベル | 0               | 0.18 *<br>VDDIO | V      |

| V <sub>bs2_3V3</sub> | ブートストラップのスレッショルド                  | モード 2、VDDIO = 3.3V ± 10%、3 レベル | 0.22 *<br>VDDIO | 0.42 *<br>VDDIO | V      |

| V <sub>bs3_3V3</sub> | ブートストラップのスレッショルド                  | モード 3、VDDIO = 3.3V ± 10%、3 レベル | 0.46 *<br>VDDIO | VDDIO           | V      |

| 温度センサ                |                                   |                                |                 |                 |        |

|                      | 温度センサの分解能 (LSB)                   | -40°C ~ 125°C                  |                 | 1.5             | °C     |

|                      | 温度センサの精度 (1 つの部品での電圧と温度による変動)     | -40°C ~ 125°C                  |                 | -7.5            | 7.5 °C |

|                      | 温度センサの精度 (電圧と温度による変動、部品間のばらつきを含む) | -40°C ~ 125°C                  |                 | -21.5           | 20 °C  |

|                      | 温度センサの範囲                          |                                |                 | -40             | 140 °C |

| 電圧センサ                |                                   |                                |                 |                 |        |

|                      | VDDA3P3 センサの範囲                    |                                | 2.66            | 3.3             | 3.96 V |

|                      | VDDA3P3 センサの分解能 (LSB)             | -40°C ~ 125°C                  |                 | 8.6             | mV     |

|                      | VDDA3P3 センサの精度 (電圧と温度による変動)       | -40°C ~ 125°C                  |                 | 8.6             | mV     |

|                      | VDDA3P3 センサの精度 (部品間のばらつきを含む)      | -40°C ~ 125°C                  | -68.8           | 68.8            | mV     |

|                      | VDD1P0 センサの範囲                     |                                | 0.8             | 1.2             | V      |

|                      | VDD1P0 センサの分解能 (LSB)              | -40°C ~ 125°C                  |                 | 2.8             | mV     |

|                      | VDD1P0 センサの精度 (電圧と温度による変動)        | -40°C ~ 125°C                  |                 | 2.8             | mV     |

|                      | VDD1P0 センサの精度 (部品間のばらつきを含む)       | -40°C ~ 125°C                  | -22.4           | 22.4            | mV     |

|                      | VDDIO センサの範囲                      |                                | 1.44            | 3.8             | V      |

|                      | VDDIO センサの分解能 (LSB)               | -40°C ~ 125°C                  |                 | 15.4            | mV     |

|                      | VDDIO センサの精度 (電圧と温度による変動)         | -40°C ~ 125°C                  |                 | 15.4            | mV     |

|                      | VDDIO センサの精度 (部品間のばらつきを含む)        | -40°C ~ 125°C                  | -78             | 78              | mV     |

(1) 製造試験、特性評価、設計によって検証済み

(2) 対象ピン: LED\_1, STRP\_1, RX\_CTRL, CLKOUT, RX\_D[3:0], RX\_CLK, LED\_0

(3) 対象ピン: MDC, INT, RESET, LED\_1, STRP\_1, RX\_CTRL, CLKOUT, RX\_D0, RX\_D1, RX\_CLK, TX\_CLK, TX\_CTRL, TX\_D2, TX\_D3, LED\_0, MDIO

(4) 対象ピン: TX\_D0, TX\_D1, RX\_D2, RX\_D3

(5) 対象ピン: LED\_1, RX\_D[3:0], RX\_CLK, LED\_0

(6) 対象ピン:STRP\_1、RX\_CTRL

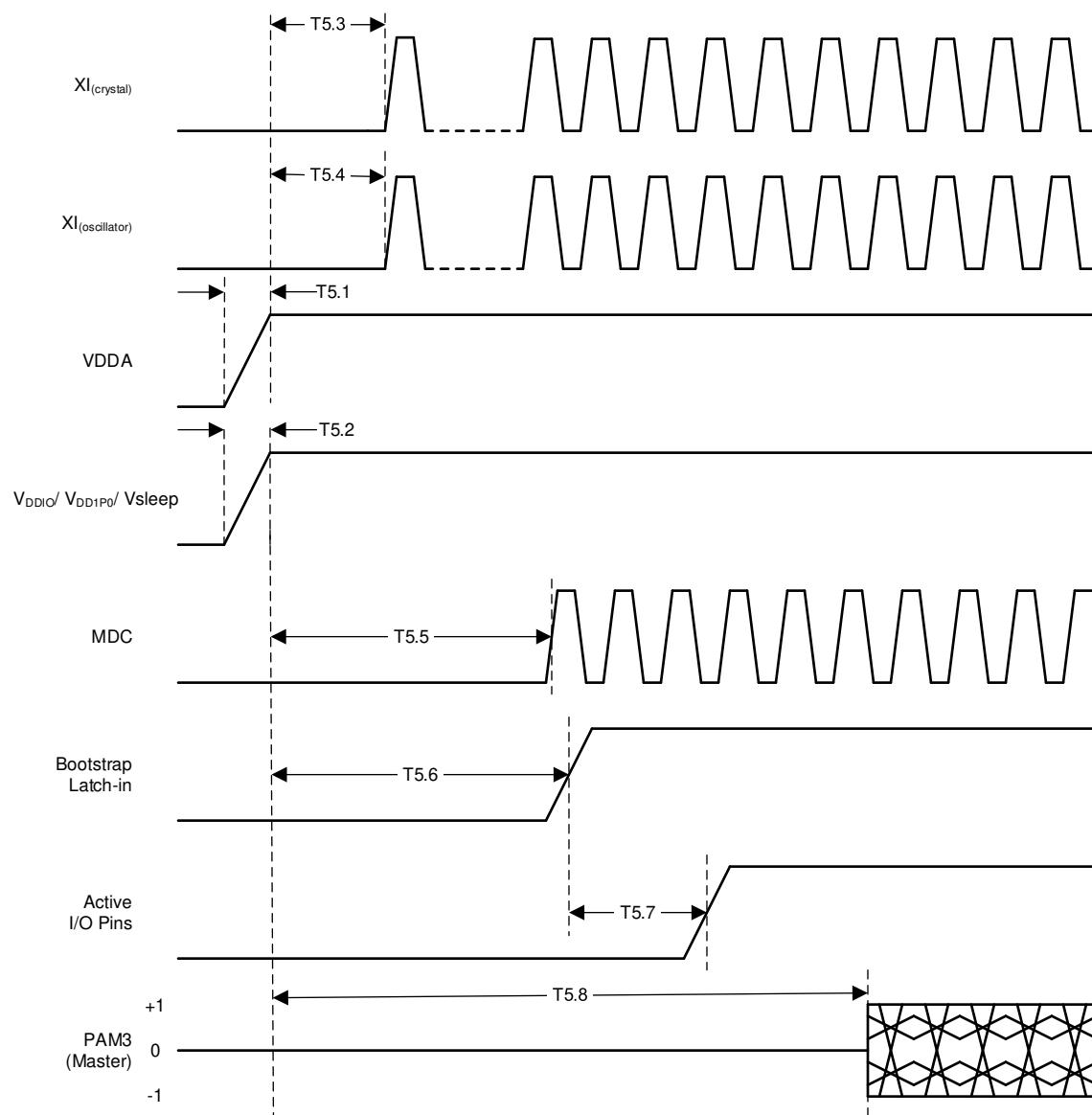

## 5.6 タイミング要件

(1)

| パラメータ                      |                                                                                | テスト条件                                   | 最小値 | 公称値  | 最大値  | 単位  |

|----------------------------|--------------------------------------------------------------------------------|-----------------------------------------|-----|------|------|-----|

| <b>電源投入のタイミング</b>          |                                                                                |                                         |     |      |      |     |

| T5.1                       | VDDA3P3 期間 (2)                                                                 | 0% ~ 100% (+/- 10% VDDA3P3)             | 0.5 | 40   | 40   | ms  |

| T5.2                       | VDD1P0 期間 (2)                                                                  | 0% ~ 100% (+/- 10% VDD1P0)              | 0.1 | 40   | 40   | ms  |

| T5.2                       | VDDIO 期間 (2)                                                                   | VDDIO = 1.8 V                           | 0.1 | 40   | 40   | ms  |

| T5.2                       | VDDIO 期間 (2)                                                                   | VDDIO = 2.5 V                           | 0.1 | 40   | 40   | ms  |

| T5.2                       | VDDIO 期間 (2)                                                                   | VDDIO = 3.3 V                           | 0.1 | 40   | 40   | ms  |

| T5.2                       | V <sub>SLEEP</sub> 期間 (2)                                                      | 0% ~ 100% (+/- 10% V <sub>SLEEP</sub> ) | 0.1 | 40   | 40   | ms  |

| T5.3                       | 電源投入後の水晶振動子の安定化時間 (最後の電源レールが 100% まで立ち上がってから)                                  |                                         |     | 1500 |      | μs  |

| T5.4                       | 電源投入後の発振器の安定化時間 (最後の電源レールが 100% まで立ち上がってから) (3)                                |                                         |     | 20   | 20   | ms  |

| T5.5                       | レジスタ アクセスの MDC プリアンブルまでの、電源投入後安定化時間                                            |                                         |     | 65   |      | ms  |

| T5.6                       | ハードウェア構成:電源投入からストラップ ラッチインまでの時間                                                |                                         |     | 60   | 60   | ms  |

| T5.7                       | ハードウェア構成:ストラップ ラッチイン完了からピンが機能モードに移行するまでの時間                                     |                                         |     | 110  | 110  | ns  |

| T5.8                       | 電源投入からの PAM3 アイドル ストリーム (マスタ モード)                                              |                                         |     | 60   | 60   | ms  |

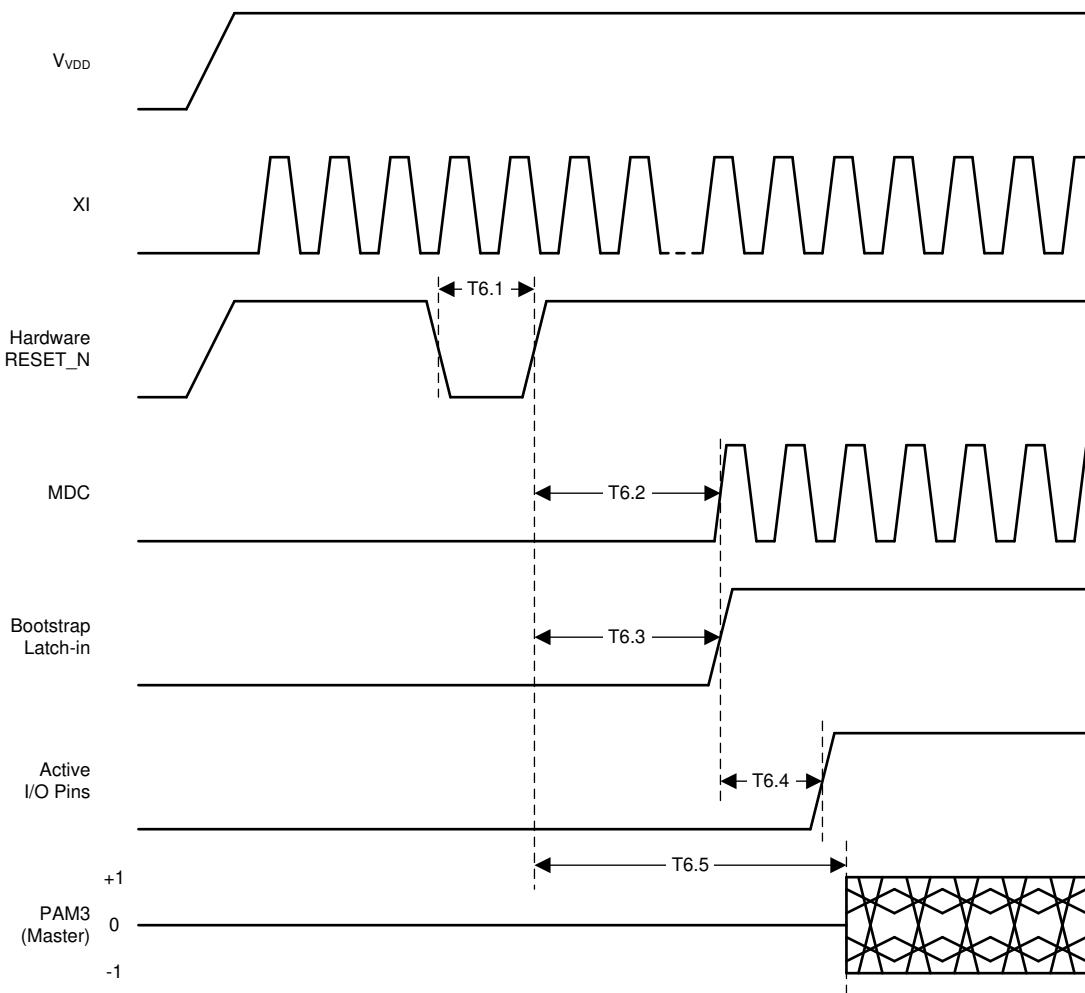

| <b>リセットタイミング (RESET_N)</b> |                                                                                |                                         |     |      |      |     |

| T6.1                       | リセットパルス幅                                                                       |                                         | 5   |      | 5    | μs  |

| T6.2                       | レジスタ アクセスの MDC プリアンブルまでの、リセット後安定化時間                                            |                                         | 1   |      | 1    | ms  |

| T6.3                       | ハードウェア構成:リセットからラッチインまでの時間                                                      |                                         |     | 2    | 2    | μs  |

| T6.4                       | ハードウェア構成:ストラップ ラッチイン完了からピンが機能モードに移行するまでの時間                                     |                                         |     | 1.5  | 1.5  | μs  |

| T6.5                       | リセットからの PAM3 アイドル ストリーム (マスタ モード)                                              |                                         |     | 1500 | 1500 | μs  |

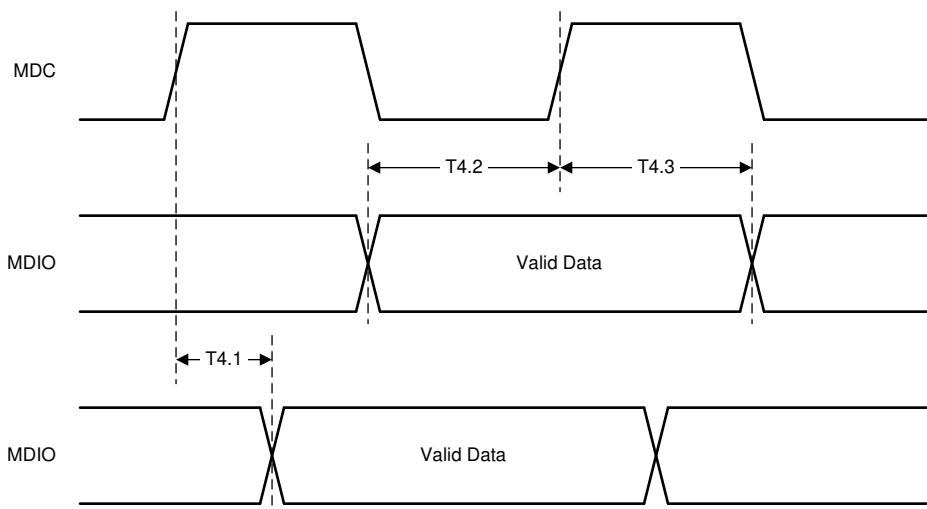

| <b>SMI タイミング</b>           |                                                                                |                                         |     |      |      |     |

| T4.1                       | MDC - MDIO (出力) 遅延時間 (25pF 負荷)                                                 |                                         | 0   | 6    | 10   | ns  |

| T4.2                       | MDC に対する MDIO (入力) のセットアップ時間                                                   |                                         | 10  |      | 10   | ns  |

| T4.3                       | MDC に対する MDIO (入力) のホールド時間                                                     |                                         | 10  |      | 10   | ns  |

|                            | MDC 周波数 (25pF 負荷)                                                              |                                         | 2.5 | 20   | 20   | MHz |

| <b>受信レイテンシ タイミング</b>       |                                                                                |                                         |     |      |      |     |

|                            | MDI の SSD シンボルから RGMII の RX_CLK の立ち上がりエッジ (RX_CTRL アサート時) まで                   |                                         |     |      | 8    | μs  |

|                            | MDI の SSD シンボルから RGMII の RX_CLK の立ち上がりエッジ (RX_CTRL アサート時) まで (RS-FEC バイパス モード) |                                         |     |      | 400  | ns  |

|                            | MDI の SSD シンボルから SGMII の最初のシンボルまで                                              |                                         |     |      | 9    | μs  |

|                            | MDI の SSD シンボルから SGMII の最初のシンボルまで (RS-FEC バイパス モード)                            |                                         |     |      | 450  | ns  |

| <b>送信レイテンシ タイミング</b>       |                                                                                |                                         |     |      |      |     |

## 5.6 タイミング要件 (続き)

(1)

| パラメータ                                                                         | テスト条件 | 最小値 | 公称値 | 最大値 | 単位 |

|-------------------------------------------------------------------------------|-------|-----|-----|-----|----|

| RGMII の TX_CLK の立ち上がりエッジ (TX_CTRL アサート時) から MDI の SSD シンボルまで                  |       |     | 0.8 |     | μs |

| RGMII の TX_CLK の立ち上がりエッジ (TX_CTRL アサート時) から MDI の SSD シンボルまで (RS-FEC バイパスモード) |       |     | 600 |     | ns |

| SGMII の最初のシンボルから MDI の SSD シンボルまで                                             |       |     | 0.9 |     | μs |

| SGMII の最初のシンボルから MDI の SSD シンボルまで (RS-FEC バイパスモード)                            |       |     | 700 |     | ns |

### 25MHz 発振器の要件

|                                            |           |      |     |     |   |

|--------------------------------------------|-----------|------|-----|-----|---|

| 周波数 (X1)                                   |           | 25   |     | MHz |   |

| 温度と経時変化に対する周波数の許容誤差と安定性                    |           | -100 | 100 | ppm |   |

| 立ち上がり / 立ち下がり時間 (10% - 90%) <sup>(6)</sup> |           | 8    |     | ns  |   |

| ジッタ (RMS)                                  | 5MHz まで積分 | 1    |     | ps  |   |

| デューティ サイクル                                 |           | 40   | 50  | 60  | % |

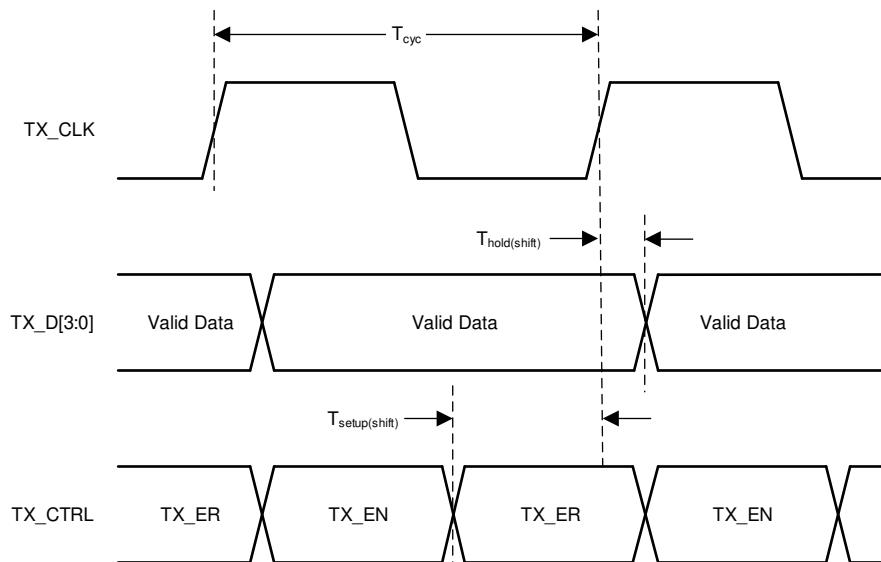

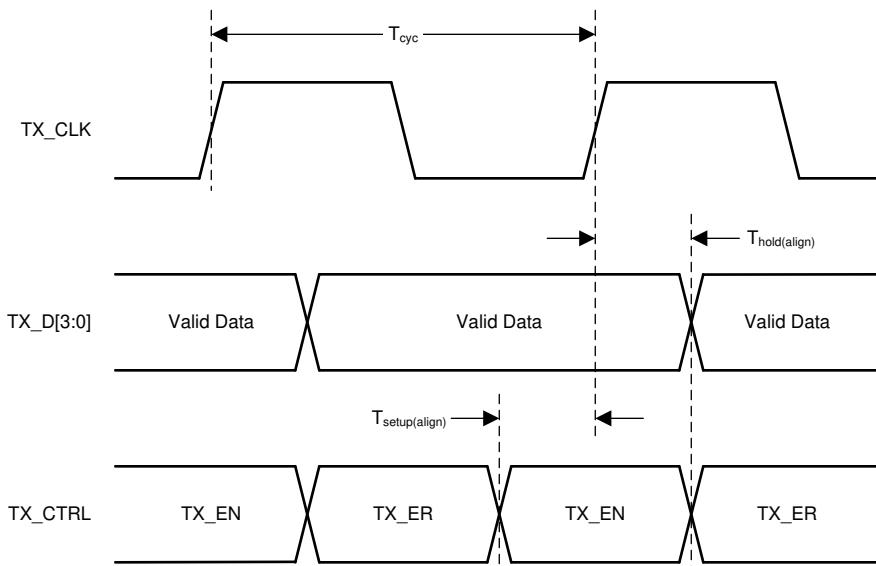

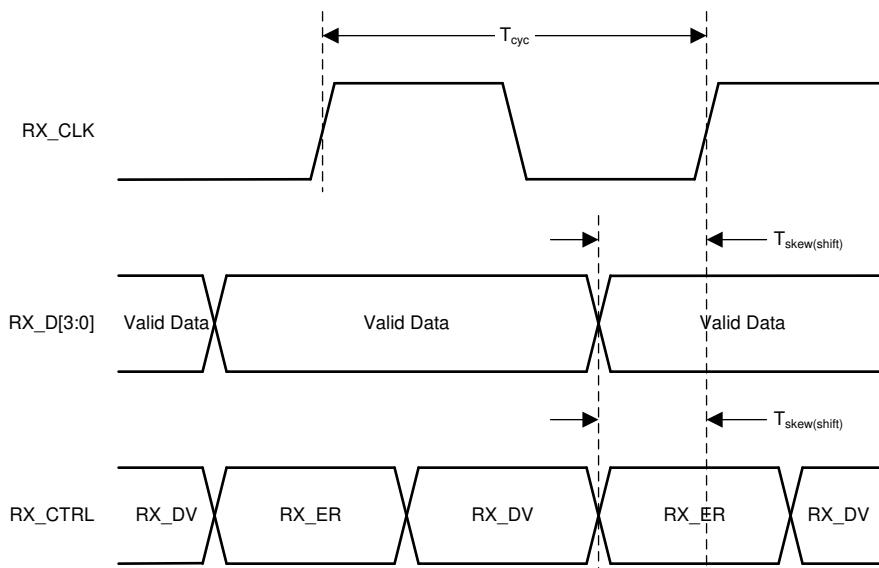

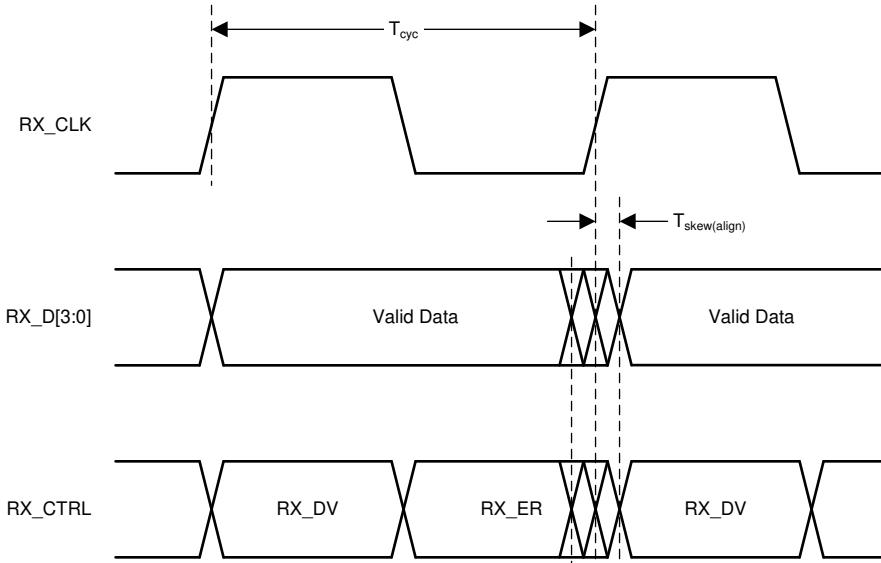

### RGMII タイミング

|                            |                                                                    |                               |       |       |       |    |

|----------------------------|--------------------------------------------------------------------|-------------------------------|-------|-------|-------|----|

| T <sub>setupR</sub>        | TX_D[3:0]、TX_CLK までの TX_CTRL のセットアップ時間                             | PHY ピン上                       | 1     | 2     | ns    |    |

| T <sub>holdR</sub>         | TX_D[3:0]、TX_CLK からの TX_CTRL のホールド時間 <sup>(5)</sup>                | PHY ピン上                       | 1     | 2     | ns    |    |

| T <sub>skewT</sub>         | RX_D[3:0]、RX_CLK からの RX_CTRL の遅延時間 (整列モード有効)                       | PHY ピン上                       | -500  | 0     | 500   | ps |

| T <sub>skewT</sub> (Shift) | RX_D[3:0]、RX_CLK からの RX_CTRL の遅延時間 (シフトモード有効、デフォルト) <sup>(4)</sup> | PHY ピン上                       | 2.190 | 2.650 | 2.970 | ns |

| T <sub>cyc</sub>           | クロック周期                                                             | RX_CLK                        | 7.2   | 8     | 8.8   | ns |

| T <sub>cyc</sub>           | クロック周期                                                             | TX_CLK                        | 7.2   | 8     | 8.8   | ns |

| Duty_G                     | デューティ サイクル                                                         | RX_CLK                        | 45    | 50    | 55    | %  |

| Duty_G                     | デューティ サイクル                                                         | TX_CLK                        | 45    | 50    | 55    | %  |

| Tr                         | 立ち上がり時間 (20% ~ 80%)                                                | CL=Ctrace=5pF                 |       | 0.75  |       | ns |

| Tf                         | 立ち下がり時間 (20%~80%)                                                  | C <sub>L</sub> = Ctrace = 5pF |       | 0.75  |       | ns |

| RGMII RX のシフトモード遅延         | DLL DLL_RX_DELAY_CTRL_SL = 0 <sup>(4)</sup>                        |                               | 0.330 | 0.650 | 0.970 | ns |

|                            | DLL DLL_RX_DELAY_CTRL_SL = 1 <sup>(4)</sup>                        |                               | 0.580 | 0.900 | 1.220 | ns |

|                            | DLL DLL_RX_DELAY_CTRL_SL = 2 <sup>(4)</sup>                        |                               | 0.830 | 1.150 | 1.470 | ns |

|                            | DLL DLL_RX_DELAY_CTRL_SL = 3 <sup>(4)</sup>                        |                               | 1.000 | 1.400 | 1.720 | ns |

|                            | DLL DLL_RX_DELAY_CTRL_SL = 4 <sup>(4)</sup>                        |                               | 1.230 | 1.650 | 1.970 | ns |

|                            | DLL DLL_RX_DELAY_CTRL_SL = 5 <sup>(4)</sup>                        |                               | 1.490 | 1.990 | 2.220 | ns |

|                            | DLL DLL_RX_DELAY_CTRL_SL = 6 <sup>(4)</sup>                        |                               | 1.690 | 2.150 | 2.470 | ns |

|                            | DLL DLL_RX_DELAY_CTRL_SL = 7 <sup>(4)</sup>                        |                               | 1.960 | 2.400 | 2.730 | ns |

|                            | DLL DLL_RX_DELAY_CTRL_SL = 8 <sup>(4)</sup>                        |                               | 2.180 | 2.650 | 2.970 | ns |

|                            | DLL DLL_RX_DELAY_CTRL_SL = 9 <sup>(4)</sup>                        |                               | 2.490 | 2.900 | 3.220 | ns |

| RGMII シフト TX モード遅延         |                                                                    |                               |       |       |       |    |

|                            | DLL DLL_TX_DELAY_CTRL_SL = 1 <sup>(4) (8)</sup>                    |                               | 0.08  | 0.25  | 0.38  | ns |

|                            | DLL DLL_TX_DELAY_CTRL_SL = 2 <sup>(4) (8)</sup>                    |                               | 0.27  | 0.49  | 0.67  | ns |

|                            | DLL DLL_TX_DELAY_CTRL_SL = 3 <sup>(4) (8)</sup>                    |                               | 0.51  | 0.73  | 0.91  | ns |

## 5.6 タイミング要件 (続き)

(1)

| パラメータ                                            | テスト条件                                                    | 最小値                                                | 公称値  | 最大値                | 単位       |         |

|--------------------------------------------------|----------------------------------------------------------|----------------------------------------------------|------|--------------------|----------|---------|

| DLL DLL_TX_DELAY_CTRL_SL = 4 <sup>(4) (8)</sup>  |                                                          | 0.75                                               | 0.97 | 1.15               | ns       |         |

| DLL DLL_TX_DELAY_CTRL_SL = 5 <sup>(4) (8)</sup>  |                                                          | 0.94                                               | 1.21 | 1.44               | ns       |         |

| DLL DLL_TX_DELAY_CTRL_SL = 6 <sup>(4) (8)</sup>  |                                                          | 1.18                                               | 1.45 | 1.68               | ns       |         |

| DLL DLL_TX_DELAY_CTRL_SL = 7 <sup>(4) (8)</sup>  |                                                          | 1.37                                               | 1.69 | 1.98               | ns       |         |

| DLL DLL_TX_DELAY_CTRL_SL = 8 <sup>(4) (8)</sup>  |                                                          | 1.61                                               | 1.93 | 2.22               | ns       |         |

| DLL DLL_TX_DELAY_CTRL_SL = 9 <sup>(4) (8)</sup>  |                                                          | 1.85                                               | 2.17 | 2.46               | ns       |         |

| DLL DLL_TX_DELAY_CTRL_SL = 10 <sup>(4) (8)</sup> |                                                          | 2.04                                               | 2.42 | 2.75               | ns       |         |

| DLL DLL_TX_DELAY_CTRL_SL = 11 <sup>(4) (8)</sup> |                                                          | 2.28                                               | 2.65 | 2.99               | ns       |         |

| DLL DLL_TX_DELAY_CTRL_SL = 12 <sup>(4) (8)</sup> |                                                          | 2.52                                               | 2.9  | 3.23               | ns       |         |

| <b>SGMII トランシミッタの AC タイミング</b>                   |                                                          |                                                    |      |                    |          |         |

|                                                  | 625MHz でのクロック信号のデューティ サイクル                               |                                                    | 48   | 52                 | %        |         |

| $T_{rise}$                                       | Vod 立ち上がり時間                                              |                                                    | 100  | 200                | ps       |         |

| $T_{fall}$                                       | Vod 立ち下がり時間                                              |                                                    | 100  | 200                | ps       |         |

| ジッタ                                              | 出力ジッタ                                                    |                                                    | 200  | 320 <sup>(7)</sup> | ps       |         |

| <b>25MHz 水晶振動子の要件</b>                            |                                                          |                                                    |      |                    |          |         |

|                                                  | 周波数                                                      |                                                    | 25   |                    | MHz      |         |

|                                                  | 温度と経時変化に対する周波数の許容誤差と安定性                                  |                                                    | -100 | 100                | ppm      |         |

|                                                  | 等価直列抵抗                                                   |                                                    |      | 100                | $\Omega$ |         |

| <b>出力クロック タイミング (CLKOUT)</b>                     |                                                          |                                                    |      |                    |          |         |

|                                                  | 周波数                                                      |                                                    | 25   |                    | MHz      |         |

|                                                  | デューティ サイクル (水晶振動子を接続した場合)                                |                                                    | 45   | 55                 | %        |         |

|                                                  | 立ち上がり / 立ち下がり時間 (10% - 90%)                              |                                                    |      | 2.5                | ns       |         |

|                                                  | ジッタ (RMS) (スレーブ モード、MAC インターフェイス: SGMII)                 |                                                    |      | 5                  | ps       |         |

|                                                  | ジッタ (RMS) (マスタ モード、MAC インターフェイス: SGMII)                  |                                                    |      | 2.4                | ps       |         |

|                                                  | ジッタ (RMS) (スレーブ モード、MAC インターフェイス: RGMII)                 |                                                    |      | 11                 | ps       |         |

|                                                  | ジッタ (RMS) (マスタ モード、MAC インターフェイス: RGMII)                  |                                                    |      | 15                 | ps       |         |

| <b>スリープへの移行とウェークアップ</b>                          |                                                          |                                                    |      |                    |          |         |

|                                                  | WAKE Low からスリープに入るまで、INH が Low に遷移                       | 通常モード、<br>MDI_Energy =<br>FALSE sleep_en =<br>TRUE |      | 64                 | 85       | us      |

|                                                  | sleep_en = True からスリープに入るまで、INH が Low に遷移 (マ<br>スタ モード)  | 通常モード、WAKE<br>= Low、MDI_Energy<br>= FALSE          |      | 5                  | 85       | us      |

|                                                  | sleep_en = TRUE からスリープに入るまで、INH が Low に遷移 (ス<br>レーブ モード) | 通常モード、WAKE<br>= Low、MDI_Energy<br>= FALSE          |      | 5000               |          | us      |

|                                                  | MDI のエネルギー喪失からスリープに入るまで、INH が Low に遷<br>移                | 通常モード、WAKE<br>= Low、sleep_en =<br>TRUE             |      |                    | 5        | ms      |

|                                                  | ローカル ウェークアップ パルス幅 (WAKE ピン)                              | スリープ モード、<br>WAKE ピン                               | 80   |                    |          | $\mu$ s |

|                                                  | MDI からのウェークアップのための Send-S/Send-T パターンの継<br>続時間           | スリープ モード、スレ<br>ーブ                                  | 1.25 |                    |          | ms      |

## 5.6 タイミング要件 (続き)

(1)

| パラメータ                                         | テスト条件                                                      | 最小値 | 公称値 | 最大値 | 単位       |

|-----------------------------------------------|------------------------------------------------------------|-----|-----|-----|----------|

| ローカル ウェークアップ、INH が High に遷移                   | スリープ モード、<br>WAKE ピンの立ち上<br>がりエッジから INH<br>の立ち上がりエッジま<br>で |     |     | 85  | us       |

| PHY がスリープ モードにとどまる上で MDI で許容される差動ノイズ<br>レベル   | スリープ モード                                                   |     | 200 |     | mV pk-pk |

| 有効なウェークアップのためのリンク パートナーの VOD (5m ケーブ<br>ルの場合) | スリープ モード                                                   | 840 |     |     | mV pk-pk |

- (1) 製造試験、特性評価、設計によって保証されています。

- (2) 電源レール間の電源シーケンスの制約はありません。

- (3) OSC クロックが遅れた場合、OSC クロックの安定化後に追加のリセットが必要です。

- (4) RX および TX 遅延コードのプログラマビリティについては、レジスタ [0x0430] を参照してください。

- (5) PHY は、最大 2ns のスキーを追加するため、TX\_CLK から TX\_D[3:0] を内部的に遅延させます。プログラマビリティについては、レジスタ [0x0430] を参照してください。

- (6) 40%~55% のデューティ サイクルの場合、最大 8ns の立ち上がり / 立ち下がり時間をサポートしています。40%~60% のデューティ サイクルの

場合、最大 6ns の立ち上がり / 立ち下がり時間をサポートしています

- (7) この最大値を 300ps に低減するため (必要な場合)、追加のレジスタ設定が利用できます。

- (8) 1.8V VDDIO のデータです。

## 5.7 タイミング図

図 5-1. 起動タイミング

図 5-2. リセットタイミング

図 5-3. RGMII の送信タイミング (内部遅延有効化)

図 5-4. RGMII の送信タイミング (内部遅延無効化)

図 5-5. RGMII の受信タイミング (内部遅延有効化)

図 5-6. RGMII の受信タイミング (内部遅延無効化)

図 5-7. シリアル マネージメントのタイミング

## 5.8 LED の駆動特性

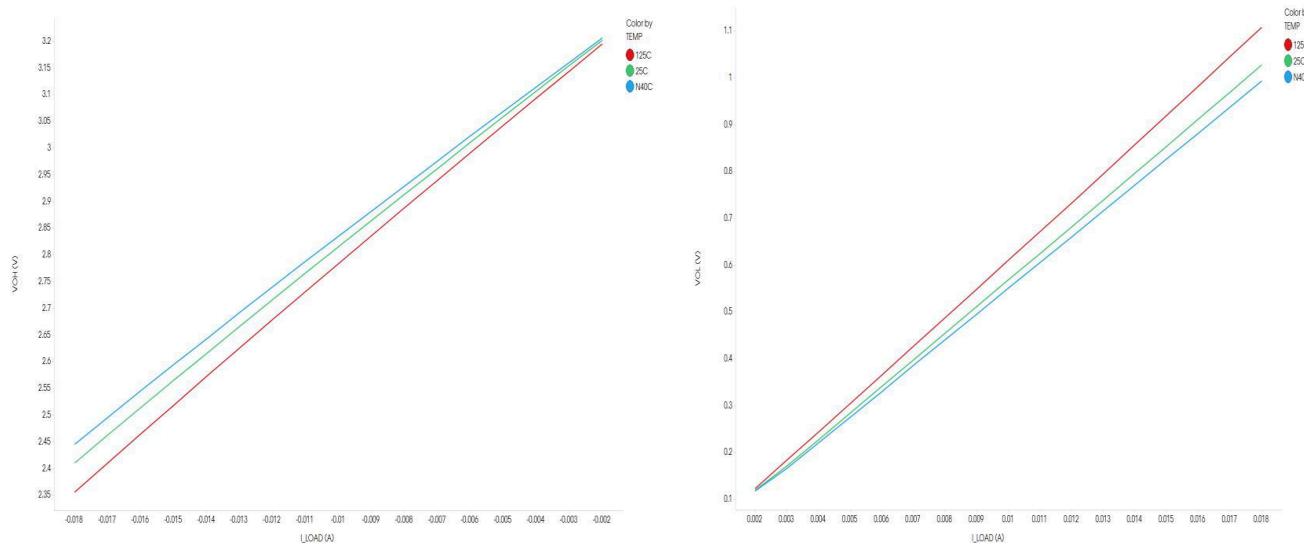

図 5-8. LED の V と I との関係 (VDDIO = 3.3V)

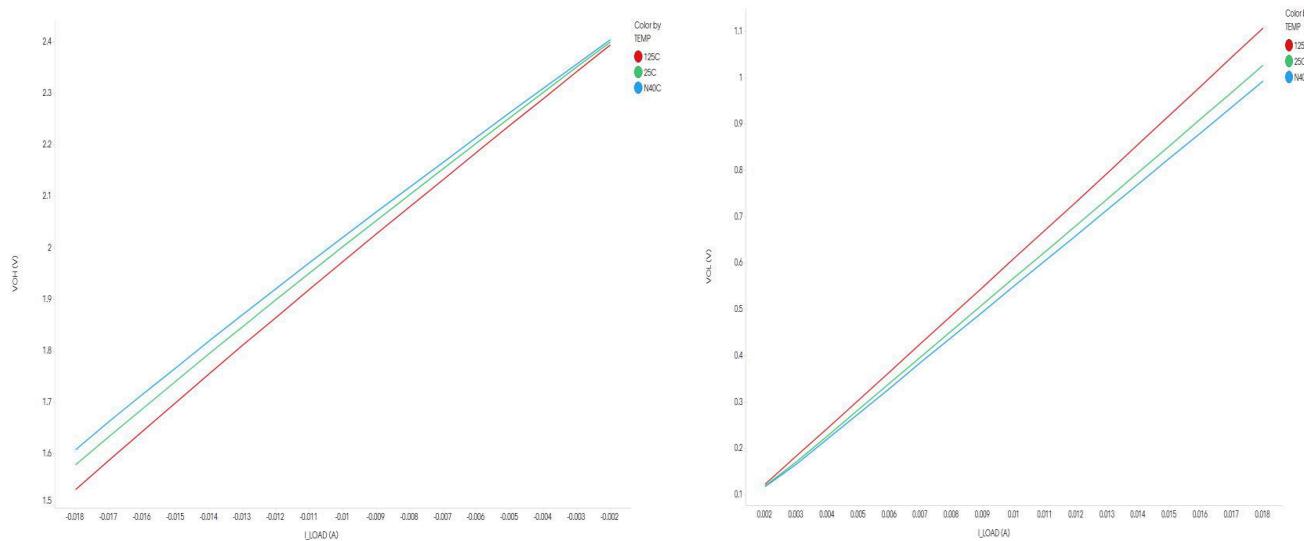

図 5-9. LED の V と I との関係 (VDDIO = 2.5V)

## 6 詳細説明

### 6.1 概要

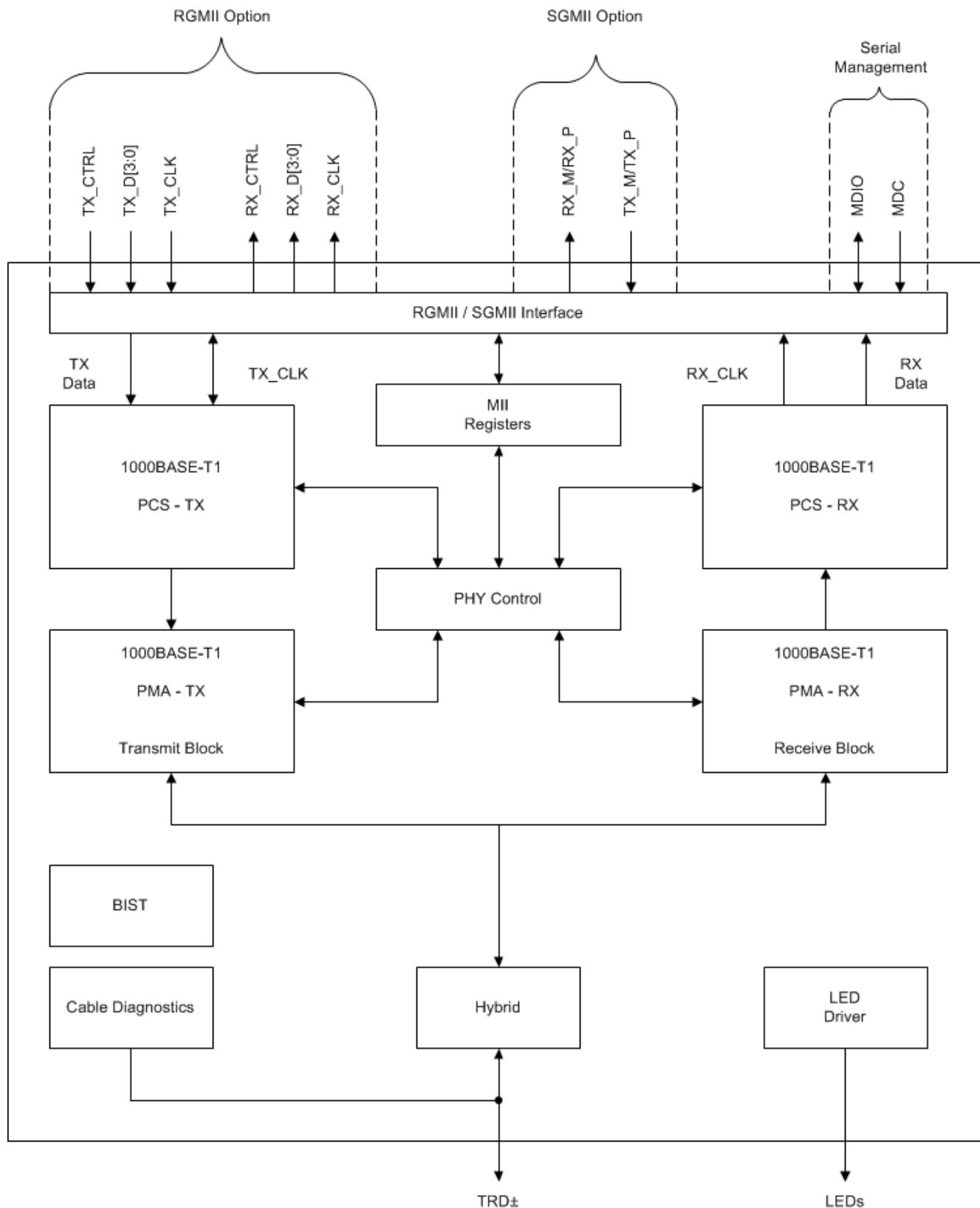

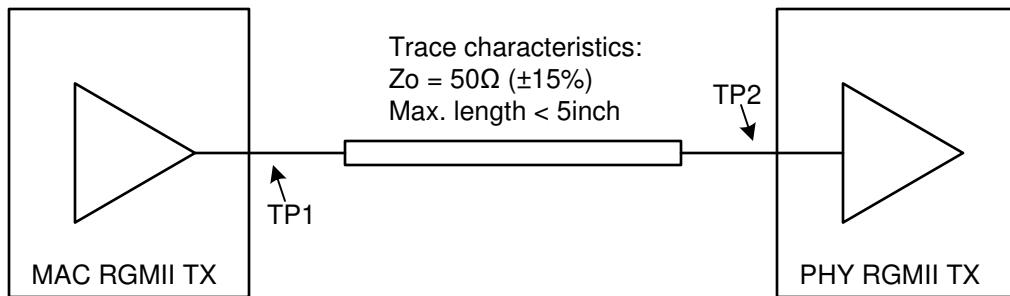

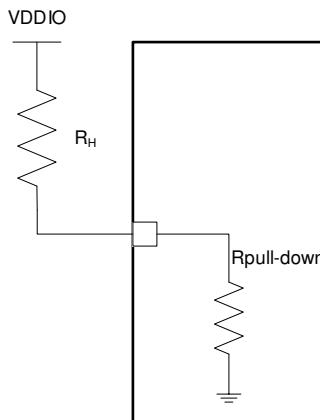

DP83TG720S-Q1 は車載用 1000BASE-T1 イーサネット物理層トランシーバです。本デバイスは IEEE 802.3bp に準拠しており、車載アプリケーション向けに AEC-Q100 認定済みです。