# DP83826 決定論的、低レイテンシ、低消費電力、10/100Mbps の産業用イーサネット PHY

## 1 特長

- 小さく決定論的なレイテンシ

- TX レイテンシ: 40ns, RX レイテンシ: 170ns

- 電源サイクル間の決定論的レイテンシ < ±2ns

- XI と TX\_CLK の位相差が一定 < ±2ns

- 堅牢かつ小型のシステム実装

- EMC を強化するための回路を内蔵

- IEC 61000-4-2 ESD: ±8kV 接触, ±15kV 気中

- IEC 61000-4-4 EFT: 5kHz, 100kHz で ±4 kV

- CISPR 22 伝導エミッション Class B

- CISPR 22 放射エミッション Class B

- 高速リンクドロップ < 10μs

- ケーブルの到達範囲: 150m 以上

- 電圧モードライアンドライバ

- MAC インターフェイスの終端を内蔵

- 許容電圧: ±10%

- 1 つのデバイスで 2 つのピン モードを選択可能

- 追加機能を持つ ENHANCED モード

- 一般的なイーサネットピン配置用の BASIC モード

- 低消費電力 < 160mW

- MAC インターフェイス: MII、RMII

- プログラム可能な省エネルギー モード

- アクティブ スリープ

- ディープ パワー ダウン

- Energy Efficient Ethernet (EEE) IEEE 802.3az

- Wake-on-LAN (WoL)

- 診断ツール: ケーブル診断、内蔵自己テスト (BIST)、ループバック モード

- 3.3V の単一電源

- I/O 電圧: 1.8V または 3.3V

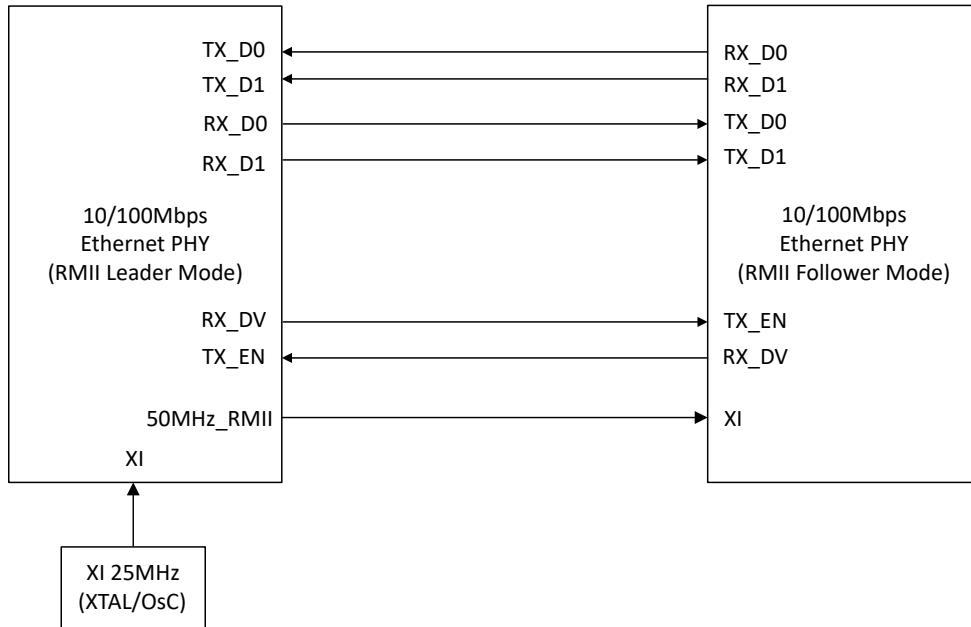

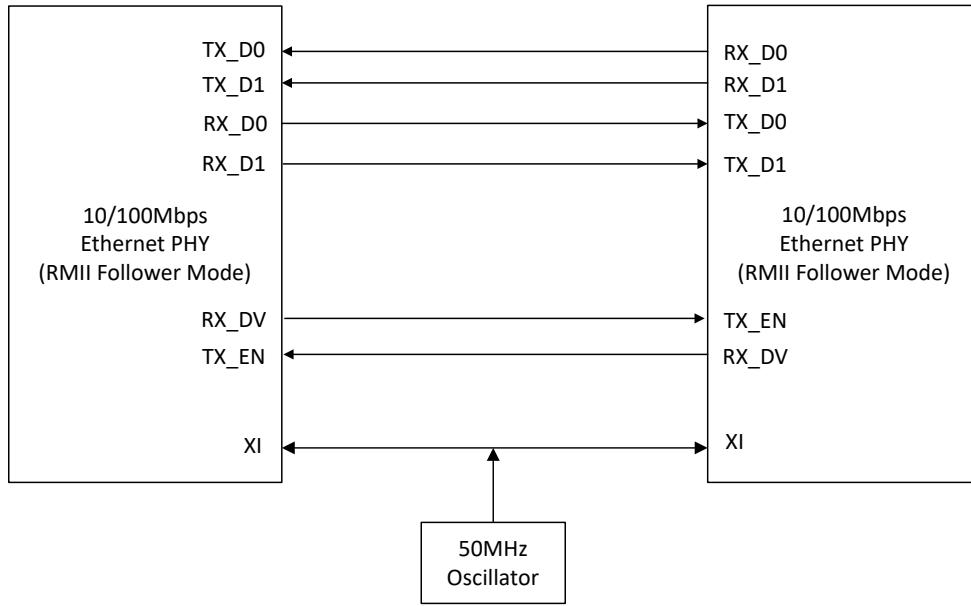

- RMII バックツー バックリピーター モード

- DP83826E の動作温度範囲: -40°C ~ 105°C

- DP83826I の動作温度範囲: -40°C ~ 85°C

- IEEE 802.3 準拠: 10BASE-T、100BASE-TX

- EtherCAT® 準拠

## 2 アプリケーション

- ファクトリ・オートメーション、ロボットおよびモーション制御

- モーター・ドライブ

- グリッド・インフラ

- ビル・オートメーション

- 産業用イーサネット・フィールドバス

## 3 説明

DP83826 は、小さく決定論的なレイテンシ、低消費電力、10BASE-T、および 100BASE-TX イーサネット プロトコルのサポートにより、リアルタイム産業用イーサネット システムの厳格な要件を満たすことができます。このデバイスは、高速なリンクアップ時間を達成するためのハードウェア ブートストラップ、高速リンク ドロップ検出モード、システム内の他のモジュールをクロック同期させるための専用基準クロック出力 (CLKOUT) を備えています。

一般的なイーサネットピン配置を使用する BASIC 標準イーサネット モードと、追加機能とハードウェア ブートストラップ構成によって標準イーサネットと複数の産業用イーサネット フィールドバス アプリケーションをサポートする ENHANCED イーサネット モードという 2 つのモードに構成できます。

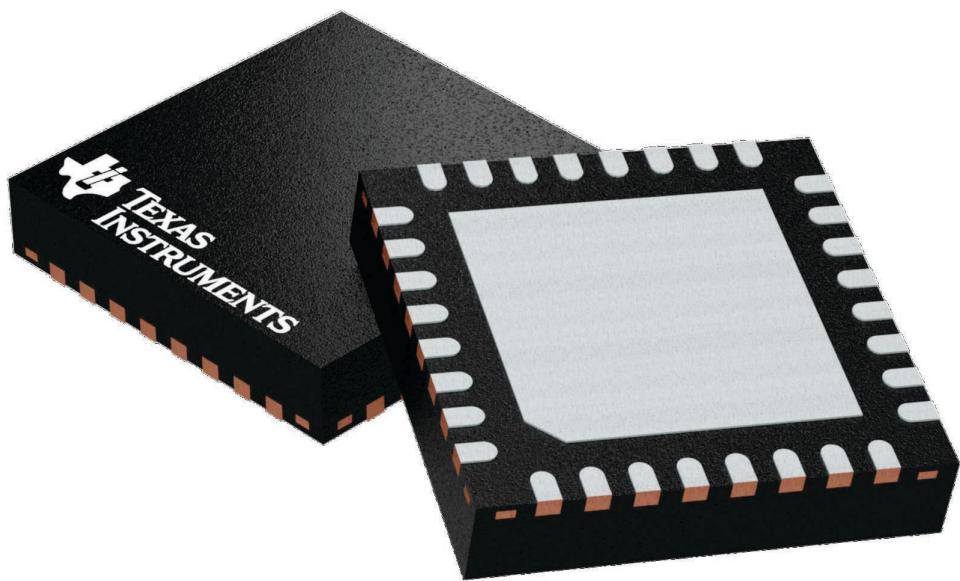

### デバイス ファミリ情報

| 部品番号 (1)         | パッケージ     | 本体サイズ (公称)      | 属性                       |

|------------------|-----------|-----------------|--------------------------|

| DP83826E/I       | VQFN (32) | 5.00mm × 5.00mm | 最小のレイテンシ、一般的なピン配置        |

| DP83825I         | WQFN (24) | 3.00mm × 3.00mm | 小さなサイズ、最適化されたソリューションコスト  |

| DP83822HF/IF/H/I | VQFN (32) | 5.00mm × 5.00mm | 広い温度範囲、ファイバー、RGMII のサポート |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

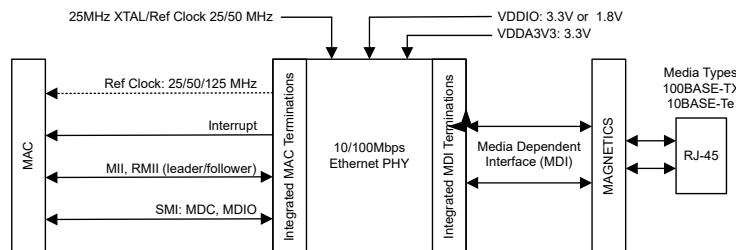

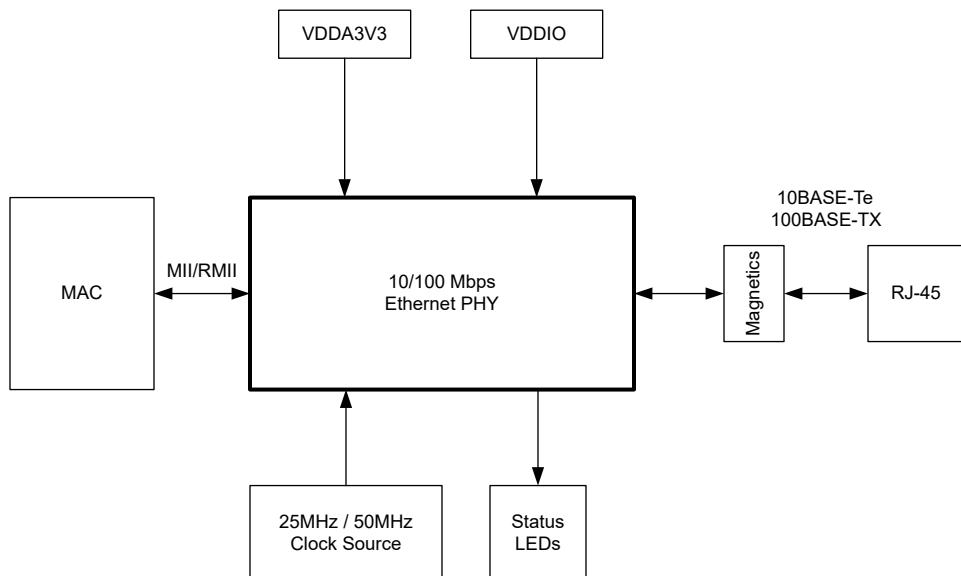

アプリケーション概略図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                                   |    |                               |     |

|-----------------------------------|----|-------------------------------|-----|

| <b>1 特長</b>                       | 1  | 8.3 機能説明                      | 26  |

| <b>2 アプリケーション</b>                 | 1  | 8.4 プログラミング                   | 50  |

| <b>3 説明</b>                       | 1  | 8.5 レジスタ マップ                  | 54  |

| <b>4 モード比較表</b>                   | 3  | <b>9 アプリケーションと実装</b>          | 99  |

| <b>5 ピン構成および機能 (ENHANCED モード)</b> | 4  | 9.1 アプリケーション情報                | 99  |

| <b>6 ピン構成および機能 (BASIC モード)</b>    | 8  | 9.2 代表的なアプリケーション              | 99  |

| <b>7 仕様</b>                       | 11 | 9.3 電源に関する推奨事項                | 103 |

| 7.1 絶対最大定格                        | 11 | 9.4 レイアウト                     | 104 |

| 7.2 ESD 定格                        | 11 | <b>10 デバイスおよびドキュメントのサポート</b>  | 107 |

| 7.3 推奨動作条件                        | 11 | 10.1 関連資料                     | 107 |

| 7.4 熱に関する情報                       | 12 | 10.2 ドキュメントの更新通知を受け取る方法       | 107 |

| 7.5 電気的特性                         | 13 | 10.3 サポートリソース                 | 107 |

| 7.6 タイミング要件                       | 16 | 10.4 商標                       | 107 |

| 7.7 タイミング図                        | 19 | 10.5 静電気放電に関する注意事項            | 107 |

| 7.8 代表的特性                         | 24 | 10.6 用語集                      | 107 |

| <b>8 詳細説明</b>                     | 25 | <b>11 改訂履歴</b>                | 107 |

| 8.1 概要                            | 25 | <b>12 メカニカル、パッケージ、および注文情報</b> | 110 |

| 8.2 機能ブロック図                       | 26 |                               |     |

## 4 モード比較表

DP83826 は、ストラップして、ENHANCED モードまたは BASIC モードで動作させることができます。ENHANCED モードでは、DP83826 は標準イーサネット アプリケーションに加えて、リアルタイム イーサネット アプリケーションもサポートできます。BASIC モードでは、DP83826 は標準イーサネット アプリケーションをサポートできます。さらに、BASIC モードでは、DP83826 のピン配置は、多くのアプリケーションで使用される一般的な PHY ピン配置と一致しています。

**表 4-1. ENHANCED モードまたは BASIC モードの選択**

| ENHANCED モード                                           | BASIC モード                   |

|--------------------------------------------------------|-----------------------------|

| ModeSelect (ピン 1) を未接続のままにするか、プルアップ抵抗を介して VDDIO に接続します | ModeSelect (ピン 1) を GND に短絡 |

**表 4-2. ENHANCED モードと BASIC モードにおけるピン マッピングの相違**

| ピン番号 | ENHANCED モード | BASIC モード  |

|------|--------------|------------|

| 31   | CLKOUT/LED1  | LED1/TX_ER |

| 21   | PWRDN/INT    | INT        |

**表 4-3. ENHANCED モードと BASIC モードにおけるハードウェア ブートストラップの相違**

| ハードウェア ブートストラップ                           | ENHANCED モード <sup>(3)</sup> | BASIC モード           |

|-------------------------------------------|-----------------------------|---------------------|

| 高速リンク ドロップのイネーブルおよびディスエーブル <sup>(1)</sup> | あり                          | なし (常にイネーブル)        |

| 高速リンク ドロップ検出メカニズム                         | ストラップ制御可能                   | RX_ERROR および信号エネルギー |

| Auto-MDIX イネーブル / ディスエーブル <sup>(1)</sup>  | あり                          | いいえ                 |

| MDI/MDIX の強制選択 <sup>(1)</sup>             | あり                          | いいえ                 |

| RMII 双方向反復モード構成 <sup>(2)</sup>            | あり                          | いいえ                 |

| MII または RMII の選択                          | あり                          | あり                  |

| 速度の選択 (10M または 100M)                      | なし                          | あり                  |

| MII 絶縁イネーブルおよびディスエーブル                     | なし                          | あり                  |

| オートネゴシエーション イネーブルおよびディスエーブル               | あり                          | あり                  |

| 使用可能な PHY アドレス数                           | 8                           | 8                   |

| 半二重または全二重の選択                              | なし                          | あり                  |

| LED1 の代わりの CLKOUT                         | あり                          | いいえ                 |

| 奇数ビブル検出                                   | ストラップ制御可能                   | デフォルトでディスエーブル       |

- (1) これらのピン ブートストラップにより、ENHANCED モード DP83826 は、リアルタイム イーサネット アプリケーションの厳しい要件を満たすことができます。

(2) このピン ブートストラップにより、ENHANCED モード DP83826 は、RMII リピータとして機能できます。

(3) ENHANCED モードには、BASIC モードのすべての動作モードが含まれています。違いは、これらの動作モードでは、ENHANCED モードでレジスタ設定が必要となることです。

### 注

一般的な標準イーサネット ピン配置を使用する既存のシステムで、DP83826 BASIC モードを使用する手順のステップ バイ ステップ アプローチについては、[SNLA338](#) を参照してください。

### 注

イーサネット関連の略語 (頭字語) 標準リストについては、『[イーサネット製品関連頭字語の中国語と英語の定義](#)

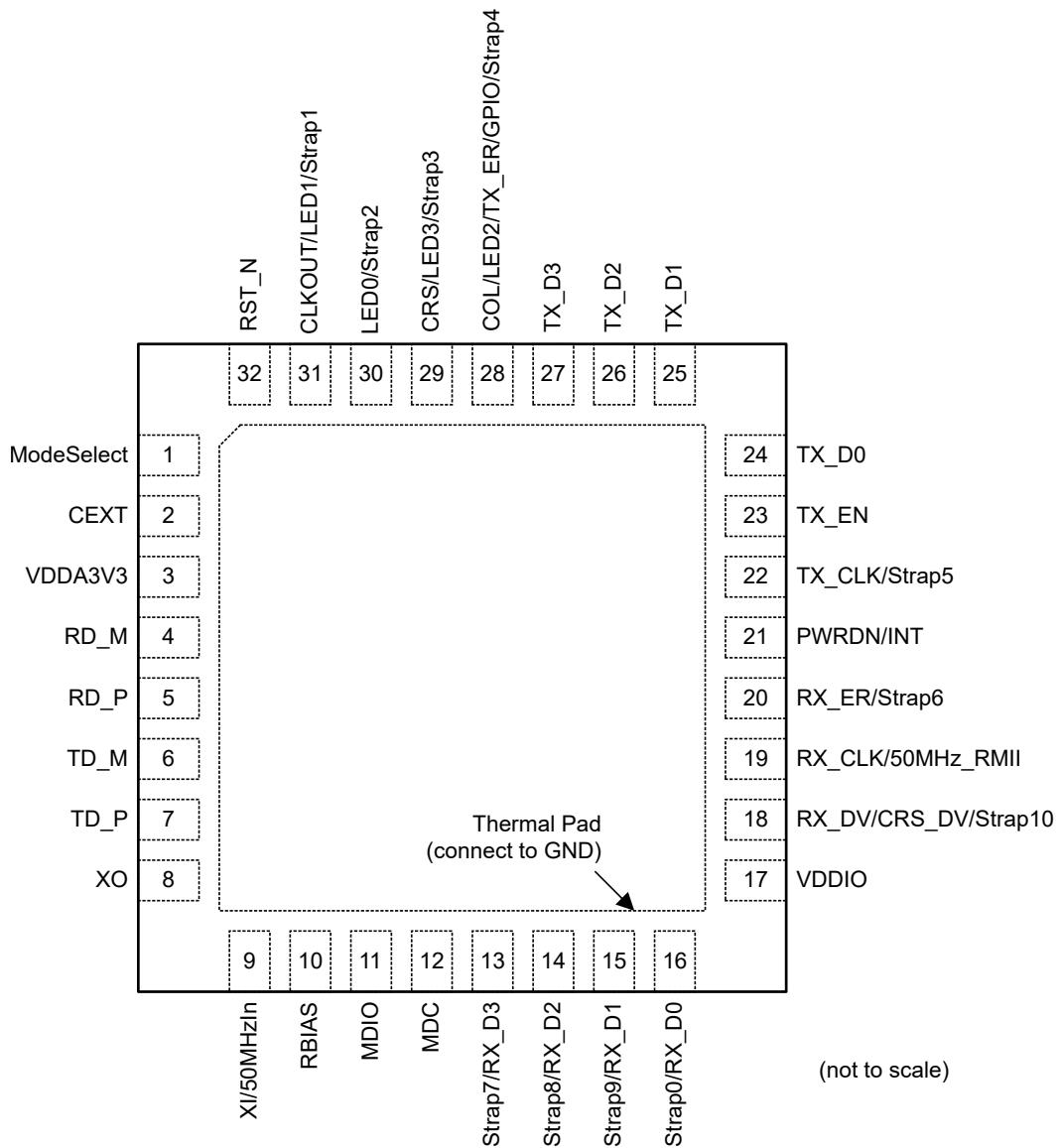

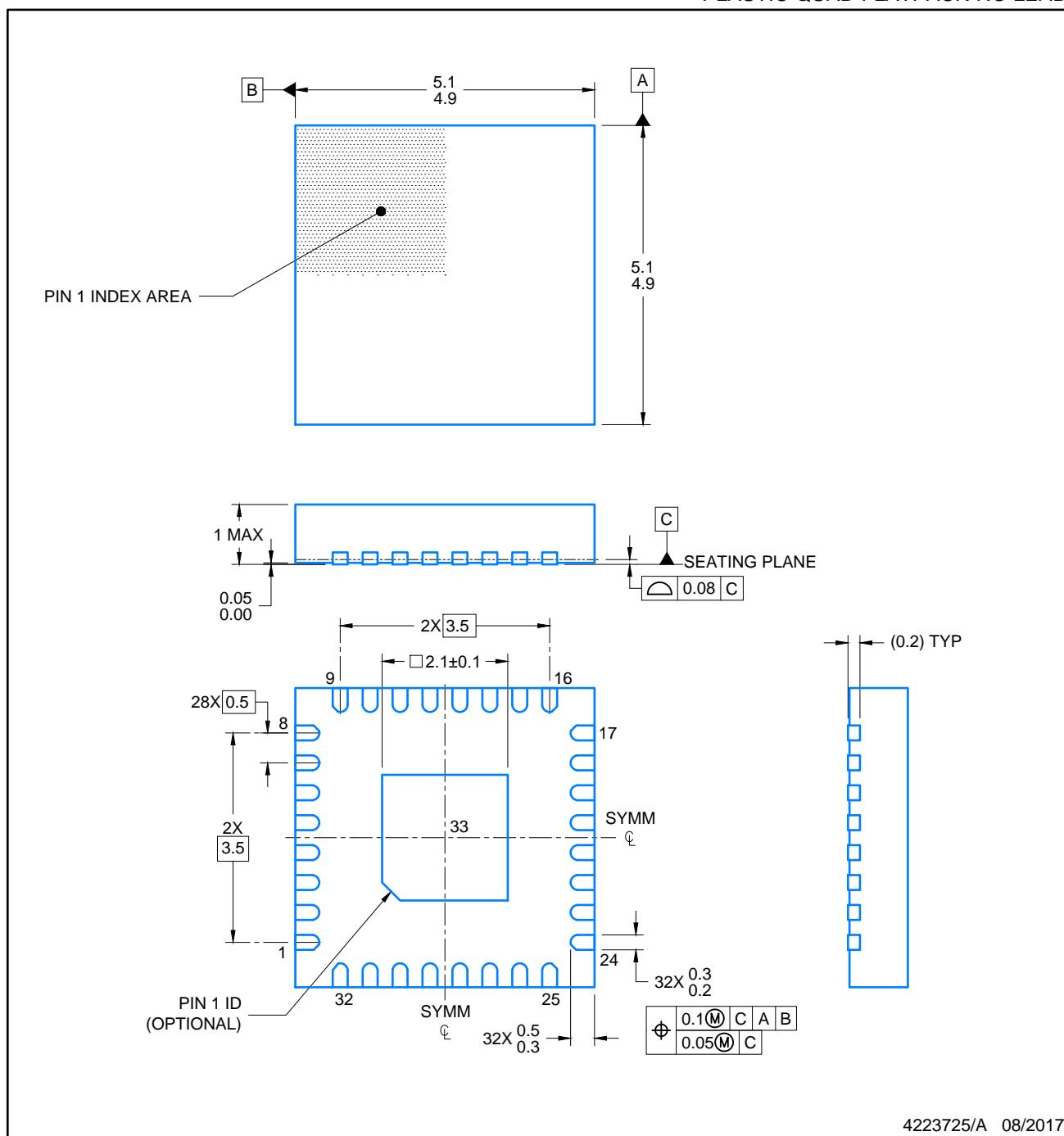

## 5 ピン構成および機能 (ENHANCED モード)

ENHANCED モードは、DP83826 がスタートアップ時に構成できる 2 つのモードのうちの 1 つです。このモードでは、DP83826 は標準イーサネット アプリケーションに加えて、リアルタイムイーサネット アプリケーションもサポートできます。DP83826 を ENHANCED モードに構成するには、ModeSelect (ピン 1) を未接続のままにするか、抵抗で VDDIO にプルアップします。

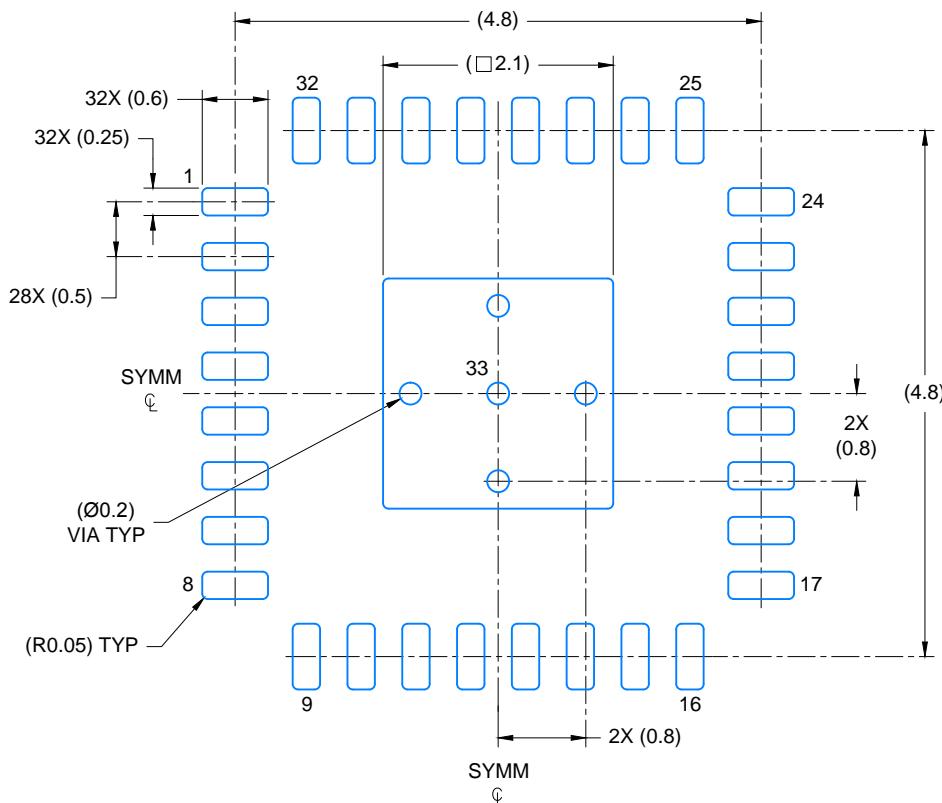

図 5-1. RHB パッケージ

32 ピン QFN

(上面図)

**表 5-1. ピン機能 (ENHANCED モード)**

| ピン                    |    | タイプ <sup>(1)</sup>            | 説明                                                                                                                                                                                                                         |

|-----------------------|----|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                    | なし |                               |                                                                                                                                                                                                                            |

| ModeSelect            | 1  | リセット:I, PU アクティブ:I, PU        | このピンは、DP83826 の次の動作モードを選択します: BASIC モードまたは ENHANCED モード。ENHANCED モードの場合、このピンは NC のままにするか、抵抗で VDDIO にプルアップします。BASIC モードでは、このピンは GND に短絡させる必要があります。                                                                          |

| CEXT                  | 2  | A                             | 外部コンデンサ: CEXT ピンは、2nF のコンデンサを通して GND に接続します。                                                                                                                                                                               |

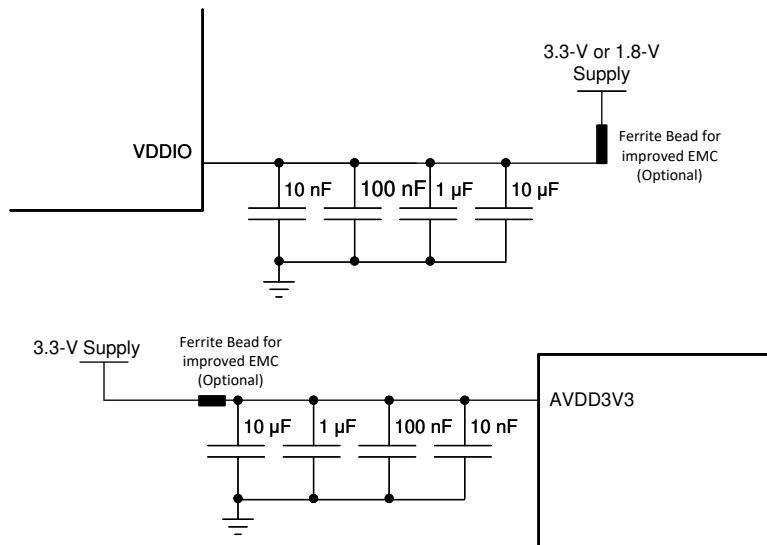

| VDDA3V3               | 3  | 電源                            | 入力アナログ電源: 3.3V デカップリングコンデンサの要件については、データシートの「電源に関する推奨事項」セクションを参照してください。                                                                                                                                                     |

| RD_M                  | 4  | A                             | 差動受信入力 (物理メディア依存:PMD): これらの差動入力は、10BASE-Te または 100BASE-TX 固有の信号モードを受け入れるように自動的に構成されます。                                                                                                                                     |

| RD_P                  | 5  | A                             |                                                                                                                                                                                                                            |

| TD_M                  | 6  | A                             | 差動送信出力 (PMD) : これらの差動出力は、PHY に選択されている構成に基づいて、10BASE-Te または 100BASE-TX のいずれかの信号モードに構成されます。                                                                                                                                  |

| TD_P                  | 7  | A                             |                                                                                                                                                                                                                            |

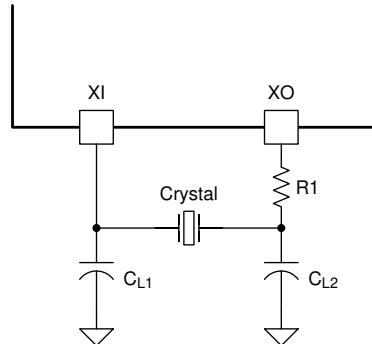

| XO                    | 8  | A                             | 水晶振動子出力: 基準クロック出力。XO ピンは水晶振動子の場合にのみ使用されます。CMOS レベル発振器を XI に接続する場合、このピンをフローティングのままにします。                                                                                                                                     |

| XI/50MHzIn            | 9  | A                             | 水晶振動子または発振器の入力クロック:<br>MII モード、RMII リーダー モード: 25MHz ± 50ppm の水晶振動子または発振器クロック。<br>RMII フォロワ モード: 50MHz ± 50ppm の CMOS レベル発振器クロック。                                                                                           |

| RBIAS                 | 10 | A                             | RBIAS (ハイアス抵抗) 値 6.49kΩ (グランドに 1% の精度で接続)。                                                                                                                                                                                 |

| MDIO                  | 11 | リセット:I, PU アクティブ:I/O, PU      | 管理データ I/O: 管理ステーションまたは PHY から出力される可能性がある双方向管理データ信号。このピンには、10kΩ への内部プルアップ抵抗が搭載されています。必要に応じて、外部プルアップ抵抗を追加できます。                                                                                                               |

| MDC                   | 12 | リセット:I, PD アクティブ:I, PD        | 管理データクロック: MDIO シリアル管理入力 / 出力データへの同期クロック。このクロックは、MAC の送信クロックおよび受信クロックと非同期にすることができます。最大クロック レートは 25MHz です。最小クロック レートはありません。                                                                                                 |

| RX_D3                 | 13 | リセット:I, PD アクティブ:O<br>Strap7  | 受信データ: ケーブルで受信されたシンボルは、RX_CLK の立ち上がりエッジに同期してデコードされ、これらのピンに表示されます。RX_DV がアサートされている場合、有効なデータが含まれています。MII モードでは、ニブル (RX_D[3:0]) を受信します。RMII モードでは、2 ビットの RX_D[1:0] を受信します。                                                    |

| RX_D2                 | 14 | リセット:I, PD アクティブ:O<br>Strap8  |                                                                                                                                                                                                                            |

| RX_D1                 | 15 | リセット:I, PD アクティブ:O<br>Strap9  |                                                                                                                                                                                                                            |

| RX_D0                 | 16 | リセット:I, PD アクティブ:O<br>Strap0  |                                                                                                                                                                                                                            |

| VDDIO                 | 17 | 電源                            | I/O 電源電圧: 3.3V または 1.8V。デカップリングコンデンサの要件については、データシートの「電源デカップリングに関する推奨事項」セクションを参照してください。                                                                                                                                     |

| RX_DV/<br>CRS_DV      | 18 | リセット:I, PD アクティブ:O<br>Strap10 | 受信データ有効: このピンは、MII モードの場合は RX_D[3:0]、RMII モードの場合は RX_D[1:0] に有効なデータが存在することを示します。MII モードでは、このピンは RX_DV として機能します。RMII モードでは、このピンは CRS_DV として機能し、RMII キャリアと受信データの有効な通知を組み合わせます。このピンは、RMII モードの RX_DV に構成し、RMII 反復モードを有効化できます。 |

| RX_CLK/<br>50MHz_RMII | 19 | リセット:I, PD アクティブ:O            | MII 受信クロック: MII 受信クロックは、速度 100bps の 25MHz 基準クロックおよび受信データストリームから取得される速度 10Mbps の 2.5MHz 基準クロックを供給します。<br>RMII リーダー モードでは、これにより 50MHz 基準クロックを供給します。RMII フォロワ モードでは、このピンは使われず、入力、プルダウンのままになります。                               |

表 5-1. ピン機能 (ENHANCED モード) (続き)

| ピン                      |    | タイプ <sup>(1)</sup>          | 説明                                                                                                                                                                                                                                                                                           |

|-------------------------|----|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                      | なし |                             |                                                                                                                                                                                                                                                                                              |

| RX_ER                   | 20 | リセット:I、PD アクティブ:O<br>Strap6 | 受信エラー:このピンは、MII モードおよび RMII モードの両方で受信パケット内にエラー シンボルが検出されたことを示します。<br>MII モードでは、RX_CLK の立ち上がりエッジに同期して、RX_ER が High にアサートされます。<br>RMII モードでは、基準クロックの立ち上がりエッジに同期して、RX_ER が High にアサートされます。受信エラー (アイドル中のエラーを含む) が発生するたびに、RX_ER が High にアサートされます。<br>このストラップは、パワーアップ時にのみラッチされ、ピンのリセット時にはラッチされません。 |

| PWRDN/INT               | 21 | リセット:I、PU アクティブ:I/O、PU      | パワーダウン (デフォルト)、割り込み:このピンのデフォルトの機能はパワーダウンです。このピンを割り込みとして構成するには、レジスタ アクセスが必要です。パワーダウン機能では、このピンにアクティブ Low 信号が印加されると、デバイスはパワーダウン モードに移行します。このピンが割り込みピンとして構成されている場合に割り込み状態が発生すると、このピンが Low にアサートされます。このピンには、弱い内部プルアップ抵抗 (9.5kΩ) のオープンドレイン出力があります。一部のアプリケーションでは、外部 PU 抵抗が必要となります。                  |

| TX_CLK                  | 22 | リセット:I、PD アクティブ:O<br>Strap5 | MII 送信クロック:MII 送信クロックは、速度 100Mbps の 25MHz 基準クロックおよび速度 10Mbps の 2.5MHz 基準クロックを提供します。MII モードでは、このクロックの位相は入力クロックを基準として一定となることに注意してください。RMII モードでは使用されません。                                                                                                                                       |

| TX_EN                   | 23 | リセット:I、PD アクティブ:I、PD        | 送信イネーブル:TX_EN は、TX_CLK の立ち上がりエッジに示されます。TX_EN は、MII モードでは TX_D[3:0]、RMII モードでは TX_D[1:0] に有効なデータ入力が存在することを示します。TX_EN はアクティブ High 信号です。                                                                                                                                                        |

| TX_D0                   | 24 | リセット:I、PD アクティブ:I、PD        | 送信データ:<br>MII モードでは、MAC から受信された送信データニブルは TX_CLK の立ち上がりエッジに同期します。                                                                                                                                                                                                                             |

| TX_D1                   | 25 | リセット:I、PD アクティブ:I、PD        | RMII モードでは、MAC から受信された TX_D[1:0] は基準クロックの立ち上がりエッジに同期します。                                                                                                                                                                                                                                     |

| TX_D2                   | 26 | リセット:I、PD アクティブ:I、PD        |                                                                                                                                                                                                                                                                                              |

| TX_D3                   | 27 | リセット:I、PD アクティブ:I、PD        |                                                                                                                                                                                                                                                                                              |

| COL/LED2/<br>TX_ER/GPIO | 28 | リセット:I、PD アクティブ:O<br>Strap4 | 衝突検出 (デフォルト):MII モードでは、ピンが衝突検出 (COL) として動作している場合、全二重モードではこのピンは常に Low になります。半二重モードでは、送信メディアと受信メディアの両方がアイドル状態でない場合にのみ、COL が High にアサートされます。このピンは、レジスタ構成によって、2 番目の追加 LED ドライバ (LED2)、MII TX_ER 信号、または汎用 I/O (GPIO) として構成することもできます。<br>RMII モードでは、このピンはデフォルトで LED2 として機能します。                     |

| CRS/LED3                | 29 | リセット:I、PD アクティブ:O<br>Strap3 | 搬送波検知 (デフォルト):<br>MII モードでは、受信メディアまたは送信メディアがアイドルでない場合、このピンが High にアサートされます。搬送波検知および受信データは有効です。レジスタ構成により、このピンを 3 番目の LED (LED3) として構成できます。<br>RMII モードでは、このピンはデフォルトで LED3 として構成されます。                                                                                                          |

| LED0                    | 30 | リセット:I、PD アクティブ:O<br>Strap2 | LED0:この LED は、リンクのステータスに加えて、送受信アクティビティを示します。リンクが正常な場合は LED が点灯します。トランスマッタまたはレシーバがアクティブになると、LED が点滅します。ピンの外部プルアップまたはプルダウンに基づいて、LED 極性は自動検出 (アクティブ Low / アクティブ High) されます。                                                                                                                     |

**表 5-1. ピン機能 (ENHANCED モード) (続き)**

| ピン              |    | タイプ <sup>(1)</sup>               | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------|----|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称              | なし |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CLKOUT/<br>LED1 | 31 | リセット:I, PU アク<br>ティブ:O<br>Strap1 | <p>このピンは、パワーオンリセット (POR) 後のデフォルト出力として、XI からの 25MHz 基準クロックを供給します。出力はリセットの影響を受けないため、他のシステムに影響を及ぼすことなく、アプリケーションは PHY をリセットできます。出力クロックは、ディープ パワー ダウンによってのみオフになります。</p> <p>ピンは、ストラップまたはレジスタ構成によって、LED1 として動作するように構成できます。ストラップは、パワーアップ時にのみラッチされ、ピンのリセット時にはラッチされません。リンクが 100Mbps の場合は LED が点灯します。リンクが 10Mbps の場合、またはリンクがない場合は、LED は消灯したままになります。</p> <p>ピンの外部プルアップまたはプルダウンに基づいて、LED 極性は自動検出 (アクティブ Low / アクティブ High) されます。</p> <p>このストラップは、パワーアップ時にのみラッチされ、ピンのリセット時にはラッチされません。</p> |

| RST_N           | 32 | リセット:I, PU アク<br>ティブ:I, PU       | リセット Low:RST_N ピンはアクティブ Low リセット入力です。このピンを 25μs 以上 Low にアサートすると、リセットプロセスが強制的に開始されます。リセットが開始されると、ストラップ ピンが再スキャンされ、PHY のすべての内部レジスタがデフォルト値にリセットされます。                                                                                                                                                                                                                                                                                                                          |

(1) I = 入力、O = 出力、I/O = 入力 / 出力、A = アナログ、PU または PD = 内部プルアップまたはプルダウン; ハードウェア ブートストラップ構成

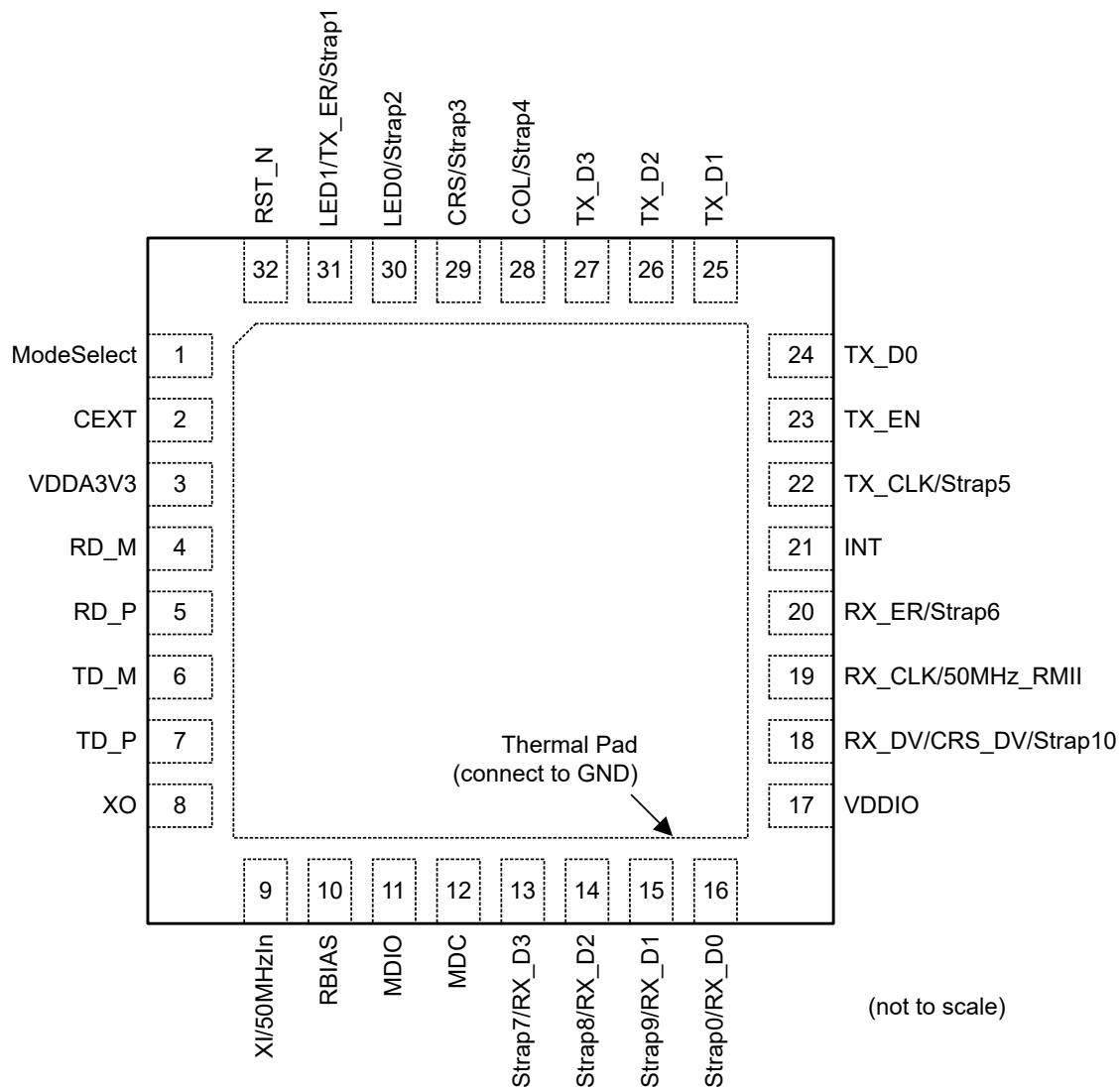

## 6 ピン構成および機能 (BASIC モード)

BASIC モードは、DP83826 がスタートアップ時に構成できる 2 つのモードのうちの 1 つです。このモードでは、DP83826 はすべての標準イーサネット アプリケーションをサポートでき、現在多くのアプリケーションで使用されている一般的なピン配置構成に一致します。DP83826 を BASIC モードに構成するには、ModeSelect (ピン 1) を GND に短絡します。

図 6-1. RHB パッケージ

32 ピン QFN

(上面図)

表 6-1. ピン機能 (BASIC モード)

| ピン         |    | タイプ <sup>(1)</sup>     | 説明                                                                                                                                                     |

|------------|----|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称         | なし |                        |                                                                                                                                                        |

| ModeSelect | 1  | リセット:I, PU アクティブ:I, PU | このピンは、次の動作モードを選択します: BASIC モードまたは ENHANCED モード。DP83826 を BASIC モードに構成するには、このピンを GND に短絡する必要があります。ENHANCED モードの場合、このピンは NC のままにするか、抵抗で VDDIO にプルアップします。 |

| CEXT       | 2  | A                      | 外部コンデンサ: CEXT ピンは、2nF のコンデンサを通して GND に接続します。                                                                                                           |

**表 6-1. ピン機能 (BASIC モード) (続き)**

| ピン                    |    | タイプ <sup>(1)</sup>            | 説明                                                                                                                                                                                                                                    |

|-----------------------|----|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                    | なし |                               |                                                                                                                                                                                                                                       |

| VDDA3V3               | 3  | 電源                            | 入力アナログ電源: 3.3V デカップリング コンデンサの要件については、データシートの「電源に関する推奨事項」セクションを参照してください。                                                                                                                                                               |

| RD_M                  | 4  | A                             | 差動受信入力 (PMD) : これらの差動入力は、10BASE-Te または 100BASE-TX 固有の信号モードを受け入れるように自動的に構成されます。                                                                                                                                                        |

| RD_P                  | 5  | A                             |                                                                                                                                                                                                                                       |

| TD_M                  | 6  | A                             | 差動送信出力 (PMD) : これらの差動出力は、PHY に選択されている構成に基づいて、10BASE-Te または 100BASE-TX のいずれかの信号モードに構成されます。                                                                                                                                             |

| TD_P                  | 7  | A                             |                                                                                                                                                                                                                                       |

| XO                    | 8  | A                             | 水晶振動子出力: 基準クロック出力。XO ピンは水晶振動子の場合にのみ使用されます。CMOS レベル発振器を XI に接続する場合、このピンをフローティングのままにします。                                                                                                                                                |

| XI/50MHzIn            | 9  | A                             | 水晶振動子または発振器の入力クロック: MII モードまたは RMII リーダー モード: 25MHz ± 50ppm の水晶振動子または発振器クロック。RMII フォロワ モード: 50MHz ± 50ppm の CMOS レベル発振器クロック。                                                                                                          |

| RBIAS                 | 10 | A                             | バイアス抵抗: $R_{BIAS}$ 値 6.49kΩ (グランドに 1% の精度で接続)。                                                                                                                                                                                        |

| MDIO                  | 11 | リセット:I, PU アクティブ:I/O, PU      | 管理データ I/O: 管理ステーションまたは PHY から出力される可能性がある双方向管理データ信号。このピンには、10kΩ への内部プルアップ抵抗が搭載されています。必要に応じて、外部プルアップ抵抗を追加できます。                                                                                                                          |

| MDC                   | 12 | リセット:I, PD アクティブ:I, PD        | 管理データクロック: MDIO シリアル管理入力 / 出力データへの同期クロック。このクロックは、MAC の送信クロックおよび受信クロックと非同期にすることができます。最大クロック レートは 25MHz です。最小クロック レートはありません。                                                                                                            |

| RX_D3                 | 13 | リセット:I, PU アクティブ:O<br>Strap7  | 受信データ: ケーブルで受信されたシンボルは、RX_CLK の立ち上がりエッジに同期してデコードされ、これらのピンに表示されます。RX_DV がアサートされている場合、有効なデータが含まれています。MII モードでは、ニブル (RX_D[3:0]) を受信します。RMII モードでは、2 ビットの RX_D[1:0] を受信します。                                                               |

| RX_D2                 | 14 | リセット:I, PD アクティブ:O<br>Strap8  |                                                                                                                                                                                                                                       |

| RX_D1                 | 15 | リセット:I, PD アクティブ:O<br>Strap9  |                                                                                                                                                                                                                                       |

| RX_D0                 | 16 | リセット:I, PU アクティブ:O<br>Strap0  |                                                                                                                                                                                                                                       |

| VDDIO                 | 17 | 電源                            | I/O 電源電圧: 3.3V または 1.8V。デカップリング コンデンサの要件については、データシートの「電源に関する推奨事項」セクションを参照してください。                                                                                                                                                      |

| RX_DV/<br>CRS_DV      | 18 | リセット:I, PD アクティブ:O<br>Strap10 | 受信データ有効: このピンは、MII モードの場合は RX_D[3:0]、RMII モードの場合は RX_D[1:0] に有効なデータが存在することを示します。MII モードでは、このピンは RX_DV として機能します。RMII モードでは、このピンは CRS_DV として機能し、RMII キャリアと受信データの有効な通知を組み合わせます。                                                          |

| RX_CLK/<br>50MHz_RMII | 19 | リセット:I, PD アクティブ:O            | MII 受信クロック: MII 受信クロックは、速度 100Mbps の 25MHz 基準クロックおよび受信データストリームから取得される速度 10Mbps の 2.5MHz 基準クロックを供給します。RMII リーダー モードでは、これにより 50MHz 基準クロックを供給します。RMII フォロワ モードでは、このピンは使われず、入力 / PD のままになります。                                             |

| RX_ER                 | 20 | リセット:I, PD アクティブ:O<br>Strap6  | 受信エラー: このピンは、MII モードおよび RMII モードの両方で受信パケット内にエラー シンボルが検出されたことを示します。MII モードでは、RX_CLK の立ち上がりエッジに同期して、RX_ER が High にアサートされます。RMII モードでは、基準クロックの立ち上がりエッジに同期して、RX_ER が High にアサートされます。受信エラー (アイドル中のエラーを含む) が発生するたびに、RX_ER が High にアサートされます。 |

| INT                   | 21 | リセット:I, PU アクティブ:O, PU        | 割り込み: 割り込み状態が発生すると、このピンは Low にアサートされます。このピンには、弱い内部プルアップ抵抗 (9.5kΩ) のオープンドレイン出力があります。一部のアプリケーションでは、外部 PU 抵抗が必要となります。                                                                                                                    |

表 6-1. ピン機能 (BASIC モード) (続き)

| ピン         |    | タイプ <sup>(1)</sup>                   | 説明                                                                                                                                                                                                                                                                                   |

|------------|----|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称         | なし |                                      |                                                                                                                                                                                                                                                                                      |

| TX_CLK     | 22 | リセット:I、PD アクティブ:I<br>タイプ:O<br>Strap5 | MII 送信クロック: MII 送信クロックは、速度 100Mbps の 25MHz 基準クロックおよび速度 10Mbps の 2.5MHz 基準クロックを提供します。MII モードでは、このクロックの位相は基準クロックを基準として一定となることに注意してください。このような一定位相を必要とするアプリケーションで、この機能を使用できます。RMII モードでは使用されません。                                                                                         |

| TX_EN      | 23 | リセット:I、PD アクティブ:I、PD                 | 送信イネーブル: TX_EN は、TX_CLK の立ち上がりエッジに示されます。TX_EN は、MII モードでは TX_D[3:0]、RMII モードでは TX_D[1:0] に有効なデータ入力が存在することを示します。TX_EN はアクティブ High 信号です。                                                                                                                                               |

| TX_D0      | 24 | リセット:I、PD アクティブ:I、PD                 | 送信データ:<br>MII モードでは、MAC から受信された送信データニブルは TX_CLK の立ち上がりエッジに同期します。                                                                                                                                                                                                                     |

| TX_D1      | 25 | リセット:I、PD アクティブ:I、PD                 | RMII モードでは、MAC から受信された TX_D[1:0] は基準クロックの立ち上がりエッジに同期します。                                                                                                                                                                                                                             |

| TX_D2      | 26 | リセット:I、PD アクティブ:I、PD                 |                                                                                                                                                                                                                                                                                      |

| TX_D3      | 27 | リセット:I、PD アクティブ:I、PD                 |                                                                                                                                                                                                                                                                                      |

| COL        | 28 | リセット:I、PD アクティブ:O<br>Strap4          | 衝突検出:<br>MII モード: 全二重モードでは、このピンは常に Low です。半二重モードでは、送信メディアと受信メディアの両方がアイドル状態でない場合にのみ、このピンが High にアサートされます。<br>RMII モードでは、このピンは使用されません。                                                                                                                                                 |

| CRS        | 29 | リセット:I、PD アクティブ:O<br>Strap3          | 搬送波検知:<br>MII モードでは、受信メディアまたは送信メディアがアイドルでない場合、このピンが High にアサートされます。<br>搬送波検知または受信データは有効です。RMII モードでは、このピンは使用されません。                                                                                                                                                                   |

| LED0       | 30 | リセット:I、PU アクティブ:O<br>Strap2          | LED0: この LED は、リンクのステータスに加えて、送受信アクティビティを示します。リンクが正常な場合は LED が点灯します。トランスマッタまたはレシーバがアクティブになると、LED が点滅します。LED 極性はアクティブ Low に固定されます。ストラップ目的で外部プルダウンを必要とする場合、LED とストラップの両方を正しく動作させるために、ストラップと LED の直列抵抗の両方を調整する必要があります。詳細については、LED セクションを参照してください。                                        |

| LED1/TX_ER | 31 | リセット:I、PU アクティブ:O<br>Strap1          | LED1: このピンは、デフォルトで LED1 として機能します。リンクが 100Mbps の場合は LED が点灯します。リンクが 10Mbps の場合、またはリンクがない場合は、LED は消灯したままになります。レジスタ設定により、このピンを TX_ER に構成できます。<br>LED 極性はアクティブ Low に固定されます。ストラップ目的で外部プルダウンを必要とする場合、LED とストラップの両方を正しく動作させるために、ストラップと LED の直列抵抗の両方を調整する必要があります。詳細については、LED セクションを参照してください。 |

| RST_N      | 32 | リセット:I、PU アクティブ:I、PU                 | リセット Low: RST_N ピンはアクティブ Low リセット入力です。このピンを 25μs 以上 Low にアサートすると、リセットプロセスが強制的に開始されます。リセットが開始されると、ストラップピンが再スキャンされ、PHY のすべての内部レジスタがデフォルト値にリセットされます。                                                                                                                                    |

(1) I = 入力、O = 出力、I/O = 入力 / 出力、A = アナログ、PU または PD = 内部プルアップまたはプルダウン: ハードウェア ブートストラップ構成

## 7 仕様

### 7.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

| パラメータ                  |                                                                            | 最小値  | 最大値 | 単位 |

|------------------------|----------------------------------------------------------------------------|------|-----|----|

| アナログ電源電圧               | VDDA3V3                                                                    | -0.3 | 4   | V  |

| IO 電源                  | VDDIO3V3                                                                   | -0.3 | 4   | V  |

| IO 電源                  | VDDIO1V8                                                                   | -0.3 | 2.1 | V  |

| 保管温度                   | Tstg                                                                       | -65  | 150 | °C |

| MDI ピン                 | TX_P, TX_M, RX_P, RX_M                                                     | -0.6 | 4   | V  |

| MAC インターフェイスピン         | TX_CLK, TX_D[3:0], TX_EN, TX_ER, RX_CLK, RX_D[3:0], RX_ER, RX_DV, CRS, COL | -0.3 | 4   | V  |

| シリアル マネージメントインターフェイスピン | MDIO, MDC                                                                  | -0.3 | 4   | V  |

| 水晶振動子 / 発振器ピン          | XI, XO                                                                     | -0.3 | 4   | V  |

| リセットピン                 | RST_N                                                                      | -0.3 | 4   | V  |

(1) 「絶対最大定格」の範囲外の動作は、デバイスに恒久的な損傷を与える可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 7.2 ESD 定格

| パラメータ       | 定義                                                                                      | 値    | 単位 |

|-------------|-----------------------------------------------------------------------------------------|------|----|

| 静電気放電 (HBM) | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup> MDI (Media Dependent Interface) ピン | ±5   | kV |

|             | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 <sup>(1)</sup> MDI ピンを除くすべてのピン                    | ±2   | kV |

| ESD (CDM)   | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 準拠 <sup>(2)</sup> 、すべてのピン                          | ±750 | V  |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。必要な予防措置をとれば、HBM ESD 耐圧が 500V 未満でも製造可能です。±5kV または ±4kV と記載されたピンは、実際にはそれよりも高い性能を持つ場合があります。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。必要な予防措置をとれば、CDM ESD 耐圧が 250V 未満でも製造可能です。±750V と記載されているピンは、実際にはそれよりも高い性能を持つ場合があります。

### 7.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ                 |                | 最小値  | 標準値 | 最大値  | 単位 |

|-----------------------|----------------|------|-----|------|----|

| アナログ電源電圧              | VDDA3V3        | 3    | 3.3 | 3.6  | V  |

| IO 電源                 | VDDIO3V3       | 3    | 3.3 | 3.6  | V  |

|                       | VDDIO1V8       | 1.62 | 1.8 | 1.98 | V  |

| 自由気流での動作温度 (DP83826E) | T <sub>A</sub> | -40  | 25  | 105  | °C |

| 自由気流での動作温度 (DP83826I) | T <sub>A</sub> | -40  | 25  | 85   | °C |

## 7.3 推奨動作条件 (続き)

自由気流での動作温度範囲内 (特に記述のない限り)

| パラメータ      |                                                                                                                                 | 最小値  | 標準値 | 最大値  | 単位 |

|------------|---------------------------------------------------------------------------------------------------------------------------------|------|-----|------|----|

| VDDIO:1.8V | TX_EN、TX_D0、TX_D1、TX_D2、TX_D3、TX_CLK、RX_D0、RX_D1、RX_D2、RX_D3、RX_DV、RX_ER、MDIO、MDC、COL/LED2、CRS、CLKOUT/LED1、INT/PWDN、RESET、TX_ER | 1.62 | 1.8 | 1.98 | V  |

|            | XI 発振器入力                                                                                                                        | 1.62 | 1.8 | 1.98 | V  |

|            | LED0                                                                                                                            | 1.62 | 1.8 | 1.98 | V  |

| VDDIO:3.3V | TX_EN、TX_D0、TX_D1、TX_D2、TX_D3、TX_CLK、RX_D0、RX_D1、RX_D2、RX_D3、RX_DV、RX_ER、MDIO、MDC、COL/LED2、CRS、CLKOUT/LED1、INT/PWDN、RESET、TX_ER | 3.0  | 3.3 | 3.6  | V  |

|            | XI 発振器入力                                                                                                                        | 3.0  | 3.3 | 3.6  | V  |

|            | LED0                                                                                                                            | 3.0  | 3.3 | 3.6  | V  |

## 7.4 热に関する情報

(1)

| 熱評価基準                |                     |      | 単位   |

|----------------------|---------------------|------|------|

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 52   | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 42   | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 | 11.9 | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 31.5 | °C/W |

| $Y_{JT}$             | 接合部から上面への特性パラメータ    | 2.1  | °C/W |

| $Y_{JB}$             | 接合部から基板への特性パラメータ    | 31.4 | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーションレポートを参照してください。

## 7.5 電気的特性

自由気流での動作温度範囲内 ( $VDDA3V3 = 3V3$ ) (特に記述のない限り)<sup>(1)</sup>

| パラメータ                                                                            | テスト条件                 | 最小値  | 標準値  | 最大値  | 単位 |

|----------------------------------------------------------------------------------|-----------------------|------|------|------|----|

| <b>IEEE Tx 準拠 (100BaseTx)</b>                                                    |                       |      |      |      |    |

| $V_{OD}$                                                                         | 差動出力電圧                |      | 950  | 1050 | mV |

| <b>IEEE Tx 準拠 (10BaseTe)</b>                                                     |                       |      |      |      |    |

| $V_{OD}$                                                                         | 出力差動電圧 <sup>(2)</sup> | 1.54 | 1.75 | 1.96 | V  |

| <b>消費電力の基準値 (アクティブ モード、50% のトラフィック、パケット サイズ:1518、ランダム コンテンツ、150m のケーブル)</b>      |                       |      |      |      |    |

| $I_{(VDDA3V3=3V3)}$                                                              | MII (100BaseTx)       |      | 45   | 53   | mA |

| $I_{(VDDA3V3=3V3)}$                                                              | MII (10BaseTe)        |      | 35   | 46   | mA |

| $I_{(VDDA3V3=3V3)}$                                                              | RMII リーダー (100BaseTx) |      | 45   | 53   | mA |

| $I_{(VDDA3V3=3V3)}$                                                              | RMII リーダー (10BaseTe)  |      | 35   | 46   | mA |

| $I_{(VDDA3V3=3V3)}$                                                              | RMII フォロワ (100BaseTx) |      | 45   | 53   | mA |

| $I_{(VDDA3V3=3V3)}$                                                              | RMII フォロワ (10BaseTe)  |      | 35   | 46   | mA |

| $I_{(VDDIO=3V3)}$                                                                | MII (100BaseTx)       |      | 8    | 14   | mA |

| $I_{(VDDIO=3V3)}$                                                                | MII (10BaseTe)        |      | 5    | 12   | mA |

| $I_{(VDDIO=3V3)}$                                                                | RMII リーダー (100BaseTx) |      | 9    | 14   | mA |

| $I_{(VDDIO=3V3)}$                                                                | RMII リーダー (10BaseTe)  |      | 9    | 12   | mA |

| $I_{(VDDIO=3V3)}$                                                                | RMII フォロワ (100BaseTx) |      | 7    | 8.5  | mA |

| $I_{(VDDIO=3V3)}$                                                                | RMII フォロワ (10BaseTe)  |      | 5    | 6    | mA |

| $I_{(VDDIO=1V8)}$                                                                | MII (100BaseTx)       |      | 5    | 7    | mA |

| $I_{(VDDIO=1V8)}$                                                                | MII (10BaseTe)        |      | 3    | 6    | mA |

| $I_{(VDDIO=1V8)}$                                                                | RMII リーダー (100BaseTx) |      | 5    | 7    | mA |

| $I_{(VDDIO=1V8)}$                                                                | RMII リーダー (10BaseTe)  |      | 5    | 6    | mA |

| $I_{(VDDIO=1V8)}$                                                                | RMII フォロワ (100BaseTx) |      | 3    | 6    | mA |

| $I_{(VDDIO=1V8)}$                                                                | RMII フォロワ (10BaseTe)  |      | 2    | 3    | mA |

| <b>消費電力 (アクティブ モードの最も厳しい条件、100% のトラフィック、パケット サイズ:1518、ランダム コンテンツ、150m のケーブル)</b> |                       |      |      |      |    |

| $I_{(VDDA3V3=3V3)}$                                                              | MII (100BaseTx)       |      | 44   | 55   | mA |

| $I_{(VDDA3V3=3V3)}$                                                              | MII (10BaseTe)        |      | 35   | 48   | mA |

## 7.5 電気的特性 (続き)

自由気流での動作温度範囲内 ( $VDDA3V3 = 3V3$ ) (特に記述のない限り)<sup>(1)</sup>

| パラメータ                         | テスト条件                          | 最小値                              | 標準値 | 最大値  | 単位    |

|-------------------------------|--------------------------------|----------------------------------|-----|------|-------|

| $I_{(VDDA3V3=3V3)}$           | RMII リーダー (100BaseTx)          |                                  |     | 44   | 55 mA |

|                               | RMII リーダー (10BaseTe)           |                                  |     | 35   | 48 mA |

|                               | RMII フォロワ (100BaseTx)          |                                  |     | 44   | 55 mA |

|                               | RMII フォロワ (10BaseTe)           |                                  |     | 35   | 48 mA |

| $I_{(VDDIO=3V3)}$             | MII (100BaseTx)                |                                  |     | 10   | 15 mA |

| $I_{(VDDIO=3V3)}$             | MII (10BaseTe)                 |                                  |     | 5    | 12 mA |

| $I_{(VDDIO=3V3)}$             | RMII リーダー (100BaseTx)          |                                  |     | 11   | 15 mA |

|                               | RMII リーダー (10BaseTe)           |                                  |     | 9    | 12 mA |

|                               | RMII フォロワ (100BaseTx)          |                                  |     | 8    | 12 mA |

|                               | RMII フォロワ (10BaseTe)           |                                  |     | 5    | 10 mA |

| $I_{(VDDIO=1V8)}$             | MII (100BaseTx)                |                                  |     | 6    | 9 mA  |

| $I_{(VDDIO=1V8)}$             | MII (10BaseTe)                 |                                  |     | 2    | 6 mA  |

| $I_{(VDDIO=1V8)}$             | RMII リーダー (100BaseTx)          |                                  |     | 6    | 9 mA  |

|                               | RMII リーダー (10BaseTe)           |                                  |     | 5    | 7 mA  |

|                               | RMII フォロワ (100BaseTx)          |                                  |     | 4    | 8 mA  |

|                               | RMII フォロワ (10BaseTe)           |                                  |     | 2    | 6 mA  |

| <b>消費電力 (低消費電力モード)</b>        |                                |                                  |     |      |       |

| $I_{(AVDD3V3=3V3)}$           | 100 BaseTx EEE モード             | EEE モードの 100 BaseTx リンク (LPI オン) |     | 15   | mA    |

| $I_{(AVDD3V3=3V3)}$           | IEEE パワーダウン                    |                                  |     | 11   | mA    |

| $I_{(AVDD3V3=3V3)}$           | アクティブ スリープ                     |                                  |     | 18   | mA    |

| $I_{(AVDD3V3=3V3)}$           | リセット                           |                                  |     | 12.5 | mA    |

| $I_{(VDDIO=3V3)}$             | 100 BaseTx EEE モード             | EEE モードの 100 BaseTx リンク (LPI オン) |     | 6    | mA    |

| $I_{(VDDIO=3V3)}$             | IEEE パワーダウン                    |                                  |     | 10.5 | mA    |

| $I_{(VDDIO=3V3)}$             | アクティブ スリープ                     |                                  |     | 10.5 | mA    |

| $I_{(VDDIO=3V3)}$             | リセット                           |                                  |     | 10.5 | mA    |

| $I_{(VDDIO=1V8)}$             | 100 BaseTx EEE モード             | EEE モードの 100 BaseTx リンク (LPI オン) |     | 4    | mA    |

| $I_{(VDDIO=1V8)}$             | IEEE パワーダウン                    |                                  |     | 5.5  | mA    |

| $I_{(VDDIO=1V8)}$             | アクティブ スリープ                     |                                  |     | 5.5  | mA    |

| $I_{(VDDIO=1V8)}$             | リセット                           |                                  |     | 5.5  | mA    |

| <b>ブートストラップ DC 特性 (2 レベル)</b> |                                |                                  |     |      |       |

| $V_{IH\_3V3}$                 | High レベルのブートストラップ スレッショルド: 3V3 |                                  |     | 1.3  | V     |

## 7.5 電気的特性 (続き)

自由気流での動作温度範囲内 ( $VDDA3V3 = 3V3$ ) (特に記述のない限り)(1)

| パラメータ          | テスト条件                          | 最小値                                             | 標準値  | 最大値                 | 単位        |

|----------------|--------------------------------|-------------------------------------------------|------|---------------------|-----------|

| $V_{IL\_3V3}$  | Low レベルのブートストラップ スレッショルド: 3V3  |                                                 |      | 0.6                 | V         |

| $V_{IH\_1V8}$  | High レベルのブートストラップ スレッショルド: 1V8 |                                                 | 1.3  |                     | V         |

| $V_{IL\_1V8}$  | Low レベルのブートストラップ スレッショルド: 1V8  |                                                 |      | 0.6                 | V         |

| <b>水晶発振器</b>   |                                |                                                 |      |                     |           |

| $C_{OSC\_EXT}$ | 外部負荷容量                         |                                                 | 15   | 30                  | pF        |

| <b>IO</b>      |                                |                                                 |      |                     |           |

| $V_{IH\_3V3}$  | High レベル入力電圧                   | $VDDIO = 3.3V \pm 10\%$                         | 1.7  |                     | V         |

| $V_{IL\_3V3}$  | Low レベル入力電圧                    | $VDDIO = 3.3V \pm 10\%$                         |      | 0.8                 | V         |

| $V_{OH\_3V3}$  | High レベル出力電圧                   | $I_{OH} = -2mA, VDDIO = 3.3V \pm 10\%$          | 2.4  |                     | V         |

| $V_{OL\_3V3}$  | Low レベル出力電圧                    | $I_{OL} = 2mA, VDDIO = 3.3V \pm 10\%$           |      | 0.4                 | V         |

| $V_{IH\_1V8}$  | High レベル入力電圧                   | $VDDIO = 1.8V \pm 10\%$                         |      | $0.65 \times VDDIO$ | V         |

| $V_{IL\_1V8}$  | Low レベル入力電圧                    | $VDDIO = 1.8V \pm 10\%$                         |      | $0.35 \times VDDIO$ | V         |

| $V_{OH\_1V8}$  | High レベル出力電圧                   | $I_{OH} = -2mA, VDDIO = 1.8V \pm 10\%$          |      | $VDDIO - 0.45$      | V         |

| $V_{OL\_1V8}$  | Low レベル出力電圧                    | $I_{OL} = 2mA, VDDIO = 1.8V \pm 10\%$           |      | 0.45                | V         |

| $I_{IH}$       | 高入力電流                          | $T_A = -40^\circ C \sim 85^\circ C, VIN=VDDIO$  |      | 15                  | $\mu A$   |

| $I_{IH}$       | 高入力電流                          | $T_A = -40^\circ C \sim 105^\circ C, VIN=VDDIO$ |      | 25                  | $\mu A$   |

| $I_{IL}$       | 入力 Low 電流                      | $T_A = -40^\circ C \sim 85^\circ C, VIN=GND$    |      | 15                  | $\mu A$   |

| $I_{IL}$       | 入力 Low 電流                      | $T_A = -40^\circ C \sim 105^\circ C, VIN=GND$   |      | 25                  | $\mu A$   |

| $I_{OZH}$      | トライステート出力高電流                   | $T_A = -40^\circ C \sim 85^\circ C$             | -15  | 15                  | $\mu A$   |

| $I_{OZH}$      | トライステート出力高電流                   | $T_A = -40^\circ C \sim 105^\circ C$            | -25  | 25                  | $\mu A$   |

| $I_{OZL}$      | トライステート出力低電流                   | $T_A = -40^\circ C \sim 85^\circ C$             | -15  | 15                  | $\mu A$   |

| $I_{OZL}$      | トライステート出力低電流                   | $T_A = -40^\circ C \sim 105^\circ C$            | -25  | 25                  | $\mu A$   |

| $R_{PD}$       | 内部プルダウン抵抗                      |                                                 | 7.5  | 10                  | $k\Omega$ |

| $R_{PU}$       | 内蔵プルアップ抵抗                      |                                                 | 7.5  | 10                  | $k\Omega$ |

| $C_{IN}$       | 入力容量                           | XI ピン                                           |      | 1                   | pF        |

| $C_{IN}$       | 入力容量                           | 入力ピン                                            |      | 5                   | pF        |

| $C_{OUT}$      | 出力容量                           | XO ピン                                           |      | 1                   | pF        |

| $C_{OUT}$      | 出力容量                           | 出力ピン                                            |      | 5                   | pF        |

| $V_{CM-OSC}$   | XI 入力発振器クロックの同相電圧              | $VDDIO = 1.8V$                                  | 0.9  |                     | V         |

| $V_{CM-OSC}$   | XI 入力発振器クロックの同相電圧              | $VDDIO = 3.3V$                                  | 1.65 |                     | V         |

| $R_{series}$   | 内蔵 MAC 直列終端抵抗                  | $RX\_D[3:0], RX\_ER, RX\_DV, RX\_CLK, TX\_CLK$  | 50   |                     | $\Omega$  |

(1) 製造試験、特性評価、設計によって検証済み

(2) レジスタ 0x030E に 0x4A40 を書き込む必要があります。

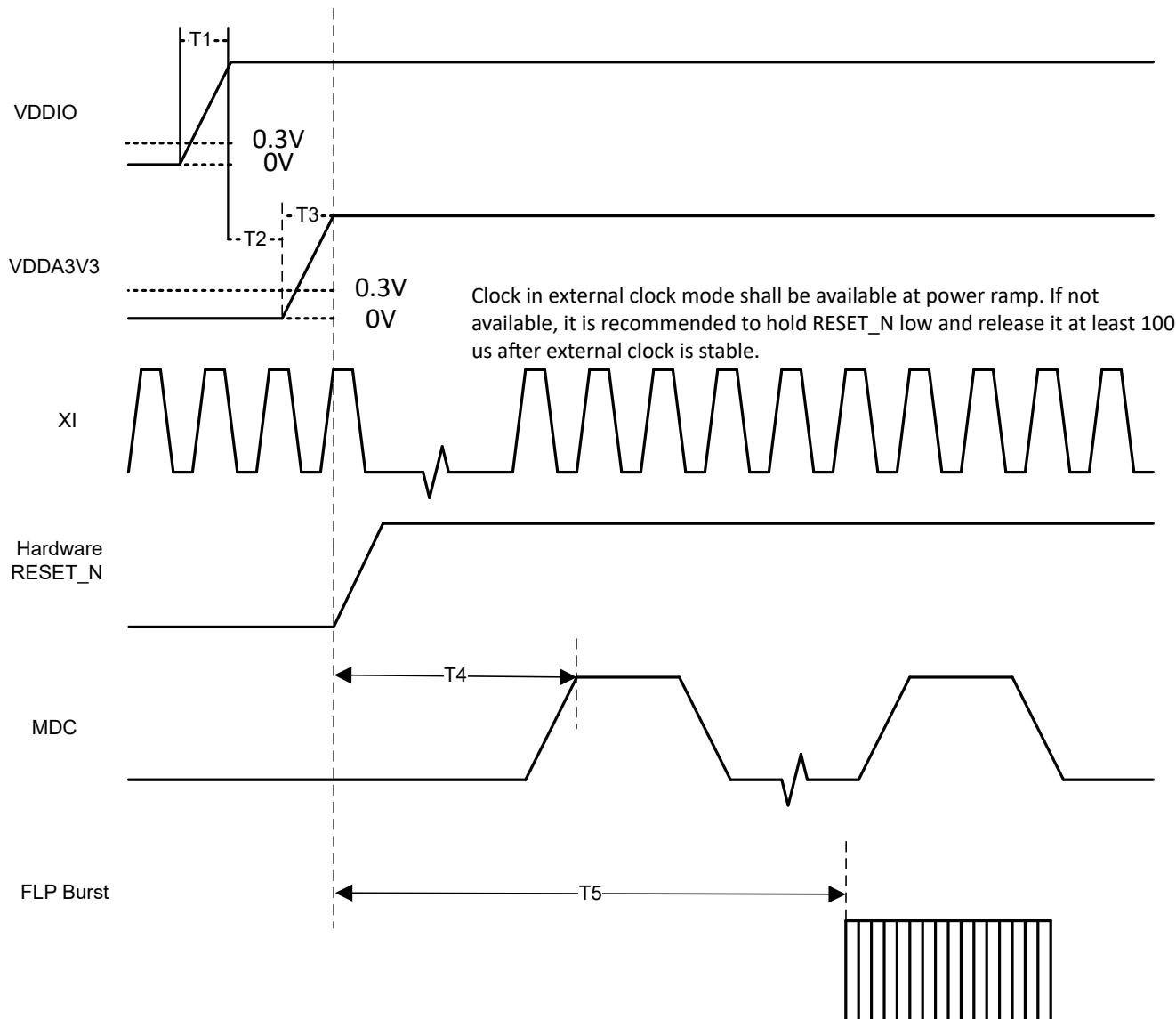

## 7.6 タイミング要件

(1)

| パラメータ                   |                                                                   | 最小値  | 公称値  | 最大値  | 単位 |

|-------------------------|-------------------------------------------------------------------|------|------|------|----|

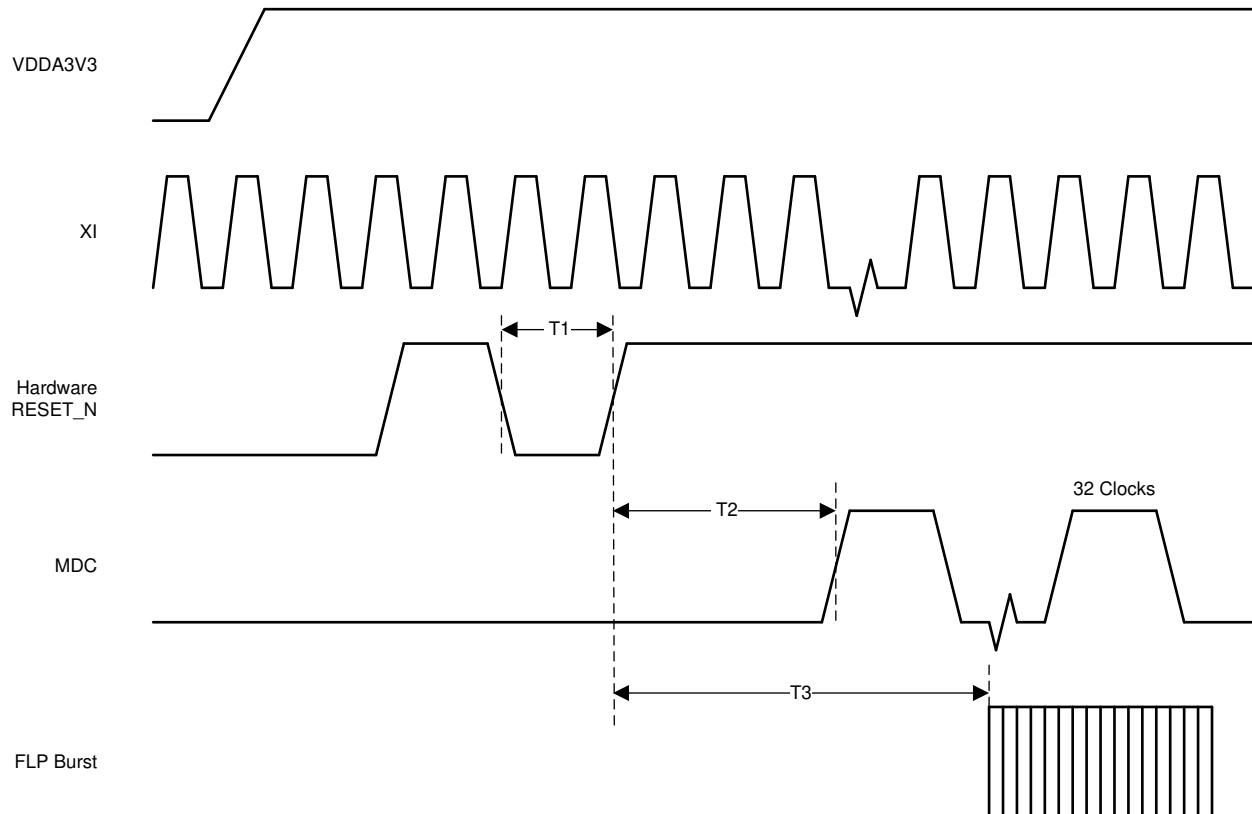

| <b>パワーアップ タイミング</b>     |                                                                   |      |      |      |    |

| T1                      | 電圧ランプ期間 (VDDIO の 0%~100%)                                         | 0.5  | 50   | ms   |    |

| T2                      | VDDA3V3 の後に VDDIO、または VDDIO の後に VDDA3V3 の順に供給 (2) (4)             | 0    | 200  | ms   |    |

| T3                      | 電圧ランプ期間 (VDDA3V3 の 0%~100%)                                       | 0.5  | 50   | ms   |    |

| T4                      | POR リリース時間 / 電源投入から SMI レディまで:レジスタ アクセスの MDC プリアンブルまでの、電源投入後安定化時間 |      | 50   | ms   |    |

| T5                      | 電源投入から FLP まで                                                     | 1500 |      | ms   |    |

|                         | 電源立ち上げの前の VDDA3V3、VDDIO のペデスタル電圧                                  |      | 0.3  | V    |    |

| <b>リセット タイミング</b>       |                                                                   |      |      |      |    |

| T1                      | リセット パルス幅:リセット可能な最小リセット パルス幅 (デバウンシング コンデンサなし)                    | 25   |      | μs   |    |

| T2                      | リセットから SMI レディまで:レジスタ アクセスの MDC プリアンブルまでの、リセット後安定化時間              |      | 2    | ms   |    |

| T3                      | リセットから FLP まで                                                     | 1500 |      | ms   |    |

|                         | リセットから 100M 信号まで (ストラップ モード)                                      | 0.5  |      | ms   |    |

|                         | リセットから RMII リーダー クロックまで                                           | 0.2  |      | ms   |    |

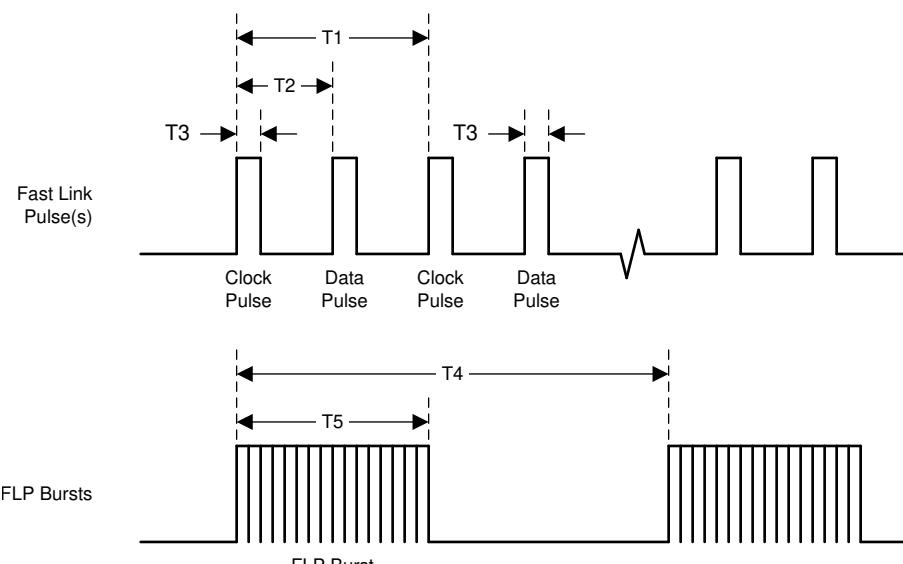

| <b>高速リンク パルス タイミング</b>  |                                                                   |      |      |      |    |

| T1                      | クロック パルスからクロック パルスまでの期間                                           | 111  | 125  | 139  | μs |

| T2                      | クロック パルスからデータ パルスまでの期間                                            | 55.5 | 62.5 | 69.5 | μs |

| T3                      | クロック / データのパルス幅                                                   |      | 104  |      | ns |

| T4                      | FLP バーストから FLP バーストまでの期間                                          | 8    | 16   | 24   | ms |

| T5                      | FLP バースト幅                                                         |      | 2    |      | ms |

|                         | バースト内のパルス幅                                                        | 17   | 33   |      |    |

| <b>リンク アップ タイミング</b>    |                                                                   |      |      |      |    |

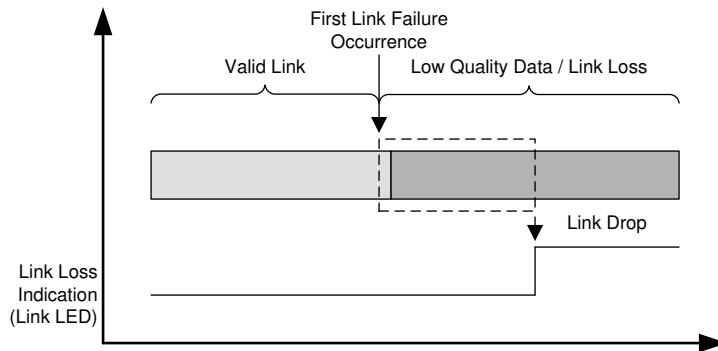

|                         | ストラップを使って有効化された高速リンクドロップ、150m ケーブル                                |      | 10   | μs   |    |

|                         | モード 1 (信号 / エネルギー喪失表示) を使用した高速リンクドロップ時間                           |      | 10   | μs   |    |

|                         | モード 2 (低信号対雑音比スレッショルド) を使用した高速リンクドロップ時間 (5)                       |      | 10   | μs   |    |

|                         | モード 3 (MLT3 エラー カウント) を使用した高速リンクドロップ時間 (5)                        |      | 10   | μs   |    |

|                         | モード 4 (RX エラー数) を使用した高速リンクドロップ時間                                  |      | 10   | μs   |    |

|                         | モード 5 (デスクランブル リンクドロップ) を使用した高速リンクドロップ時間 (5)                      |      | 11   | μs   |    |

| <b>100M EEE のタイミング</b>  |                                                                   |      |      |      |    |

|                         | スリープ時間                                                            | 210  |      | μs   |    |

|                         | 静穏時間                                                              | 20   |      | ms   |    |

|                         | ウェーク時間 (Tw_sys_tx)                                                | 36   |      | μs   |    |

|                         | リフレッシュ時間                                                          | 200  |      | μs   |    |

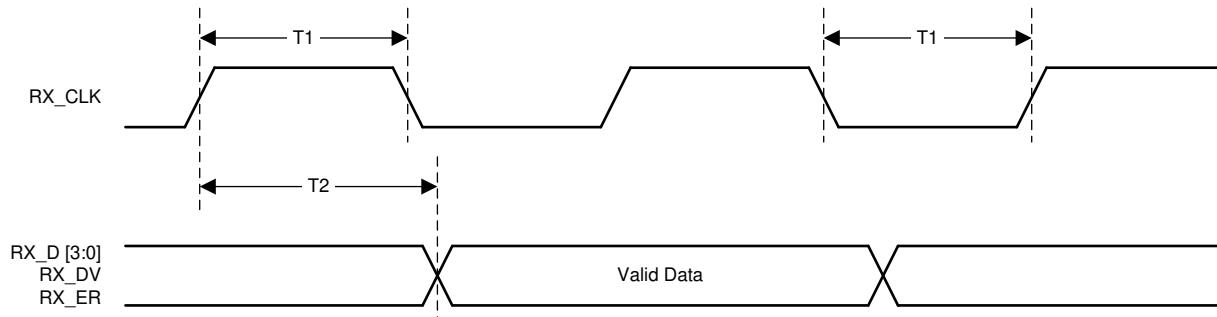

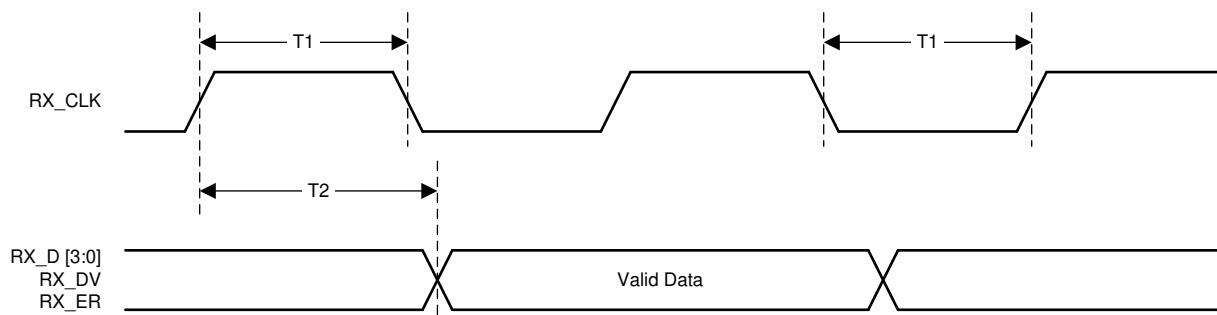

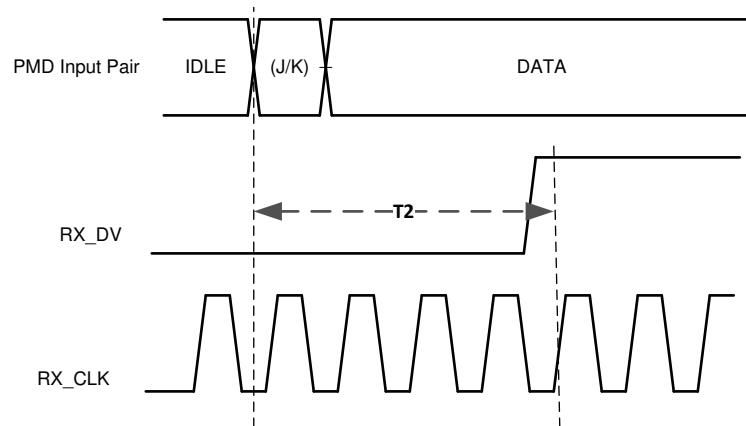

| <b>100M MII 受信タイミング</b> |                                                                   |      |      |      |    |

| T1                      | RX_CLK High/Low 時間                                                | 16   | 20   | 24   | ns |

| T2                      | RX_CLK 立ち上がりからの RX_D[3:0]、RX_ER、RX_DV の遅延                         | 20   |      | 28   | ns |

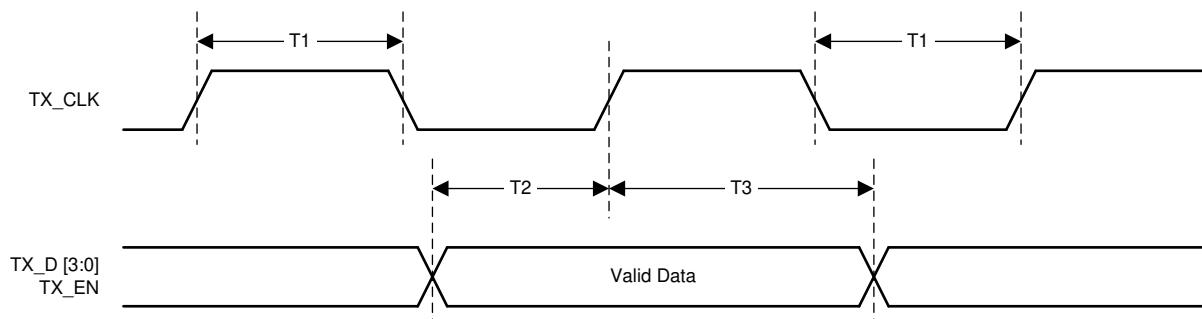

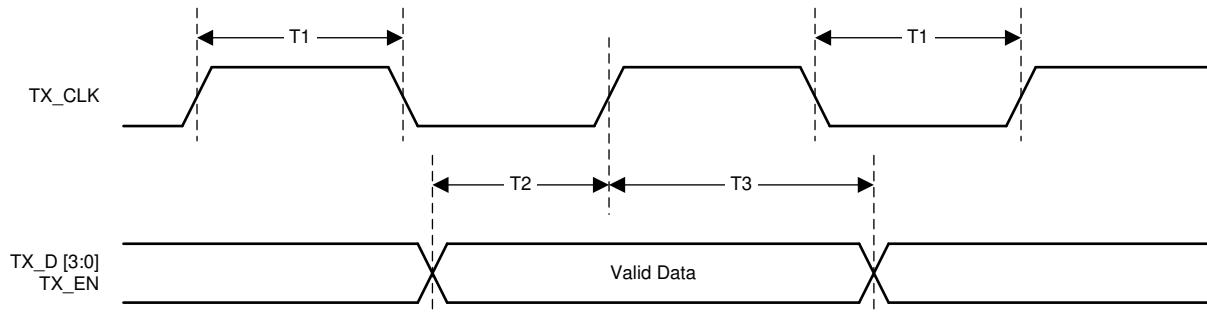

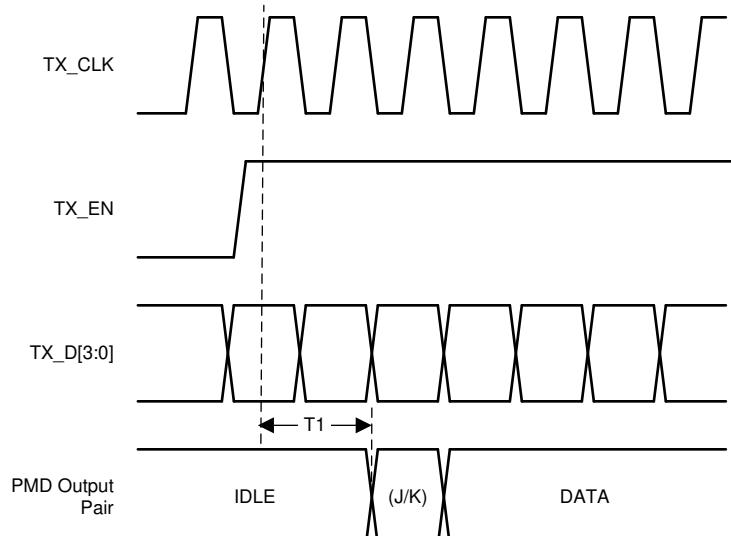

| <b>100M MII 送信タイミング</b> |                                                                   |      |      |      |    |

| T1                      | TX_CLK High/Low 時間                                                | 16   | 20   | 24   | ns |

| T2                      | TX_CLK までの TX_D[3:0]、TX_ER、TX_EN のセットアップ                          | 10   |      | ns   |    |

## 7.6 タイミング要件 (続き)

(1)

| パラメータ                                                                      |  | 最小値  | 公称値 | 最大値    | 単位  |

|----------------------------------------------------------------------------|--|------|-----|--------|-----|

| T3 TX_CLK からの TX_D[3:0]、TX_ER、TX_EN のホールド                                  |  | 0    |     | ns     |     |

| <b>10M MII 受信タイミング</b>                                                     |  |      |     |        |     |

| T1 RX_CLK High/Low 時間 <sup>(3)</sup>                                       |  | 160  |     | 200    | 240 |

| T2 RX_CLK 立ち上がりからの RX_D[3:0]、RX_ER、RX_DV の遅延 <sup>(3)</sup>                |  | 100  |     | 300    | ns  |

| <b>10M MII 送信タイミング</b>                                                     |  |      |     |        |     |

| T1 TX_CLK High/Low 時間                                                      |  | 190  |     | 200    | 210 |

| T2 TX_CLK までの TX_D[3:0]、TX_ER、TX_EN のセットアップ                                |  | 25   |     | ns     |     |

| T3 TX_CLK からの TX_D[3:0]、TX_ER、TX_EN のホールド                                  |  | 0    |     | ns     |     |

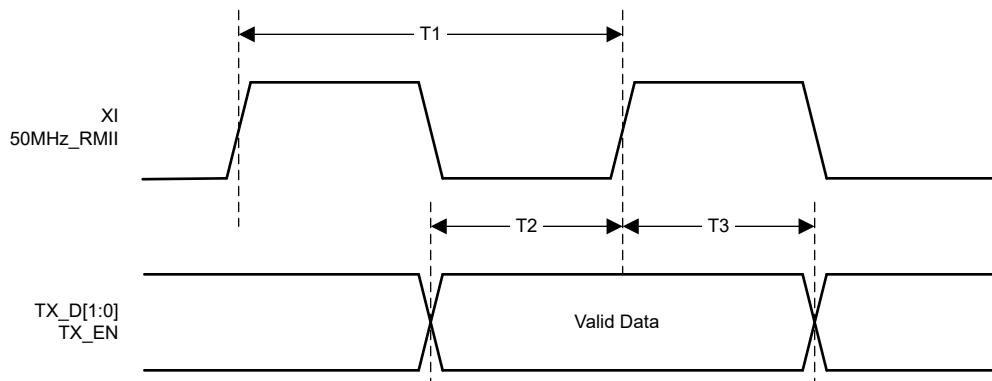

| <b>100M RMII リーダー タイミング</b>                                                |  |      |     |        |     |

| RMII リーダー クロック周期                                                           |  | 20   |     | ns     |     |

| RMII リーダー クロック デューティ サイクル                                                  |  | 35   |     | 65     | %   |

| <b>100M RMII フォロワ タイミング</b>                                                |  |      |     |        |     |

| T2 基準クロックの立ち上がりまでの TX_D[1:0]、TX_ER、TX_EN のセットアップ<br>RMII 送信タイミングを参照してください。 |  | 4    |     | ns     |     |

| T3 基準クロックの立ち上がりからの TX_D[1:0]、TX_ER、TX_EN のホールド RMII 送信タイミングを参照してください。      |  | 2    |     | ns     |     |

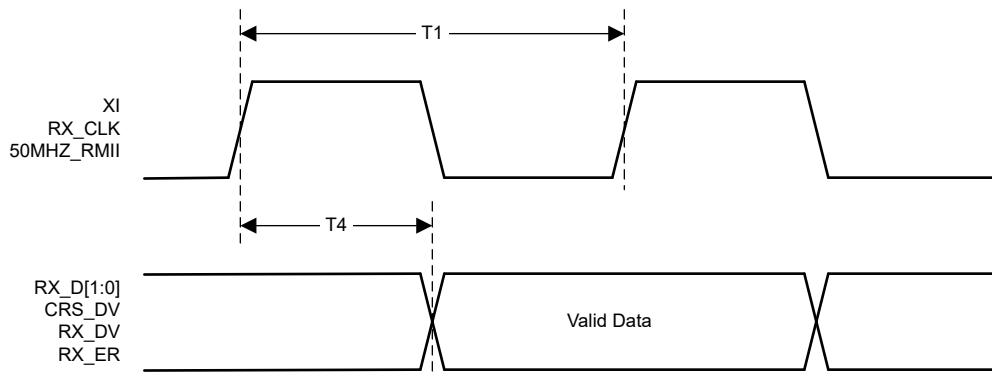

| T4 基準クロックの立ち上がりからの RX_D[1:0]、RX_ER、CRS_DV の遅延 RMII 受信タイミングを参照してください。       |  | 4    |     | 14     | ns  |

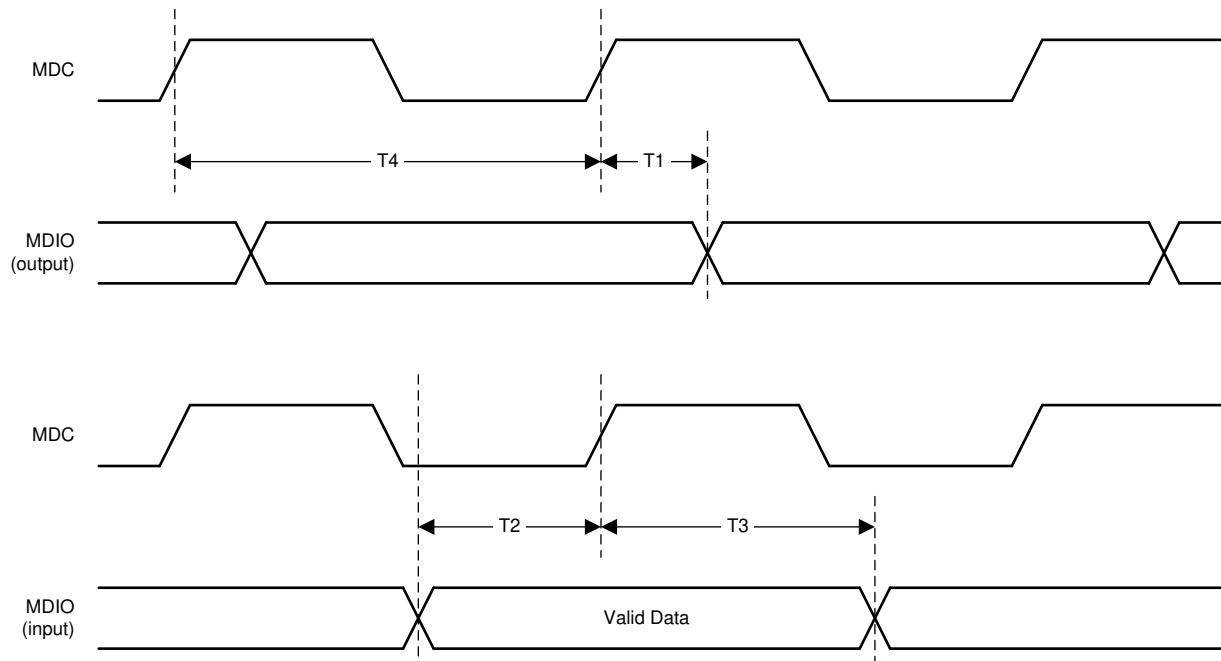

| <b>SMI タイミング</b>                                                           |  |      |     |        |     |

| T1 MDC から MDIO (出力) までの遅延時間                                                |  | 0    |     | 13     | ns  |

| T2 MDC に対する MDIO (入力) のセットアップ時間                                            |  | 10   |     | ns     |     |

| T3 MDC に対する MDIO (入力) のホールド時間                                              |  | 10   |     | ns     |     |

| T4 MDC 周波数                                                                 |  | 2.5  |     | 24     | MHz |

| <b>出力クロック タイミング (50M RMII リーダー クロック)</b>                                   |  |      |     |        |     |

| 周波数 (PPM)                                                                  |  | 50   |     | ppm    |     |

| ジッタ (長期 500 サイクル)                                                          |  | 450  |     | ps     |     |

| 立ち上がり / 立ち下がり時間                                                            |  | 5    |     | ns     |     |

| デューティ サイクル                                                                 |  | 40   |     | 60     | %   |

| <b>出力クロック タイミング (25M クロック出力)</b>                                           |  |      |     |        |     |

| 周波数 (PPM)                                                                  |  | 50   |     | ppm    |     |

| デューティ サイクル                                                                 |  | 35   |     | 65     | %   |

| 立ち上がり時間                                                                    |  | 4000 |     | ps     |     |

| 立ち下がり時間                                                                    |  | 5000 |     | ps     |     |

| ジッタ (長期: 500 サイクル)                                                         |  | 300  |     | ps     |     |

| ジッタ (短期)                                                                   |  | 250  |     | ps     |     |

| 周波数                                                                        |  | 25   |     | MHz    |     |

| <b>25MHz 入力クロック許容誤差</b>                                                    |  |      |     |        |     |

| 周波数許容誤差 (ElectChar_Sections セクションの「PLL 出力周波数 PPM」と同じ)                      |  | -50  |     | 50     | ppm |

| 立ち上がり / 立ち下がり時間                                                            |  | 5    |     | ns     |     |

| ジッタ許容誤差 (RMS)                                                              |  | 50   |     | ps     |     |

| 1kHz での入力位相ノイズ                                                             |  | -98  |     | dBc/Hz |     |

## 7.6 タイミング要件 (続き)

(1)

| パラメータ                                                                                                                                    | 最小値  | 公称値  | 最大値  | 単位     |

|------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------|

| 10kHz での入力位相ノイズ                                                                                                                          |      |      | -113 | dBc/Hz |

| 100kHz での入力位相ノイズ                                                                                                                         |      |      | -113 | dBc/Hz |

| 1MHz での入力位相ノイズ                                                                                                                           |      |      | -113 | dBc/Hz |

| 10MHz での入力位相ノイズ                                                                                                                          |      |      | -113 | dBc/Hz |

| デューティサイクル                                                                                                                                | 40   | 60   | %    |        |

| <b>50MHz 入力クロック許容誤差</b>                                                                                                                  |      |      |      |        |

| 周波数許容誤差                                                                                                                                  | -50  | 50   | 50   | ppm    |

| 立ち上がり / 立ち下がり時間                                                                                                                          |      |      | 5    | ns     |

| ジッタ許容誤差 (RMS)                                                                                                                            |      |      | 50   | ps     |

| ジッタ許容誤差: 位相ノイズから算出された長期ジッタ (100,000 サイクル)                                                                                                |      |      |      | ps     |

| 1kHz での入力位相ノイズ                                                                                                                           |      |      | -87  | dBc/Hz |

| 10kHz での入力位相ノイズ                                                                                                                          |      |      | -107 | dBc/Hz |

| 100kHz での入力位相ノイズ                                                                                                                         |      |      | -107 | dBc/Hz |

| 1MHz での入力位相ノイズ                                                                                                                           |      |      | -107 | dBc/Hz |

| 10MHz での入力位相ノイズ                                                                                                                          |      |      | -107 | dBc/Hz |

| デューティサイクル                                                                                                                                | 40   | 60   | %    |        |

| <b>レイテンシタイミング</b>                                                                                                                        |      |      |      |        |

| MII 100M Tx (MII から MDI まで): TX_CLK の立ち上がりエッジ (TX_EN アサート時) から MDI の SSD シンボルまで、高速 RX_DV 有効、100m ケーブル                                    | 38   | 40   | 40   | ns     |

| MII 100 Rx (MDI から MII まで): MDI の SSD シンボルから RX_CLK の立ち上がりエッジ (RX_DV アサート時) まで、高速 RX_DV 有効、100m ケーブル                                     | 166  | 170  | 170  | ns     |

| MII 10M Tx (MII から MDI まで): TX_CLK の立ち上がりエッジ (TX_EN アサート時) から MDI の SSD シンボルまで                                                           |      |      | 540  | ns     |

| RMII フォロワ 100M Tx (RMII から MDI): フォロワー RMII は、TX_EN のアサートとともに XI クロックの立ち上がりエッジを使用して、MDI 上の SSD シンボルを生成し、FAST RX_DV が有効で、100 メートルのケーブルを使用 | 88   | 96   | 96   | ns     |

| RMII リーダー 100M Tx (RMII から MDI まで): RMII リーダーのクロックの立ち上がりエッジ (TX_EN アサート時) から MDI の SSD シンボルまで、高速 RX_DV 有効、100m ケーブル                      | 88   | 96   | 96   | ns     |

| RMII フォロワ 10M Tx (RMII から MDI まで): RMII フォロワの XI クロックの立ち上がりエッジ (TX_EN アサート時) から MDI の SSD シンボルまで                                         |      |      | 1360 | ns     |

| RMII リーダー 10M Tx (RMII から MDI まで): RMII リーダーのクロックの立ち上がりエッジ (TX_EN アサート時) から MDI の SSD シンボルまで                                             |      |      | 1360 | ns     |

| MII 10M Rx (MDI から MII まで): MDI の SSD シンボルから RX_CLK の立ち上がりエッジ (RX_DV アサート時) まで、高速 RX_DV 有効、100m ケーブル                                     |      |      | 1640 | ns     |

| RMII フォロワ 100M Rx (MDI から RMII まで): MDI の SSD シンボルから RMII フォロワの XI クロックの立ち上がりエッジ (CRS_DV アサート時) まで、高速 RX_DV 有効、100m ケーブル                 | 268  | 288  | 288  | ns     |

| RMII リーダー 100M Rx (MDI から RMII まで): MDI の SSD シンボルから RMII リーダーのリーダークロックの立ち上がりエッジ (CRS_DV アサート時) まで                                       | 252  | 270  | 270  | ns     |

| RMII フォロワ 10M (MDI から RMII まで): MDI の SSD シンボルから RMII フォロワの XI クロックの立ち上がりエッジ (CRS_DV アサート時) まで (10M)                                     | 2110 | 2152 | 2152 | ns     |

| RMII リーダー 10M (MDI から RMII まで): MDI の SSD シンボルから RMII リーダーのリーダークロックの立ち上がりエッジ (CRS_DV アサート時) まで (10M)                                     | 2110 | 2152 | 2152 | ns     |

## 7.6 タイミング要件 (続き)

(1)

| パラメータ                                         | 最小値 | 公称値 | 最大値 | 単位 |

|-----------------------------------------------|-----|-----|-----|----|

| MII:XI と TXCLK の間の位相差 (複数回のリセット、パワー サイクルを挟んで) | 0   | 2   | 4   | ns |

- (1) 製造試験、特性評価、設計によって検証

- (2) 電源の立ち上げ開始時にクロックが利用可能である必要があります。クロックが遅れた場合、POR 完了後に追加の RESET\_N が必要です。クロックの安定化と POR 完了の 100 $\mu$ s 後にリセットを開始できます

- (3) 最初のニブルのデータを受信中に、PHY はソースをローカル クロックから再生クロックに切り替え、RX\_CLK をストレッチして、RX\_CLK から RX\_DV までの遅延に影響を及ぼします。

- (4) VDDIO 電源と AVDD 電源は、同時に立ち上げることも、どちらかの立ち上げを (遅延の最大値まで) 遅らせることもできます。

- (5) Rx\_Error カウントまたは信号 / エネルギー損失表示を有効化して、最大限度を満たします。

## 7.7 タイミング図

図 7-1. パワーアップ タイミング (電源シーケンス)

図 7-2. リセットタイミング (POR)

図 7-3. シリアルマネージメントのタイミング

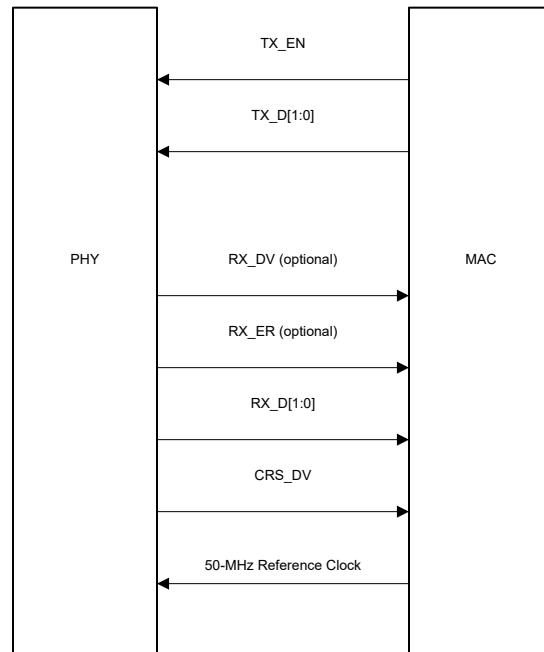

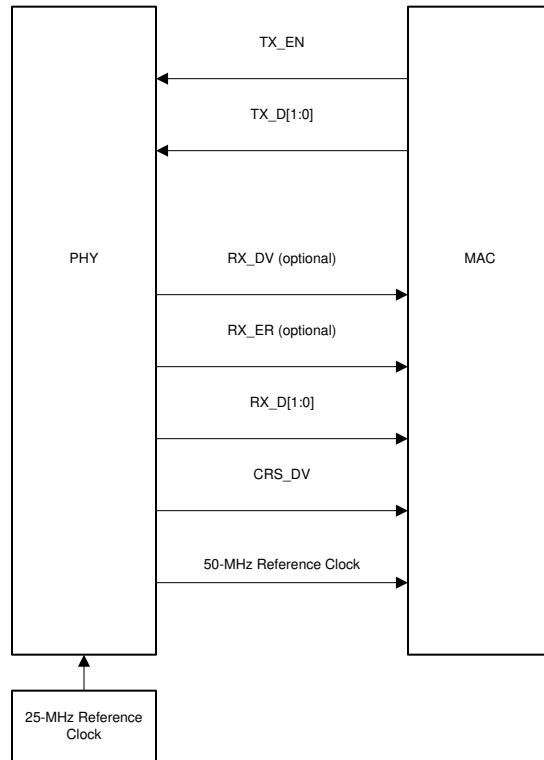

図 7-4. RMII 送信タイミング

図 7-5. RMII 受信タイミング

図 7-6. 100m MII 送信タイミング

図 7-7. 100m MII 受信タイミング

図 7-8. 10M MII 送信タイミング

図 7-9. 10m MII 受信タイミング

図 7-10. 高速リンク パルス タイミング

図 7-11. 100BASE-TX 送信レイテンシ タイミング

図 7-12. 100BASE-TX 受信レイテンシ タイミング

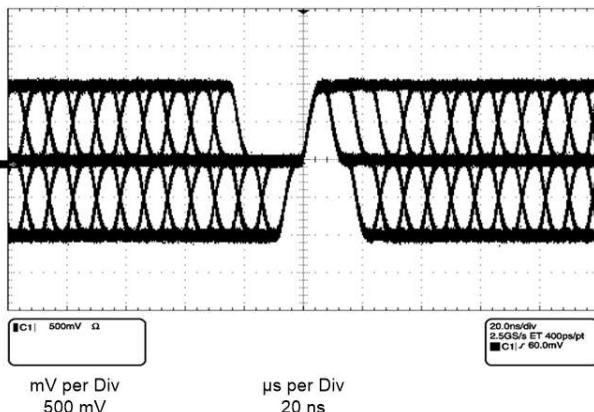

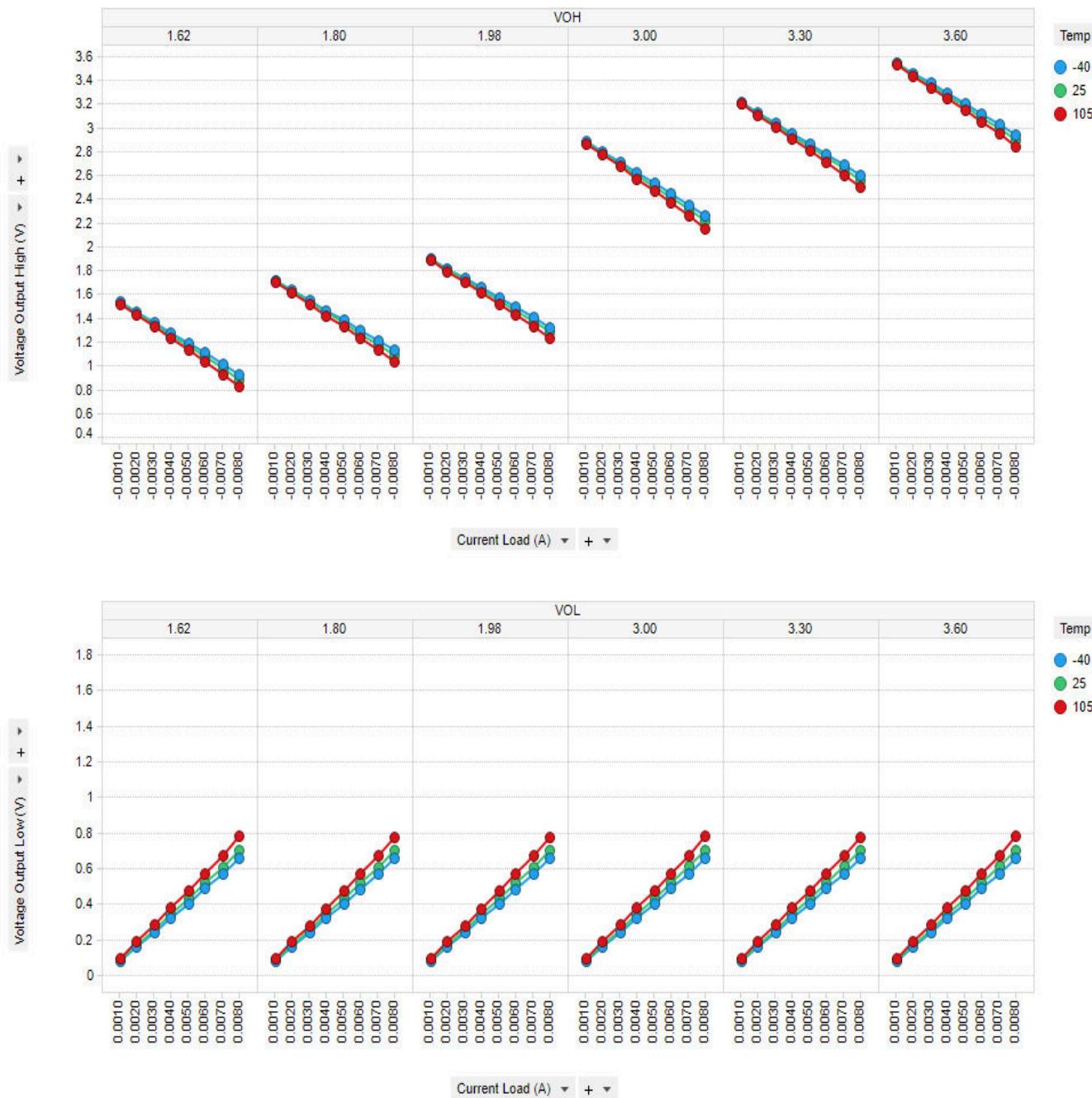

## 7.8 代表的特性

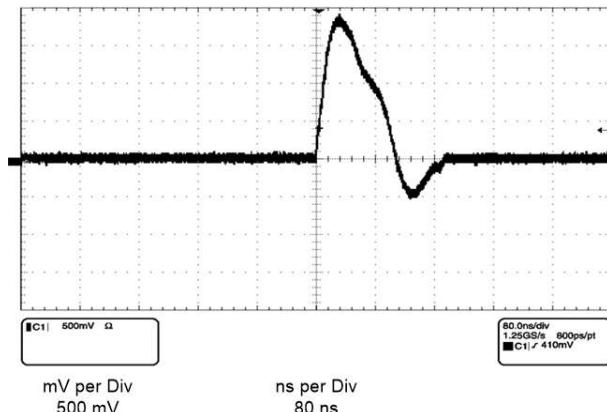

図 7-13. 100BASE-TX PMD アイ波形

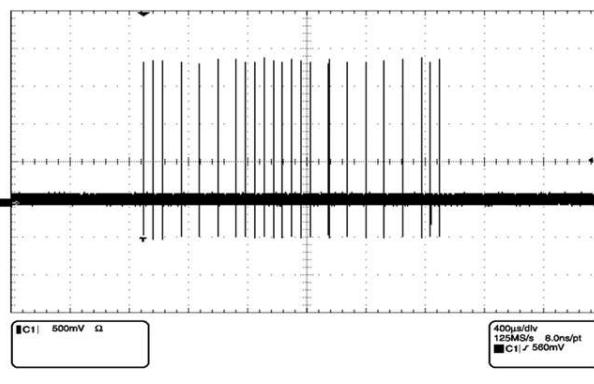

図 7-14. 10BASE-Te リンク パルスの波形

図 7-15. オートネゴシエーション高速リンク パルスの波形

## 8 詳細説明

### 8.1 概要

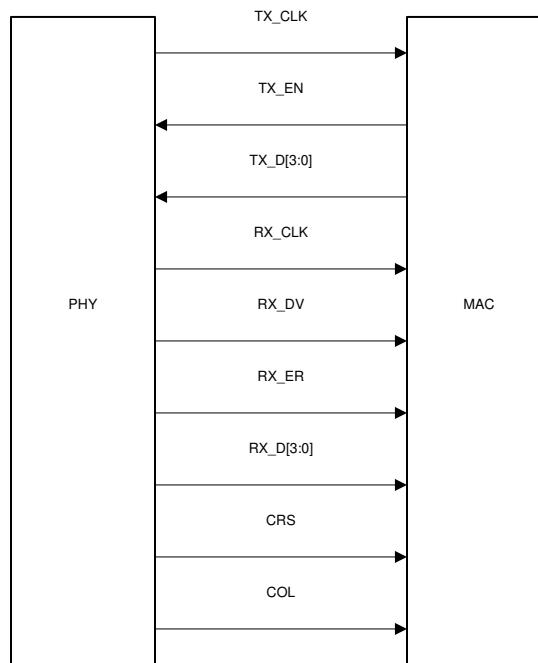

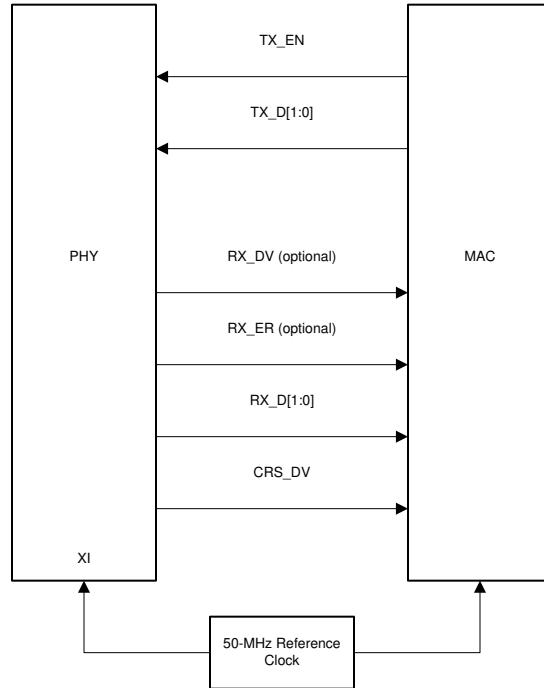

DP83826 は、IEEE802.3 10BASE-T<sub>e</sub> および 100BASE-TX 規格に準拠したシングル ポートの物理層トランシーバです。DP83826 は、厳格な産業用フィールドバス アプリケーションのニーズを満たすように設計されており、非常に低いレイテンシ、レイテンシの確定的な変動 (リセット、電源サイクル全体)、XI と TX\_CLK 間の固定位相、低消費電力、高速リンクアップを実現するハードウェア ブートストラップを使用した構成を提供します。このデバイスは、MAC (媒体アクセス制御) に直接接続するための標準の MII および RMII (リーダー モードおよびフォロワ モード) をサポートしています。このデバイス専用の CLKOUT ピンを使用して、システム上の他のモジュールをクロック駆動できます。さらに、PWRDN ピンはパワー オン リセット (POR) から DP83826 のリンクアップを制御し、DP83826 の非同期パワーアップおよびホスト SoC (システム オン チップ) または FPGA (フィールド プログラマブル ゲート アレイ) コントローラの設計に有用です。

デバイスは 3.3V 単一電源で動作し、LDO を内蔵しているので、内部ブロックに必要な電圧レールを供給できます。デバイスは 3.3V または 1.8V の I/O 電圧インターフェイスに対応できるため、DP83826 は単一電源 PHY として動作できます。DP83826 内の自動電源構成により、追加の構成設定を必要とせずに、VDDIO 電源を自由に組み合わせて使用できます。

DP83826 では、ミクスド シグナル処理を使用してイコライゼーション、データの回復、および誤り訂正が行われるため、ケーブル長が 150m 以上の CAT5e ツイストペア配線で信頼性の高い動作を実現できます。

DP83826 は、パワーアップ シーケンス時にハードウェア ブートストラップを使用して、2 つのモードを選択できます。

- BASIC モード

- ENHANCED モード

BASIC モードは、標準イーサネット アプリケーションに必要なすべての機能を提供します。また、現在の多くのアプリケーションで使用されている一般的なピン配置の構成を使用しているので、既存のプラットフォームでの評価とテストを簡素化できます。DP83826 を使用すれば、MAC と MDI 終端を内蔵しているため、ボードの設計を効率化できます。必要なすべてのクロック出力は、25MHz 外部水晶振動子または発振器入力を備えた単一の PLL から生成されます。

#### 注

一般的な標準イーサネット ピン配置を使用する既存のシステムで、DP83826 BASIC モードを使用する手順のステップ-バイステップ アプローチについては、[SNLA338](#) を参照してください。

ENHANCED モードには、BASIC モードで説明されているすべての動作モードが含まれていますが、ピンを変更することで追加の機能が可能になります。ENHANCED モードの DP83826 は、標準イーサネット アプリケーションに加えてイーサネット フィールドバス アプリケーションでも使用できます。機能には以下が含まれます：

- 専用基準クロック出力: CLKOUT (ピン 31) を使用すると、システム全体を同期して、レイテンシを短縮できます (MAC での FIFO の減少)。このクロックは POR で有効化され、リセットを通して使用可能に維持されます。この機能により、他の PHY およびボード上のホスト SoC/FPGA 用の専用クロックの必要性も低下します。

- 専用 HW ストラップで強制モード、MDI、MDIX を使用することで、POR およびリセットからの高速リンクアップが実現します。

- IEEE パワーダウン ピン: PWRDN (ピン 21) は、DP83826 の非同期パワーアップとホスト SoC/FPGA 制御に有用で、この専用ピンを介して DP83826 リンクアップを引き続き管理できます。

- MAC インターフェイス ピン以外の PHY アドレス ハードウェア ブートストラップにより、MII および RMII MAC インターフェイス ピンのシグナル インテグリティが向上します。

両方のモードのピン マッピングについては、セクション [セクション 5](#) および [セクション 6](#) を参照してください。

両方のモードのハードウェア ブートストラップの構成については、セクション [セクション 8.4.1.1](#) および [セクション 8.4.1.2](#) を参照してください。

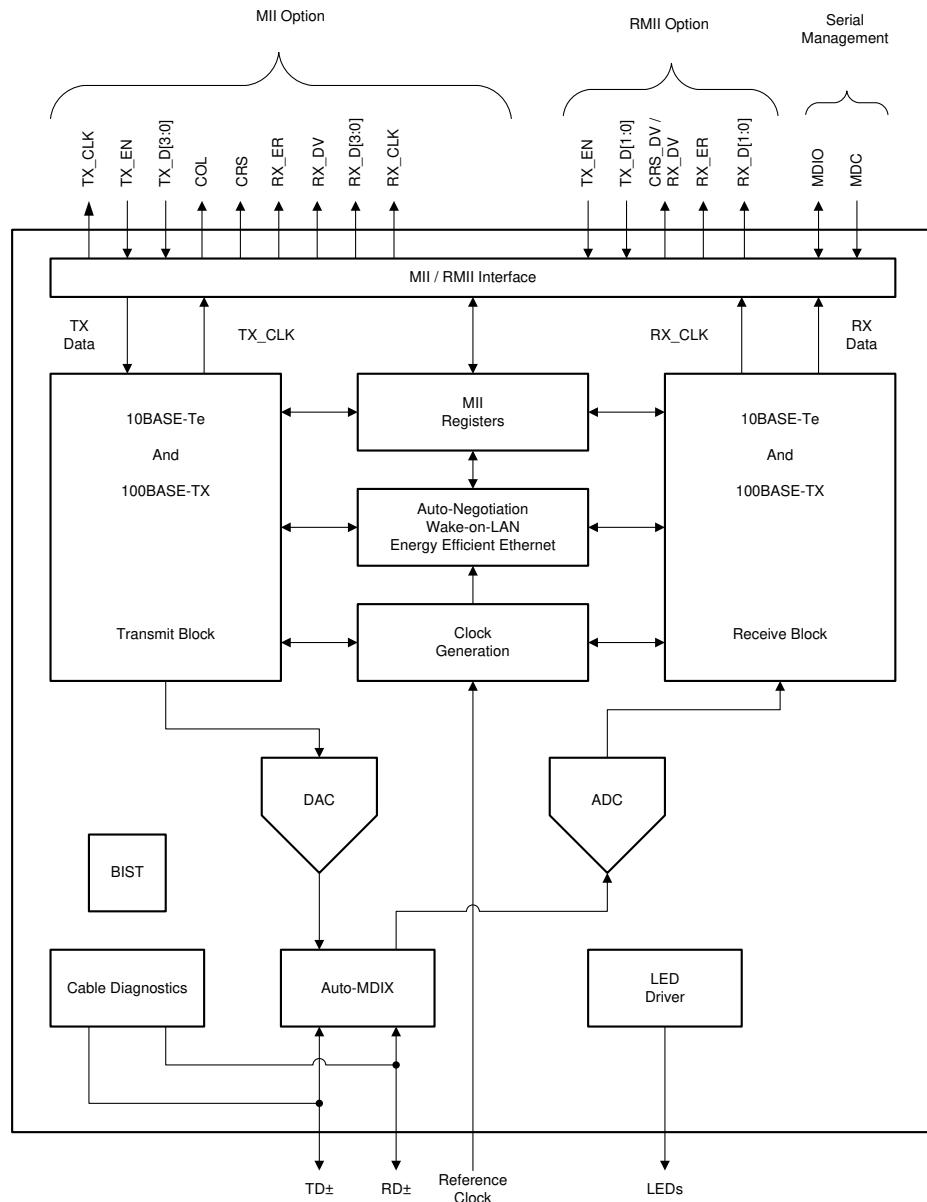

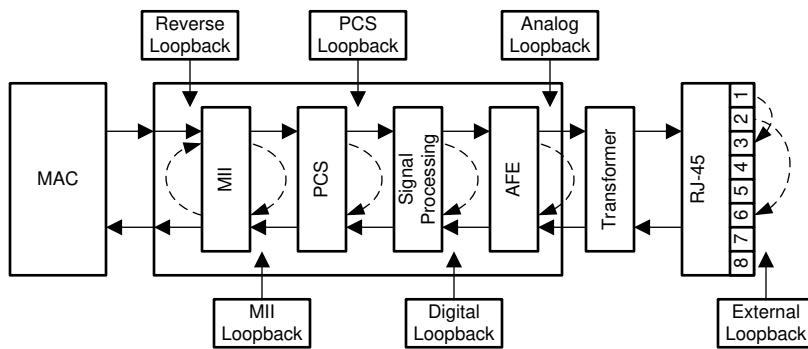

## 8.2 機能ブロック図

## 8.3 機能説明

### 8.3.1 オートネゴシエーション(速度/二重モード選択)

オートネゴシエーションは、リンク セグメントの両端間で設定情報を交換するメカニズムを提供します。このメカニズムは、高速リンク パルス (FLP) を交換することによって実装されます。FLPS は、リンク セグメントの各終端にある 2 つのデバイス間の機能を通信するために使用される情報を提供するバースト パルスです。DP83826 は、オートネゴシエーションのために 100BASE-TX および 10BASE-Te の動作モードをサポートしています。オートネゴシエーションにより、リンク パートナーとローカル デバイスのアドバタイズされた能力に基づいて、最も高い共通速度が選択されるようになります。オートネゴシエーションは、BASIC モード制御レジスタ (BMCR、アドレス 0x0000) のビット [12] を使って、ブートストラップを使用して、またはレジスタ設定を使用して、ハードウェアで有効化または無効化できます。オートネゴシエーションの詳細については、IEEE 802.3 条項 28 の仕様を参照してください。

### 8.3.2 Auto-MDIX の解決

DP83826 は、リンク パートナーへの接続に「ストレート」ケーブルと「クロスオーバー」ケーブルのいずれを使用しているかを判断できます。DP83826 は、TD (MDI) チャネルと Rd (MDIX) チャネルを自動的に再割り当てし、リンク パートナーとのリンクを確立できます。Auto-MDIX 解決は、機能をアドバタイズするために FLP を交換する実際のオートネゴシエーション プロセスよりも前に行われます。自動 MDI/MDIX は IEEE 802.3 条項 40、40.8.2 節に記述されており、10BASE-Te および 100BASE-TX には必要な実装ではありません。Auto-MDIX は、PHY を強制モードで動作させる際にも使用できます。

Auto-MDIX は、ハードウェア ブートストラップを使用して、またはレジスタ構成を行うことで、PHY 制御レジスタ (PHYCR、アドレス 0x0019) のビット [15] を使用して有効化または無効化できます。Auto-MDIX が無効化されている場合、PMA は MDI (ストレート) または MDIX (クロスオーバー) のいずれかに強制されます。MDI または MDIX の手動構成は、PHYCR のビット [14] を使用して、またはハードウェア ブートストラップを ENHANCED モードで使用することで、レジスタ構成を使用して行うこともできます。

### 8.3.3 EEE (Energy Efficient Ethernet)

#### 8.3.3.1 EEE の概要

IEEE 802.3az で定義されている省電力型イーサネット (EEE) は、低消費電力アイドル (LPI) モードで動作するレイヤ 1 (物理層) およびレイヤ 2 (データリンク層) に統合された機能です。LPI モードでは、パケットの使用率が低いときに電力が節約されます。EEE は、リンクのドロップまたはパケットの破損を発生させずに、LPI モードの移行および終了を実行するプロトコルを定義します。

DP83826 EEE は、100Mbps および 10Mbps の速度をサポートします。EEE は、MII と RMII 両方の MAC インターフェイスでサポートされています。10BASE-Te 動作では、EEE は 10BASE-T PHY と完全に相互運用可能な低い送信振幅で動作します。

EEE は、レジスタのプログラミングによって有効化する必要があります。以下の手順では、MDC/MDIO インターフェイスを使用して、DP83826 を EEE 用に構成する方法について説明します。

| レジスタ・アドレス | データ   |

|-----------|-------|

| 001Fh     | 8000h |

| 203Ch     | 0002h |

| 04D1h     | 008Bh |

| 04D3h     | 4F12h |

| 04DFh     | 0180h |

| 033Eh     | A681h |

| 033Fh     | 0003h |

| 0123h     | 0800h |

| 031Bh     | 8848h |

| 0466h     | FE00h |

| 04CFh     | 261Dh |

| 0416h     | 1F30h |

| 04F5h     | 2864h |

| 04E0h     | FFF2h |

| 031Fh     | FE36h |

| 0308h     | 0000h |

| 04F4h     | 0800h |

| レジスタ・アドレス | データ   |

|-----------|-------|

| 0000h     | 3300h |

### 8.3.3.2 EEE ネゴシエーション

EEE は、オートネゴシエーション中にアドバタイズされます。オートネゴシエーションは、パワーアップ時、管理コマンド時、リンク障害後、またはユーザ介入によって実行されます。EEE は、両方のリンク パートナーが EEE 機能をアドバタイズする場合にのみサポートされます。EEE がサポートされていない場合、すべての EEE 機能が無効になり、MAC は LPI をアサートしません。EEE 機能をアドバタイズするため、PHY は追加のフォーマット済み次ページと未フォーマットの次ページを順番に交換する必要があります。

EEE ネゴシエーションは、レジスタ アクセスを使用して有効化できます。IEEE 802.3az では、MMD3 および MMD7 が EEE 制御およびステータス レジスタの場所として定義されています。MMD3 レジスタ 0x1014、0x1001、0x1016、および MMD7 レジスタ 0x203C、0x203D には、EEE の動作に必要なすべての制御とステータス表示が含まれています。省電力型イーサネット構成レジスタ 3 (EEECFG3、アドレス 0x04D1) には、EEE 構成バイパスの制御が含まれています。

デフォルトでは、EEE 機能はバイパスされます。MMD3 および MMD7 レジスタに基づいて EEE をアドバタイズするには、EEE 機能バイパスを無効化 (0x04D1.0 = 1、0x04D1.3 = 1) し、EEE アドバタイズメントを有効化 (MMD7 0x203C.1 = 1) する必要があります。

### 8.3.4 802.3az をサポートしていないレガシー MAC のための EEE

デバイスは、レジスタのプログラミングによって LPI 信号 (アイドルおよびリフレッシュ) を開始するように構成することもできます。この機能により、使用されている MAC が EEE をサポートしていない場合でも、システムは EEE を実行できます。このモードでは、ホスト コントローラ アプリケーションによって、LPI 信号のイネーブル / ディスエーブルが決まります。\*DP83826\* が LPI 信号モードの場合、アプリケーションは DP83826 をアクティブ モードに移行してから、MAC インタフェース経由でデータを送信します。

DP83826 には、LPI 信号モード中にデータを保存するためのバッファリング機能はありません。レジスタ設定によって EEE を有効化するには、以下のレジスタを設定する必要があります。

1. 0x04D1.0 = 1、0x04D1.3 = 1 を書き込むことで、EEE 機能を有効化します

2. 書き込み (MMD7 0x203C.1 = 1) により、オート ネゴシエーション中に EEE 機能をアドバタイズします

3. 0x0000.9 = 1 を書き込むことで、リンクを再ネゴシエーションします

4. 0x04D1.12 = 1 を書き込むことで、強制的に Tx LPI をアイドル状態にします

5. LPI アイドルの送信を停止するには、0x04D1.12 = 0 を書き込みます

### 8.3.5 WoL (Wake-on-LAN) パケット検出

Wake-on-LAN (WoL) は、特定のフレームを検出し、レジスタ ステータスの変更、GPIO 表示、割り込みフラグのいずれかを通じて接続コントローラに通知するメカニズムを提供します。DP83826 デバイスの WoL 機能により、物理層より上位にある接続デバイスは、適格な資格情報を持つフレームが検出されるまで低消費電力状態を維持できます。このデバイスは、WoL マジック パケット™ フレーム タイプをサポートしています。適格 WoL フレームを受信すると、デバイス WoL ロジック回路は、GPIO ピンによってユーザー定義イベント (パルスまたはレベル変化) またはステータス割り込みフラグを生成し、接続コントローラにウェーク イベントが発生したことを通知します。このデバイスにはサイクル冗長性チェック (CRC) ゲートが内蔵されており、無効なパケットによってウェークアップ イベントがトリガされることを防止します。Wake-on-LAN 機能には以下が含まれます。

- サポートされているすべての速度 (100BASE-TX および 10BASE-T) での WoL フレームの識別

- WoL フレーム受信時のウェークアップ割り込み生成

- 無効なフレームからの割り込み生成を防止するための WoL フレーム CRC エラー チェック

- SecureOn パスワード保護を備えたマジック パケット技術

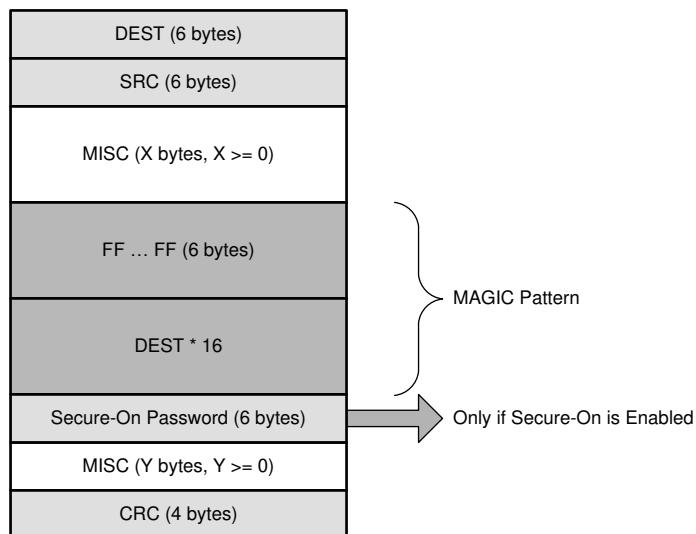

### 8.3.5.1 マジック パケット構造

マジック パケット検出を構成した場合、DP83826 は、ノードにアドレス指定された受信フレームすべてを、特定のデータ シーケンスでスキャンします。このシーケンスにより、フレームがマジック パケットフレームとして識別されます。

マジック パケットフレームは、送信元アドレス、宛先アドレス(受信ステーションの IEEE アドレスまたはブロードキャストアドレス)、CRC など、選択した LAN 技術の基本的な要件も満たしている必要があります。

特定のマジック パケットシーケンスは、このノードの MAC アドレスを 16 個複製したもので、中断や中断はありません。セキュリティが有効な場合は、Secure-On パスワードが続きます。このシーケンスはパケット内の任意の場所に配置できますが、同期ストリームの前に配置する必要があります。同期ストリームは、6 バイトの 0xFF として定義されます。

図 8-1. マジック パケット構造

### 8.3.5.2 マジック パケットの例

以下は、宛先アドレス 11h 22h 33h 44h 55h 66h および SecureOn パスワード 2Ah 2Bh 2Ch 2Dh 2Eh 2Fh のマジック パケットの例です。

| DESTINATION       | SOURCE            | MISC              | FF                |

|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 |

| 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 |

| 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 |

| 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 | 11 22 33 44 55 66 |

| 11 22 33 44 55 66 | 2A 2B 2C 2D 2E 2F | MISC              | CRC               |                   |                   |                   |                   |                   |                   |

### 8.3.5.3 Wake-on-LAN の構成と状態

Wake-on-LAN 機能は、受信構成レジスタ (RXFCFG、アドレス 0x04A0) を使って構成します。レシーバステータス レジスタ (RXFS、アドレス 0x04A1) に Wake-on-LAN ステータスが通知されます。Wake-on-LAN 割り込みフラグの構成と状態は、MII 割り込みステータス レジスタ 2 (MISR2、アドレス 0x0013) にあります。

### 8.3.6 低消費電力モード

DP83826 デバイスは、3 つの低消費電力モードをサポートしています。このセクションでは、これらの低消費電力モードの背後にある原理、およびそれらを有効にする構成について説明します。

### 8.3.6.1 アクティブスリープ

アクティブスリープモードにより、リンクパートナーが接続されていない場合の消費電力が低減されます。この機能を有効化するには、PHYの初期化時にPHYSCRレジスタに正しいビットを書き込む必要があります。この機能は、BISCRレジスタを読み出すことで確認できます。

アクティブスリープが有効化されており、PHYがケーブル接続を検出しない場合、PHYは自動的にアクティブスリープモードに遷移します。デバイスがこのモードに遷移すると、TD $\pm$ およびRD $\pm$ ピンのSMI回路とエネルギー検出回路を除くすべての内部回路がシャットダウンします。アクティブスリープモードでは、デバイスは1.4秒ごとに通常のリンクパルス(NLP)を送信して、リンクパートナーの存在を確認します。リンクパートナーが検出されると、PHYは自動的に通常モードに戻り、内部回路の他の部分に電力を供給します。

デバイスは、PHY固有の制御レジスタ(PHYSCR、アドレス0x0011)のビット[14:12]=0b110を設定することで、アクティブスリープモードを有効化します。

### 8.3.6.2 IEEEパワーダウン

IEEEパワーダウンスイッチは、SMIおよび内部クロック回路を除くすべてのPHY回路を無効にします。

IEEEパワーダウンスイッチは、レジスタアクセスによって、またはピンがパワーダウン機能に構成されている場合に、INTR/PWRDNピンのいずれかを使用して有効化できます。

INTR/PWRDNピンによるIEEEパワーダウンスイッチを有効化するには、このピンをLowにしてグランドに駆動する必要があります。

SMIによるIEEEパワーダウンスイッチを有効化するには、BASICモード制御レジスタ(BMCR、アドレス0x0000)のビット[11]を1に設定します。

### 8.3.6.3 ディープパワー ダウン状態

ディープパワー ダウン状態(DPD)は、SMIを除くすべてのPHY回路を無効化します。このモードでは、デバイスはPHYPLLを無効化して、消費電力をさらに低減します。

デバイスは、このシーケンスを使用して、DPD状態に移行します。

1. DPD状態を有効化(0x0428.2=1)

2. IEEEパワーダウン状態を有効化(ピンまたは0x0000.11=1)

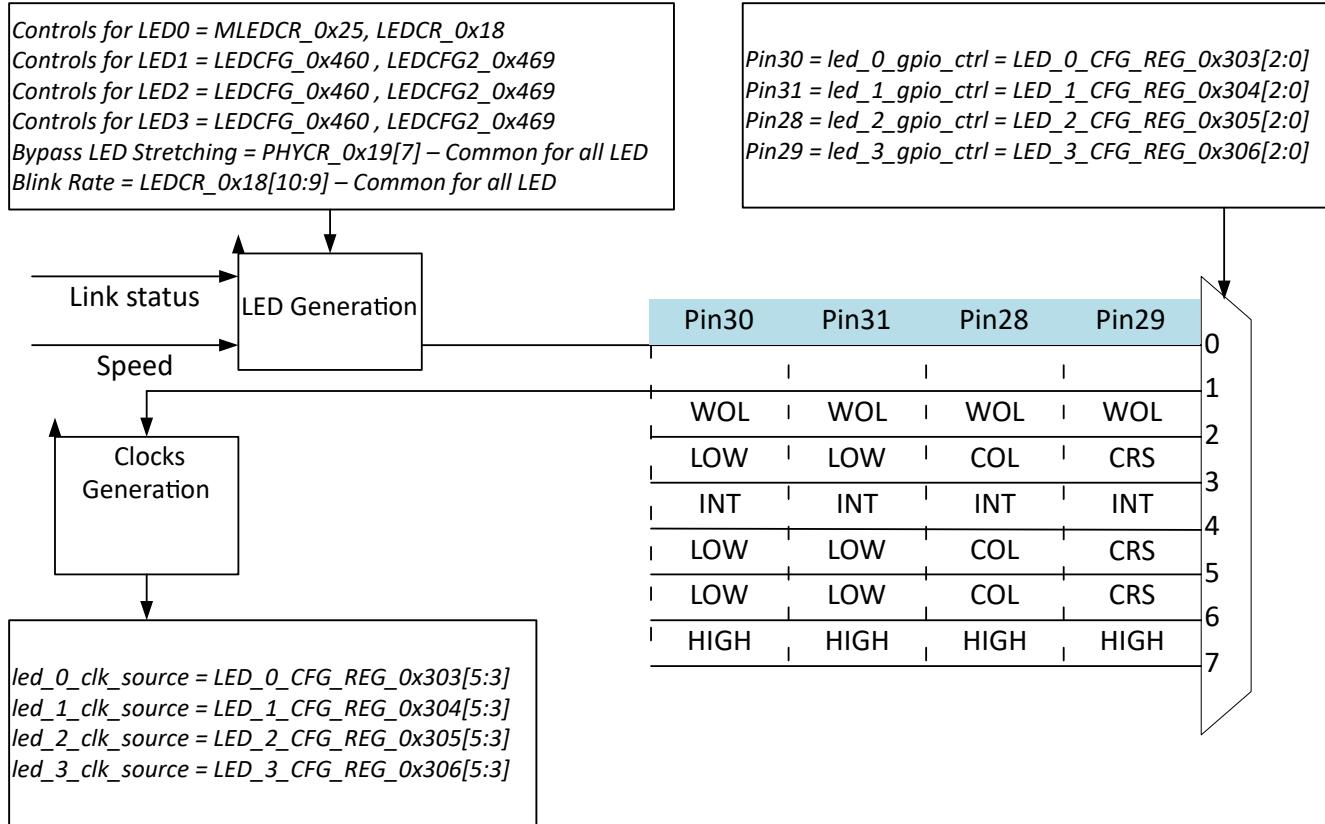

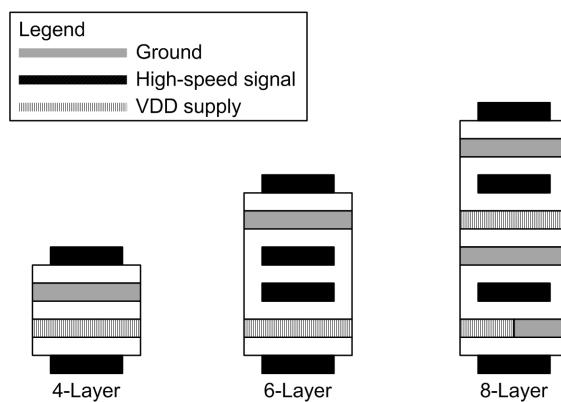

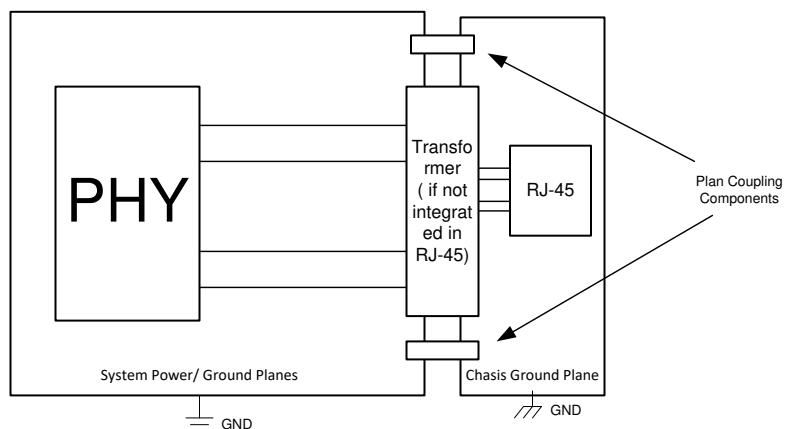

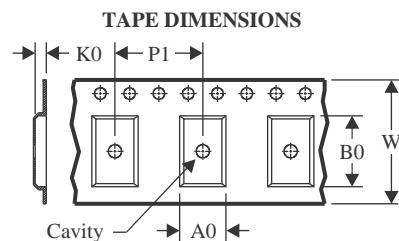

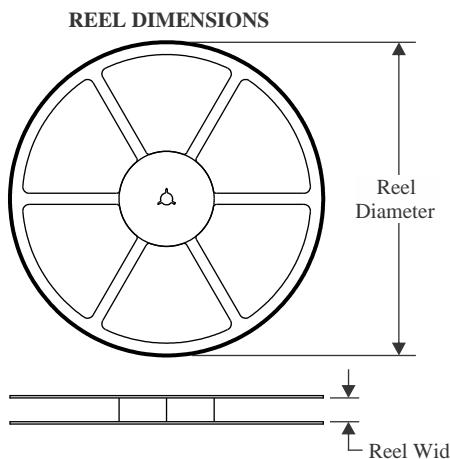

### 8.3.7 RMIIリピータモード