## DLPC8445、DLPC8445V、DLPC8455 高解像度コントローラ

### 1 特長

- DLPC84x5 コントローラのサポート

- 60Hz で最大 4K UHD

- 240Hz (2D) および 120Hz (3D) で最大 1080p

- DLPC84x5 コントローラは、以下の 4K UHD DMD をサポートしています。

- DLPC8445 および DLPC8445V は、DLP472TP および DLP391TP DMD をサポートしています

- DLPC8455 は DLP473TE DMD をサポートしています

- 1, 2, 4、または 8 レーンの V-by-One® HS ビデオ入力ポート × 1

- 最大 600MHz のピクセルクロックと 60Hz で 2160p

- 最大 3.0Gbps の入力伝送レート

- サポートされている入力形式

- RGB および YCbCr

- 4:4:4 と 4:2:2

- 内蔵 Arm® プロセッサ

- 52 本の構成可能な GPIO

- PWM ジェネレータ

- キャプチャタイマおよび遅延タイマ

- USB 2.0 高速コントローラ

- SPI および I<sup>2</sup>C コントローラー

- UART および割り込みコントローラ

- ワーピング エンジン

- 1D および 2D キーストーン補正

- ビデオ処理用の組み込み部分フレーム メモリ

- 追加の画像処理

- オーバーラップ カラー対応 (DLPC8445V および DLPC8455 のみ)

- 可変リフレッシュ レート (VRR) 対応

- ローリング バッファによるフレーム レイテンシの短縮

- DynamicBlack

- フレーム レートの乗算

- 色座標調整

- 色温度調整

- 逆ガンマ補正をプログラム可能

- 読み出し側の空間分割 / 時分割多重化

- 3D ディスプレイの統合サポート

- スプラッシュスクリーン ディスプレイ

- マイクロプロセッサおよび PWM シーケンス用のシリアル フラッシュ

- システム制御

- DMD 電源およびリセット ドライバ制御

- DMD 画像の左右 / 上下反転

- JTAG バウンダリスキャン テストをサポート

- LED、RGB レーザー、レーザー蛍光ベースのシステムをサポート

### 2 アプリケーション

- モバイル スマート TV

- モバイル プロジェクタ

- デジタル サイネージ

- レーザー TV

### 3 説明

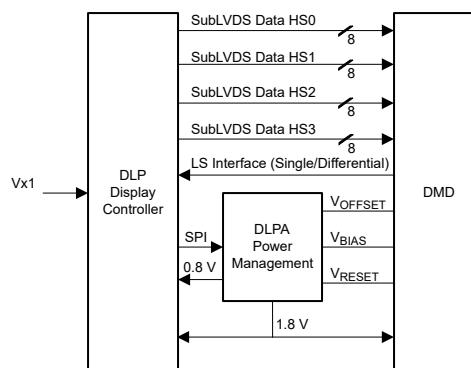

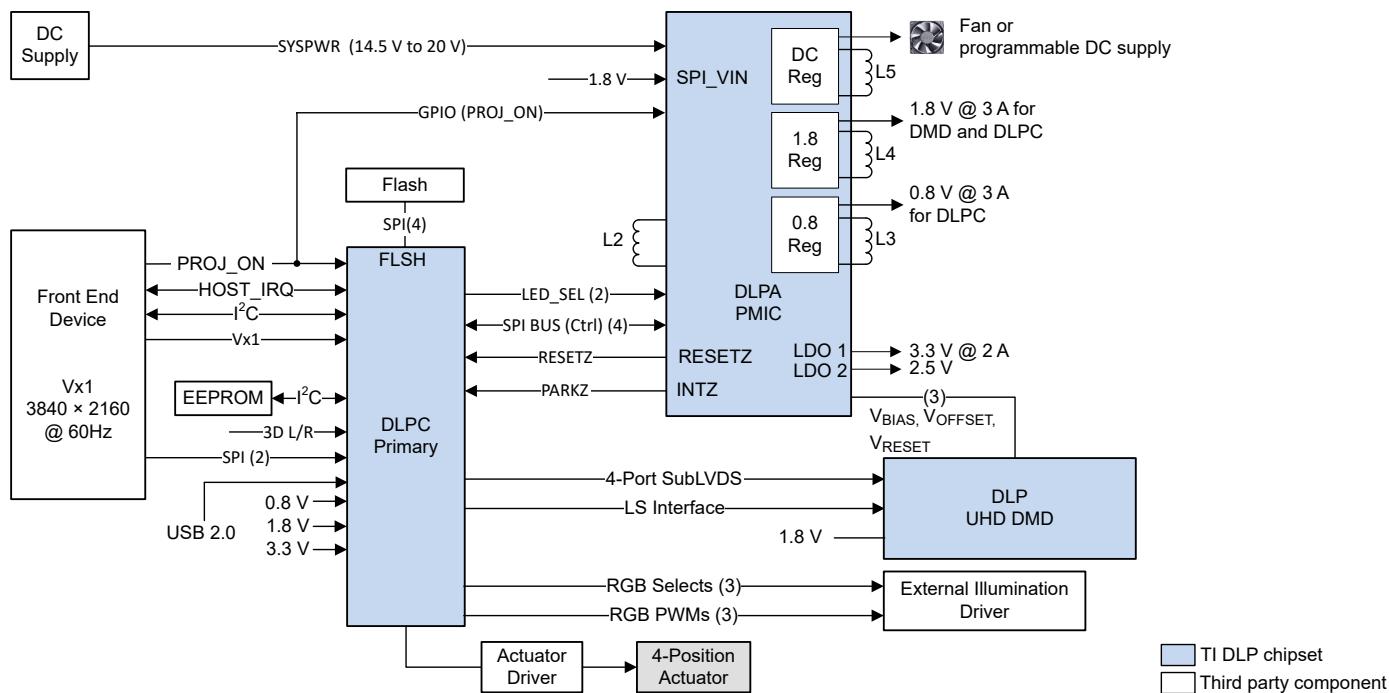

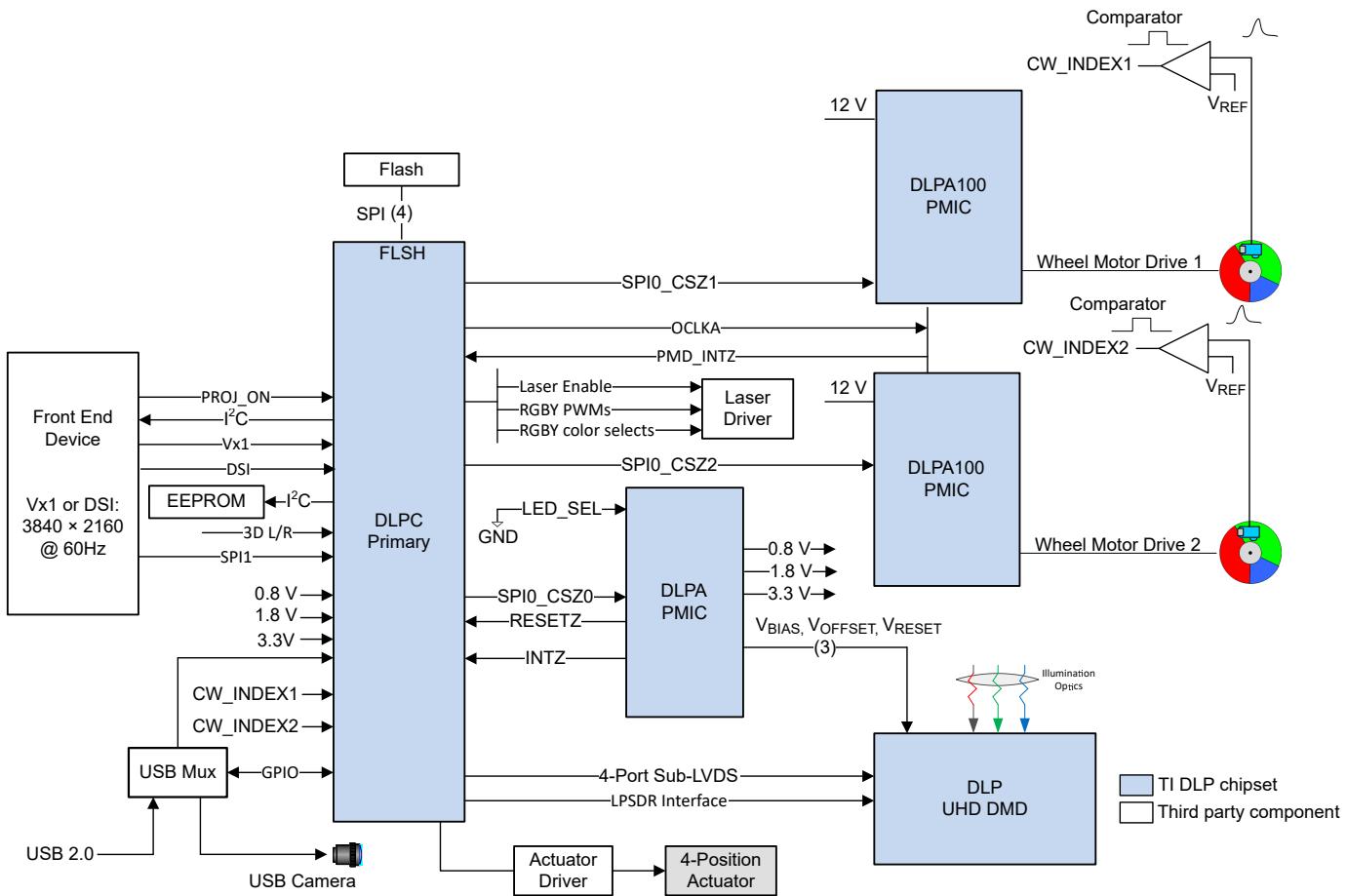

DLPC8445、DLPC8445V、DLPC8455 は、TI の DLP® 製品用の 4K UHD デジタル ディスプレイ コントローラです。DLP チップ セットは、1 つのディスプレイ コントローラ、1 つのマッチングされた DMD、DLPA3085 または DLPA3082 パワー マネージメント IC、DLPA100 モータードライバ IC (レーザー蛍光照明システムのみ) で構成されています。このチップ セットは、小型で高解像度と高輝度を必要とするディスプレイ システムに適しています。信頼性の高い動作を保証するために、DLPC8445、DLPC8445V、または DLPC8455 ディスプレイ コントローラは、常に DMD と DLPA3085 または DLPA3082 PMIC と組み合わせて使用する必要があります。注: DLPA3085 は、DLPC8455 ではサポートされていません。

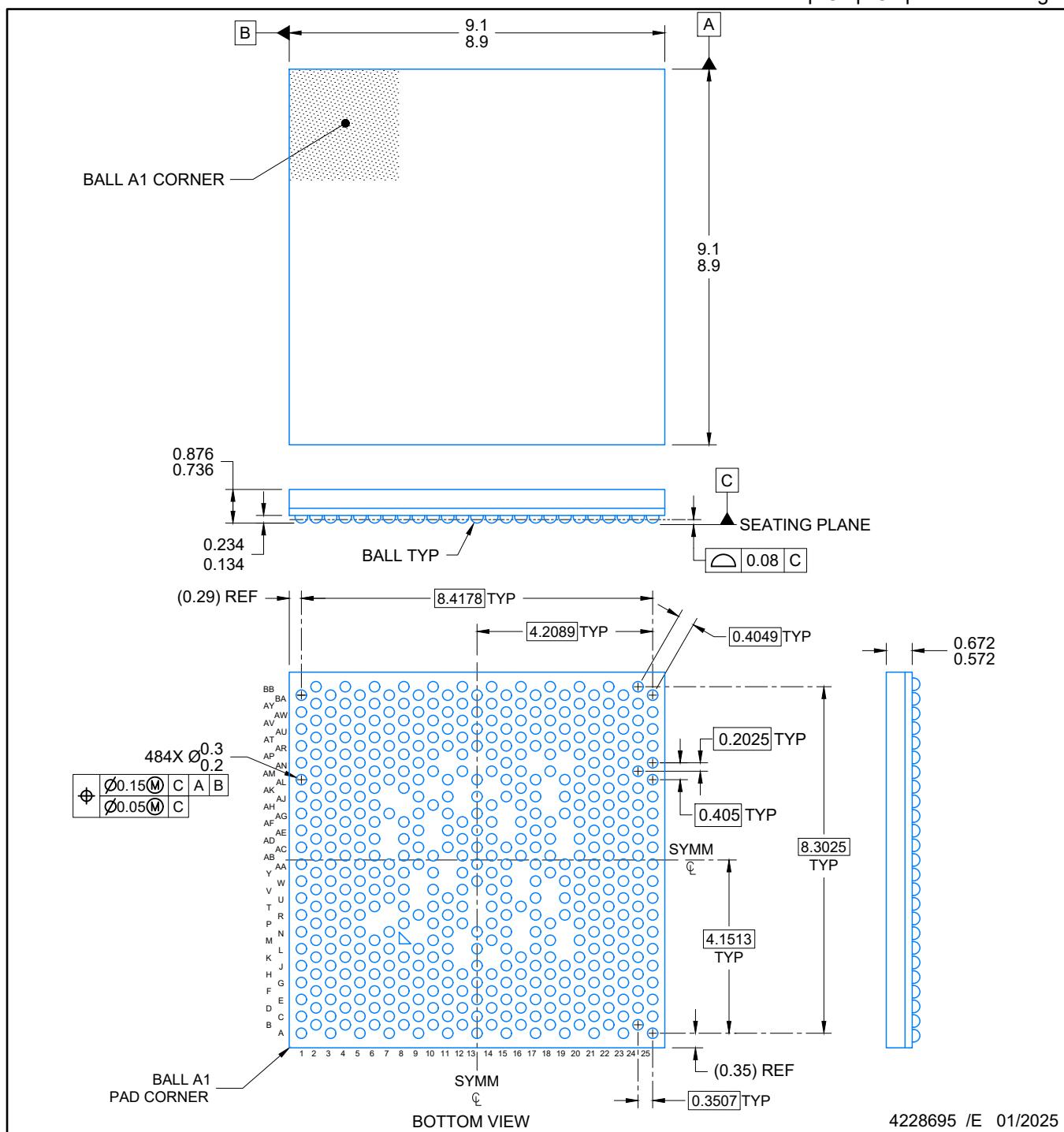

#### 製品情報

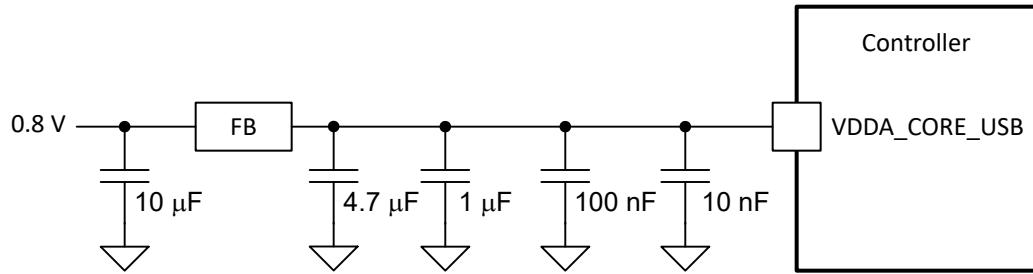

| 部品番号         | パッケージ <sup>(1)</sup> | パッケージ<br>サイズ    |

|--------------|----------------------|-----------------|

| DLPC8445AMD  | FCCSP (484)          | 9.00mm × 9.00mm |

| DLPC8445VAMD | FCCSP (484)          | 9.00mm × 9.00mm |

| DLPC8455AMD  | FCCSP (484)          | 9.00mm × 9.00mm |

(1) 詳細については、「メカニカル、パッケージ、および注文情報」を参照してください。

4K UHD ディスプレイ チップセット

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                                                                            |    |                                             |    |

|----------------------------------------------------------------------------|----|---------------------------------------------|----|

| <b>1 特長</b>                                                                | 1  | 5.14 フラッシュインターフェイスのタイミング要件                  | 30 |

| <b>2 アプリケーション</b>                                                          | 1  | 5.15 ソースフレームのタイミング要件                        | 31 |

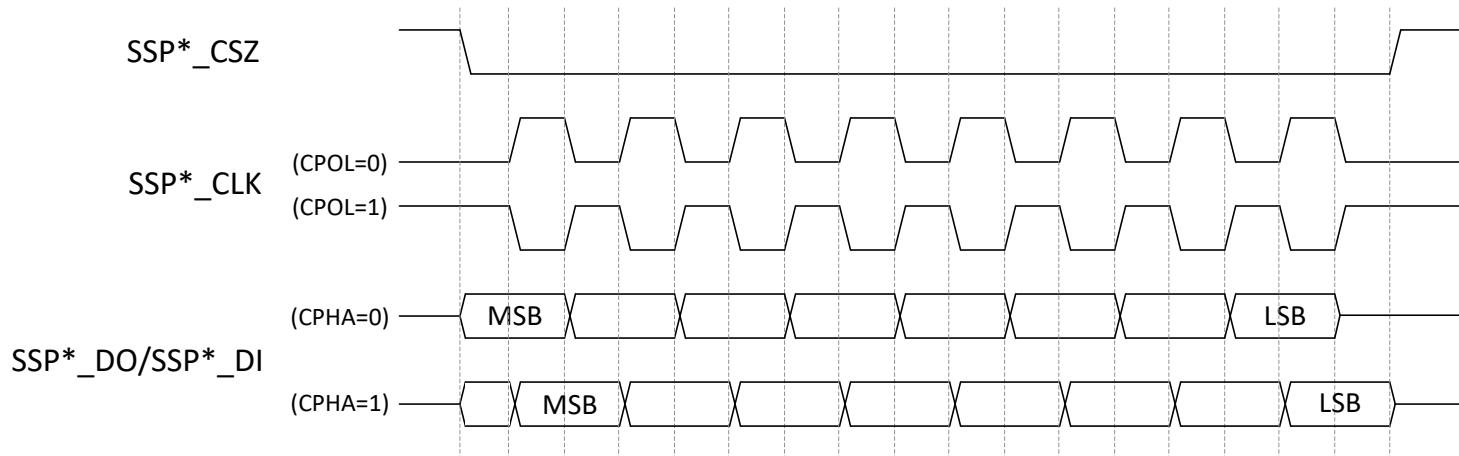

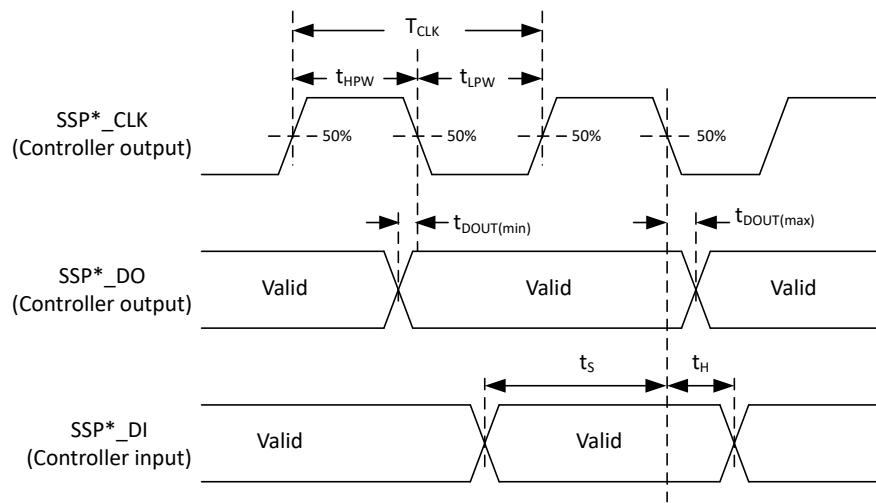

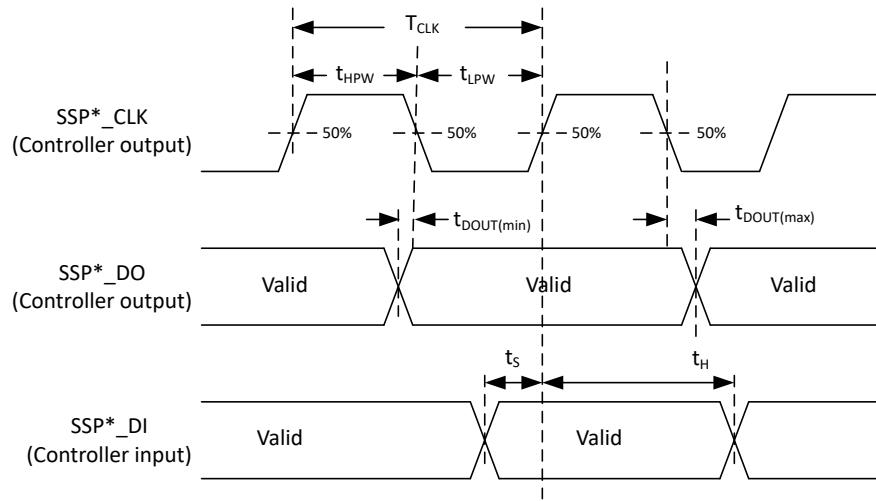

| <b>3 説明</b>                                                                | 1  | 5.16 同期シリアルポートインターフェイスのタイミング要件              | 32 |

| <b>4 ピン構成および機能</b>                                                         | 3  | 5.17 I <sup>2</sup> Cインターフェイスタイミングの要件       | 34 |

| 4.1 初期化、基板レベル テスト、デバッグ                                                     | 3  | 5.18 プログラマブル出力クロックのタイミング要件                  | 34 |

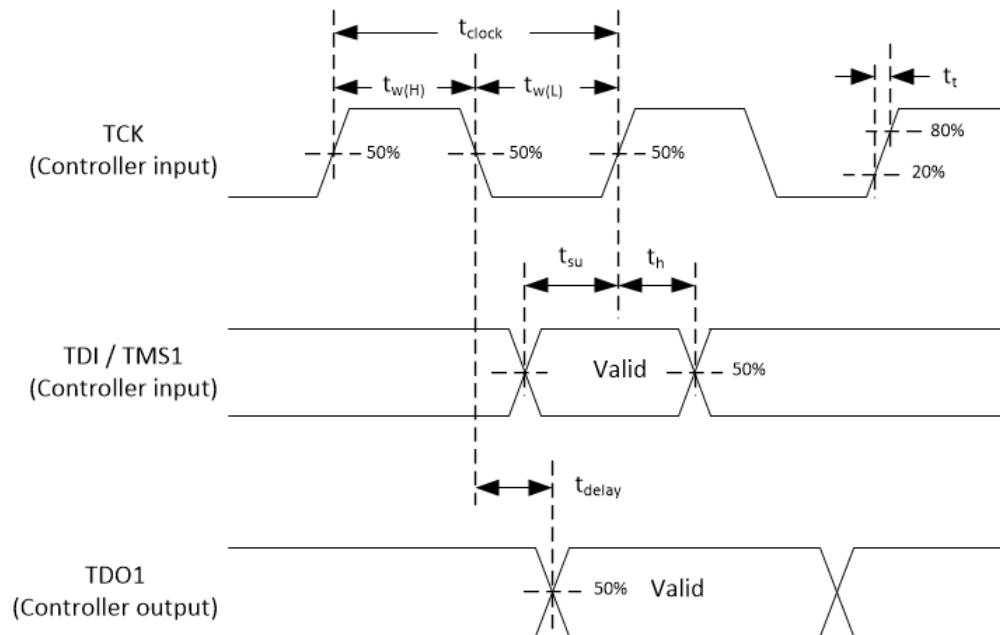

| 4.2 V-by-One インターフェイスの入力データおよび制御                                           | 5  | 5.19 JTAG バウンダリスキャンインターフェイスのタイミング要件(デバッグのみ) | 34 |

| 4.3 FPD-Link ポートの入力データおよび制御<br>(DLPC8445、DLPC8445V、DLPC8455 ではサポートされていません) | 6  | 5.20 DMD 低速インターフェイスのタイミング要件                 | 36 |

| 4.4 DSI 入力データおよびクロック(DLPC8445、<br>DLPC8445V、DLPC8455 ではサポートされていません)        | 7  | 5.21 DMD SubLVDS インターフェイスのタイミング要件           | 36 |

| 4.5 DMD SubLVDS インターフェイス                                                   | 8  | <b>6 詳細説明</b>                               | 37 |

| 4.6 DMD リセットおよび低速インターフェイス                                                  | 10 | 6.1 概要                                      | 37 |

| 4.7 フラッシュインターフェイス                                                          | 10 | 6.2 機能ブロック図                                 | 37 |

| 4.8 ペリフェラルインターフェイス                                                         | 11 | 6.3 機能説明                                    | 39 |

| 4.9 GPIO ペリフェラルインターフェイス                                                    | 12 | <b>7 電源に関する推奨事項</b>                         | 52 |

| 4.10 クロックおよびPLL のサポート                                                      | 17 | 7.1 システムのパワーアップおよびパワーダウンシーケンス               | 52 |

| 4.11 電源およびグランド                                                             | 17 | 7.2 DMD 高速パーク制御(PARKZ)                      | 54 |

| 4.12 I/O タイプのサブスクリプト定義                                                     | 19 | 7.3 パワーマネージメント                              | 55 |

| 4.13 内部プルアップおよびプルダウンの特性                                                    | 19 | 7.4 ホットプラグの使用法                              | 55 |

| <b>5 仕様</b>                                                                | 20 | 7.5 未使用の入力ソースインターフェイスの電源                    | 55 |

| 5.1 絶対最大定格                                                                 | 20 | 7.6 電源                                      | 55 |

| 5.2 ESD 定格                                                                 | 21 | <b>8 レイアウト</b>                              | 56 |

| 5.3 推奨動作条件                                                                 | 21 | 8.1 レイアウトのガイドライン                            | 56 |

| 5.4 熱に関する情報                                                                | 22 | 8.2 熱に関する注意事項                               | 62 |

| 5.5 電源の電気的特性                                                               | 22 | <b>9 デバイスおよびドキュメントのサポート</b>                 | 63 |

| 5.6 ピンの電気的特性                                                               | 23 | 9.1 サードパーティ製品に関する免責事項                       | 63 |

| 5.7 DMD SubLVDS インターフェイスの電気的特性                                             | 24 | 9.2 ドキュメントのサポート                             | 63 |

| 5.8 DMD 低速インターフェイスの電気的特性                                                   | 25 | 9.3 ドキュメントの更新通知を受け取る方法                      | 63 |

| 5.9 V-by-One インターフェイスの電気的特性                                                | 25 | 9.4 サポートリソース                                | 63 |

| 5.10 USB の電気的特性                                                            | 26 | 9.5 デバイスの命名規則                               | 64 |

| 5.11 システム発振器のタイミング要件                                                       | 26 | 9.6 商標                                      | 64 |

| 5.12 電源およびリセットのタイミング要件                                                     | 28 | 9.7 静電気放電に関する注意事項                           | 64 |

| 5.13 V-by-One インターフェイスの一般的なタイミング要件                                         | 29 | 9.8 用語集                                     | 64 |

|                                                                            |    | <b>10 改訂履歴</b>                              | 66 |

|                                                                            |    | <b>11 メカニカル、パッケージ、および注文情報</b>               | 66 |

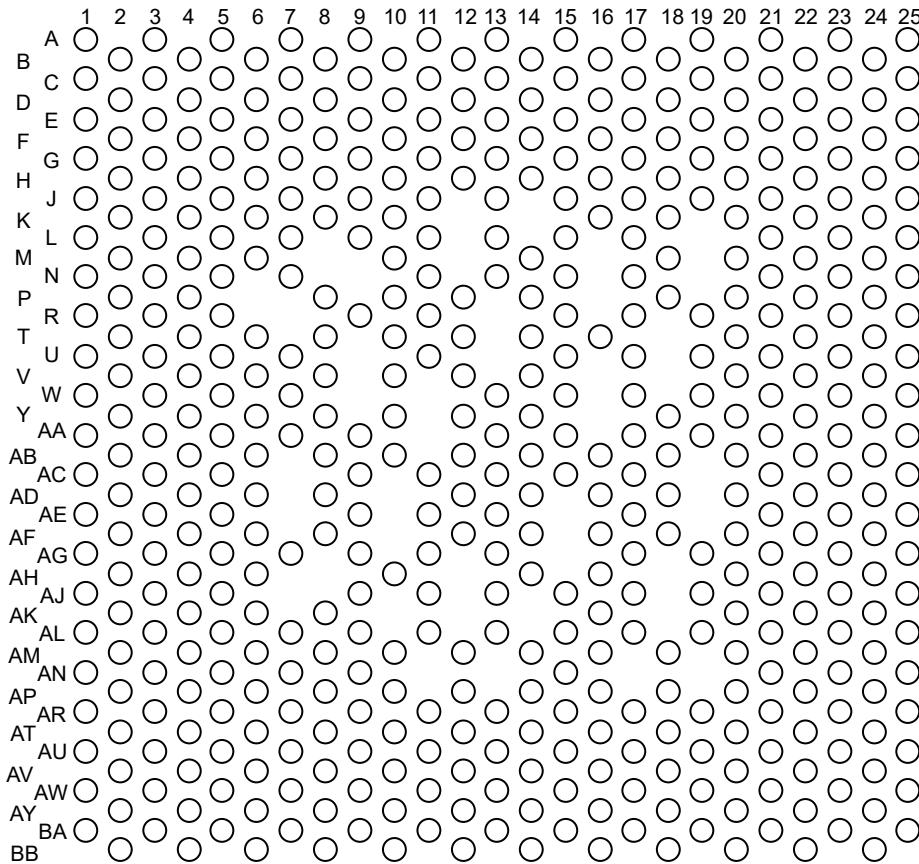

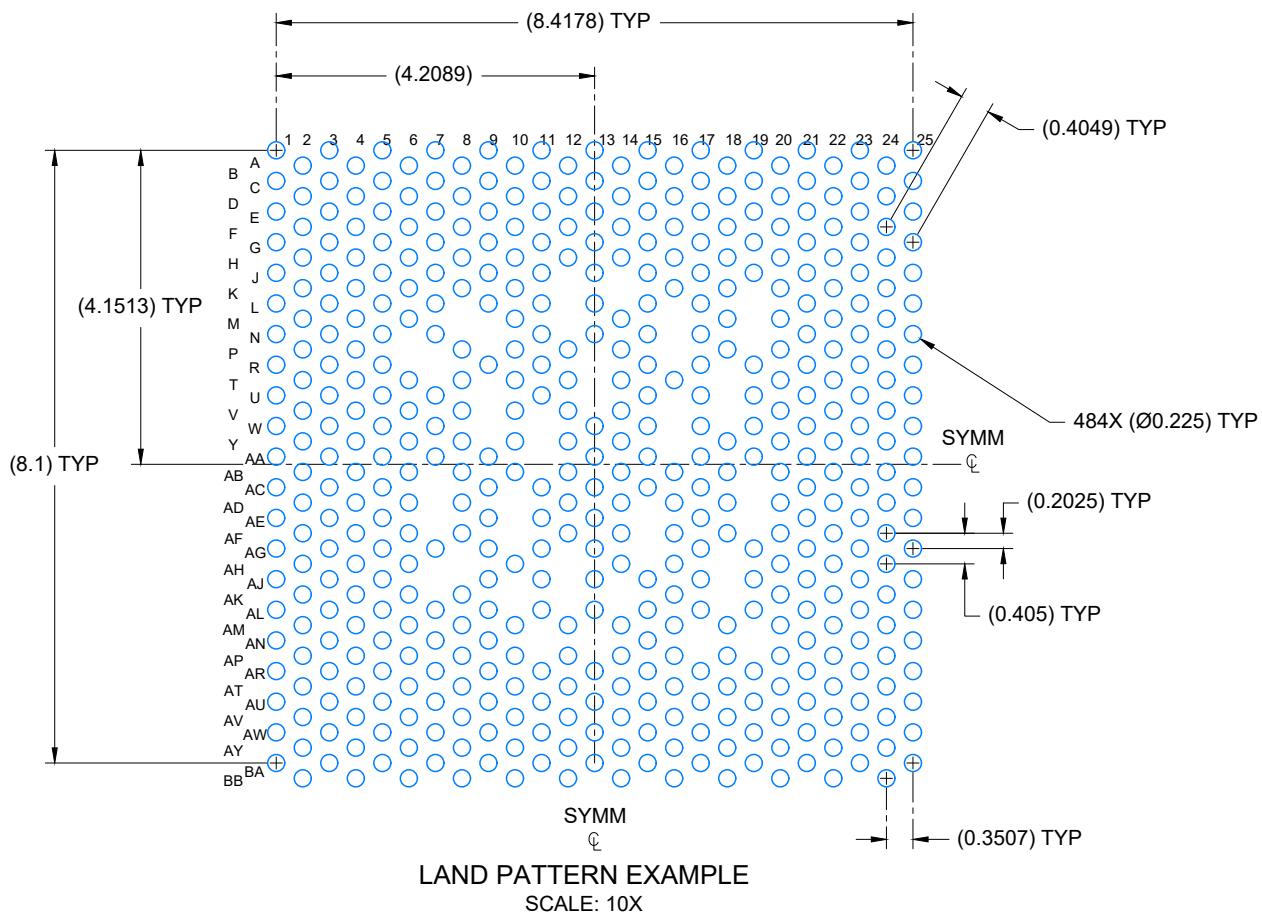

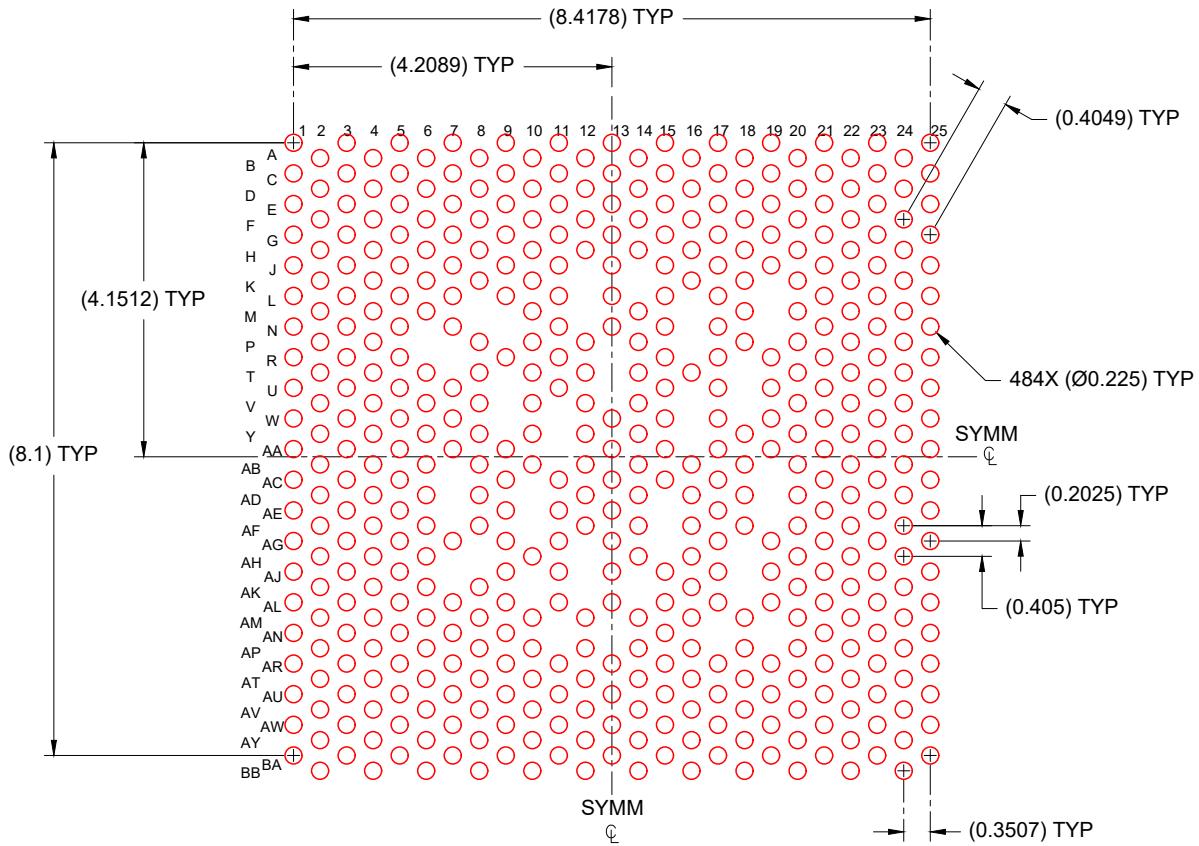

## 4 ピン構成および機能

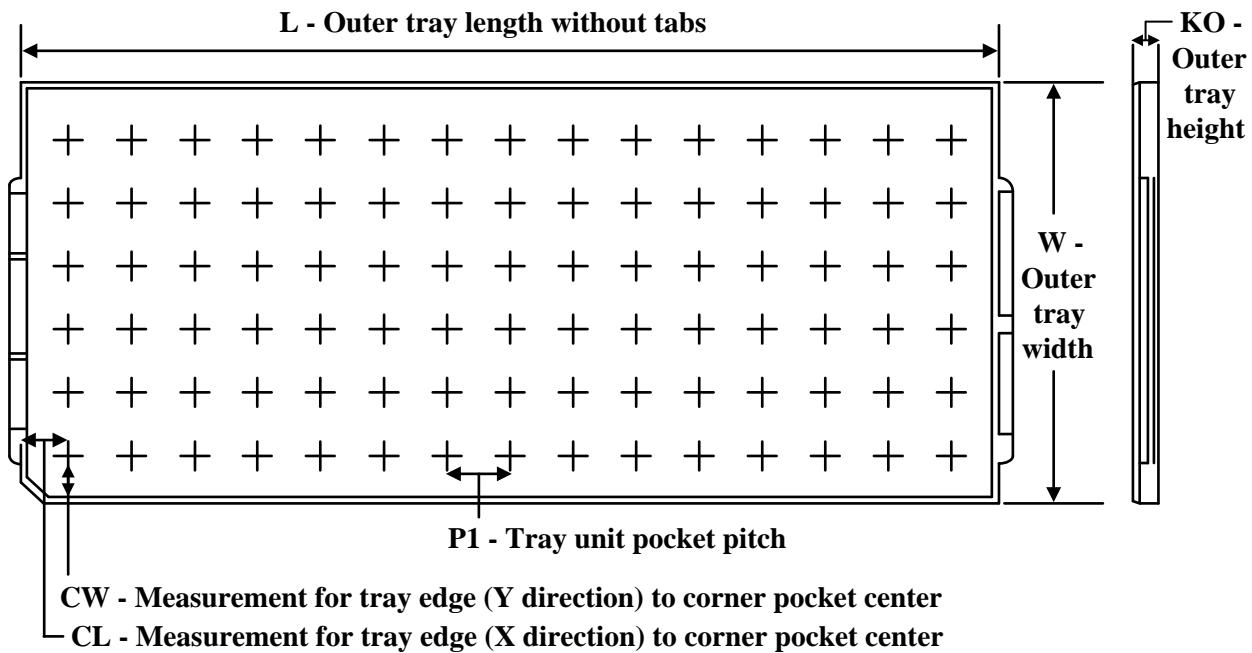

図 4-1. AMD パッケージ 484 ピン FCCSP 上面図

### 4.1 初期化、基板レベルテスト、デバッグ

表 4-1. 初期化、基板レベルテスト、デバッグ

| 名称       | ピン番号 | I/O (1) | 説明                                                                                                                                                                                                                       |

|----------|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROJ_ON  | AP2  | I1      | 通常ミラー パーキング要求 (アクティブ Low): ホストの PROJ_ON 出力によって駆動されます。この信号がロジック Low になると、コントローラは DMD を PARK ますが、DMD のパワードウンは行いません (DLPA が代わりに行います)。最小 High 時間は 200ms です。最小 Low 時間は 200ms です。                                              |

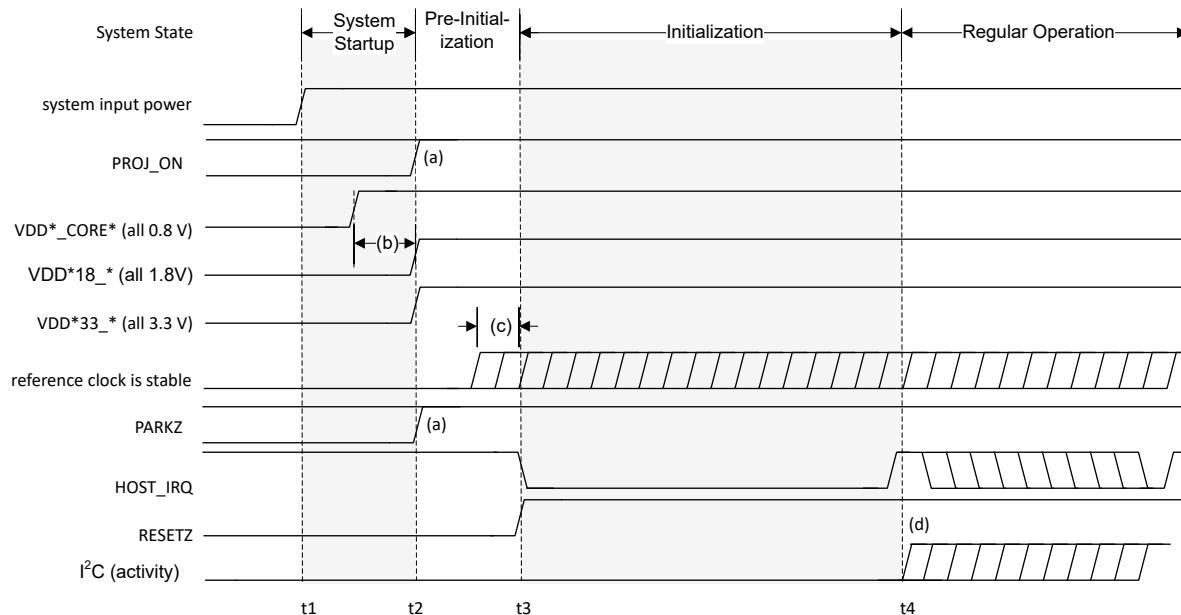

| RESETZ   | P2   | I1      | パワーオン リセット (ヒステリシス バッファを備えたアクティブ Low 入力)。RESETZ で Low から High への遷移が検出されると、自己構成が開始されます。このリセットがデアサートされる前に、すべてのコントローラの電源とクロックが安定している必要があります。RESETZ がアサートされている間は、どの信号もアクティブ状態ではありません。このピンは通常、DLPA PMIC の RESETZ ピンに接続されています。 |

| PARKZ    | AR1  | I1      | DMD 高速パーク制御 (ヒステリシス バッファを備えたアクティブ Low 入力)。電力損失が迫っている場合に、この信号を使用して DMD を素早くパークさせることができます。DMD の最長寿命は高速パーク動作では達成できない可能性があるため、この信号は通常パーク動作が完了できない場合にのみアサートされることを意図しています。PARKZ 信号は通常、DLPA 割り込み出力信号から供給されます。                   |

| JTAGTCK  | V24  | I2      | JTAG と ARM-ICE のシリアル データ クロック。この信号は、JTAG と ARM-ICE 間の動作 (テキサス・インスツルメンツのテストのみ) で共有されます。弱い内部プルダウンを含みます。                                                                                                                    |

| JTAGTMS1 | U23  | I2      | JTAG テスト モード選択。弱い内部プルアップを含みます。                                                                                                                                                                                           |

表 4-1. 初期化、基板レベル テスト、デバッグ (続き)

| ピン             |      | I/O (1) | 説明                                                                                                                                                                                                            |

|----------------|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称             | 番号   |         |                                                                                                                                                                                                               |

| JTAGTMS2       | W25  | I2      | ARM-ICE テストモード選択通常動作では、このピンはオープンのままにするか、未接続のままにする必要があります。弱い内部プルアップを含みます。                                                                                                                                      |

| JTAGTRSTZ      | AA25 | I2      | JTAG、ARM-ICE リセット。<br>通常動作では、このピンは $8k\Omega$ 以下の外付け抵抗を介してグランドにプルする必要があります。通常動作中にこのピンを Low にしないと、起動時や初期化に問題が発生します。<br>JTAG バウンダリスキャンと ARM-ICE デバッグ動作では、このピンはプルアップするか、接続しないままにする必要があります。弱い内部プルアップとヒステリシスを含みます。 |

| JTAGTDI        | Y24  | I2      | JTAG、ARM-ICE、CPU MBIST:シリアル データ入力。弱い内部プルアップを含みます。                                                                                                                                                             |

| JTAGTDO1       | V22  | B14     | JTAG シリアル データ出力                                                                                                                                                                                               |

| JTAGTDO2       | W23  | B14     | ARM-ICE シリアル データ出力。通常動作では、このピンには $\leq 9.15k\Omega$ の外付けプルアップ抵抗が必要です。                                                                                                                                         |

| ETM_TRACECLK   | U25  | O14     | 予約済みピン、未接続のままにする必要があります。                                                                                                                                                                                      |

| ETM_TRACECTL   | T24  | O14     | 予約済みピン、未接続のままにする必要があります。                                                                                                                                                                                      |

| TSTPT_0        | T22  | B14     | テストピン 0<br>このピンには内部プルダウンがあり、 $\leq 9.15k\Omega$ の外付けプルアップ抵抗 (プルアップなし:通常ブート、プルアップあり:ホストコマンド待機) が必要な場合があります。                                                                                                    |

| TSTPT_1        | R25  | B14     | テストピン 1<br>このピンには、通常ブート動作用の内部プルダウンがあります。                                                                                                                                                                      |

| TSTPT_2        | R23  | B14     | テストピン 2<br>このピンには内部プルダウンがあり、 $\leq 9.15k\Omega$ の外付けプルアップ抵抗 (プルアップなし: $I^2C$ アドレス = 0x36、プルアップあり: $I^2C$ アドレス = 0x34) が必要な場合があります。                                                                            |

| TSTPT_3        | P24  | B14     | テストピン 3<br>このピンには内部プルダウンがあり、 $\leq 9.15k\Omega$ の外付けプルアップ抵抗 (プルアップなし:ホストインターフェイスが USB または $I^2C$ 、プルアップあり:ホストインターフェイスが $I^2C$ のみ) が必要な場合があります。                                                                |

| TSTPT_4        | N25  | B14     | テストピン 4<br>このピンには内部プルダウン抵抗があります。                                                                                                                                                                              |

| TSTPT_5        | P22  | B14     | テストピン 5<br>このピンには内部プルダウン抵抗があります。                                                                                                                                                                              |

| TSTPT_6        | N23  | B14     | テストピン 6<br>このピンには内部プルダウン抵抗があります。                                                                                                                                                                              |

| TSTPT_7        | M24  | B14     | テストピン 7<br>このピンには内部プルダウン抵抗があります。                                                                                                                                                                              |

| GPTP0          | AA23 | B13     | 汎用テストピン 0<br>このピンには内部プルダウンがあり、 $\leq 9.15k\Omega$ の外付けプルアップ抵抗 (プルアップなし:外部水晶振動子、プルアップあり:外部クロック) が必要な場合があります。                                                                                                   |

| GPTP1          | AB22 | B13     | 汎用テストピン 1<br>このピンには内部にプルダウン抵抗があります。                                                                                                                                                                           |

| GPTP2          | AC25 | B13     | 汎用テストピン 2<br>このピンには内部にプルダウン抵抗があります。                                                                                                                                                                           |

| ATB_0_H        | AH4  | PWR     | 予約済みピン、未接続のままにする必要があります。                                                                                                                                                                                      |

| ATB_1_H        | AJ5  | PWR     | 予約済みピン、未接続のままにする必要があります。                                                                                                                                                                                      |

| ATEST          | G13  | PWR     | 予約済みピン、未接続のままにする必要があります。                                                                                                                                                                                      |

| CAP_VDD_S_FLSH | AD22 | PWR     | 外部バイアス容量                                                                                                                                                                                                      |

| CAP_VDD_S_INTF | AJ21 | PWR     | 外部バイアス容量                                                                                                                                                                                                      |

| IFORCE         | L3   | PWR     | 製造用途のみ。グランドに接続する必要があります。                                                                                                                                                                                      |

| VSENSE         | K2   | PWR     | 予約済みピン、未接続のままにする必要があります。                                                                                                                                                                                      |

**表 4-1. 初期化、基板レベル テスト、デバッグ (続き)**

| ピン        |     | I/O <sup>(1)</sup> | 説明                                                                      |

|-----------|-----|--------------------|-------------------------------------------------------------------------|

| 名称        | 番号  |                    |                                                                         |

| HWTEST_EN | Y22 | I2                 | 予約済みピン。<br>通常動作では、この信号を PCB 上のグランドに直接接続する必要があります。弱い内部プルダウンとヒステリシスを含みます。 |

(1) I/O 定義の詳細については、[セクション 4.12](#) を参照してください。

## 4.2 V-by-One インターフェイスの入力データおよび制御

| ピン          |      | I/O <sup>(1)</sup> | 説明 <sup>(2) (3) (4)</sup>                                                                                                            |

|-------------|------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| 名称          | 番号   |                    |                                                                                                                                      |

| P1_VX1_D0_P | AV8  | I5                 | V-by-One インターフェイス データ レーン                                                                                                            |

| P1_VX1_D0_N | AU9  |                    |                                                                                                                                      |

| P1_VX1_D1_P | BB8  |                    |                                                                                                                                      |

| P1_VX1_D1_N | AY8  |                    |                                                                                                                                      |

| P1_VX1_D2_P | BA9  |                    |                                                                                                                                      |

| P1_VX1_D2_N | AW9  |                    |                                                                                                                                      |

| P1_VX1_D3_P | BB10 |                    |                                                                                                                                      |

| P1_VX1_D3_N | AY10 |                    |                                                                                                                                      |

| P1_VX1_D4_P | BA11 |                    |                                                                                                                                      |

| P1_VX1_D4_N | AW11 |                    |                                                                                                                                      |

| P1_VX1_D5_P | AV12 |                    |                                                                                                                                      |

| P1_VX1_D5_N | AU13 |                    |                                                                                                                                      |

| P1_VX1_D6_P | BB12 |                    |                                                                                                                                      |

| P1_VX1_D6_N | AY12 |                    |                                                                                                                                      |

| P1_VX1_D7_P | BA13 |                    |                                                                                                                                      |

| P1_VX1_D7_N | AW13 |                    |                                                                                                                                      |

| P1_HTPDN    | AN3  | O10                | V-by-One インターフェイスのホットプラグ検出 (コントローラレシーバはこの信号を Low にプルして、トランスマッタに存在を示します)。この信号はコントローラ出力のオープンドレインです。トランスマッタにはプルアップ抵抗が必要です。              |

| P1_LOCKN    | AM4  | O10                | V-by-One インターフェイスのクロックがロックを検出します (コントローラレシーバはこの信号を Low にプルして、トランスマッタにクロック抽出ロックを示します)。この信号はコントローラ出力のオープンドレインです。トランスマッタにはプルアップ抵抗が必要です。 |

| P1_RREF     | AU11 | PWR                | V-by-One バイアス抵抗入力                                                                                                                    |

- (1) I/O 定義の詳細については、「[I/O タイプのサブスクリプト定義](#)」を参照してください。

- (2) このシステムは、入力ソースの帯域幅要件に基づいて、1 レーン、2 レーン、4 レーン、8 レーンでの動作をサポートしています。未使用のデータ レーンの入力はオープンのままにする必要があります。すべてのレーンを使用するわけではありません。V-by-One ビデオインターフェイスをまったく使用しない場合は、ピンをグランドに接続する必要があります。

- (3) V-by-One ポートは、基板レイアウトの最適化に役立つよう、限定的なレーンの再マッピングをサポートしています。詳細については、「[V-by-One インターフェイス](#)」を参照してください。

- (4) 本書では、V-by-One と Vx1 という用語を同じ意味で使用しています。

## 4.3 FPD-Link ポートの入力データおよび制御 (DLPC8445、DLPC8445V、DLPC8455 ではサポートされていません)

| ピン            |      | I/O <sup>(1)</sup> | 説明 <sup>(2) (3) (4)</sup> |

|---------------|------|--------------------|---------------------------|

| 名称            | 番号   |                    |                           |

| P2A_LVDS_C_P  | BA17 | I4                 | 予約済み                      |

| P2A_LVDS_C_N  | AW17 | I4                 |                           |

| P2A_LVDS_D0_P | BA15 | I4                 |                           |

| P2A_LVDS_D0_N | AW15 | I4                 |                           |

| P2A_LVDS_D1_P | BB16 | I4                 |                           |

| P2A_LVDS_D1_N | AY16 | I4                 |                           |

| P2A_LVDS_D2_P | AV16 | I4                 |                           |

| P2A_LVDS_D2_N | AU15 | I4                 |                           |

| P2A_LVDS_D3_P | BB18 | I4                 |                           |

| P2A_LVDS_D3_N | AY18 | I4                 |                           |

| P2A_LVDS_D4_P | AV18 | I4                 | 予約済み                      |

| P2A_LVDS_D4_N | AU17 | I4                 |                           |

| P2A_LVDS_RPI  | AT16 | PWR                |                           |

| P2B_LVDS_C_P  | BA21 | I4                 |                           |

| P2B_LVDS_C_N  | AW21 | I4                 |                           |

| P2B_LVDS_D0_P | BB20 | I4                 |                           |

| P2B_LVDS_D0_N | AY20 | I4                 |                           |

| P2B_LVDS_D1_P | AV20 | I4                 |                           |

| P2B_LVDS_D1_N | AU19 | I4                 |                           |

| P2B_LVDS_D2_P | AV22 | I4                 |                           |

| P2B_LVDS_D2_N | AU21 | I4                 |                           |

| P2B_LVDS_D3_P | BB22 | I4                 | 予約済み                      |

| P2B_LVDS_D3_N | AY22 | I4                 |                           |

| P2B_LVDS_D4_P | BA23 | I4                 |                           |

| P2B_LVDS_D4_N | AW23 | I4                 |                           |

| P2B_LVDS_RPI  | AT20 | PWR                | 予約済み                      |

- (1) I/O 定義の詳細については、[セクション 4.12](#) を参照してください。

- (2) 本書では、FPD および FPD リンクという用語は FPD リンク I を指します。

- (3) 未使用ポートの入力はグランドに接続するか、外付け抵抗を介してグランドにプルしてください。

- (4) これら 2 つのポートのうちの 1 つだけが必要な場合は、どちらかのポートを使用し、もう一方のポートは未使用ポートとして扱われます。

## 4.4 DSI 入力データおよびクロック (DLPC8445、DLPC8445V、DLPC8455 ではサポートされていません)

| ピン            |     | I/O <sup>(1)</sup> | 説明 <sup>(2)</sup> |

|---------------|-----|--------------------|-------------------|

| 名称            | 番号  |                    |                   |

| P3_DSI_C_P    | BB6 | I6                 | 予約済み              |

| P3_DSI_C_N    | AY6 | I6                 |                   |

| P3_DSI_D0_P   | BA5 | I6                 |                   |

| P3_DSI_D0_N   | AW5 | I6                 |                   |

| P3_DSI_D1_P   | BB4 | I6                 |                   |

| P3_DSI_D1_N   | AY4 | I6                 |                   |

| P3_DSI_D2_P   | AV4 | I6                 | 予約済み              |

| P3_DSI_D2_N   | AU5 | I6                 |                   |

| P3_DSI_D3_P   | BA3 | I6                 |                   |

| P3_DSI_D3_N   | AW3 | I6                 |                   |

| P3_DSI_RCALIB | AV6 | PWR                | 予約済み              |

(1) I/O 定義の詳細については、[セクション 4.12](#) を参照してください。

(2) 未使用ポートの入力はグランドに接続するか、外付け抵抗を介してグランドにプルしてください。

## 4.5 DMD SubLVDS インターフェイス

| ピン               |     | I/O (1) | 説明                          |

|------------------|-----|---------|-----------------------------|

| 名称               | 番号  |         |                             |

| DMD_HS0_CLK_P    | B6  | O15     | チャネル 0 DMD SubLVDS クロック レーン |

| DMD_HS0_CLK_N    | D6  |         |                             |

| DMD_HS0_WDATA0_P | A3  |         |                             |

| DMD_HS0_WDATA0_N | C3  |         |                             |

| DMD_HS0_WDATA1_P | F4  |         |                             |

| DMD_HS0_WDATA1_N | E5  |         |                             |

| DMD_HS0_WDATA2_P | B4  |         |                             |

| DMD_HS0_WDATA2_N | D4  |         |                             |

| DMD_HS0_WDATA3_P | A5  |         |                             |

| DMD_HS0_WDATA3_N | C5  |         |                             |

| DMD_HS0_WDATA4_P | F6  |         |                             |

| DMD_HS0_WDATA4_N | E7  |         |                             |

| DMD_HS0_WDATA5_P | A7  |         |                             |

| DMD_HS0_WDATA5_N | C7  |         |                             |

| DMD_HS0_WDATA6_P | F8  |         |                             |

| DMD_HS0_WDATA6_N | E9  |         |                             |

| DMD_HS0_WDATA7_P | B8  | O15     | チャネル 0 DMD SubLVDS データ レーン  |

| DMD_HS0_WDATA7_N | D8  |         |                             |

| DMD_HS1_CLK_P    | A13 |         |                             |

| DMD_HS1_CLK_N    | C13 |         |                             |

| DMD_HS1_WDATA0_P | B10 |         |                             |

| DMD_HS1_WDATA0_N | D10 |         |                             |

| DMD_HS1_WDATA1_P | A11 |         |                             |

| DMD_HS1_WDATA1_N | C11 |         |                             |

| DMD_HS1_WDATA2_P | F10 |         |                             |

| DMD_HS1_WDATA2_N | E11 |         |                             |

| DMD_HS1_WDATA3_P | B12 |         |                             |

| DMD_HS1_WDATA3_N | D12 |         |                             |

| DMD_HS1_WDATA4_P | B14 |         |                             |

| DMD_HS1_WDATA4_N | D14 |         |                             |

| DMD_HS1_WDATA5_P | F12 |         |                             |

| DMD_HS1_WDATA5_N | E13 |         |                             |

| DMD_HS1_WDATA6_P | A15 | O15     | チャネル 1 DMD SubLVDS データ レーン  |

| DMD_HS1_WDATA6_N | C15 |         |                             |

| DMD_HS1_WDATA7_P | F14 |         |                             |

| DMD_HS1_WDATA7_N | E15 |         |                             |

| DMD_HS2_CLK_P    | A19 |         |                             |

| DMD_HS2_CLK_N    | C19 |         |                             |

## 4.5 DMD SubLVDS インターフェイス (続き)

| ピン               |     | I/O <sup>(1)</sup> | 説明                          |

|------------------|-----|--------------------|-----------------------------|

| 名称               | 番号  |                    |                             |

| DMD_HS2_WDATA0_P | A17 | O15                | チャネル 2 DMD SubLVDS データ レーン  |

| DMD_HS2_WDATA0_N | C17 |                    |                             |

| DMD_HS2_WDATA1_P | F16 |                    |                             |

| DMD_HS2_WDATA1_N | E17 |                    |                             |

| DMD_HS2_WDATA2_P | B18 |                    |                             |

| DMD_HS2_WDATA2_N | D18 |                    |                             |

| DMD_HS2_WDATA3_P | F18 |                    |                             |

| DMD_HS2_WDATA3_N | E19 |                    |                             |

| DMD_HS2_WDATA4_P | B20 |                    |                             |

| DMD_HS2_WDATA4_N | D20 |                    |                             |

| DMD_HS2_WDATA5_P | A21 |                    |                             |

| DMD_HS2_WDATA5_N | C21 |                    |                             |

| DMD_HS2_WDATA6_P | F20 |                    |                             |

| DMD_HS2_WDATA6_N | E21 |                    |                             |

| DMD_HS2_WDATA7_P | B22 |                    |                             |

| DMD_HS2_WDATA7_N | D22 |                    |                             |

| DMD_HS3_CLK_P    | H24 | O15                | チャネル 3 DMD SubLVDS クロック レーン |

| DMD_HS3_CLK_N    | J25 |                    |                             |

| DMD_HS3_WDATA0_P | B24 |                    |                             |

| DMD_HS3_WDATA0_N | C25 |                    |                             |

| DMD_HS3_WDATA1_P | D24 |                    |                             |

| DMD_HS3_WDATA1_N | E25 |                    |                             |

| DMD_HS3_WDATA2_P | F22 |                    |                             |

| DMD_HS3_WDATA2_N | E23 |                    |                             |

| DMD_HS3_WDATA3_P | F24 |                    |                             |

| DMD_HS3_WDATA3_N | G25 |                    |                             |

| DMD_HS3_WDATA4_P | H22 |                    |                             |

| DMD_HS3_WDATA4_N | G23 |                    |                             |

| DMD_HS3_WDATA5_P | K24 |                    |                             |

| DMD_HS3_WDATA5_N | L25 |                    |                             |

| DMD_HS3_WDATA6_P | K22 |                    |                             |

| DMD_HS3_WDATA6_N | J23 |                    |                             |

| DMD_HS3_WDATA7_P | M22 |                    |                             |

| DMD_HS3_WDATA7_N | L23 |                    |                             |

(1) I/O 定義の詳細については、[セクション 4.12](#) を参照してください。

## 4.6 DMD リセットおよび低速インターフェイス

| ピン              |    | I/O <sup>(1)</sup> | 説明                                                                                                                                                                                                                                      |

|-----------------|----|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称              | 番号 |                    |                                                                                                                                                                                                                                         |

| DMD_LS0_CLK_P   | F2 | O15                | DMD 低速差動インターフェイス、ポート 0 クロック                                                                                                                                                                                                             |

| DMD_LS0_CLK_N   | E1 | O15                |                                                                                                                                                                                                                                         |

| DMD_LS0_WDATA_P | B2 | O15                | DMD 低速差動インターフェイス、ポート 0 書き込みデータ                                                                                                                                                                                                          |

| DMD_LS0_WDATA_N | C1 | O15                |                                                                                                                                                                                                                                         |

| DMD_LS1_CLK     | G1 | O12                | DMD 低速シングルエンドインターフェイス、ポート 1 クロック                                                                                                                                                                                                        |

| DMD_LS1_WDATA   | E3 | O12                | DMD 低速シングルエンドインターフェイス、ポート 1 書き込みデータ                                                                                                                                                                                                     |

| DMD_LS2_CLK     | H2 | O12                | DMD 低速シングルエンドインターフェイス、ポート 2 クロック                                                                                                                                                                                                        |

| DMD_LS2_WDATA   | G3 | O12                | DMD 低速シングルエンドインターフェイス、ポート 2 書き込みデータ                                                                                                                                                                                                     |

| DMD_LS0_RDATA   | H4 | I1                 | DMD、低速シングルエンドシリアルインターフェイス、ポート 0 読み取りデータ <sup>(2)</sup>                                                                                                                                                                                  |

| DMD_LS1_RDATA   | J3 | I1                 | DMD、低速シングルエンドシリアルインターフェイス、ポート 1 読み取りデータ <sup>(2)</sup> このポートを使用しない場合、この入力がフローティングにならないように、外部プルアップまたはプルダウンが必要です。                                                                                                                         |

| DMD_LS2_RDATA   | M4 | I1                 | DMD、低速シングルエンドシリアルインターフェイス、ポート 2 読み取りデータ <sup>(2)</sup> このポートを使用しない場合、この入力がフローティングにならないように、外部プルアップまたはプルダウンが必要です。                                                                                                                         |

| DMD_LS3_RDATA   | K4 | I1                 | DMD、低速シングルエンドシリアルインターフェイス、ポート 3 読み取りデータ <sup>(2)</sup> このポートを使用しない場合、この入力がフローティングにならないように、外部プルアップまたはプルダウンが必要です。                                                                                                                         |

| DMD_DEN_ARSTZ   | J1 | O10                | DMD ドライバインエーブル信号 / アクティブ Low 非同期リセット (1 = イネーブル、0 = リセット)<br>この信号は、DMD がパークされた後、DMD から電源が切断される前に、Low に駆動されます。<br>コントローラの 1.8V 電源が DMD の 1.8V 電源から独立している場合、DMD 電源が供給されている間コントローラ電源が非アクティブになった場合に信号を Low に保持するために、外付けプルダウン抵抗を使用する必要があります。 |

(1) I/O 定義の詳細については、[セクション 4.12](#) を参照してください。

(2) すべての制御インターフェイスの読み取りは、シングルエンドの低速信号を使用します。読み取りデータは、低速の差動書き込みクロックによってクロックされます。

## 4.7 フラッシュインターフェイス

| ピン         |      | I/O <sup>(1)</sup> | 説明                                                      |

|------------|------|--------------------|---------------------------------------------------------|

| 名称         | 番号   |                    |                                                         |

| FLSH_CSZ   | AG23 | B16                | チップセレクト: ブート FLASHのみ (ブート FLASH はこのチップセレクトを使用する必要があります) |

| FLSH_CLK   | AG25 | B16                | フラッシュクロック                                               |

| FLSH_DATA0 | AH22 | B16                | アドレスビット 0 (LSB)                                         |

| FLSH_DATA1 | AH24 | B16                | アドレスビット 1                                               |

| FLSH_DATA2 | AJ25 | B16                | アドレスビット 2                                               |

| FLSH_DATA3 | AJ23 | B16                | アドレスビット 3                                               |

(1) I/O 定義の詳細については、[セクション 4.12](#) を参照してください。

## 4.8 ペリフェラル インターフェイス

| ピン          |      | I/O <sup>(1)</sup> | 説明                                                                                                                                                                  |

|-------------|------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称          | 番号   |                    |                                                                                                                                                                     |

| IIC0_SCL    | AL25 | B18                | I2C ポート 0 (プライマリ - セカンダリ)、通常はホストからコントローラへのコマンドおよび制御用としてセカンダリ、SCL (双方向、オープンドレイン) : 外部プルアップが必要です。このプルアップの最小許容値は $470\Omega$ です。                                       |

| IIC0_SDA    | AK24 | B18                |                                                                                                                                                                     |

| SSP0_DO     | AP24 | O17                | SSP/SPI ポート 0 データ出力 (プライマリ): 送信データピン                                                                                                                                |

| SSP0_DI     | AN23 | I3                 | SSP/SPI ポート 0 データ入力 (プライマリ): 受信データピン                                                                                                                                |

| SSP0_CLK    | AN25 | O17                | SSP/SPI ポート 0 クロック (プライマリ): クロックピン                                                                                                                                  |

| SSP0_CSZ_0  | AM22 | O17                | SPI ポート 0 チップ セレクト 0 (プライマリ): チップセレクト (アクティブ Low)。<br>外部デバイスへのチップ セレクト入力がフローティングにならないように、外付けプルアップ抵抗 ( $\leq 10k\Omega$ ) を推奨します。                                    |

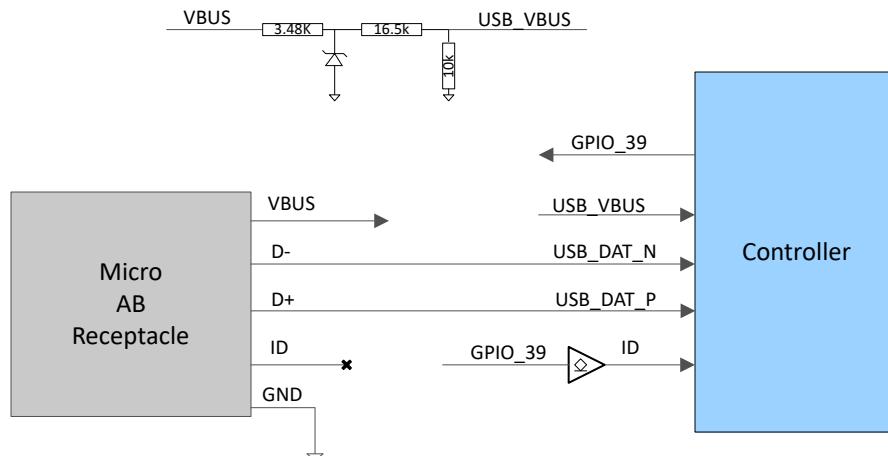

| USB_DAT_P   | AU1  | B7                 | USB OTG データレーン                                                                                                                                                      |

| USB_DAT_N   | AW1  | B7                 |                                                                                                                                                                     |

| USB_VBUS    | AP4  | B7                 | USB OTG 5V 電源検出                                                                                                                                                     |

| USB_ID      | AT2  | I7                 | USB OTG ミニ レセプタクルの識別                                                                                                                                                |

| USB_TXRTUNE | AR3  | PWR                | RTTRIM USB OTG リファレンス抵抗:<br>オンチップ抵抗のキャリブレーション用外付けリファレンス抵抗は、 $499\Omega$ の値で接続する必要があります。                                                                             |

| HOST_IRQ    | AK22 | O17                | ホスト割り込み (出力):<br>HOST_IRQ は、DLPC の自動初期化が進行中であること、および最も重要なのはその完了時を示します。また、HOST_IRQ はコマンド処理中にも切り替わり、実行中であることを示します。このピンはリセット中にトライステートになります。この信号には外付けプルアップを接続する必要があります。 |

(1) I/O 定義の詳細については、[セクション 4.12](#) を参照してください。

## 4.9 GPIO ペリフェラル インターフェイス

| ピン      |      | I/O (1) | 説明 (2) (3) (4)                                                                                      |

|---------|------|---------|-----------------------------------------------------------------------------------------------------|

| 名称      | 番号   |         |                                                                                                     |

| GPIO_00 | AR25 | B17     | 汎用 I/O 00:<br>オプション:<br>1.Alt 0:SSP1_SCLK (O-P/I-S)<br>2.Alt 1:XY_IF_SCLK (I)<br>3.SW GPIO (B)      |

| GPIO_01 | AU25 | B17     | 汎用 I/O 01:<br>オプション:<br>1.Alt 0:SSP1_DI (I)<br>2.Alt 1:XY_IF_DI(I)<br>3.SW GPIO (B)                 |

| GPIO_02 | AW25 | B17     | 汎用 I/O 02:<br>オプション:<br>1.Alt 0:SSP1_DO (O)<br>2.Alt 1:XY_IF_DO (O)<br>3.SW GPIO (B)                |

| GPIO_03 | AT24 | B17     | 汎用 I/O 03:<br>オプション:<br>1.Alt 0:SSP1_CSZ_0 (O-P/I-S)<br>2.Alt 1:XY_IF_CSZ (I)<br>3.SW GPIO (B)      |

| GPIO_04 | AV24 | B17     | 汎用 I/O 04:<br>オプション:1.Alt<br>0: SSP1_CSZ_1 (O-P/I-S)<br>2.Alt 1:該当なし<br>3.SW GPIO (B)               |

| GPIO_05 | AR23 | B17     | 汎用 I/O 05:<br>オプション:<br>1.Alt 0:SSP1_CSZ_2 (O-P/I-S)<br>2.Alt 1:該当なし<br>3.SW GPIO (B)               |

| GPIO_06 | AP22 | B17     | 汎用 I/O 06:<br>オプション:<br>1.Alt 0:SSP0_BCSZ (O-P/I-S)<br>2.Alt 1:SSP1_BCSZ (O-P/I-S)<br>3.SW GPIO (B) |

| GPIO_07 | AL23 | B17     | 汎用 I/O 07:<br>オプション:<br>1.Alt 0:IIC1_SCL (B)<br>2.Alt 1:該当なし<br>3.SW GPIO (B)                       |

| GPIO_08 | AM24 | B17     | 汎用 I/O 08:<br>オプション:<br>1.Alt 0:IIC1_SDA (B)<br>2.Alt 1:該当なし<br>3.SW GPIO (B)                       |

| GPIO_09 | N3   | B10     | 汎用 I/O 09:<br>オプション:<br>1.Alt 0:WPC_COLOR_SENSOR_VSYNC(O)<br>2.Alt 1:MEMAUX_1(O)<br>3.SW GPIO (B)   |

| GPIO_10 | P4   | B9      | 汎用 I/O 10:<br>オプション:<br>1.Alt 0:UART1_RSTZ (O)<br>2.Alt 1:該当なし<br>3.SW GPIO (B)                     |

## 4.9 GPIO ペリフェラル インターフェイス (続き)

| ピン      |      | I/O <sup>(1)</sup> | 説明 <sup>(2) (3) (4)</sup>                                                                |

|---------|------|--------------------|------------------------------------------------------------------------------------------|

| 名称      | 番号   |                    |                                                                                          |

| GPIO_11 | T4   | B10                | 汎用 I/O 11:<br>オプション:<br>1.Alt 0:UART1_CTSZ(I)<br>2.Alt 1:該当なし<br>3.SW GPIO (B)           |

| GPIO_12 | V4   | B10                | 汎用 I/O 12:<br>オプション:<br>1.Alt 0:DMD_PWR_EN (O)<br>2.Alt 1:RC_CHARGE (O)<br>3.SW GPIO (B) |

| GPIO_13 | AD24 | B14                | 汎用 I/O 13:<br>オプション:<br>1.Alt 0:PAUX0 (O)<br>2.Alt 1:LED_SEL0 (O)<br>3.SW GPIO (B)       |

| GPIO_14 | AC23 | B14                | 汎用 I/O 14:<br>オプション:<br>1.Alt 0:PAUX1 (O)<br>2.Alt 1:LED_SEL1 (O)<br>3.SW GPIO (B)       |

| GPIO_15 | AE25 | B14                | 汎用 I/O 15:<br>オプション:<br>1.Alt 0:PAUX2 (O)<br>2.Alt 1:LED_SEL2 (O)<br>3.SW GPIO (B)       |

| GPIO_16 | AE23 | B14                | 汎用 I/O 16:<br>オプション:<br>1.Alt 0:PAUX3 (O)<br>2.Alt 1:LED_SEL3 (O)<br>3.SW GPIO (B)       |

| GPIO_17 | AF24 | B13                | 汎用 I/O 17:<br>オプション:<br>1.Alt 0:PAUX4 (O)<br>2.Alt 1:LED_SEL4 (O)<br>3.SW GPIO (B)       |

| GPIO_18 | AF22 | B13                | 汎用 I/O 18:<br>オプション:<br>1.Alt 0:PAUX5 (O)<br>2.Alt 1:LED_SEL5 (O)<br>3.SW GPIO (B)       |

| GPIO_19 | R1   | B10                | 汎用 I/O 19:<br>オプション:<br>1.Alt 0:PAUX6 (O)<br>2.Alt 1:該当なし<br>3.SW GPIO (B)               |

| GPIO_20 | R3   | B10                | 汎用 I/O 20:<br>オプション:<br>1.Alt 0:PAUX7 (O)<br>2.Alt 1:SL_Trigger (I)<br>3.SW GPIO (B)     |

| GPIO_21 | U1   | B10                | 汎用 I/O 21:<br>オプション:<br>1.Alt 0:PAUX8 (O)<br>2.Alt 1:該当なし<br>3.SW GPIO (B)               |

## 4.9 GPIO ペリフェラル インターフェイス (続き)

| ピン      |     | I/O <sup>(1)</sup> | 説明 <sup>(2) (3) (4)</sup>                                                                   |

|---------|-----|--------------------|---------------------------------------------------------------------------------------------|

| 名称      | 番号  |                    |                                                                                             |

| GPIO_22 | T2  | B9                 | 汎用 I/O 22:<br>オプション:<br>1.Alt 0:PAUX9 (O)<br>2.Alt 1:CW_INDEX0 (I)<br>3.SW GPIO (B)         |

| GPIO_23 | U3  | B10                | 汎用 I/O 23:<br>オプション:<br>1.Alt 0:PAUX10 (O)<br>2.Alt 1:PWM_OUT_CW0 (O)<br>3.SW GPIO (B)      |

| GPIO_24 | W1  | B10                | 汎用 I/O 24:<br>オプション:<br>1.Alt 0:PAUX11 (O)<br>2.Alt 1:PWM_OUT_CW1 (O)<br>3.SW GPIO (B)      |

| GPIO_25 | V2  | B10                | 汎用 I/O 25:<br>オプション:<br>1.Alt 0:PWM_OUT_RLED (O)<br>2.Alt 1:CMP_MSEL_0 (O)<br>3.SW GPIO (B) |

| GPIO_26 | W3  | B10                | 汎用 I/O 26:<br>オプション:<br>1.Alt 0:PWM_OUT_GLED (O)<br>2.Alt 1:CMP_PWM (O)<br>3.SW GPIO (B)    |

| GPIO_27 | AA1 | B10                | 汎用 I/O 27:<br>オプション:<br>1.Alt 0:PWM_OUT_BLED (O)<br>2.Alt 1:CMP_OUT (I)<br>3.SW GPIO (B)    |

| GPIO_28 | Y4  | B10                | 汎用 I/O 28:<br>オプション:<br>1.Alt 0:PWM_OUT_IRLED (O)<br>2.Alt 1:LS_PWR (O)<br>3.SW GPIO (B)    |

| GPIO_29 | Y2  | B10                | 汎用 I/O 29:<br>オプション: 1.Alt 0:PWM_OUT_UVLED (O)<br>2.Alt 1:CW_INDEX_1 (I)<br>3.SW GPIO (B)   |

| GPIO_30 | AA3 | B11                | 汎用 I/O 30:<br>オプション:<br>1.Alt 0:HBT_CLKOUT (O)<br>2.Alt 1:該当なし<br>3.SW GPIO (B)             |

| GPIO_31 | AB4 | B10                | 汎用 I/O 31:<br>オプション:<br>1.Alt 0:HBT_DO (O)<br>2.Alt 1:該当なし<br>3.SW GPIO (B)                 |

| GPIO_32 | AC1 | B10                | 汎用 I/O 32:<br>オプション:<br>1.Alt 0:HBT_CLKIN_0 (I)<br>2.Alt 1:該当なし<br>3.SW GPIO (B)            |

## 4.9 GPIO ペリフェラルインターフェイス (続き)

| ピン      |     | I/O <sup>(1)</sup> | 説明 <sup>(2) (3) (4)</sup>                                                                           |

|---------|-----|--------------------|-----------------------------------------------------------------------------------------------------|

| 名称      | 番号  |                    |                                                                                                     |

| GPIO_33 | AB2 | B10                | 汎用 I/O 33:<br>オプション:<br>1.Alt 0:HBT_DI_0 (I)<br>2.Alt 1:該当なし<br>3.SW GPIO (B)                       |

| GPIO_34 | AC3 | B9                 | 汎用 I/O 34:<br>オプション:<br>1.Alt 0:HBT_CLKIN_1 (I)<br>2.Alt 1:GP_CLK2 (O)<br>3.SW GPIO (B)             |

| GPIO_35 | AD4 | B10                | 汎用 I/O 35:<br>オプション:<br>1.Alt 0:HBT_DI_1 (I)<br>2.Alt 1:CAL_PWR(O)<br>3.SW GPIO (B)                 |

| GPIO_36 | AE1 | B10                | 汎用 I/O 36:<br>オプション:<br>1.Alt 0:HBT_CLKIN_2 (I)<br>2.Alt 1:該当なし<br>3.SW GPIO (B)                    |

| GPIO_37 | AD2 | B10                | 汎用 I/O 37:<br>オプション:<br>1.Alt 0:HBT_DI_2 (I)<br>2.Alt 1:該当なし<br>3.SW GPIO (B)                       |

| GPIO_38 | AE3 | B10                | 汎用 I/O 38:<br>オプション:<br>1.Alt 0:EFSYNC (O)/DASYNC(I)<br>2.Alt 1:該当なし<br>3.SW GPIO (B)               |

| GPIO_39 | AG1 | B10                | 汎用 I/O 39:<br>オプション:<br>1.Alt 0:SEQ_SYNC (B - オープンドレイン)<br>2.Alt 1:該当なし<br>3.SW GPIO (B)            |

| GPIO_40 | AF4 | B10                | 汎用 I/O 40:<br>オプション:<br>1.Alt 0:AWC0_DACCLK_0_1 (O)<br>2.Alt 1:該当なし<br>3.SW GPIO (B)                |

| GPIO_41 | AF2 | B11                | 汎用 I/O 41:<br>オプション:<br>1.Alt 0:AWC0_DACCLK_0_1 (O)<br>2.Alt 1:該当なし<br>3.SW GPIO (B)                |

| GPIO_42 | AJ1 | B10                | 汎用 I/O 42:<br>オプション:<br>1.Alt 0:AWC0_DACS_PWMA_0 (O)<br>2.Alt 1:該当なし<br>3.SW GPIO (B)               |

| GPIO_43 | AG3 | B10                | 汎用 I/O 43:<br>オプション:<br>1.Alt 0:AWC0_DACD_PWMB_0 (O)<br>2.Alt 1:PWM_OUT_BLED_2 (O)<br>3.SW GPIO (B) |

## 4.9 GPIO ペリフェラル インターフェイス (続き)

| ピン      |     | I/O <sup>(1)</sup> | 説明 <sup>(2) (3) (4)</sup>                                                                      |

|---------|-----|--------------------|------------------------------------------------------------------------------------------------|

| 名称      | 番号  |                    |                                                                                                |

| GPIO_44 | AH2 | B10                | 汎用 I/O 44:<br>オプション:<br>1.Alt 0:AWC0_DACS_PWMA_1 (O)<br>2.Alt 1:PAUX_INT0 (O)<br>3.SW GPIO (B) |

| GPIO_45 | AJ3 | B10                | 汎用 I/O 45:<br>オプション:<br>1.Alt 0:AWC0_DACD_PWMB_1 (O)<br>2.Alt 1:PAUX_INT1 (O)<br>3.SW GPIO (B) |

| GPIO_46 | AL1 | B10                | 汎用 I/O 46:<br>オプション:<br>1.Alt 0:該当なし<br>2.Alt 1:PAUX_INT2 (O)<br>3.SW GPIO (B)                 |

| GPIO_47 | AK4 | B11                | 汎用 I/O 47:<br>オプション:<br>1.Alt 0:AWC1_DACCLK_0_1 (O)<br>2.Alt 1:PAUX_INT3 (O)<br>3.SW GPIO (B)  |

| GPIO_48 | AK2 | B10                | 汎用 I/O 48:<br>オプション:<br>1.Alt 0:AWC1_DACS_PWMA_0 (O)<br>2.Alt 1:SF_SEL_0 (O)<br>3.SW GPIO (B)  |

| GPIO_49 | AN1 | B10                | 汎用 I/O 49:<br>オプション:<br>1.Alt 0:AWC1_DACD_PWMB_0 (O)<br>2.Alt 1:SF_SEL_1 (O)<br>3.SW GPIO (B)  |

| GPIO_50 | AL3 | B10                | 汎用 I/O 50:<br>オプション:<br>1.Alt 0:AWC1_DACS_PWMA_1 (O)<br>2.Alt 1:SF_SEL_2 (O)<br>3.SW GPIO (B)  |

| GPIO_51 | AM2 | B10                | 汎用 I/O 51:<br>オプション:<br>1.Alt 0:AWC1_DACD_PWMB_1 (O)<br>2.Alt 1:SF_SEL_3 (O)<br>3.SW GPIO (B)  |

- (1) I/O 定義の詳細については、[セクション 4.12](#) を参照してください。

- (2) この表は、コントローラの GPIO 機能を定義しています。これらの GPIO の特定の製品構成割り当てについては、[GPIO の機能](#) を参照してください。

- (3) ほとんどの GPIO は、汎用 I/O として利用可能であるだけでなく、少なくとも 1 つの代替ハードウェア機能の用途を持っています。製品構成によっては、代替ハードウェア機能として使用するために GPIO が特別に予約されている場合があります（その場合、汎用 I/O としては使用できません）。特定の製品構成の GPIO の割り当て詳細については、[GPIO の機能](#) を参照してください。

- (4) 汎用 I/O として使用可能なすべての GPIO は、入力、標準出力、またはオープンドレイン出力として構成される必要があります。これはフラッシュ構成で設定されます。未使用的 GPIO をロジック 0 出力として構成し、未接続のままにします。それ以外の場合は、フローティング入力を避けるために外付けプルアップ抵抗またはプルダウン抵抗が必要です。すべての GPIO のリセットのデフォルトは入力信号です。オープンドレイン出力として構成された各信号には、外付けプルアップ抵抗 ( $\leq 10\text{k}\Omega$ ) が必要です。

## 4.10 クロックおよびPLL のサポート

| ピン       |      | I/O <sup>(1)</sup> | 説明                                                                                                                                                                                               |

|----------|------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称       | 番号   |                    |                                                                                                                                                                                                  |

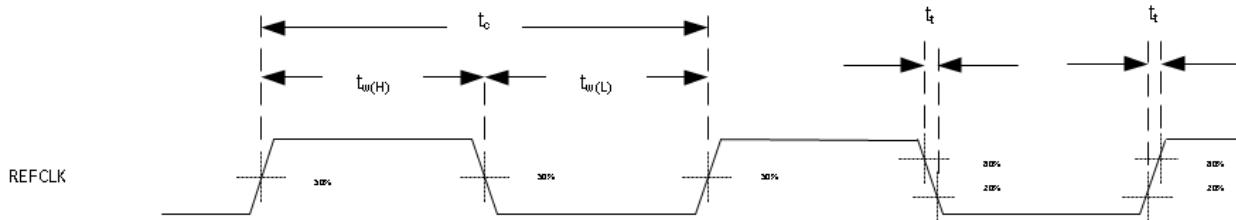

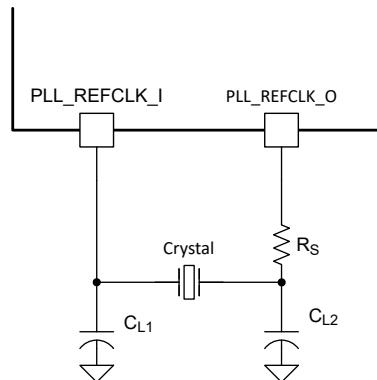

| REFCLK_I | N1   | I8                 | 水晶振動子入力:リファレンス クロックの水晶振動子入力 <sup>(2) (3)</sup>                                                                                                                                                   |

| REFCLK_O | L1   | O8                 | 水晶振動子出力:リファレンス クロックの水晶振動子出力 <sup>(2) (5)</sup>                                                                                                                                                   |

| OCLKA    | AB24 | O14                | 汎用出力クロック A <sup>(4)</sup><br>カラー ホイール モーター コントローラ駆動用。周波数はソフトウェアでプログラム可能で、電源オン時のデフォルト周波数は 0.99MHz です。<br>注:出力周波数は、パワーアップ以外のリセット動作の影響を受けません(つまり、システムの電源をオフにしてから再度オンになるまで、システムは最後にプログラムされた値を保持します)。 |

- (1) I/O 定義の詳細については、「[I/O テーブル](#)」を参照してください。

(2) この信号の詳細については、「[システム発振器のタイミング](#)」を参照してください。

(3) 水晶振動子の代わりに外部発振器を使用するアプリケーションでは、発振器を使用してこのピンを駆動します。

(4) この信号の詳細については、「[プログラマブル出力クロック タイミング](#)」を参照してください。

(5) 水晶振動子の代わりに外部発振器を使用するアプリケーションでは、このピンを接地する必要があります。

## 4.11 電源およびグランド

| ピン            |                                                                                                                                                                                                       | I/O <sup>(1)</sup> | 説明                                       |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------------------|

| 名称            | 番号                                                                                                                                                                                                    |                    |                                          |

| VDDA18_PLLM   | AL11                                                                                                                                                                                                  | PWR                | メイン I/F PLL 用 1.8V (公称)                  |

| VDDA18_PLLD   | J13                                                                                                                                                                                                   | PWR                | DMD I/F PLL 用 1.8V (公称)                  |

| VDD_CORE      | AA13, AA15, AA21, AB16, AC13, AD6, AD8, AD18, AD20, AE9, AE11, AF14, AF16, AF20, AG7, AH6, AJ11, AL9, AL13, AL17, AL19, K8, K18, L9, L13, M6, M20, N15, N17, T6, T12, T14, T20, U19, V8, V10, Y6, Y20 | PWR                |                                          |

| VDDAR_CORE    | AB10, AB12, AJ9, AJ13, AJ15, AJ17, AJ19, AK8, N11, N13, P8, P18, R9, R19, W15, W17                                                                                                                    | PWR                |                                          |

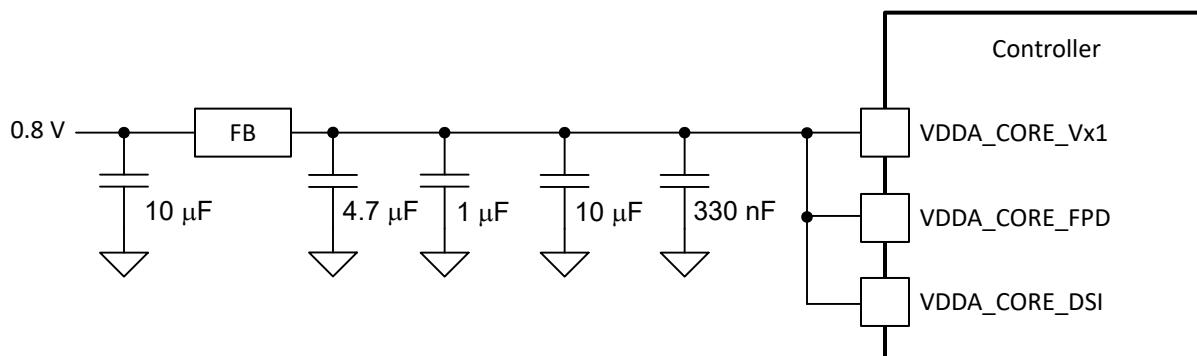

| VDDA_CORE_DSI | AR7                                                                                                                                                                                                   | PWR                |                                          |

| VDDA_CORE_FPD | AM16, AM18, AM20                                                                                                                                                                                      | PWR                | FPD コア用 0.8V (公称) 固定電源                   |

| VDDA_CORE_USB | AM6                                                                                                                                                                                                   | PWR                | USB コントローラ用 0.8V (公称)                    |

| VDDA_CORE_Vx1 | AM10, AM14                                                                                                                                                                                            | PWR                | Vx1 コア用 0.8V (公称) 固定電源                   |

| VDDA18_DDI    | J7, J9, J11, J15, J17, J19                                                                                                                                                                            | PWR                | SubLVDS DMD インターフェイス用 1.8V (公称) 固定 IO 電源 |

| VDDA18_DSI    | AP8                                                                                                                                                                                                   | PWR                | DSI 用 1.8V (公称)                          |

| VDDA18_FPD    | AN15, AP16, AP18, AR19                                                                                                                                                                                | PWR                | FPD I/O 用 1.8V (公称) 固定電源                 |

| VDDA18_USB    | AN7                                                                                                                                                                                                   | PWR                | USB PHY 用 1.8V (公称)                      |

| VDDA18_Vx1    | AM12, AP10, AP14                                                                                                                                                                                      | PWR                | Vx1 I/O 用 1.8V (公称) 固定電源                 |

| VDDA33_USB    | AP6                                                                                                                                                                                                   | PWR                | USB PHY 用 3.3V (公称)                      |

## 4.11 電源およびグランド (続き)

| ピン             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I/O <sup>(1)</sup> | 説明                                                                                                                          |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 名称             | 番号                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    |                                                                                                                             |

| VDDS18_LVCMOS1 | AA5, AE5, AG5, AL5, W5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                    |                                                                                                                             |

| VDDS18_LVCMOS2 | N21, R21, U21, W21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                    |                                                                                                                             |

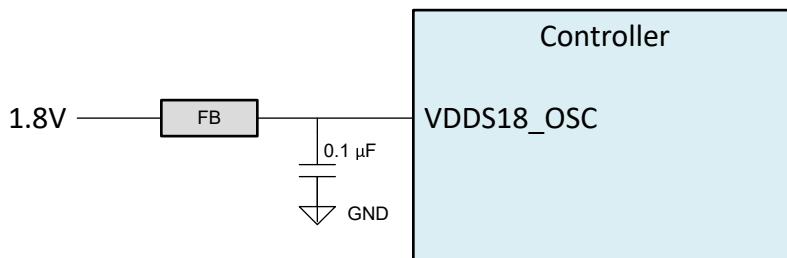

| VDDS18_OSC     | U5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PWR                | リファレンス発振器 I/O 用 1.8V (公称) 固定電源                                                                                              |

| VDDSHV_FLSH    | AC21, AE21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PWR                | クワッドシリアル フラッシュ インターフェイス用 1.8V または 3.3V (公称) マルチ電圧 IO 電源                                                                     |

| VDDSHV_INTF    | AG21, AL21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PWR                | PMIC I/O の代わりに PAD1000 をサポートするための、SPI および I <sup>2</sup> C I/O 用 1.8V または 3.3V (公称) マルチ電圧 IO 電源 (GPIO[8:0] を含む)。また、HOST_IRQ |

| VSS            | A1, A9, A23, A25, AA7, AA9, AA17, AA19, AB6, AB8, AB14, AB18, AB20, AC5, AC9, AC11, AC15, AC17, AD12, AD14, AD16, AE13, AE17, AF6, AF8, AF12, AF18, AG9, AG11, AG13, AG17, AG19, AH10, AH14, AH16, AH20, AK6, AK16, AK20, AL7, AL15, AM8, AN5, AN9, AN21, AP12, AP20, AR5, AR9, AR11, AR13, AR15, AR17, AR21, AT4, AT6, AT8, AT10, AT12, AT14, AT18, AT22, AU3, AU7, AU23, AV2, AV10, AV14, AW7, AW19, AY2, AY14, AY24, B16, BA1, BA7, BA19, BA25, BB2, BB14, BB24, C9, C23, D2, D16, G5, G7, G9, G11, G15, G17, G19, G21, H6, H8, H10, H12, H14, H16, H18, H20, J5, J21, K6, K10, K16, K20, L5, L7, L11, L15, L17, M2, M10, M14, M18, N5, N7, P10, P12, P14, P20, R5, R11, R15, R17, T8, T10, T16, U7, U11, U15, U17, V6, V12, V14, V20, W7, W13, W19, Y8, Y10, Y12, Y14, Y18 | RTN                | グランド、パッケージ レベルではすべてのグランドは VSS に接続                                                                                           |

| VPP            | L21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RTN                | 製造用途のみ (eFuse)。グランドに接続する必要があります                                                                                             |

(1) I/O 定義の詳細については、セクション 4.12 を参照してください。

## 4.12 I/O タイプのサブスクリプト定義

| I/O     |                                   |                           |                         |

|---------|-----------------------------------|---------------------------|-------------------------|

| サブスクリプト | 説明                                | 電源リファレンス                  | ESD 構造                  |

| 1       | LVC MOS 1.8V のみ                   | VDDS18_LVC MOS1           | 電源レールと GND への ESD ダイオード |

| 2       | LVC MOS 1.8V のみ                   | VDDS18_LVC MOS2           | 電源レールと GND への ESD ダイオード |

| 3       | LVC MOS 1.8/3.3V                  | VDD SHV_INTF              | 電源レールと GND への ESD ダイオード |

| 4       | 差動 FPD LVDS                       | VDDA18_FPD                | 電源レールと GND への ESD ダイオード |

| 5       | 差動 V-by-One                       | VDDA18_VX1                | 電源レールと GND への ESD ダイオード |

| 6       | 差動 DSI                            | VDDA18_DSI                | 電源レールと GND への ESD ダイオード |

| 7       | USB 2.0                           | VDDA18_USB、<br>VDDA33_USB | 電源レールと GND への ESD ダイオード |

| 8       | 基準発振器入力                           | VDDS18_OSC                | 電源レールと GND への ESD ダイオード |

| 9       | LVC MOS 1.8V のみ 6.5mA             | VDDS18_LVC MOS1           | 電源レールと GND への ESD ダイオード |

| 10      | LVC MOS 1.8V のみ 8mA               | VDDS18_LVC MOS1           | 電源レールと GND への ESD ダイオード |

| 11      | LVC MOS 1.8V のみ 12mA              | VDDS18_LVC MOS1           | 電源レールと GND への ESD ダイオード |

| 12      | LVC MOS 1.8V のみ 24mA              | VDDS18_LVC MOS1           | 電源レールと GND への ESD ダイオード |

| 13      | LVC MOS 1.8V のみ 6.5mA             | VDDS18_LVC MOS2           | 電源レールと GND への ESD ダイオード |

| 14      | LVC MOS 1.8V のみ 8mA               | VDDS18_LVC MOS2           | 電源レールと GND への ESD ダイオード |

| 15      | 差動 SubLVDS 1.8V                   | VDDA18_DDI                | 電源レールと GND への ESD ダイオード |

| 16      | LVC MOS 1.8/3.3V 8mA              | VDD SHV_FLSH              | 電源レールと GND への ESD ダイオード |

| 17      | LVC MOS 1.8/3.3V 7.5mA            | VDD SHV_INTF              | 電源レールと GND への ESD ダイオード |

| 18      | i <sup>2</sup> c 1.8/3.3V3mA@3.3V | VDD SHV_INTF              | 電源レールと GND への ESD ダイオード |

| タイプ     |                                   |                           |                         |

| I       | 入力                                | 該当なし                      |                         |

| O       | 出力                                |                           |                         |

| B       | 双方向                               |                           |                         |

| PWR     | 電源                                |                           |                         |

| RTN     | グランドリターン                          |                           |                         |

## 4.13 内部プルアップおよびプルダウンの特性

| 内部プルアップ抵抗およびプルダウン抵抗の特性 <sup>(1)</sup>                                                                                                | 条件              | 最小値 | 最大値 | 単位 |

|--------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|----|

| 弱いプルアップ抵抗 - FLSH_CSZ                                                                                                                 | VDD_FLSH = 3.3V | 42  | 59  | kΩ |

| 弱いプルアップ抵抗 - SSP0_CSZ_0                                                                                                               | VDD_INTF = 3.3V | 18  | 26  | kΩ |

| 弱いプルアップ抵抗 - JTAGTRSTZ, JTAGTDI,<br>JTAGTMS1, JTAGTMS2,                                                                               | VDD18 = 1.8 V   | 31  | 84  | kΩ |

| 弱いプルダウン抵抗 - JTAGTCK, HWTEST_EN,<br>TSTPT_0, TSTPT_1, TSTPT_2, TSTPT_3,<br>TSTPT_4, TSTPT_5, TSTPT_6, TSTPT_7,<br>GPTP0, GPTP1, GPTP2 | VDD18 = 1.8 V   | 31  | 71  | kΩ |

- (1) 5.7kΩ 以下の外付けプルアップ抵抗またはプルダウン抵抗(必要な場合)は、どの電圧条件でも、関連する内部プルアップ抵抗またはプルダウン抵抗を適切に無効化するのに十分です。

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

| パラメータ                      |                                                                                                                              | 最小値  | 標準値     | 最大値     | 単位 |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------|------|---------|---------|----|

| <b>電源電圧 (2)</b>            |                                                                                                                              |      |         |         |    |

| VDD_CORE                   | コア ロジック用 0.8V (公称)                                                                                                           | -0.3 | 1.05    | 1.05    | V  |

| VDDAR_CORE                 | SRAM コア (0.8V 公称)                                                                                                            | -0.3 | 1.05    | 1.05    | V  |

| VDDS18_LVCMOS1             | 1.8V (公称) 固定 IO 電源、左側                                                                                                        | -0.3 | 2.2     | 2.2     | V  |

| VDDS18_LVCMOS2             | 1.8V (公称) 固定 IO 電源、右側                                                                                                        | -0.3 | 2.2     | 2.2     | V  |

| VDDA_CORE_DSI              | DSI 用 0.8V (公称)                                                                                                              | -0.3 | 1.05    | 1.05    | V  |

| VDDA18_DSI                 | DSI 用 1.8V (公称)                                                                                                              | -0.3 | 2.2     | 2.2     | V  |

| VDDA_CORE_FPD              | FPD コア用 0.8V (公称) 固定電源                                                                                                       | -0.3 | 1.05    | 1.05    | V  |

| VDDA18_FPD                 | FPD I/O 用 1.8V (公称) 固定電源                                                                                                     | -0.3 | 2.2     | 2.2     | V  |

| VDDA_CORE_Vx1              | Vx1 コア用 0.8V (公称) 固定電源                                                                                                       | -0.3 | 1.05    | 1.05    | V  |

| VDDA18_Vx1                 | Vx1 I/O 用 1.8V (公称) 固定電源                                                                                                     | -0.3 | 2.2     | 2.2     | V  |

| VDDA_CORE_USB              | USB コントローラ用 0.8V (公称)                                                                                                        | -0.3 | 1.05    | 1.05    | V  |

| VDDA18_USB                 | USB PHY 用 1.8V (公称)                                                                                                          | -0.3 | 2.2     | 2.2     | V  |

| VDDA33_USB                 | USB PHY 用 3.3V (公称)                                                                                                          | -0.3 | 3.6     | 3.6     | V  |

| VDDSHV_INTF                | PMIC I/O の代わりに PAD1000 をサポートするための、SPI および I <sup>2</sup> C I/O 用 1.8V または 3.3V (公称) マルチ電圧 IO 電源 (GPIO[8:0] を含む)。また、HOST_IRQ。 | -0.3 | 3.8     | 3.8     | V  |

| VDDSHV_FLSH                | クワッドシリアル フラッシュインターフェイス用 1.8V または 3.3V (公称) マルチ電圧 IO 電源                                                                       | -0.3 | 3.8     | 3.8     | V  |

| VDDA18_DDI                 | SubLVDS DMD インターフェイス用 1.8V (公称) 固定 IO 電源                                                                                     | -0.3 | 2.2     | 2.2     | V  |

| VDDS18_OSC                 | リファレンス発振器 I/O 用 1.8V (公称) 固定電源                                                                                               | -0.3 | 2.2     | 2.2     | V  |

| VDDA18_PLLM                | メイン I/F PLL 用 1.8V (公称)                                                                                                      | -0.3 | 2.2     | 2.2     | V  |

| VDDA18_PLDD                | DMD I/F PLL 用 1.8V (公称)                                                                                                      | -0.3 | 2.2     | 2.2     | V  |

| <b>LDO INTF</b>            |                                                                                                                              |      |         |         |    |

| CAP_VDDS_INTF              | 3.3V/1.8V デュアル電圧インターフェイス I/O 用外付けコンデンサ                                                                                       | 1.8  | 1.98    | V       |    |

| CAP_VDDS_FLSH              | 3.3V/1.8V デュアル電圧フラッシュ I/O 用外付け部コンデンサ                                                                                         |      |         |         |    |

| <b>一般</b>                  |                                                                                                                              |      |         |         |    |

| T <sub>J</sub>             | 動作時接合部温度                                                                                                                     | -30  | 115     | 115     | °C |

| T <sub>C</sub>             | 動作時のケース温度                                                                                                                    | -30  | 105     | 105     | °C |

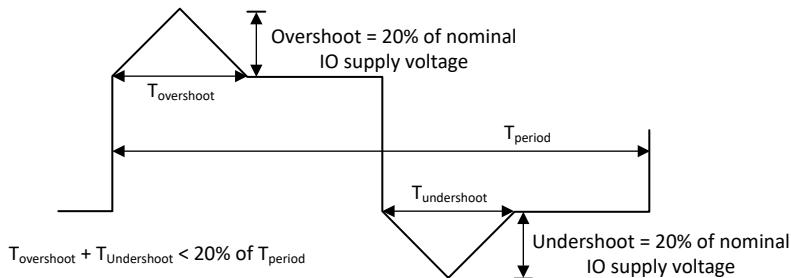

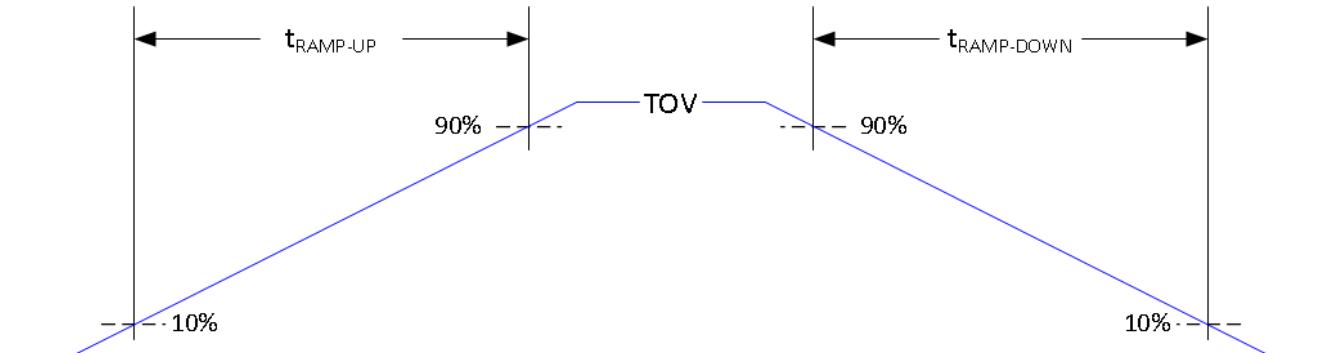

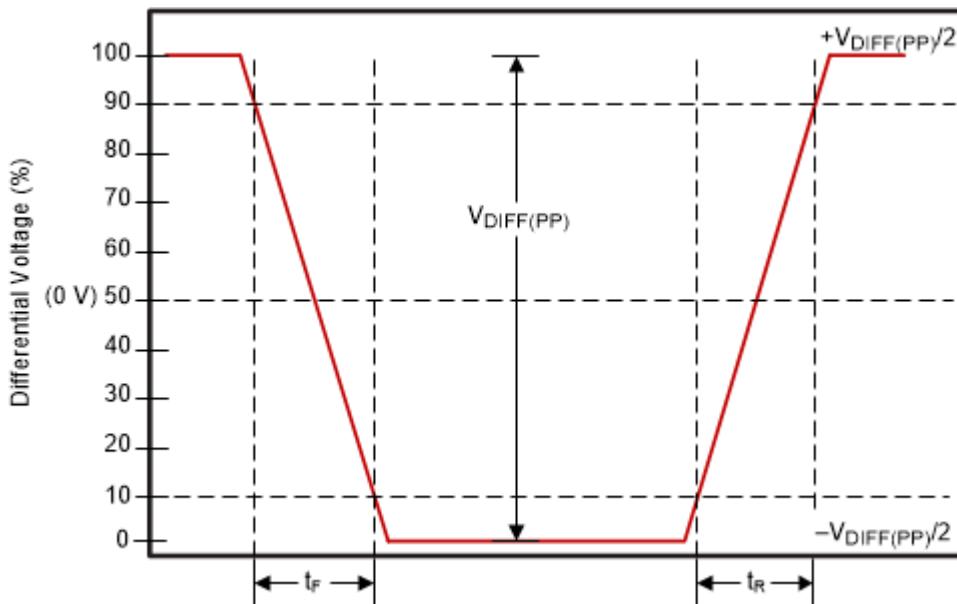

| O ピンの過渡オーバーシュートおよびアンダーシュート | 信号周期の最大 20% にわたって IO 電源電圧の 20% (図 5-1、IO 過渡電圧範囲を参照)                                                                          |      | 0.2×VDD | 0.2×VDD | V  |

| T <sub>stg</sub>           | 保管温度範囲                                                                                                                       | -40  | 125     | 125     | °C |

- (1) 「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

- (2) すべての電圧値は、GND を基準としたものです。

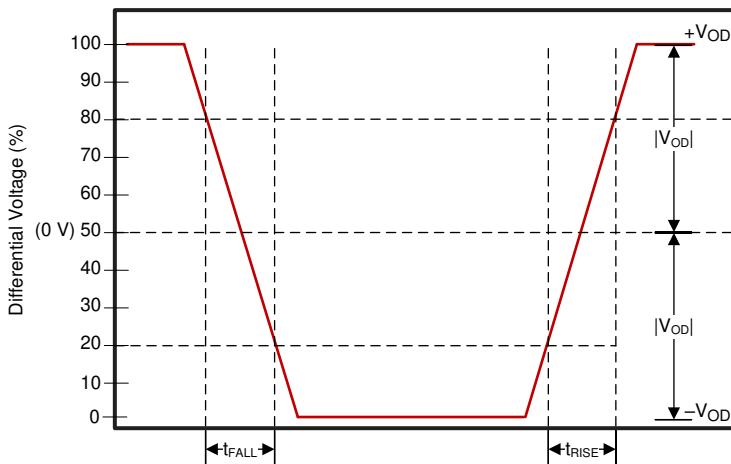

図 5-1. IO 過渡電圧範囲

## 5.2 ESD 定格

ANSI/ESDA/JEDEC JS-002

| パラメータ       |      |                                                              | 値          | 単位 |

|-------------|------|--------------------------------------------------------------|------------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup> | $\pm 1000$ | V  |

|             |      | デバイス帶電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠 <sup>(2)</sup>    | $\pm 250$  |    |

(1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 5.3 推奨動作条件

| パラメータ          |                                                                                                                              | 許容誤差 | 最小値   | 標準値 | 最大値   | 単位 |

|----------------|------------------------------------------------------------------------------------------------------------------------------|------|-------|-----|-------|----|

| <b>電源電圧</b>    |                                                                                                                              |      |       |     |       |    |

| VDD_CORE       | コア ロジック用 0.8V (公称)                                                                                                           |      | 0.76  | 0.8 | 0.84  | V  |

| VDDAR_CORE     | SRAM コア (0.8V 公称)                                                                                                            |      | 0.76  | 0.8 | 0.84  | V  |

| VDDS18_LVCMOS1 | 1.8V (公称) 固定 IO 電源、左側                                                                                                        |      | 1.647 | 1.8 | 1.953 | V  |

| VDDS18_LVCMOS2 | 1.8V (公称) 固定 IO 電源、右側                                                                                                        |      | 1.647 | 1.8 | 1.953 | V  |

| VDDA_CORE_DSI  | DSI 用 0.8V (公称)                                                                                                              |      | 0.76  | 0.8 | 0.84  | V  |

| VDDA18_DSI     | DSI 用 1.8V (公称)                                                                                                              |      | 1.647 | 1.8 | 1.953 | V  |

| VDDA_CORE_FPD  | FPD コア用 0.8V (公称) 固定電源                                                                                                       |      | 0.76  | 0.8 | 0.84  | V  |

| VDDA18_FPD     | FPD I/O 用 1.8V (公称) 固定電源                                                                                                     |      | 1.647 | 1.8 | 1.953 | V  |

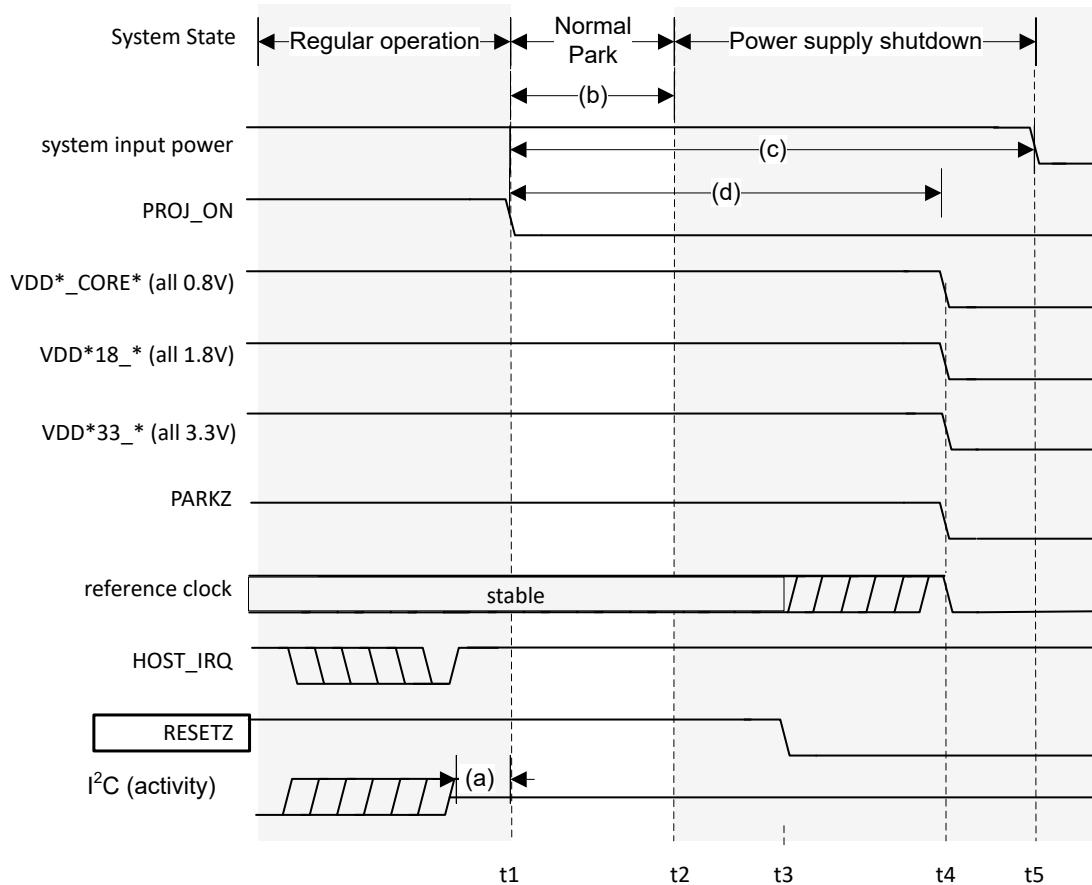

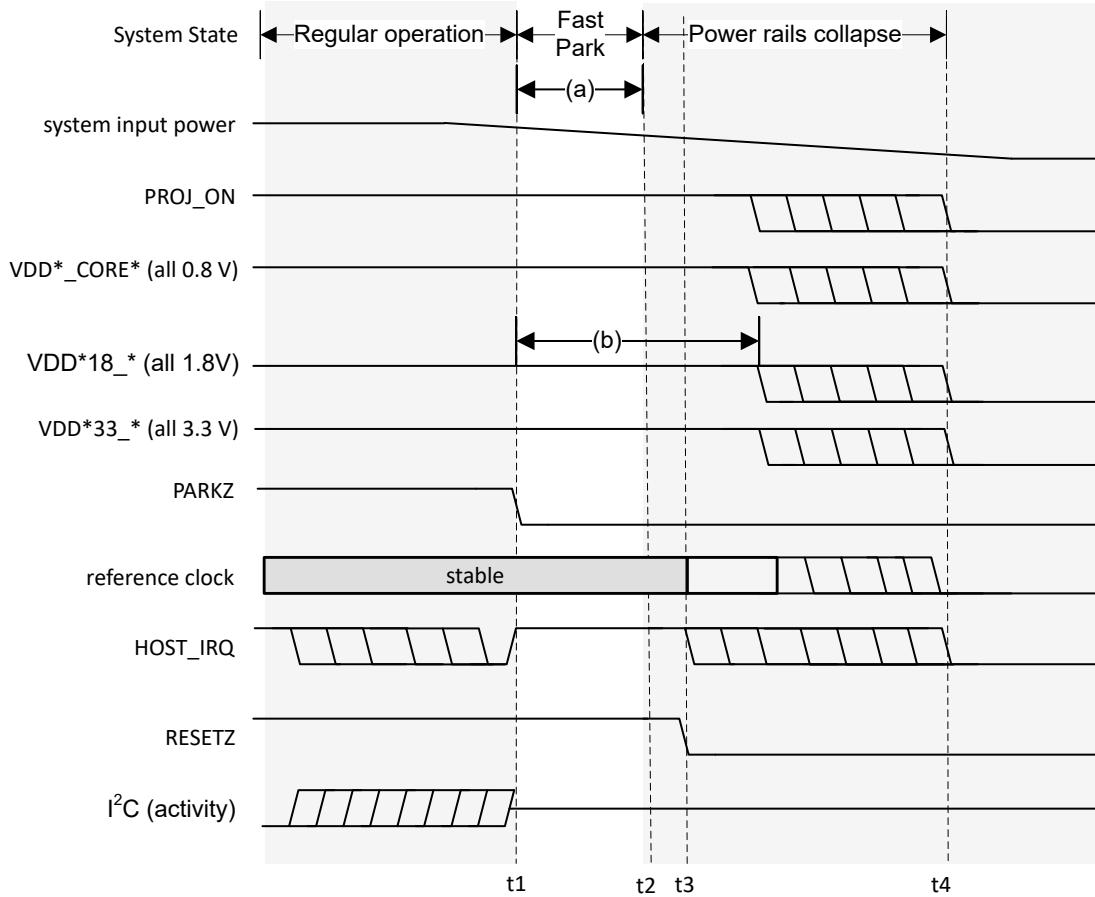

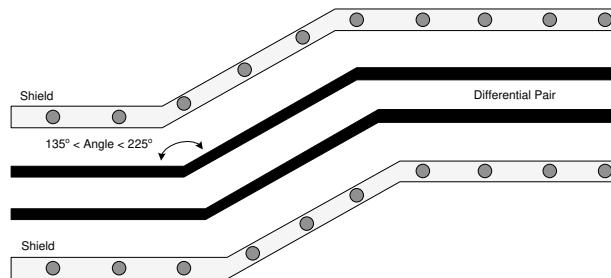

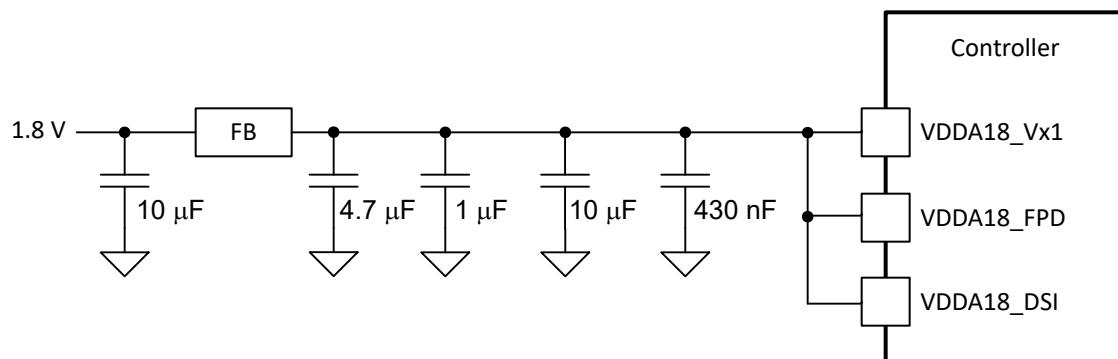

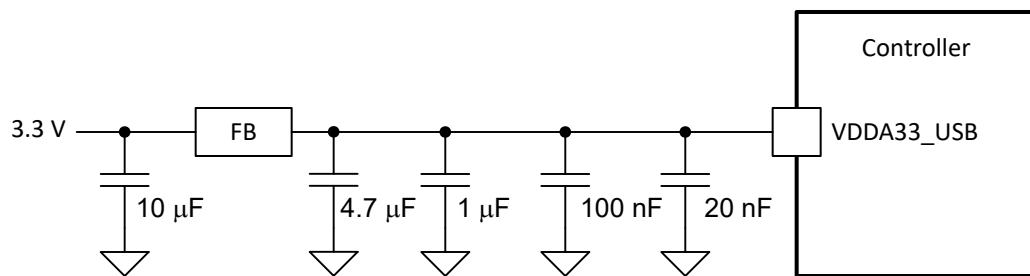

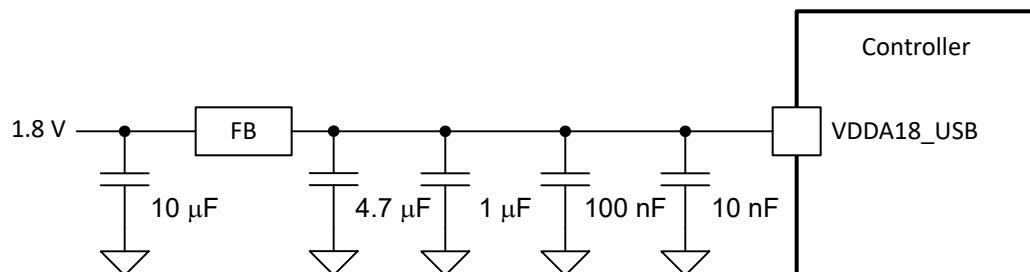

| VDDA_CORE_Vx1  | Vx1 コア用 0.8V (公称) 固定電源                                                                                                       |      | 0.76  | 0.8 | 0.84  | V  |