## DLPC6422 DLP® デジタルコントローラ

### 1 特長

- DLP78TUV (.78 インチ 8.3-メガピクセル) DMD 向けデジタルコントローラ

- デュアルコントローラ、60Hz で最大 4K

- シングルコントローラ、120Hz で最大 1080p

- シングル 30 ビットまたはデュアル 60 ビットの入力ピクセル インターフェイスを提供:

- YUV、YCrCb、RGB データ形式

- RGB データフォーマット

- 8、9、10 ビット/カラー

- 最大 320MHz のピクセル クロック (シングル コントローラでデュアル 30 ビット モード時)

- 最大 600MHz のピクセル クロック (デュアル コントローラ、デュアル 30 ビット モード時)

- 高速、低電圧差動信号 (LVDS) DMD インターフェイス

- 150MHz ARM946™ マイクロプロセッサ

- マイクロプロセッサ ペリフェラル

- プログラマブル パルス幅変調 (PWM) およびキャプチャ タイマ

- 3 つの I2C ポート、3 つの UART ポート、3 つの SSP ポート

- 1 つの USB 1.1 セカンダリ ポート

- 画像処理

- 複数の画像処理アルゴリズム

- フレーム レート変換

- 色座標調整

- プログラム可能な色空間の変換

- プログラム可能なデガンマおよびスプラッシュ

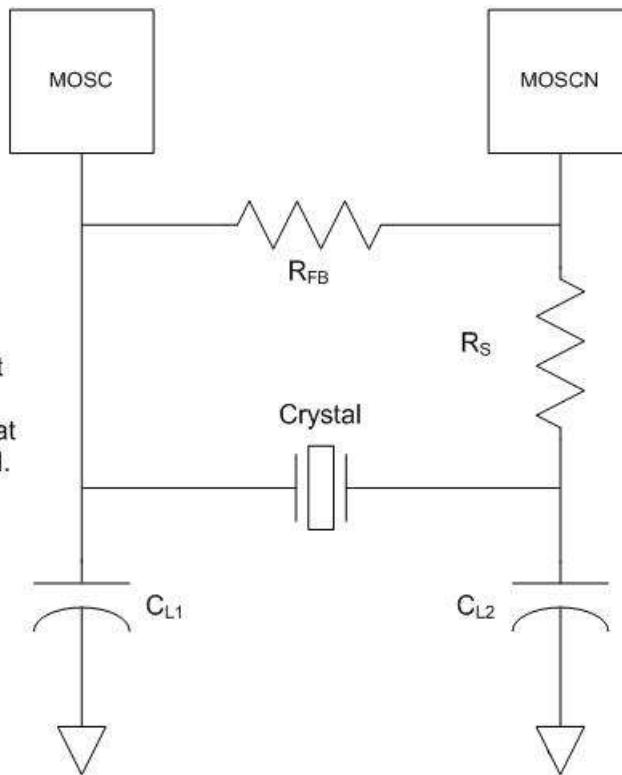

- クロック生成回路内蔵

- 単一の 20MHz クリスタルで動作

- スペクトラム拡散クロッキングを内蔵

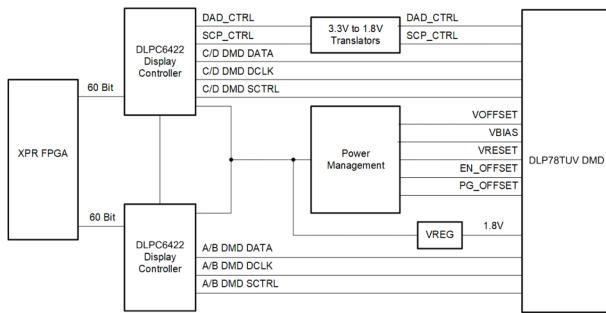

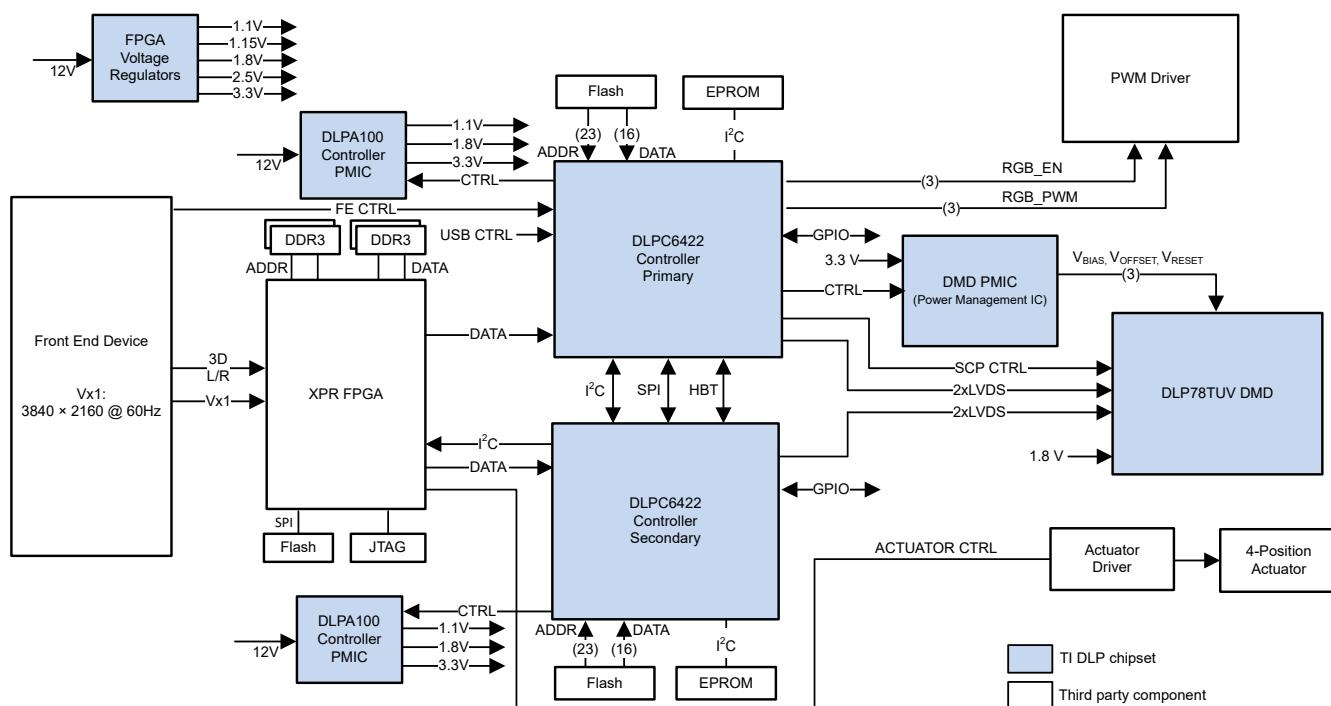

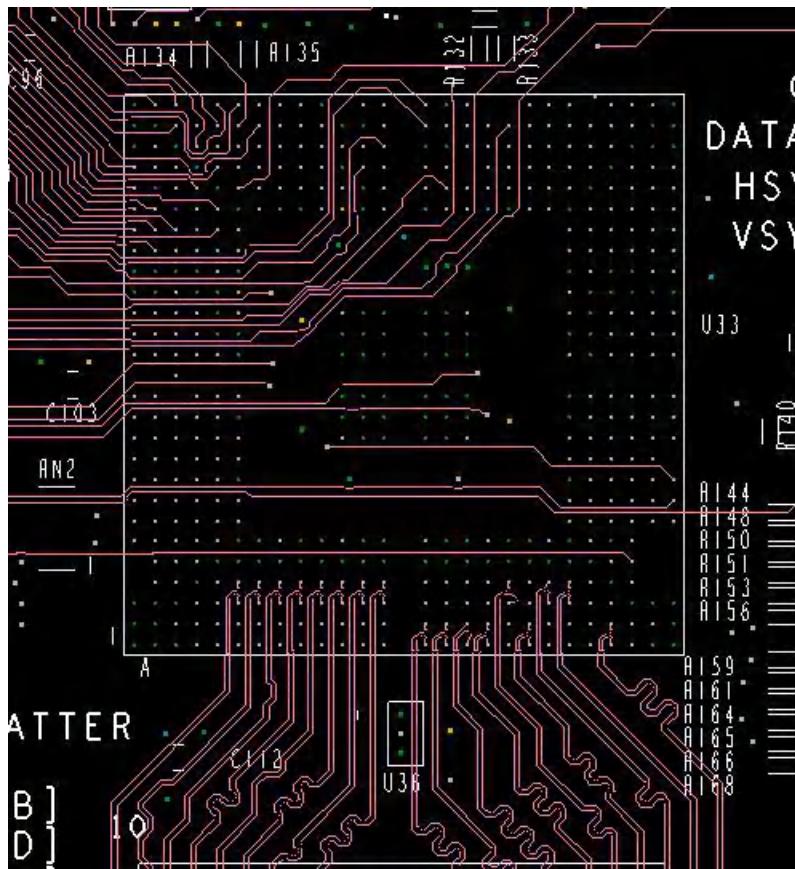

デュアルコントローラシステムの概略回路図

- 外部メモリに対応

- マイクロプロセッサおよび PWM シーケンス用のパラレル フラッシュ

- 516 ピンのプラスチック ボール グリッド アレイ パッケージ

- LED およびレーザー ハイブリッド照明をサポート

### 2 アプリケーション

- 3D プリンタ

- レーザー マーキング

- レーザー 製造

- デジタルイメージングと露光

### 3 説明

DLPC6422 は、DLP® イメージング チップセット用のデジタル ライト コントローラです。このチップセットは、DLPC6422 ライトコントローラ、DLP デジタルマイクロミラーデバイス (DMD) DLP78TUV、DLPA100 パワーマネジメントデバイス、DLPA300 DMD マイクロミラードライバで構成されます (DMD データシートを参照)。このシステムは、高速、高分解能、UV 波長、高光量スループット、堅牢なシステムを必要とする DLP 3D プリントやその他の画像処理アプリケーションに最適です。信頼性の高い動作を保証するため、DLPC6422 ライトコントローラは、DLP DMD DLP78TUV および対応する DLP パワー マネジメントデバイスと一緒に使用する必要があります。

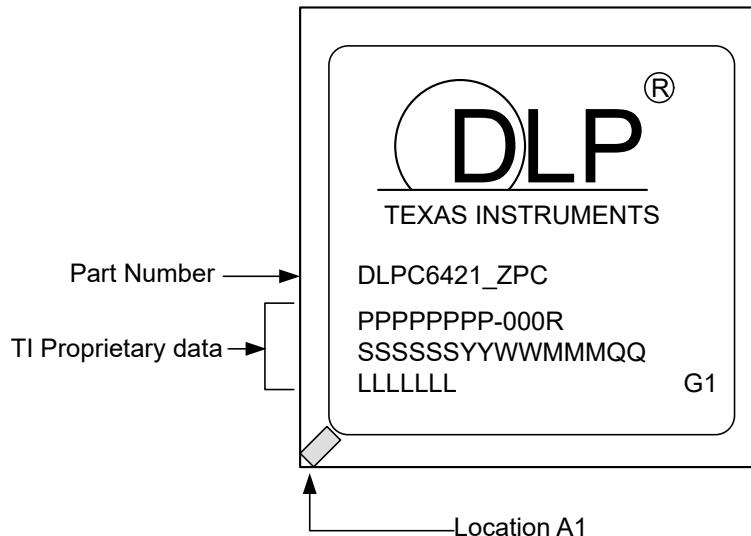

#### パッケージ情報

| 部品番号     | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|----------|----------------------|--------------------------|

| DLPC6422 | ZPC (516)            | 27.00mm × 27.00mm        |

(1) 詳細については、[セクション 10](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンも含まれます。

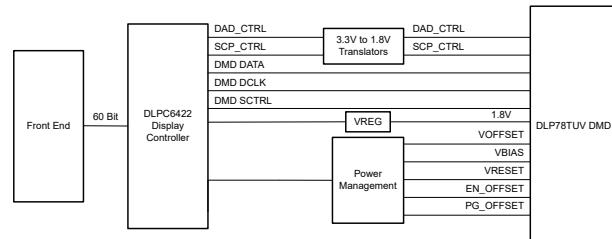

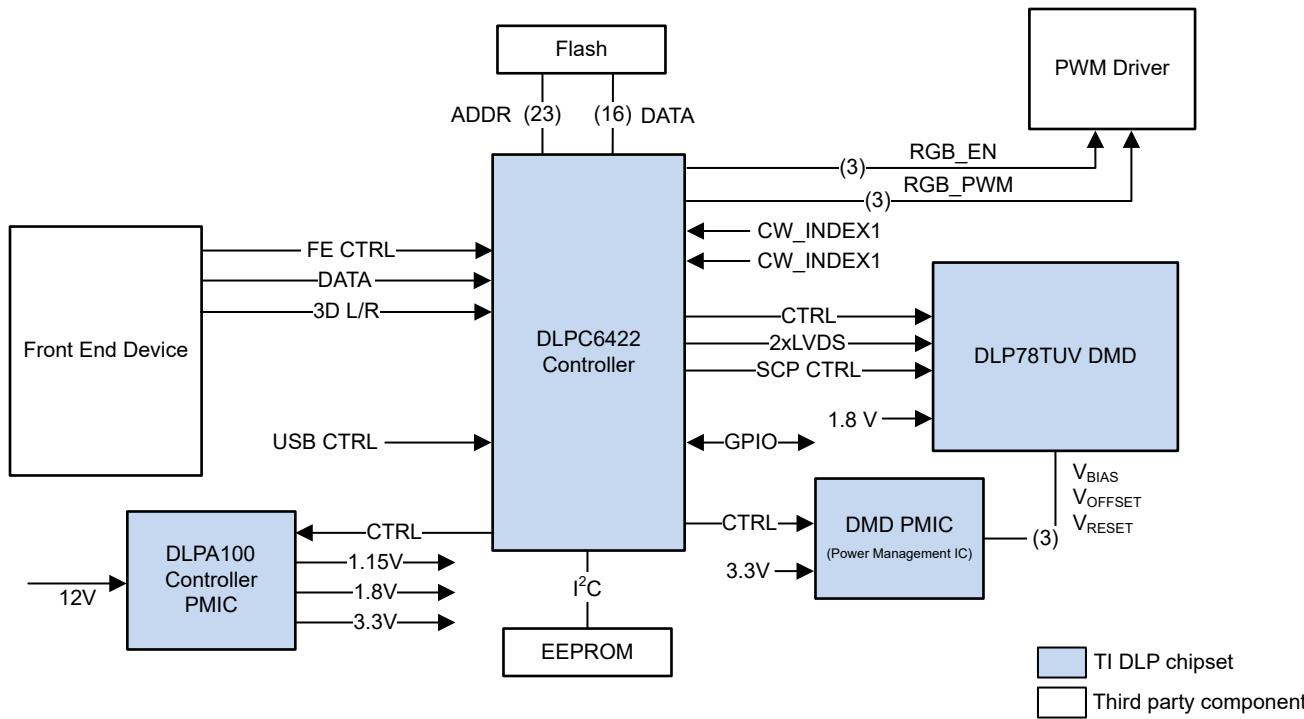

シングルコントローラシステムの概略回路図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                                                          |           |                                                                     |           |

|----------------------------------------------------------|-----------|---------------------------------------------------------------------|-----------|

| <b>1 特長</b> .....                                        | <b>1</b>  | <b>5.15 JTAG インターフェイス:I/O バウンダリスキャンアプ<br/>リケーションのスイッチング特性</b> ..... | <b>25</b> |

| <b>2 アプリケーション</b> .....                                  | <b>1</b>  | <b>6 詳細説明</b> .....                                                 | <b>28</b> |

| <b>3 説明</b> .....                                        | <b>1</b>  | 6.1 概要.....                                                         | <b>28</b> |

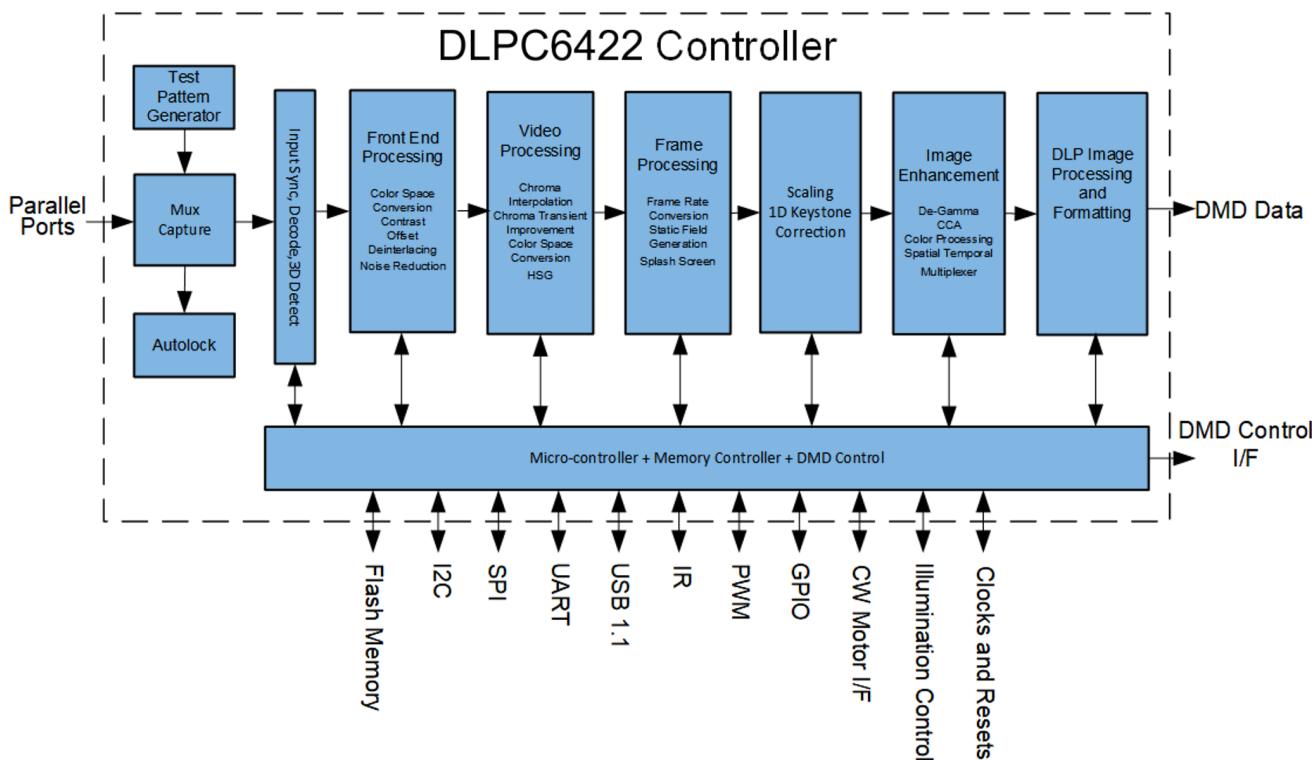

| <b>4 ピン構成および機能</b> .....                                 | <b>3</b>  | 6.2 機能ブロック図.....                                                    | <b>28</b> |

| <b>5 仕様</b> .....                                        | <b>14</b> | 6.3 機能説明.....                                                       | <b>28</b> |

| 5.1 絶対最大定格.....                                          | <b>14</b> | 6.4 デバイスの機能モード.....                                                 | <b>32</b> |

| 5.2 推奨動作条件.....                                          | <b>14</b> | <b>7 アプリケーションと実装</b> .....                                          | <b>33</b> |

| 5.3 熱に関する情報.....                                         | <b>15</b> | 7.1 アプリケーション情報.....                                                 | <b>33</b> |

| 5.4 電気的特性.....                                           | <b>16</b> | 7.2 代表的なアプリケーション.....                                               | <b>33</b> |

| 5.5 ESD 定格.....                                          | <b>18</b> | 7.3 電源要件および推奨事項.....                                                | <b>35</b> |

| 5.6 システム振動子のタイミング要件.....                                 | <b>18</b> | 7.4 レイアウト.....                                                      | <b>37</b> |

| 5.7 テストおよびリセットのタイミング要件.....                              | <b>18</b> | <b>8 デバイスおよびドキュメントのサポート</b> .....                                   | <b>44</b> |

| 5.8 JTAG インターフェイス:I/O バウンダリスキャンアプ<br>リケーションのタイミング要件..... | <b>19</b> | 8.1 サード・パーティ製品に関する免責事項.....                                         | <b>44</b> |

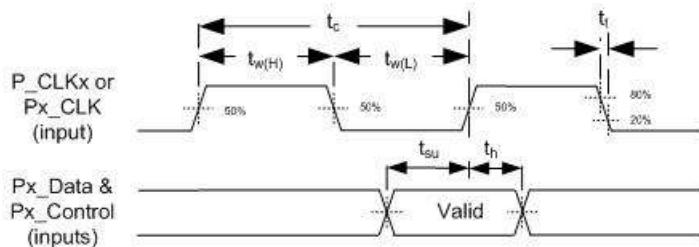

| 5.9 ポート 1 入力ピクセルのタイミング要件.....                            | <b>19</b> | 8.2 デバイス サポート.....                                                  | <b>44</b> |

| 5.10 ポート 3 入力ピクセルインターフェイス (GPIO 経<br>由) のタイミング要件.....    | <b>21</b> | 8.3 ドキュメントのサポート.....                                                | <b>45</b> |

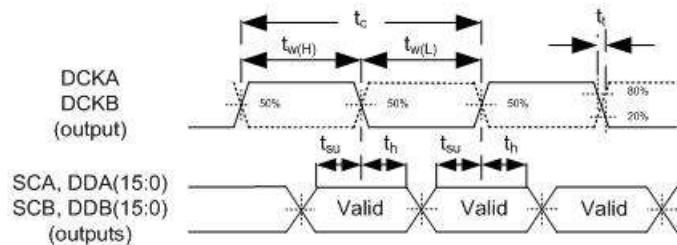

| 5.11 DMD LVDS インターフェイスのタイミング要件.....                      | <b>21</b> | 8.4 ドキュメントの更新通知を受け取る方法.....                                         | <b>46</b> |

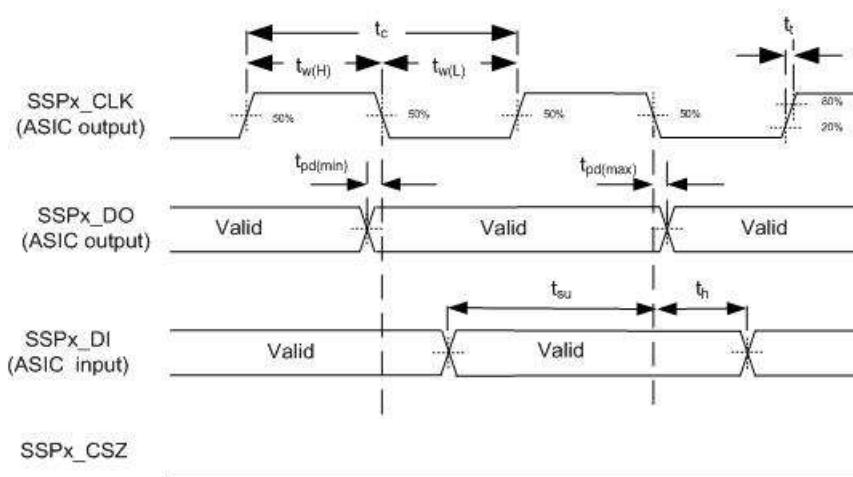

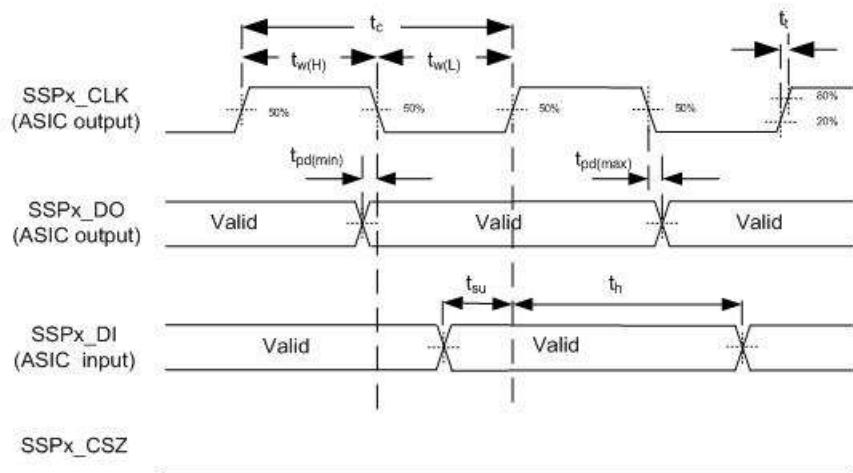

| 5.12 同期シリアルポート (SSP) インターフェイスのタイ<br>ミング要件.....           | <b>22</b> | 8.5 サポート・リソース.....                                                  | <b>46</b> |

| 5.13 プログラム可能出力クロックのスイッチング特性.....                         | <b>23</b> | 8.6 商標.....                                                         | <b>46</b> |

| 5.14 同期式シリアルインターフェイス (SSP) のスイッチ<br>ング特性.....            | <b>23</b> | 8.7 静電気放電に関する注意事項.....                                              | <b>46</b> |

|                                                          |           | 8.8 用語集.....                                                        | <b>46</b> |

|                                                          |           | <b>9 改訂履歴</b> .....                                                 | <b>46</b> |

|                                                          |           | <b>10 メカニカル、パッケージ、および注文情報</b> .....                                 | <b>47</b> |

## 4 ピン構成および機能

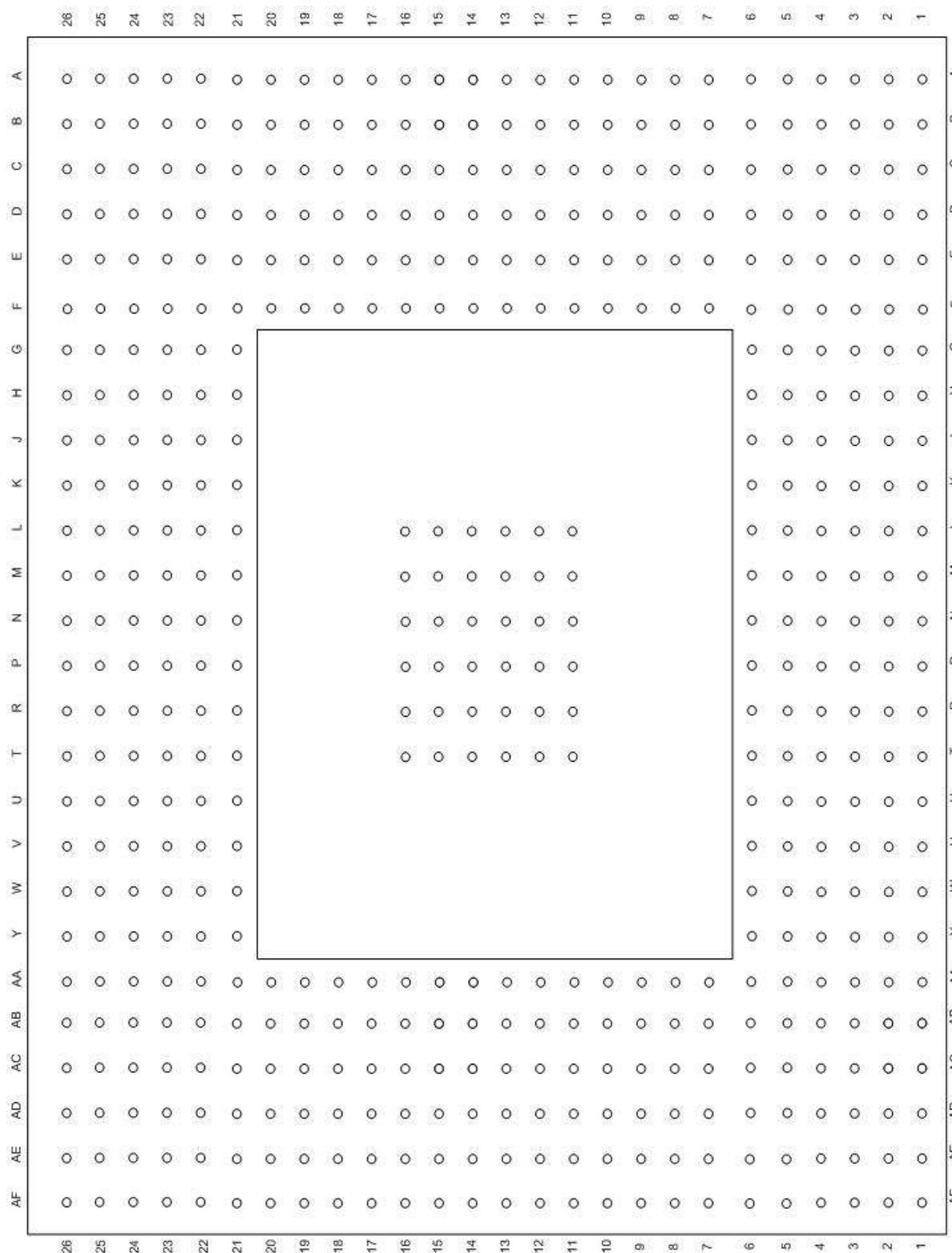

図 4-1. ピン構成

**表 4-1. ピンの機能**

| ピン <sup>(1)</sup>             |     | タイプ <sup>(2)</sup> | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------|-----|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                            | 番号  |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

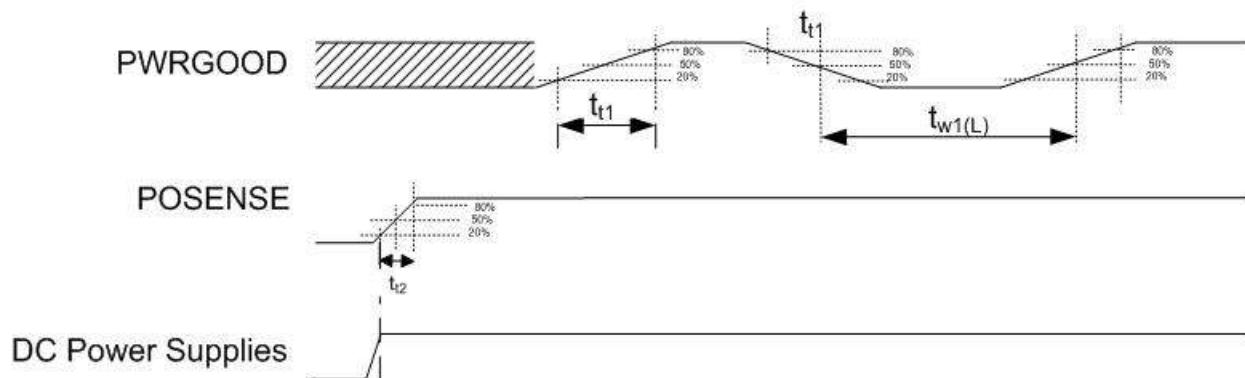

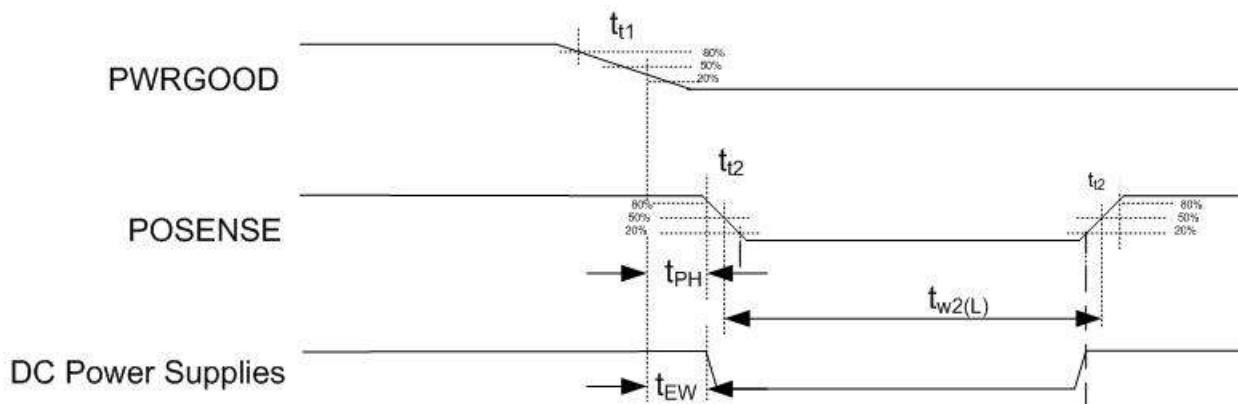

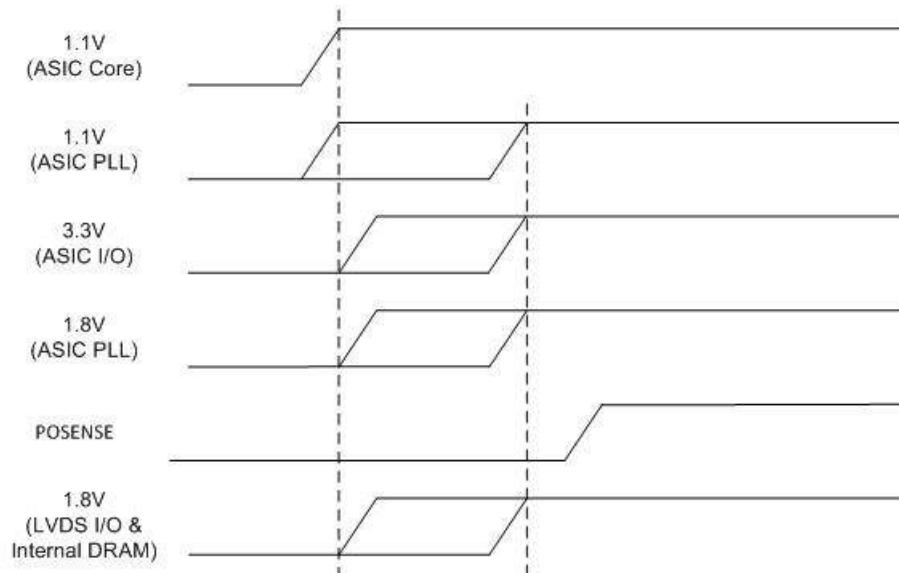

| POSENSE                       | P22 | I <sub>4</sub>     | 電源投入検出 (High True)、外部電圧監視回路から供給される信号。この信号は、すべての ASIC 電源電圧が指定された最小電圧の 90% に達したときにアクティブ (High) に駆動されます。この信号は、指定されたように PWRGOOD の立ち下がりエッジ後、非アクティブ (Low) になります。                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PWRGOOD                       | T26 | I <sub>4</sub>     | パワーグッド、ハイタルー、外部電源または電圧モニタからの信号。ハイバリューは、すべての電源が動作電圧仕様の範囲内であり、システムがリセット状態を終了しても安全であることを示します。High から Low への遷移は、コントローラまたは DMD 電源電圧が定格最低レベルを下回ったことを示すために使用されます。この遷移は、仕様で規定されている電源電圧降下の前に生じさせる必要があります。この期間中、POSENSE はアクティブ High のままである必要があります。これは停電状態が迫っていることを知らせる警告です。この警告は、長期的な DMD の信頼性向上のために必要です。PWRGOOD が指定された最小時間 Low になると、DLPC6422 コントローラは DMD パーク処理を実行して、コントローラを完全にリセットし、DMD を保護します。この最小アサート解除時間は、グリッヂから入力を保護するために使用されます。この後、PWRGOOD が Low の間、DLPC6422 コントローラはリセット状態に保持されます。正常に動作させるためには、PWRGOOD 信号を High に駆動する必要があります。DLPC6422 コントローラは、指定された最小時間にわたって High に駆動されると、PWRGOOD をアクティブであるとして認識します。ヒステリシスを使用します |

| EXT_ARSTZ                     | T24 | O <sub>2</sub>     | 汎用、low true、出力リセット。この出力は、パワーアップリセット (POSENSE) を Low にアサートすると、即座に Low にアサートされ、POSENSE が Low で維持されている間 Low で保持されます。EXT_ARSTZ は、パワーアップリセットの解除後 (つまり POSENSE が High に設定された状態)、ソフトウェアによって解除されるまで Low に維持されます。EXT_ARSTZ 信号も、PWRGOOD または内部で生成されるリセットが検出された後、ほぼ 5μs で Low にアサートされます。いずれの場合も、2ms 以上の間アクティブとなります。ASIC には、この出力を独立して駆動するために使用できるソフトウェアレジスタが含まれていることにご注意ください。                                                                                                                                                                                                                                             |

| MTR_ARSTZ                     | T25 | O <sub>2</sub>     | カラーホールモーターコントローラ、Low True、リセット出力。この出力は、パワーアップリセット (POSENSE) を Low にアサートすると、即座に Low にアサートされ、POSENSE が Low で維持されています。MTR_ARSTZ は、パワーアップリセットの解除後 (つまり POSENSE が High に設定された状態)、ソフトウェアによって解除されるまで Low に維持されます。MTR_ARSTZ 信号も、オプションで、PWRGOOD または内部で生成されるリセットが検出された後、ほぼ 5μs で Low にアサートされます。いずれの場合も、2ms 以上の間アクティブとなります。ASIC には、この出力を独立して駆動するために使用できるソフトウェアレジスタが含まれていることにご注意ください。ASIC にはソフトウェアレジスタも含まれており、ランプストライクリセット時にモーターリセットのアサートを無効にするために使用できます。                                                                                                                                                                |

| ポートレベルのテストと初期化 <sup>(3)</sup> |     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

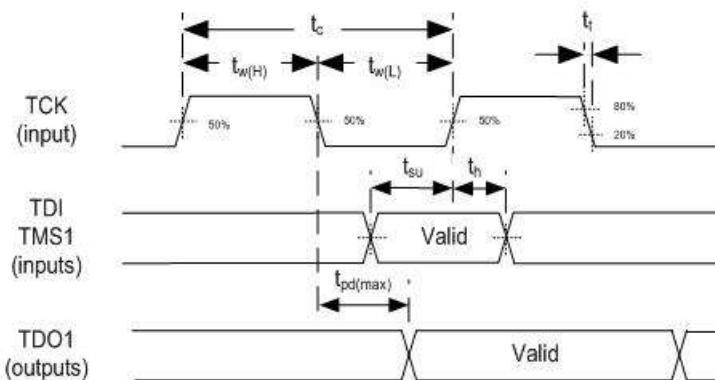

| TDI                           | N25 | I <sub>4</sub>     | JTAG シリアルデータ入力。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TCK                           | N24 | I <sub>4</sub>     | JTAG シリアルデータクロック                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| TMS1                          | P25 | I <sub>4</sub>     | JTAG テスト モード選択                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TMS2                          | P26 | I <sub>4</sub>     | JTAG テスト モード選択                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TDO1                          | N23 | O <sub>5</sub>     | JTAG シリアル データ出力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TDO2                          | N22 | O <sub>5</sub>     | JTAG シリアル データ出力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TRSTZ                         | M23 | I <sub>4</sub>     | JTAG リセット。この信号には内部プルアップが含まれ、ヒステリシスを利用してしています。このピンは、JTAG インターフェイスがパウンダリスキヤンまたは ARM デバッグに使用されている場合、High (または未接続状態) になります。そうでない場合、このピンはグランドに接続されます。通常動作中にこのピンを Low に固定しないと、起動や初期化で問題が生じます。                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RTCK                          | E4  | O <sub>2</sub>     | JTAG リターンクロック                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ETM_PIPESTAT_2                | A4  | B <sub>2</sub>     | ETM トレースポートパイプラインステータス。ARM コアのパイプラインステータスを示します。これらの信号には、内部プルダウンが含まれます。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ETM_PIPESTAT_1                | B5  | B <sub>2</sub>     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ETM_PIPESTAT_0                | C6  | B <sub>2</sub>     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ETM_TRACESYNC                 | A5  | B <sub>2</sub>     | ETM トレースポート同期信号、トレースパケットポート上のプランチシーケンスの開始を示します。この信号には、内部プルダウンが含まれます。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ETM_TRACECLK                  | D7  | B <sub>2</sub>     | ETM トレースポートクロック。この信号には、内部プルダウンが含まれます。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ICTSEN                        | M24 | I <sub>4</sub>     | IC トライステートイネーブル (アクティブ High)。High をアサートすると、JTAG インターフェイスを除くすべての出力がトライステートになります。この信号には内部プルダウンが含まれますが、保護機能強化のために外付けプルダウンが推奨されます。ヒステリシスを使用します                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TSTPT_7                       | E8  | B <sub>2</sub>     | テストピン 7 この信号で、内部プルダウンが生じます。<br>通常使用: テスト出力用に予約されています。通常使用のために、オープンのままにするか、未接続にすることが推奨されます                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TSTPT_6                       | B4  | B <sub>2</sub>     | テストピン 6 この信号で、内部プルダウンが生じます。<br>通常使用: テスト出力用に予約されています。通常使用のために、オープンのままにするか、未接続にすることが推奨されます                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TSTPT_5                       | C4  | B <sub>2</sub>     | テストピン 5 この信号で、内部プルダウンが生じます。<br>通常使用: テスト出力用に予約されています。通常使用のために、オープンのままにするか、未接続にすることが推奨されます                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TSTPT_4                       | E7  | B <sub>2</sub>     | テストピン 4 この信号で、内部プルダウンが生じます。<br>通常使用: テスト出力用に予約されています。通常使用のために、オープンのままにするか、未接続にすることが推奨されます                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TSTPT_3                       | D5  | B <sub>2</sub>     | テストピン 3 この信号で、内部プルダウンが生じます。<br>通常使用: テスト出力用に予約されています。通常使用のために、オープンのままにするか、未接続にすることが推奨されます                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TSTPT_2                       | E6  | B <sub>2</sub>     | テストピン 2 この信号で、内部プルダウンが生じます。さらに、TSTPT (2:0) を外部プルアップに接続するためのジャンパー オプションを提供することを推奨します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TSTPT_1                       | D3  | B <sub>2</sub>     | テストピン 1 この信号で、内部プルダウンが生じます。さらに、TSTPT (2:0) を外部プルアップに接続するためのジャンパー オプションを提供することを推奨します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TSTPT_0                       | C2  | B <sub>2</sub>     | テストピン 0 この信号で、内部プルダウンが生じます。さらに、TSTPT (2:0) を外部プルアップに接続するためのジャンパー オプションを提供することを推奨します。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| デバイステスト                       |     |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

表 4-1. ピンの機能 (続き)

| ピン <sup>(1)</sup>                                          |      | タイプ <sup>(2)</sup> | 説明                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------|------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                                                         | 番号   |                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

| HW_TEST_EN                                                 | M25  | I <sub>4</sub>     | デバイス製造テストイネーブル。この信号には内部ブルダウンが含まれ、ヒステリシスを利用しています。保護機能強化のため、この信号は通常動作で外部グランドに固定することが推奨されます。                                                                                                                                                                                                                                                                                                          |

| アナログ フロントエンド                                               |      |                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

| AFE_ARSTZ                                                  | AC12 | O <sub>2</sub>     | アナログフロントエンド、LOW True、リセット出力。この出力は、パワーアップリセット (POSENSE) を Low にアサートすると、即座に Low にアサートされ、POSENSE が Low で維持されている間 Low で保持されます。AFE_ARSTZ は、パワーアップリセットの解除後 (つまり POSENSE が High に設定された状態)、ソフトウェアによって解除されるまで Low に維持されます。AFE_ARSTZ 信号も、PWRGOOD または内部で生成されるリセットが検出された後、ほぼ 5μs で Low にアサートされます。いずれの場合も、ソフトウェアによってリセット状態が解除されてから 2ms 以上の間アクティブとなります。ASIC には、この出力を独立して駆動するために使用できるソフトウェアレジスタが含まれていることにご注意ください。 |

| AFE_CLK                                                    | AD12 | O <sub>6</sub>     | ビデオデコーダ動作作用のアナログフロントエンド外部クロック出力。プログラム可能出力ドライブをサポート                                                                                                                                                                                                                                                                                                                                                 |

| AFE IRQ                                                    | AB13 | I <sub>4</sub>     | アナログフロントエンド割り込み (アクティブ High)。この信号には内部ブルダウンが含まれ、ヒステリシスを利用しています。                                                                                                                                                                                                                                                                                                                                     |

| ポート 1 およびポート 2 チャネルデータおよびコントロール <sup>(4) (5) (6) (7)</sup> |      |                    |                                                                                                                                                                                                                                                                                                                                                                                                    |

| P_CLK1                                                     | AE22 | I <sub>4</sub>     | 入力ポートデータピクセル書き込みクロック (立ち上がりエッジまたは立ち下がりエッジトリガとして選択可能、およびそれが関連付けられているポート (A または B または (A および B))。この信号には、内部ブルダウンが含まれます。                                                                                                                                                                                                                                                                               |

| P_CLK2                                                     | W25  | I <sub>4</sub>     | 入力ポートデータピクセル書き込みクロック (立ち上がりエッジまたは立ち下がりエッジトリガとして選択可能、およびそれが関連付けられているポート (A または B または (A および B))。この信号には、内部ブルダウンが含まれます。                                                                                                                                                                                                                                                                               |

| P_CLK3                                                     | AF23 | I <sub>4</sub>     | 入力ポートデータピクセル書き込みクロック (立ち上がりエッジまたは立ち下がりエッジトリガとして選択可能、およびそれが関連付けられているポート (A または B または (A および B))。この信号には、内部ブルダウンが含まれます。                                                                                                                                                                                                                                                                               |

| P_DATAEN1                                                  | AF22 | I <sub>4</sub>     | アクティブ High データ イネーブル関連付けられているポート (A または B、または (A および B)) を選択可能。この信号には内部ブルダウンが含まれます。                                                                                                                                                                                                                                                                                                                |

| P_DATAEN2                                                  | W24  | I <sub>4</sub>     | アクティブ High データ イネーブル関連付けられているポート (A または B、または (A および B)) を選択可能。この信号には内部ブルダウンが含まれます。                                                                                                                                                                                                                                                                                                                |

| P1_A_9                                                     | AD15 | I <sub>4</sub>     | ポート 1A チャネル入力ピクセルデータ (ビットウェイト 128)                                                                                                                                                                                                                                                                                                                                                                 |

| P1_A_8                                                     | AE15 | I <sub>4</sub>     | ポート 1A チャネル入力ピクセルデータ (ビットウェイト 64)                                                                                                                                                                                                                                                                                                                                                                  |

| P1_A_7                                                     | AE14 | I <sub>4</sub>     | ポート 1A チャネル入力ピクセルデータ (ビットウェイト 32)                                                                                                                                                                                                                                                                                                                                                                  |

| P1_A_6                                                     | AE13 | I <sub>4</sub>     | ポート 1A チャネル入力ピクセルデータ (ビットウェイト 16)                                                                                                                                                                                                                                                                                                                                                                  |

| P1_A_5                                                     | AD13 | I <sub>4</sub>     | ポート 1A チャネル入力ピクセルデータ (ビットウェイト 8)                                                                                                                                                                                                                                                                                                                                                                   |

| P1_A_4                                                     | AC13 | I <sub>4</sub>     | ポート 1A チャネル入力ピクセルデータ (ビットウェイト 4)                                                                                                                                                                                                                                                                                                                                                                   |

| P1_A_3                                                     | AF14 | I <sub>4</sub>     | ポート 1A チャネル入力ピクセルデータ (ビットウェイト 2)                                                                                                                                                                                                                                                                                                                                                                   |

| P1_A_2                                                     | AF13 | I <sub>4</sub>     | ポート 1A チャネル入力ピクセルデータ (ビットウェイト 1)                                                                                                                                                                                                                                                                                                                                                                   |

| P1_A_1                                                     | AF12 | I <sub>4</sub>     | ポート 1A チャネル入力ピクセルデータ (ビットウェイト 0.5)                                                                                                                                                                                                                                                                                                                                                                 |

| P1_A_0                                                     | AE12 | I <sub>4</sub>     | ポート 1A チャネル入力ピクセルデータ (ビットウェイト 0.25)                                                                                                                                                                                                                                                                                                                                                                |

| P1_B_9                                                     | AF18 | I <sub>4</sub>     | ポート 1B チャネルの入力ピクセルデータ (ビットウェイト 128)                                                                                                                                                                                                                                                                                                                                                                |

| P1_B_8                                                     | AB18 | I <sub>4</sub>     | ポート 1B チャネルの入力ピクセルデータ (ビットウェイト 64)                                                                                                                                                                                                                                                                                                                                                                 |

| P1_B_7                                                     | AC15 | I <sub>4</sub>     | ポート 1B チャネルの入力ピクセルデータ (ビットウェイト 32)                                                                                                                                                                                                                                                                                                                                                                 |

| P1_B_6                                                     | AC16 | I <sub>4</sub>     | ポート 1B チャネルの入力ピクセルデータ (ビットウェイト 16)                                                                                                                                                                                                                                                                                                                                                                 |

| P1_B_5                                                     | AD16 | I <sub>4</sub>     | ポート 1B チャネルの入力ピクセルデータ (ビットウェイト 8)                                                                                                                                                                                                                                                                                                                                                                  |

| P1_B_4                                                     | AE16 | I <sub>4</sub>     | ポート 1B チャネルの入力ピクセルデータ (ビットウェイト 4)                                                                                                                                                                                                                                                                                                                                                                  |

| P1_B_3                                                     | AF16 | I <sub>4</sub>     | ポート 1B チャネルの入力ピクセルデータ (ビットウェイト 2)                                                                                                                                                                                                                                                                                                                                                                  |

| P1_B_2                                                     | AF15 | I <sub>4</sub>     | ポート 1B チャネルの入力ピクセルデータ (ビットウェイト 1)                                                                                                                                                                                                                                                                                                                                                                  |

| P1_B_1                                                     | AC14 | I <sub>4</sub>     | ポート 1B チャネルの入力ピクセルデータ (ビットウェイト 0.5)                                                                                                                                                                                                                                                                                                                                                                |

| P1_B_0                                                     | AD14 | I <sub>4</sub>     | ポート 1B チャネルの入力ピクセルデータ (ビットウェイト 0.25)                                                                                                                                                                                                                                                                                                                                                               |

| P1_C_9                                                     | AD20 | I <sub>4</sub>     | ポート 1C チャネルの入力ピクセルデータ (ビットウェイト 128)                                                                                                                                                                                                                                                                                                                                                                |

| P1_C_8                                                     | AE20 | I <sub>4</sub>     | ポート 1C チャネルの入力ピクセルデータ (ビットウェイト 64)                                                                                                                                                                                                                                                                                                                                                                 |

| P1_C_7                                                     | AE21 | I <sub>4</sub>     | ポート 1C チャネルの入力ピクセルデータ (ビットウェイト 32)                                                                                                                                                                                                                                                                                                                                                                 |

| P1_C_6                                                     | AF21 | I <sub>4</sub>     | ポート 1C チャネルの入力ピクセルデータ (ビットウェイト 16)                                                                                                                                                                                                                                                                                                                                                                 |

| P1_C_5                                                     | AD19 | I <sub>4</sub>     | ポート 1C チャネルの入力ピクセルデータ (ビットウェイト 8)                                                                                                                                                                                                                                                                                                                                                                  |

| P1_C_4                                                     | AE19 | I <sub>4</sub>     | ポート 1C チャネルの入力ピクセルデータ (ビットウェイト 4)                                                                                                                                                                                                                                                                                                                                                                  |

| P1_C_3                                                     | AF19 | I <sub>4</sub>     | ポート 1C チャネルの入力ピクセルデータ (ビットウェイト 2)                                                                                                                                                                                                                                                                                                                                                                  |

| P1_C_2                                                     | AF20 | I <sub>4</sub>     | ポート 1C チャネルの入力ピクセルデータ (ビットウェイト 1)                                                                                                                                                                                                                                                                                                                                                                  |

| P1_C_1                                                     | AC19 | I <sub>4</sub>     | ポート 1C チャネルの入力ピクセルデータ (ビットウェイト 0.5)                                                                                                                                                                                                                                                                                                                                                                |

| P1_C_0                                                     | AE18 | I <sub>4</sub>     | ポート 1C チャネルの入力ピクセルデータ (ビットウェイト 0.25)                                                                                                                                                                                                                                                                                                                                                               |

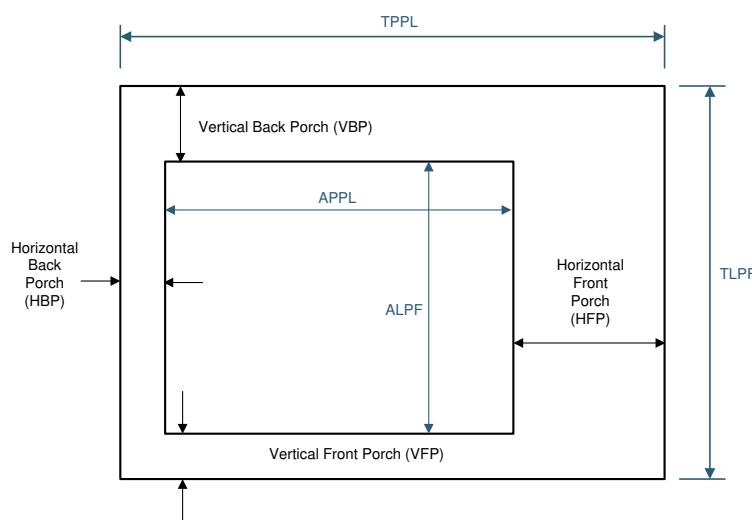

| P1_VSYNC                                                   | AC20 | B <sub>2</sub>     | ポート 1 の垂直同期この信号には、内部ブルダウンが含まれます。ポート 1 と関連付けられるように意図されていますが、ポート 2 で使用するようにプログラム可能です。                                                                                                                                                                                                                                                                                                                |

| P1_HSYNC                                                   | AD21 | B <sub>2</sub>     | ポート 1 水平同期この信号には、内部ブルダウンが含まれます。ポート 1 と関連付けされるように意図されていますが、ポート 2 で使用するようにプログラム可能です。                                                                                                                                                                                                                                                                                                                 |

表 4-1. ピンの機能 (続き)

| ピン <sup>(1)</sup>            |      | タイプ <sup>(2)</sup> | 説明                                                                                  |

|------------------------------|------|--------------------|-------------------------------------------------------------------------------------|

| 名称                           | 番号   |                    |                                                                                     |

| P2_A_9                       | AD26 | I <sub>4</sub>     | ポート 2 A チャネル入力ピクセルデータ (ビットウェイト 128)                                                 |

| P2_A_8                       | AD25 | I <sub>4</sub>     | ポート 2 A チャネル入力ピクセルデータ (ビットウェイト 64)                                                  |

| P2_A_7                       | AB21 | I <sub>4</sub>     | ポート 2 A チャネル入力ピクセルデータ (ビットウェイト 32)                                                  |

| P2_A_6                       | AC22 | I <sub>4</sub>     | ポート 2 A チャネル入力ピクセルデータ (ビットウェイト 16)                                                  |

| P2_A_5                       | AD23 | I <sub>4</sub>     | ポート 1 A チャネル入力ピクセルデータ (ビットウェイト 8)                                                   |

| P2_A_4                       | AB20 | I <sub>4</sub>     | ポート 2 A チャネル入力ピクセルデータ (ビットウェイト 4)                                                   |

| P2_A_3                       | AC21 | I <sub>4</sub>     | ポート 2 A チャネル入力ピクセルデータ (ビットウェイト 2)                                                   |

| P2_A_2                       | AD22 | I <sub>4</sub>     | ポート 2 A チャネル入力ピクセルデータ (ビットウェイト 1)                                                   |

| P2_A_1                       | AE23 | I <sub>4</sub>     | ポート 2 A チャネル入力ピクセルデータ (ビットウェイト 0.5)                                                 |

| P2_A_0                       | AB19 | I <sub>4</sub>     | ポート 2 A チャネル入力ピクセルデータ (ビットウェイト 0.25)                                                |

| P2_B_9                       | Y22  | I <sub>4</sub>     | ポート 2 B チャネルの入力ピクセルデータ (ビットウェイト 128)                                                |

| P2_B_8                       | AB26 | I <sub>4</sub>     | ポート 2 B チャネルの入力ピクセルデータ (ビットウェイト 64)                                                 |

| P2_B_7                       | AA23 | I <sub>4</sub>     | ポート 2 B チャネルの入力ピクセルデータ (ビットウェイト 32)                                                 |

| P2_B_6                       | AB25 | I <sub>4</sub>     | ポート 2 B チャネルの入力ピクセルデータ (ビットウェイト 16)                                                 |

| P2_B_5                       | AA22 | I <sub>4</sub>     | ポート 2 B チャネルの入力ピクセルデータ (ビットウェイト 8)                                                  |

| P2_B_4                       | AB24 | I <sub>4</sub>     | ポート 2 B チャネルの入力ピクセルデータ (ビットウェイト 4)                                                  |

| P2_B_3                       | AC26 | I <sub>4</sub>     | ポート 2 B チャネルの入力ピクセルデータ (ビットウェイト 2)                                                  |

| P2_B_2                       | AB23 | I <sub>4</sub>     | ポート 2 B チャネルの入力ピクセルデータ (ビットウェイト 1)                                                  |

| P2_B_1                       | AC25 | I <sub>4</sub>     | ポート 2 B チャネルの入力ピクセルデータ (ビットウェイト 0.5)                                                |

| P2_B_0                       | AC24 | I <sub>4</sub>     | ポート 2 B チャネルの入力ピクセルデータ (ビットウェイト 0.25)                                               |

| P2_C_9                       | W23  | I <sub>4</sub>     | ポート 2 C チャネル入力ピクセルデータ (ビットウェイト 128)                                                 |

| P2_C_8                       | V22  | I <sub>4</sub>     | ポート 2 B チャネルの入力ピクセルデータ (ビットウェイト 64)                                                 |

| P2_C_7                       | Y26  | I <sub>4</sub>     | ポート 2 C チャネル入力ピクセルデータ (ビットウェイト 32)                                                  |

| P2_C_6                       | Y25  | I <sub>4</sub>     | ポート 2 B チャネルの入力ピクセルデータ (ビットウェイト 16)                                                 |

| P2_C_5                       | Y24  | I <sub>4</sub>     | ポート 2 C チャネル入力ピクセルデータ (ビットウェイト 8)                                                   |

| P2_C_4                       | Y23  | I <sub>4</sub>     | ポート 2 B チャネルの入力ピクセルデータ (ビットウェイト 4)                                                  |

| P2_C_3                       | W22  | I <sub>4</sub>     | ポート 2 C チャネル入力ピクセルデータ (ビットウェイト 2)                                                   |

| P2_C_2                       | AA26 | I <sub>4</sub>     | ポート 2 B チャネルの入力ピクセルデータ (ビットウェイト 1)                                                  |

| P2_C_1                       | AA25 | I <sub>4</sub>     | ポート 2 C チャネル入力ピクセルデータ (ビットウェイト 0.5)                                                 |

| P2_C_0                       | AA24 | I <sub>4</sub>     | ポート 2 B チャネルの入力ピクセルデータ (ビットウェイト 0.25)                                               |

| P2_VSYNC                     | U22  | B <sub>2</sub>     | ポート 2 の垂直同期この信号には、内部プルダウンが含まれます。ポート 2 と関連付けられるように意図されていますが、ポート 1 で使用するようにプログラム可能です。 |

| P2_HSYNC                     | W26  | B <sub>2</sub>     | ポート 2 水平同期この信号には、内部プルダウンが含まれます。ポート 2 と関連付けされるように意図されていますが、ポート 1 で使用するようにプログラム可能です。  |

| <b>ALF 入力ポートコントロール</b>       |      |                    |                                                                                     |

| ALF_VSYNC                    | AF11 | I <sub>4</sub>     | オートロック専用垂直同期。この信号には内部プルダウンが含まれており、ヒステリシスを使用します。                                     |

| ALF_HSYNC                    | AD11 | I <sub>4</sub>     | オートロック専用水平同期この信号には内部プルダウンが含まれており、ヒステリシスを使用します。                                      |

| ALF_CSYNC                    | AE11 | I <sub>4</sub>     | オートロック専用複合同期 (緑色で同期)。この信号には内部プルダウンが含まれており、ヒステリシスを使用します。                             |

| <b>DMD リセットおよびバイアスコントロール</b> |      |                    |                                                                                     |

| DADOEZ                       | AE7  | O <sub>5</sub>     | DAD (DLPA200/DLPA300) 出力イネーブル (アクティブ Low)                                           |

| DADADDR_3                    | AD6  | O <sub>5</sub>     | DAD アドレス                                                                            |

| DADADDR_2                    | AE5  | O <sub>5</sub>     |                                                                                     |

| DADADDR_1                    | AF4  | O <sub>5</sub>     |                                                                                     |

| DADADDR_0                    | AB8  | O <sub>5</sub>     |                                                                                     |

| DADMODE_1                    | AD7  | O <sub>5</sub>     | DAD モード                                                                             |

| DADMODE_0                    | AE6  | O <sub>5</sub>     |                                                                                     |

| DADSEL_1                     | AE4  | O <sub>5</sub>     | DAD 選択                                                                              |

| DADSEL_0                     | AC7  | O <sub>5</sub>     |                                                                                     |

| DADSTRB                      | AF5  | O <sub>5</sub>     | DAD ストローブ                                                                           |

| DAD_INTZ                     | AC8  | I <sub>4</sub>     | DAD 割り込み (アクティブ Low)。この信号は通常外部プルアップを必要とし、ヒステリシスを使用します。                              |

| <b>DMD LVDS インターフェイス</b>     |      |                    |                                                                                     |

表 4-1. ピンの機能 (続き)

| ピン <sup>(1)</sup> |     | タイプ <sup>(2)</sup> | 説明                               |

|-------------------|-----|--------------------|----------------------------------|

| 名称                | 番号  |                    |                                  |

| DCKA_P            | V4  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動クロック       |

| DCKA_N            | V3  | O <sub>7</sub>     |                                  |

| SCA_P             | V2  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルコントロール |

| SCA_N             | V1  | O <sub>7</sub>     |                                  |

| DDA_P_15          | P4  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_N_15          | P3  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_P_14          | P2  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_N_14          | P1  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_N_12          | R1  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_P_11          | T4  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_N_11          | T3  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_P_10          | T2  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_N_10          | T1  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_P_9           | U4  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_N_9           | U3  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_P_8           | U2  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_N_8           | U1  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_P_7           | W4  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_N_7           | W3  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_P_6           | W2  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_N_6           | W1  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_P_5           | Y2  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_N_5           | Y1  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_P_4           | Y4  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_N_4           | Y3  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_P_3           | AA2 | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_N_3           | AA1 | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_P_2           | AA4 | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_N_2           | AA3 | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_P_1           | AB2 | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_N_1           | AB1 | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_P_0           | AC2 | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DDA_N_0           | AC1 | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルデータ    |

| DCKB_P            | J3  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動クロック       |

| DCKB_N            | J4  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動クロック       |

| SCB_P             | J1  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルコントロール |

| SCB_N             | J2  | O <sub>7</sub>     | DMD、LVDS I/F チャネル A、差動シリアルコントロール |

| DDB_P_15          | N1  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ    |

| DDB_N_15          | N2  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ    |

| DDB_P_14          | N3  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ    |

| DDB_N_14          | N4  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ    |

| DDB_P_13          | M2  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ    |

| DDB_N_13          | M1  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ    |

| DDB_P_12          | M3  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ    |

| DDB_N_12          | M4  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ    |

| DDB_P_11          | L1  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ    |

| DDB_N_11          | L2  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ    |

| DDB_P_10          | L3  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ    |

| DDB_N_10          | L4  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ    |

| DDB_P_9           | K1  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ    |

| DDB_N_9           | K2  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ    |

表 4-1. ピンの機能 (続き)

| ピン <sup>(1)</sup>                 |     | タイプ <sup>(2)</sup> | 説明                                   |

|-----------------------------------|-----|--------------------|--------------------------------------|

| 名称                                | 番号  |                    |                                      |

| DDB_P_8                           | K3  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ        |

| DDB_N_8                           | K4  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ        |

| DDB_P_7                           | H1  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ        |

| DDB_N_7                           | H2  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ        |

| DDB_P_6                           | H3  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ        |

| DDB_N_6                           | H4  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ        |

| DDB_P_5                           | G1  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ        |

| DDB_N_5                           | G2  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ        |

| DDB_P_4                           | G3  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ        |

| DDB_N_4                           | G4  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ        |

| DDB_P_3                           | F1  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ        |

| DDB_N_3                           | F2  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ        |

| DDB_P_2                           | F3  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ        |

| DDB_N_2                           | F4  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ        |

| DDB_P_1                           | E1  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ        |

| DDB_N_1                           | E2  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ        |

| DDB_P_0                           | D1  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ        |

| DDB_N_0                           | D2  | O <sub>7</sub>     | DMD、LVDS I/F チャネル B、差動シリアルデータ        |

| プログラムメモリ (フラッシュおよび SRAM) インターフェイス |     |                    |                                      |

| PM_CSZ_0                          | D13 | O <sub>5</sub>     | 入力バス D データビット 3。<br>100Ω 内部 LVDS 終端  |

| PM_CSZ_1                          | E12 | O <sub>5</sub>     |                                      |

| PM_CSZ_2                          | A13 | O <sub>5</sub>     | 入力バス D データビット 5。<br>100Ω 内部 LVDS 終端  |

| PM_ADDR_22<br>(GPIO 36)           | A12 | B <sub>5</sub>     |                                      |

| PM_ADDR_21<br>(GPIO 35)           | E11 | B <sub>5</sub>     | 入力バス D データビット 10。<br>100Ω 内部 LVDS 終端 |

| PM_ADDR_20                        | D12 | O <sub>5</sub>     |                                      |

| PM_ADDR_19                        | C12 | O <sub>5</sub>     | 入力バス D データビット 11。<br>100Ω 内部 LVDS 終端 |

| PM_ADDR_18                        | B11 | O <sub>5</sub>     |                                      |

| PM_ADDR_17                        | A11 | O <sub>5</sub>     | 入力バス D データビット 12。<br>100Ω 内部 LVDS 終端 |

| PM_ADDR_16                        | D11 | O <sub>5</sub>     |                                      |

| PM_ADDR_15                        | C11 | O <sub>5</sub>     | 入力バス D データビット 13。<br>100Ω 内部 LVDS 終端 |

| PM_ADDR_14                        | E10 | O <sub>5</sub>     |                                      |

| PM_ADDR_13                        | D10 | O <sub>5</sub>     | 入力バス D データビット 14。<br>100Ω 内部 LVDS 終端 |

| PM_ADDR_12                        | C10 | O <sub>5</sub>     |                                      |

| PM_ADDR_11                        | B9  | O <sub>5</sub>     | 入力バス D データビット 15。<br>100Ω 内部 LVDS 終端 |

| PM_ADDR_10                        | A9  | O <sub>5</sub>     |                                      |

| PM_ADDR_9                         | E9  | O <sub>5</sub>     | 出力バス A データビット 0 から DMD               |

| PM_ADDR_8                         | D9  | O <sub>5</sub>     |                                      |

| PM_ADDR_7                         | C9  | O <sub>5</sub>     | 出力バス A データビット 1 から DMD               |

| PM_ADDR_6                         | B8  | O <sub>5</sub>     |                                      |

| PM_ADDR_5                         | A8  | O <sub>5</sub>     | 出力バス A データビット 2 から DMD               |

| PM_ADDR_4                         | D8  | O <sub>5</sub>     |                                      |

| PM_ADDR_3                         | C8  | O <sub>5</sub>     | 出力バス A データビット 3 から DMD               |

| PM_ADDR_2                         | B7  | O <sub>5</sub>     |                                      |

| PM_ADDR_1                         | A7  | O <sub>5</sub>     | 出力バス A データビット 4 から DMD               |

| PM_ADDR_0                         | C7  | O <sub>5</sub>     |                                      |

| PM_WEZ                            | B12 | O <sub>5</sub>     | 出力バス A データビット 5 から DMD               |

| PM_OEZ                            | C13 | O <sub>5</sub>     |                                      |

| PM_BLSZ_1                         | B6  | O <sub>5</sub>     | 出力バス A データビット 6 から DMD               |

| PM_BLSZ_0                         | A6  | O <sub>5</sub>     |                                      |

表 4-1. ピンの機能 (続き)

| ピン <sup>(1)</sup>            |      | タイプ <sup>(2)</sup> | 説明                                                                                                                                    |                   |

|------------------------------|------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 名称                           | 番号   |                    |                                                                                                                                       |                   |

| PM_DATA_15                   | C17  | B <sub>5</sub>     | 出力バス A データビット 7 から DMD                                                                                                                |                   |

| PM_DATA_14                   | B16  | B <sub>5</sub>     |                                                                                                                                       |                   |

| PM_DATA_13                   | A16  | B <sub>5</sub>     |                                                                                                                                       |                   |

| PM_DATA_12                   | A15  | B <sub>5</sub>     |                                                                                                                                       |                   |

| PM_DATA_11                   | B15  | B <sub>5</sub>     |                                                                                                                                       |                   |

| PM_DATA_10                   | D16  | B <sub>5</sub>     |                                                                                                                                       |                   |

| PM_DATA_9                    | C16  | B <sub>5</sub>     |                                                                                                                                       |                   |

| PM_DATA_8                    | E14  | B <sub>5</sub>     |                                                                                                                                       |                   |

| PM_DATA_7                    | D15  | B <sub>5</sub>     |                                                                                                                                       |                   |

| PM_DATA_6                    | C15  | B <sub>5</sub>     |                                                                                                                                       |                   |

| PM_DATA_5                    | B14  | B <sub>5</sub>     |                                                                                                                                       |                   |

| PM_DATA_4                    | A14  | B <sub>5</sub>     |                                                                                                                                       |                   |

| PM_DATA_3                    | E13  | B <sub>5</sub>     |                                                                                                                                       |                   |

| PM_DATA_2                    | D14  | B <sub>5</sub>     |                                                                                                                                       |                   |

| PM_DATA_1                    | C14  | B <sub>5</sub>     |                                                                                                                                       |                   |

| PM_DATA_0                    | B13  | B <sub>5</sub>     |                                                                                                                                       |                   |

| ペリフェラルインターフェイス               |      |                    |                                                                                                                                       |                   |

| IIC0_SCL                     | A10  | B <sub>8</sub>     | I <sub>2</sub> C バス 0、クロック。このバスは 400kHz の高速モード操作をサポートしています。この信号には、3.3V への外付けプルアップ抵抗が必要です。許容される最小プルアップ値は 1kΩ です。この入力は 5V トレンジトではありません。 |                   |

| IIC0_SDA                     | B10  | B <sub>8</sub>     | 2C バス 0、データ。このバスは 400kHz の高速モード操作をサポートしています。この信号には、3.3V への外付けプルアップ抵抗が必要です。許容される最小プルアップ値は 1kΩ です。この入力は 5V トレンジトではありません。                |                   |

| SSP0_CLK                     | AD4  | B <sub>5</sub>     | 同期シリアルポート 0、クロック                                                                                                                      |                   |

| SSP0_RXD                     | AD5  | I <sub>4</sub>     | 同期シリアルポート 0、受信データ入力                                                                                                                   |                   |

| SSP0_TXD                     | AB7  | O <sub>5</sub>     | 同期シリアルポート 0、送信データ出力                                                                                                                   |                   |

| SSP0_CSZ_0                   | AC5  | B <sub>5</sub>     | 同期シリアルポート 0、チップセレクト 0 (アクティブ Low)                                                                                                     |                   |

| SSP0_CSZ_1                   | AB6  | B <sub>5</sub>     | 同期シリアルポート 0、チップセレクト 1 (アクティブ Low)                                                                                                     |                   |

| SSP0_CSZ_2                   | AC3  | B <sub>5</sub>     | 同期シリアルポート 0、チップセレクト 2 (アクティブ Low)                                                                                                     |                   |

| UART0_TXD                    | AB3  | O <sub>5</sub>     | UART0 送信データ出力                                                                                                                         |                   |

| UART0_RXD                    | AD1  | O <sub>5</sub>     | UART0 受信データ入力                                                                                                                         |                   |

| UART0_RTSZ                   | AD2  | O <sub>5</sub>     | UART0 ハードウェアフローコントロール出力を送信する準備完了 (アクティブ Low)                                                                                          |                   |

| UART0_CTSZ                   | AE2  | I <sub>4</sub>     | UART0 CTS (Clear to Send) ハードウェアフローコントロール入力 (アクティブ Low)                                                                               |                   |

| USB_DAT_N                    | C5   | B <sub>9</sub>     | USB D- I/O                                                                                                                            |                   |

| USB_DAT_P                    | D6   | B <sub>9</sub>     | USB D+ I/O                                                                                                                            |                   |

| PMD_INTZ                     | AE8  | I <sub>4</sub>     | DLPA100 (アクティブ Low) からの割り込み。この信号には外部プルアップが必要です。ヒステリシスを使用します                                                                           |                   |

| CW_PWM                       | AD8  | O <sub>5</sub>     | カラーホールコントロール PWM 出力                                                                                                                   |                   |

| CW_INDEX                     | AF7  | O <sub>5</sub>     | カラーホールインデックス。ヒステリシスを使用します                                                                                                             |                   |

| LMPCTRL                      | AC9  | O <sub>5</sub>     | ランプコントロール出力ランプのイネーブルとパラストへの同期                                                                                                         |                   |

| LMPSTAT                      | AF8  | I <sub>4</sub>     | ランプステータス入力。ランプが点灯すると、パラストから High に駆動されます。                                                                                             |                   |

| 汎用 I/O (GPIO) <sup>(8)</sup> |      |                    | 代替機能 1                                                                                                                                | 代替機能 2            |

| GPIO_82                      | E3   | B <sub>5</sub>     | 該当なし                                                                                                                                  | 該当なし              |

| GPIO_81                      | AB10 | B <sub>2</sub>     | 予約済み                                                                                                                                  | 該当なし              |

| GPIO_80                      | AD9  | B <sub>2</sub>     | IR_ENABLE (O)                                                                                                                         | 該当なし              |

| GPIO_79                      | AE9  | B <sub>2</sub>     | 予約済み                                                                                                                                  | 該当なし              |

| GPIO_78                      | AF9  | B <sub>2</sub>     | FIELD_3D_LR (I)                                                                                                                       | 該当なし              |

| GPIO_77                      | AB11 | B <sub>2</sub>     | SAS_INTGTR_EN (O)                                                                                                                     | SENSE_PWM_OUT (O) |

| GPIO_76                      | AC10 | B <sub>2</sub>     | SAS_CSZ (O)                                                                                                                           | 該当なし              |

| GPIO_75                      | AD10 | B <sub>2</sub>     | SAS_DO (O)                                                                                                                            | SENSE_FREQ_IN (I) |

| GPIO_74                      | AE10 | B <sub>2</sub>     | SAS_DI (I)                                                                                                                            | SENSE_COMP_IN (I) |

| GPIO_73                      | AF10 | B <sub>2</sub>     | SAS_CLK (O)                                                                                                                           | 該当なし              |

| GPIO_72                      | K24  | B <sub>2</sub>     | SSP2_DI (I)                                                                                                                           | 該当なし              |

| GPIO_71                      | K23  | B <sub>2</sub>     | SSP2_CLK (B)                                                                                                                          | 該当なし              |

| GPIO_70                      | K22  | B <sub>2</sub>     | SSP2_CSZ_1 (B)                                                                                                                        | 該当なし              |

| GPIO_69                      | J26  | B <sub>2</sub>     | SSP2_CSZ_0 (B)                                                                                                                        | 該当なし              |

表 4-1. ピンの機能 (続き)

| ピン <sup>(1)</sup> |      | タイプ <sup>(2)</sup> | 説明                  |                     |

|-------------------|------|--------------------|---------------------|---------------------|

| 名称                | 番号   |                    |                     |                     |

| GPIO_68           | J25  | B <sub>2</sub>     | SSP2_DO (O)         | 該当なし                |

| GPIO_67           | J24  | B <sub>2</sub>     | SP_Data_7 (O)       | SSP2_CSZ_2 (B)      |

| GPIO_66           | J23  | B <sub>2</sub>     | SP_Data_6 (O)       | SSP0_CSZ_5 (B)      |

| GPIO_65           | J22  | B <sub>2</sub>     | SP_Data_5 (O)       | 該当なし                |