## DLP991UV 産業用デジタルマイクロミラー デバイス (DMD)

### 1 特長

- 高解像度の  $4096 \times 2176$  マイクロミラー アレイ

- > 890 万個を超えるマイクロミラー

- $5.4\mu\text{m}$  のマイクロミラー ピッチ

- 対角  $0.99$  インチのマイクロミラー アレイ

- マイクロミラー傾斜角  $\pm 12^\circ$  (フラット状態に対して)

- コーナーイルミネーション(対角照射)対応

- マイクロミラードライバ回路を内蔵

- UV 波長を  $343\text{nm}$  から  $410\text{nm}$  まで操作できるように設計

- 97% のウインドウ転送 (ウインドウ パスごと)

- マイクロミラーの反射率 88%

- 91% の平均回折効率 ( $343\text{nm} \sim 410\text{nm}$ , f/3 照明と f/2.4 プロジェクションの場合)

- オン状態のアレイの充填率: 90%

### 2 アプリケーション

- 産業用

- ダイレクトイメージング リソグラフィ

- 3D プリンティング

- マシンビジョンと品質管理

- レーザー マーキングおよびリペア

- 医療

- 眼科用機器

- 四肢および皮膚測定用の 3D スキャナ

- ハイパースペクトラル イメージング / スキャン

- ディスプレイ

- 3D 画像処理顕微鏡

### 3 説明

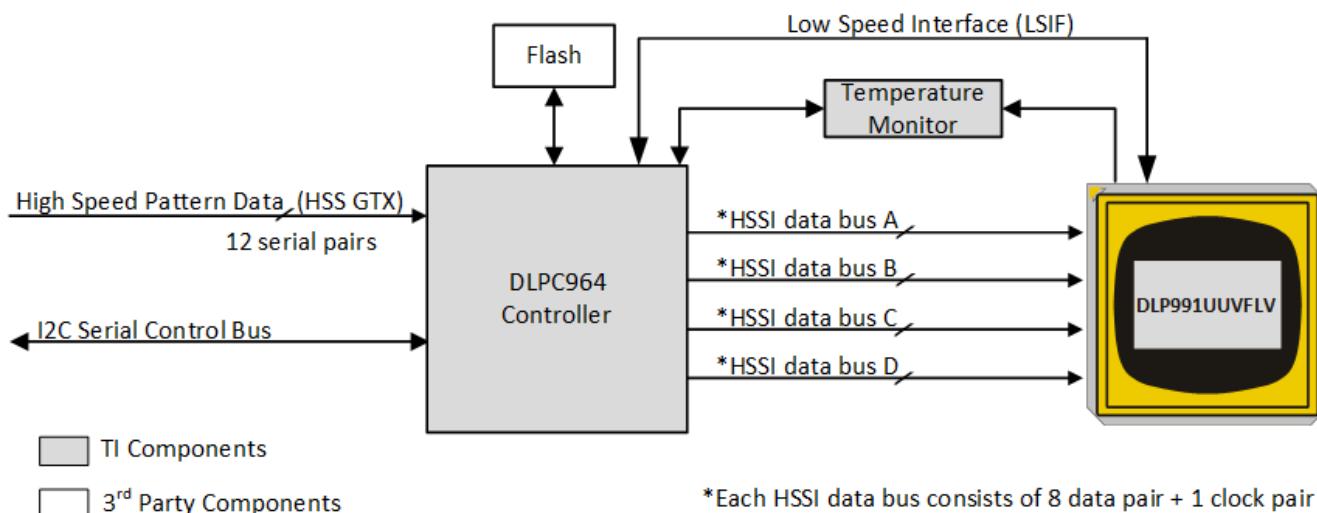

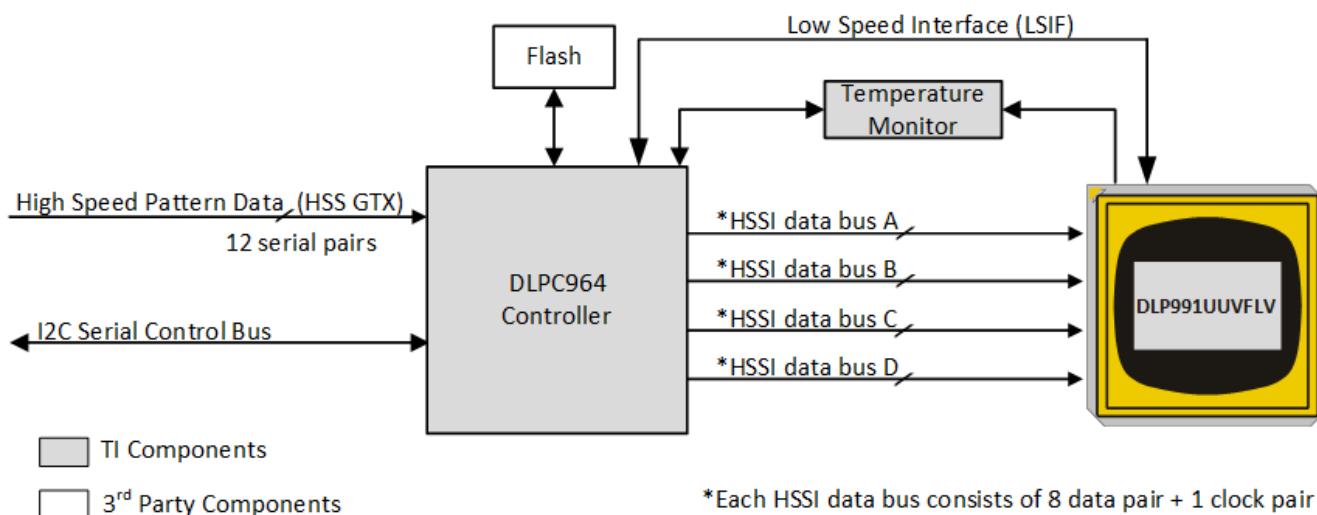

890 万個を超えるマイクロミラーを搭載した高解像度 DLP991UV デジタルマイクロミラー デバイス (DMD) は、入射光の振幅、方向、または位相を変調する空間光変調器 (SLM) です。この高度な光制御テクノロジには、産業用、医療用、コンシューマ市場向けに数多くの用途があります。DLP991UV DMD と DLPC964 コントローラはストリーミング機能を備えているため、このデバイスはダイレクトイメージング (LDI) 用途における高速かつ連続的なデータストリーミングに非常に適しています。DMD (デジタルマイクロミラー デバイス) は、さまざまな 3D プリンティング用途において、大きな 3D ビルドと超高精細な解像度を実現します。高分解能は、3D マシンビジョン アプリケーションで大型の物体をスキャンする際に直接的な利点があります。

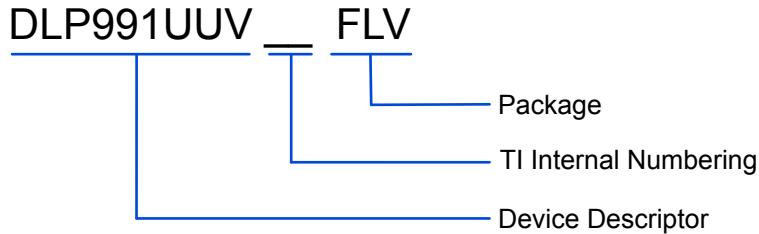

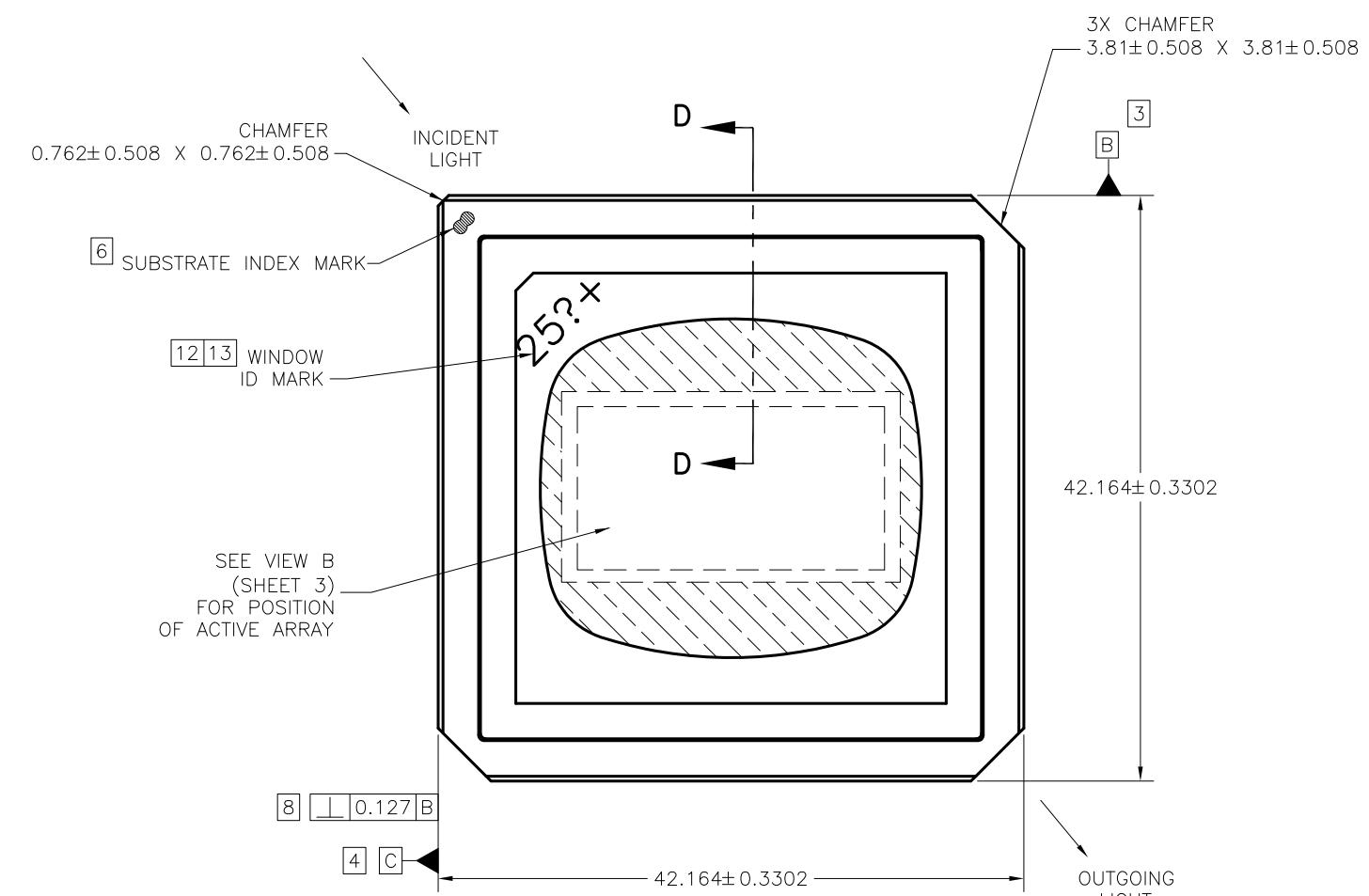

#### 製品情報

| 部品番号        | パッケージ <sup>(1)</sup> | パッケージ<br>サイズ      |

|-------------|----------------------|-------------------|

| DLP991UVFLV | FLV (321)            | 42.16mm × 42.16mm |

(1) 詳細については、「メカニカル、パッケージ、および注文情報」を参照してください。

アプリケーション概略図

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール(機械翻訳)を使用していることがあります。TIでは翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                                  |           |                                           |           |

|----------------------------------|-----------|-------------------------------------------|-----------|

| <b>1 特長</b>                      | <b>1</b>  | 6.6 DMD 温度の計算                             | 24        |

| <b>2 アプリケーション</b>                | <b>1</b>  | 6.7 マイクロミラーの電力密度の計算                       | 26        |

| <b>3 説明</b>                      | <b>1</b>  | 6.8 マイクロミラーのランデッド オン / ランデッド オフ デューティサイクル | 27        |

| <b>4 ピン構成および機能</b>               | <b>3</b>  | <b>7 アプリケーションと実装</b>                      | <b>29</b> |

| <b>5 仕様</b>                      | <b>8</b>  | 7.1 アプリケーション情報                            | 29        |

| 5.1 絶対最大定格                       | 8         | 7.2 代表的なアプリケーション                          | 29        |

| 5.2 保存条件                         | 9         | 7.3 DMD ダイ温度センシング                         | 31        |

| 5.3 ESD 定格                       | 9         | <b>8 電源に関する推奨事項</b>                       | <b>32</b> |

| 5.4 推奨動作条件                       | 9         | 8.1 DMD 電源のパワーアップ手順                       | 32        |

| 5.5 熱に関する情報                      | 11        | 8.2 DMD 電源のパワードウン手順                       | 32        |

| 5.6 電気的特性                        | 11        | <b>9 レイアウト</b>                            | <b>34</b> |

| 5.7 スイッチング特性                     | 12        | 9.1 レイアウトのガイドライン                          | 34        |

| 5.8 タイミング要件                      | 13        | <b>10 デバイスおよびドキュメントのサポート</b>              | <b>38</b> |

| 5.9 システム実装インターフェイスの荷重            | 17        | 10.1 デバイス サポート                            | 38        |

| 5.10 マイクロミラー アレイの物理特性            | 18        | 10.2 ドキュメントのサポート                          | 38        |

| 5.11 マイクロミラー アレイの光学特性            | 20        | 10.3 ドキュメントの更新通知を受け取る方法                   | 39        |

| 5.12 ウィンドウの特性                    | 21        | 10.4 サポート・リソース                            | 39        |

| 5.13 チップセットコンポーネントの使用方法の仕様       | 21        | 10.5 商標                                   | 39        |

| <b>6 詳細説明</b>                    | <b>22</b> | 10.6 静電気放電に関する注意事項                        | 39        |

| 6.1 概要                           | 22        | 10.7 用語集                                  | 39        |

| 6.2 機能ブロック図                      | 22        | <b>11 改訂履歴</b>                            | <b>39</b> |

| 6.3 機能説明                         | 23        | <b>12 メカニカル、パッケージ、および注文情報</b>             | <b>40</b> |

| 6.4 デバイスの機能モード                   | 23        | 12.1 付録: パッケージオプション                       | 41        |

| 6.5 光学インターフェイスおよびシステムの画質に関する検討事項 | 23        |                                           |           |

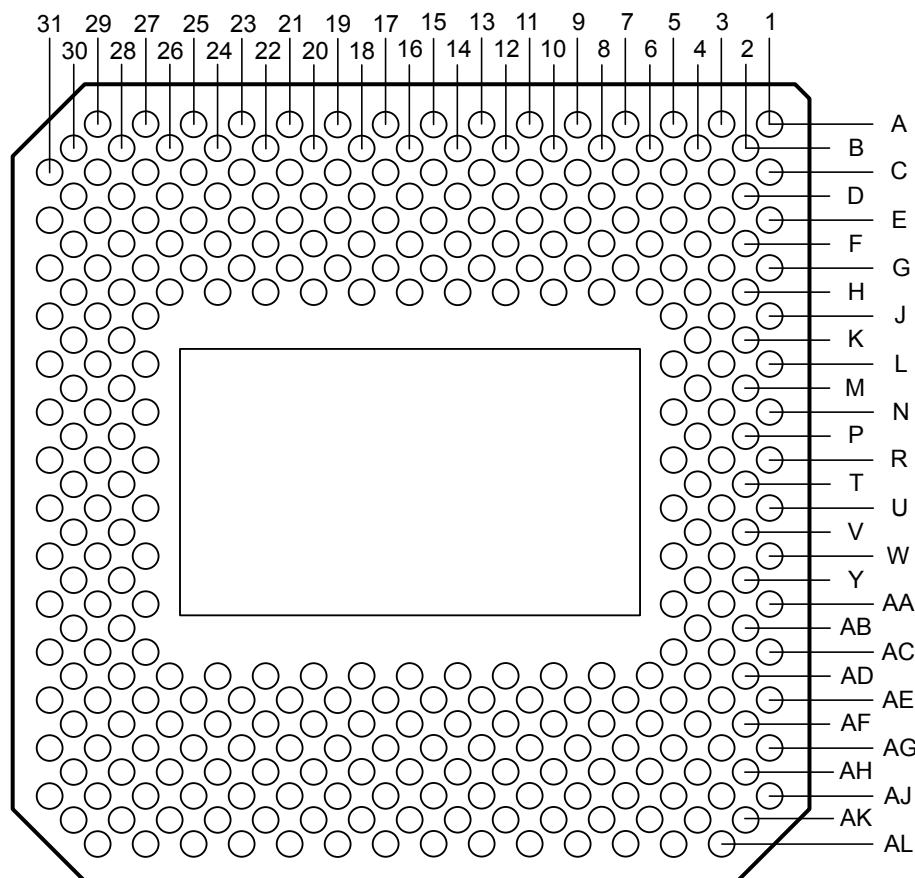

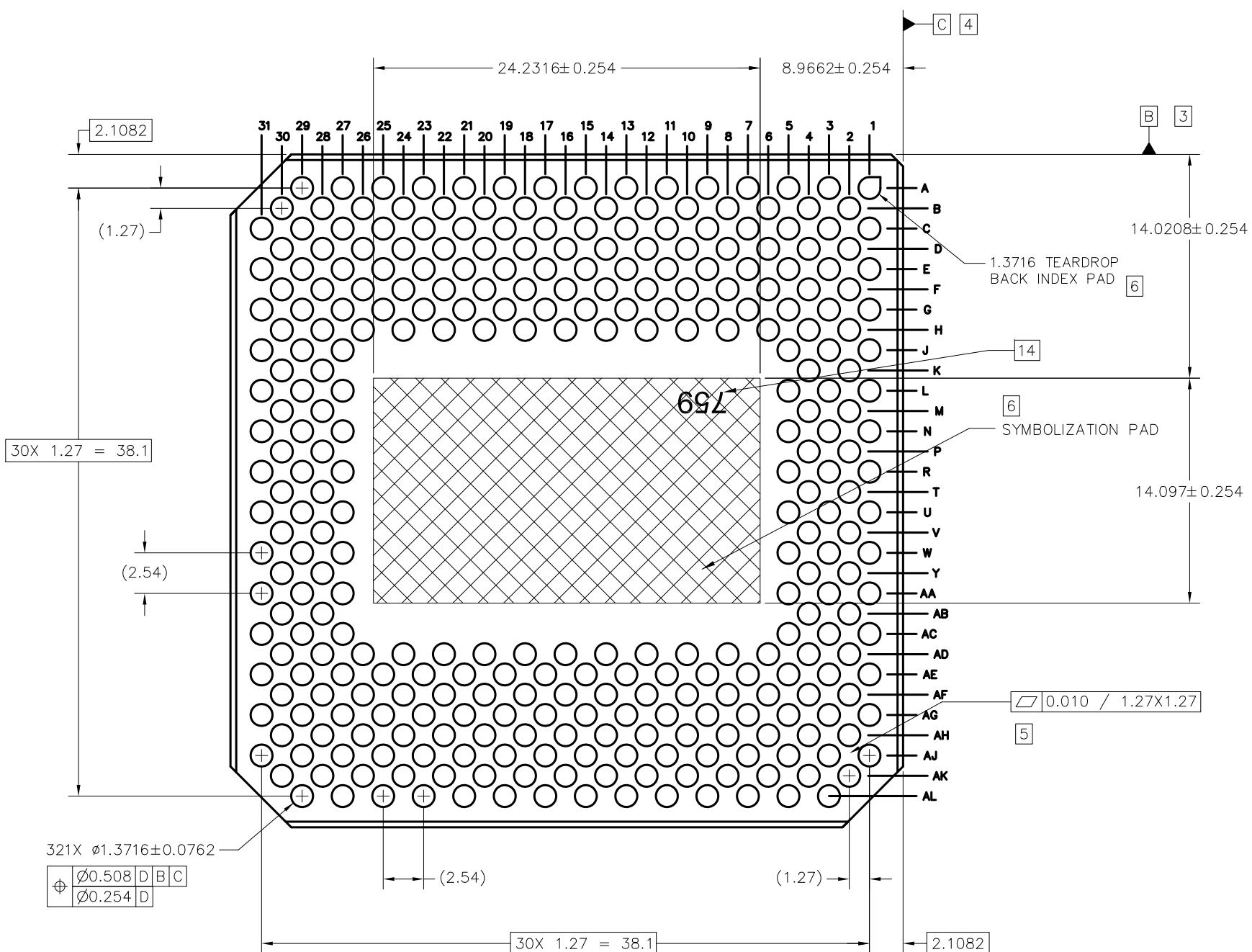

## 4 ピン構成および機能

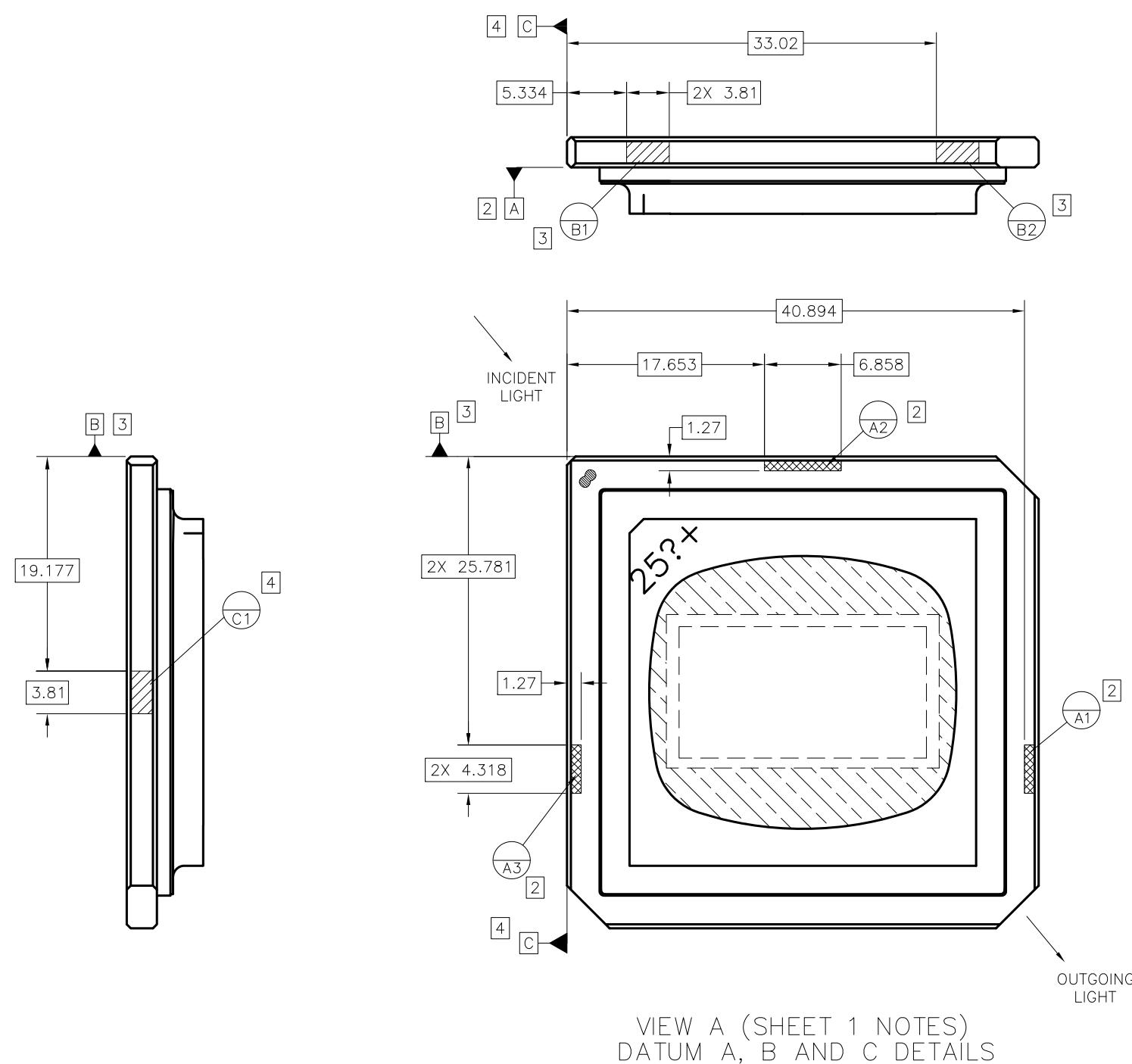

図 4-1. FLV パッケージ 321 ピン LGA 底面図

### 注意

DLP991UV DMD の信頼性が高く、長期にわたって安定した動作を確保するためには、以下の表に示す信号のレイアウトおよび動作を適切に管理することが極めて重要です。具体的な詳細とガイドラインについては、**DLP® 標準 SST デジタル マイクロミラー デバイスの PCB 設計要件**を参照してください

**表 4-1. パッケージのピン配置**

| ピン       |        | 入力と出力<br>(1) | ピンの説明             | 終端      | パターン<br>長 (mm) |

|----------|--------|--------------|-------------------|---------|----------------|

| 名称       | パッド ID |              |                   |         |                |

| D_AP (0) | E1     | I            | HSSI バス A 信号 A0+  | 差動 100Ω | 10.79          |

| D_AN (0) | F2     | I            | HSSI バス A 信号 A0 - | 差動 100Ω | 10.77          |

| D_AP (1) | J1     | I            | HSSI バス A 信号 A1+  | 差動 100Ω | 13.77          |

| D_AN (1) | G1     | I            | HSSI バス A 信号 A1 - | 差動 100Ω | 13.76          |

| D_AP (2) | A5     | I            | HSSI バス A 信号 A2+  | 差動 100Ω | 10.34          |

| D_AN (2) | B6     | I            | HSSI バス A 信号 A2 - | 差動 100Ω | 10.35          |

| D_AP (3) | K2     | I            | HSSI バス A 信号 A3+  | 差動 100Ω | 12.36          |

| D_AN (3) | L1     | I            | HSSI バス A 信号 A3 - | 差動 100Ω | 12.33          |

| D_AP (4) | B8     | I            | HSSI バス A 信号 A4+  | 差動 100Ω | 9.64           |

| D_AN (4) | A7     | I            | HSSI バス A 信号 A4 - | 差動 100Ω | 9.65           |

| D_AP (5) | A11    | I            | HSSI バス A 信号 A5+  | 差動 100Ω | 11.96          |

| D_AN (5) | A9     | I            | HSSI バス A 信号 A5 - | 差動 100Ω | 11.95          |

| D_AP (6) | R1     | I            | HSSI バス A 信号 A6+  | 差動 100Ω | 17.77          |

| D_AN (6) | T2     | I            | HSSI バス A 信号 A6 - | 差動 100Ω | 17.73          |

| D_AP (7) | W1     | I            | HSSI バス A 信号 A7+  | 差動 100Ω | 21.44          |

| D_AN (7) | U1     | I            | HSSI バス A 信号 A7 - | 差動 100Ω | 21.44          |

| DCLK_AP  | P2     | I            | HSSI バス A クロック+   | 差動 100Ω | 16.02          |

| DCLK_AN  | N1     | I            | HSSI バス A クロック-   | 差動 100Ω | 16.01          |

| D_BP (0) | A13    | I            | HSSI バス B 信号 B0+  | 差動 100Ω | 8.39           |

| D_BN (0) | B12    | I            | HSSI バス B 信号 B0-  | 差動 100Ω | 8.40           |

| D_BP (1) | P30    | I            | HSSI バス B 信号 B1+  | 差動 100Ω | 30.31          |

| D_BN (1) | R31    | I            | HSSI バス B 信号 B1-  | 差動 100Ω | 30.31          |

| D_BP (2) | B14    | I            | HSSI バス B 信号 B2+  | 差動 100Ω | 9.53           |

| D_BN (2) | A15    | I            | HSSI バス B 信号 B2-  | 差動 100Ω | 9.53           |

| D_BP (3) | A17    | I            | HSSI バス B 信号 B3+  | 差動 100Ω | 11.23          |

| D_BN (3) | B16    | I            | HSSI バス B 信号 B3-  | 差動 100Ω | 11.24          |

| D_BP (4) | B20    | I            | HSSI バス B 信号 B4+  | 差動 100Ω | 13.82          |

| D_BN (4) | A21    | I            | HSSI バス B 信号 B4-  | 差動 100Ω | 13.83          |

| D_BP (5) | N31    | I            | HSSI バス B 信号 B5+  | 差動 100Ω | 26.98          |

| D_BN (5) | L31    | I            | HSSI バス B 信号 B5-  | 差動 100Ω | 27.00          |

| D_BP (6) | G31    | I            | HSSI バス B 信号 B6+  | 差動 100Ω | 24.55          |

| D_BN (6) | J31    | I            | HSSI バス B 信号 B6-  | 差動 100Ω | 24.52          |

| D_BP (7) | B22    | I            | HSSI バス B 信号 B7+  | 差動 100Ω | 16.27          |

| D_BN (7) | A23    | I            | HSSI バス B 信号 B7-  | 差動 100Ω | 16.30          |

| DCLK_BP  | A19    | I            | HSSI バス B クロック+   | 差動 100Ω | 12.98          |

**表 4-1. パッケージのピン配置 (続き)**

| ピン       |        | 入力と出力<br>(1) | ピンの説明             | 終端      | パターン<br>長 (mm) |

|----------|--------|--------------|-------------------|---------|----------------|

| 名称       | パッド ID |              |                   |         |                |

| DCLK_BN  | B18    | I            | HSSI バス B クロック-   | 差動 100Ω | 12.99          |

| D_CP (0) | AL7    | I            | HSSI バス C 信号 C0+  | 差動 100Ω | 18.56          |

| D_CN (0) | AL5    | I            | HSSI バス C 信号 C0 - | 差動 100Ω | 18.58          |

| D_CP (1) | AG1    | I            | HSSI バス C 信号 C1+  | 差動 100Ω | 23.82          |

| D_CN (1) | AF2    | I            | HSSI バス C 信号 C1 - | 差動 100Ω | 23.80          |

| D_CP (2) | AC1    | I            | HSSI バス C 信号 C2+  | 差動 100Ω | 26.32          |

| D_CN (2) | AE1    | I            | HSSI バス C 信号 C2 - | 差動 100Ω | 26.33          |

| D_CP (3) | AA1    | I            | HSSI バス C 信号 C3+  | 差動 100Ω | 24.98          |

| D_CN (3) | AB2    | I            | HSSI バス C 信号 C3 - | 差動 100Ω | 24.99          |

| D_CP (4) | AK10   | I            | HSSI バス C 信号 C4+  | 差動 100Ω | 17.77          |

| D_CN (4) | AL9    | I            | HSSI バス C 信号 C4 - | 差動 100Ω | 17.75          |

| D_CP (5) | AL15   | I            | HSSI バス C 信号 C5+  | 差動 100Ω | 14.23          |

| D_CN (5) | AK14   | I            | HSSI バス C 信号 C5 - | 差動 100Ω | 14.23          |

| D_CP (6) | AK18   | I            | HSSI バス C 信号 C6+  | 差動 100Ω | 12.92          |

| D_CN (6) | AL17   | I            | HSSI バス C 信号 C6 - | 差動 100Ω | 12.93          |

| D_CP (7) | AL19   | I            | HSSI バス C 信号 C7+  | 差動 100Ω | 12.24          |

| D_CN (7) | AL21   | I            | HSSI バス C 信号 C7 - | 差動 100Ω | 12.21          |

| DCLK_CP  | AL13   | I            | HSSI バス C クロック+   | 差動 100Ω | 14.81          |

| DCLK_CN  | AL11   | I            | HSSI バス C クロック-   | 差動 100Ω | 14.81          |

| D_DP (0) | AL23   | I            | HSSI バス D 信号 D0+  | 差動 100Ω | 8.814          |

| D_DN (0) | AK22   | I            | HSSI バス D 信号 D0 - | 差動 100Ω | 8.82           |

| D_DP (1) | AL25   | I            | HSSI バス D 信号 D1+  | 差動 100Ω | 10.21          |

| D_DN (1) | AK24   | I            | HSSI バス D 信号 D1 - | 差動 100Ω | 10.21          |

| D_DP (2) | AK26   | I            | HSSI バス D 信号 D2+  | 差動 100Ω | 11.98          |

| D_DN (2) | AL27   | I            | HSSI バス D 信号 D2 - | 差動 100Ω | 11.98          |

| D_DP (3) | V30    | I            | HSSI バス D 信号 D3+  | 差動 100Ω | 17.09          |

| D_DN (3) | U31    | I            | HSSI バス D 信号 D3 - | 差動 100Ω | 17.05          |

| D_DP (4) | AF30   | I            | HSSI バス D 信号 D4+  | 差動 100Ω | 12.25          |

| D_DN (4) | AE31   | I            | HSSI バス D 信号 D4 - | 差動 100Ω | 12.23          |

| D_DP (5) | W31    | I            | HSSI バス D 信号 D5+  | 差動 100Ω | 14.36          |

| D_DN (5) | Y30    | I            | HSSI バス D 信号 D5 - | 差動 100Ω | 14.32          |

| D_DP (6) | AB30   | I            | HSSI バス D 信号 D6+  | 差動 100Ω | 11.16          |

| D_DN (6) | AA31   | I            | HSSI バス D 信号 D6 - | 差動 100Ω | 11.16          |

| D_DP (7) | AD30   | I            | HSSI バス D 信号 D7+  | 差動 100Ω | 13.11          |

| D_DN (7) | AC31   | I            | HSSI バス D 信号 D7 - | 差動 100Ω | 13.11          |

表 4-1. パッケージのピン配置(続き)

| ピン           |                                                                                                                                                                                                                                                                                     | 入力と出力<br>(1) | ピンの説明                       | 終端           | パターン<br>長(mm) |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------|--------------|---------------|

| 名称           | パッド ID                                                                                                                                                                                                                                                                              |              |                             |              |               |

| DCLK_DP      | AG31                                                                                                                                                                                                                                                                                | I            | HSSI バス D クロック+             | 差動 100Ω      | 13.93         |

| DCLK_DN      | AH30                                                                                                                                                                                                                                                                                | I            | HSSI バス D クロック-             | 差動 100Ω      | 13.93         |

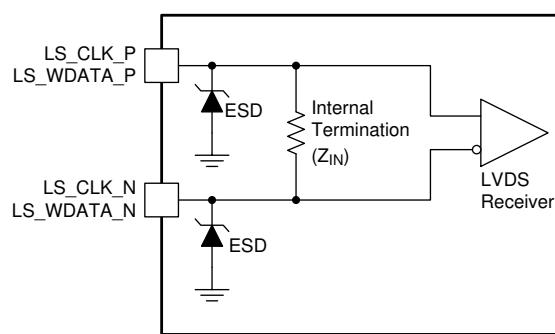

| LS_WDATA_P   | B26                                                                                                                                                                                                                                                                                 | I            | LSIF LVDS データ +             | 差動 100Ω      | 10.90         |

| LS_WDATA_N   | A27                                                                                                                                                                                                                                                                                 | I            | LSIF LVDS データ -             | 差動 100Ω      | 10.90         |

| LS_CLK_P     | B24                                                                                                                                                                                                                                                                                 | I            | LSIF LVDS CLK+              | 差動 100Ω      | 11.05         |

| LS_CLK_N     | A25                                                                                                                                                                                                                                                                                 | I            | LSIF LVDS CLK -             | 差動 100Ω      | 11.03         |

| LS_RDATA_A   | F24                                                                                                                                                                                                                                                                                 | O            | LVC MOS 出力                  |              | 2.04          |

| LS_RDATA_B   | D26                                                                                                                                                                                                                                                                                 | O            | LVC MOS 出力                  |              | 5.26          |

| LS_RDATA_C   | F30                                                                                                                                                                                                                                                                                 | O            | LVC MOS 出力                  |              | 9.57          |

| LS_RDATA_D   | C27                                                                                                                                                                                                                                                                                 | O            | LVC MOS 出力                  |              | 7.15          |

| AMUX_OUT     | E17                                                                                                                                                                                                                                                                                 | O            | アナログ テスト マルチプレクサ            |              | 6.36          |

| DMUX_OUT     | E29                                                                                                                                                                                                                                                                                 | O            | デジタル テスト マルチプレクサ            |              | 7.22          |

| DMD_EN_ARSTZ | AE23、E27、Y4                                                                                                                                                                                                                                                                         | I            | ARSTZ                       | 17.5kΩ ブルダウン | 63.74         |

| TEMP_N       | E23                                                                                                                                                                                                                                                                                 | I            | 温度ダイオード N                   |              | 3.21          |

| TEMP_P       | F22                                                                                                                                                                                                                                                                                 | I            | 温度ダイオード P                   |              | 2.86          |

| VDD          | A29、A3、AA29、AB4、AD10、AD12、AD28、AD8、AE13、AE15、AF10、AF12、AF18、AF22、AF24、AF26、AF28、AF6、AH10、AH12、AH14、AH16、AH18、AJ1、AJ11、AJ21、AJ29、AJ31、AJ5、AK2、AL29、B4、C1、C13、C21、C29、C31、D12、D16、D18、D20、D24、D8、F10、F12、F16、F18、F20、F8、H16、H18、H20、H22、H24、H28、K4、L3、M4、N29、P28、P4、T28、T4、V28、V4、Y28 | P            | デジタル コア電源電圧                 | 平面           |               |

| VDDA         | AB28、AD14、AD16、AD18、AD22、AD24、AE19、AE27、AF20、AH20、AH24、D10、D14、F6、G11、G15、H10、H12、H14、H26、H8、K28                                                                                                                                                                                    | P            | HSSI 電源電圧                   | 平面           |               |

| VRESET       | AF4、AG5、D6、E5                                                                                                                                                                                                                                                                       | P            | マイクロミラーのリセット信号用の負のバイアスの供給電圧 | 平面           |               |

| VBIAS        | AD4、AE3、D4                                                                                                                                                                                                                                                                          | P            | マイクロミラーのリセット信号用の正のバイアスの供給電圧 | 平面           |               |

**表 4-1. パッケージのピン配置 (続き)**

| ピン      |                                                                                                                                                                                                                                                                                                                                           | 入力と出力<br>(1) | ピンの説明                           | 終端 | パターン長 (mm) |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------|----|------------|

| 名称      | パッド ID                                                                                                                                                                                                                                                                                                                                    |              |                                 |    |            |

| VOFFSET | AD26、AE5、F26、F4、H4                                                                                                                                                                                                                                                                                                                        | P            | HVCMOS ロジック用の供給電圧、昇圧されたロジック レベル |    | 平面         |

| VSS     | A1、AA3、AC29、AC3、AD20、AD6、AE11、AE17、AE21、AE25、AE29、AE7、AE9、AF14、AF16、AF8、AG11、AG13、AG15、AG17、AG19、AG21、AG23、AG25、AG27、AG29、AG3、AH2、AH26、AH4、AH6、AK30、AK4、AK8、AL3、C3、D2、D22、D28、D30、E11、E13、E15、E19、E21、E25、E3、E31、E7、F14、G13、G17、G19、G21、G23、G25、G27、G29、G3、G5、G7、G9、H2、H30、H6、J29、J3、K30、L29、M2、M28、M30、N3、R29、R3、T30、U29、U3、V2、W29、W3、Y2 | G            | グランド                            | 平面 |            |

| VSSA    | AD2、AH22、AH28、AJ13、AJ15、AJ17、AJ19、AJ23、AJ25、AJ27、AJ3、AJ7、AJ9、AK12、AK16、AK20、AK28、AK6、B10、B2、B28、B30、C11、C15、C17、C19、C23、C25、C5、C7、C9、E9                                                                                                                                                                                                   | G            | グランド                            |    | 平面         |

| N/C     | AA5、AA27、AC5、AC27、AG7、AG9、AH8、F28、J5、J27、L5、L27、N27、R27、N5、R5、U5、U27、W5、W27                                                                                                                                                                                                                                                               | NC           | 接続なし                            |    |            |

(1) I = 入力、O = 出力、P = 電源、G = グランド、NC = 未接続

## 5 仕様

### 5.1 絶対最大定格

「絶対最大定格」の範囲外の動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

| パラメータ                        | 説明                                                             | 最小値  | 最大値       | 単位  |

|------------------------------|----------------------------------------------------------------|------|-----------|-----|

| <b>電源電圧</b>                  |                                                                |      |           |     |

| $V_{DD}$                     | LVC MOS コアロジックと LVC MOS 低速インターフェイス (LSIF) の電源電圧 <sup>(1)</sup> | -0.5 | 2.3       | V   |

| $V_{DDA}$                    | 高速シリアルインターフェイス (HSSI) レシーバの電源電圧 <sup>(1)</sup>                 | -0.3 | 2.2       | V   |

| $V_{OFFSET}$                 | HVC MOS およびマイクロミラー電極の電源電圧 <sup>(1) (2)</sup>                   | -0.5 | 11        | V   |

| $V_{BIAS}$                   | マイクロミラー電極の電源電圧 <sup>(1)</sup>                                  | -0.5 | 19        | V   |

| $V_{RESET}$                  | マイクロミラー電極の電源電圧 <sup>(1)</sup>                                  | -15  | 0.5       | V   |

| $ V_{DDA} - V_{DD} $         | 電源電圧差 (絶対値) <sup>(3)</sup>                                     |      | 0.3       | V   |

| $ V_{BIAS} - V_{OFFSET} $    | 電源電圧差 (絶対値) <sup>(4)</sup>                                     |      | 11        | V   |

| $ V_{BIAS} - V_{RESET} $     | 電源電圧差 (絶対値) <sup>(5)</sup>                                     |      | 34        | V   |

| <b>入力電圧</b>                  |                                                                |      |           |     |

|                              | その他の入力の入力電圧 - LVDS および LVC MOS <sup>(1)</sup>                  | -0.5 | 2.45      | V   |

|                              | その他の入力の入力電圧 - HSSI <sup>(1) (6)</sup>                          | -0.2 | $V_{DDA}$ | V   |

| <b>低速インターフェイス (LSIF)</b>     |                                                                |      |           |     |

| $f_{CLOCK}$                  | LSIF クロック周波数 (LS_CLK)                                          |      | 130       | MHz |

| $ V_{ID} $                   | LSIF 差動入力電圧の振幅 <sup>(6)</sup>                                  |      | 810       | mV  |

| $I_{ID}$                     | LSIF 差動入力電流 <sup>(7)</sup>                                     |      | 10        | mA  |

| <b>高速シリアルインターフェイス (HSSI)</b> |                                                                |      |           |     |

| $f_{CLOCK}$                  | HSSI クロック周波数 (DCLK)                                            |      | 1.65      | GHz |

| $ V_{ID} $                   | HSSI 差動入力電圧振幅データレーン                                            |      | 700       | mV  |

| $ V_{ID} $                   | HSSI 差動入力電圧振幅クロック レーン                                          |      | 700       | mV  |

| <b>環境</b>                    |                                                                |      |           |     |

| $T_{ARRAY}$                  | 温度、動作時 <sup>(8)</sup>                                          | 0    | 90        | °C  |

|                              | 温度、非動作時 <sup>(8)</sup>                                         | -40  | 90        | °C  |

| $T_{WINDOW}$                 | 温度、動作時 <sup>(8)</sup>                                          | 0    | 70        | °C  |

|                              | 温度、非動作時 <sup>(8)</sup>                                         | -40  | 90        | °C  |

| $T_{DELTA\_MAX}$             | [TP2 または TP3 の最小値] から $T_{MIN\_ARRAY}$ <sup>(9)</sup> を引いた値    |      | 5         | °C  |

| $T_{DELTA\_MIN}$             | [TP2 または TP3 の最小値] から $T_{MAX\_ARRAY}$ を引いた値 <sup>(9)</sup>    | -30  |           | °C  |

| RH                           | 相対湿度、動作中および非動作中                                                |      | 95%       |     |

- (1) すべての電圧値は、グランド端末 ( $V_{SS}$ ) を基準としたものです。DMD を適切に動作させるには、以下に示す必要な電源を接続する必要があります： $V_{DD}$ 、 $V_{DDA}$ 、 $V_{OFFSET}$ 、 $V_{BIAS}$  および  $V_{RESET}$ 。すべての  $V_{SS}$  接続も必要です。

- (2)  $V_{OFFSET}$  電源過渡電圧は、規定電圧内に収まる必要があります。

- (3)  $V_{DDA}$  と  $V_{DD}$  の間の許容される絶対電圧差を超えると、過剰な電流が流れます。

- (4)  $V_{BIAS}$  と  $V_{OFFSET}$  の間の許容される絶対電圧差を超えると、過剰な電流が流れます。

- (5)  $V_{BIAS}$  と  $V_{RESET}$  の間の許容される絶対電圧差を超えると、過剰な電流が流れます。

- (6) この最大入力電圧定格は、差動ペアの各入力電圧が同じ電位のときに適用されます。LVDS 差動入力は、指定限界値を超えないようにする必要があります。さもなくば、内部終端抵抗が損傷する可能性があります。

- (7) 差動入力は、指定限界値を超えないようにする必要があります。さもなくば、内部終端抵抗が損傷する可能性があります。この仕様は、高速シリアルインターフェイス (HSSI) と低速インターフェイス (LSI) の両方に適用されます。

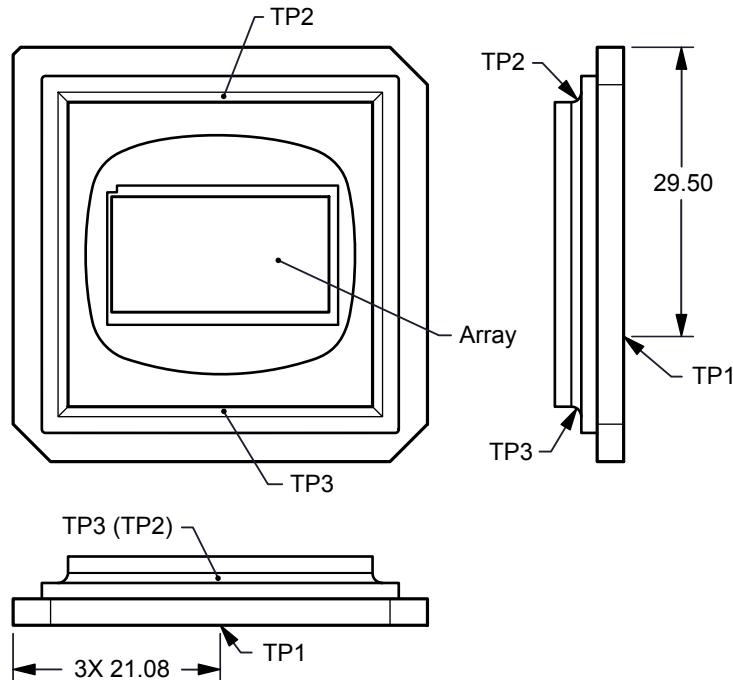

- (8) アレイの温度は直接測定することができないため、図 6-1 に示されているテスト ポイント 1 (TP1) で測定された温度と、パッケージの熱抵抗をもとに、セクション 6.6 の計算式を用いて解析的に算出する必要があります。

- (9) 計算については、セクション 6.6 を参照します。

## 5.2 保存条件

部品としての DMD、またはシステムで動作していない DMD に適用できます。

| 記号               | パラメータ       | 最小値 | 最大値 | 単位 |

|------------------|-------------|-----|-----|----|

| T <sub>DMD</sub> | DMD の保存温度   | -40 | 80  | C  |

| RH               | 相対湿度 (結露なし) |     | 95% |    |

## 5.3 ESD 定格

| 記号                 | パラメータ | 説明                                          | 値     | 単位 |

|--------------------|-------|---------------------------------------------|-------|----|

| V <sub>(ESD)</sub> | 静電放電  | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠 (1)   | ±2000 | V  |

|                    |       | デバイス帯電モデル (CDM)、JEDEC 仕様 JESD22-C101 準拠 (2) | ±500  | V  |

(1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

(2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。

## 5.4 推奨動作条件

自由気流での動作温度範囲および電源電圧内 (特に記述のない限り) (1)

| パラメータ名                                  |                                                                | 最小値                   | 標準値 | 最大値                   | 単位  |

|-----------------------------------------|----------------------------------------------------------------|-----------------------|-----|-----------------------|-----|

| <b>電源電圧</b>                             |                                                                |                       |     |                       |     |

| V <sub>DD</sub>                         | LVC MOS コアロジックおよび低速インターフェイス (LSIF) のための電源電圧(2)                 | 1.85                  | 1.9 | 1.95                  | V   |

| V <sub>DDA</sub>                        | 高速シリアルインターフェイス (HSSI) レシーバの電源電圧(2)                             | 1.85                  | 1.9 | 1.95                  | V   |

| V <sub>OFFSET</sub>                     | HVC MOS およびマイクロミラー電極の電源電圧(2) (3) (4)                           | 9.5                   | 10  | 10.5                  | V   |

| V <sub>BIAS</sub>                       | マイクロミラー電極の電源電圧(2)                                              | 17.5                  | 18  | 18.5                  | V   |

| V <sub>RESET</sub>                      | マイクロミラー電極の電源電圧(2)                                              | -14.5                 | -14 | -13.5                 | V   |

| V <sub>DDA</sub> - V <sub>DD</sub>      | 電源電圧のデルタ、絶対値(5)                                                |                       |     | 0.3                   | V   |

| V <sub>BIAS</sub> - V <sub>OFFSET</sub> | 電源電圧のデルタ、絶対値(6)                                                |                       |     | 10.5                  | V   |

| V <sub>BIAS</sub> - V <sub>RESET</sub>  | 電源電圧のデルタ、絶対値                                                   |                       |     | 33                    | V   |

| <b>LVC MOS 入力</b>                       |                                                                |                       |     |                       |     |

| V <sub>IH</sub>                         | 高レベル入力電圧(2) (7)                                                | 0.7 × V <sub>DD</sub> |     |                       | V   |

| V <sub>IL</sub>                         | 低レベル入力電圧(2) (7)                                                |                       |     | 0.3 × V <sub>DD</sub> | V   |

| <b>低速インターフェイス (LSIF)</b>                |                                                                |                       |     |                       |     |

| f <sub>CLOCK</sub>                      | LSIF クロック周波数 (LS_CLK) <sup>(9)</sup>                           | 108                   | 120 | 130                   | MHz |

| DCD <sub>IN</sub>                       | LSIF デューティ サイクル歪み (LS_CLK)                                     | 44%                   |     | 56%                   |     |

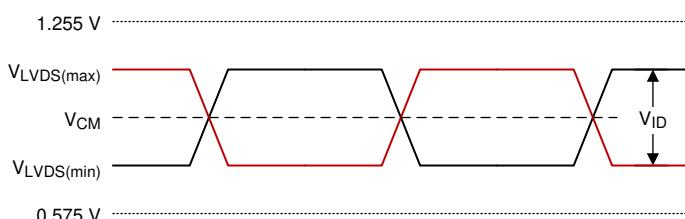

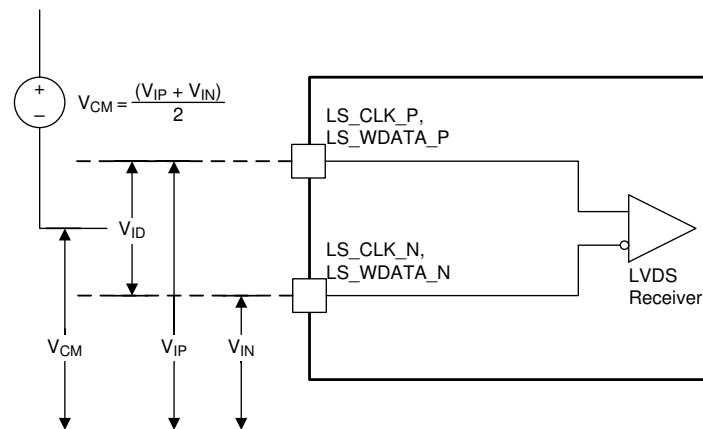

| V <sub>ID</sub>                         | LSIF 差動入力電圧の振幅 <sup>(9)</sup>                                  | 150                   | 350 | 440                   | mV  |

| V <sub>LVDS</sub>                       | LSIF 電圧 <sup>(9)</sup>                                         | 575                   |     | 1520                  | mV  |

| V <sub>CM</sub>                         | 同相電圧 <sup>(9)</sup>                                            | 700                   | 900 | 1300                  | mV  |

| Z <sub>LINE</sub>                       | ライン差動インピーダンス (PWB / パターン)                                      | 90                    | 100 | 110                   | Ω   |

| Z <sub>IN</sub>                         | 内部差動終端抵抗                                                       | 80                    | 100 | 120                   | Ω   |

| <b>高速シリアルインターフェイス (HSSI)</b>            |                                                                |                       |     |                       |     |

| f <sub>CLOCK</sub>                      | HSSI クロック周波数 (DCLK) <sup>(8)</sup>                             | 1.8                   | 1.8 | 1.8                   | GHz |

| DCD <sub>IN</sub>                       | HSSI デューティ サイクル歪み (DCLK)                                       | 44%                   | 50% | 56%                   |     |

| V <sub>ID</sub>   Data                  | HSSI 差動入力電圧振幅データレーン <sup>(8)</sup>                             | 100                   | 400 | 600                   | mV  |

| V <sub>ID</sub>   CLK                   | HSSI 差動入力電圧振幅クロックレー <sup>(8)</sup>                             | 300                   | 400 | 600                   | mV  |

| VCM <sub>DC</sub> Data                  | 入力同相電圧 (DC) データレーン <sup>(8)</sup>                              | 200                   | 600 | 800                   | mV  |

| VCM <sub>DC</sub> CLK                   | 入力同相電圧 (DC) クロックレーン <sup>(8)</sup>                             | 200                   | 600 | 800                   | mV  |

| VCM <sub>ACp-p</sub>                    | データレーンおよびクロックレーンの同相モード電圧における AC ピークツーピーク (リップル) <sup>(8)</sup> |                       |     | 100                   | mV  |

| Z <sub>LINE</sub>                       | ライン差動インピーダンス (PWB / パターン)                                      |                       | 100 |                       | Ω   |

| Z <sub>IN</sub>                         | 内部差動終端抵抗 (R <sub>Xterm</sub> )                                 | 80                    | 100 | 120                   | Ω   |

## 5.4 推奨動作条件 (続き)

自由気流での動作温度範囲および電源電圧内 (特に記述のない限り) <sup>(1)</sup>

| パラメータ名                 | 環境                                                                 | 最小値 | 標準値 | 最大値  | 単位                 |

|------------------------|--------------------------------------------------------------------|-----|-----|------|--------------------|

| <b>環境</b>              |                                                                    |     |     |      |                    |

| T <sub>ARRAY</sub>     | アレイ温度、長期動作 <sup>(10) (11) (12) (14)</sup>                          | 20  |     | 30   | °C                 |

| T <sub>WINDOW</sub>    | ウインドウ温度、動作可能、TP2 および TP3                                           | 10  |     | 30   | °C                 |

| T <sub>DELTA_MAX</sub> | [TP2 または TP3 の最小値] から T <sub>MIN_ARRAY</sub> <sup>(14)</sup> を引いた値 |     |     | 5    | °C                 |

| T <sub>DELTA_MIN</sub> | [TP2 または TP3 の最小値] から T <sub>MAX_ARRAY</sub> を引いた値 <sup>(14)</sup> | -10 |     |      | °C                 |

| RH                     | 相対湿度 (結露なし)                                                        |     |     | 95%  |                    |

| デューティサイクル              | 動作時の着地デューティサイクル <sup>(17)</sup>                                    |     | 50% |      |                    |

| ILL <sub>UV7</sub>     | 波長 < 341nm における照明強度 <sup>(13) (15) (16) (19)</sup>                 |     |     | 10   | mW/cm <sup>2</sup> |

| ILL <sub>UV6</sub>     | 343nm 以上 345nm 未満の波長における照明強度 <sup>(13) (15) (16) (19)</sup>        |     |     | 2.7  | W/cm <sup>2</sup>  |

| ILL <sub>UV5</sub>     | 345nm 以上 355nm 未満の波長における照明強度 <sup>(13) (15) (19)</sup>             |     |     | 2.9  | W/cm <sup>2</sup>  |

| ILL <sub>UV4</sub>     | 355nm 以上 365nm 未満の波長における照明強度 <sup>(13) (15) (19)</sup>             |     |     | 4.1  | W/cm <sup>2</sup>  |

| ILL <sub>UV3</sub>     | 365nm 以上 385nm 未満の波長における照明強度 <sup>(13) (15)</sup>                  |     |     | 5.9  | W/cm <sup>2</sup>  |

| ILL <sub>UV2</sub>     | 385nm 以上 400nm 未満の波長における照明強度 <sup>(13) (15)</sup>                  |     |     | 11.8 | W/cm <sup>2</sup>  |

| ILL <sub>UV1</sub>     | 400nm 以上 410nm 未満の波長における照明強度 <sup>(13) (15)</sup>                  |     |     | 22.5 | W/cm <sup>2</sup>  |

| ILL <sub>UV</sub>      | 365nm 以上 410nm 未満の波長における照明強度 <sup>(13) (15) (18)</sup>             |     |     | 22.5 | W/cm <sup>2</sup>  |

| ILL <sub>vis</sub>     | 410nm 以上 800nm 未満の波長における照明強度 <sup>(13) (15)</sup>                  |     |     | 60   | W/cm <sup>2</sup>  |

- (1) 推奨動作条件は、最終製品に DMD を取り付けた後に適用されます。

- (2) DMD を動作させるには、すべての電源接続が必要です。V<sub>DD</sub>、V<sub>DDA</sub>、V<sub>OFFSET</sub>、V<sub>BIAIS</sub> および V<sub>RESET</sub>。DMD を動作させるには、すべての V<sub>SS</sub> 接続が必要です。

- (3) すべての電圧値は、V<sub>SS</sub> グランド ピンを基準としたものです。

- (4) V<sub>OFFSET</sub> 電源過渡電圧は、規定最大電圧内に収まる必要があります。

- (5) 過剰な電流を防止するため、電源電圧のデルタ |V<sub>DDA</sub> – V<sub>DD</sub>| は、指定限界値よりも小さい必要があります。

- (6) 過剰な電流を防止するため、電源電圧のデルタ |V<sub>BIAIS</sub> – V<sub>OFFSET</sub>| は、指定限界値よりも小さい必要があります。

- (7) LVC MOS 入力ピンは DMD\_DEN\_ARSTZ です。

- (8) **タイミング要件** の高速シリアルインターフェイス (HSSI) のタイミング要件を参照してください。

- (9) **タイミング要件** の低速インターフェイス (LSIF) のタイミング要件を参照してください。

- (10) DMD を最 **推奨動作条件** の温度および UV 照明に同時に曝露すると、デバイスの寿命が短くなります。

- (11) アレイの温度は直接測定することができないため、**DMD の熱テストポイント** に示されているテストポイント (TP1) で測定された温度と、パッケージの熱抵抗を用いて、**DMD 温度計算式** により解析的に算出する必要があります。

- (12) 長期は、デバイスの使用可能寿命と定義されます。

- (13) DMD に照射可能な最大光学パワーは、各波長範囲ごとに規定された最大光出力密度およびマイクロミラー アレイの温度 (T<sub>ARRAY</sub>) によって制限されます。

- (14) 計算例については、『**DMD 温度の計算**』を参照してください。

- (15) 計算例については、『**マイクロミラーの電力密度の計算**』を参照してください。

- (16) 343nm 以上のあらゆる照明光源には、カットオフ フィルタを使用し、341nm でこのパワーレベル以下に抑える必要があります。343nm から 341nm にかけての照明電力は徐々に減少することが想定されており、それにより 341nm における最大許容パワー制限が達成可能となります。

- (17) 着地デューティサイクルとは、個々のマイクロミラーがある一方の状態 (12.0° または -12.0°) に着地している時間の割合を、反対の状態 (-12.0° または 12.0°) に対する割合として示したものです。50% は、ミラーがオン状態で 50%、オフ状態で 50% に達した 50/50 のデューティサイクルに相当します。着地デューティサイクルの詳細については、「**マイクロミラーの着地オンと着地オフのデューティサイクルの定義**」を参照してください。

- (18) 内蔵照明の総電力密度 (365nm ~ 410nm) は 22.5W/cm<sup>2</sup> を超えないようにする必要があります。そのため、5.9W/cm<sup>2</sup> の照明を 365nm ~ 385nm の範囲で使用し、11.8W/cm<sup>2</sup> を 385nm ~ 400nm の範囲で使用する場合、400nm ~ 410nm の範囲の照明は 4.8W/cm<sup>2</sup> に制限する必要があります。

- (19) 365nm 未満の複数の波長帯域の照明は、他の波長帯域と同時に使用できない場合があります。たとえば、344nm 照明 (343nm 以上および 345nm 未満) を使用する場合、この帯域外の別の波長を同時に使用することはできません。

## 5.5 熱に関する情報

| 熱評価基準                         |  | DLP991UUV                                        |  | 単位   |  |

|-------------------------------|--|--------------------------------------------------|--|------|--|

|                               |  | FLV パッケージ                                        |  |      |  |

|                               |  | 321 ピン                                           |  |      |  |

| $R_{MAX\_ARRAY\_TO\_CERAMIC}$ |  | 熱抵抗、テストポイント 1 (TP1) に対する最大アクティブ領域 <sup>(1)</sup> |  | 0.55 |  |

| $R_{MIN\_ARRAY\_TO\_CERAMIC}$ |  | 熱抵抗、テストポイント 1 (TP1) に対する最小アクティブ領域 <sup>(1)</sup> |  | 0.30 |  |

|                               |  |                                                  |  | °C/W |  |

- (1) DMD は、吸収・発散された熱をパッケージ背面に伝導するよう設計されており、適切なヒートシンクによってその熱を放散できます。ヒートシンクおよび冷却システムは、指定された動作温度内でパッケージを維持できる必要があります。DMD の合計熱負荷は、主にアクティブ領域によって吸収される入射光によって決まりますが、その他の寄与としてウインドウ開口部によって吸収される光エネルギーやアレイの消費電力があります。光学システムは、ウインドウの開放口から外れた光エネルギーを最小限に抑えるよう設計する必要があります。これは、この領域に熱負荷が増大すると、デバイスの信頼性が大幅に低下する可能性があるためです。TP1 の場所については、『図 6-1』を参照してください。

## 5.6 電気的特性

自由気流での動作温度範囲および電源電圧内 (特に記述のない限り)

| 記号                | パラメータ <sup>(2) (3)</sup>               | テスト条件 <sup>(2)</sup>                         | 最小値                 | 標準値  | 最大値                 | 単位            |

|-------------------|----------------------------------------|----------------------------------------------|---------------------|------|---------------------|---------------|

| <b>電流—標準</b>      |                                        |                                              |                     |      |                     |               |

| $I_{DD}$          | 消費電流 $V_{DD}$ <sup>(4)</sup>           |                                              |                     | 1.5  | 1.9                 | A             |

| $I_{DDA}$         | 消費電流 $V_{DDA}$ <sup>(4)</sup>          |                                              |                     | 1.4  | 1.9                 | A             |

| $I_{OFFSET}$      | 消費電流 $V_{OFFSET}$ <sup>(5) (6)</sup>   |                                              |                     | 37   | 50                  | mA            |

| $I_{BIAS}$        | 消費電流 $V_{BIAS}$ <sup>(5) (6)</sup>     |                                              |                     | 12.0 | 50                  | mA            |

| $I_{RESET}$       | 消費電流 $V_{RESET}$ <sup>(6)</sup>        |                                              | -50                 | -25  |                     | mA            |

| <b>パワー—標準</b>     |                                        |                                              |                     |      |                     |               |

| $P_{DD}$          | 電源消費電力 $V_{DD}$ <sup>(4)</sup>         |                                              |                     | 2710 | 3710                | mW            |

| $P_{DDA}$         | 電源消費電力 $V_{DDA}$ <sup>(4)</sup>        |                                              |                     | 2500 | 3600                | mW            |

| $P_{OFFSET}$      | 電源消費電力 $V_{OFFSET}$ <sup>(5) (6)</sup> |                                              |                     | 370  | 525                 | mW            |

| $P_{BIAS}$        | 電源消費電力 $V_{BIAS}$ <sup>(5) (6)</sup>   |                                              |                     | 216  | 925                 | mW            |

| $P_{RESET}$       | 電源消費電力 $V_{RESET}$ <sup>(6)</sup>      |                                              |                     | 350  | 725                 | mW            |

| $P_{TOTAL}$       | 電源の合計消費電力                              |                                              |                     | 6146 | 9485                | mW            |

| <b>LVC MOS 入力</b> |                                        |                                              |                     |      |                     |               |

| $I_{IL}$          | 低レベル入力電流 <sup>(7)</sup>                | $V_{DD} = 1.95\text{ V}, V_I = 0\text{V}$    | -100                |      |                     | nA            |

| $I_{IH}$          | 高レベル入力電流 <sup>(7)</sup>                | $V_{DD} = 1.95\text{ V}, V_I = 1.95\text{V}$ |                     |      | 135                 | $\mu\text{A}$ |

| <b>LVC MOS 出力</b> |                                        |                                              |                     |      |                     |               |

| $V_{OH}$          | DC 出力高電圧 <sup>(8)</sup>                | $I_{OH} = -2\text{mA}$                       | $0.8 \times V_{DD}$ |      |                     | V             |

| $V_{OL}$          | DC 出力低電圧 <sup>(8)</sup>                | $I_{OL} = 2\text{mA}$                        |                     |      | $0.2 \times V_{DD}$ | V             |

| <b>レシーバのアイ特性</b>  |                                        |                                              |                     |      |                     |               |

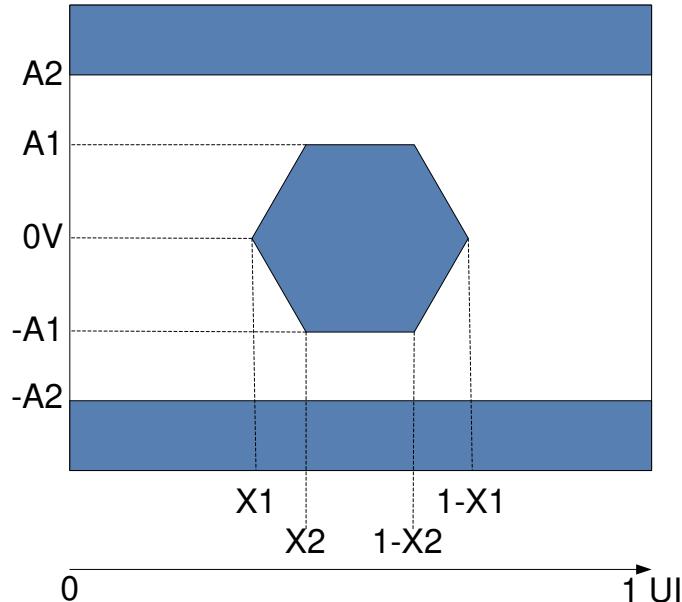

| A1                | 最小アイ開口 <sup>(9)</sup>                  |                                              | 100                 | 400  | 600                 | mV            |

| A2                | 最大信号スイング <sup>(9) (10)</sup>           |                                              |                     |      | 600                 | mV            |

| X1                | 最大アイクロージャ <sup>(9)</sup>               |                                              |                     |      | 0.275               | UI            |

| X2                | 最大アイクロージャ <sup>(9)</sup>               |                                              |                     |      | 0.4                 | UI            |

| $ t_{DRIFT} $     | トレーニング パターン間のクロックとデータのドリフト             |                                              |                     |      | 20                  | ps            |

| <b>容量</b>         |                                        |                                              |                     |      |                     |               |

| $C_{IN}$          | 入力容量 LVC MOS                           | $f = 1\text{MHz}$                            |                     |      | 30                  | pF            |

| $C_{IN}$          | 入力容量 LSIF (低速インターフェイス)                 | $f = 1\text{MHz}$                            |                     |      | 20                  | pF            |

## 5.6 電気的特性 (続き)

自由気流での動作温度範囲および電源電圧内 (特に記述のない限り)

| 記号               | パラメータ <sup>(2) (3)</sup>                            | テスト条件 <sup>(2)</sup> | 最小値 | 標準値 | 最大値 | 単位 |

|------------------|-----------------------------------------------------|----------------------|-----|-----|-----|----|

| C <sub>IN</sub>  | 入力キャパシタンス HSSI (高速シリアルインターフェイス) - 差動 - クロックピンとデータピン | f = 1MHz             |     |     | 5   | pF |

| C <sub>OUT</sub> | 出力容量                                                | f = 1MHz             |     |     | 10  | pF |

- (1) 特に注記がない限り、デバイスの電気的特性は 推奨動作条件下での値です。

- (2) DMD を動作させるには、すべての電源接続が必要です。V<sub>DD</sub>、V<sub>DDA</sub>、V<sub>OFFSET</sub>、V<sub>BIA</sub>S および V<sub>RESET</sub>。DMD を動作させるには、すべての V<sub>SS</sub> 接続が必要です。

- (3) すべての電圧値は、グランドピン (V<sub>SS</sub>) を基準としたものです。

- (4) 過剰な電流を防止するため、電源電圧のデルタ |V<sub>DDA</sub> - V<sub>DD</sub>| は、指定限界値よりも小さい必要があります。

- (5) 過剰な電流を防止するため、電源電圧のデルタ |V<sub>BIA</sub>S - V<sub>OFFSET</sub>| は、指定限界値よりも小さい必要があります。

- (6) 90μs 内での 1 回のフェーズリセット、1 回のアレイ負荷、および 1 回のグローバルリセットに基づいた消費電力

- (7) LVC MOS 入力仕様は、ピン DMD\_DEN\_ARSTZ に対するものです。

- (8) LVC MOS 出力仕様は、ピン LS\_RDATA\_A および LS\_RDATA\_B に対するものです。

- (9) 図 5-10、レシーバ アイマスク (1e-12 BER) を参照します。

- (10) セクション 5.4 に定義されています

## 5.7 スイッチング特性

自由気流での動作温度範囲および電源電圧内 (特に記述のない限り)

| 記号              | パラメータ                                                                            | テスト条件                           | 最小値 | 標準値 | 最大値  | 単位   |

|-----------------|----------------------------------------------------------------------------------|---------------------------------|-----|-----|------|------|

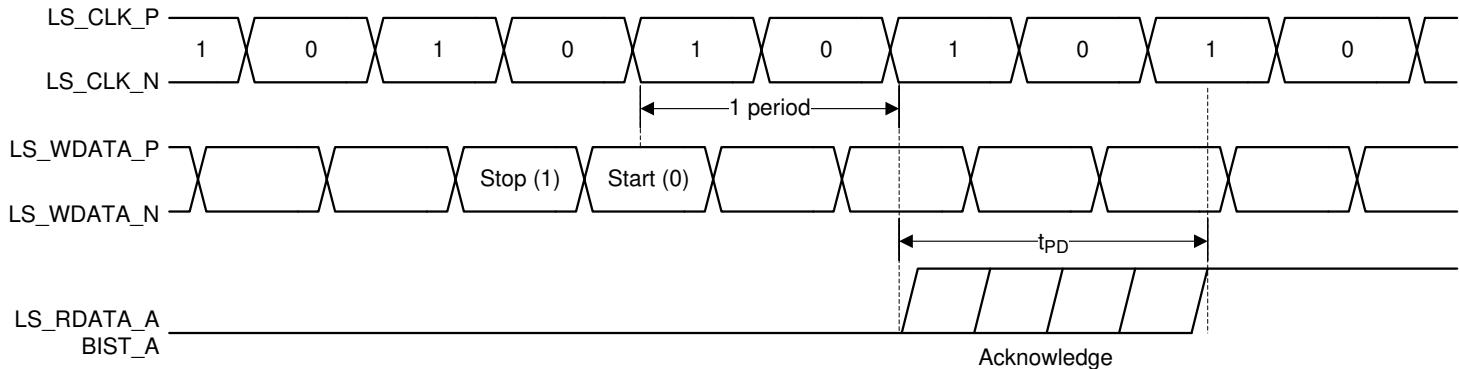

| t <sub>pd</sub> | 出力伝搬、クロックから Q まで、LS_CLK (差動クロック信号)<br>入力の立ち上がりエッジから LS_RDATA 出力まで <sup>(1)</sup> | C <sub>L</sub> = 5pF            |     |     | 11.1 | ns   |

| t <sub>pd</sub> | 出力伝搬、クロックから Q まで、LS_CLK (差動クロック信号)<br>入力の立ち上がりエッジから LS_RDATA 出力まで <sup>(1)</sup> | C <sub>L</sub> = 10pF           |     |     | 11.3 | ns   |

|                 | スルーレート、LS_RDATA                                                                  | 20% ~ 80%, C <sub>L</sub> < 10p | 0.5 |     |      | V/ns |

|                 | 出力デューティサイクル歪み、LS_RDATA                                                           |                                 | 40% |     | 60%  |      |

- (1) 図 5-1 を参照してください。

図 5-1. スイッチング特性

## 5.8 タイミング要件

自由気流での動作温度範囲および電源電圧内 (特に記述のない限り)

| 記号                           | パラメータ                   | テスト条件                                      | 最小値 | 標準値 | 最大値 | 単位 |

|------------------------------|-------------------------|--------------------------------------------|-----|-----|-----|----|

| <b>LVC MOS</b>               |                         |                                            |     |     |     |    |

| $t_r$                        | 立ち上がり時間 <sup>(1)</sup>  | 20% ~ 80%のリファレンス ポイント                      |     |     | 25  | ns |

| $t_f$                        | 立ち下がり時間 <sup>(1)</sup>  | 80% ~ 20%のリファレンス ポイント                      |     |     | 25  | ns |

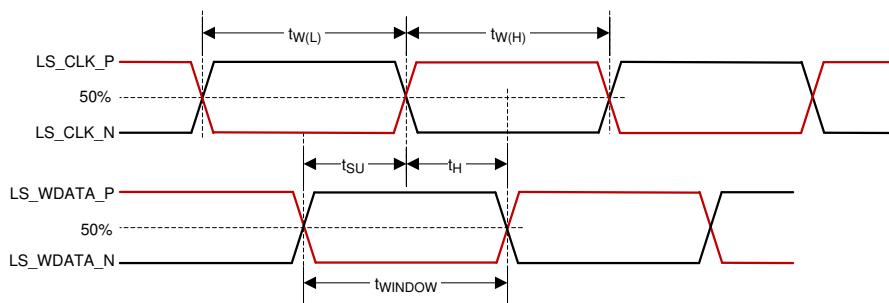

| <b>低速インターフェイス (LSIF)</b>     |                         |                                            |     |     |     |    |

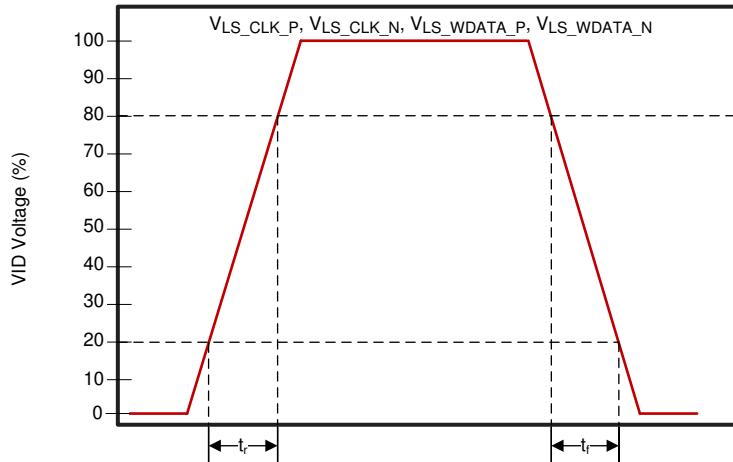

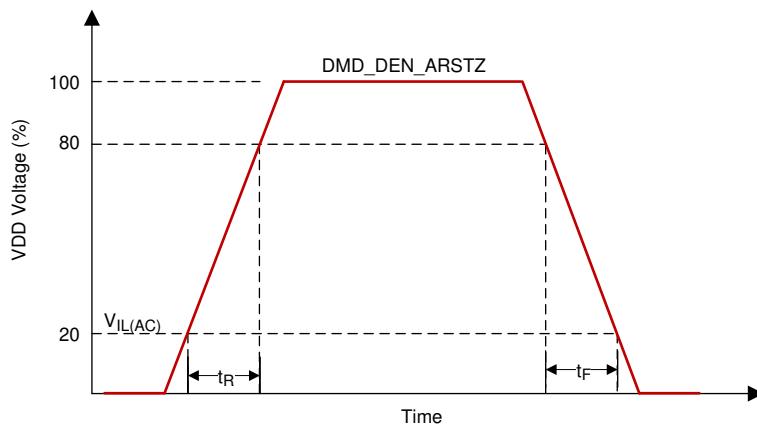

| $t_r$                        | 立ち上がり時間 <sup>(2)</sup>  | 20% ~ 80%のリファレンス ポイント                      |     |     | 450 | ps |

| $t_f$                        | 立ち下がり時間 <sup>(2)</sup>  | 80% ~ 20%のリファレンス ポイント                      |     |     | 450 | ps |

| $t_{SU}$                     | セットアップ時間 <sup>(3)</sup> | LS_WDATA が有効になってから LS_CLK の立ち上がりエッジまで (差分) | 1.5 |     |     | ns |

| $t_h$                        | ホールド時間 <sup>(3)</sup>   | LS_CLK の立ち上がりエッジの後に LS_WDATA 有効            | 1.5 |     |     | ns |

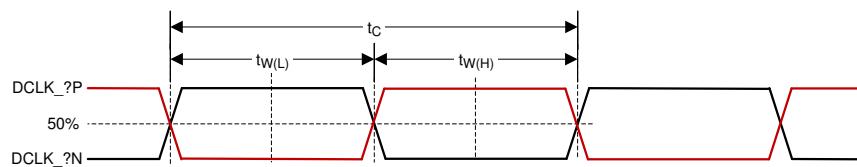

| <b>高速シリアルインターフェイス (HSSI)</b> |                         |                                            |     |     |     |    |

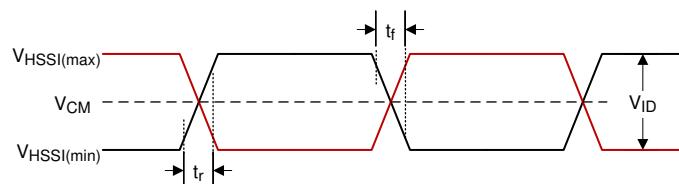

| $t_r$                        | 立ち上がり時間 <sup>(4)</sup>  | -A1 から A1 までの最小アイ高仕様                       | 50  |     | 100 | ps |

| $t_f$                        | 立ち下がり時間 <sup>(4)</sup>  | A1 から -A1 までの最小アイ高仕様                       | 50  |     | 100 | ps |

(1) LVC MOS の立ち上がり時間および立ち下がり時間について、図 5-8 を参照します。

(2) LSIF の立ち上がり時間および立ち下がり時間について、図 5-4 を参照します。

(3) LSIF のセットアップ時間およびホールド時間については、図 5-3 を参照します。

(4) HSSI の立ち上がり時間および立ち下がり時間について、図 5-9 を参照します。

図 5-2. LSIF 波形要件

$$V_{LVDS\ (max)} = V_{CM\ (max)} + \left| \frac{1}{2} \times V_{ID\ (max)} \right|$$

$$V_{LVDS\ (min)} = V_{CM\ (min)} - \left| \frac{1}{2} \times V_{ID\ (max)} \right|$$

図 5-3. LSIF のタイミング要件

図 5-4. LSIF 立ち上がり/立ち下がり時間のスルーライン

図 5-5. LSIF 電圧要件

図 5-6. LSIF 等価入力

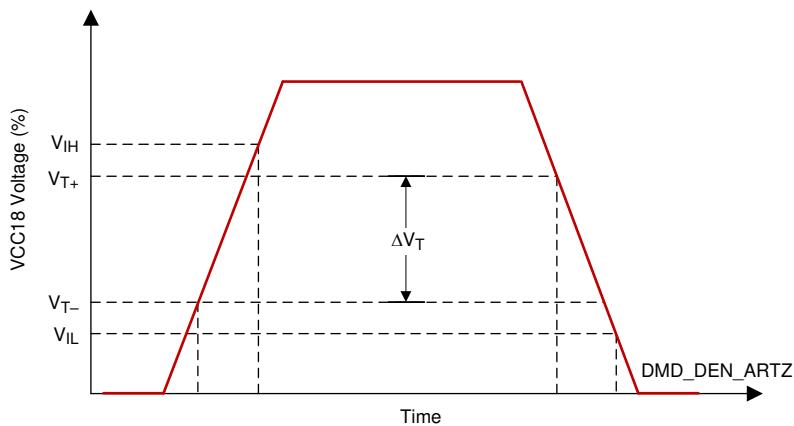

図 5-7. LVC MOS 入力ヒステリシス

図 5-8. LVC MOS の立ち上がり/立ち下がり時間のスルーレート

$$V_{HSSI(max)} = V_{CM(max)} + \left| \frac{1}{2} \times V_{ID(max)} \right|$$

$$V_{HSSI(min)} = V_{CM(min)} - \left| \frac{1}{2} \times V_{ID(max)} \right|$$

図 5-9. HSSI 波形要件

図 5-10. HSSI アイ特性

図 5-11. HSSI の CLK 特性

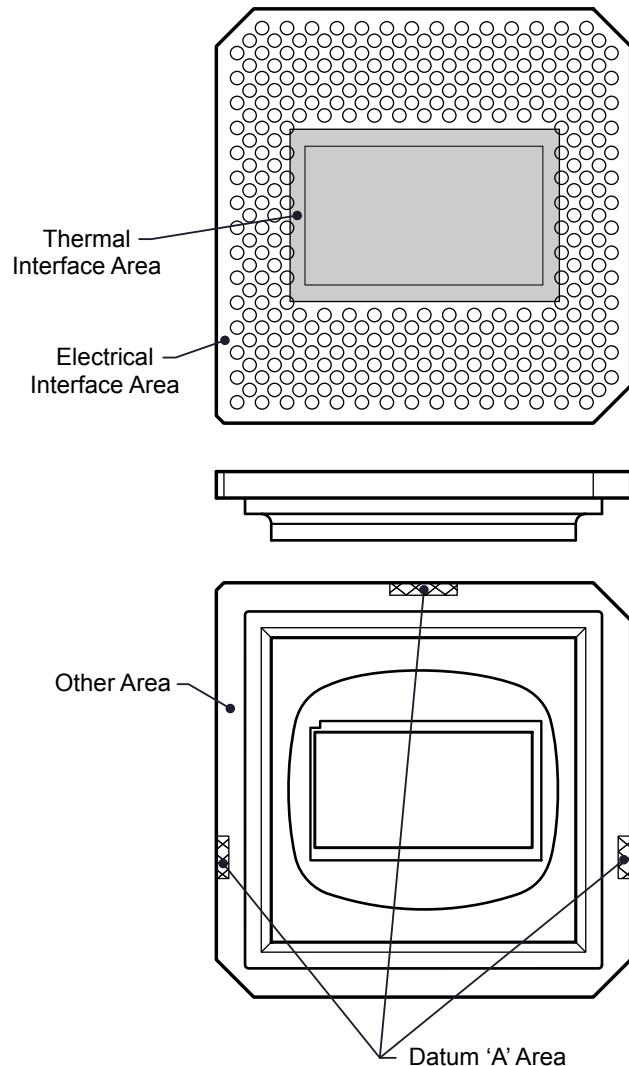

## 5.9 システム実装インターフェイスの荷重

| パラメータ                                    | 最小値 | 標準値 | 最大値  | 単位 |

|------------------------------------------|-----|-----|------|----|

| 電気インターフェイス領域に適用される最大荷重 <sup>(2)</sup>    |     |     | 1334 | N  |

| 基準面 A の接触領域に加えられる最大荷重 <sup>(1) (2)</sup> |     |     | 712  | N  |

| サーマルインターフェイス領域に適用される最大負荷 <sup>(2)</sup>  |     |     | 200  | N  |

- (1) 热インターフェース領域および電気インターフェース領域に加わる荷重の合計が基準面 A に許容される荷重を超える場合、その超過分の荷重は、基準面 A 領域 ( $1334+200 - \text{基準面 A}$ ) 外に均等に分散させるか、もしくは熱および電気インターフェース領域の荷重を減らす必要があります。

- (2) 図 5-12 に示す領域内に均一に分布しています

図 5-12. システム実装インターフェイスの荷重

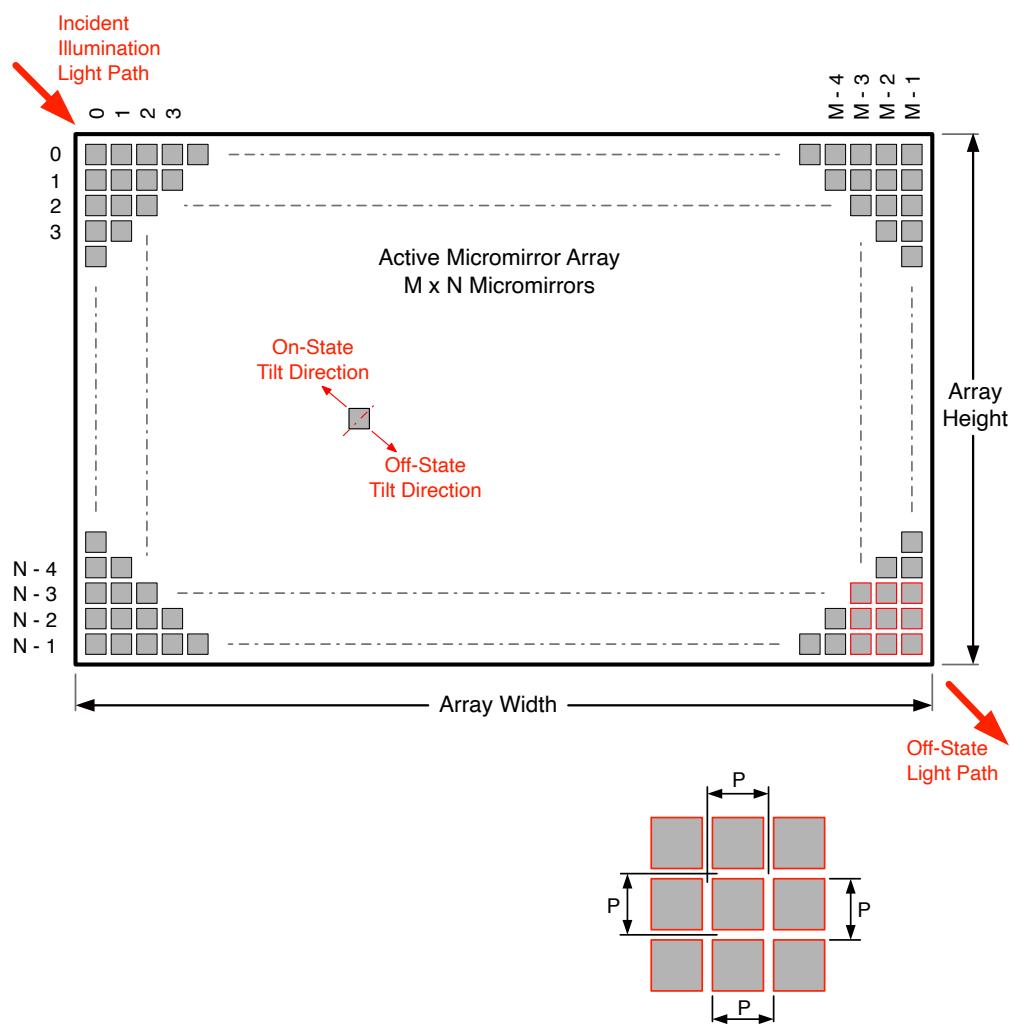

## 5.10 マイクロミラー アレイの物理特性

| パラメータ                               | 説明                                | 値       | 単位            |

|-------------------------------------|-----------------------------------|---------|---------------|

| M                                   | アクティブな列の数 <sup>(1)</sup>          | 4096    | マイクロミラー       |

| N                                   | アクティブな行の数 <sup>(1)</sup>          | 2176    | マイクロミラー       |

| P                                   | マイクロミラー (ピクセル) ピッチ <sup>(1)</sup> | 5.4     | μm            |

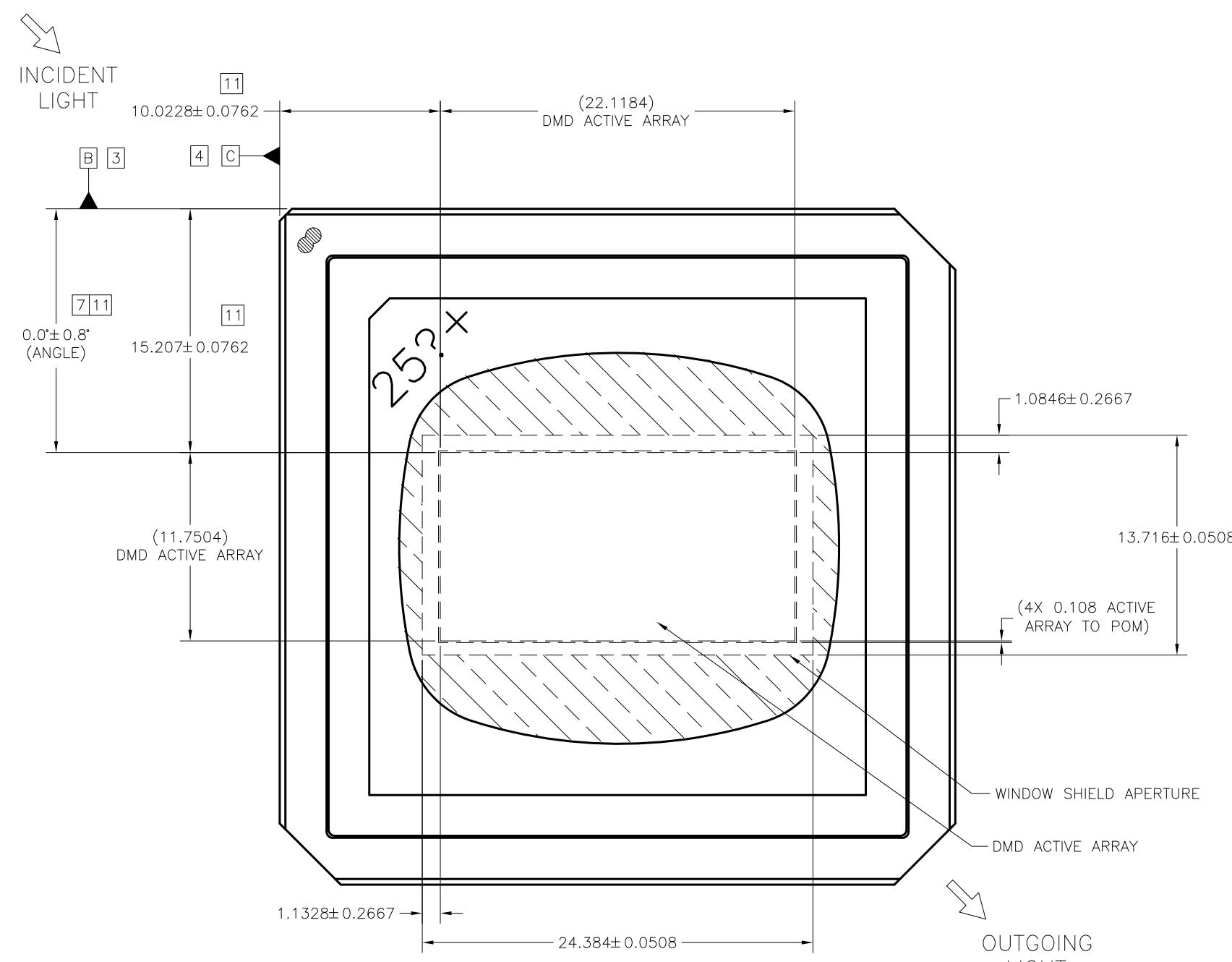

| マイクロミラーのアクティブ アレイの幅 <sup>(1)</sup>  | マイクロミラーのピッチ × アクティブ列の数            | 22.1184 | mm            |

| マイクロミラーのアクティブ アレイの高さ <sup>(1)</sup> | マイクロミラーのピッチ × アクティブ列の数            | 11.7504 | mm            |

| マイクロミラーのアクティブ境界 (上下) <sup>(2)</sup> | マイクロミラーの池 (POM)                   | 20      | マイクロミラー / サイド |

| マイクロミラーのアクティブ境界 (左右) <sup>(2)</sup> | マイクロミラーの池 (POM)                   | 20      | マイクロミラー / サイド |

(1) 図 5-13 を参照してください。

(2) アクティブアレイの周囲の構造と特性には、部分的に機能するマイクロミラーで POM と呼ばれる帶状の領域が含まれています。これらのマイクロミラーは構造的および / または電気的に、明るい状態またはオン状態へ傾けることを防止しますが、オフ状態へ傾けるには電気的バイアスが必要です。

図 5-13. マイクロミラー アレイの物理特性

## 5.11 マイクロミラー アレイの光学特性

| 記号  | パラメータ                                                       | テスト条件               | 最小値  | 標準値 | 最大値  | 単位      |

|-----|-------------------------------------------------------------|---------------------|------|-----|------|---------|

|     | マイクロミラーの傾斜角 <sup>(2) (3) (4) (5)</sup>                      | 着地状態 <sup>(1)</sup> | 11.0 |     | 13.0 | 度       |

| COT | マイクロミラーのクロスオーバー時間 <sup>(6)</sup>                            | 標準的性能               |      | 1   | 3    | μs      |

|     | マイクロミラーのスイッチング時間 <sup>(7)</sup>                             | 標準的性能               | 6    |     |      | μs      |

|     | マイクロミラーの回転軸の方向 <sup>(8)</sup>                               |                     | 44   |     | 46   | 度       |

|     | マイクロミラー アレイの光効率が 343nm ~ 410nm の波長範囲に対応 <sup>(9) (10)</sup> |                     |      | 68% |      |         |

|     | 非動作マイクロミラー <sup>(11)</sup>                                  | 非隣接マイクロミラー          |      |     | 10   | マイクロミラー |

|     |                                                             | 隣接するマイクロミラー         |      |     | 0    |         |

- (1) マイクロミラー アレイ全体から形成されるプレーンを基準として測定されます。

(2) マイクロミラー アレイとパッケージのデータム間には、さらに大きな変動があります。

(3) 公称着地傾斜角に対する着地傾斜角の変動を表します。

(4) 同じデバイス上または異なるデバイス上に配置された任意の 2 つの個別マイクロミラー間で発生する可能性のある変動を表しています。

(5) 一部のアプリケーションでは、システム全体の光学設計においてマイクロミラーの傾斜角の変動を考慮することが重要です。一部のシステム光学設計では、デバイス内のマイクロミラーの傾斜角が変動すると、マイクロミラー アレイから反射された光磁界では不均一性が認識される場合があります。一部のシステム光学設計では、デバイス間でマイクロミラーの傾斜角が変動すると、色測定のバラツキ、システム効率のバラツキ、またはシステムコントラストのバラツキが生じる場合があります。

(6) マイクロミラーがある着地状態から反対側の着地状態に公称遷移するために必要な時間。

(7) ミラー・クロック パルスの終了で、マイクロミラーが連続して遷移してから、次のミラー クロック パルスの開始までの最小時間。

(8) パッケージ基準面「B」および「C」を基準に測定。

(9) 特定のアプリケーションで観察される DMD の最小または最大の光学効率は、以下のような多数のアプリケーション固有の設計変数に依存します。

- 照明波長、帯域幅/ライン幅、干渉度

- 照明角度 + 角度公差

- システムの光学経路内での、照明および投影のアーチャのサイズと位置

- DMD マイクロミラー アレイの照射オーバーフィル

- 照射用光源や照射経路に異常がある場合

- 投影パスに異常が存在

規定された公称の DMD 光学効率は、以下の使用条件に基づいています。

- 343nm ~ 410nm の範囲の照明

- 入力照明の光軸がウインドウの法線に対して 24° の角度で配置されている

- ウインドウの法線に対して 0° に向けた光軸を投影している

- f/3 照明開口部

- f/2.4 投影開口

使用条件に基づき、公称の DMD 光学効率は以下の 4 つの要素から成り立っています。

- マイクロミラー アレイのフィル ファクタ: 公称値 90%

- マイクロミラー アレイの回折効率: 公称 91%

- マイクロミラー表面の反射率: 公称 88%

- ウインドウの透過率: 公称値 97% (单一通過、2 つの表面遷移を通過)

- (10) これは、アプリケーションに依存するマイクロミラーのスイッチング デューティ サイクルの影響を考慮していません。マイクロミラーのスイッチング デューティ サイクルとは、マイクロミラーが光学照明経路から光学投影経路へ実際に光を反射している時間の割合を示します。このサイクルは、照明開口のサイズ、投影開口のサイズ、およびマイクロミラー アレイの更新レートに依存します。

- (11) 非動作マイクロミラーとは、「OFF」位置から「ON」位置、またはその逆への正常な遷移ができないマイクロミラーのことを指します。

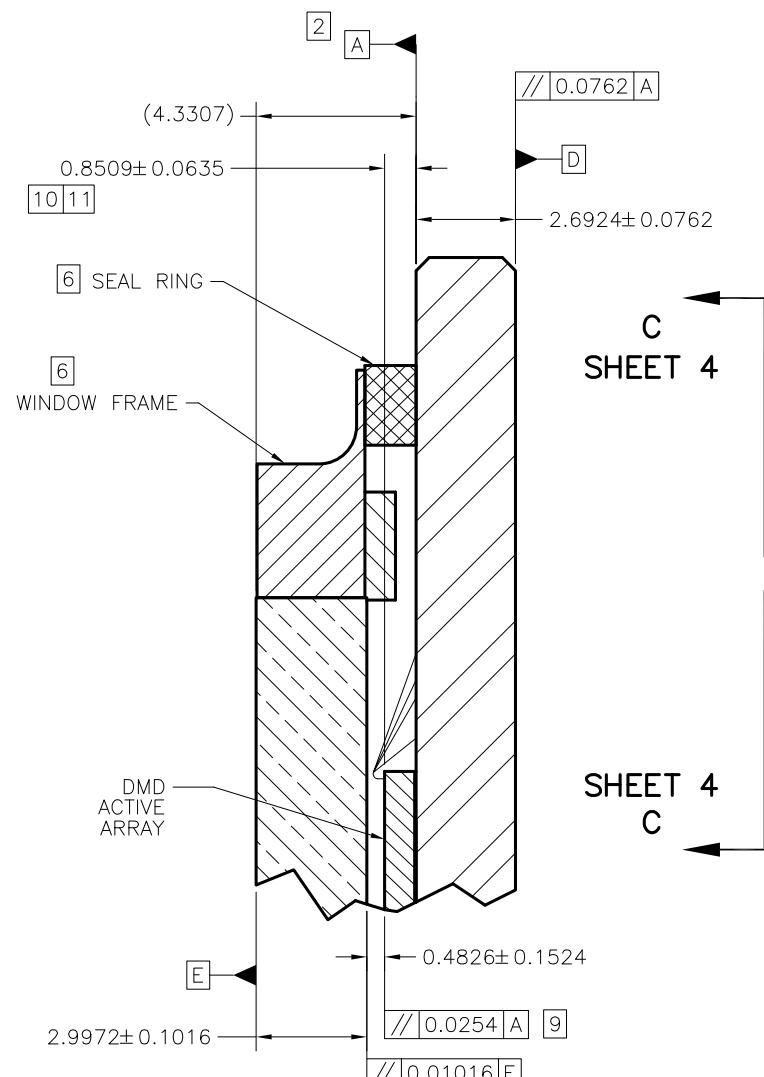

## 5.12 ウィンドウの特性

| パラメータ                               | テスト条件                                  | 最小値 | 標準値        | 最大値 | 単位 |

|-------------------------------------|----------------------------------------|-----|------------|-----|----|

| ウィンドウ材料名称                           |                                        |     | ヨーニング 7056 |     |    |

| ウィンドウ屈折率                            | 波長 589nm の場合                           |     | 1.487      |     |    |

| ウィンドウ透過率、波長範囲 343nm ~ 410nm における最小値 | すべての角度 0~30 AOI に適用 <sup>(1) (2)</sup> |     | 97%        |     |    |

(1) 両面およびガラスをシングルパスで通過

(2) 入射角 (AOI) は、入射光線と反射面または屈折面の法線との間の角度です。

## 5.13 チップセット コンポーネントの使用方法の仕様

DLPC991UV DMD の信頼性の高い機能と動作を実現するには、TI の DMD 制御テクノロジーを採用または実装する部品など、該当する DLP チップセットの他の部品と組み合わせて DMD を使用する必要があります。TI DMD 制御テクノロジーとは、DLP DMD を動作・制御するための TI のテクノロジーとデバイスのことです。

## 6 詳細説明

### 6.1 概要

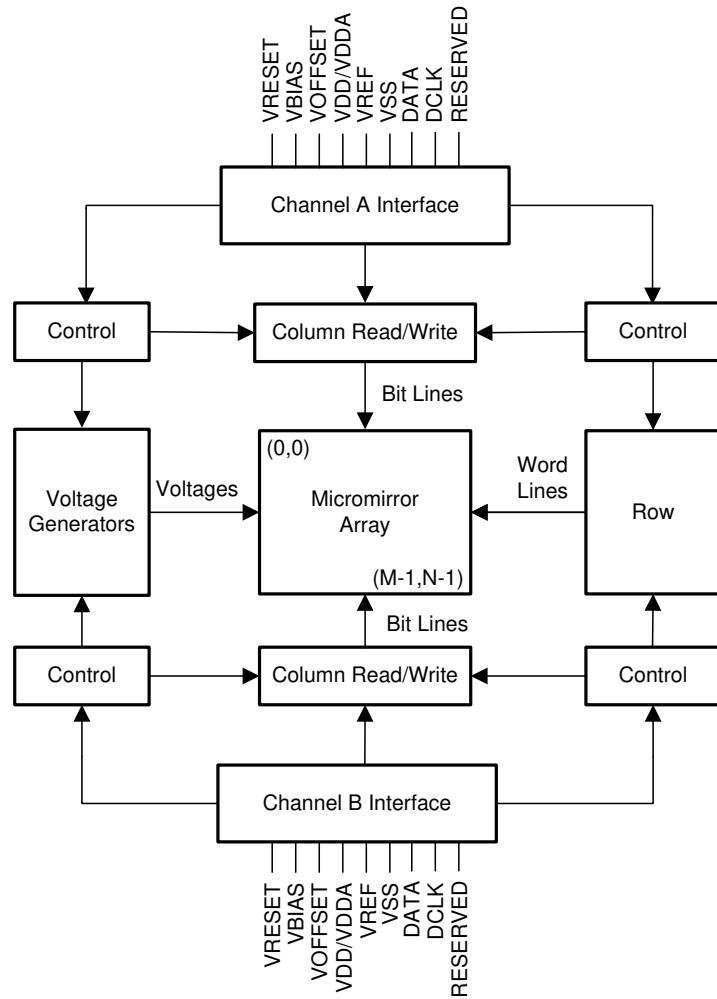

DLP991UUV デジタルマイクロミラー デバイス(DMD)は、対角 0.99 インチの空間光変調器で、高反射率のアルミニウム製マイクロミラーのアレイで構成されています。DMD は、電気入力、光出力の光マイクロマシン (MEMS) です。入力電気的データインターフェイスは、差動高速シリアルインターフェイス (HSSI) です。DMD は、1 ビット CMOS メモリセルの 2 次元アレイで構成されます。アレイは、M 個のメモリセル列と N 個のメモリセル行の格子状に編成されます。[図 5-13](#) を参照してください。マイクロミラーの正または負の傾斜角は、それぞれのメモリセルに「1」または「0」を書き込むことで個別に制御でき、これにより下層の CMOS アドレッシング回路のアドレス電圧が変化します。

信頼性の高い動作を保証するため、常に DLP991UUV DMD を TI DLPC964 産業用コントローラと組み合わせて使用します。

### 6.2 機能ブロック図

チャネル A、B、C、D のピンの詳細については、[セクション 4](#)、および [セクション 5.8](#) の HSSI インターフェイスセクションを参照してください。

チャネル C とチャネル D は A と B と同じように接続されていますが、明確にするためにこの画像からは省略されています。

## 6.3 機能説明

### 6.3.1 電源インターフェイス

DLP991UV DMD を適切に動作させるためには、5 つの DC 電圧が必要です。 $V_{DD}$ 、 $V_{DDA}$ 、 $V_{OFFSET}$ 、 $V_{RESET}$  および  $V_{BIAS}$ 。 $V_{DD}/V_{DDA}$  電源入力には、1.9V 電源が必要です。DMD には  $V_{OFFSET}$ (10V)、 $V_{RESET}$ (-14V)、 $V_{BIAS}$ (18V) を供給し、マイクロミラー作動制御を実現します。

### 6.3.2 タイミング

データシートには、デバイスピンでのタイミングが記載されています。出力タイミング解析では、テスタのピンエレクトロニクスとその伝送ラインの影響を考慮に入れる必要があります。タイミング基準負荷は、特定のシステム環境を精密に表現したり、製造試験で示される実際の負荷を表現したりすることを意図したものではありません。システム設計者は、IBIS または他のシミュレーションツールを使用して、タイミング基準負荷をシステム環境に関連付ける必要があります。記載されている負荷容量値は、AC タイミング信号の特性評価と測定のみを目的としています。この負荷容量の値は、デバイスが駆動可能な最大負荷を示しているわけではありません。

## 6.4 デバイスの機能モード

DMD の機能モードは、ディスプレイコントローラによって制御されます。詳細については、『[DLPC964 デジタルマイクロミラーデバイスコントローラデータシート](#)』を参照するか、TI のアプリケーションエンジニアにお問い合わせください。

## 6.5 光学インターフェイスおよびシステムの画質に関する検討事項

### 注

TI は、前述の制限を超える光学システムの動作条件によって発生する画質のアーチファクトまたは DMD の故障については、一切責任を負いません。

TI は、最終製品の光学性能について一切責任を負いません。目的の最終製品の光学性能を実現するには、多数の部品とシステム設計パラメータとの間でトレードオフを決定する必要があります。システムの光学性能と画像品質の最適化は、光学システム設計のパラメータのトレードオフに大きく関係しています。想定可能なすべてのアプリケーションを予測できるわけではありませんが、プロジェクタの画質と光学性能は、以下のセクションに示す光学システムの動作条件への準拠によって決まります。

### 6.5.1 開口数および迷光制御

照明と投影光学素子の開口数で定義される角度は、照明および投影瞳孔に適切な開口部を追加して、投影レンズからの平面光および迷光をブロックする場合を除いて、公称デバイスのマイクロミラー傾斜角を超えないようにする必要があります。マイクロミラーの傾斜角により、DMD の「オン」光路をその他のライトパスから分離できます。これには、DMD ウィンドウからの望ましくない平面状態の反射、DMD の境界構造、または DMD 付近にあるプリズムやレンズ表面などのその他のシステム表面などが含まれます。開口数がマイクロミラーの傾斜角を超えていたり、投影側の数値開口角が照明側の数値開口角よりも 2 度以上大きい場合、ディスプレイの縁や表示領域内に目障りなアーチファクトが発生する可能性があります。

### 6.5.2 瞳孔一致

光学的品質および画質に関する TI の仕様は、照明用光学素子の射出瞳が公称値として投影光学素子の入射瞳から 2° 以内の位置を中心としていると仮定しています。瞳孔のずれは、ディスプレイ境界とアクティブ領域に不快なアーチファクトを発生させる可能性があり、特にシステムの開口数がピクセルチルト角度を超える場合は、制御するために追加のシステム開口部が必要になる場合があります。

### 6.5.3 オーバーフィル照射

デバイスのアクティブ領域は、DMD チップアセンブリの構造を通常の視界から覆い隠す、DMD ウィンドウ面の内側にある開口部で囲まれ、複数の光学動作条件を想定したサイズとなっています。ウィンドウ開口部を照らすオーバーフィル光は、ウィンドウ開口部の端からアーチファクトが発生したり、その他の表面異常が画面に表示されたりする可能性があります。照明光学システムは、ウィンドウ開口部上の任意の場所に入射する光束が、アクティブ領域の平均光束レベルの約

10% を超えないように設計する必要があります。ウィンドウ開口部に照射される照明光の量を最小限に抑えることをお勧めします。

## 6.6 DMD 温度の計算

図 6-1. DMD の温度テスト ポイント

マイクロミラー アレイの温度は、パッケージ外部の測定点、パッケージの熱抵抗、電力消費、および照明による熱負荷から解析的に算出できます。マイクロミラー アレイの温度と基準セラミック温度との関係は、以下の式で示されます。

$$T_{MAX\_ARRAY} = T_{CERAMIC} + (Q_{ARRAY} \times R_{MAX\_ARRAY-TO-CERAMIC})$$

$$T_{MIN\_ARRAY} = T_{CERAMIC} + (Q_{ARRAY} \times R_{MIN\_ARRAY-TO-CERAMIC})$$

$$T_{DELTA\_MIN} = [\text{minimum of } TP2 \text{ or } TP3] - T_{MAX\_ARRAY}$$

$$T_{DELTA\_MAX} = [\text{maximum of } TP2 \text{ or } TP3] - T_{MIN\_ARRAY}$$

$$Q_{ARRAY} = Q_{ELECTRICAL} + Q_{ILLUMINATION}$$

ここで、

- $T_{ARRAY}$  = 算出されたアレイ温度 ( $^{\circ}\text{C}$ )

- $T_{CERAMIC}$  = 測定されたアレイ温度 ( $^{\circ}\text{C}$ ) (TP1 の場所)

- $R_{ARRAY-TO-CERAMIC}$  = アレイからセラミック TP1 までのパッケージの熱抵抗 ( $^{\circ}\text{C}/\text{ワット}$ )

- $Q_{ARRAY}$  = アレイ上の DMD 全体の消費電力 (ワット) (電力 + 吸収光)

- $Q_{ELECTRICAL}$  = 公称電力

- $Q_{INCIDENT}$  = DMD に入射する光の総光学パワー

- $Q_{ILLUMINATION} = (\text{DMD 平均熱吸収率} \times Q_{INCIDENT})$  (セクション 5.4 を参照。)

- DMD の平均熱吸収率 (オン状態) = 0.26

- DMD の平均熱吸収率 (オフ状態) = 0.42

DMD の消費電力は変数で、電圧、データレート、動作周波数に依存します。アレイ温度を計算するには、DMD の電力損失( $Q_{ELECTRICAL}$ )として 9.5 ワットの値を使用します。照射用光源から吸収される電力は変数で、マイクロミラーの動作状態と光源の強度に依存します。上記の式は、システム内の各 DMD チップに対して有効です。この想定では、アクティブ アレイで 91.0%、アレイ境界で 9.0% の照度分布を想定しています。

オフ状態およびオン状態のサンプル計算を以下に示します。

### 6.6.1 オフ状態熱差動 ( $T_{\Delta\text{MIN}}$ )

$$TP1 (\text{ceramic}) = 20.0^\circ\text{C} (\text{measured})$$

$$TP2 (\text{window}) = 27.0^\circ\text{C} (\text{measured})$$

$$TP3 (\text{window}) = 29.0^\circ\text{C} (\text{measured})$$

$$Q_{\text{INCIDENT}} = 20.0\text{W} (\text{measured})$$

$$Q_{\text{ELECTRICAL}} = 9.5\text{W}$$

$$R_{\text{MAX\_ARRAY-TO-CERAMIC}} = 0.55^\circ\text{C/W}$$

$$Q_{\text{ARRAY}} = 9.5\text{W} + (20.0\text{W} \times 0.42) = 17.9\text{W}$$

$$T_{\text{MAX\_ARRAY}} = 20.0^\circ\text{C} + (17.9\text{W} \times 0.55^\circ\text{C/W}) = 29.85^\circ\text{C}$$

$$T_{\Delta\text{MIN}} = [\text{minimum of TP2 or TP3}] - T_{\text{MAX\_ARRAY}} = 27.0^\circ\text{C} - 29.85^\circ\text{C} = -2.85^\circ\text{C}$$

### 6.6.2 オン状態の熱差動 ( $T_{\Delta\text{MAX}}$ )

$$TP1 (\text{ceramic}) = 20.0^\circ\text{C} (\text{measured})$$

$$TP2 (\text{window}) = 27.0^\circ\text{C} (\text{measured})$$

$$TP3 (\text{window}) = 29.0^\circ\text{C} (\text{measured})$$

$$Q_{\text{INCIDENT}} = 20.0\text{W} (\text{measured})$$

$$Q_{\text{ELECTRICAL}} = 9.5\text{W}$$

$$R_{\text{MIN\_ARRAY-TO-CERAMIC}} = 0.30^\circ\text{C/W}$$

$$Q_{\text{ARRAY}} = 9.5\text{W} + (20.0\text{W} \times 0.26) = 14.7\text{W}$$

$$T_{\text{MIN\_ARRAY}} = 20.0^\circ\text{C} + (14.7\text{W} \times 0.30^\circ\text{C/W}) = 24.41^\circ\text{C}$$

$$T_{\Delta\text{MAX}} = [\text{maximum of TP2 or TP3}] - T_{\text{MIN\_ARRAY}} = 29.0^\circ\text{C} - 24.41^\circ\text{C} = 4.59^\circ\text{C}$$

## 6.7 マイクロミラーの電力密度の計算

さまざまな波長帯域で DMD 上の照明の光出力密度を計算するには、DMD で測定された合計光出力、照明のオーバーフィル率、アクティブ アレイの面積、目的の波長帯域でのスペクトルの合計光出力に対する比率を使用します。

- $ILL_{UV7} = [OP_{UV-RATIO} \times Q_{INCIDENT}] \times 1000 \text{ (mW/W)} \div A_{ILL} \text{ (mW/cm}^2\text{)}$

- $ILL_{UV6} = [OP_{VIS-RATIO} \times Q_{INCIDENT}] \div A_{ILL} \text{ (W/cm}^2\text{)}$

- $ILL_{UV5} = [OP_{VIS-RATIO} \times Q_{INCIDENT}] \div A_{ILL} \text{ (W/cm}^2\text{)}$

- $ILL_{UV4} = [OP_{VIS-RATIO} \times Q_{INCIDENT}] \div A_{ILL} \text{ (W/cm}^2\text{)}$

- $ILL_{UV3} = [OP_{VIS-RATIO} \times Q_{INCIDENT}] \div A_{ILL} \text{ (W/cm}^2\text{)}$

- $ILL_{UV2} = [OP_{IR-RATIO} \times Q_{INCIDENT}] \div A_{ILL} \text{ (W/cm}^2\text{)}$

- $ILL_{UV1} = [OP_{IR-RATIO} \times Q_{INCIDENT}] \div A_{ILL} \text{ (W/cm}^2\text{)}$

- $ILL_{UV} = [OP_{IR-RATIO} \times Q_{INCIDENT}] \div A_{ILL} \text{ (W/cm}^2\text{)}$

- $ILL_{VIS} = [OP_{BLU1-RATIO} \times Q_{INCIDENT}] \div A_{ILL} \text{ (W/cm}^2\text{)}$

- $A_{ILL} = A_{ARRAY} \div (1 - OV_{ILL}) \text{ (cm}^2\text{)}$

ここで

- $ILL_{UV7}$  = DMD での UV7 照明の電力密度 ( $\text{mW/cm}^2$ )

- $ILL_{UV6}$  = DMD での UV6 照明の電力密度 ( $\text{W/cm}^2$ )

- $ILL_{UV5}$  = DMD での UV5 照明の電力密度 ( $\text{W/cm}^2$ )

- $ILL_{UV4}$  = DMD での UV4 照明の電力密度 ( $\text{W/cm}^2$ )

- $ILL_{UV3}$  = DMD での UV3 照明の電力密度 ( $\text{W/cm}^2$ )

- $ILL_{UV2}$  = DMD での UV2 照明の電力密度 ( $\text{W/cm}^2$ )

- $ILL_{UV1}$  = DMD での UV1 照明の電力密度 ( $\text{W/cm}^2$ )

- $ILL_{UV}$  = DMD での UV 照明の電力密度 ( $\text{W/cm}^2$ )

- $ILL_{VIS}$  = DMD での VIS 照明の電力密度 ( $\text{W/cm}^2$ )

- $A_{ILL}$  = DMD での照明領域 ( $\text{cm}^2$ )

- $Q_{INCIDENT}$  = DMD での総入射光パワー (W) (測定値)

- $A_{ARRAY}$  = アレイの面積 ( $\text{cm}^2$ ) (データシート)

- $OV_{ILL}$  = アレイ外の DMD の総照明パーセント (%) (光学モデル)

- $OP_{UV7-RATIO}$  = 照明スペクトルにおける、波長が 341nm 未満の光パワーの合計に対する、総光パワーに対する比率 (スペクトル測定)

- $OP_{UV6-RATIO}$  = 照明スペクトルの総光出力に対する、波長が 343nm 以上 345nm 以下の場合の光出力比 (スペクトル測定)

- $OP_{UV5-RATIO}$  = 照明スペクトルの総光出力に対する、波長が 345nm 以上 355nm 以下の場合の光出力比 (スペクトル測定)

- $OP_{UV4-RATIO}$  = 照明スペクトルの総光出力に対する、波長が 355nm 以上 365nm 以下の場合の光出力比 (スペクトル測定)

- $OP_{UV3-RATIO}$  = 照明スペクトルの総光出力に対する、波長が 365nm 以上 385nm 以下の場合の光出力比 (スペクトル測定)

- $OP_{UV2-RATIO}$  = 照明スペクトルの総光出力に対する、波長が 385nm 以上 400nm 以下の場合の光出力比 (スペクトル測定)

- $OP_{UV1-RATIO}$  = 照明スペクトルの総光出力に対する、波長が 400nm 以上 410nm 以下の場合の光出力比 (スペクトル測定)

- $OP_{UV-RATIO}$  = 照明スペクトルの総光出力に対する、波長が 365nm 以上 410nm 以下の場合の光出力比 (スペクトル測定)

- $OP_{VIS-RATIO}$  = 照明スペクトルの総光出力に対する、波長が 410nm 以上 800nm 以下の場合の光出力比 (スペクトル測定)

照明領域は、照明オーバーフィルによって異なります。DMD 上の総照明領域は、アレイ領域と、アレイの周囲のオーバーフィル領域です。光学モデルを使用して、アレイの外部にある DMD 上の全照明の割合 ( $OV_{ILL}$ ) と、アクティブ アレイ

上にある全照明の割合を決定します。これらの値から、照明領域 ( $A_{ILL}$ ) が計算されます。照明は、アレイ全体で一様であると仮定します。

測定された照明スペクトルから、総光出力に対する、対象の波長帯域における光出力との比が計算されます。

### サンプル計算 - 照明 365nm ~ 410nm

$$Q_{INCIDENT} = 33.5\text{W} \text{ (measured)}$$

$$A_{ARRAY} = (22.1184\text{mm} \times 11.7504\text{mm}) \div 100 \text{ (mm/cm)} = 2.599\text{cm}^2 \text{ (data sheet)}$$

$$OV_{ILL} = 9\% \text{ (optical model)}$$

$$OP_{UV3-RATIO} = 0.49962 \text{ (spectral measurement)}$$

$$OP_{UV2-RATIO} = 0.49962 \text{ (spectral measurement)}$$

$$OP_{UV1-RATIO} = 0.00076 \text{ (spectral measurement)}$$

$$A_{ILL} = 2.599\text{cm}^2 \div (1 - 0.09) = 2.8560\text{cm}^2$$

$$ILL_{UV} = [1.0 \times 33.5\text{W}] \div 2.8560\text{cm}^2 = 11.730\text{W/cm}^2$$

$$ILL_{UV3} = [0.49962 \times 33.5\text{W}] \div 2.8560\text{cm}^2 = 5.860\text{W/cm}^2$$

$$ILL_{UV2} = [0.49962 \times 33.5\text{W}] \div 2.8560\text{cm}^2 = 5.860\text{W/cm}^2$$

$$ILL_{UV1} = [0.00076 \times 33.5\text{W}] \div 2.8560\text{cm}^2 = 0.009\text{W/cm}^2$$

## 6.8 マイクロミラーのランデッド オン / ランデッド オフ デューティ サイクル

### 6.8.1 マイクロミラーのランデッド オン / ランデッド オフ デューティ サイクルの定義

マイクロミラーのオン/オフ着地デューティサイクル(着地デューティサイクル)は、個々のマイクロミラーが「オン」状態に着地している時間の割合(%)を、「オフ」状態に着地している時間と比較したものを示します。

たとえば、ランデッド デューティ サイクルが 75/25 の場合、対象のピクセルは全体の 75% の時間「オン」状態(25%は「オフ」状態)にあることを意味します。一方、25/75 の場合は、そのピクセルが全体の 75% の時間「オフ」状態にあることを示します。同様に、50/50 はピクセルがオン状態の時間 50%、オフ状態の時間 50% になっていることを示します。

なお、ランデッド デューティ サイクルを評価する際、一方の状態(オンまたはオフ)から他方の状態(オフまたはオン)に切り替わるのに要する時間は無視できるものと見なされます。

マイクロミラーはどちらか一方の状態(オンまたはオフ)でしか着地できないため、2 つの数値(パーセンテージ)の合計は必ず 100 になります。

### 6.8.2 DMD のランデッド デューティ サイクルと有効寿命

(最終製品またはアプリケーションの) 長期平均ランデッド デューティ サイクルを把握することが重要です。DMD マイクロミラー アレイ(アクティブ アレイとも呼ばれます)のすべて(または一部)を非対称ランデッド デューティ サイクルに長時間適用すると、DMD の有効寿命が短くなるためです。

ランデッド デューティ サイクルの対称性 / 非対称性が関連することに注意してください。ランデッド デューティ サイクルの対称性は、2 つの数値(パーセンテージ)がどれだけ等しいかによって決まります。たとえば、50/50 のランデッド デューティ サイクルは完全に対称ですが、100/0 または 0/100 のランデッド デューティ サイクルは完全に非対称です。

### 6.8.3 製品またはアプリケーションの長期平均ランデッド デューティ サイクルの推定

所定の期間中、特定のピクセルのランデッド デューティ サイクルは、そのピクセルによって表示される画像内容から追従します。

たとえば、最も単純なケースでは、ある一定の期間、あるピクセルに純粋な白を表示する場合、そのピクセルはその期間中に 100/0 ランデッド デューティサイクル下で動作します。同様に、純粋な黒を表示する場合、ピクセルは 0/100 ランデッド デューティサイクル下で動作します。

この 2 つの極端な値の間 (入力画像に適用される色と画像処理をとりあえず無視します)、ランデッド デューティ サイクルは、表 6-1 に示すように、グレイスケール値で 1 対 1 を追跡します。

**表 6-1. グレイスケール値とランデッド デューティ サイクル**

| グレイスケール値 | ランデッド デューティ サイクル |

|----------|------------------|

| 0%       | 0/100            |

| 10%      | 10/90            |

| 20%      | 20/80            |

| 30%      | 30/70            |

| 40%      | 40/60            |

| 50%      | 50/50            |

| 60%      | 60/40            |

| 70%      | 70/30            |

| 80%      | 80/20            |

| 90%      | 90/10            |

| 100%     | 100/0            |

## 7 アプリケーションと実装

### 注

以下のアプリケーション情報は、テキサス・インスツルメンツの製品仕様に含まれるものではなく、テキサス・インスツルメンツはその正確性も完全性も保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。また、お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 7.1 アプリケーション情報

テキサス・インスツルメンツの DLP テクノロジーは、デジタルマイクロミラー デバイス (DMD) を使用して光を変調する微小電気機械システム (MEMS) 技術です。DMD は 890 万個強のマイクロミラーを内蔵でき、さまざまな解像度とサイズで提供されています。DMD の各マイクロミラーは独立して制御され、照明装置やカメラと同期させることができます。さまざまなアプリケーションを実現できます。DLP 技術は、世界中のさまざまな産業製品を実現しています。これには、大型リソグラフィー機器に組み込まれたデジタルイメージングエンジンから、高解像度の 3D プリンティング機器までが含まれます。

テキサス・インスツルメンツの最新のチップセットは、SST という画期的なマイクロミラー技術に基づいています。5.4 $\mu\text{m}$  の小さなピクセルピッチと 12 度の傾斜角を持つ SST チップセットは、より高い解像度を小型のフォームファクタで実現し、優れた画像処理機能を提供しながら、高い光学効率を維持します。DLP チップセットは、高速変調で高解像度のプロジェクションを実現するあらゆるシステムに最適です。

### 7.2 代表的なアプリケーション

DLP991UV DMD は、4096 × 2176 の解像度を持つ DLP デジタルマイクロミラー デバイスです。TI の DLPC964 産業用コントローラおよびその他の電気的・光学的・機械的部品と組み合わせることで、DLP991UV DMD は産業用ダイレクトイメージングや 3D プリンタ用途に優れたシステムを提供します。DLP991UV DMD を使用した代表的なシングルチップシステムアプリケーションを図 7-1 に示します。

図 7-1. 代表的な DLP991UV アプリケーション図

表 7-1. DMD の概要

| DMD      | ARRAY       | 単一行のロード時間 (ns) | 単一ブロックの読み込み時間 (μs) | グローバルリセットモードフルアレイ (パターン/秒) | クワッドブロックリセットモードフルアレイ (パターン/秒) |

|----------|-------------|----------------|--------------------|----------------------------|-------------------------------|

| DLP991UV | 4096 × 2176 | 37.09          | 5.04               | 11,273                     | 12,390                        |

### 7.2.1 設計要件

高レベルでは、DLP991UV DMD システムは、照明光源、光学エンジン、電子部品、およびソフトウェアで構成されています。設計者はまず、照明光源を選定し、光学系と照明光源の関係を考慮しながら光学エンジンを設計する必要があります。次に設計者は、DMD システムにおける電子部品について理解する必要があります。アプリケーション用の PCB ボードは、DLP991UV DMD を駆動・制御するために必要なすべての電子部品をサポートしており、これには DLPC964 産業用コントローラ、電源、DMD デバイスなどが含まれます。

### 7.2.2 詳細な設計手順

DLPC964 産業用コントローラと DLP991UV DMD の間の電気接続を設計する際、お客様をサポートするために、TI はリファレンス設計の回路図およびレイアウトガイドラインを提供しています。信頼性の高いプロジェクトサブシステムを実現するために、これらのガイドラインに従うことを推奨します。DLP システムを完成させるには、DMD、関連する照明光源、光学要素、必要な機械部品、さらに推奨される熱設計の概念とガイドラインを含む光学モジュールまたはライトエンジンが必要です。

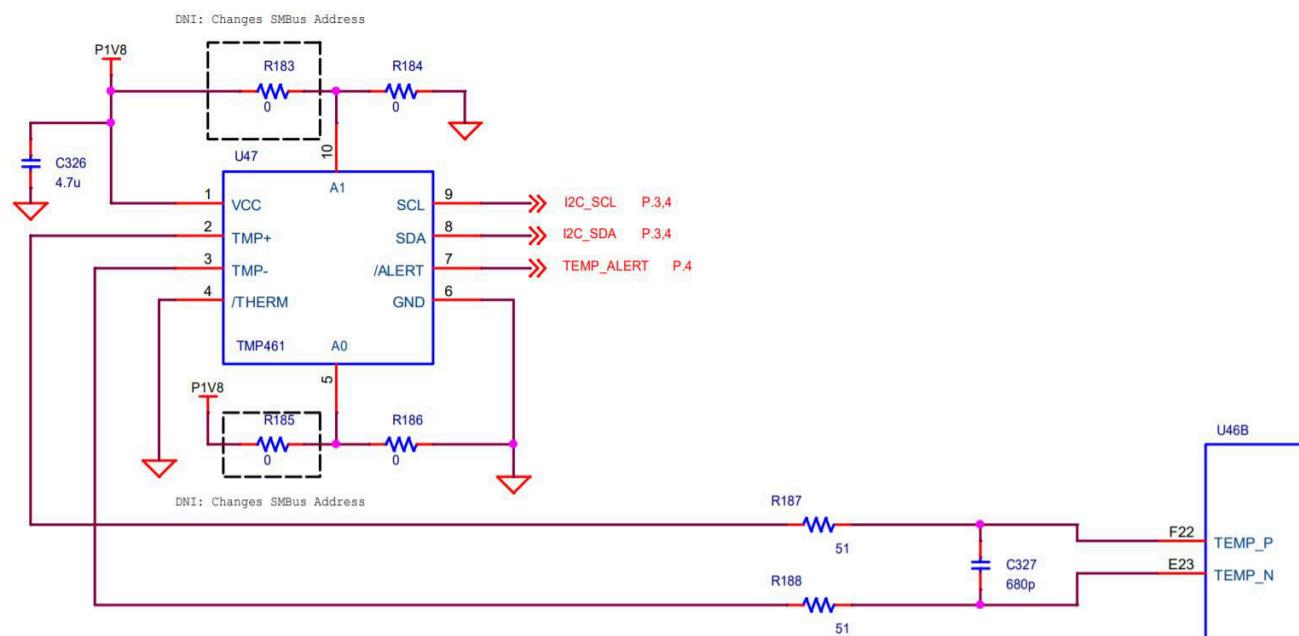

## 7.3 DMD ダイ温度センシング

DMD には、マイクロミラー アレイの外側にあるダイの一角の温度を測定するための内蔵サーマル ダイオードが搭載されています。サーマルダイオードは、図 7-2 に示すように TMP461 温度センサと接続できます。TMP461 からのシリアルバスは DLPC964 産業用コントローラに接続することで、温度検知機能を有効にできます。温度の読み取り値を照会する方法の詳細については、『[DLPC964 産業用コントローラのデータシート](#)』を参照してください。

DLPC964 インダストリアル コントローラは、TMP461 を設定して DMD 温度センサ ダイオードを読み取ることができます。このデータは、照明のパワー調整、ファンの回転速度、アクティブ冷却の温度や流量など、全体システム設計に追加機能を組み込むために活用できます。I<sup>2</sup>C インターフェイスを使用して、TMP461 と DLPC964 コントローラ間のすべての通信を完了します。[ピン構成および機能](#)に概要を示したように、TMP461 はピン E23 と F22 を経由して DMD に接続されます。

図 7-2. 温度センサのシステム基板の配線例

- わかりやすくするために、詳細は省略しています。DLPC964 産業用コントローラへの接続については、TI リファレンス デザインを参照してください。

- システム基板レイアウトの推奨事項については、『[TMP461 高精度、リモートおよびローカル温度センサ、ピンプログラマブルバスアドレス付きデータシート](#)』を参照してください。

- R1、R2、R3、R4、C1 の推奨部品の値については、『[TMP461 高精度、リモートおよびローカル温度センサ、ピンプログラマブルバスアドレス付きデータシート](#)』および TI のリファレンスデザインを参照してください。

- R5 = 0Ω。R6 = 0Ω。0 Ω の抵抗は、DMD パッケージのピンの近くに配置する必要があります。

## 8 電源に関する推奨事項

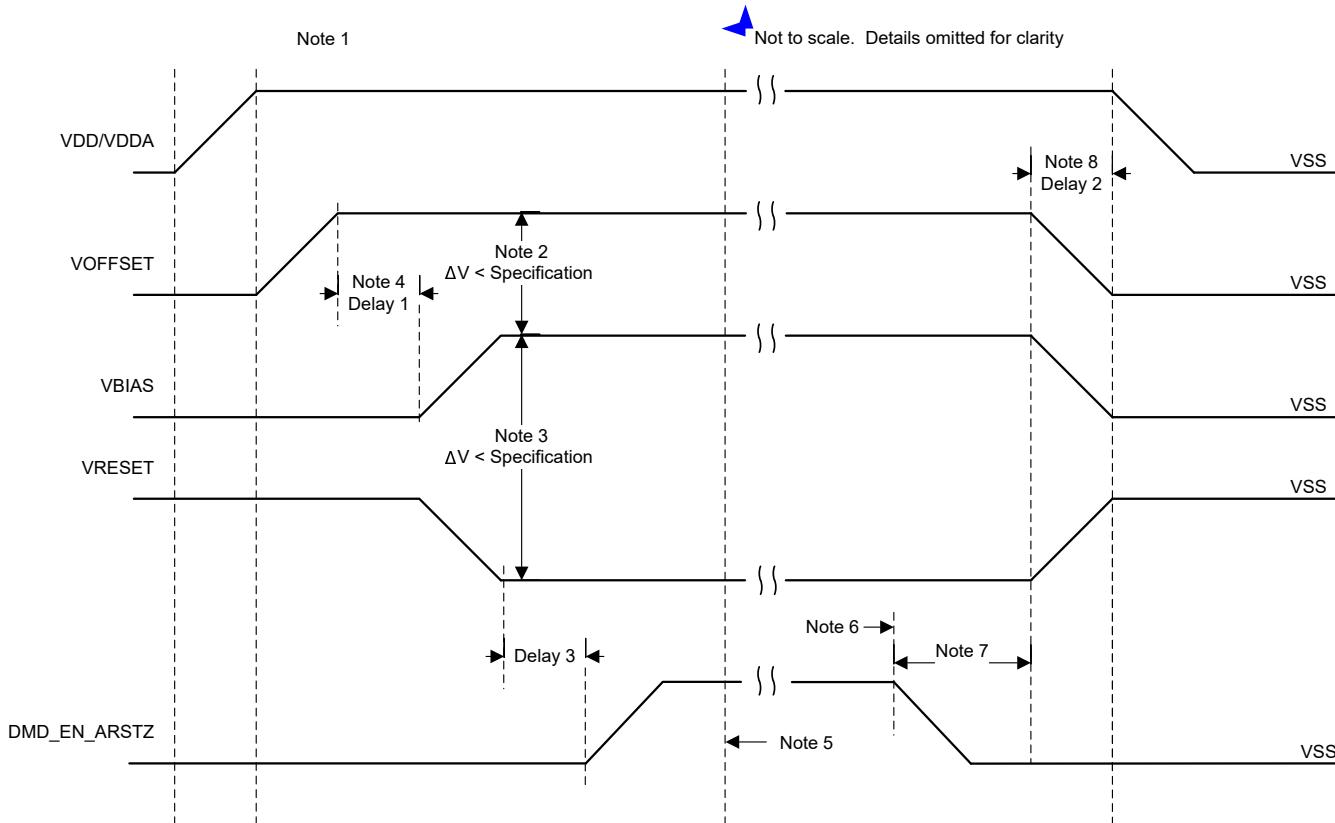

DMD の動作には、以下の電源装置がすべて必要です。 $V_{DD}$ 、 $V_{DDA}$ 、 $V_{BIAS}$ 、 $V_{OFFSET}$  および  $V_{RESET}$ 。DMD のパワーアップ / パワーダウンシーケンシングは、DLP ディスプレイコントローラによって厳密に制御されます。

### 注

DMD を確実に動作させるには、以下の電源シーケンシング要件に従う必要があります。規定されたパワーアップおよびパワーダウン要件のいずれかに準拠しない場合、デバイスの信頼性に影響を及ぼす可能性があります。DMD 電源シーケンシング要件を参照してください。

$V_{DD}$ 、 $V_{DDA}$ 、 $V_{BIAS}$ 、 $V_{OFFSET}$ 、 $V_{RESET}$  電源をパワーアップおよびパワーダウン動作時に調整する必要があります。以下の各要件のいずれかに適合していない場合、DMD の信頼性と寿命が大幅に低下します。共通のグランド  $VSS$  も接続する必要があります。

**表 8-1. 電源シーケンス要件**

| 記号           | パラメータ   | 説明                                        | 最小値 | 標準値 | 最大値 | 単位 |

|--------------|---------|-------------------------------------------|-----|-----|-----|----|

| $t_{DELAY}$  | 遅延要件    | $V_{OFFSET}$ パワーアップから $V_{BIAS}$ パワーアップまで | 2   |     |     | ms |

| $V_{OFFSET}$ | 電源電圧レベル | パワーアップ シーケンスの遅延の開始時 <sup>(1)</sup>        |     | 6   |     | V  |

| $V_{BIAS}$   | 電源電圧レベル | パワーアップ シーケンスの遅延の終了時 <sup>(1)</sup>        |     | 6   |     | V  |

(1) 「シーケンスの遅延の要件」を参照してください。

### 8.1 DMD 電源のパワーアップ手順

- パワーアップ時には常に、 $V_{OFFSET}$  に表 8-2 で指定された Delay1 を加えた電圧、 $V_{BIAS}$ 、および  $V_{RESET}$  電圧が DMD に印加される前に、 $V_{DD}$  および  $V_{DDA}$  が起動および安定する必要があります。

- パワーアップ時には、 $V_{BIAS}$  と  $V_{OFFSET}$  の電圧差が、セクション 5.4 に示される指定限界内でなければならないという厳しい要件があります。

- パワーアップ中、 $V_{BIAS}$  を基準とした  $V_{RESET}$  の相対タイミングは不要です。

- 過渡電圧レベルが、セクション 5.1、セクション 5.4 で規定されている要件に従えば、パワーアップ時の電源スルーレートを柔軟に設定できます。

- パワーアップ時には、 $V_{DD}$  および  $V_{DDA}$  がセクション 5.4 に記載されている動作電圧まで安定するまで、LVCMOS 入力ピンを High にしないでください。

### 8.2 DMD 電源のパワーダウン手順

- パワーダウン時には、 $V_{BIAS}$ 、 $V_{RESET}$ 、および  $V_{OFFSET}$  がグランドの指定限界内で放電されるまで、 $V_{DD}$  および  $V_{DDA}$  を供給する必要があります。表 8-2 を参照してください。

- パワーダウン時には、 $V_{BIAS}$  と  $V_{OFFSET}$  の電圧デルタが、セクション 5.4 に示される指定限界内でなければならないという厳しい要件があります。

- パワーダウン中、 $V_{BIAS}$  を基準とした  $V_{RESET}$  の相対タイミングは不要です。

- 過渡電圧レベルが、セクション 5.1、セクション 5.4 で規定されている要件に従えば、パワーダウン時の電源スルーレートを柔軟に設定できます。

- パワーダウン時は、LVCMOS 入力ピンをセクション 5.4 で規定されている値未満にする必要があります。

図 8-1. DMD 電源要件

1. ピン構成および機能を参照してください。

2. 過剰な電流を防止するため、電源電圧のデルタ  $|V_{BIAS} - V_{OFFSET}|$  は、セクション 5.4 で指定されている限界値よりも小さい必要があります。

3. 過剰な電流を防止するため、電源電圧のデルタ  $|V_{BIAS} - V_{RESET}|$  は、セクション 5.4 の指定限界値よりも小さい必要があります。

4.  $V_{BIAS}$  は、 $V_{OFFSET}$  がパワーアップした後に、表 8-2 の Delay1 仕様に従ってパワーアップする必要があります。

5. DLP コントローラソフトウェアにより、グローバル  $V_{BIAS}$  コマンドが開始されます。

6. DMD のマイクロミラー パーク シーケンスの完了後、DLP コントローラソフトウェアはハードウェアパワーダウンを開始し、 $DMD\_EN\_ARSTZ$  を有効にして、 $V_{BIAS}$ 、 $V_{RESET}$ 、 $V_{OFFSET}$  を無効化します。

7. 電力損失条件下で、DLP コントローラのハードウェア  $DMD\_EN\_ARSTZ$  によって緊急 DMD マイクロミラー パーク手順が実行されている場合は、Low になります。

8. 表 8-2 の Delay2 仕様に準拠して、 $V_{OFFSET}$ 、 $V_{BIAS}$ 、および  $V_{RESET}$  が Low になるまで、 $V_{DD}$  は High に維持する必要があります。

9. 過剰な電流を防止するため、電源電圧のデルタ  $|V_{DDA} - V_{DD}|$  は、セクション 5.4 の指定限界値よりも小さい必要があります。

表 8-2. DMD 電源要件

| パラメータ  | 説明                                                                                   | 最小値 | 公称値 | 最大値 | 単位 |

|--------|--------------------------------------------------------------------------------------|-----|-----|-----|----|

| Delay1 | $V_{OFFSET}$ が推奨動作電圧で安定してから、 $V_{BIAS}$ および $V_{RESET}$ のパワーアップまでの遅延                 | 1   | 2   |     | ms |

| Delay2 | $V_{OFFSET}$ 、 $V_{BIAS}$ 、および $V_{RESET}$ のパワーダウンから遅延 $V_{DD}$ を High に保持する必要があります。 | 50  |     |     | μs |

| Delay3 | $V_{BIAS}$ および $V_{RESET}$ が推奨動作電圧で安定してから、 $DMD\_EN\_ARSTZ$ がアサートされるまでの遅延。           | 20  |     |     | μs |

## 9 レイアウト

### 9.1 レイアウトのガイドライン

これらのガイドラインは、DLP991UV DMD を使用した PCB 基板の設計を対象としています。DMD 基板は、高速デジタルロジックを主体とした高速多層 PCB で、DMD まで接続される 3.6Gbps の差動データバスを含みます。TI は、 $V_{OFFSET}$ 、 $V_{RESET}$ 、および  $V_{BIAS}$  には、フルまたはミニ電源プレーンを使用することを推奨しています。グランドにはソリッドプレーンが必要です。表 9-2 に示すように、PCB 上のシングルエンドトレースの目標インピーダンスは、差動トレースの場合  $50\Omega \pm 10\%$  および  $100\Omega \pm 10\%$  です。TI では、高品質の FR-4 材料を使用して PCB を製造することを推奨します。

#### 9.1.1 PCB 設計規格

業界設計仕様に示す業界仕様に従って PCB を設計および構築します。

**表 9-1. 業界設計仕様**

| 業界仕様                                        | 適用           |

|---------------------------------------------|--------------|

| IPC-2221 および IPC-2222、クラス 2、レベル B の製造容易性に準拠 | ボード設計        |

| IPC-6011 および IPC-6012、クラス 2                 | PWB 製造       |

| IPC-SM-840、クラス 3                            | PWB 半田マスクを完成 |

| UL94V-0 可燃性定格およびマーキング                       | 完成 PWB       |

| UL796 定格およびマーキング                            | 完成 PWB       |

#### 9.1.2 一般的な PCB 配線

##### 9.1.2.1 パターンのインピーダンスと配線の優先度

TI は、最高の性能を得るために、単端信号に対して PCB の目標インピーダンスを  $50\Omega \pm 10\%$  にすることを推奨しています。 $100\Omega \pm 10\%$  の差動信号については、表 9-2 を参照してください。

**表 9-2. パターンのインピーダンス**

| 信号                                                                    | 差動インピーダンス      |

|-----------------------------------------------------------------------|----------------|

| HSSI DMD インターフェイス - DMD_D_(A, B, C, D)[7:0],<br>DMD_DCLK_(A, B, C, D) | $100\Omega$ 差動 |

| DMD LS インターフェイス - DMD_LS_CLK, DMD_LS_WDATA                            | $100\Omega$ 差動 |

表 9-3 に、信号の配線優先度を示します。

**表 9-3. ルーティングの優先度**

| 信号                                                                    | 優先順位 |

|-----------------------------------------------------------------------|------|

| HSSI DMD インターフェイス - DMD_D_(A, B, C, D)[7:0],<br>DMD_DCLK_(A, B, C, D) | 1    |

| DMD LS インターフェイス - DMD_LS_CLK, DMD_LS_WDATA                            | 2    |

| 他のすべての信号                                                              | 3    |

##### 9.1.2.2 PCB 層構成の例

システムの設計要件を満たすため、PCB 層の設計に細心の注意を払う必要があります。表 9-4 は、PCB スタックアップの例を示します。HSSI DMD 入力インターフェイスを構成する高速差動信号の信号整合性を最大化するために、差動信号は内部層に配線され、安定したグランドプレーンを基準として配置されています。DMD ボードの信号整合性をさらに向上させるために、HSSI DMD 入力インターフェースの性能を高める目的で、信号の立ち上がり速度を改善できる誘電体材料として Nelco N4000-13 SI が使用されています。

**表 9-4. PCB 層構成の例**

| レイヤ番号 | レイヤ名                         | 銅の重量                       | 備考                                                                                                                     |

|-------|------------------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------|

| 1     | サイド A - 主要コンポーネント            | 1/2 oz (メッキ前)              | 電源回路やデータ入力コネクタを含む上面のコンポーネント。低周波信号の配線取り回し。銅箔 (GND) の厚さを最大 1oz にメッキすることを希望します。#2 層のインピーダンスリファレンス。                        |

| 2     | 信号 (高周波)                     | 1/2 オンス                    | 高速信号層。入力コネクタから DMD への高速差動データバス。データラインは、第 1 層のグランドプレーンの下に保持されます。                                                        |

| 3     | グランド                         | 1/2 オンス                    | 信号層 #2 および #4 に対するリファレンスとしてのソリッドグランドプレーン (GND ネット)                                                                     |

| 4     | 信号 (高周波)                     | 1/2 オンス                    | 高速信号層。入力コネクタから DMD への高速差動データバス                                                                                         |

| 5     | グランド                         | 1/2 オンス                    | 信号層 #4, #6 のソリッドグランドプレーン (ネット GND) リファレンス                                                                              |

| 6     | 信号 (高周波)                     | 1/2 オンス                    | 高速信号層。入力コネクタから DMD への高速差動データバス                                                                                         |

| 7     | グランド                         | 1/2 オンス                    | 信号層 #6, 8 のソリッドグランドプレーン (ネット GND) のリファレンス                                                                              |

| 8     | サイド B - DMD、電源プレーン、および 2 次部品 | 1/2 oz (メッキ前) <sup>1</sup> | DMD とエスケープデータ入力コネクタ。1.8V, 3.3V, 10V, -14V, 18V 用の 1 次側分割電源プレーン。必要に応じて個別部品を使用。低周波信号の配線取り回し。銅箔の厚さを最大 1oz にメッキすることを希望します。 |

1. DLP991UV DMD の機械的 ICD 図面に記載されているとおり、DMD デバイスのパッドは、30 マイクロインチ以上の電解金の下に、50 ~ 100 マイクロインチの電解ニッケルでメッキされている必要があります。

### 9.1.2.3 パターン幅、間隔

特に指定がない限り、TI はすべての信号が 0.005 インチ/0.0015 インチ (トレース幅/スペーシング) の設計ルールに従うことを推奨しています。インピーダンスおよびスタックアップ要件の分析を使用して、実際のトレース幅を決定し、計算します。

スペースが許す限り、すべての電圧信号の幅を最大化します。

表 9-5 および表 9-6 に記載されている幅と間隔の要件に従ってください。

**表 9-5. パターンの最小間隔**

| 信号                                                                          | PWR | GND | シングル エンド           | 差動ペア               | 単位 |

|-----------------------------------------------------------------------------|-----|-----|--------------------|--------------------|----|

|                                                                             |     |     |                    | ペアツーペア             |    |

| PWR                                                                         | 15  | 5   | 15                 | 15                 | ミル |

| GND                                                                         | 5   |     | 5                  | 5                  | ミル |

| HSSI DMD インターフェイス -<br>DMD_D_(A, B, C, D)[7:0],<br>DMD_DCLK_(A, B, C, D),   | 15  | 5   | 3x ペア内 (P-to-N) 間隔 | 3x ペア内 (P-to-N) 間隔 | ミル |

| DMD LS インターフェイス -<br>DMD_LS_CLK, DMD_LS_WDATA,<br>DMD_LS_RDATA_(A, B, C, D) | 15  | 5   | トレース幅の 3 倍         | 3x ペア内 (P-to-N) 間隔 | ミル |

| 他のすべての信号                                                                    | 15  | 5   | トレース幅の 3 倍         | 3x ペア内 (P-to-N) 間隔 | ミル |

**表 9-6. 電圧パターンの幅と間隔に関する推奨事項**