**DDC112**

JAJS210

# デュアル電流入力 20ビット AD コンバータ

# 特長

- モノリシック電荷測定 AD コンバータ

- デジタル・フィルタによるノイズ低減:3.2ppm、RMS

- 積分直線性:±0.005% Reading ±0.5ppm FSR

- 高精度真の積分機能

- プログラマブル・フルスケール

- 単電源

- カスケード可能出力

# アプリケーション

- ダイレクト 光センサ・デジタル変換

- CT スキャナ DAS

- 赤外線パイロメータ

米国特許 #5841310 による保護対象

- 高精度プロセス制御

- 液体/ガスクロマトグラフィ

- 血液分析

# 概要

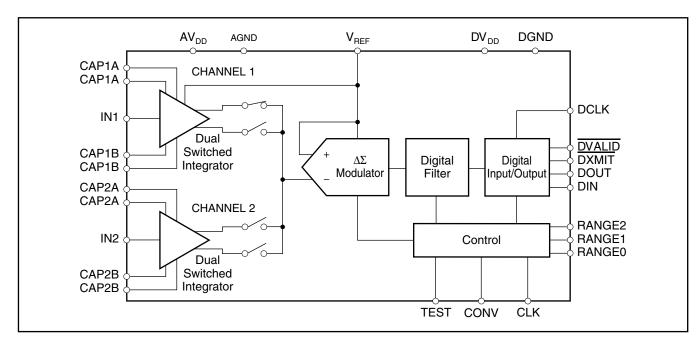

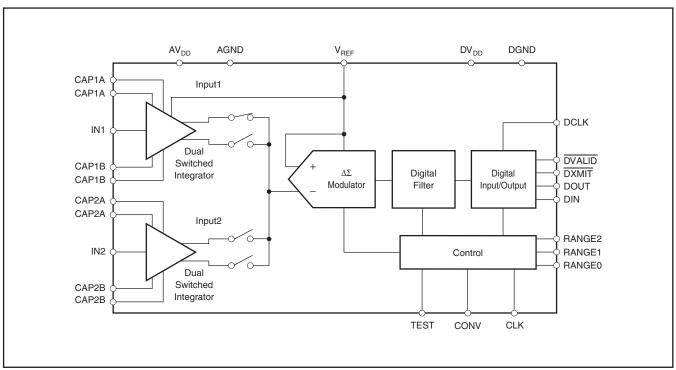

DDC112は、デュアル入力、広ダイナミック・レンジ、電荷デジタイジングの分解能20ビットのADコンバータです。また、光センサ等の低電流出力デバイスを、ADコンバータ入力に直接接続可能です。各入力に2つの積分器を持ち、一方がデジタル変換中に他方が積分を行う為、電荷積分は連続して行います。

高精度/高ダイナミックレンジのデジタル出力を得るため、2 入力のそれぞれについてDDC112は、電流/電圧変換、連続積分、プログラマブルなフルスケール・レンジ、AD変換、およびデジタルフィルタなどの機能を組み合わせています。プログラマブルな内蔵フルスケール・レンジに加え、外付けの積分コンデンサを使用する事により最大1000pCの、ユーザー・プログラマブルなフルスケール・レンジが可能です。

すべての商標および登録商標は、それぞれの所有者に帰属します。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ (日本TI) が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。 日本TIによる和文資料は、あくまでもTI正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料を ご確認下さい。

TIおよび日本TIは、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如

何なる責任も負いません。

SBAS085B 翻訳版

単電源動作を実現するため、内蔵ADコンバータは差動入力となっており、正入力は $V_{REF}$ に接続されています。各積分サイクルの初期のリセット区間で、積分コンデンサは $V_{REF}$ に充電されます。この電荷は、入力電流に比例して放電され、積分サイクルの終了時、残電圧が $V_{REF}$ と比較されます。

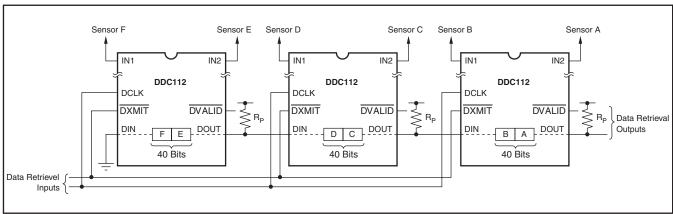

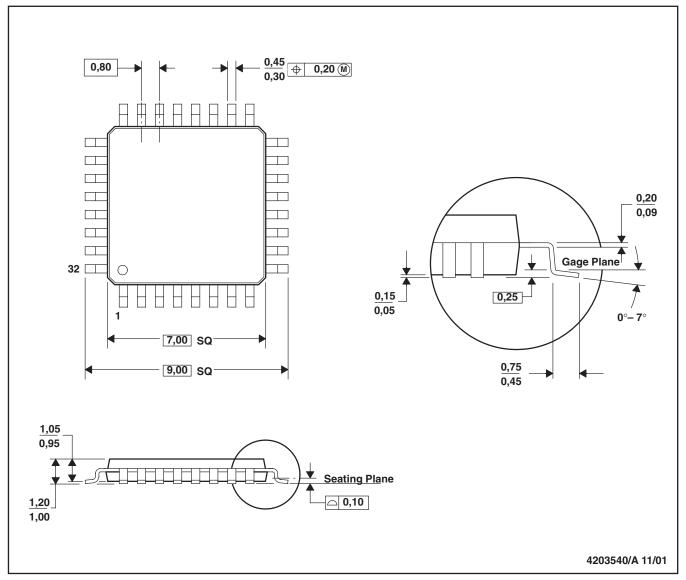

直前の変換結果を保持する高速シリアル・シフト・レジスタは、複数のDDC112ユニットのカスケード構成が可能で、相互接続線数を最小限とします。DDC112は、SO-28またはTQFP-32パッケージで供給され、2つの性能グレードがあります。

# 静電気放電対策

これらのデバイスは、限定的なESD(静電破壊)保護機能を 内蔵しています。保存時または取り扱い時に、MOSゲートに 対する静電破壊を防止するために、リード線どうしを短絡して おくか、デバイスを伝導性のフォームに入れる必要があります。

#### 絶対最大定格(1)

| $AV_{DD} \sim DV_{DD}$          | -0.3V ∼ +6V                    |

|---------------------------------|--------------------------------|

|                                 |                                |

| AV <sub>DD</sub> ~ AGND         | −0.3V ~ +6V                    |

| DV <sub>DD</sub> ~ DGND         | −0.3V ~ +6V                    |

| AGND ~ DGND                     | ±0.3V                          |

| V <sub>REF</sub> 電圧 ~ AGND      | $-0.3V \sim AV_{DD} + 0.3V$    |

| デジタル入力 ~ DGND                   | −0.3V ~ DVDD + 0.3V            |

| デジタル出力 ~ DGND                   | −0.3V ~ DVDD + 0.3V            |

| パッケージ許容損失                       | $(T_{JMAX} - T_A)/\theta_{JA}$ |

| 最大ジャンクション温度(T <sub>JMAX</sub> ) | +150°C                         |

| 熱抵抗、SO、θ <sub>JA</sub>          | +150°C/W                       |

| 熱抵抗、TQFP、θ <sub>JA</sub>        | +100°C/W                       |

| 端子温度(半田付け、10秒)                  | +300°C                         |

<sup>- (1)</sup> 絶対最大定格を超えるストレスは、デバイスに永久的な損傷を与えます。 絶対最大定格の状態で長時間動作させると、デバイスの信頼性が低下します。 これはストレスの定格のみについて示してあり、規定された値で、またはこれらの値を越える状態での本製品の機能動作を意味するものではありません。

#### 製品情報(1)

| 製品名      | 最大積分直線性誤差               | 規定温度範囲        | パッケージ   | パッケージ・コード | 製品型番 <sup>(2)</sup> | 出荷形態    |

|----------|-------------------------|---------------|---------|-----------|---------------------|---------|

| DDC112U  | ±0.025% Reading 1.0ppm  | –40° ∼ +85°C  | SO-28   | DW        | DDC112U             | レール     |

| DDC1120  | FSR±                    | _40 · 9 +65 C | 30-28   | DVV       | DDC112U/1K          | テープ・リール |

| DDC112UK | ±0.025% Reading ±1.0ppm | 0°C ∼ +70°C   | SO-28   | DW        | DDC112UK            | レール     |

| DDC1120K | FSR                     | 0 0 ~ +70 0   | 50-28   |           | DDC112UK/1K         | テープ・リール |

| DDC112Y  | ±0.025% 読み取り値           | –40° ∼ +85°C  | TQFP-32 | PJT       | DDC112Y/250         | テープ・リール |

| DDC1121  | ±1.0ppm FSR             | -40 ~ +65 C   | TQFF-32 |           | DDC112Y/2K          | テープ・リール |

| DDC112YK | ±0.025% Reading ±1.0ppm | 0°C ∼ +70°C   | TQFP-32 | PJT       | DDC112YK/250        | テープ・リール |

| DDCTIZIK | FSR                     | 0 0 ~ +70 0   | 1077-32 |           | DDC112YK/2K         | テープ・リール |

<sup>(1)</sup> 最新のパッケージ情報と発注情報については、このデータシートの末尾にある「付録:パッケージ・オプション」を参照するか、www.ti.comまたは www.tij.co.jp にあるTI のWeb サイトを参照してください。

<sup>(2)</sup> テープ・リールの形態で供給されるスラッシュ (/) の付いたモデルは、表示の数量 ( $\lceil$ /1K $\rfloor$ はリールあたり1,000 個のデバイス) で供給されます。 DDC112U/1Kにて1,000個を注文すると、1,000個巻のリールが1点出荷されます。

# 電気的特性

特記のない限り、 $T_A=+25^{\circ}$ C、A $V_{DD}=DV_{DD}=+5V$ 、(DDC112U、Y:  $T_{INT}=500\mu s$ 、CLK = 10MHz)、 (DDC112UK、YK:  $T_{INT}=333.3\mu s$ 、CLK = 15MHz)、 $V_{REF}=+4.096V$ 、連続モード動作、および内蔵積分コンデンサ使用。

| パラメータ                                                | DDC112U、Y                                              |       | J、Y                             | DDC112UK、YK      |        |                                 | 当位               |                                   |

|------------------------------------------------------|--------------------------------------------------------|-------|---------------------------------|------------------|--------|---------------------------------|------------------|-----------------------------------|

| 773-9                                                | 条件                                                     | MIN   | TYP                             | MAX              | MIN    | TYP                             | MAX              | 単位                                |

| アナログ入力                                               |                                                        |       |                                 |                  |        |                                 |                  |                                   |

| 外部、+側フルスケール                                          |                                                        |       |                                 |                  |        |                                 |                  |                                   |

| レンジ 0                                                | $C_{EXT} = 250pF$                                      |       |                                 | 1000             |        |                                 | 1000             | pC                                |

| 内蔵、+側フルスケール                                          |                                                        |       |                                 |                  |        |                                 |                  |                                   |

| レンジ 1                                                |                                                        | 47.5  | 50                              | 52.5             | 47.5   | 50                              | 52.5             | pC                                |

| レンジ 2                                                |                                                        | 95    | 100                             | 105              | 95     | 100                             | 105              | pC                                |

| レンジ3                                                 |                                                        | 142.5 | 150                             | 157.5            | 142.5  | 150                             | 157.5            | pC                                |

| レンジ 4                                                |                                                        | 190   | 200                             | 210              | 190    | 200                             | 210              | pC                                |

| レンジ 5                                                |                                                        | 237.5 | 250                             | 262.5            | 237.5  | 250                             | 262.5            | pC                                |

| レンジ 6                                                |                                                        | 285   | 300                             | 315              | 285    | 300                             | 315              | pC                                |

| レンジ 7                                                |                                                        | 332.5 | 350                             | 367.5            | 332.5  | 350                             | 367.5            | pC                                |

| -側フルスケール入力                                           |                                                        | +フル   | スケール                            | の -0.4%          | +フル    | スケール                            | の -0.4%          | pC                                |

| ダイナミック特性                                             |                                                        |       |                                 |                  |        |                                 |                  |                                   |

| 変換レート                                                |                                                        |       |                                 | 2                |        |                                 | 3                | kHz                               |

| 積分時間、T <sub>INT</sub>                                | 連続モード                                                  | 500   |                                 | 1,000,000        | 333.3  |                                 | 1,000,000        | μs                                |

| 積分時間、T <sub>INT</sub>                                | 不連続モード                                                 | 50    |                                 |                  | 50     |                                 |                  | μs                                |

| システム・クロック<br>入力(CLK)                                 |                                                        | 1     | 10                              | 12               | 1      | 10                              | 15               | MHz                               |

| データ・クロック(DCLK)                                       |                                                        |       |                                 | 12               |        |                                 | 15               | MHz                               |

| 精度                                                   |                                                        |       |                                 |                  |        |                                 |                  |                                   |

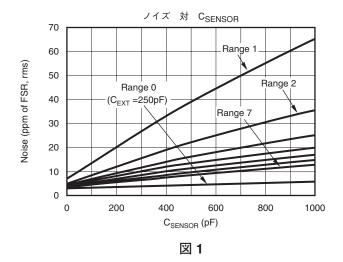

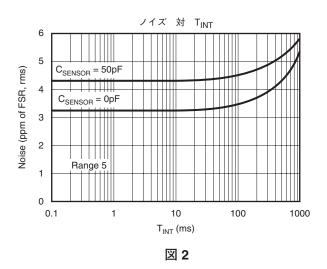

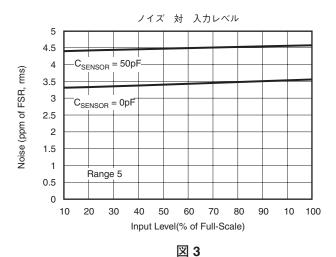

| ノイズ、<br>  "Low" レベルの電流入力 <sup>(1)</sup>              | C <sub>SENSOR</sub> <sup>(2)</sup> = 0pF レンジ 5 (250pC) |       | 3.2                             |                  |        | 3.2                             |                  | ppm of FSR, <sup>(3)</sup><br>rms |

|                                                      | C <sub>SENSOR</sub> = 25pF レンジ5 (250pC)                |       | 3.8                             |                  |        | 3.8                             |                  | ppm of FSR,<br>rms                |

|                                                      | C <sub>SENSOR</sub> = 50pF レンジ5 (250pC)                |       | 4.2                             | 6.0              |        | 4.2                             | 7                | ppm of FSR,<br>rms                |

| 微分直線性誤差                                              |                                                        |       | '<br>% Readin<br>FSR(M <i>F</i> | g ±0.5ppm<br>AX) |        | '<br>% Readin<br>FSR(M <i>A</i> | g ±0.5ppm<br>AX) |                                   |

| 積分直線性誤差(4)                                           |                                                        |       | % Readin                        | g ±0.5ppm<br>P)  | ±0.005 | % Readin<br>FSR(TY              | g ±0.5ppm<br>P)  |                                   |

|                                                      |                                                        |       | % Readin                        | g ±1.0ppm<br>X)  | ±0.025 | % Readin<br>FSR(M               | g ±1.0ppm<br>AX) |                                   |

| ノー・ミッシング・コード                                         |                                                        |       | 20                              |                  |        | 20                              |                  | Bits                              |

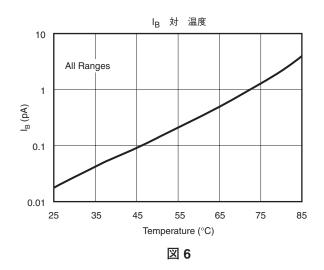

| 入力バイアス電流                                             | $T_A = +25^{\circ}C$                                   |       | 0.1                             | 10               |        | 0.1                             | 10               | pA                                |

| レンジ誤差                                                | レンジ 5 (250pC)                                          |       |                                 | 5                |        |                                 | 5                | % of FSR                          |

| レンジ誤差 マッチング <sup>(5)</sup>                           | 全レンジ                                                   |       | 0.1                             | 0.5              |        | 0.1                             | 0.5              | % of FSR                          |

| V <sub>REF</sub> に対するレンジ感度                           | $V_{REF} = 4.096 \pm 0.1 V$                            |       | 1:1                             |                  |        | 1:1                             |                  |                                   |

| オフセット誤差                                              | レンジ 5、 (250pC)                                         |       | ±200                            |                  |        | ±200                            | ±600             | ppm of FSR                        |

| オフセット誤差の<br>マッチング <sup>(5)</sup>                     |                                                        |       | ±100                            |                  |        | ±100                            |                  | ppm of FSR                        |

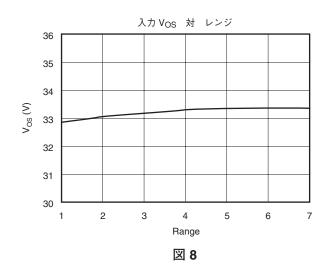

| DC バイアス電圧 <sup>(6)</sup><br>(Input V <sub>OS</sub> ) |                                                        |       | ±0.05                           | ±2               |        | ±0.05                           | ±2               | mV                                |

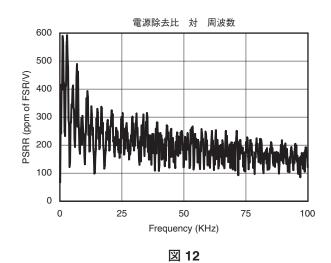

| 電源除去比                                                |                                                        |       | ±25                             | ±200             |        | ±25                             | ±200             | ppm of FSR                        |

| 内蔵テスト信号                                              |                                                        |       | 13                              |                  |        | 13                              |                  | pC                                |

| 内蔵テストの精度                                             |                                                        |       | ±10                             |                  |        | ±10                             |                  | %                                 |

- (1) フルスケールの1%以下入力時。

(2) CSENSORは、フォトダイオード/結線側からみたDDC112の入力容量です。

(3) FSRは、フルスケール範囲(Full-Scale Range)です。

(4) 直線性の測定には、近似直線を使用しました。

(5) A側/B側のマッチング。入力1/入力2ではありません。

(6) DDC112の入力側でDDC112によって生成される電圧であり、センサに対してこれが印加されます。

# 電気的特性

特記のない限り、T<sub>A</sub> = +25°C、AV<sub>DD</sub> = DV<sub>DD</sub> = +5V、(DDC112U、Y: T<sub>INT</sub> = 500μs、CLK = 10MHz)、 (DDC112UK、YK:T<sub>INT</sub> = 333.3μs、CLK = 15MHz)、V<sub>REF</sub> = +4.096V、連続モード動作、および内蔵積分コンデンサ使用。

| パラメータ                             | 条件                                    |       | DDC112U | 、 Y                     | DDC112UK、YK |       |                        | *** (-            |

|-----------------------------------|---------------------------------------|-------|---------|-------------------------|-------------|-------|------------------------|-------------------|

| ハラメータ                             | <b>余</b> 什                            | MIN   | TYP     | MAX                     | MIN         | TYP   | MAX                    | 単位                |

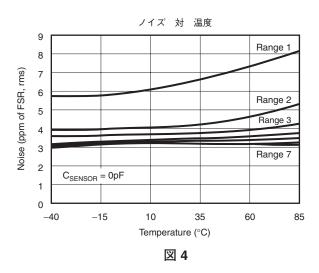

| 温度特性                              |                                       |       |         |                         |             |       |                        |                   |

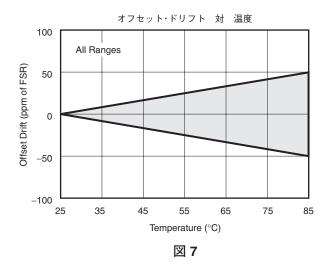

| オフセット・ドリフト                        |                                       |       | ±0.5    |                         |             |       | ±3 <sup>(7)</sup>      | ppm of<br>FSR/°C  |

| オフセット・ドリフト安定性                     |                                       |       | ±0.2    |                         |             | ±0.2  | ±0.7 <sup>(7)</sup>    | ppm of<br>FSR/min |

| DC バイアス電圧ドリフト                     | センサ入力に重畳                              |       | 3       |                         |             | 1±    |                        | μV/°C             |

| 入力バイアス電流ドリフト                      | +25°C ∼ +45°C                         |       | 0.01    | <b>1</b> <sup>(7)</sup> |             | 0.01  | 1 <sup>(7)</sup>       | pA/°C             |

| 入力バイアス電流                          | T <sub>A</sub> = +75°C                |       | 2       | 50 <sup>(7)</sup>       |             | 2     | 50 <sup>(7)</sup>      | pA                |

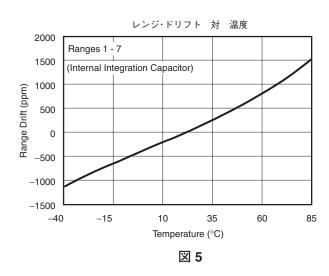

| レンジ・ドリフト <sup>(8)</sup>           | レンジ 5(250pC)                          |       | 25      |                         | 0           | 25    | 50 <sup>(7)</sup>      | ppm/°C            |

| レンジ・ドリフト・<br>マッチング <sup>(5)</sup> | レンジ 5(250pC)                          |       | ±0.05   |                         |             | ±0.05 |                        | ppm/°C            |

| リファレンス                            |                                       |       |         |                         |             |       |                        |                   |

| 電圧                                |                                       | 4.000 | 4.096   | 4.200                   | 4.000       | 4.096 | 4.200                  | V                 |

| 入力電流 <sup>(9)</sup>               | T <sub>INT</sub> = 500μs              |       | 150     |                         |             | 225   | 275                    | μΑ                |

| デジタル入出力                           |                                       |       |         |                         |             |       |                        |                   |

| ロジック・レベル                          |                                       |       |         |                         |             |       |                        |                   |

| V <sub>IH</sub>                   |                                       | 4.0   |         | DV <sub>DD</sub> + 0.3  | 4.0         |       | DV <sub>DD</sub> + 0.3 | V                 |

| V <sub>IL</sub>                   |                                       | -0.3  |         | +0.8                    | -0.3        |       | +0.8                   | V                 |

| V <sub>OH</sub>                   | $I_{OH} = -500 \mu A$                 | 4.5   |         |                         | 4.5         |       |                        | V                 |

| V <sub>OL</sub>                   | I <sub>OL</sub> = 500μA               |       |         | 0.4                     |             |       | 0.4                    | V                 |

| 入力電流、I <sub>IN</sub>              |                                       | -10   |         | +10                     | -10         |       | +10                    | μΑ                |

| データ形式 <sup>(10)</sup>             |                                       | スト    | レート・バ   | イナリ                     | ストレート・バイナリ  |       | イナリ                    |                   |

| 電源                                |                                       |       |         |                         |             |       |                        |                   |

| 電源電圧                              | AV <sub>DD</sub> および DV <sub>DD</sub> | 4.75  |         | 5.25                    | 4.75        |       | 5.25                   | V                 |

| 供給電流                              |                                       |       |         |                         |             |       |                        |                   |

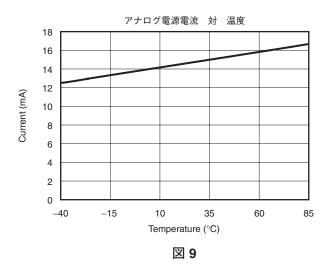

| アナログ電流                            | $AV_{DD} = +5V$                       |       | 14.8    |                         |             | 15.2  |                        | mA                |

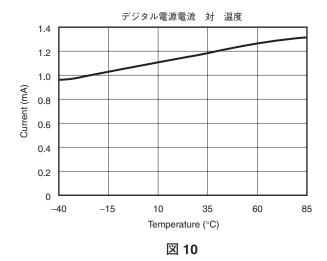

| デジタル電流                            | $DV_{DD} = +5V$                       |       | 1.2     |                         |             | 1.8   |                        | mA                |

| 全消費電力                             |                                       |       | 80      | 100                     |             | 85    | 130                    | mW                |

| 温度範囲                              |                                       |       |         |                         |             |       |                        |                   |

| 規定                                |                                       | -40   |         | +85                     | 0           |       | +70                    | °C                |

| 保存                                |                                       | -60   |         | +100                    | -60         |       | +100                   | °C                |

- (7) 設計にて検証、実デバイス・テストではありません。

(8) レンジ・ドリフトは、外部基準電圧ドリフトを含みません。

(9) T<sub>INT</sub>が大きくなるに従って、入力基準の電流は小さくなります(「電圧リファレンス」セクションを参照)。

(10) データ形式はストレート・バイナリで、わずかなオフセットが存在します(「データ取得」セクションを参照)。

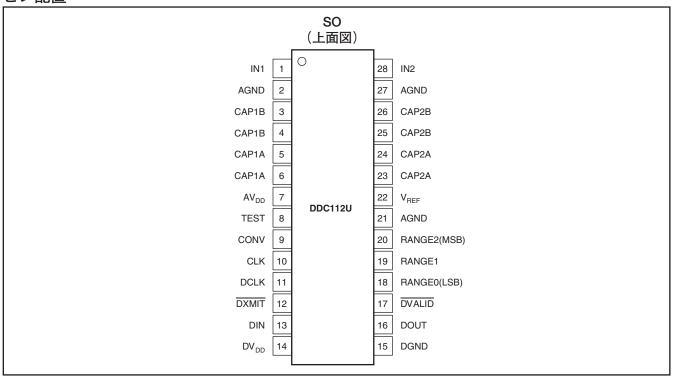

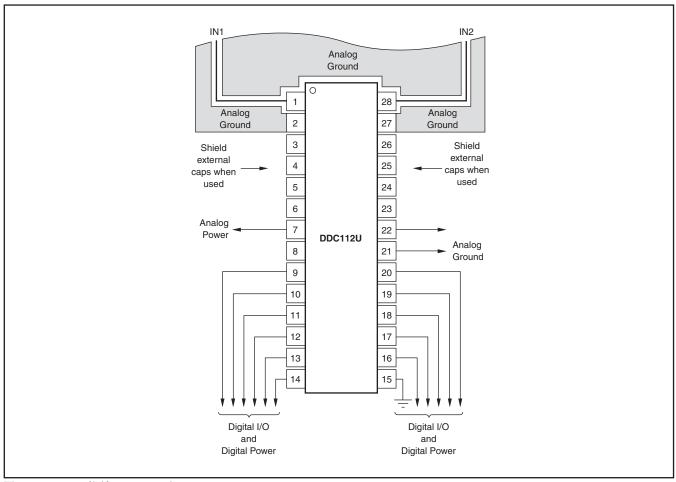

# ピン配置

# 端子機能 (DDC112U)

| ピン番号 | 名称               | 説明                                                                                                               |

|------|------------------|------------------------------------------------------------------------------------------------------------------|

| 1    | IN1              | 入力1:積分器1Aおよび1Bに対するアナログ入力。アクティブな積分器は、CONV入力により決定されます。                                                             |

| 2    | AGND             | アナログ・グランド                                                                                                        |

| 3    | CAP1B            | 外部コンデンサ、積分器1B用                                                                                                   |

| 4    | CAP1B            | 外部コンデンサ、積分器1B用                                                                                                   |

| 5    | CAP1A            | 外部コンデンサ、積分器1A用                                                                                                   |

| 6    | CAP1A            | 外部コンデンサ、積分器1A用                                                                                                   |

| 7    | AV <sub>DD</sub> | アナログ電源、定格+5V                                                                                                     |

| 8    | TEST             | テスト用制御入力"High"の時、CONV遷移毎にAまたはBの積分器に対してテスト電荷が印加されます。                                                              |

| 9    | CONV             | A、Bどちら側の積分器を入力に接続するか制御します。連続モードでは、CONV = "High" →サイドAで積分、CONV = "Low" →サイドBで積分します。CONVは、CLKに同期させる必要があります(図14参照)。 |

| 10   | CLK              | システム・クロック入力、10MHz                                                                                                |

| 11   | DCLK             | シリアル・データ・クロック入力。この入力は、シリアルI/Oシフト・レジスタを動作させます。                                                                    |

| 12   | DXMIT            | シリアル·データ送信のイネーブル入力。"Low"で内部シリアル·シフト·レジスタがイネーブルになります。                                                             |

| 13   | DIN              | シリアル・デジタル入力。複数のDDC112をカスケード接続する場合に使用します。                                                                         |

| 14   | $DV_DD$          | デジタル電源、+5V                                                                                                       |

| 15   | DGND             | デジタル・グランド                                                                                                        |

| 16   | DOUT             | シリアル・データ出力、DXMIT= "High"でハイ・インピーダンス (Hi-Z)                                                                       |

| 17   | DVALID           | データ有効出力。 "Low"で、シリアルI/Oレジスタに確定データがあることを意味します。                                                                    |

| 18   | RANGE 0          | レンジ制御入力0(LSB)                                                                                                    |

| 19   | RANGE 1          | レンジ制御入力1                                                                                                         |

| 20   | RANGE 2          | レンジ制御入力2 (MSB)                                                                                                   |

| 21   | AGND             | アナログ・グランド                                                                                                        |

| 22   | $V_{REF}$        | 外部基準電圧入力、+4.096V                                                                                                 |

| 23   | CAP2A            | 外部コンデンサ、積分器2A用                                                                                                   |

| 24   | CAP2A            | 外部コンデンサ、積分器2A用                                                                                                   |

| 25   | CAP2B            | 外部コンデンサ、積分器2B用                                                                                                   |

| 26   | CAP2B            | 外部コンデンサ、積分器2B用                                                                                                   |

| 27   | AGND             | アナログ・グランド                                                                                                        |

| 28   | IN2              | 入力2:積分器2Aおよび2Bに対するアナログ入力。アクティブな積分器は、CONV入力により決定されます。                                                             |

**表 1**. 端子説明

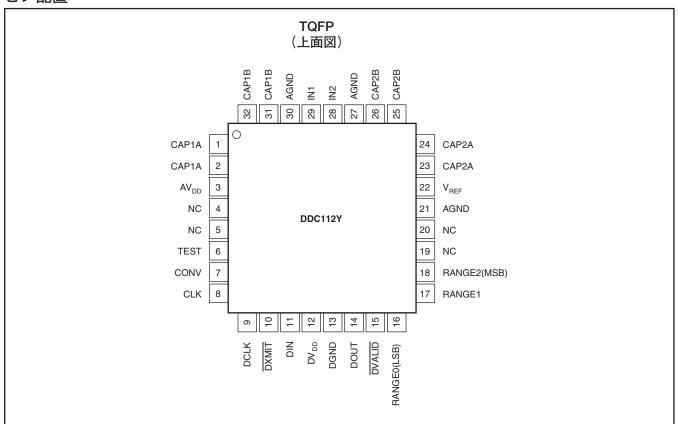

# 端子機能(DDC112Y)

| 端端   | 子         | =1 10                                                                                                    |

|------|-----------|----------------------------------------------------------------------------------------------------------|

| ピン番号 | 名称        | ¬説明                                                                                                      |

| 1    | CAP1A     | 外部コンデンサ、積分器1A用                                                                                           |

| 2    | CAP1A     | 外部コンデンサ、積分器1A用                                                                                           |

| 3    | $AV_DD$   | アナログ電源、+5V                                                                                               |

| 4    | NC        | 未接続                                                                                                      |

| 5    | NC        | 未接続                                                                                                      |

| 6    | TEST      | テスト用制御入力 "High" の時、CONV遷移毎にAまたはBの積分器に対してテスト電荷が印加されます。                                                    |

| 7    | CONV      | A、Bどちら側の積分器を入力に接続するか制御します。連続モードでは、CONV = "High" サイドA で積分、CONV = "Low" サイドBで積分します。CONVは、CLKに同期させる必要があります。 |

| 8    | CLK       | システム・クロック入力、10MHz                                                                                        |

| 9    | DCLK      | シリアル・データ・クロック入力。この入力は、シリアルI/Oシフト・レジスタを動作させます。                                                            |

| 10   | DXMIT     | シリアル·データ送信のイネーブル入力。 "Low"で内部シリアル·シフト·レジスタがイネーブルになります。                                                    |

| 11   | DIN       | DIN11シリアル・デジタル入力。複数のDDC112をカスケード接続する場合に使用します。                                                            |

| 12   | $DV_DD$   | デジタル電源、+5V                                                                                               |

| 13   | DGND      | デジタル・グランド                                                                                                |

| 14   | DOUT      | シリアル・データ出力、DXMIT = "High"でハイ・インピーダンス (Hi-Z)                                                              |

| 15   | DVALID    | データ有効出力。"Low"で、シリアルI/Oレジスタに確定データがあることを意味します。                                                             |

| 16   | RANGE 0   | レンジ制御入力0 (LSB)                                                                                           |

| 17   | RANGE 1   | レンジ制御入力1                                                                                                 |

| 18   | RANGE 2   | レンジ制御入力2 (MSB)                                                                                           |

| 19   | NC        | 未接続                                                                                                      |

| 20   | NC        | 未接続                                                                                                      |

| 21   | AGND      | アナログ・グランド                                                                                                |

| 22   | $V_{REF}$ | 外部基準電圧入力、+4.096V                                                                                         |

| 23   | CAP2A     | 外部コンデンサ、積分器2A用                                                                                           |

| 24   | CAP2A     | 外部コンデンサ、積分器2A用                                                                                           |

| 25   | CAP2B     | 外部コンデンサ、積分器2B用                                                                                           |

| 26   | CAP2B     | 外部コンデンサ、積分器2B用                                                                                           |

| 27   | AGND      | アナログ・グランド                                                                                                |

| 28   | IN2       | 入力2:積分器2Aおよび2Bに対するアナログ入力。アクティブな積分器は、CONV入力により<br>決定されます。                                                 |

| 29   | IN1       | 入力1:積分器1Aおよび1Bに対するアナログ入力。アクティブな積分器は、CONV入力により<br>決定されます。                                                 |

| 30   | AGND      | アナログ・グランド                                                                                                |

| 31   | CAP1B     | 外部コンデンサ、積分器1B用                                                                                           |

| 32   | CAP1B     | 外部コンデンサ、積分器1B用                                                                                           |

表 2. 端子説明

# 代表的特性

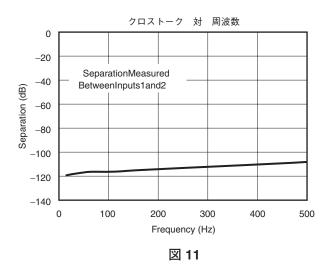

特記のない限り、 $T_A=+25^{\circ}C$ 、レンジ5(250pC)、 $T_{INT}=500\mu s$ 、 $V_{REF}=+4.096$ 、 $AV_{DD}=DV_{DD}=+5V$ 、および CLK=10MHzにて特性測定。

# 代表的特性

特記のない限り、 $T_A=+25^{\circ}$ C、レンジ5(250pC)、 $T_{INT}=500\mu s$ 、 $V_{REF}=+4.096$ 、 $AV_{DD}=DV_{DD}=+5V$ 、および CLK = 10MHzにて特性測定。

#### 動作原理

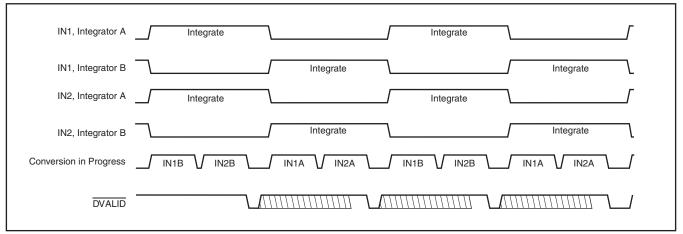

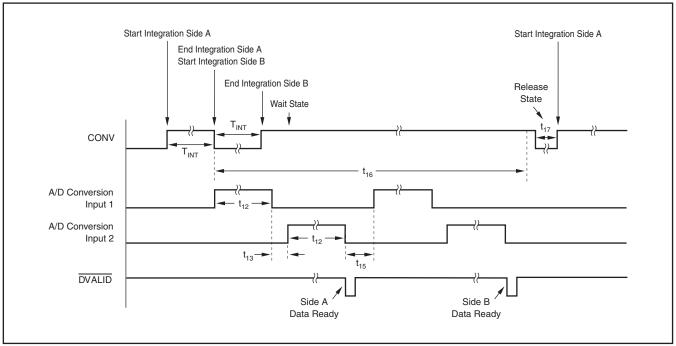

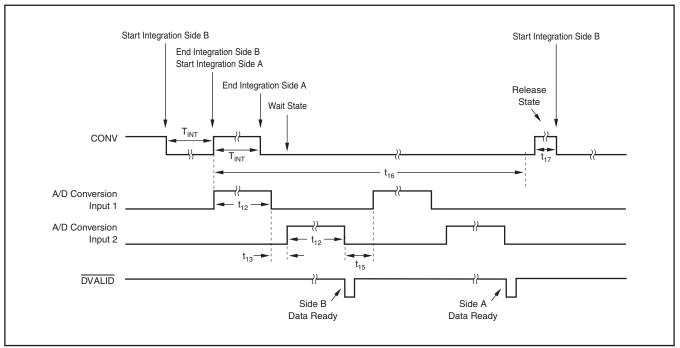

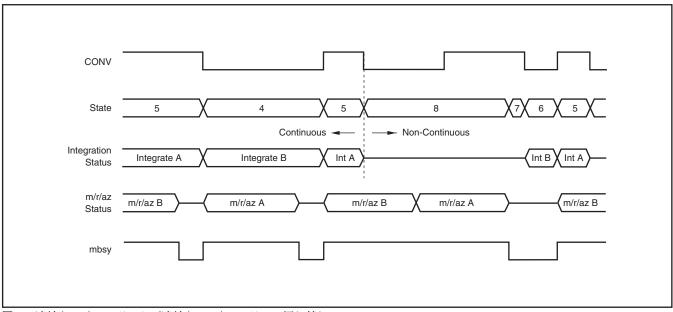

DDC112の基本動作を図13に示します。このデバイスには2つの同等な入力があり、それぞれI/V変換、入力切替後、AD変換されます。またそれぞれの入力には2つずつの積分器があり、交互使用により連続での積分が可能です。4つの積分器出力は、入力マルチプレクサによりその1つが選択され、1つのデルタ・シグマ(ΔΣ)型ADコンバータに送られます。DDC112の連続積分モードでは、両入力の2つの片側積分器が積分中に、他方の2つの積分器出力をそれぞれAD変換します。この様子を図14に示します。この積分とAD変換プロセスは、システム・クロック(CLK)により制御されます。10MHzのシステム・クロックでは、積分器とデルタ・シグマ型ADコンバータは、約220μsにて1回の20bit AD変換が行われます。各入力のA側、B側の結果は、シリアル出力シフト・レジスタに保存されます。シフト・レジスタに有効なデータが入ると、DVALID出力は"Low"になります。

DDC112のデジタル・インターフェイスは、同期シリアル・インターフェイスであり、データ・クロック (DCLK)、送信イネーブル ( $/\overline{DXMIT}$ )、シリアル・データ出力 (DOUT)、及びシリアル・データ入力 (DIN)を使用して、データを送信します。DDC112は、1つのADコンバータのみである為、図14に示す様に、2入力のAD変換プロセスは多重化されています。積分とAD変換は、基本的に独立したデータ取得プロセスです。従って、CLK周波数とDCLK周波数は、同じである必要はありません。DINは、複数のコンバータをカスケード接続する時のみ使用し、それ以外ではDGNDに接続します。  $T_{INT}$ 、CLK、およびDCLKにもよりますが、100個以上のコンバータのデイジーチェーン接続が可能です。これにより、数多くのコンバータが必要なケースでは、デジタル出力の接続は大変容易になります。

図 13. ブロック図

図 14. DDC112での積分/変換の基本タイミング(連続モード)

#### デバイス動作

#### 基本積分サイクル

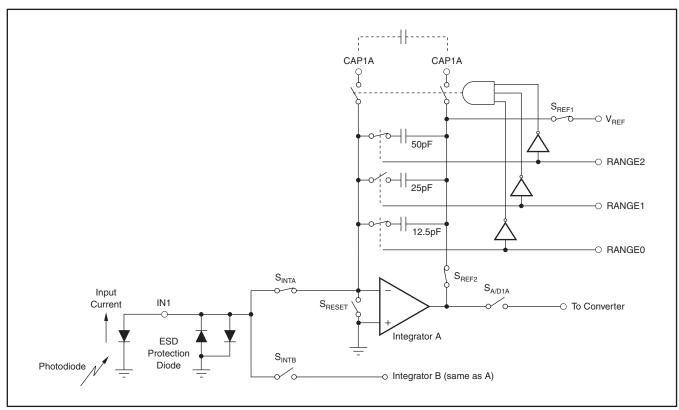

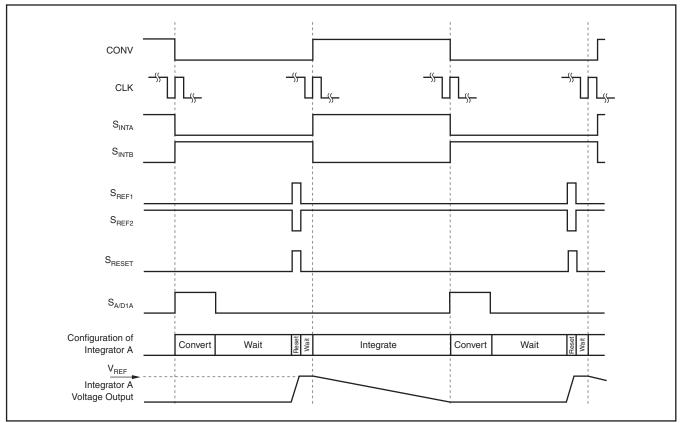

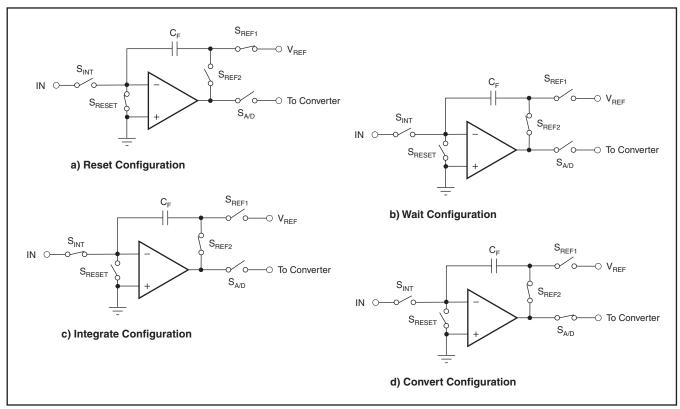

DDC112でのフロント・エンドの基本的なトポロジは、図15に示す様に従来型のアナログ積分回路です。この図は、入力 1 のみを示しています。この入力部は、オペアンプ、選択可能なフィードバック・コンデンサ回路  $(C_F)$ 、および複数個のスイッチにより構成され、積分サイクルを実行します。図15で示すスイッチのタイミングを図16に示します。図16は、DDC112の積分器の動作の考え方を説明しておりますが、設計の為の正確なタイミングを示すものではありません。DDC112積分器部のリセット、積分、AD変換、およびウェイト・サイクルの等価回路を図17に示します。この内部スイッチ回路は、変換命令(CONV)、レンジ選択ピン (RANGEO-RANGE2)、およびシステム・クロック (CLK)により、外部より制御されます。最良のノイズ性能を得るため、CONV信号はCLKの立ち上がりエッジに同期させる必要があります。またCONV信号は、CLKの立ち上がりエッジに対して $\pm 10$ ns以内で反転 (F)0、動作させる事を推奨します。

積分器の非反転入力は、内部でGNDに接続されています。従って、DDC112のアナログGNDは、ノイズが出来るだけ少ない事が必要です。レンジ・スイッチにより、内蔵/外部コンデンサは、オペアンプの反転入力と出力間に並列に接続されます。表3に、各レンジでの積分コンデンサ  $(C_F)$  容量を示します。AD変換開始時、 $S_{A/D}$ 、 $S_{INTA}$ 、 $S_{INTB}$ 、 $S_{REF1}$ 、 $S_{REF2}$ 、および $S_{RESET}$ の各スイッチがセットされます(図16参照)。

AD変換の完了時に、積分コンデンサ  $(C_F)$  の電荷量は、 $S_{REF1}$ と $S_{RESET}$ によってリセットされます (図16および図17a参照)。これは、リセット期間で実行されます。このリセットにより選択されたコンデンサは、基準電圧 $V_{REF}$ まで充電されます。

積分コンデンサの充電が完了すると、 $S_{REF1}$ および $S_{RESET}$ は切り替り、 $V_{REF}$ とアンプ回路は切断され、積分開始を待ちます(図17b参照)。CONV信号の立ち上がりエッジで、 $S_{INTA}$ はONとなり、A側の積分が開始されます。これにより積分器は、積分モードに移行します(図17c参照)。

| RANGE2 | RANGE1 | RANGE0 | C <sub>F</sub><br>(pF,typ) | 入力レンジ<br>(pC,typ) |

|--------|--------|--------|----------------------------|-------------------|

| 0      | 0      | 0      | 外部<br>12.5 ~ 250           | 最大 1000           |

| 0      | 0      | 1      | 12.5                       | −0.2 ~ 50         |

| 0      | 1      | 0      | 25                         | −0.4 ~ 100        |

| 0      | 1      | 1      | 37.5                       | −0.6 ~ 150        |

| 1      | 0      | 0      | 50                         | −0.8 ~ 200        |

| 1      | 0      | 1      | 62.5                       | −0.1 ~ 250        |

| 1      | 1      | 0      | 75                         | −1.2 ~ 300        |

| 1      | 1      | 1      | 87.5                       | −1.4 ~ 350        |

表 3. DDC112のレンジ選択

入力信号の電荷は積分コンデンサに集められ、それに従いアンプの電圧出力は降下します。CONV信号の立ち下がりエッジで入力信号はA側からB側に切り替わり  $(S_{INTA}$ および $S_{INTB})$ 、A側の積分は停止します。CONV信号の立ち下がりエッジより前のA側の積分中に、B側ではADコンバータによるAD変換が行われリセットされています。CONV信号の立ち下がりエッジで、B側での入力信号の積分を開始します。この段階で、A側のオペアンプからの出力電圧が、 $\Delta\Sigma$  ADコンバータの入力に印加されます (図 17d参照)。

図 15. 入力1積分器の基本的な構成 - 入力レンジは250pC (CF = 62.5pF)の設定。

図 16. 図15で示した回路に対応する積分器の基本的なタイミング図

図 17. DDC112 のフロント·エンド積分器、4モード構成図

#### 積分コンデンサ(CF)の値の決定

積分器のフィードバック・コンデンサの値、積分期間、および基準電圧によって、DDC112の+側のフルスケール (+FS) 値が決まります。DDC112の+側フルスケールの近似値は、次の式で求められます。

$$Q_{IN} = I_{IN} \times T_{IN}$$

$$Q_{FS} = (0.96) V_{REF} \times C_{F}$$

$$I_{FS} = \frac{(0.96) V_{REF} \times C_{F}}{T_{INT}}$$

(1)

または

$$C_{F} = \frac{I_{FS} \times T_{INT}}{(0.96)V_{BFF}}$$

(2)

係数0.96を使用する事により、GNDレベルまでスイングする事無しに、フロント・エンドの積分器をフルスケールまで使用する事ができます。—側のフルスケール (-FS) 範囲は、+側のフルスケール範囲に対して約0.4%です。たとえば、レンジ5の+FSレンジは、250pCです。これに対応する-FSレンジは、約-1pCです。この比率は外部コンデンサに関しても同様で、 $V_{REF}$ からも独立しています ( $V_{REF}$ の許容範囲については、「電気的特性」の表を参照)。

#### 積分コンデンサ

DDC112には、各チャネル、および各A/B側にそれぞれ7個のコンデンサがオンチップで用意されています。これらの内蔵コンデンサは製造時に調整され、DDC112の誤差性能を満たします。レンジ制御ピン (RANGE0-RANGE2) は、4個すべての積分器のコンデンサの値を、同時に変更します。その為、各入力及びA/B側の入力は、外部コンデンサを使用しない限り、常に同じフルスケール範囲を持ちます。

外部積分コンデンサは[RANGE2-RANGE0 = 000]を設定する事で、内蔵コンデンサの代わりに使用する事ができます。外部コンデンサのピン接続を表 4に示します。一般的には4つの外部コンデンサは同じ容量のものを使用しますが、DDC112の入力1と入力2で、別容量のペアとして使用する事も可能です。容量値にかかわらず、A/B側の容量は同じ値とすることを強く推奨します。

| 外部コンデン     | サの接続端子     | 積分器  |      |  |

|------------|------------|------|------|--|

| DDC112U、UK | DDC112Y、YK | チャネル | A/B側 |  |

| 5 と 6      | 1と2        | 1    | Α    |  |

| 3 と 4      | 31 と 32    | 1    | В    |  |

| 23 と 24    | 23 E 24    | 2    | Α    |  |

| 25 と 26    | 25 と 26    | 2    | В    |  |

**表 4**. 範囲構成をRANGE2-RANGE0 = 000にした場合の 外部コンデンサ接続

各レンジの精度は、積分コンデンサの精度に依存する為、コンデンサの選択には注意が必要です。外部積分コンデンサは、低電圧特性および温度特性が良く、メモリ効果、及びリークの少ない事が必要です。最良の選択かどうかは、アプリケーション毎の必要特性に依存します。良いタイプは、チップ・オン・ガラス(COG)セラミック、ポリカーボネート、ポリスチレン、及びシルバードマイカ等です。

#### リファレンス電圧

外部リファレンス電圧は、積分サイクル開始前の積分コンデンサに対するリセットに使用されます。 また、積分サイクル終了後の積分電圧測定や、ADコンバータでも使用されます。このサンプリング時、外部リファレンス電圧はADコンバータに供給されなければなりません。 $500\mu$ sの積分時間では、電荷量は約 $150\mu$ Aの $V_{REF}$ 電流として変換されます。ADコンバータで必要な電荷は積分時間とは無関係です。従って積分時間を長くすると、平均電流は減少します。例えば $1000\mu$ sの積分時間では、平均 $V_{REF}$ 電流は $75\mu$ Aとなります。

$V_{REF}$ は図17での個々のモードに於いて、安定である事が重要です。 $\Delta\Sigma$  ADコンバータは、 $V_{REF}$ に対する積分器出力の電圧差を測定します。積分コンデンサは最初に $V_{REF}$ 電圧にリセットされますので、コンデンサ・リセット時の $V_{REF}$ 電圧と測定時とに差があると、オフセットが発生します。また $V_{REF}$ 電圧はフルスケール・レンジに直接関係しますので、長時間安定度も重要です。最後に、 $V_{REF}$ にはノイズが最小である事が必要です。

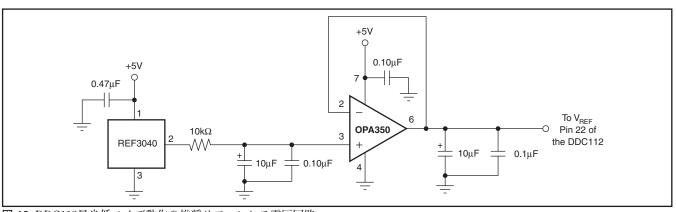

上記の理由のため、外部リファレンス電圧にはオペアンプに よるバッファを使用する事を強く推奨します(図18参照)。この 回路では、基準電圧は4.096Vを発生します。

ノイズを減少させるLPFを使用し、オペアンプをバッファとして使用します。このアンプは、ユニティ・ゲインでの帯域幅は4MHz以上、低ノイズで、入出力同相電圧は $V_{REF}$ 電圧以上である事が必要です。バッファの後には、DDC112  $V_{REF}$ 端子直近にコンデンサを使用します。

図 18. DDC112最良低ノイズ動作の推奨リファレンス電圧回路

図18に示した回路で、使用する大容量コンデンサによる不安定が考えられますが、殆どのオペアンプでは問題なく動作します。オペアンプの安定動作の為に出力に直列抵抗を入れる事は、 $V_{REF}$ の低下を生じ、大きなオフセットを生じる為推奨しません。

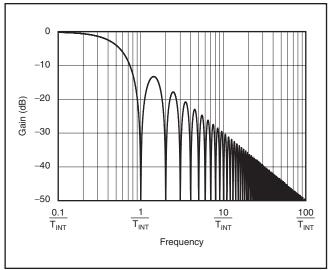

#### DDC112周波数特性

DDC112の周波数特性は、従来の連続時間型のフロント・エンド積分器により決定され(図19参照)、T<sub>INT</sub>を調整することにより、3dB帯域幅とノッチ周波数を変更できます。フロント・エンド積分器の後段にあるADコンバータの周波数特性は、積分器からのホールド電圧をサンプリングするため影響を及ぼしません。つまり、ADコンバータに対する入力は常にDC信号です。フロント・エンド積分器の出力はサンプリングされるので、エイリアシングが発生する可能性があります。入力信号周波数がサンプリング・レートの半分を上回ったときは、エイリアシングが発生します。

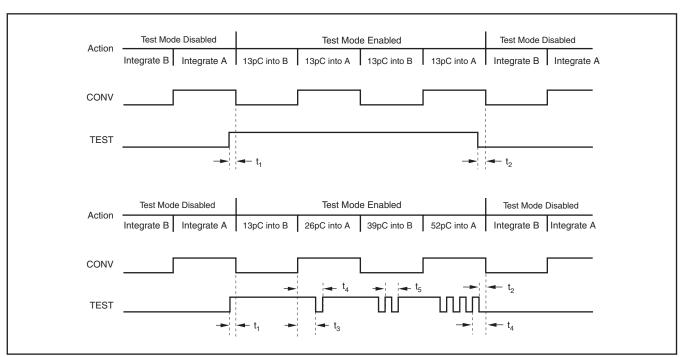

#### テスト・モード

TEST時は、ピンIN1とピンIN2はGNDに接続され、約13pC の電荷パケットが入力1と入力2両方の積分コンデンサに転送されます。この固定電荷量は積分サイクルの間に、積分コンデンサに1回、または複数回にわたって、転送することができます。

積分時間中に複数回の電荷パケット転送が行われる時は、毎回 13pCづつ追加されます。このモードは、連続モード/不連続モードのどちらでも使用できます。テスト・モードのタイミング図を 図20に示します。図20に示す上側3本の線は、13pCの1つの電荷パケットを積分コンデンサに転送するタイミングを示します。下側3本の線は、複数の電荷パケットを積分コンデンサに 転送するタイミングを示します。

図 19. DDC112 の周波数特性

図 20. DDC112 のテスト·モードのタイミング図

|                |                               | CLK = 10MHz |     | CLK = 15MHz |     |     |     |    |

|----------------|-------------------------------|-------------|-----|-------------|-----|-----|-----|----|

| シンボル           | 概要                            | MIN         | TYP | MAX         | MIN | TYP | MAX | 単位 |

| t <sub>1</sub> | テスト・モード・イネーブルのセットアップ時間        | 100         |     |             | 100 |     |     | ns |

| t <sub>2</sub> | テスト・モード・ディセーブルのセットアップ時間       | 100         |     |             | 100 |     |     | ns |

| t <sub>3</sub> | テスト・モード・イネーブルのホールド時間          | 100         |     |             | 100 |     |     | ns |

| t <sub>4</sub> | テスト・モード時の TEST立ち上がりから CONV 反転 | 5.4         |     |             | 3.6 |     |     | μs |

| t <sub>5</sub> | TEST の立ち上がり周期                 | 5.4         |     |             | 3.6 |     |     | μs |

表 5. DDC112 のテスト・モードのタイミング

この電荷パケット転送機能は、TESTとCONV両信号にて動作します。CONV信号反転以前にTESTが"High"となる事で、テスト・モードに入ります。この時点で、CONVのエッジはアナログ入力をGND接続し、13pCの電荷パケットが積分コンデンサに対して転送されます。TESTが"High"の状態が2回の変換(CONVの立ち上がりと立ち下がり)以上で維持されている場合、4個の積分器すべてに13pCの電荷パケットが充電されます。AD変換終了時、このデータシートの「連続および不連続動作モード」セクションに説明されるとおり、積分器の出力電圧はデジタル値化されます。テスト・モードは、TESTが"Low"の時にCONV信号が反転する事で終了します。

上記の様にテスト・モードに入った後は、TEST信号は必要回数、何回でもサイクルすることができます。このような操作が行われると、13pCの電荷はTEST信号の立ち上がり毎に追加充電されます。複数電荷パケットの追加充電は、CONV信号反転時にTEST信号が"Low"でない限り行われます。

#### デジタル関連事項

DDC112のデジタル・インターフェイスは、データ・クロック (DCLK)、送信イネーブル・ピン (DXMIT)、データ有効ピン (DVALID)、シリアル・データ出力ピン (DOUT)、およびシリアル・データ入力ピン (DIN)の構成で、同期シリアル・インターフェイスを提供します。DDC112は、ADコンバータ1つを内蔵しており、2入力はインターリーブされて処理されます (図14を参照)。積分と変換のプロセスは、基本的にはデータ取得プロセスとは独立しています。その為、CLK周波数とDCLK周波数は

同じである必要はありません。DINは、複数のコンバータをカスケード接続する場合のみ使用します。多数のコンバータが必要な場合は、カスケードまたはデイジーチェーンする事により、デジタル出力の相互接続とルーティングは大幅に簡素化されます。詳細については、このデータシートの「複数のコンバータのカスケード接続」部を参照してください。

DDC112の変換レートは、積分時間 (ユーザーが決定) とAD 変換速度で決定されます。AD変換時間は、主にシステム・クロック (CLK) 周波数の関数です。1回のAD変換サイクルは、2信号 (DDC112の各入力) の変換、および2回の積分に対する積分器のリセット時間によって構成されます。ほとんどの状況では、AD変換時間は積分時間より短くなります。この状況では、DDC112は連続モードで動作します。DDC112が連続モードで動作している場合、センサ出力は各入力のA/B側交互で連続的に積分されます。

AD変換が積分時間より長い時間を要する場合は、DDC112 は不連続モードに切り替わります。不連続モードでは、ADコンバータは積分プロセス時間に追従する事が出来ません。したがって、デジタイズ・プロセスが追いつくまで、積分プロセスは定期的に停止することになります。DDC112の2つの基本的な動作モードである、"連続モード"と"不連続モード"については、このデータシートの「連続および不連続動作モード」セクションで説明します。

#### 連続および不連続動作モード

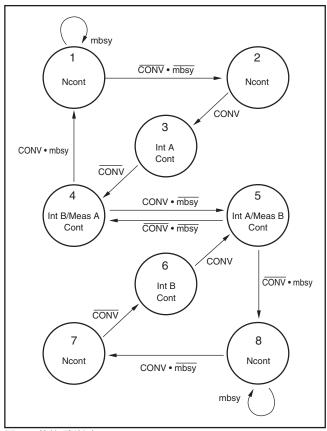

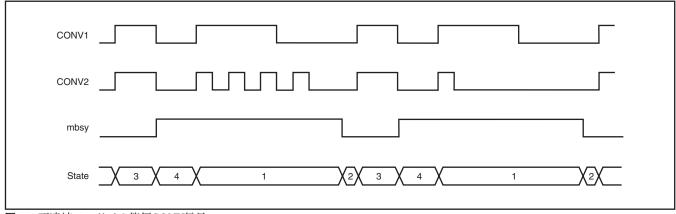

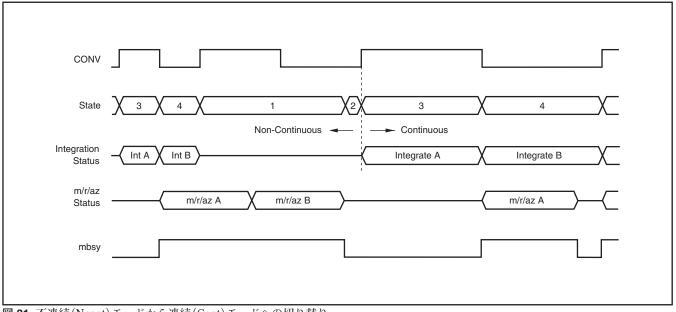

DDC112の状態遷移図を図 21に示します。全部で、8つの状態があります。表6に於いて概要を示します。

図 21. 状態遷移図

| 状態 | モード   | 説明                                                                                  |  |

|----|-------|-------------------------------------------------------------------------------------|--|

| 1  | Ncont | A側 m/r/az (測定、リセット、オートゼロ) を完了し<br>次にB側(直前の状態が状態4)を行う。<br>CONVが"High"状態での電源投入時の初期状態。 |  |

| 2  | Ncont | A側での積分準備。                                                                           |  |

| 3  | Cont  | A側積分                                                                                |  |

| 4  | Cont  | B側で積分;A側はm/r/az                                                                     |  |

| 5  | Cont  | A側で積分;B側はm/r/az                                                                     |  |

| 6  | Cont  | B側積分                                                                                |  |

| 7  | Ncont | B側での積分準備                                                                            |  |

| 8  | Ncont | B側m/r/azを完了し、次にB側(直前の状態が状態5)を<br>行う。<br>CONVが"Low"状態での電源投入時の初期状態。                   |  |

表 6. 状態説明

4つの信号が、状態遷移図での状態遷移に使用されます;これらはCONVとmbsy、およびそれぞれの反転信号です。状態変移はレベルにより遷移し、CONV信号の反転するエッジで状態を遷移させます。mbsyは内部で使用される信号で、ユーザーは制御できません。測定/リセット/オートゼロ(m/r/az)サイクル動作時、アクティブになります。

連続モード(Cont)時のmbsyは、CONV信号反転時には非アクティブです。積分を行っていない側は、他方側の積分が終了した時、常に次の積分を開始できます。従って、現状ステータスを知るには、CONV信号の状態を知れば状態遷移が分かります。連続モードの動作は、状態3~6に相当します。この内、3と6の状態のみで積分を行います。(m/r/azサイクルではない)

mbsyは非連続モード (Ncont) で、1,2,7 及び8の状態で重要となります。mbsyがアクティブの時にCONV信号を反転させると、DDC112はNcont 1 (又は8)の状態に入るか、入ったままの状態となります。mbsyが非アクティブになった後、状態2(または7)になります。この状態は、必要とされる側の積分前の準備状態です。前述の様に、Ncont状態ではDDC112の入力はGND接続されます。

状態遷移図で分かる事は、積分は常にA側とB側交互であり、この関係は、どの様なCONV信号パターンでも保たれ、モードには関係しません。状態2と7により、Ncontモードでもこの関係が保証されます。

DDC112への電源投入時の最初の状態は、CONV信号の初期レベルにより1か8になります。CONV信号が"High"での電源投入時は、最初の状態は1となります。同様に、CONV="Low"での電源投入時は、8の状態となります。全体として状態は、1と8、2と7、3と6、及び4と5は対称となります。CONV信号の反転は、状態遷移で対称に移動します。

#### タイミング例

#### 連続(Cont)モード

状態遷移の動作を、以下のタイミング図を使用して説明します。これらを、図22から図31に示します。表7に全体タイミングをCLK数で示します。表 7の " $\mu$ s" の時間値は、与えられたCLK数により計算できます。例えばCLK=10MHzではCLK周期=0.1 $\mu$ sなので、表7に示す $t_6$ は、479.4 $\mu$ sとなります。

| シンボル            | 説明                     | 值(CLK 期間)                         |

|-----------------|------------------------|-----------------------------------|

| t <sub>6</sub>  | Contモード m/r/az サイクル    | 4794                              |

| t <sub>7</sub>  | Contモード データ・レディ        | 4212 (t <sub>INT</sub> > 4794)    |

|                 |                        | 4212 ±3 (t <sub>INT</sub> = 4794) |

| t <sub>8</sub>  | Ncontモードの最初のデータ・レディ    | 4212 ±3                           |

| t <sub>9</sub>  | Ncontモードの 2 番目のデータ・レディ | 4548                              |

| t <sub>10</sub> | Ncontモードm/r/azサイクル     | 9108                              |

表7. クロック周期で表したタイミング規格

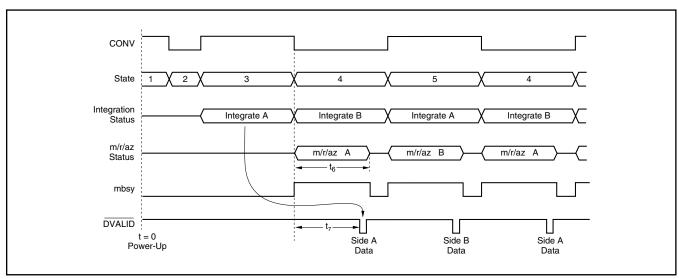

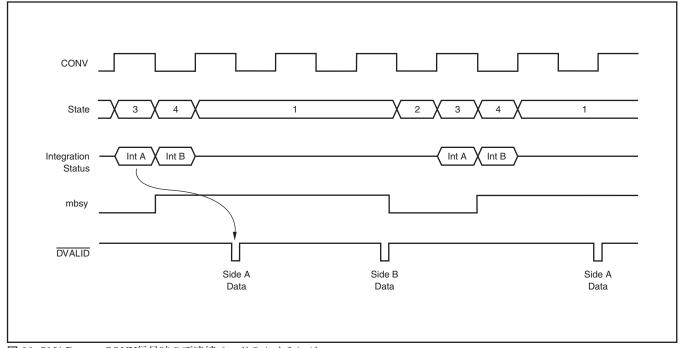

図22では連続モードに於ける電源投入後の数積分サイクルを示します。最上部はCONV信号で、外部より供給します。2番目は状態遷移図での状態を示します。次の2つが行われている積分と測定サイクルを示し、次に内部信号のmbsy、最後に、 $\overline{DVALID}$ を示します。データシートに示されている様に、 $\overline{DVALID}$ はDDC112よりデータ取得が可能となると "Low" アクティブになり、ユーザーにより $\overline{DXMIT}$ が "Low" にされるまで "Low" を継続します。図22およびそれ以降のタイミング図では、 $\overline{DVALID}$ が "Low" となってすぐユーザーにより $\overline{DXMIT}$ を "Low" にされたタイミングで示しています。 $\overline{DVALID}$ 波形下の文章はどちら側かのデータかを示し、矢印にて対応する積分サイクルを示します。図22から図31は、ほぼ同じタイミング・スケールで表しています。

図22で最初の状態は "Ncont1"です。また、DDC112の電源投入時は、常にNcont (非連続) モードです。この例では、最初の状態はCONV信号が電源投入時に "High"である為、状態1となります。最初の2つの状態経過後にCont状態に達し、状態は4と5のトグル動作となります。これ以降、入力信号はA側、又はB側に於いて連続して積分されます。m/r/az サイクルに必要な時間 " $t_6$ " は、先に述べたContモードとNcontモードの切り替わりタイミングと同じになります。 $\overline{DVALID}$  は、CONV信号が反転して " $t_7$ " 時間後に "Low"となり、データ取得可能を示します。表8に示すように、" $t_7$ " は $T_{INT}$ により2つの値があります。この理由は、後の "特別な考慮事項" 部で説明します。

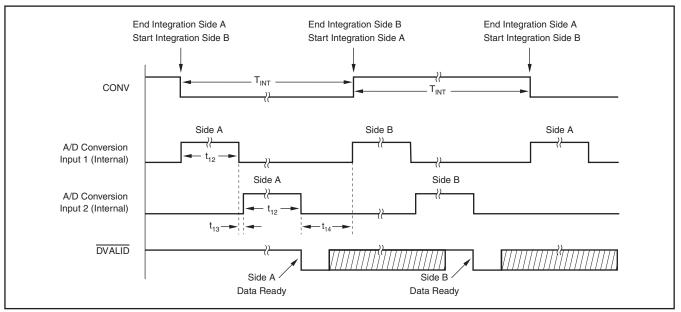

図23にはCONV信号反転時の状況を示します。此処で異なるのは、最初の3つの状態のみです。それ以降は前の状態と同様に、状態4と5を繰り返します。図24は連続モードでの内部動作のタイミング・ダイアグラムです。

図 22. 連続モードのタイミング (電源投入時に CONVが "High")

| シンボル           | 説明                   | 值 (CLK = 10MHz)                                                                              | 值 (CLK = 15MHz)                                                                   |

|----------------|----------------------|----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| t <sub>6</sub> | Cont モード m/r/az サイクル | 479.4µs                                                                                      | 319.6μs                                                                           |

| t <sub>7</sub> | Cont モード データ・レディ     | 421.2 $\mu$ s ( $T_{INT} > 479.4 \mu$ s)<br>421.2 $\pm 0.3 \mu$ s ( $T_{INT} = 479.4 \mu$ s) | 280.8μs (T <sub>INT</sub> > 319.6μs)<br>280.8 ±0.2μs (T <sub>INT</sub> = 319.6μs) |

表 8. 連続モードでのDDC112のタイミング

図 23. 連続モードのタイミング (電源投入時にCONVが "Low")

図 24. 連続モードでのDDC112の内部動作タイミング

|                  |                      | CLK = 10MHz |       |           | C   |       |           |    |

|------------------|----------------------|-------------|-------|-----------|-----|-------|-----------|----|

| シンボル             | 説明                   | MIN         | TYP   | MAX       | MIN | TYP   | MAX       | 単位 |

| T <sub>INT</sub> | 積分期間(連続モード)          | 500         |       | 1,000,000 | 333 |       | 1,000,000 | μs |

| t <sub>12</sub>  | AD 変換時間(内部制御)        |             | 202.2 |           |     | 134.8 |           | μs |

| t <sub>13</sub>  | AD 変換リセット時間(内部制御)    |             | 13.2  |           |     | 8.8   |           | μs |

| t <sub>14</sub>  | 積分器とAD変換リセット時間(内部制御) |             | 61.8  |           |     | 41.2  |           | μs |

表 9. 連続モードでの内部動作タイミング

#### 非連続 (Ncont) モード

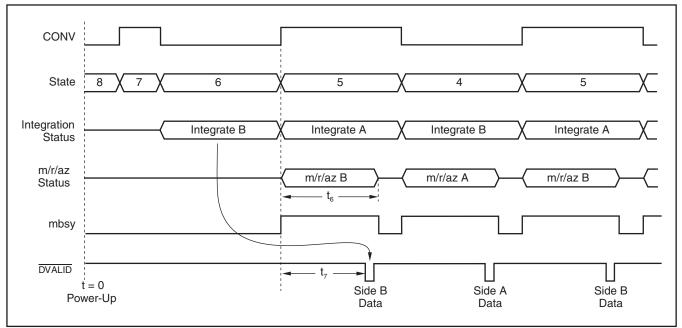

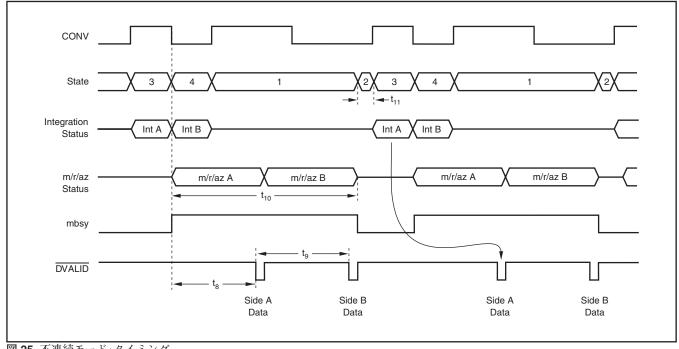

図25にNcontモードでの動作を示します。積分は組(A/Bまた はB/A) で行なわれ、次に積分が行われない時間が続きます。 この時、前の積分値の測定、リセット、およびオート・ゼロが 行われます。DDC112の状態が"3"又は"6"に進む前に、A 側とB側はm/r/azが終了していなければならず、" $t_{10}$ "の時間 がかかります。m/r/azサイクル終了後、" $t_{11}$ " の時間が次の積 分の準備に必要です。この時間はNcontモードとして必要で、 Ncontモードのm/r/azサイクルはContモードのm/r/azサイク ルと少し異なります。最初の積分サイクル終了後、DVALIDは "t8" 時間後に "Low" となります。これは、Contモードと同

じ時間です。2番目のデータは、最初のデータがレディになっ た後、"tg"の時間後にレディとなります。このアプリケーション 資料で使用している名称付けは、DDC112がNcontモードの時、 Ncontモード状態とContモード状態を通過する為です。たとえ ば図25で、状態遷移パターンは3、4、1、2、3、4、1、2、3、 4...となり、3と4はContモードの状態です。Ncontモードの定義 は、ある時間に於いてA側、B側共に積分が行われていない、 という事です。積分を実行する状態をContモード状態、積分を 実行しない状態をNcontモード状態と呼びます。積分はNcont モードで行われますが、これは単に連続して行われない事を示 し、あるContモード状態はNcontモード状態を経由しなければ なりません。

図 25. 不連続モード・タイミング

| シンボル            | 説明                    | 值 (CLK = 10MHz) | 值 (CLK = 15MHz) |

|-----------------|-----------------------|-----------------|-----------------|

| t <sub>8</sub>  | 最初のNcont モード・データ・レディ  | 421.2 ±0.3μs    | 280.8 ±0.2μs    |

| t <sub>9</sub>  | 2番目のNcont モード・データ・レディ | 454.8μs         | 303.2μs         |

| t <sub>10</sub> | Ncont モード m/r/az サイクル | 910.8µs         | 607.2μs         |

| t <sub>11</sub> | 積分の実行準備               | ≥ 24.0µs        | ≥ 24.0µs        |

表 10. 不連続モードでの DDC112 のタイミング

図 26. 非連続モードで、A側積分が最初に行われる変換動作の内部状態詳細

|                  |                         |     | CLK = 10MHz |           |     | CLK = 15MHz |           |    |  |

|------------------|-------------------------|-----|-------------|-----------|-----|-------------|-----------|----|--|

| シンボル             | 説明                      | MIN | TYP         | MAX       | MIN | TYP         | MAX       | 単位 |  |

| T <sub>INT</sub> | 積分時間 (不連続モード)           | 50  |             | 1,000,000 | 50  |             | 1,000,000 | μs |  |

| t <sub>12</sub>  | AD 変換時間(内部制御)           |     | 202.2       |           |     | 134.8       |           | μs |  |

| t <sub>13</sub>  | AD 変換リセット時間(内部制御)       |     | 13.2        |           |     | 8.8         |           | μs |  |

| t <sub>15</sub>  | 積分器と AD 変換 リセット時間(内部制御) |     | 37.8        |           |     | 25.2        |           | μs |  |

| t <sub>16</sub>  | AD 変換とリセットの合計時間(内部制御)   |     | 910.8       |           |     | 607.2       |           | μs |  |

| t <sub>17</sub>  | リリース時間                  | 24  |             |           | 24  |             |           | μs |  |

表 11. 不連続モードでの DDC112 の内部タイミング

図 27. 非連続モードで、B側積分が最初に行われる変換動作の内部タイミング図

状態遷移図を見ますと、状態遷移を行う為のCONV信号のパターンは特殊ではない事が分かります。状態1又は8になった後は、DDC112はmbsyが "Low"になるまで、CONV信号は関係なくその状態に保持されます。m/r/azサイクルの実行中は、ステート・マシンはCONVを無視します(図21を参照)。上部2信号は異なったCONV信号パターンですが、同じ状態となります。少々分かり難いかもしれませんが、この事により非連続モードでのCONV信号パターンに柔軟性が持たせられます。例えばDDC112評価キットでは、非連続モードで、 $t_6$ 時間以下のパルス幅の方形波を使用しています。図29では、50%Duty、 $T_{INT}$  = 1620CLK周期での非連続モードの動作を示しています。方形波

のCONV信号を使用する時は注意が必要です。特定の積分時間は、状態2(またはCONV信号反転時は状態7)の間隔が短くなり過ぎるので、避ける必要があります。状態遷移図で、状態2から3へは、CONV信号が"High"となると遷移します。ステート・マシンは、次の側の積分に備えた準備の為に、状態2の時間が十分な長さ( $t_{11}$ )である事を保証しません。ユーザーがCONVの適切なタイミングを設定する必要があります。例えば、CONV信号が $T_{\rm INT}$  = 3042CLKの周期を持つ方形波である場合、状態2はわずか18CLK の周期でしかなく、 $t_{11}$ の条件を満たせません。

図 28. 不連続モードでの等価CONV信号

**図 29**. 50% Duty、CONV信号時の不連続モードのタイミング

#### モードの切り替わり

ContモードからNcontモードへの切り替わりは、 $T_{INT} < t_6$ である場合に起こります。図30にこの遷移の例を示します。この図では、B側でのm/r/azサイクル完了前にA側での積分が終了した時、不連続 (Ncont) モードに入ります。DDC112は、状態8と7にてB側とA側の測定を行い、その時入力はGNDに短絡します。Ncontの積分は、状態6で始まります。

NcontモードからContモードへの切り替わりは、 $T_{INT}$ が長くなり、常に $T_{INT}$   $\geq$   $t_6$ になった時に切り変わります(図26を参照)。  $T_{INT}$  が長い時には、次の積分開始までにm/r/az サイクルが完了する十分な時間が確保される為、入力信号の連続的な積分が可能になります。Contモードへの切り替わり時の最初の積分での特別なケースとして、 $T_{INT}$  は $t_6$ より短くなる事があります。これは状態3ではB側でのm/r/az サイクルが必要なく、A側の積分を待つ必要が無い為許容されます。

図 30. 連続(Cont)モードから不連続(Ncont)モードへの切り替り

図 31. 不連続(Ncont)モードから連続(Cont)モードへの切り替り

# 特別な考慮事項 非連続モードでの積分時間

DDC112は、比較的高速なクロックを使用します。CONVは CLKに同期させる必要がある為、CLK = 10 MHzでは $T_{\text{INT}}$ は 100 ns ステップで調整することができます。しかしながら、内部の測定、リセット、およびオートゼロ動作では、より遅いクロックの方が効率が良くなります。その為、DDC112ではCLKを6分周し、600 ns 周期の低速クロックを使用してm/r/az サイクルとデータ・レディ・ロジックを実行します。

この分周器により、積分期間は低速クロック周期の整数倍とならない事があります。例えば、 $T_{\rm INT}$  = 5000 CLK周期 (CLK = 10MHzで500 $\mu$ s) の時、積分期間は833 1/3低速クロック数となります。この $T_{\rm INT}$ と低速クロック周期の非整数倍となる関係により、積分毎の低速クロック・エッジ数の異なりを生じさせます。この積分毎の低速エッジ数の異なりは、積分周期毎に異なり、ノイズとして発生します。このエッジ数の異なりはランダムでなく、3積分周期毎に繰り返されます。この積分器でのノイズは、この繰返し周期と同じ周波数のトーンとして現われます。

連続モードではこの問題を避ける為に、低速クロックをm/r/azサイクル終了後の必要無くなった時点で停止させます。低速クロックの再開は、次の積分開始時に行われます。CONV信号反転時には低速クロックは常に停止状態である為、積分周期内での低速クロック数は、積分時間に関係なく一定の数となります。従って、 $T_{INT} \ge 4794$  CLK周期の時はこの問題は発生しません。

一方、Ncontモードでは、低速クロックは常に動作させておく必要があります。m/r/azサイクルは、積分終了時には未だ終了していません。従って、この問題が発生する事があります。このノイズは、DDC112の基板レイアウトに大きく左右されます。確実な接地と良くデカップリングされた電源では、大きく減少させる事も可能です。しかしながら、非連続モードでの性能を確保する為には、積分時間は $1/(2f_{SLOWCLOCK})$ の整数倍に選ぶ必要があります。CLK = 10MHz時、積分時間は、 $T_{INT}$  = 100nsの整数倍では無く、300nsの整数倍にする必要があります。従って、 $T_{INT}$  =  $100\mu s$ ではなく、 $T_{INT}$  =  $99\mu s$ が良い選択肢です。

#### データ・レディ

データの読み取り可能 (データ・レディ) を示す $\overline{DVALID}$ は、内部低速クロックを使用して作られます。このクロック (低速クロック) とCLKとの位相関係は、電源投入時に決まり、その時によりランダムです。CONV信号はCLKに同期している為、低速クロックとの位相関係はランダムとなります。 $T_{INT} > t_6$ の時、前述の様に低速クロックは一時停止します。この一時停止により、内部クロックはCONV信号と同期し、CONV信号と $\overline{DVALID}$ が "Low" となるタイミング  $(t_7 \ge t_8)$  は、固定となります。

$T_{INT} < t_6$ の時、内部低速クロックは停止する事が出来ず、同期する事もありません。従って、CONV信号反転時とデータ・レディを示す $\overline{DVALID}$ のタイミングは、CONV信号と低速クロックの位相が固定されないため、固定になりません。この変化量は、 $\pm 1/$ ( $2f_{SLOWCLOCK}$ )又は $\pm 3/f_{CLK}$ です。Ncontモードで、 $\overline{DVALID}$ の2番目のとのタイミングは、最初の $\overline{DVALID}$ の時 ( $t_9$ )にこの変化が起き、両方とも低速クロックで動作している為、2番目にはこの変化はありません。

データ・レディを確認する $\overline{DVALID}$ のポーリングは、読み取りタイミングが自動的に調整される為、この変化を気にする必要はありません。もし読み取りタイミングが $\overline{CONV}$ 信号反転から直接トリガー(ポーリングで無く)している時は、読み取りタイミングを最大 $t_7$ 、又は $t_8$ の待ち時間を持たせる事で、データが常に読み取り可能となります。

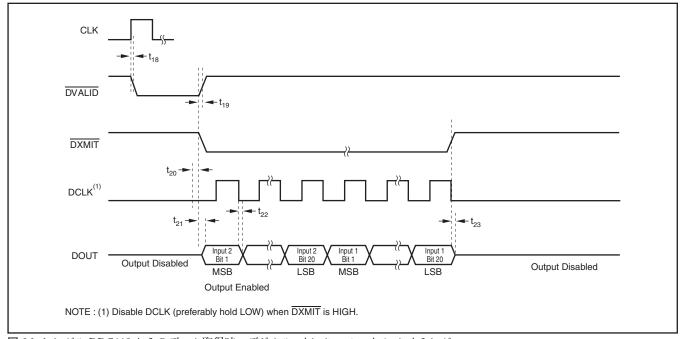

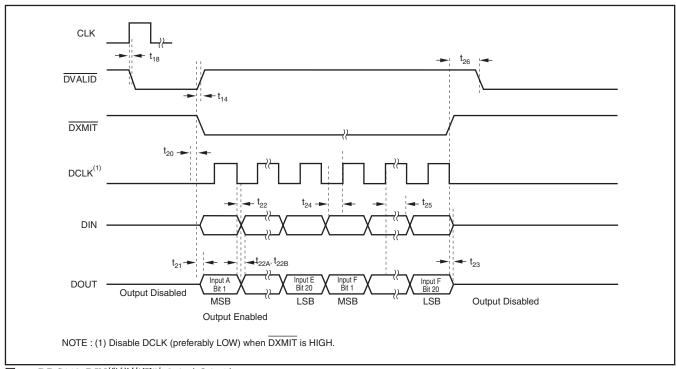

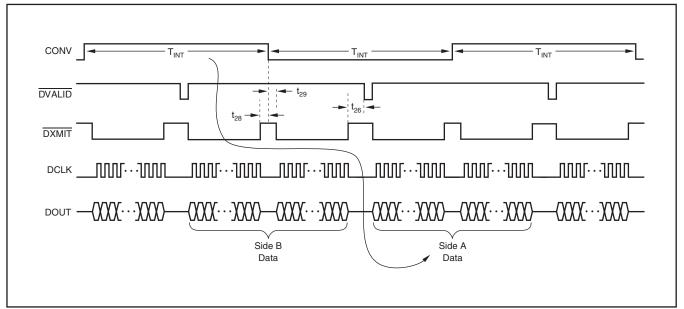

#### データ取得

連続モードと非連続モードに於いて、変換済みのデータは DVALIDが "Low"となるタイミングで取得可能となります。 (図34を参照)。 DXMITの立下りとデータ・クロック (DCLK) の組み合わせで、DDC112からのデータはシリアル送信を開始します。一般的にDDC112からのデータは、 DVALIDが立ち下がってからすぐより、次のCONV信号の反転 (LowからHigh、又はその逆)前に取得されます。もしそうで無い場合には、CONV信号反転の10us付近ではDCLK、及びそれに伴うDOUTの停止に注意する必要があります。もしこの注意を怠ると、CONV信号により開始される積分に対して、ノイズが重畳される事があります。

DOUTのシリアル出力データは、表12に示す様に、ストレート・バイナリ・コードです。DDCにより入力信号の"0"近辺以下に出力オフセットが生成されます。この為、フルスケールの"-0.4%"までの基板でのリーク電流は、"0"にクリップされずに許容されます。

| コード                      | 入力信号      |

|--------------------------|-----------|

| 1111 1111 1111 1111 1111 | FS        |

| 1111 1111 1111 1111 1110 | FS – 1LSB |

| 0000 0001 0000 0000 0001 | +1LSB     |

| 0000 0001 0000 0000 0000 | Zero      |

| 0000 0000 0000 0000 0000 | -0.4% FS  |

表 **12**. ストレート·バイナリ·コードの表

#### 複数のコンバータのカスケード接続

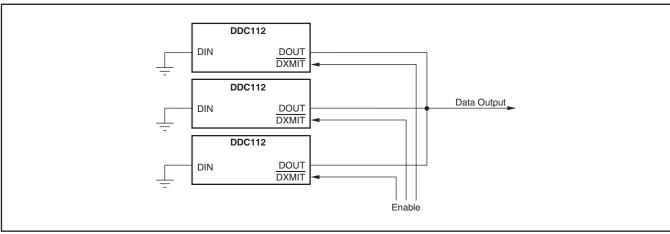

複数のDDC112を、図32および図33に示す様に、シリアル、 又はパラレルに接続できます

複数のデバイスのDOUTをDINと共にデイジーチェーン接続

し、接続線数を削減可能です。このモードでの動作では、図32 の様にシリアルデータは複数のDDC112によりシフトされます。

$R_{PULLUP}$ は、 $\overline{DXMIT}$ が"High"のとき、DINがフローティングになるのを防ぎます。CLK = 15MHz時は、DOUTの容量性負荷を小さくする様、注意が必要です

図 32. DDC112のデイジーチェーン接続

図 33. DDC112の並列接続

図 34. シングル DDC112 からのデータ取得時、デジタル・インターフェイス・タイミング

| シンボル                            | 説 明                                          | MIN | TYP | MAX | 単位 |

|---------------------------------|----------------------------------------------|-----|-----|-----|----|

| t <sub>18</sub>                 | CLKの立ち上がりエッジからDVALIDが"Low"になるまでの伝播遅延         | 30  |     |     | ns |

| t <sub>19</sub>                 | DXMITが "Low" になってからDVALIDが "High" になるまでの伝播遅延 | 30  |     |     | ns |

| t <sub>20</sub>                 | DCLKが "Low"になってからDXMITが "Low"になるまでのセットアップ時間  |     | 20  |     | ns |

| t <sub>21</sub>                 | DXMITが"Low"になってからDOUTが有効になるまでの伝播遅延           |     |     | 30  | ns |

| t <sub>22</sub>                 | DCLKの立ち下がりエッジ後の有効DOUTホールド時間                  | 5   |     |     | ns |

| t <sub>23</sub>                 |                                              |     | 30  |     | ns |

| t <sub>22A</sub> <sup>(1)</sup> | DCLKの立ち下がりエッジからDOUTが有効になるまでの伝播遅延             |     |     | 25  | ns |

| t <sub>22B</sub> (2)            | DCLKの立ち下がりエッジからDOUTが有効になるまでの伝播遅延             |     |     | 30  | ns |

- (1) DDC112UK、YKのみに適用。DDC112UK、YKのDIN (4pF || Typ) に負荷 (5pF || 100kΩ) を追加した最大負荷。(2) DDC112U、Yのみに適用。DDC112U、YのDIN (4pF || Typ) に負荷 (5pF || 100kΩ) を追加した最大負荷。

表 13. DDC112 データ取得タイミング

**図 35**. DDC112 DIN機能使用時のタイミング

|                 |                                                    | CLK = 10MHz |     |     | CLK = 15MHz |     |     |    |

|-----------------|----------------------------------------------------|-------------|-----|-----|-------------|-----|-----|----|

| シンボル            | 説明                                                 | MIN         | TYP | MAX | MIN         | TYP | MAX | 単位 |

| t <sub>24</sub> | DINからDCLKの立ち上がりエッジまでのセットアップ時間                      | 10          |     |     | 5           |     |     | ns |

| t <sub>25</sub> | DCLKの立ち上がりエッジが発生した後、DINまでのホールド時間                   | 10          |     | 0   | 10          |     |     | ns |

| t <sub>26</sub> | DVALIDの立ち上がりエッジが発生するまでにDXMITを<br>"High"に維持するホールド時間 | 2           |     |     | 1.33        |     |     | μs |

**表 14**. DINを使用時のDDC112データ取得タイミング

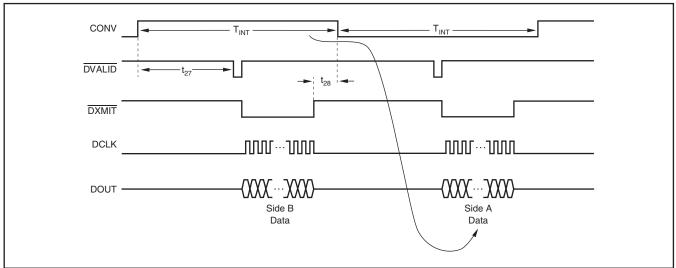

#### CONV信号反転前のデータ取得(連続モード)

この方法は最も基本的な方法です。データの取得は $\overline{\text{DVALID}}$ が "Low" になった直後に開始し、CONVが反転する前に終了します。図36に示します。最良の性能を得るには、CONVを反転させる前にデータ取得を  $t_{28}$ 時間前で終了させる必要があります。この方法は、積分時間がより長い場合に最適です。 読み取りに利用出来る最長時間は、 $T_{\text{INT}}-t_{27}-t_{28}$ です。DCLK及びCLK = 10MHzの時、デイジーチェーン接続可能なDDC112の最大数は;

$$\frac{T_{INT} - 431.2\mu s}{40\tau_{DCLK}} \tag{3}$$

ここで、 $\tau_{DCLK}$ はデータ・クロック周期です。 例えば、 $T_{INT}$  = 1000 $\mu$ s、DCLK = 10MHzの時、DDC112の最大数は;

$$\frac{1000\mu s - 431.2\mu s}{(40)(100ns)} = 142.2 \rightarrow 142DDC112s \qquad (4)$$

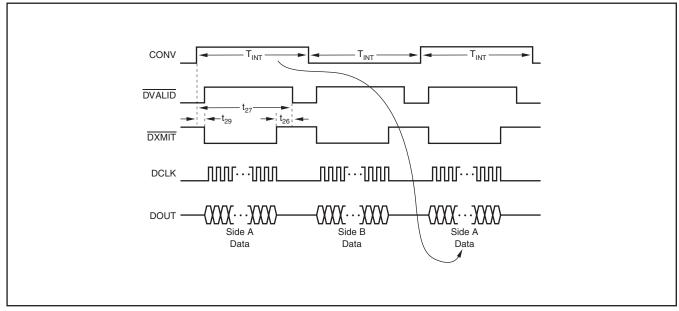

#### CONV信号反転後のデータ取得(連続モード)

積分時間がより短い場合は、CONV信号の反転後にデータ取得を開始し、次のデータ・レディ前に取得を終了する方法で、より多くの時間が利用できます。 データ取得を開始は、CONV信号の反転後、 $t_{29}$ の時間待つ必要があります。図37に、この例を示します。取得に利用できる最長時間は、 $T_{\rm INT}$ に関わり無く、 $t_{27}$  –  $t_{29}$  –  $t_{26}$  (CLK = 10MHz の時、421.2 $\mu$ s – 10 $\mu$ s – 2 $\mu$ s) です。 デイジーチェーン接続可能なDDC112の最大数は;

$$\frac{409.2\mu s}{40\tau_{DCLK}}\tag{5}$$

DCLK = 10MHzの時、DDC112の最大接続可能数は102です。

図 36. CONV信号反転前のデータ取得

|                 |                  | CLK = 10MHz |       |     | C   |       |     |    |

|-----------------|------------------|-------------|-------|-----|-----|-------|-----|----|

| シンボル            | 説明               | MIN         | TYP   | MAX | MIN | TYP   | MAX | 単位 |

| t <sub>27</sub> | Cont モード データ・レディ |             | 421.2 |     |     | 280.8 |     | μs |

| t <sub>28</sub> | Conv 反転前のデータ取得終了 | 10          |       |     | 10  |       |     | μs |

表 15. CONV信号反転前のデータ取得のタイミング

図 37. CONV 信号反転後のDDC112 データ取得

|                                    |                                       | CLK = 10MHz |       |     | C    |       |     |          |

|------------------------------------|---------------------------------------|-------------|-------|-----|------|-------|-----|----------|

| シンボル                               | 説明                                    | MIN         | TYP   | MAX | MIN  | TYP   | MAX | 単位       |

| t <sub>26</sub>                    |                                       | 2           |       |     | 1.33 |       |     | μs       |

| t <sub>27</sub><br>t <sub>29</sub> | Cont モード データ・レディ<br>CONV信号反転後のデータ取得開始 | 10          | 421.2 |     | 10   | 280.8 |     | μs<br>μs |

表 16. CONV 信号反転後のDDC112 データ取得タイミング

#### CONV信号反転の前後に於けるデータ取得

データ取得の絶対最大時間は、CONV信号反転の前および後の時間を使用したデータ取得です。 $T_{INT}$ のほぼ全期間をデータ取得に利用できます。 図38に、前記の2つの手法を組み合わせてこれを実行する方法を示します。デジタル・ノイズを防止する為、前述の様にCONV信号反転時はデータ取得を停止し、次のデータ・レディ前に取得を終了します。この場合のデイジーチェーン接続可能なDDC112の最大数は;

$$\frac{T_{INT} - 20\mu s - 2\mu s}{40\tau_{DCLK}} \tag{6}$$

$T_{\rm INT}$  = 500 $\mu$ s、 DCLK = 10MHzでは、DDC112の接続最大数は119です。

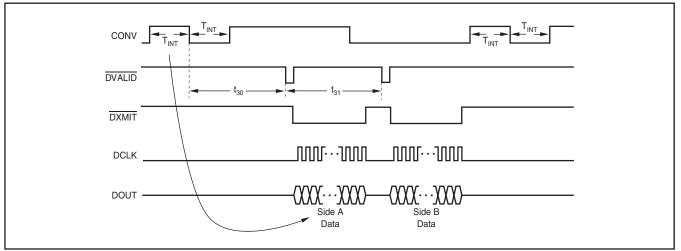

#### データ取得:不連続モード

不連続モードでの取得は、連続モードと多少異ります。図39に示す様に、また、アプリケーション資料SBAA024 (www.ti.comでダウンロード可能) で詳細に説明されていますが、最初の積分が完了から、 $t_{30}$ 期間後に、 $\overline{DVALID}$ は "Low" になります。  $T_{INT}$ がこの時間より短い場合は、他の側のデータ・レディ前の $t_{31}$ 全体を利用したデータ取得が可能です。 $T_{INT} > t_{30}$ の時、最初の積分データは2番目の積分完了前にレディとなります。デー

タ取得は、取得可能時間が短くなる為、2番目の積分終了まで 待つ必要があります。利用可能な時間は $t_{31}$  –  $(T_{INT}-t_{30})$ です。 2番目の積分によって得られたデータは、次の積分動作が開始 する前に取得する必要があります。この時間は、CONVを生成 するために使用されるパターンに大きく依存します。連続モー ドと同様、CONVが反転する前と後で、データ取得を停止し  $(t_{28}$ と $t_{29}$ )、新しいデータが準備できる前に取得を完了する必要 があります  $(t_{26})$ 。

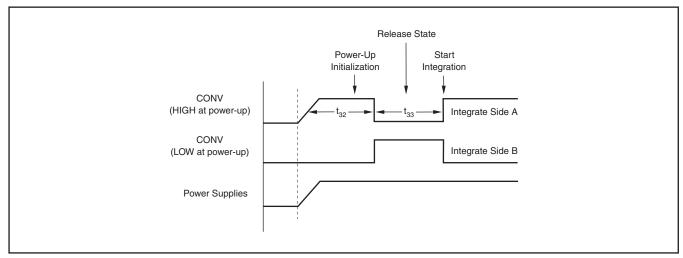

#### 電源投入シーケンス

電源投入の前に、すべてのデジタル入力ピンとアナログ入力ピンを "Low" にしておく必要があります。電源投入の時点で、これらの信号入力を0V以外の電圧にバイアスすることも可能です。ただし、それらの電圧はAV $_D$ DまたはDV $_D$ Dを上回ってはなりません。電源投入時のCONV信号レベルは、どちら側(AまたはB)を最初に積分するのか決定します。ただし、積分が開始可能になる前に、CONV信号をトグルする必要があります。図40を参照して下さい。

図 38. CONV信号反転の前後でのデータ読み取り

|                 |                                           | CLK = 10MHz |     |     | CLK = 15MHz |     |     |    |

|-----------------|-------------------------------------------|-------------|-----|-----|-------------|-----|-----|----|

| シンボル            | 説明                                        | MIN         | TYP | MAX | MIN         | TYP | MAX | 単位 |

| t <sub>26</sub> | DVALID立ち下がり前のDXMIT "High" に<br>維持するホールド時間 | 2           |     |     | 1.33        |     |     | μs |

| t <sub>28</sub> | CONV信号反転前のデータ取得停止                         | 10          |     |     | 10          |     |     | μs |

| t <sub>29</sub> | CONV信号反転後のデータ取得開始                         | 10          |     |     | 10          |     |     | μs |

表 17. DDC112CONV信号反転の前後でのデータ読み取りタイミング

図39. 不連続モードのデータ読み取り

|                                    |                                                                     | CLK = 10MHz |                     |     | CLK = 15MHz |                |     |          |

|------------------------------------|---------------------------------------------------------------------|-------------|---------------------|-----|-------------|----------------|-----|----------|

| シンボル                               | 説明                                                                  | MIN         | TYP                 | MAX | MIN         | TYP            | MAX | 単位       |

| t <sub>30</sub><br>t <sub>31</sub> | 最初のNcontモードデータ・レディ (SBAA024を参照)<br>2番目のNcontモードデータ・レディ (SBAA024を参照) |             | 421.1 ±0.3<br>454.8 |     |             | 280.8<br>303.2 |     | μs<br>μs |

表 18. DDC112不連続モードのデータ読み取りタイミング

**図 40**. DDC112電源投入タイミング

| シンボル                               | 説明                              | MIN      | TYP | MAX | 単位       |

|------------------------------------|---------------------------------|----------|-----|-----|----------|

| t <sub>32</sub><br>t <sub>33</sub> | 電源投入時の初期化期間<br>初期化リリースから積分の開始まで | 50<br>50 |     |     | μs<br>μs |

表 **19**. DDC112 電源投入シーケンス·タイミング

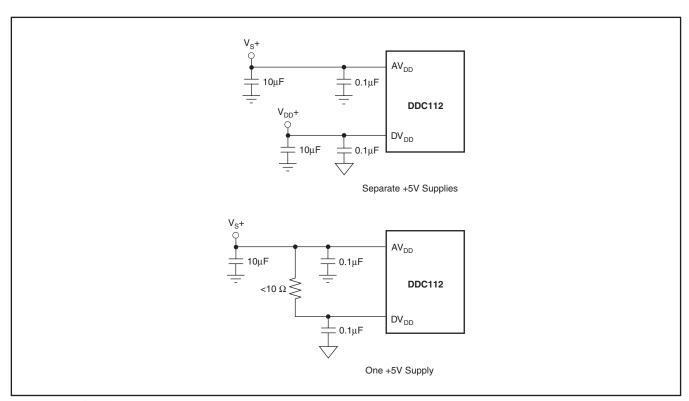

# レイアウト 電源とグランド

$AV_{DD}$ と $DV_{DD}$ は、両方ともできるだけノイズが少ない事が必要です。特に  $AV_{DD}$ はDDC112の動作に対して非同期のため、ノイズが少ない事は重要です。図41に、DDC112への電源に可能な2つの方法を示します。最初の事例では、2つの+5V電源を $AV_{DD}$ と $DV_{DD}$ に対して個別に供給します。この事例では、 $10\mu$ F の固体タンタル・コンデンサと $0.1\mu$ F のセラミック・コンデンサを使用して、DDC112の各+5V電源をバイパスする必要があります。2番目の事例では、 $AV_{DD}$ の電源から $10\Omega$ 未満の抵抗を通して $DV_{DD}$ 電源を供給しています。どちらの事例でも、 $0.1\mu$ FのコンデンサをDDC112パッケージの直近に配置する必要があります。

#### アナログ信号パスのシールド

他の高精度回路と同様、慎重にPCBをレイアウトすることにより、最良の性能が保証されます。相互接続をできるだけ短くして直接結線し、浮遊容量を避けることが特にアナログ入力ピンでは重要です。PCB上で、デジタル信号をアナログ入力信号からできるだけ遠ざける必要があります。

DDC112に関する回路レイアウトを設計するときは、入力シールドを考慮する必要があります。DDC112の入力はハイ・インピーダンスであり、外部ノイズに対して特に敏感です。シールドが行われていない場合、PCBのトレース相互間のリークはDDC112の入力バイアス電流を上回る可能性があります。図42に、可能な方法を示します。DDC112の入力の周囲に、グランド・パターンを配置します。このシールドは、入力ピンに対する結合ノイズを最小限に抑えるのに役立ちます。さらに、外部コンデンサを使用する場合は、外部コンデンサの接続ピンをグランド・パターンで保護する必要があります。

上記のアプローチは、低インピーダンスのアナログ・グランドを使用してこれらの影響されるピンを取り囲むことにより、リークの影響を緩和します。回路の他の部分で発生するリーク電流は、DDC112のアナログ入力段ではなく、低インピーダンスのアナログ・グランドに流入するので、実害をもたらしません。

図 41. 電源接続オプション

**図 42**. DDC112U推奨シールド·デザイン

#### パッケージ・オプション

#### 製品情報

| Orderable Device | Status (1) | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| DDC112U          | ACTIVE     | SOIC            | DW                 | 28   | 20             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| DDC112U/1K       | ACTIVE     | SOIC            | DW                 | 28   | 1000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| DDC112U/1KG4     | ACTIVE     | SOIC            | DW                 | 28   | 1000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| DDC112UG4        | ACTIVE     | SOIC            | DW                 | 28   | 20             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| DDC112UK         | ACTIVE     | SOIC            | DW                 | 28   | 20             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| DDC112UK/1K      | ACTIVE     | SOIC            | DW                 | 28   | 1000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| DDC112UK/1KG4    | ACTIVE     | SOIC            | DW                 | 28   | 1000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| DDC112Y/250      | ACTIVE     | TQFP            | PJT                | 32   | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| DDC112Y/250G4    | ACTIVE     | TQFP            | PJT                | 32   | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| DDC112Y/2K       | ACTIVE     | TQFP            | PJT                | 32   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| DDC112Y/2KG4     | ACTIVE     | TQFP            | PJT                | 32   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| DDC112YK/250     | ACTIVE     | TQFP            | PJT                | 32   | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| DDC112YK/250G4   | ACTIVE     | TQFP            | PJT                | 32   | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| DDC112YK/2K      | ACTIVE     | TQFP            | PJT                | 32   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| DDC112YK/2KG4    | ACTIVE     | TQFP            | PJT                | 32   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

(1) マーケティング・ステータスは次のように定義されています。

ACTIVE:製品デバイスが新規設計用に推奨されています。

LIFEBUY: TIによりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

NRND:新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TIでは新規設計にこの部品を使用することを推奨していません。

PREVIEW:デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

OBSOLETE: TIによりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free (RoHS)、Pb-Free (RoHS Expert) およびGreen (RoHS & no Sb/Br) があります。最新情報および製品内容の詳細については、http://www.ti.com/productcontentでご確認ください。

TBD: Pb-Free/Green変換プランが策定されていません。

Pb-Free (RoHS): TIにおける "Lead-Free" または "Pb-Free"(鉛フリー) は、6つの物質すべてに対して現在のRoHS要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が0.1%を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TIの鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

Pb-Free (RoHS Exempt): この部品は、1) ダイとパッケージの間に鉛ベースの半田バンプ使用、または 2) ダイとリードフレーム間に鉛ベースの接着剤を使用、が除外されています。それ以外は上記の様にPb-Free (RoHS) と考えられます。

**Green (RoHS & no Sb/Br):**TIにおける "Green" は、"Pb-Free" (RoHS互換) に加えて、臭素 (Br) およびアンチモン (Sb) をベースとした難燃材を含まない (均質 な材質中のBrまたはSb重量が0.1%を超えない) ことを意味しています。

<sup>(3)</sup> MSL、ピーク温度 -- JEDEC業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

重要な情報および免責事項:このページに記載された情報は、記載された日付時点でのTIの知識および見解を表しています。TIの知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TIでは、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TIおよびTI製品の供給者は、特定の情報を機密情報として扱っているため、CAS番号やその他の制限された情報が公開されない場合があります。

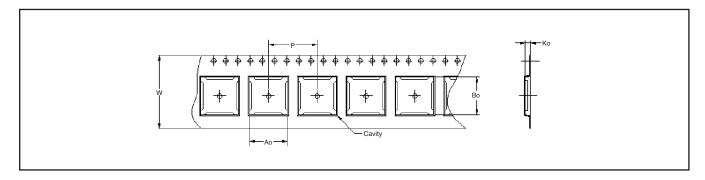

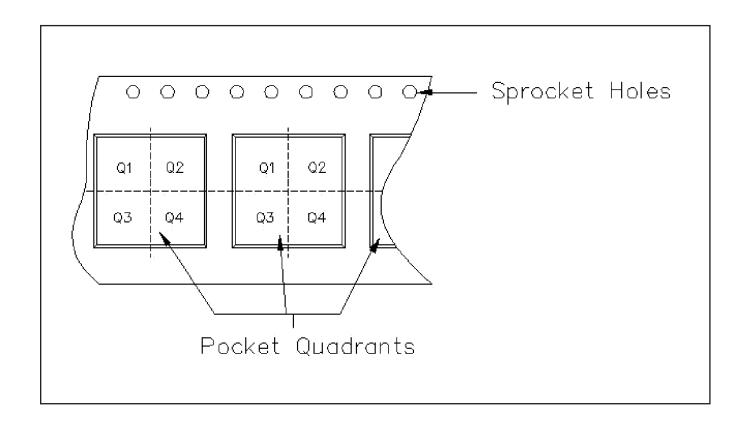

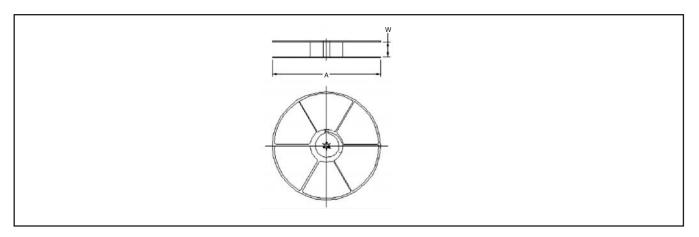

# PACKAGE MATERIALS INFORMATION

Carrier tape design is defined largely by the component lentgh, width, and thickness.

| Ao =                                         | Dimension | designed | to | accommodate | the | component | width.     |  |  |

|----------------------------------------------|-----------|----------|----|-------------|-----|-----------|------------|--|--|

| Bo =                                         | Dimension | designed | to | accommodate | the | component | length.    |  |  |

|                                              |           |          |    | accommodate | the | component | thickness. |  |  |

| W = Overall width of the carrier tape.       |           |          |    |             |     |           |            |  |  |

| P = Pitch between successive cavity centers. |           |          |    |             |     |           |            |  |  |

# PACKAGE MATERIALS INFORMATION

# テープ / リール情報

| Device       | Package | Pins | Site | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>(mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant   |

|--------------|---------|------|------|--------------------------|-----------------------|---------|---------|---------|------------|-----------|--------------------|

| DDC112U/1K   | DW      | 28   | TAI  | 330                      | 32                    | 11.35   | 18.67   | 3.1     | 16         | 32        | PKGORN<br>T1TR-MSP |

| DDC112UK/1K  | DW      | 28   | TAI  | 330                      | 32                    | 11.35   | 18.67   | 3.1     | 16         | 32        | PKGORN<br>T1TR-MSP |

| DDC112Y/250  | PJT     | 32   | TAI  | 330                      | 16                    | 9.6     | 9.6     | 1.5     | 12         | 16        | PKGORN<br>T2TR-MSP |

| DDC112Y/2K   | PJT     | 32   | TAI  | 330                      | 16                    | 9.6     | 9.6     | 1.5     | 12         | 16        | PKGORN<br>T2TR-MSP |

| DDC112YK/250 | PJT     | 32   | TAI  | 330                      | 16                    | 9.6     | 9.6     | 1.5     | 12         | 16        | PKGORN<br>T2TR-MSP |

| DDC112YK/2K  | PJT     | 32   | TAI  | 330                      | 16                    | 9.6     | 9.6     | 1.5     | 12         | 16        | PKGORN<br>T2TR-MSP |

# テープ/リール・ボックス情報

| Device       | Package | Pins | Site | Length (mm) | Width (mm) | Height (mm) |

|--------------|---------|------|------|-------------|------------|-------------|

| DDC112U/1K   | DW      | 28   | TAI  | 0.0         | 0.0        | 0.0         |

| DDC112UK/1K  | DW      | 28   | TAI  | 346.0       | 346.0      | 49.0        |

| DDC112Y/250  | PJT     | 32   | TAI  | 346.0       | 346.0      | 33.0        |

| DDC112Y/2K   | PJT     | 32   | TAI  | 346.0       | 346.0      | 33.0        |

| DDC112YK/250 | PJT     | 32   | TAI  | 346.0       | 346.0      | 33.0        |

| DDC112YK/2K  | PJT     | 32   | TAI  | 346.0       | 346.0      | 33.0        |

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-013 variation AE.

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Falls within JEDEC MS-026

(SBAS085B)

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。丁!製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。丁!製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえてがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定していない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2009, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

#### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。

1. 静電気

素手で半導体製品単体を触らないこと。どうしても触る必要がある 場合は、リストストラップ等で人体からアースをとり、導電性手袋 等をして取り扱うこと。

弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

前記のリストストラップ・導電性手袋・テーブル表面及び実装装置類の接地等の静電気帯電防止措置は、常に管理されその機能が確認されていること。

#### 2. 温·湿度環境

温度:0~40 、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

直射日光があたる状態で保管・輸送しないこと。

3. 防湿梱包

防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装 すること。

4. 機械的衝擊

梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

5. 熱衝擊

はんだ付け時は、最低限260 以上の高温状態に、10秒以上さらさないこと。(個別推奨条件がある時はそれに従うこと。)

6. 汚染

はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。 はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上