# 16ビット、シングル・チャネル、±18V出力（バッファなし）、超低消費電力、シリアル・インターフェイス、DAコンバータ

## 特 長

- 16ビット分解能

- 出力：±18V（±18Vリファレンス電圧入力）

- ±18V電源動作

- 超低消費電力

- 高精度INL：1LSB

- 低ノイズ： $10\text{nV}/\sqrt{\text{Hz}}$

- 高速セトリング：1LSBまで $1\mu\text{s}$

- 高速SPI™インターフェイス：最大50MHz

- 16ピンTSSOPパッケージ

- ゼロまたはミッドスケールへ選択リセット

## ア プ リ ケ シ ョ ン

- 携帯機器

- 自動試験装置

- 産業用プロセス制御

- データ・アクイジション・システム

- 光ネットワーク

## 解 説

DAC8871は16ビット、シングル・チャネル、シリアル入力、電圧出力型のDAコンバータ（DAC）です。出力範囲はリファレンス電圧 $V_{REFH}$ および $V_{REFL}$ により定まります。リファレンス電圧を適切に選択することで、出力をユニポーラあるいはバイポーラに設定でき、最大出力電圧は±18Vです。このコンバータは規定の動作温度範囲-40°C～+105°Cにわたって、優れた直線性（1LSBのINL）、低ノイズ、および高速セトリング特性（フルスケール出力で $1\mu\text{s}/1\text{LSB}$ ）を提供します。出力バッファがないため、消費電力およびバッファ起因の誤差が低減されます。本デバイスは、標準的な高速クロック（最大50MHz）の3Vまたは5VのSPIシリアル・インターフェイスによってDSPやマイクロプロセッサと通信を行います。

最適な特性を得るために、外部リファレンス電圧をケルビン接続する端子を備えています。DAC8871はTSSOP-16パッケージで提供します。

Gate Drive、PowerPAD は、テキサス・インスツルメンツの商標です。

この資料は、Texas Instruments Incorporated (TI) が英文で記述した資料を、皆様のご理解の一助として頂くために日本テキサス・インスツルメンツ(日本 TI)が英文から和文へ翻訳して作成したものです。

資料によっては正規英語版資料の更新に対応していないものがあります。

日本 TI による和文資料は、あくまでも TI 正規英語版をご理解頂くための補助的参考資料としてご使用下さい。

製品のご検討およびご採用にあたりましては必ず正規英語版の最新資料をご確認下さい。

TI および日本 TI は、正規英語版にて更新の情報を提供しているにもかかわらず、更新以前の情報に基づいて発生した問題や障害等につきましては如何なる責任も負いません。

# 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。すべての集積回路は、適切な ESD 保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

## 製品情報<sup>(1)</sup>

| 製品型番     | 最小相対精度<br>(LSB) | 微分非直線性<br>(LSB) | 温度範囲            | パッケージ捺印 | パッケージ    | パッケージ<br>・コード |

|----------|-----------------|-----------------|-----------------|---------|----------|---------------|

| DAC8871B | ±1              | ±1              | −40°C to +105°C | 8871    | TSSOP-16 | PW            |

| DAC8871  | ±3              | ±1              | −40°C to +105°C | 8871    | TSSOP-16 | PW            |

(1) 最新のパッケージ情報と発注情報については、このデーター・シート末尾のパッケージ・オプション追捕または、TIのウェップ・サイト ([www.tij.co.jp](http://www.tij.co.jp), [www.ti.com](http://www.ti.com)) を参照してください。

## 絶対最大定格<sup>(1)</sup>

|                          | DAC8871                             | 単位   |

|--------------------------|-------------------------------------|------|

| $V_{DD}$ ~ GND           | −0.3 ~ +7                           | V    |

| デジタル入力電圧 ~ GND           | −0.3 ~ ( $V_{DD}$ + 0.3)            | V    |

| AGND ~ DGND              | −0.3 ~ +0.3                         | V    |

| $V_{CC}$ ~ $V_{SS}$      | −0.3 ~ +39.6                        | V    |

| $V_{CC}$ ~ AGND          | −0.3 ~ +19.8                        | V    |

| $V_{SS}$ ~ AGND          | +0.3 ~ −19.8                        | V    |

| $V_{REFH}$ ~ $V_{REFL}$  | −0.3 ~ +39.6                        | V    |

| $V_{REFH}$ ~ AGND        | −0.3 ~ +19.8                        | V    |

| $V_{REFL}$ ~ AGND        | −19.8 ~ +17.5                       | V    |

| 動作温度範囲                   | −40 ~ +105                          | °C   |

| 保存温度範囲                   | −65 ~ +150                          | °C   |

| 最大ジャンクション温度 ( $T_J$ max) | +150                                | °C   |

| 許容損失                     | $(T_J$ max − $T_A)$ / $\theta_{JA}$ | W    |

| 熱抵抗, $\theta_{JA}$       | 161.4                               | °C/W |

(1) 絶対最大定格を超えるストレスが加わった場合、デバイスが永続的なダメージを受ける事があります。

また、絶対最大定格の状態が続いた場合、デバイスの信頼性に影響を与える事があります。

## 電気的特性

(特に記述の無い限り)  $T_A = T_{MIN} \sim T_{MAX}$ ,  $V_{CC} = +15V$ ,  $V_{SS} = -15V$ ,  $V_{REFH} = +10V$ ,  $V_{REFL} = -10V$ ,  $V_{DD} = +5V$

| パラメータ                          | 測定条件           | DAC8871                              |                   |                | 単位        |  |  |

|--------------------------------|----------------|--------------------------------------|-------------------|----------------|-----------|--|--|

|                                |                | MIN                                  | TYP               | MAX            |           |  |  |

| <b>静特性</b>                     |                |                                      |                   |                |           |  |  |

| 分解能                            |                | 16                                   |                   | ビット            |           |  |  |

| 直線性誤差                          | DAC8871B       | $V_{REFH} = 10V$ , $V_{REFL} = -5V$  | $\pm 0.75$        | $\pm 1$        | LSB       |  |  |

|                                |                | $V_{REFH} = 10V$ , $V_{REFL} = -10V$ | $\pm 1$           | $\pm 1.5$      | LSB       |  |  |

| DAC8871                        |                | $\pm 1$                              |                   | $\pm 3$        | LSB       |  |  |

| 微分直線性誤差                        |                | $\pm 0.25$                           |                   | $\pm 1$        | LSB       |  |  |

| ゲイン誤差                          |                | $\pm 0.5$                            |                   | 2              | LSB       |  |  |

| ゲイン・ドリフト                       |                | $\pm 0.1$                            |                   | $ppm/^\circ C$ |           |  |  |

| バイポーラ・ゼロ誤差                     |                | $\pm 1$                              |                   | $\pm 4$        | LSB       |  |  |

| バイポーラ・ドリフト                     |                | $\pm 0.1$                            |                   | $ppm/^\circ C$ |           |  |  |

| ゼロ・コード誤差                       |                | $\pm 0.5$                            |                   | $\pm 2$        | LSB       |  |  |

| ゼロ・コード・ドリフト                    |                | $\pm 0.05$                           |                   | $ppm/^\circ C$ |           |  |  |

| <b>出力特性</b>                    |                |                                      |                   |                |           |  |  |

| 出力電圧                           |                | $V_{REFL}$                           | $V_{REFH}$        | V              |           |  |  |

| 出力インピーダンス                      |                | 6.25                                 |                   | $k\Omega$      |           |  |  |

| セトリング時間                        |                | FSの1 LSBまで, $C_L = 15pF$             |                   | 1              | $\mu s$   |  |  |

| スルーレート <sup>(1)</sup>          |                | $C_L = 15pF$                         |                   | 40             | $V/\mu s$ |  |  |

| デジタル・フィードスルー <sup>(2)</sup>    |                | 0.2                                  |                   | $nV\cdot s$    |           |  |  |

| 出力ノイズ                          |                | 10                                   |                   | $nV/\sqrt{Hz}$ |           |  |  |

| 電源除去                           |                | 1                                    |                   | LSB            |           |  |  |

| <b>リファレンス入力</b>                |                |                                      |                   |                |           |  |  |

| $V_{REFH}$ Ref high 入力電圧範囲     |                | 0                                    | $+18$             |                | V         |  |  |

| $V_{REFL}$ Ref low 入力電圧範囲      |                | -18                                  | $V_{REFH} - 1.25$ |                | V         |  |  |

| Ref high 入力電流                  |                | 1.3                                  |                   | $mA$           |           |  |  |

| Ref low 入力電流                   |                | -1.3                                 |                   | $mA$           |           |  |  |

| リファレンス入力インピーダンス <sup>(3)</sup> |                | 7.5                                  |                   | $k\Omega$      |           |  |  |

| リファレンス入力容量                     | Code = 0000h   | 75                                   |                   | $pF$           |           |  |  |

|                                | Code = FFFFh   | 120                                  |                   | $pF$           |           |  |  |

| <b>デジタル入力</b>                  |                |                                      |                   |                |           |  |  |

| $V_{IL}$ "L" 入力電圧              | $V_{DD} = +5V$ | DGND                                 | 0.8               | V              |           |  |  |

|                                | $V_{DD} = +3V$ | DGND                                 | 0.6               | V              |           |  |  |

| $V_{IH}$ "H" 入力電圧              | $V_{DD} = +5V$ | 2.6                                  | $V_{DD}$          | V              |           |  |  |

|                                | $V_{DD} = +3V$ | 2.1                                  | $V_{DD}$          | V              |           |  |  |

| 入力電流                           |                | $\pm 1$                              |                   | $\mu A$        |           |  |  |

| 入力容量                           |                | 10                                   |                   | $pF$           |           |  |  |

(1) スルーレートは、出力が0からフルスケールに変化するときの遷移の10%から90%を測定しています。

(2) デジタル・フィードスルーは、デジタル入力からアナログ出力へ注入されるインパルスとして定義されます。これは、 $\overline{CS}$ を "High" に保ちSCLKおよびDIN信号がトグルしている、DAC出力が変化しない条件下で測定されます。このときのSDIバスにおけるフルスケールのコード変化（すなわち、0000hから1111h、およびその逆）で規定されます。

(3) リファレンス電圧入力抵抗にはコード依存性があり、最小値は8555hのときです。

## 電気的特性（続き）

（特に記述の無い限り） $T_A = T_{MIN} \sim T_{MAX}$ ,  $V_{CC} = +15V$ ,  $V_{SS} = -15V$ ,  $V_{REFH} = +10V$ ,  $V_{REFL} = -10V$ ,  $V_{DD} = +5V$

| パラメータ       | 測定条件 | DAC8871 |     |       | 単位          |

|-------------|------|---------|-----|-------|-------------|

|             |      | MIN     | TYP | MAX   |             |

| <b>電源</b>   |      |         |     |       |             |

| $V_{CC}$    |      | +13.5   | +15 | +19.8 | V           |

| $V_{SS}$    |      | -19.8   | -15 | -13.5 | V           |

| $V_{DD}$    |      | +2.7    |     | +5.5  | V           |

| $I_{CC}$    |      | 0.01    | 2   |       | $\mu A$     |

| $I_{SS}$    |      | -0.01   | -2  |       | $\mu A$     |

| $I_{DD}$    |      | 3       | 10  |       | $\mu A$     |

| 消費電力        |      | 15      | 30  |       | $\mu W$     |

| <b>温度範囲</b> |      |         |     |       |             |

| 規定          |      | -40     |     | +105  | $^{\circ}C$ |

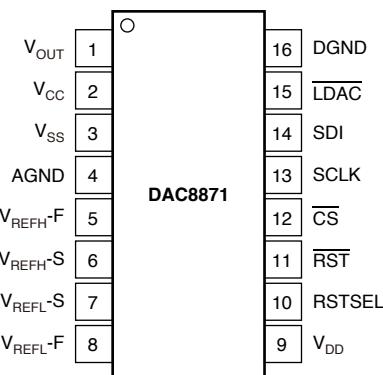

## ピン配置

PWパッケージ

TSSOP-16

(上面図)

## ピン構成

| 端子  | 説明                                                                                                                                                                                                                                             |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | 名称                                                                                                                                                                                                                                             |

| 1   | V <sub>OUT</sub> DACアナログ出力                                                                                                                                                                                                                     |

| 2   | V <sub>CC</sub> アナログ正電源: +15V                                                                                                                                                                                                                  |

| 3   | V <sub>SS</sub> アナログ負電源: -15V                                                                                                                                                                                                                  |

| 4   | AGND アナログ・グランド                                                                                                                                                                                                                                 |

| 5   | V <sub>REFH</sub> -F V <sub>REFH</sub> リファレンス入力 (フォース) 、外部 V <sub>REFH</sub> に接続                                                                                                                                                               |

| 6   | V <sub>REFH</sub> -S V <sub>REFH</sub> リファレンス入力 (センス) 、外部 V <sub>REFH</sub> に接続                                                                                                                                                                |

| 7   | V <sub>REFL</sub> -S V <sub>REFL</sub> リファレンス入力 (センス) 、外部 V <sub>REFL</sub> に接続                                                                                                                                                                |

| 8   | V <sub>REFL</sub> -F V <sub>REFL</sub> リファレンス入力 (フォース) 、外部 V <sub>REFL</sub> に接続                                                                                                                                                               |

| 9   | V <sub>DD</sub> デジタル電源、5Vロジックのインターフェースの場合 +5V, 3Vロジックのインターフェースの場合 +3V                                                                                                                                                                          |

| 10  | RSTSEL パワーオン・リセットの選択、パワーオン・リセット後の V <sub>OUT</sub> を決める。V <sub>DD</sub> に接続の場合、DACラッチがパワーオン後にミッドスケールに設定され、V <sub>OUT</sub> = (V <sub>REFH</sub> - V <sub>REFL</sub> ) / 2。DGNDに接続の場合、DACラッチはクリアされ ('0')、V <sub>OUT</sub> = V <sub>REFL</sub> 。 |

| 11  | RST リセット (アクティブ "Low" )                                                                                                                                                                                                                        |

| 12  | CS チップ・セレクト入力 (アクティブ "Low" ) 、CS が "Low" のときデータをSDIへクロック入力                                                                                                                                                                                     |

| 13  | SCLK シリアル・クロック入力                                                                                                                                                                                                                               |

| 14  | SDI シリアル・データ入力、データはSCLKの立ち上がりエッジでレジスタにラッチ                                                                                                                                                                                                      |

| 15  | LDAC Load DAC 制御入力(アクティブ"Low")、LDAC が "Low" のときDACラッチにラッチすると同時に入力レジスタの内容を更新                                                                                                                                                                    |

| 16  | DGND デジタル・グランド                                                                                                                                                                                                                                 |

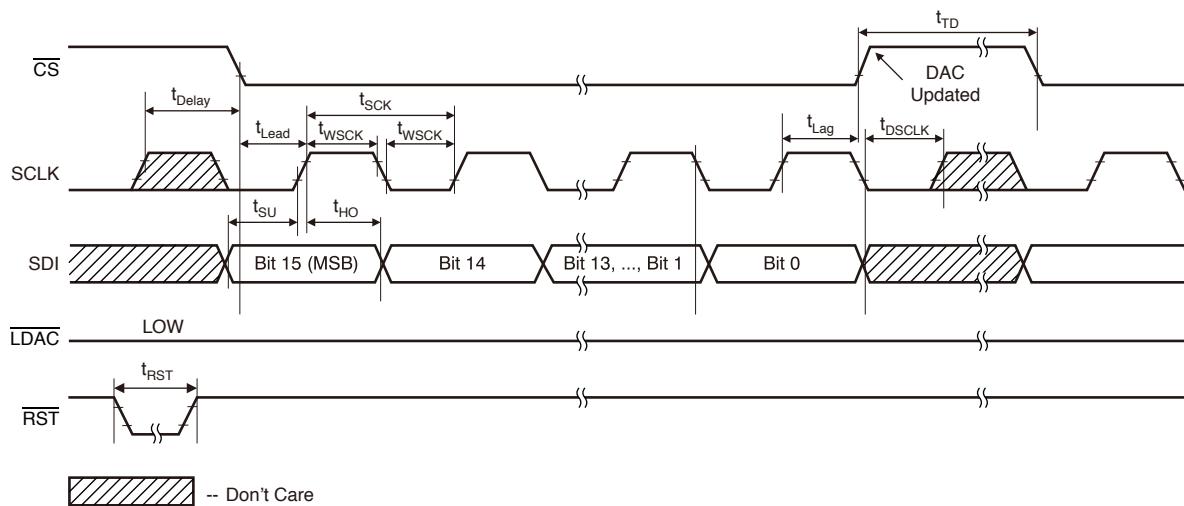

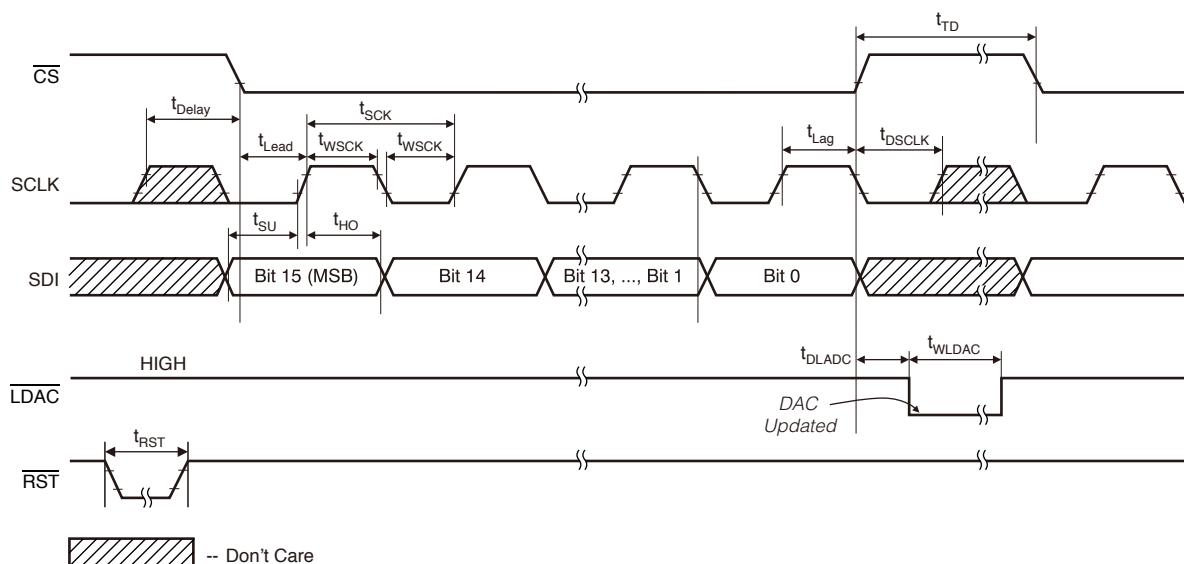

## タイミング図

図1.  $\overline{\text{LDAC}}$ が“Low”固定の場合

図2.  $\overline{\text{LDAC}}$ をアクティブにする場合

タイミング特性 :  $V_{DD}=+5V$ <sup>(1)</sup>(<sup>(2)</sup>)

(特に記述の無い限り)  $T_A = -40 \sim +105^\circ C$

|             | パラメータ                                                     | MIN | MAX | UNIT    |

|-------------|-----------------------------------------------------------|-----|-----|---------|

| $t_{SCK}$   | SCLK 周期                                                   | 20  |     | ns      |

| $t_{WSCK}$  | SCLK "High" / "Low" 時間                                    | 10  |     | ns      |

| $t_{Delay}$ | SCLK "High" から $\overline{CS}$ "Low" までの遅延時間              | 10  |     | ns      |

| $t_{Lead}$  | $\overline{CS}$ イネーブルになる時間                                | 10  |     | ns      |

| $t_{Lag}$   | $\overline{CS}$ イネーブルの遅れ時間                                | 10  |     | ns      |

| $t_{DSCLK}$ | $\overline{CS}$ "High" から SCLK "High" までの遅延時間             | 10  |     | ns      |

| $t_{TD}$    | $\overline{CS}$ のアクティブからアクティブ間の $\overline{CS}$ "High" 時間 | 30  |     | ns      |

| $t_{SU}$    | データ・セットアップ時間 (入力)                                         | 10  |     | ns      |

| $t_{HO}$    | データ・ホールド時間 (入力)                                           | 0   |     | ns      |

| $t_{WLDAc}$ | $\overline{LDAC}$ 幅                                       | 30  |     | ns      |

| $t_{DLDAc}$ | $\overline{CS}$ "High" から $\overline{LDAC}$ "Low" までの遅延時間 | 30  |     | ns      |

| $t_{RST}$   | リセット ( $\overline{RST}$ ) "Low" 時間                        | 10  |     | ns      |

|             | $V_{DD}$ "High" から $\overline{CS}$ "Low" まで (パワーアップ遅延時間)  | 10  |     | $\mu s$ |

(1) 設計でのデータ。製造時に試験はしていません。

(2) 出荷開始時に抜き取りサンプル・テスト、その後は再設計やプロセス変更時に試験を行いこのパラメータに反映します。

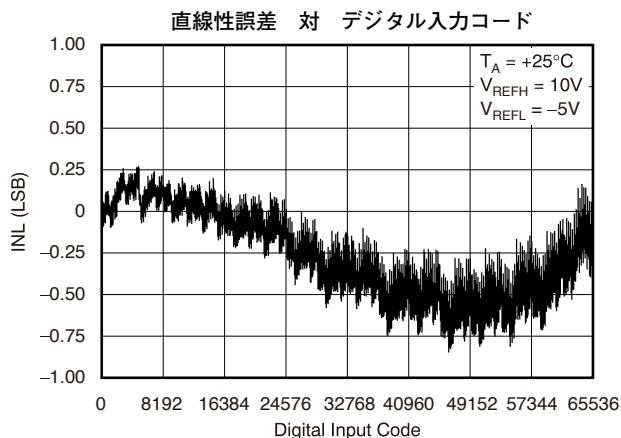

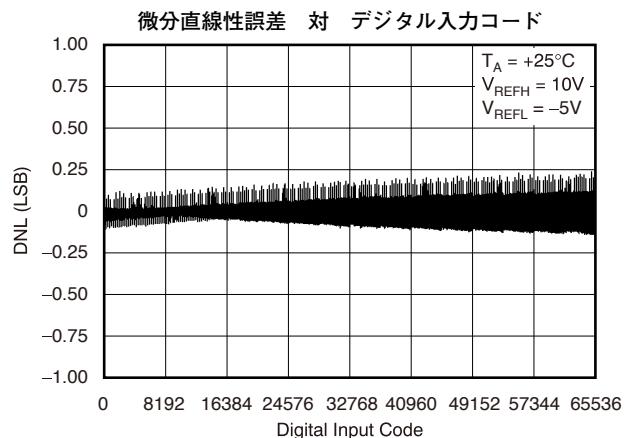

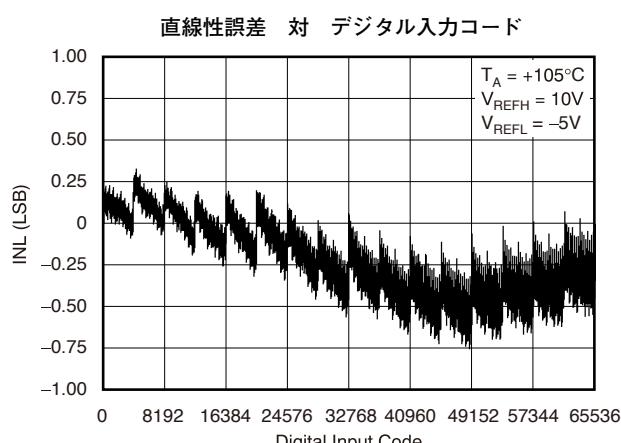

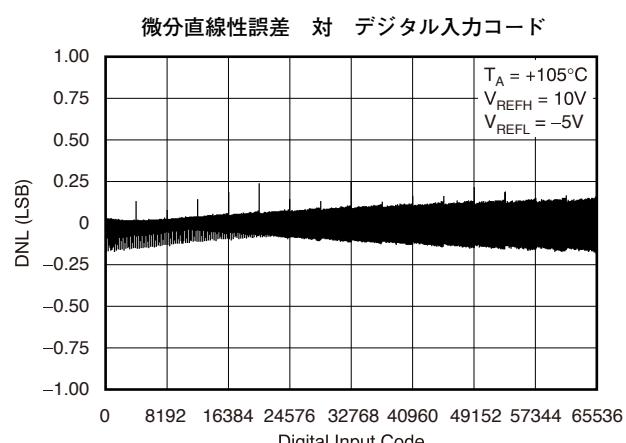

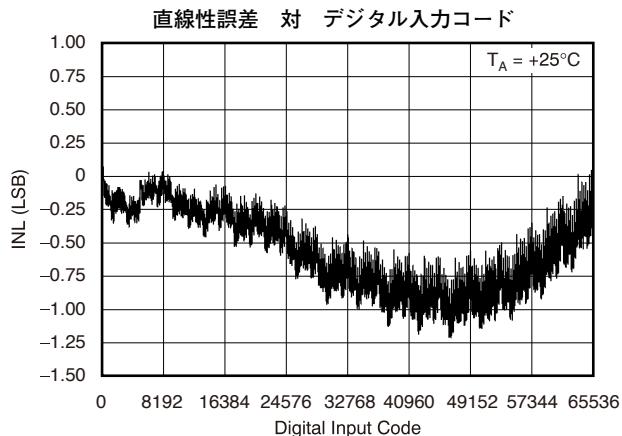

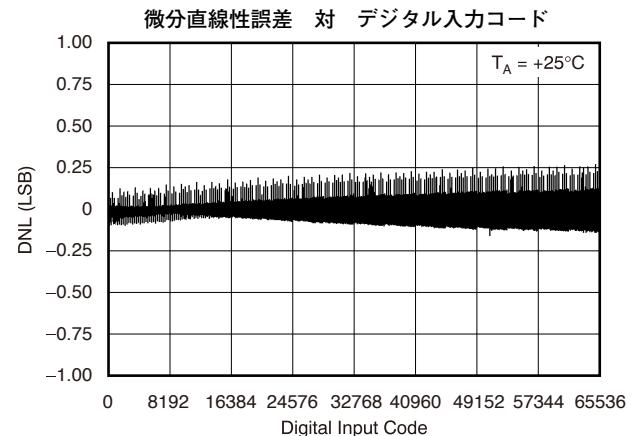

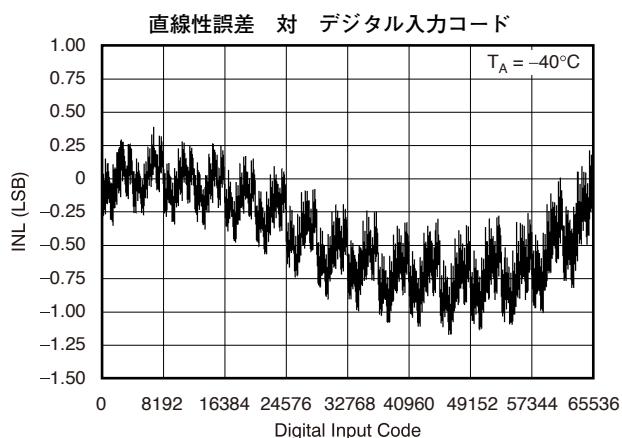

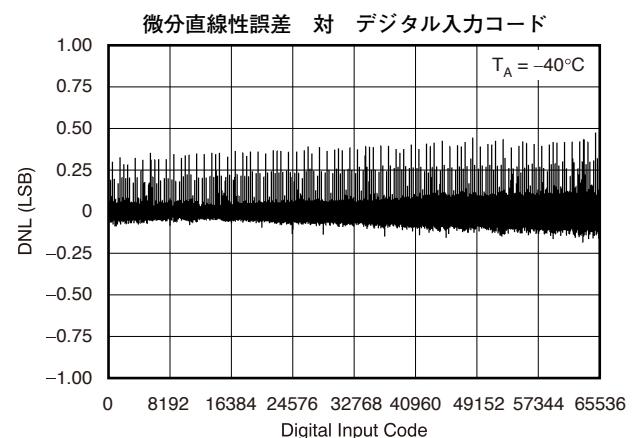

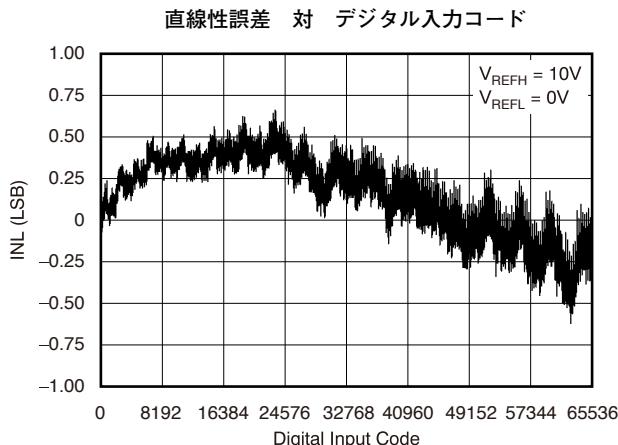

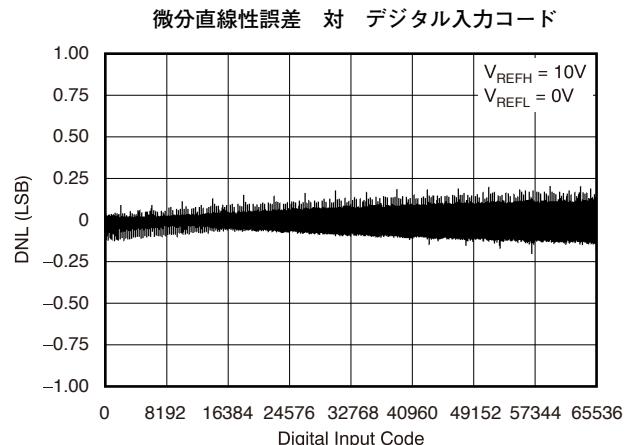

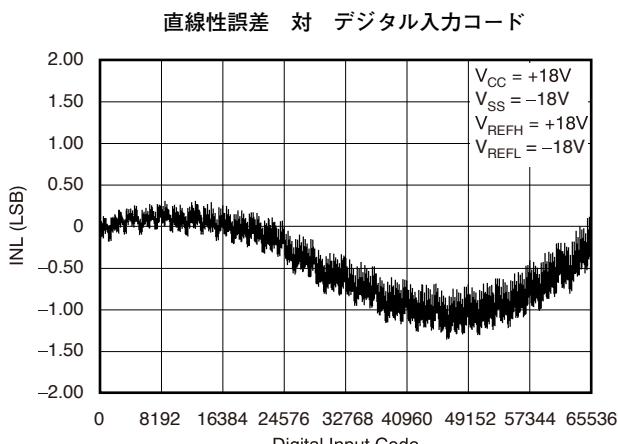

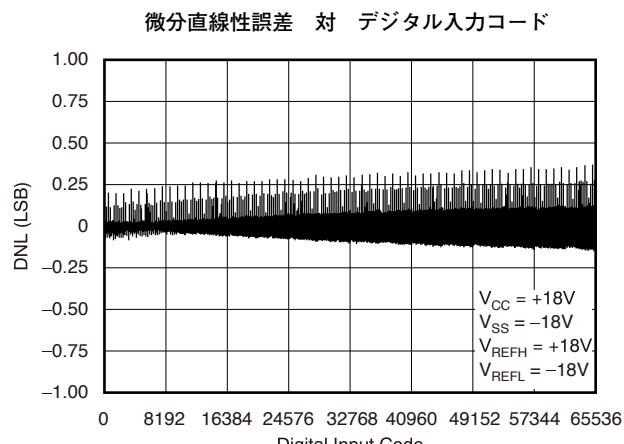

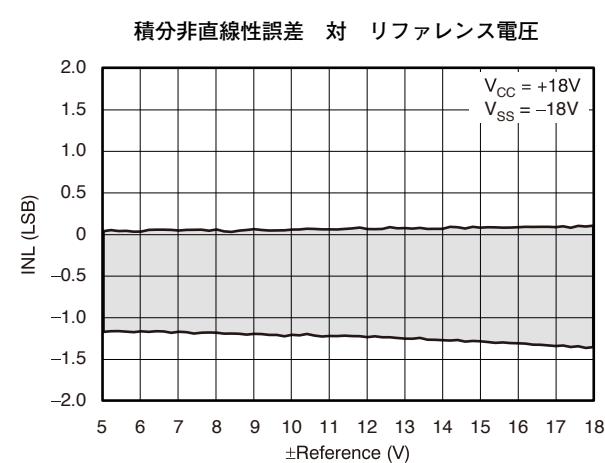

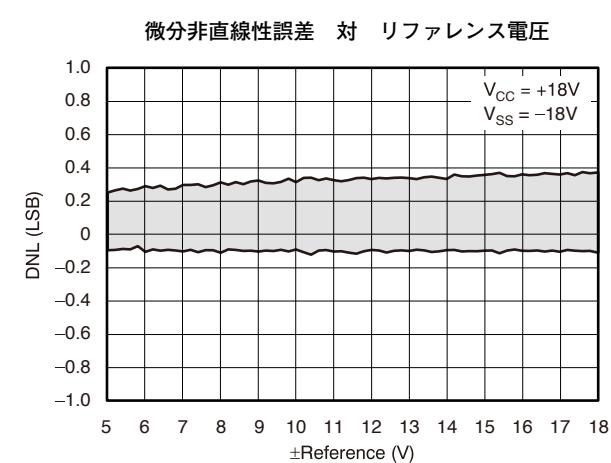

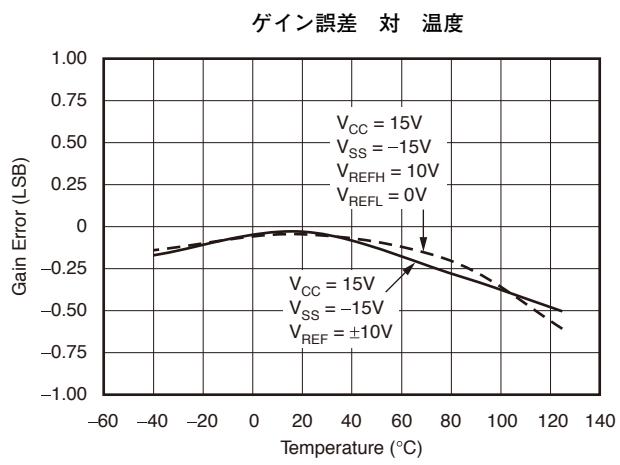

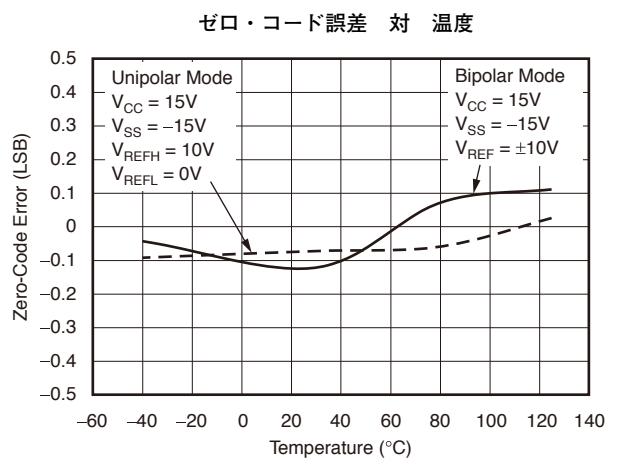

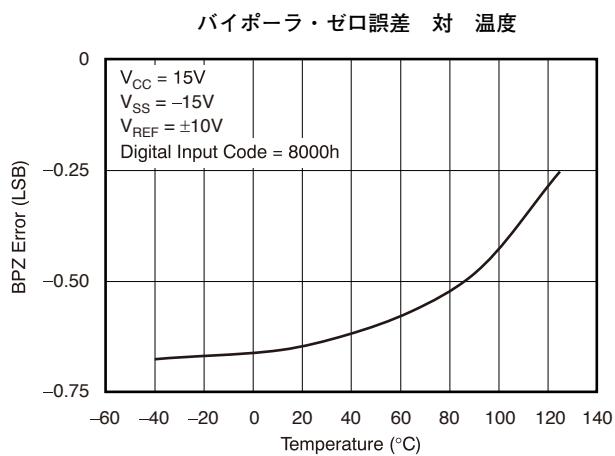

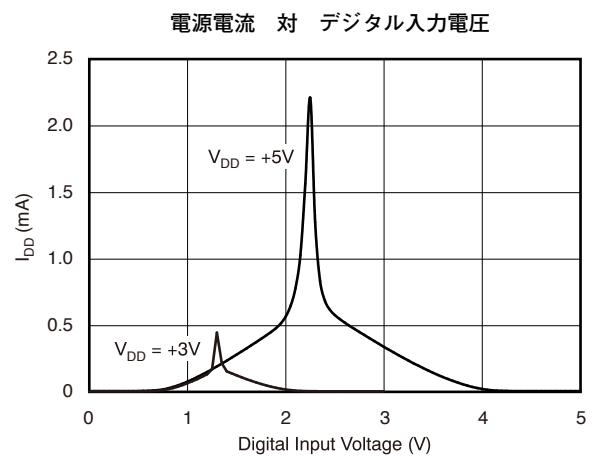

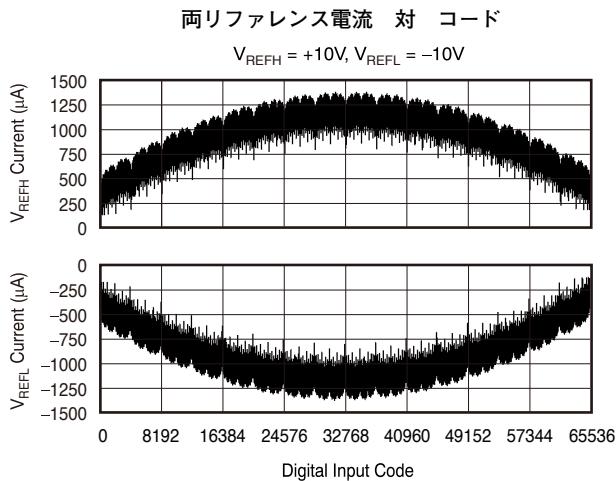

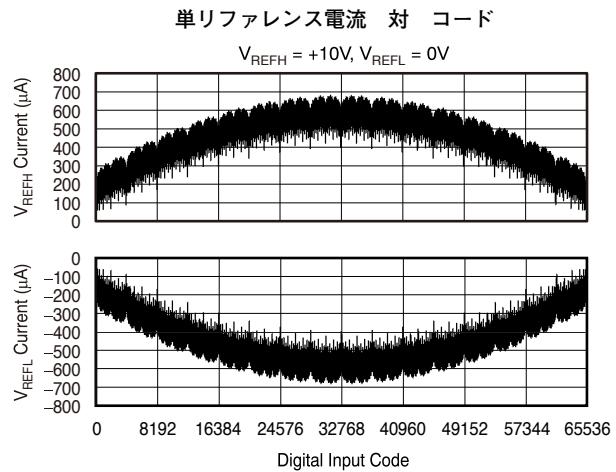

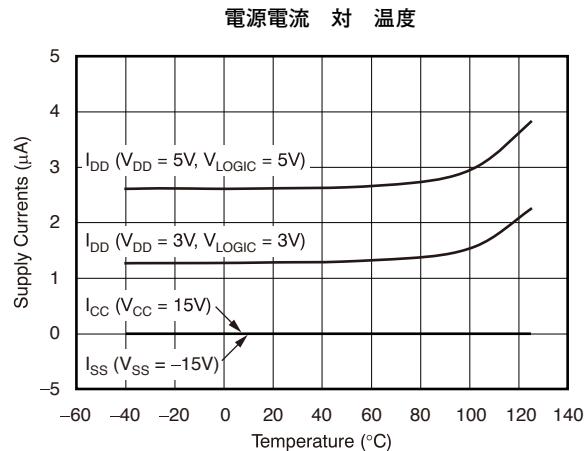

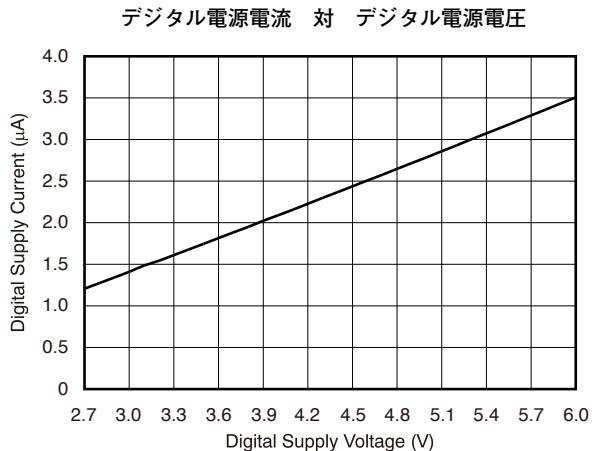

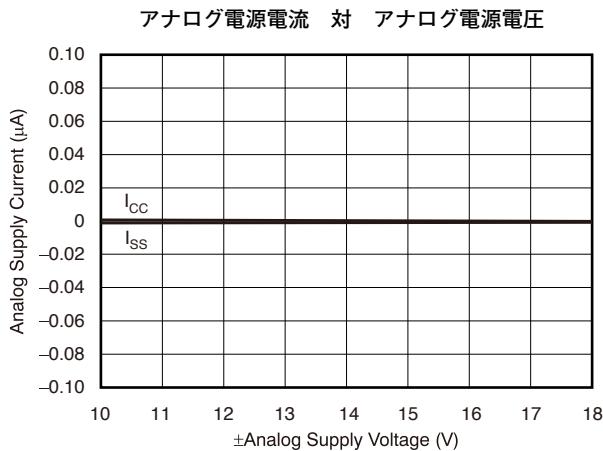

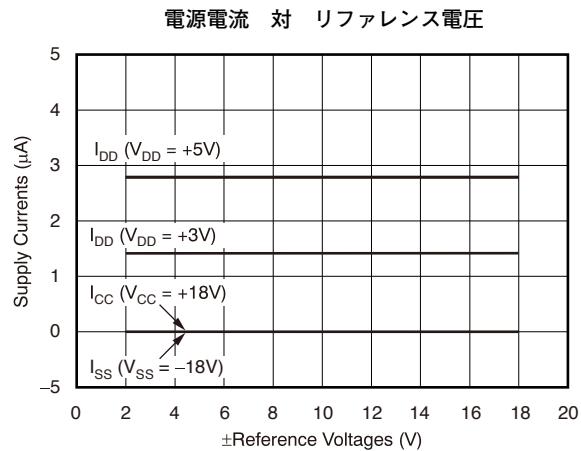

## 代表的特性

(特に記述の無い限り)  $T_A = +25^\circ\text{C}$ ,  $V_{DD} = +5\text{V}$ ,  $V_{CC} = +15\text{V}$ ,  $V_{SS} = -15\text{V}$ ,  $V_{REFH} = +10\text{V}$ ,  $V_{REFL} = -10\text{V}$

図3

図4

図5

図6

図7

図8

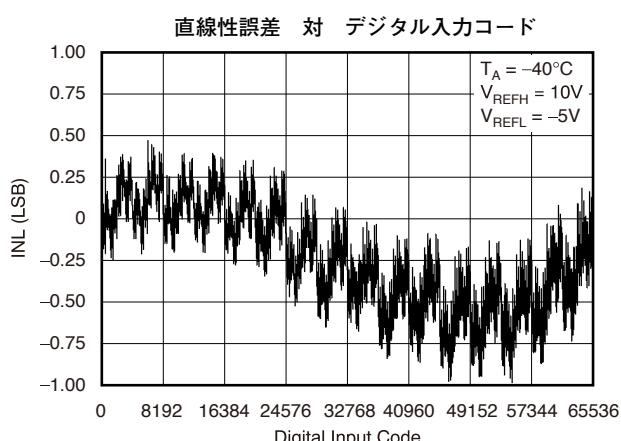

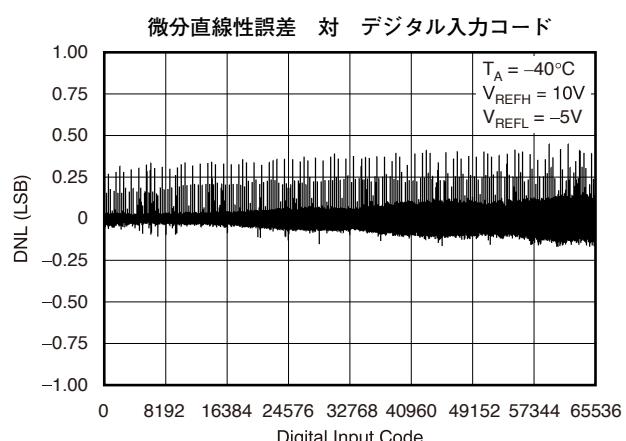

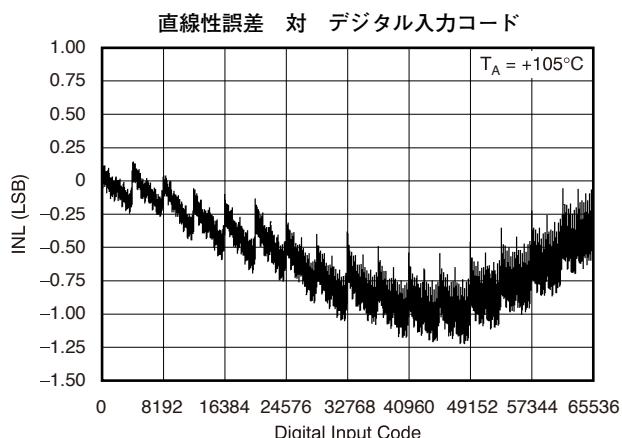

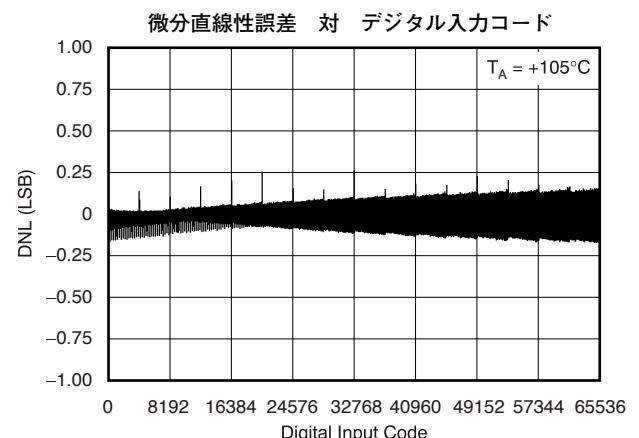

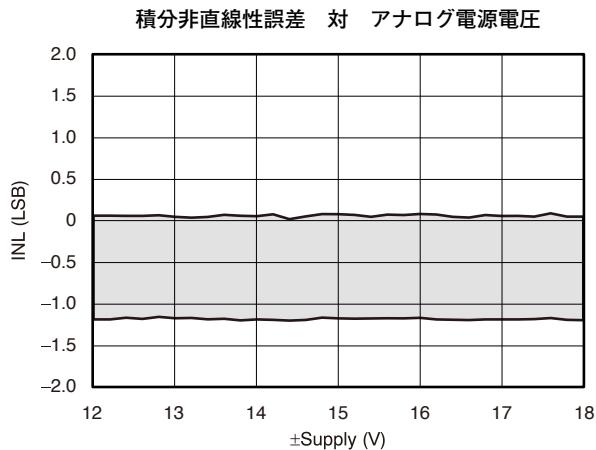

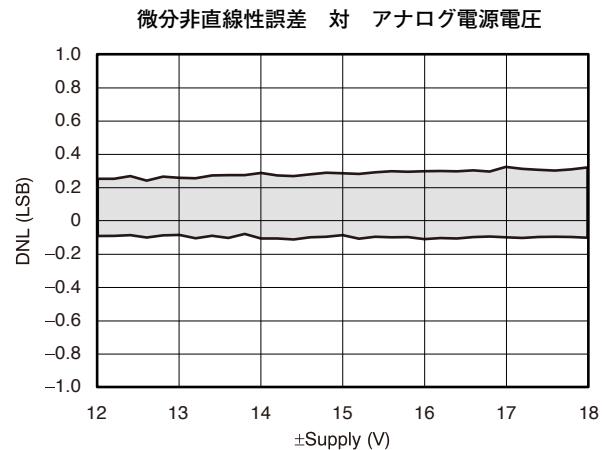

## 代表的特性 (続き)

(特に記述の無い限り)  $T_A = +25^\circ\text{C}$ ,  $V_{DD} = +5\text{V}$ ,  $V_{CC} = +15\text{V}$ ,  $V_{SS} = -15\text{V}$ ,  $V_{REFH} = +10\text{V}$ ,  $V_{REFL} = -10\text{V}$

図9

図10

図11

図12

図13

図14

## 代表的特性 (続き)

(特に記述の無い限り)  $T_A = +25^\circ\text{C}$ ,  $V_{DD} = +5\text{V}$ ,  $V_{CC} = +15\text{V}$ ,  $V_{SS} = -15\text{V}$ ,  $V_{REFH} = +10\text{V}$ ,  $V_{REFL} = -10\text{V}$

図15

図16

図17

図18

図19

図20

## 代表的特性 (続き)

(特に記述の無い限り)  $T_A = +25^\circ\text{C}$ ,  $V_{DD} = +5\text{V}$ ,  $V_{CC} = +15\text{V}$ ,  $V_{SS} = -15\text{V}$ ,  $V_{REFH} = +10\text{V}$ ,  $V_{REFL} = -10\text{V}$

図21

図22

図23

図24

図25

図26

## 代表的特性 (続き)

(特に記述の無い限り)  $T_A = +25^\circ\text{C}$ ,  $V_{DD} = +5\text{V}$ ,  $V_{CC} = +15\text{V}$ ,  $V_{SS} = -15\text{V}$ ,  $V_{REFH} = +10\text{V}$ ,  $V_{REFL} = -10\text{V}$

図27

図28

図29

図30

図31

図32

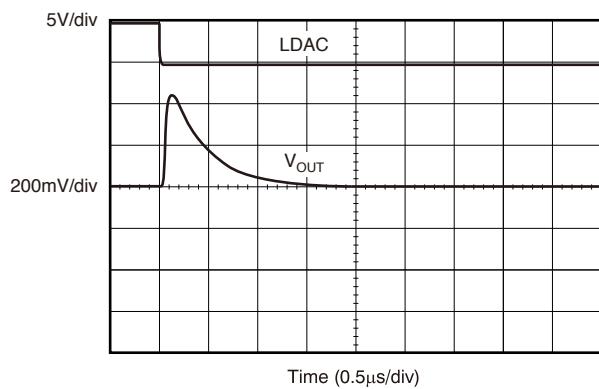

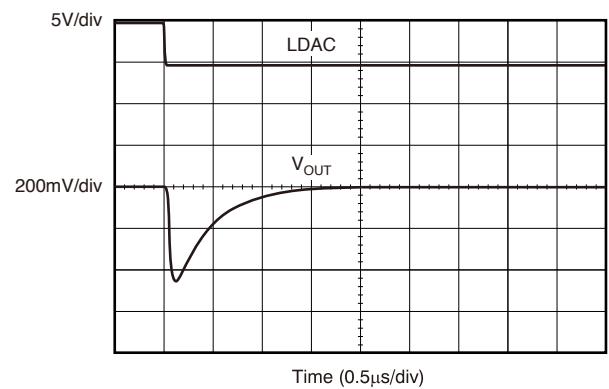

## 代表的特性（続き）

（特に記述の無い限り） $T_A = +25^\circ\text{C}$ ,  $V_{DD} = +5\text{V}$ ,  $V_{CC} = +15\text{V}$ ,  $V_{SS} = -15\text{V}$ ,  $V_{REFH} = +10\text{V}$ ,  $V_{REFL} = -10\text{V}$

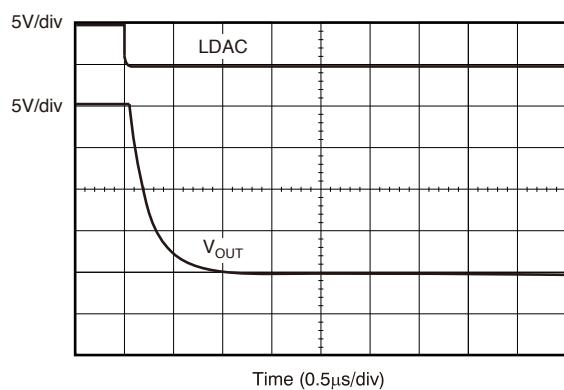

メジャー・キャリー・グリッチ（立下り）

図33

メジャー・キャリー・グリッチ（立上り）

図34

DACセトリング・タイム（立下り）

図35

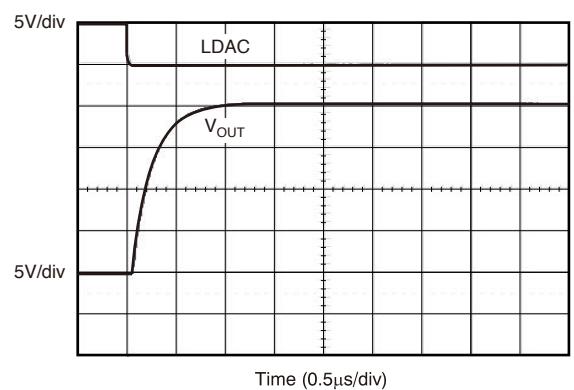

DACセトリング・タイム（立上り）

図36

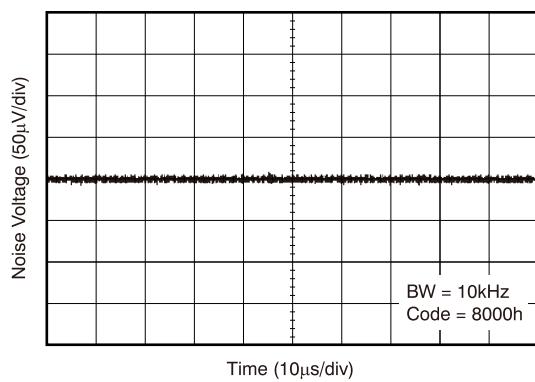

広帯域ノイズ

図37

## 動作理論

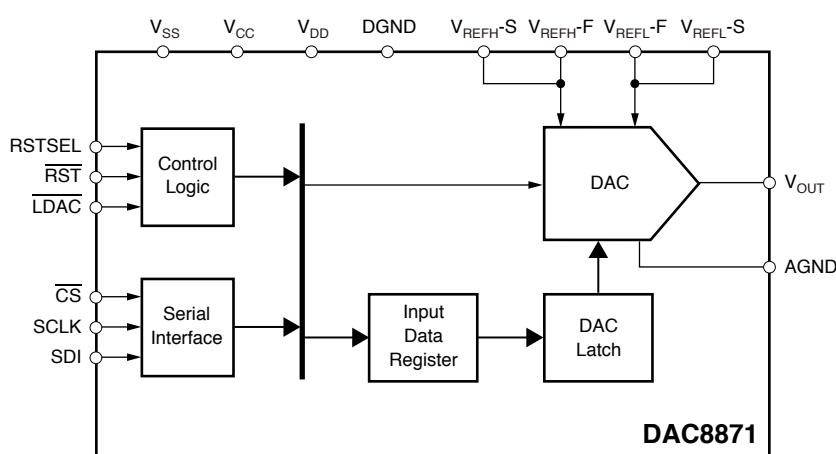

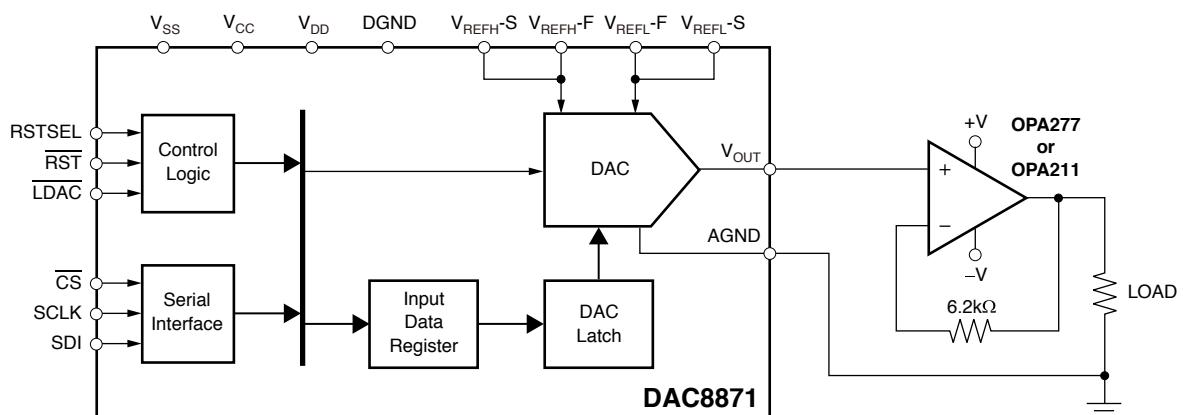

### 概要

DAC8871は、16ビット、シングル・チャネル、シリアル入力、電圧出力のDACです。 $\pm 13.5V$ から $\pm 19.8V$ までの範囲のデュアル電源で動作し、 $10\mu A$  (Typ) の消費電流となります。その出力範囲は $V_{REFL}$ から $V_{REFH}$ です。データは16ビット・ワード・フォーマットで、SPIシリアル・インターフェイスを経由してDAC8871に書き込みます。DAC8871は、電源投入時に出力を既知の状態にするようにパワーオン・リセット機能が組込まれています。パワーオン後、RSTSEL端子の状態により入力レジスタの値およびDACラッチが設定され、このDACラッチが $V_{OUT}$ 端子の出力状態を設定します。詳細は、「パワーオン・リセットおよびハードウェア・リセット」節を参照してください。

DAC8871には、リファレンス電圧およびアナログ・グランド用のケルビン接続用端子も備えています。

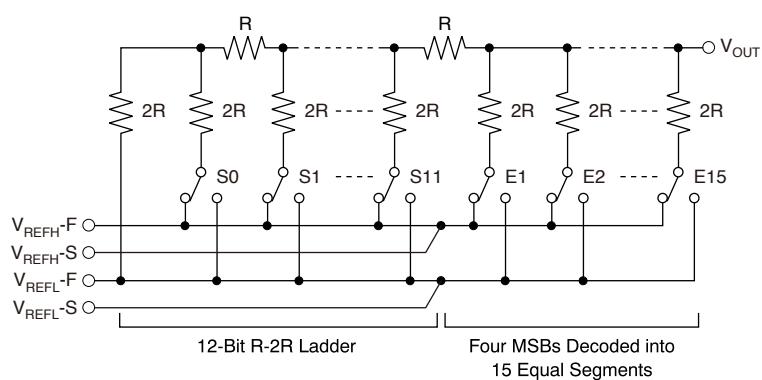

### デジタル・アナログ変換部

DAC8871のDACアーキテクチャは2つのマッチドDACで構成され、かつ、セグメント化されています。その単純化した回路図を図38に示します。16ビット・データ・ワードの上位 (MSB) 4ビットは、デコードされて15個のスイッチE1からE15をドライブします。これらスイッチの各々が、15個の同じ抵抗値の抵抗の1個をAGNDあるいは $V_{REF}$ のいずれかに接続します。データ・ワードの残りの12ビットは、12ビット電圧モードR-2Rラダー抵抗網のスイッチS0からS11をドライブします。

図38. DACのアーキテクチャ

### 出力範囲

DACの出力は次式のようになります。

$$V_{OUT} = \frac{(V_{REFH} - V_{REFL}) \times \text{Code}}{65536} + V_{REFL} \quad (1)$$

ここで、Code (コード) とはDACラッチにロードされる10進データ・ワードです。

例えば、 $V_{REFH}$ が $+10V$ および $V_{REFL}$ が $-10V$ の場合、 $V_{OUT}$ の範囲は $-10V$  (Code=0000h) から $+10V$  (Code=FFFFh) になります。

$V_{REFL}$ の範囲は $-18V$ から ( $V_{REFH}-1.25V$ ) であり、 $V_{REFH}$ の範囲は $0V$ から $+18V$ です。DAC8871の出力は、適切な $V_{REFL}$ および $V_{REFH}$ の値を設定することにより、ユニポーラ (0Vから $+18V$ ) またはバイポーラにすることができます。

## パワーオン・リセットおよびハードウェア・リセット

DAC8871にはパワーオン・リセット機能があります。RSTSEL端子が“Low”(DGNDに接続)で、パワーオンまたはハードウェア・リセット信号で $\overline{RST}$ 端子を有効にしたとき、DACラッチは('0')にクリアされ、V<sub>OUT</sub>端子は負のフルスケールに設定されます。RSTSEL端子が“High”的場合、DACラッチおよびV<sub>OUT</sub>はミッドスケールに設定されます。

## シリアル・インターフェイス

DAC8871のデジタル・インターフェイスは、SPI、QSPI<sup>TM</sup>、Microwire<sup>TM</sup>およびTI DSP<sup>TM</sup>インターフェイスと互換性のある標準的な3線式であり、最大50Mビット/秒の伝送速度まで動作できます。データ伝送はチップ・セレクト( $\overline{CS}$ )信号によりフレーム化されます。DACはバス・スレーブとして動作します。バス・マスターは同期クロック(SCLK)を発生し、データ伝送を開始します。 $\overline{CS}$ が“High”的場合、DACはアクセスされず、SCLKとSDIは無視されます。バス・マスターは、 $\overline{CS}$ を“Low”にドライブしてDACにアクセスします。 $\overline{CS}$ の“High”から“Low”への遷移の直後に、SDI端子へのシリアル入力データはSCLKの立ち上がりエッジに同期してバス・マスターからシフト出力され、SCLKの立ち上がりエッジで入力シフトレジスタにMSBファーストでラッチされます。 $\overline{CS}$ の“Low”から“High”への遷移により、入力シフトレジスタの内容は入力レジスタへ転送されます。

データ・レジスタは、すべて16ビットです。DAC8871に1データ・ワードを転送するには16SCLKサイクルが必要です。1データ・ワード全体の転送を完了するには、16番目のSCLKが入力された直後に $\overline{CS}$ が“High”になる必要があります。 $\overline{CS}$ が“Low”的間にSCLKが16サイクル以上供給されると、最後の16ビットが $\overline{CS}$ の立ち上がりエッジで入力レジスタへ転送されます。しかし、 $\overline{CS}$ が16SCLKサイクルの途中で“High”になると、データは破損されます。この場合、DACへ新規の16ビット・ワードを再ロードします。

DAC8871にはLDAC端子があり、 $\overline{CS}$ が“High”になった後でLDACを“Low”にすることにより、DACラッチを非同期で更新することができます。この場合、 $\overline{CS}$ が“Low”的間LDACを“High”に保つ必要があります。 $\overline{LDAC}$ を“Low”に固定すると、DACラッチは入力レジスタがロードされた直後に更新されます(これは、 $\overline{CS}$ の“Low”から“High”への遷移によります)。

## 外付けアンプの選定

DAC8871の出力はバッファされていません。その出力インピーダンスは約6.2k $\Omega$ です。外付けのバッファ・アンプを要するアプリケーションの場合、出力オフセットのトリミングを不要にするため、低オフセット電圧(出力範囲が±10Vで1LSB=305 $\mu$ V)のアンプを選ぶ必要があります。また、入力バイアス電流とDAC出力インピーダンス(およそ6.25k $\Omega$ )の積がゼロ・コード誤差に加算されるため、入力バイアス電流も低いアンプにします。入出力レール・ツー・レール特性も必要になります。セトリングの高速性については、オペアンプのスルーレートによりDACのセトリング・タイムが妨害されないようにします。DACの出力インピーダンスは一定であり、コードに依存しません。しかし、ゲイン誤差を最小にするために、出力アンプの入力インピーダンスは可能な限り高くなります。さらに、アンプの3dB帯域幅は1MHz以上にします。アンプによりシステムに対して別個の時定数が加わるため、出力のセトリング・タイムは増加します。したがって、アンプの3dB帯域幅が高いと、DACとアンプを組み合わせた実効的なセトリング・タイムは短いものになります。

図39. 外部アンプを付けたDAC8871

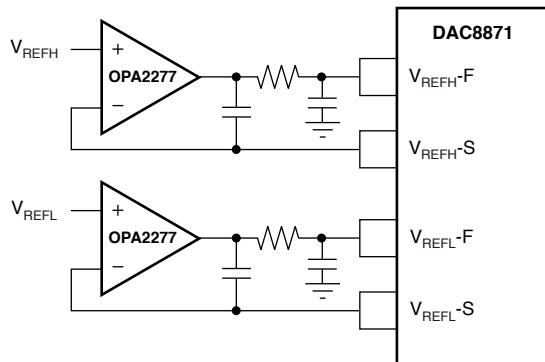

## リファレンス電圧入力

DACのフルスケール出力電圧は、「出力範囲」節で示したように、リファレンス電圧により定まります。

リファレンス電圧入力  $V_{REFH}$  は、0Vから+18Vまでの任意の電圧に設定できます。また、リファレンス電圧入力  $V_{REFL}$  は、-18Vから  $(V_{REFH} - 1.25V)$  までの任意の電圧に設定できます。 $V_{REFH}$  入力に流入し、 $V_{REFL}$  から流出する電流は、DACの出力電圧に依存します。詳細は図27および図28を参照してください。リファレンス電圧入力は、リファレンス電圧源に対して変動する負荷になります。リファレンス電圧源が所要の電流をシンクまたはソースできる場合、リファレンス電圧バッファは不要です。DAC8871にはリファレンス電圧ドライブ（フォース）およびセンス接続があり、リファレンス電圧電流および回路インピーダンスの変化により生じる内部誤差を最小にします。図40に標準的なリファレンス電圧構成を示します。

図40. バッファされたリファレンス電圧の接続

## 電源のバイパス

高精度、高分解能の特性を実現するために、 $10\mu F$ のタンタル・コンデンサと $0.1\mu F$ のセラミック・コンデンサの各1個を並列にして、電源端子をバイパスするように推奨します。

## 電源立ち上げシーケンス

アナログ電源 (VCC と VSS) はデジタル電源 (VDD) より先に立ち上げてください。これら全ての電源はリファレンス電源 ( $V_{REFH}$  と  $V_{REFL}$ ) より必ず先に立ち上げなければなりません。更に、DACの入力シフトレジスタはパワーオン・リセット（もしくは  $\overline{RST}$  ピンによるハードウェア・リセット）によってリセットされませんから、電源が立ち上がるまでは  $\overline{CS}$  ピンは間違っても絶対にアサートしないで下さい。不適当なパワーアップに備えるためにも、 $\overline{CS}$  ピンは抵抗を介して VDD へプルアップされることをお薦め致します。

同様に、パワーアップしている期間は、 $\overline{LDAC}$  ピンの状態を絶対に変えないで下さい。 $\overline{LDAC}$  ピンは、抵抗を介して VDD へプルアップされることをお薦めいたします。もし全く使用されない場合には GND へ固定接続してください。

ESD保護回路が起動されることを確実に防ぐために、他の全部のデジタル信号ピンは、VDD が立ち上がるまで必ず GND 電位を保持して下さい。

## パッケージ情報

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|--------------|-----------------|------|-------------|-------------------------|------------------|------------------------------|

| DAC8871SBPW      | ACTIVE                | TSSOP        | PW              | 16   | 90          | Green (RoHS & no Sb/Br) | Call TI          | Level-2-260C-1 YEAR          |

| DAC8871SBPWG4    | ACTIVE                | TSSOP        | PW              | 16   | 90          | Green (RoHS & no Sb/Br) | Call TI          | Level-2-260C-1 YEAR          |

| DAC8871SBPWR     | ACTIVE                | TSSOP        | PW              | 16   | 2000        | Green (RoHS & no Sb/Br) | Call TI          | Level-2-260C-1 YEAR          |

| DAC8871SBPWRG4   | ACTIVE                | TSSOP        | PW              | 16   | 2000        | Green (RoHS & no Sb/Br) | Call TI          | Level-2-260C-1 YEAR          |

| DAC8871SPW       | ACTIVE                | TSSOP        | PW              | 16   | 90          | Green (RoHS & no Sb/Br) | Call TI          | Level-2-260C-1 YEAR          |

| DAC8871SPWG4     | ACTIVE                | TSSOP        | PW              | 16   | 90          | Green (RoHS & no Sb/Br) | Call TI          | Level-2-260C-1 YEAR          |

| DAC8871SPWR      | ACTIVE                | TSSOP        | PW              | 16   | 2000        | Green (RoHS & no Sb/Br) | Call TI          | Level-2-260C-1 YEAR          |

| DAC8871SPWRG4    | ACTIVE                | TSSOP        | PW              | 16   | 2000        | Green (RoHS & no Sb/Br) | Call TI          | Level-2-260C-1 YEAR          |

(1) マーケティング・ステータスは次のように定義されています。

ACTIVE : 製品デバイスが新規設計用に推奨されています。

LIFEBUY : TI によりデバイスの生産中止予定が発表され、ライフタイム購入期間が有効です。

NRND : 新規設計用に推奨されていません。デバイスは既存の顧客をサポートするために生産されていますが、TI では新規設計にこの部品を使用することを推奨していません。

PREVIEW : デバイスは発表済みですが、まだ生産が開始されていません。サンプルが提供される場合と、提供されない場合があります。

OBSOLETE : TI によりデバイスの生産が中止されました。

(2) エコ・プラン - 環境に配慮した製品分類プランであり、Pb-Free (RoHS)、Pb-Free (RoHS Expert) および Green (RoHS & no Sb/Br) があります。最新情報および製品内容の詳細については、<http://www.ti.com/productcontent> でご確認ください。

TBD : Pb-Free/Green 変換プランが策定されていません。

Pb-Free (RoHS) : TI における “Lead-Free” または “Pb-Free” (鉛フリー) は、6 つの物質すべてに対して現在の RoHS 要件を満たしている半導体製品を意味します。これには、同種の材質内で鉛の重量が 0.1% を超えないという要件も含まれます。高温で半田付けするように設計されている場合、TI の鉛フリー製品は指定された鉛フリー・プロセスでの使用に適しています。

Pb-Free (RoHS Exempt) : この部品は、1) ダイとパッケージの間に鉛ベースの半田バンプ使用、または 2) ダイとリードフレーム間に鉛ベースの接着剤を使用、が除外されています。それ以外は上記の様に Pb-Free (RoHS) と考えられます。

Green(RoHS & no Sb/Br) : TI における “Green” は、“Pb-Free” (RoHS 互換) に加えて、臭素 (Br) およびアンチモン (Sb) をベースとした難燃材を含まない (均質な材質中の Br または Sb 重量が 0.1% を超えない) ことを意味しています。

(3) MSL、ピーク温度 -- JEDEC 業界標準分類に従った耐湿性レベル、およびピーク半田温度です。

重要な情報および免責事項 : このページに記載された情報は、記載された日付時点での TI の知識および見解を表しています。TI の知識および見解は、第三者によって提供された情報に基づいており、そのような情報の正確性について何らの表明および保証も行うものではありません。第三者からの情報をより良く統合するための努力は続けております。TI では、事実を適切に表す正確な情報を提供すべく妥当な手順を踏み、引き続きそれを継続してゆきますが、受け入れる部材および化学物質に対して破壊試験や化学分析は実行していない場合があります。TI および TI 製品の供給者は、特定の情報を機密情報として扱っているため、CAS 番号やその他の制限された情報が公開されない場合があります。

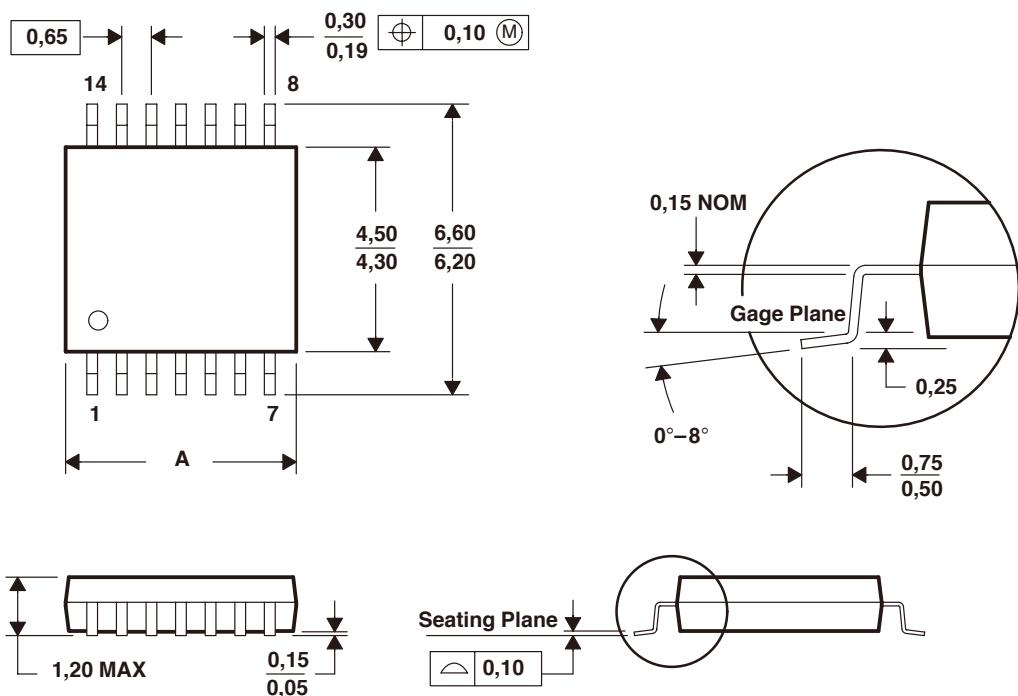

14 PINS SHOWN

| DIM   | PINS ** | 8    | 14   | 16   | 20   | 24   | 28   |

|-------|---------|------|------|------|------|------|------|

| A MAX |         | 3,10 | 5,10 | 5,10 | 6,60 | 7,90 | 9,80 |

| A MIN |         | 2,90 | 4,90 | 4,90 | 6,40 | 7,70 | 9,60 |

4040064/F 01/97

## 注記 :

- A. 尺法はすべてミリメートルです。

- B. 本図は予告なく変更することがあります。

- C. ボディの寸法には、0,15 を超えるモールド・フラッシュや突起は含まれません。

- D. JEDEC MO-153 に準拠します。

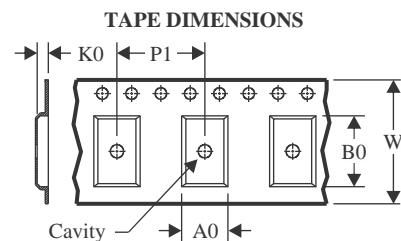

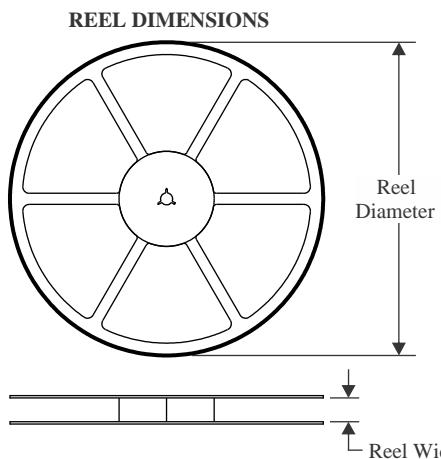

**TAPE AND REEL INFORMATION**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

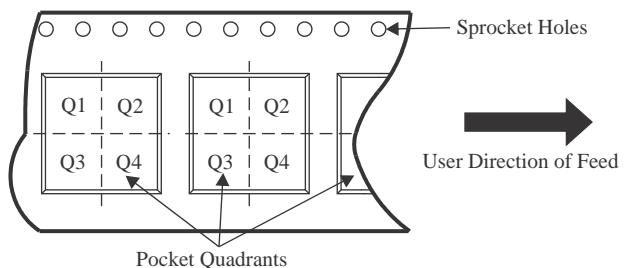

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|--------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| DAC8871SBPWR | TSSOP        | PW              | 16   | 2000 | 330.0              | 12.4               | 6.9     | 5.6     | 1.6     | 8.0     | 12.0   | Q1            |

| DAC8871SPWR  | TSSOP        | PW              | 16   | 2000 | 330.0              | 12.4               | 6.9     | 5.6     | 1.6     | 8.0     | 12.0   | Q1            |

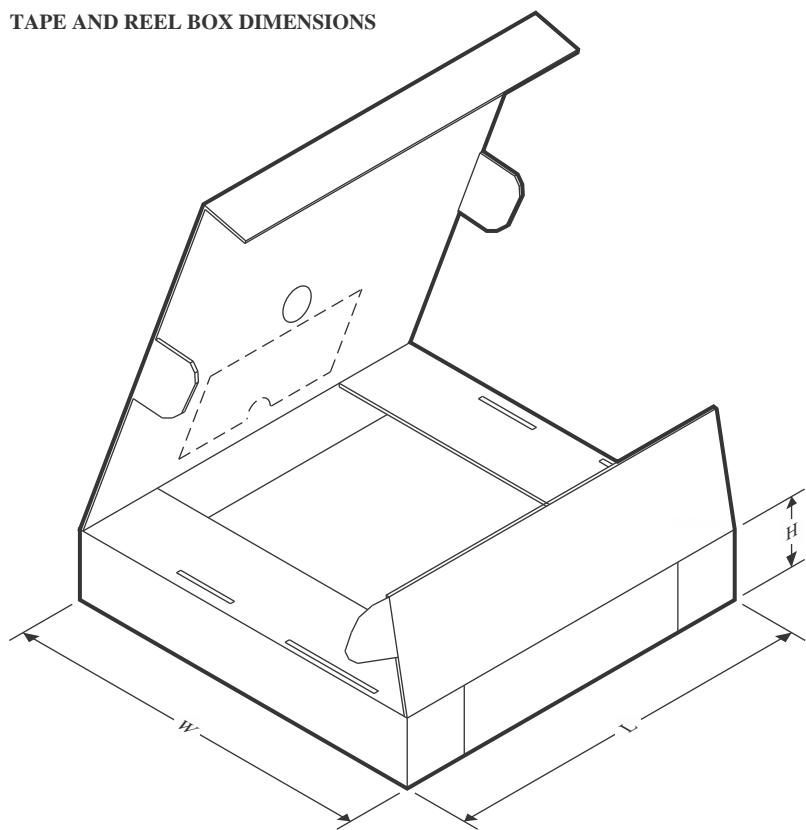

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DAC8871SBPWR | TSSOP        | PW              | 16   | 2000 | 350.0       | 350.0      | 43.0        |

| DAC8871SPWR  | TSSOP        | PW              | 16   | 2000 | 350.0       | 350.0      | 43.0        |

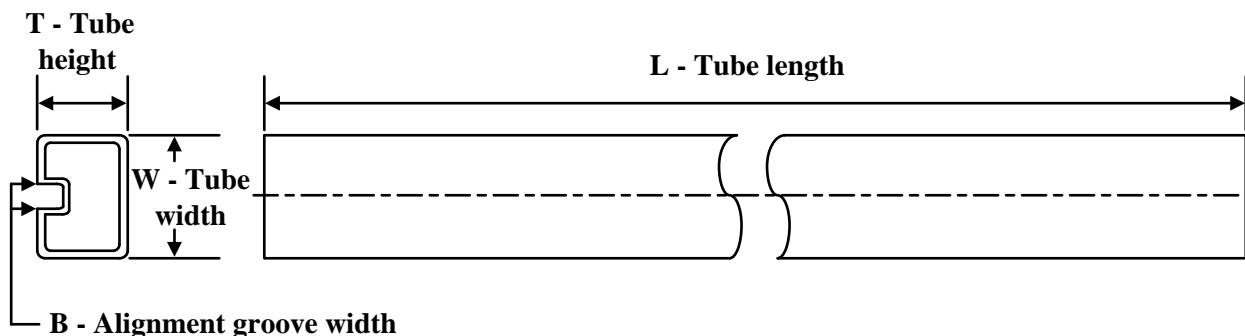

**TUBE**

\*All dimensions are nominal

| Device        | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T ( $\mu$ m) | B (mm) |

|---------------|--------------|--------------|------|-----|--------|--------|--------------|--------|

| DAC8871SBPW   | PW           | TSSOP        | 16   | 90  | 530    | 10.2   | 3600         | 3.5    |

| DAC8871SBPW.A | PW           | TSSOP        | 16   | 90  | 530    | 10.2   | 3600         | 3.5    |

| DAC8871SPW    | PW           | TSSOP        | 16   | 90  | 530    | 10.2   | 3600         | 3.5    |

| DAC8871SPW.A  | PW           | TSSOP        | 16   | 90  | 530    | 10.2   | 3600         | 3.5    |

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適したテキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかるテキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所 : Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated