# DAC539E4W LUT ベースのスタンドアロン障害管理向け、I<sup>2</sup>C または SPI 自動検出機能付き、10 ビット・スマート DAC

## 1 特長

- クワッドコンパレータ入力

- 10ビットの独立コンパレータスレッショルド

- 1 LSB の DNL

- 1×、1.5×、2×、3×、4× のゲイン

- クワッド汎用出力 (GPO)

- LUT に基づくコンパレータから GPO へのマッピング

- SPI および I<sup>2</sup>C インターフェイスの自動検出

- $V_{IH}$ : 1.62V ( $V_{DD} = 5.5V$  の場合)

- MODE ピンにより、プログラミングモードとスタンドアロンモードを選択

- ユーザーがプログラム可能な不揮発性メモリ (NVM)

- リファレンス: 内部、外部、VDD

- 広い動作範囲

- 電源: 1.8V ~ 5.5V

- 温度: -40°C ~ +125°C

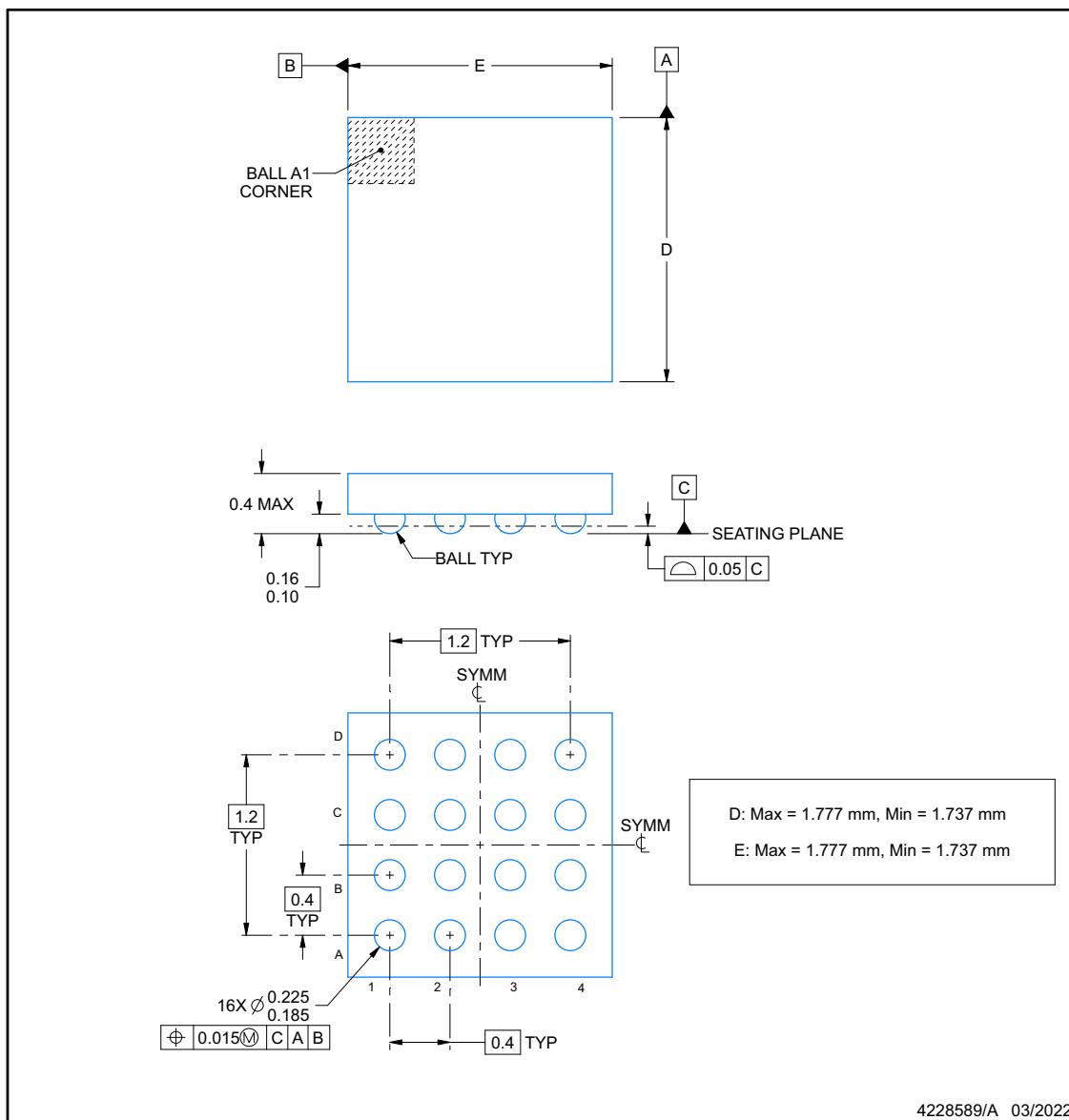

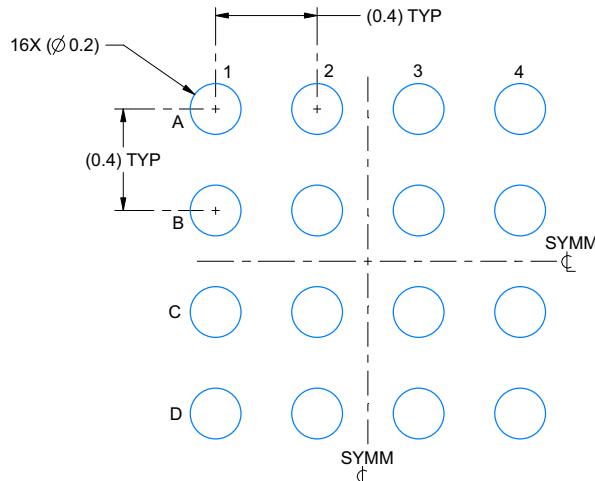

- 超小型パッケージ:

- 16 ピン DSBGA: 1.76mm × 1.76mm (公称値)

## 2 アプリケーション

- コードレス電動工具

- ロボット掃除機

- 空気清浄機と加湿器

## 3 概要

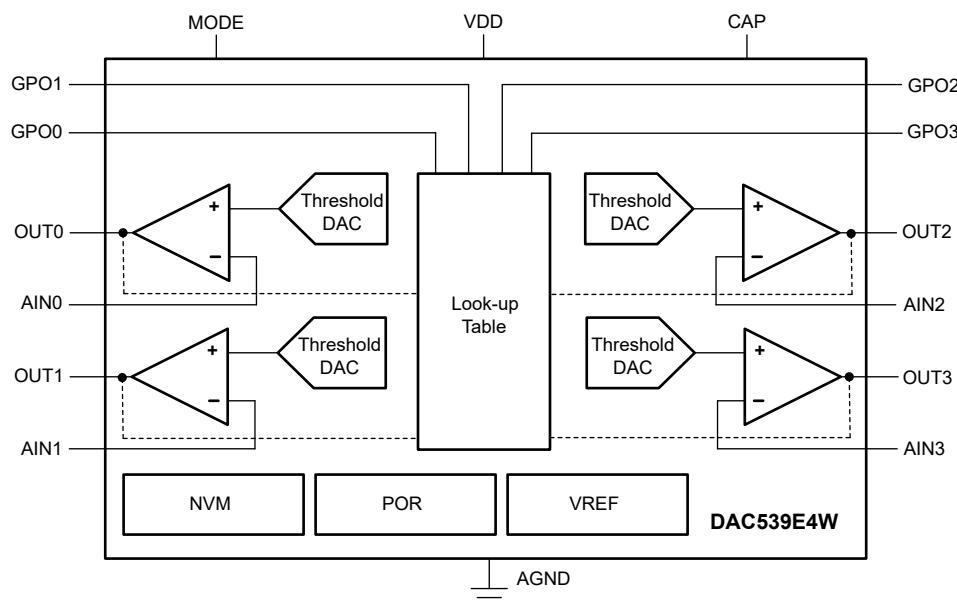

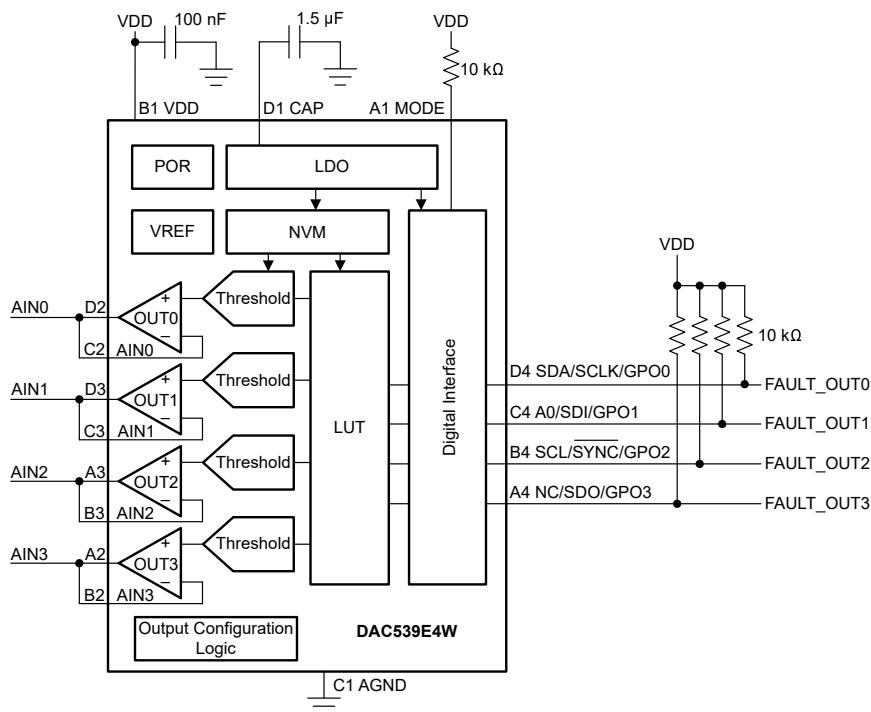

DAC539E4W は、クワッドプログラマブルコンパレータ入力とクワッド汎用出力を備えた 10 ビットスマート D/A コンバータ (DAC) です。ロックアップテーブルにより、コンパレータ入力が GPO にマッピングされます。また、DAC539E4W は遅延をプログラム可能で、入力の遷移を安定させることもできます。これらのデバイスは、構成を保存するための NVM を提供します。このスマート DAC は、LUT と NVM を使用するプロセッサを必要とせずに動作します (プロセッサレス動作)。

このデバイスには、SPI および I<sup>2</sup>C インターフェイスの自動検出と内部基準電圧が搭載されています。スマート DAC は、機能セット、小型パッケージ、低消費電力により、フォルト管理アプリケーションに非常に適しています。

### パッケージ情報

| 部品番号      | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-----------|----------------------|--------------------------|

| DAC539E4W | YBH (DSBGA, 16)      | 1.76mm × 1.76mm          |

- (1) 詳細については、[セクション 10](#) を参照してください。

(2) パッケージサイズ(長さ × 幅)は公称値であり、該当する場合はピンを含みます。

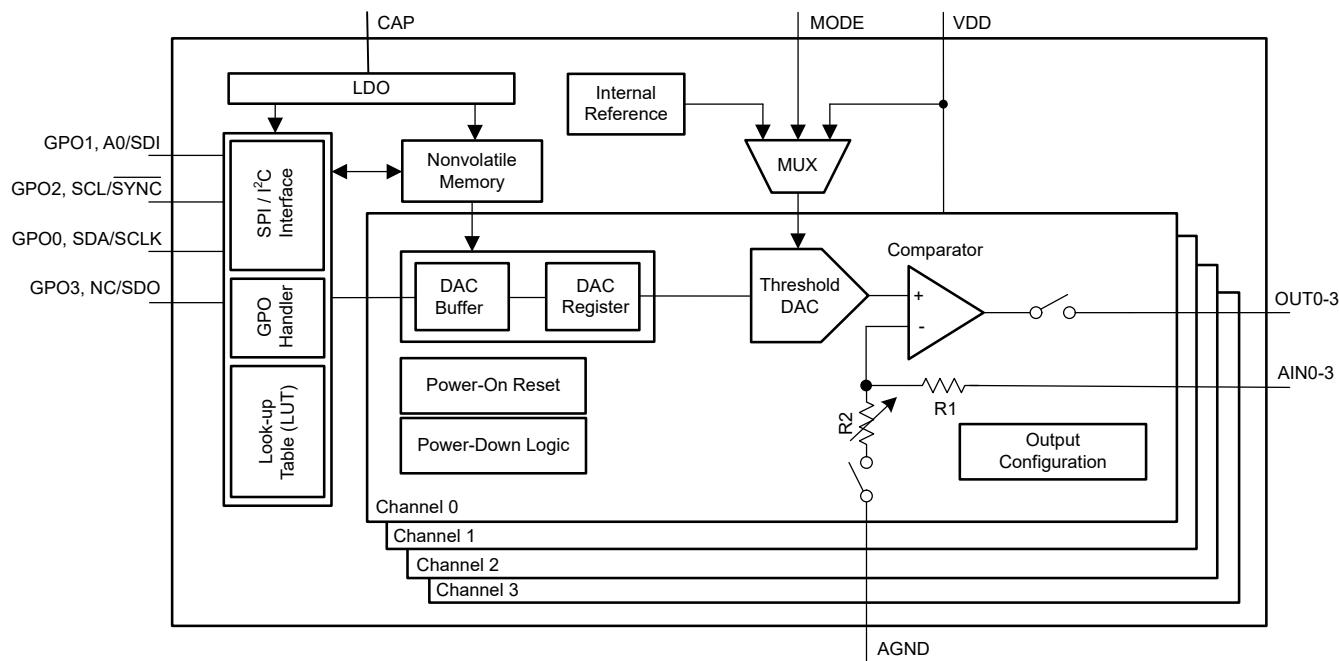

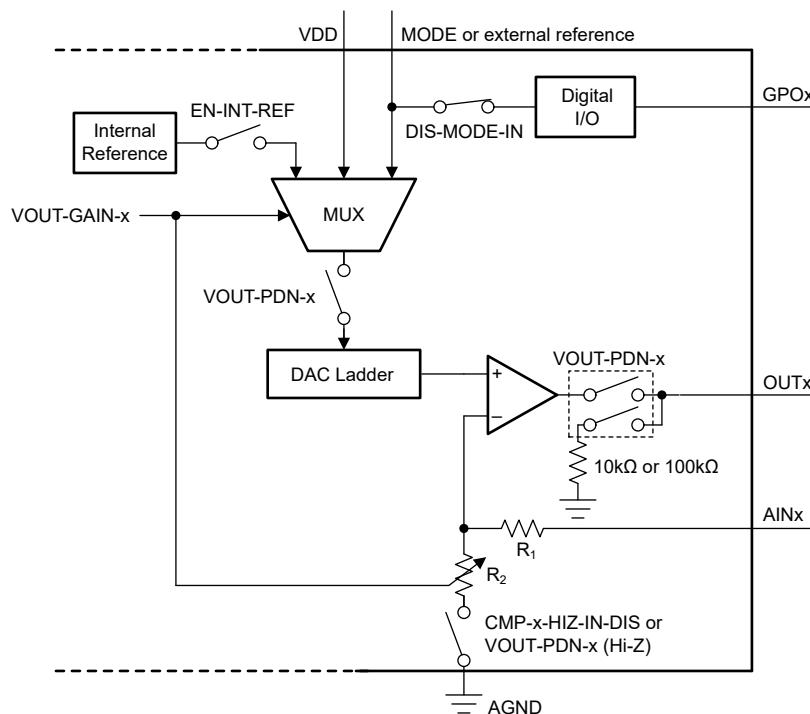

概略ブロック図

## 目次

|                                                |          |                               |           |

|------------------------------------------------|----------|-------------------------------|-----------|

| <b>1 特長</b>                                    | <b>1</b> | 5.15 代表的特性                    | 13        |

| <b>2 アプリケーション</b>                              | <b>1</b> | <b>6 詳細説明</b>                 | <b>17</b> |

| <b>3 概要</b>                                    | <b>1</b> | 6.1 概要                        | 17        |

| <b>4 ピン構成および機能</b>                             | <b>3</b> | 6.2 機能ブロック図                   | 17        |

| <b>5 仕様</b>                                    | <b>5</b> | 6.3 機能説明                      | 18        |

| 5.1 絶対最大定格                                     | 5        | 6.4 デバイスの機能モード                | 25        |

| 5.2 ESD 定格                                     | 5        | 6.5 プログラミング                   | 29        |

| 5.3 推奨動作条件                                     | 5        | 6.6 レジスタマップ                   | 36        |

| 5.4 熱に関する情報                                    | 5        | <b>7 アプリケーションと実装</b>          | <b>48</b> |

| 5.5 電気的特性:スレッショルド DAC                          | 6        | 7.1 アプリケーション情報                | 48        |

| 5.6 電気的特性:コンパレータ                               | 7        | 7.2 代表的なアプリケーション              | 48        |

| 5.7 電気的特性:総則                                   | 8        | 7.3 電源に関する推奨事項                | 54        |

| 5.8 タイミング要件:I <sup>2</sup> C スタンダードモード         | 9        | 7.4 レイアウト                     | 54        |

| 5.9 タイミング要件:I <sup>2</sup> C 高速モード             | 9        | <b>8 デバイスおよびドキュメントのサポート</b>   | <b>56</b> |

| 5.10 タイミング要件:I <sup>2</sup> C 高速モードプラス         | 9        | 8.1 ドキュメントの更新通知を受け取る方法        | 56        |

| 5.11 タイミング要件:SPI 書き込み動作                        | 10       | 8.2 サポート・リソース                 | 56        |

| 5.12 タイミング要件:SPI 読み出しおよびデイジー チェーン動作 (FSDO = 0) | 10       | 8.3 商標                        | 56        |

| 5.13 タイミング要件:SPI 読み出しおよびデイジー チェーン動作 (FSDO = 1) | 10       | 8.4 静電気放電に関する注意事項             | 56        |

| 5.14 タイミング図                                    | 11       | 8.5 用語集                       | 56        |

|                                                |          | <b>9 改訂履歴</b>                 | <b>56</b> |

|                                                |          | <b>10 メカニカル、パッケージ、および注文情報</b> | <b>56</b> |

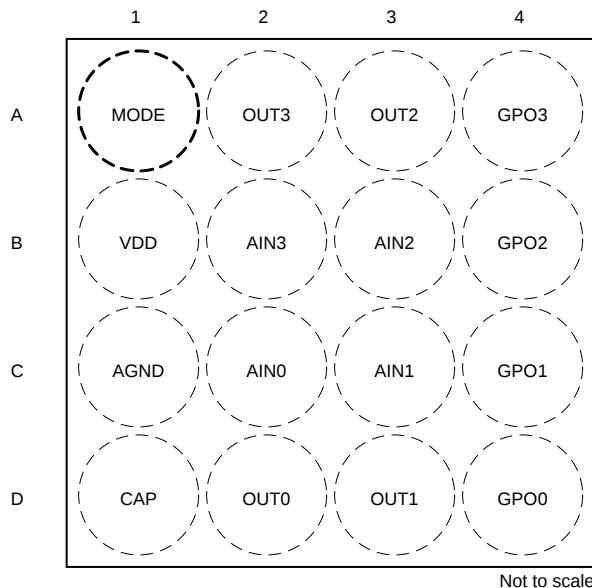

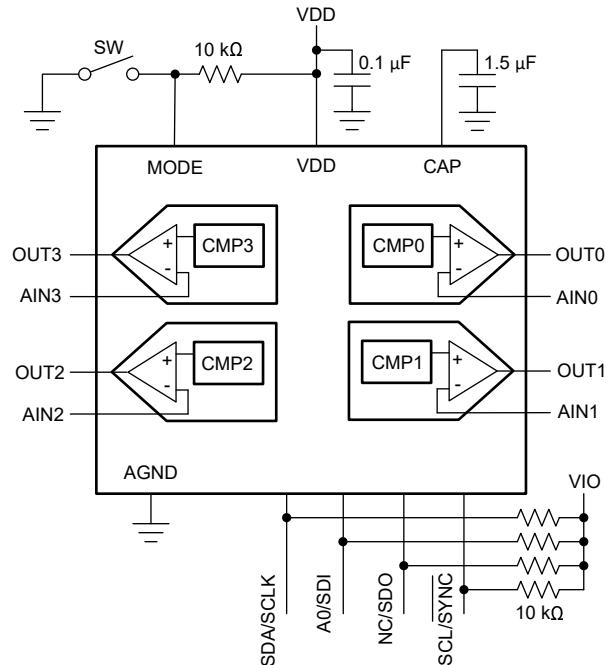

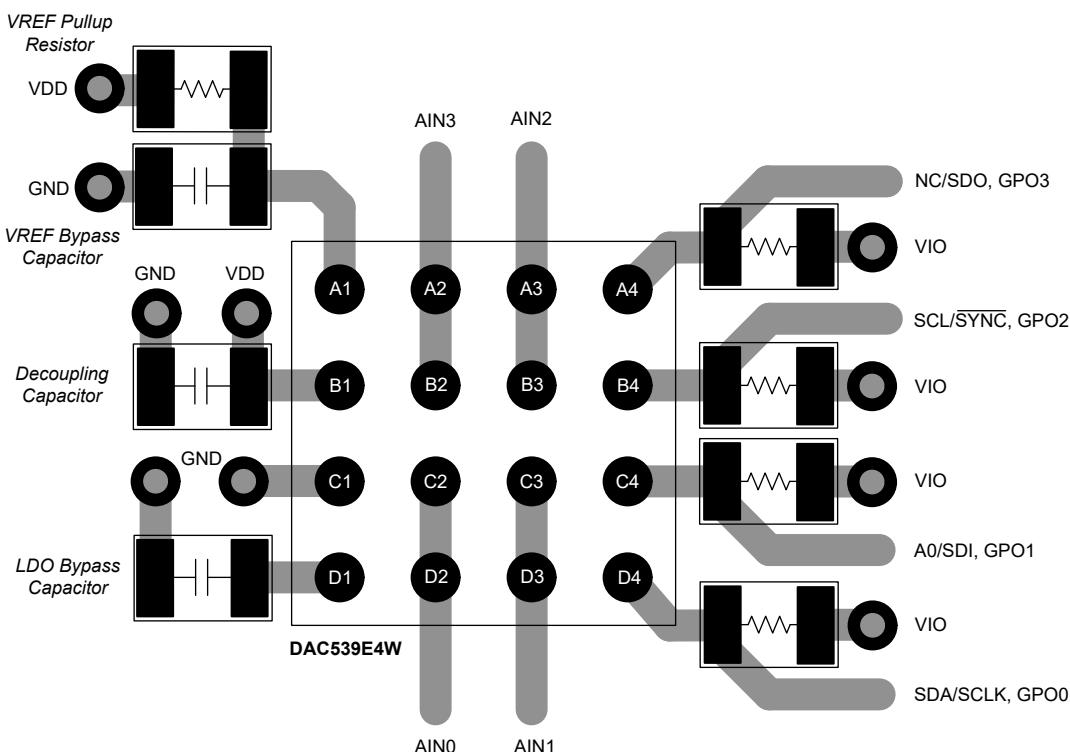

## 4 ピン構成および機能

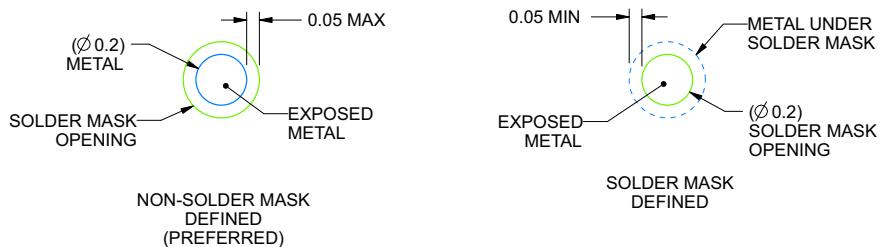

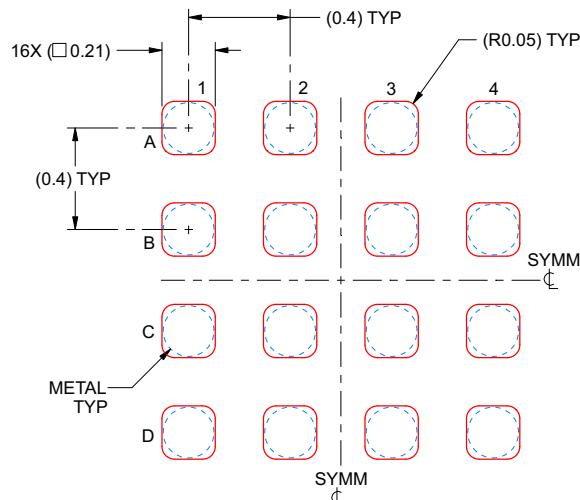

図 4-1. YBH パッケージ、16 ピン DSBGA (上面図)

表 4-1. ピンの機能

| 番号 | ピン<br>名称 | タイプ     | 説明                                                                                                                                                                                                                                                                     |

|----|----------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1 | モード      | 電源      | 外部リファレンス (VREF) または MODE 入力。MODE と AGND の間にコンデンサ (約 0.1μF) を接続します。<br>外部リファレンスを使用しない場合は、VDD に対してプルアップ抵抗を使用します。このピンは VDD より前に上昇させないでください。外部リファレンスを使用する場合は、VDD の後にリファレンスが上昇することを確認してください。<br>プログラミングモードでは、このピンを Low にします。スタンダードアロンモードの場合、このピンを High にするか、外部リファレンスに接続します。 |

| A2 | OUT3     | 出力      | コンパレータ出力 3。PCB の配線を簡単にするために、レジスタ設定を使用してこのピンを Hi-Z にし、AIN3 と OUT3 を短絡させます。                                                                                                                                                                                              |

| A3 | OUT2     | 出力      | コンパレータ出力 2。PCB の配線を簡単にするために、レジスタ設定を使用してこのピンを Hi-Z にし、AIN2 と OUT2 を短絡させます。                                                                                                                                                                                              |

| A4 | GPO3     | 出力      | プログラミングモード: このピンは SDO として構成できます。SDO 機能の場合、外部プルアップ抵抗を使用してピンを I/O 電圧に接続します。使用しない場合は、外付け抵抗を使用してこのピンを VDD または AGND に接続します。このピンは VDD よりも先に上昇できます。<br>スタンダードアロンモード: 汎用出力 3。このピンは外付けプルアップ抵抗を使用して I/O 電圧に接続します。                                                                |

| B1 | VDD      | 電源      | 電源電圧。                                                                                                                                                                                                                                                                  |

| B2 | AIN3     | 入力      | チャネル 3 用アナログ入力ピン。                                                                                                                                                                                                                                                      |

| B3 | AIN2     | 入力      | チャネル 2 用アナログ入力ピン。                                                                                                                                                                                                                                                      |

| B4 | GPO2     | 入力 / 出力 | プログラミングモード (SCL/SYNC): I <sup>2</sup> C シリアルインターフェースクロックまたは SPI チップセレクト入力。これは外付けプルアップ抵抗を使用して I/O 電圧に接続します。このピンは VDD よりも先に上昇できます。<br>スタンダードアロンモード: 汎用出力 2。このピンは外付けプルアップ抵抗を使用して I/O 電圧に接続します。                                                                            |

| C1 | AGND     | グランド    | デバイスの全回路のグランドリファレンスポイント。                                                                                                                                                                                                                                               |

| C2 | AIN0     | 入力      | チャネル 0 用アナログ入力ピン。                                                                                                                                                                                                                                                      |

| C3 | AIN1     | 入力      | チャネル 1 用アナログ入力ピン。                                                                                                                                                                                                                                                      |

**表 4-1. ピンの機能 (続き)**

| ピン |      | タイプ     | 説明                                                                                                                                                                                                                                                    |

|----|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 番号 | 名称   |         |                                                                                                                                                                                                                                                       |

| C4 | GPO1 | 入力 / 出力 | プログラミングモード (A0/SDI): I <sup>2</sup> C または SPI 用シリアルデータ入力のアドレス構成ピン。<br>A0 の場合、アドレス構成のために、このピンを VDD、AGND、SDA、SCL のいずれかに接続します。<br>SDI の場合、このピンをプルアップまたはプルダウンする必要はありません。このピンは VDD よりも先に上昇できます。<br>スタンダードアロンモード: 汎用出力 1。このピンは外付けプルアップ抵抗を使用して I/O 電圧に接続します。 |

| D1 | CAP  | 電源      | 内部 LDO 用の外部バイパスコンデンサ。CAP と AGND の間にコンデンサ (約 1.5µF) を接続します。                                                                                                                                                                                            |

| D2 | OUT0 | 出力      | コンバレータ出力 0。PCB の配線を簡単にするため、レジスタ設定を使用してこのピンを Hi-Z にし、AIN0 と OUT0 を短絡させます。                                                                                                                                                                              |

| D3 | OUT1 | 出力      | コンバレータ出力 1。PCB の配線を簡単にするため、レジスタ設定を使用してこのピンを Hi-Z にし、AIN1 と OUT1 を短絡させます。                                                                                                                                                                              |

| D4 | GPO0 | 入力 / 出力 | プログラミングモード (SDA/SCLK): 双方向 I <sup>2</sup> C シリアルデータバスまたは SPI クロック入力。このピンは I <sup>2</sup> C モードで外部プルアップ抵抗を使用して I/O 電圧に接続します。このピンは VDD よりも先に上昇できます。<br>スタンダードアロンモード: 汎用出力 0。このピンは外付けプルアップ抵抗を使用して I/O 電圧に接続します。                                          |

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|           |                                | 最小値  | 最大値            | 単位 |

|-----------|--------------------------------|------|----------------|----|

| $V_{DD}$  | $V_{DD}$ から AGND への電源電圧        | -0.3 | 6              | V  |

|           | デジタル入力から AGND                  | -0.3 | $V_{DD} + 0.3$ | V  |

|           | $V_{AINX}$ から AGND             | -0.3 | $V_{DD} + 0.3$ | V  |

|           | $V_{OUTX}$ から AGND             | -0.3 | $V_{DD} + 0.3$ | V  |

| $V_{REF}$ | 外部リファレンス、 $V_{REF}$ から AGND    | -0.3 | $V_{DD} + 0.3$ | V  |

|           | OUTX、VDD、AGND ピンを除く任意のピンに流れる電流 | -10  | 10             | mA |

| $T_J$     | 接合部温度                          | -40  | 150            | °C |

| $T_{stg}$ | 保存温度                           | -65  | 150            | °C |

- (1) 「絶対最大定格」の範囲外での動作は、デバイスの永続的な損傷の原因となる可能性があります。「絶対最大定格」は、これらの条件において、または「推奨動作条件」に示された値を超える他のいかなる条件でも、本製品が正しく動作することを意味するものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用すると、デバイスが完全に機能しない可能性があり、デバイスの信頼性、機能、性能に影響を及ぼし、デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|             |      |                                                                  | 値     | 単位 |

|-------------|------|------------------------------------------------------------------|-------|----|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>     | ±2000 | V  |

|             |      | デバイス帯電モデル (CDM)、ANSI/ESDA/JEDEC JS-002 に準拠、すべてのピン <sup>(2)</sup> | ±500  |    |

(1) JEDEC ドキュメント JEP155 には、500V HBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250V CDM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|           |                                           | 最小値  | 公称値 | 最大値      | 単位 |

|-----------|-------------------------------------------|------|-----|----------|----|

| $V_{DD}$  | グランドへの正の電源電圧 (AGND)                       | 1.7  | 5.5 | 5.5      | V  |

| $V_{REF}$ | グランドへの外部リファレンス (AGND)                     | 1.7  |     | $V_{DD}$ | V  |

| $V_{IH}$  | デジタル入力 High 電圧、 $1.7V < V_{DD} \leq 5.5V$ | 1.62 |     |          | V  |

| $V_{IL}$  | デジタル入力 Low 電圧                             |      |     | 0.4      | V  |

| $C_{CAP}$ | CAP ピンの外付けコンデンサ                           | 0.5  |     | 15       | μF |

| $T_A$     | 周囲温度                                      | -40  |     | 125      | °C |

### 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>        |                     | DAC539E4W   | 単位   |

|-----------------------------|---------------------|-------------|------|

|                             |                     | YBH (DSBGA) |      |

|                             |                     | 16 ピン       |      |

| $R_{\theta JA}$             | 接合部から周囲への熱抵抗        | 81.2        | °C/W |

| $R_{\theta JC(\text{top})}$ | 接合部からケース (上面) への熱抵抗 | 0.3         | °C/W |

| $R_{\theta JB}$             | 接合部から基板への熱抵抗        | 20.3        | °C/W |

| $\Psi_{JT}$                 | 接合部から上面への特性パラメータ    | 0.2         | °C/W |

| $\Psi_{JB}$                 | 接合部から基板への特性パラメータ    | 20.3        | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション レポートを参照してください。

## 5.5 電気的特性：スレッショルド DAC

すべての最小/最大仕様 ( $-40^{\circ}\text{C} \leq T_A \leq +125^{\circ}\text{C}$  時) および標準仕様 ( $T_A = 25^{\circ}\text{C}$ 、 $1.7\text{V} \leq V_{DD} \leq 5.5\text{V}$  時)、DAC リファレンスを  $VDD$  に接続、ゲイン =  $1 \times$ 、および  $VDD$  または  $AGND$  でのデジタル入力 (特に記述のない限り)

| パラメータ                      | テスト条件                                                                         | 最小値                                                                                                                                   | 標準値  | 最大値     | 単位   |

|----------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|---------|------|

| <b>安定動作</b>                |                                                                               |                                                                                                                                       |      |         |      |

|                            | 分解能                                                                           | 10                                                                                                                                    |      |         | ビット  |

| INL                        | 積分非直線性 <sup>(1)</sup>                                                         | -1.25                                                                                                                                 | 1.25 |         | LSB  |

| DNL                        | 微分非直線性 <sup>(1)</sup>                                                         | -1                                                                                                                                    | 1    |         | LSB  |

| オフセット誤差 <sup>(3)</sup>     | $1.7\text{V} \leq V_{DD} < 2.7\text{V}$ 、AINx ピンを $OUTx$ に短絡、DAC コード:8d       | -0.75                                                                                                                                 | 0.3  | 0.75    | %FSR |

|                            | $2.7\text{V} \leq V_{DD} \leq 5.5\text{V}$ 、AINx ピンを $V_{OUT}$ に短絡、DAC コード:8d | -0.5                                                                                                                                  | 0.25 | 0.5     |      |

| オフセット誤差温度係数 <sup>(3)</sup> | AINx ピンを $OUTx$ に短絡、DAC コード:8d                                                | $\pm 0.0003$                                                                                                                          |      | %FSR/°C |      |

| ゲイン誤差 <sup>(3)</sup>       | エンドポイントコード間:8d~1016d                                                          | -0.5                                                                                                                                  | 0.25 | 0.5     | %FSR |

| ゲイン誤差温度係数 <sup>(3)</sup>   | エンドポイントコード間:8d~1016d                                                          | $\pm 0.0008$                                                                                                                          |      | %FSR/°C |      |

| <b>出力</b>                  |                                                                               |                                                                                                                                       |      |         |      |

| $Z_O$                      | $V_{AIN}$ DC 出力インピーダンス <sup>(3)</sup>                                         | DAC 出力イネーブルおよび内部リファレンス (ゲイン = $1.5 \times$ または $2 \times$ ) または $V_{DD}$ での外部リファレンス (ゲイン = $1 \times$ )、 $V_{REF}$ ピンは $V_{DD}$ に短絡なし | 400  | 500     | 600  |

|                            |                                                                               | DAC 出力イネーブル、内部 $V_{REF}$ 、ゲイン = $3 \times$ または $4 \times$                                                                             | 325  | 400     | 485  |

(1) 出力を無負荷で測定。外部リファレンスと内部リファレンス  $V_{DD} \geq 1.21 \times$  ゲイン +  $0.2\text{V}$ 、エンドポイントコード間:8d ~ 1016d。

(2) 内部リファレンスを使用する場合のリファレンス値に対して  $200\text{mV}$  のヘッドルームで規定。

(3) 出力を無負荷で測定。

## 5.6 電気的特性：コンパレータ

すべての最小/最大仕様 ( $-40^{\circ}\text{C} \leq T_A \leq +125^{\circ}\text{C}$  時) および標準仕様 ( $T_A = 25^{\circ}\text{C}$ 、 $1.7\text{V} \leq V_{DD} \leq 5.5\text{V}$  時)、DAC リファレンスを VDD に接続、電圧出力モードでゲイン = 1 ×、および VDD または AGND でのデジタル入力 (特に記述のない限り)

| パラメータ                         | テスト条件                                                                                                                                                                | 最小値                                                                                                                                                                                                                             | 標準値                           | 最大値      | 単位 |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------|----|

| <b>安定動作</b>                   |                                                                                                                                                                      |                                                                                                                                                                                                                                 |                               |          |    |

| オフセット誤差 <sup>(1) (2)</sup>    | $1.7\text{V} \leq V_{DD} \leq 5.5\text{V}$ 、ミッドスケールの DAC、Hi-Z のコンパレータ入力、外部リファレンスで動作する DAC。                                                                           | -6                                                                                                                                                                                                                              | 0                             | 6        | mV |

| オフセット誤差の時間ドリフト <sup>(1)</sup> | $V_{DD} = 5.5\text{V}$ 、外部リファレンス、 $T_A = 125^{\circ}\text{C}$ 、Hi-Z モードの AINx、フルスケールで 0V 時の $V_{AINX}$ の DAC またはゼロスケールで 1.84V 時の $V_{AINX}$ の DAC、10 年連続動作のためのドリフト指定 |                                                                                                                                                                                                                                 | 4                             |          | mV |

| <b>出力</b>                     |                                                                                                                                                                      |                                                                                                                                                                                                                                 |                               |          |    |

| 入力電圧                          | $V_{REF}$ を $V_{DD}$ に接続、AINx 抵抗回路網をグランドに接続                                                                                                                          | 0                                                                                                                                                                                                                               |                               | $V_{DD}$ | V  |

|                               | $V_{REF}$ を $V_{DD}$ に接続、AINx 抵抗回路網をグランドから接続解除                                                                                                                       | 0                                                                                                                                                                                                                               | $V_{DD} \times (1/3 - 1/100)$ |          |    |

| $V_{OL}$                      | ロジック Low 出力電圧                                                                                                                                                        | $I_{LOAD} = 100\mu\text{A}$ 、オープンドレインモードで出力                                                                                                                                                                                     | 0.1                           |          | V  |

| <b>ダイナミック性能</b>               |                                                                                                                                                                      |                                                                                                                                                                                                                                 |                               |          |    |

| $t_{resp}$                    | 出力応答時間                                                                                                                                                               | 10 ビット分解能のミッドスケールの DAC、Hi-Z の AINx 入力、AINx ノードの遷移ステップは ( $V_{DAC} - 2 \text{ LSB}$ ) から ( $V_{DAC} + 2 \text{ LSB}$ )、遷移時間を出力の出力構成 10% ~ 90% で測定、 $100\mu\text{A}$ の出力電流、コンパレータの出力をプッシュプルモードに構成、コンパレータ出力の負荷コンデンサは $25\text{pF}$ | 10                            |          | μs |

- (1) 設計と特性評価による仕様で、製造試験は未実施。

(2) この仕様には、DAC の総合未調整誤差 (TUE) は含まれていません。

## 5.7 電気的特性：総則

すべての最小/最大仕様 ( $-40^{\circ}\text{C} \leq T_A \leq +125^{\circ}\text{C}$  時) および標準仕様 ( $T_A = 25^{\circ}\text{C}$ ,  $1.7\text{V} \leq V_{DD} \leq 5.5\text{V}$  時), DAC リファレンスを VDD に接続、ゲイン = 1 ×、および VDD または AGND でのデジタル入力 (特に記述のない限り)

| パラメータ                                   | テスト条件                                                                                                      | 最小値                                                         | 標準値            | 最大値                     | 単位               |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------|-------------------------|------------------|

| <b>内部リファレンス</b>                         |                                                                                                            |                                                             |                |                         |                  |

| 初期精度                                    | すべての測定において $T_A = 25^{\circ}\text{C}$                                                                      | 1.1979                                                      | 1.212          | 1.224                   | V                |

| リファレンス出力の温度係数 <sup>(1) (2)</sup>        |                                                                                                            |                                                             | 50             | ppm/ $^{\circ}\text{C}$ |                  |

| <b>EXTERNAL REFERENCE</b>               |                                                                                                            |                                                             |                |                         |                  |

| $V_{REF}$ 入力インピーダンス <sup>(1) (3)</sup>  |                                                                                                            | 192                                                         | k $\Omega$ -ch |                         |                  |

| <b>EEPROM</b>                           |                                                                                                            |                                                             |                |                         |                  |

| 耐久性 <sup>(1)</sup>                      | $-40^{\circ}\text{C} \leq T_A \leq +85^{\circ}\text{C}$                                                    | 20000                                                       |                |                         | サイクル             |

|                                         | $T_A = 125^{\circ}\text{C}$                                                                                | 1000                                                        |                |                         |                  |

| データ保持期間 <sup>(1)</sup>                  |                                                                                                            | 50                                                          | 年              |                         |                  |

| EEPROM プログラミング書き込みサイクル時間 <sup>(1)</sup> |                                                                                                            | 200                                                         | ms             |                         |                  |

| デバイスの起動時間 <sup>(1)</sup>                | 電源有効 ( $V_{DD} \geq 1.7\text{V}$ ) から出力有効状態 (EEPROM でプログラムされた出力状態) までに要する時間、CAP ピンの $0.5\mu\text{F}$ コンデンサ | 5                                                           | ms             |                         |                  |

| <b>デジタル入力</b>                           |                                                                                                            |                                                             |                |                         |                  |

| ピン容量 1                                  | ピンごと                                                                                                       | 10                                                          | pF             |                         |                  |

| <b>電源</b>                               |                                                                                                            |                                                             |                |                         |                  |

| $I_{DD}$                                | VDD に流れる電流                                                                                                 | スリープモードの DAC、内部リファレンスはパワーダウン、<br>$5.5\text{V}$ の外部リファレンス    | 28             |                         | $\mu\text{A}$    |

|                                         | VDD に流れる電流 <sup>(1)</sup>                                                                                  | スリープモードの DAC、内部リファレンス有効、内部リファレンスを流れる追加電流                    | 10             |                         |                  |

|                                         |                                                                                                            | DAC チャネル有効、内部リファレンス有効、電圧出力モードで DAC チャネルごとに内部リファレンスを流れる追加電流  | 12.5           |                         | $\mu\text{A-ch}$ |

|                                         |                                                                                                            | 通常動作、ステートマシン有効                                              | 1.53           |                         | mA               |

| <b>ハイインピーダンス出力</b>                      |                                                                                                            |                                                             |                |                         |                  |

| $I_{LEAK}$                              | OUTx と AINx に流れる電流                                                                                         | Hi-Z 出力モードの DAC、 $1.7\text{V} \leq V_{DD} \leq 5.5\text{V}$ | 10             | nA                      |                  |

(1) 設計と特性評価による仕様で、製造試験は未実施。

(2)  $-40^{\circ}\text{C}$  および  $+125^{\circ}\text{C}$  で測定し、勾配を計算。

(3) DAC チャネルのインピーダンスを並列に接続。

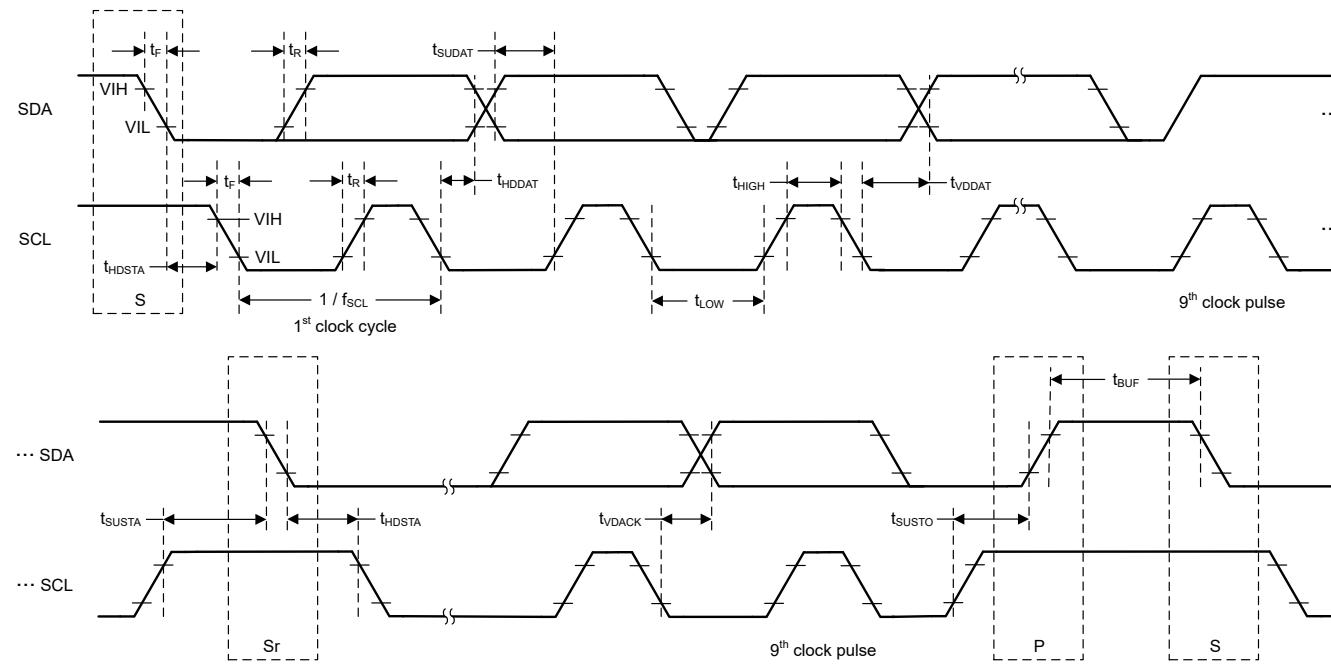

## 5.8 タイミング要件 : I<sup>2</sup>C スタンダードモード

すべての入力信号は、V<sub>IIL</sub> から V<sub>pull-up</sub> の 70%、1.7V ≤ V<sub>DD</sub> ≤ 5.5V、−40°C ≤ T<sub>A</sub> ≤ +125°C、1.7V ≤ V<sub>pull-up</sub> ≤ V<sub>DD</sub> V でタイミング設定されます

|                    |                                                                                     | 最小値  | 公称値 | 最大値  | 単位  |

|--------------------|-------------------------------------------------------------------------------------|------|-----|------|-----|

| f <sub>SCL</sub>   | SCL 周波数                                                                             |      |     | 100  | kHz |

| t <sub>BUF</sub>   | ストップ条件とスタート条件の間のバスフリー時間                                                             | 4.7  |     |      | μs  |

| t <sub>HDSTA</sub> | リピートスタート後のホールド時間                                                                    | 4    |     |      | μs  |

| t <sub>SUSTA</sub> | 繰り返しスタートのセットアップ時間                                                                   | 4.7  |     |      | μs  |

| t <sub>SUSTO</sub> | STOP 条件のセットアップ時間                                                                    | 4    |     |      | μs  |

| t <sub>HDDAT</sub> | データホールド時間                                                                           | 0    |     |      | ns  |

| t <sub>SUDAT</sub> | データセットアップ時間                                                                         | 250  |     |      | ns  |

| t <sub>LOW</sub>   | SCL クロックの Low 期間                                                                    | 4700 |     |      | ns  |

| t <sub>HIGH</sub>  | SCL クロックの High 期間                                                                   | 4000 |     |      | ns  |

| t <sub>F</sub>     | クロック / データの立ち下がり時間                                                                  |      |     | 300  | ns  |

| t <sub>R</sub>     | クロック / データの立ち上がり時間                                                                  |      |     | 1000 | ns  |

| t <sub>VDDAT</sub> | データ有効時間、R = 360 Ω、C <sub>trace</sub> = 23pF、C <sub>probe</sub> = 10pF               |      |     | 3.45 | μs  |

| t <sub>VDACK</sub> | データ有効アクノリッジ (受信確認) 時間、R = 360 Ω、C <sub>trace</sub> = 23pF、C <sub>probe</sub> = 10pF |      |     | 3.45 | μs  |

## 5.9 タイミング要件 : I<sup>2</sup>C 高速モード

すべての入力信号は、V<sub>IIL</sub> から V<sub>pull-up</sub> の 70%、1.7V ≤ V<sub>DD</sub> ≤ 5.5V、−40°C ≤ T<sub>A</sub> ≤ +125°C、1.7V ≤ V<sub>pull-up</sub> ≤ V<sub>DD</sub> V でタイミング設定されます

|                    |                                                                                    | 最小値  | 公称値 | 最大値 | 単位  |

|--------------------|------------------------------------------------------------------------------------|------|-----|-----|-----|

| f <sub>SCL</sub>   | SCL 周波数                                                                            |      |     | 400 | kHz |

| t <sub>BUF</sub>   | ストップ条件とスタート条件の間のバスフリー時間                                                            | 1.3  |     |     | μs  |

| t <sub>HDSTA</sub> | リピートスタート後のホールド時間                                                                   | 0.6  |     |     | μs  |

| t <sub>SUSTA</sub> | 繰り返しスタートのセットアップ時間                                                                  | 0.6  |     |     | μs  |

| t <sub>SUSTO</sub> | STOP 条件のセットアップ時間                                                                   | 0.6  |     |     | μs  |

| t <sub>HDDAT</sub> | データホールド時間                                                                          | 0    |     |     | ns  |

| t <sub>SUDAT</sub> | データセットアップ時間                                                                        | 100  |     |     | ns  |

| t <sub>LOW</sub>   | SCL クロックの Low 期間                                                                   | 1300 |     |     | ns  |

| t <sub>HIGH</sub>  | SCL クロックの High 期間                                                                  | 600  |     |     | ns  |

| t <sub>F</sub>     | クロック / データの立ち下がり時間                                                                 |      |     | 300 | ns  |

| t <sub>R</sub>     | クロック / データの立ち上がり時間                                                                 |      |     | 300 | ns  |

| t <sub>VDDAT</sub> | データ有効時間、R = 360Ω、C <sub>trace</sub> = 23pF、C <sub>probe</sub> = 10pF               |      |     | 0.9 | μs  |

| t <sub>VDACK</sub> | データ有効アクノリッジ (受信確認) 時間、R = 360Ω、C <sub>trace</sub> = 23pF、C <sub>probe</sub> = 10pF |      |     | 0.9 | μs  |

## 5.10 タイミング要件 : I<sup>2</sup>C 高速モードプラス

すべての入力信号は、V<sub>IIL</sub> から V<sub>pull-up</sub> の 70%、1.7V ≤ V<sub>DD</sub> ≤ 5.5V、−40°C ≤ T<sub>A</sub> ≤ +125°C、1.7V ≤ V<sub>pull-up</sub> ≤ V<sub>DD</sub> V でタイミング設定されます

|                    |                         | 最小値  | 公称値 | 最大値 | 単位  |

|--------------------|-------------------------|------|-----|-----|-----|

| f <sub>SCL</sub>   | SCL 周波数                 |      |     | 1   | MHz |

| t <sub>BUF</sub>   | ストップ条件とスタート条件の間のバスフリー時間 | 0.5  |     |     | μs  |

| t <sub>HDSTA</sub> | リピートスタート後のホールド時間        | 0.26 |     |     | μs  |

| t <sub>SUSTA</sub> | 繰り返しスタートのセットアップ時間       | 0.26 |     |     | μs  |

| t <sub>SUSTO</sub> | STOP 条件のセットアップ時間        | 0.26 |     |     | μs  |

| t <sub>HDDAT</sub> | データホールド時間               | 0    |     |     | ns  |

| t <sub>SUDAT</sub> | データセットアップ時間             | 50   |     |     | ns  |

| t <sub>LOW</sub>   | SCL クロックの Low 期間        | 0.5  |     |     | μs  |

| t <sub>HIGH</sub>  | SCL クロックの High 期間       | 0.26 |     |     | μs  |

すべての入力信号は、V<sub>I</sub>L から V<sub>pull-up</sub> の 70%、1.7V ≤ V<sub>DD</sub> ≤ 5.5V、−40°C ≤ T<sub>A</sub> ≤ +125°C、1.7V ≤ V<sub>pull-up</sub> ≤ V<sub>DD</sub> V でタイミング設定されます

|                    |                                                                                     | 最小値 | 公称値 | 最大値  | 単位 |

|--------------------|-------------------------------------------------------------------------------------|-----|-----|------|----|

| t <sub>F</sub>     | クロック / データの立ち下がり時間                                                                  |     |     | 120  | ns |

| t <sub>R</sub>     | クロック / データの立ち上がり時間                                                                  |     |     | 120  | ns |

| t <sub>VDDAT</sub> | データ有効時間、R = 360 Ω、C <sub>trace</sub> = 23pF、C <sub>probe</sub> = 10pF               |     |     | 0.45 | μs |

| t <sub>VDACK</sub> | データ有効アノリジング (受信確認) 時間、R = 360 Ω、C <sub>trace</sub> = 23pF、C <sub>probe</sub> = 10pF |     |     | 0.45 | μs |

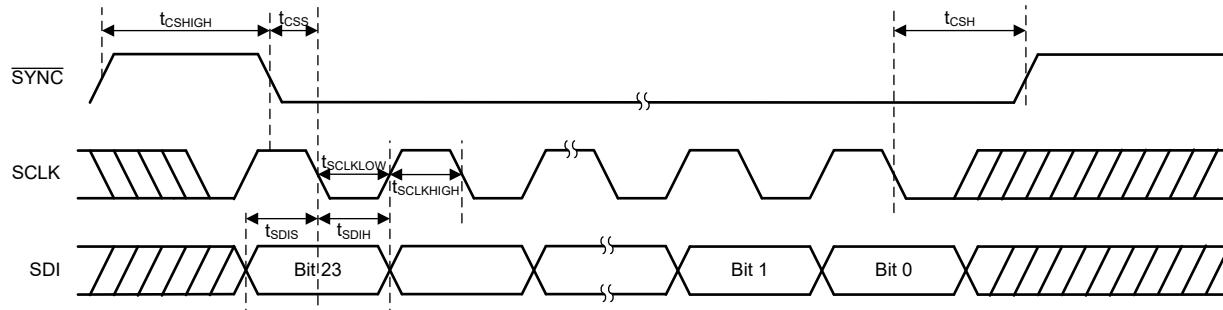

### 5.11 タイミング要件 : SPI 書き込み動作

すべての入力信号は t<sub>r</sub> = t<sub>f</sub> = 1V/ns (V<sub>IO</sub> の 10% ~ 90%) で指定され、(V<sub>I</sub>L + V<sub>I</sub>H)/2、1.7V ≤ V<sub>IO</sub> ≤ 5.5V、1.7V ≤ V<sub>DD</sub> ≤ 5.5V の電圧レベルおよび −40°C ≤ T<sub>A</sub> ≤ +125°C からタイミング設定されます

|                       |                                                    | 最小値 | 公称値 | 最大値 | 単位  |

|-----------------------|----------------------------------------------------|-----|-----|-----|-----|

| f <sub>SCLK</sub>     | シリアル クロック周波数                                       |     |     | 50  | MHz |

| t <sub>SCLKHIGH</sub> | SCLK High 時間                                       | 9   |     |     | ns  |

| t <sub>SCLKLOW</sub>  | SCLK Low 時間                                        | 9   |     |     | ns  |

| t <sub>SDIS</sub>     | SDI のセットアップ時間                                      | 8   |     |     | ns  |

| t <sub>SDIH</sub>     | SDI のホールド時間                                        | 8   |     |     | ns  |

| t <sub>css</sub>      | SYNC から SCLK 立ち下がりエッジまでのセットアップ時間                   | 18  |     |     | ns  |

| t <sub>CSH</sub>      | SCLK 立ち下がりエッジから SYNC 立ち上がりエッジまで                    | 10  |     |     | ns  |

| t <sub>CSHIGH</sub>   | SYNC High 時間                                       | 50  |     |     | ns  |

| t <sub>DACWAIT</sub>  | 同じチャネルのシーケンシャル DAC 更新の待機時間 (後続の SYNC 立ち下がりエッジ間の時間) | 2   |     |     | μs  |

### 5.12 タイミング要件 : SPI 読み出しおよびデイジー チェーン動作 (FSDO = 0)

すべての入力信号は t<sub>r</sub> = t<sub>f</sub> = 1V/ns (V<sub>IO</sub> の 10% ~ 90%) で指定され、(V<sub>I</sub>L + V<sub>I</sub>H)/2、1.7V ≤ V<sub>IO</sub> ≤ 5.5V、1.7V ≤ V<sub>DD</sub> ≤ 5.5V、−40°C ≤ T<sub>A</sub> ≤ +125°C、FSDO = 0 の電圧レベルからタイミング設定されます

|                       |                                                                             | 最小値 | 公称値 | 最大値  | 単位  |

|-----------------------|-----------------------------------------------------------------------------|-----|-----|------|-----|

| f <sub>SCLK</sub>     | シリアル クロック周波数                                                                |     |     | 1.25 | MHz |

| t <sub>SCLKHIGH</sub> | SCLK High 時間                                                                | 350 |     |      | ns  |

| t <sub>SCLKLOW</sub>  | SCLK Low 時間                                                                 | 350 |     |      | ns  |

| t <sub>SDIS</sub>     | SDI のセットアップ時間                                                               | 8   |     |      | ns  |

| t <sub>SDIH</sub>     | SDI のホールド時間                                                                 | 8   |     |      | ns  |

| t <sub>css</sub>      | SYNC から SCLK 立ち下がりエッジまでのセットアップ時間                                            | 400 |     |      | ns  |

| t <sub>CSH</sub>      | SCLK 立ち下がりエッジから SYNC 立ち上がりエッジまで                                             | 400 |     |      | ns  |

| t <sub>CSHIGH</sub>   | SYNC High 時間                                                                | 1   |     |      | μs  |

| t <sub>SDODLY</sub>   | SCLK 立ち上がりエッジから SDO 立ち下がりエッジまで、I <sub>OL</sub> ≤ 5mA、C <sub>L</sub> = 20pF。 |     |     | 300  | ns  |

### 5.13 タイミング要件 : SPI 読み出しおよびデイジー チェーン動作 (FSDO = 1)

すべての入力信号は t<sub>r</sub> = t<sub>f</sub> = 1V/ns (V<sub>IO</sub> の 10% ~ 90%) で指定され、(V<sub>I</sub>L + V<sub>I</sub>H)/2、1.7V ≤ V<sub>IO</sub> ≤ 5.5V、1.7V ≤ V<sub>DD</sub> ≤ 5.5V、−40°C ≤ T<sub>A</sub> ≤ +125°C、FSDO = 1 の電圧レベルからタイミング設定されます

|                       |               | 最小値 | 公称値 | 最大値 | 単位  |

|-----------------------|---------------|-----|-----|-----|-----|

| f <sub>SCLK</sub>     | シリアル クロック周波数  |     |     | 2.5 | MHz |

| t <sub>SCLKHIGH</sub> | SCLK High 時間  | 175 |     |     | ns  |

| t <sub>SCLKLOW</sub>  | SCLK Low 時間   | 175 |     |     | ns  |

| t <sub>SDIS</sub>     | SDI のセットアップ時間 | 8   |     |     | ns  |

すべての入力信号は  $t_f = t_r = 1V/ns$  ( $V_{IO}$  の 10% ~ 90%) で指定され、 $(V_{IL} + V_{IH})/2$ 、

$1.7V \leq V_{IO} \leq 5.5V$ 、 $1.7V \leq V_{DD} \leq 5.5V$ 、 $-40^{\circ}C \leq T_A \leq +125^{\circ}C$ 、 $FSDO = 1$  の電圧レベルからタイミング設定されます

|              |                                                                    | 最小値 | 公称値 | 最大値 | 単位 |

|--------------|--------------------------------------------------------------------|-----|-----|-----|----|

| $t_{SDIH}$   | SDI のホールド時間                                                        |     | 8   |     | ns |

| $t_{CSS}$    | SYNC から SCLK 立ち下がりエッジまでのセットアップ時間                                   |     | 300 |     | ns |

| $t_{CSH}$    | SCLK 立ち下がりエッジから SYNC 立ち上がりエッジまで                                    |     | 300 |     | ns |

| $t_{CSHIGH}$ | SYNC High 時間                                                       |     | 1   |     | μs |

| $t_{SDODLY}$ | SCLK 立ち上がりエッジから SDO 立ち下がりエッジまで、 $I_{OL} \leq 5mA$ 、 $C_L = 20pF$ 。 |     |     | 300 | ns |

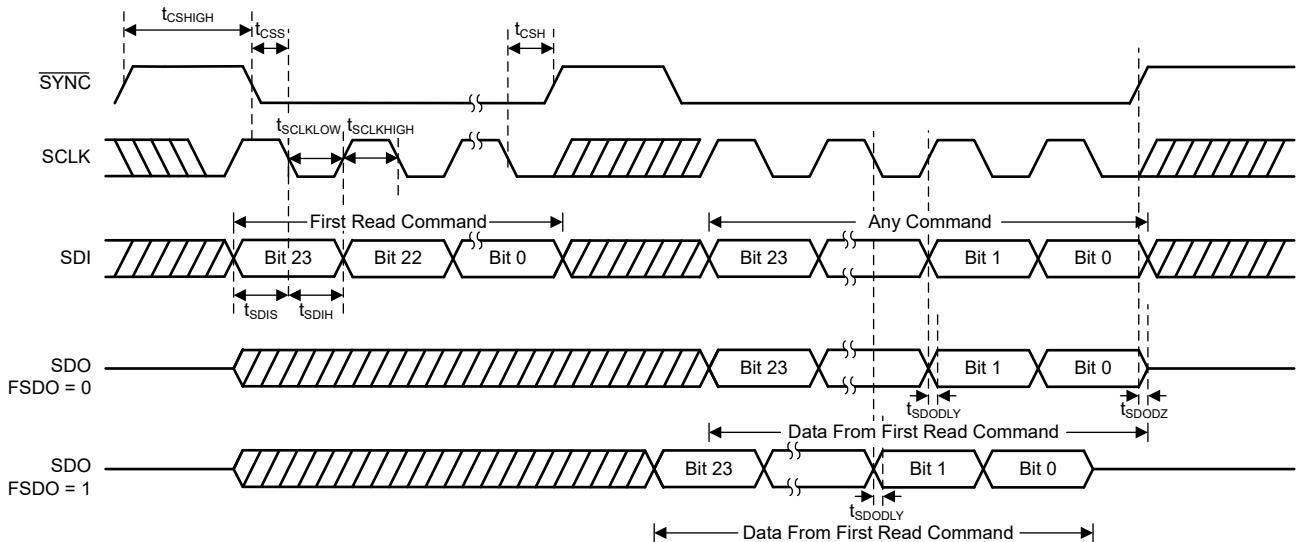

## 5.14 タイミング図

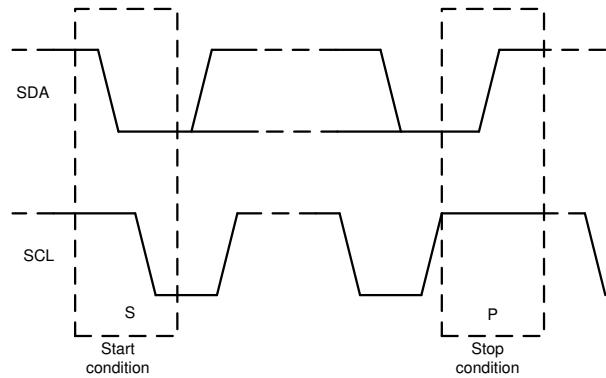

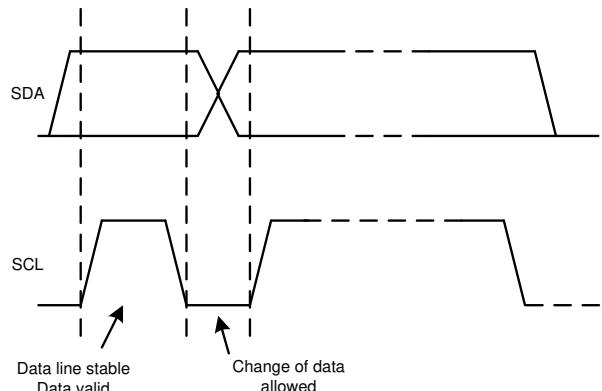

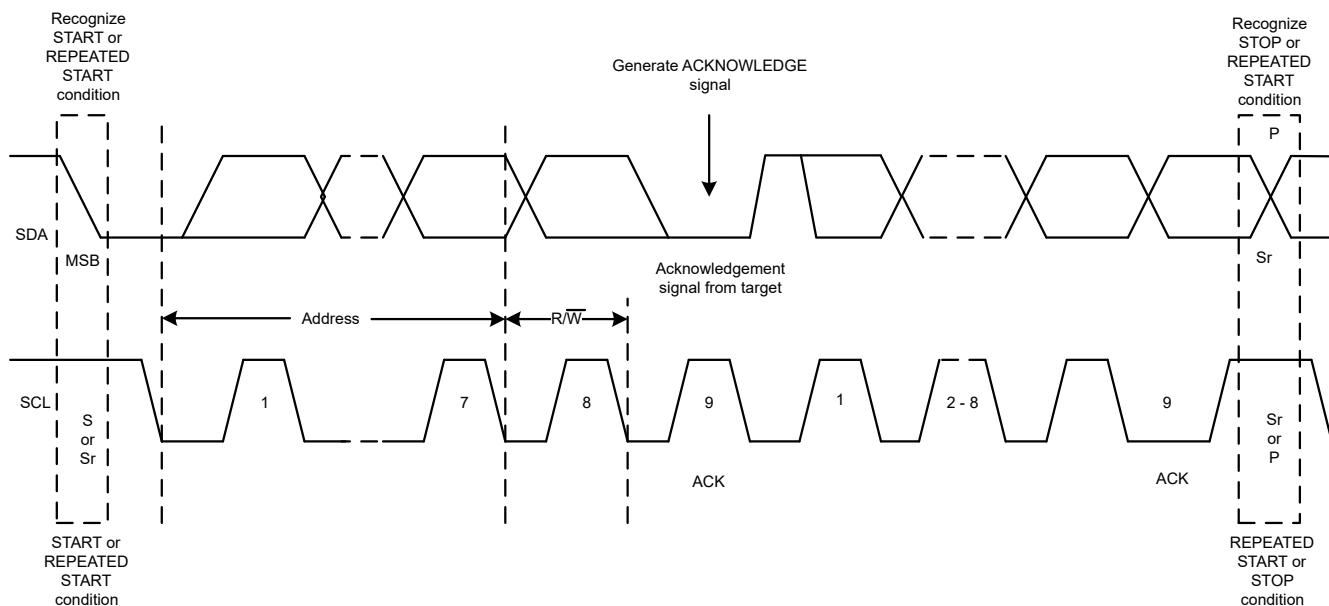

S: Start bit, Sr: Repeated start bit, P: Stop bit

図 5-1. I<sup>2</sup>C のタイミング図

図 5-2. SPI 書き込みタイミング図

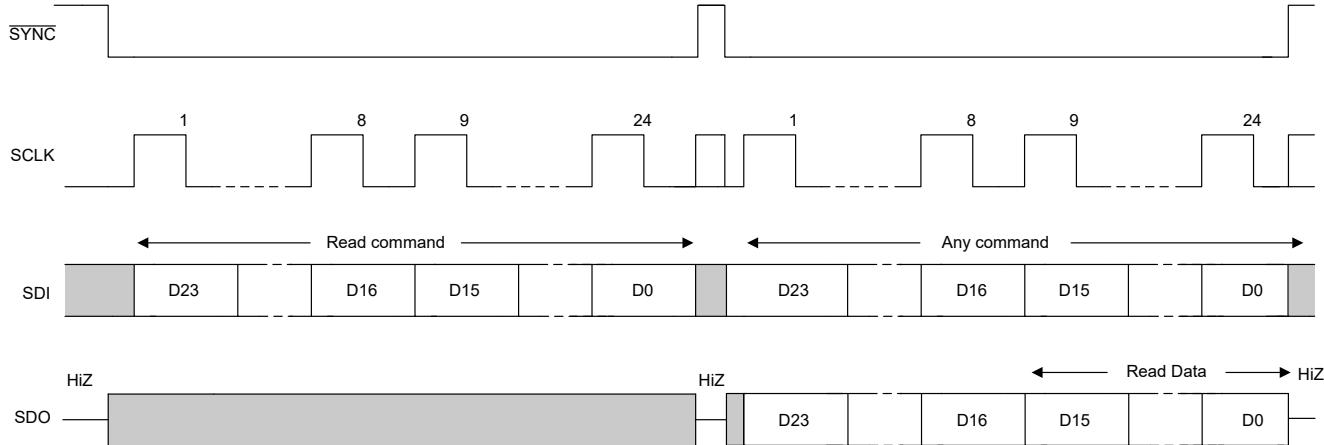

図 5-3. SPI 読み出しのタイミング図

## 5.15 代表的特性

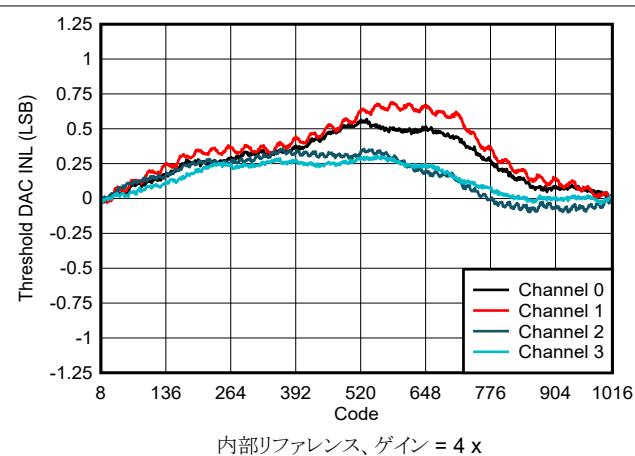

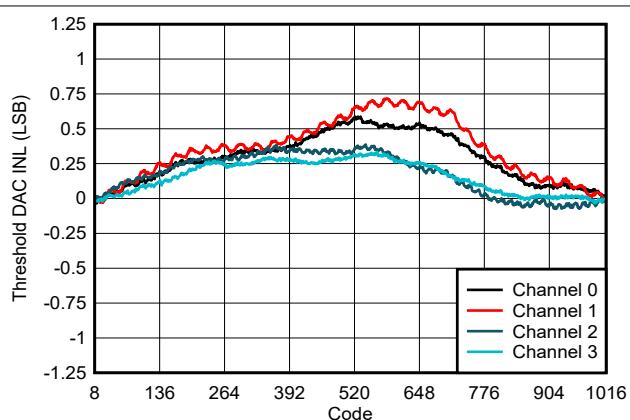

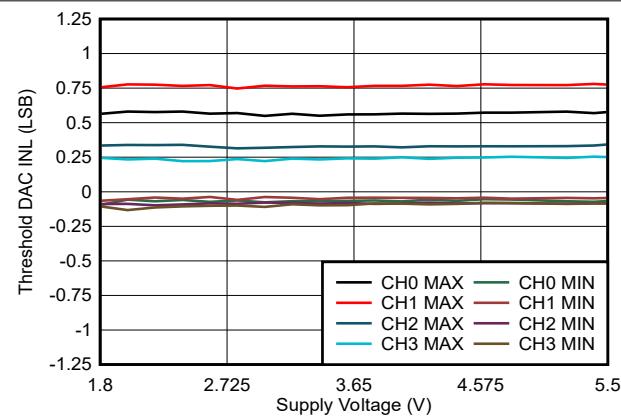

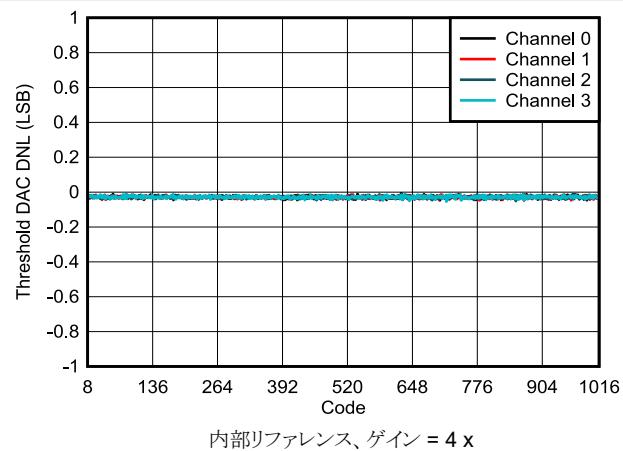

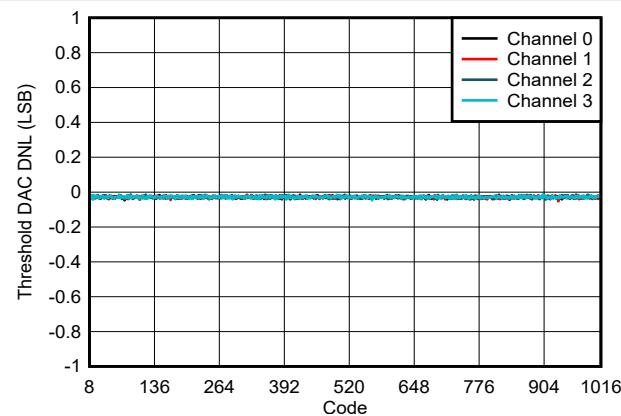

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5.5\text{V}$ 、外部リファレンス =  $5.5\text{V}$ 、ゲイン =  $1 \times$ 、AINx ピン (Hi-Z モード)、および出力無負荷時 (特に記述のない限り)

図 5-4. スレッショルド DAC INL とデジタル入力コードとの関係

図 5-5. スレッショルド DAC INL とデジタル入力コードとの関係

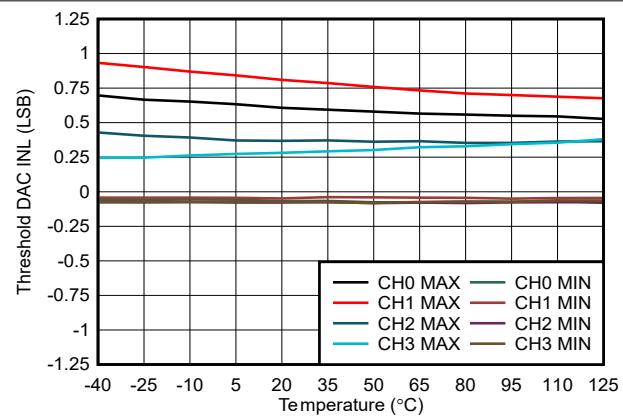

図 5-6. スレッショルド DAC INL と温度との関係

図 5-7. スレッショルド DAC INL と電源電圧との関係

図 5-8. スレッショルド DAC DNL とデジタル入力コードとの関係

図 5-9. スレッショルド DAC DNL とデジタル入力コードとの関係

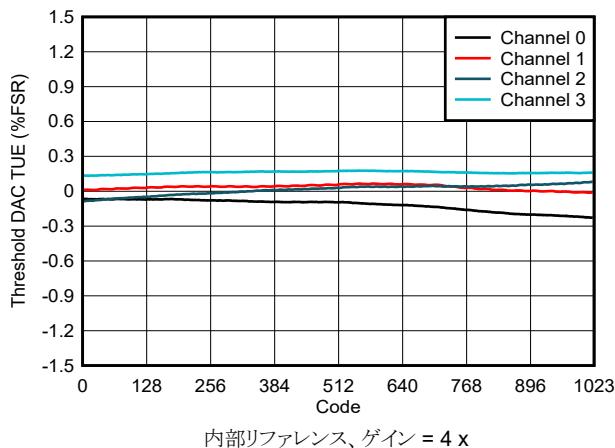

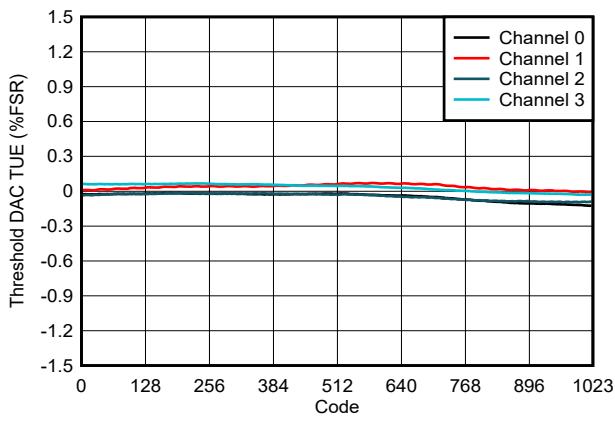

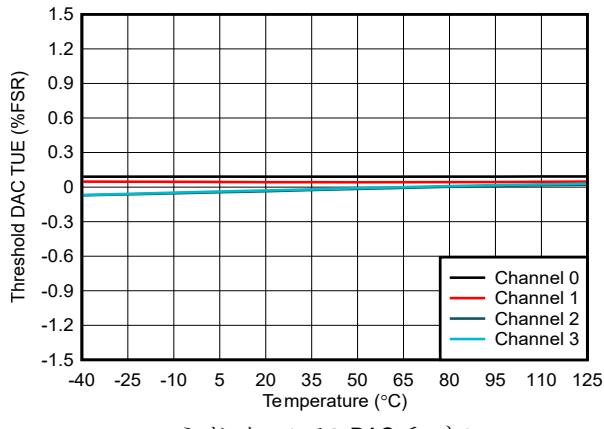

## 5.15 代表的特性 (続き)

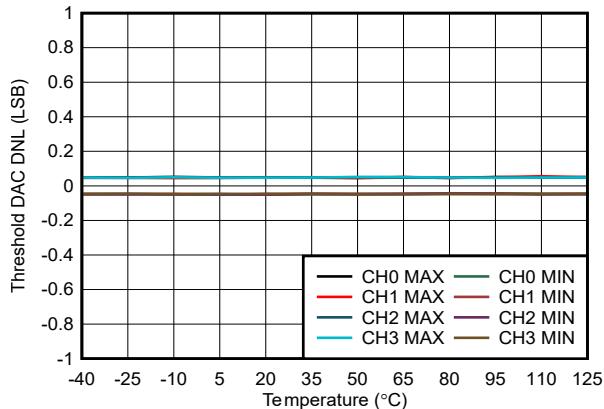

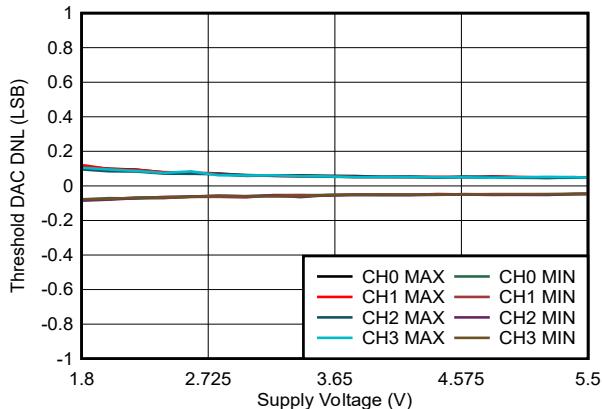

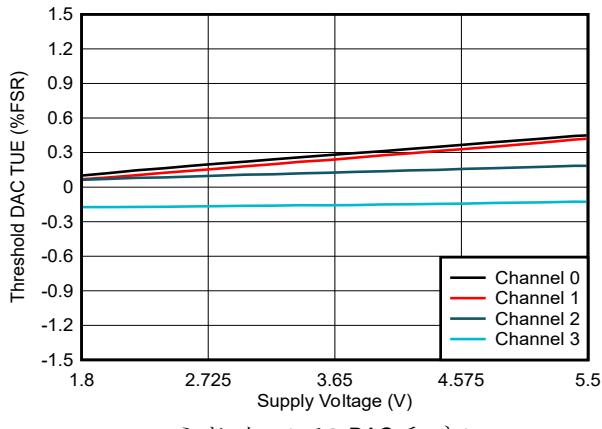

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5.5\text{V}$ 、外部リファレンス =  $5.5\text{V}$ 、ゲイン =  $1 \times$ 、AINx ピン (Hi-Z モード)、および出力無負荷時 (特に記述のない限り)

図 5-10. スレッショルド DAC DNL と温度との関係

図 5-11. スレッショルド DAC DNL と電源電圧との関係

内部リファレンス、ゲイン =  $4 \times$

図 5-12. スレッショルド DAC 総合未調整誤差 (TUE) とデジタル入力コードとの関係

図 5-13. スレッショルド DAC 総合未調整誤差 (TUE) とデジタル入力コードとの関係

ミッドスケールでの DAC チャネル

図 5-14. スレッショルド DAC 総合未調整誤差 (TUE) と温度との関係

ミッドスケールでの DAC チャネル

図 5-15. スレッショルド DAC 総合未調整誤差 (TUE) と電源電圧との関係

## 5.15 代表的特性 (続き)

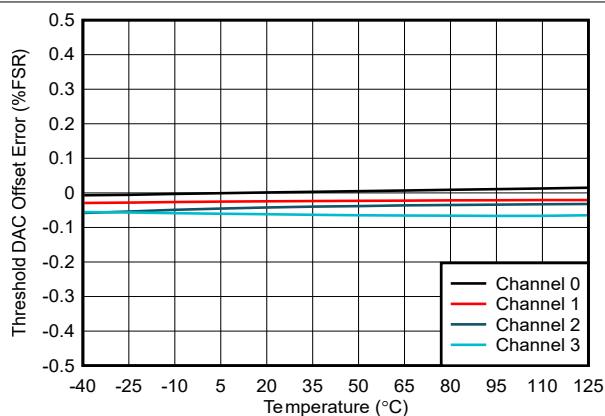

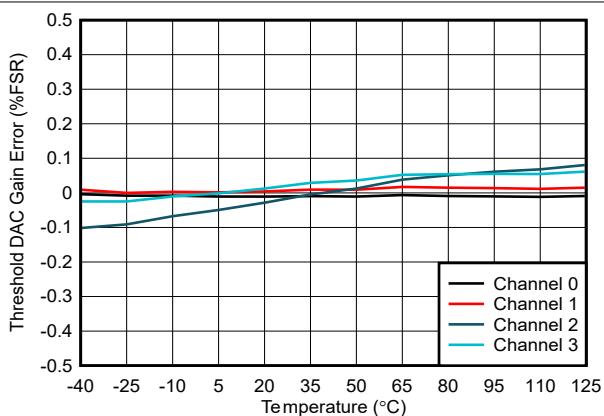

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5.5\text{V}$ 、外部リファレンス = 5.5V、ゲイン = 1 ×、AINx ピン (Hi-Z モード)、および出力無負荷時 (特に記述のない限り)

図 5-16. スレッショルド DAC オフセット誤差と温度との関係

図 5-17. スレッショルド DAC ゲイン誤差と温度との関係

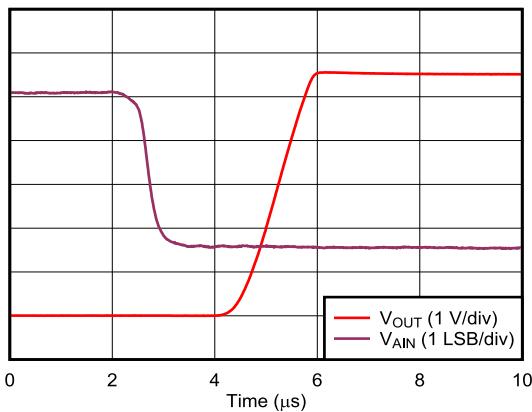

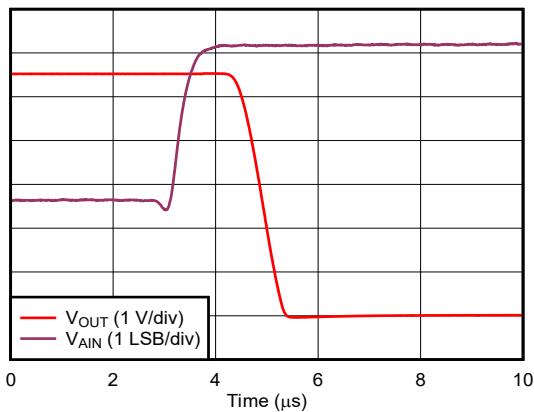

プッシュプルモードでのコンパレータ出力

図 5-18. コンパレータの応答時間 : Low から High への遷移

プッシュプルモードでのコンパレータ出力

図 5-19. コンパレータの応答時間 : High から Low への遷移

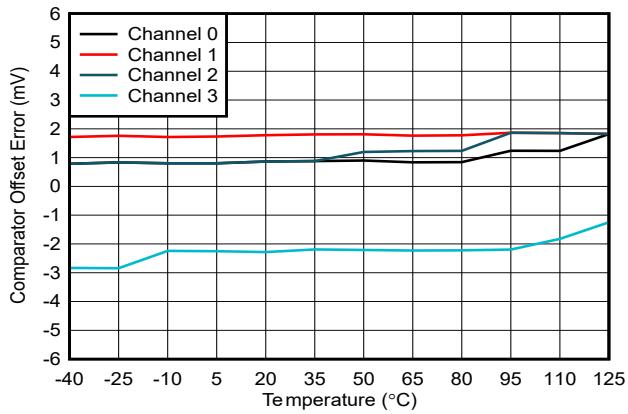

図 5-20. コンパレータのオフセット誤差と温度との関係

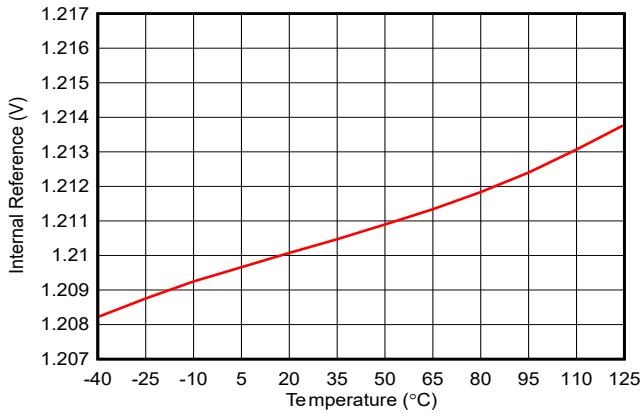

内部リファレンス

図 5-21. 内部リファレンスと温度との関係

## 5.15 代表的特性 (続き)

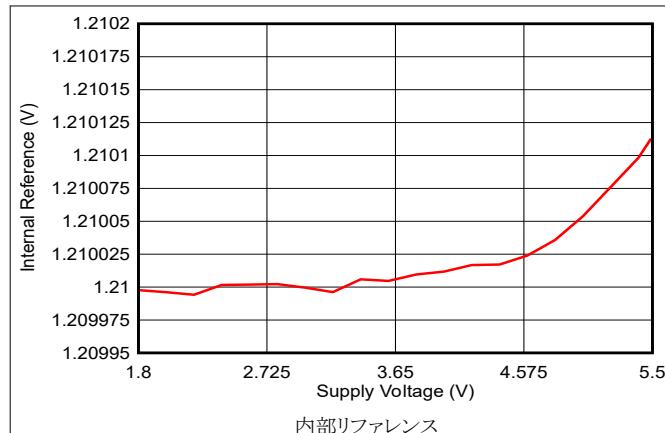

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5.5\text{V}$ 、外部リファレンス =  $5.5\text{V}$ 、ゲイン =  $1 \times$ 、AINx ピン (Hi-Z モード)、および出力無負荷時 (特に記述のない限り)

図 5-22. 内部リファレンスと電源電圧との関係

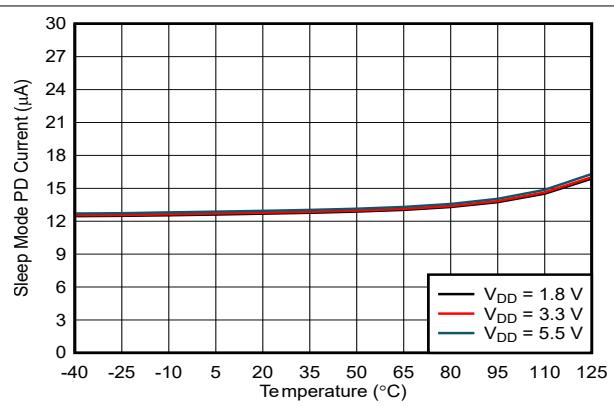

図 5-23. パワーダウン電流と温度との関係

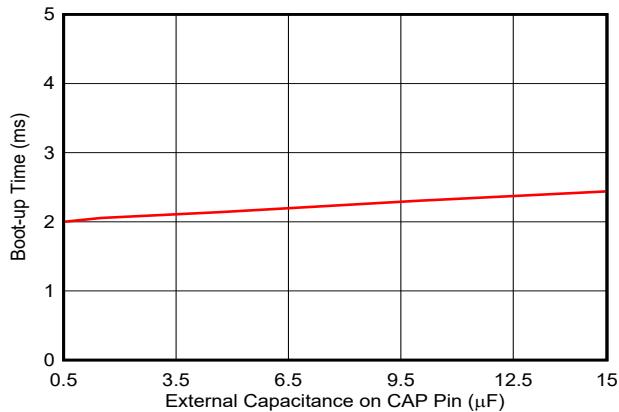

図 5-24. ブートアップ時間と CAP ピンの容量との関係

## 6 詳細説明

### 6.1 概要

DAC539E4W は、プログラマブルコンパレータと参照テーブルベースの汎用出力を備えた、10 ビット、クワッドスマート D/A コンバータ (DAC) です。コンパレータ出力はオプションとして直接利用できます。コンパレータ入力は、VDD/3 の入力範囲では Hi-Z として、または全入力範囲では有限の抵抗として構成できます。コンパレータは、リファレンスとして 4 つのスレッショルド DAC を使用します。すべてのスレッショルド DAC は独立して構成でき、設定を NVM に保存できます。

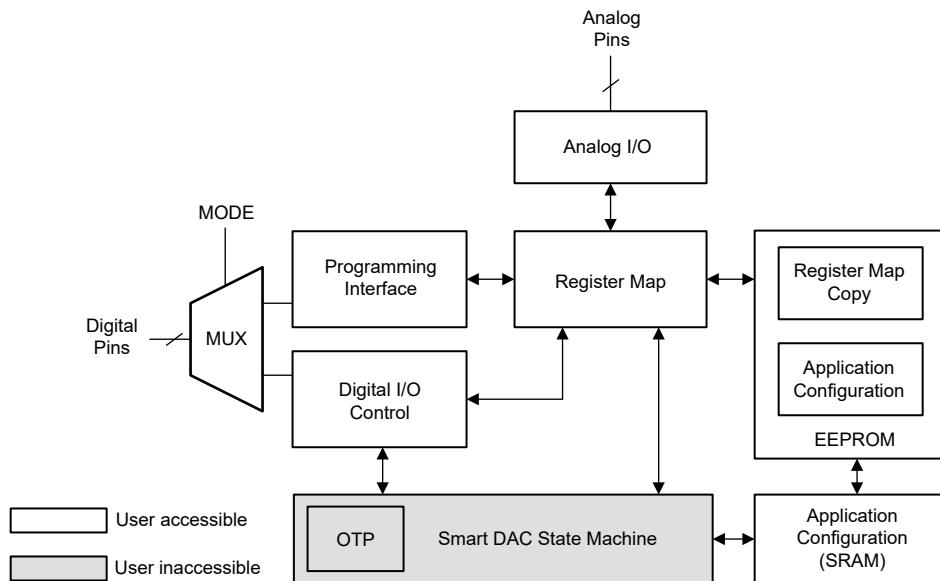

DAC539E4W は MODE ピンを使用して、プログラミングモード ( $\text{I}^2\text{C}$  または SPI) とスタンダードアロンモードを選択します。このデバイスは不揮発性メモリ (NVM) を備えており、SPI または  $\text{I}^2\text{C}$  インターフェイスを使用して工場出荷時にレジスタ設定を保存します。プログラム後、このデバイスはプロセッサを必要とせずに、自律動作します。

### 6.2 機能ブロック図

## 6.3 機能説明

### 6.3.1 スマート D/A コンバータ (DAC) アーキテクチャ

DAC539E4W はスレッショルド DAC とそれに続くコンパレータにストリングアーキテクチャを使用します。セクション 6.2 はブロック図内の DAC アーキテクチャを示しています。これは 1.8V ~ 5.5V の電源で動作します。

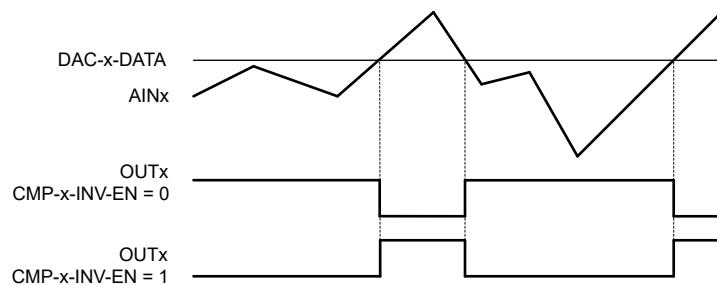

スレッショルド DAC は、1.21V の内部電源リファレンス、MODE ピンの外部リファレンス、または電源の、3 つのリファレンスオプションのいずれかを使用します。スレッショルド DAC は複数のプログラマブル出力範囲をサポートしています。

コンパレータ出力はレジスタ設定を使用して反転できます。コンパレータ出力はプッシュアップまたはオーブンドレインでできます。各種入力範囲をサポートするため、アナログ入力は Hi-Z または有限インピーダンスとして構成できます。*margin-high* と *margin-low* レジスタフィールドは NVM に保存されていませんが、コンパレータは *margin-high* と *margin-low* レジスタフィールドとラッチコンパレータを使用してプログラマブルヒステリシスをサポートします。コンパレータ出力はデバイスから内部的にアクセスできます。

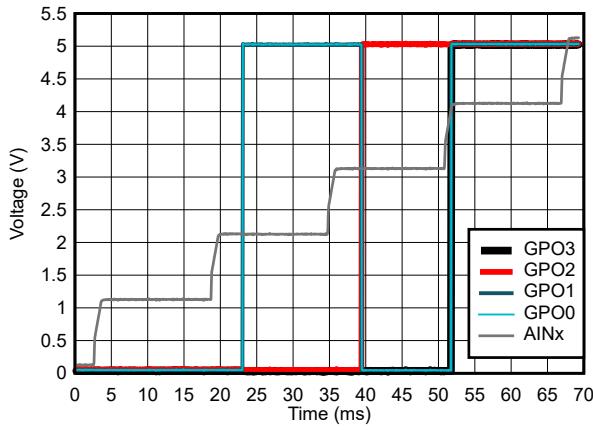

DAC539E4W は、図 6-1 に示すように、算術、ロジック、タイミングの各演算をサポートするプログラマブルステートマシンを装備しています。このステートマシンは、コンパレータ出力を DAC539E4W の GPO にマッピングする、参照テーブルとしてあらかじめプログラムされています。ステートマシンはレジスタマップを使用して設定され、パラメータは NVM に保存できます。ステートマシンは、プロセッサと接続せずにスタンダロンモードで動作できます（プロセッサレス動作）。

図 6-1. スマート DAC アーキテクチャ

### 6.3.2 スレッショルド DAC

各チャネルのスレッショルド DAC は、COMMON-CONFIG レジスタの VOUT-PDN-x フィールドのパワーアップオプションを選択することでイネーブルにできます。目的のスレッショルド電圧を実現するには、正しいリファレンスオプションを選択して、必要な出力範囲のゲインを選択し、各チャネルの DAC-x-DATA レジスタに DAC コードをプログラムします。

#### 6.3.2.1 基準電圧と DAC 伝達関数

DAC539E4W には、内部リファレンス、外部リファレンス、電源の 3 つの電圧リファレンスオプションがあります (図 6-2 を参照)。スレッショルド DAC の伝達関数は、電圧リファレンスの選択に基づいて変化します。

図 6-2. 電圧リファレンスの選択とパワーダウンロジック

##### 6.3.2.1.1 基準電圧としての電源

デフォルトでは、DAC539E4W は電源ピン (VDD) をリファレンスとして動作します。式 1 は電源ピンをリファレンスとして使用した場合のスレッショルド DAC の伝達関数を示します。出力段のゲインは常に 1 倍です。

$$V_{THLD} = \frac{DAC\_DATA}{2^N} \times V_{DD} \quad (1)$$

ここで

- N は DAC539E4W のビット単位の分解能で、10 ビットです。

- DAC\_DATA は DAC-x-DATA レジスタの DAC-x-DATA フィールドにロードされるバイナリコードの 10 進数と等しくなります。

- DAC\_DATA の範囲は  $0 \sim 2^N - 1$  です。

- $V_{DD}$  は DAC のリファレンス電圧として使用します。

### 6.3.2.1.2 内部リファレンス

DAC539E4W には内部リファレンスが搭載されており、デフォルトでディスエーブルになっています。内部リファレンスをイネーブルにするには、COMMON-CONFIG レジスタのビット EN-INT-REF に 1 を書き込みます。内部リファレンスは固定 1.21V 電圧 (標準値) を生成します。DAC-x-VOUT-CMP-CONFIG レジスタの VOUT-GAIN-x フィールドを使用して、DAC 出力電圧 ( $V_{THLD}$ ) で  $1.5\times$ 、 $2\times$ 、 $3\times$ 、 $4\times$  のゲインを実現します。[式 2](#) は内部リファレンスを使用した DAC 伝達関数を示しています。

$$V_{THLD} = \frac{DAC\_DATA}{2^N} \times V_{REF} \times GAIN \quad (2)$$

ここで

- N は DAC539E4W のビット単位の分解能で、10 ビットです。

- DAC\_DATA は DAC-x-DATA レジスタの DAC-x-DATA フィールドにロードされるバイナリコードの 10 進数と等しくなります。

- DAC\_DATA の範囲は  $0 \sim 2^N - 1$  です。

- $V_{REF}$  は内部リファレンス電圧です (1.21V)。

- VOUT-GAIN-X ビットに基づき、ゲイン =  $1.5\times$ 、 $2\times$ 、 $3\times$ 、 $4\times$ 。

### 6.3.2.1.3 外部リファレンス

DAC539E4W は外部リファレンス入力 (MODE ピン) を提供します。DAC-x-VOUT-CMP-CONFIG レジスタの VOUT-GAIN-X フィールドを適切に構成し、外部リファレンスオプションを選択します。MODE ピン機能を使用しない場合、DEVICE-MODE-CONFIG レジスタの DIS-MODE-IN ビットに 1 を書き込んで、静止電流を最小化します。外部リファレンスは 1.8V ~ VDD にすることができます。[式 3](#) は外部リファレンスを使用する場合のスレッショルド DAC の伝達関数を示しています。

#### 注

外部リファレンスは、過渡状態と定常状態の両方で VDD を下回っている必要があります。したがって、外部リファレンスは VDD の後に上昇し、VDD の前に下降する必要があります。

$$V_{THLD} = \frac{DAC\_DATA}{2^N} \times V_{REF} \quad (3)$$

ここで

- N は DAC539E4W のビット単位の分解能で、10 ビットです。

- DAC\_DATA は DAC-x-DATA レジスタの DAC-x-DATA フィールドにロードされるバイナリコードの 10 進数と等しくなります。

- DAC\_DATA の範囲は  $0 \sim 2^N - 1$  です。

- $V_{REF}$  は外部リファレンス電圧です。

### 6.3.3 参照テーブル (LUT)

DAC539E4W には、コンパレータ入力を GPO にマッピングするユーザーがプログラムできる参照テーブルが用意されています。この LUT は、スタンダードアロン動作では NVM に保存できます。表 6-1 および 表 6-2 は、DAC-x-VOUT-CMP-CONFIG レジスタの CMP-x-INV-EN ビットの各種設定を使用してユーザーがプログラム可能な LUT を示しています。表 6-3 は、プログラミングモードとスタンダードアロンモードの間のピンマッピングを示しています。

**表 6-1. コンパレータ入力から GPO へのマップ (CMP-x-INV-EN = 0、デフォルト)**

| コンパレータ入力 |      |      |      | ユーザーがプログラム可能な出力<br>(デフォルト値) |      |      |      | SRAM の位置  | 名称          |

|----------|------|------|------|-----------------------------|------|------|------|-----------|-------------|

| AIN3     | AIN2 | AIN1 | AIN0 | GPO3                        | GPO2 | GPO1 | GPO0 |           |             |

| 0        | 0    | 0    | 0    | 1                           | 1    | 1    | 1    | 0x25[3:0] | LUT-0-DATA  |

| 0        | 0    | 0    | 1    | 1                           | 1    | 1    | 0    | 0x26[3:0] | LUT-1-DATA  |

| 0        | 0    | 1    | 0    | 1                           | 1    | 0    | 1    | 0x27[3:0] | LUT-2-DATA  |

| 0        | 0    | 1    | 1    | 1                           | 1    | 0    | 0    | 0x28[3:0] | LUT-3-DATA  |

| 0        | 1    | 0    | 0    | 1                           | 0    | 1    | 1    | 0x29[3:0] | LUT-4-DATA  |

| 0        | 1    | 0    | 1    | 1                           | 0    | 1    | 0    | 0x2A[3:0] | LUT-5-DATA  |

| 0        | 1    | 1    | 0    | 1                           | 0    | 0    | 1    | 0x2B[3:0] | LUT-6-DATA  |

| 0        | 1    | 1    | 1    | 1                           | 0    | 0    | 0    | 0x2C[3:0] | LUT-7-DATA  |

| 1        | 0    | 0    | 0    | 0                           | 1    | 1    | 1    | 0x2D[3:0] | LUT-8-DATA  |

| 1        | 0    | 0    | 1    | 0                           | 1    | 1    | 0    | 0x2E[3:0] | LUT-9-DATA  |

| 1        | 0    | 1    | 0    | 0                           | 1    | 0    | 1    | 0x2F[3:0] | LUT-10-DATA |

| 1        | 0    | 1    | 1    | 0                           | 1    | 0    | 0    | 0x30[3:0] | LUT-11-DATA |

| 1        | 1    | 0    | 0    | 0                           | 0    | 1    | 1    | 0x31[3:0] | LUT-12-DATA |

| 1        | 1    | 0    | 1    | 0                           | 0    | 1    | 0    | 0x32[3:0] | LUT-13-DATA |

| 1        | 1    | 1    | 0    | 0                           | 0    | 0    | 1    | 0x33[3:0] | LUT-14-DATA |

| 1        | 1    | 1    | 1    | 0                           | 0    | 0    | 0    | 0x34[3:0] | LUT-15-DATA |

**表 6-2. コンパレータ入力から GPO へのマップ (CMP-x-INV-EN = 1)**

| コンパレータ入力 |      |      |      | ユーザーがプログラム可能な出力<br>(デフォルト値) |      |      |      | SRAM の位置  | 名称          |

|----------|------|------|------|-----------------------------|------|------|------|-----------|-------------|

| AIN3     | AIN2 | AIN1 | AIN0 | GPO3                        | GPO2 | GPO1 | GPO0 |           |             |

| 0        | 0    | 0    | 0    | 0                           | 0    | 0    | 0    | 0x25[3:0] | LUT-0-DATA  |

| 0        | 0    | 0    | 1    | 0                           | 0    | 0    | 1    | 0x26[3:0] | LUT-1-DATA  |

| 0        | 0    | 1    | 0    | 0                           | 0    | 1    | 0    | 0x27[3:0] | LUT-2-DATA  |

| 0        | 0    | 1    | 1    | 0                           | 0    | 1    | 1    | 0x28[3:0] | LUT-3-DATA  |

| 0        | 1    | 0    | 0    | 0                           | 1    | 0    | 0    | 0x29[3:0] | LUT-4-DATA  |

| 0        | 1    | 0    | 1    | 0                           | 1    | 0    | 1    | 0x2A[3:0] | LUT-5-DATA  |

| 0        | 1    | 1    | 0    | 0                           | 1    | 1    | 0    | 0x2B[3:0] | LUT-6-DATA  |

| 0        | 1    | 1    | 1    | 0                           | 1    | 1    | 1    | 0x2C[3:0] | LUT-7-DATA  |

| 1        | 0    | 0    | 0    | 1                           | 0    | 0    | 0    | 0x2D[3:0] | LUT-8-DATA  |

| 1        | 0    | 0    | 1    | 1                           | 0    | 0    | 1    | 0x2E[3:0] | LUT-9-DATA  |

| 1        | 0    | 1    | 0    | 1                           | 0    | 1    | 0    | 0x2F[3:0] | LUT-10-DATA |

| 1        | 0    | 1    | 1    | 0                           | 1    | 1    | 0    | 0x30[3:0] | LUT-11-DATA |

| 1        | 1    | 0    | 0    | 1                           | 1    | 0    | 0    | 0x31[3:0] | LUT-12-DATA |

| 1        | 1    | 0    | 1    | 1                           | 1    | 0    | 1    | 0x32[3:0] | LUT-13-DATA |

| 1        | 1    | 1    | 0    | 1                           | 1    | 1    | 0    | 0x33[3:0] | LUT-14-DATA |

| 1        | 1    | 1    | 1    | 1                           | 1    | 1    | 1    | 0x34[3:0] | LUT-15-DATA |

**表 6-3. GPO ピンマッピング**

| スタンダロンモード<br>(MODE ピンが High) | プログラミングモード<br>(MODE ピンが Low) | ピン番号 |

|------------------------------|------------------------------|------|

| GPO0                         | SDA/SCLK                     | 8    |

| GPO1                         | A0/SDI                       | 7    |

| GPO2                         | SCL/SYNC                     | 6    |

| GPO3                         | NC/SDO                       | 5    |

DAC539E4W には、コンパレータ出力と GPO との間のプログラマブル遅延が搭載され、アナログ入力の遷移を安定化できます。この遅延は、LOOP-WAIT レジスタの LOOP-REFRESH フィールドを使用して指定します。[式 4](#) は LOOP-REFRESH フィールドの 10 進値を使用して合計遅延を秒単位で計算します。

$$\text{DELAY\_TIME} = \frac{2^{\text{LOOP\_REFRESH} + 1}}{25.6 \times 10^6} \quad (4)$$

### 6.3.4 プログラミングインターフェイス

DAC539E4W には、I<sup>2</sup>C と SPI を含む 4 つのデジタル I/O ピンがあります。これらのデバイスは、電源投入後に最初の通信が成功したときに I<sup>2</sup>C と SPI プロトコルを自動的に検出し、検出済みインターフェイスに接続します。インターフェイスプロトコルが接続されると、プロトコルの変更はすべて無視されます。I<sup>2</sup>C インターフェイスは、A0 ピンを使用して 4 つのアドレスオプションから選択します。SPI はデフォルトでは 3 線インターフェイスです。このモードではリードバック機能を使用できません。NC/SDO ピンはレジスタマップで構成してから、SDO 出力として NVM にプログラムできます。SPI リードバックモードは書き込みモードよりも低速です。プログラミングインターフェイスのピンは次のとおりです：

- I<sup>2</sup>C:SCL, SDA, A0

- SPI:SCLK, SDI, SYNC, NC/SDO

出力として使用する場合、すべてのデジタルピンはオープンドレインです。そのため、すべての出力ピンは、外部レジスタを使用して必要な I/O 電圧にプルアップする必要があります。

### 6.3.5 不揮発性メモリ (NVM)

DAC539E4W には不揮発性メモリ (NVM) ビットが内蔵されています。これらのメモリビットはユーザーがプログラムおよび消去でき、電源がない場合でも設定値を保持します。「レジスタマップ」セクションの強調表示された灰色のセルが示すように、COMMON-TRIGGER レジスタで NVM-PROG = 1 に設定すると、すべてのレジスタビットを NVM に保存できます。これは自動リセットされるビットです。NVM の書き込み動作またはリロード動作が進行中の場合、GENERAL-STATUS レジスタの NVM-BUSY ビットはデバイスにより 1 に設定されます。この期間中、デバイスによってデバイスに対するすべての読み取り/書き込み動作がブロックされます。書き込み動作またはリロード動作が完了すると、NVM-BUSY ビットは 0 に設定されます。この時点で、デバイスに対するすべての読み取り/書き込み操作が許可されます。DAC539E4W のすべてのレジスタのデフォルト値は、POR イベントが発行されるとすぐに NVM からロードされます。

また、DAC539E4W は COMMON-TRIGGER レジスタに NVM-RELOAD ビットも実装しています。このビットを 1 に設定すると、デバイスは NVM リロード動作を開始します。NVM リロード動作は、NVM から保存されたデータでレジスタマップを上書きします。完了後、デバイスはこのビットを 0 に自動的にリセットします。NVM-RELOAD 動作中、NVM-BUSY ビットは 1 に設定されます。

#### 6.3.5.1 NVM 巡回冗長検査 (CRC)

DAC539E4W は、NVM に保存されたデータが破損していないことを確認するための、NVM 用巡回冗長検査 (CRC) 機能を実装しています。DAC539E4W には次の 2 種類の CRC アラームビットが実装されています。

- NVM-CRC-FAIL-USER

- NVM-CRC-FAIL-INT

NVM-CRC-FAIL-USER ビットはユーザーがプログラム可能な NVM ビットのステータスを示し、NVM-CRC-FAIL-INT ビットは内部 NVM ビットのステータスを示します。CRC 機能は、NVM プログラム操作 (書き込みまたはリロード) が実行されるたび、およびデバイスの起動中に、16 ビットの CRC (CRC-16-CCITT) と NVM データを保存することによって実装されます。デバイスは NVM データを読み取り、保存済みの CRC を使用してデータを検証します。CRC アラームビット (GENERAL-STATUS レジスタの NVM-CRC-FAIL-USER と NVM-CRC-FAIL-INT) は、デバイスの NVM からデータを読み取った後、エラーを報告します。

---

注

アラームビットはブートアップ時にのみ設定されます。

---

##### 6.3.5.1.1 NVM-CRC-FAIL-USER ビット

NVM-CRC-FAIL-USER ビットのロジック 1 は、ユーザーがプログラム可能な NVM データが破損していることを示します。この状態では、デバイス内のすべてのレジスタが工場出荷時のリセット値で初期化され、任意のデバイスレジスタへの書き込みまたは読み取りが可能です。このアラームビットを 0 にリセットするには、ソフトウェアリセット (セクション 6.3.7 を参照) コマンドを発行するか、デバイスの電源を入れ直します。ソフトウェアリセットまたは電源入れ直しの際にも、ユーザーがプログラム可能な NVM ビットがリロードされます。問題が解決しない場合は、NVM を再プログラムしてください。

##### 6.3.5.1.2 NVM-CRC-FAIL-INT ビット

NVM-CRC-FAIL-INT ビットのロジック 1 は、内部 NVM データが破損していることを示します。この状態では、デバイス内のすべてのレジスタが工場出荷時のリセット値で初期化され、任意のデバイスレジスタへの書き込みまたは読み取りが可能です。一時的な障害の場合、アラームビットを 0 にリセットするには、ソフトウェアリセット (セクション 6.3.7 を参照) コマンドを発行するか、デバイスの電源を入れ直します。NVM に永続的な障害が発生すると、デバイスは使用できなくなります。

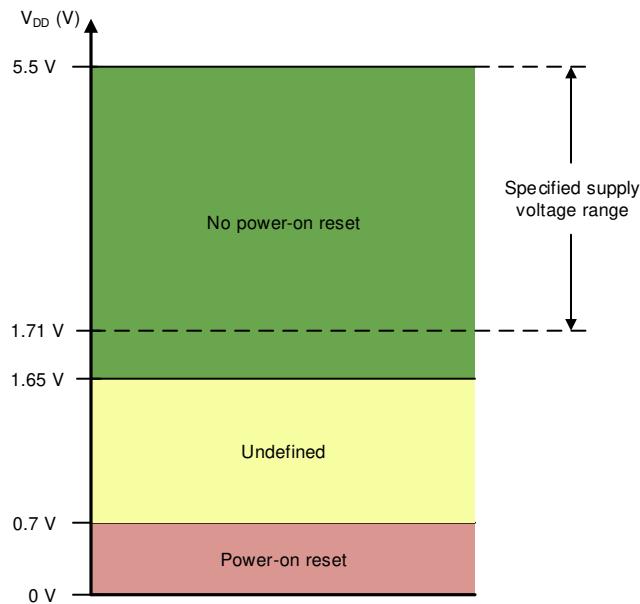

### 6.3.6 パワーオン リセット (POR)

DAC539E4W は、電源投入時に出力電圧を制御するパワーオンリセット (POR) 機能を備えています。 $V_{DD}$  電源が立ち上がりると、POR イベントが発行されます。POR により、全レジスタはデフォルト値に初期化され、POR (ブートアップ) 遅延の後にのみデバイスとの通信が有効になります。DAC539E4W のすべてのレジスタのデフォルト値は、POR イベントが発行されるとすぐに NVM からロードされます。

デバイスに電源が投入されると、デバイスは POR 回路によりデフォルトモードに設定されます。POR 回路では、図 6-3 に示すように、電源投入時に内部コンデンサが放電されてデバイスがリセットされるように、規定の  $V_{DD}$  レベルが必要です。POR が発生するようにするには、 $V_{DD}$  が少なくとも 1ms の間、0.7V 未満である必要があります。 $V_{DD}$  が 1.65V 未満に低下しても 0.7V を超えている場合 (未定義の領域として表示)、デバイスのリセットは、指定されたすべての温度および電源条件下で決定的ではありません。この場合は、POR を開始します。 $V_{DD}$  が 1.65V を超えたままになると、POR は発生しません。

図 6-3.  $V_{DD}$  POR 回路のスレッショルドレベル

### 6.3.7 外部リセット

デバイスへの外部リセットはレジスタマップを介してトリガできます。デバイスソフトウェアのリセットイベントを開始するには、COMMON-TRIGGER レジスタの RESET フィールドに予約コード 1010b を書き込みます。このソフトウェアリセットにより POR イベントが開始されます。

### 6.3.8 レジスタ マップロック

DAC539E4W は、DAC レジスタへの偶発的な (意図しない) 書き込みを防止するレジスタマップロック機能を実装しています。COMMON-CONFIG レジスタの DEV-LOCK ビットが 1 にセットされると、デバイスはすべてのレジスタをロックします。DEV-LOCK 設定をバイパスするには、COMMON-TRIGGER レジスタの DEV-UNLOCK ビットに 0101b を書き込みます。

## 6.4 デバイスの機能モード

### 6.4.1 コンパレータ モード

あるチャネルのコンパレータを有効にするには、それぞれの DAC-x-VOUT-CMP-CONFIG レジスタの CMP-x-EN ビットと CMP-x-OUT-EN ビットに 1 を書き込みます。コンパレータの出力は、CMP-x-OD-EN ビットを使用して、プッシュプルまたはオープンドレインとして構成できます。コンパレータの出力を反転するには、CMP-x-INV-EN ビットに 1 を書き込みます。AINx ピンのインピーダンスは有限です。AINx ピンのハイインピーダンスを無効化するには、CMP-x-HIZ-IN-DIS ビットに 1 を書き込みます。[表 6-4](#) は各種ビット設定に対するピンのコンパレータ出力を示しています。[表 6-5](#) はコンパレータのフルスケールのアナログ入力設定を示しています。それより高い入力電圧はカットされます。

**表 6-4. コンパレータの出力構成**

| CMP-x-EN | CMP-x-OUT-EN | CMP-x-OD-EN | CMP-x-INV-EN | OUTx ピン <sup>(1)</sup> |

|----------|--------------|-------------|--------------|------------------------|

| 0        | X            | X           | X            | コンパレータは有効にされません。       |

| 1        | 0            | X           | X            | Hi-Z 出力。               |

| 1        | 1            | 0           | 0            | プッシュプル出力。              |

| 1        | 1            | 0           | 1            | プッシュプルおよび反転出力。         |

| 1        | 1            | 1           | 0            | オープンドレイン出力。            |

| 1        | 1            | 1           | 1            | オープンドレインおよび反転出力。       |

(1) コンパレータが有効なとき、コンパレータの出力値は、出力ピン (OUTx) の設定に関係なく LUT からアクセスできます。

**表 6-5. フルスケールのアナログ入力  $V_{FS}$**

| リファレンス (VREF) | ゲイン   | $V_{FS}$ (Hi-Z 入力モード) | $V_{FS}$ (有限インピーダンス入力モード) |

|---------------|-------|-----------------------|---------------------------|

| 電源            | 1 ×   | VDD / 3               | VDD                       |

| 外部            | 1 ×   | VREF / 3              | VREF                      |

| 内部            | 1.5 × | (VREF × GAIN) / 3     | VREF × GAIN               |

|               | 2 ×   | (VREF × GAIN) / 3     | VREF × GAIN               |

|               | 3 ×   | (VREF × GAIN) / 6     | (VREF × GAIN) / 2         |

|               | 4 ×   | (VREF × GAIN) / 6     | (VREF × GAIN) / 2         |

各 DAC-x-CMP-MODE-CONFIG レジスタの CMP-x-MODE フィールドを使用すると、個々のコンパレータチャネルを、ヒステリシスなし、ヒステリシスあり、ラッチコンパレータモードに構成できます。

**注**

NVM ではヒステリシスなしモードのみがサポートされています。ヒステリシスマードまたはラッチコンパレータモードは、レジスタマップでのみ動作可能です。

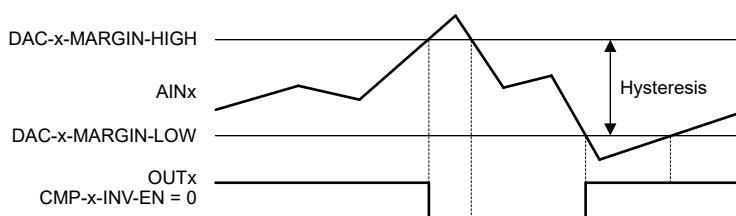

図 6-4 はコンパレータのインターフェイス回路を示しています。図 6-5 はプログラマブルコンパレータの動作を示しています。表 6-6 に示すように、DAC-x-CMP-MODE-CONFIG レジスタの CMP-x-MODE ビットを使用すると、個々のコンパレータチャネルを、ヒステリシスなし、ヒステリシスありのモードに構成できます。

図 6-4. コンパレータのインターフェイス

図 6-5. プログラマブルコンパレータの動作

表 6-6. コンパレータモードの選択

| CMP-x-MODE ビットフィールド | コンパレータの構成                                                                                     |

|---------------------|-----------------------------------------------------------------------------------------------|

| 00                  | 通常のコンパレータモード。ヒステリシス動作なし。                                                                      |

| 01                  | ヒステリシスコンパレータモード (NVM ではサポートされていません)。DAC-x-MARGIN-HIGH および DAC-x-MARGIN-LOW レジスタはヒステリシスを設定します。 |

| 10                  | 無効な設定。                                                                                        |

| 11                  | 無効な設定。                                                                                        |

#### 6.4.1.1 プログラマブルヒステリシスコンパレータ

表 6-6 に示すように、CMP-x MODE ビットが 01b に設定されると、コンパレータはヒステリシスを供給します。ヒステリシスは、図 6-6 に示すように、DAC-x-MARGIN-HIGH と DAC-x-MARGIN-LOW レジスタによって供給されます。

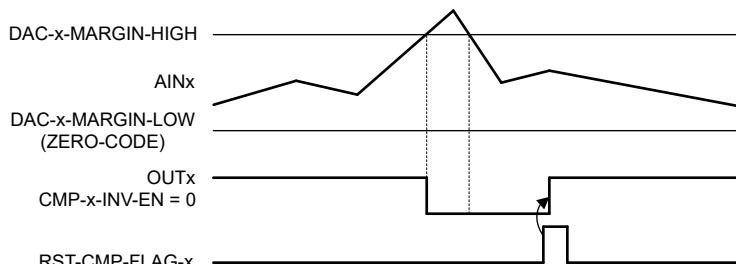

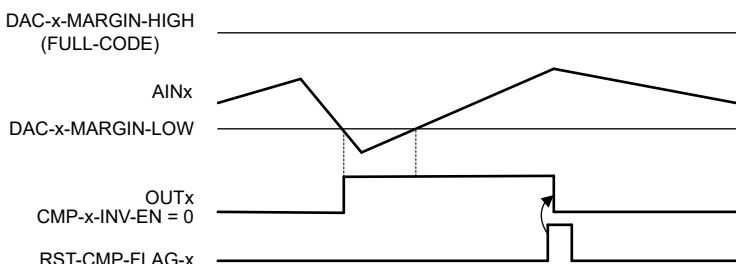

DAC-x-MARGIN-HIGH がフルコードに設定されるか、DAC-x-MARGIN-LOW がゼロコードに設定されると、コンパレータはラッチコンパレータとして動作し、スレッショルドを超えた後に出力がラッチされます。ラッチされた出力は、COMMON-DAC-TRIG レジスタの対応する RST-CMP-FLAG-x ビットに書き込むことによりセットできます。図 6-7 はアクティブ Low 出力のラッチコンパレータの動作を示し、図 6-8 はアクティブ High 出力のラッチコンパレータの動作を示しています。

##### 注

DAC-x-MARGIN-HIGH レジスタの値は、DAC-x-MARGIN-LOW レジスタの値より大きくする必要があります。ヒステリシスマードのコンパレータ出力は非反転型のみでできます。つまり、DAC-x-VOUT-CMP-CONFIG レジスタの CMP-x-INV-EN ビットを 0 に設定する必要があります。ラッチモードでリセットを有効にするには、入力電圧が DAC-x-MARGIN-HIGH と DAC-x-MARGIN-LOW の範囲内である必要があります。

図 6-6. 出力のラッチがないプログラマブルヒステリシス

図 6-7. アクティブ Low 出力付きラッチコンパレータ

図 6-8. アクティブ High 出力付きラッチコンパレータ

### 6.4.2 パワーダウン モード

図 6-2 に示すように、DAC539E4W のコンパレータと内部リファレンスは、COMMON-CONFIG レジスタの EN-INT-REF および VOUT-PDN-x ビットを介して個別にパワーダウンできます。電源オン時に、DAC 出力と内部リファレンスはデフォルトで無効化されます。パワーダウンモードでは、コンパレータ出力 (OUTx ピン) はハイインピーダンス状態になります。この状態を  $10\text{k}\Omega\text{-AGND}$  または  $100\text{k}\Omega\text{-AGND}$  (パワーアップ時) に変更するには、VOUT-PDN-x ビットを使用します。

コンパレータのパワーアップ状態は、NVM を使用して任意の状態 (パワーダウンまたは通常モード) にプログラムできます。表 6-7 はコンパレータのパワーダウンビットを示しています。

表 6-7. コンパレータのパワーダウンビット

| レジスタ          | VOUT-PDN-x[1] | VOUT-PDN-x[0] | 説明                                                 |

|---------------|---------------|---------------|----------------------------------------------------|

| COMMON-CONFIG | 0             | 0             | チャネル x をパワーアップします。                                 |

|               | 0             | 1             | $10\text{k}\Omega$ を AGND に接続してチャネル x をパワーダウンします。  |

|               | 1             | 0             | $100\text{k}\Omega$ を AGND に接続してチャネル x をパワーダウンします。 |

|               | 1             | 1             | チャネル x を Hi-Z にパワーダウンします (デフォルト)。                  |

## 6.5 プログラミング

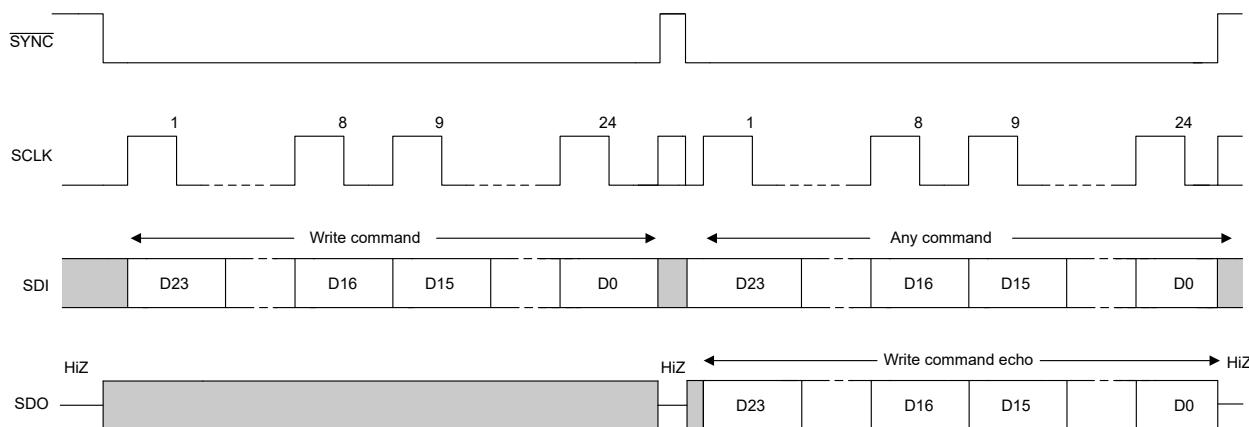

### 6.5.1 SPI プログラミングモード

DAC539E4W の SPI アクセスサイクルを開始するには、SYNC ピンを Low にアサートします。シリアルクロック SCLK は、連続クロックまたはゲートクロックです。SDI データは、SCLK の立ち下がりエッジに同期します。DAC539E4W の SPI フレームは 24 ビット長です。そのため、SYNC ピンは、少なくとも 24 個の SCLK の立ち下がりエッジの間、Low に維持されます。SYNC ピンが High にデアサートされると、アクセス サイクルは終了します。アクセス サイクルに最小クロック エッジよりも短い場合、通信は無視されます。デフォルトでは、SDO ピンはイネーブルではありません (3 線式 SPI)。3 線式 SPI モードでは、アクセス サイクルで最小クロックエッジ数を超える場合、デバイスは最初の 24 ビットのみを使用します。SYNC が High のとき、SCLK および SDI 信号がブロックされ、SDO は Hi-Z になり、バス上に接続されている他のデバイスのデータのリードバックが可能になります。

24 ビット SPI アクセスサイクルのフォーマットを、表 6-8 と 図 6-9 に示します。SDI への最初のバイト入力は命令サイクルです。命令サイクルは、読み取りまたは書き込みコマンドと、アクセスする 7 ビットアドレスとして、リクエストを識別します。サイクルの最後の 16 ビットはデータサイクルを形成します。

表 6-8. SPI 読み取り/書き込みアクセスサイクル

| ビット   | フィールド    | 説明                                                                                                     |

|-------|----------|--------------------------------------------------------------------------------------------------------|

| 23    | R/W      | アドレスレジスタに対する読み取りまたは書き込みコマンドとして通信を識別します: R/W = 0 は書き込み動作を設定します。R/W = 1 は読み取り動作を設定します                    |

| 22-16 | A[6:0]   | レジスタアドレス: 読み取りまたは書き込み動作中にアクセスするレジスタを指定します                                                              |

| 15-0  | DI[15:0] | データサイクルビット: 書き込みコマンドの場合、データ サイクルのビットはアドレス A[6:0] のレジスタに書き込まれる値となります。読み取りコマンドの場合、データサイクルのビットは未使用値となります。 |

図 6-9. SPI 書き込みサイクル

読み取り動作には、まず INTERFACE-CONFIG レジスタの SDO-EN ビットを設定して SDO ピンを有効化する必要があります。この構成を 4 線式 SPI と呼びます。読み取り操作は、読み取りコマンドのアクセス サイクルを発行することで開始されます。読み取りコマンドの後、リクエストされたデータを取得するため、2 回目のアクセスサイクルを発行する必要があります。表 6-9 および 図 6-10 は出力データのフォーマットを示しています。データは、FSDO ビットに応じて、SCLK の立ち下がりエッジまたは立ち上がりエッジのいずれかの SDO ピンでクロック出力されます。図 5-3 を参照してください。

表 6-9. SDO 出力アクセスサイクル

| ビット   | フィールド    | 説明                            |

|-------|----------|-------------------------------|

| 23    | R/W      | 前回のアクセスサイクルのエコー R/W           |

| 22-16 | A[6:0]   | 前回のアクセスサイクルのエコーレジスタアドレス       |

| 15-0  | DI[15:0] | 前のアクセスサイクルでリクエストされたデータのリードバック |

図 6-10. SPI 読み取りサイクル

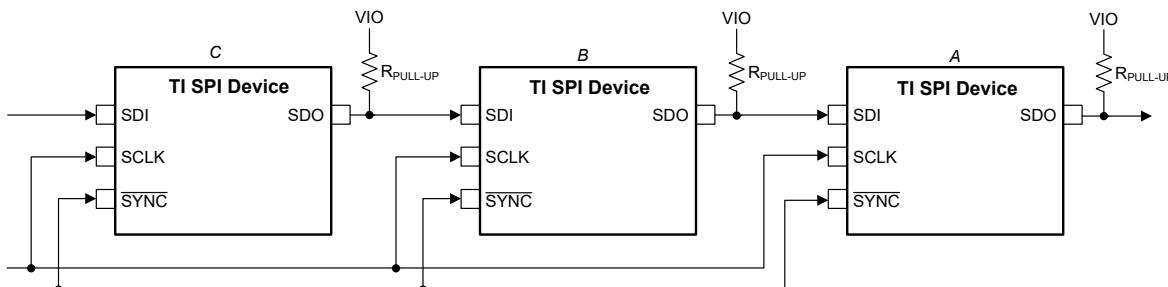

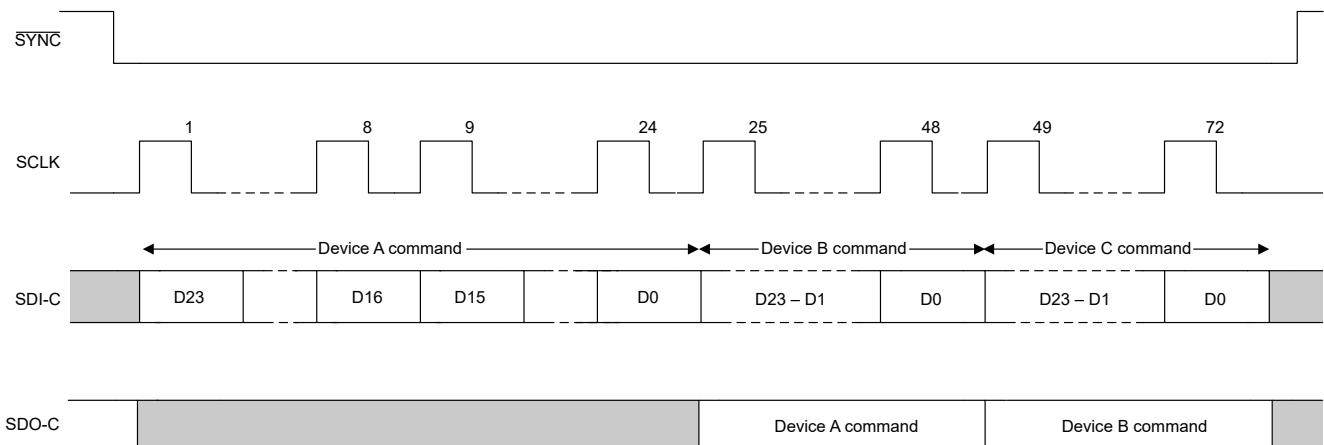

デイジーチェーン動作は SDO ピンでもイネーブルになります。デイジーチェーンモードでは、図 6-11 に示すように、デバイスのいずれかの SDO ピンを以下のデバイスの SDI ピンに接続して、複数のデバイスをチェーンで接続します。SPI ホストはチェーン内の最初のデバイスの SDI ピンを駆動します。チェーンの最後のデバイスの SDO ピンは、SPI ホストの POCI ピンに接続されます。4 線式 SPI モードでは、アクセスサイクルに 24 クロックエッジの倍数が含まれる場合、チェーン内の最初のデバイスは最後の 24 ビットのみを使用します。アクセスサイクルに、24 の倍数でないクロックエッジが含まれている場合、デバイスは SPI パケットを無視します。図 6-12 はデイジーチェーン書き込みサイクルのパケットフォーマットを示しています。

図 6-11. SPI デイジーチェーンの接続

図 6-12. SPI デイジーチェーンの書き込みサイクル

### 6.5.2 I<sup>2</sup>C プログラミング モード

DAC539E4W には、「ピン構成および機能」セクションのピン図に示すように、2 線シリアルインターフェース (SCL および SDA) と、1 つのアドレスピン (A0) があります。I<sup>2</sup>C バスは、プルアップ構造を持つデータライン (SDA) とクロックライン (SCL) で構成されます。バスがアイドルのときは、SDA ラインと SCL ラインの両方が High にプルされます。I<sup>2</sup>C 互換のデバイスはすべて、オープンドレインの I/O ピンである SDA および SCL を介して I<sup>2</sup>C バスに接続します。

I<sup>2</sup>C 仕様では、通信を制御するデバイスをコントローラ、コントローラによって制御されるデバイスをターゲットと規定しています。コントローラは SCL 信号を生成します。また、コントローラは、データ転送の開始または停止を示すために、バス上に特別なタイミング条件 (スタート条件、繰り返しスタート条件、ストップ条件) を生成します。デバイスアドレッシングはコントローラが実行します。I<sup>2</sup>C バス上のコントローラは通常、マイコンまたはデジタル信号プロセッサ (DSP) です。DAC539E4W は I<sup>2</sup>C バス上でターゲットとして動作します。ターゲットはコントローラコマンドをアクノリッジ (受信確認) して、コントローラの制御時にデータを受信または送信します。

通常、DAC539E4W はターゲットレシーバとして動作します。コントローラは、ターゲットレシーバである DAC539E4W に対して書き込みを行います。ただし、コントローラが DAC539E4W の内部レジスタデータを必要とする場合は、DAC539E4W がターゲットトランスマッタとして動作します。このケースでは、コントローラは DAC539E4W からデータを読み取ります。I<sup>2</sup>C の専門用語によれば、読み取りと書き込みはコントローラに言及しています。

DAC539E4W は以下のデータ転送モードをサポートしています：

- スタンダードモード (100Kbps)

- 高速モード (400Kbps)

- 高速モードプラス (1.0Mbps)

スタンダードモードと高速モードのデータ転送プロトコルはまったく同じであるため、このデータシートではこれらのモードを F/S モードと呼びます。高速モードプラスのプロトコルはデータ転送速度の点ではサポートされますが、出力電流の点ではサポートされません。Low レベル出力電流は 3mA で、スタンダードモードおよび高速モードの場合と同様です。DAC539E4W は 7 ビットアドレッシングをサポートします。10 ビットアドレッシング モードはサポートしていません。また、ジエネラルコールリセット機能をサポートしています。次のシーケンスを送信すると、デバイス内でソフトウェアリセット (スタートまたは再スタート、0x00、0x06、ストップ) が起動します。リセットは、2 バイト目に続く ACK ビットの立ち上がりエッジで、デバイス内でアサートされます。

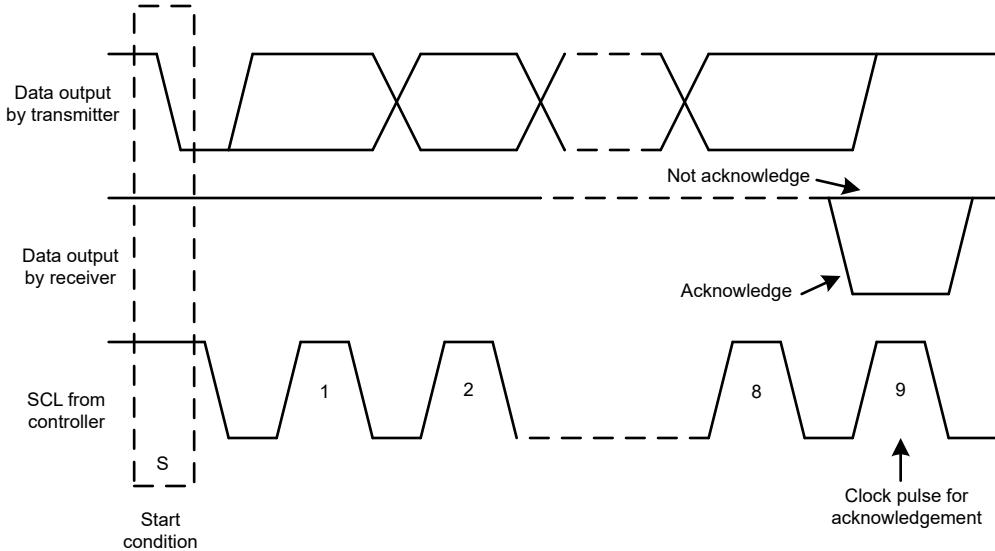

指定のタイミング信号を除いて、I<sup>2</sup>C インターフェイスではシリアルバイトを扱います。各バイトの最後に、9 回目のクロックサイクルで確認応答信号が生成および検出されます。アクノリッジ (受信確認) は、9 回目のクロックサイクルの High 期間中 SDA ラインを Low にすることで行われます。アクノリッジなしは、図 6-13 に示すように 9 回目のクロックサイクルの High 期間中 SDA ラインを High のまま保持することで行われます。

図 6-13. I<sup>2</sup>C バスのアクノリッジ(受信確認)とアクノリッジなし

#### 6.5.2.1 F/S モードのプロトコル

次の手順では、F/S モードのトランザクションの完了について説明します。

1. コントローラは、スタート条件を生成することで、データ転送を開始します。図 6-14 で示されているように、SCL がハイの状態で SDA ラインにハイからローへの遷移が発生すると、スタート条件となります。すべての I<sup>2</sup>C 互換デバイスは、スタート条件を認識します。

2. 次に、コントローラは SCL パルスを生成し、7 ビットのアドレスと読み取り/書き込み方向ビット (R/W) を SDA ライン上で送信します。すべての送信中、コントローラはデータが有効であることを確認します。有効なデータ条件では、図 6-15 に示すように、クロックパルスのハイ期間全体にわたって SDA ラインが安定している必要があります。すべてのデバイスは、コントローラによって送信されたアドレスを認識して、そのアドレスを内部の各固定アドレスと比較します。図 6-13 に示すように、一致するアドレスを持つターゲットデバイスだけが、9 番目の SCL サイクルのハイ期間全体にわたって SDA ラインをローにすることで、アクノリッジを生成します。コントローラがこのアクノリッジ(受信確認)を検出すると、ターゲットとの通信リンクが確立されます。

3. コントローラは、データをターゲットへ送信するか (R/W ビット 0)、ターゲットからデータを受信するため (R/W ビット 1)、さらに SCL サイクルを生成します。どちらの場合も、トランシミッタから送信されたデータに対してレシーバがアクノリッジ(受信確認)を返す必要があります。アクノリッジ(受信確認)信号は、コントローラまたはターゲットのどちらが受信者であるかによって、コントローラまたはターゲットのどちらかによって生成されます。8 ビットのデータとアクノリッジ(受信確認)1 ビットから構成される 9 ビットの有効なデータシーケンスを、必要なだけ続けることができます。

4. 図 6-14 に示すように、データ転送の終了を通知するために、コントローラは SCL ラインがハイの状態で SDA ラインをローからハイに引き上げることでストップ条件を生成します。このアクションによってバスが解放され、アドレス指定されたターゲットとの通信リンクが停止します。すべての I<sup>2</sup>C 互換デバイスがストップ条件を認識します。ストップ条件の受信によって、バスは解放され、すべてのターゲットデバイスはスタート条件および一致するアドレスが送信されるのを待ちます。

図 6-14. START 条件と STOP 条件

図 6-15. I<sup>2</sup>C バスのビット転送

### 6.5.2.2 I<sup>2</sup>C 更新シーケンス

表 6-10 に示すように、DAC539E4W は 1 回の更新のために、スタート条件、有効な I<sup>2</sup>C アドレスバイト、コマンドバイト、2 つのデータバイトを必要とします。

表 6-10. 更新シーケンス

| MSB                             | ...                        | LSB | ACK | MSB           | ... | LSB | ACK           | MSB | ... | LSB | ACK | MSB | ... | LSB | ACK |

|---------------------------------|----------------------------|-----|-----|---------------|-----|-----|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

| アドレス (A) バイト<br>セクション 6.5.2.2.1 | コマンドバイト<br>セクション 6.5.2.2.2 |     |     | データバイト - MSDB |     |     | データバイト - LSDB |     |     |     |     |     |     |     |     |

| DB [31:24]                      | DB [23:16]                 |     |     | DB [15:8]     |     |     | DB [7:0]      |     |     |     |     |     |     |     |     |

図 6-16 に示すように、各バイトの受信後、DAC539E4W は 1 つのクロックパルスの High 期間中に SDA ラインを Low にすることで、確認応答を行います。この 4 つのバイトと確認応答サイクルにより、1 回の更新を実行するために必要な 36 のクロック サイクルが生成されます。有効な I<sup>2</sup>C アドレスバイトによって、DAC539E4W が選択されます。

図 6-16. I<sup>2</sup>C バス プロトコル

コマンドバイトは、選択された DAC539E4W の動作モードを設定します。このバイトによって動作モードが選択されると、DAC539E4W デバイスは、データ更新を実行するために、最上位データバイト (MSDB) と最下位データバイト (LSDB) という 2 つのデータバイトを受信する必要があります。DAC539E4W デバイスは、LSDB に続くアクリッジ (受信確認) 信号の立ち下がりエッジで更新を実行します。

高速モード (クロック = 400kHz) を使用する場合、最大 DAC 更新レートは 10kSPS に制限されます。高速モードプラス (クロック = 1MHz) を使用すると、最大 DAC 更新レートは 25kSPS に制限されます。ストップ条件を受信すると、DAC539E4W デバイスは I<sup>2</sup>C バスを解放し、新しいスタート条件を待ちます。

### 6.5.2.2.1 アドレスバイト

表 6-11 に示すアドレスバイトは、コントローラデバイスからスタート条件に続いて受信する最初のバイトです。アドレスの最初の 4 ビット (MSB) は工場出荷時に 1001b にプリセットされています。アドレスの次の 3 ビットは、A0 ピンによって制御されます。A0 ピン入力は、VDD、AGND、SCL、または SDA に接続できます。各データフレームの最初のバイトにおいて A0 ピンがサンプリングされて、アドレスが決定します。デバイスはアドレスピンの値をラッピングし、その結果として、表 6-12 に従ってその特定のアドレスに応答します。

**表 6-11. アドレスバイト**

| 備考            | MSB |     |     |     |                             |     |     | LSB     |

|---------------|-----|-----|-----|-----|-----------------------------|-----|-----|---------|

| —             | AD6 | AD5 | AD4 | AD3 | AD2                         | AD1 | AD0 | R/W     |

| ジェネラル アドレス    | 1   | 0   | 0   | 1   | 表 6-12<br>(ターゲットアドレスの列) を参照 |     |     | 0 または 1 |

| ブロードキャスト アドレス | 1   | 0   | 0   | 0   | 1                           | 1   | 1   | 0       |

**表 6-12. アドレスフォーマット**

| ターゲットのアドレス | A0 ピン |

|------------|-------|

| 000        | AGND  |

| 001        | VDD   |

| 010        | SDA   |

| 011        | SCL   |

DAC539E4W は、複数の DAC539E4W デバイスの同期更新やパワーダウンに使用できる、ブロードキャストアドレッシングをサポートしています。ブロードキャストアドレスを使用すると、DAC539E4W はアドレスピンの状態に関係なく応答します。ブロードキャストは書き込みモードでのみサポートされます。

### 6.5.2.2.2 コマンドバイト

「レジスタマップ」セクションの「レジスタ名」表には ADDRESS 列のコマンドバイトが一覧表示されています。

### 6.5.2.3 I<sup>2</sup>C 読み出しシーケンス

レジスタを読み取るには、次のコマンドシーケンスを使用する必要があります。

- スタートまたは再スタートコマンドとターゲットアドレス、書き込みの 0 に設定した R/W ビットを送信します。デバイスはこのイベントをアクノリッジ (受信確認) します。

- 読み取り対象レジスタのコマンドバイトを送信します。デバイスはこのイベントを再度アクノリッジ (受信確認) します。

- 再スタートとターゲットアドレス、読み取りの 1 に設定した R/W ビットを送信します。デバイスはこのイベントをアクノリッジ (受信確認) します。

- デバイスはアドレスレジスタの MSDB バイトに書き込みます。コントローラはこのバイトをアクノリッジ (受信確認) する必要があります。

- 最後に、デバイスはレジスタの LSDB に書き込みます。

ブロードキャストアドレスは読み取りに使用できません。

**表 6-13. 読み取りシーケンス**

| S | MSB                        | ... | R/W<br>(0) | ACK | MSB                        | ... | LSB   | ACK | Sr                         | MSB | ...   | R/W<br>(1) | ACK     | MSB | ...    | LSB  | ACK     | MSB | ...    | LSB | ACK |

|---|----------------------------|-----|------------|-----|----------------------------|-----|-------|-----|----------------------------|-----|-------|------------|---------|-----|--------|------|---------|-----|--------|-----|-----|

|   | アドレスバイト<br>セクション 6.5.2.2.1 |     |            |     | コマンドバイト<br>セクション 6.5.2.2.2 |     |       | Sr  | アドレスバイト<br>セクション 6.5.2.2.1 |     |       |            | MSDB    |     |        | LSDB |         |     |        |     |     |

|   | コントローラから                   |     | ターゲット      |     | コントローラから                   |     | ターゲット |     | コントローラから                   |     | ターゲット |            | ターゲットから |     | コントローラ |      | ターゲットから |     | コントローラ |     |     |

## 6.6 レジスタマップ

表 6-14. レジスタマップ

| レジスタ                  | 最上位データバイト (MSDB)  |                   |             |            |                |            |            |            | 最下位データバイト (LSDB) |             |              |                  |                |            |        |      |  |  |  |  |  |  |  |  |  |  |

|-----------------------|-------------------|-------------------|-------------|------------|----------------|------------|------------|------------|------------------|-------------|--------------|------------------|----------------|------------|--------|------|--|--|--|--|--|--|--|--|--|--|

|                       | BIT15             | BIT14             | BIT13       | BIT12      | BIT11          | BIT10      | BIT9       | BIT8       | BIT7             | BIT6        | BIT5         | BIT4             | BIT3           | BIT2       | BIT1   | BIT0 |  |  |  |  |  |  |  |  |  |  |

| NOP                   | NOP               |                   |             |            |                |            |            |            |                  |             |              |                  |                |            |        |      |  |  |  |  |  |  |  |  |  |  |

| DAC-x-MARGIN-HIGH     | DAC-x-MARGIN-HIGH |                   |             |            |                |            |            |            |                  |             |              |                  |                |            |        |      |  |  |  |  |  |  |  |  |  |  |

| DAC-x-MARGIN-LOW      | DAC-x-MARGIN-LOW  |                   |             |            |                |            |            |            |                  |             |              |                  |                |            |        |      |  |  |  |  |  |  |  |  |  |  |

| DAC-x-VOUT-CMP-CONFIG | X                 |                   | VOUT-GAIN-x |            |                | X          |            |            |                  | CMP-x-OD-EN | CMP-x-OUT-EN | CMP-x-HIZ-IN-DIS | CMP-x-INV-EN   | CMP-x-EN   |        |      |  |  |  |  |  |  |  |  |  |  |

| DAC-x-CMP-MODE-CONFIG | X                 |                   |             | CMP-x-MODE |                | X          |            |            |                  |             |              |                  |                |            |        |      |  |  |  |  |  |  |  |  |  |  |

| COMMON-CONFIG         | 予約済み              | DEV-LOCK          | 予約済み        | EN-INT-REF | VOUT-PDN-3     |            | 予約済み       | VOUT-PDN-2 |                  | 予約済み        | VOUT-PDN-1   |                  | 予約済み           | VOUT-PDN-0 |        | 予約済み |  |  |  |  |  |  |  |  |  |  |

| COMMON-TRIGGER        | DEV-UNLOCK        |                   |             |            | リセット           |            |            | 予約済み       |                  |             |              |                  | NVM-PROG       | NVM-RELOAD |        |      |  |  |  |  |  |  |  |  |  |  |

| COMMON-DAC-TRIG       | RST-CMP-FLAG-0    | 予約済み              |             |            | RST-CMP-FLAG-1 | 予約済み       |            |            | RST-CMP-FLAG-2   | 予約済み        |              |                  | RST-CMP-FLAG-3 | 予約済み       |        |      |  |  |  |  |  |  |  |  |  |  |

| GENERAL-STATUS        | NVM-CRC-FAIL-INT  | NVM-CRC-FAIL-USER | X           | DAC-3-BUSY | DAC-2-BUSY     | DAC-1-BUSY | DAC-0-BUSY | NVM-BUSY   | DEVICE-ID        |             |              |                  |                | VERSION-ID |        |      |  |  |  |  |  |  |  |  |  |  |

| CMP-STATUS            | X                 |                   |             |            |                |            |            |            |                  |             |              |                  |                |            |        |      |  |  |  |  |  |  |  |  |  |  |

| DEVICE-MODE-CONFIG    | 予約済み              | DIS-MODE-IN       | 予約済み        |            |                |            |            |            |                  |             | X            |                  |                |            |        |      |  |  |  |  |  |  |  |  |  |  |

| INTERFACE-CONFIG      | X                 |                   |             | TIMEOUT-EN | X              |            |            |            |                  |             |              |                  | FSDO-EN        | X          | SDO-EN |      |  |  |  |  |  |  |  |  |  |  |

| STATE-MACHINE-CONFIG0 | 予約済み              |                   |             |            |                |            |            |            |                  |             |              |                  |                |            |        |      |  |  |  |  |  |  |  |  |  |  |

| SRAM-CONFIG           | X                 |                   |             |            |                |            |            |            | SRAM-ADDR        |             |              |                  |                |            |        |      |  |  |  |  |  |  |  |  |  |  |

| SRAM-DATA             | SRAM-DATA         |                   |             |            |                |            |            |            |                  |             |              |                  |                |            |        |      |  |  |  |  |  |  |  |  |  |  |

| DAC-x-DATA            | DAC-x-DATA        |                   |             |            |                |            |            |            |                  |             |              |                  |                |            |        |      |  |  |  |  |  |  |  |  |  |  |

| LUT-x-DATA            | 予約済み              |                   |             |            |                |            |            |            |                  |             |              |                  |                |            |        |      |  |  |  |  |  |  |  |  |  |  |

| LOOP-WAIT             | 予約済み              |                   |             |            |                |            |            |            | LOOP-WAIT        |             |              |                  |                |            |        |      |  |  |  |  |  |  |  |  |  |  |

注: 陰影のあるセルは NVM に保存されているレジスタビットまたはフィールドを示します。

注: X = 未使用。

**表 6-15. レジスタ名**

| I <sup>2</sup> C/SPI アドレス | SRAM アドレス | レジスタ名                 | セクション                        |

|---------------------------|-----------|-----------------------|------------------------------|

| 00h                       | —         | NOP                   | <a href="#">セクション 6.6.1</a>  |

| 01h                       | —         | DAC-0-MARGIN-HIGH     | <a href="#">セクション 6.6.2</a>  |

| 02h                       | —         | DAC-0-MARGIN_LOW      | <a href="#">セクション 6.6.3</a>  |

| 03h                       | —         | DAC-0-VOUT-CMP-CONFIG | <a href="#">セクション 6.6.4</a>  |

| 05h                       | —         | DAC-0-CMP-MODE-CONFIG | <a href="#">セクション 6.6.5</a>  |

| 07h                       | —         | DAC-1-MARGIN-HIGH     | <a href="#">セクション 6.6.2</a>  |

| 08h                       | —         | DAC-1-MARGIN_LOW      | <a href="#">セクション 6.6.3</a>  |

| 09h                       | —         | DAC-1-VOUT-CMP-CONFIG | <a href="#">セクション 6.6.4</a>  |

| 0Bh                       | —         | DAC-1-CMP-MODE-CONFIG | <a href="#">セクション 6.6.5</a>  |

| 0Dh                       | —         | DAC-2-MARGIN-HIGH     | <a href="#">セクション 6.6.2</a>  |

| 0Eh                       | —         | DAC-2-MARGIN_LOW      | <a href="#">セクション 6.6.3</a>  |

| 0Fh                       | —         | DAC-2-VOUT-CMP-CONFIG | <a href="#">セクション 6.6.4</a>  |

| 11h                       | —         | DAC-2-CMP-MODE-CONFIG | <a href="#">セクション 6.6.5</a>  |

| 13h                       | —         | DAC-3-MARGIN-HIGH     | <a href="#">セクション 6.6.2</a>  |

| 14h                       | —         | DAC-3-MARGIN_LOW      | <a href="#">セクション 6.6.3</a>  |

| 15h                       | —         | DAC-3-VOUT-CMP-CONFIG | <a href="#">セクション 6.6.4</a>  |