# DACx3608 オクタル、10 ビットまたは 8 ビット、I<sup>2</sup>C<sup>TM</sup> インターフェイス、超小型 3 × 3 WQFN パッケージのバッファ付き電圧出力 DAC

## 1 特長

- ±1LSB INL および DNL

- 広い動作範囲

- 電源: 1.8V～5.5V

- 温度範囲: -40°C～+125°C

- I<sup>2</sup>C<sup>TM</sup> シリアル・インターフェイス

- Standard, Fast, Fast+ モード

- VIH: 2.4V ( $V_{DD} = 5.5V$ )

- LDAC ピンによる出力の同時更新

- 超低消費電力 : 0.1mA / チャネル (1.8V)

- 低消費電力起動モード：出力を 10K 状態にパワーダウン

- 超小型パッケージ

- 16 ピン WQFN (3mm × 3mm)

## 2 アプリケーション

- プログラム可能な電源

- プログラマブル・ウィンドウ・コンバレータ

- ディスプレイ・パネルのVCOMバイアス印加

- 多機能プリンタのレーザー・ドライバ

- オート・フォーカスのデジタル・カメラ用レンズ

- ATM、現金計数器、バーコード・リーダー

- IPネットワーク・カメラ、プロジェクタ

## 3 概要

DAC53608 および DAC43608 (DACx3608) は、低消費電力、8 チャネル、10 ビットまたは 8 ビットの電圧出力デジタル・アナログ・コンバータ (DAC) です。DACx3608 は 1.8V～5.5V の広い電源電圧範囲にわたって単調性を維持するように設計されています。外部リファレンスを使用して、1.8V～5.5V のフルスケール出力電圧範囲に対応する一方、消費する静止電流はチャネル当たり 0.1mA です。また、チャネルごとにユーザーがプログラム可能なパワーダウン・レジスタも内蔵しています。これらのレジスタにより、DAC 出力バッファは起動時は 10K 状態にパワーダウンされ、これらの出力バッファにパワーアップ・コマンドが発行されるまで、この状態を維持します。

低静止電流で電源電圧範囲が広く、チャネル単位のパワーダウン・オプションを備えた DACx3608 は、低消費電力のバッテリ駆動システムに最適です。

I<sup>2</sup>C<sup>TM</sup> インターフェイスで通信し、I<sup>2</sup>C<sup>TM</sup> の Standard モード (100kbps)、Fast モード (400kbps)、Fast+ モード (1Mbps) をサポートしています。また、DAC を同時に更新できるロード DAC (LDAC) ピンも備えています。

DACx3608 は小型の 3mm × 3mm、16 ピン WQFN パッケージで供給されます。これらのデバイスは、拡張産業用温度範囲の -40°C～+125°C で完全に動作が規定されています。

### 製品情報<sup>(1)</sup>

| 型番       | パッケージ     | 本体サイズ(公称)     |

|----------|-----------|---------------|

| DAC53608 | WQFN (16) | 3.00mm×3.00mm |

| DAC43608 | WQFN (16) | 3.00mm×3.00mm |

(1) 利用可能なすべてのパッケージについては、このデータシートの末尾にある注文情報を参照してください。

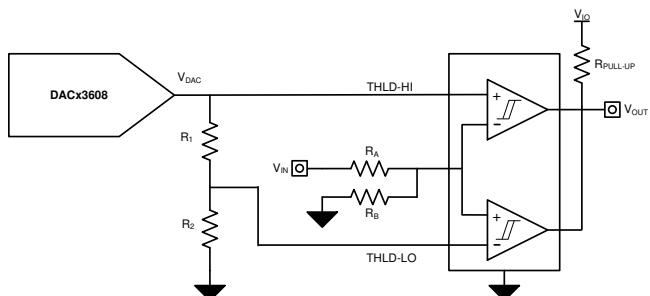

## プログラマブル・ウィンドウ・コンバレータ

## ブロック概略図

## 目次

|          |                                                           |    |           |                           |    |

|----------|-----------------------------------------------------------|----|-----------|---------------------------|----|

| <b>1</b> | 特長 .....                                                  | 1  | 8.2       | 機能ブロック図 .....             | 19 |

| <b>2</b> | アプリケーション .....                                            | 1  | 8.3       | 機能説明 .....                | 20 |

| <b>3</b> | 概要 .....                                                  | 1  | 8.4       | デバイスの機能モード .....          | 21 |

| <b>4</b> | 改訂履歴 .....                                                | 2  | 8.5       | プログラミング .....             | 22 |

| <b>5</b> | デバイス比較表 .....                                             | 3  | 8.6       | レジスタ・マップ .....            | 28 |

| <b>6</b> | ピン構成および機能 .....                                           | 3  | <b>9</b>  | アプリケーションと実装 .....         | 31 |

| <b>7</b> | 仕様 .....                                                  | 4  | 9.1       | アプリケーション情報 .....          | 31 |

| 7.1      | 絶対最大定格 .....                                              | 4  | 9.2       | 代表的なアプリケーション .....        | 31 |

| 7.2      | ESD定格 .....                                               | 4  | <b>10</b> | 電源に関する推奨事項 .....          | 34 |

| 7.3      | 推奨動作条件 .....                                              | 4  | <b>11</b> | レイアウト .....               | 35 |

| 7.4      | 熱特性 .....                                                 | 4  | 11.1      | レイアウトの注意点 .....           | 35 |

| 7.5      | 電気的特性 .....                                               | 5  | 11.2      | レイアウト例 .....              | 35 |

| 7.6      | タイミング要件:I <sup>2</sup> C <sup>TM</sup> Standard モード ..... | 7  | <b>12</b> | デバイスおよびドキュメントのサポート .....  | 36 |

| 7.7      | タイミング要件:I <sup>2</sup> C <sup>TM</sup> Fast モード .....     | 7  | 12.1      | ドキュメントのサポート .....         | 36 |

| 7.8      | タイミング要件:I <sup>2</sup> C <sup>TM</sup> Fast+ モード .....    | 8  | 12.2      | 関連リンク .....               | 36 |

| 7.9      | タイミング要件:ロジック .....                                        | 8  | 12.3      | ドキュメントの更新通知を受け取る方法 .....  | 36 |

| 7.10     | 代表的特性:1.8V .....                                          | 10 | 12.4      | コミュニティ・リソース .....         | 36 |

| 7.11     | 代表的特性:5.5V .....                                          | 12 | 12.5      | 商標 .....                  | 36 |

| 7.12     | 代表的特性 .....                                               | 17 | 12.6      | 静電気放電に関する注意事項 .....       | 36 |

| 7.13     | 代表的特性 .....                                               | 18 | 12.7      | Glossary .....            | 36 |

| <b>8</b> | 詳細説明 .....                                                | 19 | <b>13</b> | メカニカル、パッケージ、および注文情報 ..... | 37 |

| 8.1      | 概要 .....                                                  | 19 |           |                           |    |

## 4 改訂履歴

2018年10月発行のものから更新

Page

- 事前情報から量産データに 変更 .....

1

## 5 デバイス比較表

| デバイス     | 分解能    |

|----------|--------|

| DAC53608 | 10 ビット |

| DAC43608 | 8 ビット  |

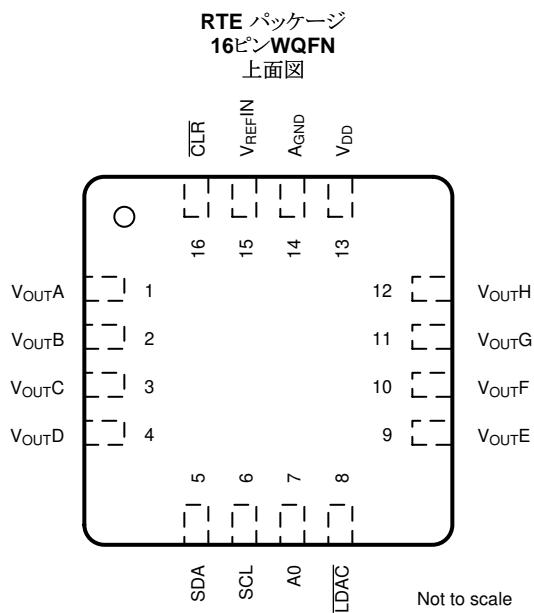

## 6 ピン構成および機能

### 端子機能

| 端子                 |    | I/O | 説明                                                                          |

|--------------------|----|-----|-----------------------------------------------------------------------------|

| 名前                 | 番号 |     |                                                                             |

| A0                 | 7  | I   | 4 ステート・アドレス入力                                                               |

| A <sub>GND</sub>   | 14 | GND | デバイスの全回路のグラウンド基準点                                                           |

| CLR                | 16 | I   | 非同期クリア・ピン (アクティブ Low)                                                       |

| LDAC               | 8  | I   | 同時出力更新用ロード DAC ピン (アクティブ Low)                                               |

| SCL                | 6  | I   | シリアル・インターフェイス・クロック                                                          |

| SDA                | 5  | I/O | 入力レジスタにデータをクロック入出力します。このピンは双方、オープン・ドレインのデータ・ラインで、外付けプルアップ抵抗で電源に接続する必要があります。 |

| V <sub>DD</sub>    | 13 | PWR | アナログ電源電圧 (1.8V~5.5V)                                                        |

| V <sub>OUTA</sub>  | 1  | O   | DAC A からのアナログ出力電圧                                                           |

| V <sub>OUTB</sub>  | 2  | O   | DAC B からのアナログ出力電圧                                                           |

| V <sub>OUTC</sub>  | 3  | O   | DAC C からのアナログ出力電圧                                                           |

| V <sub>OUTD</sub>  | 4  | O   | DAC D からのアナログ出力電圧                                                           |

| V <sub>OUTE</sub>  | 9  | O   | DAC E からのアナログ出力電圧                                                           |

| V <sub>OUTF</sub>  | 10 | O   | DAC F からのアナログ出力電圧                                                           |

| V <sub>OUTG</sub>  | 11 | O   | DAC G からのアナログ出力電圧                                                           |

| V <sub>OUTH</sub>  | 12 | O   | DAC H からのアナログ出力電圧                                                           |

| V <sub>REFIN</sub> | 15 | I/O | デバイスへのリファレンス入力                                                              |

## 7 仕様

### 7.1 絶対最大定格

自由通気で動作温度範囲内(特に記述のない限り)<sup>(1)</sup>

|      |                                          | MIN  | MAX                   | UNIT |

|------|------------------------------------------|------|-----------------------|------|

| 入力電圧 | A <sub>GND</sub> に対する V <sub>DD</sub>    | -0.3 | 6                     | V    |

|      | A <sub>GND</sub> に対する V <sub>REFIN</sub> | -0.3 | V <sub>DD</sub> + 0.3 |      |

|      | A <sub>GND</sub> に対するデジタル入力              | -0.3 | V <sub>DD</sub> + 0.3 |      |

| 出力電圧 | A <sub>GND</sub> に対する V <sub>OUT</sub>   | -0.3 | V <sub>DD</sub> + 0.3 | V    |

| 入力電流 | ピンへの電流                                   | -10  | 10                    | mA   |

| 温度   | 接合部温度、T <sub>J</sub>                     | -40  | 150                   | °C   |

|      | 保管温度、T <sub>stg</sub>                    | -65  | 150                   |      |

- (1) 絶対最大定格を上回るストレスが加わった場合、デバイスに永続的な損傷が発生する可能性があります。これはストレスの定格のみについて示してあり、このデータシートの「推奨動作条件」に示された値を超える状態で本製品が正常に動作することを暗黙的に示すものではありません。絶対最大定格の状態に長時間置くと、本製品の信頼性に影響を与えることがあります。

### 7.2 ESD定格

|                    |      |                                                               | VALUE | UNIT |

|--------------------|------|---------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 準拠、すべてのピン <sup>(1)</sup>   | ±1000 | V    |

|                    |      | デバイス帯電モデル (CDM)、JEDEC 規格 JESD22-C101 準拠、すべてのピン <sup>(2)</sup> | ±500  |      |

- (1) JEDEC のドキュメント JEP155 に、500V HBM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。[次の文はオプション、wiki を参照。] 必要な予防措置をとれば、HBM の ESD 耐圧が 500V 未満でも製造可能です。[次の文はオプション、wiki を参照。] ±WWWWV や ±XXXV と表示されるピンは、より高い性能を備えています。

- (2) JEDEC のドキュメント JEP157 に、250V CDM では標準の ESD 管理プロセスで安全な製造が可能であると規定されています。[次の文はオプション、wiki を参照。] 必要な予防措置をとれば、CDM の ESD 耐圧が 250V 未満でも製造可能です。[次の文はオプション、wiki を参照。] ±YYYYV や ±ZZZV と表示されるピンは、より高い性能を備えています。

### 7.3 推奨動作条件

自由気流での動作温度範囲内(特に記述のない限り)

|                                          |                                            | MIN | NOM                   | MAX             | UNIT |

|------------------------------------------|--------------------------------------------|-----|-----------------------|-----------------|------|

| A <sub>GND</sub> に対する V <sub>DD</sub>    | グランドに対する正電源電圧                              | 1.8 | 5.5                   |                 | V    |

| A <sub>GND</sub> に対する V <sub>REFIN</sub> | グランドに対する基準入力電源電圧                           | 1.8 |                       | V <sub>DD</sub> | V    |

| VIH                                      | デジタル入力 High 電圧、1.8 ≤ V <sub>DD</sub> ≤ 2.7 |     | V <sub>DD</sub> - 0.3 |                 | V    |

| VIH                                      | デジタル入力 High 電圧、2.7 < V <sub>DD</sub> ≤ 5.5 |     | 2.4                   |                 | V    |

| VIL                                      | デジタル入力 Low 電圧                              |     |                       | 0.5             | V    |

| T <sub>A</sub>                           | 周囲温度                                       | -40 |                       | 125             | °C   |

### 7.4 热特性

| 熱特性 <sup>(1)</sup>    |                   | DACx3608   | 単位   |

|-----------------------|-------------------|------------|------|

|                       |                   | RTE (WQFN) |      |

|                       |                   | 16 ピン      |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗      | 49         | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース(上面)への熱抵抗 | 50         | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗      | 24.1       | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への熱特性      | 1.1        | °C/W |

| Y <sub>JB</sub>       | 接合部から基板への熱特性      | 24.1       | °C/W |

| R <sub>θJC(bot)</sub> | 接合部からケース(底面)への熱抵抗 | 8.7        | °C/W |

- (1) 新旧熱評価基準の詳細については、アプリケーション・レポート『Semiconductor and IC Package Thermal Metrics』(英語) を参照してください。

## 7.5 電気的特性

すべての最小値 / 最大値は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、すべての標準値は  $T_A = 25^\circ\text{C}$ 、 $1.8\text{V} \leq V_{DD} \leq 5.5\text{V}$ 、 $V_{DD} \geq 2.7\text{V}$  では  $V_{REFIN} = 2.5\text{V}$ 、 $V_{DD} \leq 2.7\text{V}$  では  $V_{REFIN} = 1.8\text{V}$ 、 $A_{GND}$  に対する  $R_L = 5\text{k}\Omega$ 、 $A_{GND}$  に対する  $C_L = 200\text{pF}$ 、 $V_{DD}$  または  $A_{GND}$  でのデジタル入力を条件として規定しています (特に記述のない限り)。

| パラメータ                      |                       | テスト条件                                                                              | MIN  | TYP     | MAX | UNIT    |

|----------------------------|-----------------------|------------------------------------------------------------------------------------|------|---------|-----|---------|

| <b>安定動作</b>                |                       |                                                                                    |      |         |     |         |

| 分解能                        |                       | DAC53608                                                                           | 10   |         |     | ビット     |

|                            |                       | DAC43608                                                                           | 8    |         |     |         |

| INL                        | 相対精度 <sup>(1)</sup>   | DAC43608、 $2.7\text{V} \leq V_{DD} \leq 5.5\text{V}$                               | -1   | 1       |     | LSB     |

|                            |                       | DAC43608、 $1.8\text{V} \leq V_{DD} \leq 2.7\text{V}$                               | -1   | 1       |     |         |

|                            |                       | DAC53608、 $2.7\text{V} \leq V_{DD} \leq 5.5\text{V}$                               | -1   | 1       |     |         |

|                            |                       | DAC53608、 $1.8\text{V} \leq V_{DD} \leq 2.7\text{V}$                               | -1   | 1       |     |         |

| DNL                        | 微分非線形性 <sup>(1)</sup> | DAC43608、 $2.7\text{V} \leq V_{DD} \leq 5.5\text{V}$                               | -1   | 1       |     | LSB     |

|                            |                       | DAC43608、 $1.8\text{V} \leq V_{DD} \leq 2.7\text{V}$                               | -1   | 1       |     |         |

|                            |                       | DAC53608、 $2.7\text{V} \leq V_{DD} \leq 5.5\text{V}$                               | -1   | 1       |     |         |

|                            |                       | DAC53608、 $1.8\text{V} \leq V_{DD} \leq 2.7\text{V}$                               | -1   | 1       |     |         |

| ゼロコード誤差                    |                       | $2.7\text{V} \leq V_{DD} \leq 5.5\text{V}$ 、コード 0d を DAC に入力                       |      | 6       | 12  | mV      |

|                            |                       | $1.8\text{V} \leq V_{DD} \leq 2.7\text{V}$ 、コード 0d を DAC に入力                       |      | 6       | 12  |         |

| ゼロコード誤差温度係数                |                       |                                                                                    |      | ±5      |     | µV/°C   |

| オフセット誤差 <sup>(1)</sup>     |                       | $2.7\text{V} \leq V_{DD} \leq 5.5\text{V}$                                         | -0.5 | 0.25    | 0.5 | %FSR    |

|                            |                       | $1.8\text{V} \leq V_{DD} \leq 2.7\text{V}$                                         | -0.5 | 0.25    | 0.5 |         |

| オフセット誤差温度係数 <sup>(1)</sup> |                       |                                                                                    |      | ±0.0003 |     | %FSR/°C |

| ゲイン誤差 <sup>(1)</sup>       |                       | $2.7\text{V} \leq V_{DD} \leq 5.5\text{V}$                                         | -0.5 | 0.25    | 0.5 | %FSR    |

|                            |                       | $1.8\text{V} \leq V_{DD} \leq 2.7\text{V}$                                         | -0.5 | 0.25    | 0.5 |         |

| ゲイン誤差温度係数 <sup>(1)</sup>   |                       |                                                                                    |      | ±0.0004 |     | %FSR/°C |

| フルスケール誤差                   |                       | $2.7\text{V} \leq V_{DD} \leq 5.5\text{V}$ 、コード 1023d を DAC に入力、ヘッドルームなし           | -0.5 | 0.25    | 0.5 | %FSR    |

|                            |                       | $1.8\text{V} \leq V_{DD} \leq 2.7\text{V}$ 、コード 1023d を DAC に入力、ヘッドルームなし           | -1   | 0.5     | 1   |         |

| フルスケール誤差温度係数               |                       |                                                                                    |      | ±0.0004 |     | %FSR/°C |

| <b>出力特性</b>                |                       |                                                                                    |      |         |     |         |

| $V_{OUTX}$                 | 出力電圧                  |                                                                                    | 0    | 5.5     |     | V       |

| $C_L$                      | 容量性負荷 <sup>(2)</sup>  | $R_L = \text{無限大}$                                                                 |      | 1       |     | nF      |

|                            |                       | $R_L = 5\text{k}\Omega$                                                            |      | 2       |     |         |

|                            | 負荷安定化                 | DAC ミッドスケール、 $-10\text{mA} \leq I_{OUT} \leq 10\text{mA}$ 、 $V_{DD} = 5.5\text{V}$ |      | 0.1     |     | mV/mA   |

| 短絡電流                       |                       | $V_{DD} = 1.8\text{V}$ 、(チャネルごとに) フルスケール出力を $A_{GND}$ に短絡またはゼロスケール出力を $V_{DD}$ に短絡 |      | 10      |     | mA      |

|                            |                       | $V_{DD} = 2.7\text{V}$ 、(チャネルごとに) フルスケール出力を $A_{GND}$ に短絡またはゼロスケール出力を $V_{DD}$ に短絡 |      | 25      |     |         |

|                            |                       | $V_{DD} = 5.5\text{V}$ 、(チャネルごとに) フルスケール出力を $A_{GND}$ に短絡またはゼロスケール出力を $V_{DD}$ に短絡 |      | 50      |     |         |

| 出力電圧ヘッドルーム                 |                       | $V_{DD}$ に対して (DAC 出力無負荷)                                                          |      | 0.05    |     | V       |

(1) コード間のエンドポイント一致 : コード 4 - コード 1016 は 10 ビット、コード 1 - コード 251 は 8 ビット。

(2) 量産では検査していません。

## 電気的特性 (continued)

すべての最小値 / 最大値は  $T_A = -40^\circ\text{C} \sim +125^\circ\text{C}$ 、すべての標準値は  $T_A = 25^\circ\text{C}$ 、 $1.8\text{V} \leq V_{DD} \leq 5.5\text{V}$ 、 $V_{DD} \geq 2.7\text{V}$  では  $V_{REFIN} = 2.5\text{V}$ 、 $V_{DD} \leq 2.7\text{V}$  では  $V_{REFIN} = 1.8\text{V}$ 、 $A_{GND}$  に対する  $R_L = 5\text{k}\Omega$ 、 $A_{GND}$  に対する  $C_L = 200\text{pF}$ 、 $V_{DD}$  または  $A_{GND}$  でのデジタル入力を条件として規定しています (特に記述のない限り)。

| パラメータ                     |                        | テスト条件                                                                                                                                                                       | MIN  | TYP | MAX                            | UNIT |  |  |

|---------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|--------------------------------|------|--|--|

| 出力電圧ヘッドルーム <sup>(2)</sup> |                        | $V_{DD}$ に対して (負荷電流 = $10\text{mA}$ @ $V_{DD} = 5.5\text{V}$ 、負荷電流 = $3\text{mA}$ @ $V_{DD} = 2.7\text{V}$ 、負荷電流 = $1\text{mA}$ @ $V_{DD} = 1.8\text{V}$ )、DAC コード = フルスケール | 10   |     | %FSR                           |      |  |  |

| $Z_O$                     | DC 出カインピーダンス           | DAC ミッドスケール                                                                                                                                                                 | 0.25 |     | $\Omega$                       |      |  |  |

|                           |                        | DAC コード 4d                                                                                                                                                                  | 0.25 |     |                                |      |  |  |

|                           |                        | DAC コード 1016                                                                                                                                                                | 0.26 |     |                                |      |  |  |

| DC-PSRR                   | 電源電圧変動除去比 (DC)         | DAC ミッドスケール、 $V_{DD} = 5\text{V} \pm 10\%$                                                                                                                                  | 0.25 |     | mV/V                           |      |  |  |

| 動的特性                      |                        |                                                                                                                                                                             |      |     |                                |      |  |  |

| $t_{sett}$                | 出力電圧セトリング時間            | 10%FSR に対する 1/4 から 3/4 スケールおよび 3/4 から 1/4 スケールへの変化時のセトリング、 $R_L = 5\text{k}\Omega$ 、 $C_L = 200\text{pF}$ 、 $V_{DD} = 5.5\text{V}$                                          | 10   |     | $\mu\text{s}$                  |      |  |  |

| SR                        | スルーレート                 | $R_L = 5\text{k}\Omega$ 、 $C_L = 200\text{pF}$ 、 $V_{DD} = 5.5\text{V}$                                                                                                     | 0.6  |     | $\text{V}/\mu\text{s}$         |      |  |  |

|                           | 電源オン時のグリッチ振幅           | $R_L = 5\text{k}\Omega$ 、 $C_L = 200\text{pF}$                                                                                                                              | 110  |     | $\text{mV}$                    |      |  |  |

| $V_n$                     | 出カノイズ                  | 0.1Hz ~ 10Hz、DAC ミッドスケール、 $V_{DD} = 5.5\text{V}$                                                                                                                            | 40   |     | $\mu\text{V}_{pp}$             |      |  |  |

| $V_n$                     | 出カノイズ                  | 帯域幅 0.1Hz ~ 100kHz、DAC ミッドスケール、 $V_{DD} = 5.5\text{V}$                                                                                                                      | 0.05 |     | $\text{mV}_{rms}$              |      |  |  |

| $V_n$                     | 出カノイズ密度                | 1kHz で測定、DAC ミッドスケール、 $V_{DD} = 5.5\text{V}$                                                                                                                                | 0.2  |     | $\mu\text{V}/\sqrt{\text{Hz}}$ |      |  |  |

|                           |                        | 10kHz で測定、DAC ミッドスケール、 $V_{DD} = 5.5\text{V}$                                                                                                                               | 0.2  |     |                                |      |  |  |

| AC-PSRR                   | 電源電圧変動除去比 (AC)         | 200mV 50/60Hz の正弦波を電源電圧に重畳、DAC ミッドスケール                                                                                                                                      | -71  |     | dB                             |      |  |  |

|                           | チャネル間 AC クロストーク        | 隣接チャネルのフルスケール・スイング                                                                                                                                                          | 1.5  |     | $\text{nV}\cdot\text{s}$       |      |  |  |

|                           | チャネル間 DC クロストーク        | 全チャネルのフルスケール・スイング、ゼロまたはフルスケールでチャネルを測定                                                                                                                                       | 0.05 |     | LSB                            |      |  |  |

|                           | コード書き換えによるグリッチ・インパルス   | ミッドコード付近の $\pm 1\text{LSB}$ の変化 (フィードスルーを含む)                                                                                                                                | 10   |     | $\text{nV}\cdot\text{s}$       |      |  |  |

|                           | コード書き換えによるグリッチ・インパルス振幅 | ミッドコード付近の $\pm 1\text{LSB}$ の変化 (フィードスルーを含む)                                                                                                                                | 25   |     | $\text{mV}$                    |      |  |  |

| 電圧リファレンス入力                |                        |                                                                                                                                                                             |      |     |                                |      |  |  |

|                           | リファレンス入カインピーダンス        | 全チャネル電源オン                                                                                                                                                                   | 12.5 |     | $\text{k}\Omega$               |      |  |  |

|                           | リファレンス入カ容量             |                                                                                                                                                                             | 50   |     | $\text{pF}$                    |      |  |  |

| デジタル入力                    |                        |                                                                                                                                                                             |      |     |                                |      |  |  |

|                           | デジタル・フィードスルー           | $SCLK = 1\text{MHz}$ 、ミッドスケールで DAC 出力静止                                                                                                                                     | 20   |     | $\text{nV}\cdot\text{s}$       |      |  |  |

|                           | ピン容量                   | ピン単位                                                                                                                                                                        | 10   |     | $\text{pF}$                    |      |  |  |

| 電源要件                      |                        |                                                                                                                                                                             |      |     |                                |      |  |  |

| $IV_{DD}$                 | $V_{DD}$ に流れ込む電流       | 通常モード、全 DAC フルスケール、SPI 静止。                                                                                                                                                  | 3    |     | $\text{mA}$                    |      |  |  |

| $IV_{DD}$                 | $V_{DD}$ に流れ込む電流       | 全 DAC パワーダウン                                                                                                                                                                | 50   |     | $\mu\text{A}$                  |      |  |  |

## 7.6 タイミング要件 : I<sup>2</sup>C<sup>TM</sup> Standard モード

すべての入力信号は VIL から  $V_{DD}$  の 70% に対して、 $1.8V \leq V_{DD} \leq 5.5V$ 、 $1.8V \leq V_{REFIN} \leq V_{DD}$ 、 $-40^{\circ}C \leq T_A \leq +125^{\circ}C$ 、 $1.8V \leq V_{DD} \leq 2.7V$  では  $V_{pull\ up} = V_{DD}$ 、 $2.7V \leq V_{DD} \leq 5.5V$  では  $V_{pull\ up} = 2.7V$  または  $V_{DD}$  を条件として時間測定しています。

|             |                       | MIN  | NOM | MAX  | UNIT |

|-------------|-----------------------|------|-----|------|------|

| $t_{SCLK}$  | SCLK 周波数              |      |     | 0.1  | MHz  |

| $t_{BUF}$   | ストップ条件とスタート条件間のバス解放時間 | 4.7  |     |      | μs   |

| $t_{HDSTA}$ | 再スタート条件生成後のホールド時間     | 4    |     |      | μs   |

| $t_{SUSTA}$ | 再スタート条件セットアップ時間       | 4.7  |     |      | μs   |

| $t_{SUSTO}$ | ストップ条件セットアップ時間        | 4    |     |      | μs   |

| $t_{HDDAT}$ | データ・ホールド時間            | 0    |     |      | ns   |

| $t_{SUDAT}$ | データ・セットアップ時間          | 250  |     |      | ns   |

| $t_{LOW}$   | SCL クロックの Low 期間      | 4700 |     |      | ns   |

| $t_{HIGH}$  | SCL クロックの High 期間     | 4700 |     |      | ns   |

| $t_F$       | クロック / データの立ち下がり時間    |      |     | 300  | ns   |

| $t_R$       | クロック / データの立ち上がり時間    |      |     | 1000 | ns   |

## 7.7 タイミング要件 : I<sup>2</sup>C<sup>TM</sup> Fast モード

すべての入力信号は VIL から  $V_{DD}$  の 70% に対して、 $1.8V \leq V_{DD} \leq 5.5V$ 、 $1.8V \leq V_{REFIN} \leq V_{DD}$ 、 $-40^{\circ}C \leq T_A \leq +125^{\circ}C$ 、 $1.8V \leq V_{DD} \leq 2.7V$  では  $V_{pull\ up} = V_{DD}$ 、 $2.7V \leq V_{DD} \leq 5.5V$  では  $V_{pull\ up} = 2.7V$  または  $V_{DD}$  を条件として時間測定しています。

|             |                       | MIN  | NOM | MAX | UNIT |

|-------------|-----------------------|------|-----|-----|------|

| $t_{SCLK}$  | SCLK 周波数              |      |     | 0.4 | MHz  |

| $t_{BUF}$   | ストップ条件とスタート条件間のバス解放時間 | 1.3  |     |     | μs   |

| $t_{HDSTA}$ | 再スタート条件生成後のホールド時間     | 0.6  |     |     | μs   |

| $t_{SUSTA}$ | 再スタート条件セットアップ時間       | 0.6  |     |     | μs   |

| $t_{SUSTO}$ | ストップ条件セットアップ時間        | 0.6  |     |     | μs   |

| $t_{HDDAT}$ | データ・ホールド時間            | 0    |     |     | ns   |

| $t_{SUDAT}$ | データ・セットアップ時間          | 100  |     |     | ns   |

| $t_{LOW}$   | SCL クロックの Low 期間      | 1300 |     |     | ns   |

| $t_{HIGH}$  | SCL クロックの High 期間     | 600  |     |     | ns   |

| $t_F$       | クロック / データの立ち下がり時間    |      |     | 300 | ns   |

| $t_R$       | クロック / データの立ち上がり時間    |      |     | 300 | ns   |

## 7.8 タイミング要件 : I<sup>2</sup>C<sup>TM</sup> Fast+ モード

すべての入力信号は VIL から  $V_{DD}$  の 70% に対して、 $1.8V \leq V_{DD} \leq 5.5V$ 、 $1.8V \leq V_{REFIN} \leq V_{DD}$ 、 $-40^{\circ}C \leq T_A \leq +125^{\circ}C$ 、 $1.8V \leq V_{DD} \leq 2.7V$  では  $V_{pull\ up} = V_{DD}$ 、 $2.7V \leq V_{DD} \leq 5.5V$  では  $V_{pull\ up} = 2.7V$  または  $V_{DD}$  を条件として時間測定しています。

|             |                       | MIN  | NOM | MAX | UNIT |

|-------------|-----------------------|------|-----|-----|------|

| $t_{SCLK}$  | SCL 周波数               |      |     | 1   | MHz  |

| $t_{BUF}$   | ストップ条件とスタート条件間のバス解放時間 | 0.5  |     |     | μs   |

| $t_{HDSTA}$ | 再スタート条件生成後のホールド時間     | 0.26 |     |     | μs   |

| $t_{SUSTA}$ | 再スタート条件セットアップ時間       | 0.26 |     |     | μs   |

| $t_{SUSTO}$ | ストップ条件セットアップ時間        | 0.26 |     |     | μs   |

| $t_{HDDAT}$ | データ・ホールド時間            | 0    |     |     | ns   |

| $t_{SUDAT}$ | データ・セットアップ時間          | 50   |     |     | ns   |

| $t_{LOW}$   | SCL クロックの Low 期間      | 0.5  |     |     | μs   |

| $t_{HIGH}$  | SCL クロックの High 期間     | 0.26 |     |     | μs   |

| $t_F$       | クロック / データの立ち下がり時間    |      |     | 120 | ns   |

| $t_R$       | クロック / データの立ち上がり時間    |      |     | 120 | ns   |

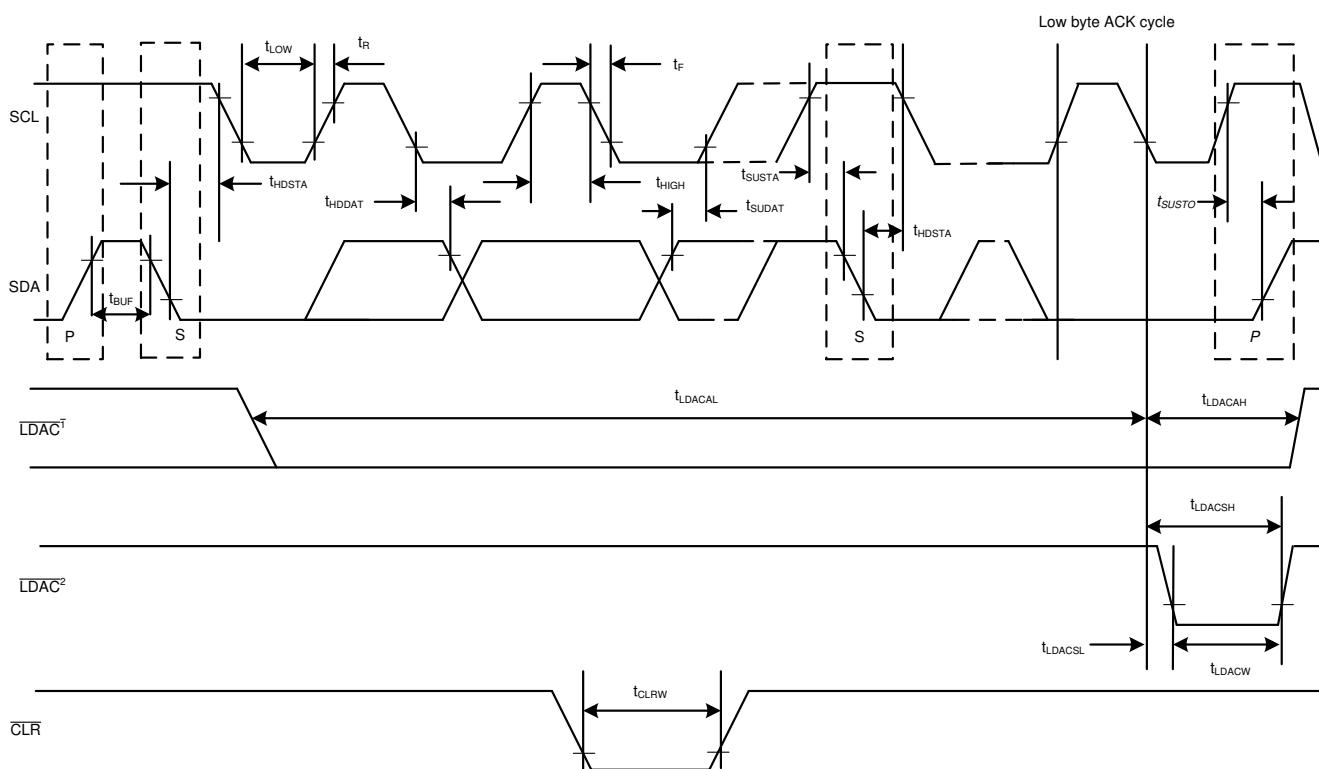

## 7.9 タイミング要件 : ロジック

すべての入力信号は VIL から  $V_{DD}$  の 70% に対して、 $1.8V \leq V_{DD} \leq 5.5V$ 、 $1.8V \leq V_{REFIN} \leq V_{DD}$ 、 $-40^{\circ}C \leq T_A \leq +125^{\circ}C$ 、 $1.8V \leq V_{DD} \leq 2.7V$  では  $V_{pull\ up} = V_{DD}$ 、 $2.7V \leq V_{DD} \leq 5.5V$  では  $V_{pull\ up} = 2.7V$  または  $V_{DD}$  を条件として時間測定しています。

|              |                                                                           | MIN | NOM | MAX | UNIT      |

|--------------|---------------------------------------------------------------------------|-----|-----|-----|-----------|

| $t_{LDACAH}$ | SCL 立ち下がりエッジから $\overline{LDAC}$ 立ち上がりエッジまで、 $1.7V \leq V_{DD} \leq 2.7V$ | 20  |     |     | ns        |

| $t_{LDACAH}$ | SCL 立ち下がりエッジから $\overline{LDAC}$ 立ち上がりエッジまで、 $2.7V < V_{DD} \leq 5.5V$    | 20  |     |     | ns        |

| $t_{LDACAL}$ | $\overline{LDAC}$ 立ち下がりエッジから SCL 立ち下がりエッジまで、 $1.7V \leq V_{DD} \leq 5.5V$ | 10  |     |     | クロック・サイクル |

| $t_{LDACSH}$ | SCL 立ち下がりエッジから $\overline{LDAC}$ 立ち上がりエッジまで、 $1.7V \leq V_{DD} \leq 2.7V$ | 80  |     |     | ns        |

| $t_{LDACSH}$ | SCL 立ち下がりエッジから $\overline{LDAC}$ 立ち上がりエッジまで、 $2.7V < V_{DD} \leq 5.5V$    | 50  |     |     | ns        |

| $t_{LDACSL}$ | SCL 立ち下がりエッジから $\overline{LDAC}$ 立ち下がりエッジまで、 $1.7V \leq V_{DD} \leq 2.7V$ | 20  |     |     | ns        |

| $t_{LDACSL}$ | SCL 立ち下がりエッジから $\overline{LDAC}$ 立ち下がりエッジまで、 $2.7V \leq V_{DD} \leq 5.5V$ | 20  |     |     | ns        |

| $t_{LDACW}$  | $\overline{LDAC}$ Low 時間、 $1.7V \leq V_{DD} < 2.7V$                       | 30  |     |     | ns        |

| $t_{LDACW}$  | $\overline{LDAC}$ Low 時間、 $2.7V \leq V_{DD} \leq 5.5V$                    | 60  |     |     | ns        |

| $t_{CLRW}$   | $\overline{CLR}$ Low 時間、 $1.7V \leq V_{DD} < 2.7V$                        | 30  |     |     | ns        |

| $t_{CLRW}$   | $\overline{CLR}$ Low 時間、 $2.7V \leq V_{DD} \leq 5.5V$                     | 60  |     |     | ns        |

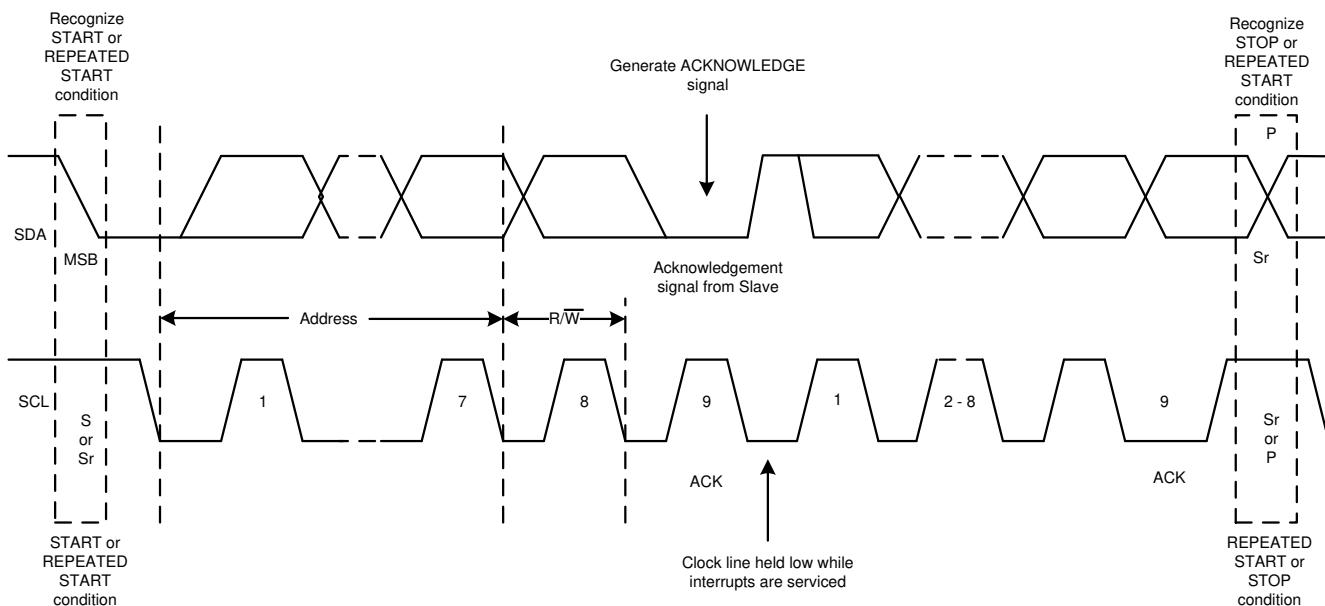

図1. シリアル・インターフェイス・タイミング図

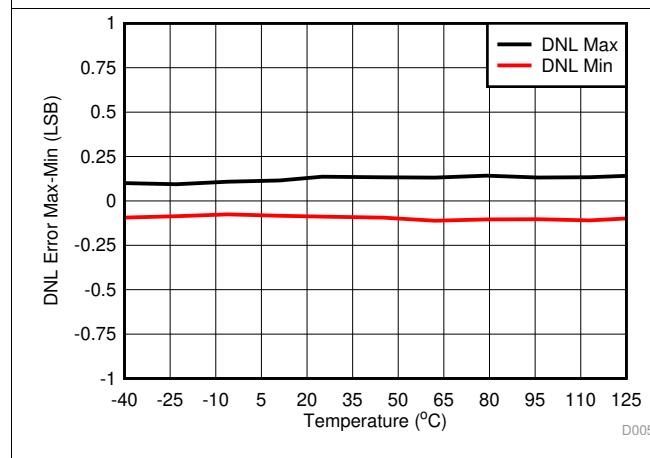

## 7.10 代表的特性 : 1.8V

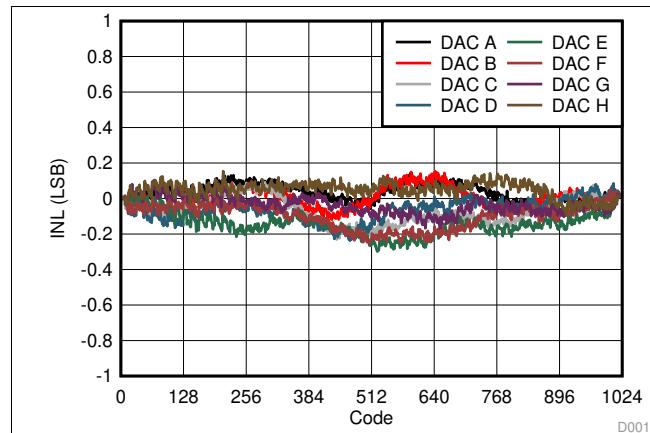

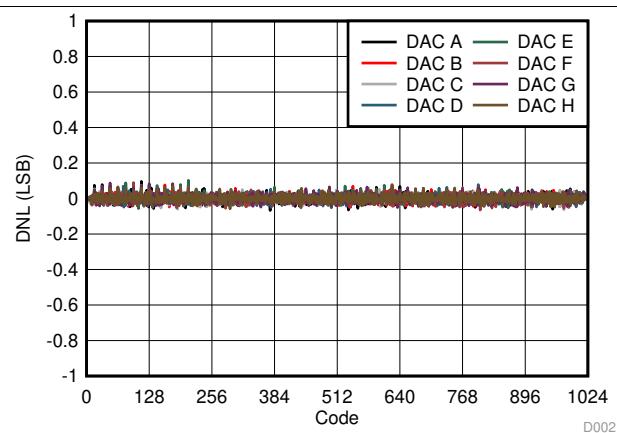

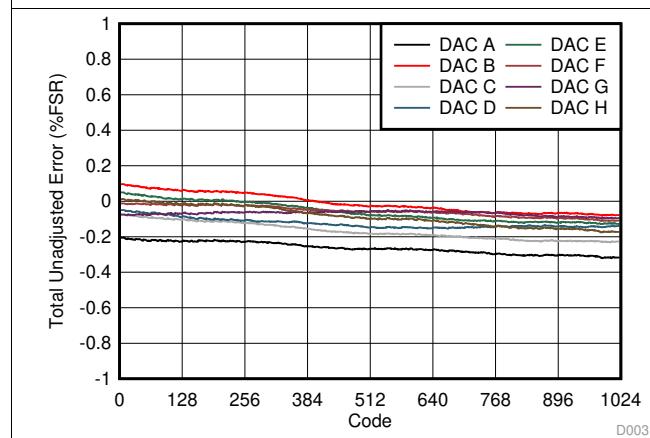

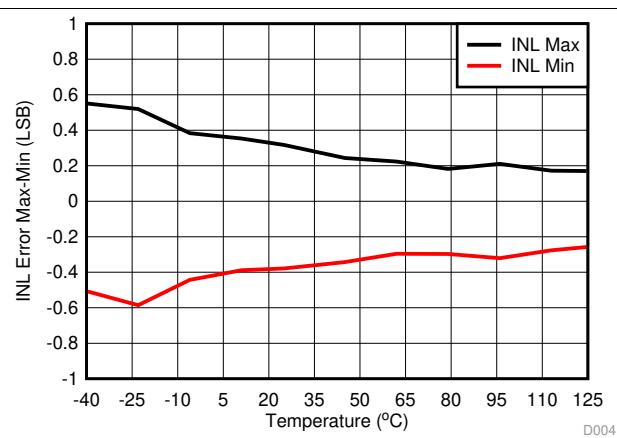

$T_A = 25^\circ\text{C}$ ,  $V_{DD} = 1.8\text{V}$ , リファレンス = 1.8V, DAC 出力は無負荷 (特に記述のない限り)

図 2. 積分直線性誤差とデジタル入力コードとの関係

図 3. 微分直線性誤差とデジタル入力コードとの関係

図 4. 総合未調整誤差とデジタル入力コードとの関係

図 5. 積分直線性誤差と温度との関係

図 6. 微分直線性誤差と温度との関係

図 7. 総合未調整誤差と温度との関係

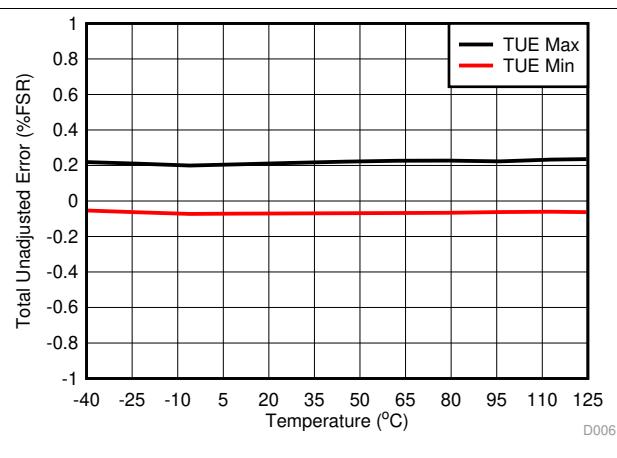

## 代表的特性 : 1.8V (continued)

$T_A = 25^\circ\text{C}$ ,  $V_{DD} = 1.8\text{V}$ , リファレンス = 1.8V, DAC 出力は無負荷 (特に記述のない限り)

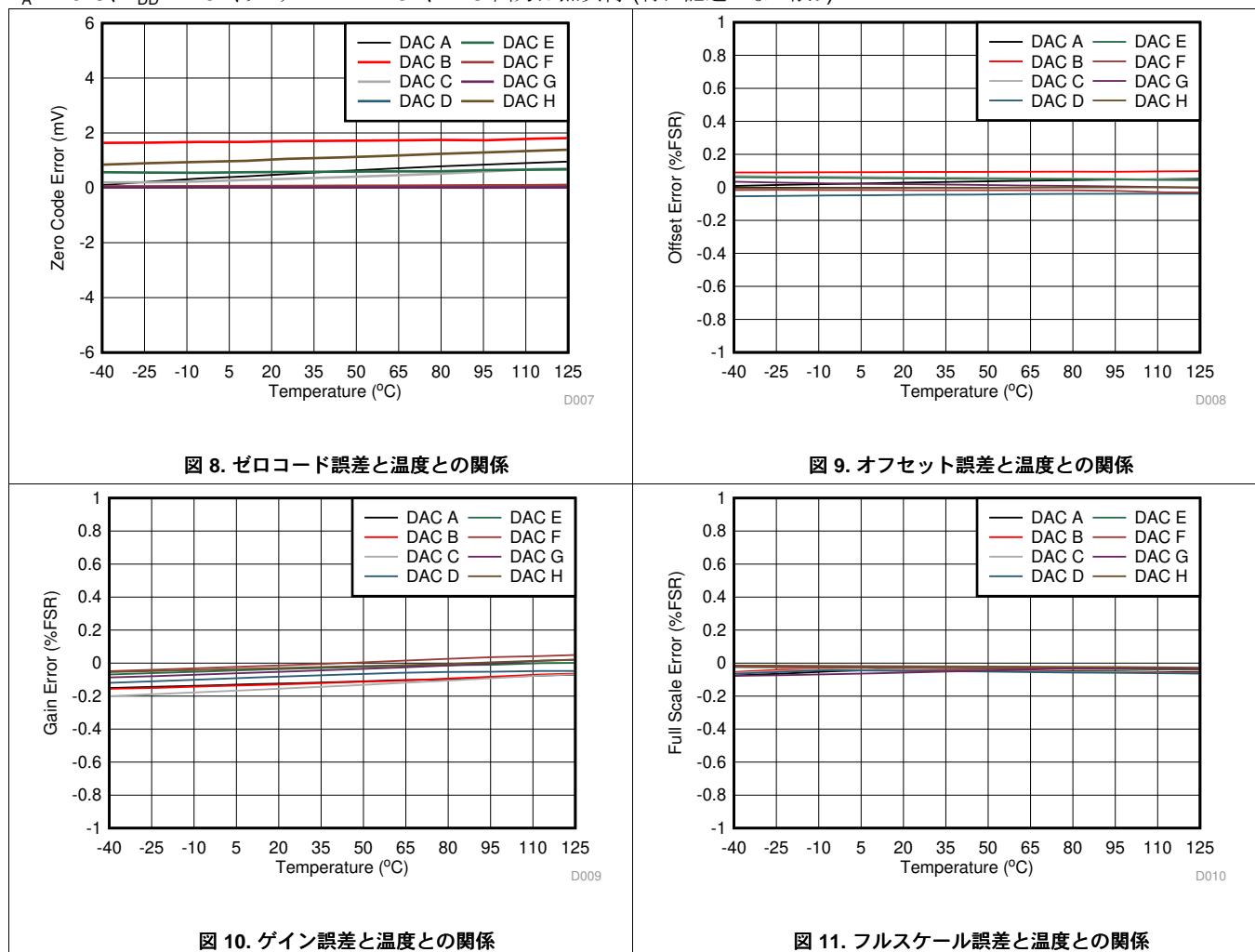

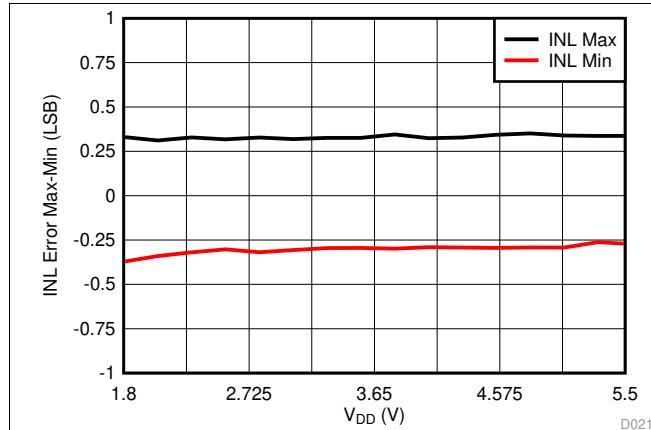

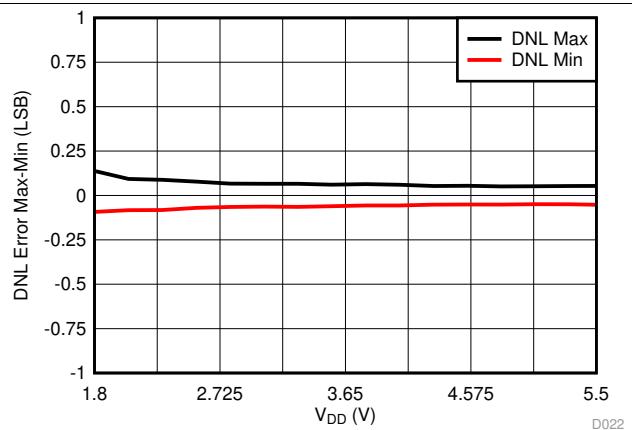

## 7.11 代表的特性 : 5.5V

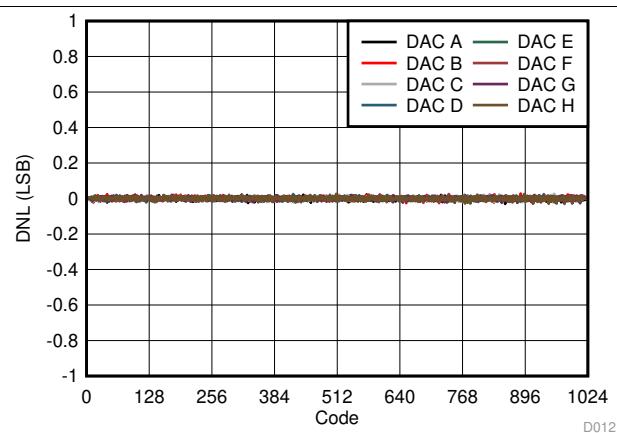

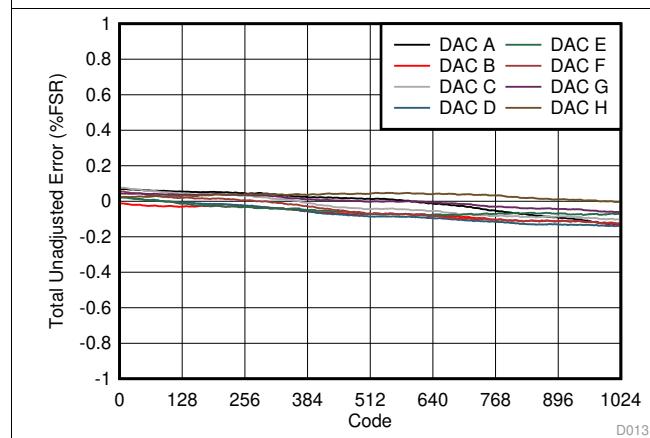

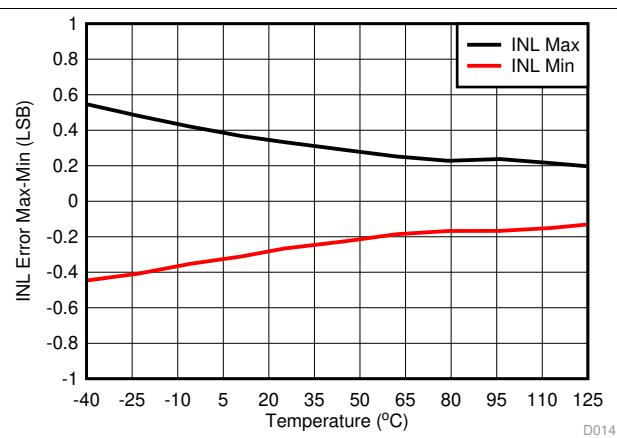

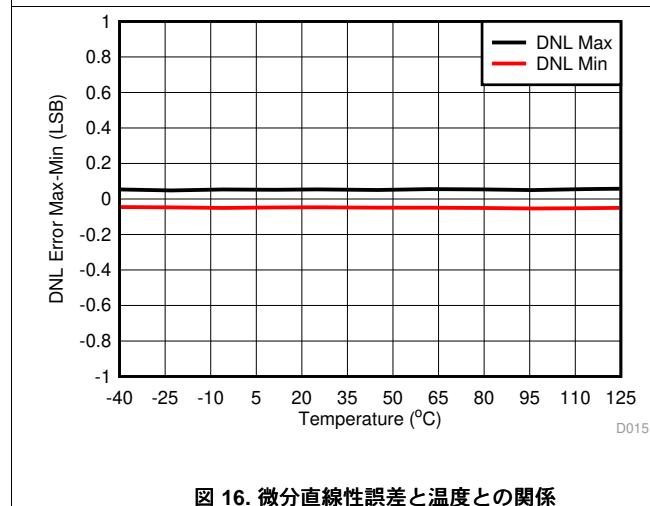

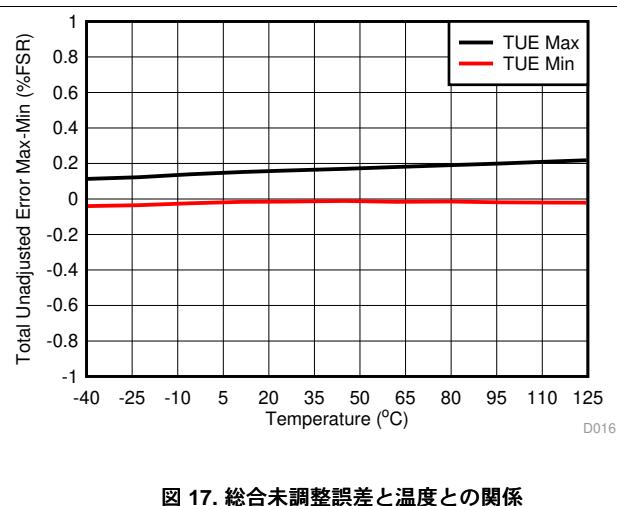

$T_A = 25^\circ\text{C}$ ,  $V_{DD} = 5.5\text{V}$ , リファレンス = 5.5V, DAC 出力は無負荷 (特に記述のない限り)

図 12. 積分直線性誤差とデジタル入力コードとの関係

図 13. 微分直線性誤差とデジタル入力コードとの関係

図 14. 総合未調整誤差とデジタル入力コードとの関係

図 15. 積分直線性誤差と温度との関係

図 16. 微分直線性誤差と温度との関係

図 17. 総合未調整誤差と温度との関係

## 代表的特性 : 5.5V (continued)

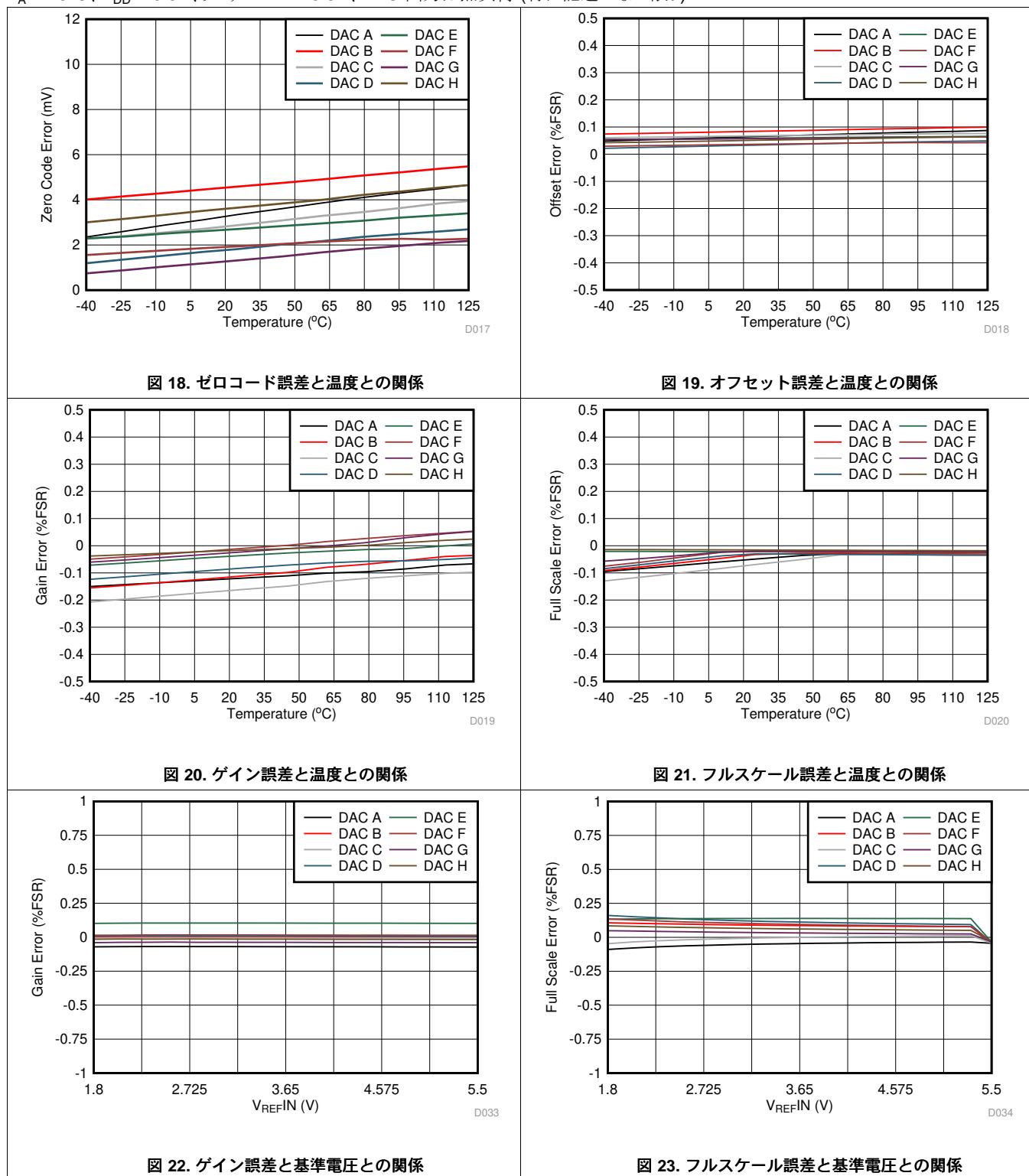

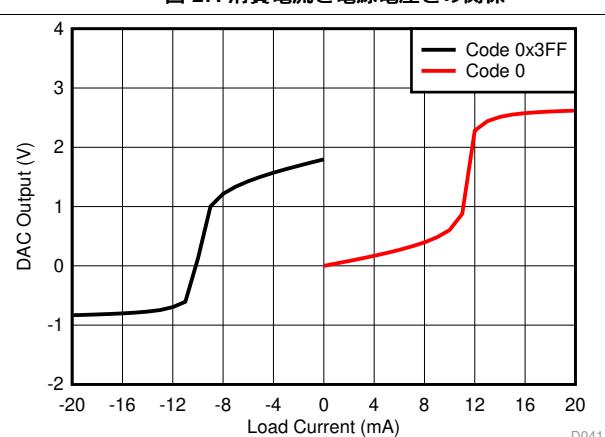

$T_A = 25^\circ\text{C}$ ,  $V_{DD} = 5.5\text{V}$ , リファレンス = 5.5V、DAC 出力は無負荷 (特に記述のない限り)

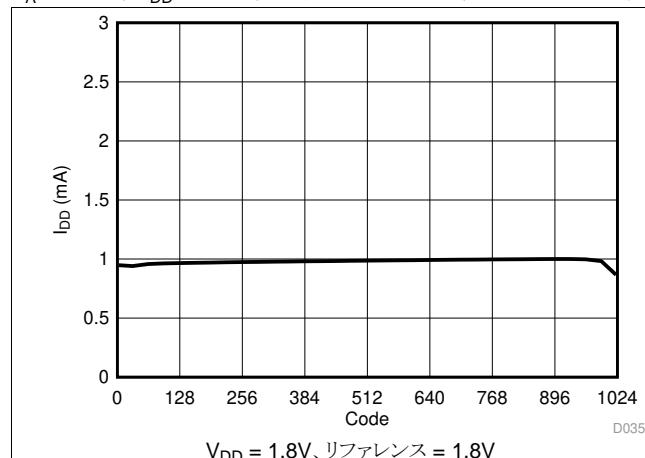

## 代表的特性 : 5.5V (continued)

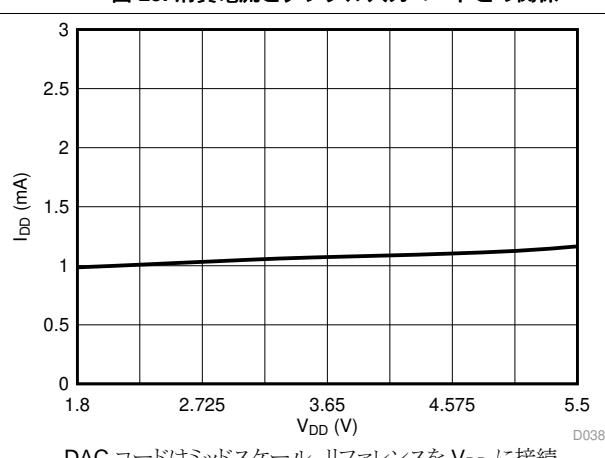

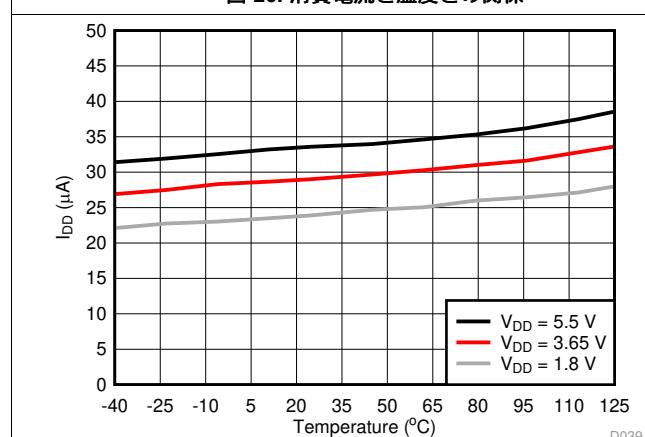

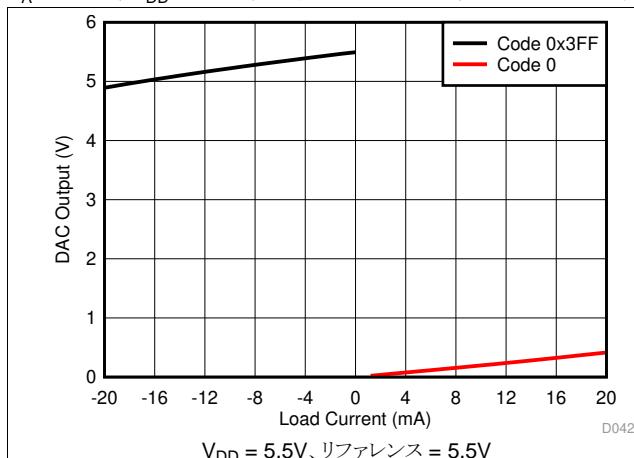

$T_A = 25^\circ\text{C}$ 、 $V_{DD} = 5.5\text{V}$ 、リファレンス = 5.5V、DAC 出力は無負荷 (特に記述のない限り)

図 24. 消費電流とデジタル入力コードとの関係

図 25. 消費電流とデジタル入力コードとの関係

図 26. 消費電流と温度との関係

図 27. 消費電流と電源電圧との関係

図 28. パワーダウン電流と温度との関係

図 29. ソース / シンク能力

## 代表的特性 : 5.5V (continued)

$T_A = 25^\circ\text{C}$ ,  $V_{DD} = 5.5\text{V}$ , リファレンス = 5.5V, DAC 出力は無負荷 (特に記述のない限り)

図 30. ソース / シンク能力

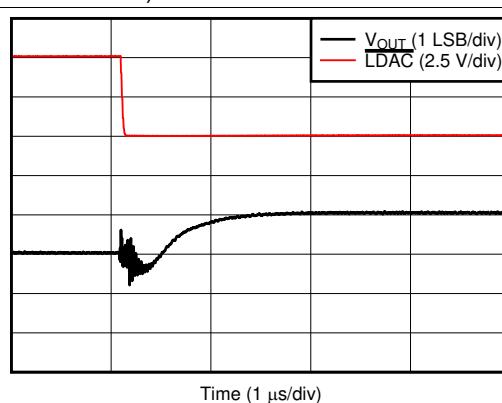

図 31. グリッヂ・インパルス、立ち上がりリエッジ、1LSB ステップ

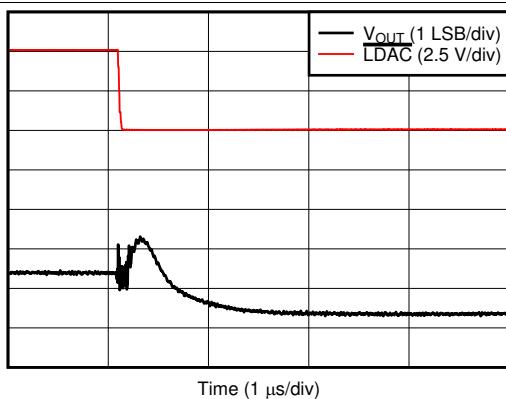

図 32. グリッヂ・インパルス、立ち下がりリエッジ、1LSB ステップ

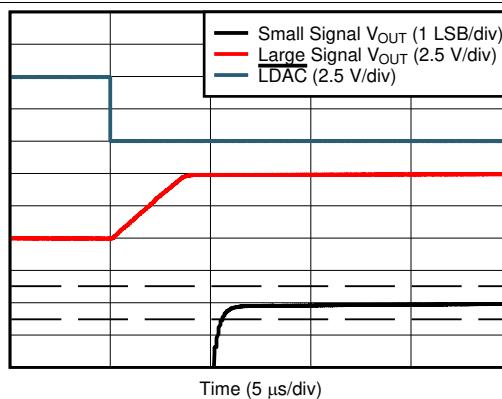

図 33. フルスケール・セトリング時間、立ち上がりリエッジ

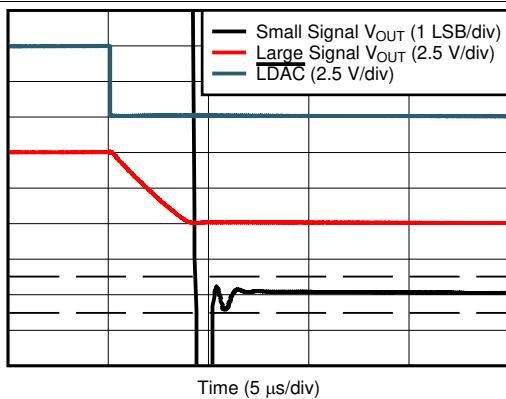

図 34. フルスケール・セトリング時間、立ち下がりリエッジ

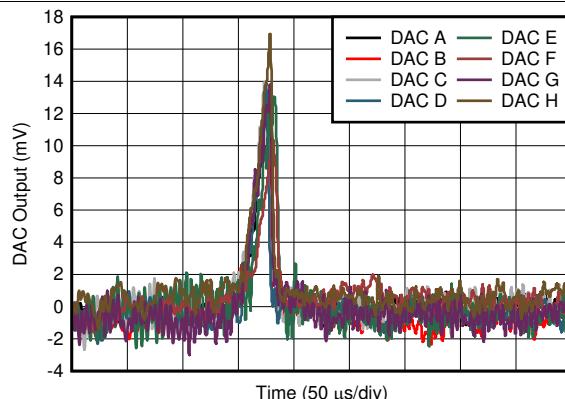

図 35. 電源オン時のグリッヂ

## 代表的特性 : 5.5V (continued)

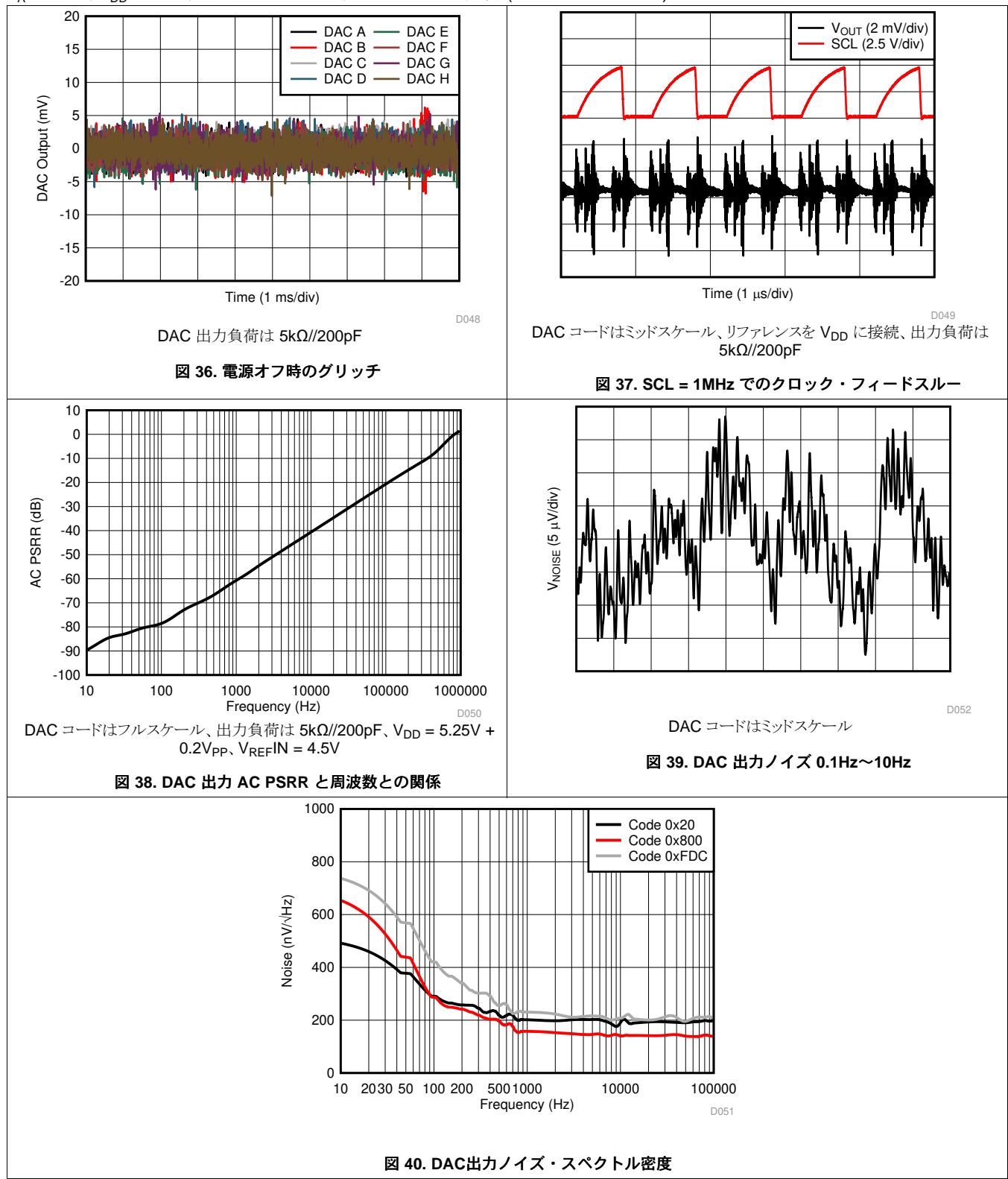

$T_A = 25^\circ\text{C}$ ,  $V_{DD} = 5.5\text{V}$ , リファレンス = 5.5V, DAC 出力は無負荷 (特に記述のない限り)

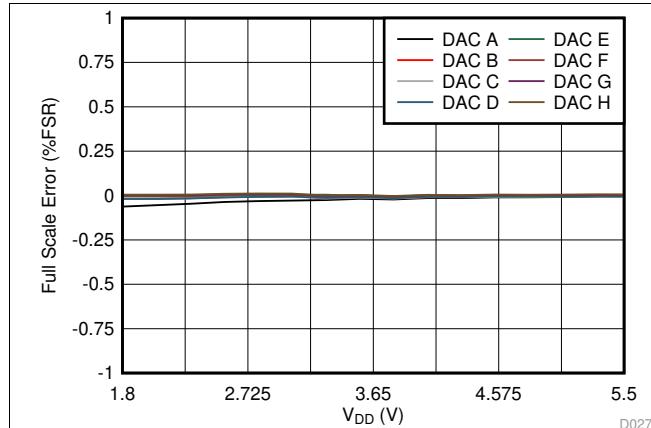

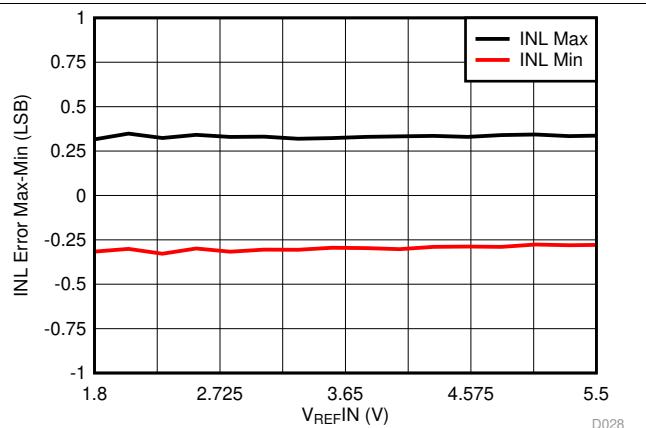

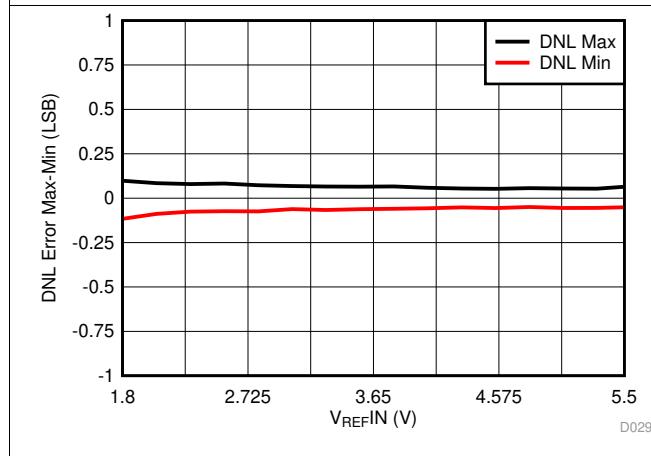

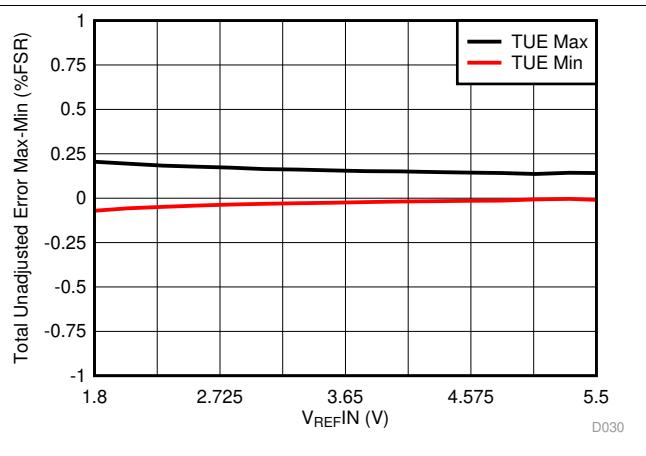

## 7.12 代表的特性

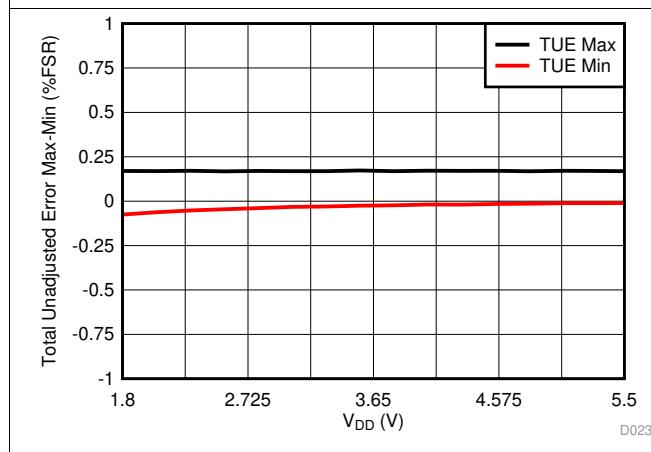

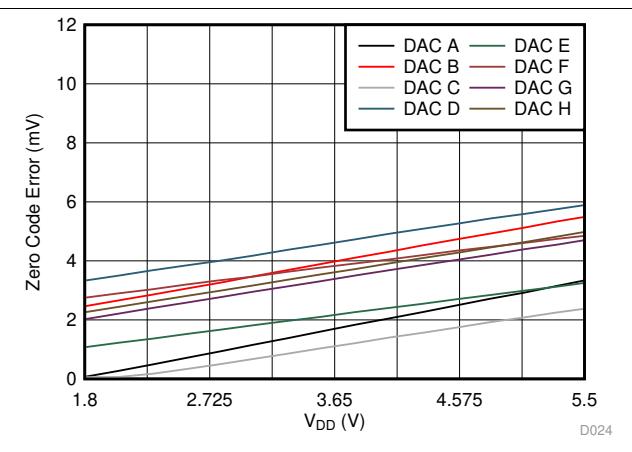

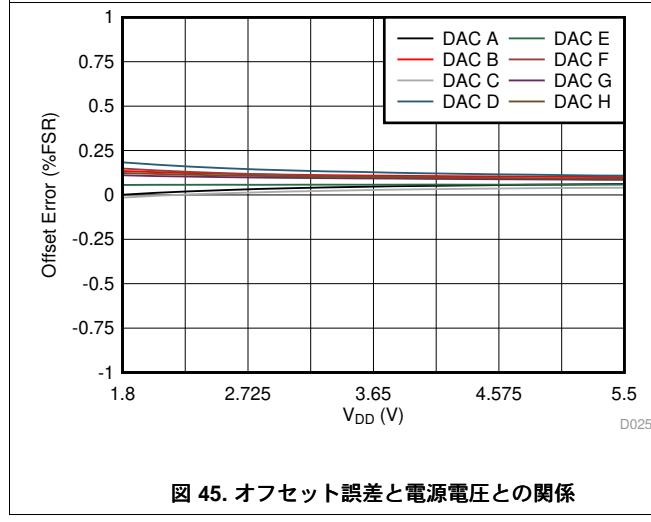

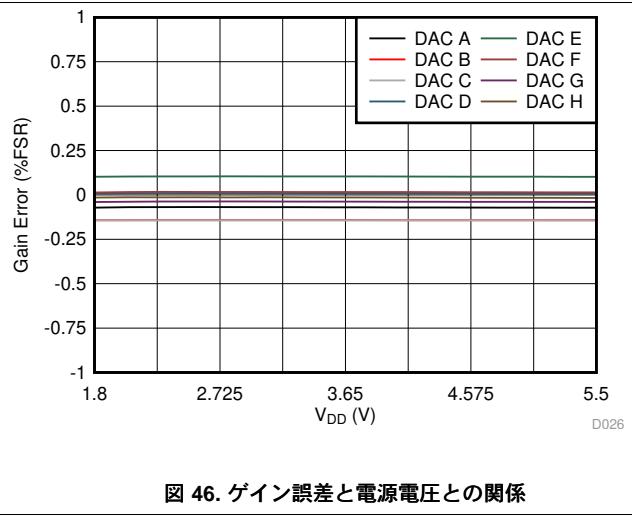

$T_A = 25^\circ\text{C}$ 、DAC 出力は無負荷 (特に記述のない限り)

図 41. 積分直線性誤差と電源電圧との関係

図 42. 微分直線性誤差と電源電圧との関係

図 43. 総合未調整誤差と電源電圧との関係

図 44. ゼロコード誤差と電源電圧との関係

図 45. オフセット誤差と電源電圧との関係

図 46. ゲイン誤差と電源電圧との関係

## 7.13 代表的特性

$T_A = 25^\circ\text{C}$ ,  $V_{DD} = 5.5\text{V}$ , DAC 出力は無負荷 (特に記述のない限り)

図 47. フルスケール誤差と電源電圧との関係

図 48. 積分直線性誤差と基準電圧との関係

図 49. 微分直線性誤差と基準電圧との関係

図 50. 総合未調整誤差と基準電圧との関係

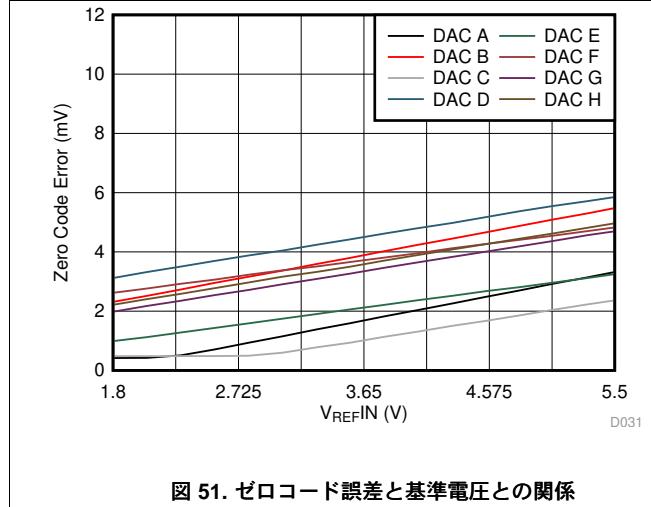

図 51. ゼロコード誤差と基準電圧との関係

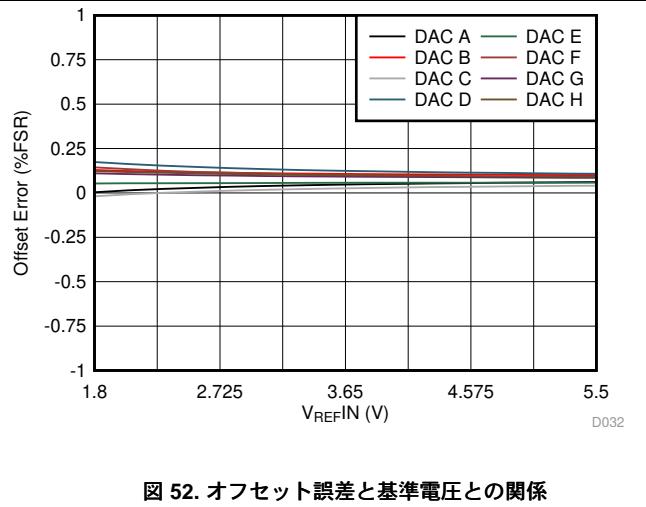

図 52. オフセット誤差と基準電圧との関係

## 8 詳細説明

### 8.1 概要

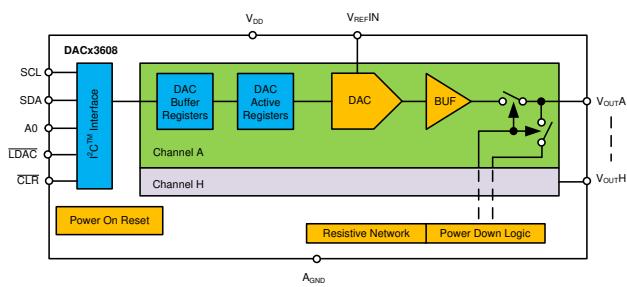

DAC53608 と DAC43608 は、10 ビットおよび 8 ビットの分解能を持つ 8 チャネル・バッファ付き電圧出力デジタル / アナログ・コンバータ (DAC) のピン互換ファミリです。1.8V～5.5V の外部リファレンスにより、1.8V～5.5V のフルスケール電圧を出力できます。全電源電圧範囲にわたって単調性を維持します。

デバイスとの通信は I<sup>2</sup>C<sup>TM</sup> 互換インターフェイスで行い、I<sup>2</sup>C<sup>TM</sup> の Standard モード (100kbps)、Fast モード (400kbps)、Fast+ モード (1Mbps) をサポートしています。また、DAC を同時に更新できるロード DAC (LDAC) ピンも備えています。

DACx3608 は -40°C～+125°C の温度範囲で仕様が規定されており、小型の QFN パッケージで供給されます。

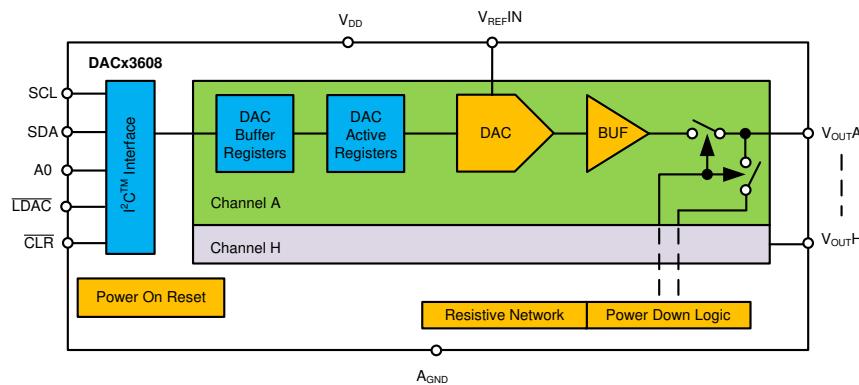

### 8.2 機能ブロック図

図 53. DACx3608 DAC のブロック図

## 8.3 機能説明

### 8.3.1 デジタル / アナログ・コンバータ (DAC) アーキテクチャ

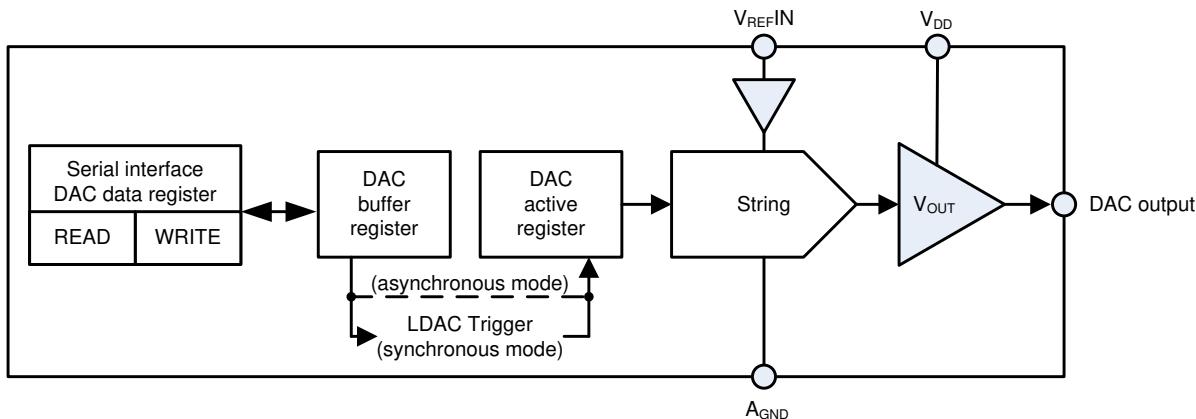

DACx3608 ファミリの各出力チャネルは、ストリング・アーキテクチャと出力バッファ・アンプで構成されています。図 54 に DAC アーキテクチャのブロック図を示します。

図 54. DACx3608 DAC のアーキテクチャ

#### 8.3.1.1 DAC の伝達関数

個々の DAC データ・レジスタに対する入力データは、ストレート・バイナリ形式で記述します。電源オンまたはリセット・イベント後に、すべての DAC レジスタはゼロコードに設定されます。式 1 に DAC 伝達関数を示します。

$$V_{\text{OUT}} = \frac{\text{DACn\_DATA}}{2^N} \times V_{\text{REFIN}}$$

ここで

- N = 分解能 (ビット)

- 10 (DAC53608) と 8 (DAC43608) のどちらか

- DACn\_DATA は DAC レジスタにロードされるバイナリ・コードに等価な 10 進数です。

- DACn\_DATA の範囲は  $0 \sim 2^N - 1$  です。

- V<sub>REFIN</sub> は DAC の基準電圧です。

- (1)

#### 8.3.1.2 DAC レジスタの更新と LDAC 機能

DAC データ・レジスタに書き込まれたデータは DAC バッファ・レジスタに保存されます。DAC バッファ・レジスタから DAC アクティブ・レジスタへのデータ転送は、即実行 (非同期モード) か LDAC トリガにより開始 (同期モード) のどちらかに設定できます。DAC アクティブ・レジスタが更新されると、DAC 出力は新しい値に変わります。

各 DAC チャネルの更新モードは、LDAC ピンの状態によって決まります。

非同期モード (DAC 書き込みコマンドより前に LDAC = 0) では、DAC データ・レジスタに書き込みを行うと、I<sup>2</sup>C<sup>TM</sup> フレームが終了した時点で DAC アクティブ・レジスタと DAC 出力が即更新されます。

同期モード (DAC 書き込みコマンドより前に LDAC = 1) では、DAC データ・レジスタに書き込みを行っても DAC 出力は自動的に更新されず、LDAC が 0 になって初めて更新が実行されます。同期更新モードでは、すべての DAC 出力を同時に更新できます。

#### 8.3.1.3 CLR 機能

CLR ピンは DAC への非同期入力ピンです。このピンが Low になると (論理 0)、DAC バッファおよび DAC アクティブ・レジスタはゼロコードになります。

## 機能説明 (continued)

### 8.3.1.4 出力アンプ

出力バッファ・アンプは、出力上に  $0V \sim V_{DD}$  の最大出力範囲でレール・ツー・レール電圧を生成します。式 1 は DAC 出力のフルスケール出力範囲が  $V_{REFIN}$  ピンの電圧によって決まることを示しています。

### 8.3.2 リファレンス

DACx3608 は、外部リファレンスを使用する必要があります。ただし、リファレンス・ピン  $V_{REFIN}$  と電源ピン  $V_{DD}$  は互いに接続できます。リファレンス入力ピンの電圧範囲は  $1.8V \sim V_{DD}$  です。全チャネルがオンになっている場合、このピンの標準的な入力インピーダンスは  $12.5k\Omega$  です。

### 8.3.3 パワーオン・リセット (POR)

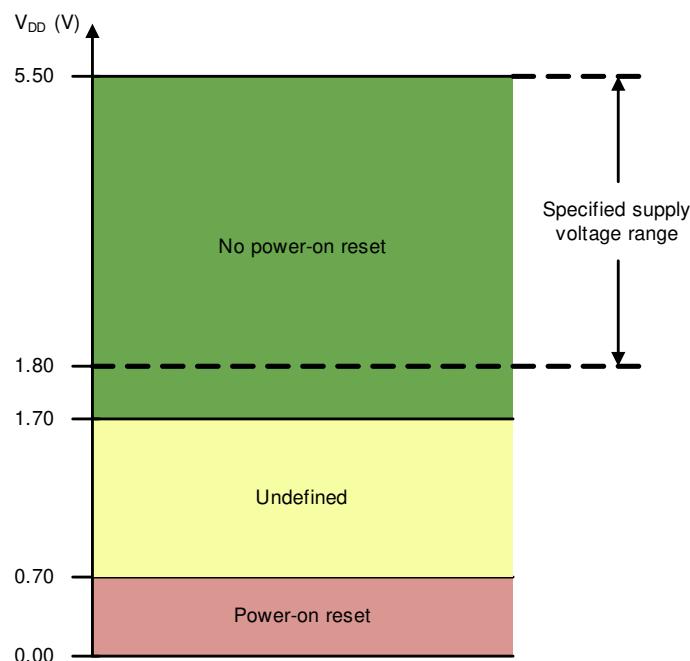

DACx3608 ファミリは、電源投入時に出力電圧を制御するパワーオン・リセット (POR) 機能を備えています。 $V_{DD}$  電源が立ち上がりると、POR イベントが発行されます。POR により、全レジスタはデフォルト値に初期化され、 $V_{DD}$  が DAC の動作電圧範囲に達した後 5ms 経過してから通信が有効になります。DAC データ・レジスタのデフォルト値はゼロコードです。DAC の出力は、有効なコマンドがチャネルに書き込まれるまで、電源投入時の電圧のままでです。

電源投入時に、POR 回路によりデバイスがデフォルト値に設定されます。電源投入時に内部コンデンサが放電しデバイスをリセットすることを確実にするには、図 55 に示す特定の  $V_{DD}$  レベルが POR 回路に必要です。POR を確実に実行するには、 $V_{DD}$  が  $0.7V$  未満の状態を 1ms 以上継続する必要があります。 $V_{DD}$  が  $1.7V$  未満に降下しても  $0.7V$  を上回っている場合 (未定義領域として表示)、温度および電源のすべての規定条件でリセットするかどうかは分かりません。この場合、POR を起動します。 $V_{DD}$  が  $1.7V$  を上回ったままであれば、POR は実行されません。

図 55.  $V_{DD}$  POR 回路のスレッショルド・レベル

### 8.3.4 ソフトウェア・リセット

ソフトウェア・リセット・イベントは、TRIGGER レジスタ (アドレス 2h) の SW-RST ビットに予約コード 0x1010 を書き込むことにより起動します。

## 8.4 デバイスの機能モード

DACx3608 には、通常モードとパワーダウン・モードという 2 つの動作モードがあります。

## デバイスの機能モード (continued)

### 8.4.1 パワーダウン・モード

DACx3608 DAC 出力アンプは、DEVICE\_CONFIG レジスタを介して、個別またはグローバルにパワーダウンできます ( $A_{GND}$  に対して  $10K$ )。この状態で、本デバイスは  $50\mu A$  ( $V_{DD} = 1.8V$ ) を消費します。全出力チャネルのバッファ・アンプが  $10K$  モードにパワーダウンした状態で起動し、チャネルごとのパワーダウン・レジスタに  $0$  が書き込まれパワーアップ・コマンドが発行されるまでその状態を維持します。

## 8.5 プログラミング

ピン構成および機能 に示すように、DACx3608 は 2 線式シリアル・インターフェイスとして SCL、SDA、1 つのアドレス・ピン A0 を備えています。 $I^2C^{TM}$  バスは、プルアップ構造を持つデータ・ライン (SDA) とクロック・ライン (SCL) で構成されます。バスがアイドルのときは、SDA と SCL の両方が High になります。 $I^2C^{TM}$  互換のデバイスはすべて、オープン・ドレインの I/O ピンである SDA および SCL を介して  $I^2C^{TM}$  バスに接続します。

$I^2C^{TM}$  仕様では、通信を制御するデバイスをマスタといい、マスタに制御されるデバイスをスレーブといいます。マスタ・デバイスは SCL 信号を生成します。また、専用のタイミング条件 (スタート条件、再スタート条件、ストップ条件) をバスに生成して、データ転送の開始または停止を通知します。デバイス・アドレッシングはマスタが実行します。 $I^2C^{TM}$  バス上のマスタ・デバイスは通常、マイクロコントローラまたはデジタル・シグナル・プロセッサ (DSP) です。DACx3608 ファミリは、 $I^2C^{TM}$  バス上でスレーブ・デバイスとして動作します。スレーブ・デバイスはマスタのコマンドに対して確認応答し、マスタの制御に従つてデータを送受信します。

通常、DACx3608 ファミリはスレーブ・レシーバとして動作します。マスタ・デバイスは、スレーブ・レシーバである DACx3608 に対して書き込みを行います。ただし、マスタ・デバイスが DACx3608 の内部レジスタ・データを必要とする場合は、DACx3608 ファミリがスレーブ・トランスマッタとして動作します。この場合、マスタ・デバイスは DACx3608 から読み取ります。 $I^2C^{TM}$  の用語では、読み取り / 書き込みといえばマスタ・デバイスを指します。

DACx3608 ファミリはスレーブであり、次のデータ転送モードをサポートしています。

- Standard モード (100kbps)

- Fast モード (400kbps)

- Fast+ モード (1.0Mbps)

Standard モードと Fast モードのデータ転送プロトコルはまったく同じであるため、このデータシートではこれらのモードを F/S モードと呼びます。Fast+ モードのプロトコルについては、データ転送速度はサポートしていますが、出力電流はサポートていません。低レベル出力電流は、Standard モードおよび Fast モードの場合と同様に  $3mA$  となります。DACx3608 ファミリは 7 ビット・アドレッシングをサポートしています。10 ビット・アドレッシング・モードはサポートていません。また、ジェネラル・コール・リセット機能をサポートしています。次のシーケンスを送信すると、デバイス内でソフトウェア・リセットが起動します。スタート / 再スタート、 $0x00$ 、 $0x06$ 、ストップ。2 番目のバイトに続く、ACK ビットの立ち上がりエッジで、リセットがデバイス内でアサートされます。

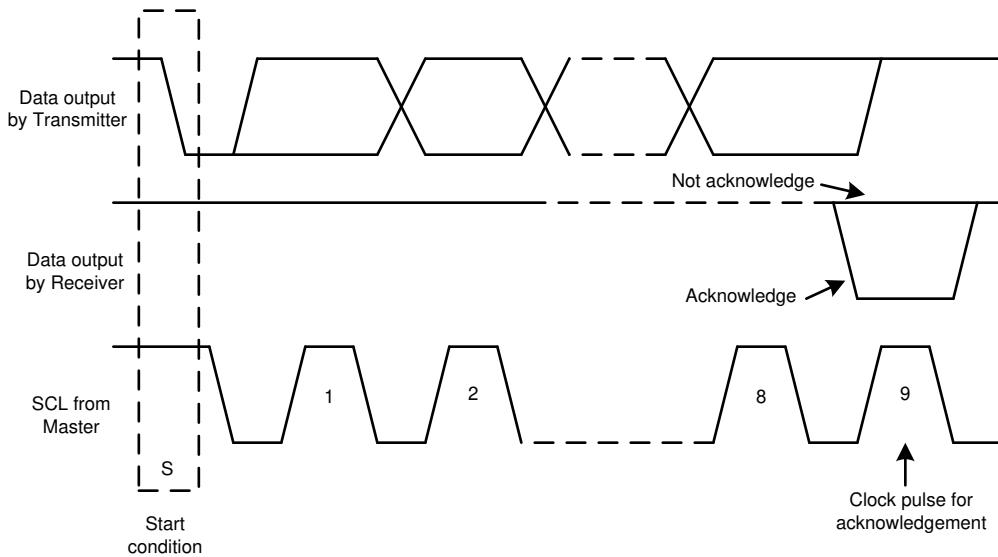

指定のタイミング信号を除いて、 $I^2C^{TM}$  インターフェイスではシリアル・バイトを扱います。各バイトの最後に、9 回目のクロック・サイクルで確認応答信号が生成および検出されます。確認応答は、9 回目のクロック・サイクルの High 期間中 SDA ラインを Low にすることで行われます。否定応答は、図 56 に示すように 9 回目のクロック・サイクルの High 期間中 SDA ラインを High のまま保持することで行われます。

## プログラミング (continued)

図 56. I<sup>2</sup>C<sup>TM</sup> バスの確認応答と否定応答

### 8.5.1 F/S モードのプロトコル

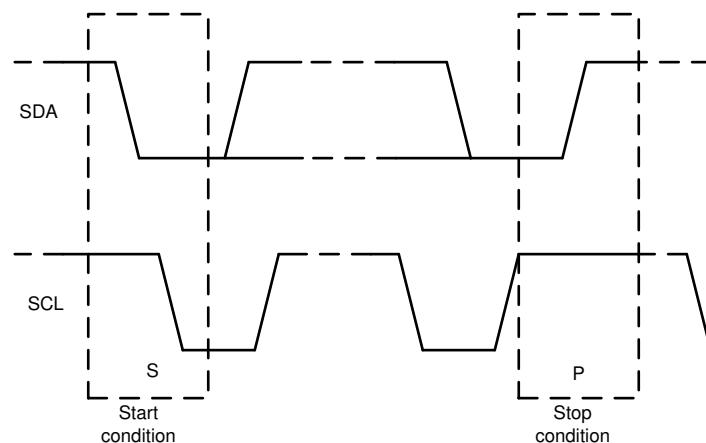

- マスターがスタート条件を生成して、データ転送を開始します。スタート条件は、図 57 に示すように SCL が High の間に SDA ラインが High から Low に遷移すると発生します。すべての I<sup>2</sup>C<sup>TM</sup> 互換デバイスが、スタート条件を認識します。

図 57. スタート条件とストップ条件

## プログラミング (continued)

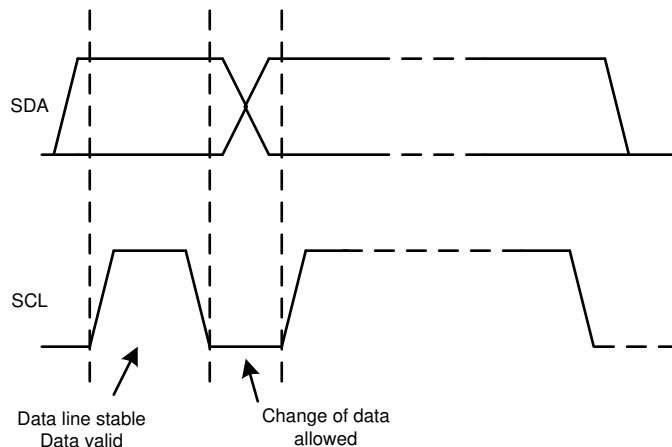

**図 58. I<sup>2</sup>C™ バスでのビット転送**

2. 次に、マスタは SCL パルスを生成し、7 ビットのアドレスと読み取り / 書き込み方向ビット (R/W) を SDA ライン上で送信します。すべての送信中、データが有効であることをマスタは確認します。**図 58** に示すように、データが有効であるためには、クロック・パルスの High 期間全体にわたって SDA ラインが安定している必要があります。すべてのデバイスは、マスタによって送信されたアドレスを認識して、デバイス内部の固定アドレスと比較します。**図 56** に示すように、一致するアドレスを持つスレーブ・デバイスだけが、9 回目の SCL サイクルの High 期間全体の間 SDA ラインを Low にすることで、確認応答を生成します。この確認応答を検出することで、マスタはスレーブとの通信リンクが確立されたことを認識します。

3. マスタは、スレーブへのデータ送信 (R/W ビット 0) またはスレーブからのデータ受信 (R/W ビット 1) を行うために、引き続き SCL サイクルを生成します。どちらの場合も、送信側から送信されたデータに対して受信側が確認応答を返す必要があります。したがって、確認応答信号は、どちらが受信側かによって、マスタが生成する場合とスレーブが生成する場合があります。8 ビットのデータと 1 ビットの確認応答で構成される 9 ビットの有効なデータ・シーケンスを、必要な長さだけ続けることができます。

4. データ転送の終わりを通知するときには、マスタは SCL ラインが High の間に SDA ラインを Low から High にすることで、ストップ条件を生成します (**図 57** を参照)。これによってバスが解放され、アドレス指定されたスレーブとの通信リンクが停止します。すべての I<sup>2</sup>C™ 互換デバイスが、ストップ条件を認識します。ストップ条件の受信によって、バスは解放され、すべてのスレーブ・デバイスはスタート条件および一致するアドレスが送信されるのを待ちます。

## プログラミング (continued)

### 8.5.2 DACx3608 の I<sup>2</sup>C<sup>TM</sup> 更新シーケンス

表 1 に示すように DACx3608 では、1 回の更新のために、スタート条件、有効な I<sup>2</sup>C<sup>TM</sup> アドレス・バイト、コマンド・バイト、2 つのデータ・バイト (最上位データ・バイト (MSDB) と最下位データ・バイト (LSDB)) を必要とします。

表 1. 更新シーケンス

| MSB          | .... | LSB        | ACK | MSB       | ... | LSB      | ACK | MSB  | ... | LSB | ACK | MSB | ... | LSB | ACK |

|--------------|------|------------|-----|-----------|-----|----------|-----|------|-----|-----|-----|-----|-----|-----|-----|

| アドレス (A) バイト |      | コマンド・バイト   |     | MSDB      |     | LSDB     |     | LSDB |     |     |     |     |     |     |     |

| DB [32:24]   |      | DB [23:16] |     | DB [15:8] |     | DB [7:0] |     |      |     |     |     |     |     |     |     |

図 59 に示すように、各バイトの受信後、DACx3608 ファミリは 1 つのクロック・パルスの High 期間中に SDA ラインを Low にすることで、確認応答を行います。この 4 つのバイトと確認応答サイクルにより、1 回の更新を実行するために必要な 36 のクロック・サイクルが生成されます。有効な I<sup>2</sup>C<sup>TM</sup> アドレス・バイトによって、DACx3608 が選択されます。

図 59. I<sup>2</sup>C<sup>TM</sup> バス・プロトコル

コマンド・バイトは、選択された DACx3608 の動作モードを設定します。このバイトによって動作モードが選択されると、DACx3608 シリーズは、データ更新を実行するために、最上位データ・バイト (MSDB) と最下位データ・バイト (LSDB) という 2 つのデータ・バイトを受信する必要があります。DACx3608 は、LSDB に続く確認応答信号の立ち下がりエッジで更新を実行します。

Fast モード (クロック = 400kHz) を使用すると、最大 DAC 更新レートは 22.22kSPS となります。Fast+ モード (クロック = 1MHz) を使用すると、最大 DAC 更新レートは 55.55kSPS となります。ストップ条件を受信すると、DACx3608 ファミリは I<sup>2</sup>C<sup>TM</sup> バスを解放し、新たなスタート条件を待ちます。

### 8.5.3 DACx3608 のアドレス・バイト

表 2 に示すアドレス・バイトは、マスター・デバイスからスタート条件に続いて受信する最初のバイトです。アドレスの最初の 4 ビット (MSB) は工場出荷時に 1001 に設定されます。次の 3 ビットは A0 ピンによって制御されます。A0 ピンの入力は V<sub>DD</sub>, A<sub>GND</sub>, SCL, または SDA に接続できます。各データ・フレームの最初のバイトにおいて A0 ピンがサンプリングされて、アドレスが決定します。デバイスはアドレス・ピンの値をラッチし、その結果として、表 3 に従ってその特定のアドレスに応答します。

DACx3608 ファミリはブロードキャスト・アドレッシングをサポートしています。ブロードキャスト・アドレッシングは、複数の DACx3608 の同期更新やパワーダウンに使用できます。DACx3608 ファミリのデバイスは、互いに組み合わせて使うことでマルチチップ同期更新をサポートするように設計されています。ブロードキャスト・アドレスを使用して、アドレス・ピンの状態に関係なく応答します。ブロードキャストは書き込みモードでのみサポートしています。

**表 2. DACx3608 のアドレス・バイト**

| 備考            | MSB |     |     |     |                       |     |         | LSB |

|---------------|-----|-----|-----|-----|-----------------------|-----|---------|-----|

|               | AD6 | AD5 | AD4 | AD3 | AD2                   | AD1 | AD0     |     |

| ジェネラル・アドレス    | 1   | 0   | 0   | 1   | 表 3 (スレーブ・アドレスの列) を参照 |     | 0 または 1 |     |

| ブロードキャスト・アドレス | 1   | 0   | 0   | 0   | 1                     | 1   | 1       | 0   |

**表 3. アドレス形式**

| スレーブ・アドレス | A0 ピン            |

|-----------|------------------|

| 1001 000  | A <sub>GND</sub> |

| 1001 001  | V <sub>DD</sub>  |

| 1001 010  | SDA              |

| 1001 011  | SCL              |

### 8.5.4 DACx3608 のコマンド・バイト

DACx3608 のコマンド・バイト (表 4 参照) は、DACx3608 シリーズに対して書き込みや読み取りを行うとき、実行するコマンドとアクセスするレジスタを制御します。

**表 4. DACx3608 のコマンド・バイト**

| B23 | B22 | B21 | B20 | B19 | B18 | B17 | B16 | 備考             |

|-----|-----|-----|-----|-----|-----|-----|-----|----------------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | DEVICE_CONFIG  |

| 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | STATUS/TRIGGER |

| 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | BRDCAST        |

| 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0   | DACA_DATA      |

| 0   | 0   | 0   | 0   | 1   | 0   | 0   | 1   | DACB_DATA      |

| 0   | 0   | 0   | 0   | 1   | 0   | 1   | 0   | DACC_DATA      |

| 0   | 0   | 0   | 0   | 1   | 0   | 1   | 1   | DACD_DATA      |

| 0   | 0   | 0   | 0   | 1   | 1   | 0   | 0   | DACE_DATA      |

| 0   | 0   | 0   | 0   | 1   | 1   | 0   | 1   | DACF_DATA      |

| 0   | 0   | 0   | 0   | 1   | 1   | 1   | 0   | DACG_DATA      |

| 0   | 0   | 0   | 0   | 1   | 1   | 1   | 1   | DACH_DATA      |

### 8.5.5 DACx3608 のデータ・バイト (MSDB と LSDB)

表 5 に示すように、MSDB と LSDB には、コマンド・バイトで指定されるレジスタに渡されるデータが含まれています。DACx3608 ファミリは、LSDB[0] ビットに続く確認応答信号の立ち下がりエッジで更新を実行します。

**表 5. DACx3608 のデータ・バイト**

| コマンド・ビット       | データ・ビット   |                                                 |     |    |                 |      |      |        |      |      |      |      |      |

|----------------|-----------|-------------------------------------------------|-----|----|-----------------|------|------|--------|------|------|------|------|------|

|                | MSDB      |                                                 |     |    | LSDB            |      |      |        |      |      |      |      |      |

| B19 - B16      | B15 - B12 | B11                                             | B10 | B9 | B8              | B7   | B6   | B5     | B4   | B3   | B2   | B1   | B0   |

| DEVICE_CONFIG  | x         | 0                                               | 0   | 0  | PD<br>N-<br>All | PDNH | PDNG | PDNF   | PDNE | PDND | PDNC | PDNB | PDNA |

| STATUS/TRIGGER | x         | DEVICE_ID                                       |     |    |                 | x    | x    | SW_RST |      |      |      |      |      |

| BRDCAST        | x         | BRDCAST_DATA[9:0] / BRDCAST_DATA[7:0] – MSB 左揃え |     |    |                 |      |      |        |      |      | x    | x    |      |

| DACA_DATA      | x         | DACA_DATA[9:0] / DACA_DATA[7:0] – MSB 左揃え       |     |    |                 |      |      |        |      |      | x    | x    |      |

| DACB_DATA      | x         | DACB_DATA[9:0] / DACB_DATA[7:0] – MSB 左揃え       |     |    |                 |      |      |        |      |      | x    | x    |      |

| DACC_DATA      | x         | DACC_DATA[9:0] / DACC_DATA[7:0] – MSB 左揃え       |     |    |                 |      |      |        |      |      | x    | x    |      |

| DACD_DATA      | x         | DACD_DATA[9:0] / DACD_DATA[7:0] – MSB 左揃え       |     |    |                 |      |      |        |      |      | x    | x    |      |

| DACE_DATA      | x         | DACE_DATA[9:0] / DACE_DATA[7:0] – MSB 左揃え       |     |    |                 |      |      |        |      |      | x    | x    |      |

| DACF_DATA      | x         | DACF_DATA[9:0] / DACF_DATA[7:0] – MSB 左揃え       |     |    |                 |      |      |        |      |      | x    | x    |      |

| DACG_DATA      | x         | DACG_DATA[9:0] / DACG_DATA[7:0] – MSB 左揃え       |     |    |                 |      |      |        |      |      | x    | x    |      |

| DACH_DATA      | x         | DACH_DATA[9:0] / DACAH_DATA[7:0] – MSB 左揃え      |     |    |                 |      |      |        |      |      | x    | x    |      |

### 8.5.6 DACx3608 の I<sup>2</sup>C<sup>TM</sup> 読み取りシーケンス

レジスタを読み取るには、次のコマンド・シーケンスを使用する必要があります。

- スタートまたは再スタート・コマンドとスレーブ・アドレス、書き込みの 0 に設定した R/W ビットを送信します。デバイスがこのイベントに対して確認応答します。

- 読み取り対象レジスタのコマンド・バイトを送信します。デバイスがこのイベントに対して再度、確認応答します。

- 再スタートとスレーブ・アドレス、読み取りの「1」に設定した R/W ビットを送信します。デバイスがこのイベントに対して確認応答します。

- デバイスがアドレス指定されたレジスタの MSDB バイトを書き込みます。マスターはこのバイトに対して確認応答する必要があります。

- 最後に、デバイスがレジスタの LSDB を書き出します。

別の読み取り方法として、書き込まれた最後のレジスタの値を読み返すこともできます。このシーケンスでは、スタートまたは再スタートとスレーブ・アドレス、1に設定した R/W ビットを送信することで、最後のレジスタの 2 バイトが読み出されます。DACx3608 ファミリのレジスタは、SW-RST レジスタ以外はすべて読み取り可能です。[表 5](#) に読み取りコマンド・セットを示します。

なお、読み取りではブロードキャスト・アドレスを使用できません。

**表 6. 読み取りシーケンス**

| S     | MSB          | ... | R/W<br>(0) | ACK   | MSB          | ... | LSB  | ACK   | Sr | MSB          | ...  | R/W<br>(1) | ACK | MSB  | ... | LSB    | ACK | MSB  | ... | LSB | ACK |  |

|-------|--------------|-----|------------|-------|--------------|-----|------|-------|----|--------------|------|------------|-----|------|-----|--------|-----|------|-----|-----|-----|--|

|       | ADDRESS BYTE |     |            |       | COMMAND BYTE |     |      |       | Sr | ADDRESS BYTE |      |            |     | MSDB |     |        |     | LSDB |     |     |     |  |

| マスタから |              |     | スレーブ       | マスタから |              |     | スレーブ | マスタから |    |              | スレーブ | スレーブから     |     |      | マスタ | スレーブから |     |      | マスタ |     |     |  |

## 8.6 レジスタ・マップ

**Table 7. レジスタ・アドレス**

| B23 | B22 | B21 | B20 | B19 | B18 | B17 | B16 | 備考             |

|-----|-----|-----|-----|-----|-----|-----|-----|----------------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | DEVICE_CONFIG  |

| 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0   | STATUS/trigger |

| 0   | 0   | 0   | 0   | 0   | 0   | 1   | 1   | BRDCAST        |

| 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0   | DACA_DATA      |

| 0   | 0   | 0   | 0   | 1   | 0   | 0   | 1   | DACB_DATA      |

| 0   | 0   | 0   | 0   | 1   | 0   | 1   | 0   | DACC_DATA      |

| 0   | 0   | 0   | 0   | 1   | 0   | 1   | 1   | DACD_DATA      |

| 0   | 0   | 0   | 0   | 1   | 1   | 0   | 0   | DACE_DATA      |

| 0   | 0   | 0   | 0   | 1   | 1   | 0   | 1   | DACF_DATA      |

| 0   | 0   | 0   | 0   | 1   | 1   | 1   | 0   | DACG_DATA      |

| 0   | 0   | 0   | 0   | 1   | 1   | 1   | 1   | DACH_DATA      |

**Table 8. レジスタ・マップ**

| コマンド・ビット       | データ・ビット   |                                                 |     |    |                 |      |      |        |      |      |      |      |      |  |  |

|----------------|-----------|-------------------------------------------------|-----|----|-----------------|------|------|--------|------|------|------|------|------|--|--|

|                | MSDB      |                                                 |     |    | LSDB            |      |      |        |      |      |      |      |      |  |  |

| B19 - B16      | B15 - B12 | B11                                             | B10 | B9 | B8              | B7   | B6   | B5     | B4   | B3   | B2   | B1   | B0   |  |  |

| DEVICE_CONFIG  | x         | 0                                               | 0   | 0  | PD<br>N-<br>All | PDNH | PDNG | PDNF   | PDNE | PDND | PDNC | PDNB | PDNA |  |  |

| STATUS/trigger | x         | DEVICE_ID                                       |     |    |                 | x    | x    | SW_RST |      |      |      |      |      |  |  |

| BRDCAST        | x         | BRDCAST_DATA[9:0] / BRDCAST_DATA[7:0] – MSB 左揃え |     |    |                 |      |      |        |      | x    | x    |      |      |  |  |

| DACA_DATA      | x         | DACA_DATA[9:0] / DACA_DATA[7:0] – MSB 左揃え       |     |    |                 |      |      |        |      | x    | x    |      |      |  |  |

| DACB_DATA      | x         | DACP_DATA[9:0] / DACB_DATA[7:0] – MSB 左揃え       |     |    |                 |      |      |        |      | x    | x    |      |      |  |  |

| DACC_DATA      | x         | DACC_DATA[9:0] / DACC_DATA[7:0] – MSB 左揃え       |     |    |                 |      |      |        |      | x    | x    |      |      |  |  |

| DACD_DATA      | x         | DACD_DATA[9:0] / DACD_DATA[7:0] – MSB 左揃え       |     |    |                 |      |      |        |      | x    | x    |      |      |  |  |

| DACE_DATA      | x         | DACE_DATA[9:0] / DACE_DATA[7:0] – MSB 左揃え       |     |    |                 |      |      |        |      | x    | x    |      |      |  |  |

| DACF_DATA      | x         | DACF_DATA[9:0] / DACF_DATA[7:0] – MSB 左揃え       |     |    |                 |      |      |        |      | x    | x    |      |      |  |  |

| DACG_DATA      | x         | DACG_DATA[9:0] / DACG_DATA[7:0] – MSB 左揃え       |     |    |                 |      |      |        |      | x    | x    |      |      |  |  |

| DACH_DATA      | x         | DACH_DATA[9:0] / DACH_DATA[7:0] – MSB 左揃え       |     |    |                 |      |      |        |      | x    | x    |      |      |  |  |

**表 9. DACx3608 レジスタ名**

| オフセット | 略称            | レジスタ名      | セクション                                           |

|-------|---------------|------------|-------------------------------------------------|

| 01h   | DEVICE_CONFIG | デバイス構成レジスタ | DEVICE_CONFIG レジスタ (オフセット = 01h) [リセット = 00FFh] |

**表 9. DACx3608 レジスタ名 (continued)**

| オフセット     | 略称             | レジスタ名             | セクション                                                                               |

|-----------|----------------|-------------------|-------------------------------------------------------------------------------------|

| 02h       | STATUS/TRIGGER | 状態およびトリガ・レジスタ     | STATUS/TRIGGER レジスタ (オフセット = 02h) [リセット = 0300h (DAC53608)、リセット = 0500h (DAC43608)] |

| 03h       | BRDCAST        | ブロードキャスト・データ・レジスタ | BRDCAST レジスタ (オフセット = 03h) [リセット = 0000h]                                           |

| 08h - 0Fh | DACn_DATA      | DACn データ・レジスタ     | DACn_DATA レジスタ (オフセット = 08h ~ 0Fh) [リセット = 0000h]                                   |

#### 8.6.1 DEVICE\_CONFIG レジスタ (オフセット = 01h) [リセット = 00FFh]

**図 60. DEVICE\_CONFIG レジスタ**

| 15             | 14 | 13 | 12 | 11 | 10      | 9    | 8    | 7                 | 6    | 5    | 4    | 3    | 2    | 1 | 0 |

|----------------|----|----|----|----|---------|------|------|-------------------|------|------|------|------|------|---|---|

| Don't Care     |    | 0  | 0  | 0  | PDN-AII | PDNH | PDNG | PDNF              | PDNE | PDND | PDNC | PDNB | PDNA |   |   |

| $\overline{W}$ |    |    |    |    |         |      |      | R/ $\overline{W}$ |      |      |      |      |      |   |   |

**表 10. DEVICE\_CONFIG レジスタ・フィールドの説明**

| ビット   | フィールド      | 種類                | リセット | 説明                                                                                                                                                                         |

|-------|------------|-------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-12 | Don't Care | $\overline{W}$    | 0h   | Don't Care                                                                                                                                                                 |

| 11-9  | 予約         | $\overline{W}$    | 00   | 予約                                                                                                                                                                         |

| 8     | PDN-AII    | R/ $\overline{W}$ | 0    | グローバル・パワーダウン・ビット、「1」に設定すると、全チャネルおよび全バイアス・ブロックがパワーダウンします。                                                                                                                   |

| 7-0   | PDNn       | R/ $\overline{W}$ | FFh  | このビットを「1」に設定すると(デフォルト)、DACn がパワーダウン・モードになります(出力バッファが $A_{GND}$ に対して 10K にパワーダウン)。全出力チャネルのバッファ・アンプが 10K モードにパワーダウンした状態で起動し、これらのレジスタに 0 を書き込んでパワーアップ・コマンドが発行されるまでその状態を維持します。 |

#### 8.6.2 STATUS/TRIGGER レジスタ (オフセット = 02h) [リセット = 0300h (DAC53608)、リセット = 0500h (DAC43608)]

**図 61. STATUS/TRIGGER レジスタ**

| 15             | 14 | 13        | 12 | 11 | 10 | 9 | 8 | 7          | 6          | 5 | 4 | 3      | 2 | 1 | 0 |

|----------------|----|-----------|----|----|----|---|---|------------|------------|---|---|--------|---|---|---|

| Don't Care     |    | DEVICE_ID |    |    |    |   |   | Don't Care | Don't Care |   |   | SW_RST |   |   |   |

| $\overline{W}$ |    |           |    |    |    |   |   | R          |            |   |   |        |   |   |   |

**表 11. STATUS/TRIGGER レジスタ・フィールドの説明**

| ビット   | フィールド      | 種類             | リセット                                               | 説明                                               |

|-------|------------|----------------|----------------------------------------------------|--------------------------------------------------|

| 15-12 | Don't Care | $\overline{W}$ | 0h                                                 | Don't Care                                       |

| 11-6  | DEVICE_ID  | R              | DAC536<br>08:<br>001100<br>DAC436<br>08:<br>010100 | デバイス識別番号<br>DAC53608: 001100<br>DAC43608: 010100 |

| 5-4   | Don't Care | $\overline{W}$ | 0h                                                 | Don't Care                                       |

| 3-0   | SW_RST     | $\overline{W}$ | 0h                                                 | このレジスタを 1010 に設定すると、デバイスがデフォルト値にリセットされます。        |

### 8.6.3 BRDCAST レジスタ (オフセット = 03h) [リセット = 0000h]

図 62. BRDCAST レジスタ

| 15         | 14                                              | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4          | 3          | 2 | 1 | 0 |

|------------|-------------------------------------------------|----|----|----|----|---|---|---|---|---|------------|------------|---|---|---|

| Don't Care | BRDCAST_DATA[9:0] / BRDCAST_DATA[7:0] – MSB 左揃え |    |    |    |    |   |   |   |   |   | Don't Care | Don't Care |   |   |   |

| W          | W                                               |    |    |    |    |   |   |   |   |   | W          | W          |   |   |   |

表 12. BRDCAST レジスタ・ フィールドの説明

| ビット   | フィールド                                 | 種類 | リセット | 説明                                                                                                                                                                                                          |

|-------|---------------------------------------|----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-12 | Don't Care                            | W  | 0h   | Don't Care                                                                                                                                                                                                  |

| 11-2  | BRDCAST_DATA[9:0] / BRDCAST_DATA[7:0] | W  | 000h | BRDCAST レジスタに書き込むことにより、DAC チャネルがそのアクティブなレジスタ・データを BRDCAST_DATA のものに更新するように強制します。<br>データはストレート・バイナリ形式で MSB 揃えとし、次の形式に従います。<br>DAC53608: { DATA[9:0] }<br>DAC43608: { DATA[7:0], x, x }<br>x – Don't Care ビット |

| 1-0   | Don't Care                            | W  | 00   | Don't Care                                                                                                                                                                                                  |

### 8.6.4 DACn\_DATA レジスタ (オフセット = 08h ~ 0Fh) [リセット = 0000h]

図 63. DACn\_DATA レジスタ

| 15         | 14                                              | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4          | 3          | 2 | 1 | 0 |

|------------|-------------------------------------------------|----|----|----|----|---|---|---|---|---|------------|------------|---|---|---|

| Don't Care | BRDCAST_DATA[9:0] / BRDCAST_DATA[7:0] – MSB 左揃え |    |    |    |    |   |   |   |   |   | Don't Care | Don't Care |   |   |   |

| W          | W                                               |    |    |    |    |   |   |   |   |   | W          | W          |   |   |   |

表 13. DACn\_DATA レジスタ・ フィールドの説明

| ビット   | フィールド                           | 種類 | リセット | 説明                                                                                                                                                                                                        |

|-------|---------------------------------|----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-12 | Don't Care                      | W  | 0h   | Don't Care                                                                                                                                                                                                |

| 11-2  | DACn_DATA[9:0] / DACn_DATA[7:0] | W  | 000h | DACn_DATA レジスタに書き込むことにより、各 DAC チャネルがそのアクティブなレジスタ・データを DACn_DATA に更新するように強制します。<br>データはストレート・バイナリ形式で MSB 揃えとし、次の形式に従います。<br>DAC53608: { DATA[9:0] }<br>DAC43608: { DATA[7:0], x, x }<br>x – Don't Care ビット |

| 1-0   | Don't Care                      | W  | 00   | Don't Care                                                                                                                                                                                                |

## 9 アプリケーションと実装

### 注

以降のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 9.1 アプリケーション情報

DACx3608 は、小型の 3X3 パッケージで供給される、8 チャネル、低消費電力のバッファ付き出力 DAC です。マルチチャネル、低消費電力、小型のパッケージを特長とするこの DAC は、幅広い最終機器のさまざまな用途に適しています。最も一般的な用途は、多機能プリンタの LED バイアス、プログラマブル・コンパレータによる電源管理、高精度回路のオフセットおよびゲイン調整、電源マージニングなどです。

### 9.2 代表的なアプリケーション

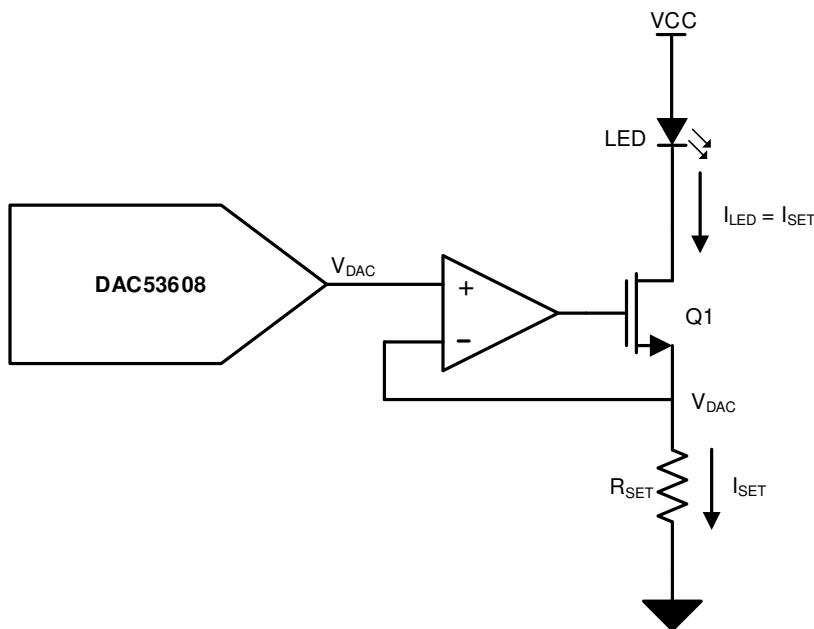

#### 9.2.1 プログラマブル LED バイアス

多機能プリンタ、プロジェクタ、EPOS などの最終機器は、LED による安定した光度を必要とします。図 64 に DACx3608 を使用した LED バイアスの概略回路図を示します。

図 64. LED のバイアス印加

##### 9.2.1.1 設計要件

- 一端が電源に接続された LED を流れるプログラム可能な定電流

- DAC の出力範囲: 0~5V

- LED の電流範囲: 0~20mA

## 代表的なアプリケーション (continued)

### 9.2.1.2 詳細な設計手順

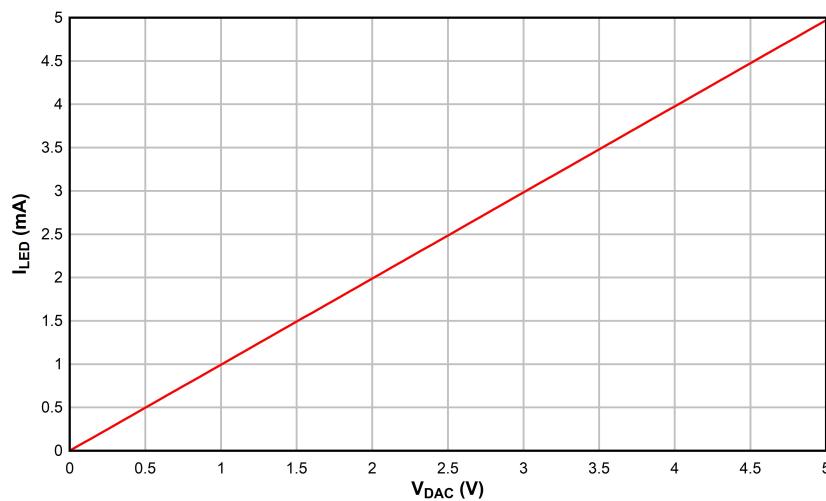

ユニティ・ゲイン・バッファを使用した MOSFET のソース電流の設定に DAC を使います (図 64 参照)。LED は、電源と MOSFET のドレインの間に接続します。この構成により、LED に流れる電流量を DAC で制御または設定できます。DAC に接続したバッファが、帰還ループ内で MOSFET のゲート・ソース電圧を制御することで、電圧降下とそれに付随する MOSFET の温度、電流、経年変化によるドリフトを補償できます。DAC で設定する LED 電流は式 2 により計算できます。DAC の出力範囲の 0~5V から 0~20mA を生成するには、250Ω の  $R_{SET}$  が必要です。

$$I_{SET} = \frac{V_{DAC}}{R_{SET}} \quad (2)$$

LED バイアス用の疑似コードは以下のとおりです。

```

//SYNTAX: WRITE <REGISTER NAME(Hex Code)>, <DATA>

//Power-up the device and channels

WRITE DEVICE_CONFIG(0x01), 0x0000

//Program mid code (or the desired voltage) on all channels

WRITE DACA_DATA(0x08), 0x07FC //10-bit MSB aligned

WRITE DACB_DATA(0x09), 0x07FC //10-bit MSB aligned

WRITE DACC_DATA(0x0A), 0x07FC //10-bit MSB aligned

WRITE DACD_DATA(0x0B), 0x07FC //10-bit MSB aligned

WRITE DACE_DATA(0x0C), 0x07FC //10-bit MSB aligned

WRITE DACF_DATA(0x0D), 0x07FC //10-bit MSB aligned

WRITE DAGC_DATA(0x0E), 0x07FC //10-bit MSB aligned

WRITE DACH_DATA(0x0F), 0x07FC //10-bit MSB aligned

```

### 9.2.1.3 アプリケーション曲線

図 65. LED バイアス回路の DC 伝達特性

## 代表的なアプリケーション (continued)

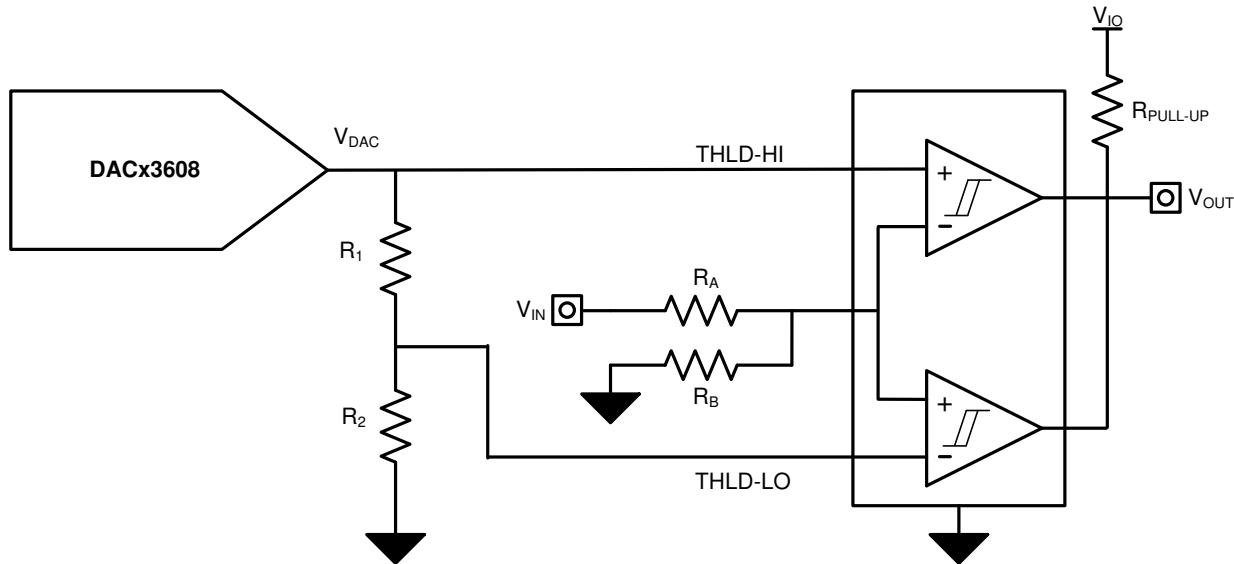

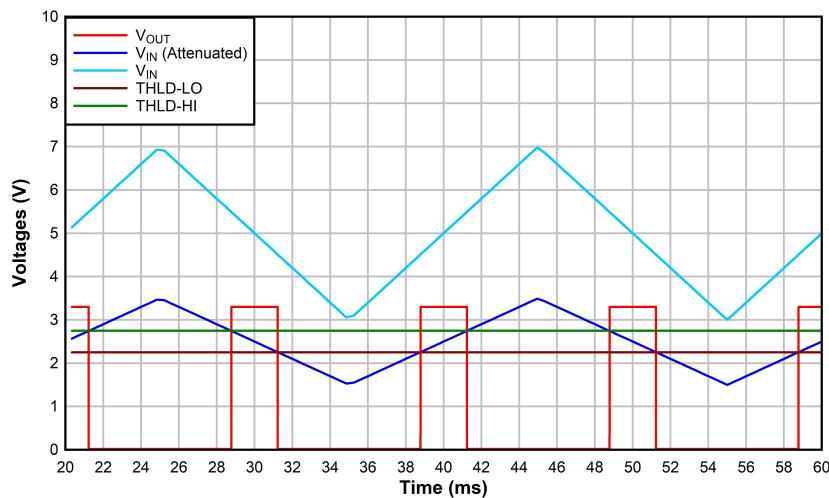

### 9.2.2 プログラマブル・ウィンドウ・コンパレータ

ネットワーク・サーバーや光モジュールといった集中電源を使用する最終機器は、部品を保護するために電力バスを監視する必要があります。この監視または管理を、ウインドウ・コンパレータを使用して実現します。ウインドウ・コンパレータは、上限 / 下限スレッショルド超過の信号入力を監視します。スレッショルド超過が発生すると、トリガ信号が生成されます。モジュールで利用可能なすべての電源を管理するには、マルチチャネル監視が必要です。**DACx3608** を使うと、使いやすく占有面積の小さい方法でこの要件を満たすことができます。

図 66. プログラマブル・ウィンドウ・コンパレータ

### 9.2.2.1 設計要件

- 監視対象電圧:5V

- High スレッショルド:5V + 10%

- Low スレッショルド:5V - 10%

- トリガ出力:3.3V オープン・ドレイン・シングル出力

### 9.2.2.2 詳細な設計手順

図 66 に、1 つの DAC チャネルを使用して High スレッショルドと Low スレッショルドの両方を比較する例を示します。図のように、DAC チャネルごとにデュアル・コンパレータを使用します。抵抗  $R_A$  と  $R_B$  からなる分圧器を使用して、信号レベルが DAC の範囲内に収まるようにします。また、抵抗  $R_1$  と  $R_2$  のペアを High スレッショルドの係数として使い、Low スレッショルドを設定します。この構成により、1 つの DAC チャネルを使用して High スレッショルド・レベルと Low スレッショルド・レベルの両方を監視できます。次の利点を得るために、コンパレータはオープン・ドレインとする必要があります。

- 監視プロセッサに適したロジック出力レベルを生成する

- シングル・トリガを生成するために2つの出力を短絡できる

図 66 に示す回路では、信号入力が High および Low スレッショルド・レベルを超えない限り、回路の出力は HIGH のままでです。どちらかのスレッショルドにかかるった時点で、出力は LOW になります。式 3 により、DAC で設定した High スレッショルドから Low スレッショルド電圧を計算できます。

$$V_{THLD+LO} = V_{DAC} \times \left( \frac{R_2}{R_1 + R_2} \right) \quad (3)$$

## 代表的なアプリケーション (continued)

5V 電源が  $\pm 10\%$  以内であることを監視するために、公称値が DAC ミッドコードになるように設定することを推奨します。DACx3608 の出力範囲が 0~5V であるため、ミッドコード電圧出力は 2.5V とします。したがって、 $R_A$  と  $R_B$  は、比較対象電圧が 2.5V になるように選定できます。この例では、 $R_A$  と  $R_B$  は等しいため、どちらにも  $10\text{k}\Omega$  の抵抗を使用できます。DACx3608 の 1 つのチャネルを  $V_{THLD-HI}$  にプログラムする必要があります。例えば  $2.5\text{V} + 5\% = 2.625\text{V}$ 。これは 10 ビットの DAC コードである  $(2^{10}/5\text{V}) \times 2.625\text{V} = 537.6$  (0x21 Ah) に相当します。2.625V から  $V_{THLD-LO}$  (例:  $2.5\text{V} - 5\% = 2.405\text{V}$ ) を生成するため、式 3 を用いて、 $R_1$  と  $R_2$  の値はそれぞれ  $7.5\text{k}\Omega$ 、 $82\text{k}\Omega$  と計算できます。プログラマブル・ウィンドウ・コンパレータ用の疑似コードと目的の DAC 値を以下に示します。

```

//SYNTAX: WRITE <REGISTER NAME(Hex Code)>, <DATA>

//Power-up the device and channels

WRITE DEVICE_CONFIG(0x01), 0x0000

//Program 2.625V on channel A

WRITE DACA_DATA(0x08), 0x0868 //10-bit MSB aligned

```

### 9.2.2.3 アプリケーション曲線

図 67. プログラマブル・コンパレータの出力波形

## 10 電源に関する推奨事項

DACx3608 ファミリは電源シーケンスを必要としません。単一電源、 $V_{DD}$  が必要です。 $V_{DD}$  ピンには、 $0.1\mu\text{F}$  のデカップリング・コンデンサを推奨します。

## 11 レイアウト

### 11.1 レイアウトの注意点

DACx3608 のピン配置では、レイアウトを最適化できるようにアナログ・ピン、デジタル・ピン、電源ピンを離しています。信号品質を確保するため、デジタル・トレースとアナログ・トレースを離し、デカップリング・コンデンサをデバイス・ピンの近くに配置することを推奨します。

### 11.2 レイアウト例

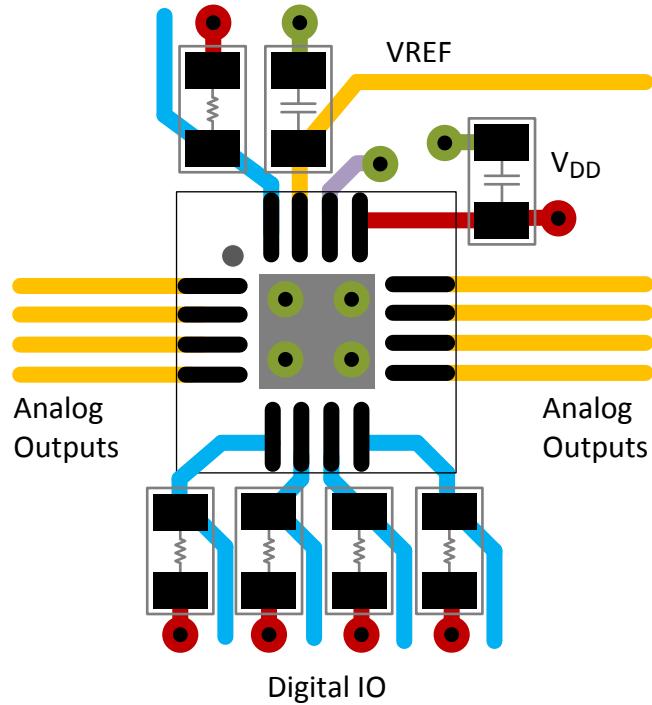

図 68 に、デカップリング・コンデンサとプルアップ抵抗を含むレイアウト図の一例を示します。

図 68. レイアウト例

## 12 デバイスおよびドキュメントのサポート

### 12.1 ドキュメントのサポート

#### 12.1.1 関連資料

関連資料については、以下を参照してください。『*DAC53608EVM ユーザー・ガイド』(SLAU790)*

#### 12.2 関連リンク

次の表に、クイック・アクセス・リンクを示します。カテゴリには、技術資料、サポートおよびコミュニティ・リソース、ツールとソフトウェア、およびサンプル注文またはご購入へのクイック・アクセスが含まれます。

**表 14. 関連リンク**

| 製品       | プロダクト・フォルダ              | ご注文はこちら                 | 技術資料                    | ツールとソフトウェア              | サポートとコミュニティ             |

|----------|-------------------------|-------------------------|-------------------------|-------------------------|-------------------------|

| DAC53608 | <a href="#">ここをクリック</a> |

| DAC43608 | <a href="#">ここをクリック</a> |

#### 12.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、ti.comのデバイス製品フォルダを開いてください。右上の隅にある「通知を受け取る」をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取れます。変更の詳細については、修正されたドキュメントに含まれている改訂履歴をご覧ください。

#### 12.4 コミュニティ・リソース

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's [Terms of Use](#).

**TI E2E™オンライン・コミュニティ** *TIのE2E ( Engineer-to-Engineer )* コミュニティ。エンジニア間の共同作業を促進するために開設されたものです。e2e.ti.comでは、他のエンジニアに質問し、知識を共有し、アイディアを検討して、問題解決に役立することができます。

**設計サポート** *TIの設計サポート* 役に立つE2Eフォーラムや、設計サポート・ツールをすばやく見つけることができます。技術サポート用の連絡先情報も参照できます。

#### 12.5 商標

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 12.6 静電気放電に関する注意事項

すべての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

#### 12.7 Glossary

**SLYZ022 — TI Glossary.**

This glossary lists and explains terms, acronyms, and definitions.

## 13 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、そのデバイスについて利用可能な最新のデータです。このデータは予告なく変更されることがあります。ドキュメントが改訂される場合もあります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| DAC43608RTER          | Active        | Production           | WQFN (RTE)   16 | 3000   LARGE T&R      | Yes         | FULL NIPDAU                          | Level-1-260C-UNLIM                | -40 to 125   | D43608              |

| DAC43608RTER.A        | Active        | Production           | WQFN (RTE)   16 | 3000   LARGE T&R      | Yes         | FULL NIPDAU                          | Level-1-260C-UNLIM                | -40 to 125   | D43608              |

| DAC43608RTERG4        | Active        | Production           | WQFN (RTE)   16 | 3000   LARGE T&R      | Yes         | FULL NIPDAU                          | Level-1-260C-UNLIM                | -40 to 125   | D43608              |

| DAC43608RTERG4.A      | Active        | Production           | WQFN (RTE)   16 | 3000   LARGE T&R      | Yes         | FULL NIPDAU                          | Level-1-260C-UNLIM                | -40 to 125   | D43608              |

| DAC43608RTET          | Active        | Production           | WQFN (RTE)   16 | 250   SMALL T&R       | Yes         | FULL NIPDAU                          | Level-1-260C-UNLIM                | -40 to 125   | D43608              |

| DAC43608RTET.A        | Active        | Production           | WQFN (RTE)   16 | 250   SMALL T&R       | Yes         | FULL NIPDAU                          | Level-1-260C-UNLIM                | -40 to 125   | D43608              |

| DAC53608RTER          | Active        | Production           | WQFN (RTE)   16 | 3000   LARGE T&R      | Yes         | FULL NIPDAU                          | Level-1-260C-UNLIM                | -40 to 125   | D53608              |

| DAC53608RTER.A        | Active        | Production           | WQFN (RTE)   16 | 3000   LARGE T&R      | Yes         | FULL NIPDAU                          | Level-1-260C-UNLIM                | -40 to 125   | D53608              |

| DAC53608RTET          | Active        | Production           | WQFN (RTE)   16 | 250   SMALL T&R       | Yes         | FULL NIPDAU                          | Level-1-260C-UNLIM                | -40 to 125   | D53608              |

| DAC53608RTET.A        | Active        | Production           | WQFN (RTE)   16 | 250   SMALL T&R       | Yes         | FULL NIPDAU                          | Level-1-260C-UNLIM                | -40 to 125   | D53608              |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "-" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative

and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

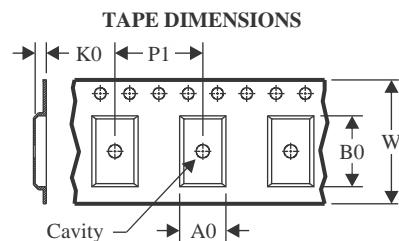

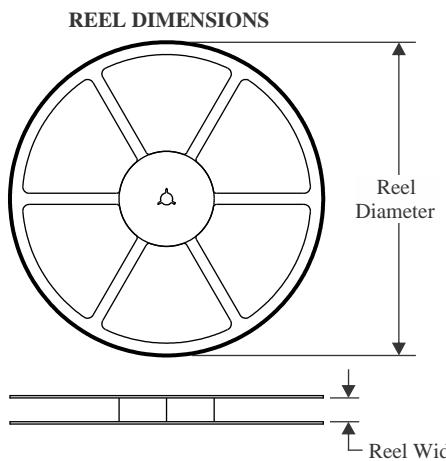

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

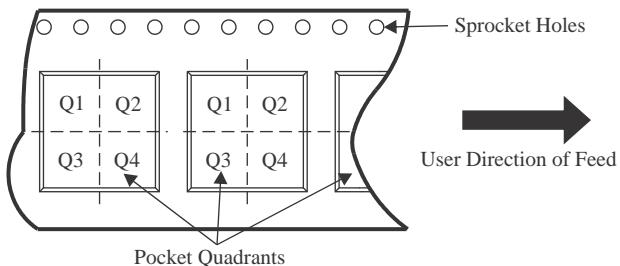

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| DAC43608RTER   | WQFN         | RTE             | 16   | 3000 | 330.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| DAC43608RTERG4 | WQFN         | RTE             | 16   | 3000 | 330.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| DAC43608RTET   | WQFN         | RTE             | 16   | 250  | 180.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| DAC53608RTER   | WQFN         | RTE             | 16   | 3000 | 330.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

| DAC53608RTET   | WQFN         | RTE             | 16   | 250  | 180.0              | 12.4               | 3.3     | 3.3     | 1.1     | 8.0     | 12.0   | Q2            |

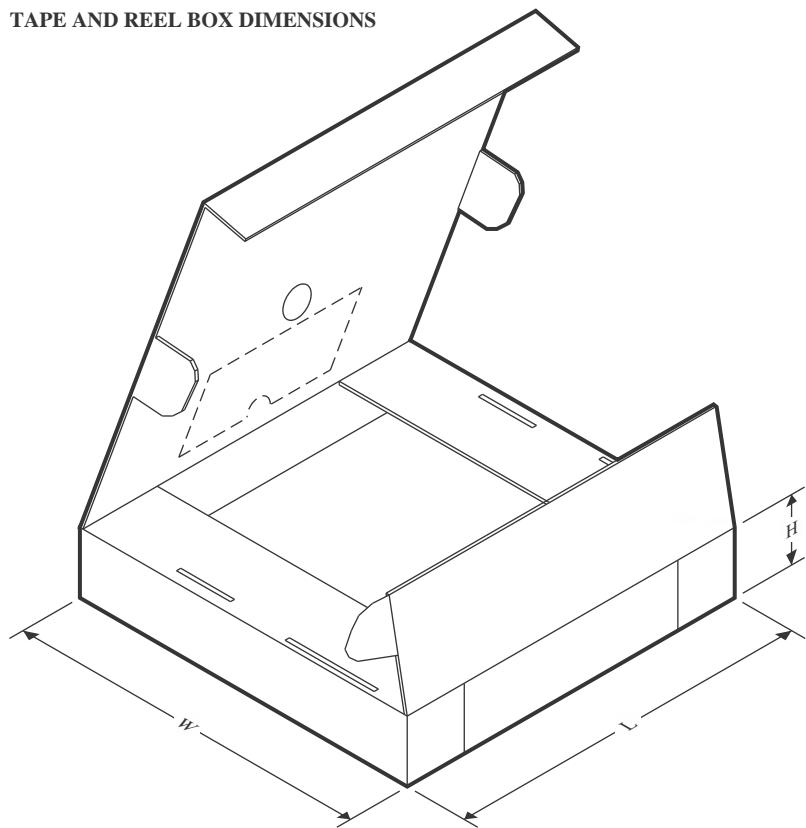

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device          | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DAC43608RTER    | WQFN         | RTE             | 16   | 3000 | 367.0       | 367.0      | 35.0        |

| DAC43608RTTERG4 | WQFN         | RTE             | 16   | 3000 | 367.0       | 367.0      | 35.0        |

| DAC43608RTET    | WQFN         | RTE             | 16   | 250  | 210.0       | 185.0      | 35.0        |

| DAC53608RTER    | WQFN         | RTE             | 16   | 3000 | 367.0       | 367.0      | 35.0        |

| DAC53608RTET    | WQFN         | RTE             | 16   | 250  | 210.0       | 185.0      | 35.0        |

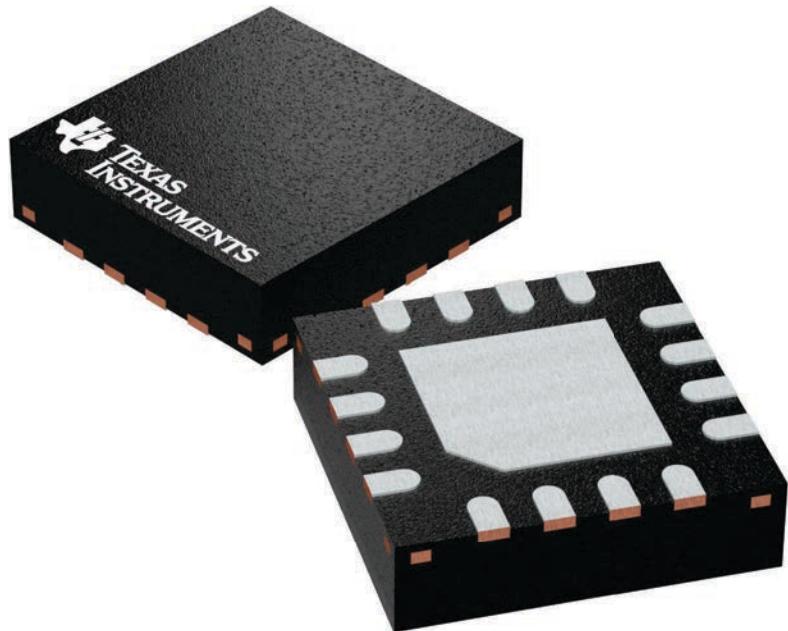

## GENERIC PACKAGE VIEW

### RTE 16

### WQFN - 0.8 mm max height

3 x 3, 0.5 mm pitch

PLASTIC QUAD FLATPACK - NO LEAD

This image is a representation of the package family, actual package may vary.

Refer to the product data sheet for package details.

4225944/A

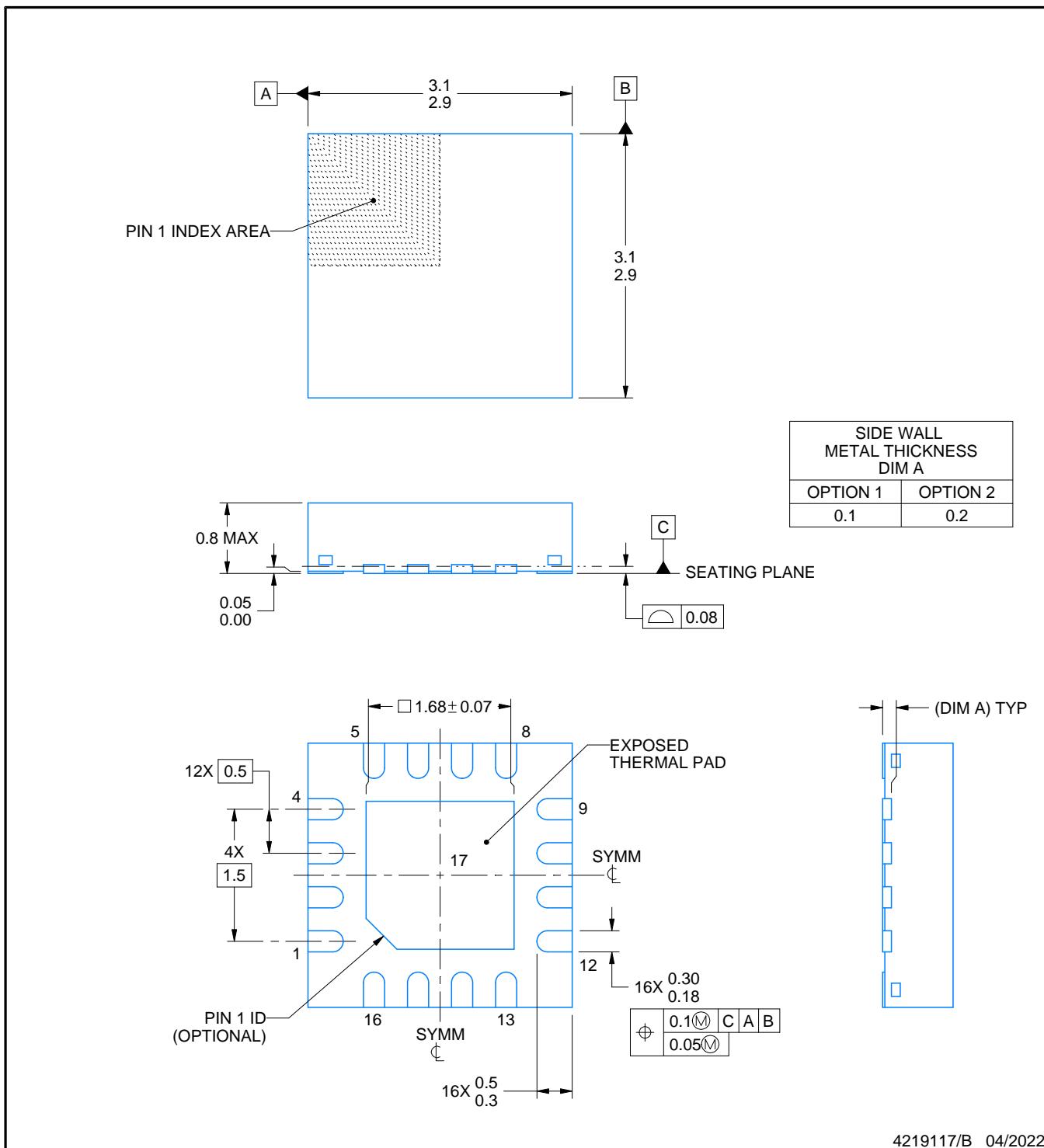

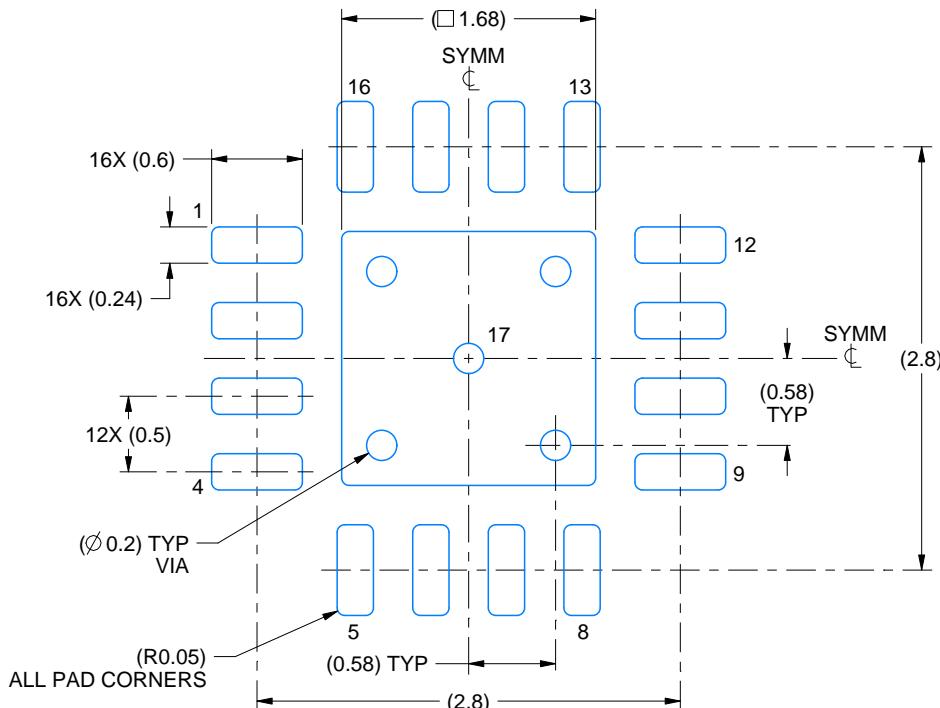

# PACKAGE OUTLINE

RTE0016C

WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

4219117/B 04/2022

## NOTES:

- All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- This drawing is subject to change without notice.

- The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

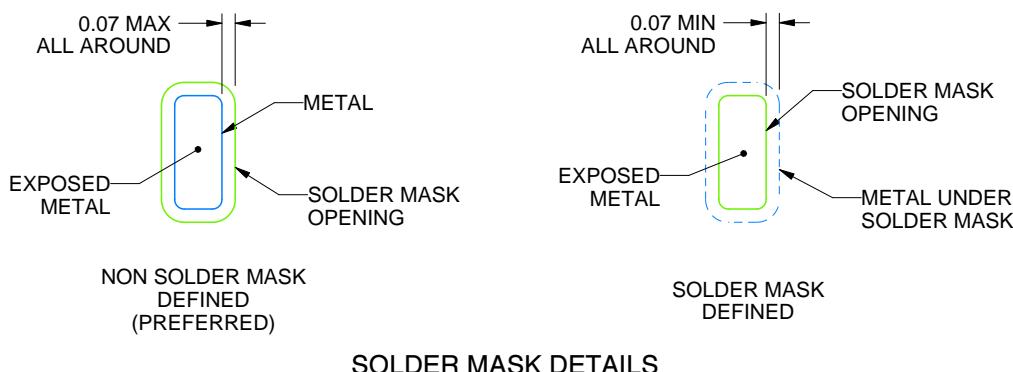

# EXAMPLE BOARD LAYOUT

RTE0016C

WQFN - 0.8 mm max height

PLASTIC QUAD FLATPACK - NO LEAD

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:20X

SOLDER MASK DETAILS

4219117/B 04/2022

NOTES: (continued)

4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 ([www.ti.com/lit/slua271](http://www.ti.com/lit/slua271)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

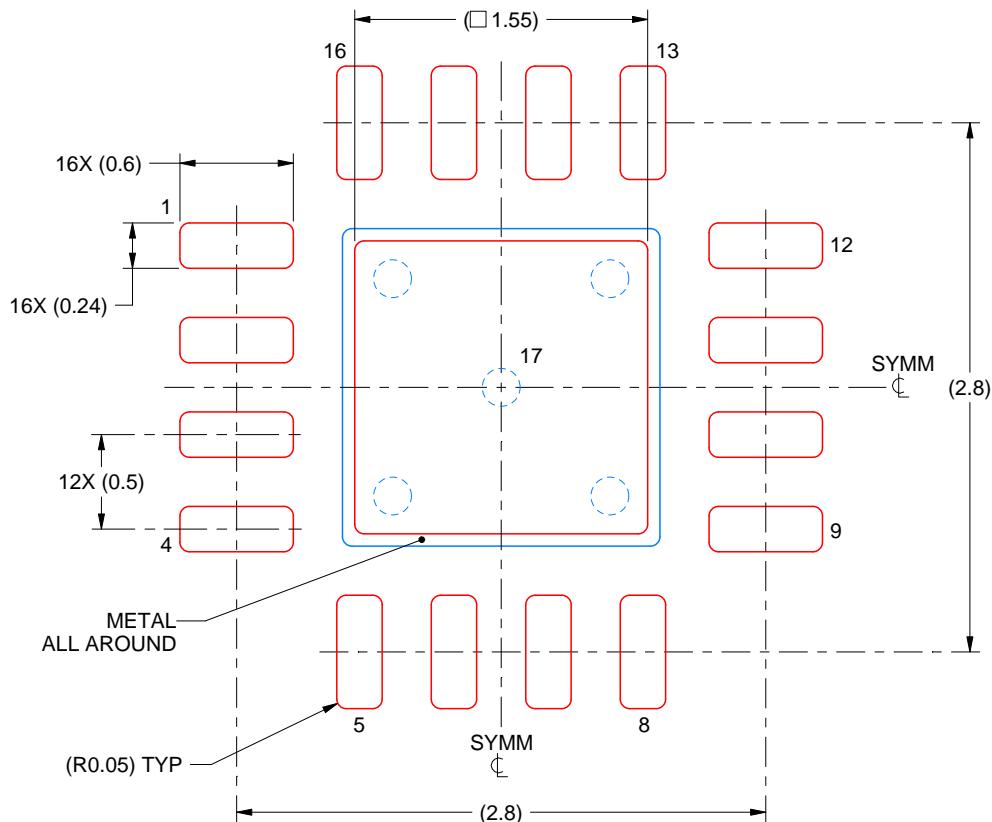

## EXAMPLE STENCIL DESIGN

RTE0016C

## **WQFN - 0.8 mm max height**

PLASTIC QUAD FLATPACK - NO LEAD

## SOLDER PASTE EXAMPLE BASED ON 0.125 mm THICK STENCIL

EXPOSED PAD 17:

85% PRINTED SOLDER COVERAGE BY AREA UNDER PACKAGE

SCALE:25X

4219117/B 04/2022

#### NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TIは、技術データと信頼性データ(データシートを含みます)、設計リソース(リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Webツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、TI製品を使用する設計の経験を積んだ開発者への提供を意図したもので、(1)お客様のアプリケーションに適したTI製品の選定、(2)お客様のアプリケーションの設計、検証、試験、(3)お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。