DAC121C081, DAC121C085

JAJSAQ5F - DECEMBER 2007 - REVISED OCTOBER 2016

# DAC121C081およびDAC121C085 12ビットMicro Power D/Aコンバータ、I<sup>2</sup>C互換インターフェイス搭載

#### 1 特長

- 12ビットの単調性を保証

- 低消費電力の動作: 3.3Vで最大値156µA

- 拡張電源電圧範囲: 2.7V~5.5V

- I<sup>2</sup>C互換の2線式インターフェイス、Standard (100kHz)、Fast (400kHz)、High-Speed (3.4MHz) モードをサポート

- レール・ツー・レール電圧出力

- 非常に小型のパッケージ

- 分解能: 12ビット

- INL: ±8LSB (最大値)

- DNL: 0.6/-0.5LSB (最大値)

- セトリング時間: 8.5µs (最大値)

- ゼロコード誤差: 10mV (最大値)

- フルスケール誤差: -0.7%FS (最大値)

- 供給電力

- 通常: 380µW (3V) / 730µW (5V) (標準値)

- パワーダウン時: 0.5μW (3V) / 0.9μW (5V) (標準値)

# 2 アプリケーション

- 産業用プロセス制御

- 携帯測定機器

- デジタル・ゲインおよびオフセットの調整

- プログラム可能な電圧源および電流源

- 試験用機器

#### 3 概要

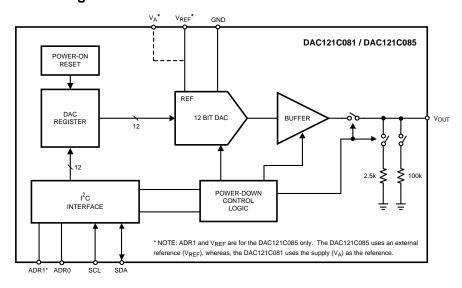

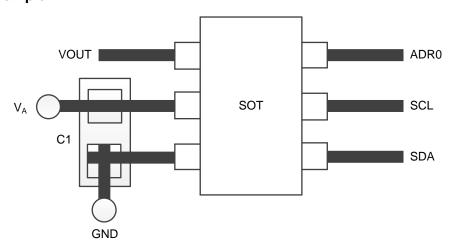

DAC121C081は12ビット、シングル・チャネル、電圧出力のD/Aコンバータ(DAC)で、2.7V~5.5Vの電源で動作します。出力アンプではレール・ツー・レールの出力が可能で、セトリング時間は8.5μsです。DAC121C081は電源電圧を基準として使い、最も広い動的出力範囲を提供します。5Vでの動作時、消費電流は通常値で132μAです。6ピンのSOTおよびWSONパッケージで供給され、3つのアドレス・オプションをピンにより選択できます。

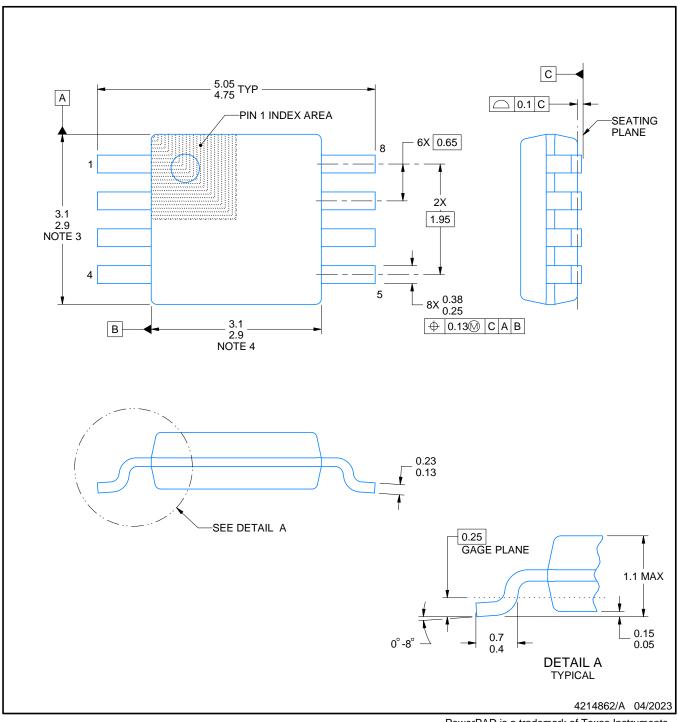

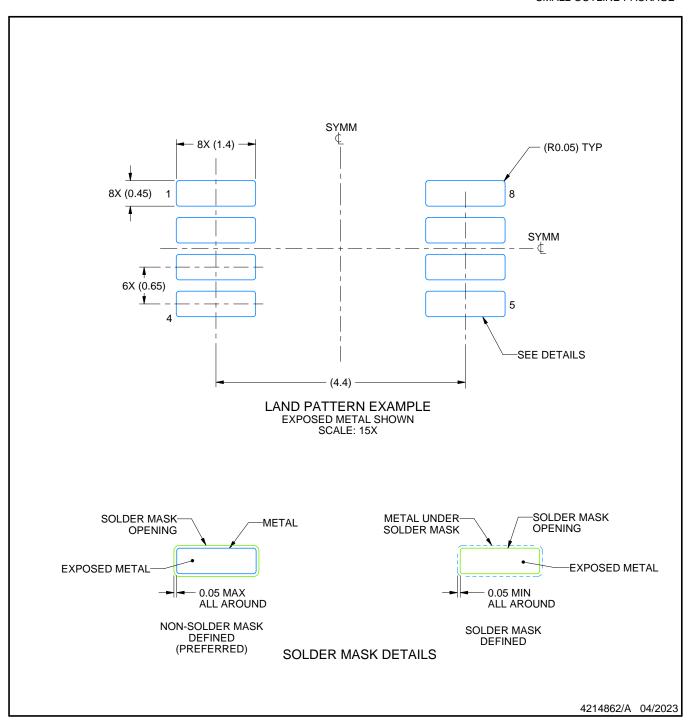

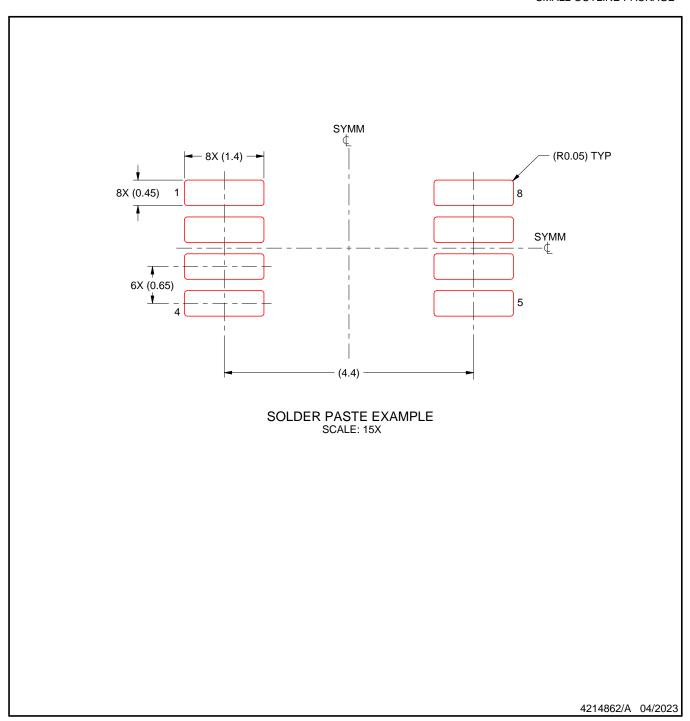

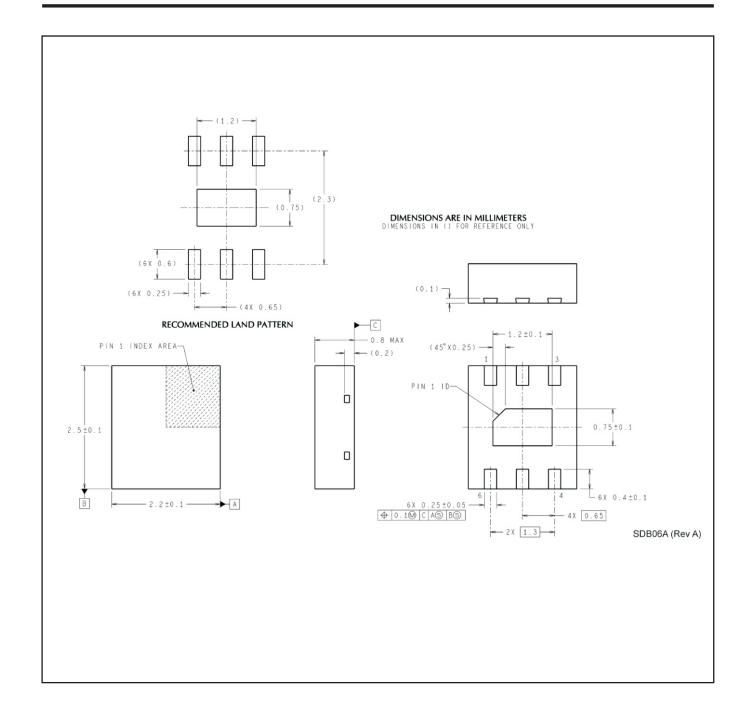

代替品として、DAC121C085は9つのI<sup>2</sup>Cアドレシング・オプションがあり、外部基準電圧を使用します。性能やセトリング時間はDAC121C081と同じで、8リードのVSSOPで供給されます。

#### 製品情報(1)

|            | - CHA 113 1184 |               |

|------------|----------------|---------------|

| 型番         | パッケージ          | 本体サイズ(公称)     |

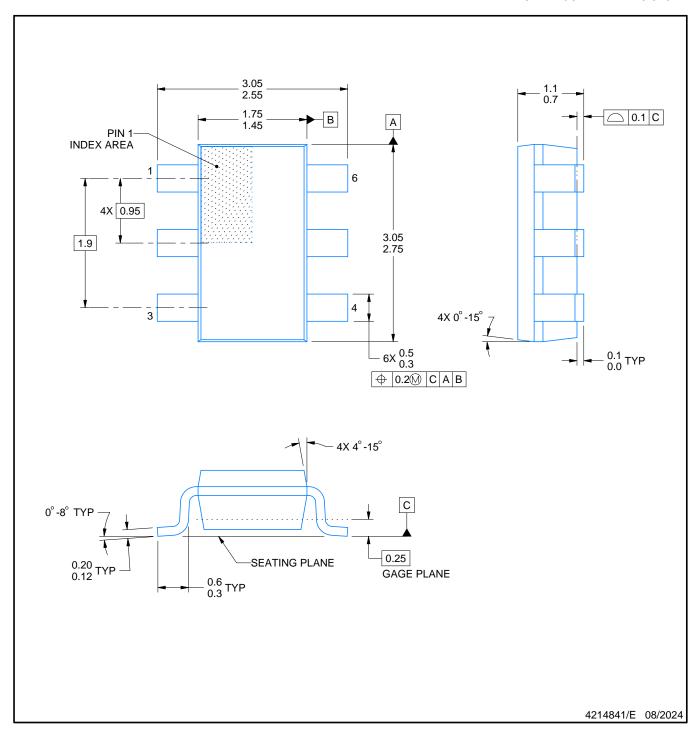

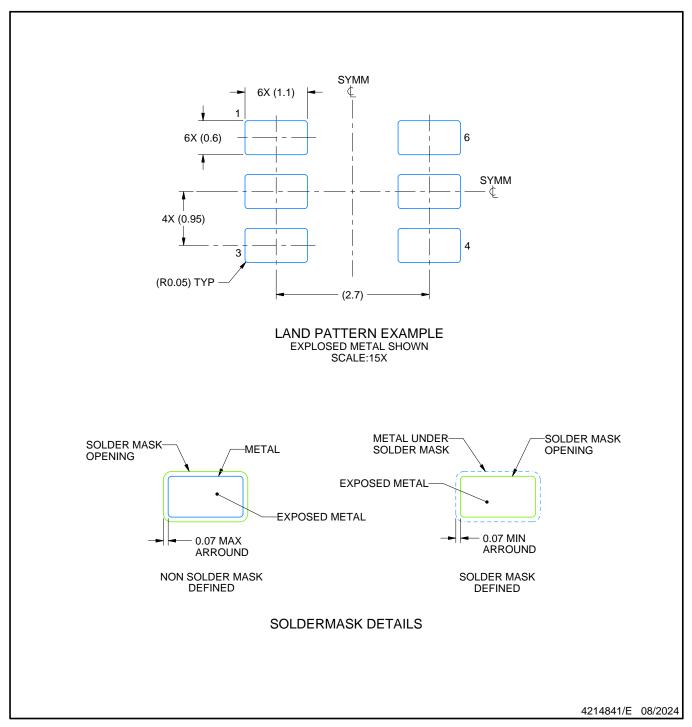

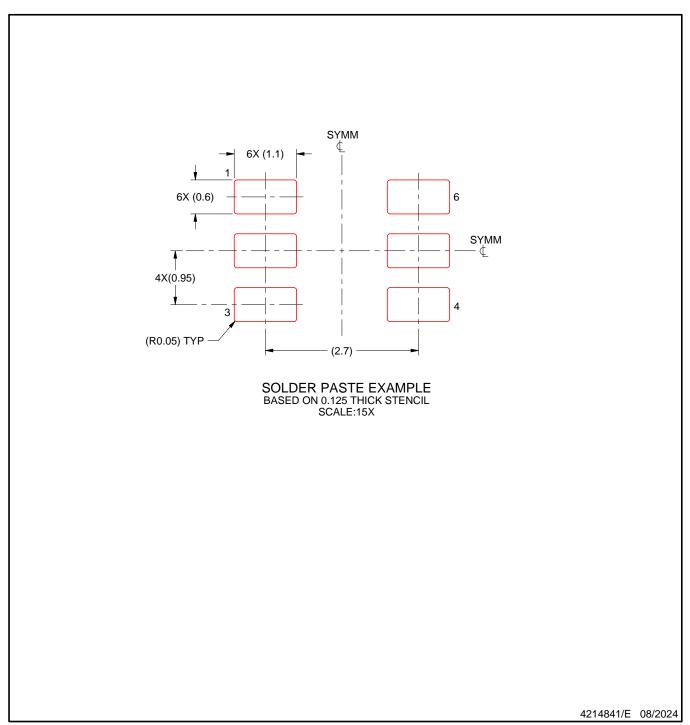

| DAC121C081 | WSON (6)       | 2.20mm×2.50mm |

|            | SOT (6)        | 1.60mm×2.90mm |

| DAC121C085 | VSSOP (8)      | 3.00mm×3.00mm |

(1) 提供されているすべてのパッケージについては、データシートの末 尾にある注文情報を参照してください。

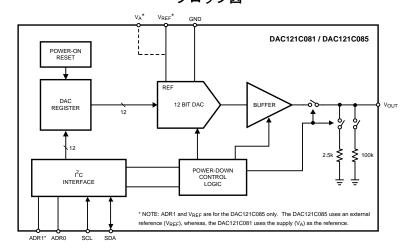

### ブロック図

| 目次 |

|----|

|----|

| 1 | 特長1                                  |    | 8.5 Programming                         | 20 |

|---|--------------------------------------|----|-----------------------------------------|----|

| 2 | アプリケーション1                            |    | 8.6 Registers                           |    |

| 3 | 概要1                                  | 9  | Application and Implementation          | 22 |

| 4 | 改訂履歴2                                |    | 9.1 Application Information             | 22 |

| 5 | 概要(続き)3                              |    | 9.2 Typical Application                 | 24 |

| 6 | Pin Configuration and Functions      | 10 | Power Supply Recommendations            | 26 |

| 7 | Specifications5                      |    | 10.1 Using References as Power Supplies | 26 |

| • | 7.1 Absolute Maximum Ratings 5       | 11 | Layout                                  | 29 |

|   | 7.2 ESD Ratings                      |    | 11.1 Layout Guidelines                  | 29 |

|   | 7.3 Recommended Operating Conditions |    | 11.2 Layout Example                     | 29 |

|   | 7.4 Thermal Information              | 12 | デバイスおよびドキュメントのサポート                      | 30 |

|   | 7.5 Electrical Characteristics       |    | 12.1 デバイス・サポート                          | 30 |

|   | 7.6 AC and Timing Characteristics9   |    | 12.2 ドキュメントのサポート                        | 30 |

|   | 7.7 Typical Characteristics          |    | 12.3 関連リンク                              | 30 |

| 8 | Detailed Description 15              |    | 12.4 商標                                 | 31 |

| • | 8.1 Overview                         |    | 12.5 静電気放電に関する注意事項                      | 31 |

|   | 8.2 Functional Block Diagram         |    | 12.6 Glossary                           | 31 |

|   | 8.3 Feature Description              | 13 | メカニカル、パッケージ、および注文情報                     | 31 |

|   | 8.4 Device Functional Modes          |    |                                         |    |

# 4 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| Revision E (January 2016) から Revision F に変更                                                                                                                          | Page |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Changed V <sub>OUT</sub> and V <sub>A</sub> descriptions.      Added column to Table 2.                                                                              |      |

| Revision D (March 2013) から Revision E に変更                                                                                                                            | Page |

| <ul> <li>「ESD定格」表、「機能説明」セクション、「デバイスの機能モード」セクション、「アプリケーションと実装」セクション、「電源に関する推奨事項」セクション、「レイアウト」セクション、「デバイスおよびドキュメントのサポート」セクション、「メカニカル、パッケージ、および注文情報」セクションを追加</li> </ul> |      |

| Added addresses that the DAC responds to on the I2C bus.                                                                                                             | 18   |

| Revision C (March 2013) から Revision D に変更                                                                                                                            | Page |

| Changed layout of National Semiconductor Data Sheet to TI format                                                                                                     | 29   |

#### 5 概要(続き)

DAC121C081およびDAC121C085で使用する2線式のI<sup>2</sup>C互換シリアル・インターフェイスは、High-Speedモード (3.4MHz)も含む3つの速度モードすべてで動作します。外部アドレス選択ピンにより、2線式バスごとに3つまでの DAC121C081、または9つまでのDAC121C085デバイスを使用できます。DAC121C081には、追加のアドレス・オプションを使用できるピン互換の代替品もあります。

DAC121C081およびDAC121C085には16ビットのレジスタが内蔵されており、動作モード、パワーダウン条件、出力電圧を制御できます。パワー・オン・リセット回路により、0VまでのDAC出力電力が保証されます。パワーダウン機能により、消費電力は1マイクロワット未満まで減少します。低消費電力と小型のパッケージから、これらのDACはバッテリ駆動の機器で使用するための非常に優れた選択肢です。各DACは、拡張産業用温度範囲の-40℃~+125℃で動作します。

DAC121C081およびDAC121C085は、どちらもピン互換なDACファミリの一部であり、このファミリには分解能が8および10ビットの製品も含まれています。8ビットDACについては、DAC081C081とDAC081C085を参照してください。10ビットDACについては、DAC101C081とDAC101C085を参照してください。

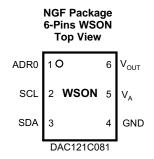

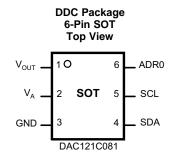

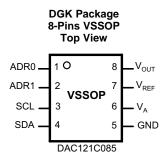

# 6 Pin Configuration and Functions

#### **Pin Functions**

|                  | PIN        |     | DESCRIPTION | FOLUNAL ENT OFFICIAL              |                                                                                                                                                                                                                                                  |                     |

|------------------|------------|-----|-------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| NAME             | WSON       | SOT | VSSOP       | TYPE                              | DESCRIPTION                                                                                                                                                                                                                                      | EQUIVALENT CIRCUIT  |

| ADR0             | 1          | 6   | 1           | Digital<br>Input,<br>three levels | Tri-state Address Selection Input. Sets the two<br>Least Significant Bits (A1 and A0) of the 7-bit<br>slave address. (see Table 1)                                                                                                               | PIN 21k \$41.5k     |

| ADR1             | _          | _   | 2           | Digital<br>Input,<br>three levels | Tri-state Address Selection Input. Sets Bits A6 and A3 of the 7-bit slave address. (see Table 1)                                                                                                                                                 | Snap<br>Back 41.5k  |

| GND              | 4          | 3   | 5           | Ground                            | Ground for all on-chip circuitry                                                                                                                                                                                                                 | _                   |

| SCL              | 2          | 5   | 3           | Digital Input                     | Serial Clock Input. SCL is used together with SDA to control the transfer of data in and out of the device.                                                                                                                                      | PIN                 |

| SDA              | 3          | 4   | 4           | Digital<br>Input/Outpu<br>t       | Serial Data bi-directional connection. Data is clocked into or out of the internal 16-bit register relative to the clock edges of SCL. This is an open-drain data line that must be pulled to the supply $(V_A)$ by an external pullup resistor. | Snap<br>Back<br>GND |

| V <sub>OUT</sub> | 6          | 1   | 8           | Analog<br>Output                  | Analog Output Voltage                                                                                                                                                                                                                            | _                   |

| V <sub>A</sub>   | 5          | 2   | 6           | Supply                            | Power supply input. For the SOT and WSON versions, this supply is used as the reference. Must be decoupled to GND.                                                                                                                               |                     |

| VREF             | _          | _   | 7           | Supply                            | Unbufferred reference voltage. For the VSSOP, this supply is used as the reference. V <sub>REF</sub> must be free of noise and decoupled to GND.                                                                                                 | _                   |

| PAD              | (LLP only) | _   | _           | Ground                            | Exposed die attach pad can be connected to ground or left floating. Soldering the pad to the PCB offers optimal thermal performance and enhances package self-alignment during reflow.                                                           | _                   |

#### 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1) (2) (3)

|                                            | MIN  | MAX                | UNIT |

|--------------------------------------------|------|--------------------|------|

| Supply voltage, V <sub>A</sub>             | -0.3 | 6.5                | V    |

| Voltage on any input pin                   | -0.3 | 6.5                | V    |

| Input current at any pin (4)               |      | ±10                | mA   |

| Package input current <sup>(4)</sup>       |      | ±20                | mA   |

| Power consumption at T <sub>A</sub> = 25°C |      | See <sup>(5)</sup> |      |

| Junction temperature, T <sub>J</sub>       |      | 150                | °C   |

| Storage temperature, T <sub>stg</sub>      | -65  | 150                | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- 2) All voltages are measured with respect to GND = 0 V, unless otherwise specified.

- (3) If Military/Aerospace specified devices are required, contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (4) When the input voltage at any pin exceeds 5.5 V or is less than GND, the current at that pin should be limited to 10 mA. The 20-mA maximum package input current ratings limits the number of pins that can safely exceed the power supplies with an input current of 10 mA to two.

- (5) The absolute maximum junction temperature (T<sub>Jmax</sub>) for this device is 150°C. The maximum allowable power dissipation is dictated by T<sub>Jmax</sub>, the junction-to-ambient thermal resistance (θ<sub>JA</sub>), and the ambient temperature (T<sub>A</sub>), and can be calculated using the formula PDMAX = (T<sub>Jmax</sub> T<sub>A</sub>) / θ<sub>JA</sub>. The values for maximum power dissipation will be reached only when the device is operated in a severe fault condition (for example, when input or output pins are driven beyond the operating ratings, or the power supply polarity is reversed).

#### 7.2 ESD Ratings

|             |                          |                                                                 |                         | VALUE | UNIT |  |

|-------------|--------------------------|-----------------------------------------------------------------|-------------------------|-------|------|--|

| DAC081      | C081 in NGF Package      |                                                                 |                         |       |      |  |

|             |                          | Human-body model (HBM), per                                     | All pins except 2 and 3 | ±2500 |      |  |

|             |                          | ANSI/ESDA/JEDEC JS-001                                          | Pins 2 and 3            | ±5000 |      |  |

| V           | Floatroototic discharge  | Charged-device model (CDM), per JEDEC                           | All pins except 2 and 3 | ±1000 |      |  |

| $V_{(ESD)}$ | Electrostatic discharge  | specification JESD22-C101                                       | Pins 2 and 3            | ±1000 | V    |  |

|             |                          | Machine model (MM)                                              | All pins except 2 and 3 | ±250  |      |  |

|             |                          | Machine model (MM)                                              | Pins 2 and 3            | ±350  |      |  |

| DAC081      | C081 in DDC Package      |                                                                 |                         |       |      |  |

|             | Electronic de de la como | Human-body model (HBM), per<br>ANSI/ESDA/JEDEC JS-001           | All pins except 4 and 5 | ±2500 |      |  |

|             |                          |                                                                 | Pins 4 and 5            | ±5000 | V    |  |

| V           |                          | Charged-device model (CDM), per JEDEC specification JESD22-C101 | All pins except 4 and 5 | ±1000 |      |  |

| $V_{(ESD)}$ | Electrostatic discharge  |                                                                 | Pins 4 and 5            | ±1000 |      |  |

|             |                          | Machine model (MM)                                              | All pins except 4 and 5 | ±250  |      |  |

|             |                          | Machine model (MM)                                              | Pins 4 and 5            | ±350  |      |  |

| DAC081      | C085 in DGK Package      |                                                                 |                         |       |      |  |

|             |                          | Human-body model (HBM), per                                     | All pins except 3 and 4 | ±2500 |      |  |

|             |                          | ANSI/ESDA/JEDEC JS-001                                          | Pins 3 and 4            | ±5000 |      |  |

| V           | Clastrostatia diasharas  | Charged-device model (CDM), per JEDEC                           | All pins except 3 and 4 | ±1000 | V    |  |

| $V_{(ESD)}$ | Electrostatic discharge  | specification JESD22-C101                                       | Pins 3 and 4            | ±1000 |      |  |

|             |                          | Machine model (MM)                                              | All pins except 3 and 4 | ±250  |      |  |

|             |                          | Machine model (MM)                                              | Pins 3 and 4            | ±350  |      |  |

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)(1)

|                                       | MIN | MAX            | UNIT |

|---------------------------------------|-----|----------------|------|

| Operating temperature, T <sub>A</sub> | -40 | 125            | ů    |

| Supply voltage, V <sub>A</sub>        | 2.7 | 5.5            | V    |

| Reference voltage, V <sub>REFIN</sub> | 1   | V <sub>A</sub> | V    |

| Digital input voltage <sup>(2)</sup>  | 0   | 5.5            | V    |

| Output load                           | 0   | 1500           | pF   |

<sup>1)</sup> All voltages are measured with respect to GND = 0 V, unless otherwise specified.

#### 7.4 Thermal Information

|                                     |                                        |            | 21C081    | DAC121C085  |      |

|-------------------------------------|----------------------------------------|------------|-----------|-------------|------|

| THERMAL METRIC <sup>(1)(2)(3)</sup> |                                        | NGF (WSON) | DDC (SOT) | DGK (VSSOP) | UNIT |

|                                     |                                        | 6 PINS     | 6 PINS    | 8 PINS      |      |

| $R_{\theta JA}$                     | Junction-to-ambient thermal resistance | 190        | 250       | 240         | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> The inputs are protected as shown in the following. Input voltage magnitudes up to 5.5 V, regardless of V<sub>A</sub>, will not cause errors in the conversion result. For example, if V<sub>A</sub> is 3 V, the digital input pins can be driven with a 5-V logic device.

<sup>(2)</sup> Soldering process must comply with Texas Instruments' Reflow Temperature Profile Specifications, SNOA549.

<sup>(3)</sup> Reflow temperature profiles are different for lead-free packages.

#### 7.5 Electrical Characteristics

The following specifications apply for  $V_A = 2.7 \text{ V}$  to 5.5 V,  $V_{REF} = V_A$ ,  $C_L = 200 \text{ pF}$  to GND, input code range 48 to 4047. All Maximum and Minimum limits apply for  $T_{MIN} \le T_A \le T_{MAX}$  and all Typical limits are at  $T_A = 25$ °C, unless otherwise specified. (1)

|                   | PARAMETER                     | TEST CONDITIONS                                                     | MIN                  | TYP <sup>(2)</sup> | MAX <sup>(2)</sup>   | UNIT   |  |

|-------------------|-------------------------------|---------------------------------------------------------------------|----------------------|--------------------|----------------------|--------|--|

| STATIC            | PERFORMANCE                   |                                                                     |                      |                    |                      |        |  |

|                   | Resolution                    |                                                                     | 12                   |                    |                      | Bits   |  |

|                   | Monotonicity                  |                                                                     | 12                   |                    |                      | Bits   |  |

| INL               |                               |                                                                     |                      | 2.2                | 8                    |        |  |

|                   | Integral Non-Linearity        |                                                                     | -8                   | -1.5               |                      | LSB    |  |

|                   |                               |                                                                     |                      | 0.18               | 0.6                  | LSB    |  |

| DNL               | Differential Non-Linearity    |                                                                     | -0.5                 | -0.12              |                      | LSB    |  |

| ZE                | Zero Code Error               | I <sub>OUT</sub> = 0                                                |                      | 1.1                | 10                   | mV     |  |

| FSE               | Full-Scale Error              | I <sub>OUT</sub> = 0                                                |                      | -0.1               | -0.7                 | %FSR   |  |

| GE                | Gain Error                    | All ones Loaded to DAC register                                     |                      | -0.2               | -0.7                 | %FSR   |  |

| ZCED              | Zero Code Error Drift         |                                                                     |                      | -20                |                      | μV/°C  |  |

|                   |                               | V <sub>A</sub> = 3 V                                                |                      | -0.7               |                      | ppm    |  |

| TC GE             | Gain Error Tempco             | V <sub>A</sub> = 5 V                                                |                      | -1                 |                      | FSR/°C |  |

| ANALOG            | OUTPUT CHARACTERISTICS        | (V <sub>OUT</sub> )                                                 |                      |                    |                      |        |  |

|                   |                               | DAC121C085                                                          | 0                    |                    | $V_{REF}$            |        |  |

|                   | Output voltage range (3)      | DAC121C081                                                          | 0                    |                    | V <sub>A</sub>       | V      |  |

|                   |                               | V <sub>A</sub> = 3 V, I <sub>OUT</sub> = 200 μA                     |                      | 1.3                |                      | mV     |  |

| ZCO               | Zero code output              | V <sub>A</sub> = 5 V, I <sub>OUT</sub> = 200 μA                     |                      | 7                  |                      |        |  |

|                   |                               | V <sub>A</sub> = 3 V, I <sub>OUT</sub> = 200 μA                     |                      | 2.984              |                      |        |  |

| FSO               | Full scale output             | V <sub>A</sub> = 5 V, I <sub>OUT</sub> = 200 μA                     |                      | 4.989              |                      | V      |  |

|                   | Output short-circuit current  | V <sub>A</sub> = 3 V, V <sub>OUT</sub> = 0 V,<br>Input Code = FFFh. |                      | 56                 |                      |        |  |

| os                | (I <sub>SOURCE</sub> )        | V <sub>A</sub> = 5 V, V <sub>OUT</sub> = 0 V,<br>Input Code = FFFh. |                      | 69                 |                      | mA     |  |

|                   | Output short-circuit current  | V <sub>A</sub> = 3 V, V <sub>OUT</sub> = 3 V,<br>Input Code = 000h. |                      | -52                |                      |        |  |

| los               | (I <sub>SINK</sub> )          | $V_A = 5 \text{ V}, V_{OUT} = 5 \text{ V},$<br>Input Code = 000h.   |                      | -75                |                      | mA     |  |

| О                 | Continuous output current (3) | Available on the DAC output                                         |                      |                    | 11                   | mA     |  |

|                   |                               | R <sub>L</sub> = ∞                                                  |                      | 1500               |                      | _      |  |

| CL                | Maximum load capacitance      | $R_L = 2 k\Omega$                                                   |                      | 1500               |                      | pF     |  |

| Z <sub>OUT</sub>  | DC output impedance           |                                                                     |                      | 7.5                |                      | Ω      |  |

| REFERE            | NCE INPUT CHARACTERISTIC      | S (DAC121C085 only)                                                 |                      |                    |                      |        |  |

|                   | Input range minimum           |                                                                     | 1                    | 0.2                |                      | V      |  |

| $V_{REF}$         | Input range maximum           |                                                                     |                      |                    | V <sub>A</sub>       | V      |  |

|                   | Input impedance               |                                                                     |                      | 120                |                      | kΩ     |  |

| OGIC I            | NPUT CHARACTERISTICS (SCI     | ., SDA)                                                             |                      |                    |                      |        |  |

| / <sub>IH</sub>   | Input high voltage            |                                                                     | 0.7 × V <sub>A</sub> |                    |                      | V      |  |

| / <sub>IL</sub>   | Input low voltage             |                                                                     |                      | <del>.</del>       | 0.3 × V <sub>A</sub> | V      |  |

| IN                | Input current                 |                                                                     |                      |                    | ±1                   | μΑ     |  |

| C <sub>IN</sub>   | Input pin capacitance (3)     |                                                                     |                      |                    | 3                    | pF     |  |

| V <sub>HYST</sub> | Input hysteresis              |                                                                     | 0.1 × V <sub>A</sub> |                    |                      | V      |  |

|                   | NPUT CHARACTERISTICS (ADI     | R0, ADR1)                                                           |                      |                    | ,                    |        |  |

| ViH               | Input high voltage            |                                                                     | V <sub>A</sub> - 0.5 |                    |                      | V      |  |

Values shown in this table are design targets and are subject to change before product release. Typical figures are at  $T_J = 25$ °C, and represent most likely parametric norms. Test limits are specified to AOQL (Average Outgoing Quality Level).

This parameter is specified by design and/or characterization and is not tested in production.

# **Electrical Characteristics (continued)**

The following specifications apply for  $V_A$  = 2.7 V to 5.5 V,  $V_{REF}$  =  $V_A$ ,  $C_L$  = 200 pF to GND, input code range 48 to 4047. All Maximum and Minimum limits apply for  $T_{MIN} \le T_A \le T_{MAX}$  and all Typical limits are at  $T_A$  = 25°C, unless otherwise specified.<sup>(1)</sup>

|                                                             | PARAMETER                                                              | TEST C                                  | ONDITIONS                               | MIN              | TYP <sup>(2)</sup> | MAX <sup>(2)</sup> | UNIT |  |

|-------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|------------------|--------------------|--------------------|------|--|

| V <sub>IL</sub>                                             | Input low voltage                                                      |                                         |                                         |                  |                    | 0.5                | V    |  |

| I <sub>IN</sub>                                             | Input current                                                          |                                         |                                         |                  |                    | ±1                 | μΑ   |  |

| LOGIC O                                                     | UTPUT CHARACTERISTICS (SD                                              | A)                                      |                                         |                  |                    |                    |      |  |

| V                                                           | Output law valtage                                                     | I <sub>SINK</sub> = 3 mA                |                                         |                  |                    | 0.4                | V    |  |

| V <sub>OL</sub>                                             | Output low voltage                                                     | I <sub>SINK</sub> = 6 mA                |                                         |                  |                    | 0.6                | V    |  |

| l <sub>OZ</sub>                                             | High-impedence output leakage current                                  |                                         |                                         |                  |                    | ±1                 | μΑ   |  |

| POWER I                                                     | REQUIREMENTS                                                           | •                                       | •                                       |                  |                    | ·                  |      |  |

| \/                                                          | Supply voltage minimum                                                 |                                         |                                         | 2.7              |                    |                    | V    |  |

| $V_A$                                                       | Supply voltage maximum                                                 |                                         |                                         |                  |                    | 5.5                | V    |  |

| Normal                                                      | V <sub>OUT</sub> set to midscale. 2-wire int                           | erface quiet (SCL                       | = SDA = V <sub>A</sub> ). (output u     | ınloaded)        |                    |                    |      |  |

|                                                             | V DAC121C081 supply current                                            | $V_A = 2.7 \text{ V to } 3.6 \text{ V}$ | /                                       |                  | 105                | 156                |      |  |

| I <sub>ST_VA-1</sub>                                        | V <sub>A</sub> <b>DAC121C081</b> supply current                        | $V_A = 4.5 \text{ V to } 5.5 \text{ V}$ | <i>J</i>                                |                  | 132                | 214                | μΑ   |  |

|                                                             | V DAC121C005 aupply ourrent                                            | $V_A = 2.7 \text{ V to } 3.6 \text{ V}$ | /                                       |                  | 86                 | 118                | μΑ   |  |

| I <sub>ST_VA-5</sub>                                        | V <sub>A</sub> <b>DAC121C085</b> supply current                        | $V_A = 4.5 \text{ V to } 5.5 \text{ V}$ | /                                       |                  | 98                 | 152                | μΑ   |  |

|                                                             | V <sub>REF</sub> supply current                                        | $V_A = 2.7 \text{ V to } 3.6 \text{ V}$ | /                                       |                  | 37                 | 43                 |      |  |

| I <sub>ST_VREF</sub>                                        | (DAC121C085 only)                                                      | $V_A = 4.5 \text{ V to } 5.5 \text{ V}$ | J                                       |                  | 53                 | 61                 | μΑ   |  |

|                                                             | Power consumption                                                      | V <sub>A</sub> = 3 V                    |                                         |                  | 380                |                    |      |  |

| P <sub>ST</sub>                                             | (V <sub>A</sub> and V <sub>REF</sub> for<br>DAC121C085) <sup>(4)</sup> | V <sub>A</sub> = 5 V                    |                                         |                  | 730                |                    | μW   |  |

| Continuo                                                    | us Operation 2-wire interface                                          | actively addressin                      | g the DAC and writing                   | to the DAC reg   | ister. (outpu      | ıt unloaded        | i)   |  |

|                                                             |                                                                        | f _400 kHz                              | $V_A = 2.7 \text{ V to } 3.6 \text{ V}$ |                  | 134                | 220                | ПΔ   |  |

|                                                             | V DAC121C091 quanty ourrent                                            | f <sub>SCL</sub> =400 kHz               | $V_A = 4.5 \text{ V to } 5.5 \text{ V}$ |                  | 192                | 300                | μA   |  |

| I <sub>CO_VA-1</sub>                                        | V <sub>A</sub> <b>DAC121C081</b> supply current                        | f _ 2 / MU-7                            | $V_A = 2.7 \text{ V to } 3.6 \text{ V}$ |                  | 225                | 320                |      |  |

|                                                             |                                                                        | f <sub>SCL</sub> = 3.4 MHz              | $V_A = 4.5 \text{ V to } 5.5 \text{ V}$ |                  | 374                | 500                | μΑ   |  |

|                                                             |                                                                        | f _ 400 kHz                             | $V_A = 2.7 \text{ V to } 3.6 \text{ V}$ |                  | 101                | 155                |      |  |

|                                                             | V DAC121COSE quanty ourrant                                            | $f_{SCL} = 400 \text{ kHz}$             | $V_A = 4.5 \text{ V to } 5.5 \text{ V}$ |                  | 142                | 220                | μΑ   |  |

| I <sub>CO_VA-5</sub>                                        | V <sub>A</sub> <b>DAC121C085</b> supply current                        | f _ 2.4 MHz                             | $V_A = 2.7 \text{ V to } 3.6 \text{ V}$ |                  | 193                | 235                |      |  |

|                                                             |                                                                        | f <sub>SCL</sub> = 3.4 MHz              | $V_A = 4.5 \text{ V to } 5.5 \text{ V}$ |                  | 325                | 410                | μΑ   |  |

|                                                             | V <sub>REF</sub> supply current                                        |                                         | $V_A = 2.7 \text{ V to } 3.6 \text{ V}$ |                  | 33.5               | 55                 |      |  |

| I <sub>CO_VREF</sub>                                        | (DAC121C085 only)                                                      |                                         | $V_A = 4.5 \text{ V to } 5.5 \text{ V}$ |                  | 49.5               | 71.4               | μΑ   |  |

|                                                             |                                                                        | f <sub>SCL</sub> = 400 kHz              | V <sub>A</sub> = 3 V                    |                  | 480                |                    | μW   |  |

| D                                                           | Power consumption                                                      |                                         | V <sub>A</sub> = 5 V                    |                  | 1.06               |                    | mW   |  |

| P <sub>CO</sub>                                             | ( $V_A$ and $V_{REF}$ for DAC121C085)                                  | f <sub>SCL</sub> = 3.4 MHz              | V <sub>A</sub> = 3 V                    |                  | 810                |                    | μW   |  |

|                                                             |                                                                        | ISCL = 3.4 IVITZ                        | V <sub>A</sub> = 5 V                    |                  | 2.06               |                    | mW   |  |

| Power Do                                                    | own 2-wire interface quiet (SC                                         | $L = SDA = V_A$ ) afte                  | r PD mode written to [                  | DAC register. (o | utput unload       | ded)               |      |  |

|                                                             | Supply current                                                         | All power-down                          | $V_A = 2.7 \text{ V to } 3.6$           |                  | 0.13               | 1.52               | μ.Λ  |  |

| I <sub>PD</sub>                                             | (V <sub>A</sub> and V <sub>REF</sub> for DAC121C085)                   | modes                                   | V <sub>A</sub> = 4.5 V to 5.5 V         |                  | 0.15               | 3.25               | μΑ   |  |

| D                                                           | Power consumption                                                      | All power-down                          | V <sub>A</sub> = 3 V                    |                  | 0.5                |                    | \^/  |  |

| $P_{PD}$ (V <sub>A</sub> and V <sub>REF</sub> for DAC121C08 | modes                                                                  | V <sub>A</sub> = 5 V                    |                                         | 0.9              |                    | μW                 |      |  |

<sup>(4)</sup> To ensure accuracy, it is required that  $V_A$  and  $V_{REF}$  be well bypassed.

# 7.6 AC and Timing Characteristics

The following specifications apply for  $V_A = 2.7 \text{ V}$  to 5.5 V,  $V_{REF} = V_A$ ,  $R_L = Infinity$ ,  $C_L = 200 \text{ pF}$  to GND. All Maximum and Minimum limits apply for  $T_{MIN} \le T_A \le T_{MAX}$  and all Typical limits are at  $T_A = 25^{\circ}\text{C}$ , unless otherwise specified. (1)

|                     | PARAMETER                                   | TEST CONDITIONS <sup>(2)</sup>                                              | MIN | TYP <sup>(3)</sup> | MAX <sup>(2)(3)</sup> | UNIT   |

|---------------------|---------------------------------------------|-----------------------------------------------------------------------------|-----|--------------------|-----------------------|--------|

| t <sub>s</sub>      | Output Voltage Settling Time <sup>(4)</sup> | 400h to C00h code change $R_L = 2 \text{ k}\Omega$ , $C_L = 200 \text{ pF}$ |     | 6                  | 8.5                   | μs     |

| SR                  | Output Slew Rate                            |                                                                             |     | 1                  |                       | V/µs   |

|                     | Glitch Impulse                              | Code change from 800h to 7FFh                                               |     | 12                 |                       | nV-sec |

|                     | Digital Feedthrough                         |                                                                             |     | 0.5                |                       | nV-sec |

|                     | Multiplying Bandwidth (5)                   | V <sub>REF</sub> = 2.5 V ± 0.1 Vpp                                          |     | 160                |                       | kHz    |

|                     | Total Harmonic Distortion (5)               | V <sub>REF</sub> = 2.5 V ± 0.1 Vpp<br>input frequency = 10 kHz              |     | 70                 |                       | dB     |

|                     | Make He Time                                | V <sub>A</sub> = 3 V                                                        |     | 0.8                |                       | μs     |

| t <sub>WU</sub>     | Wake-Up Time                                | V <sub>A</sub> = 5 V                                                        |     | 0.5                |                       | μs     |

| DIGITA              | L TIMING SPECS (SCL, SDA)                   |                                                                             |     |                    |                       |        |

|                     |                                             | Standard Mode                                                               |     |                    | 100                   |        |

|                     | 0 0 5                                       | Fast Mode                                                                   |     |                    | 400                   | kHz    |

| f <sub>SCL</sub>    | Serial Clock Frequency                      | High Speed Mode, C <sub>b</sub> = 100 pF                                    |     |                    | 3.4                   |        |

|                     |                                             | High Speed Mode, C <sub>b</sub> = 400 pF                                    |     |                    | 1.7                   | MHz    |

|                     |                                             | Standard Mode                                                               | 4.7 |                    |                       |        |

|                     |                                             | Fast Mode                                                                   | 1.3 |                    |                       | μs     |

| LOW                 | SCL Low Time                                | High Speed Mode, C <sub>b</sub> = 100 pF                                    | 160 |                    |                       |        |

|                     |                                             | High Speed Mode, C <sub>b</sub> = 400 pF                                    | 320 |                    |                       | ns     |

|                     |                                             | Standard Mode                                                               | 4   |                    |                       |        |

|                     |                                             | Fast Mode                                                                   | 0.6 |                    |                       | μs     |

| tHIGH               | SCL High Time                               | High Speed Mode, C <sub>b</sub> = 100 pF                                    | 60  |                    |                       |        |

|                     |                                             | High Speed Mode, C <sub>b</sub> = 400 pF                                    | 120 |                    |                       | ns     |

|                     |                                             | Standard Mode                                                               | 250 |                    |                       |        |

| t <sub>SU;DAT</sub> | Data Setup Time                             | Fast Mode                                                                   | 100 |                    |                       | ns     |

| ,                   |                                             | High Speed Mode                                                             | 10  |                    |                       |        |

|                     |                                             | Standard Mode                                                               | 0   |                    | 3.45                  |        |

|                     |                                             | Fast Mode                                                                   | 0   |                    | 0.9                   | μs     |

| HD;DAT              | Data Hold Time                              | High Speed Mode, C <sub>b</sub> = 100 pF                                    | 0   |                    | 70                    |        |

|                     |                                             | High Speed Mode, C <sub>b</sub> = 400 pF                                    | 0   |                    | 150                   | ns     |

|                     |                                             | Standard Mode                                                               | 4.7 |                    |                       |        |

| t <sub>SU;STA</sub> | Setup time for a start or a                 | Fast Mode                                                                   | 0.6 |                    |                       | μs     |

| ,                   | repeated start condition                    | High Speed Mode                                                             | 160 |                    |                       | ns     |

|                     |                                             | Standard Mode                                                               | 4   |                    |                       |        |

| HD;STA              | Hold time for a start or a                  | Fast Mode                                                                   | 0.6 |                    |                       | μs     |

| ,5171               | repeated start condition                    | High Speed Mode                                                             | 160 |                    |                       | ns     |

|                     | Bus free time between a stop                | Standard Mode                                                               | 4.7 |                    |                       |        |

| t <sub>BUF</sub>    | and start condition                         | Fast Mode                                                                   | 1.3 |                    |                       | μs     |

|                     |                                             | Standard Mode                                                               | 4   |                    |                       |        |

| SU;STO              | Setup time for a stop condition             | Fast Mode                                                                   | 0.6 |                    |                       | μs     |

| 55,510              | Cotap time for a stop containon             | High Speed Mode                                                             | 160 |                    |                       | ns     |

<sup>(1)</sup> Values shown in this table are design targets and are subject to change before product release.

$C_b$  refers to the capacitance of one bus line.  $C_b$  is expressed in pF units.

Typical figures are at  $T_J = 25$ °C, and represent most likely parametric norms. Test limits are specified to AOQL (Average Outgoing Quality Level).

This parameter is specified by design and/or characterization and is not tested in production.

Applies to the Multiplying DAC configuration. In this configuration, the reference is used as the analog input. The value loaded in the DAC Register will digitally attenuate the signal at Vout.

### **AC and Timing Characteristics (continued)**

The following specifications apply for  $V_A$  = 2.7 V to 5.5 V,  $V_{REF}$  =  $V_A$ ,  $R_L$  = Infinity,  $C_L$  = 200 pF to GND. All Maximum and Minimum limits apply for  $T_{MIN} \le T_A \le T_{MAX}$  and all Typical limits are at  $T_A$  = 25°C, unless otherwise specified.<sup>(1)</sup>

|                   | PARAMETER                                                                              | TEST CONDITIONS <sup>(2)</sup>           | MIN                  | TYP <sup>(3)</sup> | MAX <sup>(2)(3)</sup> | UNIT |  |  |  |

|-------------------|----------------------------------------------------------------------------------------|------------------------------------------|----------------------|--------------------|-----------------------|------|--|--|--|

|                   |                                                                                        | Standard Mode                            |                      |                    | 1000                  |      |  |  |  |

|                   | Disa time of CDA simus!                                                                | Fast Mode                                | 20+0.1C <sub>b</sub> |                    | 300                   |      |  |  |  |

| $t_{rDA}$         | Rise time of SDA signal                                                                | High Speed Mode, C <sub>b</sub> = 100 pF | 10                   |                    | 80                    | ns   |  |  |  |

|                   |                                                                                        | High Speed Mode, C <sub>b</sub> = 400 pF | 20                   |                    | 160                   |      |  |  |  |

|                   |                                                                                        | Standard Mode                            |                      |                    | 250                   |      |  |  |  |

|                   | Fall time of CDA signal                                                                | Fast Mode                                |                      |                    |                       |      |  |  |  |

| $t_{fDA}$         | Fall time of SDA signal                                                                | High Speed Mode, C <sub>b</sub> = 100 pF | 10                   |                    | 80                    | ns   |  |  |  |

|                   |                                                                                        | High Speed Mode, C <sub>b</sub> = 400 pF | 20                   |                    | 160                   |      |  |  |  |

|                   |                                                                                        | Standard Mode                            |                      |                    | 1000                  |      |  |  |  |

|                   | Disa time of CCI signal                                                                | Fast Mode                                | 20+0.1C <sub>b</sub> |                    | 300                   | ns   |  |  |  |

| t <sub>rCL</sub>  | Rise time of SCL signal                                                                | High Speed Mode, C <sub>b</sub> = 100 pF | 10                   |                    | 40                    |      |  |  |  |

|                   |                                                                                        | High Speed Mode, C <sub>b</sub> = 400 pF | 20                   |                    | 80                    |      |  |  |  |

|                   |                                                                                        | Standard Mode                            |                      |                    | 1000                  | ns   |  |  |  |

|                   | Rise time of SCL signal after a repeated start condition and after an acknowledge bit. | Fast Mode                                | 20+0.1C <sub>b</sub> |                    | 300                   |      |  |  |  |

| t <sub>rCL1</sub> |                                                                                        | High Speed Mode, C <sub>b</sub> = 100 pF | 10                   |                    | 80                    |      |  |  |  |

|                   |                                                                                        | High Speed Mode, C <sub>b</sub> = 400 pF | 20                   |                    | 160                   |      |  |  |  |

|                   |                                                                                        | Standard Mode                            |                      |                    | 300                   |      |  |  |  |

|                   | Fall time of a COL since!                                                              | Fast Mode                                | 20+0.1C <sub>b</sub> |                    | 300                   | ļ    |  |  |  |

| t <sub>fCL</sub>  | Fall time of a SCL signal                                                              | High Speed Mode, C <sub>b</sub> = 100 pF | 10                   |                    | 40                    | ns   |  |  |  |

|                   |                                                                                        | High Speed Mode, C <sub>b</sub> = 400 pF | 20                   |                    | 80                    |      |  |  |  |

| C <sub>b</sub>    | Capacitive load for each bus line (SCL and SDA)                                        |                                          |                      |                    | 400                   | pF   |  |  |  |

|                   | Pulse Width of spike                                                                   | Fast Mode                                |                      |                    | 50                    |      |  |  |  |

| t <sub>SP</sub>   | Pulse Width of spike suppressed (6)(4)                                                 | High Speed Mode                          |                      | 10                 | ns                    |      |  |  |  |

|                   | SDA output delay (see the                                                              | Fast Mode                                |                      | 87                 | 270                   |      |  |  |  |

| t <sub>outz</sub> | Additional Timing Information section)                                                 | High Speed Mode                          |                      | 38                 | 60                    | ns   |  |  |  |

<sup>(6)</sup> Spike suppression filtering on SCL and SDA will supress spikes that are less than 50 ns for standard-fast mode and less than 10ns for hs-mode.

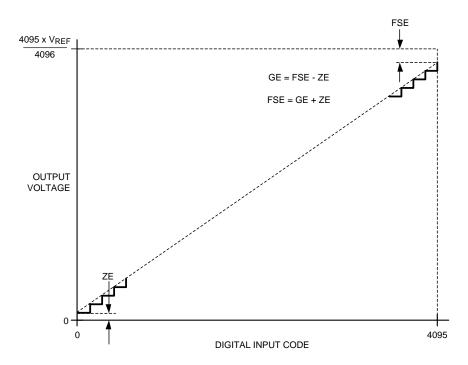

Figure 1. Input / Output Transfer Characteristic

Figure 2. Serial Timing Diagram

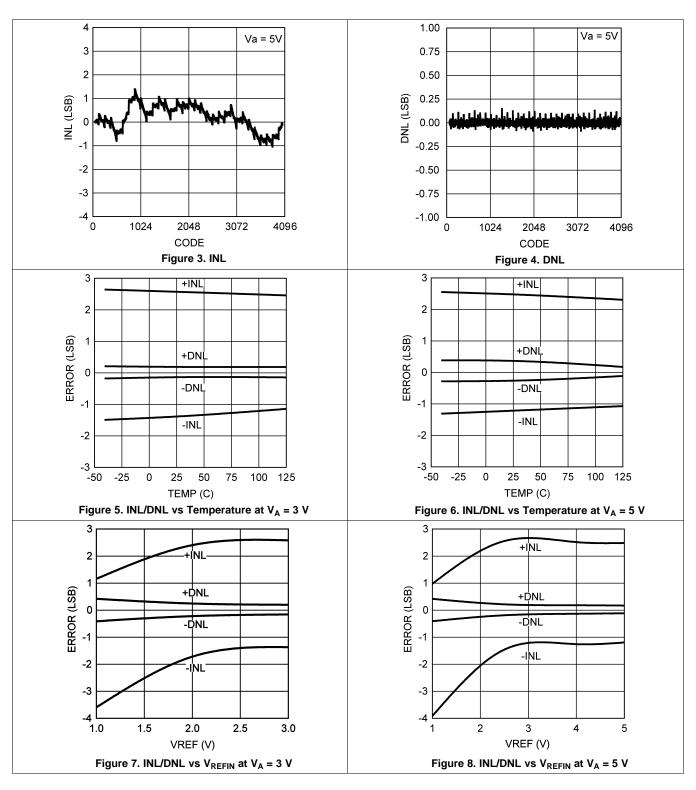

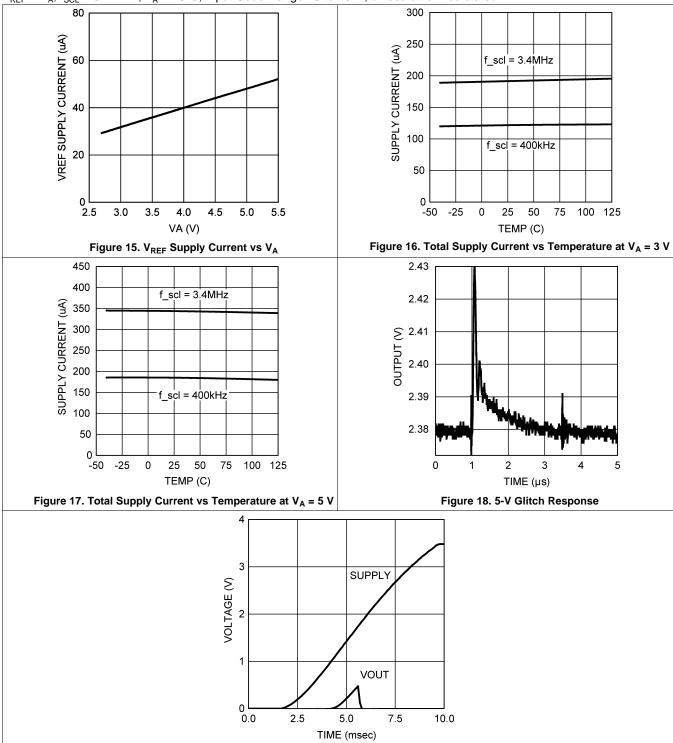

#### 7.7 Typical Characteristics

$V_{REF} = V_A$ ,  $f_{SCL} = 3.4$  MHz,  $T_A = 25$ °C, Input Code Range 48 to 4047, unless otherwise stated.

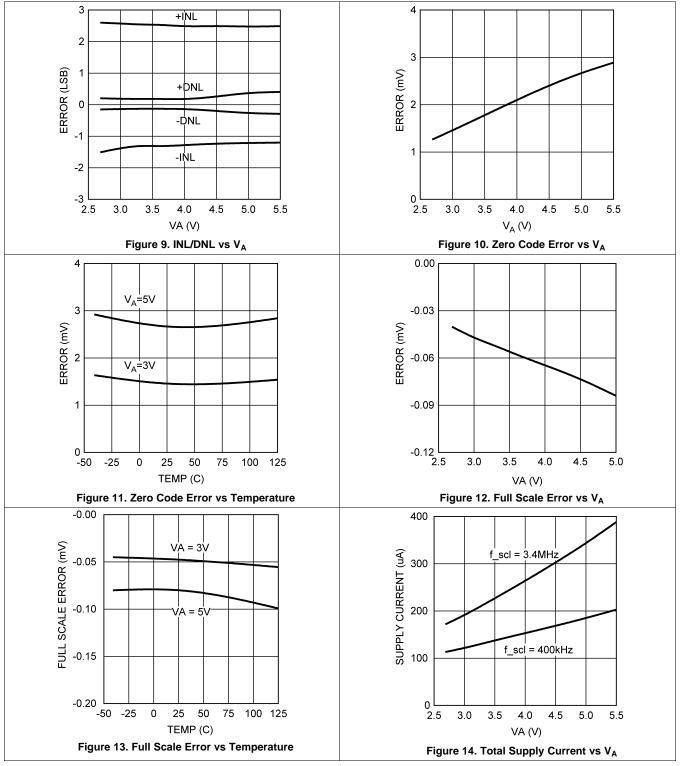

# **Typical Characteristics (continued)**

$V_{REF} = V_A$ ,  $f_{SCL} = 3.4$  MHz,  $T_A = 25$ °C, Input Code Range 48 to 4047, unless otherwise stated.

# TEXAS INSTRUMENTS

### **Typical Characteristics (continued)**

$V_{REF} = V_A$ ,  $f_{SCL} = 3.4$  MHz,  $T_A = 25$ °C, Input Code Range 48 to 4047, unless otherwise stated.

Figure 19. Power-On Reset

# 8 Detailed Description

#### 8.1 Overview

The DAC121C081 is fabricated on a CMOS process with an architecture that consists of switches and resistor strings that are followed by an output buffer.

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

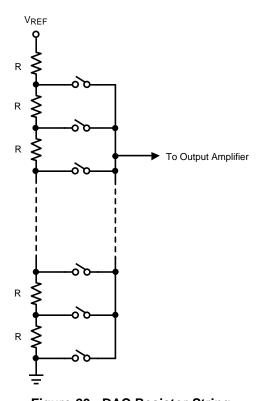

#### 8.3.1 DAC Section

The DAC121C081 is fabricated on a CMOS process with an architecture that consists of switches and resistor strings that are followed by an output buffer.

For simplicity, a single resistor string is shown in Figure 20. This string consists of 4096 equal valued resistors with a switch at each junction of two resistors, plus a switch to ground. The code loaded into the DAC register determines which switch is closed, connecting the proper node to the amplifier. The input coding is straight binary with an ideal output voltage of:

$$V_{OUT} = V_{REF} \times (D / 4096)$$

where D is the decimal equivalent of the binary code that is loaded into the DAC register. (1)

D can take on any integer value from 0 to 4095. This configuration ensures that the DAC is monotonic.

Figure 20. DAC Resistor String

# 8.3.2 Output Amplifier

The output amplifier is rail-to-rail, providing an output voltage range of 0 V to  $V_A$  when the reference is  $V_A$ . All amplifiers, even rail-to-rail types, exhibit a loss of linearity as the output approaches the supply rails (0 V and  $V_A$ , in this case). For this reason, linearity is specified over less than the full output range of the DAC. However, if the reference is less than  $V_A$ , there is only a loss in linearity in the lowest codes. The output capabilities of the amplifier are described in the *Electrical Characteristics*.

The output amplifiers are capable of driving a load of 2 k $\Omega$  in parallel with 1500 pF to ground or to  $V_A$ . The zero-code and full-scale outputs for given load currents are available in the *Electrical Characteristics*.

#### 8.3.3 Reference Voltage

The DAC121C081 uses the supply  $(V_A)$  as the reference. With that said,  $V_A$  must be treated as a reference. The analog output is only as clean as the reference  $(V_A)$ . TI recommends driving the reference with a voltage source with low-output impedance.

The DAC121C085 comes with an external reference supply pin ( $V_{REF}$ ). For the DAC121C085, it is important that  $V_{REF}$  be kept as clean as possible.

Applications Information describes a handful of ways to drive the reference appropriately. See *Using References* as *Power Supplies* for details.

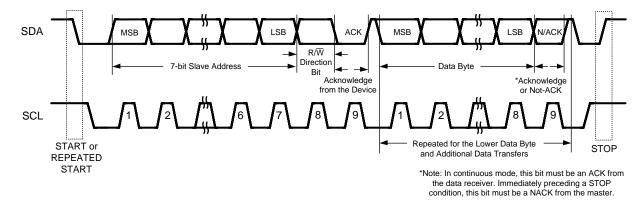

#### 8.3.4 Serial Interface

The I<sup>2</sup>C-compatible interface operates in all three speed modes. Standard mode (100 kHz) and Fast mode (400 kHz) are functionally the same and will be referred to as Standard-Fast mode in this document. High-Speed mode (3.4MHz) is an extension of Standard-Fast mode and will be referred to as Hs-mode in this document. The following diagrams describe the timing relationships of the clock (SCL) and data (SDA) signals. Pullup resistors or current sources are required on the SCL and SDA busses to pull them high when they are not being driven low. A logic zero is transmitted by driving the output low. A logic high is transmitted by releasing the output and allowing it to be pulled up externally. The appropriate pullup resistor values depends on the total bus capacitance and operating speed.

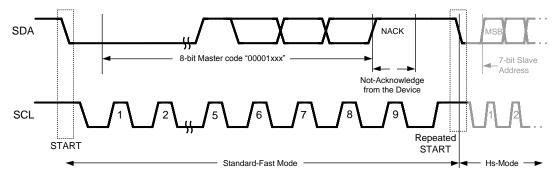

#### 8.3.4.1 Basic PC Protocol

The I<sup>2</sup>C interface is bi-directional and allows multiple devices to operate on the same bus. To facilitate this bus configuration, each device has a unique hardware address which is referred to as the slave address. To communicate with a particular device on the bus, the controller (master) sends the slave address and listens for a response from the slave. This response is referred to as an acknowledge bit. If a slave on the bus is addressed correctly, it Acknowledges (ACKs) the master by driving the SDA bus low. If the address doesn't match a device's slave address, it Not-acknowledges (NACKs) the master by letting SDA be pulled high. ACKs also occur on the bus when data is being transmitted. When the master is writing data, the slave ACKs after every data byte is successfully received. When the master is reading data, the master ACKs after every data byte is received to let the slave know it wants to receive another data byte. When the master wants to stop reading, it NACKs after the last data byte and creates a Stop condition on the bus.

All communication on the bus begins with either a Start condition or a Repeated Start condition. The protocol for starting the bus varies between Standard-Fast mode and Hs-mode. In Standard-Fast mode, the master generates a Start condition by driving SDA from high to low while SCL is high. In Hs-mode, starting the bus is more complicated. See *High-Speed (Hs) Mode* for the full details of a Hs-mode Start condition. A Repeated Start is generated to either address a different device, or switch between read and write modes. The master generates a Repeated Start condition by driving SDA low while SCL is high. Following the Repeated Start, the master sends out the slave address and a read/write bit as shown in Figure 21. The bus continues to operate in the same speed mode as before the Repeated Start condition.

All communication on the bus ends with a Stop condition. In either Standard-Fast mode or Hs-Mode, a Stop condition occurs when SDA is pulled from low to high while SCL is high. After a Stop condition, the bus remains idle until a master generates a Start condition.

See the Phillips I<sup>2</sup>C<sup>®</sup> Specification (Version 2.1 Jan, 2000) for a detailed description of the serial interface.

Figure 21. Basic Operation

#### 8.3.4.2 Standard-Fast Mode

In Standard-Fast mode, the master generates a start condition by driving SDA from high to low while SCL is high. The Start condition is always followed by a 7-bit slave address and a Read/Write bit. After these eight bits have been transmitted by the master, SDA is released by the master and the DAC121C081 either ACKs or NACKs the address. If the slave address matches, the DAC121C081 ACKs the master. If the address doesn't match, the DAC121C081 NACKs the master.

For a **write** operation, the master follows the ACK by sending the upper eight data bits to the DAC121C081. Then the DAC121C081 ACKs the transfer by driving SDA low. Next, the lower eight data bits are sent by the master. The DAC121C081 then ACKs the transfer. At this point, the DAC output updates to reflect the contents of the 16-bit DAC register. Next, the master either sends another pair of data bytes, generates a Stop condition to end communication, or generates a Repeated Start condition to communicate with another device on the bus.

For a **read** operation, the DAC121C081 sends out the upper eight data bits of the DAC register. This is followed by an ACK by the master. Next, the lower eight data bits of the DAC register are sent to the master. The master then produces a NACK by letting SDA be pulled high. The NACK is followed by a master-generated Stop condition to end communication on the bus, or a Repeated Start to communicate with another device on the bus.

#### 8.3.4.3 High-Speed (Hs) Mode

For Hs-mode, the sequence of events to begin communication differ slightly from Standard-Fast mode. Figure 22 describes this in further detail. Initially, the bus begins running in Standard-Fast mode. The master generates a Start condition and sends the 8-bit Hs master code (00001XXX) to the DAC121C081. Next, the DAC121C081 responds with a NACK. Once the SCL line has been pulled to a high level, the master switches to Hs-mode by increasing the bus speed and generating a Repeated Start condition (driving SDA low while SCL is pulled high). At this point, the master sends the slave address to the DAC121C081, and communication continues as shown in Figure 21.

When the master generates a Repeated Start condition while in Hs-mode, the bus stays in Hs-mode awaiting the slave address from the master. The bus continues to run in Hs-mode until a Stop condition is generated by the master. When the master generates a Stop condition on the bus, the bus must be started in Standard-Fast mode again before increasing the bus speed and switching to Hs-mode. ns16705

Figure 22. Beginning Hs-Mode Communication

#### 8.3.4.4 PC Slave (Hardware) Address

The DAC has a seven-bit  $I^2C$  slave address. For the VSSOP version of the DAC, this address is configured by the ADR0 and ADR1 address selection inputs. For the DAC121C081, the address is configured by the ADR0 address selection input. ADR0 and ADR1 can be grounded, left floating, or tied to  $V_A$ . If desired, the address selection inputs can be set to  $V_A/2$  rather than left floating. The state of these inputs sets the address the DAC responds to on the  $I^2C$  bus (see Table 1). In addition to the selectable slave address, there is also a broadcast address (1001000) for all DAC121C081's and DAC121C085's on the 2-wire bus. When the bus is addressed by the broadcast address, all the DAC121C081's and DAC121C085's will respond and update synchronously. Figure 24 and Figure 25 describe how the master device should address the DAC through the  $I^2C$ -Compatible interface.

Keep in mind that the address selection inputs (ADR0 and ADR1) are only sampled until the DAC is correctly addressed with a non-broadcast address. At this point, the ADR0 and ADR1 inputs TRI-STATE and the slave address is locked. Changes to ADR0 and ADR1 will not update the selected slave address until the device is power-cycled.

Table 1. Slave Addresses

| Slave Address | DAC121C0       | 085 (VSSOP)    | DAC121C081 (SOT<br>AND WSON) <sup>(1)</sup> | Do Not Use <sup>(2)</sup> |

|---------------|----------------|----------------|---------------------------------------------|---------------------------|

| [A6 - A0]     | ADR1           | ADR0           | ADR0                                        |                           |

| 0001100       | Floating       | Floating       | Floating                                    | 1000110                   |

| 0001101       | Floating       | GND            | GND                                         | 1000110                   |

| 0001110       | Floating       | $V_{A}$        | V <sub>A</sub>                              | 1000111                   |

| 0001000       | GND            | Floating       |                                             | 1000100                   |

| 0001001       | GND            | GND            |                                             | 1000100                   |

| 0001010       | GND            | V <sub>A</sub> |                                             | 1000101                   |

| 1001100       | V <sub>A</sub> | Floating       |                                             | 1100110                   |

| 1001101       | $V_{A}$        | GND            |                                             | 1100110                   |

| 1001110       | V <sub>A</sub> | V <sub>A</sub> |                                             | 1100111                   |

| 1001000       |                |                | 1100100                                     |                           |

<sup>(1)</sup> Pin-compatible alternatives to the DAC121C081 options are available with additional address options.

#### 8.3.5 Power-On Reset

The power-on reset circuit controls the output voltage of the DAC during power up. Upon application of power, the DAC register is filled with zeros and the output voltage is 0 V. The output remains at 0 V until a valid write sequence is made to the DAC.

When resetting the device, it is crutial that the  $V_A$  supply be lowered to a maximum of 200 mV before the supply is raised again to power up the device. Dropping the supply to within 200 mV of GND during a reset will ensure the ADC performs as specified.

#### 8.3.6 Simultaneous Reset

The broadcast address allows the  $I^2C$  master to write a single word to multiple DACs simultaneously. Provided that all of the DACs exist on a single  $I^2C$  bus, every DAC updates when the broadcast address is used to address the bus. This feature allows the master to reset all of the DACs on a shared  $I^2C$  bus to a specific digital code. For instance, if the master writes a power-down code to the bus with the broadcast address, all of the DACs powers down simultaneously.

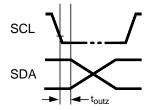

#### 8.3.7 Additional Timing Information: toutz

The  $t_{outz}$  specification is provided to aid the design of the  $I^2C$  bus. After the SCL bus is driven low by the  $I^2C$  master, the SDA bus will be held for a short time by the DAC121C081. This time is referred to as  $t_{outz}$ . The following figure illustrates the relationship between the fall of SCL, at the 30% threshold, to the time when the DAC begins to transition the SDA bus. The  $t_{outz}$  specification only applies when the DAC is in control of the SDA bus. The DAC is only in control of the bus during an ACK by the DAC121C081 or a data byte read from the DAC (see Figure 25).

<sup>(2)</sup> These addresses should not be used by other I<sup>2</sup>C devices on the I<sup>2</sup>C bus. Using these addresses can cause the DAC121C081/085 to not respond when addressed by the assigned Slave Address.

Figure 23. Data Output Timing

The t<sub>outz</sub> specification is typically 87 ns in Standard-Fast Mode and 38 ns in Hs-Mode.

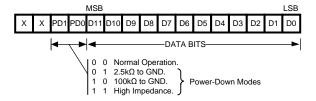

#### 8.4 Device Functional Modes

#### 8.4.1 Power-Down Modes

The DAC121C081 has three power-down modes. In power-down mode, the supply current drops to 0.13  $\mu$ A at 3 V and 0.15  $\mu$ A at 5 V (typical). The DAC121C081 is put into power-down mode by writing a one to PD1 and/or PD0. The outputs can be set to high impedance, terminated by 2.5 k $\Omega$  to GND, or terminated by 100 k $\Omega$  to GND (see Figure 26).

The bias generator, output amplifier, resistor string, and other linear circuitry are all shut down in any of the power-down modes. When the DAC121C081 is powered down, the value written to the DAC register, including the power-down bits, is saved. While the DAC is in power-down, the saved DAC register contents can be read back. When the DAC is brought out of power-down mode, the DAC register contents will be overwritten and  $V_{OUT}$  will be updated with the new 12-bit data value.

The time to exit power-down (Wake-Up Time) is typically 0.8  $\mu$ s at 3 V and 0.5  $\mu$ s at 5 V.

#### 8.5 Programming

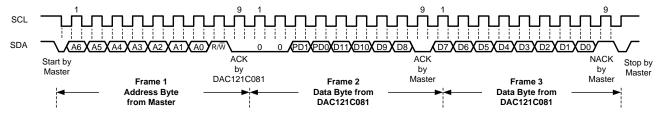

#### 8.5.1 Writing to the DAC Register

To write to the DAC, the master addresses the part with the correct slave address (A6-A0) and writes a zero to the read/write bit. If addressed correctly, the DAC returns an ACK to the master. The master then sends out the upper data byte. The DAC responds by sending an ACK to the master. Next, the master sends the lower data byte to the DAC. The DAC responds by sending an ACK again. At this point, the master either sends the upper byte of the next data word to be converted by the DAC, generates a Stop condition to end communication, or generates a Repeated Start condition to begin communication with another device on the bus. Until generating a Stop condition, the master can continuously write the upper and lower data bytes to the DAC register. This allows for a maximum DAC conversion rate of 188.9 kilo-conversions per second in Hs-mode.

Figure 24. Typical Write to the DAC Register

#### **Programming (continued)**

#### 8.5.2 Reading from the DAC Register

To read from the DAC register, the master addresses the part with the correct slave address (A6-A0) and writes a one to the read/write bit. If addressed correctly, the DAC returns an ACK to the master. Next, the DAC sends out the upper data byte. The master responds by sending an ACK to the DAC to indicate that it wants to receive another data byte. Then the DAC sends the lower data byte to the master. Assuming only one 16-bit data word is read, the master sends a NACK after receiving the lower data byte. At this point, the master either generates a Stop condition to end communication, or a Repeated Start condition to begin communication with another device on the bus.

Figure 25. Typical Read from the DAC Register

#### 8.6 Registers

#### 8.6.1 DAC Register

The DAC register, Figure 26, has sixteen bits. The first two bits are always zero. The next two bits determine the mode of operation (normal mode or one of three power-down modes). The final twelve bits of the shift register are the data bits. The data format is straight binary (MSB first, LSB last), with twelve 0s corresponding to an output of 0 V and twelve 1s corresponding to a full-scale output of  $V_A - 1$  LSB. When writing to the DAC Register,  $V_{OUT}$  will update on the rising edge of the ACK following the lower data byte.

Figure 26. DAC Register Contents

(2)

#### 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Information

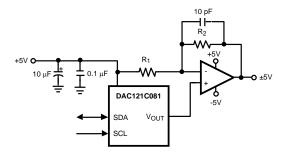

#### 9.1.1 Bipolar Operation

The DAC121C081 is designed for single supply operation and thus has a unipolar output. However, a bipolar output may be obtained with the circuit in Figure 27. This circuit provides an output voltage range of ±5 V. A rail-to-rail amplifier should be used if the amplifier supplies are limited to ±5 V.

Figure 27. Bipolar Operation

The output voltage of this circuit for any code is found to be, as shown in Equation 2:

$$V_O = (V_A \times (D / 4096) \times ((R1 + R2) / R1) - V_A \times R2 / R1)$$

Equation 3 shows that with  $V_A = 5 \text{ V}$  and R1 = R2,

$$V_0 = (10 \times D / 4096) - 5 V$$

(3)

A list of rail-to-rail amplifiers suitable for this application are indicated in Table 2.

#### Table 2. Some Rail-to-Rail Amplifiers

| AMP     | PKGS         | Typ V <sub>OS</sub> | Typ I <sub>SUPPLY</sub> |

|---------|--------------|---------------------|-------------------------|

| LMP7701 | SOT-23       | 37 uV               | 0.79 mA                 |

| LMV841  | SC70-5       | 50 uV               | 1 mA                    |

| LMC7111 | SOT-23       | 0.9 mV              | 25 μΑ                   |

| LM7301  | SO-8, SOT-23 | 0.03 mV             | 620 µA                  |

| LM8261  | SOT-23       | 0.7 mV              | 1 mA                    |

#### 9.1.2 DSP/Microprocessor Interfacing

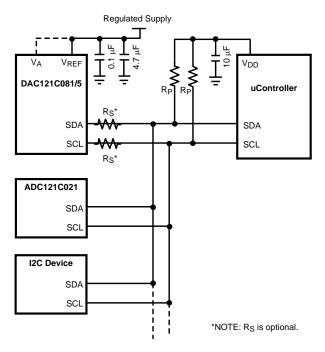

Interfacing the DAC121C081 to microprocessors and DSPs is quite simple. The following guidelines are offered to simplify the design process.

#### 9.1.2.1 Interfacing to the 2-wire Bus

Figure 28 shows a microcontroller interfacing to the DAC121C081 through the 2-wire bus. Pullup resistors (Rp) should be chosen to create an appropriate bus rise time and to limit the current that will be sunk by the opendrain outputs of the devices on the bus. See the  $I^2C^{\$}$  Specification for further details. Typical pullup values to use in Standard-Fast mode bus applications are 2 k $\Omega$  to 10 k $\Omega$ . SCL and SDA series resisters (R<sub>S</sub>) near the DAC121C081 are optional. If high-voltage spikes are expected on the 2-wire bus, series resistors should be used to filter the voltage on SDA and SCL. The value of the series resistance must be picked to ensure the V<sub>IL</sub> threshold can be achieved. If used, R<sub>S</sub> is typically 51  $\Omega$ .

Figure 28. Serial Interface Connection Diagram

#### 9.1.2.2 Interfacing to a Hs-mode Bus

Interfacing to a Hs-mode bus is very similar to interfacing to a Standard-Fast mode bus. In Hs-mode, the specified rise time of SCL is shortened. To create a faster rise time, the master device (microcontroller) can drive the SCL bus high and low. In other words, the microcontroller can drive the line high rather than leaving it to the pullup resistor. It is also possible to decrease the value of the pullup resistors or increase the pullup current to meet the tighter timing specs. See the  $I^2C^{\otimes}$  Specification for further details.

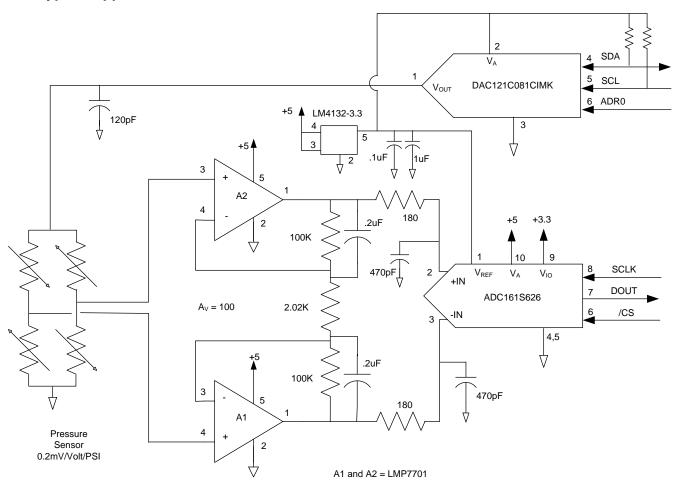

#### 9.2 Typical Application

Figure 29. Pressure Sensor Gain Adjust

#### 9.2.1 Design Requirements

A positive supply only data acquisition system capable of digitizing a pressure sensor output. In addition to digitizing the pressure sensor output, the system designer can use the DAC121C081 to correct for gain errors in the pressure sensor output by adjusting the bias voltage to the bridge pressure sensor.

#### 9.2.2 Detailed Design Procedure

As shown in Equation 4, the output of the pressure sensor is relative to the imbalance of the resistive bridge times the output of the DAC121C081, thus providing the desired gain correction.

Pressure Sensor Output =

$$(DAC_Output \times [(R2/(R1 + R2) - (R4/(R3 + R4))]))$$

(4)

Likewise for the ADC161S626, Equation 5 shows that the ADC output is function of the Pressure Sensor Output times relative to the ratio of the ADC input divided by the DAC121C081 output voltage.

ADC161S626 Output = (Pressure Sensor Output

$$\times$$

100 /(2  $\times$  VREF) )  $\times$  2<sup>16</sup> (5)

# **Typical Application (continued)**

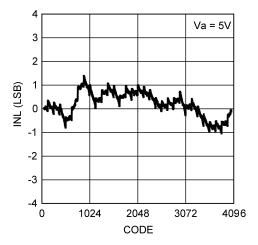

# 9.2.3 Application Curve

Figure 30. INL vs Input Code

#### 10 Power Supply Recommendations

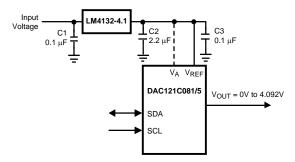

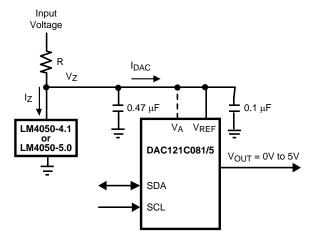

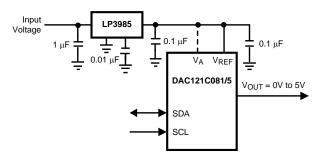

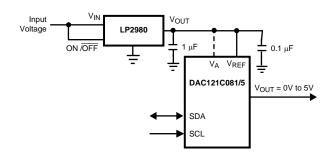

#### 10.1 Using References as Power Supplies