# **DAC101S101**

DAC101S101/DAC101S101Q 10-Bit Micro Power, RRO Digital-to-Analog Converter

Literature Number: JAJSAE9

National Semiconductor 2008年12月

# DAC101S101/DAC101S101Q

10 ビット、マイクロパワー、フルスイング出力対応 D/A コンバータ

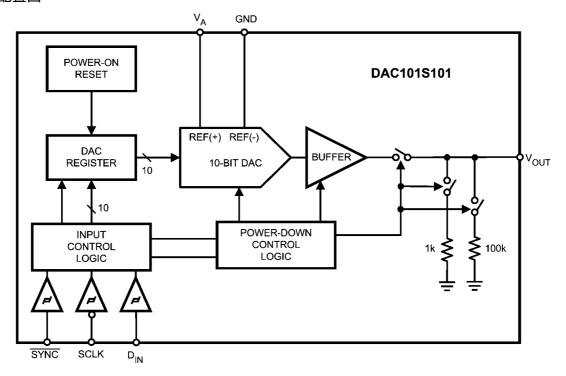

### 概要

DAC101S101 は、変換に必要な機能をすべて備えた、汎用 10 ビット電圧出力 D/A コンバータ (DAC) です。  $+2.7V \sim +5.5V$  の範囲の単一電源で動作し、消費電流は 3.6V で  $175\,\mu A$  です。 フルスイングが得られる出力アンプを内蔵しているほか、全電源電圧範囲にわたって最高  $30 \mathrm{MHz}$  のクロックレートで動作する  $3 \,$  線式 シリアル・インタフェースを備えています。  $\mathrm{SPI}^{\mathrm{TM}}$  、QSPI、

MICROWIRE、DSP インタフェースとの互換性があります。 他社 の競合デバイスは、動作電圧は 2.7V から 3.6V の範囲と狭く、また 20MHz 動作が限界です。

DAC101S101 の電源電圧はリファレンス電圧源として用いられ、できるだけ広い出力ダイナミックレンジを実現します。DAC 出力はパワーオン・リセット回路によってパワーアップ時に 0V に設定され、デバイスに有効な書き込みがあるまで維持されます。パワーダウン機能により消費電力をマイクロワット未満に抑えます。

DAC101S101は消費電力が小さく小型パッケージを採用している ため、バッテリで動作する機器に最適です。

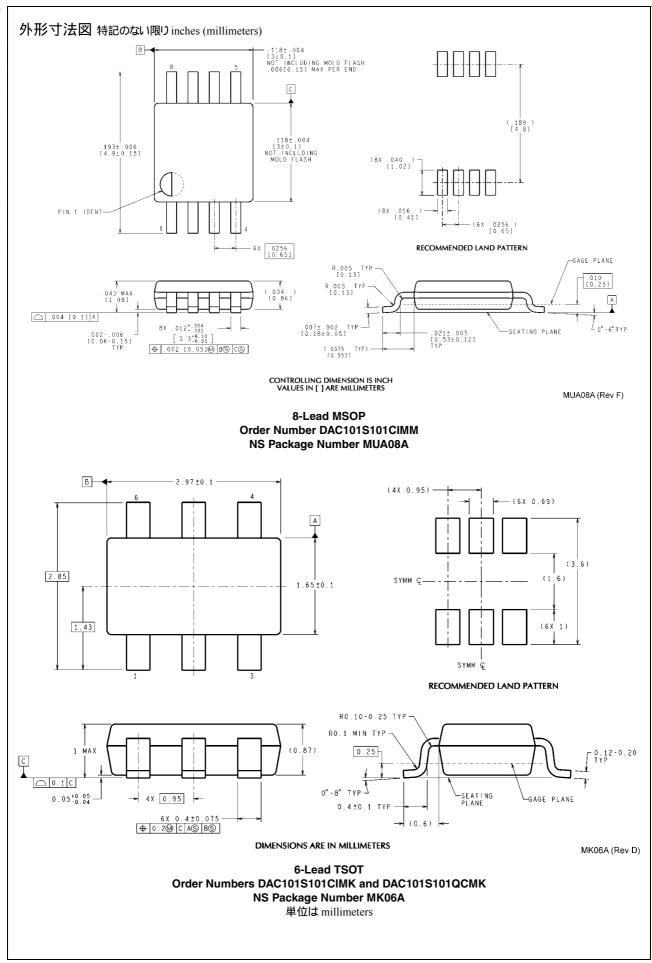

DAC101S101 は AD5310 の上位代替品として最適です。また、8 ビットの DAC081S101 や 12 ビットの DAC121S101 など、ピン互換 DAC ファミリの一員です。 DAC101S101 は拡張工業用温度範囲である-40 ~+105 で動作します。 DAC101S101Q の動作温度範囲は、自動車 / 拡張温度範囲である-40 ~+125 に対応しています。 DAC101S101 は 6 ピンの TSOT パッケージおよび 8 ピンの MSOP パッケージで提供され、DAC101S101Qは6ピンのTSOT パッケージのみで提供されます。

### 特長

DAC101S101Q は、AEC-Q100 グレード 1 認定、車載グレード製品の生産フローで製造されます。

モノトニック(単調上昇)を保証

低消費電力動作

フルスイング電圧出力

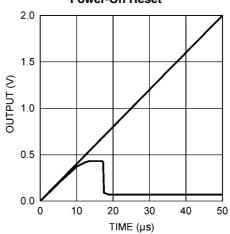

パワーオン・リセット時に出力 0V

広い動作温度範囲(-40~+125)

広い電源電圧範囲 (+2.7V~+5.5V)

小型パッケージ

パワーダウン機能

## 主な仕様

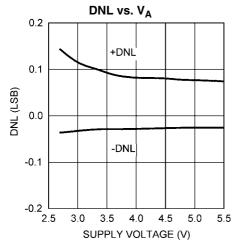

分解能10 ビットDNL+ 0.15、 - 0.05LSB (typ)出力セトノング時間8 µs (typ)ゼロコード誤差3.3mV (typ)フルスケール誤差- 0.06%FS (typ)

消費電力

通常モード 0.63mW (3.6V) /1.41mW (5.5V) (typ) パワーダウン・モード 0.14 µW (3.6V) /0.33 µW (5.5V ) (typ)

### アプリケーション

バッテリ駆動の測定機器 デジタルによるゲインとオフセット制御 プログラマブルな電圧源および電流源 プログラマブルなアッテネータ 車載用

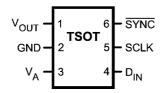

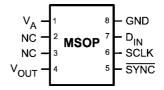

### ピン配置図

SPI™ は Motorola, Inc. の商標です。

# 製品情報

| Order Numbers   | Temperature Range               | Package  | Top Mark | Feature                                        |

|-----------------|---------------------------------|----------|----------|------------------------------------------------|

| DAC101S101CIMM  | -40°C ≤ T <sub>A</sub> ≤ +105°C | MSOP     | V-000    |                                                |

| DAC101S101CIMMX | -40°C ≤ T <sub>A</sub> ≤ +105°C | MSOP T/R | X62C     |                                                |

| DAC101S101CIMK  | -40°C ≤ T <sub>A</sub> ≤ +105°C | TSOT     |          |                                                |

| DAC101S101CIMKX | -40°C ≤ T <sub>A</sub> ≤ +105°C | TSOT T/R | X63C     |                                                |

| DAC101S101QCMK  | -40°C ≤ T <sub>A</sub> ≤ +125°C | TSOT     |          | AEC-Q100 Grade 1                               |

| DAC101S101QCMKX | -40°C ≤ T <sub>A</sub> ≤ +125°C | TSOT T/R | Q63C     | Qualified; Automotive<br>Grade Production Flow |

| DAC101S101EVAL  | Evaluation Board                | TSOT     |          |                                                |

# ピン配置図

# ピン説明

| TSOT<br>(SOT-23)<br>ピン番号 | MSOP<br>ピン番号 | シンボル              | 説明                                                                                                                                                                                               |

|--------------------------|--------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                        | 4            | V <sub>OUTA</sub> | DAC アナログ出力電圧。                                                                                                                                                                                    |

| 2                        | 8            | GND               | 全オンチップ回路のグラウンド。                                                                                                                                                                                  |

| 3                        | 1            | $V_{A}$           | 電源電圧およびリファレンス入力。 GND に対してデカップリングしてください。                                                                                                                                                          |

| 4                        | 7            | D <sub>IN</sub>   | シリアル・データ入力。 データは SYNC が Low になったあとの SCLK の立ち下がリエッジで 16 ビット・シフトレジスタに取り込まれます。                                                                                                                      |

| 5                        | 6            | SCLK              | シリアル・クロック入力。 データはこのクロックの立ち下がりエッジでシフト<br>レジスタに取り込まれます。                                                                                                                                            |

| 6                        | 5            | SYNC              | データ入力のフレーム同期。このピンを Low にすると入力シフトレジスタが有効になり、データは SCLK の立ち下がりエッジでシフトレジスタに取り込まれます。 16 番目の SCLK クロックの前に SYNC を High にして、SYNC の立ち上がりをライト・シーケンスを無視させる割り込みとして DAC に与えない限り、DAC 出力は16番目のクロック・サイクルで更新されます。 |

|                          | 2, 3         | NC                | 未接続。これらのピンは内部接続されていません。                                                                                                                                                                          |

www.national.com/jpn/

## 絶対最大定格 (Note 1、2)

本データシートには軍用・航空宇宙用の規格は記載されていません。 関連する電気的信頼性試験方法の規格を参照ください。

電源電圧 (V<sub>A</sub>) 6.5V 各入力端子電圧 - 0.3V ~ (V<sub>A</sub> + 0.3V) 各端子の入力電流 (Note 3) 10mA パッケージ入力電流 (Note 3) 20mA

消費電力 (T<sub>A</sub> = 25 ) Note 4 参照

ESD 耐性 (Note 5)2500V人体モデル250Vマシン・モデル250Vハンダ付け温度、赤外線

(10 秒) (Note 6)

235

保存温度範囲

- 65 ~ + 150

# 動作定格 (Note 1、2)

動作温度範囲

# パッケージ熱抵抗

| Package     | $\theta_{JA}$ |

|-------------|---------------|

| 8-Lead MSOP | 240°C/W       |

| 6-Lead TSOT | 250°C/W       |

# 電気的特性

以下の仕様は、 $V_A$  = + 2.7V ~ + 5.5V、 $R_L$  = 2k ~ GND、 $C_L$  = GND に対して 200pF、 $f_{SCLK}$  = 30MHz、入力コード範囲 12 ~ 1011 という条件に対して適用されます。 特記のない限り、太字のリミット値は  $T_{MIN}$   $T_A$   $T_{MAX}$  に適用され、他のリミット値は  $T_A$  = 25 に適用されます。

| Symbol    | Parameter                  | Conditions                                    | Typical  | Limits              | Units              |

|-----------|----------------------------|-----------------------------------------------|----------|---------------------|--------------------|

|           |                            |                                               | (Note 9) | (Note 9)            | (Limits)           |

| STATIC PE | RFORMANCE                  |                                               |          |                     |                    |

|           | Resolution                 |                                               |          | 10                  | Bits (min)         |

|           | Monotonicity               |                                               |          | 10                  | Bits (min)         |

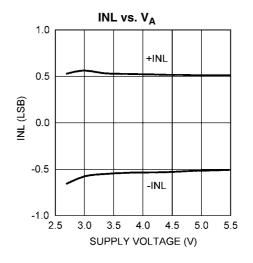

| INL       | Integral Non-Linearity     | Over Decimal codes 12 to 1011                 | ±0.6     | ±2.8                | LSB (max)          |

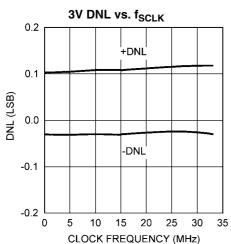

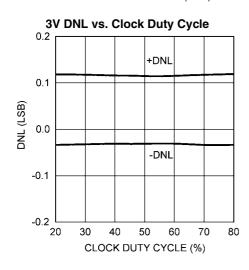

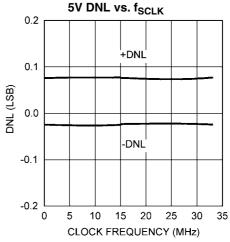

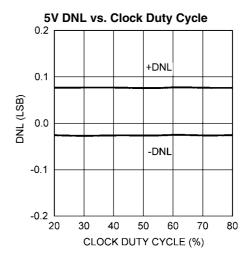

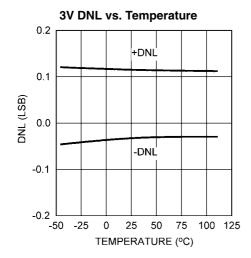

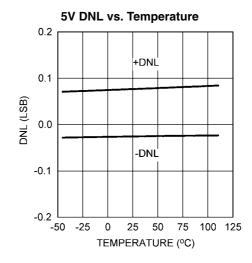

| DNL       | Differential Non-Linearity | $V_A = 2.7V \text{ to } 5.5V$                 | +0.15    | +0.35               | LSB (max)          |

|           |                            |                                               | -0.05    | -0.2                | LSB (min)          |

| ZE        | Zero Code Error            | I <sub>OUT</sub> = 0                          | +3.3     | +15                 | mV (max)           |

| FSE       | Full-Scale Error           | $I_{OUT} = 0$                                 | -0.06    | -1.0                | %FSR (max)         |

| GE        | Gain Error                 | All ones Loaded to DAC register               | -0.10    | ±1.0                | %FSR (max)         |

| ZCED      | Zero Code Error Drift      |                                               | -20      |                     | μV/°C              |

| TC GE     | Gain Error Tempco          | V <sub>A</sub> = 3V                           | -0.7     |                     | ppm/°C             |

|           | Gain Error Tempeo          | V <sub>A</sub> = 5V                           | -1.0     |                     | ppm/°C             |

| OUTPUT C  | HARACTERISTICS             |                                               |          | -                   |                    |

|           | Output Voltage Range       | (Note 10)                                     |          | 0<br>V <sub>A</sub> | V (min)<br>V (max) |

|           |                            | V <sub>A</sub> = 3V, I <sub>OUT</sub> = 10 μA | 1.8      |                     | m∨                 |

| zco       | Zero Code Output           | $V_A = 3V$ , $I_{OUT} = 100 \mu A$            | 5.0      |                     | mV                 |

| 200       |                            | $V_A = 5V$ , $I_{OUT} = 10 \mu A$             | 3.7      |                     | mV                 |

|           |                            | $V_A = 5V$ , $I_{OUT} = 100 \mu A$            | 5.4      |                     | mV                 |

|           | Full Scale Output          | $V_A = 3V$ , $I_{OUT} = 10 \mu A$             | 2.997    |                     | ٧                  |

| FSO       |                            | $V_A = 3V$ , $I_{OUT} = 100 \mu A$            | 2.990    |                     | ٧                  |

|           | Tan Source Suput           | $V_A = 5V$ , $I_{OUT} = 10 \mu A$             | 4.995    |                     | ٧                  |

|           |                            | $V_A = 5V$ , $I_{OUT} = 100 \mu A$            | 4.992    |                     | ٧                  |

|           | Maximum Load Capacitance   | R <sub>L</sub> = ∞                            | 1500     |                     | pF                 |

| ····      | Hazimum Load Capacitance   | $R_L = 2k\Omega$                              | 1500     |                     | pF                 |

|           | DC Output Impedance        |                                               | 1.3      |                     | Ohm                |

# 電気的特性(つづき)

以下の仕様は、 $V_A$  = + 2.7V ~ + 5.5V、 $R_L$  = 2k ~ GND、 $C_L$  = GND に対して 200pF、 $f_{SCLK}$  = 30MHz、入力コード範囲 12 ~ 1011 という条件に対して適用されます。 特記のない限り、太字のリミット値は  $T_{MIN}$   $T_A$   $T_{MAX}$  に適用され、他のリミット値は  $T_A$  = 25 に適用されます。

| Symbol                            | Parameter                        | Conditions                                      |                       | Typical<br>(Note 9) | Limits<br>(Note 9) | Units<br>(Limits) |

|-----------------------------------|----------------------------------|-------------------------------------------------|-----------------------|---------------------|--------------------|-------------------|

| I <sub>OS</sub> Outpu             |                                  | $V_A = 5V$ , $V_{OUT} = 0V$ , Input code = 3FFh |                       | -63                 |                    | mA                |

|                                   |                                  | $V_A = 3V, V_{OUT} = 0V,$<br>Input code = 3FFh  |                       | -50                 |                    | mA                |

|                                   | Output Short Circuit Current     | $V_A = 5V, V_{OUT} = 5V,$<br>Input code = 000h  |                       | 74                  |                    | mA                |

|                                   |                                  | $V_A = 3V, V_{OUT} = 3V,$<br>Input code = 000h  |                       | 53                  |                    | mA                |

| OGIC INP                          | UT                               |                                                 |                       |                     |                    |                   |

| I <sub>IN</sub>                   | Input Current (Note 10)          |                                                 |                       |                     | ±1                 | μA (max)          |

| V                                 | Input Law Voltage (Note 10)      | V <sub>A</sub> = 5V                             |                       |                     | 0.8                | V (max)           |

| $V_{IL}$                          | Input Low Voltage (Note 10)      | $V_A = 3V$                                      |                       |                     | 0.5                | V (max)           |

| V                                 | Input Ligh Voltage (Note 10)     | $V_A = 5V$                                      |                       |                     | 2.4                | V (min)           |

| $V_{iH}$                          | Input High Voltage (Note 10)     | $V_A = 3V$                                      |                       |                     | 2.1                | V (min)           |

| C <sub>IN</sub>                   | Input Capacitance (Note 10)      |                                                 |                       |                     | 3                  | pF (max)          |

| OWER RE                           | QUIREMENTS                       | -                                               |                       | -                   |                    | -                 |

|                                   |                                  | Normal Mode                                     | $V_A = 5.5V$          | 256                 | 332                | μΑ (max)          |

|                                   |                                  | f <sub>SCLK</sub> = 30 MHz                      | $V_A = 3.6V$          | 174                 | 226                | μΑ (max)          |

|                                   |                                  | Normal Mode                                     | V <sub>A</sub> = 5.5V | 221                 | 297                | μΑ (max)          |

|                                   |                                  | f <sub>SCLK</sub> = 20 MHz                      | $V_A = 3.6V$          | 154                 | 207                | μA (max)          |

|                                   |                                  | Normal Mode                                     | V <sub>A</sub> = 5.5V | 145                 |                    | μA (max)          |

|                                   |                                  | f <sub>SCLK</sub> = 0                           | $V_A = 3.6V$          | 113                 |                    | μA (max)          |

| I <sub>A</sub>                    | Supply Current (output unloaded) | All PD Modes,                                   | V <sub>A</sub> = 5.0V | 83                  |                    | μΑ (max)          |

|                                   |                                  | f <sub>SCLK</sub> = 30 MHz                      | $V_A = 3.0V$          | 42                  |                    | μA (max)          |

|                                   |                                  | All PD Modes,                                   | V <sub>A</sub> = 5.0V | 56                  |                    | μA (max)          |

|                                   |                                  | f <sub>SCLK</sub> = 20 MHz                      | $V_A = 3.0V$          | 28                  |                    | μA (max)          |

|                                   |                                  | All PD Modes,                                   | V <sub>A</sub> = 5.5V | 0.06                | 1.0                | μΑ (max)          |

|                                   |                                  | f <sub>SCLK</sub> = 0 (Note 10)                 | $V_A = 3.6V$          | 0.04                | 1.0                | μΑ (max)          |

|                                   |                                  | Normal Mode                                     | V <sub>A</sub> = 5.5V | 1.41                | 1.83               | mW (max           |

|                                   |                                  | f <sub>SCLK</sub> = 30 MHz                      | $V_A = 3.6V$          | 0.63                | 0.81               | mW (max           |

|                                   |                                  | Normal Mode                                     | V <sub>A</sub> = 5.5V | 1.22                | 1.63               | mW (max           |

|                                   | Power Consumption (output        | f <sub>SCLK</sub> = 20 MHz                      | $V_A = 3.6V$          | 0.55                | 0.74               | mW (max           |

| <br>                              |                                  | Normal Mode                                     | V <sub>A</sub> = 5.5V | 0.80                |                    | μW (max)          |

|                                   |                                  | f <sub>SCLK</sub> = 0                           | $V_A = 3.6V$          | 0.41                |                    | μW (max)          |

| $P_{C}$                           | unloaded)                        | All PD Modes,                                   | V <sub>A</sub> = 5.0V | 0.42                |                    | μW (max)          |

|                                   | ·                                | f <sub>SCLK</sub> = 30 MHz                      | $V_A = 3.0V$          | 0.13                |                    | μW (max)          |

|                                   |                                  | All PD Modes,                                   | V <sub>A</sub> = 5.0V | 0.28                |                    | μW (max)          |

|                                   |                                  | f <sub>SCLK</sub> = 20 MHz                      | $V_A = 3.0V$          | 0.08                |                    | μW (max)          |

|                                   |                                  | All PD Modes,                                   | V <sub>A</sub> = 5.5V | 0.33                | 5.5                | μW (max)          |

|                                   |                                  | f <sub>SCLK</sub> = 0 (Note 10)                 | $V_A = 3.6V$          | 0.14                | 3.6                | μW (max)          |

| 1 /1                              | Power Efficiency                 | $I_{LOAD} = 2mA$ $V_A = 5V$ $V_A = 3V$          | V <sub>A</sub> = 5V   | 91                  | •                  | %                 |

| I <sub>OUT</sub> / I <sub>A</sub> |                                  |                                                 | 94                    |                     | %                  |                   |

www.national.com/jpn/ 4

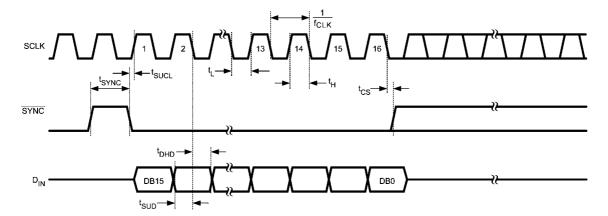

### AC 特性とタイミング仕様

以下の仕様は、 $V_A$  = + 2.7V ~ + 5.5V、 $R_L$  = 2k ~ GND、 $C_L$  = GND に対して 200pF、 $f_{SCLK}$  = 30MHz、入力コード範囲 12 ~ 1011 という条件に対して適用されます。 特記のない限り、太字のリミット値は  $T_{MIN}$   $T_{A}$   $T_{MAX}$  に適用され、他のリミット値は  $T_A$  = 25 に適用されます。

| Symbol                       | Parameter                              | Conductions                                |                         | Typical | Limits | Units<br>(Limits) |

|------------------------------|----------------------------------------|--------------------------------------------|-------------------------|---------|--------|-------------------|

| f <sub>SCLK</sub>            | SCLK Frequency                         |                                            |                         |         | 30     | MHz (max)         |

| t <sub>s</sub>               | Output Voltage Settling Time (Note 10) | 100h to 300h code change, $R_L = 2k\Omega$ | C <sub>L</sub> ≤ 200 pF | . 5     | 7.5    | μs (max)          |

| SR                           | Output Slew Rate                       |                                            |                         | 1       |        | V/µs              |

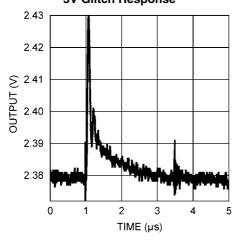

|                              | Glitch Impulse                         | Code change from 20                        | 0h to 1FFh              | 12      |        | nV-sec            |

|                              | Digital Feedthrough                    |                                            |                         | 0.5     |        | nV-sec            |

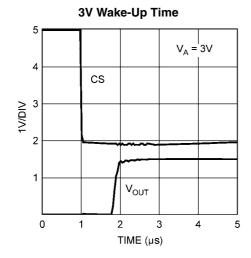

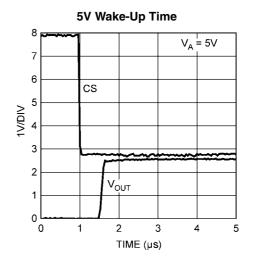

| + Walsa I la Tima            | Wake-Up Time                           | V <sub>A</sub> = 5V                        |                         | 6       |        | μs                |

| t <sub>wu</sub> Wake-Up Time |                                        | V <sub>A</sub> = 3V                        |                         | 39      |        | μs                |

| 1/f <sub>SCLK</sub>          | SCLK Cycle Time                        |                                            |                         |         | 33     | ns (min)          |

| t <sub>H</sub>               | SCLK High time                         |                                            |                         | 5       | 13     | ns (min)          |

| tլ                           | SCLK Low Time                          |                                            |                         | 5       | 13     | ns (min)          |

| t <sub>sucL</sub>            | Set-up Time SYNC to SCLK Rising Edge   |                                            |                         | -15     | 0      | ns (min)          |

| t <sub>sup</sub>             | Data Set-Up Time                       |                                            |                         | 2.5     | 5      | ns (min)          |

| t <sub>DHD</sub>             | Data Hold Time                         |                                            |                         | 2.5     | 4.5    | ns (min)          |

|                              | SCLK fall to rise of SYNC              | V <sub>A</sub> = 5V                        |                         | 0       | 3      | ns (min)          |

| t <sub>cs</sub>              | SOLN IAII IO FISE OF STING             | V <sub>A</sub> = 3V                        |                         | -2      | 1      | ns (min)          |

|                              | SYNC High Time                         | 2.7 ≤ V <sub>A</sub> ≤ 3.6                 |                         | 9       | 20     | ns (min)          |

| t <sub>SYNC</sub>            | STI40 Filgir Filme                     | $3.6 \le V_A \le 5.5$                      |                         | 5       | 10     | ns (min)          |

Note 1: 絶対最大定格とは、IC に破壊が発生する可能性があるリミナ値をいいます。動作定格とはデバイスが機能する条件を示しますが、特定の性能リミナ値を保証するものではありません。保証された仕様、および試験条件については「電気的特性」を参照してください。保証された仕様はリストに示された試験条件でのみ適用されます。また、記載の試験条件以外でデバイスを動作させると、性能特性が低下することがあります。

**Note 2:** 特記のない限り、全電圧は GND = 0 を基準にして測定されます。

Note 3: いずれかのピンで入力電圧  $(V_{IN})$  が電源電圧を超えた場合 (すなわち  $V_{IN} < GND$ 、または  $V_{IN} > V_A$  のどき )、そのピンの入力電流を 10mA 以下に制限しなければなほせん。最大パッケージ入力定格電流(20mA)におり、電源電圧を超えて10mAの電流を流すことができるピン数は2本に制限されます。

Note 4: 温度上昇時の動作では、最大消費電力の定格を T<sub>J</sub>max (最大接合部温度:このデバイスの場合、T<sub>J</sub>max は 150 )、 J<sub>A</sub> (接合部・周囲温度間熱抵抗)、T<sub>A</sub> (周囲温度)に従ってディレーティングしなければな)ません。任意温度における最大許容消費電力は、P<sub>D</sub>MAX = (T<sub>J</sub>max - T<sub>A</sub>)/ J<sub>A</sub> または「絶対最大定格」で示される値のうち、いずれか低い方の値です。デバイスが重大な障害 (たとえば入力ピンや出力ピンが電源電圧を超えて駆動されている場合、あるいは電源の極性が反転している場合)にある場合にのみ最大消費電力値に到達することがあります。明らかにこのような条件での動作は避けなければな)ません。

Note 5: 人体モデルの場合、100pF のコンデンサから直列抵抗 1.5k を通して各ピンに放電させます。 マシン・モデルの場合は、220pF のコンデンサから直接 各ピンに放電させます。

Note 6: 面実装デバイスのハンダ付け方法については、1986 年以降に発行された「National Semiconductor Linear Data Book」の "Surface Mount" セクション を参照してください。

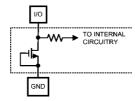

Note 7: 以下に示すように、各アナログ入出力ピンは 1 個のツェナーダイオードで保護されています。 入力電圧が最大  $V_A$  + 300mV もしくは GND の 300mV 以内の電圧までの振幅の場合にはデバイスが損傷を受けることはありません。 しかし、入力電圧が  $V_A$  より 100mV を超えて上昇するか GND が 100mV より下回る場合は変換結果に誤差を生じる可能性があります。 例えば、 $V_A$  =  $2.7V_{DC}$  の場合、変換精度を確保するには - 100mV 入力電圧  $2.8V_{DC}$  にする必要があります。

**Note 8:** 精度を保証するために、 $V_A$  ピンにはそれぞれ別個のバイパス・コンデンサを設けて同一電源に接続します。

**Note 9:** 代表値 (typ) は、T<sub>J</sub> = 25 で得られる最も標準的な数値です。テスト・リミット値はナショナル セミコンダクターの平均出荷品質レベル AOQL に基づき保証されます。

Note 10: このパラメータは設計と特性評価によって保証されています。 製造時の試験は行っていません。

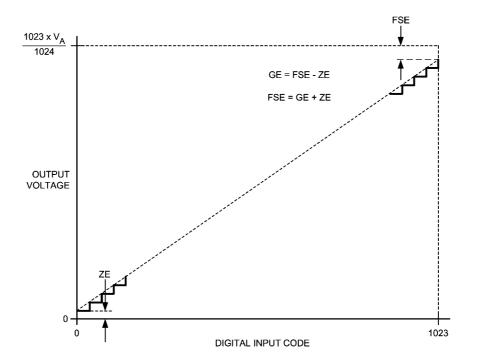

### 用語の定義

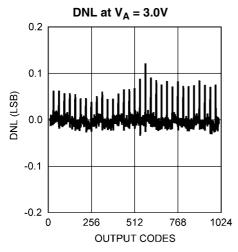

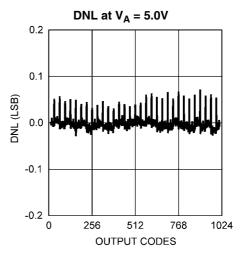

微分非直線性 (DIFFERENTIAL NON-LINEARITY: DNL) は 理想的な 1LSB ステップからの最大偏差を表します。 1LSB は  $V_{REF}/1024$  =  $V_{A}/1024$  です。

デジタル・フィードスルー(DIGITAL FEEDTHROUGH) は、DAC 出力が更新されないときに、デジタル入力から DAC のアナログ出力に注入されるエネルギーです。 データバス上のフルスケール・コード変化を用いて測定します。

フルスケール誤差 **(FULL-SCALE ERROR)** は、DAC にフルスケール・コード (3FFh) をロードしたときの実際の出力電圧と  $V_A \times 1023/1024$  の値との差です。

ゲイン誤差 (GAIN ERROR) は、伝達関数の理想カーブからの偏差です。 ゲイン誤差 GE はゼロスケール誤差 ZE とフルスケール誤差 FSE から、GE = FSE - ZE として求められます。

グリッチ・インパルス (GLITCH IMPULSE) は DAC レジスタへの入力コードが変化したときにアナログ出力に注入されるエネルギーです。 単位を nV-s (ナノボルト秒)とするグリッチ面積で規定されます。

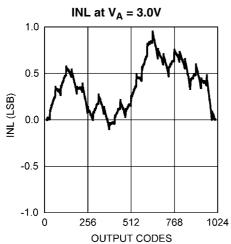

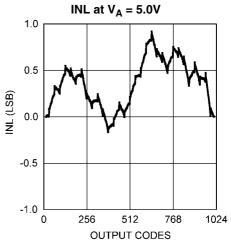

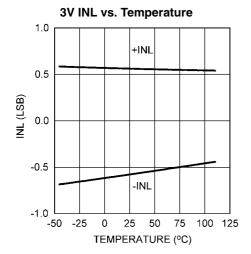

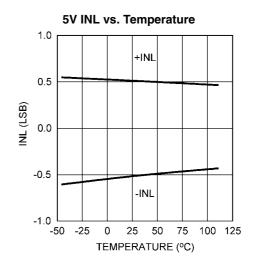

積分非直線性 (INTEGRAL NON-LINEARITY: INL) は、入力から出力への伝達関数を通る直線を基準とした、各個別コードの偏差を表します。この直線から任意のコードとの偏差は、各コード値の中央から測定します。 エンド・ポイント法が用いられます。この製品の INL は電気的特性のとおり制限付き範囲に対して規定されます。

LSB (LEAST SIGNIFICANT BIT) は、全ビットのうち、最も小さな値、または最も小さな重みを持ったビットです。 LSB の値は、

LSB =

$$V_{REF}/2^n$$

ここで  $V_{REF}$  は製品の電源電圧、"n" は単位をビットとする DAC の分解能で DAC101S101 の場合は 10 です。

最大負荷容量 (MAXIMUM LOAD CAPACITANCE) は出力が 安定したままの状態で DAC が駆動できる最大容量です。

単調性 (MONOTONICITY) とは、入力コードを増加させたときに DAC 出力が決して減少しない、単調上昇となる条件を指します。

最上位ビット (MSB) は、ワード中のすべてのビットのうち、最も値の大きなビット、あるいは最も重みの重いビットを指します。 MSB の値は  $V_{\rm RFF}$  の 1/2 です。

電力効率(POWER EFFICIENCY)は全消費電流に対する出力電流の比です。出力電流は電源から与えられます。消費電流と出力電流の差は、負荷がない状態でデバイスが消費する電力です。

セトリング時間 (SETTLING TIME) は、出力が最終値の 1/2LSB の範囲内に落ち着くまでの時間です。

ウェイクアップ時間 (WAKE-UP TIME) は、デバイスにパワーダウン・モードからアクティブ・モードに復帰する指示が出された後で、出力が最終値の 1/2LSB の範囲内に落ち着くまでの時間です。

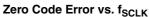

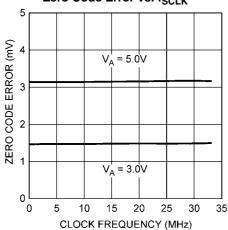

ゼロコード誤差 (ZERO CODE ERROR) は、コード 000h を入力 したときに DAC 出力に現れる、出力誤差あるいは電圧です。

# 变換特性

FIGURE 1. Input / Output Transfer Characteristic

# タイミング図

FIGURE 2. DAC101S101 Timing

# 代表的な性能特性

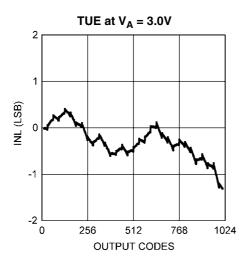

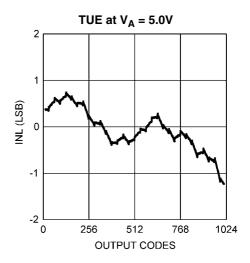

特記のない限り、f<sub>SCLK</sub> = 30MHz、T<sub>A</sub> = 25 、入力コード・レンジ 12 ~ 1011。

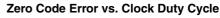

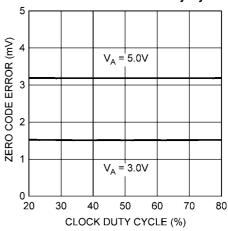

## **Zero Code Error vs. Temperature**

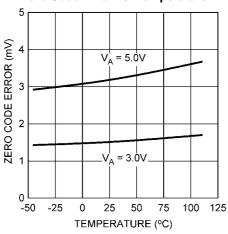

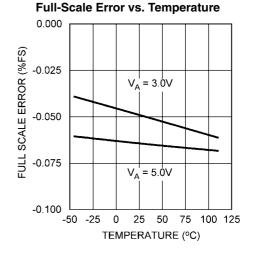

# Full-Scale Error vs. f<sub>SCLK</sub>

特記のない限り、f<sub>SCLK</sub> = 30MHz、T<sub>A</sub> = 25 、入力コード・レンジ 12 ~ 1011。

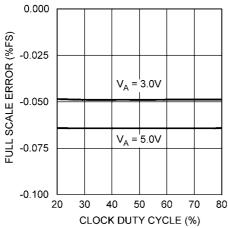

# Full-Scale Error vs. Clock Duty Cycle

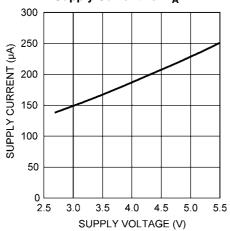

# Supply Current vs. V<sub>A</sub>

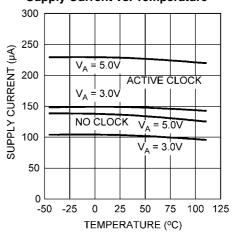

## Supply Current vs. Temperature

# **5V Glitch Response**

# Power-On Reset

#### 1.0 機能説明

#### 1.1 DAC セクション

DAC101S101 は CMOS プロセスで製造され、出力バッファの前段を抵抗ストリングとスイッチで構成するアーキテクチャを採用しています。 電源は、リファレンス電圧として機能します。 入力コードの形式はストレート・バイナリで理想出力電圧は次のとおりです。

$$V_{OUT} = V_A \times (D/1024)$$

ここで、D は DAC レジスタにロードされたバイナリ・コードと等価な 10 進数であり、0 ~ 1023 の範囲の値となります。

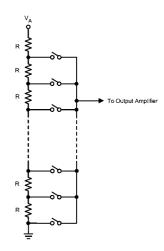

#### 1.2 抵抗ストリング

Figure 3 に抵抗ストリングを示します。この抵抗列は値の等しい 1024 本の直列抵抗から構成され、このうちの 2 本の抵抗の接点に対して 1 つの割合でスイッチがあります。 さらに、最後のスイッチの一端はグラウンドに接続されています。 DAC レジスタにロードされたコードによって閉じるべきスイッチ回路が決まり、適切なノードがアンプに接続されます。この動作は DAC のモノトニック性(単調上昇)を保証します。

FIGURE 3. DAC Resistor String

### 1.3 出力アンプ

出力バッファ・アンプはフルスイングに対応しており、0V から  $V_A$  の範囲の出力電圧が得られます。フルスイング・アンプであってもあらゆるアンプは出力電圧が電源レール (この場合で 0V と  $V_A$ ) に近づくにつれてリニアリティが悪化します。 そのため、リニアリティは DAC の全出力範囲より洗練い範囲で規定されます。アンプの出力能力は電気的特性の表に規定されています。

#### 1.4 シリアル・インタフェース

3 線式インタフェースは SPI、QSPI、MICROWIRE、およびほと んどの DSP インタフェースと互換性があります。 ライト・シーケンス の詳細はタイミング図を参照してください。

ライト・シーケンスは SYNC 信号を Low にした時点から始まはす。 SYNC を Low にすると、 D<sub>IN</sub> ピンのデータは SCLK クロックの立ち下がりエッジで 16 ビット・シリアル入力レジスタに取り込まれます。 16 番目の立ち下がりエッジで最終データ・ビットが取り込まれ、プログラミングされた機能が実行されます (動作モード指定、レジスタ内容の変更)。 この時点で SYNC ピンは Low に維持したままでも、 あるいは High にしてもかまいません。 いずれの場合も、 SYNC の立ち下がりエッジで次の書き込みサイクルを開始するには、次のライト・シーケンスの前に最小規定時間以上 High にしなければなりません。

SYNC バッファとD<sub>IN</sub> バッファはそれぞれピン電圧が High のときに より多くの電流を引き込むため、消費電力を抑えるにはライト・シーケンス中以外は Low に維持してください。

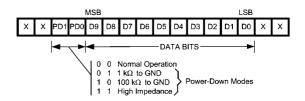

#### 1.5 入力シフトレジスタ

入力シフトレジスタは Figure 4 のとおり 16 ビットで構成されています。 先頭の 2 ビットは "don't cares" であり、この後ろに動作モード ( ノーマル・モードまたは 3 つのパワーダウン・モードのうちの 1 つ ) を決定する 2 つのビットが続きます。 シリアル入力レジスタの内容は SCLK の 16 番目の立ち下がりエッジで DAC レジスタに転送されます。 Figure 2 のタイミング図を参照してください。

FIGURE 4. Input Register Contents

通常、SYNC 信号は SCLK の 16 個の立ち下がリエッジ期間中は Low に維持します。 DAC は 16 番目の立ち下がリエッジで更新されます。 ただし、16 番目の立ち下がリエッジの前に SYNCが High になると、シフト・レジスタがリセットされ、ライト・シーケンスが無効となります。 DAC レジスタは更新されず、動作モードの変更の更新は行われません。

### 1.6 パワーオン・リセット

パワーオン・リセット回路はパワーアップ中の出力電圧を制御します。電源投入時、DAC レジスタには 0 で満たされており、出力電圧は 0V であり、DAC に有効なライト・シーケンスがあるまでこの状態が維持されます。

### 1.7 パワーダウン・モード

DAC101S101 には、4 つの動作モードがあります。 これらのモードは、コントロール・レジスタの 2 つのビット (DB13 と DB12) で設定されます。

**TABLE 1. Modes of Operation**

| DB13 | DB12 | Operating Mode               |  |

|------|------|------------------------------|--|

| 0    | 0    | Normal Operation             |  |

| 0    | 1    | Power-Down with 1kΩ to GND   |  |

| 1    | 0    | Power-Down with 100kΩ to GND |  |

| 1    | 1    | Power-Down with Hi-Z         |  |

DB13とDB12 が両方とも0 である場合、デバイスは通常の動作をします。これらのビットの他の3 つの組み合わせについては、Table 1 に示すとおり、消費電流がパワーダウン・レベルまで低下し、1k または100k の抵抗でプルダウンされるか、ハイ・インピーダンス状態に置かれます。

いずれのパワーダウン・モードでも、バイアス・ジェネレータ、出力アンプ、抵抗ストリング、およびその他のリニア回路はすべてシャットダウンされます。 ただし、DAC レジスタの内容はパワーダウン・モードによる影響を受けないため、パワーダウンから復旧したときには、出力電圧はパワーダウン前の電圧に戻ります。 消費電力は、パワーダウン・モードに加えて、 $\overline{SYNC}$  と $D_{IN}$ を Low にして SCLK を停止したときに最も小さくなります。 パワーダウンからの復帰時間 (ウェイクアップ時間) は、AC 特性とタイミング仕様の表に示すように通常  $t_{WII}$  µs です。

### 2.0 アプリケーション情報

DAC101S101 は構成が単純で使い勝手に優れています。ただし、電源をリファレンス電圧として利用しているデータ・コンバータは本質的に電源電圧除去比 (Power Supply Rejection Ratio: PSRR)を備えていないことを理解しておく必要があります。そのためデバイスにはノイズのないクリーンな電源を与えなければなりません。

#### 2.1 DSP/ マイクロプロセッサとのインタフェース

DAC101S101 とマイクロプロセッサや DSP とのインタフェースはご く単純です。 以下のガイドラインを活用して設計プロセス期間を短縮してください。

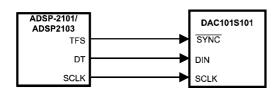

#### 2.1.1 ADSP-2101/ADSP2103 とのインタフェース

Figure 5 に DAC101S101 と ADSP-2101/ADSP2103 間のシリア ル・インタフェースを示します。 DSP は SPORT Transmit Alternate Framing Mode 動作に設定します。プログラミングは SPORT 制御レジスタを介して行い、Internal Clock Operation、Active Low Framing、16-bit Word Length に構成します。 転送は SPORT モードをイネーブルにしたあとの Tx レジスタへのワード書き込みで始まります。

FIGURE 5. ADSP-2101/2103 Interface

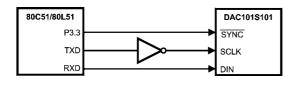

### 2.1.2 80C51/80L51 とのインタフェース

DAC101S101 と80C51/80L51 マイクロコントローラ間のシリアル・インタフェースを Figure 6 に示します。 SYNC 信号はマイクロコントローラのビットプログラマブル・ピンから出力されます。 この例ではポート・ライン P3.3 を使用しています。この信号はデータがDAC101S101 に転送されるときに Low になります。80C51/80L51は8 ビット・バイトを転送するため、送信サイクルには立ち下がリクロック・エッジは8 個しか存在しません。DAC にデータをロードするには1回目の8 ビット転送後もP3.3 信号を Low に維持しておく必要があります。2回目の書き込みサイクルを開始してデータの第2 バイトを転送したあとで、ポートライン P3.3 を High にします。80C51/80L51が LSBを先頭にデータを送信するのに対してDAC101S101は MSBを先頭にロードする点に注意して、80C51/80L51の送信ルーチンを作成してください。

FIGURE 6. 80C51/80L51 Interface

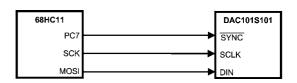

#### 2.1.3 68HC11 インタフェース

DAC101S101と68HC11マイクロコントローラ間のシリアル・インタフェースを Figure 7に示します。DAC101S101の SYNC 信号は80C51/80L51と同様にポート・ラインから駆動します(図の PC7)。

68HC11 の CPOL ビットをゼロに設定し CPHA ビットを 1 に設定してください。この設定によって MOSI 出力のデータは SCLK クロッ

クの立ち下がリエッジで有効になます。PC7がLowになるとDACにデータが転送されます。68HC11は8ビット・バイトのデータを8つのクロックの立ち下がリエッジに同期して送信します。 データはMSBを先頭に送信されます。 PC7は1回目の8ビット転送が終わったあともLowに維持しておかなければなりません。2回目の書き込みサイクルを開始してDACに2番目のデータを転送したあと、PC7をHighにしてライト・シーケンスを終了します。

FIGURE 7. 68HC11 Interface

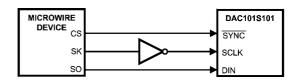

#### 2.1.4 Microwire インタフェース

Figure 8 に Microwire 互換デバイスと DAC1018101 間のインタフェースを示します。 データは SCLK 信号の立ち上がりエッジで出力されます。

FIGURE 8. Microwire Interface

#### 2.2 リファレンス電圧を電源として使用

電源電圧をリファレンス電圧として使用するデバイスには、待機時供給源が必要であることを念頭に入れてください。

DAC1014S101 はきわめて少ない電力しか消費しませんので、リファレンス・ソースを電源としても使用することが可能です。 電圧レギュレータをリファレンス・ソースとして使うメリットは精度と安定性です。 DAC101S101 の電源電圧として一部の低ノイズ・レギュレータも使えます。以下に DAC101S101 の電源として好適なデバイスをリストアップしておきます。

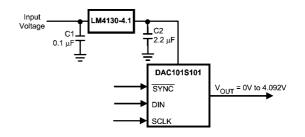

### 2.2.1 LM4130

温度範囲にわたって 0.05% の精度を持つ LM4130 は DAC101S101 のリファレンス・ソースとして好適です。この製品の主な欠点は、3Vと5Vのバージョンがないことです。しかし 0V ~ 4.096V の出力範囲が好ましい場合、あるいは許容される場合、4.096V 品が使えます。 VIN ピンを 0.1 μF コンデンサでバイパスし、 VOUT ピンを 2.2 μF でバイパスすると、安定性が高まり出力ノイズが減少します。 LM4130 は小型 5 ピン SOT23 パッケージで供給されます。

FIGURE 9. The LM4130 as a power supply

### 2.0 アプリケーション情報(つづき)

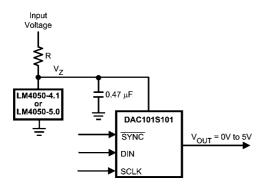

#### 2.2.2 LM4050

精度 0.44% の LM4050 シャント・リファレンスも DAC101S101 の電源レギュレータとして好適です。この製品には 3V 品はありませんが、4.096V 品と 5V 品とがあります。 LM4050 は小型 3 ピンSOT23 パッケージで供給されます。

FIGURE 10. The LM4050 as a power supply

Figure 10 の回路で抵抗 R の最小値は、LM4050 を流れる最大電流が定格の 15mA を超えないように選択してください。電流が最大となる条件は、入力電圧が最も高く、LM4050 の出力電圧が最も低く、抵抗の誤差が最も小さい側にあって、DAC101S101がゼロ電流を引き込んでいる場合です。また、抵抗 R の最大値は、LM4050 がレギュレーションに必要とする最小電流に加えて、DAC101S101 がフル動作をしたときの最大電流が流せるように設定します。電流が最小となる条件は、入力電圧が最も低く、LM4050 の出力電圧が最も高く、抵抗の誤差が最も大きい側にあって、DAC101S101 が最大電流を引き込んでいる場合です。これらの条件は次のように記述することができます。

$R(min) = (V_{IN}(max) - V_{Z}(min) / (I_{A}(min) + I_{Z}(max))$  および

$R(max) = (V_{IN}(min) - V_{Z}(max)) / (I_{A}(max) + I_{Z}(min))$

ここで  $V_Z(min)$  と  $V_Z(max)$  は LM4050 の公称出力電圧±温度に対する LM4050 の出力変動、 $I_Z(max)$  は LM4050 を流れる最大許容可能電流、 $I_Z(min)$  は LM4050 が適切なレギュレーションに必要とする最小電流、 $I_A(max)$  は DAC101S101 の最大消費電流、 $I_A(min)$  は DAC101S101 の最小消費電流です。

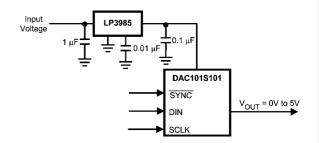

#### 2.2.3 LP3985

LP3985 は低ノイズの超低ドロップアウト電圧レギュレータで、精度は温度範囲にわたって 3% です。 高精度なリファレンスを必要としない DAC101S101 アプリケーションに好適です。3.0V 品、3.3V 品、5V 品などがあり、低周波数の 30µV という低ノイズを誇ます。低周波ノイズはフィルタリングが難しいため、この仕様は一部のアプリケーションでは問題になります。 LP3985 は小型 5 ピンSOT23 パッケージと 5 バンプ micro SMD パッケージで供給されます。

FIGURE 11. Using the LP3985 regulator

入力コンデンサは 1.0μF で LP3985 の入力側にはいかなる ESR 要件も必要としません。一方、出力には 5m から 500m の範囲の ESR を持つ 1.0μF のセラシック・コンデンサが必要です。デバイスの適切な動作を確保するため、コンデンサの仕様は十分注意して読み解いてください。

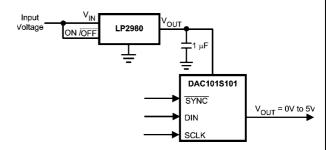

#### 2.2.4 LP2980

LP2980 は超低ドロップアウト・レギュレータで、精度はグレードに応じて異なり、温度範囲にわたって 0.5% または 1.0% です。 3.0V 品、 3.3V 品、 5V 品などがあります。

FIGURE 12. Using the LP2980 regulator

他の低ドロップアウト・レギュレータと同様に、LP2980 はループ安定性を確保するために出力コンデンサを必要とします。出力コンデンサは温度範囲にわたって少なくとも1.0 μF の容量が必要であり、2.2 μF 以上でより良好な性能が得られます。コンデンサの ESR は LP2980 データシートで規定される範囲内になければなりません。面実装ダンタル・コンデンサが物理的な大きさと ESR の両面で適当です。セラミック・コンデンサはその小ささが特長ですが、LP2980 に使用するには一般に ESR 値が小さすぎます。アルミ電解コンデンサはサイズが大きく低温側で ESR 値が高くなるため、一般に適切ではありません。

## 2.0 アプリケーション情報(つづき)

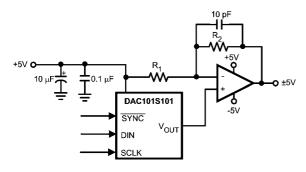

## 2.3 バイポーラ動作

DAC101S101 は単一電源動作で設計されているため、出力はユニポーラです。 ただし、Figure 13 の回路を使用すればバイポーラ出力が得られます。 この回路の出力電圧範囲は± 5V です。アンプ電源が± 5V の場合はフルスイング・アンプを使用してください。

FIGURE 13. Bipolar Operation

あるコードが与えられたとき、この回路の出力電圧は次のとおりです。

$V_{O}$  =  $(V_{A} \times (D / 1024) \times ((R1 + R2) / R1) - V_{A} \times R2 / R1)$  ここで、D は 10 進で表した入力コードです。  $V_{A}$  = 5V、R1 = R2 のとき、

$$V_O = (10 \times D / 1024) - 5V$$

このアプリケーションに好適なフルスイング・アンプの一覧を Table 2 に示します。

TABLE 2. Some Rail-to-Rail Amplifiers

| AMP     | PKGS             | Typ V <sub>os</sub> | Typ I <sub>SUPPLY</sub> |

|---------|------------------|---------------------|-------------------------|

| LMC7111 | DIP-8<br>SOT23-5 | 0.9 mV              | 25 μΑ                   |

| LM7301  | SO-8<br>SOT23-5  | 0.03 mV             | 620 µA                  |

| LM8261  | SOT23-5          | 0.7 mV              | 1 mA                    |

### 2.4 レイアウト、グラウンド、バイパス

変換精度を可能な限り高めノイズをできるだけ抑えるには、 DAC101S101 を実装するプリント回路板上でアナログ領域とデジ タル領域とを分離する必要があります。これらの領域はアナログ電 源層とデジタル電源層の割り当てによって決まります。両方の電源 層は同一の基板層に配置してください。また、グラウンド層は単 ーグラウンドとして構成してください。単一グラウンド層が適切な条 件は、デジタル・リターン電流がアナログ・グラウンド領域を流れ ない場合です。一般に単一グラウンド層設計では、「遮断」テク ニックを使ってアナログ・グラウンド電流とデジタル・グラウンド電流 との混入を防止します。個別グラウンド層は遮断テクニックが不適 切な場合にのみ使用してください。個別グラウンド層の場合は、 可能ならば DAC101S101 の近くで、一点でのみ互いを接続しま す。エッジ・レートが高速なデジタル信号がグラウンド層の分割境 界をまたがないように十分注意してください。このようなデジタル信 号は信号トレースの直下に連続したリターン・パスを形成してしま うからです。

DAC101S101 の電源はデバイスの近くに配置した  $10\mu F \ge 0.1\mu F$  コンデンサでバイパスしてください。  $0.1\mu F$  をデバイスの電源側に配置します。  $10\mu F$  コンデンサにはタンタル・タイプを使用してください。  $0.1\mu F$  コンデンサは低 ESL かつ低 ESR でなければなりません。 DAC101S101 に与える電源はアナログ回路とのみ共用してください。

アナログ信号とデジタル信号の交差は避け、クロックとデータ・ラインは基板の部品面にルーティングしてください。 クロックとデータ・ラインの各トレースは管理されたインピーダンスで設計します。

このドキュメントの内容はナショナル セミコンダクター社製品の関連情報として提供されます。ナショナル セミコンダクター社は、この発行物の内容の正確性または完全性について、いかなる表明または保証もいたしません。また、仕様と製品説明を予告なく変更する権利を有します。このドキュメントはいかなる知的財産権に対するライセンスも、明示的、黙示的、禁反言による惹起、またはその他を問わず、付与するものではありません。

試験や品質管理は、ナショナル セミコンダクター社が自社の製品保証を維持するために必要と考える範囲に用いられます。政府が 課す要件によって指定される場合を除き、各製品のすべてのパラメータの試験を必ずしも実施するわけではありません。ナショナ ル セミコンダクター社は製品適用の援助や購入者の製品設計に対する義務は負いかねます。ナショナル セミコンダクター社の部品 を使用した製品および製品適用の責任は購入者にあります。ナショナル セミコンダクター社の製品を用いたいかなる製品の使用ま たは供給に先立ち、購入者は、適切な設計、試験、および動作上の安全手段を講じなければなりません。

それら製品の販売に関するナショナル セミコンダクター社との取引条件で規定される場合を除き、ナショナル セミコンダクター社 は一切の義務を負わないものとし、また、ナショナル セミコンダクター社の製品の販売か使用、またはその両方に関連する特定目的への適合性、商品の機能性、ないしは特許、著作権、または他の知的財産権の侵害に関連した義務または保証を含むいかなる表明または黙示的保証も行いません。

### 生命維持装置への使用について

ナショナル セミコンダクター社の製品は、ナショナル セミコンダクター社の最高経営責任者 (CEO) および法務部門 (GENERAL COUNSEL) の事前の書面による承諾がない限り、生命維持装置または生命維持システム内のきわめて重要な部品に使用することは認められていません。

こって、生命維持装置またはシステムとは (a) 体内に外科的に使用されることを意図されたもの、または (b) 生命を維持あるいは 支持するものをいい、ラベルにより表示される使用法に従って適切に使用された場合に、これの不具合が使用者に身体的障害を与 えると予想されるものをいいます。重要な部品とは、生命維持にかかわる装置またはシステム内のすべての部品をいい、これの不 具合が生命維持用の装置またはシステムの不具合の原因となりそれらの安全性や機能に影響を及ぼすことが予想されるものをいい ます。

- National Semiconductor とナショナル セミコンダクターのロゴはナショナル セミコンダクター コーポレーションの登録商標です。 その他のプランド や製品名は各権利所有者の商標または登録商標です。

Copyright © 2009 National Semiconductor Corporation 製品の最新情報については www.national.com をご覧ください。

## ナショナル セミコンダクター ジャパン株式会社

本社 / 〒 135-0042 東京都江東区木場 2-17-16

TEL.(03)5639-7300

技術資料(日本語/英語)はホームページより入手可能です。

www.national.com/jpn/

本資料に掲載されているすべての回路の使用に起因する第三者の特許権その他の権利侵害に関して、弊社ではその責を負いません。また掲載内容は予告無く変更されることがありますのでご了承ください。

# ご注意

日本テキサス・インスツルメンツ株式会社(以下TIJといいます)及びTexas Instruments Incorporated(TIJの親会社、以下TIJないしTexas Instruments Incorporatedを総称してTIといいます)は、その製品及びサービスを任意に修正し、改善、改良、その他の変更をし、もしくは製品の製造中止またはサービスの提供を中止する権利を留保します。従いまして、お客様は、発注される前に、関連する最新の情報を取得して頂き、その情報が現在有効かつ完全なものであるかどうかご確認下さい。全ての製品は、お客様とTIJとの間に取引契約が締結されている場合は、当該契約条件に基づき、また当該取引契約が締結されていない場合は、ご注文の受諾の際に提示されるTIJの標準販売契約約款に従って販売されます。

TIは、そのハードウェア製品が、TIの標準保証条件に従い販売時の仕様に対応した性能を有していること、またはお客様とTIJとの間で合意された保証条件に従い合意された仕様に対応した性能を有していることを保証します。検査およびその他の品質管理技法は、TIが当該保証を支援するのに必要とみなす範囲で行なわれております。各デバイスの全てのパラメーターに関する固有の検査は、政府がそれ等の実行を義務づけている場合を除き、必ずしも行なわれておりません。

TIは、製品のアプリケーションに関する支援もしくはお客様の製品の設計について責任を負うことはありません。TI製部品を使用しているお客様の製品及びそのアプリケーションについての責任はお客様にあります。TI製部品を使用したお客様の製品及びアプリケーションについて想定されうる危険を最小のものとするため、適切な設計上および操作上の安全対策は、必ずお客様にてお取り下さい。

TIは、TIの製品もしくはサービスが使用されている組み合せ、機械装置、もしくは方法に関連しているTIの特許権、著作権、回路配置利用権、その他のTIの知的財産権に基づいて何らかのライセンスを許諾するということは明示的にも黙示的にも保証も表明もしておりません。TIが第三者の製品もしくはサービスについて情報を提供することは、TIが当該製品もしくはサービスを使用することについてライセンスを与えるとか、保証もしくは是認するということを意味しません。そのような情報を使用するには第三者の特許その他の知的財産権に基づき当該第三者からライセンスを得なければならない場合もあり、またTIの特許その他の知的財産権に基づきTIからライセンスを得て頂かなければならない場合もあります。

TIのデータ・ブックもしくはデータ・シートの中にある情報を複製することは、その情報に一切の変更を加えること無く、かつその情報と結び付られた全ての保証、条件、制限及び通知と共に複製がなされる限りにおいて許されるものとします。当該情報に変更を加えて複製することは不公正で誤認を生じさせる行為です。TIは、そのような変更された情報や複製については何の義務も責任も負いません。

TIの製品もしくはサービスについてTIにより示された数値、特性、条件その他のパラメーターと異なる、あるいは、それを超えてなされた説明で当該TI製品もしくはサービスを再販売することは、当該TI製品もしくはサービスに対する全ての明示的保証、及び何らかの黙示的保証を無効にし、かつ不公正で誤認を生じさせる行為です。TIは、そのような説明については何の義務も責任もありません。

TIは、TIの製品が、安全でないことが致命的となる用途ないしアプリケーション(例えば、生命維持装置のように、TI製品に不良があった場合に、その不良により相当な確率で死傷等の重篤な事故が発生するようなもの)に使用されることを認めておりません。但し、お客様とTIの双方の権限有る役員が書面でそのような使用について明確に合意した場合は除きます。たとえTIがアプリケーションに関連した情報やサポートを提供したとしても、お客様は、そのようなアプリケーションの安全面及び規制面から見た諸問題を解決するために必要とされる専門的知識及び技術を持ち、かつ、お客様の製品について、またTI製品をそのような安全でないことが致命的となる用途に使用することについて、お客様が全ての法的責任、規制を遵守する責任、及び安全に関する要求事項を満足させる責任を負っていることを認め、かつそのことに同意します。さらに、もし万一、TIの製品がそのような安全でないことが致命的となる用途に使用されたことによって損害が発生し、TIないしその代表者がその損害を賠償した場合は、お客様がTIないしその代表者にその全額の補償をするものとします。

TI製品は、軍事的用途もしくは宇宙航空アプリケーションないし軍事的環境、航空宇宙環境にて使用されるようには設計もされていませんし、使用されることを意図されておりません。但し、当該TI製品が、軍需対応グレード品、若しくは「強化プラスティック」製品としてTIが特別に指定した製品である場合は除きます。TIが軍需対応グレード品として指定した製品のみが軍需品の仕様書に合致いたします。お客様は、TIが軍需対応グレード品として指定して収ない製品を、軍事的用途もしくは軍事的環境下で使用することは、もっぱらお客様の危険負担においてなされるということ、及び、お客様がもっぱら責任をもって、そのような使用に関して必要とされる全ての法的要求事項及び規制上の要求事項を満足させなければならないことを認め、かつ同意します。

TI製品は、自動車用アプリケーションないし自動車の環境において使用されるようには設計されていませんし、また使用されることを意図されておりません。但し、TIがISO/TS 16949の要求事項を満たしていると特別に指定したTI製品は除きます。お客様は、お客様が当該TI指定品以外のTI製品を自動車用アプリケーションに使用しても、TIは当該要求事項を満たしていなかったことについて、いかなる責任も負わないことを認め、かつ同意します。

Copyright © 2011, Texas Instruments Incorporated 日本語版 日本テキサス・インスツルメンツ株式会社

### 弊社半導体製品の取り扱い・保管について

半導体製品は、取り扱い、保管・輸送環境、基板実装条件によっては、お客様での実装前後に破壊/劣化、または故障を起こすことがあります。

弊社半導体製品のお取り扱い、ご使用にあたっては下記の点を遵守して下さい。 1. 熱電気

- 素手で半導体製品単体を触らないこと。どうしても触る必要がある場合は、リストストラップ等で人体からアースをとり、導電性手袋等をして取り扱うこと。

- 弊社出荷梱包単位(外装から取り出された内装及び個装)又は製品 単品で取り扱いを行う場合は、接地された導電性のテーブル上で(導 電性マットにアースをとったもの等)、アースをした作業者が行う こと。また、コンテナ等も、導電性のものを使うこと。

- マウンタやはんだ付け設備等、半導体の実装に関わる全ての装置類は、静電気の帯電を防止する措置を施すこと。

- 前記のリストストラップ・導電性手袋・テーブル表面及び実装装置 類の接地等の静電気帯電防止措置は、常に管理されその機能が確認 されていること。

### 2. 温·湿度環境

■ 温度:0~40℃、相対湿度:40~85%で保管・輸送及び取り扱いを行うこと。(但し、結露しないこと。)

- 直射日光があたる状態で保管・輸送しないこと。

- 3. 防湿梱包

- 防湿梱包品は、開封後は個別推奨保管環境及び期間に従い基板実装すること。

- 4. 機械的衝擊

- 梱包品(外装、内装、個装)及び製品単品を落下させたり、衝撃を 与えないこと。

- 5. 熱衝撃

- はんだ付け時は、最低限260℃以上の高温状態に、10秒以上さら さないこと。(個別推奨条件がある時はそれに従うこと。)

- 6. 汚染

- はんだ付け性を損なう、又はアルミ配線腐食の原因となるような汚染物質(硫黄、塩素等ハロゲン)のある環境で保管・輸送しないこと。

- はんだ付け後は十分にフラックスの洗浄を行うこと。(不純物含有率が一定以下に保証された無洗浄タイプのフラックスは除く。)

以上