CSD88584Q5DC JAJSD35E - MAY 2017 - REVISED JUNE 2024

# CSD88584Q5DC 40V ハーフ ブリッジ NexFET™ パワー ブロック

# 1 特長

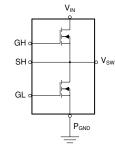

- ハーフ ブリッジ パワー ブロック

- 高密度 SON、占有面積 5mm×6mm

- 低い R<sub>DS(ON)</sub> により伝導損失を最小化 - 35A において P<sub>Loss</sub> 2.4W

- 放熱特性の優れた DualCool™ パッケージ

- インダクタンスの非常に低いパッケージ

- RoHS に準拠

- ハロゲン不使用

- 鉛フリーの端子メッキ処理

# 2 アプリケーション

- ブラシレス DC モータ制御用の三相ブリッジ

- 最大8バッテリの電動工具

- その他ハーフおよびフル ブリッジ トポロジ

Copyright © 2017, Texas Instruments Incorporated

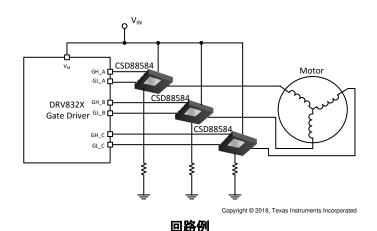

## パワー ブロックの回路図

# 3 概要

**CSD88584Q5DC 40V** パワー ブロックは、手持ち式工 具、コードレス ガーデン ツール、電動工具など大電流の モータ制御アプリケーションに最適化された設計です。こ のデバイスは、テキサス・インスツルメンツの特許取得済み の積層ダイテクノロジを活用し、寄生インダクタンスを最小 化するとともに、省スペースで放熱特性の優れた DualCool™ 5mm × 6mm パッケージで完全なハーフ ブリ ッジを提供します。このパワー ブロック デバイスは金属の 上面が露出しており、パッケージの上面から熱を引き出 し、基板から逃がすための簡単なヒートシンクとして機能 するため、多くのモータ制御用途で要求される大電流に おいて優れた放熱性能を発揮します。

製品情報

| デバイス          | 数量   | メディア           | パッケージ                  | 出荷形<br>態 |

|---------------|------|----------------|------------------------|----------|

| CSD88584Q5DC  | 2500 | 13 インチ リー<br>ル | SON<br>5.00mm × 6.00mm | テープアンドリ  |

| CSD88584Q5DCT | 250  | 7 インチ リール      | プラスチック パッケー<br>ジ       | ール       |

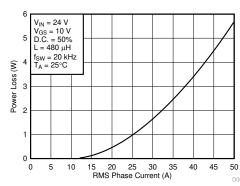

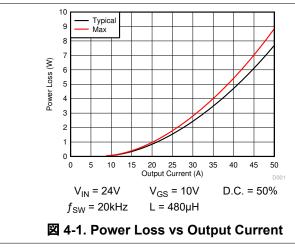

電力損失と出力電流との関係

# **Table of Contents**

| 1 特長 1                                           | 5.5 Normalized Power Loss Curves                   | 12 |

|--------------------------------------------------|----------------------------------------------------|----|

| 2 アプリケーション1                                      | 5.6 Design Example – Regulate Current to Maintain  |    |

| 3 概要1                                            | Safe Operation                                     | 12 |

| 4 Specifications3                                | 5.7 Design Example – Regulate Board and Case       |    |

| 4.1 Absolute Maximum Ratings3                    | Temperature to Maintain Safe Operation             | 13 |

| 4.2 Recommended Operating Conditions3            | 6 Layout                                           | 14 |

| 4.3 Power Block Performance3                     | 6.1 Layout Guidelines                              | 14 |

| 4.4 Thermal Information4                         | 6.2 Layout Example                                 | 16 |

| 4.5 Electrical Characteristics4                  | 7 Device and Documentation Support                 | 17 |

| 4.6 Typical Power Block Device Characteristics6  | 7.1 ドキュメントの更新通知を受け取る方法                             | 17 |

| 4.7 Typical Power Block MOSFET Characteristics7  | 7.2 サポート・リソース                                      | 17 |

| 5 Application and Implementation9                | 7.3 Trademarks                                     | 17 |

| 5.1 Application Information9                     | 7.4 静電気放電に関する注意事項                                  | 17 |

| 5.2 Brushless DC Motor With Trapezoidal Control9 | 7.5 用語集                                            |    |

| 5.3 Power Loss Curves11                          | 8 Revision History                                 |    |

| 5.4 Safe Operating Area (SOA) Curve12            | 9 Mechanical, Packaging, and Orderable Information |    |

# 4 Specifications

# 4.1 Absolute Maximum Ratings

$T_{.I} = 25^{\circ}C$  (unless otherwise noted)(1)

| PARAMETER                                  | CONDITIONS                                      | MIN                      | MAX | UNIT |

|--------------------------------------------|-------------------------------------------------|--------------------------|-----|------|

|                                            | V <sub>IN</sub> to P <sub>GND</sub>             | -0.8                     | 40  |      |

| Voltage                                    | V <sub>SW</sub> to P <sub>GND</sub>             | -0.3                     | 40  |      |

| Voltage                                    | GH to SH                                        | -20 20 V<br>-20 20 400 A |     |      |

|                                            | GL to P <sub>GND</sub>                          | -20                      | 20  |      |

| Pulsed current rating, I <sub>DM</sub> (2) |                                                 |                          | 400 | Α    |

| Power dissipation, P <sub>D</sub>          |                                                 |                          | 12  | W    |

| Avalanche energy, E <sub>AS</sub>          | High-side FET, I <sub>D</sub> = 103A, L = 0.1mH |                          | 525 | I    |

| Avaianche energy, EAS                      | Low-side FET, $I_D = 103A$ , $L = 0.1$ mH       |                          | 525 | - mJ |

| Operating junction temperate               | ure, T <sub>J</sub>                             | -55                      | 150 | °C   |

| Storage temperature, T <sub>stg</sub>      |                                                 | <b>–</b> 55              | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 4.2 Recommended Operating Conditions

T<sub>.I</sub> = 25°C (unless otherwise noted)

|                  | PARAMETER                           | CONDITIONS                     | MIN | MAX | UNIT |

|------------------|-------------------------------------|--------------------------------|-----|-----|------|

| $V_{GS}$         | Gate drive voltage                  |                                | 4.5 | 16  | V    |

| V <sub>IN</sub>  | Input supply voltage <sup>(1)</sup> |                                |     | 36  | V    |

| $f_{\sf SW}$     | Switching frequency                 | C <sub>BST</sub> = 0.1µF (min) | 5   | 50  | kHz  |

| I <sub>OUT</sub> | RMS motor winding current           |                                |     | 50  | Α    |

| TJ               | Operating temperature               |                                |     | 125 | °C   |

<sup>(1)</sup> Up to 32V input use one capacitor per phase, MLCC 10nF, 100V, X7S, 0402, PN: C1005X7S2A103K050BB from V<sub>IN</sub> to GND return. Between 32V to 36V input operation, add RC switch-node snubber as described in the セクション 6.1.1 section of this data sheet.

#### 4.3 Power Block Performance

$T_J = 25$ °C (unless otherwise noted)

|                   | PARAMETER                 | CONDITIONS                                                                                                                     | MIN | TYP | MAX | UNIT |

|-------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| P <sub>LOSS</sub> | Power loss <sup>(1)</sup> | $V_{IN}$ = 24V, $V_{GS}$ = 10V,<br>$I_{OUT}$ = 35A, $f_{SW}$ = 20kHz,<br>$T_{J}$ = 25°C, duty cycle = 50%,<br>L = 480 $\mu$ H  |     | 2.4 |     | W    |

| P <sub>LOSS</sub> | Power loss                | $V_{IN}$ = 24V, $V_{GS}$ = 10V,<br>$I_{OUT}$ = 35A, $f_{SW}$ = 20kHz,<br>$T_{J}$ = 125°C, duty cycle = 50%,<br>L = 480 $\mu$ H |     | 3.5 |     | W    |

Measurement made with eight 10μF, 50V, ±10% X5R (TDK C3225X5R1H106K250AB or equivalent) ceramic capacitors placed across V<sub>IN</sub> to P<sub>GND</sub> pins and using UCC27210DDAR 100V, 4A driver IC.

Single FET conduction, max  $R_{\theta JC}$  = 1.1°C/W, pulse duration  $\leq$  100 $\mu$ s, single pulse.

#### 4.4 Thermal Information

## $T_J = 25$ °C (unless otherwise stated)

|                 | THERMAL METRIC                                                           | MIN | TYP | MAX | UNIT |

|-----------------|--------------------------------------------------------------------------|-----|-----|-----|------|

| Р               | Junction-to-ambient thermal resistance (min Cu) <sup>(2)</sup>           |     |     | 125 | °C/W |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance (max Cu) <sup>(2)</sup> (1)       |     |     | 50  | C/VV |

| Ь               | Junction-to-case thermal resistance (top of package) <sup>(2)</sup>      |     |     | 2.1 | °C/W |

| $R_{\theta JC}$ | Junction-to-case thermal resistance (V <sub>IN</sub> pin) <sup>(2)</sup> |     |     | 1.1 | C/VV |

<sup>(1)</sup> Device mounted on FR4 material with 1in<sup>2</sup> (6.45cm<sup>2</sup>) Cu.

#### 4.5 Electrical Characteristics

T<sub>.I</sub> = 25°C (unless otherwise stated)

|                     | PARAMETER                        | TEST CONDITIONS                                 | MIN | TYP  | MAX   | UNIT      |

|---------------------|----------------------------------|-------------------------------------------------|-----|------|-------|-----------|

| STATIC CH           | IARACTERISTICS                   |                                                 |     |      |       |           |

| BV <sub>DSS</sub>   | Drain-to-source voltage          | V <sub>GS</sub> = 0V, I <sub>DS</sub> = 250μA   | 40  |      |       | V         |

| I <sub>DSS</sub>    | Drain-to-source leakage current  | V <sub>GS</sub> = 0V, V <sub>DS</sub> = 32V     |     |      | 1     | μΑ        |

| I <sub>GSS</sub>    | Gate-to-source leakage current   | V <sub>DS</sub> = 0V, V <sub>GS</sub> = 20V     |     | ,    | 100   | nA        |

| V <sub>GS(th)</sub> | Gate-to-source threshold voltage | $V_{DS} = V_{GS}, I_{DS} = 250 \mu A$           | 1.2 | 1.7  | 2.3   | V         |

| В                   | Drain to source on registance    | V <sub>GS</sub> = 4.5V, I <sub>DS</sub> = 30A   |     | 1.0  | 1.5   | <b>~0</b> |

| R <sub>DS(on)</sub> | Drain-to-source on resistance    | V <sub>GS</sub> = 10V, I <sub>DS</sub> = 30A    |     | 0.68 | 0.95  | mΩ        |

| g <sub>fs</sub>     | Transconductance                 | V <sub>DS</sub> = 4V, I <sub>DS</sub> = 30A     |     | 149  |       | S         |

| DYNAMIC             | CHARACTERISTICS                  |                                                 | 1   |      |       |           |

| C <sub>ISS</sub>    | Input capacitance                |                                                 |     | 9540 | 12400 | pF        |

| Coss                | Output capacitance               | $V_{GS} = 0V$ , $V_{DS} = 20V$ ,<br>f = 1MHz    |     | 957  | 1240  | pF        |

| C <sub>RSS</sub>    | Reverse transfer capacitance     | ,2                                              |     | 474  | 616   | pF        |

| R <sub>G</sub>      | Series gate resistance           |                                                 |     | 1.0  | 2.0   | Ω         |

| Qg                  | Gate charge total (4.5 V)        |                                                 |     | 68   | 88    | nC        |

| Qg                  | Gate charge total (10 V)         |                                                 |     | 137  | 178   | nC        |

| Q <sub>gd</sub>     | Gate charge gate-to-drain        | V <sub>DS</sub> = 20V,<br>I <sub>DS</sub> = 30A |     | 26   |       | nC        |

| Q <sub>gs</sub>     | Gate charge gate-to-source       |                                                 |     | 24   |       | nC        |

| Q <sub>g(th)</sub>  | Gate charge at V <sub>th</sub>   |                                                 |     | 16   |       | nC        |

| Q <sub>OSS</sub>    | Output charge                    | V <sub>DS</sub> = 20V, V <sub>GS</sub> = 0V     |     | 42   |       | nC        |

| t <sub>d(on)</sub>  | Turnon delay time                |                                                 |     | 11   |       | ns        |

| t <sub>r</sub>      | Rise time                        | V <sub>DS</sub> = 20V, V <sub>GS</sub> = 10V,   |     | 24   |       | ns        |

| t <sub>d(off)</sub> | Turnoff delay time               | $I_{DS} = 30A$ , $R_G = 0\Omega$                |     | 53   |       | ns        |

| t <sub>f</sub>      | Fall time                        |                                                 |     | 17   |       | ns        |

| DIODE CH            | ARACTERISTICS                    |                                                 | •   |      | '     |           |

| V <sub>SD</sub>     | Diode forward voltage            | I <sub>DS</sub> = 30A, V <sub>GS</sub> = 0V     |     | 0.75 | 1.0   | V         |

| Q <sub>rr</sub>     | Reverse recovery charge          | V <sub>DS</sub> = 20V, I <sub>F</sub> = 30A,    |     | 34   |       | nC        |

| t <sub>rr</sub>     | Reverse recovery time            | di/dt = 300A/µs                                 |     | 24   |       | ns        |

資料に関するフィードバック (ご意見やお問い合わせ) を送信

Copyright © 2024 Texas Instruments Incorporated

4

R<sub>BJC</sub> is determined with the device mounted on a 1in<sup>2</sup> (6.45cm<sup>2</sup>), 2oz (0.071mm) thick Cu pad on a 1.5in × 1.5in (3.81cm × 3.81cm), 0.06in (1.52mm) thick FR4 board. R<sub>BJC</sub> is specified by design while R<sub>BJA</sub> is determined by the user's board design.

Max  $R_{\theta JA}$  = 50°C/W when mounted on 1in² (6.45cm²) of 2oz (0.071mm) thick Cu.

Max  $R_{\theta JA}$  = 125°C/W when mounted on minimum pad area of 2oz (0.071mm) thick Cu.

# 4.6 Typical Power Block Device Characteristics

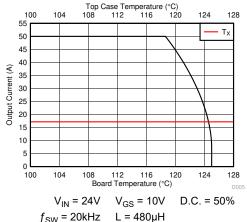

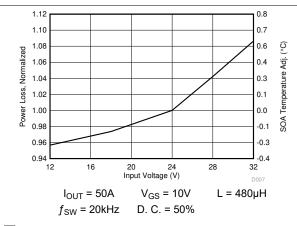

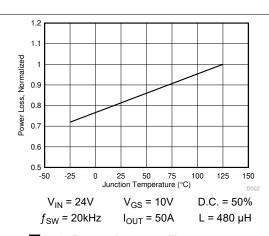

The typical power block system characteristic curves ( $\boxtimes$  4-1 through  $\boxtimes$  4-6) are based on measurements made on a PCB design with dimensions of 4in (W) × 3.5in (L) × 0.062in (H) and 6 copper layers of 2oz copper thickness. See  $2000 \times 5$  section for detailed explanation.  $T_J = 125^{\circ}C$ , unless stated otherwise.

図 4-3. Typical Safe Operating Area

図 4-5. Normalized Power Loss vs Input Voltage

図 4-2. Power Loss vs Temperature

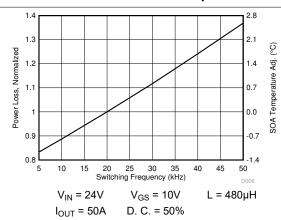

図 4-4. Normalized Power Loss vs Switching Frequency

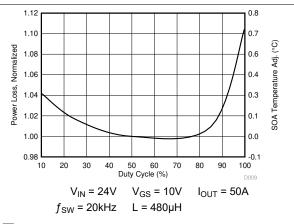

図 4-6. Normalized Power Loss vs Duty Cycle

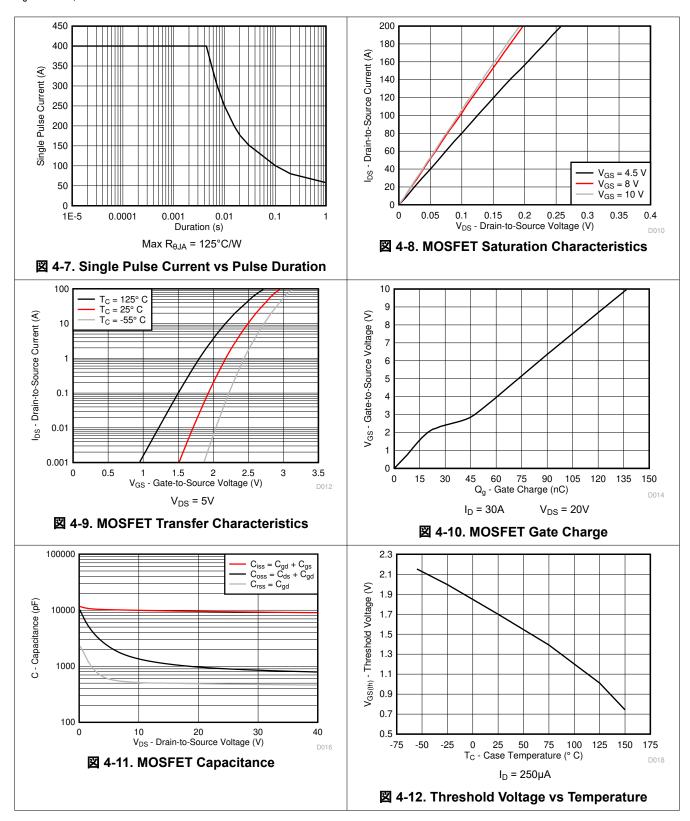

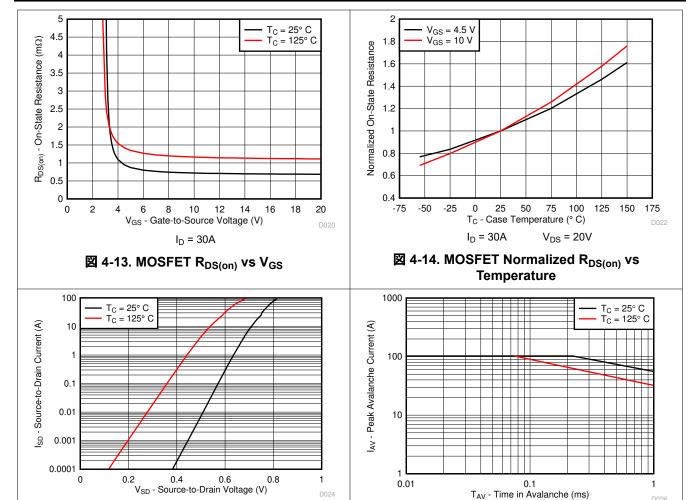

# 4.7 Typical Power Block MOSFET Characteristics

$T_J = 25$ °C, unless stated otherwise.

# 5 Application and Implementation

注

以下のアプリケーション情報は、TIの製品仕様に含まれるものではなく、TIではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

## **5.1 Application Information**

Historically, battery powered tools have favored brushed DC configurations to spin their primary motors, but more recently, the advantages offered by brushless DC operation (BLDC) operation have brought about the advent of popular designs that favor the latter. Those advantages include, but are not limited to higher efficiency and therefore longer battery life, superior reliability, greater peak torque capability, and smooth operation over a wider range of speeds. However, BLDC designs put increased demand for higher power density and current handling capabilities on the power stage responsible for driving the motor.

The CSD88584Q5DC is part of TI's power block product family and is a highly optimized product designed explicitly for the purpose driving higher current DC motors in power and gardening tools. It incorporates TI's latest generation silicon which has been optimized for low resistance to minimize conduction losses and offer excellent thermal performance. The power block utilizes TI's stacked die technology to offer one complete half bridge vertically integrated into a single 5mm × 6mm package with a DualCool exposed metal case. This feature allows the designer to apply a heatsink to the top of the package and pull heat away from the PCB, thus maximizing the power density while reducing the power stage footprint by up to 50%.

#### 5.2 Brushless DC Motor With Trapezoidal Control

The trapezoidal commutation control is simple and has fewer switching losses compared to sinusoidal control.

Copyright © 2017, Texas Instruments Incorporated

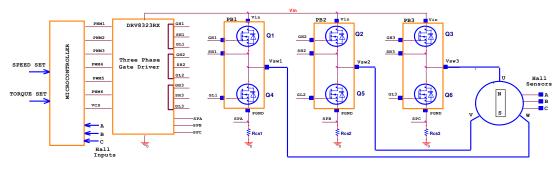

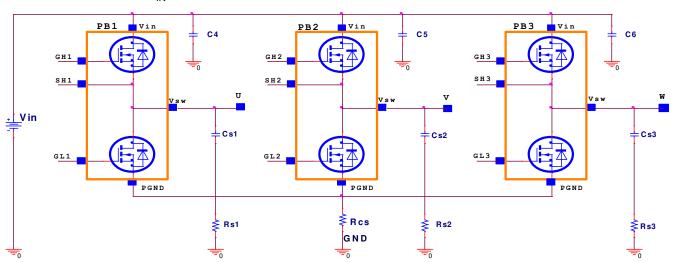

#### 図 5-1. Functional Block Diagram

The block diagram shown in 🗵 5-1 offers a simple instruction of what is required to drive a BLDC motor: one microcontroller, one three-phase driver IC, 3 power blocks (historically 6 power MOSFETs) and 3 Hall effect sensors. The microcontroller responsible for block commutation must always know the rotor orientation or its position relative to the stator coils. This is easy achieved with a brushed DC motor due to the fixed geometry and position of the rotor windings, shaft and commutator.

A three-phase BLDC motor requires three Hall effect sensors or a rotary encoder to detect the rotor position in relation to stator armature windings. Combining these three Hall effect sensors output signals, the microcontroller can determine the proper commutation sequence. The three Hall sensors named A, B, and C are mounted on the stator core at 120° intervals and the stator phase windings are implemented in a star configuration. For every 60° of motor rotation, one Hall sensor changes its state. Based on the Hall sensor outputs code, at the end of each block commutation interval the ampere conductors are commutated to the next position. There are 6 steps needed to complete a full electrical cycle. The number of block commutation cycles to complete a full mechanical rotation is determined by the number of rotor pole pairs.

Copyright © 2024 Texas Instruments Incorporated

資料に関するフィードバック(ご意見やお問い合わせ) を送信

9

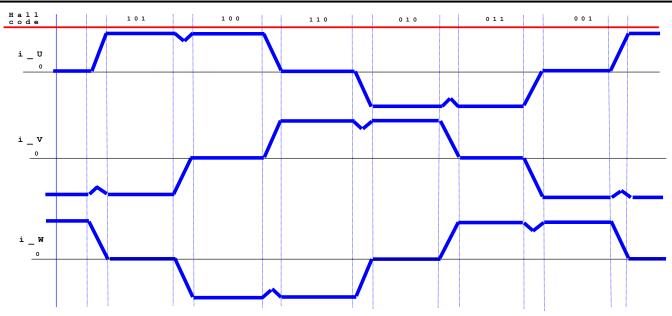

図 5-2. Winding Current Waveforms on a BLDC Motor

☑ 5-2 above shows the three phase motor winding currents i\_U, i\_V, and i\_W when running at 100% duty cycle.

Trapezoidal commutation control offers the following advantages:

- Only two windings in series carry the phase winding current at any time while the third winding is open.

- · Only one current sensor is necessary for all 3 windings U, V, and W.

- The position of the current sensor allows the use of low-cost shunt resistors.

However, trapezoidal commutation control has the disadvantage of commutation torque ripple. The current sense on a three-phase inverter can be configured to use a single-shunt or three different sense resistors. For cost sensitive applications targeting sensorless control, the three Hall effect sensors can be replaced with BEMF voltage feedback dividers.

To obtain faster motor rotations and higher revolutions per minute (RPM), shorter periods and higher  $V_{\text{IN}}$  voltage are necessary. Contrarily, to reduce the rotational speed of the motor, it is necessary to lower the RMS voltage applied across stator windings. This can easily be easily achieved by modulating the duty cycle, while maintain a constant switching frequency. Frequency for the three-phase inverter chosen is usually low between 10kHz to 50kHz to reduce winding losses and to avoid audible noise.

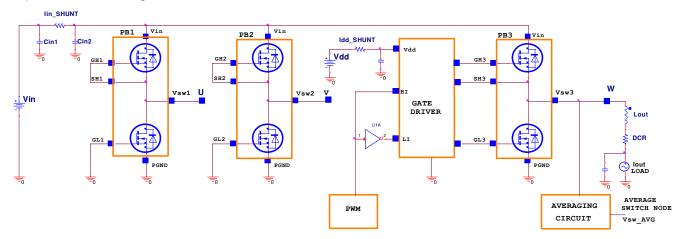

#### 5.3 Power Loss Curves

CSD88584Q5DC was designed to operate up to 7-cell Li-lon battery voltage applications ranging from 18V to 32V, typical 24V. For 8s, input voltages between 32V to 36V, RC snubbers are required for each switch-node U, V, and W. To reduce ringing, refer to the セクション 6.1.1 section. In an effort to simplify the design process, Texas Instruments has provided measured power loss performance curves over a variety of typical conditions.

☑ 4-1 plots the CSD88584Q5DC power loss as a function of load current. The measured power loss includes both input conversion loss and gate drive loss.

式 1 is used to generate the power loss curve:

Power loss (W) =

$$(V_{IN} \times I_{IN} \text{ SHUNT}) + (V_{DD} \times I_{DD} \text{ SHUNT}) - (V_{SW} \text{ AVG} \times I_{OUT})$$

(1)

The power loss measurements were made on the circuit shown in  $\boxtimes$  5-3, power block devices for legs U and V, PB1 and PB2 were disabled by shorting the CSD88584Q5DC high-side and low-side FETs gate-to-source terminals. Current shunt lin\_shunt provides Input current and Idd\_SHUNT provides driver supply current measurements. The winding current is measured from the DC load. An averaging circuit provides switch node W equivalent RMS voltage.

Copyright © 2017, Texas Instruments Incorporated

#### 図 5-3. Power Loss Test Circuit

The RMS current on the CSD88584Q5DC device depends on the motor winding current. For trapezoidal control, the MOSFET RMS current is calculated using ₹ 2.

$$I_{RMS} = I_{OUT} \times \sqrt{2}$$

(2)

Taking into consideration system tolerances with the current measurement scheme, the inverter design needs to withstand a 20% overload current.

Winding RMS Current (A)

CSD88584Q5DC I<sub>RMS</sub> (A)

Overload 120% × I<sub>RMS</sub> (A)

30

42

51

40

56

68

50

70

85

表 5-1. RMS and Overload Current Calculations

English Data Sheet: SLPS598

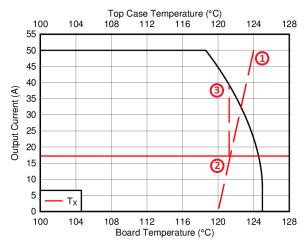

#### 5.4 Safe Operating Area (SOA) Curve

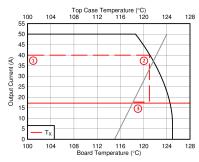

The SOA curve in  $\boxtimes$  4-3 provide guidance on the temperature boundaries within an operating system by incorporating the thermal resistance and system power loss. This curve outlines the board and case temperatures required for a given load current. The area under the curve dictates the safe operating area. This curve is based on measurements made on a PCB design with dimensions of 4in (W) × 3.5in (L) × 0.062in (H) and 6 copper layers of 2oz copper thickness.

#### 5.5 Normalized Power Loss Curves

The normalized curves in the CSD88584Q5DC data sheet provide guidance on the power loss and SOA adjustments based on application specific needs. These curves show how the power loss and SOA temperature boundaries will adjust for different operation conditions. The primary Y-axis is the normalized change in power loss while the secondary Y-axis is the change in system temperature required in order to comply with the SOA curve. The change in power loss is a multiplier for the typical power loss. The change in SOA temperature is subtracted from the SOA curve.

# 5.6 Design Example - Regulate Current to Maintain Safe Operation

If the case and board temperature of the power block are known, the SOA can be used to determine the maximum allowed current that will maintain operation within the safe operating area of the device. The following procedure outlines how to determine the RMS current limit while maintaining operation within the confines of the SOA, assuming the temperatures of the top of the package and PCB directly underneath the part are known.

- 1. Start at the maximum current of the device on the Y-axis and draw a line from this point at the known top case temperature to the known PCB temperature.

- 2. Observe where this point intersects the T<sub>x</sub> line.

- 3. At this intersection with the T<sub>X</sub> line, draw vertical line until you hit the SOA current limit. This intercept is the maximum allowed current at the corresponding power block PCB and case temperatures.

In the example below, we show how to achieve this for the temperatures  $T_C$  = 124°C and  $T_B$  = 120°C. First we draw from 50 A on the Y-axis at 124°C to 120°C on the X-axis. Then, we draw a line up from where this line crosses the  $T_X$  line to see that this line intercepts the SOA at 39A. Thus we can assume if we are measuring a PCB temperature of 124°C, and a top case temperature of 120°C, the power block can handle 39A RMS, at the normalized conditions. At conditions that differ from those in  $\boxtimes$  4-1, the user may be required to make an SOA temperature adjustment on the  $T_X$  line, as shown in the next section.

図 5-4. Regulating Current to Maintain Safe Operation

## 5.7 Design Example – Regulate Board and Case Temperature to Maintain Safe Operation

In the previous example we showed how given the PCB and case temperature, the current of the power block could be limited to ensure operation within the SOA. Conversely, if the current and other application conditions are known, one can determine from the SOA what board or case temperature the user will need to limit their design to. The user can estimate product loss and SOA boundaries by arithmetic means (see  $\cancel{to}\cancel{2}\cancel{2}\cancel{2}\cancel{2}\cancel{2}\cancel{2}$  5.7.1 section). Though the power loss and SOA curves in this data sheet are taken for a specific set of test conditions, the following procedure outlines the steps the user should take to predict product performance for any set of system conditions.

#### 5.7.1 Operating Conditions

- Winding output current (I<sub>OUT</sub>) = 40A

- Input voltage (V<sub>IN</sub>) = 32V

- Switching frequency (F<sub>SW</sub>) = 40kHz

- Duty cycle (D.C.) = 95%

#### 5.7.2 Calculating Power Loss

- Power loss at 40A ≈ 4.7W (図 4-1)

- Normalized power loss for input voltage ≈ 1.09 (

4-5)

- Normalized power loss for duty cycle ≈ 1.06 (

4-6)

- Final calculated power loss = 4.7W × 1.24 × 1.09 × 1.06 ≈ 6.7W

#### 5.7.3 Calculating SOA Adjustments

- SOA adjustment for input voltage ≈ 0.6°C (図 4-5)

- SOA adjustment for duty cycle ≈ 0.4°C (

✓ 4-6)

- Final calculated SOA adjustment = 1.7 + 0.6 + 0.4 ≈ 2.7°C

In the  $2722 \times 5.6$  section above, the estimated power loss of the CSD88584Q5DC would increase to 6.7W. In addition, the maximum allowable board temperature would have to increase by 2.7°C. In 35-5, the SOA graph was adjusted accordingly.

- 1. Start by drawing a horizontal line from the application current (40A) to the SOA curve.

- 2. Draw a vertical line from the SOA curve intercept down to the T<sub>X</sub> line.

- 3. Adjust the intersection point by subtracting the temperature adjustment value.

In this design example, the SOA board/ambient temperature adjustment yields a decrease of allowed junction temperature of  $2.7^{\circ}$ C from  $121.0^{\circ}$ C to  $118.3^{\circ}$ C. Now it is known that the intersection of the case and PCB temperatures on the  $T_X$  line must stay below this point. For instance, if the power block case is observed operating at  $124^{\circ}$ C, the PCB temperature must in turn be kept under  $115^{\circ}$ C to maintain this crossover point.

図 5-5. Regulate Temperature to Maintain Safe Operation

資料に関するフィードバック(ご意見やお問い合わせ)を送信

13

#### 6 Layout

The two key system-level parameters that can be optimized with proper PCB design are electrical and thermal performance. A proper PCB layout will yield maximum performance in both areas. Below are some tips for how to address each.

## 6.1 Layout Guidelines

#### 6.1.1 Electrical Performance

The CSD88584Q5DC power block has the ability to switch at voltage rates greater than 1kV/µs. Special care must be then taken with the PCB layout design and placement of the input capacitors; high-current, high dl/dT switching path; current shunt resistors; and GND return planes. As with any high-power inverter operated in hard switching mode, there will be voltage ringing present on the switch nodes U, V, and W. Switch-node ringing appears mainly at the HS FET turnon commutation with positive winding current direction. The U, V, and W phase connections to the BLDC motor can be usually excluded from the ringing behavior since they are subjected to high-peak currents but low dl/dT slew-rates. However, a compact PCB design with short and low-parasitic loop inductances is critical to achieve low ringing and compliance with EMI specifications.

For safe and reliable operation of the three-phase inverter, motor phase currents have to be accurately monitored and reported to the system microcontroller. One current sensor needs to be connected on each motor phase winding U, V, and W. This sensing method is best for current sensing as it provides good accuracy over a wide range of duty cycles, motor torque, and winding currents. Using current sensors is recommended because it is less intrusive to the  $V_{\text{IN}}$  and GND connections.

Copyright © 2017, Texas Instruments Incorporated

#### 図 6-1. Recommended Ringing Reduction Components

However, for cost sensitive applications, current sensors are generally replaced with current sense resistors.

- For designs using the 60V three-phase smart gate driver DRV8320SRHBR, current sense resistor R<sub>CS</sub> can be placed between common source terminals for all 3 power block devices CSD88584Q5DC to P<sub>GND</sub> and measured using an external current sense amplifier as depicted in ⋈ 6-1 above.

- For designs using the 60V three-phase gate driver DRV8323RSRGZT, three current sense resistors R<sub>CS1</sub>, R<sub>CS2</sub> and R<sub>CS3</sub> can be used between each CSD88584Q5DC source terminal to GND and measured by the included DRV8323 current sense amplifiers. The three-phase driver IC should be placed as close as possible to the power block gate GL and GH terminals.

Copyright © 2024 Texas Instruments Incorporated

Breaking the high-current flow path from the source terminals of the power block to GND by introducing the  $R_{CS}$  current shunt resistors introduces parasitic PCB inductance. In the event the switch node waveforms exhibits peak ringing that reaches undesirable levels, the ringing can be reduced by using the following ringing reduction components:

- The use of a high-side gate resistor in series with the GH pin is one effective way to reduce peak ringing. The recommended HS FET gate resistor value will range between 4.7Ω to 10Ω depending on the driver IC output characteristics used in conjunction with the power block device. The low-side FET gate pin GL should connect directly to the driver IC output to avoid any parasitic cdV/dT turnon effect.

- Low inductance MLCC caps C4, C5, and C6 can be used across each power block device from V<sub>IN</sub> to the source terminal P<sub>GND</sub>. MLCC 10nF, 100V, ±10%, X7S, 0402, PN: C1005X7S2A103K050BB are recommended.

- Ringing can be reduced via the implementation of RC snubbers from each switch node U, V, and W to GND.

Recommended snubber component values are as follows:

- Snubber resistors Rs1, Rs2, Rs3: 2.21Ω, 1%, 0.125W, 0805, PN: CRCW08052R21FKEA

- Snubber caps Cs1, Cs2, and Cs3: MLCC 4.7nF, 100V, X7S, 0402, PN: C1005X7S2A472M050BB

With a switching frequency of 20kHz on the three-phase inverter, the power dissipation on the RC snubber resistor is 80mW per channel. As a result, 0805 package size for resistors Rs1, Rs2, and Rs3 is adequate.

#### 6.1.2 Thermal Considerations

The CSD88584Q5DC power block device has the ability to utilize the PCB copper planes as the primary thermal path. As such, the use of thermal vias included in the footprint is an effective way to pull away heat from the device and into the system board. Concerns regarding solder voids and manufacturability issues can be addressed through the use of three basic tactics to minimize the amount of solder attach that will wick down the via barrel:

- Intentionally space out the vias from one another to avoid a cluster of holes in a given area.

- Use the smallest drill size allowed by the design. The example in ☒ 6-2 uses vias with a 10mil drill hole and a 16mil solder pad.

- Tent the opposite side of the via with solder-mask. Ultimately the number and drill size of the thermal vias should align with the end user's PCB design rules and manufacturing capabilities.

To take advantage of the DualCool thermally enhanced package, an external heatsink can be applied on top of the power block devices. For low EMI, the heatsink is usually connected to GND through the mounting screws to the PCB. Gap pad insulators with good thermal conductivity should be used between the top of the package and the heatsink. The Bergquist Sil-Pad 980 is recommended which provides excellent thermal impedance of 1.07°C/W at 50psi.

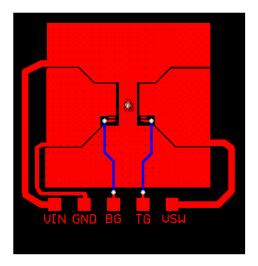

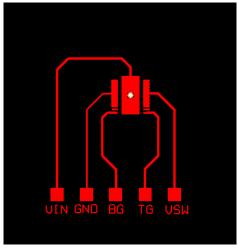

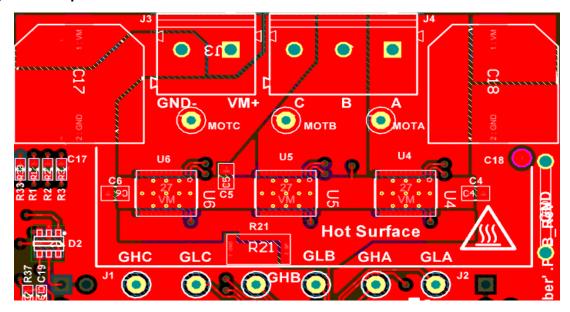

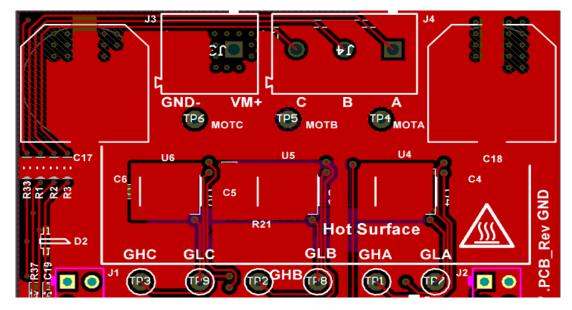

## 6.2 Layout Example

図 6-2. Top Layer

図 6-3. Bottom Layer

The placement of the input capacitors C4, C5, and C6 relative to  $V_{IN}$  and  $P_{GND}$  pins of CSD88584Q5DC device should have the highest priority during the component placement routine. It is critical to minimize the  $V_{IN}$  to GND parasitic loop inductance. A shunt resistor R21 is used between all three U4, U5, and U6 power block source terminals to the input supply GND return pin.

Input RMS current filtering is achieved via two bulk caps C17 and C18. Based on the RMS current ratings, the recommended part number for input bulk is CAP AL, 330µF, 63V, ±20%, PN: EMVA630ADA331MKG5S.

# 7 Device and Documentation Support

# 7.1 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、www.tij.co.jp のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。 変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

#### 7.2 サポート・リソース

テキサス・インスツルメンツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インスツルメンツの仕様を構成するものではなく、必ずしもテキサス・インスツルメンツの見解を反映したものではありません。テキサス・インスツルメンツの使用条件を参照してください。

#### 7.3 Trademarks

NexFET<sup>™</sup> and DualCool<sup>™</sup> are trademarks of TI. テキサス・インスツルメンツ E2E<sup>™</sup> is a trademark of Texas Instruments. すべての商標は、それぞれの所有者に帰属します。

#### 7.4 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インスツルメンツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

#### 7.5 用語集

テキサス・インスツルメンツ用語集 この用語集には、用語や略語の一覧および定義が記載されています。

17

Product Folder Links: CSD88584Q5DC

# **8 Revision History**

| Changes from                  | Revision D (December 2018) to Revision E (June 2024)                                                                                                                                       | Page             |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| <ul><li>ドキュメント á</li></ul>    | 全体にわたって表、図、相互参照の採番方法を更新                                                                                                                                                                    | 1                |

|                               | /配置図に PGND を追加                                                                                                                                                                             |                  |

|                               |                                                                                                                                                                                            |                  |

| Changes from                  | Revision C (January 2018) to Revision D (December 2018)                                                                                                                                    | Page             |

| Updated cu                    | rrent sense resistor description in applications section                                                                                                                                   | 14               |

|                               |                                                                                                                                                                                            | _                |

|                               | Revision B (September 2017) to Revision C (January 2018)                                                                                                                                   | Page             |

| <ul> <li>Changed V</li> </ul> | :出力電流との関係電力損失と出力電流との関係」プロットで、V <sub>DD</sub> = 10V を V <sub>GS</sub> = 10V<br><sub>DD</sub> to V <sub>GS</sub> in sections <i>Recommended Operating Conditions, Block Performanc</i> e, an | d <i>Typical</i> |

|                               | k Device Characteristics                                                                                                                                                                   |                  |

| • Changed I <sub>D</sub>      | test condition from 20V to 32V in the Electrical Characteristics table                                                                                                                     | 4                |

| Changes from                  | n Revision A (May 2017) to Revision B (September 2017)                                                                                                                                     | Page             |

| • Updated ⊠                   | 4-3 to extend to 50A                                                                                                                                                                       | 6                |

| Changes from                  | n Revision * (May 2017) to Revision A (May 2017)                                                                                                                                           | Page             |

|                               | 図でゲートドライバの部品番号を更新                                                                                                                                                                          | <u> </u>         |

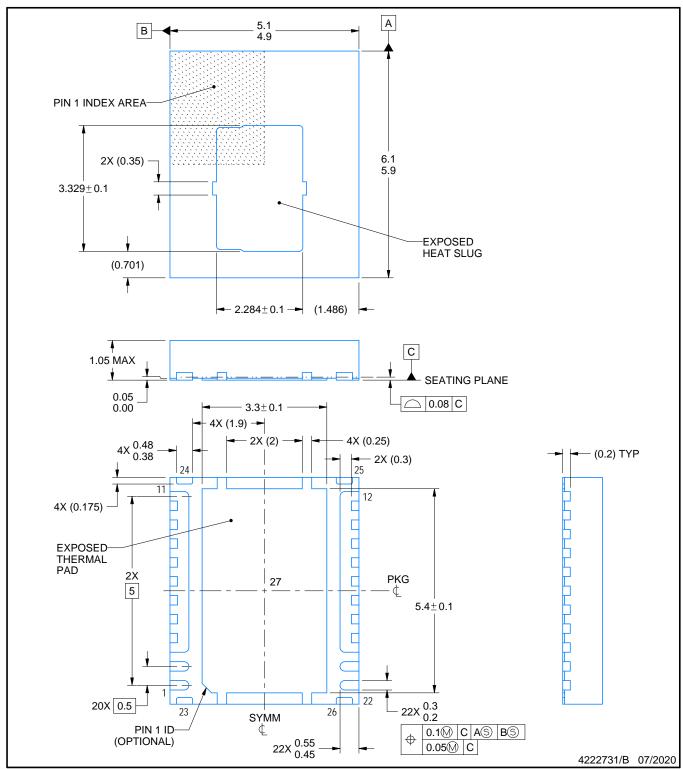

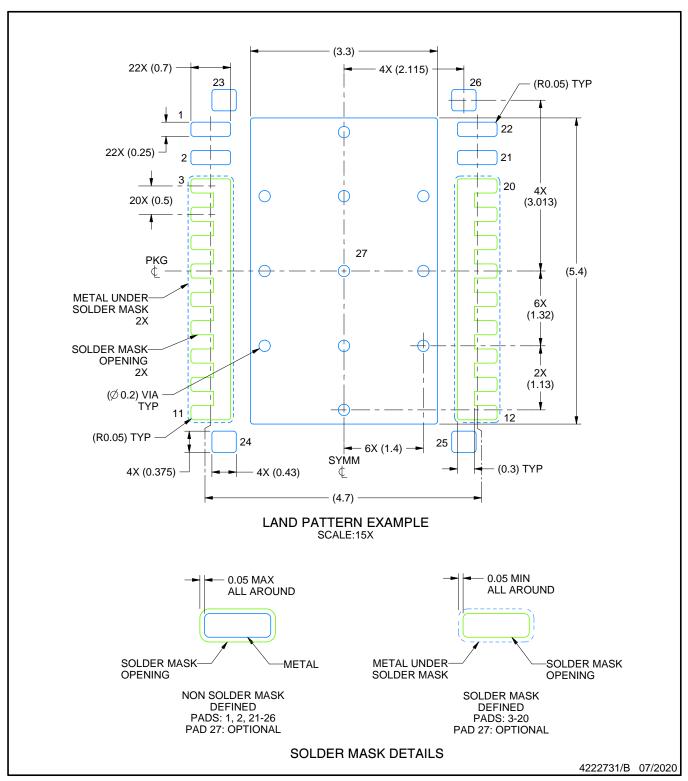

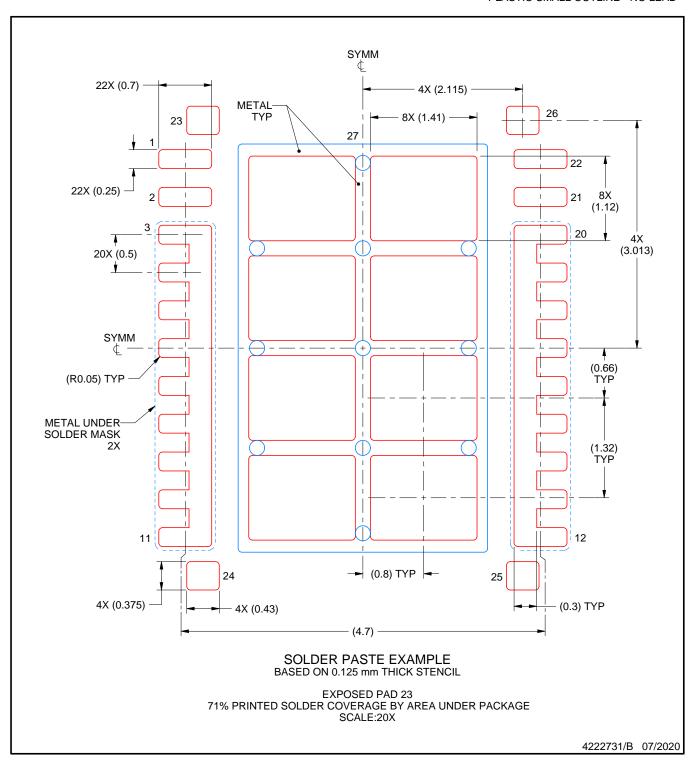

# 9 Mechanical, Packaging, and Orderable Information

The following pages include mechanical packaging and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

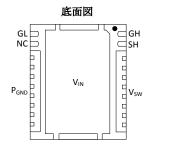

表 9-1. Pin Configuration Table

| POSITION | PIN NAME        | DESCRIPTION           |  |  |  |  |  |  |  |  |

|----------|-----------------|-----------------------|--|--|--|--|--|--|--|--|

| 1        | GH              | High Side Gate        |  |  |  |  |  |  |  |  |

| 2        | SH              | High Side Gate Return |  |  |  |  |  |  |  |  |

| 3-11     | V <sub>SW</sub> | Switch Node           |  |  |  |  |  |  |  |  |

| 12-20    | $P_{GND}$       | Power Ground          |  |  |  |  |  |  |  |  |

| 21       | NC              | No Connect            |  |  |  |  |  |  |  |  |

| 22       | GL              | Low Side Gate         |  |  |  |  |  |  |  |  |

| 23-26    | NC              | No Connect            |  |  |  |  |  |  |  |  |

| 27       | V <sub>IN</sub> | Input Voltage         |  |  |  |  |  |  |  |  |

19

Product Folder Links: CSD88584Q5DC

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されているテキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、テキサス・インスツルメンツの販売条件、または ti.com やかかる テキサス・インスツルメンツ製品の関連資料などのいずれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated www.ti.com 8-Nov-2025

#### PACKAGING INFORMATION

| Orderable part number | Status | Material type | Package   Pins          | Package qty   Carrier | RoHS        | Lead finish/<br>Ball material | MSL rating/<br>Peak reflow | Op temp (°C) | Part marking (6) |

|-----------------------|--------|---------------|-------------------------|-----------------------|-------------|-------------------------------|----------------------------|--------------|------------------|

|                       |        |               |                         |                       |             | (4)                           | (5)                        |              |                  |

| CSD88584Q5DC          | Active | Production    | VSON-CLIP<br>(DMM)   22 | 2500   LARGE T&R      | ROHS Exempt | SN                            | Level-1-260C-UNLIM         | -55 to 150   | 88584            |

| CSD88584Q5DC.B        | Active | Production    | VSON-CLIP<br>(DMM)   22 | 2500   LARGE T&R      | ROHS Exempt | SN                            | Level-1-260C-UNLIM         | -55 to 150   | 88584            |

| CSD88584Q5DCT         | Active | Production    | VSON-CLIP<br>(DMM)   22 | 250   SMALL T&R       | ROHS Exempt | SN                            | Level-1-260C-UNLIM         | -55 to 150   | 88584            |

| CSD88584Q5DCT.B       | Active | Production    | VSON-CLIP<br>(DMM)   22 | 250   SMALL T&R       | ROHS Exempt | SN                            | Level-1-260C-UNLIM         | -55 to 150   | 88584            |

<sup>(1)</sup> Status: For more details on status, see our product life cycle.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

<sup>(2)</sup> Material type: When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> RoHS values: Yes, No, RoHS Exempt. See the TI RoHS Statement for additional information and value definition.

<sup>(4)</sup> Lead finish/Ball material: Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> MSL rating/Peak reflow: The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> Part marking: There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

# **PACKAGE OPTION ADDENDUM**

www.ti.com 8-Nov-2025

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 25-Sep-2024

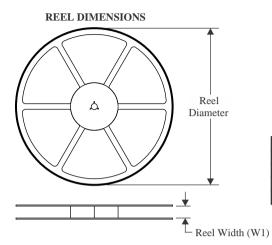

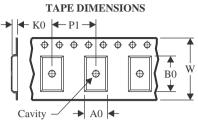

## TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |  |  |  |  |  |  |

|----|-----------------------------------------------------------|--|--|--|--|--|--|

| В0 | Dimension designed to accommodate the component length    |  |  |  |  |  |  |

| K0 | Dimension designed to accommodate the component thickness |  |  |  |  |  |  |

| W  | Overall width of the carrier tape                         |  |  |  |  |  |  |

| P1 | Pitch between successive cavity centers                   |  |  |  |  |  |  |

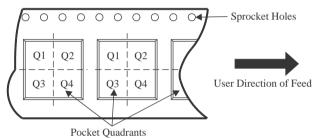

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | ,   | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|-----|------------|------------|------------|-----------|------------------|

| CSD88584Q5DC  | VSON-<br>CLIP   | DMM                | 22 | 2500 | 330.0                    | 15.4                     | 6.3 | 5.3        | 1.2        | 8.0        | 12.0      | Q2               |

| CSD88584Q5DCT | VSON-<br>CLIP   | DMM                | 22 | 250  | 178.0                    | 12.4                     | 6.3 | 5.3        | 1.2        | 8.0        | 12.0      | Q2               |

www.ti.com 25-Sep-2024

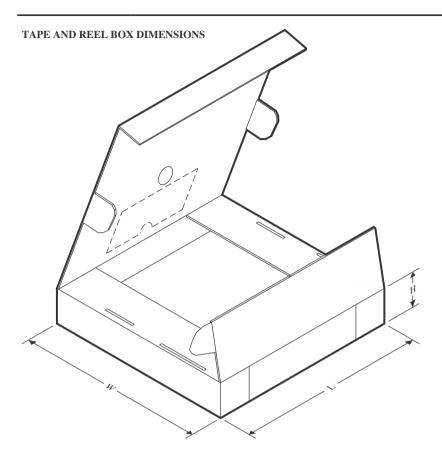

#### \*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| CSD88584Q5DC  | VSON-CLIP    | DMM             | 22   | 2500 | 333.2       | 345.9      | 28.6        |

| CSD88584Q5DCT | VSON-CLIP    | DMM             | 22   | 250  | 180.0       | 180.0      | 79.0        |

PLASTIC SMALL OUTLINE - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

- 4. Tie bar size and position may vary.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

- 5. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 6. Vias are optional depending on application, refer to device data sheet. If some or all are implemented, recommended via locations are shown.

PLASTIC SMALL OUTLINE - NO LEAD

NOTES: (continued)

7. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

## 重要なお知らせと免責事項

TI は、技術データと信頼性データ (データシートを含みます)、設計リソース (リファレンス デザインを含みます)、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の黙示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または黙示的にかかわらず拒否します。

これらのリソースは、TI 製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した TI 製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている TI 製品を使用するアプリケーションの開発の目的でのみ、TI はその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。TI や第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、TI およびその代理人を完全に補償するものとし、TI は一切の責任を拒否します。

TIの製品は、TIの販売条件、TIの総合的な品質ガイドライン、 ti.com または TI 製品などに関連して提供される他の適用条件に従い提供されます。TI がこれらのリソースを提供することは、適用される TI の保証または他の保証の放棄の拡大や変更を意味するものではありません。 TI がカスタム、またはカスタマー仕様として明示的に指定していない限り、TI の製品は標準的なカタログに掲載される汎用機器です。

お客様がいかなる追加条項または代替条項を提案する場合も、TIはそれらに異議を唱え、拒否します。

Copyright © 2025, Texas Instruments Incorporated

最終更新日:2025 年 10 月