# CDCE6214-Q1 超低消費電力クロック・ジェネレータ、1つのPLL、4つの差動出力、2つの入力、EEPROM内蔵

## 1 特長

- 車載アプリケーション向けに AEC-Q100 認証済み

- 溫度グレード 2: -40°C ~ 105°C

- **機能安全対応**

- 機能安全システムの設計に役立つ資料を利用可能

- 設定可能な高性能低消費電力フラクショナル N PLL (スプリアスによる RMS ジッタ (12kHz~20MHz,  $F_{out} > 100MHz$ ) は以下のとおり)

- 整数モード:

- 差動出力: 350fs (標準)、600fs (最大)

- LVC MOS 出力: 標準 1.05ps、最大 1.5ps

- 分数モード:

- 差動出力: 標準 1.7ps、最大 2.1ps

- LVC MOS 出力: 標準 2.0ps、最大 4.0ps

- SSC 付きの PCIe Gen 1/2/3/4、SSC なしの 1/2/3/4/5/6 をサポート

- 標準消費電力: 4 出力チャネルで 65mA、1 出力チャネルで 23mA

- ユニバーサル クロック入力

- 差動 AC 結合または LVC MOS: 10 MHz ~ 200 MHz

- 水晶振動子: 10 MHz ~ 50 MHz

- 柔軟な出力クロック分配

- 4 チャネル分周器: 24kHz~328.125MHz の最大 5 つの固定出力周波数

- OUT0~OUT4 ピンで疑似 LVDS、LP-HCSL、LVC MOS 出力の組み合わせ

- 出力分周器のグリッチレス スイッチングと出力チャネル同期

- GPIO とレジスタによる個別の出力有効化

- 周波数マージニング オプション

- DCO モード: 10ppb 以下のステップ サイズで周波数を増減

- 完全統合された設定可能なループ帯域幅: 100 kHz ~ 1.6 MHz

- 単一電源または複数電源 (レベル変換用): 1.8V、2.5V、3.3V

- 設定可能な GPIO と柔軟な設定オプション

- I<sup>2</sup>C 互換インターフェイス: 最高 400kHz

- 2 つのページと外部選択ピンを持つ内蔵 EEPROM その場で設定が可能

- 100Ω システムをサポート

- 低い電磁放射

- 小さい占有面積: 24 ピン VQFN (4mm × 4mm)

## 2 アプリケーション

- PCIe Gen 1~Gen 6 のクロック処理

- ADAS (先進運転支援システム) - センサ フュージョン

- インフォテインメントとクラスター - 車載向けヘッド ユニット - eAVB

- データ センターおよびエンターブラインズ コンピューティング

- PC、ノート PC

- 企業向け機器 - 多機能プリンタ

- テストおよび測定 - ハンドヘルド機器

## 3 説明

CDCE6214-Q1 は、各種ドライバ モードを選択可能な 5 つの独立したクロック出力を生成できる、4 チャネル、超低消費電力、中グレード ジッタの車載用クロック ジェネレータです。入力信号源にはシングルエンドまたは差動入力のクロック ソース、あるいは水晶振動子を使用できます。CDCE6214-Q1 は、任意の入力周波数から無関係のベース周波数を合成するフラクショナル N PLL を備えています。

CDCE6214-Q1 は、フォールバック モードでのみ I<sup>2</sup>C インターフェイスを使用して構成できます。シリアル インターフェイスが使用できないときは、GPIO ピンをピン モードで使用し、デバイスを独自の構成に設定できます。

オンチップの EEPROM を使用して構成を変更できます (ピンで事前選択可能)。このデバイスは、グリッチなしの動作による周波数マージニング機能を備えており、システム設計検証テスト (DVT) とイーサネット オーディオ ビデオ プリッジ (eAVB) をサポートできます。DCO モードで分数帰還分周器を調整することで、すべての出力チャネルで細かい周波数マージニングが可能です。

内蔵パワー コンディショニングは、優れた電源リップル除去 (PSRR) を提供し、電力供給ネットワークのコストと複雑さを低減します。アナログおよびデジタル コア ブロックは 1.8V、2.5V、または 3.3V ±5% 電源で動作し、出力ブロックは 1.8V、2.5V、または 3.3V ±5% 電源で動作します。

CDCE6214-Q1 を使用すると、1 つの基準クロックで動作する高性能クロック ツリーを非常に低い消費電力と小さなフットプリントで実現できます。CDCE6214-Q1 は、EEPROM 機能を工場でプログラムすることもユーザーがプログラムすることもできるため、使いやすく即座に起動できる低消費電力クロック供給デバイスとして理想的です。

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール (機械翻訳) を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

**表 3-1. パッケージ情報**

| 部品番号        | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-------------|----------------------|--------------------------|

| CDCE6214-Q1 | RGE (VQFN, 24)       | 4.00mm × 4.00mm          |

(1) 詳細については、[セクション 11](#) を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はピンを含みます。

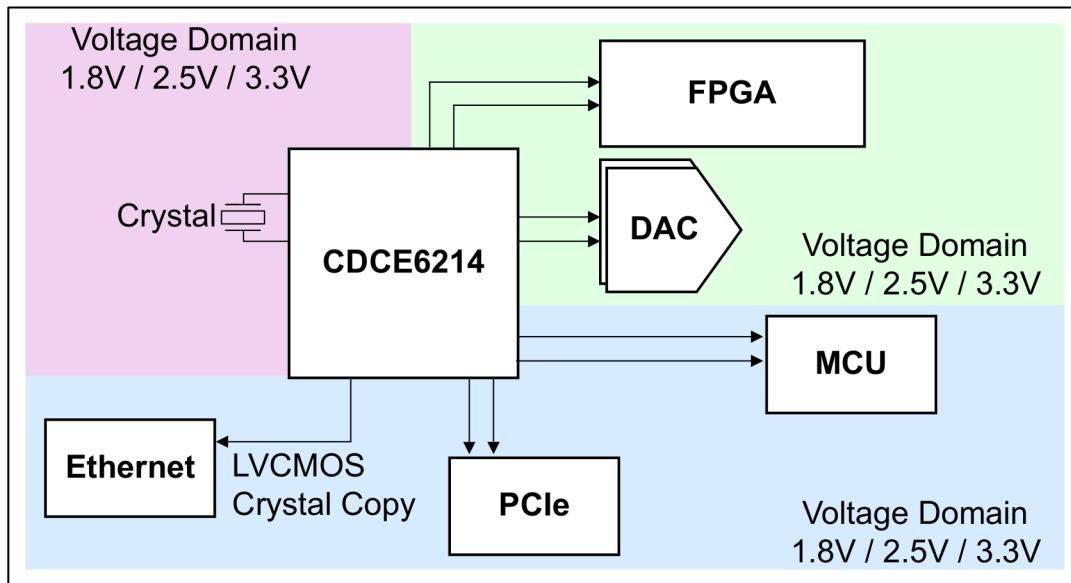

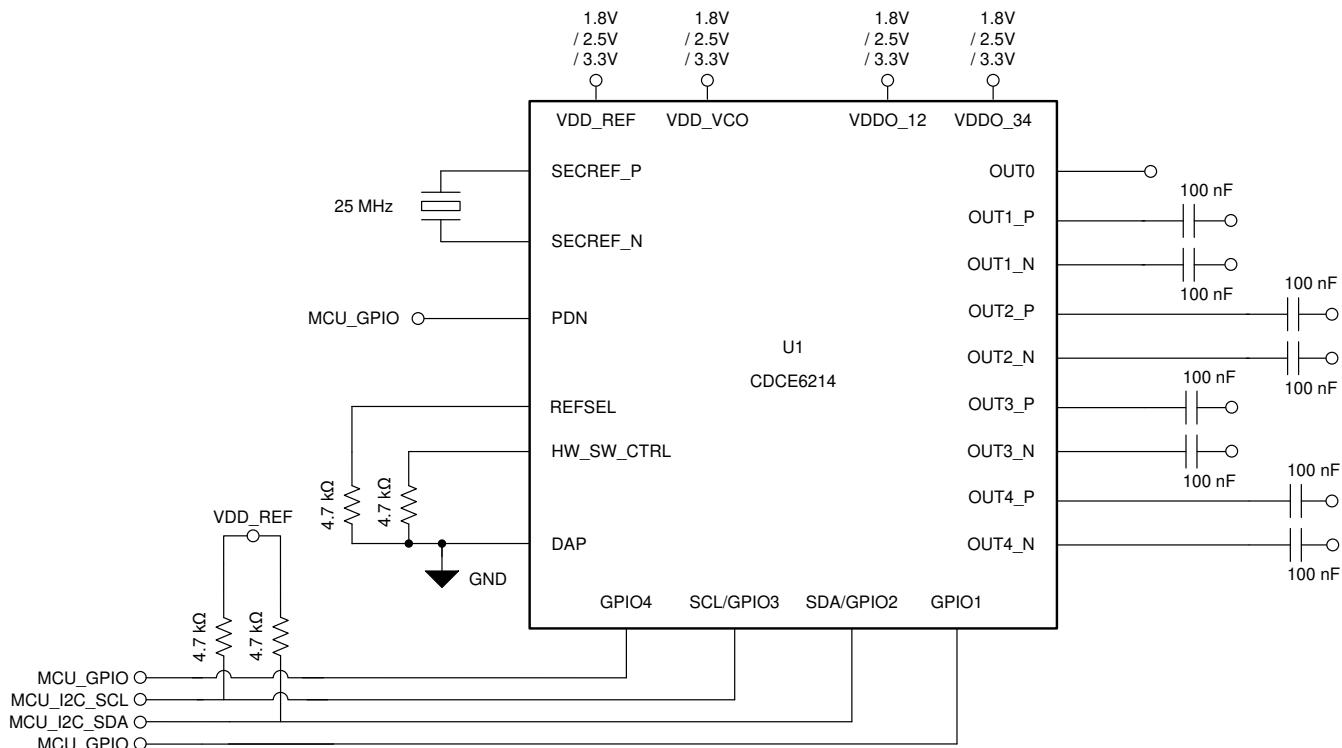

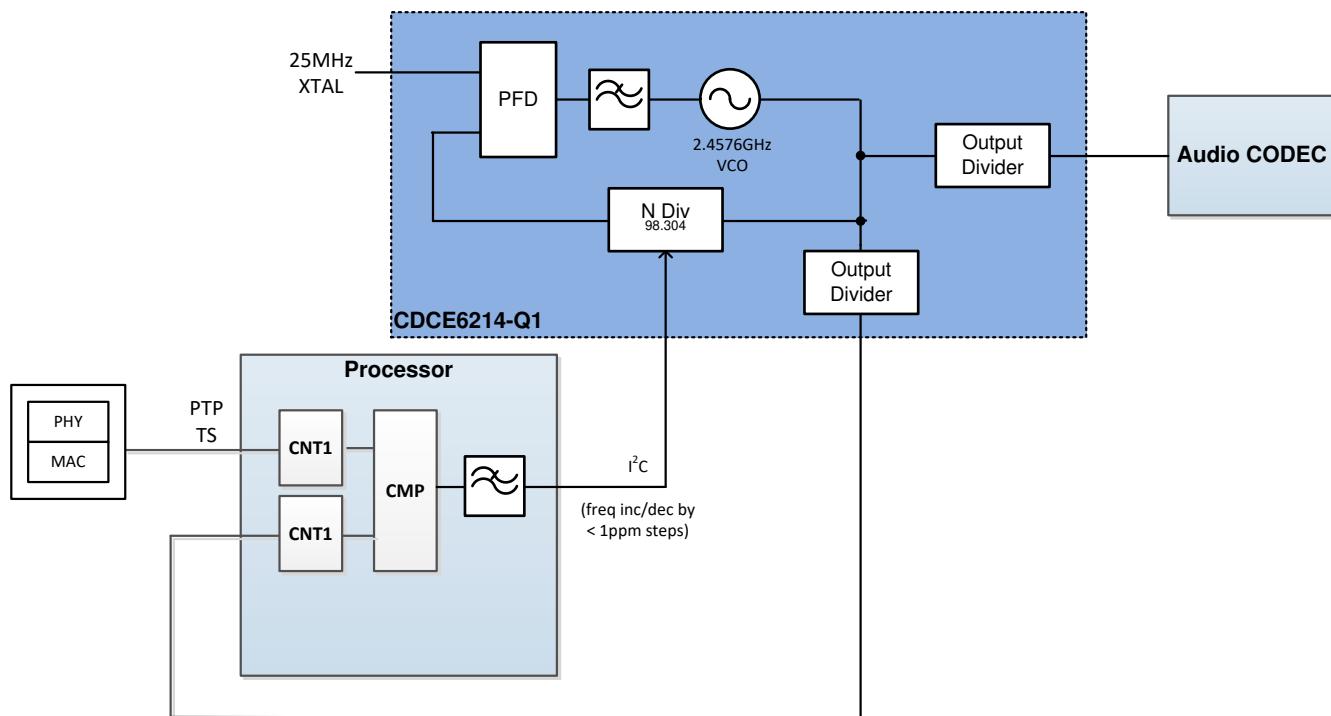

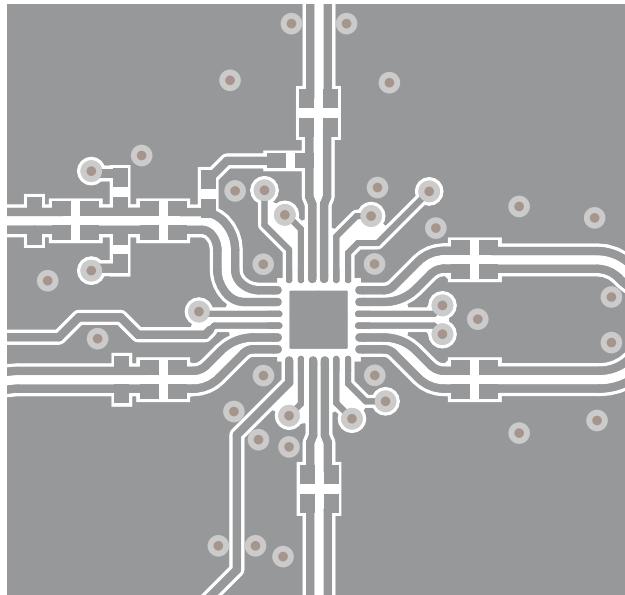

**アプリケーションの例 CDCE6214-Q1**

## 目次

|                                               |          |                               |           |

|-----------------------------------------------|----------|-------------------------------|-----------|

| <b>1 特長</b>                                   | <b>1</b> | <b>6 パラメータ測定情報</b>            | <b>17</b> |

| <b>2 アプリケーション</b>                             | <b>1</b> | <b>6.1 リファレンス入力</b>           | <b>17</b> |

| <b>3 説明</b>                                   | <b>1</b> | <b>6.2 出力</b>                 | <b>17</b> |

| <b>4 ピン構成および機能</b>                            | <b>4</b> | <b>6.3 シリアル・インターフェイス</b>      | <b>18</b> |

| <b>5 仕様</b>                                   | <b>7</b> | <b>6.4 PSNR テスト</b>           | <b>18</b> |

| 5.1 絶対最大定格                                    | 7        | <b>6.5 クロックのインターフェイスと終端</b>   | <b>19</b> |

| 5.2 ESD 定格                                    | 7        | <b>7 詳細説明</b>                 | <b>20</b> |

| 5.3 推奨動作条件                                    | 7        | <b>7.1 概要</b>                 | <b>20</b> |

| 5.4 熱に関する情報                                   | 7        | <b>7.2 機能ブロック図</b>            | <b>20</b> |

| 5.5 EEPROM の特性                                | 8        | <b>7.3 機能説明</b>               | <b>21</b> |

| 5.6 リファレンス入力、シングルエンド特性                        | 8        | <b>7.4 デバイスの機能モード</b>         | <b>35</b> |

| 5.7 リファレンス入力、差動特性                             | 8        | <b>7.5 プログラミング</b>            | <b>36</b> |

| 5.8 リファレンス入力、水晶振動子モードの特性                      | 8        | <b>8 アプリケーションと実装</b>          | <b>46</b> |

| 5.9 汎用入力特性                                    | 9        | <b>8.1 アプリケーション情報</b>         | <b>46</b> |

| 5.10 トリプル・レベル入力特性                             | 9        | <b>8.2 代表的なアプリケーション</b>       | <b>47</b> |

| 5.11 ロジック出力特性                                 | 9        | <b>8.3 電源に関する推奨事項</b>         | <b>49</b> |

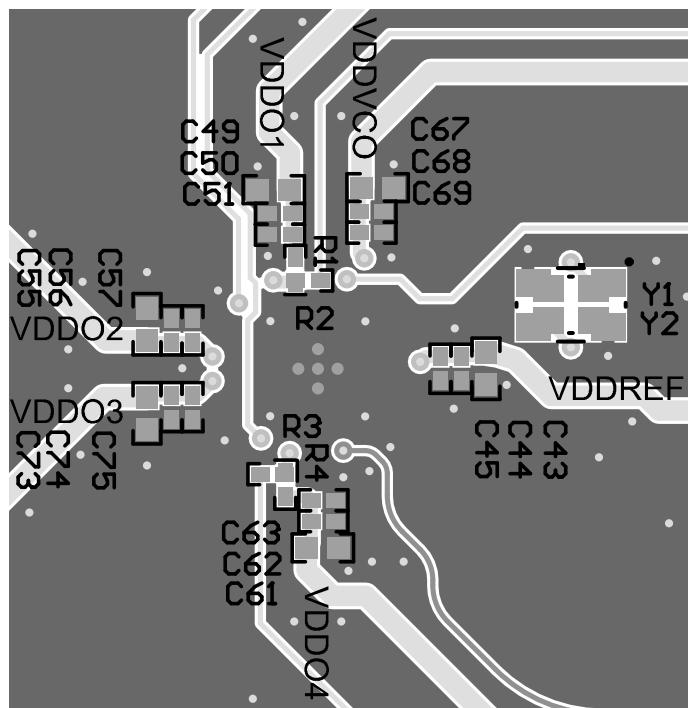

| 5.12 フェーズロック ループ特性                            | 9        | <b>8.4 レイアウト</b>              | <b>50</b> |

| 5.13 閉ループ出力ジッタの特性                             | 10       | <b>9 デバイスおよびドキュメントのサポート</b>   | <b>52</b> |

| 5.14 入力および出力絶縁                                | 10       | <b>9.1 デバイスサポート</b>           | <b>52</b> |

| 5.15 バッファ モードの特性                              | 10       | <b>9.2 ドキュメントのサポート</b>        | <b>52</b> |

| 5.16 PCIe スペクトラム拡散ジェネレータ                      | 11       | <b>9.3 ドキュメントの更新通知を受け取る方法</b> | <b>52</b> |

| 5.17 LVCMOS 出力特性                              | 11       | <b>9.4 サポート・リソース</b>          | <b>52</b> |

| 5.18 LP-HCSL 出力特性                             | 12       | <b>9.5 商標</b>                 | <b>52</b> |

| 5.19 LVDS 出力特性                                | 12       | <b>9.6 静電気放電に関する注意事項</b>      | <b>52</b> |

| 5.20 出力同期特性                                   | 12       | <b>9.7 用語集</b>                | <b>52</b> |

| 5.21 パワーオンリセット特性                              | 13       | <b>10 改訂履歴</b>                | <b>52</b> |

| 5.22 I <sup>2</sup> C 互換シリアル インターフェイスの特性      | 13       | <b>11 メカニカル、パッケージ、および注文情報</b> | <b>53</b> |

| 5.23 タイミング要件、I <sup>2</sup> C 互換シリアル インターフェイス | 13       | <b>11.1 付録:パッケージオプション</b>     | <b>57</b> |

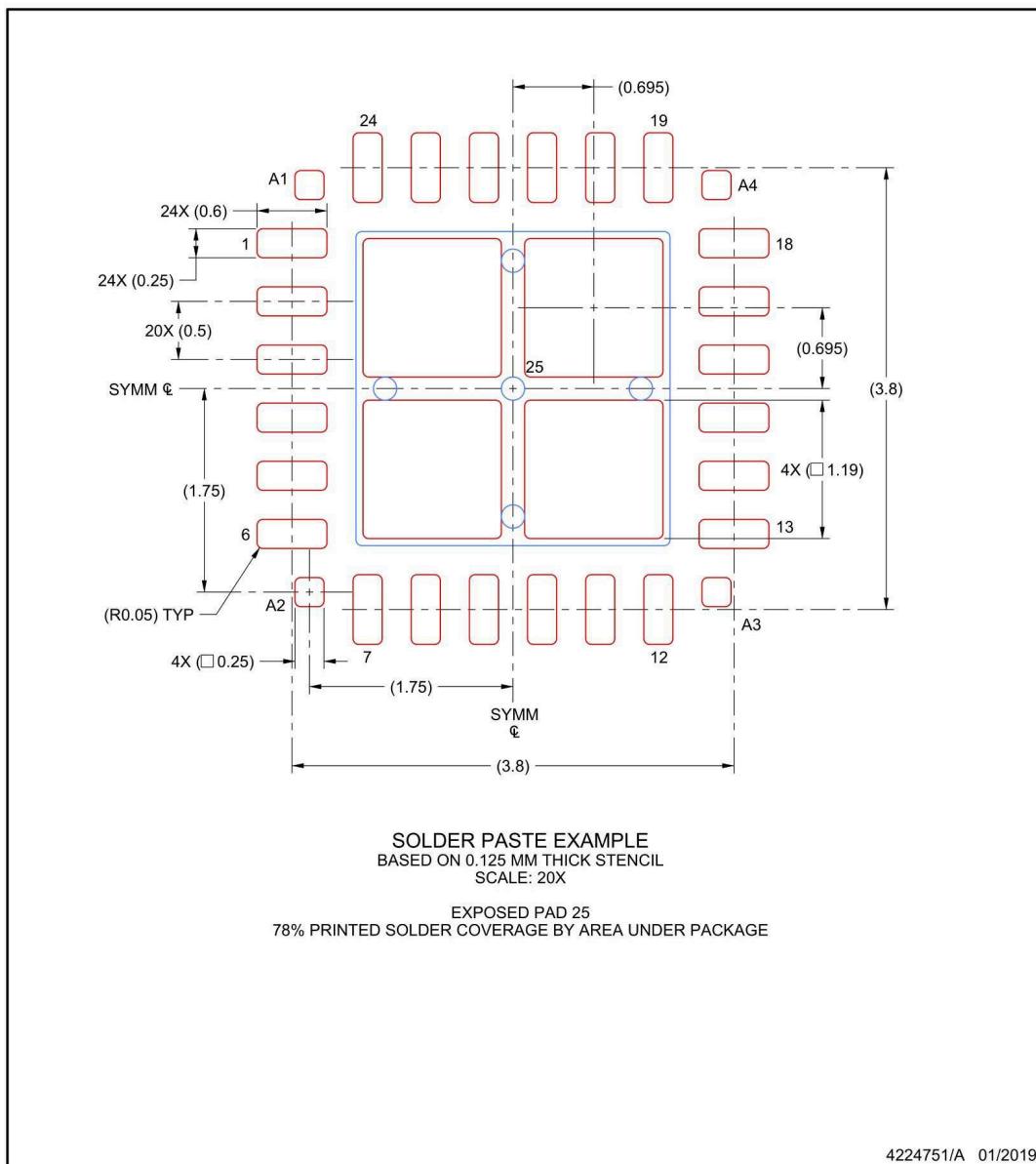

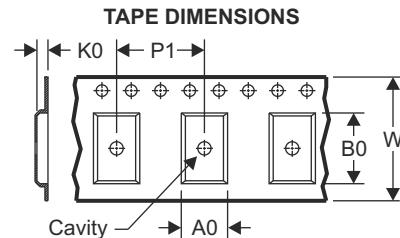

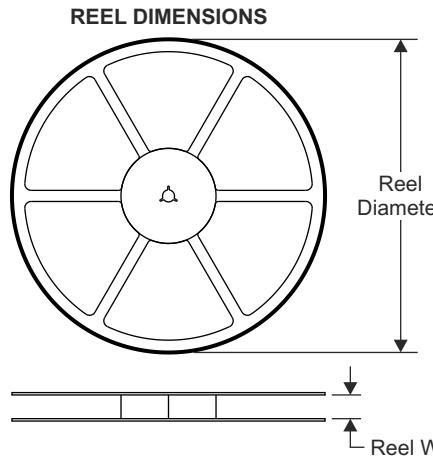

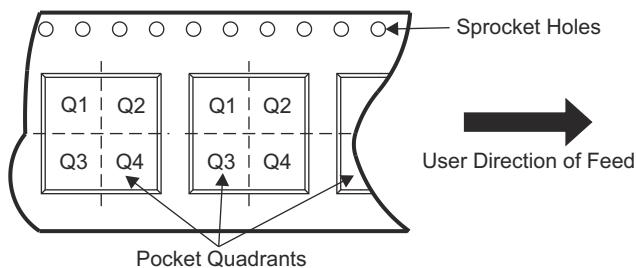

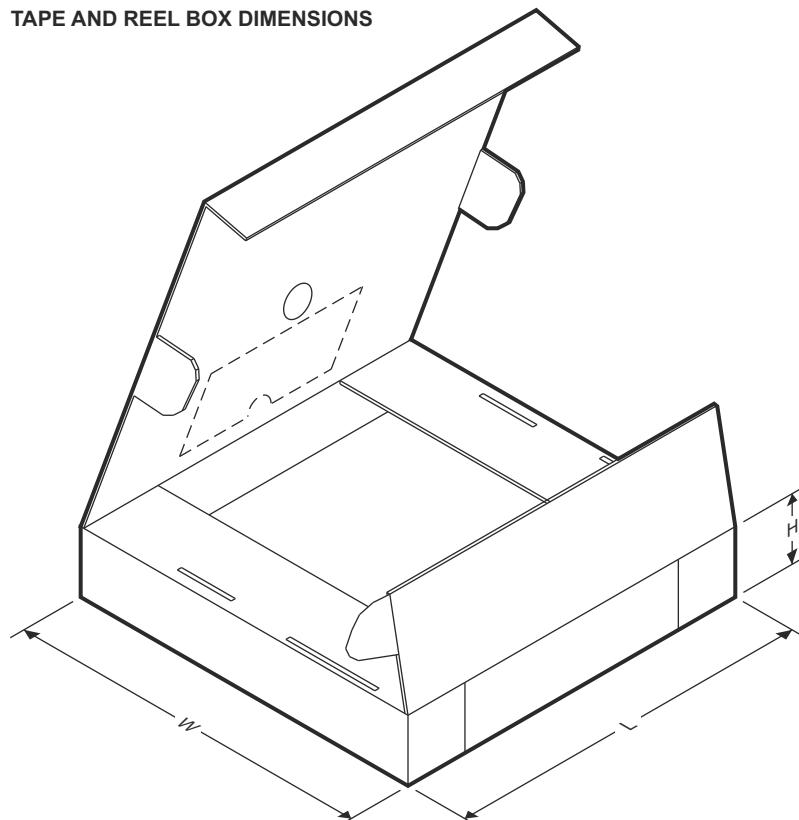

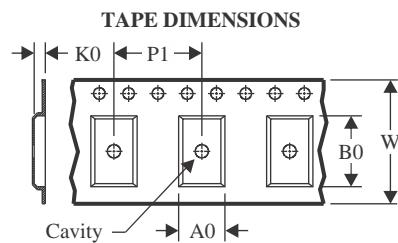

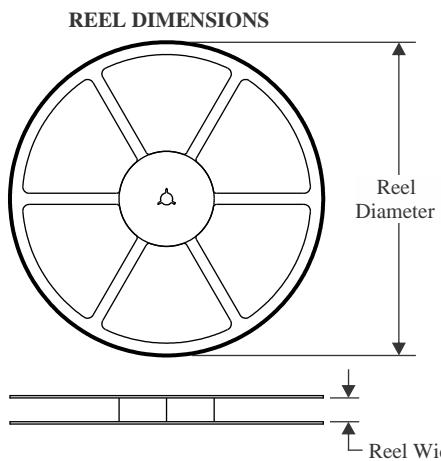

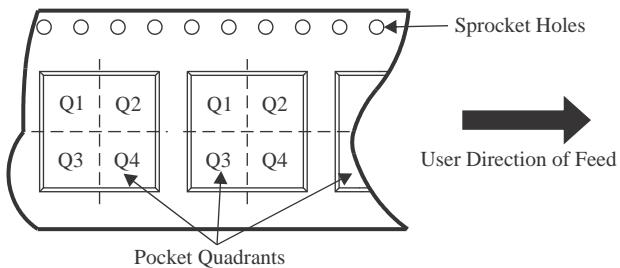

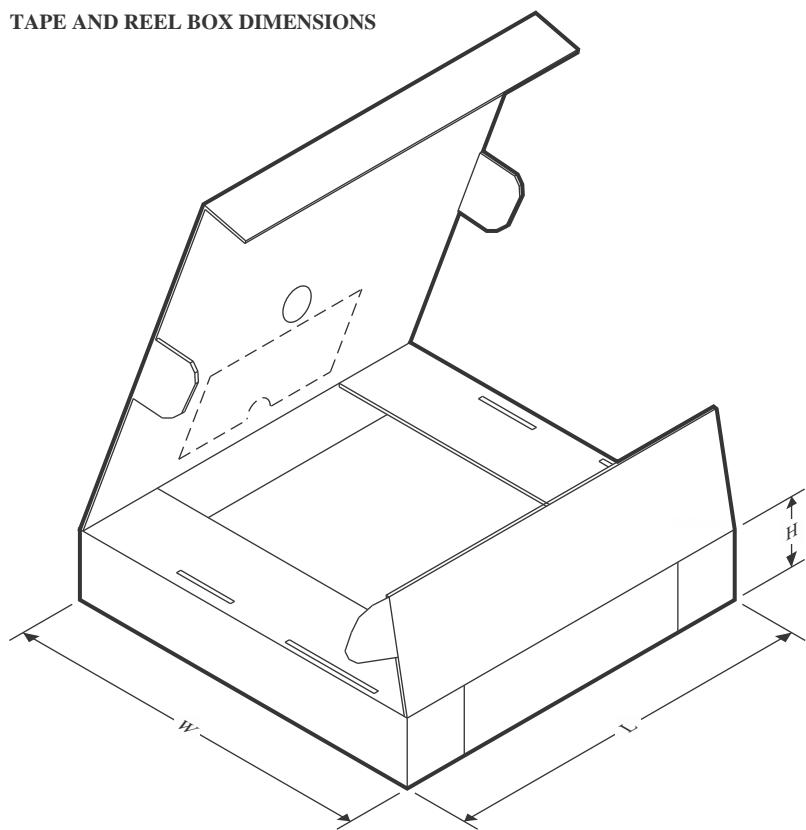

| 5.24 電源特性                                     | 14       | <b>11.2 テープおよびリール情報</b>       | <b>58</b> |

| 5.25 代表的特性                                    | 14       |                               |           |

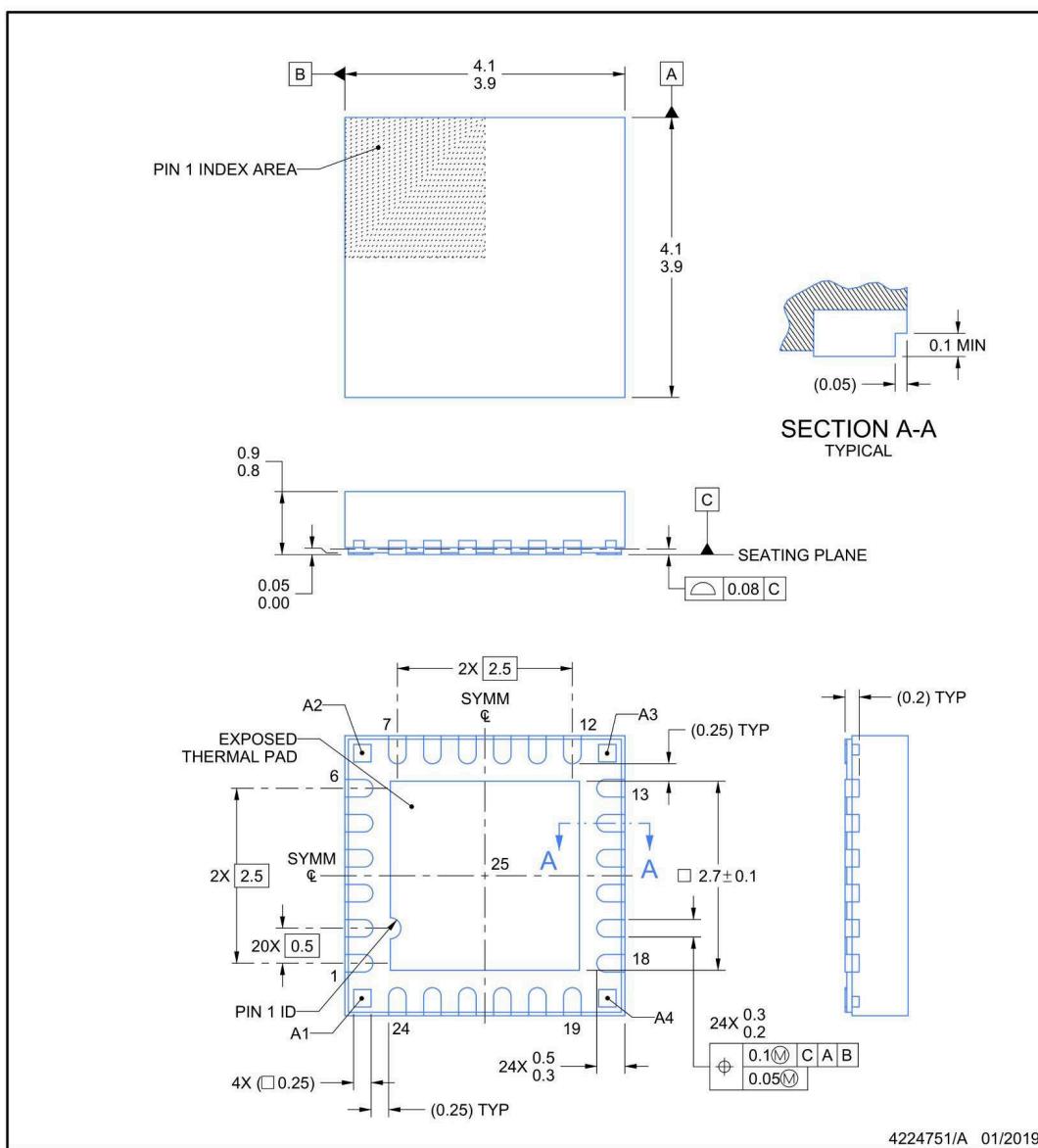

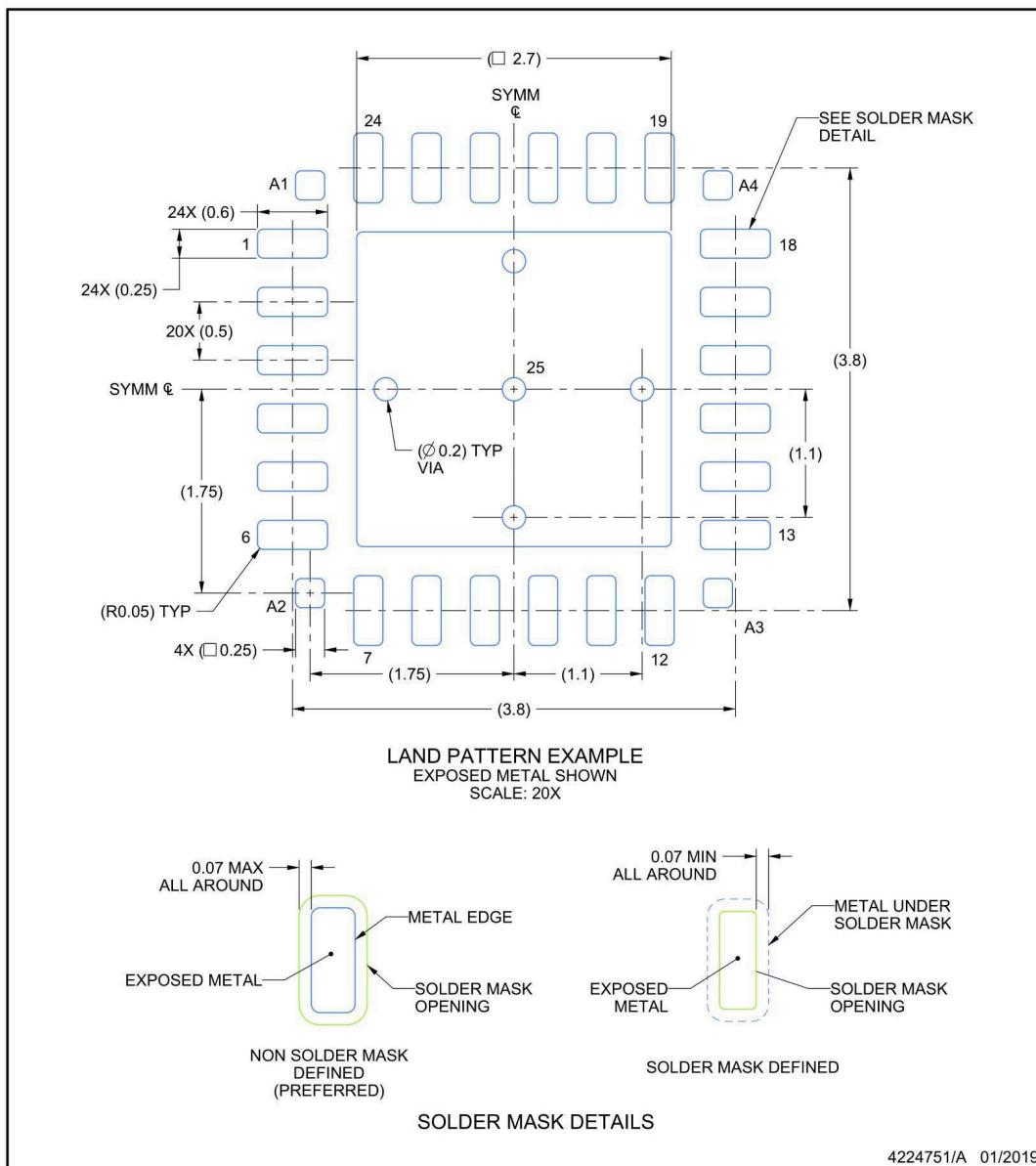

## 4 ピン構成および機能

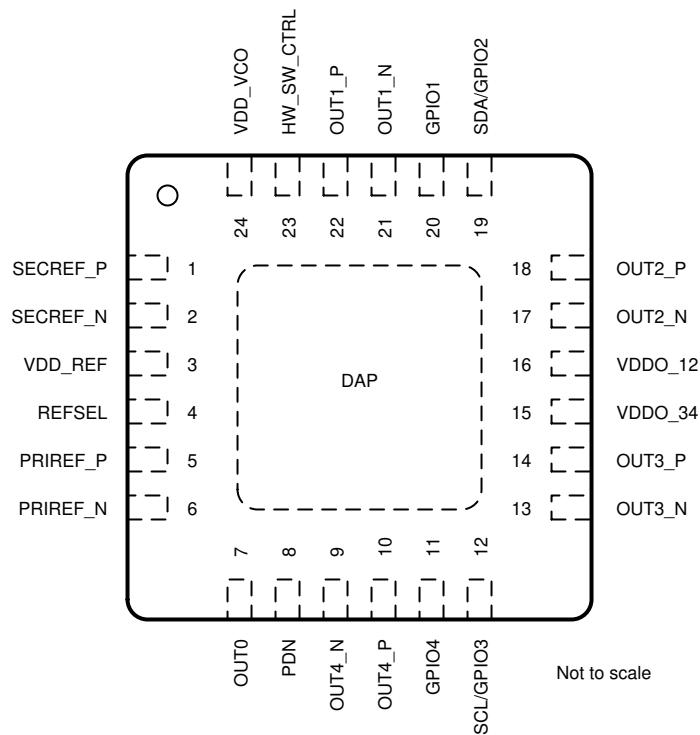

図 4-1. RGE パッケージ 24 ピン VQFN 上面図

**表 4-1. ピンの機能**

| ピン                       |    | タイプ <sup>(1)</sup> | 説明                                                                                                                                                                                  |

|--------------------------|----|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称                       | 番号 |                    |                                                                                                                                                                                     |

| <b>電源</b>                |    |                    |                                                                                                                                                                                     |

| DAP                      | —  | G                  | ダイ取り付けパッド。DAP は、電気的接続であり、放熱経路を提供します。デバイスの適切な電気的性能および放熱性能を得るために、DAP を PCB のグランドプレーンに接続する必要があります。                                                                                     |

| VDD_REF                  | 3  | P                  | リファレンス入力およびデジタル用の 1.8V、2.5V、または 3.3V 電源。                                                                                                                                            |

| VDD_VCO                  | 24 | P                  | PLL/VCO 用の 1.8V、2.5V、または 3.3V 電源。                                                                                                                                                   |

| VDDO_12                  | 16 | P                  | OUT1 および OUT2 チャネル用の 1.8V、2.5V、または 3.3V 電源                                                                                                                                          |

| VDDO_34                  | 15 | P                  | OUT0、OUT3、および OUT4 チャネル用の 1.8V、2.5V、または 3.3V 電源                                                                                                                                     |

| <b>入力ブロック</b>            |    |                    |                                                                                                                                                                                     |

| HW_SW_C_TRL              | 23 | I, RPUPD           | EEPROM ページの手動選択ピン (トライステート)。弱いプルアップ / プルダウン。R <sub>PU</sub> = 50kΩ。R <sub>PD</sub> = 50kΩ。                                                                                          |

| PRIREF_P                 | 5  | I                  | プライマリ基準クロック。差動入力またはシングルエンド入力を受け入れます。差動モードでは、入力ピンに AC 結合コンデンサと内部バイアスが必要です。LVCMOS の場合、入力は PRIREF_P に供給し、非駆動入力ピンはグランドにプルダウンする必要があります。シングルエンドモードでは、差動モードの場合の内部バイアスはディスエーブルになります。        |

| PRIREF_N                 | 6  | I                  |                                                                                                                                                                                     |

| REFSEL                   | 4  | I, RPUPD           | リファレンス入力の手動選択ピン (トライステート)。弱いプルアップ / プルダウン。R <sub>PU</sub> = 50kΩ。R <sub>PD</sub> = 50kΩ。                                                                                            |

| SECREF_P                 | 1  | I                  | セカンダリ基準クロック。差動入力、シングルエンド入力、または XTAL を受け入れます。差動モードでは、入力ピンに AC 結合コンデンサと内部バイアスが必要です。XTAL 入力の場合、SECREF_P ピンと SECREF_N ピンの間に水晶振動子を接続します。                                                 |

| SECREF_N                 | 2  | I                  | SECREF_P は XOUT で、SECREF_N は XIN です。このデバイスでは、XOUT に電力制限抵抗は必要ありません。LVCMOS 入力の場合、入力は SECREF_P に供給し、非駆動入力ピンはグランドにプルダウンする必要があります。シングルエンドモードおよび XTAL モードでは、差動モードの場合の内部バイアスはディスエーブルになります。 |

| <b>出力ブロック</b>            |    |                    |                                                                                                                                                                                     |

| OUT0                     | 7  | O                  | LVCMOS 出力 0。リファレンス入力は、この出力にバイパスできます。すべての LVCMOS 出力で出力スルーレートを構成可能です。                                                                                                                 |

| OUT1_P                   | 22 | O                  | 疑似 LVDS/LP-HCSL/LVCMOS 出力ペア 1。疑似 LVDS/LP-HCSL または 2x LVCMOS 出力付きプログラマブルドライバ。                                                                                                        |

| OUT1_N                   | 21 | O                  |                                                                                                                                                                                     |

| OUT2_P                   | 18 | O                  | 疑似 LVDS/LP-HCSL 出力ペア 2。疑似 LVDS/LP-HCSL 出力付きプログラマブルドライバ。                                                                                                                             |

| OUT2_N                   | 17 | O                  |                                                                                                                                                                                     |

| OUT3_P                   | 14 | O                  | 疑似 LVDS/LP-HCSL 出力ペア 3。疑似 LVDS/LP-HCSL 出力付きプログラマブルドライバ。                                                                                                                             |

| OUT3_N                   | 13 | O                  |                                                                                                                                                                                     |

| OUT4_P                   | 10 | O                  | 疑似 LVDS/LP-HCSL/LVCMOS 出力ペア 4。疑似 LVDS/LP-HCSL または 2x LVCMOS 出力付きプログラマブルドライバ。                                                                                                        |

| OUT4_N                   | 9  | O                  |                                                                                                                                                                                     |

| <b>デジタル制御 / インターフェイス</b> |    |                    |                                                                                                                                                                                     |

| GPIO1                    | 20 | I/O                | ステータス出力または GPIO1 入力。                                                                                                                                                                |

| GPIO4                    | 11 | I/O                | ステータス出力または GPIO4 入力。                                                                                                                                                                |

| PDN                      | 8  | I, R <sub>PU</sub> | デバイスのパワーダウン / RESET (アクティブ Low) または SYNCN。弱いプルアップ抵抗 R <sub>PU</sub> = 50kΩ。出力モードでは、プルアップ抵抗がディスエーブルになります。                                                                            |

表 4-1. ピンの機能 (続き)

| ピン        |    | タイプ <sup>(1)</sup> | 説明                                                                                                                                                           |

|-----------|----|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称        | 番号 |                    |                                                                                                                                                              |

| SDA/GPIO2 | 19 | I/O                | I <sup>2</sup> C シリアル データ(双方向、オープンドレイン)または GPIO2 入力。I <sup>2</sup> C モードでは、VDD_REF への外部プルアップ抵抗が必要です。I <sup>2</sup> C アドレスは、オンチップ EEPROM から初期化されます。フェイルセーフ入力。 |

| SCL/GPIO3 | 12 | I                  | I <sup>2</sup> C シリアル クロックまたは GPIO3 入力。I <sup>2</sup> C モードでは、VDD_REF への外部プルアップ抵抗が必要です。フェイルセーフ入力。                                                            |

(1) 種類:

- G = グランド

- P = 電源

- I = 入力

- I/O = 入出力

- O = 出力

- I, RPUPD = 入力、抵抗性プルアップおよびプルダウン付き

- I, RPU = 入力、抵抗性プルアップ付き

- I/O, RPU = 入出力、抵抗性プルアップ付き

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                                                                             |       | 最小値  | 最大値                         | 単位 |

|-----------------------------------------------------------------------------|-------|------|-----------------------------|----|

| VDD_REF、VDD_VCO、VDDO_12、VDDO_34                                             | 電源電圧  | -0.3 | 3.63                        | V  |

| PRIREF_P、PRIREF_N、SECREF_P、SECREF_N                                         | 入力電圧  | -0.3 | VDD_REF + 0.3               | V  |

| GPIO1、SDA(GPIO2、SCL(GPIO3、GPIO4、REFSEL、HW_SW_CTRL、PDN                       | 入力電圧  | -0.3 | VDD_REF + 0.3               | V  |

| OUT0、OUT1_P、OUT1_N、OUT2_P、OUT2_N、OUT3_P、OUT3_N、OUT4_P、OUT4_N <sup>(2)</sup> | 出力電圧  | -0.3 | VDDO_X <sup>(2)</sup> + 0.3 | V  |

| T <sub>J</sub>                                                              | 接合部温度 |      | 125                         | °C |

| T <sub>stg</sub>                                                            | 保存温度  | -65  | 150                         | °C |

- (1) 「絶対最大定格」を超えた動作は、デバイスに恒久的な損傷を与える可能性があります。絶対最大定格は、これらの条件において、または推奨動作条件に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

- (2) VDDO\_X は、特定の出力チャネルの出力電源を表します。ここで、X はチャネルインデックスを表します。

### 5.2 ESD 定格

|                    |      |                                                            | 値    | 単位 |

|--------------------|------|------------------------------------------------------------|------|----|

| V <sub>(ESD)</sub> | 静電放電 | 人体モデル (HBM)、AEC Q100-002、HBM ESD 分類レベル 2 準拠 <sup>(1)</sup> | 2000 | V  |

|                    |      | デバイス帶電モデル (CDM)、AEC Q100-011 CDM ESD 分類レベル C5 準拠           | 750  | V  |

- (1) AEC Q100-002 は、HBM ストレス試験を ANSI/ESDA/JEDEC JS-001 仕様に従って実施しなければならないと規定しています。

### 5.3 推奨動作条件

自由気流での動作温度範囲内 (特に記述のない限り)

|                   |                                | 最小値  | 公称値         | 最大値   | 単位 |

|-------------------|--------------------------------|------|-------------|-------|----|

| VDD_VCO           | コア電源電圧                         | 1.71 | 1.8、2.5、3.3 | 3.465 | V  |

| VDDO_12、VDDO_34   | 出力電源電圧                         | 1.71 | 1.8、2.5、3.3 | 3.465 | V  |

| VDD_REF           | リファレンス電源電圧                     | 1.71 | 1.8、2.5、3.3 | 3.465 | V  |

| T <sub>A</sub>    | 周囲温度                           | -40  |             | 105   | °C |

| T <sub>J</sub>    | 接合部温度                          | -40  |             | 125   | °C |

| T <sub>LOCK</sub> | 全温度範囲での連続ロック (VCO キャリブレーションなし) |      |             | 145   | °C |

| t <sub>RAMP</sub> | 最大電源電圧ランプ時間 <sup>(1)</sup>     | 0.1  |             | 30    | ms |

- (1) VDD ピンは、電源ランプ時間内に最終値の 95% に単調に到達する必要があります。この評価のために、すべての VDD ピンは互いに接続されました。非単調または低速の電源ランプの場合、VDD ピンが最終値の 95% に達するまで PDN ピンをプルダウンすることをお勧めします。PDN ピンには 50kΩ のプルアップ抵抗があります。PDN ピンをアクティブに制御できない場合、PDN ピンの GND にコンデンサを追加して、リセットの解除を遅延させることを推奨します。

### 5.4 熱に関する情報

| 熱評価基準 <sup>(1)</sup>  |                     | CDCE6214Q1<br>TM | 単位   |

|-----------------------|---------------------|------------------|------|

|                       |                     | RGE (VQFN)       |      |

|                       |                     | 24 ピン            |      |

| R <sub>θJA</sub>      | 接合部から周囲への熱抵抗        | 32.5             | °C/W |

| R <sub>θJC(top)</sub> | 接合部からケース (上面) への熱抵抗 | 32.5             | °C/W |

| R <sub>θJB</sub>      | 接合部から基板への熱抵抗        | 12.2             | °C/W |

| 熱評価基準 <sup>(1)</sup>  |                   | CDCE6214Q1<br>TM | 単位   |

|-----------------------|-------------------|------------------|------|

|                       |                   | RGE (VQFN)       |      |

|                       |                   | 24 ピン            |      |

|                       |                   |                  |      |

| R <sub>θJC(bot)</sub> | 接合部からケース(底面)への熱抵抗 | 2.0              | °C/W |

| Ψ <sub>JT</sub>       | 接合部から上面への特性パラメータ  | 0.4              | °C/W |

| Ψ <sub>JB</sub>       | 接合部から基板への特性パラメータ  | 12.2             | °C/W |

(1) 従来および最新の熱評価基準の詳細については、『半導体およびICパッケージの熱評価基準』アプリケーションノートを参照してください。

## 5.5 EEPROM の特性

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、T<sub>A</sub> = -40°C~105°C

| パラメータ              | テスト条件               | 最小値  | 標準値 | 最大値 | 単位   |

|--------------------|---------------------|------|-----|-----|------|

| n <sub>EEcyc</sub> | EEPROM プログラミング サイクル | 各ワード | 10  |     | サイクル |

| t <sub>EERet</sub> | EEPROM データ保持        |      | 10  |     | 年    |

## 5.6 リファレンス入力、シングルエンド特性

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、T<sub>A</sub> = -40°C~105°C

| パラメータ                   | テスト条件        | 最小値            | 代表値           | 最大値 | 単位   |

|-------------------------|--------------|----------------|---------------|-----|------|

| f <sub>IN_Ref</sub>     | リファレンス周波数    |                | 10            | 200 | MHz  |

| V <sub>IH</sub>         | 入力 HIGH 電圧   | LVC MOS 入力バッファ | 0.8 × VDD_REF |     | V    |

| V <sub>IL</sub>         | 入力 LOW 電圧    | LVC MOS 入力バッファ | 0.2 × VDD_REF |     | V    |

| dV <sub>IN</sub> /dT    | 入力スルーレート     | 20%~80%        | 1             |     | V/ns |

| IDC                     | 入力デューティ・サイクル |                | 40            | 60  | %    |

| I <sub>IN_LEAKAGE</sub> | 入力リーク電流      |                | -100          | 100 | μA   |

| C <sub>IN_REF</sub>     | 入力容量         | 25°C           |               | 5   | pF   |

## 5.7 リファレンス入力、差動特性

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、T<sub>A</sub> = -40°C~105°C

| パラメータ                   | テスト条件                 | 最小値                 | 代表値  | 最大値 | 単位   |

|-------------------------|-----------------------|---------------------|------|-----|------|

| f <sub>IN_Ref</sub>     | リファレンス周波数             |                     | 10   | 200 | MHz  |

| V <sub>IN_DIFF</sub>    | 差動入力電圧スイング、ピーク・ツー・ピーク | VDD_REF = 2.5V/3.3V | 0.4  | 1.6 | V    |

| V <sub>IN_DIFF</sub>    | 差動入力電圧スイング、ピーク・ツー・ピーク | VDD_REF = 1.8V      | 0.4  | 1.0 | V    |

| dV <sub>IN</sub> /dT    | 入力スルーレート              | 20%~80%             | 1    |     | V/ns |

| IDC                     | 入力デューティ・サイクル          |                     | 40   | 60  | %    |

| I <sub>IN_LEAKAGE</sub> | 入力リーク電流               |                     | -100 | 100 | μA   |

| C <sub>IN_REF</sub>     | 入力容量                  | 25°C                |      | 5   | pF   |

## 5.8 リファレンス入力、水晶振動子モードの特性

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、T<sub>A</sub> = -40°C~105°C<sup>(1)</sup>

| パラメータ                | テスト条件           | 最小値                             | 代表値 | 最大値  | 単位  |

|----------------------|-----------------|---------------------------------|-----|------|-----|

| f <sub>IN_Xtal</sub> | 水晶周波数           | 基本モード                           | 10  | 50   | MHz |

| Z <sub>ESR</sub>     | 水晶振動子の等価直列抵抗    | f <sub>Xtal</sub> = 10MHz~16MHz |     | 60   | Ω   |

| Z <sub>ESR</sub>     | 水晶振動子の等価直列抵抗    | f <sub>Xtal</sub> = 16MHz~30MHz |     | 50   | Ω   |

| Z <sub>ESR</sub>     | 水晶振動子の等価直列抵抗    | f <sub>Xtal</sub> = 30MHz~50MHz |     | 30   | Ω   |

| C <sub>L</sub>       | 水晶振動子の負荷容量      | オンチップ負荷容量を使用。サポートされている水晶振動子の範囲  | 5   | 12.8 | pF  |

| P <sub>Xtal</sub>    | 水晶振動子で許容される駆動電力 | サポートされている水晶振動子の最大許容             |     | 200  | μW  |

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、TA = -40°C~105°C<sup>(1)</sup>

| パラメータ                 | テスト条件                                | 最小値 | 代表値 | 最大値 | 単位 |

|-----------------------|--------------------------------------|-----|-----|-----|----|

| C <sub>XIN_LOAD</sub> | オンチップ負荷容量<br>代表値の 200fF ステップでプログラム可能 | 3   | 9.1 | 9.1 | pF |

(1) XTAL 入力の構成に関する詳細なアプリケーション・レポートについては、『[SNA331: CDCI6214 および CDCE6214-Q1 水晶振動子入力を使用する設計](#)』を参照してください。

## 5.9 汎用入力特性

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、TA = -40°C~105°C

| パラメータ                     | テスト条件         | 最小値                                       | 代表値           | 最大値 | 単位   |

|---------------------------|---------------|-------------------------------------------|---------------|-----|------|

| V <sub>IH</sub>           | 入力 HIGH 電圧    | 0.8 × VDD_REF                             |               |     | V    |

| V <sub>IL</sub>           | 入力 LOW 電圧     |                                           | 0.2 × VDD_REF |     | V    |

| I <sub>IH</sub>           | 入力 HIGH レベル電流 | V <sub>IH</sub> = VDD_REF、GPIO[1:4]、PDN   | -5            | 5   | μA   |

| I <sub>IL</sub>           | 入力 LOW レベル電流  | V <sub>IL</sub> = GND、GPIO[2:3]           | -5            | 5   | μA   |

| I <sub>IL</sub>           | 入力 LOW レベル電流  | V <sub>IL</sub> = GND、GPIO[1]、GPIO[4]、PDN | -100          | 100 | μA   |

| dV <sub>IN</sub> /dT      | 入力スルーレート      | 20%~80%                                   | 0.5           |     | V/ns |

| T <sub>PULSE_WIDT_H</sub> | 正常動作のパルス幅     |                                           | 10            |     | ns   |

| R <sub>PU</sub>           | プルアップ抵抗       | ピン PDN、GPIO[1]、GPIO[4]                    | 30            | 55  | kΩ   |

| C <sub>IN</sub>           | ピン容量          |                                           |               | 10  | pF   |

## 5.10 トリプル・レベル入力特性

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、TA = -40°C~105°C

| パラメータ           | テスト条件         | 最小値                       | 代表値           | 最大値            | 単位  |

|-----------------|---------------|---------------------------|---------------|----------------|-----|

| V <sub>IH</sub> | 入力 HIGH 電圧    | 0.8 × VDD_REF             |               |                | V   |

| V <sub>IM</sub> | 入力 MID 電圧     | 0.41 × VDD_REF            | 0.5 × VDD_REF | 0.58 × VDD_REF | V   |

| V <sub>IL</sub> | 入力 LOW 電圧     |                           | 0.2 × VDD_REF |                | V   |

| I <sub>IH</sub> | 入力 HIGH レベル電流 | V <sub>IH</sub> = VDD_REF | 20            | 50             | 100 |

| I <sub>IL</sub> | 入力 LOW レベル電流  | V <sub>IL</sub> = GND     | -100          | -50            | -20 |

## 5.11 ロジック出力特性

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、TA = -40°C~105°C

| パラメータ | テスト条件      | 最小値           | 代表値           | 最大値 | 単位 |

|-------|------------|---------------|---------------|-----|----|

| VOH   | 出力 HIGH 電圧 | 0.8 × VDD_REF |               |     | V  |

| VOL   | 出力 LOW 電圧  |               | 0.2 × VDD_REF |     | V  |

## 5.12 フェーズロックループ特性

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、TA = -40°C~105°C

| パラメータ            | テスト条件             | 最小値                       | 標準値  | 最大値  | 単位    |

|------------------|-------------------|---------------------------|------|------|-------|

| f <sub>PFD</sub> | 位相検出器周波数          | 整数およびフラクショナル PLL モード      | 1    | 100  | MHz   |

| f <sub>vco</sub> | 電圧制御発振器の周波数       |                           | 2335 | 2625 | MHz   |

| f <sub>BW</sub>  | 構成可能な閉ループ PLL 帯域幅 | REF = 25MHz               | 100  | 1600 | kHz   |

| K <sub>vco</sub> | 電圧制御発振器のゲイン       | f <sub>vco</sub> = 2.4GHz |      | 140  | MHz/V |

| K <sub>vco</sub> | 電圧制御発振器のゲイン       | f <sub>vco</sub> = 2.5GHz |      | 175  | MHz/V |

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、T<sub>A</sub> = -40°C~105°C

| パラメータ                  |                                  | テスト条件           | 最小値 | 標準値 | 最大値 | 単位  |

|------------------------|----------------------------------|-----------------|-----|-----|-----|-----|

| ΔT <sub>CL</sub>       | 連続ロックで許容される温度ドリフト <sup>(1)</sup> | dT/dt ≤ 20K/min |     | 145 |     | °C  |

| f <sub>MAX-ERROR</sub> | フランクショナル N PLL での最大周波数誤差         |                 |     | 0.1 |     | ppm |

- (1) 連続ロックの最大許容温度ドリフト: 温度ドリフト全体にわたって PLL がロック状態にある間にオンチップ VCO がキャリブレーションされたときに、以前の値からいざれかの方向に温度がドリフト可能な範囲。内部 VCO キャリブレーションの実行: デバイスの起動時、および RESET ピンを使用してデバイスをリセットしたとき、およびレジスタビットが変更されたとき。これは、デバイスが全周波数範囲で動作することを意味しますが、温度が連続ロックの最大許容温度ドリフトを超えてドリフトした場合、適切な REGISTER ビットを使用して VCO を再キャリブレーションし、PLL をロック状態に維持する必要があります。最初にキャリブレーションを行った温度にかかわらず、-40°C ~ 105°C の周囲温度範囲を超える温度ドリフトは決して発生しません。

## 5.13 閉ループ出力ジッタの特性

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、T<sub>A</sub> = -40°C~105°C

| パラメータ                    |                          | テスト条件                                                                                              | 最小値 | 代表値  | 最大値  | 単位 |

|--------------------------|--------------------------|----------------------------------------------------------------------------------------------------|-----|------|------|----|

| t <sub>RJ_CL</sub>       | RMS 位相ジッタ                | 12kHz~20MHz のスプリアスによる RMS ジッタ、入力水晶振動子 = 25MHz、差動 OUTx > 100MHz、整数 PLL                              |     | 350  | 600  | fs |

| t <sub>RJ_CL</sub>       | RMS 位相ジッタ <sup>(1)</sup> | 12kHz~20MHz のスプリアスによる RMS ジッタ、水晶振動子入力 = 25MHz、差動 OUTx > 100MHz、フランクショナル PLL                        |     | 1600 | 2100 | fs |

| t <sub>RJ_CL, PCIE</sub> | RMS 位相ジッタ                | PCIe Gen 3 フィルタ適用済み、XIN = 水晶振動子 25MHz、OUTx = 100MHz、フランクショナル N PLL、SSC あり / なし、LP-HCSL または LVDS 出力 |     | 475  | 1000 | fs |

- (1) F<sub>IN</sub> = 25MHz、F<sub>OUT</sub> = 161.1328MHz、F<sub>PFD</sub> = 25MHz、RMS ノイズ = 1.83ps。F<sub>IN</sub> = 25MHz、F<sub>OUT</sub> = 161.1328MHz、F<sub>PFD</sub> = 50MHz、RMS ノイズ = 1.33ps。F<sub>IN</sub> = 25MHz、F<sub>OUT</sub> = 148.5MHz、F<sub>PFD</sub> = 25MHz、RMS ノイズ = 1.74ps。F<sub>IN</sub> = 25MHz、F<sub>OUT</sub> = 148.5MHz、F<sub>PFD</sub> = 50MHz、RMS ノイズ = 1.43ps。F<sub>IN</sub> = 25MHz、F<sub>OUT</sub> = 148.3516MHz、F<sub>PFD</sub> = 25MHz、RMS ノイズ = 1.6ps。F<sub>IN</sub> = 25MHz、F<sub>OUT</sub> = 148.3516MHz、F<sub>PFD</sub> = 50MHz、RMS ノイズ = 1.5ps。F<sub>IN</sub> = 25MHz、F<sub>OUT</sub> = 106.5MHz、F<sub>PFD</sub> = 25MHz、RMS ノイズ = 0.8ps。F<sub>IN</sub> = 25MHz、F<sub>OUT</sub> = 106.5MHz、F<sub>PFD</sub> = 50MHz、RMS ノイズ = 1.3ps。

## 5.14 入力および出力絶縁

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、T<sub>A</sub> = -40°C~105°C

| パラメータ                  |            | テスト条件                                                                         | 最小値 | 代表値 | 最大値 | 単位 |

|------------------------|------------|-------------------------------------------------------------------------------|-----|-----|-----|----|

| P <sub>ISOLATION</sub> | リファレンス入力絶縁 | リファレンス入力間のクロストーク、PRIREF = 27MHz LVC MOS、SECREF = 25MHz XTAL                   |     | -64 |     | dB |

| P <sub>ISOLATION</sub> | リファレンス入力絶縁 | リファレンス入力間のクロストーク、PRIREF = 100MHz LVDS、SECREF = 25MHz LVC MOS                  |     | -72 |     | dB |

| P <sub>ISOLATION</sub> | クロック出力絶縁   | クロック出力間のクロストーク、OUT1 = 100MHz LP-HCSL、OUT2 = 156.25MHz LVDS、PFD = 25MHz、整数 PLL |     | -65 |     | dB |

| P <sub>ISOLATION</sub> | クロック出力絶縁   | クロック出力間のクロストーク、OUT1 = 156.25MHz LVDS、OUT0 = 25MHz LVC MOS                     |     | -42 |     | dB |

## 5.15 バッファモードの特性

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、T<sub>A</sub> = -40°C~105°C

| パラメータ                      |                        | テスト条件                                                                 | 最小値 | 標準値 | 最大値 | 単位 |

|----------------------------|------------------------|-----------------------------------------------------------------------|-----|-----|-----|----|

| t <sub>RJ_ADD</sub>        | 追加の RMS 位相ジッタ、システム レベル | 整数モード、10kHz~20MHz の範囲、REF = HCSL 100MHz、0.5V/ns、OUTx = 100MHz LP-HCSL |     | 350 |     | fs |

| t <sub>PROP, LVC MOS</sub> | 入力から出力までの伝搬遅延          | REF = LVC MOS 25MHz、OUTx = 25MHz LVC MOS                              | 1   |     |     | ns |

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、T<sub>A</sub> = -40°C~105°C

| パラメータ                            |                              | テスト条件                                                                | 最小値  | 標準値 | 最大値 | 単位 |

|----------------------------------|------------------------------|----------------------------------------------------------------------|------|-----|-----|----|

| t <sub>PROP</sub> , Differential | 入力から出力までの伝搬遅延 <sup>(1)</sup> | REF = AC-LVDS 100MHz, OUTx = 100MHz, OUT0 で測定                        |      | 2.3 |     | ns |

| t <sub>PROP-VARIATION</sub>      | ZDB モードでの入力から出力までの遅延変動       | ZDB モード、LVCMOS 入力 = LVCMOS 出力 = 25MHz, PLL BW = 300kHz~900kHz, 全温度範囲 | -400 |     | 400 | ps |

(1) OUT1/OUT4 と OUT2/OUT3 はペア単位でマッチングされます。OUT1/OUT4 には LVCMOS バッファがあるのに対し、OUT2/OUT3 には LVCMOS バッファがありません。OUT1/OUT4 と OUT2/OUT3 の間に、追加のスキー 150ps ~ 250ps があります。

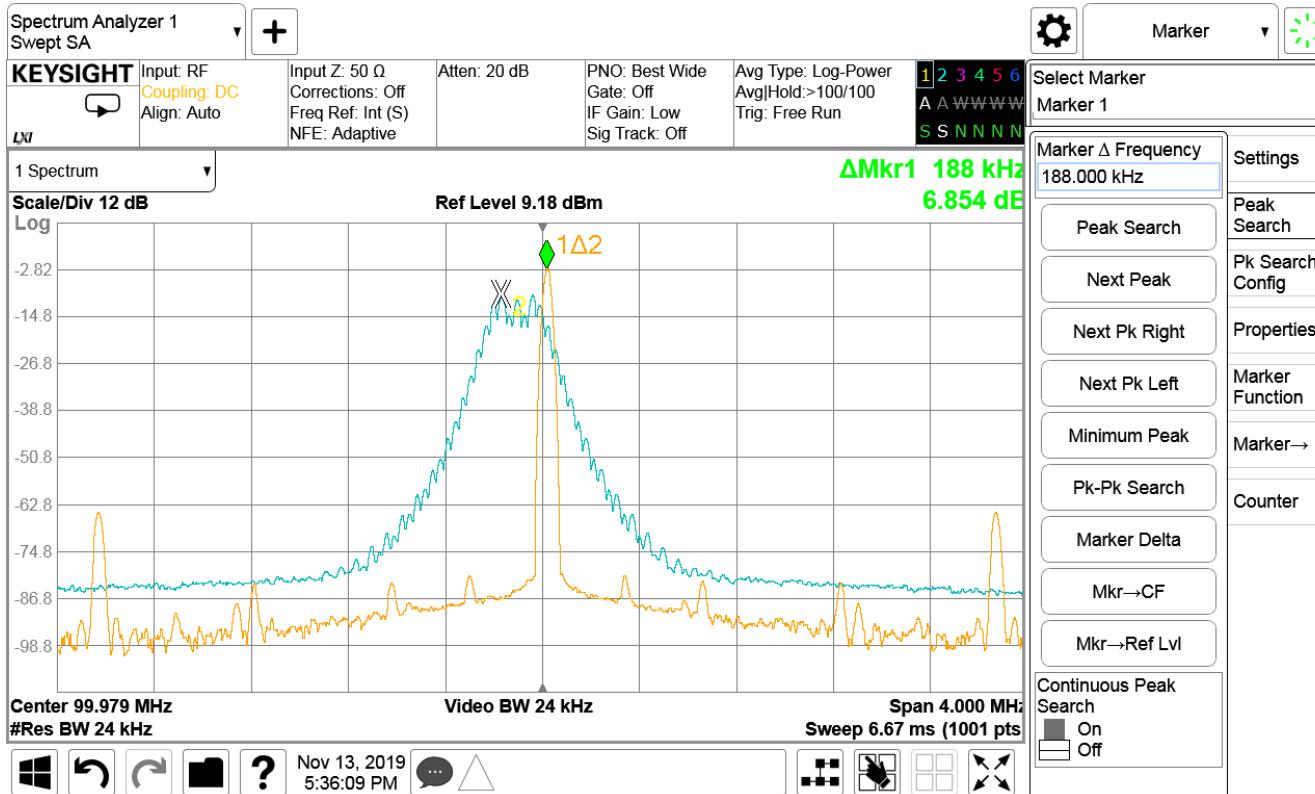

## 5.16 PCIe スペクトラム拡散ジェネレータ

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、T<sub>A</sub> = -40°C~105°C

| パラメータ                           |                               | テスト条件                                                 | 最小値  | 標準値  | 最大値 | 単位  |

|---------------------------------|-------------------------------|-------------------------------------------------------|------|------|-----|-----|

| f <sub>SSC-RATE</sub>           | SSC 変調レート                     | OUTx = 100MHz                                         | 30   | 31.5 | 33  | kHz |

| P <sub>AMPL-RED</sub>           | SSC 振幅縮小                      | OUTx = 100MHz, -0.25% ダウンスプレッド                        |      | 6.8  |     | dB  |

| P <sub>AMPL-RED</sub>           | SSC 振幅縮小                      | OUTx = 100MHz, -0.50% ダウンスプレッド                        |      | 9.9  |     | dB  |

| f <sub>SSC-STEP</sub>           | ダウンおよびセンター スプレッド SSC ステップ サイズ | OUTx = 100MHz                                         |      | 0.25 |     | %   |

| t <sub>SSC_FREQ_DEVIATION</sub> | ダウンスプレッドの最小 / 最大偏差            | OUTx = 100MHz F <sub>PFD</sub> = 25MHz, 50MHz, 100MHz | -0.5 |      | 0   | %   |

| t <sub>SSC_FREQ_DEVIATION</sub> | センター スプレッドの最小 / 最大偏差          | OUTx = 100MHz F <sub>PFD</sub> = 25MHz, 50MHz, 100MHz | -0.5 |      | 0.5 | %   |

## 5.17 LVCMOS 出力特性

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、T<sub>A</sub> = -40°C~105°C

| パラメータ                  |                       | テスト条件                                         | 最小値          | 代表値   | 最大値 | 単位  |

|------------------------|-----------------------|-----------------------------------------------|--------------|-------|-----|-----|

| f <sub>O_LVCMOS</sub>  | 出力周波数                 | GND に 2pF、通常モード                               | 0.024        |       | 200 | MHz |

| V <sub>OH_LVCMOS</sub> | 出力 HIGH 電圧            | I <sub>OH</sub> = 1mA、VDDO_x は対応する電源電圧です。     | 0.8 × VDDO_x |       |     | V   |

| V <sub>OL_LVCMOS</sub> | 出力 LOW 電圧             | I <sub>OL</sub> = 1mA、VDDO_x は対応する電源電圧です。     | 0.2 × VDDO_x |       |     | V   |

| I <sub>OH</sub>        | 出力 HIGH 電流            | Vout = 0.8 × VDDO_x, VDDO_x = 1.8V            |              | -6    |     | mA  |

| I <sub>OH</sub>        | 出力 HIGH 電流            | Vout = 0.8 × VDDO_x, VDDO_x = 2.5V            |              | -8.5  |     | mA  |

| I <sub>OH</sub>        | 出力 HIGH 電流            | Vout = 0.8 × VDDO_x, VDDO_x = 3.3V            |              | -11.2 |     | mA  |

| I <sub>OL</sub>        | 出力 LOW 電流             | Vout = 0.2 × VDDO_x, VDDO_x = 1.8V            |              | 6     |     | mA  |

| I <sub>OL</sub>        | 出力 LOW 電流             | Vout = 0.2 × VDDO_x, VDDO_x = 2.5V            |              | 8.5   |     | mA  |

| I <sub>OL</sub>        | 出力 LOW 電流             | Vout = 0.2 × VDDO_x, VDDO_x = 3.3V            |              | 11.2  |     | mA  |

| T <sub>RISE-FALL</sub> | 出力立ち上がり / 立ち下がり時間     | 20/80%, C <sub>L</sub> = 5pF、通常モード            | 300          | 500   | 700 | ps  |

| T <sub>RISE-FALL</sub> | 出力立ち上がり / 立ち下がり時間     | 20/80%, C <sub>L</sub> = 5pF、スロー・モード、OUT0 で測定 |              | 1000  |     | ps  |

| T <sub>SKEW</sub>      | 出力間スキー <sup>(1)</sup> | LVCMOS 出力間、同じ分周値                              |              | 100   |     | ps  |

| T <sub>SKEW</sub>      | 出力間スキー <sup>(1)</sup> | LVCMOS 出力から差動出力、同じ分周値                         |              | 400   |     | ps  |

| ODC                    | 出力デューティ・サイクル          | PLL バイパス・モードではありません                           | 45           |       | 55  | %   |

| R <sub>ON_LVCMOS</sub> | 出力インピーダンス             | 通常モード                                         | 45           | 60    | 75  | Ω   |

| R <sub>ON_LVCMOS</sub> | 出力インピーダンス             | スロー・モード                                       | 50           | 65    | 85  | Ω   |

(1) OUT1/OUT4 と OUT2/OUT3 はペア単位でマッチングされます。OUT1/OUT4 には LVCMOS バッファがあるのに対し、OUT2/OUT3 には LVCMOS バッファがありません。OUT1/OUT4 は T<sub>OUT-SKEW</sub> 内でマッチングされます。OUT2/OUT3 は T<sub>OUT-SKEW</sub> 内でマッチングされます。

## 5.18 LP-HCSL 出力特性

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、TA = -40°C~105°C

| パラメータ                 | テスト条件                      | 最小値                                                                           | 標準値  | 最大値     | 単位   |

|-----------------------|----------------------------|-------------------------------------------------------------------------------|------|---------|------|

| f <sub>O_HCSL</sub>   | 出力周波数                      | 0.024                                                                         |      | 328.125 | MHz  |

| V <sub>OH</sub>       | 出力 HIGH 電圧 <sup>(3)</sup>  | 660                                                                           |      | 850     | mV   |

| V <sub>OL</sub>       | 出力 LOW 電圧                  | -150                                                                          |      | 150     | mV   |

| Z <sub>DIFF</sub>     | 差動出力インピーダンス <sup>(3)</sup> | 90                                                                            | 100  | 110     | Ω    |

| V <sub>CROSS</sub>    | 絶対交差ポイント                   | 12 インチ、100Ω ± 10% 差動パターン、FR4 でピンあたり 2pF ± 5%。                                 | 250  | 550     | mV   |

| ΔV <sub>CROSS</sub>   | 相対交差ポイントの変動                | 平均的な交差ポイントを基準にします                                                             |      | 140     | mV   |

| dV/dt                 | 立ち上がりエッジと立ち下がりエッジのスルーレート   | 差動、V <sub>CROSS</sub> ± 150mV、f <sub>O_HCSL</sub> = 100MHz <sup>(1)</sup>     | 1    | 4       | V/ns |

| ΔdV/dt                | スルーレートマッチング                | シングルエンド、V <sub>CROSS</sub> ± 75mV、f <sub>O_HCSL</sub> = 100MHz <sup>(1)</sup> |      | 20      | %    |

| V <sub>rb</sub>       | 出力リングバック電圧                 | 100MHz の差動出力で測定され、ゼロ交差からの最小電圧を指定します                                           | -100 | 100     | mV   |

| T <sub>stable</sub>   | リングバックまでの経過時間              | リングバックが許容されるまでの最小時間                                                           | 500  |         | ps   |

| ODC                   | 出力デューティサイクル                | PLL バイパス モードではありません                                                           | 45   | 55      | %    |

| T <sub>OUT-SKEW</sub> | 出力スキュー <sup>(2)</sup>      | 同じ分周値、LP-HCSL から LP-HCSL まで                                                   |      | 100     | ps   |

- (1) PCIe テスト負荷スルーレート

- (2) OUT1/OUT4 と OUT2/OUT3 はペア単位でマッチングされます。OUT1/OUT4 には LVCMSO バッファがあるのに対し、OUT2/OUT3 には LVCMSO バッファがありません。OUT1/OUT4 は T<sub>OUT-SKEW</sub> 内でマッチングされます。OUT2/OUT3 は T<sub>OUT-SKEW</sub> 内でマッチングされます。OUT1/OUT4 と OUT2/OUT3 の間に、追加のスキュー 150ps ~ 250ps があります。

- (3) 差動出力特性は出荷時にトリミングされ、トリミング設定は EEPROM に保存されます。パラメータは、フォールバック モードでは無効です。

## 5.19 LVDS 出力特性

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、TA = -40°C~105°C

| パラメータ                 | テスト条件                  | 最小値                                                  | 標準値   | 最大値     | 単位    |    |

|-----------------------|------------------------|------------------------------------------------------|-------|---------|-------|----|

| f <sub>O_PRG_AC</sub> | 出力周波数                  | 0.024                                                |       | 328.125 | MHz   |    |

| V <sub>CM</sub>       | 出力同相モード <sup>(1)</sup> | VDDO_X = 2.5V、3.3V                                   | 1.025 | 1.2     | 1.375 | V  |

| V <sub>CM</sub>       | 出力同相モード <sup>(1)</sup> | VDDO_X = 1.8V                                        | 0.85  | 0.95    | 1.05  | V  |

| V <sub>OD</sub>       | 差動出力電圧 <sup>(1)</sup>  | VDDO_X = 1.8V (F <sub>out</sub> < 200MHz)、2.5V、3.3V。 | 0.25  | 0.30    | 0.45  | V  |

| V <sub>OD</sub>       | 差動出力電圧 <sup>(1)</sup>  | VDDO_X = 1.8V、F <sub>OUT</sub> > 200MHz              | 0.22  | 0.30    | 0.45  | V  |

| t <sub>RF</sub>       | 出力立ち上がり / 立ち下がり時間      | LVDS (20%~80%)                                       | 450   | 650     | 900   | ps |

| ODC                   | 出力デューティサイクル            | PLL バイパス モードではありません                                  | 45    | 55      | %     |    |

| T <sub>OUT-SKEW</sub> | 出力スキュー <sup>(2)</sup>  | 同じ分周値、LVDS 出力間                                       |       | 100     | ps    |    |

- (1) 出力同相電圧および差動出力スイングは、レジスタ設定 DIFFBUF\_IBIAS\_TRIM、LVDS\_CMTRIM\_DEC、および LVDS\_CMTRIM\_INC に依存します。DIFFBUF\_IBIAS\_TRIM=6h、LVDS\_CMTRIM\_DEC=0h、および LVDS\_CMTRIM\_INC=0h に対して定義されたパラメータ。DC でテストされた出力同相モード。

- (2) OUT1/OUT4 と OUT2/OUT3 はペア単位でマッチングされます。OUT1/OUT4 には LVCMSO バッファがあるのに対し、OUT2/OUT3 には LVCMSO バッファがありません。OUT1/OUT4 は T<sub>OUT-SKEW</sub> 内でマッチングされます。OUT2/OUT3 は T<sub>OUT-SKEW</sub> 内でマッチングされます。OUT1/OUT4 と OUT2/OUT3 の間に、追加のスキュー 150ps ~ 250ps があります。

## 5.20 出力同期特性

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、TA = -40°C~105°C

| パラメータ                | テスト条件          | 最小値                                         | 標準値 | 最大値 | 単位 |

|----------------------|----------------|---------------------------------------------|-----|-----|----|

| t <sub>SU_SYNC</sub> | セットアップ時間の同期パルス | R = 1 で 100MHz での PLL リファレンス立ち上がりエッジを基準にします | 3   |     | ns |

| t <sub>H_SYNC</sub>  | ホールド時間の同期パルス   | R = 1 で 100MHz での PLL リファレンス立ち上がりエッジを基準にします |     | 3   | ns |

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、T<sub>A</sub> = -40°C~105°C

| パラメータ                 | テスト条件                         | 最小値                                      | 標準値 | 最大値 | 単位  |

|-----------------------|-------------------------------|------------------------------------------|-----|-----|-----|

| t <sub>PWH_SYNC</sub> | 同期の High パルス幅                 | R = 1 で、2 PFD 期間以上 + 24 フィードバック ブリスケーラ期間 | 60  |     | ns  |

| t <sub>PWL_SYNC</sub> | 同期の Low パルス幅                  | R = 1 で、1 PFD 期間以上                       | 6   |     | ns  |

| t <sub>EN</sub>       | 個別の出力イネーブル時間 <sup>(1)</sup>   | トライステートから最初の有効な立ち上がりエッジまで                |     | 4   | nCK |

| t <sub>DIS</sub>      | 個別の出力ディスエーブル時間 <sup>(1)</sup> | 最後の有効な立ち下がりエッジからトライステートまで                |     | 4   | nCK |

(1) 各出力チャネルの出力クロック サイクル。デジタル ロジックで処理されるグローバル出力イネーブルでは、さらに伝搬が追加されます。

## 5.21 パワーオン リセット特性

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、T<sub>A</sub> = -40°C~105°C

| パラメータ                  | テスト条件                        | 最小値                                                                        | 標準値   | 最大値 | 単位 |

|------------------------|------------------------------|----------------------------------------------------------------------------|-------|-----|----|

| V <sub>THRESHOLD</sub> | POR スレッショルド電圧 <sup>(1)</sup> | 0.875                                                                      | 1.275 |     | V  |

| t <sub>STARTUP</sub>   | 起動時間                         | スタートアップ時間は、VDD が 95% に到達した後、出力が正しい周波数でトグルする (入力 = 水晶振動子または外部クロック) までの時間です。 | 9     |     | ms |

| t <sub>VDD</sub>       | 電源ランプ時間 <sup>(2)</sup>       | PDN=LOW のときのすべての VDD ピンのタイミング要件                                            | 0.1   | 30  | ms |

- (1) POR スレッショルド電圧は、内部リセットがデアサートされる電源電圧です。スレッショルド電圧は PDN によって内部的に認定されます。

(2) VDD ピンは、電源ランプ時間内に最終値の 95% に単調に到達する必要があります。パラメータは特性により規定されています。この評価のために、すべての VDD ピンは互いに接続されました。非単調または低速の電源ランプの場合、VDD ピンが最終値の 95% に達するまで PDN ピンをプルダウンすることをお勧めします。PDN ピンには 50kΩ のプルアップ抵抗があります。PDN ピンをアクティブに制御できない場合、PDN ピンの GND にコンデンサを追加して、リセットの解除を遅延させることを推奨します。

## 5.22 I<sup>2</sup>C 互換シリアルインターフェイスの特性

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、T<sub>A</sub> = -40°C~105°C

| パラメータ            | テスト条件          | 最小値                                   | 標準値                                   | 最大値 | 単位 |

|------------------|----------------|---------------------------------------|---------------------------------------|-----|----|

| V <sub>IH</sub>  | 入力電圧、ロジック High | 0.7 × V <sub>D<sub>DD</sub>_REF</sub> |                                       |     | V  |

| V <sub>IL</sub>  | 入力電圧、ロジック Low  |                                       | 0.3 × V <sub>D<sub>DD</sub>_REF</sub> |     | V  |

| I <sub>IH</sub>  | 入力リーコンデンサ      | V <sub>D<sub>DD</sub>_REF</sub> ± 10% | -5                                    | 5   | μA |

| V <sub>OL</sub>  | Low レベル出力電圧    | 3mA のシンク電流                            |                                       | 0.4 | V  |

| C <sub>IN</sub>  | 入力容量           |                                       |                                       | 10  | pF |

| C <sub>OUT</sub> | 出力容量           | ピンあたりの最大バス容量                          |                                       | 400 | pF |

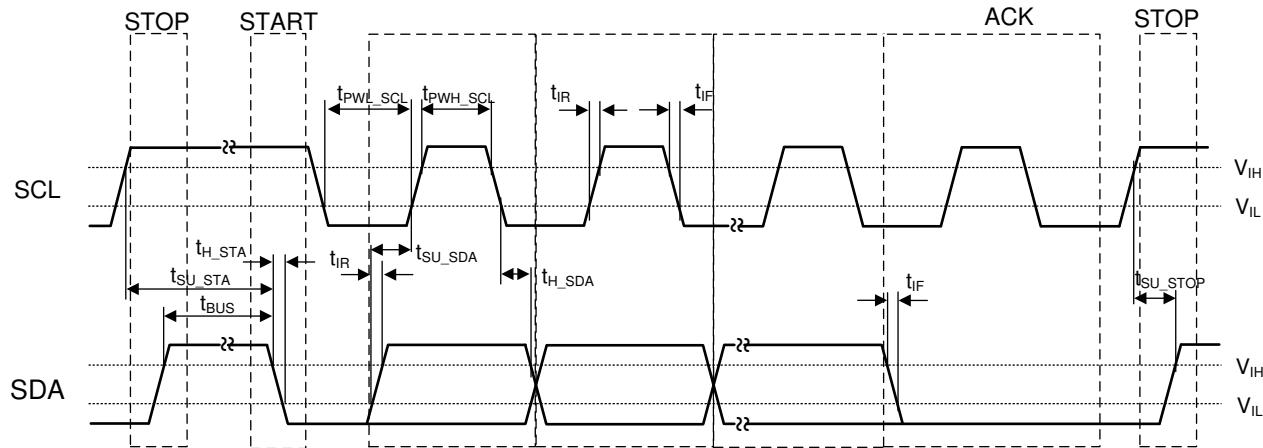

## 5.23 タイミング要件、I<sup>2</sup>C 互換シリアルインターフェイス

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、T<sub>A</sub> = -40°C~105°C

| パラメータ               | テスト条件                 | 最小値                                                                       | 標準値 | 最大値 | 単位  |

|---------------------|-----------------------|---------------------------------------------------------------------------|-----|-----|-----|

| t <sub>PW_G</sub>   | 抑制されたグリッチのパルス幅        |                                                                           |     | 50  | ns  |

| f <sub>SCL</sub>    | SCL クロック周波数           | 標準                                                                        | 100 |     | kHz |

| f <sub>SCL</sub>    | SCL クロック周波数           | ファースト モード                                                                 | 400 |     | kHz |

| t <sub>SU_STA</sub> | スタート コンディションのセットアップ時間 | SDA=V <sub>IL</sub> の前に SCL=V <sub>IH</sub>                               | 0.6 |     | μs  |

| t <sub>H_STA</sub>  | スタート コンディションのホールド時間   | SCL=V <sub>IL</sub> の後に SCL=V <sub>IL</sub> 。この時間の経過後に、最初のクロック エッジが生成される。 | 0.6 |     | μs  |

| t <sub>SU_SDA</sub> | データ セットアップ時間          | SDA が有効、f <sub>SCL</sub> =100kHz                                          | 250 |     | ns  |

| t <sub>SU_SDA</sub> | データ セットアップ時間          | SDA が有効、f <sub>SCL</sub> =400kHz                                          | 100 |     | ns  |

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、T<sub>A</sub> = -40°C~105°C

| パラメータ                | テスト条件                    | 最小値                                     | 標準値              | 最大値  | 単位 |

|----------------------|--------------------------|-----------------------------------------|------------------|------|----|

| t <sub>H_SDA</sub>   | データホールド時間 <sup>(1)</sup> | SCL=V <sub>IH</sub> の前に SDA が有効         | 0 <sup>(2)</sup> | (3)  | μs |

| t <sub>VD_SDA</sub>  | 有効なデータまたはアクリッジ時間         | f <sub>SCL</sub> =100kHz <sup>(3)</sup> |                  | 3.45 | μs |

| t <sub>VD_SDA</sub>  | 有効なデータまたはアクリッジ時間         | f <sub>SCL</sub> =400kHz <sup>(2)</sup> |                  | 0.9  | μs |

| t <sub>PWH_SCL</sub> | パルス幅 High、SCL            | f <sub>SCL</sub> =100kHz                | 4.0              |      | μs |

| t <sub>PWH_SCL</sub> | パルス幅 High、SCL            | f <sub>SCL</sub> =400kHz                | 0.6              |      | μs |

| t <sub>PWL_SCL</sub> | パルス幅 Low、SCL             | f <sub>SCL</sub> =100kHz                | 4.7              |      | μs |

| t <sub>PWL_SCL</sub> | パルス幅 Low、SCL             | f <sub>SCL</sub> =400kHz                | 1.3              |      | μs |

| t <sub>IR</sub>      | 入力立ち上がり時間                |                                         |                  | 300  | ns |

| t <sub>IF</sub>      | 入力立ち下がり時間                |                                         |                  | 300  | ns |

| t <sub>OF</sub>      | 出力立ち下がり時間                | 10pF ≤ C <sub>OUT</sub> ≤ 400pF         |                  | 250  | ns |

| t <sub>SU_STOP</sub> | ストップ コンディションのセットアップ時間    |                                         |                  | 0.6  | μs |

| t <sub>BUS</sub>     | バスフリー時間                  | ストップ コンディションからスタート コンディションまでの時間         |                  | 1.3  | μs |

- (1) t<sub>H\_SDA</sub> は、SCL の立ち下がりエッジから測定されたデータホールド時間であり、送信中のデータとアクリッジに適用されます。

- (2) SCL 信号の立ち下がりエッジの未定義領域をブリッジするため、デバイスは SDA 信号のために (SCL 信号の V<sub>IH(min)</sub> を基準として) 300ns 以上のホールド時間を内部的に確保する必要があります。

- (3) t<sub>H\_SDA</sub> の最大値は、スタンダード モードで 3.45μs、ファースト モードで 0.9μs ですが、t<sub>VD\_SDA</sub> の最大値より遷移時間の分だけ小さくする必要があります。この最大値を満たす必要があるのは、SCL 信号の Low 期間 (t<sub>PWL\_SCL</sub>) を本デバイスがストレッチ (延長) しない場合に限られます。クロックが SCL をストレッチする場合、I<sup>2</sup>C Master がクロックをリリースする前に、セットアップ時間までにデータが有効になっている必要があります。

## 5.24 電源特性

VDD\_VCO、VDDO\_12、VDDO\_34、VDD\_REF = 1.8V ± 5%、2.5V ± 5%、3.3V ± 5%、T<sub>A</sub> = -40°C~105°C

| パラメータ               | テスト条件          | 最小値                                                          | 標準値 | 最大値  | 単位 |

|---------------------|----------------|--------------------------------------------------------------|-----|------|----|

| I <sub>DD_REF</sub> | VDD_REF 電源電流   | 25MHz XTAL、DBL ON                                            |     | 8    | mA |

| I <sub>DD_VCO</sub> | VCO および PLL 電流 | f <sub>VCO</sub> =2400MHz、PSA = PSB = 4、N 分周器 = 48           |     | 14   | mA |

| I <sub>DD_OUT</sub> | 出力チャネル電流       | IOD=6、LP-HCSL、OUT3 および OUT4 で 100MHz、OUT0 で 25MHz            |     | 22   | mA |

| I <sub>DD_OUT</sub> | 出力チャネル電流       | IOD = 6、LP-HCSL、OUT1 および OUT2 で 100MHz                       |     | 17.5 | mA |

| I <sub>DD_PDN</sub> | パワーダウン電流       | リセットピン / ビットを使用                                              | 2.8 | 5    | mA |

| I <sub>DD_TYP</sub> | 標準電流           | 水晶振動子入力とダブラーを使用した 4 × 100MHz LVDS のケース、SSC オフ                | 50  | 70   | mA |

| I <sub>DD_TYP</sub> | 標準電流           | 水晶振動子入力とダブルを使用した 4 × 100MHz LP-HCSL のケース、SSC オフ              | 65  | 90   | mA |

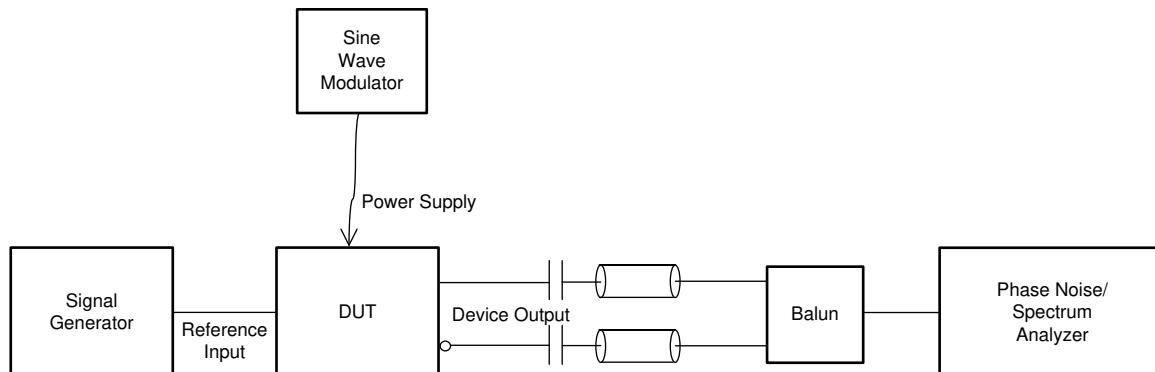

| L <sub>PSNR</sub>   | 電源ノイズ除去        | OUTx = 100MHz 差動、f <sub>INJ</sub> = 100kHz で VDDx 注入正弦波の 1 つ | -61 |      | dB |

| L <sub>PSNR</sub>   | 電源ノイズ除去        | OUTx = 100MHz 差動、f <sub>INJ</sub> = 1MHz で VDDx 注入正弦波の 1 つ   | -57 |      | dB |

## 5.25 代表的特性

室温で測定

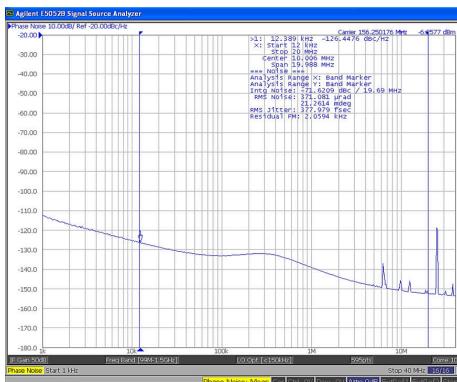

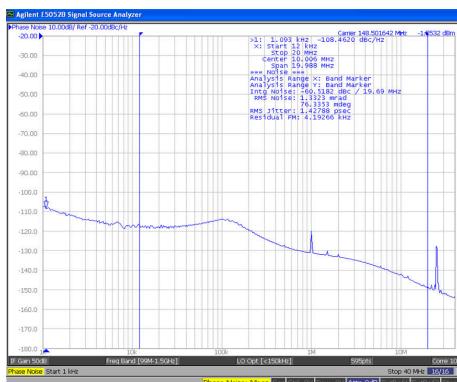

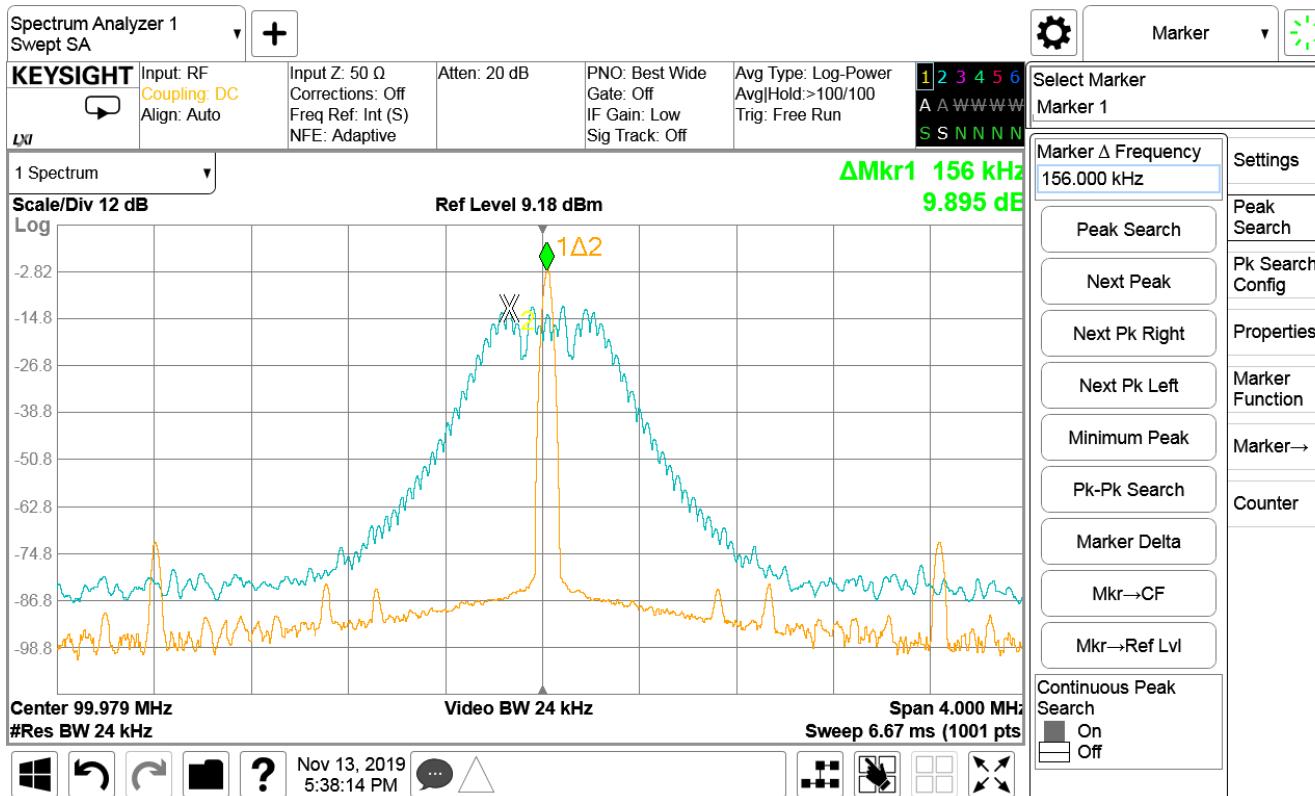

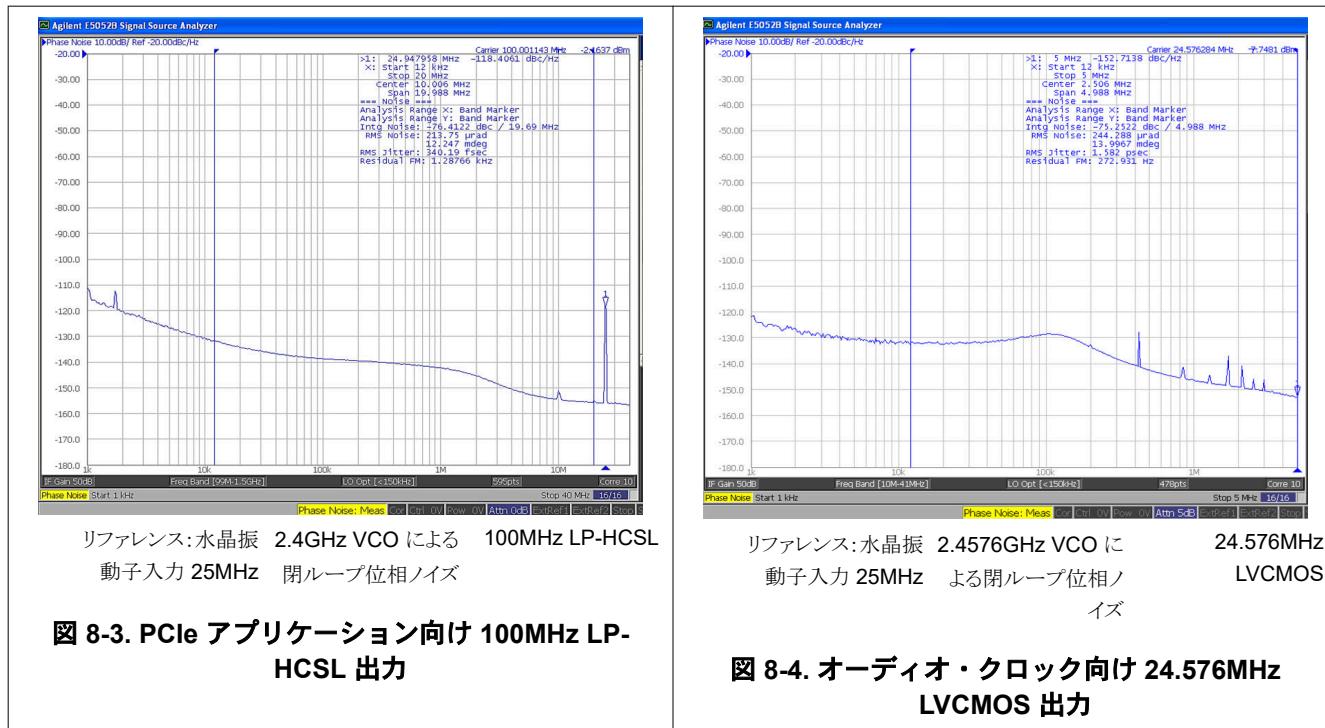

リファレンス:水晶振動子 2.5GHz VCO による 156.25MHz LVDS

動子入力 25MHz 閉ループ位相ノイズ

図 5-1. 156.25MHz LVDS 出力

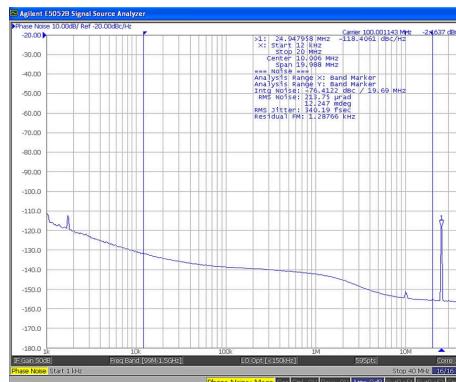

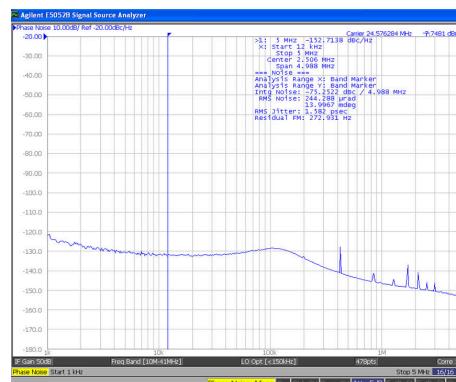

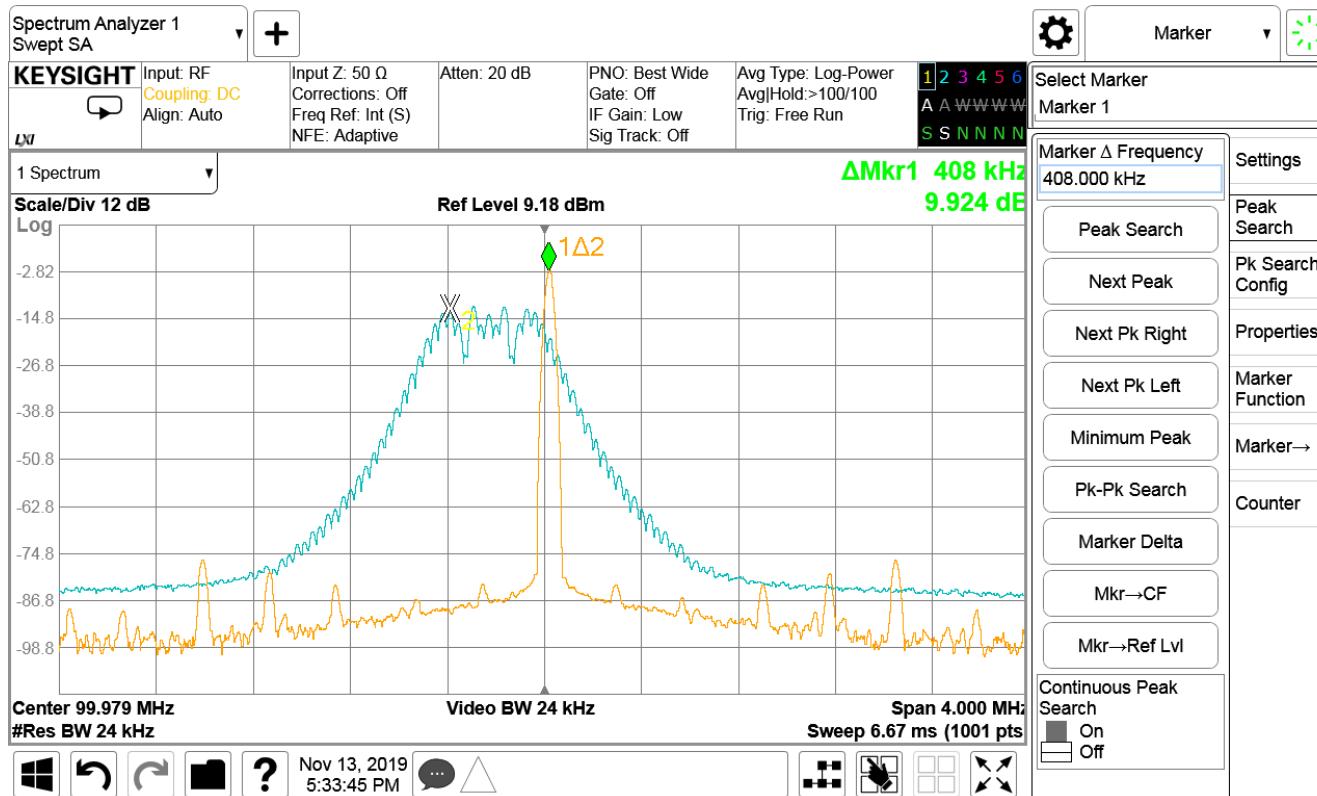

リファレンス:水晶振 2.4GHz VCO による 100MHz LP-HCSL

動子入力 25MHz 閉ループ位相ノイズ

図 5-2. 100MHz LP-HCSL 出力

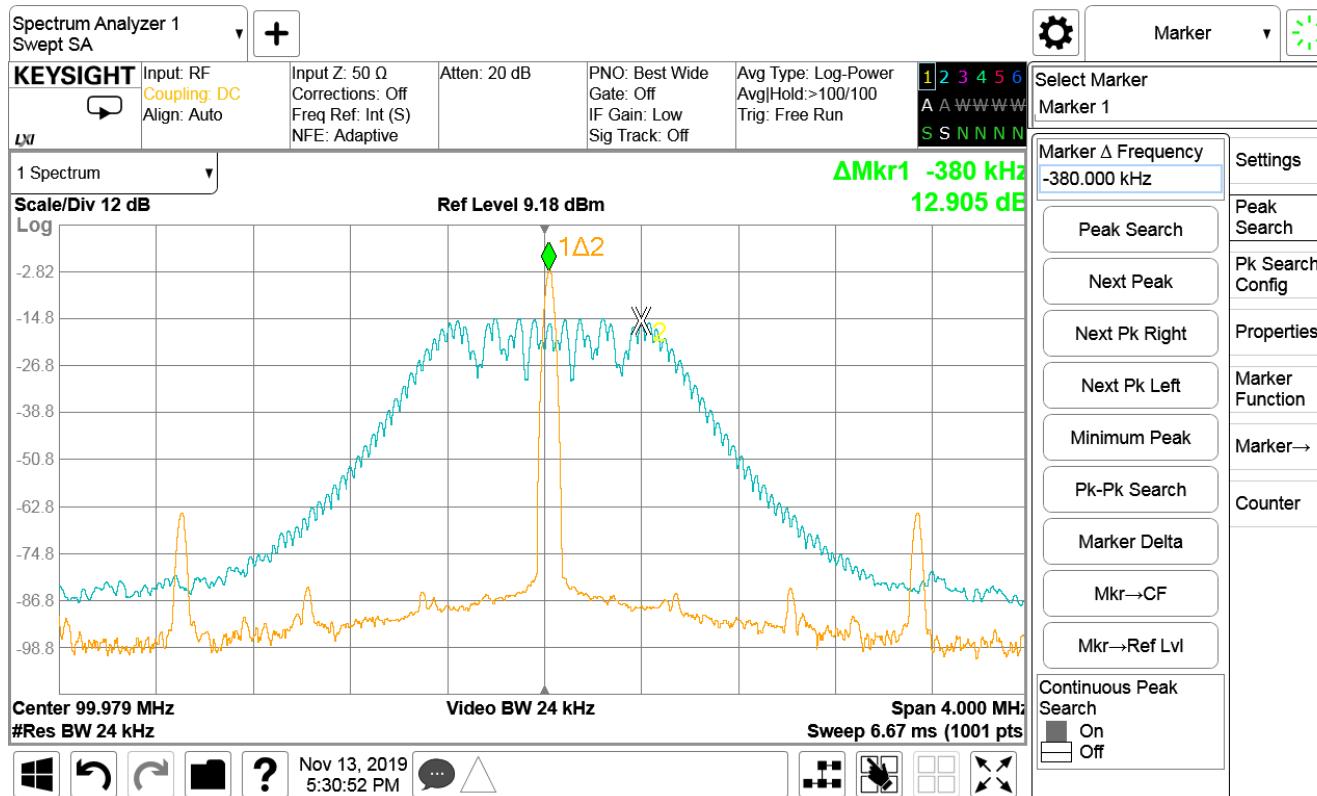

リファレンス:水晶振動子入力 25MHz 2.376GHz VCO による閉ループ位相ノイズ 148.5MHz LVDS

図 5-3. 148.5MHz LVDS 出力

リファレンス:水晶振動子 2.4576GHz VCO に

動子入力 25MHz よる閉ループ位相ノイズ

図 5-4. 24.576MHz LVC MOS 出力

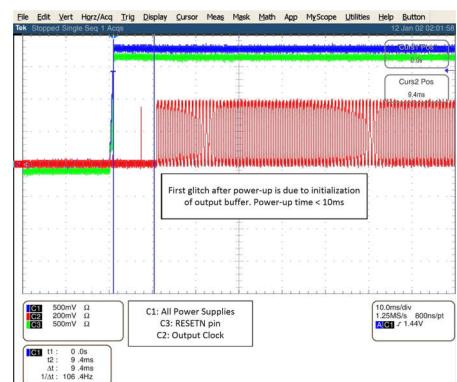

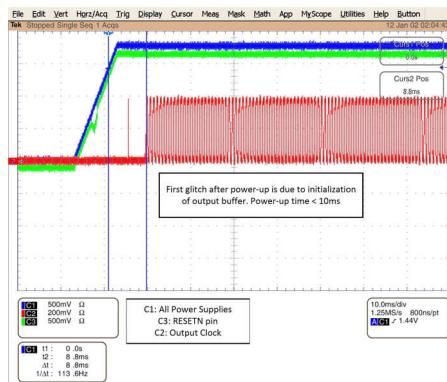

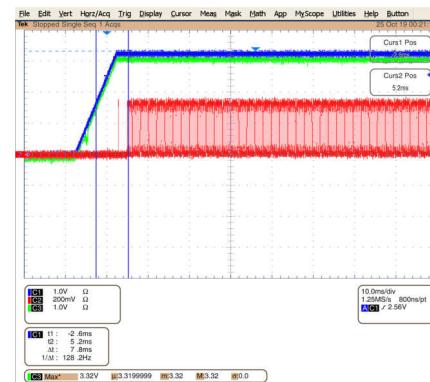

図 5-5. すべての電源 = 1.8V、VDD ランプ時間 = 1ms

図 5-6. すべての電源 = 3.3V、VDD ランプ時間 = 1ms

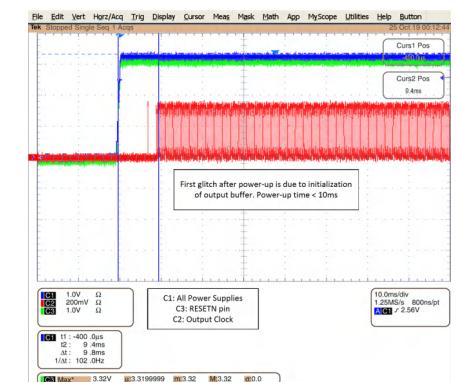

図 5-7. すべての電源 = 1.8V、VDD ランプ時間 = 10ms

図 5-8. すべての電源 = 3.3V、VDD ランプ時間 = 10ms

## 6 パラメータ測定情報

### 6.1 リファレンス入力

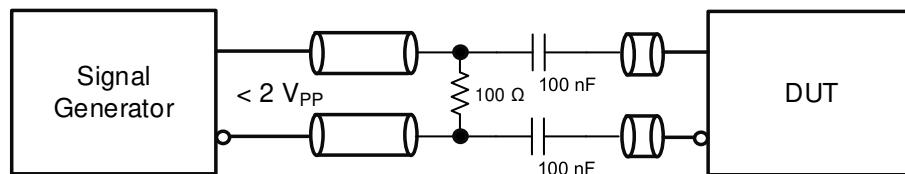

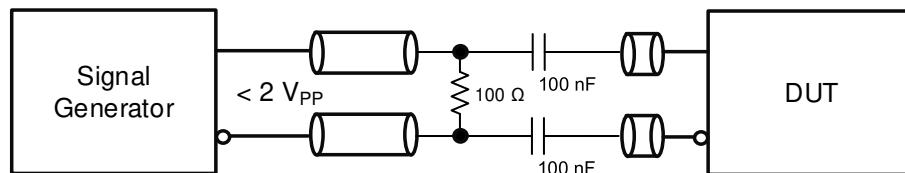

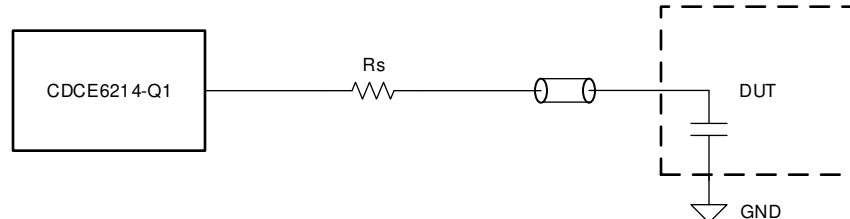

図 6-1. 差動 AC 結合入力

### 6.2 出力

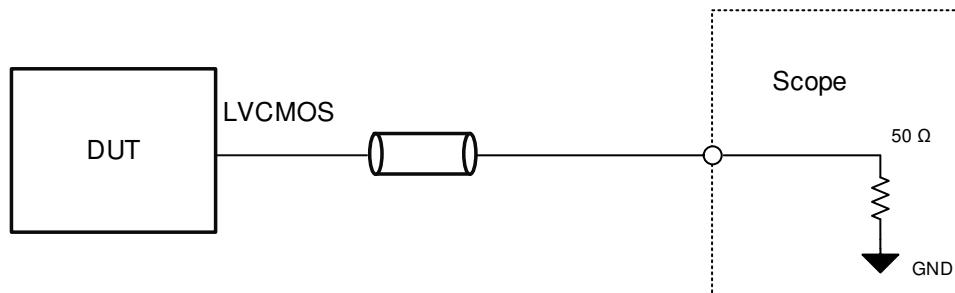

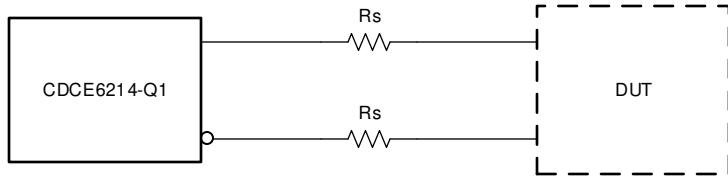

図 6-2. LVCMOS 出力テスト構成

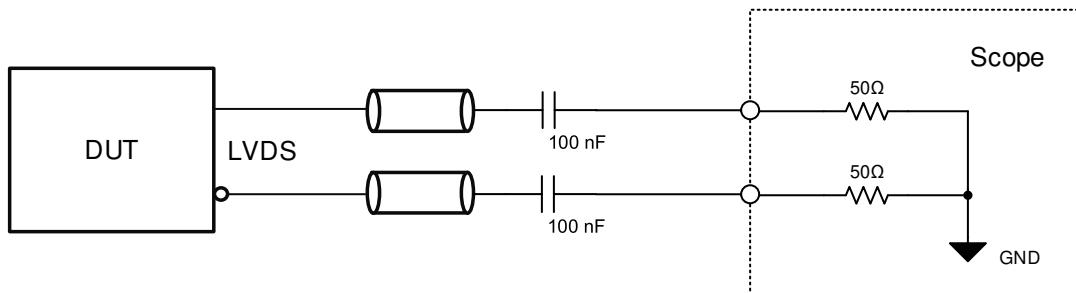

図 6-3. LVDS 出力テスト構成、AC 結合

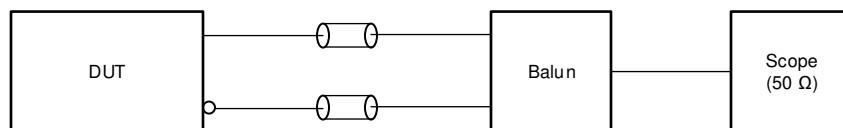

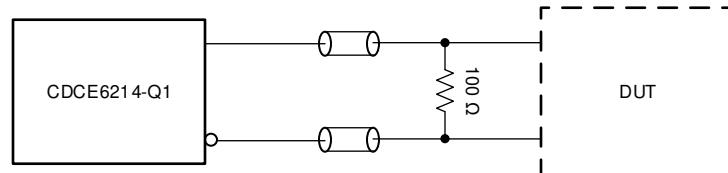

図 6-4. LP-HCSL テスト構成、DC 結合

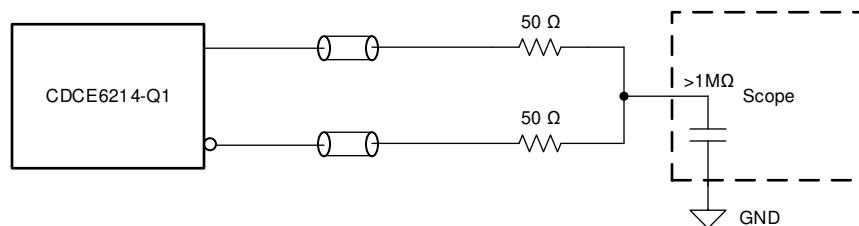

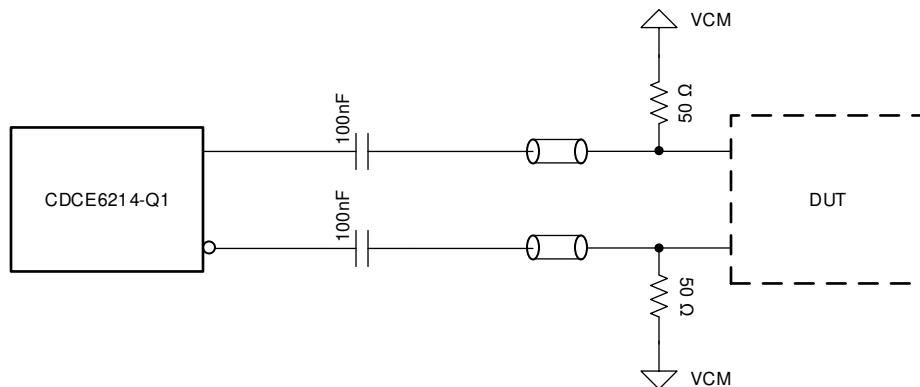

図 6-5. LVDS 同相電圧、DC 結合

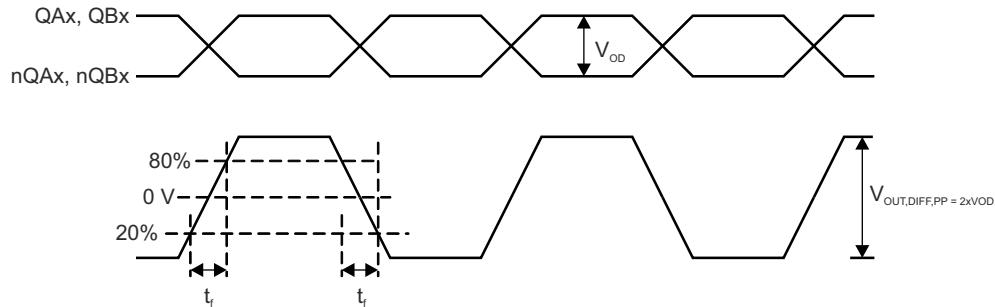

図 6-6. 差動出力電圧と立ち上がり / 立ち下がり時間

### 6.3 シリアル・インターフェイス

図 6-7. I<sup>2</sup>C タイミング

### 6.4 PSNR テスト

図 6-8. PSNR テスト構成

## 6.5 クロックのインターフェイスと終端

### 6.5.1 リファレンス入力

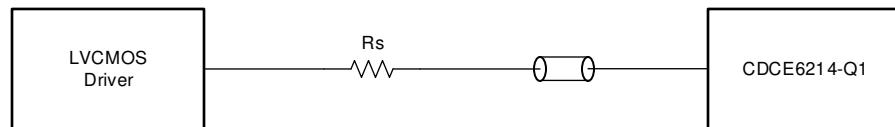

図 6-9. シングルエンド LVC MOS からリファレンス

図 6-10. 差動入力からリファレンス

### 6.5.2 出力

図 6-11. LVC MOS 出力

A. 100Ω の抵抗を DUT の近くに配置します

図 6-12. LVDS 出力 - DC 結合

図 6-13. LVDS 出力 - AC 結合

図 6-14. LP-HCSL 出力

## 7 詳細説明

### 7.1 概要

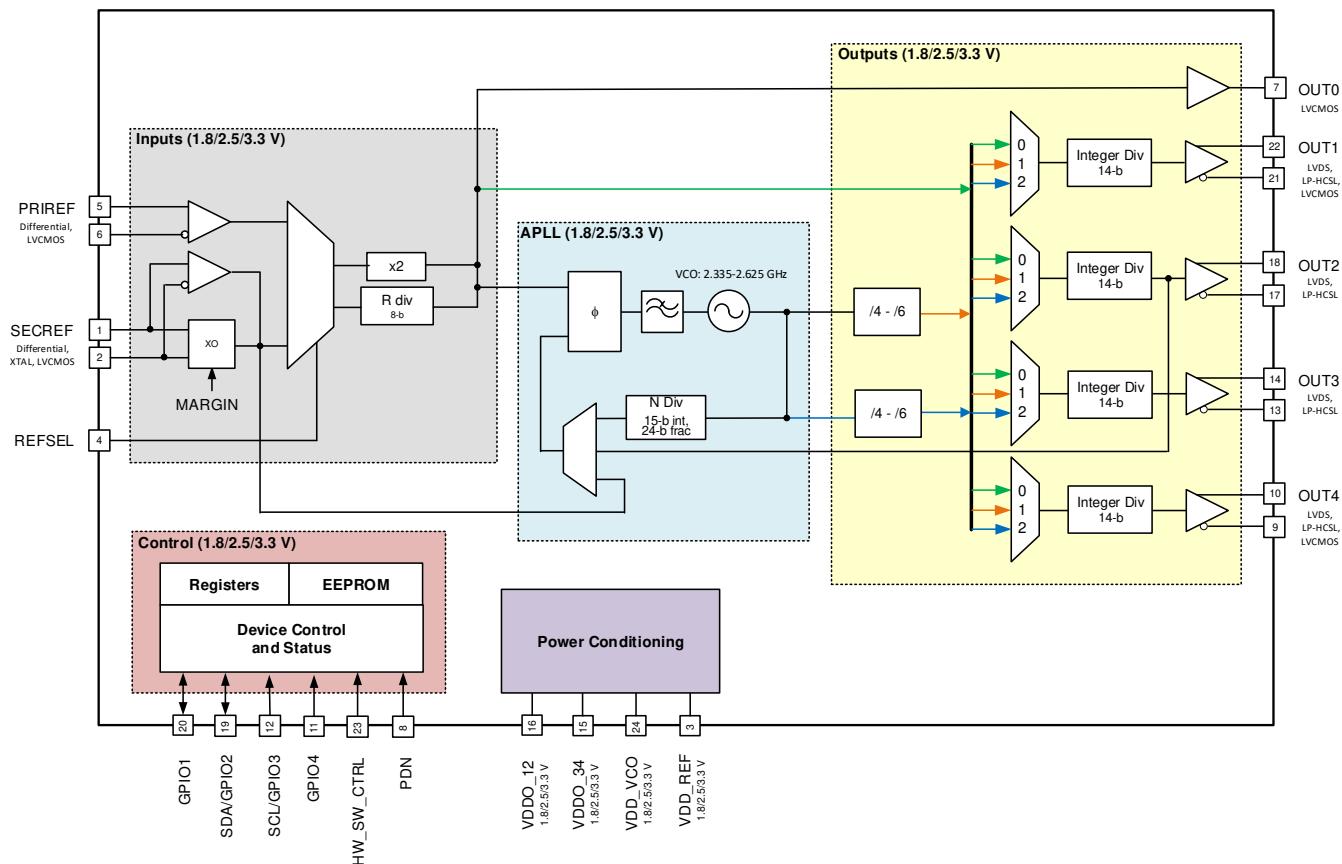

CDCE6214-Q1 車載向けクロック・ジェネレータは、電圧制御発振器 (VCO) 内蔵、および選択可能な入力リファレンスを備えたループ フィルタ内蔵のフェーズ ロック ループ (PLL) です。入力リファレンスは、XTAL、差動およびシングルエンド LVCMS 入力をサポートしています。PLL にはフラクショナル N PLL があり、内蔵 VCO の範囲は 2335 MHz ~ 2625 MHz です。VCO の出力は、複数の周波数分周器とマルチプレクサを含むクロック分配ネットワークに接続されています。これらのネットワークの出力は、構成可能な差動バッファとシングルエンド バッファを使用して肆つの出力チャネルに接続されています。肆つの電源ピンがあり、1.8V、2.5V、3.3V の電源電圧に個別に構成できます。デフォルトでは、CDCE6214-Q1 は、電源オン時にフォールバック モードでのみ I<sup>2</sup>C シリアル インターフェイスを使用して構成でき、I<sup>2</sup>C モードは EEPROM ページの両方でパワーアップ時に無効になります。このデバイスは、GPIO、I<sup>2</sup>C、内部または外部ゼロ遅延モードを介したデジタル制御発振器 (DCO) などのさまざまなモードをサポートします。

### 7.2 機能ブロック図

図 7-1. CDCE6214-Q1 クロック・ジェネレータ、2 入力、1 つのフラクショナル N PLL、4 出力付き

## 7.3 機能説明

以下のセクションでは、CDCE6214-Q1 超低消費電力クロック・ジェネレータの個々のブロックについて説明します。

### 7.3.1 リファレンス ブロック

PLL への基準クロックは、ピン 1 (SECREF\_P) および 2 (SECREF\_N)、またはピン 5 (PRIREF\_P) および 6 (PRIREF\_N) に供給されます。さまざまな基準クロックに対応するために、複数の入力段があります。ピン 1 とピン 2 を使用して、クロックの両端に XTAL を接続するか、外部シングルエンド LVC MOS クロックまたは差動クロックを供給することができます。これらのモードは、レジスタのプログラミングにより選択できます。差動モードを選択すると、ピンに適切なバイアスが印加されます。差動モードの場合は、外部 AC 結合コンデンサが必要です。XTAL または LVC MOS モードを選択すると、バイアス回路が解除されます。ピン 5 とピン 6 を使用して、外部シングルエンド LVC MOS クロックまたは差動クロックを供給できます。

リファレンス マルチプレクサは、PLL の基準クロックを選択します。REFSEL ピン = L に設定すると SECREF 入力が選択され、REFSEL ピン = H に設定すると PRIREF 入力が選択されます。または、レジスタ設定を使用してこれを構成することもできます。

**表 7-1. リファレンス入力の選択**

| レジスタ ビット アドレス | レジスタ ビット フィールド名   | 値         | 説明                                                |

|---------------|-------------------|-----------|---------------------------------------------------|

| R2[1:0]       | REFSEL_SW         | 0h または 1h | 入力リファレンス マルチプレクサはピン 4 (REFSEL) で制御                |

|               | (デフォルト:0h)        | 2h        | ピン 1 / ピン 2 の SECREF 入力を選択。これはピン 4 のステータスとは無関係です。 |

|               |                   | 3h        | ピン 5 / ピン 6 の PRIREF 入力を選択。これはピン 4 のステータスとは無関係です。 |

| R24[1:0]      | IP_SECREF_BUF_SEL | 0h        | XO をイネーブル。SECREF ピンで有効。                           |

|               | (デフォルト:0h)        | 1h        | LVC MOS バッファをイネーブル。SECREF ピンで有効。                  |

|               |                   | 2h または 3h | 差動バッファをイネーブル。SECREF ピンで有効。                        |

| R24[15]       | IP_PRIREF_BUF_SEL | 0h        | LVC MOS バッファをイネーブル。PRIREF ピンで有効。                  |

|               | (デフォルト:0h)        | 1h        | 差動バッファをイネーブル。PRIREF ピンで有効。                        |

基準分周器またはクロック ダブラーを使用して、基準クロックをさらに乗算 (2x) するか、PLL に分周することができます。IP\_RDIV[7:0] を使用して分周器の値を設定できます。IP\_RDIV[7:0] を 00h に設定するとダブラー機能が有効になります。

リファレンス ブロックからの出力クロックは、OUT0 およびその他の出力チャネルにバイパスできます。バイパスされたクロックは、入力クロックと PFD クロックのどちらかを選択できます。[表 7-9](#) を参照してください。

SECREF\_P および SECREF\_N ピンは、基本モードの水晶振動子を 10MHz~50MHz の範囲で駆動する水晶発振器の段を提供します。水晶発振器の入力段には、最大 9pF の調節可能な負荷コンデンサ アレイが内蔵されており、R24[12:8] によりプログラムできます。発振器の駆動能力は、R24[5:2] によりプログラムできます。

LVC MOS 入力バッファのスレッショルド電圧は、VDD\_REF に従います。このデバイスは、出力に個別の電源があるため、レベル シフタとして使用できます。

### 7.3.1.1 ゼロ遅延モード、内部バスおよび外部バス

CDCE6214-Q1 は、内部および外部フィードバックにより、ゼロ遅延モードで動作できます。ゼロ遅延モードでは、PRIREF クロックが PFD への基準クロックとして使用されます。SECREF 入力クロックを使用して、外部ソースを PFD へのフィードバック クロックとして供給できます。ゼロ遅延動作には、外部フィードバック パスを推奨します。さらに、出力チャネル 2 から供給される追加の内部フィードバック パスもあります。内部ゼロ遅延モードでは、入力出力伝播遅延は外部よりも高くなることが予想されます。

**表 7-2. ゼロ遅延動作**

| 動作 <sup>(1)</sup> <sup>(2)</sup> | REFSEL | R2[1:0] -<br>REFSEL_SW | R24[1:0] -<br>IP_SECREF_B<br>UF_SEL <sup>(3)</sup> | R24[15] -<br>IP_PRIREF_BU<br>F_SEL <sup>(3)</sup> | R0[8] -<br>ZDM_EN | R0[10] -<br>ZDM_CLOCKSEL | 説明                                                  |

|----------------------------------|--------|------------------------|----------------------------------------------------|---------------------------------------------------|-------------------|--------------------------|-----------------------------------------------------|

| 通常動作、XTAL<br>入力                  | L      | 0h、1h、または<br>2h        | 0h                                                 | X                                                 | 0h                | 0h                       | 通常動作、XTAL<br>入力                                     |

| 通常動作、差動<br>入力                    | L      | 0h、1h、または<br>2h        | 2h または 3h                                          | X                                                 | 0h                | 0h                       | SECREF / 差動<br>入力                                   |

| 通常動作、差動<br>入力                    | H      | 0h、1h、または<br>3h        | X                                                  | 1h                                                | 0h                | 0h                       | PRIREF / 差動<br>入力                                   |

| 通常動作、<br>LVC MOS 入力              | L      | 0h、1h、または<br>2h        | 1h                                                 | X                                                 | 0h                | 0h                       | SECREF/<br>LVC MOS 入力                               |

| 通常動作、<br>LVC MOS 入力              | H      | 0h、1h、または<br>3h        | X                                                  | 0h                                                | 0h                | 0h                       | PRIREF/<br>LVC MOS 入力                               |

| 外部ゼロ遅延モ<br>ード、差動入力               | H      | 0h、1h、または<br>3h        | 2h または 3h                                          | 1h                                                | 1h                | 1h                       | PRIREF の入力<br>クロック、<br>SECREF のフィ<br>ードバック クロッ<br>ク |

| 外部ゼロ遅延モ<br>ード、LVC MOS<br>入力      | H      | 0h、1h、または<br>3h        | 1h                                                 | 0h                                                | 1h                | 1h                       | PRIREF の入力<br>クロック、<br>SECREF のフィ<br>ードバック クロッ<br>ク |

| 内部ゼロ遅延モ<br>ード、差動入力               | H      | 0h、1h、または<br>3h        | X                                                  | 1h                                                | 1h                | 0h                       | PRIREF の入力<br>クロック                                  |

| 内部ゼロ遅延モ<br>ード、差動入力               | H      | 0h、1h、または<br>3h        | X                                                  | 0h                                                | 1h                | 0h                       | PRIREF の入力<br>クロック                                  |

- (1) ゼロ遅延モードでは、PLL がロックできるようにすべての分周器をプログラムする必要があります。ゼロ遅延モードでのパワーアップ時に、PLL は自動的にロックされます

- (2) 外部ゼロ遅延モードでは、チャネル 2 が必要です。チャネル 2 はパワーダウンしないでください

- (3) 「X」は機能に影響を与えずに、あらゆるビットフィールド値を許可します。

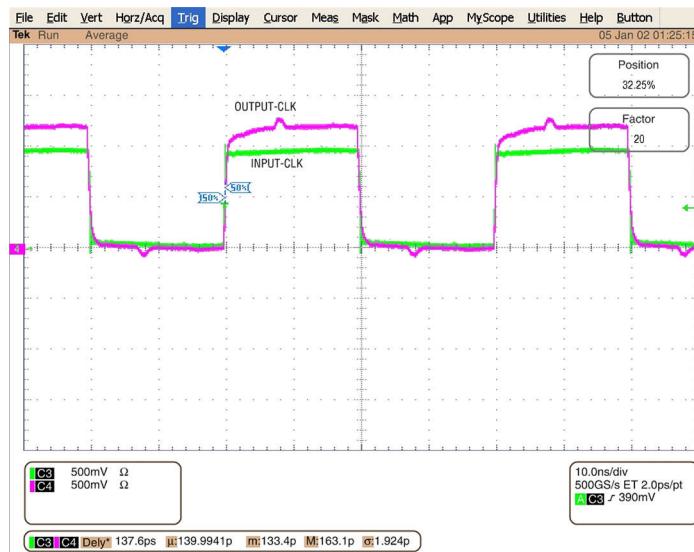

図 7-2. LVC MOS 出力の外部ゼロ遅延モードでの入力 / 出力アライメント

### 7.3.2 フェーズロックループ(PLL)

CDCE6214-Q1 は、完全に統合されたフェーズロックループ(PLL)回路を備えています。位相周波数検出器で、リファレンス位相と内部フィードバック位相の間の誤差が比較されます。比較結果は、内蔵ループフィルタに接続されているチャージポンプに供給されます。ループフィルタから生成される制御電圧によって、内蔵の電圧制御発振器(VCO)が調整されます。VCO の周波数は、帰還分周器(Nカウンタ)を経由して PFD に返されます。

- 整数およびフラクショナル N PLL 動作モード。

- 分数モードでの 1 次、2 次、または 3 次の MASH 動作。

- 24 ビットの分子と分母を使用して、0ppb の周波数精度で分数周波数を生成できます。

- PFD は 1MHz~100MHz で動作します。

- ライブロック検出器(R7[0] または GPIO の PLL\_LOCK)は、PLL ロックステータスを提供します(分数モードで SSC がイネーブルの場合、ロック検出ウインドウを拡大する必要があります。R50[10:8] = 7h)。さらに、ステイッキー ビットロック検出(R7[1])により、ロックの一時的損失があったかどうかが検出されます。

- 選択可能なフィルタコンポーネントを内蔵しています。

- 25MHz の PFD 周波数では、100kHz~1.6MHz の PFD 帯域幅を実現して、リファレンス入力への PLL を最適化できます。

- 電圧制御発振器(VCO)の範囲は 2335MHz~2615MHz です。

- 0.25% および 0.5% のセンターおよびダウンスプレッドスペクトラムクロック(SSC)をサポートしています。さらに、VCO は PCIe クロック用に 100MHz で最大 0.5% の SSC 基準電圧もサポートしています。

表 7-3. 一般的なクロックジェネレータのループフィルタ設定

| f <sub>VCO</sub> (MHz) | f <sub>PFD</sub> (MHz) | 帯域幅 (MHz 単位) | 位相マージン (°) | 減衰係数 | I <sub>CP</sub> (mA) | C <sub>Pcap</sub> (pF) | R <sub>Res</sub> (kΩ) | C <sub>Zcap</sub> (pF) |

|------------------------|------------------------|--------------|------------|------|----------------------|------------------------|-----------------------|------------------------|

| 2400                   | 25                     | 0.469        | 70         | 0.5  | 0.60                 | 16.1                   | 2.5                   | 580                    |

| 2400                   | 50                     | 0.938        | 70         | 2    | 0.60                 | 8.2                    | 2.5                   | 276                    |

| 2400                   | 100                    | 1.60         | 70         | 0.5  | 0.80                 | 8.2                    | 2.5                   | 303                    |

| 2457.6                 | 61.44                  | 1.04         | 70         | 1.15 | 0.60                 | 9.2                    | 2.0                   | 331                    |

| 2500                   | 25                     | 0.49         | 70         | 0.4  | 0.60                 | 13.5                   | 2.5                   | 497                    |

| 2500                   | 50                     | 0.93         | 70         | 1.0  | 0.60                 | 11.7                   | 2.5                   | 386                    |

| 2400                   | 50                     | 400          | 65         | 0.1  | 0.40                 | 11.7                   | 1.5                   | 636                    |

表 7-4. 一般的な PLL 分周器設定<sup>1</sup>

| 入力周波数<br>(MHz) | f <sub>PFD</sub> (MHz) | 出力周波数<br>(MHz) | f <sub>VCO</sub> | N カウンタ分周値 | 分子      | 分母       | PSA | 出力分周器 |

|----------------|------------------------|----------------|------------------|-----------|---------|----------|-----|-------|

| 25             | 50                     | 100            | 2400             | 48        | 該当なし    | 該当なし     | 4   | 6     |

| 25             | 25                     | 100            | 2400             | 96        | 該当なし    | 該当なし     | 4   | 6     |

| 25             | 50                     | 156.25         | 2500             | 50        | 該当なし    | 該当なし     | 4   | 4     |

| 25             | 25                     | 25             | 2400             | 96        | 該当なし    | 該当なし     | 4   | 24    |

| 25             | 25                     | 24.576         | 2457.6           | 98        | 5071614 | 16682942 | 4   | 25    |

| 25             | 25                     | 148.5          | 2376             | 95        | 664983  | 16624579 | 4   | 4     |

### 7.3.2.1 PLL 構成および分周器の設定

$$f_{PFD} = F_{in}/F_{factor} \quad (1)$$

$F_{factor}$  は、R25[7:0] - ip\_ref\_div によって決まります。ip\_ref\_div = 0 のときは  $F_{factor} = 0.5$ 、それ以外のときは  $F_{factor} = ip\_ref\_div$  です。

$$f_{VCO} = f_{PFD} \times (N + Num/Den). \quad (2)$$

N は、R30[14:0] - PLL\_NDIV によって設定されます。Num は分数の分子で、{R32[7:0], R31[15:0]} によって設定されます。Den は分数の分母で、R34[7:0], R33[15:0] によって設定されます。{R34[7:0], R33[15:0]} = 0 のとき、Den=2<sup>24</sup> です。

シグマ デルタ モジュレータは、量子化ノイズを形成するために、異なる次数の MASH をサポートしています。整数モードの場合、R27[1:0] は 0h として設定されます。分数モードでは、R27[1:0] は、1 次では 1h、2 次では 2h、3 次では 3h にそれぞれ設定できます。

整数モードでは、R51[6]=1h に設定することにより、PLL がシングルエンド PFD 構成で設定されます。分数モードでは、R51[6]=0h に設定することにより、PLL を差動 PFD 構成で設定する必要があります。さらに、R51[10] は、分数モードでは 1h として、整数モードでは 0h として設定されます。

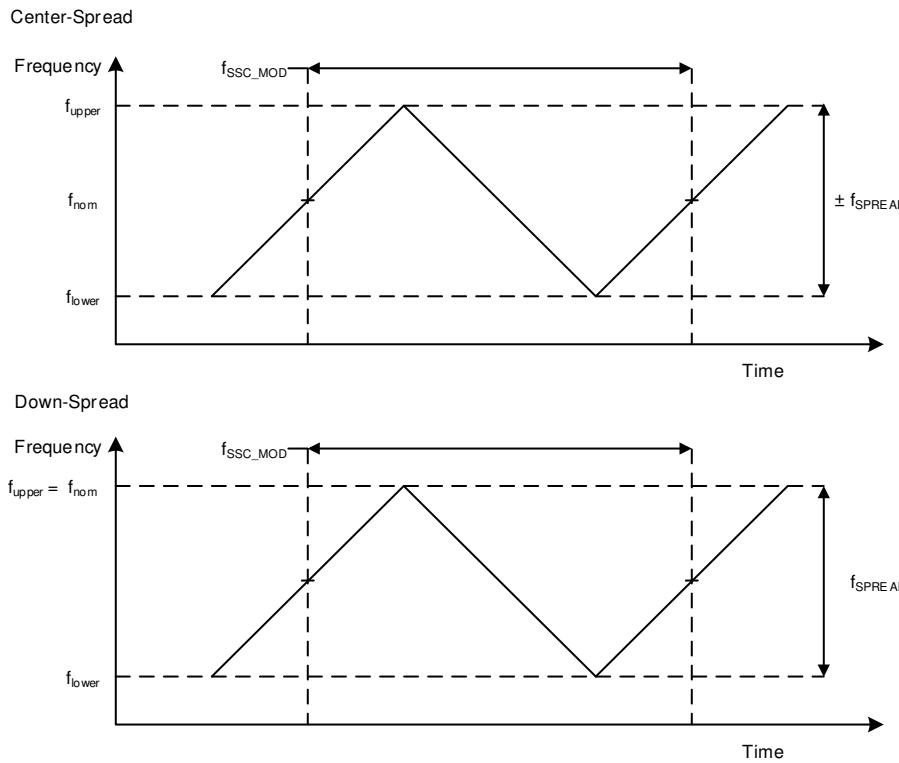

### 7.3.2.2 拡散スペクトラム クロック処理

矩形クロック信号からの高調波エネルギーは、特定の周波数範囲に拡散できます。この周波数偏差は、高調波の平均振幅の低下につながります。これは、レシーバがこの動作モードをサポートしている場合に、システムの電磁干渉 (EMI) の課題対応に役立ちます。変調の形状は三角波です。

SSC クロックは、フラクショナル N PLL を介して生成されます。SSC がイネーブルのとき、SSC クロックは、PLL から生成されるすべてのクロックで使用できます。基準クロックまたは PFD クロックは、OUT1～OUT4 ピンで使用できます。

ダウン スプレッドとセンター スプレッドをサポートしています。以下のモードをサポートしています。

- PFD 周波数: 25MHz または 50MHz

- ダウン スプレッド: -0.25% および ±0.5%

- センター スプレッド: ±0.25% および ±0.5%

これらの組み合わせのいずれかを選択するには、事前構成済み設定を使用できます。

これらの事前構成済み設定を使用すると、31.5kHz の fmod が合成され、100MHz の出力クロックが得られます。

<sup>1</sup> 分数モード設定は、DCO モードのステップ サイズである 0.1ppm に基づいています

図 7-3. 拡散スペクトラム クロック

表 7-5. 拡散スペクトラム設定 (2)

| R41[15] - SSC_EN | R42[5] - SSC_TYPE <sup>(1)</sup> | R42[3:1] - SSC_SEL <sup>(1)</sup> | 説明                                                               |

|------------------|----------------------------------|-----------------------------------|------------------------------------------------------------------|

| 0h               | X                                | X                                 | 出力に SSC 変調なし                                                     |

| 1h               | 0h                               | X                                 | ダウン スプレッド SSC 変調。SSC 拡散は、ssc_sel によって決まります                       |

| 1h               | 1h                               | X                                 | センター スプレッド SSC 変調。<br>SSC 拡散は、ssc_sel によって決まります                  |

| 1h               | X                                | 0h                                | 25MHz PFD、センター スプレッドの場合は $\pm 0.25\%$ 、ダウン スプレッドの場合は $-0.25\%$ 。 |

| 1h               | X                                | 1h                                | 25MHz PFD、センター スプレッドの場合は $\pm 0.50\%$ 、ダウン スプレッドの場合は $-0.50\%$ 。 |

| 1h               | X                                | 2h                                | 50MHz PFD、センター スプレッドの場合は $\pm 0.25\%$ 、ダウン スプレッドの場合は $-0.25\%$ 。 |

| 1h               | X                                | 3h                                | 50MHz PFD、センター スプレッドの場合は $\pm 0.50\%$ 、ダウン スプレッドの場合は $-0.50\%$ 。 |

| 1h               | X                                | 4h-7h                             | 使用できません。                                                         |

(1) 「X」は、このビットフィールドが任意の値を取ることを示します

(2) その他の SSC 拡散および変調レートについては、テキサス・インスツルメンツの担当者にお問い合わせください。

図 7-4. 100MHz、-0.25% のダウンスプレッド、パターンあり / なし

図 7-5. 100MHz、±0.25% のセンター スpread、パターンあり / なし

図 7-6. 100MHz、-0.5% のダウンスプレッド、パターンあり / なし

図 7-7. 100MHz、±0.5% のセンター スpread、パターンあり / なし

**表 7-6. PCI Express 準拠測定**

| 番号 | CLASS | データレート | アーキテクチャ | PNA 測定方式 | スコープ測定方式 | 仕様限界  | 結果 |

|----|-------|--------|---------|----------|----------|-------|----|

| 1  | Gen4  | 16Gb/s | CC      | 195fs    | 260fs    | 500fs | 合格 |

| 2  | Gen4  | 16Gb/s | SRIS    | -        | 490fs    | 500fs | 合格 |

| 3  | Gen5  | 32Gb/s | CC      | 87fs     | 111fs    | 150fs | 合格 |

| 4  | Gen5  | 32Gb/s | SRIS    | -        | 157fs    | *     | *  |

### 7.3.2.3 デジタル制御発振器と周波数インクリメントまたはデクリメント - シリアルインターフェイス モードと GPIO モード

このモードでは、出力クロック周波数を固定周波数ステップでインクリメントまたはデクリメントできます。周波数ステップ サイズは、レジスタ R43[15:0] によって決まります。この値は、シグマ デルタ変調器の分子に加算または減算されます。FREQ\_INC 信号の立ち上がりエッジごとに出力周波数が上昇し、FREQ\_DEC 信号の立ち上がりエッジごとに出力周波数が低下します。インクリメント / デクリメントをトリガする方法は 2 つあります。

1. GPIO を適切に構成し、外部マイコンまたは ASIC 経由で FREQ\_INC または FREQ\_DEC 信号を送信します。

2. シリアルインターフェイスで制御されるレジスタビットフィールドを使用します。

**表 7-7. 周波数インクリメントまたはデクリメント機能のレジスタ設定**

| レジスタビット アドレス | レジスタビット フィールド名             | 説明                                             |

|--------------|----------------------------|------------------------------------------------|

| R3[3]        | FREQ_INC_DEC_EN            | DCO モードを有効化 / 無効化します                           |

| R3[4]        | FREQ_INC_DEC_REG_MODE      | GPIO またはシリアルインターフェイスを使用して DCO トリガを選択します。       |

| R3[6:5]      | FREQ_DEC_REG, FREQ_INC_REG | シリアルインターフェイス経由で FREQ_INC または FREQ_DEC 信号を生成します |

| R43[15:0]    | FREQ_INC_DEC_DELTA         | 周波数インクリメントまたはデクリメントのステップ サイズ                   |

**表 7-8. DCO モードでの分周器設定の計算**

| パラメータ                                    | 値(例)      | 説明                                                                                                                                                                           |

|------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 入力 PFD 周波数 ( $F_{PFD}$ )                 | 25MHz     | $F_{PFD}$ に従って設定します。                                                                                                                                                         |

| 期待される VCO 周波数 ( $F_{VCO}$ )              | 2457.6MHz | $F_{VCO}$ は、2335MHz~2625MHz の VCO 動作範囲内に設定されます。PSA / PSB / 出力分周器が整数になるように $F_{VCO}$ が選択されます。                                                                                 |

| 期待される出力周波数 ( $F_{OUT}$ )                 | 24.576MHz | $PSA = 4, IOD = 25, F_{VCO} = PSA \times IOD \times F_{OUT}$                                                                                                                 |

| 期待されるステップ サイズ (ppm 単位) ( $F_{step}$ )    | 0.1       | $FREQ\_INC$ または $FREQ\_DEC$ の立ち上がりエッジごとに、出力はこのステップ サイズで変化します。                                                                                                                |

| N 分周器の値 (N)                              | 98        | $INT(F_{VCO}/F_{PFD})$                                                                                                                                                       |

| 0ppb の精度を満たす最小の分子値 (Num)                 | 76        | これらの値は、出力の精度要件を満たすよう計算されます。 $2^{24}$ 未満である必要があります。                                                                                                                           |

| 0ppb の精度を満たす最小の分母 (Den)                  | 250       |                                                                                                                                                                              |

| ppm ステップ サイズを満たす最小の分母値 ( $F_{DEN,min}$ ) | 101725.26 | $1/(F_{step} \times 1e6) / (F_{VCO}/F_{PFD})$                                                                                                                                |

| 最終的な分母値 ( $F_{DEN,final}$ )              | 500000    | $F_{DEN,final}$ は、 $F_{DEN,min}$ よりも大きく、 $2^{24}$ よりも大きい必要があります。 $F_{DEN,final}$ および $F_{NUM,final}$ はそれぞれ、Den と Num の整数倍である必要があります。 $F_{DEN,final}/Den = F_{NUM,final}/Num$ |

| 最終的な分子値 ( $F_{NUM,final}$ )              | 152000    |                                                                                                                                                                              |

| ステップ サイズをインクリメントまたはデクリメントします             | 5         | この値は $2^{16}-1$ 未満である必要があります。 $F_{DEN,final}$ は、 $F_{DEN,min}$ の最も近い整数倍である必要があります。                                                                                           |

### 7.3.3 クロックディストリビューション

VCO 出力は、オンチップ クロック分配の供給源である個別構成可能な 2 つのプリスケーラ分周器、PSA と PSB に接続されます。PSA と PSB は、 $/4$ 、 $/5$ 、または  $/6$  の分周値として互いに独立して構成できます。

クロック分配は、4 つの出力チャネルで構成されています。各出力チャネルには、グリッチレス スイッチングおよび同期機能を備えた整数分周器 (IOD) が内蔵されています。

IOD は、PSA、PSB、または基準クロックのいずれかをソースにすることができます。IOD をバイパスすると、出力で基準クロックを供給できます。

OUT0、OUT1、OUT2、OUT3、OUT4 の 5 つの出力チャネルがあります。

OUT0 はスルーレート制御可能な LVC MOS 出力です。基準クロックか PFD クロックのいずれかを、クロック分配ネットワーク経由でこの出力に配線できます。

OUT1 と OUT4 は同一の出力チャネルです。このチャネルの出力バッファは、LVC MOS、LP-HCSL、疑似 LVDS など、さまざまな信号規格と互換性があります。

OUT2 と OUT3 は同一の出力チャネルです。このチャネルの出力バッファは、LP-HCSL や 疑似 LVDS など、さまざまな信号規格と互換性があります。

- LP-HCSL 出力バッファは、GND への終端抵抗なしでレシーバに直接接続できます。LP-HCSL の出力インピーダンスは、 $50\Omega \pm 10\%$  にトリミングされます。直列抵抗を使用して、ト雷斯のインピーダンスに適応できます。

- 疑似 LVDS では、正と負の極性の出力ピンの間に差動終端を接続する必要があります。終端は、直接接続することも、AC 結合コンデンサを経由することもできます。 $50\Omega$  のシステムには、 $100\Omega$  の差動終端が適切です。

- LVC MOS 出力は、容量性負荷専用として設計されています。正および負の出力ピンの極性は、個別に構成できます。

差動バッファは、最大 328.125MHz の広範囲の出力周波数をサポートします。LVC MOS は最大 200MHz をサポートします。

**表 7-9. 入力基準クロック、PFD クロック、または PLL クロックから出力までの構成 (1)**

| レジスタ ビット アドレス | レジスタ ビット フィールド名                                                                     | 説明                                    |

|---------------|-------------------------------------------------------------------------------------|---------------------------------------|

| R25[10]       | IP_BYP_OUT0_EN                                                                      | OUT0 に対する基準クロックまたは PFD クロックをイネーブルにします |

| R25[9]        | REF_CH_MUX                                                                          | PFD クロックまたは入力基準クロックを選択します             |

| R25[14:11]    | IP_REF_TO_OUT4_EN、<br>IP_REF_TO_OUT3_EN、<br>IP_REF_TO_OUT2_EN、<br>IP_REF_TO_OUT1_EN | OUT1～OUT4 への基準クロックを選択します              |

| R56[15:14]    | CH1_MUX                                                                             | OUT1 のクロック選択 MUX 制御                   |

| R62[15:14]    | CH2_MUX                                                                             | OUT2 のクロック選択 MUX 制御                   |

| R67[15:14]    | CH3_MUX                                                                             | OUT3 のクロック選択 MUX 制御                   |

| R72[15:14]    | CH4_MUX                                                                             | OUT4 のクロック選択 MUX 制御                   |

(1) クロストーク低減のため、クロックを使用していないときはすべてディスエーブルにすることを推奨します

**表 7-10. クロック分配ネットワークの構成**

| レジスタ ビット アドレス | レジスタ ビット フィールド名 | 説明                    |

|---------------|-----------------|-----------------------|

| R47[6:5]      | PLL_PSB         | プログラマブル プリスケーラ分周器 PSB |

| R47[4:3]      | PLL_PSA         | プログラマブル プリスケーラ分周器 PSA |

| R56[13:0]     | CH1_DIV         | OUT1 整数分周器の値          |

| R62[13:0]     | CH2_DIV         | OUT2 整数分周器の値          |

| R67[13:0]     | CH3_DIV         | OUT3 整数分周器の値          |

**表 7-10. クロック分配ネットワークの構成 (続き)**

| レジスタ ビット アドレス | レジスタ ビット フィールド名 | 説明           |

|---------------|-----------------|--------------|

| R72[13:0]     | CH4_DIV         | OUT4 整数分周器の値 |

**表 7-11. LVCMOS 出力バッファの構成 (1) (2)**

| レジスタ ビット アドレス      | レジスタ ビット フィールド名                                  | 説明                                   |

|--------------------|--------------------------------------------------|--------------------------------------|

| R78[12]            | CH0_EN                                           | OUT0 LVCMOS バッファをイネーブルにします           |

| R79[3:0]           | CH0_CMOS_SLEW_RATE_CTRL                          | OUT0 LVCMOS バッファの出力スルーレートを制御します      |

| R59[14], R75[14]   | CH1_CMOSN_EN, CH4_CMOSP_EN                       | OUT1N/OUT4P LVCMOS バッファをイネーブルにします    |

| R59[13], R75[13]   | CH1_CMOSP_EN, CH4_CMOSN_EN                       | OUT1P/OUT4N LVCMOS バッファをイネーブルにします    |

| R59[12], R75[12]   | CH1_CMOSN_POL, CH4_CMOSP_POL                     | OUT1N/OUT4P LVCMOS バッファの出力極性を設定します   |

| R59[11], R75[11]   | CH1_CMOSP_POL, CH4_CMOSN_POL                     | OUT1P/OUT4N LVCMOS バッファの出力極性を設定します   |

| R60[3:0], R76[3:0] | CH1_CMOS_SLEW_RATE_CTRL, CH4_CMOS_SLEW_RATE_CTRL | OUT1/OUT4 LVCMOS バッファの出力スルーレートを制御します |

(1) 複数の出力バッファを同時に有効にしてはいけません。

(2) VDDO レベルに基づき、ch1\_1p8vdet, ch2\_1p8vdet, ch3\_1p8vdet, ch4\_1p8vdet を適宜設定する必要があります。1.8V に設定する場合は、safety\_1p8v\_mode を設定する必要があります。

**表 7-12. LP-HCSL 出力バッファの構成 (1) (2) (3)**

| レジスタ ビット アドレス                      | レジスタ ビット フィールド名                                    | 説明                                           |

|------------------------------------|----------------------------------------------------|----------------------------------------------|

| R57[14], R63[13], R68[13], R73[13] | CH1_HCSL_EN, CH2_HCSL_EN, CH3_HCSL_EN, CH4_HCSL_EN | OUT1/OUT2/OUT3/OUT4 で LP-HCSL バッファをイネーブルにします |

(1) 複数の出力バッファを同時に有効にしてはいけません。

(2) 外部終端は不要です。電圧モードドライバ。

(3) VDDO レベルに基づき、ch1\_1p8vdet, ch2\_1p8vdet, ch3\_1p8vdet, ch4\_1p8vdet を適宜設定する必要があります。1.8V に設定する場合は、safety\_1p8v\_mode を設定する必要があります。

**表 7-13. 疑似 LVDS 出力バッファの構成 (1) (2) (3)**

| レジスタ ビット アドレス                             | レジスタ ビット フィールド名                                                                                | 説明                                                          |

|-------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| R59[15], R65[11], R70[11], R75[15]        | CH1_LVDS_EN, CH2_LVDS_EN, CH3_LVDS_EN, CH4_LVDS_EN                                             | OUT1/OUT2/OUT3/OUT4 で疑似 LVDS バッファをイネーブルにします                 |

| R60[15:12], R66[3:0], R71[3:0], R76[9:6]  | CH1_DIFFBUF_IBIAS_TRIM, CH2_DIFFBUF_IBIAS_TRIM, CH3_DIFFBUF_IBIAS_TRIM, CH4_DIFFBUF_IBIAS_TRIM | OUT1/OUT2/OUT3/OUT4 の出力スイングと出力同相モードを設定します                   |

| R60[11:10], R66[5:4], R71[5:4], R76[5:4]  | CH1_LVDS_CMTRIM_INC, CH2_LVDS_CMTRIM_INC, CH3_LVDS_CMTRIM_INC, CH4_LVDS_CMTRIM_INC             | OUT1/OUT2/OUT3/OUT4 の出力同相モードを引き上げます。2.5V/3.3V モードのみ。        |

| R60[5:4], R65[14:13], R71[10:9], R77[1:0] | CH1_LVDS_CMTRIM_DEC, CH2_LVDS_CMTRIM_DEC, CH3_LVDS_CMTRIM_DEC, CH4_LVDS_CMTRIM_DEC             | OUT1/OUT2/OUT3/OUT4 の出力同相モードを引き下げます。2.5V または 3.3V モードの場合のみ。 |

(1) 複数の出力バッファを同時に有効にしてはいけません。

(2) DC 結合モードでは、100Ω の差動終端が必要です。AC 結合モードでは、50Ω のシングルエンド終端または 100Ω の差動終端が必要です。

(3) VDDO レベルに基づき、ch1\_1p8vdet, ch2\_1p8vdet, ch3\_1p8vdet, ch4\_1p8vdet を適宜設定する必要があります。1.8V に設定する場合は、safety\_1p8v\_mode を設定する必要があります。

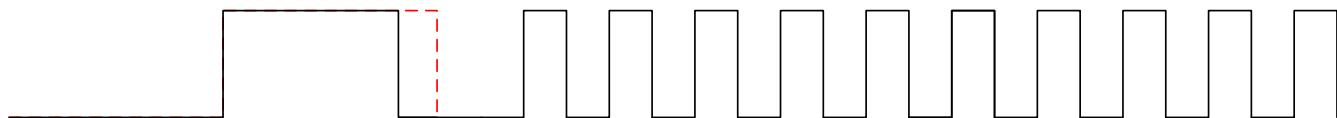

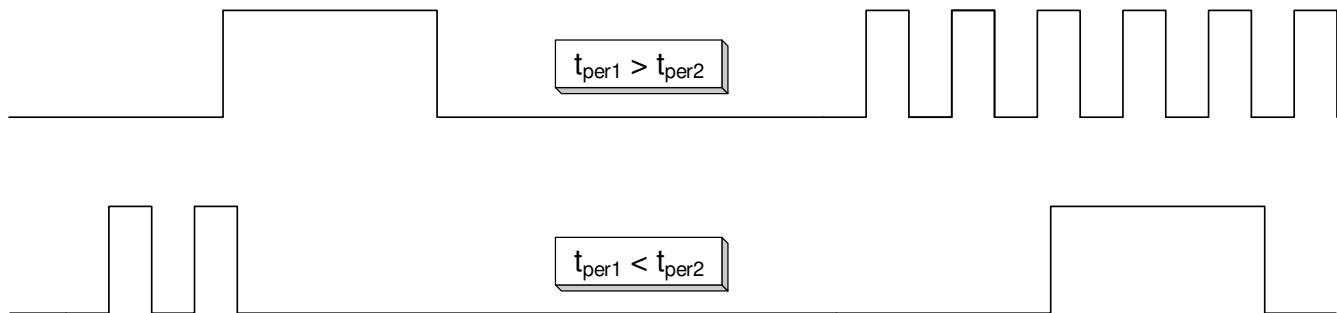

### 7.3.3.1 グリッチレス動作

ビットフィールド `ch{x}_glitchless_en` を使用して、グリッチレス出力分周器の更新を有効にできます。この機能により、クロック周期の **High** パルスが出力分周器の更新プロセスによって遮断されないことが保証されます。この機能は、レシーバのセットアップ時間とホールド時間が違反されていないことも保証します。以前の期間から新しい期間への遷移時の **Low** パルスが適宜延長されます。

Glitch-Less Divider Disabled:

Glitch-Less Divider Enabled:

図 7-8. グリッチレス分周器の更新

### 7.3.3.2 分周器の同期

出力分周器は、決定論的な方法でリセットできます。これは、同期ビットまたは **PDN** ピンを使用して行うことができます。ビンのレベルは、**PFD** 入力の基準周波数を使用して内部的に判定されます。**SYNCN** ピンまたは同期ビットが **Low** レベルになると、出力がミュートされます。**High** レベルになると、すべての出力分周器が同期的に解放されて動作し、すべての出力が共通の立ち上がりエッジを共有します。最初の立ち上がりエッジは、それぞれのプリスケーラ期間のステップで個別に遅延させることができます。`ch{x}_sync_delay` を使用して最大 32 サイクルまで遅延可能です。これにより、**FPGA** 設計でロジックゲートが引き起こす配線ミスマッチ、ケーブル、固有遅延などの外部遅延を補償できます。各チャネルは、同期プロセスに含めることも、除外することもできます。分周器の同期は、`ch{x}_sync_en` によって個別に有効にできます。

パワー サイクルでの入力から出力までの確定的な動作を実現するには、基準分周器を 1 に設定する必要があります。リファレンス分周器がリファレンスクロックを分割したり、リファレンスダブラーを使用したりしてはいけません。

図 7-9. 出力分周器の同期

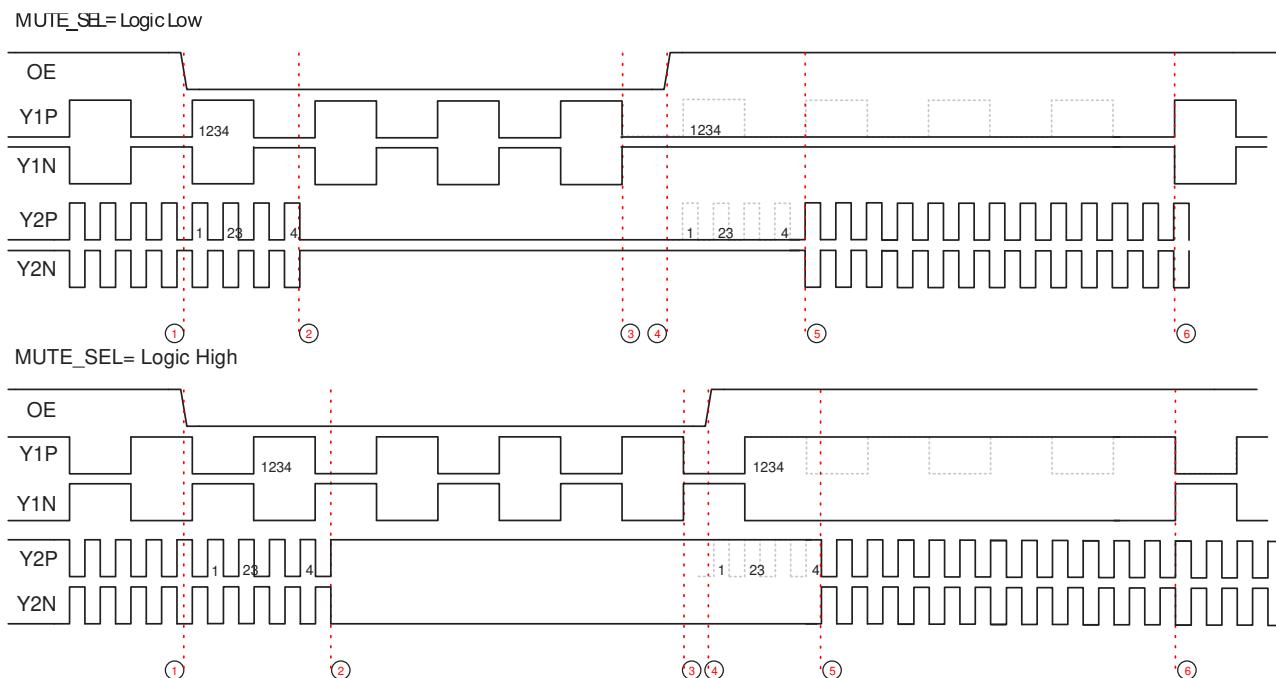

### 7.3.3.3 グローバルおよび個別の出力イネーブル

出力イネーブル機能により、ユーザーはすべてまたは特定の出力バッファをイネーブルまたはディスエーブルすることができます。OUT0 のバイパス コピーは、グローバル出力イネーブル信号から除外されます。出力がディスエーブルのとき、この信号は構成可能なミュート状態を駆動します。シリアル インターフェイスが非アクティブになっているときは、個別の出力イネーブル信号をすべて同時に使用できます。個別の出力イネーブル信号は、クロックをゲートするために、それぞれの出力チャネルの整数分周器を制御します。したがって、各整数分周器をアクティブにする必要があります。

個別の出力イネーブル信号により、それぞれの出力が確定的な方法でイネーブルおよびディスエーブルになります。したがって、信号の High および Low レベルは、それぞれの出力クロックの 4 サイクルをカウントすることで判定されます。

図 7-10. 個別の出力の有効化と無効化

**表 7-14. グリッチレス動作と分周器の同期**

| レジスタ ビット アドレス                  | レジスタ ビット フィールド名                                                                     | 説明                                           |

|--------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------|

| R0[14]                         | PDN_INPUT_SEL                                                                       | PDN ピンを PDN または SYNCN として構成します               |

| R0[5]                          | SYNC                                                                                | シリアル インターフェイス経由で同期信号を生成します                   |

| R57[9], R63[9], R68[9], R73[9] | CH1_GLITCHLESS_EN,<br>CH2_GLITCHLESS_EN,<br>CH3_GLITCHLESS_EN,<br>CH4_GLITCHLESS_EN | OUT1/OUT2/OUT3/OUT4 のグリッチレス スイッチングをイネーブルにします |

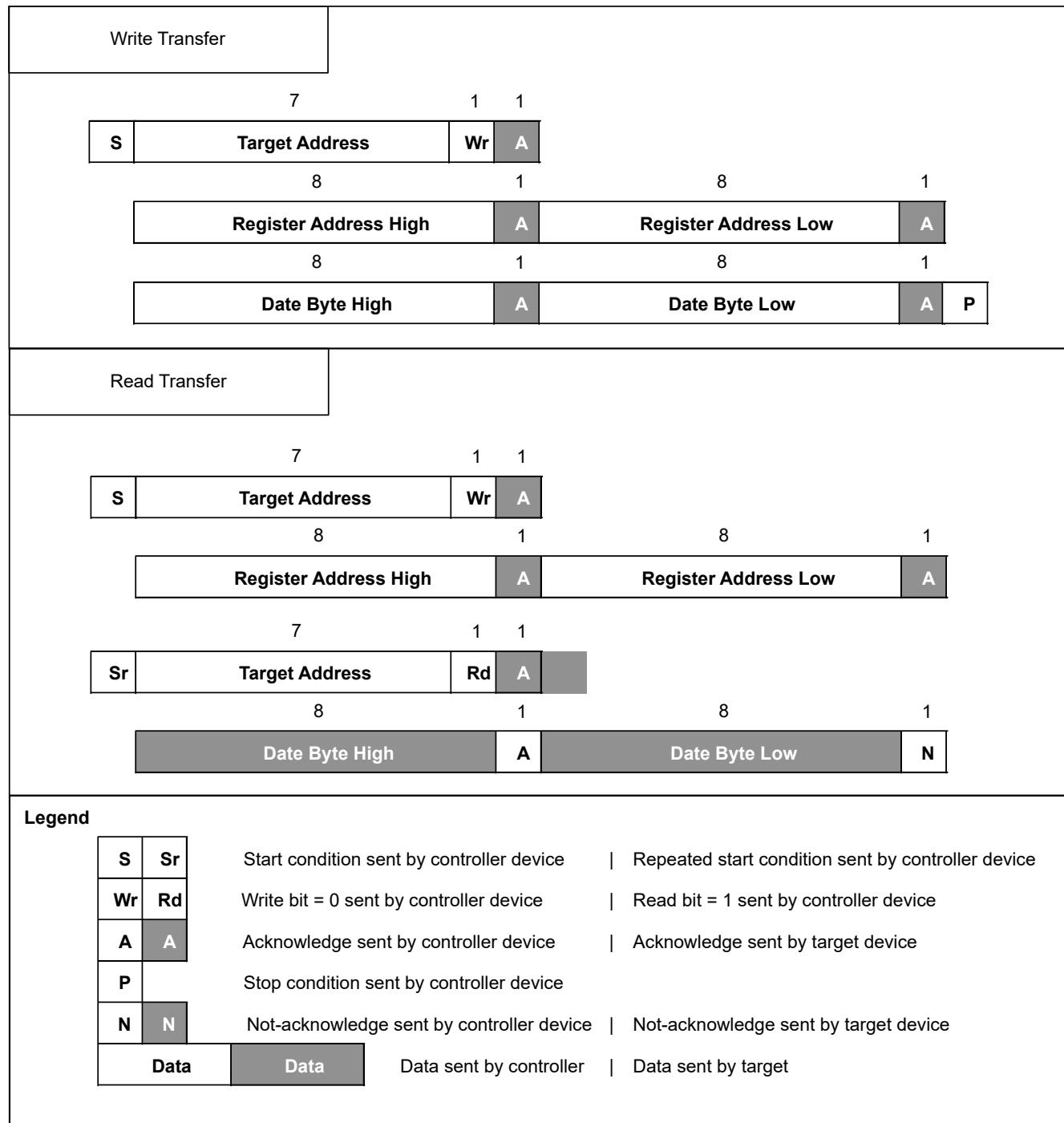

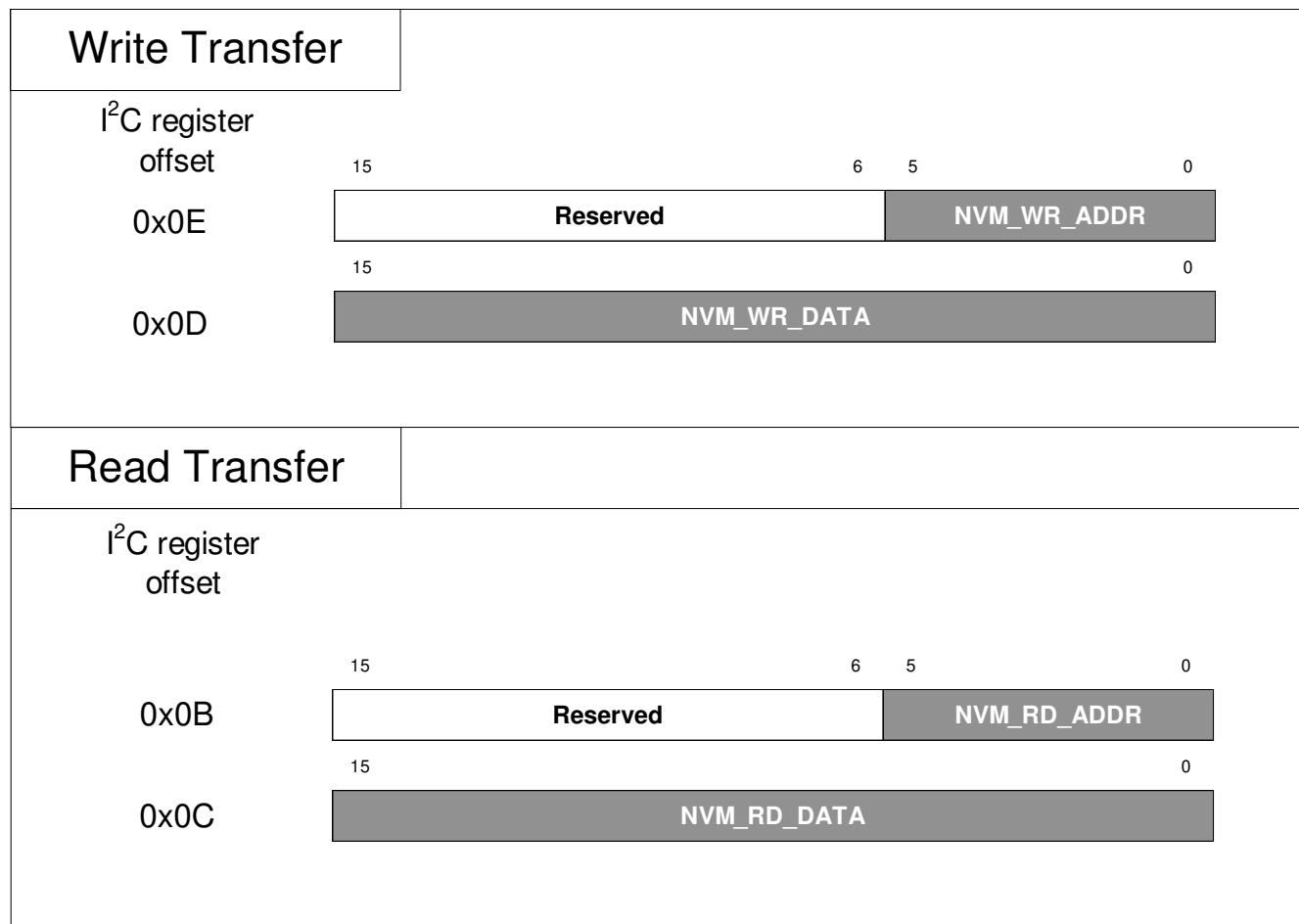

| R57[3], R63[3], R68[3], R73[3] | CH1_SYNC_EN, CH2_SYNC_EN,<br>CH3_SYNC_EN, CH4_SYNC_EN                               | OUT1/OUT2/OUT3/OUT4 の同期をイネーブルにします            |