# CDCDB2000 PCIe Gen 1～Gen 7 用 DB2000QL 準拠 20 出力クロック バッファ

## 1 特長

- 85Ω の出力終端を内蔵した 20 の LP-HCSL 出力

- 8 つのハードウェア出力イネーブル (OE#) 制御

- DB2000QL フィルタ後の付加位相ジッタ: < 0.08ps rms

- PCIe Gen 6 および Gen 7 Common Clock (CC) および Individual Reference (IR) アーキテクチャをサポート

- スペクトラム拡散対応

- サイクル間ジッタ:< 50ps

- 出力間スキー:< 50ps

- 入出力間遅延:3ns 未満

- コアおよび入出力電源電圧:3.3V

- ハードウェア制御による低消費電力モード (PD#)

- PD# モードでの出力制御のためのサイドバンド インタフェイス (SBI)

- 9 つの選択可能な SMBus アドレス

- 消費電力:600mW 未満

- 6mm × 6mm の 80 ピン TLGA/GQFN パッケージ

## 2 アプリケーション

- マイクロサーバーおよびタワー サーバー

- ストレージ エリア ネットワーク (SAN) とホストバス アダプタ (HBA) カード

- ネットワーク接続ストレージ

- ハードウェア アクセラレータ

## 3 説明

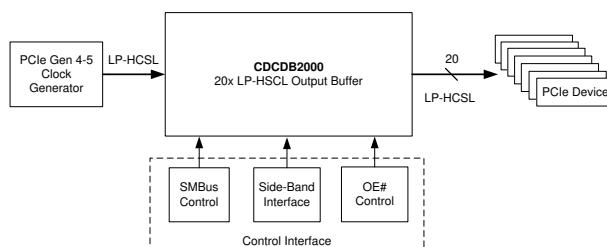

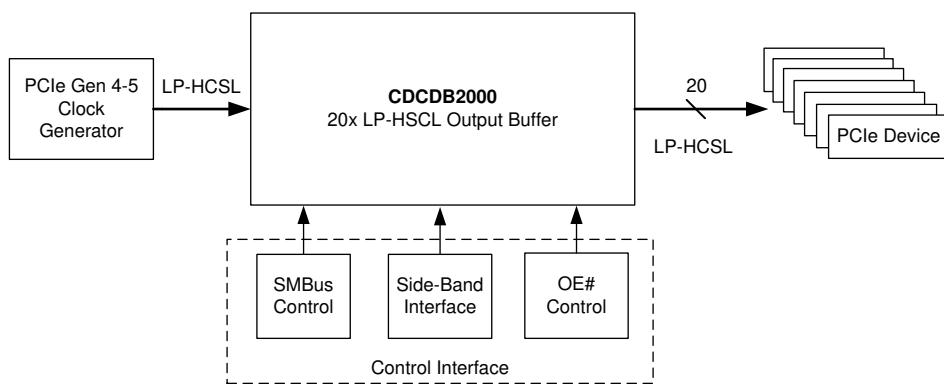

CDCDB2000 は、PCIe Gen 1～7、QuickPath Interconnect (QPI)、UPI、SAS、SATA インターフェイス用のリファレンス クロックを分配できる 20 出力 LP-HCSL、DB2000QL 準拠クロック バッファです。SMBus、SBI、8 つの出力イネーブルピンにより、20 の出力すべてを個別に設定および制御できます。CDCDB2000 は DB2000QL から派生したバッファであり、DB2000QL 仕様のシステム パラメータを満たし、または上回る性能を備えています。CDCDB2000 は 80 ピンの 6mm × 6mm TLGA/GQFN パッケージに封止されています。

### パッケージ情報

| 部品番号      | パッケージ <sup>(1)</sup> | パッケージ サイズ <sup>(2)</sup> |

|-----------|----------------------|--------------------------|

| CDCDB2000 | TLGA (80)            | 6.00mm × 6.00mm          |

- (1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

(2) パッケージ サイズ (長さ × 幅) は公称値であり、該当する場合はビンを含みます。

**CDCDB2000 のシステム図**

このリソースの元の言語は英語です。翻訳は概要を便宜的に提供するもので、自動化ツール（機械翻訳）を使用していることがあり、TI では翻訳の正確性および妥当性につきましては一切保証いたしません。実際の設計などの前には、ti.com で必ず最新の英語版をご参照くださいますようお願いいたします。

## 目次

|                |    |                        |    |

|----------------|----|------------------------|----|

| 1 特長           | 1  | 7 レジスタマップ              | 17 |

| 2 アプリケーション     | 1  | 7.1 CDCDB2000 のレジスタ    | 17 |

| 3 説明           | 1  | 8 アプリケーションと実装          | 24 |

| 4 ピン構成および機能    | 2  | 8.1 アプリケーション情報         | 24 |

| 5 仕様           | 7  | 8.2 代表的なアプリケーション       | 24 |

| 5.1 絶対最大定格     | 7  | 8.3 電源に関する推奨事項         | 25 |

| 5.2 ESD 定格     | 7  | 8.4 レイアウト              | 26 |

| 5.3 推奨動作条件     | 7  | 9 デバイスおよびドキュメントのサポート   | 29 |

| 5.4 熱に関する情報    | 7  | 9.1 デバイス サポート          | 29 |

| 5.5 電気的特性      | 8  | 9.2 ドキュメントのサポート        | 29 |

| 5.6 タイミング要件    | 9  | 9.3 ドキュメントの更新通知を受け取る方法 | 29 |

| 5.7 代表的特性      | 11 | 9.4 サポート・リソース          | 29 |

| 6 詳細説明         | 12 | 9.5 商標                 | 29 |

| 6.1 概要         | 12 | 9.6 静電気放電に関する注意事項      | 29 |

| 6.2 機能ブロック図    | 12 | 9.7 用語集                | 29 |

| 6.3 機能説明       | 12 | 10 改訂履歴                | 29 |

| 6.4 デバイスの機能モード | 13 | 11 メカニカル、パッケージ、および注文情報 | 30 |

| 6.5 プログラミング    | 15 |                        |    |

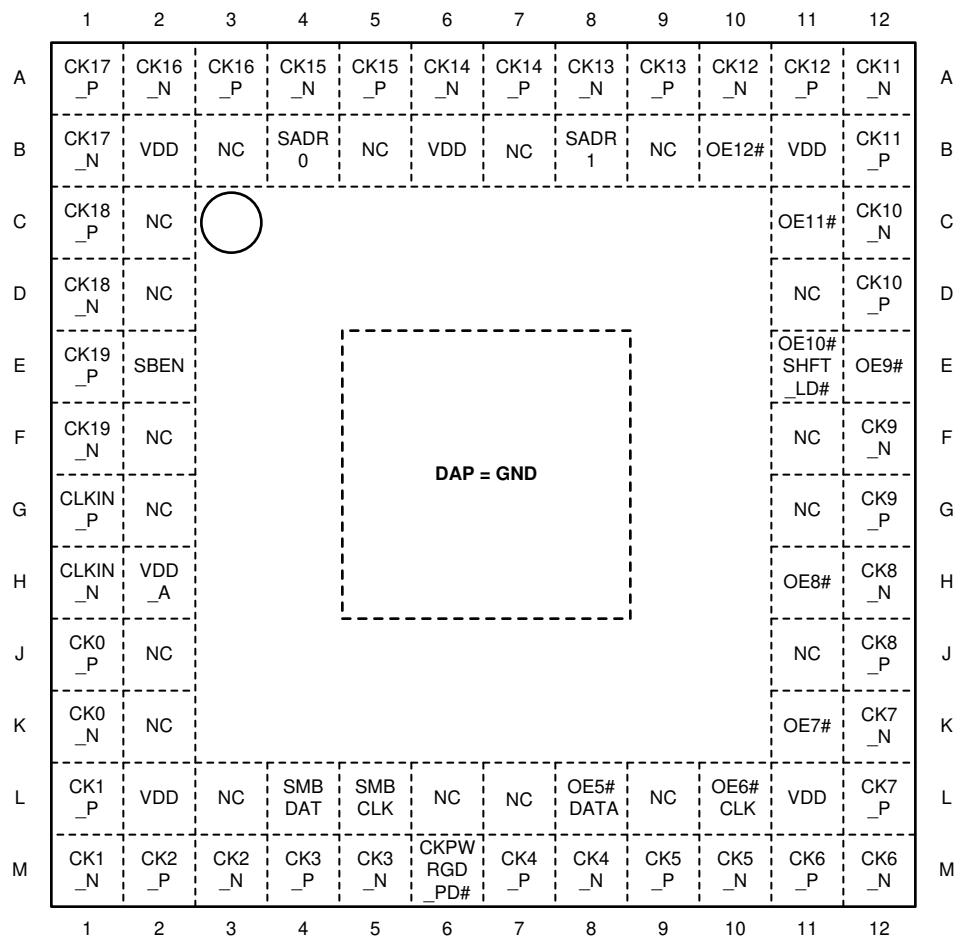

## 4 ピン構成および機能

図 4-1. CDCDB2000 NPP パッケージ 80 ピン TLGA 上面図

**表 4-1. ピンの機能**

| ピン                |     | 入出力タイプ<br>(2) | 説明                                                                                                                                              |

|-------------------|-----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称 <sup>(1)</sup> | 番号  |               |                                                                                                                                                 |

| <b>入力クロック</b>     |     |               |                                                                                                                                                 |

| CLKIN_P           | G1  | I             | LP-HCSL 差動クロック入力。通常、クロック ソースの差動出力に直接接続します。                                                                                                      |

| CLKIN_N           | H1  | I             |                                                                                                                                                 |

| <b>出力クロック</b>     |     |               |                                                                                                                                                 |

| CK0_P             | J1  | O             | チャネル 0 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。使用しない場合は、ピンを未接続のままにしておくことができます。                                                              |

| CK0_N             | K1  | O             |                                                                                                                                                 |

| CK1_P             | L1  | O             | チャネル 1 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。使用しない場合は、ピンを未接続のままにしておくことができます。                                                              |

| CK1_N             | M1  | O             |                                                                                                                                                 |

| CK2_P             | M2  | O             | チャネル 2 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。使用しない場合は、ピンを未接続のままにしておくことができます。                                                              |

| CK2_N             | M3  | O             |                                                                                                                                                 |

| CK3_P             | M4  | O             | チャネル 3 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。使用しない場合は、ピンを未接続のままにしておくことができます。                                                              |

| CK3_N             | M5  | O             |                                                                                                                                                 |

| CK4_P             | M7  | O             | チャネル 4 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。使用しない場合は、ピンを未接続のままにしておくことができます。                                                              |

| CK4_N             | M8  | O             |                                                                                                                                                 |

| CK5_P             | M9  | O             | チャネル 5 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。未使用の場合、ピンは接続せずにままででき、ピン L8 (OE5#/DATA) はデータ モードにするか high にすることを推奨します。                        |

| CK5_N             | M10 | O             |                                                                                                                                                 |

| CK6_P             | M11 | O             | チャネル 6 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。未使用の場合、ピンは接続せずにままででき、ピン L10 (OE6#/CLK) はデータ モードにするか high にすることを推奨します。                        |

| CK6_N             | M12 | O             |                                                                                                                                                 |

| CK7_P             | L12 | O             | チャネル 7 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。使用しない場合、これらのピンを未接続のままにでき、チャネル 7 の出力をディセーブルにするには、ピン K11 (OE7#) を high にすることを推奨します。            |

| CK7_N             | K12 | O             |                                                                                                                                                 |

| CK8_P             | J12 | O             | チャネル 8 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。使用しない場合、これらのピンを未接続のままにでき、チャネル 8 の出力をディセーブルにするには、ピン H11 (OE8#) を high にすることを推奨します。            |

| CK8_N             | H12 | O             |                                                                                                                                                 |

| CK9_P             | G12 | O             | チャネル 9 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。使用しない場合、これらのピンを未接続のままにでき、チャネル 9 の出力をディセーブルにするには、ピン E12 (OE9#) を high にすることを推奨します。            |

| CK9_N             | F12 | O             |                                                                                                                                                 |

| CK10_P            | D12 | O             | チャネル 10 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。使用しない場合、これらのピンは接続せずにままででき、ピン E11 (OE10#/SHFT_LD#) は SHFT_LD# モードまたは high にブリッアップすることを推奨します。 |

| CK10_N            | C12 | O             |                                                                                                                                                 |

| CK11_P            | B12 | O             | チャネル 11 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。使用しない場合、これらのピンを未接続のままにでき、チャネル 11 の出力をディセーブルにするには、ピン C11 (OE11#) を high にすることを推奨します。         |

| CK11_N            | A12 | O             |                                                                                                                                                 |

| CK12_P            | A11 | O             | チャネル 12 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。使用しない場合、これらのピンを未接続のままにでき、チャネル 12 の出力をディセーブルにするには、ピン B10 (OE12#) を high にすることを推奨します。         |

| CK12_N            | A10 | O             |                                                                                                                                                 |

| CK13_P            | A9  | O             | チャネル 13 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。使用しない場合は、ピンを未接続のままにしておくことができます。                                                             |

| CK13_N            | A8  | O             |                                                                                                                                                 |

| CK14_P            | A7  | O             | チャネル 14 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。使用しない場合は、ピンを未接続のままにしておくことができます。                                                             |

| CK14_N            | A6  | O             |                                                                                                                                                 |

| CK15_P            | A5  | O             | チャネル 15 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。使用しない場合は、ピンを未接続のままにしておくことができます。                                                             |

| CK15_N            | A4  | O             |                                                                                                                                                 |

| CK16_P            | A3  | O             | チャネル 16 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。使用しない場合は、ピンを未接続のままにしておくことができます。                                                             |

| CK16_N            | A2  | O             |                                                                                                                                                 |

表 4-1. ピンの機能(続き)

| ピン                |     | 入出力タイプ<br>(2) | 説明                                                                                                                                                                                                                                                                                                  |

|-------------------|-----|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称 <sup>(1)</sup> | 番号  |               |                                                                                                                                                                                                                                                                                                     |

| CK17_P            | A1  | O             | チャネル 17 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。使用しない場合は、ピンを未接続のままにしておくことができます。                                                                                                                                                                                                                 |

| CK17_N            | B1  | O             |                                                                                                                                                                                                                                                                                                     |

| CK18_P            | C1  | O             | チャネル 18 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。使用しない場合は、ピンを未接続のままにしておくことができます。                                                                                                                                                                                                                 |

| CK18_N            | D1  | O             |                                                                                                                                                                                                                                                                                                     |

| CK19_P            | E1  | O             | チャネル 19 の LP-HCSL 差動クロック出力。通常、PCIe 差動クロック入力に直接接続します。使用しない場合は、ピンを未接続のままにしておくことができます。                                                                                                                                                                                                                 |

| CK19_N            | F1  | O             |                                                                                                                                                                                                                                                                                                     |

| <b>管理と制御</b>      |     |               |                                                                                                                                                                                                                                                                                                     |

| CKPWRGD_PD#       | M6  | I, PD         | クロック パワー グッドおよびパワー ダウン マルチファンクション入力ピン、内部 120kΩ プルダウン。通常、マイクロ コントローラの GPIO に接続します。使用しない場合は、ピンを未接続のままにしておくことができます。最初の high 遷移で、PWRGD はラッ奇された Sadr[1:0] 入力をサンプリングし、デバイスを起動します。PWRGD が初めて high にアサートされた後、このピンは PD# ピンになります。このピンでパワーダウン モードを制御します。<br>LOW:パワーダウン モード、すべての出力チャネルトライステート。<br>HIGH:通常動作モード。 |

| OE5#_DATA         | L8  | I, PD         | チャネル 5 およびサイドバンド インターフェイス データ マルチファンクションピンの出力イネーブル、内部 120kΩ プルダウン付き。通常、マイクロ コントローラの GPIO に接続します。両方のモードを使わない場合、このピンは接続なしのままにできます。ピン E 2 = LOW の場合、OE5# モード。チャネル 5 の出力イネーブル、アクティブ low。<br>LOW:出力チャネル 5 を有効化します。<br>HIGH:出力チャネル 5 を無効化します。ピン E2 = HIGH のとき、data モード。サイドバンド インターフェイス データ ピン。            |

| OE6#_CLK          | L10 | I, PD         | チャネル 6 およびサイドバンド インターフェイス クロック マルチファンクションピンの出力イネーブル、内部 120kΩ プルダウン付き。通常、マイクロ コントローラの GPIO に接続します。両方のモードを使わない場合、このピンは接続なしのままにできます。ピン E 2 = LOW の場合、OE6# モード。チャネル 6 の出力イネーブル、アクティブ Low。<br>LOW:出力チャネル 6 を有効化します。<br>HIGH:出力チャネル 6 を無効化します。ピン E2 = HIGH のとき、CLK モード。サイドバンド インターフェイス クロック ピン。           |

| OE7#              | K11 | I, PD         | チャネル 7 の出力イネーブル、120kΩ の内部プルダウン、アクティブ low。通常、マイクロ コントローラの GPIO に接続します。使用しない場合は、ピンを未接続のままにしておくことができます。<br>LOW:出力チャネル 7 を有効化します。<br>HIGH:出力チャネル 7 を無効化します。                                                                                                                                             |

| OE8#              | H11 | I, PD         | チャネル 8 の出力イネーブル、120kΩ の内部プルダウン、アクティブ low。通常、マイクロ コントローラの GPIO に接続します。使用しない場合は、ピンを未接続のままにしておくことができます。<br>LOW:出力チャネル 8 を有効化します。<br>HIGH:出力チャネル 8 を無効化します。                                                                                                                                             |

| OE9#              | E12 | I, PD         | チャネル 9 の出力イネーブル、120kΩ の内部プルダウン、アクティブ low。通常、マイクロ コントローラの GPIO に接続します。使用しない場合は、ピンを未接続のままにしておくことができます。<br>LOW:出力チャネル 9 を有効化します。<br>HIGH:出力チャネル 9 を無効化します。                                                                                                                                             |

**表 4-1. ピンの機能(続き)**

| ピン                |     | 入出力タイプ<br>(2) | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------|-----|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 名称 <sup>(1)</sup> | 番号  |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| OE10#<br>SHFT_LD# | E11 | I, PD         | <p>チャネル 10 の出力イネーブルおよびサイドバンド インターフェイス負荷シフトレジスタ <math>120\Omega</math> の内部プルダウン付きマルチファンクション ピン。通常、マイクロコントローラの GPIO に接続します。両方のモードを使わない場合、このピンは接続なしのままにできます。ピン E2 = LOW の場合、OE10# モード。チャネル 10 の出力イネーブル、アクティブ low。</p> <p>LOW: 出力チャネル 10 を有効化します。</p> <p>HIGH: 出力チャネル 10 を無効化します。ピン E2 = HIGH の場合、SHFT_LD# モード。サイドバンド インターフェイス ロード シフトレジスタ ピン。</p> <p>LOW: サイドバンド インターフェイス シフトレジスタをディセーブルにします。</p> <p>HIGH: サイドバンド インターフェイス シフトレジスタをイネーブルします。</p> <p>立ち下がりエッジにより、サイドバンド シフトレジスタの内容が出力レジスタに転送されます。</p> |

| OE11#             | C11 | I, PD         | <p>チャネル 11 の出力イネーブル、<math>120\text{k}\Omega</math> の内部プルダウン、アクティブ low。通常、マイクロコントローラの GPIO に接続します。使用しない場合は、ピンを未接続のままにしておくことができます。</p> <p>LOW: 出力チャネル 11 を有効化します。</p> <p>HIGH: 出力チャネル 11 を無効化します。</p>                                                                                                                                                                                                                                                                                               |

| OE12#             | B10 | I, PD         | <p>チャネル 12 の出力イネーブル、<math>120\text{k}\Omega</math> の内部プルダウン、アクティブ low。通常、マイクロコントローラの GPIO に接続します。使用しない場合は、ピンを未接続のままにしておくことができます。</p> <p>LOW: 出力チャネル 12 を有効化します。</p> <p>HIGH: 出力チャネル 12 を無効化します。</p>                                                                                                                                                                                                                                                                                               |

| SBEN              | E2  | I, S, PD      | <p>サイドバンド インターフェイスのイネーブル入力、内部 <math>120\text{k}\Omega</math> プルダウン付き。通常、マイクロコントローラの GPIO に接続します。使用しない場合は、ピンを未接続のままにしておくことができます。このピンがアサートされると、出力イネーブル (OE#) ピンがディセーブルになります。</p> <p>LOW: OE# ピンと SMBus イネーブル ビット制御出力、サイドバンド インターフェイスはディセーブル。</p> <p>HIGH: サイドバンド インターフェイスによる出力、OE# ピン、SMBus イネーブル ビットがディセーブルです。</p>                                                                                                                                                                                 |

**SMBus および SMBus アドレス**

|        |    |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------|----|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SADR0  | B4 | I, S, PU/ PD | <p>SMBus アドレス ストラップ ビット [0]。これは 3 レベル入力で、ピン B8 と組み合わせてデコードされ、SMBus アドレスを設定します。このピンには、接続されていない場合に VDD/2 にバイアスされる内部 <math>120\text{k}\Omega</math> プルアップまたはプルダウン ネットワークがあります。</p> <p>high レベル入力構成では、ピンを <math>1\text{k} \sim 5\text{k}</math> の外部プルアップ抵抗を介して、許容誤差 5% で <math>3.3\text{VDD}</math> にプルアップする必要があります。</p> <p>低レベル入力構成入力では、外部プルダウン抵抗を介して、<math>1\text{k} \sim 5\text{k}</math> の範囲内に、許容誤差 5% でグランドにプルダウンする必要があります。</p> <p>中間レベル入力構成の場合、このピンをフローティングのままにし、VDD にもグランドにも接続しないでください。</p>      |

| SADR1  | B8 | I, S, PU/ PD | <p>SMBus アドレス ストラップ ビット [1]。これは 3 レベル入力で、ピン B4 と組み合わせてデコードされ、SMBus アドレスを設定します。このピンには、接続されていない場合に VDD/2 にバイアスされる内部 <math>120\text{k}\Omega</math> プルアップまたはプルダウン ネットワークがあります。</p> <p>high レベル入力構成では、このピンを外付けプルアップ抵抗を介して、許容誤差 5% で <math>1\text{k} \sim 5\text{k}</math> の範囲で <math>3.3\text{VDD}</math> にプルアップする必要があります。</p> <p>low レベル入力構成では、外部プルダウン抵抗を介して、<math>1\text{k} \sim 5\text{k}</math> の範囲、許容誤差 5% でグランドにプルダウンする必要があります。</p> <p>中間レベル入力構成の場合、このピンをフローティングのままにし、VDD にもグランドにも接続しないでください。</p> |

| SMBCLK | L5 | I            | SMBus インターフェイスのクロック ピン。通常は外付けプルアップ抵抗を使用して $3.3\text{V}$ VDD にプルアップします。推奨 プルアップ レジスタ 値は $8.5\text{k}$ を超えます。                                                                                                                                                                                                                                                                                                                                                                                         |

| SMBDAT | L4 | I/O          | SMBus インターフェイスのデータ ピン。通常は外付けプルアップ抵抗を使用して $3.3\text{V}$ VDD にプルアップします。推奨 プルアップ レジスタ 値は $8.5\text{k}$ を超えます。                                                                                                                                                                                                                                                                                                                                                                                          |

表 4-1. ピンの機能 (続き)

| ピン<br>名称 <sup>(1)</sup> | 番号                                                                         | 入出力タイプ<br><sup>(2)</sup> | 説明                                                                                                        |

|-------------------------|----------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------|

| <b>電源電圧およびグラウン</b>      |                                                                            |                          |                                                                                                           |

| GND                     | DAP                                                                        | G                        | グランド。グランド パッドはシステム グランドに接続します。                                                                            |

| VDD                     | B2、B6、B11、L2、<br>L11                                                       | P                        | LP-HCSL クロック出力チャネルの電源入力。デカップリング コンデンサを GND に接続して 3.3V 電源レールに接続します。電源とグランドとの間に各電源ピンの近くに 0.1μF コンデンサを配置します。 |

| VDD_A を必要としま<br>す       | H2                                                                         | P                        | 差動入力クロックの電源入力。デカップリング コンデンサを GND に接続して 3.3V 電源レールに接続します。ピン付近の両端に 0.1μF のコンデンサを配置します。                      |

| <b>内部接続なし</b>           |                                                                            |                          |                                                                                                           |

| NC                      | B3、B5、B7、B9、<br>C2、D2、D11、F2、<br>F11、G2、G11、J2、<br>J11、K2、L3、L6、<br>L7、L9、 | —                        | GND または VDD プレーンには接続しないでください。                                                                             |

(1) ピン名の末尾にある「#」記号は、信号が低電圧レベルのときにアクティブ状態が発生することを示しています。「#」が存在しない場合、信号はアクティブ high です。

(2) 各ピンの I/O タイプの定義は次のとおりです。

- I = 入力

- O = 出力

- I/O = 入出力

- PU/PD = VDD/2 への内部 120kΩ プルアップ/プルダウン ネットワーク バイアス

- PD = 120kΩ の内部プルダウン

- S = ハードウェア構成ピン

- P = 電源

- G = グランド

## 5 仕様

### 5.1 絶対最大定格

自由気流での動作温度範囲内 (特に記述のない限り) <sup>(1)</sup>

|                        |         | 最小値  | 最大値            | 単位 |

|------------------------|---------|------|----------------|----|

| $V_{DD}$ , $V_{DD\_A}$ | 電源電圧    | -0.3 | 3.6            | V  |

| $V_{IN}$               | IO 入力電圧 | GND  | $V_{DD} + 0.5$ | V  |

| $T_J$                  | 接合部温度   |      | 125            | °C |

| $T_{stg}$              | 保存温度    | -65  | 150            | °C |

- (1) 「絶対最大定格」の範囲外での動作は、デバイスの永続的な損傷の原因となる可能性があります。絶対最大定格は、これらの条件において、または推奨動作条件に示された値を超える他のいかなる条件でも、本製品が正しく動作することを暗に示すものではありません。「絶対最大定格」の範囲内であっても「推奨動作条件」の範囲外で使用した場合、本デバイスは完全に機能するとは限らず、このことが本デバイスの信頼性、機能、性能に影響を及ぼし、本デバイスの寿命を縮める可能性があります。

### 5.2 ESD 定格

|             |      | 値                                                              | 単位    |

|-------------|------|----------------------------------------------------------------|-------|

| $V_{(ESD)}$ | 静電放電 | 人体モデル (HBM)、ANSI/ESDA/JEDEC JS-001 に準拠、すべてのピン <sup>(1)</sup>   | ±3000 |

|             |      | デバイス帶電モデル (CDM)、JEDEC 仕様 JESD22-C101 に準拠、すべてのピン <sup>(2)</sup> |       |

- (1) JEDEC ドキュメント JEP155 には、500VHBM であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

(2) JEDEC ドキュメント JEP157 には、250VCMD であれば標準的な ESD 管理プロセスにより安全な製造が可能であると記載されています。

### 5.3 推奨動作条件

自由空気での動作温度範囲内 (特に記述のない限り)

|             |        | 最小値   | 公称値 | 最大値   | 単位 |

|-------------|--------|-------|-----|-------|----|

| $V_{DD}$    | IO 電源  | 3.135 | 3.3 | 3.465 | V  |

| $V_{DD\_A}$ | コア電源電圧 | 3.135 | 3.3 | 3.465 | V  |

| $T_A$       | 周囲温度   | -40   |     | 85    | °C |

| $T_J$       | 接合部温度  |       |     | 125   | °C |

### 5.4 热に関する情報

| 熱評価基準 <sup>(1)</sup> |                     | CDCDB2000  | 単位   |

|----------------------|---------------------|------------|------|

|                      |                     | NPP (GQFN) |      |

|                      |                     | 80 ピン      |      |

| $R_{\theta JA}$      | 接合部から周囲への熱抵抗        | 32.7       | °C/W |

| $R_{\theta JC(top)}$ | 接合部からケース (上面) への熱抵抗 | 31.2       | °C/W |

| $R_{\theta JB}$      | 接合部から基板への熱抵抗        | 15.9       | °C/W |

| $\Psi_{JT}$          | 接合部から上面への特性パラメータ    | 0.4        | °C/W |

| $\Psi_{JB}$          | 接合部から基板への特性パラメータ    | 15.8       | °C/W |

| $R_{\theta JC(bot)}$ | 接合部からケース (底面) への熱抵抗 | 1.5        | °C/W |

- (1) 従来および最新の熱評価基準の詳細については、『半導体および IC パッケージの熱評価基準』アプリケーション ノートを参照してください。

## 5.5 電気的特性

VDD、VDD\_A = 3.3V±5%、-40°C≤TA≤85°C。標準値は、VDD = VDD\_A = 3.3V、25°C のときです (特に記述のない限り)

| パラメータ                  |                               | テスト条件                                                                               | 最小値                    | 標準値  | 最大値                 | 単位                      |

|------------------------|-------------------------------|-------------------------------------------------------------------------------------|------------------------|------|---------------------|-------------------------|

| <b>消費電流</b>            |                               |                                                                                     |                        |      |                     |                         |

| I <sub>DD_A</sub>      | コア消費電流                        | アクティブ モード。CKPWRGD_PD# = 1                                                           | 12                     |      |                     | mA                      |

|                        |                               | パワーダウン モード。CKPWRGD_PD# = 0                                                          | 8                      |      |                     |                         |

| I <sub>DD</sub>        | IO 出力ごとの出力電源電流                | 全出力ディセーブル                                                                           | 20                     |      |                     | mA                      |

|                        |                               | 全出力アクティブ、100MHz                                                                     | 200                    |      |                     |                         |

|                        |                               | パワーダウン モード。CKPWRGD_PD# = 0                                                          | 8                      |      |                     |                         |

| <b>クロック入力</b>          |                               |                                                                                     |                        |      |                     |                         |

| f <sub>IN</sub>        | 入力周波数                         |                                                                                     | 50                     | 100  | 250                 | MHz                     |

| V <sub>IN</sub>        | 入力電圧スイング                      | CLKIN_P と CLKIN_N <sup>(1)</sup> の間の差動電圧                                            | 200                    | 2300 |                     | mV <sub>Diff-peak</sub> |

| dV/dt                  | 入力電圧エッジレート                    | 入力スイングの 20% ~ 80%                                                                   | 0.7                    |      |                     | V/ns                    |

| DV <sub>CROSS</sub>    | V <sub>CROSS</sub> の合計変動      | V <sub>CROSS</sub> での合計変動                                                           | 140                    |      |                     | mV                      |

| DC <sub>IN</sub>       | 入力デューティ サイクル                  |                                                                                     | 40                     | 60   |                     | %                       |

| C <sub>IN</sub>        | 入力キャパシタンス <sup>(2)</sup>      | CLKIN_P ピンと CLKIN_N ピンの間の差動容量                                                       | 2.2                    |      |                     | pF                      |

| <b>クロック出力</b>          |                               |                                                                                     |                        |      |                     |                         |

| f <sub>OUT</sub>       | 出力周波数                         |                                                                                     | 50                     | 100  | 250                 | MHz                     |

| C <sub>OUT</sub>       | 出力キャパシタンス <sup>(1)</sup>      | CKx_P ピンと CKx_N ピンの間の差動容量                                                           | 2.2                    |      |                     | pF                      |

| V <sub>OH</sub>        | 出力 HIGH 電圧                    | シングル エンド <sup>(2) (3)</sup>                                                         | 225                    | 270  |                     | mV                      |

| V <sub>OL</sub>        | 出力 LOW 電圧                     |                                                                                     | 10                     | 150  |                     |                         |

| V <sub>CROSS</sub>     | 交差点電圧                         | 入力 V <sub>CROSS</sub> を 140mV 変化させた。 <sup>(3) (4)</sup>                             | 130                    | 200  |                     |                         |

| DV <sub>CROSS</sub>    | V <sub>CROSS</sub> の合計変動      | 入力 V <sub>CROSS</sub> を 140mV 変化させました。<br>V <sub>CROSS</sub> <sup>(3) (4)</sup> の変動 | 35                     |      |                     |                         |

| V <sub>ovs</sub>       | オーバーシュート電圧                    | <sup>(3)</sup>                                                                      |                        |      | V <sub>OH</sub> +75 |                         |

| V <sub>uds</sub>       | アンダーシュート電圧                    | <sup>(3)</sup>                                                                      |                        |      | V <sub>OL</sub> -75 |                         |

| Z <sub>DIFF</sub>      | 差動インピーダンス                     | V <sub>OL</sub> /V <sub>OH</sub> で測定                                                | 81                     | 85   | 89                  | Ω                       |

| Z <sub>DIFF_CROS</sub> | 差動インピーダンス                     | V <sub>CROSS</sub> で測定                                                              | 68                     | 85   | 102                 |                         |

| t <sub>EDGE</sub>      | エッジレート                        | V <sub>CROSS</sub> で測定                                                              | 2                      | 20   |                     | V/ns                    |

| Dt <sub>EDGE</sub>     | エッジレートマッチング                   | V <sub>CROSS</sub> で測定                                                              |                        |      | 20                  | %                       |

| t <sub>STABLE</sub>    | 安定したクロック出力へのパワー グッド アサート      | CKPWRGD_PD# ピンが 0 から 1 に遷移、f <sub>IN</sub> = 100MHz                                 | PWRGD が 0.2V に達したときに測定 | 1.8  |                     | ms                      |

| t <sub>DRIVE_PD#</sub> | 出力が high に駆動されるへのパワー グッド アサート | CKPWRGD_PD# ピンが 0 から 1 に遷移、f <sub>IN</sub> = 100MHz                                 | PWRGD が 0.2V に達したときに測定 | 300  |                     | μs                      |

| t <sub>OE</sub>        | 安定したクロック出力への出力イネーブルのアサート      | OEx# ピンが 1 から 0 に遷移します                                                              |                        | 10   |                     | CLKIN 周期                |

| t <sub>OD</sub>        | 出力イネーブルのデアサートからクロックなし出力へ      | OEx# ピンが 0 から 1 に遷移します                                                              |                        | 10   |                     |                         |

| t <sub>PD</sub>        | 電源オフ アサートからクロックなし出力へ          | CKPWRGD_PD# ピンが 1 から 0 に遷移します                                                       |                        | 3    |                     |                         |

| t <sub>DCD</sub>       | デューティ サイクルの歪み                 | 差動、f <sub>IN</sub> = 100MHz、f <sub>IN_DC</sub> = 50%                                | -1.0                   | 1.0  |                     | %                       |

## 5.5 電気的特性 (続き)

VDD、VDD\_A = 3.3V±5%、-40°C≤TA≤85°C。標準値は、VDD = VDD\_A = 3.3V、25°C のときです (特に記述のない限り)

| パラメータ                 |              | テスト条件                                                                 | 最小値                         | 標準値  | 最大値     | 単位 |

|-----------------------|--------------|-----------------------------------------------------------------------|-----------------------------|------|---------|----|

| t <sub>DLY</sub>      | 伝搬遅延         | (5)                                                                   |                             | 0.5  | 3       | ns |

| t <sub>SKew</sub>     | 出力間のスキー      | (6)                                                                   |                             |      | 50      | ps |

| J <sub>CKx_PCIE</sub> | 付加ジッタ        | DB2000QL フィルタ                                                         |                             | 0.08 | ps, rms |    |

|                       | PCIe7 の追加ジッタ | PCIe7.0 フィルタ                                                          |                             | 11.3 | fs, rms |    |

|                       | PCIe6 の追加ジッタ | PCIe6.0 フィルタ                                                          |                             | 16.1 | fs, rms |    |

|                       | PCIe5 の追加ジッタ | PCIe5.0 フィルタ                                                          |                             | 26.4 | fs, rms |    |

|                       | PCIe4 の追加ジッタ | PLL BW = 2 ~ 5MHz, CDR = 10MHz                                        | 入力クロックスルーレート $\geq 1.8V/ns$ | 0.08 | ps, rms |    |

|                       | PCIe3 の追加ジッタ |                                                                       | 入力クロックスルーレート $\geq 0.6V/ns$ | 0.15 | ps, rms |    |

| J <sub>CKx_PCIE</sub> | PCIe2 の追加ジッタ | PCIe2 フィルタ                                                            |                             | 0.2  | ps, rms |    |

| J <sub>CKx_PCIE</sub> | PCIe1 の追加ジッタ | PCIe1 フィルタ                                                            |                             | 5    | ps, rms |    |

| J <sub>CKx</sub>      | 付加ジッタ        | f <sub>IN</sub> = 100Mhz、スルーレート $\geq (3V/ns)$ 、12kHz ~ 20Mhz の積分帯域幅。 |                             | 155  | fs, rms |    |

### SMBus インターフェイス、サイドバンド インターフェイス、OEx#、CKPWRGD\_PD#、SBEN

|                  |              |                 |                       |     |    |

|------------------|--------------|-----------------|-----------------------|-----|----|

| V <sub>IH</sub>  | High レベル入力電圧 |                 | 2.0                   |     | V  |

| V <sub>IL</sub>  | Low レベル入力電圧  |                 |                       | 0.8 |    |

| I <sub>IL</sub>  | 入力リーク電流      | 内部プルアップ/プルダウン付き | GND < V <sub>IN</sub> | -30 | μA |

|                  |              | 内部プルアップ/プルダウンなし | < V <sub>DD</sub>     | -5  |    |

| C <sub>IN</sub>  | 入力容量         |                 |                       | 4.5 | pF |

| C <sub>OUT</sub> | 出力容量         |                 |                       | 4.5 | pF |

### 3-LEVEL のデジタル インターフェイス (SA\_0, SA\_1)

|                   |              |                                                          |                       |                    |    |

|-------------------|--------------|----------------------------------------------------------|-----------------------|--------------------|----|

| V <sub>IHT</sub>  | High レベル入力電圧 |                                                          | 2.4                   |                    | V  |

| V <sub>IMT</sub>  | Mid レベル入力電圧  |                                                          | 1.3                   | V <sub>DD</sub> /2 |    |

| V <sub>ILT</sub>  | Low レベル入力電圧  |                                                          |                       | 1.8                |    |

| I <sub>INT</sub>  | 入力 high 電流   | V <sub>IN</sub> = V <sub>DD</sub> 、V <sub>IN</sub> = GND | -10                   | 10                 | μA |

| I <sub>Leak</sub> | 入力リーク電流      | 内部プルアップ/プルダウン付き                                          | GND < V <sub>IN</sub> | -30                |    |

|                   |              |                                                          | < V <sub>DD</sub>     | 30                 |    |

- (1) 電圧スイングにオーバーシュートが含まれます。

- (2) 量産時にはテストを行っていません。設計と特性評価により検証されています。

- (3) DC テスト負荷内で測定。

- (4) V<sub>CROSS</sub> は、システム グランドを基準として CKx\_P = CKx\_N の場合のシングルエンド電圧です。CKx\_P が立ち上がりの場合、CKx の立ち上がりエッジでのみ有効です。

- (5) CLK\_IN の立ち上がりエッジから、任意の CKx 出力まで測定。

- (6) 任意の CKx 出力の立ち上がりエッジから、他の CKx 出力との間で測定。

## 5.6 タイミング要件

VDD、VDD\_A = 3.3V±5%、-40°C < TA < 85°C。標準値は、VDD = VDD\_A = 3.3V、25°C のときです (特に記述のない限り)。

|                               |              | 最小値 | 公称値 | 最大値 | 単位  |

|-------------------------------|--------------|-----|-----|-----|-----|

| <b>SMBUS 互換インターフェース タイミング</b> |              |     |     |     |     |

| f <sub>SMB</sub>              | SMBus の動作周波数 |     | 10  | 100 | kHz |

VDD、VDD\_A = 3.3V $\pm$ 5%、-40°C < TA < 85°C。標準値は、VDD = VDD\_A = 3.3V、25°C のときです (特に記述のない限り)。

|               |                                      | 最小値  | 公称値 | 最大値 | 単位      |

|---------------|--------------------------------------|------|-----|-----|---------|

| $t_{BUF}$     | STOP と START 間のバス解放時間                | 4.7  |     |     | $\mu s$ |

| $t_{HD\_STA}$ | START 条件のホールド時間                      | 4    |     |     |         |

| $t_{SU\_STA}$ | START 条件のセットアップ時間                    | 4.7  |     |     |         |

| $t_{SU\_STO}$ | ストップ条件のセットアップ時間                      | 4    |     |     |         |

| $t_{HD\_DAT}$ | SMBDAT のホールド時間                       | 300  |     |     | $ns$    |

| $t_{SU\_DAT}$ | SMBDAT のセットアップ時間                     | 250  |     |     |         |

| $t_{TIMEOUT}$ | SMBCLK low 検出のタイムアウト                 | 25   | 35  | ms  |         |

| $t_{LOW}$     | SMBCLK の Low 期間                      | 4.7  |     |     | $\mu s$ |

| $t_{HIGH}$    | SMBCLK の High 期間                     | 4    | 50  |     |         |

| $t_{LOW\_SL}$ | 累積クロック low の拡張時間                     | 25   | ms  |     |         |

| $t_F$         | SMBCLK/SMBDAT 立ち下がり時間 <sup>(1)</sup> | 300  |     |     | $ns$    |

| $t_R$         | SMBCLK/SMBDAT 立ち上がり時間 <sup>(2)</sup> | 1000 |     |     |         |

#### サイドバンド インターフェイスのタイミング

|              |                 |     |    |        |

|--------------|-----------------|-----|----|--------|

| $t_{PERIOD}$ | クロック周期          | 40  |    | $ns$   |

| $t_{SETUP}$  | クロックまでのセットアップ時間 | 25  |    |        |

| $t_{DSU}$    | データ セットアップ時間    | 10  |    |        |

| $t_{DHOLD}$  | データ ホールド時間      | 5   |    |        |

| $t_{DELAY}$  | 遅延時間            | 25  |    |        |

| $t_{PDLY}$   | 伝搬遅延            | 4   | 10 | CLK 周期 |

| $t_{SLEW}$   | クロックのスルーレート     | 0.2 | 3  | V/ns   |

(1)  $TF = (VIHMIN + 0.15) \sim (VILMAX - 0.15)$

(2)  $TR = (VILMAX - 0.15) \sim (VIHMIN + 0.15)$

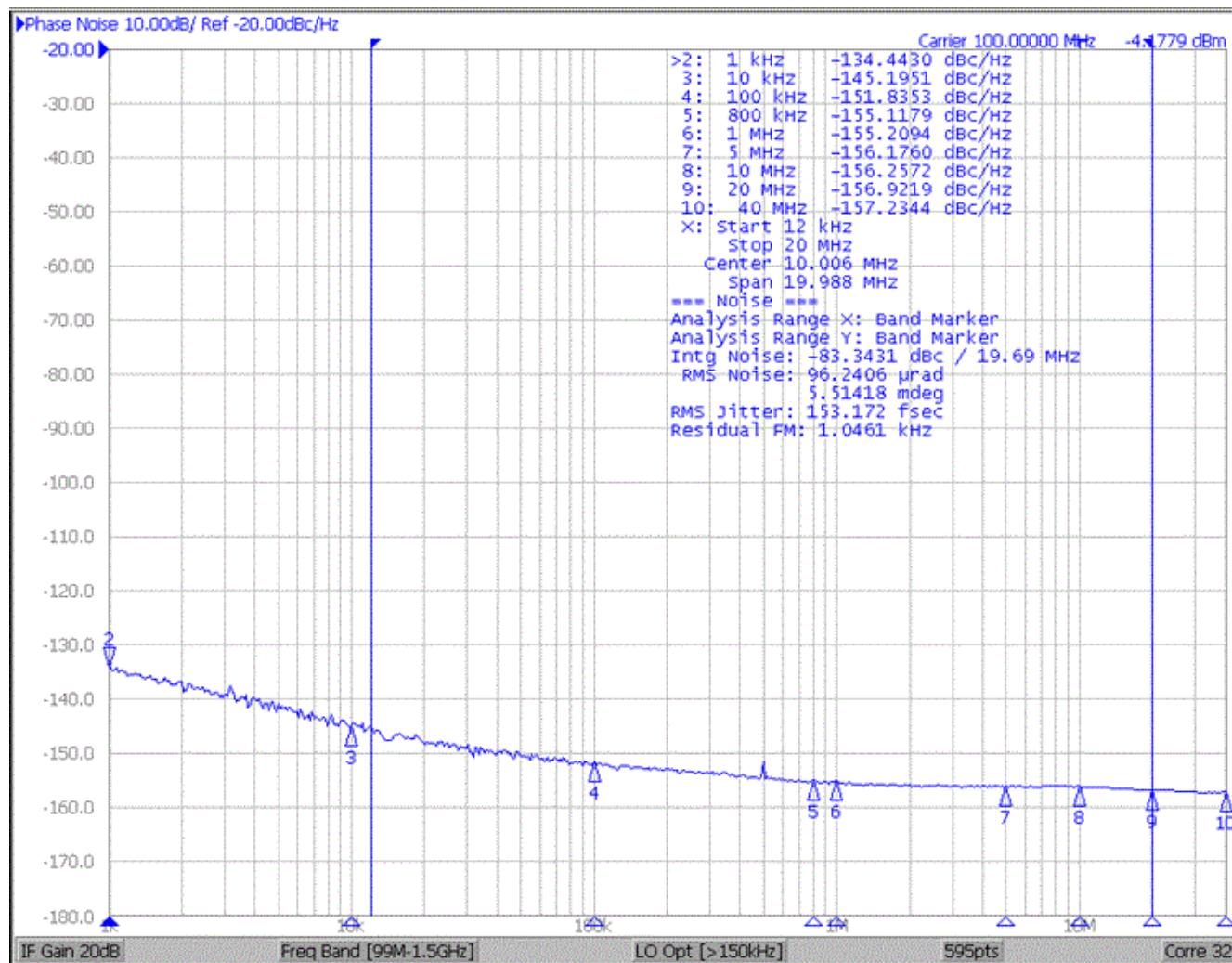

## 5.7 代表的特性

図 5-1. CDCDB2000 クロック出力 (CK0:19) 位相ノイズ

## 6 詳細説明

### 6.1 概要

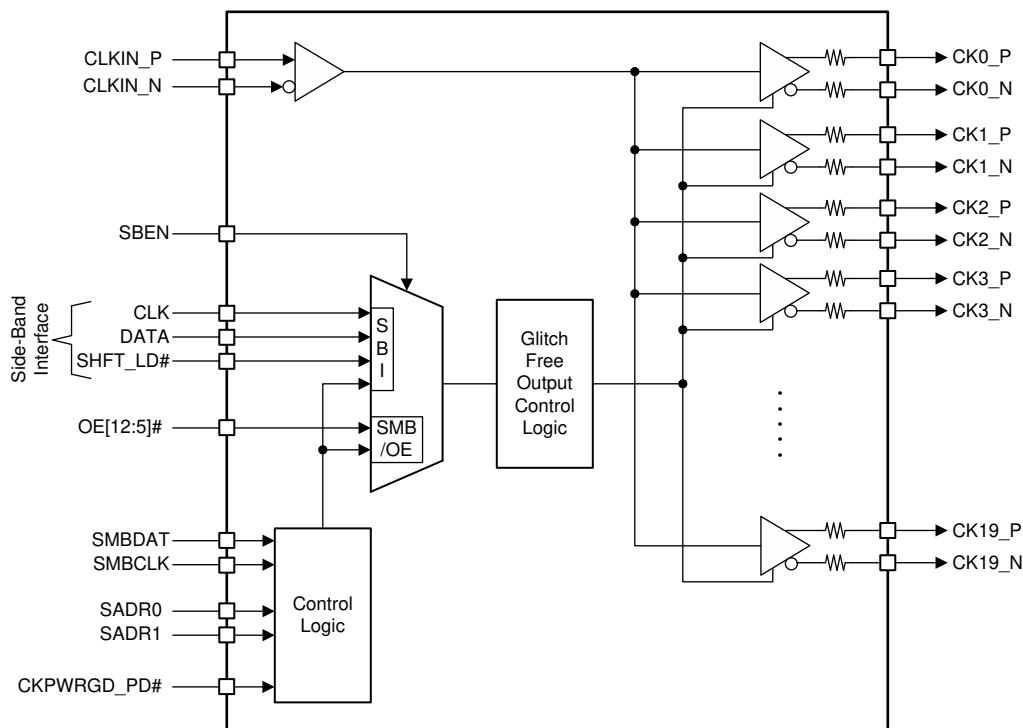

CDCDB2000 は、付加ジッタが小さい伝搬遅延のクロック バッファであり、PCIe Gen 1 ~ 7、QPI、UPI の各基準クロックの厳格な性能要件を満たすように設計されています。CDCDB2000 を使用すると、単一のクロック ソースを LP-HCSL 形式で最大 20 の個別出力のバッファリングと複製が可能です。CDCDB2000 の出力は、サイドバンド制御インターフェイスを使用して出力を有効化する前に設定できます。CDCDB2000 には、SMBus バージョン 2.0 準拠のインターフェイスからアクセスできるステータスおよび制御レジスタも含まれています。このデバイスは、大量の外部受動部品を内蔵しているため、システム全体のコストを削減できます。

### 6.2 機能ブロック図

### 6.3 機能説明

#### 6.3.1 出力イネーブルの制御

CDCDB2000 では、出力チャネルの状態を制御するために次の 2 つの方法を使用できます。SMBUS/OE#、およびサイドバンドインターフェイス。いつでもアクティブにできるのは 2 つの方法のうちの 1 つのみであり、アクティブインターフェイスは SBEN ピンの状態によって選択されます。どちらの出力制御方法も、各出力の状態を個別に割り当てることができます。

SMBUS/OE# 制御を選択すると、OE# ピンがアクティブになります。OE# ピンは、同じ値で出力の状態を制御します。たとえば、OE# ピンは CK5 出力ドライバの状態を制御します。SMBus レジスタは、必要に応じて OE# ピンの状態に関係なく、出力をイネーブルまたはディセーブルにできます。

#### 6.3.2 SMBus

CDCDB2000 には、CKPWRGD\_PD# = 1 のときのみアクティブになる SMBus インターフェイスがあります。SMBus では、SBEN ピンを使用して SMBus モードを選択した場合、各出力を個別にイネーブル/ディセーブルできます。

CKPWRGD\_PD# = 0 の場合、SMBus ピンは Hi-Z 状態になりますが、すべてのレジスタ設定は保持されます。SMBus レジスタ値は、VDD\_A が推奨動作電圧の範囲内に維持されている間のみ保持されます。

### 6.3.2.1 SMBus アドレス割り当て

SMBus アドレスは、それぞれが 3 レベルをサポートする 2 本のピン (SADR1 および SADR0) の構成によって割り当てられます。この構成により、CDCDB2000 は 9 つの異なる SMBus アドレスを想定できます。

SMBus アドレス ピンは、サンプリングされた PWRGD は 1 に設定されている。アドレス ピンの構成については、表 6-1 を参照してください。デバイスの電源をオフにして PWRGD 状態がクリアされるまで、アドレスを変更できません。

**表 6-1. SMBus アドレス割り当て**

| SADR1 | SADR0 | SMBus アドレス |

|-------|-------|------------|

| L     | L     | 0xD8       |

| L     | M     | 0xDA       |

| L     | H     | 0xDE       |

| M     | L     | 0xC2       |

| M     | M     | 0xC4       |

| M     | H     | 0xC6       |

| H     | L     | 0xCA       |

| H     | M     | 0xCC       |

| H     | H     | 0xCE       |

### 6.3.3 サイドバンド インターフェイス

サイドバンド インターフェイス (SBI) は、DATA、CLK、SHFT\_LD# ピンで構成される基本的な 3 線式インターフェイスです。SBI は、データを 20 ビット長のシフト レジスタにシフトするために使用されます。SHFT\_LD# ピンが high のとき、CLK の立ち上がりエッジでデータがシフト レジスタにシフトインされる可能性があります。データのシフト後、SHFT\_LD# の立ち下がりエッジは、シフト レジスタの内容を SBI 出力レジスタにクロックします。

SBEN ピンによって SBI がイネーブルになっている間、OE[7:9, 11, 12]# ピンがディセーブルされて、データ、CLK および SHFT\_LD# が OE5# ピン、OE6# ピン、OE10# ピンでそれぞれイネーブルになります。

電源が印加され、SBEN = 1 のとき、CKPWRGD\_PD# ピンの状態に関係なく SBI はアクティブになります。この特性により、CKPWRGD\_PD# ピンが最初にアサートされる前に、シフト レジスタのロードと内容の SBI 出力レジスタへの転送が可能になります。

## 6.4 デバイスの機能モード

### 6.4.1 CKPWRGD\_PD# 機能

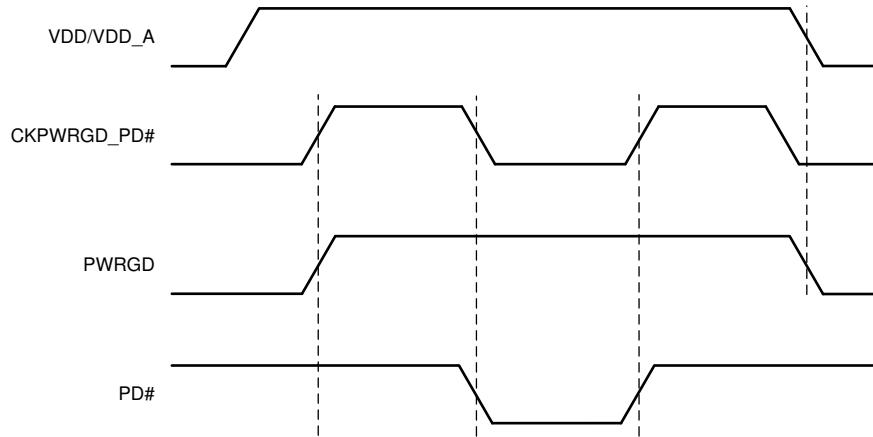

CKPWRGD\_PD# ピンは、デバイス内で次の 2 つの状態変数を設定するために使用されます。PWRGD、PD #。PWRGD および PD# 変数は、デバイスのどの機能がいつでもアクティブになるか、および入力および出力ピンの状態を制御します。

PWRGD および PD# 状態は、CKPWRGD\_PD# ピンで多重化されます。CKPWRGD\_PD# は、VDD、VDD\_A、CLKIN が存在し推奨動作条件内になるまで、VOL を下回り、VDD\_A + 0.3V を超えないようにする必要があります。

CKPWRGD\_PD# ピンの最初の立ち上がりエッジで PWRGD = 1 が設定されます。PWRGD が 1 に設定された後、CKPWRGD\_PD# ピンを使用して、PD# モードのみをアサートします。PWRGD 変数は、VDD と VDD\_A を削除すると、0 にのみクリアされます。

図 6-1. PWRGD と PD# の状態が変更されます

#### 6.4.2 OE[12:5]# および SMBus 出力イネーブル

各出力チャネル 0 ~ 19 は、SMB イネーブル ビットと呼ばれる SMBus 制御レジスタ ビットによって個別にイネーブルまたはディセーブルできます。さらに、12 ~ 5 の各出力チャネルには、専用の対応する OE[12:5]# ハードウェアピンがあります。OE[12:5]# ピンは非同期的にアサートされた low 信号で、出力をイネーブルまたはディセーブルできます。

ハードウェアとソフトウェアを介した出力のイネーブルとディセーブルについては、表 6-2 を参照してください。出力チャネルをアクティブにするには、SMB イネーブルビットを両方とも 1 にし、OEx# ピンを入力 low 電圧「0」にする必要があることに注意してください。

表 6-2 が有効なのは、SBEN 信号が low (SBEN = 0) のときのみです。

表 6-2. SBEN = 0 のとき OE[12:5]# 機能

| 入力    |     |       | OE[12:5]# ハードウェア ピンと SMBus 制御レジスタ ビット |           |          |                |

|-------|-----|-------|---------------------------------------|-----------|----------|----------------|

| PWRGD | PD# | CLKIN | SMBus ENABLE ビット (バイト[2:0])           | OE[12:5]# | CK[12:5] | CK[19:13, 4:0] |

| 0     | X   | X     | X                                     | X         | Low      | Low            |

| 1     | 0   | X     | X                                     | X         | トライステート  | トライステート        |

| 1     | 1   | ランニング | 0                                     | X         | 0        | 0              |

| 1     | 1   | ランニング | 1                                     | 0         | ランニング    | ランニング          |

| 1     | 1   | ランニング | 1                                     | 1         | 0        | ランニング          |

## 6.5 プログラミング

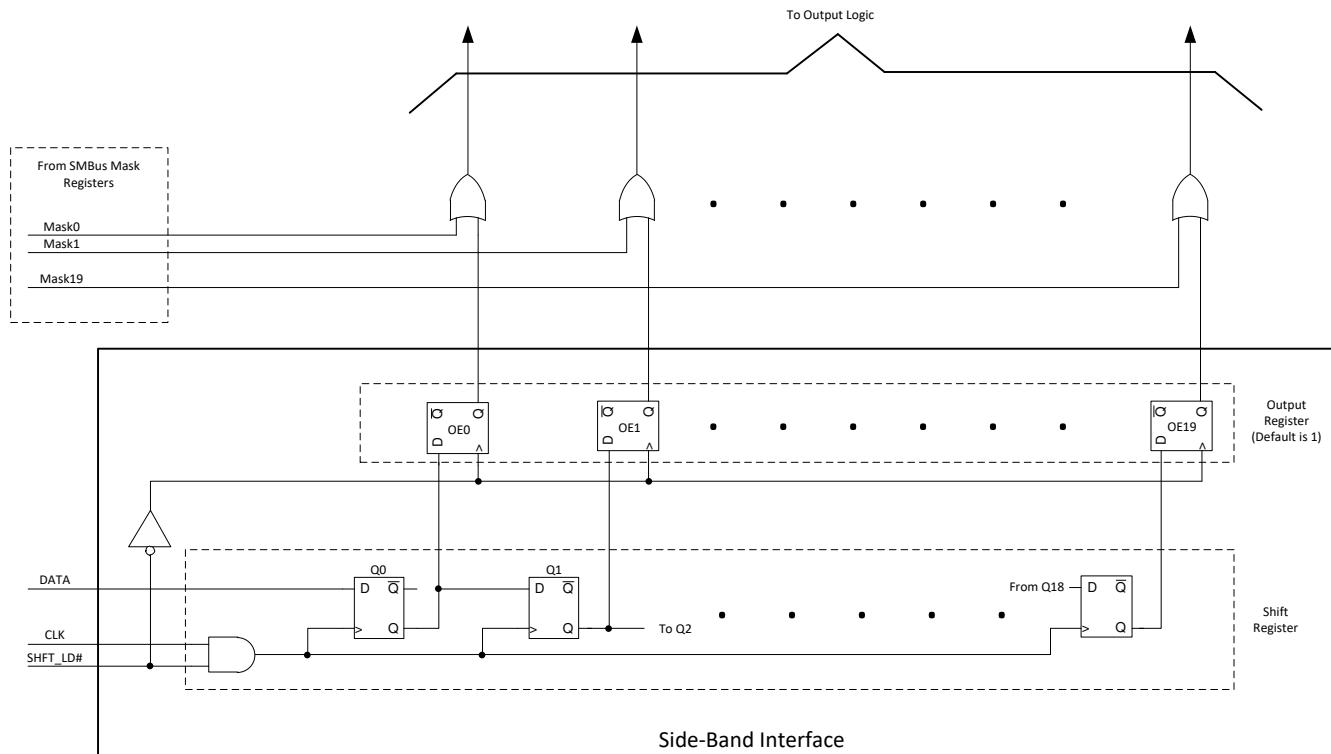

CDCDB2000 には、20 の出力ドライバの状態をプログラムする方法が 2 つあります。SMBus と SBI です。

SMBus インターフェイスと SBI インターフェイスを選択するには、SBEN ピンを使用します。SBEN を high レベルにプルすると、SBI がイネーブルになります。SBEN ピンをグランドにプルすると、SMBus インターフェイスがイネーブルされます。SBI をイネーブルにすると、SMBus マスク レジスタがアクティブになります。SMBus マスク レジスタにより、SBI シフト レジスタの機能をディセーブルにし、各チャネルをイネーブルに設定できます。各出力をイネーブル/ディセーブルするために、SMBus マスク レジスタと SBI シフト レジスタがどのように機能しているかの図については、図 6-2 を参照してください。

図 6-2. SMBus マスク レジスタと SBI シフト レジスタ ロジック

### 6.5.1 SMBus

SMBus プログラミングについてはを参照セクション 6.3.2 し、レジスタについてはを参照してくださいセクション 7。

### 6.5.2 SBI

サイドバンド インターフェイス (SBI) は、シンプルな 3 線式シリアル インターフェイスです。このインターフェイスは DATA ピン、CLK ピン、SHFT\_LD# ピンで構成されます。SHFT\_LD# ピンが high のとき、CLK クロック データの立ち上がりエッジからシフトレジスタへのデータです。データをシフトした後、SHFT\_LD# の立ち下がりエッジにより、シフトレジスタの内容が出力レジスタにロードされます。SBI と従来型の SMBus インターフェイスは両方とも、共通の出力イネーブル/ディスエーブル同期ロジックを供給し、使用する方法に関係なくグリッチのないイネーブル/ディスエーブル出力を提供します。

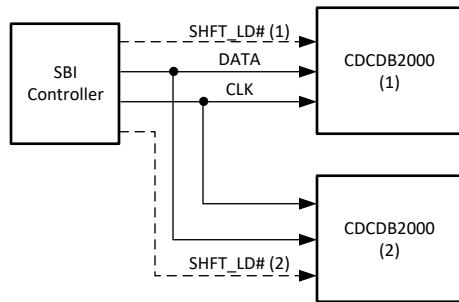

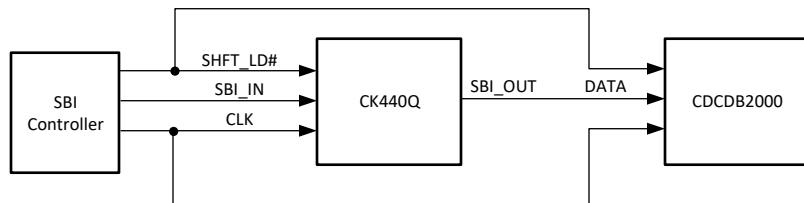

SBI は、スタート ポロジ、デイジー チェーン ポロジ、および直接の 3 つの方法でシステム レベルで構成できます。このデバイスのスタート ポロジを [図 6-3](#) に示します。デイジー チェーン ポロジを、[図 6-4](#) に示します。

図 6-3. SBI スタート ポロジ

図 6-4. SBI デイジー チェーン ポロジ

## 7 レジスタマップ

### 7.1 CDCDB2000 のレジスタ

表 7-1 に、CDCDB2000 レジスタの一覧を示します。表 7-1 にないレジスタ位置はすべて予約済みと見なす必要があります。レジスタ内容は変更しないでください。

**表 7-1. CDCDB2000 のレジスタ**

| アドレス | 略称               | レジスタ名                       | セクション |

|------|------------------|-----------------------------|-------|

| 0h   | OECR1            | 出力イネーブルの制御 1                | 表示    |

| 1h   | OECR2            | 出力イネーブルの制御 2                | 表示    |

| 2h   | OECR3            | 出力イネーブルの制御 3                | 表示    |

| 3h   | OERDBK           | 出力が有効:読み取り専用                | 表示    |

| 4h   | SBRDBK を参照してください | SBEN リード バック                | 表示    |

| 5h   | VDRREVID         | ベンダーリビジョンの識別                | 表示    |

| 6h   | DEVID            | デバイス識別情報                    | 表示    |

| 7h   | BTRDCNT          | バイト読み取りカウント制御               | 表示    |

| 8h   | SBIMSK1          | サイドバンド インターフェース オーバーライド制御 1 | 表示    |

| 9h   | SBIMSK2          | サイドバンド インターフェース オーバーライド制御 2 | 表示    |

| Ah   | SBIMSK3          | サイドバンド インターフェース オーバーライド制御 3 | 表示    |

表の小さなセルに収まるように、複雑なビット アクセス タイプを記号で表記しています。表 7-2 に、このセクションでアクセス タイプに使用しているコードを示します。

**表 7-2. CDCDB2000 のアクセス タイプ コード**

| アクセス タイプ      | コード | 説明               |

|---------------|-----|------------------|

| 読み取りタイプ       |     |                  |

| R             | R   | 読み出し             |

| 書き込みタイプ       |     |                  |

| W             | W   | 書き込み             |

| リセットまたはデフォルト値 |     |                  |

| -n            |     | リセット後の値またはデフォルト値 |

#### 7.1.1 OECR1 レジスタ (アドレス = 0h) [リセット = 78h]

OECR1 を表 7-3 に示します。

概略表に戻ります。

OECR1 レジスタには、個別の出力クロック チャネル [19:16] をイネーブルまたはディセーブルにするビットが含まれています

**表 7-3. OECR1 レジスタのフィールドの説明**

| ビット | フィールド        | タイプ | リセット | 説明                                                                             |

|-----|--------------|-----|------|--------------------------------------------------------------------------------|

| 7   | 予約済み         | R   | 0h   | 予約済み                                                                           |

| 6   | 出力イネーブル、CK19 | R/W | 1h   | このビットは、出力チャネル CK19_P/CK19_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル |

**表 7-3. OECR1 レジスタのフィールドの説明 (続き)**

| ビット | フィールド        | タイプ | リセット | 説明                                                                             |

|-----|--------------|-----|------|--------------------------------------------------------------------------------|

| 5   | 出力イネーブル、CK18 | R/W | 1h   | このビットは、出力チャネル CK18_P/CK18_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル |

| 4   | 出力イネーブル、CK17 | R/W | 1h   | このビットは、出力チャネル CK17_P/CK17_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル |

| 3   | 出力イネーブル、CK16 | R/W | 1h   | このビットは、出力チャネル CK16_P/CK16_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル |

| 2-0 | 予約済み         | R   | 0h   | 予約済み                                                                           |

### 7.1.2 OECR2 レジスタ (アドレス = 1h) [リセット = FFh]

OECR2 を表 7-4 に示します。

概略表に戻ります。

OECR2 レジスタには、各出力クロック チャネル [7:0] をイネーブルまたはディセーブルにするビットが含まれています。

**表 7-4. OECR2 レジスタのフィールドの説明**

| ビット | フィールド       | タイプ | リセット | 説明                                                                           |

|-----|-------------|-----|------|------------------------------------------------------------------------------|

| 7   | 出力イネーブル、CK7 | R/W | 1h   | このビットは、出力チャネル CK7_P/CK7_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル |

| 6   | 出力イネーブル、CK6 | R/W | 1h   | このビットは、出力チャネル CK6_P/CK6_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル |

| 5   | 出力イネーブル、CK5 | R/W | 1h   | このビットは、出力チャネル CK5_P/CK5_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル |

| 4   | 出力イネーブル、CK4 | R/W | 1h   | このビットは、出力チャネル CK4_P/CK4_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル |

| 3   | 出力イネーブル、CK3 | R/W | 1h   | このビットは、出力チャネル CK3_P/CK3_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル |

| 2   | 出力イネーブル、CK2 | R/W | 1h   | このビットは、出力チャネル CK2_P/CK2_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル |

**表 7-4. OECR2 レジスタのフィールドの説明 (続き)**

| ピット | フィールド       | タイプ | リセット | 説明                                                                           |

|-----|-------------|-----|------|------------------------------------------------------------------------------|

| 1   | 出力イネーブル、CK1 | R/W | 1h   | このビットは、出力チャネル CK1_P/CK1_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル |

| 0   | 出力イネーブル、CK0 | R/W | 1h   | このビットは、出力チャネル CK0_P/CK0_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル |

### 7.1.3 OECR3 レジスタ (アドレス = 2h) [リセット = FFh]

OECR3 を表 7-5 に示します。

概略表に戻ります。

OECR3 レジスタには、各出力クロック チャネル [15:8] をイネーブルまたはディセーブルにするビットが含まれています。

**表 7-5. OECR3 レジスタのフィールドの説明**

| ピット | フィールド        | タイプ | リセット | 説明                                                                             |

|-----|--------------|-----|------|--------------------------------------------------------------------------------|

| 7   | 出力イネーブル、CK15 | R/W | 1h   | このビットは、出力チャネル CK15_P/CK15_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル |

| 6   | 出力イネーブル、CK14 | R/W | 1h   | このビットは、出力チャネル CK14_P/CK14_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル |

| 5   | 出力イネーブル、CK13 | R/W | 1h   | このビットは、出力チャネル CK13_P/CK13_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル |

| 4   | 出力イネーブル、CK12 | R/W | 1h   | このビットは、出力チャネル CK12_P/CK12_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル |

| 3   | 出力イネーブル、CK11 | R/W | 1h   | このビットは、出力チャネル CK11_P/CK11_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル |

| 2   | 出力イネーブル、CK10 | R/W | 1h   | このビットは、出力チャネル CK10_P/CK10_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル |

| 1   | 出力イネーブル、CK9  | R/W | 1h   | このビットは、出力チャネル CK9_P/CK9_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル   |

**表 7-5. OECR3 レジスタのフィールドの説明 (続き)**

| ビット | フィールド       | タイプ | リセット | 説明                                                                           |

|-----|-------------|-----|------|------------------------------------------------------------------------------|

| 0   | 出力イネーブル、CK8 | R/W | 1h   | このビットは、出力チャネル CK8_P/CK8_N の出力イネーブル信号を制御します。<br>0h = 出力ディセーブル<br>1h = 出力イネーブル |

**7.1.4 OERDBK レジスタ (アドレス = 3h) [リセット = 0h]**

OERDBK を表 7-6 に示します。

概略表に戻ります。

OERDBK レジスタには、OE[12:5]# 入力ピンの現在の状態を通知するビットが含まれています。

**表 7-6. OERDBK レジスタ フィールドの説明**

| ビット | フィールド    | タイプ | リセット | 説明                                  |

|-----|----------|-----|------|-------------------------------------|

| 7   | OE12# 状態 | R   | 0h   | このビットは、OE12# ピンに存在するロジック レベルを報告します。 |

| 6   | OE11# 状態 | R   | 0h   | このビットは、OE11# ピンに存在するロジック レベルを報告します。 |

| 5   | OE10# 状態 | R   | 0h   | このビットは、OE10# ピンに存在するロジック レベルを報告します。 |

| 4   | OE9# 状態  | R   | 0h   | このビットは、OE9# ピンに存在するロジック レベルを報告します。  |

| 3   | OE8# 状態  | R   | 0h   | このビットは、OE8# ピンに存在するロジック レベルを報告します。  |

| 2   | OE7# 状態  | R   | 0h   | このビットは、OE7# ピンに存在するロジック レベルを報告します。  |

| 1   | OE6# 状態  | R   | 0h   | このビットは、OE6# ピンに存在するロジック レベルを報告します。  |

| 0   | OE5# 状態  | R   | 0h   | このビットは、OE5# ピンに存在するロジック レベルを報告します。  |

**7.1.5 SBRDBK レジスタ (アドレス = 4h) [リセット = 1h]**

SBRDBK を表 7-7 に示します。

概略表に戻ります。

SBRDBK レジスタには、SBEN 入力ピンの現在の状態を通知するビットが含まれています。

**表 7-7. SBRDBK レジスタ フィールドの説明**

| ビット | フィールド   | タイプ | リセット | 説明                                 |

|-----|---------|-----|------|------------------------------------|

| 7-1 | 予約済み    | R   | 0h   | 予約済み                               |

| 0   | SBEN 状態 | R/W | 1h   | このビットは、SBEN ピンに存在するロジック レベルを報告します。 |

**7.1.6 VDRREVID レジスタ (アドレス = 5h) [リセット = X]**

表 7-8 に、VDRREVID を示します。

概略表に戻ります。

VDRREVID レジスタには、ベンダ識別コードシリコン リビジョン コードが含まれています。

**表 7-8. VDRREVID レジスタ フィールドの説明**

| ビット | フィールド           | タイプ | リセット | 説明                                                                        |

|-----|-----------------|-----|------|---------------------------------------------------------------------------|

| 7-4 | リビジョン コード [3:0] | R   | X    | シリコンのリビジョン コード。<br>シリコン リビジョン コード ビット [3:0] はレジスタ ビット [7:4] に直接マップされています。 |

**表 7-8. VDRREVID レジスタ フィールドの説明 (続き)**

| ピット | フィールド       | タイプ | リセット | 説明                                                           |

|-----|-------------|-----|------|--------------------------------------------------------------|

| 3-0 | ベンダ ID[3:0] | R   | X    | ベンダー識別コード。<br>ベンダ ID ピット [3:0] はレジスタ ピット [3:0] に直接マップされています。 |

### 7.1.7 DEVID レジスタ (アドレス = 6h) [リセット = X]

DEVID を表 7-9 に示します。

概略表に戻ります。

DEVID レジスタには、デバイス識別コードが含まれています。

**表 7-9. DEVID レジスタ フィールドの説明**

| ピット | フィールド        | タイプ | リセット | 説明                                                              |

|-----|--------------|-----|------|-----------------------------------------------------------------|

| 7-0 | デバイス ID[7:0] | R   | X    | デバイス ID コード。<br>デバイス ID ピット [7:0] はレジスタ ピット [7:0] に直接マップされています。 |

### 7.1.8 BTRDCNT レジスタ (アドレス = 7h) [リセット = 8h]

表 7-10 に、BTRDCNT を示します。

概略表に戻ります。

BTRDCNT レジスタを使用すると、発行された読み出しコマンド時に SMBus インターフェイスから読み戻すバイト数を構成できます。

**表 7-10. BTRDCNT レジスタ フィールドの説明**

| ピット | フィールド          | タイプ | リセット | 説明                           |

|-----|----------------|-----|------|------------------------------|

| 7-6 | 予約済み           | R   | 0h   | 予約済み                         |

| 5-0 | 読み出しバイト数 [5:0] | R/W | 8h   | このレジスタに書き込むと、読み戻すバイト数を設定します。 |

### 7.1.9 SBIMSK1 レジスタ (アドレス = 8h) [リセット = 0h]

SBIMSK1 を表 7-11 に示します。

概略表に戻ります。

SBIMSK1 レジスタを使用すると、CDCDB2000 がサイドバンド インターフェイス モードのときに、SMBus は各出力チャネルを個別に強制的にイネーブルにできます。

**表 7-11. SBIMSK1 レジスタのフィールドの説明**

| ピット | フィールド         | タイプ | リセット | 説明                                                                           |

|-----|---------------|-----|------|------------------------------------------------------------------------------|

| 7   | SBI 出力マスク、CK7 | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK7 が有効。 |

| 6   | SBI 出力マスク、CK6 | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK6 が有効。 |

**表 7-11. SBIMSK1 レジスタのフィールドの説明 (続き)**

| ビット | フィールド         | タイプ | リセット | 説明                                                                           |

|-----|---------------|-----|------|------------------------------------------------------------------------------|

| 5   | SBI 出力マスク、CK5 | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK5 が有効。 |

| 4   | SBI 出力マスク、CK4 | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK4 が有効。 |

| 3   | SBI 出力マスク、CK3 | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK3 が有効。 |

| 2   | SBI 出力マスク、CK2 | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK2 が有効。 |

| 1   | SBI 出力マスク、CK1 | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK1 が有効。 |

| 0   | SBI 出力マスク、CK0 | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK0 が有効。 |

### 7.1.10 SBIMSK2 レジスタ (アドレス = 9h) [リセット = 0h]

SBIMSK2 を表 7-12 に示します。

概略表に戻ります。

SBIMSK2 レジスタを使用すると、CDCDB2000 がサイドバンド インターフェイス モードのときに、SMBus は各出力チャネルを個別に強制的にイネーブルにできます。

**表 7-12. SBIMSK2 レジスタのフィールドの説明**

| ビット | フィールド          | タイプ | リセット | 説明                                                                            |

|-----|----------------|-----|------|-------------------------------------------------------------------------------|

| 7   | SBI 出力マスク、CK15 | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK15 が有効。 |

| 6   | SBI 出力マスク、CK14 | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK14 が有効。 |

| 5   | SBI 出力マスク、CK13 | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK13 が有効。 |

**表 7-12. SBIMSK2 レジスタのフィールドの説明 (続き)**

| ピット | フィールド          | タイプ | リセット | 説明                                                                            |

|-----|----------------|-----|------|-------------------------------------------------------------------------------|

| 4   | SBI 出力マスク、CK12 | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK12 が有効。 |

| 3   | SBI 出力マスク、CK11 | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK11 が有効。 |

| 2   | SBI 出力マスク、CK10 | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK10 が有効。 |

| 1   | SBI 出力マスク、CK9  | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK9 が有効。  |

| 0   | SBI 出力マスク、CK8  | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK8 が有効。  |

### 7.1.11 SBIMSK3 レジスタ (アドレス = Ah) [リセット = 0h]

SBIMSK3 を表 7-13 に示します。

概略表に戻ります。

SBIMSK3 レジスタを使用すると、CDCDB2000 がサイドバンド インターフェイス モードのときに、SMBus は各出力チャネルを個別に強制的にイネーブルにできます。

**表 7-13. SBIMSK3 レジスタのフィールドの説明**

| ピット | フィールド          | タイプ | リセット | 説明                                                                            |

|-----|----------------|-----|------|-------------------------------------------------------------------------------|

| 7-4 | 予約済み           | R   | 0h   | 予約済み                                                                          |

| 3   | SBI 出力マスク、CK19 | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK19 が有効。 |

| 2   | SBI 出力マスク、CK18 | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK18 が有効。 |

| 1   | SBI 出力マスク、CK17 | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK17 が有効。 |

| 0   | SBI 出力マスク、CK16 | R/W | 0h   | このビットは、設定されている場合、SBI 出力の無効化よりも優先されます。<br>0h = SBI は出力を制御<br>1h = 出力 CK16 が有効。 |

## 8 アプリケーションと実装

### 注

以下のアプリケーション情報は、TI の製品仕様に含まれるものではなく、TI ではその正確性または完全性を保証いたしません。個々の目的に対する製品の適合性については、お客様の責任で判断していただくことになります。お客様は自身の設計実装を検証しテストすることで、システムの機能を確認する必要があります。

### 8.1 アプリケーション情報

CDCDB2000 は、PCIe 第 6 世代および PCIe 第 7 世代 REFCLK 分配をサポートするファンアウト バッファです。これは、通常 100MHzclock の最大 20 個のコピーを作成および配布するために使用されます。

### 8.2 代表的なアプリケーション

図 8-1 に CDCDB2000 の代表的なアプリケーションを示します。このアプリケーションでは、クロック ジェネレータは CDCDB2000 に 100MHz のリファレンスを提供し、そのクロックを PCIe エンドポイントに分配します。クロック ジェネレータとして、LMK03328 などのディスクリート クロック ジェネレータを使用することも、クロック ジェネレータを PCH またはアプリケーション プロセッサなどのより大きなコンポーネントに統合することもできます。

図 8-1. 代表的なアプリケーション

#### 8.2.1 設計要件

プロセッサ チップセットの PCH から複数のエンドポイントに 100MHzPCIe リファレンス クロックを分配する必要がある、代表的なサーバー マザーボード アプリケーションを考えてみましょう。クロックの入力および出力要件の例を次に示します。

- クロック入力:

- 100MHzLP-HCSL

- クロック出力:

- 2 個の 100MHzto プロセッサ、LP-HCSL

- 2 個の 100MHz ライザーリタイマ、LP-HCSL

- 2 個の 100MHzto DDR メモリ コントローラ、LP-HCSL

以下のセクションでは、上記のシナリオの周波数を出力するように CDCDB2000 を構成するための設計手順について説明します。

## 8.2.2 詳細な設計手順

CDCDB2000 ソケットの設計を開始する前に、次の項目を決定する必要があります。

- 出力イネーブルの制御方法

### 8.2.2.1 出力イネーブルの制御方法

このデバイスには、SMBus にプログラムされたレジスタ（ソフトウェア）を使用して出力を制御するか、またはハードウェア OE# ピンを使用して出力を制御するオプションがあります。ソフトウェアを使用して出力を制御する場合、ハードウェア OE# ピンはフローティングのままにしておくことができます。これらの各ピンにはグランドへのプルダウンがあるためです。レジスタのプログラムの詳細情報については、「[セクション 7](#)」セクションを参照してください。

ハードウェア OE# ピンを使用して出力を制御する場合、たとえば、これらのピンを GPIO コントローラに接続し、[セクション 4](#) セクションに従って出力を HIGH/LOW に設定することができます。出力の制御に使用される OUT\_EN\_CLK7 ~ OUT\_EN\_CLK0 ビットを、レジスタ OECR1 のフィールドの説明に示します。これらのレジスタ ビットはデフォルトで 1 に設定されており、出力が「ソフトウェア イネーブル」であり、したがって状態がハードウェア OE# ピンによって設定されていることを検証します。

### 8.2.2.2 SMBus アドレス

SMBus アドレスは、[表 8-1](#) に示された電位アドレスから選択する必要があります。表に示すように、適切なプルアップ抵抗またはプルダウン抵抗を SADR<sub>x</sub> ピンに配置する必要があります。競合を回避するため、SMBus アドレスがまだ使用されていないことを確認します。

**表 8-1. SMBus アドレス割り当て**

| SADR1 | SADR0 | SMBus アドレス |

|-------|-------|------------|

| L     | L     | 0xD8       |

| L     | M     | 0xDA       |

| L     | H     | 0xDE       |

| M     | L     | 0xC2       |

| M     | M     | 0xC4       |

| M     | H     | 0xC6       |

| H     | L     | 0xCA       |

| H     | M     | 0xCC       |

| H     | H     | 0xCE       |

### 8.2.3 アプリケーション曲線

[表 8-2](#) に示すグラフは、アプリケーション曲線と代表的特性の両方のプロットとして使用されます（[セクション 5.7](#) セクションを参照）。

**表 8-2. グラフ一覧**

| タイトル                            | 図     |

|---------------------------------|-------|

| CDCDB2000 クロック出力 (CK0:19) 位相ノイズ | 図 5-1 |

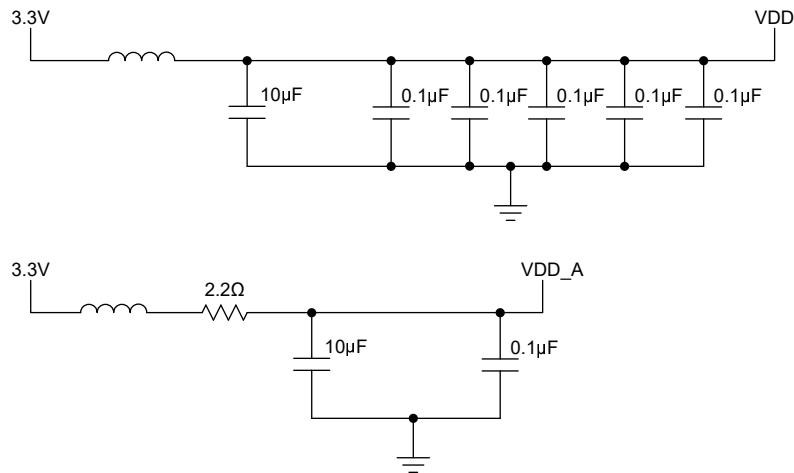

## 8.3 電源に関する推奨事項

高性能クロック バッファは、電源のノイズに敏感であり、バッファの付加ジッタが大幅に増加する可能性があります。そのため、特にアプリケーションでジッタと位相ノイズが重要な場合は、システム電源からのノイズを低減することが不可欠です。

フィルタコンデンサを使用して、電源からの低周波数ノイズを除去すると、バイパスコンデンサが高周波ノイズに対する非常に低いインピーダンス パスとして機能し、電源システムを誘導性の変動から保護できます。このバイパスコンデンサは、デバイスの必要に応じて瞬間的な電流サージを発生させます。またバイパスコンデンサの等価直列抵抗 (ESR) を小さくする必要があります。バイパスコンデンサを適切に使用するには、電源端子の近くに配置し、短いループでレイアウトしてインダクタンスを最小限に抑えます。基板電源とチップ電源の間にフェライトビーズを挿入し、クロック バッファによって生

成される高周波スイッチングノイズを絶縁することを推奨します。これらのビーズは、スイッチングノイズが基板の電源に漏れるのを防止します。基板電源とチップ電源を適切に絶縁し、適切な動作に必要な最小電圧を上回る電源端子の電圧を維持するため、DC抵抗が非常に小さく適切なフェライトビーズを選定します。

図 8-2 に、この推奨される電源フィルタリングおよびデカップリング方法を示します。

図 8-2. 電源のデカップリング

## 8.4 レイアウト

### 8.4.1 レイアウトのガイドライン

以下のセクションでは、CDCDB2000 の良好な熱性能と電源接続を実現するためのレイアウトのガイドラインを示します。

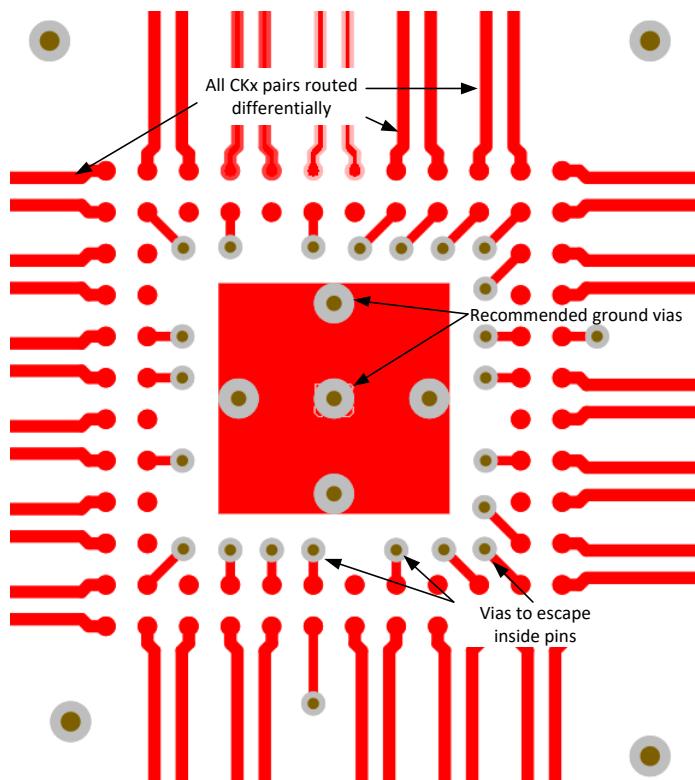

### 8.4.2 レイアウト例

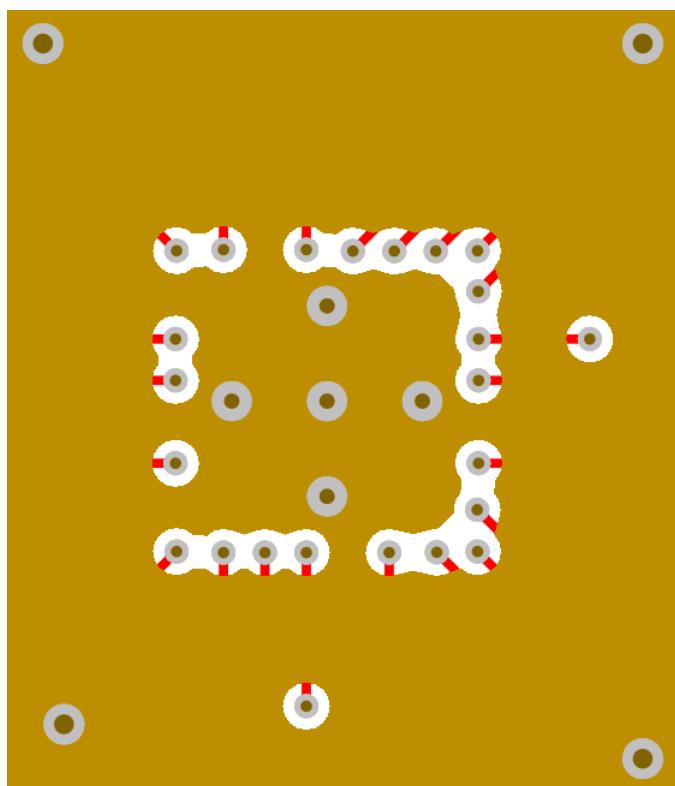

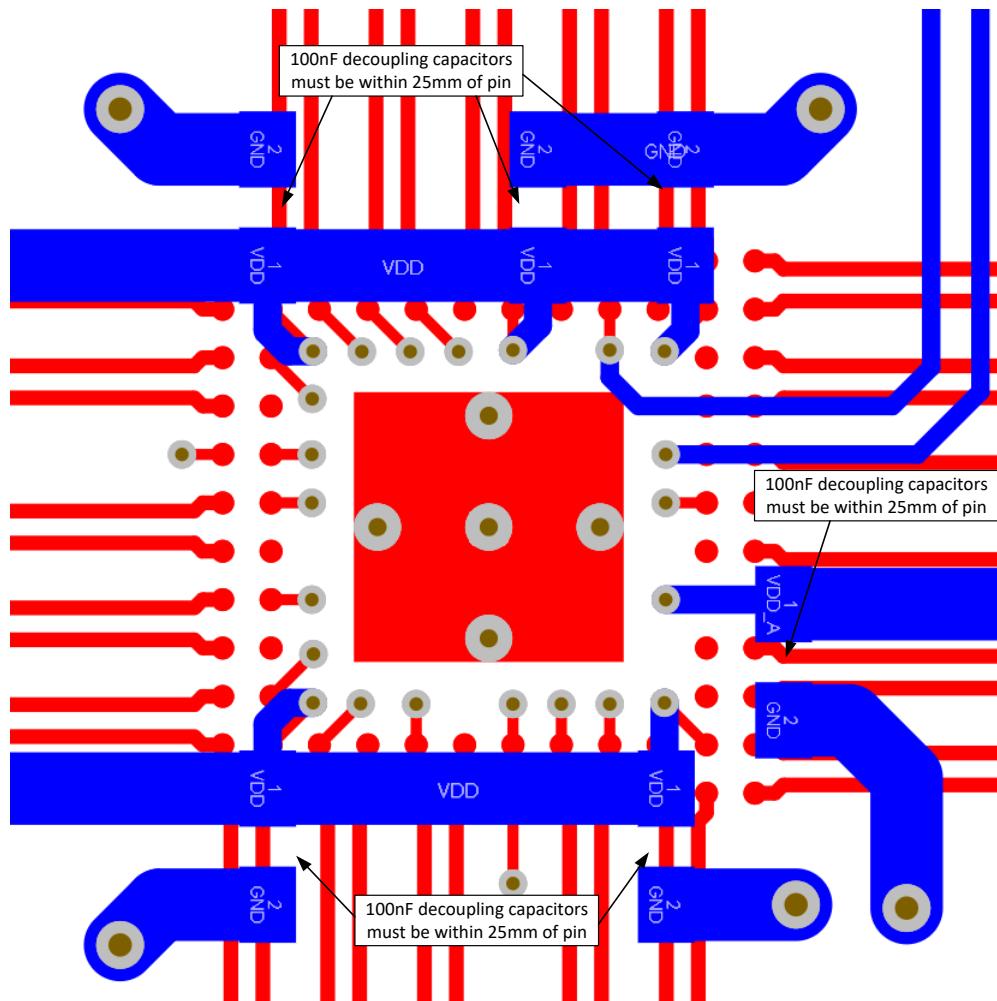

図 8-3 および図 8-4 は、熱設計手法のアプリケーションと、デバイスの DAP と PCB 間の低インダクタンスのグランド接続を示すプリント基板 (PCB) レイアウトの例です。

CDCDB2000 には、 $85\Omega$  の差動出力インピーダンス LP-HCSL フォーマットドライバが搭載されています。CKx ピンに接続されるすべての伝送ラインは、反射を防止し、放射エミッションの増加を防止するために、 $85\Omega$  の差動インピーダンス、 $42.5\Omega$  のシングルエンドインピーダンスとする必要があります。伝送ライン上のスタブを除去または削減するように注意してください。

図 8-3. CDCDB2000 の PCB レイアウト例、最上層

図 8-4. CDCDB2000 の PCB レイアウト例、GND 層

図 8-5. CDCDB2000 の PCB レイアウト例、最下層

## 9 デバイスおよびドキュメントのサポート

### 9.1 デバイス サポート

#### 9.1.1 TICS Pro

TICS Pro は、EVM プログラミングおよびレジスタ マップ生成用オフライン ソフトウェア ツールであり、個々の用途に合わせてデバイス構成をプログラミングできます。TICS Pro の場合、<http://www.ti.com/tool/TICSPRO-SW> にアクセスしてください。

### 9.2 ドキュメントのサポート

#### 9.2.1 関連資料

- テキサス インstrumentツ、[CDCDB2000 ユーザーガイド](#)

### 9.3 ドキュメントの更新通知を受け取る方法

ドキュメントの更新についての通知を受け取るには、[www.tij.co.jp](http://www.tij.co.jp) のデバイス製品フォルダを開いてください。[通知] をクリックして登録すると、変更されたすべての製品情報に関するダイジェストを毎週受け取ることができます。変更の詳細については、改訂されたドキュメントに含まれている改訂履歴をご覧ください。

### 9.4 サポート・リソース

テキサス・インstrumentツ E2E™ サポート・フォーラムは、エンジニアが検証済みの回答と設計に関するヒントをエキスパートから迅速かつ直接得ることができる場所です。既存の回答を検索したり、独自の質問をしたりすることで、設計で必要な支援を迅速に得ることができます。

リンクされているコンテンツは、各寄稿者により「現状のまま」提供されるものです。これらはテキサス・インstrumentツの仕様を構成するものではなく、必ずしもテキサス・インstrumentツの見解を反映したものではありません。テキサス・インstrumentツの[使用条件](#)を参照してください。

### 9.5 商標

テキサス・インstrumentツ E2E™ is a trademark of Texas Instruments.

すべての商標は、それぞれの所有者に帰属します。

### 9.6 静電気放電に関する注意事項

この IC は、ESD によって破損する可能性があります。テキサス・インstrumentツは、IC を取り扱う際には常に適切な注意を払うことを推奨します。正しい取り扱いおよび設置手順に従わない場合、デバイスを破損するおそれがあります。

ESD による破損は、わずかな性能低下からデバイスの完全な故障まで多岐にわたります。精密な IC の場合、パラメータがわずかに変化するだけで公表されている仕様から外れる可能性があるため、破損が発生しやすくなっています。

### 9.7 用語集

#### テキサス・インstrumentツ用語集

この用語集には、用語や略語の一覧および定義が記載されています。

## 10 改訂履歴

資料番号末尾の英字は改訂を表しています。その改訂履歴は英語版に準じています。

| <b>Changes from Revision B (October 2024) to Revision C (August 2025)</b> | <b>Page</b> |

|---------------------------------------------------------------------------|-------------|

| • 「特長」、「アプリケーション」、「概要」セクションに PCIe Gen 7 の仕様を追加.....                       | 1           |

| • 「概要」セクションに PCIe Gen 7 の仕様を追加.....                                       | 12          |

| Changes from Revision A (February 2020) to Revision B (October 2024) | Page |

|----------------------------------------------------------------------|------|

| • ドキュメント全体にわたって表、図、相互参照の採番方法を更新.....                                 | 1    |

| Changes from Revision * (November 2019) to Revision A (February 2020) | Page |

|-----------------------------------------------------------------------|------|

| • 最大入力電圧を VDD + 0.3V から VDD+ 0.5V に変更 .....                           | 7    |

## 11 メカニカル、パッケージ、および注文情報

以降のページには、メカニカル、パッケージ、および注文に関する情報が記載されています。この情報は、指定のデバイスに使用できる最新のデータです。このデータは、予告なく、このドキュメントを改訂せずに変更される場合があります。本データシートのブラウザ版を使用されている場合は、画面左側の説明をご覧ください。

## 重要なお知らせと免責事項

テキサス・インスツルメンツは、技術データと信頼性データ（データシートを含みます）、設計リソース（リファレンス デザインを含みます）、アプリケーションや設計に関する各種アドバイス、Web ツール、安全性情報、その他のリソースを、欠陥が存在する可能性のある「現状のまま」提供しており、商品性および特定目的に対する適合性の默示保証、第三者の知的財産権の非侵害保証を含むいかなる保証も、明示的または默示的にかかわらず拒否します。

これらのリソースは、テキサス・インスツルメンツ製品を使用する設計の経験を積んだ開発者への提供を意図したものです。(1) お客様のアプリケーションに適した テキサス・インスツルメンツ製品の選定、(2) お客様のアプリケーションの設計、検証、試験、(3) お客様のアプリケーションに該当する各種規格や、その他のあらゆる安全性、セキュリティ、規制、または他の要件への確実な適合に関する責任を、お客様のみが単独で負うものとします。

上記の各種リソースは、予告なく変更される可能性があります。これらのリソースは、リソースで説明されている テキサス・インスツルメンツ製品を使用するアプリケーションの開発の目的でのみ、テキサス・インスツルメンツはその使用をお客様に許諾します。これらのリソースに関して、他の目的で複製することや掲載することは禁止されています。テキサス・インスツルメンツや第三者の知的財産権のライセンスが付与されている訳ではありません。お客様は、これらのリソースを自身で使用した結果発生するあらゆる申し立て、損害、費用、損失、責任について、テキサス・インスツルメンツおよびその代理人を完全に補償するものとし、テキサス・インスツルメンツは一切の責任を拒否します。

テキサス・インスツルメンツの製品は、[テキサス・インスツルメンツの販売条件](#)、または [ti.com](http://ti.com) やかかる テキサス・インスツルメンツ製品の関連資料などのいづれかを通じて提供する適用可能な条項の下で提供されています。テキサス・インスツルメンツがこれらのリソースを提供することは、適用されるテキサス・インスツルメンツの保証または他の保証の放棄の拡大や変更を意味するものではありません。

お客様がいかなる追加条項または代替条項を提案した場合でも、テキサス・インスツルメンツはそれらに異議を唱え、拒否します。

郵送先住所: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2025, Texas Instruments Incorporated

**PACKAGING INFORMATION**

| Orderable part number | Status<br>(1) | Material type<br>(2) | Package   Pins  | Package qty   Carrier | RoHS<br>(3) | Lead finish/<br>Ball material<br>(4) | MSL rating/<br>Peak reflow<br>(5) | Op temp (°C) | Part marking<br>(6) |

|-----------------------|---------------|----------------------|-----------------|-----------------------|-------------|--------------------------------------|-----------------------------------|--------------|---------------------|

| CDCDB2000ENPPR        | Active        | Production           | TLGA (NPP)   80 | 4000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 85    | CDCDB 2000          |

| CDCDB2000ENPPR.A      | Active        | Production           | TLGA (NPP)   80 | 4000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 85    | CDCDB 2000          |

| CDCDB2000ENPPT        | Active        | Production           | TLGA (NPP)   80 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 85    | CDCDB 2000          |

| CDCDB2000ENPPT.A      | Active        | Production           | TLGA (NPP)   80 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 85    | CDCDB 2000          |

| CDCDB2000NPPR         | Active        | Production           | TLGA (NPP)   80 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 85    | CDCDB 2000          |

| CDCDB2000NPPR.A       | Active        | Production           | TLGA (NPP)   80 | 3000   LARGE T&R      | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 85    | CDCDB 2000          |

| CDCDB2000NPPT         | Active        | Production           | TLGA (NPP)   80 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 85    | CDCDB 2000          |

| CDCDB2000NPPT.A       | Active        | Production           | TLGA (NPP)   80 | 250   SMALL T&R       | Yes         | NIPDAU                               | Level-3-260C-168 HR               | -40 to 85    | CDCDB 2000          |

<sup>(1)</sup> **Status:** For more details on status, see our [product life cycle](#).

<sup>(2)</sup> **Material type:** When designated, preproduction parts are prototypes/experimental devices, and are not yet approved or released for full production. Testing and final process, including without limitation quality assurance, reliability performance testing, and/or process qualification, may not yet be complete, and this item is subject to further changes or possible discontinuation. If available for ordering, purchases will be subject to an additional waiver at checkout, and are intended for early internal evaluation purposes only. These items are sold without warranties of any kind.

<sup>(3)</sup> **RoHS values:** Yes, No, RoHS Exempt. See the [TI RoHS Statement](#) for additional information and value definition.

<sup>(4)</sup> **Lead finish/Ball material:** Parts may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

<sup>(5)</sup> **MSL rating/Peak reflow:** The moisture sensitivity level ratings and peak solder (reflow) temperatures. In the event that a part has multiple moisture sensitivity ratings, only the lowest level per JEDEC standards is shown. Refer to the shipping label for the actual reflow temperature that will be used to mount the part to the printed circuit board.

<sup>(6)</sup> **Part marking:** There may be an additional marking, which relates to the logo, the lot trace code information, or the environmental category of the part.

Multiple part markings will be inside parentheses. Only one part marking contained in parentheses and separated by a "~" will appear on a part. If a line is indented then it is a continuation of the previous line and the two combined represent the entire part marking for that device.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

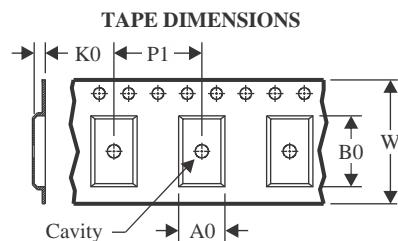

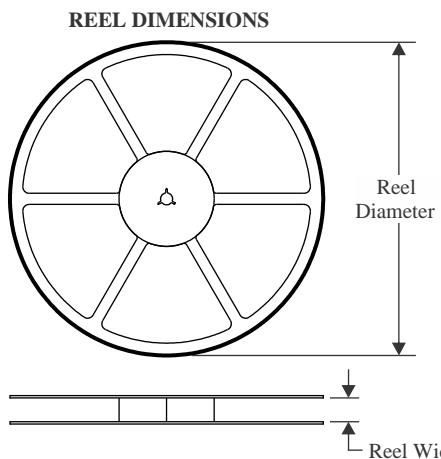

## TAPE AND REEL INFORMATION

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

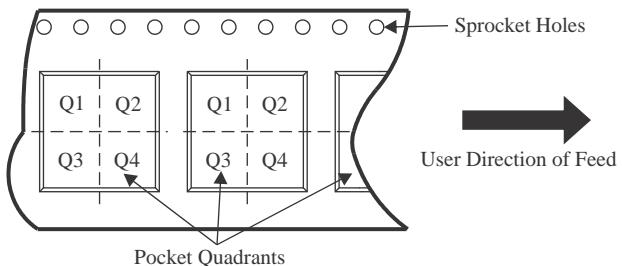

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|----------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| CDCDB2000ENPPR | TLGA         | NPP             | 80   | 4000 | 330.0              | 16.4               | 6.3     | 6.3     | 1.1     | 12.0    | 16.0   | Q1            |

| CDCDB2000ENPPT | TLGA         | NPP             | 80   | 250  | 180.0              | 16.4               | 6.3     | 6.3     | 1.1     | 12.0    | 16.0   | Q1            |

| CDCDB2000NPPR  | TLGA         | NPP             | 80   | 3000 | 330.0              | 16.4               | 6.3     | 6.3     | 1.1     | 12.0    | 16.0   | Q2            |

| CDCDB2000NPPT  | TLGA         | NPP             | 80   | 250  | 180.0              | 16.4               | 6.3     | 6.3     | 1.1     | 12.0    | 16.0   | Q2            |

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| CDCDB2000ENPPR | TLGA         | NPP             | 80   | 4000 | 367.0       | 367.0      | 38.0        |

| CDCDB2000ENPPT | TLGA         | NPP             | 80   | 250  | 210.0       | 185.0      | 35.0        |

| CDCDB2000NPPR  | TLGA         | NPP             | 80   | 3000 | 367.0       | 367.0      | 38.0        |

| CDCDB2000NPPT  | TLGA         | NPP             | 80   | 250  | 210.0       | 185.0      | 35.0        |

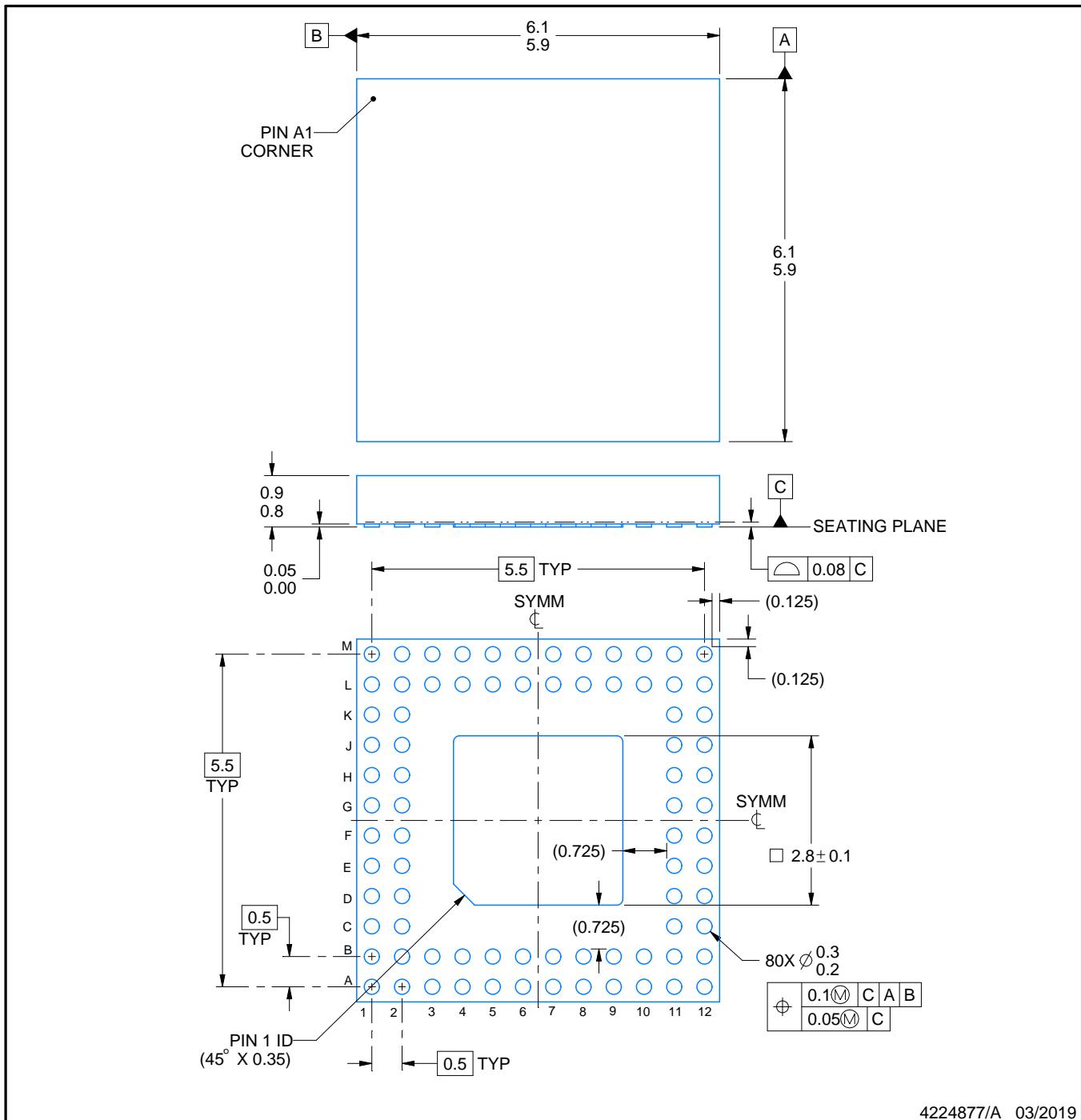

NPP0080A

# PACKAGE OUTLINE

TLGA - 0.9 mm max height

THIN LAND GRID ARRAY

4224877/A 03/2019

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

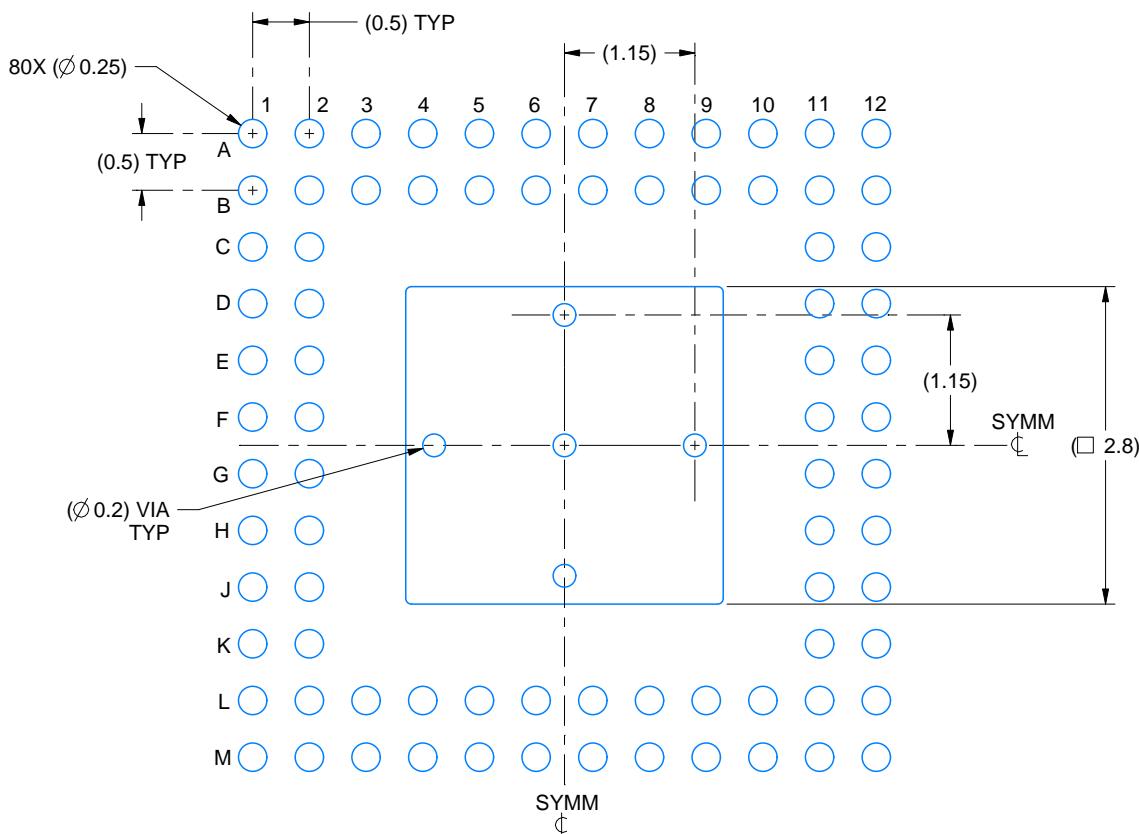

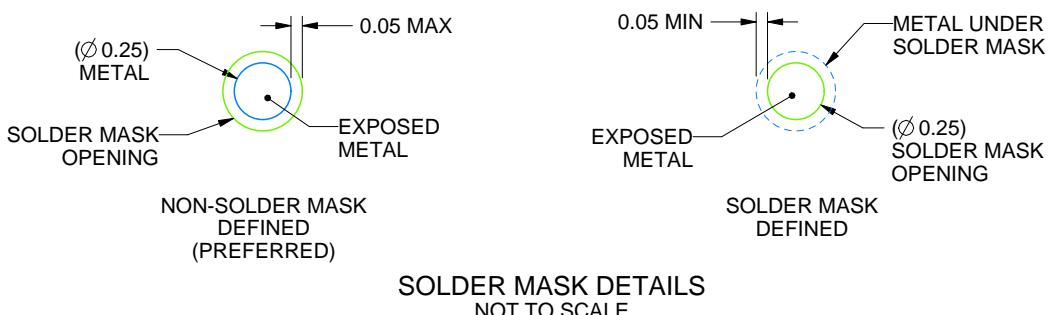

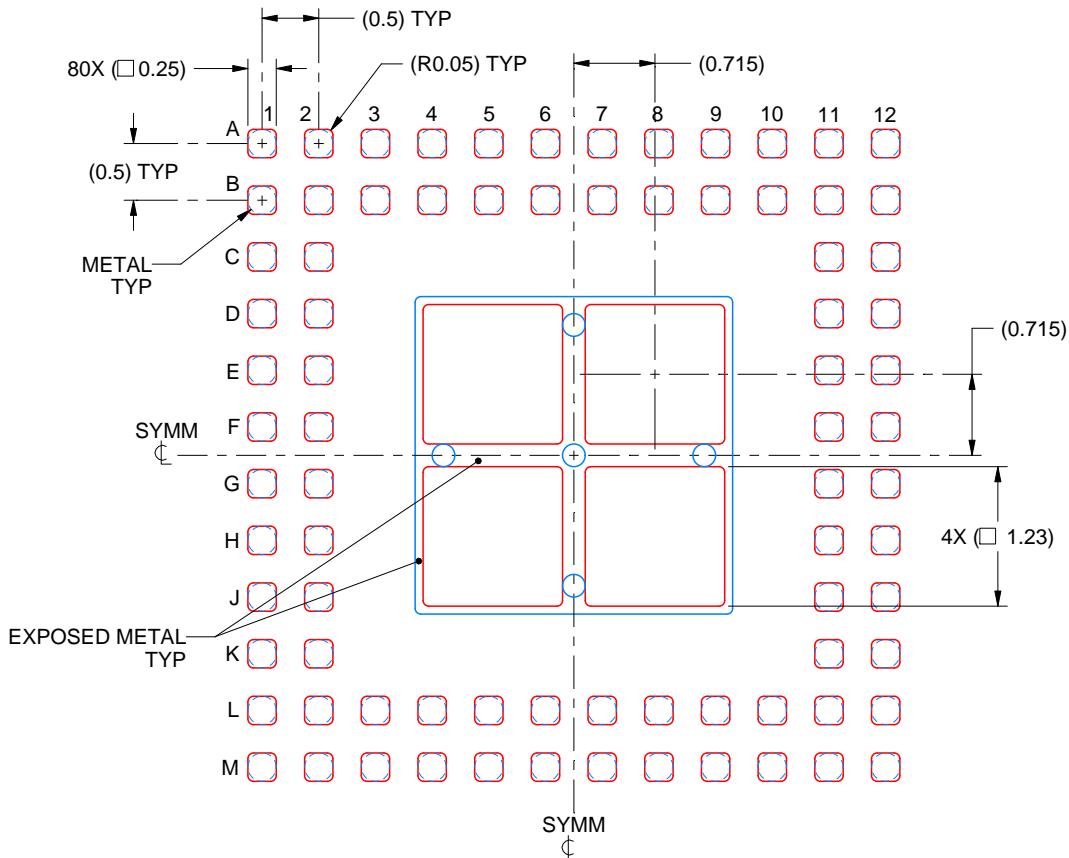

## **EXAMPLE BOARD LAYOUT**

**NPP0080A**

## **TLGA - 0.9 mm max height**

THIN LAND GRID ARRAY

**LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE: 15X**

4224877/A 03/2019

#### NOTES: (continued)

4. Final dimensions may vary due to manufacturing tolerance considerations and also routing constraints.

See Texas Instruments Literature No. SNVA009 ([www.ti.com/lit/snva009](http://www.ti.com/lit/snva009)).

5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

# EXAMPLE STENCIL DESIGN

NPP0080A

TLGA - 0.9 mm max height

THIN LAND GRID ARRAY

SOLDER PASTE EXAMPLE

BASED ON 0.1 mm THICK STENCIL

SCALE: 15X

4224877/A 03/2019

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release.